# PERFORMANCE EVALUATION OF NEUTRAL POINT CLAMPED ACTIVE RECTIFIER

# **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree of

MASTER OF TECHNOLOGY

in

# ELECTRICAL ENGINEERING

(With Specialization in Electric Drives and Power Electronics)

By

# **ASHOK PEDDI**

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA) JUNE, 2011

# **CANDIDATE'S DECLARATION**

I hereby declare that the work that is being presented in this dissertation entitled "PERFORMANCE EVALUATION OF NEUTRAL POINT CLAMPED ACTIVE RECTIFIER" in partial fulfillment of the requirements for the award of the degree of Master of Technology in Electrical Engineering with specialization in "Electric Drives and Power Electronics" submitted to the Department of Electrical Engineering, Indian Institute of Technology, Roorkee, INDIA is an authentic record of my own work carried under the guidance of Dr. Sharmili Das, Assistant Professor & Dr. Pramod Agarwal, Professor, Department of Electrical Engineering, Indian Institute of Technology, Roorkee.

The matter embodied in this dissertation has not been submitted for the award of any other degree or diploma.

Date: 30/06/2011

Place: Rookee

Ashokp (ASHOK PEDDI)

This is to certify that the above statement made by the candidate is true to the best of my knowledge.

i

Sharmili Das.

(**Dr. Sharmili Das**) Assistant Professor, Department of Electrical Engineering IIT Roorkee, INDIA.

(**Dr. Pramod Agarwal**) Professor, Department of Electrical Engineering IIT Roorkee, INDIA.

# ACKNOWLEDGEMENT

It is to my proud privilege to express my deep sense of gratitude and sincere thanks towards **Dr. Sharmili Das**, Assistant Professor & **Dr. Pramod Agarwal**, Professor, Department of Electrical Engineering, Indian Institute of Technology, Roorkee, for their esteem guidance, and valuable suggestions without which it would not have been possible to complete this dissertation work in present form. This work is simply the reflection of their thoughts, ideas and concepts. I am highly indebted to them for their kind and valuable suggestions and of course their valuable time during the period of this work. The huge quantum of knowledge I had gained during their inspiring guidance would be immensely beneficial for my future endeavors.

I thank all the **teaching** and **non teaching staff members** of the department who have contributed directly or indirectly in successful completion of my dissertation work.

I am extremely grateful to friends and well-wishers for their help, meaningful suggestions and persistent encouragement given to me at different stages of my work.

Finally, I would like to say that I am indebted to my **parents** for everything that they have given to me. I thank them for the sacrifices they made so that I could grow up in a learning environment. They have always stood by me in everything I have done, providing constant support, encouragement and love.

Finally, I would like to thank almighty to whom I owe everything.

Date: Place: Rookee

#### **ASHOK PEDDI**

The AC-DC converters, also known as rectifiers, are developed using diodes and thyristors to provide uncontrolled and controlled, unidirectional and bidirectional dc power. However, these rectifiers can pollute AC supply with significant levels of low frequency harmonics, pulsating input current (electromagnetic interference (EMI)), and excessive VAR. with tough regulations and severe economic restraints, the design of Active rectifier which draws nearly sinusoidal current with unity power factor is very important from the point of view of energy saving and also to satisfy harmonic standards such as IEEE 1000-3-2.

In response to these problems, a significant amount of research has been devoted to the area of switch-mode rectifiers (SMRs), power-factor correctors (PFCs), pulse widthmodulation (PWM) rectifiers and multilevel rectifiers. Current research has been focusing recently on decreasing the number of power switches to simplify the circuit, complexity of control circuit and increase its reliability.

In the present work, a four switch Single-phase neutral-point diode-clamped active rectifier (reduced switch topology) is considered. Detailed power circuit analysis for the undertaken topology is presented. Two high performance control strategies (two level PWM and three level PWM) are discussed and verified through simulations. These control schemes for single-phase diode-clamped active rectifier is proposed to achieve a unity power factor, balanced neutral-point voltage and constant DC-bus voltage. The application of considered active rectifier topology is to improvement of power quality is investigated. The considered rectifier can also be used for harmonic current filtering. Finally experimental prototype of the considered four switch single-phase diode-clamped rectifier is developed and tested.

Theoretical and practical results of the system show that the developed system can eliminate the harmonics and achieve unity power factor with minimum complexity.

| 2 21         | Venieur en ferrer ef Elein e en eiter den stand en ter                                       | 41                     |

|--------------|----------------------------------------------------------------------------------------------|------------------------|

| 3.21<br>3.22 | Various waveforms of Flying capacitor three level converter                                  | 41                     |

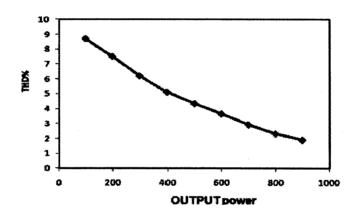

| 3.22         | Waveform and harmonic spectrum of input current<br>Total harmonic distortion vs output power | 42                     |

| 3.23         | Power Factor vs output power                                                                 | 42<br>43               |

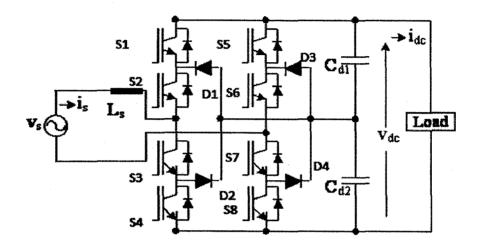

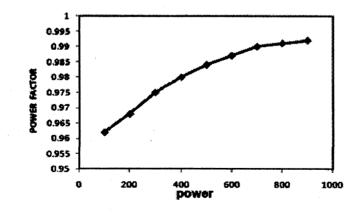

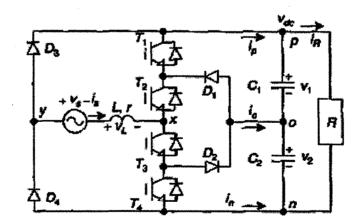

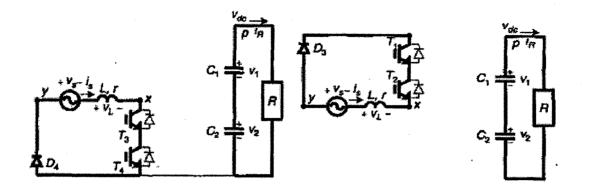

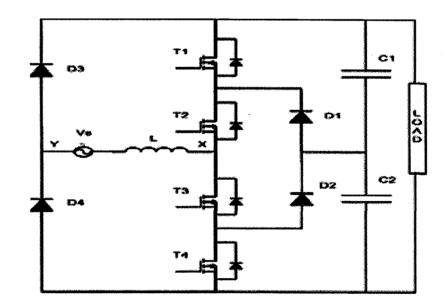

| 4.1          | Circuit configuration of neutral-point diode-clamped rectifier                               | 43<br>44               |

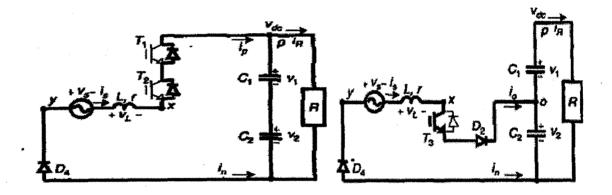

| 4.2          | Operation in a) mode-1 & b) mode-2                                                           | 44                     |

| 4.3          | Operation in a) mode-3 & b) mode-4                                                           | 46                     |

| 4.4          | Operation in a) mode-5 & b) mode-6                                                           | 46                     |

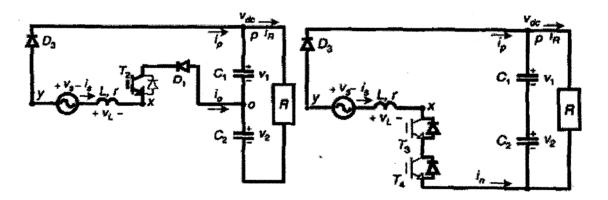

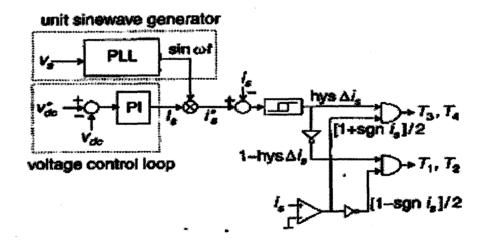

| 4.5          | Control circuit for PFC converter system                                                     | 49                     |

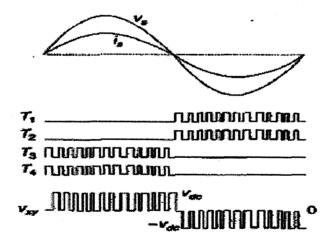

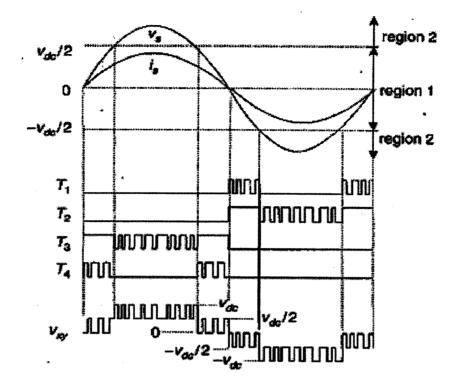

| 4.6          | Switching-signals and ac side voltages of two-level PWM                                      | 50                     |

| 1.0          | Rectifier                                                                                    | 50                     |

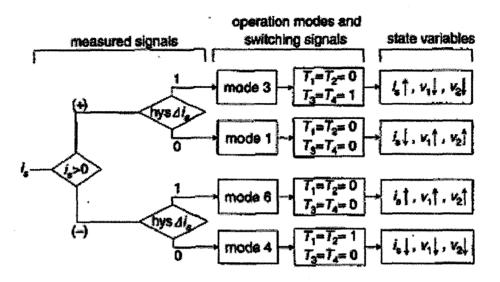

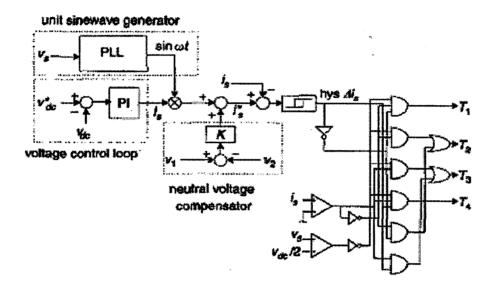

| 4.7          | Control strategy (two-level PWM)                                                             | 51                     |

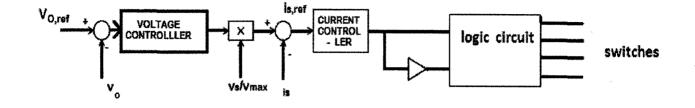

| 4.9          | Switching signals and AC-side voltage of three-level PWM                                     | 53                     |

|              | Rectifier                                                                                    |                        |

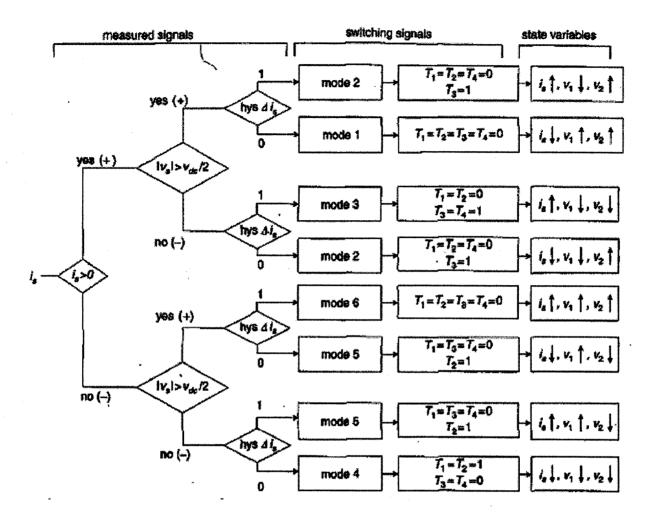

| 4.10         | Control strategy (three-level P WM)                                                          | 55                     |

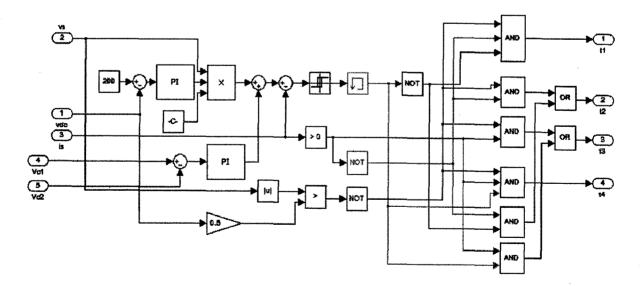

| 4.11         | Control block diagram (three-level PWM)                                                      | 56                     |

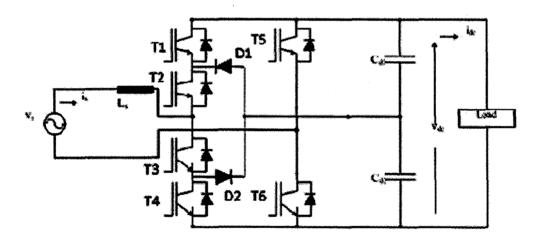

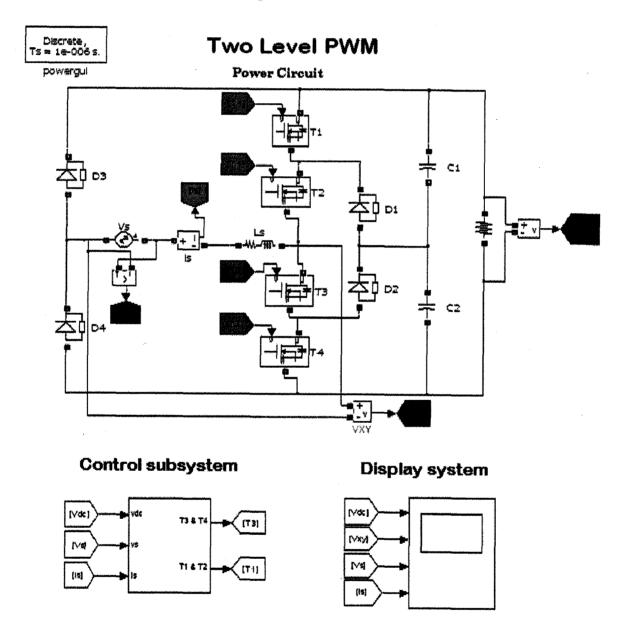

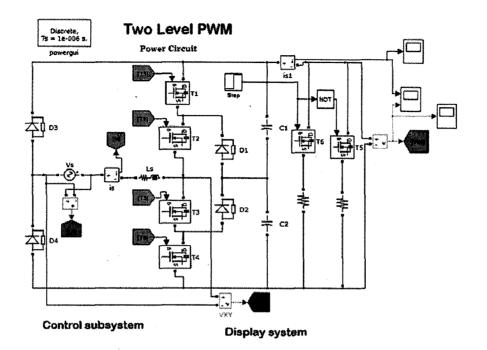

| 5.1          | SIMULINK model of single-phase active rectifier for Two-Level                                | 58                     |

|              | PWM                                                                                          |                        |

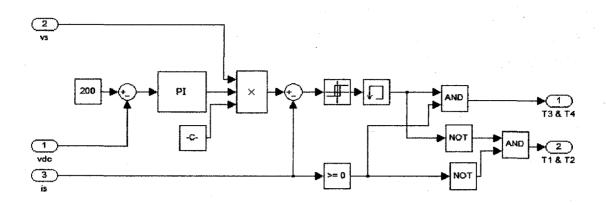

| 5.2          | Control block diagram for Two-Level PWM scheme                                               | 59                     |

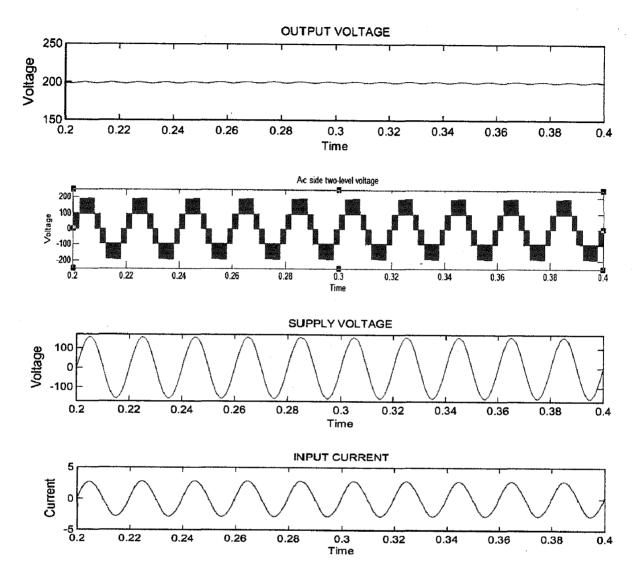

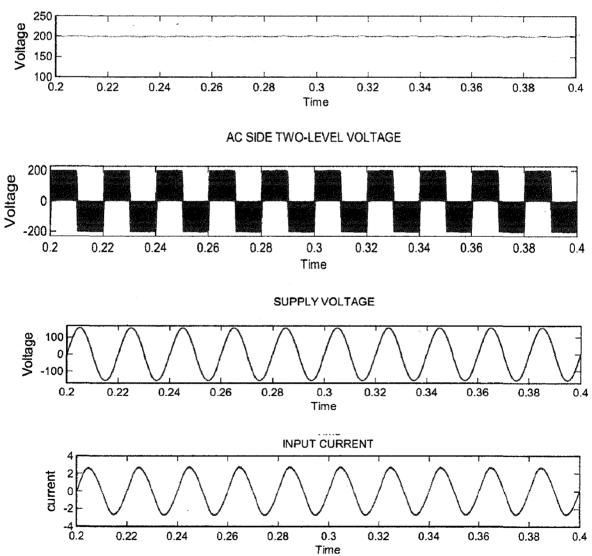

| 5.3          | Various simulation results                                                                   | 59                     |

| 5.4          | Supply voltage & current                                                                     | <b>60</b> <sup>+</sup> |

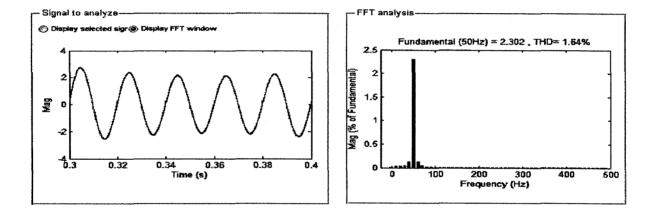

| 5.5          | Input current waveform and harmonic spectrum                                                 | 60                     |

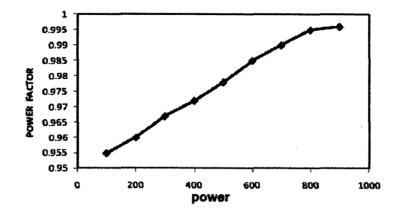

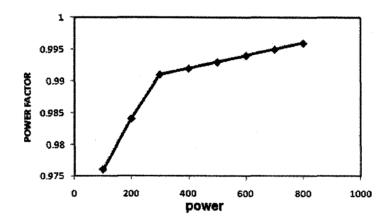

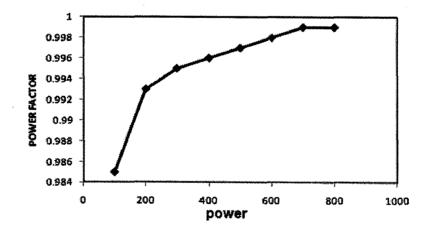

| 5.6          | Power factor vs output power                                                                 | 61                     |

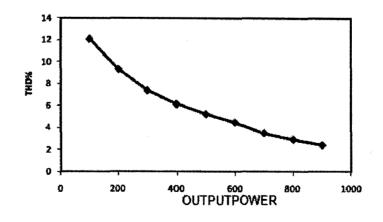

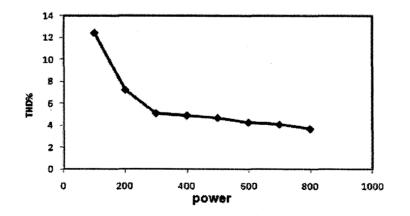

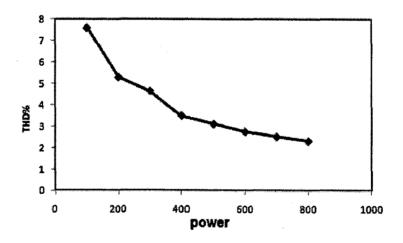

| 5.7          | Total harmonic distortion vs output power                                                    | 61                     |

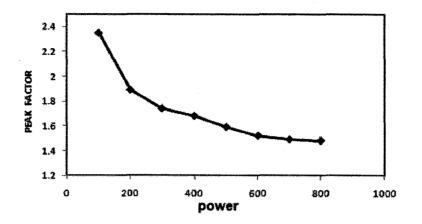

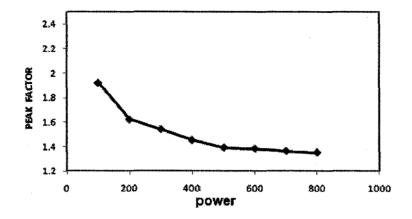

| 5.8          | Peak factor vs output power                                                                  | 62                     |

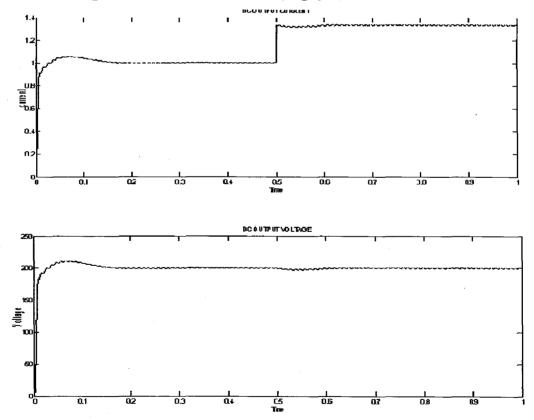

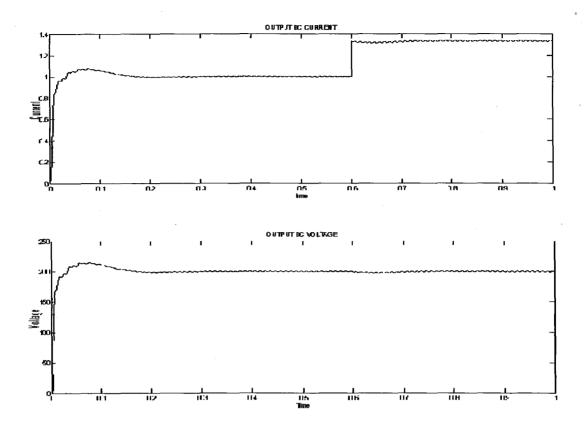

| 5.9          | Converter with load change from $200\Omega$ to $150\Omega$                                   | 63                     |

| 5.10         | Output current (above) and voltage (below) for change in load condition                      | 63                     |

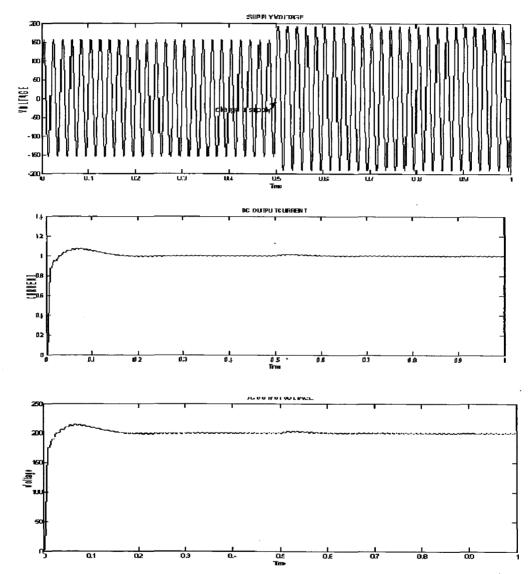

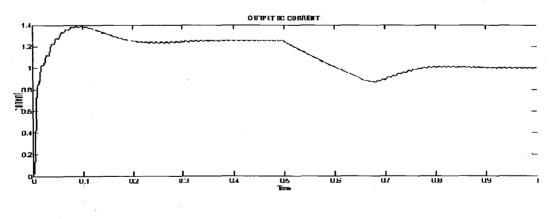

| 5.11         | Waveforms of change in supply (above), output current (middle)                               | 64                     |

|              | and output voltage (below)                                                                   | 0.                     |

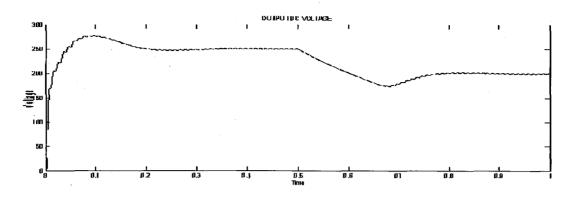

| 5.12         | Output voltage and current for change in reference                                           | 65                     |

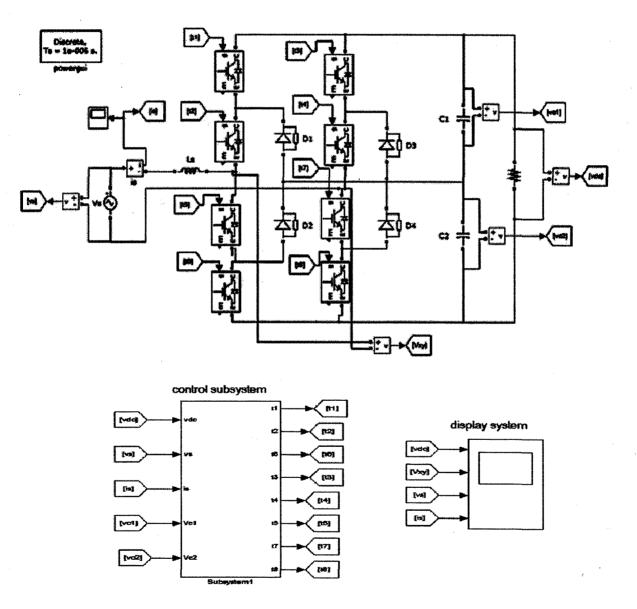

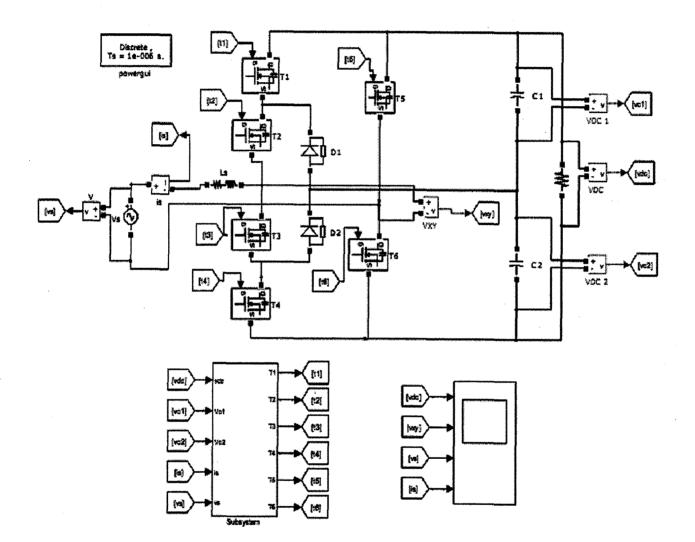

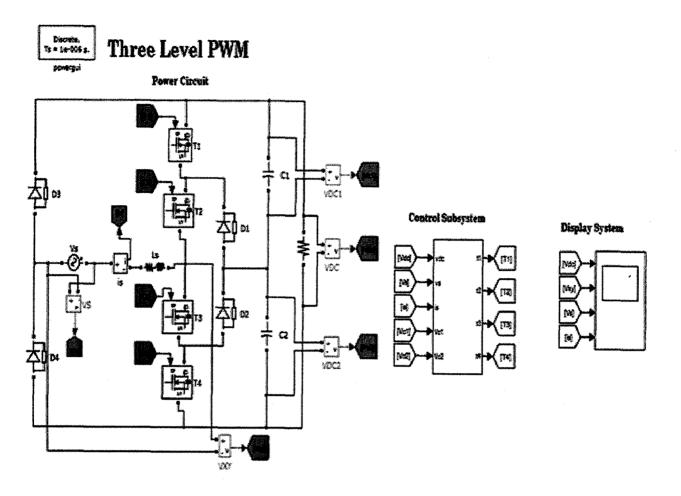

| 5.13         | SIMULINK model of single-phase active rectifier for Three-<br>Level PWM                      | 66                     |

| 5.14         | Control block diagram for Three-Level PWM scheme                                             | 66                     |

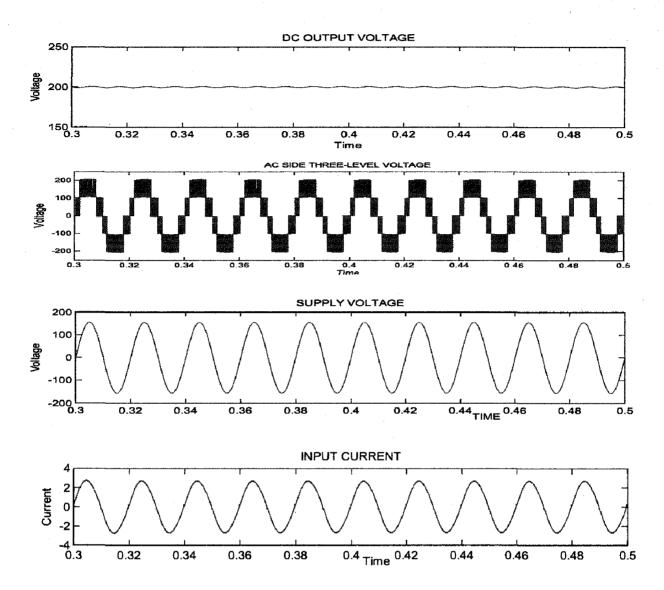

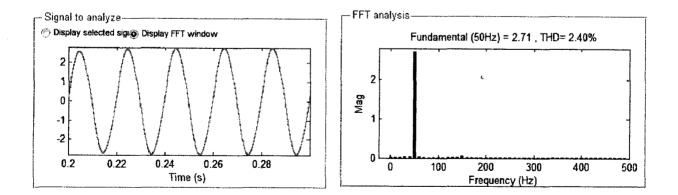

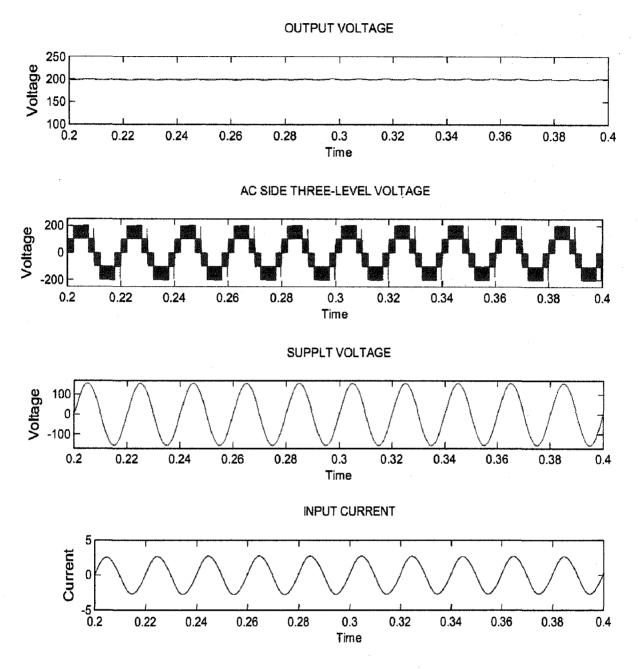

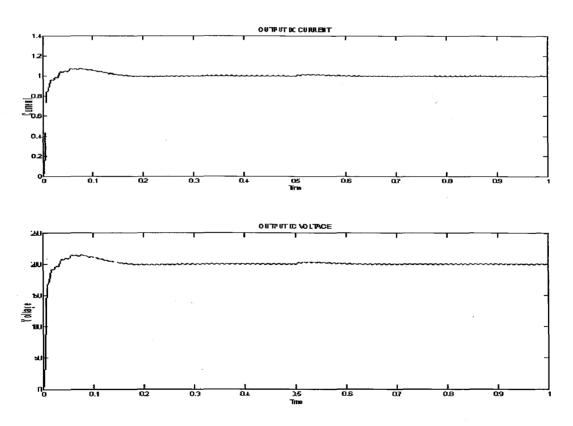

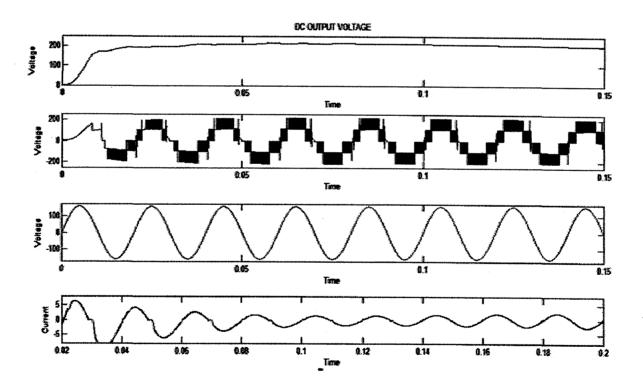

| 5.14         | Simulation results                                                                           | 66<br>67               |

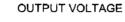

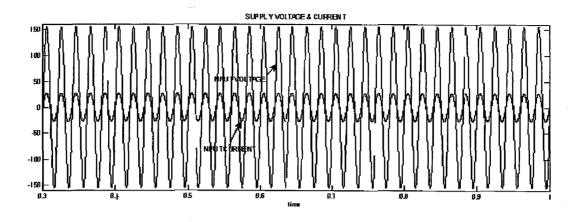

| 5.15<br>5.16 | Supply voltage & current                                                                     |                        |

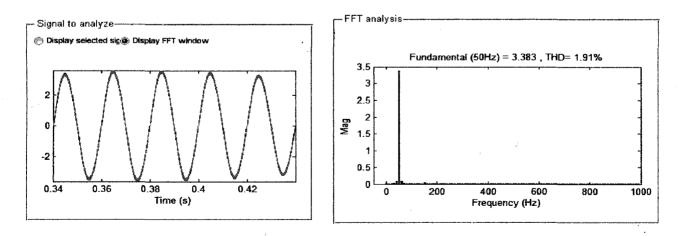

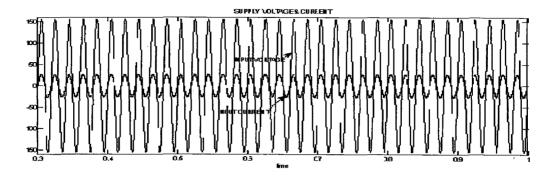

| 5.10<br>5.17 |                                                                                              | 68                     |

| J.17         | Input current waveform and harmonic spectrum                                                 | 68                     |

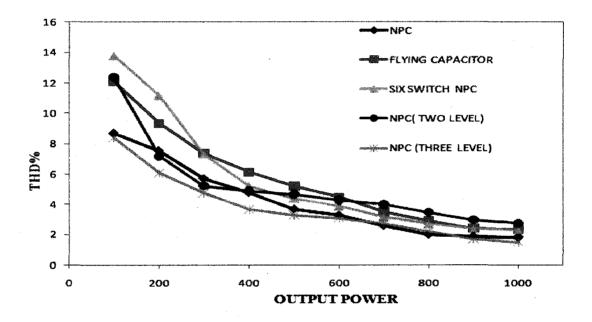

| 5.18 | Total harmonic distortion vs output power                     | 69 |

|------|---------------------------------------------------------------|----|

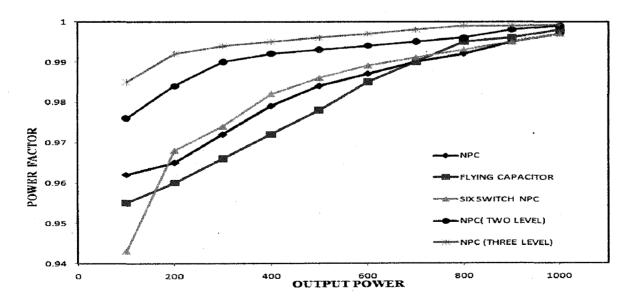

| 5.19 | Power factor vs output power                                  | 69 |

| 5.20 | Peak factor vs output power                                   | 70 |

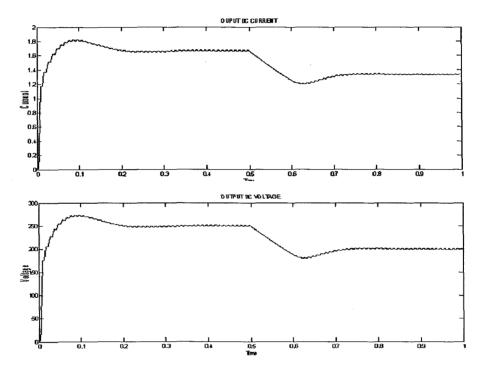

| 5.21 | Output current (above) and voltage (below) for change in load | 71 |

|      | condition                                                     |    |

| 5.22 | Output current for change in reference                        | 72 |

| 5.23 | Output voltage for change reference                           | 72 |

| 5.24 | Output current (above), output voltage (below) for change in  | 72 |

|      | supply                                                        |    |

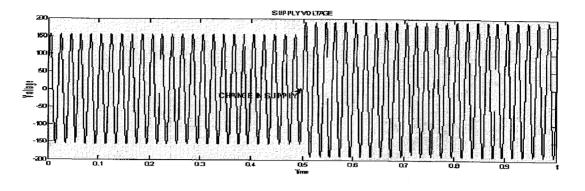

| 5.25 | Change in supply voltage at $t=0.5$ sec.                      | 73 |

| 5.26 | Step in response of active rectifier                          | 73 |

| 5.27 | Total harmonic distortion vs output power                     | 74 |

| 5.28 | Peak factor vs output power                                   | 74 |

| 6.1  | Power circuit of a single-phase Neutral-Point diode-Clamped   | 77 |

|      | Rectifier                                                     |    |

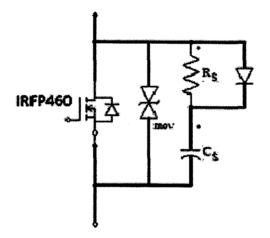

| 6.2  | Snubber circuit for MOSFET protection                         | 79 |

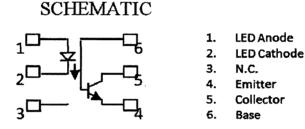

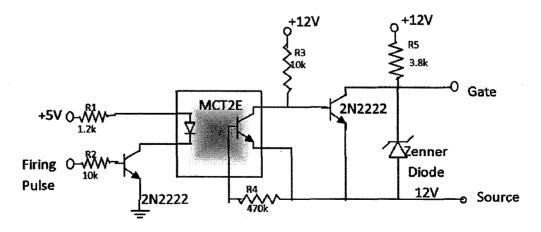

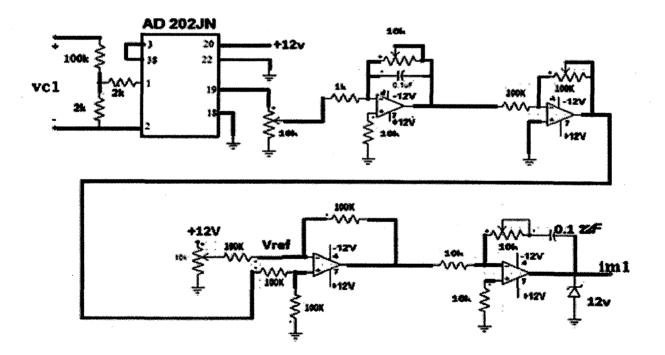

| 6.3  | Pulse amplification and isolation circuit diagram             | 80 |

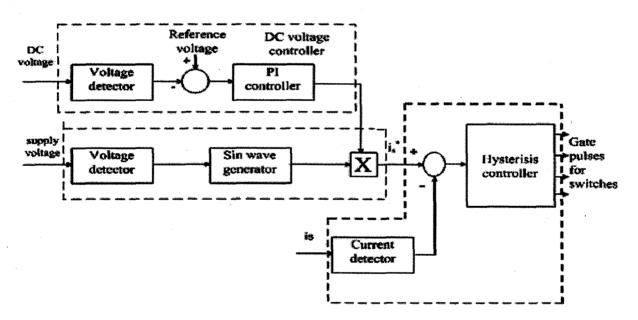

| 6.4  | Control Scheme Realization                                    | 81 |

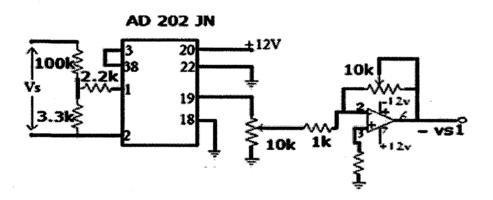

| 6.5  | AC Voltage sensing circuit.                                   | 82 |

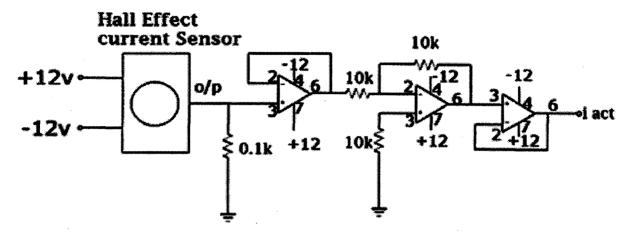

| 6.6  | AC Current sensing circuit.                                   | 83 |

| 6.7  | DC voltage sensing along with the PI controller circuit.      | 83 |

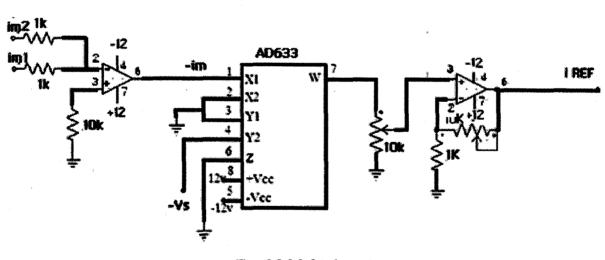

| 6.8  | Multiplier circuit                                            | 84 |

| 6.9  | Hysteresis Controller with Dead band circuit.                 | 85 |

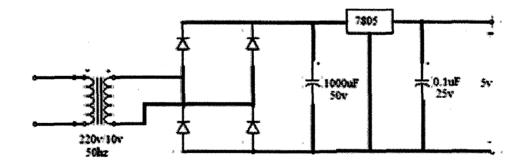

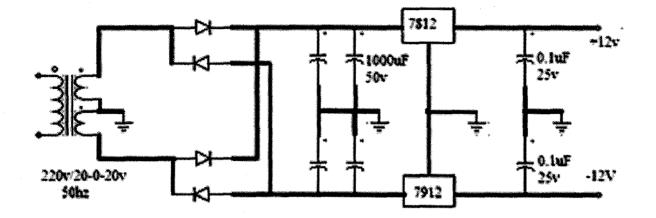

| 6.10 | +5V Regulated DC supply.                                      | 86 |

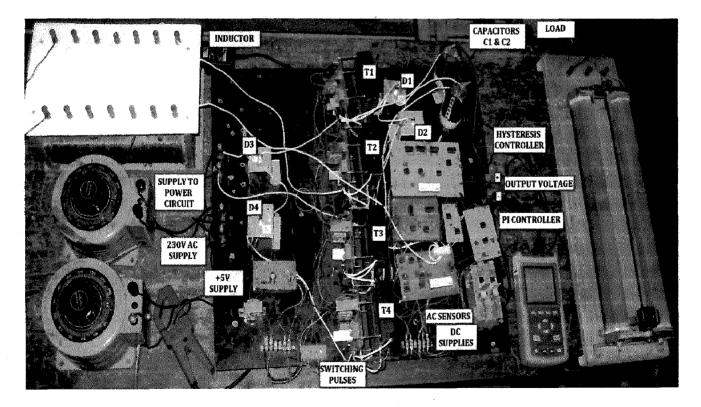

| 7.1  | LABORATORY EXPERIMENTAL SETUP                                 | 88 |

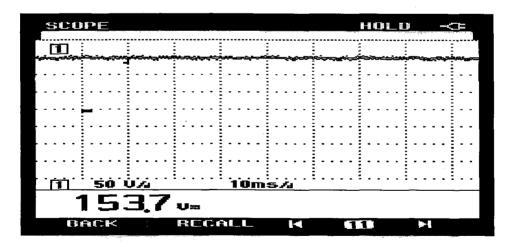

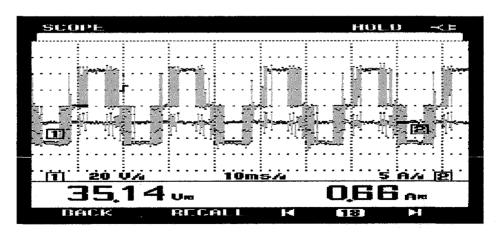

| 7.2  | Output Dc voltage                                             | 89 |

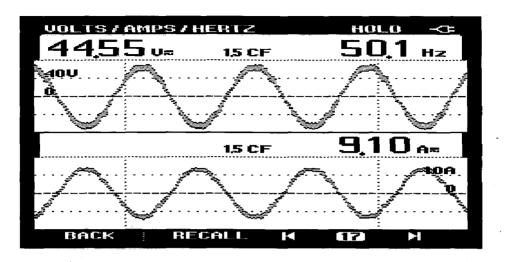

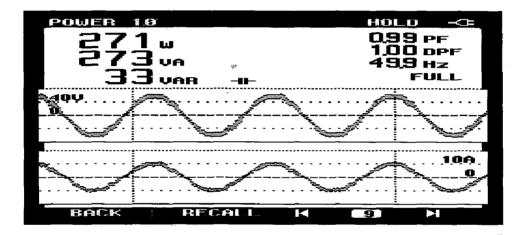

| 7.3  | Source voltage & current                                      | 90 |

| 7.4  | Power Factor of input current                                 | 90 |

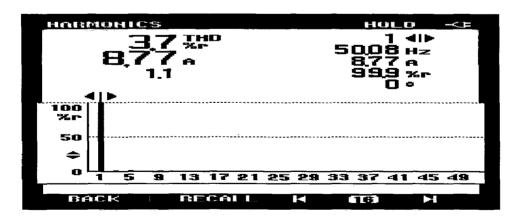

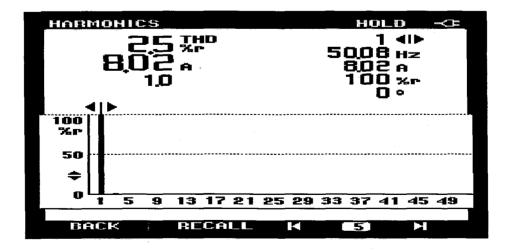

| 7.5  | Total Harmonic Distortion of input current                    | 90 |

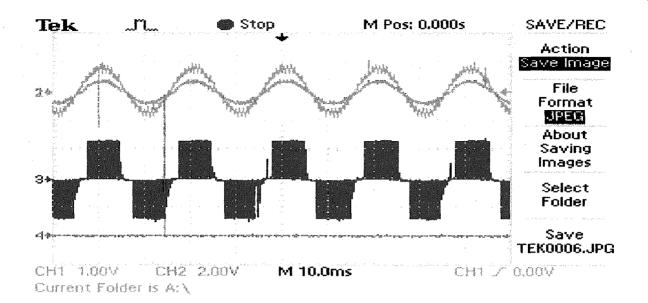

| 7.6  | Ac side two level voltage                                     | 91 |

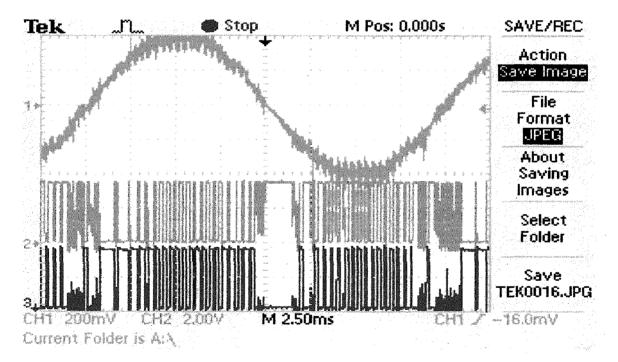

| 7.7  | Switching pulses                                              | 91 |

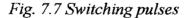

| 7.8  | Source voltage & current                                      | 92 |

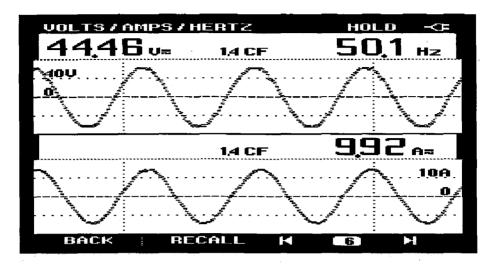

| 7.9  | Power Factor of input current                                 | 92 |

| 7.10 | Total Harmonic Distortion of input current                    | 92 |

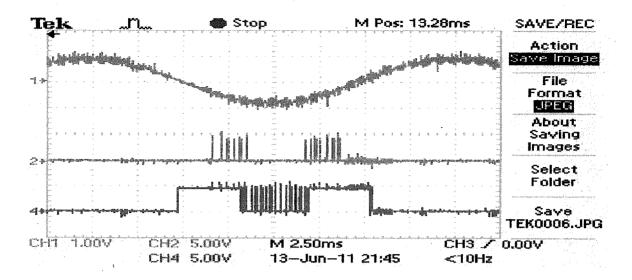

| 7.11 | Switching pulses for switches T1 and T2                       | 93 |

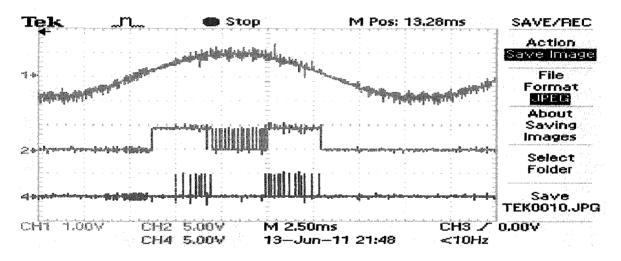

| 7.12 | Switching pulses for switches T3 and T4                       | 93 |

| 7.13 | Ac side three level voltage                                   | 93 |

# LIST OF TABLES

| T. No. | Caption                                                | P. No. |

|--------|--------------------------------------------------------|--------|

| 2.1    | Examples of linear loads.                              | 10     |

| 2.2    | Examples of some nonlinear loads.                      | 11     |

| 2.3    | Limits for Class A equipment in standard IEC 1000-3-2. | 14     |

| 2.4    | Limits for Class B equipment in standard IEC 1000-3-2. | 15     |

| 2.5    | Limits for Class C equipment in standard IEC 1000-3-2. | 15     |

| 4.1    | Switching states and modes of operation rectifier.     | 47     |

| 5.1    | Harmonic components of supply current                  | 60     |

| 5.2    | Harmonic components of supply current                  | 68     |

| 5.3    | Comparison of converter topologies                     | 74     |

# **CONTENTS**

| CANDIDATE D  | ECLA | RATION                                               | i    |

|--------------|------|------------------------------------------------------|------|

| ACKNOWLED    | EGEM | <b>ENT</b>                                           | ii   |

| ABSTRACT     |      |                                                      | iii  |

| LIST OF FIGU | RES  |                                                      | iv   |

| LIST OF TABL | ES   |                                                      | vii  |

| CHAPTER - 1  | INT  | RODUTION AND LITURETURE REVIEW                       | 1    |

|              | 1.1  | Introduction                                         | 1    |

| <u>.</u> .   | 1.2  | Literature review                                    | 3    |

|              | 1.3  | Dissertation organization                            | 4    |

| CHAPTER - 2  | HAR  | RMONICS AND POWER FACTOR                             | 6    |

| •            |      | Introduction                                         | 6    |

|              | 2.1  | Harmonics                                            | 6    |

|              | 2.2  | Linear and Non-Linear Loads                          | 9    |

|              |      | 2.2.1 Linear Loads                                   | 9    |

|              |      | 2.2.2 Non Linear Loads                               | 10   |

|              | 2.3  | Sources of Harmonics                                 | 12   |

|              |      | 2.3.1 Effects of harmonics                           | 12   |

|              | 2.4  | Standards regulating line current harmonics          | 13   |

|              | 2.5  | Power Factor                                         | 16   |

|              | 2.6  | Power Factor Correction                              | 18   |

|              | 2.7  | Desirable features of a PFC technique                | 19   |

|              |      | 2.7.1 Input side features:                           | 19   |

|              |      | 2.7.2 Output side features:                          |      |

| CHAPTER - 3  | MU   | LTILEVEL CONVERTERS                                  | 20   |

|              |      | Introduction                                         | 20   |

|              | 3.1  | Classification of rectifiers                         | 20   |

|              |      | 3.1.1 Problems with Conventional Rectifiers:         | 22   |

|              | 3.2  | Improved Power Quality Converters (IPQCs):           | 22   |

|              |      | 3.2.1 Topology-Based Classification                  | - 24 |

|              |      | 3.2.2 Converter-based classification                 | 25   |

|              | 3.3  | Multilevel Converters for PFC                        | 25   |

|              |      | 3.3.1 Configurations                                 | 26   |

|              |      | 3.3.2 Advantages of multilevel converters:           | 27   |

|              | 3.4  | Classification of Single Phase Multilevel Converters | 28   |

|              | 3.5  | Topologies of Three Level PWM Converters             | 30   |

|             | 3.6  | Diode Clamped Three Level Converter:                                           | 31       |

|-------------|------|--------------------------------------------------------------------------------|----------|

|             |      | 3.6.1 Simulation results                                                       | 32       |

|             |      | 3.6.2 Varying load condition:                                                  | 34       |

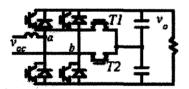

|             | 3.7  | Six switch Diode Clamped Three Level Converter                                 | 35       |

|             |      | 3.7.1 Simulation results                                                       | 36       |

|             |      | 3.7.2 Varying load condition:                                                  | 38       |

|             | 3.8  | Flying capacitor three level converter:                                        | 39       |

|             |      | 3.8.1 Simulation results                                                       | 40       |

|             |      | 3.8.2 Varying load condition:                                                  | 42       |

|             | 3.9  | Conclusion                                                                     | 43       |

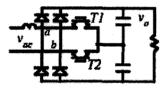

| CHAPTER - 4 | SINC | GLE PHASE NEUTRAL POINT DIODE CLAMPED                                          | 44       |

|             | REC  | TIFIER                                                                         |          |

|             | 4.1  | Introduction                                                                   | 44       |

|             | 4.2  | Principle of operation:                                                        | 45       |

|             | 4.3  | Control schemes                                                                | 48       |

|             |      | 4.3.1 Two-level PWM control strategy                                           | 49       |

|             |      | 4.3.2 Three-level PWM control strategy                                         | 52       |

| CHAPTER - 5 | PER  | FORMANCE EVALUATION OF SINGLE PHASE                                            | 57       |

|             | NEU  | TRAL POINT DIODE CLAMPED RECTIFIER                                             |          |

|             |      | Introduction                                                                   | 57       |

|             | 5.1  | Two-level PWM control scheme                                                   | 58       |

|             |      | 5.1.1 Steady state performance evaluation                                      | 58       |

|             |      | 5.1.2 Performance under varying load condition:                                | 61       |

|             |      | 5.1.3 Dynamic Performance Evaluation:                                          | 62       |

|             | 5.2  | Three-level PWM control scheme                                                 | 65       |

|             |      | 5.2.1 Steady state performance evaluation                                      | 69       |

|             |      | 5.2.2 Performance under varying load condition:                                | 70       |

|             |      | 5.2.3 Dynamic Performance Evaluation:                                          | 73       |

|             | 5.3  | Comparative analysis of converters                                             | 74       |

|             |      | 5.3.1 Various load conditions                                                  | 75       |

|             | 5.4  | Conclusion                                                                     | 76       |

| CHAPTER - 6 |      | TEM HARDWARE DEVELOPMENT                                                       | 77       |

|             | 6.1  | Hardware Development                                                           | 77       |

|             | 6.2  | Power Circuit development                                                      | 77       |

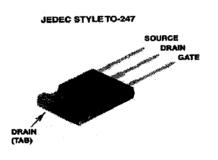

|             |      | 6.2.1 Switches                                                                 | 78       |

|             |      | 6.2.2 Snubber circuit<br>6.2.3 Pulse Amplification and Isolation Circuit       | 78       |

|             | 6.3  | 6.2.3 Pulse Amplification and Isolation Circuit<br>Control circuit realization | 80<br>82 |

|             | 0.0  | 6.3.1 AC voltage sensing circuit:                                              | 82       |

|             |      |                                                                                | 112      |

2000 K

|             |       | 6.3.2 Current Sensing Circuit:                      | 82 |

|-------------|-------|-----------------------------------------------------|----|

|             |       | 6.3.3 DC Voltage Sensing and PI controller circuit: | 83 |

|             |       | 6.3.4 Multiplier Circuit:                           | 84 |

|             |       | 6.3.5 Hysteresis current controller:                | 85 |

|             | 6.4   | Power supplies                                      | 86 |

|             | 6.5   | Conclusion                                          | 86 |

| CHAPTER - 7 | EXP   | ERIMENTAL RESULTS                                   | 87 |

|             | 7.1 C | Condusion                                           | 94 |

| CHAPTER - 8 | CON   | <b>ICLUSIONS AND FUTURE SCOPE</b>                   | 95 |

|             | 8.1   | CONCLUSIONS                                         | 95 |

|             | 8.2   | SCOPE FOR FUTURE WORK                               | 96 |

| REFERENCES  |       |                                                     | 97 |

#### REFERENCES

# CHAPTER 1

# **INTRODUCTION AND LITERATURE REVIEW**

# 1.1 Introduction

The most familiar loads on electrical power system were the constant power, constant impedance and constant current loads or a linear combination of thereof. In these cases, the voltage and current wave shapes are nearly pure sinusoidal. But this is no longer the case with modern electric power system. Massive use of the nonlinear and time varying devices has led to distortion of voltage and current waveforms. As a consequence, recently the issue of power quality has become important. Both electric utility and end users of electric power are becoming increasingly concerned about the quality of electric power. The term "power quality" has been used to describe the variation of the voltage, current and frequency on the power system beyond a limit.

The equipment connected to an electricity distribution network usually needs some kind of power conditioning, typically rectification, which produces a non sinusoidal line current due to the nonlinear input characteristic. The most significant examples of nonlinear loads are AC-DC converters. These AC-DC Power Converters are extensively used in various applications like power supplies, dc motor drives and front-end converters in adjustable-speed ac drives, HVDC transmission, switched-mode power supplies, and utility interfacing with conventional energy sources and so on. Traditionally, ac-dc power conversion has been dominated by diode or phase controlled rectifiers which act as non-linear loads on the power systems. These Conventional Converter system demands reactive power from the supply lines for proper commutation of the devices used in the system. Therefore conventional converter system has low overall power factor and draw input currents which are rich in harmonics .These harmonics lead to additional power losses in electrical equipment. This creates the power quality problem for the power distribution network and for other electrical systems in the vicinity of rectifier. This is why power factor correction (PFC) on the device side has become an important part of the final design for so many products. Hence present day's technology is heading towards achieving

sinusoidal current in phase with the supply voltage especially while using power electronic equipment.

In electric equipments, PFC technology can increase power factor, reduce harmonic pollution on grid and improve power utilization. The PFC techniques reduce the input current harmonics and improved power factor operation of converters is important from the energy saving point of view and also to satisfy the standards like IEC-1000-3-2, IEC-555 or IEEE-519. For improving the quality of power some techniques are developed. The techniques for improving power factor and to reduce current harmonics are classifies as follows:

- Passive filters.

- Active filters.

- Hybrid filters

- New circuits and control techniques.

Because of severity of power quality problems passive filters, active filters (AFs), and hybrid filters along with conventional rectifiers, have been extensively developed especially in high power rating and already existing installations. However, these filters are quite costly, heavy, and bulky and have reasonable losses which reduce overall efficiency of the complete system. Even in some cases the rating of converter used in AF is almost close to the rating of the load. Under these observations, it is considered better option to include new circuits and control techniques as an inherent part of the system of ac–dc conversion. Under this a new breed of rectifiers has been developed using new solid state self commutating devices those are switchmode rectifiers (SMRs), power-factor correctors (PFCs), pulse width-modulation (PWM) rectifiers and multilevel rectifiers.

Multilevel rectifiers have been developed now at a reasonably matured level for ac-dc conversion with reduced harmonic currents, high power factor, low electromagnetic interference (EMI) and low radio frequency interference (RFI) at input ac mains and well-regulated and good quality dc output to feed loads ranging from fraction of Watt to several hundred kilowatts (Kw) power ratings in large number of applications. These have the advantages of low stresses on the devices, low losses and thus, high efficiency, and are suitable for high-power applications. It has a stepped voltage waveform instead of PWM and has reduced high-frequency currents. The switching frequency of high power semiconductor switches is usually limited by the maximum

power loss. According to the voltage level of the power semiconductor, there are two-level and multilevel pulse-width modulation (PWM). The voltage stress of power switches can be reduced significantly if the voltage levels are increasing, but the circuit complexity, voltage balance problem and control scheme become more difficult. Recently, much literature has paid attention to multilevel converters for high power or high voltage applications. Multilevel converters take advantage of series connection of low voltage power switches (such as IGBT or IGCT) to handle high voltage stress, operation at higher switching frequency which allows a reduction in the size of passive components, and low harmonic distortion in comparison with two-level converters.

#### **1.2 Literature review**

The reason for harmonics in the systems is because of undesirable ac line current harmonics, and low power factors, of conventional rectifiers. These effects include: unsafe neutral current magnitudes in three-phase systems, heating and reduction of life in transformers and Induction Motors, degradation of system voltage waveforms, unsafe currents in power-factor-correction capacitors, and malfunctioning of certain power system protection elements are explained by Anibal T. De Almeida [1], [2].

Multilevel converters-a new breed of converters by J.S Lai and F.Z. Peng [4], [5] has described the multilevel voltage source converters are emerging as a new breed of power converter options for high-power applications. Three main topologies and their operating principle, features, constraints, and potential applications of these converters will be discussed. This paper also explains the application of multilevel converters in reactive power compensation and filtering current harmonics. In these topologies main drawbacks like voltage unbalance between levels and the complexity of control schemes are explained.

The papers [6], [7] by B. R. Lin explained the use of multilevel converters and their use for high power medium voltage applications for AC drive using front end multilevel rectifier as AC/DC/AC converters for AC drive applications. Single phase three level PWM converters [8], [9], [10] for reducing current harmonics are discussed.

The papers related to author B. R. Lin with different fellow scientists has done research on multilevel converters of various topologies and reducing the complexity of power circuit and control circuit by reducing the no. of power switches that are used in the converter. Here he discussed various control schemes [11] for multilevel converters. He discussed drawbacks of conventional diode/thyristor rectifiers related to power factor decrement and increasing harmonics in the input current. He also given the advantages of three level converters [12], [13] and various control techniques and controllers ( PI & Hysteresis current controller for capacitor voltage balancing with reference current generated from supply voltage template) which can be implemented to get better power quality and better eliminating current harmonics [14], [15].He has discussed different topologies and PWM schemes in various papers.

The papers [16], [17], [18] discuss single phase neutral-point diode clamped converter for getting high power factor with balancing output voltage. The practical problems regarding balancing DC-link voltage in multilevel converter is explained by Mario Marchesoni and Pierluigi Tenca [24]. The redundancy in switching states of power devices in diode clamped topology is to avoid capacitor voltage imbalance [16]. In this technique we don't require extra circuitry and is easy to implement. The capacitor clamped topology [19] for high power factor also discussed.

Hysteresis controller is one of the good control strategies for AC-DC converters. It can be applied to single phase rectifiers and three phase rectifiers. Green Boys [21] have explained the principle of HCC for AC-DC converters. But in HCC switching frequency does not remain constant.

Some papers [22], [23], [25] also discuss the most important information about the operation of multilevel PWM converters. N. Schibli and A. Rufer[28] in this paper the use single phase three level traction applications are discussed.

In [31], Mohan N has briefly presented different power converters, their control techniques and applications. B. K. Bose has explained control techniques in detail.

#### **1.3 Dissertation organization**

The dissertation is organized into seven chapters and the work included in each chapter is briefly outlined as follows:

The Present Chapter 1 describes an overview of the use of conventional AC-DC converters and their adverse effects on system are of low overall power factor and draw input currents which are rich in harmonics. Brief literature review on power factor circuits (PFC), Switch Mode Rectifiers (SMRs) and multilevel converters for improving power quality by harmonics mitigation and also conclusions.

The **Chapter 2** deals the harmonics definition and the effect of harmonics in the system. Also deals with different types of linear and non linear loads, harmonic producing equipment and standard regulating line current harmonics. The causes of low power factor, how does it affect the system, different disadvantages of low power factor and the need of power factor correction are discussed.

The Chapter 3 deals with the adverse effects of conventional rectifier's on the system and classification of rectifiers. The use of improved power quality converters and there classification is discussed. Multilevel converter topologies their advantages are discussed. Single phase three level converter topologies are discussed for eliminating current harmonics. Simulation models are developed using MATLAB/SIMULINK. Elaborate simulation study was done to check the performance of converters under varying load conditions and conclusions.

The **Chapter 4** describes the circuit topology of reduced switch single phase neutral point diode clamped rectifier for high power factor is described. The modes of operation of power circuits are explained. The control strategies for the operation of rectifier are discussed.

The **Chapter 5** deals simulation models of active rectifier using MATLAB/SIMULINK. Elaborating simulation study was done to check the performance of rectifier under varying load condition with two control schemes that are proposed to rectifier. It also gives details about the dynamic performance of converter under sudden changes in load, reference and supply voltage. The harmonic analysis for source current, THD of source current is observed. And the comparative analysis has done for various converters.

The Chapter 6 gives the hardware implementation of single phase neutral point diode clamped rectifier for experimental validation. The fabrication of power circuit and control circuit is briefly discussed.

The Chapter 7 presents the recorded experimental results is displayed.

The Chapter 8 highlights the main conclusions drawn from the work done. Future scope for the improvements to get better performance is presented.

#### CHAPTER 2

# HARMONICS AND POWER FACTOR

#### Introduction

The equipment connected to an electricity distribution network usually needs some kind of power conditioning, typically rectification, which produces a non sinusoidal line current due to the nonlinear input characteristics. Line-frequency diode rectifiers convert AC input voltage into DC output voltage in an uncontrolled manner. Single-phase diode rectifiers are needed in relatively low power equipment that need some kind of power conditioning, such as electronic equipment (e.g. TVs, office equipment, battery chargers, electronic ballasts) and household appliances. For higher power, three-phase diode rectifiers are used, e.g. in variable-speed drives and industrial equipment. In both single-phase and three-phase rectifiers, a large filtering capacitor is connected across the rectifier output to obtain DC output voltage with low ripple. As a consequence, the line current is non sinusoidal i.e it consists of harmonics.

In most of these cases, the amplitude of odd harmonics of the line current is considerable with respect to the fundamental. The normalized amplitudes of the 3rd, 5th, 7th and 9th harmonics are significant. While the effect of a single low power nonlinear load on the network can be considered negligible, the cumulative effect of several nonlinear loads is important. Line current harmonics have a number of undesirable effects on both the distribution network and consumers.

#### 2.1 Harmonics

A harmonic is defined as steady state voltage or currents having frequencies that are an integer multiple of the system fundamental frequency. Electricity generation is normally produced at constant frequencies of 50 Hz or 60 Hz and the generators e.m.f can be considered practically sinusoidal. However, when a source of sinusoidal voltage is applied to a nonlinear device or load, the resulting current is not perfectly sinusoidal. In the presence of system impedance this current causes a non-sinusoidal voltage drop and, therefore, produces voltage distortion at the load terminals, i.e. the latter contains harmonics.

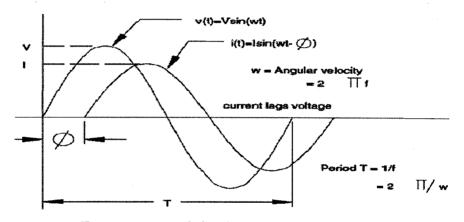

A sinusoidal voltage or current function that is dependent on time t may be represented by the following expressions:

Voltage function,

Current function,

(2.2)

Where  $\omega = 2 \times \pi \times f$  is known as the angular frequency of the periodic waveform and is the difference in phase angle between the voltage and the current waveforms referred to as a common axis. The sign of phase angle is positive if the current leads the voltage and negative if the current lags the voltage is shown in Fig.2.1.

Fig.2.1 Sinusoidal voltage and current

Fig.2.2 Non-sinusoidal voltage waveform

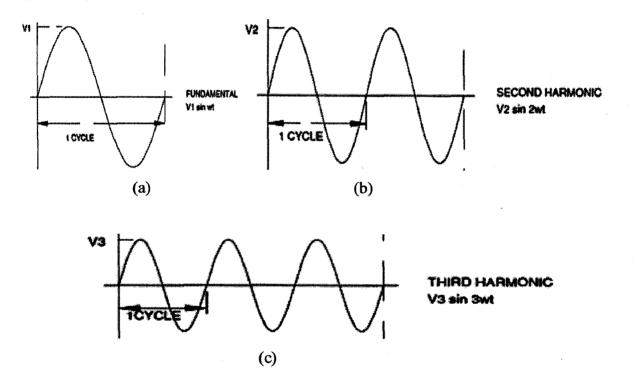

The fundamental (or first harmonic) frequency has a frequency of  $f_I$ , the second harmonic has a frequency of  $2 \times f_I$ , the third harmonic has a frequency of  $3 \times f_I$ , and the  $n^{th}$  harmonic has a frequency of  $n \times f_I$ . If the fundamental frequency is 50 Hz, the second harmonic

frequency is 100 Hz, and the third harmonic frequency is 150 Hz etc. Fig.2.2 shows non-sinusoidal voltage waveform.

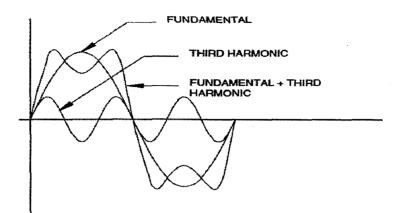

The significance of harmonic frequencies can be seen in Fig.2.3 the second harmonic undergoes two complete cycles during one cycle of the fundamental frequency, and the third harmonic traverses three complete cycles during one cycle of the fundamental frequency.  $V_1$ ,  $V_2$ , and  $V_3$  are the peak values of the harmonic components that comprise the composite waveform, which also has a frequency of f. For a periodic voltage wave with fundamental frequency of  $\omega = 2\pi f$ . The Fig. 2.4 gives sum of two harmonic frequency i.e. fundamental and third harmonic frequencies.

Fig.2.3 (a) Fundamental voltage, (b) second harmonics two cycles in half cycle of fundamental and (c) third harmonics three cycles in half cycle of fundamental

Fig.2.4 Nonlinear waveform by adding the fundamental and third harmonic frequency waveforms

# 2. 2 Linear and Non-Linear Loads

#### 2.2.1 Linear loads

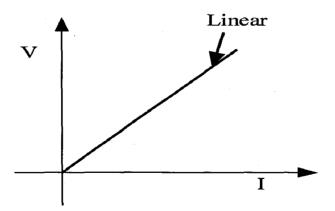

Linear loads are those in which voltage and current signals follow one another very closely, such as the voltage drop that develops across a constant resistance, which varies as a direct function of the current that passes through it. This relation is better known as Ohm's law and states that the current through a resistance fed by a varying voltage source is equal to the relation between the voltage and the resistance, as described below. Fig.2.5 shows the voltage and current profile linear.

$$I(t) = \frac{V(t)}{R} \tag{2.3}$$

Linear loads, such as electrical motors driving fans, water pumps, oil pumps, cranes, elevators, etc., not supplied through power conversion devices like variable frequency drives or any other form or rectification/inversion of current will incorporate magnetic core losses that depend on iron and copper physical characteristics. Table 2.1 describes a list of linear loads [20].

| Resistive                                                                                         | Inductive                                                                                                                                                                         | Capacitive                                                                                                                                                             |  |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| elements                                                                                          | elements                                                                                                                                                                          | elements                                                                                                                                                               |  |

| elements <ul> <li>Incandescent <ul> <li>lighting</li> <li>Electric heaters</li> </ul> </li> </ul> | elements <ul> <li>Induction motors</li> <li>Current limiting reactors</li> <li>Induction generators (Wind mills)</li> <li>Damping reactors used to attenuate harmonics</li> </ul> | elements <ul> <li>Power factor correction capacitor banks</li> <li>Underground cables</li> <li>Insulated cables</li> <li>Capacitor used in harmonic filters</li> </ul> |  |

|                                                                                                   | • Tuning reactors in harmonic filters                                                                                                                                             |                                                                                                                                                                        |  |

| Table 2.1: | Examples | oflinear | loads |

|------------|----------|----------|-------|

|------------|----------|----------|-------|

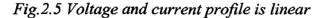

### 2. 2.2 Non Linear loads

Nonlinear loads are loads in which the current waveform does not be similar to the applied voltage waveform due to a number of reasons, for example, the use of electronic switches that conduct load current only during a fraction of the power frequency period. Therefore, we can conceive non linear loads as those in which Ohm's law cannot describe the relation between V and I. Among the most common nonlinear loads in power systems are all types of rectifying devices like those found in power converters, power sources, uninterruptible power supply (UPS) units, and arc devices like electric furnaces and fluorescent lamps. Table 2.2

provides a more extensive list of various devices in this category. Fig.2.6 Shows voltage and current profile is non linear.

Nonlinear loads cause a number of disturbances like voltage waveform distortion, overheating in transformers and other power devices, over current on equipment neutral connection leads, telephone interference, and microprocessor control problems.

## Fig.2.6 Voltage and current profile is non linear

Nonlinear loads cause a number of disturbances like voltage waveform distortion, overheating in transformers and other power devices, over current on equipment neutral connection leads, telephone interference, and microprocessor control problems.

| <b>Power electronics</b>                                                                                                                                                                                                                                         | Classical devices                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| <ul> <li>Power converters</li> <li>Variable frequency drives</li> <li>DC motor controllers</li> <li>Cyclo-converters Cranes</li> <li>Elevators</li> <li>Steel mills</li> <li>Power supplies</li> <li>UPS</li> <li>Battery chargers</li> <li>Inverters</li> </ul> | <ul> <li>Transformers</li> <li>Rotating machines</li> <li>Fluorescent lamps</li> <li>ARC furnaces</li> </ul> |

#### Table 2.2: Examples of some nonlinear loads

## 2. 3 Sources of Harmonics

Harmonic producing equipments are found in varied locations from offices to manufacturing plants and they are becoming inevitable in daily life. Various harmonic producing equipments are [1]:

- Personal computers

- Electronic lighting ballasts

- Variable and adjustable speed drives

- Industrial process controls

- Electronic test equipment

- Solid state controls

- UPS systems

- Medical equipment

- Electronic household appliances.

Harmonic currents generated by office equipment increase power system heat losses and the power bills of end users. Generally harmonic problems in office buildings are caused by nonlinear loads causing harmonic current injection. The injected current is propagated to all distribution circuits and leads to harmonic voltage distortion on the system. Harmonic currents can cause such problems as [3]:

#### 2.3.1 Effects of harmonics:

- Excessive current in the neutral conductor of three-phase four-wire systems, caused by odd triplen current harmonics (triplen: 3rd, 9th, 15th, etc.). This leads to overheating of the neutral conductor( over loading), tripping of the protective relay and overheating or de-rating of transformer

- Reduced power factor, hence less active power available from a wall outlet having a certain apparent power rating.

- Excessive heating of wiring and connections

- Damaging of capacitor banks

- Resonance

- Malfunction of electronic equipment & errors in metering equipments

- Communication interference & increased audio noise

- Distorted supply voltage

- Increased power losses

- Logic faults in digital devices

- Errors in power metering

- Inadvertent thermal tripping of relays, circuit breakers and protective devices

- Cogging or crawling in induction motors, mechanical oscillation in a turbine-generator combination or in a motor-load system.

## 2.4 Standards regulating line current harmonics

The reason for the low power factor is the undesirable ac line current harmonics, of conventional peak-detection and phase-controlled rectifiers. The previously mentioned negative effects of line current distortion have prompted a need for setting limits for the line current harmonics of equipment connected to the electricity distribution network. Standardization activities in this area have been carried out for many years. As early as 1982, the International Electro technical Committee - IEC published its standard IEC 555-2 [IEC82], which was also adopted in 1987 as European standard EN 60555-2, by the European Committee for Electro technical Standardization - CENELEC. Standard IEC 555-2 has been replaced in 1995 by standard IEC 1000-3-2 [IEC95], also adopted by CENELEC as European standard EN 61000-3-2. Standard IEC 1000-3-2 applies to equipment with a rated current up to and including 16Arms per phase which is to be connected to 50Hz or 60Hz, 220-240Vrms single-phase, or 380-415Vrms three-phase mains. Items of electrical equipment are categorized into four classes (A, B, C and D), for which specific limits are set for the harmonic content of the line current. The standard has been revised several times and a second edition was published in 2000 [IEC00] with an amendment in 2001 [IEC01]. Next, we present the current harmonic limits and the present status in equipment classification, with a discussion on the changes in the definition of Class D equipment.

Class A includes: Balanced three-phase equipment; household appliances, excluding equipment identified as Class D; tools, excluding portable tools; dimmers for incandescent lamps; and audio equipment. Equipment not specified in one of the other three classes should be considered as Class A equipment. The limits for Class A are presented.

Class B equipment includes: Portable tools; and nonprofessional arc welding equipment. The limits for this class are those shown in Table 2.3 multiplied by a factor of 1.5.

Class C includes: Lighting equipment. For an active input power greater than 25W, the harmonic currents should not exceed the limits presented in Table 2.4 (except for dimmers for incandescent lamps, which belong to Class A). Discharge lighting equipment having an active input power smaller than or equal to 25W should comply with one of the following two sets of requirements: the harmonic currents should not exceed the Class D power-related limits, shown in Table2.5.The harmonic limits for Class D are presented in Table2.5. The Class D includes equipment having an active input power less than or equal to 600W, of the following types: personal computers, personal computer monitors; and television receivers.

| Harmonic order    | Maximum permissible       |

|-------------------|---------------------------|

| n                 | harmonic current<br>A     |

| Odd 1             | larmonics                 |

| 3                 | 2.30                      |

| 5                 | 1.14                      |

| 7                 | 0.77                      |

| 9                 | 0.40                      |

| 11                | 0.33                      |

| 13                | 0.21                      |

| $15 \le n \le 39$ | $0.15 \cdot \frac{15}{n}$ |

| Even              | harmonics                 |

| 2                 | 1.08                      |

| 4                 | 0.43                      |

| 6                 | 0.30                      |

| 8 ≤ <i>n</i> ≤ 40 | $0.23 \cdot \frac{8}{n}$  |

Table 2.3 Limits for Class A equipment in standard IEC 1000-3-2.

| Harmonic order                     | Maximum permissible harmonic current<br>expressed as a percentage of the input<br>current at the fundamental frequency |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| n                                  | %                                                                                                                      |

| 2                                  | 2                                                                                                                      |

| 3                                  | 30 · PF *                                                                                                              |

| 5                                  | 10                                                                                                                     |

| 7                                  | 7                                                                                                                      |

| 9                                  | 5                                                                                                                      |

| $11 \le n \le 39$                  | 3                                                                                                                      |

| (odd harmonics only)               |                                                                                                                        |

| $PF^*$ is the circuit power factor |                                                                                                                        |

Table 2.4 Limits for Class B equipment in standard IEC 1000-3-2.

Table 2.5 Limits for Class C equipment in standard IEC 1000-3-2.

| Harmonic order   | Maximum permissible<br>harmonic current per<br>watt | Maximum permissible<br>harmonic current |

|------------------|-----------------------------------------------------|-----------------------------------------|

| n                | mA/W                                                | A                                       |

| 3                | 3.4                                                 | 2.30                                    |

| 5                | 1.9                                                 | 1.14                                    |

| 7                | 1.0                                                 | 0.77                                    |

| 9                | 0.5                                                 | 0.40                                    |

| 11               | 0.35                                                | 0.33                                    |

| 13 <i>≤n</i> ≤39 | $\frac{3.85}{n}$                                    | As in Class A                           |

Standard IEEE 519-1992 [IEE92] gives recommended practices and requirements for harmonic control in electrical power systems, for both individual consumers and utilities. The limits for line current harmonics are given as a percentage of the maximum demand load current  $I_L$ (fundamental frequency component) at the Point of Common Coupling – PCC at the utility. They decrease as the ratio *I*sc/  $I_L$  decreases, where *I*sc is the maximum short-circuit current at the PCC, meaning that the limits are lower in weaker grids. The standard covers also high voltage loads, of much higher power, which are not addressed by IEC 1000-3-2.

# **2.5 Power Factor**

Reduction of line current harmonics is needed in order to comply with the standard. This is commonly referred to as the Power Factor Correction – PFC, which may be misleading. Therefore, some clarification is needed. The power factor PF is defined as the ratio of the active power P to the apparent power S:

## PF=P/S

For purely sinusoidal voltage and current, the classical definition is obtained

$$PF=COS \varphi$$

(2.4)

Where  $\varphi$  is the displacement angle between phase voltage and phase current. We assume the line voltage to be sinusoidal, since in most cases the total harmonic voltage distortion is quite low, e.g. the total harmonic distortion of the line voltage is *THD*=2%. However, the line current is non sinusoidal when the load is nonlinear. Therefore, the classical definition of the power factor does not apply. For sinusoidal voltage and non sinusoidal current can be expressed as:

$$PF = \frac{V_{rms}I_{1,rms}\cos\varphi}{V_{rms}I_{rms}} = \frac{I_{1,rms}}{I_{rms}}\cos\varphi = K_P\cos\varphi = D.F\cos\varphi \quad (2.5)$$

The factor (Distortion Factor)

$$K_P = D.F = \frac{I_{1,rms}}{I_{rms}}, K_P \in [0,1]$$

(2.6)

It describes the harmonic content of the current with respect to the fundamental. This factor is called distortion factor. In a classical sense, PFC means compensation of the displacement factor In this case; the power factor depends on both harmonic content and displacement factor. It appears that there is no standard term which can be used to denote the factor defined above .Some authors refer to it as the 'purity factor' while others as the 'distortion factor' We believe that 'purity factor' describes its meaning more accurately, as the factor is unity for a pure sinusoidal current, and it decreases as the harmonic content increases. Moreover, defining it as 'distortion factor' is in contradiction with the definition given by the IEEE

Standard Dictionary on Electrical and Electronics ,which considers it as a synonym for the total harmonic distortion factor, the latter being defined for the line current as:

$$THD_i = \frac{\sqrt{\sum_{n=2}^{\infty} I_{n,rms}^2}}{I_{1,rms}}$$

(2.7)

It is straightforward to show that the relation between Kp and THDi is:

$$K_P = \frac{1}{\sqrt{1 + THD_i^2}} \tag{2.8}$$

Standard IEC 1000-3-2 sets limits on the harmonic content of the current but does not specifically regulate the purity factor Kp or the total harmonic distortion of the line current  $THD_i$

The values of Kp and  $THD_i$  for which compliance with IEC 1000-3-2 is achieved depend on the power level. For low power level, even a relatively distorted line current may comply with the standard. In addition to this, it can be seen from (that the distortion factor Kp of a waveform with a moderate  $THD_i$  is close to unity (e.g. Kp = 0.989 for  $THD_i = 15\%$ ). Considering as well, the following statements can be made: A high power factor can be achieved even with a substantial harmonic content. The power factor PF is not significantly degraded by harmonics, unless their amplitude is quite large (low Kp, very large  $THD_i$ ). Low harmonic content does not guarantee high power factor (Kp close to unity, but low cos $\phi$ ).

Some of the disadvantages of low power factor are [1]:

- Because of large current, the losses in the generators and transmission line increases and causing over heating of the system components.

- It causes poor voltage regulation at the load.

- As the load voltage increases due to poor voltage regulation the power transfer capacity is adversely affected.

- The investment in system facilities per KW of load supplied increases with decreases in supply power factor.

Improving the power factor brings three major benefits:

- Power distribution costs for the electric company are reduced, making the power company much happier. A side benefit is to reduce the tendency of the current peaks to "flatten" the tops of the input voltage sinusoidal waveform.

- More power can be drawn from a line of a given current rating, allowing more powerful equipment to be connected without having to re-wire a building, saving time and money.

- Various governmental and quasi-governmental agencies are passing laws requiring improved power factors on certain types of equipment, especially those which draw a lot of power. These laws make it illegal to sell certain types of equipment without testing and certification of a minimum power factor. To continue to sell medium to high power supplies in the future, power supply manufacturers will have to deal with power factor correction.

Because of the severity of problems due to low power factor, some options such as passive filters, active filters and hybrid filters to be used along with traditional thyristor/diode rectifiers have been extensively developed, especially in large rating and already existing installations.

# **2.6 Power Factor Correction**

Most of the research on Power Factor Correction (PFC) for nonlinear loads actually related to the reduction of the harmonic content of the line current. There are several solutions to achieve PFC Depending on whether active switches (controllable by an external control input) are used or not, PFC solutions can be categorized as passive or active. In passive PFC, only passive elements are used in addition to the diode bridge rectifier, to improve the shape of the line current. Obviously, the output voltage is not controllable. For active PFC, active switches are used in conjunction with reactive elements in order to increase the effectiveness of the line current shaping and to obtain controllable output voltage. The switching frequency further differentiates the active PFC solutions into two classes. In low-frequency active PFC, switching takes place at low-order harmonics of the line-frequency and it is synchronized with the line

voltage. In high-frequency active PFC, the switching frequency is much higher than the line frequency. An overview of methods for PFC is presented.

# 2.7 Desirable features of a PFC technique

#### 2.7.1 Input side features:

(1) Sinusoidal input current with close to unity PF operation.

(2) Reduced EMI.

(3) Insensitive to small signal perturbations in the load Output side features:

#### 2.7.2 Output side features:

(1) Good line and load regulation.

(2) Low output voltage ripple.

(3) Fast output dynamics (i.e., high bandwidth).

(4) Multiple output voltage, levels if needed by the application.

However the filters that are used PFC are quite costly, bulky, and have reasonable losses, which reduce overall efficiency of the complete system. Even in some cases the rating of converter use in active filters is almost close to the rating of the load. Under such circumstances, it is considered better option to use such converters as an inherent part of system of AC-DC conversion, which provides reduced size, high efficiency, and well controlled and regulated DC to provide comfortable and flexible operation of the system.

# CHAPTER 3

# **MULTILEVEL CONVERTERS**

## Introduction

The AC–DC conversion is used increasingly in a wide diversity of applications: power supplies for microelectronics, household electric appliances, electronic ballasts, battery charging, dc motor drives, power conversion, etc.

#### **3.1 Classification of rectifiers**

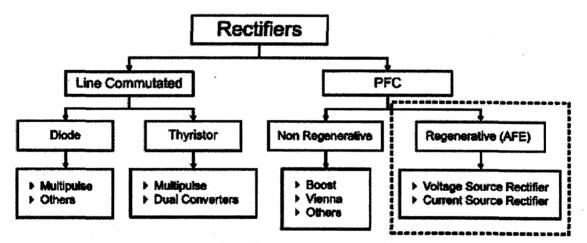

As shown in Figure 3.1 below ac-dc converters can be classified to different topologies working with low switching frequency (line commutated) and other topologies which operate with high switching frequency. The simplest line-commutated converters use diodes to transform the electrical energy from ac to dc. The use of thyristors allows for the control the power flow. The main disadvantage of these naturally commutated converters is the generation of harmonics and drawing reactive power. Harmonics have a negative effect on the operation of the electrical system and, therefore, attention is paid to their generation and control. One basic and typical method to reduce input current harmonics is the use of multi pulse connections based on transformers with multiple windings.

The main feature of the multi pulse rectifier [2] lies in its ability to reduce the line current harmonic distortion. This is achieved by the phase shifting transformer, through which some of the low-order harmonic currents generated by the six-pulse rectifiers are canceled. In general, the higher the number of rectifier pulses, the lower the line current distortion is. The rectifiers with more than 30 pulses are seldom used in practice mainly due to increased transformer costs and limited performance improvements. The multi pulse rectifier has a number of other features. It normally does not require any LC filters or power factor compensators, which leads to the elimination of possible LC resonances. The use of the phase-shifting transformer provides an effective means to block common-mode voltages generated by the rectifier and inverter in medium voltage drives, which would otherwise appear on motor terminals, leading to a premature failure of winding insulation.

Another conceptually different way of harmonics reduction is the so-called powerfactor correction (PFC). In these converters, controlled power switches like insulated gate bipolar transistors (IGBTs), gate-turn-off thyristors (GTOs), or integrated gate controlled thyristors (IGCTs) are included in the power circuit of the rectifier to change actively the waveform of the input current, reducing the distortion .These circuits reduce harmonics and consequently they improve the power factor, which is the origin of their generic name of PFC. Several PFC topologies like boost and Vienna rectifiers discussed further, are suited for applications, where power is transmitted only from the ac source to the dc load. However, there are several applications where energy flow can be reversed during the operation. Examples are: locomotives, downhill conveyors, cranes, etc. In all these applications, the line-side converter must be able to deliver energy back to the power supply, which is known as power regeneration. A regenerative rectifier is a rectifier capable of power regeneration These rectifiers, also known as active front end (AFE), can be classified as voltage-source rectifiers (VSRs) and current-source rectifiers (CSRs).

Fig.3.1 Classification of rectifiers

Though passive rectifiers are simple, these present themselves as nonlinear loads to the utility. The input currents of these rectifiers are having considerable lower order harmonics. These also cause considerable overheating in the distribution lines and the distribution transformer supplying the loads, and electromagnetic interference (EMI) with communication and control lines in the proximity. Further, a diode-bridge rectifier cannot regulate its output dc voltage against input voltage regulation. It also cannot regenerate, which is essential in the certain motor drive applications. The other associated problems of these converters include [4]:

#### **3.1.1 Problems with Conventional Rectifiers:**

- i) Large reactive power drawn by the rectifiers from the power system which requires that the distribution equipment handle large power, thus increasing its volt-ampere ratings;

- ii) Voltage drops at the buses;

- iii) Higher input current harmonics resulting in the distorted line current which tends to distort the line voltage waveform. This often creates problems in the reliable operation of sensitive equipment operating on the same bus;

- iv) Increased losses in the equipments ( due to harmonics) such as transformers and motors connected to the utility;

- v) Electromagnetic interference with the nearby communication lines;

- vi) Blown-fuses on power factor correction capacitors due to high voltages and currents from resonance with line impedance and capacitor bank failures;

- vii)Nuisance operation of protective devices including false tripping of relays;

- viii) Damaging dielectric heating in cables and so on.

In order to comply with such harmonic standards, bulk input passive filters and harmonic traps have been used at the input sides of the passive rectifiers. These not only increase the volume and weight of the rectifiers, but also deteriorate the dynamic response and the overall efficiency.

With the advent of new solid state self commutating devices such as MOSFETs, insulated gate bipolar transistors (IGBTs), gate turn-off thyristors (GTOs), etc., even some of which have either not been thought or not possible to be developed earlier using diodes and thyristors. Such pieces of equipment are generally known as converters. These converters are used for power quality purpose so; these are called improved power quality converters (IPQCs):

# **3.2 Improved Power Quality Converters (IPQCs):**

Conventional ac-dc converters have the demerits of poor power quality in terms of injected current harmonics, caused voltage distortion and poor power factor at input ac mains and slow varying rippled dc output at load end, low efficiency and large size of ac and dc filters as discussed above. In light of their increased applications, a new breed of rectifiers has been developed using new solid state self commutating devices such as MOSFETs, insulated gate

bipolar transistors (IGBTs), gate turn-off thyristors (GTOs), etc., even some of which have either not been thought or not possible to be developed earlier using diodes and thyristors. Such pieces of equpipment are generally known as converters, but specifically named as switch-mode rectifiers (SMRs), power-factor correctors (PFCs), pulse width-modulation (PWM) rectifiers and multilevel rectifiers. Because of strict requirement of power quality at input ac mains several standards have been developed and are being enforced on the consumers. Because of severity of power quality problems some other options such as passive filters, active filters (AFs), and hybrid filters along with conventional rectifiers, have been extensively developed especially in high power rating and already existing installations. However, these filters are quite costly, heavy, and bulky and have reasonable losses which reduce overall efficiency of the complete system. Even in some cases the rating of converter used in AF is almost close to the rating of the load. Under these observations, it is considered better option to include such converters as an inherent part of the system of ac–dc conversion, which provides reduced size, higher efficiency, and well controlled and regulated dc to provide comfortable and flexible operation of the system. The following are some advantages of PWM active rectifiers over passive rectifiers are:

- i. Sinusoidal input current operation

- ii. Adjustable input power factor which means these are used as PFC circuits

- iii. well-regulated and good quality dc output voltage/current to feed loads ranging from fraction of Watt to several hundred kilowatts power ratings.

- iv. Low-valued energy storage elements (inductors and capacitors)

- v. Low electromagnetic interference (EMI) and radio frequency interference (RFI) at input ac mains

- vi. Good dynamic response against sudden changes in input voltage and load current vii. Higher efficiency of power conversion

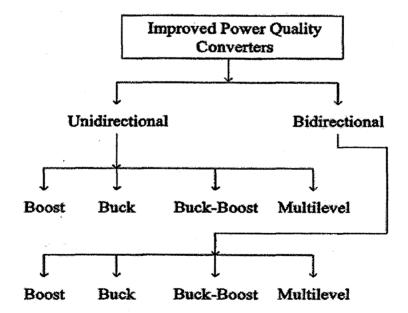

Improved power quality converters (IPQCs) have been classified on the basis of the converter topology as Boost, Buck, Buck-Boost and Multilevel converters with unidirectional and bi-directional power flow and the type of converter used as unidirectional and bi-directional converters. However, for high-voltage and high-power applications, the concept of multilevel converters is developed which may avoid a low-frequency transformer and reduces the switching frequency of the devices.

The IPQC technology has been developed now at a reasonably matured level for ac-dc conversion with reduced harmonic currents, high power factor, low electromagnetic interference (EMI) and radio frequency interference (RFI) at input ac mains and well-regulated and good quality dc output to feed loads ranging from fraction of Watt to several hundred kilowatts power ratings in large number of applications. IPQCs are classified on the basis of topology and type of converter used. The topology-based classification is categorized on the basis of boost, buck, buck-boost, multilevel, unidirectional and bidirectional voltage, current, and power flow. The converter type can be step-up and step-down choppers, voltage source and current-source inverters, bridge structure, etc.

#### **3.2.1 Topology-Based Classification**

This classification of IPQC is based on the topology used in the converters. These are classified as boost, buck, buck–boost, and multilevel with unidirectional and bidirectional power flow. Fig. 3.2 shows the tree of topology-based classification of IPQCs. These converters are developed in such vastly varying configurations to fulfill the very close and exact requirement in variety.

Fig.3.2 Classification of improved power quality converters

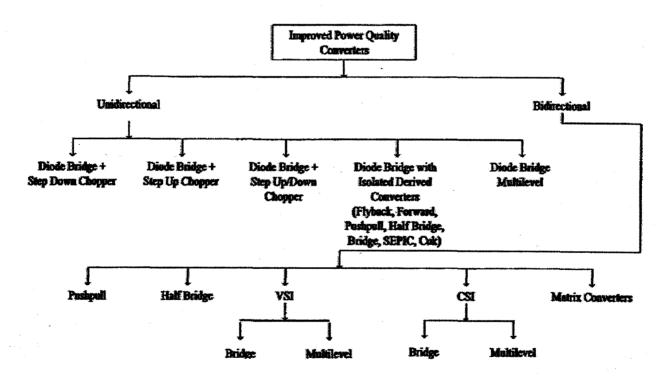

## 3.2.2 Converter-based classification

This type of classification is based on the converter used as shown in Fig. 3.3. These are broadly classified into two types, namely, unidirectional and bidirectional converters.

Unidirectional converters are realized using a diode bridge in conjunction with other basic power electronic converters, namely, step-down chopper, step-up chopper, step-up/down chopper, isolated, forward, fly back, push pull, half bridge, bridge, SEPIC, Cuk, Zeta, etc., and multilevel converters. Bidirectional ac-dc converters consist of basic converters normally used in inverters such as push-pull, half-bridge, voltage-source inverters, and current-source inverters employing MOSFETs for low-power, IGBTs for medium-power, and GTOs for high-power converters. These ac-dc converters are extensively employed for adjustable-speed drives used to drive active loads such as a hoist, a crane, traction, etc., line interactive UPS, and BESS. Four-quadrant ac-dc converters are normally implemented using matrix converters.

Fig.3.3 Classification based on converter used

# **3.3 Multilevel Converters for PFC**

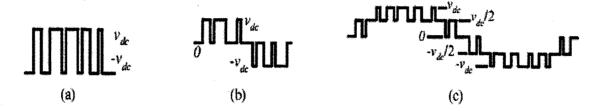

Multilevel converters have the advantages of low stresses on the devices, low losses and thus, high efficiency, and are suitable for high-power applications [7]. It has a stepped voltage

waveform instead of PWM and has reduced high-frequency currents. The switching frequency of high power semiconductor switches is usually limited by the maximum power loss. According to the voltage level of the power semiconductor, there are two-level and multilevel pulse-width modulation (PWM) schemes the two-level and three-level PWM pattern [4]. The voltage stress of power switches can be reduced significantly if the voltage levels are increasing, but the circuit complexity, voltage balance problem and control scheme become more difficult. Recently, much literature has paid attention to multilevel converters for high power or high voltage applications [5]. Multilevel converters take advantage of series connection of low voltage power switches (such as IGBT or IGCT) to handle high voltage stress, operation at higher switching frequency which allows a reduction in the size of passive components, and low harmonic distortion in comparison with two-level converters.

#### **3.3.1 Configurations:**

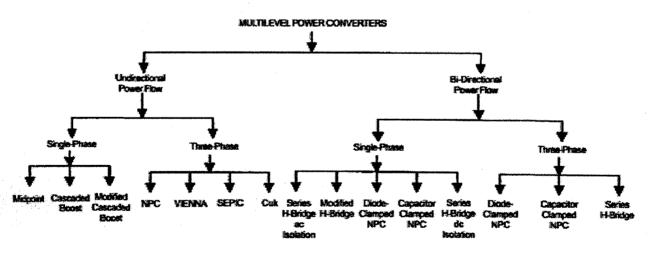

Circuit configurations of MPCs are classified on the basis of number of phases and power flow capability as shown in Fig .3.4 the first category consists of single-phase and threephase MPCs with unidirectional power flow. Single phase and three-phase MPCs with bidirectional power flow from the second category.

Fig.3.4 Classification of multilevel power converters

MSPC (Multilevel Static Power Conversion) technology has reached a mature level and is increasingly being applied to a number of medium and high voltage applications. Application of MPC with bi-directional power flow in electric drives forms an important area of research in MSPC. MPCs were initially proposed in ac motor drives applications due to their ability to generate low harmonics, multi-tier waveforms. Permanent magnet brushless motor (PMSM) drives in high power three-phase industrial drive and as well as in single phase traction drives. Series H-Bridge MLI with isolated dc sources for each level has been proposed for Electric Vehicle (EV) drives applications [22]. This converter provides a modular structure, adds redundancy and is uniquely suited for the applications drawing power from independent batteries and fuel cells.

As power levels reach multiple kW in single-phase applications, multilevel techniques have been proposed in single-phase ac-dc power conversion with unidirectional power flow for two-quadrant rectifier- inverter drives and high voltage front-end power factor pre-regulators.

Use of low voltage power devices in these power factor correction (PFC) converters allows high switching frequency operation required for PFC. a number of three level topologies have been proposed for single-phase rectification [11] achieving compliance to relevant international standards albeit at more complex control strategy than two level rectifiers[12]. Three-phase MPCs with unidirectional power flow have been proposed for high performance power supplies and rectifiers in non-regenerative ac drive applications.

A number of configurations including diode clamped NPC converter, VIENNA rectifiers and series H-bridge converters have been introduced in electric drives, utility system and power supplies applications with excellent results and their widespread adaptation is certain in near future.

#### 3.3.2 Advantages of multilevel converters:

- 1. Trend in development of power devices indicates a tradeoff in voltage rating and switching frequency as well as overall performance. Voltage stresses on devices in MPCs are just a fraction of overall voltage rating of the converter. This allows use of high performance devices available at low voltage rating.

- Large changes in voltage levels at high frequency can cause common mode voltages and electromagnetic interference (EMI). Common mode voltages can cause premature bearing and insulation failure in electric motors, conducted EMI and other problems. Common mode voltages are reduced in these converters as the voltage is synthesized in smaller steps with low dv/dt.

- Voltage handling capacity of MPCs is not restricted by voltage rating of power devices. Semiconductor devices impose a limit on voltage rating of conventional converters leading to high current design of system, which limits the power rating and increases losses.

- 4. Voltage and current harmonics are significantly reduced in MPCs. Multilevel PWM and step modulation methods have been proposed to synthesize voltages with high spectral quality even at low switching frequency. This is an important criterion if GTOs and other high power devices are used, as well as high efficiency is desired in converters.

- 5. High voltage handling capability and improved spectral performance reduce the need for step-down and multi-pulse/poly-phase transformers which are used in two level and multi-pulse converters in high voltage applications. Substantial reduction in cost, size, weight and losses are possible by reduction of transformers.

# **3.4 Classification of Single Phase Multilevel Converters**