## A THEORETICAL STUDY OF A TERNARY III-V COMPOUND MIS-FIELD EFFECT DEVICE

### A THESIS

submitted in fulfilment of the requirements for the award of the degree of

DOCTOR OF PHILOSOPHY

in PHYSICS

## RAJ KUMAR SHAR.

DEPARTMENT OF PHYSICS UNIVERSITY OF ROORKEE ROORKEE-247 667 (INDIA)

MARCH, 1991

Dedicated

•

Г, My Parents

.

•

### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the thesis entitled "A THEORETICAL STUDY OF A TERNARY III-V DEVICE" in fulfilment of the COMPOUND MIS-FIELD EFFECT requirement for the award of the Degree of Doctor of Philosophy, submitted in the Department of PHYSICS of the university, is an authentic record of my own work carried out during a period from to MARCH 1991 under the supervision of Lecturer, Department of Physics and NOVEMBER 1984 to DR. V.K. TONDON. DR. SANKAR SARKAR, Reader, Department of Electronics and Computer Engineering, University of Roorkee, Roorkee.

The matter embodied in this thesis has not been submitted by me for the award of any other Degree.

RhShame (RAJ KUMAR SHARMA)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

Sankar Sarkan (SANKAR SARKAR) Reader. Department of Electronics and Computer Engineering, University of Roorkee, ROORKEE - 247667 INDIA

rondon)

Lecturer. Department of Physics, University of Roorkee, ROORKEE - 247667 INDIA

Date: March 30, 1991.

The Ph.D. Viva-Voce examination of Shri RAJ KUMAR SHARMA, Research Scholar has been held on

Signature of Guides

Signature of External Examiners

### ABSTRACT

The growing need for high-speed digital circuits and high-frequency applications are generally met by devices made on high carrier mobility III - V semiconductors such as GaAs, InP, InGaAsP and InGaAs. Considerable attention needs to be focused on the development of III - V compound MIS-technology. In view of the reports that the fabrication of n-channel inversion-mode MISFETs InGaAsP and InGaAs substrates is а possibility. in InP. Experimental investigations show that of these, the InGaAs-based MISFETs are of highest inversion layer mobility and best insulator-semiconductor interface properties. As InGaAs has turned the most useful semiconductor for photodetector out to be applications, InGaAs MISFET is also a competent device for applications such as integrated optics.

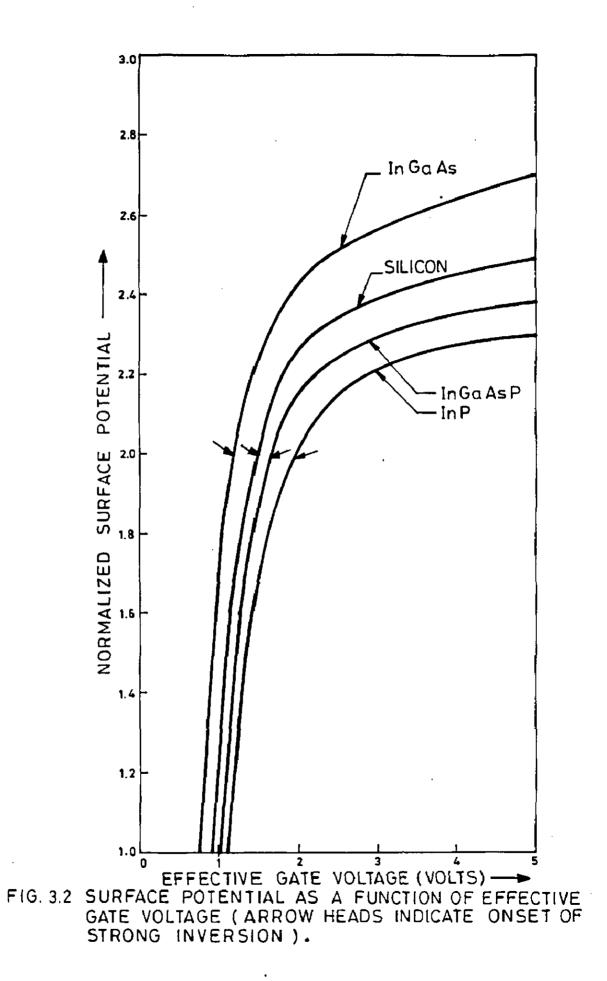

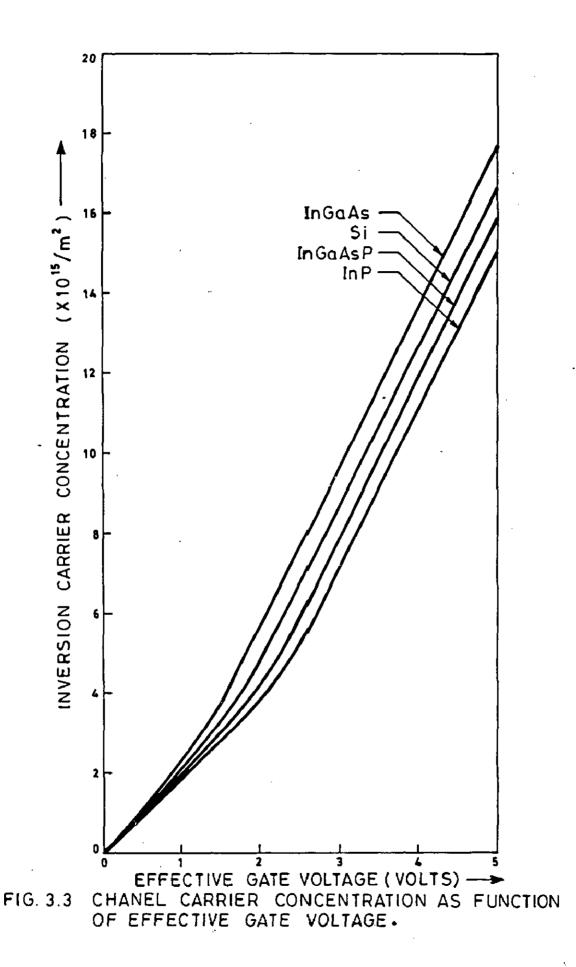

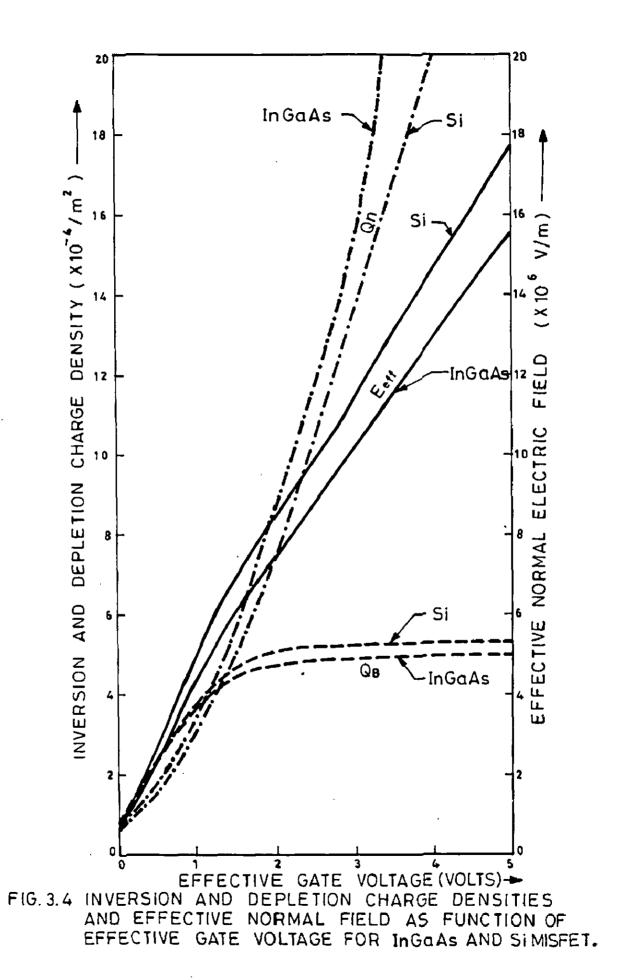

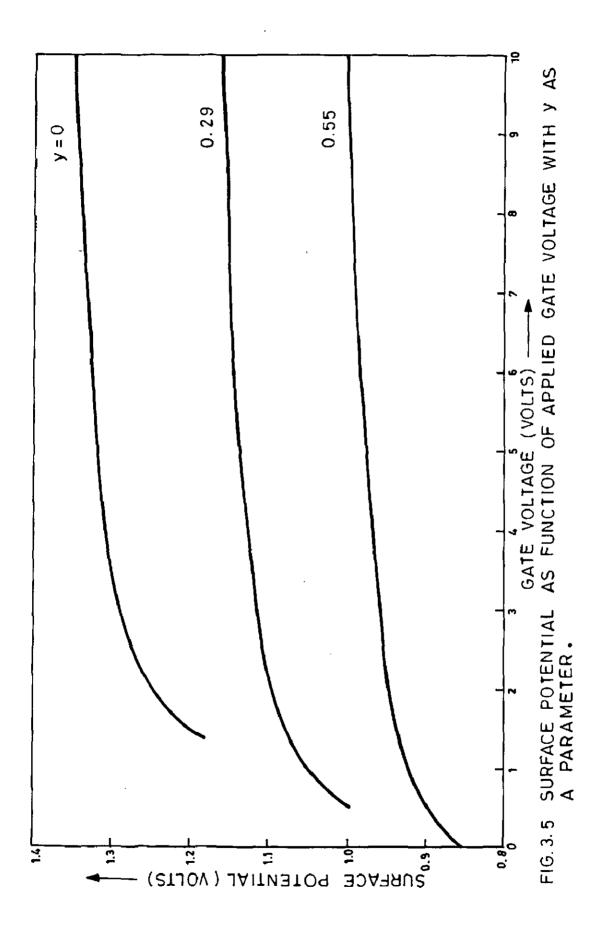

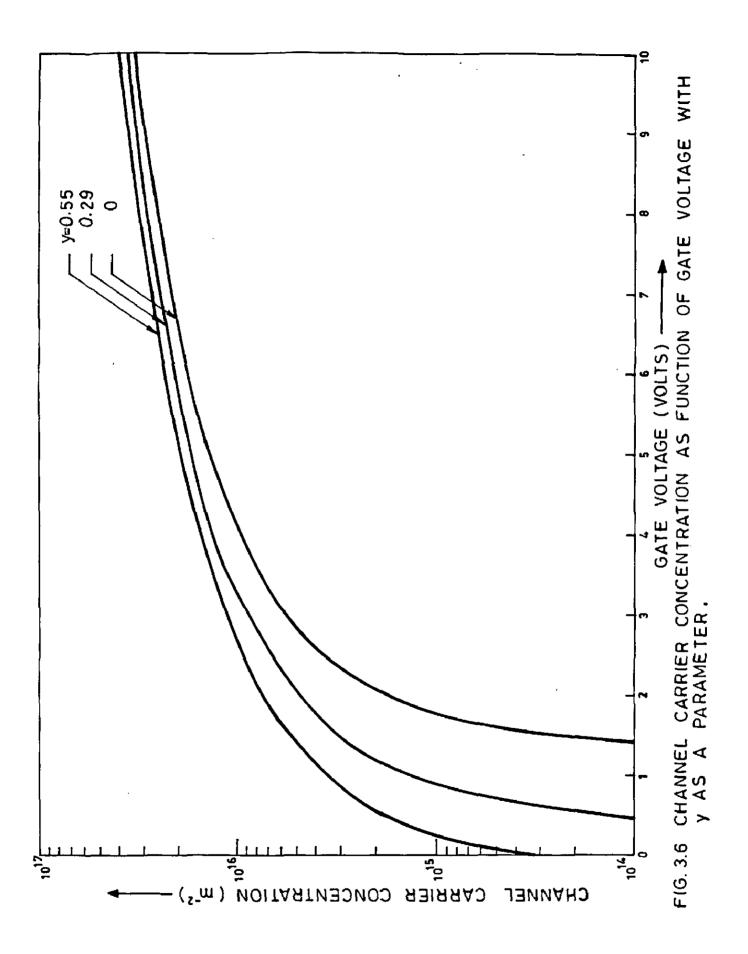

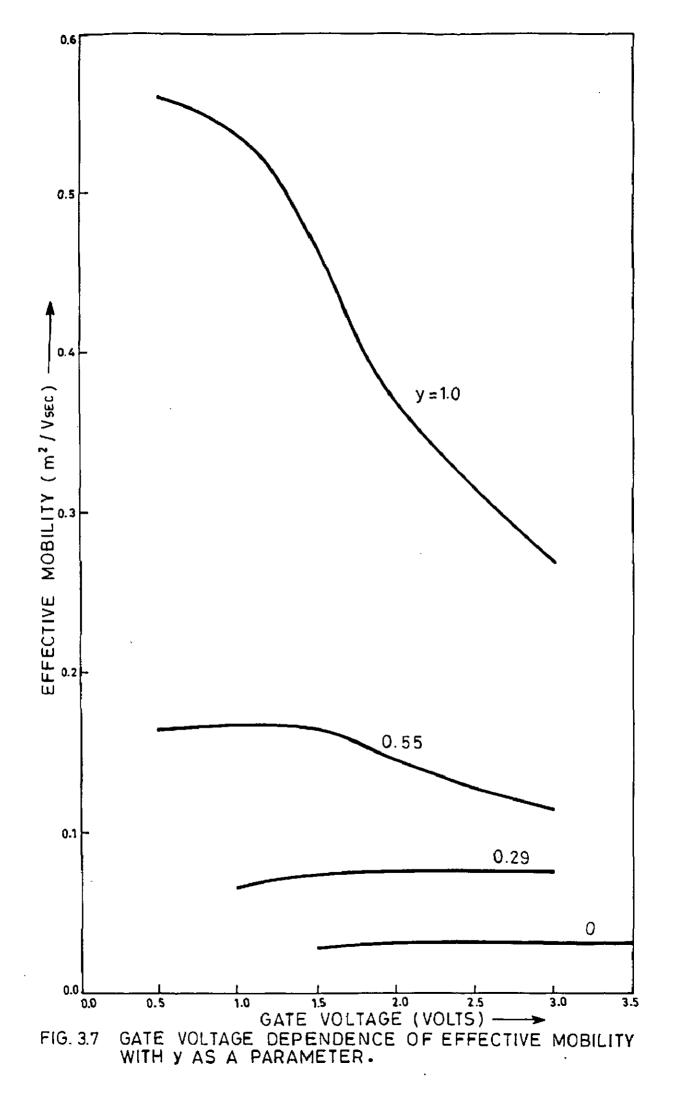

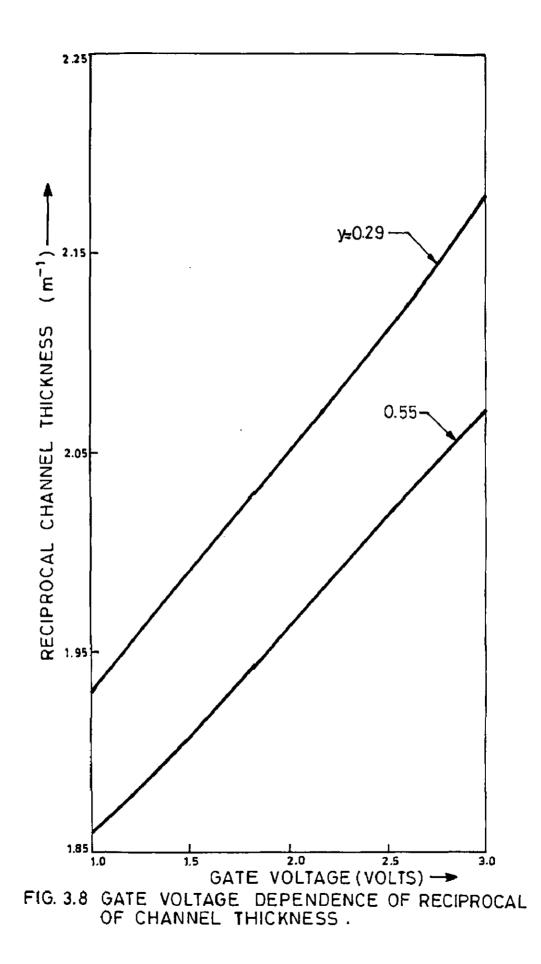

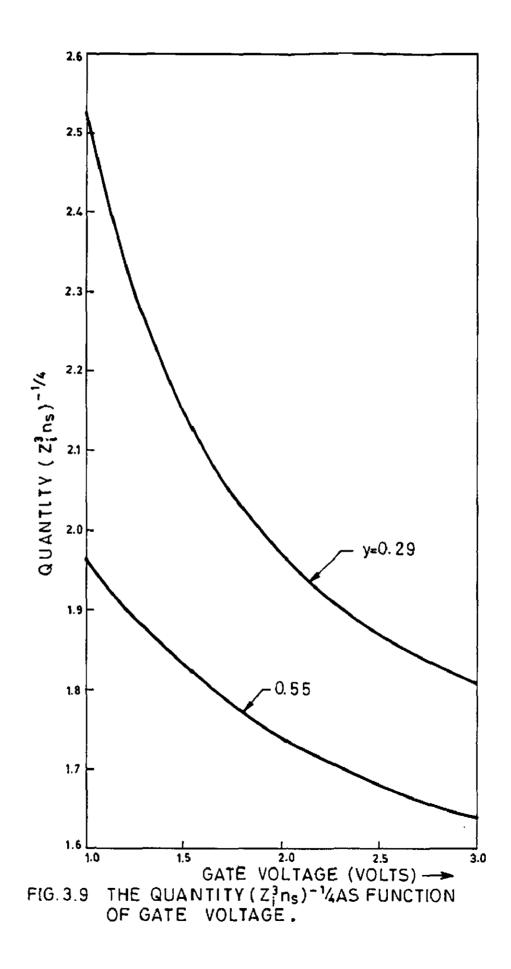

An analysis of the properties of inversion layer formed on p-type InGaAs shows that in an inversion-mode InGaAs MIS device an excellent control of surface potential can be achieved by the application of a gate voltage. Onset of strong inversion in InGaAs MIS device requires much lower effective gate voltage than other known MISFET materials. Normal effective field in an inverted InGaAs substrate is relatively higher than in an inverted silicon surface. The effective carrier mobility in an n-type inversion layer in InGaAs is extremely high because of its lower electron effective mass and thicker inversion layer. Furthermore, the lower electron effective mobility in n-inversion layer on InGaAs degrades severely with increase in gate voltage. The analysis shows that this is caused by a high rate of decrease of channel thickness with increase in gate voltage. InGaAs is the ternary limit of the quaternary alloy system of  $In_{1-x}Ga_xAs_vP_{1-v}$ . Considering the effective mobility in InGaAs MISFET is compared

with that in other members of the quaternary family. In the past, the effective mobility of InGaAsP MISFETs have been reported to be alloy composition dependent. A degradation of effective mobility with increase in gate voltage was also reported. In order to explain these observations, a Matthiessen's rule approach is taken in the present thesis. In the process two factors, namely, the scattering and screening factors have been identified. These factors are dependent on the gate as well as on alloy composition. In agreement with the experimental observations available in literature, the analysis shows that the effective mobility degradation with increase in gate voltage becomes more and more pronounced if the y-composition parameter is increased.

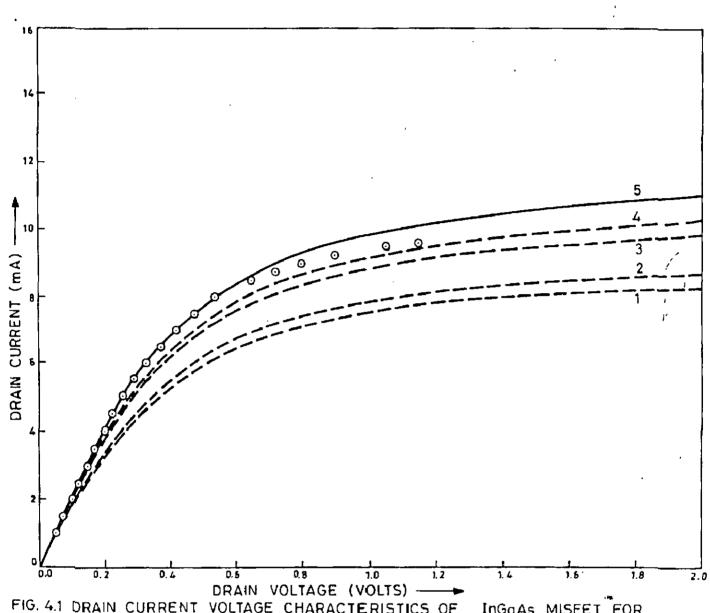

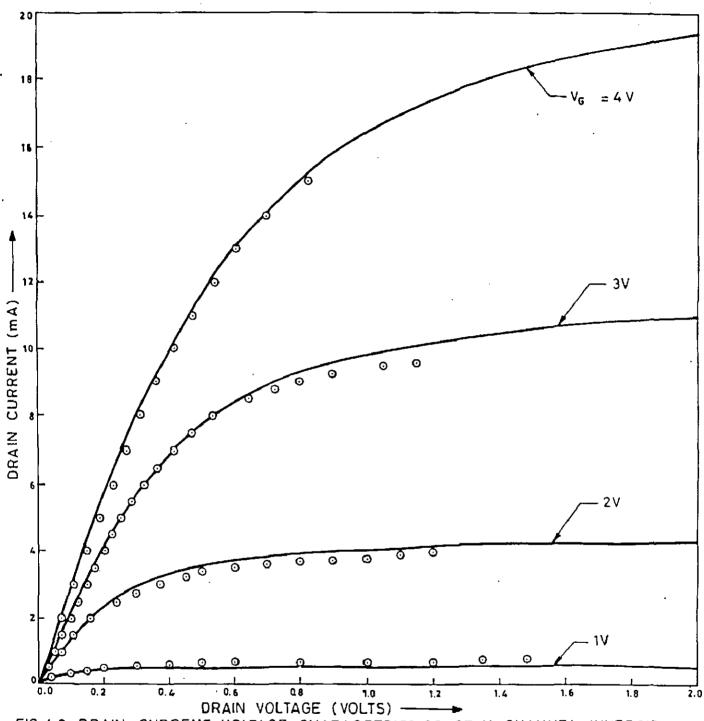

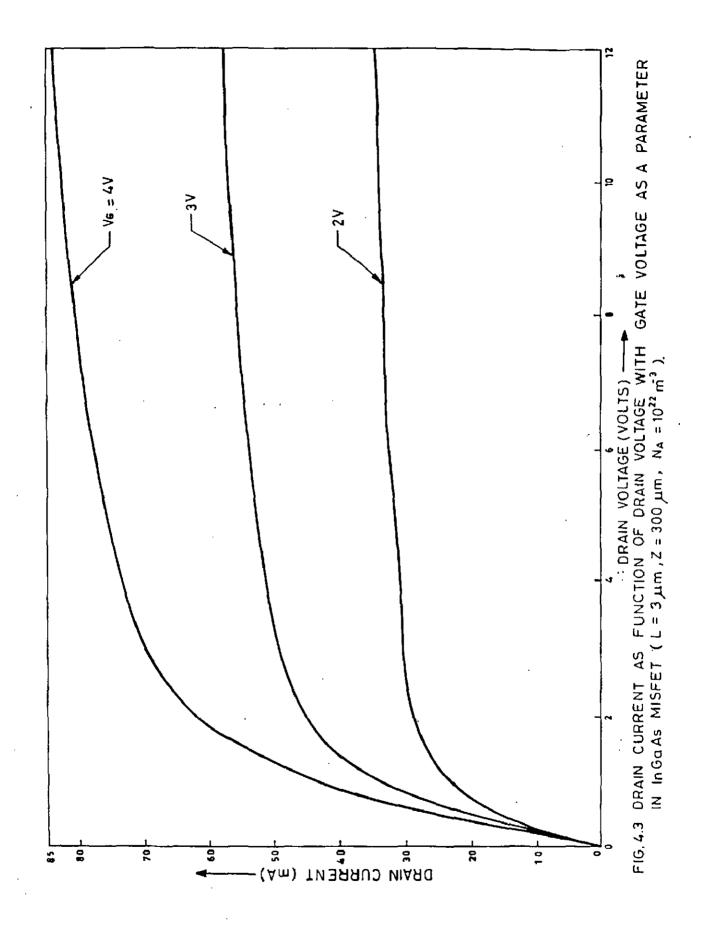

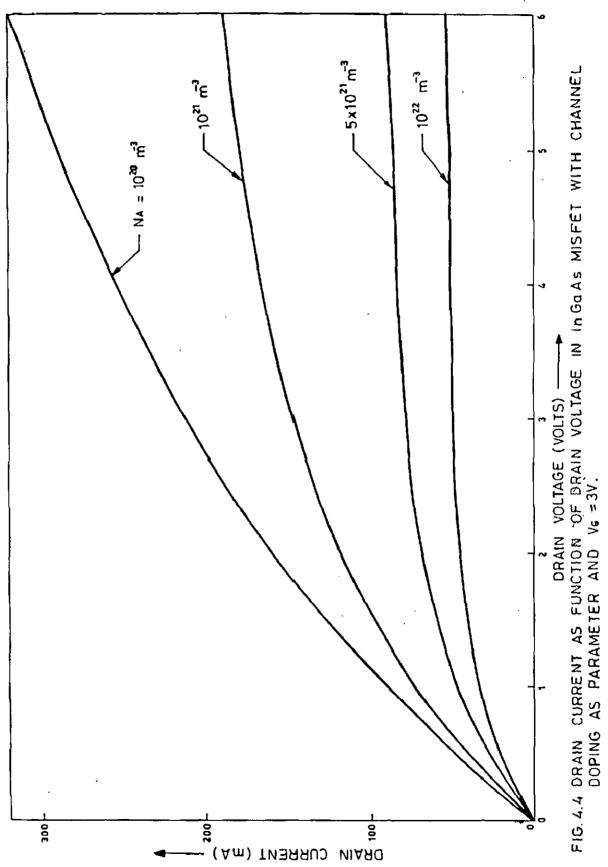

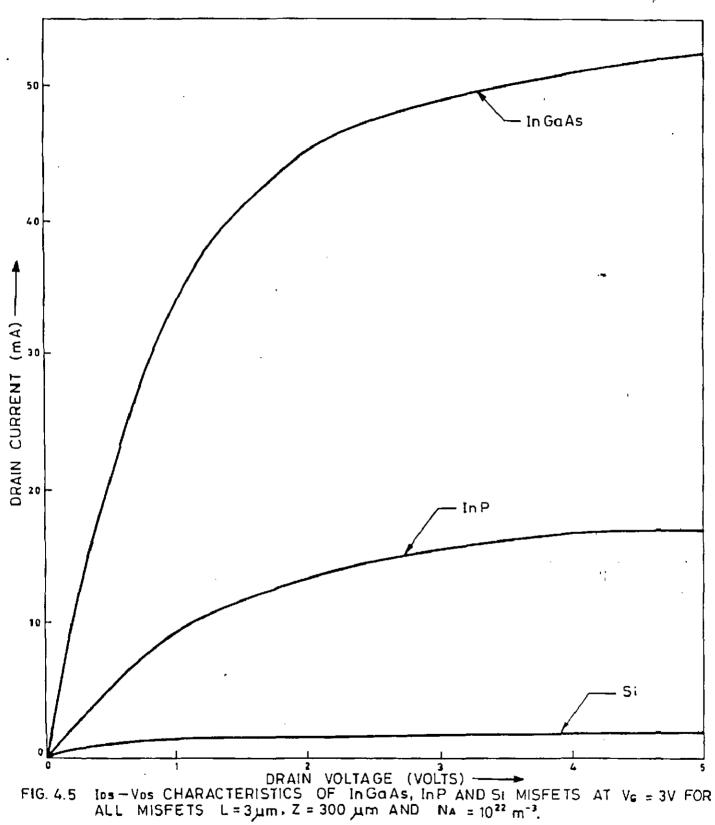

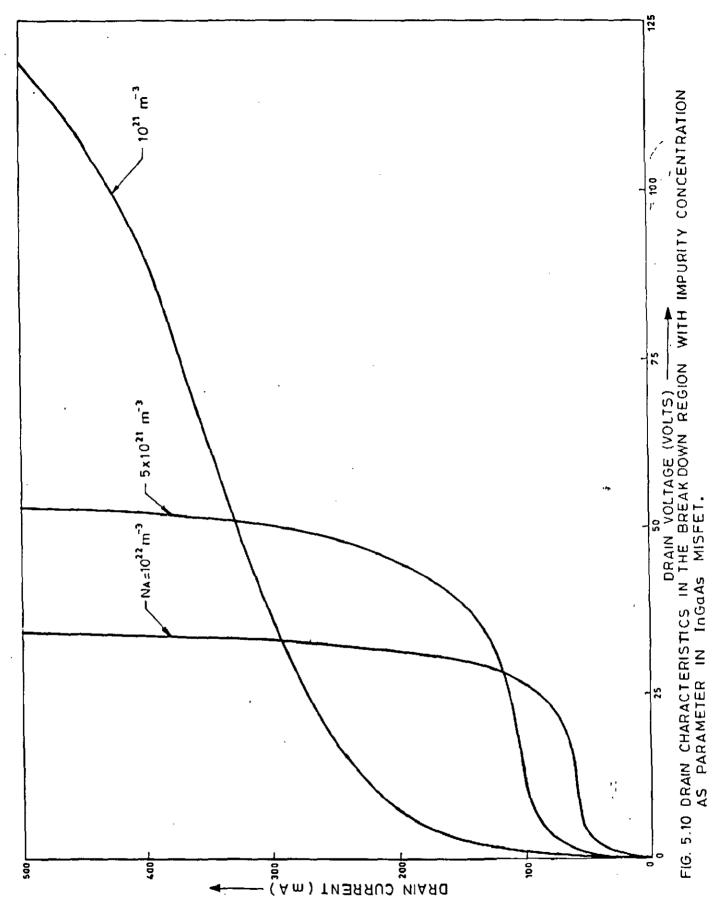

The study of the drain characteristics (drain characteristics) current-drain voltage of the n-channel inversion-mode long-channel InGaAs MISFETs is carried out through the development of an appropriate MISFET-model. The model uses an effective mobility model that has been widely used in silicon MISFET analysis. This mobility expression involves a number of mobility parameters which are generally determined by elaborate laboratory experiments. It has been shown that using the basic MISFET-model developed, the mobility parameters can he approximated with nominal experimental data. The model is then used to study the drain characteristics of InGaAs MISFET. The validity of the model is first checked by comparing the calculated drain characteristics with experimental data available in literature. The MISFET-model is then used to study the effects of substrate doping level on the drain characteristics of an InGaAs MISFET. It is found that for higher doping levels, the saturation drain current and the drain voltage for pinch-off are both lower.

(ii)

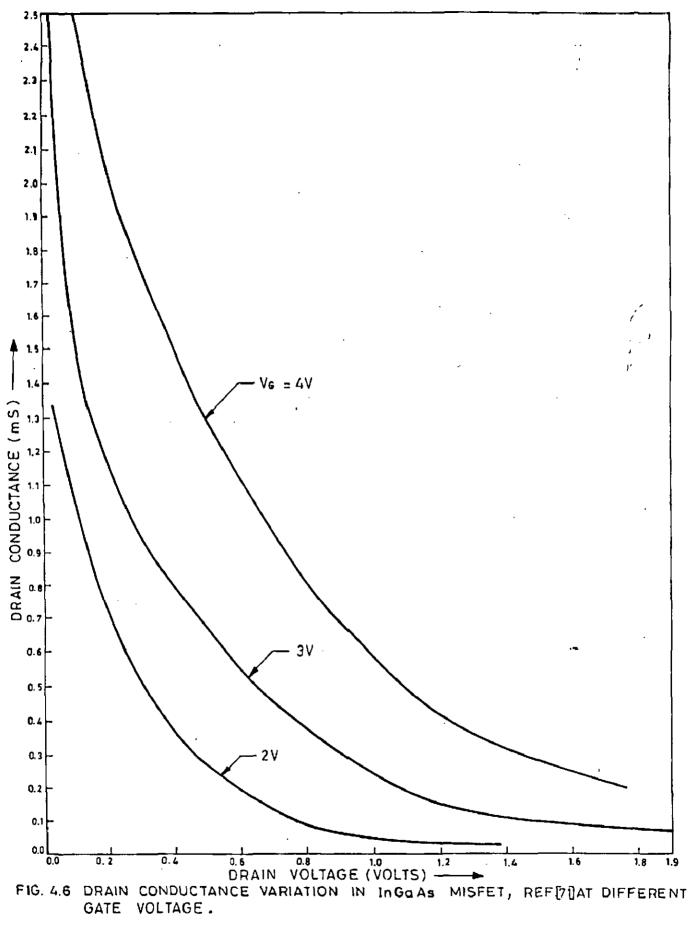

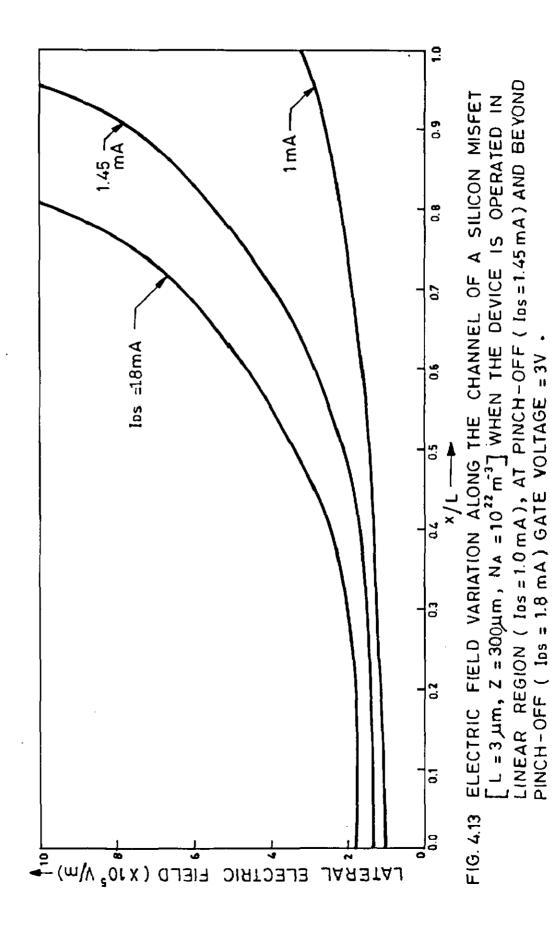

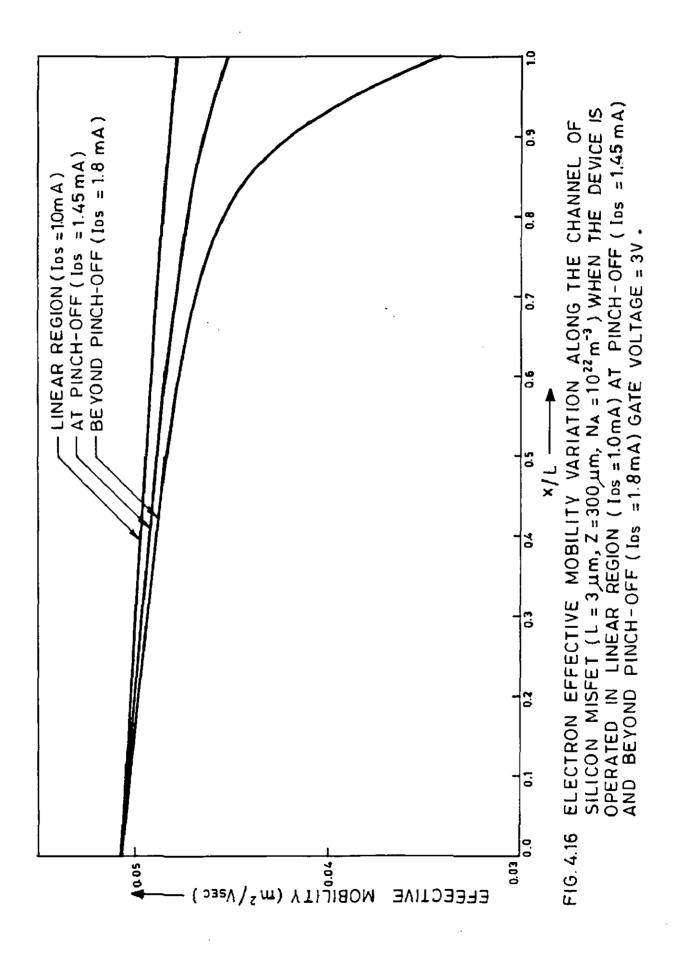

For the sake of comparison, the model is applied to InP and silicon MISFETS. It is observed that the level of operating drain current in InGaAs MISFET is comparatively higher than in InP and silicon MISFETS. A high drain conductance in InGaAs MISFET is also indicated by the study.

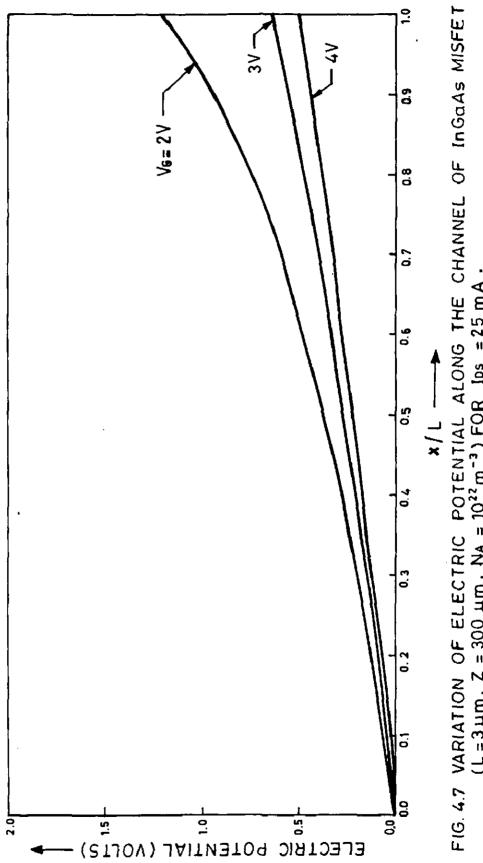

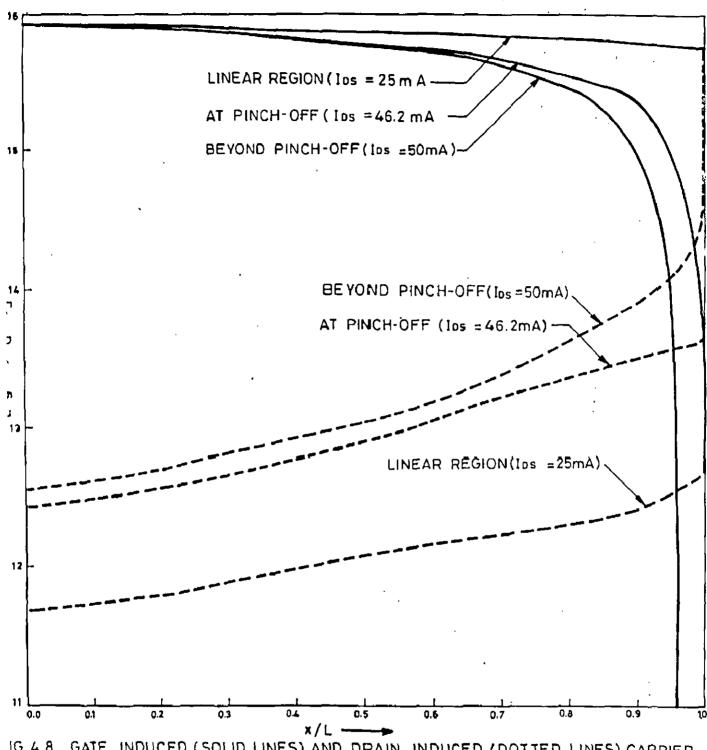

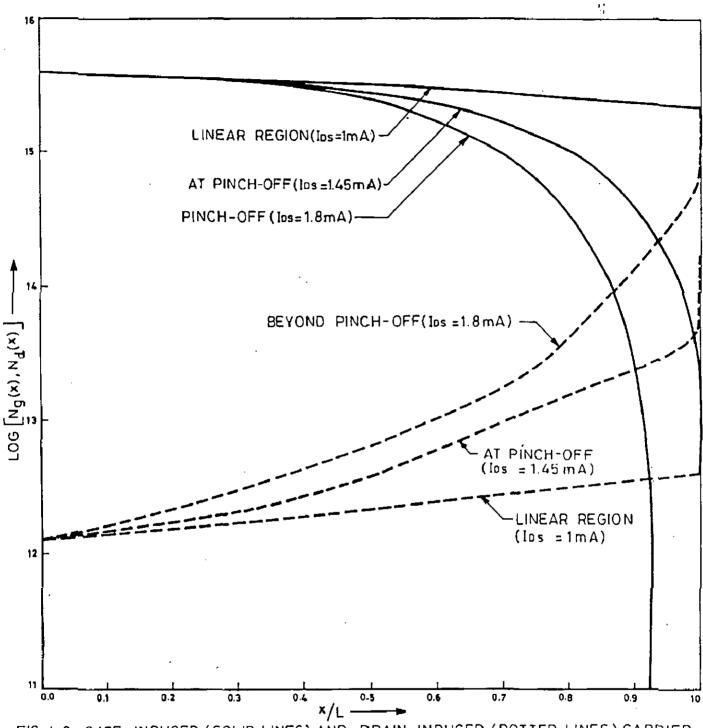

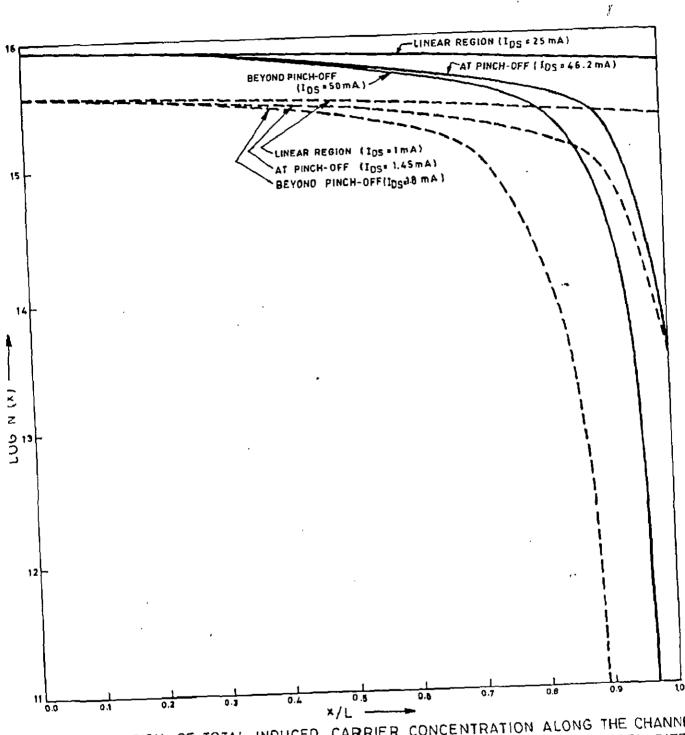

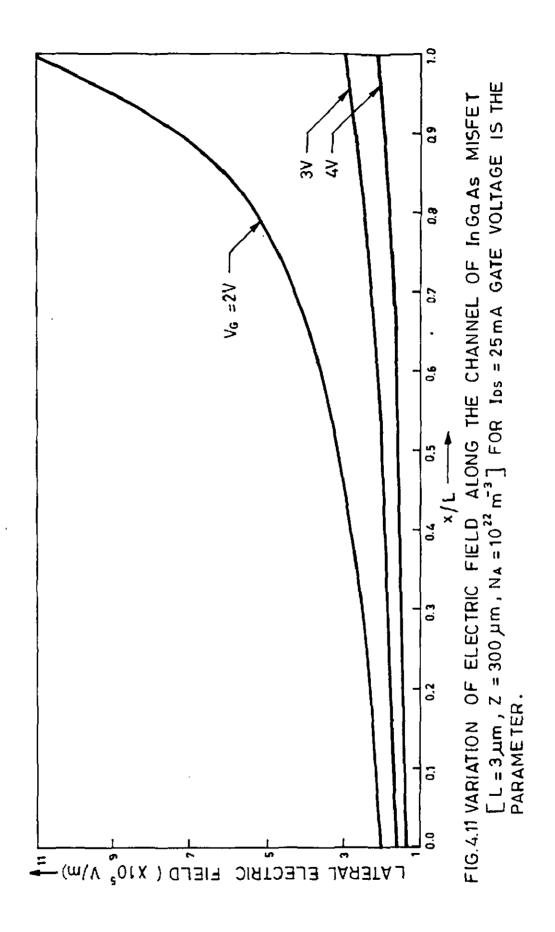

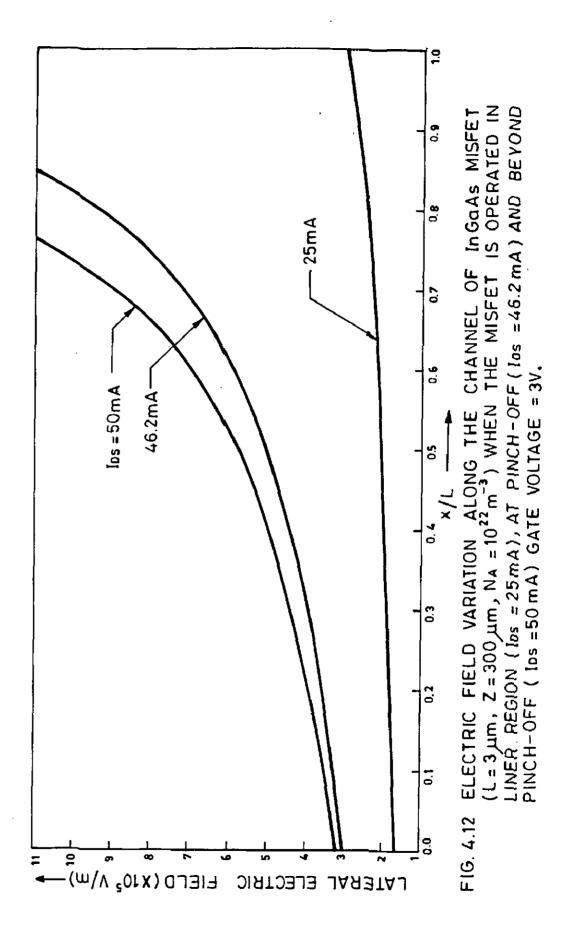

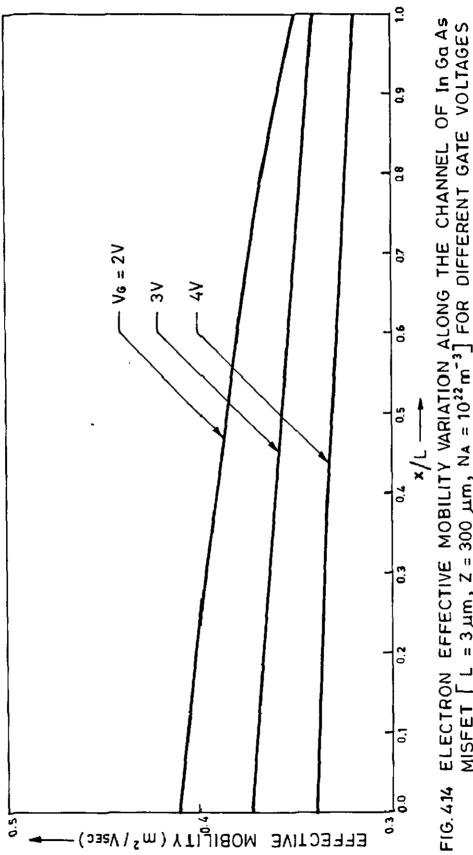

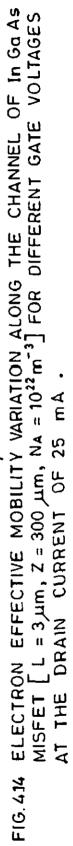

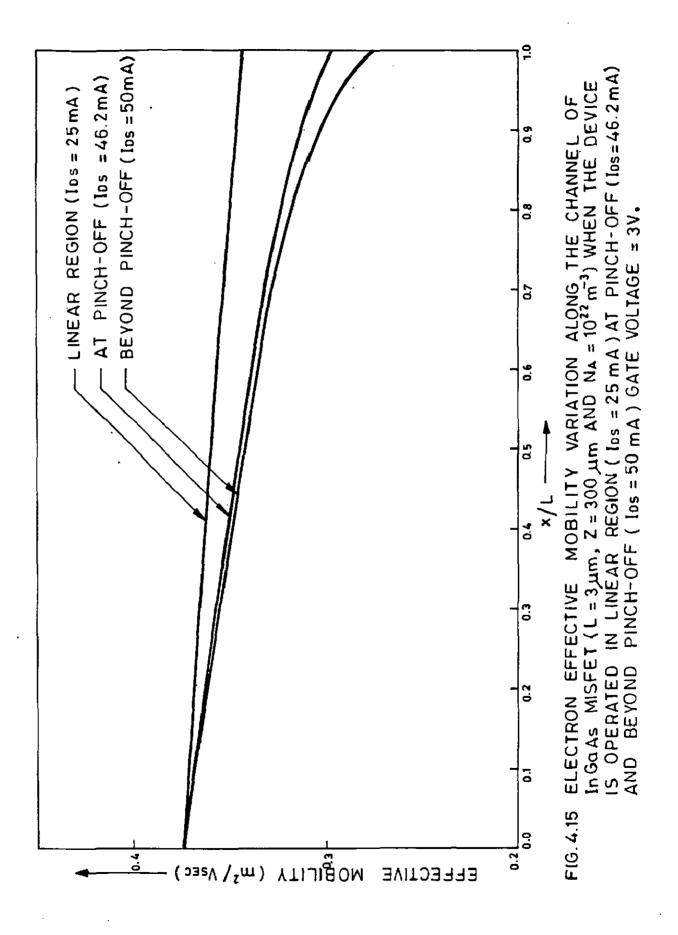

The MISFET-model is self-sufficient to give a picture of potential and electric field variation along the channel. It is also capable of determining the distribution of gate induced and drain induced carriers along the channel. It has been shown that these quantities vary in a similar manner as in silicon MISFETs. However, the magnitudes of each of these quantities are higher in InGaAs MISFET. The analysis also considers the variation of effective mobility along the channel. It is shown that effective towards the drain mobility decreases end. This mobility degradation is enhanced by lowering of gate voltage.

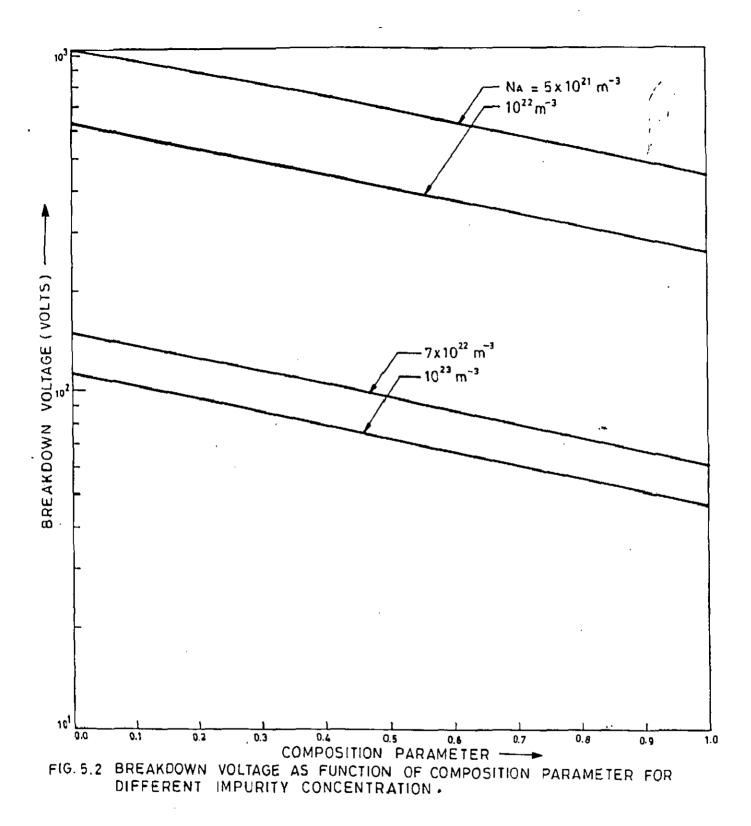

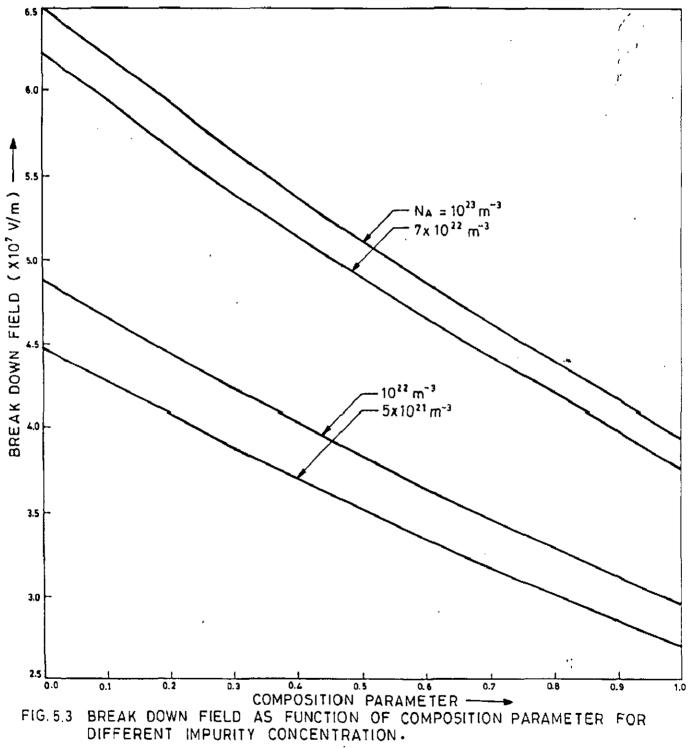

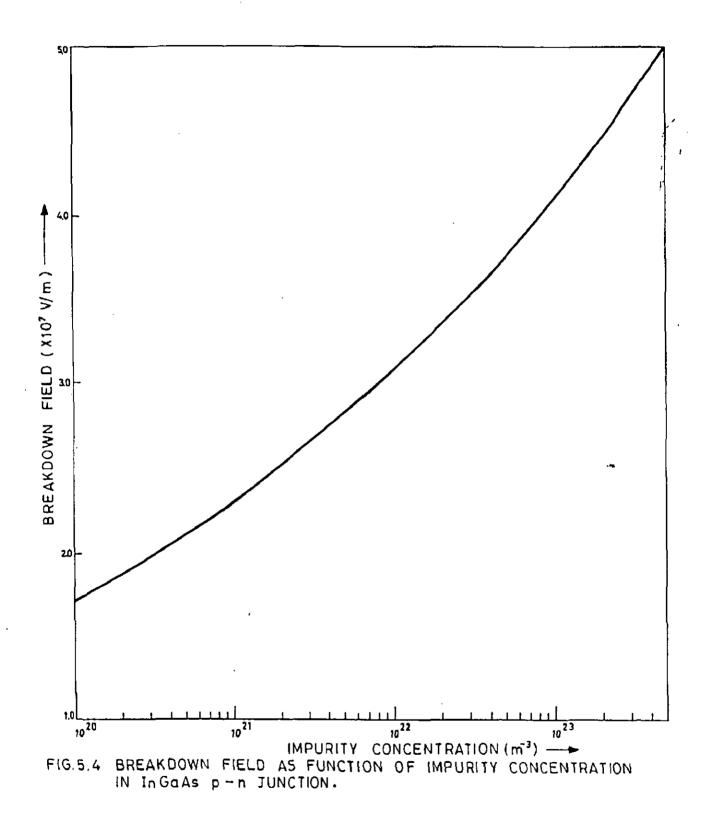

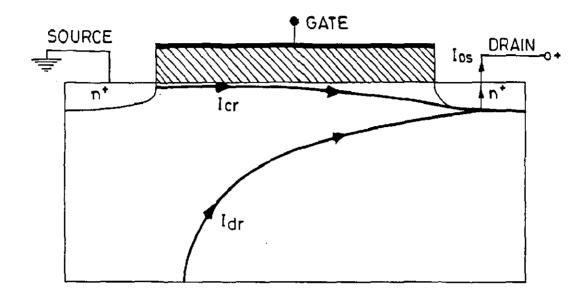

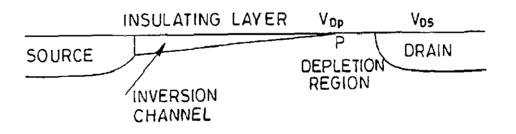

In a MISFET the channel carrier concentration is enhanced by impact ionization at high drain voltages and also there is possibility of avalanche breakdown in the p-n junction formed by the drain and substrate. In order to account for the influence of current multiplication by the above two processes, it is necessary to deal with drain breakdown mechanism and its effect on the characteristics of an InGaAs MISFET. The analysis of the drain breakdown mechanism has been carried out in the light of the well established impact ionization theories. To this effect the breakdown parameters for InGaAs and related semiconductors are that for In<sub>1-x</sub>Ga<sub>x</sub>As<sub>y</sub>P<sub>1-y</sub>, analysed. first It is shown the breakdown voltage and breakdown fields are both dependent on the alloy composition parameters. InGaAs, which is the ternary limit

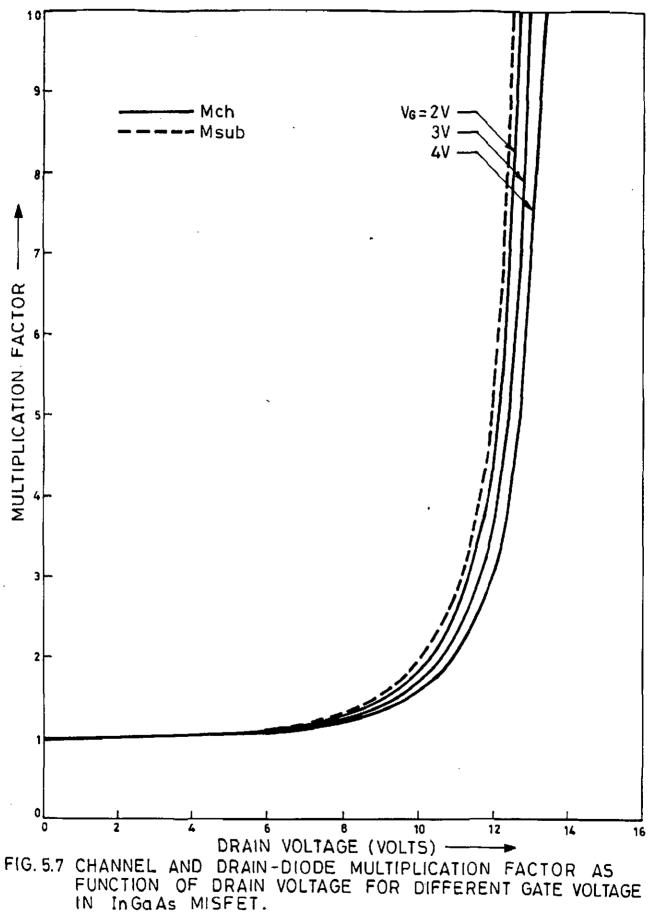

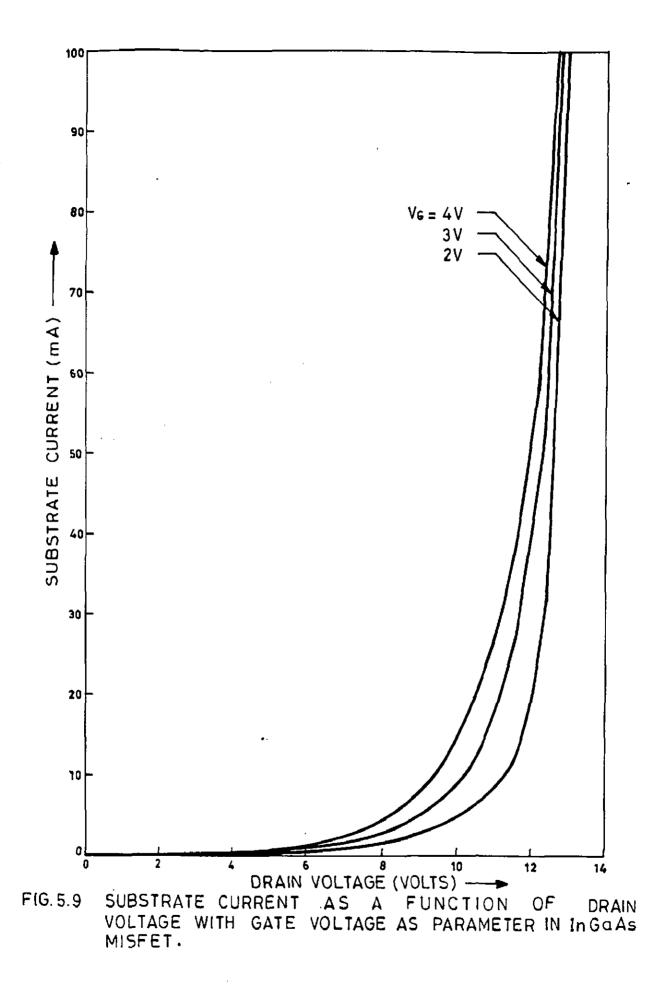

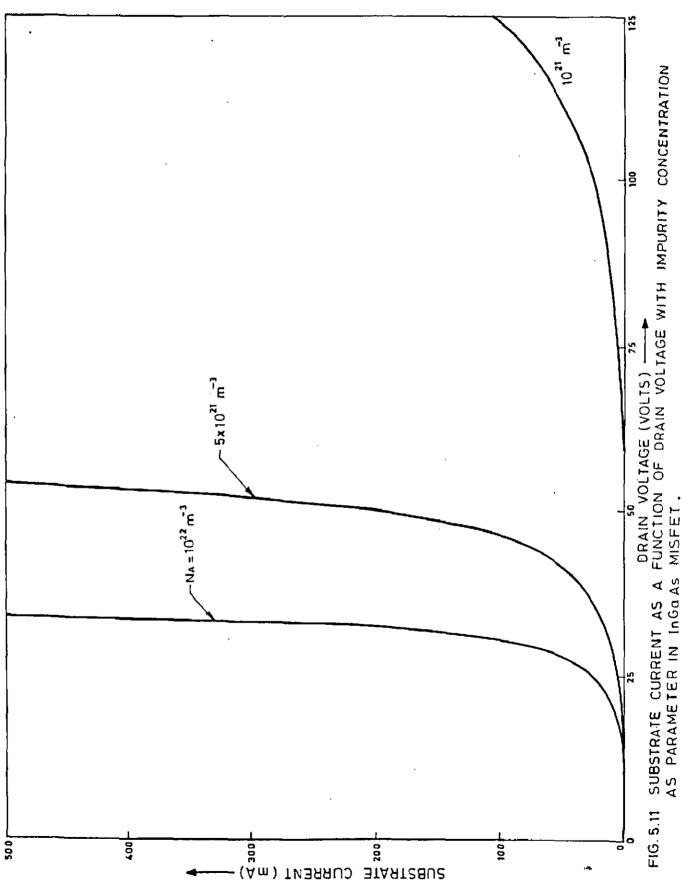

of the guaternary alloy system has the lowest breakdown voltage and breakdown field. The breakdown field in InGaAs is a slowly varying function of the doping level. A most important breakdown parameter is multiplication factor. Two distinct multiplication factors are defined for a MISFET, viz., the channel multiplication factor and drain-diode multiplication factor or substrate multiplication factor. The channel multiplication factor is related to impact ionization in the channel of the MISFET, while the other multiplication factor arises out of avalanche breakdown in the drain-diode at high drain voltage. It has been shown analytically that the channel multiplication factor is controlled by the gate voltage. It decreases with increase in gate voltage. The drain-diode multiplication factor on the other hand is independent of gate voltage.

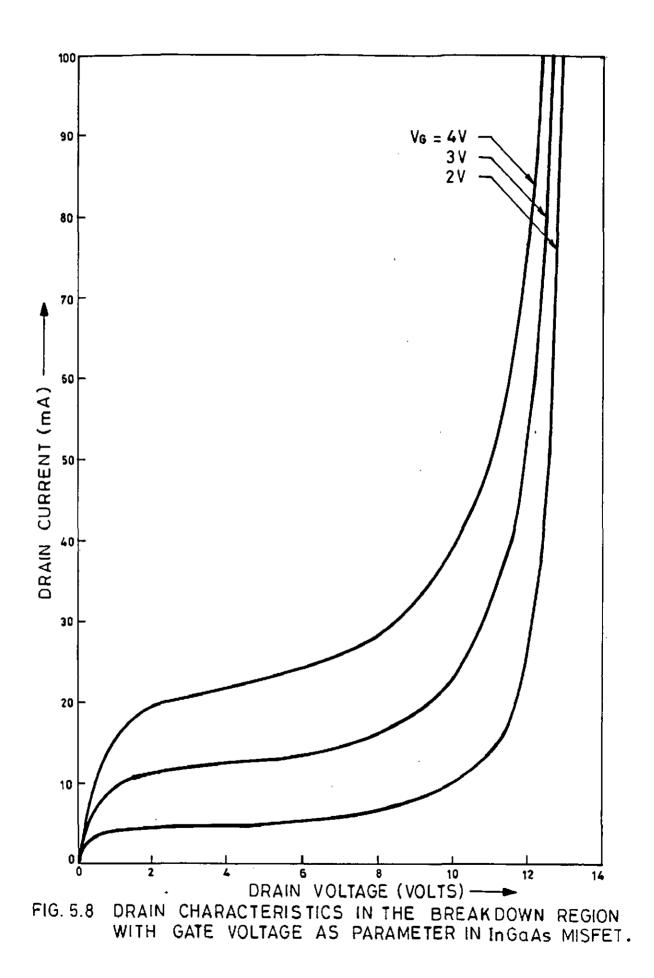

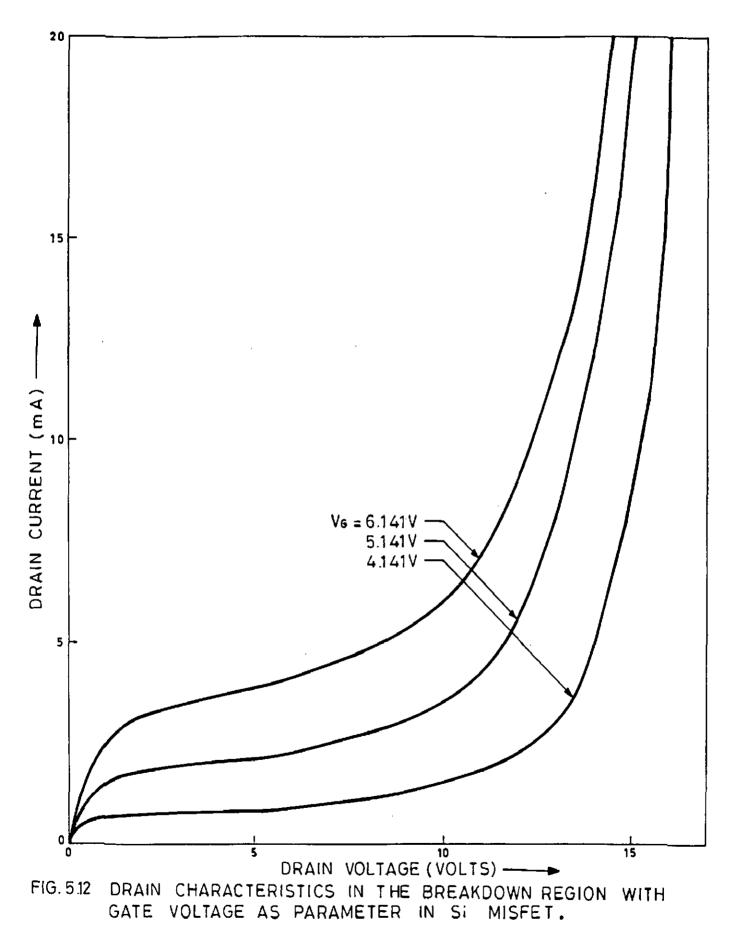

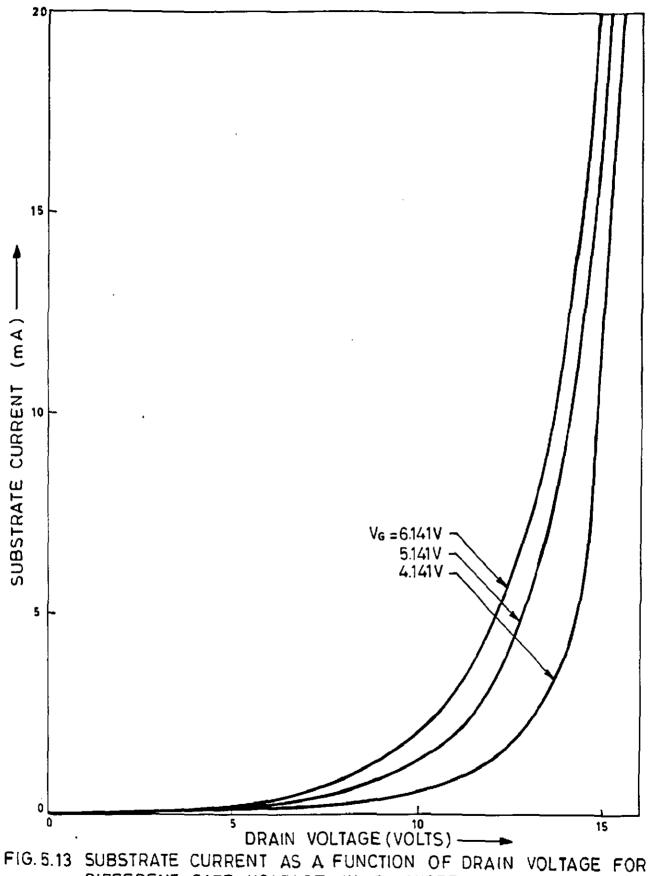

For the analysis of the influence of impact ionization on the drain characteristics of the InGaAs MISFET, the drain current is assumed to be composed of two components. One of the component is the multiplied channel current and the other is the drain-diode current. The multiplied channel current is obtained by the product of channel multiplication factor and the drain current obtained from the MISFET-model developed. The analysis shows that influence of impact ionization in channel and drain-diode depletion layer on the drain characteristics of an InGaAs MISFET is similar to what has been observed in silicon MISFETs. The analysis also shows that the drain breakdown voltage at which avalanche breakdown occurs either in the channel or drain-diode, increases with increase in gate voltage. Furthermore, the drain breakdown voltage in a silicon MISFET is comparatively lower than that in a comparable InGaAs MISFET.

- (i) R.K. Sharma, S. Sarkar and V.K. Tondon, "Influence of normal field on electron mobility in inverted p-InGaAsP surface", Int. Conf. on Semiconductor Materials, New Delhi, Dec.13-16, 1988.

- (ii) R.K. Sharma, S. Sarkar and V.K. Tondon, "A theoretical analysis of inversion mode InGaAsP-MISFETS", Foundation Meeting of the Materials Research Society of India, Hyderabad, Feb.10, 1989.

- (iii) R.K. Sharma, S. Sarkar and V.K. Tondon, "An improved Matthiessen's rule based mobility model for MIS-inversion layer", NACONECS-89, Roorkee, Nov.2-4, 1989.

- (iv) S. Sarkar, R.K. Sharma and V.K. Tondon, "Gate voltage control of surface potential in inversion mode InGaAsP-MISFETs", Accepted for Publication in Solid-State Electronics.

- (v) R.K. Sharma, S. Sarkar and V.K. Tondon, "Modeling inversion mode InGaAs-MISFET", Communicated to IEEE Trans. Electron Devices.

- (vi) V.K. Tondon, R.K. Sharma and S. Sarkar, "An analysis of MIS-inversion layer effective mobility", Communicated to J. of Microelectronics.

I am extremely grateful to Supervisors Dr. V.K. Tondon and Dr. S. Sarkar for their invaluable guidance and perpetual encouragement throughout the course of this investigation.

I am thankful to Dr. M.K. Srivastava, Head, Department of Physics, University of Roorkee, for providing all the necessary facilities. I am also grateful to Dr. S.K. Joshi, Director, National Physical Laboratory, for his valuable help in the early stage of research work.

I also record my appreciation and thankfulness to Dr. Keshav Kumar, Dr. Arun K. Katiyar, Dr. Arvind K. Jain and Mr. S.P. Purohit for their kind co-operation during my reaserch work.

I would thank University Grants Commission, New Delhi for financial assistance in the form of Teacher Fellowship.

RK Shanne

(RAJ KUMAR SHARMA)

CONTENTS

| CHAPTER |        |                                                     | Page No. |

|---------|--------|-----------------------------------------------------|----------|

| I       | INTRO  | 1-10                                                |          |

|         | 1.1    | Introduction                                        | 1        |

|         | 1.2    | Statement of the Problem                            | 7        |

|         | 1.3    | Organization of Thesis                              | 8        |

| II      | III -  | V COMPOUND SEMICONDUCTOR MISFETs - A REVIEW         | 11-59    |

|         | 2.1    | Introduction                                        | 11       |

|         | 2.2    | III - V Compound Semiconductor for MIS              |          |

|         |        | Devices                                             | 12       |

|         |        | 2.2.1 Semiconductor-dielectric interfaces           | 12       |

|         |        | 2.2.2 Drain current drift                           | 20       |

|         | 2.3    | III - V Semiconductor MIS-Technology                | 26       |

|         |        | 2.3.1 Semi-insulating substrates                    | 26       |

|         |        | 2.3.2 Growth of III - V compound                    |          |

|         |        | semiconductors                                      | 27       |

|         |        | 2.3.3 Ion-implantation                              | 30       |

|         |        | 2.3.4 Dielectric growth techniques                  | 34       |

|         | 2.4    | III - V Semiconductor MISFETs                       | 37       |

|         |        | 2.4.1 GaAs MISFET                                   | 37       |

|         |        | 2.4.2 InSb MISFET                                   | 41       |

|         |        | 2.4.3 InP MISFET                                    | 42       |

| •       |        | 2.4.4 InGaAsP and InGaAs MISFET                     | 50       |

|         | 2.5    | Conclusion                                          | 57       |

| III     | ELECTI | RON MOBILITY IN $In_{1-x}Ga_x As_y P_{1-y}$ MISFETs | 60-86    |

|         | 3.1    | Introduction                                        | 60       |

|         | 3.2    | Surface Potential in Inverted p-InGaAs              |          |

|         |        | and Related Compound Semiconductors                 | 61       |

|         |        | 3.2.1 Fundamental equations                         | 62       |

|         |        | 3.2.2 Quantitative analysis                         | 64.      |

|    | 3.3   | Charge and Field in Inversion Layer            | 67      |

|----|-------|------------------------------------------------|---------|

|    |       | 3.3.1 Depletion and inversion charge densities | 68      |

|    |       | 3.3.2 Effective normal field                   | 70      |

|    | 3.4   | Carrier Mobility in Inversion Channel          | 72      |

|    |       | 3.4.1 Scattering mechanism in inversion channe | 1 72    |

|    |       | 3.4.2 Effective mobility                       | 76      |

|    | 3.5   | Conclusion                                     | 86      |

| IV | ANALY | SIS OF n-CHANNEL INVERSION-MODE InGaAs MISFET  | 87-116  |

|    | 4.1   | Introduction                                   | 87      |

|    | 4.2   | The Basic Model                                | 88      |

|    |       | 4.2.1 Effective mobility parameter extraction  | 94      |

|    | 4.3   | Analysis of the Drain Characteristics of       |         |

|    |       | InGaAs MISFET                                  | 99      |

|    |       | 4.3.1 A more generalized effective mobility    |         |

|    |       | expression                                     | 99      |

|    |       | 4.3.2 Effect of channel doping on drain        |         |

|    |       | characteristic <b>s</b>                        | 102     |

|    | 4.4   | Electric Potential Variation along the         |         |

|    |       | Channel and Its Effect                         | 107     |

|    |       | 4.4.1 Potential and field variation along      |         |

|    |       | the channel                                    | 108     |

|    |       | 4.4.2 Effective mobility variation along       |         |

|    |       | the channel                                    | 113     |

|    | 4.5   | Conclusion                                     | 115     |

| V  | DRAIN | BREAKDOWN IN InGaAs MISFET                     | 117-148 |

|    | 5.1   | Introduction                                   | 117     |

|    | 5,2   | Theory of Impact Ionization                    | 118     |

|    |       | 5.2.1 Avalanche breakdown and ionization       |         |

|    |       | integarls                                      | 118     |

|    |       | 5.2.2 Ionization rates                         | 121     |

.

.

.

| 5,2,3 The breakdown field                   | 124 |  |

|---------------------------------------------|-----|--|

| 5.2.4 Evaluation of multiplication factors  | 125 |  |

| 5.2.5 A theoretical estimation of breakdown |     |  |

| parameters in InGaAs and related            |     |  |

| semiconductors                              | 127 |  |

| 5.3 Drain Breakdown in MIS Transistor       | 130 |  |

| 5.4 Influence of Impact Ionization on Drain |     |  |

| Characteristics                             | 132 |  |

| 5.4.1 Avalanche ionization in the channel   | 133 |  |

| 5.4.2 Junction breakdown in MIS device      | 136 |  |

| 5,4,3 Substrate current                     | 138 |  |

| 5.5 Influence of Gate Voltage and Impurity  | •   |  |

| Concentration on InGaAs MISFET Drain        |     |  |

| Characteristics in the Breakdown Range      | 139 |  |

| 5.5.1 Effect of gate voltage on drain and   |     |  |

| substrate current in the breakdown          |     |  |

| region                                      | 139 |  |

| 5.5.2 Effect of impurity concentration on   |     |  |

| drain current in the breakdown region       | 143 |  |

| 5.5.3 A comparison with silicon MISFET      | 144 |  |

| 5.6 Conclusion                              | 147 |  |

| CONCLUSIONS AND SUGGESTIONS FOR FUTURE WORK |     |  |

| 6.1 Introduction                            | 149 |  |

| 6.2 Summary and Conclusions                 | 150 |  |

| 6.3 Scope for Further Work                  | 168 |  |

| REFERENCES                                  |     |  |

•

VI

## chapter I

· .

.

.

.

### 1.1 INTRODUCTION

The introduction of the concept of a surface field-effect device dates back to the early 30s, when Lilienfeld and Heil [36,220], independently proposed a device in which current through a thin layer of semiconductor is controlled by a surface electric field. In their field-effect devices, the controlling electric fields were created by the application of a potential drop across an insulator with the semiconductor and metal as the two electrodes. The modern version of these devices are known as metal-insulator-semiconductor field-effect transistors the (MISFETs). This device has two other acronyms, namely, MOSFET (metal-oxide-semiconductor field-effect transistor) and IGFET (insulated-gate field-effect transistor). Although the basic principle of operation of the MISFETs was conceived in the first half of the century, the major break-through in MIS-technology long time for the want of a wait a reliable had to insulator-semiconductor combination. In 1959. Atalla [8] demonstrated that by thermally growing SiO<sub>2</sub> on a Si-surface, a MIS device grade insulator-semiconductor system can be achieved. A year later Kahng and Atalla [114] proposed a Si-SiO2 MISFET. The device was further developed by Hofstein and Heiman [104]. Thus, silicon MISFET emerged as a potential device for many electronic applications.

The MISFET device essentially consists of a lightly doped silicon substrate into which two lightly doped regions are diffused. These regions are known as the source and the drain. A potential difference between the source and drain makes a majority carrier current conduction through the space between

them. The conducting path between the drain and source is known as the channel. If the carriers in transit through the channel are electrons, the device is an n-channel MISFET. If the current is due to transit of holes between source and the drain, the device is a p-channel MISFET. Hofstein and Heiman [91,104] also demonstrated that the MISFETs can operate in two distinct modes. namely, inversion-mode operation and depletion-mode. In inversion-mode operation, the channel is formed by surface inversion of the semiconductor. In the depletion-mode operation, the channel is provided by the bulk of the semiconductor lying under a surface depletion layer. In either case, a voltage applied at the metal electrode on the insulator surface modulates the channel conductivity, thereby controlling the current. This metallic film is known as the gate of the device. As appreciable surface inversion requires substantive gate voltage, an inversion-mode MISFET does not conduct a significant current at zero or very low gate voltage. Thus, an inversion-mode MISFET is a normally 'off' device. On the other hand, a depletion-mode MISFET operates even at zero gate voltage. Because of this characteristics, a depletion-mode MISFET is categorized as a normally 'on' device.

The pressing need for microminiaturization led to the emergence of integrated circuit (IC) technology. Once again silicon turned out to be the most suitable material as substrate for the IC-chips. SiO<sub>2</sub> proved to be a versatile impurity mask and surface passivation layer for silicon IC-wafers. The common intrests in IC-technology and silicon MIS-technology made the two benefit from the progress of one another. It was soon realized that a MISFET is more compatible with the integrated circuits

than the bipolar and junction field-effect transistors. Comparatively lesser number of processing step and smaller area requirements made the MISFETs to be more convenient for IC-applications. These advantages of MISFETs have made LSIs and VLSIs to be possible. As elements in integrated circuits, the silicon MISFETs found applications wide in semiconductor memories, switching circuits, logic circuits, microprocessors and many other circuits, subsystems and systems. Because of the 'off' character, the inversion-mode MISFETs find an normally ample use in the switching and logic circuits. As speed is of concern in these applications, n-channel inversion-mode MISFETs with high channel carrier mobility are more commonly used.

The trends of microminiaturization and demand for economy anđ reliability led millimeter microwave, wave and opto-electronics to adopt semoconductor technology. The parameter of primary concern for high-frequency devices is short carrier transit time, while direct and wide bandgap which are of utmost importance for a semiconductor to be useful for opto-electronic applications. Carrier transit time can be shortened to some extent by reducing device dimension. But technological constraints to this technique of put limit transit time reduction. An alternative is the use of a high mobility and high saturation velocity semiconductor. For opto-electronic applications a direct and wide gap semiconductor is essential as it ensures efficient operation in the optical range of the electromagnetic spectrum. Unfortunately, silicon with its fully mature device technology does not quite meet these requirements. Consequently, attention was drawn towards the high electron mobility and wide bandgap III - V compound semiconductors such

З

GaAs, InP etc. By mid sixties, several III - V compound as semiconductors microwave and opto-electronic devices such as Gunn's, GaAs-IMPATT's, GaAs-varactor's, p-n junction LASER's, PIN photodetector's, avalanche photodetector's and a few other were developed. Side by side with these inventions, more III ~ V compound semiconductors were found to be useful for opto-electronic and high-frequency applications. Prominent amongst these are InGaAsP, InGaAs, GaAlAs and GaAsP.

The seventies and eighties were marked by advances in low-loss-low-dispersion silica fibre for the 1.0 1.7 um wavelength transmission. Investigations show that wavelength which offers minimum loss extends from 1.3 µm to 1.6 µm region [151]. This opened a new era for communication systems. Systems using silica fibre as transmission line and semiconductor optical sources and detectors began to develop concurrent with these developments the concept of integrated optics also found its place in the communication systems [108]. The implementation of the idea of integrated optics along with the fact that an optical communication signal is usually modulated at microwave frequencies, necessitates the use of a semiconductor that satisfy both bandgap and mobility requirements. The semiconductor that meets these requirements happens to be  $In_{1-x}Ga_xAs_yP_{1-y}$  grown on InP under lattice match condition of  $y \approx 2.2$  x. From its binary limit of InP (y = 0) to the ternary limit InGaAs (y = 1), the bandgap of the quaternary varies from 1.35 eV to 0.75 eV. Between the same limits the electron mobility of InGaAsP varies from 0.46 to approximately 1.0  $m^2/V$ -s. The most satisfactory feature from the optical fibre communication point of view is the fact that the bandgap range of this alloy system corresponds to a

wavelength range from 0.9 µm to 1.65 µm. Another attractive property of InGaAsP is that it has a direct bandgap over its entire alloy composition range. On the basis of these properties, InGaAsP is finding immense application in optical communication systems, especially as the substrate material for LASER and photodetectors [176]. Investigations also show that of all the possible compositions of the quaternary, InGaAs suits best for photodetectors. From these results it can be safely said that InGaAs is a potential candidate for use as substrate material in an integrated optical receiver. Such an application of InGaAs will be possible, if all the devices comprising a receiver unit can be built in the semiconductor. The recent communication systems make extensive use of digital signal processing. Thus due to the fact that n-channel inversion-mode MISFETs are important components in signal processing circuits, the development of InGaAs-based n-channel inversion-mode MISFETs is of much practical significance.

The of silicon MIS-technology success encouraged scientists and technologists to embark upon the development of III v compound MIS-technology. Initial efforts were concentrated on GaAs MIS devices. However, these efforts were not rewarded, as high density of interface states pins Fermi level in the lower half of the bandgap. More recently, with the growing  $In_{1-x}Ga_xAs_vP_{1-v}$  alloy family for electronic importance of applications, attentions were drawn towards the possibility of fabricating MISFETs on InP, InGaAsP and InGaAs substrates. Ultimately, it was demonstrated that n-channel inversion-mode MISFETs on InP, InGaAsP and InGaAs are possible [65,71,202]. Investigations showed that the InGaAs MISFETs are the most

promising of these devices. Reasonably low interface state density and extremely high field-effect mobility has been reported for n-channel inversion-mode InGaAs MISFETs [65,71].

Notwithstanding the bright prospects that the preliminary investigations suggest for InGaAs MISFET, the technology of this device has yet to earn maturity. Interface state density in  $SiO_2$ -InGaAs or  $Al_2O_3$ -InGaAs systems vary over the range of  $10^{15}$  -  $10^{16}$  m<sup>-2</sup> [65,71] as compared with  $10^{14}$  m<sup>-2</sup> for  $SiO_2/Si$  that is achieved with silicon MIS-technology of the present times [220]. Another most menacing disadvantage with the InGaAs MISFETs is the drain current drift caused by the presence of traps in the insulator-semiconductor interfacial layer. However, it may be hoped that with time, these technological hurdles will be overcome and inversion channel InGaAs MISFETs will turn out to be a potential device for many applications, such as G-bit signal processing and integrated optical communication systems.

The development of any device immensely depends on the understanding of its physics. Such an understanding is achieved through theoretical analysis and the modeling of the device. So far most of the work carried out in the area of InGaAs MISFET are laboratory oriented. Very little analysis of the physics of the device has been made. In absence of a strong theoretical background, the laboratory developments of the device relied on the presumption that the silicon MISFET theory is applicable to all other MISFTEs, irrespective of the substrate material. Although some success has been achieved with this approach, the applicability of the existing MIS-theory to the case of InGaAs needs to be thoroughly analysed.

The present thesis analyses and models n-channel inversion-mode InGaAs MISFET in the light of the existing MIS-theory developed with silicon MISFET in view. The theoretical approach presented in the thesis is a study of three fundamental aspects of the device. These are :

- evaluation of InGaAs as a substrate material for inversion-mode MISFETs,

- 2. basic device physics that leads to the observed characteristics and

- 3. the factors governing the limits imposed on the operating current and voltage of the device.

### 1.2 STATEMENT OF THE PROBLEM

In an inversion-mode MISFET, the substrate material parameters such as the permittivity, intrinsic carrier concentration, carrier effective mass and doping level have profound influence on the behaviour of the channel. The channel behaviour is characterized by several independent parameters. These are surface potential, effective normal field, effective carrier mobility etc. The control of gate voltage on these channel parameters depend to a very great extent on the material parameters of the semiconductor used. The assessment of the suitability of a semiconductor for inversion-mode MISFET applicaton therefore requires analysis of the channel an parameters as functions of the various material parameters. The present thesis meets this objective through the well established MISFET relations which have been successfully applied to the study of the silicon MISFETs. Experimental data as reported in literature show that the effective electron mobility in n-channel

inversion-mode InGaAs MISFET is generally extremely high. In search of explanations for such observations a Matthiessen's rule approach is adopted in the present analysis and the factors governing effective mobility are identified. The influence of the material parameters on these factors is then studied. For a meaningful analysis of the device physics that leads to the observed output characteristics of the n-channel inversion-mode InGaAs MISFTES, a suitable MISFET-model is developed. The model is used to study the MISFET under various bias conditions. Finally, impact ionization in InGaAs is studied and the analytical results are applied to analyse drain breakdown in n-channel inversion-mode InGaAs MISFET. Thus, the salient features of the study of n-channel inversion-mode InGaAs MISFET may be stated as below :

- study of InGaAs as a material for n-channel inversion-mode MISFET,

- 2. analysis of channel field, carrier distribution, channel mobility and drain characteristics (drain current-drain voltage) for an n-channel inversion-mode InGaAs MISFET,

- 3. study of drain breakdown in n-channel inversion-mode InGaAs MISFET and

- 4. assessment of performance capabilities of n-channel enhancement-mode InGaAs MISFET on the basis of the above analytical studies.

### 1.3 ORGANIZATON OF THESIS

The thesis consists of six chapters. First chapter (that is the present chapter) focuses on the objectives, scope and importance of an analytical study of InGaAs MIS field-effect

Ŋ

devices.

The second chapter is a review of the earlier work in the area of III - V compound semiconductor MISFETs. In view of decisive role played by high electron mobility and low interface state density for high-speed applications, a large amount of work has been carried out in search of a suitable material for this purpose. Most of the available informations on III - V compound semiconductor demonstrate that the InGaAs MISFETs are potential devices for meeting high-speed requirements of the modern electronic circuits and systems.

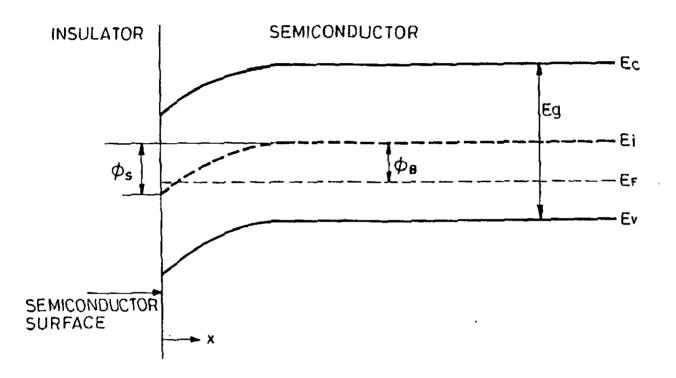

The successful application of а semiconductor in inversion-mode depends upon the influence of normal electic field on inversion layer parameters. The primary parameters which characterize an inversion channel are surface potential, channel charge density and channel carrier mobility. From inversion-mode theory, it is well known that channel properties greatly depend upon material parameters such as bandgap, effective mass and semiconductor permittivity which are composition dependent. Thus InGaAsP MISFETs of differing alloy composition have different channel properties and performance as a device. The third chapter presents a comprehensive theoretical analysis of the behaviour of these parameters of an InGaAsP MIS device. Through this analysis InGaAs is assessed as a material for inversion-mode MISFET.

The performance of MISFET depends on the electric field profile and carrier distribution in the channel. In order to study the internal fields and carrier distribution, a MISFET-model is developed and presented in the fourth chapter of

the thesis. This chapter is thus devoted to the analysis of the characteristics of InGaAs MISFET by the aid of the MISFET-model. In the process a simple method for mobility parameter extraction is also suggested. The dependence of effective carrier mobility on the various parameters of the channel are also analysed in this chapter.

The fifth chapter of the thesis deals with drain breakdown in n-channel inversion-mode InGaAs MISFET. The impact ionization in the channel and in the drain-diode depletion regions are studied with the help of existing theories and relevant experimental data available in the literature. The effect of impact ionization in channel and drain-diode on the drain characteristics are studied. The influence of gate voltage on drain breakdown is also investigated.

A critical examination of all the analytical results obtained is presented in the sixth and final chapter. Important conclusions are drawn and the inferences as well as limitations of n-channel inversion-mode InGaAs MISFET are highlighted. The scope for further work in this area is also discussed.

# chapter II

.

.

.

.

### III - V COMPOUND SEMICONDUCTOR MISFETs - A REVIEW

### 2.1 INTRODUCTION

The growing demand for digital processing at frequencies higher than a few G-bits or more resulted in an interest in developing a high-speed MISFETS. In spite of its highly developed technology the silicon MISFETS fail to meet such requirements owing to limited carrier mobility. In this respect, the III - V compound semiconductor alloy such as GaAs, InP, InGaAsP and InGaAs with high electron mobility, are better candidates for the purpose. Recently, the applications of binary, quaternary and ternary semiconductors have increased manifold and have reached a stage where indium based compounds have emerged as the most important semiconductors. While these materials have already established themselves as materials for various opto-electronic applications (LEDs, APDs and LASERs etc.), some effort have also been made to use them as the basic material for a high-speed MIS-technology.

The aim of this chapter is to present a review of the important developments in the area of III - V compound semiconductor MIS-technology. The review begins with a brief look at the III - V compound semiconductor MIS (or MOS)-technology, its present status and problem. Subsequently the emergence of III - V compound semiconductor MISFETs which derive much of its technology from that of the Si MISFET is discussed. The achievements and failures of this new MIS-technology are all critically reviewed in this chapter.

### 2.2 III - V COMPOUND SEMICONDUCTOR FOR MIS DEVICES

The utilization of the advantages of a III - V compound semiconductor insulated gate FET to a great extent depends upon the electrical properties of its semiconductor-dielectric interface and the control of drain current drift. Therefore, a thorough understanding and technological control of interfaces between these semiconductors and their native oxides and synthetic dielectric layers are equally important. In III - V compound MISFETs, drift in drain current with applied steady state drain and gate voltage, is the most serious problem that degrades the performance of these devices. This section deals with past studies on interfacial and drain current drift parameters of III - V compound MIS devices.

### 2.2.1 Semiconductor-Dielectric Interfaces

A MISFET material is required to have high low-field carrier mobility, peak carrier velocity and I-L intervalley separation. Besides these, another requirement which is of particular importance for successful MIS application is low surface state densities at the semiconductor-dielectric interafce. III - V semiconductors which satisfy the first three requirements are GaAs, InP and InGaAs. In order to develop a viable III - V semiconductor MIS-technology, the dielectricsemiconductor interface properties of these three semiconductors have been extensively studied.

Chye et al. [35] and Van Laar et al. [236] obtained most reliable data on surface band structure of  $In_{1-x}Ga_xAs_vP_{1-v}$  semiconductor on (110) surface cleaved in ultra-high vacuum. The surface with few cleavage steps have a surface Fermi level  $E_f^*$  as the same energy level as the bulk Fermi level  $E_f$ . They also reported that unlike Si, in  $In_{1-x}Ga_xAs_yP_{1-y}$ ,  $E_f^*$  is not pinned by intrinsic surface states. These are located within the valence and conduction bands and not in the bandgap. Duke and Meyer [52] explained the non-existance of intrinsic states in the bandgap by assuming that surface atoms relax forming a distorted tetrahedral environment, the anions move outward and the cations move inward. Theoretical calculations suggest that such a relaxation may force the surface states into the bandgap producing a slight overlap of the respective band edges but these results could not explain satisfactorily pinning of  $E_f^*$  within the bandgap.

Extensive X-ray photo-emission (XPS) and ultraviolet photo-emission spectroscopic (UPS) measurements by Spicer et al. [211] indicate that  $E_f^*$  is displaced from its bulk position if a fraction of a monolayer of oxygen or metal is adsorbed on the surface of an originally clean, cleaved (110) surface. The steady state position of  $E_f^*$  is a specific material parameter. The defect model of Fermi level pinning supposes that defects are created in the surface region of semiconductor when another species is adsorbed upon it, such defects may have energy levels located within the semiconductor bandgap and control the position of  $E_f^*$ . It is these extrinsic surface states that play a significant role in determining the surface and interfacial properties of the III - V semiconducting compounds that have special relevance for FET and other devices.

The performance of MISFET is dependent not only on the

semiconductor surface properties but also on semiconductor-insulator interface. V compound In III semiconductor MIS device, the insulator-semiconductor interfaces great technological significance today, are of since the operation of semiconductor devices and integrated circuits rely interfaces. Therefore. such the upon understanding and technological control of the interfaces between these semiconductors and their native oxides that evolve upon contact with the ambient environment and of synthetic dielectric layers deposited on their surfaces. The native oxides are neither stoichiometric nor spatially homogeneous and are much too conductive to qualify as dielectric layers adequate for MISFETs. However, the native oxide plays an important role in affecting device performance, as they grow guite unintentionally on the surface of the semiconductor.

Homomorphic and heteromorphic dielectric layers on GaAs have been the most extensively investigated III - V compound MISstructure with the expectation that a suitable dielectric interface will be formed to make GaAs MISFET-technology feasible. Homomorphic layers have been made by Hasegawa et al.[85,861, Hasegawa and Hartnagel [87] with anodic oxidation, Weinreich [250] with microwave plasma oxidation, Sugano and Mori [216] with rf gaseous oxidation and Chang and Sinha [26] with magnetically confined plasma beam oxidation. A large number of investigations were made on anodically oxidized dielectric layers using an aqueous solution of glycol as well as other electrolytes by Weimann and Schlapp [249]. Detailed investigation made by Chang et al.[25] using AES augmented by neutron activation analysis indicates that the free oxide surface is As deficient while the oxide in the vicinity of the semiconductor interface contains a gradient of excess As that may occupy up to 20 % of the total oxide thickness. Meiners [140] reported that the fast surface states respond to frequencies in excess of 10 MHz.

Heteromorphic MIS-structure on GaAs have been tried by Wilmsen and Szpak [256], Zeisse et al. [267] and Semushkina et al. [196] with a variety of insulators. It was observed that the location of a high density of surface states, near the middle of the GaAs fundamental bandgap, pins the Fermi level. Meiners [140] studied both p- and n-type MIS-structures with homomorphic and heteromorphic dielectric layers. He observed that the position of zero gate bias  $E_f^*$  lies between 0.6 and 0.7 eV above the valence band maximum for p-type and between 0.8 and 0.9 eV below the conduction band minimum for n-type GaAs. These observations were made on the basis of C-V and G-V measurements and were in good agreement with XPS measurement of Fermi level pinning on clean GaAs surfaces. The surface state density distribution was U-shaped. The surface potential excursion was limited to 0.45 eV in the lower half of the bandgap with a minimum of  $2 \times 10^6$  m<sup>-2</sup> eV<sup>-1</sup> surface state density which rises to more than  $10^{17} \text{ m}^{-2} \text{ev}^{-1}$  at the zone boundaries. Neither flat-band nor surface inversion could be attained in either p-type or n-type MIS-structures. Meiners [140] also suggested that these properties are independent of deposition procedure for anodic oxide, silicon oxide or silicon nitride dielectric layers.

Lile and Collins [129] pointed out that surface state density is not the only cause which limits GaAs for MIS-structure. The major impediment is the location of the Fermi

тЭ

level pinning position near the midgap. This results in limited displacement of surface potential which reduces the dynamic range of such MISFETs. Furthermore, these surface state appear to be quite slow, thereby affecting low-frequency response of MIS-structures for more than the high-frequency response. At low-frequencies the surface potential is pinned by filling of the surface traps. It was observed that 1 V change in gate voltage produces a surface potential change of a about 0.45 V at high-frequencies (>1 kHz), the same gate voltage swing produces a surface potential change of only 0.02 V at low frequencies  $(\approx 1 \text{Hz})$ . C-V measurements showed hysteresis as well as frequency dispersion in GaAs MIS-system [89,209]. Hysteresis seen in C-V curves are consistent with trap filling mechanism and indicate deep depletion for high gate voltage sweep rates. Frequency dispersion in GaAs MIS-system is generally very high [61]. Traps distributed in a metamorphic layer between GaAs and insulator appears to be the cause of much abnormally high-frequency dispersion.

On the whole the available homomorphic and heteromorphic dielectric layers in GaAs MISFET applications are unsatisfactory and most of the GaAs-dielectric interfacial problem remains unanswered. It would be highly desirable to find a more suitable dielectric layer that would eliminate Fermi level pinning near midgap, reduces hysteresis of C-V loops and surface states density by at least one order and preferably two order of magnitude.

The properties of thermally grown oxides (dry oxygen) on InP were investigated by Wager and Wilmsen [245]. They reported

-

that oxides composed of 70-75 %  $In_2O_3$  and 25-30 %  $P_2O_5$ , grow very slowly at temperature below 340  $^{\circ}$ C and rapidly above this temperature. The composition of such oxides differs from that of native oxide. Wilmsen [254] was the first to investigate the properties of InP MIS capacitors with elctrochemically anodized insulating layers. He found that the surface potential can be varied by an applied gate voltage. This is in contrast with MIS capacitors made with sputter deposited SiO2, which had their Fermi level pinned in accumulation. Probably this was due to a high density of fixed positive density of surface donor centers on the InP substrate. Meiners [141] deposited SiO, layers on InP substrates by means of low temperature, rf plasma-assisted chemical vapor deposition (CVD) process. From measured data, Meiners [141] obtained surface state density as a function of energy within the fundamental bandgap. He found that in comparison with n-type, the p-type InP surface is strongly depleted. The equilibrium surface Fermi level  $E_f^* = 1.12 \text{ eV}$ for p-type substrate was much larger than that of the n-type InP  $(E_f^* = 0.12 \text{ eV})$  [141]. This value is in good agreement with Fermi level pinning at 1.1 eV determined by Spicer et al. [210] using XPS measurements on (110) oriented cleaved InP. It is also in fair agreement with the measurements of Waldrop et al. [247] which were made on (100) oriented native oxide covered p-type InP surface.  $E_{f}^{*}$  values between 1.2 and 0.9 eV were obtained by Waldrop et al. [247]. Furthermore, from their data it is evident that surface preparation and thermal treatment can affect the position of  $E_{f}^{*}$  within the bandgap. Similar conclusions have been reached by Brillson and Shapira [22]. They used surface photo voltage and Auger electron spectroscopic measurments to investigate ultra-high vacuum cleaved and chemically treated InP

(110) surfaces.

Fermi level pinning near the conduction band edge of p-type InP allows the displacement of Fermi level over a substantial portion of the bandgap. Inversion of the surface of p-type InP MIS-structure is feasible because the Fermi level is pinned near conduction band minimum in contrast with GaAs MIS-structures. A11 these measurements [22, 141, 210, 247]demonstrate the presence of a surface acceptor level  $E_{as} \approx 0.5 \text{ eV}$ and a surface donor level  $E_{ds} \simeq 0.1$  eV with respect to the conduction band edge of n-type InP. It is also indicated that surface state density distribution is V-shaped within the bandgap of InP. These measurements are also consistent with the theoretical analysis of Dow and Allen [50]. The acceptor center ( $E_{as} \approx 0.5 \text{ eV}$ ) is considered to be due to an antisite  $P_{in}$  defect and the shallow donor center ( $E_{ds} \simeq 0.1$  eV) is attributed to  $V_p$ , a phosphorus vacancy. Furthermore, the surface state density near midgap is smaller by approximately one order of magnitude compared to that of GaAs. The above investigations also reveal that, the position of equilibrium  $E_{f}^{*}$  for zero gate bias is near the conduction band minimum in InP. Thisis of great significance for MISFET applications.

Wager and Wilmsen [244] investigated the thermodynamics of reactions between the depositing dielectric species and the InP substrate. For deposition temperature in excess of 350  $^{\circ}$ C a substantial oxidation of InP coupled with out diffusion of In from the substrate into the SiO<sub>2</sub> was found to occur. This was found to be thermodynamically stable in the presence of InP or its native oxides. While Si and SiO<sub>2</sub> were predicted to reduce the InP native oxide producing either  ${\rm SiO}_2$  or a combination of elemental In, P or their suboxides. Wager and Wilmsen [246] reported that rf plasma-assisted growth of  ${\rm SiO}_2$  profiles indicate the presence of 10 - 25 Å thick native oxide. This is presumed to be primarily InPO<sub>4</sub>, whose composition appears to be relatively independent of the deposition process. Wager et al.[243] found that the oxide growth rate is a function of the reactor configuration and is greater than the thermal oxidation rate for temperature less than 350  $^{\rm O}$ C.

More recently, a range of variable bandgap III ~ V compounds of the form  $In_{1-x}Ga_xAs_yP_{1-y}$  has been available. This alloy system can be lattice matched to semi-insulating InP to a high degree of perfection. Shinoda and Kobayashi [202] reported a study of  $In_{1-x}Ga_xAs_yP_{1-y}$  interface. The dielectric layer was deposited by CVD technique using aluminium triisopropoxide. They observed that interface state density is compositional dependent. Wieder [252] studied Ga0.47 In0.53 As dielectric interface and reported that for zero bias, equilibrium surface Fermi level  $(E_f^*)$  $\tilde{}$  0.2 eV). These results are consistent with the Schottky barrier height measurements of Kajiyama et al. [115]. It is also consistent with the barrier height measurements for p-type  $Ga_{0.47}In_{0.53}As$  as reported by Veteran et al.[240] and  $E_f^* \approx 0.2 \text{ eV}$ reported by Mullin and Wieder [158]. Based on their theoretical calculations, Allen and Dow [3] predicted that the antisite defect In<sub>As</sub> produces a donor level  $E_{ds} \approx 0.7$  eV and the antisite defect In<sub>As</sub> is associated with a donor level  $E_{ds} \approx 0.65$  eV. They calculated density of the surface donor and surface acceptor concentrations for zero gate bias, from C-V and galvanomagnetic measurements.  $N_{ds} \simeq 5 \times 10^{16}$  and  $N_{as} \simeq 10^{15} m^{-2}$  were obtained.

The value of N<sub>ds</sub> thus obtained is smaller by more than one order of magnitude and that of  $N_{as}$  is smaller by nearly two order of magnitude in comparison with the corresponding values for InP. The Fermi level pinning position within 0.2 eV of the conduction band minimum was obtained for both n-type and p-type Ga0.47 In0.53 As. This is similar to that of InP. The low density of interface state are factors of significance for MISFET applications of InGaAs. Mullin and Wieder [158] reported that low temperature annealing of MIS-structure decreases density of sruface acceptor and allows the displacement of the surface potential over a substantial portion of the bandgap in Ga0.47In0.53As MIS-structure with Al203 dielectric layers. Similar results were obtained by Kaumanns et al.[117] and Shinoda and Kobayashi [203] for Al<sub>2</sub>O<sub>3</sub>-Ga<sub>0.47</sub>In<sub>0.53</sub>As MIS-system. Interface state density variation within the bandgap is U-shaped. Annealing brodens the minimum and reduces its value by one order of magnitude as compared to that of virgin speciman.

### 2.2.2 Drain Current Drift

An important requirement of a MISFET operation is that the inversion charge density is time invariant under dc bias condition. In practice, however, most III - V semiconductor MISFETs exhibit a gradual decay in drain current with time, even under dc bias condition. This phenomenon is known as the drain current drift (DCD).

The first discussion of drain current drift was provided by Fritzsche [64]. He interpreted the change in the channel conductivity with time in inversion-mode operation of MISFET in

ΔV

terms of electron tunneling into traps distributed throughout native oxide. The density of oxide traps was assumed to increase abruptly above a few kT/q of the InP conduction level minimum. This explains the temperature dependence of the drain current drift. Van Staa et al.[238] interpreted their constant capacitance deep level transient spectroscopy ( CC DLTS } measurements in terms of spatial and energetic distribution of traps within the native oxide. The traps were assumed to be distributed both spatially and energetically within the InP-bandgap. Electrons from the conduction band were captured by the traps via tunneling while emission occurs by two-stage process involving first tunneling and then a thermally activated transition.

For an Al<sub>2</sub>O<sub>3</sub>-III - V compound semiconductor system, Okamura and Kobayashi [167,168] proposed a model that indicate one trapping level in the synthetic dielectric  $Al_2O_3$  layer and a second trapping level located in the native oxide. Tunneling into the former is considered the primary transport mechanism with a long time constant and this trap which is located below the Fermi level, is presumed to be insensitive to temperature. The trap in the native oxide is above the Fermi level; it is presumed to be temperature dependent. Thus according to this model, the elimination of the native oxide should reduce the contribution of these traps. These assumptions were confirmed by their experimental data. Using HCl to etch and remove the native oxide prior to the deposition of the synthetic dielectric, they were able to reduce the trap induced instability. Kobayashi et al. [121] reported that by first oxidizing the InP surface and then depositing the Al<sub>2</sub>O<sub>3</sub> gate dielectric layer also led to a

reduction in drift.

Lile and Taylor [132] employed drain current drift model [167,168] to analyse 'their MIS-systems and estimated an activation energy of 16 MeV, which is in good agreement with that obtained by Okamura and Kobayashi [167,168]. Wager et al. [242] carried out an extensive study of dielectric-InP interface. Based on the results of these studies Goodnick et al.[77] developed an analytical model. The model illustrates occurance of thermally activated tunneling of electron within the InP conduction band into an In<sub>2</sub>O<sub>3</sub> conducting layer. The layer of In<sub>2</sub>O<sub>3</sub> is seperated from the InP by a wider gap InPO4.

Hasegawa and Sawada [88,89] developed an interface state band (ISB) model to account for various dynamic properties of compound semiconductor-insulator interfaces. They suggested the formation of an amorphous, nonstoichiometric layer at the semiconductor surface and the interface states associated with this layer are responsible for many of the anomalous dynamic properties of III - V compound semiconductor MIS devices.

Van Vechten and Wager [239] suggested that in InP MIS devices wafer processing P-vacancies  $(V_p)$  are induced near the interface. They concluded that these vacancies are responsible for the observed drift in drain current. It was also pointed out that from one of the four nearest neighbours an In atoms could hop into the  $V_p$ , thereby annihilating the  $V_p$ . As a consequence a new defect complex consisting of an In vacancy and an antisite defect is created. As electrons are required for each annihilation, electrons are trapped in the process. This loss of electrons from the channel results in drain current drift. Wilmsen et al.[257] and Geib et al.[73] suggested that traps located within deposited dielectric layers are responsible for drain current drift. Hence insulators or deposition techniques which produce insulators with traps within or near the InP conduction band are not desirable for MIS device applications. Geib et al.[73] studied  $SiO_2$ -InP systems. The interfaces were prepared by various techniques. They found no detectable traps in  $SiO_2$ -InP system which could cause drain current drift. On this basis  $SiO_2$  seems to be a better choice than  $Si_3N_4$  and  $Al_2O_3$ .

Shinoda and Okamura [202,206] reported experimental studies on n-channel InGaAsP MISFETs with  $Al_2O_3$  as dielectric layer. The dielectric was deposited by CVD using aluminium triisopropoxide. The current drift behaviour of the InGaAsP MISFETs exhibited almost the same form as that for InP MISFETs, which has been attributed to channel electron trappings. The dominant trapping centers appears to be located in an InP-native oxide surface layer and in the CVD- $Al_2O_3$  gate insulator. These studies indicated that it is quite likely that the current drift in InGaAsP MISFETs stems from the same origin as that for InP MISFETs.

Fritzsche et al.[66] were the first to report on the behaviour of  $Ga_{0.47}In_{0.53}As$ -dielectric interface. Their studies indicated sufficiently low electron trap densities which is in the range of  $10^{16}$  m<sup>-2</sup>eV<sup>-1</sup>. Fritzsche et al.[65] also reported interfacial properties of  $Ga_{0.47}In_{0.53}As$  and CVD-SiO<sub>2</sub> deposited with HCl addition at 310 - 340 <sup>O</sup>C. A drain current drift of approximately 15 % was observed for the first 1000 s. This is

less pronounced than in similar InP MISFETs (~30 %). Fritzsche et al. [65] attributed this to electron tunneling into interfacial layer. The interface state density near the conduction band edge was found to be negligibly small, while in the bandgap center a high density of donor traps was obtained as in case of InP MIS-system. Gardner et al. [71] also studied drain current drift Ga0 47 In0 53 As MISFETs which were fabricated by in n-channel using low temperature deposited SiO2. They observed annealing in hydrogen at 300 <sup>0</sup>C for several hours substantially improves the interface properties. Interface state densities of about 5 - $7 \times 10^{14} \text{ m}^{-2} \text{ev}^{-1}$  were measured near flat-bands. The fixed oxide charge density was  $4 \times 10^{14}$  m<sup>-2</sup>. The 1 MHz C-V curve had a clockwise hysteresis at room temperature of about 0.6 V. They developed non-self-aligned gate MESFETs in which anomalous inversion layer was found with negative gate bias. The drain current drifts with time and the drain current-time curve indicates that there are possibly three time constants involved. This agrees with the model of Shinoda and Kobayashi [205] in which there is a donor trap below the Fermi level in addition to the two acceptor like traps above the Fermi level. They also suggested that some of the drain current instabilities may be due to charge injection, trapping and space charge buildup within a leaky dielectric. Furthermore, the ion-implanted self-aligned gate MISFETs showed minimum (less than 2 %) drift in drain current and insignificant anomalous inversion layer formation, giving very encouraging results. The reason for the dramatic improvement in drain current drift for the ion-implanted self-aligned gate devices are not as yet understood. This requires further study to elucidate the mechanism involved.

Selders and Beneking [195] reported the drift behaviour of GaInAs n-channel inversion-mode MISFETs with CVD-SiO2 gate dielectric layer. They abserved that rapid thermal cycle with a maximum temperature of 700 <sup>0</sup>C reduces the short-term drift, for times up to 10 s. The instabilities for the time region 10 and 10<sup>4</sup> s are not affected by the annealing step. A reduction of the oxide deposition temperature down to 250 <sup>0</sup>C results in improved stability with only 5 % reduction in drain current after 10<sup>4</sup> s of operation. Splettstosser and Beneking [214] dealt with observed increase in drain current in n-channel inversion-mode GaInAs MISFET at negative gate bias. They were of the opinion that the increase of drain current for a negative gate bias could be caused by the omission of electrons from donor like traps located in the residual native oxide. Due to increase of positive charge at the interface, the drain current increases. For a positive applied bias, traps at interface are filled with electrons. This leads to a decrease of positive charges at the interface, and consequently drain current decreases. From the shift in threshold voltage a total saturated captured charge at the interface of  $10^{15} \text{ m}^{-2}$  after  $10^5$  s was estimated.

Thus for III - V compound MISFETs, large number of models have been discussed to explain drift in drain current. Briefly speaking, it is possibly due to native oxide, distributed traps, discrete traps and traps in insulating layer. The native oxide which is present at the semiconductor-insulator interface, may have been intentionally formed but more often results from the unintentional growth during device processing. There is no general agreement whether a native oxide is an advantage or a liablity. Pande and Gutierrez [171] suggest that native oxide

4.)

improves device performance, at the same time Okamura and Kobayashi [167,168] eliminate the native oxide to improve device performance. Therefore, at this stage of III - V compound MISFET development, there is no general agreement over the accuracy of the models reported in literature so far. The topic of drain current drift on III - V MIS-structures requires detailed study for better understanding and its elimination.

# 2.3 III - V SEMICONDUCTOR MIS-TECHNOLOGY

As mentioned earlier, options available for the development of high-speed MISFET technology critically depends on the fundamental surface and interfacial properties of the binary,quaternary and ternary III - V compounds. The basic interface requirements are that it must be possible to accumulate electrons at the interface, these electrons must remain in the channel and not be trapped and they must travel with high velocity under the gate and with high mobility in the channel. Considering these important MIS requirements, various alloy and dielectric growth techniques suitable for III - V compound semiconductors have been tried by many authors. This section reviews these activities.

#### 2.3.1 Semi-Insulating Substrates

The prospects for a VLSI device technology based on the properties of III - V compound MISFETs are enahanced by the availability of semi-insulating GaAs and InP substrates. Pruniaux et al.[181] reported Cr-compensated GaAs substrate for MIS device applications. Mullin et al.[157], Antypas [4] and

**6** - 4

Henery and Swiggard [93] reported preparation of SI-InP from liquid phase encapsulation Czochralski (LEC) growth using boric oxide as an enacapsulant and Cr as a compensating impurity. Mizuno and Watanabe [154] have shown that Fe-compensated SI-InP has larger resistivity than Cr-doped InP. The SI-substrates are expected to provide isolation between devices on the same chips and such isolation appears adequate for GaAs MSI it is likely to be less than satisfactory for LSI and VLSI unless sidegating between adjacent FETs is eliminated. This interaction between adjacent FET depends on the type, distribution, density and time constant of electron traps in the SI-substrates and on their homogeneity and distribution following post ion-implatation annealing. When SI-GaAs and InP are used as substrate, lattice matched  $In_{1-x}Ga_xAs_vP_{1-v}$  alloy can be grown whose bandgap spans the energy range between 0.6 < $\lambda$  < 0.9 µm on GaAs and 0.95 < $\lambda$  < 1.7 µm on InP substrates.

## 2.3.2 Growth of III - V Compound Semiconductors

The development of a device technology requires high quality device grade material. For semiconductors these requirements are more stringent than any other materials. Two important requirements are that the semiconductor must be available in a single crystal form and it should be of high purity. Over the years several methods of growing III - V compound semiconductors have been developed. Full advantage of these techniques are taken for growing semiconductors for the fabrication of III - V compound semiconductor MISFETs. The most commonly used methods are (i) Liquid Phase Epitaxy (LPE) (ii) Vapor Phase Epitaxy (VPE) (iii) Molcular Beam Epitaxy (MBE). The

applications of these methods are briefly discussed in the following paragraphs.

(i) Liquid Phase Epitaxy - LPE growth of GaAs depends for its operation on the fact that the solubilities of As in Ga-rich solution decreases with increase in temperature. LPE growth of GaAs was first reported by Nelson [161] using tipping technique. In this technique growth is initiated by tipping the furnace containing growth tube and contents so that melt covers the substrate and is terminated by tipping the furnace back to its original position. Rupprecht [183] reported dipping technique for LPE growth of GaAs. In this technique, growth is initiated by lowering the holder to immerse the substrate in the solution and is terminated by raising the holder to its original position. These techniques are not suitable for growing multilayer structures. Panish et al.[173] reported multiwell graphite sliding boat arrangement for growing multilayer structure. [5], Nahory et al.[168], Sankaran Antypas and Moon et al.[187,188] and Pollack et al.[180] reported growth of InGaAsP and InGaAs layers on SI-InP substrate. The grown crystals are not delequescent and are chemically stable in the atmosphere. For these compounds surface oxidation is also a lesser problem than that for crystals containing Al. Therefore, complicated structures can be prepared by a two step LPE growth and/or selective etching technique. However, with LPE techniques to growing reproducible InP and InGaAsP alloys having low carrier concentration level  $(10^{21} \text{ m}^{-3})$  is still an unsolved problem. LPE technique is simple and inexpensive. Its drawbacks include growth problem with InGaAsP alloys for wavelength greater 1.4 µm. Furthermore, non-uniform growth, melt carry over and terrace

formation are some of the problems yet to be solved.

(ii) Vapor Phase Epitaxy - Shaw [199,200] Olson and Zamerowski [169], Genter and Cadoret [74] and Heyen and Balk [95,96] reported growth of GaAs layers by chloride transport technique. The trichloride and hydride processes are both variations of chloride transport system in which Ga is transported in the form of chloride of gallium and reacted with arsenic. The surface morphology of the grown layers is superior. to that produced by LPE growth. Sugiyama et al. [217], Enda [57], Hyder [106], Hyder et al. [107], Susa et al. [219] and Vohl et al.[241] reported growth of InP, InGaAsP and InGaAs layers on SI-InP. The process has demonstrated good thickness compositonal uniformity, flexible control of alloy composition and ability to scaled up for mass production. Its drawbacks be include . difficulties in growing compounds with Al and Sb contents potential for hillock, haze formation and interfacial decomposition during 'preheat' stage.

Low Pressure Metal Organic Chemical Vapor Deposition -MOCVD growth of GaAs involves the pyrolysis of a vapor phase mixture of arsenic and triethylgallium (TEG) or trimethylgallium (TMG). Free Ga atoms and arsenic molecules thus formed and these components recombine on the substrate surface to form GaAs. Bass and Oliver [13], Manasevit and Simpson [135], Duchemin et al. [51] and Hersee and Duchemin [94] reported growth of GaAs layers by MOCVD. Manasevit and Hess [134], Yoshino et al.[266] and Hirtz et al.[101,102] reported growth of  $In_{1-x}Ga_xAs_yP_{1-y}$  layers on SI-InP by metal organic chemical vapor deposition. This deposition process is based on the pyrolysis of alkyls of group III element in an atmosphere of the hydrides of group V elements, is a widely applied growth technique for the preparation of a wide range of III - V materials and heterostructures such as InAs, InP, InGaAsP and InGaAs on InP. The low pressure growth offers an improved thickness uniformity and compositonal homogeniety in addition to the suppression of autodoping memory effects. This, coupled with the reduction of parasitic decomposition in the gase phase, allows the growth of a high purity and good quality material over a large surface area for growth. Its main drawbacks are the use of toxic gases and relatively slow growth rate.

(iii) Molecular Beam Epitaxy - Cho[32], Cho and Arthur [33] and Wood [261] reported growth of GaAs layers by the impingement of directed, thermal energy atomic or molecular beams on a crystalline surface under ultra-high vacuum conditions. Chang et al.[24], Wood [261], Foxon and Joyce [62] and Cheng et al. [28,29] reported growth of  $In_{1-x}Ga_xAs_yP_{1-y}$  layers on SI-InP with special attention to the problems associated with background gas and non-congruent sublimation, interface exchange and strain induced interdiffusion. This growth technique has low temperature and excellent thickness control, expensive ultra-high vacuum requirement and difficulty of growing III - V compounds containing phosphorus.

#### 2.3.3 Ion-Implantation

The most common technique of doping an elemental semiconductor is diffusion of impurity which is a high temperature process. Such a process does not suit a III - V

**.**...

compound semiconductor as the group V element tends to undergo outdiffusion from the surface of the semiconductor. This results in vacancies and antisite defect near the surface. An useful alternative to high temperature diffusion is the implantation of energetic impurity ions into the semiconductor. In this process a beam of impurity ions is accelerated to kinetic energies ranging from several keV to several MeV and is directed on the surface of the semiconductor. As the impurity atoms enter the crystal, they give up their energy to the lattice by collisions and finally come to rest at some average penetration depth, called the range' which depends upon impurity and 'projected its implantation energy.

ىر ب

The most important application of ion-implantation is in the n- or p-type doping of the material for fabricating semiconductor devices and integrated circuts. N-type doping of GaAs by ion-implantaion can be achieved by doping ions either column VI elements ( Se, Te, S ) or column IV elements (Si, Sn). Davies et al.[42], Eisen and Welch [54], Eisen et al.[55], Gamo et al.[67] and Inada et al.[109] reported implantaion of Se, Te and S ions in GaAs. For the implantated ions to become electrically active they must occupy substitutional lattice sites, but since GaAs is a binary compound this introduces the extra complication of placing the implanted ions on the correct sublattice. It was observed that for high dose (  $>10^{18}$  ions m<sup>-2</sup>), the implantation of Se, Te and S must be carried out into heated substrates ( > 150 <sup>0</sup>C) for the dopants to be substitutionally located following post-implantation annealing. Sze and Irvin [222], Miyazaki and Mimura [152] and Tandon et al. [227] reported implantation of Si ions in GaAs. Si and Sn impurity atoms behave

in a different manner since in order to act as donor atoms they must occupy gallium sites. Woodcock et al.[262] and Donnelly et al.[49] reported that implantaion of Si<sup>+</sup> at elevated temperatures results in a smaller increase in doping efficiency than is observed for column VI dopants. Woodcock et al.[262] also observed that Sn was found to behave like group VI ions showing substantial increase in electrical activity after 'hot' implantation.

Nishioka and Ohmachi [163] reported the implantation of Si as n-type dopant in InP. Donnelly and Ferrante [47] and Davies et al.[41] observed good activation of low doses of implanted dopants but activation decreased as the implanted dose is raised above  $10^{18}$  m<sup>-2</sup>. They also observed that the maximum electron concentration available in InP by implantation are about 2-3 times larger (i.e.  $10^{25} \text{ m}^{-3}$ ) than those obtained in GaAs. The electron mobility in samples implanted at elevated temperatures (200  $^{0}$ C) is about a factor of 2 higher than those measured in samples implanted at room temperature. Implantation at 200  $^{0}$ C also gives broadening of electron concentration profile in comparison to that observed for samples implanted at room temperature with  $10^{19}$  m<sup>-2</sup> doses of silicon. Donnelly and Armiento [46] reported the use of Be as p-type dopant in InP and measurements on Be implanted InP suggest that the diffusion behaviour is similar to that observed in InGaAs and excessive diffusion is observed when Be concentration exceeds  $3 \times 10^{24}$  m<sup>-3</sup>. Law et al. [122] and Donnelly and Armiento [46] reported the use of Be as p-type dopants in GaInAsP and it may be possible to achieve hole concentration as high as  $(2 - 3) \times 10^{24} \text{ m}^{-3}$ .

Ion-implantation has advantages that it can be done at low temperature, implanted-ions can be blocked by metals or photo resist layers and very shallow doping levels can be achieved by this method. Ion-implantation has the major advantage that precise control of impurity concentration is possible. Since the ion beam current can be measured accurately during implantation, a precise quantity of impurity can be added. The distribution of impurities about the projected range is approximately Gaussion. A uniformly doped region can be created by performing several implantation at different energies. The control over impurity level, along with the impurity of the implant over the wafer surface, make ion-implantation praticularly attractive for the fabrication of integrated circuits.

During ion-implantation in III - V compound alloys, there are chances of lattice damage which results from collision between ions and the lattice atoms. However, most of this damage can be minimized by heating the crystal after ion-implantation. This process is called annealing.

In III - V compound alloys during implantation performed at elevated temperature elements of group V dissociate. In GaAs and InP, substantial vaporization of the As or P can occur at the temperatures required for post-implantation annealing. This dissociation may be prevented or minimized by encapsulating the semiconductor wafer with a suitable material or by maintaining an overpressure of the volatile constituent from the wafer. Harris et al.[82], Foyt et al.[63] and Eisen [53] have used  $Si_3N_4$ ,  $SiO_2$ and AlN as encapsulants on GaAs. Eisen [53] also suggested that the activation of high-speed of the group VI n-type dopants

J J

(S, Se and Te) has been found to be strongly affacted by the choice and method of deposition of the encapsulating material on GaAs. Donnelly and Hurwitz [48], Gleason et al.[75] and Nishioka and Ohmachi [163] used phosphosilicate glass ( PSG ),  $\text{Si}_3\text{N}_4$  and  $\text{SiO}_2$  as encapsulants for InP. Shinoda and Kobayashi [202] used  $\text{CVD-SiO}_2$  for encapsulation in InGaAsP. Woodall et al.[260] and Doerbeck et al.[44] reported suitable methods for maintaining overpressure to prevent loss of group V constituents during implantation.

The temperature required for post-implantation annealing varies with particular III - V material. Donnelly [45], Eisen and Welch [54] and Eisen et al.[55] reported that annealing temperature for ion-implanted GaAs is usually between 800 and 900  ${}^{0}C$ , although both higher and lower temperature have been used in some special cases. Eisen and Welch [54] and Eisen et al.[55] reported that annealing temperature has been maintained between 700 to 750  ${}^{0}C$  for successful ion-implantation of InP. Law et al.[122] reported that annealing temperature was maintained at 560  ${}^{0}C$  for Be<sup>-</sup> implanted GaInAsP.

### 2.3.4 Dielectric Growth Techniques

The most remarkable features of Si MIS-technology are the fortuitous native oxide  $(SiO_2)$  and the electrical properties of the  $Si/SiO_2$  system. An attractive feature of a native oxide-semiconductor system is the homomorphic nature of the interface. Such an interface is free from mismatch and associated trap states. Since the oxidation process results in the formation of a subsurface interface, the contamination problems are avoided

or at least minimized. In view of these advantages, earlier III -V semiconductor MIS-technology relied on the use of native oxides grown by wet anodization, thermal oxidation, plasma anodization and so forth. The native oxides thus grown on III v semiconductor were studied by Hartnagel [83], Sugano and Mori [216], Hasegawa et al. [85] and Wilmsen and Meiners [255]. Unfortunately, the native oxides of the III - V semiconductors be neither stoichiometric nor were found to spatially homogeneous. Native oxides of GaAs are composed of Ga<sub>2</sub>O<sub>3</sub> and As<sub>2</sub>O<sub>3</sub>, while those of InP are constituted by  $In_2O_3$  and  $P_2O_5$ . Such heterogeneous dielectrics display interfacial polarization due to accumulation of charge at phase boundaries. The III - V native oxides also allow ionic transport and are conductive. Some of these native oxides are highly porous and hygroscopic, which result of makes them unstable. As а these undesirable characterization, the native oxides are not suitable for III - V semiconductor MIS-technology.

An alternative approach of forming a dielectric on III -V semiconductor is deposition of a metal, such as aluminium and subsequently oxidation of the metal is a wet anodization, plasma oxidation or some other technique [15,98,190]. The dielectrics produced by this approach yielded some success. However, these dielectrics are of poor quality and it is difficult to terminate oxidation at the metal-semiconductor interface.

The deposition techniques have given the most successful results so far. Chemical vapor deposition ( CVD ) has been most widely used for dielectric growth on the III - V compound semiconductors. The most straight forward method of this family

is thermal CVD or pyrolysis where reactive gases are introduced into a heated chamber in which the substrate is located, An important requirement of treating a III - V semiconductor is maintaining a low substrate temperature. This is to avoid loss of group V constituents. This constituent can, however, be avoided by maintaining a group V overpressure. Peters [178] suggested two alternatives, plasma-enhanced and photo-enhanced CVD techniques. These methods rely upon excitation of gas species to enhance the reaction and thus permit lower temperature for growth and to minimize the surface damage by plasma. For such a process it would be desirable to seperate the growth zone from the vicinity of the ionized gas. Woodward et al.[263] used various combinations of SiH<sub>4</sub>, N<sub>2</sub>, NH<sub>3</sub> and H<sub>2</sub> as reactant gases for Si<sub>3</sub>N<sub>4</sub> deposition. For the SiO<sub>2</sub> deposition, tetraethoxysilane ( TEOS ) vapor was decomposed in an oxygen plasma. Meiners [142] reported indirect plasma-enhanced CVD technique which is convenient and appropriate for low temperature and low energy growth of a variety of dielectrics on III - V semiconductors.

Okamura and Kobayashi [167,168] reported deposition of  $Al_2O_3$  gate insulator on InGaAsP wafer at 350  ${}^{0}C$  by conventional CVD technique using alumunium triisopropoxide  $[Al(OC_3H_7)_3]$  in N<sub>2</sub>. Gardner et al.[71] reported deposition of SiO<sub>2</sub> layers on InGaAs by photo stimulated reaction of N<sub>2</sub>O and SiH<sub>4</sub> at substrate temperature of 170  ${}^{0}C$ . Such a low temperature process minimizes the formation of native oxide on III - V semiconductor surface during SiO<sub>2</sub> deposition. Cameron et al.[23] reported that  $Al_2O_3$  film shows higher dielectric constant both at higher and lower (100 kHz and 10 Hz) freqencies in comparison with SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>. On the other hand, Si<sub>3</sub>N<sub>4</sub> shows higher resistivity and

breakdown field under optimized conditions for deposition.

#### 2.4 III - V SEMICONDUCTOR MISFETS