## **ANALYSIS OF INTERCONNECT PERFORMANCE**

### **USING FDTD TECHNIQUE**

By

**SHAILESH MITTAL**

Enrolment no.: 10550010

A dissertation submitted in partial satisfaction of the Requirements for the degree Of Master of Technology

in

**Solid State Electronic Materials**

Dissertation Supervisor: Dr. K.L. Yadav Dr. B. K. Kaushik

#### DEPARTMENT OF PHYSICS INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247667 (INDIA) April, 2012

#### **CANDIDATE'S DECLARATION**

I hereby declare that the work presented in this seminar report entitled "Analysis of Interconnect Performance using FDTD Technique" for the partial fulfillment of the requirements for the award of the degree of "Master of Technology" in "Solid State Electronic Materials" is submitted in the Department of Physics, Indian Institute of Technology Roorkee. This report is authentic records of my own work carried out under the guidance of Dr. K. L. Yadav (Department of Physics) and Dr. B. K. Kaushik (Department of Electronics & Computer Engineering), Indian Institute of Technology Roorkee.

The matter embodied in this report work has not been submitted for the award of any other degree.

Date: 3/04/12 Place: Roorkee

Sharles Hul Shailesh Mittal

#### **CERTIFICATE**

This is to certify that the above statement made by the candidate is correct to the best of my knowledge and belief.

i

Dr. K. L. Yadav Assistant Professor Department of Physics IIT Roorkee 247667

Sha she

Dr. B.K. Kaushik Assistant Professor Department of ECE IIT Roorkee 247667

Date ... 30/April/2012

Date.....

#### **CANDIDATE'S DECLARATION**

I hereby declare that the work presented in this seminar report entitled "Analysis of Interconnect Performance using FDTD Technique" for the partial fulfillment of the requirements for the award of the degree of "Master of Technology" in "Solid State Electronic Materials" is submitted in the Department of Physics, Indian Institute of Technology Roorkee. This report is authentic records of my own work carried out under the guidance of Dr. K. L. Yadav (Department of Physics) and Dr. B. K. Kaushik (Department of Electronics & Computer Engineering), Indian Institute of Technology Roorkee.

The matter embodied in this report work has not been submitted for the award of any other degree.

Date: 30/04/12\_ Place: Roorkee

Shailesh Mittal)

#### **<u>CERTIFICATE</u>**

This is to certify that the above statement made by the candidate is correct to the best of my knowledge and belief.

Dr. K. L. Yadav Associate Professor Department of Physics IIT Roorkee 247667 Dr. B.K. Kaushik Assistant Professor Department of ECE IIT Roorkee 247667

Date.....

Date.....

#### ACKNOWLEDGEMENT

It gives me great pleasure to take this opportunity to thank and express my deep sense of gratitude to my guide Dr. B. K. Kaushik, Assistant Professor, Department of Electronic and Computer Engineering, and Dr. K. L. Yadav, Associate Professor, Department of Physics, Indian Institute of Technology Roorkee, for sharing his industry experience and valuable guidance. It is under my professor's valuable tutorship that I have learnt different aspects of research study.

I would like to thank research scholars of Semiconductor Devices and VLSI Technology group and the VLSI Lab staff for their help in learning HSPICE and MATLAB tool and installation of various tools for carrying out my dissertation work.

I am thankful to Prof. Padam Kumar, Head of ECE Department and Prof. A. K. Jain Head of Physics Department for providing me the necessary facilities to complete this work. I would also like to thank research scholars of ECE department for their helpful discussions and suggestions about my project work without which this work would always remain incomplete.

Shailesh Mittal

#### ABSTRACT

Device scaling in deep Submicron technology shrinkage the spacing between adjacent interconnect, which leads to increase coupling effect between wires. Continuous device scaling much improved the gates delay. However, interconnect delays have not scaled in that proportion Therefore a need for accurate and computationally effective models in the early stages of the chip design process to assess or optimize issues affecting these interconnects becomes necessary.

This thesis presents the description of a finite difference time domain (FDTD) method that is intended for estimation of voltages and currents on transmission line. Interconnect performance such as crosstalk, delay, crosstalk induce delay are analyzed using FDTD technique. For motivation, analytical results based on proposed model is also compared with HSPICE simulated result. Analytical results are observed in closed agreement with HSPICE results, which proves the validity of proposed model.

### **CONTENTS**

3.1.1 Working with FDTD

| CANDIDATE'S DECLARATION    | i   |

|----------------------------|-----|

| CERTIFICATE                | i   |

| ACKNOWLEDGMENTS            | ii  |

| ABSTRACT                   | iii |

| CONTENTS                   | iv  |

|                            |     |

| 1. Introduction            | 1-4 |

| 1.1 Deep Submicron Effects | ſ   |

| 1.1 Deep Submicron Effects | 1 |

|----------------------------|---|

| 1.2 Problem Statement      | 3 |

| 1.3 Thesis Organization    | 4 |

| 2. R   | eview of Literature      |  | 5-13       |

|--------|--------------------------|--|------------|

| 2.1 In | terconnect Parasitic     |  | 5          |

| 2.1.1  | Interconnect Resistance  |  | 5          |

| 2.1.2  | Interconnect Capacitance |  | 7          |

| 2.1.3  | Interconnect Inductance  |  | <b>9</b> · |

15

2.2 Different approaches for analysis of Interconnect Performance102.2.1 Interconnect Modeling102.2.2 Alpha-power law MOSFET Model122.3 Motivation133. The FDTD Technique14-353.1 Introduction14

3.1.2Strengths of FDTD Technique153.1.3Stability criterion for FFDTD16

iv

| 3.1.4   | Central difference approximation                        | 16 |

|---------|---------------------------------------------------------|----|

| 3.2 FD  | OTD Model                                               | 18 |

| 3.2.1   | Transmission's line equations                           | 18 |

| 3.2.2   | Discretization in Space and Time                        | 19 |

| 3.2.3   | Leapfrog time-stepping                                  | 22 |

| 3.2.4   | Incorporation of boundary condition                     | 23 |

| 3.2.4.1 | Boundary matching at source end                         | 24 |

| 3.2.4.2 | Boundary matching at load end                           | 25 |

| 3.3 FD  | TD Model for Interconnect terminated by Resistive load  | 26 |

| 3.4 FD  | TD Model for Interconnect terminated by capacitive load | 28 |

| 3.5 FD  | TD Model for Interconnect driven by Resistive driver    | 29 |

| 3.6 FD  | TD Model for coupled transmission line                  | 31 |

| 3.7 FD  | TD Model for CMOS-gate driven Interconnect              | 32 |

| 4. Analysis of Interconnect Performance     | 36-44 |

|---------------------------------------------|-------|

| 4.1 Crosstalk Noise                         |       |

| 4.1.1 Functional Crosstalk                  | 37    |

| 4.1.2 Dynamic Crosstalk                     | 38    |

| 4.2 Crosstalk-induce delay                  | 41    |

| 4.3 Effect of Line Resistance Variation     | 42    |

| 4.4 Effect of interconnect length Variation | 42    |

| 4.5 HSPICE Simulation                       |       |

|                                             |       |

| 5. Conclusion and Future Scope              | 46    |

| 5.1 Conclusion                              | 46    |

| 5.2 Future Scope                            | 46    |

.

#### LIST OF FIGURES:

- Figure 1.1: Delay for interconnect.

- Figure 2.1: Parallel-plate capacitance model of interconnect wire.

- Figure 2.2: Fringing field Capacitance.

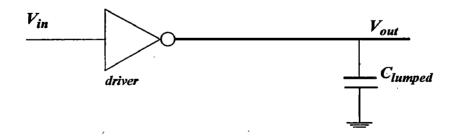

- Figure 2.3: Lumped Capacitor model for interconnect.

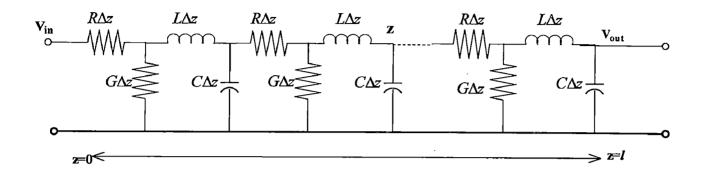

- Figure 3.1: distributed *RLGC* transmission line.

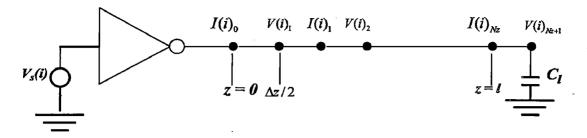

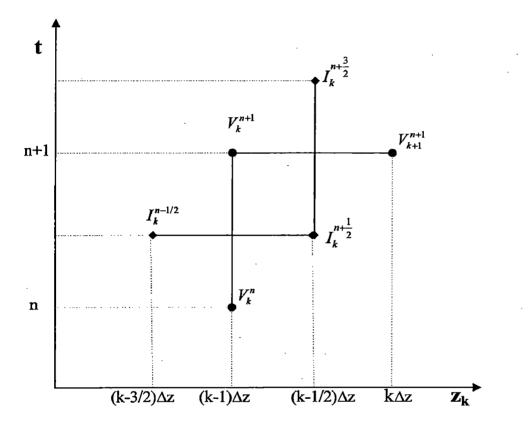

- Figure 3.2: Illustration of the discretization of the  $i^{th}$  line for the implementation of the FDTD.

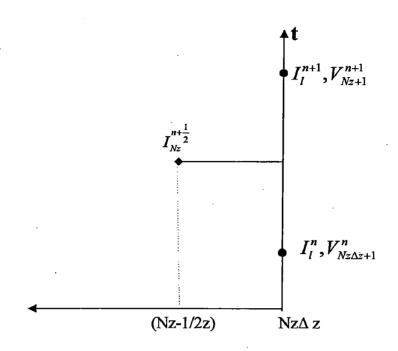

- Figure 3.3: Interlacing the current and voltage solutions in space and time for the FDTD analysis.

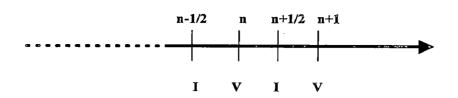

- Figure 3.4: Timeline showing when E and H fields are updated.

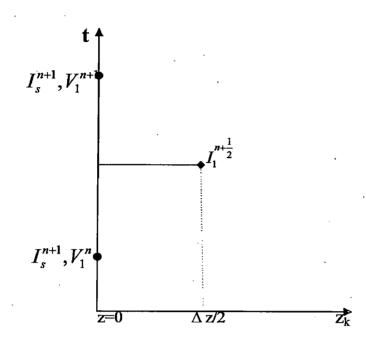

- Figure 3.5: Discretizing the terminal voltages and currents of the line at source end in order to incorporate the terminal constraints

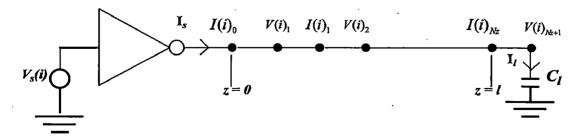

- Figure 3.6: Discretizing of line with source and load current

- Figure 3.7: Discretizing the terminal voltages and currents of the line at load end in order to incorporate the terminal constraints.

- Figure 3.8: Interconnect terminated by Resistance.

- Figure 3.9: Interconnect terminated by capacitive load.

- Figure 3.10: Interconnect driven by Resistive driver.

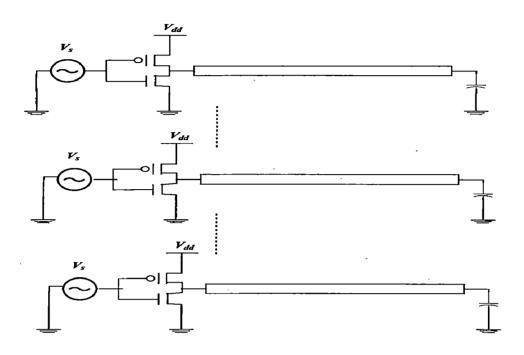

- Figure 3.11: M coupled transmission lines driven by CMOS gates.

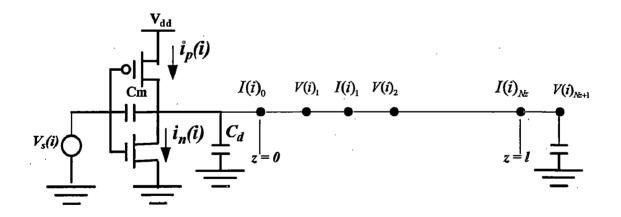

- Figure 3.12: Macro model for CMOS-gate driven interconnect.

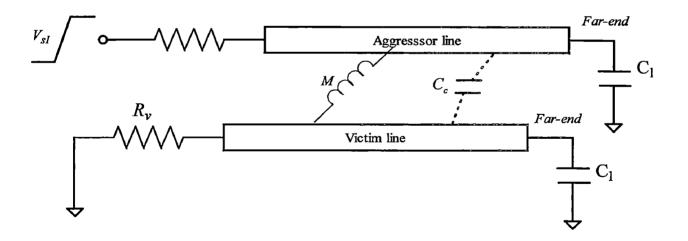

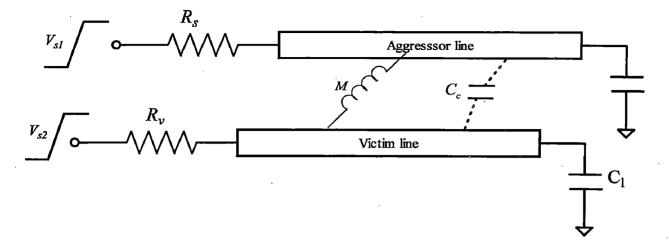

- Figure 4.1: Coupled *RLGC* interconnect configuration for functional crosstalk.

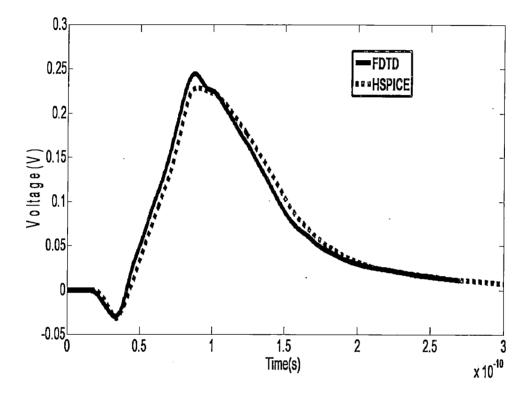

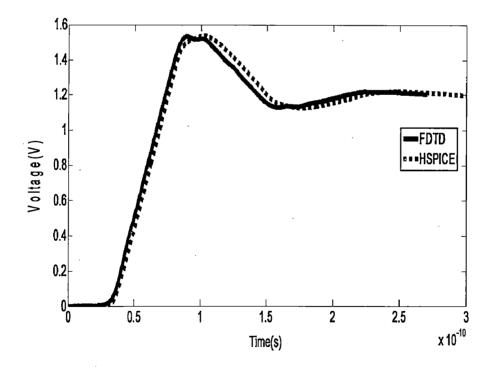

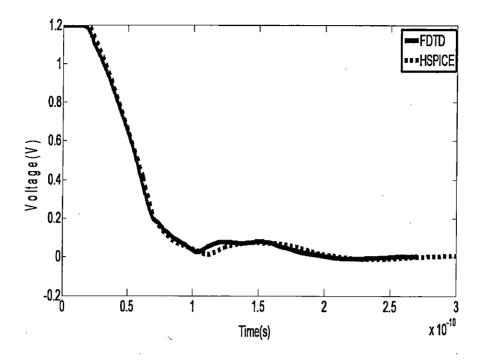

- Figure 4.2: Comparison of SPICE and FDTD generated waveforms at far-end of victim line.

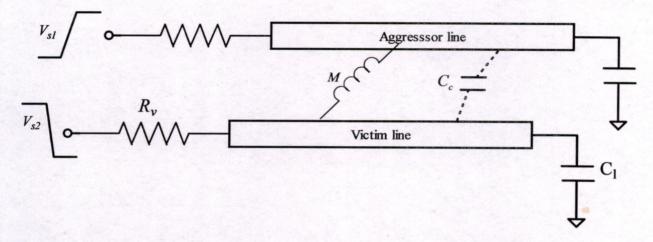

- Figure 4.3: Coupled line configurations for dynamic crosstalk analysis (in-phase switching).

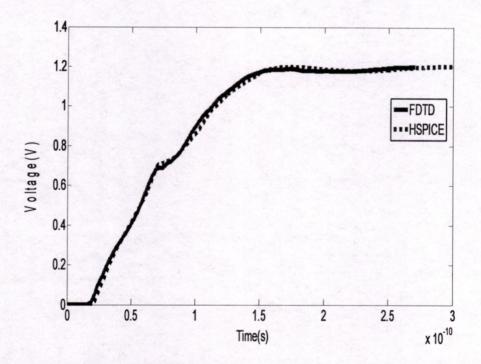

- Figure 4.4: Comparison of SPICE and FDTD generated waveforms at far-end of victim line for under in-phase switching.

- Figure 4.5: Coupled line configurations for dynamic crosstalk analysis (Out-of-phase switching).

Figure 4.6: Comparison of SPICE and FDTD generated waveforms at far-end of aggressor line under out-of-phase switching.

Figure 4.7: Comparison of SPICE and FDTD generated waveforms at far-end of victim line for under out-of-phase switching.

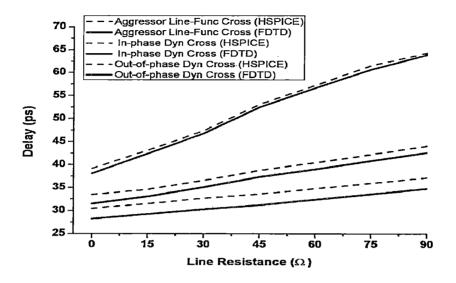

Figure 4.8: 50% Propagation delay variation with line resistance.

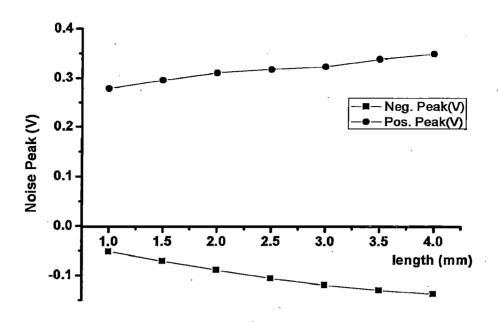

Figure 4.9: Noise Peak variation with interconnect length.

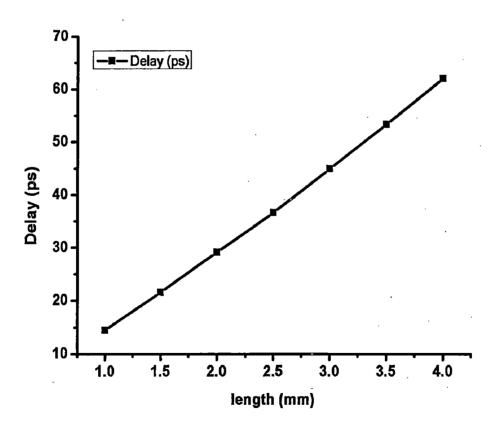

Figure 4.10: 50% delay variation with interconnect length.

#### LIST OF TABLE:

ł

Table 4.1: Delay analysis of functional and dynamic crosstalk with variation in line resistance

# Chapter 1 Introduction

On-chip interconnect system is used for distributing the clock and power supply and connecting signals among circuits. Interconnects in an integrated circuit can be loosely divided into local, intermediate and global interconnects depending on their length, size and metal layer. Local interconnects are the first, or lowest, level of interconnects. They usually connect gates, sources and drain in MOS technology, whereas the semi-global interconnect spanning over large circuits block to connecting devices. Global interconnect span the entire chip connecting the separate functional blocks on integrated circuits. Actually, Global interconnects are used as on-chip interconnect for distributing clock and power signals

In early days, the operating speed of an integrated circuit was limited by speed of a logic gate. Interconnects between the gates were considered as ideal conductors that propagated signals instantaneously and had little effect on circuit operation. However, after introduce of submicron semiconductor devices, this ideal behavior of interconnect is no longer remain adequate [1].

#### **1.1 Deep Submicron Effects**

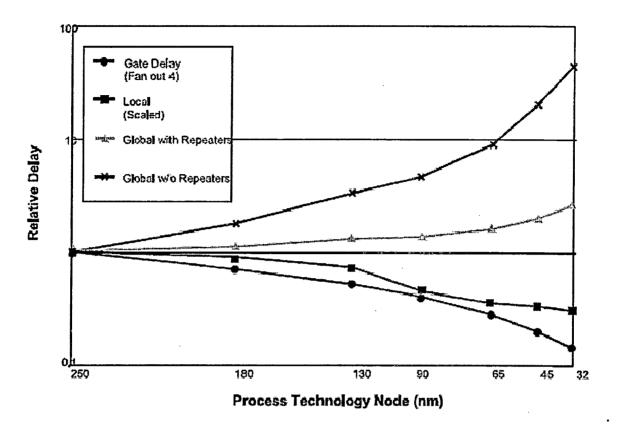

Deep submicron technology build very complicated chips with millions of very fast transistors. Much improvement in chip performance has been due to technology scaling, allowing increased densities at higher clock frequencies. Gate delays which are reduced as their dimensions become smaller. On the other hand, delay of fixed-length wire increases, when its dimensions are scaled [2]. Unfortunately, interconnect delay does not scale with the feature size.

Figure 1.1 Delay for interconnect [3].

Figure 1.1 shows the projections of gate and interconnect delays. The local interconnect is scaled with feature size, while intermediate and global interconnections certainly do not.

For local wires this delay increase is alleviated by the fact that their length is reduced with scaling since they need to connect nearby gates whose sizes diminish with scaling. However, the length of global wires is not scaled with technology since they may need to run across the chip. This has resulted in a growing delay gap between gates and global interconnect.

As the number of devices per unit area increases, interconnection between them must evolve towards a reduced cross-sectional dimension. The reducing cross-sectional dimension leads to more tightly coupled interconnections, and therefore a higher probability of unwanted crosstalk interference between them. Crosstalk noise can affect the circuit performance in two ways, either by disturbing a quiet line, or by changing the response speed of adjacent switching line. The current is injected into quiet line (victim) during the switching of adjacent line (aggressor) is defined as functional crosstalk. On the other hand, dynamic crosstalk appears due to the simultaneous switching at adjacent lines either in same phase or in opposite phase. Both functional and dynamic coupling noises have equal importance due to the following reasons: (1) the first type of crosstalk noise can cause device or logic failure due to unexpected voltage spike, (2) the second type impacts the critical issue of timing by changing the response time.

In addition, the increase in device density forces a reduction in cross-sectional dimensions that increases Resistance of interconnect wire. This increase in Resistance produces a double effect: one hand, adding to the delay, and on the other hand, producing a signal distortion. Device (transistor) driving capability increases as a result of technology scaling. This means higher frequency components in signals are transmitted through interconnections. as chip speed continually increases, the inductance effect of interconnects tends to increase, which will cause ringing at signal rise/fall edge and changes of crosstalk characteristics. In addition, aggressive usage of high-speed circuit families, scaling of power supply and threshold voltages, and mixed-signal integration combine to make the chips more noise-sensitive [4].

#### **1.2 Problem Statement**

The impact of interconnects on circuit performance is ever increasing. No longer interconnects can be treated as ideal wire. Crosstalk, delay, ringing and reflection are just some issues that degrading the time-domain performance of interconnect. Due to these growing delay, signal integrity in interconnects, there has been a shift of focus from devices to wires. This has resulted in a need for novel design tools and models that can be used to analyze and optimize on-chip interconnect.

The investigation reported in this thesis is aimed to develop a finite difference time domain (FDTD) model, for accurate analysis of time-domain performance of interconnect.

3

#### **1.3 Thesis Organization**

This thesis addresses time-domain effects in long on-chip interconnect. More specifically, the focus is on multiple parallel coupled interconnects that are a commonly a part of integrated circuits. The FDTD based model is developed in this thesis for time-domain analysis of coupled interconnect line. Thesis has the following section.

- Chapter 1 introduces the effect of deep submicron technology on Interconnect performance and discusses our research objective.

- Chapter 2 presents different approaches for accurate CMOS-gate driven interconnect. Interconnect modeling and CMOS-gate modeling using alpha-power law model is also discussed.

- Chapter 3 presents a numerical based finite difference time domain, which analytically developed for analysis of interconnect performance.

- Chapter 4 analyze time domain behavior of coupled interconnect based on result obtained through FDTD model. Analytical results also compared with HSPICE simulated result.

- Chapter 5 summarized the work present in this thesis. Future work that can be carried out on this interesting problem is also suggested here.

# Chapter 2 Review of Literature

#### **2.1 Interconnect Parasitic**

As discussed in last chapter, careful and in-depth analysis of the role and the behavior of the interconnect wire in a semiconductor technology is not only desirable, but even essential. With the introduction of deep-submicron semiconductor technologies, this picture is undergoing rapid changes. The parasitic effects introduced by the wires display a scaling behavior that differs from the active devices such as transistors, and tend to gain in importance as device dimensions are reduced and circuit speed is increased. In fact, they start to dominate some of the relevant metrics of digital integrated circuits such as speed, energy-consumption, and reliability [1].

#### 2.1.1 Interconnect Resistance

It is also called line resistance of interconnect. The resistance of a rectangular interconnects having length L and cross section area A can be expressed as:

$$R = \frac{\rho L}{A} = \frac{\rho L}{HW}$$

(2.1)

where the constant  $\rho$  is the resistivity of the material (in  $\Omega$ -m). H and W are height and width of interconnect wire respectively. Aluminum is the interconnect material most often used in

integrated circuits because of its low cost and its compatibility with the standard integratedcircuit fabrication process.

Eq. (2.1) is sufficient at low signal frequencies when the entire cross section of the wire carries the current. However, as the signal frequency increases, the current density starts to fall off exponentially into the conductor. This phenomenon is called skin effect since most of the current is now flowing through the "skin" of the conductor. The skin depth is the depth at which the current density has decreased by a factor  $e^{-1}$  of its value at the surface and is given by:

$$\delta = \sqrt{\frac{\rho}{\pi f \mu}} \tag{2.2}$$

Where f is signal frequency and  $\mu$  is permeability. The onset of the skin effect occurs for frequencies above  $f_s$ , the skin frequency. For micro strip interconnects,  $f_s$  is the frequency at which  $\delta$  equals the interconnect thickness and can be solved for by setting  $\delta = H$  and  $f = f_s$  in equation (2.2), which gives:

$$f_s = \frac{\rho}{\pi H^2 \mu} \tag{2.3}$$

Skin effect decreases the effective cross sectional area that carries the current, which causes resistance to increase. Around 63 % of the total current flows within one skin depth, but one usually makes the approximation that all current flows uniformly within this outer shell of thickness  $\delta$ . Thus, at high frequencies, the AC-resistance per unit length for a micro strip interconnects is given by:

$$R_{ac} = \sqrt{\frac{\rho \pi f \mu}{W}}$$

(2.4)

highly resistive interconnects cause large signal attenuation. As chip complexity and device density increases, wires have to be made narrower, which increases wire resistance according to the basic Eq. (2.1). By making interconnects taller, the cross sectional area of the conductor grows, which helps to lower the resistance.

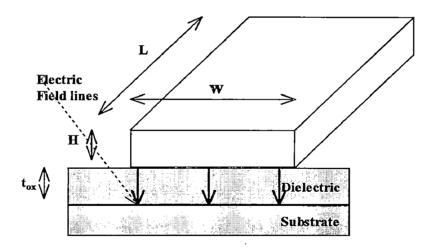

#### 2.1.2 Interconnect Capacitance

Interconnect Capacitance of a wire is a function of its shape, its environment, its distance to the substrate, and the distance to surrounding wires. Consider first a simple micro strip structure in which, rectangular interconnect wire placed above the semiconductor substrate, as shown in figure 2.1. If the width of the wire is substantially larger than the thickness of the insulating material, it may be assumed that the electrical-field lines are orthogonal to the capacitor plates,

Figure 2.1: Parallel-plate capacitance model of interconnect wire.

and that its capacitance can be modeled by the parallel-plate capacitor. For this, the total capacitance of the wire can be approximated as equation (2.5).

$$C_{\rm int.} = \frac{\varepsilon_{\rm ox}}{t_{\rm ox}} WL \tag{2.5}$$

where W and L are respectively the width and length of the wire, and  $t_{ox}$  and  $\varepsilon_{ox}$  represent the thickness of the dielectric layer and its permittivity.

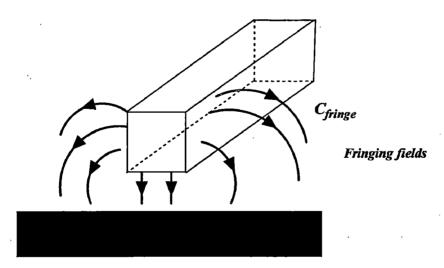

The capacitance between the side-walls of the wires and the substrate, called the fringing capacitance, can no longer be ignored and contributes to the overall capacitance. This effect is illustrated in Figure 2.2. So, capacitance per unit length for the single isolated interconnect wire

can be approximated by:

$$C = C_{pp} + C_{fring} = \frac{W \varepsilon_{0x}}{t_{0x}} + \frac{2\pi\varepsilon_{0x}}{\ln(t_{ox} / H)}$$

(2.6)

Figure 2.2: Fringing field Capacitance.

where  $C_{pp}$  is the "parallel-plate" (bottom area-to-substrate) capacitance,  $C_{fring}$  is the fringing (side-wall-to-substrate) capacitance per unit length. This simplification is only useful for estimating rough capacitance values. In reality, a wire is surrounded by a large number of other wires on the same layer and adjacent layers of the multi-level interconnect hierarchies offered in today processes.

#### 2.1.3 Interconnect Inductance

The most basic definition of inductance originates from a fundamental relation between the voltage, V, and the current, I associated with the loop. A voltage drop is created when the current flow through the loop changes:

$$\Delta V = l \frac{dI}{dt} \tag{2.7}$$

In cases when a conductor is completely surrounded by a homogeneous uniform dielectric, the capacitance, C, and inductance, l, per unit length are related by:

$$lC = \varepsilon \mu \tag{2.8}$$

where  $\varepsilon$  is the dielectric constant and  $\mu$  is the permeability For lossless lines, inductance can also be calculated from capacitance through Eq. 2.9, which describes the speed,  $\nu$ , at which an electromagnetic wave travels through a medium

$$\nu = \frac{1}{\sqrt{lC}} = \frac{1}{\sqrt{\mu\varepsilon}}$$

(2.9)

#### 2.2 Different approaches for analysis of interconnect performance

In the early days of VLSI design, signal integrity effects include interconnect delay, crosstalk, transmission line effects, substrate coupling, power supply integrity, and noise-ondelay effects were negligible because of relative slow chip speed and low integration density. However, with the introduction of technology generations at about the 0.25µm scale and below, there are many significant changes in wiring and electrical characteristics [6]. Interconnect started to be a dominating factor for chip performance and robustness. In Integrated circuit, the signal on interconnect is routed through CMOS driver. There are three approaches for analysis of CMOS-gate driven interconnects.

One approach focuses on CMOS-gate modeling with the load interconnect approximated by a lumped circuit and gate is modeled using alpha-power law model.

#### 2.2.1 Interconnect Modeling

The circuits parasitic of a wire are distributed along its length and are not lumped into a single position. Yet, when only a single parasitic component is dominant, when the interaction between the components is small, or when looking at only one aspect of the circuit behavior, it is often useful to lump the different fractions into a single circuit element. As long as the resistive component of the wire is small and the switching frequencies are in the low to medium range, it is meaningful to consider only the capacitive component of the wire, and to lump the distributed capacitance into a single capacitor as shown in Figure 2.3.

Figure 2.3: Lumped Capacitor model for interconnect.

Delay formulas were developed for CMOS gate driving interconnects line [7], [8]. In which Interconnect is modeled in lumped (C) model and then extended to include the influences of short-circuit current and gate-drain coupling capacitance [9].

On-chip metal wires of over a few millimeter lengths have a significant resistance. The equipotential assumption, presented in the lumped-capacitor model, is no longer adequate, and a resistive-capacitive model has to be adopted. With the resistive component of interconnect becoming comparable to the gate output impedance, modeling of CMOS gate driving resistor-capacitor (RC) line was presented in [10]–[12]. A first approach lumps the total wire resistance of each wire segment into one single R and similarly combines the global capacitance into a single capacitor C. This simple model, called the lumped RC model is pessimistic and inaccurate for long interconnect wires, which are more adequately represented by a distributed RC model. Now, current operating frequencies are reached in GHz range, which make necessary to include inductance effect in interconnect analysis. Kaushik *et al.* [13] has analyzed CMOS gate driving resistor-inductor-capacitor (RLC) line to allow for inductive effect of interconnects.

The second approach performs interconnect analysis by simplifying CMOS driver gate as a resistor. With this linear driver model, the Elmore delay model was first developed for lumped RC lines in [14] and then extended for lumped RLC lines in [15] and [16]. Crosstalk noise models for lumped RC coupled lines were given in [17]–[20]. Bai [20] improved the linear driver model by calculating the effective resistance of victim driver considering the nonlinearity. With the transmission line effect taken into account, Davis proposed a closed-form delay model for a distributed RLC line [21] and a crosstalk model for two and three coupled distributed RLC lines [22]. Based on even-odd mode propagated in lossless transmission lines, a crosstalk model was proposed for two-coupled lossless lines and then modified for low-loss lines to capture noise peak [23].

The third approach cosimulate nonlinear CMOS gates and distributed interconnects. The analysis of distributed transmission lines in the presence of nonlinear elements suffers from the mixed frequency/time problem, which arises from the fact that transmission lines are described by partial differential equations which are traditionally solved in the frequency domain, whereas the nonlinear elements are described only in the time domain [24].

#### 2.2.2 Alpha-power law MOSFET Model

1

There is two main discrepancies with Shockley model. One is Saturation voltage is different from the predicted value. The other is that drain current in the saturation region does not show Shockley's square-law dependence on gate-source voltage. These two discrepancies, that is, the shift of drain saturation voltage and discrepancies in the saturation region *I-V* curve, both come from the velocity saturation effects observed in short-channel MOSFET's [25].

So, a new MOSFET's model, namely alpha-power model is proposed to include the velocity saturation effect in short channel MOSFETs. PMOS and NMOS currents are represented by the alpha-power law MOS model in equation (2.10) and (2.11) respectively.

$$i_{p} = \begin{cases} 0 & V_{s} \geq V_{dd} - |V_{tp}| \quad (off) \\ K_{lp}(V_{dd} - V_{s} - |V_{tp}|)^{\alpha p^{2}} (V_{dd} - V_{1}) & V_{s} < V_{dd} - |V_{tp}| \& \quad (lin) \\ V_{1} > V_{dd} - |V_{Dsat_{p}}| \\ K_{sp}(V_{dd} - V_{s} - |V_{tp}|)^{\alpha p} & V_{s} < V_{dd} - |V_{tp}| \& \quad (sat) \\ V_{1} > V_{dd} - |V_{Dsat_{p}}| \end{cases}$$

$$(2.10)$$

where *lin, sat and off* denote linear, saturation and cut-off regions, respectively. The drain saturation current for PMOS is denoted as

$$V_{Dsat_p} = \frac{K_{sp}}{K_{lp}} (V_{dd} - V_s - |V_{tp}|)^{\alpha_p/2}$$

(2.11)

$$i_{n} = \begin{cases} 0 & V_{s} \leq V_{dd} - \left| V_{tp} \right| \quad (off) \\ K_{\ln} (V_{s} - V_{tn})^{\alpha_{n}/2} (V_{1}) & V_{s} > V_{tn} \& V_{1} < V_{Dsat_{n}} \quad (lin) \\ K_{sn} (V_{s} - V_{tn})^{\alpha_{n}} & V_{s} > V_{tn} \& V_{1} \geq V_{Dsat_{n}} \quad (sat) \end{cases}$$

$$(2.12)$$

The drain saturation current for NMOS and PMOS is denoted as

$$V_{Dsat_{n}} = \frac{K_{sn}}{K_{ln}} (V_{s} - V_{tn})^{\alpha_{n}/2}$$

(2.13)

The parameters of alpha-power law model used are velocity saturation index  $\alpha$ , the transconductance parameters  $K_i$  and  $K_s$ , and threshold voltage  $V_i$ . The subscript *n* and *p* denote for NMOS and PMOS, respectively.

#### **2.3 Motivation**

The main focus of aforementioned research work is towards the functional crosstalk category. But, for complete analysis of crosstalk noise it is necessary to include dynamic crosstalk noise also. A brief discussion of dynamic crosstalk is given by Agarwal *et al.* [23], which is based on decoupling of symmetric coupled line in single one. Furthermore, a dynamic crosstalk noise model based on even-odd mode is also discussed [26], but applicable to lossless (low-loss) coupled lines only that to limited to two lines in number only.

This paper proposes a numerical based FDTD model for accurate analysis of dynamic crosstalk induced glitch and delay in lossy coupled transmission line. This concept can be further extended for multi-transmission lines as well. Non-linear termination in algorithm, lesser numbers of assumptions and accurate accounts of transmission line effects increase the importance of FDTD over other existing methods.

## Chapter 3

## **The FDTD Technique**

#### **3.1Introduction**

Finite-difference time-domain (FDTD) is a popular computational electrodynamics modeling technique. This firstly implemented to solve Maxwell's equation. The time-dependent partial differentials are discretized using central-difference approximations to the space and time partial derivatives. The resulting finite-difference equations are solved in either software or hardware in a leapfrog manner, firstly implemented by Yee *et al.* [20] for Maxwell's equation solution. In this thesis FDTD is implemented on transmission line equation where relative parameters are line voltage (V) and current (I) like as electrical field (E) and magnetic field (H) in Maxwell's equation.

To implement an FDTD solution of transmission's equations, a computational domain must first be established. The computational domain is simply the physical region over which the model will be performed (here, interconnect modeled into *RLGC* transmission line is computational domain with relative parameter V and I). The V and I fields are determined at every point in space within that computational domain. The Line parasitic such as Resistance (R), Capacitance (C), Conductance (G) and Inductance (L) of each cell within the computational domain must be specified. For coupled line configuration the coupling factors such as coupling capacitance ( $C_c$ ) and mutual inductance (M) should be added in computational domain.

Once the computational domain is established a source is specified. The source can be linear or non linear voltage source. Current source can be also used. Likewise for computational domain a termination load is also specified, which is almost capacitor in case of on-chip interconnects. After specifying the load and source, the boundary condition is used at the interference of computational domain and terminals end to matching the FDTD solution for voltage and Current at that time and space point.

#### 3.1.1 Working with FDTD method

When transmission's differential equations are examined, it can be notice that the change in the voltage (V) in time (the time derivative) is dependent on the change in the current (I) across space (the curl). These results in the basic FDTD time-stepping relation that, at any point in space, the updated value of the V in time is dependent on the stored value of the V and the numerical curl of the local distribution of the I in space.

The I is time-stepped in a similar manner. At any point in space, the updated value of I in time is dependent on the stored value of I and the numerical curl of the local distribution of the V in space. Iterating I and V updates results in a explicit marching-in-time process where in sampleddata analogs of the continuous electromagnetic signal under consideration propagate in a

numerical grid stored in the computer memory [20].

#### 3.1.2 Strengths of FDTD technique

G. G. 21893 (p) S ACC No Date. 18/12/12 Date. 18/12/12

- FDTD technique used to solve differential equation. It is intuitive, so can easily understand who to use in a model.

- It is a time domain technique. In which response of the system over a wide range of frequencies can be obtained with a single simulation.

- FDTD calculate relative parameter such as E and H in case of Maxwell's equation and V and I in case of transmission line equation, everywhere in the computational domain as they evolve in time. That provides the importance picture of field movement throughout the model. This type of display is useful in understanding what is going on in the model, and to help ensure that the model is working correctly.

- The FDTD technique allows the user to specify the computational domain. A wide variety of linear and nonlinear medium can be naturally and easily modeled.

#### 3.1.3 Stability Criterion for FDTD

The numerical stability of the FDTD method is determined by the Courant-Friedrichs-Lewy (CFL) condition, which simply requires a signal that cannot be allowed to travel more than one space size during one time step. The CFL condition is a necessary condition for convergence while solving certain partial differential equations numerically by the method of finite differences. It arises when explicit time-marching schemes are used for the numerical solution [21].

For stability of the FDTD solution, the position and time discretization must satisfy the Courant condition. Numerically the time and space discretization should follow the following equation.

$$\Delta t \le \frac{\Delta z}{\nu} \tag{3.1}$$

where  $\nu$  is signal velocity in line. The Courant stability condition provides that for stability of the solution the time step must be no greater than the propagation time over each cell.

#### 3.1.4 Central difference approximation

Consider a function of one variable f(t). Expanding this in a Taylor series in a neighborhood of a desired point  $t_0$  gives

where the primes denote the various derivatives with respect tot of the function. Solving this for the first derivative gives

Thus first order derivative can be approximated as

$$f'(t_0) = \frac{f(t_0 + \Delta t) - f(t_0)}{\Delta t} + \theta(\Delta t)$$

(3.4)

Where  $\theta(\Delta t)$  denotes that the error in truncating the series is on the order of  $\Delta t$ . So the first derivative may be approximated with the forward difference

$$f'(t_0) \cong \frac{f(t_0 + \Delta t) - f(t_0)}{\Delta t}$$

(3.5)

This amounts to approximating the derivative of f(t) as with its region of the desired point. If we expand the Taylor's series as

which can be approximate by

$$f'(t_0) \cong \frac{f(t_0) - f(t_0 - \Delta t)}{\Delta t}$$

(3.7)

This gives the backward approximate equation for derivative.

Other approximations known as central differences can be found by subtracting equation (3.3) from equation (3.6) to yield the first derivative central difference approximation

$$f'(t_0) \cong \frac{f(t_0) - f(t_0 - \Delta t)}{\Delta t}$$

(3.8)

with a truncation error of  $\Delta t^2$ . Similarly, the second derivative central difference is obtained by adding (2) and (5) to yield

$$f''(t_0) \cong \frac{f(t_0 + \Delta t) - 2f(\Delta t) + f(t_0 - \Delta t)}{\Delta t^2}$$

(3.9)

with a truncation error on the order of  $\Delta t^2$ . Due to second order error truncation in central difference approximation, FDTD termed as FDTD solution with second order accuracy.

#### **3.2FDTD MODEL**

This section presents the formalization of a finite difference time domain (FDTD) method that is intended for estimation of voltages and currents on interconnects which are modeled as *RLGC* transmission line.

#### 3.2.1 Transmission line's equation

In general, interconnect behaves as a waveguide that can be analyzed using Maxwell's equations. Interconnect can also be analyzed using transmission line equations, if it is assumed that the waves on the line propagate in the transverse electromagnetic (TEM) mode [22]. Interconnect models based on transmission lines with distributed *RLGC* segments are thus normally used in on-chip interconnect analysis

Figure 3.1: distributed RLGC transmission line.

Figure 3.1 show the *RLGC* distributed transmission line, where *R*, *L*, *G*, *C* per unit length resistance, inductance, conductance and capacitance of transmission line of length *l*, respectively. Consider the point z along the transmission line of Figure 3.1 at time t. The following set of equations holds:

$$\frac{d}{dz}V(z,t) = -RI(z,t) - L\frac{d}{dz}I(z,t)$$

(3.10a)

$$\frac{d}{dz}I(z,t) = -GV(z,t) - C\frac{d}{dz}V(z,t)$$

(3.10b)

#### 3.2.2 Discretization in space and time

To implement FDTD on equation (3.10), first we divide transmission line into Nz section, each of length  $\Delta z$  as shown in figure 3.2. Similarly, we divide the total solution time into Nt segments of length  $\Delta t$ . Discretization of voltage and current and relation with time and space is shown in figure 3.3. In order to ensure stability of the discretization and to ensure second-order accuracy,

of the FDTD

Figure 3.3: Interlacing the current and voltage solutions in space and time for the FDTD analysis.

we interlace the  $N_z$  +1 voltage points,  $V_I$ ,  $V_2$ ,...,  $V_{N_z}$  and the  $N_z$  current points,  $I_1$ ,  $I_2$ , ...,  $I_{N_z}$ . Each voltage and adjacent current solution point is separated by  $\Delta z/2$ . The time points also be interlaced and each voltage time point and adjacent current time point are separated by  $\Delta t/2$ , as also shown in figure 3.3. Now using central differential approximation on equation (3.10a)

$$\frac{V_{K+1}^{n+1} - V_{K}^{n+1}}{\Delta z} + L \frac{I_{K}^{n+3/2} - I_{K}^{n+1/2}}{\Delta t} + R \frac{I_{K}^{n+3/2} + I_{K}^{n+1/2}}{2} = 0$$

(3.11)

for K =1, 2, 3, ....., Nz and similarly applying central difference approximation on equation (3.10b) become

$$\frac{I_{K}^{n+1/2} - I_{K-1}^{n+1/2}}{\Delta z} + C \frac{V_{K}^{n+1} - V_{K}^{n}}{\Delta t} + G \frac{V_{K}^{n+1} + I_{K}^{n}}{2} = 0$$

(3.12)

for  $K=2, 3, 4, \ldots, Nz$ , where we denote voltage and current as

$$V_{i}^{j} = V[(i-1)\Delta z, j\Delta t]$$

$$I_{i}^{j} = I[(i-1/2)\Delta z, j\Delta t]$$

(3.13a)

(3.13b)

Now by rearranging equation (3.11) and (3.12) the recursive relation of voltage and current at interior point of interconnect can be given as

$$V_{k}^{n+1} = ABV_{k}^{n} + \frac{A}{\Delta z} \left( I_{k-1}^{n+1/2} - I_{k}^{n+1/2} \right)$$

(3.14)

for K =1, 2, 3, ...., *Nz* and

$$I_{k}^{n+3/2} = EFI_{k}^{n+1/2} + \frac{E}{\Delta z} \left( V_{k}^{n+1} - V_{k+1}^{n+1} \right)$$

(3.15)

for K= 2, 3, 4, ...., Nz

21

where

$$A = \left(\frac{C}{\Delta t} + \frac{G}{2}\right)^{-1}, B = \left(\frac{C}{\Delta t} - \frac{G}{2}\right), E = \left(\frac{L}{\Delta t} + \frac{R}{2}\right)^{-1} \text{ and } F = \left(\frac{L}{\Delta t} - \frac{R}{2}\right)$$

(3.16)

Equation (3.14) and (3.15) are recursive relation is used to estimation the voltage and current at different point of line at different time for signal transmission line. This can be extended for multi-transmission line. For N transmission line the Voltage and Current can be can be replaced by vector of order of  $1 \times N$  as

$$V = [V(1) V(2) V(3) \dots V(N)]^T$$

(3.17a)

$$I = [I(1) I(2) I(3) \dots I(N)]^{2}$$

(3.17b)

where V(1), V(2)... are voltage point for line 1, 2... respectively, similarly apply for current points. line parameter such as R, L, G, C and all other derived parameter as A, B, E, F are replaced by  $N \times N$  matrix for N transmission line.

#### 3.2.3 Leapfrog time-stepping

As shown in the previous section, Current is updated at  $t = (n+1/2)\Delta t$  using the previous current value at  $t = (n-1/2)\Delta t$  and voltage at  $t = n\Delta t$ . Voltage, on the other hand, is updated at  $t = (n+1)\Delta t$  using the previous at  $t = n\Delta t$  and current at  $t = (n+1/2)\Delta t$ . Figure 3.4 shows timeline when I and V are updated.

Figure 3.4: Timeline showing when E and H fields are updated.

To remain numerically stable, the time-step must obey the Courant Stability Condition

$$\Delta t < \frac{1}{C\Delta z} \tag{3.18}$$

To obtain good spatial resolution, the cell size should be less than a tenth of the shortest wavelength [24]

$$\Delta z < \frac{\lambda_{\min}}{10} \tag{3.19}$$

#### 3.2.4 Incorporation of boundary condition

This section considers incorporation of terminal condition with FDTD solution. The essential problem in incorporating the terminal conditions is that the FDTD voltages and currents at each end of the line,  $V_I$ ,  $I_I$ , and  $V_{Nz+I}$ ,  $I_{Nz}$  are not collocated in space or time, whereas the terminal conditions relate the voltage and current at the same position and at the same time [23]. This section can be divided into two parts such as (1) boundary matching at source and line interface and (2) boundary matching at load and line interference.

#### 3.2.4.1 Boundary matching at source end

Figure 3.5: Discretizing the terminal voltages and currents of the line at source end in order to incorporate the terminal constraints.

Let the source current is  $I_s$  at source terminal (z=0) as shown in figure 3.6. To match the source current at boundary Equation (3.14) is discretized at the source by averaging the source currents  $I_s$  to obtain a value that is located in time at the same time point at  $I_0^{n+1/2}$  as,

Figure 3.6: Discretizing of line with source and load current.

24

$$I_0^{n+1/2} = \frac{I_s^{n+1} + I_s^n}{2} \tag{3.20}$$

Now using equation (3.14) and (3.20), recursive relation for voltage and current at source and line interference can be given as

$$\frac{1}{\Delta z/2} \left[ I_1^{n+1/2} - \frac{I_s^{n+1} + I_s^n}{2} \right] + \frac{1}{\Delta t} C \left[ V_1^{n+1} - V_1^n \right] + \frac{G}{2} \left[ V_1^{n+1} + V_1^n \right] = 0$$

(3.21)

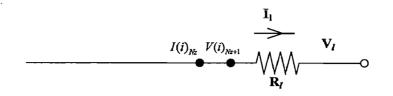

#### 3.2.4.2 Boundary matching at load end

The load current at load terminal is shown in figure 3.6. Similarly, the transmission-line equation (3.14), is discretized at the load by averaging the load currents  $I_l$  in order to obtain a value that is located in time at the same point as  $I_{Nz}^{n+1/2}$  as

$$I_{Nz+1}^{n+1} = \frac{I_i^{n+1} + I_i^n}{2}$$

(3.22)

Now using equation (3.14) and (3.22), recursive relation between voltage and current at load end and line interference can be written as

$$\frac{1}{\Delta z/2} \left[ \frac{I_l^{n+1} + I_l^n}{2} - I_{Nz}^{n+1/2} \right] + \frac{1}{\Delta t} C \left[ V_{Nz+1}^{n+1} - V_{Nz+1}^n \right] + \frac{G}{2} \left[ V_{Nz+1}^{n+1} + V_{Nz+1}^n \right] = 0$$

(3.23)

First, the voltages along the line are obtained, for a fixed time, from equation (3.14) in terms of

Figure 3.7: Discretizing the terminal voltages and currents of the line at load end in order to incorporate the terminal constraints.

the previous solutions. Then the currents are obtained from (3.15) in terms of the voltages as well as previously obtained current values.

#### **3.3** FDTD Model for Interconnect terminated by Resistive load

Let interconnect is terminated by resistor at load end. Now using figure 3.8 the relation between load current  $I_l$  and load voltage  $V_l$  (zero in mostly cases, where line is terminated by ground resistive load) can be given as

$$V_{Nz+1} = V_l + I_l R_l$$

(3.24)

26

Figure 3.8: Interconnect terminated by Resistance.

Discretizing this into time domain simply gives

.

$$V_{Nz+1}^{n+1} = V_l^{n+1} + I_l^{n+1} R_l$$

(3.25)

On rearranging equation (3.25)

$$I_{l}^{n+1} = \frac{V_{Nz+1}^{n+1} - V_{l}^{n+1}}{R_{l}}$$

(3.26)

Now using equation (3.26) and relation derived in equation (3.23), recursive relation for voltage at resistive load can be given as

$$V_{Nz+1}^{n+1} = K_1 K_2 V_{Nz}^n + \frac{2A}{\Delta z} \left[ I_{Nz}^{n+1/2} + \frac{V_l^n - V_l^{n+1}}{R_l} \right]$$

(3.27)

where

$$K_1 = [1 + 2A / \Delta z]^{-1} \text{ and } K_2 = [AB - 2A / \Delta z]$$

(3.28)

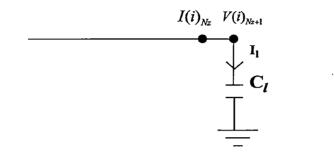

#### 3.4 FDTD Model for Interconnect terminated by capacitive load

Figure 3.9: Interconnect terminated by capacitive load

Let the second case in which interconnect is terminated by capacitor at load end. Again using figure 3.9 the relation between load current  $I_l$  and load voltage  $V_{Nz+1}$  can be given as

$$I_l = C_l \frac{d}{dt} V_{Nz+1} \tag{3.29}$$

Discretizing the equation (3.29) in time domain

$$I_{l}^{n+1} = C_{l} \frac{\left( V_{Nz+1}^{n+1} - V_{Nz+1}^{n} \right)}{\Delta t}$$

(3.30)

Now, using equation (3.30) and (3.23), the interface equation for voltage at capacitive load end is given by

$$V_{Nz+1}^{n+1} = K_1 K_2 V_{Nz}^n + \frac{2A}{\Delta z} \left[ I_{Nz}^{n+1/2} \right]$$

(3.31)

where

$$K_{1} = \left[1 + 2AC_{l} / \Delta t \Delta z\right]^{-1} \text{ and } K_{2} = \left[AB - 2AC_{l} / \Delta t \Delta z\right]$$

(3.32)

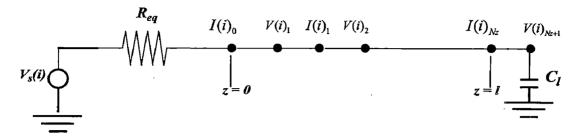

#### **3.5** FDTD Model for Interconnect driven by Resistive driver

CMOS driver is usually represented by a linear circuit which uses the equivalent PMOS resistance for falling ramp input or the equivalent NMOS resistance for rising ramp input. In CMOS-gate driven interconnect, for simplification CMOS driver is replaced by its equivalent on resistance in series with power supply. The equivalent MOS resistance  $R_{eq}$  can be approximated by just averaging the values of the resistance at the midpoint (where MOS transistor is in saturation state) during switching, which is in the form of [24].

$$R_{eq} = \frac{3}{4} \frac{V_{dd}}{I_{sat}} \left( 1 - \frac{7}{9} \lambda V_{dd} \right)$$

(3.33)

where  $V_{dd}$  is power supply voltage,  $I_{Sat}$  is the drain saturation current, and  $\lambda$  is channel-length modulation. In this section the CMOS driver is modeled into linear resistor in series with voltage source. The CMOS driver is replaced by equivalent the vnin resistance ( $R_{eq}$ ).

The termination circuit as shown in figure 3.10, at the source end of interconnect line consists of a resistor and voltage source connected in such a way that can be described by following relation

Figure 3.10: Interconnect driven by Resistive driver

$$I_{s} = \frac{V_{1} - V_{s}}{R_{eq}}$$

(3.34)

On rearranging (3.34)

$$V_1 = V_s - I_s R_{eq} \tag{3.35}$$

To implemented FDTD equation (3.35) should be discretized in time domain as

$$V_1^{n+1} = V_s^{n+1} - I_s^{n+1} R_{eq}$$

(3.36)

Using equation (3.21) and (3.36) recursion relations at source interface for  $V_1$  can be given as

$$V_1^{n+1} = K_1 K_2 V_1^n + K_1 K_3 (V_s^n + V_s^{n+1}) - 2K_1 K_3 R_{eq} I_1^{n+1/2}$$

(3.37)

and

$$K_1 = (U + K_3)^{-1}$$

,  $K_2 = (AB - K_3)$  and  $K_3 = A / \Delta z R_s$  (3.38)

#### 3.6 FDTD Model for coupled transmission line

In this section, two distributed coupled *RLC* lines are considered. Let *R*, *L* and *C* be per unit length line resistance, self-inductance, and ground capacitance of the line, respectively. Subscription 1 and 2 is used for line 1 and line 2, respectively.  $C_c$  and *M* represent the coupling capacitance per unit length and mutual inductance per unit length between the lines. At any point *z* along the line, voltage and current waveforms on line 1 and line 2 satisfy the following set of differential equations,

$$\frac{\partial}{\partial z}V_{1}(z,t) + L_{1}\frac{\partial}{\partial t}I_{1}(z,t) + M\frac{\partial}{\partial t}I_{2}(z,t) + R_{1}I_{1}(z,t) = 0$$

(3.39a)

$$\frac{\partial}{\partial z}V_2(z,t) + L_2\frac{\partial}{\partial t}I_2(z,t) + M\frac{\partial}{\partial t}I_1(z,t) + R_2I_2(z,t) = 0$$

(3.39b)

$$\frac{\partial}{\partial z}I_{1}(z,t) + (C_{1} + C_{c})\frac{\partial}{\partial t}V_{1}(z,t) - C_{c}\frac{\partial}{\partial t}V_{2}(z,t) + G_{1}V_{1}(z,t) = 0$$

(3.39c)

$$\frac{\partial}{\partial z}I_2(z,t) + (C_2 + C_c)\frac{\partial}{\partial t}V_2(z,t) - C_c\frac{\partial}{\partial t}V_1(z,t) + G_2V_2(z,t) = 0$$

(3.39d)

which can be written in matrix form as,

$$\frac{\partial}{\partial z}V(z,t) + L\frac{\partial}{\partial t}I(z,t) + RI(z,t) = 0$$

(3.40a)

$$\frac{\partial}{\partial z}I(z,t) + C\frac{\partial}{\partial t}V(z,t) + GV(z,t) = 0$$

(3.40b)

where I and V are in  $2 \times 1$  matrix form and R, L, G, C are in  $2 \times 2$  matrix form given as

$$R = \begin{pmatrix} R_{1} & 0 \\ 0 & R_{2} \end{pmatrix}, \quad L = \begin{pmatrix} L_{1} & M \\ M & L_{2} \end{pmatrix}, \quad G = \begin{pmatrix} G_{1} & 0 \\ 0 & G_{2} \end{pmatrix}, \text{ and}$$

$$C = \begin{pmatrix} C_{1} + C_{c} & -C_{c} \\ -C_{c} & C_{1} + C_{c} \end{pmatrix}$$

(3.41)

for N number of coupled transmission lines, I and V are converted into  $N \times 1$  matrix and R, L, G, C are in  $N \times N$  matrix. Now equation (3.40) can be solved similarly as the equation (3.14). All previous recursive relation derived for interconnect is applicable for coupled line just changing the parameter matrix.

#### 3.7 FDTD Model for CMOS-gate driven Interconnect

In chapter 3, CMOS driver is simplified as a linear circuit in which a constant resistance is used to approximate the nonlinear and time-varying MOS resistance. FDTD is implemented for linear behavior of driver in that section, whereas this chapter presents a FDTD method for transient analysis of lossy transmission lines in the presence of the nonlinear behavior of CMOS gates.

Signal integrity is strongly affected by both the transmission line behavior of interconnects and the nonlinear behavior of CMOS drivers. Therefore, accurate prediction of time delay and crosstalk noise should combine the effect of transmission line that propagates quasi TEM with precise transistor level modeling of CMOS-gate [24]. The nonlinear behavior of CMOS gates is represented by alpha-power law model [31], with the drain current described by piecewise linear function of the drain voltage and discretized in time domain for the FDTD implementation.

Figure 3.11 shows M coupled transmission lines driven by CMOS gates. The input signal is  $N \times 1$  vector of voltage, denoted as  $V_s = [V_s(1) V_s(2) V_s(3) \dots V_s(N)]^{-1}$ . The alpha power-law

model [31] is used for modeling the CMOS gates. A detail of alpha power model is given in section 2.3. Figure 3.12 shows the macro model used for FDTD implement.

Figure 3.11: M coupled transmission lines driven by CMOS gates.

Figure 3.12: Macro model for CMOS-gate driven interconnect.

PMOS and NMOS currents are represented by the alpha-power law MOS model and discretized in time domain, shown in (2) and (3), respectively.

$$i_{p}^{n+1} = \begin{cases} 0 & V_{s}^{n+1} \ge V_{dd} - |V_{tp}| \\ K_{lp}(V_{dd} - V_{s}^{n+1} - |V_{tp}|)^{\alpha_{p}/2} (V_{dd} - V_{1}^{n}) & V_{s}^{n+1} < V_{dd} - |V_{tp}| \& \\ V_{1}^{n} > V_{dd} - |V_{Dsatp}| \\ K_{sp}(V_{dd} - V_{s}^{n+1} - |V_{tp}|)^{\alpha_{p}} & V_{s}^{n+1} < V_{dd} - |V_{tp}| \& \\ V_{1}^{n} > V_{dd} - |V_{Dsatp}| \end{cases}$$

(3.42)

$$i_{n}^{n+1} = \begin{cases} 0 & V_{s}^{n+1} \leq V_{dd} - \left| V_{tp} \right| \\ K_{\ln} \left( V_{s}^{n+1} - V_{tn} \right)^{\alpha_{n}/2} \left( V_{1}^{n} \right) & V_{s}^{n+1} > V_{tn} \& V_{1}^{n} < V_{Dsat_{n}}^{n} \\ K_{sn} \left( V_{s}^{n+1} - V_{tn} \right)^{\alpha_{n}} & V_{s}^{n+1} > V_{tn} \& V_{1}^{n} \geq V_{Dsat_{n}}^{n} \end{cases}$$

(3.43)

where discretized saturation current is represented as

$$V_{Dsat_{p}}^{n} = \frac{K_{sp}}{K_{lp}} (V_{dd} - V_{s}^{n} - |V_{tp}|)^{\alpha_{p}/2}$$

(3.44)

$$V_{Dsat_n}^n = \frac{K_{sn}}{K_{ln}} (V_s^n - V_{tn})^{\alpha_n/2}$$

(3.45)

Applying KCL at source and interconnect interface according to figure 3.12, results in

$$I_{s} = C_{m} \left[ \frac{d(V_{s} - V_{1})}{dx} \right] + i_{p} - i_{n} - C_{d} \frac{dV_{1}}{dx}$$

(3.46)

where  $C_m$  and  $C_d$  are drain to coupling capacitance and the drain diffusion capacitance of CMOS driver.

Source Current  $I_s$ , in discretized form can be written as

$$I_{S}^{n+1} = C_{m} \frac{V_{S}^{n+1} - V_{S}^{n}}{\Delta t} + i_{p}^{n+1} - i_{n}^{n+1} - (C_{m} + C_{d})(\frac{V_{1}^{n+1} - V_{1}^{n}}{\Delta t})$$

(3.47)

Now solving equation (3.47) and (3.23) the recursive relation for voltage at CMOS-gate and interconnect interface can be given as

$$V_1^{n+1} = K_1 V_1^n - K_2 I_1^{n+1/2} + \frac{K_2}{2} \left[ i_p^{n+1} - i_n^{n+1} \right] + K_3$$

(3.48)

where

$$K_{1} = \left[\Delta z \Delta t U + A(C_{m} + C_{l})\right]^{-1} \left[\Delta z \Delta t A B + A(C_{m} + C_{l})\right]$$

$$K_{2} = 2A \Delta t \left[\Delta z \Delta t U + A(C_{m} + C_{l})\right]^{-1}, \quad K_{3} = \frac{K_{2}}{2} \left[I_{s}^{n} + \frac{C_{m}}{\Delta t}(V_{s}^{n+1} - V_{s}^{n})\right]$$

$$(3.49)$$

### **Chapter 4**

# **Analysis of Interconnect Performance**

As discussed in earlier chapter, interconnects are used for distributing clock-signals, power supply and connecting signals among integrated circuits. In other manner, we can say that interconnects are medium in IC for propagation of signals from one device to other connect device. So, interconnect perform well, if the propagating signal at far end of interconnect reach at desired time and desired waveform shape.

However, after introduces of sub micron device technology a significant change is noticed in interconnect performance. Typical time-domain effects include interconnect delay, crosstalk, transmission line effects, noise-on-delay effects highly degraded the performance of interconnects. This chapter presents a detail time-domain analysis based on FDTD model developed in last chapter for coupled interconnect configuration.

#### 4.1 Crosstalk Noise

Aggressive usage of high-speed circuit families, scaling of power supply and threshold voltages, and mixed-signal integration combine to make the chips more noise-sensitive. Crosstalk noise in IC is results of coupling effects between interconnect line. Noise, cause by one signal, being coupled into a different signal is called crosstalk. Crosstalk noise can affect the circuit performance in two ways, either by disturbing a quiet line, or by changing the response speed of adjacent switching line.

#### 4.1.1 Functional Crosstalk

The current is injected into quiet line (victim) during the switching of adjacent line (aggressor) is defined as functional crosstalk. Or, an undesirable voltage spike generated at quiet line (victim) during the switching of adjacent line is defined as functional crosstalk. This type of crosstalk noise can cause device or logic failure due to unexpected.

A simple set-up for functional-crosstalk analysis is presented here. Figure 4.1 shows the experimental set-up for coupled interconnect configuration driven by resistive driver. One of the lines is identified as aggressor and the other as victim. The driver of aggressor line is excited by a rising ramp source of  $V_s = 1.2$ V with 50ps transient time, in series with a linear resistance  $R_s=75\Omega$ . On the other hand, the driver of victim line is grounded through a linear resistance  $R_v=50 \Omega$ .

Coupled interconnect wire of 2mm length is considered for crosstalk analysis. The interconnect wire has parameters such as ground capacitance (C) = 257fF, self-inductance (L) = 2.15nH, coupling capacitance ( $C_c$ ) = 184fF and mutual- inductance (M) = 1.68nH. Interconnect is terminated by a load capacitance ( $C_l$ ) of 30fF.

Figure 4.1: Coupled *RLGC* interconnect configuration for functional crosstalk.

The response of victim line at far-end is shown in Figure 4.2. An aggressor line switching, results in a voltage spike of 0.234 V at far end of victim-lime. If a device connected at far end of victim has threshold voltage in this range, a logical failure or false switching of gate may occurs.

Figure 4.3: Comparison of SPICE and FDTD generated waveforms at far-end of victim line.

#### 4.1.2 Dynamic Crosstalk

Dynamic crosstalk appears due to the simultaneous switching at adjacent lines either in same phase or in opposite phase. This noise impacts the critical issue of timing by changing the response time of adjacent signal.

Analyzing the dynamic crosstalk noise case is equally important as modeling of functional crosstalk noise, particularly since CMOS logic gates tend to have very good functional-noise rejection capabilities, so dynamic case is essential for complete analysis of onship performance.

Figure 4.3: Coupled line configurations for dynamic crosstalk analysis (in-phase switching).

Using Set-up shown in figure 4.3, dynamic crosstalk is analyzed, when both aggressor and victim lines are simultaneously switched in same phase by rising ramp signal  $(0-V_s)$  with 50ps

Figure 4.4: Comparison of SPICE and FDTD generated waveforms at far-end of victim line for under inphase switching.

transition time. Time domain response is shown in Fig. 4.4. The positive peak at far end of victim line reached up to 1.57V for 1.2V input ramp signal.

Figure 4.5: Coupled line configurations for dynamic crosstalk analysis (Out-of-phase switching).

Figure 4.6: Comparison of SPICE and FDTD generated waveforms at far-end of aggressor line under outof-phase switching.

Figure 4.7: Comparison of SPICE and FDTD generated waveforms at far-end of victim line under out-ofphase switching.

In second case of dynamic crosstalk interconnects lines is excited in out-of-phase as shown in figure 4.5. A rising-ramp signal is applied at aggressor line where falling-ramp is used for victim line. The time domain response at far end of both lines is shown in Figure 4.6 and figure 4.7, respectively.

#### 4.2 Crosstalk-induce delay

As discusses earlier, dynamic crosstalk highly influence the timing issue of signal. The change is response time of a signal due to switching in adjacent line is known as crosstalk-induce delay.

The delay of interconnect line is reduces, when adjacent line is switching in same case. It can be easily understand using couple transmission line theory, that when both line switching in same direction the effecting coupling capacitance between lines is reduces. That's way delay is also reduced. Similarly, in other case the delay is increase when adjacent line is switched in out-of-phase, because in this case effect coupling capacitance is doubled.

Figure 4.8: 50% Propagation delay variation with line resistance.

#### 4.3 Effect of Line Resistance Variation

Fig. 4.8 presents the variation of 50% propagation delay with line resistance for three cases *viz.* (i) Aggressor line under functional crosstalk scenario (*Aggressor Line-Func Cross*) (ii) Inphase dynamic crosstalk scenario (*In-phase Dyn Cross*); (iii) Out-of-phase dynamic crosstalk scenario (*Out-of-phase Dyn Cross*). It has been observed that the delay reduces for in-phase case, while, it increases for out-of-phase switching scenario. However, as the line resistance increases, the propagation delay for all three cases increases due to increase in RC delay of line.

#### 4.4 Effect of interconnect length Variation

A similar functional crosstalk analysis set-up is used. Interconnect length is vary from 1mm to 4mm. In all case line parasitic is calculated, and FDTD model is implemented for output response. Figure 4.9 shows the variation in noise peak at far-end of victim line with

Figure 4.9: Noise Peak variation with interconnect length.

Figure 4.10: 50% delay variation with interconnect length.

43

interconnect length. Where figure 4.10 show the delay variation at aggressor line end with respect to interconnect length. According to figure 4.10, increment in delay is linearly vary with interconnect line.

#### TABLE 4.1

#### DELAY ANALYSIS OF FUNCTIONAL AND DYNAMIC CROSSTALK WITH VARIATION IN LINE RESISTANCE

| Line<br>Resistance<br>(Q) | Propagation Delay in 2mm Long Interconnect |                |              |              |                |              |                        |                |              |

|---------------------------|--------------------------------------------|----------------|--------------|--------------|----------------|--------------|------------------------|----------------|--------------|

|                           | Dynamic Crosstalk Delay                    |                |              |              |                |              | Functional Crosstalk   |                |              |

|                           | In- Phase                                  |                |              | Out-of-Phase |                |              | (Aggressor Line Delay) |                |              |

|                           | FDTD<br>(ps)                               | HSPICE<br>(ps) | Error<br>(%) | FDTD<br>(ps) | HSPICE<br>(ps) | Error<br>(%) | FDTD<br>(ps)           | HSPICE<br>(ps) | Error<br>(%) |

|                           |                                            |                |              |              |                |              |                        |                |              |

| 15                        | 29.25                                      | 31.53          | 7.3          | 42.40        | 43.10          | 1.6          | 33.10                  | 34.67          | 4.5          |

| 30                        | 30.30                                      | 32.72          | 7.3          | 46.80        | 47.37          | 1.2          | 35.10                  | 36.58          | 4.0          |

| 45                        | 31.20                                      | 33.59          | 7.1          | 52.50        | 53.13          | 1.1          | 37.30                  | 38.76          | 3.7          |

| 60                        | 32.40                                      | 34.78          | 6.8          | 56.70        | 57.25          | 0.9          | 39.00                  | 40.45          | 3.5          |

| 75                        | 33.60                                      | 35.97          | 6.6          | 60.70        | 61.19          | 0.8          | 40.80                  | 42.19          | 3.3          |

| 90                        | 34.80                                      | 37.16          | 6.3          | 63.90        | 64.35          | 0.7          | 42.60                  | 44.04          | 3.2          |

#### 4.5 HSPICE Simulation

.

The HSPICE simulation used W element model to represent a transmission line. RLGC parameter matrix is external define for W-element model. For all above discusses cases the HSPICE simulation result is also obtain for same RLGC matrix.

For self motivation and to verify the analytically result based on FDTD model, comparison with HSPICE is also made. In almost cases, the FDTD based waveforms closely matches with HSPICE waveforms, which validates the accuracy of proposed method.

Table 4.1 compares propagation delay between proposed FDTD model and HSPICE simulation results. Propagation delay is presented for line resistance varying from 0 to  $90\Omega$ . It has been observed that the percentage error reduces with increasing line resistance. For the proposed model an average error of 4.1% with respect to HSPICE results is observed. The comparisons of FDTD results with HSPICE demonstrates that the proposed method captures waveform shapes, peak timing and 50% propagation delay with high accuracy for both functional and dynamic crosstalk scenarios. As compared to HSPICE, the analytical model results in an error that ranges from 0.7% to 7.5% only.

Therefore, it can be concluded that the analytical results for proposed FDTD model is in close agreement with HSPICE results.

## **Chapter 5**

### **Conclusion and Future Scope**

#### **5.1 Conclusion**

In this dissertation, a set of general finite-difference time-domain updating equations is derived for interconnect analysis. The accuracy of FDTD is improved by using appropriate discretization in space and time point. All analyses were carried out on practical problems and they are supported with simulation results. The measurement results were in good agreement with simulation results, thus leading to the conclusion that all stipulated theories are accurate.

#### **5.2 Future Scope**

All the objectives aimed for are achieved at the end of the project. However, there is future work to be continued more on this direction. Following are the potential areas where future work can be extended:

- The effect of crosstalk and crosstalk induce delay is estimate for two coupled line interconnect. It can be extended for more number of lines.

- Although the FDTD method is widely used in the field of computational electromagnetic, the long computational time and large memory requirement have always been a concern with the technique. A deep research can be done in this area.

46

#### References

[1] J. Rabaey, A. Chandrakasan, and B. Nikolic, Digital Integrated Circuits: A Design Perspective, 2<sup>nd</sup> ed. Englewood Cliffs, Nj: Prentice-Hall, 2003.

[2] H. B. Bakoglu, Circuits, Interconnections, and Packaging for VLSI, Addison-Wesley Publishing Company, 1990.

[3] International Technology Roadmap for Semiconductors Interconnect, 2005, 2007 and 2009 editions, http://www.itrs.net.

[4] Francesc Moll, Miquel Roca, Interconnection Noise in VLSI Circuits, 2004.

[5] D. Sylvester and K. Keutzer, "Getting to the bottom of deep submicron," in Proc. International Conference on Computer Aided Design, pp.203-211, 1998.

[5] P. S. Hung, An Interconnect-driven System-On-Chip Floor planning Framework, August, 2002.

[6] F. Moll, M. Roca, A. Rubio, "Inductance in VLSI interconnection modeling", IEE Proc -Circuits Devices Syst, Vol. 145, no 3, June 1998.

[7] T. Sakurai and A. R. Newton, "Alpha-power model and its applications to CMOS inverter delay and other formulas," IEEE J. Solid-State Circuits, vol. 25, no. 2, pp. 584–594, Apr. 1990.

[8] S. Dutta, S. S. M. Shetti, and S. L. Lusky, "A comprehensive delay model for CMOS inverters," IEEE J. Solid-State Circuits, vol. 30, no. 8, pp. 864–871, Aug. 1995.

[9] L. Bisdounis, S. Nikolaidis, and O. Koufopavlou, "Analytical transient response and propagation delay evaluation of the CMOS inverter for short-channel devices," IEEE J. Solid-State Circuits, vol. 33, no. 2, pp. 302–306, Feb. 1998.

[10] J. Qian, S. Pullela, and L. Pillage, "Modeling the 'effective capacitance' for the RC interconnect of CMOS gates," IEEE Trans. Comput.-Aided Des., vol. 13, no. 12, pp. 1526–1535, Dec. 1994.

[11] M. Hafed, M. Oulmane, and N. C. Rumin, "Delay and current estimation in a CMOS inverter with an RC load," IEEE Trans. Comput.-Aided Des., vol. 20, no. 1, pp. 80–89, Jan. 2001.

[12] A. Chatzigeorgiou, S. Nikolaidis, and I. Tsoukalas, "Modeling CMOS gates driving RC interconnect loads," *IEEE Trans. Circuits Syst. II: Analog Digital Signal Process.*, vol. 48, no. 4, pp. 413–418, Apr. 2001.

[13] B. K. Kaushik, S. Sarkara, and R. P. Agarwala, "Waveform analysis and delay prediction for a CMOS gate driving RLC interconnect load," Integration, Very Large Scale Integr. J., vol. 40, no. 4, pp. 394–405, Jul. 2007.

[14] J. Rubinstein, P. Penfield, and M. A. Horowitz, "Signal delay in RC tree networks," IEEE Trans. Comput.-Aided Des., vol. 2, no. 3, pp. 202–211, Jul. 1983.

[15] A. Kahng and S. Muddu, "An analytical delay model for RLC interconnects," IEEE Trans. Comput.-Aided Des., vol. 16, no. 2, pp. 1507–1514, Dec. 1997.

[16] Y. I. Ismail, E. G. Friedman, and J. L. Neves, "Equivalent Elmore delay for RLC trees," IEEE Trans. Comput.-Aided Des., vol. 19, no. 1, pp. 83–97, Jan. 2000.

[17] T. Sakurai, "Closed-form expressions for interconnect delay, coupling, and crosstalk in VLSIs," IEEE Trans. Electron Devices, vol. 40, no. 1, pp. 118–124, Jan. 1993.

[18] Y. Eo, W. R. Eisenstadt, J. Y. Jeong, and O.-K. Kwon, "A new on-chip interconnect crosstalk model and experimental verification for CMOS VLSI circuit design," IEEE Trans. Electron Devices, vol. 47, no. 1, pp. 129–140, Jan. 2000.

[19] L. Ding, D. Blaauw, and P. Mazumder, "Accurate crosstalk modeling for early signal integrity analysis," IEEE Trans. Comput.-Aided Des., vol. 22, no. 5, pp. 627–635, May 2003.

[20] X. Bai, R. Chandra, S. Dey, and P. V. Srinivas, "Interconnect couplingaware driver modeling in static noise analysis for nanometer circuits," IEEE Trans. Comput.-Aided Des., vol. 23, no. 8, pp. 1256–1263, Aug. 2004.

[21] J. A. Davis and J. D. Meindl, "Compact distributed RLC models, part I: Single line transient, time delay, and overshoot expressions," IEEE Trans. Electron Devices, vol. 47, no. 11, pp. 2068–2077, Nov. 2000.

[22] J. A. Davis and J. D. Meindl, "Compact distributed RLC models, part II: Coupled line transient expressions and peak crosstalk in multilevel networks," IEEE Trans. Electron Devices, vol. 47, no. 11, pp. 2078–2087, Nov. 2000.

49

[23] K. Agarwal, D. Sylvester, and D. Blaauw, "Modeling and analysis of crosstalk noise in coupled RLC interconnects," IEEE Trans. Comput.- Aided Des., vol. 25, no. 5, pp. 892–901, May 2006.

[24] X. Li, J. Mao, and M. Swaminathan, "Transiant analysis of CMOS- Gate –Driven RLGC interconnects based on FDTD, "IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, vol. 30, no. 4, pp. 574-583, Apr. 2011.

[26] B. K. Kaushik, S. Sarkar, R. P. Agarwal and R. C. Joshi, "crosstalk Analysis of simultaneously switching coupled interconnects driven by unipolar inputs through heterogeneous resistive drivers," proc. IEEE Int. Conf. Emerging Technologies ICET, pp.278-283, 12-13 Nov. 2007.

[27] Kane Yee (1966), "Numerical solution of initial boundary value problems involving Maxwell's equations in isotropic media", IEEE Trans. on Antennas and Propagation, vol. 14, no. 3, page 302-307, 1966.

[28] R.Courant, K. Friedrichs and H. Lewy, "On the partial difference equations of mathematical physics," IBM Journal, March 1967, pp. 215-234, English translation of the 1928 German original.

[29] C. R. Paul, "Decoupling the multi conductor transmission line equations," IEEE Transactions on Microwave Theory and Techniques, 44(8):1429–1440, Aug. 1996.

[30] C. R. Paul, "Incorporation of terminal constraints in the FDTD analysis of transmission lines," IEEE Trans. Electromagnetic Compatibility, vol. 36, no. 2, pp. 85–91, May 1994.

[31] T. Sakurai and A. R. Newton, "Alpha-power model and its applications to CMOS inverter delay and other formulas," IEEE J. Solid-State Circuits, vol. 25, no. 2, pp. 584–594, Apr. 1990.

[32] K.K. Ng and W.T. Lynch, 'The impact of intrinsic series resistance on MOSFET scaling,' IEEE Trans. Electron Devices, vol. ED-34, pp. 503-511, Mar. 1987.

#### **List of Publication**

[1] Shailesh Mittal, B. K. Kaushik, K. L. Yadav, Manoj Kumar Majumder, "Dynamic Crosstalk Analysis in RLC Modeled Interconnects using FDTD Method," submitted to IEEE International Conference on Computer and Communication Technology (ICCCT), 23-25 Nov. 2012, MNNIT Allahabad. (Review result awaited)

[2] Shailesh Mittal, B. K. Kaushik, K. L. Yadav, Manoj Kumar Majumder," Analysis of Dynamic Crosstalk Delay in Coupled Interconnect using FDTD," submitted to International Conference on Communication, Computing & Security (ICCCS), 8-10 Oct. 2012, NIT Rourkela ,. (Review result awaited)