# INFLUENCE OF HIGH FIELDS ON STANDBY POWER DISSIPATION OF CMOS GATES

### **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree

of

**MASTER OF TECHNOLOGY**

in

**SOLID STATE ELECTRONIC MATERIALS**

By SANGHAMITRA GHOSH

DEPARTMENT OF PHYSICS

INDIAN INSTITUTE OF TECHNOLOGY ROORKEE

ROORKEE -247 667 (INDIA)

February, 2003

CANDIDATE'S DECLARATION

I hereby declare that the work which is being presented in this dissertation entitled

" INFLUENCE OF HIGH FIELDS ON STANDBY POWER DISSIPATION OF

CMOS GATES", in partial fulfillment of the requirements for the award of the degree

of Master of Technology in Solid State Electronic Materials, submitted in the

Department of Physics, Indian Institute of Technology Roorkee, Roorkee, is an authentic

record of my own work carried out during the period from June 2002 to February 2003,

under the supervision of Prof. S. Sarkar, Department of Electronics and Computer

Engineering and Prof. R. Nath, Department of Physics, Indian Institute of Technology

Roorkee, Roorkee.

The matter embodied in this dissertation has not been submitted by me for the award

of any other degree.

Date: 24.02.2003

Place: IIT Roorkee.

(Sanghamitra Ghosh)

It is certified that the above statement made by the candidate is correct to the best of

my knowledge and belief.

Date: 24.02.2003

Place: IIT Roorkee.

(Prof. S. Sarkar)

(Prof. R. Nath)

i

### **ABSTRACT**

The main contribution to standby power dissipation comes from the subthreshold leakage current. Hence, it is mandatory to develop a holistic model which accounts for all important physical phenomena taking place in the subthreshold regime. These include drift-diffusion, thermionic emission, short channel effects and high field effects. The subthreshold model has been specifically modified to include the high field effect in subthreshold region i.e., impact ionization which ultimately leads to avalanche breakdown. The standby power dissipation of a CMOS circuit is calculated using the concept of dominant leakage states, input state probabilities and the model mentioned above. Finally, the effect of multiplication on the standby power dissipation of the circuit is studied with respect to the applied inputs.

**ACKNOWLEDGEMENT**

I wish to convey my deep regards to Prof. S. Sarkar, Department of Electronics and

Computer Engineering, Indian Institute of Technology Roorkee, Roorkee, for his

esteemed guidance and healthy initiative at all stages of this dissertation. I specially thank

him for his patience and readiness to help at all times in the course of this work.

I express my sincere gratitude to Prof. R. Nath, Department of Physics, Indian

Institute of Technology Roorkee, Roorkee for his direction, help and support.

My sincere acknowledgement to Prof. Ishwar Singh Tyagi, Head, Department of

Physics, Indian Institute of Technology Roorkee, Roorkee for providing the necessary

facilities to carry out this work.

I thank my friends for their kind cooperation and encouragement.

I owe it to the blessings of my parents that I have been able to complete this work in

due time.

Date: 24.02.2003

(Sanghamitra Ghosh)

iii

## **CONTENTS**

| CANDIDATE'   | S DECLARATION                                | i    |

|--------------|----------------------------------------------|------|

| ABSTRACT     | •                                            | ii   |

| ACKNOWLEI    | OGEMENTS                                     | iii  |

| CONTENTS     |                                              | iv   |

| LIST OF FIGU | URES                                         | vi   |

| LIST OF TAB  | LES                                          | viii |

| NOMENCLAT    | TURE                                         | х    |

| CHAPTER 1    | INTRODUCTION                                 | 1    |

|              | 1.1 Overview                                 | 1    |

|              | 1.2 Objectives                               | 2    |

|              | 1.2.1 Statement of purpose                   | 2    |

|              | 1.2.2 Problem Statements                     | 2    |

|              | 1.3 Organization                             | 3    |

| CHAPTER 2    | LITERATURE RIVIEW                            | 4    |

| CHAPTER 3    | NMOS SUBTHRESHOLD CURRENT MODEL              | 9    |

|              | 3.1 Long channel model                       | 9    |

|              | 3.2 Short channel effects                    | 11   |

|              | 3.2.1 Charge sharing                         | 11   |

|              | 3.2.2 Drain induced barrier lowering         | 14   |

|              | 3.3 Drain current due to thermionic emission | 19   |

|              | 3.4 Conclusion                               | 20   |

| CHAPTER 4       | EFFECTS OF HIGH FIELDS AND SCALING ON                          | 21   |

|-----------------|----------------------------------------------------------------|------|

|                 | SUBTHRESHOLD CURRENT                                           |      |

|                 | 4.1 Impact ionization                                          | 21   |

|                 | 4.2 Scaling                                                    | 25   |

| CHAPTER 5       | STANDBY POWER ESTIMATION OF A DIGITAL                          | 27   |

|                 | CIRCUIT                                                        |      |

|                 | 5.1 Dominant leakage states                                    | 28   |

|                 | 5.2 Determination of state probabilities                       | 31   |

|                 | 5.2.1 Correlation coefficients and state probabilities         | 32   |

|                 | 5.2.2 Observability                                            | 36   |

|                 | 5.2.3 Algorithm                                                | 37   |

|                 | 5.3 Standby power calculation for each dominant leakage state. | 39   |

| CHAPTER 6       | RESULT AND DISSCUSSION                                         | 41   |

| CHAPTER 7       | CONCLUSION                                                     | . 62 |

| REFERENCES      |                                                                | 63   |

| APPENDICES<br>A | DEVICE PARAMETERS AND PHYSICAL CONSTANTS                       | A.1  |

| В               | NUMERICAL COMPUTATION OF NMOS DIBL COEFICIENT                  | B.1  |

| C               | GRAPHICAL DEDUCTION OF THRESHOLD VOLTAGE SHIFT                 | C.1  |

| D               | PROGRAMS                                                       | D.1  |

# LIST OF FIGURES

| Fig. No. | Figure Name                                                                                        | Page No. |

|----------|----------------------------------------------------------------------------------------------------|----------|

| 3.1      | NMOS energy and potential profile at the interface.                                                | 13       |

| 3.2      | Schematic illustration of depletion zones in an NMOS.                                              | 13       |

| 3.3      | Distribution of induced charge in an NMOS.                                                         | 16       |

| 3.4      | Simplified model of the drain bias induced charge.                                                 | 16       |

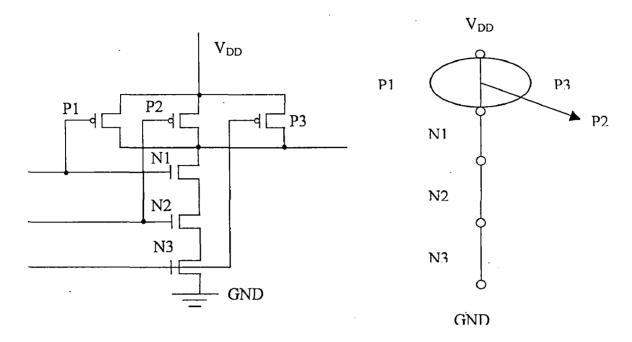

| 5.1a     | Circuit diagram of a NAND3 gate.                                                                   | 29       |

| 5.1b     | Euler Graph of a NAND3 gate.                                                                       | 29       |

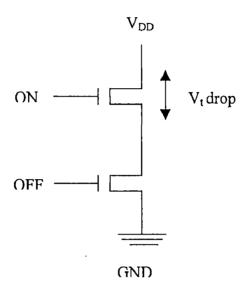

| 5.2      | Fig. 5.2: $V_T$ drop across the ON NMOS in an NMOS inverter.                                       | 31       |

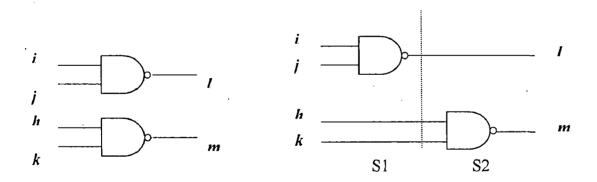

| 5.3      | Extension of the rules in Table 5.2 to calculate $C_{l,m}$ for two AND gates.                      | 35       |

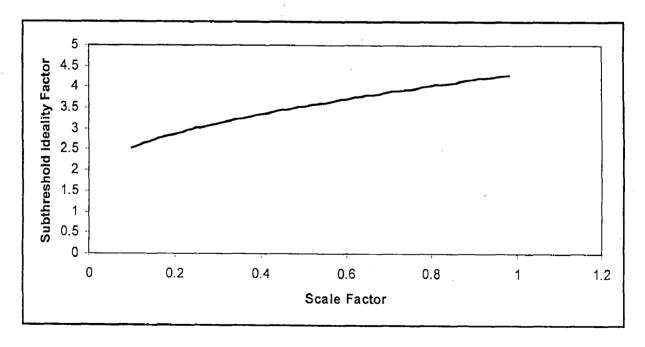

| 6.1      | Variation of subthreshold ideality factor with scale factor.                                       | 41       |

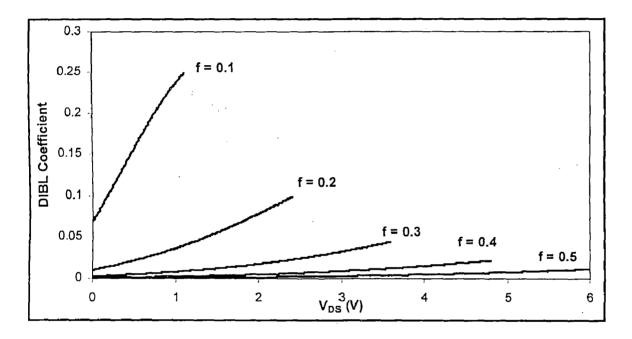

| 6.2      | Variation of DIBL coefficient with drain source voltage for different scale factors.               | 42       |

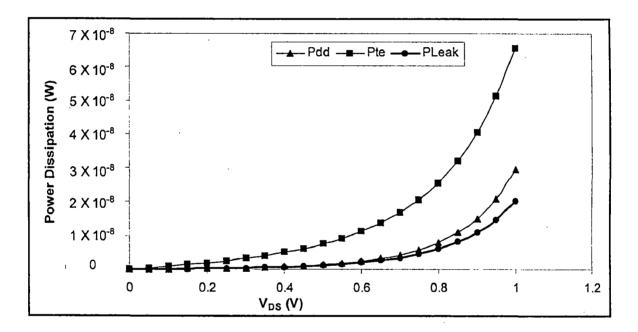

| 6.3      | Power dissipation ( $P_{Leak}$ , $P_{dd}$ , $P_{te}$ ) versus drain source voltage.                | .43      |

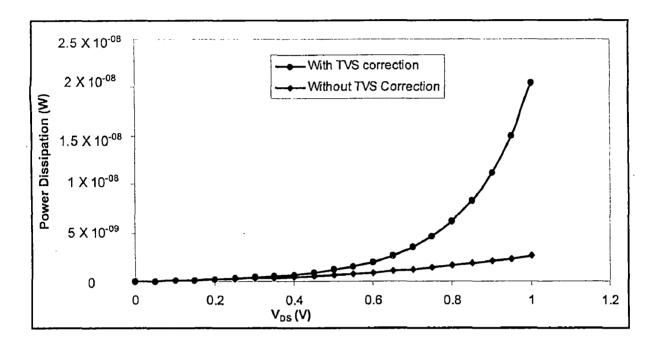

| 6.4      | Power dissipation versus drain-source voltage with and without threshold voltage shift correction. | 44       |

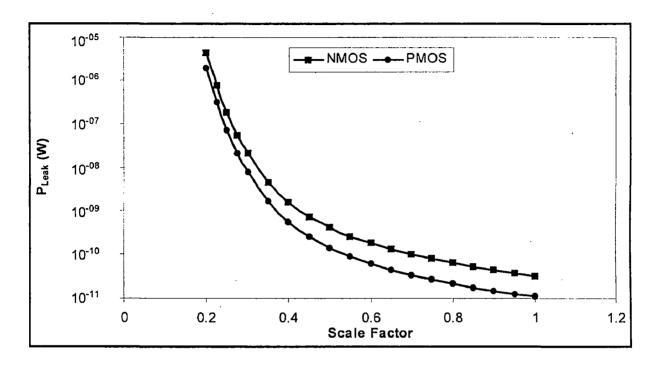

| 6.5      | Power dissipation versus scale factor.                                                             | 45       |

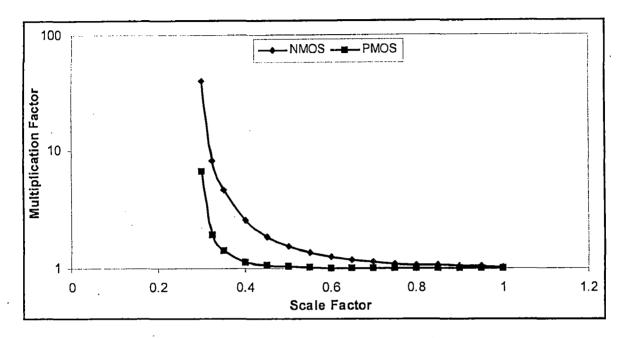

| 6.6      | Multiplication factor versus scale factor.                                                         | 46       |

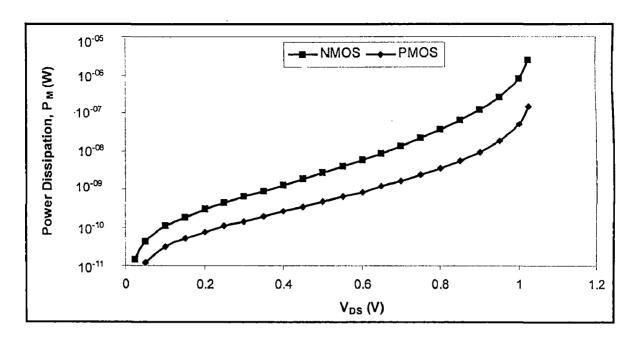

| 6.7      | Power dissipation $(P_M)$ versus drain source voltage.                                             | 47       |

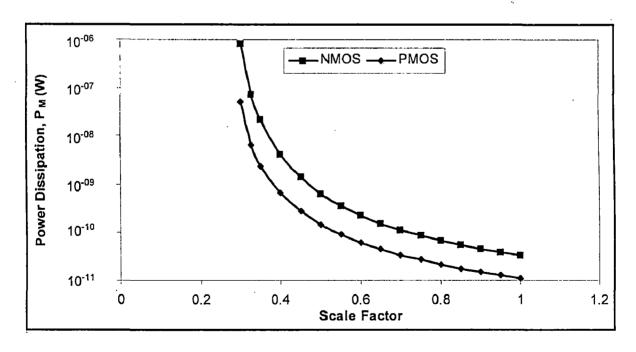

| 6.8      | Power dissipation $(P_M)$ versus scale factor.                                                     | 47       |

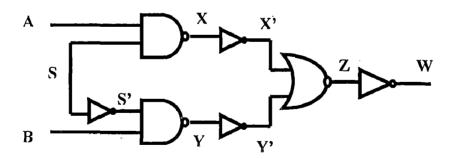

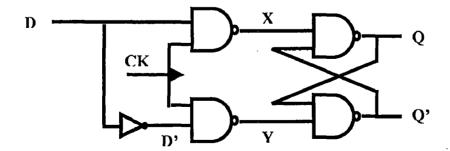

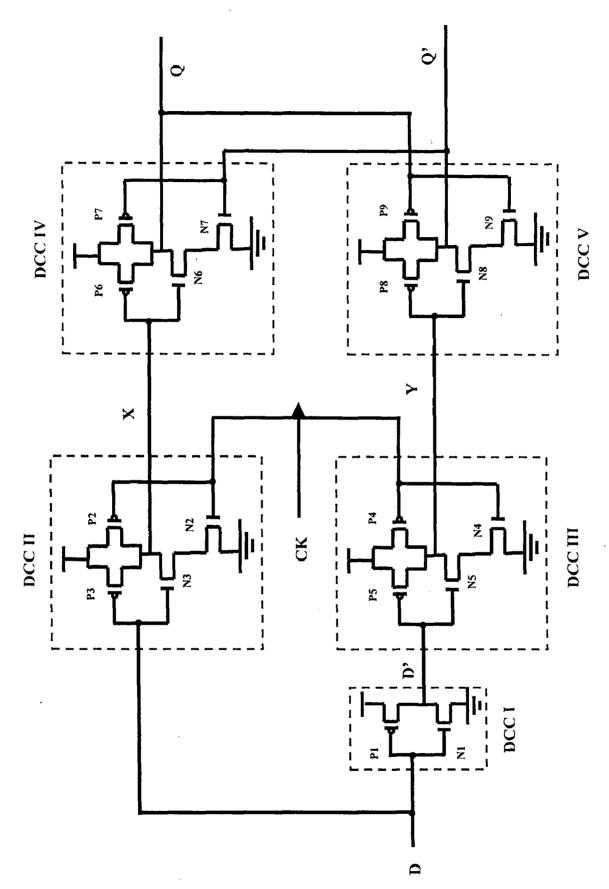

| 6.9      | Gate level diagram of a two input multiplexer.                                                     | 48       |

| Fig. No. | Figure Name                                                      | Page No |

|----------|------------------------------------------------------------------|---------|

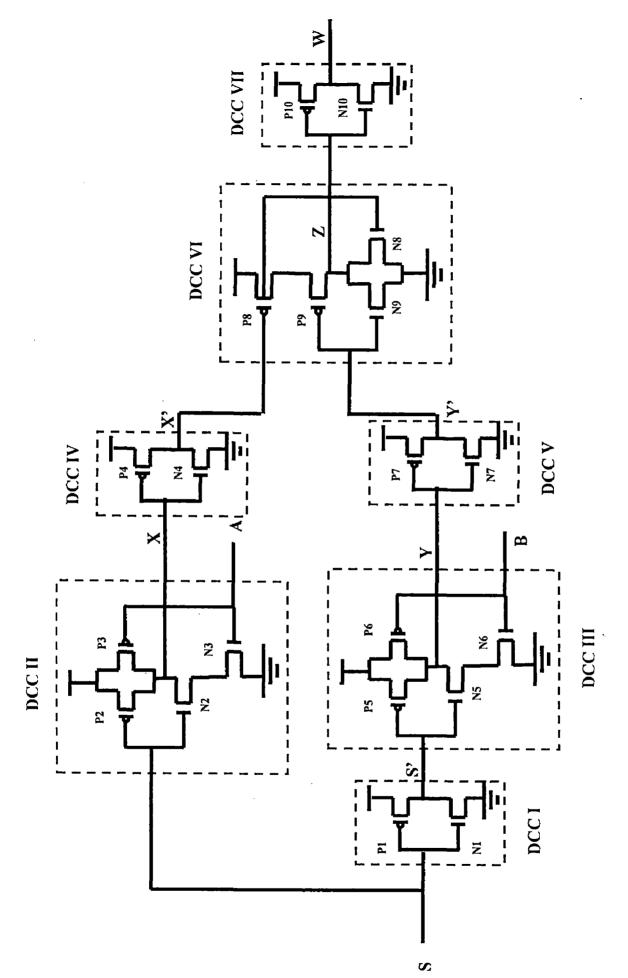

| 6.10     | CMOS circuit diagram of a two input multiplexer.                 | 49      |

| 6.11     | Gate level diagram of a D flip flop.                             | 51      |

| 6.12     | CMOS circuit diagram of a D flip flop.                           | 52      |

| C.1      | Variation of threshold voltage shift versus gate source voltage. | C.2     |

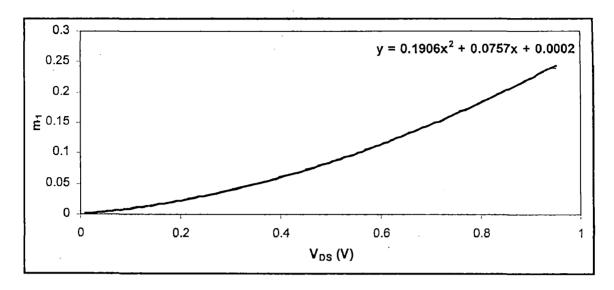

| C.2      | Variation of $m_1$ versus drain source voltage.                  | C.3     |

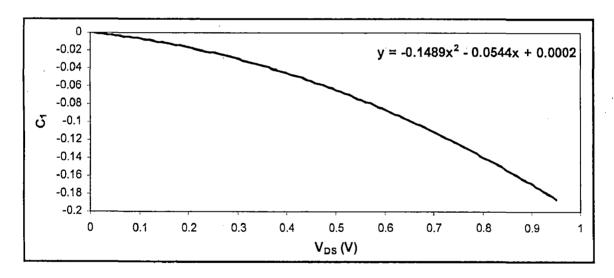

| C.3      | Variation of C <sub>I</sub> versus drain source voltage.         | C.3     |

| C.4      | Variation of threshold voltage shift with drain source voltage.  | C.4     |

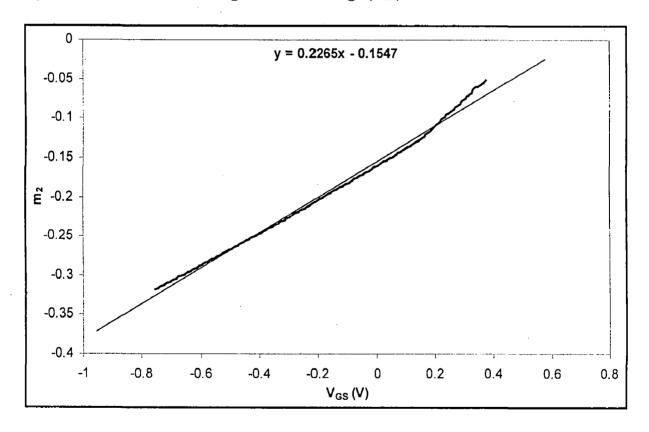

| C.5      | Variation of $m_2$ with gate source voltage.                     | C.4     |

# LIST OF TABLES

| Гable No. | Name                                                                                                                                                 | Page No. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.1       | Rules for calculating the node signal probability through the correlation coefficients.                                                              | 33       |

| 5.2       | Rules for determining the output correlation coefficients of a pair of signals given the input correlation coefficients and the input probabilities. | 34       |

| 5.3       | Rules for calculating the node observabilities through the correlation coefficients.                                                                 | 37       |

| 6.1       | Leakage power calculations for a NAND3 circuit with substrate doping of value $5 \times 10^{22}$ m <sup>-3</sup> .                                   | 54       |

| 6.2       | Leakage power calculations for a NAND3 circuit with substrate doping of value 10 <sup>23</sup> m <sup>-3</sup> .                                     | 55       |

| 6.3a      | Input states for DC connected components of a two input multiplexer.                                                                                 | 56       |

| 6.3b      | Transistors contributing to leakage in each DC connected component of a two input multiplexer.                                                       | 56       |

| 6.4       | Power dissipation of dominant leakage states for each DC connected component of a two input multiplexer.                                             | 57       |

| 6.5a      | Node probabilities corresponding to each DC connected component of a two input multiplexer.                                                          | 58       |

| 6.5b      | Output observabilities probabilities corresponding to each DC connected component of a two input multiplexer.                                        | 58       |

| 6.5c      | State probabilities corresponding to each DC connected component of a two input multiplexer.                                                         | 58       |

| 6.6       | Standby power dissipation of a two input multiplexer without considering the effect of multiplication.                                               | 59       |

| Table No. | Name                                                                                           | Page No |

|-----------|------------------------------------------------------------------------------------------------|---------|

| 6.7       | Standby power dissipation of a two input multiplexer considering the effect of multiplication. | 59      |

| 6.8       | Input states of a two input multiplexer in descending order of power dissipation.              | 60      |

| 6.9       | Average standby power dissipation of a two input multiplexer.                                  | 60      |

| 6.10a     | Input states for DC connected components of a D flip flop.                                     | 61      |

| 6.10b     | Transistors contributing to leakage in each DC connected component of a D flip flop.           | 61      |

| 6.11      | Total and average standby power dissipation of a D flip flop.                                  | 61      |

### **NOMENCLATURE**

| Symbol                           | Description                                                    |

|----------------------------------|----------------------------------------------------------------|

| $\alpha_n$                       | Electron ionization coefficient                                |

| $eta_{\!\scriptscriptstyle P}$   | Hole ionization coefficient                                    |

| $lpha_B$                         | Electron ionization coefficient at E <sub>B</sub>              |

| $eta_{B}$                        | Hole ionization coefficient at E <sub>B</sub>                  |

| $lpha_{M}$                       | Electron ionization coefficient at E <sub>M</sub>              |

| $eta_{\!\scriptscriptstyle M}$   | Hole ionization coefficient at E <sub>M</sub>                  |

| δ                                | Effective channel thickness                                    |

| $\mathcal{E}_{ox}$               | Oxide permittivity                                             |

| $\mathcal{E}_{\mathcal{S}}$      | Substrate permittivity                                         |

| η                                | Subthreshold ideality factor                                   |

| $\phi_b = V_{th} \log (N_a/n_i)$ | Position of Fermi level relative to the intrinsic level of the |

|                                  | doped substrate                                                |

| $\phi_{ms}$                      | Metal to semiconductor work function difference                |

| $\mu_n$                          | Effective mobility                                             |

| χ                                | Ratio of depletion charges induced in the channel to the total |

|                                  | additional depletion charge                                    |

| σ                                | Drain induced barrier lowering coefficient                     |

| $\psi(x,y)$                      | Two dimensional potential of the channel w.r.t source          |

| $\psi_{ST}^o$                    | Interface potential in the channel region at threshold         |

| $\psi^o_s$                         | Constant interface potential in the absence of drain bias below      |

|------------------------------------|----------------------------------------------------------------------|

|                                    | threshold                                                            |

| $\psi_s(x)$                        | Interface potential at a position x in the channel on applying a     |

|                                    | drain bias                                                           |

| $\psi_{sn}^{o}$ , $\psi_{sp}^{o}$  | NMOS and PMOS interface potential below threshold                    |

| <b>A</b>                           | Richardson's constant                                                |

| $C_{dep}(x)$                       | Channel depletion capacitance per unit area                          |

| $C_{ox} = \varepsilon_{ox}/t_{ox}$ | Gate oxide capacitance                                               |

| $d_{dep}$                          | Gate depletion width on application of a drain bias                  |

| $D_n = \mu_n \ V_{th}$             | Electron diffusion coefficient                                       |

| $d_o$                              | Gate depletion width in the absence of drain bias                    |

| $E_B$                              | Breakdown electric field                                             |

| $E_{g}$                            | Band gap                                                             |

| $E_M$                              | Maximum electric field                                               |

| $E_{nM}$ , $E_{pM}$                | Maximum electric field in NMOS and PMOS channel                      |

| $E_s$                              | Electric field at the Si-SiO <sub>2</sub> interface                  |

| $F_x$                              | Electric field component along the interface                         |

| $F_{y}$                            | Electric field component normal to the Si-SiO <sub>2</sub> interface |

| $F_{y}(o)$                         | Normal component of electric field component at the interface        |

| $I_d$                              | Subthreshold drain current                                           |

| $I_{dd}$                           | Subthreshold drift diffusion current                                 |

| $I_{dn}$ , $I_{dp}$                | Electron and hole subthreshold drain current                         |

| $I_{DS}$                           | Total drain source current considering multiplication                |

| $I_{DSn}$ , $I_{DSp}$ | NMOS and PMOS avalanche current                     |

|-----------------------|-----------------------------------------------------|

| $I_{s 	o d}^{o}$      | Thermionic emission current from source to drain at |

|                       | equilibrium                                         |

| $I_{d \to s}^{o}$     | Thermionic emission current from drain to source at |

|                       | equilibrium                                         |

| $I_{s \to d}$         | Thermionic emission current from source to drain    |

| $I_{d \to s}$         | Thermionic emission current from drain to source    |

| $I_{te}$              | Net thermionic emission current                     |

| $J_n$                 | n-channel current density per unit area             |

| K                     | Boltzman's constant                                 |

| L                     | Length of Gate                                      |

| M                     | Avalanche multiplication factor                     |

| $M_n$ , $M_p$         | Elecron and hole initiated multiplication           |

| $N_a$                 | Substrate doing per unit volume                     |

| $N_d$                 | Source and drain contact doping per unit volume     |

| $n_i$                 | Intrinsic carrier concentration per unit volume     |

| n = n(x)              | Electron density per unit area at position x        |

Average standby power dissipation  $P_{Avg}$ Standby power dissipation due to  $I_{dd}$  $P_{dd}$ Standby power dissipation due to  $I_d$  $P_{Leak}$ Standby power dissipation due to multiplication  $P_{M}$ Average standby power dissipation due to multiplication  $P_{MAvg}$ Total standby power dissipation due to multiplication in  $P_{MN}$ ,  $P_{MP}$ NMOS and PMOS Standby power dissipation due to  $I_{te}$  $P_{te}$ Electron charge Q Bulk charge in the MOS channel  $Q_b$ Total additional depletion charge  $\Delta Q$ Sheet charge distribution along the channel  $\Delta q(x)$ Drain biased induced charge in the substrate  $\Delta Q_1$ Drain biased induced charge at the gate  $\Delta Q_2$ Induced channel depletion charge  $\Delta Q_{ch}$ TTemperature Gate Oxide thickness  $t_{ox}$ V = V(x)Positive contribution to the potential due to drain bias  $V_{bi} = V_{th} \log \left( N_a N_D / n_i^2 \right)$ Built in voltage between the source contact and the substrate  $V_{DD}$ Supply voltage Applied drawn source voltage  $V_{DS}$  $V_{FB}$ Flat band voltage Applied gate source voltage  $V_{GS}$

$V_{min}$  Potential at the source-channel junction  $V_T$  Threshold voltage

$\Delta V_T$  Threshold voltage shift

$V_{th} = KT/q$  Thermal voltage

$V_{To}$  Threshold voltage at zero drain vias

$\dot{W}$  Width of Gate

$W_{eq}$  Equivalent junction width

$W_{eqn}$ ,  $W_{eqp}$  Equivalent junction width for  $n^+p$  and  $p^+n$ -junction

$x_d$ Drain-channel depletion width

$x_s$  Source-channel depletion width

#### INTRODUCTION

#### 1.1 Overview

For the last four decades, the semiconductor industry has been improving itself with rapid pace by betterment of its products. These have resulted principally from the industry's ability to continually follow Moore's Law i.e., exponentially scale down the minimum feature sizes of devices used to fabricate integrated circuits. As per the current scaling trend, the number of components per chip doubles every 18 months.

Standby power dissipation in a CMOS circuit occurs due to the existence of leakage currents in the NMOS and PMOS transistors even when they are not undergoing any switching event. Of the two leakage components, the subthreshold current is due to carrier diffusion between the drain and source of a MOS transistor in the weak inversion region of operation. A MOSFET is said to operate in the subthreshold region when the applied gate voltage is below the threshold voltage i.e., the conducting channel is weakly inverted. This region corresponds to the OFF state of the MOS device. But, there always exists some leakage current due to finite amount of charge at Si-SiO<sub>2</sub> interface. Another component, the reverse saturation current flows when the pnjunction between the drain and the bulk of a transistor is reverse biased. Since, junction leakage is two to three orders of magnitude smaller than the subthreshold component, it can be ignored for all practical purposes.

With decreasing feature sizes, the power supply voltage is also reduced. Hence, the threshold voltage of transistors is scaled down to maintain a constant switching speed. Since, the subthreshold leakage rises exponentially with decreasing threshold voltage, the leakage power dissipation in the standby mode increases significantly with scaling. Therefore, the contribution

of standby power dissipation to total average power dissipation increases with reduction in device dimensions.

As a MOS device is scaled down, the electric field in the subthreshold regime rises, leading to impact ionization. This finally causes avalanche breakdown. Therefore, the study of effect of impact ionization on CMOS circuits is important as high electric fields put a practical limit on the power handling capability of CMOS gates. So, the main objective of this work is to determine the standby power dissipation of a CMOS circuit, with and without the impact ionization consideration and compare the two results.

#### 1.2 Objectives

#### 1.2.1 Statement of Purpose

To study the influence of high fields on standby power dissipation of CMOS gates.

#### 1.2.2 Problem Statements

- a. To select an accurate subthreshold current model, its interpretation and complete mathematical analysis, for simulation purposes.

- Calculation of subthreshold ideality factor  $(\eta)$  and its variation with scaling.

- Calculation of threshold voltage shift/ DIBL coefficient ( $\sigma$ ) and study of its behavior.

- Determination of model parameters as a function of the scale factor.

- Extension of the model to PMOS device.

- b. To include the effect of high fields on this model and hence develop a modified current model.

- Calculation of maximum electric field.

- Calculation of multiplication factor.

- Extension to a PMOS device.

- c. To devise a method to calculate the standby power dissipation of a digital circuit using this model.

- Segregation of the circuit into DC-Connected Components (DCC).

- Calculation of Input State Propagation Probabilities for each DCC.

- Determination of Dominant Leakage States (DLS) for each DCC.

- Determination of standby power for each DLS using the model developed.

- Combining the results for different DCCs using state probabilities.

#### 1.3 Organization

This report is divided into six chapters. The first chapter is introduces the reader to the problems of this dissertation. The remaining part of the dissertation is organized as follows:

Prior work carried out in context of this dissertation is discussed in chapter 2. In chapter 3, the NMOS subthreshold current model used for the purpose of this study is discussed. The effects of constant electric field scaling and impact ionization on the drain current are presented in chapter 3. In chapter 4, a method to estimate the standby or leakage power dissipation of a digital circuit is described. Chapter 5 presents the results. In chapter 6 the study is concluded.

#### LITERATURE REVIEW

Estimation of standby power dissipation is time-consuming and expensive because of repeated leakage current evaluation using non-linear simulation models in large digital circuits. Leakage current calculation is complicated due to highly nonlinear behavior of the MOS drain current with respect to the drain-source voltage in the subthreshold regime of operation.

The basic theory for subthreshold current of MOSFETs [1] works well for long channel devices and with minor adjustments, can even account for some short channel effects. However, as device dimensions continue to scale down drastically to submicron range and further, constraints on the drain current increase [2]. One of the most important short channel effects is the lowering of the energy barrier between the source and the channel known as Drain Induced Barrier Lowering or DIBL [3]. Experimental studies [4] confirmed that DIBL leads to threshold voltage shift in short channel MOSFETs. Many theoretical models have been developed for the subthreshold current. For example, the BSIM current model [5] takes the threshold voltage shift into consideration. But, being empirical in nature, it is not suitable for modeling deep submicron devices. Fjeldly and Shur proposed a completely analytical model for the subthreshold regime [6]. This model is based on the concept of charge sharing. The drain induced depletion charge in the channel is estimated using this concept and an expression for the distribution of charge along the channel is found by using two-dimensional Poisson's equation. It is possible to determine the DIBL and hence the threshold voltage shift using this distribution.

Two mechanisms, namely the phenomenon of drift-diffusion and thermionic emission determine the current in the MOS channel. The currents corresponding to both the

mechanisms depend on the Si-SiO<sub>2</sub> interface potential, which is a function of the threshold voltage shift among other parameters. The current limiting mechanism that leads to the highest impedance dominates the total channel current. This implies that the drain current is dominated by the smaller of the two.

With device scaling, electric field in the channel region increases. In the submicron regime, the field may rise to the order of 10<sup>7</sup> Vm<sup>-1</sup> for a moderate drain voltage. Such a high field may bring about multiplication in the subthreshold regime. Multiplication factors must account for the different ionization rates in electron and holes. Analytical approximations for the multiplication factors due to holes and electrons in germanium and silicon one-sided abrupt junctions are available in Ref. [9]. This analysis is quite accurate. The approach followed is that of a uniform field equivalent junction. The actual depletion width of the drain junction is replaced by an equivalent width corresponding to an equivalent electric field with the same multiplication factor. The ratio of equivalent width to actual width is calculated for an abrupt junction using the condition that, the magnitude of multiplication factor tends to infinity just at the point of breakdown. Resulting expressions for multiplication factors are quite accurate and have zero error at the breakdown field, which is important when using it for high multiplications. Spirito [9] also discusses different cases corresponding to low multiplication levels (which depend on single ionization rate i.e., either electron ionization rate or hole ionization rate) and high multiplication levels.

Troutman [10] presents a model specifically developed for low level multiplication in MOSFETs and discusses the results of both theoretical and experimental analyses. At high multiplication levels, the ionization integral is a function of ionization rates of both electrons and holes. For example, in an NMOS channel when the electric field is high enough, the secondary holes can also gain enough energy to cause impact ionization. In the saturation

region, channel current consists of electrons that are thermally emitted over the potential barrier at the source. Since, electric field is maximum just beneath the drain, electrons are collected by the reverse biased drain junction. Some of the primary electrons can gain enough energy to cause impact ionization of an electron-hole pair. The secondary electrons with energy higher than the Si-SiO<sub>2</sub> energy barrier are injected into the gate oxide. The secondary holes thus collected at the drain are prevented from reaching the source by the built in potential and are collected at the substrate. Therefore, experimental values of multiplication factor in the saturation regime are determined by measuring channel and substrate currents.

Assumptions used in deriving the expression for multiplication in the saturation region are invalid in the subthreshold region. An approximation used in calculation of ionization integral is that the drain junction is a one-dimensional abrupt n<sup>+</sup>p-junction. On application of drain-source voltage, electric field from source to drain reaches peak value in a linear fashion. Implicit in the above assumption is that only the lateral field or the field parallel to the channel current is important for determining subthreshold multiplication behavior. Such an approximation is not valid for saturation region where gate-source voltage plays an equally important part. In the subthreshold region, unlike saturation region, multiplication hardly depends on gate source voltage.

The model leads to reasonable agreement with experimental data for a long channel device in the range of low-level multiplication. Comparison with experimental results for variation of multiplication with drain source voltage when extended to higher multiplication levels for subthreshold regime, indicate a sharper breakdown than indicated by the model.

As the device thresholds are reduced to maintain performance in large circuits, the subthreshold current becomes significant due to the exponential relation between device

current and threshold voltage. This necessitates the need for developing accurate standby power estimation techniques.

Chen et al. [13] have developed a simple model for leakage estimation using the concept of transistor stacks. The subthreshold current of MOSFETs constituting the stack is modeled using the BSIM2 subthreshold current equation. Steady state leakage values are estimated as a function of the number of transistors that are turned off. Since, the subthreshold current flowing through each transistor in a series stack is the same, the current through each transistor is equated and solved for voltage across each transistor. These voltages are then used to determine the magnitude of current and finally the power dissipation. The standby power of a circuit for a given primary input state is calculated by simply summing the leakage power consumed by off transistors. The voltage across on transistors is assumed to be negligible due to small amounts of currents involved and they are treated as short circuit. This is one of the major disadvantages of this model leading to erroneous leakage estimation. Not all on transistors in the stack can be treated as a short circuit because of the threshold voltage drop across some of them.

Chen et al. [13] mainly focus on calculating the maximum leakage across all permutations of the unspecified inputs using genetic algorithm technique. However, a leakage model is meaningful only when the device has been idle for some time. A device becomes idle many times during the lifetime of its battery, each time with a random setting for the unspecified input signals. Furthermore, the state of a circuit's inputs is typically partially defined when the device enters standby mode. To obtain a reliable estimate of average battery lifetime, the average rather than the maximum circuit leakage must be calculated.

Sirichotiyakul et al. [14] describe a new approach for efficient estimation of standby power dissipation. The method proposed by them uses a variety of problem reduction techniques like dominant leakage states and state probabilities [15] combined with graph reduction techniques. The average standby power dissipation of a circuit is obtained from leakage of individual DC connected components. The notion of dominant leakage states is introduced for each DC connected component. A state with more than one off transistor in the  $V_{DD}$ -ground leakage path is far less leaky than a state with only one transistor off in the  $V_{DD}$ -ground path. The latter states are called dominant leakage states, which are usually very small compared to the number of all possible states. This eliminates the need to simulate all possible states for a DC connected component, saving simulation time. The leakage power of each dominant leakage state of a DC connected component is obtained from precharacterized tables of current values based on Newton-Raphson iterations. These iterated values are derived from a subthreshold current model similar to the BSIM2. The average leakage of a circuit for a particular primary input state is obtained from leakage of individual DC connected components and from their state probabilities. This method claims to achieve speedups of three to four orders of magnitude over exhaustive SPICE simulations while maintaining very good accuracy.

### NMOS SUBTHRESHOLD CURRENT MODEL

The existing subthreshold current model as proposed by Fjeldly and Shur [6] is described below.

### 3.1 The long channel model

In the subthreshold region, the MOSFET behaves almost like a Bipolar Junction Transistor with the channel as a long base. The n<sup>+</sup> source acts as an emitter and the drain acts as the collector. Therefore, for a long channel device, most of the voltage applied at the drain will drop across the reverse biased n<sup>+</sup>p junction, the longitudinal electric field component being much smaller than the component normal to the Si-SiO<sub>2</sub> interface. The current is then simply the sum of drift and diffusion terms as for a BJT. The current density is given by [6]

$$J_n = -q \left( -n\mu_n \frac{d\psi}{dx} + D_n \frac{dn}{dx} \right) = -qD_n \left( -\frac{n}{V_{th}} \frac{d\psi}{dx} + \frac{dn}{dx} \right) \qquad \dots (3.1)$$

Multiplying (3.1), by the integrating factor  $exp(-\psi/V_{th})$ , and integrating from source (x=0) to drain (x=L), gives

$$J_{n} = qD_{n} \frac{n(0) \exp\left(-\frac{\psi(0, y)}{V_{th}}\right) - n(L) \exp\left(-\frac{\psi(L, y)}{V_{th}}\right)}{\int_{0}^{L} \exp\left(-\frac{\psi(x, y)}{V_{th}}\right) dx} \dots (3.2)$$

Implicit in (3.2), is the assumption that the current density is independent of position of carriers in the channel. Disregarding degeneracy, the source contact concentration n(0) and the drain contact n(L) are both equal, i.e.,  $N_d \neq N_a$ . Conventionally, the source contact being the potential reference,  $\psi(0, y) = 0$  and  $\psi(L, y) = V_{DS}$ .

The drift-diffusion current is then obtained by integrating (3.2) over the cross-section of the conducting channel,

$$I_{dd} = q N_d W \delta D_n \frac{\left[1 - \exp\left(-\frac{V_{DS}}{V_{th}}\right)\right]}{\int\limits_{0}^{L} \exp\left(-\frac{\psi(x, y)}{V_{th}}\right) dx} \qquad \dots (3.3)$$

The effective channel thickness  $\delta$ , normal to the Si-SiO<sub>2</sub> interface depends on the interface potential. At threshold, the interface potential in the channel is given by

$$\psi_{sT}^{o} = -V_{bi} + 2\phi_{b} \qquad ...(3.4)$$

Below threshold, the interface potential can be expressed as

$$\psi_s^o = \psi_{sT}^o + \frac{V_{GT}}{\eta} = -V_{bi} + 2\phi_b + \frac{V_{GT}}{\eta} \qquad ...(3.5)$$

where, the subthreshold ideality factor  $\eta$  [7] reflects division of gate voltage between the depletion layer capacitance and the gate oxide capacitance. The voltage,  $V_{GT} = V_{GS} - V_T$ . The threshold voltage  $V_T$  is given by

$$V_T = \phi_{ms} - \frac{Q_{ss}}{C_{ox}} - \frac{Q_b}{C_{ox}} + 2\phi_b = V_{FB} - \frac{Q_b}{C_{ox}} + 2\phi_b \qquad ...(3.6)$$

where [2],

$$\phi_{ms} = -\frac{E_g}{2q} - \phi_b \qquad \dots (3.7)$$

Since, the electron density in the channel is exponentially dependant on the interface potential  $\psi_s^o$ ,  $\delta$  corresponds to the thickness of the channel with respect to the interface where the potential has decreased by  $V_{th}[1]$ . Therefore,

$$\delta = V_{th} / E_s \qquad \dots (3.8)$$

From Gauss's law,

$$E_s = -Q_h / \varepsilon_s \qquad \dots (3.9)$$

where,

$$Q_{h} = -\sqrt{2q\varepsilon_{s}N_{a}(\psi_{s}^{o} + V_{bi})} \qquad ...(3.10)$$

Therefore,

$$\delta = V_{th} \sqrt{\frac{\varepsilon_s}{2qN_a(2\phi_b + V_{GT}/\eta)}} \qquad ...(3.11)$$

The above expression is valid when  $-2\varphi_b < V_{GT}/\eta < 0$  i.e., in the weak inversion and depletion region.

#### 3.2 Short channel effects

As the gate length of the MOS device is reduced, departures from long channel behavior take place due to two dimensionality of the electric field. The potential distribution now depends on both the transverse field due to the gate and the longitudinal field due to the drain bias. Therefore, the potential distribution becomes two-dimensional and GCA is no longer valid.

#### 3.2.1 Charge sharing

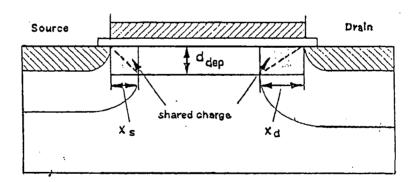

At short gate lengths, the drain depletion region and the source depletion region may represent a considerable fraction of channel length. The source and drain depletion regions intrude into the channel even without bias and in effect take part of the channel charge otherwise controlled by the gate. Therefore, in the denominator of (3.3), the integral becomes very small in the junction depletion zones as the potential increases rapidly. Hence, one of the considerations of the short channel effect is to replace the limits of the integral from  $0 \rightarrow L$  to  $x_s \rightarrow L$ - $x_d$ .

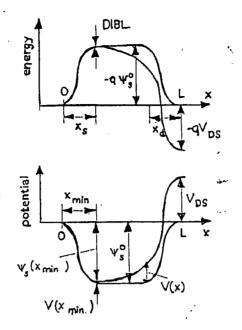

Fig. 3.1: Band diagram (top) and potential profile (bottom) at the semiconductor-insulator interface of an n-channel MOSFET. The symmetrical profiles correspond to  $V_{DS} = 0$ , and the asymmetrical profiles to  $V_{DS} > 0$ . The figure indicates the origin of DIBL. The symbols are defined in the text.

Fig. 3.2: Schematic illustration of the depletion zones associated with the source, drain and gate for an applied  $V_{DS}$ . The shaded areas near source and drain indicate the regions of charge sharing.

#### 3.2.2 Drain induced barrier lowering (DIBL)

With increase in positive drain bias, the drain depletion zone can grow to the extent that it begins to interact with the source channel junction. This is responsible for two basic effects:

a. The drain bias induces a positive shift V(x) in potential such that V(0) = 0 and  $V(L) = V_{DS}$ . Therefore,

$$\psi_s = \psi_s^o + V(x) \tag{3.14}$$

The interface potential is now a function of x as shown in Fig. 3.1. At the source channel boundary,  $V(x) = V(x_s) = V_{min}$ . Therefore,

$$\psi_{s}(x_{s}) = \psi_{s}^{a} + V(x_{s})$$

...(3.15)

The reduction in the potential at the source leads to a lowering of the interface energy barrier between the source and channel by  $-qV_{min}$ . As a result, the charge injection from the source to the channel increases.

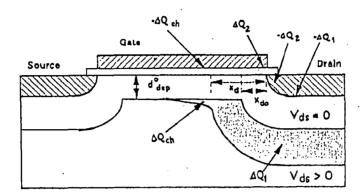

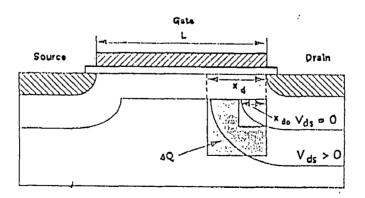

b. With a large depletion region, the additional induced drain depletion charge is distributed non-uniformly from drain to source (Fig. 3.3). Using, the principle of charge sharing, the charges and their counter charges can be paired, such that, a fraction of the additional drain charge  $\Delta Q_{ch}$  has its counter charge  $-\Delta Q_{ch}$  on the gate electrode. The remaining charges and counter charges are between the drain and the substrate  $(\Delta Q_1, -\Delta Q_1)$  and between drain and gate  $(\Delta Q_2, -\Delta Q_2)$ .

Both these effects can be taken care of by beginning with the Poisson's equation for the depletion region under the gate, away from source and drain depletion zones.

$$\frac{\partial F_x}{\partial x} + \frac{\partial F_y}{\partial y} = -\frac{qN_a}{\varepsilon_s} \qquad \dots (3.16)$$

Integrating with respect to y from the Si-SiO2 interface through the depletion region yields

$$\left\langle \frac{\partial F_x}{\partial x} \right\rangle d_{dep} - F_y(0) = -\frac{qN_a d_{dep}}{\varepsilon_s} \qquad \dots (3.17)$$

From one dimensional theory,

$$d_{dep} \approx \sqrt{\frac{2\varepsilon_s}{qN_a}(\psi_s + V_{bi})} = d_o \sqrt{1 + \frac{V(x)}{\psi_s^o + V_{bi}}} \qquad ...(3.18)$$

From the principle of continuity of electric field across a boundary,

$$F_{y}(0) = \frac{C_{ox}}{\varepsilon} (V_{GS} - V_{FB} - \psi_{s} - V_{bi}) \qquad ...(3.19)$$

Away from source and drain,  $\langle \partial F/\partial x \rangle = 0$  when  $V_{DS} = 0$ . Considering (3.17) with and without an applied drain bias and taking the difference,

$$\frac{\partial^2 V}{\partial x^2} d_{dep}(x) - \frac{C_{ox}}{\varepsilon_s} V(x) = \frac{qN_a}{\varepsilon_s} \left[ d_{dep}(x) - d_o \right] \qquad \dots (3.20)$$

Since, V(x) and its x-derivatives are small outside the drain depletion region, first order expansion of (3.20) in V(x) yields

$$\frac{\partial^2 V}{\partial x^2} - \frac{V}{\lambda^2} = 0 \tag{3.21}$$

where,

$$\lambda = d_o \left( 1 + \frac{\varepsilon_{ox} d_o}{\varepsilon_{s} t_{ox}} \right)^{-1/2} \dots (3.22)$$

Without much error, it can be assumed that (3.21) is valid for  $x < x_s$  also. Therefore, the boundary condition becomes V(x = 0) = 0. Using this Condition, the solution of (3.22) is

$$V(x) = V_0 \sinh(x/\lambda) \qquad \dots (3.23)$$

where,  $V_o$  is a constant to be determined.

Fig. 3.3: Distribution of depletion charge induced by an applied drain-source bias, indicated by the shaded region  $\Delta Q_{ch}$  is part of the induced charge located in the central channel region and has its counter charge on the gate electrode.

Fig. 3.4: Simplified model of the drain-bias induced charge  $\Delta Q$  in the substrate under the gate. The induced channel charge  $\Delta Q_{ch}$  is taken to be a fraction of  $\Delta Q$ , according to the principle of charge sharing.

The charge distribution at any point x in the channel is given by

$$\Delta q(x) = C_{dep} V(x) \approx \frac{V_o \varepsilon_s}{d_o} \sinh(x/\lambda)$$

...(3.24)

where,

$C_{dep}(x)$  has been expanded to lowest order in V(x). Assuming that, in the range  $x_s \le x \le L - x_d$ , the integral of  $\Delta q(x)$  is  $\Delta Q_{ch}$ ,  $V_o$  is obtained as

$$V_o = \frac{\Delta Q_{ch} d_o}{W \lambda \varepsilon_s} \left[ \cosh(\frac{L - x_d}{\lambda}) - \cosh(\frac{x_s}{\lambda}) \right]^{-1} \qquad \dots (3.25)$$

The shaded region in Fig. 3.4 gives an approximate estimate of the additional depletion charge under the gate electrode.

$$\Delta Q \approx qWN_a (x_d^2 - x_{do}^2) \tag{3.26}$$

Let  $\Delta Q_{ch}$  be some fraction  $\chi$  of the charge  $\Delta Q$ . With  $x_{do} \approx x_s$ ,

$$\Delta Q_{ch} \approx \chi q W N_a (x_d^2 - x_{do}^2) \approx 2 \chi W \varepsilon_s V_{DS} \qquad ...(3.27)$$

From (3.24) and (3.26),  $V_o$  is obtained as

$$V_o \approx \frac{2\chi V_{DS} d_o}{\lambda} \left[ \cosh(\frac{L - x_d}{\lambda}) - \cosh(\frac{x_s}{\lambda}) \right]$$

...(3.28)

Therefore, the potential corresponding to the barrier lowering at the source channel boundary is

$$V(x_s) \approx \frac{2\chi V_{DS} d_o \sinh(x_s/\lambda)}{\lambda} \left[ \cosh(\frac{L - x_d}{\lambda}) - \cosh(\frac{x_s}{\lambda}) \right]^{-1} \qquad \dots (3.29)$$

As a consequence of barrier lowering, there is a drain-bias-induced shift in the threshold voltage. From (3.5), the threshold voltage shift can be taken as,

$$\Delta V_T = -\eta V(x_s) \tag{3.30}$$

Combining (3.29) and (3.30) gives,

$$\Delta V_T = -\eta V(x_s) = -\sigma V_{DS} \qquad \dots (3.31)$$

where,  $\sigma$  is the drain induced barrier lowering coefficient.

The main improvisation on the model proposed by Fjeldly and Shur is the numerical computation of the subthreshold ideality factor and the DIBL coefficient. Although, the model given in [6] is purely analytical, both  $\eta$  and  $\sigma$  are calculated numerically with the constraint that they both satisfy  $L >= x_s + x_d$  and equation (3.29). This is done to account for the effect of these parameters on the model current equation. The method used for numerical computation is bisection method because of surety of convergence of this particular numerical method. The detailed calculation of  $\eta$  and  $\sigma$  are given in appendix C.

Considering the above mentioned short channel effects, the integrand in the denominator of (3) can now be evaluated. Since, the integrand is exponentially dependent on the potential, the hyperbolic sine function in (3.23) can be expanded to first order in x, i.e.,

$$\int_{x_{s}}^{L-x} d \exp(-\frac{\psi(x)}{V_{th}}) dx \approx \exp(-\frac{\psi_{s}^{o}}{V_{th}}) \int_{x_{s}}^{L-x} d \exp\left(-\frac{V_{o}x}{V_{th}\lambda}\right) dx$$

$$\approx \frac{\lambda V_{th}}{V_{o}} \exp\left(-\frac{\psi_{s}^{o} + V(x_{s})}{V_{th}}\right) \left\{1 - \exp\left(-\frac{V_{o}(L - x_{s} - x_{d})}{V_{th}\lambda}\right)\right\}$$

...(3.32)

Therefore, the drift diffusion current is obtained as

$$I_{dd} = \frac{qN_d W \delta D_n V_o}{\lambda V_{th}} \frac{\exp((\psi_s^O + V(x_s)) / V_{th}) [1 - \exp(-V_{DS} / V_{th})]}{1 - \exp(-V_o (L - x_s - x_d) / V_{th} \lambda)} \qquad ...(3.33)$$

#### 3.3 Drain Current due to thermionic emission

The net drain current due to thermionic emission is zero at zero drain-source bias. Therefore, the equilibrium thermionic emission current from source to drain,  $I_{s\to d}^o$ , and from drain to source,  $I_{d\to s}^o$ , are given by

$$I_{s \to d}^o = I_{d \to s}^o = I_o \exp(\frac{\psi_s^o}{V_{th}}) \qquad \dots (3.34)$$

and

$$I_{o} = W \delta A T^{2} \qquad \dots (3.35)$$

where A is the Richardson's constant. When a finite voltage is applied to the drain, the phenomenon of DIBL also contributes to the current. Thus,

$$I_{s \to d} = I_o \exp(\frac{\psi_s(x_s)}{V_{th}}) = I_o \exp(\frac{\psi_s^o + V(x_s)}{V_{th}}) \qquad ...(3.36)$$

$$I_{d\to s} = I_{s\to d} \exp(-\frac{V_{DS}}{V_{th}}) \qquad \dots (3.37)$$

The net thermionic emission current under a drain-source bias from (3.36) and (3.37) is

$$I_{ie} = I_{s \to d} - I_{d \to s} = I_o \exp(\frac{\psi_s^o + V(x_s)}{V_{th}}) [1 - \exp(-\frac{V_{DS}}{V_{th}})] \qquad ...(3.38)$$

It is observed that the mechanisms of drift-diffusion and thermionic emission act predominantly in a serial fashion. The drain current will be limited by the one, which corresponds to the highest impedance. Therefore, the total drain current can be written as a combination of (3.33) and (3.38) as

$$I_d \approx \left[\frac{1}{I_{dd}} + \frac{1}{I_{te}}\right]^{-1} \tag{3.39}$$

As can be seen from the above expression, the current limiting mechanism at small gate lengths is thermionic emission, whereas drift-diffusion dominates at larger gate lengths.

Consequently, the standby power dissipation is given by

$$P_{l,eak} = I_d V_{DS} \tag{3.40}$$

#### 3.4 Conclusion

The expressions for NMOS drain current and leakage power dissipation ignoring impact ionization are given by (3.39) and (3.40). Further analysis presented in this dissertation is based on these equations. The model equations for PMOS have been obtained as well through similar analysis. Therefore, PMOS modeling is not being described here.

### EFFECTS OF HIGH FIELDS AND SCALING ON SUBTHRESHOLD CURRENT

The model of Fjeldly and Shur [6] ignores the effects of very high fields in the MOS channel. This is a good approximation for long channel and above submicron devices. As the channel length is reduced, electric field in the channel increases. One of the important high field effects is impact ionization. For large drain voltages, impact ionization can become a deciding factor for drain current and hence, leakage power dissipation.

#### 4.1 Impact ionization

When a semiconductor is subjected to an increasing electric field, a point is reached where the carrier velocities approach their saturation values. Any further increase in electric field leads to an increase in their average kinetic energies. At fields of the order of 10<sup>7</sup> Vm<sup>-1</sup>, significant numbers of carriers acquire energies higher than the band gap. These primary hot carriers collide with the lattice atoms to generate secondary electron hole pairs (EHPs). This process continues resulting in carrier multiplication and is known as the avalanche process.

In connection with the secondary EHP generation, the ionization coefficient ( $\alpha$  for electrons and  $\beta$  for holes) is defined as number of EHPs produced per carrier on moving a unit distance along the electric field. For the given MOS device, the electric field is highest just below the Si-SiO<sub>2</sub> interface. The drain current in NMOS due to electron multiplication is given by [8]

$$I_{DS} = M_n I_{dn} \qquad \dots (4.1a)$$

Similarly, drain current in PMOS due to hole multiplication is given by

$$I_{DS} = M_p I_{dp} \qquad \dots (4.1b)$$

The ionization integral, is a measure of number of secondary EHPs generated per electron or hole.

For electron initiated multiplication, ionization integral is given by

$$1 - \frac{1}{M_n} = \int_{0}^{E_M} \alpha_n \exp\left(-k_n \int_{0}^{E} (\alpha_n - \beta_p) dE'\right) dE \qquad \dots (4.2a)$$

For hole initiated multiplication, ionization integral is given by

$$1 - \frac{1}{M_p} = \int_{0}^{E_M} \beta_p \exp\left(-k \int_{E}^{E_M} (\beta_p - \alpha_n) dE'\right) dE \qquad ...(4.2b)$$

where,

$$\alpha_n = A_n \exp(-\frac{b_1}{E_M}) \qquad \dots (4.3)$$

$$\beta_p = B_p \exp(\frac{-b_2}{E_M}) \qquad \dots (4.4)$$

$$k_n = \frac{\mathcal{E}_s}{N_c} \qquad \dots (4.5a)$$

and

$$k_p = \frac{\varepsilon_s}{N_d} \qquad \dots (4.5b)$$

Considering the drain as an one dimensional abrupt junction, the actual depletion width, say W, can be replaced by an equivalent one,  $W_{eq}$ , with the same multiplication of the actual junction such that [9]

For an n<sup>+</sup>p-junction,

$$1 - \frac{1}{M_n} = \frac{\alpha_M}{\beta_M - \alpha_M} \left[ \exp\left( (\beta_M - \alpha_M) W_{eqn}(E_M) \right) - 1 \right] \qquad \dots (4.6a)$$

For an p<sup>+</sup>n-junction,

$$1 - \frac{1}{M_p} = \frac{\beta_M}{\alpha_M - \beta_M} \left[ \exp\left((\alpha_M - \beta_M)W_{eqp}(E_M)\right) - 1 \right] \qquad \dots (4.6b)$$

where,

$$W_{enn}(E_M) = m_n W_n = m_n k_n E_M \qquad \dots (4.7a)$$

and

$$W_{eqp}(E_M) = m_p W_p = m_p k_p E_M$$

...(4.7b)

$m_n$  and  $m_p$  are proportionality factors less than 1.

The multiplication factor is now a function of peak electric field through the equivalent junction width and carrier ionization coefficients as can be seen from equations (4.3), (4.4) and (4.7).

The breakdown field  $E_B$ , is that critical value of electric field, above which carrier multiplication by impact ionization sets in. If the electric field increases any further on account of increase in the drain-source voltage, the drain looses control of the current because of avalanche breakdown. The typical value of breakdown field for silicon is about  $3 \times 10^7 \text{ Vm}^{-1}$ . For  $E_M >> E_B$ ,  $M \to \infty$  and hence,  $1-1/M \to 1$ . Therefore, for  $E_M \ge E_B$ ,  $m_n$  and  $m_p$  can be approximated as

$$m_{nB} = \frac{\ln(\alpha_B / \beta_B)}{\alpha_B - \beta_B} \frac{1}{k_n E_B} \qquad \dots (4.8a)$$

$$m_{pB} = \frac{\ln(\alpha_B / \beta_B)}{\alpha_B - \beta_B} \frac{1}{k_p E_B} \dots (4.8b)$$

At breakdown,

$$m_n = m_{nB} (E_M / E_B) \qquad \dots (4.9a)$$

$$m_p = m_{pB}(E_M / E_B) \qquad \dots (4.9b)$$

Using, (4.9a) in (4.6a), the multiplication factor for electrons is obtained as

$$M_n = 1/[1 - \alpha_M/(\beta_M - \alpha_M)(\exp(m_{nB}E_M/E_B) - 1)]$$

...(4.10a)

Using, (4.9b) in (4.6b), the multiplication factor for holes is obtained as

$$M_p = 1/[1 - \beta_M/(\alpha_M - \beta_M)(\exp(m_{pB}E_M/E_B) - 1)]$$

...(4.10b)

The maximum field depends on the drain source voltage as well as the gate source voltage through the following relation [10], [11]

$$E_{nM} = \sqrt{\frac{2qN_a}{\varepsilon_s} \left( V_{DS} - b_n \phi_{bn} + V_{bin} \right)} \qquad ...(4.11a)$$

$$E_{pM} = \sqrt{\frac{2qN_d}{\varepsilon_s} \left( V_{SD} + b_p \phi_{bp} - V_{bip} \right)} \qquad ...(4.11b)$$

where,

$$b_n = \left| \frac{\psi_{sn}^o}{\phi_{bn}} \right| \qquad \dots (4.12a)$$

$$b_p = \frac{\left|\psi_{sp}^{o}\right|}{\left|\phi_{bp}\right|} \qquad \dots (4.12b)$$

The NMOS interface potential below threshold,  $\psi^o_{sn}$  is given by equation (3.5) of chapter 3. The PMOS interface potential,  $\psi^o_{sp}$  can be obtained similarly.

For the subthreshold region, 1 < b < 2. Therefore, (4.11) can be written as

$$E_{nM} = \sqrt{\frac{2qN_a}{\varepsilon_s} \left( V_{DS} - \psi_{sn}^o + V_{bin} \right)} \qquad \dots (4.13a)$$

$$E_{pM} = \sqrt{\frac{2qN_d}{\varepsilon_s} \left( V_{SD} + \psi_{sp}^o - V_{bip} \right)} \qquad \dots (4.13b)$$

Equation (4.10) describes the impact ionization model for electron as well as hole initiated multiplication. A complete subthreshold impact ionization current model can now be obtained from (4.1). The NMOS drain current for this model is

$$I_{DSn} = \frac{I_{dn}}{(1 - \alpha_M / (\beta_M - \alpha_M)(\exp(m_{nR} E_M / E_R) - 1))}$$

...(4.14a)

The PMOS drain current can be written as

$$I_{DSp} = \frac{I_{dp}}{(1 - \beta_M / (\alpha_M - \beta_M)(\exp(m_{pR} E_M / E_R) - 1))}$$

...(4.14b)

Consequently, the leakage power dissipation for an NMOS is given by

$$P_{MN} = I_{DSn}V_{DS} \qquad \dots (4.15a)$$

Similarly, the PMOS leakage power dissipation is given by

$$P_{MP} = I_{DSp}V_{SD} \qquad \dots (4.15b)$$

It can be concluded from equation (4.13a) and (4.13b) that, interface potential and built-in voltage being small quantities compared to bias voltage, the peak electric field is dominated by the bias voltage. This leads to high multiplication factors (4.10) for slight increase in the applied voltage finally affecting  $P_{MN}$  and  $P_{MP}$ .

# 4.2 Scaling

A long geometry device is reduced to a small geometry device by scaling it down.

According to the constant electric field scaling model, the scaling rule [12] is

$$V_{sf} = sV \qquad \dots (4.16a)$$

$$x_{sf} = sx \tag{4.16b}$$

For NMOS,

$$N_{asf} = \frac{N_a}{s} \tag{4.16c}$$

For PMOS,

$$N_{dsf} = \frac{N_d}{s} \qquad \dots (4.16d)$$

where the scale factor,  $s \le 1$ .

This implies that  $N_{asf}$  and  $N_{dsf}$  increase with scaling leading to higher electric fields in smaller MOS devices (refer to equations 4.13a and 4.13b). Therefore, power dissipation as may be obtained from equations 4.15a and 4.15b is now an increasing function of scaling. The dependence of power dissipation on scaling is through drain current. The increase in power dissipation is expected to be sharp for small values of scale factors.

# STANDBY POWER ESTIMATION OF A DIGITAL CIRCUIT

A novel approach for accurate and efficient calculation of standby power dissipation is given by Sirichotiyakul et al. [14]. This is done, by introducing the concepts of Dominant Leakage States and state probabilities combined with graph reduction techniques. This method claims to achieve speedups of three to four orders of magnitude over exhaustive SPICE simulations while maintaining very good accuracy. Therefore, the method proposed in [14] is used in conjunction with the subthreshold impact ionization model developed in previous chapters to determine circuit leakage.

Simulation complexity is overcome through a series of techniques mentioned below.

• Segregation of the circuit into DC-Connected Components (DCC).

This eliminates the need to simulate the entire network, instead simulating only one DCC at a time, thus reducing complexity.

Calculation of State Probabilities for each DCC.

State probabilities are calculated using primary input probabilities.

Determination of Dominant Leakage States (DLS) for each DCC.

This implies that for each DCC, only a small subset instead of all possible 2<sup>N</sup> states are evaluated for leakage. Here, N is the number of primary inputs.

Determination of standby power for each DLS using the model developed.

Each state in the dominant leakage set of a DCC is simulated using the subthreshold impact ionization model.

Combining the results for different DCCs using state probabilities.

# 5.1 Dominant Leakage States (DLS)

It is known that leakage of a gate is significantly less in some states than in others. A state with more than one transistor OFF in a path from  $V_{DD}$  to GND is far less leaky than a state with only one transistor OFF in any  $V_{DD}$ -GND path. The latter states are called Dominant Leakage States (DLS). The set of DLSs is usually very small compared to the set of all possible states. The key idea is to ignore the leakage of insignificant or nondominant states in the average leakage calculation without loosing significant accuracy. For example, for a two input NAND gate, the set of DLSs are D= $\{01, 10, 11\}$ , i.e. the total number of DLS are three. Whereas, the number of DLS in a three input NAND are four and in four input NAND, only five. Considering only these states, the average leakage is, at the most, only about 5 % less than the exact average. Such accuracy is obtained by simulating only three out of eight possible states for a NAND3 gate. This tradeoff becomes even more attractive for DCCs with a large number of inputs.

#### Stepwise procedure to obtain DLS

a. Draw the Euler graph for each DCC. Let G(V, E) be an Euler graph representing a DCC in the circuit, such that each  $v \in V$  represents a node in the DCC and each  $e \in E$  represents a transistor in the DCC whose drain and source nodes are the end points of e. Since, G represents a DCC, it has only one connected component. Also |V| > 1, as there are at least two nodes,  $V_{DD}$  and GND.

For example, a NAND3 gate can be represented as

Fig. 5.1a: A NAND3 gate.

Fig. 5.1b: Euler Graph of a NAND3 gate.

A disconnecting set of edges in a connected graph G is any set of edges in G whose removal results in more than one connected component. If  $F \subseteq E(G)$  is a disconnecting set, G(V, E-F) has more than one component. For example, for Fig. 5.1,  $\{P1, P2, P3\}$ ,  $\{N1\}$ ,  $\{N2\}$ ,  $\{N3\}$ ,  $\{N1, N2\}$ ,  $\{N2, N3\}$ ,  $\{N1, N3\}$ ,  $\{N1, N2, N3\}$  are all disconnecting sets.

A cutset of G is defined as a minimal disconnecting set of G. Since it is minimal, a cutset always leaves a graph with exactly two components. Given a non empty set  $S \subset V(G)$ , [S, S'] denotes a cutset of G, the set of edges each having one end point in S and another in S'. For example, for Fig. 5.1b,  $\{P1, P2, P3\}$ ,  $\{N1\}$ ,  $\{N2\}$ ,  $\{N3\}$  are all cutsets.

V<sub>DD</sub> is always in S.

b. Determine the set of OFF transistors for each DCC for a particular input state. Let this set be called OFF(b). Let B be the set of all possible Boolean states for a gate's inputs such that

$b \in B$ . An edge is called an OFF edge if its corresponding transistor is OFF in a given state. It is imperative that OFF(b) is a disconnecting set for G such that  $V_{DD}$  and GND lie in different components of G(V, E-OFF(b)). Otherwise, there will be a short circuit in b.

c. Determine the subset of transistors out of these OFF ones, which contribute to leakage. Let this set be called LEAK (b) i.e., LEAK(b) is a set of transistors that contribute to subthreshold leakage in state b. It is clear that LEAK(b)  $\subseteq$  OFF(b) and that the end points of each edge of LEAK(b) are in different components of G(V, E-OFF(b)). If both the drain and source nodes of a transistor are in the same component of G(V, E-OFF(b)), then there is a conducting path between them consisting of other transistors of the component. Such a transistor will not contribute to subthreshold leakage. LEAK(b) is also a disconnecting set of G.

d. Check if LEAK (b) is a minimal set. A state b is said to be a Dominant Leakage State if LEAK (b) is minimal i.e., if there exists no other state a∈B such that LEAK(a) LEAK(b). If b is a DLS, LEAK(b) is a dominant-leakage set. This will happen for those input states where a single transistor in a series stack is OFF or all the transistors connected in parallel are OFF.

By above definition, a dominant leakage set is a minimal disconnecting set of G, and is hence, a cutset [S, S'] of G, such that  $V_{DD}$  is in S and GND is in S'. That is, when b is a DLS, G(V, E-LEAK(b)) has exactly two components, with  $V_{DD}$  and GND in different components. Vice versa, a cutset is qualified as a dominant leakage set only if 1) removing its edges partitions  $V_{DD}$  and GND into different partitions and 2) all of its edges can be logically OFF at the same time.

Therefore, {P1, P2, P3}, {N1}, {N2} and {N3} are dominant leakage sets for the input states {111}, {011}, {101} and {110} respectively. Hence, these input states are called Dominant Leakage States for the NAND3 gate.

For each DLS, there are two types of ON transistors, which contribute to leakage. If in a transistor stack, two transistors are in series such that the ON transistor is connected to  $V_{DD}$  and the OFF transistor is connected to GND, there is a  $V_T$  drop across the ON transistor as shown in Fig. 5.2.

Fig. 5.2:  $V_T$  drop across the ON NMOS in an NMOS inverter.

On the other hand, if a transistor is of native type, there will be no V<sub>t</sub> drop across the transistor when it is ON i.e., its source and drain nodes will be at equal potentials. In Fig. 5.1, for the input state {110}, there is a potential drop of V<sub>t</sub> across N2 whereas there is practically no voltage drop across N1 and {P1, P2, P3}. Therefore, the voltage drop across the leaking transistor N3 is now V<sub>DD</sub>-V<sub>t</sub>. Since, the subthreshold current is a non-linear function of the voltage drop, the leakage power dissipation decreases significantly.

#### 5.2 Determination of State Probabilities

Ercolani et al. [15] describe a procedure for propagating the probabilities of primary inputs to all internal and primary output signals while accounting for the first order spatial

correlation between signals. The procedure uses correlation between every pair of signals and hence is called Correlation Coefficient Method (CCM). The coefficients are propagated along with the probabilities. This procedure is applied to calculate the probabilities and correlation coefficients of all signals in the circuit and thereby calculate the state probabilities of the DCCs.

#### Notations and definitions [15]:

- a. The quantity p(j) is the signal probability of node j, namely, the probability that a randomly selected vector sets j to 1. Considering the possible interaction between different nodes, p(j/i) is the probability of node j being 1 conditioned by node i being 1.

- b. B(j) is the probability that a randomly selected vector propagates the value on j to at least one of circuit primary inputs.

- c. B1(j) (B0(j)) is the probability that a randomly chosen vector among all those controlling j at 1(0) allows j to be observed at primary outputs.

- **d.** dl(j) (d0(j)) is the probability that a randomly selected vector detects j stuck at 1 or 0.

- e. d1(j/f = x) (d0(j/f = x)) is the detection probability of node j stuck at 1(0) conditioned by node f being at the logic value x.

# 5.2.1 Correlation Coefficients and Signal Probabilities

The correlation coefficient method explicitly accounts for the effects of statistical correlation between signals.

From probability theory, given two events A and B, the probability P(AB) of  $AB = A \cap B$  is given by P(AB)=P(A/B)P(B), where P(A/B) represents the probability of A given B.

In terms of correlation coefficients  $C_{A,B}$ , defined by the equation  $P(AB)=P(A)P(B)C_{A,B}$ . Hence,

$$C_{A,B} = \frac{P(AB)}{P(A)P(B)} = \frac{P(A/B)}{P(A)} = \frac{P(B/A)}{P(B)} \qquad \dots (5.1)$$

If A and B are independent events,

$$P(AB)=P(A)P(B) \qquad \dots (5.2)$$

Thus,  $C_{A,B}=1$ .

In a combinational network, an event is a node at 1; hence P(A) = P(j = 1) = p(j) and

$$C_{i,j} = C_{j,i} = \frac{p(ij)}{p(i)p(j)} = \frac{p(i/j)}{p(i)} = \frac{p(j/i)}{p(j)} \qquad \dots (5.3)$$

$$p(i/j) = p(i)C_{i,j}$$

...(5.4)

Given a gate with two inputs (i, j), the probability p(l) at the output l can be calculated by means of p(i), p(j) and their correlation coefficient  $C_{i,j}$  as shown in Table. 5.1.

Table 5.1 Rules for calculating the node signal probability through the correlation coefficients.

$$p(l) = 1 - p(i)p(j)C_{i,j}$$

$$0 \le p(l) \le 1$$

$$0 \le C_{i,j} \le \frac{1}{p(i)p(j)}$$

$$p(l) = 1 - p(i) - p(j) + p(i)p(j)C_{i,j}$$

$$0 \le p(l) \le 1$$

$$\frac{p(i) + p(j) - 1}{p(i)p(j)} \le C_{i,j} \le \frac{p(i) + p(j)}{p(i)p(j)}$$

The correlation coefficients can be derived analytically by means of the set of basic rules given in Table. 5.2.

Table 5. 2. Rules for determining the output correlation coefficients of a pair of signals given the input correlation coefficients and the input probabilities.

| Primary Inputs                                | Signals are assumed to be independent:                                                                              |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                                               | p(i/j) = p(i), p(j/i) = p(j)                                                                                        |

|                                               | $C_{i,j} = 1$                                                                                                       |

|                                               | $i \equiv l \equiv m \Rightarrow p(l) = p(m) = p(i)$                                                                |

| i                                             | p(l/m)=1                                                                                                            |

|                                               | $p(l)C_{l,m}=1$                                                                                                     |

| m                                             | $C_{l,m} = \frac{1}{p(l)}$                                                                                          |

|                                               |                                                                                                                     |

| , ,                                           | $i \equiv \bar{i} \implies p(l) = 1 - p(i)$                                                                         |

| ,                                             | p(l/m) = 1 - p(i/j)                                                                                                 |

| j m                                           | $p(l)C_{l,m} = 1 - p(i)C_{i,j}$                                                                                     |

|                                               | $C_{I,m} = \frac{1 - p(i)C_{i,j}}{1 - p(i)}$                                                                        |

|                                               |                                                                                                                     |

| i                                             | $l \equiv i \cap j \Rightarrow p(l) = 1 - p(i)p(j)C_{i,j}$                                                          |

| <i>i</i> ———————————————————————————————————— | $p(l/m) = 1 - p(i/h)p(j/h)C_{i,j}$                                                                                  |

| h —m                                          | $p(l)C_{l,m} = 1 - p(i)p(j)C_{i,h}C_{j,h}C_{i,j}$                                                                   |

|                                               | $C_{i,m} = \frac{1 - p(i)p(j)C_{i,h}C_{j,h}C_{i,j}}{1 - p(i)p(j)C_{i,j}}$                                           |

|                                               |                                                                                                                     |

| i   \( \sigma \)                              | $l \equiv \overline{i \cup j} \Rightarrow p(l) = 1 - p(i) - p(j) + p(i)p(j)C_{i,j}$                                 |

|                                               | $p(l/m) = 1 - p(i/h) - p(j/h) + p(i/h)p(j/h)C_{i,j}$                                                                |

| h — m                                         | $p(l)C_{l,m} = 1 - p(i)C_{i,h} - p(j)C_{j,h} + p(i)p(j)C_{i,h}C_{j,h}C_{i}$                                         |

| •                                             | $\int_{C_{i,h}} 1 - p(i)C_{i,h} - p(j)C_{j,h} + p(i)p(j)C_{i,h}C_{j,h}C_{i,j}$                                      |

|                                               | $C_{l,m} = \frac{1 - p(i)C_{i,h} - p(j)C_{j,h} + p(i)p(j)C_{i,h}C_{j,h}C_{i,j}}{1 - p(i) - p(j) + p(i)p(j)C_{i,j}}$ |

In Table 5.2, an approximation has been introduced while calculating the correlation coefficients in the last two cases. The correlation of two signals to a third is neglected i.e., the effect of higher order conditional probabilities are not taken into account. To verify this approximation, exhaustive simulations were made on several circuits by Ercolani et al. [15]. It was found that the simulated values considering higher order conditional probabilities and those calculated by means of above equations are comparable even at gates presenting signal reconvergencies.

Because of this approximation, the calculated coefficients lead to gate output probabilities outside the 0-1 interval. To avoid this, the correlation coefficients are limited within the bounds given in Table 5.1.

By using the rules of Table 5.2, it is possible to compute the correlation coefficients between any two signals at the output of a circuit block. Consider, for example the two NAND gates on the left hand side of Fig. 5.3.

Fig. 5. 3. An example of extension of the rules in Table 5.2 to calculate  $C_{l,m}$  for two AND gates.

By splitting the circuit as shown on the right hand side, and applying rules in Table 5.2 to S1,  $C_{l,h}$  and  $C_{lk}$  are calculated. Then,  $C_{l,m}$  is computed by applying the same rule to S2. The

rules given here are only for two input gates, but can be easily extended to the multiple-input case by simply considering a multiple input gate as a cascade of two input elementary devices.

The above method can be used only for combinational circuits. Sequential circuits or in circuits with feedbacks, the nodes with feedbacks are assigned initial values for signal probabilities and correlation coefficients. The procedure mentioned above is then applied on the whole circuit in an iterative loop until a particular accuracy for the updated values is reached.

#### 5.2.2 Observability

For each signal j, the conditional observability is given by B1(j) and B0(j). To illustrate the rules for their computation, a NAND gate with inputs (i, j) and output l is considered as an example. Then,

$$B1(i) = \text{Prob (observe } (l) \& j = 1/i = 0)$$

...(5.5a)

$$B0(i) = \text{Prob (observe } (l) \& j = 1/i = 1)$$

...(5.5b)

It is assumed for simplicity, that the observability of the gate output l, is independent of the value of its inputs (i, j). Introducing the correlation coefficients,

$$B1(i) = B0(l)p(j)\frac{1 - p(i)C_{i,j}}{1 - p(i)} \qquad ...(5.6a)$$

$$B0(i) = B1(l)p(j)C_{i,j}$$

...(5.6b)

This assumption is correct as long as the observability of l does not depend on signals statistically correlated to i or j. Table 5.3 summarizes the rules used to calculate the observability at output (1/0) of a gate. As can be easily verified, the rules for calculating B1 for an NAND gate and B0 for an NOR gate include the equivalence conditions.

Table 5.3 Rules for calculating the node observabilities through the correlation coefficients.

| i               | B1(i) = B0(l) $B0(i) = B1(l)$                                                                                |

|-----------------|--------------------------------------------------------------------------------------------------------------|

| i               | $B1(i) = B0(l)p(j)\frac{1 - p(i)C_{i,j}}{1 - p(i)}$ $B0(i) = B1(l)p(j)C_{i,j}$                               |

| i               | $B1(i) = B0(l)(1 - p(j)\frac{1 - p(i) - p(j) + p(i)p(j)C_{i,j}}{1 - p(i)})$ $B0(i) = B1(l)(1 - p(j)C_{i,j})$ |

| $i$ $i_1$ $i_2$ | $B1(i) = 1 - (1 - B1(i_1))(1 - B1(i_2))$ $B0(i) = 1 - (1 - B0(i_1))(1 - B0(i_2))$                            |

# 5.2.3 The Algorithm

The Correlation Coefficient Method (CCM) for a combinational circuit splits the calculation of state probabilities into two phases. A first step is used to compute signal probabilities by means of rules of Tables 5.1 and 5.2, successively applied proceeding from primary inputs to outputs. Then from the rules of Table 5.3, backtracking is performed to derive node observabilities. Finally, the state probability is obtained by multiplying the corresponding signal probability and observability.

```

The pseudocode for the algorithm is

ecm()

{

for (each primary input j)

{/* initialize primary input values*/

p(j) = 0.5;

for (each primary input i \neq j)

{C_{i,j}=1;}

}

for (each level in the network, from the inputs)

{/*forward step, for signal probabilities and correlation coefficients */

for (each node j of level)

p(j) = \text{SignalProbability}(level); /* from rules of Table 4.1*/

for (each node i of level, i \neq j)

C_{ij} = CorrelationCoefficients(level); /* from rules of Table 4.2 */

}

}

}

for (each primary output j)

{/* initialize output observabilities */

B0(j) = B1(j) = 1;

}

```

To save computation time it is useful to recognize during circuit compilation all the couples of independent signals and the gates not involved in fan-out reconvergencies.

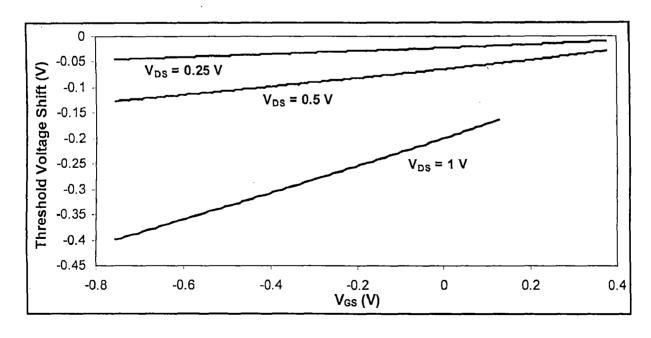

# 5.3 Standby Power calculation for each DLS

To determine the standby power dissipation for a DLS, the gate-source voltage ( $V_{GS}$ ) and the drain-source voltage ( $V_{DS}$ ) for each leaking transistor must be calculated. It is observed that either a single OFF transistor in series or all the OFF transistors connected in parallel between two nodes contribute to leakage in a particular Dominant Leakage State for a DCC. The potential drop across a native ON transistor is zero whereas the potential drop across a non-native one is  $V_T$ . Therefore, both  $V_{DS}$  and  $V_{GS}$  are functions of the threshold voltage  $V_T$ ,

which in turn is a function of the threshold voltage shift  $(\Delta V_T)$ . Hence,  $\Delta V_T$  must be determined correctly for different scale factors. For this purpose,  $\Delta V_T$  is plotted against  $V_{GS}$  for varying  $V_{DS}$  using the subthreshold model described in chapter 2 and the equation, which best fits the curve is considered. In case, the plots are linear in nature,

$$\Delta V_T = m_1(V_{DS}) \ V_{GS} + C_1 \ \dots (5.7)$$