## ANALYTICAL MODELING OF DOUBLE GATE FinFET AND ITS APPLICATIONS TO SRAM CELL DESIGN

### **A THESIS**

## Submitted in partial fulfilment of the requirements for the award of the degree of DOCTOR OF PHILOSOPHY in ELECTRONICS AND COMPUTER ENGINEERING

by

### **BALWINDER RAJ**

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE - 247 667 (INDIA) DECEMBER, 2009 ©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE, 2009 ALL RIGHTS RESERVED

.

### INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

#### **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled "ANALYTICAL MODELING OF DOUBLE GATE FinFET AND ITS APPLICATIONS TO SRAM CELL DESIGN" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electronics and Computer Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from July 2006 to December 2009 under the supervision of **Dr. A. K. Saxena**, Professor and **Dr. S. Dasgupta**, Assistant Professor, Department of Electronics and Computer Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

5 08 ×11/09 Dasgupta) Supervisor

(A. K. Saxena) Supervisor

Date:

Frand Le Dos Juph

Signature of External Examiner

## Abstract

Transistor dimensions have been scaled down to nanoscale dimensions to enhance the driving capability and switching speed. International Technology Roadmap for Semiconductor (ITRS)-2007 report shows an industry wide consensus on the "best current estimate" of the industry's research and development needs. Silicon has taken a vital role in semiconductor industry while III-V semiconductor devices play a major role for various electronics applications. The limiting factors in the bulk MOSFET downscaling is the power consumption due to Short Channel Effects (SCEs), leakage current and subthreshold slope degradation. Novel devices are being investigated very rigorously to continue the scaling trends. In the device research community, researchers are looking for such a device which has low leakage and low threshold voltage without compromising on performance, resulting in multiple gate structures. Such examples are the Double Gate MOSFET and FinFET device. A self aligned Double Gate (DG) FinFET reduces leakage currents, process parameter variations and also eliminates short channel effect.

This thesis deals with modeling and simulation of FinFET device and subsequent application to the design of FinFET based 6T-SRAM cell as well as analysis of design issues and performance metrics. In this thesis, an extensive literature survey of the state of the art in the area of study is presented. Many important research papers are referred and cited which allows one to fully appreciate the usefulness of such novel devices in present day circuits. Various research gaps are also investigated.

i

One dimensional potential modeling of single or double gate MOSFET is not enough to explain its various physical facts within the device in nanoscale regime. At extremely low dimensions, electric field in both longitudinal and transverse directions becomes substantially large. Hence, two dimensional (2D) device modeling is required to enhance the accuracy of the results. 2D models gives a more accurate result but at the cost of the computation time. The Quantum Mechanical (QM) analytical modeling of potential for the FinFET device under study carried out. This gives closed form solution of surface potential.

Further, the threshold voltage evaluation becomes an important issue in order to undertake power dissipation characteristics. Hence extractions of threshold voltage and parasitic source/drain resistance modeling have been also carried out in order to understand the switching behaviour of the device. Various potential profiles such as surface potential, front gate to back gate potential, source to drain potential and 3D potential plot for the FinFET device under study have also been presented. Key issues including FinFET device structure, design parameters, potential modeling, process parameter variation effects and device scaling limit have been undertaken quantitatively as well as qualitatively. The results obtained on the basis of our proposed analytical model have been compared and contrasted with the reported experimental results and a close match was found.

The analytical modeling for Quantum mechanical (QM) inversion charge, field dependent mobility and drain current for nanoscale Double Gate (DG) FinFET have been evaluated. As the device dimensions are excessively reduced and the dimensions of the device becomes of the order of the de-Broglie wavelength of electron, it is imperative to undertake an extensive Quantum Mechanical (QM) modeling for the device under study. An extensive analytical modeling of FinFET

ii

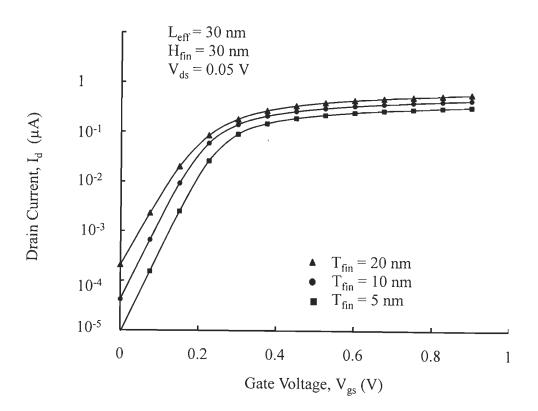

device has been carried out for extracting QM inversion charge. Analytical model has been developed to estimate the drain current. Further, variation of drain current with various process/device parameters is carried out for the FinFET device structure under study. The effect of fin thickness ( $T_{fin}$ ) and fin height ( $H_{fin}$ ) on drain current has been modeled and discussed. In order to evaluate the output drain current, a comprehensive mobility model for the charge carriers has been carried out. Various mobility models have been studied and implemented during the course of work and appropriate mobility model is taken up in order to evaluate the drain current. The results obtained on the basis of our model are compared with our TCAD Sentaurus simulation result as well as reported experimental results for the purpose of validation.

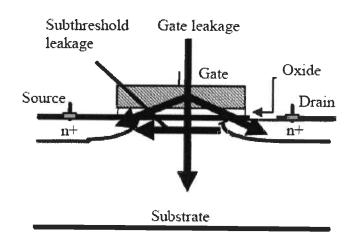

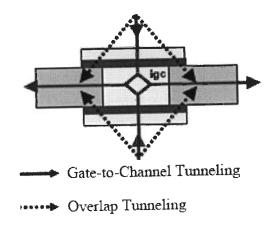

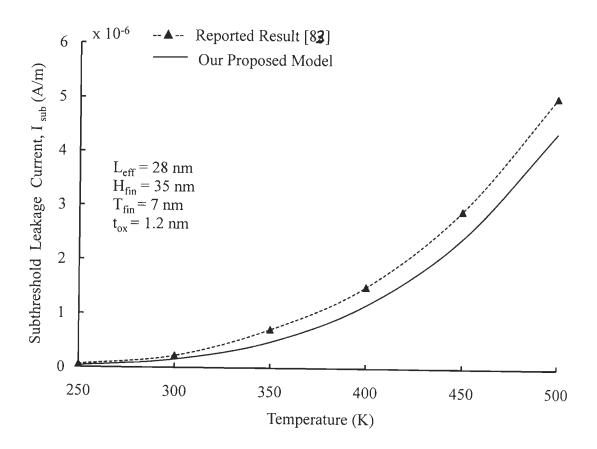

The analytical modeling and estimation of various types of leakage currents associated with the FinFET device are presented, as low leakage devices are required for low power consumption for various applications. The various leakage current components in FinFET device have been evaluated such as subthreshold leakage current, gate tunneling leakage current and its dependence on various device/process parameters. The subthreshold leakage current is primarily due to diffusion of carriers and has been modeled analytically. Gate to channel leakage is primarily due to tunneling of electrons from inverted surface channel to gate. We have also analytically calculated subthreshold swing for FinFET to evaluate the subthreshold leakage current. As the device dimensions are reduced, the off state leakage current substantially increases because of many QM effects. This result in larger power dissipation of the device and the matter assumes critical importance in SRAM, as FinFET SRAM designs are prone to larger power dissipation. The results obtained have shown that at same technology node, the leakages in FinFETs are lower as compared to DG-MOS devices. Further, our analysis shows the improvement in the performance due to reduction in leakage current of FinFET device.

It can be appreciated that the devices by themselves don't add to the existing integration era. But until, a circuit analysis using the proposed devices is undertaken, the full benefits of integration cannot be captured. Logic and memory circuit design in nanoscale regime requires control over leakage currents with device level parameter variations. FinFET based 6T SRAM cell design using device/circuit co-design approach also carried out. Our analysis shows that use of FinFET devices with intrinsic body doping reduces leakage current and short channel effects. Hence, we conclude that FinFET devices can emerge as one of the promising candidate for reducing leakage components with minimum body transition time, making it efficient for low power and high performance circuit design in nanoscale regime. Further, FinFET based SRAM cell usually uses the smallest device on chip packed very closely together to achieve high density. Thus they are more sensitive to process variations.

The FinFET based 6T SRAM cell uses cross coupled inverter structure to store bits. The mismatch between cell devices can cause data flipping during read operation. Thus the primary goal of the proposed design includes maximizing stability and minimizing leakage in SRAM, besides achieving maximum density. Design considerations for maximizing performance and yield of FinFET-based 6-T SRAM at the 32 nm have been examined. It is shown that, FinFET based SRAM cells have enhanced performance over planar bulk-Si MOSFET SRAM cells. Our proposed FinFET based 6T-SRAM cells have improved the 'read' and 'write' margin, without compromising on the area requirement. The simulations have been carried out in HSPICE with appropriate structuring of model file containing various device parameters both independent and extracted. The analysis for the performance metric of FinFET based SRAM cell such as SNM, RNM, WNM, power, delay have been also carried out.

Our analysis shows that, use of FinFET device with intrinsic body reduces leakage current and enhances the driving capability. Hence, we conclude that FinFET can emerge as one of the promising candidate for reducing leakage components making it efficient for low power and high performance SRAM cell design in nanoscale regime.

## Acknowledgement

I wish to express my heartfelt regards and gratitude to Dr. S. Dasgupta, Assistant Professor and Dr. A. K. Saxena, Professor, Semiconductor Devices and VLSI Technology (SDVT) Group, Department of Electronics and Computer Engineering, Indian Institute of Technology Roorkee for their invaluable guidance and inspiration in successful completion of the present work. Their creative ideas, constant monitoring research activities, hardworking nature, encouragement and moral support were extremely beneficial for this research work. With their wide experience, sharp and incisive intellect, maestro ability combined with astute research methodology and deep insight of subject have unerringly steered the work on smooth and steady course. I sincerely appreciate their pronounced individualities, humanistic and warm personal approach which have given me the strength and will to carry this research work. I humbly acknowledge a lifetime deep gratitude to my supervisors.

I am thankful to Dr. S. Manhas and Dr. Anand Bulusu, Asst. Professors, SDVT Group, E & CE, IIT Roorkee for providing guidance and support. I am also grateful to Dr. S. N. Sinha, Professor and Head, E & CE, DRC Chairman, Prof. R. Mitra, Prof. M. J. Nigam, Professor, E & CE, Prof. R. Nath, Department of Physics for being member of my research committee and sparing their time for critically examining the work and providing valuable suggestions.

My sincere thanks to Mr. Naveen and Mr. Dinesh Sharma, SDVT Group, E & CE, IIT Roorkee for their constant help during the research work. I would like sincerely thank to research scholars of SDVT group, Jitendra Kanungo, R. S. Rathod, Ramesh Vaddi, Gaurav Koshal and M. Tech. friends for discussing technical

vii

problems. My sincere thanks to my Ph.D. seniors of SDVT group Mr. S. K. Visvakarma and Dr. Brajesh Kaushik for guiding me at various stages of research. I also want to express my sincere thanks to my friends Dr. Gaurav Raheja, Dr. Samarjeet Rawat, Dr. Nilesh Sharma, Dr. Vikas Chawla, Dr. Ramesh Sunkaria and many more those who helped me directly or indirectly in various aspects to improve the quality of thesis and pleasant stay in IIT campus. Special thanks to my friends Vinod, B.B Gupta, Rajiv, Balwinder Singh, Pushpinder Singh and RK.Vishvakarma who always encouraged me throughout research tenure.

My special thanks and heartfelt gratitude goes to Mrs. T. Dasgupta and Mrs. Shobha Saxena for ever making me feel owned, loved and a part of their families.

Finally, I wish to express my sincere appreciation to my father Shri. Krishan Lal, mother Smt. Parkasho Rani, my elder brothers Balwan Chand and Balwant Raj, my family and relatives without their efforts, cooperation and support this research effort would not have been possible.

This thesis is dedicated to my teachers and family.

Date:

Place:

(Balwinder Raj)

## Contents

|                         | Page No. |

|-------------------------|----------|

| Copyright               |          |

| Candidate's Declaration |          |

| Abstract                | i        |

| Acknowledgement         | vii      |

| Contents                | ix       |

| List of Figures         | XV       |

| List of Tables          | xxi      |

| List of Symbols         | xxiii    |

| List of Abbreviation    | xxvii    |

### **CHAPTER 1: INTRODUCTION**

| 1.1 | Introd | uction                                                      | 1  |

|-----|--------|-------------------------------------------------------------|----|

| 1.2 | Scalin | g of Semiconductor Devices                                  | 5  |

| 1.3 | Motiv  | ation of Work                                               | 7  |

| 1.4 | Proble | ems Description                                             | 9  |

|     | 1.4.1  | QM Analytical Modeling of Nanoscale DG FinFET:              | 11 |

|     |        | Evaluation of Potential, Threshold Voltage and              |    |

|     |        | Source/Drain Resistance                                     |    |

|     | 1.4.2  | Analytical Modeling of nanoscale Double Gate FinFET:        | 12 |

|     |        | Evaluation of Inversion Charge, Mobility and                |    |

|     |        | Drain Current                                               |    |

|     | 1.4.3  | Modeling of Subthreshold Leakage Current, Subthreshold      | 13 |

|     |        | Swing factor and Gate Leakage Currents for DG FinFET Device |    |

|     | 1.4.4 FinFET Based Nanoscale Static Random Access Memory     | 13 |

|-----|--------------------------------------------------------------|----|

|     | (SRAM) Cell Design: Analysis of Performance metric,          |    |

|     | Process variation, Underlapped FinFET and Temperature effect |    |

|     | 1.4.5 Performance Evaluation of FinFET based SRAM            | 15 |

| 1.5 | Thesis Organization                                          | 16 |

| 1.6 | Conclusion                                                   | 17 |

## CHAPTER 2: LITERATURE REVIEW

| 2.1 | Introduction                                                | 19 |

|-----|-------------------------------------------------------------|----|

| 2.2 | Scaling of Bulk MOSFET                                      | 22 |

|     | 2.2.1 Bulk CMOS Challenges                                  | 25 |

|     | 2.2.2 Disadvantages of Bulk MOSFET                          | 26 |

|     | 2.2.3 Nanoscale CMOS Design Problems                        | 26 |

| 2.3 | Advanced MOSFET Structures                                  | 29 |

|     | 2.3.1 Ultra-Thin Body (UTB) MOSFET                          | 29 |

|     | 2.3.2 DG MOSET                                              | 30 |

|     | 2.3.3 SOI MOSFET                                            | 32 |

|     | 2.3.4 Multiple-Gate MOSFET                                  | 34 |

| 2.4 | FinFET Device: A Review                                     | 37 |

|     | 2.4.1 FinFET Benefits, Drawbacks, and Alternatives          | 39 |

|     | 2.4.2 FinFET Device Modeling: Potential, Threshold Voltage, | 40 |

|     | S/D Resistance, Inversion Charge, Mobility and Drain        |    |

|     | Current Modeling                                            |    |

| 2.5 | Leakage currents in Bulk MOSFET and FinFET device | 43 |

|-----|---------------------------------------------------|----|

|     | 2.5.1 Subthreshold Leakage Currents               | 44 |

|     | 2.5.2 Gate Leakage Current                        | 45 |

| 2.6 | FinFET based SRAM Design Issues                   | 46 |

| 2.7 | Conclusion                                        | 49 |

## CHAPTER 3: Quantum Mechanical Analytical Modeling of Nanoscale DG FinFET: Evaluation of Potential, Threshold Voltage and Source/Drain Resistance

| 3.1 | Introduction                               | 51 |

|-----|--------------------------------------------|----|

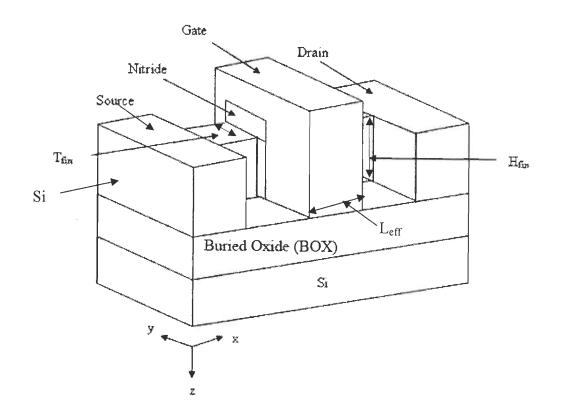

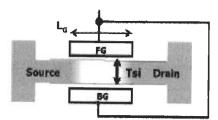

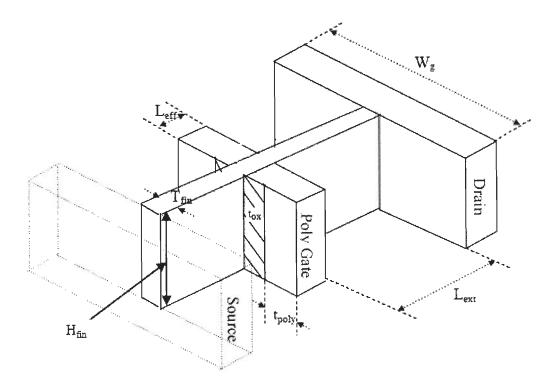

| 3.2 | FinFET Structure                           | 53 |

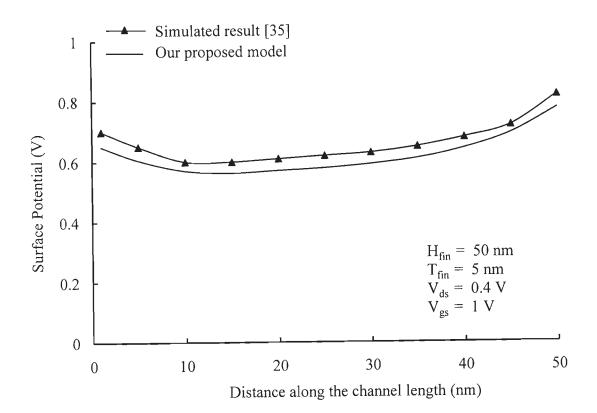

| 3.3 | Quantum Mechanical (QM) Potential Modeling | 55 |

| 3.4 | Threshold Voltage Modeling                 | 59 |

| 3.5 | Source/Drain (S/D) Resistance Modeling     | 60 |

| 3.6 | Results and Discussion                     | 63 |

| 3.7 | Conclusion                                 | 71 |

## CHAPTER 4: Analytical Modeling of Nanoscale DoubleGate FinFET: Evaluation of Inversion Charge, Mobility and Drain Current

| 4.1 | Introduction                      | 73 |

|-----|-----------------------------------|----|

| 4.2 | Quantum Inversion Charge Modeling | 75 |

| 4.3 | Mobility Modeling                 | 77 |

| 4.4 | Drain Current Modeling            | 78 |

| 4.5 | Results and Discussion            | 80 |

| 4.6 | Conclusion                        | 94 |

CHAPTER 5: Modeling of Subthreshold Leakage Current, Subthreshold Swing Factor and Gate Leakage Currents for DG FinFET Device

| 5.1 | Introduction                          | 95  |

|-----|---------------------------------------|-----|

| 5.2 | Subthreshold Swing Modeling           | 97  |

| 5.3 | Subthreshold Leakage Current Modeling | 98  |

| 5.4 | Gate Leakage Current modeling         | 100 |

| 5.5 | Results and Discussion                | 102 |

| 5.6 | Conclusion                            | 114 |

## CHAPTER 6: FinFET Based Nanoscale Static Random Access Memory (SRAM) Cell Design: Analysis of Performance metric, Process variation, Underlapped FinFET and Temperature effect

| 6.1 | Introdu | action                                            | 117 |

|-----|---------|---------------------------------------------------|-----|

| 6.2 | Bulk S  | RAM cell Design Problems                          | 120 |

| 6.3 | SRAM    | I Design Tradeoffs                                | 122 |

|     | 6.3.1 A | Area vs. Yield                                    | 122 |

|     | 6.3.2 F | Read vs. Write Stability                          | 122 |

|     | 6.3.3 § | Speed vs. Leakage Current                         | 122 |

| 6.4 | FinFE   | T based SRAM cell Design                          | 123 |

|     | 6.4.1 I | FinFET Based SRAM Performance Metrics             | 125 |

| 6.5 | Effect  | of Process Variation on FinFET                    | 127 |

| 6.6 | Under   | lapped FinFET Device                              | 129 |

|     | 6.6.1   | Various Parameters of Underlapped FinFET          | 131 |

|     | 6.6.2   | Monte Carlo Analysis of FinFET Process Variations | 131 |

|     | 6.6.3   | Effect of Temperature on FinFET's Performance     | 132 |

|     |         |                                                   |     |

| 6.7  | Results and Discussion                          | 133 |

|------|-------------------------------------------------|-----|

| 6.8  | Conclusion                                      | 147 |

| СНА  | PTER 7: CONCLUSION AND FURTHER SCOPE            |     |

| 7.1  | Conclusion                                      | 149 |

| 7.2  | Further Scope                                   | 152 |

| APP  | ENDIX: PHYSICAL CONSTANTS AND DEVICE PARAMETERS | 155 |

| BIBI | LIOGRAPHY                                       | 157 |

| LIST | OF PUBLICATIONS                                 | 185 |

xiv

# List of Figures

| Figure     | Caption                                                         | Page No. |

|------------|-----------------------------------------------------------------|----------|

| No.        |                                                                 |          |

|            |                                                                 |          |

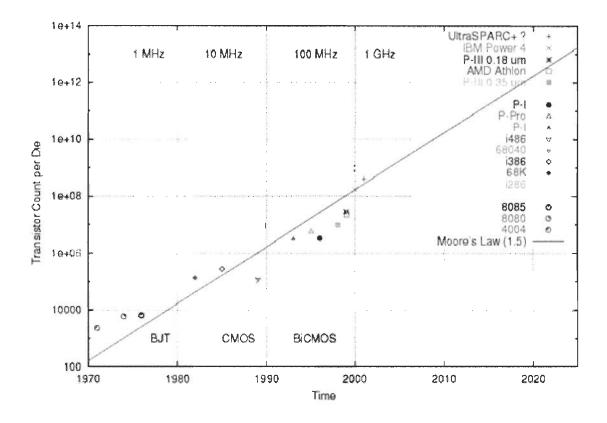

| Fig. 1.1   | Moore's law of scaling.                                         | 6        |

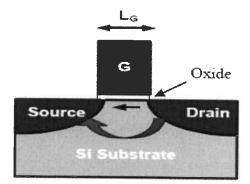

| Fig. 2.1   | Bulk MOSFET.                                                    | 23       |

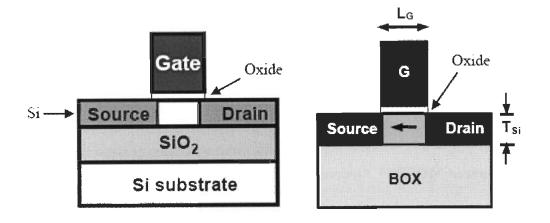

| Fig. 2.2   | Ultra Thin Body MOSFET.                                         | 30       |

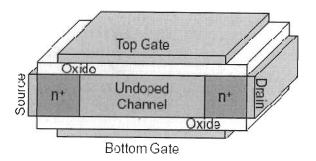

| Fig. 2.3   | Double gate MOSFET.                                             | 31       |

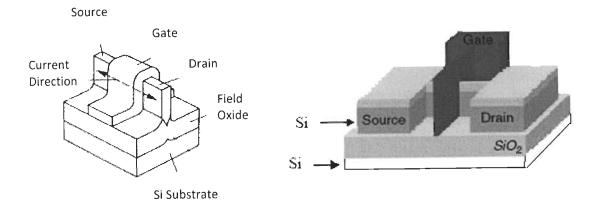

| Fig. 2.4.a | DELTA transistor.                                               | 38       |

| Fig. 2.4.b | FinFET transistor.                                              | 38       |

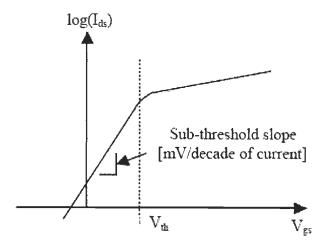

| Fig. 2.5   | Variation of subthreshold current with gate voltage.            | 45       |

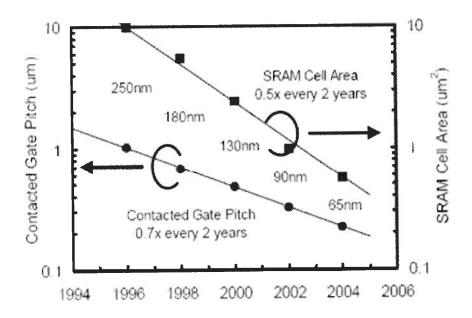

| Fig. 2.6   | SRAM cell size has been scaling at $\sim 0.5$ x per generation. | 48       |

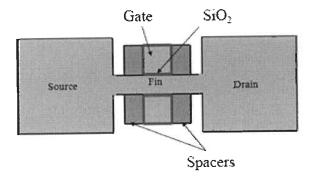

| Fig. 3.1   | Structure of FinFET.                                            | 53       |

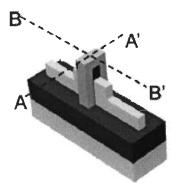

| Fig. 3.2   | Geometry of the FinFET device [6].                              | 62       |

| Fig. 3.3   | Surface potential variations along the channel length for       | 64       |

|            | comparing our quantum result and through reported               |          |

|            | simulation result [35].                                         |          |

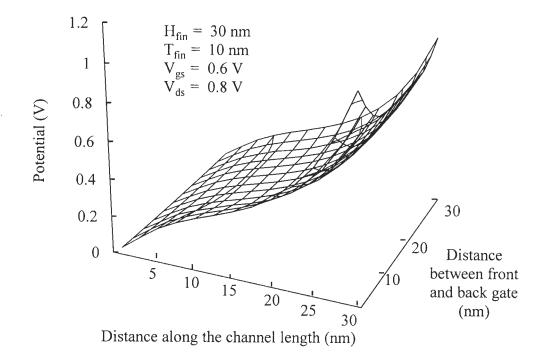

| Fig. 3.4   | 3D potential plot of FinFET for 30 nm channel length            | 65       |

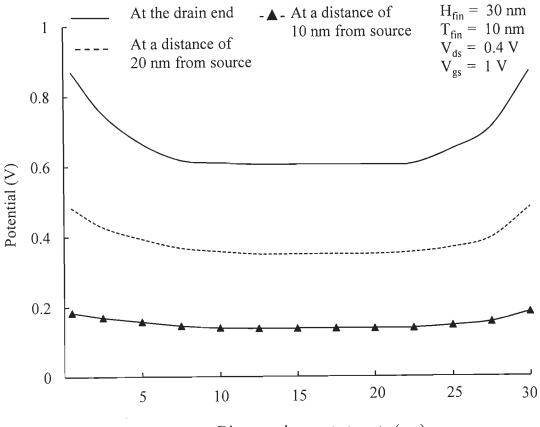

| Fig. 3.5   | Potential variations from front gate to back gate at various    | 66       |

|            | positions along the channel length.                             |          |

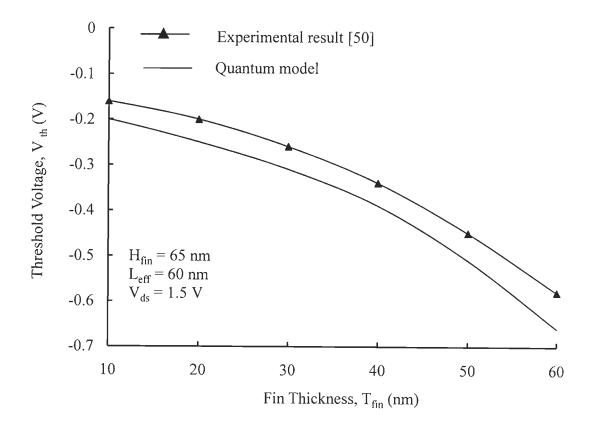

| Fig. 3.6   | Variation of threshold voltage with Fin thickness for our       | 67       |

|            | proposed QM model, classical model and experimental             |          |

|            | reported result [50].                                           |          |

xv

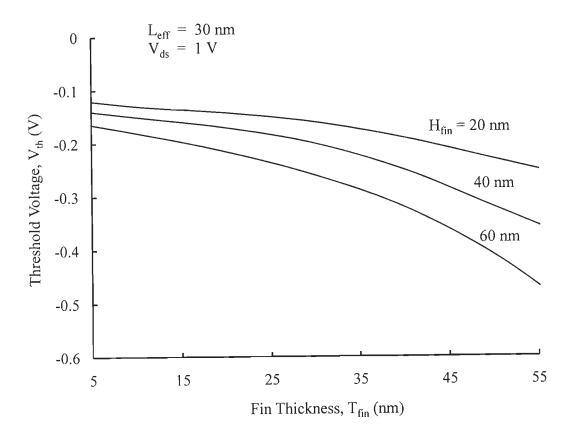

| Fig. 3.7  | Variation of threshold voltage with fin thickness for            | 68   |

|-----------|------------------------------------------------------------------|------|

|           | various fin height.                                              |      |

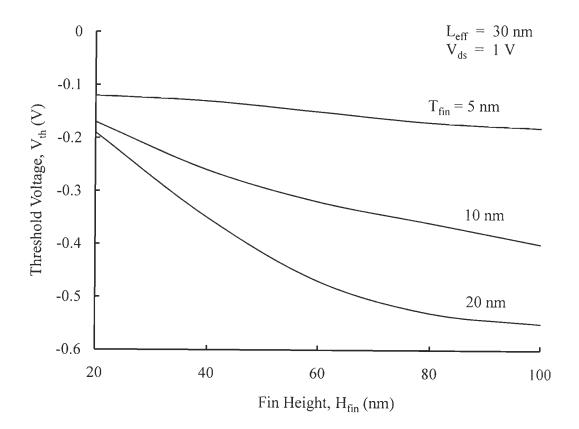

| Fig. 3.8  | Variation of threshold voltage with fin height for various       | 69   |

|           | fin thickness.                                                   |      |

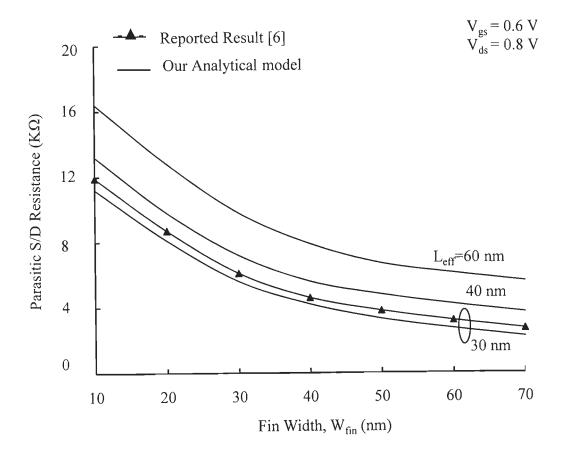

| Fig. 3.9  | Variation of parasitic S/D resistance with varying Fin           | 70   |

|           | width for proposed analytical model and reported result.         |      |

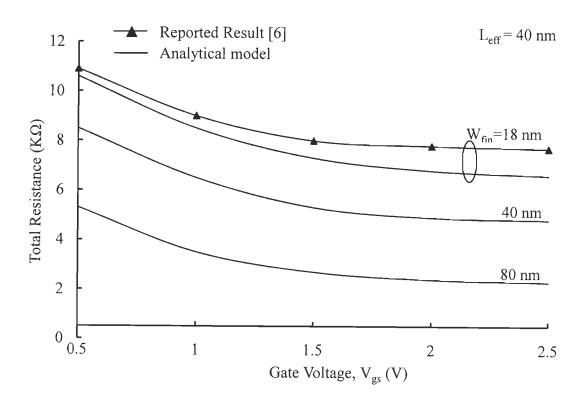

| Fig. 3.10 | Variation of total resistance with variation of gate voltage for | 71   |

|           | varying Fin width.                                               |      |

| Fig. 4.1  | FinFET 2D Structure used in the Sentaurus simulations.           | 80 . |

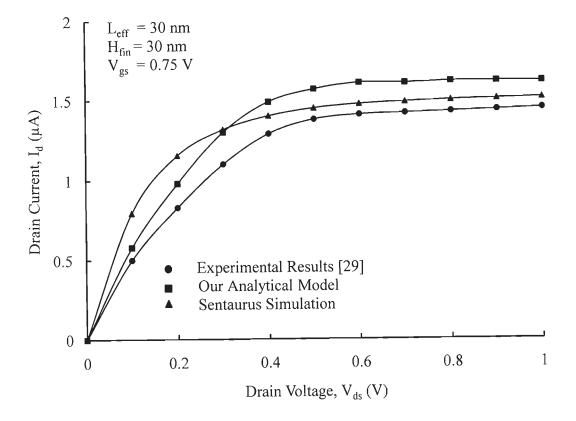

| Fig. 4.2  | Variation of drain current with drain voltage according to our   | 82   |

|           | analytical quantum mechanical model, reported experimental       |      |

|           | results [29] and our Sentaurus simulation results.               |      |

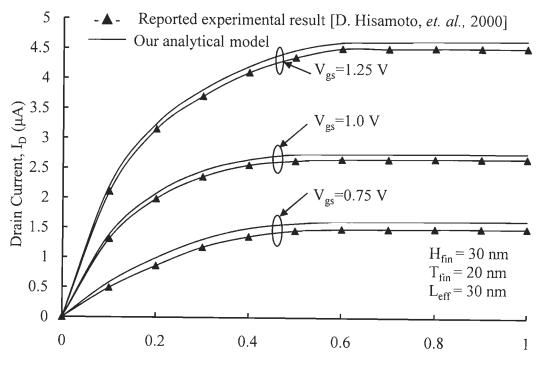

| Fig. 4.3  | Variation of drain current with drain voltage obtained           | 83   |

|           | through our model and reported experimental results [29].        |      |

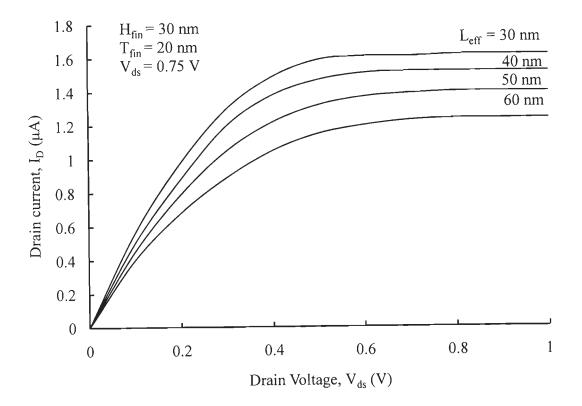

| Fig. 4.4  | Variation of drain current with drain voltage for various        | 84   |

|           | effective gate lengths.                                          |      |

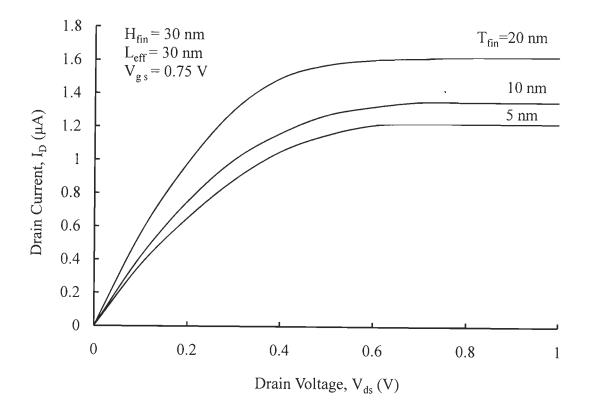

| Fig. 4.5  | Variation of drain current with applied drain voltage for        | 85   |

|           | varying Fin thickness.                                           |      |

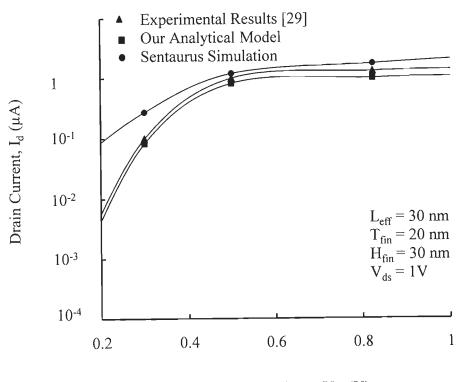

| Fig. 4.6  | Variation of drain current with gate voltage for our             | 86   |

|           | analytical model, reported experimental results [29] and         |      |

|           | Sentaurus simulated results.                                     |      |

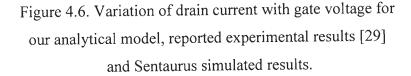

| Fig. 4.7  | Variation of drain current with applied gate voltage for our     | 87   |

|           | model and reported experimental results [29].                    |      |

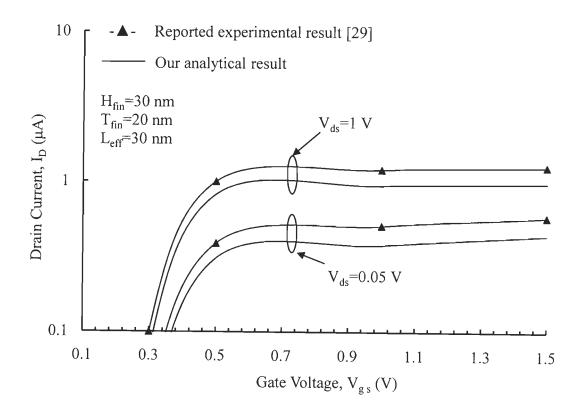

| Fig. 4.8  | Variation of drain current with applied gate voltage for         | 88   |

|           | various effective gate lengths.                                  |      |

xvi

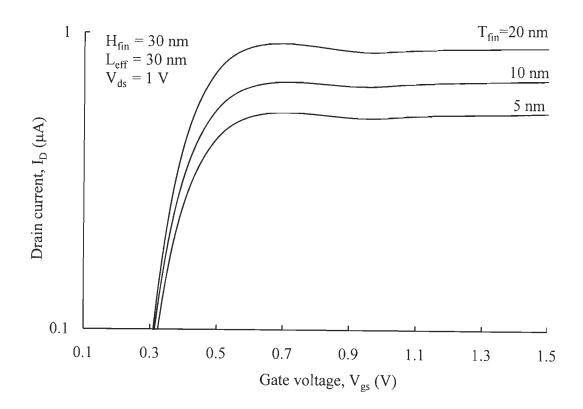

- Fig. 4.9 Variation of drain current with gate voltage for fin thickness of 5 nm and 20 nm for the comparison between classical and quantum model.

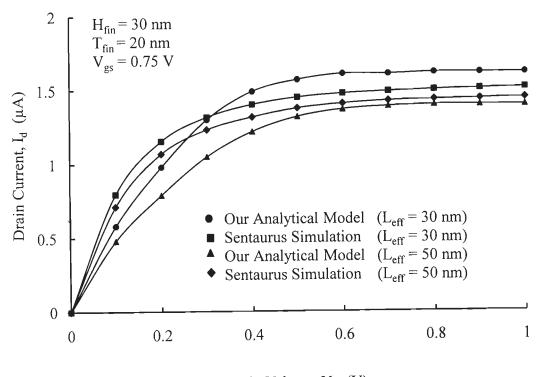

- Fig. 4.10 Comparison of our analytical quantum mechanical model 90 with Sentaurus simulation results for  $I_d$ - $V_d$  characteristics for gate lengths of 30 nm and 50 nm.

89

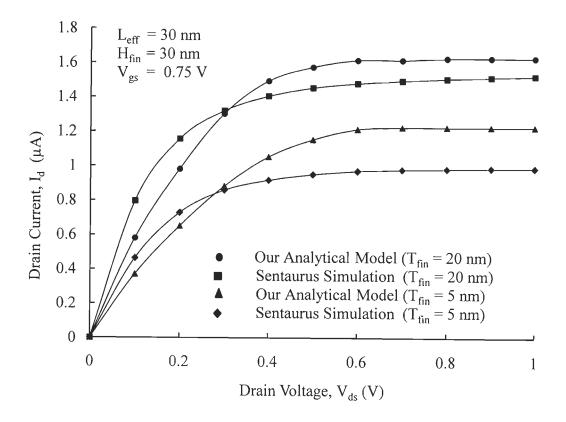

- Fig. 4.11 Variation of drain current with drain voltage and 91 comparison for our analytical quantum mechanical model and Sentaurus simulation results for T<sub>fin</sub> of 20 nm and 5 nm

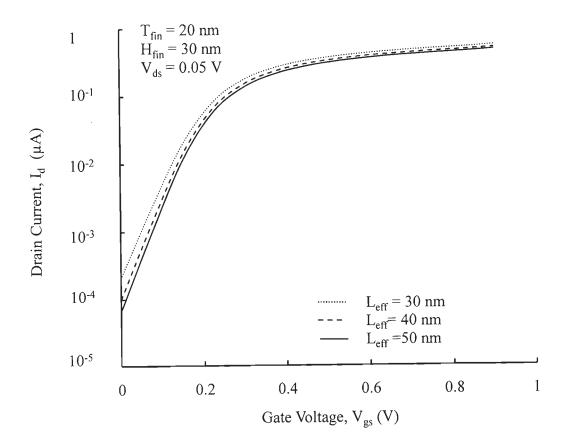

- Fig. 4.12 Variation of drain current with applied gate voltage for 92 varying channel length of 30 nm, 40 nm and 50 nm using Sentaurus.

- Fig. 4.13Variation of drain current with applied gate voltage for Fin93thicknesses of 5 nm, 10 nm and 20 nm using Sentaurus.

- Fig. 5.1Subthreshold and Gate Leakage Currents [4]99

- Fig. 5.2 Gate Leakage Current in Double Gate FinFET Device 100 [145].

- Fig. 5.3 Variation of subthreshold leakage current  $(I_{sub})$  with 103 variation of absolute temperature for our proposed model and reported result [82].

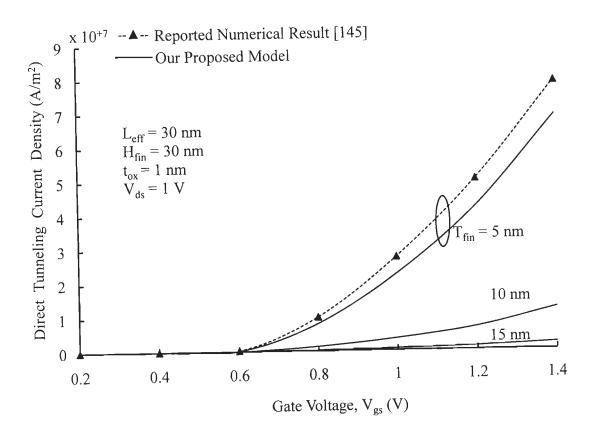

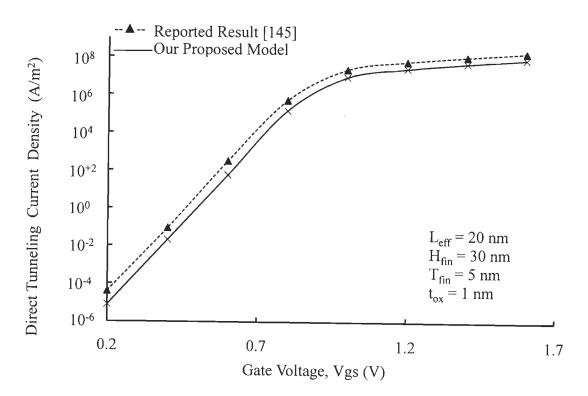

- Fig. 5.4 Variation of direct tunneling current density with gate 104 voltage for Fin thickness (T<sub>fin</sub>) of 5 nm, 10 nm and 15 nm.

- Fig. 5.5 Variation of direct tunneling current density with gate 105 voltage for our proposed model and reported result [145].

xvii

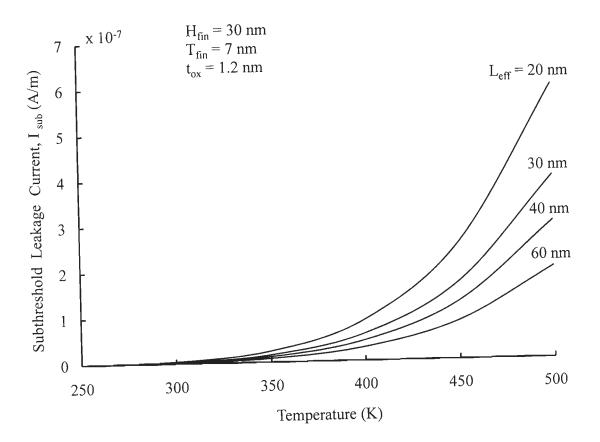

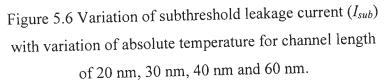

- Fig. 5.6 Variation of subthreshold leakage current  $(I_{sub})$  with 106 variation of absolute temperature for channel length of 20 nm, 30 nm, 40 nm and 60 nm.

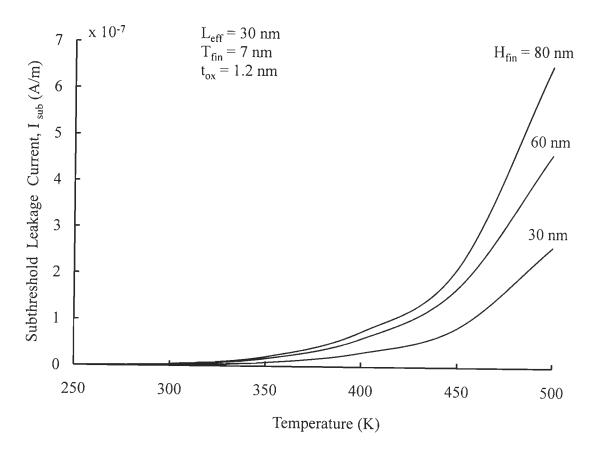

- Fig. 5.7 Variation of subthreshold leakage current (*I<sub>sub</sub>*) with 107 variation of absolute temperature for Fin height of 20 nm, 60 nm and 80 nm.

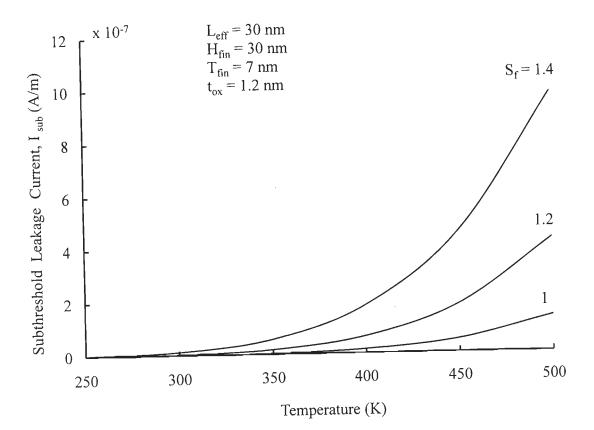

- Fig. 5.8 Variation of subthreshold leakage current  $(I_{sub})$  with 108 variation of absolute temperature for subthreshold swing factor of 1, 1.2 and 1.4.

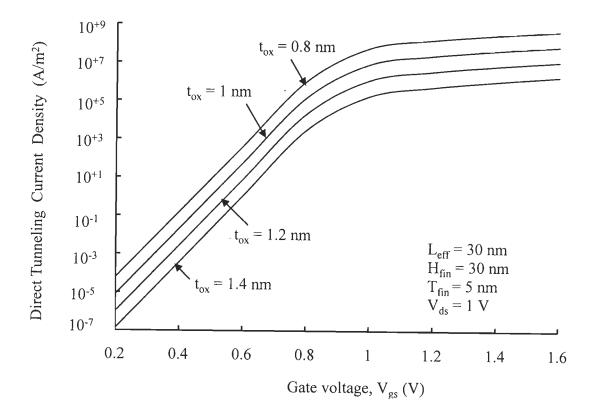

- Fig. 5.9 Variation of direct tunneling current densitywith gate 109 voltage for oxide thickness (t<sub>ox</sub>) of 0.8 nm, 1 nm, 1.2 nm and 1.4 nm.

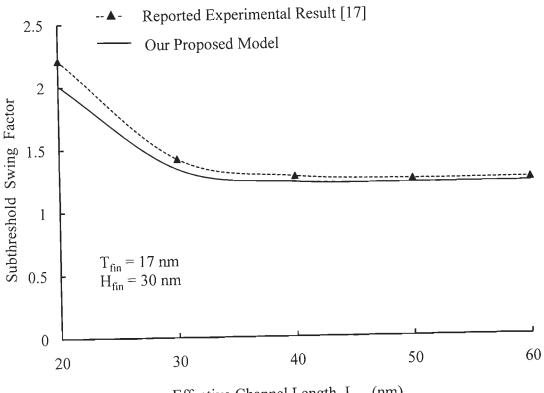

- Fig. 5.10 Variation of subthreshold swing factor with the variation 110 of channel length for Our proposed model and reported experimental result [17].

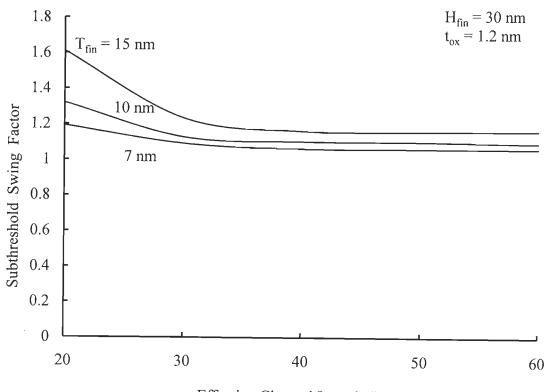

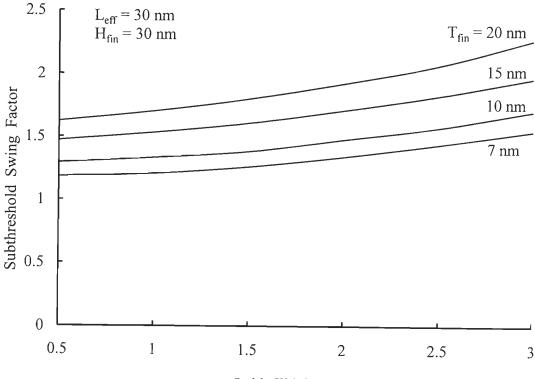

- Fig. 5.11 Variation of subthreshold swing factor with the variation 111 of channel length for Fin thickness of 7 nm, 10 nm and 15 nm.

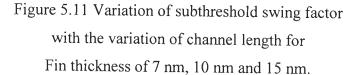

- Fig. 5.12 Variation of subthreshold swing factor with the fin 112 thickness for channel length of 20 nm, 30nm and 40 nm.

- Fig. 5.13 Variation of subthreshold swing factor with oxide 113 thickness for Fin thickness of 7 nm, 10 nm, 15 nm and 20 nm.

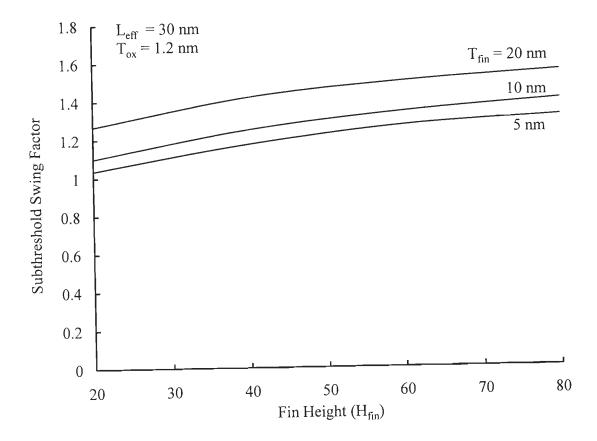

- Fig. 5.14 Variation of subthreshold swing with fin height for 114 various fin thickness.

xviii

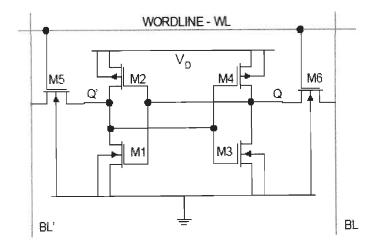

| Fig. 6.1   | Double Gate FinFET.                                                       | 123 |

|------------|---------------------------------------------------------------------------|-----|

| Fig. 6.2   | 6T SRAM cell [44].                                                        | 124 |

| Fig. 6.3   | A typical underlapped FinFET device.                                      | 130 |

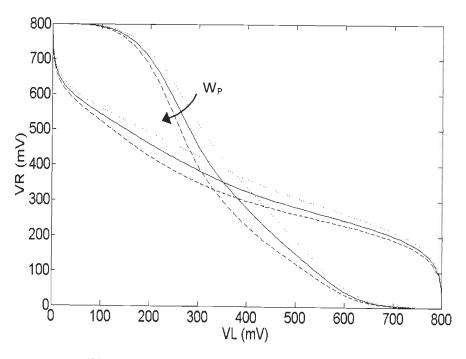

| Fig. 6.4   | SNM variations with width of Load.                                        | 133 |

| Fig. 6.5   | SNM variations with width of Driver.                                      | 134 |

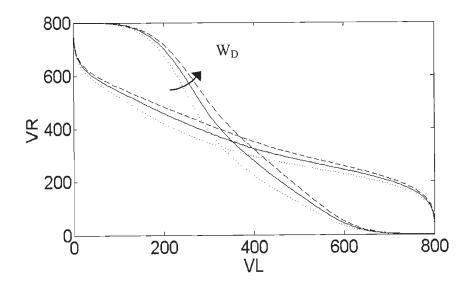

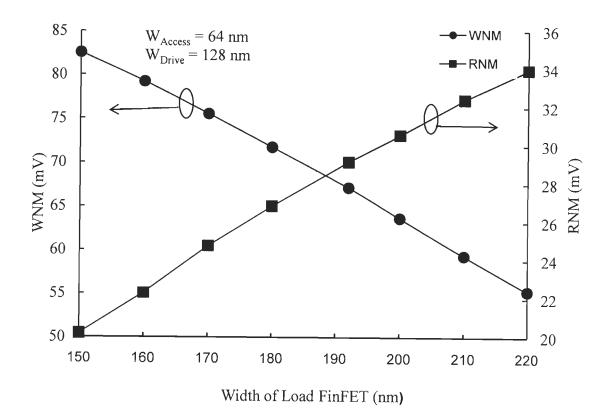

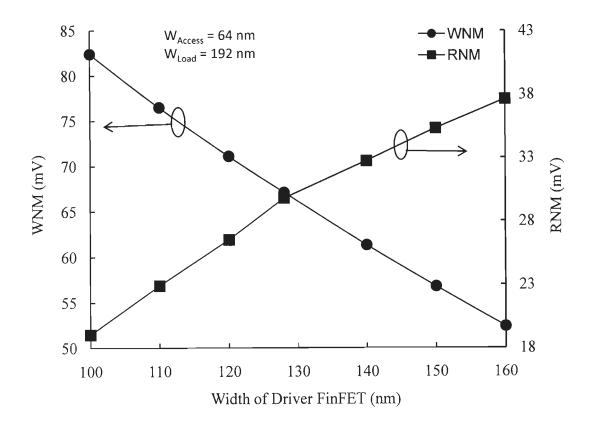

| Fig. 6.6   | WNM and RNM variation with width of Load FinFET.                          | 135 |

| Fig. 6.7   | WNM and RNM variation with width of Driver FinFET.                        | 136 |

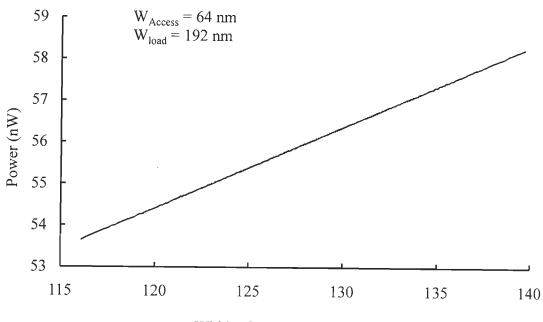

| Fig. 6.8.a | Static power variation with width of Driver FinFET.                       | 137 |

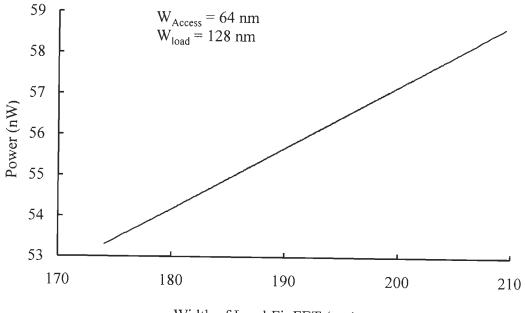

| Fig. 6.8.b | Static power variation with width of Load FinFET.                         | 137 |

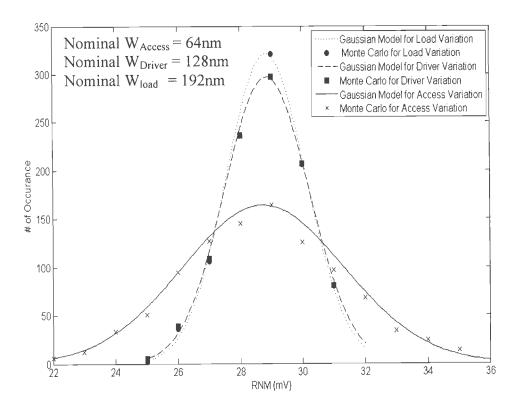

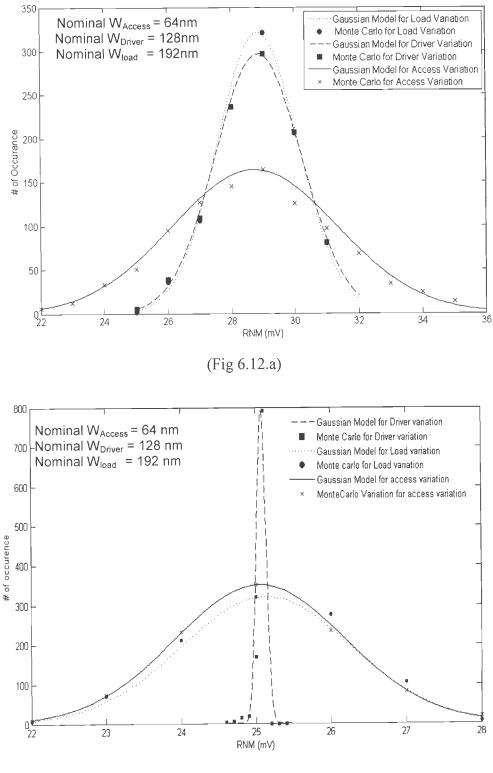

| Fig. 6.9.a | Variations and distribution of RNM                                        | 138 |

| Fig. 6.9.b | Variations and distribution of WNM                                        | 138 |

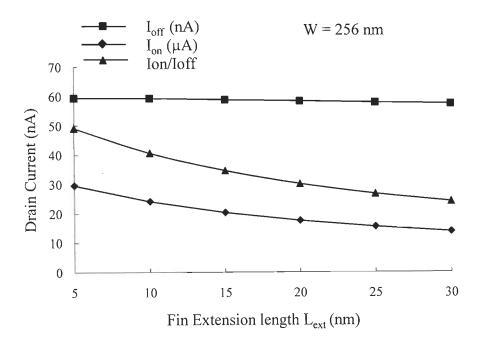

| Fig. 6.10  | Variation of $I_{ON}$ and $I_{OFF}$ with Fin extension length $(L_{ext})$ | 140 |

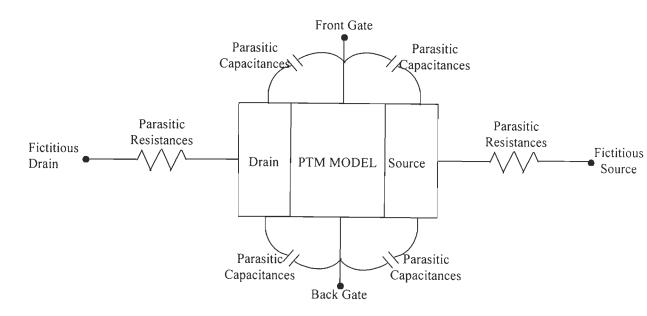

| Fig. 6.11  | Underlapped FinFET derived from PTM model                                 | 141 |

| Fig. 6.12  | Monte Carlo results for variation of RNM with load, driver                | 142 |

|            | and access FinFET widths for (a) PTM model                                |     |

|            | (b) Underlapped model (with fin extension regions)                        |     |

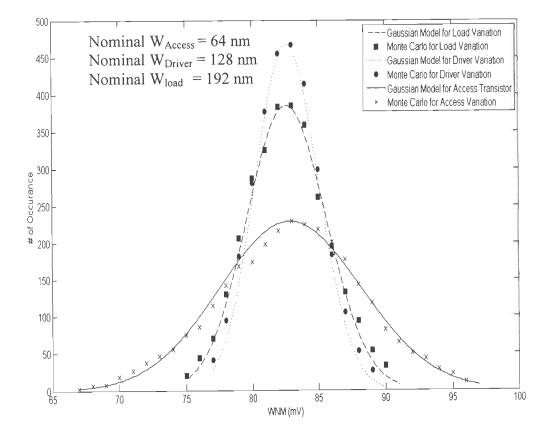

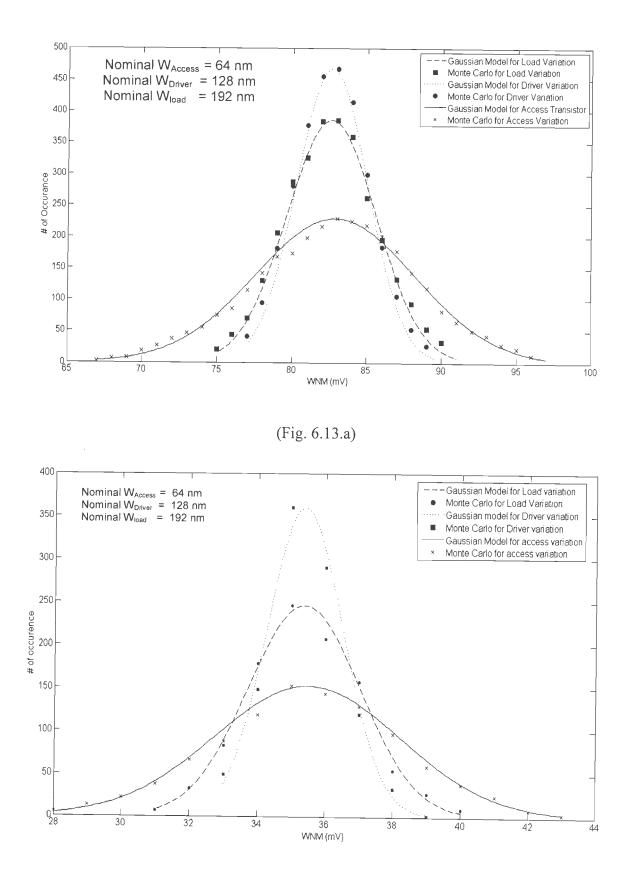

| Fig. 6.13  | Monte Carlo results for variation of WNM with load,                       | 145 |

|            | driver and access FinFETs widths for (a) PTM model                        |     |

|            | (b) Underlapped model (with fin extension regions)                        |     |

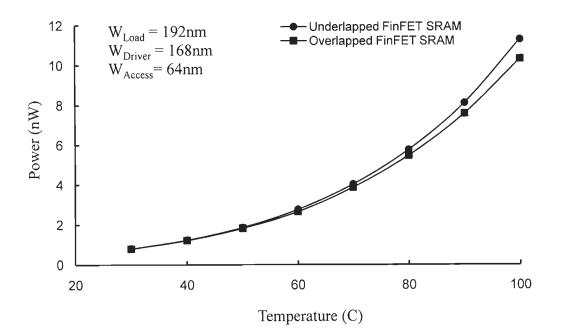

| Fig. 6.14  | Effect of temperature variation on static power for PTM                   | 146 |

|            | FinFET model and underlapped FinFET model SRAM                            |     |

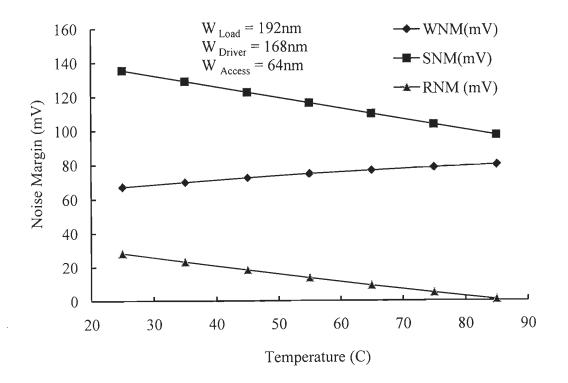

| Fig. 6.15  | Effect of temperature variation on static noise margin, read              | 146 |

|            | noise margin and write noise margin for PTM FinFET                        |     |

|            | model                                                                     |     |

xix

~

# List of Tables

| Table | No.   | Title                                                    | Page No. |

|-------|-------|----------------------------------------------------------|----------|

| Table | 4.1   | Value of Parameters                                      | 81       |

| Table | 5.1   | Value of Parameters                                      | 102      |

| Table | 6.1   | Parameters used in simulation                            | 129      |

| Table | 6.2.a | Mean and Standard Deviation of RNM Monte Carlo Analysis  | s 139    |

| Table | 6.2.b | Mean and standard Deviation of WNM Monte Carlo Analysi   | s 139    |

| Table | 6.3   | Parameters for the Underlapped FinFET Device             | 140      |

| Table | 6.4   | Mean and Standard Deviation values of RNM with Variation | 143      |

|       |       | in FinFET Widths                                         |          |

| Table | 6.5   | Mean and Standard Deviation Value of WNM with Variation  | 144      |

|       |       | in FinFET widths                                         |          |

.

# List of Symbols

| L <sub>eff</sub>        | Effective Channel Length         |

|-------------------------|----------------------------------|

| $L_g$                   | Physical Gate Length             |

| <i>H</i> <sub>fin</sub> | FinFET Height                    |

| T <sub>fin</sub>        | FinFET Thickness                 |

| <i>t</i> <sub>ox</sub>  | Equivalent Oxide Layer Thickness |

| Λ                       | Scale Length                     |

| q                       | Electronic Charge                |

| N <sub>A</sub>          | Channel Doping Concentration     |

| N <sub>D/S</sub>        | Drain/Source Doping Density      |

| n <sub>i</sub>          | Intrinsic Carriers Concentration |

| $\mathcal{E}_{si}$      | Silicon Permittivity             |

| E <sub>ox</sub>         | Oxide Permittivity               |

| $\mathcal{E}_{ins}$     | Insulator Permittivity           |

| $\Psi_s$                | Surface Potential                |

| ${\psi}_o$              | Centre Potential                 |

| arphi                   | Electron Wave Function           |

| $V_{gs}$                | Gate Voltage                     |

| V <sub>ds</sub>         | Applied Drain to Source Voltage  |

| $V_S$                   | Potential at Source Terminal     |

| V <sub>bi</sub>         | Built in Potential               |

| V <sub>FB</sub>         | Flat Band Voltage                |

| $V_{T}$                      | Thermal Voltage                                      |

|------------------------------|------------------------------------------------------|

| V <sub>th</sub>              | Threshold Voltage of the Device                      |

| $\Delta V_{th}$              | Threshold Voltage Roll-off                           |

| $V_{\text{th,QM}}$           | Quantum Mechanical Threshold Voltage                 |

| I <sub>ds</sub>              | Channel Current from Drain to Source                 |

| Isub                         | Subthreshold Current                                 |

| Cox                          | Capacitance of Oxide Layer Per Unit Area             |

| $k_B$                        | Boltzman's Constant                                  |

| $E_{g}$                      | Band Gap Energy                                      |

| $E_{G(ins)}$                 | Energy Band Gap for Insulators                       |

| E <sub>ins</sub>             | Electric Field in the Insulator Region               |

| $E_{F}$                      | Fermi Energy Level                                   |

| $E_{eff}$                    | Effective Electric Field                             |

| $\mathcal{Q}_b$              | Bulk Charge                                          |

| $q_i$                        | Inversion Charge                                     |

| $C_{ins}$                    | Insulator Capacitance                                |

| $C_{si}$                     | Channel Capacitance                                  |

| $C_{g}$                      | Gate Capacitance                                     |

| $C_{\scriptscriptstyle dep}$ | Depletion Capacitance                                |

| m <sub>ox</sub>              | Electron Effective Mass of Insulators                |

| m <sub>o</sub>               | Free Electron Mass                                   |

| <i>m</i> ,*                  | Effective Mass of Electron in Transverse Direction   |

| $m_i^*$                      | Effective Mass of Electron in Longitudinal Direction |

| h                              | Planck's Constant                  |

|--------------------------------|------------------------------------|

| $\mu_n$                        | Mobility of Electron               |

| $\mu_p$                        | Mobility of Hole                   |

| $\mu_{\scriptscriptstyle eff}$ | Effective Mobility                 |

| ν                              | Channel Potential                  |

| S                              | Subthreshold Slope                 |

| $S_f$                          | Subthreshold Slope Factor          |

| Т                              | Temperature                        |

| η                              | Fitting Parameter                  |

| $X_{j}$                        | Source/Drain Junction Depth        |

| $ ho_{ m int}$                 | Contact Resistivity                |

| $ \rho_{ext} $                 | Resistivity of the S/D Extension   |

| L <sub>ext</sub>               | Length of the Fin Extension Region |

| $T_{poly}$                     | Thickness Ploysilicon Layer        |

xxvi

# List of Abbreviations

| AC     | Access                                  |

|--------|-----------------------------------------|

| BL     | Bit Line                                |

| BOX    | Buried Oxide                            |

| CMOS   | Complementary Metal Oxide Semiconductor |

| CR     | Cell Ratio                              |

| DG     | Double Gate                             |

| DIBL   | Drain Induced Barrier Lowering          |

| DOS    | Density of States                       |

| DRAM   | Dynamic Random Access Memory            |

| EC     | Electrical Confinement                  |

| EOT    | Effective Oxide Thickness               |

| FDSOI  | Fully Depleted Silicon-On-Insulator     |

| FinFET | Fin Field Effect Transistor             |

| GAA    | Gate-All-Around                         |

| GIDL   | Gate Induced Drain Lowering             |

| HDD    | Heavily Doped S/D                       |

| IC     | Integrated Circuits                     |

| ITRS   | International Technology Roadmap for Semiconductor |

|--------|----------------------------------------------------|

| MOSFET | Metal Oxide Semiconductor Field effect Transistor  |

| MuGFET | Multi Gate Field Effect Transistor                 |

| PD     | Pull Down                                          |

| PDSOI  | Partially Depleted Silicon-On-Insulator            |

| PTM    | Predictive Technology Model                        |

| PU     | Pull Up                                            |

| QG MOS | Quadruple Gate MOS                                 |

| QME    | Quantum Mechanical Effects                         |

| R&D    | Research and Development                           |

| RDF    | Random Dopant Fluctuations                         |

| RNM    | Read Noise Margin                                  |

| S/D    | Source/Drain                                       |

| SC     | Structural Confinement                             |

| SCEs   | Short Channel Effects                              |

| SNM    | Static Noise Margin                                |

| SoC    | System on Chip                                     |

| SOI    | Silicon on Insulator                               |

| SP `   | Schrodinger-Poisson                                |

| SRAM | Static Random Access Memory      |

|------|----------------------------------|

| ULSI | Ultra Large Scale Integration    |

| UTB  | Ultra Thin Body                  |

| VTC  | Voltage Transfer Characteristics |

| VLSI | Very Large Scale Integration     |

| WL   | World Line                       |

| WNM  | Write Noise Margin               |

#### Introduction

#### **1.1 Introduction**

Continued miniaturization of bulk silicon Complementary Metal Oxide Semiconductor (CMOS) transistors is being limited by Short Channel Effects (SCE's). SCE is the decrease of the MOSFET threshold voltage as the channel length is reduced. Other SCE's are mobility degradation and Drain Induced Barrier Lowering (DIBL). Higher channel doping, shallower source/drain junctions and thinner gate dielectrics have been employed to improve gate control and enhance performance as the gate length is scaled down [40]. However, these techniques are rapidly approaching present material and process limits. Alternate transistor architectures such as the planar Ultra-Thin Body (UTB), Double-Gate Metal Oxide Semiconductor Field Effect Transistor (DG MOSFET) and Fin Field Effect Transistor (FinFET) may be necessary to continue gate length scaling down to the sub-32 nm regime [20, 80].

The silicon-based microelectronics industry has been growing rapidly for the past four decades following Moore's law of scaling [45, 46]. However, fundamental physical limits are nearly at the end of conventional linear scaling of transistor dimensions and the new era of MOS scaling constrained by power dissipation and process-induced variations. FinFET is the most promising double-gate structure for integrated circuit manufacturing [62] in the near future. With MOSFET as an unit component of most high-performance ICs, the focus is on developing transistors that are faster and smaller than their predecessors, maintaining a high degree of reliability

and low cost. These often-conflicting goals are the driving force behind transistor research in academia and industry. With many groups working on near and long-term solutions to the demands of the IC industry, one type of device has garnered attention of some prominent researchers and industry heavyweights – the FinFET. This device presents a solution that promises excellent performance and scalability, while carrying with it a great degree of risk in a manufacturing environment or fabrication [27, 43].

Fundamental changes in device architecture may be necessary to continue scaling trends with thin-body MOSFETs such as UTB-FETs and FinFETs emerging as leading contenders. Constant scaling of CMOS devices is the well-known driver of advancement and growth in the microelectronic industry with today's advanced technology delivering high-performing devices at the 90nm and 65nm technology nodes [57, 60, 90]. A major problem in scaling MOS devices with nanoscale gate length is the difficulty in controlling the leakage current when the device is switched off. In standard planar MOS technology, doping profile may be used to mitigate part of this problem. But the drawback of increased channel doping would result in reduction of mobility and hence the driving capability of the device. One can reduce the oxide layer thickness to maintain the device performance but below a certain limit, the gate leakage current exceeds more than the tolerance limit. Advanced devices have focused on highly confined channel to improve source-drain isolation. Practical structures utilize a vertical configuration such as FinFET [29], also known as trigate MOSFET. Such devices in general provide a good source to drain isolation but offer somewhat moderate current rate [16].

Semiconductor memory arrays capable of storing large quantities of information are essential to all digital system. The amount of memory required in a particular system depends on the type of application with the requirement of high

2

density on-chip memory for digital systems. Conventional MOS based memory would not be able to meet such demand due to reasons stated earlier such as SCEs, leakage, power dissipation etc. Hence, the requirement of FinFET as memory element would be essential to mitigate above problems. The ever increasing demand for large storage capacity has driven the fabrication technology and memory development towards more compact design rules and consequently towards higher data storage densities. On-chip memory arrays have become widely used subsystems in VLSI circuits and commercially available single chip read/write memory capacity has reached more than 2 GB [36, 55].

The semiconductor memory is generally classified according to the type of data storage and data access. Read/Write memory or Random Access Memory (RAM) must permit the modification of data bits stored in the memory array, as well as their retrieval demand [39]. Based on the operation type of individual data storage cells, RAMs are classified into two main categories:

- 1. Dynamic RAM (DRAM)

- 2. Static RAM (SRAM).

As the continuing trend for high-density memories favors small memory cell sizes, the dynamic RAM cell with a small structure has become a popular choice, where binary data are stored as a charge in a capacitor and the presence or absence of stored charge determines the value of the stored bit. The data stored in a capacitor cannot retain indefinitely, because the leakage currents eventually remove or modify the stored data. Thus the DRAM cell requires a periodic refreshing of the stored data, so that unwanted modifications due to leakage are prevented before they occur [22]. The usage of a capacitor as a primary storage device generally enables the DRAM cell to be realized in a much smaller silicon area compared to the typical SRAM cell.

3

The FinFET based SRAM cell consists of latch so the cell data is kept as long as power is turned on and refresh operation is not required. SRAM is mainly used for the cache memory in microprocessor, mainframe computers, engineering workstations and memory in handheld devices due to its high speed and low power consumption. Memories are said to be static if no periodic clock signals are required to refresh and retain the stored data indefinitely. Memory cells in these circuits have a direct path to supply or ground or both. Read-Write memory cell arrays based on flip-flop circuits are commonly referred to as SRAMs. The FinFET based SRAM cell consists of two cross-coupled inverters and two access transistors. The access FinFET's are connected to the wordline at their respective gate terminals and the bitlines at their source/drain terminals. The wordline is used to select the cell while the bitlines are used to perform read or write operations on the cell. Internally, the cell holds the stored value on one side and its complement on the other side. The two complementary bitlines are used to improve speed and noise rejection properties [41, 90].

This chapter provides an introduction and brief idea about the whole work carried in this thesis. Section 1.1 deals with introduction and international technology roadmap for semiconductor with reference to ITRS-2007 report, section 1.2 describes the scaling of semiconductor devices. Section 1.3 gives the motivation behind the research work carried. Further, section 1.4 deals with the problem description and section 1.5 describe the thesis organization. The conclusion of this chapter is drawn in section 1.6.

In particular, the International Technology Roadmap for Semiconductors (ITRS) has identified several types of devices such as Ultra Thin Body (UTB), Double Gate MOSFET and FinFET that could augment or eventually replace classical

4

CMOS devices. The Emerging Research Devices section of the ITRS report [65] discusses several emerging technologies including UTB multiple gate field effect transistors.

All of these improvement trends, sometimes called "scaling" trends, have been enabled by large R&D investments. In the last two decades, the growing size of the required investments has motivated industry collaboration with many R&D partnerships and other cooperative ventures. The ITRS has been successful worldwide cooperation endeavor. It presents an industry-wide consensus on the "best current estimate" of the industry's research and development needs to a 15-year horizon. As such, it provides a guide to the efforts of companies, research organizations and governments. The ITRS has improved the quality of R&D investment decisions made at all levels and has helped channel research efforts to areas that truly need research breakthroughs. ITRS to large extent helps to do technology forecasting within semiconductor industry as well as in academic domain.

#### **1.2 Scaling of Semiconductor Devices**

Moore's law describes the rate of increase in transistor density with progressing years as shown in figure 1.1. Reduction of the physical MOS device dimensions have improved both circuit speed and density [46, 58]. The major aim of pursuing Moor's law or finding alternative solution is to further increase the performance. It can be inferred from figure 1.1 that:

a) Circuit operational frequency 'f' increases with a reduction in gate length,  $L_g$ , as  $\sim 1/L_g$ ; allowing for faster circuits,

5

b) It can be shown that chip area decreases (due to increased density) as  $\sim L_g^2$ ; enabling higher transistor density and cheaper ICs.

Figure 1.1 Moore's law of scaling [Source: Intel, IBM, TI, Polsson].

Since its conception, there has been an exponential scaling down of transistor dimensions (following the trend predicted by G. E. Moore [46].) targeted towards making the circuits smaller in order to fit more and more functionalities in a given chip area. The modern day circuits have over 100 million transistors per chip and this exponential growth since early 1960s is expected to continue for at least another decade [65]

The main goals behind scaling down transistors in a circuit are to achieve improved performance, more on-chip functionality and reduced cost per functionality. The transistors in ICs have been traditionally implemented using Bulk Silicon CMOS technology. As the lateral and vertical dimensions of the transistor are scaled down, several effects come into play which make further scaling down of the traditional device architecture increasingly challenging [12]. As the gate length ( $L_g$ ) of a transistor is decreased (lateral scaling), the source and drain regions come closer and the drain electric field starts reducing the source-channel potential barrier. The capacitively coupled gate tends to lose control on the channel, especially in the subsurface region. This capacitive coupling can be improved by decreasing the gate dielectric thickness (vertical scaling). The chief outcome of this is an increase in the off-state leakage current ( $I_{OFF}$ ) of the transistors which contributes to the total stand-by power in a circuit [13, 23].

#### 1.3 Motivation of Work

Microelectronic devices have evolved rapidly in terms of size, cost and performance. Scaling of device dimensions has been the engine of the semiconductor industry [123] allowing manufacturers to produce consecutive generations of integrated circuits of ever decreasing dimensions and increasing transistor densities. This trend has resulted in feature sizes with nanometer dimensions. Current physical gate lengths of transistors used in high performance integrated circuits are around 50 nm and will go down to 32 nm and 18 nm by 2010 and 2016 respectively, according to projections made in the 2007 International Technology Roadmap of Semiconductors (ITRS) [65]. Prototype transistors with gate lengths as small as 22 nm have already been fabricated in research labs around the world [18, 43].

7

Clearly the microelectronic industry has entered the nanotechnology era and is manufacturing millions of nanoscale transistors on a phenomenal scale.

Consequently, scaling of FinFET device dimensions is important in order to improve the drivability and to achieve higher-performance and functional VLSI's. Hence, an accurate assessment of device characteristics and performance in nanoscale range is of fundamental importance to understand the ultimate limits of FinFET device as well as to develop innovative device concepts. Nanometer scale dimensions (1-100 nm) are comparable to (if not smaller than) the mean free path (~100 nm) as well as the de-Broglie wavelength (~ 10 nm) of electrons in typical semiconductors and metals. Hence, standard macroscopic models (for example, the drift diffusion model of current flow) which include scattering effects using lumped parameters (like mobility) and neglecting quantum effects (like the wave nature of electrons) are not applicable to nanostructures and new models and methods need to be developed.

It is well known fact that as the channel length reduces, more Short Channel Effects (SCEs) are prevalent in the device which tend to degrade the performance and hence the functionality of the chip. The control of SCEs is more challenging in progressive scaling of MOSFETs. The double gate MOSFET and FinFET structures have emerged as the main candidates to provide the electrostatic integrity needed to scale down FinFETs to minimal channel lengths. In addition to better electrostatics than the single gate MOSFETs, the use of these devices have the advantages relative to the carrier transport mainly due to 1) reduced surface roughness scattering and 2) reduction of the coulomb scattering because the channel is made up of undoped/ low doped Silicon. Compact analytical and semi-empirical models of these device structures remain an issue and have been looked into in this thesis.

Technology trends have resulted in static power dissipation (leakage) emerging as a first design consideration in high-performance processor design. Historically, architectural innovations for improving performance relied on exploiting ever larger number of transistors operating at higher frequencies. To keep the resulting switching power dissipation at bay, successive technology generations have relied on reducing the supply voltage. In order to maintain performance, however, a corresponding reduction in the transistor threshold voltage ( $V_{th}$ ) is required. Since the Metal Oxide Semiconductor Field Effect Transistor (MOSFET) sub-threshold leakage current increases exponentially with reduced  $V_{th}$ , static power dissipation has grown to be a significant fraction of overall chip power dissipation in modern deep-sub-micron processes. Analysis of nanoscale device such as FinFET provides high performance and reduced leakage currents with reduced sensitivity to process parameter variations.

Since leakage power is proportional to the number of FinFETs, much of the recent work in reducing static power has focused on Static Random Access Memory (SRAM)-based structures, such as the caches that comprise the vast majority of onchip transistors. Existing circuit-level leakage reduction techniques are oblivious to program behavior and trade off performance for reduced leakage where ever possible.

#### **1.4 Problems Description**

The proposed work during the period of research is expected to yield an optimized design for a conventional 6T based FinFET SRAM for its operation in low power domain showing less SCEs, ultra small access time and high stability. It is felt that in order to properly understand the FinFET based SRAM design, one has to undertake a study to evaluate the full output characteristics of FinFET so that we are able to appreciate the variation of output characteristics with process parameter variations which are quite substantial at such low dimensions.

In view of the above observations, the whole work during the period of research has been divided into two primary phases. Initially, during the starting phase, the study of FinFET as a device has been carried out. The device dimensions taken during the study is primarily dictated by the technology node as predicted by ITRS report. Subsequently, the results obtained in the first phase have been utilized for FinFET based SRAM design in the second phase of the research work. The requisite design parameters have been obtained through reported literature or nodes predicted by ITRS. Since the work carried out is purely theoretical in nature, verification and validation of the results obtained becomes an issue of prime importance in order to substantiate our work. In order to do so, comparison of our results with those obtained through reported experimental/simulated results have been undertaken during each stage of the work.

After extensive literature survey, various technical gaps came to light for the current research work in this area. These are stated as under:

- (i) For the prediction of device performance of FinFET structure, 2D/3D device simulation is inevitable. There are research papers where FinFET 2D/3D model have been proposed but detailed study of variation in the output characteristics with process parameters variation, device structure etc have not been carried out.

- (ii) It is felt that a full Quantum Mechanical (QM) analytical modeling needed to be carried out in order to appreciate qualitatively the behavior of FinFET under various bias/process conditions.

10

- (iii) No universal mobility model has been proposed for charge carriers in FinFET structure. The evaluation of effective mobility under all conditions of process parameters variation would be required for determining the driving capability of FinFET structure.

- (iv)Extensive QM corrections are required for predicting accurate picture of device. Density of State (DOS) based correction model is not well reported in literature. Moreover outputs from TCAD simulator have not been reported in literature.

- (v) To the best of our knowledge, very few research papers have actually dealt with the leakage aspect of FinFET. The study is critical in order to estimate analytically or otherwise the power dissipation of FinFET device under bias. Evaluation of subthreshold and gate leakage current of FinFET have not been reported extensively.

- (vi) At subsystem level, very few papers have been reported on FinFET based SRAM design. Most of the papers in this area are based on fabrication/process technology for generation of SRAM cell by DG MOSFET.

In view of above research gaps, the detailed research problems have been presented as:

## 1.4.1 QM Analytical Modeling of Nanoscale DG FinFET: Evaluation of Potential, Threshold Voltage and Source/Drain Resistance

In order to evaluate the output current, it is essential to find out the potential variation within the active area of the device. In order to approach such a problem, analytical modeling scheme for FinFET has been carried out with device parameters. Key issues including FinFET device structure, design parameters, potential modeling, process parameter variation effects and device scaling limit have been undertaken quantitatively as well as qualitatively. Variation of potential along source-to-drain region as well as from gate to gate has been presented. The threshold voltage evaluation becomes an important issue in order to undertake power dissipation characteristics. Hence extraction of threshold voltage is also carried out in order to understand the switching behaviour of the device. The analytical modeling for threshold voltage and parasitic source/drain resistance has been carried out for the FinFET device structure under study. The results obtained on the basis of our proposed analytical model have been compared and contrasted with the reported experimental results.

## 1.4.2 Analytical Modeling of Nanoscale Double Gate FinFET: Evaluation of Inversion Charge, Mobility and Drain Current

As the device dimensions are excessively reduced and the channel length of the device becomes of the order of the de-broglie wavelength of electron, it becomes imperative to undertake an extensive Quantum Mechanical (QM) modeling for the device under study. The QM inversion charge analytical modeling of FinFET device has been carried out. Further, evaluation of quantum inversion charge is to be taken up in order to appreciate the amount of charge storage under various external bias conditions. This has been essential to understand SRAM behaviour. In order to evaluate the output drain current, a comprehensive mobility model for the charge carriers has been carried out. Various mobility models are studied and implemented during the course of study and appropriate model is taken up in order to evaluate the drain current. The results obtained on the basis of our model are compared with our TCAD Sentaurus simulation result as well as reported experimental results. The aim of the work carried out is to explore FinFET with ultra thin body. They are chosen because of their high scalability. The problem stated above has been overcome by doing a full quantum mechanical treatment of the FinFET device.

## 1.4.3 Modeling of Subthreshold Leakage Current, Subthreshold Swing factor and Gate Leakage Currents for DG FinFET Device

As the device dimensions are reduced, the off state leakage current substantially increases because of many Quantum Mechanical (QM) effects. This results in a larger power dissipation of the device and the matter assumes critical importance in SRAM as FinFET SRAM designs are prone to larger power dissipations. Reported results have shown that at the same technology node, the leakage in FinFET is lower as compared to bulk MOSFET. The various leakage current components in FinFET device have been evaluated such as subthreshold, gate tunneling leakage current and its dependence on various device/process parameters. This information would be critical in arriving at those device/process dimensions which would result in minimizing the power dissipation.

## 1.4.4 FinFET Based Nanoscale Static Random Access Memory (SRAM) Cell Design: Analysis of Performance metric, Process variation, Underlapped FinFET and Temperature effect

Embedded SRAM arrays are expected to contribute the largest fraction of chip area and device count in future ICs. These arrays are likely to be the primary source of chip leakage. Further, FinFET based SRAM cell usually uses the smallest device on chip packed very closely together to achieve high density. Thus they are more sensitive to process variations. The FinFET based 6T SRAM cell uses cross coupled inverter structure to store bit. The mismatch between cell devices can cause data flipping during read operation. Thus the primary goal of the proposed design includes maximizing stability and minimizing leakage in SRAM, besides achieving maximum density. To the best of our knowledge, very few research papers are available that explore FinFET structure/technology from an SRAM circuit standpoint. The existing literature assumes promise for scaling CMOS into the sub-45nm regime, particularly for low-power applications such as memory [115, 170].

Design considerations for maximizing performance and yield of FinFET-based 6-T SRAM at the 32 nm have been examined. It is known that SCEs are effectively suppressed by a narrow silicon fin which allows for gate-length scaling down to the 32 nm regime without the use of heavy channel/body doping. But at such low dimensions of FinFET, there might be issues related to reliable fabrication. There might be a large increase in the parasitic, which would result in hindrance for high speed applications. It also allows FinFET devices to have negligible depletion charge and capacitance, which yield a steep sub-threshold slope. In addition, FinFETs have lower parasitic device capacitance because both depletion and junction capacitances are effectively eliminated, which reduces the bitline capacitive load. Finally, the elimination of heavy doping in the channel minimizes V<sub>th</sub> variations due to statistical dopant fluctuation effects. Therefore, FinFET based SRAM cells have enhanced performance over planar bulk-Si MOSFET SRAM cells. FinFET based SRAM cell have improved 'read' and 'write' margin of the SRAM cell without compromising on the area requirement. The simulations have been carried out in HSPICE with appropriate structuring of model file containing various device parameters both independent and extracted.

### 1.4.5 Performance Evaluation of FinFET based SRAM

### 1.4.5.1 Static and Dynamic Noise Margin

The Static Noise Margin (SNM) is the maximum amount of noise voltage that can be introduced at the outputs of the two inverters such that the cell retains its data. SNM quantifies the amount of noise voltage required at the internal nodes of a bit cell to flip the FinFET based SRAM cell's contents. When the bit cell is holding data, its wordline is 'LOW' so the nFinFET access transistors are 'OFF'. In order to hold its data properly, the back-to-back inverters must maintain bi-stable operating points. The best measure of the ability of these inverters to maintain their state is the bitcell's Static Noise Margin (SNM). For the 32 nm node FinFET, we have evaluated the SNMs under various bias conditions and process conditions. This would be useful for fabrication engineers to design benchmarks for future nanoscale FinFET based SRAM with respect to process tolerances.

#### 1.4.5.2 Read/Write Noise Margin

Utilizing higher FinFET threshold voltages also negatively impact the access time due to the lower read current. However, it improves the 'read' and 'write' margins. While high threshold voltage pFinFET loads decreases the inverter trip point, high threshold nFinFET Pull-Down Device (NPD) tends to increase it. Since the current driving ability of the NPD is larger than that of the pFinFET load, increasing the threshold voltage of the nFinFET transistors tends to have a stronger impact on the trip voltage, thus resulting in larger read and write margins.

15

#### **1.4.5.3 Power Evaluation**

Large FinFET based SRAM consumes a significant portion of the overall power of an application processor. Power consumption in an SRAM consists of short active periods and very long idle periods. For SRAM, standby power consumption is a major issue. Therefore, leakage reduction in large memory arrays has become essential for low-power VLSI applications. FinFET based SRAM cell leakage is commonly suppressed by either using longer channel lengths or higher transistor threshold voltages. Another method is to use multiple threshold voltage devices. Using longer channel lengths increases the cell area and in addition, also increases word line and bit line capacitances, thus increasing access time and active power. Therefore, longer channel lengths are used sparingly.

#### **1.5 Thesis Organization**

This thesis is organized into seven chapters as follows:

Chapter 1 Deals with introduction portion.

**Chapter 2** The review of existing literature for modeling of proposed device is presented in chapter 2. This chapter contains the literature review on bulk MOSFET, advanced MOSFET structures such as UTB, DG and FinFET, various leakage currents associated with the MOSFET and FinFET devices and circuit aspect of FinFET based nanoscale SRAM design.

16

- **Chapter 3** Deals with the full quantum mechanical analytical modeling of two dimensional potential with surface potential approach for the work function engineered Double Gate FinFET device. This chapter also evaluates the threshold voltage and parasitic source/drain resistance analytical modeling of FinFET device.

- **Chapter 4** Describes the analytical modeling of the quantum inversion charge, field dependent mobility and drain current for FinFET device.

- Chapter 5 Describes the analytical modeling and estimation of various types of leakage currents associated with the FinFET device.

- Chapter 6 Deals with the FinFET based nanoscale SRAM cell design with device/circuit co-design approach.

- Chapter 7 Summarizes all key findings and discussion on them to reach targeted conclusion and finally we will list out the potential directions for future work.

#### **1.6 Conclusion**

In this chapter, the reader is introduced with various concepts of FinFET device and nanoscale SRAM design. A brief idea about the international technology roadmap of semiconductor and its applications with reference to ITRS-2007 is also given in this chapter. It concludes by giving a brief organization of the thesis. The outcome of the present work is expected to help future VLSI/ULSI designer and device modeling community to develop such integration schemes that will not only enhance the performance criterion in terms of speed but also a reduction in the overall power dissipation.

## **Literature Review**

#### 2.1 Introduction

Transistor dimensions have been scaled down to nanoscale dimensions with passing years. Down scaling has the advantage in term of low power consumption, high speed and high packaging density. Microelectronic devices will play a key role in the future of nanoelectronics. Traditional microelectronic devices such as CMOS (Complementary Metal Oxide Semiconductor) transistors are entering the nanoscale regime and are giving rise to extremely inexpensive but extraordinary powerful circuits and systems. Also current CMOS circuits and process technology will be used as a foundation on which to build future nanoelectronic structures. It is not unthinkable that a hybrid between microelectronic and nanoelectronic technology will give rise to powerful structures and systems. Certain novel nano devices with some modifications in traditional CMOS transistors such as Double Gate (DG) MOSFET, Silicon on Insulator (SOI), Metal Gate (MG) MOSFET and FinFET device are also becoming popular. Understanding the operation and the limitations of CMOS transistors is important to understand these new device structures.

Scaling of CMOS into nanometer regime requires new device architectures. Suitable candidates are SOI devices with multiple gates such as double-gate FinFET structures, which can be scaled more aggressively than conventional bulk-Si devices [30, 68, 12, 73]. The key feature of multi-gate SOI MOSFETs is strong gate control of the channel region suppressing effectively the short-channel effects. Moreover the role of Quantum Mechanical (QM) effects becomes more important in these devices with an ultra-thin gate dielectric and Si body. Scaling conventional CMOS transistors much below 50 nm is difficult due to high Short Channel Effects (SCE's) and leakage currents [141, 164]. Control of leakage currents require gate dielectrics so thin and bodies doped so heavily that a process window sufficiently large for manufacturing might not be found. Double-Gate FinFET structures can overcome these and other limitations to transistor scaling [110, 153, 162]. By placing a second gate on the opposite side of the device, the channel to gate capacitance is doubled and the channel potential is better controlled by the gate electrode, thus limiting the leakage current [52]. With this perspective in mind, fully-depleted devices such as FinFETs are very promising candidates due to their immunity against short-channel effects [19, 50]. FinFET devices with a gate width of only 10 nm have already been reported [17].

In contrast to bulk MOSFETs, these devices inherently require twodimensional investigations [70, 103, 117]. Unfortunately with shrinking device dimensions, classical device simulation becomes more inaccurate. A rigorous Schrödinger-Poisson solver would be necessary to accurately describe the device behavior. As such, simulations are computationally extremely demanding due to the large number of grid points in two-dimensional problems. They are normally not appropriate. Instead, classical device simulations with additional quantum correction models can be used. However, the validity of these models for ultra thin silicon layers is currently under discussion.

FinFETs were developed due to their process simplicity and compatibility with current process flow for bulk planar MOSFETs. The self alignment for the FinFET structure makes it inherentaly advantageous as compared to bulk CMOS technology or standard double gate MOSFET because of lower values of intrinsic gate to source and gate to drain capacitances, which in turn result in high speed of operation. Further, by vary nature of structure of the FinFET, there is a reduction in the leakage current and hence an increase in  $I_{on}/I_{off}$ . MOSFET device size has been scaled quite aggressively due to the fast progress of process techniques. As MOSFET device is scaled down, short channel effects increase and leakage currents are enhanced. Double Gate FinFET was proposed to suppress the short channel effects in future nanoscale device [93, 125]. For extremely scaled devices within the tiny volume of the Si channel, even a small variation in the number of impurity atoms will have a very significant impact on the effective doping density. Hence, according to the classical relationship between the threshold voltage and doping density, controlling  $V_{th}$  very precisely will remain a challenging task and is likely to become a critical issue due to doping density fluctuation. Although some early papers [3, 67, 71, 79] have addressed this issue, this mainly focused on the conventional high doping strategy for controlling  $V_{th}$ .

To extend the scaling limits for nanoscale technologies, advanced Fully Depleted (FD) SOI and double-gate (DG) FinFET [20, 40] with undoped or lowdoped ultra-thin body are emerging [33]. The increase in threshold voltage has been observed in thin-body structure device. Previous works calculated the threshold voltage shift numerically [51, 105, 106] and treated the quantum effect with the effect of a high doping concentration. A simple analytical model is desirable for understanding the experimental data and providing quick guide to the threshold voltage adjustment for Ultra Thin Body Field Effect Transistor (UTBFET).

Given such a promising importance, device modeling of FinFET has become a necessity for possible future applications. The leakage currents associated with bulk MOSFET and Double Gate FinFET have been described in detail [52, 82] while the

circuit aspects of FinFET based SRAM have been studied by Nowak et, al., [39]. Qin et. al., [56] and Sriram et, al., [80] showed that because of excellent control of short channel effect in FinFET, there is a lower subthreshold leakage current and therefore, FinFET emerged as one of the most promising device for circuit design in nanoscale regime.

In this chapter, the review of existing literature is presented. Various research papers, books and monographs are referred which take care of various aspects such as: classical and QM modeling of FinFET device in order to understand the timeliness of the work being carried out as well as to understand the various technical gaps in the area of FinFET modeling and its application to FinFET based nanoscale memory design. Section 2.2; covers the literature on scaling of bulk MOSFET device and section 2.3; deals with a survey of various advanced MOSFET structures, inversion charge density and drain current. Further, in this chapter, section 2.4; describes the review of FinFET device, section 2.5; enumerates the research done on leakage currents associated with the FinFET device. The circuit aspect of FinFET device has been presented for design of FinFET based SRAM through various research papers in section 2.6 and this chapter concludes with section 2.7.

#### 2.2 Scaling of Bulk MOSFET

The planar bulk-silicon MOSFET shown in Figure 2.1 has been the workhorse of the semiconductor industry over the last 4 decades. In 1980's, many alternative models to bulk silicon MOSFET's have been proposed. However, the scaling down of bulk MOSFET becomes increasingly difficult for gate lengths below ~20 nm expected by the year 2010. As the gate length is reduced, the capacitive coupling of the channel

potential to the source and drain increases relative to the gate, leading to significantly degraded Short-Channel Effects (SCE). The main driving forces for reducing the dimensions have increased circuit density per unit chip area, increased speed of operation and lower cost per function. Device scaling requires a balance between device functionality and device reliability. Both of these have to be maintained as one scales channel length to smaller sizes. As critical transistor dimensions are scaled, reliability concerns become more pronounced. This manifests itself as [31, 57, 58, 59, 133, 134]: a) Increased OFF-state leakage, b) Threshold voltage (V<sub>th</sub>) roll-off, c) reduction of V<sub>th</sub> with increasing drain bias due to a modulation of the source-channel potential barrier by the drain voltage, also called Drain-Induced Barrier Lowering (DIBL).

Figure 2.1 Bulk MOSFET.

In order to maintain the relatively strong gate control of the channel potential in bulk devices, various technological improvements such as ultra-thin gate dielectrics [97], ultra-shallow source/drain junctions [167], halo implants [27, 28] and advance channel dopant profile engineering techniques such as super-steep retrograde wells [86] have been necessary. Each of these technologies is now approaching fundamental physical limitations which may, in turn, limit further scaling of device dimensions [66, 97].

In MOS devices, the gate dielectric thickness is the single most important device dimension to enable device scaling and has also been the most aggressively scaled one. A thin gate dielectric increases capacitive coupling from gate to channel, thereby reducing the source/drain influence on the channel. A larger gate capacitance also leads to a larger inversion charge density or increased ON-state drive current. However, gate dielectrics are already so thin that quantum mechanical direct tunneling through them results in significant gate leakage currents below ~20Å. The use of alternative high-k gate dielectric materials can provide a small effective oxide thickness to maintain adequate gate control needed for Lg scaling while providing a large physical barrier to gate-oxide tunneling, thereby reducing gate leakage [58, 89]. In order to scale bulk-Si transistors, heavy body doping is also necessary to eliminate leakage paths far from the gate dielectric interface and to increase back-gate (substrate) control of the body. For sub-100nm gate length devices, a strong halo implant is generally used to suppress sub-surface leakage, but this tends to increase the average channel doping in small Lg devices. High channel doping concentration, however, reduces carrier mobility due to impurity scattering and increased transverse electric field increases subthreshold slope, enhances band-to-band tunneling leakage and increases depletion and junction capacitances. These factors may combine to significantly degrade device performance [1, 11, 15, 17, 22].

In summary, from a device design point of view, in order to achieve good electrostatic integrity or good control of Short Channel Effects (SCE), the gate dielectric thickness,  $T_{OX}$ , the source/drain junction depth ( $X_J$ ), and the channel depletion depth  $X_{DEP}$ , need to be scaled down. The scale length for a bulk device,  $I_{BULK}$ , is an indication of how short L<sub>G</sub> can be made before the SCE are excessive. For a bulk MOSFET, gate leakage limits T<sub>OX</sub> scaling,  $X_{DEP}$  scaling is limited to about

10 nm due to substrate-to-drain and band-to-band tunneling current limitations on body doping.  $X_J$  is limited by process limits for forming ultra shallow junctions with abrupt doping profiles [60, 181, 182, 183].

#### 2.2.1 Bulk CMOS Challenges