### **TEST PATTERN GENERATION FOR VLSI CIRCUITS**

#### A THESIS

submitted in fulfilment of the requirements for the award of the degree of DOCTOR OF PHILOSOPHY

in

ELECTRONICS AND COMPUTER ENGINEERING

By

#### **GOPAL KRISHAN SHARMA**

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247 667 (INDIA)

**JANUARY, 1997**

Gratis

.

.

•

### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the thesis entitled **Test Pattern Generation for VLSI Circuits** in fulfilment of the requirement for the award of the Degree of **Doctor of Philosophy** and submitted in the Department of Electronics and Computer Engineering of the University is an authentic record of my own work carried out during a period from September 1993 to January 1997 under the supervision of Dr. R.P. Agarwal, Dr. J.P. Gupta, Dr. S. Sarkar and Dr. S. Ahmad.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other University.

(GOPAL K. SHARMA)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

l. l. WW (Dr. S. Sarkar) Professor

Dept. of Electronics & Computer Engg. University of Roorkee, Roorkee – 247 667

Rb opanel

(Dr. R.P. Agarwal) Professor Dept. of Electronics & Computer Engg. University of Roorkee, Roorkee – 247 667

I ahuad

(Dr. S. Ahmad) Deputy Director Central Electronics Engg. Research Institute, Pilani – 333 031

(Dr. J.P. Gupta)

Member Secretary All India Council for Technical Education, New Delhi – 110 002

Date: 15th January 1997

The Ph.D. Viva-Voce examination of Mr. Gopal K. Sharma, Research Scholar, has been held on  $\frac{13/9/97 \text{ at } 103 \text{ been}}{1. \text{Rb7}}$

2. . mm

4.

(Signature of Supervisors)

(Signature of HIO.D.)

(Signature of External Examiner)

### Abstract

Test pattern generation problem is known to be NP-complete and conventionally, automatic generation of test patterns for circuits with N number of primary inputs is characterized as a search of N-dimensional 0-1 state space. Several Automatic Test Pattern Generation (ATPG) algorithms have been developed in the past. But, in spite of considerable progress in the development of these algorithms, the computational resources required for ATPG are still enormous because the efficiency of these algorithms has not kept pace with the increasing complexity of VLSI circuits which is of the order of several tens of thousands of gates. Furthermore, these algorithms are targeted for serial computers. However, massively parallel computers and distributed network of powerful workstations, available in most of the VLSI-CAD environments, present a promising paradigm for solving such compute-intensive ATPG problems for combinational as well as sequential circuits. With the availability of these paradigms, new approaches and cost-effective methods, are therefore, imperative in order to efficiently solve the ATPG problem. Efforts have been made to investigate new test generation algorithms so that they could be easily extended to parallel and distributed computing paradigms.

Recently, two different ATPG approaches have been developed in which the problem of test pattern generation is formulated either as a Boolean satisfiability (SAT) or an optimization problem. These approaches are radically different from the conventional methods of generating test patterns for circuits from their gate level description. In these approaches, the generation of test patterns is done in two steps. In the first step, a formula is constructed which will be either an energy function or a Boolean truth (false) function representing *Boolean difference* between the fault-free and faulty circuits. In the second step, energy minimization techniques are applied to minimize the energy function or the Boolean false function and SAT algorithms are applied to satisfy the Boolean truth function. Although energy minimization and SAT problems are as hard as ATPG problem itself, these approaches have two significant advantages. First, since the function of the circuit is mathematically expressed, several new techniques may be investigated to solve the ATPG problem. Second, the non-causal form of the model would allow the use of parallel processing.

New techniques for the ATPG approaches as described above have been attempted in this thesis. In the optimization based approach, a new quadratic 0-1 programming technique to minimize the energy function, which is of the form of pseudo-Boolean quadratic function:  $E(\mathbf{x}) = \mathbf{x}^T \mathbf{Q} \mathbf{x} + \mathbf{c}^T \mathbf{x}$ , has been developed and applied to obtain test patterns. Other test generation methods developed are based on Genetic Algorithms (GAs). In these methods, an objective function is derived from either an energy function or a Boolean false function. In order to apply GAs, the constrained ATPG problem has been transformed into the unconstrained one by modifying the objective function with the help of a penalty method which is developed by using schema design. The objective function so obtained has been mapped into fitness form which is then maximized to generate test patterns. The above ATPG process has been further accelerated by incorporating a transitive closure algorithm to reduce the Boolean false function to be minimized by GAs.

Finally, the proposed ATPG methods have been implemented by developing a CAD tool to run on a Sun Sparc 10 UNIX workstation. This tool has been exercised by generating test patterns for a set of stuck-at faults in several practical example circuits. Experimental results in terms of average CPU time per fault for the example circuits are reported in the thesis. The results obtained by the proposed ATPG methods have also been compared to the results published in the literature for the same example circuits which shows the efficiency and effectiveness of the proposed methods.

### Acknowledgements

I wish to express my heartfelt gratitude to my supervisors Dr. R.P. Agarwal, Dr. J.P. Gupta, Dr. S. Sarkar and Dr. S. Ahmad for offering guidance, encouragement, help and useful suggestions throughout. I consider myself very fortunate for having been associated with them.

The cooperation and help extended by the Head of the Department of Electronics and Computer Engineering is gratefully acknowledged.

Thanks are due to the authorities of Central Electronics Engineering Research Institute (CEERI), Pilani (Rajasthan) and Council of Scientific & Industrial Research (CSIR), New Delhi for granting necessary leave in this regard. My special thanks are due to **Prof. R.N. Biswas**, Director, CEERI and **Dr. Chandra Shekhar**, Group Leader, IC Design Group, CEERI for by extending the facilities available in the VLSI Design Center.

I am grateful to Dr. Vishwani D. Agarwal, Distinguished Member of Technical Staff at the AT&T Bell Laboratories in Murray Hill, NJ (USA) and Dr. Kewal K. Saluja, Professor, Department of Electrical & Computer Engineering, University of Wisconsin-Madison (USA) for bringing me in this important area of research and in fact, they are my main motivator.

I am highly grateful to **Prof. M.P. Kapoor**, Director, Thapar Institute of Engineering & Technology, Patiala for his constant encouragement, valuable suggestions and moral support.

It is difficult to express my gratitude to my wife and children as anything said would be inadequate to compensate for the neglect that is sadly and inevitably the outcome of undertaking doctoral research. Finally, I thank all my relatives and friends for their valuable help and co-operation during my thesis work.

# Contents

-

| Candidate's | Declaration |

|-------------|-------------|

|-------------|-------------|

•

-

|   | Ab               | stract |                              | i   |

|---|------------------|--------|------------------------------|-----|

|   | Acknowledgements |        |                              | iii |

| 1 | Int              | roduct | ion                          | 8   |

| 2 | Tes              | t Gene | eration Algorithms: A Review | 17  |

|   | 2.1              | Algeb  | raic Algorithms              | 19  |

|   | 2.2              | Struct | tural Algorithms             | 20  |

|   |                  | 2.2.1  | Combinational Algorithms     | 21  |

|   |                  | 2.2.2  | Sequential Algorithms        | 38  |

|   | 2.3              | Parall | el Processing Techniques     | 43  |

|   |                  | 2.3.1  | Fault Partitioning           | 44  |

|   |                  | 2.3.2  | Heuristic Parallelization    | 46  |

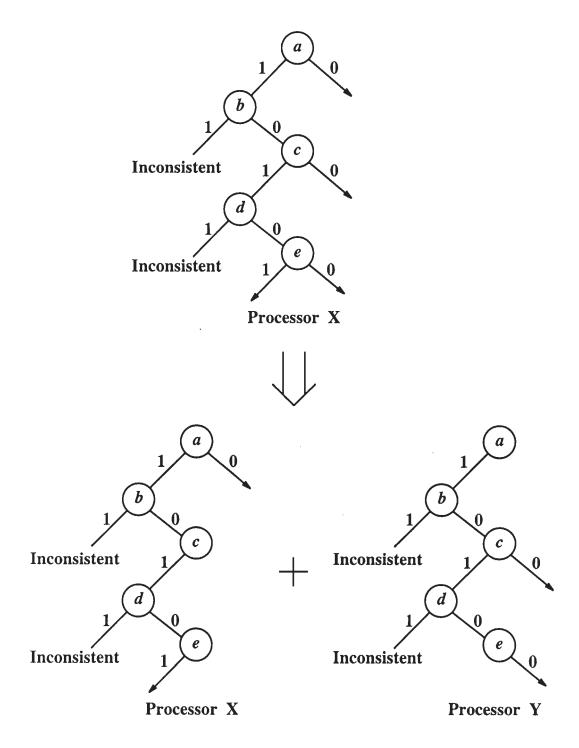

|   |                  | 2.3.3  | Search-Space Partitioning    | 47  |

|   |                  | 2.3.4  | Algorithmic Partitioning     | 49  |

|   |     | 2.3.5  | Topological Partitioning                     | 50  |

|---|-----|--------|----------------------------------------------|-----|

|   | 2.4 | Recen  | t Approaches                                 | 52  |

|   |     | 2.4.1  | ATPG Constraint Network                      | 53  |

|   |     | 2.4.2  | Optimization Methods for Test Generation     | 54  |

|   |     | 2.4.3  | Test Generation Using Boolean Satisfiability | 59  |

|   | 2.5 | Proble | m Formulation                                | 64  |

| 3 | AN  | vew Qi | adratic 0-1 Programming for Test Generation  | 67  |

|   | 3.1 | Quadr  | atic 0-1 Programming Technique               | 69  |

|   | 3.2 | A New  | Quadratic 0-1 Programming Technique          | 74  |

|   |     | 3.2.1  | Stability Race Condition                     | 76  |

|   |     | 3.2.2  | Criteria for Fixation of Variables           | 78  |

|   |     | 3.2.3  | Backtracking Procedure                       | 83  |

|   | 3.3 | Examp  | oles                                         | 83  |

|   | 3.4 | Compu  | Itational Algorithm                          | 95  |

|   | 3.5 | Compl  | exity Analysis                               | 98  |

| 4 | Gen | etic A | lgorithm Based Test Generation               | 100 |

|   | 4.1 | Geneti | c Algorithms in Search and Optimization      | 103 |

|   |     | 4.1.1  | A Simple Genetic Algorithm                   | 103 |

|   |     | 4.1.2  | Adaptive Genetic Algorithms                  | 109 |

|   | 4.2 | Geneti | c Algorithms for Test Generation Problem     | 111 |

|   | 4.3 | Energy | Minimization Approach                        | 113 |

|   |                                                                                          | 4.3.1                                                                 | Schema Design                                                                                                                                      | . 114                                                                                    |

|---|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|   |                                                                                          | 4.3.2                                                                 | Penalty Method                                                                                                                                     | . 115                                                                                    |

|   |                                                                                          | 4.3.3                                                                 | Mapping Objective Function to Fitness Form                                                                                                         | . 116                                                                                    |

|   |                                                                                          | 4.3.4                                                                 | Example                                                                                                                                            | . 116                                                                                    |

|   | 4.4                                                                                      | Boolea                                                                | an Satisfiability Approach                                                                                                                         | . 119                                                                                    |

|   | 4.5                                                                                      | Test G                                                                | Generation Algorithm                                                                                                                               | . 121                                                                                    |

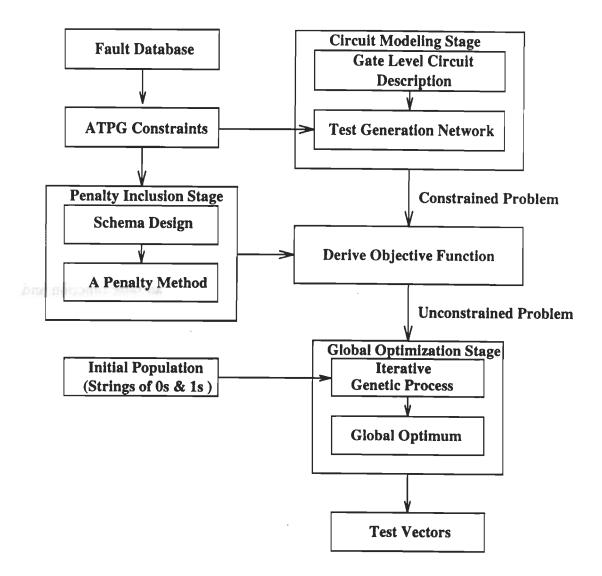

|   | 4.6                                                                                      | Auton                                                                 | natic Test Pattern Generation CAD Tool                                                                                                             | . 127                                                                                    |

|   |                                                                                          | 4.6.1                                                                 | Circuit Modeling                                                                                                                                   | . 127                                                                                    |

|   |                                                                                          | 4.6.2                                                                 | Objective Function Evaluation                                                                                                                      | . 129                                                                                    |

|   |                                                                                          | 4.6.3                                                                 | Penalty Inclusion                                                                                                                                  | 130                                                                                      |

|   |                                                                                          | 4.6.4                                                                 | Global Optimization                                                                                                                                | 130                                                                                      |

|   |                                                                                          |                                                                       |                                                                                                                                                    |                                                                                          |

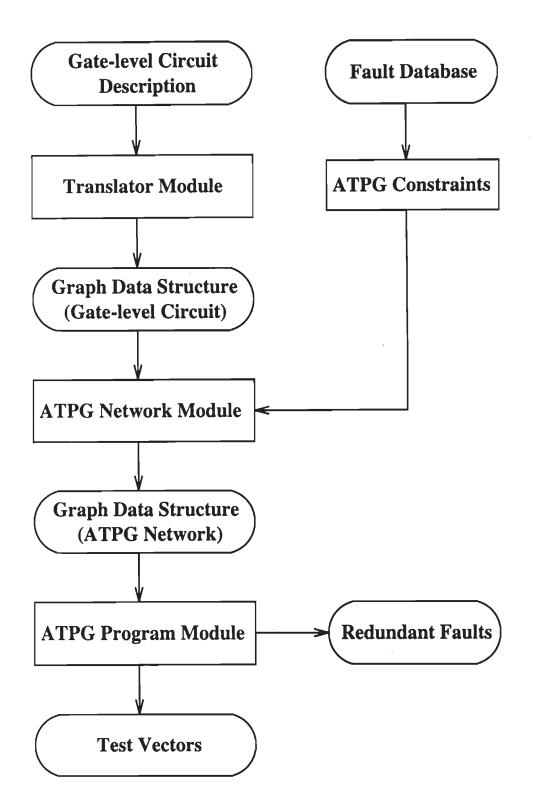

| 5 | Imp                                                                                      | olemen                                                                | tation Details and Experimental Results                                                                                                            | 132                                                                                      |

| 5 | <b>Imp</b><br>5.1                                                                        |                                                                       | tation Details and Experimental Results<br>ator Module                                                                                             |                                                                                          |

| 5 |                                                                                          | Transl                                                                |                                                                                                                                                    | 134                                                                                      |

| 5 | 5.1                                                                                      | Transla<br>ATPG                                                       | ator Module                                                                                                                                        | 134<br>136                                                                               |

| 5 | 5.1<br>5.2<br>5.3                                                                        | Transla<br>ATPG<br>ATPG                                               | ator Module                                                                                                                                        | 134<br>136<br>138                                                                        |

| 5 | 5.1<br>5.2<br>5.3                                                                        | Transla<br>ATPG<br>ATPG                                               | ator Module                                                                                                                                        | 134<br>136<br>138<br>139                                                                 |

| 5 | 5.1<br>5.2<br>5.3                                                                        | Transla<br>ATPG<br>ATPG<br>5.3.1<br>5.3.2                             | ator Module                                                                                                                                        | 134<br>136<br>138<br>139<br>141                                                          |

|   | 5.1<br>5.2<br>5.3                                                                        | Transla<br>ATPG<br>ATPG<br>5.3.1<br>5.3.2<br>clusion                  | ator Module Network Module   Program Module Program Module   QUADTEST GATEST   GATEST Program Module                                               | <ol> <li>134</li> <li>136</li> <li>138</li> <li>139</li> <li>141</li> <li>151</li> </ol> |

|   | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Con</li></ul>                                | Transla<br>ATPG<br>ATPG<br>5.3.1<br>5.3.2<br><b>clusion</b><br>Conclu | ator Module Network Module   Program Module Program Module   QUADTEST GATEST   GATEST Program Module   GATEST Program Module   Sion Program Module | <ol> <li>134</li> <li>136</li> <li>138</li> <li>139</li> <li>141</li> <li>151</li> </ol> |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Con</li> <li>6.1</li> <li>6.2</li> </ul> | Transla<br>ATPG<br>ATPG<br>5.3.1<br>5.3.2<br><b>clusion</b><br>Conclu | ator Module Network Module   Program Module Program Module   QUADTEST GATEST   GATEST Program Module                                               | <ol> <li>134</li> <li>136</li> <li>138</li> <li>139</li> <li>141</li> <li>151</li> </ol> |

# List of Figures

t

\*

| 1.1  | Design and test development cycle of VLSI chip realization.                 | 9  |

|------|-----------------------------------------------------------------------------|----|

| 2.1  | AND gate D-cubes                                                            | 22 |

| 2.2  | An example combinational circuit                                            | 24 |

| 2.3  | D-algorithm example                                                         | 24 |

| 2.4  | A generic combinational circuit                                             | 26 |

| 2.5  | Podem search-space graph                                                    | 28 |

| 2.6  | A Fan example                                                               | 30 |

| 2.7  | A block schematic of the ATPG tool                                          | 33 |

| 2.8  | Abstract problem representation of deterministic test generation            | 35 |

| 2.9  | (a) Canonical structure of a synchronous sequential circuit, and (b) its    |    |

|      | combinational iterative array model                                         | 40 |

| 2.10 | An example circuit for sequential test generation.                          | 41 |

| 2.11 | Time frame expansion of the example circuit for sequential test generation. | 42 |

| 2.12 | Search-space partitioning                                                   | 48 |

| 2.13 | ATPG Constraint Network.                                                    | 53 |

0

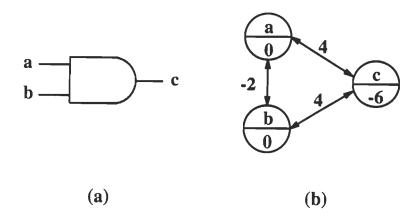

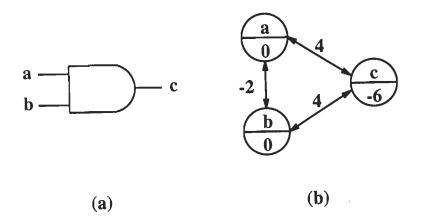

| 2.14 | (a) 2-input AND gate and (b) its neural network model                                           | 55  |

|------|-------------------------------------------------------------------------------------------------|-----|

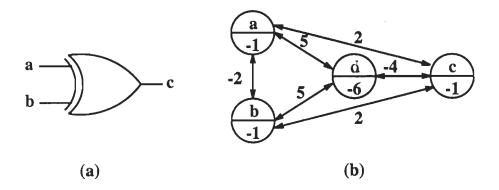

| 2.15 | (a) 2-input XOR gate and (b) its neural network representation                                  | 56  |

| 2.16 | CNF formulas for the basic gates                                                                | 60  |

| 2.17 | (a) An example circuit and (b) its implication graph                                            | 61  |

| 2.18 | Reduced implication graph                                                                       | 62  |

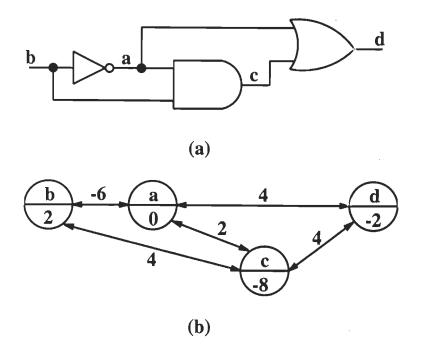

| 3.1  | (a) An AND gate and (b) its neural network model                                                | 70  |

| 3.2  | (a) An example circuit (b) Neural network representation of the example                         |     |

|      | circuit for $d$ stuck-at-0 fault                                                                | 72  |

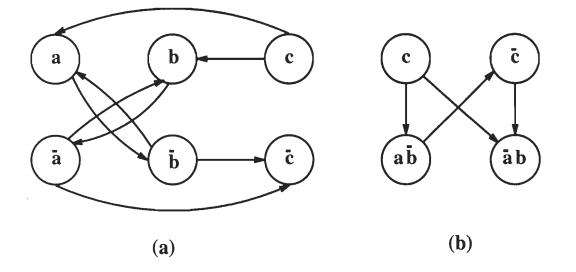

| 3.3  | (a) Implication graph for the example circuit and (b) its condensed form.                       | 74  |

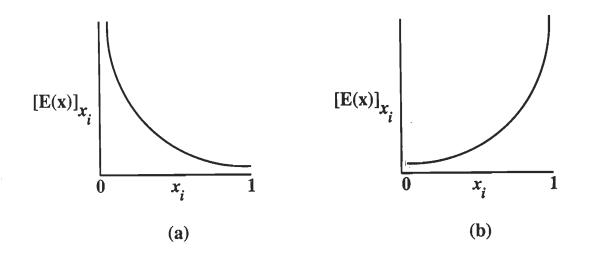

| 3.4  | $[E(\mathbf{x})]_{x_i}$ as function of $x_i$                                                    | 76  |

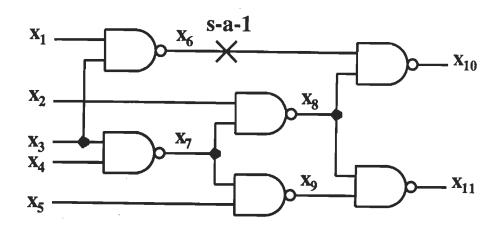

| 3.5  | (a) An ISCAS'85 circuit: c17.isc (b) Modified ISCAS circuit for the                             |     |

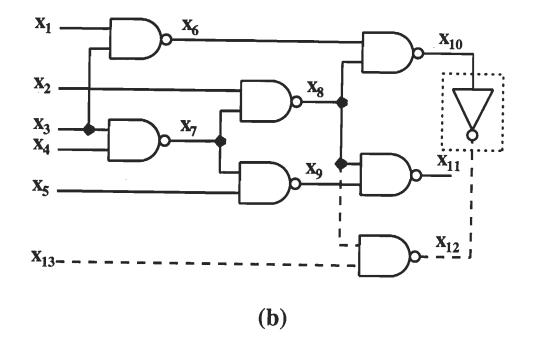

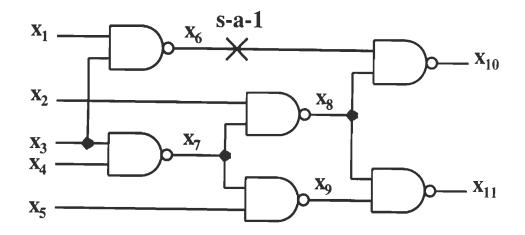

|      | stuck-at-1 fault on line $x_6$                                                                  | 87  |

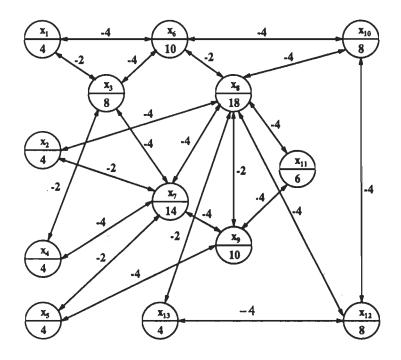

| 3.6  | ATPG neural graph for the ISCAS circuit                                                         | 88  |

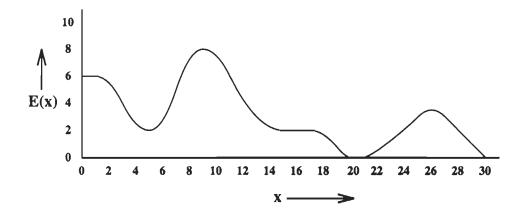

| 4.1  | A plot for the energy function                                                                  | 101 |

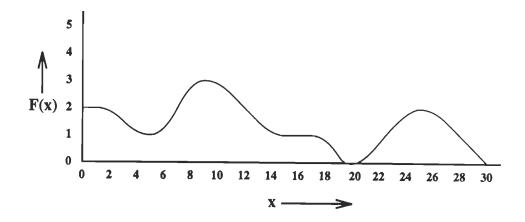

| 4.2  | A plot for the Boolean false function                                                           | 102 |

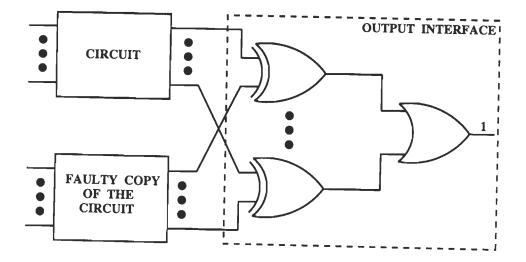

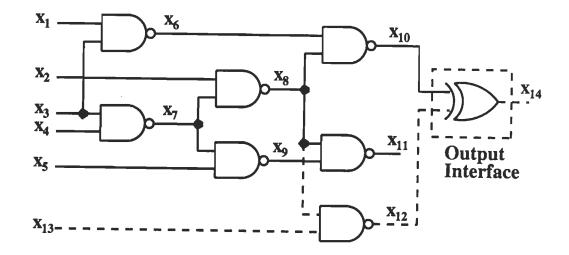

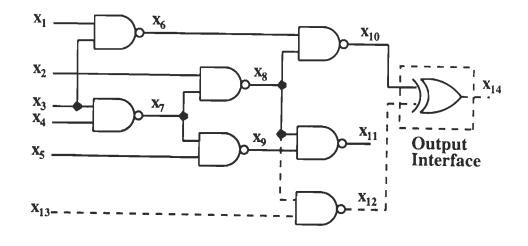

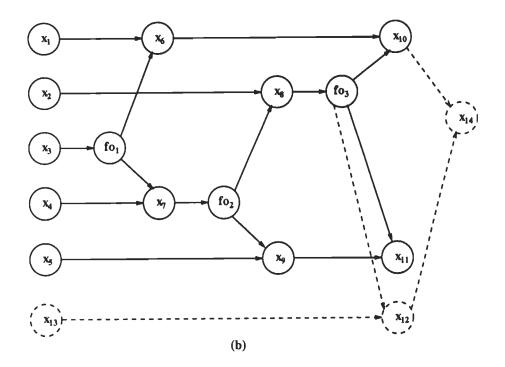

| 4.3  | The ISCAS '85 circuit with XOR as an output interface                                           | 120 |

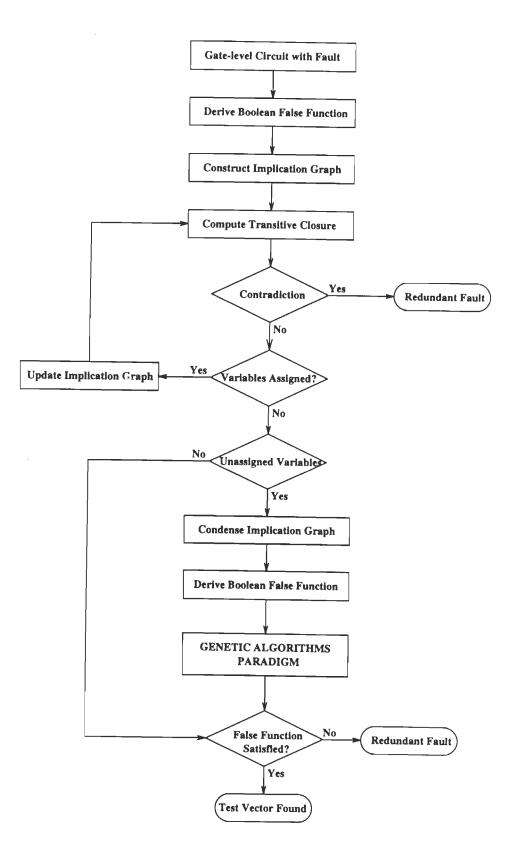

| 4.4  | Genetic Algorithms Based Test Generation Method                                                 | 122 |

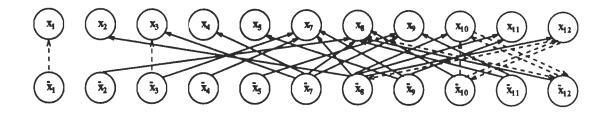

| 4.5  | Implication graph of the example ISCAS circuit with $x_6 = 0$ , $x_{13} = 0$ ,                  |     |

|      | and $x_{14} = 1$                                                                                | 124 |

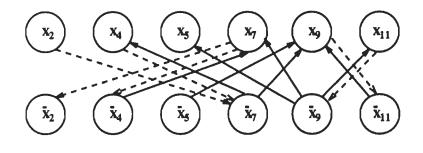

| 4.6  | (a) Reduced version of the implication graph shown in Figure 4.4 after                          |     |

|      | fixing the variables, $x_1 = 1$ , $x_3 = 1$ , $x_{10} = 1$ , $x_{12} = 0$ , and $x_8 = 1$ , (b) |     |

|      | Condensed form of the implication graph (a)                                                     | 125 |

•

| 4.7 | A CAD Tool for Automatic Test Pattern Generation.                       | 128 |

|-----|-------------------------------------------------------------------------|-----|

| 5.1 | Abstract view of the CAD tool                                           | 133 |

| 5.2 | c17.isc: An ISCAS'85 circuit                                            | 136 |

| 5.3 | Graph representation for the c17.isc circuit                            | 137 |

| 5.4 | ATPG constraint network of the ISCAS circuit c17.isc for stuck-at-1     |     |

|     | fault on line $x_6$                                                     | 138 |

| 5.5 | Graph representation for the ATPG constraint network of c17.isc circuit | 139 |

.

\*

# List of Tables

.

| 5.1 | Experimental Results: | QUADTEST | 141 |

|-----|-----------------------|----------|-----|

| 5.2 | Experimental Results: | GATEST   | 148 |

## Chapter 1

# Introduction

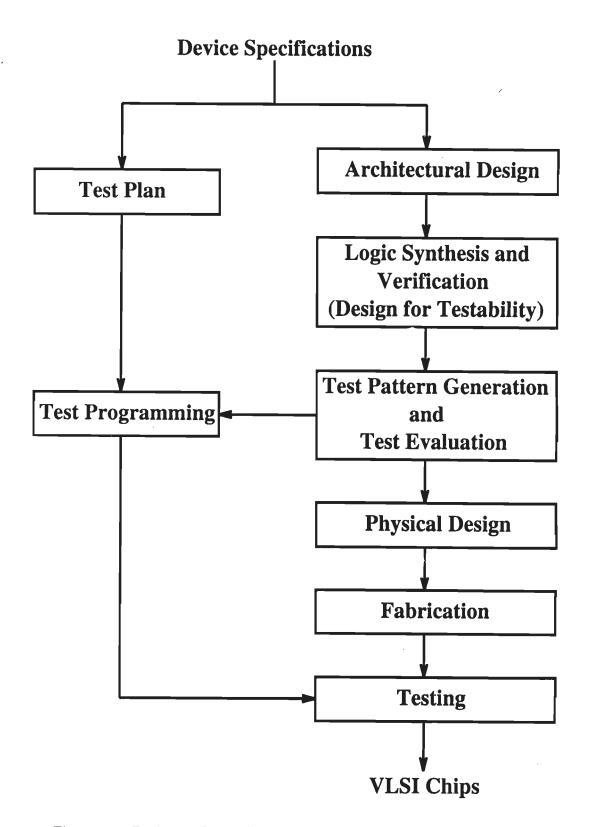

Recent advances in integrated circuit (IC) technology have made it possible to fabricate digital circuits with a very large number of devices on a single chip. Very Large Scale Integration (VLSI) is the fabrication of millions of components and interconnections on a chip by a common set of manufacturing steps. In the era of Ultra Large Scale Integration (ULSI), it is expected to have as many as 100 million transistors or even more on a single chip by the end of this century. Because of this dramatic increase in the circuit size, the design and test development of the VLSI chips becomes a costly affair with a very large turn around time. The complete design and test development cycle of the VLSI chip realization is depicted in Figure 1.1. The design and test planning of VLSI chips begins with specifications. In VLSI design, architectural design is the first step which consists of partitioning of a VLSI chip into realizable functional blocks. Logic design comes after the architectural design step and includes several test activities. In the logic design, either the logic is synthesized in a testable form or the synthesized logic is analyzed for testability. After logic synthesis, test patterns are generated and combined with the test plan to develop a program for the Automatic Test Equipment (ATE). The actual testing of VLSI chips takes place after the phys-

Figure 1.1: Design and test development cycle of VLSI chip realization.

ical design (layout, timing verification and mask generation) and fabrication (wafer processing).

Testing of VLSI circuits, because of their increased complexities and reduced geometries, becomes much more difficult and expensive as it costs more than 50 per cent of the total chip cost. The advantages of VLSI, *i.e.* reduced system cost, better performance, greater relibility, would be lost unless the chips can be tested economically. The testing process detects the physical defects produced during the fabrication of the systems. A sequence of input stimuli, known as *test patterns* or *tests*, is required to test a VLSI chip. These tests are supposed to determine correctness of each component (transistor *etc.*) and each interconnection fabricated on the chip. The test patterns are developed so that they should thoroughly check every node of the circuit. Normally, these tests are required to detect a very high fraction (*i.e.* close to 100 percent) of the *modeled faults* in the circuit which means that the device should be defect-free. The detected fraction of faults is called the *fault coverage* of the tests.

Test patterns for a circuit are developed in two phases. In the first phase, known as design verification, tests are generated to verify logical correctness and timing behavior of the circuit through simulation. The second phase of test generation consists of generation of manufacturing tests in order to ensure that circuit is fabricated correctly. However, these tests do not determine whether the circuit has been designed correctly. These test vectors are generated (either manually or automatically) after a complete design by driving the effect of faults within the circuit to a circuit output where the fault can be detected. Automatic Test Pattern Generation (ATPG) involves the generation of test vectors automatically in order to detect failures in the VLSI chip. The ATPG process is driven by the single stuck-at fault model which assumes that all faults can be modeled by a line being either permanently 0 or 1. After test pattern generation, the vectors and their expected responses must be moved to a piece of ATE, which applies the vectors to the input pins of the VLSI chip and compares the output pin responses with the expected responses to determine whether a fault is present within the circuit or not. Since the same set of vectors will be applied to a large number (a million or more in many cases) of copies of the chip, short test sequences are desirable.

Generating test patterns for digital integrated circuits is a very hard problem. Sequential circuits, because of their memory elements, might require many vectors to test one fault. The time required to generate these vectors is too large for VLSI chips. To solve this problem, circuit designers use *design-for-testability* techniques. One such technique is scan design which converts sequential circuits into combinational circuits by chaining all the flip-flops in the circuit into one or several shift registers. This allows using faster combinational test generation algorithms for vector generation. Another technique known as built-in-self-test adds IC hardware to generate random patterns that can be applied to the chip's combinational logic. This technique has the advantages of applying long vector sequences at circuit speed and there is little or no need of test generation. However, the disadvantage of this technique is that the chip becomes more complex leading to performance penalties. Both the techniques have gained wide and growing acceptance as devices become more complex. Further discussion on these techniques is beyond the scope of this thesis as the focus is on the test pattern generation.

The problem of Automatic Test Pattern Generation is known to be NPcomplete [55], [32] and conventionally, the generation of tests is characterized as a search of N-dimensional 0-1 state space, where N is the number of primary inputs in the circuit to be tested. A wide range of ATPG algorithms have been developed in the past and focussed uniprocessors machines as their hardware platforms. Major emphasis has been on the increase in the efficiency of these serial algorithms through better heuristics and data structures. However, the overall gains achieved through these developments have not kept pace with the increasing complexity of the VLSI circuits as sometimes hours and days are required in generating tests for the practical circuits of even moderate complexity. The complexity of the circuits on which test generation tools are used is growing faster than the speed of the computers on which they run. Therefore, new algorithms and techniques for test generation are required for both the circuits of today and tomarrow.

The availability of affordable parallel machines and distributed network of idle workstations in most of the VLSI-CAD environments has opened a new front for the development of efficient parallel/distributed algorithms for the compute-intensive test generation problem. In order to harness the computational power of these machines, several parallelization techniques have been investigated in the recent past. These techniques have tried to parallelize some of the portions of the conventional uniprocessor algorithms and executed them in parallel. Although, these techniques have shown some promising results, but much work remains since no effective parallel algorithms have been found.

Most recently altogether different approaches are developed in which the testing problem has been reformulated so that the algorithms for test generation can be easily parallelized to run on massively parallel and distributed computing platforms. In these approaches, the test generation problem is transformed into an optimization or Boolean satisfiability problem. Although both the optimization and satisfiability problems are as hard as test generation itself, but they have two signifiant advantages. First, several operation research and graph-theoretic techniques may become applicable and second, the non-causal form of the model makes parallel processing possible for such compute-intensive test generation problem.

12

The optimization based test generation radically differs from the conventional methods that generate test vectors for circuits from their gate level description. The circuit is modeled as a network of idealized computing elements, known as *neurons*, connected through bidirectional links and the neuron is a binary (0-1) element. The relationship between the input and output signal states of a logic gate is expressed by an *energy function* such that the zero energy (also the minimum energy) states correspond to the gate's logic function. Using this neural network modeling technique, the test generation problem has been transformed into an energy minimization problem for which various techniques like directed search augmented by probabilistic relaxation have been attempted to determine its global minimum. A quadratic 0-1 programming technique has also been devised for test pattern generation since the energy function is of the form of pseudo-Boolean quadratic function  $E(\mathbf{x}) = \mathbf{x}^T \mathbf{Q} \mathbf{x} + \mathbf{c}^T \mathbf{x}$  with  $\mathbf{x} \in \{0, 1\}^n$ , where  $\mathbf{Q}$  is an  $n \times n$  symmetric matrix of constants,  $\mathbf{c}$  is a vector of constants,  $\mathbf{x}$  is a vector of n Boolean variables, and  $\mathbf{x}^T$  is the transpose of  $\mathbf{x}$ .

Test pattern generation method using Boolean satisfiability constructs a formula expressing the *Boolean difference* between fault-free and its corresponding faulty circuit. This formula may be derived in the form of a Boolean truth function or a false function. In order to generate a test pattern for a given fault, one needs to satisfy the formula using the Boolean satisfiability algorithm when the formula is in the form of a truth function. As far as the false function is concerned, it is to be minimized to 0 and quite similar to the energy minimization approach. Test generation methods using both kinds of functions has been developed and reported in the literature.

The thesis is mainly focused on the development of new algorithms and tools for test pattern generation based on optimization and Boolean satisfiability approaches because these approaches have significant advantages as discussed above. In the optimization based test generation approach, the ATPG problem is formulated as energy minimization for which several algorithms have been proposed. In this kind of ATPG formulation, the function to be minimized is of the form of pseudo-Boolean quadratic function for which a new quadratic 0-1 programming technique has been developed to find its global minimum. Although this is a mathematical technique, it has several advantages. One important advantage is that the exploitation of the special structure of the quadratic function arising from the test generation problem has become possible as the proposed technique uses the circuit specific knowledge with ATPG constraints. Other significant advantage is that efficient heuristics can be easily incorporated which further accelerate the minimization process. Some of the heuristics are described in detail by illustrating specific examples. A computational algorithm has been developed which efficiently minimizes the energy function with moderate number of variables for small practical example circuits [104]. However, its efficiency decreases for the large number of variables due to branch-and-bound process used in the algorithm.

Other methods based on Genetic Algorithms (GAs) for generating test patterns have been developed which do not incorporate branch-and-bound process at any stage of the ATPG. In these methods, GAs are applied to both kinds of ATPG problem formulation viz. optimization as well as Boolean satisfiability. In the optimization based approach, GAs are used to find the global minimum of the energy function for generating test patterns for a given set of faults. In the Boolean satisfiability approach, instead of deriving a Boolean truth function in Conjunctive Normal Form (CNF), a Boolean false function is derived which is then minimized to find test patterns. This is an advantage as both kinds of problem formulations ultimately lead to minimization problem and thus can be solved by using GAs. The behaviour of both the energy and Boolean false functions derived for the test generation of stuck-at faults in combinational circuits has been studied and it is found that these functions are of multimodal type. The global optimum solution of the problem represented by these functions can be located in a multimodal landscape which further confirms the suitability of GAs known to be the most effective search and optimization algorithms in such problem spaces. Furthermore, GAs have a proven track record of being one of the most robust search and optimization algorithms applied in a number of combinatorial optimization problems. Other important features of GAs are that they are innovative and have inherent amenability to be processed in parallel.

In order to apply GAs for minimization of energy function or Boolean false function, an objective function is derived which is essentially required to guide GAbased search. This objective function is then modified to transform the constrained ATPG problem into an unconstrained one by using a penalty method. This penalty method has been developed with the help of schema design. The objective function so obtained is then mapped into fitness form (maximization form) by using a mapping procedure. The fitness function is then maximized using GAs and test patterns are obtained for all the detectable faults. A GA-based CAD tool for the ATPG problem has been developed and experimental results have been reported in the thesis.

### Organization of the Thesis

The research contribution made in this thesis is organized in six chapters as given below.

• Chapter 2: Test Generation Algorithms: A Review. This chapter reviews the work carried out in the area of test pattern generation for digital logic circuits. Most important test generation algorithms for combinational as well as sequential circuits are reported in this chapter. Various parallelization techniques are discussed. Most recently developed optimization and Boolean satisfiability test generation approaches are also presented in this chapter. The chapter concludes with a brief description of the problem formulation.

- Chapter 3: A New Quadratic 0-1 Programming Technique. A new quadratic 0-1 programming technique applicable to the optimization based test generation approach has been proposed in this chapter. The applicability of this technique has been demonstrated by solving the test generation problem for some example circuits. Various heuristics and their role in the energy minimization process are discussed in brief. A computational algorithm based on the proposed technique is also given in this chapter. This chapter concludes with a brief discussion on this new technique.

- Chapter 4: Genetic Algorithm Based Test Generation. This chapter proposes new test generation methods using Genetic Algorithms. It starts with an introduction to Genetic Algorithms (GA) and describes their applications to the test generation problem. Issues involved in the proposed GA-based methods are discussed and a test generation algorithm has been proposed. Finally, a CAD tool based on GAs has been proposed.

- Chapter 5: Implementation Details and Experimental Results. The implementation details of the test generation algorithms proposed in Chapter 3 and 4 are given in this chapter. A prototype CAD tool proposed in Chapter 4 has been developed. Experimental results in terms of CPU time are also presented by running the ATPG CAD tool for generating test patterns for practical example circuits. These results are also compared to the results reported in the literature.

- Chapter 6: Conclusion and Future Scope of Work. Finally, conclusions are drawn and future scope of work in the area of the thesis is discussed in this chapter.

### Chapter 2

# Test Generation Algorithms: A Review

Intensive research efforts have been made in the development of efficient test generation algorithms for combinational as well as sequential logic circuits. Test pattern generation is usually more difficult for sequential circuits than the combinational ones mainly due to the poor controllability and observability of sequential logic. Putting storage elements of a sequential logic in a desired state would require a sequence of external inputs applied over a set of clock cycles and similar is the case for observing their values through the external outputs. This implies that the sequential test generation is not only more difficult (complex) than the combinational test generation but the resulting test length is also usually much larger. However, the popular *Design for Testability* (DFT) techniques, particularly *scan designs* [31], [37], [108], increase the controllability and the observability of the storage elements in the feedback path of sequential circuits. This would reduce the complexity of sequential test generation to that of combinational test generation by transforming the sequential circuit to a combinational logic in the test mode. Hence, for sequential circuits implemented with the use of scan techniques, it is sufficient to develop efficient test generation algorithms only for combinational circuits. Due to this reason, there has been a heavy emphasis on test pattern generation algorithms for combinational circuits.

A wide range of techniques has been proposed for combinational circuit test generation. At one end of the spectrum are the exhaustive and random techniques. Exhaustive test generation means the generation of all possible input patterns and may be an obvious choice for circuits with small number of primary inputs. Random Test Generation (RTG) [4] is another simple technique that generates input vectors probabilistically and simulates whether these vectors detect fault(s) in the circuit. If a random vector detects a fault, then it is retained as a test. In RTG, a large set of random tests is needed in order to achieve high-quality tests usually determined by a *fault simulation method* in terms of *fault coverage*. Various fault simulation methods and their role in test generation are described later in this chapter. In RTG, though the test generation process itself is simple, determining the test quality by fault simulation may be an expensive process. Moreover, a longer test set costs more to apply because it increases the testing time and the memory requirements of the tester.

At the other end of the spectrum, there are deterministic techniques that can be divided into two groups: one consisting of *algebraic algorithms* and the other of *structural algorithms*. These techniques generate tests by processing a model of the circuit in contrast to RTG which do not consider the structure of the circuit-under-test. Compared to RTG, deterministic techniques are more expensive in terms of CPU time, but they produce shorter and high quality tests. Algebraic algorithms use the Boolean difference formulation (Section 2.1) to solve the problem symbolically [34], [90] and structural algorithms perform a topological search of the circuit-under-test. Algebraic algorithms have not been very practical for two reasons: (1) symbolic solutions require excessive storage and (2) heuristics required to solve practical test generation problems symbolically are not available. Structural algorithms use a data structure representing the circuit-under-test instead of deriving a Boolean expression. These algorithms systematically enumerate the search space using branch-and-bound method and employ heuristics to guide the search process. The most successful structural algorithms are described in Section 2.2.

### 2.1 Algebraic Algorithms

The most popular algebraic method is the Boolean difference method developed by Sellers et al. [90]. In this approach, a Boolean formula is constructed for a combinational circuit as its output realizes a logic (Boolean) function. Let  $F(x_1, x_2, ..., x_n)$  be a logic function of the input Boolean variables  $x_1, x_2, ..., x_n$ . The Boolean difference of  $F(\mathbf{x})$ with respect to its input variable  $x_i$  is defined as

$$F(x_1,\ldots,x_i,\ldots,x_n)\oplus F(x_1,\ldots,\bar{x_i},\ldots,x_n)$$

and is denoted by  $\frac{dF(\mathbf{x})}{dx_i}$ , where  $\oplus$  denotes the logical exclusive-OR (XOR) operation. It can also be represented as

$$\frac{dF(\mathbf{x})}{dx_i} = F_i(0) \oplus F_i(1)$$

where,

$$F_i(0) = F(x_1, \dots, x_{i-1}, 0, x_{i+1}, \dots, x_n),$$

$$F_i(1) = F(x_1, \dots, x_{i-1}, 1, x_{i+1}, \dots, x_n),$$

The set of tests for  $x_i$  stuck-at 0 is

$$X_i.\frac{dF(\mathbf{x})}{dx_i}.$$

where,  $X_i$  is the function representing the output of the sub-circuit with output at  $x_i$ . Similarly, the set of tests for  $x_i$  stuck-at 1 is given by

$$\bar{X}_i.\frac{dF(\mathbf{x})}{dx_i}.$$

The effect of two faults at the input of a logic circuit on its output can be analyzed by defining the double Boolean difference as

$$\frac{dF(\mathbf{x})}{d(x_ix_j)} = F(x_1,\ldots,x_i,\ldots,x_j,\ldots,x_n) \oplus F(x_1,\ldots,\bar{x_i},\ldots,\bar{x_j},\ldots,x_n)$$

Thus, test generation for multiple stuck-at faults can be generalized by using multiple Boolean differences [62].

Test generation using Boolean difference approach can be characterized as algebraic in a sense that it manipulates circuit equations to generate test patterns. Other algebraic test generation methods developed are the propositional method of Poage [81], the equivalent normal form [8], the cause-effect equation [17], the SPOOF procedure [28], and the structure description function [57]. All these methods derive equations for a fault-free circuit and manipulate the equations to generate test patterns. However, it is an arduous task to manipulate algebraic equations for large circuits and therefore, can not be generalized. Furthermore, the tedious nature of the algebraic manipulations of these methods lead to be impractical for test generation.

### 2.2 Structural Algorithms

A number of structural algorithms have been developed for test generation of combinational and sequential circuits. The test generation algorithms for combinational and sequential circuits are known as combinational and sequential algorithms respectively. These algorithms are briefly discussed in this section.

#### 2.2.1 Combinational Algorithms

In combinational test generation algorithms, a test pattern is generated in two steps: (1) assign values to create a change (*i.e.* fault-effect) at the fault-site, and (2) search for consistent values on all signal lines in the circuit such that the fault-effect is successfully propagated to at least one of its primary output (PO). The most successful test generation systems are based on structural algorithms. Some of the notable ones are D-algorithm [85], Podem [45], Fan [33], [35], Tops [58], Socrates [88], [89], Cont [102], [103], and Est [41]. All these algorithms are briefly described in the following subsections.

#### The D-Algorithm

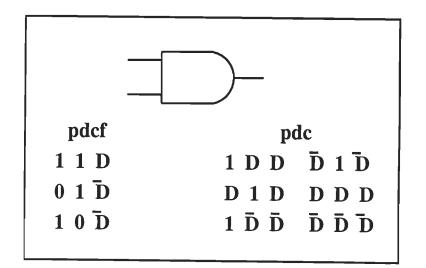

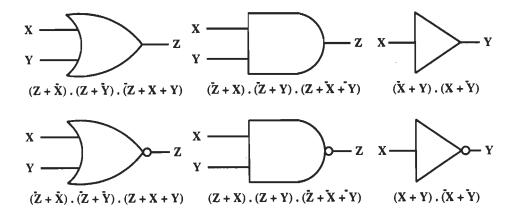

The D-algorithm is the first complete test pattern generation algorithm developed by Roth in 1966 [85] which introduces a D notation and a five-valued calculus in order to activate a single stuck-at fault and to propagate its fault-effect to at least one PO of the circuit. The five-valued calculus consists of logic values 0, 1, X (an unknown value), and two additional values D and  $\overline{D}$ . A D value signifies a logic value of 1 in the fault-free (good) circuit and 0 in the faulty circuit. A  $\overline{D}$  value signifies a logic value of 0 in the fault-free (good) circuit and 1 in the faulty circuit. The D-algorithm defines two D-cubes associated with each gate in the circuit: a primitive D-cube of a fault (pdcf) and a propagation D-cube (pdc). A pdcf is a set of inputs that produces an error signal on the output of that gate if it contains a fault. A pdc specifies the input values necessary to propagate an error signal on an input of a gate to its output. The pdcf and pdc of a two input AND gate are shown in Figure 2.1.

The basic operation of the D-algorithm is the repeated intersection of the Dcubes necessary to perform the tasks required to generate a test for a specific fault. The test generation is accomplished in three steps: fault sensitization, fault propagation

Figure 2.1: AND gate D-cubes.

and line justification. Fault sensitization is the process by which a circuit node is made to produce an erroneous value as a result of the fault. Sensitization is done by specifying an input combination for the circuit element containing the fault, using the pdcf that cause the output to take on the appropriate D value. Fault propagation is the process of propagating the D values to the primary outputs so that they can be monitored. The list of all gates whose output value is currently logical X but have one or more error signals (either D or  $\overline{D}$ s) on their inputs is called the *D*-frontier. Fault propagation process selects one gate from the D-frontier and assigns values to the unspecified gate inputs so that the gate output becomes D or  $\overline{D}$ . This process sensitizes all possible paths from the fault site to the primary outputs. This feature, referred to as multiple-path sensitization is necessary for the D-algorithm to guarantee its completeness. During fault sensitization and fault propagation, certain nodes of the circuit require to have specific values. Assigning values on the primary inputs to achieve the required value on the node is called line justification. The primary inputs to be used to justify a goal are usually determined by backtracing through circuit topology from the node in question to the primary inputs. A value is assigned to one of these primary inputs and a simulation-like process, called forward implication, is performed to see whether the current input assignment while satisfying the goal is consistent or not. If it satisfies the goal, a test is generated which means that the fault is sensitized and the fault-effect (error) is successfully propagated to the primary outputs. However, if it does not, a different value is selected and the process is repeated until either the test is generated or in case of any inconsistency, the fault under consideration is declared as redundant fault.

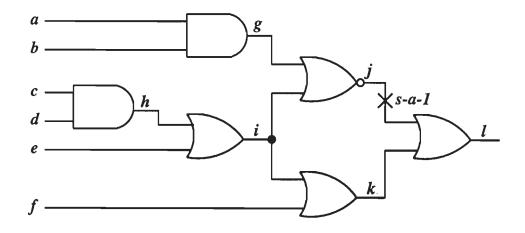

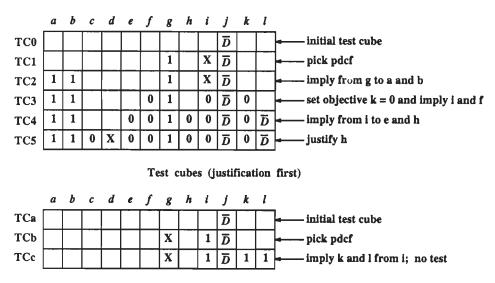

To illustrate the D-algorithm, let us consider a combinational circuit as shown in Figure 2.2 which is to be tested for a stuck-at-1 fault on signal line j. According to the first step of the D-algorithm, the fault is to be sensitized by producing an error value, *i.e.*  $\overline{D}$ , on the line j and it is shown by test cube, TC0 in Figure 2.3. The fault is sensitized using a pcdf of the NOR gate (TC1), *i.e.* by setting g = 1. Using the backward implication procedure, both the inputs, a and b, of the AND gate g must have 1 value which means a = b = 1 and TC2 shows these assignments. In order to advance the D-frontier, a 0 value is required on k node which in turn implies that both the inputs, i and f, of the OR gate k must have 0 values (TC3). The 0 value on the output of the OR gate i implies e = h = 0 (TC4). In the justification step, h has to be justified to 0, which can be done by assigning either input of the AND gate h to a 0 value. By setting c to a value 0 (TC5), a test is generated by the D-algorithm.

Now consider the test cubes (propagation first) as given in Figure 2.3 for pdcf selection. When selecting the test cube TCb for the initial fault, its forward implication determines that the value on the signal lines k and l to be 1. Since error is not visible on the primary output l, no test is generated (TCc). In this case, the algorithm would backtrack to the last decision made and select the alternate choice to proceed further. In the D-algorithm, choices are available at many internal nodes in the circuit and

Figure 2.2: An example combinational circuit

Test cubes (propagation first)

Figure 2.3: D-algorithm example.

more than two choices may be present in the case of more than two-input gates in the circuit. Due to this fact, the size of the algorithm's search space increases and makes backtracking more complex.

In fact, the original D-algorithm does not mention about the order of the

processes – fault sensitization, fault propagation and justification – to be performed. However, the efficiency of the test generation depends heavily on the order of these operations and the most efficient order is determined by the circuit topology. As an example, in test generation for j stuck-at-1 fault in the circuit of Figure 2.2, if fault propagation is done before selecting a pdcf, the unique 0 value required on node i will be discovered and the pdcf for faulty gate will be fixed. Then the test generation can proceed without any possibility of backtracking. Subsequently developed algorithms attempted to reduce the size of the solution space that must be searched. Goel made an attempt in the same direction and developed Podem (Path-Oriented DEcision Making) algorithm [45] as D-algorithm turned out to be extremely inefficient in generating tests for the class of combinational circuits that implement error-correction and translation (ECAT) type functions [45].

#### The Podem Algorithm

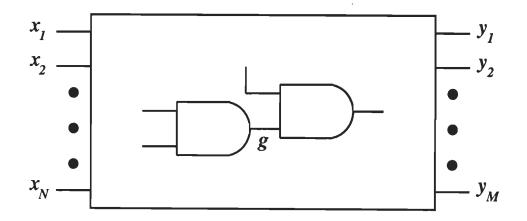

Podem is an implicit enumeration algorithm in which all possible primary input patterns are implicitly, but exhaustively, examined as tests for a given fault. In Podem, the test generation problem is formulated as a search of the N-dimensional 0-1 state space constrained by a set of Boolean equations, where N is the number of primary inputs of a combinational circuit. To view the test generation as a finite space search problem, let us consider the combinational circuit shown in Figure 2.4, where g is an internal net and the objective is to generate a test pattern for the g stuck-at-0 fault. The state on g can be expressed as a Boolean function of the primary inputs,  $x_1, x_2, \ldots, x_N$ . Similarly, each primary output  $(y_j, j = 1, 2, \ldots, M)$  can be expressed as a Boolean function of the state on net g as well as the primary inputs  $x_1, x_2, \ldots, x_N$ . Let

$$g = G(x_1, x_2, \ldots, x_N)$$

Figure 2.4: A generic combinational circuit.

and

$$y_j = Y_j(g, x_1, x_2, \ldots, x_N)$$

where  $1 \le j \le M$  and  $x_i = 0$  or 1 for  $1 \le i \le N$

The problem of test generation for g stuck-at-0 can be stated as one of solving the following set of Boolean equations:

$$G(x_1, x_2, \dots, x_N) = 1$$

$$Y_j(1, x_1, x_2, \dots, x_N) \oplus Y_j(0, x_1, x_2, \dots, x_N) = 1$$

for at least one  $j, 1 \leq j \leq M$  and  $x_i = 0$  or 1 for  $1 \leq i \leq N$

In order to generate test pattern for g stuck-at-1 fault, the same set of equations are to be solved except that G is set equal to 0. Hence, test generation can be viewed as a search of N-dimensional 0-1 state space subject to satisfying the above set of equations.

The Podem algorithm begins by trying to justify D or  $\overline{D}$  at the node under test, similar to the D-algorithm. In Podem, this justification is done by assigning values to primary inputs that affect the node in question. These primary inputs may be found by backtracing through the circuit topology. When an input assignment is made, *i.e. branching* in the context of *branch-and-bound algorithms*, forward implication (a simulation-like process) is carried out to evaluate all node values implied by the assignment. In case of any inconsistency found due to this assignment in order to achieve the goal, the complementary value is tried. When both assignment choices at a node are rejected, the algorithm backtracks efficiently to the previous input assignment. The rejection of a primary input assignment results in a *bounding* of the decision tree, in the context of the branch-and-bound algorithms. This process finally results in an orderly search methodology that will implicitly search the entire solution space.

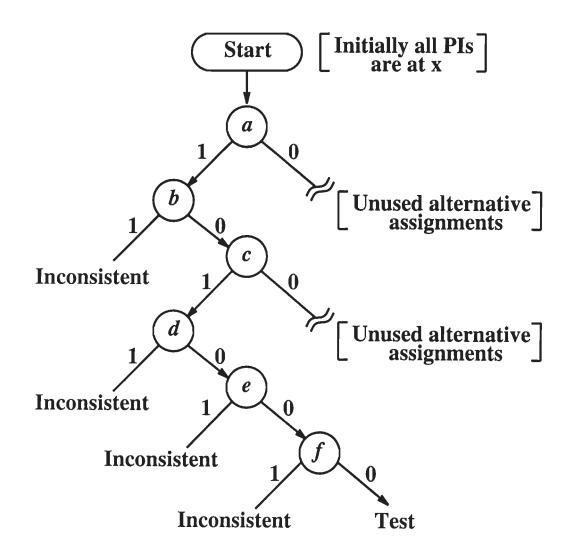

The search methodology of Podem is represented by a decision tree structure illustrated in Figure 2.5. After the value at the faulty node is justified, subsequent objectives are set up to propagate the D-frontier along a path or paths to the primary output(s). The exact order in which this process occurs is again implementation dependent. The important characteristics of Podem is that the strategy of assigning values only to primary inputs orders the search space. This procedure lets the search methodology prune the search space implicitly and increase efficiency.

To illustrate the test generation using Podem, let us consider the combinational circuit shown in Figure 2.2 with a slight modification that fault at node j is stuck-at-0 instead of stuck-at-1 fault. In order to generate test pattern for the fault under consideration, Podem orders the binary search space as shown in the form of a decision tree (Figure 2.5). A simple heuristic is used to construct this search space that always prefers to assign a logical 1 value on a primary input. Initially, all primary inputs of the example circuit are at logical X value, *i.e.* unknown value. Using this simple heuristic, the node a is assigned to a logical 1 value which also provides consistency in the circuit. Now the assignment of a logical value 1 on node b in the circuit leads to inconsistency, therefore, all assignments with b = 1 in the solution space should be

21

ų

Figure 2.5: Podem search-space graph.

pruned as shown in the decision tree. Hence, the remaining alternate value on b, *i.e.* b = 0 is tried and the decision tree is further explored. The entire process is iteratively continued till a test pattern is found. For the example circuit, the test pattern for the given fault j stuck-at-0 is thus obtained by assigning a = 1, b = 0, c = 1, d = 0, e = 0 and f = 0 as shown in Figure 2.5. Podem is a complete test generation algorithm in that a test pattern will be found if one exists.

#### The Fan Algorithm

In Podem, the test generation may become time-consuming for the circuits with large number of fan-outs and therefore, needs improvements in order to handle such circuits. The Fan (Fan-out oriented test generation algorithm) [33], [35] is an improved version of the Podem algorithm in the sense that the test generation process is accelerated by incorporating several techniques. The important goals of Fan are to reduce the number of backtracks in the binary decision tree and shorten the process time between backtracks. The Fan algorithm introduces the following two major extensions to the backtracing concept of Podem.

- Termination of backtracing in Fan at *internal lines* than stopping at primary inputs.

- Usage of a *multiple-backtrace* procedure to simultaneously satisfy a set of objectives rather than trying to satisfy one objective at a time.

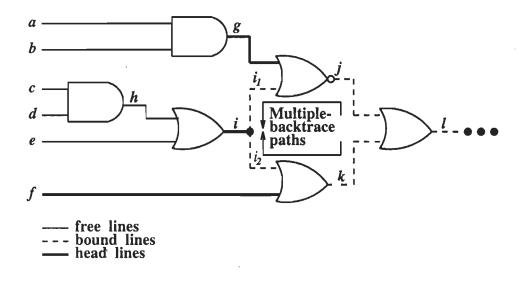

Fan defines internal lines as bound, free and head line where it stops backtracing. A bound line is a signal line reachable from some fan-out point, *i.e.* there exists a path from some fan-out point to a signal line. A signal line that is not bound is said to be a *free line* and a *head line* is a free line that is adjacent to some bound line.

In the circuit shown in Figure 2.6, signal lines  $i_1$ ,  $i_2$ , j, k, and l are bound lines. Lines a, b, c, d, e, f, g, h, and i are all free lines. Among the free lines, g, i, and f are head lines of the circuit since these lines are adjacent to the bound lines j,  $i_1$  or  $i_2$ , and k respectively. As far as the value assignments on these lines are concerned, free lines may have a uniquely assigned value whereas bound lines can not have unique (independent) values assigned to them. By definition, head lines can also be assigned values arbitrarily because they are free lines and can always be independently justified.

Figure 2.6: A Fan example.

Therefore, they can be treated as primary inputs in the justification process. Once 'a test is found by treating headlines as primary inputs, the values on them can be justified at the end of the test generation process.

Multiple-backtrace procedure is an important characteristic of the Fan algorithm which handles re-convergent fan-out branches buried in the circuit. This procedure reduces the number of backtracks that must be made in the search. In the multiple-backtrace of Fan, an objective is defined by a triplet

$$(s, n_0(s), n_1(s))$$

where s is an objective line,  $n_0(s)$  is the number of times the object value 0 is required to be set on line s, and  $n_1(s)$  is the number of times the object value 1 is required to be set on line s. The multiple-backtrace procedure starts with a set of *initial objectives* and defines different set of objectives. Starting from the set of initial objectives, a set of objectives that appear during the procedure is called a set of *current objectives*. A set of objectives that is obtained at head lines is called a set of *head objectives*. A set of objectives on fanout points is called a set of fanout-point objectives.

Multiple-backtrace procedure of Fan is illustrated here by considering the circuit shown in Figure 2.6 as an example. Assume that this circuit is a part of some larger circuit and during the test generation process, certain value is necessary at node l in the circuit. In Podem, a single backtrace could be made along the path  $l \rightarrow j \rightarrow g \rightarrow a, b$ . The values for inputs a and b could be chosen so that the goal is satisfied with a unique value on nodes i and k. Suppose the value on k can not be achieved with the value chosen for i. Then, a significant amount of backtracking could result in the search of binary decision tree. In Fan, a multiple-backtrace procedure would backtrace both the  $l \rightarrow j \rightarrow i$  and  $l \rightarrow k \rightarrow i$  paths (Figure 2.6) and determine the value needed at i to satisfy the goal. This value would then set a requirement for the justification of the value at node l. This in turn would increase the efficiency of the Fan algorithm significantly for the combinational circuits with numerous buried re-convergent fan-outs.

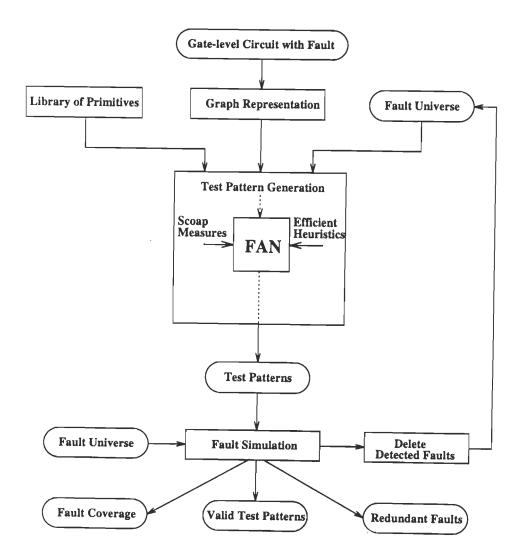

A CAD tool [92] has been developed to generate test patterns automatically for a given set of faults in a combinational logic circuit. The block schematic of the CAD tool for Automatic Test Pattern Generation (ATPG) is shown in Figure 2.7. The Fan algorithm has been implemented as a core of the CAD tool for ATPG. Fan algorithm was chosen because it is significantly faster than Podem algorithm as the search-space ordered by the Fan is relatively less than the Podem. The search-space ordered by the Fan may be further pruned with the use of efficient heuristics. These heuristics basically provide help in accelerating ATPG process by reducing the number of backtracks or bad decision. Heuristics based on centrollability/observability (C/O) measures, such as Scoap [47], [48], Savir's cutting algorithm [86], Predict [91] *etc.* have been considered in order to couple within the ATPG framework. In the heuristic development phase of the CAD tool, it is found that the popular Scoap measures lack essentially in the assumption of signal independence of fan-out signals [5]. It gives rise to errors when re-convergence is encountered. Moreover, they are also unable to provide a way to calibrate the circuit controllability/observability information in an absolute way. A new efficient heuristic based on probabilistic estimation has been proposed which considers the correlation of the inputs in a re-convergent fan-out path and provides more accurate calculations of node controllabilities than Predict.

The quality of test patterns generated by the CAD tool is determined by a fault simulator which has been incorporated with in the ATPG framework and depicted in Figure 2.7. Among the various fault simulation methods [68], [82], [106] developed in the past, a Parallel Pattern Single Fault Propagation (PPSFP) algorithm [106] has been implemented in this CAD tool. The fault simulator provides the information about the quality of the test patterns in terms of fault coverage, undetected and undetectable faults. Moreover, this simulator may be used for automatic fault dictionary generation for diagnosis of complex digital systems [93].

#### The Socrates Algorithm

Schulz et al. [88] developed an Automatic Test Pattern Generation (ATPG) system called Socrates based on the Fan algorithm. This ATPG system incorporates several distinct techniques to accelerate the ATPG process for combinational or scan-based circuits. The application of these techniques results in an earlier recognition of conflicts and redundancies and in a reduction of the number of backtracks. In particular, these techniques provide improvements in implication, unique sensitization, and multiple backtrace procedures. Among these techniques, the most important one is a *learning*

Figure 2.7: A block schematic of the ATPG tool.

procedure which is performed during the pre-processing phase of Socrates. The overall strategy of the learning procedure is to assign a logic value to a certain signal of the circuit, to perform all implications from that assignment and to learn from the results of the implications. The implications are performed by using a *logical identity* called *contrapositive*, *i.e.*

$$(P \Rightarrow Q) \Leftrightarrow (\neg Q \Rightarrow \neg P)$$

where P and Q are arbitrary assertion variables. In order to decide efficiently whether an implication is worthwhile learning or not, the following *learning criterion* is used.

• Let *i* be the signal at which the current learning step is initialized by the assignment  $i = v_i$  and let *j* be a signal at which a fixed logic value  $v_j$  (0 or 1) is assigned during the implication procedure, *i.e.*

$$(i = v_i) \Rightarrow (j = v_j)$$

• Furthermore, let j be the output of a gate, say g. If  $v_j$  requires all inputs of g to have non-controlling values and a forward implication has contributed the assignment  $j = v_j$ , then the implication

$$(j = \bar{v_j}) \Rightarrow (i = \bar{v_i})$$

is considered to be worthwhile learning.

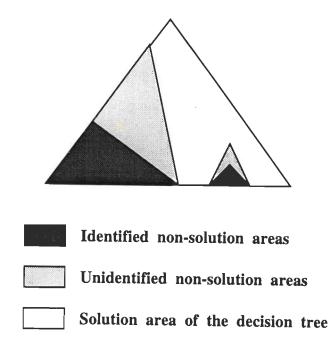

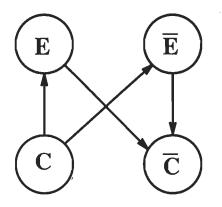

In Socrates, the test generation problem is also viewed as a search problem for which algorithms usually build a decision tree and apply a backtracking procedure [33], [35], [45] in order to find a solution of the problem. However, the decision tree can be represented as a triangle shown in Figure 2.8 and can be divided into a *solution area* and several *non-solution areas* as shown in the triangle. It is important to note that whenever a search procedure enters into one of the non-solution areas, no solution can be obtained by making additional assignments on the primary inputs of the circuit and only possibility to leave the non-solution area is through backtracking.

Majority of the deterministic test generation algorithms are not able to identify the entire non-solution areas and identify only parts of them. During the search procedure, whenever a test generation algorithm enters into an identified non-solution area, immediately backtracking will take place as soon as it is recognized that a solution can not be found with the current assignment. Contrary to this, the unidentified

Figure 2.8: Abstract problem representation of deterministic test generation.

non-solution area causes the most serious problem to the test generation algorithms as it will require a lot of backtracking in order to leave the non-solution area. Hence, the following two global goals are aimed in the development of Socrates:

- 1. Minimization of the unidentified non-solution areas, and

- 2. Avoidance of entire non-solution areas during the search process.

### The Est Algorithm

The Est algorithm [41] is an acronym for Equivalent STate Hashing algorithm which accelerates any combinational circuit test generation algorithm. Est detects equivalent search states, which are saved for all faults during test pattern generation. The search space is reduced by using Binary Decision Diagram (BDD) further than other algorithms can [33], [35], [45], [58], [85]. This algorithm made the following contributions:

- It characterizes the search state of the test generation algorithm using the *E*frontier, a cut-set of the circuit induced by a set of primary input assignments. The frontier is a partition between the circuit part labeled with 0, 1, D, and  $\overline{D}$ signals and the part labeled with X signals.

- It uses the matching of E-frontiers to cause early backup from infeasible searches or early search termination with a test pattern.

- It is the first test pattern generation algorithm which uses knowledge about the search space for a prior fault to accelerate search for a test of the current fault.

- It also uses first time the knowledge of opportunistically-discovered redundant faults in the circuit to further reduce the search space for later faults.

Est accelerated the TOPS [58] test generation algorithm 328 times and enabled it to handle all faults in the ISCAS '85 combinational benchmark circuits. Est also accelerated the Socrates algorithm 5.81 times on the same benchmark circuits. Extensions to the Est algorithm are reported in [42].

### Other ATPG Algorithms

The TOPS algorithm [58] uses the Fan's concept of the independent justification of headlines a step further by introducing a new type of node called a *basis node*. A basis node is the absolute dominator of all nodes that precede in the circuit graph. The concept of dominator nodes has come from graph theory. A node dominates another node if all paths from that node to the root pass through the dominator. All free lines and head lines in a circuit are basis nodes as they are all points of total re-convergence. In the circuit shown in Figure 2.6, the free lines *a* through *i* are basis nodes. Since node *l* is a point of total re-convergence, it is also a basis node. As a basis node, node

l can have any value required to generate a test in the remainder of the circuit, and the justification of that value at the total-re-convergence node l can be postponed in the same way as the justification of a head line.

A backtrace-stop line used in Fast (Fault-oriented Algorithm for Sensitizedpath Testing) algorithm [2] represents another generalization of the head-line concept, based on an analysis that is both topological and functional. In Fast, a line l is a backtrace-stop line for value v, if the assignment l = v can be justified without conflicts. For example, in Figure 2.6, l is a backtrace-stop line for value 0, because l = 0 can be justified by a = b = 1 and f = 0 that is without assigning any line with re-convergent fanout.

The Cont algorithm [102] implements a different approach in which if the target fault is not detected by the current input vector, Cont switches over to a new target fault. Candidate faults for target switching are identified by interleaving fault simulation steps with incremental test generation steps. In the second version [103] of the Cont algorithm, all unspecified inputs are randomly assigned prior to fault simulation.

Other test generation methods that combine features of deterministic algorithms with those of RTG are Raps [44] and Smart [2]. The Raps (**Random Path** Sensitization) algorithm attempts to create random critical paths between PIs and POs. Initially all values are at X. Raps starts by randomly selecting a PO, say z and a binary value v. Then the objective (z, v) is mapped into a PI assignment  $(i, v_i)$  by a random backtrace procedure Rbacktrace. Rbacktrace is similar to the backtrace procedure used by Podem except that the selection of a gate input is random. In Podem, this selection is guided by heuristics. The assignment  $i = v_i$  is then simulated using 3-value simulation and the process is repeated until the value of PO z becomes binary. After all the POs have binary values, a second phase of Raps assigns the PIs (if any) with X values. The entire procedure is repeated to generate tests as needed. As a result, test sets generated by Raps are smaller and achieve a higher fault coverage than those obtained by RTG.

Smart (Sensitizing Method for Algorithmic Random Testing) is also a combined deterministic and random test generation method which corrects the problems encountered by Raps. Smart generates a vector incrementally and relies on a close interaction with fault simulation. The partial vector generated at each step is simulated using critical-path tracing [1] which guides the test generation process. This interaction is based on two by-products of the critical-path tracing: stop lines and restart gates. Stop lines delimit areas of the circuit where additional fault coverage can not be obtained, while restart gates point to areas where new faults are likely to be detected with little effort. Experimental results reported in [2] show that Smart achieves higher fault coverage with smaller test sets and requires less CPU time as compared to Raps.

## 2.2.2 Sequential Algorithms

Test generation for sequential circuits is recognized to be a more complex problem than for the combinational circuits. Primarily, most sequential test generation methods have been devised on the basis of the fundamental combinational algorithms like D-algorithm [85] and Podem [45]. The extended D-algorithm of Kubo [63] and Putzolu and Roth [83] and the nine-valued model of Muth [75] are some basic procedures that are good for use in the test generation for sequential circuits. However, these algorithms are found difficult to implement and highly inefficient for large practical sequential circuits.

Considerable research has been done in the development of sequential test generation methods and a number of sequential test generators have been reported in the literature. The taxonomy of the sequential test generation methods is given below:

1. Time frame expansion based,

2. Simulation based, and

3. Rule based or expert systems.

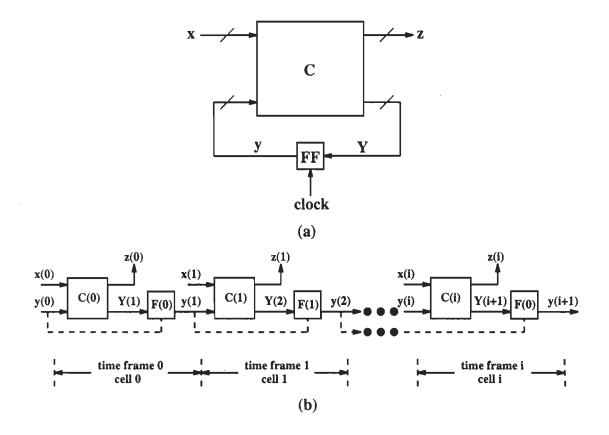

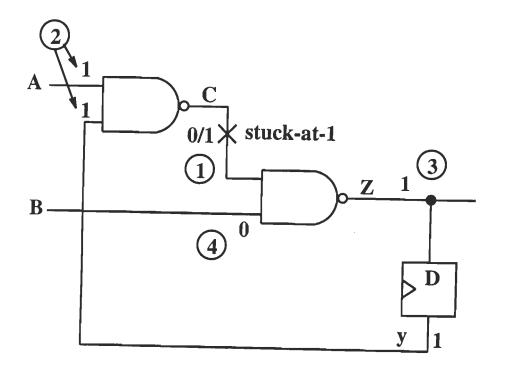

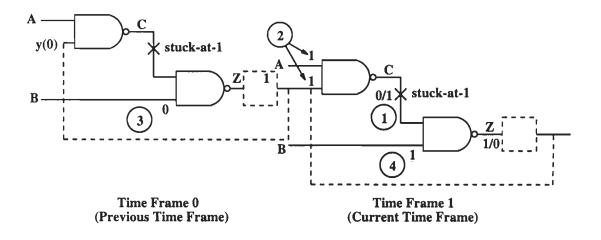

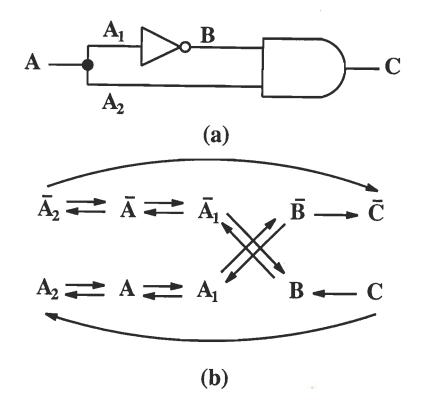

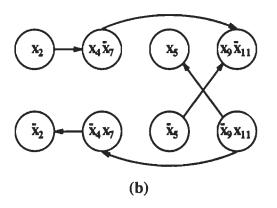

In time frame expansion based test generation methods, a synchronous sequential circuit, S is transformed into a combinational iterative array by cutting the feedback loops of the clocked flip-flops as shown in Figure 2.9(b). Each cell C(i) of the array is identical to the combinational circuit C of Figure 2.9(a). In this transformation, the clocked flip-flops (FF) of S are modeled as combinational elements F(i) which are referred to as pseudo flip-flops. In Figure 2.9(b), C(i) and F(i) correspond to time frame *i*. Suppose that an input sequence  $x(0) x(1) \dots x(k)$  is applied to the sequential circuit S in initial state y(0) and S generates the output sequence  $z(0) z(1) \dots z(k)$  with the state sequence  $y(1) y(2) \dots y(k+1)$ . Then the iterative array will generate the output z(i)from cell *i*, in response to the input x(i) to cell  $i (1 \le i \le k)$ . This modeling technique maps the time domain response of the sequential circuit into a space domain response of the iterative array. A time frame expansion of the example sequential circuit given in Figure 2.10 is illustrated in Figure 2.11. Due to this transformation, the test generation methods developed for combinational circuits could be extended to the sequential circuits. A similar technique exists for asynchronous sequential circuits.

The time frame expansion based test generation can be further subdivided into algorithms that do test generation in

• forward time,

• reverse time, and

Figure 2.9: (a) Canonical structure of a synchronous sequential circuit, and (b) its combinational iterative array model.

#### • a combination of forward time and reverse time

The extended D-algorithm and Muth's method both perform test generation in forward time. Sequential test generation algorithms based on path sensitization methods in a multiple time frame environment are reported in [12], [25], [26], [49], [72], [73]. The methods proposed in [25], [26], [72], [73] rely on reverse-time processing of the circuit. In reverse-time processing, an output for the target fault is determined first and then the algorithm works backward in time from the primary output to the fault site and finally to an uninitialized state. STG1 [72], STG2 [25], STG3 [72], and Dust [49], use multiple path sensitization based on D-algorithm framework, while Marlett [73]

Figure 2.10: An example circuit for sequential test generation.

developed the algorithm based on a single path-sensitization technique combined with a 16-valued logic model and a reevaluation method. The advantage of the reverse-time processing methods is that they are memory efficient since only the current timeframe and previous timeframe need to be in memory at a time. The disadvantages of these methods are that they are unnecessarily complex and inefficient because they work backward in time and are D-algorithm based. Some of the disadvantages are overcome by Essential [12] which uses static and dynamic information during test generation and information from the preprocessing phase to keep the search space as small as possible.

Hitest [15], Stallion [71], Steed [40] and Fastest [56] are the only known sequential circuit test generators that make use of Podem which has been much ignored as the basis for sequential circuit test generation. Hitest is a knowledge-based interactive test generation system and uses Podem for one timeframe, treating flip-flop outputs as

Figure 2.11: Time frame expansion of the example circuit for sequential test generation.