# STUDIES ON THE PERFORMANCE EVALUATION OF A LINEARLY EXTENSIBLE MULTIPROCESSOR NETWORK

## A THESIS

submitted in fulfilment of the requirements for the award of the degree

of

DOCTOR OF PHILOSOPHY

in

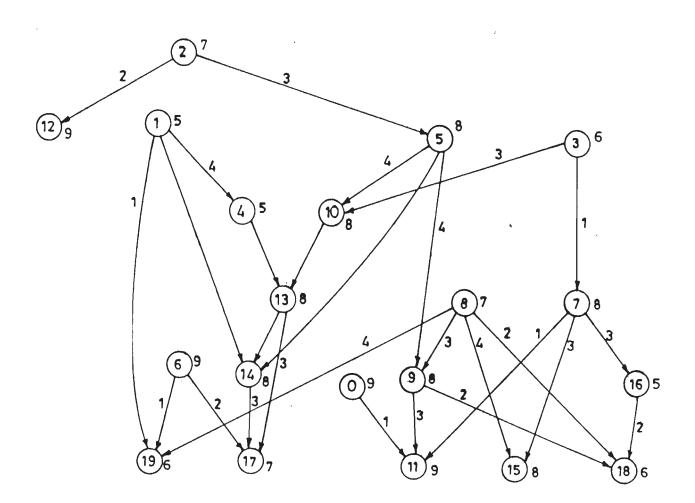

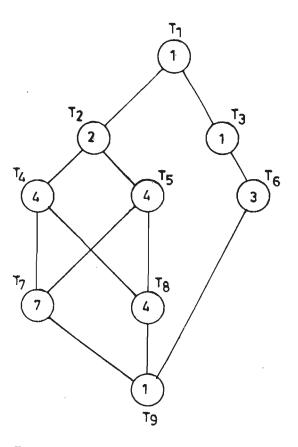

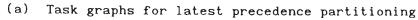

## ELECTRONICS AND COMPUTER ENGINEERING

CENTRAL LIBRARY INDIAN INSTITUTE OF TECHNOLOGY ROCRKEE-247 667 S10975

By

11-7-02

MOHAMMAD QASIM RAFIQ

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING UNIVERSITY OF ROORKEE ROORKEE – 247 667 (INDIA)

SEPTEMBER, 1995

# **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled "STUDIES ON THE PERFORMANCE EVALUATION OF A LINEARLY EXTENSIBLE MULTIPROCESSOR NETWORK" in fulfilment of the requirement for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electronics & Computer Engineering of the University is an authentic record of my own work carried out during a period from May, 1993 to September, 1995 under the supervision of Prof. J.P. Gupta, and Dr.Padam Kumar.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other university.

(MOHAMMAD QASIM RAFIQ)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

Date: 01.09.95 Dr. Padam Kumar Reader, Department of Electronics & Computer Engg. University of Roorkee

PGu

**Prof. J.P. Gupta** Member Secretary, AICTE, New Delhi

The Ph.D. viva-voce examination of MOHAMMAD QASIM RAFIQ Research Scholar, has been held on  $\frac{37}{7}/\frac{7}{9}$

Signature of Supervisors

Signature of

External Examiner

Signature of H.O.D.

Dr. R. P. ACARWAL PROFESSUR ANJ HEAD DEPARTMENT OF FLECTPUNICS ANT COMPLETE IN CONFERENCE UNIVERSITY OF FOOT SEE EUOTIME-SAL 007

#### ABSTRACT

Exploiting parallelism is now a necessity to improve the throughput of the computer systems. In terms of hardware, this typically means providing multiple, simultaneously active processors. In terms of software, it means structuring a program as a set of largely independent subtasks. The structuring of a program is usually represented by a problem graph. The nodes of the graph denote the subtasks of a program and the links/arcs between them represent the precedence data relations among the subtasks. Research is active in the direction of developing new multiprocessor architectures and schedule the partitioned program onto it in order to achieve higher execution speeds and/or increased programming comfort.

The present work, reported in this thesis, is concerned with the development of a new multiprocessor network, called a Linearly Extensible Tree (LET) network and a dynamic scheduling scheme, named as Minimum Distance Scheduling (MDS) scheme, for parallel execution of tree-structured problems. In addition to this, simulation studies are carried out to compare the performance of LET multiprocessor network and the proposed scheduling scheme MDS with other similar multiprocessor networks and related scheduling schemes available in literature, on different types of problem graphs- general and tree-structured in particular.

The model proposed is a linearly extensible tree (LET) multiprocessor network, which exhibits the desirable properties of similar types of multiproceesor networks. The LET network combines linear extensibility with small number of processing elements per extension. The network has lower diameter, hence reduces the average path-length travelled by all messages and contains a constant degree per node.

A dynamic scheduling scheme MDS has been developed, which forces minimum distance constraint, based upon only the adjacency matrix information of the LET network, and with relatively small overhead, it oversees that the task arrives at the proper processor maintaining the

(i)

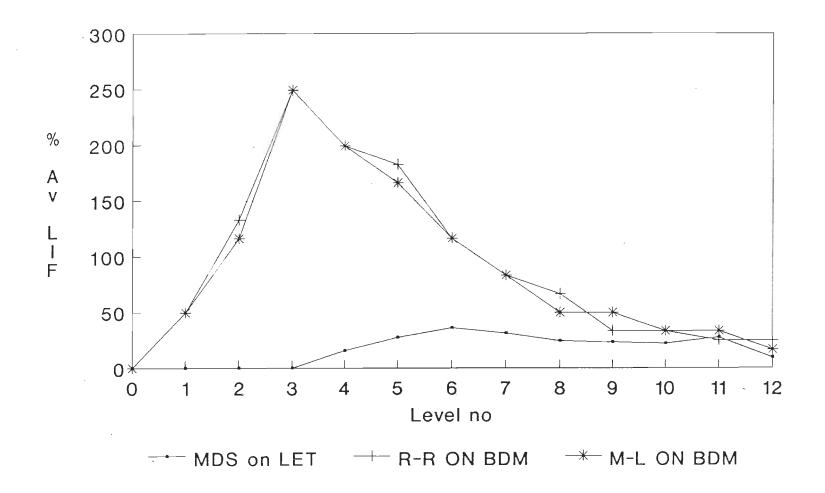

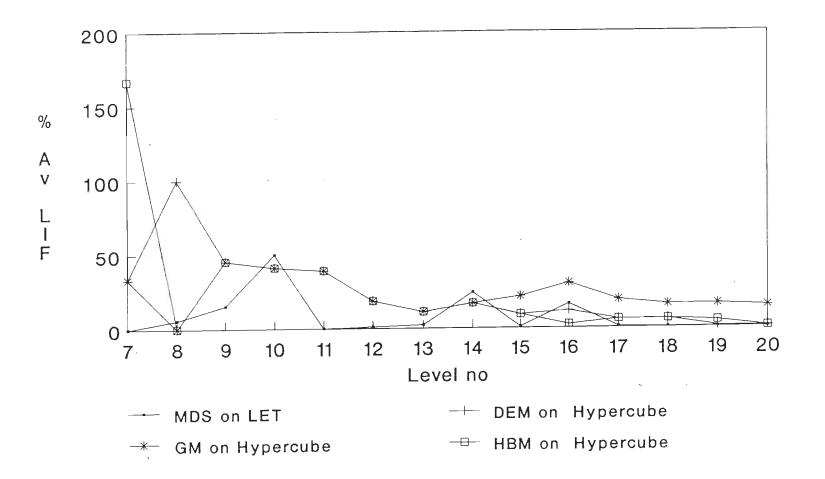

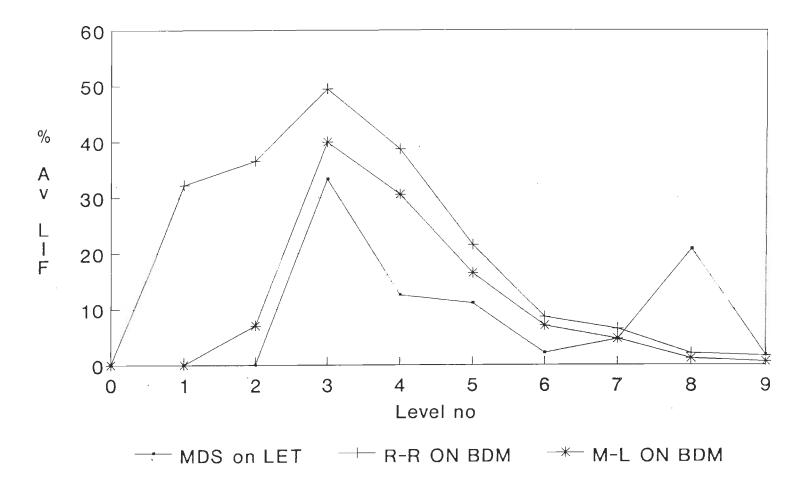

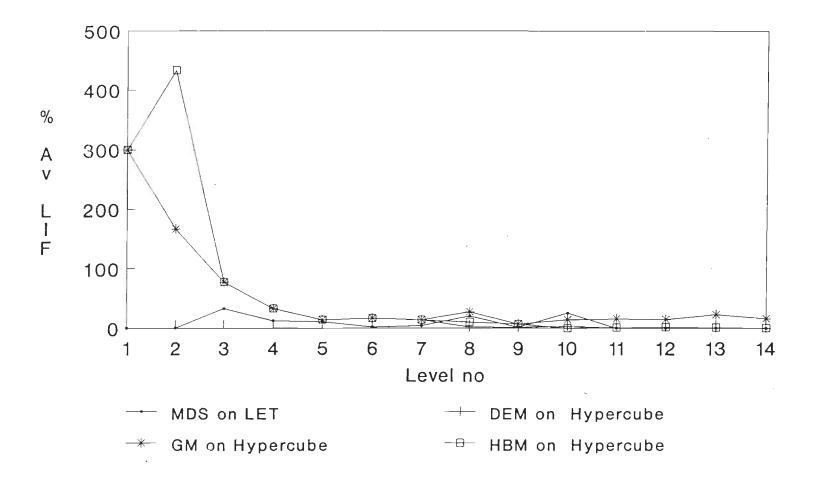

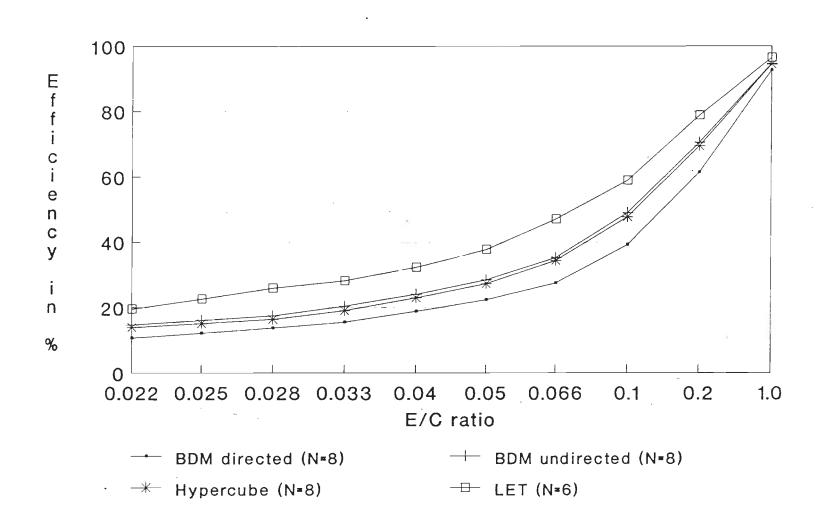

task relations even for grossly unbalanced problem graphs or in the presence of failing nodes or links. This scheduling scheme is compared with other available static and dynamic scheduling schemes in the literature for implementation on LET network and other similar multiprocessor networks for graph problems in general and tree-structured problems in particular. The superiority of the developed organisation i.e. LET network and MDS scheme on other existing organisation such as Binary deBruijn Multiprocessor (BDM) network and Round-Robin (R-R) scheme, BDM network and Minimum Load (ML) scheduling, hypercube and Dimension Exchange Method (DEM) scheme, hypercube network and Gradient Model (GM) scheme, and hypercube network and Hierarchical Balance Method (HBM) has been established.

Performance of LET network has also been studied for problems having an Acyclic Precedence Graph (APG) structures. In this connection a static Latest Precedence Scheduling (LPS) algorithm has been developed which runs faster compared to a similar other algorithm. The LPS algorithm preserves minimum distance. Performance of LET under this algorithm for APG'S has been tested and compared to other networks.

# ACKNOWLEDGEMENTS

It is with deep sense of gratitude and reverence that I express my sincere thanks to my supervisors, **Prof. J.P. Gupta.** Prof. of Electronics and Computer Engineering and presently *Member Secretary*, All India Council for Technical Education, Govt. of India, and **Dr. Padam Kumar**. *Reader*, Electronics and Computer Engineering Department, University of Roorkee, for their erudite guidance and advice, constant keen interest at every stage of this work. Their untiring and painstaking efforts, constant encouragement and suggestions, methodical approach and invaluable help throughout, made it possible for me to complete this work in time. I consider myself very fortunate to be associated with such scholars of the subject, whose affection, guidance and scientific approach served a veritable incentive for completion of this work.

I was very fortunate to come in contact with **Prof. Derek R. Wilson**, professor at the University of Westminster, London, UK during his two visits to Roorkee. His valuable suggestions and the time spared for highly fruitful discussions is gratefully acknowledged.

I shall ever remain indebted to **Prof. R. P. Agarwal**. Head, Department of Electronics and Computer Engineering, for the facilities provided to me by the department and his kindness and generous help extended during the completion of the work.

I gratefully acknowledge the financial support received from the Government of India, Ministry of Human Resources under QIP scheme and also the administration of A.M.U. Aligarh for deputing me under this scheme. I am much obliged to **Prof. S.C. Handa**, Coordinator, QIP, for extending the facilities during my stay at the University Of Roorkee.

I am grateful to my elder brother **Prof.** M.A. Siddiqui, Prof. of Medicine, Principal & CMS, JN Medical College, AMU, Aligarh, for his kind support, concern, encouragement and advice throughout my life. His own achievements have greatly inspired me. His constant moral support and sharing of my household responsibilities enabled me to devote myself fully to my work at Roorkee.

I also take this opportunity to thank and acknowledge to bhabhis, Mrs. Rafat Siddiqui, Mrs. Kamlesh Gupta and Mrs. Anita Kumar, who were a constant source of encouragement and inspiration for me during my stay at Roorkee. I can not but remember the smile, devotion, understanding and trust that my wife, Tazeen and children, Saman, Mansoor and Saboor, who bore my neglect and separation from them which was inevitable to complete this research work.

Although it is not possible to name them individually, I can not forget my well wishers at A.M.U., Aligarh, especially Prof. R.K. Gupta, Prof. A.K. Gupta, Prof. S. Basu, Prof. E. Hussain, Prof. F. Ghani, Prof. G.C. Upretti, Prof. K.A. Khan, Prof. M.T. Ahmad, Prof. S.A. Abbasi, Dr. S.K.A.Qasmi, Dr. Jamal Ahmad, Mr. S.H. Hasan, Mr. M.Naim Akhter, Dr. Sattar Husain and Mr. Z.H. Zaidi, for their persistent support and cooperation.

This acknowledgement would be incomplete if I fail to express my deep sense of obligations to all my friends and colleagues at the University of Roorkee, for their warm friendship, encouragement, cooperation and valuable suggestions during my stay, especially M/S Bahar Alam, A. Hasan, Zulfequar Ahmad, Khalid Moin, Rajiv Saxena, S.K. Sinha, M. Arif, S.A. Ansari, Ziauddin Ahmad, P. Mustajab and M.Shakeel.

# **MOHAMMAD QASIM RAFIQ**

# CONTENTS

| ABSTR | ACT                                          |                                                                                            |                                                               | (i)                   |

|-------|----------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------|

| ACKNO | WLEDGE                                       | <b>ENTS</b>                                                                                |                                                               | (iii)                 |

| CONTE | NTS                                          |                                                                                            |                                                               | (iv)                  |

| 1.    |                                              | INTROI                                                                                     | DUCTION                                                       | 1                     |

|       | 1.1                                          | Parallelism as a conc                                                                      | ept                                                           | 2                     |

|       |                                              |                                                                                            | sors                                                          | 2<br>3<br>3<br>3<br>4 |

|       |                                              | Need for performance<br>Motivation<br>Statement of the prob<br>Organization of the t       | lem                                                           | 6<br>7<br>8<br>9      |

| 2.    | REVIE<br>SCHEM                               |                                                                                            | CHITECTURES AND SCHEDULING                                    | 11                    |

|       | 2.1                                          | Multiprocessor archit                                                                      | ecture                                                        | 12                    |

|       |                                              | 2.1.1 Shared-memory<br>2.1.2 Message passi                                                 | -                                                             | 13<br>14              |

|       | 2.2                                          | ultiprocessors interconnection networks                                                    |                                                               | 16                    |

|       |                                              | 2.2.2 Network chara<br>2.2.3 Hypercube int                                                 | erconnection network                                          | 16<br>16<br>18        |

|       |                                              | 2.2.3.1 Hyp                                                                                | ercube topology                                               | 18                    |

|       |                                              | 2.2.4 Basic concept                                                                        | of tree                                                       | 21                    |

|       |                                              | 2.2.4.2 Bir                                                                                | ertree network<br>ary de-Bruijn multiprocessor<br>DM) network | 23<br>24              |

|       |                                              | 2.2.4.3 Hyp                                                                                | er de-Bruijn network                                          | 26                    |

|       | 2.3 Properties of an interconnection network |                                                                                            | rconnection network                                           | 26                    |

|       | 2.4                                          | Review of scheduling schmes                                                                |                                                               | 29                    |

|       |                                              | <ul><li>2.4.1 Introduction</li><li>2.4.2 Definitions</li><li>2.4.3 The classific</li></ul> | ation scheme                                                  | 29<br>30<br>33        |

|      |                                                                       | 2.4.3.1<br>2.4.3.2                                                  | Hierarchical classification<br>Flat classification<br>characteristics                   | 33<br>39                   |

|------|-----------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------|

|      | 2.6 Multipr                                                           |                                                                     | s<br>chitectures<br>scheduling algorithms                                               | 43<br>43<br>48             |

| 3.   | LINEARLY EXTE                                                         | NSIBLE TRE                                                          | E NETWORK                                                                               | 59                         |

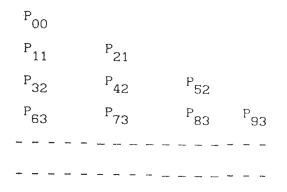

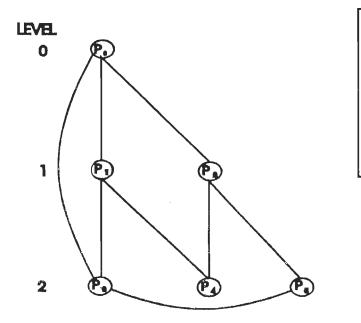

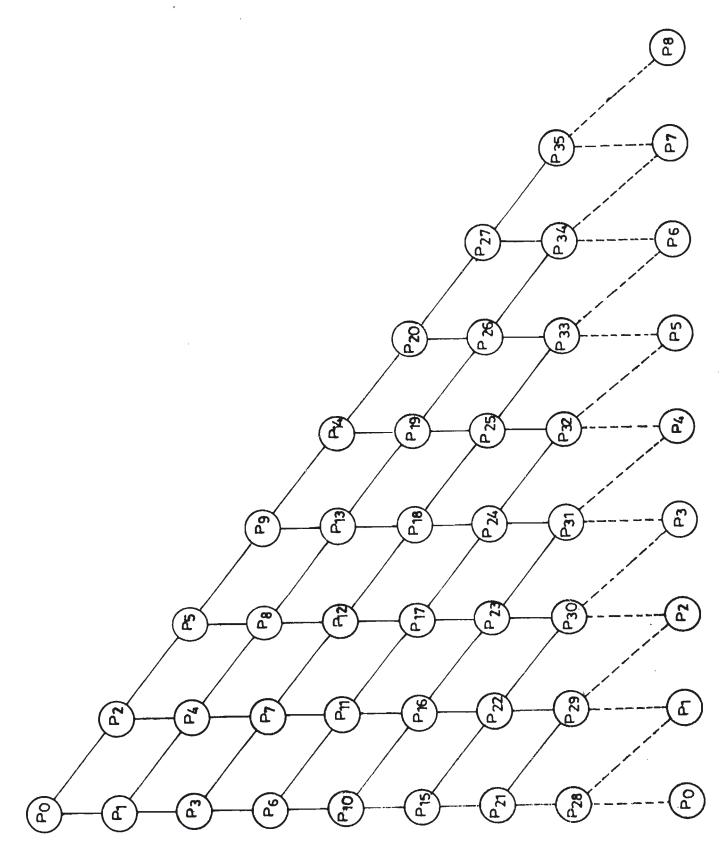

|      | 3.2 Binalry                                                           | de-Bruijn<br>y extensib                                             | terconnection networks<br>Multiporcessor (BDM) networ<br>le tree (LET) multiprocessor   | 59<br>k 60<br>62           |

|      |                                                                       | Design and<br>Properties                                            | d analysis<br>s of LET network                                                          | 62<br>64                   |

| 4.   | MINIMUM DISTA                                                         | NCE DYNAMI                                                          | C SCHEDULING SCHEME                                                                     | 71                         |

|      | <ul><li>4.2 Minimum</li><li>4.3 Minimum</li><li>4.4 The MDS</li></ul> | eduling teo<br>distance p<br>Distance S<br>algorithm<br>ion results | property<br>Sheduling (MDS) scheme                                                      | 72<br>73<br>74<br>76<br>80 |

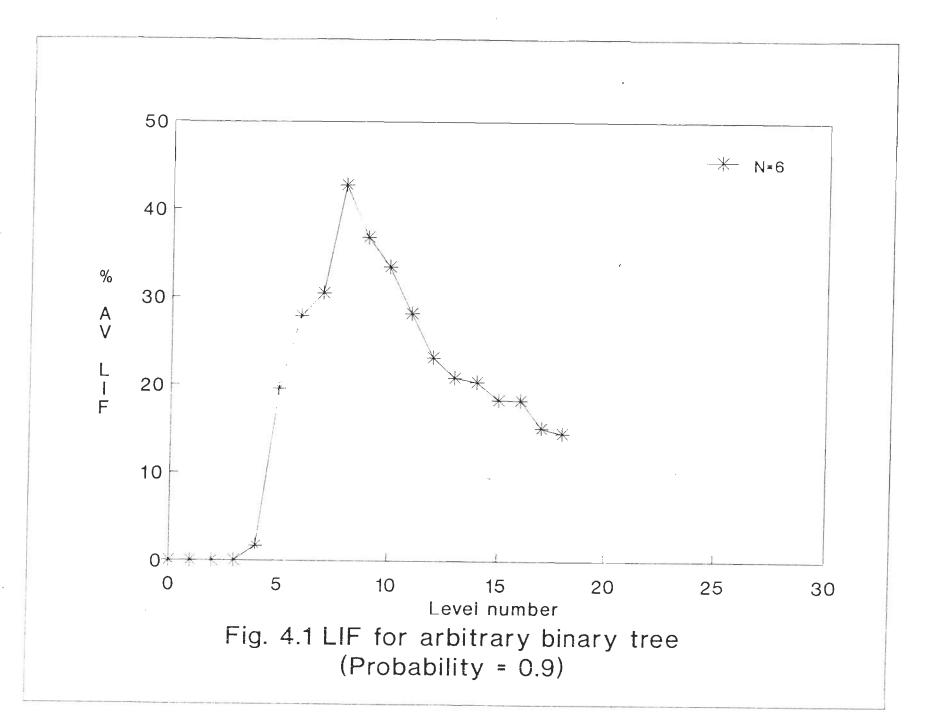

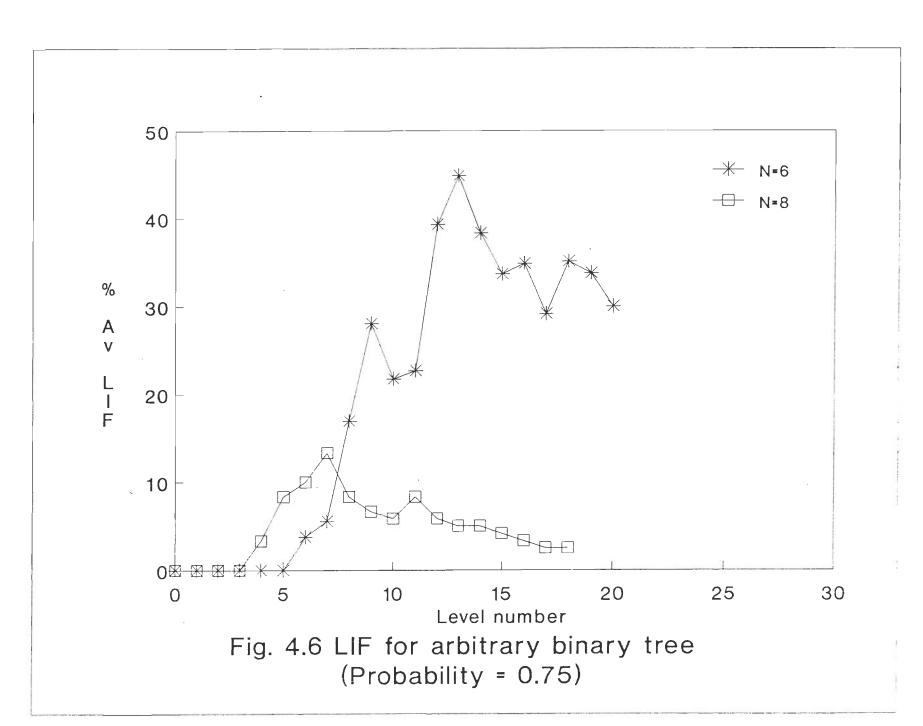

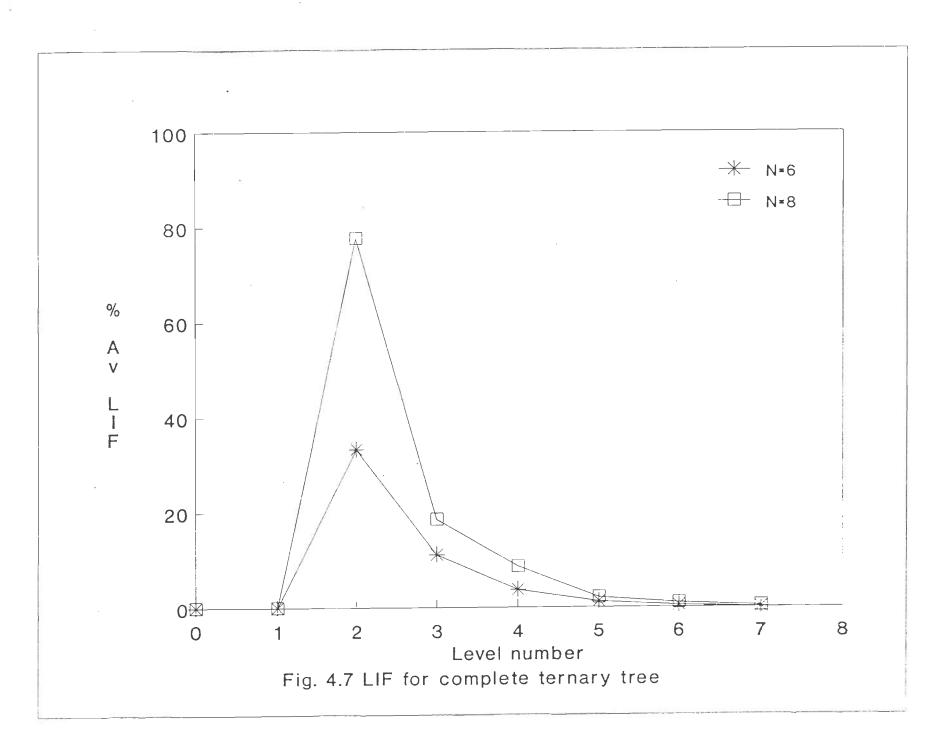

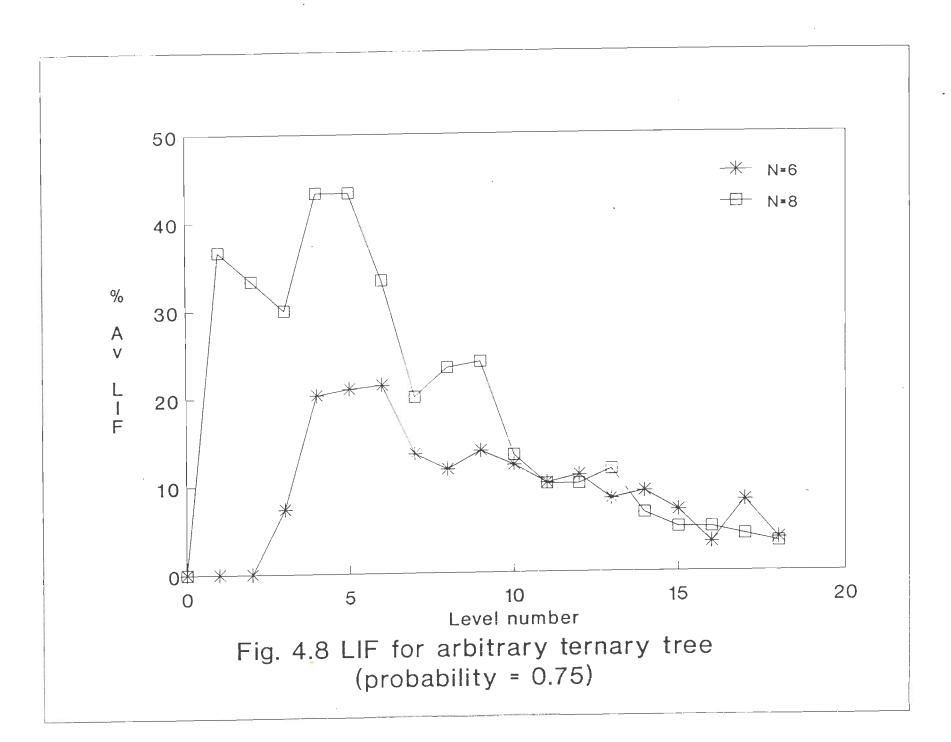

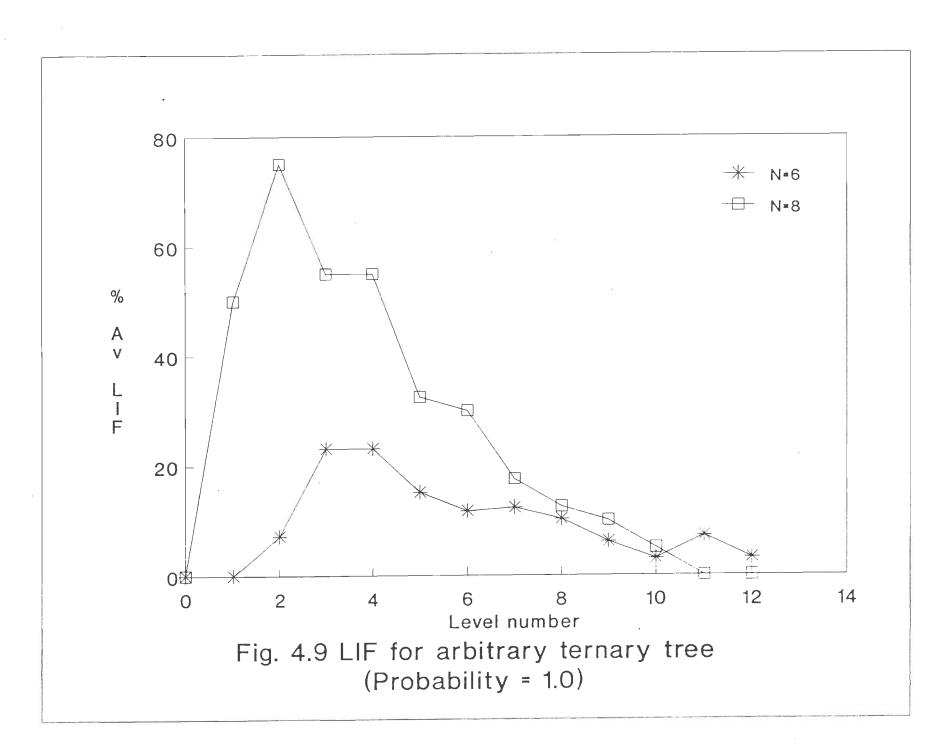

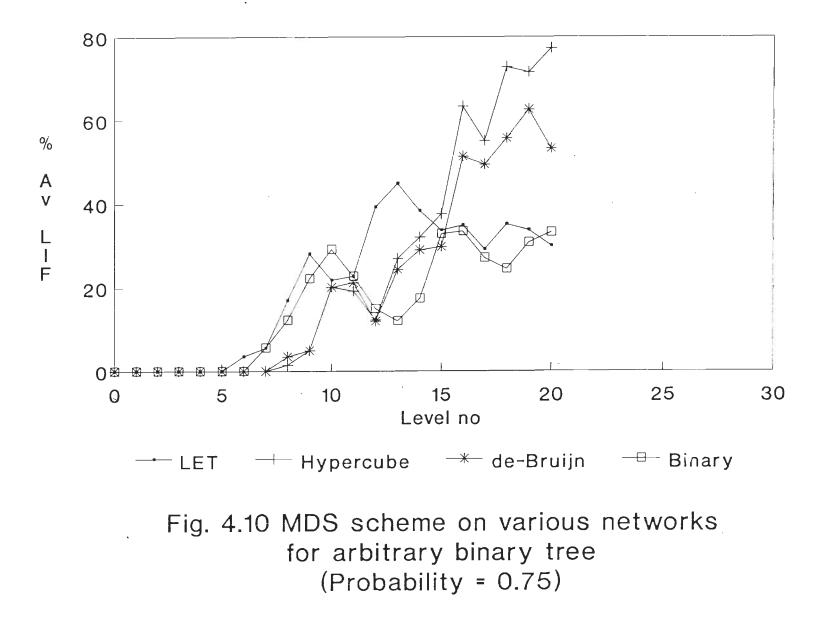

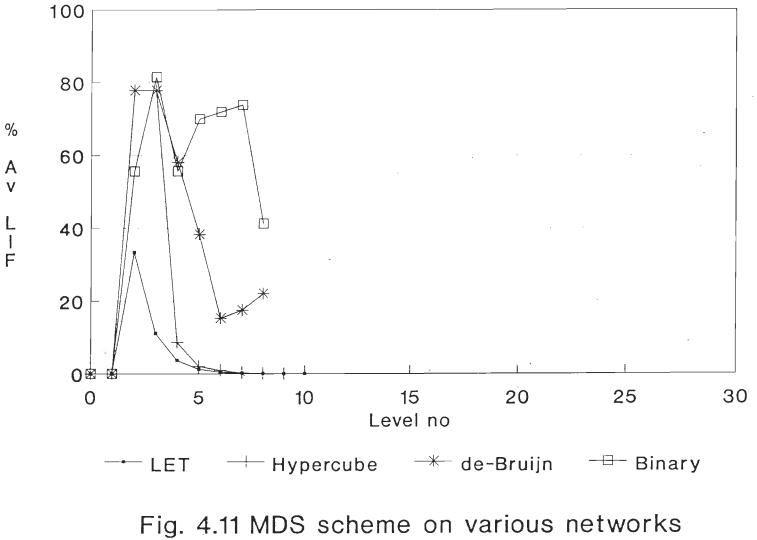

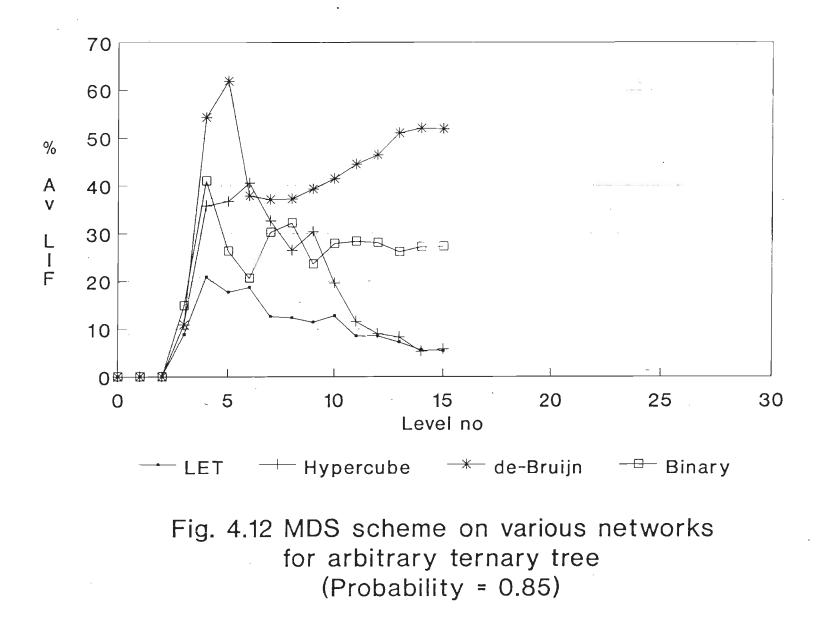

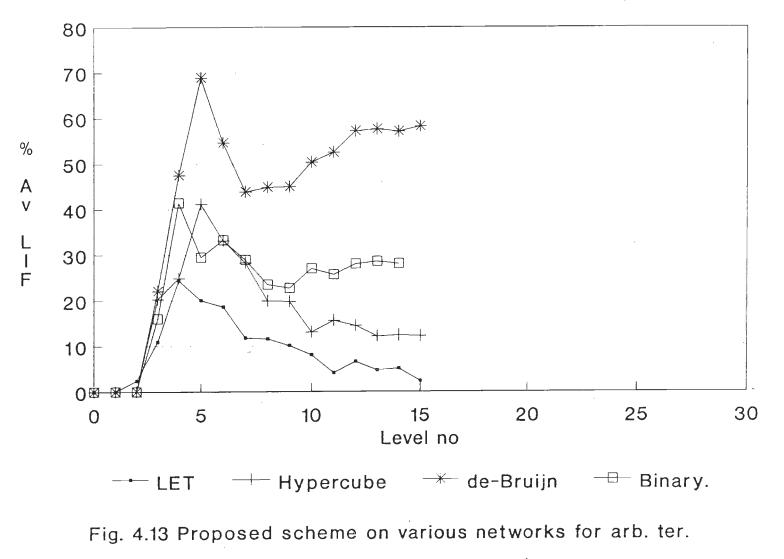

|      | 4.5.1<br>4.5.2<br>4.5.3                                               |                                                                     | oad model<br>e on LET network<br>n with other networks                                  | 81<br>84<br>89             |

| 5. ( | COMPARISON OF                                                         | MDS SCHEME                                                          | WITH OTHER SCHEDULING SCHEN                                                             | <b>ÆS</b> 101              |

| 5    | .1 Other sch                                                          | eduling sch                                                         | nemes ·                                                                                 | 101                        |

|      | 5.1.1<br>5.1.2<br>5.1.3                                               | Minimum-Lo                                                          | n (R-R) xcheduling scheme<br>ad (M-L) scheduling scheme<br>Exchange Method (DEM) schedu | 101<br>102<br>11ing 104    |

|      | 5.1.4                                                                 | Hierarchic<br>scheduling                                            | al Balancing Method (HBM)                                                               | 105                        |

|      | 5.1.5                                                                 |                                                                     | lodel (GM) schedulig scheme                                                             | 105                        |

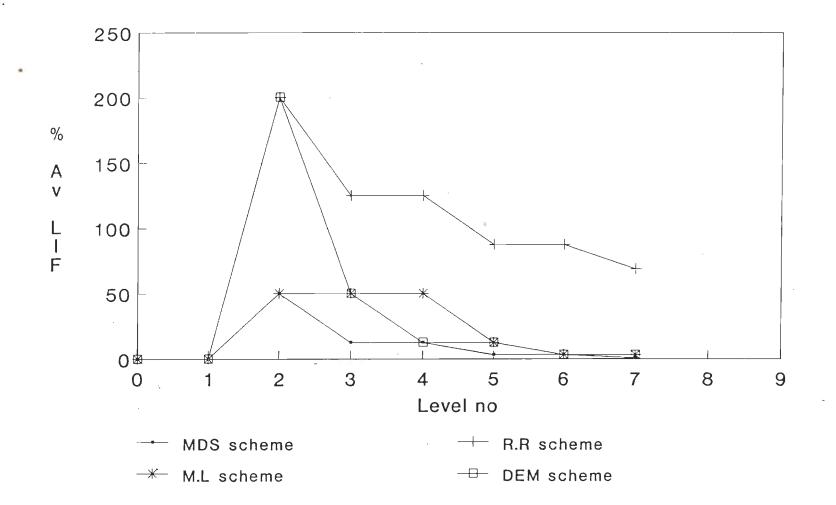

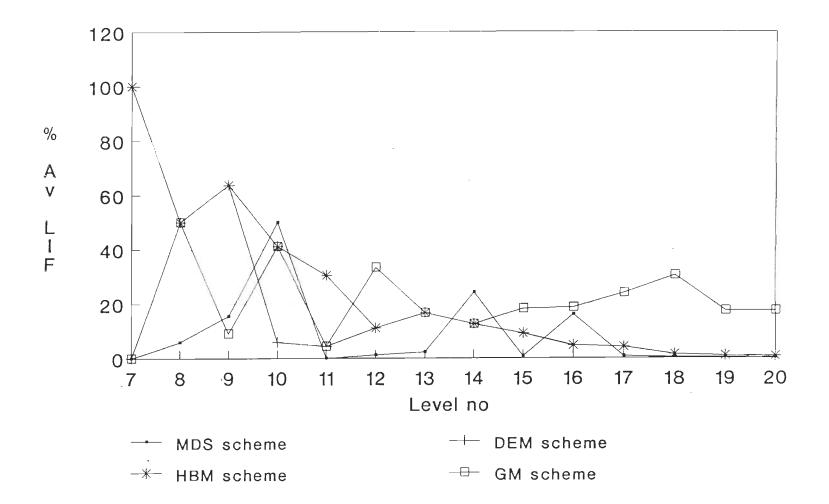

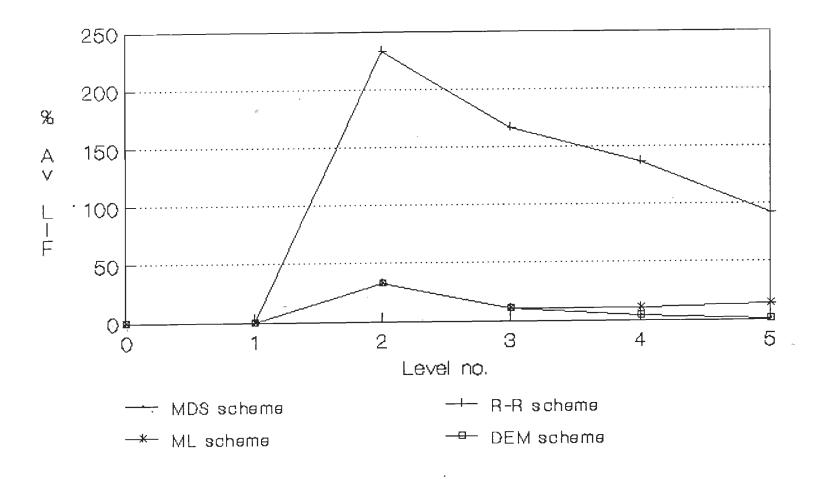

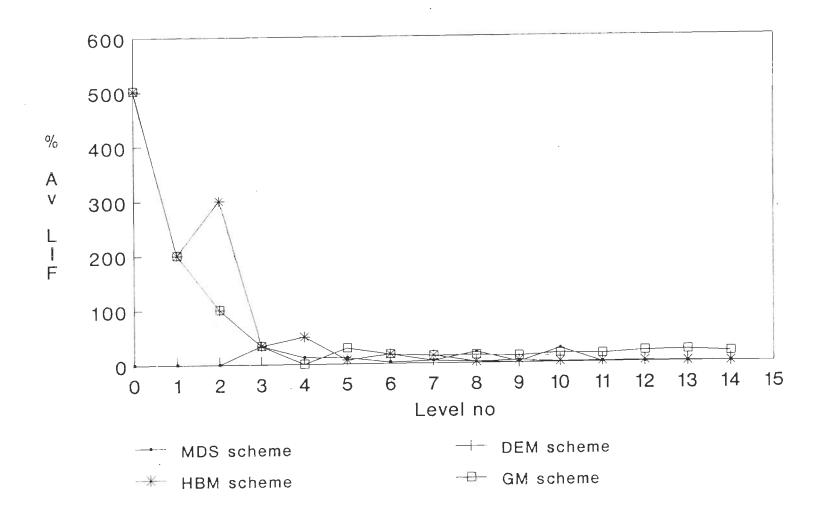

| 5.   | .2 Performan<br>on LET                                                | nce Study c                                                         | f the MDS and other schemes                                                             | 105                        |

|      |                                                                       | tional mode<br>nce of vari                                          | l<br>ous organizational models                                                          | 111<br>112                 |

|      | Į.                                                                    | Simuation                                                           |                                                                                         | 112                        |

| 025  |                                                                       |                                                                     |                                                                                         | 110                        |

| 6. | PERFORMANCE OF LET FOR GRAPHSTRUCTUED PROBLEMS |                                                                                                    |                   |

|----|------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------|

|    | 6.1<br>6.2                                     | Introduction<br>Latest Precedence scheduling strategy                                              | 121<br>123        |

|    |                                                | <ul><li>6.2.1 List Scheduling</li><li>6.2.2. HDLF algorithm</li><li>6.2.3 Task Selection</li></ul> | 124<br>124<br>126 |

|    |                                                | Lates precedence schedulng algorithm<br>Graph generation<br>Performance of LET and other network   | 128<br>130<br>132 |

| 7  | CONC                                           | LUSIONS AND FUTURE WORK                                                                            | 143               |

|    |                                                | Conclusions<br>Future work                                                                         | 144<br>146        |

REFERENCES

-----

Ę

147

÷

#### INTRODUCTION

High speed computing is essential to modern research and development as the demands for more and more computational power continue to grow. We have started relying more and more on computer simulation rather than on analysis or experimentation. A strong high-performance computer industry is essential for a successful modern economy. Critical security areas and a broad range of private sector activities depend on high-performance computers.

Most of the computer performance improvements made so far, have been based on technological developments. In fact the so called four generations of computers are defined by improved technologies (from tubes to VLSI). Semiconductor technology already has reached a point of maturity that significant switching-speed improvements are difficult to obtain. The fundamental limitation is the speed of light, because electrons can not move faster than this speed limit. Thus the source for increasing computing power must be looked for in an area other than switching technology. This has forced the designers to embrace parallel processing and to look for new architectural concepts that have the capability of providing orders-of magnitude performance increases. It is in this context that parallel processing plays a growing role in the computer industry [58,71].

The basis of most high-performance computer systems, according to Flynn's taxonomy[morgan], is the Multiple Instruction-stream and Multiple Data-stream (MIMD) organization. These systems employ multiple

processors which execute independent instruction streams accessing data autonomously. The design of such systems requires careful consideration of the number of processors and their interconnection topology, besides the proper choice of scheduling strategies for allocating the work.

Initial MIMD models often called *multiprocessors*, were based on the shared memory concept where the processors were connected to a number of memory modules to form a common global shared memory. However, such models can produce severe memory contention problems when processors try to access data residing on the same memory module. To overcome the memory contention problem the distributed memory MIMD model was introduced. In such a configuration the memory is distributed amongst the processors, with each processor and its associated local memory implemented on the same hardware device. If data needs to be accessed from local memory of another processor, then it is transferred using the interconnection network. Thus, the distributed MIMD model is scalable to higher orders of parallelism compared to shared memory model. However, the distributed model is associated with the overhead of interprocessor communication.

#### 1.1 PARALLELISM AS A CONCEPT

It was natural that the first efforts in parallel processing were extensions of the sequential von Neumann Model [6]. The main techniques used to extend the sequential von Neumann model to parallel architectures are by employing the concept of 'Pipelining, Vector processors, Array processors and Multiprocessors.

#### 1.1.1 Pipelined processors :

The process of pipelining divides a task T into subtasks

$T_1, T_2, \ldots T_K$  and assigns them to a chain of processing stations. These sections are called pipeline segment processors. Parallelism is achieved when several segments operate simultaneously.

1.1.2 Vector processors :

Vector processors are specially designed to handle computations formulated in terms of vectors. A vector processor has a set of instructions that treat vectors as single operands. Since vectors are one-dimensional arrays and the same sequence of operation is repeated for every vector element, vector processing is ideally suited to pipeline arithmatic.

1.1.3 Array processors :

The term array processor refers to a synchronous parallel computer, in which the same instruction is performed on different data that each processor fetches from its own memory. This is why this model is sometimes called data-parallel model. The interconnection network facilitates data communication among the processing units, memory processing units and memories. This type of computer is also called Single-Instruction-Multiple-Data (SIMD) computer. The source of parallelism in SIMD computers is that one instruction operates on several operands simultaneously.

1.1.4 Shared-memory multiprocessors:

Another way of introducing parallelism is to use several processors, each including a control unit, an ALU, shared memory and I/O modules. Communication between processors is via a common memory. Each processor operates its own instruction stream, fetched either from the

local memory or from shared memory on the data fetched from the shared memory. The interconnection network facilitates data exchanges between processors, and between processor and shared memory.

1.1.5 Message passing multiprocessors:

In this model, the memory is distributed among the processors such that each processor has its own program and data memory. The communication of shared data is achieved via messages exchanged directly between processors through an interconnection network. It has been shown that this model is scaleable to several hundred, possibly thousands of processor/memory units and that this is the defacto standard of high performance parallel computers. However the design and optimisation of the interconnection network in these large parallel machines is an area that still requires considerable research and development.

Following terms are commonly used in multiprocessors:

a) Processor complexity - It refers to the CPU power and the internal structure of each processing element. Processor complexity varies from one architecture to another. Homogeneous systems - These systems have all processors with identical capabilities. Heterogeneous systems -These systems have processors which are not identical.

b) Mode of operation - It is a general term referring to both instruction control and data handling. The traditional mode of operation is command-flow, so called because the flow of events is triggered by commands derived from instruction sequences. Another method is to trigger operations as soon as their operands become available. This is known as data-flow operation. In this case, the control is determined by the availability of data. Yet another mode of control is demand-flow, in

which computations takes place only if their results are required by other computations. Combinations of these control modes are also possible.

c) Memory structure - It refers to the mode of operation and the organization of computer memory. In some new computer models, such as connectionist architecture and neural networks, memory consists of interconnection weights that indicate how easily connection can be made. In ordinary computers, memory organization and the size of the memory files are closely related to data structure.

d) Interconnection network - It refers to the hardware connections among processors and between processors and memories. The architecture of interconnection network should match the algorithm communication geometry as closely as possible. Computers with simple interconnection networks are efficient only for a small number of algorithms, whereas complex interconnection networks can be configured for a broad range of applications. Of course, the price paid in this case is increased cost and extra switching time.

e) Number of processors and memory size - It simply indicates how many processors the parallel system contains and how large the main memory is. In general, more processors provide more computing power which enables the system to approach more complex problems. When the size of the algorithm is greater than the size of the system, algorithm partitioning is required. Algorithm partitioning may have undesired side-effects, so ideally the number of processors should match the size of the algorithm.

#### 1.2 NEED FOR PERFORMANCE EVALUATION

Currently, one of the most important issues in parallel processing is how to effectively utilize parallel computers that have become increasingly complex. It is estimated that many modern super computers and parallel processors deliver only 10 percent or less of their peak performance potential in a variety of applications. Yet high performance is the very reason why people build complex machines.

The causes of performance degradation are many. Performance losses occur because of mismatches among application, software, and hardware. In complex systems, mismatches may occur among software modules or hardware modules. The communication network bandwidth may not correspond to the speed of the processor or that of memory introducing unwanted latency.

Mapping applications to parallel computers and balancing parallel processors is indeed a very difficult task, and the state of understanding in this area is quite inadequate. Moreover, small changes in problem size while using different algorithms or different applications may have undesirable effects and can lead to performance degradation.

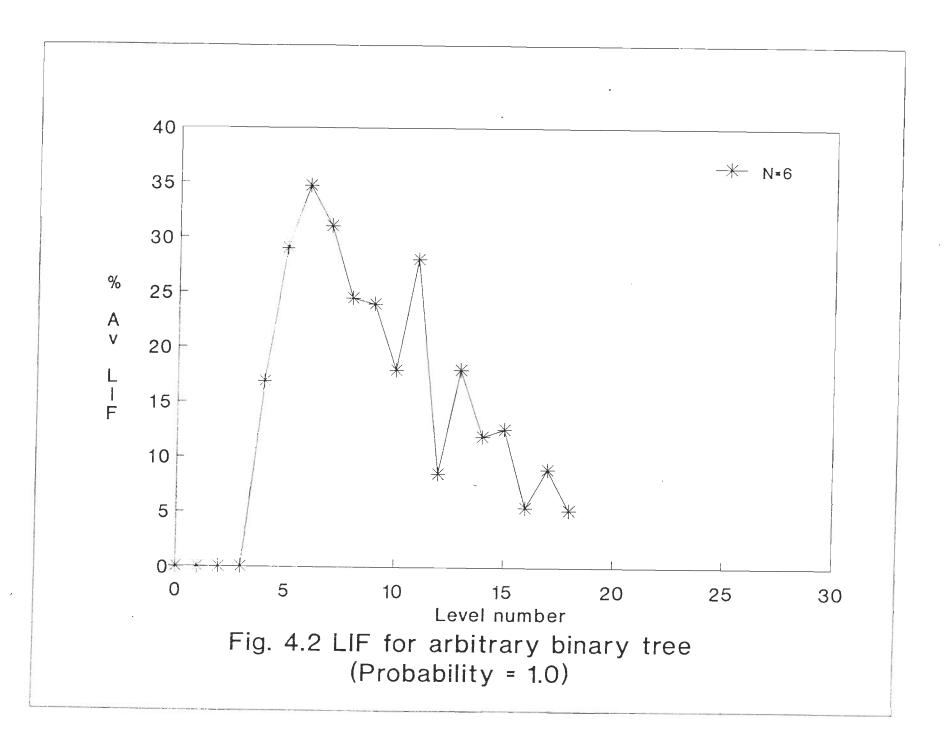

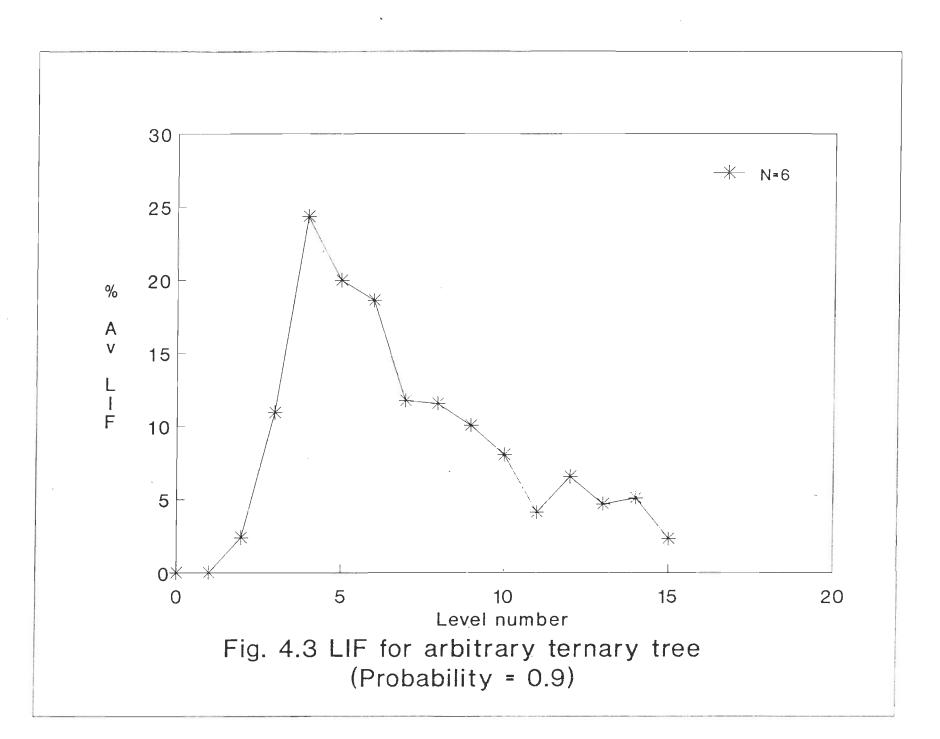

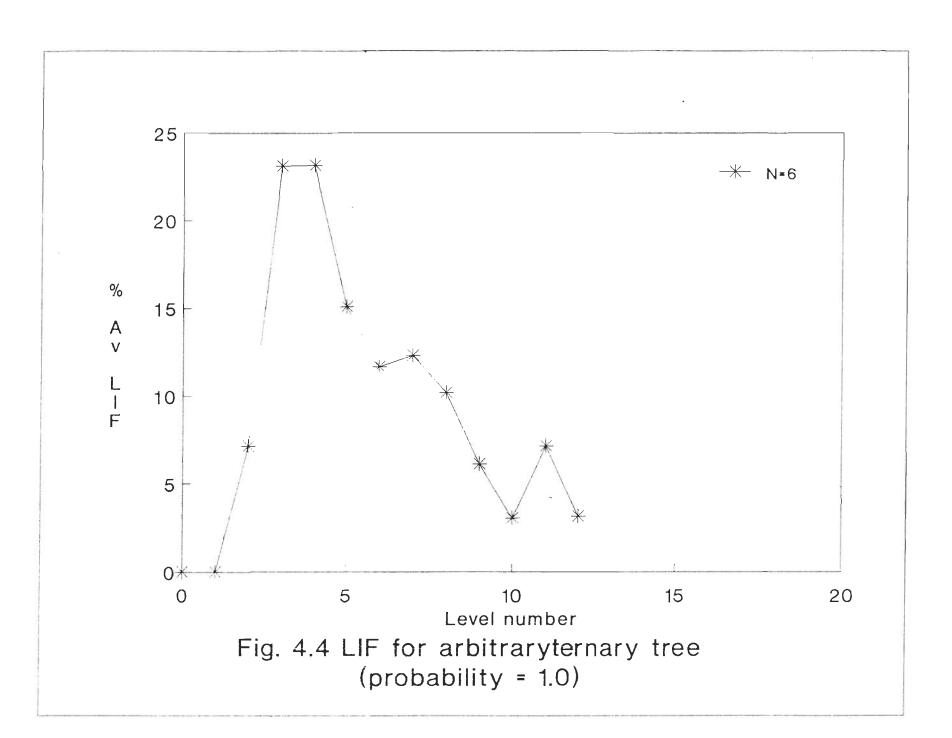

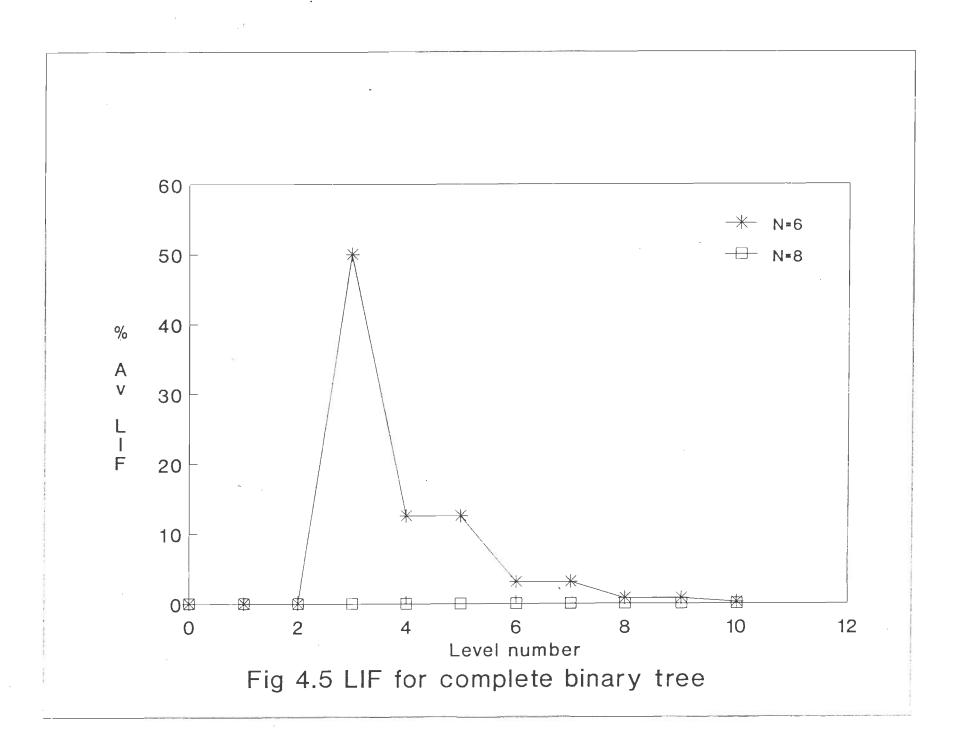

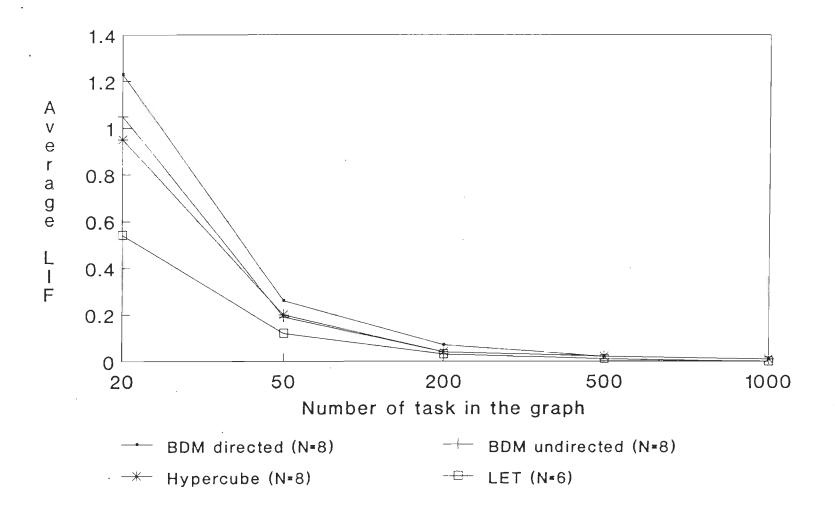

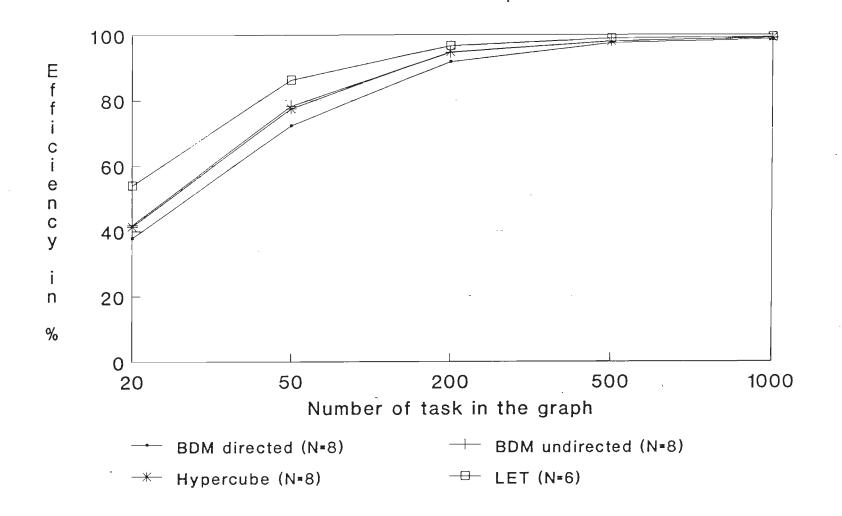

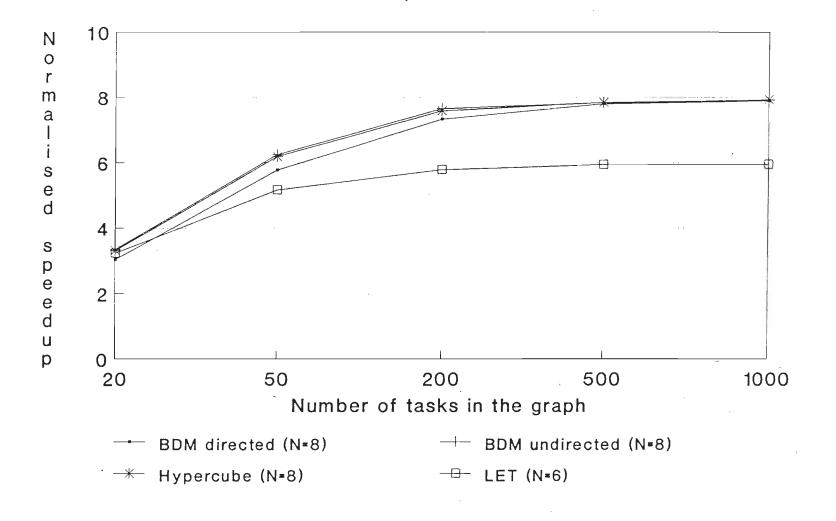

The various indices responsible for system performance include Load Imbalance Factor (LIF) and communication overhead, the complexity of the system and algorithm, efficiency of the system and speedup which are measures of different aspects of a computer system's performance. It is precisely in this area that the work presented in this thesis is based and it will be shown that a Linearly Extensible Tree (LET) network with high overall performance has been instantiated.

#### 1.3 MOTIVATION

A declarative machine project, known as CTDNet, is being undertaken by the University Of Roorkee (India) in collaboration with University of Westminster (U.K) supported by UGC (India) and British Council. The main object of the project has been the development of an extensible parallel machine to support functional programming languages. Some background of the project, which has been the main motivation behind the work carried out in this thesis, is given below.

The first phase, which was named CTDNet [20], introduced the development of a reduction machine that was designed originally for a Cube Type Distributed (CTD) multiprocessor. A CTDNet program is a binary lambda graph in which every node represents an application expression. The evaluation strategy was basically eager, which encouraged concurrent computation, with lazy implementation of conditional and iteration structures. One major criticism of CTDNet relates to its efficiency: in simulation runs, the number of messages generated and the number of process instantiations were very high. Another criticism is that it had no provision for modeling input/output within the lambda calculus framework.

A later version CTDNet-2 was developed to overcome the shortcomings of the original version [86]. This handles program expressions by graph reduction rather than string reduction, which improved CTDnet-2's performance. However, the major drawback in such networks is due to the small grain size of the computation and the consequent heavy communication overhead.

In an effort to overcome the short comings of the original CTDNet, due to the development of supercombinators, which had a profound effect

on the design of the machine model and, not surprisingly, on CTDNet model as well, the latest version of CTDNet, known as CTDNet-3, was developed with the main objective of increasing the grain size in order to minimize the communication overheads.

For efficient implementation of functional language programmes (which are mostly tree structured task graphs), on parallel machines, apart from designing a parallel evaluation model, it is essential that a suitable topology for processor interconnection coupled with appropriate scheduling strategy is used and parallelism is exploited to the optimum extent possible. Suitable topology and appropriate scheduling strategy, referred to as an organization model, depends on various factors including the dynamic behavior of the programs. In CTDNet project [86], several types of networks were experimented for executing functional programs such as shared bus, ring network, tree structure, hypercube, de-Bruijn network etc., but the optimal network of any particular type of architecture was not established.

The present work is motivated by the requirement for the design and development of network model which can improve upon the results for other networks experimented on. The proposed architecture has been tested for binary, ternary and arbitrary task trees. Randomly generated structured task graphs, which are most commonly generated out of the functional language programs, have also been incorporated in the simulation runs for testing the performance of organisation model.

#### 1.4 STATEMENT OF THE PROBLEM

The complete work, as presented in this thesis, can be divided into three parts. The first part is concerned with the design and development

of a tree structured network model. The main aim of this model is to reduce the run time overheads and therefore reduce latency in the interconnection network. The second part is concerned with the development of a scheduling scheme that can maintain a highly balanced load profile on the new network (LET) for tree structured problems and randomly generated task graph structures. Repeated simulation experiments have been performed to evaluate the performance of the interconnection system. The third and the last part of the thesis presents the implementation of different static/dynamic scheduling schemes on the developed systems and compares it with various other similar networks. A comparative simulation study has been carried out and the superiority of the system is established.

#### 1.5 ORGANIZATION OF THE THESIS

This thesis is organized as follows:

\* Chapter 2: Review of the multiprocessors architectures and scheduling schemes. In this chapter the basic concepts and properties of various tree-structured multiprocessor network has been discussed in the first part. In the second part, a review of the scheduling schemes, starting from the classification to the present scenario, based on tree structured problems and the tree type architectures is presented. Various factors influencing the run time overheads have been discussed.

\* Chapter 3: Linearly extensible tree network. This chapter discusses the design and analysis of a linearly extensible tree network and its various properties followed by its comparision with the BDM and hypercube.

\* Chapter 4: Minimum distance dynamic scheduling scheme. This chapter discusses different dynamic scheduling schemes suitable for tree type networks. A new dynamic scheduling scheme called Minimum Distance Scheduling (MDS) scheme has been described for LET network. The MDS scheme has been implemented, through simulation, on the LET network and other networks in order to confirm the performance of scheme.

\* Chapter 5: Comparison of MDS scheme with other scheduling schemes. In this chapter other scheduling schemes have been discussed briefly. The MDS scheme along with these static/dynamic scheduling schemes have been implemented on LET network. The concept of organisation model i.e. the implementation of a scheduling scheme on a network has been discussed in short and a comparison of proposed organisation model with existing models has been done in the last.

\* Chapter 6: Performance of LET for graph - structured problems. This chapter addressed the issue of static scheduling for graph structured problems. A static scheduling algorithm called latest precedence scheduling for acyclic precendence graphs has been described. The scheme has been implemented on the LET and other networks for graph structured problems. Various simulation experiments carried out have been reported here.

\* Chapter 7: Conclusion and future work. This chapter presents conclusions and recommendations for future extensions of the work.

# REVIEW OF MULTIPROCESSOR ARCHITECTURES AND SCHEDULING SCHEMES

Multiprocessing is the simultaneous execution of task on a parallel asynchronous computer system. A parallel asynchronous computer is a system whose active nodes are either processors or simple computers that cooperate closely but independently. These are multiple-instruction multiple-data stream (MIMD) computers. There are two basic multiprocessor models: shared-memory and message-passing systems. The shared-memory model provides a globally shared physical address space, which is highly desirable from the programmer's point of view. However, simultaneous access to shared-memory by many processors complicates the design of such systems. In contrast, message-passing model provides memory assoicated with each processor and data between processors is passed through messages.

MIMD computers are suitable for a much larger class of computations because they are inherently more flexible. This flexibility is achieved at the cost of a considerable more difficult mode of operation.

The organisation of this chapter is divided in two parts. In the first part of this chapter theory of shared memory and message passing multiprocessor architecture has been discussed. The properties of commonly used four multiprocessor architectures using Hypercube, de-Bruijn, hypertree and hyper de-Bruijn networks have been explained in detail. The second part of this chapter deals with basic definition and various classifications of scheduling schemes. Finally a review of different scheduling schemes on related multiprocessor networks has been given.

#### 2.1 MULTIPROCESSOR ARCHITECTURE

A multiprocessor system is a single computer incorporating a number of independent processors that work together to solve a given problem. Figure 2.1 shows the relations among algorithm granularity, degree of hardware coupling and communication mode, and the difference between distributed and parallel processing. Distributed processing occurs when hardware resources cooperate loosely to process jobs. Examples of distributed processing are use of multiple-computers connected through networks to solve different jobs. Whereas in parallel processing hardware resources cooperate closely to process tasks simultaneously [22,34,58,59,71].

| JOB LEVEL                                        | DISTRIBUTED<br>SYSTEMS            | COMPUTER NETWORKS | MESSAGE               |

|--------------------------------------------------|-----------------------------------|-------------------|-----------------------|

| TASK LEVEL<br>PROCESS LEVEL                      | 5151205                           |                   | PASSING               |

| INSTRUCTION LEVEL<br>VARIABLE LEVEL<br>BIT LEVEL | PARALLEL<br>PROCESSING<br>SYSTEMS | MULTIPROCESSORS   | SHARED<br>MEMORY      |

|                                                  |                                   | HARDWARE          | COMMUNICATION<br>MODE |

ALGORITHMIC GRANULARITY

#### DEGREE OF COUPLING

# Figure 2.1 Relation between algorithmic granularity and multiprocessing systems.

There is an important difference between multiprocessors and multiple computers. A multiple computer consists of several computers each with its own processor(s), memory, I/O and operating system, whereas a multiprocessor system has only one operating system and its processors share memory and I/O resources through an interconnection

network. As the number of processors increases, the interconnection network plays an important role in the overall performance of the system. Multiprocessors can be classified as shared-memory systems or message-passing systems.

#### 2.1.1 Shared-memory systems

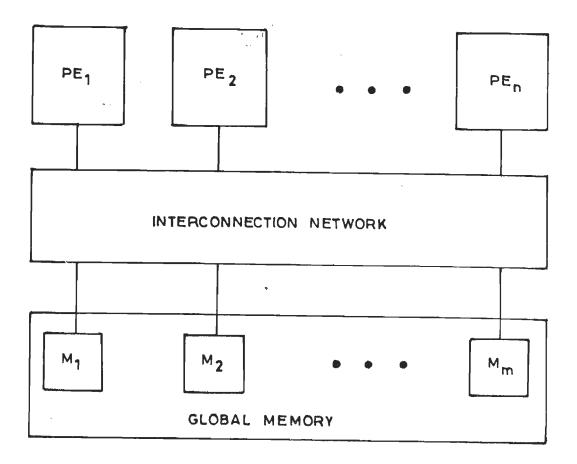

Multiprocessor architectures with shared-memory, also known as tightly coupled systems, have complete connectivity between processors and memory modules. A simplified block diagram of shared-memory systems is shown in Figure 2.2. It consists of a set of n processor elements, not necessarily identical, a set of m memory modules, and an interconnection network. The primary memory may be centralized (m=1) or partitioned into several modules. The common memory must be accessed by all processors in the system [71].

Data exchange between processors and memories is frequent and intense. The interconnection network is a potential bottleneck for these systems. While memory contention (memory access conflict) has always been a performance factor in uniprocessor systems, it becomes more important in parallel shared-memory systems simply because of the need of many processors to simultaneously access the same memory locations. To decrease the communication traffic in the network and the chance of memory contention, several alternative solutions exist. A local memory (LM), directly accessed by the processor, may be placed near the processor, thus reducing the number of memory requests through the interconnection network. Also, a cache memory may be provided in order to increase the memory bandwidth. A memory mapping (MM) unit is required to decide which memory requests are local and which are global.

Figure 2.2 Shared-memory systems

The major limitation of a shared-memory system is the possibility of primary memory access conflicts. This restriction tends to put an upper bound on the number of processors that can be effectively incorporated in the system and supported by a single operating system. Shared-memory systems are efficient for small to medium sized multiprocessors.

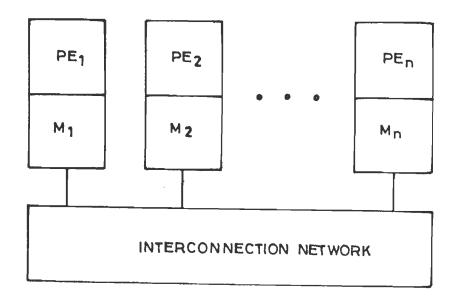

#### 2.1.2 Message-passing systems

Message-passing systems, also known as loosely coupled systems, consist of several computer modules and an interconnection network. Each

computer module has a processor, a memory and an I/O interface. Data communication is carried out through messages, not through shared variables as in the previous case. The length of message varies, but usually each message consists of a number of fixed-size packets. Inter computer communication follows a predetermined communication protocol. Thus the active node in a message-passing system is a computer and the degree is not as great as that of shared-variable systems [58,71] as shown in Figure 2.3.

Figure 2.3 Message-passing systems

Shared-memory models can perform message-passing primitives easily, but the reverse is not true. This is because data structures are shared among processors in the former model. Properties such as simplicity and scalability make message-passing multiprocessors prime candidates for very large systems. Message-passing systems are more efficient for problems that can be partitioned into larger tasks that do not interact very frequently.

## 2.2 MULTIPROCESSOR INTERCONNECTION NETWORKS

## 2.2.1 Interconnection organisation

As a result of increasing the number of functional modules in a multiprocessor, the interconnection network becomes increasingly complex. Examples of multiprocessor interconnection networks are time-shared or common buses, crossbar switches, multiport memories, Hypercubes, meshes and multistage interconnection networks. The multistage interconnection networks are feasible interconnections for large multiprocessor systems. Multistage interconnections allow processor-to-processor and processor-to-memory communications in a more general way than the other organisations [46-48,58,59,71].

#### 2.2.2 Network characteristics

Some important characteristics of a multistage interconnection network are its mode of operation, switching technique, routing technique and interconnection network topology [34,58,59,71].

#### (i) Operation modes

There are two basic modes of network operation: synchronous and asynchronous. In the synchronous mode, the network is centrally supervised. The connection paths are established simultaneously and remain set until the control disconnects them. In the asynchronous mode, connection paths are setup or disconnected on an individual basis. The asynchronous mode of operation is more appropriate for multiprocessor systems.

#### (ii) Switching techniques

There are three basic switching techniques: circuit switching, packet switching and wormhole switching. Circuit switching sets up the switches and ports and establishes a dedicated path between an input-output pair. This technique is efficient for larger transmissions. Packet switching refers to a technique in which messages between any two terminals are broken into several shorter, fixed-length packets, which are routed independently to their destination using store-and-forward procedures. In wormhole switching a message is also broken into smaller parts (called flits), as in packet switching; however, the difference is that here all flits follow the same route. Compared with circuit switching, packet switching is efficient for shorter and more frequent transmissions.

#### (iii) Routing techniques

The routing technique is the method of establishing communication paths and resolving conflicts. Three basic routing techniques have been considered: centralized, distributed and adaptive. In the centralized routing scheme, a central control makes all the logic decisions needed to setup communication paths. This scheme is more flexible for small to medium scale systems. In the distributed scheme, logical decisions are made locally, based on current conditions. In adaptive scheme, information about the network is collected globally, but routing decisions are made locally.

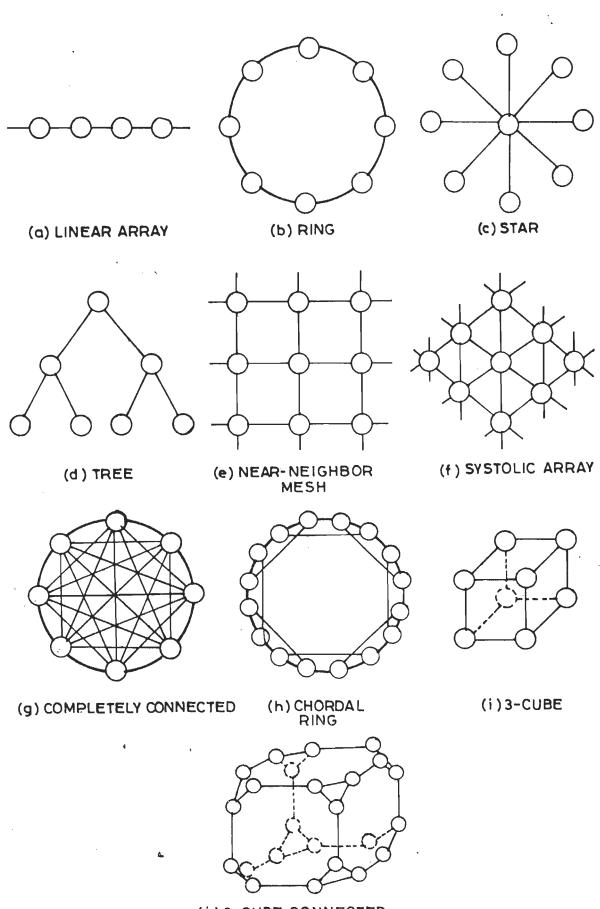

# (iv) Interconnection network topology

The network topology is the way in which the switches are

interconnected. The topology is perhaps the most important factor determining network performance. The binary Hypercube having a robust topology, is highlighted in the next section.

#### 2.2.3 Hypercube interconnection network

Many interconnection structures for loosely-coupled multiprocessors have been proposed in the literature. Examples includes: Binary tree, Lattice structure, Flip net, Omega net, Indirect n-cube, de-Bruijn net, Hypertree [9,37,40] and Hyper de-Bruijn network [37]. Some of the most successful networks are based on the Hypercube.

The Hypercube represents a class of message-passing architectures using cube (or exchange) interconnection topology. Hypercube networks are some of the first and most successful commercial multiprocessors. Each node in this network is connected through bidirectional, asynchronous point-to-point communication channels to n other nodes. The first Hypercube system was built at Caltech in the early 1980's as an experimental parallel computer for scientific numeric computation [22,58,61,71].

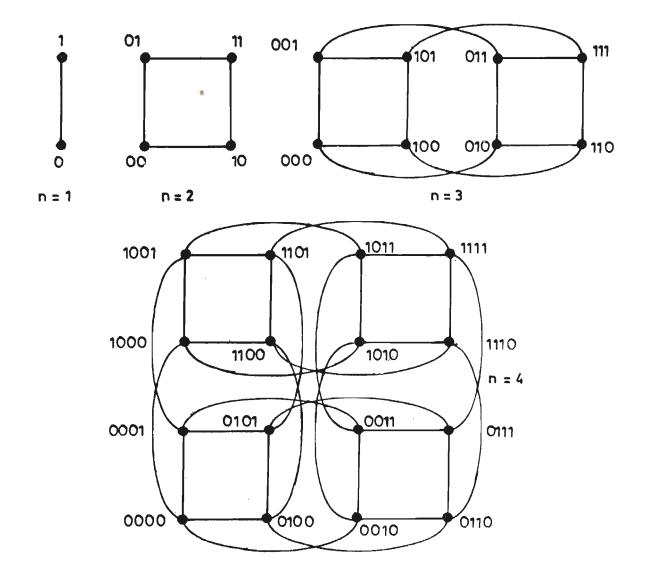

#### 2.2.3.1 Hypercube topology

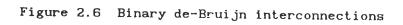

A Hypercube multiprocessor consists of  $2^n$  processors. Consecutively numbered with binary integers using a string of n bits. Each processor is connected to every other processor whose binary number differs from its own by exactly one bit. The connection scheme places the processors at the vertices of an n-dimensional cube. Hypercube interconnection networks for n nodes varying from 1 to 4 are shown in Figure 2.4. The Hypercube has the property that it can be defined inductively. A

Hypercube of order 0 is a single node, and the Hypercube of the order n+1 is constructed by taking two Hypercubes of order n and connecting their respective nodes. important Some properties of this interconnection used in parallel processing, are given below [10, 20, 37, 89]:

- As the number of processor increases, the number of connection wires and related hardware (such as ports) increases only logarithmically, so that the systems with a very large number of processors become feasible.

- 2) A Hypercube is a super set of other interconnection networks such as rings, multistage cube network, trees etc. because these can be embedded into a Hypercube by ignoring some Hypercube connections [10,20,89].

- 3) Hypercubes are scalable a property that results directly from the fact that Hypercube interconnections can be defined recursively.

- 4) Hypercubes have simple routing schemes. A message-routing policy may send a message to the neighbour whose binary tag agrees with the tag of the final destination in the next bit position, with the bits scanned in some order. The path length for sending a message between any two nodes is exactly the number of bits in which their tag bits differ. Numerous possible paths connecting any two nodes exist; this redundancy can be used to enhance the communication bandwidth and the fault tolerance of the Hypercube.

Hypercube nodes are usually identical. However, they do not have to be identical as long as their message-routing protocols are the same. In a heterogeneous system, some nodes may have special I/O or processing capabilities [10,46-48,51,58,59,85].

Figure 2.4 Hypercube interconnections

Hypercube computers have been contemplated since the appearance of microprocessors in 1970's. The first Hypercube multiprocessor was built and used at Caltech in 1983. Since then, interest in this type of parallel computer has grown so fast that today there are several companies offering a wide range of Hypercubes largely classified under two generation of Hypercubes. The machine in the first generation include the Caltech Cosmic Cube, the Intel iPCS 1, the AMETEK System 14, the NCUBE/ten and the Floating Point Systems T Series. Whereas the second generation of Hypercubes began with the advent of some more powerful message-passing schemes in 1988. Representative machines of this generation are the Intel iPSC 2 and AMETEK 2010 series. The main characteristics of this generation are: 1) 32-bit processors with integrated floating-point accelerators, 2) large node memory facilitated by the availability of megabyte-chip RAM technology, and 3) message routing that is performed in hardware and become invisible to programmer [58,61,71]. The elimination of software overhead for message-passing, coupled with the technological improvements in CPU and memory, has improved the node performance by one or two orders of magnitude.

The disadvantage of this network from requirements point of view, is that it is not truly expansible. Whenever the number of nodes grows beyond a power of two, all nodes have to be changed since they have to be provided with an additional port. Thus, the module of this network is not constant predefinable building block. Moreover, a useful expansion of this structure has to occur by doubling the number of nodes.

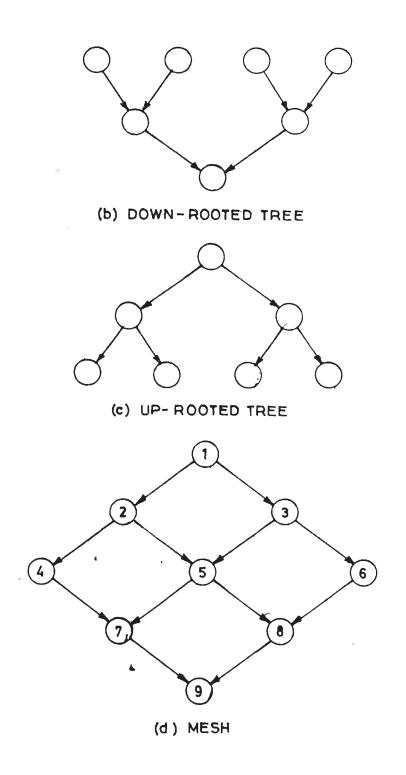

#### 2.2.4 Basic concept of tree

A tree is an acyclic connected graph [32,70]. The following theorem summarizes the basic properties of trees:

Let G(V, E) be a graph. Then G is a tree if and only if one of the following properties holds:

1) G is connected and |E| = |V| - 1,

2) G is acyclic and |E| = |V| - 1,

3) There exists a unique path between every pair of vertices in G.

The proof of this theorem is straight forward. An end point of a tree is a tree vertex of degree one. A nontrivial tree has from 2 to |V| - 1 end points. A center of a tree is a tree vertex of minimum eccentricity. A tree has exactly 1 or 2 centers. A star is a tree of diameter 1 or 2. An arbitrary acyclic graph is called forest.

A rooted tree is a tree in which a distinguish vertex V, call as the root. The level of a vertex is defined as: vertices at a distance i from the root lie at level (i+1); V itself lies at level 1. The height of the rooted tree is defined as its maximum level.

We call onward a digraph a tree if its underlying undirected graph is a tree in the sense; a vertex V is a root of a digraph G if there are directed paths from V to every other vertex in G. A digraph is a directed tree and contains a root; a vertex of outdegree zero is an end point in a directed tree.

An ordered tree is a directed tree in which the set of children of each vertex is ordered. A binary tree is an ordered tree in which no vertex has more than two children. One of the children is called the left child, while the other is called a right child. The sub tree rooted at the left child of V is called the left sub tree of V, and the one at the right is the right sub tree of V. In a complete binary tree, every vertex has either two children or none. In a balanced complete binary tree, every end point has the same level.

An N-ary tree is a generalization of binary trees where we allow each vertex to have as many as N ordered children. In a complete balanced N-ary tree, every end point has the same level.

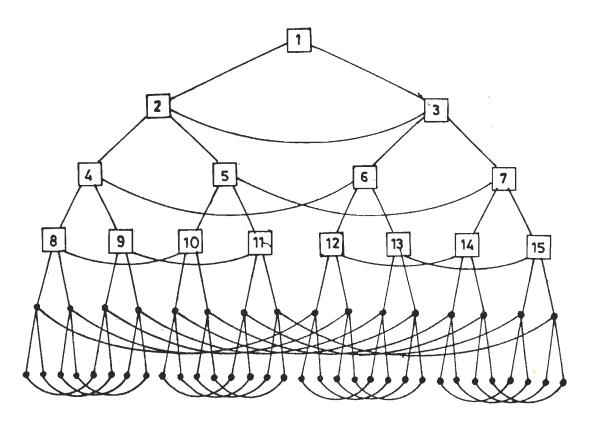

#### 2.2.4.1 Hypertree network

A hypertree network combines the best features of the binary tree and the n-dimensional Hypercube [9,40,42]. The basic skeleton of Hypertree is a binary tree structure, and as in the half-ring or full-ring structures, additional links in Hypertree are horizontal and connect nodes which lie in the same level of the tree. In particular, they are chosen to be a set of n-cube connections, connecting nodes which differ by only one bit in their address, shown in Figure 2.5.

Figure 2.5 Hypertree interconnections

The two underlying structures permit two distinct logical views of the system. Problems which map particularly nicely onto a tree structure can take advantage of the binary tree, while those that can use the symmetry of the n-cube can be assigned to the processors in a way that

efficiently uses the n-cube links. The regular structure allows the implementation of simple routing algorithms, which require no detailed knowledge of network interconnections. With relatively small additional overhead, a routing algorithm can be constructed that is robust enough, so that messages will arrive at the proper node even for grossly unbalanced trees or in the presence of failing nodes or links. This is a requirement for easy expansibility of the system and for graceful degradation in the presence of communication hardware failures. The network is readily expansible in an incremental way. All nodes have a fix number of ports regardless of the size of the network.

# 2.2.4.2 Binary de-Bruijn Multiprocessor (BDM) network

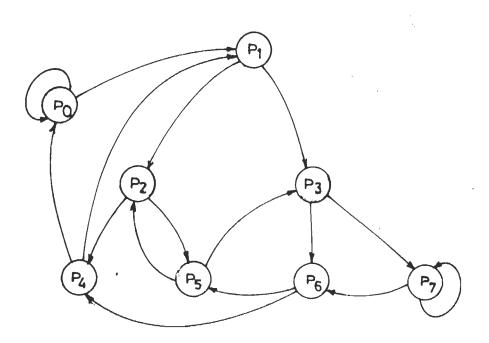

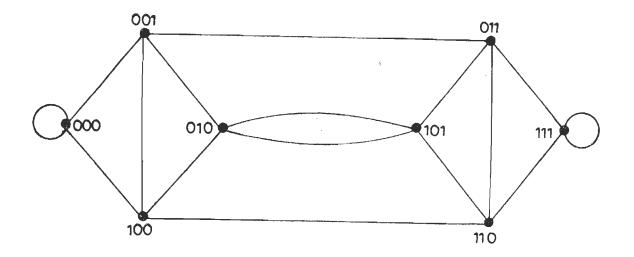

The de-Bruijn interconnection network has the property of a binary tree folding onto itself giving the appearance of infinite depth [82,83,90]. Let Q be a set of N identical processors, the topology then can be defined in terms of two functions L and R, which map Q into Q. The function L and R establish links from the processor P to the left and right child processors L(P) and R(P), respectively, for each processor P in Q. It turns out, as a result of the above definition, that each processor has a connectivity of four in the network depicted in Figure 2.6.

The network possesses a versatile topology. It admits an N-node linear array, an N-node ring, (N-1) node complete binary trees etc. The de-Bruijn networks are proven to be fault tolerant as well as extensible.

Interconnection scheme for eight processors

Undirected binary deBruijn graph

### 2.2.4.3 Hyper de-Bruijn network

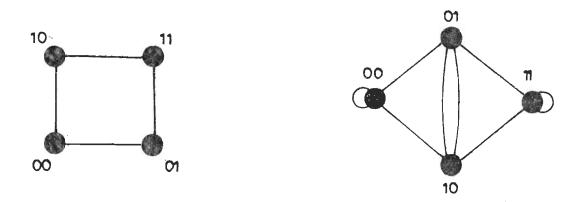

The new class of graph called the Hyper de-Bruijn graph [37] have the following properties:

- These networks allows the construction of large networks with any desired degree. In particular, 2<sup>n</sup> node network (for n≥4) can be designed to have any degree in the range of 4 to n.

- 2) These networks admit simple routing algorithms. They are flexible and fault tolerant, scalable and partitionable.

- 3) These networks have many computationally important topologies as sub networks, shown in Figure 2.7.

Figure 2.7 Hyper de-Bruijn interconnections

## 2.3 PROPERTIES OF AN INTERCONNECTION NETWORK

The selection of right topological layout for processing elements requires the incorporation of some important topological properties. These properties are listed below [37,40,47] : 1) Worst case distances : One important measure of the power of an interconnection network is the distance that message must travel in the network. It is advantageous to make this parameter as low as possible, since it will not only reduce traveling time for messages but also minimize message density in the links.

2) Average distance : Of even more importance may be the average path length travelled by all messages. In order to obtain a meaningful comparison between different networks, some normalization has to be made, in particular if networks between processors with different numbers of ports per node are considered. With no limits on the number of ports, a fully interconnected network could be designed, which would lead to an average distance of one. For a constant communication bandwidth per node, the bandwidth available through each port is then B/p, where p is the number of ports and B is the total bandwidth available from that processor [40].

Another factor influencing the average message path length is the distribution of pairs of communicating nodes. In the absence of any specific information about the communication patterns required by a particular task, one might assume a uniform distribution in which all nodes send messages with equal probability to all other nodes.

3) Routing algorithms : One of the desirable requirements for a large network of processors is that messages can be routed by each intermediate processor without total knowledge of all the details of the network, since the storage of that information within each node can use up an exorbitant amount of memory space. The requirement that this

information be resident at each node also enormously complicates the process of modifying the network.

4) Message density : Another major goal in the design of an efficient network topology is to distribute traffic as evenly as possible over all existing links.

5) Expansibility : Among the important parameters of the network are its modularity and expansibility, and specifically the smallest increment by which the system can be expanded in a useful way. It is generally unreasonable to demand that a system must remain balanced in all stages of expansion. Since this may imply that its size must be increased in large steps, i.e. powers of two.

6) Fault tolerance : The requirements for fault tolerance have greatly increased in recent years as systems have become increasingly complex. Certainly, an important feature of structures is that it must continue to work correctly, although perhaps with reduced performance, when one or more components have failed. Specifically, we expect such a system to continue to operate properly in the presence of failure of a single link or even a single node with all its attached links, as long as that particular node is not involved in the computation, i.e. the node is neither the source nor the destination for any messages [40,42].

When problem structure is such that it recursively decomposes itself into identical subproblems, it is natural to select an interconnection network which can be viewed as a virtual tree structure of arbitrary depth.

In addition to designing an appropriate network, the efficient management of parallelism on an interconnection network involves optimizing conflicting performance indices, like the minimization of communication and scheduling overheads and uniform distribution of load among the processors. Such issues are addressed at the organisational level by appropriate scheduling mechanisms. An introduction and a review of the scheduling schemes follows in the next section.

#### 2.4 REVIEW OF SCHEDULING SCHEMES

### 2.4.1 Introduction

In response to ever-growing need for speeding up computationally intensive tasks, a number of parallel computer architectures, where several processing elements are connected by an interconnection network, have been proposed. Most of these architectures may be classified into : (a) Dedicated architectures which aim at maximizing the achievable performance for a particular task or a class of similar tasks. There usually exists relatively little room for optimizing the assignment of decomposed sub tasks on these architectures. and (b) General purpose architectures, which provide a good average performance for a broad range of tasks. Therefore, scheduling becomes an important problem for such type of architectures, since it has a substantial effect on the system performance and utilization [14-17,25,57]. To determine which task module of a parallel program has to be executed on which processor of a multiprocessor system, so as to minimize the total execution time of the program is a classical multiprocessor scheduling problem [23,29,30,36,77].

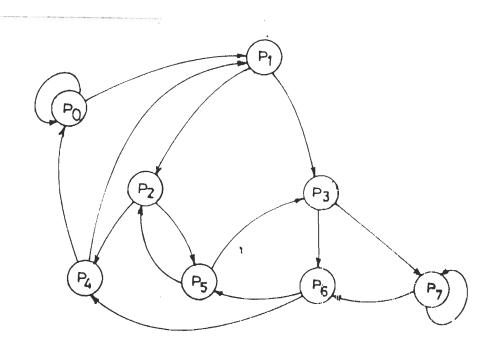

The scheduling problem assumes a set of processors and a set of tasks (jobs) which are to be serviced by these processors according to a specific policy. Depending on the nature and constraints of the tasks as well as of the processors, the problem is to find an efficient policy for managing the access to and alternatively the use of processors by various tasks to optimize some desired performance measure. То effectively exploit a more powerful computing facility of а multiprocessor, the architecture of the processor network and the problem structure both should be studied separately for the consideration of scheduling policy.

The basic scheduling theory, classification and existing scheduling schemes are now described.

## 2.4.2 Definitions

The core of all the efforts to exploit the potential power of distributed computation are the issues related to the management and allocation of system resources relative to the computational load of the system. The general scheduling problem has been described a number of times and in a number of different ways [28,39,59,100] and is usually a restatement of the classical notions of job sequencing in the study of production management. For the purposes of distributed process scheduling, the broader view of the scheduling function is taken as a *resource management* which is basically a mechanism or policy used to efficiently and effectively manage the access to and use of a resource by its various consumers. Hence, the scheduling problem may be viewed as consisting of the following three main components :

1) Consumer(s).

2) Resource(s).

3) Scheduler and Policy.

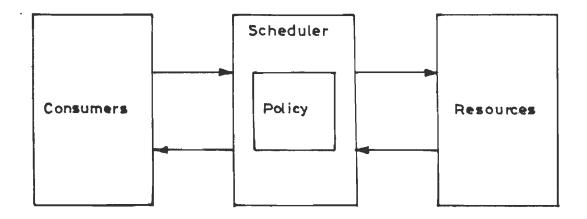

One can observe the behavior of the scheduler in terms of how the *policy* affects the *resources* and *consumers*. The scheduler may be viewed in terms of how it affects either or both resources and consumers. This relationship between the scheduler, policies, consumers, and resources is show in Figure 2.8.

Figure 2.8 Scheduling system

One by-product of the general scheduling problem is the unification of the two terms in common use in the literature [10,23,53,59,84]. There is often an implicit distinction between the terms *scheduling* and *allocation*. However, it can be argued that these are merely alternative formulations of the same problem, with allocation posed in terms of resource allocation (from the resources point of view), and scheduling viewed from the consumers point of view. Thus, allocation and

scheduling are merely two terms describing the same general mechanism, but described from different view points.

When considering the decision-making policy of a scheduling system, there are two fundamental components: responsibility and authority. When responsibility for making and carrying out policy decisions is shared among the entities in a distributed system, we say that the scheduler is *distributed*. When authority is distributed to the entities of a resource management system, we call this *decentralized*. This differentiation exists in many other organization structures. Any system which possesses decentralized authority must have distributed responsibility, but it is possible to allocate responsibility for gathering information. and carrying out policy decisions, without giving the authority to change past or make future decisions.

The terms dynamic scheduling and adaptive scheduling are quite often attached to various proposed algorithms in the literature [25,59,84] but there appears to be some confusion as to the actual difference between these two concepts. The more common property to find in a scheduler (or resource management subsystem) is the dynamic property. In dynamic situation, the scheduler takes into account the current state of affairs as it perceives them in the system. This is done during the normal operation of the system under a dynamic and unpredictable load. In an adaptive system, the scheduling policy itself reflects changes in its environment. The difference here is one of level in the hierarchical solution to the scheduling problem. Whereas a dynamic solution takes environmental inputs into account when making its decisions, an adaptive solution takes environmental stimuli into account to modify the scheduling policy itself.

#### 2.4.3 The classification scheme

The usefulness of the four-category taxonomy of computer architecture presented by Flynn [23] has been well demonstrated by the ability to compare the systems through their relation to that taxonomy. The goal of the taxonomy given here is to provide a commonly accepted set of terms and to provide a mechanism to allow comparison of past work in the area of distributed scheduling in a qualitative way. In addition, it is hoped that the categories and their relationships to each other have been chosen carefully enough to indicate areas in need of future work as well as to help classify future work.

The taxonomy will be kept as small as possible by proceeding in a hierarchical fashion for as long as possible, but some choices of characteristics may be made independent of previous design choices, and thus will be specified as a set of descriptors from which a subset may be chosen. The taxonomy, while discussed and presented in terms of distributed process scheduling, is applicable to a larger set of resources. In fact, the taxonomy could usefully be employed to classify any set of resource management systems. However, the attention is focused on the area of process management since it is in this area which we hope to drive relationships useful in determining potential areas for future work.

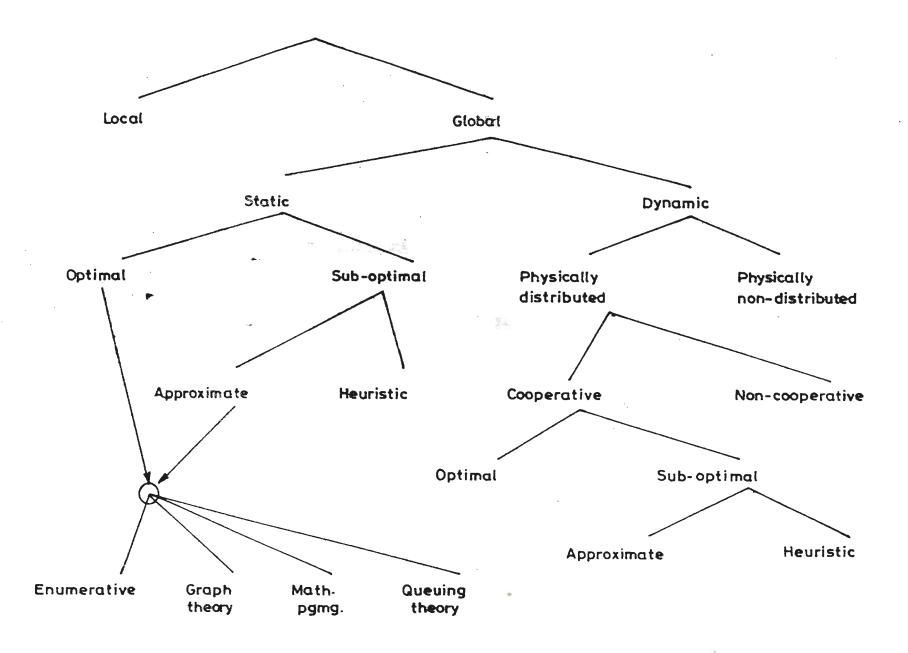

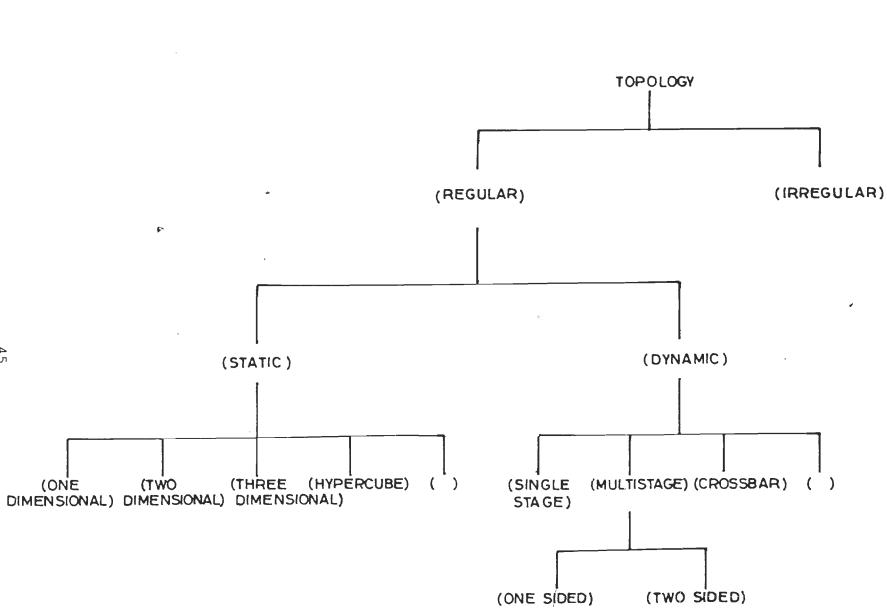

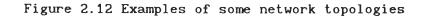

# 2.4.3.1 Hierarchical classification

The structure of the hierarchical portion of the taxonomy is shown in Figure 2.9. A discussion of the hierarchical portion then follows. 1) Local versus Global: At the highest level, we may distinguish between local and global scheduling. Local scheduling is involved with the

Figure 2.9 Task scheduling characteristics

ω 4 ÷.

assignment of processes to the time-slices of a single processor. Since the area of scheduling on single processor systems [25,28,84] as well as the area of sequencing or job-shop scheduling [20,29,53,84] has been actively studied for a number of years, this taxonomy will focus on global scheduling. Global scheduling is the problem of deciding where to execute a process, and the job of local scheduling is left to the operating system of the processor to which the process is ultimately allocated. This allows the processors in a multiprocessor environment to work with increased autonomy while reducing the responsibility (and consequently overhead) of the global scheduling must be done by a single central authority. Rather, the problems of local and global scheduling view as separate issues, and (at least logically) separate mechanisms are at work solving each of them.

2) Static versus Dynamic: The next level of hierarchy (beneath global scheduling) is a choice between static and dynamic scheduling. This choice indicates the time at which the scheduling or assignment decisions are made.

a) Static scheduling : In the case of static scheduling, information regarding the total mix of processes in the system as well as all the independent subtasks involved in a job or task force, is assumed to be available by the time the program object modules are linked into load modules. Hence, each executable image in a system has a static assignment to a particular processor, and each time that process image is submitted for execution, it is assigned to that processor. A more relaxed definition of static scheduling may include algorithms that

schedule task forces for a particular hardware configuration. Over a period of time, the topology of the system may change, but characteristics describing the task force remain the same. Hence, the scheduler may generate a new assignment of processes to processors to serve as the schedule until the topology changes again. This can be further subdivided into the following:

Optimal versus Sub-optimal: In the case that all information regarding the state of the system as well as the resource needs of a process are known, an optimal assignment can be made based on some criterion function [10,15,84]. Examples of optimization measure are minimizing total process completion time, maximizing utilization of resources in the system, or maximizing system throughput. In the event that these problems are computationally not feasible, sub-optimal solutions may be tried [66,84]. Within the realm of sub-optimal solutions to the scheduling problem, we may think of two general categories.

Approximate versus Heuristic: In approximate scheduling we use the same formal computational model for the algorithm, but instead of searching the entire solution space for an optimal solution, one is satisfied when we find a good one. These solutions are categorized as suboptimal-approximate. The assumption that a good solution can be recognized may not be so significant, but in the cases where the metric is available for evaluating a solution, this technique can be used to decrease the time taken to find an acceptable solution (schedule).

The second branch beneath the sub-optimal category is labeled heuristic [23,84]. This branch represents the category of static

algorithms which make the most realistic assumptions about a priori knowledge of the concerned process and system loading characteristics. It also represents the solution to the static scheduling problem which require the most reasonable amount of time and other system resources to perform their function. The most distinguishing feature of heuristic schedulers is that they make use of special parameters which affect the system in indirect ways. Often, the parameter being monitored is correlated to system performance in an indirect way rather than a direct way, and this alternate parameter is much simpler to monitor or calculate.

*Optimal versus* Sub-optimal Approximate techniques : Regardless of wheather a static solution is optimal or sub-optimal approximate, there are four basic categories of task allocation algorithms which can be used to arrive at an assignment of processes to processors :

1) Solution space enumeration and search [93]

2) Graph theoretic [42,69,97]

3) Mathematical programming [14,17,67,83]

4) Queuing theoretic [17,18].

The graph theoretic technique uses a graph to represent a task, and applies the minimal-cut algorithm to the graph to get the task assignment with minimum interprocessor communication. The mathematical programming approach formulates task assignment as an optimization problem, and solves it with mathematical programming techniques.

b) Dynamic scheduling: In the dynamic scheduling problem, the more realistic assumption is made that very little a priori knowledge is

available about the resource needs of a process. It is also unknown that in what environment the process will be executed during its lifetime. In the static case, a decision is made for a process image before it is ever executed, while in the dynamic case no decision is made until a process begins its life in the dynamic environment of the system. Since it is the responsibility of the running system to decide where a process is to execute, it is only natural to next ask where the decision itself is to be made.

Distributed versus Non-distributed: Dynamic scheduling is further subdivided into distributed and non-distributed scheduling. In distributed scheduling the work involved in making decisions is physically distributed among the processors [22,23,54,84], whereas in non-distributed scheduling the responsibility for the task of global dynamic scheduling physically resides on a single processor [2,71,77,87]. Here the concern is with the logical authority of the decision-making process.

Cooperative versus Non-cooperative: Within the realm of distributed dynamic global scheduling, we may also distinguish between those mechanisms which involve cooperation between the distributed components (cooperative) and those in which the individual processors make decisions independent of the actions of the other processors (non-cooperative). Here the degree of autonomy is the parameter which each processor has in determining how its own resources should be used. In the non-cooperative case individual processors act alone as autonomous entities and arrive at decisions regarding the use of their

resources independent of the effect of their decision on the rest of the system. In the cooperative case each processor has the responsibility to carry out its own portion of the scheduling task, but all processors are working towards a common system-wide goal.

As in the static case, the taxonomy tree has reached a point where we may consider optimal, sub-optimal approximate, and sub-optimal heuristic solutions. The same discussion as was presented above for static case applies here as well.

In addition to the hierarchical portion of taxonomy already discussed, there are a number of other distinguishing characteristics which scheduling systems may have. The following sections which do not fit uniquely under any particular branch of the tree-structured taxonomy given so far, are presented here as a flat extension to the scheme, but are still important in the way that they describe the behavior of the scheduler. The placement of these characteristics near the bottom of the tree is not intended to be an indication of their relative importance or any other relation to other categories of the hierarchical portion. Their position are primarily to reduce the size of the description of the taxonomy.

# 2.4.3.2 Flat classification characteristics

1) Adaptive versus Non-adaptive: An adaptive solution to the scheduling problem is one in which the algorithms and parameters used to implement the scheduling policy change dynamically according to the previous and current behavior of the system in response to previous decisions made by the scheduling system. In contrast to an adaptive scheduler, a non-adaptive scheduler would be one which does not necessarily modify

its basic control mechanism on the basis of the history of the system activity. An example of the nonadaptive scheduler would be the one which always weighs its inputs in the same way regardless of the history of the systems behavior.

2) Load Balancing: This category of policies, which has received a great deal of attention recently [10,11,16,26,36,44,60,65], approaches the problem with the philosophy that being fair to the hardware resources of the system is good for the users of that system. The basic idea is to attempt to balance the load on all processors in such a way as to allow progress by all processes on all nodes to proceed at approximately the same rate. This solution is more effective when the nodes of a system are homogeneous since this allows all nodes to know a great deal about the structure of the other nodes. Normally, information would be passed about the network periodically or on demand [6,15,41,56,89], in order to allow all nodes to obtain a local estimate concerning the global state of the system. Then the nodes act together in order to remove work from heavily loaded nodes and place it at lightly loaded nodes. This is a class of solution which relies heavily on the assumption that the information at each node is quite accurate in order to prevent processes from endlessly being circulated about the system without making much progress. Another concern here is deciding on the basic unit used to measure the load on individual nodes.

3) Bidding: In this class of policy mechanisms, a basic protocol framework exists which describes the way in which the processes are assigned to processors. The resulting scheduler is one which is usually

cooperative in the sense that enough information is exchanged (between nodes with tasks to execute and nodes which may be able to execute tasks) so that an assignment of tasks to processors can be made which is beneficial to all nodes in the system as a whole. A wide variety of possibilities exist concerning the type and amount of information exchanged in order to make decisions [1,18,23,84]. Each node in the network is responsible for two roles with respect to the bidding process: manager and contractor. The manager represents the task in need of a location to execute, and the contractor represents a node which is able to do work for other nodes. A single node may take on both of these roles, and that there are no nodes which are strictly managers or contractors alone. The manager announces the existence of a task in need of execution by a task announcement, then receives bids from the other nodes (contractors). The amount and type of information exchanged are the major factors in determining the effectiveness and performance of a scheduler employing the notion of bidding. A very important feature of this class of schedulers is that all nodes generally have full autonomy.

4) Probabilistic: This classification has existed in scheduling systems for some time [6,29,41,50,56]. The basic idea for this scheme is motivated by the fact that in many assignment problems the number of permutations of the available work and the number of mappings to processors so large, that in order to analytically examine the entire solution space would require extremely large amount of time. One of the solutions is to randomly choose some process as the next to assign. Repeatedly using this method, a number of different schedules may be generated, and then this set is analyzed to choose the best from among

those randomly generated. An alternative view of probabilistic schedulers are those which employ the principles of decision theory in the form of team theory [23,84]. These would be classified as probabilistic.

5) One-Time Assignment versus Dynamic Reassignment: In this classification, we consider the entities to be scheduled. If the entities are jobs in the traditional batch processing sense of the term [17,20,23], then we consider the single point in time in which a decision is made as to where and when the job is to execute. While this technique technically corresponds to a dynamic approach, it is also static in the sense that once a decision is made to place and execute a job, no further decisions are made concerning the job. We would characterize this class as one-time assignment. In this mechanism, the only information usable by the scheduler to make its decision is the information given to it by the user or submitter of the job.

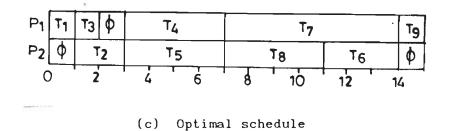

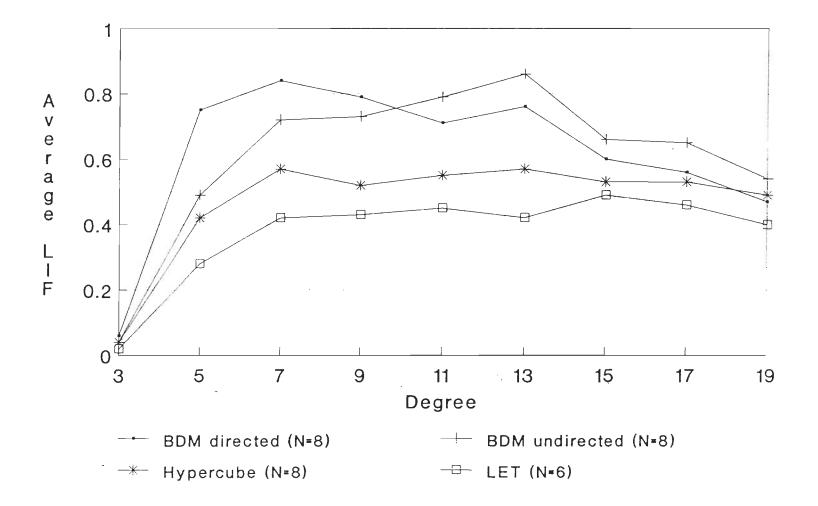

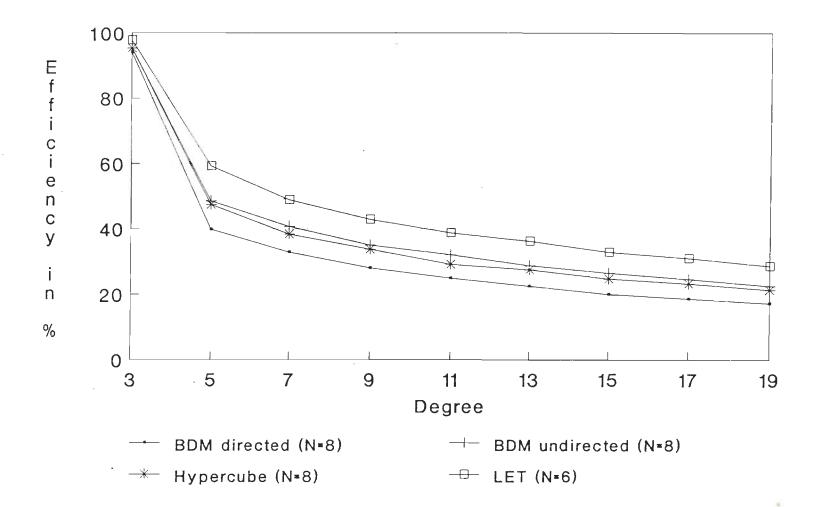

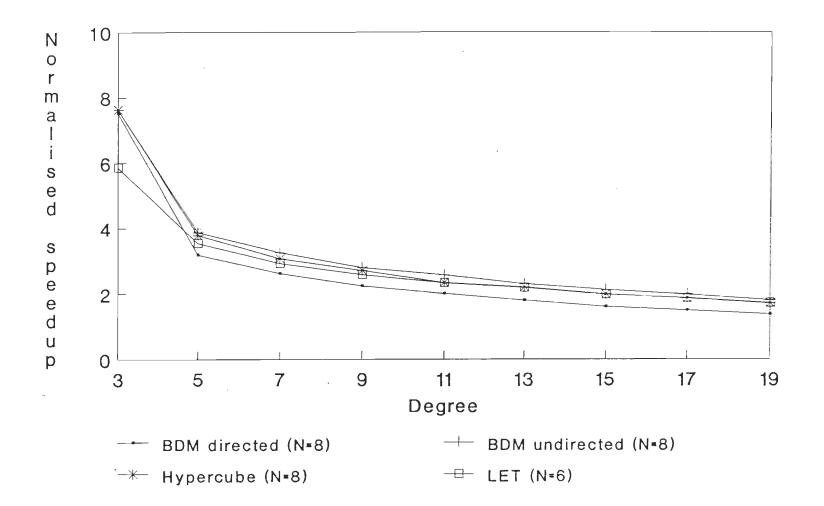

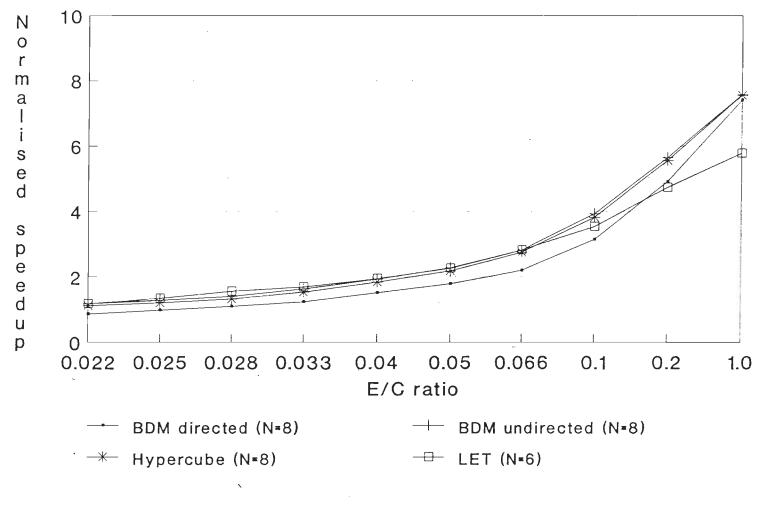

In contrast, solutions in the dynamic reassignment class try to improve on earlier decisions by using information on smaller computation units the executing subtasks of jobs or task forces. This adaptation takes the form of migrating processes (including current process state information).