# FAULT-TOLERANT MINs FOR PARALLEL PROCESSING

D65-92

PAW

# A THESIS

submitted in fulfilment of the requirements for the award of the degree

# of

DOCTOR OF PHILOSOPHY

# in

ELECTRONICS AND COMPUTER ENGINEERING

By

PAWAN KUMAR

Acc. No

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247 667 (INDIA)

APRIL, 1992

#### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the thesis entitled Fault-Tolerant MINs for Parallel Processing in fulfilment of the requirement for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electronics and Computer Engineering of the University is an authentic record of my own work carried out during a period from October 1988 to April 1992 under the supervision of Dr.R.C.Joshi and Dr.Kuldip Singh.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other University.

Pawankumar

(Pawan Kumar)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

Gra Au

(R.C.Joshi) Professor and Head, Dept. of Electronics and Computer Engineering

(Kuldip Singh)

Reader Dept. of Continuing Education

Date: 27. 4. 1992

The Ph.D Viva-Voce examination of Sri Pawan Kumar Research Scholar, has been held on

Signature of Supervisors Signature of External Examiner

625 Jesti

Signature of H.O.D.

## ABSTRACT ~

This thesis addresses the techniques for the design of reliable fault-tolerant multistage interconnection networks (MINs) used in multiprocessor systems. Statically as well as dynamically reroutable MINs are studied. Methods for the construction of regular fault-tolerant MINs are described. Their characteristics pertaining to performance and reliability are analyzed and compared with the previously proposed networks. It is shown that these multipath regular MINs are of higher reliability than other MINs having similar fault-tolerant capabilities and give better performance. The effect of component failures on the performance of these networks is also evaluated. is observed that although faults do not significantly affect It the overall network performance, they degrade the performance of some parts of the system resulting in an increase in network cycle time. New type of irregular fault-tolerant multistage networks are introduced and analyzed. Various algorithms are developed to study their characteristics. Compared to regular networks, these irregular networks have lesser hardware complexity and more computational speed because of their shorter path lengths between a processor and its favourite memory modules. The results of analysis show that it is worthwhile to employ the proposed irregular techniques in designing faulttolerant MINs. Modular implementation has been proposed to simplify the design of statically reroutable networks. The proposed fault-tolerant networks have many attractive features for use in multiprocessor systems.

#### ACKNOWLEDGEMENTS

I wish to express my heartfelt gratitude for the inspiration, encouragement and the expert guidance that Dr.R.C.Joshi and Dr.Kuldip Singh have given me throughout my stay at the University of Roorkee, Roorkee. I consider myself very fortunate for having been associated with them.

The co-operation and help extended by the Head, Department of Electronics and Computer Engineering, is gratefully acknowledged.

I am grateful to Dr. Arun Kumar, Reader E and CE Department for his help and friendly advice during my stay at Roorkee. I am also grateful to all my fellow researchers and friends, who have provided me encouragement and timely support.

I am thankful to my wife Neeta and children Neha and Rohit, not only for their patience during my research work, but also for the inspiration they have given me.

Last but not the least, I am thankful to my parent Institute i.e Thapar Institute of Engineering and Technology, Patiala, for sponsoring me under Quality Improvement Programme. In particular, I wish to record my gratitude to Prof. A.K. Sawhney for his co-operation during the period.

# CONTENTS

|    |      |         |                                         | Page  |

|----|------|---------|-----------------------------------------|-------|

|    | ABST | RACT    |                                         | (i)   |

|    | ACKN | OWLEDGE | MENTS                                   | (ii)  |

|    | CONT | ENTS    |                                         | (iii) |

| 1. | INTR | ODUCTIO | N                                       | 1     |

|    | 1.1  | Introd  | uction                                  | 1     |

|    | 1.2  | Statem  | ent of the Problem                      | 3     |

|    | 1.3  | Organi  | zation of the Thesis                    | 5     |

| 2. | REVI | EW OF F | AULT-TOLERANCE TECHNIQUES               | 6     |

|    | 2.1  | Introd  | uction                                  | 6     |

|    | 2.2  | Interc  | onnection Methods                       | 6     |

|    | 2.3  | Multis  | tage Interconnection Networks           | 8     |

|    | 2.4  | Fault-  | Tolerant MINs                           | 14    |

|    | 2.5  | Fault-  | Tolerance Techniques                    | 15    |

|    |      | 2.5.1   | Redundancy at the Network Level         | 16    |

|    |      | 2.5.2   | Redundant Stages in the Network         | 20    |

|    |      | 2.5.3   | Chaining Switches within a Stage of the | 24    |

|    |      |         | Network                                 |       |

|    |      | 2.5.4   | Other Fault-Tolerant designs for        | 26    |

|    |      |         | Full Access                             |       |

|    |      | 2.5.5   | Time Redundancy for Dynamic Full Access | 28    |

|    | 2.6  | Conclu  | sion                                    | 31    |

| S. MODOLINK MLINOKK | 3. | MODULAR | NETWORK |

|---------------------|----|---------|---------|

|---------------------|----|---------|---------|

| 3.1  | Introduction                           | 32 |  |

|------|----------------------------------------|----|--|

| 3.2  | Construction                           | 32 |  |

| 3.3  | Routing                                | 33 |  |

| 3.4  | Fault-Tolerance and Repair             | 37 |  |

| 3.5  | Reliability Analysis                   | 38 |  |

| 3.6  | Comparison with other Networks         | 41 |  |

|      | 3.6.1 Baseline Network                 | 41 |  |

|      | 3.6.2 Extra Stage Cube (ESC) Network   | 42 |  |

|      | 3.6.3 3-Replicated Network             | 43 |  |

|      | 3.6.4 INDRA Network                    | 43 |  |

| 3.7  | Cost Analysis                          | 44 |  |

| 3.8  | Reliability/Cost Ratio                 | 46 |  |

| 3.9  | Performance Model                      | 46 |  |

|      | 3.9.1 Assumptions                      | 49 |  |

|      | 3.9.2 Performance Analysis             | 50 |  |

| 3.10 | Conclusion                             | 58 |  |

| AUGM | ENTED BASELINE NETWORK                 | 60 |  |

| 4.1  | Introduction                           | 60 |  |

| 4.2  | Construction                           | 60 |  |

| 4.3  | Routing Scheme                         | 63 |  |

| 4.4  | Fault-Tolerance                        |    |  |

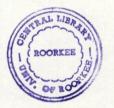

| 4.5  | Reliability Analysis                   | 70 |  |

|      | 4.5.1 Augmented Baseline Network (ABN) | 70 |  |

|      | 4.5.2 Unique-Path Baseline Network     | 73 |  |

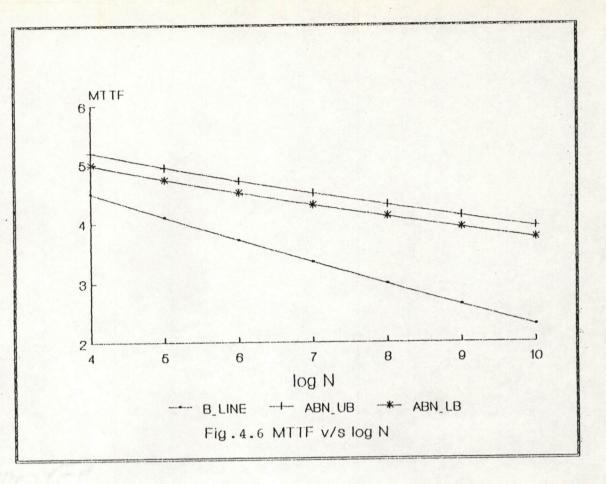

|    | 4.6   | Cost-Effectiveness                              | 74  |

|----|-------|-------------------------------------------------|-----|

|    | 4.7   | Performance Analysis                            | 76  |

|    | 4.8   | Conclusion                                      | 86  |

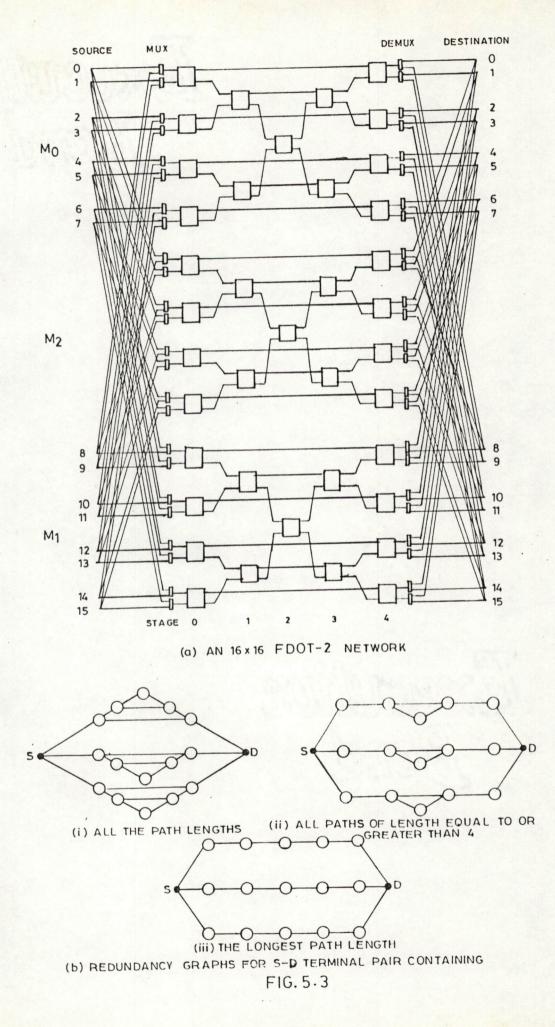

| •  | MODII | FIED FAULT-TOLERANT DOUBLE TREE (MFDOT) NETWORK | 88  |

|    | 5.1   | Introduction                                    | 88  |

|    | 5.2   | Modified Double Tree (MDOT) Network             | 88  |

|    | 5.3   | Fault-Tolerant Double Tree (FDOT) Network       | 91  |

|    | 5.4   | Modified Fault-Tolerant Double Tree (MFDOT)     | 92  |

|    |       | Network                                         |     |

|    | 5.5   | Routing Scheme of MFDOT Network                 | 95  |

|    |       | 5.5.1 Path Length Algorithm                     | 95  |

|    |       | 5.5.2 Routing Tag Algorithm                     | 96  |

|    |       | 5.5.3 Routing Procedure                         | 98  |

|    | 5.6   | Fault-Tolerance of MFDOT Network                | 99  |

|    | 5.7   | Permutation Capability of MFDOT Network         | 100 |

|    | 5.8   | Reliability and Repairability of MFDOT Network  | 100 |

|    | 5.9   | Communication Delay in MFDOT Network            | 101 |

|    | 5.10  | Conclusion                                      | 101 |

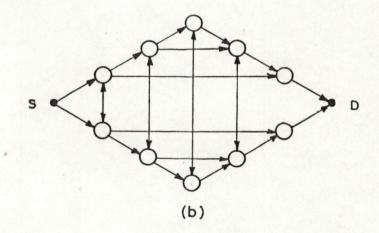

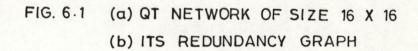

| i. | QUAD  | TREE (QT) NETWORK                               | 103 |

|    | 6.1   | Introduction                                    | 103 |

|    | 6.2   | Construction                                    | 103 |

|    | 6.3   | Routing Scheme                                  | 105 |

|    |       | 6.3.1 Path Length Algorithm                     | 105 |

|    |       | 6.3.2 Routing Tag Algorithm                     | 107 |

|    |       | 6.3.3 Routing Procedure                         | 110 |

|    | 6.4  | Fault-Tolerance                                  | 112 |

|----|------|--------------------------------------------------|-----|

|    | 6.5  | Cost Analysis and Comparison with other Networks | 114 |

|    | 6.6  | Conclusion                                       | 116 |

| 7. | CONC | LUSIONS                                          | 117 |

|    | 7.1  | Conclusions                                      | 117 |

|    | 7.2  | Suggestion for Future Investigations             | 120 |

|    | REFE | RENCES                                           | 122 |

|    | APPE | NDIX                                             | 131 |

|    | RESE | ARCH PAPERS OUT OF THE WORK                      | 124 |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 INTRODUCTION

Quest for higher and higher computational speeds has driven the hardware technology almost to the physical limits of response time of electronic circuits, but the demand for more processing power continues to grow. As a result the computer scientists are now exploring multiprocessor architectures where several processors can work concurrently in a co-operative manner. In such a multiprocessing system, processors may spend a considerable amount of time just communicating among themselves unless an efficient interconnection network (IN) connects them. A suitable IN, thus, inevitably becomes a critical system component since a communication vehicle is needed to synchronize processes and to co-ordinate processor resources.

Multistage interconnection networks (MINs) are recognized as cost-effective means to provide high-bandwidth communication in multiprocessor systems, as opposed to crossbar switches which are highly efficient but are prohibitively expensive, with  $O(N^2)$  cost (where N is the number of input and output terminals) and the time shared buses which are inexpensive but have unacceptable throughput when the number of processors connected to them is large.

A MIN consists of multiple stages of switching elements (SEs) and is categorised as regular or irregular, based upon the

number of SEs in each stage of the network. If the number of SES are same in each stage then the network is said to be regular otherwise irregular. A majority of the proposed regular MINs belong to a class of networks which in their basic form, consist of log\_N stages of mxm SEs connecting N input terminals to N output terminals. The SEs in adjacent stages are connected by an interconnection pattern that allows any input to be connected to any output. Such MINs have O(NlogN) hardware cost, O(log N) path length, and the ability to provide up to N simultaneous connections. In addition, they can employ simple and distributed routing algorithms which eliminate the need for a central controller and reduce the connection set up time. These properties make MINs attractive for multiprocessor applications.

The irregular double tree (DOT) network [58,63,81] has many desirable properties for use in multiprocessor systems, but lacks fault-tolerant capability. The useful properties of DOT network are: full access capability and shorter path lengths for a connection between a processor and its favourite memory modules as compared to regular multistage networks.

An important characteristic of these MINs is that there is a unique-path between any input-output pair. This leads to two serious disadvantages: a) poor performance and b) lack of faulttolerance and reliability. Performance of unique-path is low because of possible blocking of an input-output connection by a previously established connection and the inability to find an alternate path. There is no fault-tolerance because even a single link or switch failure can disconnect paths between several

input-output pairs. This lack of fault-tolerant capability has received considerable attention, and many ways of providing fault-tolerance to the regular multistage interconnection networks have been proposed. An exhaustive survey has been presented by Adams et al [2].

The basic idea for fault-tolerance is to provide multiple paths for an input-output pair so that alternate paths can be used in case of faults. The methods include increasing the number of stages [1], using multiple links between stages [20,61,69], increasing the size of switches [65], partitioning a unique-path network into several subnetworks [43], and incorporating multiple copies of a basic network [51,74]. For example, an Extra Stage Cube (ESC) network [1] has a redundant stage to provide two paths for every input-output pair, while a d-replicated network [51] (or layered banyan network [34]) provides redundant paths by replicating d identical basic networks. Compared to unique-path networks, these multiple path networks certainly have higher reliability but with increased hardware complexity, which not only increases cost, but also puts wrinkle on the claim of enhanced reliability.

# 1.2 STATEMENT OF THE PROBLEM

The general goals for the design of fault-tolerant MINs are high reliability, good performance even in the presence of faults, high computational speed, low cost and simple control. However, most fault-tolerant MINs proposed in the literature cannot achieve all of these goals at the same time. Most of the

Ś

regular MINs proposed in the literature have path length O(logN), which puts a limitation on the computational speed of a MIN. Some of the networks fail to tolerate faults in the first and or the last stages. Some others can tolerate faults in any stage, but they cannot maintain permutation capability when any single fault occurs. A few exceptions such as replicated networks and INDRA [75] network can maintain permutation capability in case of faults, but they are, in general, too costly.

The main objective of the present research work is to explore the techniques for the design of reliable, computationally faster, fault-tolerant and cost-effective MIN having good performance. The problem of improving the reliability and performance of the existing regular faulttolerant MINs have been examined. This thesis also investigates the possibility of constructing irregular fault-tolerant MINs having shorter path length compared to regular fault-tolerant MINs. Specifically, the problems considered in this thesis can be stated as follows:

- To propose newer and or augmenting the existing regular networks, in order to improve their reliability and performance.

- To develop irregular fault-tolerant MINs which are costeffective and have shorter path length compared to regular fault-tolerant MINs.

The efforts in exploring the above objectives result in the development of the following networks:

- . Modular Network (MN)

- . Augmented Baseline Network (ABN)

- . Modified Fault-Tolerant Double Tree (MFDOT) Network, and

- . Quad Tree (QT) Network.

#### **1.3 ORGANIZATION OF THE THESIS**

The background and the related research reported by others, are outlined in chapter 2, which is helpful for the design of reliable MINS. Chapter 3 contains the performance analysis of the modular network (MN). The improvement obtained over the performance of unique-path networks is quantified and comparison of the analyses of MTTF and cost-effectiveness with other multipath networks is given. Performance under faulty conditions is also described. Chapter 4 deals with the reliability and performance analyses of augmented baseline network (ABN). The effect of component failures on the performance of ABN are also studied.

Statically re-routable irregular modified fault-tolerant double tree (MFDOT) network is described in chapter 5. The path length and routing algorithms are proposed and the faulttolerance properties are examined. Chapter 6 covers the dynamically reroutable irregular quad tree (QT) network. The routing algorithms are formulated and a comparison with the hardware cost of other fault-tolerant MINs is presented. Finally, conclusions and proposals for further research needed in this area are given in chapter 7.

#### REVIEW

# 2.1 INTRODUCTION

Fault-tolerance is an important factor in the study of multistage interconnection networks used in large multiprocessor systems for their continuous operation over a relatively long period of time. In such networks, the failure of a switching element or connecting link destroys the communication capability between one or more pair(s) of source and destination terminals. Many techniques exist for designing multistage interconnection networks that tolerate switch and/or link failures without losing connectivity. In this chapter, interconnection methods, multistage interconnection networks and the fault-tolerance techniques are reviewed.

## 2.2 INTERCONNECTION METHODS

The interconnection of N processors to N memory modules in multiprocessor systems is an important and challenging problem for large values of N. A crossbar network provides a fast means of interconnecting the resources in a multiprocessor system. Unfortunately, the complexity and the cost of such networks grows with the square of the network size N.

Several network topologies have been designed which require much less hardware than crossbars and they can be broadly classified as static and dynamic [5]. In a static scheme, each

processor is connected by dedicated links to a subset of processors. Several static structures with regular topology have been proposed - these include ring [60], tree [35], near neighbor mesh [8], hypercubes [79], systolic arrays [42], and pyramids [95]. A comparative study by Wittie [108] describes these static networks. In these networks, each processor can communicate only with a small number of processors directly and communication with others involves the transfer of information through one or more intermediate processors.

Dynamic networks allow different connections to be set up between processing elements by changing their internal states. Multistage interconnection networks, which consist of multiple stages of switching elements, are networks with a dynamic topology. Several MINs with N inputs and N outputs have been reported in the literature [31,90]. These networks have hardware complexity O(NlogN) compared to O(N<sup>2</sup>) required by crossbars.

At the other end of the spectrum, the linear bus offers a simple and inexpensive means of communication, but they do not admit simultaneous communication between distinct processor/processor or processor/memory pairs. Thus, they are inefficient and becomes unacceptably slow for even a moderate number of processors. Use of multiple buses is helpful, but to achieve significant improvement in performance, a large number of buses ( $\approx N^2/2$ ) must be employed [22,64] which makes them no longer economically attractive.

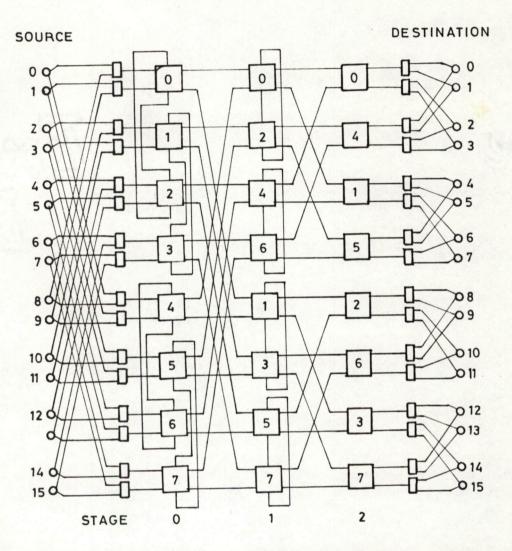

#### 2.3 MULTISTAGE INTERCONNECTION NETWORKS

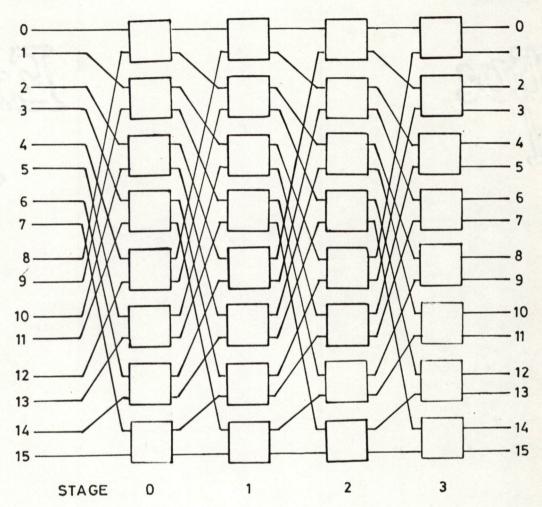

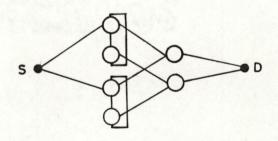

A multistage interconnection network consists of multiple stages of switching elements. Popular among them is a class of regular networks which, in their basic form, consist of log\_N mxm SEs connecting N input terminals to N output stages of terminals. If the number of switches in each stage of the network are equal then the network is said to be regular otherwise the network is irregular. They can also be built using larger SEs and correspondingly have less number of stages, with similar properties. There exist many different topologies for MINs which are characterized by the pattern of the connecting links between stages. The omega network shown in Figure 2.1, maintains a uniform connection pattern between stages, known as perfect shuffle [54,93]; many other multistage networks have non-uniform connection patterns between stages. The minimum requirement of any of these networks is to provide full access capability, which means that any input terminal of the network should be able to access any output terminal in one pass through the network.

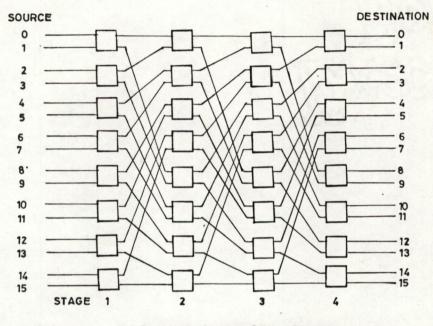

Multistage networks differ in the interconnection pattern between stages, the type and operation of individual SEs, and the control scheme for setting up the SEs. Examples include the baseline [109], omega [54], banyan [34], the indirect binary n-cube [71], flip [10], and delta [70] networks. The topological equivalence of several of these networks has been established [4,67,109]. In multistage networks, data must flow through several switching stages. Hence, these networks have a longer internal delay as compared to a crossbar.

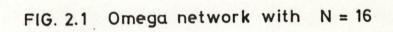

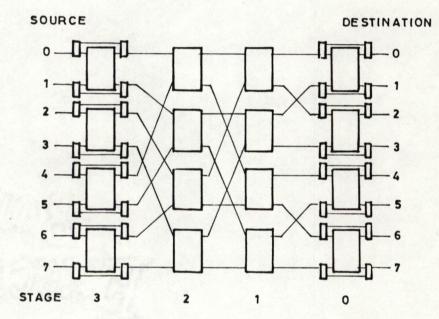

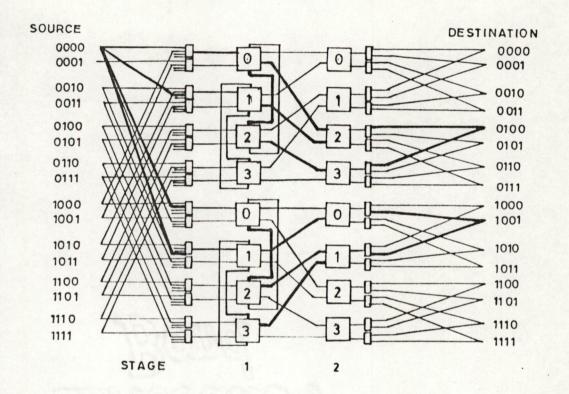

DESTINATION

An important characteristic of these MINs is the unique-path property. This means that each source has exactly one path through the network to reach any particular destination. Moreover, the routing of data from source to destination can be performed in a distributed manner using the destination address as routing tag. For example, Figure 2.2 represents a baseline network in which the route taken by a source with binary address  $s_{n-1} s_{n-2} \dots s_0$  to destination  $d_{n-1} d_{n-2} \dots d_0$  will be uniquely specified by the path code as  $s_{n-1} s_{n-2} \dots s_0 d_{n-1} d_{n-2} \dots d_0$ . The position of the path in any intermediate stage of the network can be found by observing a n bit long window in the path code (where n =  $log_2N$ ). Conflicts can arise while routing multiple connections (or permutations) through such networks when two inputs request the same output link of a switch in some intermediate stage.

This class of networks does not realize all the possible permutations of data between inputs and outputs. Networks capable of realizing all the N! permutations between the N inputs and outputs are known as rearrangeable networks. The baseline network does not possess this property since many permutations cause conflicts in one or more of the switching stages. The number of passable permutations can be increased by increasing the number of stages. This also includes multiple paths between source and destination terminals. However, the control algorithm to find non-conflicting paths for arbitrary permutations in such networks can be quite complex. A well studied multistage rearrangeable network is the benes network [11] which consists of 2  $log_2N-1$

FIG. 2.2 Baseline network with N = 16

stages of 2x2 SEs. A serial cascade of the omega network with its inverse network also displays this property.

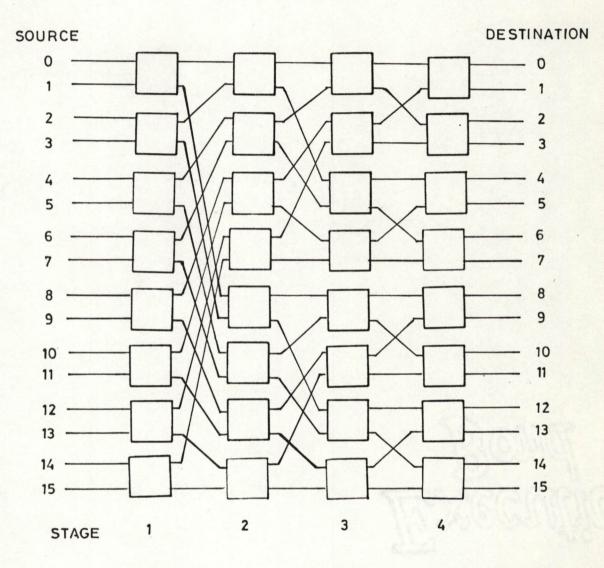

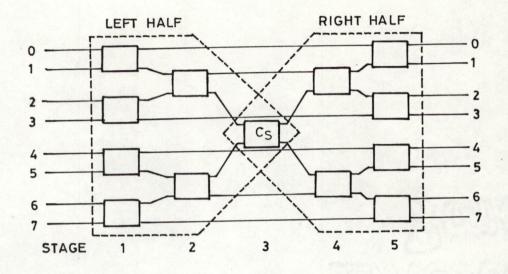

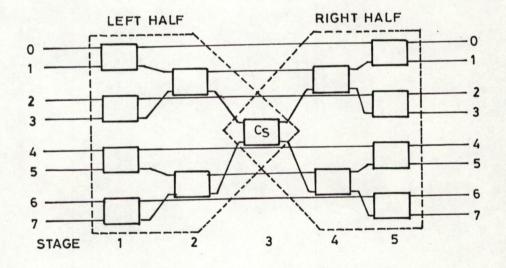

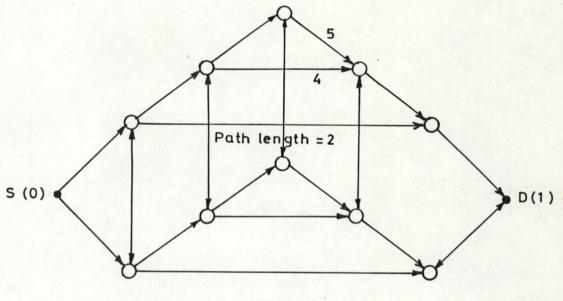

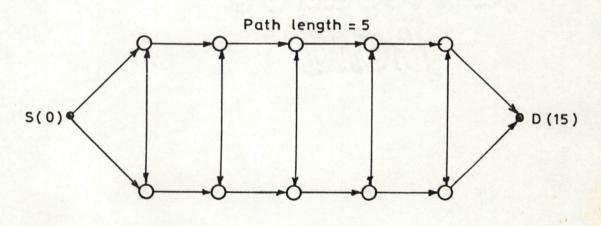

The irregular double tree (DOT) multistage network was originally proposed by Levitt et al [58]. It has found an application in the design of MIT data flow processor [57]. A DOT network shown in Figure 2.3 consists of a right and a left half. Each half of the network resembles a binary tree. The left and right trees are mirror images of each other. A DOT network of size NXN has N source and N destination terminals and 2n-1 number of stages (where  $n=log_2N$ ). Further, it has  $(2^{n+1}-3)$  SEs. An ith and (2n-i)th stage has  $2^{n-i}$  SEs of size 2x2 for i = 1,2,3,...,n. DOT network possesses the property of full access. Compared to regular networks, the DOT network has shorter path length for a connection between a processor and its favourite memory modules. Thus, DOT network has many attractive properties for use in multiprocessor systems, but lacks in fault-tolerant capability.

Only a limited set of permutations are required in some computational environments, and multistage unique-path networks are usually adequate in such cases. A control algorithm is required to set up the SEs for performing various permutations. It is necessary to have small set up times in an environment where the switching permutations change rapidly. While the control of a crossbar is relatively straightforward, the algorithm for finding the switch settings in some multistage networks is more complex.

FIG. 2.3 DOT NETWORK WITH N=8

#### 2.4 FAULT-TOLERANT MINS

A number of multistage interconnection networks have been proposed in the literature and majority of them belong to a class of networks, which in their basic form, consist of log N stages connecting N inputs to N outputs. These networks possess the full access property; in addition, a unique-path exists from any input terminal of the network to any output terminal. The uniquepath property facilitates the use of simple and efficient routing algorithms for setting up connections through the network. However, unique-path MINs have the following two major problems:

- i) Lack of fault-tolerance and poor reliability. Since there is a unique-path between any input-output pair, the presence of a single failure among the SEs or the connecting links destroys the full access property. Even though the failure of individual components in the network are usually very small, the failure rate of the entire network can be quite high in systems of large size.

- ii) Poor performance in random access environment. Since there are no alternate paths between input-output pairs, blocked requests can cause significant deterioration in performance.

Thus, fault-tolerance is a necessary attribute for the continued operation of such systems. The basic idea for faulttolerance is to provide multiple paths for a input-output pair so that alternate paths can be used in case of faults. Availability of multiple paths results in increased reliability and performance, because an alternate path can be chosen in the event

of a request being blocked or a faulty link or switch being encountered.

Rerouting or selection of alternate path in a MIN may be either static or dynamic. If a multipath MIN allows rerouting to be made only at the source or at some fixed points in the network, where the alternate path fork exists, then it is statically reroutable. In such MINs, if blocking occurs or faults are encountered, it may be necessary to backtrack to the stage where a fork occurs and attempt an alternate path from there. In dynamically reroutable multipath MIN, the paths between any given source-destination pair have a fork available at every stage. Thus, rerouting decisions can be made by the switches at any stage, on the fly, as faulty switches or links are encountered or as blocking occurs.

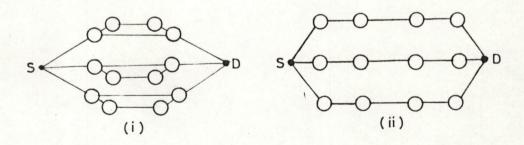

A convenient way of determining the degree of faulttolerance of multipath MIN, and to find out whether it allows static or dynamic reroutability, is by the use of its redundancy graph. The redundancy graph in a MIN shows all the available paths between a input-output pair [65,68].

# 2.5 FAULT-TOLERANCE TECHNIQUES

Many ways of providing fault-tolerance to the multistage interconnection networks have been proposed. A survey is found in [2]. Most of the proposed techniques fall somewhere between 0 and 100 percent redundancy. These techniques are briefly reviewed in this section.

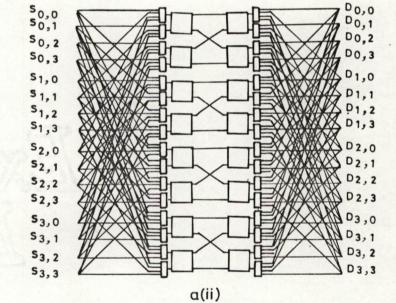

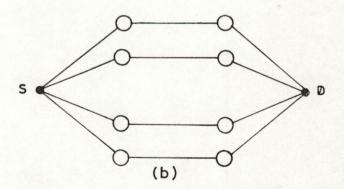

### 2.5.1 Redundancy at the Network Level

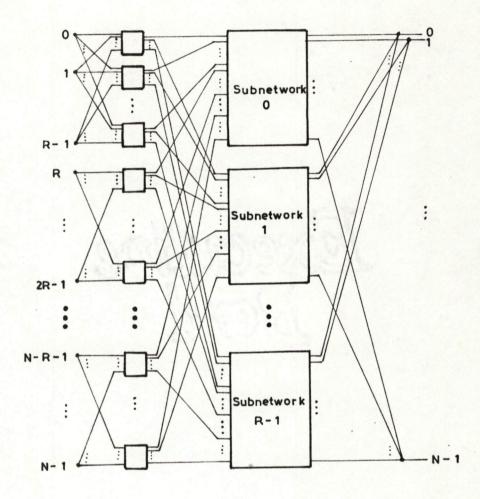

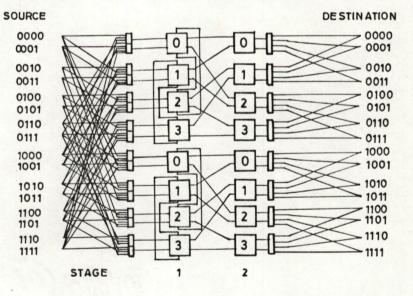

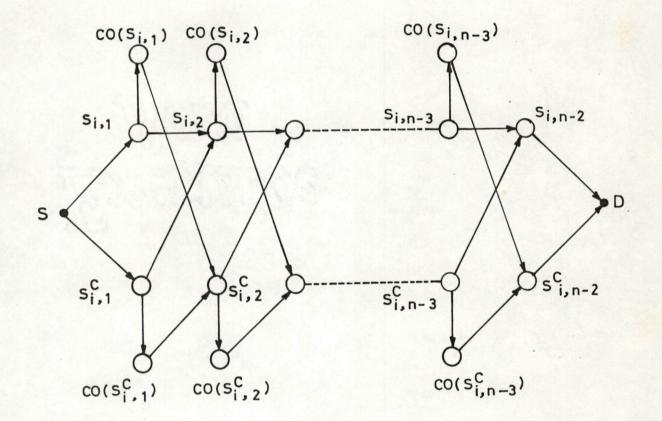

An approach to design fault-tolerant networks is to use multiple copies of the basic network such as the omega network. Examples include INDRA network [75], Merged Delta Network (MDN) [76], Augmented C-Network (ACN) [76], and d-replicated network INDRA network can be viewed as the union of R parallel [51]. layers (or copies) of a basic network with an initial distribution stage. INDRA network is constructed using RxR switches for  $N = R^n$  inputs and outputs, and provides  $R^2$  different paths between any input-output pair. The network can be visualized as a shuffle exchange MIN of size NxR, with each of the N sources connected to a specified set of R switches in the first stage, and each destination receiving connections from R specified switches in the last stage. The network is shown in Figure 2.4. Up to (R-1) failures can be tolerated and only static rerouting is possible.

The Merged Delta Network (MDN) [76] is constructed by combining d identical layers (copies) of N/d x N/d delta network to form a network with N inputs and outputs. The basic difference between an MDN and a INDRA network is that the MDN allows connections to cross layers between stages of the network, whereas a connection is confined to a single layer in the case of INDRA network. Given d copies of delta networks, each with N/d inputs and outputs and consisting of R x R SEs, an MDN is constructed as follows:

FIG. 2. 4 INDRA network shown as the union of R subnetworks

- 1. Increase the size of all SEs to R.d x R.d.

- 2. If an input (output) terminal i of the network was orginally connected to switch j in the input (output) stage of one of the delta networks, connect it to switch j in the input (output) stage of all the delta networks.

- 3. If a switch j in some stage i of the delta network was orginally connected to switch k of the stage (i + 1), connect it to switch k in stage (i + 1) of all the delta networks.

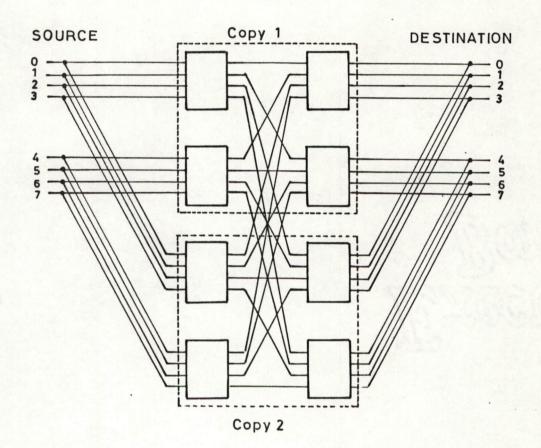

An MDN constructed from d copies of delta networks is referred to as a d-MDN. Figure 2.5 shows a 2-MDN consisting of 8 inputs and outputs constructed from two identical copies of delta networks of size 4x4.

Another example of combining multiple layer of networks to obtain fault-tolerance is the class of Augmented C-Network (ACN). The omega network has the property that for each SE in every stage, except the last, another SE exists in the same stage such that they are connected to a common pair of switches in the next stage. Such a pair of switches is called "conjugates" [76] or "output buddies" [4]. Networks satisfying this property are called C-networks and can be used to construct Augmented C-Network (ACN) [76]. An ACN with N =  $2^n$  inputs and outputs is constructed from an omega network of the same size as follows:

1. Replace each 2x2 switch by a 4x4 switch.

If an input terminal in the orginal network is connected to a switch j in the input stage of the network, connect the input terminal to the conjugate of j also.

FIG. 2.5 A 2-MDN with 8 inputs and outputs

- 3. If an input terminal of the network was initially connected to switch j of the network, connect it also to the switch  $(j + N/4) \mod N/2$ .

- 4. For every stage i except the last, if a switch j is connected to switches k, k' of stage (i + 1), connect its two new outputs to the conjugates of k and k' in stage (i + 1).

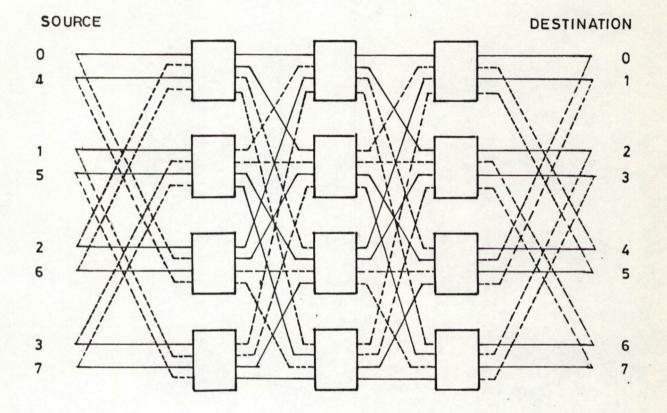

Figure 2.6 shows an ACN with N = 8 inputs and outputs constructed from an omega network of the same size. The added links are shown by broken lines.

## 2.5.2 Redundant Stages in the Network

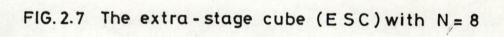

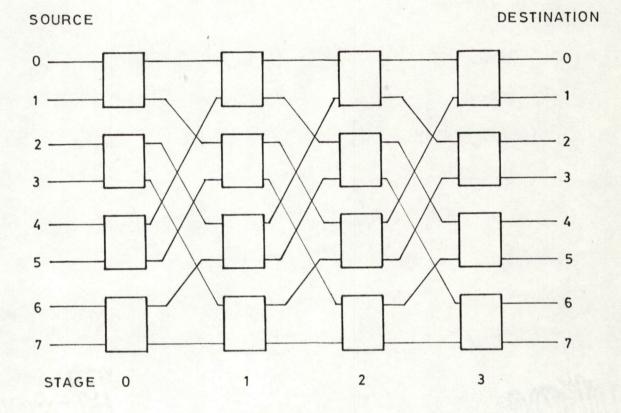

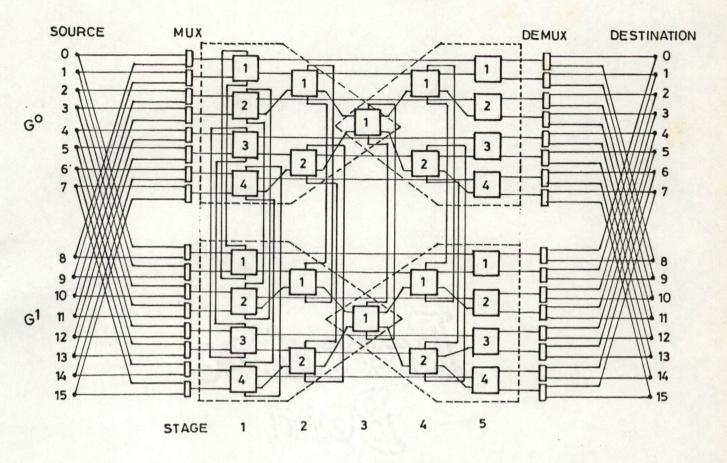

Adding redundant copies of networks is an expensive solution, but allows routing of classes of permutations even when there are multiple switch failures. If only the full access capability is required, then extra switching stages can be used to provide multiple disjoint paths between source and destination pairs. This technique provides fault-tolerance at a modest overhead. Examples include the Extra-Stage Cube (ESC) network [1], extra-stage omega network [104] and banyan networks [18]. The Extra Stage Cube network is constructed from the generalized cube network [1] by adding an extra stage at the front end of the network. The switches in this extra stage and in the final stage are equipped with demultiplexers at the inputs and multiplexers at the outputs, respectively. This arrangement makes it possible to tolerate a single switch failure in any stage of the network. Figure 2.7 shows an ESC network. Figure 2.8 shows an extra-stage

FIG. 2.6 An ACN with N = 8

FIG. 2.8 The extra-stage omega network with N = 8

omega network obtained by adding a redundant switching stage at the input of the network. The extra stage allows the network to retain its full-access capability in the presence of single switch failures in any stage except the first and the last. For all single failures in the intermediate stages, the network can also route permutations by performing multiple passes, each pass realizing a submap of the permutation [104].

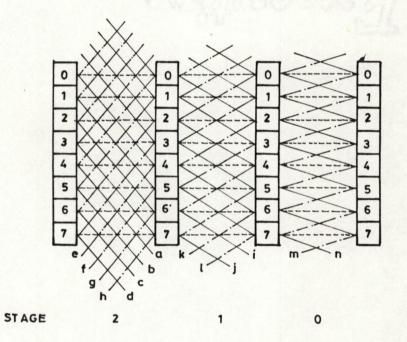

# 2.5.3 Chaining Switches within a Stage of the Network

The technique, achieves fault-tolerance by providing additional links between switches belonging to the same stage, so that data can sidestep a faulty switch. Examples include Augmented Shuffle Exchange Network (ASEN) [46]. Figure 2.9 shows an ASEN-2. ASEN is a multipath MIN which features links among switches belonging to the same stage. It has the property that for every loop of switches, there exists another loop which is connected to the same set of switches in the next stage. An ASEN is self routing. Each source has a primary multiplexer and SE and a secondary multiplexer and SE. Each source attempts entry into the ASEN via its primary multiplexer and SE. If either primary component is faulty, the request is sent to the secondary multiplexer. If the secondary multiplexer is also faulty, the ASEN fails. For stages 1 through log, N - 2, requests are first routed through the usual output link, if it is busy or if the successor SE (in the next stage) is faulty, routing is attempted via the auxiliary link. A faulty demultiplexer at the output of the ASEN is regarded as a failure of its associated SE in stage

FIG. 2.9 A augmented shuffle-exchange network (ASEN-2) with N = 16

$\log_2 N - 1$ . This strategy essentially enables a SE to detect a failure of its successor SE and re-route the request whenever possible. The ASEN is failed if a request that is not blocked does not find a path to its destination.

This technique has two benefits. First, the network can tolerate the failure of both switches in a conjugate loop. Second, the network provides a topology which lends itself to online repair and maintainability. That is, a loop can be removed from the ASEN without disrupting the operation of the network.

# 2.5.4 Other Fault-Tolerant Designs for Full Access

Multistage networks designed to provide full access in the presence of faults include the Augmented Data Manipulator (ADM) [62], Inverse Augmented Data Manipulator (IADM) [61], the Gamma network [69], the F-network [19], and the modified omega network [65,66]. These networks use enhanced SEs and/or additional links between stages to provide multiple paths between input/output pairs, thereby achieving fault-tolerance.

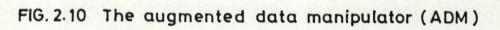

The ADM, Inverse ADM (IADM) as well as the Gamma network are based on  $\pm 2^{i}$  interconnection between stages. They use SEs with three inputs and outputs, except in the input and output stages, where the switches are 1 x 3 and 3 x 1 respectively. Each of these networks has (n + 1) switching stages for N =  $2^{n}$  inputs and outputs. At stage i of the IADM, the outputs of a switch j are connected to the switches j,  $(j + 2^{i}) \mod N$ , and  $(j - 2^{i}) \mod N$ , of the (i + 1)th stage. Figure 2.10 shows the ADM network. The Gamma network uses the same interconnection patterns as the IADM.

The difference between the ADM/IADM and the Gamma network is that the SEs in the former networks allow only one connection to be routed at a time, whereas the SEs in the latter are 3x3 crossbars.

Figure 2.11 shows the Gamma network for N = 8. The set of paths between a source-destination pair in the Gamma network can be specified using the binary fully-redundant number system. Under this system, a digit can take one of the three values - 0, 1, 1 (1 stands for -1). An input-output connection can be routed by means of a n-digit routing tag which is the modulo-N difference between the destination and the source expressed in binary redundant number system. The value of the routing tag can be used in a straightforward manner to set up the path in the network. A switch in stage i needs to examine only the ith digit of the tag: if this digit is 0, the straight connection is used, 1 then the downward  $(+2^{1})$  link is used, and if 1 then the if upward (-2<sup>i</sup>) link is used. When the source and the destination are distinct, there are multiple representations for the routing tag; hence there are multiple paths for routing the connection in the network.

# 2.5.5 Time-Redundancy for Dynamic Full Access

The techniques discussed above achieve their fault-tolerance by means of redundant hardware. An alternative approach to faulttolerance is obtained by means of redundancy in time. Thus, data may be routed in a unique-path network in the presence of faults by performing multiple passes through the network. When a fault-

FIG. 2.11 The gamma-network for N= 8

free path is not available, it may still be possible to route data from the input terminal to the output terminal in multiple passes by routing through intermediate destinations if the input and output terminals of the network are connected to the same set of nodes. This approach is useful when a unique-path network is used for processor-processor connection. The network is said to possess dynamic full access (DFA) capability if every processor in the system can communicate with every other processor in a finite number of passes through the network, routing the data through intermediate processing elements (PEs) if necessary [83]. Even though the failure of a single component destroys the full access capability of the omega network, a large number of faults do not destroy the DFA capability. Thus, by devising a routing procedure that allows routing through intermediate processors, connectivity of the system can be maintained.

It has been shown that the DFA capability is maintained under a large number of faults. A maximum of  $(\log_2 N - 2)$  passes through the network are shown to be sufficient for the communication between any two processors in the system for a network of size  $N \ge 32$  if the faults satisfy certain conditions [104]. The reconfigured system operates in a degraded mode owing to the increased latency and the additional blocking and congestion introduced by the loss of paths. However, a large waste of computational effort and resources associated with the reassignment of processors is prevented under this scheme.

## 2.6 CONCLUSION

In this chapter, unique-path and multipath multistage interconnection networks have been examined. Some of the commonly used techniques for providing fault-tolerance in the multistage interconnection networks were reviewed. These techniques are important in the design of fault-tolerant MINs. The next chapter describes the performance analysis of modular network (MN).

#### CHAPTER 3

#### MODULAR NETWORK

## 3.1 INTRODUCTION

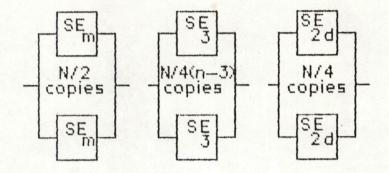

This chapter introduces a class of fault-tolerant statically reroutable regular multistage interconnection network named as modular network (MN). Scheme for augmenting unique-path multistage interconnection networks to create redundant paths between every source-destination pair is presented. The proposed modular networks are designed to have a number of identical independent unique-path MIN modules such that a connection path between each source-destination pair can be established through any of the modules. Although an individual component failure reduces MN performance, it does not cause a total network failure. In this chapter, the analyses pertaining to, performance that incorporates the effect of faults, cost and reliability/cost presented to provide a quantitative measurement of the are capabilities of MNs.

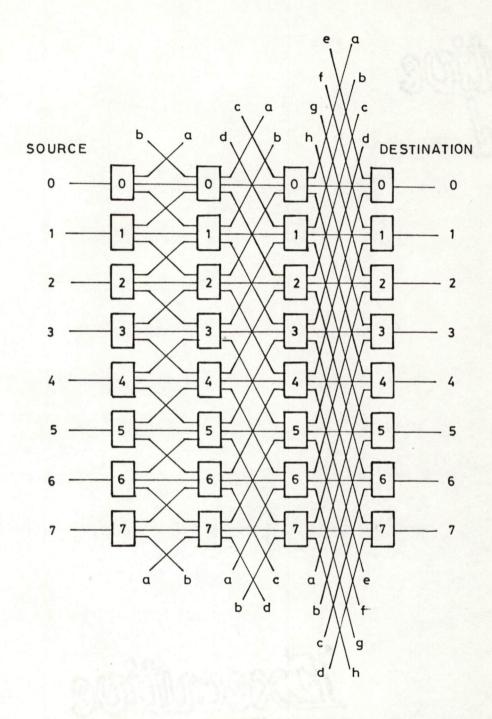

## 3.2 CONSTRUCTION

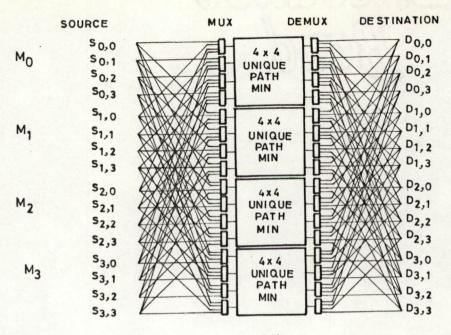

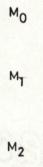

Modular network MN-k of size NxN is designed by interconnecting k disjoint subnetworks, each consisting of regular unique-path MIN of size N/kxN/k where k ( $\geq 2$ ) and N (> k) are the powers of 2. Although it is possible to have different types of regular unique-path MINs in each subnetwork but it is assumed that all the k subnetworks are of identical

type and each subnetwork consists of a baseline network [109] of size N/kxN/k. The sources and destinations are connected to each of k subnetworks through kx1 multiplexers and 1xk demultiplexers. Each subnetwork consisting of a unique-path MIN along with its associated multiplexers and demultiplexers is called a module, and are denoted as  $M_0, M_1, \ldots, M_{k-1}$ . Thus each module of MN-k consists of N/k number of kx1 multiplexers and an equal number of 1xk demultiplexers. Further, there are n (n =  $\log_2 N/k$ ) intermediate stages having (n - 1)N/k 2x2 crossbar switches.

A network resulting from this construction is named modular networks (MN-k). An example of MN-2 of size 8x8 and MN-4 of size 16x16 along with their redundancy graphs are illustrated in Figures 3.1 and 3.2 respectively. The above construction procedure of MNs can be applied to the networks consisting of rxr crossbar switches (where  $r \ge 2$ ).

#### 3.3 ROUTING

Let  $S_{i,j}$  and  $D_{m,n}$  denote the source j and destination n, which are associated with modules  $M_i$  and  $M_m$  respectively based on the partition  $0 \le i,m \le k-1$  and  $0 \le j,n \le N/k-1$  and are represented in mixed radix as :

> $S_{i,j} = s_i$ ,  $s_{(n-1)}$ ,  $\dots$ ,  $s_1 s_0$ .  $D_{m,n} = d_m$ ,  $d_{(n-1)}$ ,  $\dots$ ,  $d_1 d_0$ .

There are two ways of selecting a path between a particular source-destination pair of an MN-k, out of the k available paths. One way is the random selection of a path i.e a path is selected

S<sub>0,0</sub> D<sub>0,0</sub> 50,1 D 0,1 D 0,2 So, 2 50,3 D0,3 S1,0 D1,0 S1,1 D1,1 S1,2 D1.2 S1,3 D1,3 a(ii)

FIG. 3.1 (a) An MN-2 of size 8, showing U-Path MIN as (i) Blocks (ii) Baseline network (b) Its rendundancy graph

Мо

M

34

a(i)

M3

FIG. 3.2 (a) An MN-4 of size 16, showing U-Path MIN as (i) blocks (ii) Baseline network (b) Redundancy graph

randomly from the available paths, each path having equal probability of selection. As one of the paths become faulty, the number of available paths decreases. In this way, one can achieve a gracefull degradation of the performance, in case of faults. The other way is the preferred path i.e the path always chosen first by the source. For example, if a source needs to communicate with a destination  $D_{m,n}$ , the preferred path can be M<sub>m</sub> module i.e the request will be sent to the through corresponding multiplexer in Mm. If the preferred path is faulty (it is assumed that some techniques of fault diagnosis are available to detect and locate faults in the network [2]), the source then may try the path in one of the modules other than Mm. If that path is faulty too, the request will be submitted to an alternative path in another available module until all the paths are faulty. In this way, one can maintain a desirable performance level.

Assuming that the selection of a path out of the k available paths is already done at source, the request is submitted to the corresponding multiplexer of the selected path and the routing is as follows:

The routing tag in mixed radix representation is given as:

Routing tag =

$$d_n - 1 \cdots d_1 d_0 d_m$$

.

Bit  $d_i$  is in radix  $r_i$ , where ith stage of every module is built by using  $r_i x r_i$  crossbar switches and  $d_m$  is in radix k,  $0 \le i < n$ .

No tag bit is consumed at the multiplexer stage, because a multiplexer has only one output. After that the routing in the

intermediate stages of a module depends upon n tag bits i.e  $(d_{n-1} \cdot \cdot \cdot d_1 \cdot d_0)$ . The request progresses through the intermediate stages as the switch in stage i uses the tag bit  $d_i$ , the stages are numbered in sequence as  $n - 1, \ldots, 1, 0$  from left to right, to route the incoming request via the output link with the label  $d_i$ . Finally, the request arriving at the output stage of demultiplexers, is routed to the proper destination with the help of  $d_m$  bit. Notice that the routing algorithm is independent of the selection of a particular subnetwork.

From the description of the routing procedure, it is clear that MN-k delivers a request from a source to an arbitrary destination in the presence of (k-1) faults. This claim is logically stated as follows :

**Thoerem 1:** Routing tag delivers a request generated by a source to the correct destination tolerating up to (k-1) module faults.

#### 3.4 FAULT-TOLERANCE AND REPAIR

The fault-tolerance of an MN-k can be analysed by defining a critical set of components. A critical set of SEs in MN-k is defined as the set of k SEs, each from different modules and having the same position, such that a failure will occur if all the k SEs become faulty simultaneously. Thus, there are  $(N/2k.\log_2N/k + 2N/k)$  number of critical sets in MN-k. The following theorem characterizes the faults, that are always tolerated in MN-k.

Theorem 2: MN-k is k-1 fault-tolerant.

Proof: In the redundancy graph of MN-k, there are k paths

available between each source-destination pair. If the faults are such that they affect k-1 or fewer SEs in a critical set, there exists at least one fault-free path between any sourcedestination pair. Thus the fault-tolerance is k-1. Q.E.D. Theorem 3: MN-k possess full access capability.

**Proof:** Since MN-k provides k distinct paths for each sourcedestination pair through the k independent modules, so it is k-1 fault-tolerant. If there are k-1 or fewer faulty modules in an MN, at least one of the module is still fault free. As every module can provide a connection for any source-destination pair, the full access capability can be maintained.

The following repair scheme is proposed. If some faults develops in any module of MN-k, then the faulty module can be simply replaced by a new one. However, the overall operation of the network need not be disrupted, as the network can continue to operate at a reduced level of performance while it is being repaired. Thus the network is on-line repairable.

## 3.5 RELIABILITY ANALYSIS-Mean Time To Failure

A well known criterion used to measure the reliability of fault-tolerant networks is full access. Under the criterion of full access, a network is assumed to be faulty, if there is any source-destination pair that cannot be connected because of faulty components in the network. Under this criterion, the reliability of a network can be measured in terms of Mean Time to Failure (MTTF) of the network. The MTTF of a MIN, is defined as the expected time elapsed before some source is disconnected from

some destination. A fault model captures the assumed effects of physical failures on the operation of a system. Three fault models are used for MINs : the stuck-at fault model, the linkfault model, and the switch-fault model. In the stuck-at fault model, a failure causes a crossbar switch to remain in a particular state regardless of the control inputs given to it, thus affecting its ability to set up proper connections. The affected switch can be used to set up paths, if the stuck-at fault is also the required state. In the link-fault model, a failure affects an individual link of a switch, leaving the remaining part of the switch operational. In the switch-fault model, the strongest of the three, a failure makes a switch totally unusable. The switch-fault model is used for the analysis of MNs. It is assumed that any of the SEs i.e crossbar switches, multiplexers or demultiplexers in an MN can fail. In this section, the MTTF of MNs is analysed. The analysis is based upon the lower and upper bounds on the reliability of the networks. To make the analysis tractable, the following assumptions are made.

- i) Switch failures occur independently in a network with a failure rate of  $\lambda$  for 2x2 crossbar switches (a reasonable estimate for  $\lambda$  is about 10<sup>-6</sup> per hour [46]).

- ii) failures of multiplexers and demultiplexers also occur independently with failure rates of  $\lambda_m$  and  $\lambda_d$  respectively, which can be different from  $\lambda$ .

In general, more complicated components lead to higher failure rate. Assuming that the hardware complexity of a

component is directly proportional to the gate counts of it [70,99], one can derive a failure rate of the components.

Based on the gate counts of crossbar switches the number of gates in a 2x2 crossbar switch is approximately equal to that in a 4x1 MUX or in a 1x4 DEMUX. To simplify the analysis it can be assumed that  $\lambda_m = \lambda k/4$  for a kx1 MUX or  $\lambda_d$  ( $= \lambda_m$ ) for a 1xk DEMUX. The analysis for the upper bounds and lower bounds of MTTF are as follows:

## Upper Bound

For a system with reliability function  $R_s(t)$ , the MTTF is given by:

$$MTTF = \int_{0}^{\infty} R_{s}(t) . dt$$

$$R_{s}(t) = e^{-\lambda t}$$

for a SE

The probability R<sub>cs</sub>(t), that a critical set of SEs is not faulty is:

$$R_{cs}(t) = 1 - (1 - e^{-\lambda' t})^k$$

where

The probability that an MN-k is not faulty is:

$$R_{MN-k} = [1 - (1 - e^{-\lambda t})^{k}]^{Nn/2k} [1 - (1 - e^{-k\lambda t/4})^{k}]^{2N/k}$$

Thus, the upper bound of MTTF is :

$$MTTF_{MN-k} = \int_{0}^{\infty} R_{MN-k}(t) . dt$$

#### Lower Bound

Here each module is considered independently and is assumed to be faulty if there is any single fault in it. Since all the modules of an MN-k cannot be simultaneously faulty if the network is to retain its connection capability. Thus, a lower bound of MTTF can be obtained based on this condition and is given as :

$$MTTF_{MN-k} = \int_{0}^{\infty} [1 - (1 - e^{-(Nn/2k + N/2)\lambda t})^{k}] dt$$

## 3.6 COMPARISON WITH OTHER NETWORKS

In this section, the MTTF expressions for some of the known redundant path interconnection networks are computed and the results are compared with those of the MNs. The networks used for comparison are Extra Stage Cube (ESC), 3-replicated and INDRA (with R=2). Though baseline is not a fault-tolerant network, but it is used as a yardstick to measure the reliability improvement. The MTTF expression of these networks are also obtained in the same way as is obtained for MNs and are given below:

## 3.6.1 Baseline Network

Since any single fault leads to a network failure under the full access criterion, so the MTTF is:

$$MTTF_{baseline} = \int_{\sigma}^{\infty} [e^{-\lambda t}]^{N/2 * \log N} . dt$$

The lower bound and upper bound expressions are the same.

## 3.6.2 Extra Stage Cube (ESC) Network

## Upper Bound

In Extra Stage Cube (ESC) network , a critical set consists of each 2x2 switch with two multiplexers (or two demultiplexers) in the input stage (or output stage), as it will cause some source-destination pairs disconnected if the switch and any one of its two associated multiplexers (or demultiplexers) become faulty. For these critical sets, the probability (R<sub>cs</sub>) that a critical set is not faulty is :

$$R_{cs} = 1 - (1 - e^{-\lambda t}) * [1 - (e^{-\lambda t/2})^2] = 1 - (1 - e^{-\lambda t})^2$$

There are two disjoint paths for each source-destination pair, in the stages except the input and output stages because of the extra stage provided. It is assumed that a critical set for the stages other than input and output consists of two switches of the same stage and consider each stage independently, for an upper bound of MTTF. Thus, the MTTF is:

$$MTTF_{ESC} = \int_{0}^{\infty} [1 - (1 - e^{-\lambda t})^{2}]^{N/4} (\log_{2} N - 1) + N. dt$$

## Lower Bound

Here, the stages other than the input and output are modeled as two subnetworks, because it provides two independent paths for each source-destination pair. However, the input and output stages still need to satisfy the same condition as for the upper bound; the failure of any critical set of switch and two multiplexers (or demultiplexers) leads to the network failure. Thus, the lower bound of MTTF can be obtained by considering the case when at least one of the subnetworks is fault free and is given as:

$$MTTF_{ESC} = \int [1 - (1 - e^{-\lambda N/4} (\log_2 N - 1)t)^2] [1 - (1 - e^{-\lambda t})^2]^N dt$$

3.6.3 3-Replicated Network

## Upper Bound

In this network the critical set includes three switches on the same stage of each subnetwork. Thus, the MTTF is:

$$MTTF_{3-rep} = \int_{b} \left[1 - (1 - e^{-\lambda t})^{3}\right]^{N/2\log_2 N} dt$$

## Lower Bound

Here the sufficient condition for the network to be operative is that at least one of the subnetworks is fault free. Thus, the MTTF is:

$$MTTF_{3-rep} = \int_{0}^{\infty} [1 - (1 - e^{-\lambda N/2 \log_2 N \cdot t})^3] \cdot dt$$

## 3.6.4 INDRA Network

## Upper Bound

In this network a critical set contains two switches either on the same stage of each subnetwork or on the distribution stage of a particular subnetwork. So the MTTF is :

$$MTTF_{INDRA} = \int_{1-(1-e^{-\lambda t})^2}^{\infty} \frac{1}{2} \sqrt{2(\log_2 N+1)} dt$$

## Lower Bound

Since an INDRA network incorporates multiple copies of a basic network but prefaces the copies with a distribution stage of switches, the sufficient condition is that at least one of the switches in every switch pair in the distribution stage is not faulty, and at least one of the basic networks is fault free. Thus, the MTTF is:

$$MTTF_{INDRA} = \int_{0}^{\infty} [1 - (1 - e^{-N/2\log_{2} N \wedge t})^{2}] [1 - (1 - e^{-\lambda t})^{2}]^{N/2} dt$$

The ratios of the upper and lower bounds of MTTF for these fault tolerant networks to that of baseline network are shown in tables 3.1 and 3.2 respectively. From these tables it is clear that in most cases MNs perform more reliably than other networks.

## 3.7 COST ANALYSIS

In this section, the hardware cost and cost-effectiveness of MNs are computed and compared with some of the known redundant path interconnection networks. The networks used for comparison are ESC [1], 3-replicated [51], INDRA [75]. Though baseline [109] is not a fault-tolerant network, but it is used to measure the improvement in cost-effectiveness. To estimate the cost of a network, one common method is to calculate the switch complexity with an assumption that the cost of a switch is proportional to the number of gates involved, which is roughly proportional to

| Network<br>Size | MN-4   | MN-2   | ESC    | 3-Rep  | INDRA  |

|-----------------|--------|--------|--------|--------|--------|

| 16              | 1.3432 | 0.9026 | 0.7749 | 1.0336 | 0.6900 |

| 32              | 1.6138 | 1.0838 | 0.9779 | 1.2761 | 0.8843 |

| 64              | 1.8787 | 1.2624 | 1.1720 | 1.5142 | 1.0720 |

| 128             | 2.1397 | 1.4388 | 1.3590 | 1.7488 | 1.2550 |

| 256             | 2.3977 | 1.6133 | 1.5433 | 1.9805 | 1.4343 |

| 512             | 2.6532 | 1.7861 | 1.7231 | 2.2097 | 1.6107 |

| 1024            | 2.9066 | 1.9573 | 1.9000 | 2.4368 | 1.7847 |

Table 3.1: Ratio of upper bounds of MTTF for the fault-tolerant networks to that of baseline network.

Table 3.2

| Network<br>Size | MN-4   | MN-2   | ESC    | 3-Rep  | INDRA  |

|-----------------|--------|--------|--------|--------|--------|

| 16              | 5.5556 | 2.4000 | 3.3641 | 1.8333 | 1.4742 |

| 32              | 5.9524 | 2.5000 | 3.5177 | 1.8333 | 1.4911 |

| 64              | 6.2500 | 2.5714 | 3.5179 | 1.8333 | 1.4968 |

| 128             | 6.4815 | 2.6250 | 3.4707 | 1.8333 | 1.4988 |

| 256             | 6.6667 | 2.6667 | 3.4178 | 1.8333 | 1.4995 |

| 512             | 6.8182 | 2.7000 | 3.3709 | 1.8333 | 1.4998 |

| 1024            | 6.9444 | 2.7273 | 3.3317 | 1.8333 | 1.4999 |

Table 3.2: Ratio of lower bounds of MTTF for the fault-tolerant networks to that of baseline network.

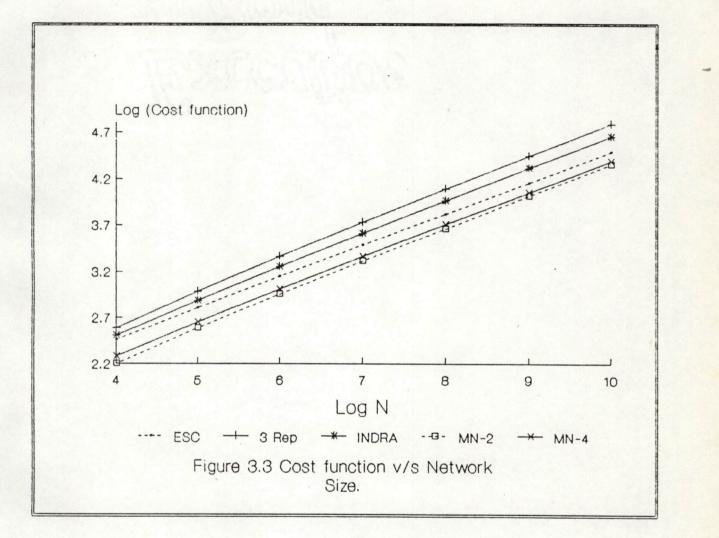

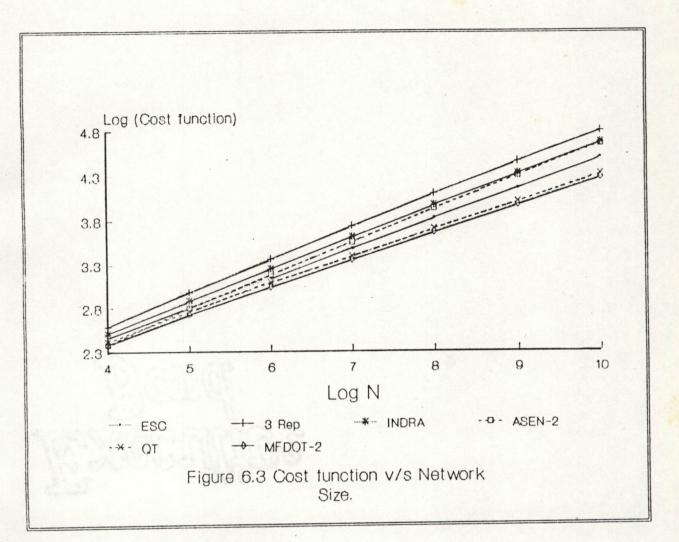

the number of `crosspoints' within a switch [70,99]. For example, a 4x4 switch has 16 units of hardware cost, whereas 2x2 switch has 4 units. For the multiplexers and demultiplexers, it is roughly assumed that each of kx1 multiplexers or 1xk demultiplexers has k units of cost. So an MN-k, ESC, 3-replicated, INDRA, and baseline have the costs of 2N(n + k), 2N(log<sub>2</sub>N+5), 6Nlog<sub>2</sub>N, 4N(log<sub>2</sub>N+1) and 2Nlog<sub>2</sub>N respectively. Graph shown in Figure 3.3 illustrates the variation of cost function with the size of the networks (2x2 switches). From the graph it is clear that MNs have lesser hardware cost than other faulttolerant networks.

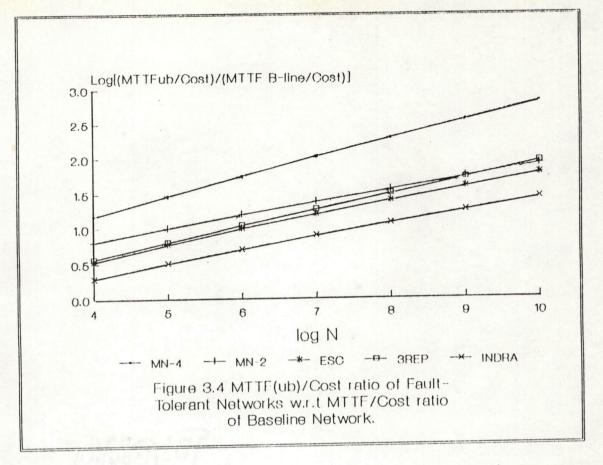

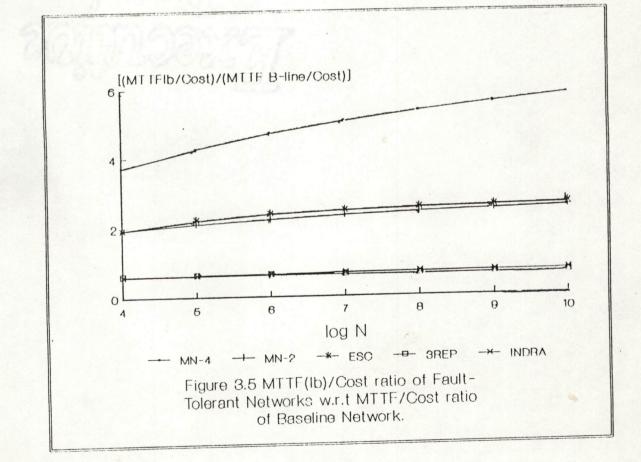

## 3.8 RELIABILITY/COST RATIO

A simple measure of the cost-effectiveness for reliability can be given by comparing MTTFs and the costs of these networks. Let the cost-effectiveness  $\eta$  of a network for reliability be the ratio of its MTTF to its cost. The MTTF/cost ratio of these networks relative to that of baseline network for both upper bound and lower bound are shown in Figures 3.4 and 3.5 respectively. From these graphs it is clear that MTTF/cost ratio of MNs are better than most other fault-tolerant networks.

## 3.9 PERFORMANCE MODEL

In this section, a model is described for circuit-switched MN performance. This model describes a numerical estimate of the probability that individual access requests can be successfully routed by an MN. The extension of this approach can be used to

evaluate network performance in the presence of faults. Previous work [19,44,75,76,99,103] employed probability of acceptance  $(p_a)$ and bandwidth as primary performance measures. Sometimes these measures are inadequate. For example, if the network provides interconnection for a multiprocessor system, a processor receiving degraded service would become a bottleneck in a parallel computation. In order to critically examine the network, a measure known as minimum reference probability is analyzed, apart from the conventional measures such as the probability of acceptance and the bandwidth. The following assumptions are made in the performance model [13,44,70].

## 3.9.1 Assumptions

- i) Sources (processors) generate requests independently. (different sources could generate requests with different probability.) Requests are mutually independent within a cycle. Blocked requests are ignored and are not resubmitted. Thus, requests in one cycle are independent of requests submitted in previous cycles. Even though this part of the assumption is unrealistic, previous analytical and simulation studies for similar systems show that not making this assumption changes the results only slightly while making the analysis much more complex [70].

- ii) Path setup time is negligible. The message time is equal to the network cycle time.

- iii) Request are generated for each destination (memories) with equal probability. Thus, traffic at every link is

symmetrical w.r.t the destinations i.e a request on any link in the network is equally likely to be intended for any possible eventual destination. Thus, incoming requests to a switch are routed to each intrastage output of the switch with equal probability.

iv) the analysis is based on preferred path routing algorithm.

## 3.9.2 Performance Analysis

In this section, the performance analysis of MNs under both fault free and fault present conditions are presented to provide a quantitative measurement of the capabilities of MNs. The measures of the network performance are probability of acceptance (defined as the probability that a request submitted successfully finds a path to the destination), bandwidth (defined as total number of requests that can be routed through the network in a cycle) and the minimum reference probability (defined as the minimum of the probability of reference among all the destinations).

The symmetry of the network is lost when faults are present. So the load is different at different locations in the network, and because of this the switches in a stage cannot be treated as identical. Thus, the performance seen by individual network sources and destinations need to be considered.

If p is the probability of request generation by a source, then the output probability at the jth multiplexer is given by:

$$p_{j} = 1 - \prod_{m} (1 - p_{m})$$

$m = 1 - \prod_{m} (1 - p_{m})$

$m = 1 - \prod_$

where

$$p_{m} = \begin{cases} p & \text{if } m = j \text{ div } (N \text{ div } k) \\ p/x & \text{if } m \neq j \text{ div } (N \text{ div } k) \end{cases}$$

x = ∞ if the module preceding the one of which jth MUX is a part i.e [ j div ( N div k) - 1 + k] mod k is non faulty.

As the output probability of a MUX becomes the input probability for a switch of stage (n-1), so the probability of presence of request at each input link of the switches of stage (n-1) are computed.

The distribution of traffic on the output links of a switch is calculated, given the distribution of traffic on its input links. Let  $p_i$  be the probability that a request is present at the ith input link of a switch and  $q_j$  be the probability that a request is present at the jth output link of a switch. Under a symmetric traffic assumptions all possible outputs are equally likely, so  $q_j$  is given by

$$q_j = 1 - \prod_i (1 - p_i/m)$$

. . . (2)

Where m represents the number of inputs and outputs of a switch.

If an input link or its associated switch is faulty, then its probability of carrying an input request is zero. If an output link is faulty or is connected to a faulty switch in the

next stage, then the probability of presence of request on that link is zero. The output probabilities would not change for the good links in the presence of faults. Since the output of a stage is the input to the next stage (except the first and the last stage), so the output probabilities can be recursively evaluated with the help of equation (2) starting from stage (n-1).

The requests which are blocked due to the faulty components in a module are to be routed by an alternate path through the first available alternate module having fault free paths corresponding to the faulty paths in the proceeding modules. So the input probabilities of the alternate module available for routing will increase to account for the additional load. The extra load in an alternate path is not uniformly directed to all the connected destinations. It is only directed to the SE which corresponds to the SE in the orginal path and thereafter it is directed uniformally to all the destinations. For a stage, if  $p_{j,extra}$  is the extra probability of request present at the input link of a switch and  $p_{j,normal}$  is the probability under fault free conditions at the jth input link of a switch, then the output probability at the ith link of the switch is given as:

$$q_{i} = 1 - \prod_{j} [1 - (p_{j,normal}/m + p_{j,extra})] \dots (3)$$

(for the output link to which the extra load is to be routed)

$$= 1 - \prod_{j \in \mathbb{N}} (1 - p_{j, \text{normal}}/m) \qquad \dots \qquad (4)$$

(for other output links)

The probability of presence of request at the output links of the switches of the final stage (i.e Oth stage) are the input probabilities for the demultiplexers. As there are no contention in the demultiplexers, so the probability of presence of request at each of the output links (leading to the destinations) is:

#

If it is fault-free, and zero if it is faulty. From these probability of presence of request for connection to different destinations, the sum of probabilities of having a connection request over all the destinations, the minimum of the probabilities of reference to any of the destinations are computed. The sum of the probabilities of all the destinations gives the bandwidth of MNs. From this the probability of acceptance of request  $(p_a)$  is calculated

## $p_a = Bandwidth/p.N$

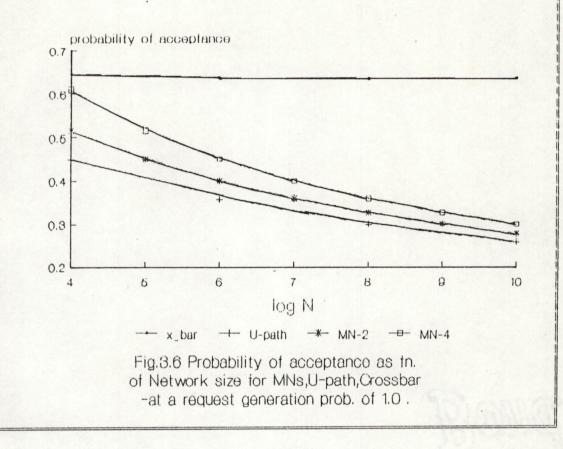

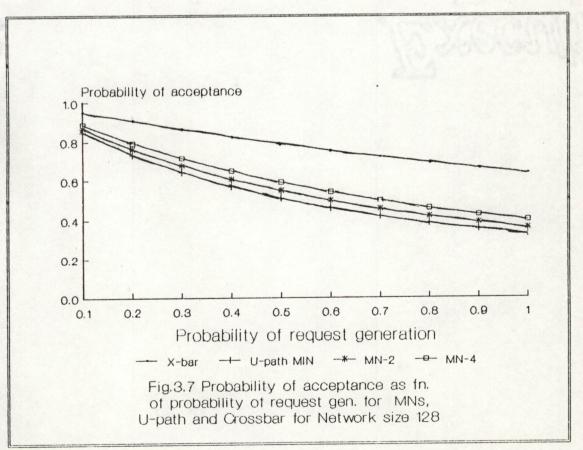

The results of the performance improvement of MNs over unique-path baseline network are shown in Figures 3.6 and 3.7. Figure 3.6 shows the variation of  $p_a$  with the size of network for request generation probability of 1.0. Figure 3.7 shows the variation of  $p_a$  with the traffic routed through the network for network size of 128 x128.

The effect of different types of fault on MN performance are illustrated by the following example.

#### Example

In this section, the effect of faults on the performance of MN of size 128 x 128 is evaluated under a variety of fault scenarios and for request generation probabilities of 1.0, 0.5, and 0.1. The performance is evaluated under the following conditions:

- i) No faults

- ii) a MUX fault

- iii) a switch fault

- iv) a DEMUX fault

- v) a module fault

For each category, the effect of fault in each stage of the network is analysed. In all there are ten performance models i.e no faults, a MUX fault, six different switch faults, a DEMUX fault and a module fault. The results of the performance are summarized in Tables 3.3, 3.4 and 3.5 for request generation probabilities of 1.0, 0.5 and 0.1 respectively. First column of each tables indicate the type of fault, II, III, V columns indicate the probability of acceptance, bandwidth and minimum reference probability respectively. Columns IV and VI show the percentage change in the probability of acceptance/bandwidth and minimum reference probability caused by each type of fault. The results show that the degradation in the probability of acceptance and bandwidth under such failures is very small O( 2% ).

Table 3.3

Network Size: 128 Prob. of req.generation by any processor: 1.00

| Sr. Fault<br>No. | Prob.of<br>acceptance | Bandwidt<br>% | h<br>change | Min.ref. pr | cob.<br>%change |

|------------------|-----------------------|---------------|-------------|-------------|-----------------|

| 1 No Fault       | 0.3594                | 46.00         | 0.0         | 0.3594      | 0.0             |

| 2 MUX            | 0.3594                | 46.00         | 0.0         | 0.3594      | 0.0             |

| 3 S5             | 0.3571                | 45.70         | 0.7         | 0.3571      | 0.7             |

| 4 S4             | 0.3564                | 45.61         | 0.8         | 0.3533      | 1.7             |

| 5 S3             | 0.3557                | 45.53         | 1.0         | 0.3445      | 4.1             |

| 6 S2             | 0.3550                | 45.44         | 1.2         | 0.3245      | 9.7             |

| 7 S1             | 0.3544                | 45.36         | 1.4         | 0.2795      | 22.2            |

| 8 S0             | 0.3538                | 45.28         | 1.6         | 0.1797      | 50.0            |

| 9 DEMUX          | 0.3566                | 45.64         | 0.8         | 0.1797      | 50.0            |

| 10 MODULE        | 0.1797                | 23.00         | 50.0        | 0.1797      | 50.0            |

(Si indicate the switch of ith stage)

## Table 3.4

Network Size: 128 Prob. of req.generation by any processor: 0.50

| r. Fault | Prob.of<br>acceptance | Bandwidt<br>% | h<br>change | Min.ref. p | rob.<br>%change |

|----------|-----------------------|---------------|-------------|------------|-----------------|

| No Fault | 0.5466                | 34.98         | -           | 0.2733     | -               |

| MUX      | 0.5466                | 34.98         | -           | 0.2733     | -               |

| S5       | 0.5435                | 34.78         | 0.6         | 0.2717     | 0.6             |

| S4       | 0.5422                | 34.70         | 0.8         | 0.2690     | 1.6             |

| 5 S3     | 0.5412                | 34.64         | 1.0         | 0.2626     | 3.9             |

| 5 S2     | 0.5403                | 34.58         | 1.1         | 0.2484     | 9.1             |

| S1       | 0.5395                | 34.53         | 1.3         | 0.2168     | 20.7            |

| S S0     | 0.5387                | 34.48         | 1.4         | 0.1476     | 46.0            |

| DEMUX    | 0.5426                | 34.73         | 0.7         | 0.1461     | 46.5            |

| O MODULE | 0.3271                | 20.93         | 40.2        | 0.1636     | 40.2            |

# Table 3.5

Network Size: 128 Prob. of req.generation by any processor: 0.10

| Sr.<br>No. | . Fault    | Prob.of<br>acceptance | Bandwidt)<br>% | n<br>change | Min.ref. p | prob.<br>%change |

|------------|------------|-----------------------|----------------|-------------|------------|------------------|

| 11         | No Fault   | 0.8668                | 11.10          | -           | 0.0867     | -                |

| 2          | MUX        | 0.8668                | 11.10          | _           | 0.0867     | _                |

| 3          | <b>S</b> 5 | 0.8651                | 11.07          | 0.2         | 0.0865     | 0.2              |

| 4          | S4         | 0.8641                | 11.06          | 0.3         | 0.0861     | 0.6              |

| 5          | S3         | 0.8633                | 11.05          | 0.4         | 0.0853     | 1.6              |

| 6          | S2         | 0.8625                | 11.04          | 0.5         | 0.0832     | 4.0              |

| 7          | S1         | 0.8618                | 11.03          | 0.6         | 0.0787     | 9.2              |

| 8          | SO         | 0.8612                | 11.02          | 0.7         | 0.0686     | 20.9             |

| 9          | DEMUX      | 0.8639                | 11.06          | 0.3         | 0.0678     | 21.7             |

| 10         | MODULE     | 0.7321                | 09.37          | 15.5        | 0.0732     | 15.5             |

Further, the performance results show that, though, faults do not significantly reduce the average performance (i.e probability of acceptance and bandwidth), the performance degradation seen by individual memories is large. Faults closer to the memories affect lesser number of memories, but affect them more strongly. If a module is faulty then the performance is reduced by 50% (for request generation probability of 1.0), but for light traffic (for request generation probability of 0.1) even module fault does not affect much, maximum degradation is less than 22%. Also faults closer to the sources affect more number of destinations, but affect them mildly. However, the associated sources though lesser in number are affected very badly as the sources find it increasingly difficult to route their requests because of faults.

## 3.10 CONCLUSION

In this chapter, a class of regular fault-tolerant multistage interconnection networks named as modular networks (MNS) has been proposed. It has been shown that reliability/cost ratio of MNs is better than that of most other fault-tolerant networks. Further, MNs provide higher probability of acceptance and bandwidth than those of unique path networks. The effect of faults on the performance of MNs has also been analysed. It has been shown that faults do not significantly affect overall network performance, but still severely degrade the performance of some parts of the system. As the number of faults increase, the performance of MNs decreases. However, for light traffic and

small size networks the performance degradation is not significant. Hence, the proposed modular networks are quite attractive for low traffic and small size networks.

#### CHAPTER 4

## AUGMENTED BASELINE NETWORK

## 4.1 INTRODUCTION

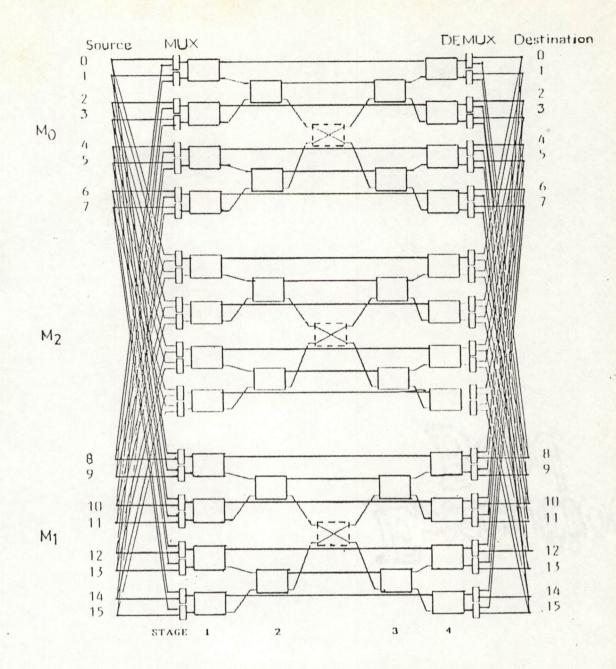

This chapter introduces a class of dynamically reroutable regular fault-tolerant multistage interconnection network named as augmented baseline network (ABN), which can achieve significant tolerance to faults and good performance with relatively low cost and simple control scheme. The proposed ABN technique results in reduced number of stages compared to the previously proposed fault-tolerant MINS. Fault-tolerance in ABN is achieved by chaining switches within a stage. The characteristics of ABN pertaining to performance, reliability and cost-effectiveness are analyzed.

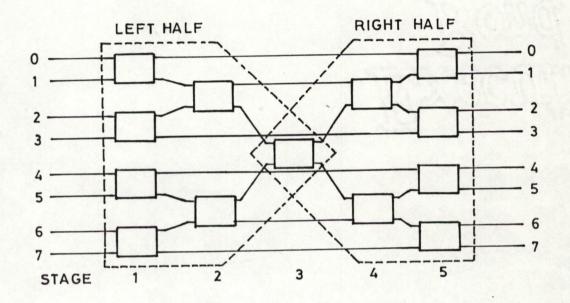

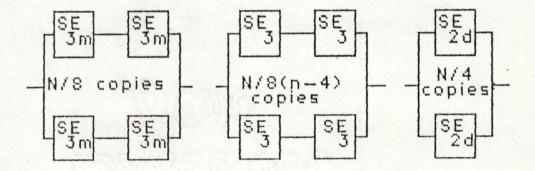

## 4.2 CONSTRUCTION

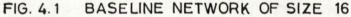

To construct an ABN of size NxN i.e with N sources and N destinations, two identical groups of N/2 sources and N/2 destinations need to be formed first. Each group consists of a multiple path, modified baseline network of size N/2. The modified baseline network is a baseline network with one less stage, and feature links among switches belonging to the same stage and forming several loops of switches. The switches in the last stage are of size 2x2 and the remaining switches in stages 1 through n-3 (n =  $\log_2 N$ ) are of size 3x3. In each stage, the switches can be grouped into conjugate pairs i.e each switch in

such a pair has the same successor switches in the next stage. These conjugate pairs can then be grouped into conjugate subsets, where a conjugate subset is composed of all switches in a particular stage that lead to the same subset of destinations. The modified baseline network achieves the multiple path property by permitting two switches in the same conjugate subset that are not a conjugate pair to communicate through auxiliary links. The switches which communicate through the use of auxiliary links form a loop. The conjugate loops are formed in such a way that the two switches which form a loop have their respective conjugate switches in a different loop.

Each source is connected to both the groups via multiplexers. There is one 4x1 MUX for each input link of a switch in stage 1 and one 1x2 DEMUX for each output link of a switch in stage n-2. Each group consisting of a modified baseline network of size N/2 x N/2 plus its associated multiplexers and demultiplexers is called a subnetwork. Thus an ABN consists of two identical subnetworks which are denoted by  $G^{i}$ . The switches in a stage of a subnetwork are being numbered from top to bottom as  $0,1,\ldots,(N/4 - 1)$ . For example, in Figure 4.2, switches 0,1,2,3 belonging to stage 1 of a subnetwork  $(G^{i})$  form a conjugate subset; within that subset, switches 0 and 1 form a 1,3 form conjugate loops.

Let the source S and destination D be represented in binary code as:

$$S = s_0 \cdot s_1 \cdot \dots \cdot s_{n-2} \cdot s_{n-1}$$

$D = d_0 \cdot d_1 \cdot \dots \cdot d_{n-2} \cdot d_{n-1}$

A source selects a particular subnetwork ( $G^i$ ) based upon the most significant bit of the destination i.e i =  $d_0$ . As there are two paths between a source-destination pair, so each source is connected to the two switches (primary and secondary) in a subnetwork. The sources are connected to the switches of stage 1 as follows:

- A source S is connected to the (s<sub>1</sub>....s<sub>n-2</sub>) primary switch in both the subnetworks through the multiplexers.

- ii) A source S is also connected to the[{(s<sub>1</sub>...s<sub>n-2</sub>)+1}mod N/4] secondary switch in both the subnetworks through the multiplexers.

Thus an ABN of size NxN consists of N 4x1 multiplexers, N 1x2 demultiplexers, and n-2 stages of N/2 switches each (the last stage has 2x2 switches and the remaining stages have 3x3 switches). Observe that this construction procedure has two benefits. First, the network can tolerate the failure of any switch in the network. Second, it provides a topology which lends itself to on-line repair and maintainability, as a loop can be removed from any stage of the ABN without disrupting the operation of the network. Since the subnetworks are identical, so VLSI implementation of the network becomes simple. The

construction procedure given in this section can be applied to a broad class of unique-path networks which are topologically equivalent [4,67,109]. A network resulting from his construction is called augmented baseline network (ABN).

An ABN of size 16x16 along with its redundancy graph is illustrated in Figure 4.2 and the multiple paths between S=0000 and D=0100, and between S=0000 and D=1001 are being highlighted in Figure 4.3. A baseline network is already given in section 2.3 and is again shown in Figure 4.1 for comparison with ABN.

#### 4.3 ROUTING SCHEME

In this section, the routing scheme of ABN is considered in the case that each source-destination pair tries to utilize only one path at a time. The non-backtracking scheme given below is easy to implement and performs quite well. This scheme assumes that sources and switches have the ability to detect faults in the switches to which they are connected. Faults in MINs can be detected by the application of test inputs [3,30], or by employing concurrent error-detection at the network level or at the switch level [33]. The ABNs are self routing. A request from any source S to a given destination D is routed through the ABN as:

- i) The source S selects one of the subnetwork  $G^{i}$  based on the most significant bit of the destination D (  $i=d_{0}$  ).

- ii) There are two paths i.e primary and secondary, between each source-destination pair. Each source attempts entry into the ABN via its primary path. If the primary path is faulty (i.e

(a)

FIG. 4.2 (a) AN ABN OF SIZE 16 (b) THE REDUNDANCY GRAPH

FIG. 4.3 An ABN of size 16, highlighting the multiple paths between S-D pair

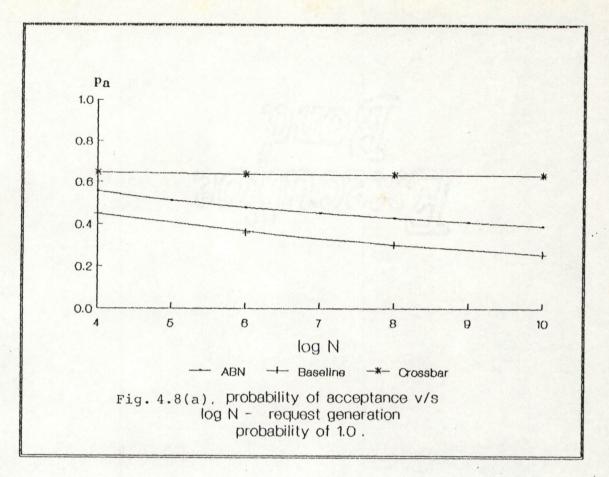

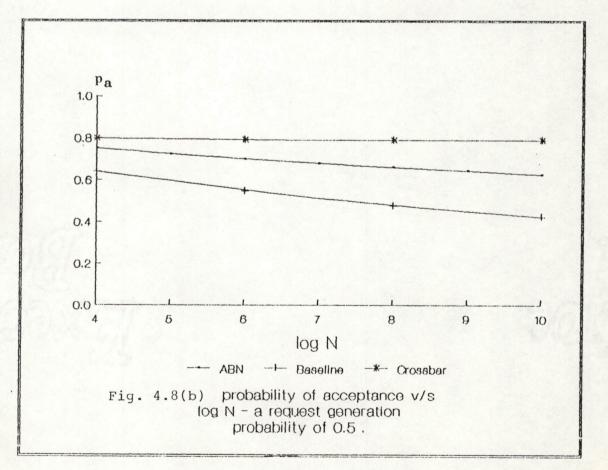

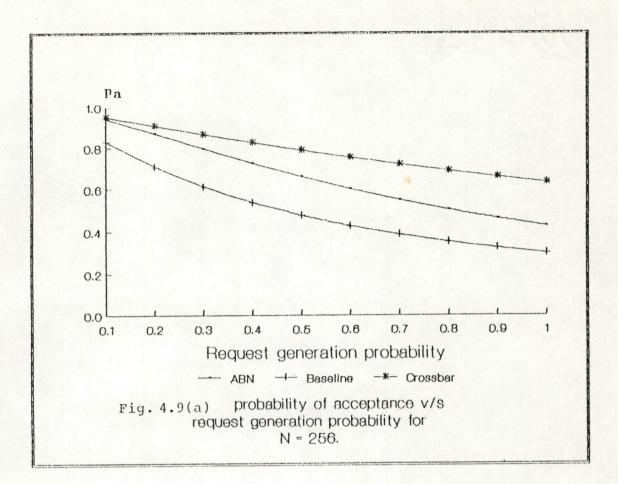

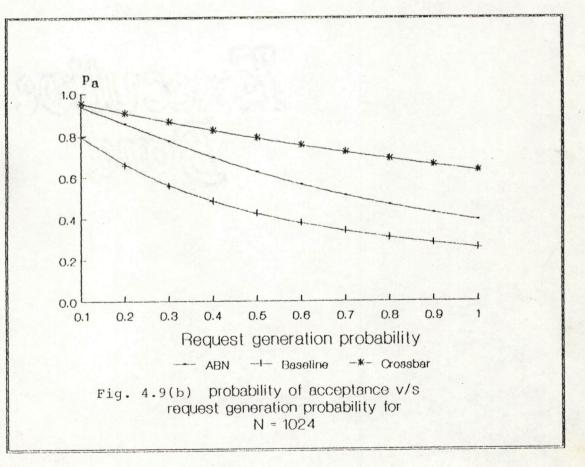

either MUX or primary switch or both are faulty), then the request is routed to the secondary path. If the secondary path is also faulty, then the ABN is failed.