# ON SOME DESIGN ASPECTS OF INTERCONNECTION NETWORKS FOR TIGHTLY COUPLED MULTIPROCESSOR SYSTEMS

## A THESIS

submitted in fulfilment of the requirements for the award of the degree of DOCTOR OF PHILOSOPHY in ELECTRONICS AND COMPUTER ENGINEERING

by

## E. VENKATESWARA PRASAD

Acc. No.

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247667 (INDIA)

**AUGUST, 1988**

Dedicated

TO MY PARENTS Smt. E. KAMESWARI AND Sri E. SRIRAMA MURTI

#### CANDIDATE'S DECLARATION

I here by certify that the work which is being presented in the thesis entitled 'ON SOME DESIGN ASPECTS OF INTERCONNECTION NETWORKS FOR TIGHTLY COUPLED MULTIPROCESSOR SYSTEMS' in fulfilment of the requirement for the award of the Degree of Doctor of Philosophy, submitted in the Department of Electronics & Computer Engineering of the University is an authentic record of my own work carried out during a period from August 1985 to August 1988 under the supervision of Dr.Suresh Rai and Dr.A.K.Sarje.

The matter embodied in this thesis has not been submitted by me for the award of any other Degree.

Date:

#### (E.V.PRASAD)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

Sursh Rn' (Dr. SURESH RAI) Reader

(Dr. A. K ÁRJE) Professor

The candidate has passed the viva-voce examination held on at . The thesis is recommended for award of the Ph.D.Degree.

1. Suresh Ra (Guide)

1. (External Examiner)

2.

(Guide)

#### ABSTRACT

Tightly connected multiprocessor systems (MPSs) are Characterized by the presence of several autonomous processors sharing multiple memory modules via some interconnection network. Since both the basic elements, processors and memory modules, are available as standard integrated circuits, the key design problem is how to put them together so that the system is efficient and reliable. The present work is a study of the interconnecting structures covering both design and analysis aspects. The interconnection networks (INs) considered are a) multiple bus b) crossbar c) multiport memory and d) multistage interconnection network. Methodologies are presented for the design of MPs by considering a variety of performance measures as no single measure gives a truly accurate estimate of the system performance. The criteria considered are : processor - memory interference, fault tolerance and some fundamental measures such as waiting time and hardware utilization.

In the design of an MPS there exists enormous number of alternative decisions. In this thesis, the major design parameters that are allowed to vary for a given architecture are number of processors, memory modules, interconnection links, and the parameters of the computation being executed, such as the memory request probability (MRP) and memory access probabilities (MAP's). The performance of multiple-bus IN for MPS is analyzed taking into account conflicts arising from memory and bus interference. Given the number of processors, the number of memory modules, the MRP and the MAP's, the model produces as output the memory bandwidth, processor utilization, memory utilization, channel utilization and waiting time of a processor while waiting to access a memory module.

Using this model it is possible to analyze the effect of input parameters on the system performance. The model presented differs from other models in its ability to allow generalized processoor demand patterns for memory access with processors of equal memory request probabilites. This model also examines the following three situations : when a memory module is equally likely to be addressed by all processors, when each processor has a different favourite memory and when all processors have the same favourite memory.

Crossbar is a special case of this analysis. The closed form solutions are compared with simulation results. This analysis is extended to partially connected bus and also to Delta Network, a multistage interconnection network.

The modeling technique adapted for the analysis is based on t-out-of-s system principle. Algorithms for computing the exact system reliability of t-out-of-s systems are proposed. These are simple, easy to implement, fast and memory and time efficient.

ii

The two types of real time systems, failure-critical and non failure-critical are considered. Using failure-critical models expressions for multiple-bus, crossbar and multiport memory INs are derived for the criterion, multiprocessing and terminal reliabilities. A technique for computing multiprocessor reliability through explicit path enumeration is also proposed. Non failure-critical models for the analysis of multiprocessing reliability and bandwidth availability are made, where coverage factors take into account the reconfiguration process for a graceful degradation in persence of failure of system components. The INs considered for analysis are multiple-bus and crossbar.

#### ACKNOWLEDGEMENT

I wish to express my deep appreciation and profound gratitude for the continuous interest taken and encouragement given by Dr.Suresh Rai and Dr.A.K.Sarje, who supervised this work. Dr.Rai's active association in the initial phase before he left to USA and regular dispatches of research material, comments and suggestions through correspondence after, had been a great help and it gives me pleasure to acknowledge him. My heartfelt thanks are due to Prof. Sarje, for his invaluable guidance, painstaking supervision, keen personal interest and meticulous scrutiny which have immensely contributed towards the successful completion of this thesis.

I express my sincere thanks to Dr.N.K.Nanda, the former Head of the Department and Dr.R.Mitra, the present Head of the Department of Electronics and Computer Engineering for informal working conditions and their encouragement.

It won't be out of place to acknowledge the financial support from the QIP scheme of Govt. of India, Ministry of Human Resources and the JNT University, Hyderabad for sponsoring the author to pursue the work. My sincere thanks go to my colleagues and Dr. M. Subbarayudu, the Head of the Deparment of Electronics and Communication Engineering, J.N.T.U. College of Engineering, Anantapur (AP) for sharing my load during my absence.

iv

It is a pleasure to acknowledge a great deal of assistance received from my friends, academic or otherwise, particularly A.U.Ravi Sankar, J.Ravi Sankar, N.S.Krishna Mohan and P.Vinod Kumar at the time of preparation of this Thesis. Thanks are due to Y.R.Singh, S.Maheswari, A. K. Singh and UPPER GANGES SYSTEMS for neat typing of the manuscript.

Task of undertaking a research involves a sacrifice on the part of many. In this connection, I would like to express my deep gratitude to my life partner, Lakshmi, for extending constant encouragement, moral support and complete cooperation throughout the course of this work. I owe a debt of gratitude to my daughters Sri Vidya, Sri Vani and Sri Valli for their patient understanding and for granting lot of time that was due to them.

As always, I owe more to my beloved parents than words can express.

#### E.V. PRASAD

## CONTENTS

|            |     | Title                             | Page No. |

|------------|-----|-----------------------------------|----------|

|            |     | ABSTRACT                          | i        |

|            |     | ACKNOWLEDGEMENT                   | iv       |

|            |     | TABLE OF CONTENTS                 | vi       |

|            |     | LIST OF TABLES                    | ix       |

|            |     | LIST OF FIGURES                   | x        |

|            |     | NOTATIONS AND ACRONYMS            | xii      |

| CHAPTER I  | INT | TRODUCTION                        | 1        |

|            | 1.1 | PARALLEL PROCESSING -AN IDEA      | .1       |

|            |     | 1.1.1 Device Technology           | 2        |

|            |     | 1.1.2 Processing Technology       | 2        |

|            |     | 1.1.3 Taxonomics                  | 4        |

|            |     | 1.1.4 Multiprocessing systems     | 5        |

|            | 1.2 | PROBLEM FORMULATION               | 8        |

|            | 1.3 | STATEMENT OF THE PROBLEM          | 9        |

|            | 1.4 | OUTLINE OF THE THESIS             | 10       |

| CHAPTER II | DE  | SIGN OF MPS- AN OVERVIEW          | 11       |

|            | 2.1 | Interconnection Networks          | 11       |

|            |     | 2.1.1 Time shared Multiple- Bus   | 12       |

|            |     | 2.1.2 Crossbar Switch             | 15       |

|            |     | 2.1.3. Multiport Memory System    | 15       |

|            |     | 2.1.4 Multistage Interconnection  | 15       |

|            |     | Networks (MINs)                   |          |

|            |     | 2.1.5 Operational Characteristics | 17       |

|            | 2.2    | SYSTEM  | EVALUATION                       | 19 |

|------------|--------|---------|----------------------------------|----|

|            |        | 2.2.1   | Evaluation Techniques            | 19 |

|            |        | 2.2.2   | t-out-of-s System:Modeling       | 23 |

|            | 2.3    | PERFOR  | MANCE EVALUATION CONSIDERATION   | 23 |

|            | 2,4    | FAULT   | TOLERANCE SYSTEM CONSIDERATION   | 24 |

|            |        | 2.4.1   | Reliability                      | 25 |

|            |        | 2.4.2   | Bandwidth Availability           | 27 |

|            |        | 2.4.3   | Evaluation Techniques-Review     | 27 |

|            | 2.5    | CONCLU  | SION                             | 29 |

| CHAPTER II | I MULT | IPROCES | SOR SYSTEM RELIABILITY           | 30 |

|            | 3.1    | MULTIP  | ROCESSING RELIABILITY            | 34 |

|            |        | 3.1.1   | Primary Method                   | 34 |

| t.         |        | 3.1.2   | Construction of Connection       |    |

|            |        |         | Matrix                           | 34 |

|            |        | 3.1.3   | Reduction of the Connection      |    |

|            |        |         | Matrix                           | 38 |

|            |        | 3.1.4   | Enumeration of Events            | 39 |

|            |        | 3.1.5   | Reliability Computation          | 43 |

|            | 3.2    | t-out-  | of-s SYSTEMS                     | 44 |

|            |        | 3.2.1   | Previous Works: A Review         | 45 |

|            |        | 3.2.2   | Theory                           | 47 |

|            |        | 3.2.3   | Algorithm Development            | 49 |

| - 28       |        | 3.2.4   | An Efficient Recursive Algorithm | 55 |

|            |        | 3.2.5   | Non-Recursive Approach           | 59 |

|            |        | 3.2.6   | Comparisons                      | 62 |

|            | 3.3    | RELIAB  | ILITY MODELING                   | 66 |

|            |        | 3.3.1   | Multiprocessing Reliability      | 66 |

|            | 1     | 3.3.2 Terminal Reliability           | 74  |

|------------|-------|--------------------------------------|-----|

|            | 3.4   | CONCLUSION                           | 76  |

| CHAPTER IV | PERF  | DRMANCE EVALUATION                   | 78  |

|            | 4.1   | CHARACTERISTICS OF MULTIPROCESSORS   | 78  |

|            | 4.2   | REVIEW OF EXISTING MEMORY            |     |

|            |       | INTERFERENCE MODELS                  | 82  |

|            | 4.3   | ASSUMPTIONS                          | 85  |

|            | 4.4   | MEMORY INTERFERENCE- ANALYSIS        | 86  |

|            |       | 4.4.1 Uniform Reference Model        | 88  |

|            |       | 4.4.2 Local Reference Model          | 97  |

|            | 1     | 4.4.3 Partial Bus System             | 107 |

|            |       | 4.4.4 Errors in Bandwidth Analysis   | 113 |

|            | 4.5   | FUNDATMENTAL MEASURES                | 114 |

|            | 4.6   | DELTA NETWORK                        | 120 |

|            | 4.7   | CONCLUSION                           | 127 |

| CHAPTER V  | FAUL  | T TOLERANCE                          | 128 |

| 1.4        | 5.1   | MULTIPLE-BUS SYSTEM                  | 130 |

|            | 5.2   | CROSSBAR SYSTEM                      | 132 |

|            | 5.3   | PARTIAL-BUS System                   | 132 |

|            | 5.4   | CONCLUSION                           | 134 |

| CHAPTER VI | CONCL | USIONS AND SCOPE OF FUTURE WORK      | 135 |

|            | 6.1   | SUMMARY AND CONCLUSIONS              | 135 |

|            | 6.2   | SUGGESTIONS FOR FUTURE INVESTIGATION | 138 |

|            |       |                                      |     |

BIBLIOGRAPHY

## LIST OF TABLES

. 1

| Table 3.1  | Variants of conservative policy                                                                                                | 48  |

|------------|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2  | Computation of Gj and H(s,t) of Example 3.7                                                                                    | 60  |

| Table 4.1  | BW of n X k X z multiple-bus MPs obtained<br>by simulation (URM)                                                               | 90  |

| Table 4.2  | BW of n x k x z multiple bus calculated<br>from equation 4.7(URM)                                                              | 91  |

| Table 4.3  | Percentage difference between calculated<br>(Table 4.2) and simulated values (Table<br>4.1) of BW of a multiple- bus MPS (URM) | 94  |

| Table 4.4  | BW of n x k crossbar MPS obtained from Eq. 4.8 with $r = 1.0$ (URM)                                                            | 95  |

| Table 4.5  | BW of n x k crossbar MPS obtained from Eq. 4.8 with $r = 0.5$ (URM)                                                            | 96  |

| Table 4.6  | BW of n x k crossbar with $r = 1.0$ , URM (Theoretical, simulation and % error)                                                | 96  |

| Table 4.7  | BW of $n \times k \times z$ multiple-bus with $\alpha = 0.8$ (UBRM)                                                            | 100 |

| Table 4.8  | BW of n x k crossbar MPS with $\alpha$ =0.8 (UBRM)                                                                             | 101 |

| Table 4.9  | BW of n x k x z multiple-bus MPS with $m = 0.8$ (NURM)                                                                         | 104 |

| Table 4.10 | BW of n x k crossbar MPS with m = 0.8<br>(NURM)                                                                                | 105 |

| Table 4.11 | Bandwidth of n x k x z partial-bus MPS obtained from Eq. 4.15 with $r = 1.0$                                                   | 111 |

| Table 4.12 | BW of partial bus: Comparison of analytical<br>results with simulation results with r=1.0<br>(URM)                             | 112 |

| Table 4.13 | Bus utilization in 8X8Xz configuration (URM)                                                                                   | 119 |

| Table 4.14 | Inputs to switches of two stage Delta<br>network                                                                               | 125 |

## LIST OF FIGURES

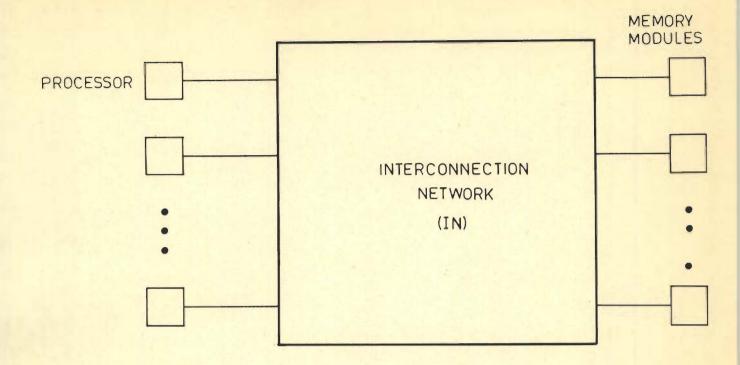

| Fig | 1.1  | A general structure of MPS                                           | 7  |

|-----|------|----------------------------------------------------------------------|----|

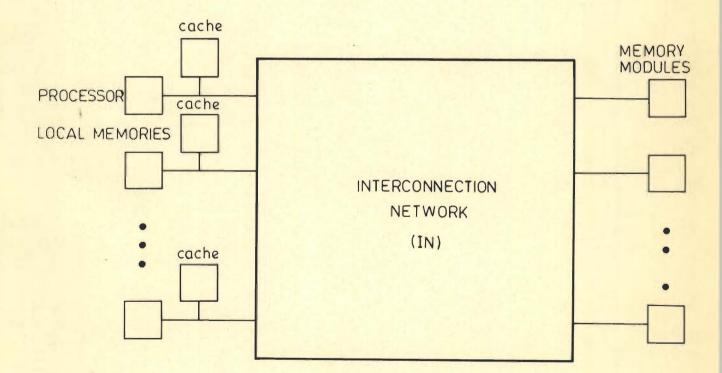

| Fig | 1.2  | A general structure of MPS with local memory                         | 7  |

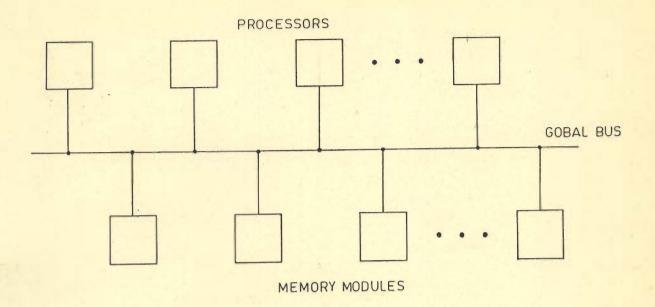

| Fig | 2.1  | Single bus multiprocessors organization                              | 13 |

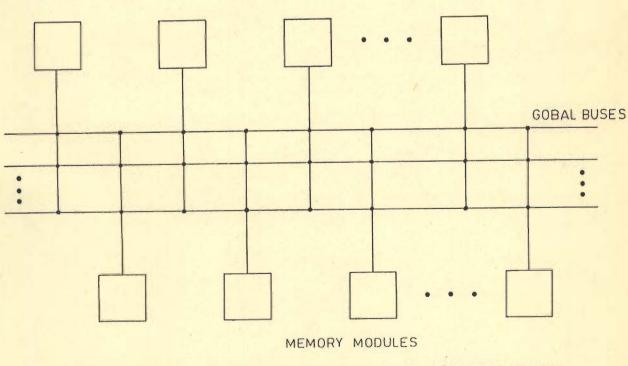

| Fig | 2.2  | Multiple-bus multiprocessor organization                             | 13 |

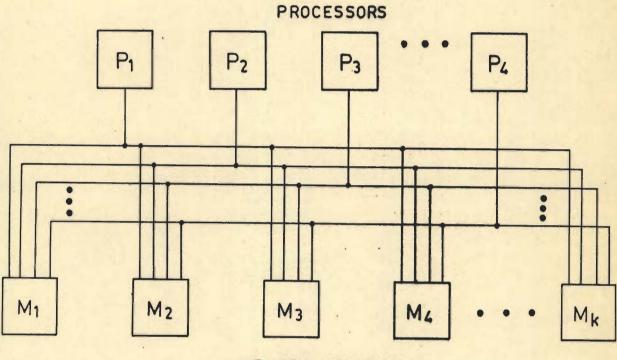

| Fig | 2.3  | Partial-bus multiprocessors organization                             | 14 |

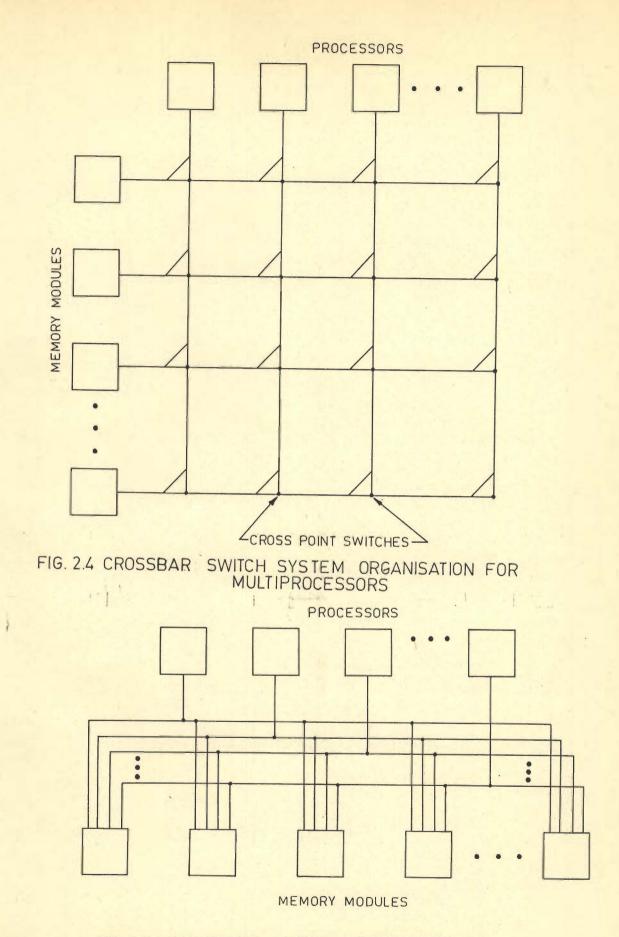

| Fig | 2.4  | Crossbar switch organization for multiprocessors                     | 16 |

| Fig | 2.5  | Multiport memory organization                                        | 16 |

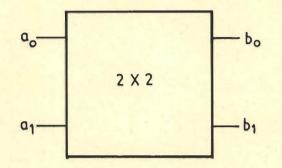

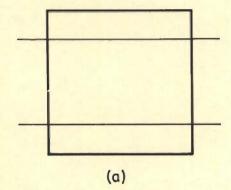

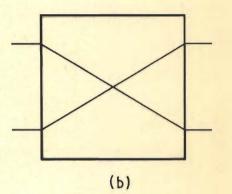

| Fig | 2.6  | 2X2 Switching element (a) Straight connection (b) Crossed connection | 18 |

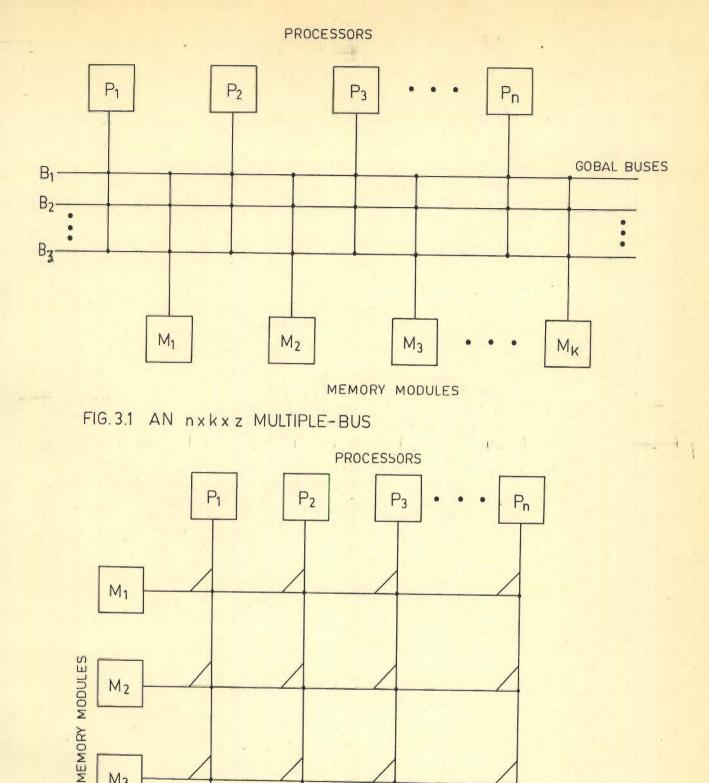

| Fig | 3.1  | An nXkXz multiple-bus                                                | 32 |

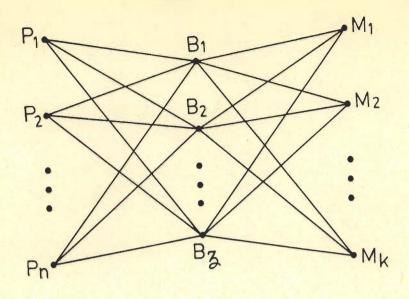

| Fig | 3.2  | An nXk crossbar multiprocessor                                       | 32 |

| Fig | 3.3  | A k n-ported memory system                                           | 33 |

| Fig | 3.4  | Graph representation of multiple-bus MPS                             | 35 |

| Fig | 3.5  | Graph respressentation of crossbar<br>swithched MPS                  | 35 |

| Fig | 3.6  | Graph respressentation of multiport memory<br>MPS                    | 36 |

| Fig | 3.7  | Connection matrix 3X3 crossbar MPS                                   | 37 |

| Fig | 3.8  | Connection matrix of 3-port memory MPS                               | 37 |

| Fig | 3.9  | Connection matrix of 3X3X2 multiple-bus MPS                          | 38 |

| Fig | 3.10 | Connection matrix of 2X2 crossbar system                             | 43 |

| Fig | 3.11 | Tableau associated with H(X;s,t) computation using Theorem 3.1       | 50 |

| Fig | 3.12 | Tableau associated with H(X;s,t) computation using Theorem 3.3       | 52 |

| Fig | 3.13 | Algorithm 3.3                                                        | 53 |

| Fig | 3.14 | Algorithm 3.4                                                        | 54 |

| Fi  | g 3.15 | Algorithm 3.5                                                            | 57               |

|-----|--------|--------------------------------------------------------------------------|------------------|

| Fi  | g 3.16 | Tableau associated with H(X;s,t-s) computation using Theorem 3.1         | 61               |

| Fi  | 3.17   | Algorithm 3.6                                                            | 63               |

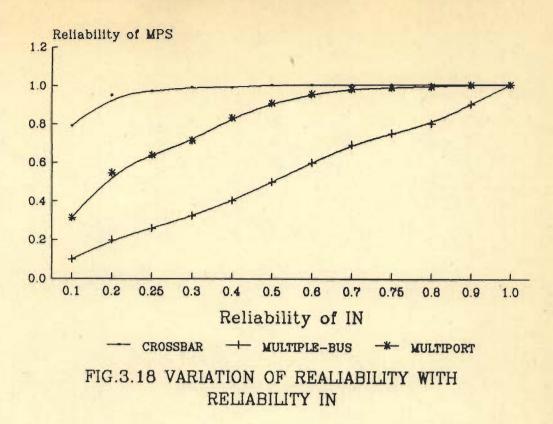

| Fi  | g 3.18 | Variation of MPS reliability on reliability of IN                        | 72               |

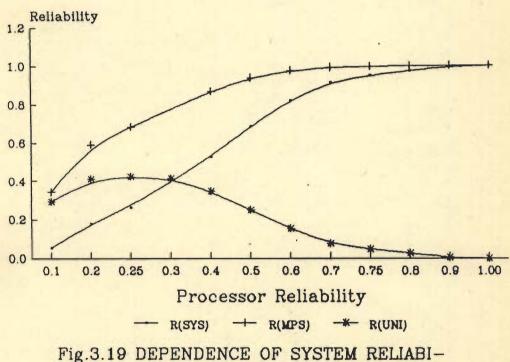

| Fi  | 3.19   | Dependence of System reliability criteria<br>processor reliability       | o <b>n</b><br>72 |

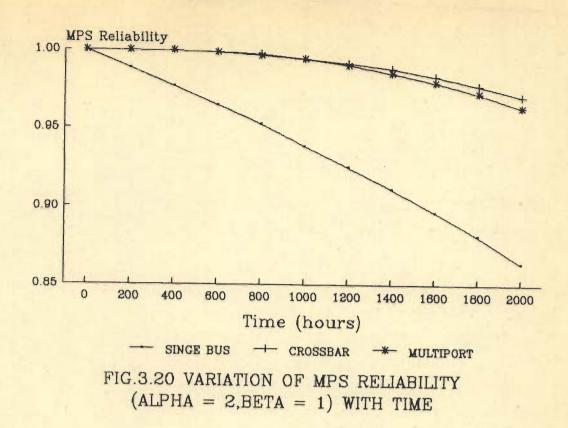

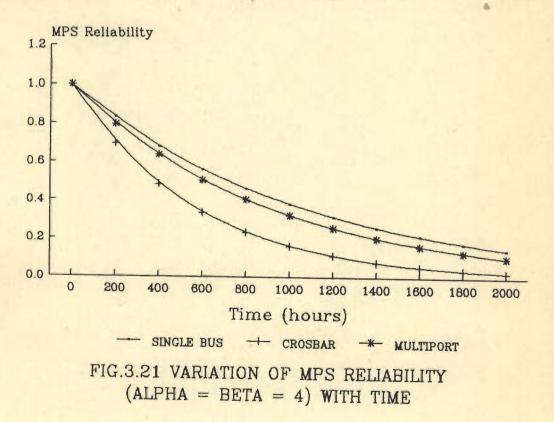

| Fi  | 3.20   | Variation of MPS reliability ( $\alpha=2,\beta=1$ ) with time            | 73               |

| Fi  | g 3.21 | Variation of MPS reliability (q=B=4) with time                           | 73               |

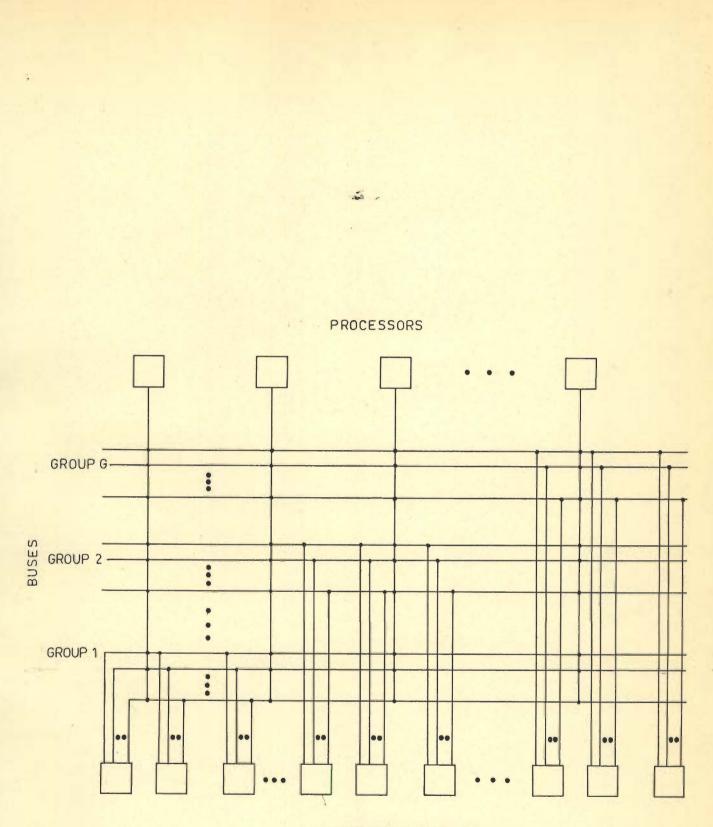

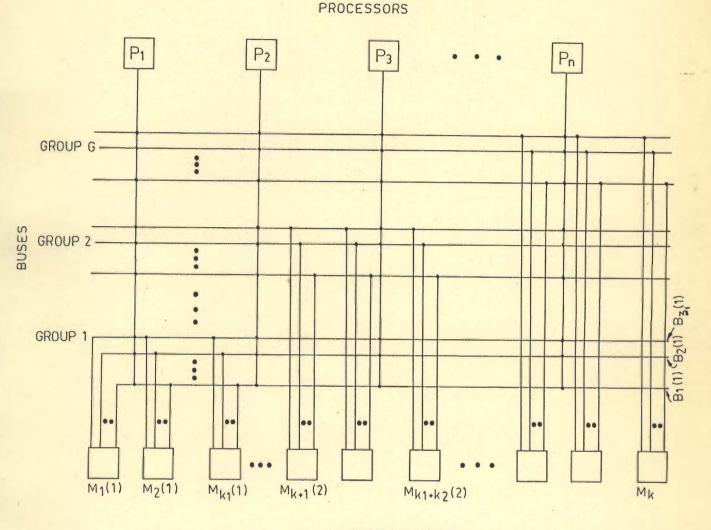

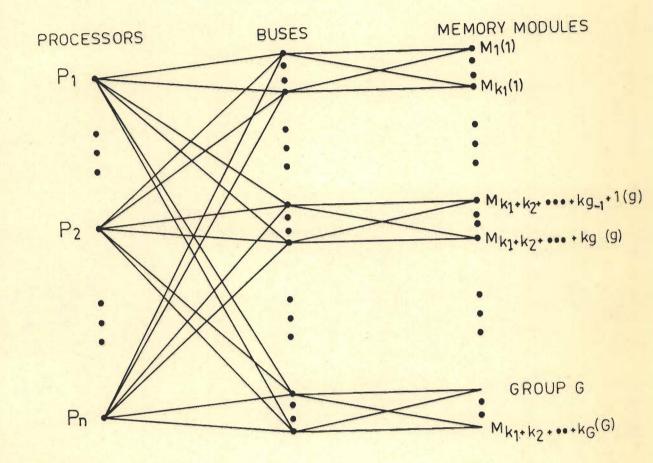

| Fi  | 9 4.1  | An nXkXz partial bus multiprocessor with G<br>groups                     | 80               |

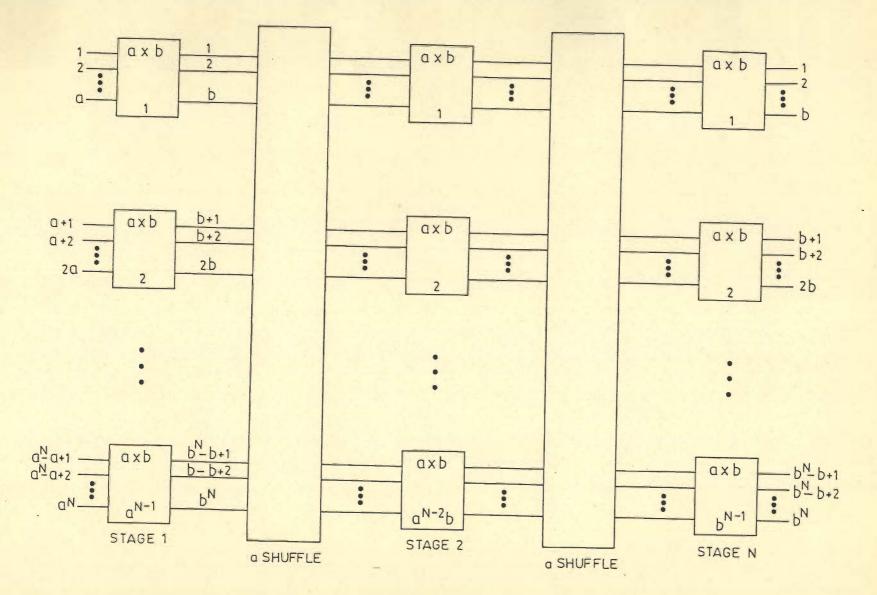

| Fi  | 9 4.2  | An a <sup>N</sup> Xb <sup>N</sup> Delta network                          | 81               |

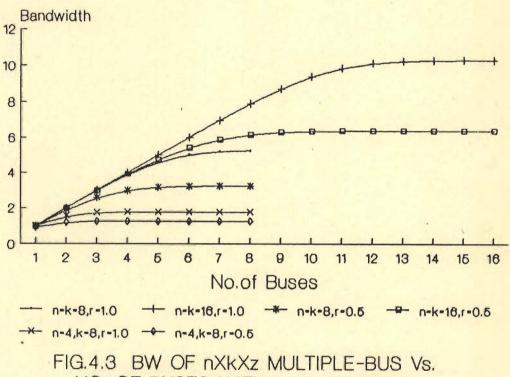

| Fi  | g 4.3  | BW of a nXkXz mulitiple-bus Vs no. of buses with, $r=1.0$ & 0.5 (URM)    | 93               |

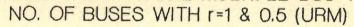

| Fi  | g 4.4  | BW of crossbar Vs no. of memory modules<br>with r=1.0 (URM)              | 98               |

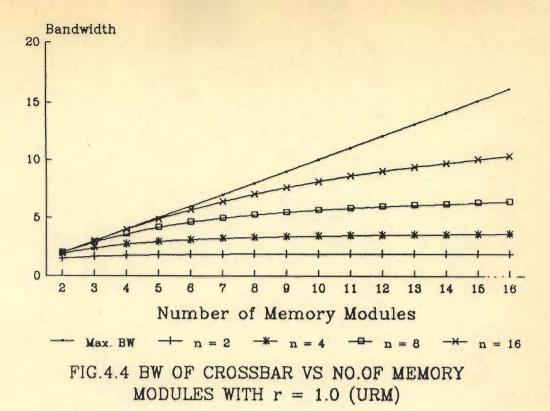

| Fi  | 9 4.5  | BW of a crossbar Vs memory request<br>probability (NURM, URM)            | 98               |

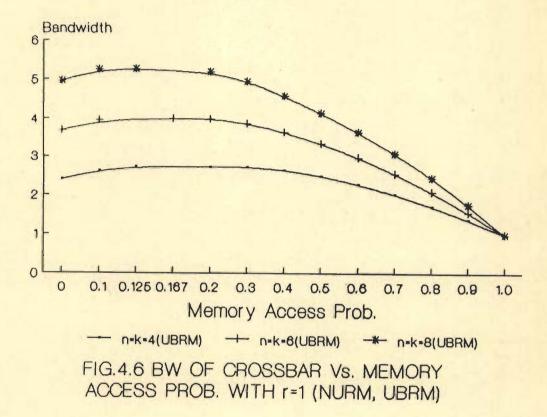

| Fi  | g 4.6  | BW of a crossbar Vs memory access<br>probability with r=1.0 (UBRM)       | 102              |

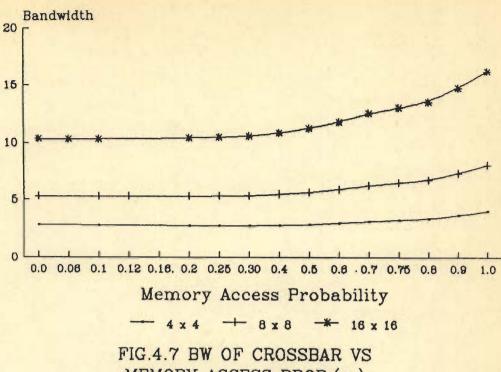

| Fid | g 4.7  | BW of a crossbar Vs memory access<br>probability (NURM)                  | 106              |

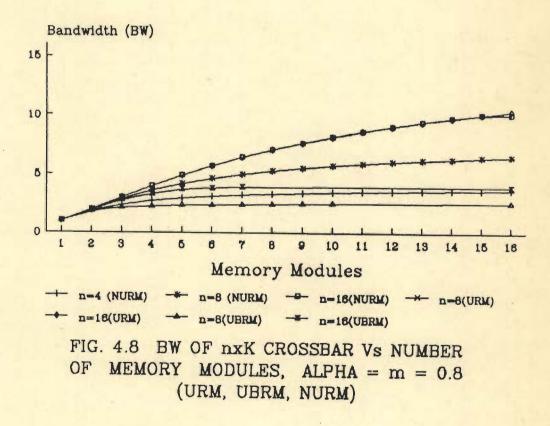

| Fi  | 9 4.8  | BW of nXk crossbar Vs no. of memory modules<br>a=m=0.8 (URM, UBRM, NURM) | 108              |

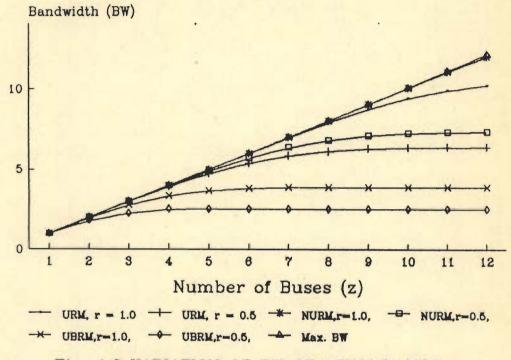

| Fid | g 4.9  | Variation of BW of 16X16Xz MPS with number<br>of buses (URM, UBRM, NURM) | 108              |

| Fig | 9 4.10 | Graph representation of partial bus MPS                                  | 109              |

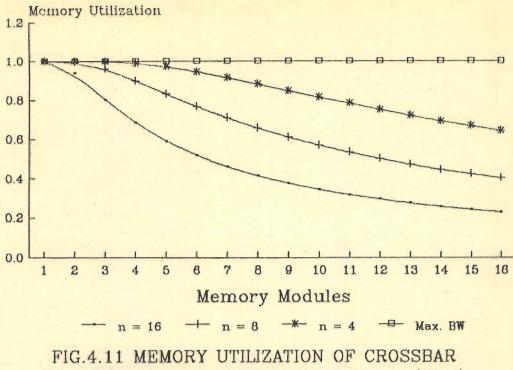

| Fig | 9 4.11 | Memory utilization of crossbar Vs no. of<br>memory modules, r=1.0 (URM)  | 116              |

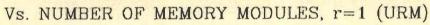

| Fig | 9 4.12 | Memory utilization of nXk crossbar with<br>r=1.0 (NURM) Vs m.            | 116              |

| Fig | 9 4.13 | A 3=X2= Delta network<br>xi                                              | 121              |

|     |        |                                                                          |                  |

## NOTATIONS & ACRONYMS

- ANSI American National Standard Institution

- BA bandwidth availability

B bus, (Bf)

- by the reliability of By and by=1-by its unreliability

- BW bandwidth

- CP conservative policy

- DFP data flow path

- END exclusive and mutually disjoint

- EP exhaustive policy

- $E(\alpha,\beta)$  the event of an MPS with  $\alpha$ -out-of-n processors updating  $\alpha$  -out-of-k memory modules while execution of a task

- H(X;s,t) pr (atleast, t units out of s are good), where  $X=(x_{\star})$

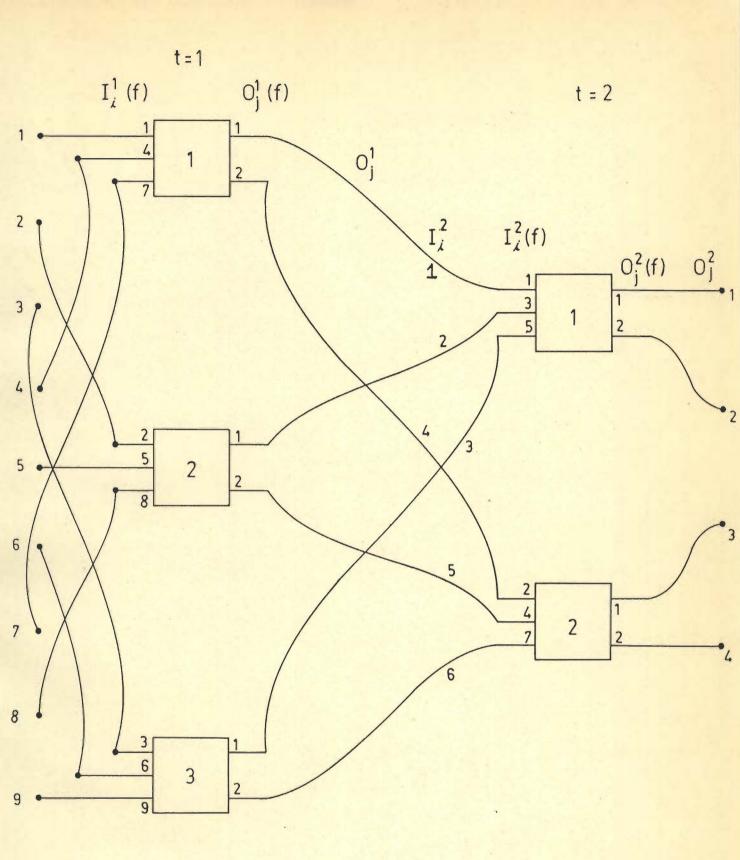

- $I^{t}_{J}(1)$  refers to the jth input index of the lth module in the t th stage of a Delta network

- I', refers to the jth input index at the tth stage of the Delta network

- k number of memory modules

- m the prob, with which processor access its favourite

memory (NURM)

- M memory module, {M₃}, 1≤j≤k

MIN multistage interconnection network

- $m_3$  the reliability of  $M_3$  and  $\overline{m}_3 = 1 m_3$  its unreliability

- $m_{3}(\tau)$   $e^{-\lambda}m_{j}\tau$ ,  $\lambda_{m_{j}}$  is the failure rate of the memory module j

- MPS multiprocessor system

- MRP memory request probability

- n number of processors

- nXk a crossbar switch with n processors and k memory modules

- nXkXz a multiple-bus with n processors, k memory modules and z buses

- NURM non uniform reference model

- O<sup>t</sup> refers to the ith output index at the tth stage of a Delta network

- $O^{t}_{1}(1)$  refers to the ith output index of the lth switch at the tth stage of a Delta network

- P processor, (P₁), 1≤i≤n

- $p_1$  the relibility of  $P_1$  and  $p_1 = 1-p_1$  its unreliability

- Pis prob. with which the ith processor access jth memory module, if already a request exists from it

- $P_{ij+}(\tau)$  the prob. that i,j,f units of processor,memory modules and buses respectively are available at time  $\tau$

- r: prob. with which the processor P: makes a request for a memory access in a cycle ;r:=r for statistically identical processor

- R(n,k) H(X; n,k)

$R_m(\tau)$  pr E {2,1}, the multiprocessing reliability

R[MMT](T) multisource - to - multi-terminal reliability

R[MST](r) multisource - to - single-terminal reliability

R[SMT](r) single source - to - multi-terminal reliability

R[SST](1) single source - to - single-terminal reliability

$R_{S}(\tau)$  pr E {1,1}, the system reliability

$R_{\alpha\beta}(\tau)$  pr E {a, B}, threshold reliability

$R_u(\tau)$   $R_g(\tau) - R_m(\tau)$ , uniprocessor reliability

$S_{13}$  crosspoint switch connecting  $P_1$  and  $M_3$

- $s_{13}$  reliability of  $S_{13}$  and  $s_{13} = 1 s_{13}$ , its unreliability

- $S_{13}(\tau) = \lambda S_{ij} \tau$ ,  $\lambda S_{ij}$  is the failure rate of  $S_{13}$

| UBRM               | unbalanced reference model                                                    |

|--------------------|-------------------------------------------------------------------------------|

| URM                | uniform reference model                                                       |

| VLSI               | Very Large Scale Integration                                                  |

| X                  | $\{X_{1}\}$ , and its reliability set $\{x_{1}\}$                             |

| ×ĭ                 | reliability of unit X and $x_{\pm}=1-x_{\pm}$ , its unreliability             |

| ZJ                 | the muliport connected to M <sub>3</sub>                                      |

| Z J                | reliability of Z <sub>3</sub> , and $z_3 = 1-z_3$ , its unreliability         |

| Ζ <sub>3</sub> (τ) | $e^{-\lambda z_j \tau}$ , $\lambda z_j$ is the failure rate of Z <sub>J</sub> |

#### CHAPTER I

#### INTRODUCTION

continuous development of computer technology The supported by the VLSI revolution stimulated the research in the field of multiprocessors. The main motivation for the change over from conventional architectures towards multiprocessor ones is the possibility to obtain a significant processing power together with the improvement of price/performance, reliability and flexibility figures. Currently such systems are moving from laboratories to real field applications. That research multiprocessing is not just an intellectual curiosity but a technique of value in real life is clearly demonstrated by writing some of the available exploratory multiprocessor systems, Cm, C. mmp, µ\*, PLURIBUS, TOMP, Intel 4321, etc., in such as. addition to so many commercial multiprocessors. Further technological advances and new generation components are likely to further enhance the trend. Whatever one's favourite reason for multiprocessor systems, it is undeniable that MPS's will play an important role in computer systems of tomorrow.

### 1.1 PARALLEL PROCESSING

Whenever a computer designer has reached for a level of performance beyond that provided by his contemporary technology, parallel processing has been his only alternative. This point will be demonstrated in three ways: by the outline of historic achievements in device technology, with a projection on the

development of the architectural features, and by a review of taxonomic types into which the spectrum of parallel processors can be divided.

#### 1.1.1. Device Technology

Computation speed has incressed by order of magnitude over the past three decades of computing with a major share of increase in speed attributable to inherently faster electronic parts. In addition to the speed of the devices, the factors reliability, reductions in hardware cost and physical size have greater effect on enhanced performance. However, better devices are not the sole factor contributing to high performance. Today we can not obtain speed increases, as we have done in the past, by simply increasing the basic speed of the logic components ; we must necessarily take other approaches to increase computation speed.

#### 1.1.2 Processing Techniques

The term parallel processing is used in a very general sense to cover methods that involve a deliberate attempt to increase speed by exploitation of concurrent events in the computing process. According to Hwang et al [1] concurency implies parallelism, simultaneity, and pipelining. Parallel events may occur at the same time instant; and pipelined events occur in overlapped time spans. Parallelism can be achieved in systems with one or more than one processing unit.

#### 1.1.2.1 Parallelism in Uniprocessors

There are some hardware and software means to promote parallelism in uniprocessors. Hardware approaches emphasis resource multiplicity and time overlapping. The operating system software approaches to achieve parallel processing with better utilization of system resources [1]. However, there is a limit to the speed obtainable from a computer based on a single processor. The closer we approach this limit, the more rapidly does the cost of such a computer rise [2]. An alternative and radically different solution is to have a newer architecture, enjoying the time tested device of parallelism i.e. using a number of operating processors.

#### 1.1.2.2 Parallel Computer Systems

State-of-the-art parallel computer systems can be characterized [1,3,4] into three structural classes : pipeline processors, array processors, and multiprocessors. The three parallel approaches to computer system design are not mutually exclusive.

Pipelined processor attains speed by dividing each processor unit into several stages. An analogy for a pipelined processor is the assembly line. Each of many sections is finely tuned to effectively perform one function on the object being assembled. Array processors consists of identical processing units under the control of a common broadcast unit. All processors perform the same operation simultaneously on different

data stored in their private memories.

Multiprocessor systems consists of several autonomous processors which can each execute separate programs. These systems can be categorized either as loosely coupled or tightly coupled. Multiprocessors which employ the shared memory interconnect approach, have been termed tightly coupled. In contrast, a loosely coupled system has disjoint primary memory address spaces and processing events do not share a common memory. A tightly coupled system, from here afterwards referred to as multiprocessor system or simply, MPS, generally requires synchronization between cooperating processors, whereas in loosely coupled system concurrent processes may be performed asynchronously.

#### 1.1.3. Taxonomics

In literature, a wide variety of different architectures have been proposed and it is natural for us to seek a taxonomy which would permit us to grasp this diversity in simple terms. The taxonomy of Flynn [5,6], Feng [7], and Shore [3] have been discussed quite widely and some of the associated technology has become a part of the language of computer science.

Flynn's classification is based on multiplicity of instruction streams and data streams. He proposed four types of computer architectures such as:single instruction stream, single data stream (SISD), single instruction multiple data stream (SIMD), multiple instruction single data stream (MISD) and

multiple instruction multiple data stream (MIMD). Feng classifies according to word length, i.e., the number of bits which are processed in parallel in a word, and the number of words which are processed in parallel. For example, a system which contains 'n' processors each with a word length 'b' bits is represented by (n,b). Shore based his classification on how the computer is organised from its constituent parts. Handler [8] compares several alternative ways of describing the architecture and introduces a more comprehensive scheme based on degree of parallelism and pipeline. His classification makes distinction at three processing levels: program control unit, arithmetic and logic unit and elementary logic circuitary.

#### 1.1.4 Multiprocessor Systems

An MPS may be viewed as a logical result of the efforts to increase computer performance by exploiting parallelism in hardware [1,3,4,9-13]. It is relatively easy to enumerate the capabilities that must be provided by the hardware based on the fundamental definition of an MPS.

#### Definition 1.1

ANSI [14] defines a multiprocessor as : " A computer employing two or more processing units under integrated control". The definition does not exclude future developments in computer architecture, but does not seem to have had any impact on contemporary architecture. Subsequently, Enslow [4] suggested a more detail definition which included :

- two or more processors having access to common memory, where private memory is not excluded,

- 2. shared 1/0,

- 3. a single integrated operating system,

- 4. hardware and software interactions at all levels,

- 5. the execution of a job must be possible on different processors, and

6. hardware interrupts.

#### 1.1.4.2 System Structure

A general model of the hardware system is shown in Fig.1.1. A set of processors and a set of memory modules are connected by means of an interconnection network (IN). More generally the processors are allowed to issue an access request to the IN in order to perform data transfer; the memory modules receive the request for an access from the processors and can accept and honour them. There are two sources of conflicts due to memory requests. First, more than one request can be made to the same memory module. Second, there may be more than one request through the same communication link of the IN to different memory units. To resolve these conflicts each IN is associated with an arbitration mechanism [1]. One way to reduce the number of processor-memory requests, and hence the IN traffic, is to have a local memory (cache) associated with each processor, as shown in Fig. 1.2 [10].

## FIG. 1.1 A GENERAL STRUCTURE OF MPS

FIG. 1.2 A GENERAL STRUCTURE OF MPS WITH LOCAL MEMORY

#### 1.2. PROBLEM FORMULATION

The major design problems in an MPS are :

- a) Network topology

- b) Control strategy

- c) Fault tolerance

- d) Performance evaluation

- e) Reconfiguration techniques

Topology design relates to interconnection structure between processors and memory modules. Control strategy concerns how to route data from a source (processor) to various destinations (memory modules). Reconfiguration techniques are used to allocate hardware resources, such as processors and connection switches. When a task requests resource through a system controller or to provide fault tolerance when the current configuration contains faulty components. Performance analysis must be performed to observe the characterstics of the hardware resources, which in turn will be used to decide whether the resources are adequate in regard to system requirements.

A fault tolerant MPS can tolerate faults to some degree and still provide reliable and gratefully degradable communication between processors and memory modules. The reliability and bandwidth availability are the two important measures of fault tolerance. Out of these, the problems of performance evaluation and fault tolerant aspects of design are considered for different IN topologies, in this dissertation.

## 1.3 STATEMENT OF THE PROBLEM

This thesis attributes itself to the problem of designing an interconnection structure considering both performance and fault tolerant issues. The object is to find efficient mathematical models that represent the system completely and accurately so that the performance of the multiprocessors could be compared under different operating conditions. To define the specific tasks which the present work is intended to cover, a list of major subproblems for the present study is given below.

- To examine the different interconnection networks, such as multiple-bus, crossbar, multiport memory system and MINs, considered for design.

- ii) to develop time and memory efficient reliability algorithm for a 't-out-of-s' redundant system, which is used as a modeling tool for the analysis of MPS's.

- iii) to obtain closed form solutions for the computation of memory interference, and hardware resources utilizations in an MPS so as to study the parameter dependence on performance. The parameters of interest are processors, memory modules, memory request probability and memory access probabilities.

- iv) to find out the responsiveness of the system for a given input request.

- v) to study the fault tolerant behaviour of the system such as reliability and bandwidth availability as these

specifications are crucial factors in the design of current and future computer systems, especially fault tolerant MPSs.

vi) to study the performance degradability due to system component failures during the execution of a task.

## 1.4 OUTLINE OF THE THESIS

Chapter II contains a general description of some existing multiprocessor architectures and characteristics of the interconnection networks. Chapter III analyzes the multiprocessor systems for reliability computation and the reliability modeling using t-out-of-s systems. Chapter IV provides tools for evaluation of performance of MPSs assuming variety of performance indices. Chapeter V considers the fault tolerance and performance degradition of non failure-critical multiprocessor models. Finally, chapter VI concludes the work carried out in the thesis along with some proposals for further research in this area.

### CHAPTER II

## DESIGN OF MPS - AN OVERVIEW

Since processors and memory modules are available as standard integrated circuits, the key design problem is how to put them together in an efficient and reliable way. Therefore, the design of interconnection structures requires special attention. The major design issues, in an MPS, considered are performance evaluation and fault-tolerance. Since the design of any system in its current state of development is as much an art or skill as it is a science, this chapter has two purposes: first to present those aspects of system evaluation criteria that are under consideration; and second to review the associated Section 2.1 gives an overview of evaluation techniques. topological aspects of interconnection networks. Section 2.2 and Section 2.3 discuss the modeling techniques and evaluation criteria for determination of performance. The fault-tolerance considerations for analysis are discussed in section 2.4. Section 2.5 concludes the chapter.

## 2.1 INTERCONNECTION NETWORKS

Focussing on the flow of data and parallelism that can be obtained with a multiprocessor, it is indeed the topology and mode of operation of the network that interconnects the functional units that becomes of paramount importance. Four main types of system organizations are possible for the processormemory switching apparatus [1,4,15]. All the four topologies are

regular and can be classified as either static or dynamic.

The system organization to be covered and the discussion on each assume that the entire system is at one physical location within distances so that unit to unit transfer can be made at full machine speed.

## 2.1.1 Time Shared Multiple-Bus

There are several degrees of complexity in the system organization depending on the number of buses. The simplest one is to have all processors and memory modules connected to a single bus which can be totally passive (ref.Fig. 2.1). It is obvious that there is no possibility for concurrent transactions in the organization. To attain more parallelism, at the price of more complexity, one can have several buses as shown in Fig. 2.2. Priorities can be given to specific units if one adds a bus and a memory arbiter to resolve the conflicts due to bus and memory interferences respectively [16]. In this case, the interconnection subsystem becomes an active device.

A modification of the multiple-bus multiprocessor that has been proposed by Lang et al [17] to provide better costeffectiveness, is known as the partial-bus architecture. Fig. 2.3 depicts a partial-bus system. The memories and buses are divided into a number of groups. All processors are connected to all buses, whereas each group of memory modules is connected to one set of buses only [18].

. . .

FIG. 2.1 SINGLE BUS MULTIPROCESSORS ORGANIZATION .

PROCESSORS

FIG. 2.2 MULTIPLE - BUS MULTIPROCESSOR ORGANIZATION .

MEMORY MODULES

FIG. 2.3 PARTIAL - BUS MULTIPROCESSORS ORGANIZATION.

#### 2.1.2 Crossbar Switch

If the number of buses in a time shared bus system is increased, a point is reached at which there is a separate path available for each memory module, as shown in Fig. 2.4. This interconnection network is called a nonblocking crossbar. This is the most extensive and expensive scheme since each crosspoint must have hardware capable of switching parallel transmissions and of resolving conflicting requests for a given memory module. The switching device becomes rapidly the dominant factor with the increase in complexity in the cost of overall system.

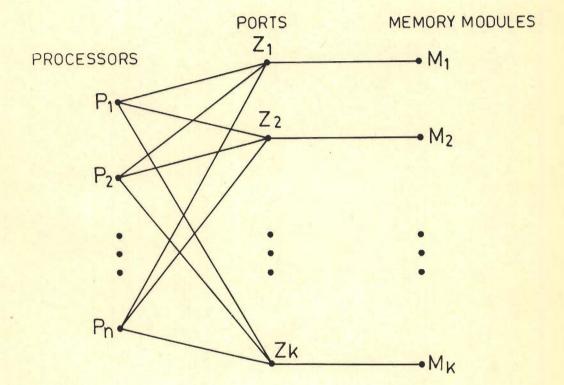

#### 2.1.3 Multiport Memory System

In this organisation (ref., Fig. 2.5) the switching is concentrated in the memory module. Each processor has access through its own bus to all memory modules and the conflicts that occur if two or more processors request access to the same memory module are in general resolved through hardware fixed priorities [19].

#### 2.1.4 Multistage Interconnection Networks (MINs)

They are well suited for communication among tightly coupled system components, and offer a good balance between cost and performance. Design, analysis, and development of MINs during the last decade have made them the most current technology [20-23].

A MIN consists of more than one stage of switching elements and is usually capable of connecting an arbitrary

FIG. 2.5 MULTIPORT MEMORY ORGANIZATION .

processor to an arbitrary memory module. Each switching element can perform a very simple circuit switching function. Consider, for example, the basic 2 x 2 switching element shown in Fig. 2.6. The swithcing element can be set in two configurations performing a straight connection, as shown in Fig. 2.6(a) and crossed connection, as shown in Fig. 2.6(b). Generally, a multistage consists of N stages where n = 2N is the number of inputs and outputs. A matrix of n log2 n basic switching elements can interconnect the set of input terminals to the set of output terminals. The interconnection patterns from stage to stage determine the network topology. In all these cases a convenient setting of basic switching elements can connect any input terminal to any output terminal.

#### 2.1.5 Operational Characteristics

In selecting the architecture of an IN, three design decisions can be identified [20, 24]. These are based on its timing, switching and control characteristics.

The timing control of an IN can be either synchronous or asynchronous. An IN transfers data using either circuit switching or packet switching. Based on control strategy, an IN may be classified as centralized or decentralized. In centralized control, a global controller receives all requests and transmits the messages in the IN. In the decentralized system, requests are handled independently by different devices in the IN. These three operational characterstics with the

FIG.2.6 2x2 SWITCHING ELEMENT

(a) STRAIGHT CONNECTION

(b) CROSSED CONNECTION

topology define an IN.

#### 2.2 SYSTEM EVALUATION

System evaluation is an essential activity in all branches of engineering. Any system which is being designed must satisfy certain specifications. Design methodologies and evaluation procedures are issued by designers to obtain system to meet these specifications [25, 26].

#### 2.2.1 Evaluation Techniques

The most popular evaluation technique can be classified into two categories : measurement techniques, and modeling techniques. There are two major problems with measurements on the system [27]. First, measurement is not feasible in the design and development stages of the system ; the system is not measurable if it is not operational. Second, measurement of most systems is a complex activity which involves considerable human and machine cost. Modeling is the alternative when measurement is intractable.

There are two major approaches of modeling systems: simulation and analytical modeling. Simulation models are more prevalent in practice because they represent aspects of the modeled system more faithfully than analytic models. However, simulation models are very expensive to use, and the results of the simulation are harder to interpret [27].

Recent advances in modeling techniques are making

analytic models increasingly capable of representing more and more aspects of the modeled system. This has promoted an increased interest in the use of analytic modeling in the design of computer systems. Modeling of a system is a two phase effort. The analysis phase is to evaluate the performance criteria of the system by considering the system architecture, work load etc. The second phase of modeling effort is the design phase.

There are at least two types of performance measures ; Determinstic and Probabilistic.

In a deterministic model all variables are deterministic If atleast one of the variable is random, the model is said to be stochastic or probabilistic. Deterministic approach is applied to worst-case or best-case studies [28,29]. Because of their potential for representing complex, highly variable phenomena in a relatively compact way, probabilistic models are much more widely applied to the study of computer systems than deterministic models.

### Probabilistic Models

These models are useful when the behaviour of the system is not predictable in deterministic fashion. The role of the probability theory is to analyse the behaviour of the system assuming the given probability assignments and distributions. The results of this analysis is as good as underlying assumptions. Probability models tend to fall into one of the three classes: i) Markov Chain , ii) Queuing theory and iii)

Combinatorial theory.

#### 2.2.1.1 Markov Models

State and state transition are the two central concepts of Markov models. The state of the system represents all that must be known to describe the system at any time i.e., it concentrates on the rate at which transition takes place between different states and then use this information to determine the probabilities that the system is in each of these states at any given time [29-31]. Markov theory is the basis of elementary queue theory [32-33].

### Drawbacks of Markov Models

- Unmanageable large state space to represent an open queue network. So this approach applies primarily to closed networks [25, 34].

- ii) In Markov modeling, using continuous parameter and discrete-parameter analysis, the processor time distribution in each state is exponential and geometrical respectively. This is in many situations an unrealistic assumption [25,30]. Continuous time models are usually less accurate than discrete time models when discrete time events are considered.

- iii) Semi-Markov process, a generalization of a Markov process, allows state durations to have arbitrary distributions. This allows certain states that can not occur in the real system and hence the results are prone to errors [34].

#### 2.2.1.2 Queuing Models

A queuing model is defined by its sources, its service centres and their interconnections. Jobs are generated by the sources. Servers are generlly used to model the resources demanded by the jobs. The interconnections specify the paths which the jobs are allowed to flow in their journey through the model from centre to centre. Each server has atleast one queue. Queuing theory encompasses the set of analytic models that most adequately describe computer systems. On the other hand, a discouragingly large fraction of practical queuing systems continue to elude exact analysis. Some researchers find these two observations a pessimestic commentary on work in queuing theory [11].

### 2.2.1.3 Combinatorial Models

Combinatorial models attempt to categorize the set of operational states of a system in terms of the functional states of its components, in such a way that the probabilities of each of these states can be determined by combinatorial means [31]. The commonly used combinatorial models are fault tree, reliability block diagrams, Sterling numbers, and t-out-of-s redundant systems. If the components are s-dependent reliability block diagrams with series-parallel (well nested) structure and fault trees, without repeated nodes can be analyzed using linear time algorithms [35]. However, if the component states are not s-dependent or the structure is not series-parallel the analysis can not in general be done using linear time. Methods for

analysing such structures use sterling numbers and t-out-of-s system concept with conditioning (using theorem of total probability). Methods based on Sterling numbers [36] are computationally complex.

### 2.2.2 t-out-of-s system : Modeling

The t-out-of-s systems are a generalization of the series-parallel model. However, instead of requiring one of the s units for the system to function t units are required. If the units are assumed to be identical, all the 't' states need not be enumerated. Any combination of the t of the s units is enumerated by s take t combinatorial coefficients, denoted by  $\binom{s}{t}$  [29,30]. It makes no difference whether the problem is defined in terms of s-dependent or s-independent component probabilities. Each term is the product of a number of component probabilities. If they are s-dependent between some of the events presented in a term, they can be accounted for by standard representation of conditional events [37]. In Chapter III, the reliability computation of t-out-of-s systems is considered.

### 2.3 PERFORMANCE EVALUATION CONSIDERATION

Performance evaluation measures the capacity of IN of a MPS in terms of parameters that represent major characteristics of an IN application model. As no single parameter can give a truly accurate measure of systems performance, different parameters are needed to characterize a system for a given application. A wide variety of performance criteria is available

in literature. In this present work an attempt has been made at evolving methodologies for the design of an MPS by considering the following criteria.

i) processor-memory interfernce [17, 34, 39-74]

ii) response time [42,47,68,73]

iii) hardware utilizations [34,42,60,68,73]

Sharing of memory modules between multiple tasks results in memory interference. This interference may be quite severe in MPS where memory modules are shared by a number of independent processors through INs. The combined effect of interference due to IN contentions and that due to memory conflicts is investigated in Chapter IV.

Response time measures, sometimes also called waiting time, describe the length of time from a request for service until the request is completed.

A measure closely related to throughput is utilization, that is, the fraction of a time a specified component (processor, memory module or bus) is busy. Utilization is an even more direct indicator of capacity of the system being used. The definitions and analysis of these performance criteria are also discussed in Chapter IV.

#### 2.4 FAULT-TOLERANCE SYSTEM CONSIDERATION

Fault-tolerant systems may be either non-degradable or degradable. In case, a component fails non-degradable systems are

able to recover by bringing up another standby component and continue operation, almost transparently, with the same computing power, i.e., system operation is not degraded by failures. Degradable systems on the otherhand operate in a degraded mode as a consequence of component failures [75]. For the performance evaluation of a degradable fault tolerance system, the important parameters of interest are reliability and bandwidth availability.

### 2.4.1 Reliability

Real time systems fall into two classes. Failurecritical and non failure-critical. In the former class of systems no down-time can be tolerated, that is, any failure during a specified interval (mission time) is construed as a mission failure. Reliability defined as the probability that no failures (at all) occur during the mission time, is an appropriate measure for this class of systems. This reliability measure and its associated measures such as multiprocessing reliability and multiterminal reliability are of great interest to the system designers and are discussed in Chapter III.

In the non failure-critical models, some down-time can be tolerated. Failures are allowed to occur as long as some constraints are met [38]. An interesting study of these systems is the computation of bandwidth availability of the system.

### 2.4.1.1 Multiprocessing Reliability

The multiprocessor approach for executing a job

introduces new requirements: first each job must be partitioned into tasks; second, each task must be scheduled for execution on one or more processors; third, each task may require to access one or more modules through atleast one of the interconnection links. In a real situation the components of multiprocesor fail at random. If a task needs at least I processors and J memory modules, different reliability criteria can be defined depending upon the availability of I and J [76].

When I = 2, and J = 1, the reliability criterion is referred to as multiprocessing reliability and when I = J = 1, it is the system reliability.

Sections 3.1, 3.3 and 5 discuss the analysis of multiprocessing reliability.

### 2.4.1.2 Terminal Reliability

These criteria find their use in packet switching communication. A meaningful measure of the reliability and availability of a communication network is the terminal reliability between the source and destination. One of the communication systems of recent interest is the MPS, where a several processors (sources) connected to a set of memory modules (destinations) through an IN (channel) [77].

Various measures for probabilistic networks have been analyzed in literature [78]. They are :

a) a source communicates with a destination (SSI reliability)

- b) a source communicates with a number of destinations (SMT reliability)

- c) a set of sources communicate with a destination (MST reliability)

- a set of sources communicate with a set of destinations

(MMT reliability)

The analysis of these reliability criteria is considered in Section 3.3.2.

### 2.4.2 Bandwidth Availability (BA)

The bandwidth availability of a gracefully degrading multiprocessor is the expected value of available BW in the system at any time 'T'. Usually in the memory interference measurement, the BW is computed by assuming non failure-critical models. The failures of the components in failure-critical models degrades the performance of the system. The simultaneous consideration of both the performance and fault-tolerance issues leads the way to the computation of BA [59].

### 2.4.3 Evaluation Techniques-Review

Many algorithms have been proposed for communication networks and a summary of these techniques can be found in [79]. These known methods can be classified as follows:

- 1) Decomposition techniques [80-82]

- 2) Graphical approach [76,83,84]

- 3) Enumeration methods [76,84-88]

### 2.4.3.1 Decomposition Techniques

The most common approach to modeling complex systems consists of structurally dividing the system into smaller subsystems (eg., processor, memory module and IN) analyzing the dependability of subsystems separately and then combining the subsystem solutions. If the subsystems fault tolerant behaviours are mutually s-independent, then a decomposition into subsystem, separate analysis of subsystems and aggregation to obtain final solution can be used [89].

### 2.4.3.2 Graphical Approach

The reliability analysis of MPS using decomposition technique or series parallell approach can be made very easily using graph models. A probabilistic graph contains a finite set of weighted vertices connected by undirected edges. Each vertex, corresponding to a physical component in the MPS, is weighted by its reliability of functioning correctly. All component reliabilities are represented in vertices. The edges are used only to specify incidence relations between vertices[76].

### 2.4.3.3. Enumeration Methods

The simplest technique for reliability evaluation is to enumerate the favourable states by examining all the elementary events. The events can be expressed using exhaustive policy (EP) or conservative policy (CP) (discussed in Chapter III). Using CP only (m+1) exclusive and mutually disjoint (EMD) events are generated as against 2m EMD terms by

EP to represent an m-variable system completely. Algorithms based on CP produces more compact results than EP and hence preferred for large systems.

Algorithms based on pathset and cutset enumeration with reduction to mutually exclusive events are generally efficient and produce compact expressions. In path (cutset) enumeration methods, the terminal reliability expression is obtained by enumeration of all simple paths (all prime cutsets) between a pair of terminal nodes which represent a complete favourable (unfavorable) non-disjoint events. To obtain reliability either the inclusion-exclusion [90], probability theory or more efficient boolean algebra [80] can be utilized for mutually exclusive events.

In all the algorithms, the most time consuming step is the disjoint process to obtain the mutually exclusive events which is required in each step of the algorithm. Chapter V considers the techniques cited above for computing the reliability criteria of an MPS.

### 2.5 Conclusion

This chapter reviews some design aspects of an MPS. We have typically considered topological performance evaluation and fault-tolerance to highlight the issue. A review of the evaluation techniques is also presented. The analysis of these criteria is carried out in detail in the chapters to follow.

### CHAPTER III

#### MULTIPROCESSOR SYSTEM RELIABILIATY

As discussed earlier, two criteria namely multiprocessing and terminal reliability, of failure-critical models are considered for performance analysis of MPSs. Because of various reasons mentioned in [88] exact/symbolic methods found their use more important than approximate techniques. The algorithms for exact reliability analysis can be divided broadly into two categories depending upon their approach in attacking the problem [ 84 ]. The algorithms of the first category are based on primary method of starting from the enumeration of multiprocessing events and compute the reliability through one of the techniques discussed in Chapter II. The other category is modeling.

We discuss in Section 3.1 the computation of multiprocessing reliability through path enumeration. The analysis of t-out-of-s systems which have been used later for modeling of MPSs, is presented in Section 3.2.

The reliability evaluation of MPS is done based on the following assumptions.

- a) Each unit and the system is either good or failed.

- b) There is no repair.

- c) The states of all units need not be mutually statistically independent.

- d) Sensing and switching of failed units out of the system is

perfect.

- e) The system is good (bad) if and only if atleast t of its s units are good (bad).

- f) Reliability of each unit is known and the units of the system are contiguously numbered.

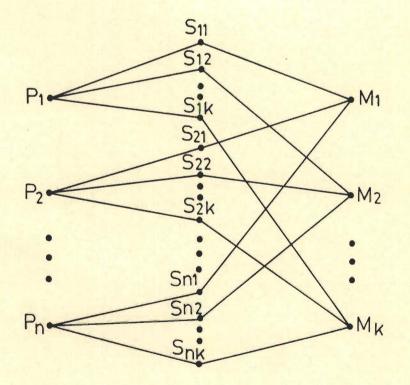

The processors are connected to the memory modules through any of the INs shown in Fig. 3.1 through 3.3. Fig. 3.1 shows an n X k X z multiple-bus architecture having n processors P1, P2,...,Pn, k memory modules, M1, M2,...,Mk, and z buses B1, B2,...,Bz. When z = k, the system behaves as an n X k crossbar, as depicted in Fig. 3.2. The processor Pi is connected to memory modules Mj through a separate crosspoint switch Sij, for all i. and j,  $1 \le i \le n$  and  $1 \le j \le k$ . In multiport system, shown in Fig. 3.3, the memory module Mj is connected to multiport Zj.

The topology of a network is the pattern of connections in its structure. This can be represented by a graph, where processors form the source nodes and memory modules the destinations. The topology is determined by the pattern of links connecting sources and destinations. Different INs are often compared graphically because comparison by topology is independent of hardware. Nodes in the graph of a IN can be numbered along with the sources and destinations and then a IN can be described in terms of the algebraic relations among the nodes. The algebraic model is useful in discussing control and communication routing strategy. The probabilistic-graphical

FIG. 3.2 AN nxk CROSSBAR MULTIPROCESSOR

CROSS POINT SWITCHES

M<sub>3</sub>

MK

MEMORY MODULES

FIG. 3.3 A k n-PORTED MEMORY SYSTEM .

.

representation of three architectures, multiple-bus, crossbar and multiport are shown in Figures 3.4 through 3.6 respectively [76].

## 3.1 MULTIPROCESSING RELIABILITY

Assuming the multiprocessor systems understudy use several processors in parallel to solve one problem, i.e., it uses a task oriented approach. The analysis of multiprocessing reliability criterion is considered below through a primary method based on path enumeration technique.

### 3.1.1 Primary Method

For determination of multiprocessing reliability it is necessary to compute all events that give rise to multiprocessing. These events can be easily obtained from the connection matrix of the system [91-92].

# 3.1.2 Construction of Connection Matrix

The connection matrix, Cn, for an MPS with n processors, is an n-row matrix. Each row of Cn corresponds to a processor; the ith row is thus labelled Fi,  $1 \le i \le n$ , for the ith processor. The number of columns in Cn depends upon the IN used. The connection matrix lists possible data flow paths (DFP's) between processors and memory modules. The construction of the connection matrix for each of the three INs is described below.

### a) Crossbar MPS

In the crossbar switched MPS, there is one unique path

# FIG. 3.4 GRAPH REPRESENTATION OF MULTIPLE-BUS MPS.

### FIG. 3.5 GRAPH REPRESENTATION OF CROSSBAR SWITCHED MPS.

FIG. 3.6 GRAPH REPRESENTATION OF MULTIPORT MEMORY MPS.

from each processor to every memory module. The connection matrix, Cn, consists of k columns, a column corresponding to a memory module. The element Ci,j of Cn represents the unique path between Pi and Mj, viz., Pi Sij Mj. These paths may be numbered as shown in the connection matrix below (Fig. 3.7), for n = k = 3. The path number is given by (i-1)k+j.

FIG. 3.7 CONNECTION MATRIX 3 x 3 CROSSBAR MPS

### b) Multiport Memory MPS

In this architecture also, there is unique path from  $P_i$ to M<sub>j</sub> through Z<sub>j</sub>, the n-ported controller for M<sub>j</sub>. The connection matrix, Cn, therefore, has k columns as shown in Fig. 3.8 for the case n = k = 3. In this case again the path number is (i-1)k+j.

FIG. 3.8 CONNECTION MATRIX OF 3-PORT MEMORY MPS

### c) Multiple-bus MPS

In this system, a processor Pi can be connected to a

memory module M<sub>j</sub> through any one of the z buses. Thus there are z paths between Pi and M<sub>j</sub>, viz., Pi Bf M<sub>j</sub>, f = 1, 2, ..., z. These paths are all numbered sequentially as shown in Fig. 3.9, for n = k = 3 and z = 2. The path number is given by (i-1) kz + (j-1)z+f.

|    | M1 B1 | M1 B2 | M2 B1 | M2 B2 | M3 B1 | M3 B2 |

|----|-------|-------|-------|-------|-------|-------|

| P1 | /1    | 2     | 3     | 4     | 5     | 6     |

| P2 | (7    | 8     | 9     | 10    | 11    | 12)   |

| Ps | 13    | 14    | 15    | 16    | 17    | 18/   |

FIG. 3.9 CONNECTION MATRIX OF 3 x 3 x 2 MULTIPLE-BUS MPS.

# 3.1.3 Reduction of the connection matrix

The matrix, Cn, gives multiprocessing events for the case when all the n processors are active in executing a task. In order to get the multiprocessing events where less than n processors (minimum 2) are active, lower order matrices are to be obtained from Cn, which contains the same number of columns as Cn, but a reduced number of rows. Thus Cn-1 contains (n-1) rows, Cn-2 contains (n-2) rows and so on. Cn-1 is obtained by removing one row at a time from Cn. There will be  $\binom{n}{n-1}$  such matrices. Cn-1 (i), i = 1, 2..., n is obtained by removing ith row from Cn. Cn-2 (i,j), i, j = 1, 2..., n, and i  $\neq$  j are obtained by removing rows i and j from Cn. In general, matrix Ca contains d rows ( $2 \leq d \leq n$ ) obtained by removing (n-d) rows from Cn. Ca will generate the multiprocessing events with d processors active. Row matrices, denoted by Ci's, will generate SISD

uniprocessing events and are not useful in determining multiprocessing reliability. Here we consider the matrices with atleast two rows. Example 3.1 illustrates the technique of reduction of a matrix.

**Example 3.1:** Consider the connection matrix, C3, given in Fig. 3.7. By reduction, we get only the lowest order matrices, C2's, and are given by

$$C_{2}(1) = \begin{pmatrix} 4 & 5 & 6 \\ 7 & 8 & 9 \end{pmatrix}, \quad C_{2}(2) = \begin{pmatrix} 1 & 2 & 3 \\ 7 & 8 & 9 \end{pmatrix}, \quad C_{2}(3) = \begin{pmatrix} 1 & 2 & 3 \\ 4 & 5 & 6 \end{pmatrix}$$

### 3.1.4 Enumeration of Events

The multiprocessing events are generated by recursively expanding each of the matrices  $C_i$ ,  $2 \le i \le n$ . Algorithm 3.1 below gives the method of expansion. Let x and y denote the number of rows and columns of the matrix,  $A_x$ , to be expanded. Multiplication and addition used in the algorithm are boolean operat=ions.

Example 3.2 illustrates this technique. Example 3.2: Consider the connection matrix of Fig. 3.7

$$\begin{pmatrix} 1 & 2 & 3 \\ 4 & 5 & 6 \\ 7 & 8 & 9 \end{pmatrix} = 1 \begin{pmatrix} 4 & 5 & 6 \\ 7 & 8 & 9 \end{pmatrix} + 2 \begin{pmatrix} 4 & 5 & 6 \\ 7 & 8 & 9 \end{pmatrix} + 3 \begin{pmatrix} 4 & 5 & 6 \\ 7 & 8 & 9 \end{pmatrix}$$

### Algorithm 3.1

Expansion of a connection matrix, Ax, for crossbar switched MPS.

> Input: x,y, Ax Output: Multiprocessing event expression with x processors active.

Step 1: Consider row 1. For the jth element, al, j generate a reduced matrix  $A_{x-1}$  (1) of size (x-1) by deleting row 1. Multiply the element al, j with  $A_{x-1}$  (1). Repeat this for each element of row 1, al, j, j = 1,2,...,y, and sum up all the terms to obtain an expression of the form

$$\sum_{j=1}^{y} a_{1,j} A_{x-1}$$

(1)

Step 2: Repeat the above procedure with each matrix in the expression till it contains only row matrices.

Step 3: Multiply the coefficient of a matrix with each element in the row matrix and add. = 1.4 (7 8 9) + 1.5 (7 8 9) + 1.6 (7 8 9) +2.4 (7 8 9) + 2.5 (7 8 9) + 2.6 (7 8 9) +3.4 (7 8 9) + 3.5 (7 8 9) + 3.6 (7 8 9)

= 1.4.7 + 1.4.8 + 1.4.9 + 1.5.7 + 1.5.8 + 1.5.9 + 1.6.7 + 1.6.8 + 1.6.9 + 2.4.7 + 2.4.8 + 2.4.9 + 2.5.7 + 2.5.8 + 2.5.9 + 2.6.7 + 2.6.8 + 2.6.9 + 3.4.7 + 3.4.8 + 3.4.9 + 3.5.7 + 3.5.8 + 3.5.9 + 3.6.7 + 3.6.8 + 3.6.9

This algorithm will directly give all the multiprocessing events for a crossbar system. Each product term in the expansion denotes an event for multiprocessing. For example 1.4.7 means the event of all the three processors and the memory module Mn are being active in the execution of a task.

The connection matrices for the multiple-bus system and the multiport memory system can also be expanded by following Algorithm 3.1. However, this will produce many duplicate terms because of some elements being common to many DFP's. This duplication can be easily avoided by slight modification of Algorithm 3.1, as shown below. This Algorithm 3.2 will produce only non-cancelling terms for multiple-bus and multiport memory system. Here we denote by  $A_{x}^{j}-1$  (i) the matrix obtained from  $A_{x}$  by deleting row i and all the columns to the left of column j. Thus  $A_{x}^{i}-1$  (i) is same as  $A_{x}-1$ (i).

Example 3.3: Consider the connection matrix of Fig. 3.8. For the first expansion matrices required are:

### Algorithm 3.2

Expansion of a connection matrix Ax for multiple-bus and multiport systems.

| Input:  | х,у,Ах            |       |            |      |   |

|---------|-------------------|-------|------------|------|---|

| Output: | multiprocessing   | event | expression | with | х |

|         | processors active |       |            |      |   |

This algorithm is same as Algorithm 3.1 except that Step 1 is modified as follows.

Step 1: Consider row 1. For the jth element in row 1, i.e., a1, j, obtain a reduced matrix  $A_{x-1}^{j}(1)$ . Multiply a1, j with  $A_{x-1}(1)$ . Repeat this for each element of row 1, a1, j, j = 1,2,...,y and sum up all the terms to obtain an expression of the form  $\sum_{j=1}^{y} a_{1,j} A_{x-1}(1)$ .

$$\begin{array}{c} 1 \\ A_{2}(1) = \begin{pmatrix} 4 & 5 & 6 \\ \\ 7 & 8 & 9 \end{pmatrix} , \begin{array}{c} 2 \\ A_{2}(1) = \begin{pmatrix} 5 & 6 \\ \\ 8 & 9 \end{pmatrix} , \begin{array}{c} 3 \\ A_{2}(1) = \begin{pmatrix} 6 \\ \\ 9 \end{pmatrix} \end{array}$$

Thus after first expansion the expression is

1.

$$\begin{pmatrix} 4 & 5 & 6 \\ 7 & 8 & 9 \end{pmatrix}$$

+ 2.  $\begin{pmatrix} 5 & 6 \\ 8 & 9 \end{pmatrix}$  + 3.  $\begin{pmatrix} 6 \\ 9 \end{pmatrix}$

and so on.

### 3.1.5 Reliability Computation

The following steps are required for computing the multiprocessing reliability, of any MPS, from the event expression.

- 1) Replace the event expression by path expression.

- 2) Disjoin the events in the path expression exhaustively to get a boolean expression, in the form of sum-of-disjoint products of the interconnecting elements involved in the paths [92].

- Replace the boolean variables with their probabilistic values to get the multiprocessing reliability.

**Example 3.4:** Consider  $2 \times 2$  crossbar system. The connection matrix is shown in Fig. 3.10.

$$\begin{array}{ccc}

M_1 & M_2 \\

P_1 & 1 & 2 \\

P_2 & 3 & 4

\end{array}$$

FIG. 3.10. CONNECTION MATRIX OF 2 X 2 CROSSBAR SYSTEM.

The event expression is  $i\delta + 14 + 23 + 24$ Path expression:  $P_1P_2S_{11}S_{21}M_1 + P_1P_2S_{11}S_{22}M_1M_2 + P_1P_2S_{12}S_{22}M_2$ Boolean expression after disjoining:  $p_1P_2S_{11}S_{21}M_1 + p_1P_2S_{11}S_{12}S_{21}M_1M_2 + p_1p_2S_{11}S_{22}S_{22}M_1M_2 +$   $p_1P_2S_{11}S_{12}S_{21}S_{22}M_2 + p_1P_2S_{11}S_{12}S_{21}S_{22}M_1M_2 + p_1p_2S_{11}S_{12}S_{21}S_{22}M_1M_2 +$   $p_1P_2S_{11}S_{12}S_{21}S_{22}M_1M_2$ Reliability of the MPS:  $2p^2s^2m + 2p^2s^2m^2 - 4p^2s^3m^2 + p^2s^4m^2$ assuming  $p_1 = p$ ,  $m_3 = m$  and  $s_{13} = s$  for all i and j.

### 3.2 t-out-of-s SYSTEMS

In this section we discuss t-out-of-s systems. The results derived here shall be used later for analysis of MPSs.

If a system with s components requires t ( $\leq$  s) or more components to function for the system to be good, then such a system is called a t-out-of-s: G system. If we let t=s, we have a series system; if we let t=1, then we have a system with parallel redundancy. A case of particular importance is a system with t=s-1. In such a system the failure of a single unit is not sufficient to cause system failure, but the failure of two units does cause system failure. This is sometimes referred to as fail-safe design.

The dual of t-out-of-s: G system is the t-out-of-s: F system which is defined as a system which requires at least t units to fail for the system to fail. Because of duality, there

is no real distinction between a t-out-of-s:G system and a t-out-of-s:F system. The probability of success of a t-out-of-s: G system is the complement of the proability of failure for an (s-t+1)-out-of-s : F. To save effort, it is only necessary to ascertain which number,  $\binom{s}{t}$  or  $\binom{s}{s-t+1}$  is larger. If the system is t-out-of-s:G and (t) is larger, the probability of system failure produces lesser number of terms for computation and hence is advantageous; otherwise the probability of succeses is advantageous. If the two numbers are equal, both the systems yield the same computation effect. Instead of discussing both the systems separately, we can consider one, say t-out-of-s:G system, and substitute t by (s-t+1) when advantageous. There has been a great deal of interest in the study of t-out-of-s systems (37,93-101) because of the following reasons. t-out-of-s systems are more general than pure series or parallel system, and some interconnections can be modeled using this technique [99,100].

### 3.2.1 Previous work : A Review

Many researchers have presented algorithms for calculating the reliability of a t-out-of-s:G system where each of the s components of the system has a given reliability. The method of inclusion-exclusion principle [102] produces a larger number of pairs of identical terms with opposite signs, and requires  $2(\frac{s}{t}) - 1$  terms and each term involves atleast t multiplications. The first success in completely supressing pairs of cancelling terms was scored by Satyanarayana et al [103] in

analysing the reliability of networks. But these results can not be applied to t-out-of-s systems, because for 1 < t < s these structures are not networks.

Cooksey [93] and Heidtmann [94] have considerably reduced the number of terms, to  $\sum_{i=t}^{s} ({t \atop t})$ , by avoiding generation of cancelling terms. However, each term has to be multiplied by a positive or negative constant which represents the number of repetitions of the term. McGrady [95] also generates the same number of terms but each term involving exactly (s-1) multiplications.

Recent algorithms [37,96-99] have further improved on the computational effort. Locks [37] used the method of disjoint products [104] and generates  $(\begin{array}{c}s\\t\end{array})$  terms. It however, involves many terms in the intermediate steps which disappear in final expression. Barlow and Heidtmann [96] used a recursive approach and is good for numerical computation but their method generates more than  $(\begin{array}{c}t\\t\end{array})$  terms. The algorithm presented by Jain and Gopal [97] generates  $(\begin{array}{c}s\\t\end{array})$  terms, but recursiveness of the evaluation process have not fully been exploited and it takes more multiplications than necessary [98].

In the following subsections we derived some efficient algorithms to obtain the exact reliability of a t-out-of-s:G system. Section 3.2.2 considers the techniques used in developing the model. Section 3.2.3 presents two recursive algorithms. An improved recursive algorithm is presented in

Section 3.2.4 and Section 3.2.5 presents an efficient non-recursive algorithm. A comparison of these algorithms [93-95,97] is done in Section 3.2.6.

### 3.2.2 Theory

In order to express the various events the two methods generally considered are conservative and exhaustive. Fratta and Montanari compared their relative merits [84]. In the present work conservative method is used for algorithm development, because it minimizes the number of disjoint events.

### Conservative Policy

Let us consider a set of boolean stochastic variables  $\{x_1 \ldots, x_m\}$ . The set of stochastic variables is first transformed into a sequence  $(x_1, x_2, \ldots, x_m)$ , i.e., an arbitrary order is choosen. The set E contains the following m+1 events.

$E_{1} = \{x_{1} = 1\}$   $E_{2} = \{x_{1} = 0; x_{2} = 1\}$   $\vdots$   $E_{m} = \{x_{1} = \dots = x_{m-1} = 0; x_{m} = 1\}$   $E_{m+1} = \{x_{1} = \dots = x_{m} = 0\}$

Note that every event except Em+1 contains exactly one positive assignment, while the number of negative assignment varies from 0 to m. This policy will be called as conservative policy while the dual policy will be called conservative negative. Both the variants of conservative policy are illustrated in Table 3.1.

### TABLE 3.1

# VARIANTS OF CONSERVATIVE POLICY

### (Variables (x1, x2..., xm)

|            |          | ignment  |

|------------|----------|----------|

| Event name | Negative | Positive |

| E1         | 0        | 1        |

| E2         | 10       | 01       |

| E3         | 110      | 001      |

|            |          |          |

|            |          |          |

|            |          |          |

| F          | 11110    | 00001    |

| Em         | 11111    | 00000    |

| Em + 1     | 11111    | 00000    |

3.2.3 Algorithm Development

Let us consider a system with 'n' units. The vectors  $X = \{p_1, p_2, ..., p_n\}$  and  $\overline{X} = \{q_1, q_2, ..., q_n\}$  represent the reliability and the unreliability values of these individual units. Then the following theorems hold.

Theorem 3.1: Let s and t be positive integers such that s2t, then in a system with n units, the reliability is given by

$R(s,t) = P_{n-s+1} H(X;s-1, t-1) + q_{n-s+1} P_{n-s+2} H(X;s-2, t-1)$ + q\_{n-s+1} q\_{n-s+2} H(X;s-2, t)

<u>Proof</u>: Consider two units with conservative positive expansion of logical 1, 01, and 00. Logical 1(0) implies that a unit is good (failed) and is replaced by p(q) value of the unit. Each factor modifies H(X;s,t) in the equation and hence the theorem is proved. Figure 3.11 illustrates the tableau for computing H(X;s,t).

Corollary 3.1 - For s=t Theorem 3.1 becomes:

$H(X;s,s) = P_{n-S+1} \quad H(X;s-1, s-1).$ which recurisivaly reduces to:

$H(X;s,s) = \frac{n}{\pi} p_1, s \neq 0$ . i=n-s+1

Theorem 3.2 - For the integer values of s and t, we have

$H(X;s.t) = \begin{bmatrix} 0; & s < t \\ 1; & t = 0 \end{bmatrix}$

<u>Proof</u>: H(X;s,t) is assumed to be  $\begin{pmatrix} S \\ t \end{pmatrix}$  hence the theorem follows

| s V .      | t   | +1       | t       |  |

|------------|-----|----------|---------|--|

|            |     |          |         |  |

| (5-2)      | (s  | 5-2,t)   | (s-2,t) |  |

| (s-1)<br>s | (5- | 5-1,t-1) | (s,t)   |  |

|            |     |          |         |  |

# FIG. 3.11 TABLEAU ASSOCIATED WITH H(x;s,t) COMPUTATION USING THEOREM 3.1

# 245423

central Library University of Poorker

from the definition of s units taken t at a time [102]

Theorem 3.3 : Let s and t be positive integers such that  $s \ge t$  then-

$H(X; s, t) = p_{n-s+1} H(X; s-1, t-1) + \dots$ +  $q_{n-s+1} \dots q_{n-t-1} p_{n-t} H(X; t, t-1)$ +  $q_{n-s+1} \dots q_{n-t} H(X; t, t)$

Proof: Same as Theorem 3.1.

Theorem 3.3 gives an expression for H(X;s,t) considering (s-t) units and applying conservative positive assignment to obtain elementary events. Thus, it has (s-t+1) terms as against only 3 terms of theroems 3.1. Fig. 3.12 illustrates the tableau for computing H(X;s,t).

Example 3.5- consider a 4-out-of-7 : G system, then

$H(X;7,4) = p_1 H(X;6,3) + q_1 p_2 H(X;5,3) + q_1 q_2 H(X;5,4)$ using theorem 3.1, and

$H(X;7,4) = p_1 H(X;6,3) + q_1 p_2 H(X;5,3) + q_1 q_2 p_3 H(X;4,3)$ + q1 q2 q3 H(X;4,4)

using Theorem 3.3. In both the cases s = n = 7 and t = k = 4.

### Recursive Approach

Algorithms 3.3 and 3.4 are directly based on Theorems 3.1 and 3.3. These are presented in Fig.3.13 , and Fig.3.14 respectively. The simplification, if any , is done using Theorems 3.2 and Corollary 3.1. The algorithms are presented in Algol-like notation.

| s t   | t-1       | t     |   |

|-------|-----------|-------|---|

| s = t | (t,t-1)   | (t,t) |   |

|       |           |       |   |

|       |           |       |   |

|       |           |       |   |

| s-2   | (s-2,t-1) |       | - |

| s-1   | (s-1,t-1) |       |   |

| 5     |           | (s,t) |   |