# GROWTH AND STUDIES OF INSULATING FILMS FOR SILICON DEVICES

## A THESIS

submitted in fulfilment of the requirements for the award of the degree of DOCTOR OF PHILOSOPHY in ELECTRONICS & COMPUTER ENGINEERING

Ву

ARUN KUMAR

DEPARTMENT OF ELECTRONICS & COMPUTER ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247 667

**OCTOBER, 1988**

#### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the thesis entitled 'GROWTH AND STUDIES OF INSULATING FILMS FOR SILICON DEVICES' in fulfilment of the requirement for the award of the Degree of Doctor of Philosophy, submitted in the Department of ELECTRONICS AND COMPUTER ENGINEE-RING of the University is an authentic record of my own work carried out during a period from Jul. 1979 to oct. 1988 under the supervision of Dr. RAGHUVIR SINGH, Professor, Department of Electrical Engineering, College of Technology, Malla, University of Aden, Aden (P.D.R.Y.) and Dr. R.P. AGARWAL, Professor, Department of Electronics and Computer Engineering, University of Roorkee, Roorkee, INDIA.

The matter embodied in this thesis has not been submitted by me for the award of any other degree.

Asun Kumar

( ARUN KUMAR )

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

( RAGHUVIR SINGA ) Professor Dept. of Electrical Engineering College of Technology, Malla University of Aden ADEN (P.D.R.Y.)

RIDogarwal

( R.P. AGARWAL ) Professor Dept. of Electronics and Computer Engineering, University of Roorkee, ROORKEE - 247 667, INDIA

Date :

The candidate has passed the Viva-Voce examination held on 27/5/89 at Elected. The thesis is recommended for award of the Ph.D. Degree.

RD garwal Signature of Guide(s)

Signature of External Examiner(s)

#### ACKNOWLEDGEMENTS

I am deeply grateful to my supervisors Dr.R.Singh, and Dr.R.P.Agarwal for providing valuable guidance and stimulating environment for working. I am specially indebted to Dr. Agarwal for his suggestions and constant encouragement particularly in the absence of Dr. Singh. His dealings as a friend rather than a supervisor, was a great source of strength to me. It was a pleasure to work under him. The gratitude to him can not be expressed in words but felt.

I express my sincere thanks to Dr.S.C.Gupta, Dr.N.K.Nanda the Ex-Heads of department and Dr.R.Mitra the present Head of the Department for providing all the necessary facilities and help during my stay at Roorkee.

I would also like to thank Dr.S.Sarkar, Dr.S.Swaminathan, Dr.Shamim Ahmed and Dr.Nisha Sarwade for helpful discussions.

I wish to acknowledge the assistance provided to me by Mr.U.S.Rawat, Mr.Sagir Khan, Mr.Amir Hasan and Mr.Ved Prakash in fabrication and developing the facilities for experimental set-ups. Thanks are also due to Mr.D.C.Bhardwaj and Mr.R.P.Singh for typing the manuscript and Mr.K.D.Saini for preparing the drawings of the thesis.

I am grateful to the Ex-Principal Dr.B.N.Sharma of M.M.Engineering College, Gorakhpur for granting me study leave. A special word of thanks to present Principal Dr.Pandey B.B.Lal for encouragement and advice in times of frustation proved to be a great source of strength.

Finally it will be injustice on my part if I fail to express my gratitude to my wife Indu and daughter Saloni specially who had to bear my negligence to their problems during the period of work.

· Asun Kumar

(ARUN KUMAR)

#### ABSTRACT

In recent years the growth and or deposition of insulating films on the surface of a semiconductor material has received considerable attention as it is used for passivation, masking, isolation, dielectric purposes (gate dielectric) etc. Quality of the insulating films govern the performance of the device and to a some extent the packing density in integrated circuits. Silicon is by far the most widely used semiconductor material for fabrication of discrete, integrated circuits, LSI, VLSI, etc. due to its well established technology and its native oxide possess the outstanding qualities. Various techniques have been developed for the growth of oxide films on silicon such as thermal oxidation, plasma anodization and wet anodization. Thermal oxidation of silicon is the most commonly used technique for the growth of oxide film, due to superior Si-SiO<sub>2</sub> interface properties. However temperature involved in oxidation generates stacking faults and dislocations; produces stress and wafer warpage; and changes the impurity profiles previously formed in the substrate. With the advent of VLSI's it was realised that for further increasing the packing density on the single chip some low temperature technique should be evolved for the growth of oxide films so that the high temperature effects may be minimized.

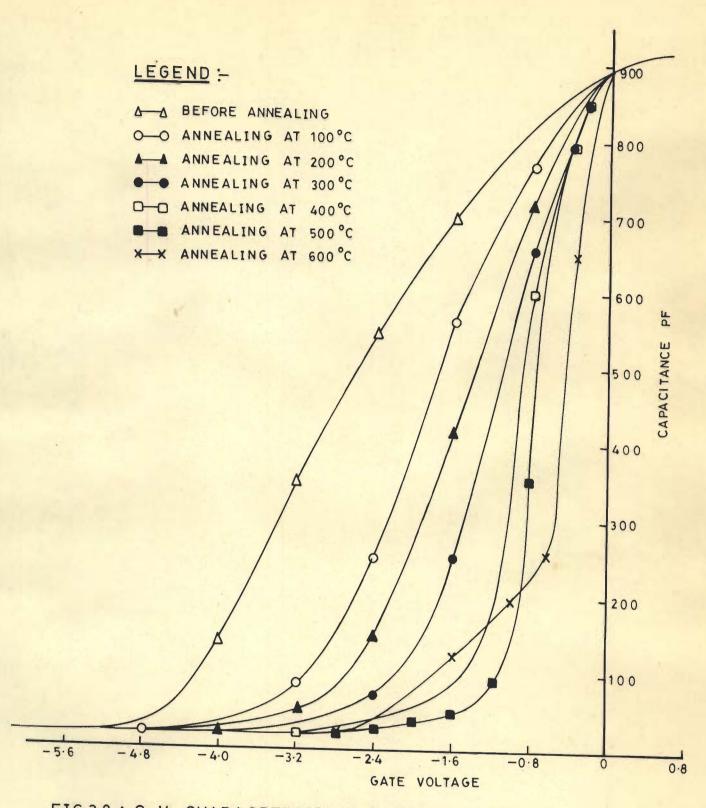

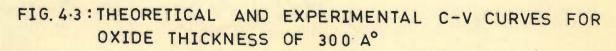

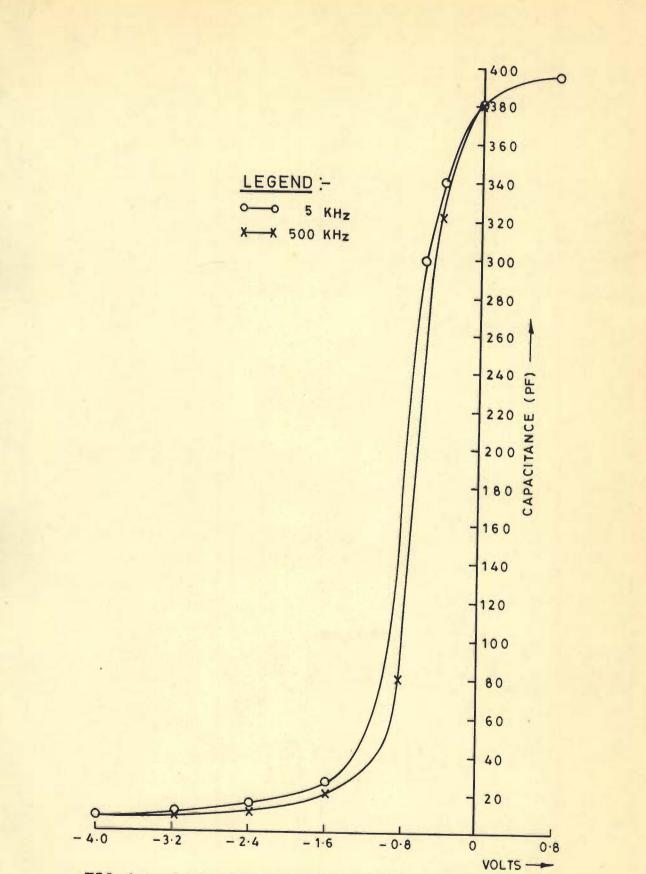

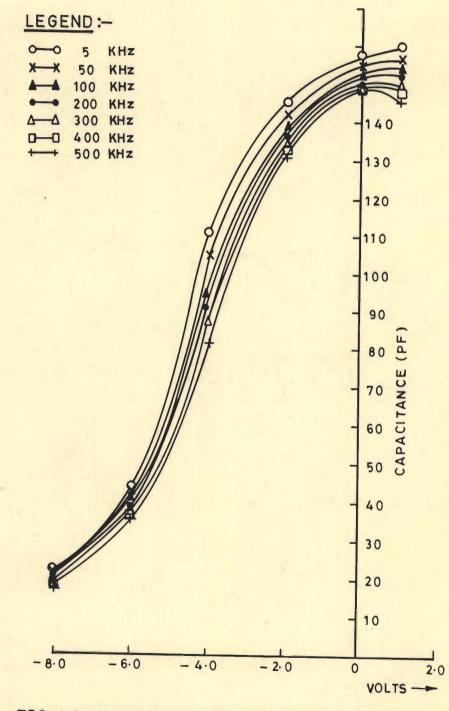

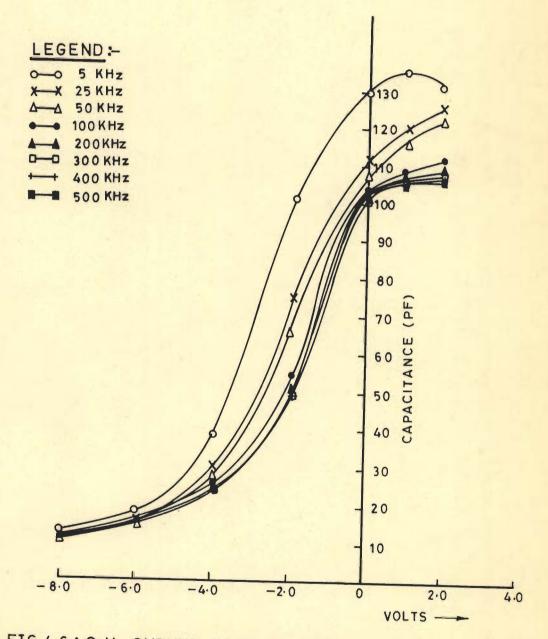

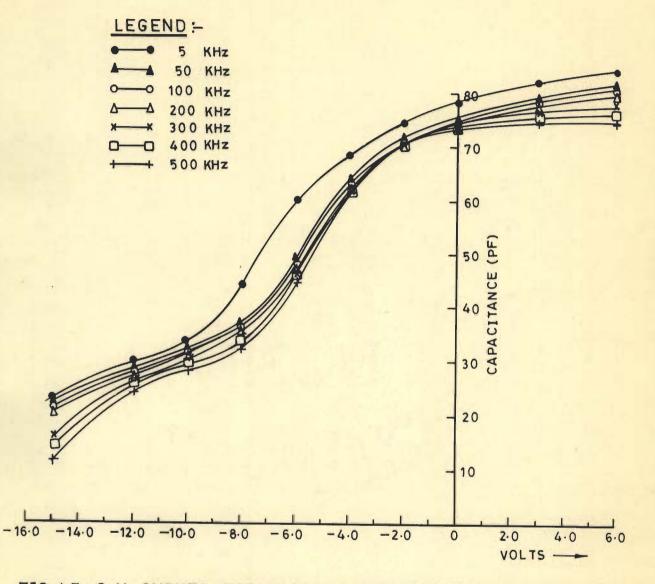

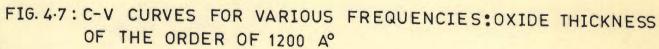

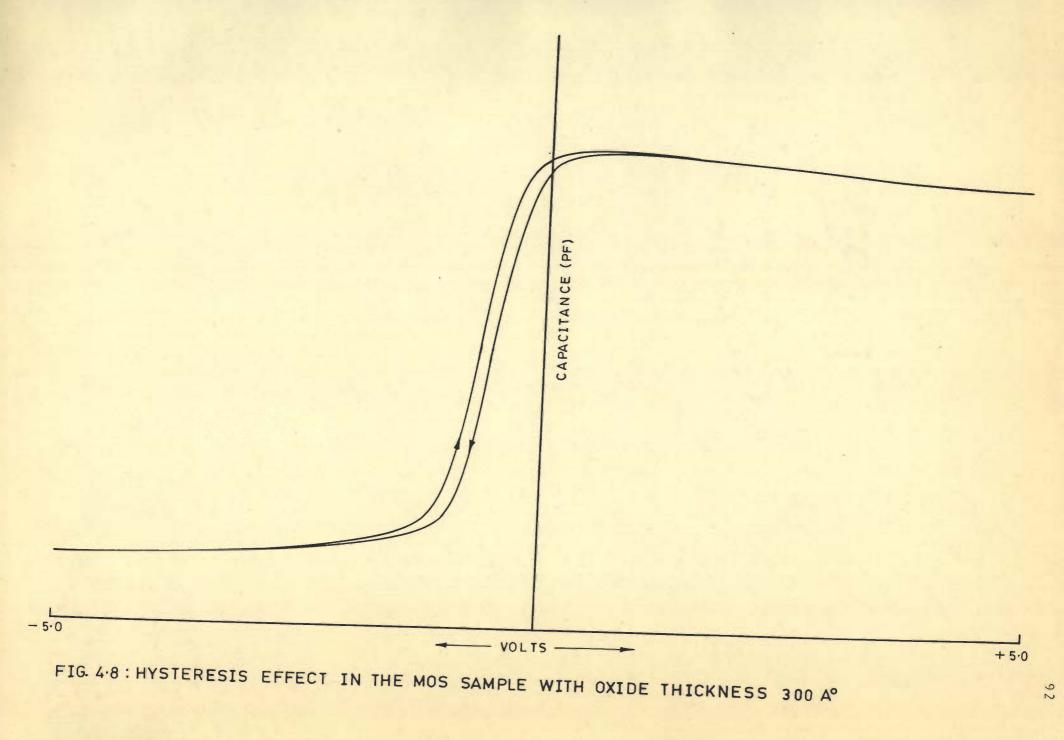

In order to avoid the undesired effects of thermal oxidation and the encouraging results of anodic oxide films on GaAs, there is a renewed interest in growing thin insulating films on silicon by anodic oxidation. Present thesis deals with the growth and or deposition insulating films on silicon at low temperatures. Due of to the ease in fabrication, simplicity of structure and the sensitivity of the C-V characteristics to physical properties, MOS structures were used to study the influence of process parameters on the properties of insulating films. The material used in the investigation was n-type epitaxially grown silicon wafer of  $\langle 111 \rangle$  orientation having resistivity of 6 to 8 ohm-cm. The resistivity of the substrate 0.005 ohm-cm. A stringent cleaning procedure based was on hydrogen peroxide solutions was used for surface preparation of samples. The electrolytic bath used for anodization was freshly prepared 0.04N KNO3 solution in Ethylene-Glycol. Anodization parameters were optimised experimentally with a view to grow thin compact SiO<sub>2</sub> layers for applications in integrated circuit technology. The anodization was carried at constant current density followed by a constant out voltage mode. Anodically oxidised samples were annealed H<sub>2</sub> atmosphere, ohmic contacts were made at the back in of anodized samples. The MOS structure was completed by evaporating ultrapure Al through a metal mask over the grown oxide film in a vacuum coating unit. The suitability of the grown SiO<sub>2</sub> film for devices was analysed by studying C-V, G-V and I-V curves. Interfacial and electrical properties such as surface state density, dielectric breakdown strength and dielectric constant were determined to assess the quality of grown oxide film. Experimental results reveal that the quality of anodically grown film of the order of 300 A° is comparable with that of thermally grown oxide films. It was also noted that the dielectric properties of the grown films deteriorates as the film thickness increases.

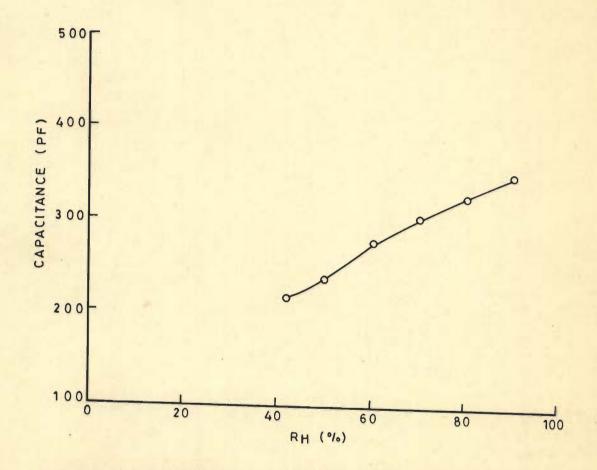

During investigations it was observed that the anodization of silicon samples at higher current density in an electrolytic bath of  $KNO_3$  in Ethylene-Glycol mixed with small quality of water at elevated temperature results in porous films. The characteristics of such anodically grown films vary with the humidity of the surrounding environment. The capacitance of the such MOS structure was measured as a function of relative humidity. Results show that the porous  $SiO_2$  films can be used to realise humidity sensors. The proposed sensors may be suitable to realise I.C. sensors as it can be fabricated on silicon I.C. chips as an integral part of the circuit.

Insulating  $Al_2O_3$  films were also deposited on silicon samples and on anodically grown layers by reactive evaporation of Aluminium to fabricate and study the MAS and MAOS structures. Aluminium oxide has higher dielectric constant, higher density and large impermeability for impurity diffusion, further  $Al_2O_3$  films gives a positive values of threshold voltage and stops fast diffusing alkali ions. Evaporation parameters and the annealing temperature were optimized for the fabrication of MAS and MAOS samples. From the measurements and results it was concluded that  $Al_2O_3$  film deposited by reactive evaporation method is useful for use as gate insulator in MOS devices alone or as an auxiliary dielectric with SiO<sub>2</sub>.

Essentially the anodization and reactive evaporation technique here used is a low temperature fabrication technique and may be suitable in VLSI and MOS technology. With the scaling down of device dimensions the use of thin SiO<sub>2</sub> films with high dielectric breakdown strength are finding importance in MOS technology. Therefore anodically grown SiO<sub>2</sub> films of thickness of the order of 300 A° is a promising substitute of the thermally grown films for VLSI and MOS technology.

(iv)

### CONTENTS

.

CHAPTER

Page No.

| ABSTRACT | T | AC | R | T | S | B | A |

|----------|---|----|---|---|---|---|---|

|----------|---|----|---|---|---|---|---|

# ACKNOWLEDGEMENTS

| 1. INTRO<br>OF T | ODUCTION AND STATEMENT<br>HE PROBLEM                         |    |

|------------------|--------------------------------------------------------------|----|

|                  | Introduction                                                 | 1  |

| 1.2              | Techniques used to form silicon dioxide<br>films on silicon  | 3  |

|                  | 1.2.1 The deposition process                                 | 4  |

|                  | 1.2.2 The native oxide growth process                        | 7  |

|                  | 1.2.3 Thermal Oxidation                                      | 7  |

|                  | 1.2.3.1 Description of thermal oxidation process methods     | 7  |

|                  | 1.2.3.2 Defects Induced by thermal oxidation                 | 10 |

|                  | 1.2.3.2 (i) Thermal Oxidation<br>stacking faults             | 11 |

|                  | 1.2.3.2 (ii) Dopant Impurity<br>Redistribution               | 11 |

|                  | 1.2.3.2 (iii) Thermal Oxidation<br>Induced Oxide<br>Stresses | 12 |

|                  | 1.2.4 Anodic Oxidation                                       | 14 |

|                  | 1.2.4.1 Plasma Anodization                                   | 14 |

|                  | 1.2.4.2 Anodization in a Liquid '<br>Electrolyte             | 14 |

| 1.               | 3 Future trends in VLSI Technology                           | 15 |

|                  | 4 Statement of the Problem                                   | 16 |

|    | 1.5 Organisation of the Thesis                                                           | 18   |

|----|------------------------------------------------------------------------------------------|------|

| 2. | CRITICAL REVIEW OF THE SILICON WET ANODIZATION                                           | 20   |

| 3. | ANODIC OXIDATION OF SILICON AND FABRICATION<br>OF MOS STRUCTURES                         | 39   |

|    | 3.1 Introduction                                                                         | 39   |

|    | 3.2 The MOS Structure                                                                    | 40   |

|    | 3.3 Surface Preparation of Silicon                                                       | 42   |

|    | 3.4 Cleaning of Accessories                                                              | 47   |

|    | 3.5 The Experimental Set-up and Fabrication of MOS Test Samples                          | 48   |

|    | 3.5.1 Electrolytic Bath                                                                  | 54   |

|    | 3.5.2 Anodization Process                                                                | 54   |

|    | 3.5.3 Electrolyte Molarity                                                               | 55   |

|    | 3.5.4 Anodization Current Density                                                        | 57   |

|    | 3.5.5 Applied Forming Voltage and Thick-<br>ness of the Grown Film                       | 60   |

|    | 3.5.6 Annealing                                                                          | 62   |

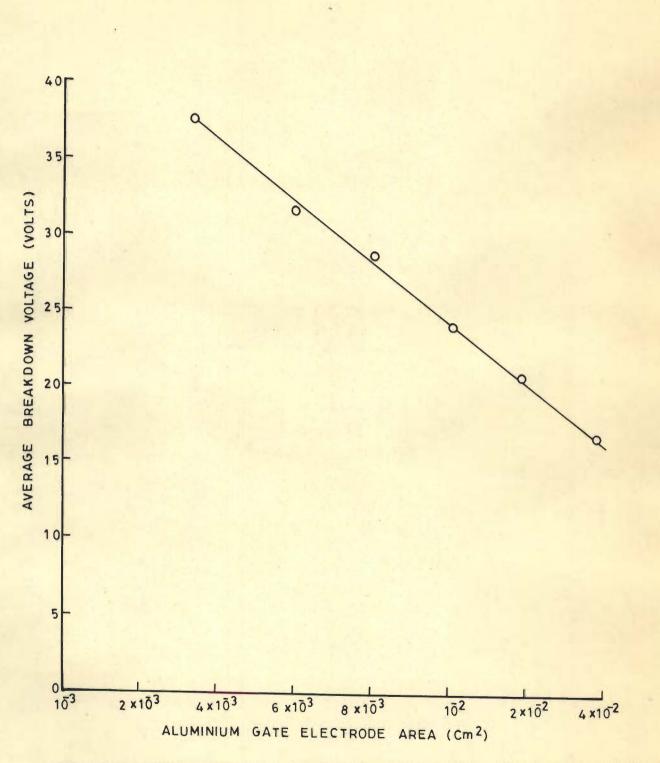

|    | 3.5.7 Gate Electrode Area                                                                | 66   |

|    | 3.5.8 Formation of Ohmic Contacts                                                        | 66   |

| 4. | CHARACTERISTICS OF ANODICALLY GROWN SiO2<br>LAYERS AND SI-SIO2 INTERFACES                | 76   |

|    | 4.1 Introduction                                                                         | 76   |

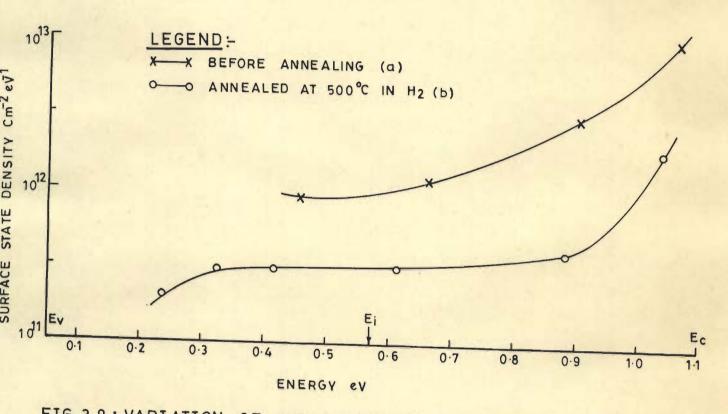

|    | 4.2 Surface States                                                                       | • 76 |

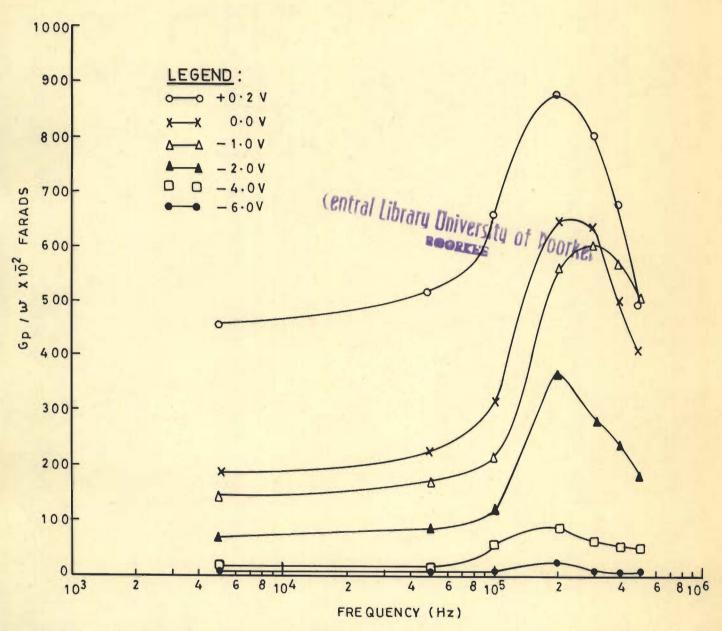

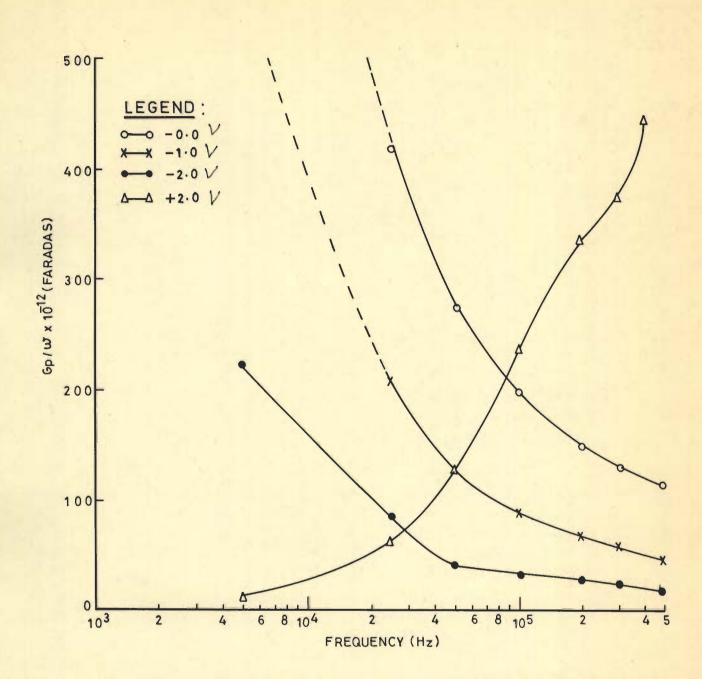

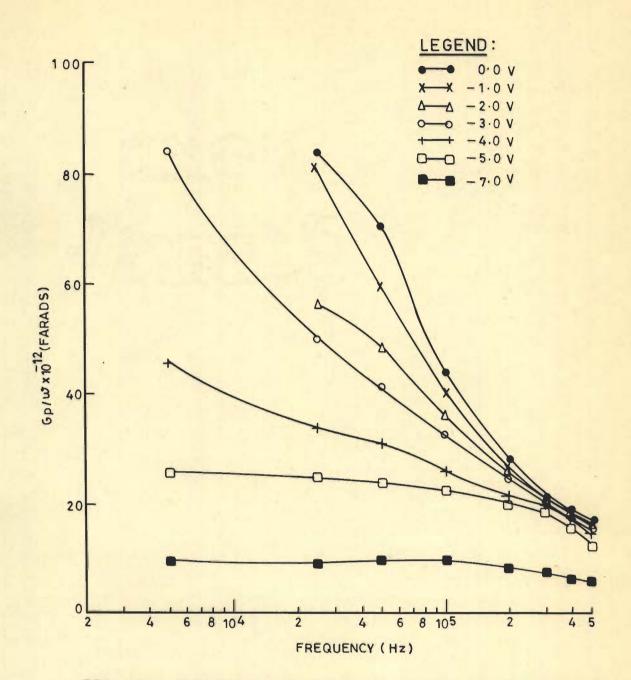

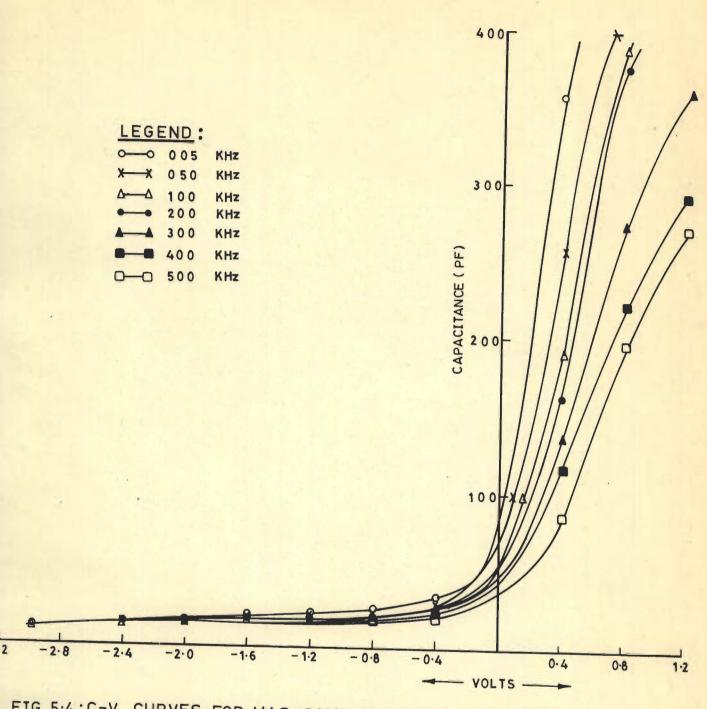

|    | 4.3 Conductance Method                                                                   | 80   |

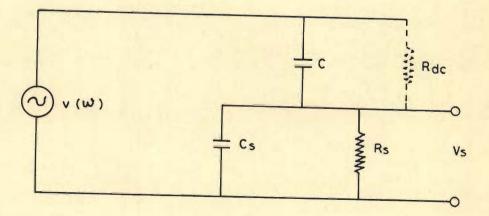

|    | 4.3.1 Measurement of the Equivalent<br>Parallel conductance (G ) of the<br>MOS Capacitor | 81   |

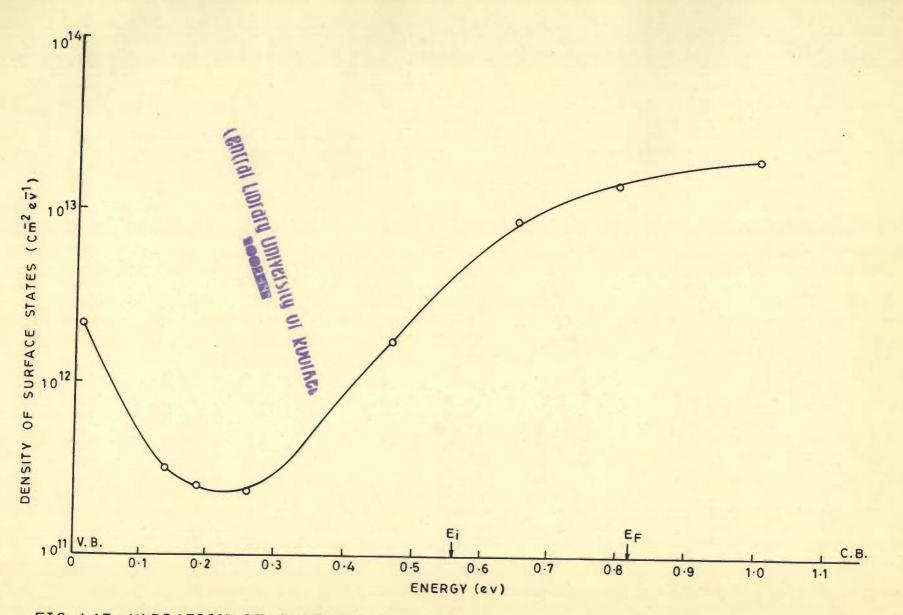

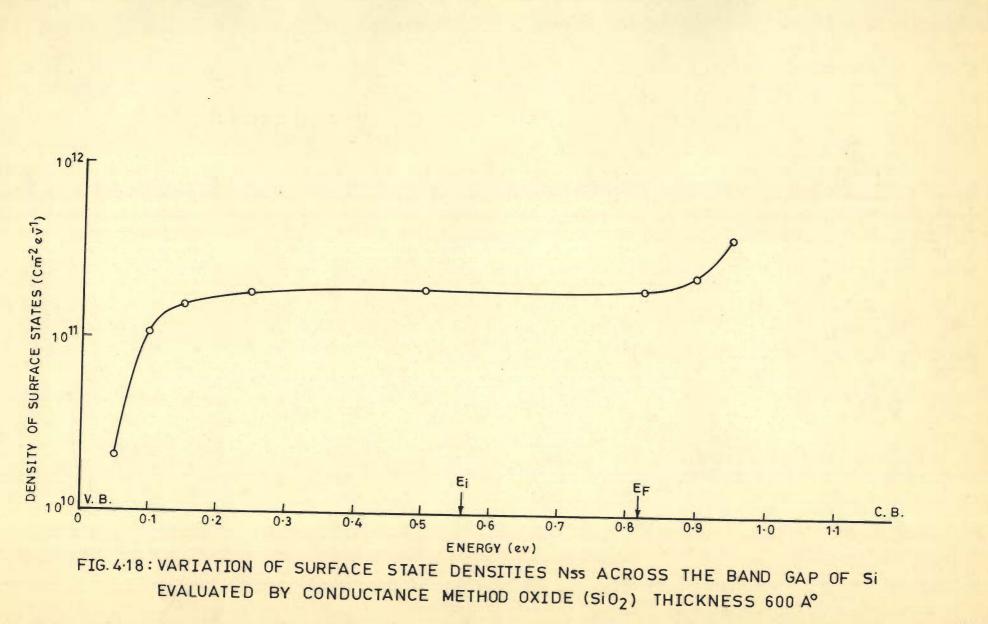

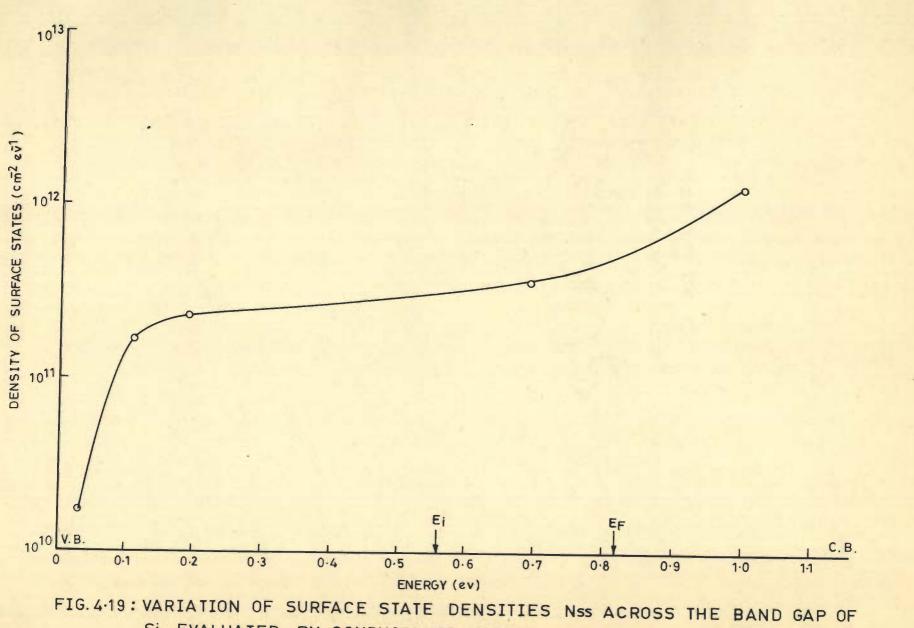

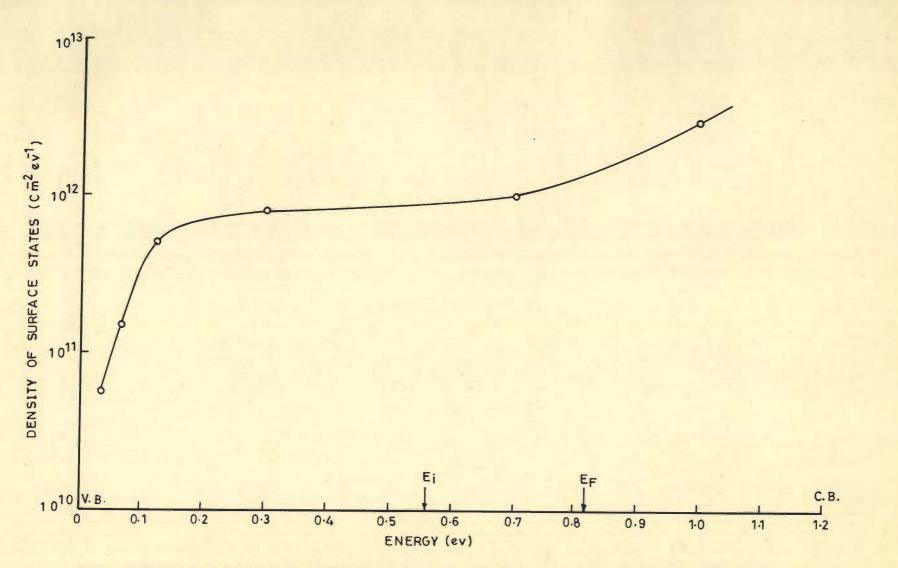

|    | 4.4 Determination of the Energy Position<br>of the Surface State Densities (Nss)<br>Across the Band Gap of Silicon       | 84         |

|----|--------------------------------------------------------------------------------------------------------------------------|------------|

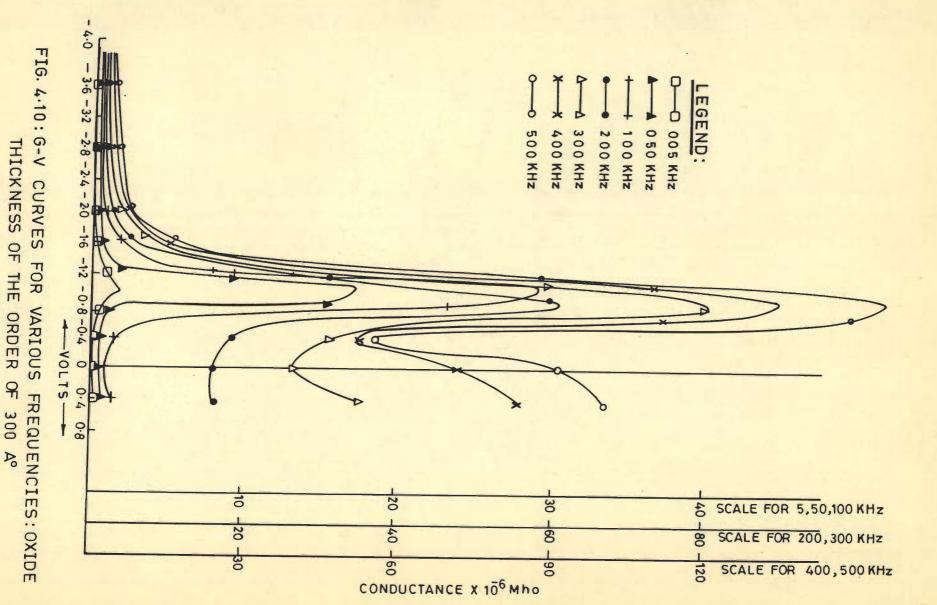

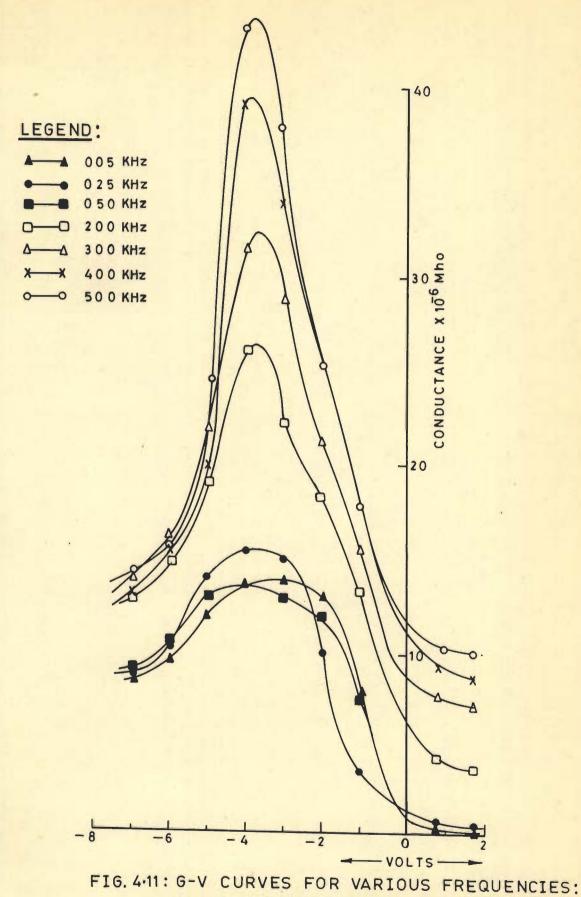

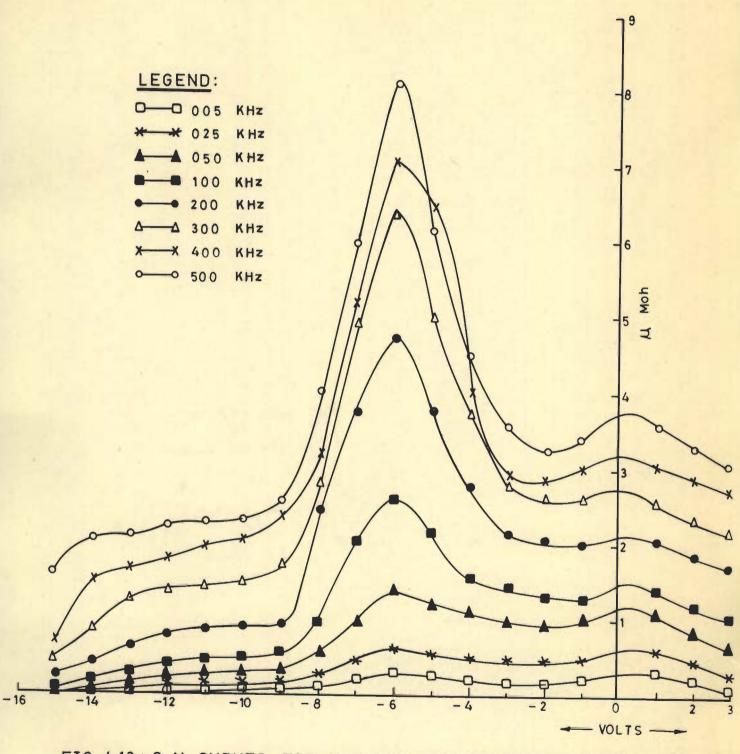

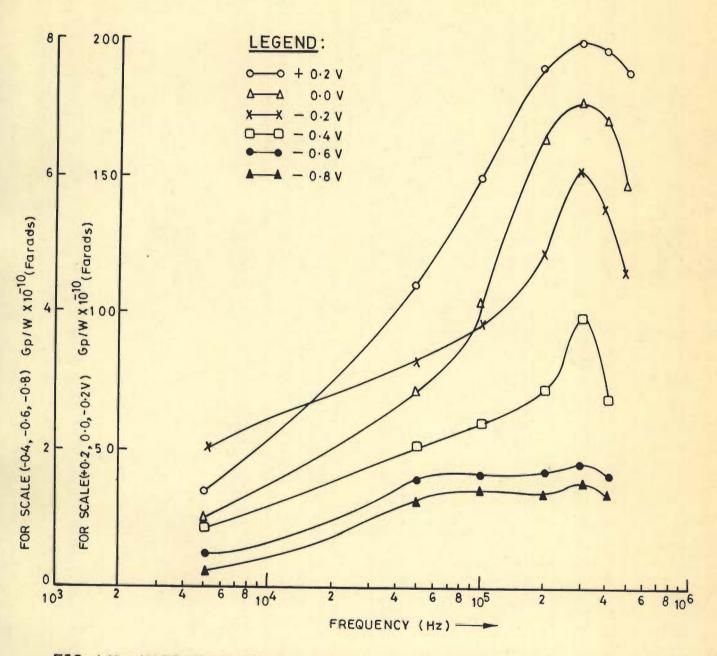

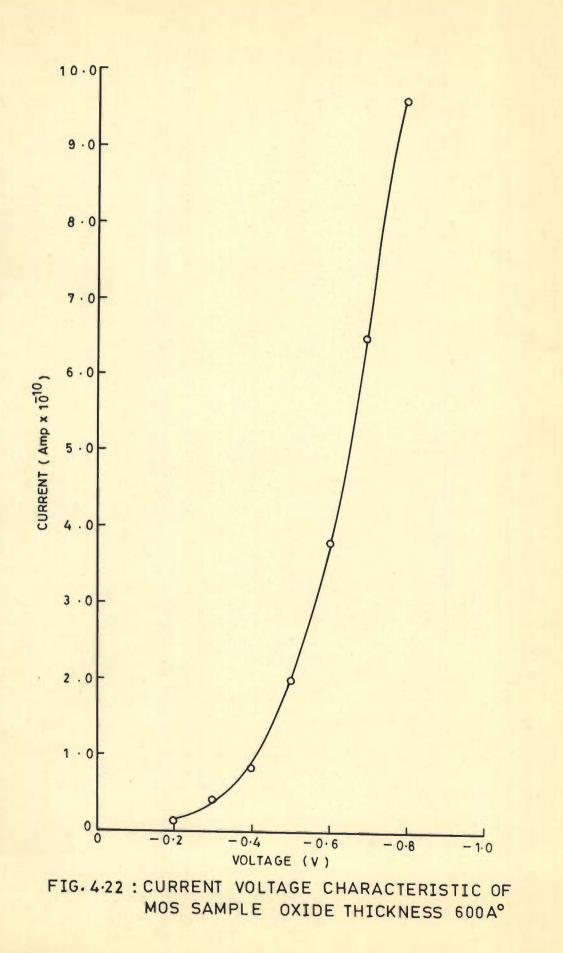

|    | 4.5 Experimental Results and Discussions                                                                                 | 85         |

| 5. | MAS, MAOS STRUCTURES AND THEIR INTERFACIAL<br>PROPERTIES                                                                 | 113        |

|    | 5.1 Introduction                                                                                                         | 113        |

|    | 5.2 Deposition of Al <sub>2</sub> O <sub>3</sub> Thin Films and<br>Fabrication of MAS Structures                         | 115<br>115 |

|    | 5.2.1 Standardisation of Deposition<br>Parameters of Al <sub>2</sub> O <sub>3</sub>                                      | 117        |

|    | 5.2.2 The Annealing of MAS Samples                                                                                       | 119        |

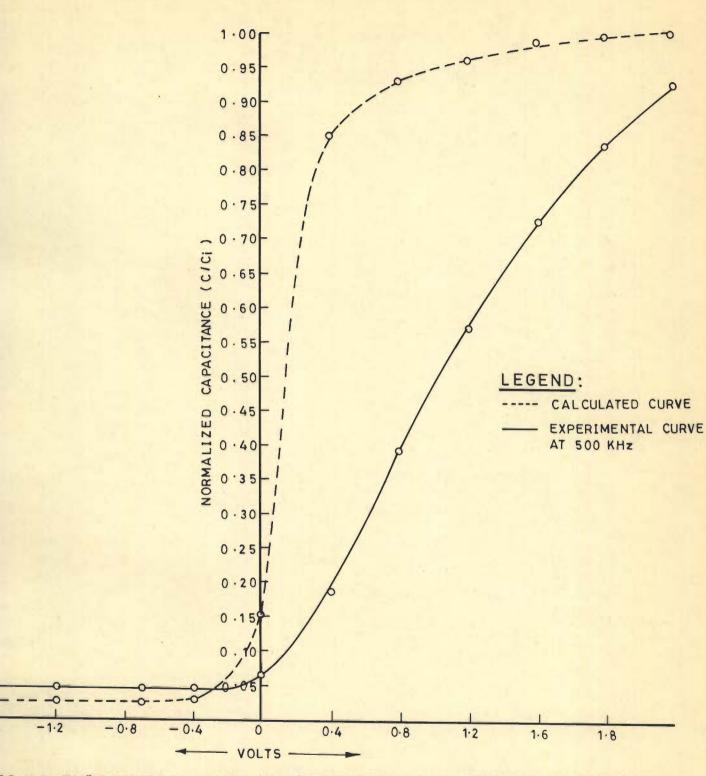

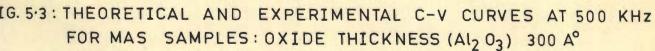

|    | 5.3 Electrical and Interfacial Properties<br>of Al-Al <sub>2</sub> O <sub>3</sub> -Si (MAS) Structures                   | 121        |

|    | 5.4 The Fabrication and characterization<br>of Al-Al <sub>2</sub> O <sub>3</sub> -SiO <sub>2</sub> -Si (MAOS) Structures | 129        |

| 6. | FABRICATION AND PERFORMANCE CHARACTERISTICS<br>OF HUMIDITY SENSITIVE SIO 2 INSULATING FILMS                              | 137        |

|    | 6.1 Introduction                                                                                                         | 137        |

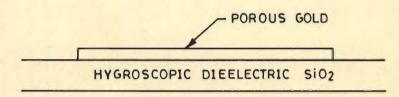

|    | 6.2 Humidity Sensitive MOS Capacitor<br>Structure                                                                        | 138        |

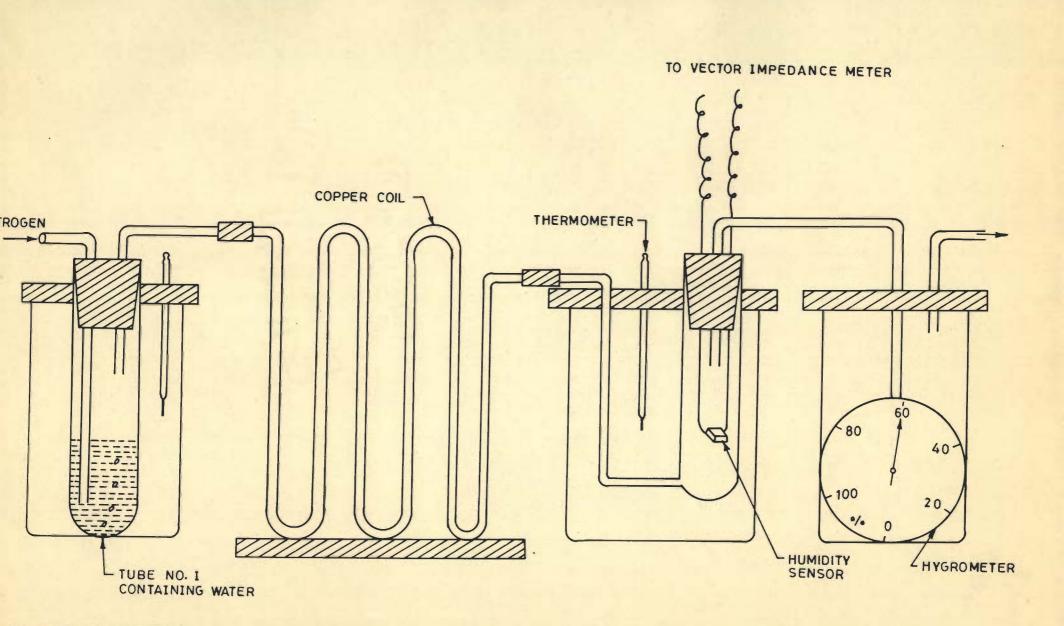

|    | 6.3 Sensor Fabrication                                                                                                   | 140        |

|    | 6.4 Experimental Results                                                                                                 | 141        |

| 7. | CONCLUSIONS AND SUGGESTIONS FOR FUTURE WORK                                                                              | 145        |

|    | 7.1 Introduction                                                                                                         | 145        |

|    | 7.2 Summary and Conclusions                                                                                              | 146        |

|    | 7.3 Suggestions for Future Work                                                                                          | 152        |

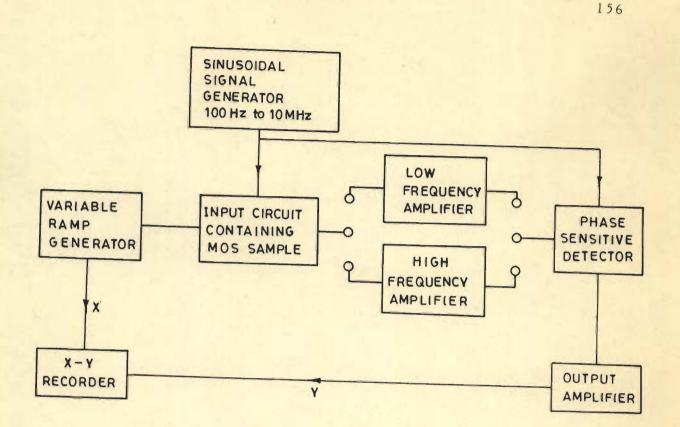

|    | APPENDIX                                                                                                                 | 154        |

|    | REFERENCES                                                                                                               | 162        |

#### CHAPTER - I

### INTRODUCTION AND STATEMENT OF THE PROBLEM

#### 1.1 INTRODUCTION

The integrated circuit complexity has advanced from small scale integration (SSI) to very large scale integration (VLSI), which has 10<sup>5</sup> or more components per chip. Present improvements on chip integration complexity are being achieved by scaling down lateral and vertical dimensions of individual devices. The shrinkage of lateral dimensions will continue to be achieved by improvements in photolithography. The reduction of vertical dimensions requires that the processing temperature, such as deposition of growth of oxide films on solicon substrate used to fabricate chips be lowered [1].

Silicon is by far the most widely used semiconductor material for fabricating discrete and integrated electronic devices and circuits as its processing technology is well established and the oxide of silicon possesses the outstanding qualities for applications. The growth or deposition of insulating films over silicon is necessary during the entire process of fabricating modern integrated circuits. The oxide layers are used for various purposes such as:

(i) For surface passivation: Passivation is accomplished

by forming a thin insulating layer on the semiconductor surface. It minimises the electrical activity of the device surface, and protects the surface from environmental contamination. Thus passivation results in a marked improvement of device performance, stability, and uniformity of characteristics from device to device.

- (ii) The oxide acts as a barrier (mask) against the diffusion of impurities into the silicon underneath thus, by cutting windows into the oxide film, impurities can be diffused into the silicon through these windows.

- (iii) The oxide provides insulation between the metallization pattern interconnecting devices in the circuit and the silicon substrate.

- (iv) The oxide insulates the gate from the silicon in field effect devices.

- (v) The oxide acts as a dielectric layer in capacitors and MOS Sensors.

The oxide films in general should have the following characteristics:

(i) Ideal interface (i.e. virtually zero surface state density) on an interface characterized by an ideal C-V curve shifted along the voltage axis to a predetermined value.

- (ii) Good insulating properties, i.e. high breakdown strength, high dielectric constant, low dielectric losses and low leakage current.

- (iii) Resistant to ionic motion at elevated temperature and/or high fields.

- (iv) High resistance to atmospheric effects.

- (v) High resistance to radiation.

The condition for a perfect-interface between semiconductor and insulating oxide films are as follows:

- (a) Strong chemical bonds between the semiconductor and the oxide layers, preventing the existence of dangling bonds.

- (b) No impurities in the interface.

- (c) The oxide layer should be chemically stable to serve as a passivating film for the interface.

- 1.2 TECHNIQUES USED TO FORM SILICON DIOXIDE FILMS ON SILICON

The techniques used to form silicon dioxide films

on silicon fall into two broad categories.

(i) The deposition process

(ii) The native oxide Growth process.

Both these processes are briefly described in the following two sub-sections.

1.2.1 THE DEPOSITION PROCESS

Silicon dioxide can be deposited by various vapour phase chemical reactions. The simplest method of vapour phase deposition is oxidation of silane  $SiH_4$ , by oxygen at low temperatures at about 500°C [2-4]. The chemical reactions for phosphorus - doped oxides are

$SiH_4 + O_2 \longrightarrow SiO_2 + 2H_2$

$4PH_3 + 50_2 \longrightarrow 2P_2O_5 + 6H_2$

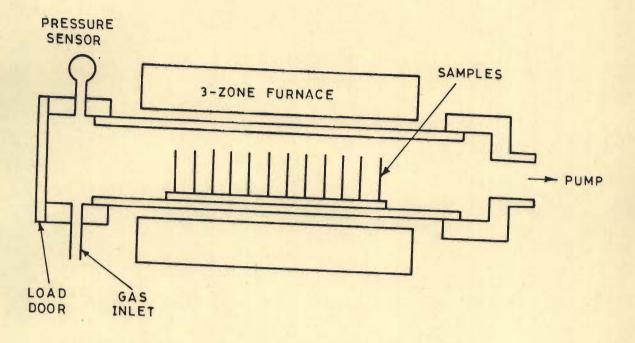

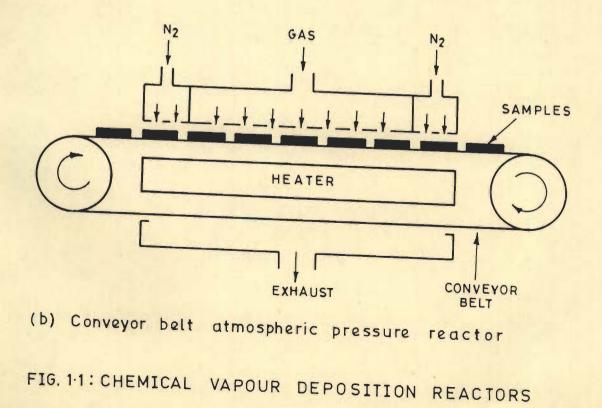

The deposition can be carried out at atmospheric pressure in a continuous reactor (Fig. 1.1b) or at reduced pressure in an LPCVD reactor (Fig. 1.1a). The main advantage of Silane-Oxygen reaction is low deposition temperature, which allows films to be deposited over aluminium metallization. Consequently, these films can be used for passivation coatings over the final device and for insulation between aluminium levels. The main disadvantages of Silane - -oxygen reaction is poor step coverage and particles caused by loosely adhering deposits on the reactor walls.

Silicon dioxide is also deposited at 650 to 750°C in an LPCVD by decomposing tetraethoxysilane,  $Si(OC_2H_5)_4$  [5,6]. The over all reaction is

Si

$$(OC_2H_5)_4 \longrightarrow SiO_2 + by products$$

where the by-products are a Complex mixture of organic and organosilicon compounds. The decomposition of  $Si(OC_2H_5)_4$  is useful for depositing insulators over polysilicon gates. The advantages of this method are excellent uniformity, conformal step coverage. The disadvantages are the hightemperature and liquid source requirements.

Silicon dioxide is also deposited at temperatures near 900°C and at reduced pressure by reacting dichlorosilane with nitrous oxide [2,7,8].

$$SiCl_2H_2 + 2N_2O \rightarrow SiO_2 + 2N_2 + 2HCl$$

This process, is used to deposit insulating layers over polysilicon; however, the oxide frequently contains small amounts of chlorine which may react with the polysilicon or cause film cracking [8].

Other deposition methods for dielectric, such as vacuum evaporation and reactive sputtering are not widely

(a) Reduced Pressure Reactor

used for VLSI processing [9]. The major problems include nonuniform depositions over many wafers, poor step coverage, and low throughput. The structure of evaporated and sputtered oxides is characterized by the composition as  $SiO_x$  where the value of x varies from one to two depending upon the deposition conditions.

1.2.2 THE NATIVE OXIDE GROWTH PROCESS

The native oxide of silicon may be grown in two ways:

(i) By thermal oxidation

(ii) By Anodic oxidation.

1.2.3 THERMAL OXIDATION [10 - 26]

1.2.3.1 DESCRIPTION OF THERMAL OXIDATION PROCESS METHODS

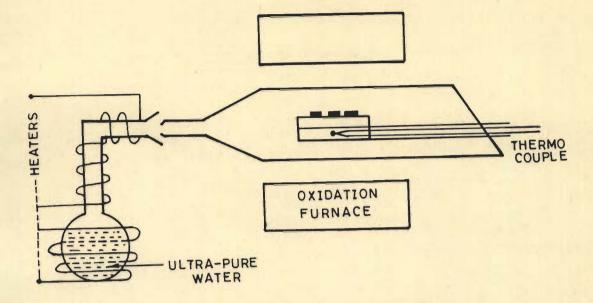

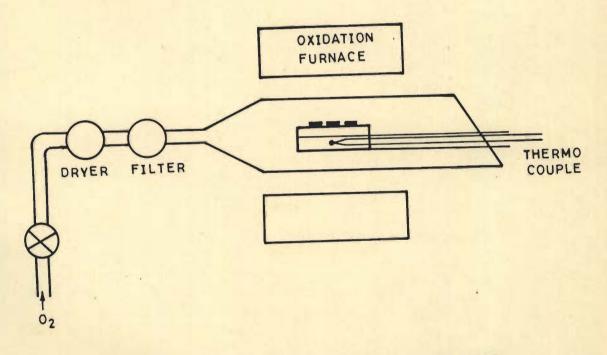

The term thermal oxides refers to those oxides formed from a thermally activated reaction of silicon with dry oxygen, wet oxygen, steam, and high - pressure steam. The first three methods are conducted in an opentube reactor where the silicon wafers are heated to a temperature in the range of 900°C to 1200°C in a steam of water vapour, oxygen, or a mixture of the two oxidants.

A wet - oxygen source is obtained by bubbling oxygen through a constant - temperature, high - purity water bath whose temperatur determines the partial pressure of water vapour in the gas stream for a specified oxygen flow rate.

For steam oxidation, the temperature of the water bath generating the steam provides a measure of the partial pressure and flow rate. Live steam yields poor grades of oxide because of the etching action of excess water. Properties of the various types of oxides grown by thermal oxidation are shown in Table I [27].

#### Table - I

#### Oxide Properties

| Туре               | Density<br>(gm/cm³) | Resistivity<br>(ohm - cm)              | Dielectric<br>strength<br>10 <sup>6</sup> V/cm |

|--------------------|---------------------|----------------------------------------|------------------------------------------------|

| Dry 0 <sub>2</sub> | 2.24 - 2.27         | 3x10 <sup>15</sup> -2x10 <sup>16</sup> | 2                                              |

| Wet O <sub>2</sub> | 2.18 - 2.21         |                                        |                                                |

| Steam<br>(l atm)   | 2.0 - 2.20          | $10^{15} - 10^{17}$                    | 6.8 - 9.0                                      |

The apparatus for the high pressure steam oxidation of silicon consists of a tight constant - volume enclosure, usually made of metal, into which a predetermined quantity of high purity water is introduced along with the silicon. The inside of the enclosure is often lined with gold or

# FIG. 1.2 : STEAM OXIDATION APPARATUS

# FIG.1.3 : DRY OXYGEN OXIDATION APPARATUS

other inert material to prevent undesired reactions between the water and the walls of the chamber. The entire system is heated to the oxidation temperature. High-pressure oxidation of silicon is particularly attractive, because thermal oxide layers can grow at relatively low temperatures comparable to typical high temp., 1-atm conditions. At 10-atm pressure and 750°C, a 300 A°-thick oxide can be grown in 30 min, the time, temperature, and pressure can be changed to vary the thickness. Such a technique has been applied to the growth of a thin gate oxide in the process to fabricate MOS dynamic RAM [28] and in the fabrication of MOS LSI [29]. In the oxidation at elevated pressure, several complications arise such as: Continuous Variations in pressure during pressurization, Small temperature variations that occur during pressurization and during the early part of the oxidation at full pressure, varying partial pressure of steam during depressurization, and grown film thickness variations from run to run and across a wafer.

#### 1.2.3.2 DEFECTS INDUCED BY THERMAL OXIDATION

In integrated circuit technology there are following important effects of thermal oxidation of silicon on bulk electrical properties of the silicon substrate and grown oxide films.

(i) Thermal Oxidation - Induced Stacking Faults

(ii) Redistribution of Dopants at interface

(iii) Thermal oxidation induced oxide stresses.

# 1.2.3.2 (i) THERMAL OXIDATION INDUCED STACKING FAULTS

The thermal oxidation process can induce stacking faults that extend from the silicon surface into the interior of the silicon [30-32]. These planar faults are structural defects in the silicon lattice consisting of an extra plane of silicon atoms bounded along the edges by dislocations. The dislocations are the transition between the extra plane of silicon atoms and the normal silicon lattice structure. Stacking faults are important in integrated circuit technology because they can be electrically active may enhance junction leakage currents and reduce minority carrier life time. The growth of oxidation-induced stacking faults is a strong function of substrate orientation, conductivity type, and defects present in nuclei. Observations show that the growth rate is greater for (100 then 111) substrates. Additionally, the density is greater for n-type conductivity than for p-type conductivity. The stacking fault.length is a strong function of oxidation temperature [33].

# 1.2.3.2 (ii) DOPANT IMPURITY REDISTRIBUTION

Dopant impurities near the silicon surface will be redistributed during thermal oxidation [34]. Redistribution

of dopant impurities in the silicon is important both from the stand point of device characteristics and in the interpretation of measurements of interface trap properties and oxide fixed charge. When silicon in thermally oxidized, an interace is formed separating the silicon from the SiO<sub>2</sub>. As oxidation proceeds this interface advances into the silicon. A doping impurity (initially present in the silicon) will redistribute at the interface until its chemical potential is the same on each side of the inteface. This redistribution may result in an abrupt change in impurity concentration across the interface. The ratio of the equilibrium concentration of the impurity (dopant) in silicon to that in SiO2 at the interface is called the equilibrium segregation coefficient. Two additional factors that influence the redistribution process are the diffusivity of the impurity in the oxide and the rate at which the interface moves with respect to the diffusion rate [35]. The segregation coefficient, as defined above increases with increasing temperature, and is orientation dependent with values for  $\langle 100 \rangle$  orientation being greater than  $\langle 111 \rangle$  orientation. Reported coefficients [36-38] are generally 0.1 to approximately 1.0 over the temperature range 850 to 1200°C.

# 1.2.3.2 (iii) THERMAL OXIDATION INDUCED OXIDE STRESSES

Stress is another effect of oxidation on silicon. Growth of an oxide film on silicon at high temperatures

puts the silicon under stress at room temperature because of the mismatch in the coefficient of thermal expansion between silicon dioxide and silicon. This stress does not directly affect the electrical properties of most devices used in integrated circuits, but if the silicon wafer is two thin, the mismatch stress can cause the wafer to warp or bow, film cracking and defect formation in the underlying silicon. Room temperature measurements following thermal oxidation of silicon show Sio, to be in a state of compression on the surface. Stress values of 3 x  $10^9$  dynes/cm<sup>2</sup> are reported [39] with the stress attributed to the difference in thermal expansion for Si and SiO<sub>2</sub>. During device processing, windows are out into the oxide resulting in a complex stress distribution. these discontinuities exceedingly high stress level At can occur. In IC fabrication, several lithography processes repeated, so alignment among the patterns is very are important when they are done on one over another. In forming patterns 2 µm or less, no more than 0.5 µm misalignment can be permitted [40]. Possible cause of the misalignment are (i) A difference in thermal expansion coefficients between silicon and silicon dioxide (ii) Shrinkage or expansion of the silicon wafer by thermal oxidation (iii) deformation of the silicon wafer or the mask plate by stress when they are brought into contact for printing.

#### 1.2.4 ANODIC OXIDATION

### 1.2.4.1 PLASMA ANODIZATION [41-43]

Plasma anodization is a vacuum process usually carried out in a pure oxygen discharge. The plasma is produced either by a high - frequency discharge or a DC electron source. Placing the wafer in a uniform density region of the plasma and biasing it positively below the plasma potential allows it to collect active charged oxygen species. The growth rate of the oxide typically increases with increasing substrate temperature, plasma density, and substrate dopant concentration. In the plasma anodization a high temperature (1000°C in H<sub>2</sub>) annealing treatment is required to obtain interfacial electrical properties comparable to thermally grown oxide films. Thus the over all process is a high temperature one. Plasma grown oxides are not superior to thermally grown oxides, and both are high temperature processes, but the apparatus needed to plasma anodization is more expensive and require more skill to use than that for thermal oxidation. Therefore, plasma anodization is not used in silicon integrated circuit manufacture.

#### 1.2.4.2 ANODIZATION IN A LIQUID ELECTROLYTE

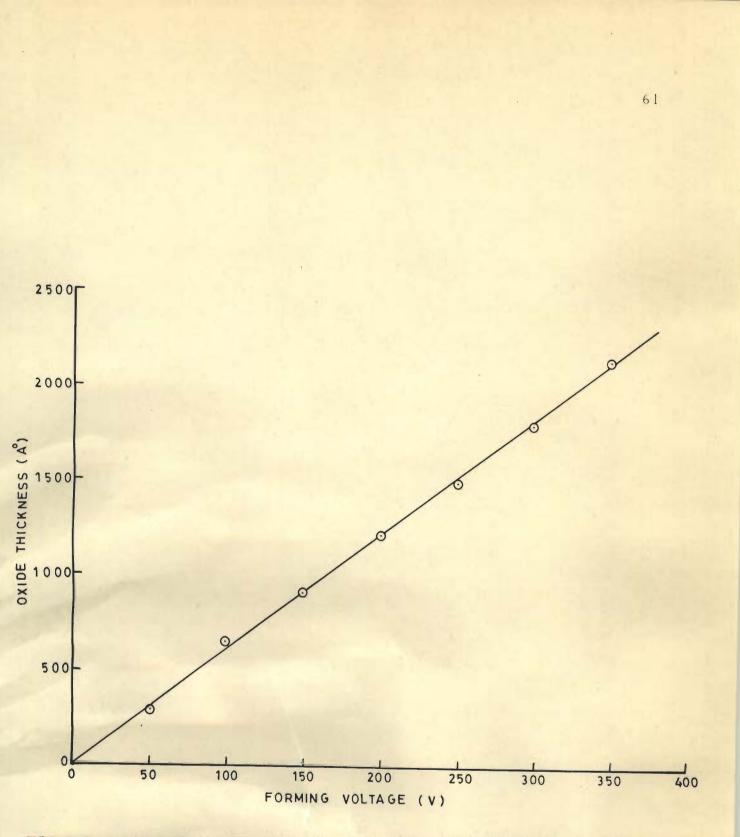

In this process the silicon wafer is made the anode of an electrolytic-cell containing an electrolyte with an oxygen bearing component, which does not dissolve silicon or its oxide, and a current is passed between the anode and an inert cathode such as platinum by applying a suitable voltage across them. An oxide film grows on the silicon surface as the current, which is predominantly electronic with a small ionic component, flows through the growing oxide layer under the applied electric field. Such a growth can be carried out at room temperature or even at temperature lower than the room temperature. The thickness of the grown oxide layer is directly proportional to the value of the forming voltage.

# 1.3 FUTURE TRENDS IN VLSI TECHNOLOGY

The total number of electronic circuit components per silicon chip increased from one in 1959 to 600,000 in eighties [44]. Although the rate of growth has slowed down in recent years because of difficulties in defining, designing and processing complicated chips, a complexity of over 1 million devices per chip will be available before 1990 [9]. This increase is made possible primarily by the advancements in photolithography process of transferring geometric shapes on a mask to a wafer surface, resulting in a continuous decrease in the device dimension from over 10 microns in the early 1960's to one micron in the early 1980's. VLSI devices having very small dimensions require not only the precise lithography and pattern transfer but also very shallow junctions. These conditions impose new requirements on the oxide film growth process. The major requirements are low processing temperature to prevent movement of the shallow junctions and low process-induced defects. One of the factors which affects the ultimate accuracy in the transfer of pattern on the wafer is the oxide thickness used in the photolithographic process. Thinner the oxide layer higher is the accuracy achieved in the pattern generation. With the scaling down of device dimensions, the use of thin SiO<sub>2</sub> films of the order to 100A° will soon become common in MOS technology [45].

The wet anodization technique, which is essentially a low, temperature technique for growing oxide films offers vast potential for manufacturing VLSI. The low-temperature processing suppresses defect formation and minimizes movement of previous diffusions.

### 1.4 STATEMENT OF THE PROBLEM

Literature survey shows that in sixties and senventies efforts were made to grow anodic-oxide films over silicon wafers under different conditions and their characteristics were studied. Due to the poor qualities of the grown films in comparison to that grown by thermal oxidation the wet anodization methods were rejected and not explored further. In order to avoid high temperature effects and the encouraging results of anodic oxide films on GaAs, there is a renewed interest in growing insulating films on silicon by anodic oxidation. An understanding of silicon-silicon dioxide interface is necessary in order to fabricate highly reliable devices. Therefore it is proposed to grow the oxide layers on silicon by anodization technique and to study the interfacial properties of the Si-SiO<sub>2</sub> interfaces in detail. Anodization parameters were optimized to obtain the best interfacial properties suitable for the fabrication of IC's.

Here an electrolytic bath consisting of KNO3 in ethylene glycol was standardised by conducting various experiments. This was done by growing oxide films on silicon in the anodic baths having different molarity of KNO3 in ethylene glycol and then evaluating the quality of grown films by determining the interface state density and dielectric breakdown strength of the fabricated MOS samples. The effects of different anodization current densities and annealing temperature in H2 atmosphere were studied to get the best results. For evaluating the electrical properties of grown films and their associated Si-SiO<sub>2</sub> interfaces MOS structures were formed on n-type  $\langle 111 \rangle$  epitaxial silicon wafers. During investigations it was observed that under certain anodization conditions the anodically grown SiO2 films become porous and humidity sensitive, therefore the use of these films for fabrication of MOS humidity sensor was also studied.

Metal - Aluminium oxide-silicon (MAS) and metal-Aluminium oxide Silicon dioxide-Silicon (MAOS) structures have also been the subject of extensive investigations. In this thesis MAS and MAOS structures are also investigated. For that  $Al_2O_3$  films were deposited by evaporating high purity Al (99.999%) in a partial pressure of  $O_2$ . The reactive evaporation of Aluminium is also a low temperature process. In the MAOS structures silicon dioxide film is grown by anodic oxidation technique.

### 1.5 ORGANISATION OF THE THESIS

The present work consists of seven chapters. First chapter reviews various oxidation processes and the drawbacks of thermal oxidation of silicon. The second chapter presents the critical review of anodic oxidation of silicon reported so far. Chapter III deals with the fabrication of MOS samples by anodic oxidation technique, which includes the surface preparation of silicon wafers, anodization process and optimisation of anodization parameters, annealing of the samples, formation of ohmic contacts and Gate electrodes. The electrical properties of anodically grown films and the Si-SiO<sub>2</sub> interfaces are evaluated in chapter IV. In the V chapter fabrication of MAS, MAOS structures, their electrical and interfacial properties are described. For the fabrication of MAS structures 300A° Al<sub>2</sub>O<sub>3</sub> film is deposited on silicon by reactive evaporation technique of aluminium, for the MAOS

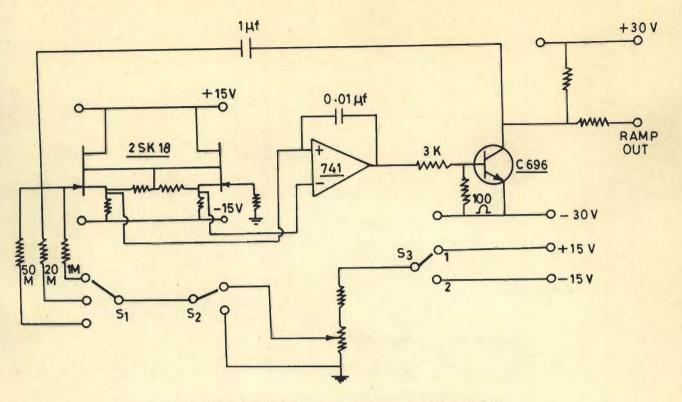

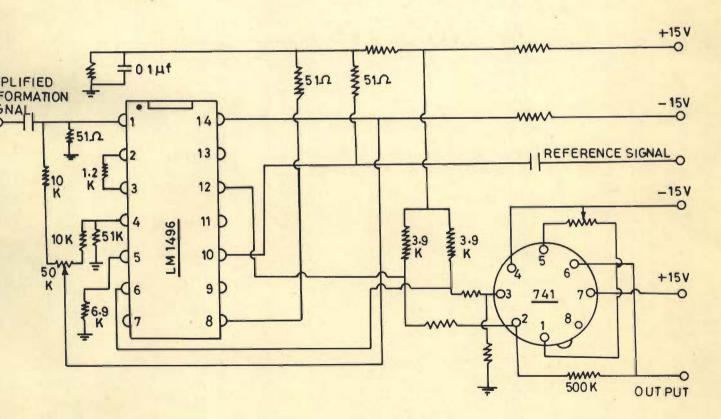

structures 300 A° of SiO<sub>2</sub> layer is grown on silicon wafers by anodic oxidation technique and the composite structure is compelted by depositing 300 A°  $Al_2O_3$  film on SiO<sub>2</sub> film by reactive evaporation technique. Chapter VI considers the fabrication and performance characteristics of humidity sensitive SiO<sub>2</sub> insulating films for MOS sensors. Humidity sensitive porous films are grown on the silicon by the anodic oxidation technique in an aqueous bath of KNO3 and ethylene glycol at temperature 50°C and high anodization current density 30mA/cm<sup>2</sup>. The last chapter VII is a concluding chapter in which conclusions are drawn on the basis of the results of IV, V and VI chapters, the scope for further work is also discussed. The APPENDIX A is devoted for the development and fabrication details of the Automatic C-V plotter and the micromanipulator developed in the laboratory.

#### CHAPTER - II

## CRITICAL REVIEW OF THE SILICON WET ANODIZATION

The anodization technique had been mostly used for anodizing the metallic films in particular aluminium for making capacitors [46, 47]. Gunter - Schulze and Betz [48] were the first Scientists who used the anodization technique for growing dense oxide films on silicon by anodic oxidation in concentrated  $H_2SO_4$ .

In 1957 Schmidt and Michel [49] tried the production of dense oxide films on n- and p-type single crystalline (111) oriented silicon of resistivity of 2-5 ohm cm using three different electrolytes viz. (i) concentrated acids, (ii) Borate electrolytes (iii) 0.04N solution of potassium nitrate in N-methylacetamide at room temperature. KNO3 was added in order to increase the conductivity of the electrolyte and in order to supply the oxygen for the anodic reaction. N-methylacetamide was used due to its high dielectric constant. In all the three above mentioned electrolytes the anodization was carried at constant current density of 4 ma/cm<sup>2</sup>. It was reported that in concentrated acids (HNO3) or (H3PO4) growth of the film does not take place beyond 160 volts, because of the large concentration of the acid anion. In ammonium borate a dense oxide of comparatively low resistivity is formed, porous oxides are formed in oxilic acid or chromate solutions. The solution of KNO<sub>3</sub> in N-methylacetamide permits forming upto 350V. If anodization at constant current density is continued after the voltage has risen to 350 volts, the oxide breaks down, the voltage starts to oscillate without rising any further, while severe damage to the oxide results. If a silicon sample is held at a constant voltage of 300V for some time, forming thereafter can be continued upto 560V. At 560 volt bright sparks appear in the solution. Thus they succeeded in forming oxide layers as thick as 2200A° at 560 volts. However they pointed out that forming at constant voltage more than 300V induces structural changes in the oxide. The field during forming is of the order 2.6x10<sup>7</sup> V/cm corresponding to a thickness increment of about 3.8A°/V. The thickness of oxide films was measured by direct weighing of the smaple, by interference colours, and by capacitance measurements. The ionic current efficiency of film growth is very low. In methylacetamide it can be increased by addition, of chloride ions or by fluoride ions.

The anodic current is in the reverse direction for a barrier on n-type silicon, consequently, the rate of the anodic growth is limited by the supply of minority carriers, holes, to the Si-oxide interface. This fact was verified by conducting anodization experiments on n-type silicon in dark and under illumination. The curve taken under illumination of the wafer is similar to that on p-type silicon.

They also reported that during the anodization process heat is generated by power dissipation across the barrier in the silicon. The measurement indicated that the temperature at a distance of 3 miles from the front surface of silicon rose to approximately 65°C within 30 sec of anodization at a current density of 6 ma/cm<sup>2</sup>, the bath temperature being 25°C.

In 1964 Schmidt et. al [50] reported the preparation phosphorus doped anodic oxide films on silicon. They of also suggested that these oxide films can be used as phosphorus diffusion sources during heat treatment. The anodization was carried out in a solution of 15 percent by volume pyrophosphoric acid in tetrahydrofurfuryl alcohol, of a constant current density in the range between 3 and at mA/cm<sup>2</sup>. The current densities below 2.5 mA/cm<sup>2</sup> lead 5 to poor oxide quality and current densities above 5 mA/cm<sup>2</sup> were not used in order to avoid Joule heating of the solution. When the desired anodization voltage was reached, the operation was continued at a constant voltage for 30 minutes, this being sufficient time for the leakage current to decay to a small value and to become practically independent of further anodization at constant voltage. Anodizations were in general carried out in non-stirred solutions at temperatures or slightly above room temperature. room At 65°C the thickness of the oxide film per volt forming voltage increases noticeably, indicating the beginning of porosity, temperature higher than  $45^{\circ}$ C were therefore avoided. The thickness/voltage increment was  $5.81A^{\circ}/V \pm 5\%$ for constant voltage operation, and  $4.66A^{\circ}/V \pm 5\%$  for constant current operation (3 mA/cm<sup>2</sup>).

In 1964 Duffeck et. al [51] used N-methylacetamide (NMA) + KNO<sub>3</sub> solutions and studied the effect of water in the anodizing solution on the grown oxide, using silicon and oxide weight analysis. The electrolysis products and reactions during anodization of silicon were examined. High purity single crystal silicon 1-2 ohm - cm p and n-type were used. Prior to anodization the silicon was etched in CP-6 (1: 5, HF: HNO<sub>3</sub>) or CP-8 (6: 10, HF HNO<sub>3</sub>), dipped in HF for several seconds, rinsed in deionized water and dried. The temperature of electrolyte was held as close to 35°C as possible. Oxide film thickness measurements vs net forming voltage at 5  $mA/cm^2$  and with 0.1 - 0.5% water in NMA showed the rate of growth of film as 5.3 A°/V from 100 to 425 volts. They investigated the effect of water concentration and current density onthe Si: O2 ratio in the oxide and concluded that 0.5% to 3% water and current densities between 3 to 10 mA/cm<sup>2</sup> produced the most Stochiometric films.

In 1965 Duffeck et. al [52] used the reagent grade ethylene glycol and 0.04N  $KNO_3$  as electrolyte to grow  $SiO_2$  films and studied the characteristic of the grown

films. For pretreatments raw, lapped silicon wafers were chemically polished in CP-6 (1: 5, HF: HNO<sub>3</sub>) or CP-8 (3: 5, HF: HNO3), dipped in HF, rinsed in deionized (DI) water and dried. Chemically polished silicon wafers were also used, they were degreased in hot trichloroethylene and rinsed in the order, acetone, deionized water, HF (49%) for 20 sec., D.I. water and dried. the temp. of electrolyte was kept at 25° - 30°C. Anodizations were carried out at constant current with current densities ranging from 1 to 25 mA/cm<sup>2</sup>. Anodization was terminated when the predetermined forming voltage was reached. The anodized wafers were rinsed in D.I. water, dried and evaluated. The thickness of films grown were measured by means of interference colour comparison to known standards. The refractive index of these films were measured. The experimental results shows that stoichiometric SiO<sub>2</sub> films canbe obtained on a reproducible basis. It is reported that the use of ethylene glycol as a solvent has the advantage of low cost, high purity, electrolyte solubility and good stability toward heat and electrolysis.

In 1966 R.Dreiner [53] anodized low resistivity ('0.02 ohm-cm) (111) oriented, p-type silicon slices in a solution of 0.04N KNO3 in ethylene glycol containing 2% water, and the dielectric behaviour of the system Si/Anodic/Sio2/ electrolyte was studied. The samples were anodized at constant current to desired voltages. No constant voltage phase followed. It was observed that the oxide started to peeloff from some areas of the substrate when low formation current densities were applied, but no such effect was observed with high current densities. Preliminary experiments indicated that the pretreatment of the substrate had an influence. The onset of peeling was delayed when the samples were chemically polished prior to formation. It was concluded that the thinner films were of better quality.

In 1967 Akos G.Revesz [54] oxidized silicon anodically using constant voltage method. The Si-SiO2 interface was investigated with the MOS capacitance method. The primary purpose of this investigation was to compare anodic oxidation with the thermal one on the basis of MOS interface behaviour. It was shown that constant voltage oxidation under clean conditions in a nonaqueous electrolyte followed by a short time annealing in helium at high temperature results in an interface that is comparable with that obtained by thermal oxidation. Chemically polished 10 ohm-cm- p-type silicon of  $\langle 111 \rangle$  and  $\langle 100 \rangle$  orientations were used. The specimens were carefully cleaned and just before anodization were submerged in hydrofluoric acid and rinsed with distilled water. The electrolyte chosen was 0.04N Solution of  $KNO_3$  in N-methylacetamide (NMA). Since it was known that this electrolyte is hygroscopic and the oxidation process is influenced by its water content, fresh electrolyte was

used for each oxidation. No attempt was made however to avoid water absorption during oxidation. The temperature during anodization was about 50°C. The cathode was a platinum sheet. The constant current density was varied from 5 to 10 mA/cm<sup>2</sup>, the highest forming voltage was 300V, and the lowest current density obtained during the constant voltage mode was 0.04 mA/cm<sup>2</sup> in about 300 min. After oxidation the specimens were rinsed in water. Some specimens were than treated in hydrogen at 500°C for 15 min., or in helium at 800°C - 1000°C. The hydrogen treatment was done in a conventional vitreous silica tube furnace, whereas the helium annealing was performed in an air cooled silica tube with radio frequency (rf) heating. For MOS capacitance measurements with a mercury probe the specimens were provided with nickel back contacts. The differential capacitance of the MOS diode as function of bias was measured at 1 MHz with an automatic measuring apparatus. The density of surface states is determined by the anodization conditions. High values were obtained by constant current anodization. In the case of constant voltage anodization the surface state density generally decreases with the anodization time i.e., with the final oxidation rate. Constant voltage anodization to low final current densities followed by annealing in helium at elevated temperature can result in 2 x 10<sup>11</sup> cm<sup>-2</sup> surface density. The relatively high perfection of this interface is shown by the lack of interface

instability effects at 300°C under high field. Under these conditions the shift of the C-V curves is quite small and voltage symmetric.

In 1968 A.G.Revesz and K.H.Zaininger [55] observed that the oxidation of silicon can be performed electrolytically by applying a sufficient overvoltage in an electrolyte that does not dissolve the oxide. The most interesting feature of anodic oxidation of silicon is the very low oxidation efficiency i.e. 0.4 to 1.6%, corresponding to a current that is overwhelmingly electronic rather than ionic. This is quite in contrast to the anodization behaviour of, say, tantalum and aluminium. During constant current oxidation, the field across the oxide is constant,  $1.2 \times 10^7$  to 1.9 x 10<sup>7</sup> volts/cm, depending on current density and the orientation of silicon. The oxidation rate is about 6 A°/V. The oxidation rate and efficiency show definite and parallel trends, they increase with increasing oxide thickness and current density. Under constant voltage anodization, the oxide thickness and current density vary with the logarithm and reciprocal of time, respectively. The oxidation rate and efficiency decreases with time and thickness. This decrease could be due to decreasing current density and/or structural changes in the oxide.

The main advantage of anodic as opposed to thermal oxidation is that it can be performed at much lower temperatures. Hence processes that deteriorate the minority carrier lifetime, can be avoided. Also, unwanted changes in the doping profile within silicon can be minimized. The disadvantages of anodic oxidation are limited thickness (2000-3000 A°) because of breakdown effects.

1969 C.R.Fritzsche [56] studied the dielectric In breakdown in anodically grown SiO2. 1 ohm-cm single crystalline silicon wafers polished on one side and nickel plated on the backside was anodized in a solution of 0.4 g  $KNO_3$  in 100 c.c. ethylene glycol at 25°C. Platinum was used as cathode and its distance from the silicon was 1.2 cm. The water content of the glycol was checked by Karl Fischver titrations and in, most cases kept between 0.06 and 0.08%. Aluminium electordes 0.5 mm in diameter were evaporated for breakdown measurement. Breakdown voltage was measured with dc as well as pulse methods, an improved pulse amplifier was used and the current limiting resistor was only 220 ohm at pulse measurement. The self-healing breakdown as well as the final breakdown which destroys the sample definitively were noted. These two types of breakdowns were called as first breakdown and definitive breakdown. It was reported that the probability of breakdown at specific point defects depends upon electrode diameter. The dielectric strength of the grown oxide layer decreases with increasing temperature and the water content of the electrolyte. It is reported

that impact ionization takes place during anodic growth of SiO<sub>2</sub>. It is found that avalanch multiplication of electrons and ionic conductivity are closely related. An improved theory is given which supplies equations for efficiency of anodization, growth at constant current, and current decay at constant voltage in excellent agreement with experimental results. The effective mass ratio of electrons to ions, the mean free time of the electrons, the mean time between ionizing collisions and the electron drift velocity are estimated from experimental data.

In 1970 R.Nannoni [57] reported that an abundant literature has been dedicated to thermal oxidation of silicon and to anodic oxidation of metal like Al, Ta, Ti, Nb, but a very few works related to the anodic oxidation of silicon have been carried out. Nannoni observed that the electrical properties of anodic oxide films and of the semiconductor oxide interface have not been investigated in detail. The results of the complex capacitance method used to characterize the semiconductor surface properties were described.

For the fabrication of MOS capacitors the silicon epitaxial wafer of  $\langle 111 \rangle$  orientation is cleaned in boiling CCl<sub>4</sub> and in boiling HNO<sub>3</sub> rinsed in deionized water and dryed in twice distilled methylic alcohol and then in

29.

ethylic ether. The wafer was anodized in a teflon cell containing the solution of 8 gm/litre of KNO3 in twice distilled diethylene glycol as electrolyte. The electrolyte bath was replaced for each preparation. A platinum grid was used as a cathode. A three step anodization process is used. In the first step the current is exactly zero. In the second step the current follows a linear increase of 0.5 mA/cm<sup>2</sup> per minute upto a density of 10 mA/cm<sup>2</sup>. In the third step the voltage limiter takes control and keeps a constant voltage U across the terminals, the current  $I_{ox}$  decreases freely reaching for instance 10 A/cm<sup>2</sup> for t<sub>ox</sub> = 24 h,  $U_{ox} = 200V$ , the oxidation temperature  $T_{ox}$  being kept constant at 30°C. After its oxidation the sampe is rinsed in ethylene alcohol then in methylic alcohol and dried in ethylic ether, then immediately stored under vacuum of 5 x 10<sup>-6</sup> torr. For electrical measurements seven gold electrodes 2 mm in diameter about 1000 A° in thickness were evaporated. The equivalent series capacitance C series and the loss tangent (tan  $\delta$ )<sub>MOS</sub> of the MOS capacitor were determined by using a capacitance bridge. These measurements were made at controlled temperature in a dry nitrogen atmosphere and in darkness. The AC voltage was maintained smaller than KT/q volts. To characterize the electrical properties of the anodic oxide MOS capacitors complex impedance values were considered and not only the imaginary part. The impedance  $Z^*_{mos}$  was calculated from the equivalent

series capacitance  $C_{series}$  and the loss factor  $(\tan \delta)_{mos}$ . Since the limit values (at a zero and infinite frequency) reached by the impedance are only capacitive, the compelx capacitance of MOS capacitor was introduced by

$$C_{\text{mos}}^* = C_{\text{mos}}' - i C_{\text{mos}}'' = \frac{1}{i Z_{\text{mos}}^*}$$

C\* representation was used in the complex plane (C" as a function of C' ) currently used for dielectric study.

The anodic oxide can be either 'dry' (moisture exposure reduced to a minimum) or 'wet' (after voluntary exposure to moisture). The study of the complex capacitance  $C_{mos}^*$  of MOS capacitors has shown the important influence of the moisture on the properties of anodic oxide MOS structures. The unambiguous determination of surface state parameters from the variations of  $C_{mos}^*$  as a function of frequency, temperature, and applied bias is discussed. A method of characterizing the distribution of Surface states was proposed. The utilization of this method permitted to explain some apparently contradictory results published in the literature, and showed that:

(i) Whatever the oxide 'Wet' or 'Dry' and Silicon-Oxide interfaces are characterized by the same energy distribution of surface states, whose density is hgih (about  $10^{13} \text{ ev}^{-1} \text{ cm}^{-2}$ ) and nearly symmetrical with respect to the middle of the gap.

- (ii) The mobile protons contained in 'Wet' oxide have no influence on the distribution of surface states.

- (iii) In order to reduce the density of surface states by thermal treatments at low temperatures (about 150°C) the oxide must be of 'wet' type.

In 1973 J.D.E.Beynon et. al [58] used the insulating  $SiO_2$  layers grown anodically to fabricate MOS capacitors and MOS transistors. The MOS capacitor structures were used for investigating the electrical properties of the oxide and also the characteristics of the Si/SiO<sub>2</sub> interface. The threshold voltages of MOS Structures were measured as a function of oxide thickness. Furthermore, the Hall mobility of the carriers in the channel of MOS transistors were ascertained by means of the specially designed Hall MOS transistor.

Mechanically polished 10 ohm-cm n-type (11) silicon substrates were used. The silicon slices were cleaned using sulphuric acid and hydrogen peroxide, followed by immersing alternately in hydroflouric acid and boiling aqua regia three times. Conventional diffusion techniques were used to form the p-type source and drain diffusion regions of the MOS transistor. Electrical contact with the silicon slice was made via a diffused P region on back of the slice, this provided a low resistance the contact to the silicon (which was made the anode in the electrolytic cell). The cathode was a thin sheet of platinum having a total surface area of 2 cm<sup>2</sup>. Several electrolytes were used but the most successful films were obtained using a mixture of 0.02N KNO3 and 0.02N KNO2 in ethylene glycol. Each silicon slices were anodised in the following way: a constant current source was maintained at an initial current density of 7 mA/cm<sup>2</sup>. As the film grew, the potential difference across it increased. When this reached to a predetermined value, the voltage was maintained at this value and the current allowed to decay. The forming voltage was maintained until the current dropped down to about 200 MA/cm<sup>2</sup>. Forming voltages between 10V and 200V were used to produce oxide thickness ranging 80 A° to 100 A°. The thickness of the oxide film was determined by ellipsometry. Due to depletion layer formation in n-type silicon at the silicon/electrolyte interface, the slice was illuminated to generate sufficient electron-hole pairs to allow growth to proceed at current densities of 7 mA/cm<sup>2</sup> at low voltages. Two metals aluminium and molybdenum were used for forming the gate. The metals were evaporated and then etched to form source, drain and gate regions. The slices were finally annealed in a mixture of hydrogen 40% and nitrogen 40% for 15 min. at 500°C.

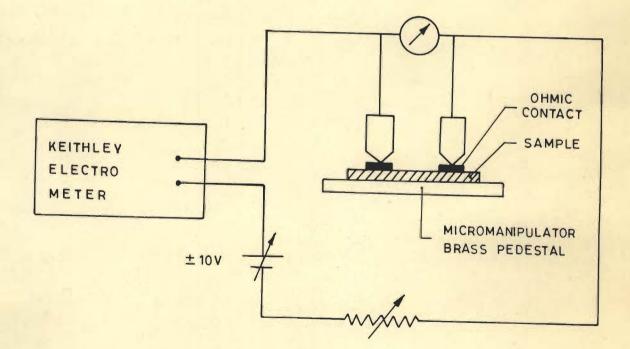

The following electrical tests were conducted on the fabricated samples. Using a keithley electrometer leakage current as low as 10<sup>-13</sup> Amp at 10V were measured for 1100 A° films, the resistivity of the anodic oxide film for thickness ranging from 200 A° to 1100 A° was found to be  $7 \pm 1 \times 10^{15}$  ohm - cm. The breakdown field strength of the oxide was deduced from the voltage required for catastrophic breakdown of the MOS capacitor. Breakdown of the oxide .was measured for positive bias voltage such that the surface of the n-type silicon immediately under the gate was in accumulation. Results indicated that the breakdown voltage is proportional to film thickness i.e. the breakdown field strength is constant. Its value was approximated 8 x 10<sup>6</sup> V/cm. From C-V measurements on aluminium MOS capacitors, it was deducted that there was a surface charge density of 2-3x10<sup>11</sup> electronic charges/cm<sup>2</sup>, this charge was found to be independent of oxide thickness. To determine the stability of the oxide, bias-temperature stress experiments were carried out on the MOS capacitors. The capacitors were heated to 150°C and maintained at this temperature for 15 min and then allowed to cool with a continuous biasing field of 10<sup>6</sup> V/cm produced by positive gate voltage. The C-V curves of the capacitors were plotted before and after the bias temperature stress to determine the shift

in flat band voltage no significant shift was detected. The threshold voltages of the MOS transistors were measured for drain currents of 1  $\mu$  amp. A quite the good agreement between the calculated and measured values of threshold voltage was reported. Hall mobility measurements were made only on device with a gate oxide thickness of 1100 A°. The average value of hall mobility of holes in the inversion layer was found tobe 210 ± 20 cm<sup>2</sup>/V.sec.

In 1977 W.D.Mackintosh and H.H.Plattner [59] identified the mobile ions during the anodic oxidation of silicon. During anodic oxidation either the cation or the anion both must migrate across the thickening oxide film. or The mobile ion can be identified or, if both move, the relative mobilities can be deduced by tagging a thin surface layer with a completely immobile marker atom and determining its position after anodizing the speciman. If the marker is found at the surface then oxidation has taken place by inward migration of the anion to form the film beneath the marked layer. If the marker is found at the substrate/oxide interface the opposite process has occured. An intermediate position indicates both cation and anion have moved and the relative mobilities are proportional to the relative thickness of the oxide on either side of the marker atoms. The inert gas atoms were chosen as markers on the grounds that they are the most likely to remain unchanged within

the oxide lattice and hence are not influenced by the application of the electrical field. In addition their large size suggests that they should not diffuse through the lattice at room temperature. The marker locations were determined by Rutherford backscattering analysis.

A variety of specimens were used. Some were thin wafers cut very closely parallel to the  $\langle 111 \rangle$  plane while others were tablets 3/8 inch thick cut from 10° off the (111) plane, most were p-type boron-doped although one n-type phosphorus doped speciman was also used. The surfaces of all specimens were prepared by vibratory polishing with 0.3 µm alumina, followed by ultrasonic cleaning to remove the abrasive. They were then degreased in trichloroethylene, etched for 5 min. in 0.5N HF and washed thoroughly. Oxidations were carried out in a Teflon cell constructed for this purpose in such a way that only 0.7 cm<sup>2</sup> of polished surface was exposed to the electrolyte. The electrical connection was made by diffusing gold into a small area back of the speciman and firmly contacting this, on the area to a copper plate contained in the body of the cell. Experiments were carried out with the following electrolytes:

(a) 0.1N aqueous solution of  $H_3BO_3$  and  $Na_2B_4O_7$ .  $10H_2O$ .

(b) 0.4N solution of  $KNO_3$  in N-methylacetamide and

(c) 0.3N solution of KNO<sub>2</sub> in tetrahydrofurfuryal alcohol.

The inert gas atoms Kr or Xe were introduced into the Si surface layers with a low energy mass separator. The amounts implaned were 5 x  $10^{14}$  atoms/cm<sup>2</sup> for Xe and 1 x  $10^{15}$  for Kr. These are the minimum amounts conveniently detected by Rutherford back scattering analysis. Specimens with prepared surfaces were anodized to give a film thickness of  $16 \mu g/cm^2$ . They were then implanted with the chosen marker at an energy that would insure that the greater part of the implanted material was located within the oxide film. Rutherford backscattering spectra were obtained. The specimens were then further anodized to a chosen voltage and analysed again. Computer analysis of the data was then carried out to obtain the position of the markers, the thickness of the oxide films, and the count of He ions back-scattered from the implanted atoms. In every case the markers were found to be very close to the outer oxide surface, showing that inward movement of the anion is responsible for oxide growth. In this respect anodic oxidation resembles thermal oxidation.

In 1979 G.C.Jain et. al [60] studied the mechanism of the constant voltage anodic oxidation of Si in a solution of ethylene glycol + 0.04N KNO<sub>3</sub>. They found that the thickness of the formed oxide vary linearly with the forming voltage at a rate of 6.3 A°/V. The anodization current for a fixed value of forming voltate decays exponentially with a linear tail. The thickness of the grown oxide obeys a parabolic law, and the ionic current efficiency tends to decrease with time up to a field  $\sim 20$  MV/cm.

Experiments were performed on rectangulared shaped silicon single crystal chips of size 45 mm x 5 mm and of thickness  $300 \mu$ m. The crystals were p-type with a resistivity of 8 ohm-cm cut parallel to the  $\langle 111 \rangle$  plane lapped flat and then polished mechanically using a submicron alumina powder as slurry followed by a light etch in the HF, HNO<sub>3</sub> and H<sub>2</sub>O system. The electrolyte used was ethylene glycol + 0.04N KNO<sub>3</sub>. trace of water (0.1 - 1%) was present in ethylene glycol. The cathode was of a noble metal (gold) foil. The thickness of the oxide was found by a comparison of the oxide colour with a standard interference colour chart.

#### CHAPTER III

### ANODIC OXIDATION OF SILICON AND FABRICATION OF MOS STRUCTURES

#### 3.1 INTRODUCTION

The literature survey shows that in last two decades efforts were made to grow anodic - oxide films over silicon wafers using different electrolytes and their characteristics were studied. However the electrical properties of anodically grown oxide films and the semiconductor oxide interfaces were not fully investigated. As the oxide films grown by thermal oxidation were found superior as compared to anodically grown films and therefore they were widely investigated and were used for fabricating insulating films for the applications in semiconductor and I.C. Technology.

As the integration of large number of devices in a single chip is increases it was realised that high temperature processes are not suitable for VLSI technology, particularly the high temperature oxidation limits the further integration of devices in a single chip and degrades the performance of the devices. Therefore it is proposed to grow high quality SiO<sub>2</sub> films at low temperatures using anodic oxidation technique for VLSI applications. Due to the ease of fabrication, simplicity of structure and the sensitivity of the C-V characteristics to physical properties MOS structures are used as a test vehicle to study the influence of process parameters on properties of insulating films grown on silicon and to study Si-SiO<sub>2</sub> interfaces. For the fabrication of MOS samples.

A stringent cleaning procedure was used to minimise the surface contamination of the samples. A proper electrolyte and its composition was selected, anodization parameters and annealing conditions were optimized. In order to grow high quality films and for obtaining the best results a large number of experiments and measurements were carried out and discussed in this chapter.

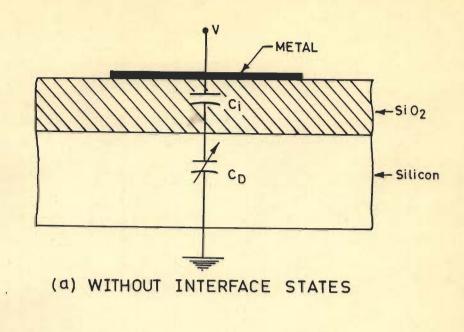

#### 3.2 THE MOS STRUCTURE

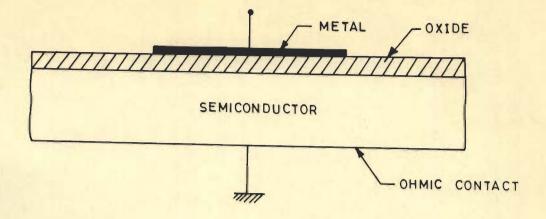

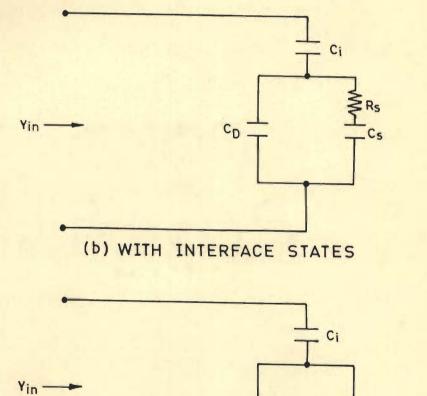

The MOS capacitor offers an incredibly powerful test structure for evaluation of the dielectric properties of grown films and for the study of electrical and interfacial properties of semiconductor – oxide interface. Schematic of MOS structure is shown in fig. 3.1. Essentially it consists of an n- or p-type semiconductor, covered by a thin oxide film with a metal electrode (gate) on top of the insulator and an ohmic contact to the semiconductor. Such devices can be an important research tool because their capacitance versus bias (C-V) characteristics contain information about the surface states present in this

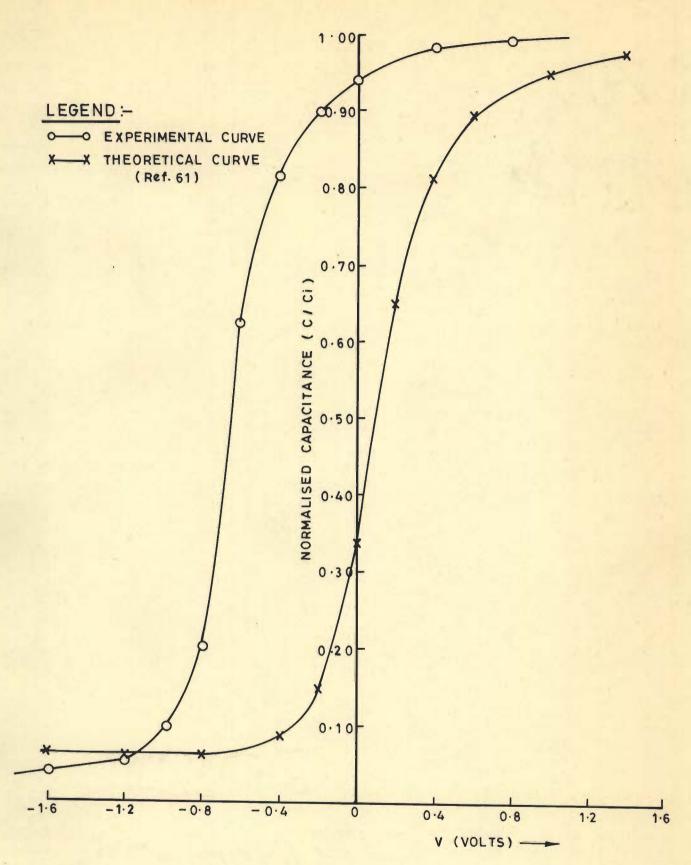

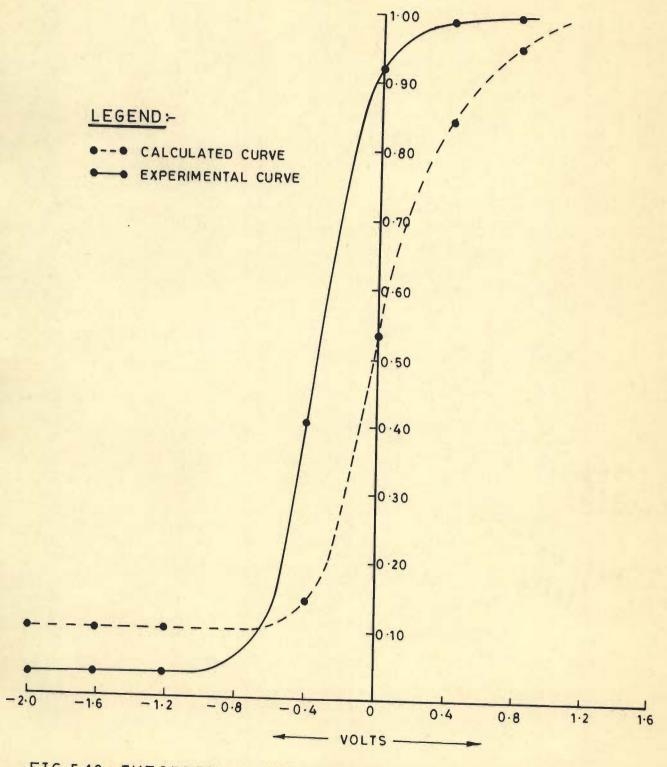

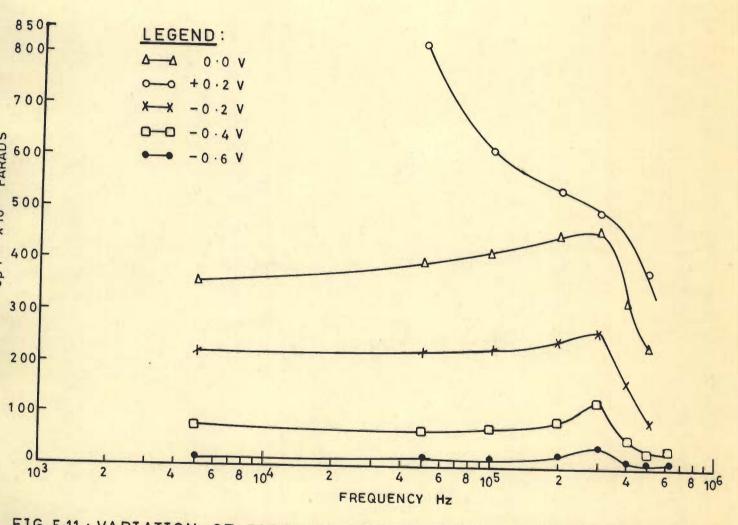

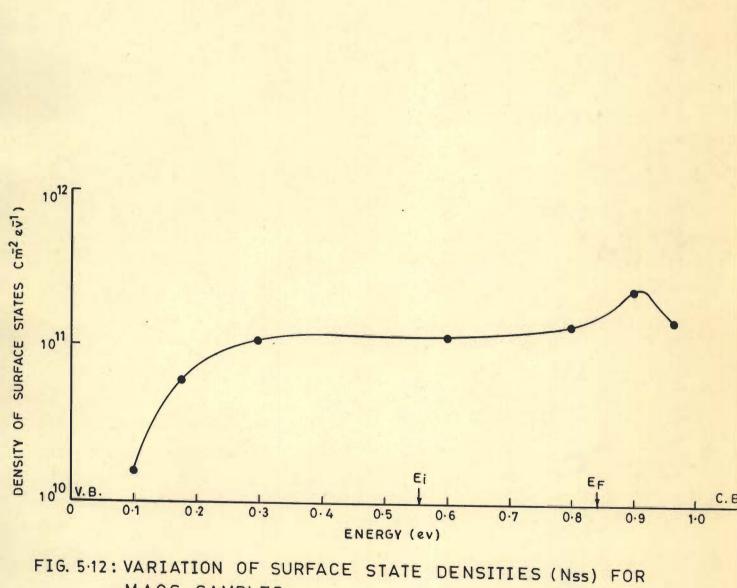

system. The performance of MOS system depends on the interface properties of the semiconductor and the oxide film grown over the semiconductor. Interface state density and dielectric breakdown strength are used to assess the quality of oxide film. Low value of interface state density and high value of breakdown field are the desired characteristics of a good insulating film. Therefore the measurement of interface state density and breakdown field are important to assess the quality of the oxide film grown on semiconductor and to optimise the process parameters associated with the fabrication of the oxide layers. To evaluate the surface states density either capacitance or conductance methods can be used. The conductance method gives the accurate results as compared to capacitance method, but it requires large number of time consuming measurements. Therefore to compare the characteristics for optimization of anodization parameters capacitance method is used. For final assessment of the grown films conductance method was used as described in chapter IV. In the MOS capacitance method, a d-c electric field is applied between the metal electrode on the oxide and the silicon. For a given value of this field, a definite charge distribution in the MOS system will arise. The differential capacitance of the silicon space charge region is then measured by superimposing a small ac voltage on the dc bias. The differential capacitance as a function of the applied dc bias is determined. These

measurements were taken with Boonton Bridge. The obtaned capacitance vs voltage (C-V) curve is compared with a calculated ideal curve [61], i.e. characteristics of a silicon-vacuum interface without surface states. If, for each value of the D.C. field, equilibrium had been established and the frequency of the small ac signal is so high that no electronic transfer between various states outside the silicon (i.e. interface, oxide states) and the space - charge region can take place during one period, then this comparison gives the density of charges residing in these states as a function of the silicon surface potential, or, what is equivalent to this, as a function of the energy position of these states in the Si forbidden band. The density of states at flatband condition i.e.  $V_s = 0$  is designated as  $N_o$  and is frequently used to characterize the MOS sample. The voltage difference between the measured and ideal C-V curves ( $\Delta V$  at flat band) can be used to calculate the surface states at flat band condition. The density of surface states in unit of cm<sup>-2</sup> is determined by Gauss law as:

$$N_{o} = \frac{C_{i} \Delta V}{q}$$

where  $C_i$  is the insulator capacitance in strong accumulation region and q is the electronic charge.

#### 3.3 SURFACE PREPARATION OF SILICON

The material used in the investigation was n-type

epitaxially grown silicon wafers of  $\langle 111 \rangle$  orientation having resistivity of 6 to 8 ohm-cm. The resistivity of the substrate was 0.005 ohm-cm. The purpose of using n-n<sup>+</sup> epitaxial wafers are to minimise the bulk series resistance to a negligible value as it causes a serious error in the extraction of interfacial properties from admittance measurements. Further it is easy to make good ohmic contact on n<sup>+</sup> silicon substrate. For the fabrication of test MOS samples wafers were cut into 8 mm x 8 mm square pieces using diamond tool scriber.

Wafer cleanliness before, during, and after oxidation is perhaps the most important requirement for growing high quality oxides [62]. Impurities present on the silicon surface prior to oxidation or during the oxide growth itself influence the homogeneity of the film, the interfacial and electrical properties of the grown films. There are three broad categories of surface contaminants:

- (a) molecular,

- (b) ionic and

- (c) atomic

Typical molecular contaminants are natural and synthetic waxes, resins and oils. They may also include grease from fingers and greasy films that are deposited when surfaces are exposed to room air or stored in plastic containers. Layers of such molecular impurities in contact with the substrate surface are usually held by weak electrostatic forces. Organic contaminants on silicon devices, especially on surface-sensitive MOS structures, may cause polarization [63] and ionic drift [64] due to the transport of protons [65]. Water insoluble organic compounds tend to make semiconductor and oxide surfaces hydrophobic, thus preventing the effective removal of absorbed ionic or metallic impurities. The removalof molecular contamination is threfore the first step in a cleaning process.

Ionic contaminants are left on the surface of the wafer after etching it in etchants containing HF acid, out of these ionic contaminants, alkali ions are particularly harmful as they may move under the influence of electric fields or at elevated temperatures, causing inversion layers, surface leakage drifts during device operation, and other instabilities [66].

Atomic contaminants present on a silicon surface include heavy metals such as gold, silver and copper. They originate from acid etchants and are usually present in the form of metallic deposits [67]. The removal of this type of contaminant generally requires reactive agents that dissolve the metal and complex the ionic from to prevent redeposition from the solution. Atomic impurities, especially the heavy metals, can seriously affect minority - carrier lifetime, surface conduction, and other device parameters governing stability of the devices [68].

Ionic contaminants are left on the surface of the wafer after etching it in etchants containing HF acid, out of these ionic contaminants, alkali ions are particularly harmful as they may move under the influence of electric fields or at elevated temperatures, causing inversion layers, surface leakage drifts during device operation, and other instabilities [66].

Atomic contaminants present on a silicon surface include heavy metals such as gold, silver and copper. They originate from acid etchants and are usually present in the form of metallic deposits [67]. The removal of this type of contaminant generally requires reactive agents that dissolve the metal and complex the ionic from to prevent redeposition from the solution. Atomic impurities, especially the heavy metals, can seriously affect monority- carrier lifetime, surface conduction, and other device parameters governing stability of the devices [68].

Since a contaminated surface is likely to contain all three types of impurities, it is necessary to first remove the gross organic residues masking the surface, then the residual organic materials, and finally the residual ionic and atomic contaminants. The following procedure was used to clean the samples.

The samples were first boiled in trichloroethylene and then ultrasonirated in acetone. The samples were treated with a solution of  $H_2O - H_2O_2 - NH_4OH$  (typically five parts by volume of  $H_2O$ , one part 30% unstabilized  $H_2O_2$  and one part  $NH_4OH$ ). It removes organic contaminants by solving action of the ammonium hydroxide and the oxidizing action of the peroxide. The sampels were then rinsed with deionized water. The samples were treated with second solution of  $H_2O - H_2O_2$ -HCl (typical composition is six parts  $H_2O$ , one part  $H_2O_2$  and one part HCl by volume). The samples were rinsed thoroughly in deionized water with several changes. Metal impurities are oxidized by the action of both the hydrogen peroxide and the chlorine in the solution resulting stable chloride complexes, the solution removes metallic impurities from the silicon surface and prevents their displacements plating back onto the silicon [69]. The main advantage of these two cleaning solutions is that they are composed of volatile components and thus leave no residues on the silicon surface. Finally the slices were dipped in dilute HF acid rinsed in deionized water treated with alcohol and blown dry before immersing them in the anodization cell.

### 3.4 CLEANING OF ACCESSORIES

Pyrrex Glass accessories such as beakers, sample holders, stirrer etc. used in the experimental work were cleaned thoroughly to remove organic and inorganic contaminants, and dust particles etc. Otherwise the impurities introdeuced from the accessories during the handling of the samples may adversely effect the quality of oxide grown. Based on experimentation the following cleaning procedure was found appropriate which gave the most satisfactory results.

(i) Boil the glasswares in teepol.

- (ii) Wash the glassware's thoroughly in water.

- (iii) Boil the glasswares in the solution of NaOH for five minutes.

- (iv) Wash the glasswares with distilled water.

- (v) Dip the glasswares in hot concentrated chromic acid for five minutes.

- (vi) Wash the glasswares again with distilled water and dry with hot air.

(vii) Rinse ultrasonically in acetone for 5 minutes.

(viii) The glasswares thus cleaned were placed in a dust free hot electric oven.

The anodization process was carried out on the horizontal laminar flow clean bench placed in the clean room. Electronic grade chemicals and ultrapure water having resistivity of the order of 14.5 M Ohm-cm were used. The ultrapue water was prepared by first distilling the tap-water, the distilled water was subjected to ultraviolet light to minimize the bactria count [70]. Finally it was passed through the sybron/Bransted water purification system.

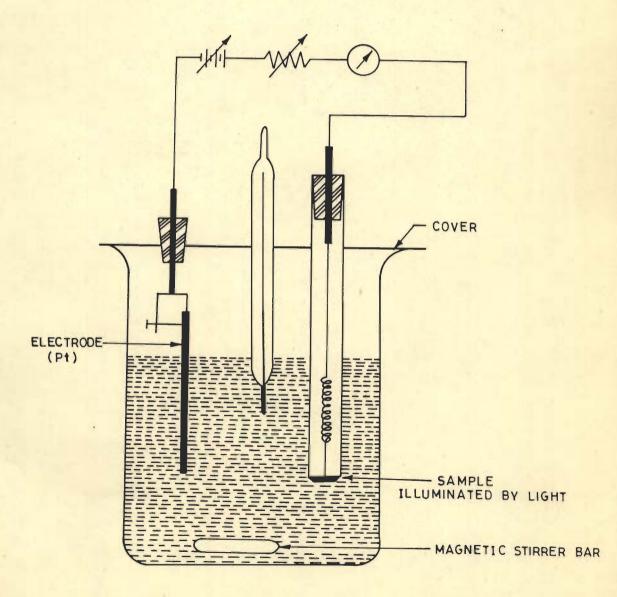

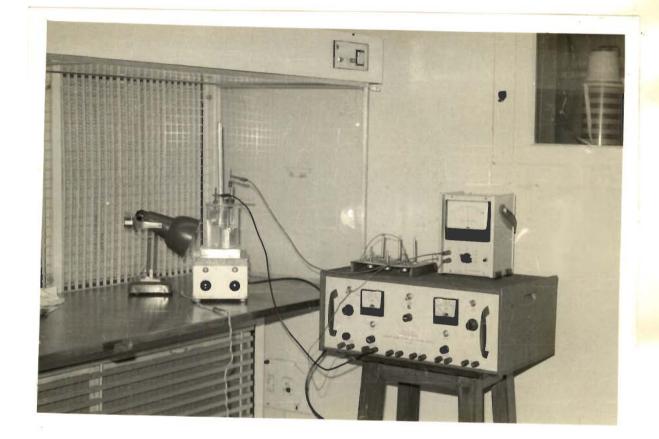

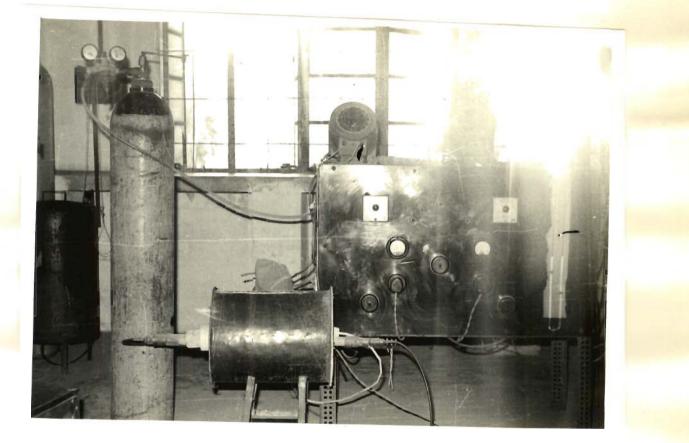

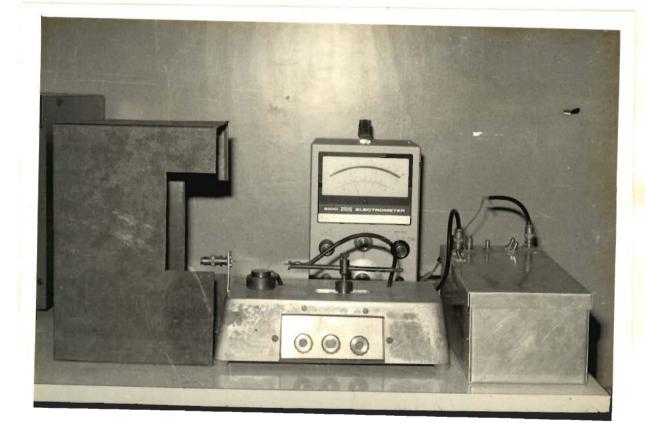

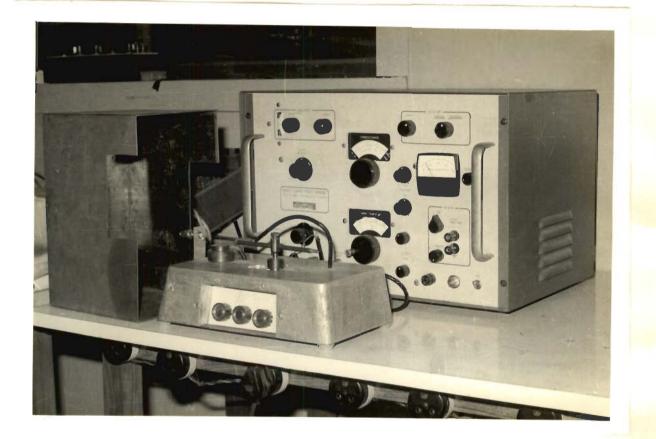

## 3.5 THE EXPERIMENTAL SET-UP AND FABRICATION OF MOS TEST SAMPLES

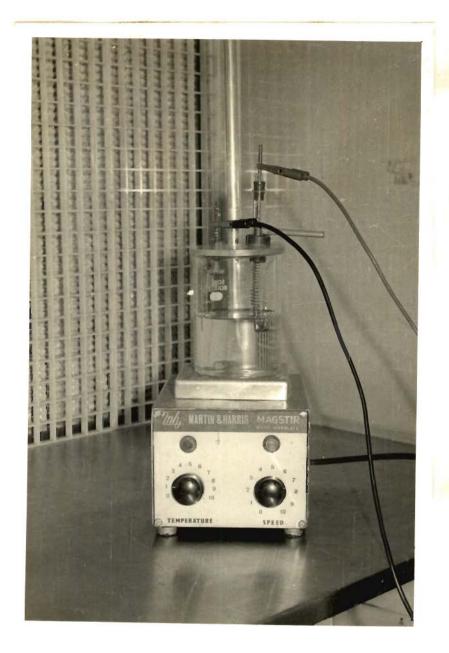

The complete anodization set-up is shown in Fig.3.2. Essentially it consits of d.c. power supply, a variable series resistance, an electrolytic-cell, a FET Nanoammeter (Aplab TF M13 Model). The electrolytic cell consits of a pyrex glass beaker having freshly prepared electrolyte. A spring loaded platinum tipped probe in contact with the sampel serves as anode of the anodization cell. The cathode must be of such conducting material which does not dissolve in or contaminate the electrolyte. Its shape should allow easy cleaning and enough surface for exposure to electrolyte, the cathode was made of a platinum flat strip of size 4 cm x 0.5 cm. Before use it was thoroughly cleaned. The electrolytic cell was placed on a magnetic stirrer (Martin and Harris Magstir) so that electrolyte

# FIG. 3-1: METAL- OXIDE- SEMICONDUCTOR (MOS) STRUCTURE

FIG 3.2: SCHEMATIC OF ANODIZATION SET- UP

may be stirred during the anodization process as shown in Fig. 3.3.

In the experimental set up a colliminated light source was used to illuminate the test sample to provide holes by photo generation.

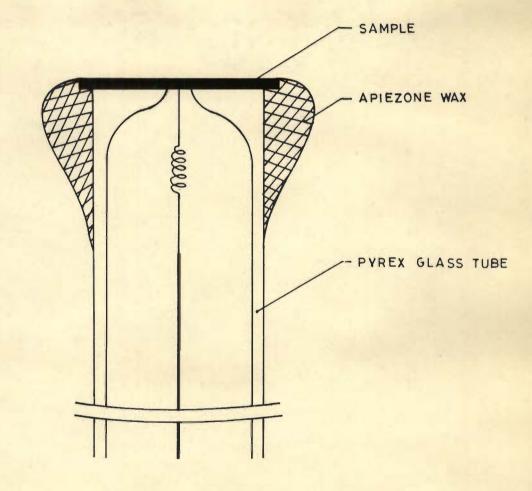

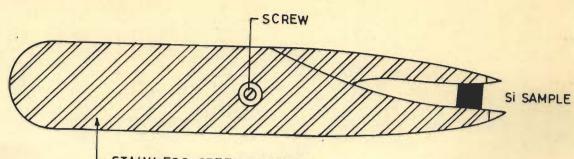

The sample to be anodized was fixed onto the sample holder as shown in Fig. 3.4 and explained as follows. The sample holder was made of pyrex glass tube. One end of this tube was made flat and had a hole of about2 mm diameter in the centre. The sample was fixed on the sample holder by Apiezone wax. The sample edges were covered with the Apiezone wax to eliminate edge effects during anodization [71].

The anodic cell should have uniform spacing between electrodes to have uniform anodic current density, therefore the sampel holder and cathode were mounted on the lid ensuring that they are parallel to each other at every point in the electrolyte. Further it was also ensured that they do not touch either the side walls or the bottom of the beaker. The lid was placed on the beaker with stirrer in position. This set-up was placed on the beaker with stirrer in position. This set-up was placed in the horizontal laminar flow clean bench and is shown in Fig.3.5.

central Library University of Ruorka

## FIG.3-3: ELECTROLYTIC - CELL

FIG. 3-4 : SAMPLE HOLDER

# FIG. 3-5: EXPERIMENTAL ARRANGEMENT FOR ANODIZATION

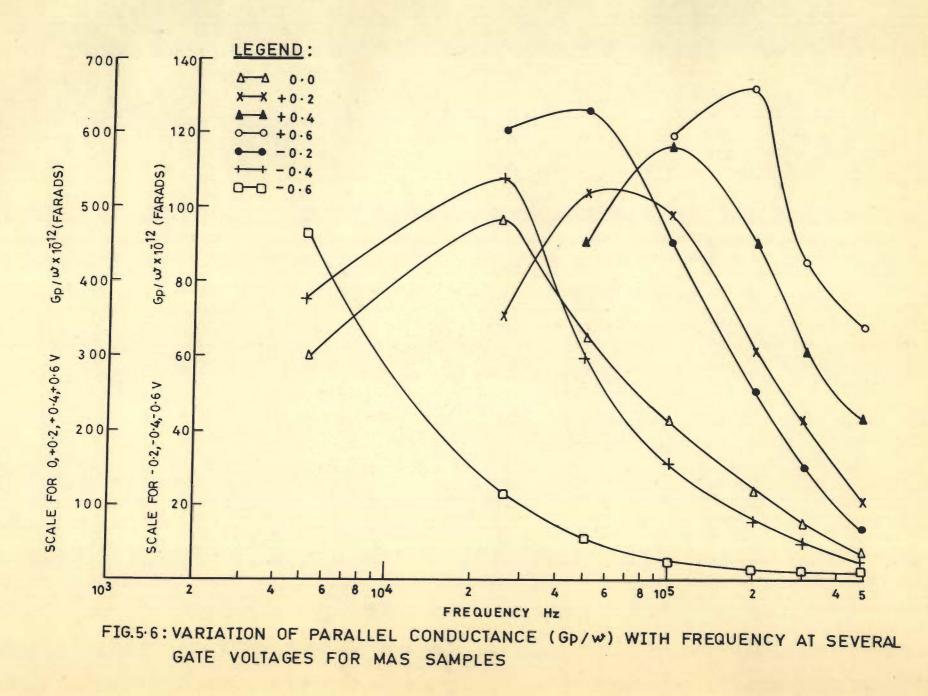

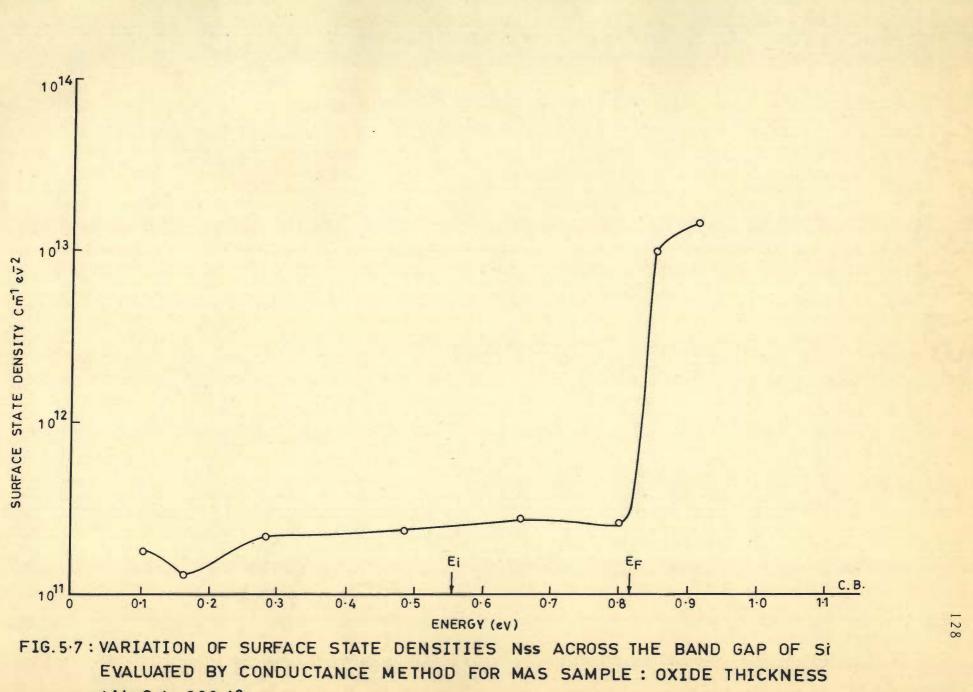

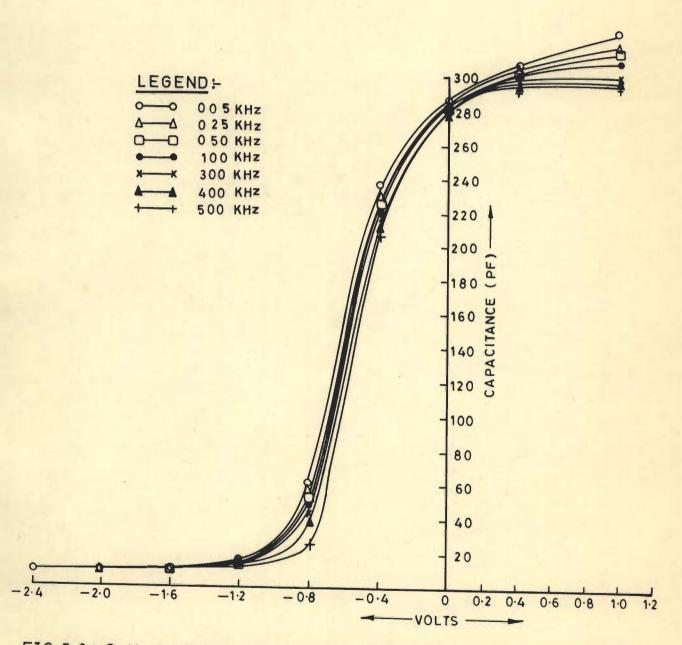

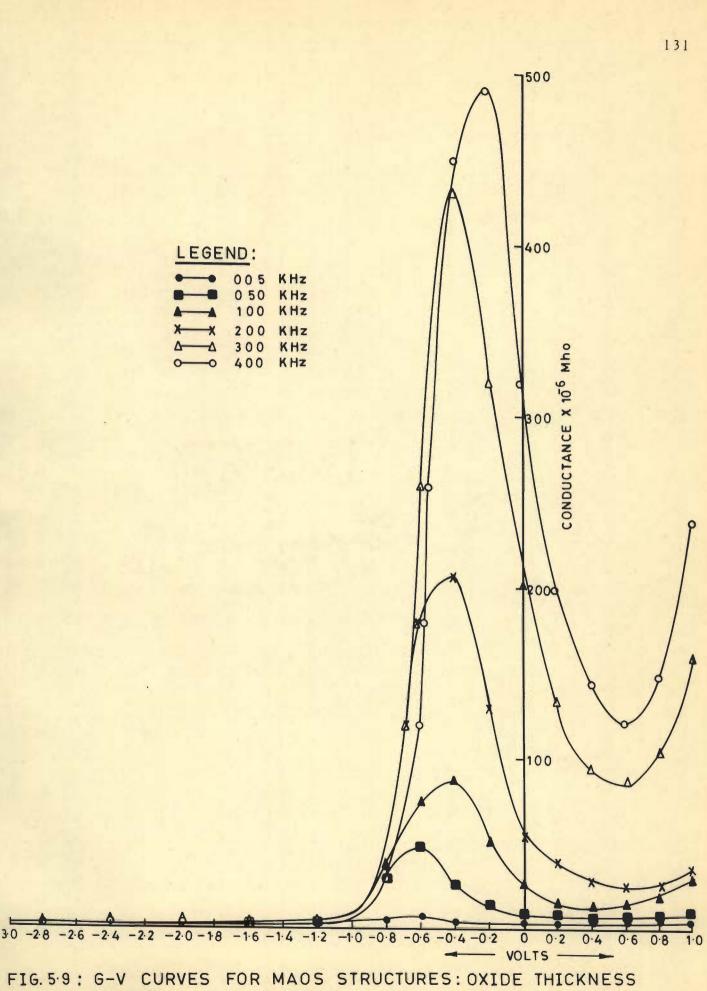

#### 3.5.1 ELECTROLYTIC BATH