# DCMIN – A NEW INTERCONNECTION NETWORK TOPOLOGY FOR PARALLEL PROCESSING

D65-87

KUL

## A THESIS

submitted in fulfilment of the requirements for the award of the degree

of

### DOCTOR OF PHILOSOPHY

in

## ELECTRONICS AND COMMUNICATION ENGINEERING

By

KULDIP SINGH

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247 667 (INDIA)

April 1987

#### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in this thesis entitled 'DCMIN - A New Interconnection Network Topology for Parallel Processing' in fulfilment of the requirement for the award of the Degree of Doctor of Philosophy submitted in the Department of Electronics and Communication Engineering of the University is an authentic record of my own work carried out during a period from Feb.1984 to April 1987 under the supervision of Dr.N.K.Nanda and Dr.R.C.Joshi.

The matter embodied in this thesis has not been submitted by me for the award of any other Degree.

(KULDIP SINGH)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

Auande 18/4/87

(N.K.NANDA) Professor and Head, Electronic and Comm. Engg. Department

Bra (M. 8.4.87 (R. C. JOSHI)

Reader, Electronics and Comm. Engg Department

The candidate has passed the Viva-Voce examination held on \_\_\_\_\_\_at\_\_\_\_. The thesis is recommended for award of Ph.D. Degree.

1. (Guide)

1. (External Examiner)

2. (Guide)

#### ABSTRACT

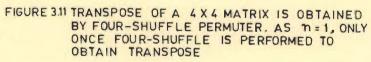

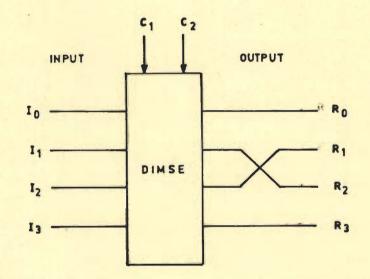

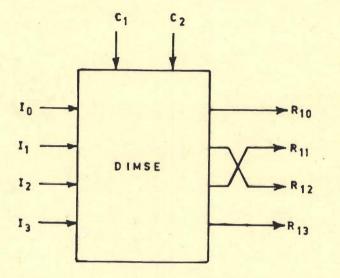

This dissertation addresses the problem of designing a reliable and computationally faster interconnection network with reduced complexity compared to the conventional multistage networks. The importance of 4-shuffle interconnection pattern for the problems requiring concurrent processing has been demonstrated. A 4x4 switch named as Dual Interconnection Modular Switching Element (DIMSE) has been proposed as an alternative to 2x2 switching element for use in Multistage Interconnection Networks (MINs). Design of a new MIN topology, designated as Dual Cube Multistage Interconnection Network (DCMIN), for use in parallel processing environments, has been proposed.

The performance and complexity of DCMIN has been evaluated and compared with the conventional cube type MINs. It has been established that in addition to being less complex and computationally faster, the DCMIN is also cost-effective. Conventional routing algorithms and relatively simpler faultdiagnosis techniques can be readily made applicable to DCMIN. Fault-tolerance capability of the proposed network is evaluated using multiple-paths through an extended topology of DCMIN called EDCMIN and multiple-passes techniques. A simple and elegant analytic model of DCMIN, using Kronecker product of matrices of DIMSEs, has been devised. DCMIN topology has the partitioning property, i.e., the network can be implemented in partitionable SIMD/MIMD environments as well.

#### ACKNOWLEDGEMENT

I wish to express my appreciation and profound gratitude for the continuous interest taken and encouragement given by Dr.N.K.Nanda and Dr.R.C.Joshi who supervised this work. Their active association through suggestions, critical comments and guidance for carrying out this research is gratefully acknowledged.

This work could not have been completed without the whole hearted help and encouragement given by Dr.P.P.Sahgal, Professor and Director, Continuing Education Department. My sincere thanks to him for providing congenial environment to carry out the work.

Special acknowledgement is due to Dr.Harpreet Singh, Professor, Department of Electrical and Computer Engineering, Wayne State University, Detroit, U.S.A. for his encouragement and fruitful discussions on several occasions.

No words can express my thanks and gratitude to Head of Electronics and Communication Engineering Department for providing me the excellent and informal working conditions in the Department to carry out this work.

I am very much grateful to my mother, wife Satpal Kaur and son Jasmeet who have been a constant source of inspiration and encouragement.

I also wish to thank my colleagues Dr.I.J.Gupta and Dr.N.Malaviya for discussions and assistance.

Finally, thanks are due to Shri Amarjeet Singh for neat typing and Shri B.R.Sharma for drawing the figures nicely.

# TABLE OF CONTENTS

|            |     |                                            | Page |

|------------|-----|--------------------------------------------|------|

|            |     | ABSTRACT                                   | i    |

|            |     | ACKNOWLEDGEMENTS                           | ii   |

|            |     | TABLE OF CONTENTS                          | iii  |

|            |     | LIST OF ABBREVIATIONS USED                 | viii |

| CHAPTER I  |     | INTRODUCTION                               | 1    |

|            | 1.1 | Interconnection Network (ICN)              | 2    |

|            | 1.2 | Multistage Interconnection Networks (MINs) | 3    |

|            | 1.3 | Fault-Tolerance                            | 4    |

|            | 1.4 | Motivation For the Present Work            | 5    |

|            | 1.5 | Statement of the Problem                   | 7    |

|            | 1.6 | Organization of the Thesis                 | 8    |

| CHAPTER II | :   | OVERVIEW OF INTERCONNECTION NETWORKS       | 10   |

|            | 2.1 | Parallel Systems                           | 11   |

|            | 2.2 | Interconnection Networks                   | 16   |

|            |     | 2.2.1 Switching Methodology                | 18   |

|            |     | 2.2.2 Interconnection Functions            | 19   |

|            |     | 2.2.3 Interconnection Network Topologies   | 23   |

|            |     | 2.2.4 Connecting Capability of             |      |

|            |     | Multistage ICN's                           | 27   |

|            |     | 2.2.5 Control Strategy                     | 29   |

|            |     | 2.2.6 Fault-Diagnosis and Fault-Tolerance  | 29   |

|            | 2.3 | Additional Modes of Parallel Architecture  | 32   |

|            |     | 2.3.1 Multiple-SIMD System                 | 33   |

| 1.1        |     | 2.3.2 Partitionable SIMD/MIMD System       | 33   |

|            | 2.4 | Conclusion                                 | 35   |

|             |           |                                         | Page |

|-------------|-----------|-----------------------------------------|------|

| CHAPTER III | <b>[:</b> | 4-SHUFFLE INTERCONNECTION PATTERN       |      |

|             |           | IN PARALLEL PROCESSING                  | 37   |

|             | 3.]       | Quaternary Number System And Its Set    |      |

|             | Ο.        | Theoretic Interpretation                | 38   |

|             | 3.2       | 2 Definition of 4-Shuffle               | 39   |

|             | 3.3       | Cube Representation of 4-Shuffle        |      |

|             |           | Permutation                             | 43   |

|             | 3.4       | 4-Shuffle Permuter (P)                  | 45   |

|             | 3.5       | Applications of 4-Shuffle Permutation   |      |

|             |           | In Parallel Processing                  | 47   |

|             |           | 3.5.1 The Fast Fourier Transform (FFT)  | 47   |

|             |           | 3.5.2 Polynomial Evaluation             | 53   |

|             |           | 3.5.3 Matrix Transposition              | 54   |

|             | 3.6       | Conclusion                              | 62   |

| CHAPTER IV: |           | DESIGN OF DUAL CUBE MULTISTAGE          |      |

|             |           | INTERCONNECTION NETWORK                 | 63   |

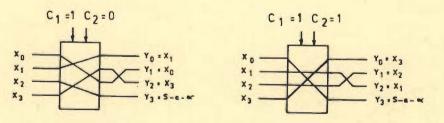

|             | 4.1       | Dual Interconnection Modular Switching  | 00   |

| 2           |           | Element (DIMSE)                         | 65   |

|             | 4.2       | Development of Single Stage Network     |      |

|             |           | Using DIMSEs                            | 71   |

| 1.1.1.1.1   | 4.3       | Multistage Interconnection Networks     |      |

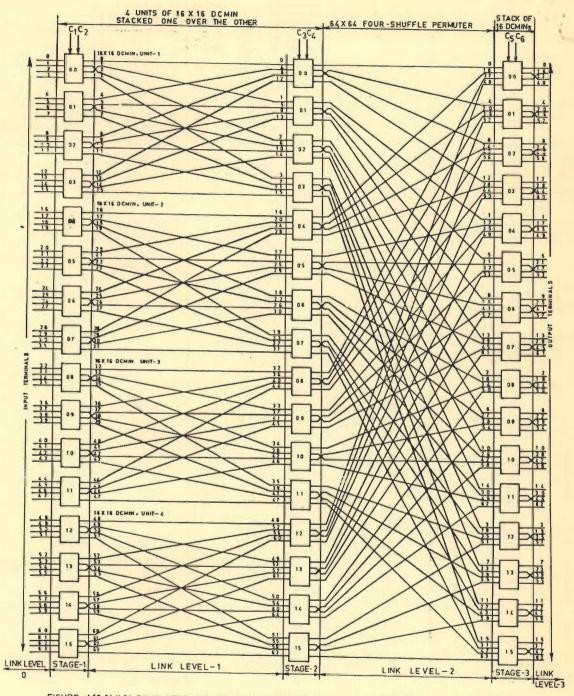

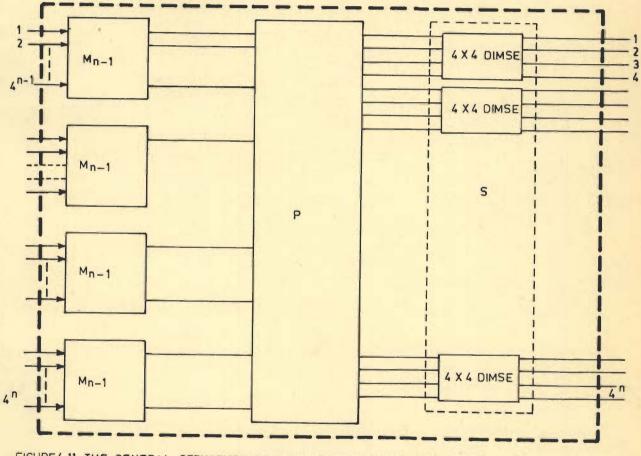

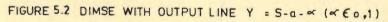

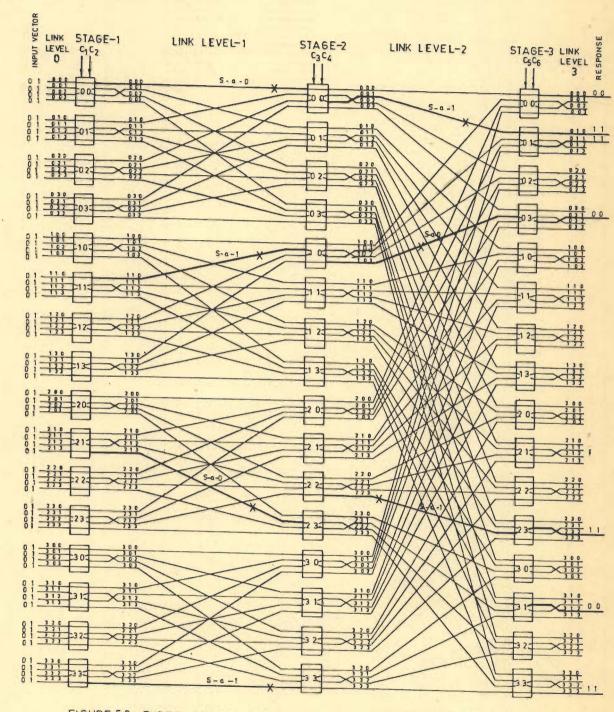

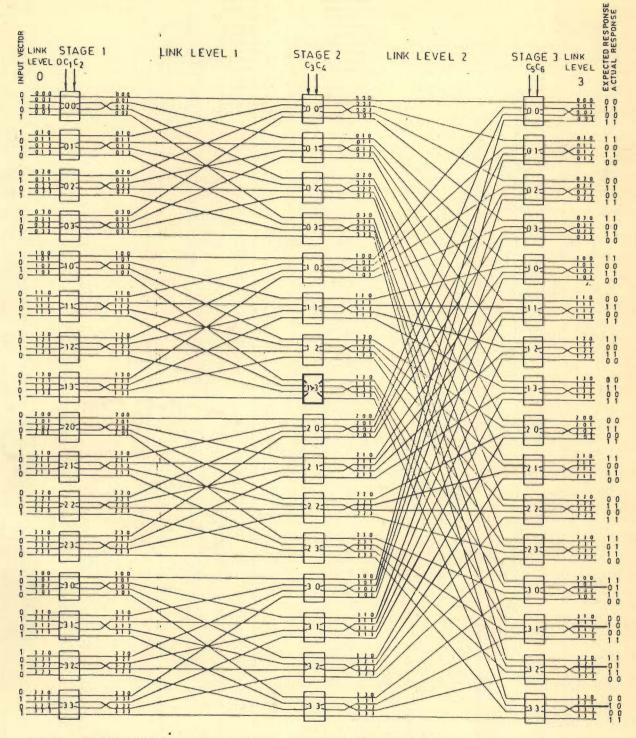

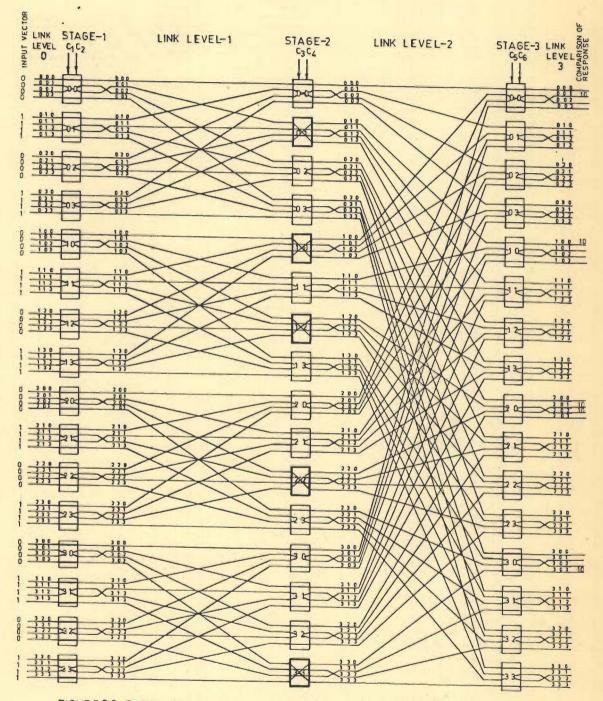

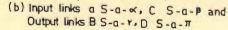

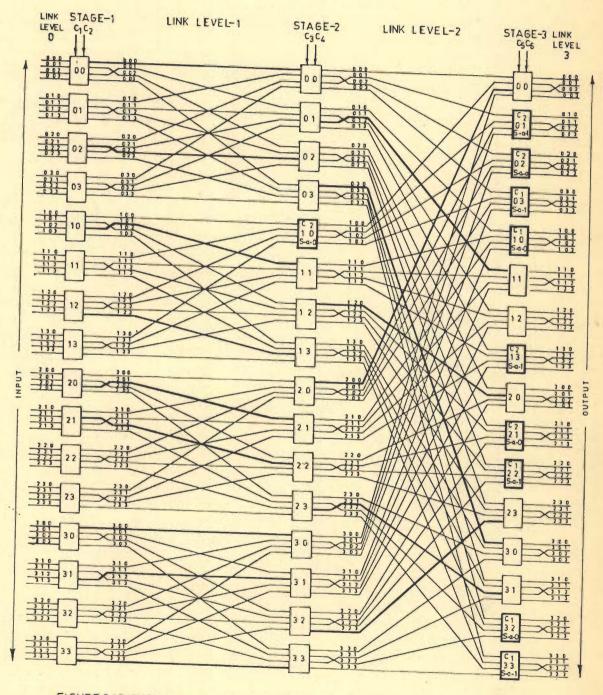

|             |           | Using DIMSEs                            | 75   |

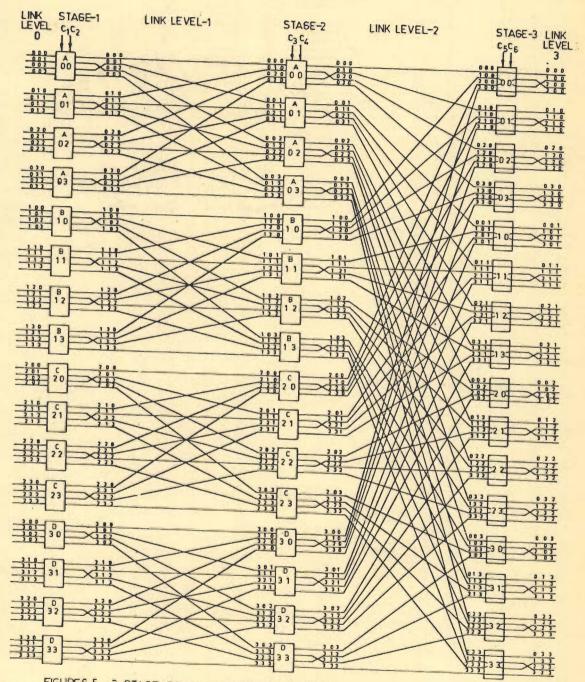

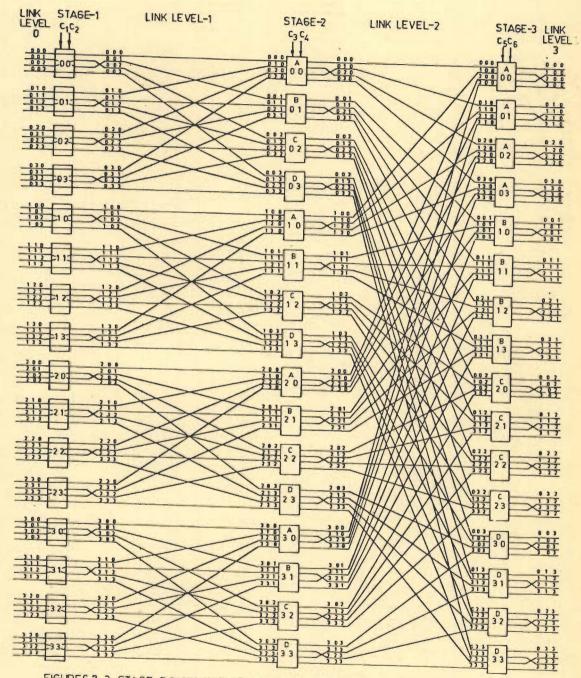

|             |           | 4.3.1 Development of DCMIN-Dual-Cube    |      |

|             |           | Multistage Interconnection Network      | 77   |

|             |           | 4.3.2 Dual Cube Analogy                 | 78   |

|             |           | 4.3.3 Generalization of DCMIN           | 80   |

|             |           | 4.3.4 Dual Cube Transformation of Three |      |

|             |           | Stage DCMIN                             | 87   |

|             | 4.4       | Interconnection Function of DCMIN       | 89   |

iv

|                                                | Page |

|------------------------------------------------|------|

| 4.5 Labeling And Addressing of Links and       |      |

| DIMSEs in DCMIN                                | 92   |

| 4.5.1 Locating the Fault-Source From           |      |

| the Known Address of the Output                |      |

| Terminal Reflecting the Fault                  | 97   |

| 4.6 Routing Schemes                            | 99   |

| 4.6.1 Destination Tag Routing                  | 100  |

| 4.6.2 Exclusive-OR Routing                     | 101  |

| 4.7 Complexity And Performance Evaluation      |      |

| of DCMIN                                       | 101  |

| 4.8 Conclusion                                 | 105  |

| CHAPTER V: FAULT-DIAGNOSIS AND FAULT-TOLERANCE |      |

| OF DCMIN                                       | 106  |

| 5.1 Fault Diagnosis of DCMIN                   | 107  |

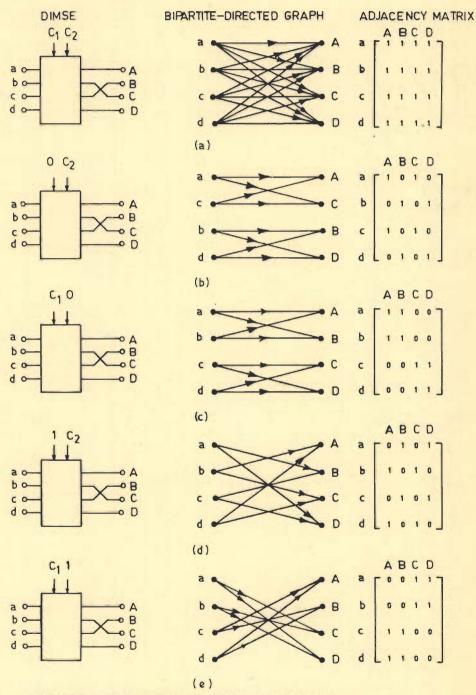

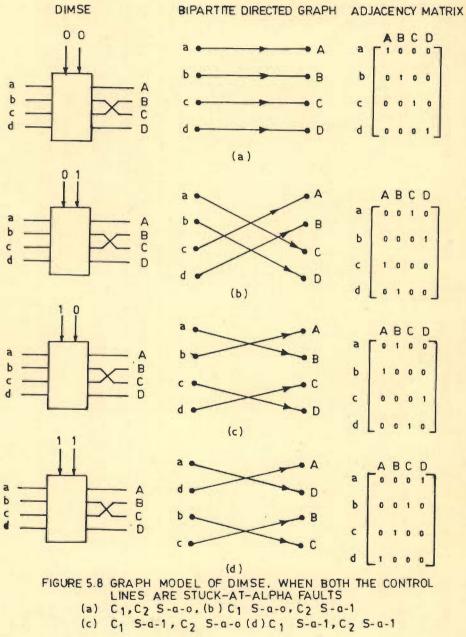

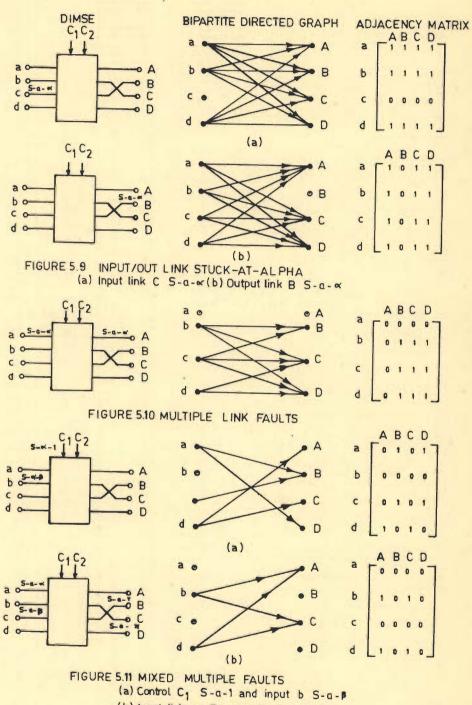

| 5.1.1 Fault Model of Dual Interconnection      |      |

| Modular Switch                                 | 107  |

| 5.1.2 Diagnosis of Fault at an External        |      |

| Link                                           | 108  |

| 5.1.3 Diagnosis of Fault at Control Lines      |      |

| 5.1.4 Multiple Faults                          | 121  |

| 5.2 Fault-Tolerance of DCMIN                   | 126  |

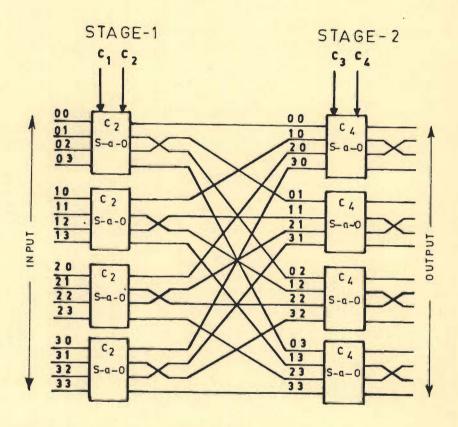

| 5.2.1 Graph Model of DIMSE                     | 126  |

| 5.2.2 Graph Model of DCMIN and Its             |      |

| DFA Capabilities                               | 130  |

| 5.3 Distance Matrix and Average Path Length    |      |

| of DCMIN                                       | 151  |

| 5.4 Conclusion                                 | 153  |

|              |                                          | Page |

|--------------|------------------------------------------|------|

| CHAPTER VI:  | GENERAL PROPERTIES OF DCMIN              | 155  |

| 6.1          | Analytical Model of DCMIN                | 155  |

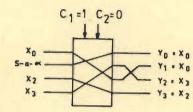

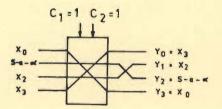

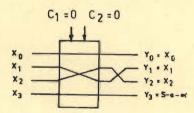

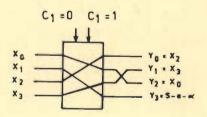

|              | 6.1.1 Matrix Representation of DIMSE     | 156  |

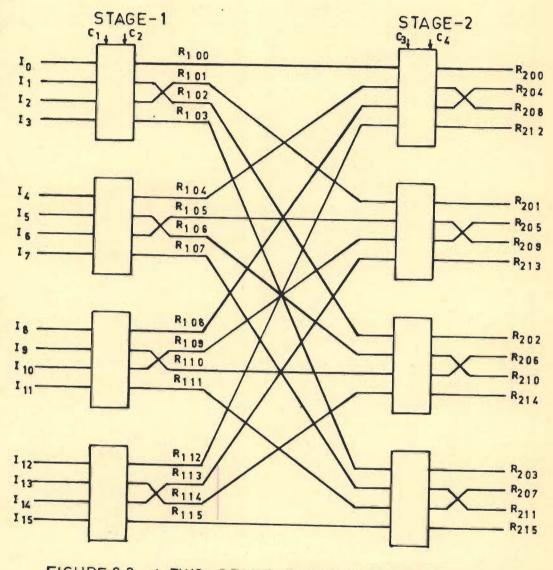

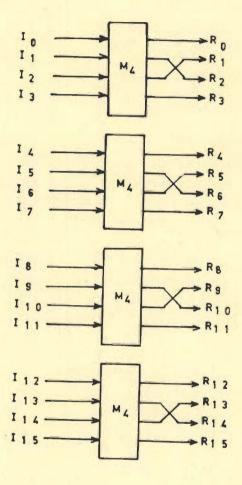

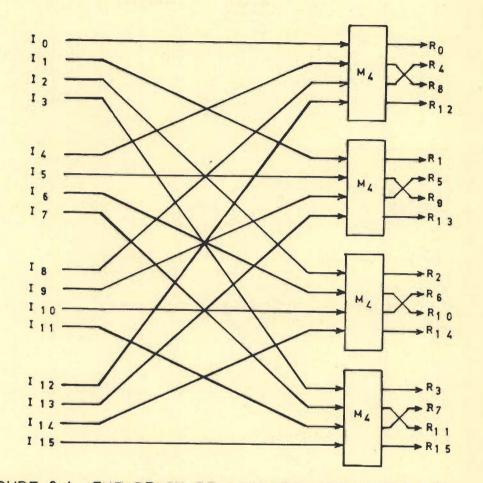

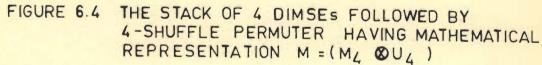

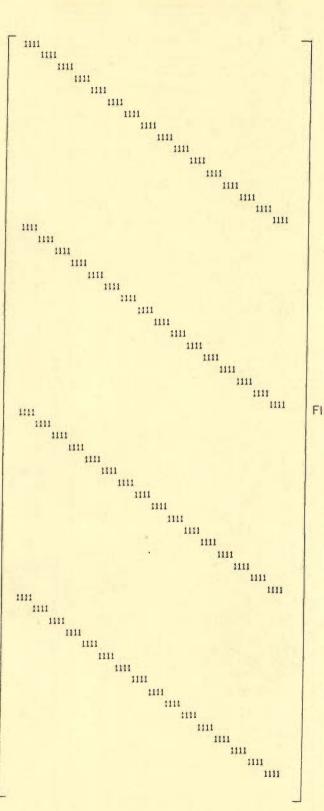

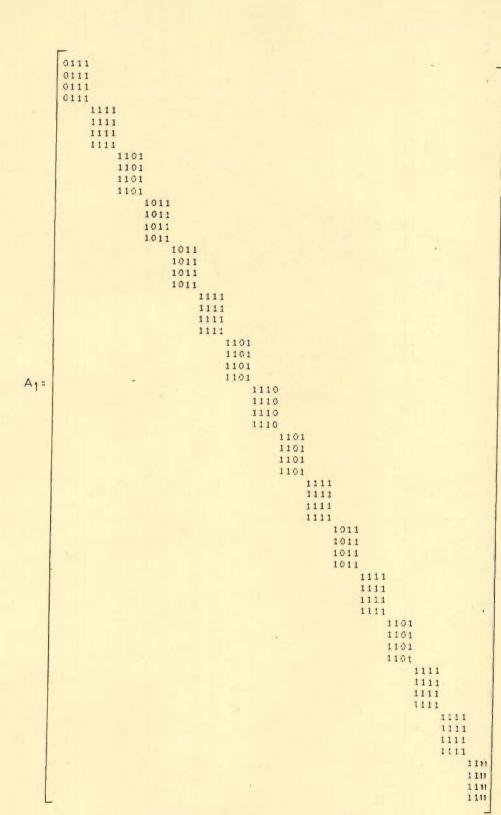

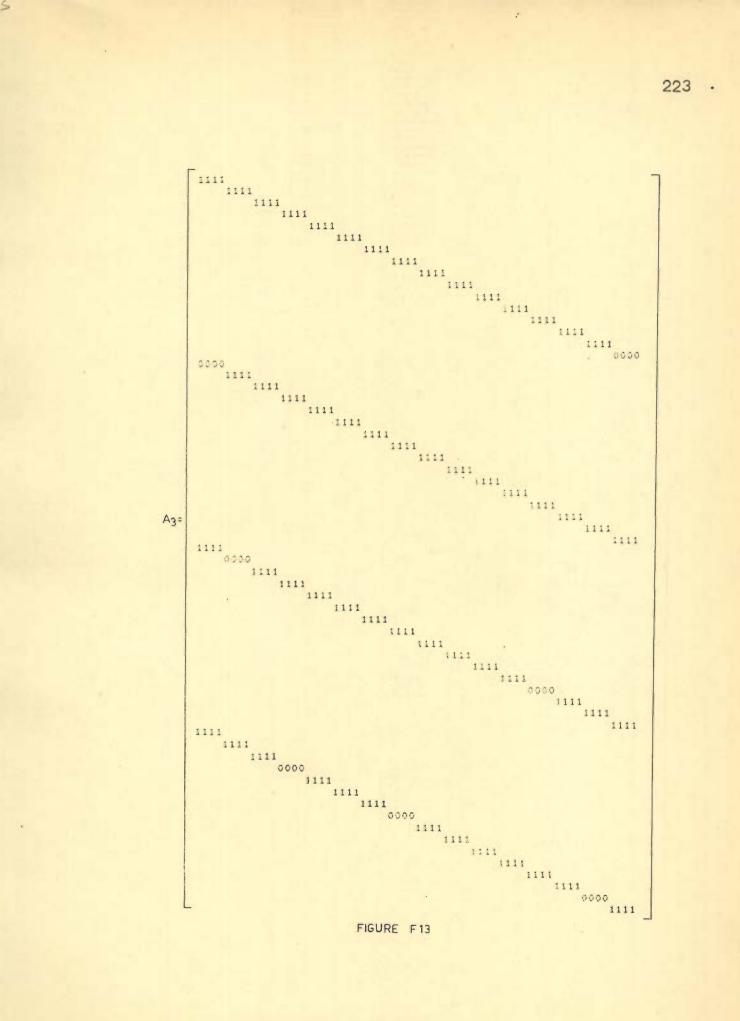

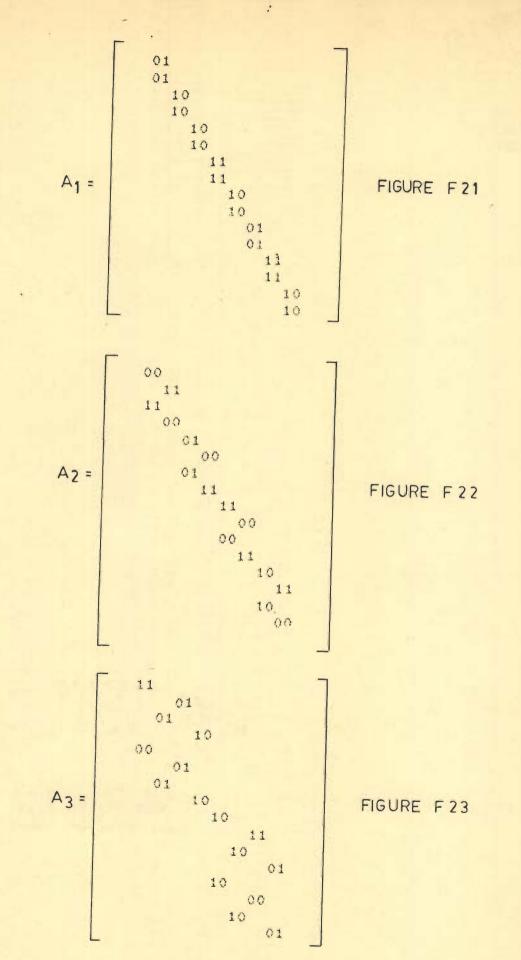

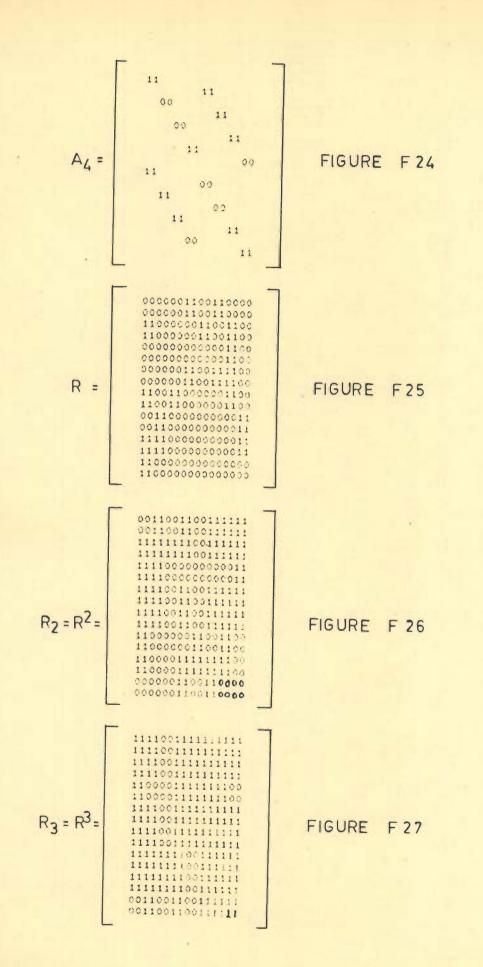

|              | 6.1.2 Matrix Representation of DCMIN     | 159  |

|              | 6.1.3 Development of DCMIN from a        |      |

|              | Given Mapping Matrix                     | 164  |

|              | 6.1.4 Properties of Mapping Matrix       |      |

|              | of DCMIN                                 | 168  |

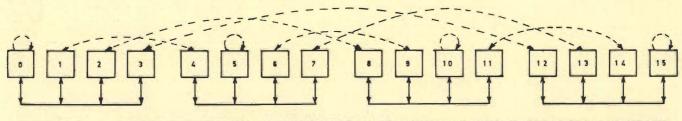

| 6.2          | Partitioning of Dual Cube Networks       | 169  |

|              | 6.2.1 Dual Cube Network Cyclic Structure | 170  |

|              | 6.2.2 Partitioning of DCMIN              | 171  |

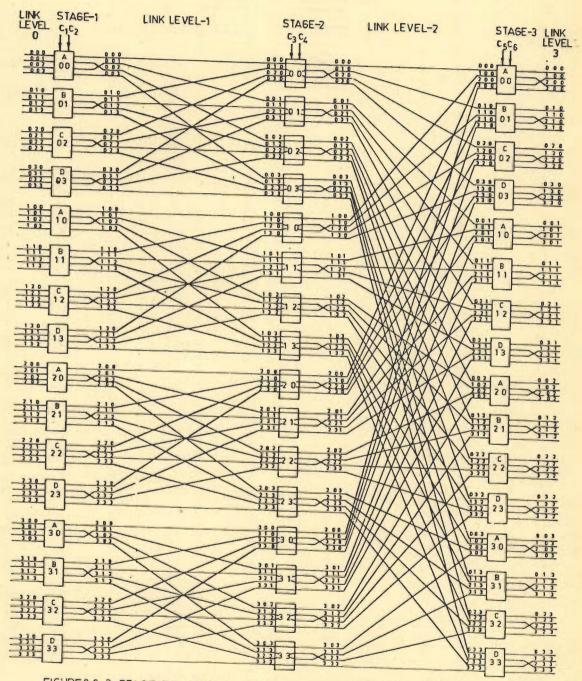

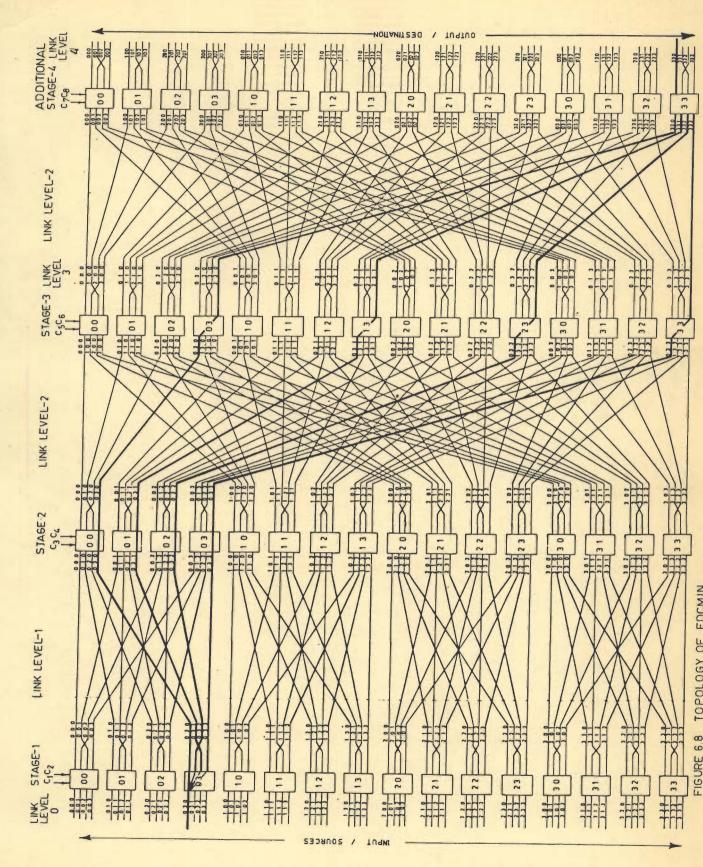

| 6.3          | The Extra Stage DCMIN (EDCMIN)           | 178  |

|              | 6.3.1 Topology of EDCMIN                 | 179  |

|              | 6.3.2 Fault-Tolerance of DCMIN           | 183  |

|              | 6.3.3 Routing Scheme for EDCMIN          | 186  |

| 6.4          | Conclusion                               | 187  |

| CHAPTER VII: | TRUNCATED DUAL CUBE MULTISTAGE           |      |

|              | INTERCONNECTION NETWORK                  | 189  |

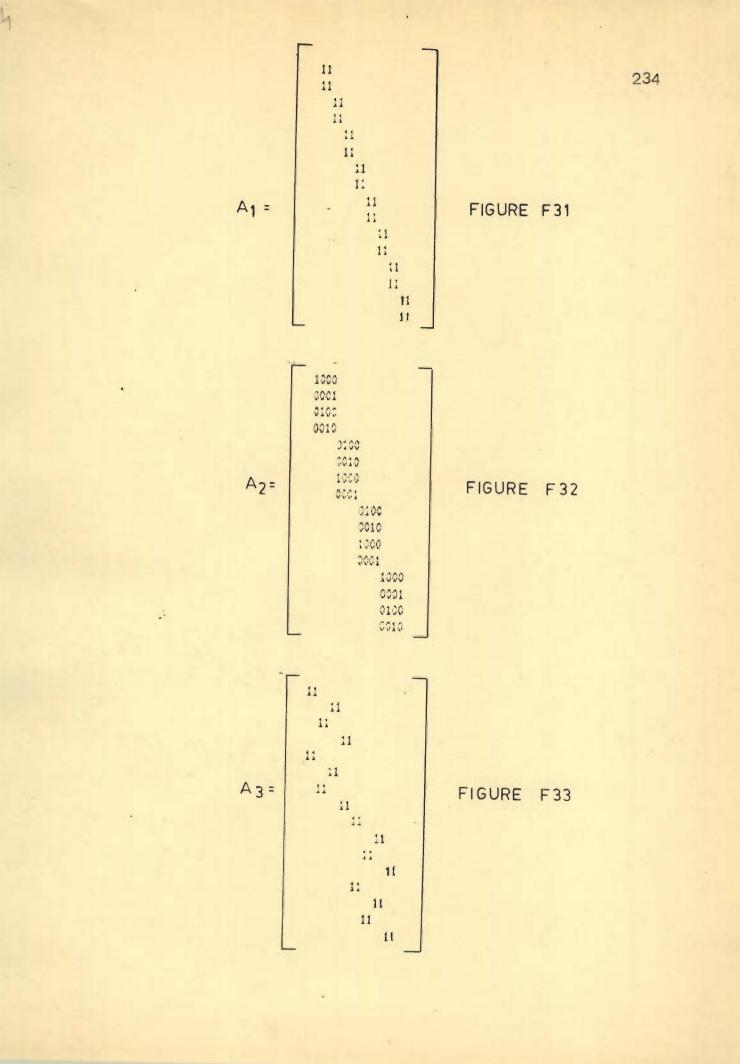

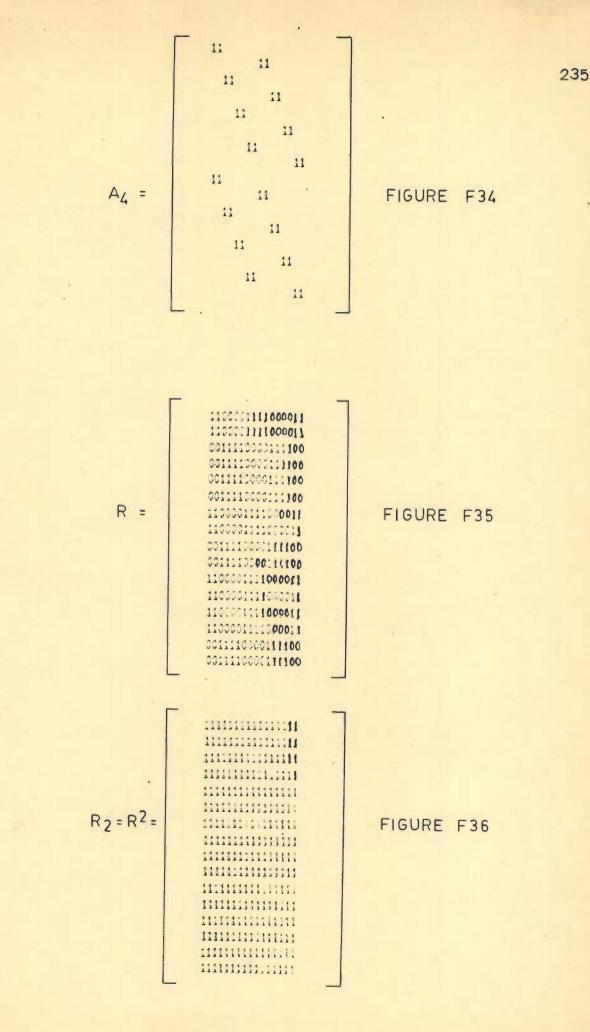

| 7.1          | Topology of TDCMIN                       | 189  |

| 7.2          | Control Strategy of TDCMIN               | 194  |

|              | Routing Scheme of TDCMIN                 | 196  |

|              | Partitioning of TDCMIN                   | 198  |

|              | 7.4.1 Partitioning Results               | 198  |

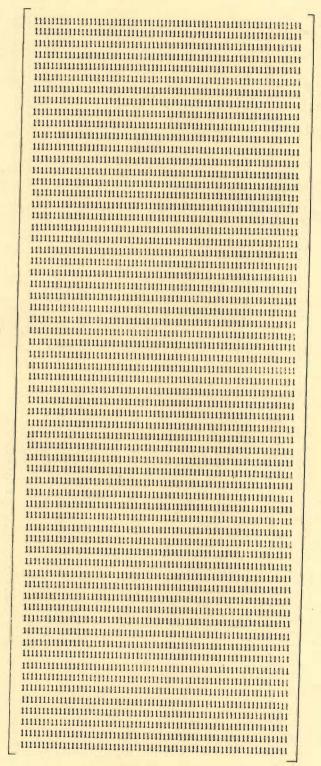

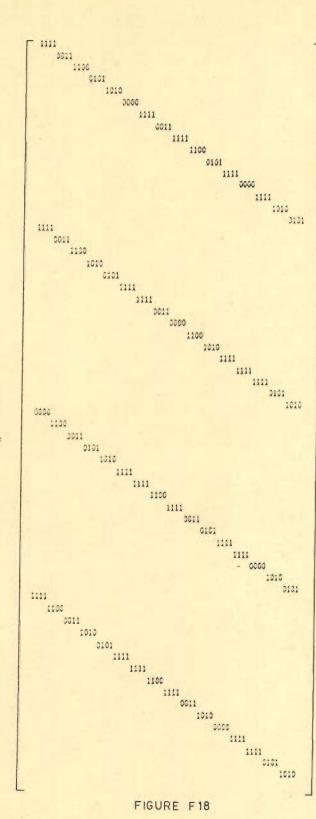

| 7.5 M        | Matrix Representation of TDCMIN          | 200  |

|              | The Extra Stage TDCMIN (ETDCMIN)         | 204  |

|              | 7.6.1 Routing Scheme                     | 205  |

| 7.7 (        | Conclusion                               | 207  |

vi

|                                           | Page |

|-------------------------------------------|------|

| CHAPTER VIII: CONCLUSIONS                 | 208  |

| 8.1 Suggestions for Future Investigations | 211  |

| APPENDIX                                  | 213  |

| BIBLIOGRAPHY                              | 236  |

vii

# LIST OF ABBREVIATIONS USED

| Augmented Data Manipulator                       |

|--------------------------------------------------|

| Central Processing Unit                          |

| Dual Cube Multistage Interconnection Network     |

| Dual Cube                                        |

| Data Transfer Register                           |

| Dynamic Full Access                              |

| Dual Interconnection Modular Switching Element   |

| Extra Stage Dual Cube Multistage Interconnection |

| Network                                          |

| Full Access                                      |

| Fast Fourier Transform                           |

| Inverse Augmented Data Manipulator               |

| Interconnection Network                          |

| Interchange                                      |

| Interconnection Networks Designed for Reliable   |

| Architecture                                     |

| Least Significant Digit                          |

| Multistage Cube Network                          |

| Multiple Instruction Multiple Data Stream        |

| Multistage Interconnection Network               |

| Multiple Instruction Single Data Stream          |

| Massively Parallel Processor                     |

| Most Significant Digit                           |

| Of the order of                                  |

| 4-Shuffle Permuter                               |

| Processing Element                               |

|                                                  |

| QR        | Quaternary Representation                      |

|-----------|------------------------------------------------|

| S         | Stack                                          |

| SE        | Switching Element                              |

| SIMD      | Single Instruction Multiple Data Stream        |

| SISD      | Single Instruction Single Data Stream          |

| TDCMIN    | Truncated Dual Cube Multistage Interconnection |

|           | Network                                        |

| ULM       | Universal Logic Module                         |

| VLSI      | Very Large Scale Integration                   |

| WSI       | Wafer Scale Integration                        |

| €         | Exclusive-OR                                   |

| $\otimes$ | Kronecker Product                              |

| σ         | General NxN Permuter                           |

#### CHAPTER I

#### INTRODUCTION

Single processor systems, which are based on the traditional Von Neumann or microprogrammed architectures, have reached their limits in computing capability. They do not provide for parallel computation of instructions and data, which makes them inappropriate for many present day applications, requiring high computational power and speed. As a result, a great deal of architectural research was directed towards overcoming the sequential barrier and evolving systems that could perform computations in parallel [9,10,38,45,46]. This culminated in the evolution of multiprocessor systems with a wide variety of applications, where higher processing speed is achieved through the concurrent or parallel operation of a number of processors.

It is predicted that the advances in VLSI and WSI technologies will, in the near future, enable designers to integrate hundreds or even thousands of processing elements on a single wafer [155]. As the component density of integrated circuits continues to increase, computer designers will be more concerned with the interconnection of the processors than with the processor design itself. One of the prominent components, which will wield great influence on such systems, is the Interconnection Network (ICN). The performance and fault-tolerance of multiprocessor systems are subsequently dictated more by the properties of ICN than by the individual units. Hence, the design of ICN assumes a significant role in parallel architectures, such as array processor and multiprocessor systems.

The time shared bus is the simplest and earliest form of ICN. In a uniprocessor architecture, functional modules are connected to a bus and the resulting systems vary widely in complexity depending upon the number and nature of the modules. A multiprocessor environment is formed by interconnecting a number of CPUs, memory units, and controllers in addition to buses. The early multiprocessor systems consisted of only a few processors. As computer systems evolved from uniprocessor to multiprocessor systems, multiple buses or cross bar switches were used to connect processors and/or memories. The advent of low cost microprocessors and the critical need of high performance computing has triggered intensive research on various ICNs. Concepts like telephone switching system [20,144] and computer communication [9,144] were used in the design and analysis of The current trend is to design ICNs in such a way that ICNs. the multiprocessor system level functions such as resource sharing and synchronization can be easily implemented by using ICN.

### 1.1 INTERCONNECTION NETWORK (ICN)

An ICN basically provides communication between the sets of source and destination ports to which different units such as processors, memories etc. are connected. Functionally, under a transfer instruction, data from a specific source node is transferred to some prespecified destination or vice-versa, following a route determined by the control signals of the network. To do this, it has to be necessarily a switching network. Accordingly, an ICN may be looked upon as a system of switches, that can be opened or closed to provide a path from a set of input

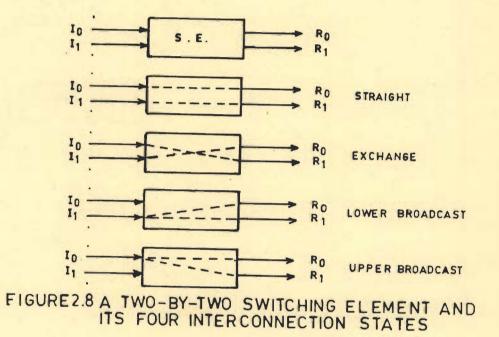

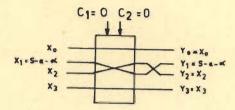

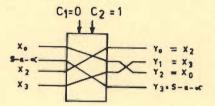

terminals to a set of output terminals. The smallest switch of interest, called Interchange (I/C) box, Switching Element (SE) or  $\beta$ -element, has two switching states corresponding to the two possible switching modes, i.e., direct or cross, depending upon the state of control signal. Usually the network is organised into several stages of switching elements, connected through links, to achieve full connectivity and is called Multistage Interconnection Network (MIN). In general, a MIN allows processor-to-processor or processor-to-memory communication.

#### 1.2 MULTISTAGE INTERCONNECTION NETWORKS (MINS)

A multistage network consists of more than one stage of switching elements and is usually capable of connecting an arbitrary input terminal to an arbitrary output terminal. Because of their structure, MINs are capable of supporting a large number of computing units and large number of simultaneous connections using a reasonable number of SEs. With proper design a connecting network can provide connections with reasonably short delays and with a relatively simple control structure. Also, MINs have built in flexibility and redundancy which can be utilized for fault-tolerance with graceful degradation in the computational speed [117]. Multistage interconnection networks mentioned in literature can be divided into three classes:

### (i) Blocking:

In blocking networks, simultaneous connections of more than one input/output terminal pair may result in conflicts in the use of network communication links.

#### (ii) Rearrangeable:

A network is called rearrangeable nonblocking network, if it can perform all possible connections between inputs and outputs, by rearranging its existing connections so that a connection path for a new inputoutput pair can always be established.

(iii) Nonblocking:

A network which can handle all possible connections without blocking is called a nonblocking network.

The Clos nonblocking network employing three stages of crossbar switches [36] was forerunner in the design hierarchy of MINs. Subsequently, Benes network [21] which is rearrangeable network, was evolved. What followed afterwards was a class of blocking networks such as Omega [79], Stran Flip [15], Indirect Binary m-cube [106], Generalized Cube [121], Generalized Shuffle [24] and Dual Cube networks [126]. In these networks, there is only one path between any source-destination pair. These networks do not realize all possible permutations of input/output combinations. However, these can perform some of the permutations which may be useful in computer communication networks. The blocking networks are advantageous because they implement simple control algorithms and employ (N/2  $log_2N$ )(2x2) or (N/4  $log_4N$ )(4x4) switches for N number of functional units.

#### 1.3 FAULT-TOLERANCE

A fault-tolerant ICN can tolerate faults to some degree and still provide reliable communication between any input/output

pair. Fault-tolerance is usually achieved by introducing redundancy in the MIN. By introducing hardware redundancy more number of alternate paths are created between source/destination pairs to augment the permutation capability of the network which makes it fault-tolerant. Hardware redundancy can be introduced in the network (i) by increasing the number of stages [3,116], (ii) by using fault-tolerant SEs [84] or (iii) by providing extra links [6,35]. These techniques have been employed in the redundant networks such as Data Manipulator [48], IADM [89, 90], Extra Stage Cube and Delta Networks [3,116], Gamma Network [103], INDRA Network [109] and Augmented C-Network [111]. An alternative approach to fault-tolerance by means of redundancy in time (multiple-passes) has been proposed in [117] and generalized in [8]. An important property of MIN is Dynamic Full Access (DFA) characteristic. A network has DFA property if each of its inputs can be connected to any one of its outputs via a finite number of passes [118].

5

1.4 MOTIVATION FOR THE PRESENT WORK

It has been observed that the nucleus of a modern day practical multiprocessor system is not so much the individual functional modules rather the interconnection network. In this respect, therefore, it is essential that the interconnection networks be designed as efficiently as possible and this is the prime justification for carrying out the work reported in this thesis. The important factors which influence the design of ICN are:

### (i) Computational Speed:

Computational speed can be increased by reducing the propagation delay in the ICN. Since the switch delay decreases with scaling, the speed at which a circuit can operate is dominated by the interconnection delay. Thus, the computational speed can be increased by reducing the number of stages in a network.

(ii) Complexity:

Complexity of the network is directly proportional to the number of switching elements used and the number of external links in the network. Accordingly, if the size of the SE is increased the number of SEs per stage will decrease. The larger size SEs with appropriate interconnection patterns can reduce the number of stages for the same number of functional units. Reduction in the number of stages will consequently reduce the number of external links.

(iii) Reliability:

Because of the system complexity, achievement of high reliability is a significant task. The ICN should have inherent fault-tolerance properties. It should be possible to achieve fault-tolerance either by adding hardware redundancy or through multiple passes. In addition the algorithms to detect and locate faulty elements, should be simple and elegant.

### (iv) Adaptability:

To suit the requirements of multiple-SIMD and partitionable SIMD/MIMD environments, it should be possible to partition the network into smaller size networks.

An NxN conventional MIN employs more than one stages of 2x2 SEs usually interconnected through perfect shuffle patterns. This gives ( $\lceil (\log_2 N) \rceil$ ) as the lower bound on the number of stages. Accordingly, the network complexity and computational speed, become proportional to ( $\lceil (\log_2 N) \rceil$ ). This puts the limitation on the capabilities of currently employed MINs in terms of computational time and complexity. With the increasing complexity of multiprocessor systems, due to the use of large number of functional elements, a logical question arises - is there an alternative MIN topology that allows the multiprocessing boundaries to be extended for the same amount of resources and cost ? It is this question to which the thesis addresses it**self**.

#### 1.5 STATEMENT OF THE PROBLEM

This thesis attributes itself to the problem of designing a simple but computationally faster and cost-effective multistage interconnection network compared to the conventional MINs. The objective is to find a new topology for a class of interconnection networks, by increasing the size of conventional 2x2 switching elements. Specifically, the problems considered in this thesis can be stated as follows:

- To examine a 4x4 switching element and propose its realization.

- (2) To investigate the link pattern to interconnect the stages of the proposed switching elements and hence evolve a new topology of a class of MIN with reduced number of stages compared to the conventional lower bound of ([~log\_N]).

- (3) To compare the performance and complexity of the proposed network topology with the conventional topology.

- (4) To evolve an analytical model of proposed MIN.

- (5) To exploit the use of the proposed topology in the various parallel processing architectures.

## 1.6 ORGANIZATION OF THE THESIS

Applications of interconnection networks and their general classification have been reviewed in Chapter II. The terminology and definitions used in Chapter II give a general base for understanding the work carried out in the thesis.

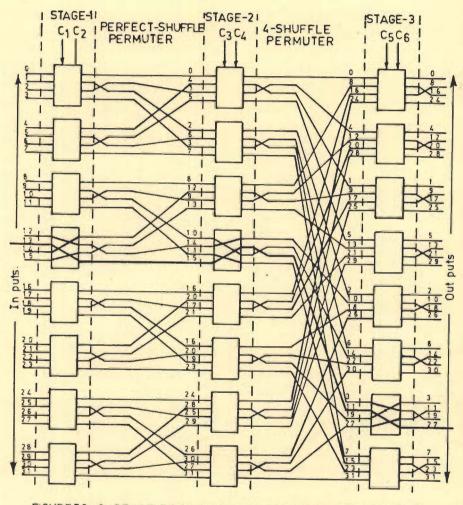

Chapter III defines 4-shuffle permutation. It has also been established that 4-shuffle interconnection pattern has an important role in parallel processing and reduces the computational complexity to  $O(\lceil \log_4 N \rceil)$ .

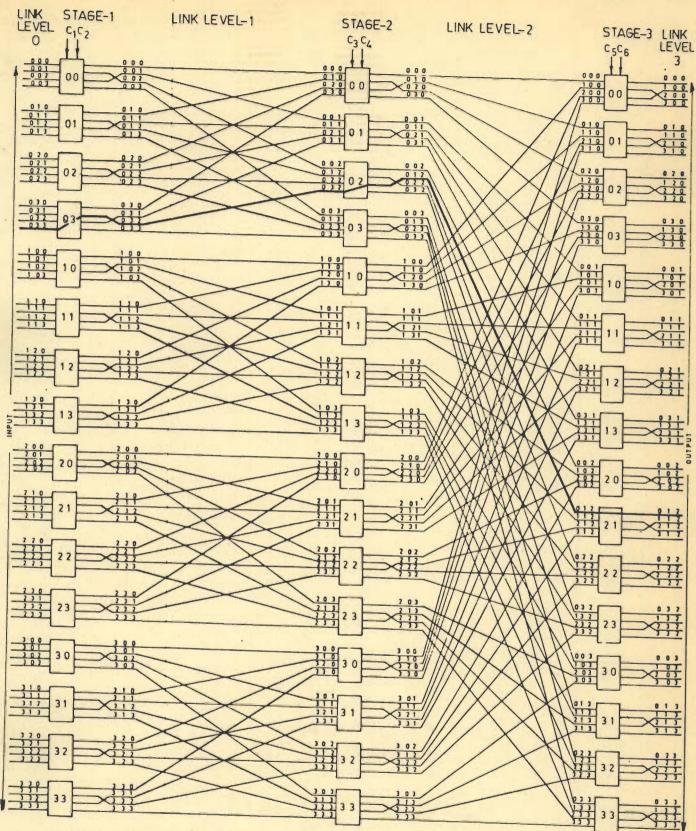

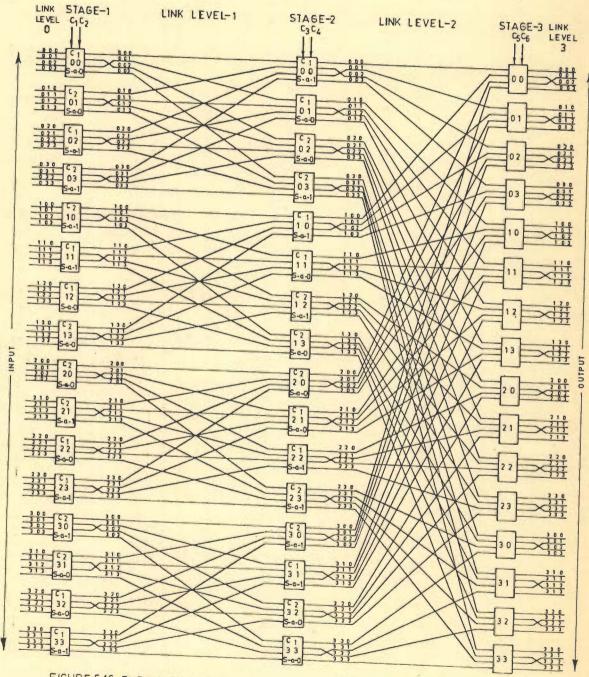

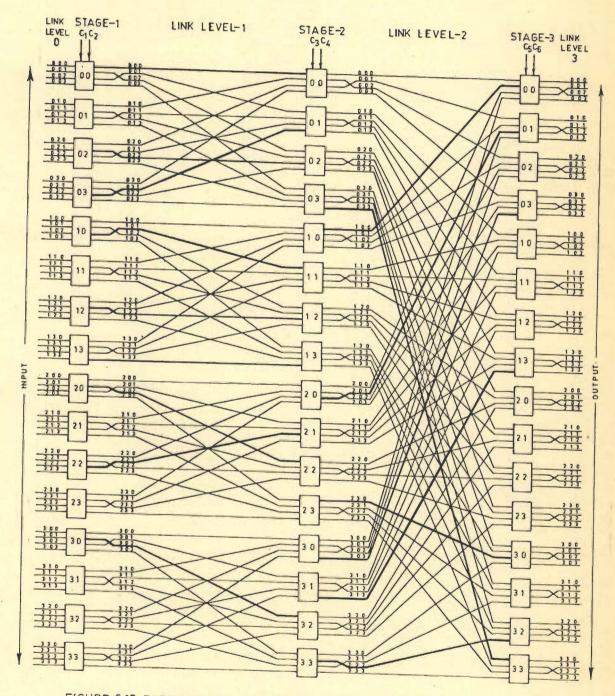

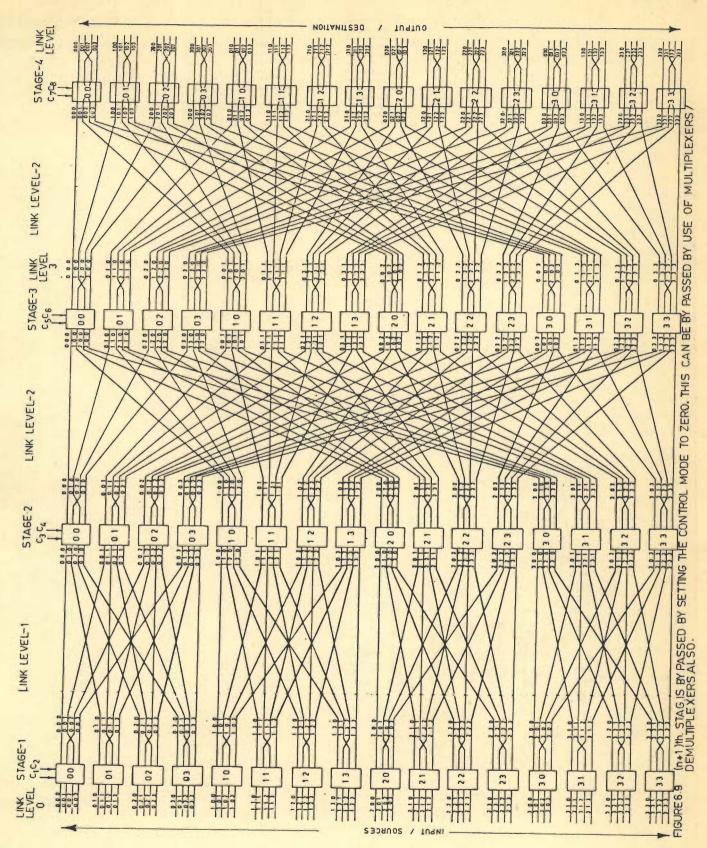

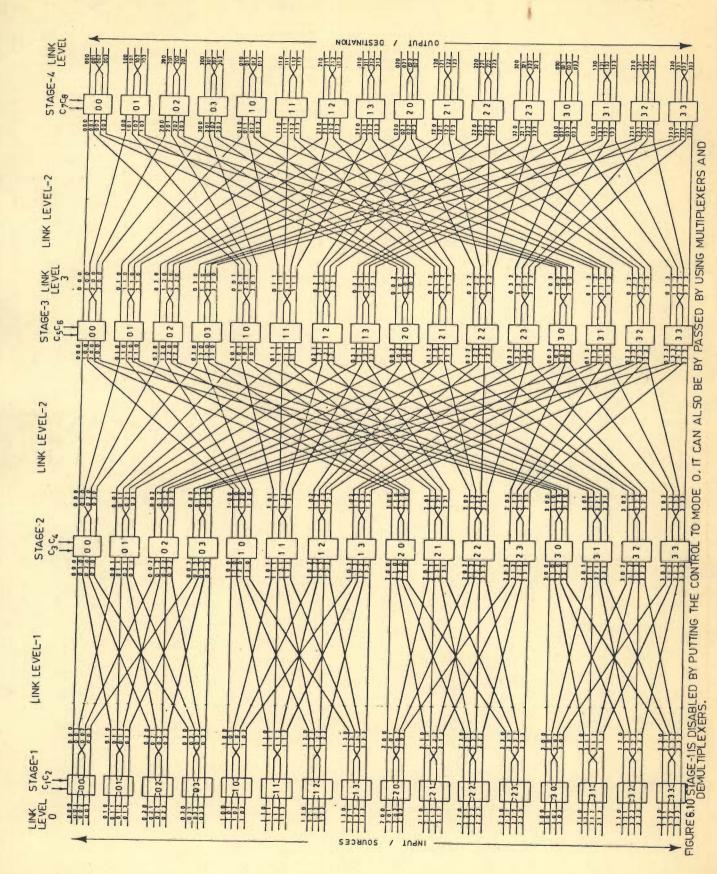

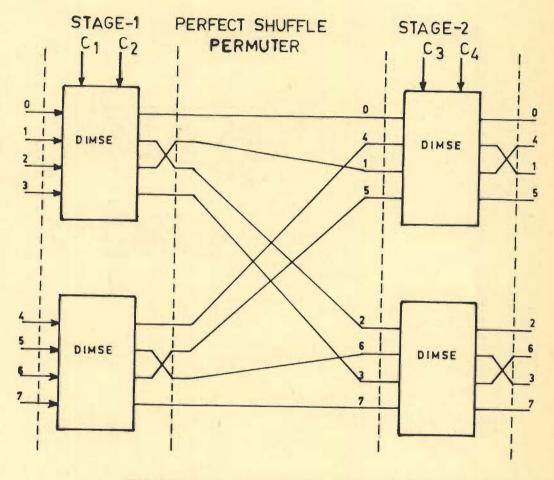

A 4x4 switch named Dual Interconnection Modular Switching Element (DIMSE) and its implementation is presented in Chapter IV, where the design of single and multistage networks using DIMSEs and 4-shuffle patterns has been given. This new multistage network topology is designated as Dual Cube Multistage Interconnection Network (DCMIN). Finally, the complexity and performance of DCMIN have been evaluated and compared with a conventional cube type network.

Reliability aspects of the proposed DCMIN are discussed in Chapter V. A description of simple procedures for fault diagnosis and evaluation of DFA capabilities of DCMIN under various fault conditions has been given.

Chapter VI is devoted to investigate the general properties of DCMIN such as modelling, adaptability and fault tolerance aspects.

TDCMIN, a derivative of DCMIN topology, when the size N of the network is such that  $N = 2^m \neq 4^n$ , has been evolved in Chapter VII. The TDCMIN topology has been evaluated from various angles.

Finally, the conclusions of the work carried out alongwith some proposals for further research in this area are given in Chapter VIII.

#### CHAPTER II

# OVERVIEW OF INTERCONNECTION NETWORKS

An interconnection network is basically a switching network, which is designed to facilitate efficient interprocess and interprocessor communication in parallel architectures. Earlier when computer systems were confined within Von Neumann architectural boundaries and the hardware cost was a significant limiting factor, interprocess and interprocessor communication were not prominent issues. Consequently, the design of a cost-effective interconnection network was a trivial and relatively unimportant task. However, contemporary IC technology and ultra high speed computational requirements have ushered in entirely new architectural challenges. It is now economically feasible and practically desirable to construct a multiprocessor system by interconnecting hundreds or thousands of processors [155]. Such systems are called parallel systems. However, the performance and utilization of such systems, in general, are limited by the extent upto which interprocessor communication is possible. Parallel processing techniques use interconnection networks to facilitate concurrent operations.

A parallel processing system comprising multiple processors is implemented with IC chips and a network interconnecting them. The IC chips though less likely to be faulty, are replaceable and the performance of a multiprocessor system is, therefore, a function of reliable operation of ICN [117]. This chapter is devoted to the study of various aspects of ICNs such as their requirements, basic interconnection functions, topologies, reliability and applications in practical parallel systems. However, before reviewing the ICNs a brief discussion on parallel systems is undertaken. ICNs also play an important role in resource allocation and reconfiguration of the parallel systems. At the end of this chapter comparatively recent modes of parallel systems are discussed briefly.

#### 2.1 PARALLEL SYSTEMS

Parallel processing has made possible the computational power and speed required by many present day real time tasks, where there is need to process immense data sets. These tasks include seismic data processing, weather forecasting, air traffic control, satellite collected imagery analysis, robot vision and speech understanding etc. The parallel systems support to meet the computational goals for all these applications. Parallel systems can be defined broadly as a unified system containing multiple processors capable of simultaneous operation. Depending upon the technique of introducing parallelism, parallel systems may be classified into the following four different categories [74]:

# (i) Multicomputer Systems

These are assembled from N computers in such a way that any two computers may communicate with each other via an interconnection bus connected with their input/output devices.

## (ii) Multiprocessor System

The interconnection bus of the multiprocessor system allows activation of a direct communication path

between any two functional units contained in the system.

(iii) Array Processor

It consists of N processors each handling same instruction issued by a single control unit, on its own data.

(iv) Pipelining

It contains pipelined processors with an instruction broken into a series of simple functions to be performed in pipelined segments, i.e., the application of assembly line technique.

The degree of complexity of such systems can be gauged from the fact that hundreds or even thousands of processors are used to achieve execution rates as high as billion floating point instructions per second [49]. Such systems have been classified on the basis of the modes of operation, i.e., how the machine relates its instructions to the data being processed [55]. Four broad classifications that have emerged are Single Instruction Single Data Stream (SISD), Single Instruction Multiple Data stream (SIMD), Multiple Instruction Single Data stream (MISD) and Multiple Instruction Multiple Data stream (MIMD). Out of these, SIMD and MIMD modes of operation are of immediate interest in parallel processing systems, involving interconnection networks.

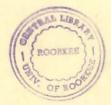

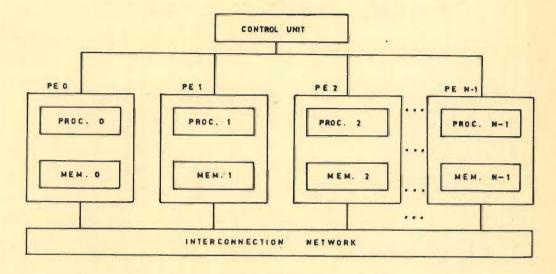

Typically, an SIMD machine is a computer system consisting of a control unit, N processors, N memory modules, and an interconnection network. The control unit broadcasts instructions to the processors, and all active processors execute the same instruction at the same time. These machines are designed to exploit the inherent parallelism of such tasks as matrix operations and such problem domains as image processing where the same operation is performed on many different matrices or image 'elements simultaneously. Detailed information about the SIMD systems is available in [11,64,66,136,144]. Examples of SIMD machines that have been actually implemented are Illiac IV [25], STARAN [15] and MPP [16,17]. Two common configurations of SIMD machines are processing olement-to-processing element organization and processor-to-memory organization as shown in Figs.2.1 and 2.2 respectively.

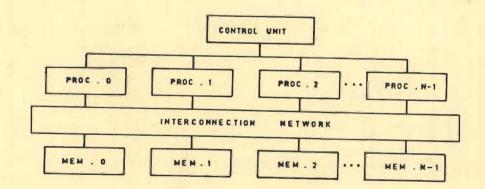

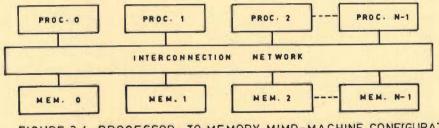

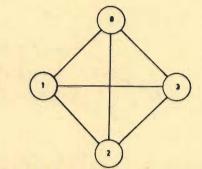

The MIMD Mode of parallelism differs from the SIMD mode in that the processors in an MIMD system operate asynchronously with respect to each other, unlike the lock - step synchronous operation of all the active processors in an SIMD machine. Typically, an MIMD machine consists of N processors, N memory modules, and an interconnection network. Each of the N processors follows its own program. Thus there are multiple instruction streams. Each processor fetches its own data on which to operate, resulting in multiple data streams, as in the SIMD systems. The interconnection network provides communication among the processors and memory modules. In an MIMD system, because each processor executes its own program, inputs to the network arrive independently, i.e., asynchronously. Examples of MIMD systems that have been implemented are Cm\* [69,138] and C.mmp [157]. MIMD machines can be organized in the processing element-toprocessing element configuration, or in the processor-to-memory configuration as depicted in Figs. 2.3 and 2.4. When using the

FIGURE 2.1 PROCESSING ELEMENT-TO-PROCESSING ELEMENT SIMD-MACHINE CONFIGURATION WITH N PROCESSING ELEMENTS (PEs)

FIGURE 2.2 PROCESSOR -TO-MEMORY SIMD-MACHINE CONFIGURATION WITH N PROCESSORS AND N MEMORIES

FIGURE 2.3 PROCESSING ELEMENT-TO- PROCESSING ELEMENT MIMD-MACHINE CONFIGURATION WITH N PROCESSING ELEMENTS

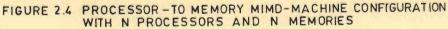

FIGURE 2.5 A SINGLE SHARED BUS PROVIDING COMMUNICATIONS FOR N DEVICES

.

processor-to-memory configuration, a cache may sometimes be associated with each processor, for example, as in an ultracomputer [61]. More information about MIMD systems and their use is available in [11,67,136].

Multiprocessor systems, incorporating a large number of processors, is a topic of continuous research and development [38,67,107]. Many distinct approaches have been persued to organize the large number of processors to achieve high performance. For example, a Massively Parallel Processor (MPP) [16, 17], consists of 2<sup>14</sup> processing elements. A major problem in designing large-scale parallel/distributed systems is the construction of an interconnection network to provide interprocessor communication, and in some cases memory access for the processors. This has been discussed hereunder in detail.

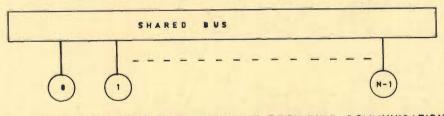

## 2.2 INTERCONNECTION NETWORKS

The interconnection scheme of processing or memory modules must provide fast and flexible communication between modules at a reasonable cost. A single shared bus, as shown in Fig.2.5, is not sufficient, because it is often desirable to allow all processors to send data to other processors simultaneously. Ideally, each processor should be linked directly to every other processor via dedicated paths so that the system is completely connected as shown in Fig.2.6. Unfortunately, these configurations are highly impractical when N is large. An alternative interconnection scheme that allows all processors to communicate simultaneously is the crossbar network shown in Fig.2.7. A normal crossbar can be defined as a switching network

.

FIGURE 2.6 A COMPLETELY CONNECTED SYSTEM FOR N=4

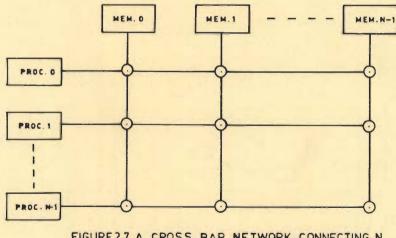

FIGURE 2.7 A CROSS BAR NETWORK CONNECTING N PROCESSORS TO N MEMORIES

.

that allows the arbitrary one to one interconnection of N inputs to N outputs without contention. A generalized crossbar also allows some input to be connected to more than one outputs (broadcasting). However, the complexity and cost of such networks increases as the square of network size N. To solve the problem of providing fast and efficient communication at reasonable cost, many different networks between the two extremes of single bus and completely connected scheme have been proposed and are reviewed in numerous survey articles and books such as [9,10,28,45,49,64,67,74,75,87,121,123,143,144,155].

These are broadly classified as static and dynamic networks which are further discussed in Section 2.2.3. Various attributes of any interconnection network are:

- (i) Switching methodology

- (ii) Interconnection functions

- (iii) Interconnection topologies

- (iv) Connecting capabilities

- (v) Control strategy

- (vi) Reliability

These aspects of interconnection networks are described briefly hereunder.

# 2.2.1 Switching Methodology

The two major switching methodologies are circuit switching and packet switching. In circuit switching, a path is physically established between a source and a destination. In packet switching, data is put in a packet and routed through the interconnection network without establishing a physical connection path. In general, circuit switching is more suitable for bulk data transmission and packet switching is more efficient for short data messages.

Another option, integrated switching, includes the capabilities of both circuit switching and packet switching. Most SIMD interconnection networks assume circuit switching operations, whereas packet switched networks have been suggested mainly for MIMD machines [87,121,123,125].

# 2.2.2 Interconnection Functions

From analytical point of view, an ICN may be viewed as a set of interconnection functions. Each interconnection function is a bijection on the set of input/output (source/destination) addresses, integers from O to N-1. A bijection is a one-to-one and onto mapping. One-to-one means that a processing element receives data from exactly one PE when interconnection function is executed. Mathematically, one-to-one implies that an integer in the set of source/destination addresses is mapped to by exactly one integer in the set when an interconnection function is applied. Onto means that every PE receives data from some other PE when an interconnection function is executed. Mathematically, onto implies that every integer in the set of PE addresses is mapped to by some integer in the set when an interconnection function is applied. In the case of interconnection networks bijection is also termed as 'permutation', i.e., from a set onto the same set [122].

Let an ordered list of elements be

0,1,2,....,(N-1)

then an interconnection function f permutes this list into

$f(0), f(1), \dots, f(N-1).$

Thus the execution of data exchange function makes a PE i to copy the contents of its Data Transfer Register (DTR) into the DTR of PE f(i) for all values of i. Mathematically,

> Let i ----> address of a processor connected as source to an ICN

then the data exchange function will result in

<pe i> ---> < pe j>

01.1

Several interconnection functions have been defined and used for implementation of ICNs [64]. However, broadly speaking most of the proposed or existing networks incorporate one of the four types of connection functions as described below:

(i) Shuffle-Exchange

The shuffle-exchange network consists of a shuffle function 'S' and an exchange function 'E' defined as  $S(b_{m-1}b_{m-2}\cdots b_{1}\cdots b_{1}b_{0}) = b_{m-2}b_{m-3}\cdots b_{1}\cdots b_{1}b_{0}b_{m-1} \cdots (2.1)$ and

$E(b_{m-1}b_{m-2}\cdots b_{1}\cdots b_{1}b_{0}) = b_{m-1}b_{m-2}\cdots b_{1}\cdots b_{1}b_{0} \qquad \dots (2.2)$ where each  $b_{1}$  is a binary bit and  $(b_{m-1}b_{m-2}\cdots b_{1}\cdots b_{1}b_{0})$  is the binary address of a functional unit. Thus, both shuffle and exchange functions manipulate a binary string which is actually an address of source or destination in binary format. Features of shuffle exchange networks are discussed in [29,30,53,93, 95,108,121,122,153].

(ii) Cube

The cube network consists of m interconnection functions defined by

$Cube_{i}(b_{m-1}b_{m-2} \cdot b_{i} \cdot b_{1}b_{0}) = b_{m-1}b_{m-2} \cdot b_{i} \cdot b_{1}b_{0} \dots (2.3)$ <br/>for  $0 \le i \le (m-1)$

The cube network forms the underlying structure of many multistage networks such as Banyan [60], STARAN Flip [15,18], Benes [21], Indirect Binary m-cube [106], Generalized Cube [125] and Extra State Cube [3]. Various properties of cube network are discussed in [53,93,94,95, 121,122,148].

The networks based on the cube and shuffle-exchange functions have been proposed for use in the systems such as PASM [124], PUMPS [27], Ultra Computer [61] and Data-Flow Machines [42].

(iii) Illiac

The Illiac network consists of four interconnection functions defined as follows:

> Illiac<sub>+1</sub>(B) = B+1 modulo N Illiac<sub>-1</sub>(B) = B-1 modulo N

Illiac<sub>+n</sub>(B) = B+n modulo N Illiac<sub>-n</sub>(B) = B-n modulo N where  $n = \sqrt{N}$  is accurate

where  $n = \sqrt{N}$  is assumed to be an integer.

This type of network is included in the MPP [16,17] and DAP [65] SIMD systems. It is similar to the eight nearest-neighbour network used in CLIP4 [56] and BASE8 [112] machines. Various properties and capabilities of illiac network are discussed in [25,97,121, 122].

(iv) PM2I

The plus-minus 2<sup>i</sup>(PM2I) network consists of 2m interconnection functions defined by

$PM2_{i}(B) = B+2^{i} \mod N$ for  $0 \le i \le (m-1)$  $PM2_{i}(B) = B-2^{i} \mod N$

The PM2I connection pattern forms the basis for the Data Manipulator [48], ADM [124] and Gamma [103] multistage networks. Various properties of PM2I network are discussed in [53,108,121,122,130].

In the above discussion of interconnection functions, the following notations have been used:  $N = 2^m$ ; the binary representation of an arbitrary PE address  $B = b_{m-1}b_{m-2}\cdots b_1b_0$ and  $\overline{b}_i$  is the complement of  $b_i$  where  $b_i'$  is binary bit and 'm' is any positive integer.

# 2.2.3 Interconnection Network Topologies

An interconnection network can be depicted by a graph in which nodes represent switching points and edges represent communication links. The overall graph representation is called network topology. Many topologies have been proposed or used for ICNs. They tend to exhibit some regular pattern and can be grouped into two broad categories (i) static and (ii) dynamic. In the static topology, each switching point is connected to a processor, while in the dynamic case only the switching points in the input/output sides are connected to processors [9].

Several static structures with regular topology have been proposed which include Ring [85], Tree [63], Near-Neighbour Mesh [12], Systolic arrays [78], Pyramids [140] and Hyper cubes [24,114]. A comparative study of these static networks can be found in [49,151]. In these networks each processor can communicate only with a small number of processors directly and communication with others involves the transfer of information through one or more intermediate processors.

Dynamic networks allow different connections to be set up between processing elements by changing their internal states. There are three topological classes in the dynamic catagory single stage, multistage and crossbar.

# (i) Single Stage

A single stage network is composed of a stage of switching elements cascaded to a link connection pattern. The single stage network is also called a recirculating network because the data item may have to recirculate through the single stage several times before reaching their final destination. The recirculating shuffle exchange network is an example of a single stage network [135]. Single stage networks are discussed in [121].

(ii) Multistage

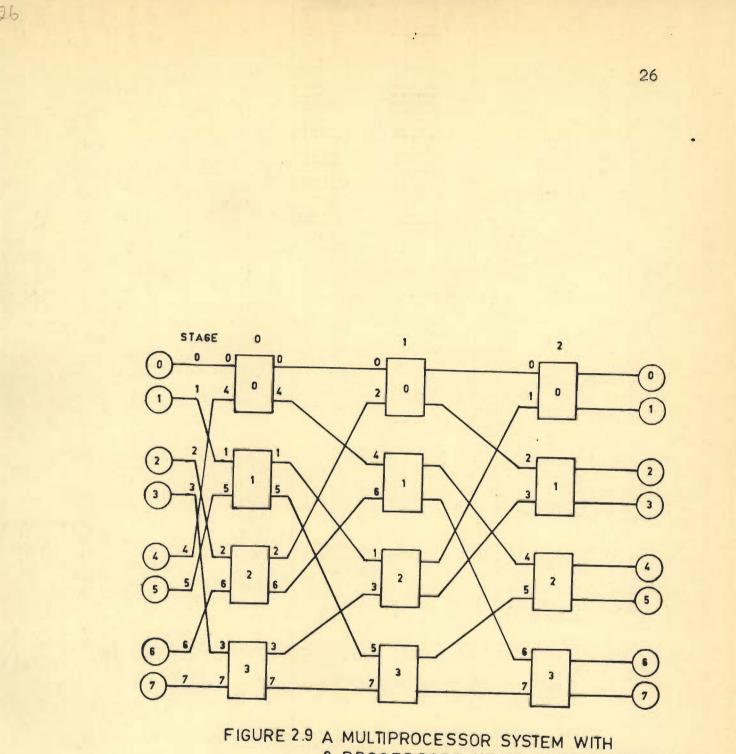

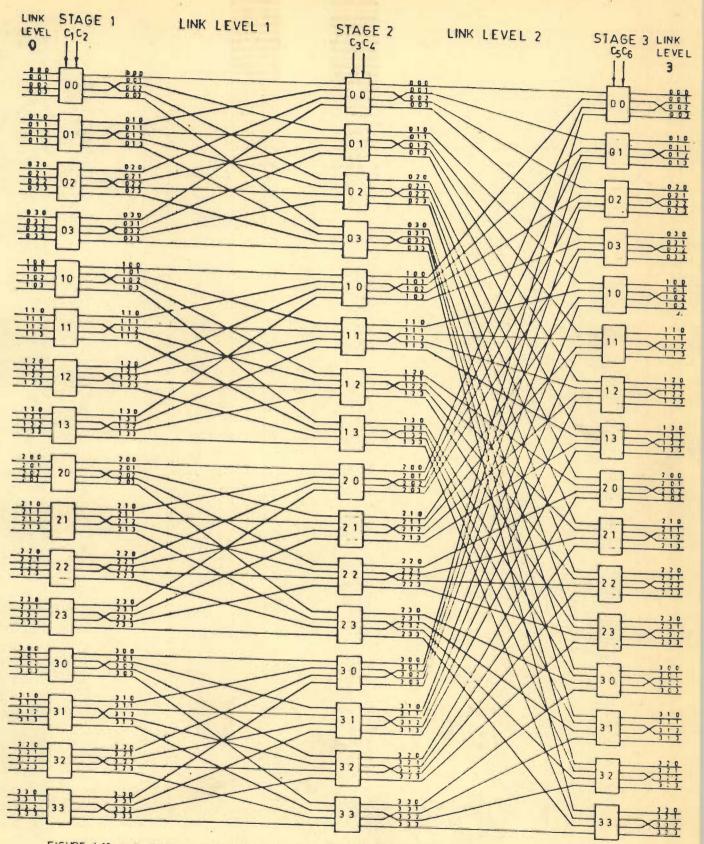

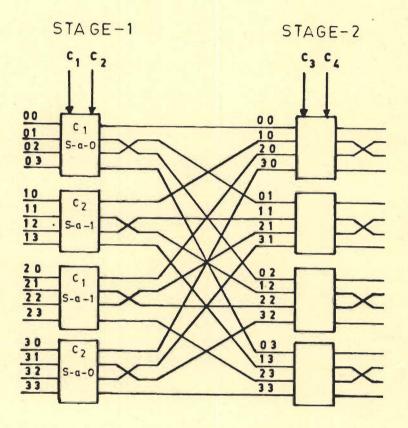

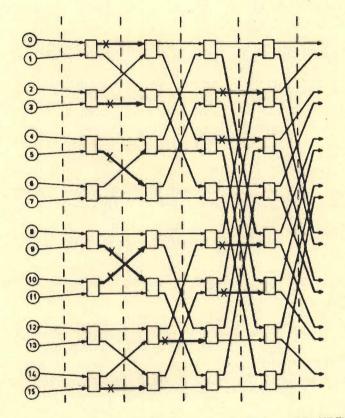

A multistage network consists of more than one stage of switching elements and is usually capable of connecting an arbitrary input terminal to an arbitrary output terminal. Several multistage networks, with  $N = 2^{m}$  inputs/outputs and  $log_{2}N$  stages of 2x2 SEs, (Fig. 2.8), have been studied in the literature [28,51, 155]. These include the Base line [152], Omega [79], Banyan [60] and Binary m-Cube [106] networks. In these networks each stage uses N/2 SEs and is connected to the next stage by atleast N paths. The network delay is proportional to the number of stages in a network. Fig. 2.9 shows a multiprocessor system with 8 processors interconnected through an omega network. There is another class of multistage networks which does not use 2x2 SEs. These networks are called redundant-path interconnection networks or data manipulator networks. Examples are the Data Manipulator [48], Augmented Data Manipulator or ADM [88,89], the Inverse Augmented Data Manipulator or IADM [124] and the Gamma network [103, 110]. A new cell based interconnection network, [156], has been introduced as a general sorting network. The proposed cell is 4x4 switch based on the concept of

.

...

8 PROCESSORS USING OMEGA NETWORK

completely interconnected set. Multistage networks differ in the interconnection pattern between stages, the type and operation of individual SEs, and the control scheme for setting up the SEs. The topological equivalance for several of these networks has been established in [5,102,152].

(iii) Crossbar

This has already been discussed in Section 2.2 and is not suitable for use in parallel processing systems because of its high cost.

2.2.4 Connecting Capability of Multistage ICNs

From connecting capability point of view multistage networks can be divided into three broad categories - blocking, rearrangeable and nonblocking [21]. In blocking networks, simultaneous connections of more than one terminal pair may result in conflicts in the use of network communication links. Examples of a blocking network are the Data Manipulator, Omega, Binary m cube, Baseline, SW Banyan and Delta networks. A network is called a rearrangeable network if it can perform all possible connections between inputs and outputs by rearranging its existing connections so that a connection path for a new input-output pair can always be established. A well defined Benes network belongs to this class [21]. The Benes rearrangeable network topology has been extensively studied for use in synchronous data permutation [68,83,96,149], and asynchronous interprocessor communication [33,48]. A network which can handle all possible connections without blocking is called nonblocking network. Two cases have been considered in the literature. In the first case, the Clos network, a one to one connection is made between an input and an output [36]. The other case considers one-tomany connections [142]. Here, a general connection network topology is generated to pass any of the multiple mappings of inputs onto outputs. The crossbar-switch network can connect every input to a free output without blocking.

A class of connecting networks having less connecting capability than the rearrangeable networks are the full access networks [117]. A network has full access property if each of the inputs can be connected to any one of the outputs. Pease's indirect binary m-cube [106] and Lawrie's Omega network [79] are examples of full access network which are neither rearrangeable nor non-blocking. The 8x8 Omega network is illustrated in Fig. 2.9. As can be observed there exists a unique route from each input to each output. An example of the network without the full access property can be obtained by deleting the third stage of switching elements in Fig. 2.9. A nonblocking network is also rearrangeable, and a rearrangeable network also possesses the full access property. A key issue in the design of connecting networks is the tradeoff between connecting capability and cost, which may be measured by the number of cross points (SEs) and links used and the complexity of the control algorithm software. Greater connecting capability normally implies higher cost. Large non blocking networks are rarely used because of their high cost. Rearrangeability is a very desirable property for telephone switching networks. However, because of the

complexity of their control algorithms, rearrangeable networks become undesirable for interconnected computers which utilize inter unit communication only.

#### 2.2.5 Control Strategy

A typical interconnection network consists of a number of switching elements and interconnecting links. Interconnection functions are realised by properly setting the control of the switching elements. The control structure of a network determines how the states of the switch boxes will be set. Two distinct types of control structures have emerged. These are (i) centralized control or flip control and (ii) individual box control or distributed control. In addition sometimes partial stage control or shift control is also used. Most existing SIMD interconnection networks use the centralized control on all the switching elements. A routing tag scheme is generally used for controlling the multistage networks. The use of tags allows network control to be distributed among the processors. The routing tags for one-to-one data transfers consists of m bits. If broadcast capabilities are also to be included then 2m bits are used where m gives the number of stages used in the network. Details about the control schemes can be found in [48,66,79,83,88,89,90].

# 2.2.6 Fault-Diagnosis and Fault-Tolerance

In parallel processing systems, reliable operation of interconnection networks is an important issue. It is desirable that the ICN should be fault-tolerant. However, in order to achieve fault-tolerance, fault detection and location must be done before the fault-tolerance scheme could be applied. Hence the reliability issue is divided into two parts - fault-diagnosis and fault-tolerance.

#### (i) Fault-Diagnosis

Fault diagnosis is concerned with detection and location of faults in interconnection networks. The fault-diagnosis problem has been studied for a class of multistage interconnection networks consisting of switching elements with two valid states [51]. The problem is approached by generating suitable fault-detection and fault-location test sets for every fault in the assumed fault model. Usually single stuck-at fault model is These test sets are then trimmed to a minimal assumed. or near minimal sets. It is important to note that to conduct the fault-diagnosis, a fault model must be obtained so that one knows what faults need to be identified and located. A fault model has been introduced, for multistage full-access network constructed from 2x2 SEs [51]. Here a simple and straight forward methodology is developed which requires only four test-sequences for single fault diagnosis, independent of network size. Many variations of this method have been studied, which include, optimization of test sequences [50,141], multiple faultdetection [86], on line diagnosis [4,58,131], fault diagnosis of multistage Banyan interconnection network [72], and distributed control interconnection network [40]. The technique has also been extended for fault analysis of FFT processors [70].

#### (ii) Fault-Tolerance

In full access multistage networks a unique path exists from any input terminal of the network to any output terminal. The presence of single failure among the SEs or the connecting links of these networks destroys the full access property. Even though the failure rates of individual components in the network are very small, the failure rate of the entire network can be quite high in systems of large size. Therefore, fault-tolerance is a necessary attribute for the continued operation of such systems. To improve upon the reliability, several interconnection networks with redundant paths between source and destination terminals, have been proposed [3,89,90,98,103,109,111,116]. Techniques for introducing fault-tolerance include augmenting the network with extra stages, increasing the size of the switching elements, and adding redundant switching elements and links. Fault-tolerance of some of these networks is limited to one-to-one connections while some networks allow permutations of data to be performed under failures. Networks capable of fault-tolerant routing of permutations include the Merged Delta Networks, Augmented C-network [111], INDRA Network [109], and Generalized INDRA network [110].

A common technique for improving the reliability and fault-tolerance of a unique path multistage interconnection network is the addition of extra switching stages. The addition of an extra switching stage in a multistage network consisting of log<sub>2</sub>N stages of 2x2 SEs, introduces an extra path for routing every input-output connection through the network. The extrastage networks provide fault-tolerance at a modest overhead. Examples include the Extra-Stage Cube network [3], Banyan networks with redundant stages [31] and Extra-Stage-Delta network [116].

An alternate approach to fault tolerance is obtained by means of redundancy in time. Thus, data may be routed in a unique-path network in the presence of faults by performing multiple passes through the network. The network is said to possess DFA capability if every processor in the system can communicate with other processor in a finite number of passes through the network, routing the data through intermediate PE's if necessary [117]. Even though the failure of a single component destroys the full-access capability, a large number of faults do not destroy the DFA capability. The general techniques for checking the DFA property of a faulty network consisting of 2x2 switching elements, with respect to a fault model, that allows only the switching elements to be stuck in one of their valid states, have been discussed in [118]. A more general fault model employing adjacency and reachability matrices of the connectivity graph of the faulty network for testing the DFA property has been used in [8]. The DFA has also been used for performance analysis of  $\beta$ -networks [119].

# 2.3 ADDITIONAL MODES OF PARALLEL ARCHITECTURE

In addition to providing communication paths in SIMD and MIMD environments, interconnection networks play an important role in other modes of parallel architecture also. These classes

of architecture include multiple-SIMD and partitionable SIMD/MIMD as defined below.

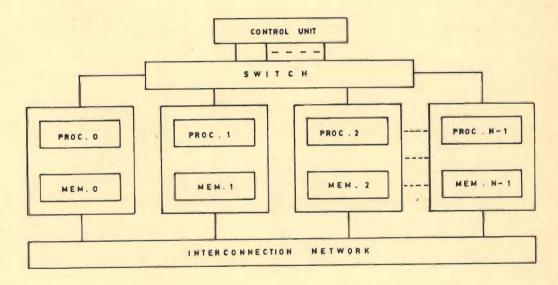

#### 2.3.1 Multiple-SIMD System

It is a parallel processing system that can be dynamically reconfigured to operate as one or more independent virtual SIMD machines of various sizes. A multiple-SIMD system consists of N processors, N memory modules, an interconnection network, and Q control units, where Q<N. The processors, memories, and interconnection network can be organized in different ways, as in SIMD machines. A general model of a multiple-SIMD machine, based on processing element-to-processing element structure, is shown in Fig.2.10. Each of the multiple control units can be connected to some subset of PEs. If PE i and PE j are assigned to different control units, they are no longer following the same instruction stream and will act independently. By assigning PEs to different control units, independent virtual SIMD machines of various sizes can be created [122].

If the virtual SIMD machines, that can be formed in a multiple-SIMD system, are to be independent the network these share must be partitionable into independent subnetworks. The partitioning of a network into independent subnetworks to suit the requirements of multiple-SIMD system, has been proposed in [122].

#### 2.3.2 Partitionable SIMD/MIMD System

A partitionable SIMD/MIMD machine is a parallel processing system that can be dynamically reconfigured to operate as one or more independent virtual SIMD and/or MIMD machines of various

#### FIGURE 2. 10 GENERAL MODEL OF A MULTIPLE-SIMD SYSTEM

.

sizes. A partitionable SIMD/MIMD machine has the same components as a multiple-SIMD machine except that each processor can follow its own instructions (MIMD operation) in addition to being capable of accepting an instruction stream from a control unit (SIMD operation). The system can be partitioned to form independent virtual machines. In this case, each virtual machine can be a SIMD machine or a MIMD machine.

The examples of multiple-SIMD and partitionable SIMD/MIMD systems are PASM [124], PM4 [26], TRAC [77,115].

#### 2.4 CONCLUSION

In this chapter the interconnection networks have been classified from various angles. Their characteristics and desired properties have been discussed in Section 2.2 whereas the applications of the interconnection networks in parallel systems have been outlined in Sections 2.1 and 2.3. Most of the work on multistage interconnection networks is limited to employing the stages of 2x2 SEs interconnected through perfect shuffle connection pattern. The natural lower bound on the number of stages for NxN MIN is ([log\_N]). Accordingly, the computational speed, complexity and cost of the network becomes proportional to ( $\lceil \log_2 N \rceil$ ). In most of the recent studies of MINs the main emphasis is on finding their equivalence and non-equivalence, comparing permutational capabilities or improving the reliability either through hardware redundancy or by decreasing the computational speed [5,6,8,72,98,100,104, 109,110,111,116,120,152]. No effort has been directed towards decreasing the number of stages thereby decreasing the computational complexity, speed and cost. In the research work undertaken, an effort has been made in this direction and a new approach has been proposed for designing an efficient and costeffective multistage network [126]. The thesis starts with defining a 4-shuffle pattern, as an improved and better alternative to perfect-shuffle pattern for parallel processing (Chapter III). A 4x4 switch instead of 2x2 conventional switching element alongwith 4-shuffle has been used in designing the multistage interconnection network. The results obtained are derived and discussed in Chapter IV. The suitability of the proposed MIN for implementation in the practical parallel systems has been examined from various angles in Chapters V, VI and VII.

#### CHAPTER III

#### 4-SHUFFLE INTERCONNECTION PATTERN IN PARALLEL PROCESSING

It has been discussed in Chapter I that an ICN plays a pivotal role in parallel processing architectures. A general review of the MINs, reveals that these employ stages of 2x2 SEs which are usually interconnected through some form of perfect shuffle pattern. Accordingly, the lower bound on the computational speed and complexity of the problems requiring concurrent processing is proportional to  $(\lceil \log_2 N \rceil)$ . In this chapter an alternative 4-shuffle pattern has been examined for use in parallel processing to interconnect the stages of MINs. 4-shuffle has been defined from different angles and an analytical model based upon cube configuration has been developed. The potential for 4-shuffle has been demonstrated by considering examples, and its general applicability for MINs has been considered at length in succeeding chapters. Specific applications considered in this chapter are the evaluation of Fast Fourier Transform, Polynomial Evaluation and Matrix Transposition. These examples exhibit inherent parallelism property. In the development of analytical model for the 4-shuffle pattern quaternary number system has been employed. This number system will also be used for the description of MINs in subsequent chapters. Therefore, before undertaking the description of 4-shuffle it is appropriate to study the quaternary number system briefly.

Let i be an integer (element) in the vector V of length  $N = 4^n$ , where n is any positive integer, and

$$Q = \{0, 1, 2, 3\}$$

then q<sub>j</sub> represents any quaternary digit such that

$$q_j \in Q$$

with  $\neq q_j = 1$

Now i can be written as

$$i = q_{n-1} 4^{n-1} + q_{n-2} 4^{n-2} + \dots + q_j 4^j + \dots + q_0, \quad 0 \le j \le (n-1)$$

...(3.1)

further, let  $q_j^k \in Q$ ,  $\forall O \leq k \leq 3$ , such that  $\# q_j^k = 1$  and

$$\begin{array}{l}

q_{j} = \{0\} \\

q_{j}^{1} = \{1\} \\

q_{j}^{2} = \{2\} \\

q_{j}^{3} = \{3\}

\end{array}$$

again, if  $q_j^{k'} \in Q$ , such that  $\not = 3, \forall 0 \leq k' \leq 3$ , i.e.,  $q_j^{k'} = Q \setminus q_j^{k}$ , giving

$$q_{j}^{O'} = \{1, 2, 3\}$$

$$q_{j}^{1'} = \{0, 2, 3\}$$

$$q_{j}^{2'} = \{0, 1, 3\}$$

$$q_{j}^{3'} = \{0, 1, 2\}$$

Then  $q_j^{k'}$  is relative complement of  $q_j^k$  with respect to  $\mathbf{Q}$ .

In this thesis,  $\bar{q}_j$  is designated as the relative complement of  $q_j$  which can be assigned three quaternary digits other than the one assigned to  $q_j$ . For example if  $q_j = 1$ , then its relative complement  $\bar{q}_j$  will be assigned values  $\{0,2,3\}$ .

The relationship derived above has been used in this and subsequent chapters.

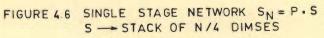

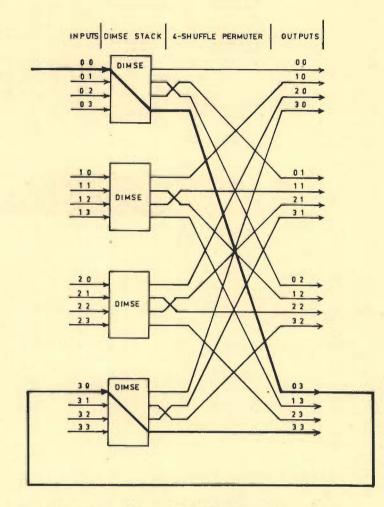

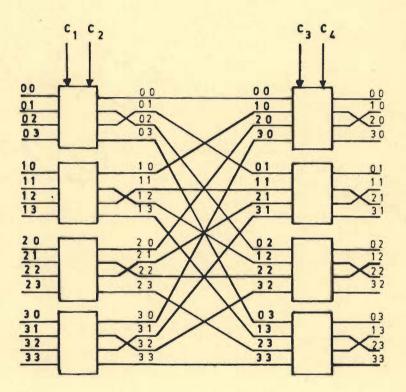

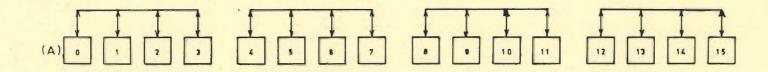

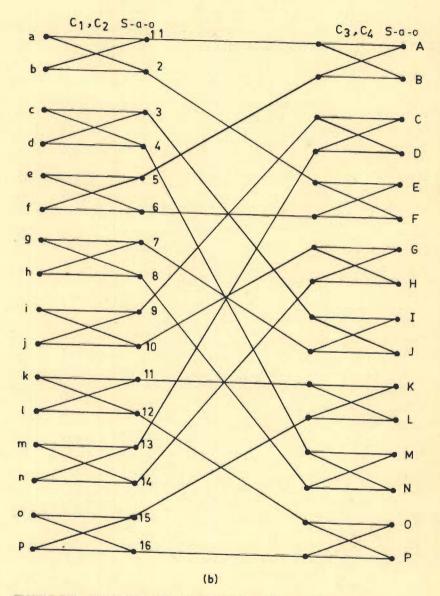

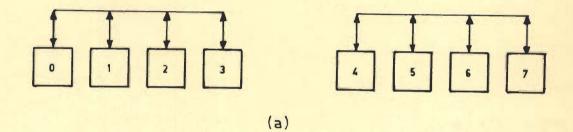

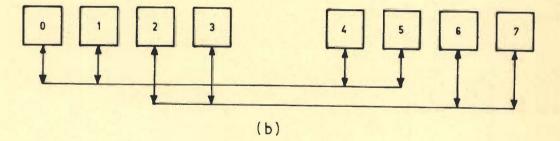

#### 3.2 DEFINITION OF 4-SHUFFLE

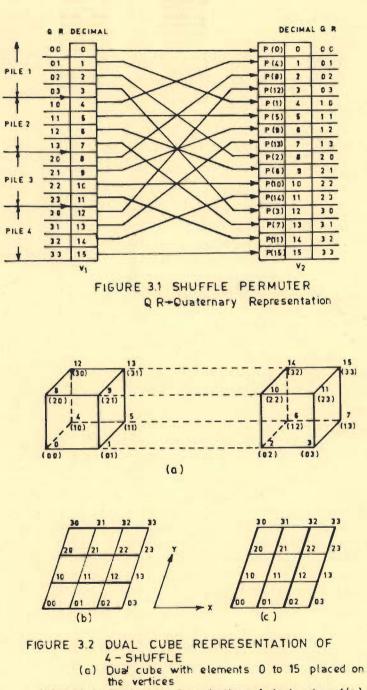

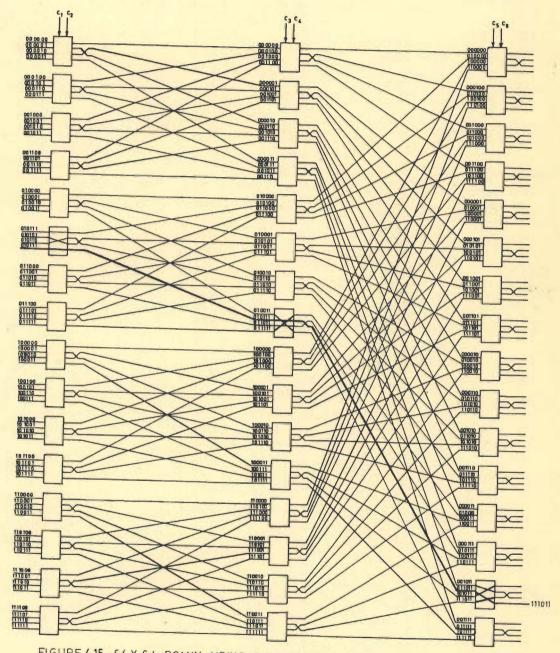

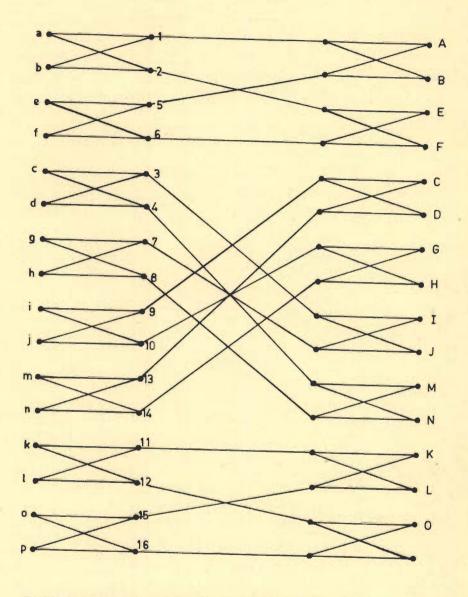

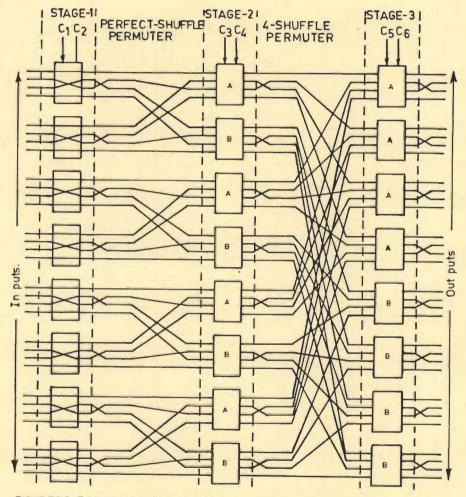

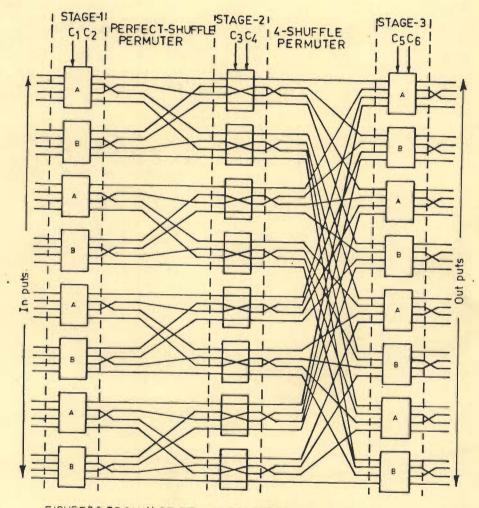

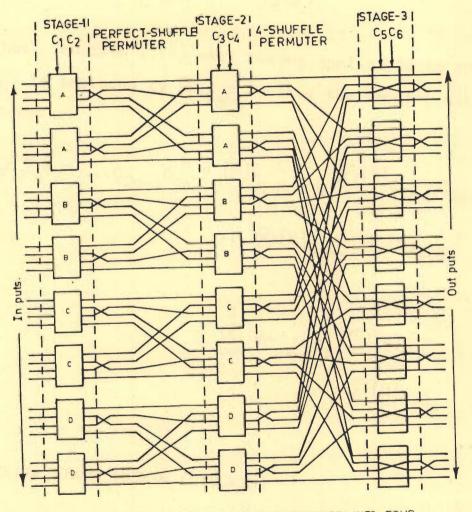

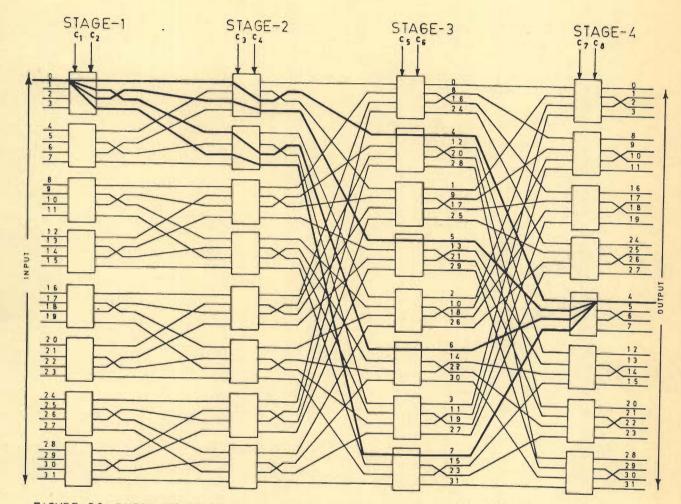

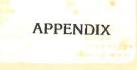

Let  $V_1$  be a vector of length N, where N is any positive integer. A 4-shuffle of N elements of the vector is obtained in two phases: (i) In the first phase, divide the N elements of the vector  $V_1$  into 4 piles of elements each, such that top pile consists of first N/4 elements, the next pile consists of subsequent N/4 elements and so on. (ii) In second phase pick the i<sup>th</sup> element from the i<sup>th</sup> pile to constitute a new pile of N/4 elements. In this way, 4 new piles with different elements will be created. This new order of the elements represents the 4-shuffle permutation of the previous order of the vector V [104]. Fig.3.1 illustrates such a shuffle for N = 16.

Mathematically, the indices of a vector  $V_1$ , can be transformed to another vector  $V_2$  with a new order through a permutation P such that

$$P(i) = 4i \mod (N-1) \qquad O \le i \le (N-1) \\ P(i) = i \qquad i = (N-1) \qquad ...(3.2)$$

The above equation gives the analytical interpretation of 4-shuffle permutation. 4-shuffle can also be seen from

(b)and (c) Back-spread projection of dual cube of (a)-Elements which differ in single digit position are on the same line •

another angle by representing the indices of the elements of the vector in quaternary number system.

Any element 'i' of the vector  $V_1$  of length N, N = 4<sup>n</sup> for some positive integer n, can be represented by Equation (3.1) as reproduced below

$i = q_{n-1}4^{n-1} + q_{n-2}4^{n-2} + \dots + q_j4^j + \dots + q_0 \dots (3.1)$

The 4-shuffle of i can be represented as

$P(i) = q_{n-2} q^{n-1} + q_{n-3} q^{n-2} + \dots + q_j q^{j+1} + \dots + q_0 q^{j+1} + q_{n-1}$ ...(3.3)

Where each q<sub>j</sub> in (3.3) has been obtained by cyclically rotating the digits in the quaternary representation of 'i' one digit to the left.

Theorem 3.1

4-shuffle permutation represented by Equation (3.1) and (3.3) together is identical to Equation (3.2).

Proof

Equation (3.2) can be expanded as

$$P(i) = 4i \qquad 0 \le i \le (\frac{N}{4} - 1)$$

= 4i + 1 - N  $\frac{N}{4} \le i \le (\frac{N}{2} - 1)$

= 4i + 2 - 2N  $\frac{N}{2} \le i \le (\frac{3N}{4} - 1)$

= 4i + 3 - 3N  $\frac{3N}{4} \le i \le (N-1)$  ...(3.4)

In Equations (3.1) and (3.3) q<sub>j</sub> being a quaternary digit, can have any value O, 1, 2 or 3. Now one can calculate the value of P(i) in (3.3) in terms of 'i' of (3.2) for four possible values of  $q_{n-1}$ .

giving P(i) =

$$4i + 3 - 3.4^n = 4i + 3 - 3_N$$

..(3.5d)

Equations (3.5a-d) put together are equivalent to Equation (3.4).

Theorem 3.2

All elements of a vector V of length  $N = 4^n$  will be shuffled to their original starting positions simultaneously, after performing 4-shuffle n times on the elements of the vector.

#### Proof

From Equations (3.2) and (3.3) it is observed that an element 'i' has n digits in its quaternary representation. Applying the cyclic shift rule on the digits of i, each time a 4-shuffle permutation is performed one digit will be shifted to the left in circular fashion. It becomes obvious that the digits will return to their original position after performing n permutations. Hence the proof.

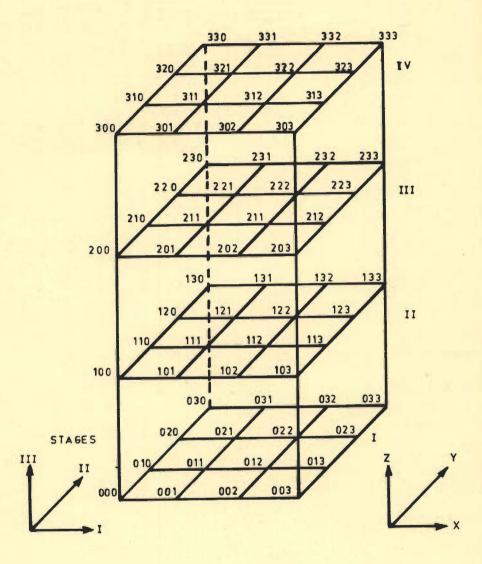

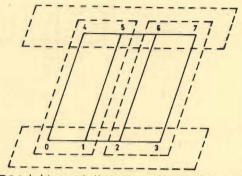

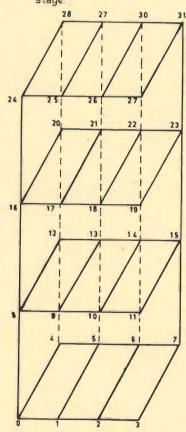

# 3.3 CUBE REPRESENTATION OF 4-SHUFFLE PERMUTATION

In this section mathematical basis and properties of 4-shuffle have been developed and postulated. These have been achieved by extending the cube model [135] and orienting it to incorporate the 4-shuffle permutation.

For this purpose a DUAL CUBE (Dcube) consisting of two cubes, as shown in Fig.3.2(a), has been proposed as the basic building block. There are 16 vertices in the dual cube which are labelled as per the following rules:

Rule 1:

Each vertex within each cube is 1-Hamming distance apart from every adjacent vertex.

Rule 2:

The corresponding elements of the two cubes are 1-Hamming distance apart.

Considering a vector  $V_1$  of length 16, the decimal equivalent of the elements of the vector and their quaternary representations are shown in Fig.3.2(a). Quaternary representation is simply obtained by considering base-4 number system. Using back-spread method of representing the cubes, the proposed dual cube can be projected as shown in Fig.3.2(b). The backspread dual cube has the following properties:

Property 1:

Each vertex has a two digit quaternary coordinate assigned to it. Traversal along any one dimension of the backspread representation will cause sequential variation of only one of the two digits while the other one will remain constant, i.e., horizontal (perpendicular) traversal will cause the second (first) coordinate to vary sequentially.

Property 2:

Each vertex in the backspread dual cube has 4 nearest neighbours, which are 1-quaternary distance apart from it.

Let 4 elements of a vector whose indices differ in their quaternary representation by one digit be put together to form a set of elements. Then the sets of elements varying in different positional digits will match on different coordinates of an n-dimensional backspread dual cube.

Theorem 3.3

If the sets of elements of a vector  $V_1$ , which differ in first digit of their quaternary representation, are matched in one dimension of the backspread dual cube, then the 4-shuffle will rotate these elements in the second dimension, matching the sets of elements, which differ in 2nd digit.

#### Proof

The sets of elements of vector  $V_1$  differing in first digit position are matched on X-coordinate lines in Fig.3.2(b) (shown with dark lines). To obtain 4-shuffle of these elements, quaternary addresses are cyclically rotated one digit position to the left. The new addresses so obtained, are the sets of elements which are matched on Y-coordinate lines in Fig.3.2(c) (shown with dark lines). This can also be verified from Fig.3.1 where vector  $V_2$  is the 4-shuffle of vector  $V_1$ .

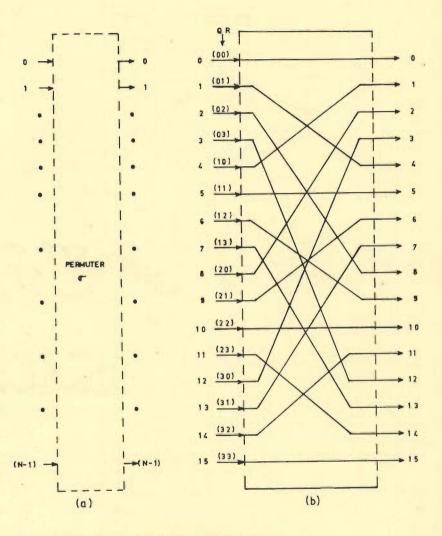

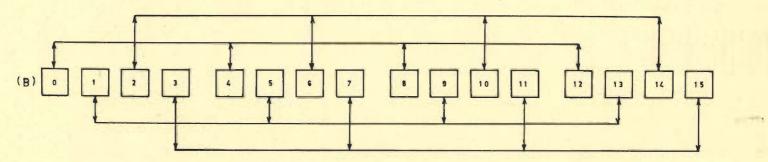

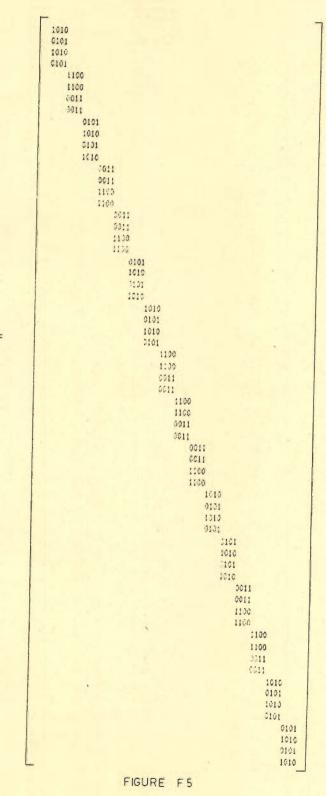

## 3.4 4-SHUFFLE PERMUTER (P)

The interconnection topology of N links in a network can be conveniently described by the permutation of its terminals. An NxN permuter ' $\sigma$ ' is defined as a network consisting of N fixed links connecting two sets of N terminals [117]. The connections realized by the permuter  $\sigma$  can be represented by a permutation of N elements.

Thus

$$\sigma = \begin{pmatrix} E_{0} & E_{1} \cdots & E_{i} \cdots & E_{N-1} \\ \sigma(E_{0}) & \sigma(E_{1}) \cdots & \sigma(E_{i}) \cdots & \sigma(E_{N-1}) \end{pmatrix}$$

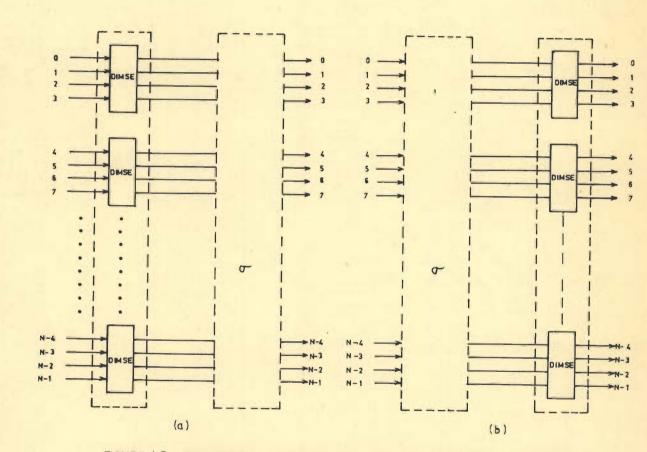

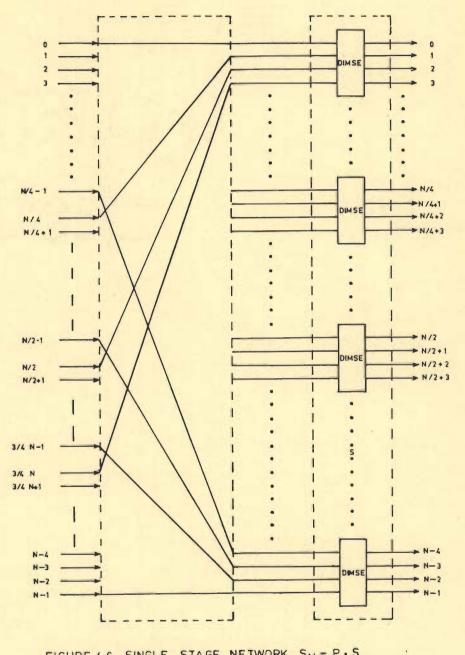

Where  $E_i$  is connected to  $\sigma(E_i)$  for i = 0, 1, 2, ..., N-1. Fig.3.3(a) depicts a general NxN permuter. In the specific case when the connections are realized using 4-shuffle permutation, the permuter is denoted as P. An example of permuter P for N = 16 is depicted in Fig.3.3(b). For the 4-shuffle Permuter P,  $\sigma$  implies left

FIGURE 3.3 (a) A general NXN permuter or (b) The 16X16 4-shuffle permuter P

cyclic shift of quaternary digits.

An NxN permuter can be considered to be a passive NxN network and can be used as a subnetwork in the construction of MINs. The concept of permuters developed here has been extensively used in Chapter IV in developing single stage and multiple stage dual cube networks.

# 3.5 APPLICATIONS OF 4-SHUFFLE PERMUTATION IN PARALLEL PROCESSING

4-shuffle has direct application in the evaluation of various mathematical problems with built in parallelism. In this section the use of 4-shuffle as an alternative to perfect shuffle in three specific problems is demonstrated. It is also shown that the computational complexity, which is proportional to  $\log_2 N$  with perfect shuffle, reduces to be proportional to  $\log_4 N$  with 4-shuffle.

3.5.1 The Fast Fourier Transform (FFT)

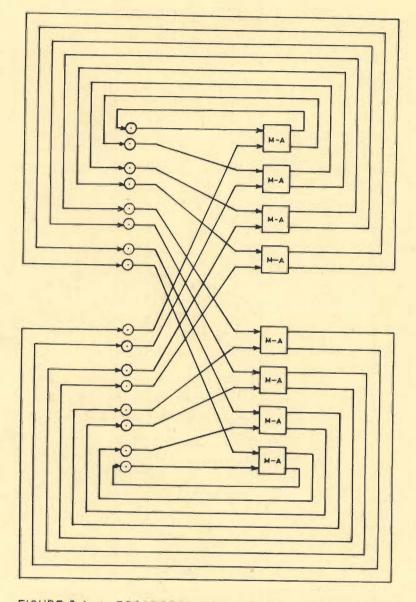

One of the computational problems which has inherent parallelism is the evaluation of FFT [37,105]. The use of perfect shuffle interconnection pattern for executing the transform algorithm on parallel processor has been demonstrated in [135]. For N samples of a time function where  $N = 2^{m}$ , m being any positive integer, the processing repeats the sequence of the following steps 'm' times to compute the fast Fourier transform [135].

(i) Perfect Shuffling

(ii) Multiply - Add

# (iii) Transfer the results back to the input of shuffle network.

This is demonstrated in Fig.3.4 for N = 16, m = 4. The network in Fig.3.4 first combines pairs of numbers whose indices differ by  $2^3 = 8$  in their binary expansion. After second shuffle, the pairs combined will differ by  $2^2 = 4$ , after third shuffle pairs will differ by  $2^1 = 2$  and finally by  $2^0 = 1$ .

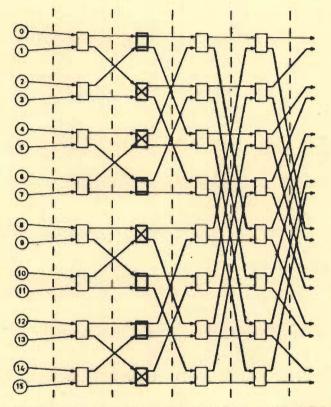

It will now be shown, that the problem can be reconfigured for evaluation of FFT using 4-shuffle permutation and it will be required to repeat the sequence of above three steps only n times, where  $N = 4^{n}$ .

Let A(k),  $k = 0, 1, \ldots, N-1$ , be N samples of a time function, sampled at instants that are spaced equally apart. It is assumed that  $N = 4^n$  where n is any positive integer. The discrete Fourier transform of A(k) is defined to be the discrete function X(j),  $j = 0, 1, \ldots, N-1$  where

$$X(j) = \sum_{\substack{k=0 \\ k=0}}^{N-1} A(k) W^{jk} \dots (3.6)$$

where  $W = e^{2\pi i/N}$

The fast Fourier transform algorithm is derived directly by forming the quaternary expansions of the indices j and k as follows:

$$j = j_{n-1} \cdot 4^{n-1} + \dots + j_1 4 + j_0 \dots (3.7)$$

and

$$k = k_{n-1} \cdot 4^{n-1} + \dots + k_1 4 + k_0 \dots (3.8)$$

where i. and k.  $\in \{0, 1, 2, 3\}$  and  $\neq 0$

where

$$j_i$$

and  $k_i \in \{0, 1, 2, 3\}$  and  $\# j_i, k_i = 1$ .

FIGURE-3.4 A PROCESSOR FOR FFT. THE 'M-A' MODULES PRODUCE WEIGHTED SUMS OF THEIR INPUTS ON THEIR OUTPUTS

Substituting the identities (3.7) and (3.8) into (3.4) one gets

$$X[j_{n-1}\cdots j_{0}] = \sum_{\substack{k_{0} \\ k_{1}}} \sum_{\substack{k_{n-1} \\ k_{n-1}}} A(k_{n-1}\cdots k_{0}) W^{jk} \dots (3.9)$$

where each of the indices k, are summed over the quaternary values 0,1,2, and 3.

To compute the Fourier transform of A(k), n different arrays, B1, B2...B are formed where each Bi is computed from  $B_{i-1}$  for i > 1. The last array of this sequence,  $B_n$  has elements that are the values of X(j), but the elements are scrambled in what is known as reverse quaternary order. The arrays are defined as follows:

$$B_{1}(j_{0}, k_{n-2}, \dots, k_{0}) = \sum_{\substack{k_{n-1} \\ k_{n-1}}} A(k_{n-1}, \dots, k_{0}) W \qquad \dots (3.10)$$

$B_{s}(j_{0}, \dots j_{s-1}, k_{n-s-1}, \dots k_{0}) =$

$\sum_{\substack{k_{n-s}}}^{\Sigma} B_{s-1}(j_0, \dots, j_{s-2}, k_{n-s}, \dots, k_0) W \xrightarrow{(j_{s-1}4^{s-1} + \dots + j_0)k_{n-s}4^{n-s}} \dots (3.11)$

for

$$s = 2, 3, ..., n$$

The relation

The relation (entral Library University of Roorkee

$$w^{jk_{n-s}} = w^{(j_{s-1}4^{s-1} + \cdots + j_0)k_{n-s}4^n}$$

may be used in the summation (3.9), giving

$$B_{n}(j_{0}, j_{1}, \dots, j_{n-1}) = \sum_{\substack{k_{0} \ k_{1} \ k_{n-1}}} \sum_{\substack{k_{n-1} \ k_{n-1}}} A(k_{n-1}, \dots, k_{s}) W^{jk}$$

$$= X(j_{n-1}, j_{n-2}, \dots, j_{0}) \qquad \dots (3.12)$$

To obtain the value of X(j) when given the vector  $B_n$ , one reverses the quaternary digits in the expression of j to obtain a new index which may be called j'. Then X(j) =  $B_n(j')$ .

The role of 4-shuffle becomes evident when Equation (3.6) is inspected. Each element of  $B_i$  is the weighted sum of four elements of  $B_{i-1}$  (or of A). To determine which four elements of  $B_{i-1}$  are combined to form  $B_i(j)$ , one forms the quaternary expansion of j, and observes the coefficients of  $4^{n-i}$ . Then the four elements of  $B_{i-1}$  that contribute to  $B_i(j)$  are the elements  $B_{i-1}(j)$  and  $B_{i-1}(j)$  where  $B_{i-1}(j)$  is the relative complement of  $B_{i-1}(j)$ . Figs. 3.2(b) and (c) show the setwise combinations that form the fast Fourier transform for N = 16.

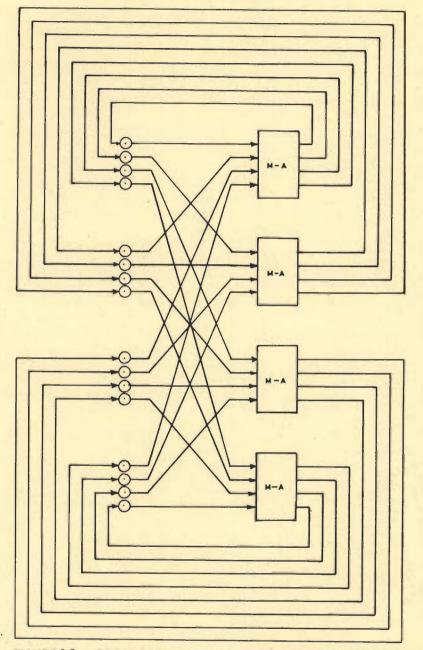

A processor for FFT for N = 16 has been reconfigured in Fig.3.5, where the perfect shuffle connections of Fig.3.4 are replaced by 4-shuffle connections and 'M-A' module is capable of computing 4 weighted sums of its 4-inputs simultaneously with the results appearing on the 4-outputs.

From Theorem 3.3, it is clear that the network in Fig.3.5 first matches the sets of elements whose indices differ by  $4^1 = 4$ and in second iteration the sets of elements whose indices differ by  $4^0 = 1$ . Accordingly, the configuration of Fig.3.5 requires two iterations, i.e., the sequence of steps are repeated only twice as compared to 4 times in configuration of Fig.3.4.

Thus, it is established that the use of 4-shuffle connection in the evaluation of FFT reduces the computational complexity to be proportional to  $\log_4 N$ .

FIGURE 3.5 A PROCESSOR FOR F FT. THE "M-A" MODULES PRODUCE WEIGHTED SUMS OF THEIR INPUTS ON THEIR OUTPUTS

### 3.5.2 Polynomial Evaluation

In this section the problem of polynomial evaluation has been taken up to demonstrate the usefulness of 4-shuffle in parallel processing. It has been demonstrated that the algorithm to evaluate polynomial of degree N can be executed on parallel processor with either perfect shuffle interconnection pattern or 4-shuffle interconnection pattern. However, the use of 4-shuffle instead of perfect-shuffle, increases the computational speed and reduces the computational complexity. The problem to be solved is as follows:

Let  $a_0, a_1, \dots, a_{n-2}$  be the coefficients of a polynomial of degree N-2. It is desired to compute  $\sum_{i=0}^{N-2} a_i X^i$  on a parallel processor that can perform upto N operations simultaneously.

The solution to this problem is now discussed. The coefficients  $a_i$ ,  $i = 0, 1, \ldots, N-2$  are arranged in consecutive locations in a block of memory and it is assumed that at each location in the block, a computation takes place. For this example the computation is multiplication. The processor operates by broadcasting a single number to all locations in the block. The numerical value of X is stored in position N-1 of the coefficient vector, the last register in the block of memory. An index register is initialized to the vector V where  $V = (0,1,0,1,0,1,\ldots,0,1)$  for perfect shuffle connections and  $V = (0,1,2,3,0,1,2,3,\ldots,0,1,2,3)$  for 4-shuffle connections.

At the end of each iteration the contents of the memory register are changed according to the following equation:

New Contents ← (Current Contents)[Contents of location(N-1)] ...(3.13) where V<sub>i</sub> is the corresponding digit in the index register.

The evaluation of polynomial of degree 14(N = 16) is presented schematically in Fig.3.6 using perfect shuffle interconnection pattern. It is observed that it requires 4 iterations of multiplications before performing the sum of the first fifteen locations in the block to get the result

$$\overset{14}{\Sigma} a_{i} X^{i} \qquad \dots (3.14)$$

The same problem has been reconfigured in Fig.3.7 with 4-shuffle interconnections. In this case only two iterations of multiplications are required before the sum is performed on the first fifteen locations in the block to get the sum of the polynomial

$$\overset{14}{\underset{i=0}{\Sigma}} a_{i} \chi^{i} \qquad \dots (3.14)$$

Again it is demonstrated that the use of 4-shuffle permutation to evaluate the polynomial reduces the lower bound on the minimum time to ( $\lceil \log_4 N \rceil$ ) from the conventional value of ( $\lceil \log_2 N \rceil$ ) with perfect shuffle.

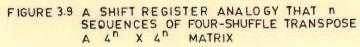

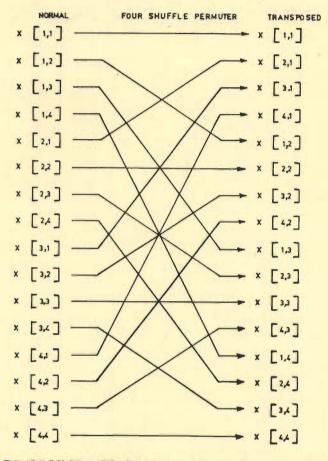

### 3.5.3 Matrix Transposition

In parallel processing sometimes it is required to rearrange the data. Two dimensional matrix calculations are particularly susceptible to these requirements. In many problems, it is necessary to have parallel access to both rows and columns of a matrix. For matrix multiplication, it is necessary to align rows of one matrix with the columns of another in order to obtain efficiency. One solution to these

| Data                                                                                                           | Index | Data              | Index | Data                           | Index | Data                           | Index | Data                            |

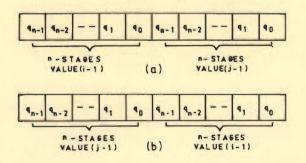

|----------------------------------------------------------------------------------------------------------------|-------|-------------------|-------|--------------------------------|-------|--------------------------------|-------|---------------------------------|