# PETRI NET APPROACH TO DESIGN AND DEVELOPMENT OF MODERN COMPUTER SYSTEMS

#### **A THESIS**

submitted in fulfilment of the requirements for the award of the degree

of

### DOCTOR OF PHILOSOPHY

in

### ELECTRONICS & COMMUNICATION ENGINEERING

By

ALI ATHAR KHAN

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247672 (INDIA)

September, 1981

# Candidate's Declaration

I hereby certify that the work which is being presented in the thesis entitled PETRI NET APPROACH TO DESIGN AND DEVELOPMENT OF MODERN COMPUTER SYSTEMS in fulfilment of the requirement for the award of the Degree of Doctor of Philosophy, submitted in the Department of Electronics & Communication Engineering of the University is an authentic record of my own work carried out during a period from August 1978 to July 1981 under the supervision of Dr. Harpreet Singh, Professor Electronics & Communication Engineering, University of Roorkee.

The matter embodied in the thesis has not been submitted by me for the award of any other degree. Roorkee University of Roorkee Thesis

University of Roomees, recommendation Certified that the increase Thesis/ Dissertation has been excepted for the award of Deg ee of Decor of Philosophy / Master of Engineering Philosophy / Master of Engineering No. Ex/ 162. Pt65 (Degree) dated With No. Ex/ 162. Pt65 (Degree) dated With

alliar

(Ali Athar Khan)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

heat

(Harpfreet Singh) Professor of Electronics & Communication Engineering University of Roorkee Roorkee (India)

Date: Sept 12, 1981

#### ABSTRACT

Petri nets (PN) have aroused considerable interest during the recent years as a model, primarily to represent and study concurrent systems. This thesis deals with the PN approach to design and development of modern computer systems. In particular several aspects of the development of PN theory, its applications to some problems of computer systems and to the problem of optimization in microprogrammed computers have been proposed.

Much of the available work on PN is scattered over various reports, dissertations and journals. The review chapter brings together the existing literature in a coherent manner so as to aid a reader in subsequent chapters.

The design and development of a system demand that a knowledge about the model be known.For this reason, the reachability tree technique and state equation for Petri nets have been proposed by earlier researchers. However, there are many unsolved problems in PN theory. For example, analysis of large PN is generally cumbersome or even impracticable. It is possible to build complex nets with desired properties from smaller nets, the analysis of which can easily be managed. This involves interconnection of nets. It is shown in this thesis how smaller nets could be connected in cascade or in parallel to preserve same properties. A state equation approach has been exploited for this purpose. Another well-known problem concerning the analysis of PN is the lack of information of firing sequences and existence of spurious solutions of corresponding state equations. This problem is studied and an algorithm is proposed to find minimal legal firing sequences to transform a given marking into another given marking.

It is a well established fact that PN can not model, as such, systems in which interruption or priorities are involved. Many extensions have earlier been proposed but they are either too specific or provide inadequate analysis technique. In this thesis such limitations in modeling capabilities of PN are overcome by proposing an inventor transition in which the token at output place is the complement of the token at input place. All the logic operations have been modeled by PN with additional invertor transitions. To analyse these, a generalized state equation is developed. It is also shown that state equation of PN proposed earlier by Murata is a special case of generalized state equation.

The state equations of Petri net appear to be very powerful. Many problems of computer science, for example, the enumeration of simple paths between two modes of graph, the terminal reliability of a computer network and program complexity evaluation are formulated in the framework of state equations and solutions for them proposed.

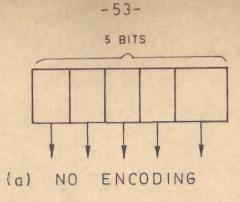

Of significant importance in the design of microprogrammed computers are microprogram optimizations. They are called for to reduce the cost of the system and to increase the efficiency. In this thesis, only bit optimization in control memory and data path optimization are taken up because of their practical utility. In the bit optimization all the maximal compatible classes of microcommands are generated using the PN state equation. From these, minimal bit solutions are obtained. The possibility of further reduction in bits, is also looked into by employing bit steering through extended PN concept.

Two approaches are proposed in this thesis to solve the problem of data path optimization. In the first approach the concept of invariance in PN is employed and solutions which include all the minimal cost solutions, are obtained. In the second approach the problem is reformulated in PN domain. The places of PN are then merged according to defined rules and minimal cost solution obtained.

Finally, the results are summarized and some suggestions alongwith critical discussions for further work are given.

(v)

#### ACKNOWLEDGMEN T

The author wishes to express his sincere gratitude to his advisor, Prof. Harpreet Singh for his excellent guidance and Encouragement without which it would have been rather impossible to carry out this research.

Special acknowledgment is due to Dr. N.K. Nanda for his keen interest and fruitful technical discussions.

Thanks are also due to Aligarh Muslim University, Aligarh for sponsoring the author under Quality Improvement Programme to persue this research and the Government of India , Ministry of Education for financial support.

The author is very much grateful to his parents, wife and children who have been a constant source of inspitation and encouragement.

Finally, the author is thankful to his friends and colloagues for extending their help directly or indirectly, during this work.

Thanks are also due to Mr. Darshan Lal Jaggi for his efficient typing of the thesis.

(vi)

## TABLE OF CONTENTS

| Chapter |                                           | Page  |

|---------|-------------------------------------------|-------|

|         | LIST OF SYMBOLS                           | xi    |

| I       | IN TRODUCTION                             |       |

|         |                                           | 1     |

|         | 1.1 Introduction                          | 1     |

|         | 1.2 Advantages of Petri Nets              | 2     |

|         | 1.3 Limitations of Petri Nets             | 4     |

|         | 1.4 Extension of Petri Nets               | 7     |

|         | 1.5 Statement of the Problem              | 8     |

|         | 1.6 Organization of the Thesis            | 9     |

| II      | CRITICAL REVIEW AND GENERAL CONSIDERATION |       |

|         | OF PETRI NETS                             | 13    |

|         | 2.1 Introduction                          | 13    |

|         | 2.2 Historical Review                     | 14    |

|         | 2.3 What are Petri Nets?                  | 16    |

|         | 2.4 Modeling with Petri Nets              | 24    |

|         | 2.4.1 Modeling of Hardware                | 25    |

|         | 2.4.2 Modeling of Software                | 26    |

|         | 2.4.3 Speed Independent Circuits          | 27    |

|         | 2.5 Subclasses of Petri Nets              | 28    |

|         | 2.5.1 Marked Graph                        | 28    |

|         | 2.5.2 State Machines                      | 29    |

|         | 2.5.3 Free-choice Petri Nets              | 29    |

|         | 2.5.4 Pure or Restricted Petri Nets       | 30    |

|         | 2.5.5 Simple Petri Nets                   | 30    |

|         | 2.6 Analysis of Petri Nets                | cone. |

|         | 2.6.1 The Reachability Tree               | 32    |

|         | 2.6.1.1 Limitations of                    | 32    |

|         | Reachability Tree                         | 37    |

| Chap ter |                                                                             | Page |

|----------|-----------------------------------------------------------------------------|------|

| III      | CRITICAL REVIEW AND GENERAL<br>CONSIDERATION OF MICROPROGRAM                |      |

|          | OP TIMIZATION                                                               | 49   |

|          | 3.1 Introduction                                                            | 49   |

|          | 3.2 Basic Concepts of Microprogramming                                      | 50   |

|          | 3.3 Strategies of Optimization                                              | 54   |

|          | 3.3.1 Bit Optimization                                                      | 55   |

|          | 3.3.1.1 Schwartz's Algorithm                                                | 57   |

|          | 3.3.1.3 Grasselli and Montanari's<br>Algorithm                              | 57   |

|          | 3.3.1.3 Linear Programming Methods                                          | 58   |

|          | 3.3.1.4 CM Cover Table Method                                               | 59   |

|          | 3.3.1.5 Branch and Bound Method                                             | 59   |

|          | 3.3.1.6 Montangero's Algorithm                                              | 60   |

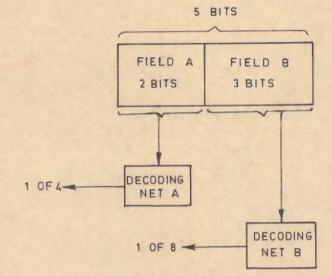

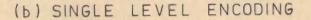

|          | 3.3.1.7 Bit Steering in Bit<br>Reduction                                    | 64   |

|          | 3.4 Data Path Optimization                                                  | 66   |

|          | 3.4.1 Interconnection Buses                                                 | 67   |

|          | 3.4.2 Dynamic Programming Approach                                          | 68   |

|          | 3.4.3 Switching Theoretic Approach                                          | 70   |

|          | 3.5 Conclusion                                                              | 73   |

| IV       | ON THE DEVELOPMENT OF PETRI NET THEORY                                      | 75   |

|          | 4.1 Introduction                                                            | 75   |

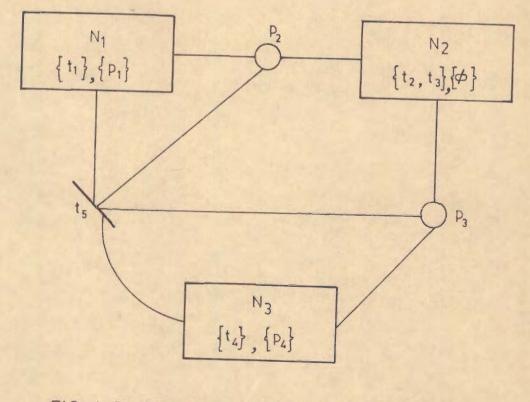

|          | 4.2 Interconnection and Decomposition of Petri Nets                         | 76   |

|          | 4.2.1 Interconnection Properties                                            | 78   |

|          | 4.2.2 Decomposition of Petri Nets                                           | 85   |

|          | 4.3 Minimal Legal Firing Sequences in Petri Nets                            |      |

|          | 4.3.1 Theory Involved                                                       | 91   |

|          | 4.3.2 Determination of Minimal Legal                                        | 92   |

|          | Firing Sequence                                                             | 94   |

|          | 4.4 State Equation Representation of<br>Logic Operations Through Petri Nets | 98   |

Chapter

V

VI

| r.                                                                    | Page |

|-----------------------------------------------------------------------|------|

| 4.4.1 Generalized State Equation                                      | 100  |

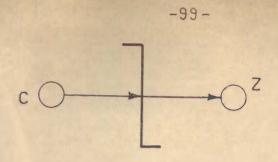

| 4.4.1.1 NOT Operation                                                 | 101  |

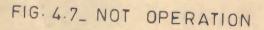

| 4.4.1.2 NAND Operation                                                | 101  |

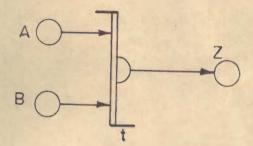

| 4.4.1.3 NOR Operation                                                 | 103  |

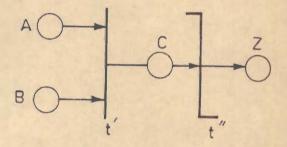

| 4.4.1.4 EX-OR Operation                                               | 103  |

| 4.5 Conclusion                                                        | 106  |

| ON THE APPLICATION OF PETRI NETS TO<br>COMPUTER HARDWARE AND SOFTWARE | 109  |

| 5.1 Introduction                                                      | 109  |

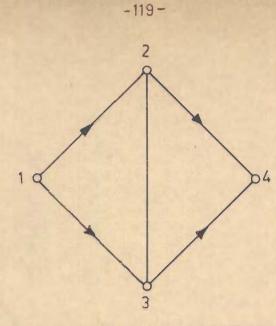

| 5.2 Enumeration of Simple Paths Between                               |      |

| two Nodes of a Graph                                                  | 110  |

| 5.2.1 Formulation                                                     | 111  |

| 5.2.2 Solution                                                        | 112  |

| 5.2.3 Maximum Iterations Needed                                       | 115  |

| 5.3 Terminal Reliability of a Computer<br>Network                     | 116  |

| 5.3.1 Probabilistic Graph and Determ-<br>-ination of Boolean Function | 117  |

| 5.3.2 Determination of Disjoint Terms<br>in F and Probability         | 120  |

| 5.4 Program Complexity Evaluation                                     | 126  |

| 5.4.1 Complexity Metrics                                              | 127  |

| 5.4.2 Execution Time                                                  | 137  |

| 5.5 Conclusion                                                        | 137  |

| PETRI NET APPROACH TO DEVELOPMENT OF                                  |      |

| M ICROPROGRAMMED COMPUTER                                             | 140  |

| 6.1 Introduction                                                      | 140  |

| 6.2 Bit Optimization                                                  | 140  |

| 6.2.1 Enumeration of Maximal Compatible<br>Classes of Microcommands   |      |

| 6.2.1.1 Formulation                                                   | 142  |

| 6.2.1.2 Enumeration Procedure                                         | 142  |

| 6.2.2 Procedure                                                       | 143  |

| 0.2.2 Frocedure                                                       | 146  |

| Cha | p | ter |

|-----|---|-----|

|-----|---|-----|

Page

(x)

| 153 |

|-----|

| 156 |

| 164 |

| 165 |

| 169 |

| 180 |

| 180 |

| 180 |

| 180 |

|     |

| 187 |

| 191 |

|     |

# LIST OF SYMBOLS

| A                | Incidence matrix                        |

|------------------|-----------------------------------------|

| В                | Number of bits                          |

| B <sub>f</sub>   | Fundamental circuit matrix              |

| Ci               | Control field i                         |

| E                | Number of edges                         |

| I                | An invariant of a PN                    |

| Mo               | Initial marking of a PN                 |

| Mn               | Marking after n th Firing in a PN       |

| M(p)             | Number of tokens in a place p           |

| Mc               | Number of microinstructions             |

| Nc               | Number of microcommands                 |

| P                | Set of Places                           |

| P                | Number of places                        |

| PN               | Petri Net                               |

| T                | Set of transitions                      |

| T                | Number of transitions                   |

| V                | Number of vertices                      |

| W                | A weighted vector                       |

| Wl               | Number of irrendundant words in a ROM   |

| a <sub>ij</sub>  | Element of incidence matrix A           |

| mi               | i th microins truction                  |

| р                | A place                                 |

| °p               | Input transitions to place p            |

| p <sup>O</sup>   | Output transitions to place p           |

| o <sub>p</sub> o | Set of transitions connected to place p |

|   | t              | A transition                            |

|---|----------------|-----------------------------------------|

|   | <sup>o</sup> t | Set of places connected to transition t |

|   | °t             | Input places to transition t            |

|   | t <sup>o</sup> | Output places of transition t           |

| 1 | W              | Weight of token in place p              |

| 1 | α              | Forward incidence function              |

| - | 3              | Backward incidence function             |

|   | U              | Union of sets                           |

|   | $\bigcap$      | Intersection of sets                    |

| 1 | A              | For all                                 |

| 1 | W              | A very large quantity                   |

#### CHAPTER I

INTRODUCTION AND STATEMENT OF THE PROBLEM

#### 1.1 INTRODUCTION

Modern computer systems comprise of multiple communicating components each of which may itself be a system. Although the interactions between them are well defined, yet they are very complex and the concepts relating to asynchrony and concurrency need close examination. The direct consequence of this is both logical and topological distribution of data, processing and control, which makes representation and performance evaluation results more and more difficult to obtain. Further, the difficulty of representation and analysis of combination of hardware and software systems has increased with the level of sophistication. Hence in order to design a secure and analysable system, the methodology must be able to depict in a formal way the system specification and must help designer to prove their correctness. In search of a formal model to do so, one finds that the tools used for modeling sequential systems are completely inadequate. For instance, block diagrams do represent the interconnections that may exist between them, but give no information about where or when these interconnections are used. A computer system can also be described by comprehensive set of logical diagrams, pertaining to the hardware, and complete listing of the code and microcode necessary to provide system operation. But obviously,

it is too much. The conventional flow diagram becomes excessively clumsy to represent concurrent systems when tried on multiprogramming and multiprocessing. Another disadvantage with flow diagram is the difficulty to represent combination of hardware and operating system, as one looses sight of parallel actions and their potential interactions. Finite state machines could be used for representation of such systems but will lead to unmanageably large single states. These difficulties have led to an extensive research to find a suitable model for modern computer systems. Among various models proposed [122], Petri nets and its subclasses [5], [97], [120], [121] have emerged as convenient and powerful tool. They can serve as an intermediate tool between program statement (ckt. diagram) - too complex to analyse and block diagrams- too simple to predict behaviour of a system. This is the prime justification for studying the application of Petri nets to design and development under taken in this thesis. Another significant achievement is that the knowledge about many models used for manipulating the systems in parallel environment is directly obtained from the study of PN. This is mainly because several models such as computation graphs, flow graph schemata, UCLA graph, vector addition system, vector replacement system, etc. are either included into or are equivalent to PN [122].

#### 1.2 ADVANTAGES OF PETRI NETS

Petri nets find their basis in a few simple rules yet they are very powerful and possess many advantages in modeling a system.

-2-

Some of them are:

- i. Petri nets often make easier to understand overall system which they represent because of their graphical and precise nature of presentation.

- ii. Petri nets are equally suited for representation of hardware and software systems.

- iii. Petri nets possess inherent concurrency and parallelism.

- iv. Asynchronous nature of Petri nets makes them suitable for representing real systems. In real life, events take variable amount of time. Petri net model reflects this variability by not depending upon a notation of time but contains all the necessary information to define the possible sequences of events of a modeled system.

- v. Petri net execution is nondeterministic. The choice as to which transition fires is made randomly i.e. nondeterministically. This feature makes Petri nets to represent real time situation where several events are occuring concurrently and the order of occurences of events is not unique.

- vi. Petri nets can be used as heirachical model. This is because they can be used at all levels including networks, register-transfer, functional, and gate etc. Interpretation can be varied to suit all the particular requirements. An entire net can be replaced by a single place or transition for modeling at more abstract level or places and transitions may be replaced by subnets to provide more detailed modeling.

-3-

- vii. The behaviour of any system can be analysed using Petri net theory. It can, thus, make use of high speed computers as computational tool for modeling and analysing larger and more complex systems than ever before.

- viii. Petri nets can be synthesized using both bottom-up and top-down approaches. Methodical design of systems with known or easily verifiable behaviour can be done [6].

- ix. Petri nets are a compromise between <u>Modeling Power</u> (ability to correct and faithful representation of the modeled system) and <u>Decision Power</u> (ability to analyse and determine properties of the modeled systems). Generally, in a model, decision and modeling powers are conflicting. For example, finite-state model possessesvery high decision as almost all questions about the model are answered, but has very low modeling power. On the other hand, Turing machines have good modeling power but poor decision power.

## 1.3 LIMITATIONS OF PETRI NETS

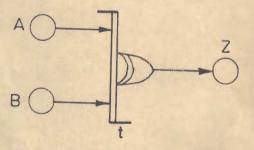

It has been found that Petri nets are too simple and limited to easily model real systems. In PN representation of the CDC 6400 operating system [105], Noe has experienced many short. comings. Normally, a Petri net transition fires when all of its inputs satisfy AND logic. On firing a transition, each output place gets one token. The transitions with such simple firing rules were inadequate to represent the above. As an example, let us consider the execution of a program ISI in operating

-4-

system of CDC 6400. This program advances a job from staging queue to input queue if the following is satisfied:

"Job in staging queue AND only one of the conditions

(i) 'No tape required-job advances', and (ii) 'tape-

job queued until tape available' is satisfied ".

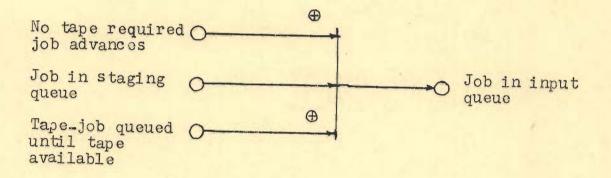

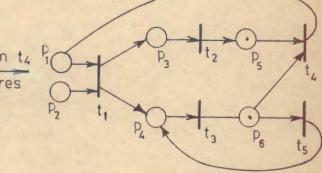

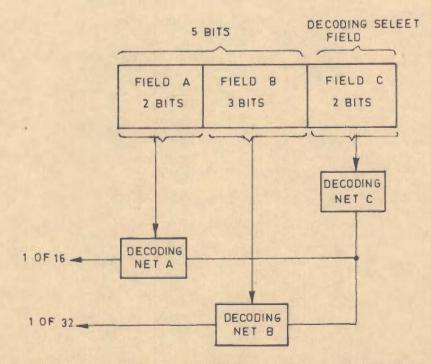

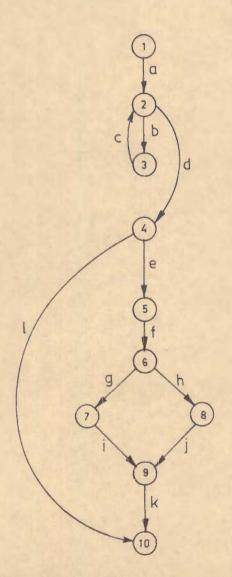

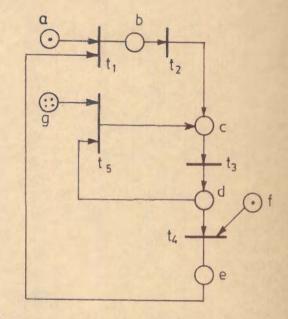

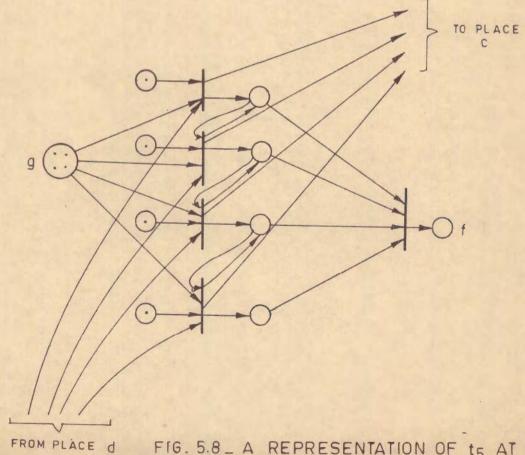

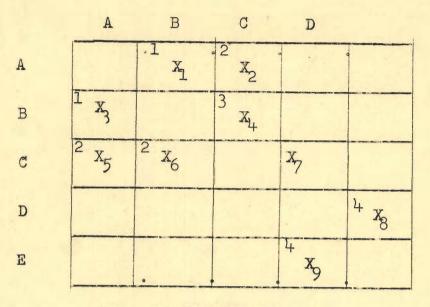

Obviously this cannot be represented by AND logic only. Noe, introduced an Exclusive-OR transition to represent this. Figure 1.1 shows the Petri net representation of the ISI program.

Fig. 1.1 PN Representation of Advancing a Job in Staging Queue of CDC 6400 Operating Systems.

Such deviations from conventional transitions made it impossible to make use of analysis techniques developed for PN.

Another point which was observed is that the tokens represented only conditions but did not carry any attribute. No data structure was associated with the location of nets. This seriously hampered the transfer of data in the system. Further, no time duration was associated with transition firing. This created another obstacle to deal with quantitative measures such as throughput and turn-around time. Baer [15] faced similar difficulties in modeling a compiler with Petri nets. He extended the PN model by the addition of OR logic, switches and token absorbers.

Patil [115] has created a synchronization problem called Cigarette Smokers Problem. He has shown that this synchronization problem cannot be represented by P and V operations on Semaphores described by Dijkstra [38] or by Petri nets. Following Patil's work, it was shown formally by Kosaraju [81] that Petri nets cannot represent systems where <u>Priority</u> constraints has also to be satisfied. He described a coordination problem of two producer/ consumer with shared channel with one producer/consumer having a priority over other. This problem has been shown to fall outside the domain of Petri nets. A similar limitation had been earlier discovered [70]. The difficulties in PN modeling of some relatively reasonable systems have been further demonstrated [3], [7].

It was felt that the limitation on Petri net modeling is due to failure of a transition to react to absence of tokens rather than only to their presence. This inability to test for a zero marking in a place, is known as <u>Zero Testing</u> [70]. Petri nets cannot test an unbounded place for zero. If the place is bounded, zero can be tested. For a bounded place p with bounded k, a complement place p' can be created such that M(p) + M(p') = k for all reachable markings. This allows to zero test M(p) by testing if M(p') is k.

-6-

# 1.4 EXTENSIONS OF PETRI NETS

To overcome some of the problems encountered in the Petri net modeling of CDC 6400 operating system, <u>Evaluation Nets</u> (E-nets) have been proposed [107], [110], [111]. E-nets are extended, interpreted model for parallel computation for performance evaluation and simulation. These represent an approach towards timing information to a Petri net. However, the five primitives proposed in E-nets proved to be too restrictive and it was difficult to model structures with more than two inputs and outputs for transitions. Some larger structures were developed [109] but were still inflexible for general use. A modification on E-nets resulted in Pro-nets [106]. The name Pro- was suggested because of the use of nets for Processors or processes. Pro-nets were allowed with multiple arcs.

Many other extensions to Petri nets like addition of inhibitor arcs [81], constraints [115], exclusive -OR transition [105], Switches [15] etc. have been suggested. Invariably all of them introduced in one way or the other, the reaction of transitions on absence of tokens as well. But they were introduced, basically to solve particular problems rather than with intention to increase the modeling capacity of Petri nets. An extensive study on the completeness of different models with extended Petri nets have been made by Agerwala et al. [1], [2], [7]-[9]. It has been observed that adding zero testing allows a Petri net to simulate a Turing machine. Thus a PN with zero testing produces a modeling scheme which can model

-7-

any system. However, many analysis questions of Petri nets become undecidable, since they are undecidable for Turing machines. This may perhaps be one of the reasons that analysis technique is not, generally, available for generalized extension of Petri nets.

In Chapter IV an invertor transition is defined which describes a NOT operation. This facilitates the representation of all logic operations with Petri nets alongwith invertor transitions. To analyse, such a Petri net, a generalized state equation is proposed. This overcomes many shortcomings in Noe's model [105] and makes the analysis of the systems possible.

### 1.5 STATEMENT OF THE PROBLEM

This thesis attributes itself to the problem of Petri net approach to the design and development of modern computer systems. Specifically, the problems considered in this thesis can be stated as follows:

- i. To evolve efficient and reliable techniques for solving some of the unsolved and outstanding problems in PN theory with a view to develop a basis for PN approach to several challenging aspects of modern computer design.

- ii. To utilize the modeling of PN (particularly, state equation representation), with a view to provide automated tools, for formulating and solving various problems of computer hardware and software.

- iii. To exploit the use of Petri nets in design and development of microprogrammed computers.

-8-

Though some aspects of the above mentioned problems have been studied by a few investigators, however, not much results have been obtained. For example, as regards the first problem a decomposition technique [137] for analysing large Petri nets does exist, but it is quite involved. Furthermore, only the necessary condition for reachability [97] has been obtained. So far as the second problem is concerned, surprisingly no work of similar nature has appeared in the literature. For the design of microprogrammed computers, only the conventional methods based upon classical approaches are available.

## 1.6 ORGANIZATION OF THE THESIS

Petri nets are becoming increasingly popular for the representation and analysis of system in general and computer systems in particular. Before it can be applied effectively some bottlenecks which appear in the theory need be removed. An attempt has been made in this thesis, to first identify those, and then to propose techniques for removing them.

Many problems in computer hardware and software can be represented by PN and can be solved by similar set of equations. Such investigation is another type of work reported in this thesis.

Invariably every modern day computer utilizes the concept of microprogramming. This has called for the need of optimization in order to have a compromise between flexibility and cost. Petri nets appear to be a natural representation for such computer systems and can provide optimization techniques in a more

-9-

systematic and easy-to-beimplemented way. This is another aspect which has been taken up here. It may be noted that almost no work except from one author [136] apart from the candidate's work on the optimization consideration of Petri net is available.

For the sake of better understanding the following arrangement has been adopted in the organization of this thesis.

The review of the existing literature related to Petri net approach in computer systems has been included in the second chapter. This chapter also contains basic concepts, important properties and applications of Petri nets scattered over many journals, reports and dissertations. Comments regarding the analysis problems of Petri nets have also been given as and when required.

Chapter III discusses the basic concepts of microprogramming, the different optimizations required therein, and the outline of the existing techniques for them. The justification for the importance of optimizations for control bit memory and interconnections of modules alongwith the comments regarding the computational complexity of the available techniques has also been made.

Chapter IV addresses to the solutions of some important problems in PN theory. First of all an investigation for the interconnection and decomposition properties of Petri nets has been carried out and useful results obtained. A new and computationally better technique for decomposition is also proposed. Another important aspect involved in the theory is that of reachability because many properties of PN are directly dependent

-10-

upon it. Therefore, it is imperative that an efficient algorithm for solving reachability problem be devised. In this direction a technique has been formulated through the determination of minimal legal firing sequences which transforms one marking into another. Furthermore, to increase modeling capabilities of a PN, an invertor transition has been proposed. This takes care of negation operation often encountered in systems. The analysis technique of PNs having such transitions has also been presented in this chapter. This technique not only allows the representation of all the logic operations by Petri net, but makes possible the analysis of many computer systems incorporating those operations. Many examples are taken up for explanation purposes.

Chapter V identifies some of the classes of state equation for Petri nets, which can solve many problems in computer hardware and software by the same technique. The proposed classes take care of the problems of enumeration of simple paths between two nodes of a graph, terminal reliability of a computer network, program complexity evaluation, and determination of maximal compatible classes (MCCs) of microcommands in control memory bit optimization. A novel technique for the solution of state equation of different classes is proposed and its superiority established by using examples considered by earlier researchers.

In Chapter VI, the application of PN to the design and development of microprogrammed computers is explored. Particularly, the optimizations involved therein have been studied. This is entirely a new approach. The control memory bit optimization is obtained first by enumerating all MCCs via PN

-11-

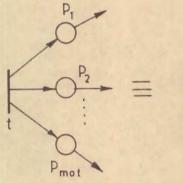

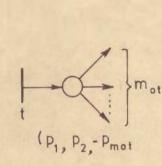

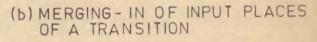

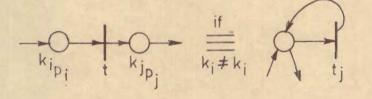

application and then putting the corresponding microcommands in different blocks so as to yield optimal solutions. From these solutions the number of bits are further reduced by exploiting the concept of bit steering [10] through extended Petri net. Advantages of the proposed technique over the existing methods have been highlighted. An example considered by many investigators, has been reconsidered to show the utility of the proposed technique. Another problem i.e. optimization of data path has been solved by first representing the data transfers among modules of the system by a Petri net and then by defining and applying the concept of merging-in of places. The proposed method is simple and requires less computational efforts. A comparison of this is made with the existing methods by way of a numerical examples considered earlier [85].

A summary of the work done has been given in Chapter VII. A brief outline for further work has been included in this chapter.

-12-

#### CHAPTER II

CRITICAL REVIEW AND GENERAL CONSIDERATIONS OF PETRI NET

#### 2.1 INTRODUCTION

Petri nets have emerged in the last decade into a very powerful and suitable model to represent, analyse and synthesise a very large and interesting class of systems exhibiting concurrency. This is because Petri nets can provide with a minimal amount of effort, a simple, natural and easy-to-understand representation. Research on Petri nets have focussed on the representation of computer hardware [5], [34], [62], [100], [108], [120], [121], computer software [5]-[7], [15], [16], [20], [28], [83], [105], [120], [121], [136], speed independent circuits [95], [112], [113], [118], production schemata [60], communication protocols [90]-[92], [100], [126], [127], asynchronous arrays [68], [117], [131], performation evaluation of computer systems [109], [111], formal language theory [19], [29], [55], [119], legal systems [89], mathematical knowledge [42], [49], propositional calculus [44], [142] etc. Analysis and synthesis of Petri nets and their subclasses with a motivation to provide some properties of the modeled system, is another area which has received a larger attention from researchers [6], [7], [11], [21], [26], [27], [43], [48], [49], [60], [67], [68], [83], [97]-[103], [136], [147], [148]. Research has also been carried out to increase the modeling capability of Petri nets [1], [2], [7],

[8], [9], [15], [81], [105], [115]. There is an ever-increasing interest in Petri nets as is evidenced by the abundance of recent work reported in most of the major conferences in the area of computers and information processing. A critical survey of the work done in this field is embodied in this chapter.

## 2.2 HISTORICAL REVIEW

The theory of Petri nets was originated in C.A. Petri's dissertation 'Kummunication mit Automaten' [123] in Germany. In his thesis, starting with the concept that many events of communication such as asynchronous and concurrent operations can be represented by purely combinatorial - topological means, Petri proposed a new model of information flow in systems. In 1965, the ideas of Petri received the attention of a group of researchers led by A. Holt at Applied Data Research, Inc., U.S.A. The group working on the Information System Theory Project [61] was concerned with finding a proper descriptive means for modeling, evaluating, and implementing systems. Here, it was shown how Petri nets could be applied to concurrent systems and the concept of Petri nets was refined and developed to such a state that it is applicable to many areas. In fact the actual definition of Petri nets, as used today, is due to Holt et al.[60].

The research on Petri net, at about same time, was also carried out under Project MAC at MIT, U.S.A. A large contribution was made particularly by the Computation Structure Group under the direction of Prof. J.B. Dennis. Examples of the use of Petri

-14-

nets for the description of control mechanisms of complex computers were given with a goal to develop automatic mechanisms for implementing the Petri net as a digital system [34]. Several Ph.D. theses, M.S. dissertations, numerous reports and papers on Petri net were produced [18], [19], [34], [35], [41], [49], [51]-[53], [56], [113]-[116], [118], [130]. The Computation Structure Group also organised the Project MAC Conference on Concurrent Systems and Parallel Computation in 1970 at Woods Hole [34] and the Conference on Petri Nets and Related Methods in 1975 at M.I.T.

The outcome of investigations at Applied Data Research and MIT, and the two conferences triggered the research activity in nature and the applications of Petri net. However, there was a similar independent research going on in Europe, particularly at the Institute fur Informationssystemforschung of the Gesellschaft fur Mathematik und Detneverarbeitung in Bonn. The institute is now involved in finding a more general and abstract theory.

Much of the work on Petri nets is in the form of theses, dissertations, reports and memos. These are neither widely circulated nor readily available. The first readily available work was by Baer [14]. However, this was mainly a survey of some of the theory developed for parallel computation. Several models including Petri nets were presented. But, there was hardly any paper in a journal of international repute, which could communicate, in a coherent manner, the work done in the field of Petri nets. In 1977, Peterson published an excellent paper [120] which is both a survey and tutorial on Petri nets. Another excellent

-15-

paper by Murata [98] came up the same year. This is a tutorial in nature but aims mainly to introduce Petri nets to those who are working in circuits and systems. These two were followed by another paper [5] which brings together a large body of work on useful applications of Petri nets.

It appears that interest in Petri nets is ever increasing. A workshop was held in Paris in 1977. Petri is still continuing his work and has extended the concepts in a form of general system theory called General Net Theory [124]. An advanced course on General Net Theory was held in Hamburg in 1979. A special interest group on Petri nets has also been formed in Germany. Research in and application of Petri nets has become widely popular.

Having given a brief historical review; the concept of Petri nets, their properties required for studying the systems modeled and recent work in the analysis of Petri nets are discussed further in the following sections.

## 2.3 WHAT ARE PETRI NETS?

Petri nets are an abstract and formal model of information flow. The concepts, properties and techniques of Petri nets are outcome of research by a number of people working at different times in different places with different backgrounds and motivations. This has resulted in many class of Petri nets and many concepts defined in different ways [27], [56], [60], [61], [113], [123]. However, there seems to be no substantial difference between

-16-

between them. Each of them is a restriction, in one way or the other, on general Petri nets. Here the most general and widely used concepts are presented.

The representation of Petri nets is done both graphically and mathematically. While the graphical representation of Petri net structure is useful in illustrating the concepts, mathematical representation is required for analysis. Both these representations are given side by side.

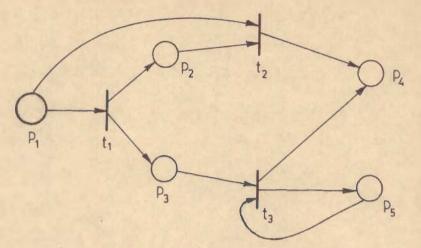

A Petri Net Graph is a <u>Directed Bipartite</u> graph with two types of <u>Nodes</u> called <u>Places</u> and <u>Transitions</u>. A <u>Circle</u> represents a place and a <u>Bar</u> represents a transition. <u>Directed Arcs</u> connect the transitions and places. Only single arc between a transition and a place is allowed in <u>Ordinary Petri Nets</u> or hereafter called Petri nets. A place p is called an <u>Input (Output)</u> place of a transition  $t_i$  if there exists a directed arc from (to) place j to (from) transition  $t_i$ . Fig. 2.1 is an example that represents a Petri net graph.

These concepts are defined mathematically as follows: <u>Definition 2.1</u> : A Petri net is a quadruple  $N = (P, T, \alpha, \beta)$ where:

P is a set of places,  $P \neq \emptyset$ T is a set of transitions,  $T \neq \emptyset$ ,  $P \bigcap T = \emptyset$ a forward incidence function  $\beta$  backward incidence function  $\alpha,\beta$  are binary relations with  $\alpha, \beta \subseteq P \times T$ , field  $(\alpha,\beta) = P \mid \mid T$

-17-

Definition 2.2: Let N = (P, T,  $\alpha$ ,  $\beta$ ) be a PN. We call <sup>o</sup>t (t<sup>o</sup>) set of input (output) places of t and by analogy, op (po) set of input (output) transitions of p where: For  $t \in T$ ,  $o_t = \{p \in P | \alpha(p, t) \neq 0\}$  and  $t^o = \{p \in P | \beta(p, t) \neq 0\}$ For  $p \in P$ ,  $^{O}p = \{t \in T | \beta(p, t) \neq 0\}$  and  $p^{O} = \{t \in T | \alpha(p, t) \neq 0\}$ The set of places (transitions) connected to a transition t

(place p) is denoted by <sup>o</sup>t<sup>o</sup> (<sup>o</sup>p<sup>o</sup>).

These notations are extended to subsets of T and P, for example, if  $P_1 \subset P$  then,  ${}^{\circ}P_1 = \bigcup_{p_1 \in P_1} {}^{\circ}p_k$

The structure of Petri nets can also be described by their Incidence Matrix [83], [97].

Definition 2.3: Let  $N = (P, T, \alpha, \beta)$  be a PN, the incidence matrix A of the PN is defined as

$A = [a_{ij}]_{|P|x|T|}$  with

a<sub>ij</sub> = { l, if i th transition has an outgoing arc to place j -l, if i th transition has an incoming arc from place j 0, otherwise

The Petri net can also be defined as N = (A, -).

The graphs as of Fig. 2.1 will represent only static (timeindependent) behaviour of the Petri net. In order to simulate the dynamic behaviour, each place in a Petri net is Marked (assigned) with a non-negative number of Tokens. The tokens are represented by Dots in circles representing places. The token distribution in

FIG. 2.1 \_ A PN GRAPH

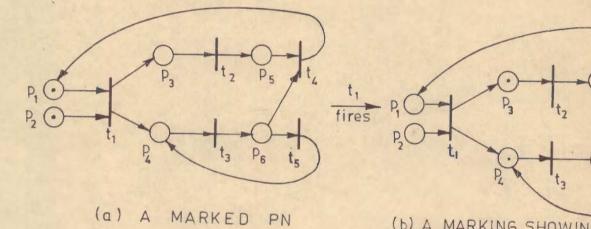

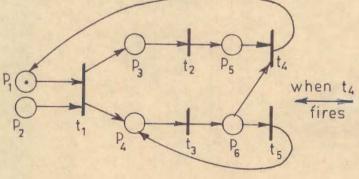

(b) A MARKING SHOWING CONCURRENCY

t<sub>2</sub> and t<sub>3</sub> fire concurrently

P5

P<sub>6</sub>

t<sub>5</sub>

(d) A MARKING SHOWING DEADLOCK

(c) MARKING SHOWING CONFLICT (Either  $t_4$  or  $t_5$  Can fire)

FIG. 2.2 \_ PN SHOWING MARKING, CONCURRENCY, CONFLICT, DEADLOCK AND REACHABILITY a Petri net is called Marking or State Space or PN.

Definition 2.4 : A marking M of a PN, N = (P, T,  $\alpha$ ,  $\beta$ ), is a mapping of P into IN (the set of natural integers : 0,1,2,...): P <u>M</u> IN. The number of tokens in a place p is denoted by M(p). A marking M can also be represented as a  $|P| \times 1$  column vector of non-negative integers, the jth entry of which denotes the number of tokens in place j.

The dynamic behaviour of a PN is obtained by the position and <u>Movement</u> of tokens i.e. change in marking. Marking of a PN changes as a result of <u>Firing</u> of a transition. Not all transitions can fire. Only those transitions which are <u>Enabled</u> can fire. However, an enabled transition will fire only if it is asked to do so. The firing of an enabled transition is called a <u>Legal</u> <u>Firing</u>. The firing rules of a transition are as follows:

- A transition is 'enabled' or 'firable' if each of its input places contains at least one token.

- 2. An enabled transition will fire on application of a control signal.

- 3. On firing an enabled transition, one token from each of its input places will be removed and one token will be added to each of its output places.

<u>Definition 2.5</u>: A PN, N = (P, T,  $\alpha$ ,  $\beta$ ) with a marking M is a <u>Marked Petri Net</u> C = (P, T,  $\alpha$ ,  $\beta$ , M) or C = (A,M).

Definition 2.6 : A transition t is enabled to fire if

Ψ p ε <sup>0</sup>t : M(p) > 0

Firing of t in M yields a new marking M' where :

$$M'(p) = \begin{cases} M(p) - 1 & \text{if } p \in {}^{\circ}t, p \notin t^{\circ} \\ M(p) + 1 & \text{if } p \in t^{\circ}, p \notin {}^{\circ}t \\ M(p) & \text{otherwise} \end{cases}$$

In Fig.2.2a, as an example, only transition  $t_1$  is enabled to fire. When  $t_1$  fires, the marking changes. The new marking is shown in Fig.2.2b. The transitions  $t_2$  and  $t_3$  now become firable. Since there is no common place input to both  $t_2$  and  $t_3$ , the two enabled transitions do not affect one another in any way. Thus  $t_2$  and  $t_3$  can fire <u>Concurrently</u>. After the firing of  $t_2$  and  $t_3$ is complete, the places  $p_5$  and  $p_6$  will have one token each (Fig.2.2c) enabling the transitions  $t_4$  and  $t_5$ . However, firing of one will <u>Disable</u> the other. This is called a <u>Conflict</u>. In such a case the decision as to which transition fires is arbitrary. This ability to represent both concurrency and conflict makes Petri nets a very powerful modeling device.

The marking of Fig.2.2b is obtained from the marking of Fig.2.2a by firing only one transition  $t_1$ . The marking of Fig.2.2b is called <u>Immediately Reachable</u> from the marking of Fig.2.2a. The marking of Fig.2.2d is obtained by firing the transitions in sequence  $t_1 t_2 t_3 t_4$  or  $t_1 t_3 t_2 t_4$ . The marking of Fig. 2.2d is said to be <u>Reachable</u> from the marking of Fig.2.2a. Thus, <u>Definition 2.7</u>: A marking M' is immediately reachable from M if the firing of some t in M yields M'. Definition 2.8 : A marking M' is reachable from M if there exists a legal firing sequence which transforms M to M'. <u>Definition 2.9</u> : The <u>Reachability Set</u>  $R_N(M)$  of a marked PN,  $N = (P, T, \alpha, \beta, M)$  is the set of all markings reachable from M. Whenever there is no ambiguity R(M) will be used instead of  $R_N(M)$ . <u>Definition 2.10</u> : The Reachability Problem is defined as: Given M', is M' $\epsilon R(M)$ ?

Other concepts of Petri nets can also be explained with the help of Fig.2.2. It is observed here that the token in any place and in any marking is atmost one. Such a PN is called <u>Safe</u> or <u>1-bounded</u>

Definition 2.11 : A place in PN, N = (P, T,  $\alpha$ ,  $\beta$ , M) is <u>k-bounded</u> if and only if there exists a fixed k such that V M' $\epsilon$  R(M) : M'(p)  $\leq$  k. A place is safe if it is 1-bounded. A marked PN is bounded if each place is k-bounded for some k. A marked PN is safe if each place is safe.

For a Petri net which is to model a real hardware device, one of the important properties is boundedness and in special case safeness. If a place is safe, then the number of tokens in the place is either 0 or 1. Thus the place can be implemented by a single flip-flop. In an ordinary PN, if a place p is not safe, then p can be forced to be safe by supplementing it by another place p' [121] in the following manner: If  $p \in {}^{\circ}t$  and  $p \notin t^{\circ}$ , then add p' to  $t^{\circ}$ If  $p \in t^{\circ}$  and  $p \notin {}^{\circ}t$ , then add p' to  ${}^{\circ}t$  However, if a place is not safe but bounded, it can be implemented by a counter. Thus a bounded PN could be realized in hardware while a PN with unbounded place can not in general be implemented.

Another important property of a PN is the representation of <u>Deadlock</u> which has been the subject of a number of studies in Computer Science [59]. A deadlock in a PN is a transition ( or a set of transitions) which can not fire. Consider Fig.2.2d. None of the transitions can fire and PN is said to be deadlocked. A transition is <u>Live</u> if it is not deadlocked.

<u>Definition 2.12</u> : A transition t in a marked PN, N = (P, T,  $\alpha,\beta,M$ ) is live if for each M' $\epsilon$  R(M) there exists a marking reachable from M' in which t can be fired. A marked PN is live if each transition is live.

<u>Definition 2.13</u> : A marked PN, N = (P, T,  $\alpha$ ,  $\beta$ , M) is free from deadlock if for V M' $\epsilon$  R(M); some t  $\epsilon$  T can fire in M'.

So far the discussion has been limited to PNs as an abstract model. When it represents a real system, a meaning or <u>Interpre-</u> <u>tation</u> is assigned to various entities - namely, transitions, places and tokens. Thus a transition in a PN may represent an event, instruction or a program. A place can represent a condition or a type of resource etc. whereas tokens will represent holding of a condition or number of resources etc.

An important property in Petri nets is <u>Conservation</u> of tokens. If toknes are used to represent resources, then the tokens must be conserved because the resources can neither be created nor destroyed. One way to do this is to maintain total number of tokens in the net, constant for every marking.

<u>Definition 2.14</u> : A marked Petri net,  $N = (P, T, \alpha, \beta, M)$  is <u>Strictly Conservative</u> if  $\forall M' \in R(M)$  :  $\Sigma M'(p) = \Sigma M(p)$ peP peP

This implies that each transition in a conservative net must have equal number of input and output places i.e.  $|^{\circ}t| = |t^{\circ}|$ . If it were not so, firing transition t will change the number of tokens in the Petri net. More generally, weights can be defined for each place as long as weighted sum is constant [84]. This still allows the conservation of resources because there is no one-to-one mapping between takens and resources. Some tokens may represent program counters etc., and a token may represent several resources. This token is later used to create one token for one resource by firing a transition. Hence a generalized conservation is defined. <u>Definition 2.15</u> : A marked Petri net, N = (P, T,  $\alpha$ ,  $\beta$ , M) is conservative with respect to a weighting vector W =  $[w_p]_{pexl}$  with  $w_p \geq 0$ , if

$$W' \in R(M): \Sigma W_{p} \cdot M'(p) = \Sigma W_{p} \cdot M(p)$$

### 2.4 MODELING WITH PETRI NETS

Petri net has found its way in modeling a variety of systems. Holt, et al. [60] have shown that Petri nets can model two aspects of the systems, <u>Events</u> and <u>Conditions</u>. In their view, a token may be thought of as representing the presence of some condition associated with its place. The firing of a transition is thought of as corresponding to the occurence of and event which may take place if all the necessary conditions are satisfied. The occurence of an event will cause some of previous conditions to cease holding, and causing other conditions to begin to hold. This is represented by a new marking. Many systems can be covered into events and conditions and, thus, can be represented by a PN [121].

#### 2.4.1 MODELING OF HARDWARE

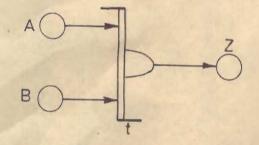

One of the important features of Petri nets is their ability to model computer hardware at different levels. At the lowest level i.e. simple memory devices and gates, computer systems can be described by state machines and hence by Petri net [121]. Though the PN discription is a bit complicated compared to state machine description, it has certain advantages in combination of machines. The combination in state machine is complex and requires a composite state with components of many submachines - a <u>Gross</u>-<u>Product</u> machine. For Petri nets, the composition is simply the <u>Cascade</u> connection (i.e. the overlapping of the output places of one net with input places of another and so on), or <u>Parallel</u> <u>Connection</u> ( i.e. duplicating the input tokens which represent input symbols). It appears such interconnections of Petri nets have not been studied so far and have been taken up in Chapter IV.

An example for modeling computer hardware at the level of registers as fundamental components of the system is the representation of n-stage pipelined operation through Petri nets [5], [100], [120], [121]. It is interesting to note that two

-25-

successive stages could be modeled in more detail by a PN, if one is interested to ensure that each pair of successive processors communicates through 'ready' and 'acknowledgement' signals.

Another approach to build very fast large computer systems, is to provide multiple functional units to perform computations on multiple registers with maximum possible parallelism. Computers such as the CDC 6600 [143] and the IBM 360/91 [12] are based on this concept. These can be modeled by Petri nets though they will require very complicated and large nets [121]. Dennis [34] has modeled through Petri nets a functional unit computer which resembles CDC 6600. Petri nets have also been used to model the interconnection of hardware modules [62], a modular microprogrammable computer [108] and I/O devices of a mini\*computer [150].

## 2.4.2 MODELING OF SOFTWARE

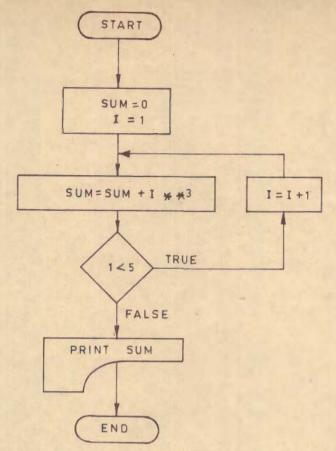

The efforts in modeling computer software have resulted in different concepts and techniques in analysis, specification and description of programs. A program has two aspects - computation and control. Petri net can represent in a straightforward manner the control aspects (i.e. the sequencing of instructions and flow of information and computation) but not the actual information values. The flowchart representation of a sequential program can easily be converted into a Petri net. The transitions are associated with the actions of the program, i.e. the computations and decisions. A token residing in a place means that the program counter is positioned ready to execute the next instruction.

-26-

Parallelism in a program has also been represented by PN [5] but can be exploited usefully only when the <u>Component</u> <u>Processes Coordinate</u>. Such a coordination requires sharing of information. Many synchronization problems arising in coordinating processes, for example mutual exclusion problem [37], producer/ consumer problem [38], the dining philosphers problem [38], and the readers/writers problem [28] have been proposed. Petri nets can clearly and explicitly represent these [5]-[7], [28], [83], [120], [121]. Also available is the analysis for system verification [5]-[7], [83].

Petri nets have been applied to compiler modeling to determine whether existing compilation algorithms are suitable for parallel processing [15], [16]. The Fortran programs for CDC 6600 computers have been converted into PN showing precedence constraints between operations [136]. This net is then merged with a PN representing the CPU. Timing information is associated with transitions, and an exhaustive search is used to determine the sequence of operations to minimize execution time. The SOLO operating system and the Scope operating system of CDC 6400 computers have also been modeled by Petri nets [20], [105]. However, the latter has used some extensions such as addition of Exclusive-OR to Petri Nets.

# 2.4.3 SPEED-INDEPENDENT CIRCUITS

In a speed independent circuit the presence of arbitrary delays in elements and connections have no effect upon circuit operations. Synthesis of music through a processor [95] is one of

-27-

many examples. Petri net has a potential for describing such circuits [118]. Places, tokens and transitions could represent wires, signals and actions. In addition to modeling, implemen tation of Petri nets has also been studied [95], [112], [113], [118], and shown to be inherently fail-secure [112]. However, there are many unsolved problems, like fault detection and isolation. This is mainly because these problems require the use of timing information.

# 2.5 SUBCLASSES OF PETRI NETS

Generalized Petri nets and for that matter Petri nets, are too powerful to analyse. Many researchers have defined, by restrictions on the structure of Petri nets, many subclasses with intentions mainly to improve their analysing capability. These subclasses do model several systems in different environments but, obviously, their modeling power is limited. The important subclasses are discussed as follows:

## 2.5.1 MARKED GRAPH

Marked graph is a subclass of Petri nets in which each place has exactly one outgoing and one incoming arc. These arcs are combined into one to represent the place. Further, a vertex represents a transition. The signals or data passing through each arc come from a predetermined source (the initial node), and are sent to predetermined destination (the terminal node). Thus, marked graphs can represent concurrency but not conflict. This limits its modeling power. However, computer systems such as

-28-

communication protocols in distributed computing [91], [128], n-stage pipelined operations used in high performance computer systems, parallel activities between central processing and disc or I/O jobs [111], and the changing operations in GRAY-1 computer [128] are but a few examples that can be modeled by marked graph [100]. Marked graph, on the other hand, has been shown to have very high decision power [26], [27], [43], [60], [64], [67], [98], [99], [101]-[103]. There are algorithms available for liveness, safeness and for solving reachability problem.

#### 2.5.2 STATE MACHINES

State machines [60], [120] are restricted Petri nets so that each transition has exactly one input and one output place. These are in the class of finite-state machines, hence are very powerful as far as decision problems are concerned. The modeling power is, however, limited.

## 2.5.3 FREE-CHOICE PETRI NETS

A free-choice Petri net is one wherein every place p is either the only input place of a transition or there is atmost one transition which has p as one of the input places. This means that either the token will remain in that place until its unique output transition fires or if there are multiple outputs for the place, then there is a free-choice of firing a transition. Hence, either all of these conflicting transitions are simultaneously enabled, or none of them are. It has been shown [26], [49] that liveness and safeness are decidable for free choice Petri nets. Although these nets are very helpful in modeling systems similar

-29-

to that of assembly-line, no work is available regarding other properties like reachability, equivalence, containment, and languages, etc.

# 2.5.4 PURE OR RESTRICTED PETRI NETS

A pure Petri net is one in which no place is both input and output of the same transition. It has good modeling power and has been shown to represent [83] a Semaphore by Dijkstra [38], bounded buffer problem [48] and five dining philosphers problem [38]. As Pure Petri nets are equivalent to PN and each can be transformed into another as far as reachability is concerned, these have the same decision power as that of Petri net. Furthermore, structural properties have been studied [83], [137] to decide many problems like liveness, broundedness in terms of invariance and consistency of pure nets.

# 2.5.5 SIMPLE PETRI NETS

In simple Petri nets [49] each transition has atmost one input place which is shared with another transition and so also serve to restrict the manner in which conflict can occur. No investigations have been made about the properties of this sub class of Petri nets.

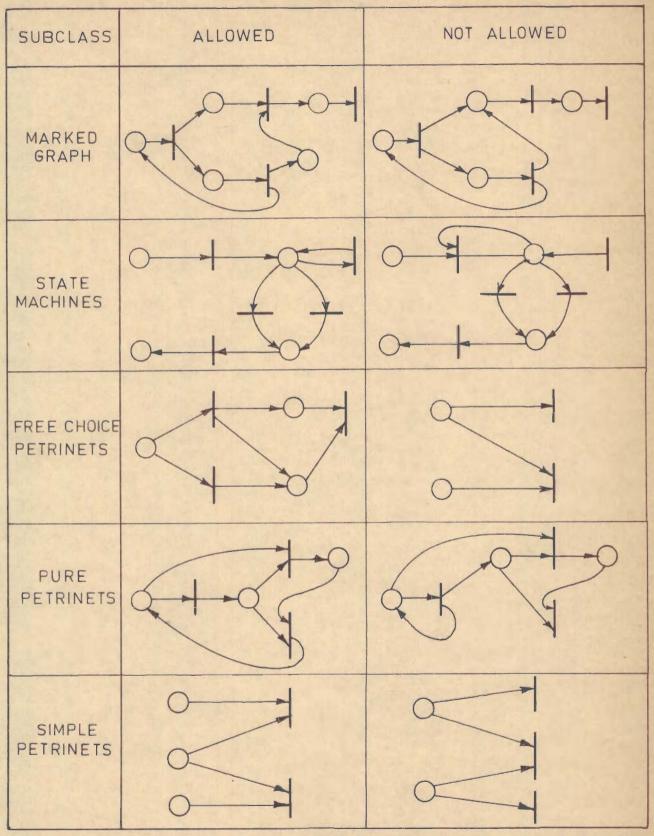

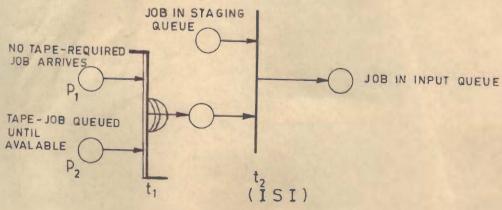

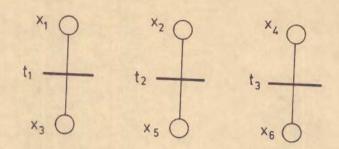

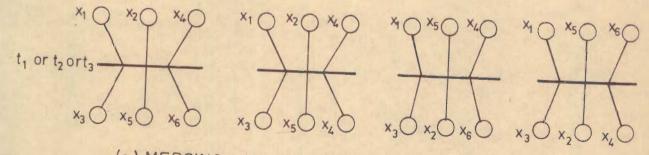

A simple chart showing some of the subclasses of Petri nets with allowed and not allowed configuration is given in Fig.2.3. It can be easily found by inspection as to why the configuration on the right hand of Fig.2.3 are not allowed.

-30-

FIG. 2.3 \_ ALLOWED AND NOT ALLOWED STRUCTURAL CONFIGURATION OF VARIOUS SUBCLASSES OF PETRINETS

1.0

## 2.6 ANALYSIS OF PETRI NETS

To study the systems through Petri nets there are two approaches available in literature. One approach is aimed at deriving properties of Petri nets, and the properties of the system modeled. In the other approach [96] the design process is carried out directly in terms of Petri nets and the resultant PN is implemented straightway [40], [113], [116]. Both these approaches require that the knowledge about the Petri net itself be available. This has led to an extensive research in the theory of Petri nets [6], [7], [21], [27], [49], [60], [82]-[84], [97], [100], [102], [120], [137], [147], [148].

The objective of the analysis of PN is to determine certain properties. Some of these such as reachability, safeness, boundedness, conservation etc. have been discussed in Section 2.3. There are other important properties as well and those will be introduced as and when needed. Obviously the analysis technique must be such that it is easily implemented on computer to allow automatic analysis of modeled systems. With this view, two major available analysis techniques are discussed as follows:

## 2.6.1 THE REACHABILITY TREE

The reachability tree of a Petri net is a tree the nodes and arcs of which represent the reachable marking and the possible changes in state resulting from the firings of transitions [69], [70], respectively. As the reachability tree is finite [121], it is possible to have a finite representation of infinite

-32-

reachability set often encountered in Petri nets. If it is found that a transition adds a token at a place every time it fires, then the number of tokens in that place is represented by w which is 'too large' such that  $w \pm x = w$ , x < w for any integer x. With these concepts, the reachability tree of PN, N = (P, T,  $\alpha$ ,  $\beta$ ,  $\frac{M}{O}$ ) where M is initial marking is constructed as follows:

Let the initial marking be the root node and tag it 'new' WHILE new markings exist DO

Select a new marking M.

If M is identical to another node in the tree which is

not new, then tag M to be old and stop processing M.

If no transition is enabled in M, tag M to be 'terminal'.

For every transition t enabled in M

- (1) Obtain the marking M' which results from joinint t in M

- (2) If there exists a path from the root to M containing a marking M" such that M'> M", then replace M'(p) by w when M'(p) > M"(p).

- (3) Introduce M as a new node, draw an arc from M to M ' labeled t, and tag M' to be 'new'.

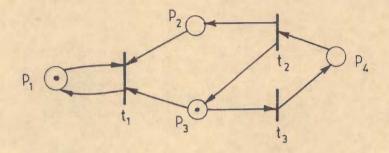

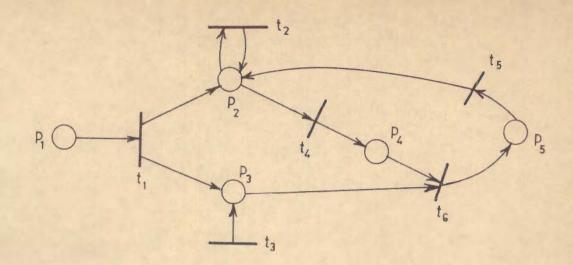

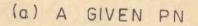

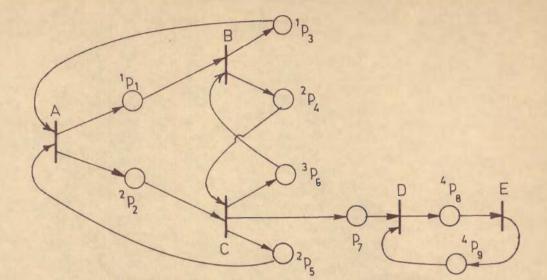

As an example, the reachability tree of a marked Petri net (Fig. 2.4) is shown in Fig.2.5.

The reachability tree can be used as a useful analysis tool to determine some of the properties of Petri nets and thus can solve several problems. The following properties are decided using the reachability tree.

FIG. 2.4 \_ A MARKED PN

FIG. 2.5 \_ THE REACHABILITY TREE OF PN IN FIG. 2.4

#### 1. Safeness and Boundedness:

If a PN is k bounded, then by definition no more than k tokens are present in any of the places. Each place can have any number of tokens given by an element of the set {0,1,2,....,k} i.e. each place can have (k+1) possible tokens. Hence the number of possible reachable markings equal (k+1)<sup>n</sup> which is a finite reachable state-space. In order to determine the bound k on a particular place, the reachability tree is first generated. If w appears in the reachability tree, the net is unbounded because w is 'too large' and there exists a sequence of transition firings which can be repeated arbitrarily many times to increase the number of tokens to an arbitrarily unbounded number. If w does not appear, then the reachability tree is scanned for the largest value of the components of the markings corresponding to that place. If bound for all place is 1, then the net is safe.

2. Conservation:

If a PN is strictly conservative, then the number of tokens in each marking remains constant. Say, this number is k. Since there are finite number of ways to partition k tokens among n places, we have a finite reachability set. Thus strict conservation of tokens can be tested by computing sum of tokens in each marking. If sums are same then the net is strictly conservative. However, if w appears in the reachability tree, then the Petri net is not strictly conservative because w, though 'too large', is different for any two markings.

WENTER A DE ROOMRED

-35-

The generalized conservation is generally given with respect to a defined weighting vector or undefined weighting vector. In the first case the weights of each place is known. If w appears in reachability tree for a place, say p and the weight of p is nonzero positive, then the weighted sum of the tokens for two markings will be different in their w component. Thus the net will not be conservative. On the other hand if the weights of all the places for which w appears are zeros, then the net is conservative. For the case when there is no defined weighting vector, a Petri net is conservative if it is conservative with respect to some weithting vector W, with  $w_p > 0$ .

3. Coverability:

An important problem in Petri nets is coverability of markings which is useful in determining the occurence of variation in mutual exclusion in a system and in testing transitions for liveness and deadlock. This is defined as follows:

<u>Definition 2.16</u>: Given a PN, N = (P, T,  $\alpha$ ,  $\beta$ , M) and a marking M' $\epsilon$  R(M). The existence of another marking M" $\epsilon$  R(M) such that M"  $\geq$  M is called a coverability problem.

This problem can be solved by inspecting reachability tree [54], [69] and searching for a node x with marking  $M_x \ge M'$ . If no node is found, the marking M' is not covered by any reachabe marking. If such a node is found, this gives a reachable marking which covers M'. Karp and Miller [69]have proposed an algorithm to determine the minimal number of transition firings to cover a given marking.

## 2.6.1.1 LIMITATIONS OF REACHABILITY TREE

The reachability tree can not solve the reachability or liveness problem. Also this can not determine which firing sequences are possible. To solve these problems it is required to know the exact number of tokens on places in different markings. This information is lost in the symbol w. However, in some particular cases reachability or liveness may be solved. For example, a Petri net whose reachability tree has terminal node (one with no successors), is not live. Similarly a marking M' may appear in the reachability tree then M' is reachable from M. Also, if a marking is not covered by some node, then it is not reachable.

## 2.6.2 STATE EQUATION OF PETRI NETS

Another approach to the analysis of Petri nets is based on state equation [97] which is quite different from that of normal dynamic systems in that the behaviour of Petri nets is essentially characterized by the control vector of non-negative integers. Even then the state variable technique of system theory can be useful in studying Petri nets. Without loss of generality (as equivalence of generalized Petri nets and singlearc nets exists [50], Petri net is considered.

Since the marking changes as a result of firing, instead of M (definition 2.4) a |P|x| column vector of nonnegative integers M<sub>k</sub> is defined. The jth entry of M<sub>k</sub> denotes the number of tokens on place j immediately after kth firing. Specifically M<sub>o</sub> denotes the initial state. Out of many enabled transitions,

-37-

which transition fires is defined by a control vector  $V_k$  as a |T|x| column vector containing exactly one nonzero entry 1 in the ith position if ith transition is fired at kth firing. The concurrent firing of more than one transitions is allowed and can be expressed as the sum of corresponding control vectors.

From the definition of firing, it is found that the state  $M_k$  resulting from another state  $M_{k-1}$  by kth firing  $V_k$  can be given in terms of following Murata's state equation:

$M_k = M_{k-1} + A^T V_k$ , k = 1,2,... (2.1) where  $A^T$  is transpose of transition-to-place incidence matrix (definition 2.3). It is noted that the ith row of A represents the token changes in |P| places when ith transition fires once. For marked graphs, A reduces to the incidence matrix of a diagraph.

Since  $M_k$  is a vector of nonnegative integers,  $V_k$  must satisfy

$$M_{k-1} + A^T V_k \ge 0$$

for each k (2.2)

Let there exists a firing sequence  $\{V_1, V_2, \dots, V_n\}$  that transforms an initial marking  $M_0$  to  $M_n$  of a Petri net. Then the solution is given by addition of the n equations of (2.1) for  $k = 1, 2, \dots, n$ .

$$M_{n} = M_{0} + A^{T} \begin{bmatrix} n \\ \Sigma \\ k=1 \end{bmatrix}$$

which can be written as

$$A^{\mathcal{L}} \Sigma = \Delta M \tag{2.3}$$

where  $\Delta M = M_n - M_o$  and  $\Sigma = \sum_{k=1}^{\Delta} V_k$  is a  $|T| \times 1$  column vector of

nonnegative integers called by <u>Firing Count Vector</u>. The ith entry of  $\Sigma$  represents the number of times the transition i would fire in a firing sequence leading from M to M<sub>n</sub>.

Based upon the above concept, the following have been obtained:

1. A necessary condition [97] that a Petri net is completely reachable i.e. any initial marking can reach any other marking is

$$Rank A = |P|$$

(2.4)

2. Given two markings M and M for a connected marked graph G, there exists a non-negative integral solution  $\Sigma$  for

$$M\Delta = \mathcal{I}^{T} \Delta$$

if and only if

$B_{r} \Delta M = 0$

where  $\Delta M = M_n - M_o$  and  $B_f$  is a fundamental circuit matrix [102].

In most of the practical applications of Petri nets, the condition (2.4) is rarely satisfied. The rank of A is generally less than the number of places in a Petri net. In such cases, the PN is uncontrollable or not completely reachable. Let the rank of A be r. Then, A can always be partitioned in the following form:

$$A = \begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix} \uparrow r$$

(2.5)

$$(2.5)$$

We can always find  $(|P|-r) \times |P|$  matrix  $B_{f}$ :

$$B_{f} = [I : A_{11}^{T} (A_{12}^{T})^{-1}]$$

(2.6)

where I is the identity matrix of order (|P|-r), such that

$$A B_{f}^{T} = 0$$

It may be noted that B<sub>f</sub> corresponds to fundamental circuit matrix in case of marked graph.

Thus, eq. (2.2) is consistent if and only if

$$B_{f} \Delta M = 0 \tag{2.7}$$

If there exists a firing sequence which transforms  $M_{o}$  to  $M_{n}$ , then the corresponding firing count vector  $\Sigma$  must exist and (2.7) must hold. Therefore,

- 3. A condition (2.7) is necessary for the existence of a firing sequence which transforms an initial marking M<sub>0</sub> to another marking M<sub>n</sub> in a Petri net [97].

- 4. In a Petri net, a state  $N_0$  cannot reach another state  $M_n$ , if their difference is a linear combination of the rows of  $B_f$  [97] i.e., if

$\Delta M = M_n - M_o = B_f^T V_n$

where  $V_n$  is a nonzero (|P|-r) x 1 column vector.

<u>Comments</u><sup>\*\*</sup>: To test if a given initial state can not reach another given state, one has to calculate  $B_f$ . For this, first A is determined for PN. Then largest nonsingular submatrix  $A_{12}$  of A is obtained in the form as in (2.5). To find  $B_f$ ,  $(A_{11}^T)^{-1}$  is determined. This is quite involved process. Thus calculation of  $B_f$  requires a lot of computation. It has been shown in the Chapter IV that the nonreachability condition can be obtained in terms of A and  $\Delta M$ . As  $B_f$  is not calculated, the testing of nonreachability becomes very simple.

The state equation approach deals basically the reachability problem. It has great promise and can solve many problems of Petri nets. It must also be noted that a similar matrix approach has been taken in independent research in Europe [21], [29], [43], [83], [137]. The liveness problem and indirectly, the reachability problem which is reducible to liveness [56] has been tackled in [21], [43], [81]. While the reference [29] uses the concept of formal languages as main vehicle, some structural properties of Petri nets have been found in [137]. Some concepts not covered in state equation and proposed by these researches in matrix approach and by others, for example [5], [7], [100], etc. are given below. As the inclusion of these concepts does not change the nature of state equation, the combined approach will be called as the state equation approach.

\*\* Denotes specific comments by the author.

• End of specific comments.

Of special interest for determining properties of Petri nets is the concept of <u>Invariance</u>. It is defined as under: <u>Definition 2.17</u> : A Petri net,  $N = (P, T, \alpha, \beta) = (A, --)$  is said to be invariant if there exists a |P| xlvector I with all its components positive such that

$$AI = 0 \tag{2.8}$$

Using eq.(2.3) and (2.8), the following is obtained

$$(\Delta M)^T I = V_K^T(AI) = 0$$

or

-

$$\mathbf{M}_{\mathbf{K}-\mathbf{l}}^{\mathbf{I}} \mathbf{I} = \mathbf{M}_{\mathbf{K}}^{\mathbf{T}} \mathbf{I}$$

(2.9)

Due to the invariant property expressed in (2.9), I is called an invariant of Petri net. However, a widely used concept [83] is that of a Simple Invariant.

Definition 2.18 : A simple Invariant is a set of places, I, such that Σ M(p) is a constant for each reachable marking M, and I does not have any proper subsets that are simple invariants.

From the definition, it is evident that the simple invariants are disjoint sets. From the set of simple invariants, some properties about the dynamic behaviour of the Petri net can be deduced [7], [83]. For example, the following properties are obtained:

#### 1. Boundedness and safeness:

If each place is in some simple invariant and the Petri net has initially a bounded marking, the net is bounded. Same is true for safe nets. This is, obviously, so because the number of tokens in a simple invariant is constant and all the places are covered by simple invariants.

2. Conservativeness:

If the set of places can be partitioned with disjoint subsets each of which is a simple invariant, the net is conservative and the total number of tokens in the net remains constant.

3. Mutual Exclusion:

If an input or output place of a transition t is contained in a simple invariant I, t is said to be a transition of I. If two transitions correspond to same simple invariant and the initial marking is such that the sum of tokens in the places of the invariant is 1, then the transitions are mutually exclusive and cannot fire simultaneously.

4. Liveness:

Under certain presuppositions, the simple invariants may be interpreted as <u>Complete System</u> of <u>Circuits</u>. When analysing liveness, so-called <u>Variants</u> are of interest, and these may be interpreted as incomplete systems of circuits [83].

In order to reduce the complexity in deciding the properties of Petri nets, the notions of boundedness and liveness have been defined so as to be independent of a given marking [137] but dependent only upon the structure of PN.

Definition 2.19 : A PN is <u>Structurally Bounded</u> if it is bounded for every marking and is <u>Structurally Live</u> if there exists a marking for which it is live. The structural boundedness and liveness have been studied [137] with a view that it is generally easier to decide if a Petri net is bounded (respectively not live) for every marking than it is bounded (respectively not live) for a given marking. A concept which has been used apart from the net invariance is Consistency.

<u>Definition 2.20</u> : A PN, N = (A, -) is <u>Consistent</u> if there exists a |T|x| vector X with all its components positive such that

$$\mathbf{A}^{\mathrm{T}}\mathbf{X} = \mathbf{0} \tag{2.10}$$

From the study of incidence matrix of pure Petri nets, the following properties have been obtained [137].

- i. If a Petri net is bounded and live then it is consistent. The converse is also true.

- ii. If a Petri net is invariant, it is bounded.

- iii. If a PN is bounded and consistent, then it is invariant and for every marked PN (A,M) the reachability set R(M) is constituted of pairwise incomparable vectors. This permits to calculate an upper bound of the cardinality of its marking classes. For example, if (A,M) is safe [49], then  $R(M) \leq {n \choose k}$  where  $k = \frac{n}{2}$  if n is even and  $k = \frac{n-1}{2}$  if n is odd.

- iv. (a) If a PN is consistent and invariant, it is bounded and live.

- (b) If a PN is invariant and nonconsistent then it is not live.

# (c) If a PN is noninvariant and nonconsistent, then it is neither bounded nor live.

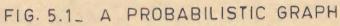

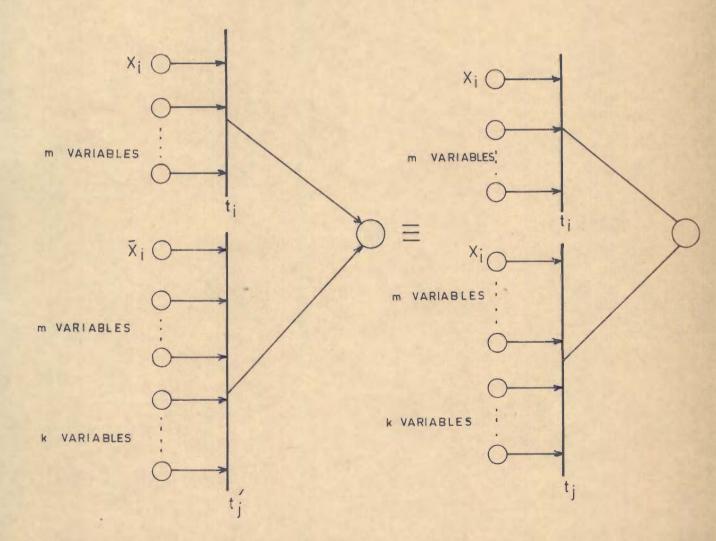

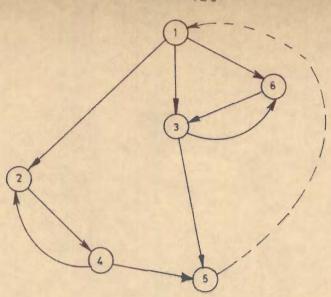

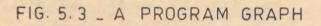

<u>Definition 2.21</u>: Given a PN, N = (P, T,  $\alpha$ ,  $\beta$ ), a Subnet of N is a PN, N<sub>1</sub> = (P<sub>1</sub>, T<sub>1</sub>,  $\alpha_1$ ,  $\beta_1$ ) such that P<sub>1</sub> P, T<sub>1</sub> T and  $\alpha_1$ ,  $\beta_1$ are the restrictions of  $\alpha$ ,  $\beta$  on P<sub>1</sub>X T<sub>1</sub>. The Union of two subnets N<sub>1</sub> = (P<sub>1</sub>, T<sub>1</sub>,  $\alpha_1$ ,  $\beta_1$ ) and N<sub>2</sub> = (P<sub>2</sub>, T<sub>2</sub>,  $\alpha_2$ ,  $\beta_2$ ) is a subnet N<sub>3</sub> = (P<sub>3</sub>, T<sub>3</sub>,  $\alpha_3$ ,  $\beta_3$ ) with P<sub>3</sub> = P<sub>1</sub>  $\bigcup$  P<sub>2</sub> and T<sub>3</sub> = T<sub>1</sub>  $\bigcup$  T<sub>2</sub>. Being given a PN, N and a set S of subnets N it is said that N is <u>Covered</u> by S or that S is a <u>Decomposition</u> of N if the union of elements of S is equal to N.