### ANALYTICAL STUDY OF CMOS-SUBTHRESHOLD OPERATION FOR LOW POWER VLSI APPLICATIONS

#### **A THESIS**

Submitted in fulfilment of the requirements for the award of the degree of DOCTOR OF PHILOSOPHY

#### in

#### ELECTRONICS AND COMPUTER ENGINEERING

by

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA) OCTOBER, 2007

# © INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, 2007

### INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

#### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the thesis entitled 'ANALYTICAL STUDY OF CMOS-SUBTHRESHOLD OPERATION FOR LOW POWER VLSI APPLICATIONS' in fulfilment of the requirements for the award of the Degree of Doctor of Philosophy submitted in the Department of Electronics and Computer Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from July 2001 to April 2006 under the supervision of Prof. R. P. Agarwal, Prof. S. Sarkar and Prof. S. C. Handa.

The suggestions have been incorporated in compliance with the examiners' remarks.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

Bhans-

(BHAVANA JHARIA)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

Date:29/10/07

Dr. R. <del>P</del>. Agarwal Professor Dept. of E & CE

I. S. Sarkar Professor (Rtd) Dept. of E & CE

Dr. S. C. Handa Prof.& Coordinator (Rtd) Q. I. P. Centre

The Ph.D. Viva-Voce examination of **Ms. BHAVANA JHARIA**, Research Scholar, has been held on 124/240-8 -.

Signature of Supervisor (s)

Sr. Handy

Signature of External Examiner

Signature of HOD

## ABSTRACT

In recent years, there has been increasing prominence of portable battery operated low power systems such as hearing aids, pacemakers, cell phones, pagers, and portable computers become more complex, prevalent, and demand increased battery life. Therefore, the demand for increased battery life will require designers to seek out new technologies and circuit techniques to maintain high performance with longer battery lifetime. Portable devices, however, are not the sole motive behind the low power and low energy design efforts. The increasing power dissipation for fixed supply devices is almost equally challenging as for portable devices.

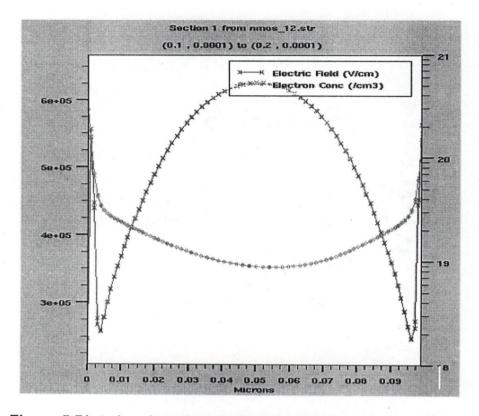

As technology feature size is reduced, the number of transistors on the chip is increased and more power is dissipated. The main components of power dissipation are switching power and leakage power. Switching power, being the dominant power component, has caught special attention in recent years. Many techniques have been introduced to control this ever-increasing power component on all levels of design abstraction. Increased leakage current due to technology feature downsizing is another challenge that faces circuit designers in the VLSI and ULSI era. In the VLSI circuits a large number of MOSFETs are often simultaneously biased in the subthreshold region of operation due to ultra-low power consumption with moderate performance degradation. In such a situation, the subthreshold currents due to the individual devices add up to a source of substantial power dissipation. This power dissipation is highly undesirable, as it causes many reliability problems. In submicron devices the problem is further aggravated by the high electric field existing in the channel region. Under the influence of high electric field the carriers multiply by impact-ionization. The result is an increased drain current.

In this thesis, an analytical approach is developed to analyze effect of scaling and impact ionization in submicron and deep submicron MOSFETs.

ii

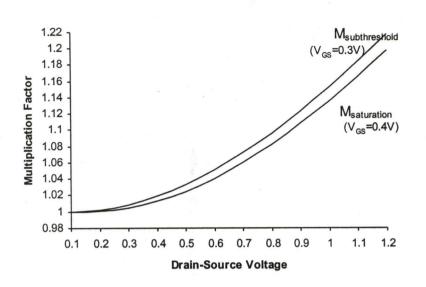

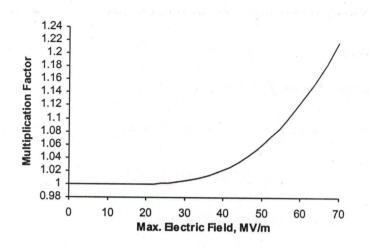

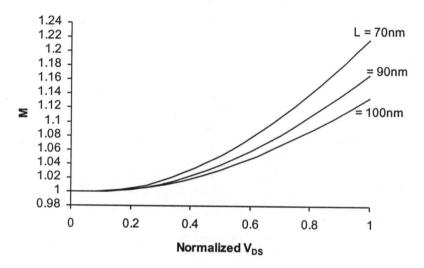

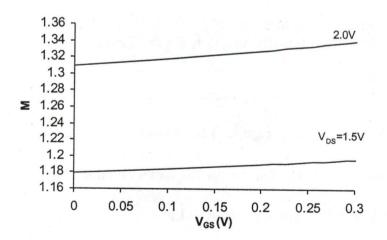

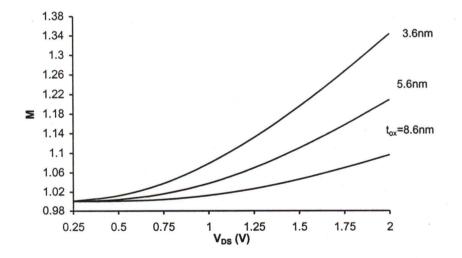

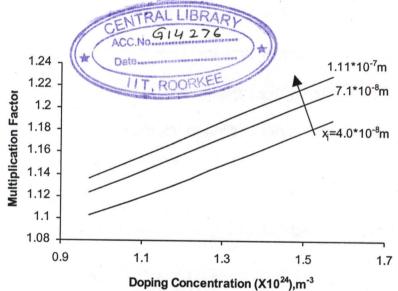

To include the effect of impact ionization on drain current, multiplication factor is first determined using well-established expressions. The analysis shows that for subthreshold operation it is important that the effect of impact ionization should be included in the analytical expression for drain current. Calculations show that multiplication factor increases with drain-source voltage,  $V_{DS}$ , and gate voltage and decreases with increase in gate oxide thickness. Calculations also show that multiplication factor increases in drain/source pn-junction depth. However, multiplication factor levels off at larger junction depths. Shallower junctions are therefore desirable if carrier multiplication is to be restricted.

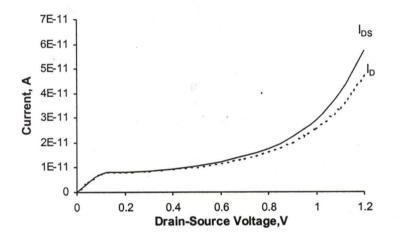

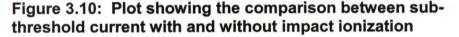

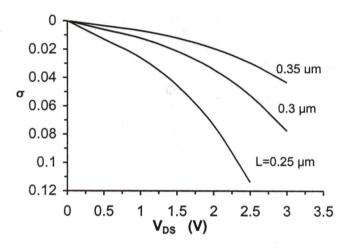

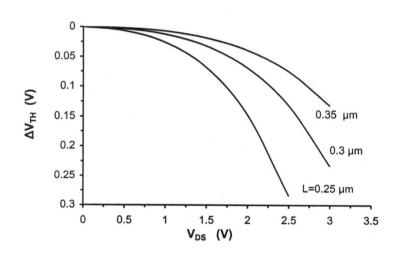

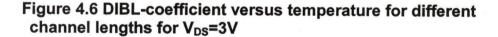

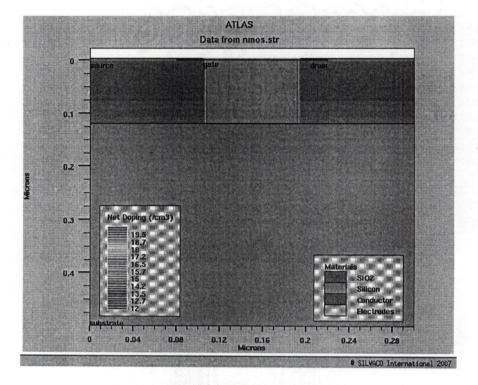

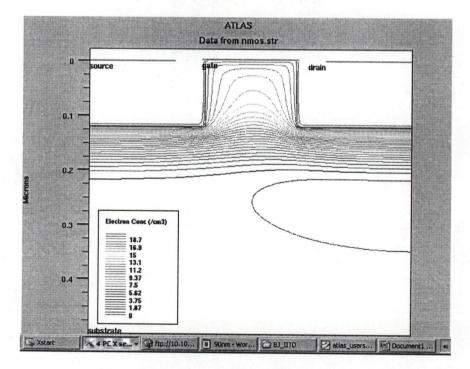

Present study considered Fjeldly and Shur's physical model for subthreshold current. While this model yields accurate results for submicron devices, it does not take into account the effect of impact ionization, which is more prominent in devices of nanometer channel length. The subthreshold current model of Fjeldly and Shur is therefore, first modified to include the effect of impact ionization, for all analytical purposes. The modified current model agrees well with results obtained from ATLAS simulation. It shows that impact ionization increases subthreshold current by few percents. Such an increase in subthreshold current model, the DIBL –coefficient was reconsidered. It has been found that this parameter is not independent of the terminal voltages of a MOSFET. The DIBL- coefficient has a strong dependence on  $V_{DS}$  and relatively lesser dependence on gate-source voltages  $V_{GS}$ . This analysis shows that, because of the strong  $V_{DS}$  dependence of the DIBL-coefficient, the threshold voltage shift is a non-linear function of  $V_{DS}$ , in contradiction to a constant DIBL-coefficient as assumed previously. It is also found that DIBL- coefficient increases with increase in temperature.

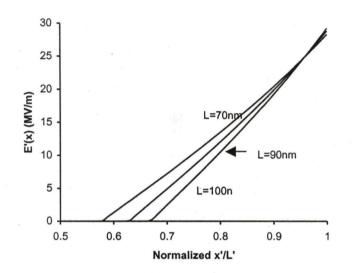

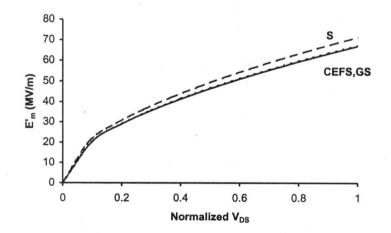

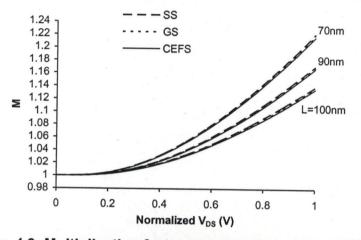

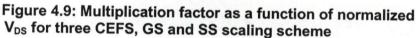

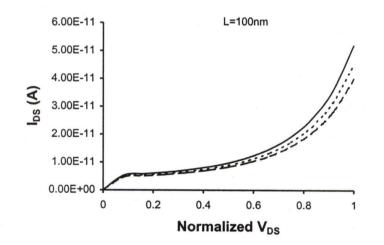

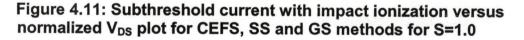

Effect of scaling methods on the subthreshold conduction of a small geometry device is also analyzed. The results show that as the channel length is scaled down, multiplication factor increases slowly in the higher regime of channel length. In the lower regime of channel length, multiplication factor rises rapidly. This result also justifies the inclusion of impact – ionization effect on subthreshold current. However, the analysis shows that there is insignificant dependence of multiplication factor on the method of scaling. Constant electric field scaling produces the largest threshold voltage shift due to DIBL. Selective scaling has the least DIBL, with generalized scaling produced DIBL falling in between the two extremes.

Finally in this thesis, an analytical approach is developed to obtain optimal  $V_{DD}$  for minimizing total power dissipation. It is well known that in above threshold CMOS operation, a tradeoff exists between propagation delay and power dissipation, when voltage is scaled. When the supply voltage is scaled down to reduce power dissipation, propagation delay is increased. SPICE simulation, however, shows that this does not hold good for subthreshold logic. For a threshold CMOS– logic operation, propagation delay in most cases first increases and then decreases with supply voltage scaling. The subthreshold current model mentioned above is used to calculate voltage dependence of propagation delay of a CMOS inverter. The results thus obtained show that, the delay increases with increase in supply voltage. An important requirement of a logic circuit is symmetric input-output characteristics. The ratio of pMOS and nMOS widths that meets this requirement is determined using the modified subthreshold current model. The ratio thus obtained is primarily mobility dependent, as in the case of above threshold logic operation. The analytical model presented shows very well match with SPICE simulations.

The results of the present investigations can be very useful in designing low power VLSI circuits, which is an immediate necessity in the modern portable electronic gadgets.

## ACKNOWLEDGMENTS

No work can be accomplished successfully and proficiently without the motivation, guidance and support of valuable persons. I am blessed to have **Prof. R. P. Agarwal**, **Prof. S. Sarkar** and **Prof. S. C. Handa** as my supervisors, who were the pillars of strength for me throughout the course of this work and supported me in hours of distress. I feel obliged to **Prof. R. P. Agarwal**, **Ex Vice-Chancellor**, **Bundelkhand University Jhansi (U.P.)**, who persuaded me to take up research in the area of Low Power VLSI. I am indeed grateful to **Prof. R. P. Agarwal** and **Prof. S. Sarkar** for their valuable assistance, dedicated support and helpful technical suggestions during the entire course of research. It was memorable experience for me to enrich myself from their vast experience, great wisdom and deep knowledge. I am beholden to **Prof. S. C. Handa** for his priceless support, advices, and encouragement throughout this research.

I also feel indebted to the Research Committee comprising of **Prof. A. K. Sarje, Prof. D. K. Mehra, Prof. A. K. Saxena and Prof. I. S. Tyagi** for their critical and constructive suggestions and comments during the initial and final scrutiny of this work.

I also want to extend my sincere thanks to **Prof. G. S. Visweswaran**, **I.I.T Delhi** for allowing me to use the laboratory facility and specially ATLAS software at **VLSI Lab.** at **IIT Delhi** to carry out my simulation work. I am highly grateful to him for providing me ample inspiration, holding useful discussion and giving me suggestions from time to time. Thanks are due to Shiva and Babu, M. Tech. students for helping me in the VLSI Lab. at IIT Delhi.

I sincerely thank all faculty members and the staff of Department of Electronics & Computer Engineering, IIT Roorkee for rendering desired help as and when needed. My special thanks are due to Co-ordinator QIP and staff who paid due attention to our problems and also showed a way to come out of it.

I acknowledge my sincere gratitude to the AICTE, MHRD Govt. of India, for financial assistance under QIP and M.I.T. Govt. of India for providing sophisticated VLSI Lab. facility under the project 'Special Manpower Development for VLSI Design and Related Softwares' Dept. of E & CE, IIT Roorkee. I owe my sincere gratitude to the Governing Body of my parent institute Govt. Engineering College, Jabalpur for allowing me to undertake this research under the QIP scheme. I have a special word of thanks for Dr. S. B. L. Beohar, Principal of my parent institute, Prof. S. K. Grover, former H.O.D. and Prof M. P. Parsai, H.O.D., Dept. of Electronics and Telecommunications for giving useful tips and suggestions.

My special thanks and heartfelt gratitude goes to **Dr. (Mrs.) Laxmi Agarwal** for ever making me feel owned, loved and a part of her family. I am thankful to **Mrs. Yashodhara Sharma**, Lecturer & Dy. Dir (HRD), Institute of Economics & Finance, Bundelkhand University, Jhansi for extending her help and support.

Thanks are due to my fellow research scholars and friends for sharing some very odd and even moments during the period.

I express my deep gratitude to my mother **Smt. Shashi Devi Jharia** for always posing a great confidence and instilling faith in me. I owe my respect and love to **Chandarji**, my brothers, sisters and brothers-in-laws for their support and good wishes.

I owe a deep sense of gratitude to All-pervading Spirit whose Divine light provided me the perseverance, guidance, inspiration, faith and strength to carry on even when the going got tough.

**Bhavana Jharia**

## **ABBREVIATIONS**

| ICs    | Integrated Circuits                                        |

|--------|------------------------------------------------------------|

| VLSI   | Very Large Scale Integration                               |

| ULSI   | Ultra Large Scale Integration                              |

| DSM    | Deep Submicron                                             |

| VTC    | Voltage Transfer Characteristic                            |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor          |

| nMOS   | n-channel MOSFET                                           |

| pMOS   | p-channel MOSFET                                           |

| CMOS   | Complimentary Metal Oxide Semiconductor                    |

| I/O    | Input-Output                                               |

| SOI    | Silicon-on-Insulator                                       |

| SOIAS  | Silicon-on-Insulator with Active Substrate                 |

| DGSOI  | Double Gate Silicon-on-Insulator                           |

| RAM    | Random Access Memory                                       |

| DRAM   | Dynamic Random Access Memory                               |

| DTMOS  | Dynamic-Threshold Metal Oxide Semiconductor                |

| VTCMOS | Variable-Threshold Complimentary Metal Oxide Semiconductor |

| MTCMOS | Multi-Threshold Complimentary Metal Oxide Semiconductor    |

| CPL    | Complimentary Pass Logic                                   |

| DIBL   | Drain-Induced Barrier Lowering                             |

| GIDL   | Gate Induced Drain Leakage                                 |

| SPICE  | Simulated Program for Integrated Circuit Emphasis          |

| LP   |   | Linear Programming              |

|------|---|---------------------------------|

| 3G   |   | 3 <sup>rd</sup> Generation      |

| nm   |   | Nano-Meter                      |

| μm   |   | Micro-Meter                     |

| MC   |   | Monte-Carlo                     |

| EED  |   | Electron Energy Distribution    |

| MBD  |   | Maxwell-Boltzmann Distribution  |

| BTE  |   | Boltzmann Transport Equation    |

| CEFS |   | Constant Electric Field Scaling |

| GS   |   | Generalized Scaling             |

| SS   |   | Selective Scaling               |

| LOCO | S | Local Oxidation of Silicon      |

| HCE  |   | Hot Carrier Effects             |

| GTC  |   | Gate Tunneling Current          |

| MLV  |   | Minimum Leakage Vector          |

| EDP  |   | Energy-Delay Product            |

|      |   |                                 |

## LIST OF SYMBOLS

| W                | Width of gate                            |

|------------------|------------------------------------------|

| L                | Length of Gate                           |

| V <sub>DS</sub>  | Drain-Source Voltage                     |

| V <sub>GS</sub>  | Gate-Source Voltage                      |

| $V_{GB}$         | Gate-Bulk Voltage                        |

| V <sub>DD</sub>  | Supply Voltage                           |

| V <sub>TH</sub>  | Threshold Voltage                        |

| V <sub>THn</sub> | Threshold Voltage for nMOS               |

| $V_{THp}$        | Threshold Voltage for pMOS               |

| V <sub>TH0</sub> | Zero-Drain-Source bias threshold Voltage |

| V <sub>T</sub>   | Thermal Voltage                          |

| V <sub>sat</sub> | Saturation Voltage                       |

| $P_{SW}$         | Average Switching Power                  |

| α                | Switching Activity Factor                |

| С                | Switching Capacitance                    |

| $\Delta V$       | Voltage Swing                            |

| f                | Switching/Signal Frequency               |

| $P_{parallel}$   | Parallel Power                           |

| P <sub>org</sub> | Original Power                           |

| $C_{org}$        | Original effective Capacitance           |

| $f_{org}$             | Original Signal Frequency                    |

|-----------------------|----------------------------------------------|

| E                     | Electric Field                               |

| $E_m$                 | Maximum Electric Field                       |

| E <sub>th</sub>       | Threshold Energy                             |

| λ                     | Mean Free path                               |

| $\alpha_i$            | Impact-Ionization Coefficient                |

| $A_i(A_n), B_i(B_n)$  | Impact-Ionization Rate Parameters            |

| М                     | Multiplication Factor                        |

| M <sub>sai</sub>      | Multiplication Factor in Saturation region   |

| $M_{lin}$             | Multiplication Factor in Linear region       |

| M <sub>sub</sub>      | Multiplication Factor in Subthreshold region |

| $l_d$                 | Characteristic Channel Length                |

| t <sub>ox</sub>       | Oxide Thickness                              |

| <i>x</i> <sub>j</sub> | Junction Depth                               |

| $L_{e\!f\!f}$         | Effective Gate Length                        |

| x <sub>s</sub>        | Source-Channel Depletion Width               |

| x <sub>d</sub>        | Drain-Channel Depletion Width                |

| I <sub>DS</sub>       | Drain Current With Impact-Ionization         |

| I <sub>D</sub>        | Drain Current (Without Impact-Ionization)    |

| I <sub>dd</sub>       | Drift-Diffusion Current                      |

| I <sub>te</sub>       | Thermionic Emission Current                  |

| $A^*$                 | Richardson's Constant                        |

| δ                     | Effective Channel Thickness                  |

х

| T               | Temperature ⁰K                                                |

|-----------------|---------------------------------------------------------------|

| η               | Subthreshold Ideality Factor                                  |

| X               | Constant                                                      |

| $d_{dep}^{0}$   | Depletion width at Zero Drain Source Bias                     |

| C <sub>ox</sub> | Gate-Oxide Capacitance                                        |

| $C_{dep}$       | Depletion Layer Capacitance                                   |

| $\varphi_b$     | Bulk Potential                                                |

| n <sub>i</sub>  | Intrinsic Carrier Density                                     |

| $N_a$           | Acceptor Doping Density                                       |

| $D_n$           | Diffusion Coefficient                                         |

| $\mu_n$         | Electron Mobility                                             |

| σ               | Drain-Induced Barrier Lowering Coefficient                    |

| $\psi_s^0$      | Potential at Si-SiO <sub>2</sub> Interface at Zero Drain Bias |

| V <sub>bi</sub> | Built-in Potential                                            |

| E(x)            | Lateral Electric Field at Distance 'x' from Source            |

| V <sub>FB</sub> | Flat-band Voltage                                             |

| $N_{sub}$       | Substrate Doping Density                                      |

| $\phi_{_F}$     | Fermi Potential                                               |

| S               | Scaling Factor                                                |

| S               | Voltage Scaling Factor                                        |

| S <sub>d</sub>  | Device Vertical Dimension Scale Factor                        |

| $S_w$           | Device Width and Wiring Dimension Scale Factor                |

| $W_p$           | pMOS Channel Width                                            |

| W <sub>n</sub>       | nMOS Channel Width                    |

|----------------------|---------------------------------------|

| I <sub>DSn</sub>     | nMOS Subthreshold Current             |

| I <sub>DSp</sub>     | pMOS Subthreshold Current             |

| $C_{load}$           | Total Load Capacitance                |

| $C_{e\!f\!f}$        | Effective Switched Capacitance        |

| I <sub>DS,on</sub>   | Drain Current with $V_{GS} = V_{THO}$ |

| t <sub>delay</sub>   | Propagation Delay                     |

| E <sub>total</sub>   | Total Energy                          |

| E <sub>dynamic</sub> | Dynamic Energy                        |

| E <sub>leak</sub>    | Leakage Energy                        |

| n                    | Number of Inverter Stages Used        |

:

## **LIST OF FIGURES**

| Figure No. | Title                                                                    | Page |

|------------|--------------------------------------------------------------------------|------|

| 2.1        | Static (Leakage) and Dynamic (Switching) Power for Different             | 14   |

|            | Technology Generations                                                   |      |

| 3.1        | Comparison of Multiplication factor in Subthreshold and                  | 41   |

|            | Saturation Regions of Operations. The Threshold Voltage of               |      |

|            | The Device is 0.33V                                                      |      |

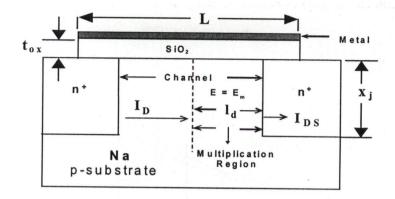

| 3.2        | Current Multiplication Model                                             | 42   |

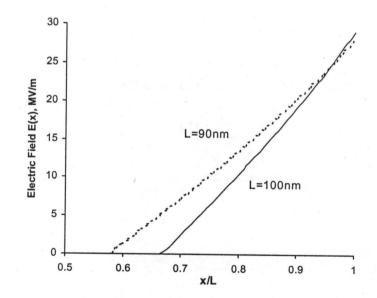

| 3.3        | Lateral Electric Field as a Function of Normalized distance              | 46   |

|            | from source. L is the Channel Length                                     |      |

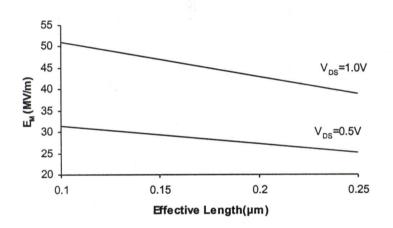

| 3.4        | Maximum Electric Field as a Function of Effective Length. $V_{DS}$       | 47   |

|            | is the Parameter                                                         |      |

| 3.5        | Multiplication factor as a Function of Maximum Electric Field            | 48   |

| 3.6        | Multiplication factor as a Function of Normalized $V_{DS}$               | 48   |

| 3.7        | Multiplication factor versus Gate Bias for Different Drain               | 48   |

|            | Voltages                                                                 |      |

| 3.8        | Multiplication factor as a Function of $V_{DS}$ for $V_{GS}$ of 0.3V and | 49   |

|            | oxide Thickness as parameter                                             |      |

| 3.9        | Multiplication factor as a Function of Doping Concentration              | 50   |

|            | and Junction $x_j$ is a Parameter                                        |      |

| 3.10       | Plot Showing The Comparison Between Subthreshold                         | 51   |

|            | Current With and Without Impact ionization                               |      |

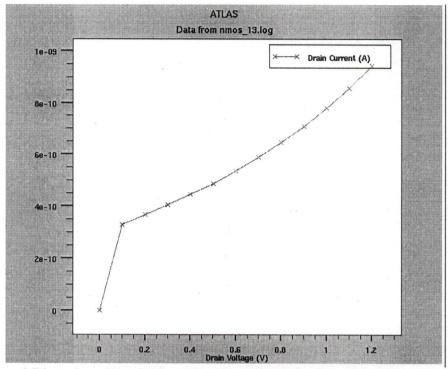

| 3.11 | Comparison of Calculated Subthreshold Current With ATLAS Simulation Result as a Function of $V_{DS}$ for $V_{GS} = 0.1V$ (Data | 51 |

|------|--------------------------------------------------------------------------------------------------------------------------------|----|

|      | given in Appendix-1)                                                                                                           |    |

| 4.1  | Drain-Induced Barrier Lowering (DIBL)                                                                                          | 58 |

| 4.2  | Variation of DIBL-Coefficient with Drain Source Voltage for<br>Different Channel Lengths                                       | 65 |

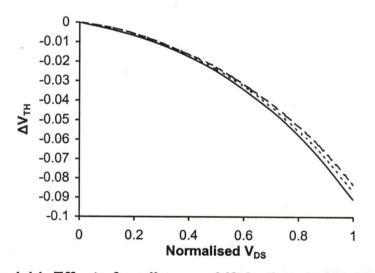

| 4.3  | Threshold Voltage Shift as a Function of Drain Bias for                                                                        | 65 |

|      | Different Channel Lengths                                                                                                      |    |

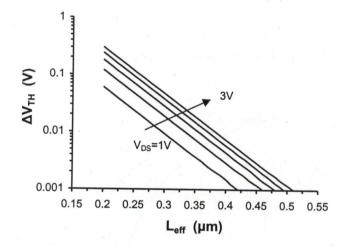

| 4.4  | Shift-in-threshold Voltage as a Function of effective Channel                                                                  | 66 |

|      | Length with $V_{DS}$ (1, 1.5, 2, 2.5 and 3V) as the Parameter                                                                  |    |

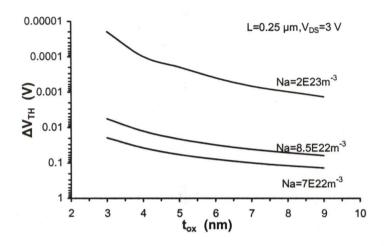

| 4.5  | Variation of Threshold Voltage Shift with Oxide Thickness for                                                                  | 67 |

|      | Different doping Concentrations                                                                                                |    |

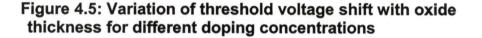

| 4.6  | DIBL-coefficient versus Temperature for Different Channel                                                                      | 67 |

|      | Lengths for $V_{DS}$ =3V                                                                                                       |    |

| 4.7  | Lateral Electric Field as a Function of Normalized Channel                                                                     | 71 |

|      | Position for Selective Scaling Method. L is Channel Length                                                                     |    |

| 4.8  | Maximum Electric Field as a Function of Normalized $V_{DS}$                                                                    | 71 |

|      | Different Scaling Method (L =90nm)                                                                                             |    |

| 4.9  | Multiplication factor as a Function of Normalized $V_{DS}$ for                                                                 | 72 |

|      | Three CEFS, GS and SS Scaling scheme                                                                                           |    |

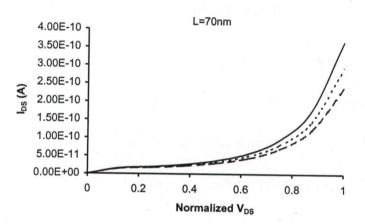

| 4.10 | Plot of Subthreshold Current with Impact ionization Versus                                                                     | 73 |

|      | Normalized $V_{DS}$ for CEFS Scaling Method                                                                                    |    |

| 4.11 | Subthreshold Current with Impact ionization Versus                                                                             | 73 |

|      | Normalized $V_{DS}$ Plot for CEFS, GS and SS Method for $S = 0.1$                                                              |    |

| 4.12 | Subthreshold Current with Impact ionization Versus                                 | 74  |

|------|------------------------------------------------------------------------------------|-----|

|      | Normalized $V_{DS}$ Plot for CEFS, GS and SS Method for $S = 0.9$                  |     |

| 4.13 | Subthreshold Current with Impact ionization Versus                                 | 74  |

|      | Normalized $V_{DS}$ Plot for CEFS, GS and SS Method for $S = 0.7$                  |     |

| 4.14 | Effect of Scaling on Shift-in-threshold Voltage in 70nm Device                     | 75  |

|      | on CEFS, Gs and SS Techniques                                                      |     |

| 5.1  | Different power Dissipation Types in CMOS Circuits                                 | 79  |

| 5.2  | CMOS Inverter for Switching Power Calculation                                      | 81  |

| 5.3  | Sizing an Inverter to have a Minimum Delay Gives a Good                            | 91  |

|      | Estimate of The Optimum Width to Minimize $V_{\text{DD}}$ Because the              |     |

|      | nMOS and pMOS are Balanced                                                         |     |

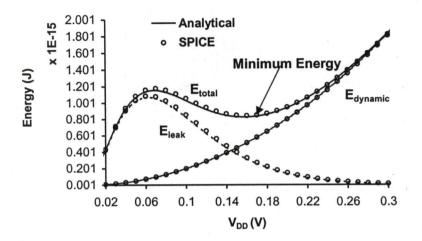

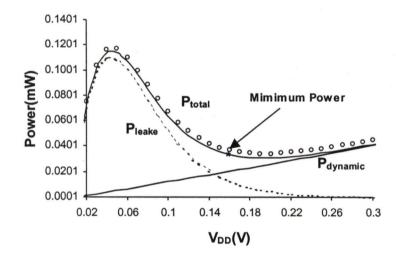

| 5.4  | Comparison of Analytical Results with SPICE Results for                            | 93  |

| 5.5  | 100nm Device. Minimum energy occurs at $V_{DD(min)}=0.16V$                         | 95  |

|      | Optimum $V_{DD}/V_{TH}$ Biasing Point Trading-off Dynamic Power                    | 90  |

|      | with Leakage Power for Constant Performance                                        |     |

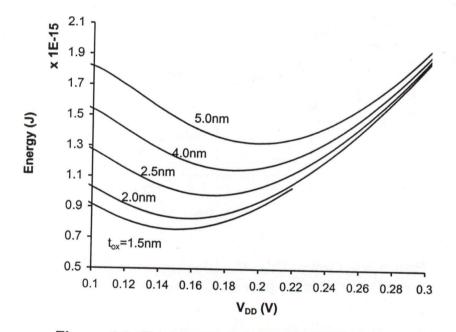

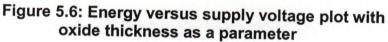

| 5.6  | Energy Versus Supply Voltage Plot with Oxide thickness as                          | 96  |

|      | Parameter                                                                          |     |

| 5.7  | Effect of Switched Capacitance variation as Optimal $V_{DD}/V_{TH}$                | 97  |

|      | Biasing Point                                                                      |     |

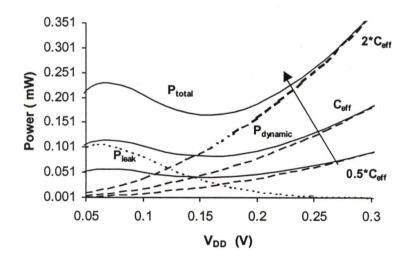

| 5.8  | Energy-Delay product for Various Power Supply Voltage                              | 98  |

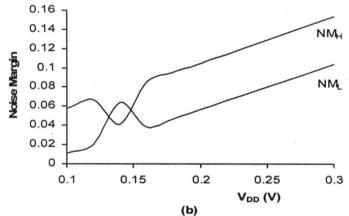

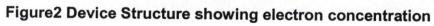

| 5.9  | (a) VTC (b) Noise Margin (High and Low) at the Minimum $V_{\scriptscriptstyle DD}$ | 101 |

|      | (Simulation). Optimum pMOS/nMOs width ratio of 3 is Shown                          |     |

|      | with others for Comparison                                                         |     |

## LIST OF TABLES

| Table No. | Title                                                        | Page |

|-----------|--------------------------------------------------------------|------|

| 2.1       | VTCMOS vs MTCMOS Techniques                                  | 27   |

| 3.1       | MOSFET Parameters                                            | 40   |

| 4.1       | Scaling Rules for Various Scaling Techniques                 | 55   |

| 4.2       | MOSFET Parameters for DIBL Analysis                          | 64   |

| 4.3       | Parameters for the Scaled Devices for CEF Scaling Method     | 70   |

| 4.4       | Subthreshold Current trends in CEFS, GS, SS at Normalized of | 74   |

|           | V <sub>DS</sub> =1V After Scaling 100nm MOSFET               |      |

| 4.5       | Various device and Technology Parameters Obtained After      | 75   |

|           | scaling 100nm Device                                         |      |

| 5.1       | Parameter values used in Comparing the Subthreshold Current  | 99   |

|           | of 100nm MOSFET [KPW02] with SPICE                           |      |

## CONTENTS

| CAN  | DIDATE   | 'S DECLARATION                                  | i    |

|------|----------|-------------------------------------------------|------|

| ABS  | TRACT    |                                                 | ii   |

| ACK  | NOWLE    | DGEMENTS                                        | v    |

| ABE  | RIVIATI  | ONS                                             | vii  |

| LIST | OF SYN   | MBOLS                                           | ix   |

| LIST | OF FIG   | URES                                            | xiii |

| LIST | OF TAE   | BLES                                            | xvi  |

| СНА  | PTER 1   | INTRODUCTION                                    | 1    |

| 1.1  | Overvie  | W                                               | 1    |

| 1.2  | Designi  | ng for Low Power                                | 2    |

| 1.3  | Motivati | ons and Objectives                              | 6    |

| 1.4  | Organiz  | ation of Thesis                                 | 7    |

|      |          |                                                 |      |

| CHA  | PTER 2   | POWER DISSIPATION in CMOS: AN OVERVIEW          | 11   |

| 2.1  | Introduc | ction                                           | 11   |

| 2.2  | Power [  | Dissipation Components in Digital CMOS Circuits | 13   |

|      | 2.2.1    | Switching Power                                 | 14   |

|      | 2.2.2    | Leakage Power                                   | 15   |

| 2.3  | Power a  | and Energy Reduction Techniques                 | 17   |

|      | 2.3.1    | Voltage Scaling                                 | 18   |

|      | 2.4.2    | Circuit Level Techniques                        | 20   |

|     | 2.3.3    | Device Level Optimizations                                      | 23 |

|-----|----------|-----------------------------------------------------------------|----|

| 2.4 | Leakage  | e Reduction Techniques                                          | 24 |

|     | 2.4.1    | Multi-Threshold COMS (MTCMOS)                                   | 25 |

|     | 2.4.2    | Variable-Threshold CMOS (VTCMOS)                                | 26 |

|     | 2.4.3    | Transistor Stacking                                             | 28 |

|     | 2.4.4    | Gate Level Leakage Reduction                                    | 29 |

| 2.5 | Ultra-Lo | w Voltage Circuit Techniques                                    | 29 |

| 2.6 | Conclus  | sions                                                           | 30 |

|     |          |                                                                 |    |

| CHA | PTER 3   | EFFECT OF IMPACT-IONIZATION ON SUBMICRON MOSFET                 | 31 |

| SUE | THRES    | HOLD CURRENT                                                    |    |

| 3.1 | Introduo | ction                                                           | 31 |

| 3.2 | Impact   | -Ionization in MOS-Channel                                      | 32 |

| 3.3 | Carrier  | Multiplication in Subthreshold Operation                        | 38 |

|     | 3.3.1    | Carrier Multiplication in The Three regions of MOSFET Operation | 38 |

|     | 3.3.2    | Subthreshold Impact Ionization Current Model                    | 41 |

| 3.4 | Analysi  | s and Results                                                   | 45 |

| 3.5 | Conclu   | sions                                                           | 52 |

|     |          |                                                                 |    |

| CHA | APTER 4  | SUBTHRESHOLD CURRENT OF SUBMICRON AND DEEP                      | 53 |

| SUE | BMICRO   | NMOSFET                                                         |    |

| 4.1 | Introdu  | ction                                                           | 53 |

| 4.2 | Scaling  | Techniques                                                      | 54 |

| 4.3 | Challer  | ges of MOSFET Scaling                                           | 57 |

|     | 4.3.1    | Short Channel effects                                           | 57 |

|     |                                                                            | 4.3.1.1                       | Length Dependent Threshold Voltage                | 58 |  |  |

|-----|----------------------------------------------------------------------------|-------------------------------|---------------------------------------------------|----|--|--|

|     |                                                                            | 4.3.1.2                       | Width Dependents threshold voltage                | 59 |  |  |

|     |                                                                            | 4.3.1.3                       | Reverse Short Channel Effects                     | 59 |  |  |

|     | 4.3.2                                                                      | Subthreshold Leakage Currents |                                                   |    |  |  |

|     |                                                                            | 4.3.2.1                       | Gate-Induced Drain Leakage                        | 60 |  |  |

|     |                                                                            | 4.3.2.2                       | Gate Tunneling Current                            | 60 |  |  |

|     | 4.3.4                                                                      | Hot Car                       | rier Effects                                      | 60 |  |  |

|     | 4.3.5 Dielectric Breakdown                                                 |                               | c Breakdown                                       | 61 |  |  |

|     | 4.3.6                                                                      | Scaling                       | the Interconnects                                 | 61 |  |  |

| 4.4 | Controlling Factors of Drain Induced Barrier Lowering Coefficient in Short |                               |                                                   |    |  |  |

|     | Channel MOSFET                                                             |                               |                                                   |    |  |  |

|     | 4.4.1                                                                      | Numeric                       | al analysis                                       | 62 |  |  |

| 4.5 | Effect of Technology Scaling on MOSFET                                     |                               |                                                   |    |  |  |

| 4.6 | Conclu                                                                     | onclusions 7                  |                                                   |    |  |  |

|     |                                                                            |                               |                                                   |    |  |  |

| CHA | PTER                                                                       | 5 OPTIM                       | UM SUPPLY VOLTAGE FOR MINIMUM POWER AND           | 77 |  |  |

| ENE | RGY                                                                        |                               |                                                   |    |  |  |

| 5.1 | Introdu                                                                    | uction                        |                                                   |    |  |  |

| 5.2 | Power and Energy Management in CMOS Circuits                               |                               |                                                   |    |  |  |

|     | 5.2.1                                                                      | Existing                      | Dynamic Power Estimation Techniques               | 80 |  |  |

|     | 5.2.2                                                                      | Existing                      | Leakage Power Estimation Techniques               | 84 |  |  |

|     | 5.2.3                                                                      | Existing                      | Total Power Estimation Techniques                 | 86 |  |  |

| 5.3 | A Simplified Analysis for Minimum Power and Energy                         |                               |                                                   |    |  |  |

|     | 5.3.1                                                                      | Optimur                       | n Sizing for Minimum Energy at a Minimum $V_{DD}$ | 88 |  |  |

|                       | 5.3.2                                             | Model Verification                                                  | 92 |  |  |

|-----------------------|---------------------------------------------------|---------------------------------------------------------------------|----|--|--|

|                       | 5.3.3                                             | $V_{DD}$ - $V_{TH}$ Optimization Overview                           | 93 |  |  |

|                       | 5.3.4                                             | Role of Switched capacitance on Optimal $V_{DD}$ - $V_{TH}$ Scaling | 97 |  |  |

|                       | 5.3.5                                             | Energy-Delay Product                                                | 98 |  |  |

|                       | 5.3.6                                             | Voltage Transfer Characteristic and Noise Margin                    | 99 |  |  |

| 5.4                   | Conclu                                            | usions                                                              |    |  |  |

|                       |                                                   |                                                                     |    |  |  |

| CHAPTER 6 CONCLUSIONS |                                                   |                                                                     |    |  |  |

| 6.1                   | 1 Summary of Important Findings and Contributions |                                                                     |    |  |  |

| 6.2                   | 2 Suggestions for Future Work                     |                                                                     |    |  |  |

|                       |                                                   |                                                                     |    |  |  |

| APP                   | APPENDIX-1                                        |                                                                     |    |  |  |

| BIBLIOGRAPHY          |                                                   |                                                                     |    |  |  |

| LIST                  | LIST OF PUBLICATIONS                              |                                                                     |    |  |  |

|                       |                                                   |                                                                     |    |  |  |

## **CHAPTER 1**

### Introduction

#### 1.1 Overview

In recent years, low power circuit operation is becoming an increasingly important metric in portable battery powered devices such as hearing aids [MBSH+99] [KR01], pacemakers, cell phones, pagers, and portable computers become more complex, prevalent, and demand increased battery life. Circuit designers are seeking out new technologies and circuit techniques to maintain high performance and long operational lifetimes. In non-portable applications, reducing power dissipation is also becoming an increasingly important issue. Thus, obtaining the required performance within a limited power budget is the most challenging goal in custom designs and in modern VLSI circuits.

Literature survey shows that sub-threshold logic circuits are preferred due to ultra-low power consumption with moderate performance degradation. Hearing aid devices are clearly one of the most suitable application areas where performance is of secondary importance [SRP00]. In subthreshold logic, circuits are powered by using supply voltage below the threshold voltage. In such circuits the delay increases but ultra-low power can be achieved without major alteration of the circuit. In the subthreshold region, the current through a transistor has an exponential dependency upon gate voltage, threshold voltage and temperature. However the width to length (W/L) ratio has a linear dependency upon the transistor current, so sizing has much less effect on the transistor current than it had in the normal strong inversion region. Therefore the disadvantages of ratioed logic in the strong inversion region such as degradation of noise margin and VTC (voltage transfer characteristic) are diminished in the sub-threshold region.

Keeping all these in mind low power design have become one of the most important design parameters for VLSI (Very Large Scale Integration) systems, which largely rely on complementary metal-oxide-semiconductor (CMOS) technology.

### 1.2 Designing for Low Power

The power dissipation attributable to the three sources viz.: short-circuit, switching, and leakage, and influences the design at different levels of the overall design process. Since the dominant component of power dissipation in CMOS circuits (due to logic transitions) varies as the square of the supply voltage, significant savings in power dissipation can be obtained by operating the devices at a reduced supply voltage. If the supply voltage is reduced while the threshold voltages stay the same, reduced noise margins result. To improve noise margins,

the threshold voltages need to be made smaller too. However, the subthreshold leakage current increases exponentially when the threshold voltage is reduced. The higher static dissipation may offset the reduction in transitions component of the dissipation. Hence the devices need to be designed to have threshold voltages that maximize the net reduction in the dissipation.

The transitions component of the dissipation also depends on the frequency or the probability of occurrence of the transitions. If a high probability of transitions is assumed and correspondingly low supply and threshold voltages chosen, to reduced the transitions components of the power dissipations and provide acceptable noise margins, respectively, the increase in the static dissipation may be large. As the supply voltage is reduced, the power-delay product of CMOS circuits decreases and the delays increase monotonically. Hence, while it is desirable to use the lowest possible supply voltage, in practice only as low a delay that can be compensated by other means, and steps can be taken to retain the system level throughput at the desired level.

One way of influencing the delay of a CMOS circuit is by changing the channel-width-to-channel-length ratio of the devices in the circuit. The power-delay product for an inverter driving another inverter through interconnects of certain length varies with the width-to-length ratio of the devices. If the interconnect capacitance is not insignificant, the power-delay product initially decreases and then increases when the width-to-length ratio is increased and the supply voltage is reduced to keep the delay constant. Hence, there exists a combination of the supply voltage and the width-to-length ratio that is optimal from the power-delay product consideration.

The way to assure that the system level throughput does not degrade as supply voltage is reduced is by exploiting parallelism and pipelining. Hence as the supply voltage is reduced, the degree of parallelism or the number of stages of pipelining is increased to compensate for the increased delay. But then the latency increases. Overhead control circuitry also has to be added. As such circuitry itself consumes power; there exist a point beyond which power, rather than decreasing, increases. Even so, great reductions in power dissipation by factors as large as 10, have been shown to be obtainable theoretically as well as in practice [CB95].

As more circuit can be accommodated per unit area, off-chip input-output (I/O) power may become the dominant power-consuming function [LS93] unless a significant amount of memory [usually static random-access memory (RAM) and in some cases dynamic RAM] and analog functions are integrated on-chip.

Circuit level choices also impact the power dissipation of CMOS circuits. Usually a number of approaches and topologies are available for implementing various logic and arithmetic functions. Choices have to be made between static versus dynamic style and pass-gate versus normal CMOS for realization of asynchronous circuits.

At the logic level, automatic tools can be used to locally transform the circuit and select realizations for its pieces from a pre-characterized library so as to reduce transitions and parasitic capacitance at circuit nodes and therefore circuit power dissipation [IP95]. At a higher level various structural choices exist for realizing any given logic functions for example for an adder one can select one of ripple-carry, carry-look-ahead, or carry-select realizations.

In synchronous circuits, even when the outputs computed by a block of combinational logic are not required, the block keeps computing its outputs from observed inputs every clock cycle. In order to save power, entire execution units comprising of combinational logic and their state registers can be put in stand-by mode by disabling the block and/or powering down the unit. Special circuitry is required to detect and power-down unused units and then power those up again when they need to be used [Kap94]. The rate of increase in the total amount of memory per chip as well as rate of increase in the memory requirement of new applications has more than kept pace with the rate of reduction in power dissipation per bit of memory. As a result, in spite of the tremendous reductions in power dissipation obtained from each generation of memory to the next, in many applications, the major portion of the instantaneous peak-power dissipation occurs in the memory.

In case of dynamic RAM (DRAM) memory, the most effective way to reduce power of any memory size is to lower the voltage and increase the effective capacitance to maintain sufficient charge in the cell. The new array organizations introduced recently [KR01] present many possibilities of lowering the power.

The literature survey reveals that many advances have been made in various research aspects, including scaling of MOS devices, low-voltage low-power CMOS design style, threshold voltage scaling for high performance designs, leakage current in CMOS circuits, leakage control techniques such as multiple VTCMOS, dynamic VTCMOS, subthreshold logic etc. [CB95] [IF97] [FS93] [LHHC+93] [DDS95a&b] [CSB92] [Mei95] [SRP01] [Sta01]. However, there are still many open research

issues, which need to be solved before low-power CMOS VLSI technology can be viable.

### 1.3 Motivations and Objectives

As the device is scaled down to submicron level the electric field in the channel region of a MOSFET becomes considerably large. The high electric field in the submicron channel has been found to be responsible for many undesirable effects. One of these effects is impact ionization. The effect of impact ionization on MOSFET operation has been the subject of study of many authors in connection with substrate current. However, the effect of impact ionization on subthreshold current has been overlooked until recently. Park et al. [PDW01] carried out a computer simulation to study the effect of impact ionization on the subthreshold current of a double-gate MOSFET. The results of the simulation show that impact ionization has substantial effect on subthreshold current of such a device. While the double-gate MOSFETs are still under study, the conventional (single gate) MOSFETs find application over a wide range of gate-length. Thus it is of interest to analyze the influence of impact ionization on the subthreshold operation of the conventional MOSFETs.

It is well known that drain induced barrier lowering (DIBL) adversely affect the operation of the submicron MOSFETs. Several workers have studied this effect in the past and currently a parameter, commonly termed as DIBL coefficient is used as a measure of the effect. However, the dependence of this parameter on gate and drain voltages, need further study.

For VLSI applications, MOS technology applies various scaling technologies viz: Ideal or Constant Electric Field Scaling, Generalized Scaling, and Selective Scaling. The different scaling schemes have their own merits and demerits. For subthreshold operation, the effects of these scaling methods need further studies. As the activities in the development of subthreshold logic grow optimization of transistor size and supply voltage for such applications has become important. Such effects should take into account both delay minimization and control of power dissipation.

More succinctly, the following course of action was adopted to achieve the planned objectives as emerging from the motivations discussed above.

- Study of the effect of impact ionization on the subthreshold current in submicron MOSFET

- An improved analysis of Drain-Induced-Barrier-Lowering (DIBL) and its effect on subthreshold current. Study of the controlling factors of DIBL coefficient

- Examination of the effects of various scaling techniques on the subthreshold current

- Optimization of transistor size and supply voltage for low-power subthreshold CMOS operation

### 1.4 Organization of the Thesis

The thesis has been organized as follows: Second chapter discusses the basic models and provides the necessary background to set the pace for going through this work. In addition, it overviews the evolution of minimum power strategies spanned over the last four decades. The survey has, primarily, been confined to minimum power based approaches, which are separately the focus of three

subsequent chapters. Chapter 3 deals with the effect of impact ionization on drain current. Multiplication factor has been determined using well-established expressions [IF97]. The drain-source voltage ( $V_{DS}$ ) dependence of multiplication factors for subthreshold, linear and saturation regions of operation of a 100nm device are compared. It is found that, subthreshold multiplication factor is highest and linear region has the lowest multiplication factor. The analysis shows that for subthreshold operation it is important that the effect of impact ionization is included in the analytical expression for drain current.

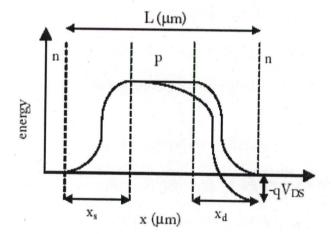

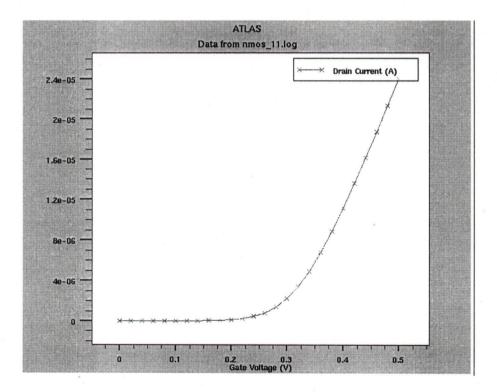

Chapter 4 focuses on subthreshold current of submicron and deep submicron MOSFET. In subthreshold CMOS logic circuit, the input voltage swing is restricted below the threshold voltage of the MOSFETs. Fieldly et al. [FS93] developed a very useful physical model for subthreshold current. This model yields accurate results for submicron devices, but does not take into account the effect of impact ionization, which is more prominent in devices of nanometer channel length. The subthreshold current model of Fjeldly et al. [FS93] is suitably modified to include the effect of impact ionization for analytical study. The modified current model agrees well with results obtained from ATLAS simulation. It shows that impact ionization increases subthreshold current by few percents. This increase in subthreshold current modifies DIBL-coefficient. It is observed that the DIBL-coefficient has a strong dependence on  $V_{DS}$  and relatively lesser dependence on gate-source voltages  $V_{GS}$ . The analysis shows that, because of the strong  $V_{DS}$  dependence of the DIBL-coefficient, the threshold voltage shift is a non-linear function of  $V_{DS}$ , in contradiction to a constant DIBL-coefficient as assumed previously [LHHC+93]. It is also found that DIBL- coefficient increases with increase in channel length and

decreases with increase in temperature. Methods of device scaling in VLSI technology have also been discussed in this chapter. The dependence of subthreshold current on applied scaling technique has been analyzed in this chapter. The results show that as the channel length is scaled down, multiplication factor increases slowly in the higher regime of channel length. In the lower regime of channel length, multiplication factor rises rapidly. This result also justifies the inclusion of impact–ionization effect on subthreshold current. Similar variations in subthreshold current with channel length scaling are shown by the analytical results. However, the analysis shows that there is insignificant dependence of multiplication factor on the method of scaling.

It has also been observed during analysis that subthreshold current also affects DIBL, and is dependant on the scaling technique. Dependence of DIBL is more significant in the higher regime of  $V_{DS}$ . Constant electric field scaling produces the largest threshold voltage shift due to DIBL. Selective scaling has the least DIBL, with generalized scaling produced DIBL falling in between the two extremes. As a result, the scaling dependence of subthreshold current follows the same pattern.

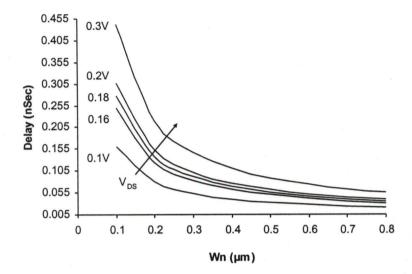

Chapter 5 addresses calculation of optimum supply voltage for minimum power and energy requirement. This chapter also deals with the proposed Modified Subthreshold Current model, which is used to study power dissipation in subthreshold CMOS operation and design of low-power CMOS logic. A tradeoff exists between propagation delay and power dissipation, when voltage is scaled. When the supply voltage is scaled down to reduce power dissipation, propagation delay is increased. SPICE simulation, however, shows that this does not hold good for subthreshold logic [Sta01] [PB03]. For a threshold CMOS–logic operation,

propagation delay in most cases first increases and then decreases with supply voltage scaling. The subthreshold current model mentioned above is used to calculate voltage dependence of propagation delay of a CMOS inverter. The results thus obtained show that, the delay increases with increase in supply voltage. An important requirement of a logic circuit is symmetric input-output characteristics. The ratio of pMOS and nMOS widths that meets this requirement is determined using the modified subthreshold current model. The ratio thus obtained is primarily mobility dependent, as in the case of above threshold logic operation.

Chapter 6 summarizes contributions and conclusions. Some future directions have also been suggested here for further exploration.

### **CHAPTER 2**

### **Power Dissipation in CMOS: An Overview**

### 2.1 Introduction

Low power and low energy issues have captivated VLSI circuit designers for the past few years in the quest for enhancing performance and extending battery lifetime [Pow95]. The increasing demand for integration of more functions with faster speeds is met by an increase in battery. For example, the third generation (3G) wireless protocol provides real-time streaming video at a high data rate on a 3G-enabled cellular phone. Such a computation intensive application can impact the battery life of the portable device. Therefore, the demand for increased battery life will require designers to seek out new technologies and circuit techniques to maintain high performance with longer battery lifetime. Portable devices, however, are not the sole motive behind the low power and low energy design efforts. The increasing power dissipation for fixed supply devices is almost equally challenging as for portable devices. As technology feature size is reduced, the number of transistors on the chip is increased and more power is dissipated. According to Moore's law, the number of transistors quadruples every two to three years. One hundred billion transistors on a single chip are projected before 2020 [Mei95]. Expensive packing techniques are essential for dissipating such extensive power generated from that large number of transistors. Also, increased power dissipation has a negative impact on device's reliability.

Several methods for power and energy reduction have been proposed in [LS93], [LM93], [KS94], [MDMA+95], [BDAM96], [KFMN+96], [KNC98], [KNBH+99], [BDAM00], [IHS01], [KHK02], [KKK03] and [WCK02]. Voltage supply,  $V_{DD}$ , scaling is considered one of the most effective elements for the process of reducing power dissipation in CMOS circuits [FSRS97]. Threshold voltage,  $V_{TH}$ , has also to be reduced to maintain the delay but reduction in  $V_{TH}$  results in an exponential increase in leakage power. With leakage power under control, the ratio ( $V_{DD}/V_{TH}$ ) tends to decrease with technology scaling [KC00] [WCK02].

Lowering supply voltage has been proved to save  $V_{TH}$  energy. Recently, a fast Fourier transform (FFT) unit was shown to work at 350 mV to provide optimal energy efficiency [WC05]. The FFT unit was also shown to function correctly at a supply voltage of 180 mV. Peak supply voltage is selected based on peak performance requirements. Occasionally, the processing unit does not require peak performance. Therefore, supply voltage can be scaled if some liberty can be taken on the performance front [BP91] [ASPB+97] [NS00]. When supply voltage is scaled,

the average energy of the system is reduced while maintaining the required throughput. As a result, battery lifetime can be extended. A typical example of such an application is the burst-mode operation of the active devices. Such an application has only two modes of operation: active and idle. The device operates at full throughput for a small period of time (active mode) before entering the idle mode (standby). Given a deadline to be met for a given task, reducing supply voltage alone would lead to timing violations. Meeting the deadline requires satisfying the circuit delay constraint. In order to meet the specified deadline at the scaled supply voltage, the threshold voltage of the device,  $V_{TH}$  is reduced. However, threshold voltage reduction leads to an exponential increase in subthreshold leakage. Therefore, leakage reduction methods are utilized to reduce leakage power during the idle mode.

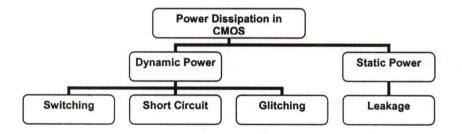

## 2.2 Power Dissipation Components in Digital CMOS Circuits

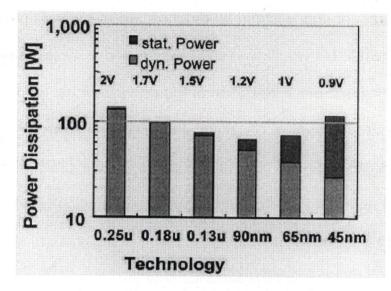

Power consumption in CMOS circuits can be divided into three main components: short-circuit power, switching power, and leakage power. Short-circuit power arises when a conducting path between supply and ground is formed. Switching power is a result of the power consumed in charging and discharging internal capacitances in the circuit. Leakage power is the power dissipated while the device is turned off. Leakage power has started to form a significant portion of the total power consumption as a result of increase in device density. Figure 2.1 shows the increase in static (leakage) power for different technology generations [ITRS03]. It is apparent that static power is dramatically increasing with technology scaling.

Figure 2.1: Static (Leakage) and Dynamic (Switching) Power for different technology generations

The ratio of leakage to total power is expected to exceed 50% in 45nm designs from about 10% in 90nm designs. Since switching and leakage power are the dominant components of power consumption, they are discussed in detail below.

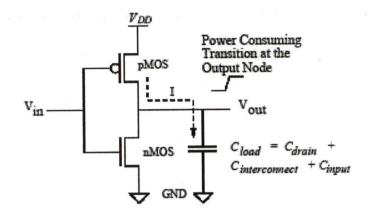

#### 2.2.1 Switching Power

Switching power is the largest contributor to the total power dissipation in conventional CMOS technologies. It is a result of switching the junction, diffusion, and interconnects capacitances. In any logic gate, if inputs to the gate are assumed to switch at a rate of f times per second, then the average switching power for that gate is given by

$$P_{SW} = \alpha C \Delta V^2 f \tag{2.1}$$

where  $\alpha$  is the switching activity factor which represents the probability of the output switching from 0 to 1, *C* is the switching capacitance,  $\Delta V$  is the voltage swing, and *f* is the switching frequency.

Generally,  $\alpha$  is less than 1. In case of a logic network of several levels of gates, the activity factor of the gate becomes a function of its inputs probabilities. For certain logic styles, however, glitching can form a non-trivial part of the overall consumption. Glitching often arises when paths with unbalanced proportional delays converge at the same node in the circuit. If glitching due to signal races is to be accounted for,  $\alpha$  might be greater than one [CSB92]. Calculations of this activity in a circuit are very difficult and require careful logic and/or circuit level characterization of the gates. Obviously, reducing any term in (2.1) will result in a reduction in switching power. However, low power techniques need to address power reduction without affecting performance or device functionality. For example, frequency reduction is beneficial in terms of power consumption but it affects the overall system speed. Therefore, it is often a challenge to reduce power dissipation while maintaining the system performance.

#### 2.2.2 Leakage Power

The different leakage current components are: (1) the reverse bias p-n junction leakage caused by barrier emission, minority carrier diffusion and band-to-band tunneling; (2)subthreshold conduction current; (3) a current component which results from the drain-induced barrier lowering (DIBL); (4) gate induced drain leakage (GIDL); (5) a component due to channel punch through; (6) current owing to hot carrier injection current; (7) oxide leakage current; (8) gate current due to hot carrier injection; The first six are OFF currents are while the last two are ON and switching currents.

• Junction Reverse Bias Current: Junction Reverse Bias Current has two components: One is minority carrier diffusion/drift near the edge of the

depletion region, and the other is due to electron hole pair generation in the depletion region of the reverse biased junction [KNBH+99]. Heavily doped junctions are also prone to Zener and band-to-band tunneling. The p-n reverse bias leakage is a function of junction area and doping concentration. It is normally a minimal contributor to total OFF current.

- Subthreshold Conduction Current: Subthreshold conduction or weak inversion current flows between source and drain when the gate voltage is below the threshold voltage  $V_{TH}$ . The subthreshold current occurs due to carrier diffusion when the gate source voltage,  $V_{GS}$ , has exceeded the week inversion point, but still below the threshold voltage, where carrier drifts is dominant. Subthreshold conduction typically dominates modern device off-state leakage as they are mostly of low threshold voltages.

- Drain-induced Barrier Lowering, DIBL: DIBL is the effect of lowering the source potential barrier near the channel surface as a result of the applied drain voltage. Ideally, DIBL does not change the subthreshold slope but does lower V<sub>TH</sub>. Higher surface and channel doping, and shallow source/drain junction depths work to reduce the DIBL mechanism.

- Gate-Induced Drain Leakage, GIDL: GIDL current arises in the high electric field under gate/drain overlap region causing a thinner depletion region of drain to well junction. GIDL results in an increase in leakage current when applying a negative voltage to the gate (NMOS case). GIDL is small for normal supply voltage but its effect rises at higher supply voltages (near burn-in).

- Punchthrough: Punchthrough occurs when source and drain depletion regions approach each other and the gate voltage loses control over the

channel current in the sub gate region. Punchthrough current varies quadratically with drain voltage. Punchthrough is often regarded as a subsurface version of DIBL.

Hot-carrier injection current: Threshold voltage tends to decrease in trench-isolated small effective channel width devices. The narrow width effect causes the threshold voltage to decrease in trench-isolated technologies for channel widths on the order of W <= 0.5µm. It can be ignored for device sizes >> 0.5µm.

Subthreshold leakage current is the largest leakage current component. It increases exponentially as a result of threshold voltage reduction. Various techniques have been developed to keep both active and leakage power under control. In the next section, some of the effective power and energy reduction methodologies are described. The intent is to focus on these particular methodologies since the work presented in this thesis builds on these methodologies.

## 2.3 **Power and Energy Reduction Techniques**

Since switching power is the major source of power dissipation in CMOS technologies, various techniques have been proposed on a variety of design levels to achieve switching power reduction. Keeping power-speed trade off in view some effort can be made at the architecture and circuit level to maintain speed at a scaled voltage. Furthermore, considering a top-down design paradigm, power and energy reduction can be achieved on the architecture, circuit, and device levels. Starting at the top level, the architecture is modified to cater to lower power dissipation and high performance requirements by introducing or adding parallelism or pipelining. When

such modifications are implemented, power can be further reduced via supply or frequency scaling. Moving down the design paradigm, both circuit and device level optimizations are required to enable energy efficient operation.

### 2.3.1 Voltage Scaling

Many designers have focused on power supply scaling as a means for low power operation. Reducing frequency or switching capacitance provides a linear reduction in switching power. On the other hand supply voltage reduction leads to quadruple savings. Furthermore, subthreshold leakage current can be reduced exponentially with supply voltage reduction. Thus, both dynamic and leakage power can be effectively reduced through supply scaling [Sak03]. Voltage reduction enables architectural level power optimizations. Parallelism or pipelining can be employed to reduce power dissipation [CSB92] [CB95]. For example if a signal of frequency f drives a logic gate at maximum applicable supply voltage, then the gate delay can be reduced by putting a duplicate unit in parallel with the original one in that case the clock frequency can reduced to  $\frac{f}{2}$  (doing the computations in parallel). Slashing the operating frequency by half allows for a 40% reduction in the supply voltage, say this reduction may vary from design to design and from one technology to another. Due to the parallelism used, the capacitance increases by a factor of 2 as a result of using a duplicate circuit. In addition, capacitance increases by another 20% (say) due to the extra routing required. Thus, the resulting reduction in power consumption of the parallel architecture compared to the original one is given by

$$P_{parallel} = CfV^2 = (2.2C_{org})(0.6V_{org})2(0.5f_{org})$$

$$= 0.4 P_{org}$$

where  $C_{org}$  is the original effective capacitance being switched per clock cycle. Apparently, the primary limitation of using parallelism to reduce overall power is the area. A considerable part of the extra area required for parallelism is the extra routing area. Wiring capacitance represents a significant part of the total capacitance of a chip. In addition, wiring capacitance does not scale as much as the feature size. Therefore, careful optimization and sophisticated routing techniques have to be utilized to fully exploit the advantage of parallelism and minimize its side effects.

(2.2)

For area constrained designs, pipelining is a viable option with much less area overhead compared to parallelism but yet a comparable throughput. It is a technique that is used to increase the throughput of a sequential set of distinct data input through a synchronous logic cascade. Pipeline architecture divides the cascade into smaller sections, the input to each section being provided by a register. That is the registers are placed between two successive sections. A faster clock is used to initiate activities in all sections at a given time. This way the overall circuit performance is improved. The power reduction achieved by this method can be more than what can be obtained from a parallel structure. Balancing the delay of all the pipelined stages is extremely important to achieve further reduction in power. That would allow for more supply voltage reduction and hence more power savings. In addition, increasing the level of pipelining also reduces the logic depth and hence the power contributed by hazards and critical races. Furthermore, exploiting both pipelining and parallelism is more attractive. This architectural choice results in further speedup and more room for supply voltage reduction.

#### 2.3.2 Circuit Level Techniques

Different static and dynamic logic styles have been introduced for the sole aim of reducing power. It is also a common design practice to combine both static and dynamic logic styles to optimize for delay and power at the same time. The merits of each logic style are explained below.

- Conventional CMOS logic style: Static CMOS logic refers to conventional • CMOS circuits, which are constructed using an nMOS pull-down network and a complementary pMOS pull-up network. Due to the complementary nature of the circuit, conventional CMOS logic style is inherently able to reject noise. The layout of CMOS gates is simple and regular due to the similar, yet complementary, pull-up and pull- down network structure. On the other hand, conventional CMOS suffers from inherent disadvantages due to the pull-up pMOS network. One of the main disadvantages is the increased gate capacitance resulting from the large size pMOS transistors. Furthermore, the pMOS transistor is usually made larger to compensate for the speed difference with nMOS due to the lower hole mobility compared to electron mobility. However, this disadvantage is diminishing as technology feature size is shrunk. The carrier drift velocities of both pMOS and nMOS approach the saturation velocity and therefore the size ratio between pMOS and nMOS devices is quickly approaching one. Another drawback of static CMOS logic is the relatively weak driving current. By adding output buffers, the driving current can be enhanced.

- Dynamic Logic Style: Dynamic logic operates in two phases: precharge and evaluation. During the precharge phase, a clock signal charges up the output node. During the evaluation phase, the clock signal switches high. Depending

upon input values, the output node is discharged or remains charged. Dynamic logic is usually faster than static CMOS due to less capacitance (pMOS network is eliminated). However, dynamic logic consumes more power. Many dynamic logic styles with improved delay and power compared to the conventional dynamic style have been reported [SRP00].

Pass-Transistor Logic Style: Unlike static and dynamic logic, pass-transistor logic provides complementary output. Moreover, inputs are connected to both the gates and the sources of transistors. Pass-transistor gates have two input categories: pass inputs and control inputs. Pass inputs are connected to the sources of the devices while control inputs are connected to the gates. The strongest advantage of pass-transistor implementation is that it can use just one network, usually nMOS, to build the logic. Also, the dual rail nature of the logic style can be used efficiently to implement multiplexing functions. However, connecting some inputs to the source causes a  $V_{\rm TH}$  drop. As a result, the voltage swing is reduced and it requires restoration at the output stage to increase noise margin and to minimize short circuit currents. As a consequence, two nMOS networks would be used in addition to the output buffering circuitry. This overhead annihilates the advantage of the low transistor count and small input capacitance. Moreover, pass-transistor logic is sensitive to voltage scaling and transistor sizing. Finally, the layout of pass-transistor logic is complicated due to the extra wiring normally required. One example of pass-transistor logic is the complementary pass-transistor logic (CPL). A CPL has two nMOS networks, one for each rail, and two inverters for level restoration [YY90]. CPL has small input capacitance, a fast differential output stage, and a high driving current. However, CPL, as a

member of the pass-transistor logic family, suffers from short circuit currents at the output and wiring complexity due to the dual rail. Other pass-transistor logic styles have been proposed. A good comparison between the different styles can be found in [ZF97]. In [ZF97], static CMOS has been shown to have superior performance over pass-transistor logic. Therefore, static and dynamic logic usually occupy a larger share of the circuit design space.

From a low power perspective, static logic dissipates less power compared to dynamic logic due to the following reasons:

- 1. Spurious Transitions: Static designs are prone to spurious transitions more than dynamic circuits due to critical races and dynamic hazards in static logic. The magnitude and the number of those undesirable transitions in a logic structure is a function of the logic design, delay skew, and logic depth. For example, an 8-bit ripple carry adder consumes an extra 30% of power due to spurious transitions [CSB92]. Dynamic logic, however, intrinsically does not suffer from spurious transitions, since any node can undergo at most one power consuming transition per clock cycle.

- Switching Capacitance: Dynamic logic has fewer devices, typically N+2 for N-input gate compared to 2N in case of CMOS. This is reflected directly on the switching capacitance and thus has a direct impact on delay and power dissipation.

- 3. Switching Activity: Dynamic logic is notorious for its high switching activity. The dynamic node has to be precharged every clock cycle even if it going to be discharged immediately after evaluation starts. For example, for a 2-input dynamic NOR gate, the switching activity is (3/4) compared to just (3/16) in case of static logic implementation. If spurious transitions are

neglected, then using dynamic logic would result in a 4 times increase in power. But if reduction in capacitance and spurious transitions were taken into account, the resulting power increase would not be that dramatic.

With fewer transistors required to implement a certain dynamic logic function compared to static logic, standby leakage current of dynamic logic can be less than its static logic counterpart. In some applications where fast evaluation time is followed by a long idle period, dynamic logic can be more attractive than static logic for its low standby leakage.

#### 2.3.3 Device Level Optimizations

As mentioned previously, CMOS is regarded as the technology of choice for low power and low energy applications. It offers a good performance and a considerable stability. However, as supply voltage is reduced, threshold voltage has to be reduced to maintain the required performance. A reduced threshold voltage directly results in an exponential increase in subthreshold current.

Some technologies have been offering a solution for the increase in subthreshold current resulting from the reduced threshold voltage. Silicon on insulator (SOI) technology has emerged with a good potential in low power and low voltage applications. In SOI technology, the thin film is totally isolated from the body by a thick film oxide. The thick oxide serves to suppress the radiation-induced current. Also, due to the thick oxide layer, the gate to source/drain capacitance is greatly reduced. As a consequence, SOI devices are faster and consume less dynamic power compared to CMOS. In terms of integration and technology down scaling, the depletion regions in bulk CMOS, which are, used for isolation put a lower

limit on feature size in bulk CMOS. The buried thick oxide in SOI makes it easier to down scale device dimensions.

Two other forms of MOS devices are of importance. These are: DTMOS SOI and DGSOI. The DTMOS is a Dynamic Threshold MOS structure; the gate is tied to the body of the SOI device. This type of connection allows for low threshold during the ON state and high threshold during the OFF state [ASPB+97]. The DGSOI is a Double-Gate SOI device in which there is a back gate separated from the body of the device by the back oxide [WZRC+02]. The DGSOI has a higher current drive for high output load in addition to an excellent ability of leakage control.