## POWER CONVERTER FOR BATTERY CHARGER IN PLUG-IN HYBRID AND ELECTRIC VEHICLES

#### A DISSERTATION

Submitted in partial fulfillment of the requirements for the award of the degree

of

#### MASTER OF TECHNOLOGY

in

**ELECTRICAL ENGINEERING** (With Specialization in Electric Drives and Power Electronics)

By

NITISH SHARMA

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247667(INDIA) May 2019

#### CANDIDATE'S DECLARATION

I hereby declare that the work which is presented in this project, entitled, "POWER CONVERTER FOR BATTERY CHARGER IN PLUG-IN HYBRID AND ELECTRIC VEHICLES", submitted in partial fulfillment of the requirement for the award of the degree of Master of Technology in "Electrical Drives & Power Electronics" in Electrical Engineering, Indian Institute of Technology Roorkee, is an authentic record of my own work carried out during the period from January 2018 to November 2018 under the supervision and guidance of Dr.M.K.Pathak, Associate professor Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee (India).

Date: May 17,2019 Place: Roorkee,India

(NITISH SHARMA)

#### CERTIFICATE

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

#### Dr.M.K.PATHAK,

#### Associate Professor,

Electrical Engineering,

Indian Institute of Technology,

Roorkee-247667

#### ACKNOWLEDGEMENT

I am using this opportunity to express my gratitude to Prof. M.K.Pathak who supported me throughout the course of this work. I am thankful for his aspiring guidance, invaluably constructive criticism and friendly advice during the seminar work. I am sincerely grateful to him for sharing his truthful and illuminating views on a number of issues related to the work.

Last but not the least I am also grateful to all faculty members and staff of Electrical Engineering, Indian Institute of Technology Roorkee.

I extend my thanks to all classmates who have given their full cooperation and valuable suggestions for my seminar work.

Thank you,

Date: May 17,2019 Place: Roorkee,India

(NITISH SHARMA)

#### ABSTRACT

Plug-in Hybrid Electric Vehicles(PHEV) and Electric Vehicles are rolled out for the consumer, and become popular in a short period of time. With the advent of Battery chargers for PHEVs there is a big opportunity for the power supply Industries to deploy large number of charging stations, affordable and easy to use, home charging station. Overall charging efficiency advancement is a important factor for the approval of these technologies, when the performance increase the charging hour and service charge decrease. Power factor correction is important to achieve regulatory standards for the AC supply mains.

Chargers with smaller size which could render more power are needed as minimal space is available in vehicle and power consumption is increasing with time, Important part of a charging system is the AC-DC converter connected in front end, which should attain high power density and high efficiency. Different front end AC-DC conventional plug in hybrid electric vehicle charger converter topologies are examined and to enhance the efficiency and performance a new bridgeless interleaved and a phase shifted semibridgeless power factor corrected converter are proposed , which is remarkable to optimize the charger size, charging time, and the amount and cost of electricity drawn from the utility. A comprehensive analytical model for these topologies is developed, with the help of which power losses and efficiency are calculated . Experimental and simulation results of prototype Bridgeless interleaved boost converter which convert the universal AC input voltage to 400 V DC at 3.4 kW are provided to authenticate the proof of concept, and analytical work discribed in this thesis. The results show a power factor greater than 0.99 from 750 W to 3.6 kW, THD less than 5% from half load to full load and a peak efficiency of 98 % at 264 V input and 1000 W load.

## Contents

| and an and a second |          |

|----------------------------------------------------------------------------------------------------------------|----------|

| Abstract                                                                                                       | iii      |

| List of Symbols                                                                                                | ix       |

| Abbreviations                                                                                                  | x        |

| 1 Introduction                                                                                                 | 1        |

| 2 Background                                                                                                   | <b>2</b> |

| 2.1 Background                                                                                                 | 2        |

| 2.1.1 Power Factor general background                                                                          | 4        |

| 3 LITERATURE REVIEW                                                                                            | 7        |

| 3.1 CLASSIFICATION                                                                                             | 7        |

| 3.2 Component stress                                                                                           | 8        |

| 3.3 Investigate Current ripple in output capacitor                                                             | 9        |

| 3.4 Solution for the Issues such as Voltage and current sensing, EMI noise                                     | 9        |

| 3.5 Current Distortion Problem at low Power                                                                    | 10       |

| 3.6 Bridgeless P.F.C. Configuration                                                                            | 10       |

| 3.7 Survey of basic AC– DC PFC topology                                                                        | 10       |

| 3.7.1 Conventional Boost Converter                                                                             | 10       |

| 3.7.2 Bridgeless Boost Converter                                                                               | 11       |

| 3.7.3 Interleaved Boost Converter                                                                              | 12       |

|                                                                                                                |          |

#### 4 PROPOSED BLIL BOOST TOPOLOGY

| <b>5</b> | OP            | ERATIONAL ANALYSIS                                                                | 16 |

|----------|---------------|-----------------------------------------------------------------------------------|----|

|          | 5.1           | CIRCUIT WORKING AND STEADY-STATE EXAMINATION                                      | 16 |

|          |               | 5.1.1 Positive Half Cycle working                                                 | 17 |

|          | 5.2           | Negative Half Cycle working                                                       | 18 |

|          |               | 5.2.1 Point by point Positive Half Cycle working and study for $\mathrm{D} > 0.5$ | 19 |

|          |               | 5.2.2 Point by point Positive Half Cycle working and study for $\mathrm{D} < 0.5$ | 25 |

| 6        | AN            | ALYTICAL MODELING                                                                 | 32 |

| 7        | $\mathbf{CA}$ | LCULATION                                                                         | 36 |

|          | 7.1           | Inductor RMS current                                                              | 36 |

|          | 7.2           | Input Bridge Diode Average Current                                                | 36 |

|          | 7.3           | Fast Diode Average Current                                                        | 37 |

|          | 7.4           | MOSFET RMS Current                                                                | 37 |

|          | 7.5           | MOSFET Intrinsic Body Diode Average Current                                       | 39 |

|          | 7.6           | Output Capacitor RMS Ripple Current (Low Frequency)                               | 39 |

|          | 7.7           | Output Capacitor RMS Ripple Current (High Frequency)                              | 39 |

| 8        | EX            | PERIMENTAL RESULTS                                                                | 42 |

|          | 8.1           | Simulation Result                                                                 | 42 |

|          | ć.            |                                                                                   |    |

| 9        | con           | clusion                                                                           | 49 |

| R        | efere         | nces                                                                              | 50 |

|          |               |                                                                                   |    |

## List of Tables

|    |     | aparent process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 4.1 | COMPARISON OF AC-DC PFC TOPOLOGIES FOR PHEV BATTERY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|    |     | CHARGING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15 |

|    |     | Contraction and the contraction of the contraction |    |

|    | 6.1 | Brief description of the component current stresses for the conventional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|    | 1   | boost,Bridgeless                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35 |

|    | 6.2 | Brief description of the component current stresses for the interleaved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 1  | 5   | boost,and BLIL PFC topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35 |

|    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    | 8.1 | Value of Parameters taken for Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42 |

|    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| ×. |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    |     | 2 1 - 3 2 Comment of Call - 1 2 P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|    | ٥.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    | 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    |     | 2 min and a few                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    |     | CONTRACT OF TECHNIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

## List of Figures

|   | 2.1  | block diagram of a universa two-stage battery charger                              | 3  |

|---|------|------------------------------------------------------------------------------------|----|

|   | 2.2  | Passive power factor correction AC main voltage and current waveforms              | 5  |

|   | 3.1  | Topology-framework based characterization of improved power quality                |    |

|   |      | converters                                                                         | 7  |

|   | 3.2  | Converter-based arrangement of improved power quality converters                   | 8  |

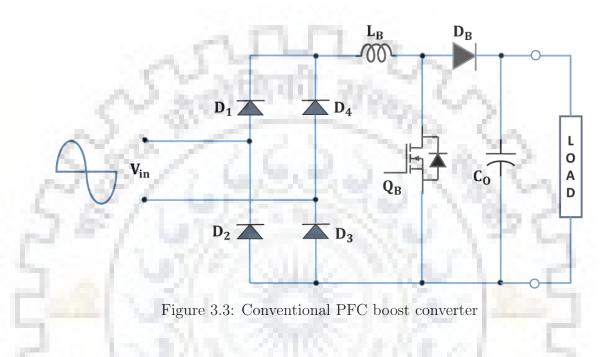

|   | 3.3  | Conventional PFC boost converter                                                   | 11 |

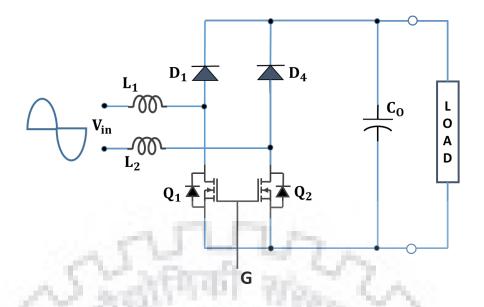

|   | 3.4  | without rectifying Bridge PFC boost converter                                      | 12 |

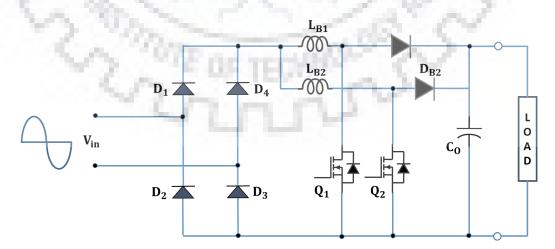

|   | 3.5  | Interleaved PFC boost converter                                                    | 12 |

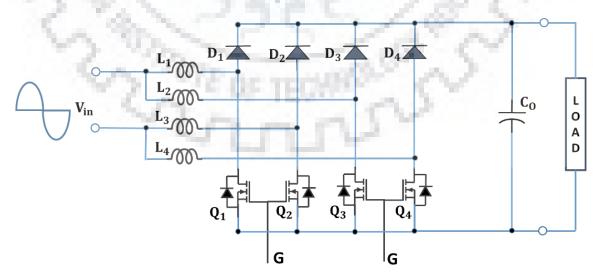

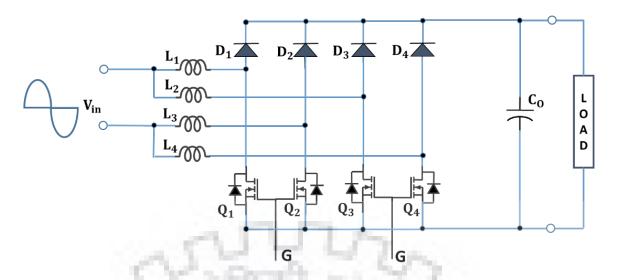

| 5 | 4.1  | Proposed BLIL PFC boost converter                                                  | 14 |

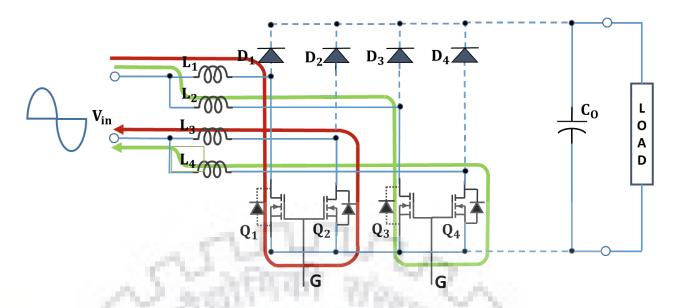

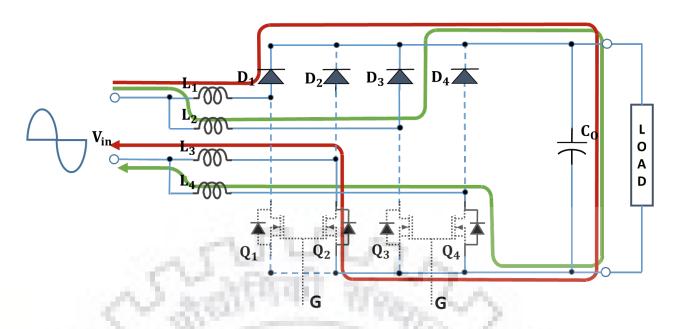

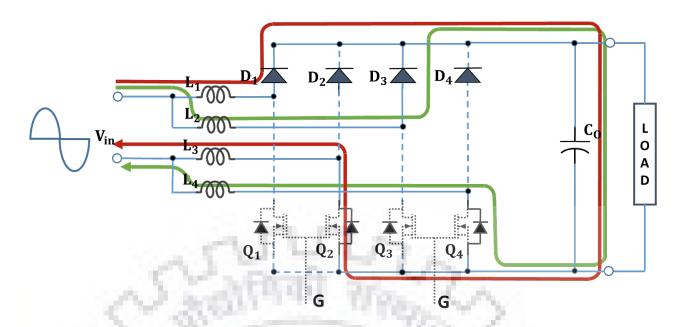

|   | 5.1  | BLIL PFC boost converter                                                           | 17 |

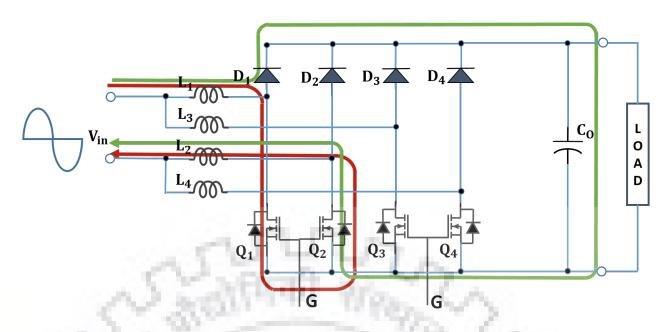

|   | 5.2  | Positive Half Cycle working                                                        | 18 |

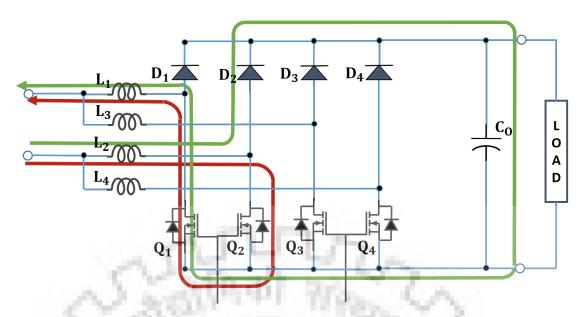

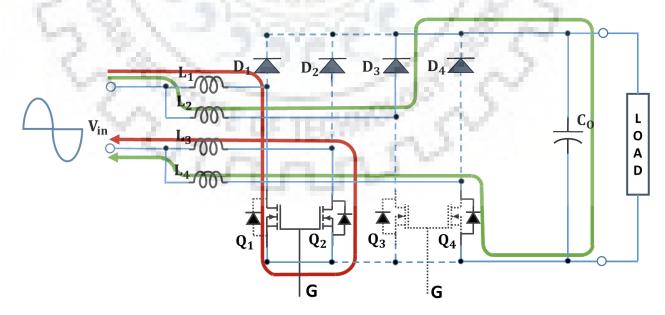

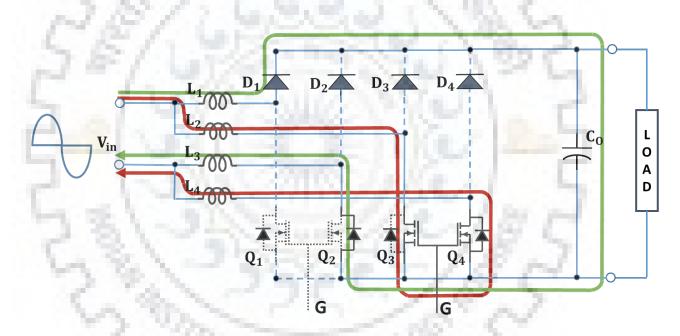

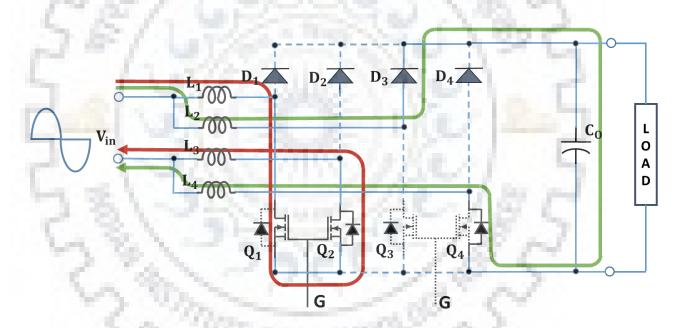

|   | 5.3  | Negative Half Cycle working                                                        | 19 |

|   | 5.4  | During Interval 1 when PAIR-1 switches are high and body diode of $Q4$             |    |

|   |      | working                                                                            | 19 |

|   | 5.5  | During Interval 2 and 4, when all switches are high                                | 20 |

|   | 5.6  | During Interval 3 PAIR-2 switches are high, and body diode of Q2 working           | 20 |

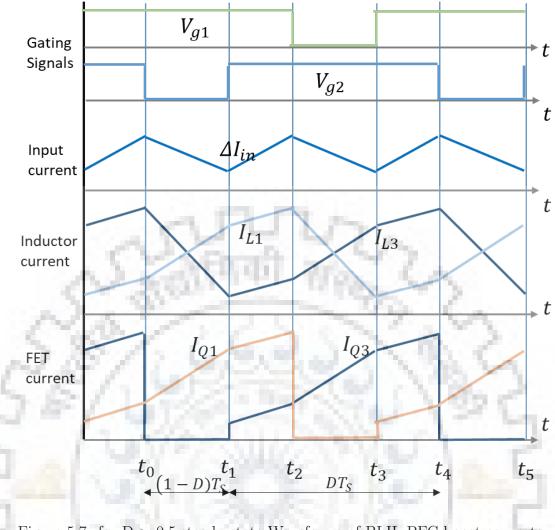

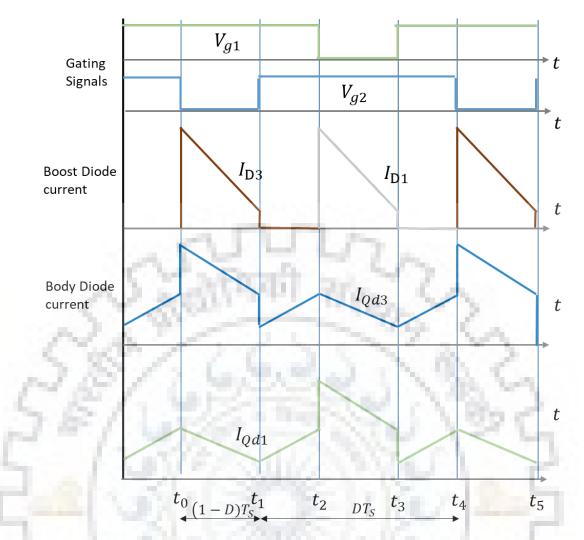

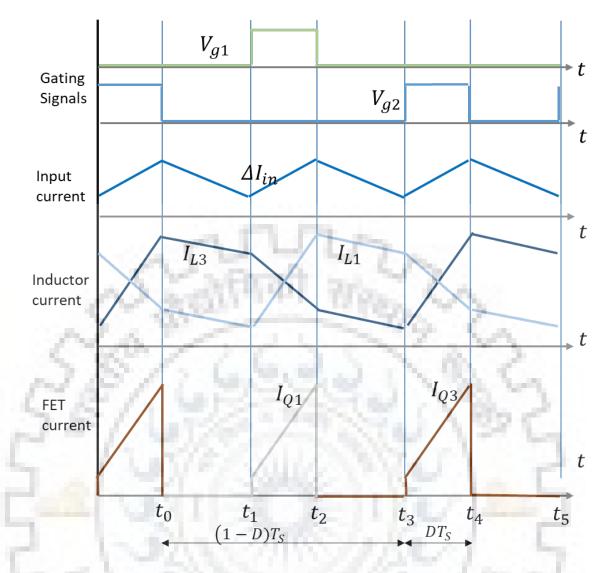

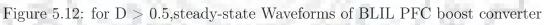

|   | 5.7  | for D $>$ 0.5,<br>steady-state Waveforms of BLIL PFC boost converter               | 24 |

|   | 5.8  | for D $>$ 0.5,<br>steady-state Waveforms of BLIL PFC boost converter $\ . \ . \ .$ | 25 |

|   | 5.9  | Body diodes of Q2 and Q4 conducts in Interval1 and $3 \dots \dots \dots \dots$     | 26 |

|   | 5.10 | PAIR-1 switches are switch ON,<br>and body diode of Q4 conducts in Interval 2      | 26 |

|   | 5.11 | PAIR-2 switches are switch ON,<br>and body diode of Q2 conducts in Interval $4$    | 27 |

|   | 5.12 | for D $>$ 0.5,<br>steady-state Waveforms of BLIL PFC boost converter $\ . \ . \ .$ | 30 |

|    | 5.13 | for D $>$ 0.5,<br>steady-state Waveforms of BLIL PFC boost converter $\ . \ . \ .$ | 31 |

|----|------|------------------------------------------------------------------------------------|----|

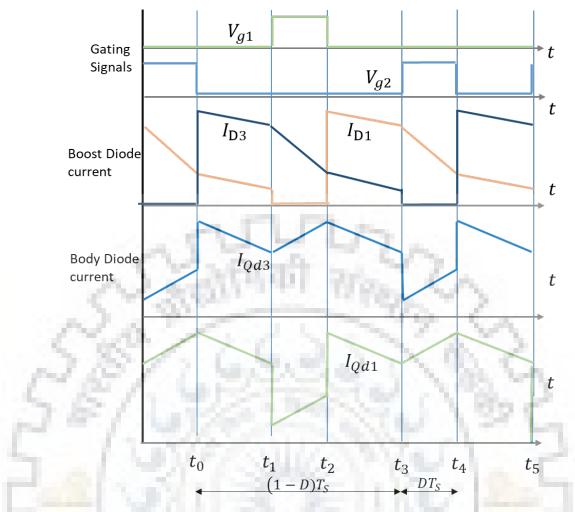

|    | 8.1  | Input current signal                                                               | 43 |

|    | 8.2  | Total Harmonic Distortion                                                          | 43 |

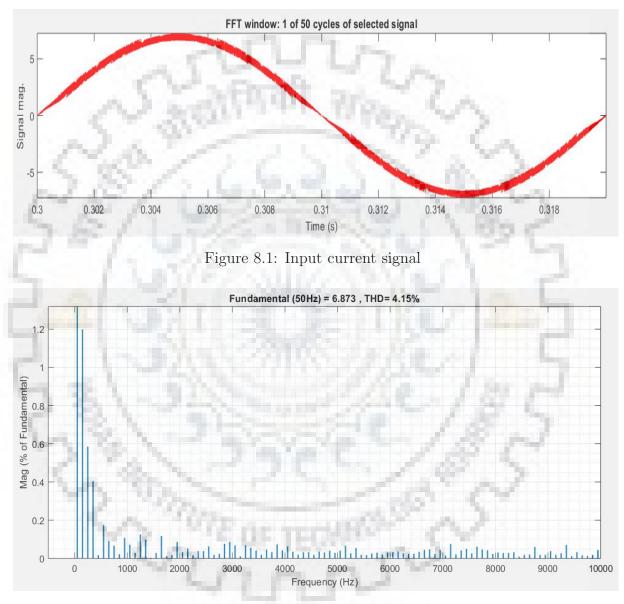

|    | 8.3  | Output current                                                                     | 44 |

|    | 8.4  | Output Voltage                                                                     | 44 |

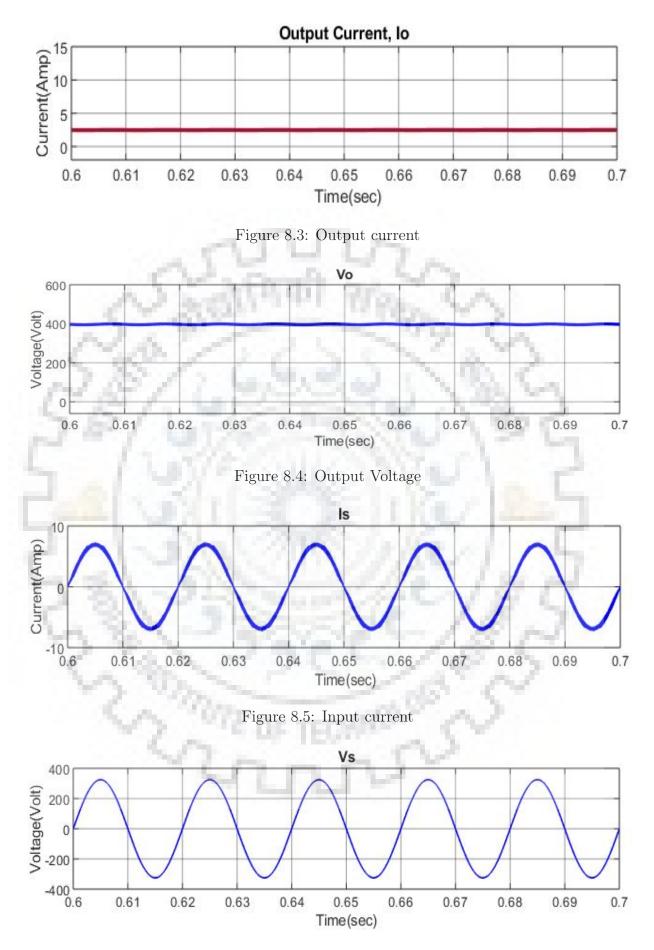

|    | 8.5  | Input current                                                                      | 44 |

|    | 8.6  | Input Voltage                                                                      | 44 |

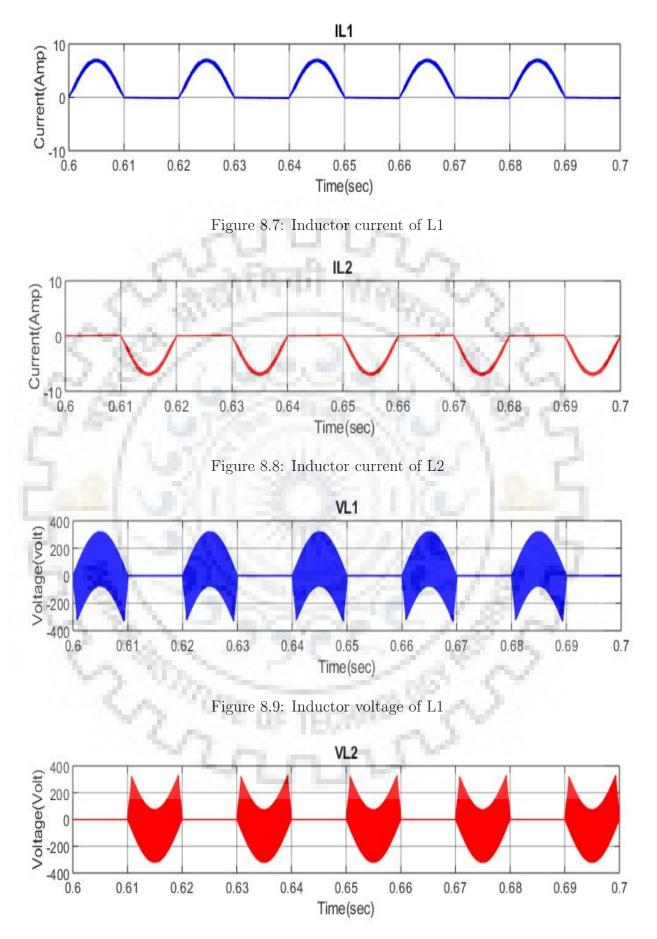

|    | 8.7  | Inductor current of L1                                                             | 45 |

|    | 8.8  | Inductor current of L2                                                             | 45 |

|    |      | Inductor voltage of L1                                                             | 45 |

|    | 8.10 | Inductor voltage of L2                                                             | 45 |

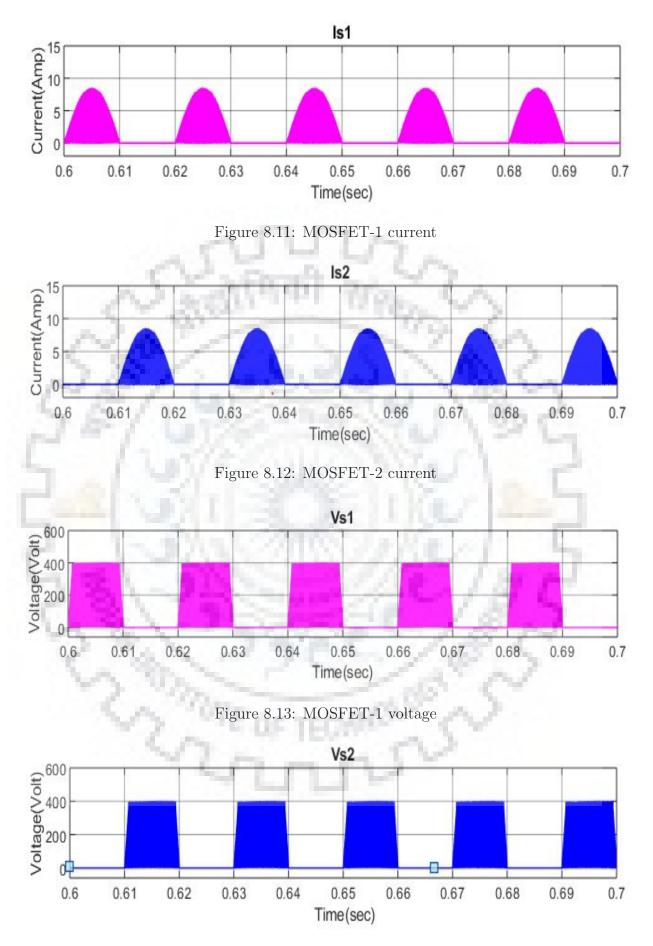

|    | 8.11 | MOSFET-1 current                                                                   | 46 |

| 12 | 8.12 | MOSFET-2 current                                                                   | 46 |

|    | 8.13 | MOSFET-1 voltage                                                                   | 46 |

|    | 8.14 | MOSFET-2 voltage                                                                   | 46 |

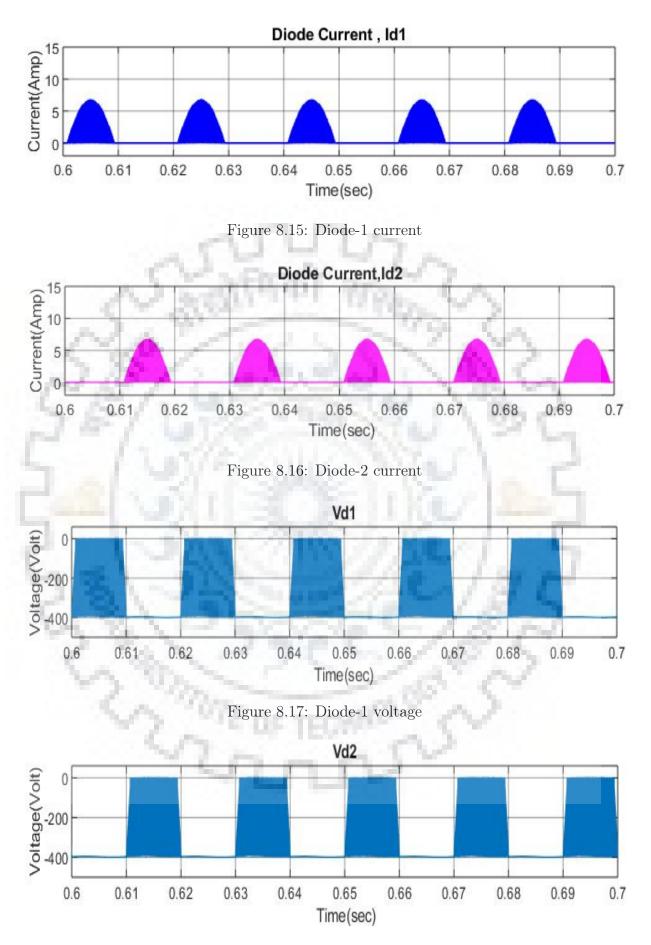

|    | 8.15 | Diode-1 current                                                                    | 47 |

| ×. | 8.16 | Diode-2 current                                                                    | 47 |

|    | 8.17 | Diode-1 voltage                                                                    | 47 |

|    | 8.18 | Diode-2 voltage                                                                    | 47 |

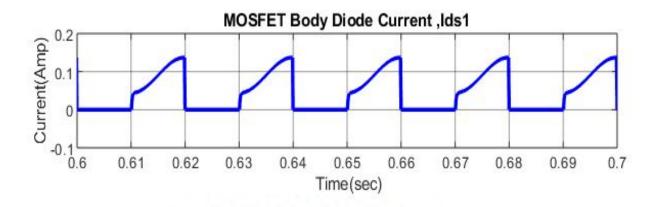

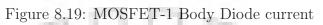

|    | 8.19 | MOSFET-1 Body Diode current                                                        | 48 |

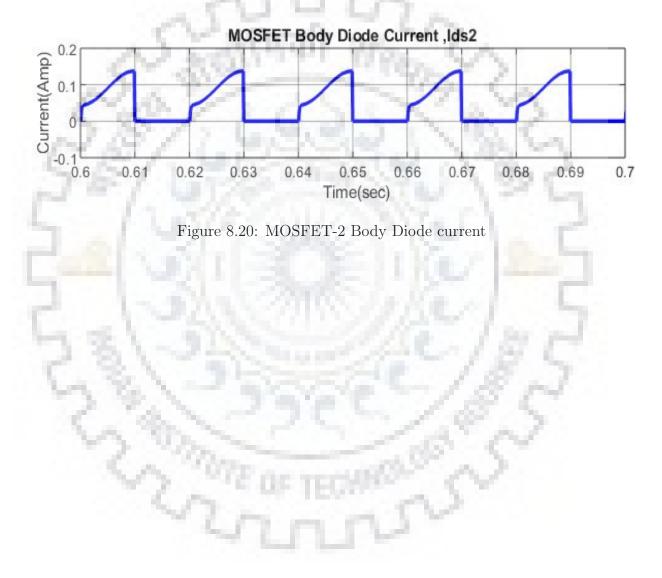

|    | 8.20 | MOSFET-2 Body Diode current                                                        | 48 |

|    |      |                                                                                    |    |

## List of Symbols

- $C_O$  Output Capacitor

- $\delta_D$  Boost Diode Duty Cycle

- $\delta_Q$  Boost Main Switch Duty Cycle

- $I_{ms}$  Total Line Current

- $I_{\rm Irms}$  Fundamental Component

- $K_d$  Distortion Factor

- $K_{\theta}$  Displacement Factor

- $T_S$  One Switching Period

- $\theta_I$  Angle between Current Fundamental and Sinusoidal Line Voltage

- $V_S$  Maximum Input Voltage

- $V_{\rm ref}$  Reference Voltage

## Abbreviations

| AC                                        | AC Alternating Current            |  |  |  |

|-------------------------------------------|-----------------------------------|--|--|--|

| ADC                                       | Analog to Digital Converter       |  |  |  |

| ASIC Application Specific Integrated Circ |                                   |  |  |  |

| BJT Bipolar Junction Transistor           |                                   |  |  |  |

| BL                                        | Bridgeless                        |  |  |  |

| BLIL                                      | Bridgeless Inte leaved            |  |  |  |

| CCM                                       | Continuous Conduction Mode        |  |  |  |

| CRM Critical Conduction Mode              |                                   |  |  |  |

| D Duty Cycle                              |                                   |  |  |  |

| DC                                        | Direct Current                    |  |  |  |

| DCM                                       | Discontinuous Conduction Mode     |  |  |  |

| DSP                                       | Digital Signal Processors         |  |  |  |

| FL Full Load                              |                                   |  |  |  |

| FPGA                                      | Field Programmable Gate Array     |  |  |  |

| IC                                        | Integrated Circuits               |  |  |  |

| IGBT                                      | Insulated Gate Bipolar Transistor |  |  |  |

| IL                                        | Interleaved                       |  |  |  |

| EMI                                       | Electrical Magnetic Interference  |  |  |  |

| EV                                        | Electric Vehicle                  |  |  |  |

| MOSFET                               | Metal Oxide Silicon Field Effect Transistor |  |  |

|--------------------------------------|---------------------------------------------|--|--|

| NL                                   | No Load                                     |  |  |

| PID                                  | Proportional Integral Derivative            |  |  |

| PF Power Factor                      |                                             |  |  |

| PFC Power Factor Correction          |                                             |  |  |

| PHEV Plug in Hybrid Electric Vehicle |                                             |  |  |

| PSFB Phase Shift Full-Bridge         |                                             |  |  |

| PWM Pulse Width Modulation           |                                             |  |  |

| RLC Resistance Inductor Capacitor    |                                             |  |  |

| RMS                                  | Root Mean Square                            |  |  |

| SR Synchronous Rectifier             |                                             |  |  |

| -                                    |                                             |  |  |

## Chapter 1

## Introduction

In the present era the energy demand increase abruptly and for the main source of energy we depend on fossil fuels as it easy to extract and cost effective. although, there is disadvantage cause by them for example air pollution which as a result effect our atmosphere, other with the price of the fossil fuel which increasing day by day. which pressurizing the Industries and Government to replacement of the fossil fuels. As a result our interest is increasing in the mean of transportation for example Plug in Hybrid Electric Vehicles (PHEV) and Electric Vehicles (EV).

In the early 19th century we were aware of the EV and PHEV technology.however,In comparison with oil the EV have high price and less energy output and the cost of storing battery was high.Now the scenario is different ,with the advent of Lithium-ion batteries and there is a hike in the price of fossil fuels and the pollution arise by them ,convince the organisation to concentrate on EV and PHEV.

when more number of EV and PHEV comes in the market and on the road ,this will impact the utility grid when the demand of charging it is at the peak level [1]. As a result in order to reduce the load on grid and decrease the charging hour there is a requirement of efficient and high power factor chargers. To keep the input current harmonics in limit drawn by these charger power factor of the charger must comply with the standards as IEC 61000-3-2 [2]

## Chapter 2

## Background

#### 2.1 Background

A hybrid vehicle with a capacity battery that could be energized by connecting a plug to an outside electricity supply coming from power source. Outlet for charging with the AC supply certainly require an on-board AC/DC charger having a power factor adjustment. An on-board 3.5 kW charger can charge an fully empty battery package in PHEVs to 95% charge within four hours by the 240 V supply [3].

efficient Chargers are additionally characterized with the dimension of power they can Make accessible to the battery package [4]:

- Level 1:typical family unit circuit, evaluated to 15 amperes and 120 volts AC . These chargers utilize the standard three-prong family unit association, and they are, for the most part thought to be convenient hardware.

- Level 2: For all time wired connected electric vehicle supply equipment utilized particularly for electric vehicle charging; evaluated up to limit of voltage 240 volts AC and current up to 60 amps, and power up to 14.4 kilowatts.

- Level 3:For all time wired electric vehicle supply gear utilized primarily for electric vehicle charging; evaluated for rating more than 14.4 kW. Quick chargers are appraised as Level 3, however not all Level 3 chargers are quick chargers. This

assignment relies upon the span of the battery package to be charged and how much time is required to charge the battery pack. A charger can be viewed as a quick charger on the off chance that it can charge a normal electric vehicle battery pack in 30 minutes or less.

The front-end AC/DC converter is a significant part of the charging system. The reason of this record is to examine how this examination will be led on the elite single-stage answers for AC/DC power factor remedied converters for PHEV battery chargers. An alternate circuit topologies and control techniques have been produced for the PFC application [5–7]. The single-stage active PFC methods can be separated into two classes: the single-stage approach and the two-stage approach. The single-stage approach is appropriate for low power applications. What's more, because of vast low frequency ripple in the output current, just lead-corrosive batteries are chargeable. Accordingly, the two-stage approach is the best possible contender for PHEV battery chargers [8], where the power rating is relatively high, and lithium-particle batteries are utilized as the fundamental energy storage system. The front end PFC area is then trailed by a DC/DC section to complete the charging system.

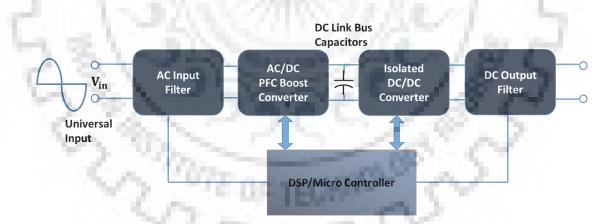

Figure 2.1: block diagram of a universa two-stage battery charger

The PFC level rectify the enter AC voltage and switch it right into a regulated intermediate DC hyperlink bus. At the equal time, power factor component correction characteristic is executed. The following DC/DC stage then converts the DC bus voltage into a regulated output DC voltage for charging batteries, which is required to fulfill the law and brief requirements.

#### 2.1.1 Power Factor general background

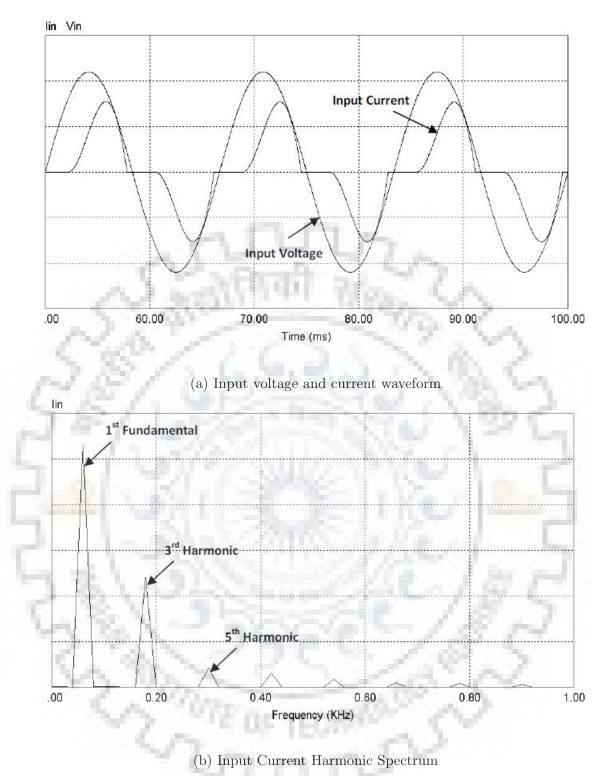

As per the requirements of input current harmonics [9] and output voltage regulation, a front-end converter is regularly actualized by a power factor correction (PFC) stage. Conventionally, a large portion of the power transformation hardware utilizes either a diode rectifier or a thyristor rectifier with a mass capacitor to converter AC voltage to DC voltage before preparing it [10]. Such rectifiers generate harmonic in the input current , which contaminates the power system and the utility lines. Power quality is turning into a noteworthy worry for some electrical users. The most straightforward type of PFC is Passive (Passive PFC). A passive PFC utilize a filter at the AC input to rectify poor power factor. The passive PFC circuitry utilize just passive components - an inductor and some capacitors, despite the fact that it is simple and robust, a passive PFC rarely achieves low Total Harmonic Distortion (THD). Also, since the circuit works at the low line power frequency of 50Hz or 60Hz, the passive elements are generally large and heavy. Figure 1-2 shows input voltage and current for a passive PFC, and the harmonic spectrum of input current. The input power factor (PF) is defined as the ratio of the real power divided by apparent power as:

Power Factor(

$$PF$$

) =  $\frac{\text{Real Power } (W)}{\text{Apparent Power } (VA)}$  (2.1)

Assuming an ideal sinusoidal input voltage source, the power factor can be expressed as the multiplication of two factors, the distortion factor and the displacement factor, as given:

$$PF = K_d K_\theta \tag{2.2}$$

The distortion factor  $K_d$  is the ratio of the fundamental RMS current to the total RMS current.

the second se

Figure 2.2: Passive power factor correction AC main voltage and current waveforms

The displacement factor,  $K_{\theta}$ , is the cosine of the displacement angle between the fundamental input current and the input voltage fundamental RMS current.

$$K_d = \frac{I_1 rms}{I_{rms}} \tag{2.3}$$

$$K_{\theta} = \cos \theta_1 \tag{2.4}$$

where, line current have  $I_{\text{Irms}}$  as the fundamental component,  $I_{\text{rms}}$  as the total line current, and  $\theta_1$  is the phase shift of the current fundamental relative to the sinusoidal line voltage. waveform in which distortion can be notice those also have the distortion factor nearly equal to one so it is not very useful for measuring the distortion practically. but Total harmonic distortion is directly related to distortion factor.

$$THD = \sqrt{\frac{I_{rms}^2 - I_{1rms}^2}{I_1 rms^2}}$$

(2.5)

$$K_d = \sqrt{\frac{1}{1 + THD^2}} \tag{2.6}$$

$K_d$  is regulated IEC 1000-3-2 [2] for lower power levels and by IEEE Std 519-1992 [11] for higher power levels, where  $K_{theta}$  is regulated by utility companies [12]

By using only the pulse width modulated (PWM) switching technique in the rectification of single phase AC supply we can diminish the current harmonics in the circuits. These converter can resemble like a resistive load and allow very little distortion in the current. these converter by using these modulation technique draw current close to sinusoidal shape with little distortion and higher PF, this method called power factor correction(PFC). By this research, the already exist based boost converter topology PFC technology with average current-mode control was noticeably improved, which increase the operating range of converter .

22

### Chapter 3

## LITERATURE REVIEW

#### 3.1 CLASSIFICATION

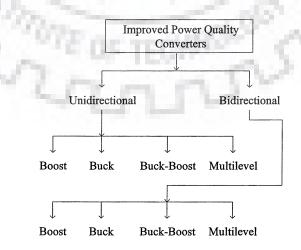

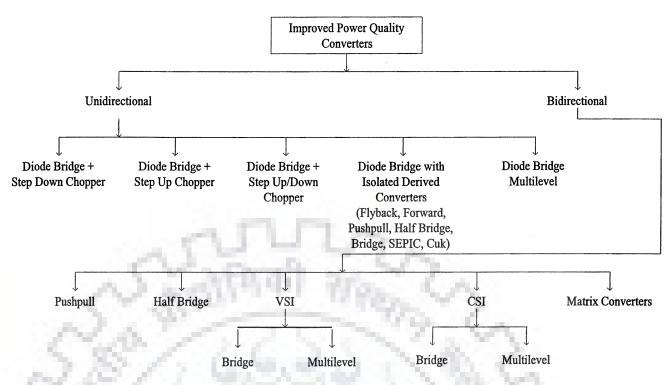

**B.** Singh et al. [5] Discuss a whole analysis of improved power quality converters (IPQCs) configurations, control of applications, components selection, design attributes, other related considerations, and their suitability and selection for precise applications. It is examined to provide a broader overview on the repute of IPQC technology. A categorized listing of more than 450 research guides on the kingdom of art of IPQC is also given for a fast reference. And also includes the sequential development and the reputation of the IPQC era, explained four essential classes namely boost, buck, buck-boost, and multilevel converters which provide higher level of power quality at the input ac source and at dc output

Figure 3.1: Topology-framework based characterization of improved power quality converters

Figure 3.2: Converter-based arrangement of improved power quality converters

#### 3.2 Component stress

L. Petersen et al. [8] In this paper, single organize topology is contrasted and the two phase topology PFC converter which utilized for the most recent decade and still proceeds. The objective of this paper is to draw the consideration on the quantitative investigation of power transferred. To think about the part stress, the after-effects of fundamental DC-DC topologies has been investigated. get the information to discover the elective arrangement of PFC converter and set against the normal two-stage solution.

With the assistance of the component load factors(CLF) looked at different converter topologies [13].other parameter Like cost, size and productivity in a roundabout way rely upon segment stress, so it is determined for fundamental topologies and considering segment stress change under various conditions .a framework of suitable arrangement are accomplished with and the investigation of what ought not to do. Bizarre segment stress is inspected with the data got from the utilization of CFL.

#### 3.3 Investigate Current ripple in output capacitor

**Dehong Xu et al.** [14]Investigated output capacitor current ripple for Boost converte ,3-level converter with switch in a require range, two lower switches converter and totem pole converter with switch in a require range. Its effect on output voltage ripple and capacitor voltage stress is examined. In output capacitors Filter current ripples for these four topologies are contrasted and the method to select output capacitor according to current ripple capability of capacitor is enumerated.

# 3.4 Solution for the Issues such as Voltage and current sensing, EMI noise

**Bing Lu at el.** [15]completed the exploration to illuminate the voltage detecting, current detecting and EMI noise by one cycle control method. Ordinary boost PFC experiences the high conduction loss in the input rectifier bridge connected in frontend. High conversion efficiency can be accomplished by utilizing the bridgeless boost topology. This new circuit has issues, for example, voltage detecting, current detecting, and EMI noise. In this paper, one cycle control procedure is utilized to unravel the issues of the voltage detecting and current detecting. Exploratory outcomes show efficiency improvement and EMI execution

2 mm

#### 3.5 Current Distortion Problem at low Power

**Costel Petrea at el.** [16]The ordinary boost power factor remedy converter has high conduction loss as a result of the input rectifier bridge. The utilization of a bridgeless PFC circuit offers high efficiency. For high powers, the bridgeless circuit will be intended to work in persistent conduction mode (CCM), utilizing a normal current mode control. The switches have parasitic capacitances that in CCM lead to switch losses, without impacting the waveform of the converters. For low loads, the intermittent conduction mode Ml D3 M2 D4 (DCM) shows up, yet the parasitic capacitances lead to the input current distortion. This paper centers around the simulation and examination of bridgeless PFC converter working at higher load and lower load and potential answers for wipe out the distortion of the current working at low power.

#### 3.6 Bridgeless P.F.C. Configuration

**Ugo Moriconi et al.** [17] portrays an inventive topology devoted to a medium to high power PFC organize. The innovation of this topology is the nonappearance of the bridge that generally is put between the EMC filter and the PFC stage. The upsides of this topology can be found as far as increased efficiency and improved thermal management.

### 3.7 Survey of basic AC– DC PFC topology

The conventional, bridgeless and interleaved boost converters are analyzed to use in frontend of ac– dc change in charging of battery in PHEV in the accompanying sub-section.

#### 3.7.1 Conventional Boost Converter

The conventioal boost topology is the most renowned topology for PFC working. In PFC working, diode bridge is utilized to rectify the AC input voltage to DC, and after this the boost converter, as appeared in Figure. The output ripple current is high in this topology and is the contrast between the DC output current and the diode current. At high power level in the diode connect ,losses become essentially expansive and decline the

effectiveness, so worried with the heat dissemination in a restricted area progresses toward becoming issue. considering above limitations, this topology is works useful for a low to medium power extend, up to about 1 kW. Above 1KW power level, architects inclines toward parallel semiconductors so as to give more output power. Size of inductor likewise turned out to be big issue at high power in view of the restricted core size accessible for the power level and the overwhelming wire check required for winding.

#### 3.7.2 Bridgeless Boost Converter

Information connect rectifier isn't required in the bridgeless boost PFC topology in contrast with the Boost AC-DC PFC converter, still, it keeps up the great boost topology. [15–21], as shown in Fig.3.4. It is useful for applications at power levels more prominent than 1 kW, where efficiency and power density are critical. This topology evacuate the issue of heat management in the input rectifier diode bridge, yet the drawback is that expanded EMI present in the circuit [22–24]. skimming input line as for the PFC organize ground is the Another bad mark of this topology, therefore without a low an optical coupler or frequency transformer it unfit to detect the input voltage. Additionally, there is a need of complex hardware so as to detect the input current, current in the MOSFET and diode ways independently, in light of the fact that every half-line cycle current path does not have a similar ground [17, 25]

Figure 3.4: without rectifying Bridge PFC boost converter

#### 3.7.3 Interleaved Boost Converter

The interleaved boost converter, shown in Figure.3.5, compose of parallelly connected two boost converter , working 180° out of phase with the help of switching pulses [19,26, 27]. The input current is the summation of the two inductors currents in  $L_{B1}$  and  $L_{B2}$ . parallel-ling of boost converter result into many merits. The ripple currents flows in these inductors are out of phase, subsequently they counteract one another, and thusly decrease the high frequency input ripple current delivered by the boost switching action, so the measure of input EMI filter is diminished [28–30].

Figure 3.5: Interleaved PFC boost converter