# SLIDING MODE CONTROL OF PUSH-PULL CONVERTER

# A DISSERTATION

Submitted in partial fulfillment of the requirements for the award of the degree

of

MASTER OF TECHNOLOGY

in ELECTRICAL ENGINEERING (With Specialization in Electric Drives and Power Electronics)

KUNAL SHIVAJI NARAD

By

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA) JUNE, 2013

# I.D. NO. MT 279 SP 2013-52

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE

# CANDIDATE'S DECLARATION

I hereby declare that the work that is being presented in this dissertation entitled, "SLIDING MODE CONTROL OF PUSH-PULL CONVERTER" in partial fulfilment of the requirements for the award of degree in Master of Technology in Electrical Engineering With Specialization in "Electric Drives & Power Electronics" submitted to the Department of Electrical Engineering, Indian Institute of Technology, Roorkee, INDIA is an authentic record of my own work carried under the guidance of Dr. S. P.Singh, Professor, Department of Electrical Engineering, Indian Institute of Technology, Roorkee.

The matter embodied in this dissertation report has not been submitted by me for the award of any other degree or diploma.

Date: 19 June 2013 Place: IIT Roorkee KUNAL SHIVAJI NARAD (M.TECH. EDPE)

# CERTIFICATE

This is to certify that the above statement made by the candidate is correct to the best of my knowledge and belief.

Date: IgJune 2013

Place: IIT Roorkee

Dr. S.P.Sing

Professor Department of Electrical Engineering IIT Roorkee-247 667 State space averaging method is used for obtaining the transfer function of Push-Pull converter. Using SISOTOOL in MATLAB tuning of PI controller is obtained. Performance of sliding mode controller for Push-Pull converter is investigated by PSIM software. The PI controller simulation results compared with sliding mode controller. From simulation results it can be observed that sliding mode controller provides better control strategy than PI controller.

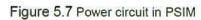

With the help of 'Simcoupler Module' which is used for co-simulation of PSIM software and MATLAB, Push Pull converter circuit in open loop configuration as well as with sliding mode controller in closed loop is simulated using Xilinx tool box. Using FPGA (Field programmable gate array) SPARTAN 3 kit, pulses required for converter operation are generated. Prototype model of Push-Pull converter is tested in open loop configuration.

The euphoria and joy, accompanying the successful completion of my task would be incomplete without the special mention of those people whose guidance and encouragement made my effort successful.

I am deeply indebted to my guide Prof. S.P.Singh in department of Department of Electrical Engineering and K.P.Guruswamy, research scholar of Indian Institute of Technology, Roorkee, whose help, stimulating suggestions and encouragement helped me in all the time to make my effort successful.

> Kunal Shivaji Narad Enrollment No. 11527013 MTech- 2<sup>nd</sup> year

# CONTENTS

| ABS  | STRACT                                                     | 1  |

|------|------------------------------------------------------------|----|

| ACK  | (NOWLEDGEMENT                                              | 2  |

| CON  | ITENTS                                                     | 3  |

| LIST | ſ OF FIGURES                                               | 5  |

|      |                                                            |    |

| CHA  | APTER 1: INTRODUCTION                                      | 7  |

| 1.1  | Various dc-to-dc Power Converters                          |    |

|      | 1.1.1 Buck converter                                       |    |

|      | 1.1.2 Boost converter                                      |    |

|      | 1.1.3 Forward converter                                    |    |

|      | 1.1.4 Push-Pull converter                                  | 8  |

| СНА  | APTER 2: STATE SPACE MODELING OF PUSH-PULL CONVERTER .     |    |

| 2.1  | Steady state analysis                                      | 14 |

| 2.2  | Small signal analysis                                      |    |

| СНА  | APTER 3: DESIGN OF PUSH-PULL CONVERTER                     | 16 |

| 3.1  | Transformer design                                         |    |

| 3.2  | Converter design                                           | 17 |

| СНА  | APTER 4: PI CONTROLLER AND SLIDING MODE CONTROLLER         | 19 |

| 4.1  | Basic structure of controller                              |    |

|      | 4.1.1 Step response of the converter without controller    |    |

| 8    | 4.1.2 Step responses of different type controllers         | 21 |

|      | 4.1.2.1 Proportional (P) Controller                        | 21 |

|      | 4.1.2.2 Integral (I) Controller                            | 22 |

|      | 4.1.2.3 Proportional-Derivative (PD) Controller            | 22 |

|      | 4.1.2.4 PI and PID Controller                              | 23 |

| 4.2  | Sliding Mode Controller                                    | 23 |

| СНА  | APTER 5: SIMULATION AND RESULTS                            | 25 |

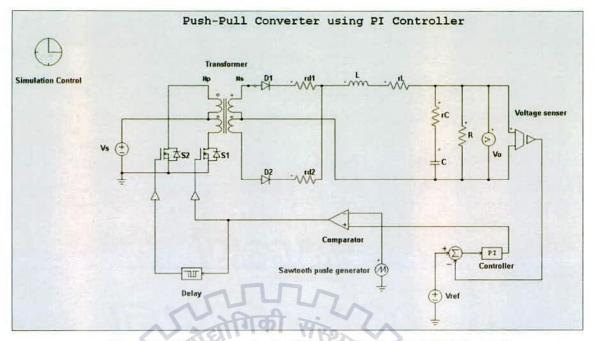

| 5.1  | PI controller for Push-Pull Converter                      | 25 |

| 5.2  | Sliding Mode Controller of Push-Pull Converter             | 26 |

| 5.3  | Comparison of sliding mode controller with PI controller   |    |

| 5.4  | FPGA based Push-Pull Converter (Open loop)                 |    |

| 5.5  | FPGA based sliding mode controller for Push-Pull Converter |    |

| СНА  | APTER 6: HARDWARE IMPLEMENTATION                           | 33 |

| 6.1  | Pulse generation using FPGA SPARTAN 3-kit                  |    |

|      | 6.1.1 Steps for pulse generation                           |    |

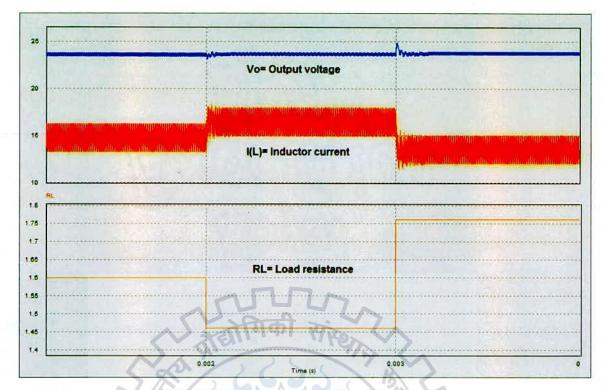

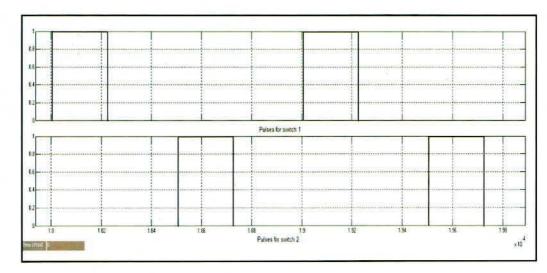

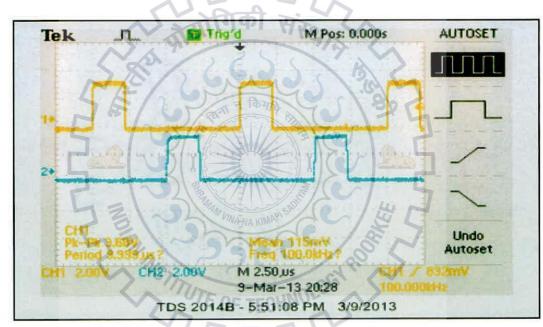

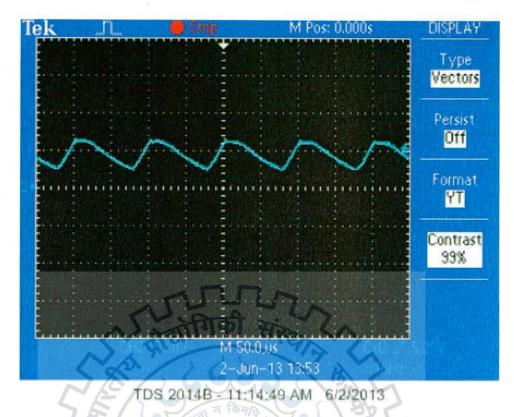

| 6.2         | 2 Simulation result and FPGA kit output |                      |    |  |  |  |

|-------------|-----------------------------------------|----------------------|----|--|--|--|

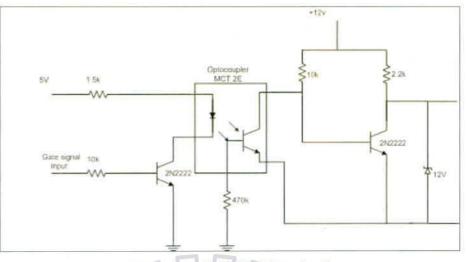

| 6.3         | Driver circu                            | uit for MOSFET       | 35 |  |  |  |

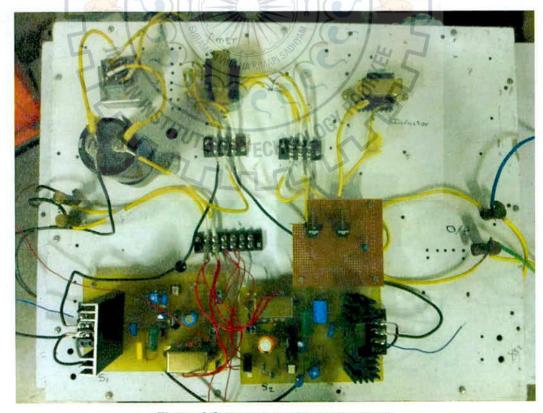

| 6.4         | Experimen                               | tal setup            | 37 |  |  |  |

| СНА         | PTER 7:                                 | CONCLUSION           | 39 |  |  |  |

| СНА         | PTER 8:                                 | BIBILIOGRAPHY        | 40 |  |  |  |

| LIST        | OF PUBLIC                               | CATIONS              | 41 |  |  |  |

| APP         | ENDIX A:                                | RM FERRITE CORE DATA | 42 |  |  |  |

| APPENDIX B: |                                         | WIRE TABLE           | 43 |  |  |  |

# LIST OF FIGURES

| Figure 1.1 Circuit of Push-Pull converter                             | 8        |

|-----------------------------------------------------------------------|----------|

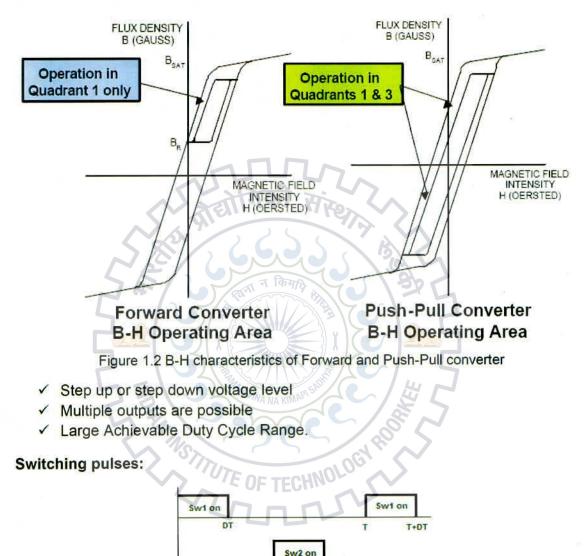

| Figure 1.2 B-H characteristics of Forward and Push-Pull converter     | 9        |

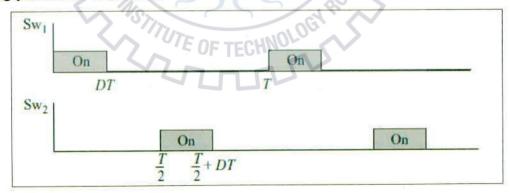

| Figure 1.3 Switching pulses for Push-Pull converter                   |          |

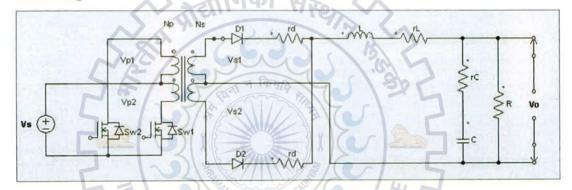

| Figure 2.1 Schematic of Push-Pull converter                           |          |

| Figure 2.2 Pulses for switches                                        |          |

| Figure 2.3 Mode 1 operation                                           |          |

| Figure 2.4 Mode 2 operation                                           |          |

| Figure 4.1 Controller structure                                       |          |

| Figure 4.2 Command window of SISOTOOL                                 |          |

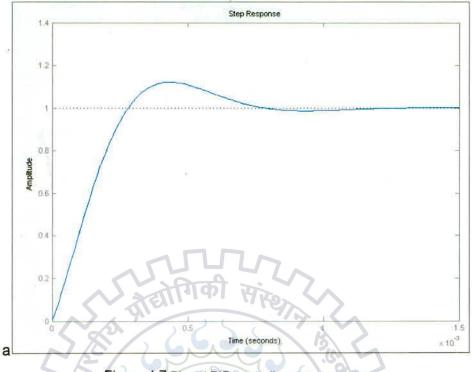

| Figure 4.3 Step response of the converter without controller          | 21       |

| Figure 4.4 Proportional controller step response                      |          |

| Figure 4.5 Integral controller step response                          |          |

| Figure 4.6 PD controller step response                                |          |

| Figure 4.7 PI and PID controller step response                        |          |

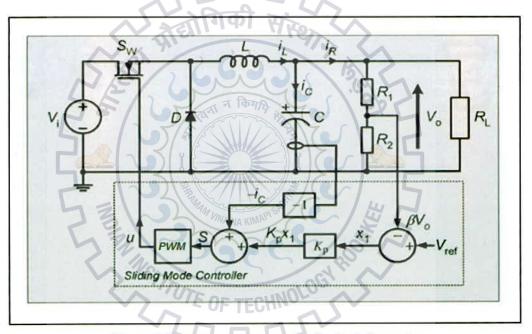

| Figure 4.8 Slinding mode controller for Buck Converter                |          |

| Figure 5.1 Simulation circuit of PI controller for Push-Pull Converte | r 26     |

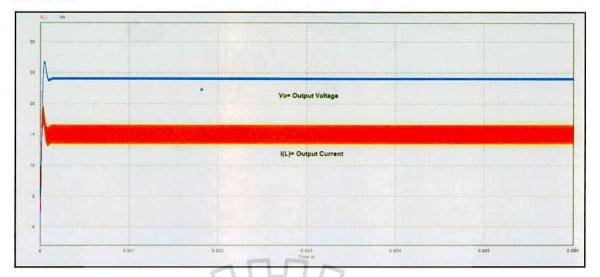

| Figure 5.2 Response of PI controller for Push-Pull Converter          |          |

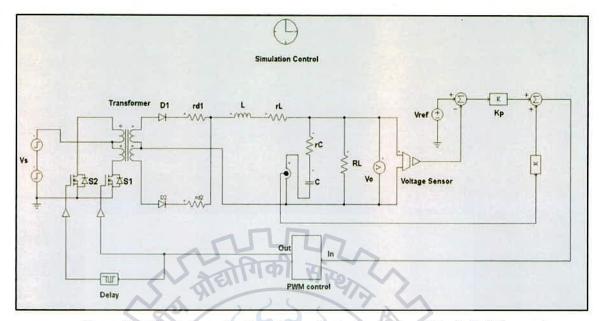

| Figure 5.3 Simulation circuit of sliding Mode Controller of Push-Pul  |          |

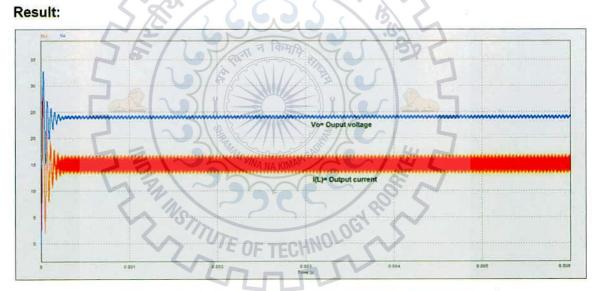

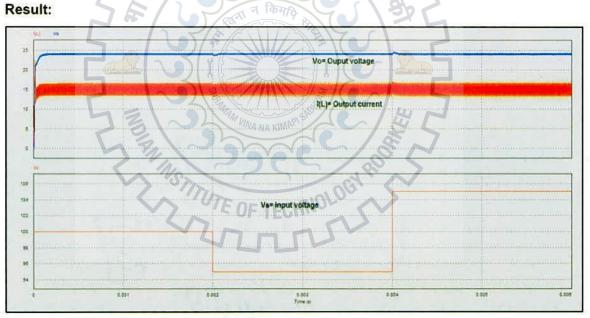

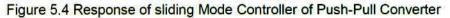

| Figure 5.4 Response of sliding Mode Controller of Push-Pull Conve     | erter 27 |

| Figure 5.5 Sliding mode controller response                           |          |

| Figure 5.6 PI Controller response                                     |          |

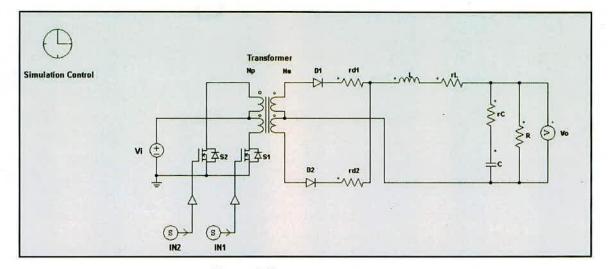

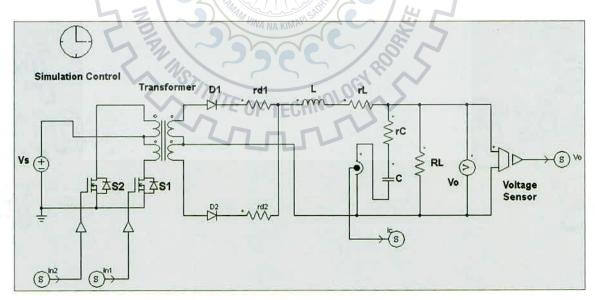

| Figure 5.7 Power circuit in PSIM                                      |          |

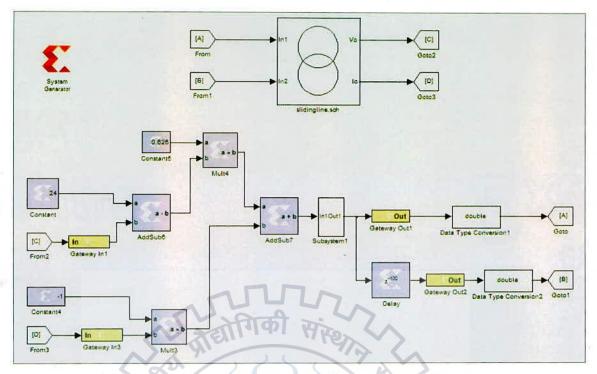

| Figure 5.8 Pulse generation circuit in MATLAB                         |          |

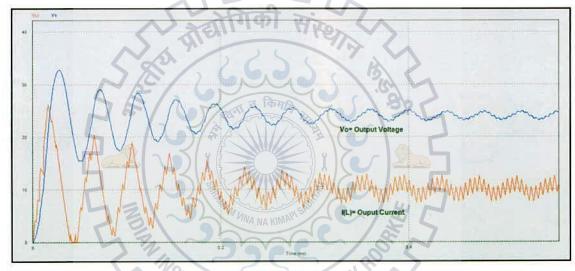

| Figure 5.9 Response of FPGA based Push-Pull Converter in open         | loop     |

| Figure 5.10 Power circuit of converter in PSIM                        |          |

| Figure 5.11 Controller circuit in MATLAB with XILINX tool box         |          |

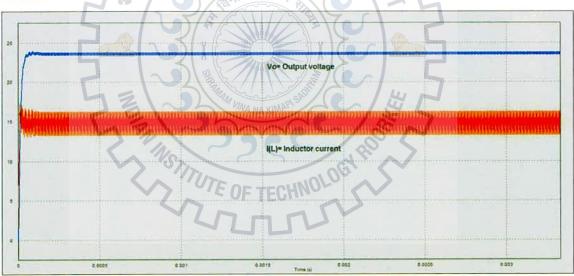

| Figure 5.12 Output voltage and output current of converter            |          |

| Figure 5.13 Response of controller with load variation                |          |

| Figure 6.1 Simulation result                                          |          |

| Figure 6.2 FPGA kit output                                            |          |

| Figure 6.3 MOSFET driver circuit                                      |          |

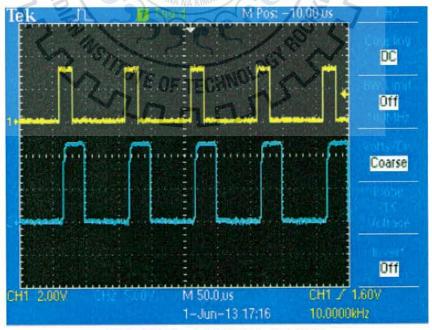

| Figure 6.4 Output of driver circuit for switch 1                      |          |

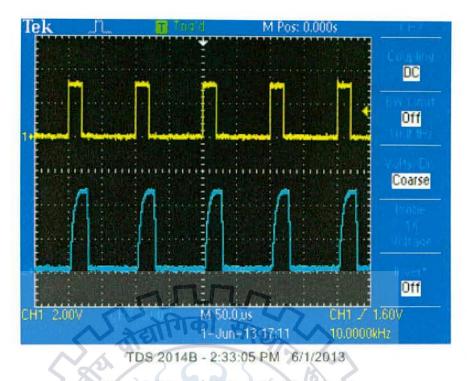

| Figure 6.5 Output of driver circuit for switch 2                      |          |

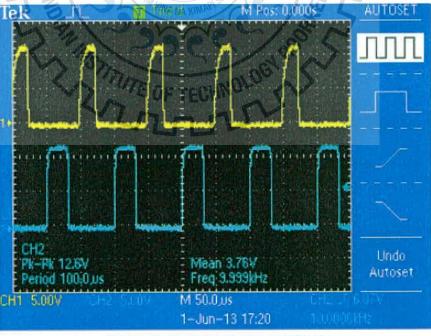

| Figure 6.6 Switching pulses from driver circuits                      |          |

| Figure 6.7 Experimental setup of Push-Pull converter                  |          |

| Figure 6.8 Close view of converter circuit                            |          |

#### **CHAPTER 1:**

Switched mode power converters (SMPS) are efficient for dc-to-dc power conversion. It consists of reactive elements and switches. DC/DC converters are basically classified as non-isolated converters and isolated converters. Buck, Boost, Buck-Boost converters are few examples of non-isolated converters. While Forward, Push-pull, Flyback converters are some examples of isolated converters. An isolated converter has many advantages over non-isolated converters. Push-Pull converter is isolated type of Buck converter. In which transformer is used to isolate load circuit from the line circuit. Push-Pull topology is similar as Forward converter with only difference is Push-Pull converter has two primaries where as Forward converter has only one primary winding. The primary switches alternately power their respective windings. In order to avoid shorting out of power supply small interval provided between turning on of the two switches. The secondary is arranged in a centre tapped configuration. The maximum power capability of a Push-Pull transformer to be twice that of a Forward transformer.

DC/DC converters are non-linear in nature. Any disturbance in line side or load side as well as if there is any situations which causes the parameter variations causes performance behaviour of the converter operation. In order to overcome this problems various kinds of controllers are used. PI controller is widely used controller for converter control operations. Sliding mode control strategy leads to large signal stability compared to the state space average method. Sliding Mode approach for Variable Structure Systems (VSS) offers an alternative way to implement a control action which exploits the inherent variable structure nature of DC-DC converters. In particular, the converter switches are driven as a function of the instantaneous values of the state variables in such a way so as to force the system trajectory to stay on a suitable selected surface on the phase space called the sliding surface. Sliding mode controller provides very robust control system.

As compared to analogue controller digital controller has many advantages like simplicity, accuracy, compactness. Digital signal processor (DSP), Microprocessors ( $\mu$ P), Field programmable gate array (FPGA) are widely used as controller techniques for dc-dc converter applications. But FPGA technique has an edge over DSP and  $\mu$ P like low power consumption, high efficiency, able to operate on higher frequencies and its simplicity of implementation.

#### 1.1 Various dc-to-dc Power Converters

- Buck Converter

- Boost Converter

- Buck-Boost Converter

- Forward Converter

- Single Ended Primary Inductor Converter

- Push-pull converter

#### 1.1.1 Buck converter

✓ Voltage step down only

- ✓ Single output only

- ✓ Very high efficiency

- ✓ Low input ripple current

- ✓ High output ripple current

## 1.1.2 Boost converter

- ✓ Voltage step up only

- Single output only

- Very high efficiency

## 1.1.3 Forward converter

- Buck type converter with an added isolation transformer

- Step up or step down voltage level

- Multiple outputs are possible

## 1.1.4 Push-Pull converter

## Circuit Diagram:

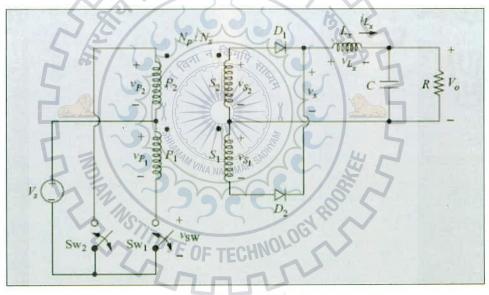

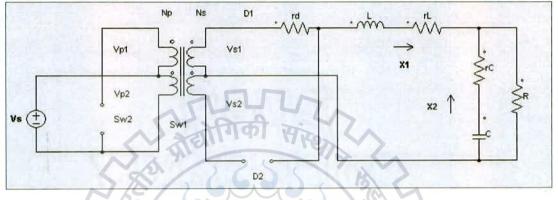

Figure 1.1 Circuit of Push-Pull converter

- Push-pull converter is similar to a forward converter except Push-Pull converter having two primaries.

- Two primary winding are alternately switched by two different primary switches.

- ✓ In order to avoid shorting out of power supply small interval provided between turnings on of the two switches.

- Primary winding as well secondary winding are arranged in a centre-tapped configuration.

- ✓ When Sw1 is turned on current starts flowing through diode D1. When switch Sw2 tuned on current starts flowing through diode D2.

- The Forward converter operates in a single quadrant of the BH curve, moving up the curve when the switch is active and resetting during the OFF time.

- ✓ The Push-Pull converter operates in two quadrants of the BH curve. Due to which the maximum power capability of a Push-Pull transformer to be twice that of a Forward transformer.

Figure 1.3 Switching pulses for Push-Pull converter

T/2

T/2 + DT

#### Working:

Push-Pull converter operated in four modes. In first mode (0 < t < DT) switch one (Sw<sub>1</sub>) is closed and switch two (Sw<sub>2</sub>) remains open, which makes upper secondary winding of transformer forward biased and lower secondary winding reverse biased. Hence diode D1 becomes forward biased and diode D2 becomes reverse biased. Current starts flowing through diode D1. In second mode ( $DT < t < \frac{T}{2}$ ) both the switches remains open. The current through inductor must maintain continuity, resulting in both diodes D1 and D2 becoming forward biased. In third mode  $\frac{T}{2} < t < \frac{T}{2} + DT$  switch two (Sw<sub>2</sub>) is closed and switch one (Sw<sub>1</sub>) is open which makes lower secondary winding of transformer become forward biased. Due to this diode D2 become forward biased and diode D1 become reversed biased and current starts flowing through D2. And in fourth mode  $\frac{T}{2} + DT < t < T$  again both the switches are remain open similar as in mode two.

O/P Voltage equation of Push-Pull converter:

$$V_{o} = 2V_{s}D\left(\frac{N_{s}}{N_{p}}\right)$$

## CHAPTER 2: STATE SPACE MODELING OF PUSH-PULL CONVERTER

In the past, the method of state space averaging had been successfully applied to characterize DC/DC converters. The variable structure system (VSS) of the DC/DC converters is an alternative method of characterizing the dc-to-dc converters in the time domain. State space averaging method essentially develops a linear, small signal, frequency domain model of nonlinear power converters. One of the widely used methods of controlling the output voltage of DC/DC converters is by means of close loop control of the duty ratio. In order to design such close loop controllers, it is necessary to obtain a dynamic model of duty ratio controlled converters The choice of average modeling method to study both large and small signal characteristics of modern power converters has become widely accepted due to its adaptability to computer simulation. When an average model is simulated, it requires with less computation time than the switched circuit model.

#### **Circuit diagram:**

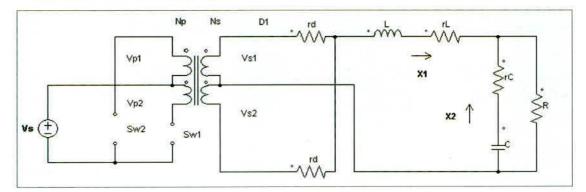

Figure 2.1 Schematic of Push-Pull converter

Firing pulses for switches:

Figure 2.2 Pulses for switches

For deriving averaged model and modelling of Pull-Pull converter following assumptions are made:

1) Both the switches (S<sub>w1</sub>, S<sub>w2</sub>) and diodes (D<sub>1</sub>, D<sub>2</sub>) are identical.

2) Both the diodes  $(D_1, D_2)$  having on resistance  $r_d$ .

- 3) Inductor and capacitor have parasitic resistance rL and rC respectively.

- 4) Converter is assumed to be operates in continuous conduction mode (CCM).

- 5) Since there are two energy storing elements inductor and capacitor, so there are two state variables including inductor current and capacitor voltage.

In each half cycle Push Pull converter has two modes of operation:

#### Mode 1: 0 < t < DT

In Mode 1, switch Sw1 is on which causes diode  $D_1$  forward bias. Current stars flowing through upper secondary winding. Circuit model for this mode is shown,

Figure 2.3 Mode 1 operation

State equations of the circuit are obtained by applying KVL and KCL. State variable for inductor current and capacitor is voltage is  $X_1$  and  $X_2$  respectively.

$$\dot{X_1} = -X_1 \frac{1}{L} \left( rd + rL + \frac{R * rC}{R + rC} \right) - X_2 \left( \frac{R}{R + rC} \right) + V_s \left( \frac{N_s}{N_p} \right)$$

$$\dot{X_2} = X_1 \left( \frac{R}{R + rC} \right) - X_2 \frac{1}{C} \left( \frac{1}{rC + R} \right)$$

$$V_o = X_1 R \left( \frac{rC}{R + rC} \right) + X_2 R \left( \frac{1}{R + rC} \right)$$

Therefore the matrices in the interval DT are:

$$\dot{X} = A_1 X + B_1 V$$

$$V_o = C_1 X$$

$$A_{1} = \begin{bmatrix} \frac{1}{L} \left( rd + rL + \frac{R * rC}{R + rC} \right) & \left( \frac{R}{R + rC} \right) \\ \left( \frac{R}{R + rC} \right) & \frac{1}{C} \left( \frac{1}{rC + R} \right) \end{bmatrix}$$

$$B_{1} = \begin{bmatrix} \frac{1}{L} \left( \frac{N_{s}}{N_{p}} \right) \\ 0 \end{bmatrix}$$

$$C_{1} = \begin{bmatrix} R \left( \frac{rC}{R + rC} \right) & R \left( \frac{1}{R + rC} \right) \end{bmatrix}$$

# Mode 2: $\frac{T}{2} < t < \frac{T}{2} + DT$

In Mode 2, both the switches  $(S_{w1}, S_{w2})$  are open and load current starts flowing through both the diodes  $(D_1, D_2)$ .

Figure 2.4 Mode 2 operation

Again there are following equations:

$$\dot{X_1} = -X_1 \frac{1}{L} \left( \frac{rd}{2} + rL + \frac{R * rC}{R + rC} \right) - X_2 \left( \frac{R}{R + rC} \right)$$

$$\dot{X_2} = X_1 \left( \frac{R}{R + rC} \right) - X_2 \frac{1}{C} \left( \frac{1}{rC + R} \right)$$

$$V_o = X_1 R \left( \frac{rC}{R + rC} \right) + X_2 R \left( \frac{1}{R + rC} \right)$$

In this mode state matrices are:

$$A_{2} = \begin{bmatrix} -\frac{1}{L} \left( \frac{rd}{2} + rL + \frac{R * rC}{R + rC} \right) & -\left( \frac{R}{R + rC} \right) \\ \left( \frac{R}{R + rC} \right) & \frac{1}{C} \left( \frac{1}{rC + R} \right) \end{bmatrix}$$

$$B_{2} = 0$$

$$C_{2} = \begin{bmatrix} R \left( \frac{rC}{R + rC} \right) & R \left( \frac{1}{R + rC} \right) \end{bmatrix} = C_{1}$$

Finally, based on averaged model concept and because the half cycle model of this converter in  $\frac{T}{2}$  as:

$$A = A_{1} + B v_{s}, \quad v_{o} = C A$$

$$A = A_{1} 2d + A_{2} (1 - 2d)$$

(a)

$$B = B_1 2d \tag{b}$$

$$C = C_1 \tag{(c)}$$

### 2.1 Steady state analysis

With the model of state space equation and matrices A, B and C we can consider small perturbation (represented by ~) and dc steady state (in upper case letters) quantities for model parameter as:

$$x = X + \tilde{x}$$

$$v_0 = V_0 + \widetilde{v_0}$$

$$d = D + \tilde{d}$$

$$v_s = V_s + \widetilde{v_s}$$

Substitution of this parameter into state equations (a), (b) and (c) yield:

$$\dot{\tilde{x}} = AX + BV_s + (A\tilde{x} + B\tilde{v}_s) + [(A_1 - A_2)X + (B_1 - B_2)V_s]2d$$

(d)

+ terms with product of  $\tilde{x}$ ,  $\tilde{d}$ ,  $\tilde{v_s}$  (negligible)

$$V_0 + \widetilde{v_0} = CX + C\tilde{X} + [(C_1 - C_2)X]2\tilde{d}$$

(e)

+ terms with product of  $\tilde{d}, \tilde{v_s}$  (negligible)

The steady state equation can be obtained from equations (d) and (e) by setting all ac components to zero. Therefore the steady state equation is,

$AX + BV_s = 0$

And for output:

$$V_0 = CX$$

From the equations (d) and (e),

$\hat{x} = A\hat{x} + B\hat{v}_s + [(A_1 - A_2)X + (B_1 - B_2)V_s]2\hat{d}$  (f)

$\tilde{v}_0 = C\hat{x} + [(C_1 - C_2)X]2\hat{d}$  (g)

## 2.2 Small signal analysis

From equations (f) and (g) that consists of ac perturbation and using Laplace transform:

$$\tilde{x}(s) = (SI - A)^{-1} [(A_1 - A_2)X + (B_1 - B_2)V_d] 2\tilde{d}(s) + (SI - A)^{-1} + B\tilde{V}_s(s)$$

(h)

$$\widetilde{V_0}(s) = C\widetilde{x}(s) + [(C_1 - C_2)X]2d(s)$$

From equations (h) and (i) we get the Laplace transform output voltage in term of duty cycle and input voltage:

(i)

$$\widetilde{v_0}(s) = \{C(SI - A)^{-1}[(A_1 - A_2)X + (B_1 - B_2)V_s] + (C_1 - C_2)X\}2\overline{d}(s) + C(SI - A)^{-1}B\widetilde{V_s}(s)$$

The perturbation of input voltage is assumed to be zero and for obtaining transfer function of output voltage to duty cycle and hence,

$$\frac{\widetilde{v_0}(s)}{\widetilde{d}(s)} = 2C(SI - A)^{-1}[(A_1 - A_2)X + (B_1 - B_2)V_s] + 2(C_1 - C_2)X$$

14

After substituting the matrix values we get the transfer function as:

# Converter transfer function:

| $\widetilde{v_0}(s)$ | 1.876e05 s + 5.717e09                   |

|----------------------|-----------------------------------------|

| $\tilde{d}(s)$       | $\overline{s^2 + 3.602e04s + 1.691e08}$ |

#### CHAPTER 3:

#### DESIGN OF PUSH-PULL CONVERTER

The push-pull switching converter is considered a transformer-isolated variation of the buck converter, and probably the most widely used type of power conversion circuit. In this design, the primary of the transformer can be connected in several ways: push-pull, half bridge or full bridge depending upon how one drives the transformer. The push-pull converter is, in fact, an arrangement of two forward converters on a single core. Push-pull converters reduce output voltage ripple by doubling the ripple current frequency to the output filter. A further advantage of push-pull operation is that magnetization is applied to the transformer core in both directions. The push-pull converter transformer, when subjected to small amounts of dc imbalance, can lead to core saturation.

## **Design Specifications:**

Input voltage  $(V_s)$ = 100v Output voltage  $(V_o)$ = 24v Output current  $(I_o)$ = 15A Operating frequency= f= 100 kHz Regulation  $(\alpha)$ = 0.5 Efficiency  $(\eta)$ = 0.95 Total dwell time  $(t_{dw})$ = 1µs Operating flux density  $(B_m)$  = 0.11T MOSFET on resistance  $(R_Q)$  = 0.1 $\Omega$ Diode voltage drop=1V

3.1 Transformer design

- 1) Maximum apparent secondary power=  $P_{ts} = I_o(V_o + V_s)\sqrt{2} = 530.33W$

- 2) Apparent power =  $P_t = P_{ts} \left( \frac{\sqrt{2}}{\eta} + 1 \right) = 1319.8W$

- 3) Electrical co-efficient =  $K_e = 0.145(f)^2 (k_f)^2 (B_m)^2 10^{-4}$

$k_f$  = waveform co - efficeint = 4(square wave)

$\therefore K_e = 28072$

4) Core geometry =  $K_g = \frac{P_t}{2K_e \alpha} = 0.047 cm^5$

(When designing with bobbin ferrite or other small bobbin cores, the core geometry is multiplied by 1.25)

$$K_g = 1.25 * 0.047 = 0.0587 \text{ cm}^5$$

- From core table RM core with core number KM-42819 is selected. (refer Appendix A)

- 6) Time period= T=  $\frac{1}{f}$ =10µs

- 7) Maximum on time=  $t = \frac{T}{2}\mu s$  $t_{on}(max) = t - t_{dw} = 4\mu s$

- 8) Maximum duty ratio=  $D_{max} = \frac{t_{on}(max)}{t} = 0.4$ 9) Current density=  $J = \frac{P_t * 10^4}{K_f K_u B_m f A_p} = 1597.71 \text{ A/cm}^2$

$$K_u$$

= window utilization = 0.3

- 10)Secondary load power= $P_{to} = I_o(V_o + V_s) = 375W$

- 11)Average primary current= $I_{in} = \frac{P_{to}}{\eta V_s} = 3.94 A$

- 12)Peak primary current=  $I_p = \frac{I_{in}}{2D_{max}} = 4.93 \text{ A}$ 13)Average primary voltage= $V_p = V_s 2D_{max}I_pR_q = 39.44v$

- 14)Primary turns=  $N_p = \frac{V_{p^{\star 10^4}}}{K_f B_m f A_c} = 9.146 \cong 10$  turns

$A_c = Iron area$

- 15)Secondary turns=N<sub>s</sub> =  $\frac{N_p(V_o + V_d)}{V_p}$  = 6.34  $\cong$  6 turns

- 16)Skin depth=  $\gamma = \frac{6.62}{\sqrt{f}} = 0.0209 \text{ cm}^{14}$

- 17)Wire area=  $\pi * r^2$ =0.00137cm<sup>2</sup> From wire table AWG#26 wire is selected. (refer Appendix B)

## 3.2 Converter design

$$V_{o} = V_{s} \left(\frac{N_{s}}{N_{p}}\right) 2D$$

Duty ratio=D=0.2

Load resistance=  $R = \frac{V_0}{I_0} = 1.6\Omega$

Assume the ripple in inductor current is 20% (= $\Delta I_{Lx}$ )

$$\Delta I_{Lx} = \frac{V_o(1/2 - D)T}{L}$$

Inductor= L= 24µH

Assume ripple in output voltage is 1%

$$0.01 = \frac{1-2D}{32f^2LC}$$

Capacitor= C= 7.81µF

Parasitic resistance of capacitor and inductor assume approximately  $0.08\Omega$  and  $0.05\Omega$ .

## Design summary:

Core= RM core (KM-42819)

Magnetic material= Ferrite core

Wire type= Litz wire

Frequency= 100kHz

Wire = AWG#26

Primary turns= 10

Secondary turns= 6

L= 24µH

C= 7.81µF

R= 1.6Ω

r

CHNOLOGYR

#### CHAPTER 4:

#### PI CONTROLLER AND SLIDING MODE CONTROLLER

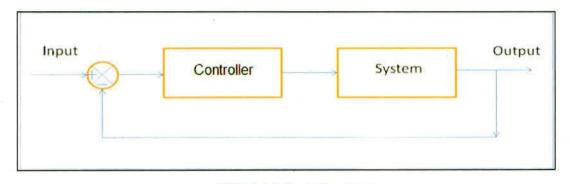

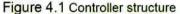

#### 4.1 Basic structure of controller

A proportional-integral-derivative controller (PID controller) is most widely used in controller for converter applications. Input to the controller is 'error' which is difference between a measured value and desired value. The controller reduces the error by adjusting the controller parameters.

The PID controller consists of three different controller parameters, namely, proportional, integral and derivative denoted P, I, and D respectively. And depending upon the required desired response, proportional and integral term of the PI controller is tuned. By tuning the proportional term rise time of the response can be reduced and by tuning the integral term steady state can be reduced to zero and with tuning of derivative term transients can be reduced.

## Tuning of PI controller using SISOTOOL

In order to get desired response of the controller it is necessary to have the controller parameters should be tuned properly. There are various methods like Manual tuning, Ziegler- Nichols method, Software tools adopted for calculation of controller gain parameters. 'SISOTOOL' which is inbuilt function in MATLAB uses converter transfer function to obtain the controller parameters. This tool enables to plot various responses like step, impulse, bode, nyquist for various controller structures, which helps to understand and select appropriate controller for converter.

#### Converter transfer function of converter

$$\frac{\widetilde{v_0}(s)}{\widetilde{d}(s)} = \frac{1.876e05 \, s \, + \, 5.717e09}{s^2 2 \, + \, 3.602e04 \, s \, + \, 1.691e08}$$

| Costrol and Estimation Toxic Manager |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Hariff - Do        |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| File Edit Help                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

| 9 6 6 5                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

| Workspace                            | Architecture Companyator Editor Graphical Tening Readyna Plots Automated Turing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

| SSO Denge Task     Denge History     | Design method /PD Turing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |

|                                      | Compensator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |

|                                      | C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |

|                                      | G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |

|                                      | Specifications Turning method. Reliant response time .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |

|                                      | The second |                    |

|                                      | Design-options<br>Controller Type OF 01 # M 0 PD 0 PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

|                                      | Design with first under descutive filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |

|                                      | Design mode Automatic (balanced performance and robustness) . •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Update Compensator |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | higher designed    |

|                                      | Stew Andréesture Steve Design Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

|                                      | 112-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |

Figure 4.2 Command window of SISOTOOL

Command window of SISOTOOL is shown in Fig. 4.2. This can be obtained from the converter transfer function. SISOTOOL enables to select the type of design method, type of tuning method, the architecture of the controller as well the controller type. By selecting desired controller and the tuning method various responses can be ploted easily.

## 4.1.1 Step response of the converter without controller

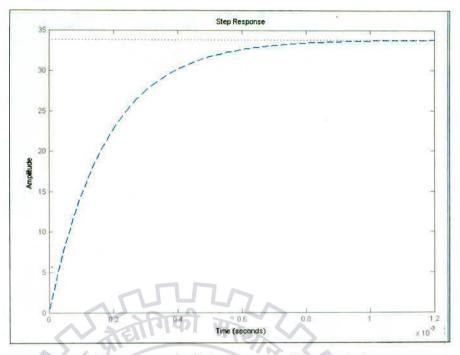

Figure 4.3 shows the step response of the converter without controller. This gives the amplitude of 34 with settling time of around 1ms. To reduce the settling time as well as to reduce the large steady state error, controller is required to get desired response.

Figure 4.3 Step response of the converter without controller

## 4.1.2 Step responses of different type controllers

# 4.1.2.1 Proportional (P) Controller

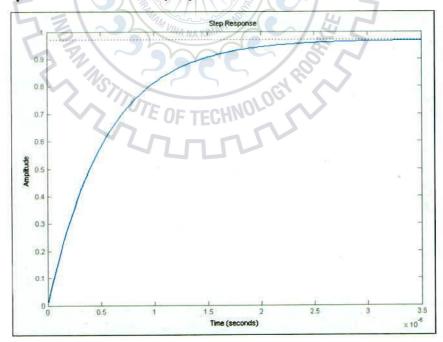

Figure 4.4 shows the step response of the converter with the proportional (P) controller. As compared to the step response without controller the settling time as well as the steady state reduces.

Figure 4.4 Proportional controller step response

## 4.1.2.2 Integral (I) Controller

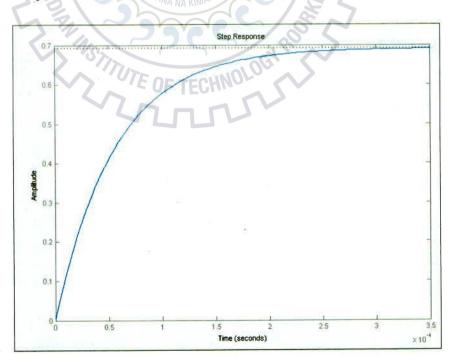

## Figure 4.5 Integral controller step response

As compared to P controller Integral (I) controller reduces the steady state error which can be seen in Fig. 4.5. But Integral control gives settling time of response more than the proportional controller.

4.1.2.3 Proportional-Derivative (PD) Controller

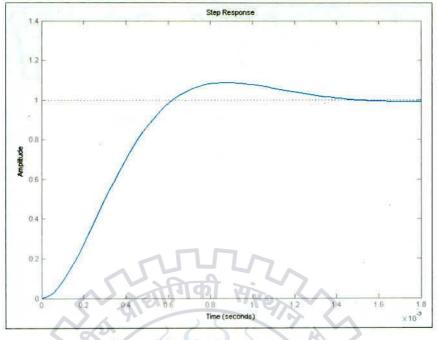

Figure 4.6 PD controller step response

#### 4.1.2.4 PI and PID Controller

Figure 4.7 Pl and PID controller step response

From the Fig. 4.7 it is clear that PI and PID controller response having zero steady state error with less settling time.

## PI Controller transfer function:

$G(s) = K^{*} (1 + sT) / (sT)$

Where,

K= Gain of the PI controller

T=Time constant T of the PI controller, in seconds.

After tuning in SISOTOOL PI controller parameters as obtained as follows,

E OF TECHN

Kp= 0.0178 T= 5.7e-05

#### 4.2 Sliding Mode Controller

Nonlinear system model imprecision may come from actual uncertainty about the plant (e.g., unknown plant parameters), or from the purposeful choice of a simplified representation of the system's dynamics. Modeling inaccuracies can be classified into two major kinds: structured (or parametric) uncertainties and unstructured uncertainties (or unmodeled dynamics). The first kind corresponds to inaccuracies on the terms actually included in the model, while the second kind corresponds to inaccuracies on the system order. Inaccuracies in modeling can have strong adverse effects on nonlinear control systems.

One of the most important approaches to dealing with model uncertainty is robust control. The typical structure of a robust controller is composed of a nominal part, similar to a feedback control law, and additional terms aimed at dealing with model uncertainty. Sliding mode controller design provides a systematic approach to the problem of maintaining stability and consistent performance in the face of modelling imprecision. The Sliding mode control (SMC) is a powerful and excellent robust nonlinear control method. SMC can ensure DC-DC converter to hold stability and good dynamic performance.

#### **Basic structure of Sliding Mode Controller:**

Sliding mode controller for Buck converter is shown in Fig. 4.8. Output of the converter is step down with the help of voltage divider circuit. Which compares with reference value ( $V_{ref}$ ). Error (X<sub>1</sub>) after comparison is multiplied with fixed gain parameter(K<sub>p</sub>). Capacitor current is multiplied with gain of value minus one. Both the signals are added which further given to PWM circuit. The switching pulses required for the switches are generated by the PWM circuit.

Figure 4.8 Slinding mode controller for Buck Converter

Where,

u= switching state

$$\beta = \frac{R2}{R1+R2}$$

$V_o = Output voltage$

$V_{ref} = Reference voltage$

$K_p = 1/\beta R_L = fix$  gain parameter

$S = K_p(V_{ref} - \beta V_o) - i_c$  = sliding mode controller equation

## **CHAPTER 5:**

#### Converter specifications:

| Parameters                                                    | Values |

|---------------------------------------------------------------|--------|

| Input voltage (V <sub>s</sub> )                               | 100 V  |

| Number of primary turns of transformer (N <sub>p</sub> )      | 10     |

| Number of secondary turns<br>of transformer (N <sub>s</sub> ) | 6      |