## SILICON NANOWIRE CMOS CIRCUIT DESIGN AND RELIABILITY

Ph.D. THESIS

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE - 247667, INDIA APRIL, 2019

## SILICON NANOWIRE CMOS CIRCUIT DESIGN AND RELIABILITY

#### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

**DOCTOR OF PHILOSOPHY**

### ELECTRONICS AND COMMUNICATION ENGINEERING

in

by

**OM PRAKASH**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) APRIL, 2019

## INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

### **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled "SILICON NANOWIRE CMOS CIRCUIT DESIGN AND RELIABILITY" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electronics and Communication Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from September, 2013 to April, 2019 under the supervision of Dr. S. K. Manhas, Associate Professor, Department of Electronics and Communication Engineering, Indian Institute of Technology Roorkee, Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

### (OM PRAKASH)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

Date:

$\mathcal{E}_{i}$

(S. K. Manhas) Supervisor

### ABSTRACT

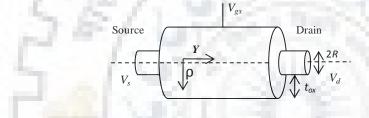

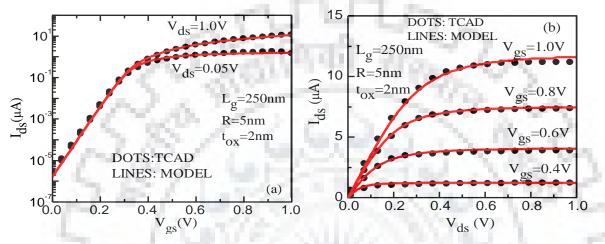

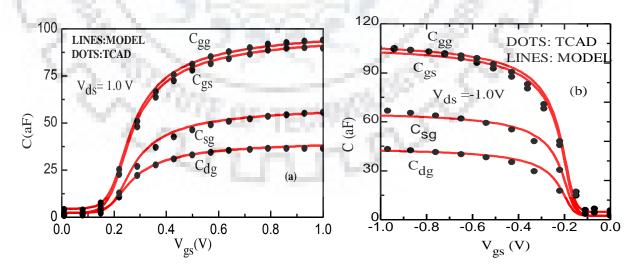

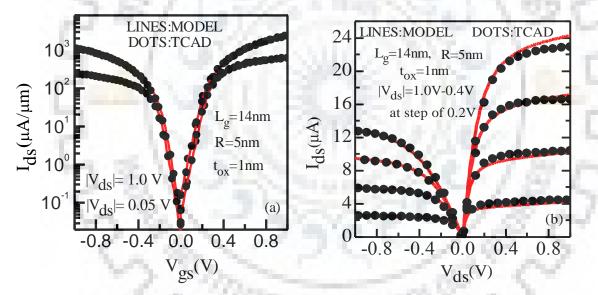

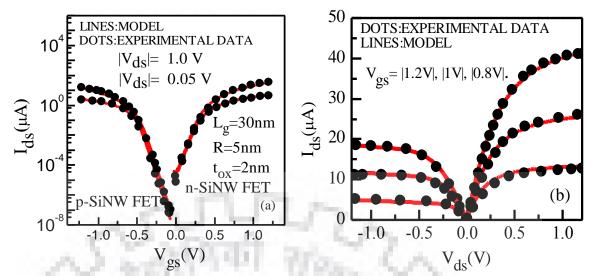

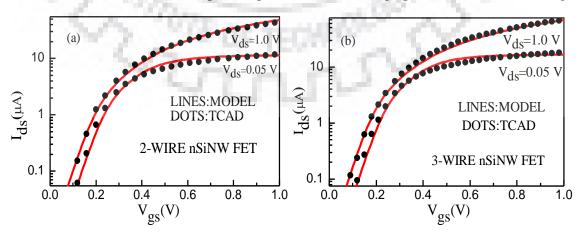

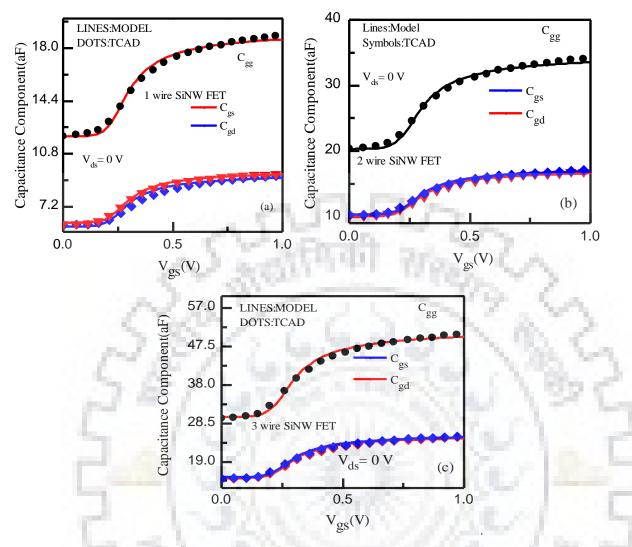

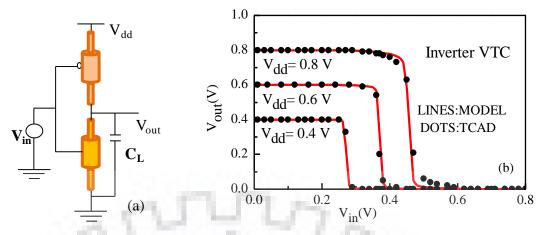

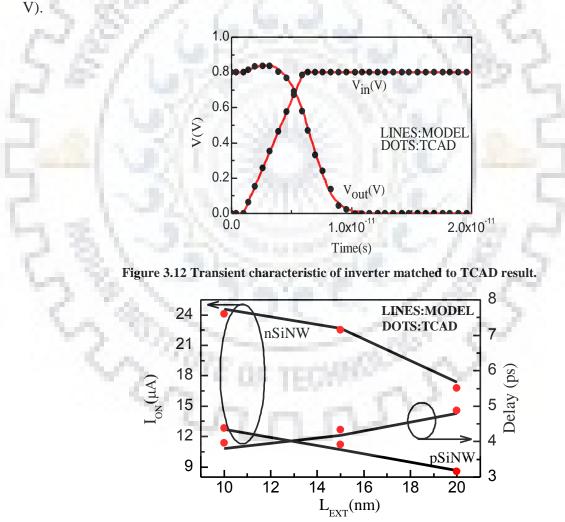

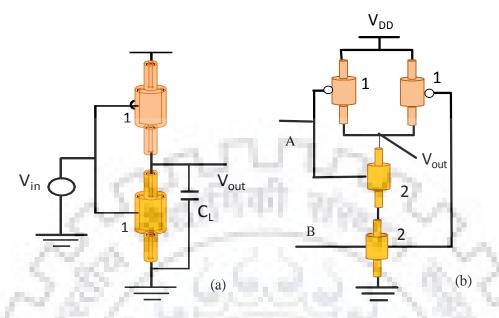

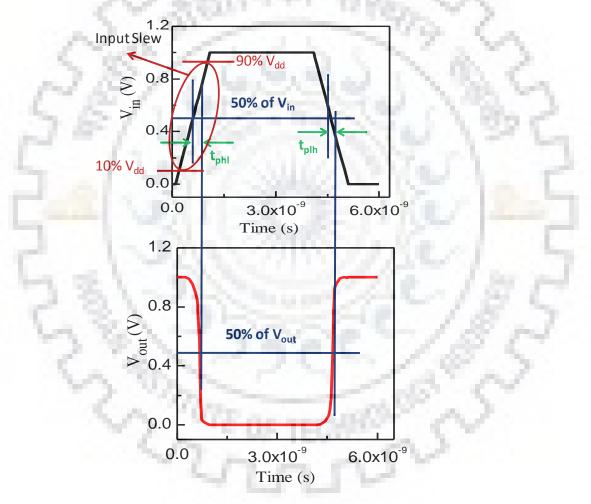

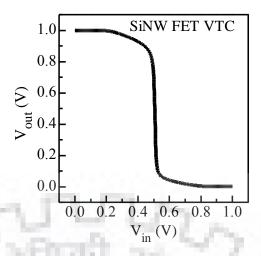

Silicon nanowire (SiNW) FET is one of the most promising candidates at extremely scaled technology nodes due to its superior channel controllability and CMOS compatibility. An accurate physics-based compact model is necessary for process and circuit design engineer to predict the available silicon data for highly scaled dimensions. Moreover, the model can also be used to accelerate the device-circuit co-optimization, which will reduce the fabrication cost and development cycle at the starting phase of future technology. In this study, we develop a unified Verilog-A compact model for lateral SiNW FET circuit design and analysis. The compact model incorporates important nanoscale effects as well as the geometry-dependent parasitic capacitances and resistance models. The parasitic models are scalable and TCAD calibrated. The Verilog-A model is calibrated to accurately match with reported experimental and TCAD based single & multiwire SiNW FET I-V and C-V characteristics.

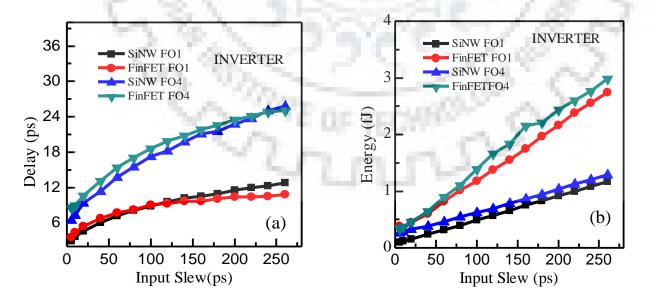

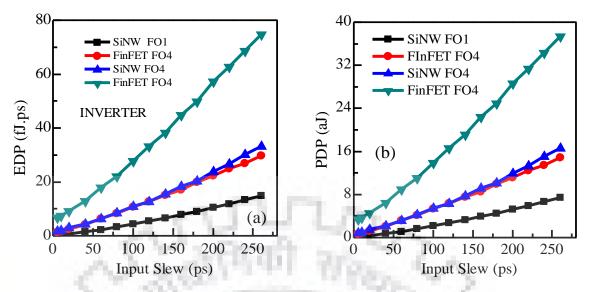

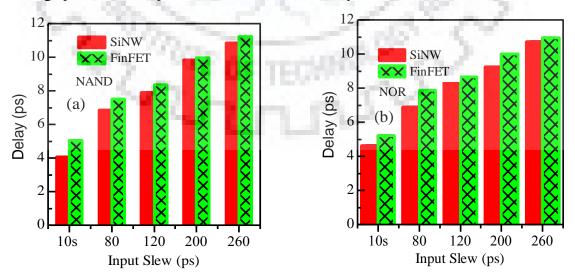

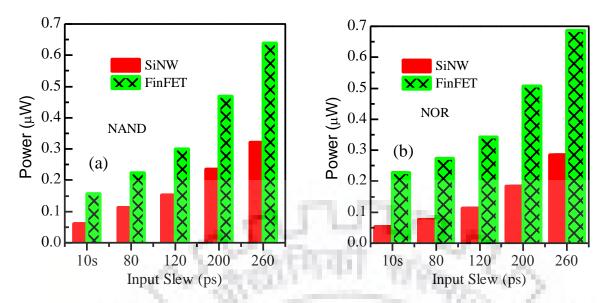

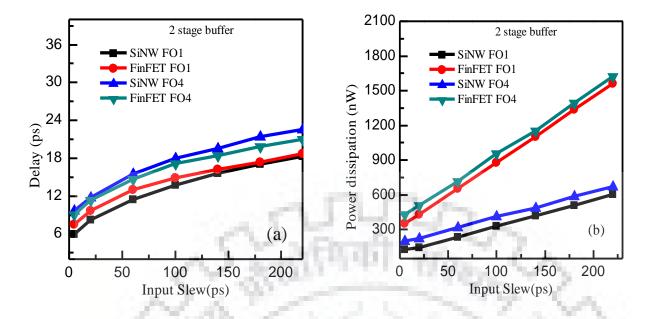

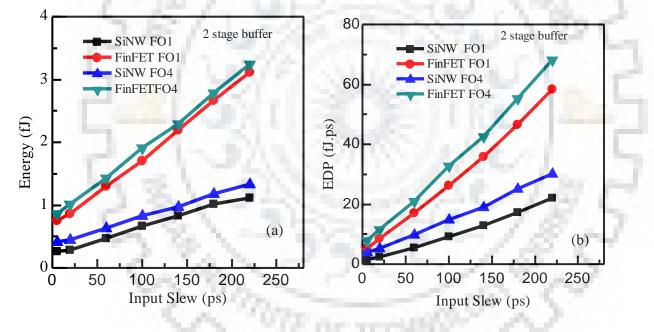

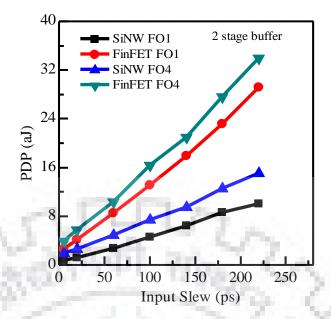

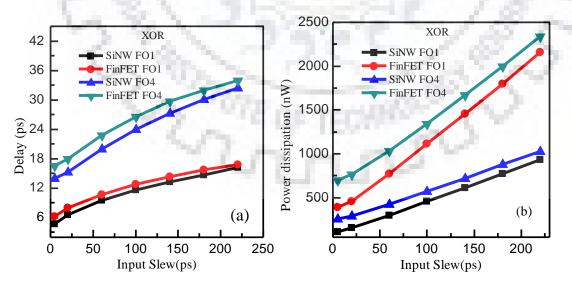

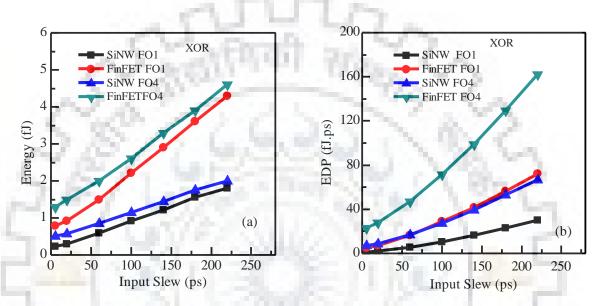

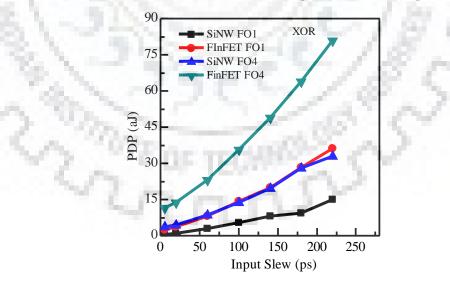

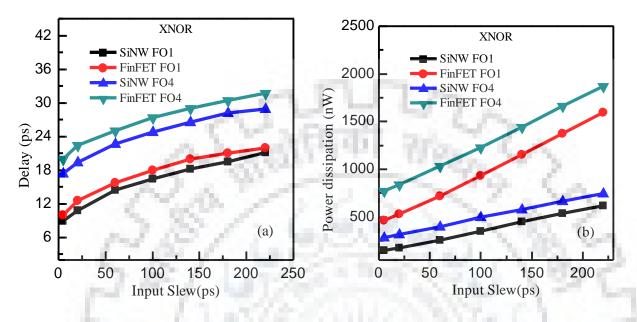

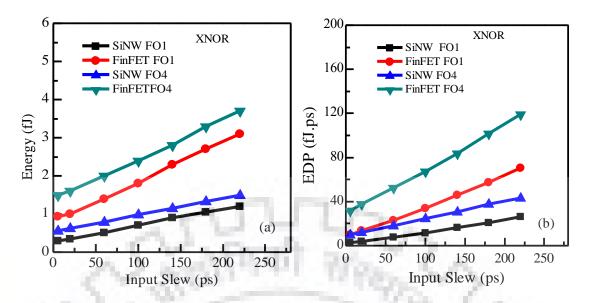

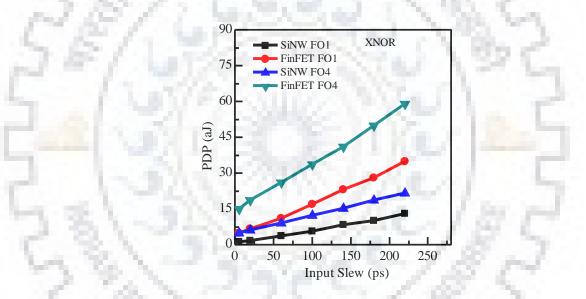

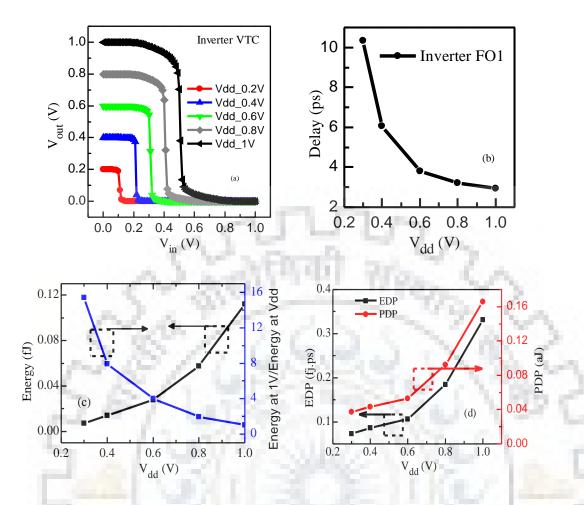

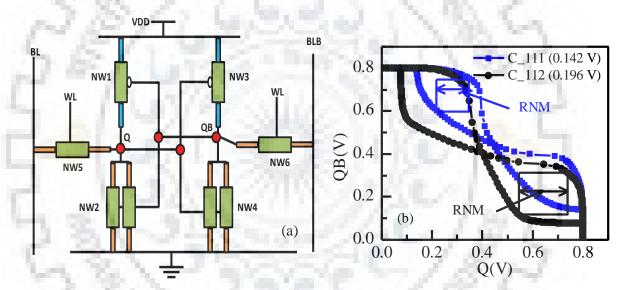

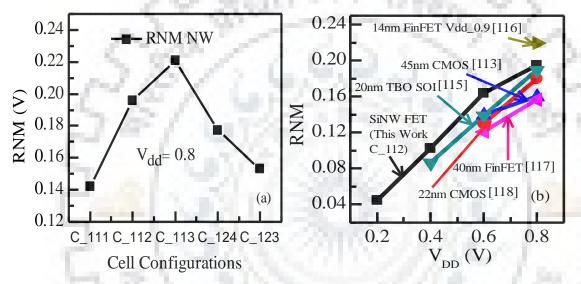

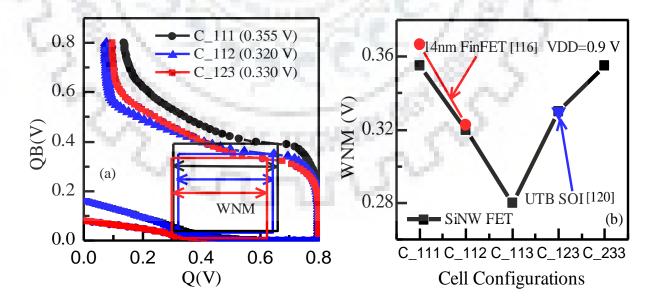

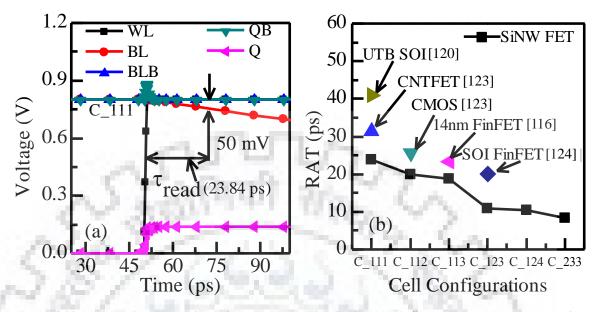

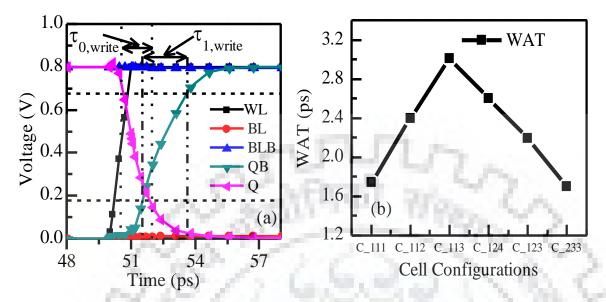

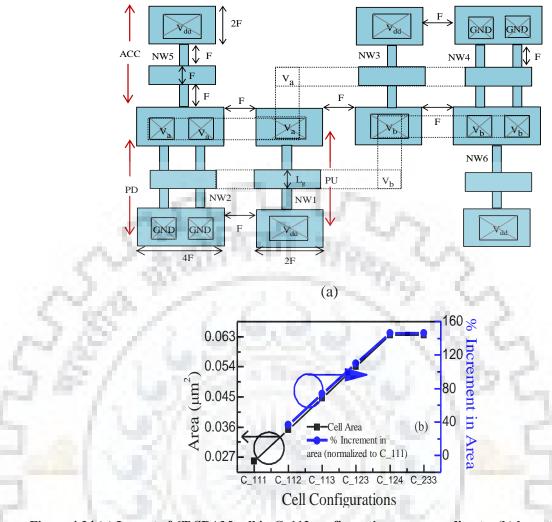

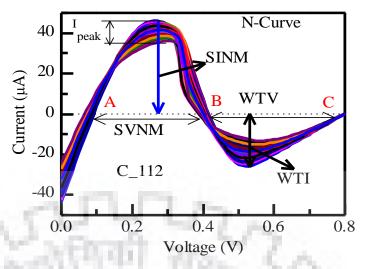

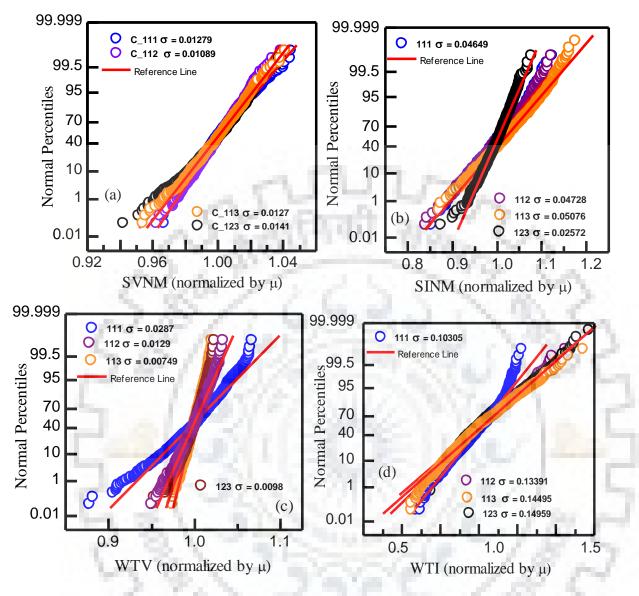

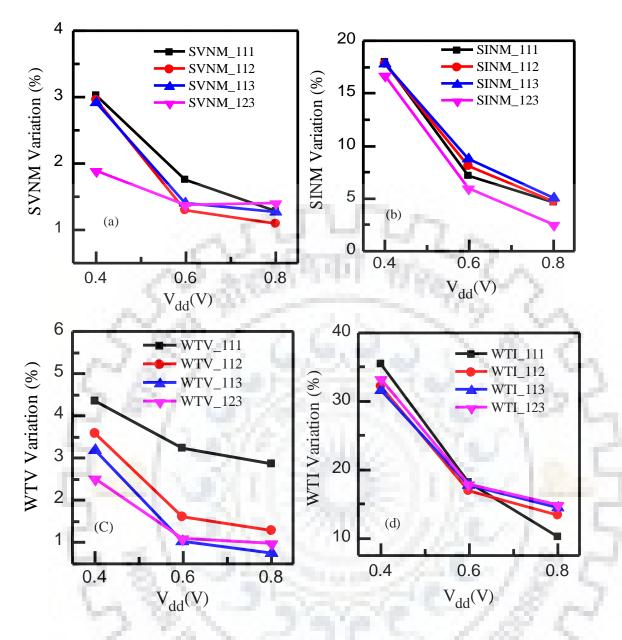

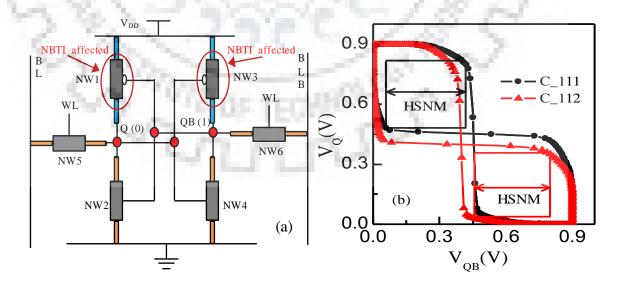

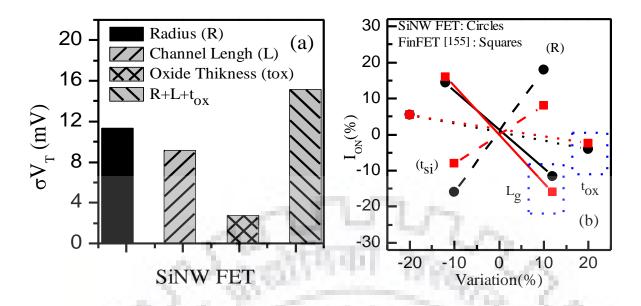

We have designed SiNW FET based basic core logic gates such as INVERTER, NAND, NOR, Buffer, XOR, XNOR and analyzed their performance. It is seen that the SiNW CMOS based logic gates have better power dissipation (~3-4X), energy-delay product (~2-3X), and power delay product (~3X) compared to corresponding FinFET based designs. Further, we have examined stability metrics (e.g., read, write noise margins and access time), geometrical variability, and layout area optimization of SiNW FET based 6T SRAM employing multiwire sizing technique. The different NW SRAM design configurations (e.g., C\_111, C\_123, etc., where C\_111 denotes the number of wires in pull up (PU), access (ACC), and pull down (PD) transistors respectively) are investigated. Among all design configurations, C\_112 is found to be the best configuration considering overall performances such as write stability, speed, layout area, and variability tolerance.

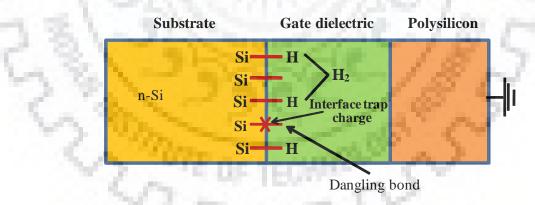

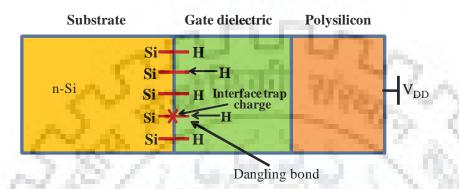

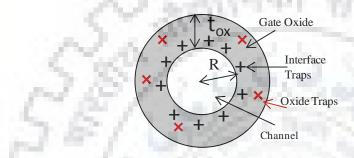

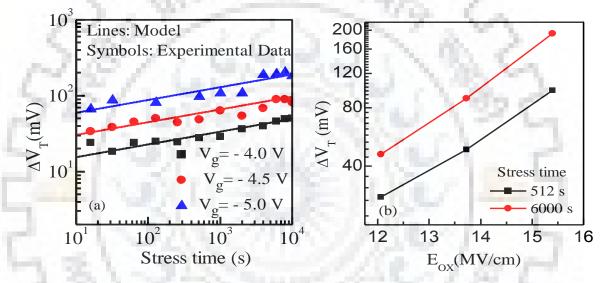

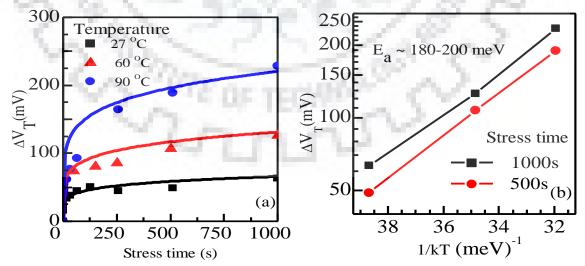

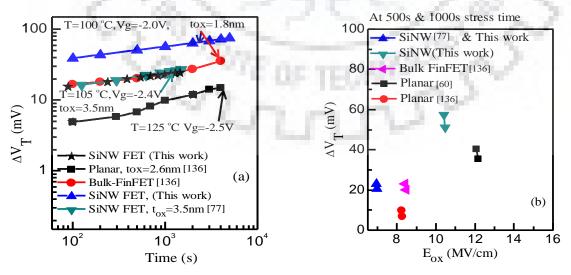

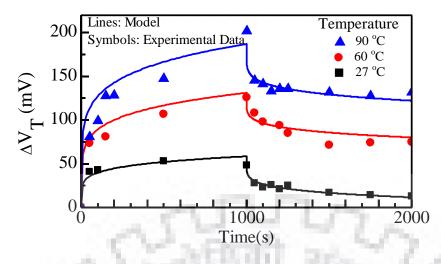

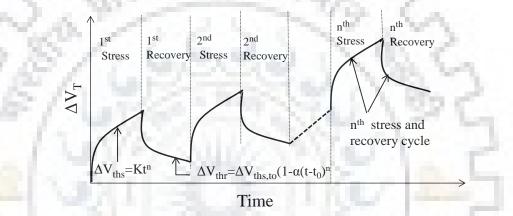

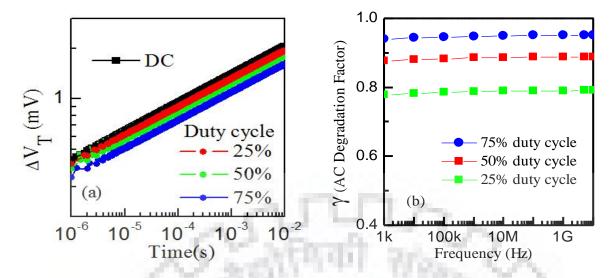

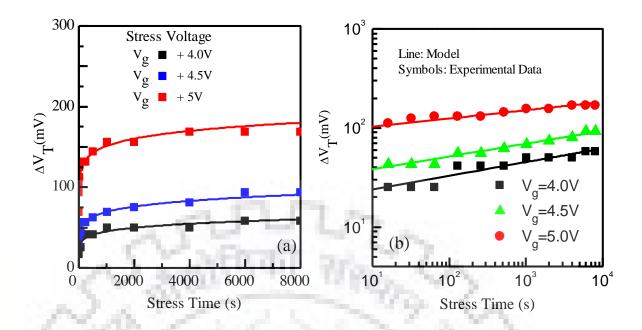

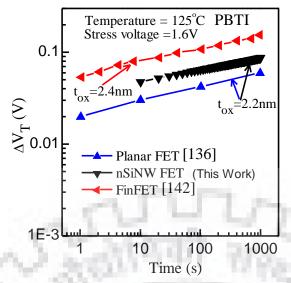

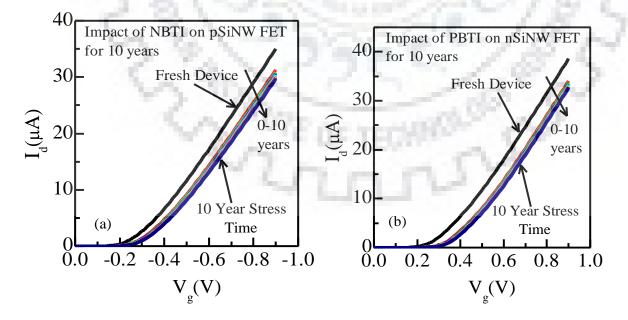

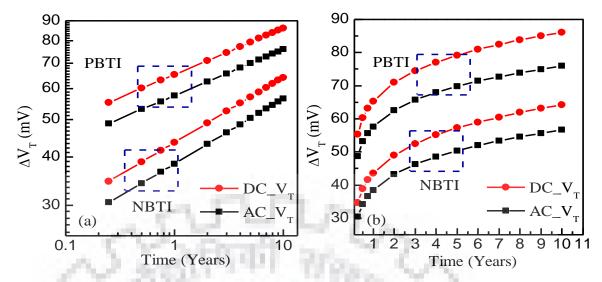

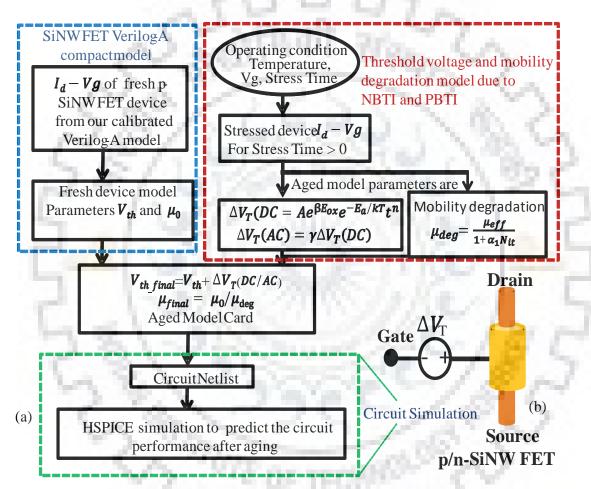

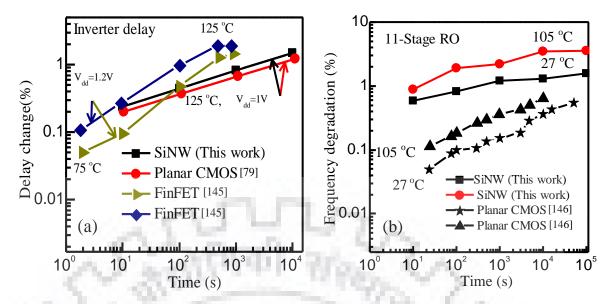

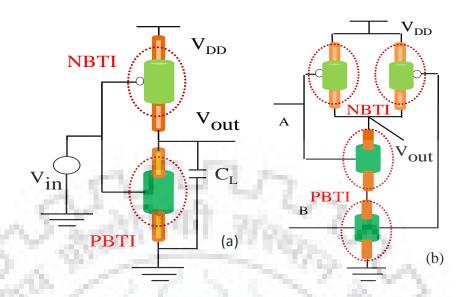

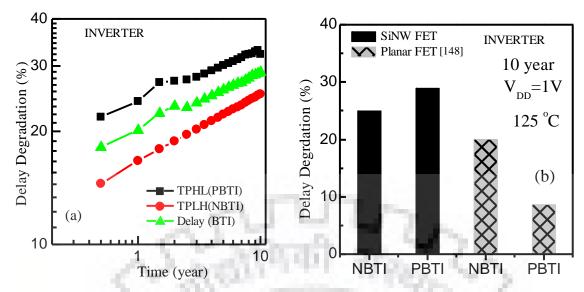

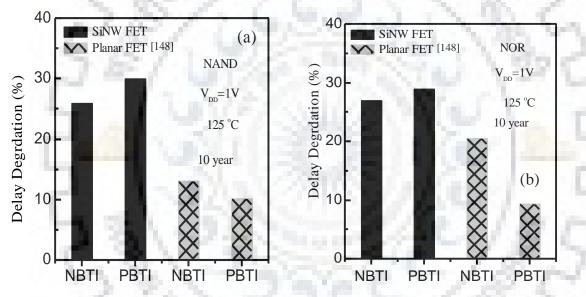

Bias temperature instability (BTI) is one of the major reliability concern at nanoscale nodes and requires an accurate model to predict device and circuit performance. BTI includes negative bias temperature instability (NBTI) and positive bias temperature instability (PBTI), which occurs on p and n-type SiNW FET devices respectively. The stress and recovery BTI model for Si NW FET is obtained from the experimental SiNW FETs using a range of stress voltage, time, and temperature. Thereafter, the developed Verilog-A compact model is integrated with

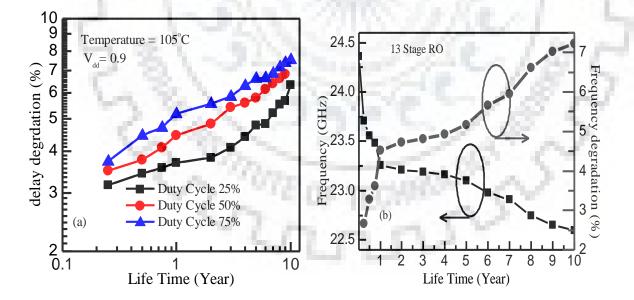

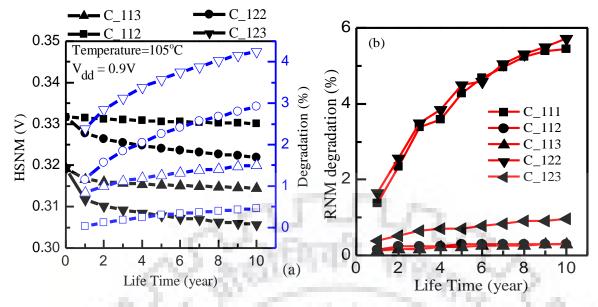

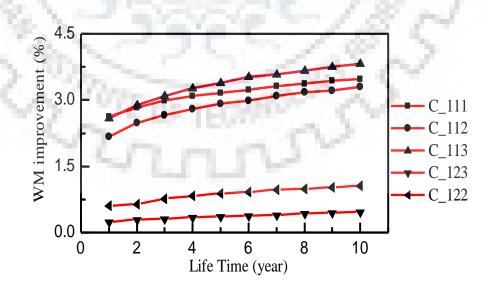

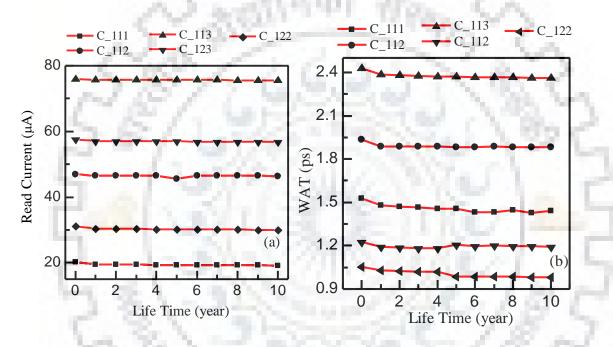

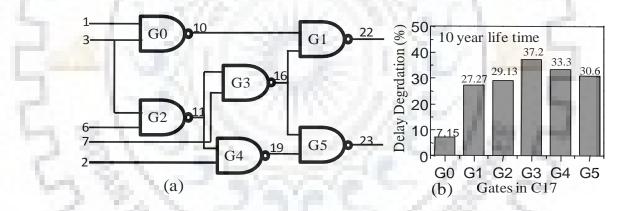

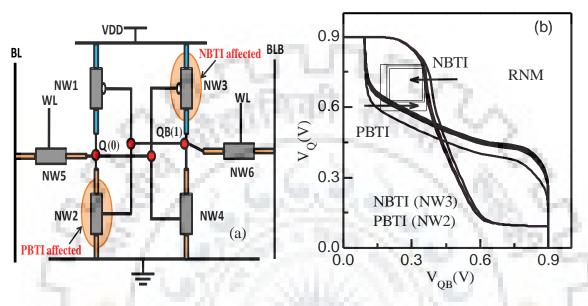

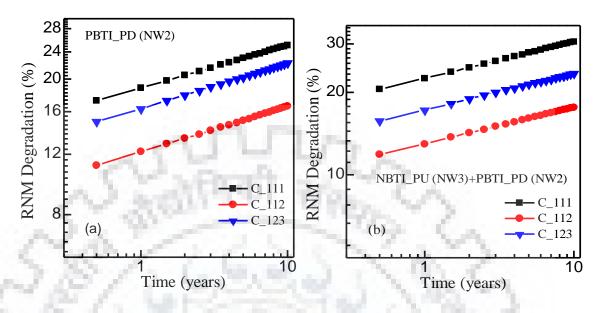

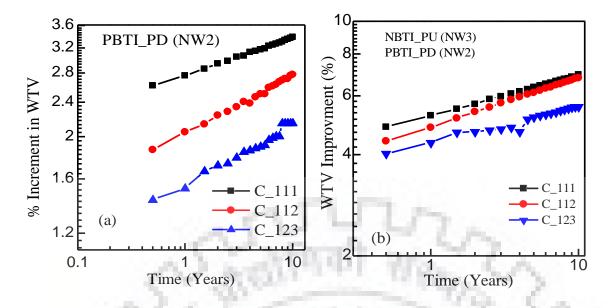

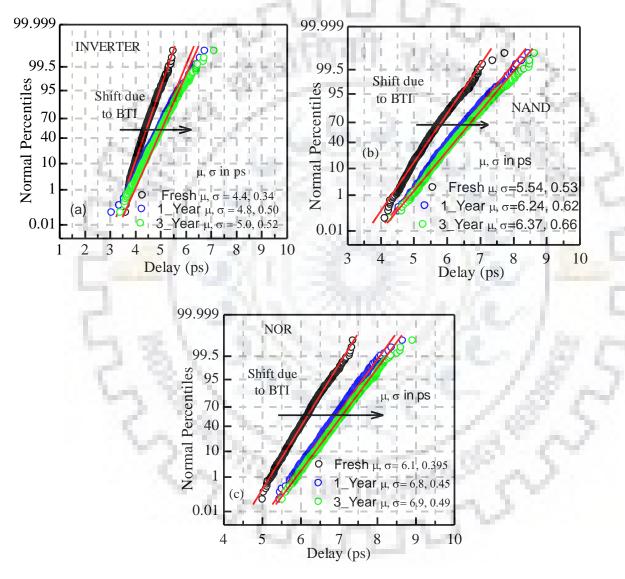

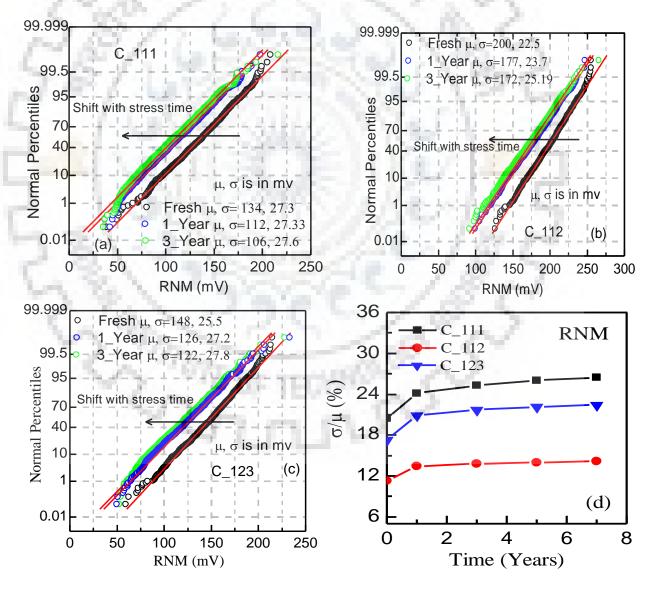

the BTI model for nanowire (NW) CMOS circuit simulation and design. It is found that NBTI is more pronounced in SiNW FET compared to FinFET and planar MOSFETs. This is attributed to its cylindrical gate structure resulting in enhanced 2-D hydrogen diffusion and stress-induced Si/SiO2 traps. Using the developed model, the impact of NBTI on NW CMOS circuits: inverter, 13-stage ring oscillator (RO), and 6T SRAM performance is analyzed. It is found that initially (for 1 year of a lifetime) due to fast trapping, inverter delay, and RO frequency degrade rapidly and saturates in long-term 10-year lifetime. Further, the combined impact of NBTI and PBTI are analyzed in circuits and a method is proposed to mitigate their impact. We demonstrated that the delay degradation is circuit topology dependent in which series-connected transistors are more prone to degradation due to PBTI (NBTI) in NAND (NOR) gates. Finally, the design of SRAM cell employing multi-wire sizing technique is investigated. It is found that the SRAM cell design margins are configuration dependent in which impact of BTI degrades the RNM by 15 % - 30 % and WNM improves by 5 % - 8 % for 10-year lifetime. We show that the BTI impact on SRAM cells is configuration dependent, which can be reduced by using appropriate design configuration. This study underscores the need for mitigating BTI degradation in NW CMOS, both at the device and circuit level.

Finally, the combined impact of time zero variability and BTI reliability on the core logic gates and read/write stability of the 6T SRAM cell is investigated. We found that the combined impact of time zero variability and BTI reliability degrades the mean and sigma value of circuit delay and SRAM RNM stability. We propose a method to minimize degradation under the influence of variability and reliability by selecting appropriate NW FET design configuration. It is found that overall the C\_112 is the best SRAM cell design configuration, having higher read/write reliability and variability tolerance. The comprehensive predictive model framework presented here is a valuable tool for variability and reliability-aware SiNW CMOS circuit design and analysis. The results and developed model of SiNW FET presented in this thesis are important benchmarks for the future studies in SiNW CMOS circuit design.

## ACKNOWLEDGEMENT

First and foremost, I would like to take this opportunity to express my gratitude to my supervisor, Dr. Sanjeev Manhas for his encouragement, advice, continuous moral support, help, and enthusiasm throughout my research work.

I would like to express my sincere thanks to Prof. A. K Saxena, Dr. SudebDasgupta, Dr. AnandBulusu of Microelectronincs and VLSI (MEV) group for their valuable suggestion, technical discussion and broadening my prospective. I am grateful to Prof. DebashisGhose, Head of Department for academic support and facilities provided to carry out the research work. I am very much obliged to Prof. G. D Verma, Department of Physics for sparing his precious time to review my Ph.D work as a external examiner at every stage.

My sincere thanks to the faculty of Microelectronics and VLSI Technology group,Department of Electronics and Communication Engineering at Indian Institute of Technology Roorkee, for the technical discussion, which have helped me in dealing with the problem I encountered during the thesis. I am grateful to Dr. Amalendu Patnaik, Chairman (DRC/SRC) for sparing his precious time regardless of all busy schedules to carefully examine my research progress time to time and provide valuable suggestions.

I would like to give special thanks to my senior Dr. Satish Maheshwaram for all the support and guidance throughout my Ph.D. It would be difficult for me to complete my Ph.D without his consistent motivation and guidance. Apart from the research work, I also would like to thanks him for the number of bike trips in Uttarakhand and Guwahati such as Bhadrinath, valley of flowers, Auli, Khursu, and Cherrapunji.

I would like to sincerely thank senior research scholar of Microelectronics and VLSI group, Dr. Baljit Kaur, Dr. Pankaj Pal, Dr. Ramesh, Dr. Manoj Majumdar, Dr. ShivamVerma, Dr. Prateek Dolas, Dr. Archana Pandey, Dr. Savitesh, Dr. Jaggu sir, Dr. Gaurav, Dr. Sneha for all the technical discussion, moral support and motivation during Ph.D.

Most Importantly, I would like to thanks my PhD friends Dinesh, Arvind, Sukwinder, Sandeep, Narendra, Inder, Upendra Mohan Bhatt, Govinda, Kumar Goodwill, Priyamwada, Poorvi, Ruchi, Himanshu, Yuvaraj, Ajeet, Abhishek, Mandeep, Satendra, Sourabh, Shashank, Navjeet, Neeraj, Prabhat, Lalit, Nitanshu for all the fun in the form of technical discussion, mess table gossip, games and trips.

I am thankful to the M.Tech students Manjeet, Ashish, Sanjay, Mohitsharma, Lalit, Yogesh, Parmeshwar, Prerna, Shilpa, Naresh, Swen, Shobhit, Richa, Shruti, Niharika, Mohit, Amit, Pitul, Raghav, Kaushal, Kaustav for all the fun like technical, nontechnical discussions specially during tea time and weekend cricket game.

I would like to thank the EICT members, Prateek, Nikhil and Shubhrata for all the support during my Ph.D and specially providing me a smart class room for presentation.

Last but not the least, I am highly indebted to my mother Smt. Savitri Devi and my father Sh. Kallu Prasad whose affection, love, believe and blessings have been a source of light for the successful completion of my work. I would like to thanks my Nana, Nani, Mama, Mami, brother, sister, sister in law and cousins for helping me during the ups and downs in the pursuit of my work. Without their encouragement and well wishes, I could not have come to this stage of life. I offer my sincere gratitude to the Almighty for giving me the right inspiration at right time, blessing me with all the good fortunes and the company of right people who helped me to move toward the aspiration of life.

|        |                      |          |      |      |      |         | 2.1       | 0.4 |

|--------|----------------------|----------|------|------|------|---------|-----------|-----|

| Date:  | 5                    |          |      |      |      |         | ~ T       |     |

| Place: | τ.,                  | A S      |      |      |      |         | (Om Praka | sh) |

|        | 23                   |          | 28   |      |      |         | -18       | 9.C |

|        | 14                   | 81       |      |      | 1.6  |         | 18        | N   |

|        | <ul> <li></li> </ul> | 19       | X    |      |      | 1       | 19°.,     | >   |

|        |                      | 22       | mo   | -    |      | and the | 8.5       |     |

|        |                      | $\sim 2$ | 100  | COF. | TEC/ | 1997 (A | SY        |     |

|        |                      |          | × 23 | 21   |      | U.      |           |     |

# CONTENTS

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | i     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| ACKNOWLEDGEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | iii   |

| CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | v     |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ix    |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| ABBREVIATIONS AND SYMBOLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | xvii  |

| 1 CHAPTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1     |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

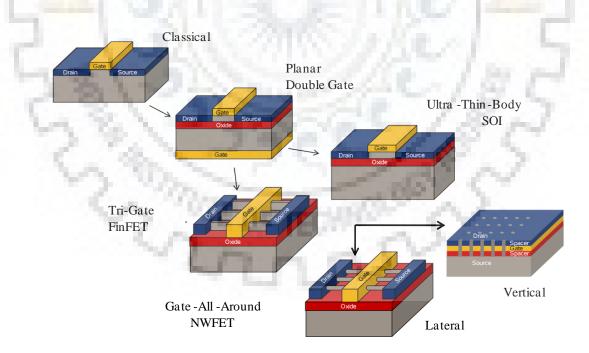

| 1.1 CMOS Scaling and Advanced MOSFET Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

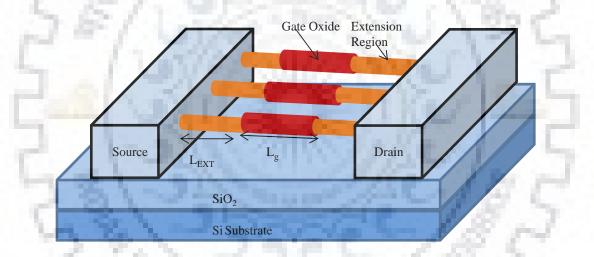

| 1.2 Lateral Silicon Nanowire Field Effect Transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2     |

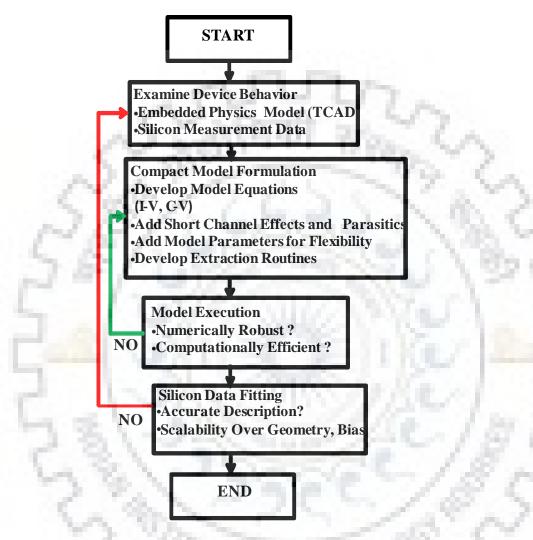

| 1.3 Compact Modeling of Multi-Gate Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3     |

| 1.4 Compact Negative/Positive Bias Temperature Instabili                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ty5   |

| 1.5 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 1.6 Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6     |

| <ul><li>1.6 Objectives</li><li>1.7 Outline of the Work</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| And the second s | 7     |

| 1.7 Outline of the Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| 1.7       Outline of the Work         2       CHAPTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7<br> |

| <ol> <li>1.7 Outline of the Work</li> <li>2 CHAPTER</li> <li>SiNW FET Compact Modeling and BTI Reliability: Literature I</li> <li>2.1 SiNW FET Compact Modeling</li> <li>2.2 Negative Bias Temperature Instability (NBTI)</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| <ol> <li>1.7 Outline of the Work</li> <li>2 CHAPTER</li> <li>SiNW FET Compact Modeling and BTI Reliability: Literature I</li> <li>2.1 SiNW FET Compact Modeling</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| <ol> <li>1.7 Outline of the Work</li> <li>2 CHAPTER</li> <li>SiNW FET Compact Modeling and BTI Reliability: Literature I</li> <li>2.1 SiNW FET Compact Modeling</li> <li>2.2 Negative Bias Temperature Instability (NBTI)</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| <ol> <li>1.7 Outline of the Work</li> <li>2 CHAPTER</li> <li>SiNW FET Compact Modeling and BTI Reliability: Literature I</li> <li>2.1 SiNW FET Compact Modeling</li> <li>2.2 Negative Bias Temperature Instability (NBTI)</li> <li>2.2.1 NBTI Background</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| <ol> <li>1.7 Outline of the Work</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| <ol> <li>Outline of the Work</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| <ol> <li>1.7 Outline of the Work</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| 3                   | CH                                                                      | APTER                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23                                                                   |

|---------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| SiN                 | W F                                                                     | ET Compact Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23                                                                   |

|                     | 3.1                                                                     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                   |

|                     | 3.2                                                                     | Core Model Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                              | 24                                                                   |

|                     | 3.3                                                                     | Advance Physical Effects for Short Channel Devices                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                   |

|                     | 3.3                                                                     | .1 Mobility Degradation                                                                                                                                                                                                                                                                                                                                                                                                                              | 30                                                                   |

|                     | 3.3                                                                     | .2 Velocity Saturation and Drain Saturation Voltage                                                                                                                                                                                                                                                                                                                                                                                                  | 30                                                                   |

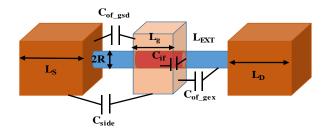

|                     | 3.4                                                                     | Geometry Dependent Parasitic Capacitance Model                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                                   |

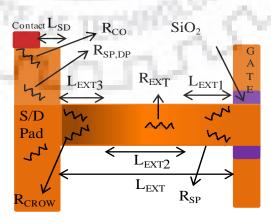

|                     | 3.5                                                                     | Geometry Dependent Parasitic Resistance Model                                                                                                                                                                                                                                                                                                                                                                                                        | 33                                                                   |

|                     | 3.6                                                                     | Asymetric SiNW FET Device                                                                                                                                                                                                                                                                                                                                                                                                                            | 34                                                                   |

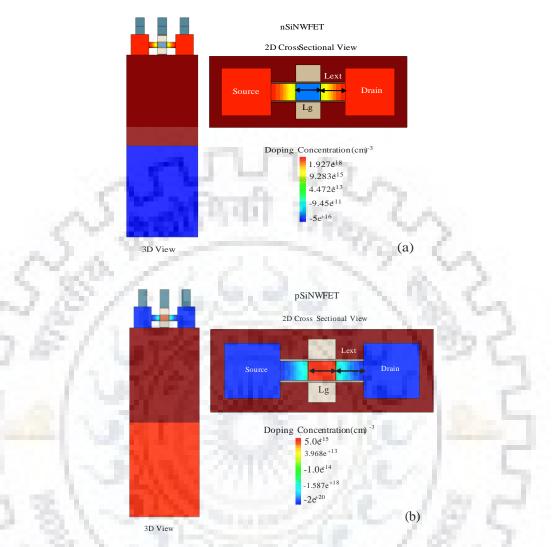

|                     | 3.7                                                                     | TCAD SETUP and SiNW FET Device Structure                                                                                                                                                                                                                                                                                                                                                                                                             | 35                                                                   |

|                     | 3.8                                                                     | Calibration of Compact Model with TCAD and Fabricated Data                                                                                                                                                                                                                                                                                                                                                                                           | 38                                                                   |

|                     | 3.8                                                                     | .1 Single wire TCAD calibration                                                                                                                                                                                                                                                                                                                                                                                                                      | 38                                                                   |

|                     |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20                                                                   |

|                     | 3.8                                                                     | .2 Multi Wire I-V and C-V Calibration                                                                                                                                                                                                                                                                                                                                                                                                                | 39                                                                   |

|                     | 3.8.<br>3.9                                                             | Implementation of Model for Circuit Simulation                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                   |

|                     |                                                                         | Implementation of Model for Circuit Simulation                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                   |

|                     | 3.9<br>3.10                                                             | Implementation of Model for Circuit Simulation                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                   |

| 4                   | 3.9<br>3.10<br>CH                                                       | Implementation of Model for Circuit Simulation                                                                                                                                                                                                                                                                                                                                                                                                       | 40<br>42<br>43                                                       |

| 4<br>Sil            | 3.9<br>3.10<br>CH<br>icon N                                             | Implementation of Model for Circuit Simulation<br>Summary<br>APTER<br>Nanowire FET based Circuit Design and Analysis                                                                                                                                                                                                                                                                                                                                 | 40<br>42<br>43<br>43                                                 |

| 4<br>Sil            | 3.9<br>3.10<br>CH<br>icon N                                             | Implementation of Model for Circuit Simulation<br>Summary<br>APTER<br>Nanowire FET based Circuit Design and Analysis                                                                                                                                                                                                                                                                                                                                 | 40<br>42<br>43<br>43                                                 |

| 4<br>Sil            | 3.9<br>3.10<br>CH<br>icon N                                             | Implementation of Model for Circuit Simulation                                                                                                                                                                                                                                                                                                                                                                                                       | 40<br>42<br>43<br>43<br>43<br>44                                     |

| 4<br>Sil            | 3.9<br>3.10<br>CH<br>icon N                                             | Implementation of Model for Circuit Simulation                                                                                                                                                                                                                                                                                                                                                                                                       | 40<br>42<br>43<br>43<br>43<br>44<br>44                               |