## DESIGN AND ANALYSIS OF NEAR THRESHOLD CMOS STORAGE ELEMENTS CONSIDERING VARIATIONS AND SOFT ERRORS

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE - 247667, INDIA JUNE, 2019

## DESIGN AND ANALYSIS OF NEAR THRESHOLD CMOS STORAGE ELEMENTS CONSIDERING VARIATIONS AND SOFT ERRORS

#### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

**DOCTOR OF PHILOSOPHY**

in

### ELECTRONICS AND COMMUNICATION ENGINEERING

by

**CHAUDHRY INDRA KUMAR**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) JUNE, 2019

## INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

## **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled "DESIGN AND ANALYSIS OF NEAR THRESHOLD CMOS STORAGE ELEMENTS CONSIDERING VARIATIONS AND SOFT ERRORS" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electronics and Communication Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from July, 2014 to June, 2019 under the supervision of Dr. Anand Bulusu, Associate Professor, Department of Electronics and Communication Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

## (CHAUDHRY INDRA KUMAR)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

Date:\_\_\_\_

(Anand Bulusu) Supervisor

The Ph. D. Viva-Voce Examination of **Mr. CHAUDHRY INDRA KUMAR**, Research Scholar, has been held on 31<sup>st</sup> August 2019.

Chairman, SRC

Signature of External Examiner

This to certify that the student has made all the corrections in the thesis.

Signature of Supervisors

Head of the Department

## ABSTRACT

Energy efficient computation is vital for the success of the next generation very large scale integration (VLSI) applications. Operating circuits in sub/near-threshold voltage (NTV) regime is one of the techniques to design energy efficient circuits. However, NTV computing has created resiliency challenges, including increasing timing faults due to process, voltage and temperature (PVT) variations and data-retention failures due to radiation-induced soft errors in modern digital circuits. To address these issues resilient circuit techniques are used to mitigate the performance degradation and data failures resulting from PVT variations and external transient noise. The work in this thesis proposes a framework to handle timing errors and soft errors issues in the NTV regime employing a resilient approach. First, we proposed a resilient latch that overcomes the timing errors issues in the NTV region. Moreover, a systematic methodology to resolve soft error issues, which are critical for memory elements (latches/SRAM) in the NTV is developed. For the same, first, an accurate model to estimate the critical charge for a static D latch is derived. Using the proposed model, soft error susceptible latches/Flip-Flop's can be identified at an initial design stage (pre-layout) and, subsequently, replaced by the radiation hardened latches. However, the reported radiation hardened latches are implemented with too large cost penalties in terms of delay, power, and area. To overcome the issue, we proposed low cost and highly reliable radiation hardened latches in the NTV regime. In this thesis we also proposed a cost effective radiation hardened SRAM cell since it is similar to a static latch.

In this thesis, first we present an energy efficient and resilient circuit design approach using novel self correcting latches (SCL). The proposed SCL technique corrects the faults due to timing violation caused by variations in data-paths and sequential elements automatically, thereby lowering PVT variation induced performance degradation. Our SCL technique employs inverse narrow width effect (INWE) in designing the self-correcting latches to reduce performance variability. The SCL technique can achieve higher performance when compared to reported resilient techniques with a much smaller area and power overhead. Consequently, most of the traditional design margins due to global and local PVT variations are eliminated which results in significant energy savings.

Further, we propose a physics based semi-analytical model to estimate the critical charge, which is a key to assessing the radiation-induced soft error susceptibility of static D-latch. To develop the model, first, we argue that the value of the critical charge increases with fan-out load of a latch. The proposed model is a function of design parameters such as transistor sizes, supply voltage and fan-out load. Consequently, it enables characterizing the spread of critical charge due to process-induced variations in these parameters. This can help circuit designers to estimate and optimize the critical charge and hence the SER at an initial design stage. The critical charge estimated by the model is in good agreement with SPECTRE simulations. Therefore, the proposed model can serve as a reliable alternative to time-intensive SPICE simulations for estimating the critical charge at design stage.

In order to limit the radiation-induced soft errors further, we propose three novel highly reliable energy efficient radiation hardened latches. The proposed latches provide the soft error tolerance by using restorer circuits (RC) to hold the correct state and Muller C-element to block the fault. The RCs are based on pull-up and pull-down paths, controlled by different susceptible nodes, results in better radiation tolerance. Furthermore, to improve the D-Q and CLK-Q transmission delay, we use INWE at the layout level of the proposed latches. The proposed latches effectively, maintain their soft error tolerance in the presence of PVT variations. We also verify the soft error rubostness of the proposed latches in TCAD mixed mode simulations.

Finally, we extend our analysis to SRAM cells. Scaling of CMOS SRAM have led to a denser packing, however, this makes SRAM cells more susceptible to a single event multiple-node upset (SEMNU). Therefore, to mitigate the effect of SEMNU in SRAM cells, we propose novel energy efficient radiation hardened memory cells in NTV regime. The proposed cells maintain its radiation-induced soft error tolerance in the presence of PVT variations. The TCAD mixed mode simulations show that our memory cells have a better performace as compared to the existing radiation hardened memory cells. Therefore, for NTV and aerospace applications our proposed memory cells would be a better choice.

## ACKNOWLEDGEMENT

# सरस्वति महाभागे विद्ये कमललोचने । विद्यारूपे विशालाक्षि विद्यां देहि नमोऽस्त् ते ॥

Completing this doctoral program was possible with the support of several people who contributed to shaping this thesis. First of all, I express my profound gratitude to my supervisor, Dr. Anand Bulusu without his guidance, encouragement and continuous moral support this work could not exist. I learned from him how to face challenges, question thoughts, and express ideas. His guidance helped me all the time, not only in research but also in leading a better life. He is not only excellent in his profession, but a gentle human being also. Words are not enough to express my gratitude to him.

I would like to express my sincere thanks to Prof. Sudeb Dasgupta, Head, Department of Electronics & Communication Engineering, Dr. A. Patnaik, Chairman DRC, Prof. D. Singh, Chairman SRC, and Dr. V. Rastogi, Department of Physics, (External expert), for being my research committee members. My sincere thank to Dr. B. K. Kaushik, Dr. B. P. Das, and Dr. B. Kumar for their lectures and discussions, which helped me to deal with the technical problems during the Ph.D. My sincere thanks to Mr. Naveen Kanwar, Microelectronics and VLSI Design Group, and other non-teaching staff of ECE Department for providing the basic lab facilities and support.

I would like to give special thanks to my senior Dr. Arvind Kumar Sharma for all the support and guidance throughout my Ph.D. His consistent motivation, valuable comments and suggestions helped me to finish the research problems efficiently. I am very grateful to my friend Dr. Abhishek Bhattacharjee for his patience and precious time to review my research papers and thesis thoroughly. I would like to sincerely thank senior research scholar of Microelectronics and VLSI group, Dr. Baljit Kaur, Dr. Pankaj Pal, Dr. Manoj Majumdar, Dr. Shivam Verma, Dr. Archana Pandey, Dr. Savitesh, Dr. Ruchi, Dr. Abhishek Acharya and Om Parkash for all the technical discussion, moral support and motivation during Ph.D.

Most Importantly, I would like to thanks my PhD friends Mandeep, Govinda, Lalit, Vikas sir, Anant sir, Sanjay sir, Sourabh, Upendra Bhatt, Satendar, Navjeet, Neeraj, Prabhat, Nitanshu, Sarita, Swati, Sonal, Amit, Rahul, Dinesh for their support, friendship and having important technical discussions related to my research. A special thanks to Priyamvada and Poorvi for all the fun time we enjoyed together and to make this Ph.D journey memorable and pleasant. I have spent a lot of time with them at IITR and memories that brings smile on my face. I want to thanks my friends, Anuj Tewari, Santosh Gupta, Mohit Maru, Balbir Awana, Puspraj Chauhan, Khaliq Ansari, Shalini and Natwar for motivating me to opt for higher studies.

Finally, I would like to thanks my beloved parents (Shri Jagpal Singh and Smt. Kamlesh Singh), caring brothers (Rajneesh bhaiya, Partap bhaiya, and Krishan bhaiya) and loving sisterin-laws (Priya bhabhi, Anu bhabhi, and Sangeeta bhabhi ) for supporting me without any expectations at every juncture of my life. I am lucky to have them in my life. I could not imagine myself at this level without the values they taught me. I offer my sincere gratitude to the Almighty for giving me the right inspiration at right time, blessing me with all the good fortunes and the company of right people who helped me to move toward the aspiration of life.

# CONTENTS

| ABSTRACT                                                        | i   |

|-----------------------------------------------------------------|-----|

| ACKNOWLEDGEMENT                                                 | iii |

| CONTENTS                                                        | V   |

| LIST OF FIGURES                                                 |     |

| LIST OF TABLES                                                  |     |

| ABBREVATIONS AND SYMBOLS                                        | XV  |

| 1 CHAPTER                                                       | 1   |

| Introduction                                                    |     |

| 1.1 Sub/near-Threshold Voltage (NTV) Operation                  |     |

| 1.2 Near-Threshold Voltage Operation Barriers                   | 3   |

| 1.2.1 Performance Variations                                    | 3   |

| 1.2.2 Functional Failure due to Soft error                      | 5   |

| 1.3 Motivation                                                  | 8   |

| 1.4 Objectives                                                  |     |

| 1.5 Organization of the Thesis                                  |     |

| 2 CHAPTER                                                       | 13  |

| Literature Survey                                               | 13  |

| 2.1 NTV Timing Error Detection and Correction (EDC) Techniques  | 13  |

| 2.2 Critical charge models to predict the circuit SEU tolerance | 16  |

| 2.3 Mitigation of Soft Errors in Static D-Latch                 |     |

| 2.3.1 Single node upset tolerant technique                      |     |

| 2.3.2 Double node upset tolerant technique                      | 20  |

| 2.3.3 Triple node upset tolerant technique                      | 21  |

| 2.4 Mitigation of Soft Errors in SRAM cell                      | 22  |

| 2.5 Technical Gaps                                              | 23  |

| 3 C                                                     | HAPTER                                                                      | 25   |

|---------------------------------------------------------|-----------------------------------------------------------------------------|------|

| Energy Efficienct Variation Aware Self Correcting latch |                                                                             |      |

| 3.1                                                     | Overview                                                                    | 25   |

| 3.2                                                     | Proposed Self Correcting Latch                                              | 26   |

| 3.                                                      | 2.1 Principle of the proposed Self Correcting Latch                         | 26   |

| 3.                                                      | 2.2 Operation of the proposed Self Correcting Latch                         | 27   |

| 3.3                                                     | Simulation Setup                                                            | 31   |

| 3.4                                                     | Simulation Results                                                          | 32   |

| 3.5                                                     | Summary                                                                     | 40   |

| 4 C                                                     | HAPTER                                                                      | 41   |

| A Phy                                                   | vsics based Variability Aware Methodology to Estimate Critical Charge for N | ear- |

| Thresh                                                  | old Voltage Latches                                                         | 41   |

| 4.1                                                     | Overview                                                                    |      |

| 4.2                                                     | Critical Charge Model for Static D-latch                                    | 42   |

| 4.3                                                     | Critical Charge Model Validation                                            | 51   |

| 4.4                                                     | Variability Analysis of the Proposed Critical Charge Model                  | 56   |

| 4.                                                      | 4.1 Supply Voltage Variation                                                | 56   |

| 4.                                                      | 4.2 Threshold Voltage Variation                                             | 57   |

| 4.                                                      | 4.3 Temperature Variation                                                   | 57   |

| 4.                                                      | 4.4 Fan-out load Variation                                                  | 57   |

| 4.                                                      | 4.5 Statistical Variability                                                 | 57   |

| 4.5                                                     | Methodology to Estimate Critical Charge                                     | 58   |

| 4.6                                                     | Summary                                                                     | 62   |

| 5 C                                                     | HAPTER                                                                      | 63   |

| Energy                                                  | / Efficient Radiation Hardened Latch Designs                                | 63   |

| 5.1                                                     | Overview                                                                    | 63   |

| 5.2                                                     | Proposed Latch Designs                                                      | 64   |

| 5.                                                      | 2.1 Proposed Single Node Upset Tolerant Latch                               | 64   |

| 5.2.2 Proposed Double Node Upset Tolerant Latch                          | 66  |

|--------------------------------------------------------------------------|-----|

| 5.2.3 Proposed Triple Node Upset Hardened Latch                          | 71  |

| 5.3 Simulation Results                                                   | 77  |

| 5.3.1 Simulation Setup                                                   | 77  |

| 5.3.2 Performance, Power and Area Comparison                             | 77  |

| 5.3.3 Variability Analysis                                               | 79  |

| 5.4 Soft Error Robustness Simulations using TCAD Tool                    | 81  |

| 5.5 Summary                                                              | 83  |

| 6 CHAPTER                                                                |     |

| Energy Efficient Radiation-Induced Soft Error Tolerant SRAM cell Designs | 85  |

| 6.1 Overview                                                             | 85  |

| 6.2 Proposed SRAM cell Designs                                           | 86  |

| 6.2.1 Proposed Single Node Upset Tolerant 10T SRAM cell                  | 86  |

| 6.2.2 Proposed Single Event Multiple Node Upset Hardened 12T SRAM cell   | 89  |

| 6.3 Simulation Results                                                   | 92  |

| 6.4 Soft Error Robustness Simulations using TCAD Tool                    | 94  |

| 6.5 Summary                                                              |     |

| 7 CHAPTER                                                                | 99  |

| Conclusion & Future Scope                                                | 99  |

| 7.1 Conclusion                                                           | 99  |

| 7.2 Future Scope                                                         |     |

| APPENDIX A                                                               |     |

| BIBLIOGRAPHY                                                             |     |

| PUBLICATIONS                                                             |     |

|                                                                          | 123 |

## **LIST OF FIGURES**

| Figure 1.1 Energy and delay in different operating regimes [19]2                                          |

|-----------------------------------------------------------------------------------------------------------|

| Figure 1.2 Classification of variations                                                                   |

| Figure 1.3 Cosmic ray intensity at different cities in the world [61]7                                    |

| Figure 1.4 Charge generation and collection mechanism from [56]7                                          |

| Figure 2.1 Conceptual timing diagrams in worst and nominal conditions [64]13                              |

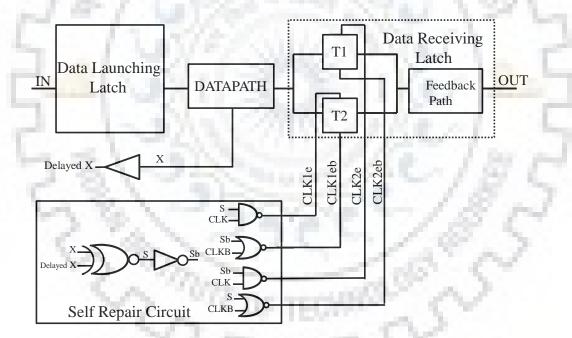

| Figure 3.1 Block diagram of proposed SCL technique consists of a conventional data launching              |

| latch, a datapath and a data receiving latch26                                                            |

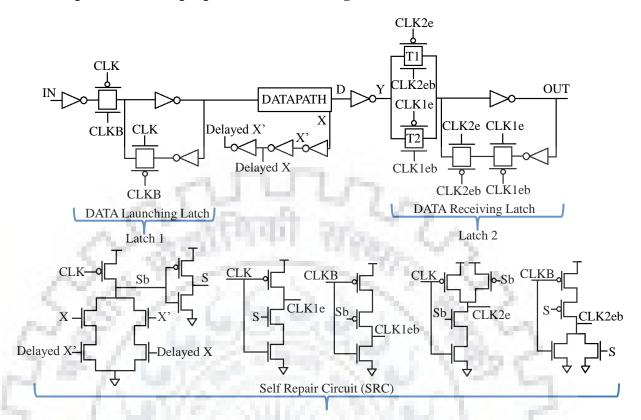

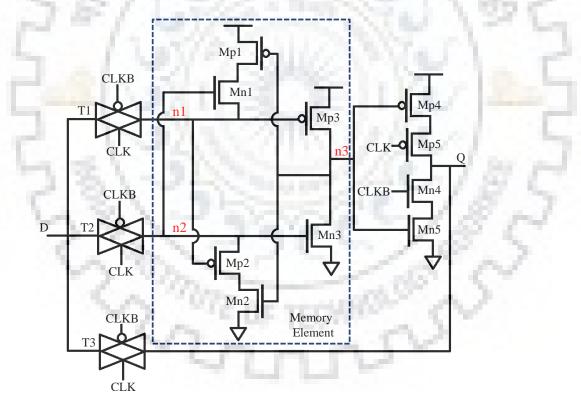

| Figure 3.2 Schematic diagram of proposed SCL technique                                                    |

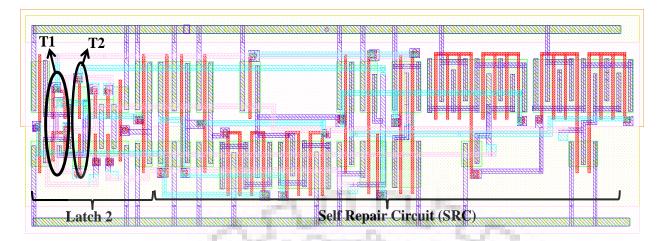

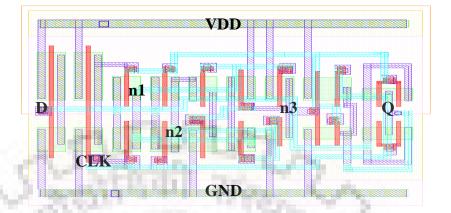

| Figure 3.3 Layout of proposed SCL technique                                                               |

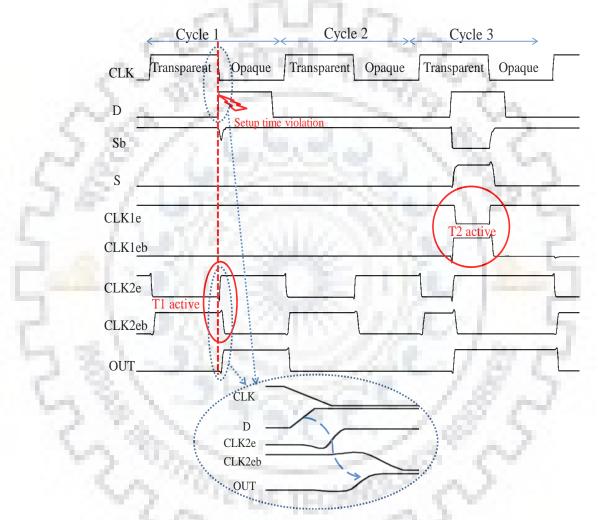

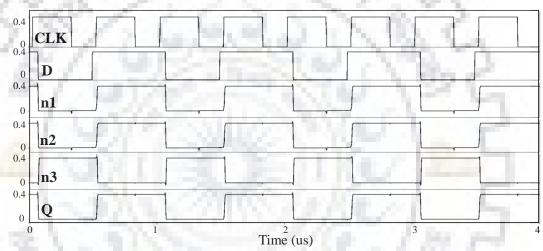

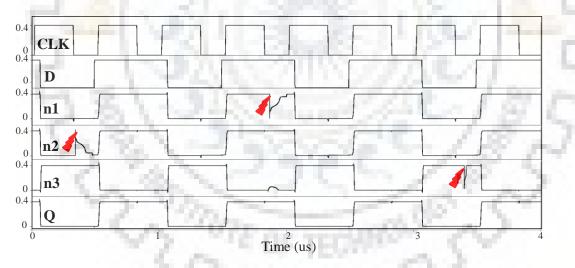

| Figure 3.4 Simulated timing diagram of the proposed methodology using S27 as a datapath29                 |

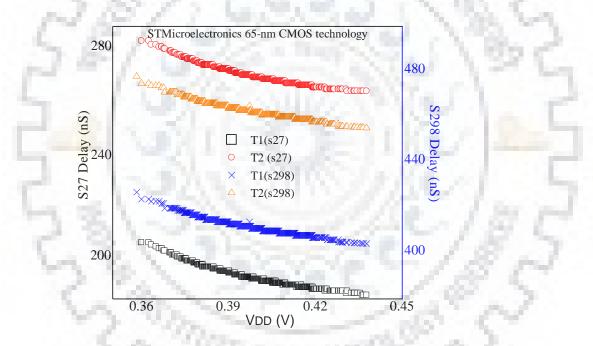

| Figure 3.5 In-Out delay (through transistor T1 and T2) vs $V_{DD}$ for S27 ISCAS circuit obtained         |

| using HSPICE 1000 MC Simulations                                                                          |

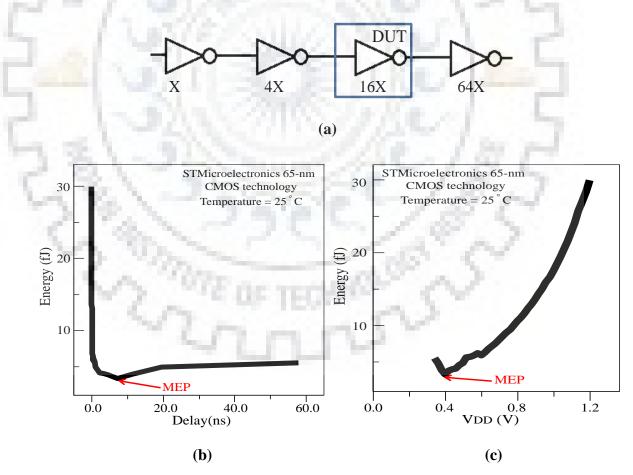

| Figure 3.6 (a) Static CMOS inverters (b) Energy Delay curve, (c) Energy v/s power supply                  |

| (V <sub>DD</sub> ) curve for an inverter                                                                  |

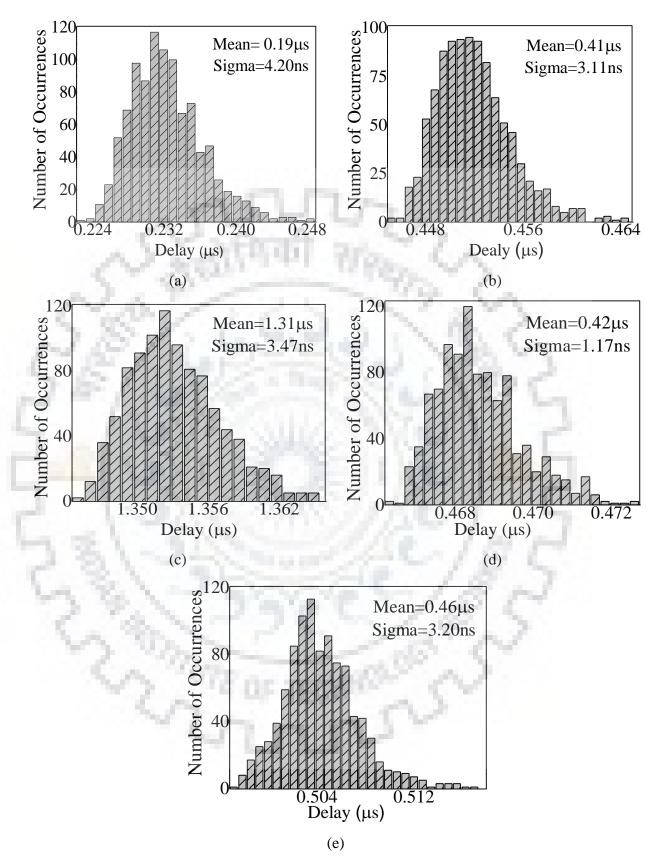

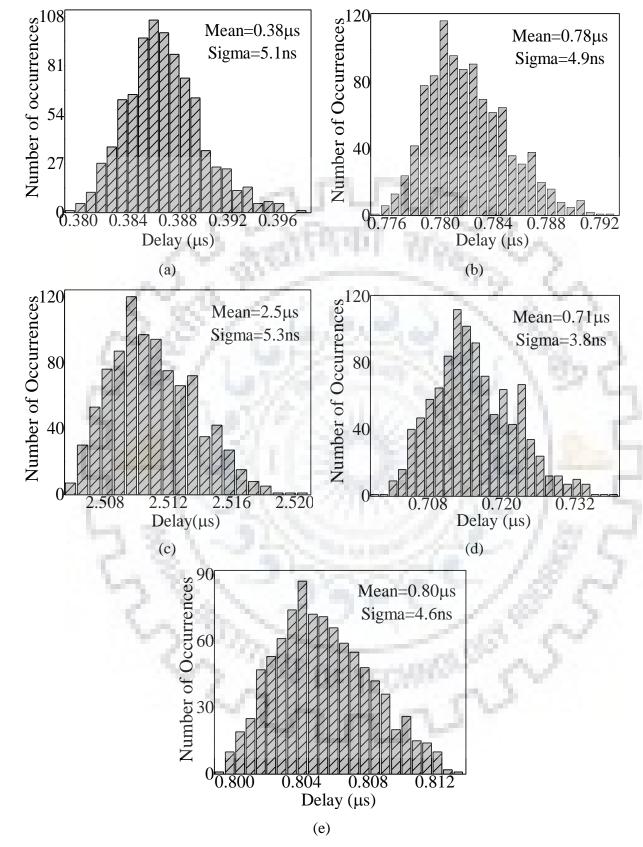

| Figure 3.7 Histogram of our SCL technique at 25 <sup>0</sup> C for (a) S27, (b) S298, (c) S344, (d) 74182 |

| and, (d) 74283                                                                                            |

| Figure 3.8 Histogram of ERFF technique at 25 <sup>o</sup> C for (a) S27, (b) S298, (c) S344, (d) 74182    |

| and, (d) 74283                                                                                            |

| Figure 3.9 Histogram of VAFF technique at 25 <sup>0</sup> C for (a) S27, (b) S298, (c) S344, (d) 74182    |

| and, (d) 74283                                                                                            |

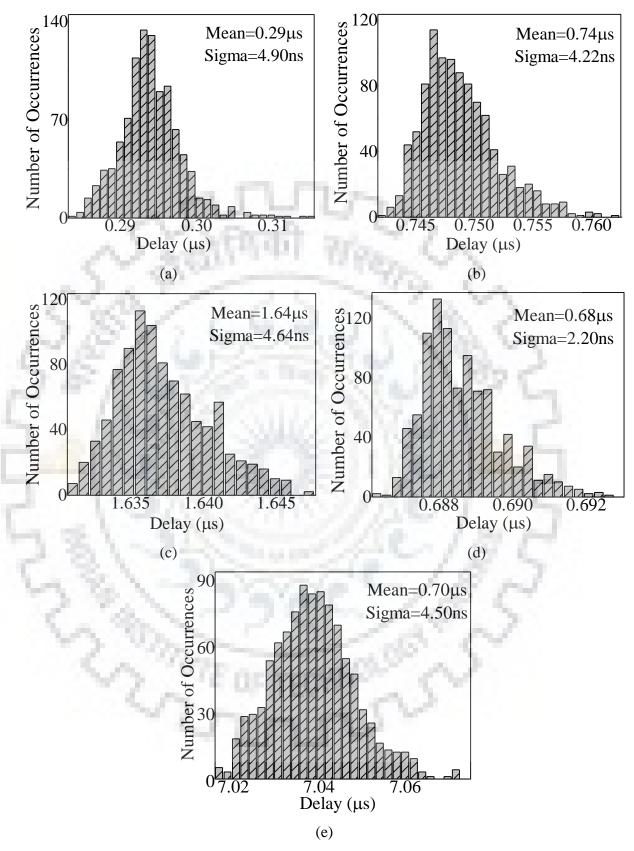

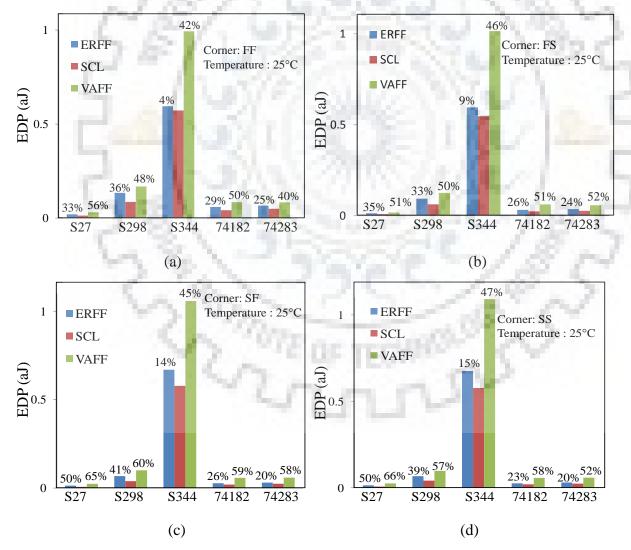

| Figure 3.10 Energy Delay Product of our SCL technique, ERFF technique and VAFF technique                  |

| for ISCAS benchmark circuits (s27, s298, s344, 74182 and 74283) at (a) -25°C, (b) 25°C and                |

| (c) 125°C                                                                                                 |

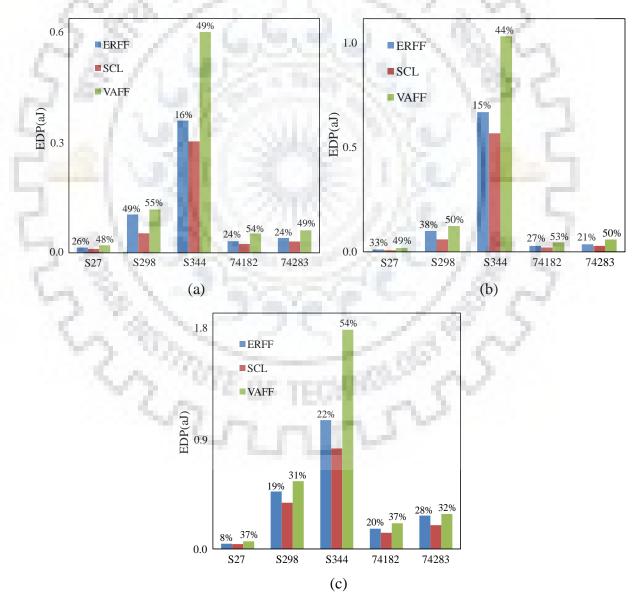

| Figure 3. 11 Energy Delay Product of our SCL technique, ERFF technique and VAFF                           |

| technique for ISCAS benchmark circuits (s27, s298, s344, 74182 and 74283) at power supply                 |

| 0.4V at room temperature (a) FF corner, (b) FS corner, (c) SF corner, and (d) SS corner38                 |

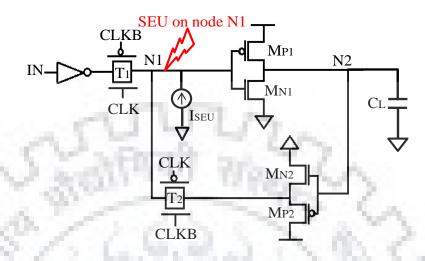

| Figure 4.1 The static D-latch, which is most commonly used, is susceptible to SEU due to                  |

| transient fault at node N1 (equivalently, node N2)                                                        |

| Figure 4.2 Simulated waveforms for Nodes N1 and N2 of the static D-latch for (a) non-flipping             |

| (< Qcritical) case, (b) flipping (> Qcritical) case due to SEU                                            |

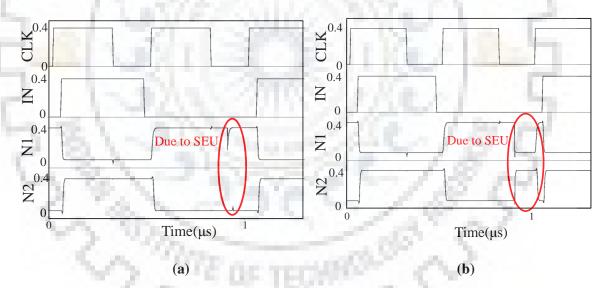

| Figure 4.3 Trip points of the static latch lie on the VTC of the feedback-path                            |

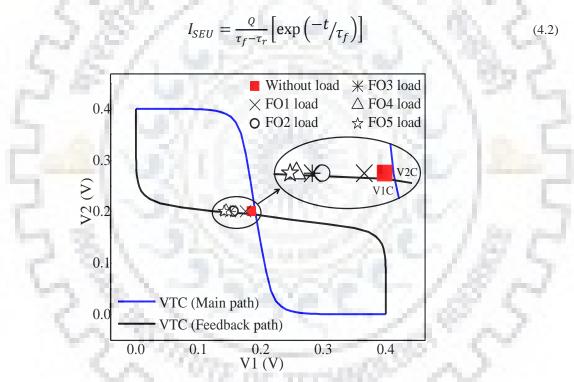

| Figure 4.4 The solid (dotted) lines show the voltage transients at node N1 and N2 for a logic                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| flipping for zero FO (FO2) case                                                                                                                                                                                                                                                        |

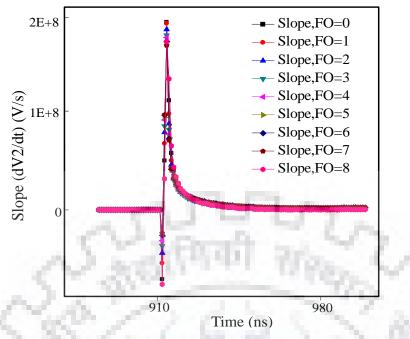

| Figure 4.5 Slope (dV2/dt) vs time overlaps at trip point independent of fan-outs                                                                                                                                                                                                       |

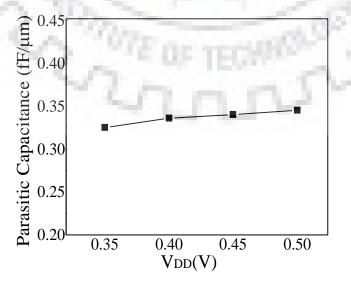

| Figure 4.6 Parasitic capacitance vs $V_{DD}$ curve independent of supply voltage at near threshold                                                                                                                                                                                     |

| regime                                                                                                                                                                                                                                                                                 |

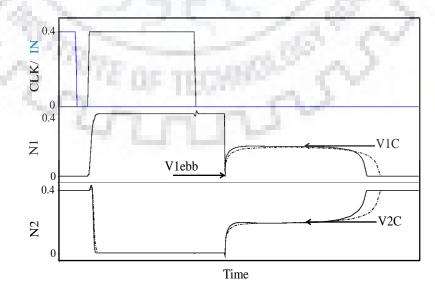

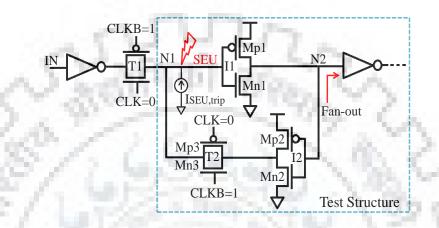

| Figure 4.7 Test circuit to emulate soft error at node N1 in the Latch with a fan-out load51                                                                                                                                                                                            |

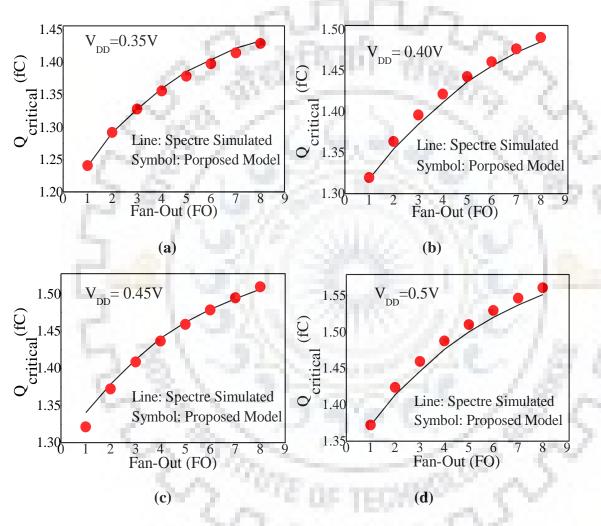

| Figure 4.8 Validation of the proposed model with SPECTRE simulation for Qcritical                                                                                                                                                                                                      |

| calculation at (a) $V_{DD} = 0.35V$ , (b) $V_{DD} = 0.4V$ , (c) $V_{DD} = 0.45$ , and (d) $V_{DD} = 0.5V$ in                                                                                                                                                                           |

| STMicroelectronics 65-nm CMOS technology at 25 <sup>0</sup> Temperature                                                                                                                                                                                                                |

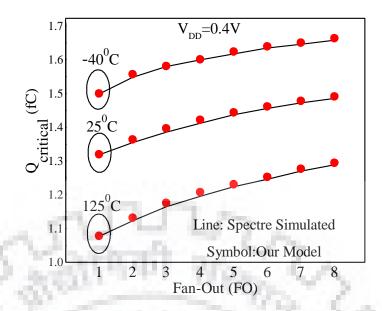

| Figure 4.9 Validation of the proposed model with SPECTRE simulation for Qcritical                                                                                                                                                                                                      |

| estimation at different temperatures (-40°C, 25°C, and 125°C) at $V_{DD}$ =0.4V in                                                                                                                                                                                                     |

| STMicroelectronics 65-nm CMOS technology                                                                                                                                                                                                                                               |

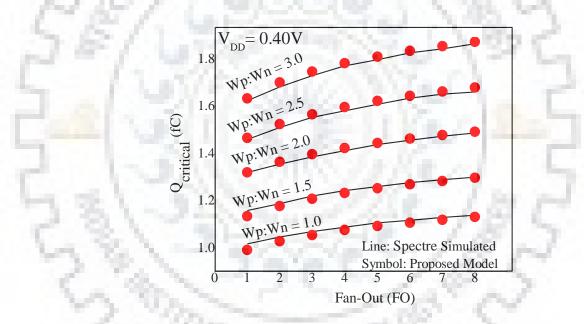

| Figure 4.10 Validation of the proposed model with SPECTRE simulation for Qcritical                                                                                                                                                                                                     |

| estimation at different beta ratio (1, 1.5, 2, 2.5, and 3) at V <sub>DD</sub> =0.4V in STMicroelectronics 65-                                                                                                                                                                          |

| nm CMOS technology at 25 <sup>0</sup> Temperature53                                                                                                                                                                                                                                    |

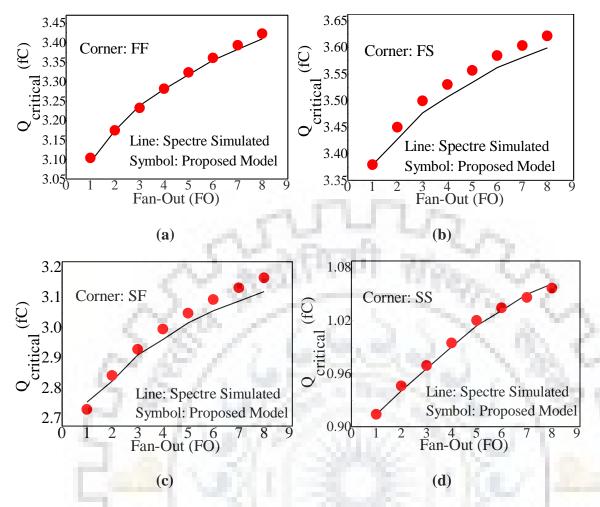

| Figure 4.11 Validation of the proposed model with SPECTRE simulation for different corners                                                                                                                                                                                             |

| Qcritical calculation at $V_{DD} = 0.40V$ in (a) FF, (b) FS, (c) SF, and (d) SS in                                                                                                                                                                                                     |

| STMicroelectronics 65-nm technology                                                                                                                                                                                                                                                    |

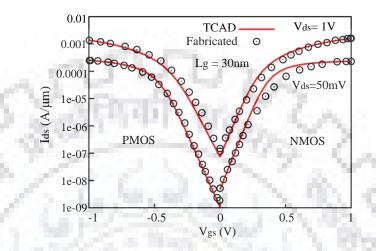

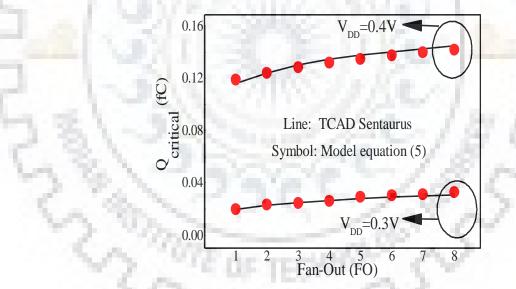

| Figure 4.12 Calibration of the TCAD models [145] with data form fabricated devices given in                                                                                                                                                                                            |

| [153] for Lg = 30 nm                                                                                                                                                                                                                                                                   |

| Figure 4.13 Validation of the proposed crtical charge model with TCAD- Sentaurus mixed                                                                                                                                                                                                 |

| mode simulations for Qcritical calculation at $V_{DD}$ = 0.30V, and $V_{DD}$ = 0.40V at 25 <sup>o</sup> C                                                                                                                                                                              |

| Temperature in 32-nm CMOS technology node55                                                                                                                                                                                                                                            |

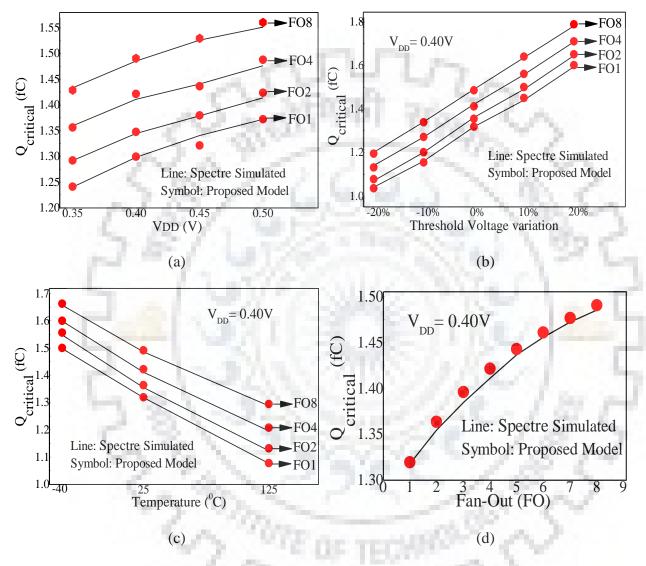

| Figure 4.14 Validation of the proposed model with SPECTRE simulation for Qcritical                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                        |

| estimation at (a) $V_{DD}$ variations, (b) $V_{TH}$ variations, (c) Temperature variations, and (d) fan-out                                                                                                                                                                            |

| estimation at (a) V <sub>DD</sub> variations, (b) V <sub>TH</sub> variations, (c) Temperature variations, and (d) fan-out load variations                                                                                                                                              |

| estimation at (a) V <sub>DD</sub> variations, (b) V <sub>TH</sub> variations, (c) Temperature variations, and (d) fan-out load variations                                                                                                                                              |

| load variations                                                                                                                                                                                                                                                                        |

| load variations                                                                                                                                                                                                                                                                        |

| load variations                                                                                                                                                                                                                                                                        |

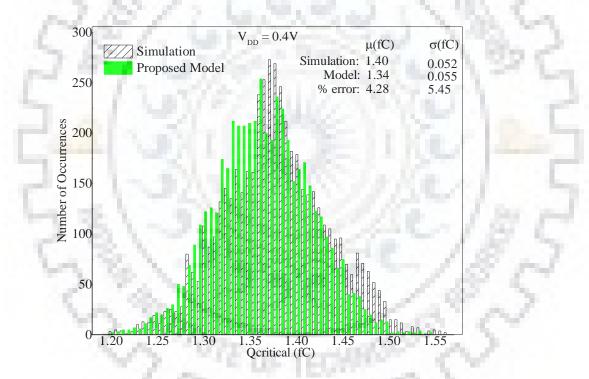

| load variations.<br>Figure 4.15 Critical charge of static D-latch with FO1 load for 5,000 Monte simulations<br>obtained using HSPICE simulations and the proposed model at $V_{DD} = 0.4V$ and<br>Temperature=25°C.<br>58                                                              |

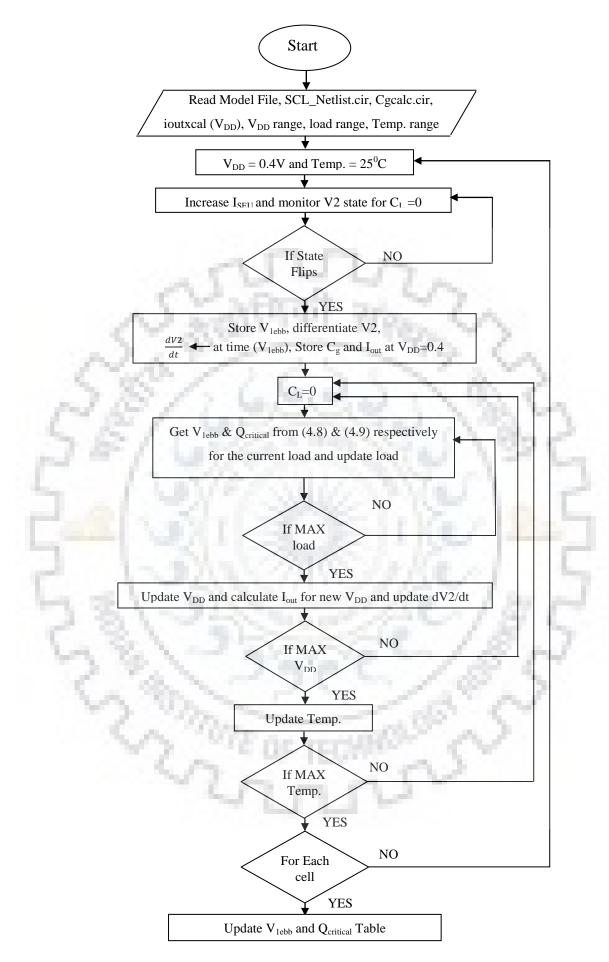

| load variations.56Figure 4.15 Critical charge of static D-latch with FO1 load for 5,000 Monte simulationsobtained using HSPICE simulations and the proposed model at $V_{DD} = 0.4V$ andTemperature=25°C.58Figure 4.16 Flow chart of the proposed methodology for estimating Qcritical |

| load variations.56Figure 4.15 Critical charge of static D-latch with FO1 load for 5,000 Monte simulationsobtained using HSPICE simulations and the proposed model at $V_{DD} = 0.4V$ andTemperature=25°C.58Figure 4.16 Flow chart of the proposed methodology for estimating Qcritical |

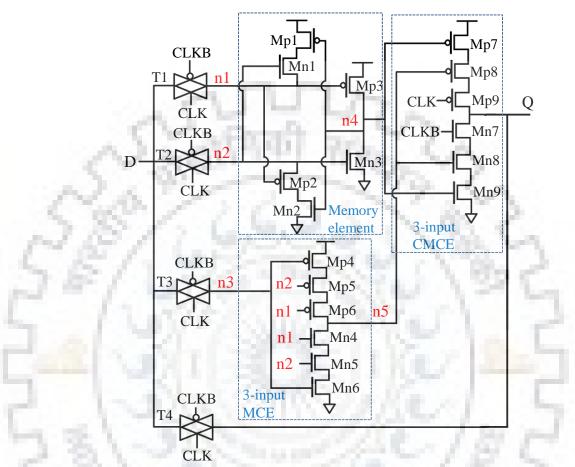

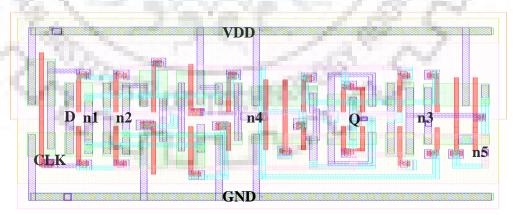

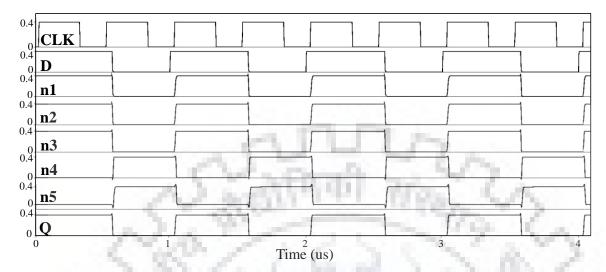

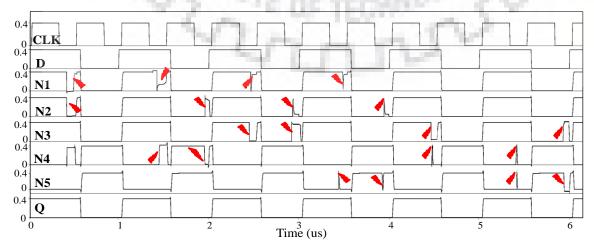

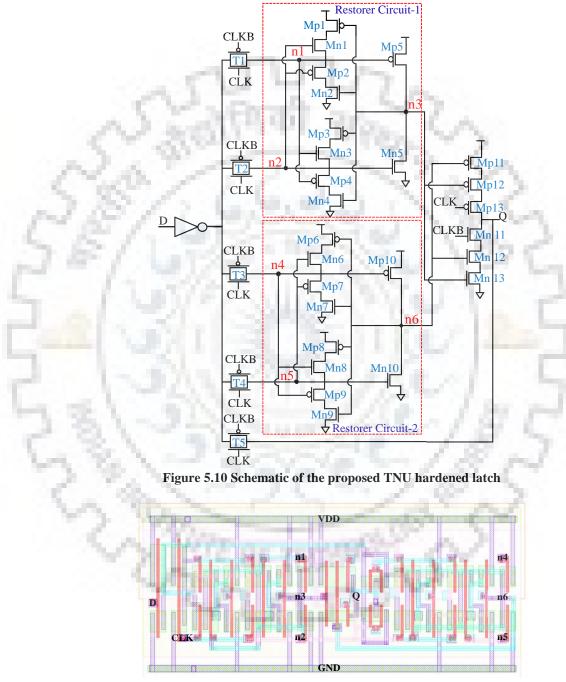

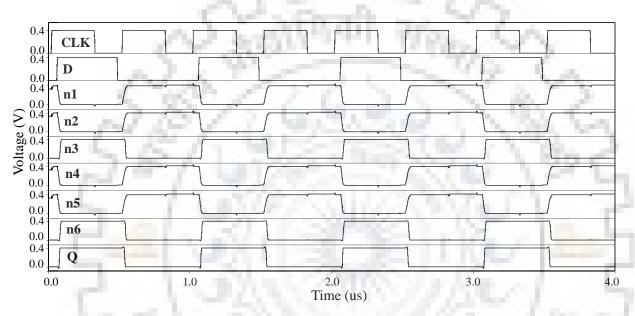

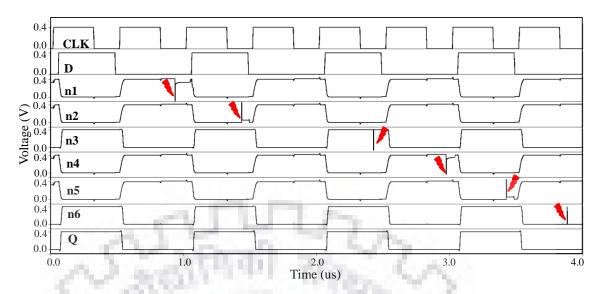

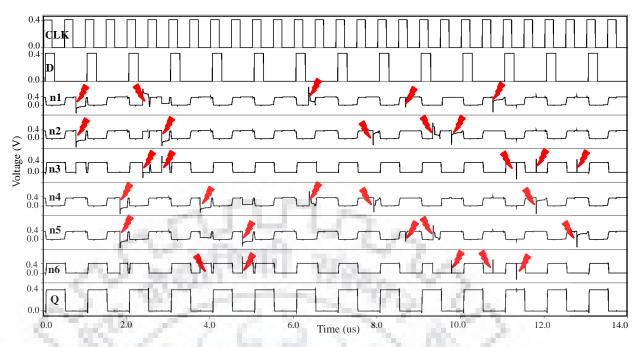

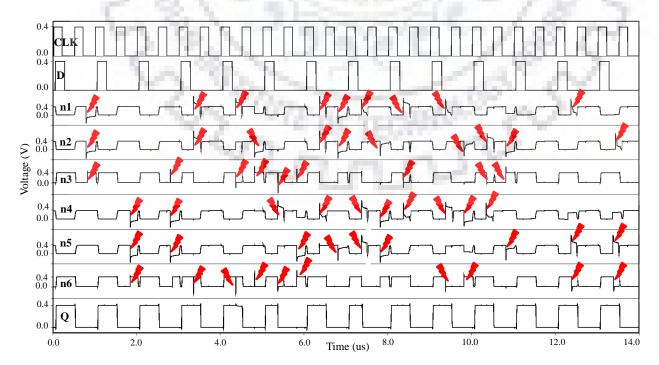

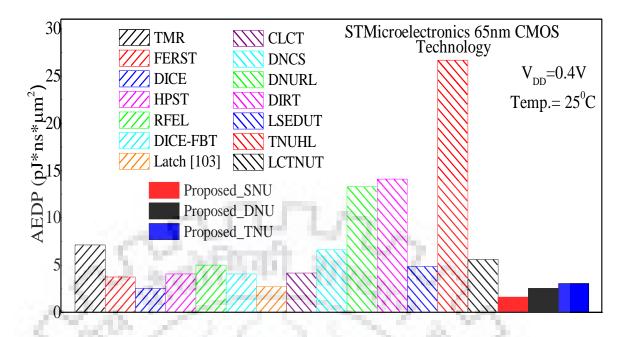

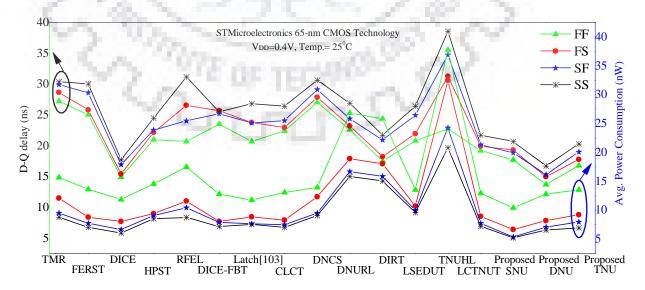

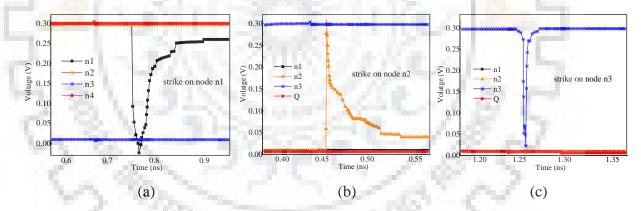

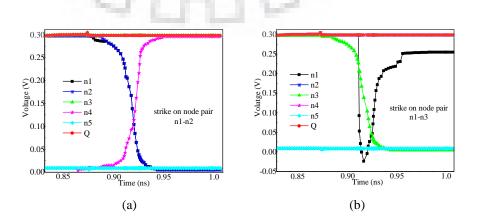

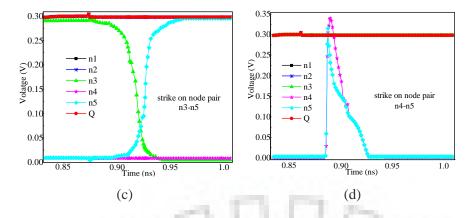

Figure 5.4 Post-layout simulated waveforms of the proposed SNU hardened latch when a Figure 5.5 Schematic of the proposed high performance, low area and DNU hardened latch...67 Figure 5.7 Post-layout simulated waveforms of the proposed DNU hardened latch for a fault Figure 5.8 Post-layout simulated waveforms of proposed DNU hardened latch for SNU Figure 5.9 Post-layout simulated waveforms of the proposed DNU hardened latch for DNU injection cases in STMicroelectronics 65-nm technology at V<sub>DD</sub> =0.4V. ......70 Figure 5.11 Layout of the proposed TNU hardened latch ......71 Figure 5.12 Post-layout simulated waveforms of proposed TNU hardened latch in fault free Figure 5.13 Post-layout simulated waveforms of proposed TNU hardened latch for SNU injection cases in STMicroelectronics 65-nm technology at 0.4V supply voltage......73 Figure 5.14 Post-layout simulated waveforms of the proposed TNU hardened latch for DNU Figure 5.15 Post-layout simulated waveforms of the proposed TNU hardened latch for TNU injection cases in STMicroelectronics 65-nm technology at 0.4V supply voltage......76 Figure 5.16 Comparison of area-energy-delay-product of the proposed radiation hardened latches with reported SNU/ DNU/ TNU hardened latches in STMicroelectronics 65-nm CMOS Figure 5.17 Comparison of D-Q delay and average power consumption at different process corners of various latches for STMicroelectronics 65-nm CMOS technology at  $V_{DD} = 0.4V...79$ Figure 5.18 Node voltages v/s time for TCAD mixed mode simulation using 32-nm CMOS technology with LET = 170 MeV-cm2/mg strike on (a) node n1, (b) node n2, and (c) node n3 Figure 5.19 Node voltages v/s time for TCAD mixed mode simulation using 32-nm CMOS technology with LET = 170 MeV-cm2/mg strike at node pairs (a) n1-n2, (b) n1-n3, (c) n3-n5, Figure 5.20 Node voltages v/s time for TCAD mixed mode simulation using 32-nm CMOS technology with LET = 170 MeV-cm2/mg strike on (a) node n1, (b) node n2, (c) node n3, (d)

| node pair n1-n2, (e) node pair n1-n4, (f) node pair n2-n6, (g) node set {n4, n5, n6}, (h) node |

|------------------------------------------------------------------------------------------------|

| set {n1, n2, n4}, and (i) node set {n1, n3, n6} of the proposed TNU hardened latch82           |

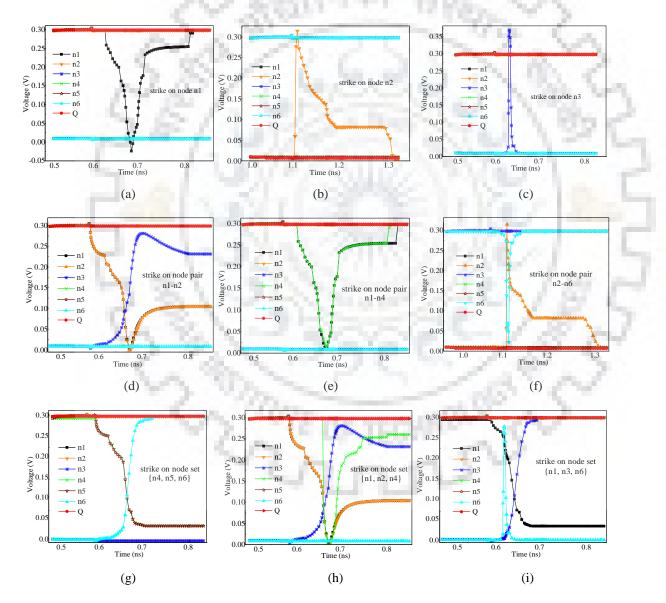

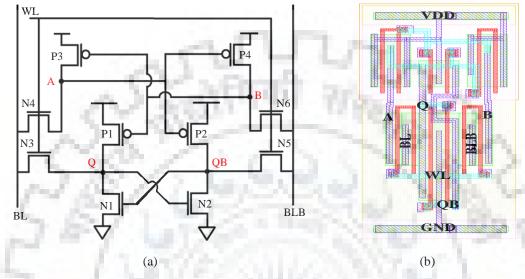

| Figure 6.1 (a) The schematic and (b) the layout of the proposed high performance, low area and |

| SEU tolerant 10T SRAM cell                                                                     |

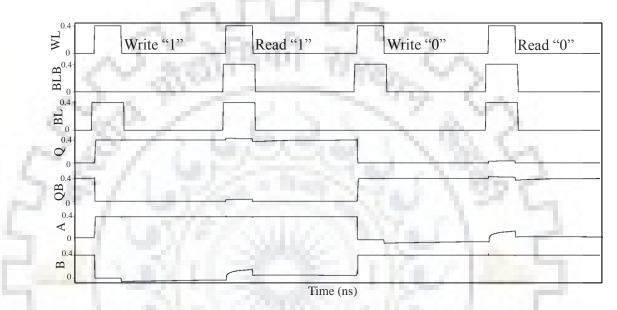

| Figure 6.2 Post-layout simulated waveforms for proposed 10T SRAM cell for fault free case in   |

| STMicroelectronics 65-nm technology at V <sub>DD</sub> =0.4 V87                                |

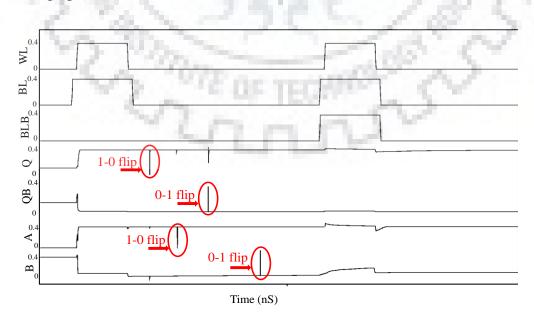

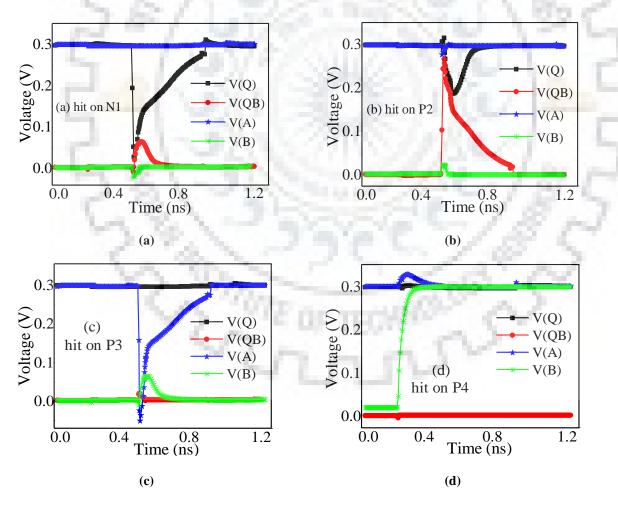

| Figure 6.3 Simulated waveforms for proposed 10T SRAM when a particle strikes on nodes Q,       |

| QB, A, and B for a STMicroelectronics 65-nm technology at 0.4 V supply voltage                 |

| Figure 6.4 (a) The schematic and (b) the layout of the proposed high performance, low area and |

| SEMNU tolerant 12T SRAM cell                                                                   |

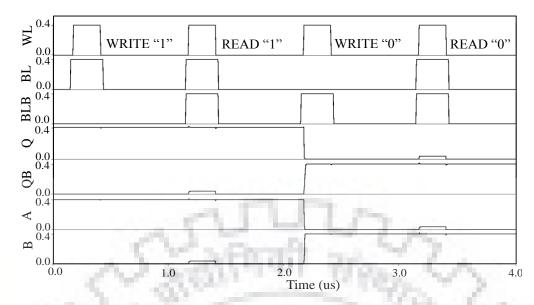

| Figure 6.5 Post-layout simulated waveforms of proposed 12T memory cell for fault free case in  |

| STMicroelectronics 65-nm technology at V <sub>DD</sub> =0.4V90                                 |

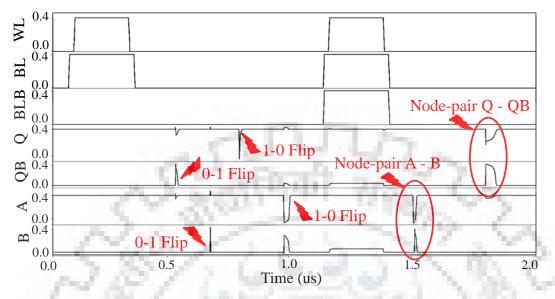

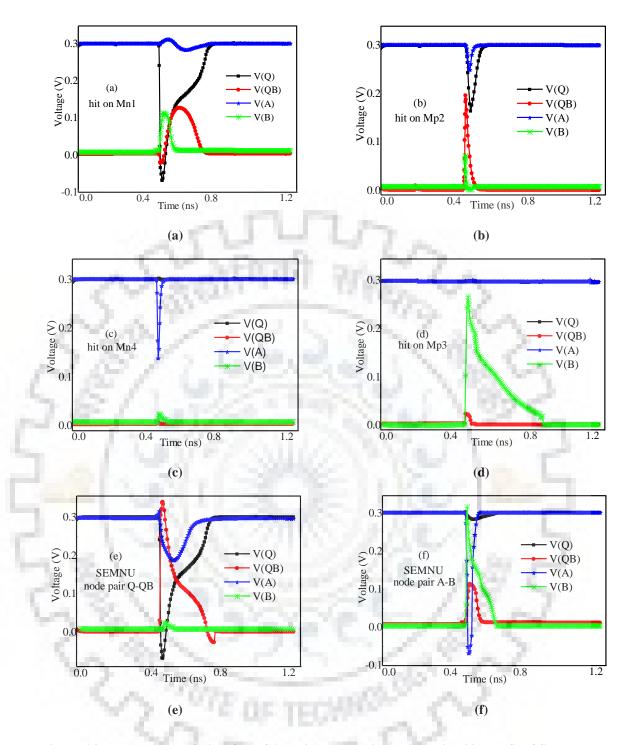

| Figure 6.6 Simulated waveforms for proposed 12T SARM cell when a particle strikes on nodes     |

| Q, QB, A, and B for an STMicroelectronics 65-nm technology at 0.4 V supply voltage92           |

| Figure 6.7 Node voltages v/s time for TCAD mixed mode simulation using 32-nm CMOS              |

| technology with LET = 30 MeV-cm2/mg strike on (a) node Q, (b) node QB, (c) node A, (d)         |

| node B for proposed 10T SRAM cell94                                                            |

| Figure 6.8 Node voltages v/s time for TCAD mixed mode simulation using 32-nm CMOS              |

| technology with LET = 30 MeV-cm2/mg strike on (a) node Q, (b) node QB, (c) node A, (d)         |

| node B, (e) node pair Q-QB, and (f) nodepair A-B for proposed 12T SRAM cell                    |

R

$\eta_{ij}$

5055

# LIST OF TABLES

| Table 3.1 Comparison summary of various parameters of ERFF and VAFF to proposed SCL             |

|-------------------------------------------------------------------------------------------------|

| technique                                                                                       |

| Table 3.2 Comparison of percentage of $3\sigma$ failure rate and Avg. power dissipation between |

| Razor, SEED and our methodology                                                                 |

| Table 3.3 Comparison summary of VAFF [71], ERFF [72], and SEED [75] to our methodology          |

| for the small datapath of [69]40                                                                |

| Table 5.1 Cost comparison of post layout parasitic extracted performance of SNU, DNU and        |

| TNU hardened latches in STMicroelectronics 65-nm CMOS technology                                |

| Table 5.2 Standard Deviation ( $\sigma$ ) for D-Q delay and Avg. Power dissipation of radiation |

| hardened latches                                                                                |

| Table 6.1 Cost comparison of post layout parasitic extracted performance of proposed 10T        |

| SRAM and 12T SRAM cells in STMicroelectronics 65-nm CMOS technology93                           |

| Table 6.2 Cost comparison of performance of proposed 10T SRAM and 12T SRAM cells in             |

| 32-nm CMOS technology                                                                           |

## **ABBREVATIONS AND SYMBOLS**

| 6T    | Six Transistor                           |

|-------|------------------------------------------|

| 10T   | Ten Transistor                           |

| 12T   | Twelve Transistor                        |

| 13T   | Thirteen Transistor                      |

| 14T   | Forteen Transistor                       |

| AEDP  | Area Energy Delay Product                |

| В     | Boron                                    |

| BL    | Bit Line                                 |

| BLB   | Bit Line Bar                             |

| BPSG  | Borophosphosilicate Glass                |

| Cg    | Gate Capacitance                         |

| CL    | Load Capacitance                         |

| Cox   | Oxide Capacitance                        |

| Cp    | Parasitic Capacitance                    |

| CG    | Clock Gating                             |

| CLCT  | Circuit and Layout Combination Technique |

| CMCE  | Clocked Muller C-element                 |

| CMOS  | Complementary Metal Oxide Semiconductor  |

| DC    | Direct Current                           |

| DIC   | Dual Interlocked Cell                    |

| DID   | Die-to-Die                               |

| DIRT  | Dual Input Inverter Radiation Tolerant   |

| DNCS  | Double Node Charge Sharing               |

| DNU   | Double Node upset                        |

| DNURL | Double Node Upset Resilient Latch        |

| DSTB  | Double Sampling with Time Borrowing      |

| DUT   | Device Under Test                        |

| ECC   | Error Correction Coding                  |

| EDC   | Error Detecting and Correcting           |

| EDP   | Energy Delay Product                     |

| EHP   | Electron Hole Pair                       |

| EMFF  | Error Masking Flip-Flop                  |

|       |                                          |

| ERFF                  | Error resilient Flip-Flop                         |

|-----------------------|---------------------------------------------------|

| FBT                   | Feedback Transistors                              |

| FERST                 | Feedback Redundant Single Event Upset Tolerant    |

| FF                    | Fast Fast                                         |

| FS                    | Fast Slow                                         |

| FO                    | Fan-Out                                           |

| FOM                   | Figures-of-Merit                                  |

| GND                   | Ground                                            |

| HPST                  | High Performance SEU Tolerant                     |

| HRDNUT                | Highly Robust Double Node Upset Tolerant          |

| HSPICE                | SPICE Simulator by Synopsis Inc.                  |

| I <sub>DS</sub>       | Drain Source Current                              |

| I <sub>dsat</sub>     | Drain Saturation Current                          |

| i <sub>Mn</sub>       | NMOS Current                                      |

| i <sub>Mp</sub>       | PMOS Current                                      |

| I <sub>out</sub>      | Output Current                                    |

| I <sub>SEU</sub>      | SEU Current due to Soft Error                     |

| I <sub>SEU,trip</sub> | Trip SEU Current due to Soft Error                |

| ITD                   | Inverse Temperature Dependence                    |

| INWE                  | Inverse Narrow Width Effect                       |

| k                     | Boltzman Constant                                 |

| KCL                   | Kirchoff's Current Law                            |

| λ                     | Channel Length Modulation Factor                  |

| L                     | Channel Length                                    |

| LCTNUT                | Low Cost and Triple Node Upset Tolerant           |

| LET                   | Linear Energy Transfer                            |

| LSEDUT                | Low-Cost Single Event Double-Upset Tolerant       |

| MC                    | Monte Carlo                                       |

| MCE                   | Muller C-Element                                  |

| MEP                   | Minimum Energy Point                              |

| MIMCAP                | Metal-Insulator-Metal Capacitor                   |

| MOSFET                | Metal Oxide Semiconductor Field Effect Transistor |

| MNDT                  | Multiple Node Disruption Tolerant                 |

| MNU                   | Multiple Node Upset                               |

| MSFF           | Master Slave Flip-Flop                              |

|----------------|-----------------------------------------------------|

| n              | Subthreshold Factor                                 |

| NTV            | Near-Threshold Voltage                              |

| PDK            | Process Design Kit                                  |

| PDP            | Power Delay Product                                 |

| PVT            | Process, Voltage, and Temperature                   |

| Qciritical     | Critical Charge                                     |

| RAT            | Read Access Time                                    |

| RC             | Restorer Circuit                                    |

| RDF            | Random Dopant Fluctuations                          |

| RFEL           | SEU Resilient and SET Filterable Robust Latch       |

| RHBD           | Radiation Hardened by Design                        |

| RSNM           | Read Static Noise Margin                            |

| σ              | Standard Deviation                                  |

| SCL            | Self-Correcting Latch                               |

| SDT            | Separated Dual Transistor                           |

| SEDU           | Single Event Double Upset                           |

| SEED           | Soft-Edge Error-Detecting                           |

| SEF            | Soft Edge Flip-Flop                                 |

| SEMNU          | Single Event Multiple Node Upset                    |

| SER            | Soft Error Rate                                     |

| SET            | Single Event Transient                              |

| SEU            | Single Event Upset                                  |

| SF             | Slow Fast                                           |

| SNTU           | Single Node Triple Upset                            |

| SNU            | Single Node Upset                                   |

| SPICE          | Simulation Program with Integrated Circuit Emphasis |

| SRAM           | Static Random Access Memory                         |

| SRC            | Self Repair Circuit                                 |

| SRCE           | SNU Resilient Cells                                 |

| SS             | Slow Slow                                           |

| STI            | Shallow Trench Isolation                            |

| t <sub>f</sub> | Fall Time                                           |

| t <sub>r</sub> | Rise Time                                           |

|                |                                                     |

| TCAD            | Technology Computer-Aided Design        |

|-----------------|-----------------------------------------|

| TDFF            | Time Dilation Flip-Flop                 |

| TDTB            | Transition Detector with Time Borrowing |

| TID             | Total Ionizing Dose                     |

| TF              | Transient Fault                         |

| TMR             | Triple Modular Redundancy               |

| TNU             | Triple Node Upset                       |

| TNUHL           | Triple Node Upset Hardened Latch        |

| TOX             | Gate Oxide Thickness                    |

| μ               | Mean                                    |

| $\mu_0$         | Mobility                                |

| V <sub>DD</sub> | Supply Voltage                          |

| V <sub>DS</sub> | Drain Source Voltage                    |

| V <sub>GS</sub> | Gate Source Voltage                     |

| V <sub>T</sub>  | Thermal Voltage                         |

| V <sub>TH</sub> | Threshold Voltage                       |

| VAFF            | Variation Aware Flip-Flop               |

| VTC             | Voltage Transfer Characteristic         |

| VLSI            | Very Large Scale Integration            |

| W               | Channel Width                           |

| W <sub>n</sub>  | Width of NMOS                           |

| W <sub>P</sub>  | Width of PMOS                           |

| WAT             | Write Access Time                       |

| WID             | Within-Die                              |

| WL              | Word Line                               |

| WSNM            | Write Static Noise Margin               |

|                 |                                         |

|                 |                                         |

## **1 CHAPTER**

## Introduction

Scaling of supply voltage (V<sub>DD</sub>) and CMOS device geometries significantly improves the energy efficiency of digital integrated circuits (IC's). To design modern energy efficient CMOS circuits, one of the necessary criteria is to operate them in sub/near-threshold voltage (NTV) regime [1], [2]. However, the major concern with NTV operation is that it leads to growing challenges in system variability and reliability [3]-[5]. As V<sub>DD</sub> reduces, setup and hold times increases while, it degrades the data storing capability. Rising process, voltage, and temperature (PVT) variations in NTV regime increases the worst case timing margins, consequently creating more timing errors and data retention failures [6]-[11]. Due to the scaling of CMOS technology and NTV operation, circuit node capacitance also gets scaled as well [12], [13]. Consequently, the signal charge representing a logic state on a node is also reduced, which makes the CMOS circuit more vulnerable to external noise due to the alpha particles and high energy neutrons, which are originated from packaging materials and intergalactic cosmic rays, respectively [14]-[16]. Therefore, resilient circuit techniques/approaches are necessary in alleviating the performance degradation and data retention failures resulting from PVT variations and external transient noise. The advantage of these techniques is that they automatically detect and correct the errors which occur because of variations and external transient noise in sequential circuits [17]. In this thesis we discuss resilient circuit design techniques to improve the tolerance against PVT variations and external transient noise. In this chapter, we briefly explain the concept of NTV operation and the circuit reliability challenges associated with it. This chapter begins with discussing the benefits of NTV operation, focusing on the trade-offs of energy and propagation delay. Thereafter, a detailed discussion is presented on the sources of variations in modern CMOS technologies. Finally, we discuss the soft error issues in NTV operation.

### 1.1 Sub/near-Threshold Voltage (NTV) Operation

Today's electronic gadgets require ultra-low power and energy efficient circuit operation. One of the most efficient methods to improve the energy efficiency is to reduce the  $V_{DD}$  into the sub/near-threshold voltage regime [18]-[21]. With NTV operation, the  $V_{DD}$  is reduced to just

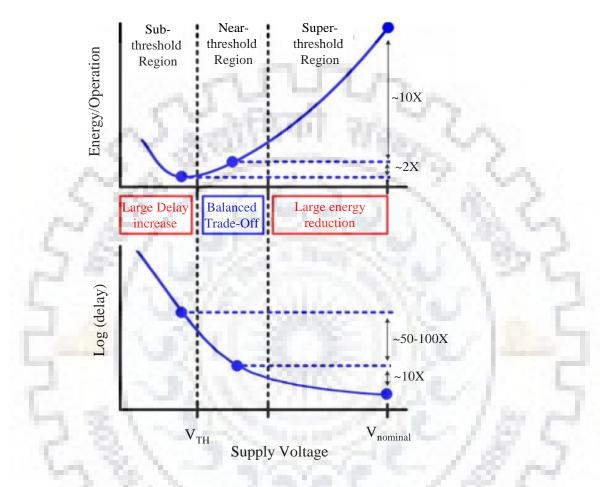

below or near to the threshold voltage ( $V_{TH}$ ) of the transistors (n-MOSFET/ p-MOSFET). Circuits operating in the NTV regime yields an energy reduction on the order of ~10X at the cost of approximately ~10X reduction in operating frequency, as compares to a nominal supply voltage (super threshold regime) as seen in Fig 1.1 [19], [22].

Figure 1.1 Energy and delay in different operating regimes [19].

Sub/near-threshold voltage operation differs from super-threshold operation (nominal supply voltages) mainly because in NTV operation the ON current depends exponentially on  $V_{DD}$  and  $V_{TH}$ , while at nominal supply voltage this dependence is linear [23]. The variation of the ON current is given in [23].

$$\frac{\sigma_{I_{sub}}}{\mu_{I_{sub}}} = \sqrt{e^{\left(\frac{\sigma V_{TH}}{n V_T}\right)} - 1}$$

(1.1)

Where  $V_T$  is the thermal voltage, n is the sub-threshold slope factor (directly proportional to  $V_{DD}$ ), and standard deviation ( $\sigma$ ) in the  $V_{TH}$  is proportional to (W. L)-1/2. This leads to more variation in the transistor ON current in sub-threshold regime. Therefore, the impact of

variations in sub/near threshold region is more adverse as compared to super-threshold region (nominal supply voltage) [24]-[27]. However, operating circuits at NTV regime is an auspicious technique to optimize the energy efficiency [28], [29]. The design techniques in NTV region would be distinct and challenging from that in the super-threshold region. For reliable operation distinct new circuits/architectures have been proposed at low supply voltages [30]-[36]. In the same direction, more research is required to improve the performance of circuits operating in the NTV regime.

### **1.2 Near-Threshold Voltage Operation Barriers**

Although NTV operation provides excellent energy-delay tradeoffs, it brings its own set of complexities. The NTV operation faces the following major challenges that must be overcome for widespread use; performance variation and reliability issues due to soft errors.

#### **1.2.1 Performance Variations**

The first and foremost barrier in NTV operation is variations. In near threshold circuits mainly two types of variations are predominant, which are: Process and Environmental variations [37], [38] as shown in Fig. 1.2. Because of the exponential relationship between transistor current and threshold voltage variations, sub/near-threshold circuit designs are highly sensitive to variations [39].

Figure 1.2 Classification of variations.

#### 1.2.1.1 Process Variation

Process variations are occurring due to the imperfect fabrication process. Process variations are spatially correlated and are common to transistors within the same area. This implies that process variations cannot only occur between the wafers, but also between areas within the same wafer. These variations are static in nature, i.e. process variations are fixed after the fabrication. Random dopant fluctuations (RDF) [40], variations in gate oxide thickness (TOX) [41], and channel length variations [42] are the main sources of process variations that affect the transistor parameters

Process variations are also classified as Die-to-Die (DID) and within-Die (WID) variations. Global or DID variation affects the physical parameter of all transistors equally with in a die. These parameters include layer thickness, channel length (L), channel width (W), body effect, and doping density [43]. Local or WID variation affects the physical parameter of each transistor with in a die differently. RDF is the main source of within-die variation and is caused by the mismatch in the amount of dopants in the channel. As a consequence, identically designed CMOS circuits may have different electrical characteristics. Global variations are only affecting the functionality of the chip but it cannot affect the yield. However, local variations only affect the yield without changing the output of the chip.

The deviation in the physical parameters of the transistor due to variations leads to changes in the electrical characteristics such as the  $V_{TH}$  of the transistor. The change in  $V_{TH}$  alters the transistor current which leads to variation in the circuit performance and power consumption, due to its exponential dependence [38], [44], [45]. It is shown in [5], [6] that variations in physical parameters of the transistor cause a ~30% variation in the chip frequency and introduce 20 X variation in the chip leakage. Traditionally, analytical models have been used to study the effect of process variations on the circuit performance [46]-[48]. The effect of static process variations at the circuit level can be reduced by changing the threshold voltage of the transistors using body or substrate biasing. Circuit-level techniques such as multiple- $V_{TH}$  [49] and gate sizing [50] have been proposed to minimize the effect of process variations.

### 1.2.1.2 Environmental Variations

The NTV circuits are also affected by environmental variations, that include supply voltage and temperature variations. These variations are dynamic in nature.

Supply voltage plays an important role in performance and power characteristics of digital circuits. Supply voltage variation is mainly due to IR drop and current derivative noise. Voltage drop or IR drop arises when the current flows on the parasitic resistance of the power grid network [51]. Current derivative noise is caused by time-varying current drawn by the parasitic

inductance of the package leads. Differences in the requirement of active current and leakage current due to IR drop across the chip lead to voltage variations [37].

As the chip density increases dramatically, temperature of the devices also increases and may affect performance dramatically. For every 100<sup>0</sup> C increase in the temperature, failure rate approximately doubles [52] due to the increased interconnect resistance and reduced carrier mobility. An increase in temperature will increase the gate delay at nominal voltages. However, the inverse is observed at low supply voltages. This phenomenon is known as the inverse temperature dependence (ITD). For ultra low voltage designs, an increment in temperature will increase the transistor switching speed. This is because a higher temperature will reduces carrier mobility and threshold voltage of the transistor. In low voltages, the effect of reduction in threshold voltage is dominant as compared to the reduction in carrier mobility. In sub/near-threshold designs, circuit switching speed is directly proportional to temperature. A temperature variation on a die mainly depends on the thermal characteristics of materials, power consumption of blocks, cooling and packaging efficiency.

Summarizing, in the NTV regime, the MOSFET current is exponentially dependent on threshold voltage, power supply, and operating temperature. Consequently, NTV circuit designs display a dramatic increase in performance uncertainty.

#### 1.2.2 Functional Failure due to Soft error

NTV circuits are vulnerable to soft errors such as single node upset (SNU) and single event multiple node upset (SEMNU) [53]. The minimum charge required to flip the logic level is lesser in NTV circuits due to the smaller supply voltage (due to NTV operation) and smaller node capacitances (due to an implementation at lower technology node). Consequently, the minimum charge required at a circuit node to change the logic level is getting reduced [12], [13]. Consequently, noise sources, such as electromagnetic interference, radiation-induced voltage transients, chip and board level signal coupling, etc. can easily change the logic state. In a properly designed architecture, voltage transients due to radiations are the major threat to the logic state integrity.

The radiation that influences the electronics architecture mainly consists of alpha particles and high energy neutrons, which are originated from chip packaging materials and intergalactic cosmic rays, respectively [54]. A soft error occurs when these energy particle strike on a

sensitive region of a transistor and generates charge carriers i.e., electron hole pairs (EHP's) in the body [55], [56]. These charge carriers are collected by the drain/source diffusion of the reverse biased drain/source-body junction. This results in the generation of a voltage transient at the node. This transient is known as a single event transient (SET) or transient fault (TF). If the duration of SET is large enough, it can flip the data (from "1" to "0" or from "0" to "1") at the node. When this corrupted logic state is processed by a sequential element (latch/ Flip-flop), it is known as a single event upset (SEU). Consequently, the transistor which is in OFF state starts conducting temporarily and changes the logic level of an affected node. A glitch at the node is thus produced, which results in TF and may result in a system failure or soft error [57]. Moreover, due to the reduction in the magnitude of node capacitance and inter node spacing, striking of a high energy particle may affect multiple nodes, which results in a multiple node upset (MNU) [58], [59].

#### 1.2.2.1 Sources of Soft error

The three main sources of radiation induced soft error in electronics circuits are: i) alpha particles from chip packaging materials, ii) high energy neutrons from intergalactic cosmic rays, and iii) the interaction of thermal neutrons from cosmic ray and <sup>10</sup>B in electronic devices containing borophosphosilicate glass (BPSG) [54]. The third soft error source is only be of concern above 180nm technology. In lower process nodes the effect of BPSG has been eliminated during the fabrication process [54].

The first major source of soft error is the alpha particles originated from chip packaging materials. Nucleus of an alpha particle is formed by two protons and two neutrons, and is emitted by radioactive materials like Lead-210 ( $^{210}$ Pb) in solder, Uranium-238 ( $^{238}$ U), Thorium-232 ( $^{232}$ Th), in packaging. Alpha particles are mostly produced by energy less than 10MeV. Consequently, an alpha particle having energy = 1 MeV, can generate approximately 44.5 fC of charge, which is enough to flip the logic state of a memory element [60].

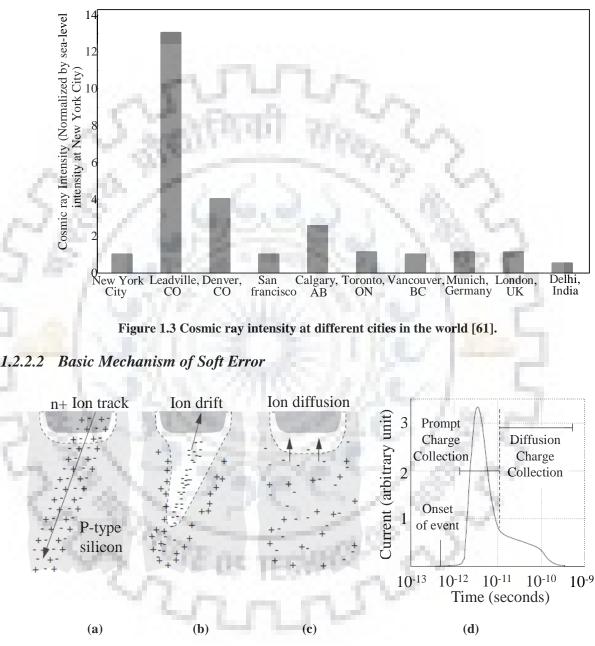

The second major source of radiation induced soft errors is high energy neutrons from cosmic rays. Cosmic rays produce a chain of nuclear interactions with the Earth's atmosphere, and generating neutrons, muons, pions, and protons before reaching sea level. The cosmic neutron flux is directly dependent on neutron energy and the altitude. Consequently, intensity of cosmic rays is different in different cities of the world as shown in Figure 1.3 [61]. As a result, neutron induced soft error rate (SER) of the same electronic circuits will be different in different cities.

A cosmic neutron generates charge through indirect ionization by interacting with silicon nucleus. When a high energy neutron collides with the silicon, it can break the nucleus into multiple fragments, each of which generates charge. The resulting charge density per distance traveled (25-150 fC/ $\mu$ m) is significantly higher than that for alpha particles (16 fC/ $\mu$ m) [54].

Figure 1.4 Charge generation and collection mechanism from [56].

The most charge sensitive part of the electronic circuits is reverse-biased junction, particularly when the junction is weakly driven or floating. As shown in Fig. 1.4 (a), when a high energy particle strike on the sensitive region of a transistor, a cylindrical charge column with a submicron radius and a high carrier (EHP's) concentration is generated. The quantity of generated charge depends on the linear energy transfer (LET) of the particles, which is a

measure of loss of particle energy per unit length. The generated charge is quickly collected on reverse-biased junction. Due to the electric field EHPs are separated; the electrons (holes) move towards the drain in n-MOSFET (p-MOSFET) and holes (electrons) move towards the substrate of n-MOSFET (p-MOSFET) (please refer Fig. 1.4 (b)). A remarkable feature of this event is the distortion of the depletion region into a funnel shape [62]. This funnel greatly enhances the drift charge collection by extending the depletion region deeper into the substrate as shown in Fig. 1.4 (b). This drift charge collection phase is completed within few tens of picoseconds and is followed by slower diffusion charge collection phase (please refer Fig. 1.4 (c)). Diffusion charge collection process continues until all extra charge carriers have been diffused away from the junction area. These generated and collected charge carriers results in a current pulse (please refer Fig. 1.4 (d)). This current pulse results a SET on the node voltage. The magnitude of the collected charge is more than a minimum charge, the logic state in a memory element is flipped and SEU or soft error occurs. This minimum charge is called the critical charge (Q<sub>ciritical</sub>).

#### **1.3 Motivation**

Due to the PVT variations and soft errors, NTV circuit designers are in a hard dilemma, while achieving reliable designs with maximum energy efficiency. Among different electronic components in every chip, sequential elements (latches/ Flip-Flop/ static random access memory (SRAM)) represent up to 50% of the chip area [63]. Sequential elements, highly affect the chip efficiency, performance and reliability. In addition, the power consumption of the clock network, in latches/Flip-Flop approximately more than half of the total chip power consumption [45]. Therefore, efficient implementation of latches and memory cells is of great importance for energy efficient and reliable integrated circuits design. Conventionally, large design margins are allocated for sub/near-threshold circuits to function in worst-case scenario. However, these worst-case margins severely degrade the performance and increase the power dissipation of a design [64]. Hence, adding these safety margins to handle PVT variations makes the design inefficient for low voltage applications. Several resilient techniques have been presented to address PVT variations [65]-[77]. The advantage of these techniques is to automatically detect and correct the errors that occur because of PVT variations in worst cases. However, these techniques detect error when data transition occurs after the edge of the clock signal, these techniques do not handle the setup time violations.

As discussed earlier, the minimum charge on the sensitive node is called the critical charge  $(Q_{ciritical})$ . This  $Q_{ciritical}$  exhibits an exponential relationship with the soft error rate. Several critical charge models have been presented to address this requirement [78]-[87]. However, these models are derived only for SRAM cells. In particular, modeling and analysis of soft errors due to SEU in sub/near-threshold latches is also vital. Therefore, an accurate model to estimate the  $Q_{critical}$  of a static D latches in sub/near-threshold regime is necessary. This  $Q_{critical}$  model will enable circuit designers to estimate and optimize the  $Q_{critical}$  and hence the SER at the schematic stage. Since the PVT variations can lead to variation in SER across the fabricated chip. This information can help the process designer to fine-tune the process in order to minimize the SER in fabricated chips.

When a static D-latch or 6T SRAM cell is operating in near threshold voltage, it becomes more susceptible to SEUs because of reducing supply voltage, increasing densities, and decreasing critical charge. Therefore, if we want to design ultra-low power memory elements in reliability critical or space applications, techniques to tolerate SEU should be applied. Error Correction Code (ECC) is a traditional approach to solve this problem. However, when multi-bit upset due to SEU occurs, ECC may not be suitable solution because the cost of complicated coding and decoding technique for multi-bit correction is too high. It will bring high power consumption and large overhead, as well as degrade the performance of the circuit. To overcome SEMNU issues, radiation-hardened by-design (RHBD) techniques are explored in [88]-[114]. The advantage of these techniques is increased immunity against soft errors in worst cases. However, the cost in terms of power, speed and area for protecting SRAM cells from a SEU is significant. Therefore, energy efficient, low cost and radiation hardened memory element (latches/ SRAM cell) designs are indispensable in NTV regime.

## 1.4 Objectives

From the above discussion, it is imminent that innovative NTV sequential circuit design techniques that not only overcome timing errors but also handle soft error issues effectively are essential. These sequential circuit designs which have reasonable area overhead as compared to conventional approaches are in great demand. In this work, the impact of PVT variations and soft errors on sequential elements' functionality/performance is discussed. The twin objectives of this research are to design PVT variation aware sub/near-threshold self correcting

ALL OF LECK

latches/SRAM and address the radiation-induced data retention failure issues. The main objectives of the thesis are:

**1.** To develop a methodology that corrects the faults due to timing violation caused by variations in data-paths and sequential elements automatically, thereby lowering PVT variation induced performance degradation.

2. To develop a physics-based variability aware methodology to estimate the critical charge of an NTV static D-latch without losing the accuracy for different fan-out loads, power supply voltages, and temperatures. Using this model, we devise a methodology to estimate the critical charge using a few DC simulations and a single transient simulation program with integrated circuit emphasis (SPICE) simulation for a given process design kit (PDK). This is an end to end method to include an accurate estimation of the critical charge for latches in NTV standard cell library characterization.

**3.** Design a highly reliable, low cost and energy efficient radiation hardened latch design for low voltage applications.

**4.** Design a novel energy efficient and higher single event multiple node upset tolerant SRAM cell designs for space applications.

### **1.5 Organization of the Thesis**

This thesis is based on the objectives discussed above. The thesis consists of seven chapters. Each chapter begins with a brief introduction to the concerned problem and motivation behind the study. Subsequently, the simulation framework, analysis, and results are discussed in a lucid manner. A brief discussion of each chapter is presented below:

**Chapter 1** provides the overall philosophy of the thesis. It provides the motivation and outline behind this research and the agenda for choosing the objectives of the work. Problem statement, objectives of the thesis and the thesis organization is presented in this chapter. It also introduces the CMOS near threshold voltage regime operation which has been considered the operating region in this thesis.

**Chapter 2** provides a comprehensive literature review on NTV techniques to incorporate timing errors due to variations in CMOS circuits. Single Event Upset due to transient fault,

Double Node upset (DNU) and triple node upset (TNU) due to charge sharing, modelling of  $Q_{critical}$  of a conventional static D-latch are also discussed. Moreover, existing design methodologies to optimize circuit performance considering circuit level variations due to NTV are reviewed.

**Chapter 3** presents a novel energy efficient self-correcting latch (SCL). The proposed technique corrects the faults due to timing violation caused by variations in datapaths and sequential elements automatically, thereby lowering PVT variation induced performance degradation. Our technique employs Inverse Narrow Width Effect (INWE) in designing the self-correcting latches to reduce performance variability. We validate the proposed methodology on several ISCAS'89 benchmark circuits and 74X series circuits.

**Chapter 4** presents a physics based semi-analytical model to estimate the critical charge Q<sub>critical</sub> of a static D-latch as a function of its fan-out load and supply voltage. The model describes the critical charge in terms of the supply voltage and transistor level parameters. The model can be used while considering PVT variations. We validate the proposed model on STMicroelectronics 65-nm CMOS technology node for different process corners. Based on this model, we propose a procedure to estimate the critical charge using a few DC simulations and a single transient simulation. This method results in an estimate of the latch's critical charge for different values of fan-out load and supply voltages.

**Chapter 5** presents high performance energy efficient radiation hardened latch designs in NTV regime. In the case of a transient fault, the proposed latches, mask the fault by a clocked Muller- C and memory elements based restorer circuit. In the transparent mode data passes through a fast and efficient path. Inverse Narrow Width Effect (INWE) is used to further improve the performance of the proposed latches at the layout level. The proposed radiation hardened latches shows a higher performance and also a better robustness against soft error occurring due to transient faults, without power consumption overhead of the earlier techniques. We validate the better SEU tolerance and improved performance of the proposed latch in STMicroelectronics 65-nm and TCAD calibrated 32-nm CMOS technologies.

**Chapter 6** presents two novel energy efficient radiation hardened by design SRAM cell designs. We validate the proposed SRAM cells in STMicroelectronics 65-nm and TCAD calibrated 32-nm CMOS technologies. The proposed SEU hardened memory cell shows better

performance (in terms of read and write access time) and also more robustness against SEU, without power consumption overhead of the earlier techniques.

**Chapter 7** concludes the thesis. The conclusions of the thesis are drawn based on the obtained results. The future scope of the work is also presented in this chapter. The thesis ends with a complete bibliography.

# **2** CHAPTER

# **Literature Survey**

In the Introduction chapter, we discussed the main challenges in near threshold circuit design. This chapter presents a comprehensive literature survey of the present and past research work that is closely related with the work presented in this thesis. The problem statement of this thesis is mainly focused on addressing the timing and soft error issues in the near threshold voltage (NTV) circuit's design, while maintaining their inherent energy-efficiency. Therefore, the works in this thesis can be classified into four parts: NTV error detection and correction (EDC) techniques (Section 2.1), critical charge modeling for static D-latch (Section 2.2), radiation hardened by design (RHBD) techniques for static D-latch (Section 2.3) and mitigation of soft error in static random access memory (SRAM) cells (Section 2.4). Finally, section 2.5 summarizes the chapter by identifying the technical gaps that we addressed in this thesis.

## 2.1 NTV Timing Error Detection and Correction (EDC) Techniques

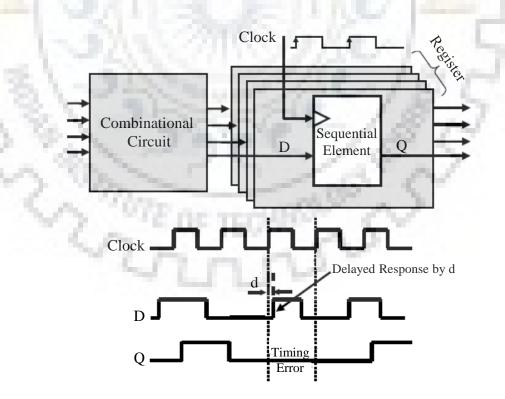

Figure 2.1 Conceptual timing diagrams in worst and nominal conditions [64].

Timing error in combinational circuits leads to delayed responses on its output node. Figure 2.1 shows that, within the presence of variations, the input data (D) arrive after the rising edge of the clock signal. Consequently, the sequential element will capture an incorrect data and a time failure error occurs. Traditionally, large design margins are allocated for NTV circuits so that the circuits can function in worst-case scenario. However, circuit designing with huge design margins results in sub-optimized designs. Therefore, the challenge to achieve a maximum yield without using large timing margins is daunting.

To overcome this issue, error detection, correction and prevention techniques are used. Employing these techniques results in high performance, while the errors encountered due to variations in worst cases are automatically detected and corrected. Various timing error detection techniques have been presented in the open literature [65] - [77]. The advantage of these techniques is to automatically detect and correct the errors which occur because of variations in a data-path in worst cases. Most of the above methodologies cited in literature are aimed to generate a post-silicon warning when process voltage and temperature (PVT) variations cause timing violations. The ICs which generate these warnings need external intervention (such as increasing the supply voltage V<sub>DD</sub>).

Razor I circuit [65] detects errors by using an error detecting latch (shadow latch) and corrects timing errors via architectural replay. However, in Razor I, if there is a setup time violation in the datapath, the error detection may not happen due to metastability of the Flip-Flop. Soft-Edge Flip-Flop (SEF) is presented in [66]. The basic principle of the SEF is to delay the master latch's clock signal so that a transparency window can be made instead of a hard boundary for sampling the data. By creating a transparency window, SEF increase the hold time. The SEF does not require any error correction operation, but it cannot instruct a controller to scale the voltage and frequency of the circuit. Consequently, it will have a very large window of transparency. In Razor II technique [67], a signal transition detector is used to make the Flip-Flop detect timing errors and do corrections. In Bubble Razor technique [68], a cycle prolongation is done in both directions of data propagation in pipeline. The main principle of bubble razor is that when timing violations occur, it broadens the operating clock cycle. However, both Razor II and Bubble Razor techniques require a huge overhead of additional circuitry for changing the clock cycle time dynamically and also increase the circuit area and clock power dissipation.

In [69], a Transition Detector with Time Borrowing (TDTB) and Double Sampling with Time Borrowing (DSTB) methodologies are proposed which are based on the principle of time borrowing. DSTB has the same issues as in the Razor I technique. In TDTB the problem of meta-stability in the main data-path's Flip-Flop was solved, however, meta-stability can occur in the error path's Flip-Flop. In [70], an error masking technique based on generic monitoring is proposed. The main drawback of this is that it is incapable to capture design characteristics, consequently giving a large error in the measurements. Therefore, the delay estimation using generic monitors is less accurate. Variability has been handled by all existing warning circuit techniques by either changing cycle time dynamically or by increasing supply voltage. In [71], a variation aware Flip-Flop (VAFF) is proposed; the VAFF generate an error signal when its input and output logic levels are different after the rising edge of the clock signal. One of the major problems in VAFF is that in case of setup time violation the final output may be erroneously chosen while in case of no setup time violations huge hold time is required. In addition, its comparator results in delay and power consumption overhead. In error resilient Flip-Flop (ERFF) [72], a late detector detects input data transition causing timing violations. The late signal converts the Flip-Flop into a latch thereby increasing the timing window dynamically. One of the major problems in ERFF technique is the possibility of race around condition because of the conversion of the Flip-Flop into a latch whenever there is late signal generated by the late detector. In addition, ERFF cannot handle meta-stability issues resulting from setup time violations.