# CHARACTERIZATION AND MITIGATION OF LINEAR AND NON-LINEAR DISTORTIONS IN SIX-PORT MODULATORS

by

CHETAN PATHAK

Submitted in partial fulfillment of the requirements of the degree of Doctor of Philosophy

to the

DEPARTMENT OF ELECTRONICS AND COMMUNICATION

ENGINEERINGINDIAN INSTITUTE OF

## TECHNOLOGY, ROORKEE

JANUARY 2019

# CHARACTERIZATION AND MITIGATION OF LINEAR AND NON-LINEAR DISTORTIONS IN SIX-PORT MODULATORS

by

**CHETAN PATHAK**

Submitted in partial fulfillment of the requirements of the degree of Doctor of Philosophy

to the

DEPARTMENT OF ELECTRONICS AND COMMUNICATION

ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY,

## ROORKEE

JANUARY 2019

### Certificate

This is to certify that the thesis entitled, "Characterization & Mitigation of Linear & Non-linear Distortions in Six-Port Modulator", being submitted by Chetan Pathak for the award of the degree of **Doctor of Philosophy** to the Department of Electronics and Communication Engineering, Indian Institute of Technology, Roorkee is a record of bonafide research work carried out by hisunder our guidance and supervision.

**Chetan Pathak** has fulfilled the requirements for the submission of this thesis, which to our knowledge has reached the requisite standard. The results contained in this thesis have not been submitted in part or in full to any other university or institute for the award of any degree or diploma.

#### (Dr. Karun Rawat)

Assistant Professor Department of Electronics and Communication Engineering Institute of Technology Roorkee Roorkee-247667, Uttarakhand, India

#### Acknowledgements

I would like to acknowledge the help of several people without whom this thesis would not have been possible. I express my deepest gratitude to all of them. I would like to begin by thanking my supervisor **Dr. Karun Rawat** for his immense support in terms of knowledge, experience, review and validation at all steps of my PhD process.

I would like to thank **Dr. Karun Rawat** for providing constant guidance and believing in my research abilities. His working attitude and organization skills are truly impressive, which I would always like to assimilate. I am grateful to him for his contribution towards my personal and professional growth.

I sincerely thank **Dr. Karun Rawat** for his scholarly inputs and valuable suggestions. His deep knowledge and enthusiasm for the subject was the continual source of inspiration to me. His intriguing questions have always inspired me to explore the things which were beyond my perception. I am thankful to him for nurturing me as a researcher.

I would also like to thank **Dr. Meenakshi Rawat** for her kind academic support and encouraging behaviour. Her cooperation and support during the entire research period is highly appreciated.

I would like to take this opportunity to express my heartfelt gratitude to all the research committee members of my doctoral program **Prof. D. Singh** for his advices, suggestions and chairing my research committee. I am also thankful to **Prof. M.V. Kartikeyan and Prof. R.S.Anand** for the advices and suggestions that have helped me grow in my research area.

I would also like to acknowledge **Dr. Meenakshi Rawat** for her insightful suggestions. She was kind enough to help with her full ability whenever I approached her in times of need.

I am thankful to Department of Science and Technology (DST), Government of India for sponsoring this research work with Extramural Grant number: SB/S3/EECE/047/2014. I would also like to thank Keysight Technologies, New Delhi and Rohde and Schwarz, India for their support in developing measurement setup under educational development program.

I am grateful to all my colleagues and labmates here in the Department of Electronics and Communication Engineering who have made this journey the most memorable and fruitful experience of my life. The moments of loud laughter and long discussions will always be cherished. I would like to Special thank **Girish Chandra Tripathi, Praveen Jaurat, Ekta Agrawal** and **Anuj Sahoo** who have always helped and supported me technically and kept me motivated and helped me abundant times in conducting long-lasting measurements.

I am thankful to all the faculty and staff members from Department of Electronics and Communication Engineering, IIT Roorkee for helping me in various ways for completing my dissertation.

Most importantly, I would like to thank my parents, **Mr. Dinesh Kumar Pathak** and **Mrs. Madhvi Pathak** to whom I owe everything. I am always being indebted to my beloved wife **Mrs. Meenal Pathak**, my daughter **Divita and** son **Rohan** who have compromised on every step and the words will fall short to thank them. They have helped

iii

me be who I am through their constant love, care and unconditional support ever. I thank them from the bottom of my heart and I will forever be grateful to them.

Over everything else, I would like to thank the Almighty God Gaud Baba, Kunwar Baba and Balaji Maharaj for bestowing me with the wisdom, health and confidence which was needed for the successful completion of this thesis which is nothing short of a dream.

#### Abstract

There is an increasing demand of lowering the complexity and power consumption in the design of the wireless terminals. Further, wideband, compact size, and low-cost digital transceivers are required to meet the demands of upcoming mobile and wireless communications. With the advent of 5G wireless communication, the expected data rate is going to exceed to an order of Gbps. This is possible with high spectral efficient modulation scheme or multiplexing techniques, where, maximum data can be transmitted within limited bandwidth. These schemes such as higher order quadrature amplitude modulation and orthogonal frequency division multiplexing result into envelope varying signals with high crest factor; which generates several linear and non-linear distortions in radio frequency modulators. The crest factor of any envelope varying signal is defined as the ratio of peak amplitude divided by r.m.s value of the signal. Moreover, the bandwidth requirement is still high to handle high data rate expected for 5G communication. Therefore, based on the availability of spectrum and the spectral efficiency of modulation scheme, both sub-6 GHz band and millimetre-wave band are recently opened for 5G communication. The power amplifiers an inevitable component of radio frequency chain which produces most of the distortion in transmitter. Therefore, one must restrict preceding stages such as RF modulator to add any distortion which may be further amplified with the PA. The conventional quadrature modulator uses mixers which are inherently non-linear components and can generate non-linear distortion. This will further reduce spectral efficiency. However, six-port reflectometer based modulator which does not use mixer is inherently linear and can be a good choice for upcoming wireless

transmitters, where, spectral efficiency requirement is quite high. Moreover, the architecture of Six-Port Modulator is simple which uses conventional passive components and schottky diodes and therefore, can easily be scaled to millimetre wave frequency. Although, these modulators are inherently linear in practice, there are several linear and non-linear distortions which appear in case of envelope varying signals with high crest factor. This thesis presents an experimental methodology to characterize these distortions using an instrument based test-bed. A hardware prototype of six-port modulator was developed to modulate in-phase (*I*) and quadrature-phase (*Q*) components of baseband signal to RF carrier of 2 GHz. Later, appropriate digital pre-compensation schemes are implemented to mitigate the distortions generated in SPM. With the implementation of proposed scheme, the SPM hardware prototype presents an excellent performance in terms of reduced error vector magnitude and adjacent channel leakage ratio.

## **Table of Contents**

| Certificate                                                                | i   |

|----------------------------------------------------------------------------|-----|

| Acknowledgements                                                           | ii  |

| Abstract                                                                   | v   |

| Table of Contents                                                          | vii |

| List of Figures and Illustrations                                          | ix  |

| List of Tables                                                             | xi  |

| List of Tables<br>List of Abbreviations                                    | xii |

|                                                                            |     |

| CHAPTER ONE: INTRODUCTION                                                  | 1   |

| 1.1 Motivation                                                             | 1   |

| 1.2 Background and Existing Methodologies                                  | 3   |

| 1.3 Problem Statements and Targeted Goals                                  | 9   |

| 1.4 Scope and Objective of Work                                            | 11  |

| 1.5 aThesis Outline                                                        | 13  |

| 1.6 Summary of Contributions                                               | 16  |

|                                                                            |     |

| CHAPTER TWO: SIX-PORT MODULATORDESIGN AND DEVELOPMENT                      |     |

| OF ITS CHARACTERIZATION TEST-BED                                           | 17  |

| 2.1 Introduction                                                           |     |

| 2.2 Six-Port Modulator Architecture and Operation                          | 17  |

| 2.3 Hardware Prototype Implementation of Six-Port Modulator                | 24  |

| 2.3.1 S-Parameters of Six-Port Modulator                                   |     |

| 2.3.2 Modulated Results in ADS/MATLAB Co-simulation                        | 32  |

| 2.4 Measurement and Characterization Test-bed for SPM                      | 34  |

| 2.5 Measurement Results                                                    | 36  |

| 2.6 Conclusion                                                             | 38  |

|                                                                            |     |

| CHAPTER THREE: CHARACTERIZATION OF LINEAR AND NON-                         |     |

| LINEAR DISTORTIONS OFSIX-PORT MODULATORAND DIGITAL                         |     |

| PRE-COMPENSATION.                                                          |     |

| 3.1 Introduction                                                           |     |

| 3.2 Six-Port Modulator Architecture in Presence of hardware Imperfections  |     |

| 3.3 Non-linearity in Schottky Diode                                        |     |

| 3.4 Behavioral Modeling of Distortion in Six-Port Modulator                | 46  |

| 3.4.1 Indirect Learning Architecture Predistortion Scheme                  | 49  |

| 3.4.2 Neural Network for Modelling: Real Valued Focused Time Delay Neural  |     |

| Network for Modelling                                                      | 51  |

| 3.4.2.1.Forward Computation                                                | 53  |

| 3.4.2.2.Backward Computation                                               | 54  |

| 3.4.3 Inverse Modeling Performance                                         |     |

| 3.5 Corrections of Linear and Non-linear Distortions in Six-Port Modulator | 62  |

| 3.6 Conclusion                                                             | 68  |

l

C

Ę

| CHAPTER FOUR: LOW COMPLEXITY POLYNOMIAL BASED MODEL                          |    |

|------------------------------------------------------------------------------|----|

| FOR LINEAR AND NON-LINEAR DISTORTION MITIGATION IN                           |    |

| SIX-PORT MODULATOR                                                           | 69 |

| 4.1 Introduction                                                             | 69 |

| 4.2 Behavioral Modeling and DPD of Six-Port Modulator Using Polynomial Based |    |

| Model                                                                        | 70 |

| 4.2.1 FIR Approach to Six-Port Modulator                                     | 71 |

| 4.2.2 IIR (Recursive) Approach to Six-Port Modulator                         | 72 |

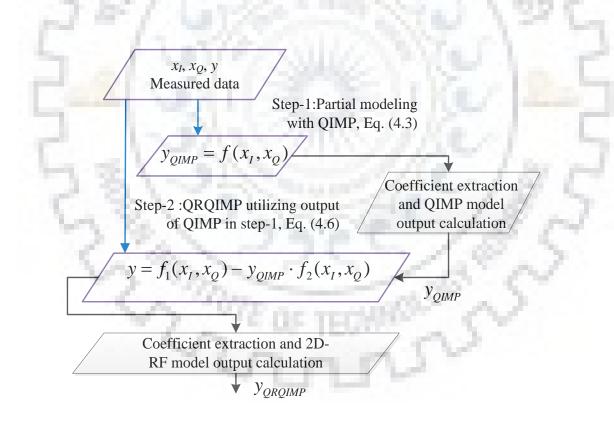

| 4.2.3 Flow Chart Implementation                                              | 74 |

| 4.2.4 Computational Calculations                                             | 76 |

| 4.3 Measurement Results                                                      | 78 |

| 4.4 Conclusion                                                               | 83 |

| A MARGINE CONTRACT OF THE ACCOUNT OF THE                                     |    |

| CHAPTER FIVE: CONCLUSION AND FUTURE SCOPE                                    | 85 |

| 5.1 Introduction                                                             | 85 |

| 5.2 Thesis Conclusion                                                        | 85 |

| 5.3 Future Scope                                                             | 87 |

| REFERENCES                                                                   | 88 |

## List of Figures and Illustrations

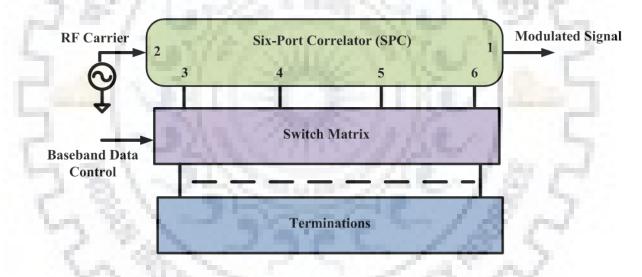

| Figure 1.1: Architecture of SPM using switchable loads.                                                                                      | 3  |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2: Topology of SPC widely used in literature.                                                                                       | 5  |

| Figure 1.3: Architecture of SPM using voltage variable loads                                                                                 | 8  |

| Figure 2.1: Architecture of SPM with SPC, diodes, and biasing circuits                                                                       | 18 |

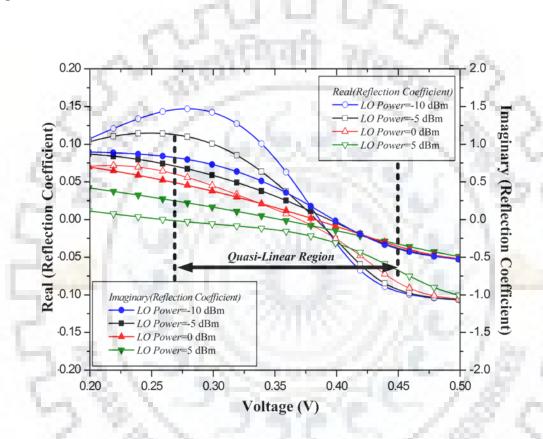

| Figure 3.1: Diode non-linearity in simulation and quasi-linear region for operation with different LO power.                                 | 45 |

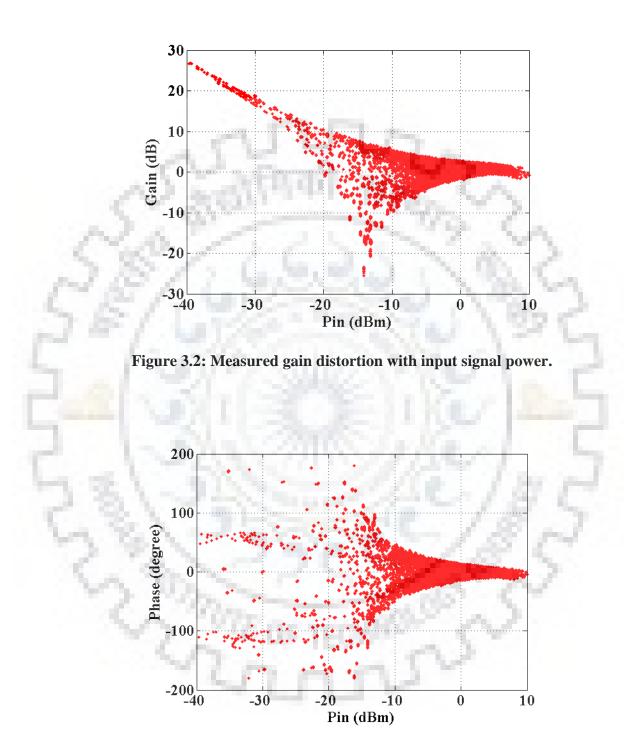

| Figure 3.2: Measured gain distortion with input signal power.                                                                                | 48 |

| Figure 3.3: Measured phase distortion with input signal power                                                                                | 48 |

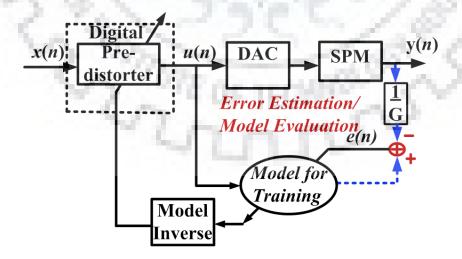

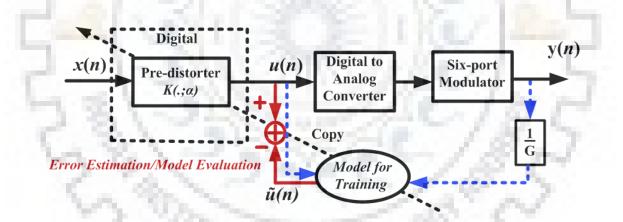

| Figure 3.4:Direct Learning Architecture of predistorters scheme                                                                              | 49 |

| Figure 3.5:Indirect Learning Architecture of predistorters scheme                                                                            | 50 |

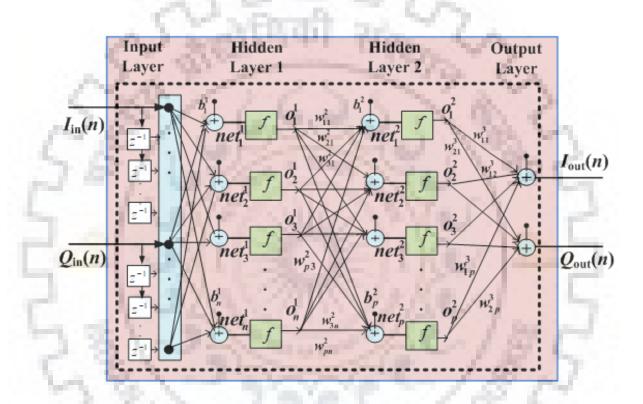

| Figure 3.6: Architecture of real-valued focused time delay neural network                                                                    | 52 |

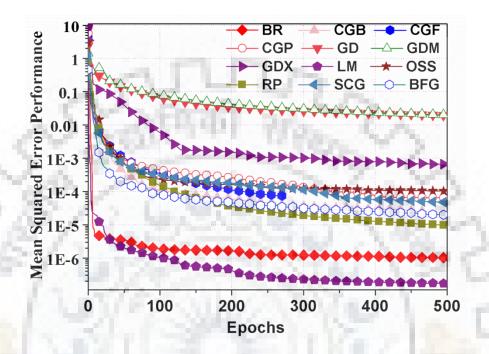

| Figure 3.7: Convergence of various NN optimization algorithms for inverse modeling of distortion in SPM.                                     | 56 |

| Figure 3.8: Convergence of model with respect to number of neurons                                                                           | 60 |

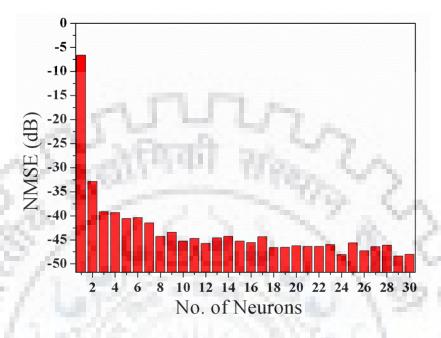

| Figure 3.9:Measured response of modulator with and without DPD correction:<br>AM/AM distortion.                                              | 64 |

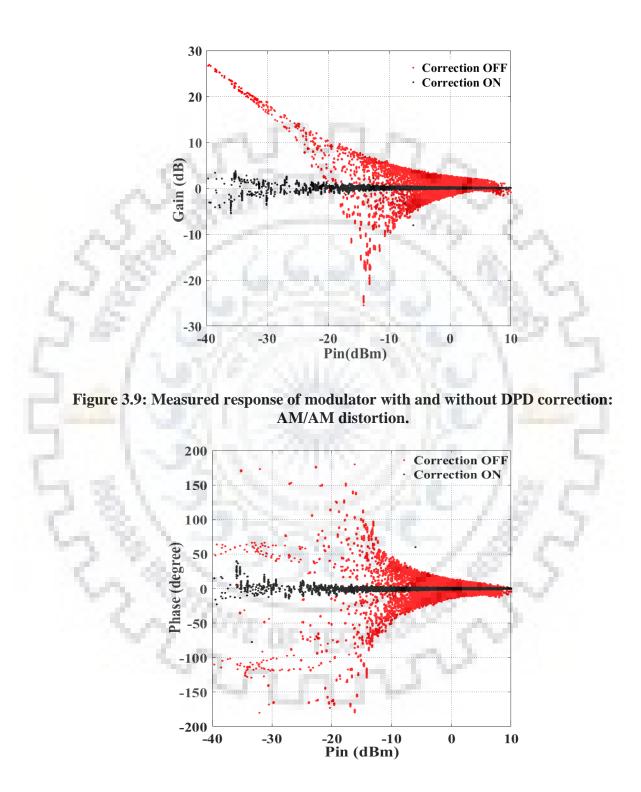

| Figure 3.10: Measured response of modulator with and without DPD correction:<br>AM/PM distortion.                                            | 64 |

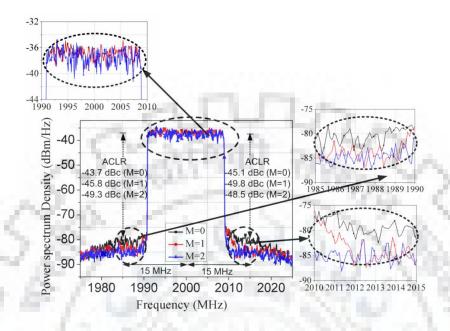

| Figure 3.11: Measured modulated spectrum of SPM with 64 QAM @ 100 Mbps with proposed scheme incorporating various memory depth.              | 65 |

| Figure 3.12: Measured constellation diagram of modulated output of SPM with 64 QAM @ 100 Mbps in presence and absence of digital correction. | 65 |

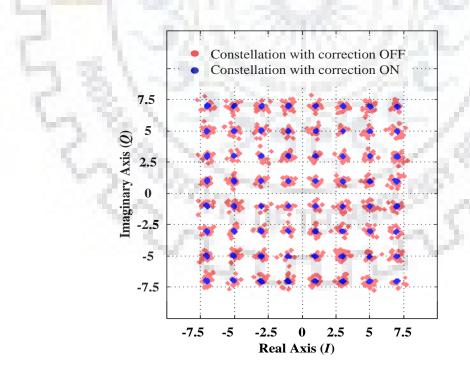

| Figure 3.13: Measured modulated spectrum of SPM with 256 QAM @ 400 Mbps. in presence and absence of digital correction.                      | 66 |

| Figure 3.14: Measured constellation diagram of SPM with 256 QAM @ 400 Mbps. in presence and absence of digital correction.                   | 67 |

| Figure 4.1: Model extraction scheme for QRQIMP model                                                                                         | 74 |

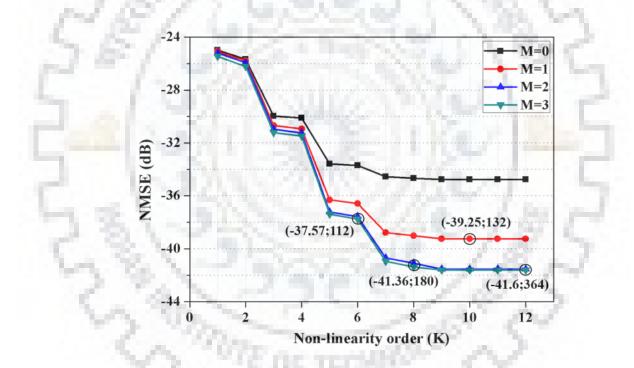

| Figure 4.2: Variation of NMSE with respect to K forQIMP Model                                                                                | 75 |

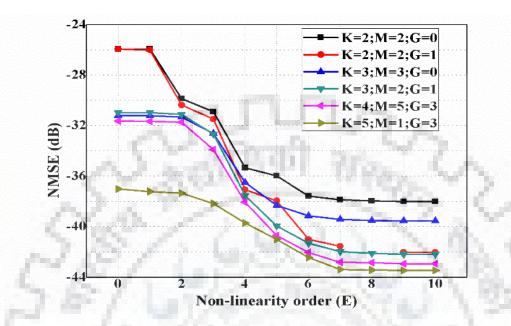

| Figure 4.3: Variation of NMSE with respect to <i>E</i> forQRQIMP Model                 | 76 |

|----------------------------------------------------------------------------------------|----|

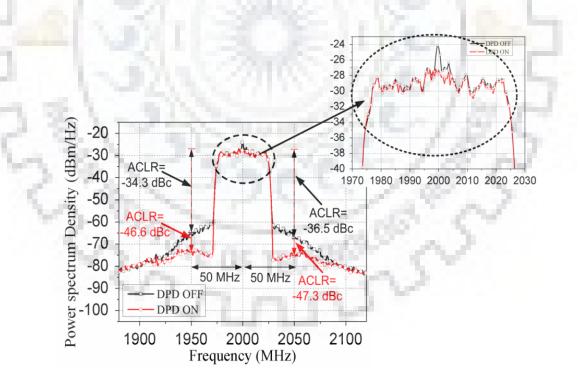

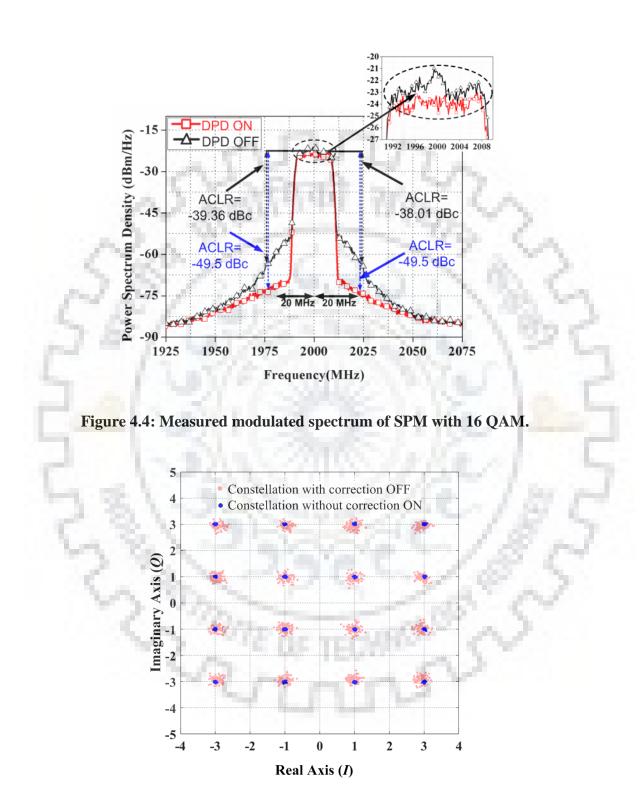

| Figure 4.4: Measured modulated spectrum of SPM with 16 QAM                             | 80 |

| Figure 4.5: Measured performance of SPM with 16 QAM in terms of constellation diagram. | 80 |

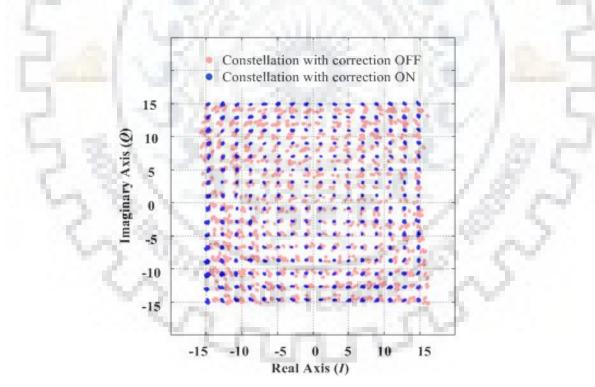

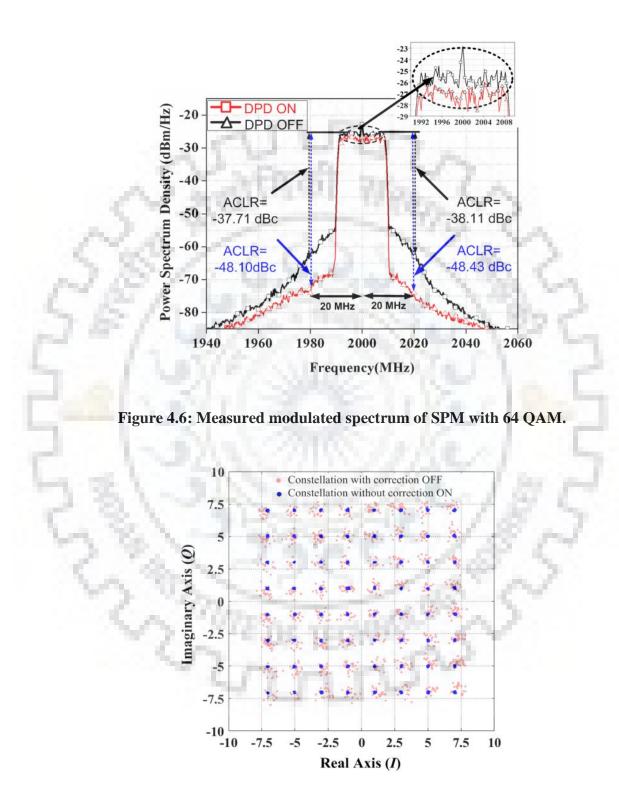

| Figure 4.6: Measured modulated spectrum of SPM with 64 QAM                             | 81 |

| Figure 4.7: Measured performance of SPM with 64 QAM in terms of constellation          |    |

## List of Tables

| Table 2.2: Spice parameters of schottky diode [87]            | 25 |

|---------------------------------------------------------------|----|

| Table 3.1: Performance comparison of various models           | 61 |

| Table 4.1: Performance comparison of various models           | 78 |

| Table 4.2: Memory of the models for different models          | 78 |

| Table 4.3: Comparison of neural network with polynomial model | 82 |

| Table 4.4: Performance comparison with state-of-the-art       | 83 |

## List of Abbreviations

| Abbreviations | Definition                      |

|---------------|---------------------------------|

| ACLR          | Adjacent Channel Leakage Ratio  |

| ACPR          | Adjacent Channel Power Ratio    |

| ADS           | Advanced Design System          |

| ATC           | American Technical Ceramics     |

| BLC           | Branch Line Coupler             |

| BPSK          | Binary Phase Shift Keying       |

| CAD           | Computer Aided design           |

| DAC           | Digital to Analog Converter     |

| DC            | Direct Current                  |

| DPD           | Digital Predistortion           |

| DSP           | Digital Signal Processing       |

| EM            | Electromagnetic                 |

| EVM           | Error Vector Magnitude          |

| FPGA          | Field Programmable Gate Array   |

| GPIB          | General Purpose Interfacing Bus |

| HCs           | Hybrid Couplers                 |

| ILA           | Indirect Learning Architecture  |

| IF            | Intermediate Frequency          |

| LTE           | Long Term Evolution             |

| LO            | Local Oscillator                |

| NMSE   | Normalized Mean Square Error                                |

|--------|-------------------------------------------------------------|

| OFDM   | Orthogonal Frequency Division Multiplexing                  |

| PA     | Power Amplifier                                             |

| РСВ    | Printed Circuit Board                                       |

| PSK    | Phase Shift Keying                                          |

| QAM    | Quadrature Amplitude Modulation                             |

| QIMP   | Quadrature-Interface Memory Polynomial                      |

| QPSK   | Quadrature Phase Shift Keying                               |

| QRQIMP | Quasi Recursive Quadrature - Interface Memory<br>Polynomial |

| RMS    | Root Mean Square                                            |

| RF     | Radio Frequency                                             |

| SPC    | Six-Port Correlator                                         |

| SPM    | Six-Port Modulator                                          |

| VNA    | Vector Network Analyzer                                     |

| VSA    | Vector Signal Analyzer                                      |

| VSG    | Vector Signal Generator                                     |

| WPD    | Wilkinson Power Divider                                     |

| 5      | OTE OF TECHNIC                                              |

| ~~~~   | La nas                                                      |

|        |                                                             |

## **Chapter One: INTRODUCTION**

#### 1.1 Motivation

The radio frequency (RF) six-port network which was originally proposed as reflectometer, now finds several applications including modulators, demodulators, network analyzers as well as beam forming and direction-finding network [1]-[85]. In each application, six-port network is comprised of passive six-port correlator (SPC) and loads terminating the SPC. The passive SPC correlates the reflected waves from its multiple ports to provide various applications. RF quadrature modulator is one such application which is an important element of wireless transmitter in modern wireless communication. This plays an important role in modulating baseband data in the form of in-phase (I) and quadrature phase (Q) components. The conventional quadrature modulator is based on mixers and quadrature hybrid couplers (HCs) [22],[51]. There is an alternative architecture based on six-port network which was proposed as modulator for wireless transmission [17],[21]-[22],[24]-[26],[28]-[36],[38]-[43].In case of six-port based modulator, the four out of six ports of SPC are terminated by either variable loads realized using schottky diodes or switches [17]-[35]. The SPC is realized using three HCs and one wilkinson power divider (WPD) as presented in [17]-[35], [46]-[47], [55]. Due to its simplified structure, low-cost and low power consumption feature along with passive nature, six-port modulator (SPM) is a good candidate for high frequency applications. For example, the passive SPC can be easily scaled to millimeter wave (mm-wave)

frequencies making SPM a potential candidate for 5G applications [66]-[72]. The schottky diode based architecture [17]-[20],[24]-[26],[28]-[32] can modulate high speed data and handle higher order quadrature amplitude modulation (QAM) with reduced complexity as compared to PIN diode or switch based architecture [21]-[22],[34],[65].However, the non-linearity of schottky diodes limits the performance of the modulator. This limitation is more visible in the case of high crest factor signals such as high order QAM. The crest factor of any envelope varying signal is defined as the ratio of peak amplitude and root mean square (RMS) value of the signal. In addition, the SPC is comprised of low-cost passive printed circuit board (PCB) components and their s-parameter performance can easily deviate from ideal values while implementing SPC. This is perhaps due to losses as well as imperfect realization of phase shifts by transmission line components. The error in the SPC realization results into linear distortion, which, along with non-linear distortion, can severely affect the performance of six-port modulator (SPM). Therefore, a suitable digital correction scheme is required to correct these distortions. This is important in order to qualify spectral mask and error vector magnitude (EVM) specifications for latest wireless standards.

This thesis presents identification and characterization of linear and non-linear distortions along with their sources in SPM. A suitable digital correction scheme is proposed to correct for the hardware impairments resulting into various distortions in SPM.

#### 1.2 Background and Existing Methodologies

As discussed in previous section, the topologies of SPMs are broadly classified under two categories. One, utilizing switchable load configuration, whereas the other operating on variable load configuration. Figure 1.1 shows the generic topology for switchable load configuration, where, a switching matrix is used to choose among various loads for terminating four different ports of SPC.

Figure 1.1: Architecture of SPM using switchable loads.

The selections of different loads are therefore controlled by switches available in switch matrix and the switching action is controlled by baseband data which is being modulated. The other two ports of six-port network are used for injection of RF carrier and obtaining modulated RF carrier as an output as shown in Figure 1.1. The implementations of this topology are given in [21]-[22],[33]-[39], [46], [50],[52]-

[53],[58],[83]. Most of these earlier works demonstrate the performance with hardware prototype of SPM using various switching configurations. The [83] presents two different configurations of switching based SPM. The primary difference is in terms of SPC topology, where, parallel modulator configuration uses two quadrature HCs connected in parallel [83]. The same topology has been used in several SPM based on switched loads as well as variable loads [17]-[20],[24]-[26],[28]-[32]. Figure 1.2 shows the most common topology of SPC widely used in literature.

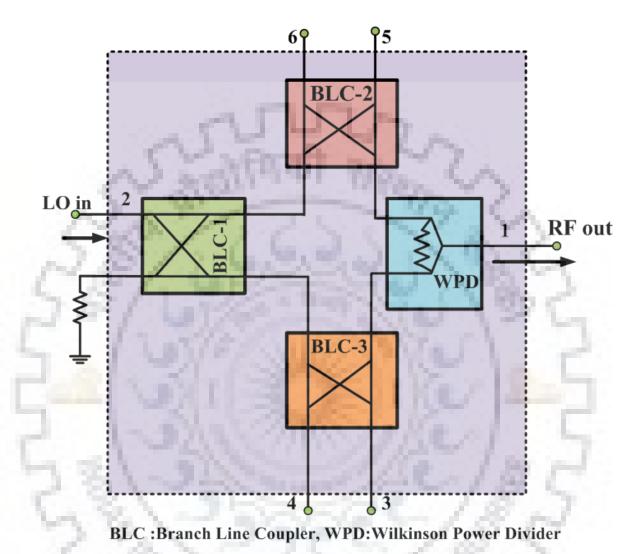

Figure 1.2: Topology of SPC widely used in literature.

This topology comprises of three quadrature HCs realized using branch line couplers (BLCs), where, two of them are connected in parallel. In case of SPM architecture as presented in [17]-[20],[24]-[26],[28]-[32], the RF carrier is applied to port 2 using BLC-1. The modulated output is available at port 1, which is internally connected to the combiner port of Wilkinson power divider (WPD) as shown in Fig. 1.2. The ports 3-6 are

used for connecting loads (switched or variable) based on the architecture of SPM.

The series configuration comprises of two BLCs connected in series [83]. The parallel modulator has better bit error probability with low conversion efficiency as compared to the serial modulator [83]. The conversion efficiency of series modulator drops fast as compared to the efficiency of parallel modulator with change in load [83].

Different configurations of SPCs are presented to scale the frequency of operation to mm-wave in case of SPM [37],[39]-[41]. The quadrature phase shift keying (QPSK) modulation is demonstrated at 62 GHz and 86 GHz for different data rates such as 100 Mbps, 500 Mbps and 1 Gbps [40]. The [37] demonstrates 16-phase shift keying (PSK) modulation at 77 GHz with 500 Mbps data rate. In addition, [34] and [42] present frequency scalability of most common SPC as shown in Fig. 1.2, where, QPSK modulation is demonstrated. The [34] demonstrates QPSK modulation at data rate of 250 Mega-baud/sec at 24 GHz. whereas, [42] demonstrates QPSK modulation at data rate of 120 Mega-baud/sec at 19 GHz. The [51] presents an SPC architecture comprising of WPD only.

The [21] presents hardware prototype capable of 16 QAM modulation upto 200 Mbps data rate at RF carrier frequency of 4.2 GHz. The modulation is performed with an EVM of 6.99%. A direct QPSK modulation is demonstrated with similar data rate in hardware at RF carrier frequency of 4.0 GHz in [22]. Similarly, [80] demonstrates hardware for QPSK modulation at 5 Mbps, 10 Mbps and 15 Mbps data rates over RF carrier frequency of 2.4 GHz.

Anultra-wideband performance of SPM is presented in [36]. The work presents

QPSK modulation at 400 Mega-Symbol/s across octave RF carrier frequency range from 4.5 GHz to 9 GHz. The [36] also analyzes various configurations of SPC to get performance over wide range of frequency. Similarly, [50] utilizes microstrip slot technique in conventional SPC architecture as shown in Figure 1.2 to enhance the bandwidth. In such case QPSK based modulation is performed over the frequency range from 4.5 GHz to 10.6 GHz [50]. The [52] uses broadside couplers in SPC configuration to achieve wide bandwidth. The binary phase shift keying (BPSK) modulation with 4Gbps data rate is demonstrated at 60 GHz using the SPM based transmitter in [52].

The [30] presents SPM hardware capable of modulating baseband data to 64 QAM with EVM of 7-7.5% at RF carrier frequency of 2.475 GHz. A higher order modulation such as 256-QAM is also demonstrated in [46], [29] at data rate of 50 M symbol/s, however, no EVM performance is reported.

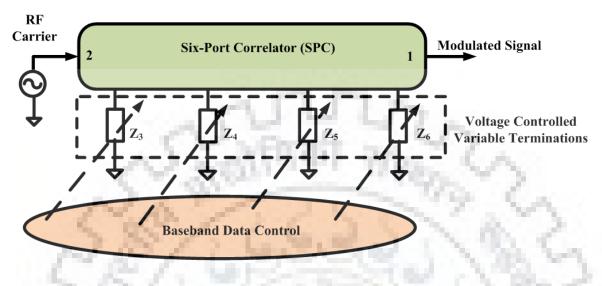

Figure 1.3 shows the other topology of SPM based on variable loads. This topology utilizes the voltage controlled loads connected to four ports of SPC. The other two ports are used for injecting RF carrier frequency and modulated output as shown in Figure 1.3.Unlike the switching load configuration, there is no requirement of any switching matrix or mechanism and a direct output of digital-to- analog converter (DAC)

Figure 1.3: Architecture of SPM using voltage variable loads.

can drive the voltage controlling the load impedances. The common strategy is to use schottky diodes, where, the impedance presented by the diode depends on bias voltage [24]-[26], [28]-[32], [47], [53], [55], the bias voltages of these diodes can be varied as per baseband signals obtained after DAC. The performance of this configuration is severely limited due to non-linearity of diode. The diode impedance varies non-linearly with the bias voltage, limiting the dynamic range of this type of SPM [28], [29], [32], [55]. Moreover, this non-linearity further exemplify due to hardware imperfections in passive SPC. Therefore, for higher order QAM modulation, the performance in terms of EVM is severely limited [24]-[26], [28]-[32], [47], [53], [55]. However, due to availability of digital access, a suitable pre-compensation technique can be implemented for correcting this non-linear effect as well as compensating for the hardware imperfections in SPC.

Apart from these generic configurations as shown in Figure 1.1 and Figure 1.2,

the polyphase networks along with power dividers/combiners are also used in implementing SPM [65]. This modulator demonstrates QPSK modulation with 3% EVM with data rate upto 20 Mbps.

#### **1.3 Problem Statements and Targeted Goals**

#### **Problem Statement #1**

The switchable architecture of SPM utilizes complex switching matrix to realize high order QAM. In such case most of the work in literature are focused on QPSK and 16 QAM modulationsas discussed in previous section. The variable load architecture however is comparatively simple and can be used for handling higher order QAM. However this scheme has limitations in terms of diode non-linearity which is being used as variable loads. The diode non-linearity restricts the dynamic range as well as further deteriorates the effect of hardware imperfection over successful modulation in this architecture. This problem must be mitigated in order to use the variable load architecture of SPM for handling the higher order QAM.[28], [30], [32], [55].

#### **Targeted Goal #1**

In order to compensate for non-linearity introduced by the diodes and linear distortions introduced by passive SPC, a nonlinear characterization setup is required to characterize these distortions in SPM. This setup should be capable of capturing linear and non-linear distortions in SPM. In addition, the setup should be able to generate in-

phase (I) and quadrature phase (Q) data corresponding to the baseband signal which will control the variable loads terminating the ports of SPC. The schottky diodes can be used for implementing variable loads.

#### **Problem Statement #2**

In the case, where, schottky diodes are used as variable loads in SPM, the performance is restricted due to the non-linearity introduced by the diode. In addition, any hardware imperfection in passive SPC will further enhance the effect of this nonlinear distortion. Therefore, an appropriate compensation is required to obtain required performance in terms of EVM.

#### **Targeted Goal #2**

The non-linear characterization scheme as discussed in problem statement 1 provides access to the digital baseband signals. This will give an opportunity to apply digital predistortion (DPD) to compensate for the linear and non-linear distortions in the SPM due to hardware imperfection in SPC as well as diode non-linearity. A suitable algorithm will be identified for developing behavioral model for SPM. Later, an inverse model will be developed to apply DPD for compensating distortions in SPM.

#### **Problem Statement #3**

The DPD scheme proposed for compensating distortions in SPM may not always be feasible to be applied in digital signal processing (DSP) / field programmable gate array (FPGA) platform. In such case, low complexity models are required for modelling and DPD application in SPM.

#### **Targeted Goal #3**

The target is to search for new low complexity model which can be easily implemented in DSP/FPGA platform with low resource consumption.

#### 1.4 Scope and Objective of Work

The overall aim of the research in this thesis is to propose digitally assisted SPM which can modulate modern wireless communication signals with minimum distortion. The thesis primarily targets three key objectives, where the summary of work under these objectives are listed as follows:

- 1. Development of Hardware prototype & characterization test-bed for digital baseband signal generation and modulation with digital correction.

- A SPM modulator is developed with passive SPC designed at 2 GHz. The schottky diode HSMS2820 by Broadcom technologies is used as variable load.

- An instrument based test-bed is developed to generate baseband data and modulate it using SPM. This comprises of vector signal generator (VSG) by Keysight (model no. MXG N5182B), which play-back the baseband *I* and *Q* data stored in its memory. The differential DAC outputs at the rear panel of VSG provide the analog signals corresponding to the *I* and *Q* data which is modulated by the SPM hardware. The vector signal analyzer (VSA) by Keysight (model no. MXA N9020B) is used to capture modulated RF carrier and extract corresponding baseband *I* and *Q* data. This output *I* and *Q* data is compared with input baseband *I* and *Q* data originally sent to VSG to retrieve gain and phase characteristic of SPM. These gain and phase characteristics are then used for behavioural modelling and DPD application.

- Characterization of Linear and Non-linear distortion of SPM & digital precompensation.

- The imperfections in SPM are characterized using instrument test-bed developed under objective 1.

- A behavioural modelling of linear and non-linear distortions is performed based on neural network.

- A DPD scheme is implemented to pre-compensate and mitigate these distortions.

- 3. Low-complexity solution for Linear and Non-linear distortion mitigation in SPM.

- A polynomial based low-complexity model is proposed which will be implemented digitally using less resources as compared to Neural Network based model.

- The model is used to apply DPD for distortion mitigation in SPM.

- The SPM is tested with high order QAM signals as well as orthogonal frequency division multiplexing (OFDM) signals complying long term evolution (LTE) standard.

#### 1.5 Thesis Outline

The thesis is organised into five chapters including introduction and conclusion. The following discussion presents the content of each chapter in brief.

The first chapter states the literature review on SPM and their performance. Various configurations based on switching or variable loads are discussed including their advantages and disadvantages. The configurations using transistors or diodes realizing the variable loads are also discussed in this chapter. The chapter also discusses the problem statements and targeted goals. The objectives of the thesis are also presented in this chapter based on these problem statements. This chapter also summarizes the contribution as well as thesis organisation.

Second chapter discusses the design of SPM using passive SPC and schottky diode as variable loads. A hardware prototype is developed using RO4350B substrate with dielectric constant of 3.66, height of 20 mil and loss tangent of 0.0037. The schottky

diode HSMS2820 by Broadcom technologies is used as variable load. The hardware prototype is designed to operate at centre frequency of 2 GHz. An instrument based testbed is also developed which can provide baseband I and Q data to the SPM for modulation of RF carrier frequency at 2 GHz. These basebands I and Q data correspond to digital modulation such as QAM which is generated in MATLB and later uploaded to the memory of VSG (Keysight MXG N5182B). The DACs inside VSG convert these baseband I and Q data to analog signals which are available in differential form at the rear panel of VSG. The SPM modulates the RF carrier with respect to these signals. Similarly, the test-bed also has VSA which captures the modulated RF carrier and saves the I and Q baseband data modulating the RF carrier. These baseband I and Q data are then used generate behavioural model of SPM so that DPD can be applied to compensate for the distortions.

The third chapter focuses on the identifying the linear and non-linear distortion components and their sources in SPM. The hardware imperfections in SPC primarily contributes to linear distortions which further add-up to the nonlinear distortions produced by the diodes. A behavioural model is developed based on real-valued focused time delay neural network to model these linear and non-linear distortions. The SPM is characterized in terms of gain and phase distortions which are captured from the test-bed developed in chapter 2. Later these distortions are modelled and inverse of this model is applied in digital domain. The I and Q baseband data when passes through this model get pre-distorted such that after modulation from SPM the output of SPM is effectively distortion free. This digital pre-compensation technique is validated with the modulation of QAM and LTE signals and the modulated signals qualify the requirements of LTE standard in terms of EVM and adjacent channel leakage ratio (ACLR).

The fourth chapter presents low-complexity quadrature interference memory polynomial (QIMP) Model and its variant. This model has better performance as compared to the state-of-art polynomial based models. In comparison to neural network based behavioural modelling of chapter 3, this model offers low resource consumption in terms of signal processing. The performance of the model is validated in hardware prototype and test-bed developed in chapter 2. The QAM as well as the LTE signals are modulated using the SPM after applying the digital predistorters based on the proposed model. The EVM and ACLR are well below the required range as specified by the standards.

The fifth chapter concludes the thesis by summarizing the research outcomes against various objectives defined in chapter 1. The chapter also discusses future work related to the thesis.

22

#### **1.6 Summary of Contributions**

#### **Journal Publication:**

- [1] C. Pathak, K. Rawat, "Nonlinear Characterization & Distortion Mitigation in Six-Port Modulator", *IEEE Transactions on Instrumentation and Measurement*, vol.68,no.4,pp.1178-1188,Apr.2019

- [2] C. Pathak, K. Rawat, "Characterization and Modelling of Hardware Imperfections in Schottky Diode Based Six-Port Modulator", Wiley International Journal of RF and Microwave Computer-Aided Engineering, vol.29, no.6, pp.1-10, Jun. 2019

#### **Conference Proceedings:**

[3] C. Pathak, K. Rawat, "Quadrature modulation using radio frequency wave correlation in multiport network," 5th IEEE International Conference on Signal Processing and Integrated Networks (SPIN), New Delhi, India, Feb 2018, pp.1-3.

# **Chapter Two: Six-Port Modulator Design and Development of Its Characterization Test-Bed**

#### 2.1 Introduction

This chapter discusses the architecture of SPM based on the architecture shown in Fig. 1.3. The modulation performed by the presented architecture is also discussed along with assumptions that will lead to ideal operation in terms of modulation. Later, a hardware prototype is developed based on this architecture to modulate the signals at RF carrier frequency of 2 GHz. The performance of this hardware prototype is validated in terms of s-parameters in simulation as well as measurement. The chapter also presents an instrument based test-bed developed to characterize and measure the performance of SPM hardware prototype in terms of LTE signals using 64-QAM modulation.

#### 2.2 Six-Port Modulator Architecture and Operation

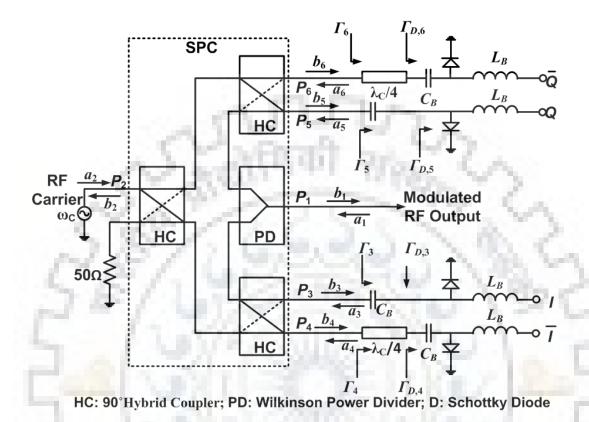

The modulator architecture based on multiport network. This comprises of passive multi-port wave correlator which correlates and combines the reflected wave from its various ports. SPM comprises of passive SPC with its four ports terminated with high speed variable impedances schottky diodes [17]-[20],[24]-[26],[28]-[32],[55]. The SPC combines these waves reflected from the ports terminated by these schottky diodes. Figure 2.1 shows the architecture of SPM, where, the RF carrier signal of frequency  $f_c$  is

Figure 2.1: Architecture of SPM with SPC, diodes, and biasing circuits.

fed from port  $P_2$ , which is reflected from ports  $P_3$  to  $P_6$  with reflection coefficients  $\Gamma_3$  to  $\Gamma_6$ . Ports  $P_3$  to  $P_6$  are terminated using schottky diodes with quarter-wave transmission lines and their bias circuitry is shown in Figure 2.1.

SPC combines these reflected waves using its s-parameter matrix and gives output modulated signal at Port 1. The reflection coefficients  $\Gamma_3$ ,  $\Gamma_4$ ,  $\Gamma_5$  and  $\Gamma_6$  depend on diodes reflection coefficients  $\Gamma_{D,3}$ ,  $\Gamma_{D,4}$ ,  $\Gamma_{D,5}$  and  $\Gamma_{D,6}$  which varies with the control signals  $I = -\overline{I}, Q = -\overline{Q}$  as shown in Figure 2.1. These control signals can be *I*, *Q* of any digital modulation schemes such as QAM produced after DAC conversion. In such case, the baseband information is modulates the RF carrier by changing reflection coefficients of the diodes according to *I* and *Q* data. The quarter-wave transmission lines of length  $\lambda_C/4$  and the injection of *I* and *Q* in differential form helps in carrier leakage suppression at output port *P*<sub>1</sub> which is described in [24]-[26],[28]-[32],[55]. The diodes are biased by the baseband inputs as common-mode signal and the bias circuitry comprises of RF chokes *L*<sub>B</sub> and blocking capacitors *C*<sub>B</sub> as shown in Figure 2.1. The RF chokes *L*<sub>B</sub> blocks the leakage of RF carrier to the baseband input side from where baseband data and direct current (DC) bias is injected. The blocking capacitors *C*<sub>B</sub> in Figure 2.1 blocks DC bias to leak towards RF path connecting to passive SPC.

The output signal  $b_1$  at port  $P_1$  in Figure 2.1 is the function of incident RF carrier signal  $a_2$ , its reflected components from various ports and s-parameters of passive SPC. Assuming  $L_B$  and  $C_B$  as ideal components, the modulated RF carrier at port  $P_1$  is given in (2.2).

$$b_{1} = a_{2} \sum_{m=3}^{6} S_{m2} \Gamma_{m} S_{1m}$$

$$a_{2} \left( S_{32} \Gamma_{3} S_{13} + S_{42} \Gamma_{4} S_{14} + S_{52} \Gamma_{5} S_{15} + S_{62} \Gamma_{6} S_{16} \right)$$

(2.2)

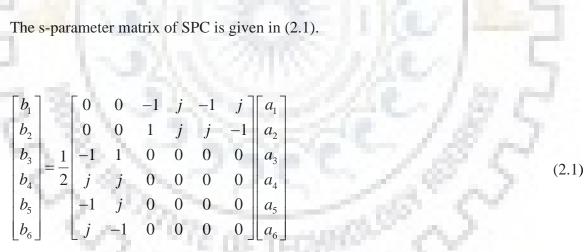

where,  $b_1$  is modulated carrier output from port  $P_1$  and  $S_{m2}$  is the s-parameter defined as ratio of voltage wave measured at  $m^{\text{th}}$  port and the voltage wave incident at port  $P_2$ , when all the other ports are terminated with matched loads. Similarly,  $S_{1m}$  is the s-parameter between port  $P_1$  and  $m^{\text{th}}$  port, which is obtained as the ratio of voltage wave measured at Port  $P_1$  and the voltage wave incident at  $m^{\text{th}}$  Port, with all the ports terminated with matched loads.  $\Gamma_m$  is the reflection coefficient at  $m^{\text{th}}$  port of SPC. Using the s-parameter matrix of ideal SPC as given in (2.1), one can write,

$$b_{1} = -\frac{a_{2}}{4} \Big[ \big( \Gamma_{3} + \Gamma_{4} \big) + j \big( \Gamma_{5} + \Gamma_{6} \big) \Big]$$

(2.3)

Thus, modulated carrier  $b_1$  depends upon reflection coefficients  $\Gamma_3, \Gamma_4, \Gamma_5$  and  $\Gamma_6$ . In order to obtain  $b_1$  as modulated carrier,  $\Gamma_3$  and  $\Gamma_4$  should replace baseband component *I*. Similarly,  $\Gamma_5$  and  $\Gamma_6$  should be function of input baseband component *Q*. This is possible since reflection coefficient  $\Gamma_m$ , at  $m^{\text{th}}$  port where, m=3,4,5,6 depends on diode reflection coefficient, which can vary with *I* and *Q* signals provided as control voltages of schottky diodes. Expanding the reflection coefficient by Taylor series at the DC bias voltage  $V_{CM}$  of the diode, one can obtain

$$\Gamma_{D,m}(V) = \Gamma_{D,m}(V_{CM}) + k_0 (V - V_{CM}) + k_1 (V - V_{CM})^2 + \dots + k_{n-1} (V - V_{CM})^{n-1}$$

(2.4)

where,

$$k_{n-1} = \frac{1}{n!} \Gamma_{D,m}^{(n)}(V_{CM}) = \frac{1}{n!} \frac{\partial^n \Gamma_{D,m}(V)}{\partial V^n} \Big|_{V = V_{CM}}; n = 1, 2, \dots$$

(2.5)

Assuming diode operation is restricted to linear region only, one can truncate (2.5) to first order term

$$\Gamma_{D,m}(V) \approx \Gamma_{D,m}(V_{CM}) + k(V - V_{CM}) = \Gamma_0 + k_0 \Delta v$$

(2.6)

where, *m* represents port numbers 3 to 6 of SPC which are connected to diodes.  $\Gamma_{D,m}$  ( $V_{CM}$ ) or  $\Gamma_0$  is the reflection coefficient due to common mode voltage applied to each diode such as DC bias. Parameter  $k_0$  governs the rate of change of reflection coefficient  $\Gamma$  with change in voltage. If the reflection coefficient as described in (2.4) is controlled by the baseband *I* and *Q* data which is in voltage form, then using (2.6) in (2.3), results into carrier signal  $b_1$  modulated with *I* and *Q* data. However, the component  $\Gamma_0$  of reflection

coefficient will reflect carrier only and hence produce carrier leakage in addition to the modulated signal. To avoid the carrier leakage at port 1, the *I* and *Q* data are applied in differential form along with quarter wave transmission line of length  $\lambda_c/4$  between diodes and ports of SPC as shown in Figure 2.1.These transmission lines give 180° phase shifts to the reflection coefficients  $\Gamma_{D,4}(V)$  and  $\Gamma_{D,6}(V)$ . The diode reflection coefficients  $\Gamma_{D,m}(V)$  and the reflection coefficients at SPC ports as shown in Figure 2.1 are related as:

200 g 100

$$\Gamma_{3}(V) = \Gamma_{D,3}(V) = \Gamma_{0} + k_{0}I$$

(2.7)

$$\Gamma_{5}(V) = \Gamma_{D,5}(V) = \Gamma_{0} + k_{0}Q$$

(2.8)

$$\Gamma_{4}(V) = e^{-j\pi}\Gamma_{D,4}(V) = -\Gamma_{D,4}(V) = -\Gamma_{0} - k_{0}\overline{I}$$

(2.9)

$$\Gamma_{6}(V) = e^{-j\pi}\Gamma_{D,6}(V) = -\Gamma_{D,6}(V) = -\Gamma_{0} - k_{0}\overline{Q}$$

(2.10)

where, factor  $e^{-j\pi}$  appears in (2.9) and (2.10) due to quarter wave transmission line of length  $\lambda_c/4$  as shown in Figure 2.1. Using (2.7) - (2.10) in (2.4), one can write

$$b_{1} = -\frac{a_{2}}{4} \left[ \left( \Gamma_{0} + k.I \right) + \left( -\Gamma_{0} - k.\overline{I} \right) + j \left\{ \left( \Gamma_{0} + k.Q \right) + \left( -\Gamma_{0} - k.\overline{Q} \right) \right\} \right]$$

(2.11)

If  $\overline{I}$  and  $\overline{Q}$  represents inverted replica of baseband *I* and *Q* signals i.e.  $I = -\overline{I}$ ,  $Q = -\overline{Q}$ , one can write (2.11) as:

$$b_1 = -\frac{|a_2|k}{2} [I + jQ] e^{j\omega_C t}$$

(2.12)

Therefore, differential *I* and *Q*, along with quarter-wave transmission line, remove the component  $\Gamma_0$  which would have contributed for carrier leakage at output if not cancelled [24],[26],[65]. Equation (2.12) represents successful modulation with following assumptions:

1. The diodes reflection coefficient should change symmetrically around  $\Gamma_0$  as described in (2.7)-(2.10).

2. The diodes reflection coefficient should be linear function of control voltages as described in (2.7)-(2.10).

3.  $\overline{I}$  and  $\overline{Q}$  should be inverted replica of baseband I and Q signals,

4. The s-parameters of SPC hardware should be same as s-parameters of ideal SPC, as shown in Figure 2.1.

Any deviation from the above four assumptions will result into poor performance of SPM and hence produce distortions in the output. The distortions occurring due to non-ideal s-parameters and errors in relation between  $I, \overline{I}, Q, \overline{Q}$  are linear distortions. The non-linear relation between reflection coefficient of diode and its baseband control voltage will result into non-linear distortion. This also disturbs the first assumption, and the reflection coefficient variation will be no more symmetric around  $\Gamma_0$  resulting into carrier leakage. No matter, how carefully the design is developed and simulated; some of these imperfections are inevitable. These imperfections are due to fabrication errors, use of low cost components, inaccurate diode models and non-ideal paths between DACs and SPM. Therefore, one must use digital corrections with SPM to obtain up-to mark performance. Fortunately, the SPM is directly connected to the baseband unit. Therefore, it is feasible to implement a system which can characterize the imperfections and apply suitable correction algorithm for accurate modulation. Following sections describe a hardware prototype developed based on the architecture of Figure 2.1. Later, an instrument based test-bed is described which is capable of capturing the linear and nonlinear distortions and applying appropriate digital corrections to digital-baseband *I*, *Q* signals for compensating distortions.

#### 2.3 Hardware Prototype Implementation of Six-Port Modulator

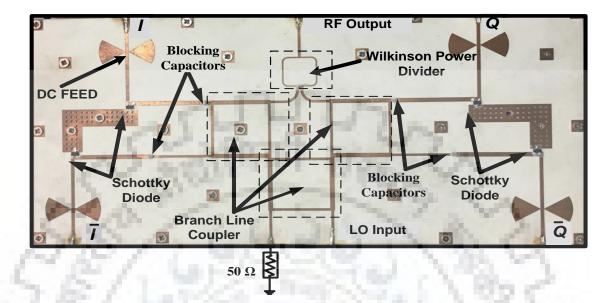

Based on the architecture of Figure 2.1, a hardware prototype is fabricated on Rogers RO4350B substrate. The Rogers RO4350 substrate has dielectric constant 3.66, height of 20 mil and loss tangent of 0.0037. Figure 2.2 shows the photograph of the hardware prototype which uses schottky diode HSMS2820 by Broadcom technologies as variable load. The diode has nominal junction capacitance  $C_{j0}$ =0.649pF and saturation current  $I_s$ =0.48nA. Table 2.2 shows the spice parameters of the diode. The diode is biased using an inductor realized by a transmission line terminated with butterfly stubs as shown in

Figure 2.2: Photograph of SPM fabricated hardware.

Table 2.2: Spice parameters of schottky diode [87]

| Parameter Type                                     | Values   |

|----------------------------------------------------|----------|

| Saturation current, Is                             | 0.48nA   |

| Ohmic resistance, R <sub>s</sub>                   | 7.8      |

| Emission coefficient, N                            | 1.067    |

| Junction capacitance at zero bias, C <sub>jo</sub> | 0.0649pF |

| Junction potential, V <sub>j</sub>                 | 0.65 V   |

| Grading Coefficient, M                             | 0.5      |

| Energy gap, Eg                                     | 0.69eV   |

| Breakdown Voltage, Bv                              | 26.7     |

| Low Level Reverse breakdown knee current, Ibv      | 100µA    |

Figure 2.2. The capacitors by American Technical Ceramics (ATC) are used as DC blocks to avoid leakage of DC bias to SPC. The bias can be supplied as common-mode voltage from differential I, Q ports.

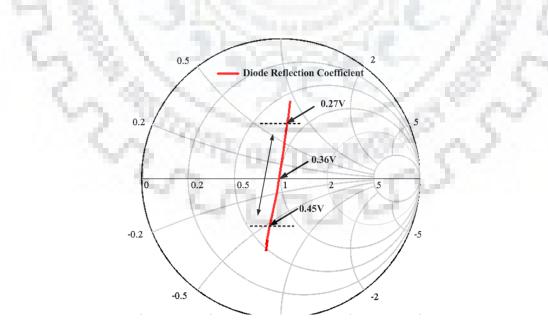

Figure 2.3 shows diode reflection coefficient with different bias voltages for RF carrier power of 0 dBm in simulation. One can see from Figure 2.3 that for carrier power of 0 dBm, the diode can operate in quasi-linear region with peak-to-peak voltage of 180 mV around the common mode bias voltage of 360 mV. While extending this region, the diode non-linearity will play an important role restricting the dynamic range of the diode and therefore modulator. In addition, a hardware imperfection will enhances this small nonlinearity further in real scenario.

Figure 2.3: Variation of reflection coefficient of diode as variable load with bias.

Therefore, a digital correction scheme is required in SPM which are described in later chapters.

#### 2.3.1 S-Parameters of Six-Port Modulator

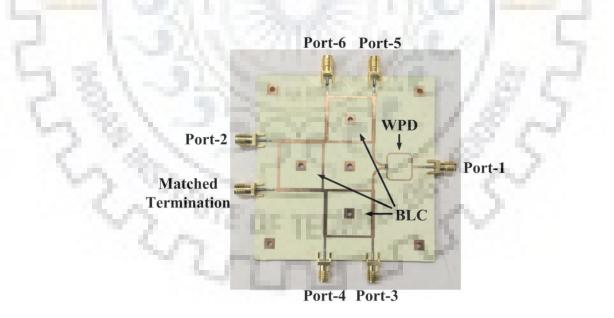

The s-parmeters of passive SPC used in SPM is seperately fabricated for measuring its s-parameters. This is shown in Figure 2.4. This SPC comprises of three BLCs and one WPD and similar to the archeitecture as described in Figure 1.2 in chapter 1. The s-parameter of this SPC is validated using electromagnetic (EM) simulation as well as in measurement using vector network anlyzer (VNA).

Figure 2.4: Photograph of SPC used in SPM.

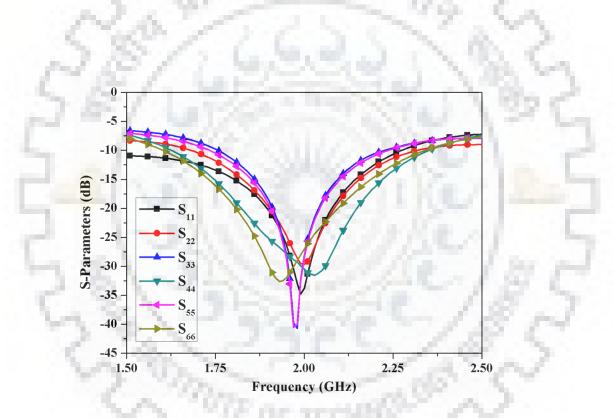

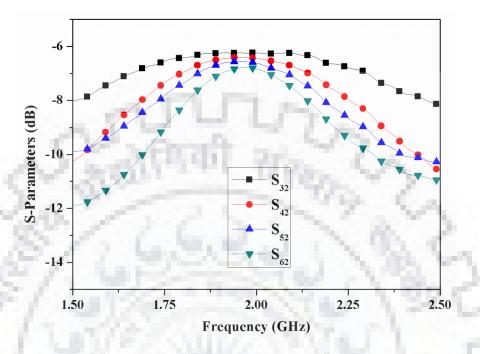

Figure 2.5 shows s-parameters  $S_{11}$ ,  $S_{22}$ ,  $S_{33}$ ,  $S_{44}$ ,  $S_{55}$  and  $S_{66}$  expressed at each port. One can see from this figure that return loss is greater than 27 dB at center frequency of 2 GHz at each port. This corresponds to the S-parameter values below 0.044 which is close to ideal value of zero as given in s-parameter matrix of (2.1). Figure 2.6 shows magnitude of s-parameters  $S_{32}$ ,  $S_{42}$ ,  $S_{52}$  and  $S_{62}$  in dB scale.

Figure.2.5: Magnitude of various s-parameters (in dB) at each port.

Figure 2.6: Magnitude of s-parameters (dB): S32, S42, S52 and S62.

One can verify from Figure 2.6 that the magnitude of these s-parameters is between -6.2 dB - 6.8 dB. This corresponds to the values of magnitude between 0.46 to 0.49 in the linear scale which is close to the ideal value of 0.5 as given in s-parameter matrix of (2.1).

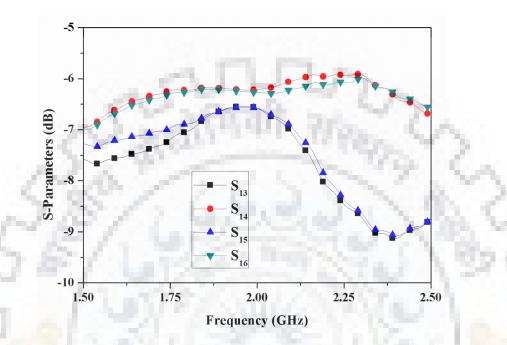

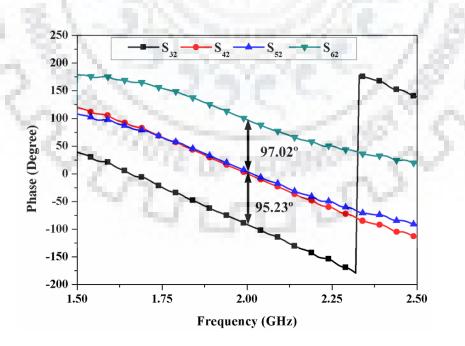

Figure 2.7 shows the measured magnitude of s-parameters  $S_{13}$ ,  $S_{14}$ ,  $S_{15}$  and  $S_{16}$  in dB scale. One can see that the values are s-parameters is between -6.2 dB to -6.5 dB. This corresponds to the values of magnitude between 0.47 to 0.49 in the linear scale which is close to the ideal value of 0.5 as given in s-parameter matrix of (2.1). Figure 2.8 represents measured phase of s-parameters  $S_{32}$ ,  $S_{42}$ ,  $S_{52}$  and  $S_{62}$ .

Figure 2.7: Magnitude of s-parameters (dB): S13, S14, S15 and S16.

Figure 2.8: Phase of s-parameters (Degree): S<sub>32</sub>, S<sub>42</sub>, S<sub>52</sub> and S<sub>62</sub>.

Assuming, initial phase due to feed lines and interconnections to be approximately-88° to -91° for de-embedding, the value of angle of s-parameters  $S_{32}$ ,  $S_{42}$ ,  $S_{52}$  and  $S_{62}$  are slightly deviated within 6° from the ideal phase as described in s-parameter matrix of (2.1).

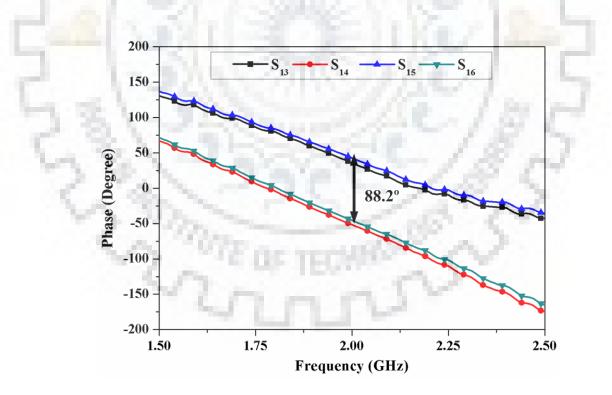

Figure 2.9 shows the phase of s-parameters:  $S_{13}$ ,  $S_{14}$ ,  $S_{15}$  and  $S_{16}$ . De-embedding, constant offset between-144° and -147° due to feedline and interconnections, the phases are close to the values as listed in (2.1) within an error of 9°.

Figure 2.9: Phase of s-parameters (Degree): S13, S14, S15 and S16.

#### 2.3.2 Modulated Results in ADS/MATLAB Co-simulation

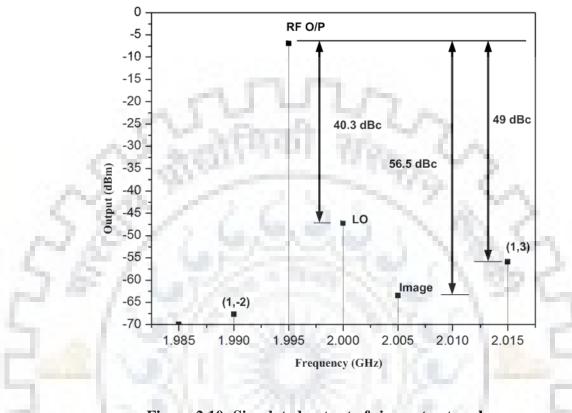

The modulating capability of SPM designed in this chapter is first validated in simulation by using Keysight advanced design system (ADS) computer aided design (CAD) tool. In such case, cosine and sine signals of 5 MHz frequency are used as I and Qdata representing an intermediate frequency (IF) signal. They are applied differentially as shown in Figure 2.1. Here, the RF carrier is represented as local oscillator (LO) of frequency 2 GHz which is applied at port  $P_2$ . The power of this LO signal is set to 2 dBm and the diodes are biased at 0.2 V. Figure 2.10 shows the spectral response of the modulated output at port  $P_1$  in Figure 2.1. The RF power is obtained as -6 dBm, whereas, LO leakage is -46 dBm. The image suppression is around 55 dBc. The other products are intermodulation products of  $f_{IF}$  and  $f_{LO}$  due to inherent diode non-linearity. Figure 2.10 validates the SPM performance in simulation, where, the spurious components such as image, LO and intermodulation products are suppressed to some extent. However, this suppression is limited due to hardware imperfections resulting into non ideal s-parameter of passive SPC. In addition, a non-linear effect may also combine with these hardware imperfections results into distortions which degrade the performance of SPM. This can be corrected digitally in baseband before DACs which is explained in the subsequent chapters.

Figure 2.10: Simulated output of six-port network.

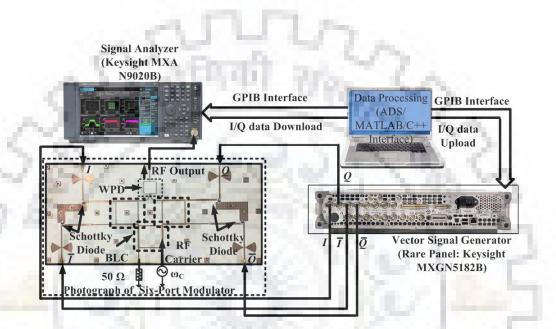

#### 2.4 Measurement and Characterization Test-bed for SPM

The characterization and distortion mitigation setup of SPM has digital baseband generation unit and a bank of DACs for converting baseband digital data into analog *I*, *Q* signals in differential form i.e.  $I = -\overline{I}$ ,  $Q = -\overline{Q}$ . Figure 2.11 shows this instrument based test-bed, where, baseband generation and DAC are realized by VSG from Keysight (model no. MXG N5182B). The computer as shown in Figure 2.11 uses MATLAB to generate different signals using different modulation schemes and data rates. The corresponding baseband data in *I* and *Q* format is uploaded in the memory of VSG using general purpose interface bus (GPIB) interface. The GPIB is common terminology for IEEE 488 short-range digital communications which uses 8-bit parallel multi-master interface bus specification. The VSG plays the baseband data into analog signals which are available  $I, -\overline{I}, Q, -\overline{Q}$  in differential form at the rear panel of VSG as shown in Figure 2.11.

These signals are then fed to six-port quadrature modulator at its respective inputs as shown in Figure 2.10. The six-port quadrature modulator is an in-house developed PCB as shown in Figure 2.2. The bias is supplied as common-mode voltage from differential I-Q ports in the rear panel of VSG. The RF modulated carrier is captured using vector signal analyzer (VSA) by Keysight (model no. MXA N9020B) as shown in Figure 2.11. The captured signal can be displayed in the form of spectrum in VSA. The VSA also has the

feature to demodulate captured signal and extract the baseband I and Q data using its internal quadrature-demodulator and analog to digital converters (ADCs).

Figure 2.11: Characterization setup for SPM.

This baseband data is sent back to computer using GPIB interface where the MATLAB is used for further processing. Once, the corresponding baseband I and Q data at the input as well as output is known, the complex gain of the system can be identified by comparing the two. An appropriate behavioral modeling is then employed to model the complex gain in terms of gain and phase compression characteristics of the system. Once, the model is complete, an inverse model can be employed in digital domain to predistort the input baseband I and Q data such that linear as well as non-linear distortion can be cancelled at the output. In order to evaluate the performance of six-port based modulator, a 20 MHz LTE signal with 100 Mbps data rate using 64-QAM modulation

scheme is modulated using the SPM as shown in Figure 2.11. The characterization setup of Figure 2.11 is also used to capture the modulated output to measure the performance in terms of ACLR and EVM.

#### **2.5 Measurement Results**

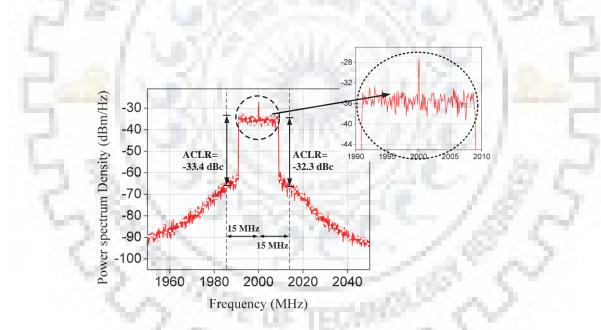

The measured output spectrum of RF carrier modulated by SPM and captured by VSA is shown in Figure 2.12. Ideally, the spectrum should not have adjacent channel leakage.

Figure 2.12: Measured distorted spectrum of RF carrier modulated with 20 MHz LTE captured at the output of SPM characterization setup.

One can see from Figure 2.12, a spectral leakage in adjacent band is appearing due to several distortions such as diode non-linearity and imperfections in passive SPC hardware. The ACLR is the measure of spectral leakage in the adjacent channel. The

ACLR is calculated as ratio of power measured in adjacent channel at certain frequency offset to the power measured within the channel. Figure 2.12 shows an ACLR of -33.4 dBc and -32.2 dBc measured at 15 MHz offset in lower and upper side of center frequency, respectively. These ACLR values do not comply with the industry requirements as described in RF physical layer specification of 3GPP TS36.141 6.2 document [88]-[89]. A carrier leakage is also appearing in the signal as shown in zoomed version of measured spectrum in Figure 2.12. This will result into an in-band distortion in this case.

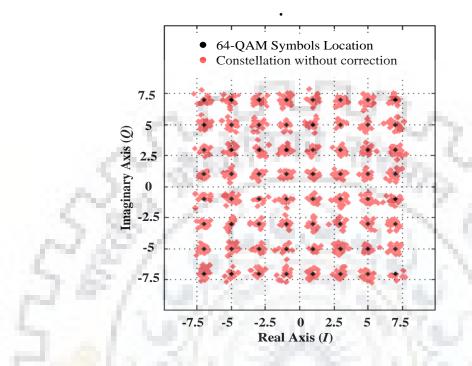

Figure 2.13 shows the constellation of 64-QAM signal after demodulation of LTE carrier captured by VSA in Figure 2.11. From Figure 2.13 one can see the symbol spreading due to distortion, as compared to the actual symbols locations. This spread is measured in terms of EVM which is a measure of the error between the predefined industry-approved constellation symbol location and the actual measured symbol after equalization [90]. The EVM of 20.14% is calculated in the present case for the modulated signal with no correction. This does not qualify the 8% requirements of LTE signal with 64-QAM modulation as described in RF physical layer specification as mentioned in 3GPP TS36.104 document [90]-[91]. Therefore, it is important to capture and model the distortion of SPM such that a suitable digital correction scheme can be employed to mitigate them.

Figure 2.13: Measured constellation diagram of 64-QAM used in LTE signal modulated by SPM.

#### 2.6 Conclusion

This chapter discusses the basic architecture of SPM and its operating principle for modulating I and Q signals of any digital modulation schemes such as QAM produced after DAC conversion. A hardware prototype based on this architecture is designed and developed to demonstrate the modulation feature of SPM. An RF instrument based characterization setup is also developed to upload I and Q signals of any digital modulation scheme and convert them to analog signals using DACs for driving six-port based modulator hardware prototype. A successful modulation of LTE signal using 64 QAM is demonstrated using the hardware prototype SPM and its characterization setup.

However, due to several distortions and hardware imperfections, the quality of modulation in terms of measured EVM is not up to mark and does not qualify the requirement set by LTE standard. Therefore, a suitable distortion mitigation scheme must be studied to utilize six-port based modulators to be used in commercial LTE transmission.

# **Chapter Three: Characterization of Linear and Non-linear Distortions of Six-Port Modulator and Digital Pre-Compensation.**

#### 3.1 Introduction

This Chapter focuses on the characterization of various distortions (linear as well as nonlinear) in SPM. The diode is the major source of non-linear distortion in SPM design, as discussed in section 2.1 of chapter 2. In addition, small hardware imperfections in implementing the correct s-parameters of passive SPC in hardware prototype further enhances these distortions. This chapter analyze the effect of these hardware imperfections in generating extra cross-modulation terms due to even weak non-linearity of diode operation. In order to digitally compensate these linear and non-linear distortions, a behavioural model is developed based on real-valued focused time delay neural network. This model is based on the characterization of the SPM prototype developed in chapter 2 using the gain and phase distortions captured from the test-bed developed in previous chapter. Later, these distortions are modelled and inverse of this model is applied in digital domain for pre-compensation. The I and Q baseband data when passes through this model get predistorted such that after modulation from SPM, the output of SPM is effectively distortion free. This digital pre-compensation technique is established with the successful modulation of QAM and LTE signals over the RF carrier at 2 GHz. The modulated carrier qualifies the requirement by LTE standard in terms of EVM and ACLR.

#### 3.2 Six-Port Modulator Architecture in Presence of hardware Imperfections

SPM architecture using schottky diodes as variable load is described in section 2.1 of chapter 2. The ideal s-parameters of SPC are given in (2.1). In case of hardware imperfections, the elements of this s-parameter matrix changes. If a small error ( $\delta$ ) is assumed in every s-parameters in terms of phase and amplitude, the modified s-parameter matrix with hardware imperfection can be given by

In order to simplify the case, the isolation and reflection coefficient of each element of SPC are assumed 0. The reciprocity i.e.  $S_{ij}=S_{ji}$ , is also considered in (3.1) as the travelling wave faces same transmission while moving from  $i^{th}$  port to  $j^{th}$  port and vice versa. In order to further simplify the analyses, all error terms are assumed to be very small and

hence same i.e.  $\delta_1 = \delta_2 = \delta_3 = \delta_4 = \dots \delta_{16} = \delta$ . For ideal case, without the above imperfections, where  $\delta_1 = \delta_2 = \delta_3 = \delta_4 = \dots \delta_{16} = \delta = 0$ , (3.1) reduces to (2.2). Using the imperfect s-parameter matrix of SPC as given by (3.1) in (2.2), one can obtain the output wave  $b_1$  as given in (3.2).

$$b_{1} = -\frac{a_{2}}{4} \left[ \left\{ \Gamma_{3} \left( 1 + 2\delta + 2\delta^{2} \right) + \Gamma_{4} \left( 1 + 2\delta \right) + 2\delta \left( 1 + \delta \right) \left( \Gamma_{5} + \Gamma_{6} \right) \right\} + j \left\{ \left( 1 + 2\delta \right) \left( \Gamma_{5} + \Gamma_{6} \right) - \Gamma_{4} 2\delta \left( \delta + 1 \right) \right\} \right]$$

(3.2)

Assuming, the diode is operating in non-linear region, one can now truncate (2.4) to third-order non-linear approximation as

$$\Gamma_{D,m}(V) \approx \Gamma_0 + k_0 \Delta v + k_1 (\Delta v)^2 + k_2 (\Delta v)^3$$

(3.3)

If the reflection coefficient  $\Gamma_{D,m}(V)$  as described in (3.3) is controlled by the baseband *I* and *Q* data which are in voltage form, then one can write

$$\Gamma_{3}(V) = \Gamma_{D,3}(V) = \Gamma_{0} + kI + k_{1}I^{2} + k_{2}I^{3}$$

(3.4)

$$\Gamma_{5}(V) = \Gamma_{D,5}(V) = \Gamma_{0} + kQ + k_{1}Q^{2} + k_{2}Q^{3}$$

(3.5)

$$\Gamma_{4}(V) = e^{-j\pi} \Gamma_{D,4}(V) = -\Gamma_{D,4}(V) = -\Gamma_{0} - k\overline{I} - k_{1}(\overline{I})^{2} - k_{2}(\overline{I})^{3}$$

(3.6)

$$\Gamma_{6}(V) = e^{-j\pi} \Gamma_{D,6}(V) = -\Gamma_{D,6}(V) = -\Gamma_{0} - k\bar{Q} - k_{1}(\bar{Q})^{2} - k_{2}(\bar{Q})^{3}$$

(3.7)

Using (3.4) to (3.7) in (3.2), the modulator output can be represented as (3.8) with various modulator imperfections. This expression is obtained assuming  $\overline{I}$  and  $\overline{Q}$  representing exact inverted replica of baseband I and Q signals i.e.  $I = -\overline{I}$ ,  $Q = -\overline{Q}$ .

$$b_{1} = -\frac{a_{2}}{4} \left[ \left\{ \frac{2k(1+\delta)^{2}I}{IComponent} + \frac{4k\delta(1+\delta)Q}{Crosstalk/Leakage of Q} + \frac{2\delta^{2}\Gamma_{0}}{DC \ offset} + \frac{2k_{1}\delta^{2}I^{2} + 2k_{2}(1+\delta)^{2}I^{3}}{NonlinearTerms of I} + \frac{4k_{2}\delta(1+\delta)Q^{3}}{NonlinearTerm of Q} \right]$$

$$+ j \left\{ \frac{2k(1+2\delta)Q}{QComponent} - \frac{2k\delta(1+\delta)I}{Crosstalk/Leakage of I} + \frac{2\delta(1+\delta)\Gamma_{0}}{DC \ offset} + \frac{2k_{2}(1+2\delta)Q^{3}}{NonlinearTerms of Q} + \frac{2k_{1}\delta(1+\delta)I^{2} - 2k_{2}\delta(1+\delta)I^{3}}{NonlinearTerms of I} \right\}$$

$$(3.8)$$

One can clearly see from (3.8) that due to imperfect realization of s-parameters of passive SPC along with non-linearity of diode, there is a crosstalk between real and imaginary part depending upon all the reflection coefficients. In addition, the common mode voltage which should cancel in ideal situation is present at the output as DC offset at both in-phase and quadrature component of output wave  $b_1$ . This DC-offset can be ignored in in-phase component considering  $\delta$  is small, however, its effect cannot be neglected in quadrature component. One can also see that slight tuning in terms of amplitude of *I* and *Q* can correct for some imbalances as discussed in [24], but cannot mitigate the DC offset. The non-linearity will further expand with small error in the s-parameter matrix as shown in (3.8) and will contribute to further cross talk. Therefore, the strategy of using differential *I* and *Q* along with quarter-wave transmission line [18]-[33],[55] cannot completely remove the component  $\Gamma_0$  contributing for carrier leakage, if SPC is realized with imperfect s-parameters.

#### 3.3 Non-linearity in Schottky Diode

Figure 3.1 shows the variation of real and imaginary parts of complex reflection coefficient  $\Gamma_m$  of diode with bias voltage. Figure 3.1 also shows this variation for different local oscillator (LO) power. The LO power here represents the RF carrier power during modulation. A non-linear model of diode in simulation has been used to estimate diode non-linearity in Figure 3.1. One can see from Figure 3.1, that for LO power of 0 dBm, the diode varies over quasi-linear region of 270 mV to 450 mV. Therefore, the diode bias can be set at 360 mV with maximum peak-to-peak voltage varying 180 mV around the common mode bias voltage of 360 mV.

Accordingly, the I and Q signal voltages are also falling within this range. In real scenario the hardware imperfections and small diode non-linearity is inevitable. Therefore, a digital correction scheme is required in SPM to keep the errors due to above imperfection under check. Like any other quadrature modulator, SPM is connected

directly to baseband digital unit. Therefore, a suitable digital predistortion scheme can correct its linear as well as non-linear distortions. Even with careful design, some of these imperfections are inevitable.

Figure 3.1: Diode non-linearity in simulation and quasi-linear region for operation with different LO power.

A setup sown in Figure 2.11 is capable of capturing the linear and non-linear distortions and applying an appropriate digital correction to digital-baseband I, Q signals for hardware compensation.

#### 3.4 Behavioral Modeling of Distortion in Six-Port Modulator

In the absence of any distortion, the impairment free modulator output should be linearly scaled version of the baseband data modulated over RF carrier [88]-[89]. If the output of modulator is captured and de-modulated, the demodulated output and the baseband inputs are related as

$$V_{out} = g\left(V_{in}\right) \tag{3.9}$$

where, the baseband input voltage is  $V_{in} = I + jQ$ , and  $V_{out}$  is the demodulated baseband output voltage. The gain represented by function g ( ) is a complex valued non-linear function representing the amplitude as well as phase change in the modulated signals with the input signal amplitude. In ideal situation, this gain and phase change is constant. However, in practice, the gain and phase change produced by the modulator can be nonlinear due to diode non-linearity and other impairments, such I/Q imbalances, cross-talks etc. occurring due to imperfect SPC as given in (3.8).

Figure 3.2 and 3.3 show distortion in gain and phase with respect to input signal power. This is obtained by comparing baseband I, Q data demodulated from the output of modulator and the input baseband I, Q data fed to the modulator after proper time delay adjustment. The output baseband data is obtained from VSA by down-converting and demodulating captured modulated RF carrier at the output of modulator. One can see

from Figure 3.2 that the non-linear gain response represents amplitude modulation to amplitude modulation (AM/AM) distortion. The large scattering of gain in Figure 3.2 is due to DC offset and I/Q imperfections in the modulators as established in literature [88]-[90].

Similarly, Figure 3.3 shows the non-linear phase difference between output and input signals of the modulator which represents amplitude modulation to phase modulation (AM/PM) distortion.

Moreover, the bias circuitry uses energy storing elements such as capacitors and inductors with finite charging and discharging time. Thus, in the presence of the modulated signals with broadband envelope, memory effect is also exhibited by the modulator, which contributes to the scattering of its gain and phase response even in the absence of DC offset, non-linearity and I/Q imbalances etc.

22

Figure 3.3: Measured phase distortion with input signal power.

#### 3.4.1 Indirect Learning Architecture Predistortion Scheme

The distortion characterization and mitigation setup of Figure 2.11 provides an option of utilizing a very powerful digital correction scheme called predistortion which can correct any type of the hardware distortion. Predistortion scheme requires a behavioral model of hardware capturing all its distortion, and the inverse of this model is implemented in the digital domain. There are two architectures generally used for model extraction i.e. direct learning architecture and indirect learning architecture. The difference between direct and indirect learning architecture has been investigated in [101]. The indirect learning architecture can be run in an open-loop fashion. While direct learning architecture is usually used in closed-loop systems. Therefore, the stability of the system is required to be maintained. The closed-loop estimation is shown in Figure 3.4, where the predistorter coefficients are updated based on linearized system input and output.

**Figure 3.4: Direct Learning Architecture of predistorters scheme**

The indirect learning approach is a well-established method for the Digital Predistortion. Figure 3.5 shows the indirect learning architecture (ILA) of predistorter [100],-[103],[113]-[114]. x(n) is input signal to predistorter, u(n) is predistorter output and input to modulator and y(n) is the output of modulator after application of predistorted signal u(n). ILA principle is based on the observation that if the  $\tilde{u}(n)$  is the output of predistorter when (y(n)/G) is input to predistorter model, then if one imposes  $u(n) = \tilde{u}(n)$ , then it leads to x(n) = (y(n)/G), where G represents small signal gain of modulator.

Figure 3.5: Indirect Learning Architecture of predistorters scheme.

In other words, one can also perceive that once required conditions are imposed, the output is linear amplified version of input given as

$$\tilde{\mathbf{u}}(n) = \psi(\mathbf{y}(n) / G) \tag{3.10}$$

if one imposes condition of  $u(n) = \tilde{u}(n)$ , predistorter coefficients estimation condition for the first iteration, predistorter has no action and input to SPM is u(n) = x(n). Now

$$x(n) = \psi(y(n)/G) \tag{3.11}$$

As x(n) and y(n) are available from the measurement data, non-linear predistortion model coefficients and subsequently  $\psi$  can be calculated using adaptive signal processing schemes. The main advantage of ILA is that predistorters can be any non-linear model  $\psi$  that maps normalized output to input available in baseband form. In this thesis, the feed forward neural network (NN) is used to represent non-linear function  $\psi$ . Once coefficients (weights/bias) for the model are extracted based on input and output data of modulator, they are digitally copied in predistorters in the digital domain before the analog hardware in the line-up shown in Figure 3.5. One can also observe from Figure 3.5 that for the first iteration, this mapping maps a relation which is inverse of normalized SPM characteristics given as  $y(n)/G = \Psi(x(n))$ .

## 3.4.2 Neural Network for Modelling: Real Valued Focused Time Delay Neural Network for Modelling

The real valued focused time-delay neural network (RVFTDNN) topology is shown in Figure 3.6. This NN topology is used to model the function, relating the pair of input I, Q

data and the pair of output I, Q data as shown in Figure 3.6. The motivation of using NN based model becomes evident from linear and non-linear distortion behaviour of six-port based modulator setup. There are linear as well as non-linear distortion in I and Q.

Figure 3.6: Architecture of real-valued focused time delay neural network.

In addition, there is a possible cross-talk between *I* and *Q* due to imperfect s-parameter of SPC as described in (3.8). In such case, NN based model is very useful as it can map all these possible combinations of cross-talks, non-linearity and dc bias which is expected from its topology as shown in Figure 3.6. The feed-forward neural network (FFNN) is a popular modelling tool, which is presented with input vectors of order  $1 \times 2(m+1)$ , including the real values of present and past inputs.

$$X(n) = [I_{in}(n), I_{in}(n-1), \dots, I_{in}(n-m), Q_{in}(n), Q_{in}(n-1), \dots, Q_{in}(n-m)]$$

(3.12)

where n denotes the present training sample and m is the memory length of the modulator system. The targeted output vector is

$$Y(n) = [I_{out}(n), Q_{out}(n)]$$

(3.13)

where,  $I_{out}(n)$  and  $Q_{out}(n)$  represents pair of output I, Q data.

### 3.4.2.1. Forward Computation

The hidden layers are fully connected, as shown in Figure 3.6. During the forward computation, data from neurons of a lower layer (i.e.,  $k^{th}$  layer) is multiplied with weight and propagated forward to neurons in the upper layer i.e.,  $(k+1)^{th}$  layer. The net input to any neuron, *i*, in any layer (k+1) is given by

$$\operatorname{net}_{i}^{k+1} = \sum_{j=1}^{p} w_{ij}^{k+1} o_{j}^{k} + b_{i}^{k+1}$$

(3.14)

If  $w_{ij}$  denotes the synaptic weight connecting the  $j^{th}$  input from the previous layer to the  $i^{th}$  neuron of the present layer, where, P denotes the total number of neurons in the previous layers,  $b_i^k$  denotes bias of the  $i^{th}$  neuron in the  $k^{th}$  layer. It is worth mentioning that the SPM output is the function of four variables  $I, \overline{I}, Q, \overline{Q}$ . The  $\overline{I}$  and  $\overline{Q}$  represents an inverted replica of baseband I and Q signals which are automatically adjusted in the bias value of neurons inherently present in the NN. The output of any layer represents an input to the next layer. The output of  $i^{th}$  neuron at any  $k^{th}$  layer is calculated as

$$o_i^k = f(\operatorname{net}_i^k) \tag{3.15}$$