# FPGA PROTOTYPING FOR MICROGRID PROTECTION

Ph.D. THESIS

by

PRAVEEN KUMAR

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) JUNE, 2019

# **FPGA PROTOTYPING FOR MICROGRID PROTECTION**

### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

### **DOCTOR OF PHILOSOPHY**

in

### **ELECTRICAL ENGINEERING**

by

PRAVEEN KUMAR

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) JUNE, 2019

## ©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2019 ALL RIGHTS RESERVED

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE

### STUDENT'S DECLARATION

I hereby certify that the work presented in the thesis entitled "**FPGA PROTOTYPING FOR MICROGRID PROTECTION**" is my own work carried out during a period from July, 2014 to June, 2019 under the supervision of Dr. Vishal Kumar, Associate Professor and Dr. Rajendra Pratap Adjunct Faculty Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in the thesis has not been submitted for the award of any other degree of this or any other Institute.

### (PRAVEEN KUMAR)

Dated: June 06, 2019

### SUPERVISOR'S DECLARATION

This is to certify that the above mentioned work is carried out under my supervision.

(Vishal Kumar) Supervisor (Rajendra Pratap) Supervisor

Dated: June 06, 2019

The Ph.D. Viva-Voce Examination of Praveen Kumar, Research Scholar, has been held on **September 14, 2019**.

Chairperson, SRC

This is to certify that the student has made all the corrections in the thesis.

### Supervisors

Head of the Department

**External Examiner**

Dated: September 14, 2019

### ABSTRACT

The recent advancement of digital technology is the re-configurable hardware i.e. field programmable gate array (FPGA), programmed by Hardware Description Language (HDL) is used for high-speed applications. It has credentials for developing intelligent electronic devices, which are used in the power system components, and smart grid applications i.e. fast relay for the protection of the microgrid (MG) asking high computational demand, low latencies, reconfigurability, high bandwidth and parallel processing. Some inherent benefit of the FPGA device is the parallelism of hardware that increases the execution speed compared to sequential software architecture based technologies ( $\mu$ P and  $\mu$ C). Due to these predominant features, the FPGA based digital relays are being considered for the protection of MGs.

MGs provides a platform for integration of various distributed generators (DGs) and renewable energy sources (RESs) like solar PVs and wind generators, loads and storage devices. These DGs and RESs serve multiple purposes viz. reducing the carbon footprint from the environment, reachability to remote demand locations, quick installation and low-cost maintenance etc. The MG is usually connected to the utility grid through a single bus called the point of common coupling (PCC) and hence, is capable of operating both in synchronism with the utility grid known as grid-connected mode and as an autonomous power island i.e. standalone mode. The small-scale MGs provide uninterrupted power supply to the end user during the period of power outages, emergencies and failures of the utility grid due to any abnormality or a fault occurring in the utility grid. There are several challenges for reliable operation of a MG in the field of monitoring, controls, and protection. Among these, the device development for the protection of the MG has been addressed in the present work.

The existing overcurrent protection relays (OCRs) developed for passive distribution networks (radial network) are not applicable for active distribution networks viz. Microgrid (MG). Since the integrated distributed energy resources (DERs) are connected through power electronic interfacing (PEI) having fast dynamics, therefore, the MG is a low-inertial system. To overcome the stated problem, a fast relay is required for the protection of MG that can isolate the faulty section, detect its mode of operation and adapt threshold settings as per the operating mode. Protective hardware is required to be developed that can sense the faster dynamics within MG and also have the feature of parallel processing by which the computation time for decision making is reduced. The FPGA is such an electronic device that is used in the power system

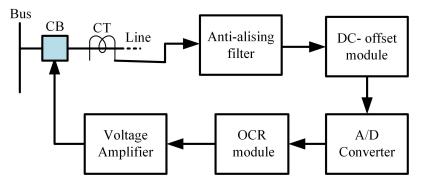

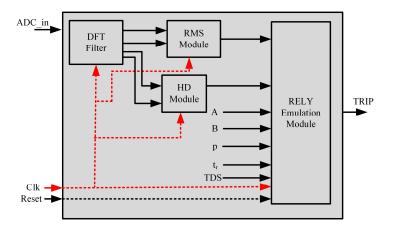

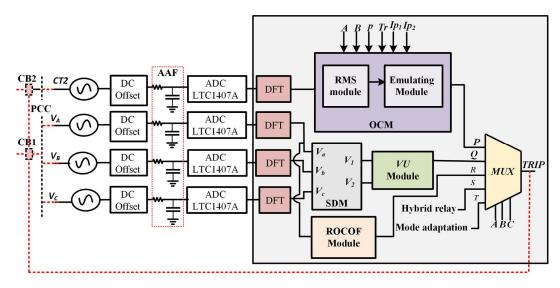

industry and smart grid applications asking for high computational demand, low latencies, reconfigurability and parallel processing. Due to these predominant features, the FPGA based digital relays are being considered for the protection of the MGs. In the present work, the FPGA based prototyping has been used for different block of OCR viz. DC-offset module, antialiasing filter, DFT filter module, harmonic detection module and relay emulation module are implemented with a higher degree of accuracy at low cost.

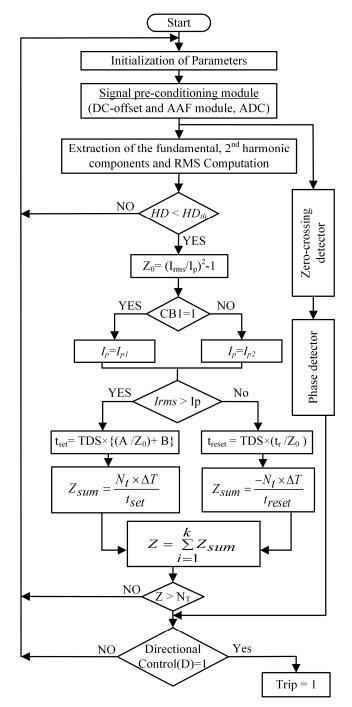

Conventional OCRs are mostly used for the protection of the radial distribution network. However, in case of microgrid protection, OCRs maloperate due to the bidirectional power flow, the need of directional feature of the relay has become necessary. Therefore, the directional feature is added to the developed OCR prototype. Here, a digital phase detection module has been developed for the estimation of direction of current flowing through the power system network using a zero-crossing detector. A parallel architecture for phase and tripping time computation has been used in the proposed design that makes the developed relay faster by reducing the computation time of the algorithm. Here also, performance of the DOCR is tested by creating the faults at different locations with different values of time dial settings and plug-point-multiplier. Hardware-in-loop (HIL) verification of the relay is carried out with the standard DOCR of the RTDS which verify the successful operation of the designed relay under different fault conditions.

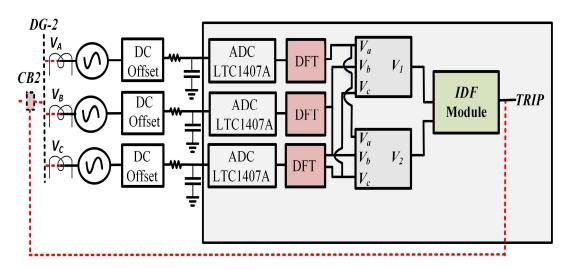

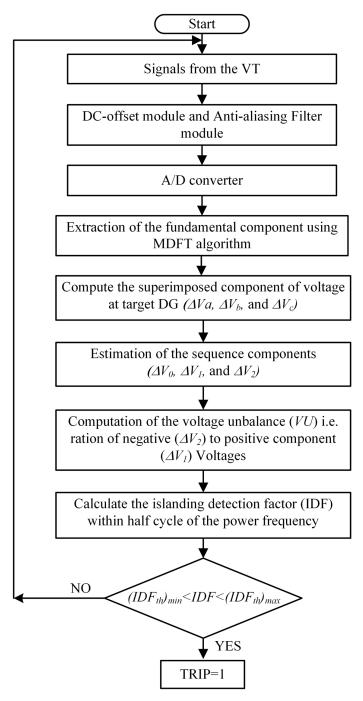

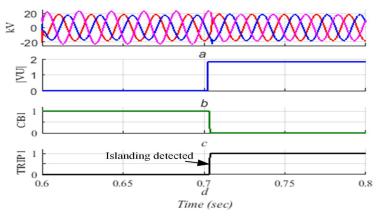

Islanding is the condition, which occurs when a portion of the distribution network (or MG) is disconnected from the utility grid and operates independently with the help of local DGs and RESs. Generally, two types of MG islanding occur i.e. intentional and unintentional. The intentional islanding is mainly performed to carry out some maintenance works within the MG and for the safety of the working personnel; whereas the unintentional islanding occurs due to the utility grid blackout by equipment failure, natural disaster or any abnormality in the power system. As per the suggested standard viz. UL-1741, IEC-62116 and IEEE 1547<sup>TM</sup> islanding must be detected and the active DGs are isolated from the MG within 2-seconds after detecting the islanding. Hence, it is an essential requirement to develop a fast relay that can detect the islanding (by sensing variation in parameters) within the stipulated time interval as well as take necessary action i.e. either isolate the affected section/DG of the MG (with non-critical loads) by generating the trip signal. In present work, the FPGA prototype for islanding detection based on the islanding discrimination factor (IDF) using the periodic maxima of superimposed voltage components is developed. A modular design approach is used to implement the islanding

detection technique (IDT) algorithm. Verilog HDL has been used to optimize the hardware resources and minimize computational complexity. HIL verification of the IDT has been performed for islanding and non-islanding events with a microgrid test system developed on RTDS. The performance of the prototype has been verified under various test cases viz. for both islanding and non-islanding events.

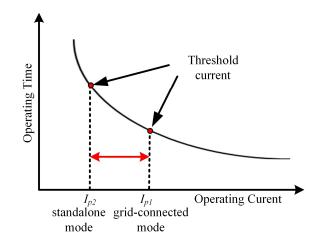

Now, the magnitude of a fault current depends on the operating mode of the MG as well as number and types of the integrated DGs placed within the MG. The contribution of the fault current by rotating machine-based sources is higher than that of PEI DERs as compared to their respective normal rated current. The magnitude of fault current is 6.0-10.0 p.u in the rotating machine whereas its magnitude is lower i.e. up to 1.0-2.0 p.u in case of PEI interfaced DERs. However, in the grid-connected mode of operation, the magnitude of fault current is greater than the magnitude of the fault current in the islanded mode of operation. Also, the trip time is more in the case of a standalone mode in comparison with the grid-connected mode. Hence, mode-adaptability of the OCR is inevitably required for the reliable operation of MG, which can be performed by changing the threshold setting i.e. pick-up current (*Ip*) setting of the OCR. In this work, a hardcore reconfigurable multifunctional relay is designed, which is used for the detection of operating modes of the MG as well as mode adaptation within the MG. Some additional functional modules viz. voltage unbalance module, rate of change of frequency (ROCOF) module and a soft controller are designed on the FPGA and added in the developed OCR prototype. HIL verification of the developed prototype is performed with the RTDS under various test conditions viz. under different power mismatches.

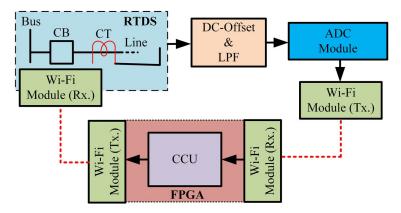

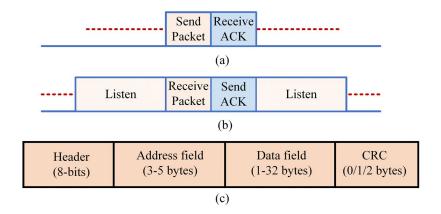

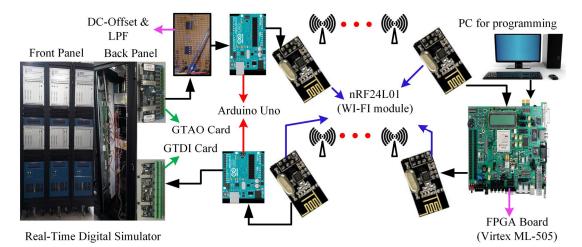

Lastly, the prototype of a communication assisted adaptive relay (CAAR) is developed by adding a communication feature with the designed OCR to achieve mode adaptability of the relay installed at various DG located remotely. The status of these modes and the working status of the DGs are communicated through the wireless network. Here nRF24L01 wireless modules are used as the transmitter and the receiver of the CAAR. Performances of the CAAR prototype has been verified in HIL on a MG test system under the environment of RTDS. Different test cases i.e. operating modes of the MG, faults at different locations, types of faults and relay coordination are tested to validate the functionality of the developed prototype of CAAR. In the present work, the FPGA based prototype of the overcurrent relay (OCR) with its internal components viz. DC-offset module, anti-aliasing filter, DFT module, harmonic detection module and relay emulation module are developed with a higher degree of accuracy and low cost. Here, Verilog HDL is used to optimize the hardware resources and minimize

computational complexity. Furthermore, the directional feature is added to the developed OCR prototype, which is works as directional-OCR. Here, a digital phase detection module is used for the estimation of the direction of current by a zero-crossing detector. Performance of the relay is tested by creating the faults at different locations with different values of time dial settings and plug-point-multiplier.

With GOD's grace, I take this opportunity to thanks all those who have supported me all through this course of research work. First and foremost, I would like to express my deepest sense of gratitude towards my supervisors Dr. Vishal Kumar, Associate Professor, Department of Electrical Engineering and Dr. Rajendra Pratap, Adjunct faculty, Department of Electrical Engineering of IIT Roorkee, for their patience, inspiring guidance, constant encouragement, moral support, and keen interest in minute details of the work.

I also express my sincere gratitude towards my research committee members Dr. Y.V. Hote (Associate Professor EED), Dr. Manoj Tripathi, (Associate Professor, EED) Dr. Dharmendra Singh, (Professor, Department of ECE) for their invaluable direction, encouragement and support, and above all the noblest treatment extended by them during the course of my research at IIT Roorkee.

I heartily extend my gratitude to Head of the Department of Electrical Engineering, and all faculty members of the department for their help, moral support, and providing the excellent infrastructure, laboratory and computing facility for the research work.

I am immensely thankful to Research scholars Mr. Sachidanda Sen, Mr. Maneesh Kumar, Mr. Sanjay Kumar, Dr. Santosh Kumar Singh and Dr. Ankit Singh for their timely help, support and encouragement during my research work.

I owe a debt of gratitude to my parents, Mr. Ram Narayan Sah and Smt. Manju Devi, my brother Naveen Kumar and my wife Smt. Sonali Gupta for their endless support, encouragement, patience and care.

May all praise be to the Almighty, the most beneficent, and the most merciful.

(Praveen Kumar)

## **CONTENTS**

| ABSTRACT                                                   |

|------------------------------------------------------------|

| ACKNOWLEDGEMENTS xi                                        |

| CONTENTSxiii                                               |

| LIST OF FIGURES xix                                        |

| LIST OF TABLES                                             |

| LIST OF SYMBOLS xxv                                        |

| LIST OF ABBREVIATIONS xxvii                                |

| Chapter 1: Introduction1                                   |

| 1.1 Overview of Relay Design1                              |

| 1.2 Overview of Microgrid1                                 |

| 1.2.1 Microgrid Protection                                 |

| 1.2.2 Importance of IDTs                                   |

| 1.2.3 Requirement of Fast Relays                           |

| 1.3 Field Programmable Gate Array                          |

| 1.3.1 FPGA Design Flow                                     |

| 1.4 Literature Review                                      |

| 1.4.1 Relay Design                                         |

| 1.4.2 Islanding Detection Technique for MGs 12             |

| 1.4.2.1 Active islanding detection techniques              |

| 1.4.2.2 Passive islanding detection techniques             |

| 1.4.2.3 Hybrid islanding detection techniques              |

| 1.4.2.4 Communication-based islanding detection techniques |

| 1.4.2.5 Advanced IDTs based on signal processing tool      |

| 1.4.3 Adaptive Protection Schemes of Microgrid             |

| 1.5 Motivation                                             |

| 1.6 Objectives and Contributions of the Thesis                              |       |

|-----------------------------------------------------------------------------|-------|

| 1.7 Organization of the Thesis                                              |       |

| Chapter 2: EMULATION OF AN OVERCURRENT RELAY ON RECONFIGU                   | RABLE |

| HARDWARE                                                                    | 27    |

| 2.1 Introduction                                                            |       |

| 2.2 Working Principle and Design Overview of OCR                            |       |

| 2.3 Internal Design of OCR                                                  | 29    |

| 2.3.1 ADC Module                                                            | 29    |

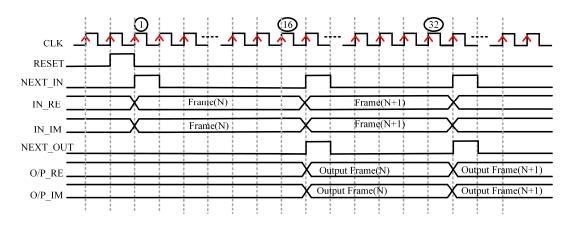

| 2.3.2 DFT Filter and RMS Estimation Module                                  | 29    |

| 2.3.3 Effect of Transformer Inrush Current and Harmonic Distortion Module   |       |

| 2.3.4 Relay Emulating Module                                                | 32    |

| 2.3.5 Operation of Designed OCR                                             | 33    |

| 2.4 Emulation Results                                                       | 34    |

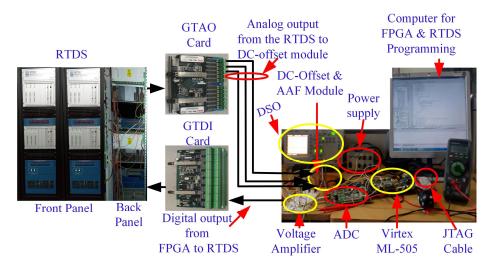

| 2.5 Experiment setup for HIL Testing of FPGA Prototype                      | 38    |

| 2.5.1 Test System                                                           | 38    |

| 2.5.2 Interfacing between FPGA and RTDS                                     | 38    |

| 2.6 Hardware-in-Loop Verification of OCR Prototype                          | 40    |

| 2.6.1 Characteristic verification of the designed OCR                       | 40    |

| 2.6.2 Operational Verification of the designed OCR                          | 44    |

| 2.6.2.1 Performance with different fault resistances and inception angles   | 48    |

| 2.6.2.2 Coordination of OCRs                                                | 51    |

| 2.6.2.3 Performance of the proposed OCR during transformer inrush condition | 53    |

| 2.7 Summary                                                                 | 54    |

| Chapter 3: FPGA based design and HIL verification OF DIRECT                 | IONAL |

| OVERCURRENT Relay                                                           | 55    |

| 3.1 Introduction:                                                           | 55    |

| 3.2 Directional Overcurrent Relay                                           | 55    |

|   | 3.3 Design Flow of the DOCR                                                     | 56 |

|---|---------------------------------------------------------------------------------|----|

|   | 3.3.1 Analog to Digital Converter                                               | 56 |

|   | 3.3.2 DFT Filter and Root Mean Square Module                                    | 56 |

|   | 3.3.3 Zero Crossing Detector Module                                             | 56 |

|   | 3.3.4 Phase Detection Module                                                    | 57 |

|   | 3.3.5 Relay Emulating Module                                                    | 58 |

|   | 3.3.6 Power system module                                                       | 59 |

|   | 3.4 Implementation of the Proposed Design                                       | 59 |

|   | 3.5 Results and Discussion                                                      | 61 |

|   | 3.5.1 Characteristics Verification of DOCR                                      | 61 |

|   | 3.5.2 Hardware setup for HIL Testing                                            | 62 |

|   | 3.6 Results and Discussion for HIL Testing                                      | 63 |

|   | 3.6.1 Testing of PD Module under Faults                                         | 63 |

|   | 3.6.2 Operational Verification of Designed DOCR                                 | 64 |

|   | 3.7 Summary                                                                     | 69 |

| С | hapter 4: Islanding Detection Technique based on Discrimination factor          | 71 |

|   | 4.1 Introduction:                                                               | 71 |

|   | 4.2 System Architecture of Designed IDT Module                                  | 72 |

|   | 4.3 Digital Design of the Proposed IDT Algorithm                                | 72 |

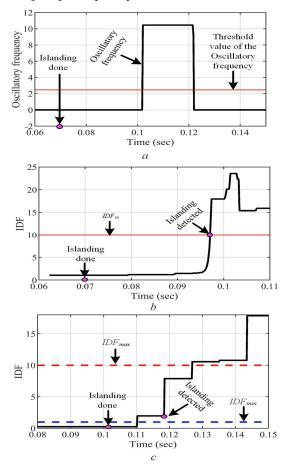

|   | 4.4 Working Principle and Design of IDT                                         | 74 |

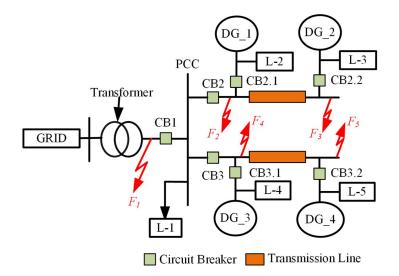

|   | 4.5 Test System                                                                 | 75 |

|   | 4.6 Experimental Setup for HIL Verification                                     | 76 |

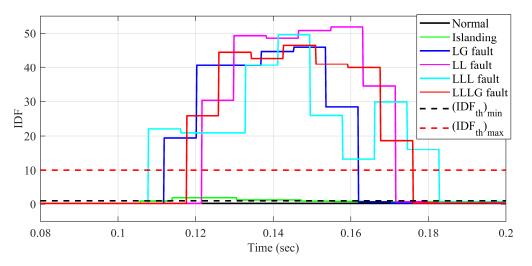

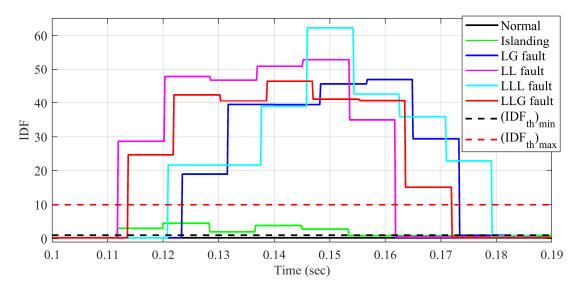

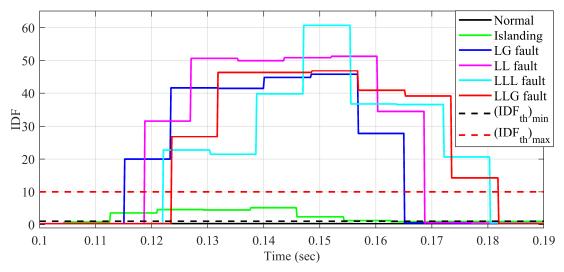

|   | 4.7 IDF Threshold Settings                                                      | 77 |

|   | 4.8 Results of HIL Verification                                                 | 79 |

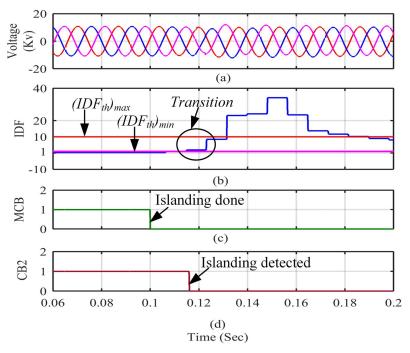

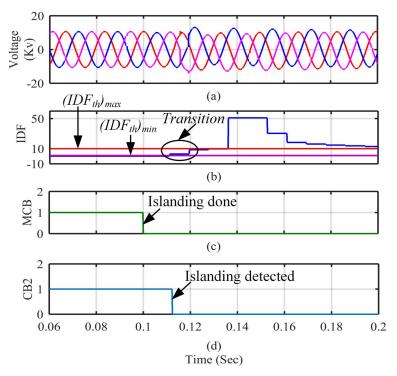

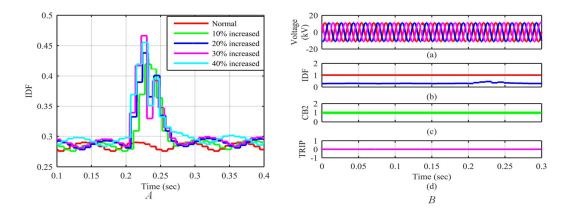

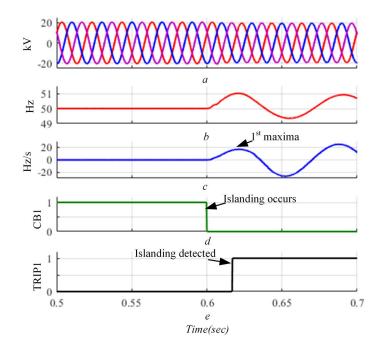

|   | 4.8.1 Operation of IDT Algorithm under Islanding Event for Zero Power Imbalance | 79 |

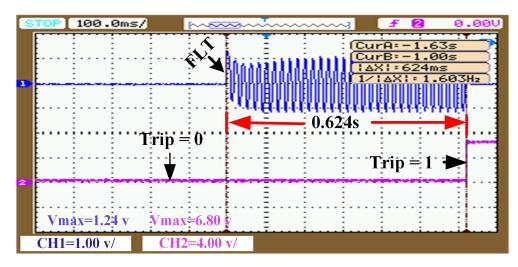

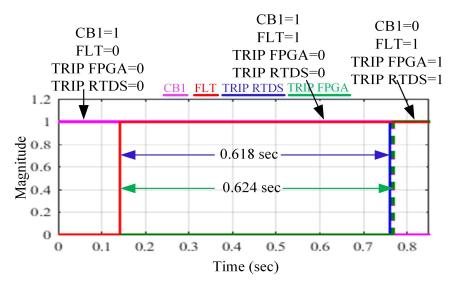

|   | 4.8.1.1 Performance verification for islanding condition                        | 79 |

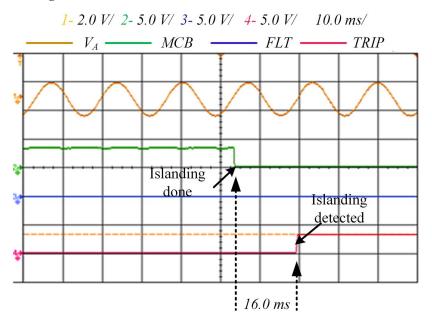

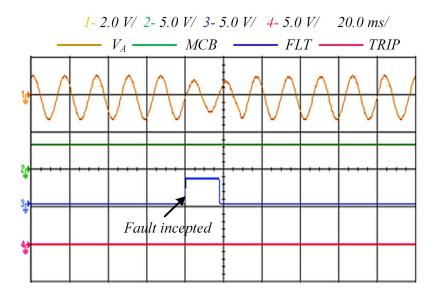

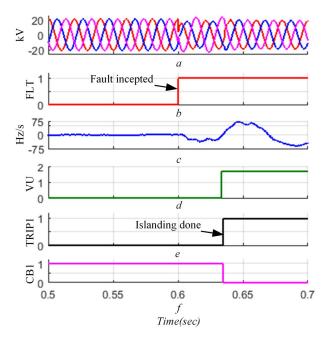

|   | 4.8.1.2 Performance verification for non-islanding event                        | 81 |

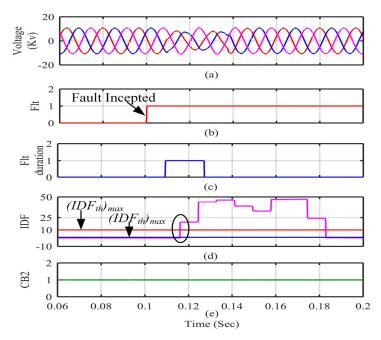

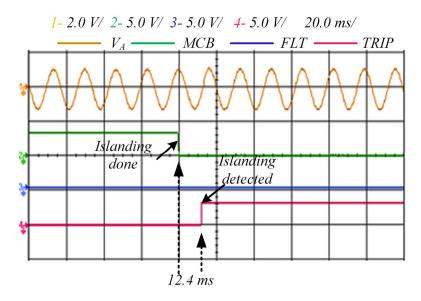

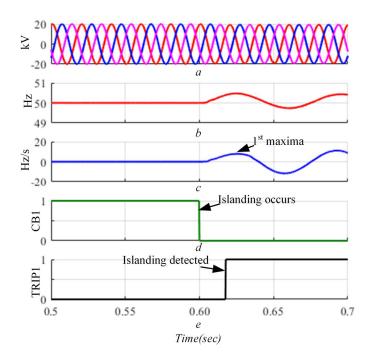

| 4.8.2 Performance Verification of Prototype under 25% Power Imbalance | 81  |

|-----------------------------------------------------------------------|-----|

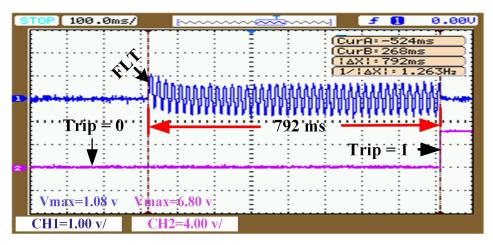

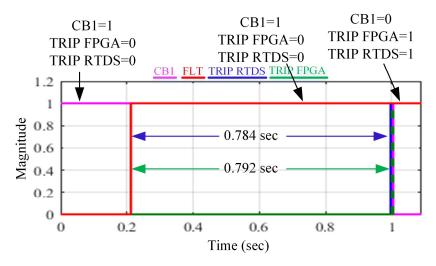

| 4.8.2.1 Performance verification for islanding condition              |     |

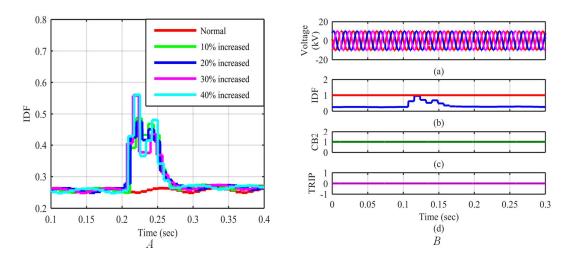

| 4.8.3 Performance Verification under other Non-Islanding Scenario     |     |

| 4.8.3.1 Sudden change in load:                                        |     |

| 4.8.3.2 Sudden change in Inductive or capacitive load:                |     |

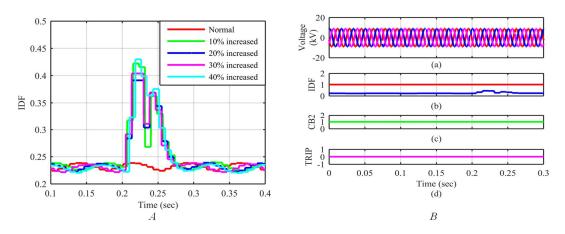

| 4.8.3.3 Sustained voltage Sag/Swell:                                  |     |

| 4.9 Comparative Study of the Proposed IDT                             |     |

| 4.10 Summary                                                          |     |

| Chapter 5: Mode adaptation Subsequent to islanding operation          | 89  |

| 5.1 Introduction                                                      |     |

| 5.2 Architecture of Microgrid                                         |     |

| 5.3 Internal Architecture of Multifunctional Relay                    |     |

| 5.3.1 Design of Over-current Module                                   | 91  |

| 5.3.2 Design of Voltage Unbalance Module                              | 91  |

| 5.3.3 Design of the Rate of Change of Frequency Module                |     |

| 5.4 Experimental Setup for HIL Verification                           |     |

| 5.5 Results and Discussion                                            | 95  |

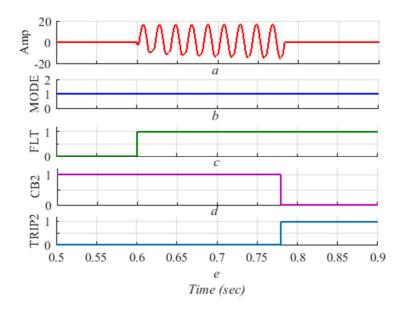

| 5.5.1 Perfectly Matched Load and Generation                           |     |

| 5.5.1.1 Verification of OCM for control input ABC=000                 | 96  |

| 5.5.1.2 Verification of VU module for control input ABC= 001          |     |

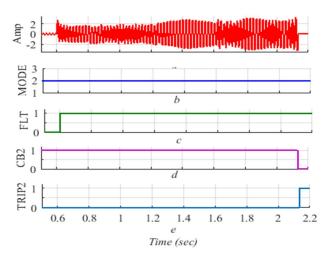

| 5.5.1.3 Verification of ROCOF module for control input ABC=010        |     |

| 5.5.1.4 Hybrid mode of operation for control input ABC= 011           |     |

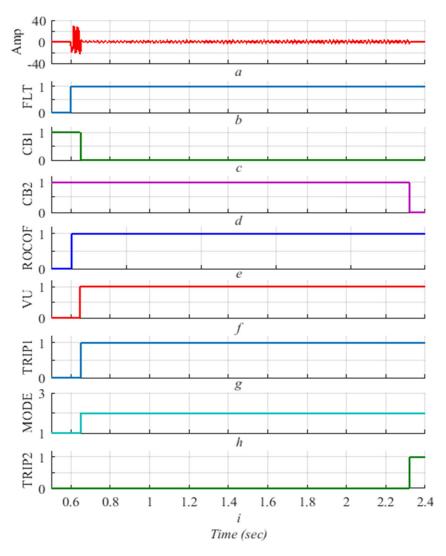

| 5.5.1.5 Verification for adaptation of relay                          | 100 |

| 5.5.2 Power Mismatch between Load and Generation is 25%               | 102 |

| 5.6 Result Discussion                                                 | 106 |

| 5.7 Summary                                                           | 107 |

| Chapter 6: Communication based adaptive protection      |  |

|---------------------------------------------------------|--|

| 6.1 Introduction                                        |  |

| 6.2 Architecture and Internal Design of Developed Relay |  |

| 6.2.1 Working of Developed Relay Module                 |  |

| 6.2.2 Signal Conditioning Module                        |  |

| 6.2.3 Analog to Digital Converter                       |  |

| 6.2.4 Wi-Fi Module                                      |  |

| 6.2.5 Control Unit Developed on FPGA Hardware           |  |

| 6.3 Flow Chart of the Developed Protection Scheme       |  |

| 6.4 Test System and Hardware-in-loop Verification       |  |

| 6.4.1 Microgrid Test System Developed in RTDS           |  |

| 6.4.2 Experimental Setup                                |  |

| 6.5 Results and Discussion                              |  |

| 6.5.1 Effect of Operating Mode of MG on Relay           |  |

| 6.5.2 Mode Adaptability of Developed Relay              |  |

| 6.5.3 Testing for Relay Coordination                    |  |

| 6.6 Summary                                             |  |

| Chapter 7: Conclusion and future work                   |  |

| 7.1 Conclusion                                          |  |

| BIBLIOGRAPHY                                            |  |

| LIST OF PUBLICATIONS                                    |  |

| APPENDIX                                                |  |

## **LIST OF FIGURES**

| Figure 1.1 Architecture of the Microgrid                                            | 2  |

|-------------------------------------------------------------------------------------|----|

| Figure 1.2 Overview of the Field Programmable Gate Array                            | 6  |

| Figure 1.3 FPGA design flow                                                         | 7  |

| Figure 1.4 Characteristics plot (time vs <i>I</i> <sub>sc</sub> ) for VI            | 9  |

| Figure 1.5 Characteristics plot (time vs <i>I</i> <sub>sc</sub> ) for EI            | 9  |

| Figure 1.6 Classification of islanding detection techniques                         | 13 |

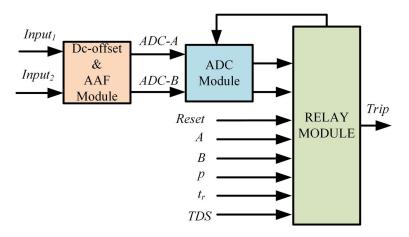

| Figure 2.1 Architecture of the proposed protection scheme                           | 28 |

| Figure 2.2 Functional block diagram of OCR module                                   | 29 |

| Figure 2.3 Timing diagram of DFT core                                               | 30 |

| Figure 2.4 Data path for emulating the relay                                        | 32 |

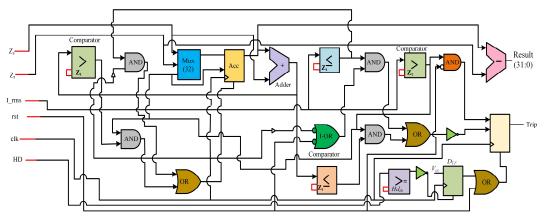

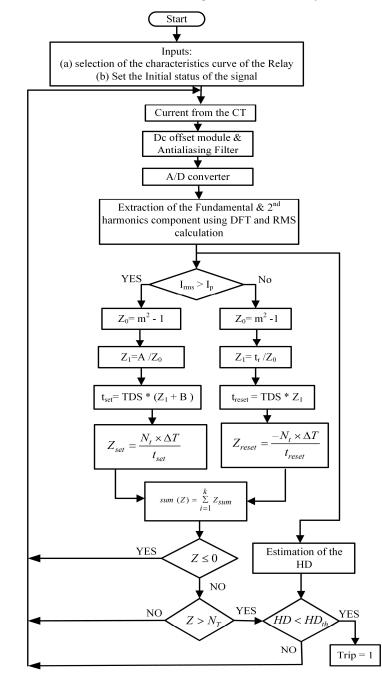

| Figure 2.5 Algorithmic chart of overcurrent relay                                   | 33 |

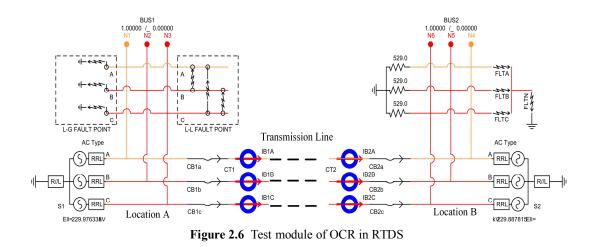

| Figure 2.6 Test module of OCR in RTDS                                               | 38 |

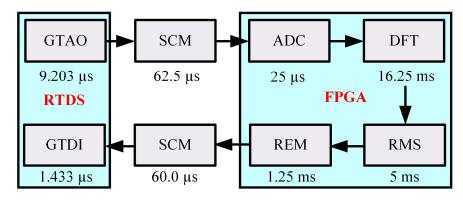

| Figure 2.7 Hardware-setup for HIL verification of OCR prototype                     | 38 |

| Figure 2.8 Latency involve in HIL verification                                      | 39 |

| Figure 2.9 Trip signal generated by FPGA at TDS=1 for EI characteristic             | 41 |

| <b>Figure 2.10</b> EI OCR at TDS = 1                                                | 41 |

| Figure 2.11 Trip signal generated by FPGA for EI OCR at TDS=2                       | 42 |

| Figure 2.12 EI OCR at TDS=2                                                         | 42 |

| Figure 2.13 Trip signal generated by FPGA at TDS=2 for VI characteristic            | 43 |

| Figure 2.14 Test results for VI characteristic at TDS=2 in close loop condition     | 43 |

| Figure 2.15 Test results for EI characteristic when LL fault occurred at location B | 45 |

| <b>Figure 2.16</b> Signal generated by FPGA and RTDS for EI OCR at TDS = 1          | 45 |

| Figure 2.17 Test results for VI characteristic when LL fault occurred at location B | 46 |

| <b>Figure 2.18</b> Signal generated by FPGA and RTDS for VI OCR at TDS = 1          | 46 |

| Figure 2.19 Test results for EI characteristic when LLLG fault occurred at location B                                                                                                                                                                                 | 47    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <b>Figure 2.20</b> EI OCR at TDS = 1                                                                                                                                                                                                                                  | 47    |

| Figure 2.21 Test results for VI characteristic when LLLG fault occurred at location B                                                                                                                                                                                 | 48    |

| Figure 2.22 Signal generated by FPGA and RTDS relay for EI OCR at TDS=1                                                                                                                                                                                               | 48    |

| Figure 2.23 Test results for EI characteristic when LG fault incepted                                                                                                                                                                                                 | 49    |

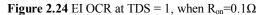

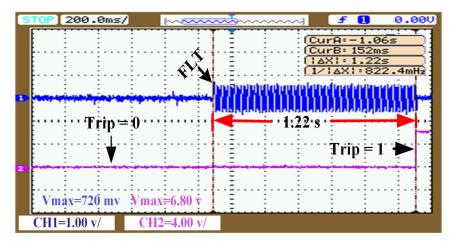

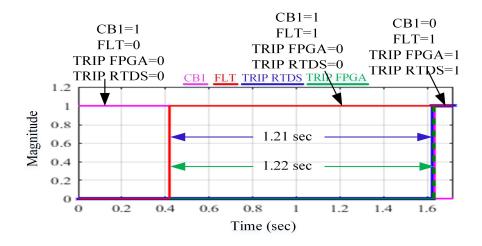

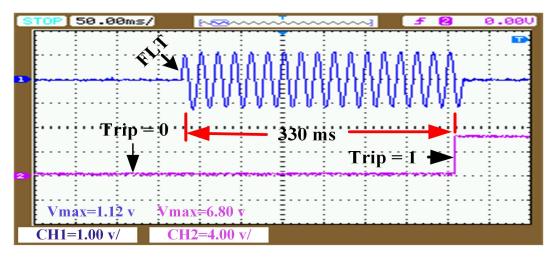

| <b>Figure 2.24</b> EI OCR at TDS = 1, when $R_{on}=0.1\Omega$                                                                                                                                                                                                         | 49    |

| <b>Figure 2.25</b> When LG (a-g) fault incepted, when $R_{on}=5\Omega$                                                                                                                                                                                                | 49    |

| Figure 2.26 VI OCR, when Ron=5 $\Omega$                                                                                                                                                                                                                               | 50    |

| Figure 2.27 Trip signal generated by FPGA for EI OCR at TDS=1                                                                                                                                                                                                         | 51    |

| Figure 2.28 Signal generated by FPGA and RTDS relay for EI OCR at TDS=1                                                                                                                                                                                               | 51    |

| Figure 2.29 Test results for EI characteristic based OCR at TDS=2                                                                                                                                                                                                     | 52    |

| Figure 2.30 Signal generated by FPGA and RTDS relay for VI OCR                                                                                                                                                                                                        | 52    |

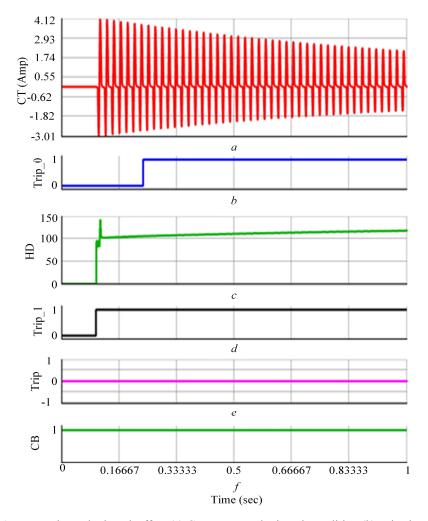

| <b>Figure 2.31</b> Test results under inrush effect (a) CT current under inrush condition (b signal generated by the FPGA (c) HD of the signal under inrush condition (d) Trip signal HDth) (e) Effective trip signal generated by the prototype (f) Status of the CB | (HD > |

| Figure 3.1 Block diagram for the RMS module                                                                                                                                                                                                                           |       |

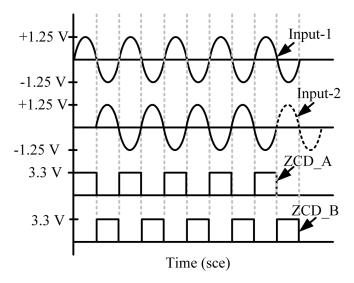

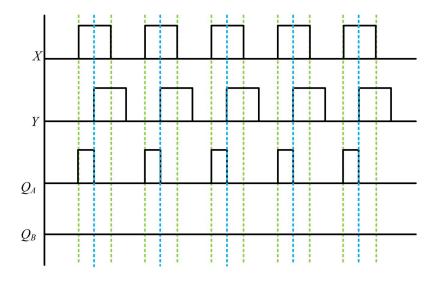

| Figure 3.2 Waveforms of the ZCD module                                                                                                                                                                                                                                | 57    |

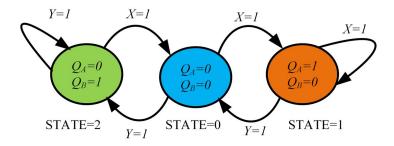

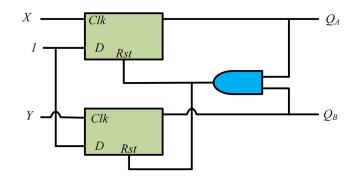

| Figure 3.3 State diagram of the PD module                                                                                                                                                                                                                             | 57    |

| Figure 3.4 Circuit diagram of the PD module                                                                                                                                                                                                                           | 58    |

| Figure 3.5 Output of PD module when X leads Y                                                                                                                                                                                                                         | 58    |

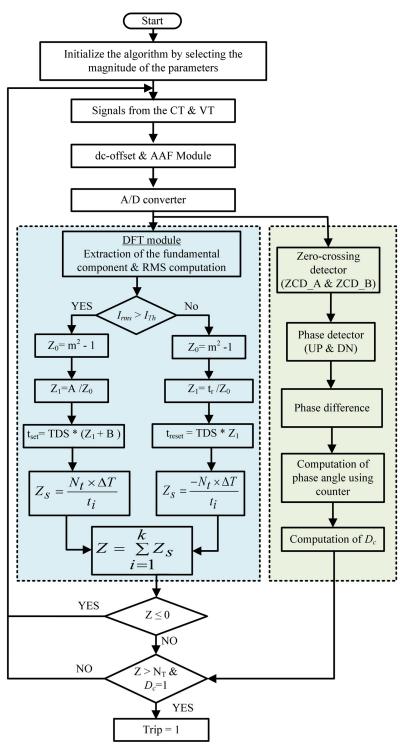

| Figure 3.6 Flow chart of the DOCR                                                                                                                                                                                                                                     | 60    |

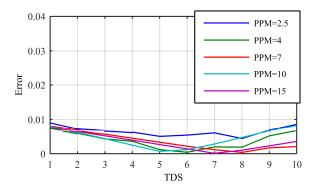

| Figure 3.7 Error between emulated and IEEE Std. relay operating                                                                                                                                                                                                       | 62    |

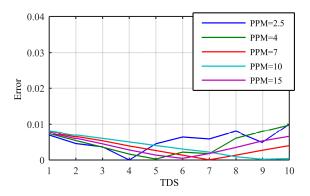

| Figure 3.8 Error between emulated and IEEE Std. relay operating time                                                                                                                                                                                                  | 62    |

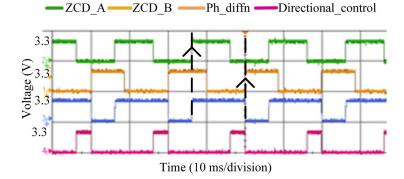

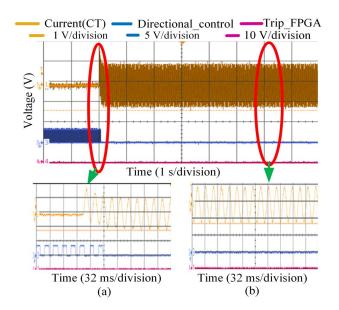

| Figure 3.9 HIL testing of PD module under normal condition                                                                                                                                                                                                            | 63    |

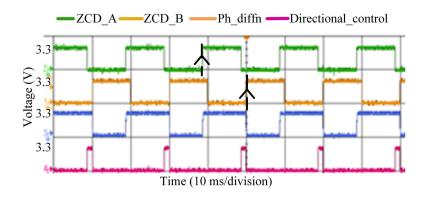

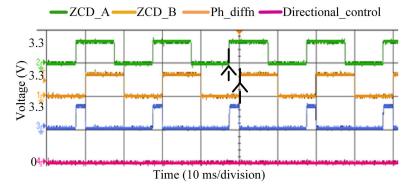

| Figure 3.10 HIL testing of PD module when fault incepted at Location-1                                                                                                                                                                                                | 64    |

| Figure 3.11 HIL testing of PD module when fault incepted at Location_2                                                                                                                                                                                                | 64    |

| Figure 3.12 HIL result for EI characteristics when LG fault occurred at location1                                                                                                                                                                                     | 65    |

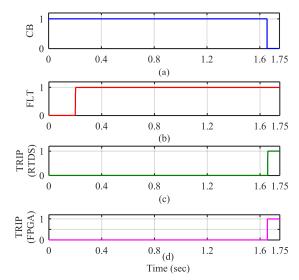

| Figure 3.13 Status of control signal when LG fault occurred at location-1                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.14 HIL result for EI characteristic when LG fault occurred at location 2                                                        |

| Figure 3.15 Status of control signal when LG fault occurred at location-2                                                                |

| Figure 3.16 HIL result for EI characteristic when LL fault occurred at location 1                                                        |

| Figure 3.17 Status of control signal when LL fault occurred at location 1                                                                |

| Figure 3.18 HIL result for EI characteristic when LL fault occurred at location 2                                                        |

| Figure 3.19 Status of control signal, when LL fault occurred at location 2                                                               |

| Figure 4.1 Overview and signal-flow of the proposed IDT                                                                                  |

| Figure 4.2 Flow-chart of the proposed islanding detection technique                                                                      |

| Figure 4.3 Microgrid test system modelled in RTDS                                                                                        |

| Figure 4.4 IDF magnitude for islanding & non- islanding events with power mismatch 0%. 77                                                |

| Figure 4.5 IDF magnitude for islanding & non-islanding events for 25% power mismatch 78                                                  |

| Figure 4.6 Values of IDF for islanding & non- islanding events for -25% power mismatch. 78                                               |

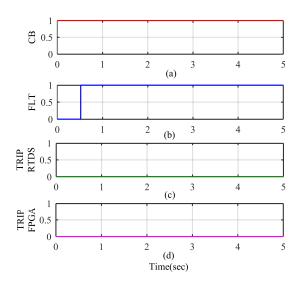

| Figure 4.7 Test results for 0% mismatch condition monitored in RTDS                                                                      |

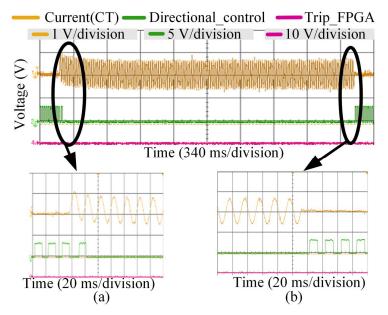

| Figure 4.8 Test results for 0% mismatch condition monitored in DSO                                                                       |

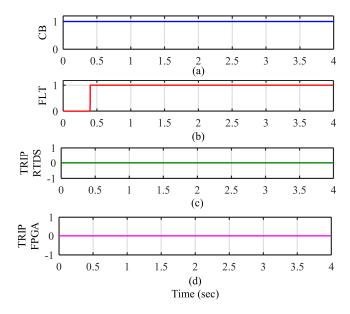

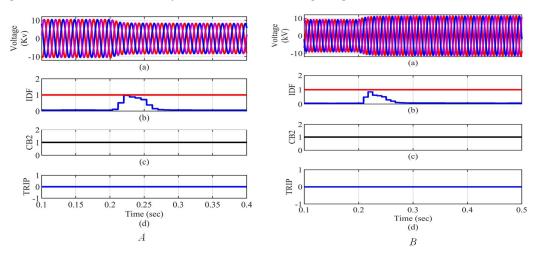

| Figure 4.9 Test results monitored in RTDS when mismatch is 25%                                                                           |

| Figure 4.10 Test results monitored in DSO, when mismatch is 25%                                                                          |

| Figure 4.11 Performance Verification of islanding condition when mismatch is 25%                                                         |

| Figure 4.12 Signal monitored in DSO for performance verification when mismatch is 25% 83                                                 |

| Figure 4.13 Variation of load at target DG (a) Magnitude of IDF (b) Under 25% power         mismatch for 50% variation.       85         |

| Figure 4.14 Variation in inductive load at target DG (a) Magnitude of IDF (b) For 50% change       85         in inductive load       85 |

| <b>Figure 4.15</b> Variation of capacitive load at target DG (a) Magnitude of IDF (b) response for 50% variation in capacitive load      |

| Figure 4.16 Performance under non-islanding events (A) under voltage sag (B) under voltage swell                                         |

| Figure 4.17 Comparison between published and proposed IDT                                                                                |

| Figure 5.1  | Microgrid test system modelled in RTDS                             | . 90 |

|-------------|--------------------------------------------------------------------|------|

| Figure 5.2  | Design-flow of the proposed design                                 | . 91 |

| Figure 5.3  | Results of the OCM for grid-connected mode                         | . 97 |

| Figure 5.4  | Results of the OCM for standalone mode                             | . 98 |

| Figure 5.5  | Status of the signal for HIL- verification of VU module            | . 98 |

| Figure 5.6  | HIL-verification of the ROCOF module for constant power load       | . 99 |

| Figure 5.7  | Operation of the hardcore relay in hybrid mode                     | 100  |

| Figure 5.8  | Performance of the relay under mode adaptation                     | 101  |

| Figure 5.9  | HIL-verification of the ROCOF module for constant impedance load   | 106  |

| Figure 6.1  | Overview of the developed overcurrent relay                        | 110  |

| Figure 6.2  | Adaptive relaying principal                                        | 111  |

| Figure 6.3  | Enhanced ShockBurst protocol engine                                | 112  |

| Figure 6.4  | Flow-chart of the proposed relay prototype                         | 114  |

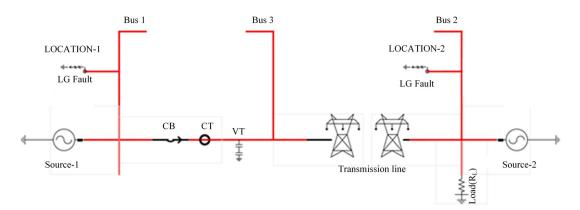

| Figure 6.5  | Layout of the Microgrid test system with control strategy          | 115  |

| Figure 6.6  | Hardware set-up for HIL verification                               | 116  |

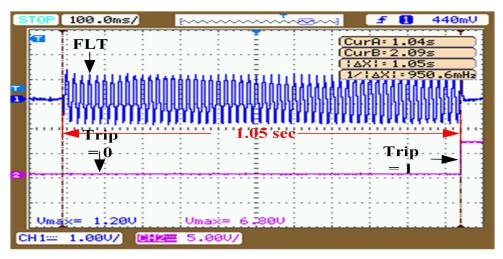

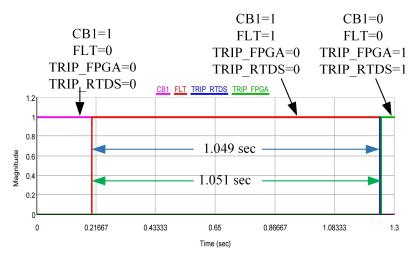

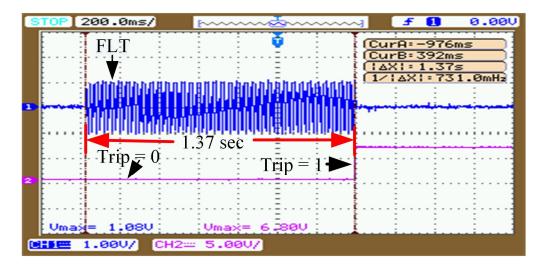

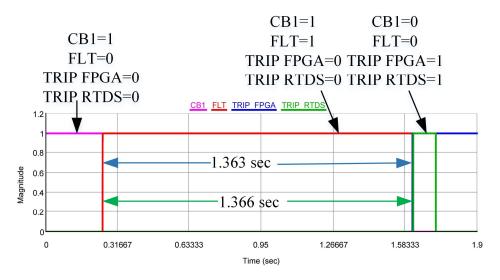

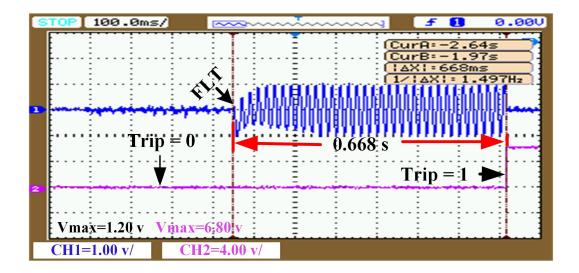

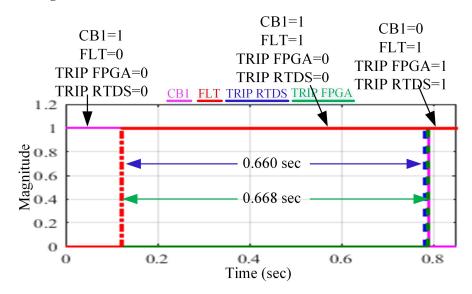

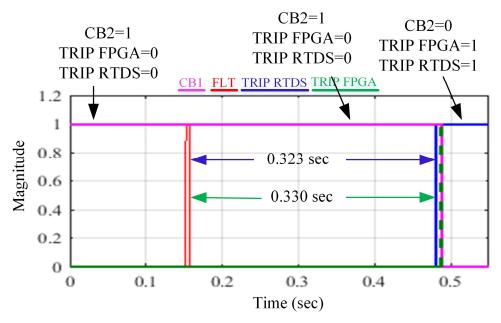

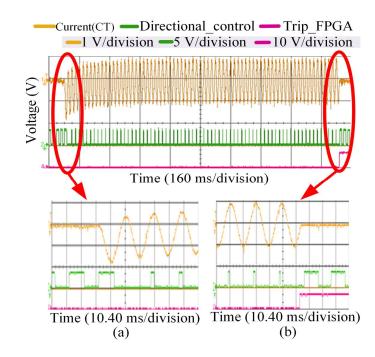

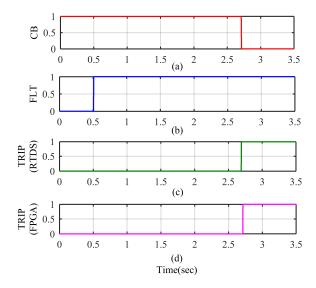

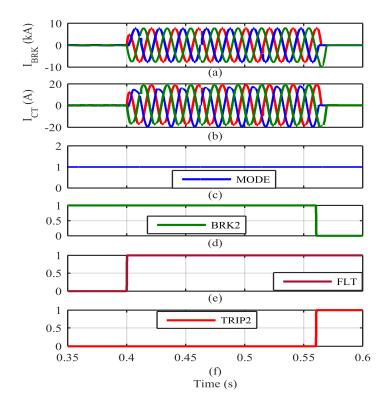

| Figure 6.7  | Test results for grid-connected MG when fault is incepted at $F_2$ | 117  |

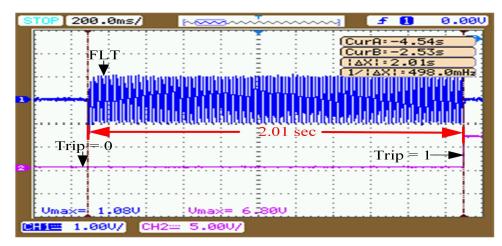

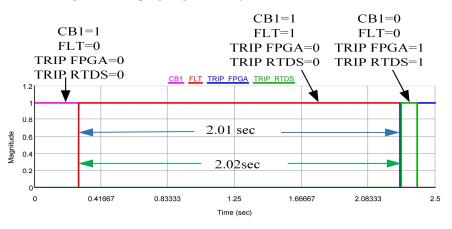

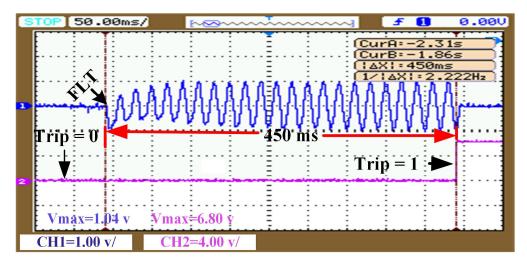

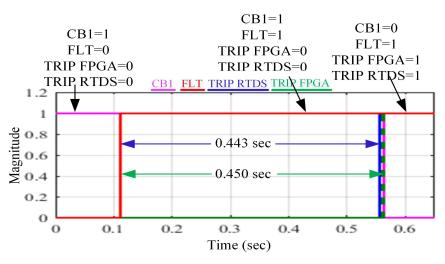

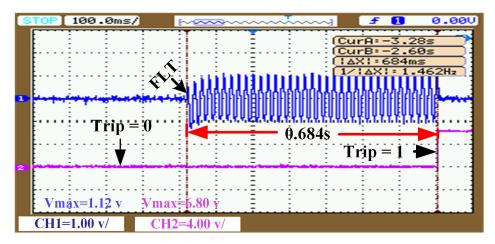

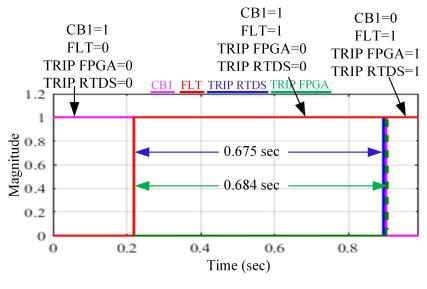

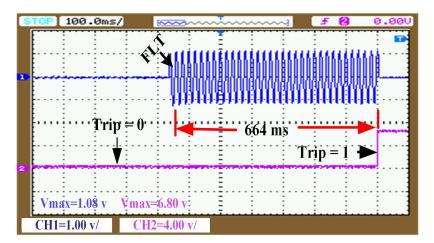

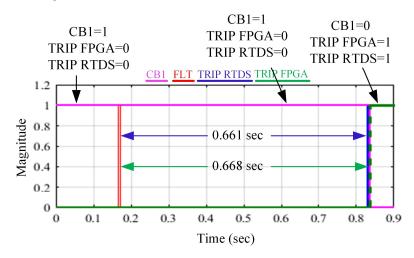

| Figure 6.8  | Results for islanded MG when fault incepted at $F_2$               | 118  |

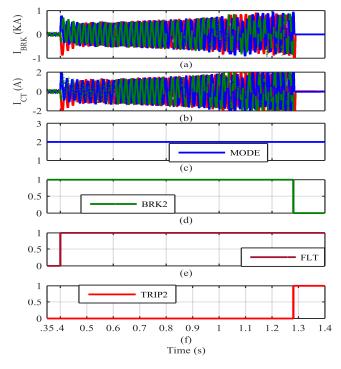

| Figure 6.9  | Operation of the OCR for mode adaptation                           | 119  |

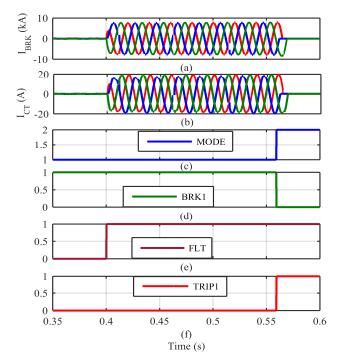

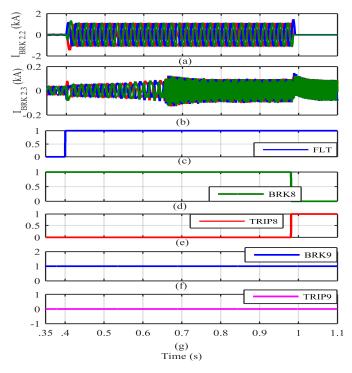

| Figure 6.10 | <b>0</b> Results for relay coordination for fault at $F_3$         | 120  |

# LIST OF TABLES

| Table 1.1 Comparison of various islanding detection method                             | 14  |

|----------------------------------------------------------------------------------------|-----|

| Table 1.2 Comparison of various active islanding method                                | 15  |

| Table 1.3 Comparison of various passive islanding method                               | 17  |

| Table 1.4 Comparison of various hybrid islanding method                                | 18  |

| Table 1.5 Comparison of various communication based islanding method                   | 19  |

| Table 1.6 Comparison of various signal processing based islanding method               | 21  |

| Table 2.1 Parameters for the relay characteristics                                     | 28  |

| Table 2.2 Summary of XC5VLX50T-3FF1136 device resource utilization                     | 34  |

| Table 2.3 IEEE standard and emulated operating time for EI time-current characteristic | 35  |

| Table 2.4 IEEE standard and emulated operating time for VI time-current characteristic | 36  |

| Table 2.5 (%) error between IEEE standard and emulated relay operating time            | 37  |

| Table 2.6 (%) error between IEEE standard and emulated relay operating time            | 37  |

| Table 2.7 Characteristics verification of the OCR with different values of Ip and TDS  | 44  |

| Table 2.8 Operational verification of the OCR with different operating conditions      | 50  |

| Table 3.1 Summary of FPGA Device Resource Utilization for DOCR                         | 61  |

| <b>Table 3.2</b> Status of signals when fault is occurred at location 1                | 65  |

| <b>Table 3.3</b> Status of signals when fault is occurred at location 2                | 66  |

| Table 4.1 Testing of the designed prototype under different power mismatch conditions  | 83  |

| Table 4.2 Testing of the designed prototype under different power mismatch conditions  | 84  |

| Table 5.1 Components settings for HIL-Verification of the proposed prototype           | 95  |

| Table 5.2 Functional modules of the relay                                              | 96  |

| Table 5.3 Verification of the designed module of the proposed relay                    | 102 |

| Table 5.4 Operation in hybrid IDT for 25 % power mismatch ("011")                      | 104 |

| Table 5.5 Adaptive operation of the proposed design                                    | 105 |

| Table 6.1 | Testing of the | relay performan | e under different | fault conditions |  |

|-----------|----------------|-----------------|-------------------|------------------|--|

|-----------|----------------|-----------------|-------------------|------------------|--|

# LIST OF SYMBOLS

| Symbols                       | Meaning                                              |

|-------------------------------|------------------------------------------------------|

| А,В,р                         | Characteristics Constant of the Relay                |

| ADC_in                        | Input of the FPGA                                    |

| Clk                           | Clock                                                |

| f                             | Frequency                                            |

| $F_1$                         | Fault at Location 1                                  |

| $F_2$                         | Fault at Location 2                                  |

| $F_3$                         | Fault at Location 3                                  |

| $F_4$                         | Fault at Location 4                                  |

| $F_5$                         | Fault at Location 5                                  |

| FLT                           | Fault                                                |

| $F_n$                         | Frequency of the Fundamental Component               |

| $F_s$                         | Sampling Frequency                                   |

| G                             | Generation Capacity                                  |

| Н                             | Moment of Inertia                                    |

| $I_F$                         | Fault Current                                        |

| Ip                            | Pick-up Current                                      |

| k                             | Scaling Factor for ROCOF                             |

| $N_0$                         | Zero Sequence Component                              |

| $N_l$                         | Positive Sequence Component                          |

| $N_2$                         | Negative Sequence Component                          |

| Na, Nb, Nc                    | Phase A,B,C Voltage                                  |

| $N_T$                         | Target Number                                        |

| $P_b$ , $Z_b$ , $P_c$ , $Z_c$ | Parameter Constant                                   |

| <i>ROCOF</i> <sub>th</sub>    | Threshold Value of Rate of change of frequency       |

| t                             | Relay Tripping Time                                  |

| $t_r$                         | Relay Reset Time                                     |

| TRIP_FPGA                     | Trip Signal Generated by FPGA Relay Prototype        |

| TRIP_ROCOF                    | Trip Generated by Rate-of-change of Frequency Module |

| TRIP_RTDS                     | Trip Signal Generated by RTDS Relay                  |

| TRIP_VU                       | Trip Generated by Voltage Unbalance Module           |

| $t_s$                         | Relay Set Time                                       |

| VU <sub>th</sub>              | Threshold Value of Voltage Unbalance                 |

| X(0)                          | DC Component of Input Signal                         |

| X(1)       | Fundamental Component of Input Signal        |

|------------|----------------------------------------------|

| X(2)       | 2nd Harmonic Component of Input Signal       |

| x(n)       | Input Signal                                 |

| Ζ          | Accumulator                                  |

| $\Delta P$ | Power Unbalances between Load and Generation |

# LIST OF ABBREVIATIONS

| Abbreviations | Meaning                                 |

|---------------|-----------------------------------------|

| AAF           | Anti-Aliasing Filter                    |

| ADC           | Analog to Digital Converter             |

| AFD           | Active Frequency Drift                  |

| ANN           | Artificial Neural Network               |

| ASIC          | Application Specific Integrated Circuit |

| BRAM          | Block Random Access Memory              |

| CAAR          | Communication Assisted Adaptive Relay   |

| CB            | Circuit Breaker                         |

| CLB           | Configurable Logic Block                |

| CORDIC        | Coordinate Rotational Digital Computer  |

| СТ            | Current Transformer                     |

| DER           | Distributed Energy Resource             |

| DFT           | Discrete Fourier Transform              |

| DG            | Distributed Generator                   |

| DOCR          | Directional Overcurrent relay           |

| DSO           | Digital Storage Oscilloscope            |

| DSP           | Digital Signal processing               |

| DT            | Definite Time                           |

| DWT           | Discrete Wavelet Transform              |

| EI            | Extreme Inverse                         |

| FPGA          | Field Programmable Gate Array           |

| GTAO          | Gigabit Transceiver Digital Output Card |

| GTDI          | Gigabit Transceiver Digital Input Card  |

| HD            | Harmonic Distortion                     |

| HDL           | Hardware Description Language           |

| HHT           | Hilbert Huyang Transform                |

| HIL           | Hardware-in-loop                        |

| I/O           | Input-output                            |

| IT            | Inverse Time                            |

| ID            | Internal Design                         |

| IDF           | Islanding Discrimination Factor         |

| IDMT          | Inverse Definite Minimum Time           |

| IDT           | Islanding Detection Technique           |

| IED           | Intelligence Electronic Device          |

| IP            | Intellectual Property                   |

| ISE           | Integrated Synthesis Environment        |

| LG            | Line-Ground                             |

| LL            | Line-Line                               |

| LLLG          | Line-Line-Ground                        |

|               |                                         |

| LUT   | Lookup Table                                                     |

|-------|------------------------------------------------------------------|

| M     | Plug Point Setting                                               |

| MCB   | Main Circuit Breaker                                             |

| MG    | Microgrid                                                        |

| MSPS  | Mega Sample Per Second                                           |

| NDZ   | Non Detection Zone                                               |

| NGC   | Native Generic Circuit                                           |

| OCR   | Overcurrent Relay                                                |

| PCC   | Point of Common Coupling                                         |

| PD    | Phase Detection                                                  |

| PD    | Phase Detection                                                  |

| PEI   | Power Electronics Interfacing                                    |

| PLC   | Power Line Communication                                         |

| PLC   | Programmable Logic Controller                                    |

| PLL   | Phase Locked Loop                                                |

| PMU   | Phasor Measurement Unit                                          |

| PSM   | Power System Module                                              |

| PV    | Photovoltaic                                                     |

| RAM   | Random Access Memory                                             |

| REM   | Relay Emulating Module                                           |

| RES   | Renewable Energy Sources                                         |

| RMS   | Root Mean Square                                                 |

| ROCOF | Rate of Change of Frequency                                      |

| ROCOP | Rate of Change of Output Power                                   |

| RPS   | Real Power Shift                                                 |

| RTDS  | Real-Time Digital Simulator                                      |

| RTL   | Register Transfer logic                                          |

| SCADA | Supervisory Control and Data Acquisition                         |

| SFS   | Sandia Frequency shift                                           |

| SMS   | Slip Mode Frequency Shift                                        |

| SOPC  | System on Programmable Chip                                      |

| SVS   | Sandia Voltage shift                                             |

| TDS   | Time Dial Setting                                                |

| THD   | Total Harmonic Distortion                                        |

| TT    | Transfer Trip                                                    |

| UCF   | User Constraint File                                             |

| VHDL  | Very High Speed Integrated Circuit Hardware Description Language |

| VHSIC | Very High Speed Integrated Circuit                               |

| VI    | Very Inverse                                                     |

| VT    | Voltage Transformer                                              |

| VU    | Voltage Unbalance                                                |

| ZCD   | Zero Crossing Detector                                           |

|       |                                                                  |

### 1.1 Overview of Relay Design

An electromagnetic relay is a fundamental relay, which works on the principle of electromagnetic effects of the current flowing through the energised winding. This relay has many limitations such as high power consumption, contact problem, slow response, a high burden on instrument transformer and adaptability. Adaptation of the diodes, transistors, capacitors and inductors in the 1980s, added a new edge in the power system industry by introducing the solid state and static relays. These relays have comparatively low cost, small size and require less maintenance. Programmability and lack of communication features were the main disadvantages of these conventional relays. The microprocessor ( $\mu$ P) and the microcontroller ( $\mu$ C) based digital numerical relays were introduced in the 1990s. These relays facilitate software programmability and support multiple objectives realization on a single controller. However, the requirement of application specific integrated circuits, programmability, memory space, computational burden, limited speed and high cost were the main constraints of these relays.

The recent advancement of digital technology is the re-configurable hardware i.e. field programmable gate array (FPGA), programmed by Hardware Description Language (HDL) is used for high-speed applications. It has credentials for developing intelligent electronic devices, which are used in the power system components, and smart grid applications i.e. fast relay for the protection of the microgrid (MG) asking high computational demand, low latencies, reconfigurability, high bandwidth and parallel processing. Some inherent benefit of the FPGA device is the parallelism of the hardware that increases the execution speed compared to sequential software architecture based technologies ( $\mu$ P and  $\mu$ C).

### **1.2 Overview of Microgrid**

The increased usage of the low-carbon emitting distributed generators (DGs) and renewable energy sources (RESs) like solar PVs and wind generators placed at the distribution level has changed the structure of the conventional power system network [1], [2]. These DGs and RESs serve multiple purposes viz. reducing the carbon footprint from the environment, reachability to remote demand locations, quick installation and low-cost maintenance etc. The term "microgrids" (MGs) was coined around one and a half decade ago, provides a platform for integration of various diesel generators, RESs, loads and storage devices [3]. These MGs are usually connected to the utility grid through a single bus called the point of common coupling (PCC) and hence, are capable of operating both in synchronism with the utility grid known as grid-connected mode and as an autonomous power island i.e. standalone mode. The small-scale MGs provides uninterrupted power supply to the end users during the period of any power outage, emergencies and failures of the main/utility grid due to any abnormality or when a fault occurs in the utility grid.

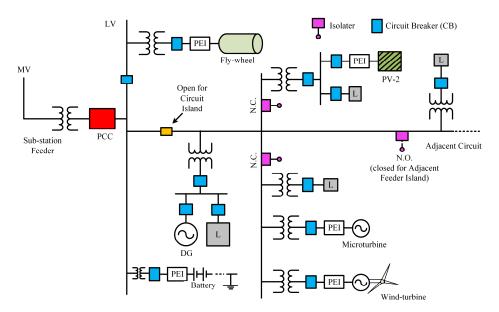

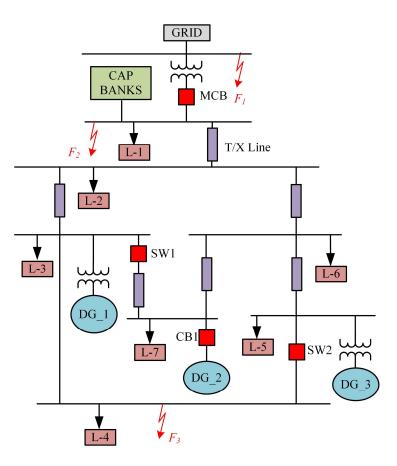

Figure 1.1 gives a simple architecture of the MG that consists of different types of generation unit i.e. solar photovoltaic (PV) cells, wind turbine, flywheel, diesel generator, batteries and microturbine. Some of these generations are RESs type i.e. PV cells and wind turbine, which are intermittent in nature and follows different generation characteristics [4], [5]. These RESs are connected to the MG through power electronics interfacing (PEI) inverters and converters, which are used to convert the generated power into different format i.e. DC-to-AC and AC-DC-AC. Different types of loads (L), Isolators and circuit breaker (CB) are also connected to the MG. The isolator is used to connect or disconnect a portion of the MG (to accommodate any change in its configuration). Whereas, the CB is a controlled switch that is used to perform the control and protection activities. The main circuit breaker (MCB) located at PCC is a centralized switch that is responsible for deciding the operating modes of the MG. Now, there are several challenges for reliable operation of the MG is of high significance. The work presented in this thesis covers various aspects of MG protection.

Figure 1.1 Architecture of the Microgrid

#### **1.2.1 Microgrid Protection**

Traditional protection schemes used in the conventional power system, are not applicable for the protection of the MG due to the integration of a large number of DERs [6] [7]. The involvement of low inertial interfacing converters, bidirectional power flow within the network and different generation characteristics make the task of MG protection a complex one. Furthermore, the magnitude of the fault current is limited and it depends on the operating mode of the MG as well as number and types of the integrated DGs placed within the MG. The contribution of the fault current by rotating machine based sources are higher than that of inverter-interfaced DERs as compared to their respective normal rated current. The magnitude of fault current is 6.0-10.0 p.u in the rotating machine whereas its magnitude is lower i.e. up to 1.0-2.0 p.u in case of inverter-interfaced DERs [8]–[11] [12]. Moreover, in the grid-connected mode of operation, the magnitude of fault current is greater than the magnitude of fault current in the islanded mode of operation. Therefore, it is important to detect the operating mode of the MG. Identification of the mode of operation of the MG is also essential for the programming of protection devices since the contribution of the fault current depends on the mode of operation of the microgrid and penetration of the DGs, RESs and storage devices that affect the satisfactory working of the traditional protective relays. Quick isolation of the DGs in case of islanding event is considered to be a significant step towards MG protection. However, it is difficult to achieve this goal by using a traditional relay. Several other protection issues of MG viz. identification of its operating mode, islanding detection, isolation of spurious or faulty sections, fault current level, the direction of power flow and blocking of false trips etc. in the presence of a large number of DGs is a challenging task [13], [14]. Out of all these, islanding detection is one of the most crucial aspects for MG protection for safe, secure and uninterrupted power supply.

#### **1.2.2 Importance of IDTs**

Islanding is the condition which occurs when a portion of the distribution network (or MG) is disconnected from the utility grid and operates independently with help of local DGs and RESs [15], [16]. Generally, two types of islanding of MG occur i.e. intentional and unintentional [17]. The intentional islanding is mainly performed to carry out some maintenance works within the MG and for the safety of the working personnel [18]; whereas the unintentional islanding occurs due to the utility grid blackout by equipment failure, natural disaster or any abnormality in the power system. System stability and power quality within the MG are adversely affected during the unintentional islanding, which can damage the electrical equipment (critical loads and DGs)

within the working islanded section. Hence, in present studies, more focus is given on the unintentional islanding of the MG [12].

Therefore, when islanding occurs at PCC, it must be detected at the DG terminals which can be disconnected from the MG feeders for the safety of the equipment. As per the suggested standard viz. UL 1741 [19], IEC-62116 [20] and IEEE 1547<sup>TM</sup> [21] islanding must be detected and the active DGs are isolated from the MG within 2-seconds after detecting the islanding. However, by isolating a DG, the reliability of the MG i.e. maintaining the uninterrupted power supply to critical loads is lost. Therefore, to improve the reliability of MG, another way to act in case of MG islanding is to reduce the output power of the DGs (equivalent to the critical load demand) instead of isolating it. In that case, for the protection of working DGs, the relay settings should be changed i.e. reduced as per the decrease in the power flowing through the network. Now, for the purpose of islanding detection, under/over voltage, under/over frequency, and phasor based techniques are mostly used [22]. Hence, it is an essential requirement to develop a fast relay that can detect the islanding (by sensing variations in these parameters) within the stipulated time interval as well as take necessary action i.e. either isolate the affected section/DG of the MG (with non-critical loads) by generating the trip signal or adapting the relays at the DG terminal i.e. reducing their threshold setting for maintaining reliability of the supply to critical loads.

#### 1.2.3 Requirement of Fast Relays

The existing overcurrent protection relay i.e. OCRs developed for passive distribution networks (radial network) are not applicable for active distribution networks viz. MG. Since MG is a lowinertial system as the integrated DERs are connected through PEI having fast dynamics. Some of the other significant protection issues for using conventional relays with respect to MGs are listed below [6] [23]:

- The level of fault current varies according to their mode of operation i.e. the protection technique developed for one mode of operation would not be applicable for another mode of operation due to the different level of fault current.

- Threshold setting of the relay become invalid because of the unpredictable dynamic characteristics of RESs based generators.

- DERs are connected to the MG using different types of interfacing PEI which limits the amount of fault current.

To overcome the stated problems, a fast relay is required for the protection of a MG that can isolate the faulty section, detect its mode of operation and also, change the setting of the

threshold as per the operating mode. Further, it is important to note that, the MG is a low-inertial system having different types of DG with faster dynamics. To tackle these issues, protective hardware is required to be developed that can sense the faster dynamics within a MG and also have the feature of parallel processing by which the computation time for decision making is reduced. Hence, a faster response is obtained. The Field programmable gate arrays (FPGA) is such an electronic device that is used in the power system industry and smart grid applications asking for high computational demand, low latencies, reconfigurability, high bandwidth and parallel processing [24].

With the help of FPGA, signal processing modules are implemented with a higher degree of accuracy at a low cost. Furthermore, they are easily reprogrammable to accommodate any changes in the design [25]. The performance of the FPGA based system is a lot better than the microcontroller i.e.  $\mu$ C and DSP based relays. Since FPGA works on the principle of parallel processing, its operations are faster [26]. Due to these predominant features, the FPGA based systems are currently being considered to perform power flow monitoring, fault identification and the protection of the distribution systems [27].

### **1.3 Field Programmable Gate Array**

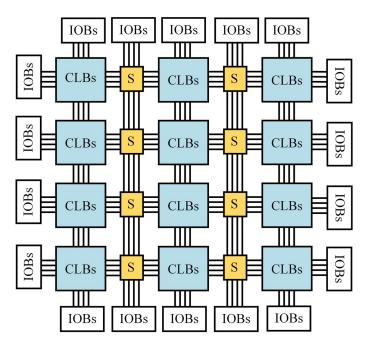

FPGAs are programmable integrated devices capable of implementing the digital design of the protective relays for MGs. Reconfigurability and re-programmability are the important features of the FPGA that provides the flexibility for developing logic circuits at low cost. Low power consumption, high-speed input-output (I/O) capabilities and parallel processing are some of the essential features of FPGA, which are used in the signal processing and found suitable for the practical platform with real-time applications [28], [29] [30]. Hardware description language (HDL) viz. VHDL or Verilog is used to implement the digital-logic on the FPGA. In VHDL, 'V' stands for Very High-Speed Integrated Circuit (VHSIC) and HDL. Figure 1.2 shows a typical architecture of the FPGA that consists of input-output blocks (IOBs), programmable switches (Ss) and configurable logic blocks (CLBs) [31]. IOBs are the special logic blocks that provide a programmable interface between the CLBs and the external peripherals. Switches provide programmable interconnections between input/output and CLBs. CLBs are the programmable logic blocks also known as slices or logic cells that are used in the digital design of an algorithm or a circuit for performing necessary computation and storage of data. Programmable combinational logic (various gates), flip-flops and look-up tables are the main elements of CLBs.

Figure 1.2 Overview of the Field Programmable Gate Array

#### 1.3.1 FPGA Design Flow

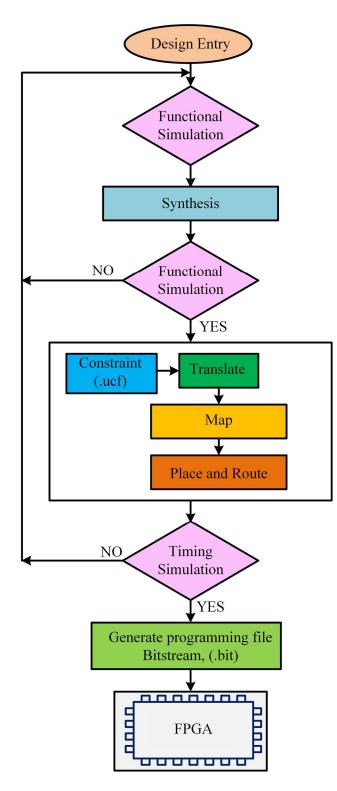

Figure 1.3 shows the simplified design flow to program an FPGA. It includes HDL coding, simulation, synthesis, and implementation as discussed below:

#### Design Entry:

At this stage, functionality and structure of the design plus I/Os of an algorithm are defined. There are different methods of the design entry viz. schematic based, HDL based and a combination of both. Schematic based design entry is easy to read, but, it is not convenient for large project (complex design). HDL based designs are more convenient and fast to implement the sophisticated design. In our work, HDL based design approach is used to implement the relaying algorithm using Verilog HDL. Target FPGA device is also selected during the design entry for the simulation and implemented of the design.

#### **RTL Design and Simulation:**

It is also known as register transfer logic (RTL) design and simulation. This simulation is performed to detect any logic error in the functionality implementation of the design. The simulation run time is not very high and it also allows one to change the HDL code if the required functionality is not met.

#### Synthesis:

In this process, input HDL viz. VHDL or Verilog is translated into a netlist, which describes a list of logical element (logic gates and flip-flops) and their connectivity. For a complex design,

multiple netlists are generated. It has three standard processes i.e. syntax check, optimization and mapping. The resulting output design netlist is in the format of Native Generic Circuit (NGC) file that is used for design implementation.

Figure 1.3 FPGA design flow

### Functional Simulation:

It is a post-synthesis simulation that gives information about the logic operation of the circuit. The functionality of the design can be tested after completion of the translation process. If the functionality of the design is not met, changes in the code can be done.

#### Implementation:

This process includes translate, mapping, placement and routing of the logic within the FPGA device. In the translation process, all netlists and constraints are combined into single large netlist (Xilinx format is Native Generic Database (NGD)). Here, constraints are defined through pin assignment and timing requirement viz. input clock period and maximum delay. This information is stored in a User Constraints File (UCF) with extention.ucf.

After that, the specified resources of the input netlist (extention.ngd) are compared with the available resources of the target FPGA during the mapping step. Here, an error message is generated if the resources are specified/defined incorrectly. The whole circuit is divided into sub-blocks to fit into the logic blocks of the target FPGA. Native Circuit Description (NCD) file is generated as an output.

Now, the place and route processes are used to mapped NCD sub-blocks into FPGA logic blocks physically, according to the defined constraints. Also, signals are routed between logic blocks to meet the timing constraints. The output NCD file carries routing information.

# Timing Analysis:

Finally, a timing simulation is performed after the place and route step, which evaluates the implemented design with all the timing constraints. The complete information of the time delay of the design is written out in the Post Place and Route timing report.

The routed NCD file is converted to a bitstream (.bit file) using BITGEN that is used to programme the target FPGA for on-chip implementation.

### **1.4 Literature Review**

As this thesis primarily focuses on the fast acting relays and MG protection, the literature review is divided into three parts: relay design, islanding detection and mode adaptability for the MG protection. A comprehensive review of these areas is carried out as follows:

### 1.4.1 Relay Design

A relay is designed to ensure the protection of an electric power supply network against faults and abnormalities in power system operation. Overcurrent relays (OCRs) are more commonly used relays for power system protection than any other type of relays [32]. These relays operate when the actuating current exceeds from a specified limit, by generating a trip

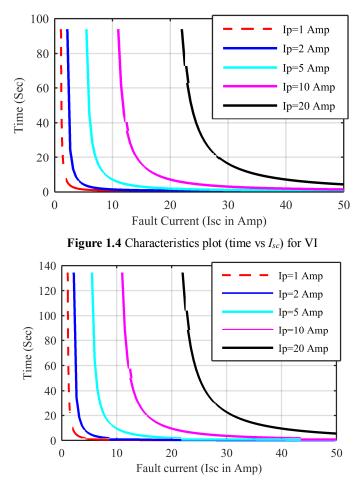

signal for the CB. These relays have been deployed to protect a wide range of power system components such as generators, sub-transmission and distribution networks, rotating machines and transformers etc. Figure 1.4 and Figure 1.5 represent the inverse characteristics i.e., Very inverse (VI) and Extremely inverse (EI) characteristics of the OCR. In these figures, y-axis represents the relay tripping time in sec whereas x-axis represents the fault current ( $I_{sc}$ ) in Amp. Each curve shows the fixed values of the  $I_p$  settings. For a given  $I_p$ , if the magnitude of fault current  $I_{sc}$  increases, the trip-time decreases. However, if plug-setting  $I_p$  is kept high (for a given fault current), then the relay tripping time would also increases.

An electromagnetic relay is a fundamental relay which works on the principle of electromagnetic effects of the current flowing through the energized winding. This relay has many limitations such as high power consumption, contact problem, slow response, a high burden on instrument transformer and adaptability. A technological transition in relaying is observed after cheap and large-scale manufacturing of the diodes, transistors, capacitors and inductors were made possible in the late 1980s. This added a new edge in the power system industry by introducing the solid state and static relays. These relays have comparatively low-

Figure 1.5 Characteristics plot (time vs Isc) for EI

cost, small size and require less maintenance. However, programmability and lack of communication features were the major drawbacks of such conventional relays.

Microprocessor and Microcontroller based digital numerical relays were introduced in the 1990s [33]–[38]. These relays facilitate software programmability and support multiple objective realizations on a single chip. However, the requirement of application specific integrated circuits (ASIC), programmability, memory space, computational burden, limited speed and high cost were the main constraints of these relays. A hybrid passive OCR equipped with an inductor and a capacitor is proposed in [39]. Here, overcurrent function is used for the detection of DC fault, while the frequency of the LC circuit is processed by the discrete wavelet transform (DWT) to detect high resistive faults. However, this relay is meant for small-scale DC grids only. In [40], a new time-current characteristic for numerical OCRs is proposed by using a customized approach having a set of successive straight lines considered as the OCR characteristics. Relay tripping time is computed using the look-up table which contains the relay operating time and magnitude of the fault current. By doing so, it was assumed that each relay should be operated at the lowest possible time. However, the operating time of the OCR is increased when the magnitude of the fault current does not fall into the look-up table. Therefore, the linear characteristic maintains a fixed time interval between the primary and backup protection relays, hence, affects their coordination. Therefore, some researchers are still trying to define better time-current characteristics than the standard ones to be used in the numerical OCRs [41], [42].

Later, OCR is developed on the FPGA hardware, which is a mature technology and used for high-speed applications. It has credentials for developing intelligent electronic devices (IEDs) which are used in power system industry and smart grid applications asking high computational demand, low latencies, reconfigurability, high bandwidth and parallel processing [24]. FPGA based OCR design is reported in [43] which uses a three-stage pipelined architecture which consists of a look-up-table, a counter, and two comparators. Although the design involves the advantages of FPGA, the effects of noise, signal conditioning and inverse characteristics of the OCR are not considered in the design. The FPGA-based wavelet transformation module is proposed in [44]. Here, the dedicated task of detecting various disturbances in power system such as voltage sags, swells, and loss of power has been carried out. This hardware design requires the allocation of huge amount of hardware resources. Another FPGA based inverse definite minimum time (IDMT) OCR is reported in [45]. The design is based upon a look-up table and the trip signal is generated after a certain delay (predefined in the look-up table) when the value of current is greater than the magnitude of stored value. Here, a preloaded lookup

table is used for determination of tripping time with respect to operating current and cannot be used under varying operating current conditions. Also, it does not follow the IEEE Standard inverse characteristics curve. In [46], a system on a programmable chip (SOPC) based OCR design is presented. Altera development board and soft processor intellectual property (IP) core are used in the design. However, this design does not report extraction of the fundamental frequency component and the proposed OCR is not tested in a closeded loop environment such as Hardware-in-Loop (HIL). Another FPGA based digital OCR is presented in [47] [48]. Here, the pipeline architecture has been used for the design, which was implemented on the Xilinx Virtex-II development board. In this design different types of fault is considered for the verification of the inverse characteristics prescribed by IEEE. However, the HIL verification has not been done for the proposed design. Here also, it lacks the verification in the form of FPGA implementation under real-time operating conditions.

In [49], a multi-functional protective relay is presented which is completely based on preexisting IP cores. The design is based on floating point arithmetic operations which increase both the hardware utilization and the computational burden. Instead of real-time, stored data for fault conditions has been used for testing and HIL verification in closed-loop condition has not been performed. These also fail to cater the requirement of restraint behaviour under inrush current effect which arises due to energization of transformers. Also, in this article, a directional-OCR (DOCR) has also been proposed. Design of the DOCR is based on the delay timer where the trip signal is initiated after a certain time delay. In this design, the inverse characteristics of the OCR have not been included. Directional protection algorithm based on the current sensing module is proposed in [50]. Here, two separate modules have been used for the detection of the magnitude of the fault and its direction. Current is considered as the polarizing quantity in this module and the direction detection module computes the phase angle difference with respect to the normal current. In this paper, inverse characteristics of the OCR is not considered and HIL verification has also not been performed. In [51], a current signal based DOCR is discussed for the transmission line protection. The pre-fault current signal is used as the polarizing quantity. The direction of the fault is detected by a superimposed component of the current signal. The design does not consider the inverse characteristics of the OCR. Also, it is not verified in a real-time environment (HIL).

Certain application of directional relay for coordinated operation is also available in the literature [52]. In [53], a directional inverse time OCR is suggested for meshed distribution systems. Here, continuous relay settings are suggested for the coordination strategy in addition to the conventional pick-up current *Ip* and time-dial settings (*TDS*). By doing so, the operating

time of the OCR is reduced. But, it fails to provide details for computing its directional element. Also, the design and testing of the directional relay in a closed-loop environment have not been discussed. In [54], a new directional element based OCR is proposed. The directional element of the asymmetrical fault is computed using the magnitude and angle of the superimposed negative sequence impedance, whereas for a symmetrical fault the same is computed using the magnitude of the superimposed positive-sequence impedance, positive sequence current and torque angle. Here, the hardware complexity is higher since computation of the sequence component of the impedance is required. Further, the speed of operation of the directional element validation of the designed relay was not reported, and only simulation studies are presented. In [55], the direction of the fault is estimated by a current-based algorithm using the sign of the imaginary part of the post-fault current phasor. However, the experiments are performed in off-line mode by considering a data logger.

#### **1.4.2 Islanding Detection Technique for MGs**

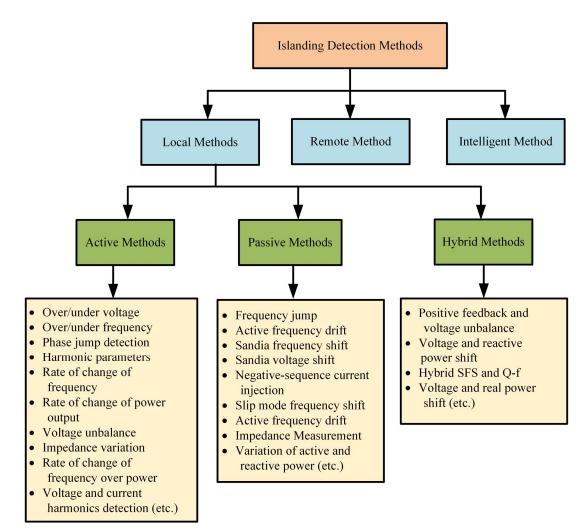

Islanding detection techniques (IDTs) are broadly classified as local, remote and intelligent IDTs as shown in Figure 1.6 [56]–[60]. Local IDTs are further categorized as active, passive, and hybrid methods. In passive IDTs, local parameters of the target DGs terminal viz. frequency, voltage, current, and phase angle are monitored to detect the islanding [61], [62]. Whereas, in active IDTs, small perturbations are introduced with the local parameter. This results in a significant change in the measured system parameters that are used to detect the islanding. In hybrid IDT, two or more methods of islanding detection from active and passive IDTs are combined. In remote IDT, variations in the electrical parameters due to system disturbance is measured at different locations within the MG and the information is transferred to the central control unit through a communication link. The decision for islanding is taken based upon an assessment of various conditions observed from the information shared. Other important category is the intelligent technique that use advanced signal processing tool viz. wavelet transform, neuro-fuzzy classifier, S-transform, artificial neural networks (ANNs), adaptive ANNs for effectively detecting and classifying islanding conditions [56], [57]. The advantages and limitations of the discussed techniques are tabulated in Table 1.1 [63].

### 1.4.2.1 Active islanding detection techniques

Active IDTs are based on estimating the response of various local parameters at the DGs terminal which are mostly generated by introducing/injecting small perturbations using an external source. In active islanding detection technique, a small noise signal is intentionally

Figure 1.6 Classification of islanding detection techniques