# MODELING, ANALYSIS AND CONTROL OF NON-ISOLATED DC-DC CONVERTERS

Ph. D. Thesis

by

### VISHWANATHA SIDDHARTHA

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) MAY, 2019

## MODELING, ANALYSIS AND CONTROL OF NON-ISOLATED DC-DC CONVERTERS

#### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

### DOCTOR OF PHILOSOPHY

in

#### **ELECTRICAL ENGINEERING**

by

#### VISHWANTHA SIDDHARTHA

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) MAY, 2019

©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2019 ALL RIGHTS RESERVED

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

## **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled "MODELING, ANALYSIS AND CONTROL OF NON-ISOLATED DC-DC CONVERTERS" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electrical Engineering of the Indian Institute of Technology Roorkee, Roorkee, is an authentic record of my own work carried out during a period from July, 2014 to May, 2019 under the supervision of Dr. Yogesh Vijay Hote, Associate Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institution.

#### (VISHWANATHA SIDDHARTHA)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

(Yogesh Vijay Hote) Supervisor

Date:

## ABSTRACT

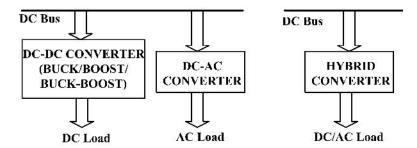

The switched mode converters grow to be popular, because of its vast applications in different fields. These are having applications mainly in micro-grid, renewable energy power generation, battery charging, power supplies, LED drivers, aero-space equipment, drives applications etc. Different applications require their individual set point voltage levels according to the requirement. Depending on the applications, various DC-DC converters have been utilized to step up/down the regulated DC voltage from the unregulated DC voltage. In practice, buck, boost and buck-boost converters are the most commonly used DC-DC converters for step down/up applications. Here, the accurate design analysis of these converter systems is very important. This is main motive to work on detailed analysis, accurate modelling and control of non-isolated DC-DC converters.

Overall, DC-DC converters can be classified as buck and boost type. In this work, the basic non-isolated DC-DC converters such as boost, buck-boost and NIBB (Non-inverting buck-boost) are mainly considered for analysis in different aspects. All major non-idealities of the converter system are considered such as equivalent series resistances (ESR) of filter elements (inductor, capacitor), resistances of input supply, semiconductor switches and diode forward drop voltage. Overall, thesis can be viewed as two parts, first part concentrates on design, modelling analysis of DC-DC converters and second part focuses on their controller design.

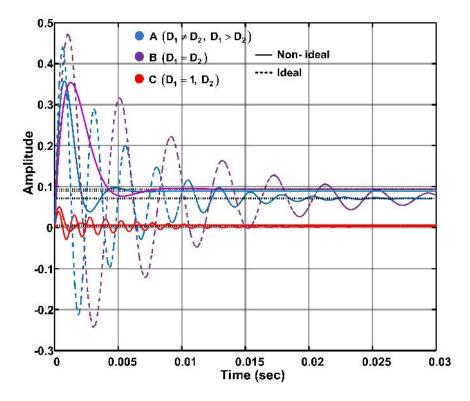

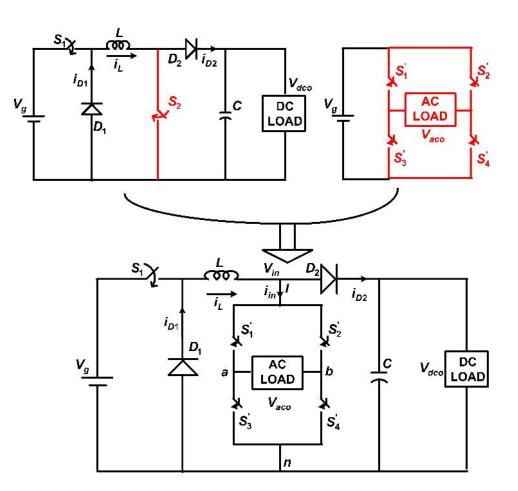

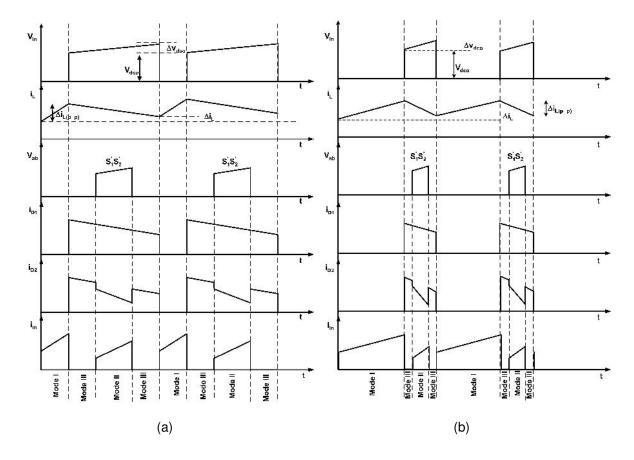

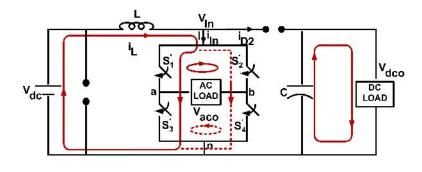

The first part mainly concentrates on power electronic related issues like design, modelling and analysis. This includes improved or accurate expressions of duty cycle, inductor and capacitor for non-ideal boost, buck-boost and NIBB converter. Here, the important discussions of maximum achievable duty cycle, voltage of converter system with the given parameters and minimum input voltage needed for the desired output are explained in detail. The exact utilization of these expressions for power and control engineers also explained. Further, OVR (Output Voltage Ripple) and ESR are analysed and also the effect of ICR (Inductor Current Ripple), OVR on capacitor design discussed in detail. Moreover, the maximum permissible ESR for specified OVR is derived. Along with this, a complete non-ideal mathematical model is developed, which gives similar response of practical system in dynamic and steady-state behaviour wise. The state-space average approach is used to develop the accurate non-ideal models. These non-ideal models are compared with the ideal models. Desired practical results are obtained by the non-ideal model with minimum tolerance. In addition, a hybrid converter namely non-inverting buck-boost derived hybrid converter (NIBBDHC) is proposed based on the knowledge of basic converter topologies. The proposed topology has a feature, which can provide both DC and AC outputs, simultaneously. Functionally as similar as conventional VSI (Voltage Source Inverter), however, shoot through is well utilized in proposed converter. Complete mathematical analysis is presented and are verified through simulation and practical implementation.

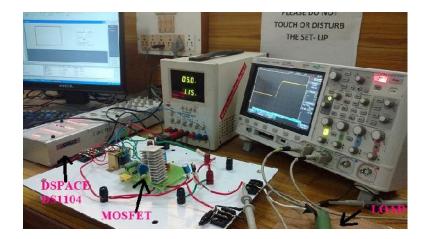

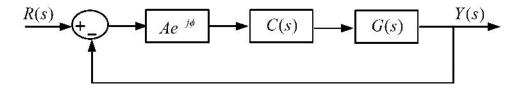

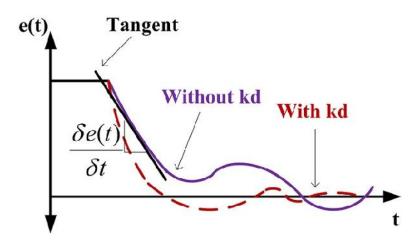

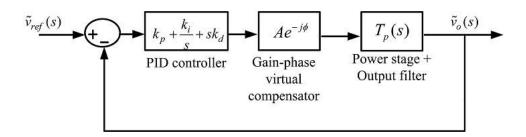

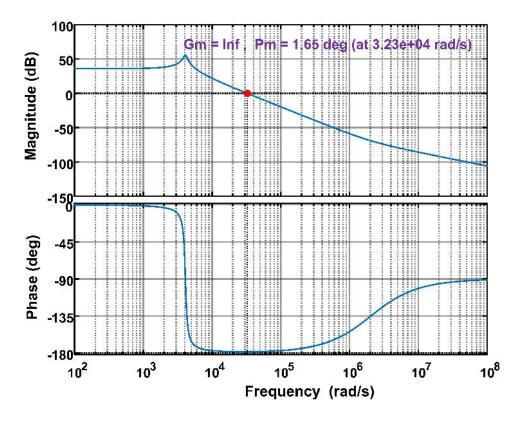

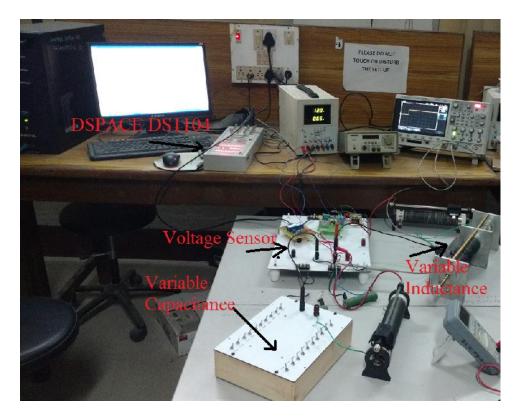

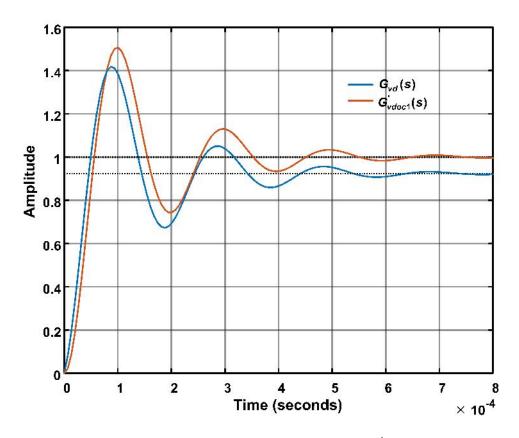

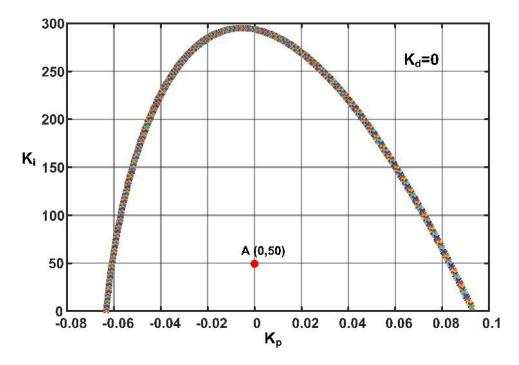

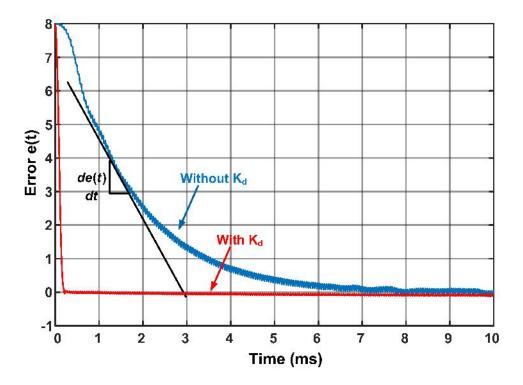

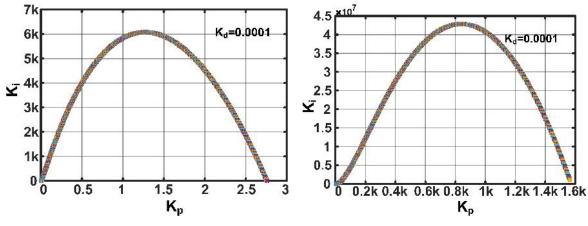

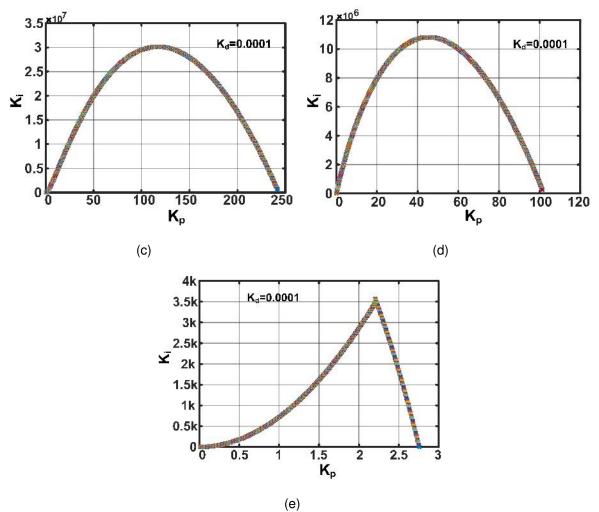

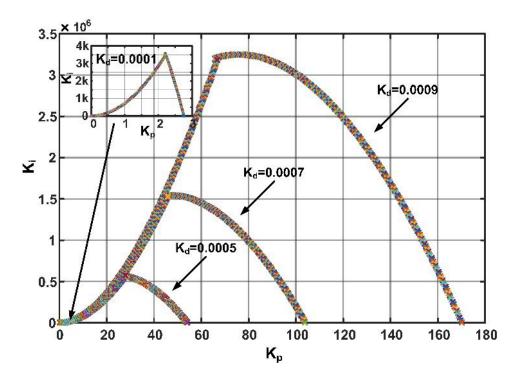

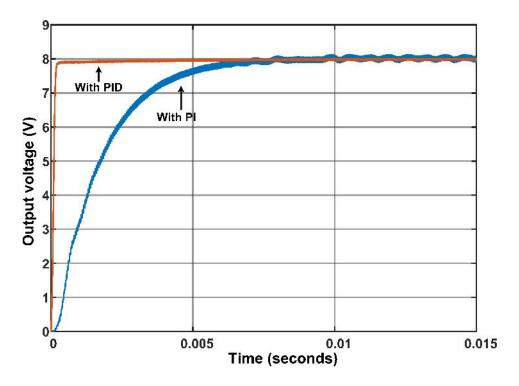

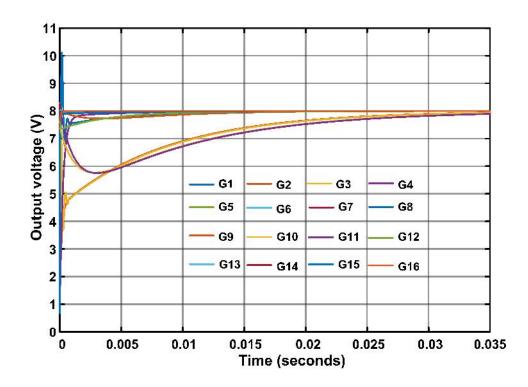

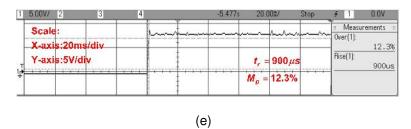

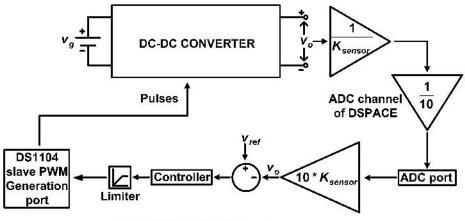

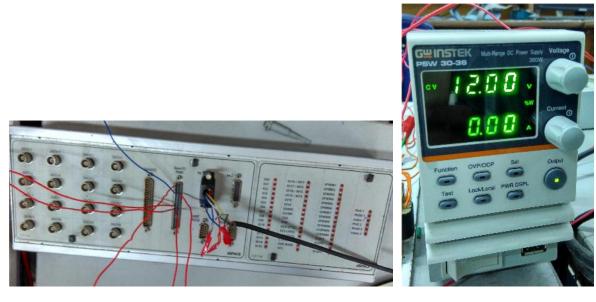

The second part of thesis is related to designing a controller for DC-DC converters. Here, IMC (Internal Model Control) is used to design the PID controller. The  $\lambda$  tuning is proposed for DC-DC converters. The main focus is to design a general PID controller for all types of converters and there is no need for trial and error method to choose PID parameters. Along with this, the designed PID can achieve desired bandwidth of the system, which is very important for the DC-DC converters. Further, when there exist parametric uncertainties, a PID controller is designed. The best part of this work is that, single PID controller can handle the parametric uncertainties (interval type of uncertainties). For this, Kharitonov theorem and stability boundary locus techniques are used. Here, a reduced polynomial approach is proposed for DC-DC converters through simulations and practical experiments. The controller is implemented on DSPACE-1104 through Hardware in loop.

ii

### ACKNOWLEDGEMENTS

Undertaking this Ph.D. has been a truly life-changing experience for me and it would not have been possible to do without the support and guidance that I received from many people. First of all, I owe it all God (Shiva) for granting me the wisdom, health and strength to undertake this research task and enabling me to its completion.

Foremost, I would like to express my sincere gratitude to my supervisor Dr. Yogesh Vijay Hote for the continuous support of my Ph.D. study and research, for his patience, motivation, enthusiasm, and immense knowledge. A person with an amicable and positive disposition, Sir has always made him available to clarify my doubts despite his busy schedule and I consider it as a great opportunity to do my doctoral programme under his guidance and to learn from his research expertise. His guidance helped me in all the time of research and writing of this thesis. I could not have imagined having a better supervisor and mentor for my Ph.D. study. Thank you Sir for all your help and support. Besides my advisor, I would like to thank to the members of my student research committee: Dr. M. K. Pathak, Associate Professor, Department of Electrical Engineering, Dr. A. Swaminathan, Associate Professor, Department of Mathematics, Dr. B. Tyagi, Associate Professor, Department of Electrical Engineering, for their encouragement, insightful comments, suggestions and hard guestions in various presentation during my research work tenure. I would like to thank Prof. M. K. Vasantha, Professor (retired), Department of Electrical Engineering, for his encouragement and motivation. I am grateful to the reviewers whose constructive suggestions and invaluable advices improved the quality of my publication derived from this work.

I would also like to acknowledge Dr. B. Das, Head of the Department of Electrical Engineering, for his help on various occasions. I am thankful to Mr. Anil Agarwal, Lab Assistant (retired), Mr. Jakir Hussain and Mr. Sandeep, Lab Assistants, Control and Robotics Laboratory, Mr. Narendra Singh, Lab Assistant, Applied Electronics Laboratory for delivering all type of help in conducting experiment during my research work. I am highly obliged to owemy sincere thanks to the technical and administrative staff of electrical engineering department, especially to Mr. Mohan Singh and Mr.

iii

Rishabh, who helped me in in all possible ways during the work.

I thank my fellow lab mates, Dr. Sahaj Saxena, Dr. Sandeep, Dr. Raju, Sudharsana Rao, Pushkar, Arvind, Jitender, Mahender, Shivan Biradar and Shivam Jain for the stimulating discussions, for the sleepless nights we were working together during some period, and for all the fun we have had in the last four and a half years. I would like to thank all my colleagues, without their support this work is unimaginable. I would like to mention some of them, Dr. Aurbindo Panda, Dr. Y. Srinivasa Rao, Dr. Santhosh Singh, Dr. Narendra Babu, Dr. Sanjeev Pannala, Dr. Ankit Singh, Naveen Yalla, Haris Ahmed, Jagannath, Bhargav, Saran and Krishna Chaitanya. I am lucky to have my friend Vinod Kumar (Research scholar, IIT BHU), Vijay Babu (Research scholar, IIT BHU), and Tirumala Rao (Research scholar, IIT Kharagpur) for supporting me in every walk of research life.

My sincere thanks to the family of my supervisor (Mrs. Swapnaja, Mrudula and Mayank) with whom I enjoyed homely treatment, birthday functions and memorable trips. Special thanks to my school friend Dinesh Reddy and other friends Sudheer, Dr. Govind, Ravi Teja and Yadgiri for their constant moral support, love, care and encouragement in the journey of achieving this might task.

Finally, I wish to express my hearty gratitude to my mother Aruna, father V Narasimhaiah and sister Dr. Santhoshi (MD General Surgeon), who always encourages and let me to pursue what I like. They are wonderful and sacrifices a lot so that I can focus on my research; for that I am infinitely grateful to them.

(Vishwanatha Siddhartha)

# TABLE OF CONTENTS

| A  | BSTR | ACT     |             |                                    |   |   | i    |

|----|------|---------|-------------|------------------------------------|---|---|------|

| A  | СКИС | WLED    | GEMENT      | S                                  |   |   | iii  |

| LI | ST O | f figu  | RES         |                                    |   |   | xii  |

| LI | ST O | F TABL  | .ES         |                                    |   | ) | xxii |

| LI | ST O | F ACRO  | ONYMS       |                                    |   | ) | κxv  |

| LI | ST O | F SYMI  | BOLS        |                                    |   | х | xvi  |

| 1  | ΙΝΤΙ | RODUC   | TION        |                                    |   |   | 1    |

|    | 1.1  | Revisi  | t to Funda  | umentals                           |   |   | 1    |

|    | 1.2  | DC-D    | C Convert   | ers: Background                    |   |   | 1    |

|    | 1.3  | Literat | ure and F   | lesearch Plan                      |   |   | 5    |

|    |      | 1.3.1   | Design o    | r Analysis of converters           |   |   | 6    |

|    |      | 1.3.2   | Modeling    | g of converters                    |   |   | 6    |

|    |      | 1.3.3   | New top     | ologies for specific applications  |   |   | 7    |

|    |      | 1.3.4   | Control o   | of DC-DC converters                |   |   | 7    |

|    |      |         | 1.3.4.1     | IMC literature                     |   |   | 9    |

|    |      |         | 1.3.4.2     | Literature on lambda tuning        |   |   | 9    |

|    |      |         | 1.3.4.3     | Literature on robust PID design    |   |   | 10   |

|    | 1.4  | Main (  | Contributio | ons                                |   |   | 11   |

|    | 1.5  | Overv   | iew of The  | esis                               | • | • | 12   |

| 2  | NOM  | N-IDEA  | L PWM D     | C-DC BOOST CONVERTER               |   |   | 15   |

|    | 2.1  | Backg   | round and   | Motivation                         |   | • | 15   |

|    | 2.2  | Funda   | mental A    | nalysis                            |   |   | 17   |

|    |      | 2.2.1   | Energy s    | storing phase ( $0 < t \le DT$ )   |   |   | 17   |

|    |      | 2.2.2   | Energy r    | eleasing phase ( $DT < t \leq T$ ) |   |   | 19   |

| 2.3 | Stead  | y-State Analysis                                              | 20 |  |  |  |

|-----|--------|---------------------------------------------------------------|----|--|--|--|

|     | 2.3.1  | Output voltage expression                                     | 21 |  |  |  |

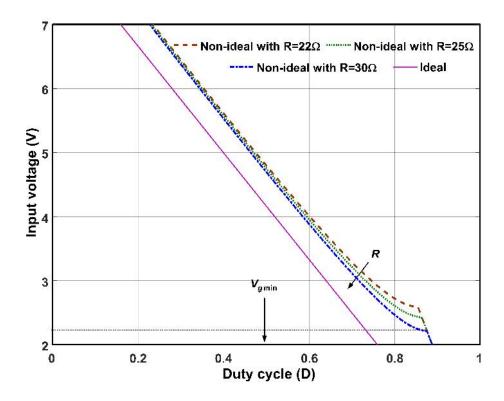

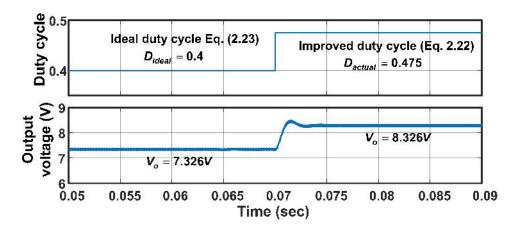

|     | 2.3.2  | Modified duty cycle expression                                | 24 |  |  |  |

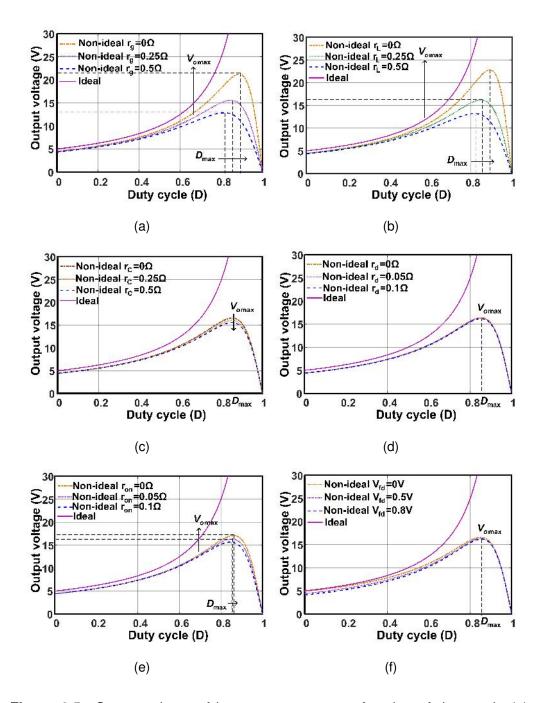

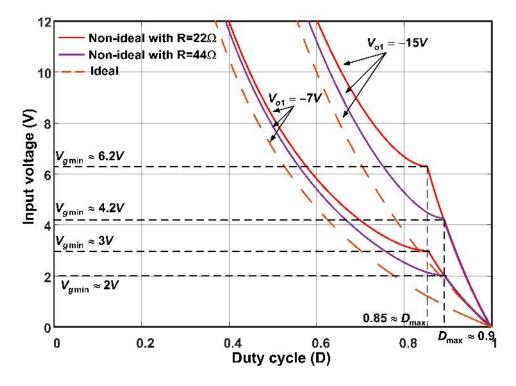

|     | 2.3.3  | Maximum achievable duty cycle and output voltage              | 26 |  |  |  |

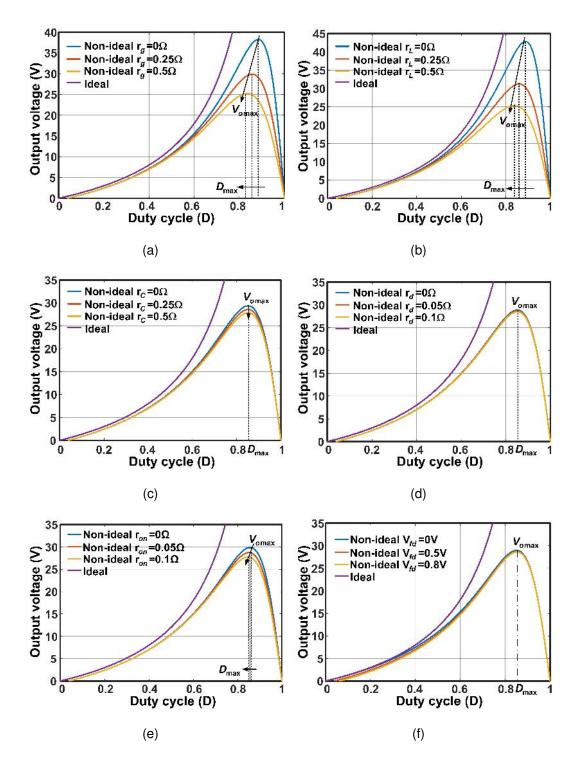

|     | 2.3.4  | Effect of parasitics                                          | 27 |  |  |  |

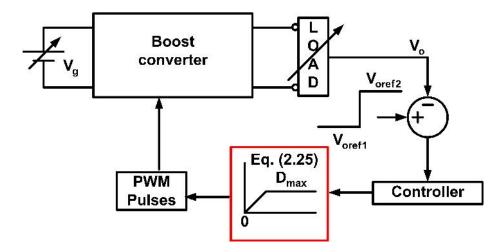

| 2.4 | Outco  | mes for Closed-loop Control                                   | 29 |  |  |  |

| 2.5 | Desig  | Design of Filter Elements                                     |    |  |  |  |

|     | 2.5.1  | Inductor current ripple (ICR) and Inductor design             | 31 |  |  |  |

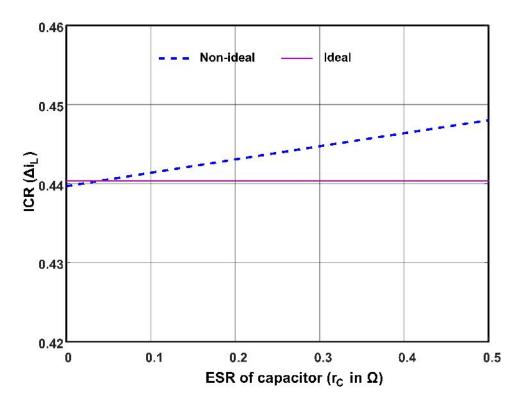

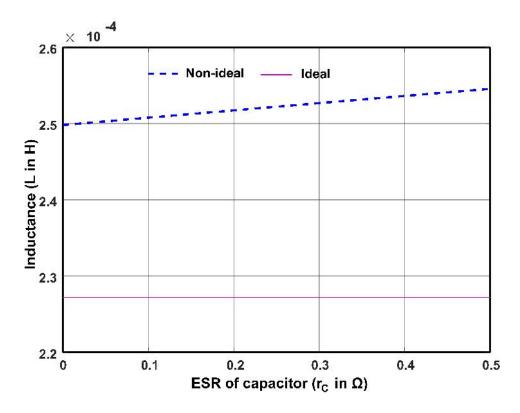

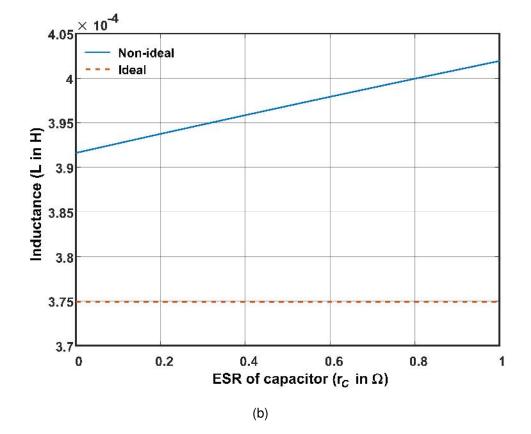

|     |        | 2.5.1.1 Effect of parasitics on ICR and inductance            | 34 |  |  |  |

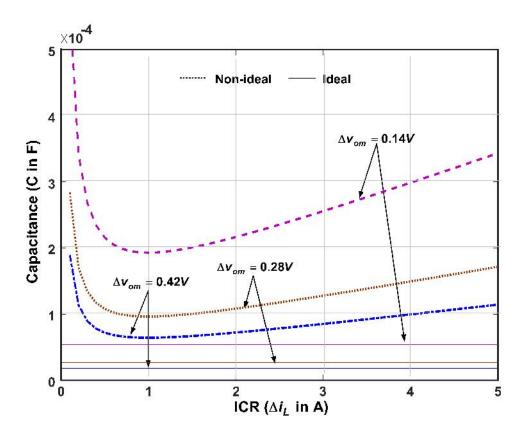

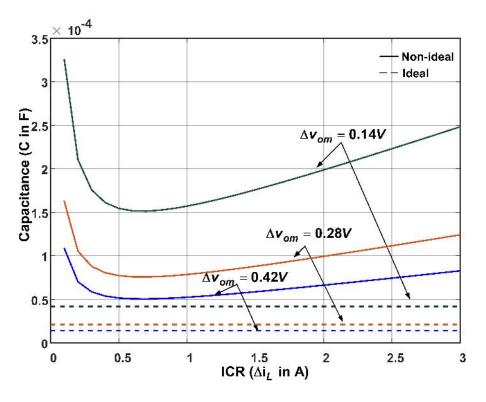

|     | 2.5.2  | Design of Capacitor                                           | 34 |  |  |  |

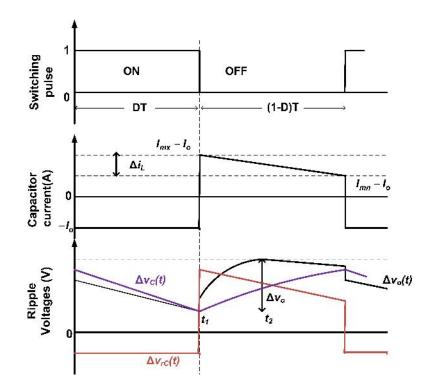

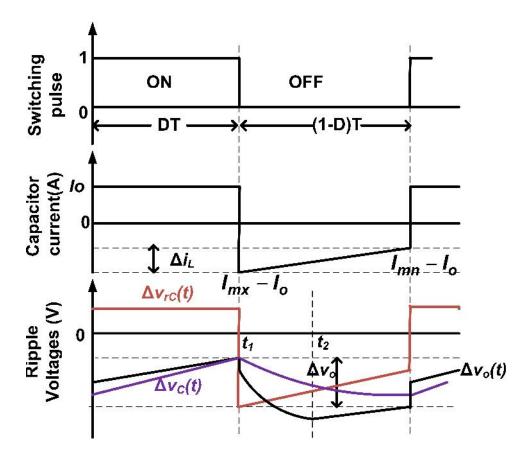

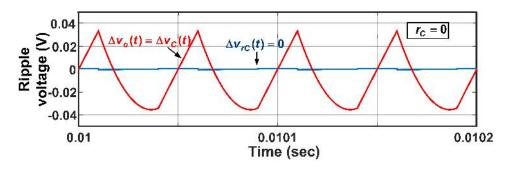

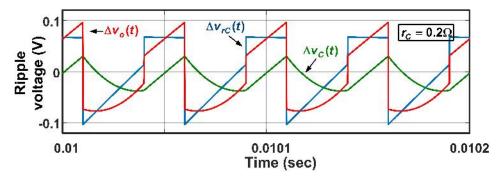

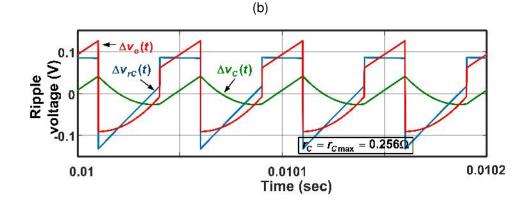

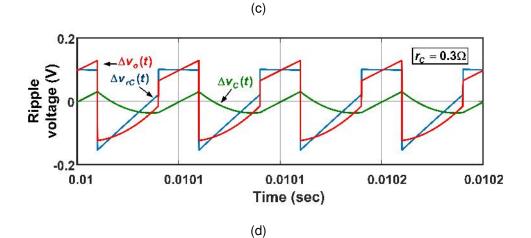

|     |        | 2.5.2.1 OVR analysis                                          | 34 |  |  |  |

|     |        | 2.5.2.2 Analysis during ON time                               | 35 |  |  |  |

|     |        | 2.5.2.3 Analysis during OFF time                              | 36 |  |  |  |

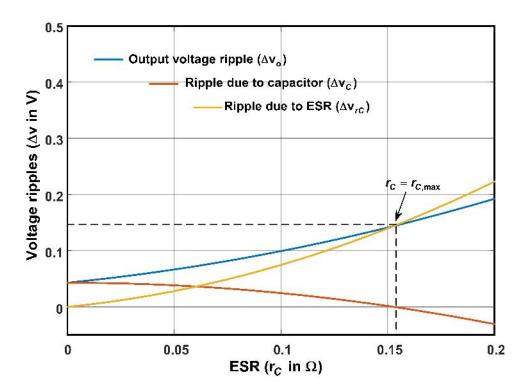

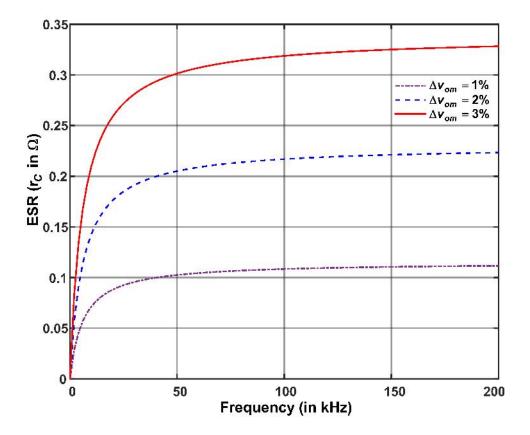

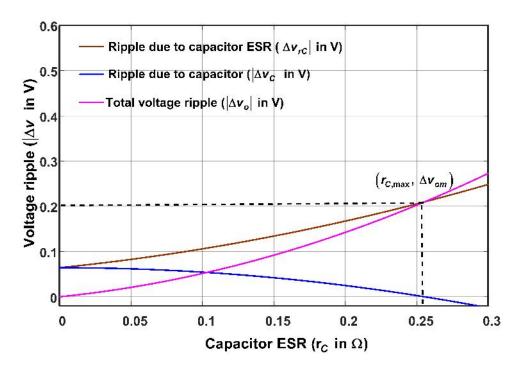

|     | 2.5.3  | Effect of ESR on OVR                                          | 38 |  |  |  |

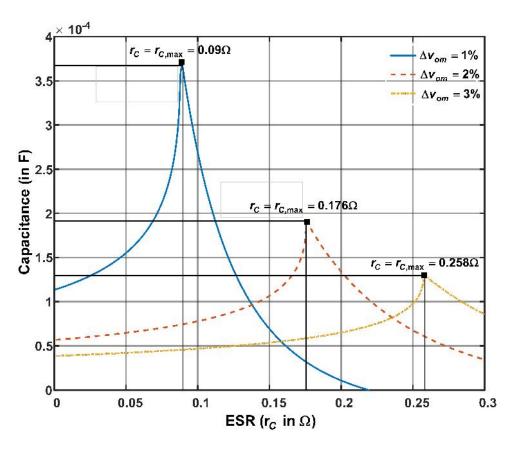

|     | 2.5.4  | Output capacitor design                                       | 38 |  |  |  |

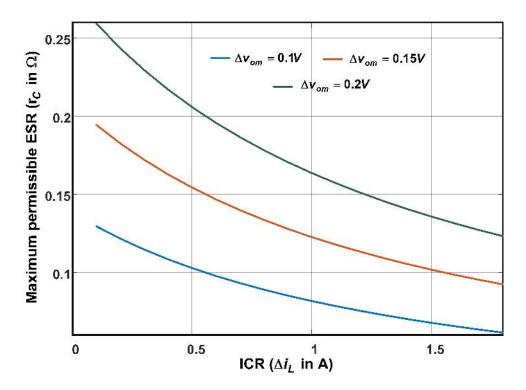

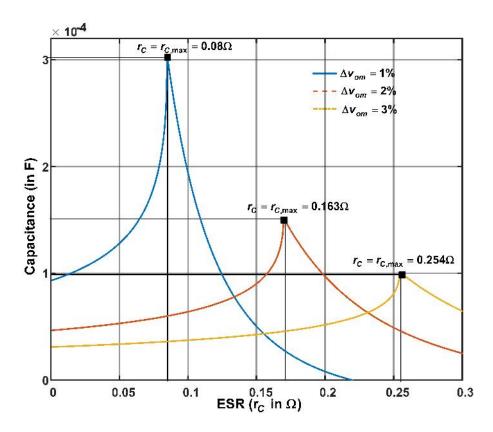

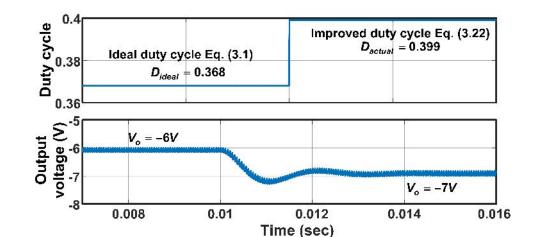

|     | 2.5.5  | Maximum permissible ESR ( $r_{C,max}$ ) and ICR effect        | 40 |  |  |  |

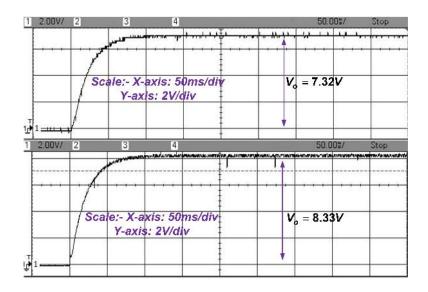

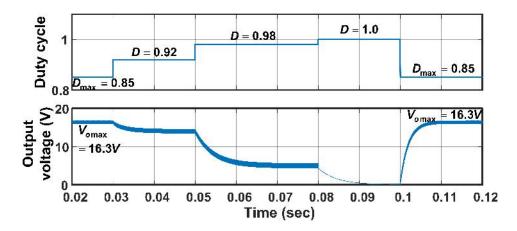

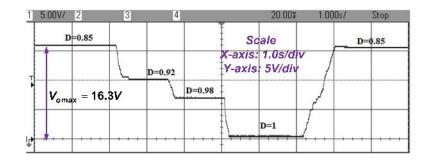

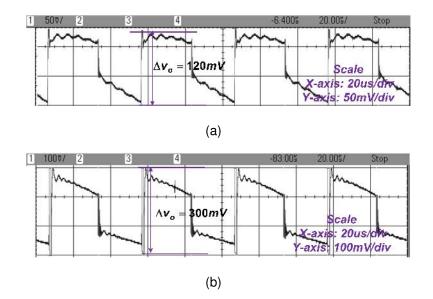

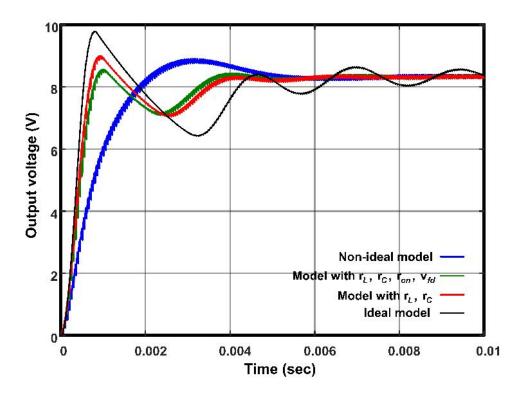

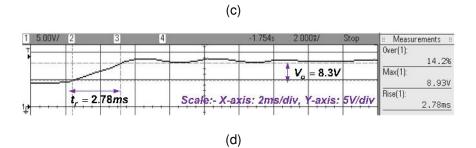

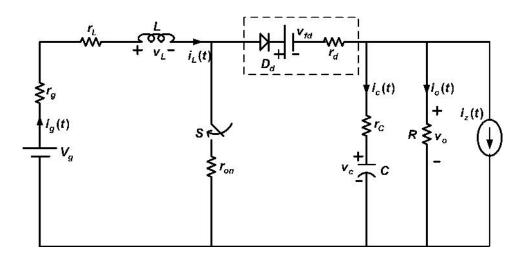

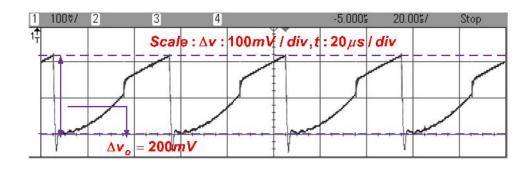

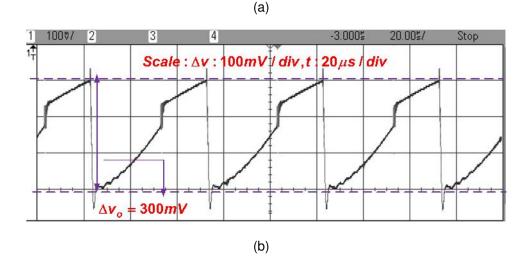

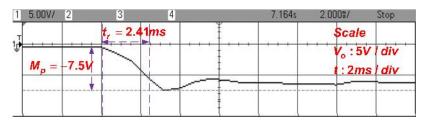

| 2.6 | Experi | imental Results and Discussion                                | 43 |  |  |  |

| 2.7 | Perfor | mance Comparison of Non-ideal Boost Converter With Other      |    |  |  |  |

|     | Semi-  | non ideal Boost Converter Models                              | 52 |  |  |  |

| 2.8 | Mathe  | matical Modelling                                             | 56 |  |  |  |

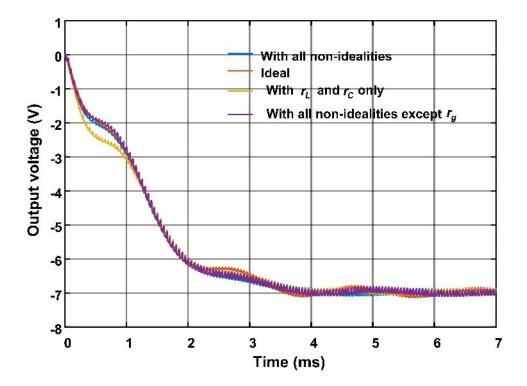

|     | 2.8.1  | Comparison of steady-state ideal and non-ideal models         | 61 |  |  |  |

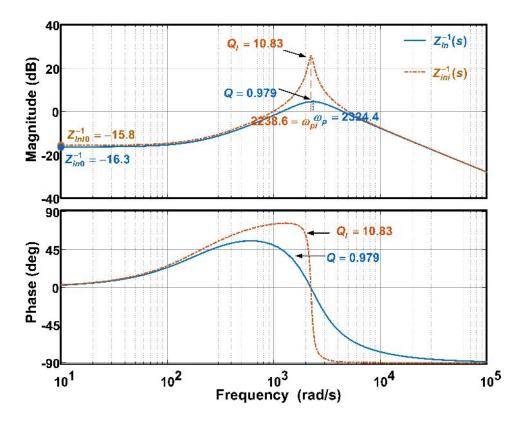

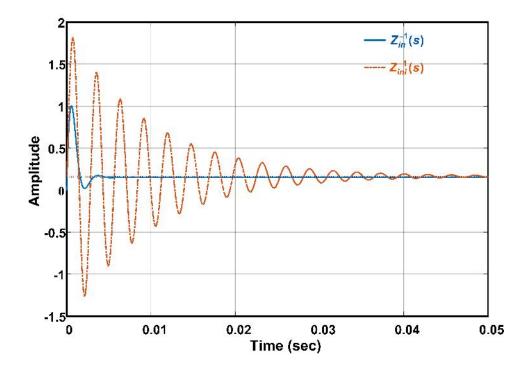

|     | 2.8.2  | Comparison of small-signal ideal and non-ideal models         | 66 |  |  |  |

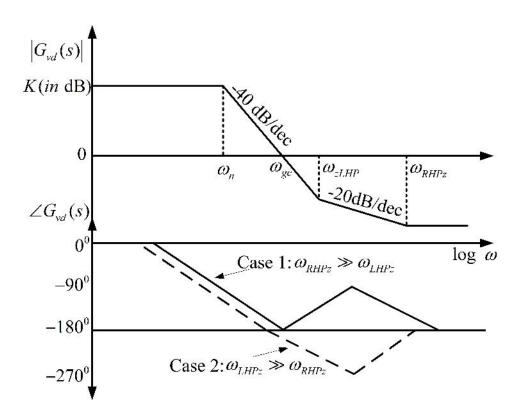

| 2.9 | Contro | ol Oriented Analysis                                          | 68 |  |  |  |

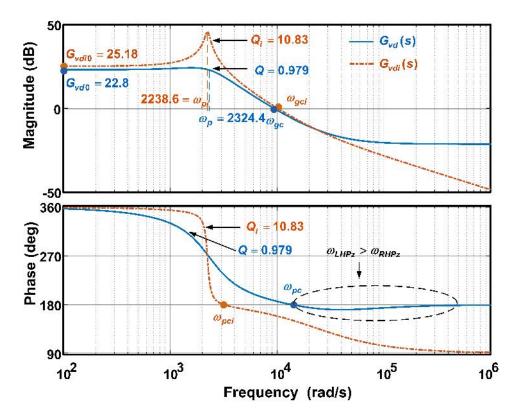

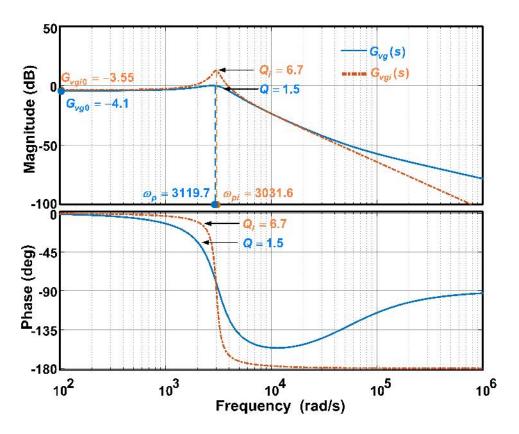

|     | 2.9.1  | Analysis of control to output voltage or control voltage gain | 68 |  |  |  |

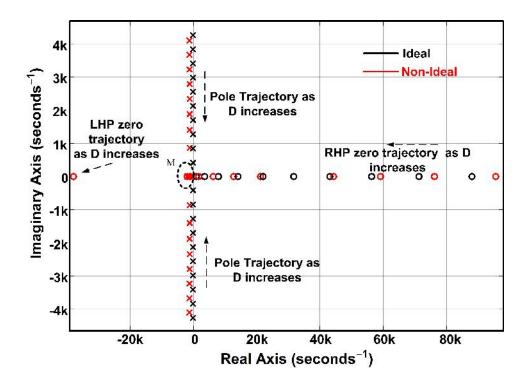

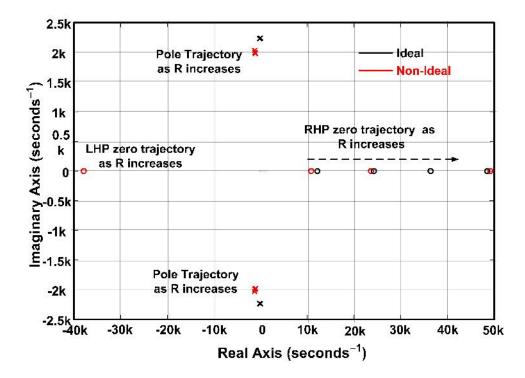

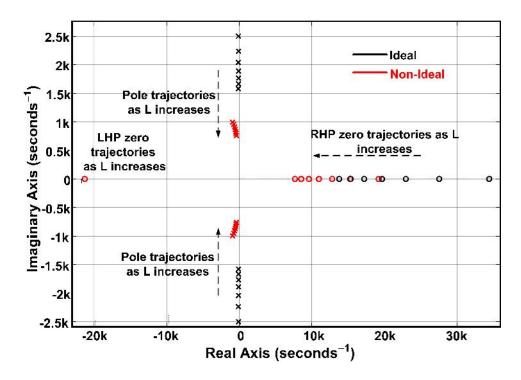

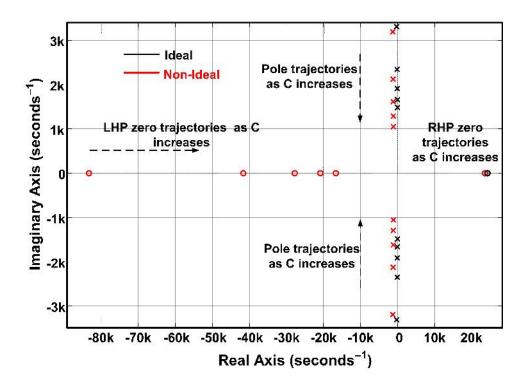

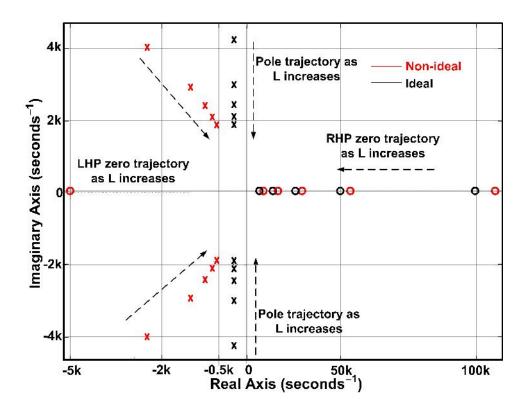

|     |        | 2.9.1.1 Parametric effect on poles and zeros                  | 68 |  |  |  |

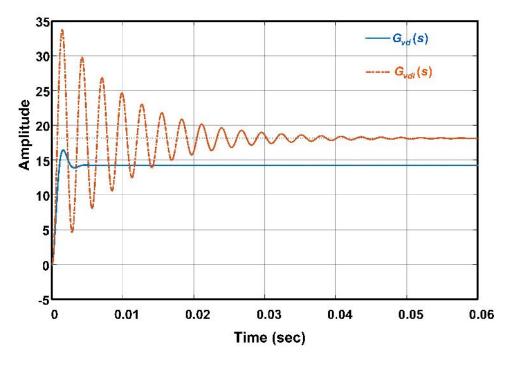

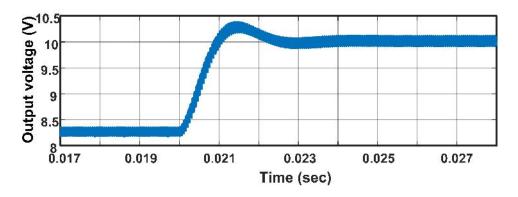

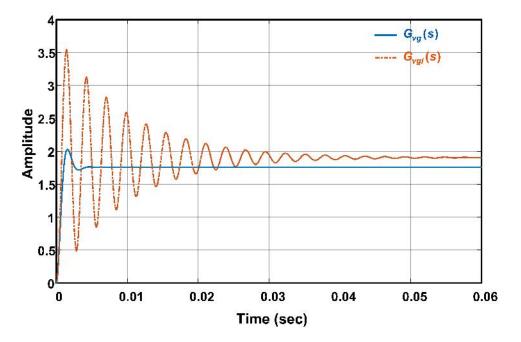

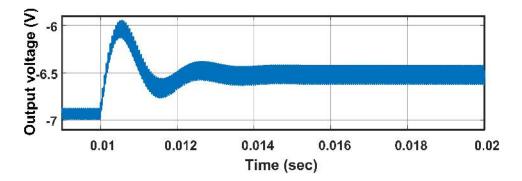

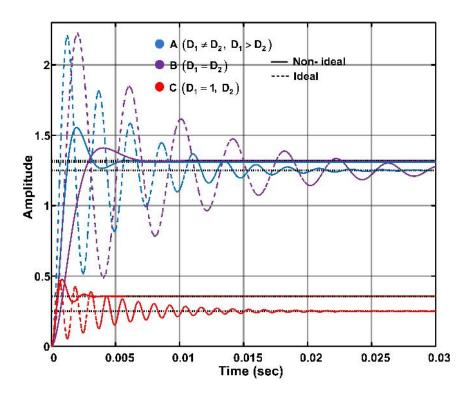

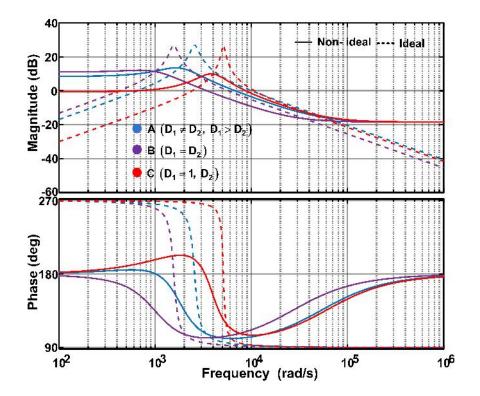

|     |        | 2.9.1.2 Time domain and frequency response analysis           | 72 |  |  |  |

|     |        | 2.9.1.3 Important observations for controller design          | 73 |  |  |  |

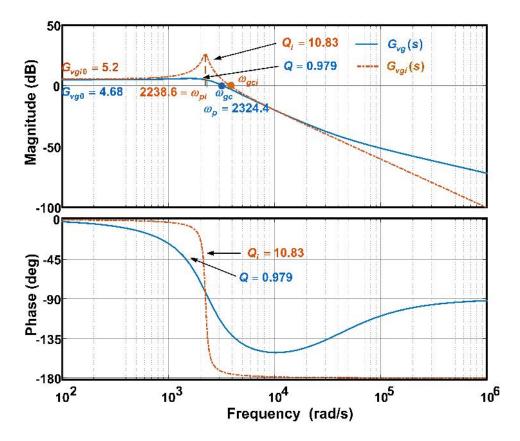

|     | 2.9.2  | Analysis of input to output voltage or audio susceptibility   | 74 |  |  |  |

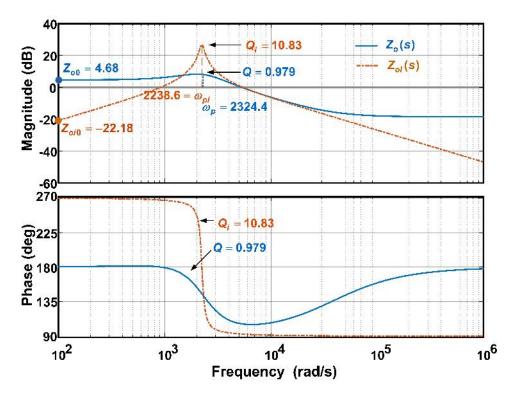

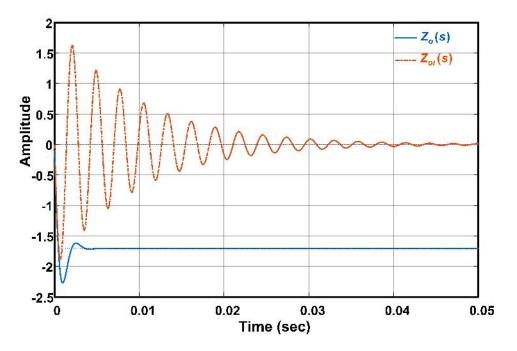

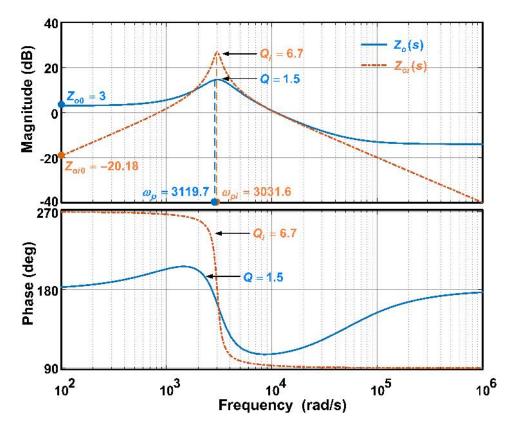

|     | 2.9.3  | Analysis of output impedance                                  | 77 |  |  |  |

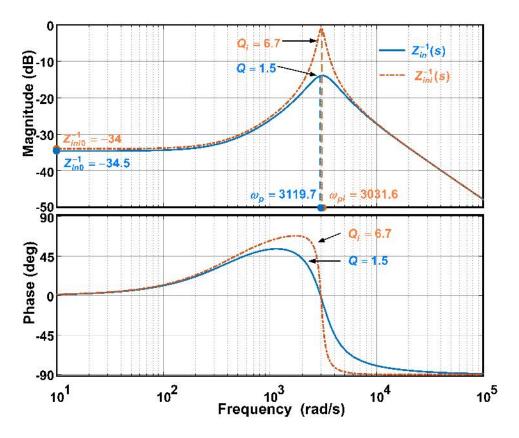

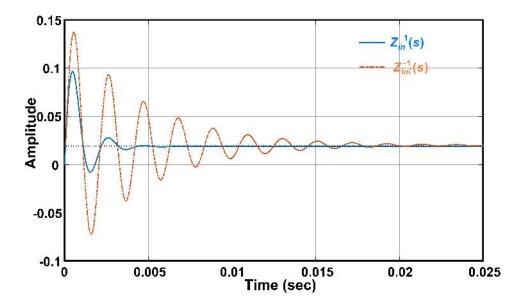

|     | 2.9.4  | Analysis of input impedance                                   | 78 |  |  |  |

|   | 2.10 | Conclu | sions                                                         |

|---|------|--------|---------------------------------------------------------------|

| 3 | NON  | I-IDEA | DC-DC BUCK-BOOST CONVERTER 83                                 |

|   | 3.1  | Backg  | ound and Motivation                                           |

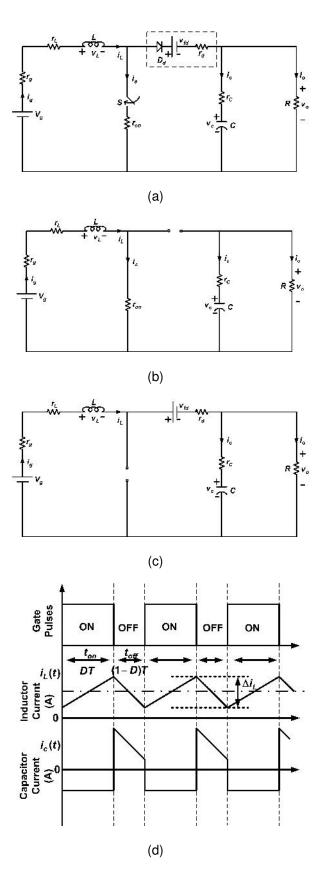

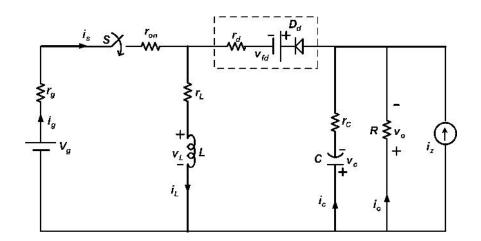

|   | 3.2  | Funda  | mental Analysis                                               |

|   |      | 3.2.1  | Energy storing phase ( $0 < t \le DT$ )                       |

|   |      | 3.2.2  | Energy releasing phase $(DT < t \le T)$                       |

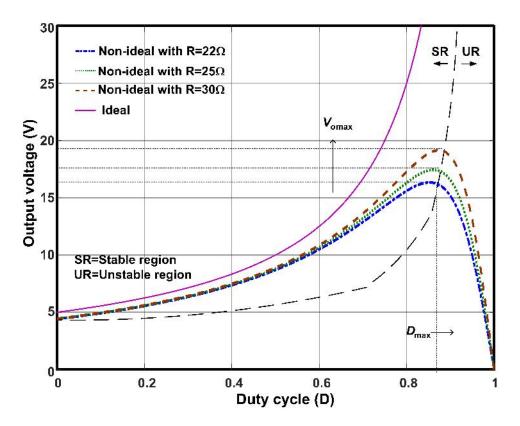

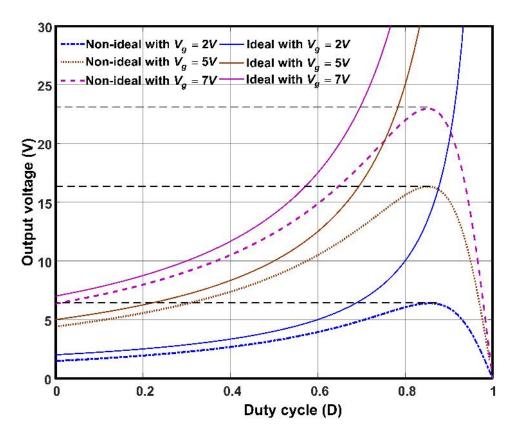

|   | 3.3  | Stead  | State Analysis                                                |

|   |      | 3.3.1  | Output voltage expression                                     |

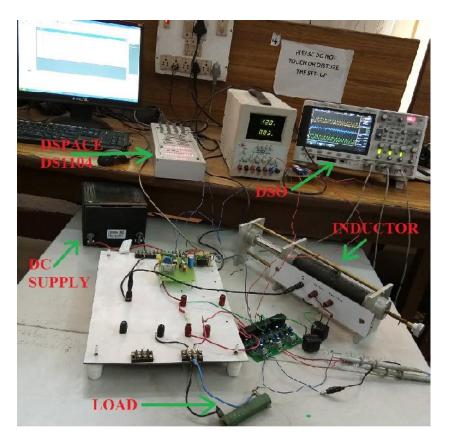

|   |      | 3.3.2  | Modified duty cycle expression                                |

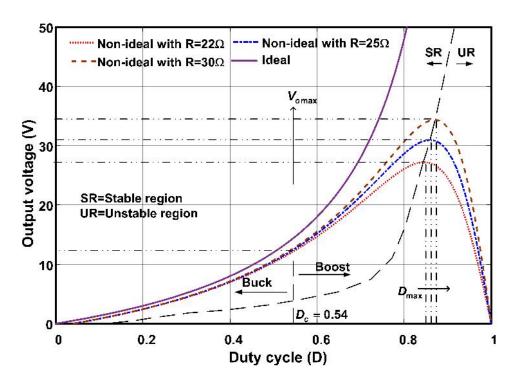

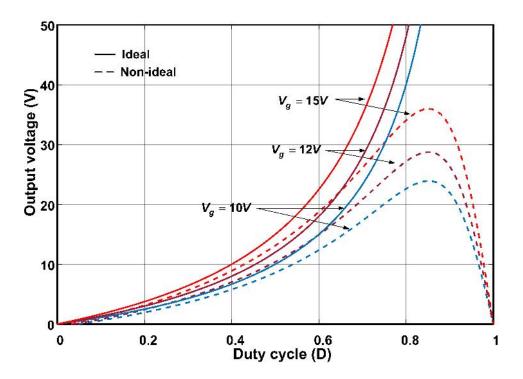

|   |      | 3.3.3  | Maximum achievable duty cycle and output voltage 93           |

|   |      | 3.3.4  | Effect of parasitics                                          |

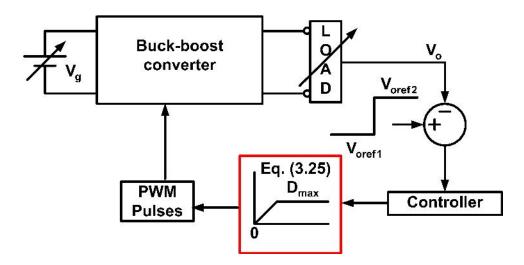

|   | 3.4  | Outco  | nes for Closed-loop Control                                   |

|   | 3.5  | Desigi | of Filter Elements                                            |

|   |      | 3.5.1  | Inductor current ripple (ICR) and Inductor design             |

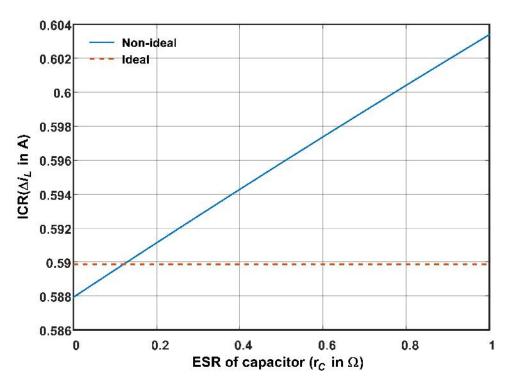

|   |      |        | 3.5.1.1 Effect of parasitics on ICR and inductance 101        |

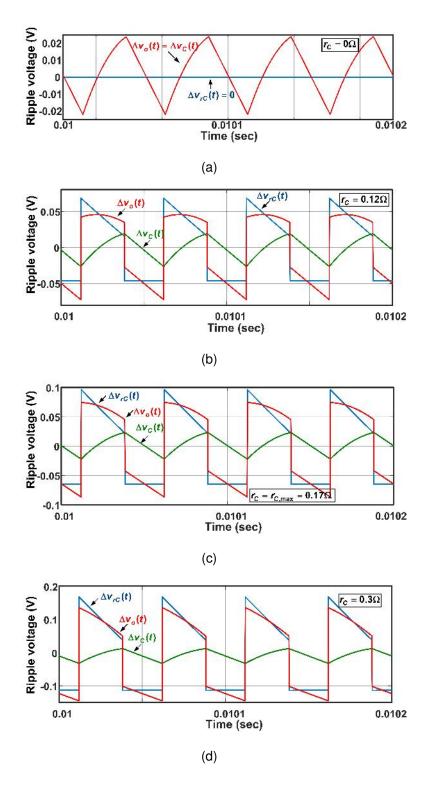

|   |      | 3.5.2  | Design of Capacitor                                           |

|   |      |        | 3.5.2.1 OVR analysis                                          |

|   |      |        | 3.5.2.2 Analysis during ON time                               |

|   |      |        | 3.5.2.3 Analysis during OFF time                              |

|   |      | 3.5.3  | Effect of ESR on OVR                                          |

|   |      | 3.5.4  | Output capacitor design                                       |

|   |      | 3.5.5  | Maximum permissible ESR ( $r_{C,max}$ ) and ICR effect 106    |

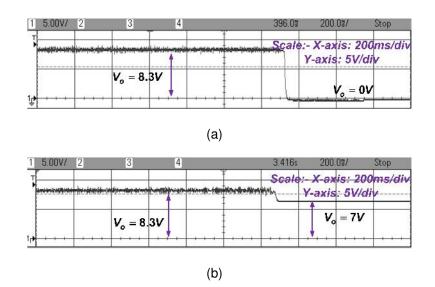

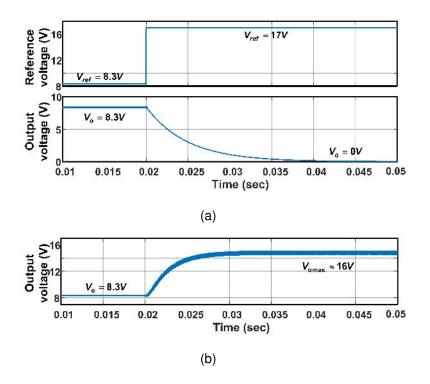

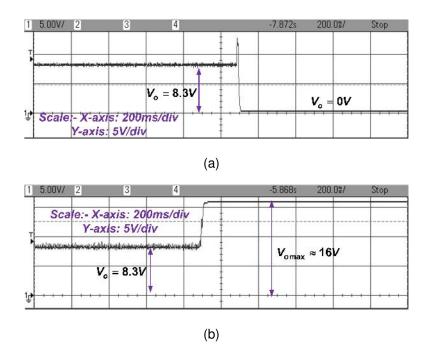

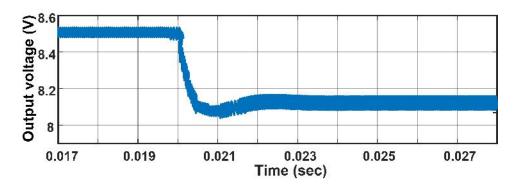

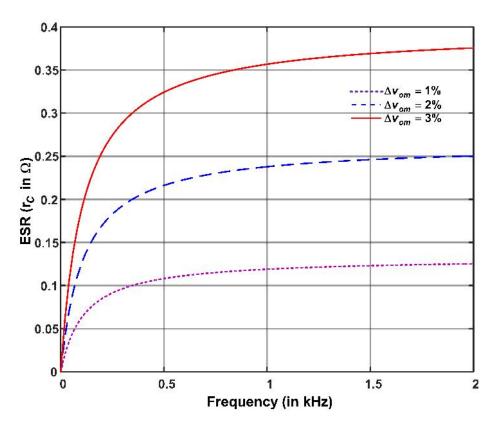

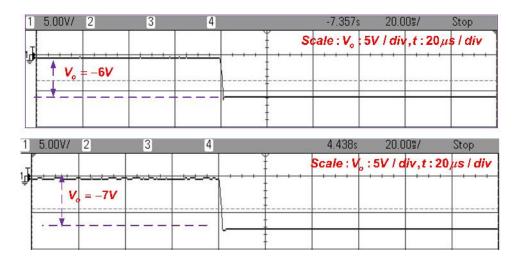

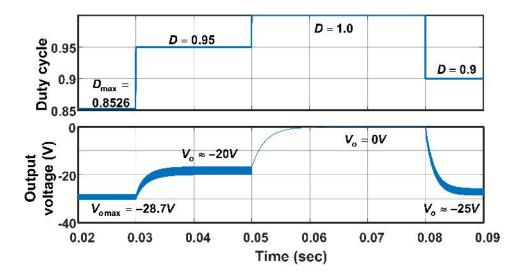

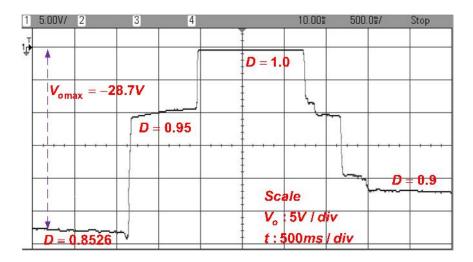

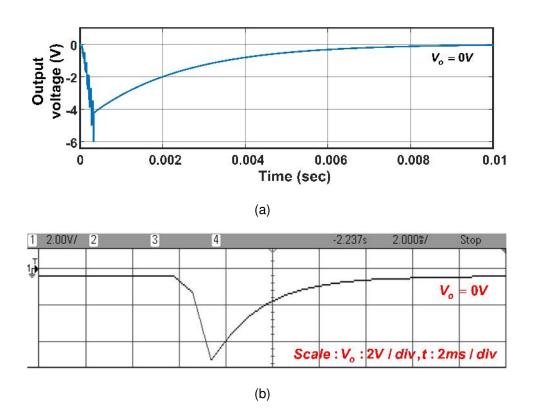

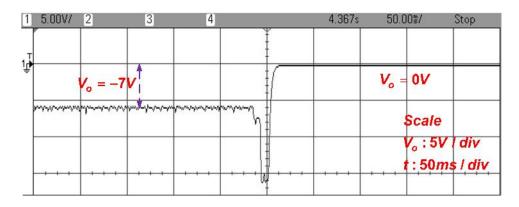

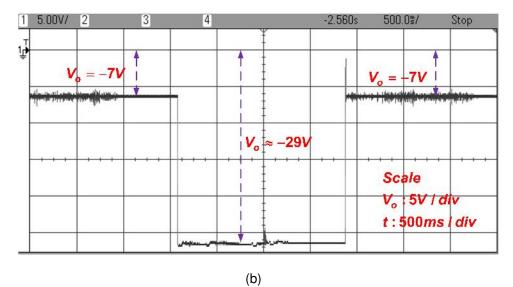

|   | 3.6  | Exper  | mental Results and Discussion                                 |

|   | 3.7  | Exper  | mental Validation of Complete Non-ideal Small Signal Model of |

|   |      | Buck-I | Boost Converter                                               |

|   | 3.8  | Mathe  | natical Modeling                                              |

|   |      | 3.8.1  | Comparison of steady-state ideal and non-ideal models 128     |

|   |      | 3.8.2  | Comparison of small-signal ideal and non-ideal models 133     |

|   | 3.9  | Contro | l Oriented Analysis                                           |

|   |      | 3.9.1 | Analysis  | of control to output voltage or control voltage gain | 135 |

|---|------|-------|-----------|------------------------------------------------------|-----|

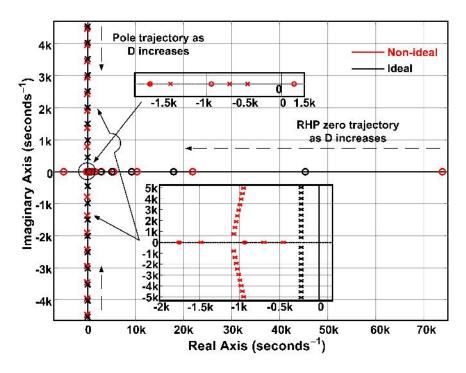

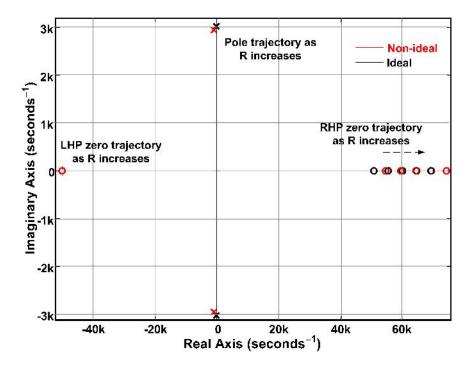

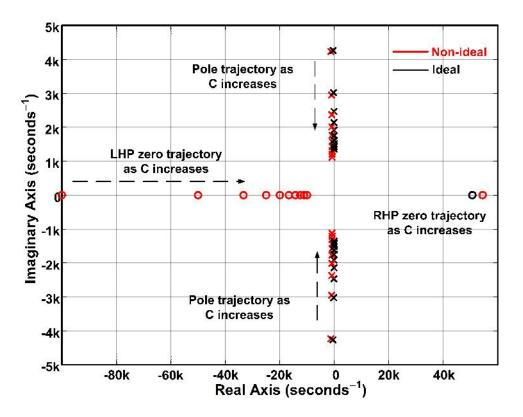

|   |      |       | 3.9.1.1   | Parametric effect on poles and zeros                 | 135 |

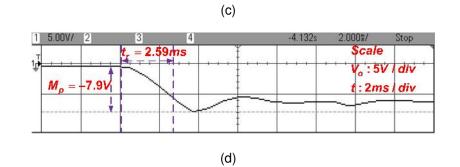

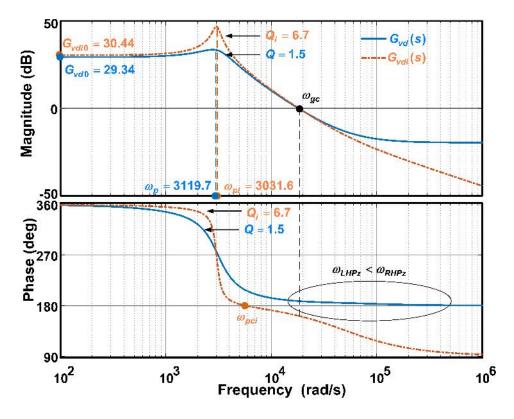

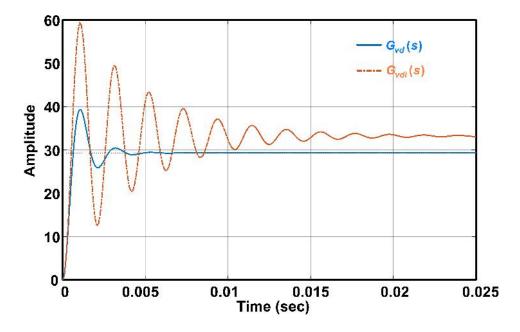

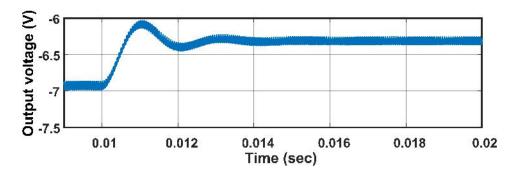

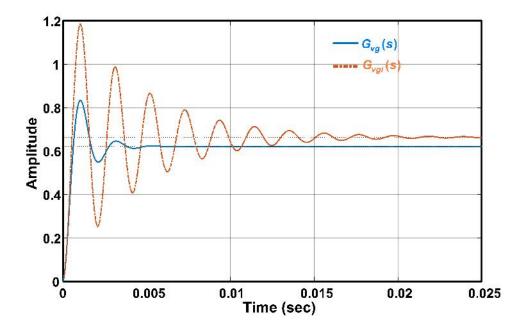

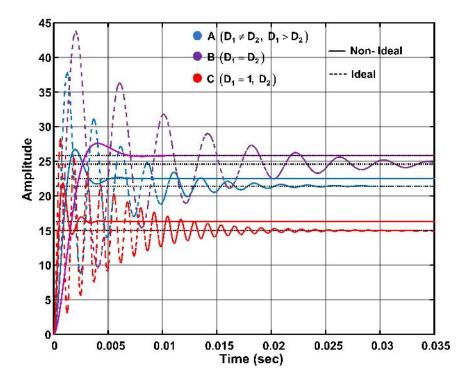

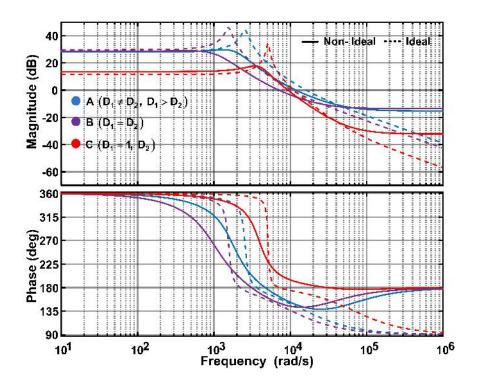

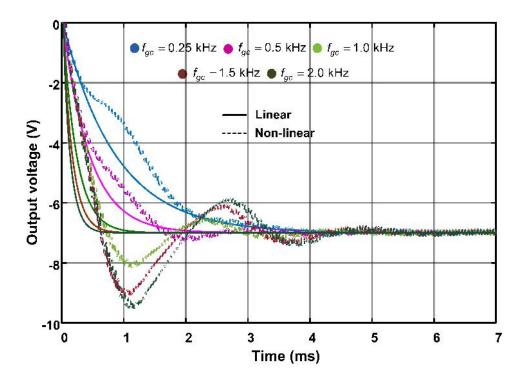

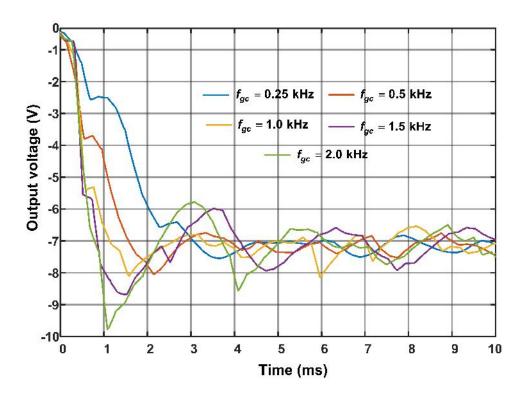

|   |      |       | 3.9.1.2   | Time domain and frequency response analysis          | 138 |

|   |      |       | 3.9.1.3   | Important observations for controller design         | 140 |

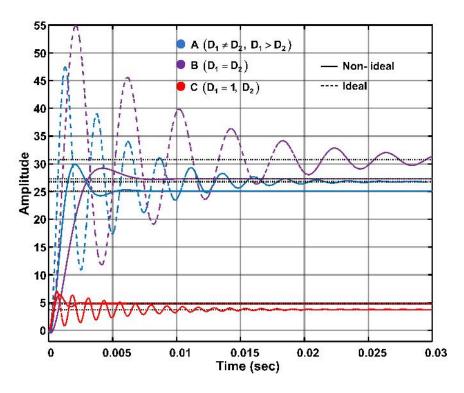

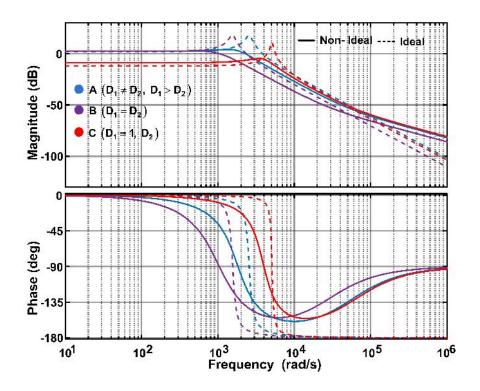

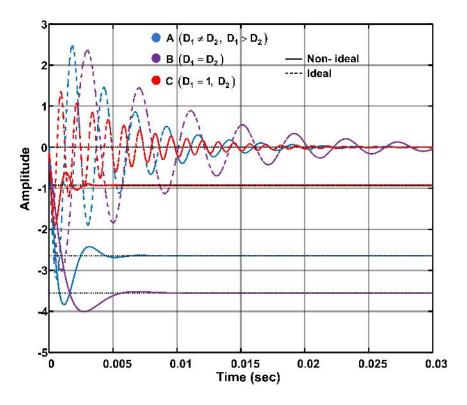

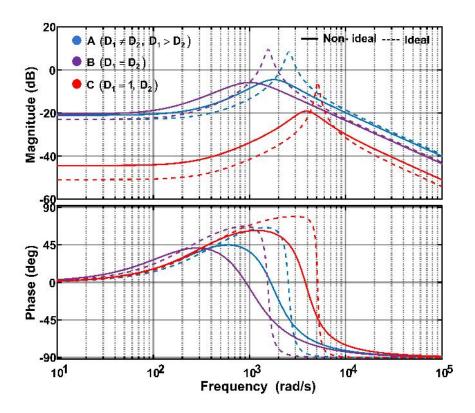

|   |      | 3.9.2 | Analysis  | s of input to output voltage or audio susceptibility | 141 |

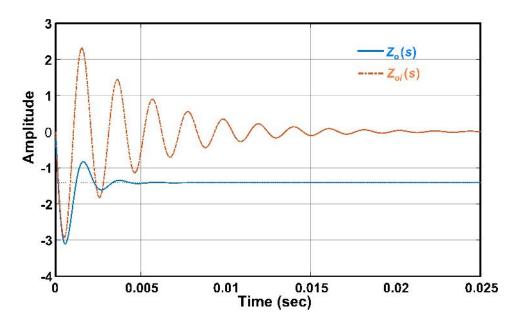

|   |      | 3.9.3 | Analysis  | of output impedance                                  | 143 |

|   |      | 3.9.4 | Analysis  | of input impedance                                   | 145 |

|   | 3.10 | Concl | usions    |                                                      | 147 |

| 4 |      |       |           | IVERTING DC-DC BUCK-BOOST CONVERTER                  | 149 |

| 7 | 4.1  |       |           |                                                      | -   |

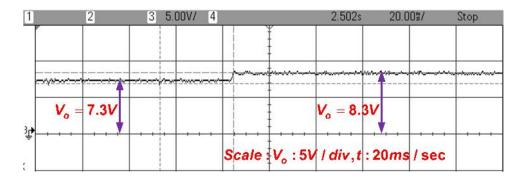

|   | 4.2  | -     |           |                                                      |     |

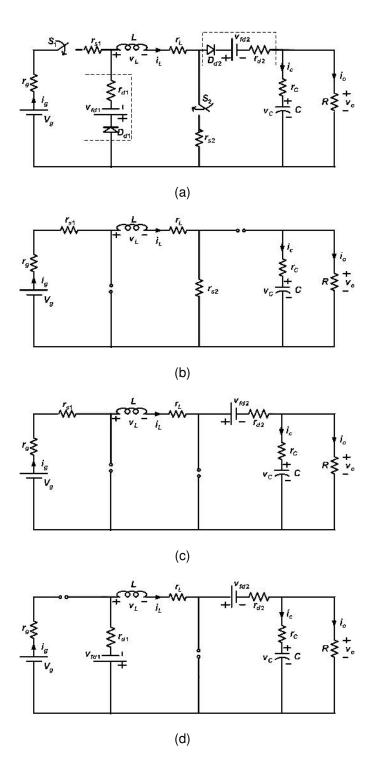

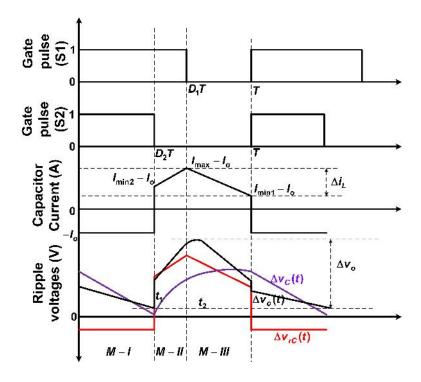

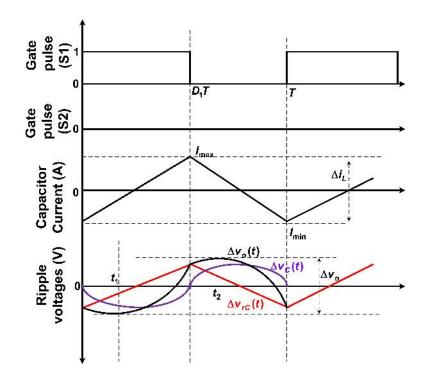

|   |      | 4.2.1 |           | Operation ( $0 < t < D_2T$ )                         |     |

|   |      | 4.2.2 |           | Operation $(D_2T < t < D_1T)$                        |     |

|   |      | 4.2.3 |           | Operation $(D_1T < t < T)$                           |     |

|   | 4.3  | Stead |           | nalysis                                              |     |

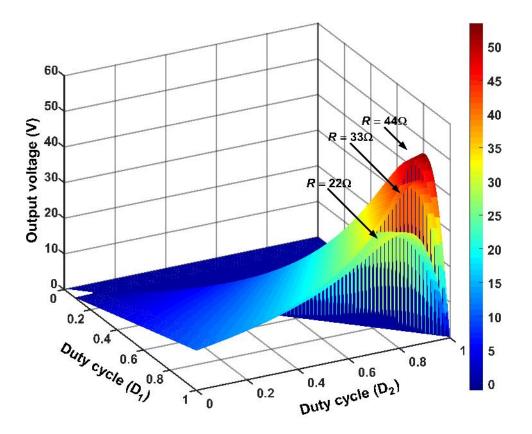

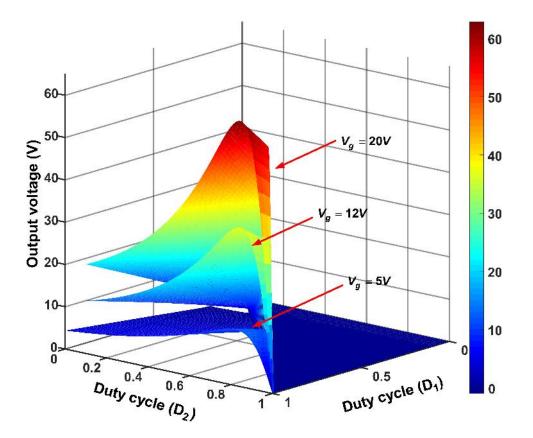

|   |      | 4.3.1 | -         | voltage expression                                   |     |

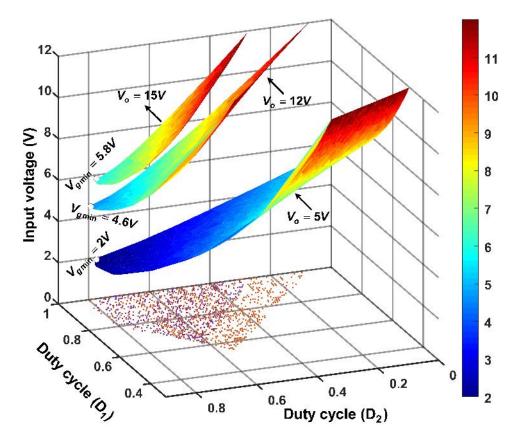

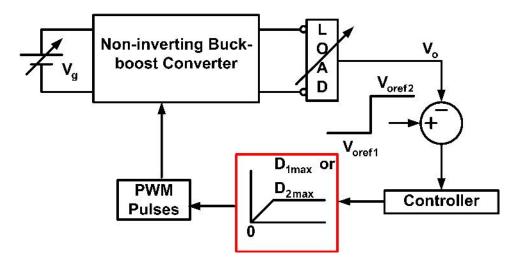

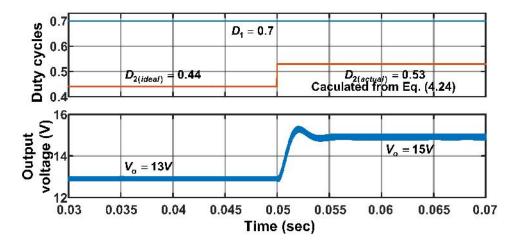

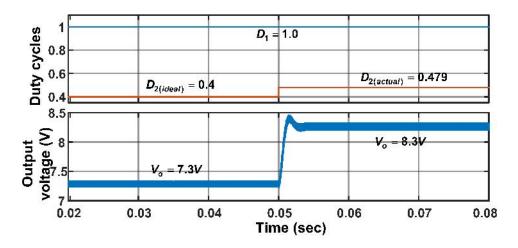

|   |      | 4.3.2 | •         | duty cycle expression                                |     |

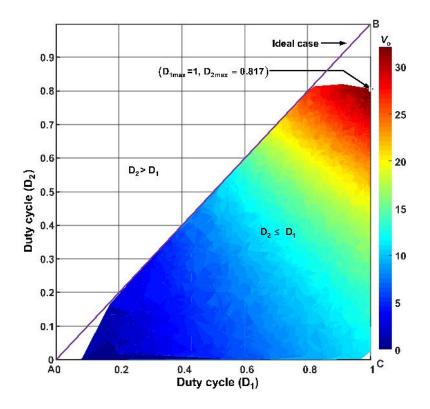

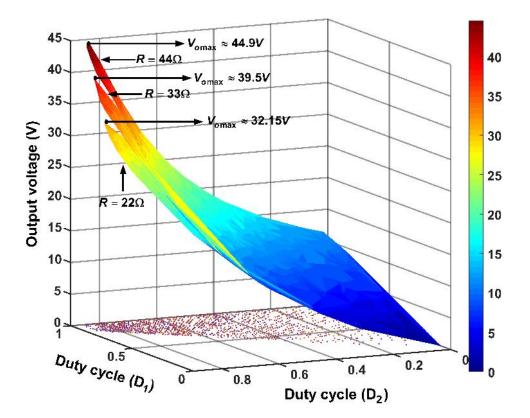

|   |      | 4.3.3 |           | m achievable duty cycle and output voltage           |     |

|   | 4.4  | Outco |           | Steady State Analysis                                |     |

|   | 4.5  |       |           | Elements                                             |     |

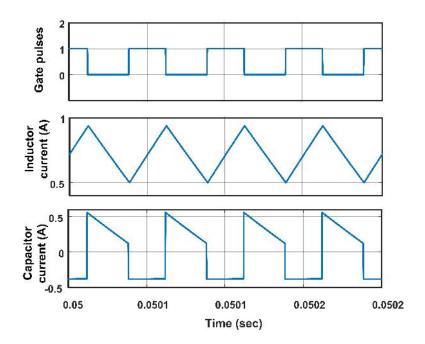

|   |      | 4.5.1 | Inductor  | current ripple (ICR) and Inductor design             | 165 |

|   |      | 4.5.2 | Design o  | of Capacitor                                         | 167 |

|   |      |       | 4.5.2.1   | OVR analysis                                         | 168 |

|   |      |       | 4.5.2.2   | Analysis during Mode I                               | 169 |

|   |      |       | 4.5.2.3   | Analysis during Mode II                              | 170 |

|   |      |       | 4.5.2.4   | Analysis during Mode III                             | 171 |

|   |      | 4.5.3 | Effect of | ESR on OVR                                           | 174 |

|   |      | 4.5.4 | Output o  | capacitor design                                     | 174 |

|   |      | 4.5.5 | Maximu    | m permissible ESR ( $r_{C,max}$ ) and ICR effect     | 176 |

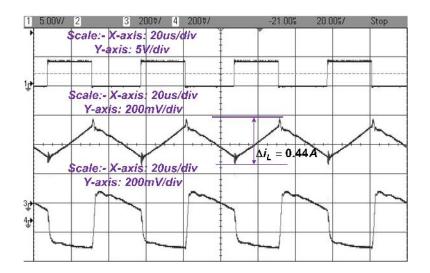

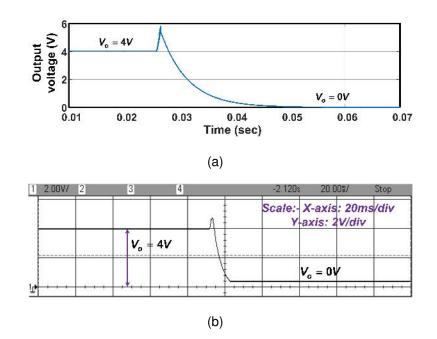

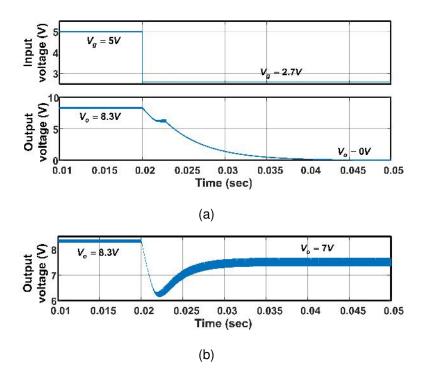

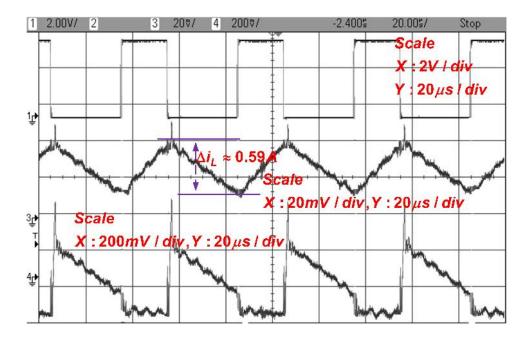

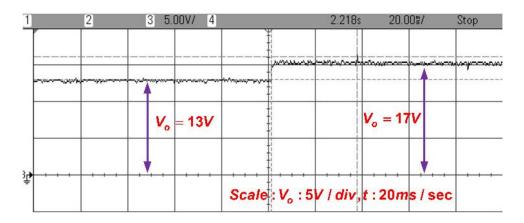

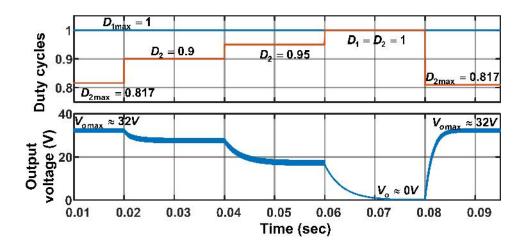

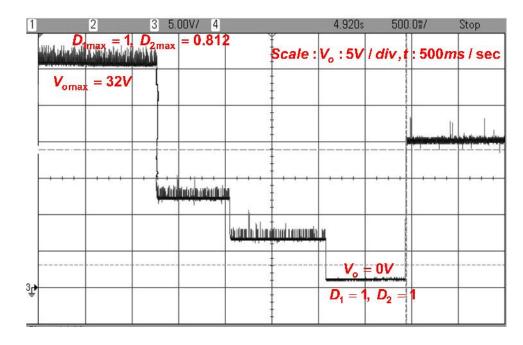

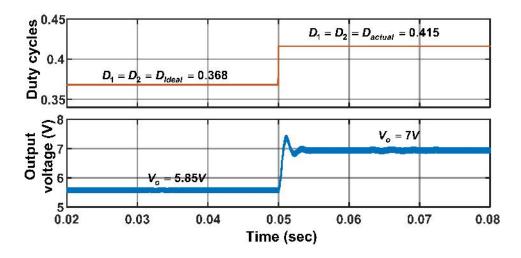

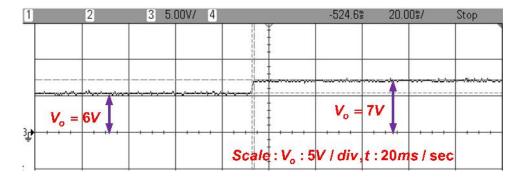

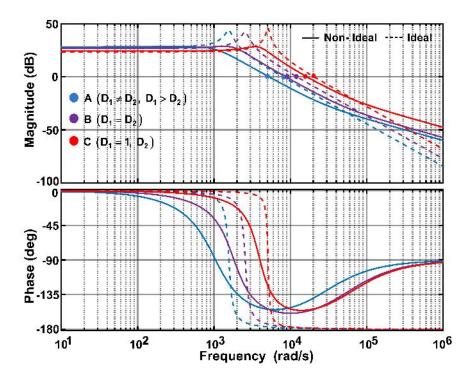

| 4.6  | Experi                                                                                             | mental R                                                                                                                                                                     | esults and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.7  | Mathe                                                                                              | matical M                                                                                                                                                                    | lodeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.7.1                                                                                              | Compari                                                                                                                                                                      | son of steady-state ideal and non-ideal models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 190                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

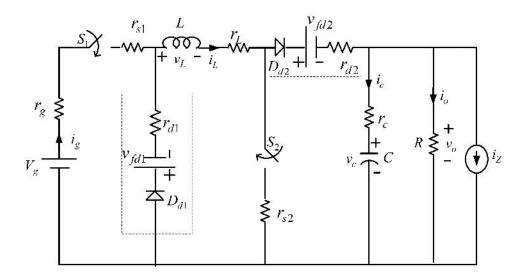

|      | 4.7.2                                                                                              | Compari                                                                                                                                                                      | son of small-signal ideal and non-ideal models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 196                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.8  | Contro                                                                                             | l Oriente                                                                                                                                                                    | d Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.8.1                                                                                              | Analysis                                                                                                                                                                     | of control to output voltage or control voltage gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                                                                                    | 4.8.1.1                                                                                                                                                                      | Parametric effect on poles and zeros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                                                                                    | 4.8.1.2                                                                                                                                                                      | Time domain and frequency response analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.8.2                                                                                              | Analysis                                                                                                                                                                     | of input to output voltage or audio susceptibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 201                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.8.3                                                                                              | Analysis                                                                                                                                                                     | of output impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.8.4                                                                                              | Analysis                                                                                                                                                                     | of input impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

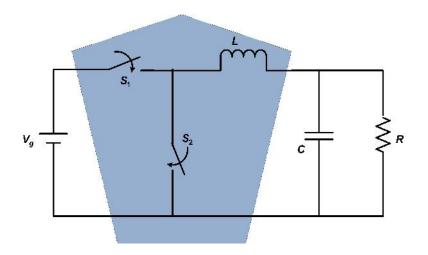

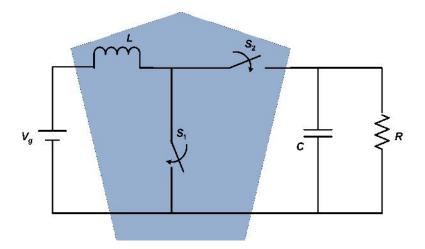

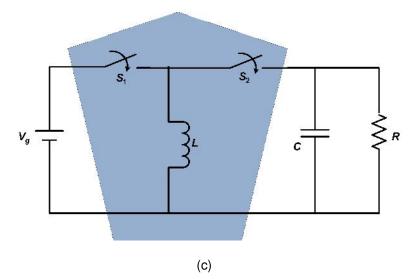

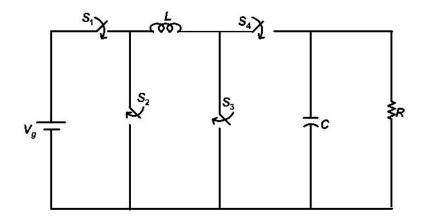

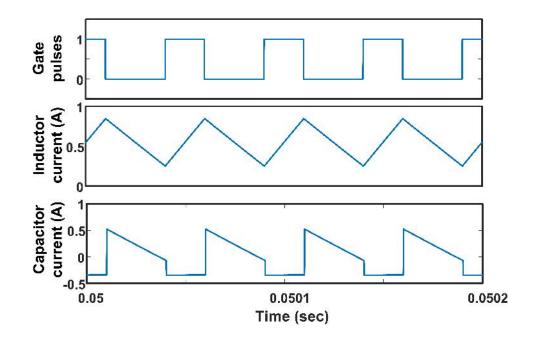

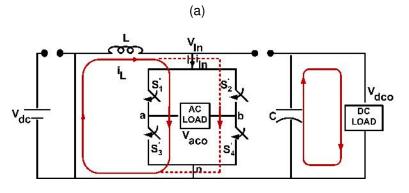

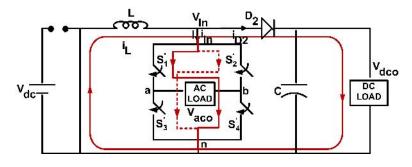

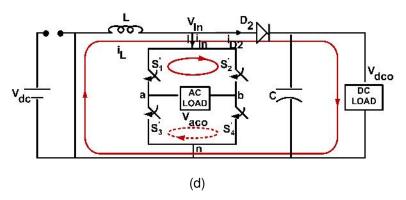

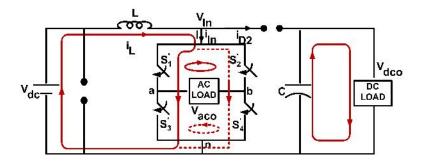

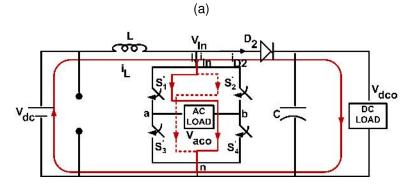

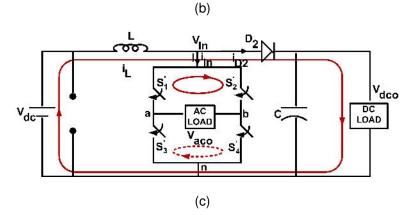

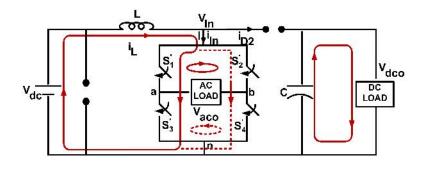

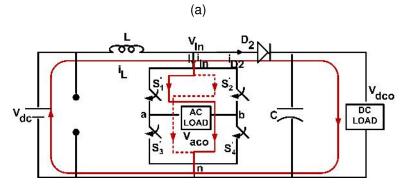

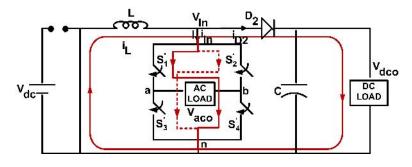

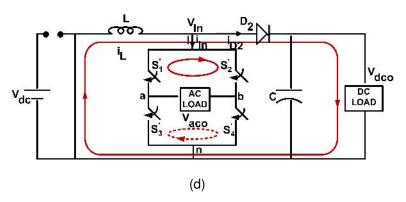

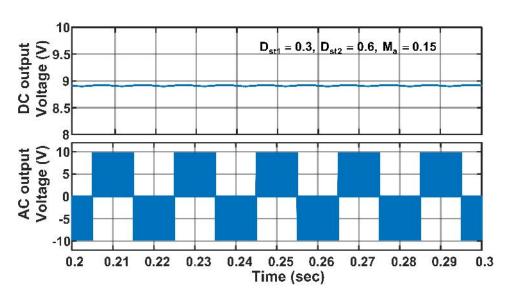

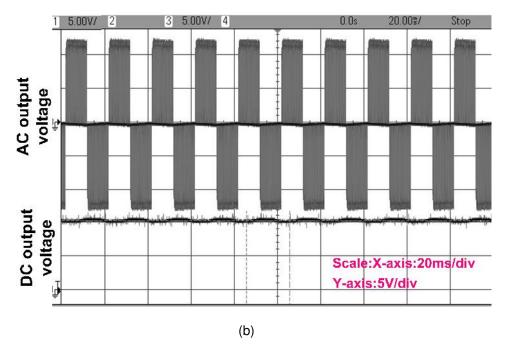

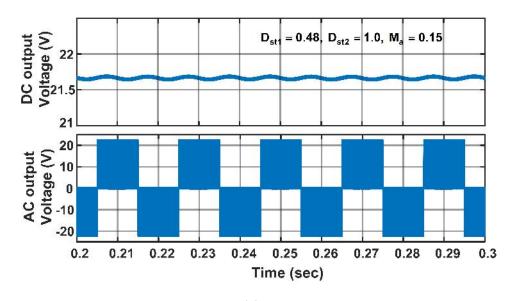

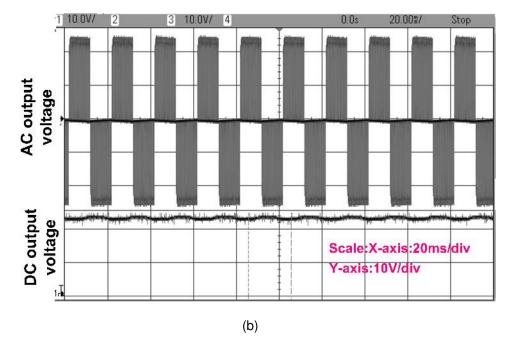

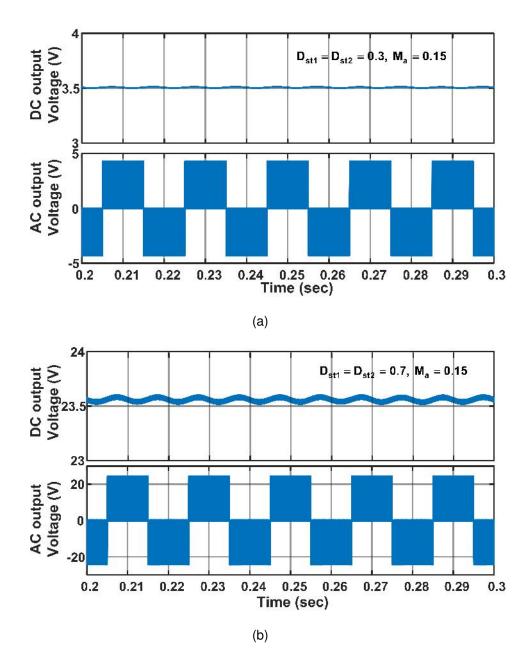

| 4.9  | Propos                                                                                             | sed NIBB                                                                                                                                                                     | Derived Hybrid Converter (NIBBDHC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 206                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.9.1                                                                                              | Synthesi                                                                                                                                                                     | is of NIBBDHC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.9.2                                                                                              | Operatio                                                                                                                                                                     | n of NIBBDHC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                                                                                    | 4.9.2.1                                                                                                                                                                      | Mode-I (Shoot-through)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 209                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                                                                                    | 4.9.2.2                                                                                                                                                                      | Mode-II (Power Period)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                                                                                    | 4.9.2.3                                                                                                                                                                      | Mode-III (Zero or null Period)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.9.3                                                                                              | Steady-s                                                                                                                                                                     | state analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 212                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                                                                                    | 4.9.3.1                                                                                                                                                                      | DC and AC output voltage gains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 212                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                                                                                    | 4.9.3.2                                                                                                                                                                      | Output power expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

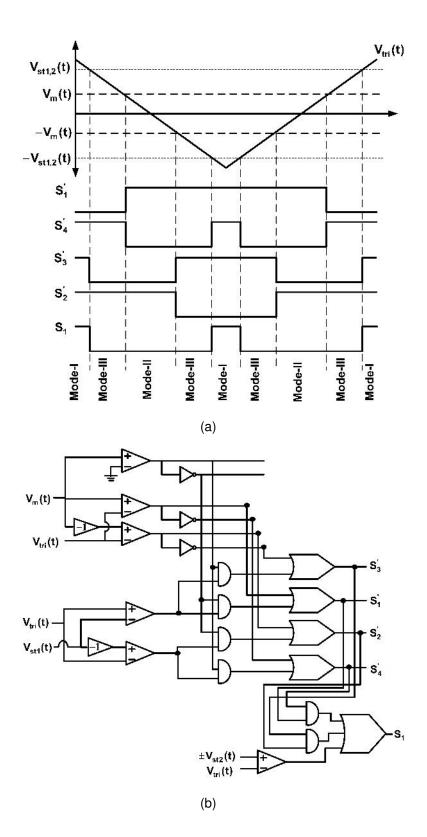

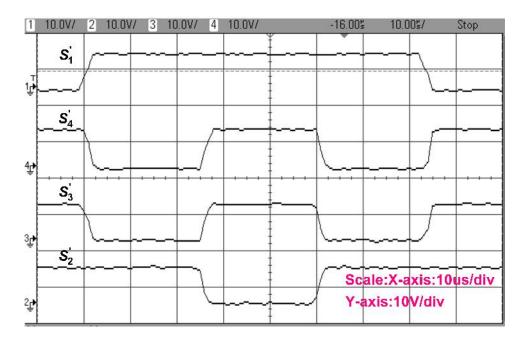

|      | 4.9.4                                                                                              | Switchin                                                                                                                                                                     | g pulses generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

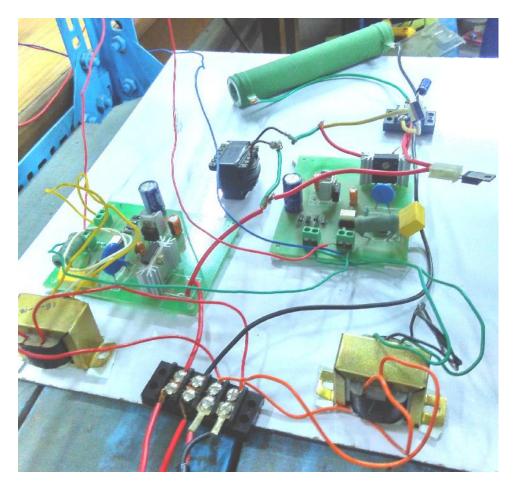

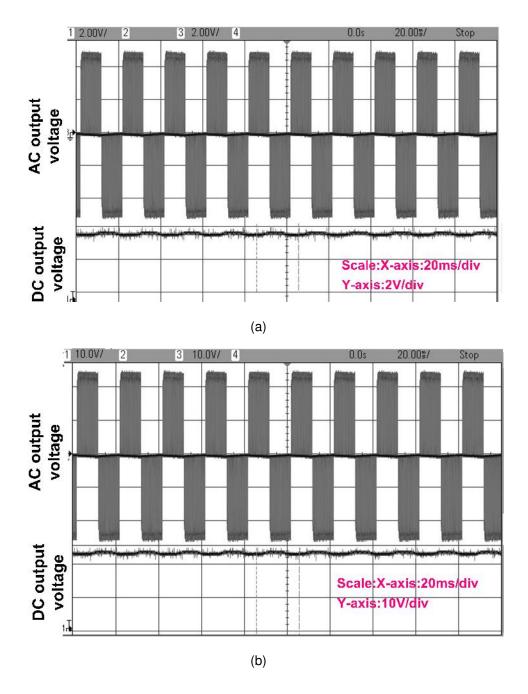

| 4.10 | Hardw                                                                                              | are Imple                                                                                                                                                                    | mentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 216                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.10.1                                                                                             | Compari                                                                                                                                                                      | son of proposed NIBBDHC with existing topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 220                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.11 | Conclu                                                                                             | usions                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 221                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CON  | ITROLI                                                                                             | LER DES                                                                                                                                                                      | IGN FOR DC-DC CONVERTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 225                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |