# INVESTIGATION ON POWER QUALITY IMPROVEMENT USING UPQC

Ph. D. Thesis

by

## JANARDHANA KOTTURU

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) FEBRUARY, 2019

# INVESTIGATION ON POWER QUALITY IMPROVEMENT USING UPQC

### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

### DOCTOR OF PHILOSOPHY

in

### **ELECTRICAL ENGINEERING**

by

#### JANARDHANA KOTTURU

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) FEBRUARY, 2019

©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2019 ALL RIGHTS RESERVED

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

## **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in this thesis entitled **"INVESTIGATION ON POWER QUALITY IMPROVEMENT USING UPQC"** in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electrical Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from January, 2013 to February, 2019 under the supervision of Prof. Pramod Agarwal, Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

## (JANARDHANA KOTTURU)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

Date: \_\_\_\_\_

(Prof. Pramod Agarwal) Supervisor

The Ph.D. Viva-Voce Examination of *Mr. Janardhana Kotturu*, Research Scholar, has been held on .....

Signature of Supervisor

Signature of External Examiner

Chairman, DRC

Head of the Department

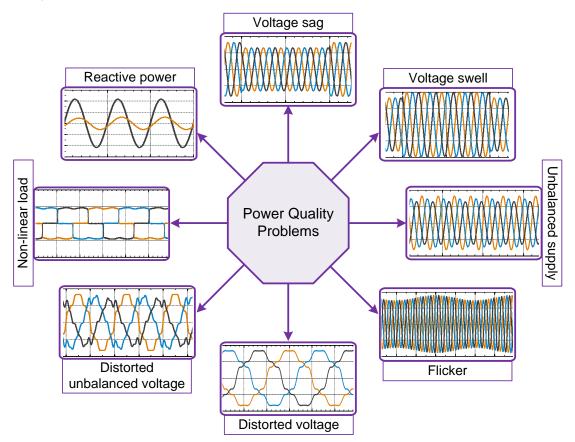

The most intensive enlargement industry wise as key equipment for modern power distribution system are the equipments based on power electronic principles. These offers a vast range of advantages for power processing like flexible control, cost reduction, overall size optimization, etc. On the contrary, utilizing these devices gives rise to numerous problems like reactive power shortage and harmonics polluting the power distribution system. The need of excessive reactive power demand leads to poor power factor, bad voltage regulation and a surge in feeder losses with reduced active power flow capabilities of the distribution system. Additionally the situation worsens in the advent of nonlinear loads raising the bar for power quality issues on distribution system. The operation of non-linear equipments on distribution systems like transformers, induction machines, electric arc furnaces, welding equipment, fluorescent lamps (with magnetic ballasts), etc. are also responsible for generation of harmonics in electric power systems. Additionally various perturbations are reported which ranges from sub cycle duration to long term steady state condition leading to distorted waveform. Short disruption, voltage sag, swell, transients of both current and voltage, distorted harmonics and waveforms, voltage fluctuations, flicker, voltage unbalance are few listed interruptions. The severity of the situation lies when there is commence of waveform distortion, flicker, and voltage imbalance at the distribution system regulation of which becomes the prime concern. A slight deviation in magnitude of voltage from its prescribed limit, current and or frequency or waveform impurity results in a potent power quality problem. These power quality problems results into interruption to the normal operation of the electrical equipments that are connected to the distribution system. Modern equipment are highly responsive to the quality of voltage that is being supplied to them. Hence, by improving the power quality takes into account both healthy and efficient distribution system as well as reduced power losses in turn saving upon the cost. To protect the interest of utility, international agencies like IEC, IEEE have been developing various standards (IEC61000, IEEE 519-1992) for harmonic specifications for point of common coupling as well as individual equipment. In addition, these guidelines promote better practices in both power systems and equipment design hence helping to minimize the operational cost.

Conventionally used power quality mitigating devices addresses to a single power quality problem at a single time. This truth lead researchers to develop dynamic and adjustable devices to mitigate multiple power quality problems. A promising approach to it is the Custom Power Devices (CDP's). These devices amends most of the problems of distribution system due to which most of the existing mitigating devices are being replaced by the CDP's reducing the cost as there are less number of overall switches involved. The family of CPDs includes distribution static synchronous compensator (DSTATCOM), dynamic

i

voltage restorer (DVR) and unified power quality conditioner (UPQC) which is used for compensating the power quality problems in the current and/or voltage waveforms.

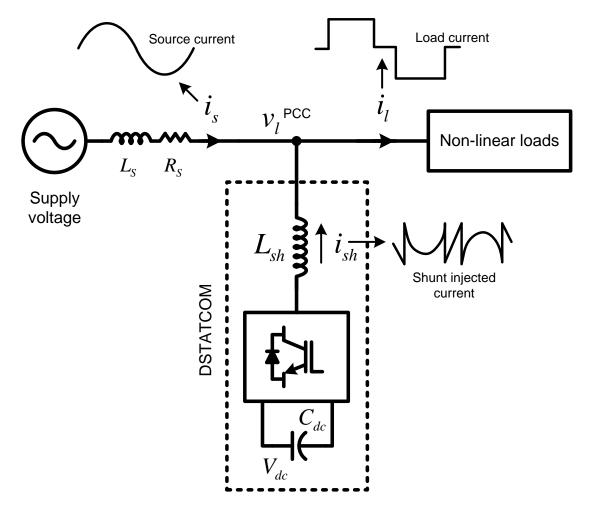

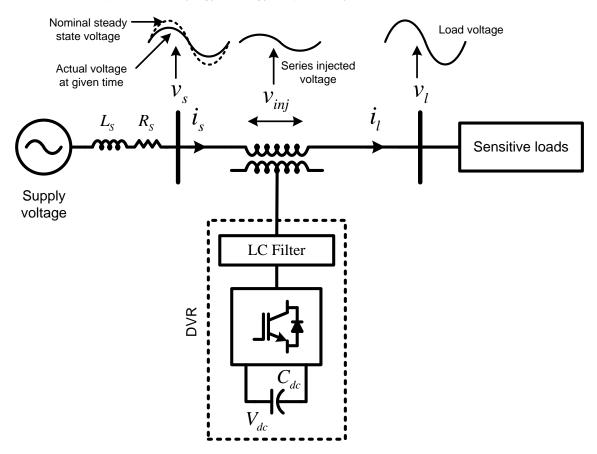

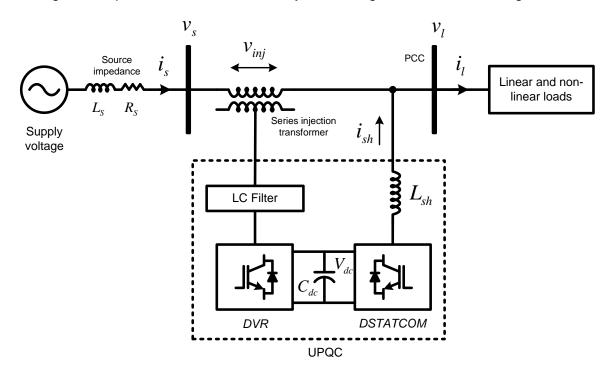

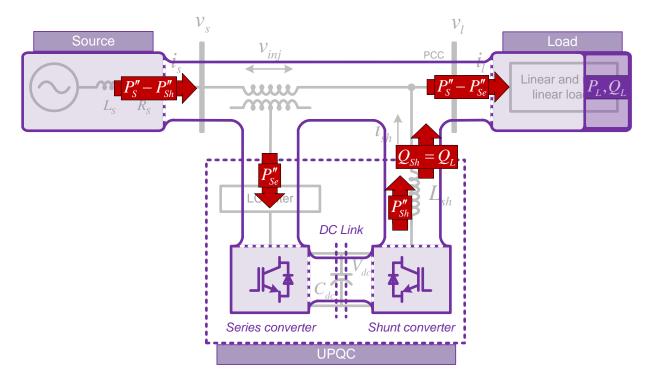

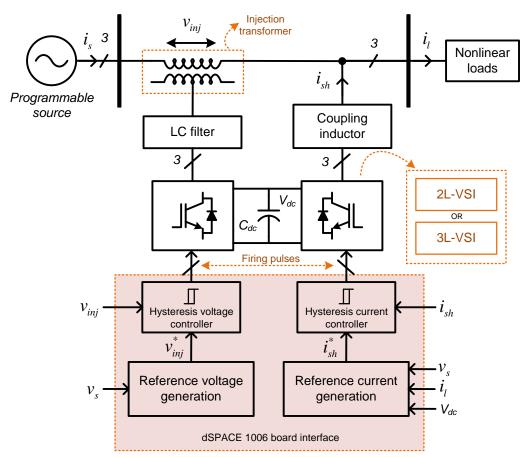

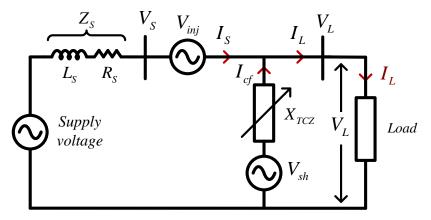

The typical custom power device is the distribution static compensator (DSTATCOM) connected in shunt at PCC. Its sole purpose is to diminish the power quality problem related to current on the distribution side. To achieve harmonic filtering, power factor correction and load balancing, the DSTATCOM injects current at the point of common coupling (PCC). An example of custom series compensation device is the dynamic voltage restorer (DVR). Its main motive is to provide protection to sensitive loads from voltage sag/ swell interruptions and harmonics in the supply side. The requisite voltage magnitude and phase angle is injected in series with the distribution feeder utilizing injection transformers and VSI accompanied by the dc-link voltage from the DC storage capacitor. A more modern and relatively versatile approach to the custom power devices is the unified power quality conditioner (UPQC). UPQC comprises of two inverters back to back in conjunction with a common dc-link. It attends to imperfections of both load current and supply voltage making it a substitute of both DSTATCOM and DVR combined.

The present work portraits an extensive and elaborate literature survey of suggested topologies, control strategies of UPQC for the sole purpose of power quality improvement. The adequacy of UPQC with two-level inverter structures has been evaluated for various power quality problems. An extended studies has been performed to multilevel structure of UPQC credits to its unique design which allows a large plethora of high voltage and also reduces the device switching frequency. It is observed that a diode clamed inverter with all the six phases of back to back converter which are sharing a common dc-link is capable of amalgamating desired waveform from several levels of DC voltage. An alluring prospect of investigation would be integration of multilevel diode clamped inverter to UPQC. There are a myriad of features offered by UPQC-ML on deciding the type of control to be used while compensating source voltage (sag, unbalanced voltage, voltage harmonics, current harmonics or reactive power). It also does the same compensating load current playing an important role in the control scheme of back to back inverters. UPQC-3L showcases a much elevated performance in comparison to UPQC-2L as it showcases superior compensating characteristics against distortion in the system. The improvement in the percentage value of THD is also observed for UPQC-3L configuration in comparison to UPQC-2L. Additionally an improved quantity of compensation is seen in with various power quality disturbances for UPQC-3L than UPQC-2L.

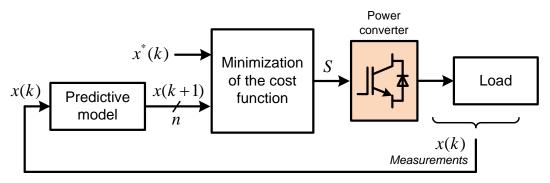

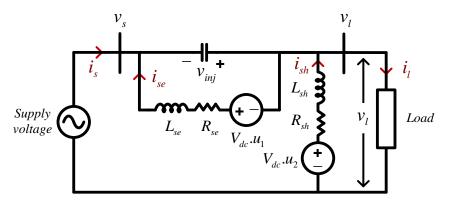

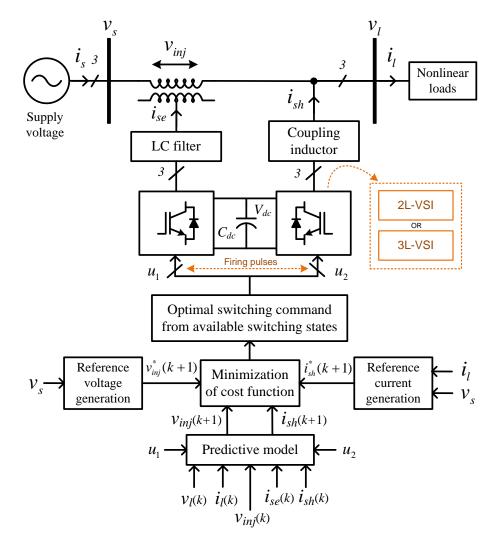

A simplified model predictive control for UPQC-2L is proposed, in which predictive voltage control for series converter to maintain a constant value of load voltage during voltage disturbances and predictive current control for shunt converter to maintain source current free from distortions is used without need of multivariable complex mathematical

ii

evaluation. The sensed voltage and current signals of source and load are used to derive the future predicted values of source current and load voltage from the discrete state space model of UPQC. The appropriate switching state is selected and applied to the converters based on the minimization of the cost function, which is selected as the square of the difference between reference and predicted values. Independent generation of reference control signals for both shunt and series converters are performed. The two reference signals are injection voltage by the series transformer into the system, considered for series converter and injectable compensation current by the shunt converter against load distortions, entitled as control reference for shunt converter. In similar way the approach is extended to UPQC-3L configuration with diode clamped multilevel inverter structure. The cost function is modified as the dc-link voltage balancing is mandatory for three-level structure along with series injecting voltage and shunt compensating current signals.

The work also focused on the reducing dc-link voltage rating of UPQC. The thorough literature has been studied on this issue. The requirement of dc-link voltage for shunt and series active filter, for UPQC are different. These fluctuation in values lead to a provocative task to assign a common dc-link of pertinent rating to achieve adequate shunt and series compensation. Conventionally, to achieve legitimate compensation the shunt filter requires higher dc-link voltage in comparison to the series active filter thus to fulfill this criterion, researchers have been left with no preference other than to choose common dc-link voltage on the basis of shunt active filter prerequisites. This leads to over rating of the series active filters as the requisites are less in comparison to shunt active filter. Thus, literature studies have revealed UPQC topologies with elevated dc-link voltage. Hence the voltage source inverters (VSIs) turn out to be bulky due to high value of dc-link capacitor. Additionally, the switch rating has to be chosen with increased value of voltage and current in return the entire cost and size upsurges.

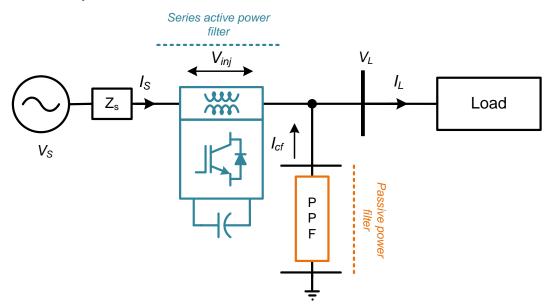

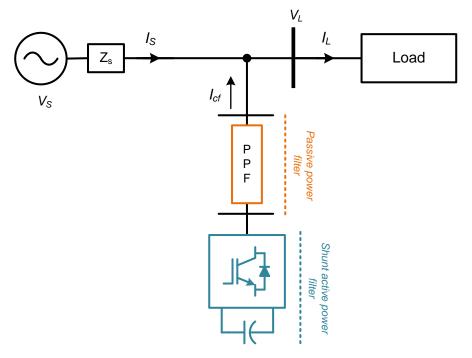

It has been observed in literatures, that few attempts have been initiated to minimize the inverter capacity by lowering the storage capacity of dc-link voltage by introducing hybrid APFs, thus intensifying system reliability. The usage of IGBTs as switching devices in the VSI of active filters cutbacks on the rating of active filter elements in hybrid filters with sensibly elevated rating. As a result it operates at very high frequency contributing to fast response and decrement in size of ripple filter passive elements and size of dc bus capacitor. A combination of shunt passive power filter (PPF) and series APF constitutes the series hybrid APF (SeHAPF). SHAF is gaining popularity due to its reduced capacity and versatile usage. An example to testify the theory would be a hybrid filter as unification of active series filter (5%) and passive series filter (20%) utilizing only 20% rating of load in case of voltage fed loads. Industrial investigation and dedicated research is directed toward series active filters as they are more popular than shunt counterpart due to its simple configuration and

iii

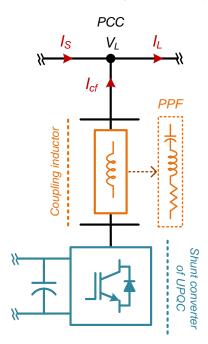

operating procedures. The shunt hybrid active power filters (SHAPFs) are series connection of passive and active filters for ease of operation at a conducive voltage and current in conjunction to high rating of active filter up to 60%-80% of the load. Unified power quality conditioner in comparison to series and shunt active filters receives less attention by the researchers by implementing hybrid structures with passive filters. A hybrid UPQC with a branch of passive filters attached to it, tuned specifically with 3<sup>rd</sup>, 5<sup>th</sup>, and 7<sup>th</sup> order harmonics has been proposed by L.H. Zhou et al. This model reduces the capacity of dc-link of shunt converter compared to conventional UPQC.

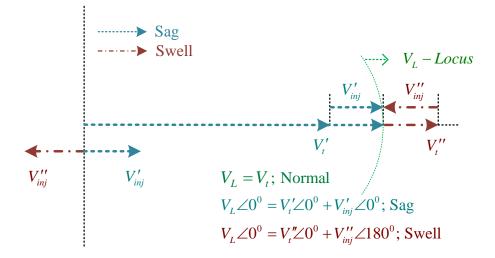

The present work proposes an analytic method to control the dc-link voltage of hybrid UPQC. In majority of the UPQC based power quality conditioner, load reactive power compensation is performed by shunt APF. It is so because the utilization factor of the shunt APF is much elevated in comparison to series APF when utilized in steady state operation and is heavily influenced by load reactive power needs. To achieve lower dc-link voltage, the compensation burden on shunt APF rating should be decreased. This can be made possible by adopting phage angle control (PAC). This method enables the sharing of reactive power between series and shunt APFs by introducing a power angle difference between source and load voltage, maintaining the magnitude of voltages for both the APFs equal. The present work makes an attempt to maintain the magnitude of voltage on the dc-link as low as possible by application of PAC to hybrid UPQC which enables to achieve further reduction in dc-link voltage in comparison to conventional UPQC. The algorithm proposed in this work, indirectly identifies the range of minimum possible dc-link voltage for a given load power factor with suitable power angle between source and load voltage. A comparative study is performed for VA loadings and utilization of power electronic converters of the designed hybrid UPQC under different conditions to the traditional UPQC. Additionally, a generalized algorithm is proposed to evaluate optimal dc-link voltage over a percentage range of voltage sag/swell combinations. Thus, the proposed algorithm gives the best fixed minimum dc-link voltage corresponding to within the range fixed by the algorithm based on the compensation level. In this work the maximum dc-link voltages are evaluated for a range of ±10% of system sag/swell index till 50%, at a given phase angle  $\delta$  varying from 0° to 45°. The analysis of minimum dc-link voltage requirement is simulated in MATLAB Simulink platform for three cases of k: no voltage sag/swell, 20% sag and swell with the combination of load lagging power factor of 0.7 and also validated experimentally.

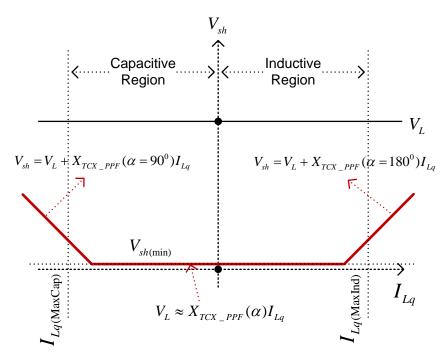

The feasibility of inclusion of Thyristor Controlled Impedance (TCZ) based PPF in hybrid UPQC is also accessed allowing for a broader range of loading reactive power from lagging to leading power factor. The TCZ-PPF enables to further minimize the dc-link voltage of hybrid UPQC in comparison to the PPF based hybrid UPQC over wide range of compensation. In an Ideal case, the dc-link voltage requirement is zero inside the

iv

compensating angle and vice-versa for outside the range of TCZ-PPF. Additionally, the minimum dc-link voltage is also evaluated for the compensation of current harmonics that are injected by the presence of nonlinear loads apart from the reactive power compensation. Three cases have been accessed to analyse the performance of the proposed topology: border point, inside the TCZ-PPF reactive power compensation range and outside the range. To accomplish minimum requirement of minimum dc-link voltage outside the compensating range, PAC control has been implemented. In addition to that, the influence of voltage sag on the dc-link voltage requirement is also scrutinized for three cases of loading reactive power.

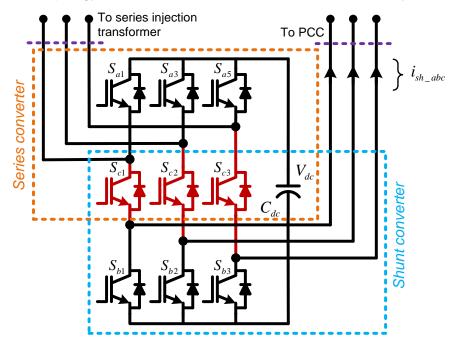

The study focuses on the reduction of cost of UPQC by downsizing the number of components. Due to its easy adaptability, an increase in research interest has taken place in which prime focus has been to improve the performance, efficiency and reduction of size and cost. Numerous topologies have come to lamplight in an effort for reduction of size and cost whilst maintaining its performance and efficiency. A reduction in the number of components can lead to a reduction in the cost of a UPQC. The major component of UPQC is series injection transformer. A Transformer-less series injection (TLSI) UPQC is an example of component reduction of UPQC. The size is so selected that it prevents problems occurring due to magnetization current demand from erratic voltage compensation and possible saturation of transformer due to DC biasing. This Thesis introduces TLSI-UPQC with its construction and explains its mode of operation. The topology integrates UPQC directly with in-coming distribution transformer averting the requirement of series injection transformer. This topology takes advantage of its location, a UPQC places in later to the distribution transformer towards the loads. The leverage provided by the topology is cost reduction and minimizing the requisite of bulky series injection transformers. This design cannot be implemented in single-phase loads due to the absence of physical neutral point. An alternative is to provide an additional forth leg in the shunt converter. Proper control strategy is designed enabling virtual neutral point for transformers on the distribution end and neutral current paths for the unbalanced loads. The proposed topology is simulated in MATLAB Simulink platform and the results are validated through an experimental prototype, which is developed in the laboratory. The experimental results show the validity and effectiveness of the proposed topology in accordance with the simulation results.

God had bestowed me the opportunity to show my sense of gratitude for all who had helped me through my journey of completion of this work. It would give me immense pleasure to express my deepest gratitude firstly and mostly to my respected supervisor Prof. Pramod Agarwal, Department of Electrical Engineering, Indian Institute of Technology Rroorkee, Roorkee, for inspiration, guidance and immense patience with constant encouragement and his uninterrupted attention to the minute details of the work. I will be indebted to his cooperation and warm approach personally and professionally and for providing me with the state of the art laboratory facility to carry out my research work.

I also express my sincere gratitude towards my research committee members Dr. B. Das (Professor EED & Chairmen SRC), Dr. S.P.Gupta, (Professor, EED), Dr. Dharmendra Singh (Professor, ECE & External Expert) for their invaluable direction, encouragement and support, and above all the noblest treatment extended by them during the course of my studies at IIT Roorkee.

I heartily extend my gratitude to Head of the Department of Electrical Engineering, and all faculty members of the department for their help, moral support, and providing the excellent infrastructure, laboratory and computing facility for the research work.

My heartfelt thanks to Dr. Bhim Singh (Professor, EED, IITD) for their valuable suggestion and inspiration during their visit at IIT Roorkee.

I acknowledge my sincere gratitude to the Ministry of Human Resources and Development (MHRD), Government of India for providing financial support during my doctoral research work.

I extend my sincere thanks to my colleagues, Dr Sukanta Halder, Dr. Srinivasa Rao, Dr. Venkata Ramana, Dr. Manmohan, Dr. Om Hari, Dr. Suresh M, Dr. Kishore, Mr. Vadtiya Jagan, Mr. Anil Konsattu, Mr. Narendra Babu, Mr. Naveen Yella, Mr. Sanjeev Reddy for sharing and supporting me during my research work. I will never forget my friends Deepshikha and Annesha Karmakar for kept me motivated by their caring words and completely hearted supports during the research work.

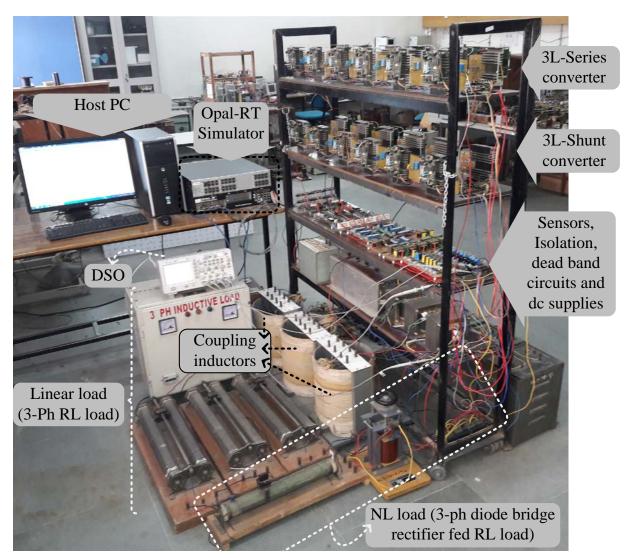

I owe gratitude to all the administrative & technical staff of the department of Electrical Engineering, IIT Roorkee, for their cooperation and necessary facility provided to me to carry out this research work. My special thanks to Mr. Amir Ahmed, Mr. Gautam Singh and Mr. Rakesh Kumar, who helped me to prepare experimental setup of my research work.

I cannot express my deepest sense of gratitude and thankfulness to my parents, for their unconditional love support, encouragement, patience, care and trust. May all praise be to the Almighty, the most beneficent, and the most merciful.

(Janardhana Kotturu)

## CONTENTS

| ABS  | TRACT   | ٢                                                         | I     |

|------|---------|-----------------------------------------------------------|-------|

| ACK  | NOWL    | EDGEMENTS                                                 | VII   |

| CON  | TENTS   | 5                                                         | IX    |

| LIST | OF FIG  | GURES                                                     | XIII  |

| LIST | OF TA   | BLES                                                      | XXV   |

| LIST | OF AC   | CRONYMS                                                   | XXVII |

| LIST | OF SY   | MBOLS                                                     | XXIX  |

| СНА  | PTER '  | 1: INTRODUCTION                                           | 1     |

| 1.1  | Electri | ic Power Quality                                          |       |

|      | 1.1.1   | Power Quality Problems                                    |       |

|      |         | Power Quality Standards                                   |       |

| 1.2  |         | y of Power Quality Problems                               |       |

| 1.3  | Solutio | ons to Power Quality Problems                             | 16    |

|      | 1.3.1   | Solutions to Harmonic Distortion                          | 16    |

|      | 1.3.2   | Solutions to Poor Power Factor                            |       |

|      | 1.3.3   | Solutions to Voltage Sag/Swell                            |       |

| 1.4  | Literat | ture Survey of Custom Power Devices                       |       |

|      | 1.4.1   | Distribution Static Compensator (DSTATCOM)                |       |

|      | 1.4.2   | Dynamic Voltage Regulator (DVR)                           | 22    |

|      | 1.4.3   | Unified Power Quality Conditioner (UPQC)                  | 24    |

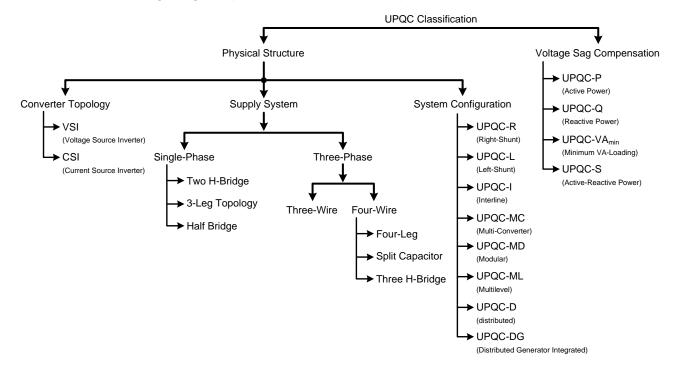

|      |         | 1.4.3.1 Classification of UPQC Topology                   |       |

|      |         | 1.4.3.2 Control Techniques of UPQC                        |       |

|      |         | 1.4.3.3 Concept of UPQC under Compensation                |       |

| 1.5  | Scope   | e of Work and Author's Contribution                       |       |

| 1.6  | Organ   | ization of the Thesis                                     | 40    |

| -    | PTER 2  |                                                           |       |

| 2.1  | Introdu | uction                                                    | 43    |

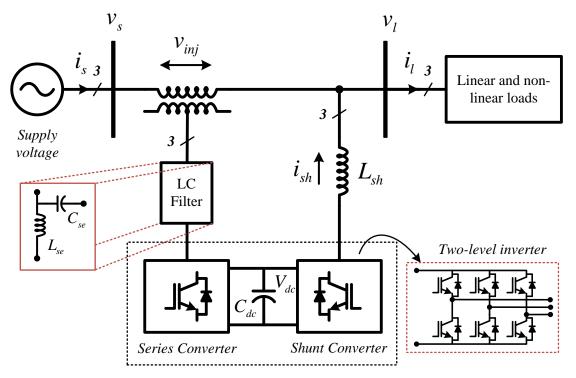

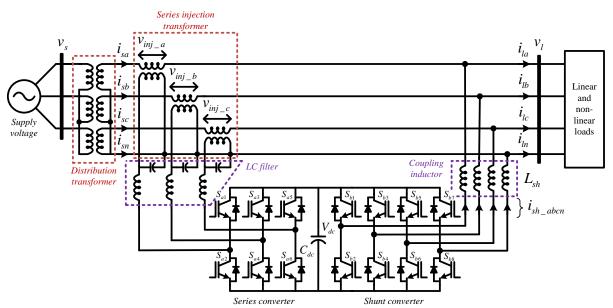

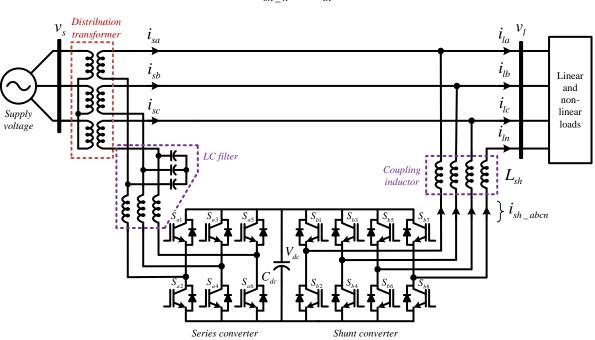

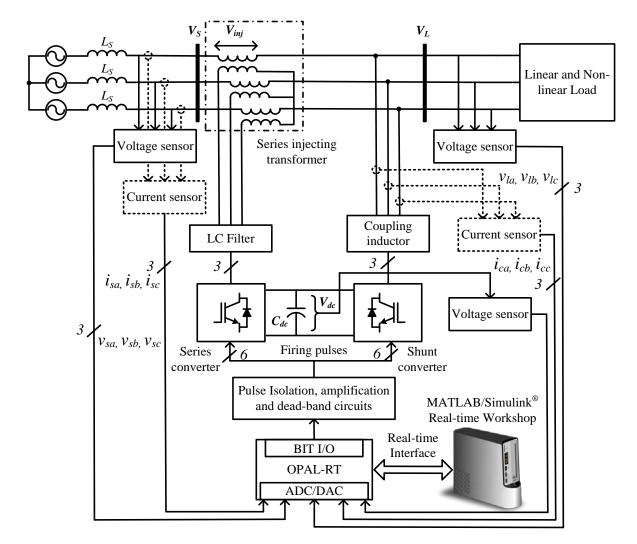

| 2.2  | Syster  | m Description                                             | 43    |

|      | 2.2.1   | Unified Power Quality Conditioner                         | 43    |

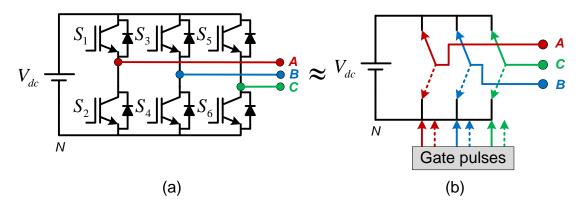

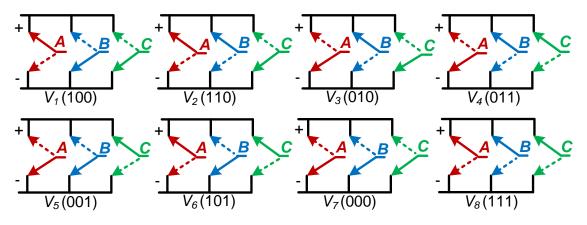

|      |         | 2.2.1.1 Two-level Inverter and Control Schemes            |       |

|      |         | 2.2.1.2 Multi-Level Inverter and Control Schemes          | 49    |

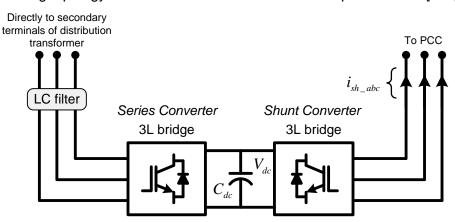

|      | 2.2.2   | Unified Power Quality Conditioner Using Three-level DCMLI | 58    |

| 2.3  | Param   | neter Estimation of Unified Power Quality Conditioner     | 58    |

|      | 2.3.1   | Design of Shunt Converter part of UPQC                    | 59    |

|      | 2.3.2   | Design of Series Converter Part of UPQC                   | 60    |

| 2.4 | Contro  | ol Strategies                                                     | 61  |

|-----|---------|-------------------------------------------------------------------|-----|

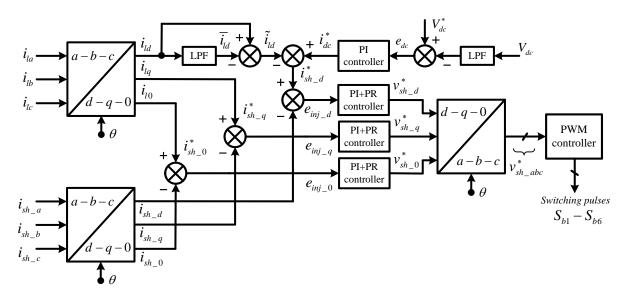

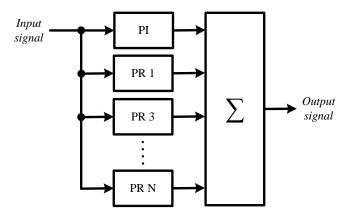

|     | 2.4.1   | Control Strategy of UPQC-2L                                       | 61  |

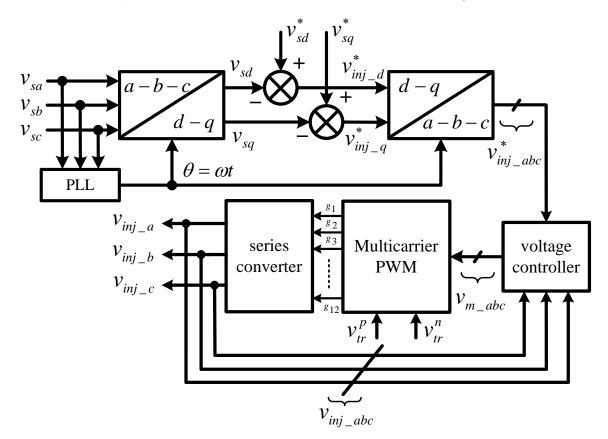

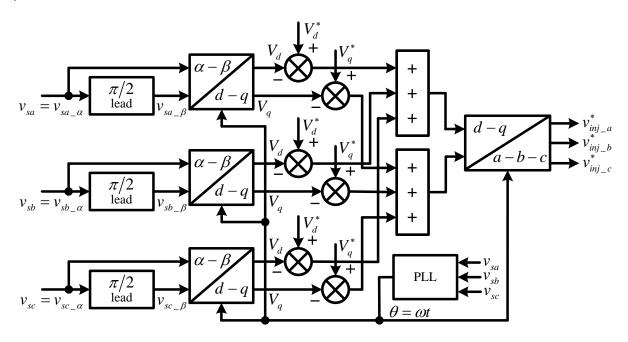

|     |         | 2.4.1.1 Control Strategy of Series Converter                      | 61  |

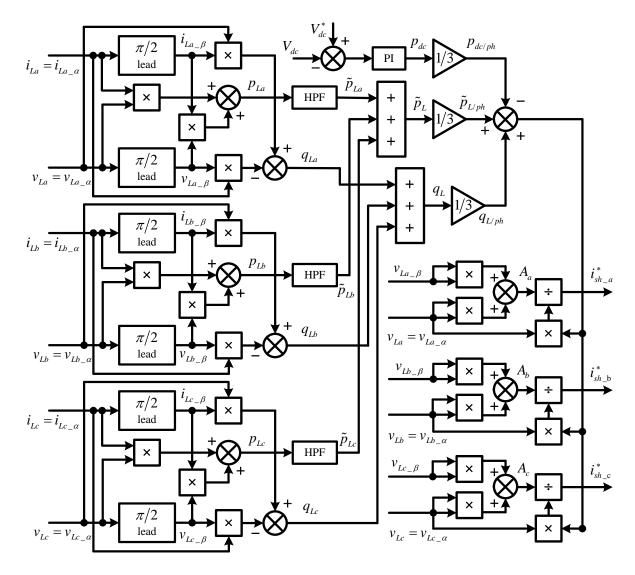

|     |         | 2.4.1.2 Control Strategy of Shunt Converter                       | 63  |

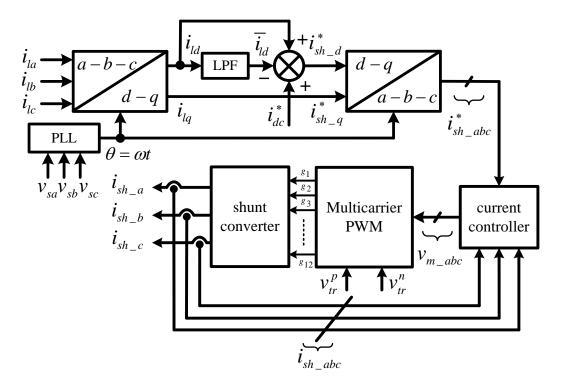

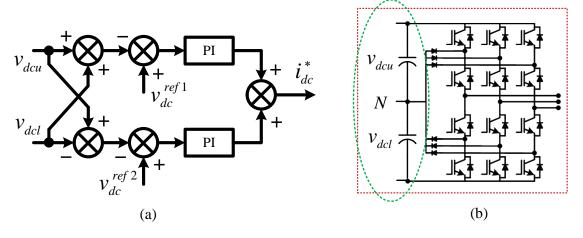

|     | 2.4.2   | Control Strategy of UPQC-3L                                       | 64  |

|     |         | 2.4.2.1 Control Strategy of Series Converter                      | 64  |

|     |         | 2.4.2.2 Control Strategy of Shunt Converter                       | 65  |

| 2.5 | Simula  | ation and Experimental Results of UPQC-2L and UPQC-3L             | 66  |

|     | 2.5.1   | Case-1: Distorted Source and Non-linear Load                      | 69  |

|     | 2.5.2   | Case-2: Voltage Sag Compensation under Non-linear Load            | 80  |

|     | 2.5.3   | Case-3: Voltage Swell Compensation under Non-linear Load          | 88  |

|     | 2.5.4   | Case-4: Unbalanced Source Voltage Compensation                    | 96  |

|     | 2.5.5   | Case-5: Unbalanced Distorted Source Voltage Compensation          | 101 |

|     | 2.5.6   | Case-6: Reactive Power Compensation                               | 108 |

| 2.6 | Conclu  | usion                                                             | 111 |

| СНА | PTER 3  | 3: SIMPLIFIED MODEL PREDICTIVE CONTROL OF UPQC                    | 113 |

| 3.1 | Introdu | uction                                                            | 113 |

| 3.2 | Model   | Predictive Control                                                | 115 |

| 3.3 | UPQC    | System Model Description                                          | 117 |

| 3.4 | Discre  | te-Time Model for Predictive Control Strategy                     | 117 |

|     | 3.4.1   | Selection of Cost Function and Optimization                       | 120 |

|     | 3.4.2   | Reference Signal Generation                                       | 123 |

| 3.5 | Simula  | ation and Experimental Results                                    | 126 |

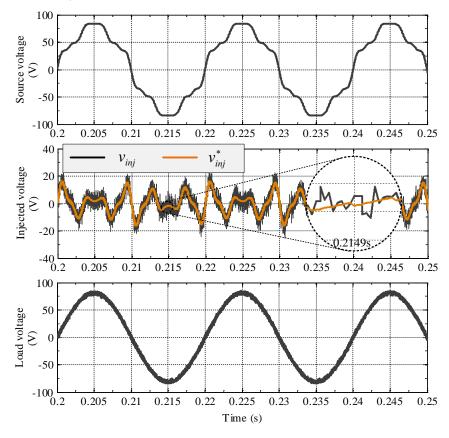

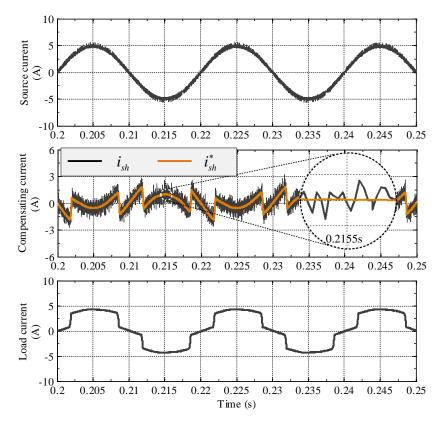

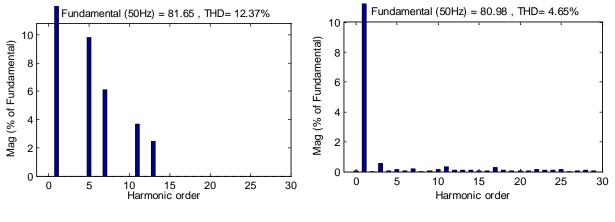

|     | 3.5.1   | Case-1: Distorted Source Voltage and Non-linear Load              | 128 |

|     | 3.5.2   | Case-2: Distorted Unbalanced Source Voltage                       | 136 |

|     | 3.5.3   | Case-3: Voltage Sag with Non-linear Load                          | 145 |

|     | 3.5.4   | Case-4: Voltage Swell with Non-linear Load                        | 151 |

| 3.6 | Conclu  | usion                                                             | 157 |

| СНА | PTER 4  | 4: HYBRID UNIFIED POWER QUALITY CONDITIONER                       | 159 |

| 4.1 |         | uction                                                            |     |

|     | 4.1.1   | Passive Power Filter                                              |     |

|     | 4.1.2   | Passive Power Filter in Hybrid Configurations                     |     |

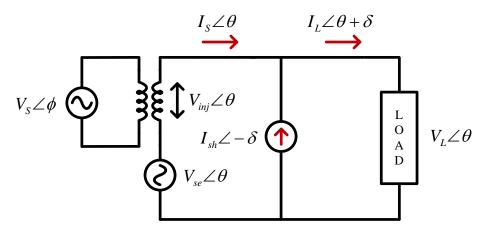

| 4.2 |         | pt Background                                                     |     |

| 4.3 |         | I UPQC Topology Description                                       |     |

|     | -       | PAC based DC-Link Voltage Estimation                              |     |

| 4.4 |         | nk Voltage Analysis of Hybrid UPQC                                |     |

|     | 4.4.1   | Analysis of Minimum DC-Link Voltage between UPQC and Hybrid UPQC. |     |

|     | 4.4.2  | Evaluation of Minimum DC-Link Voltage using PAC Approach       | 173       |

|-----|--------|----------------------------------------------------------------|-----------|

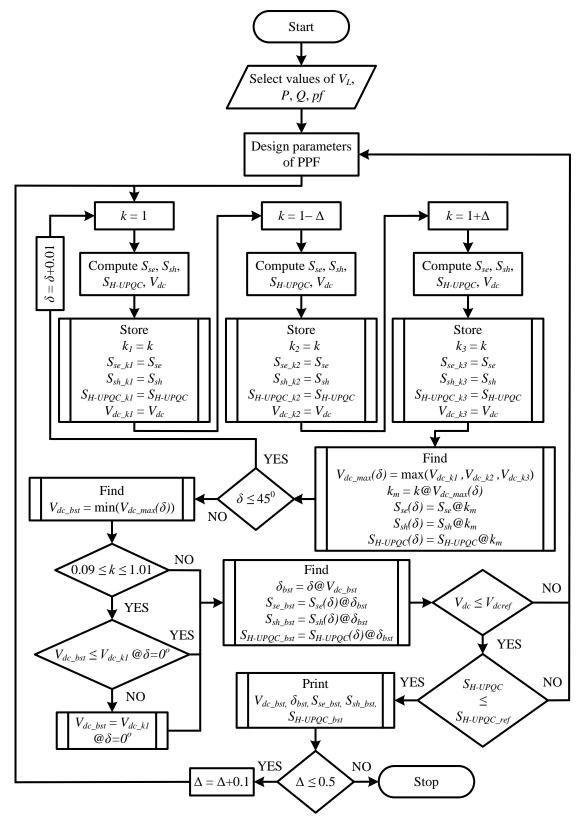

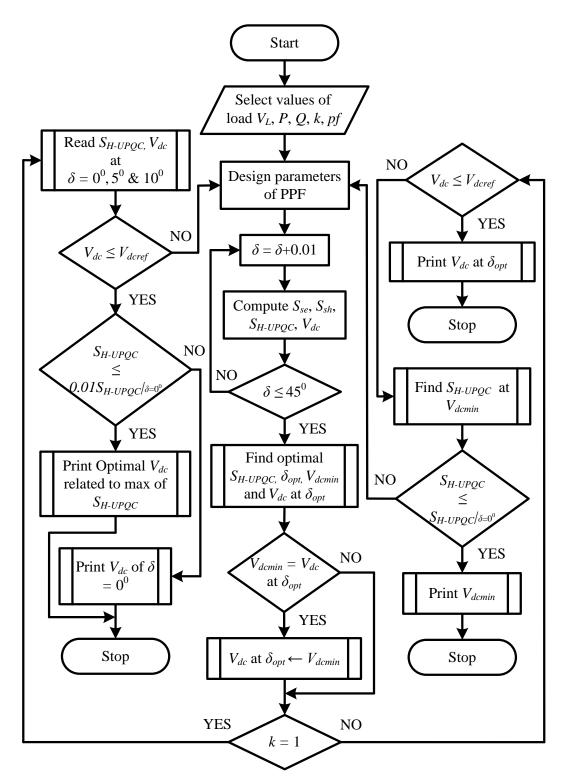

|     | 4.4.3  | Algorithm to Evaluate Optimal DC-Link Voltage                  | 175       |

| 4.5 | Contro | oller for Hybrid-UPQC                                          | 177       |

|     | 4.5.1  | Reference Signal Generation for Series Converter               | 177       |

|     | 4.5.2  | Reference Signal Generation for Shunt Converter                |           |

| 4.6 | Simula | ation Study of Proposed Algorithm of DC-Link Voltage Analysis  |           |

| 4.7 | Exper  | imental Verification                                           |           |

| 4.8 | Concl  | usion                                                          |           |

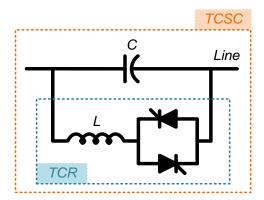

| СНА | PTER   | 5: TCZ-PPF BASED HYBRID UNIFIED POWER QUALITY COND             | TIONER189 |

| 5.1 | Introd | uction                                                         |           |

|     | 5.1.1  | Concept Background                                             |           |

| 5.2 | Topol  | bgy Description                                                |           |

| 5.3 | Paran  | neter Design of TCZ-PPF Hybrid UPQC                            |           |

| 5.4 |        | nk Voltage Requirement of TCZ-PPF Hybrid UPQC                  |           |

|     | 5.4.1  | Analysis of Minimum DC-Link Voltage Requirement                | 199       |

|     | 5.4.2  | Algorithm to Evaluate Optimal DC-Link Voltage                  |           |

| 5.5 | Contro | oller for Hybrid-UPQC                                          | 204       |

|     | 5.5.1  | Generation of Reference Signals for Series and Shunt Converter |           |

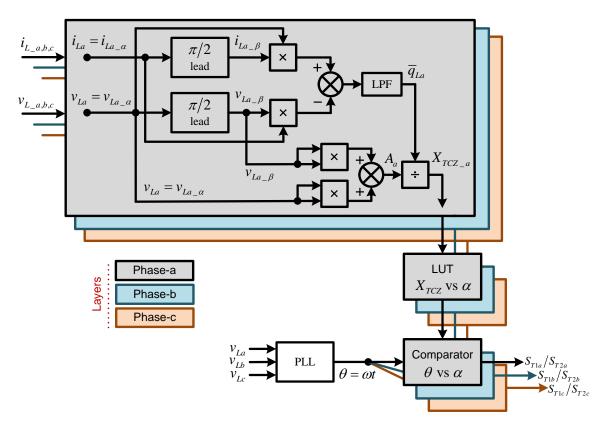

|     | 5.5.2  | Generation Firing Commands for TCR of TCZ-PPF                  |           |

| 5.6 | Simula | ation Study                                                    | 205       |

| 5.7 | Exper  | imental Verification                                           | 207       |

| 5.8 | Concl  | usion                                                          | 210       |

| СНА | PTER   | 6: TRANSFORMERLESS SERIES INJECTION BASED UPQC                 | 211       |

| 6.1 | Introd | uction                                                         | 211       |

| 6.2 | Struct | ure Description                                                | 215       |

|     | 6.2.1  | Features and Challenges                                        | 217       |

|     | 6.2.2  | Equivalent Circuit and Operation:                              | 217       |

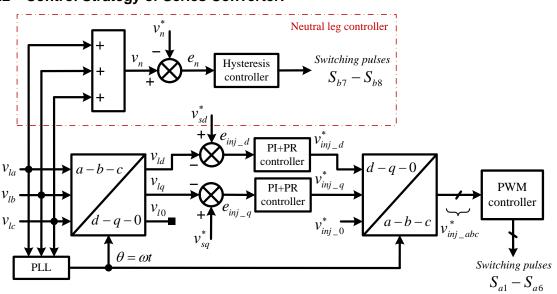

| 6.3 | Contro | ol Strategy of TLSI-UPQC                                       | 218       |

|     | 6.3.1  | Control Strategy of Shunt Converter:                           | 218       |

|     | 6.3.2  | Control Strategy of Series Converter:                          |           |

| 6.4 | Simula | ation and Experimental Results                                 |           |

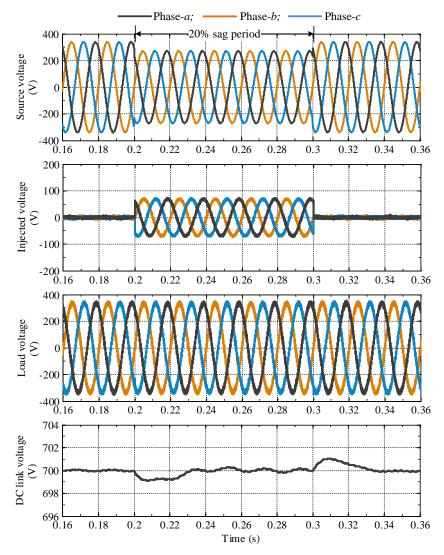

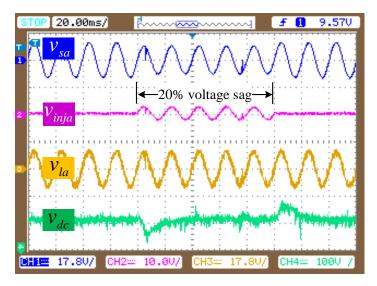

|     | 6.4.1  | Source Voltage Sag with Nonlinear Load:                        | 224       |

|     | 6.4.2  | Distorted Source Voltage with Nonlinear Load:                  |           |

|     | 6.4.3  | Unbalanced Source Voltage:                                     | 232       |

|     | 6.4.4  | Unbalanced Linear Load:                                        | 233       |

|     | 6.4.5  | Unbalanced Non-linear Load:                                    | 238       |

|     | 6.4.6  | Unbalanced Linear and Non-linear Load:                         | 242       |

| 6.5  | Conclusion               | 245 |

|------|--------------------------|-----|

| СНА  | PTER 7: CONCLUSIONS      | 247 |

| 7.1  | Conclusion               | 247 |

| 7.2  | Future Scope of Research | 249 |

| DIIR | LICATIONS EPOM THE WORK  | 251 |

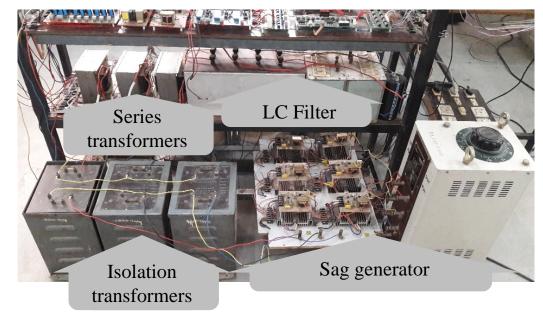

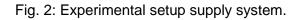

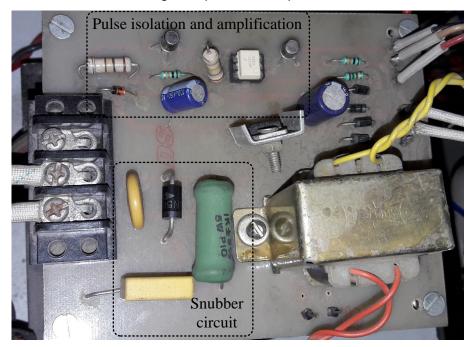

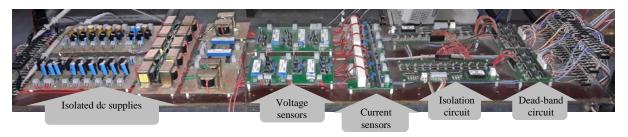

| PHOTOGRAPHS OF THE EXPERIMENTAL SETUP | 253 |

|---------------------------------------|-----|

| BIBLIOGRAPHY                          | 257 |

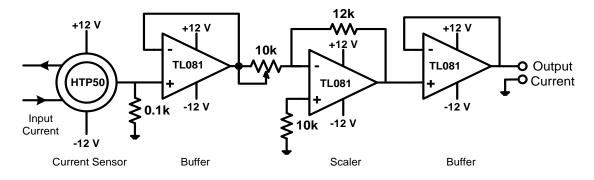

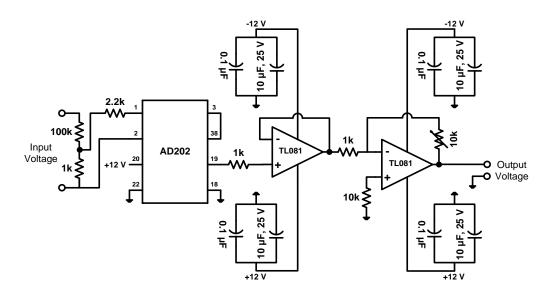

| APPENDIX – A: SYSTEM HARDWARE         | 279 |

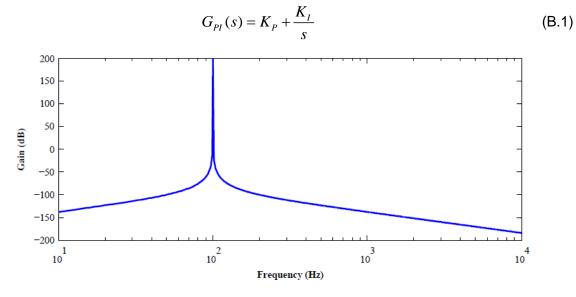

| APPENDIX – B: PR CONTROLLER           |     |

## LIST OF FIGURES

| Fig. 1.1: Pictorial view of major power quality problems4                                     |

|-----------------------------------------------------------------------------------------------|

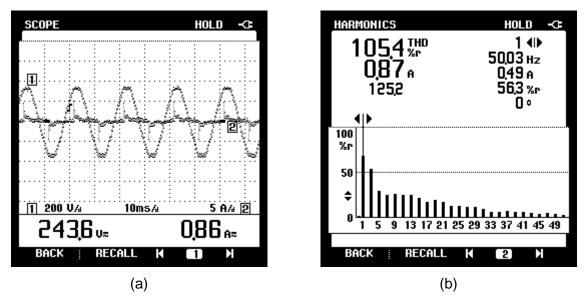

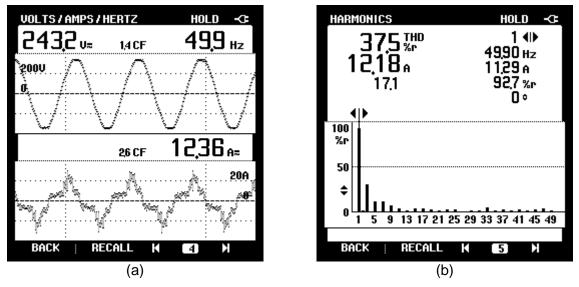

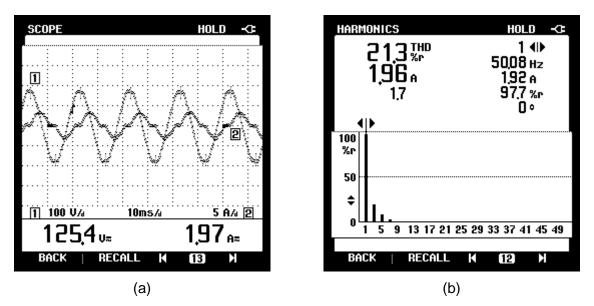

| Fig. 1.2: Mobile charger: (a) Voltage and current waveforms; (b) Harmonic spectrum of         |

| current9                                                                                      |

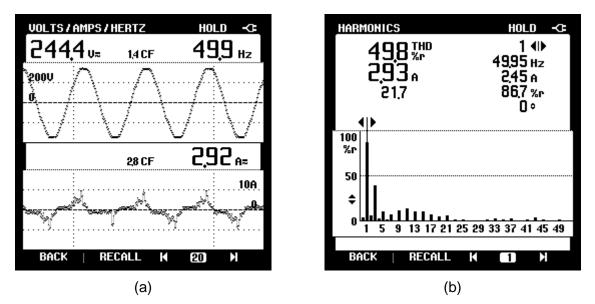

| Fig. 1.3: Personal computer: (a) Voltage and current waveforms; (b) Harmonic spectrum of      |

| current9                                                                                      |

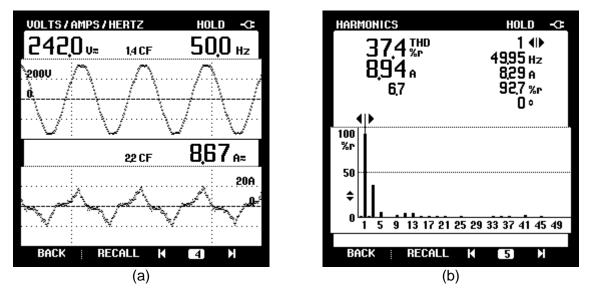

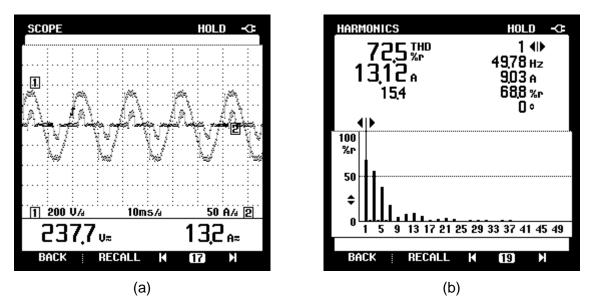

| Fig. 1.4: Uninterruptable power supply: (a) Voltage and current waveforms; (b) Harmonic       |

| spectrum of current10                                                                         |

| Fig. 1.5: Opal-RT Simulator: (a) Voltage and current waveforms; (b) Harmonic spectrum of      |

| current                                                                                       |

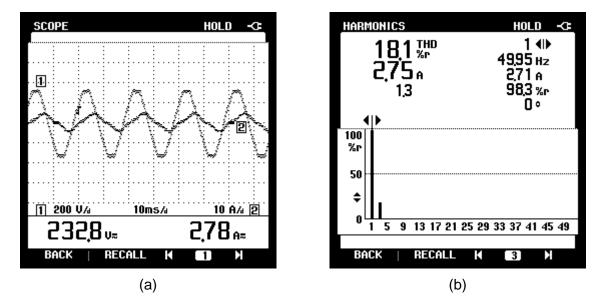

| Fig. 1.6: Central UPS system of computer lab: (a) Voltage and current waveforms; (b)          |

| Harmonic spectrum of current11                                                                |

| Fig. 1.7: Single fluorescent lamp: (a) Voltage and current waveforms; (b) Harmonic spectrum   |

| of current                                                                                    |

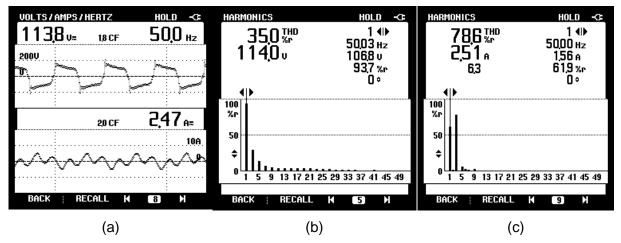

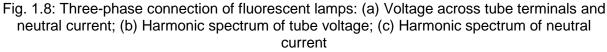

| Fig. 1.8: Three-phase connection of fluorescent lamps: (a) Voltage across tube terminals and  |

| neutral current; (b) Harmonic spectrum of tube voltage; (c) Harmonic spectrum of neutral      |

| current12                                                                                     |

| Fig. 1.9: CFL: (a) Voltage and current waveforms; (b) Harmonic spectrum of current            |

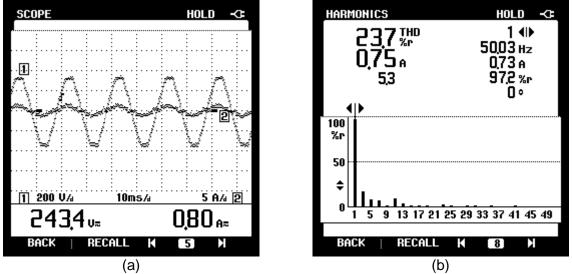

| Fig. 1.10: Water cooler: (a) Voltage and current waveforms; (b) Harmonic spectrum of          |

| current13                                                                                     |

| Fig. 1.11: Air conditioner: (a) Input current waveform; (b) Harmonic spectrum                 |

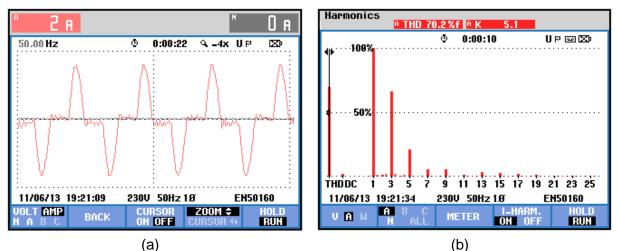

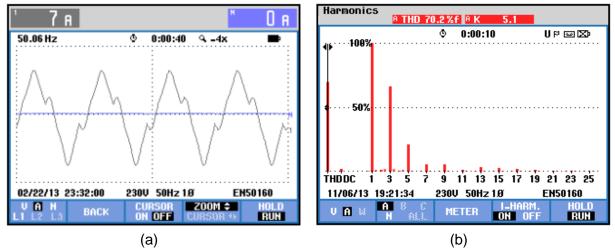

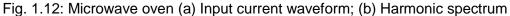

| Fig. 1.12: Microwave oven (a) Input current waveform; (b) Harmonic spectrum                   |

| Fig. 1.13: Three-phase diode bridge rectifier with RL load: (a) Voltage and current waveforms |

| of phase- <i>a</i> ; (b) Harmonic spectrum of current15                                       |

| Fig. 1.14: Single-phase voltage regulator with RL load: (a) Voltage and current waveforms of  |

| phase- <i>a</i> ; (b) Harmonic spectrum of current15                                          |

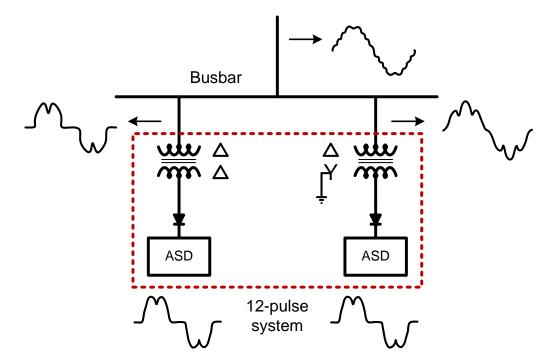

| Fig. 1.15: Phase multiplication technique for harmonic compensation in the load [7]           |

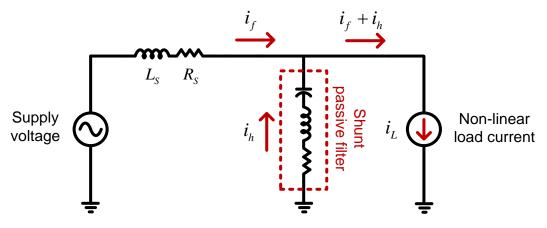

| Fig. 1.16: Shunt passive filter installed in the network [7]17                                |

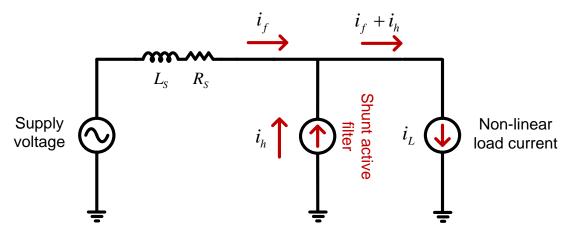

| Fig. 1.17: Shunt active filter installed in the network [7]18                                 |

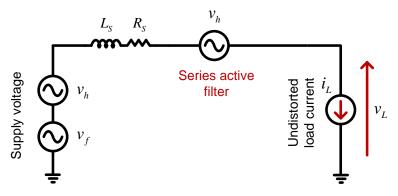

| Fig. 1.18: Series active filter installed in the network [7]19                                |

| Fig. 1.19: System configuration of DSTATCOM                                                   |

| Fig. 1.20: System configuration of DVR23                                                      |

| Fig. 1.21: System configuration of UPQC24                                                     |

| Fig. 1.22: Classification of UPQC topology [231]26                                            |

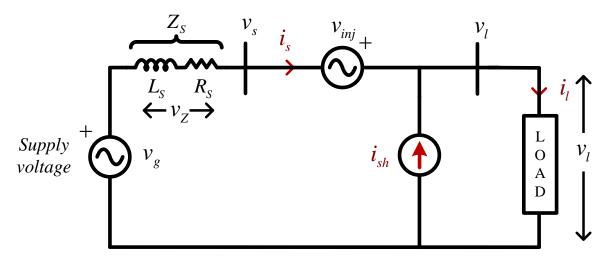

| Fig. 1.23: Single-phase equivalent circuit of UPQC [143]                                      |

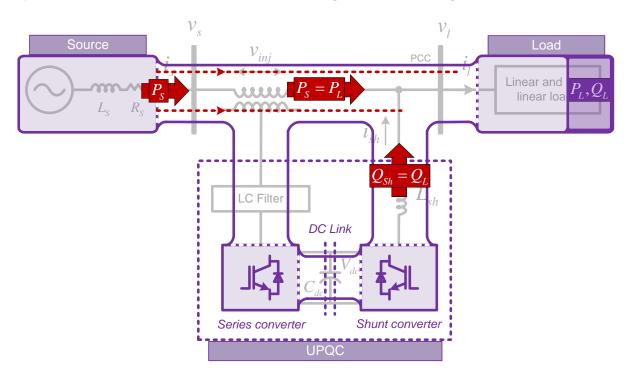

| Fig. 1.24: Power flow during normal working condition of UPQC                                 |

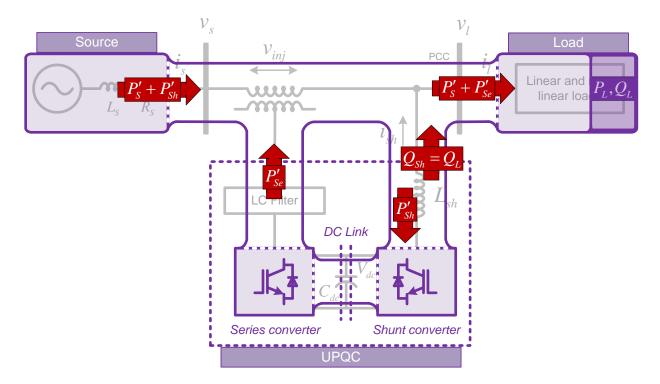

| Fig. 1.25: Power flow analysis during sag compensation                                        |

| Fig. 1.26: Power analysis during swell compensation                                       | 37    |

|-------------------------------------------------------------------------------------------|-------|

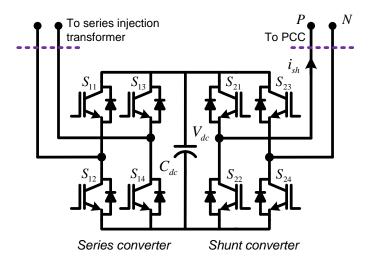

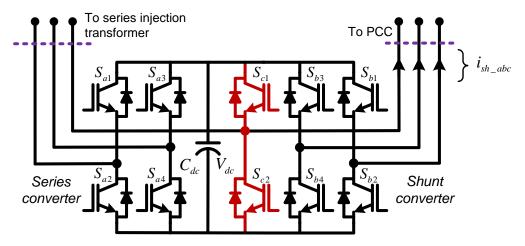

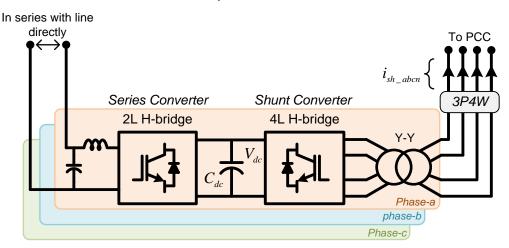

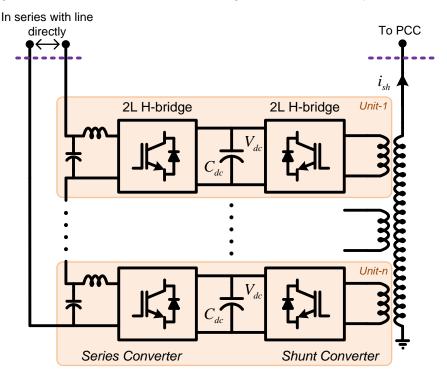

| Fig. 2.1: Structure of unified power quality conditioner with two-level inverters         | 44    |

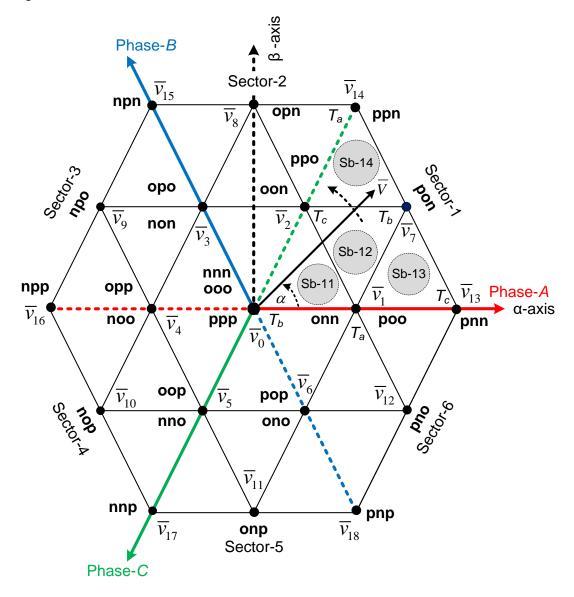

| Fig. 2.2: Three-phase two-level inverter [258]                                            | 45    |

| Fig. 2.3: Switching states for two-level inverter                                         | 45    |

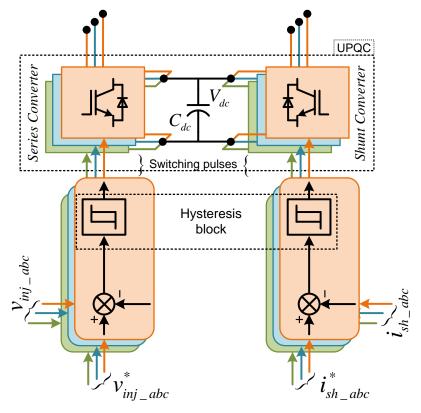

| Fig. 2.4: Application of hysteresis controller for two-level inverter in UPQC             | 46    |

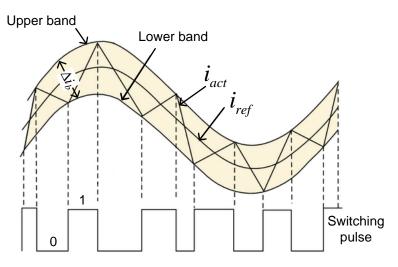

| Fig. 2.5: Hysteresis controller                                                           | 46    |

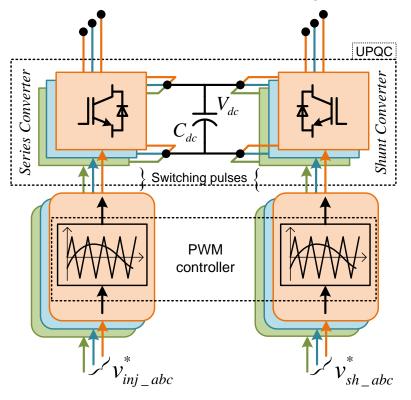

| Fig. 2.6: Application of PWM controller for two-level inverter in UPQC                    | 47    |

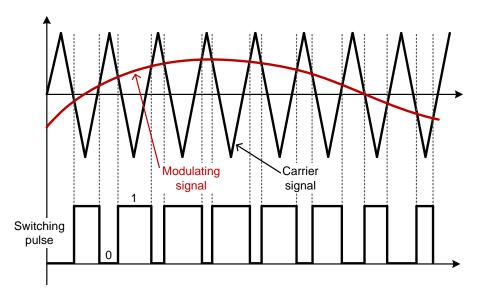

| Fig. 2.7: SPWM controller for two-level inverter                                          | 47    |

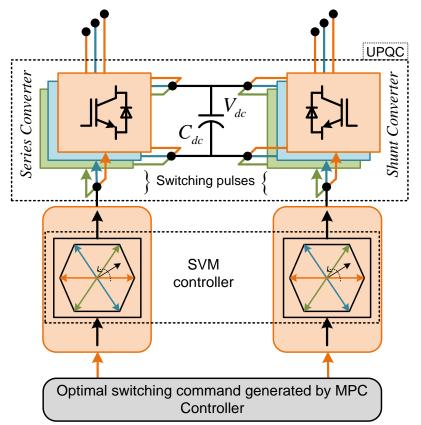

| Fig. 2.8: Application of SVM controller for two-level inverter in UPQC                    | 48    |

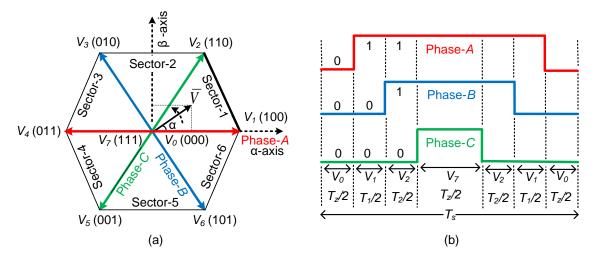

| Fig. 2.9: (a) Vector representation for two-level inverter, (b) Pulse pattern of sector-1 | 49    |

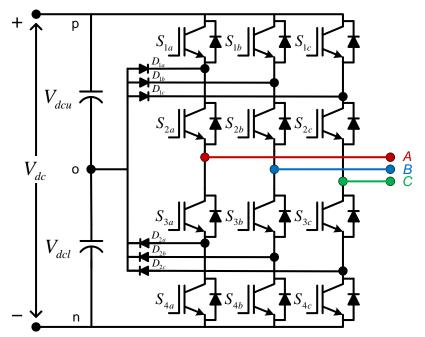

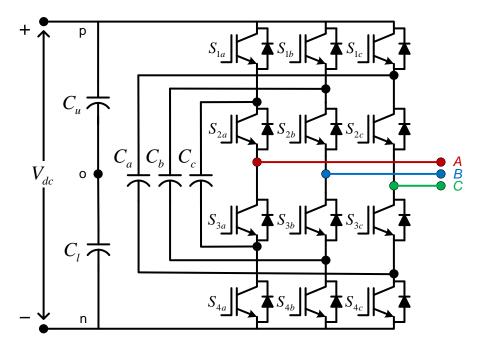

| Fig. 2.10: DCMLI structure of three-level inverter                                        | 50    |

| Fig. 2.11: FCMLI structure of three-level inverter                                        | 51    |

| Fig. 2.12: Single-phase of CHBMLI structure with two DC sources                           | 51    |

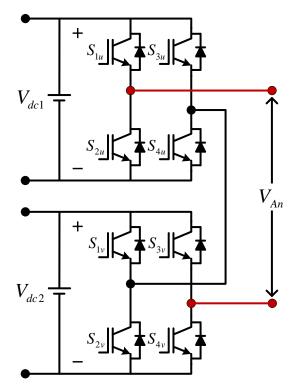

| Fig. 2.13: (a). In-phase level shift modulation, (b). Phase leg of three-level diode clam | nped  |

| multilevel inverter [268]                                                                 | 53    |

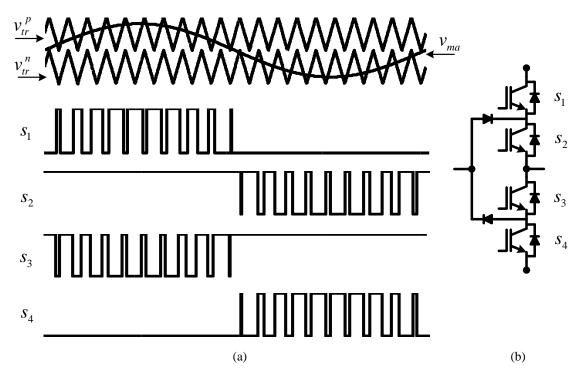

| Fig. 2.14: Space vector diagram for three-level inverter [268]                            | 54    |

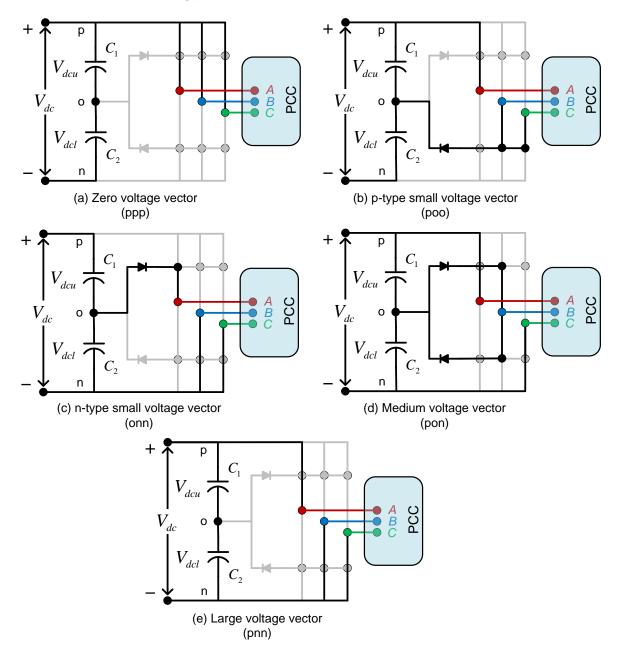

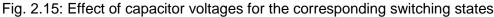

| Fig. 2.15: Effect of capacitor voltages for the corresponding switching states            | 57    |

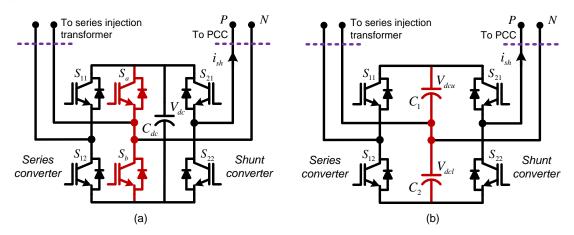

| Fig. 2.16: Structure of unified power quality conditioner with three-level inverters      | 58    |

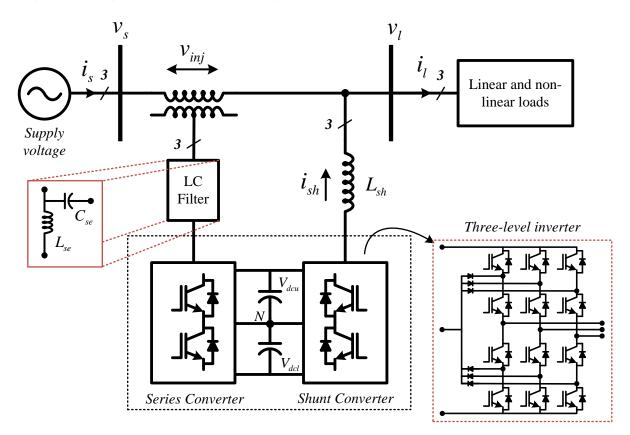

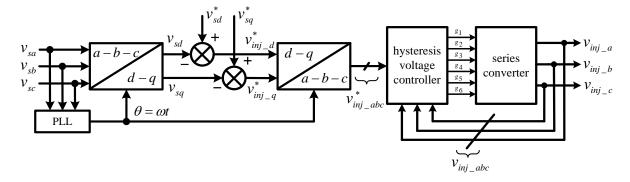

| Fig. 2.17: Control strategy of series converter                                           | 62    |

| Fig. 2.18: Control strategy of shunt converter                                            | 63    |

| Fig. 2.19: Control strategy of series converter                                           | 65    |

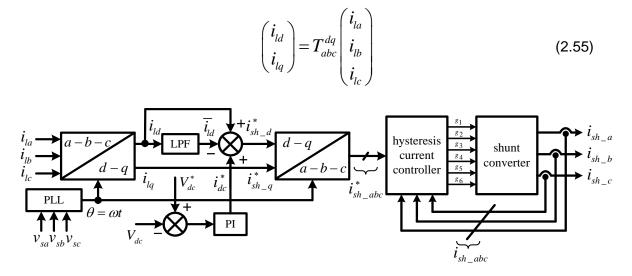

| Fig. 2.20: Control strategy of shunt converter                                            | 66    |

| Fig. 2.21: Control strategy of shunt converter                                            | 66    |

| Fig. 2.22: Block diagram of system topology under evaluation                              | 68    |

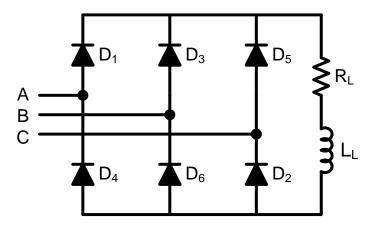

| Fig. 2.23: Uncontrolled bridge rectifier with RL load                                     | 69    |

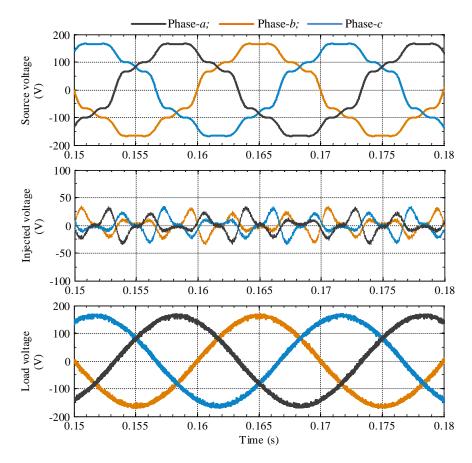

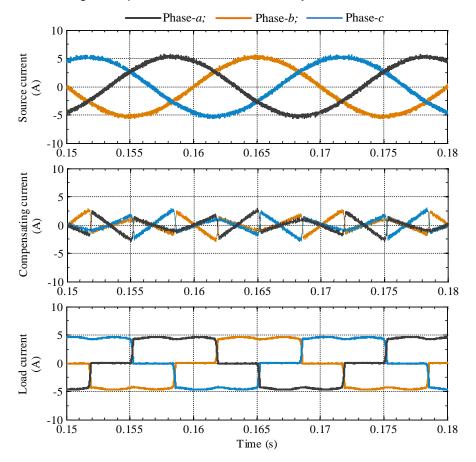

| Fig. 2.24: Voltage compensation characteristics by shunt converter of UPQC-2L             | 70    |

| Fig. 2.25: Current compensation characteristics by shunt converter of UPQC-2L             | 70    |

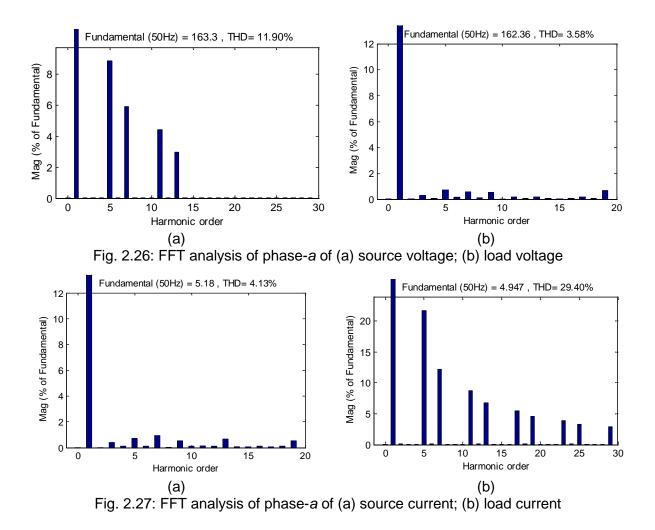

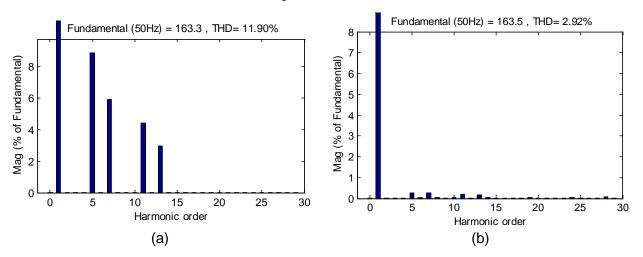

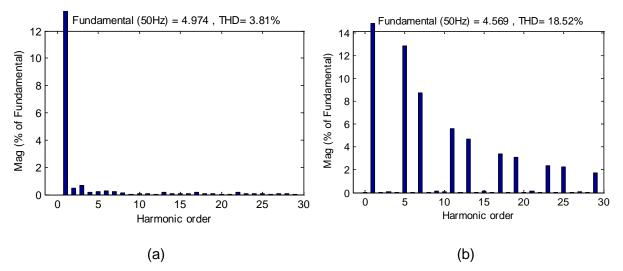

| Fig. 2.26: FFT analysis of phase-a of (a) source voltage; (b) load voltage                | 71    |

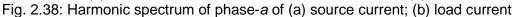

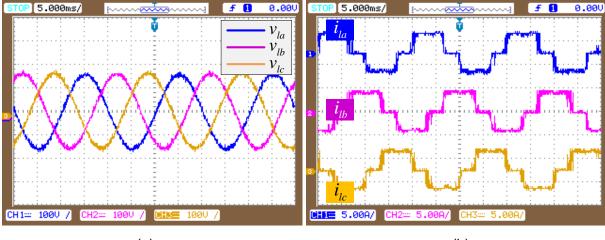

| Fig. 2.27: FFT analysis of phase- <i>a</i> of (a) source current; (b) load current        | 71    |

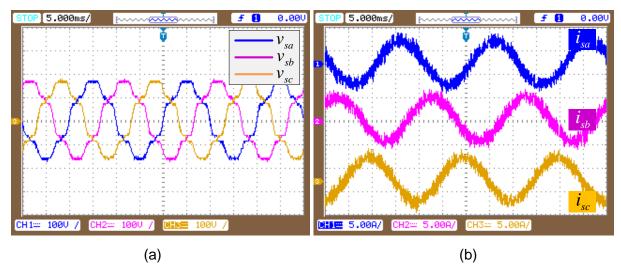

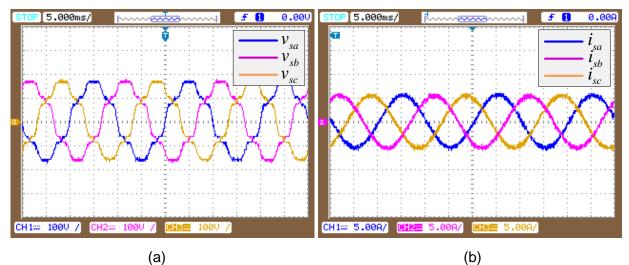

| Fig. 2.28: (a). Three-phase source voltages and (b). Source currents for case-1 in UPQ0   | C-2L  |

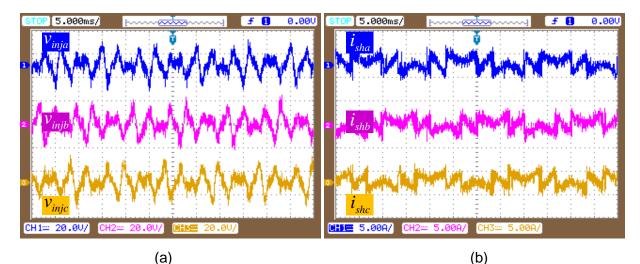

|                                                                                           | 72    |

| Fig. 2.29: (a). Three-phase series injected voltages and (b). Shunt compensating current  | s for |

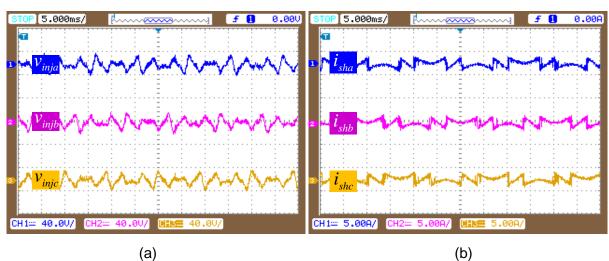

| case-1 in UPQC-2L                                                                         | 73    |

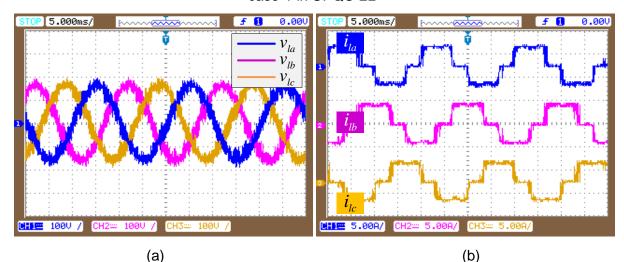

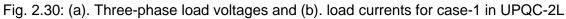

| Fig. 2.30: (a). Three-phase load voltages and (b). load currents for case-1 in UPQC-2L    | 73    |

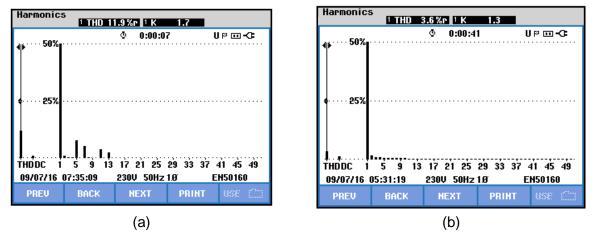

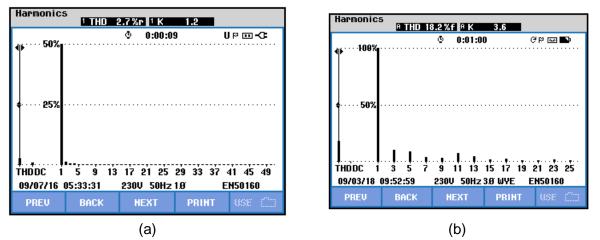

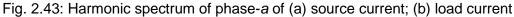

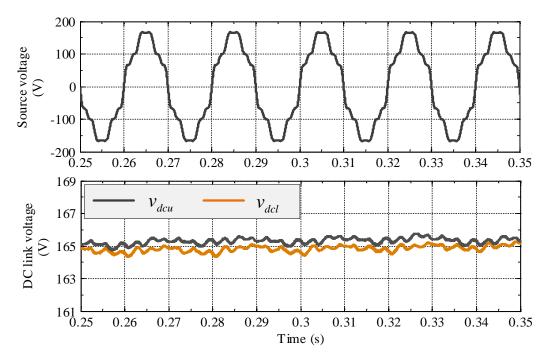

| Fig. 2.31: Harmonic spectrum of phase-a of (a) source voltage; (b) load voltage           | 73    |

| Fig. 2.32: Harmonic spectrum of phase-a of (a) source current; (b) load current           | 74    |

| Fig. 2.33: Simulation results showing dc-link voltage variation during case-1 with UPQC-2 | 2L74  |

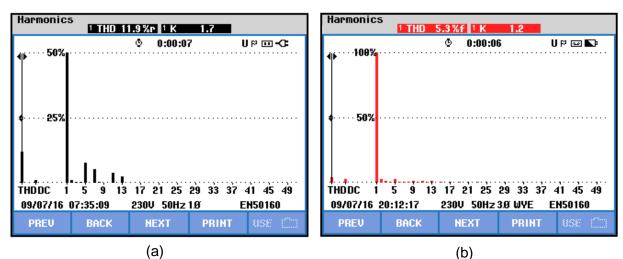

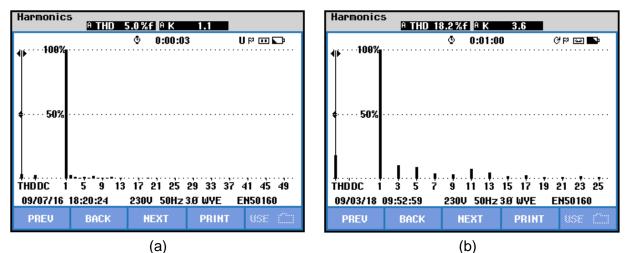

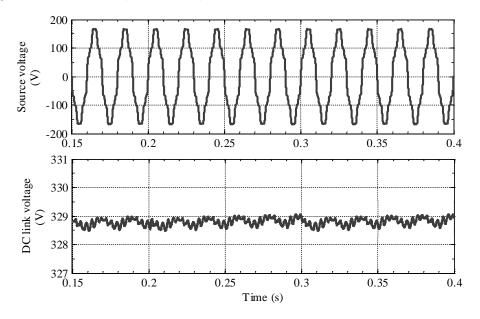

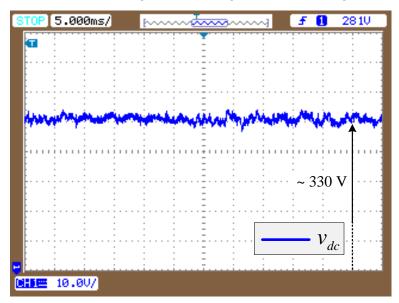

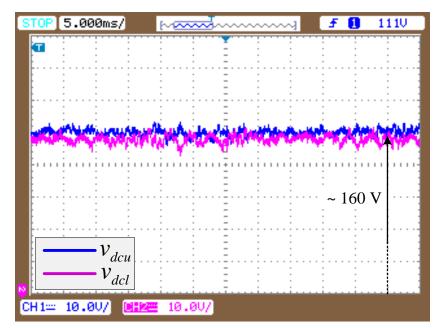

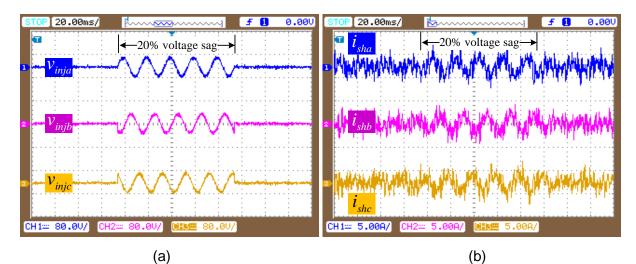

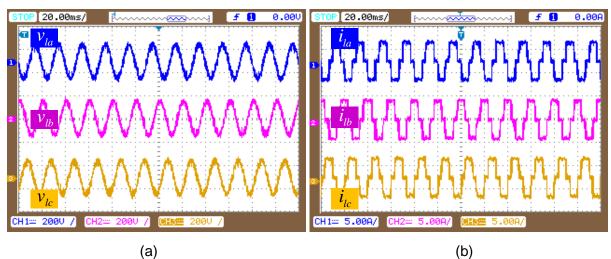

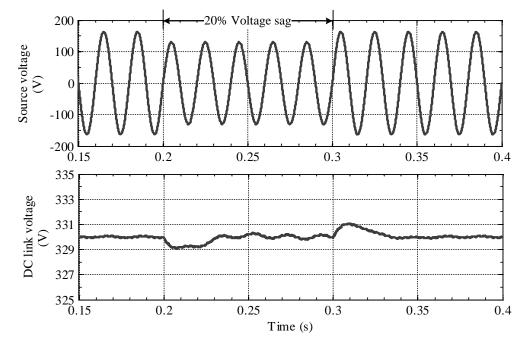

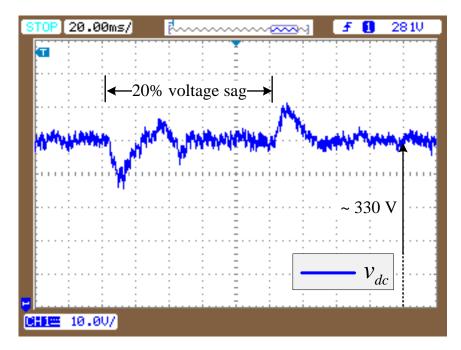

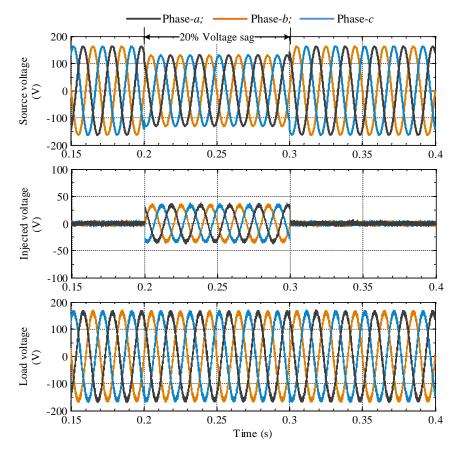

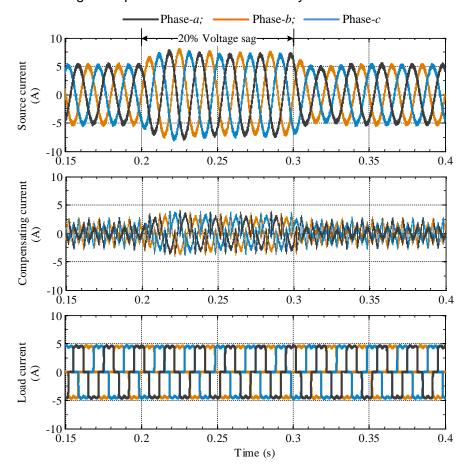

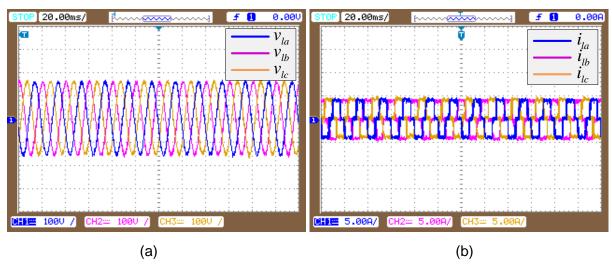

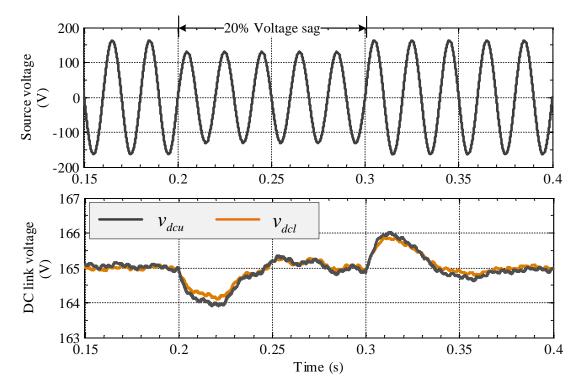

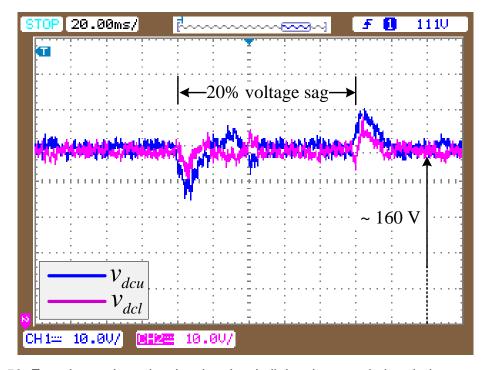

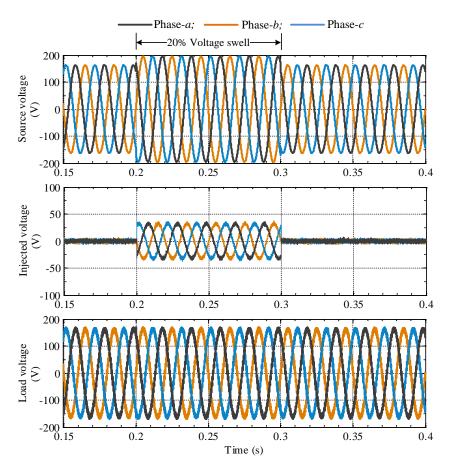

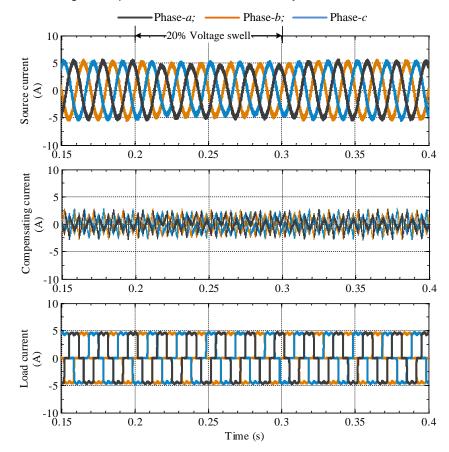

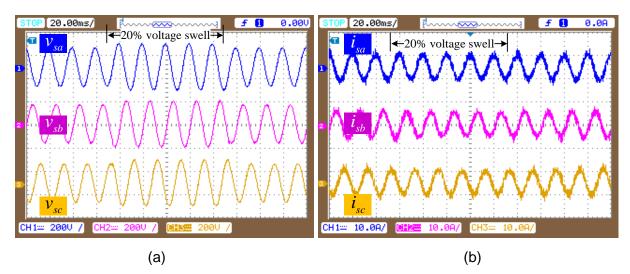

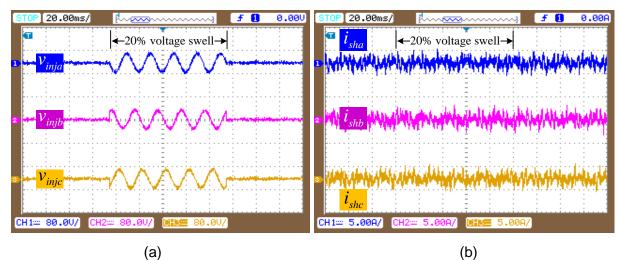

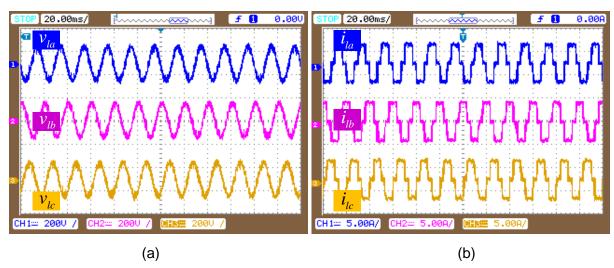

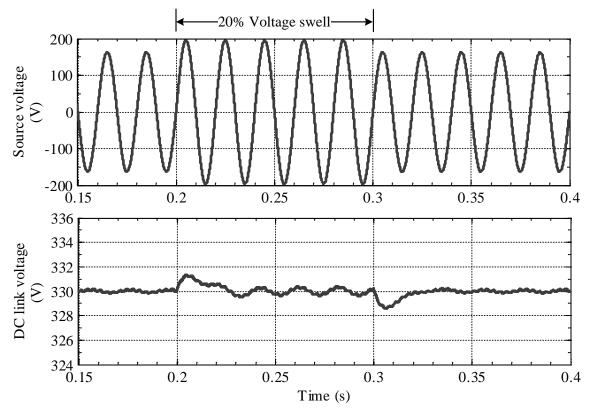

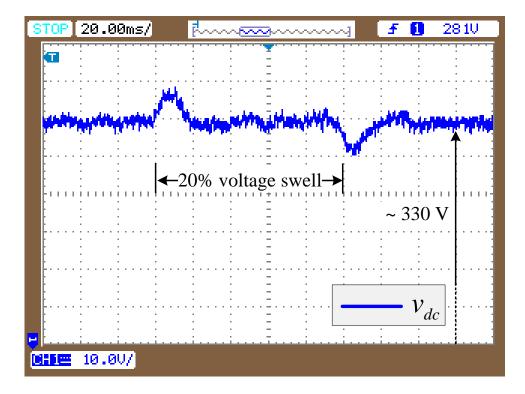

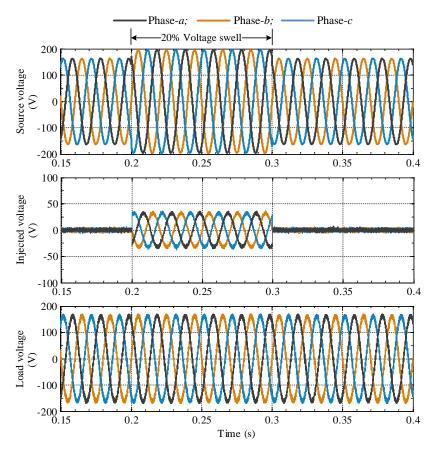

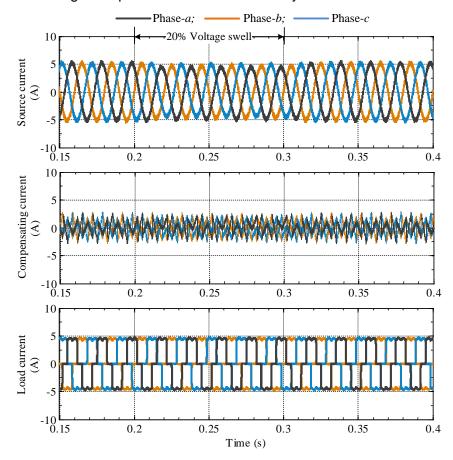

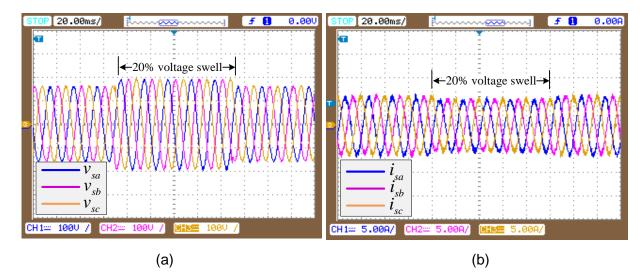

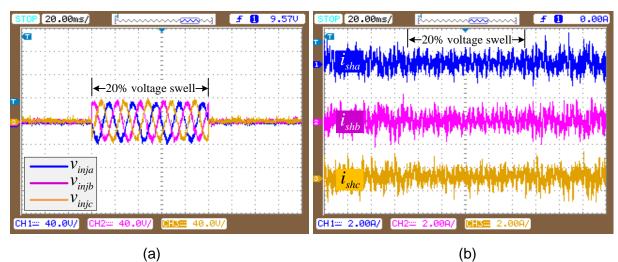

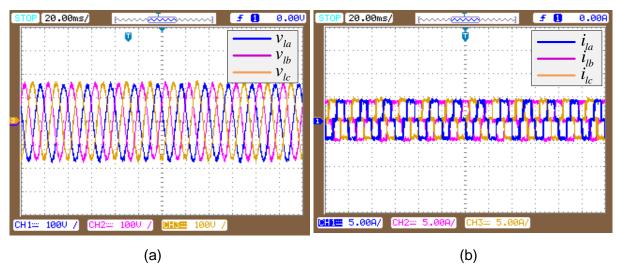

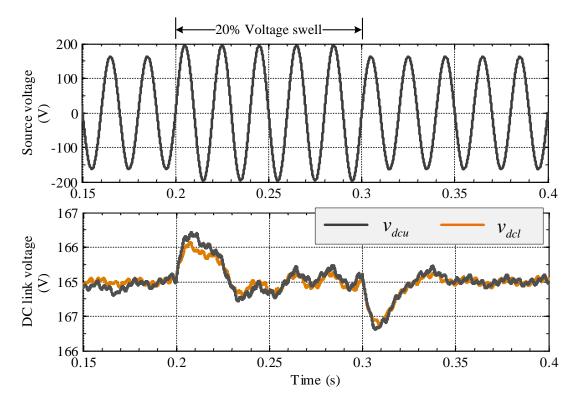

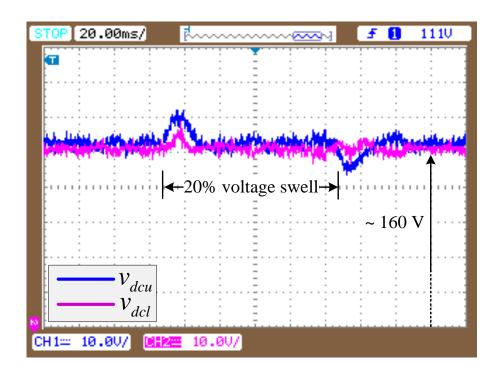

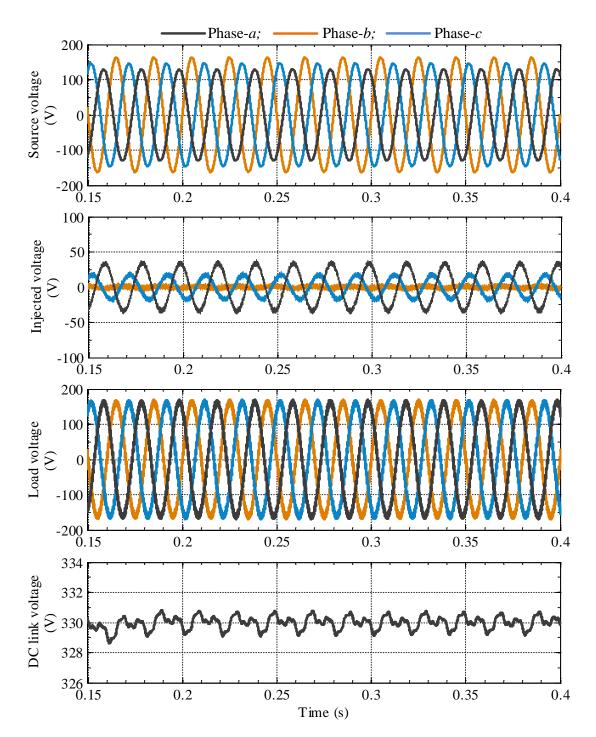

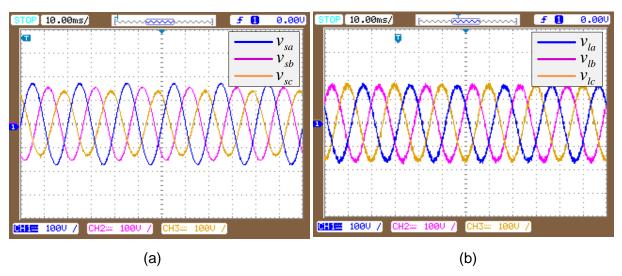

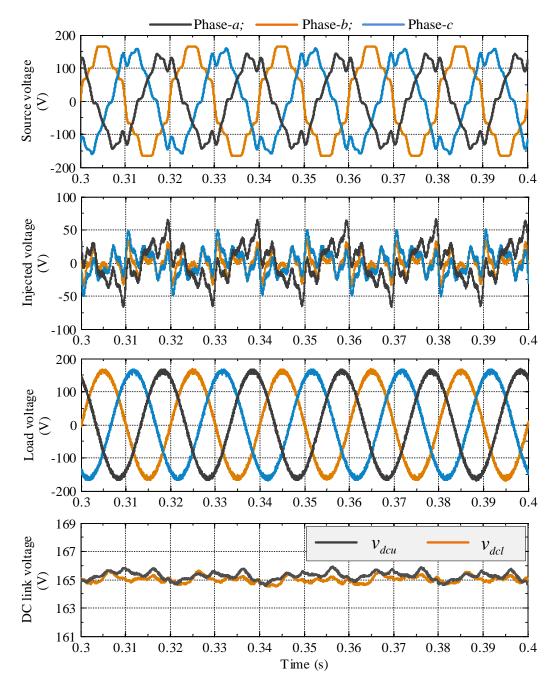

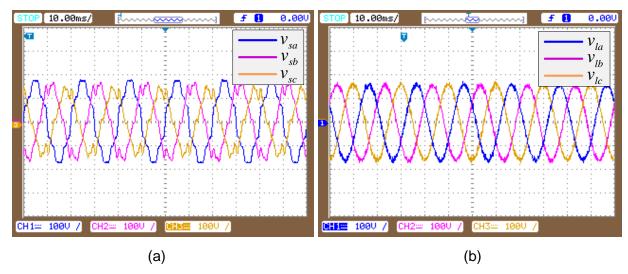

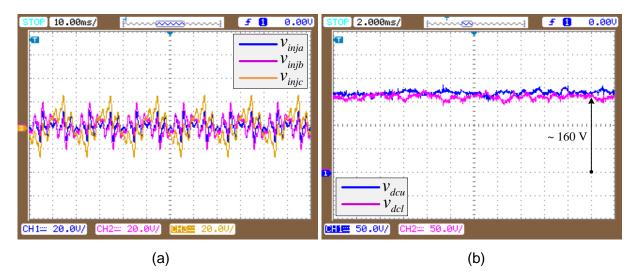

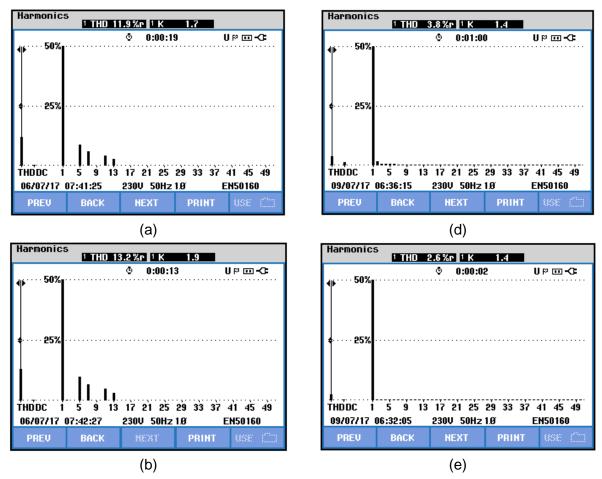

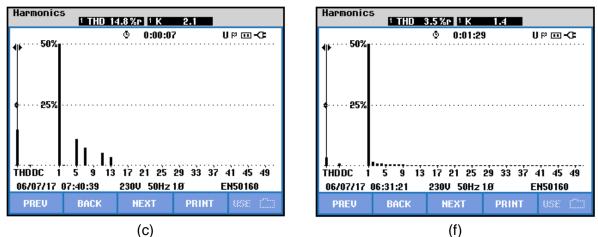

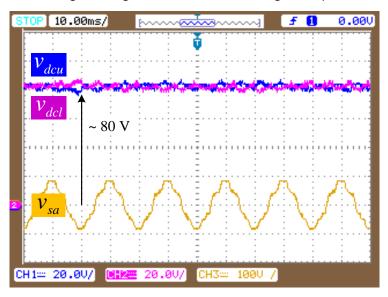

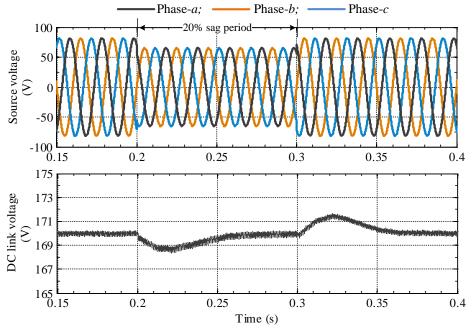

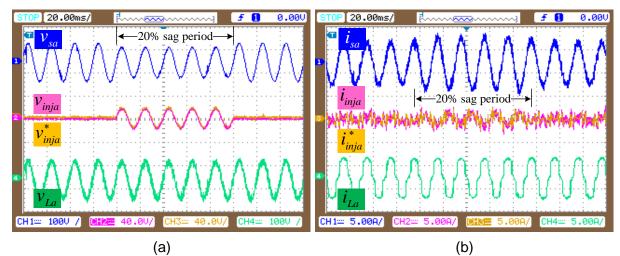

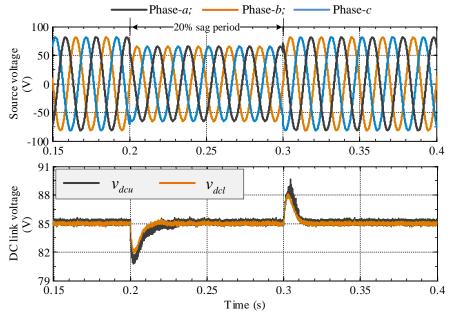

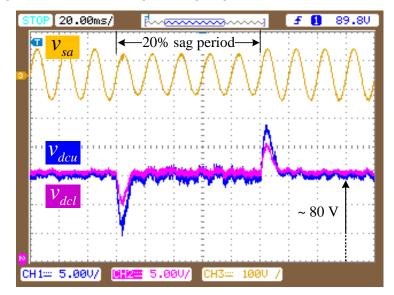

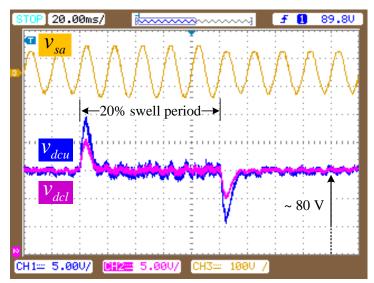

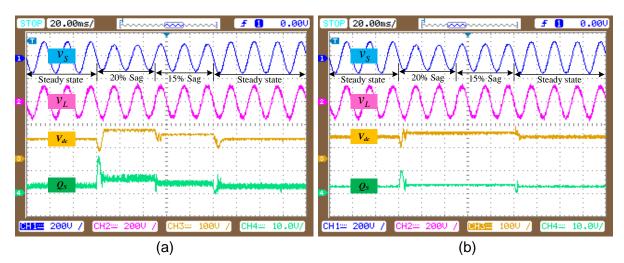

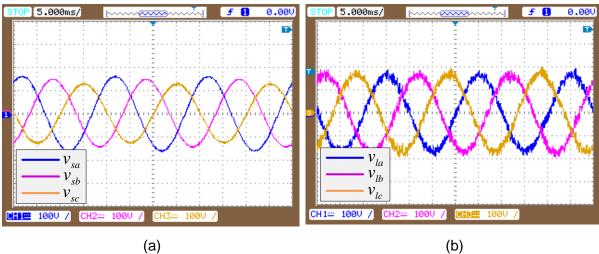

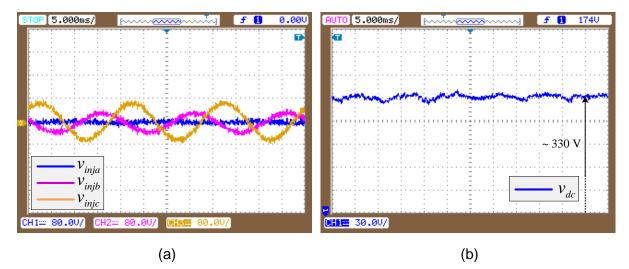

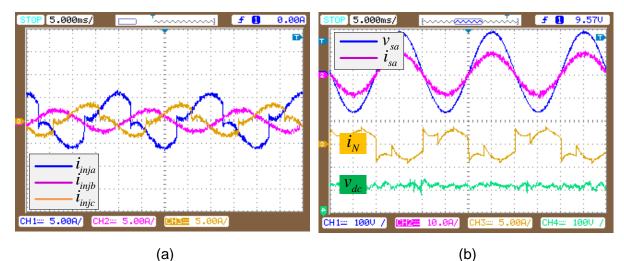

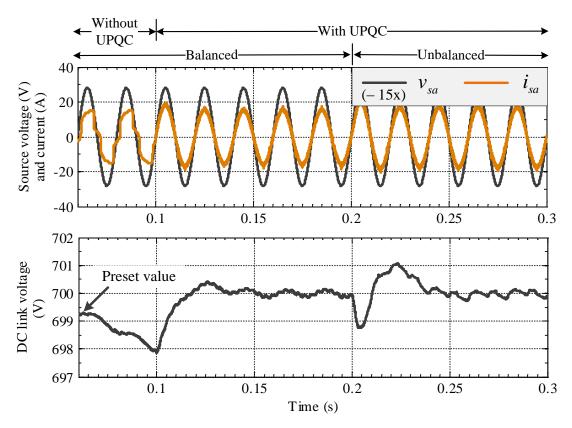

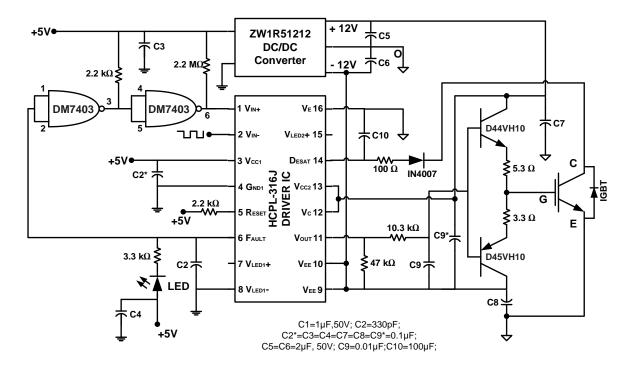

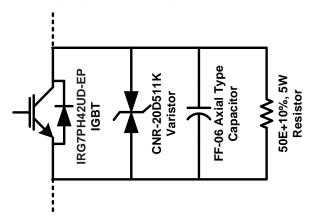

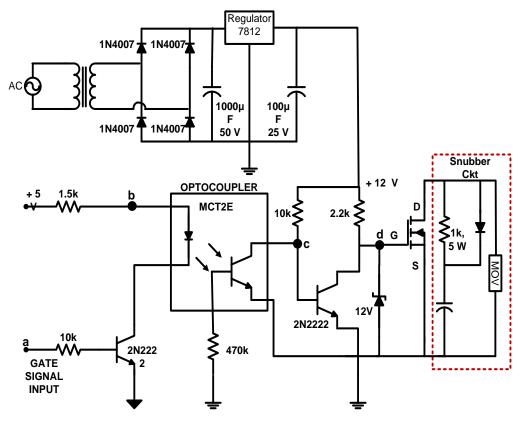

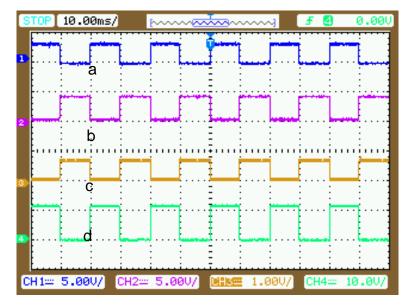

Fig. 2.34: Experimental results showing the dc-link voltage variation during case-1 with Fig. 2.35: Current compensation characteristics by shunt converter of UPQC-3L ......75 Fig. 2.36: Voltage compensation characteristics by shunt converter of UPQC-3L ......75 Fig. 2.39: (a). Three-phase source voltages and (b). Source currents for case-1 with UPQC-3L .....77 Fig. 2.40: (a). Three-phase series injected voltages and (b). Shunt compensating currents for case-1 with UPQC-3L ......77 Fig. 2.41: (a). Three-phase load voltages and (b). load currents for case-1 with UPQC-3L..78 Fig. 2.44: Simulation results showing the dc-link voltage variation during case-1 with UPQC-Fig. 2.45: Experimental results showing the dc-link voltage variation during case-1 with Fig. 2.48: (a). Three-phase source voltages and (b). Source currents for case-2 with UPQC-Fig. 2.49: (a). Three-phase series injected voltages and (b). Shunt compensating currents for Fig. 2.50: (a). Three-phase load voltages and (b). load currents for case-2 with UPQC-2L..83 Fig. 2.51: Simulation results showing dc-link voltage variation during case-2 with UPQC-2L83 Fig. 2.52: Experimental results showing the dc-link voltage variation during vcase-2 with Fig. 2.55: (a). Three-phase source voltages and (b). three-phase source currents for case-2 Fig. 2.56: (a). Three-phase series injected voltages and (b). Shunt compensating currents for Fig. 2.57: (a). Three-phase load voltages and (b). three-phase load currents for case-2 with Fig. 2.58: Simulation results showing dc-link voltage variation during case-2 with UPQC-3L87

| Fig. 2.59: Experimental results showing the dc-link voltage variation during case-2 with UPQC-3L        |

|---------------------------------------------------------------------------------------------------------|

| Fig. 2.60: Voltage compensation characteristics by shunt converter of UPQC-2L                           |

| Fig. 2.61: Current compensation characteristics by shunt converter of UPQC-2L                           |

| Fig. 2.62: (a). Three-phase source voltages and (b). three-phase source currents for case-3             |

| with UPQC-2L90                                                                                          |

| Fig. 2.63: (a). Three-phase series injected voltages and (b). Shunt compensating currents for           |

| case-3 with UPQC-2L90                                                                                   |

| Fig. 2.64: (a). Three-phase load voltages and (b). three-phase load currents for case-3 with            |

| UPQC-2L                                                                                                 |

| Fig. 2.65: Simulation results showing the dc-link voltage variation during case-3 with UPQC-            |

| 2L91                                                                                                    |

| Fig. 2.66: Experimental results showing the dc-link voltage variation during case-3 with                |

| UPQC-2L                                                                                                 |

| Fig. 2.67: Voltage compensation characteristics by shunt converter of UPQC-3L                           |

| Fig. 2.68: Current compensation characteristics by shunt converter of UPQC-3L93                         |

| Fig. 2.69: (a). Three-phase source voltages and (b). three-phase source currents for case-3             |

| with UPQC-3L94                                                                                          |

| Fig. 2.70: (a). Three-phase series injected voltages and (b). Shunt compensating currents for           |

| case-3 with UPQC-3L94                                                                                   |

| Fig. 2.71: (a). Three-phase load voltages and (b). three-phase load currents for case-3 with            |

| UPQC-3L                                                                                                 |

| Fig. 2.72: Simulation results showing the dc-link voltage variation during case-3 with UPQC-         3L |

| Fig. 2.73: Experimental results showing the dc-link voltage variation during case-3 with                |

| UPQC-3L                                                                                                 |

| Fig. 2.74: Steady state voltage compensation characteristics of UPQC-2L under case-497                  |

| Fig. 2.75: (a). Three-phase source voltages and (b). Load voltages for case-4 with UPQC-2L              |

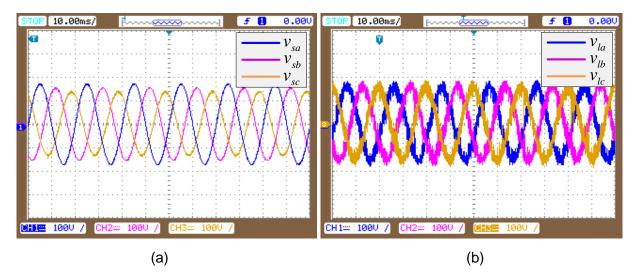

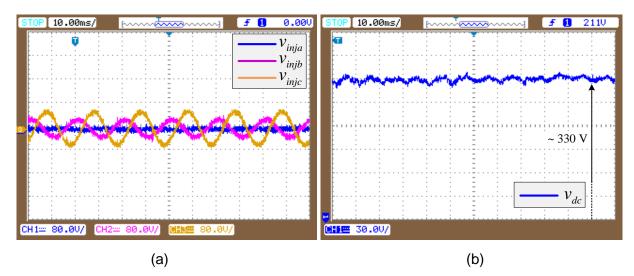

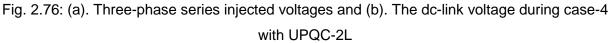

| Fig. 2.76: (a). Three-phase series injected voltages and (b). The dc-link voltage during case-          |

| 4 with UPQC-2L                                                                                          |

| Fig. 2.77: Voltage compensation characteristics by shunt converter of UPQC-3L                           |

| Fig. 2.78: (a). Unbalanced three-phase source voltages and (b). load voltages after                     |

| compensation for case-4 with UPQC-3L99                                                                  |

| Fig. 2.79: (a). Three-phase series injected voltages and (b). dc-link voltage during case-4 by UPQC-3L  |

| Fig. 2.80: Voltage compensation characteristics by shunt converter of UPQC-2L                           |

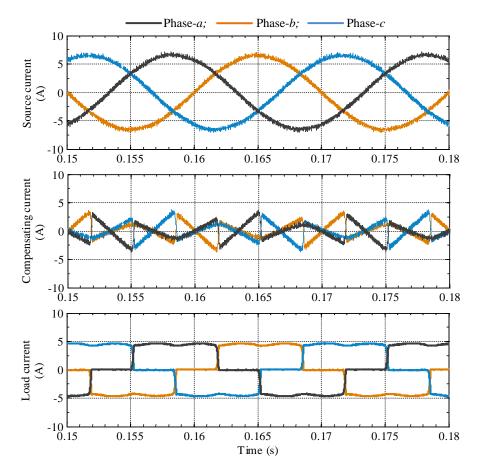

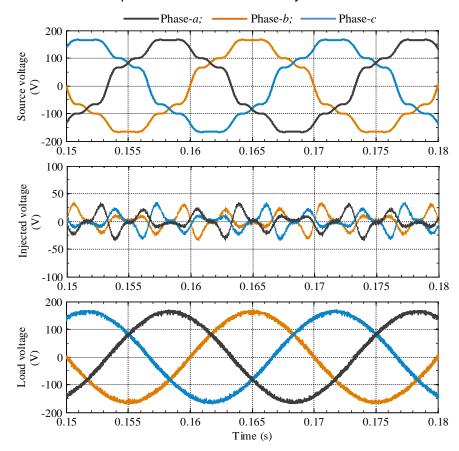

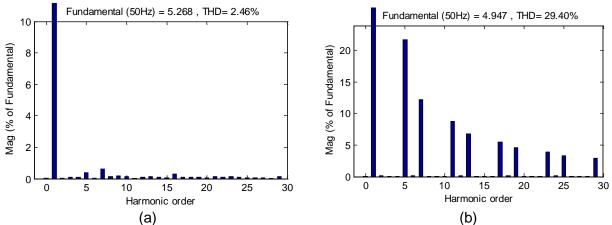

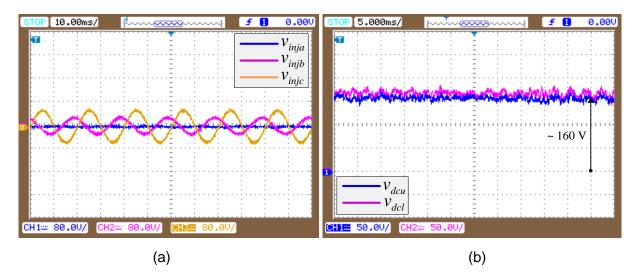

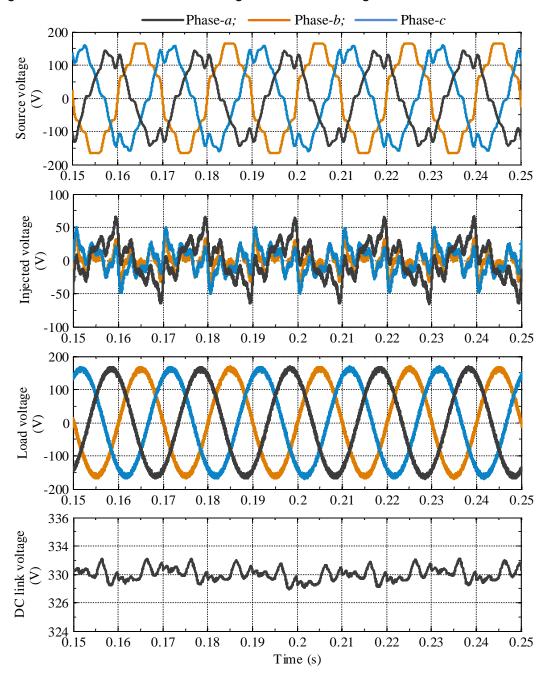

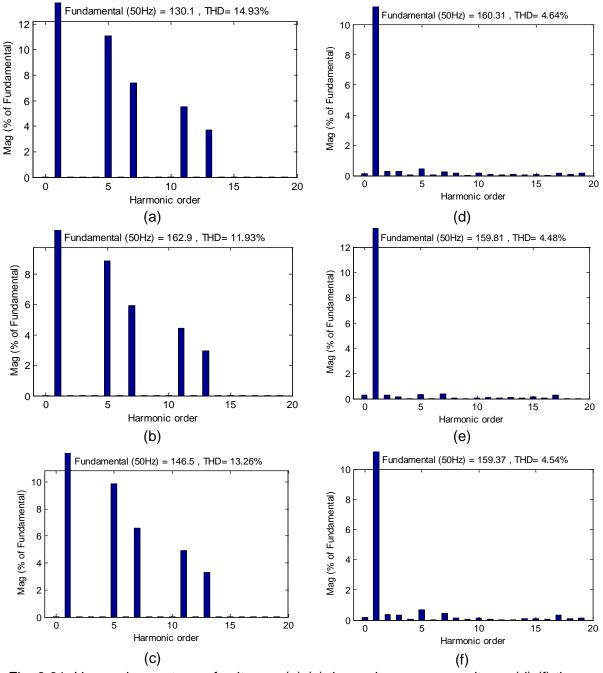

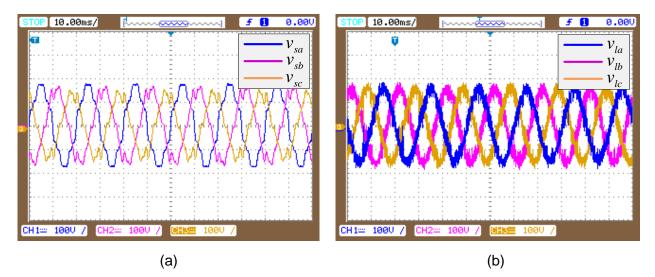

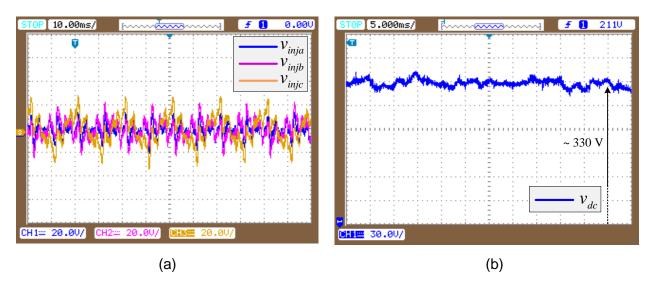

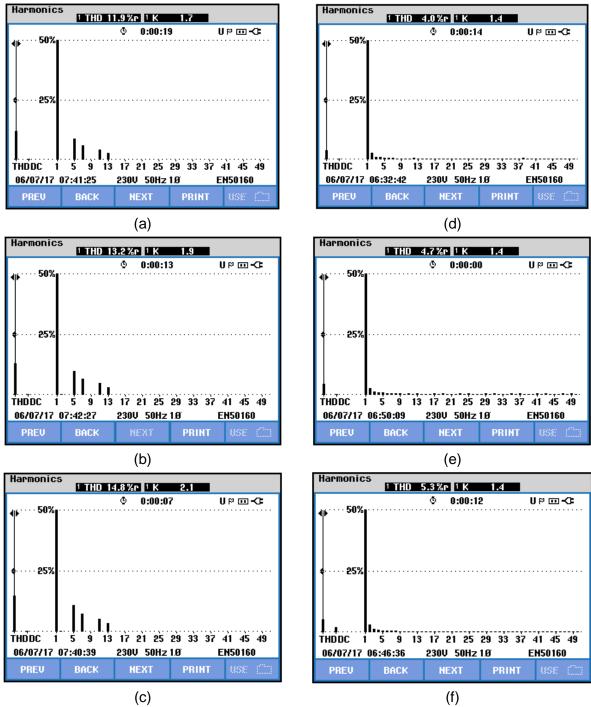

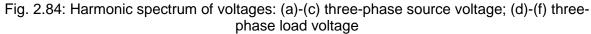

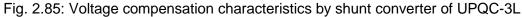

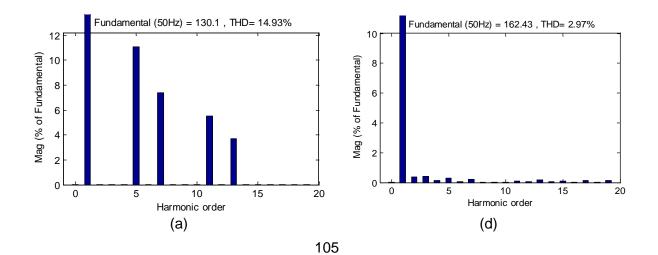

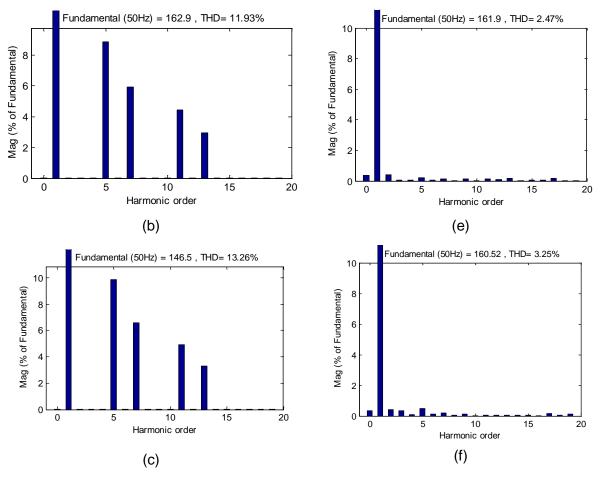

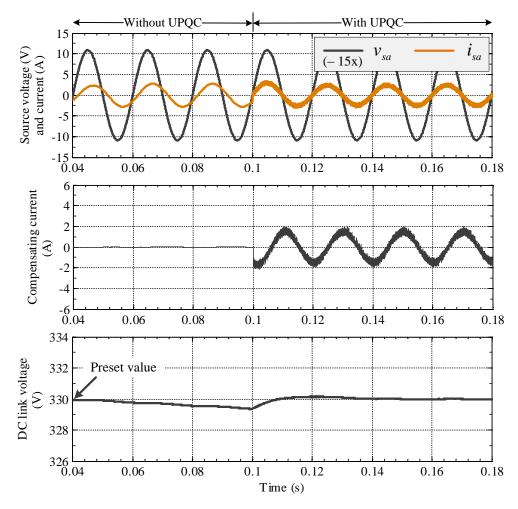

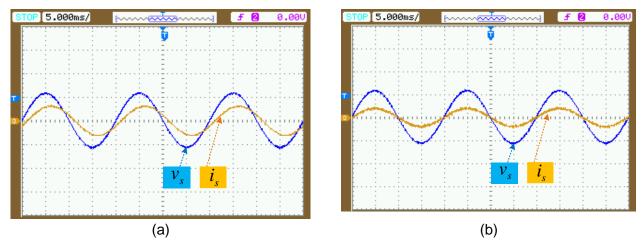

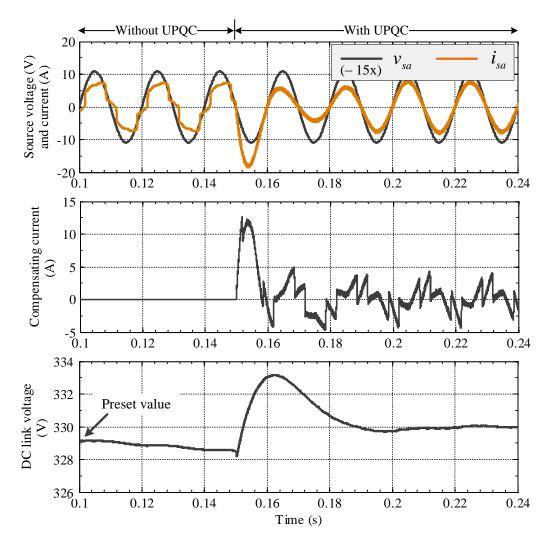

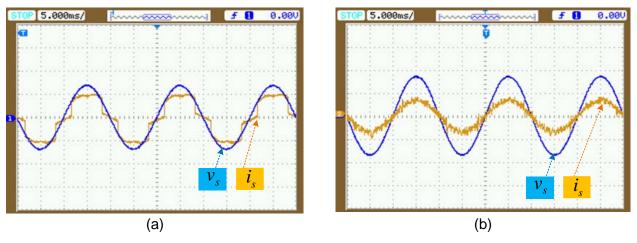

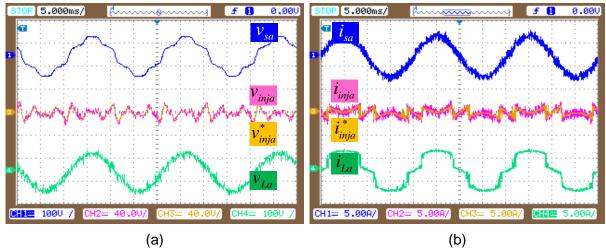

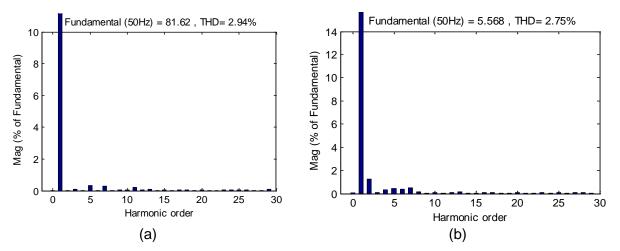

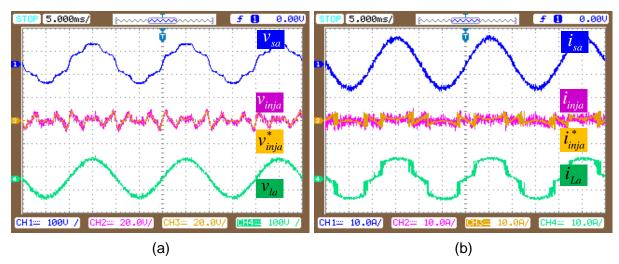

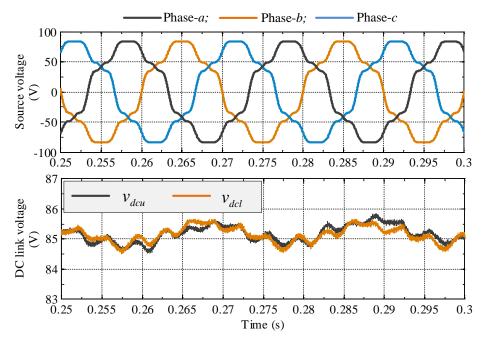

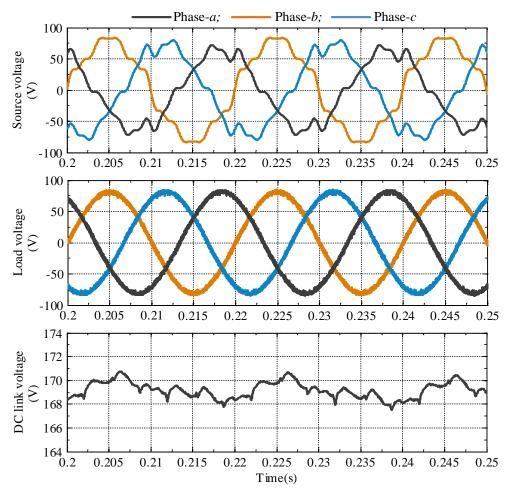

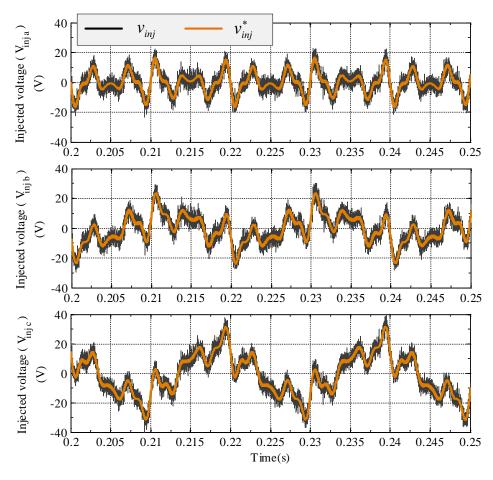

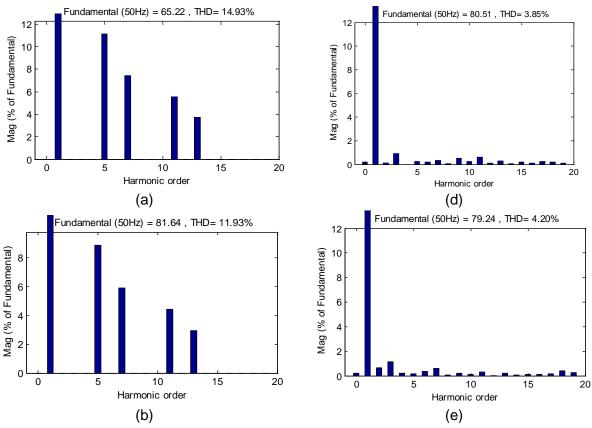

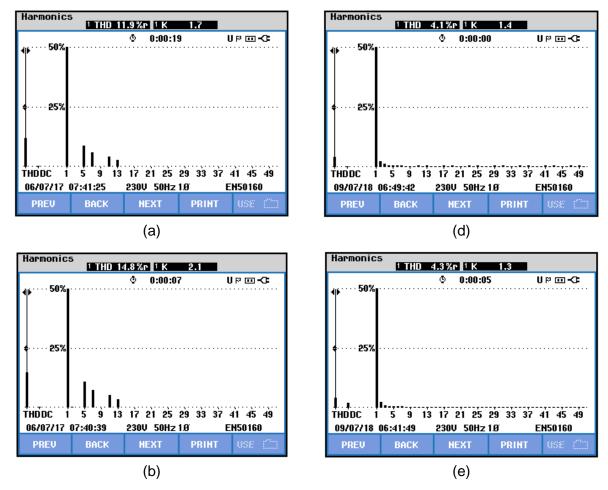

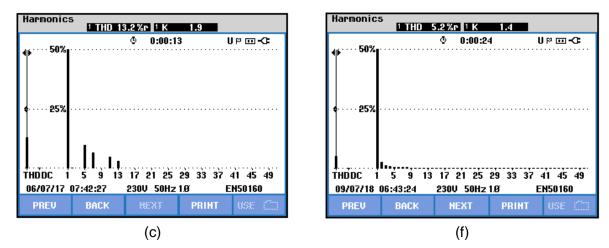

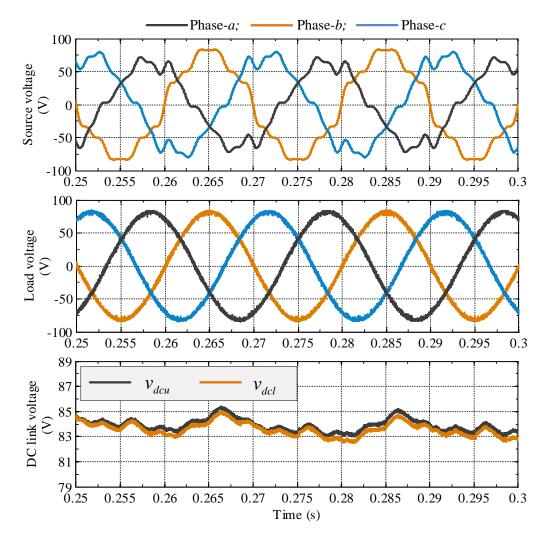

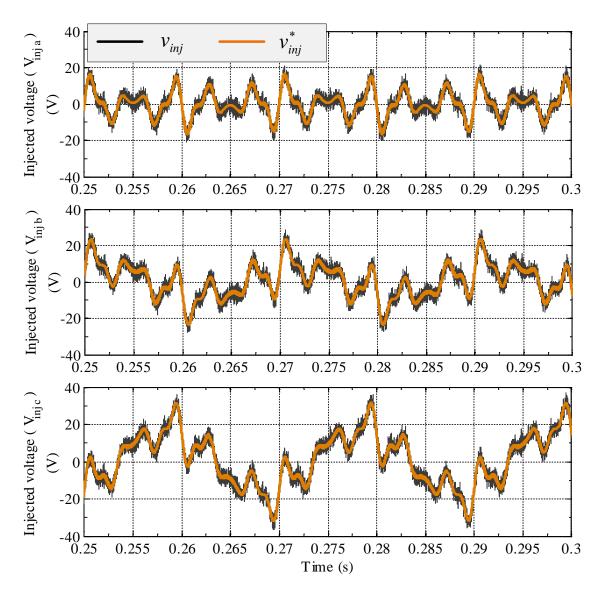

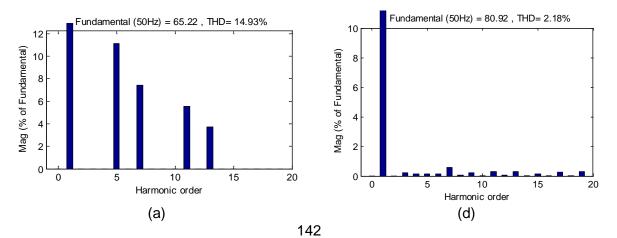

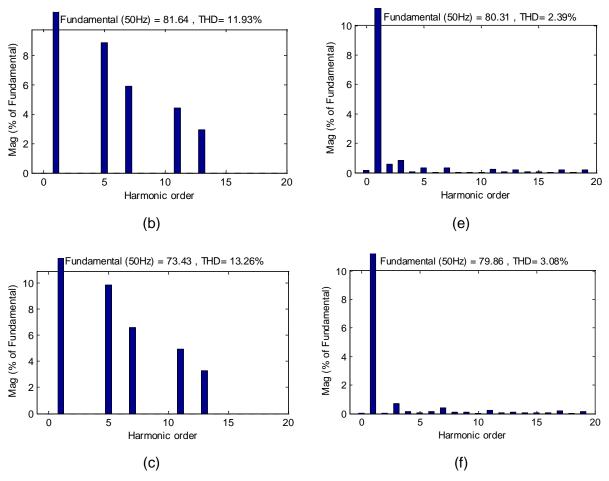

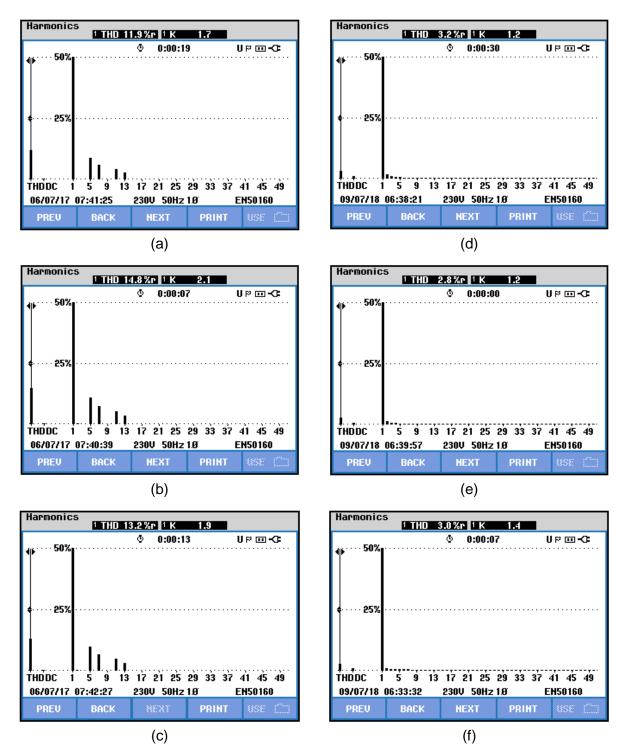

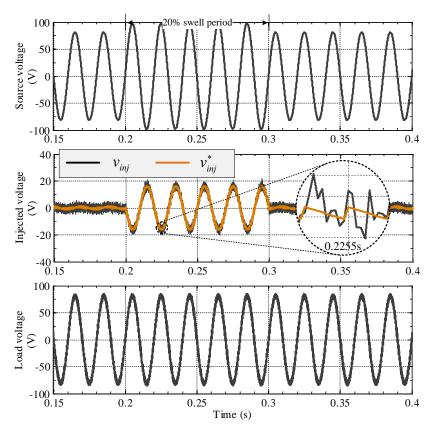

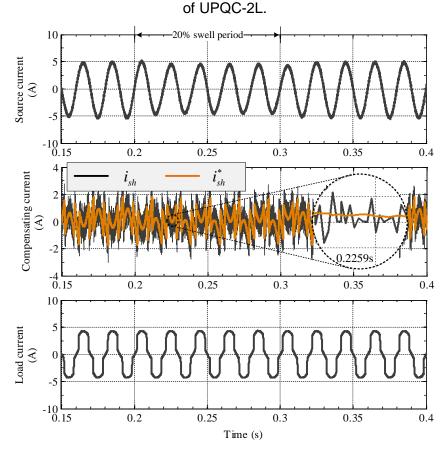

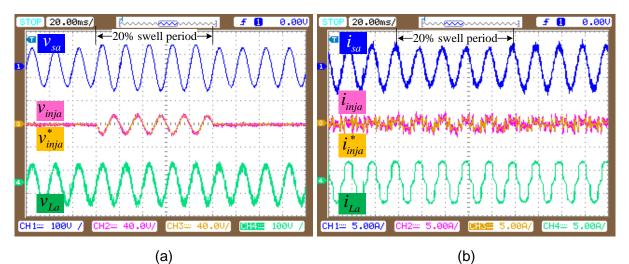

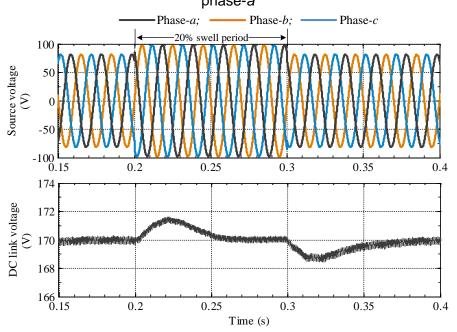

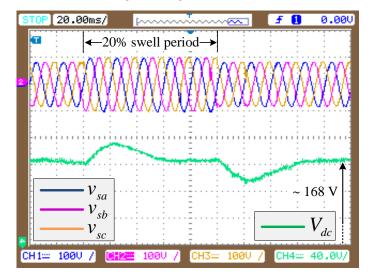

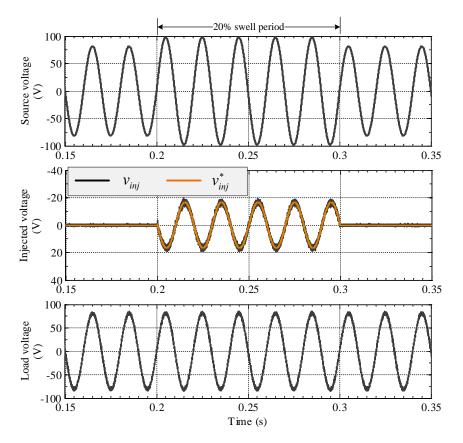

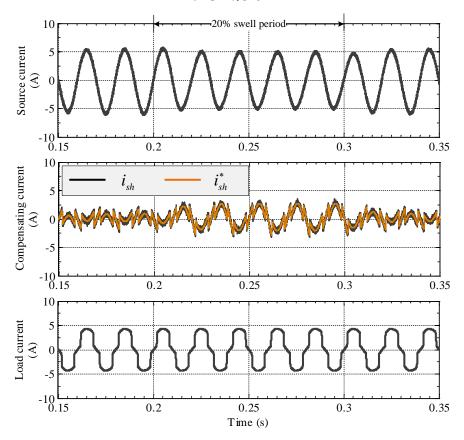

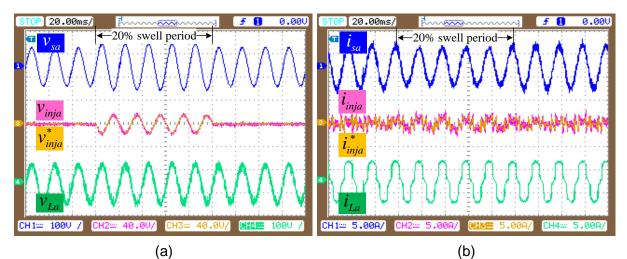

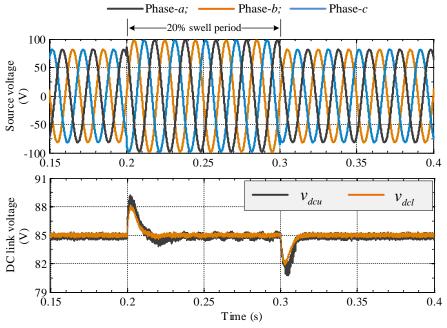

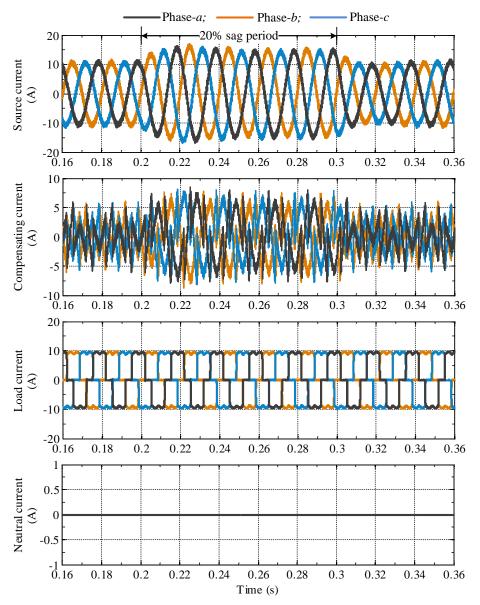

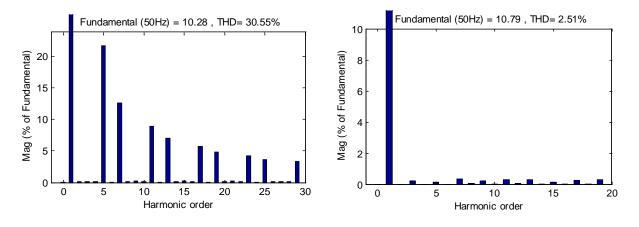

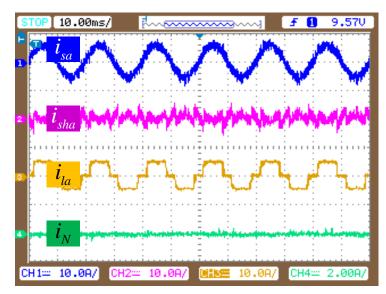

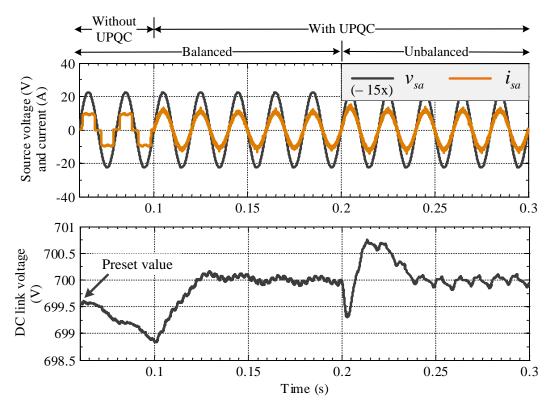

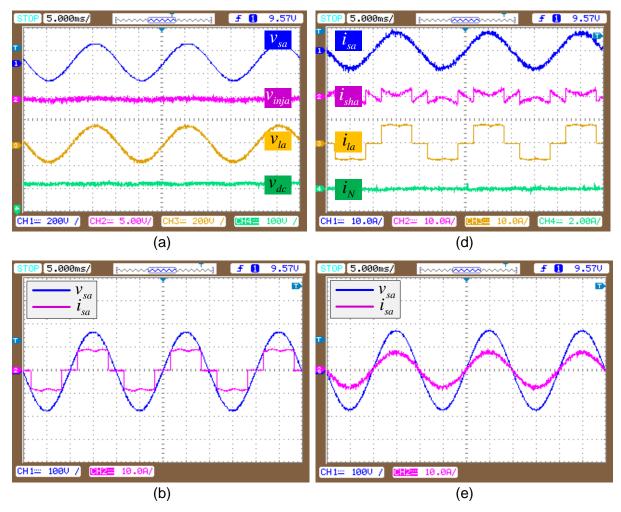

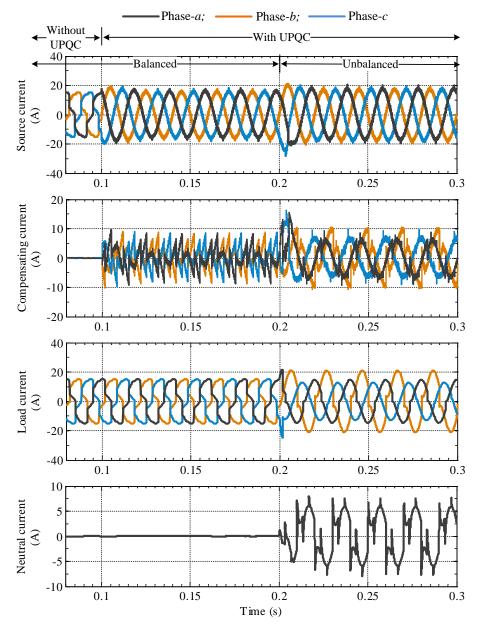

Fig. 2.81: Harmonic spectrum of voltages: (a)-(c) three-phase source voltage; (d)-(f) threephase load voltage......102 Fig. 2.82: (a). Unbalanced and distorted three-phase source voltages and (b). Load voltages after voltage compensation with UPQC-2L ......103 Fig. 2.83: (a). Three-phase series injected voltages and (b). The dc link voltage during Fig. 2.84: Harmonic spectrum of voltages: (a)-(c) three-phase source voltage; (d)-(f) threephase load voltage......104 Fig. 2.85: Voltage compensation characteristics by shunt converter of UPQC-3L ...... 105 Fig. 2.86: Harmonic spectrum of voltages: (a)-(c) three-phase source voltage; (d)-(f) threephase load voltage......106 Fig. 2.87: (a). Unbalanced distorted three-phase source voltages and (b). load voltages after Fig. 2.88: (a). Three-phase series injected voltages and (b). dc link voltage during case-5 by Fig. 2.89: Harmonic spectrum of voltages: (a)-(c) three-phase source voltage; (d)-(f) three-Fig. 2.90: Linear load current compensation (three-phase RL load) by shunt converter of Fig. 2.91: Phase-a source voltage and current (a) before compensation; (b) after compensation with UPQC-2L with linear load ......109 Fig. 2.92: Nonlinear load current compensation (three phase bridge rectifier fed RL load) by shunt converter of UPQC-2L......110 Fig. 2.93: Phase-a source voltage and current (a) before compensation; (b) after Fig. 3.1: General MPC scheme......116 Fig. 3.6: Distorted voltage compensation by the proposed control scheme showing for phase-a of UPQC-2L......128 Fig. 3.7: Compensation of source current during distorted voltage along with non-linear load

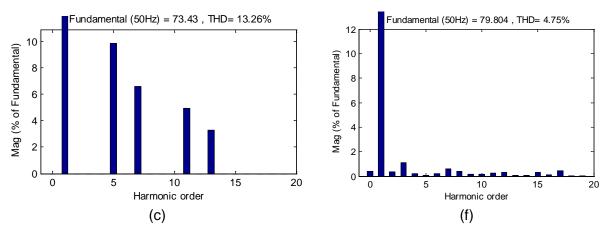

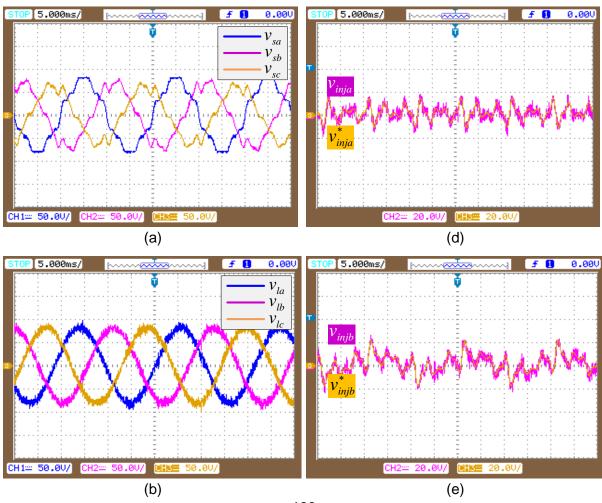

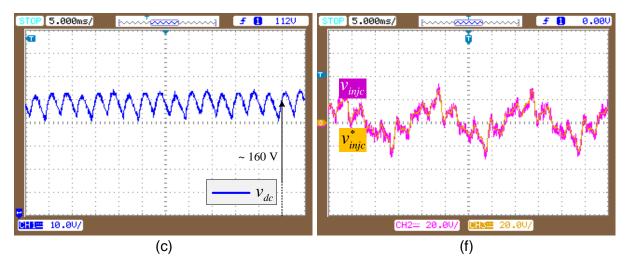

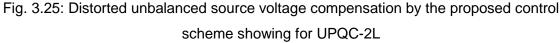

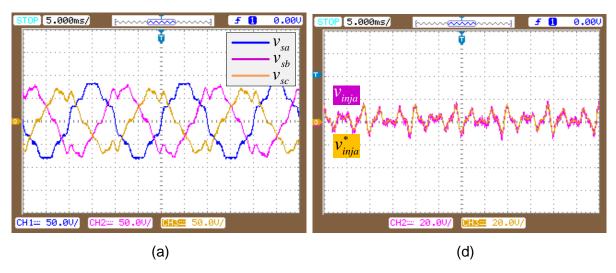

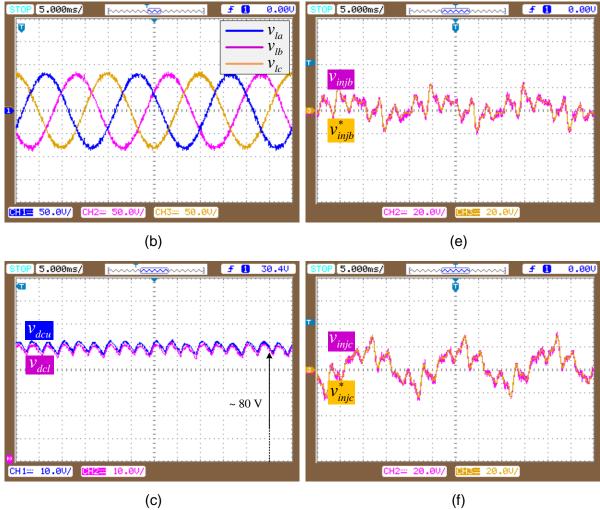

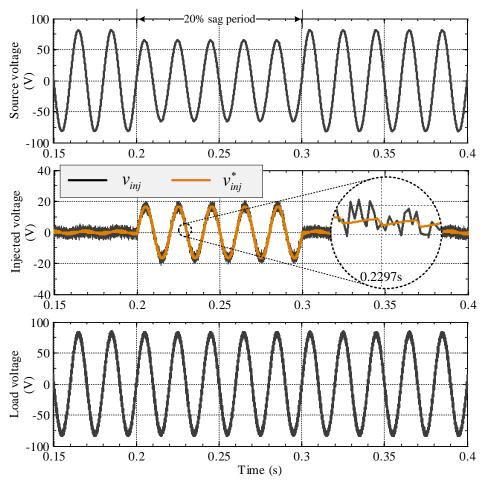

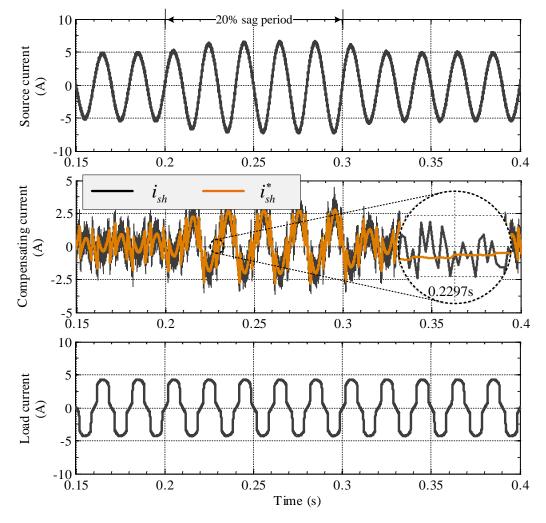

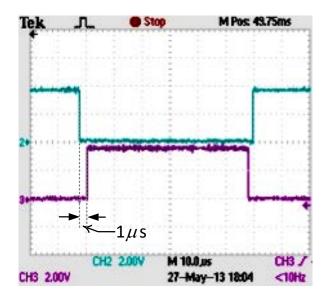

Fig. 3.10: Distorted voltage compensation by the proposed control scheme showing for Fig. 3.14: Experimental scope results showing dc-link voltage during distorted voltage Fig. 3.15: Distorted source voltage compensation by the proposed control scheme showing Fig. 3.16: Compensation of source current during distorted source voltage along with non-Fig. 3.20: DC-link voltage during distorted source voltage compensation of UPQC-3L ..... 135 Fig. 3.21: Experimental scope results showing dc-link voltage during distorted source voltage Fig. 3.22: Distorted unbalanced source voltage compensation by the proposed control Fig. 3.23: Three-phase injected voltages during distorted unbalanced source voltage Fig. 3.24: Harmonic spectrum of voltages: (a)-(c) three-phase source voltage; (d)-(f) threephase load voltage......139 Fig. 3.25: Distorted unbalanced source voltage compensation by the proposed control scheme showing for UPQC-2L.....140 Fig. 3.26: Harmonic spectrum of voltages: (a)-(c) three-phase source voltage; (d)-(f) threephase load voltage.....141 Fig. 3.27: Distorted unbalanced source voltage compensation by the proposed control scheme showing for phase-a of UPQC-3L. .....141 Fig. 3.28: Three-phase injected voltages during distorted unbalanced source voltage Fig. 3.29: Harmonic spectrum of voltages: (a)-(c) three-phase source voltage; (d)-(f) threephase load voltage......143 Fig. 3.30: Distorted unbalanced source voltage compensation by the proposed control scheme showing for UPQC-3L......144 Fig. 3.31: Harmonic spectrum of voltages: (a)-(c) three-phase source voltage; (d)-(f) threephase load voltage......145

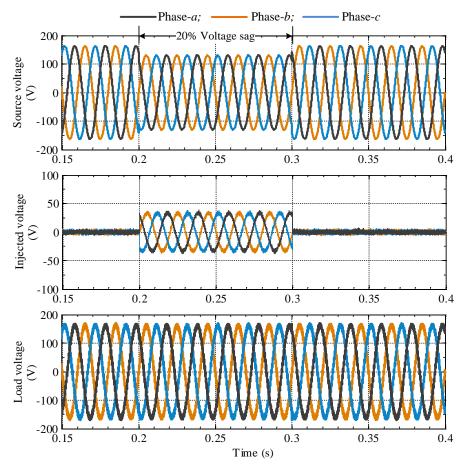

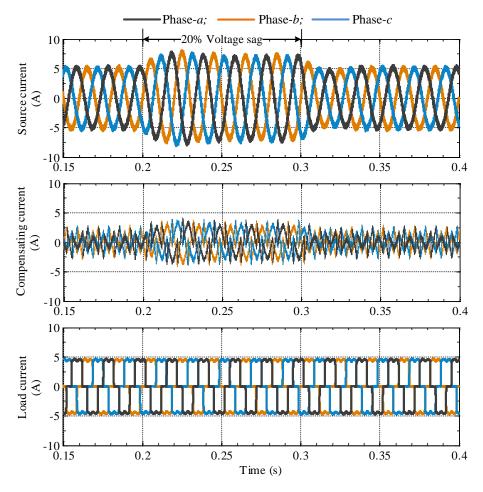

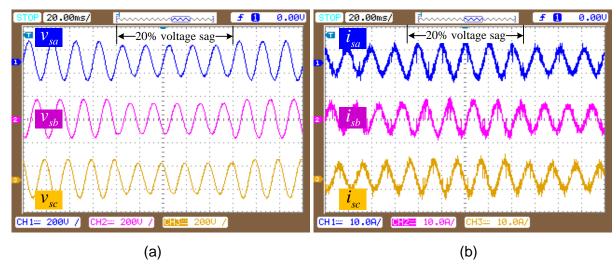

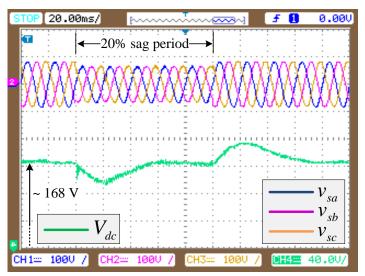

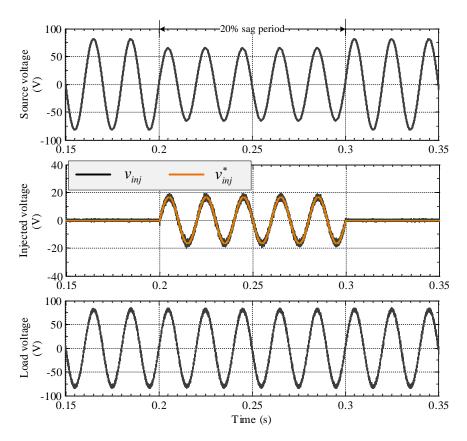

| Fig. 3.32: Voltage sag compensation by the proposed control scheme showing for phase- <i>a</i> of UPQC-2L                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 3.33: Compensation of source current during voltage sag along with non-linear load by the proposed control scheme showing for phase- <i>a</i> of UPQC-2L |

| Fig. 3.34: Voltage swell compensation by the proposed control scheme showing for phase-a                                                                      |

| Fig. 3.35: DC-link voltage during sag compensation of UPQC-2L                                                                                                 |

| Fig. 3.36: Experimental scope results showing dc-link voltage during sag compensation of UPQC-2L                                                              |

| Fig. 3.37: Voltage sag compensation by the proposed control scheme showing for phase-a of UPQC-3L                                                             |

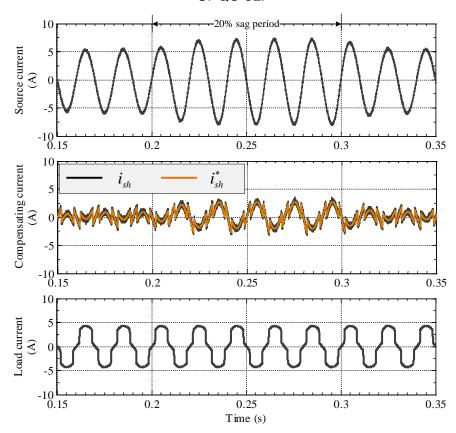

| Fig. 3.38: Compensation of source current during voltage sag along with non-linear load by                                                                    |

| the proposed control scheme showing for phase-a of UPQC-3L149                                                                                                 |

| Fig. 3.39: Voltage swell compensation by the proposed control scheme showing for phase-a                                                                      |

| Fig. 3.40: DC-link voltage during sag compensation of UPQC-3L 150                                                                                             |

| Fig. 3.41: Experimental scope results showing dc-link voltage during sag compensation of UPQC-3L                                                              |

| Fig. 3.42: Voltage swell compensation by the proposed control scheme showing for phase-a of UPQC-2L                                                           |

| Fig. 3.43: Compensation of source current during voltage swell along with non-linear load by                                                                  |

| the proposed control scheme showing for phase-a of UPQC-2L                                                                                                    |

| Fig. 3.44: Voltage swell compensation by the proposed control scheme showing for phase-a                                                                      |

| Fig. 3.45: DC-link voltage during swell compensation of UPQC-2L                                                                                               |

| Fig. 3.46: Experimental scope results showing dc-link voltage during swell compensation of UPQC-2L                                                            |

| Fig. 3.47: Voltage swell compensation by the proposed control scheme showing for phase-a of UPQC-3L                                                           |

| Fig. 3.48: Compensation of source current during voltage swell along with non-linear load by                                                                  |

| the proposed control scheme showing for phase-a of UPQC-3L                                                                                                    |

| Fig. 3.49: Voltage swell compensation by the proposed control scheme showing for phase-a                                                                      |

| Fig. 3.50: DC-link voltage during swell compensation of UPQC-3L                                                                                               |

| Fig. 3.51: Experimental scope results showing dc-link voltage during swell compensation of UPQC-3L                                                            |

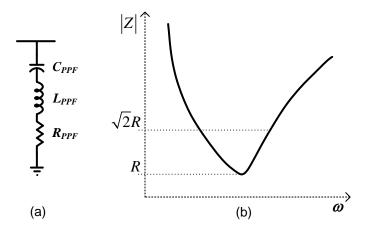

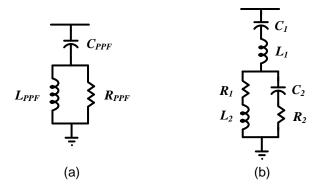

| Fig. 4.1: Band-pass filter and its impedance frequency plot                                                                                                   |

| Fig. 4.2: (a) High-pass, (b) Double band-pass filter                                            | 161    |

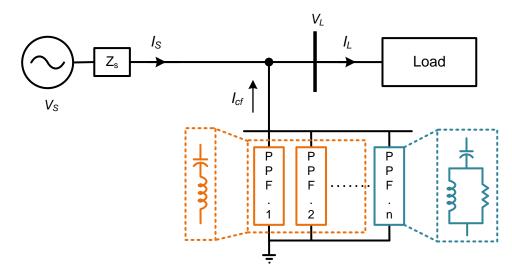

|-------------------------------------------------------------------------------------------------|--------|

| Fig. 4.3: Shunt passive power filters in distribution network                                   | 161    |

| Fig. 4.4: Structure of series hybrid active power filter                                        | 162    |

| Fig. 4.5: Structure of shunt hybrid active power filter                                         | 163    |

| Fig. 4.6: Placement of passive power filter (PPF) in the UPQC application.                      | 163    |

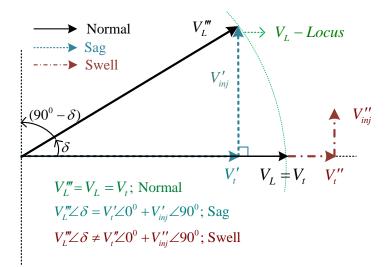

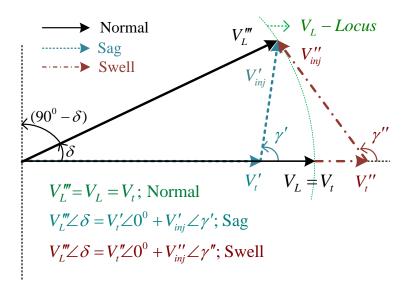

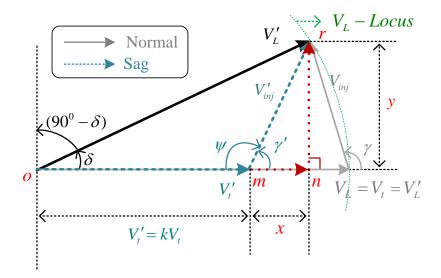

| Fig. 4.7: Phasor representation of voltage compensation using UPQC-P [231]                      | 165    |

| Fig. 4.8: Phasor representation of voltage compensation using UPQC-Q [231]                      | 166    |

| Fig. 4.9: Phasor representation of voltage compensation using UPQC-S [231]                      | 166    |

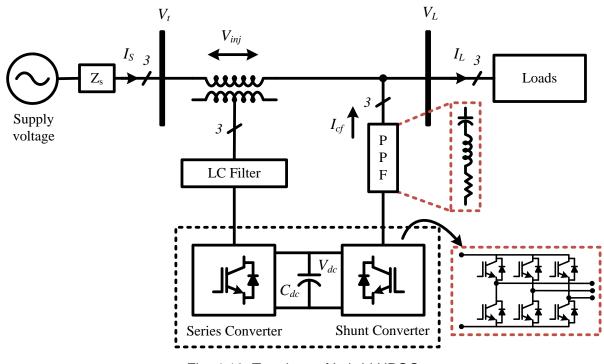

| Fig. 4.10: Topology of hybrid UPQC                                                              | 167    |

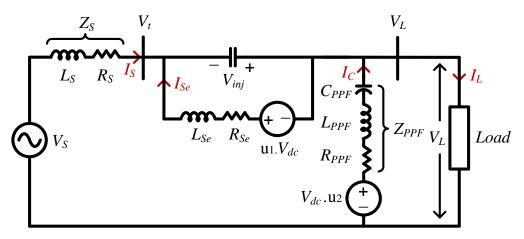

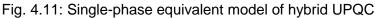

| Fig. 4.11: Single-phase equivalent model of hybrid UPQC                                         |        |

| Fig. 4.12: PAC approach to hybrid UPQC                                                          | 170    |

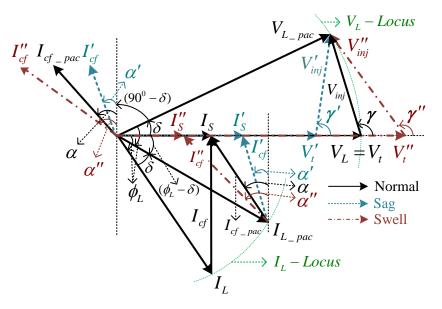

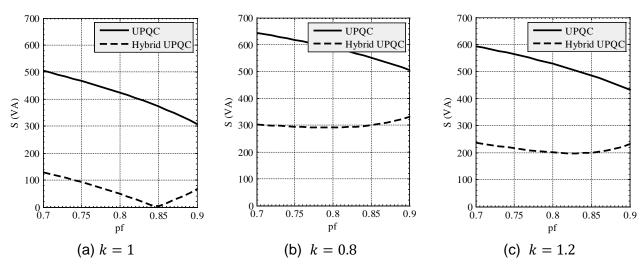

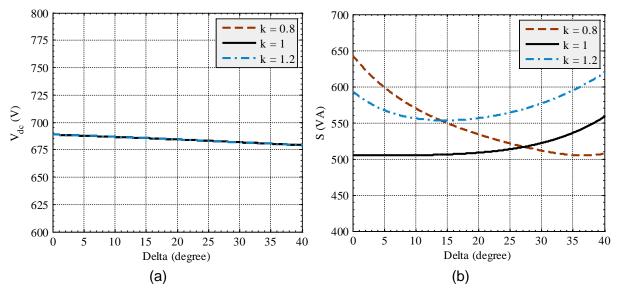

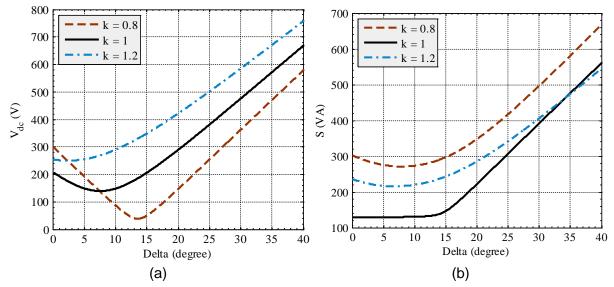

| Fig. 4.13: The variation of $Vdc$ of UPQC and hybrid UPQC with respect to power factor.         | 172    |

| Fig. 4.14: The variation of VA loading of UPQC and hybrid UPQC with respect to I                | power  |

| factor                                                                                          | 172    |

| Fig. 4.15: The variation of dc-link voltage and VA loading with respect to $\delta$ of conver   |        |

| UPQC                                                                                            | 173    |

| Fig. 4.16: The variation of dc-link voltage and VA loading with respect to $\delta$ of hybrid L |        |

|                                                                                                 | 173    |

| Fig. 4.17: Flowchart of the proposed algorithm to select optimal dc-link voltage of I           | •      |

| UPQC                                                                                            | 176    |

| Fig. 4.18: Phasor diagram to estimate the series converter parameters                           |        |

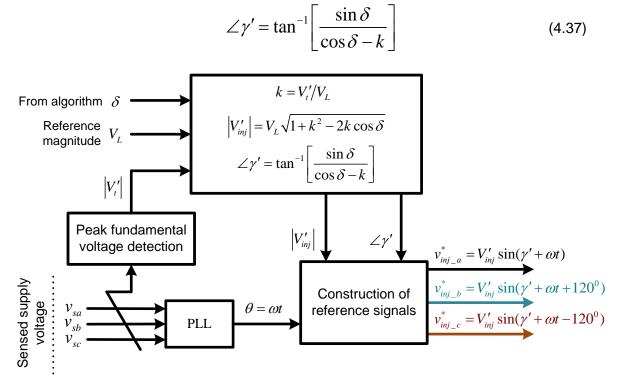

| Fig. 4.19: Reference voltage signal generation of series converter                              | 178    |

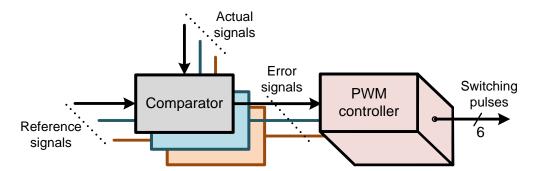

| Fig. 4.20: PWM controller for generating switching pulses for converter switches                |        |

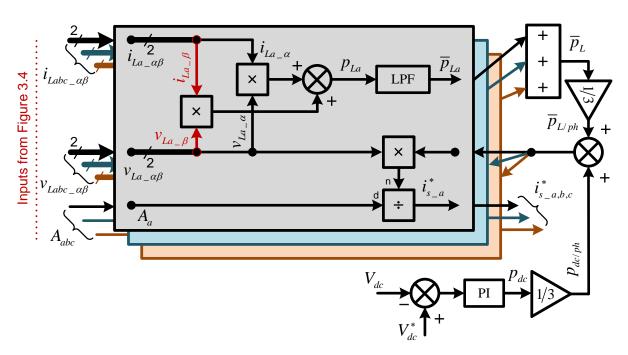

| Fig. 4.21: Reference current signal generation for shunt converter                              | 180    |

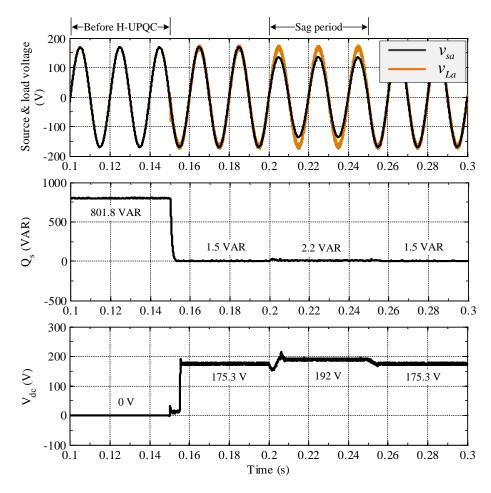

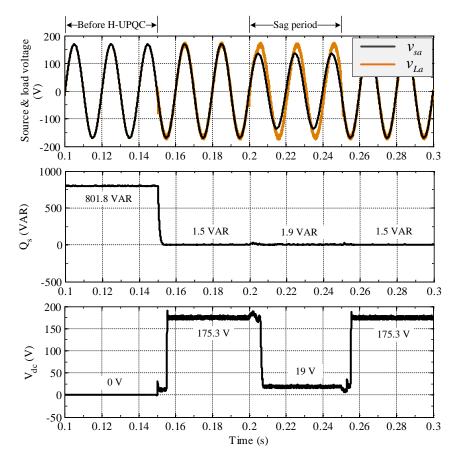

| Fig. 4.22: Simulation results of minimum dc-link voltage requirement during voltage             | e sag  |

| condition.                                                                                      | 181    |

| Fig. 4.23: Simulation results of minimum dc-link voltage requirement during voltage             | e sag  |

| condition with proposed algorithm                                                               | 182    |

| Fig. 4.24: Simulation results of minimum dc-link voltage requirement during variable vo         | oltage |

| sag condition (a) with without application of PAC approach and (b) with proposed algo           |        |

|                                                                                                 |        |

| Fig. 4.25: Simulation results of minimum dc-link voltage requirement during voltage             |        |

| condition.                                                                                      |        |

| Fig. 4.26: Simulation results of minimum dc-link voltage requirement during voltage             |        |

| condition with proposed algorithm                                                               | 185    |

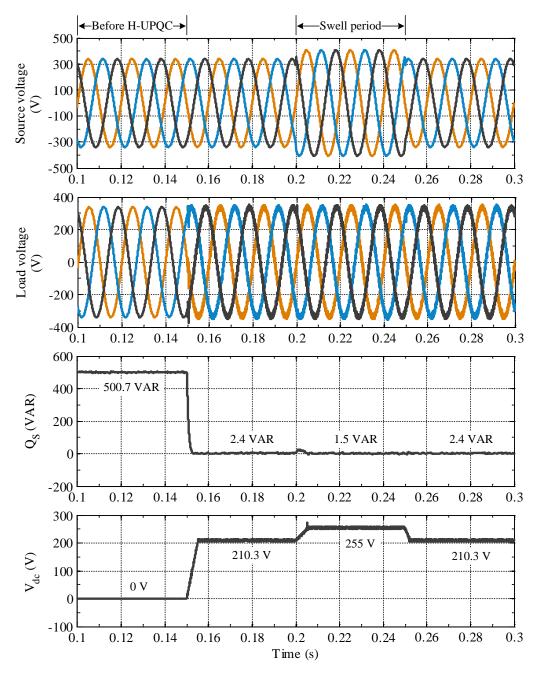

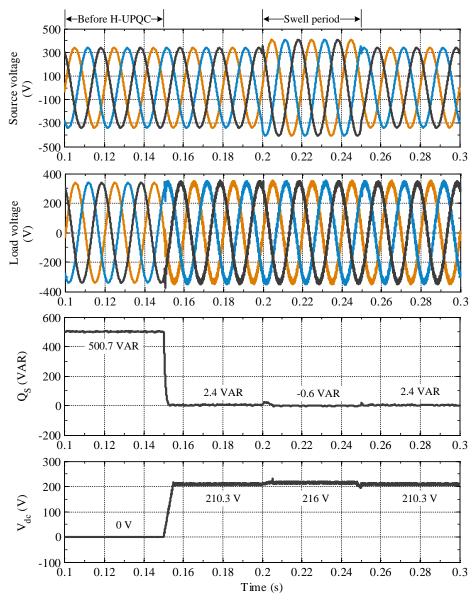

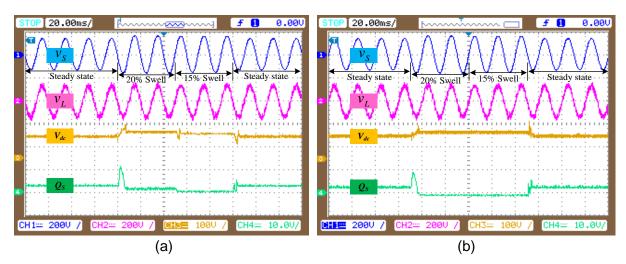

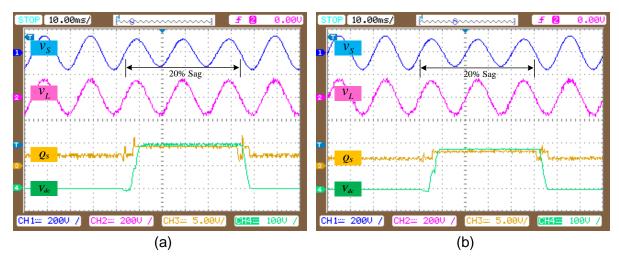

Fig. 4.27: Simulation results of minimum dc-link voltage requirement during variable voltage swell condition (a) with without application of PAC approach and (b) with proposed algorithm.

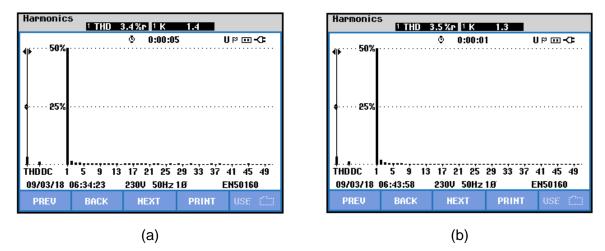

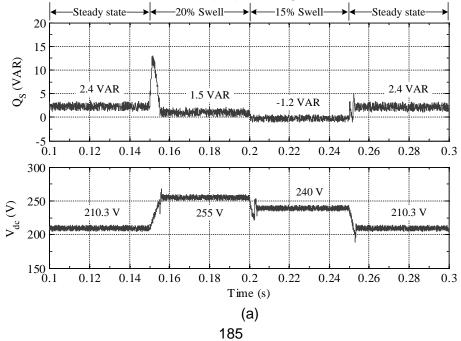

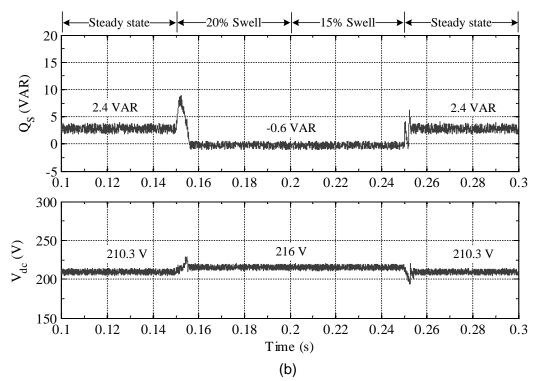

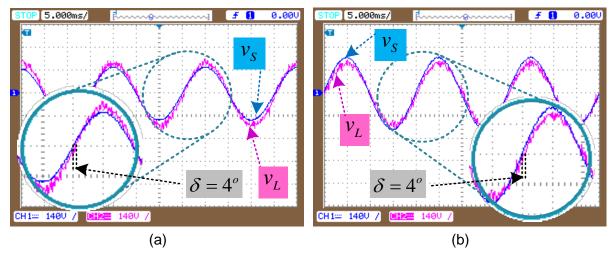

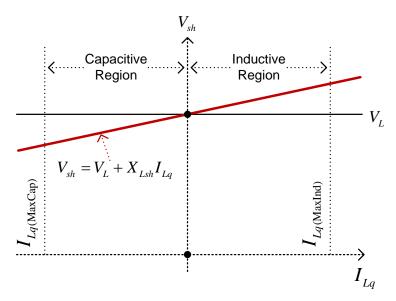

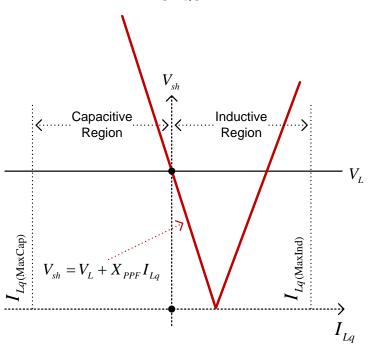

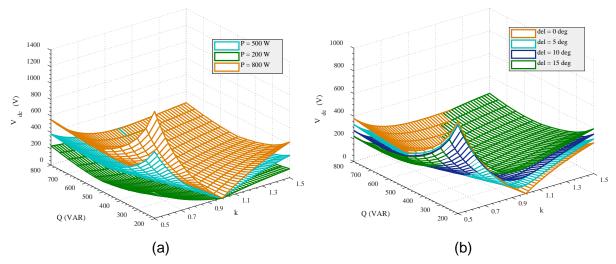

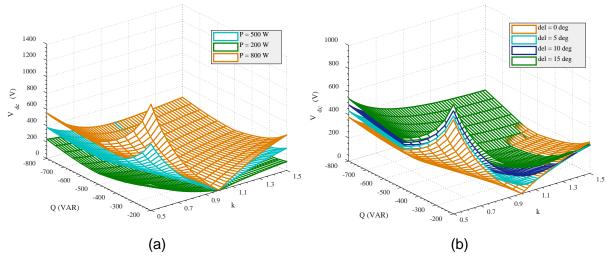

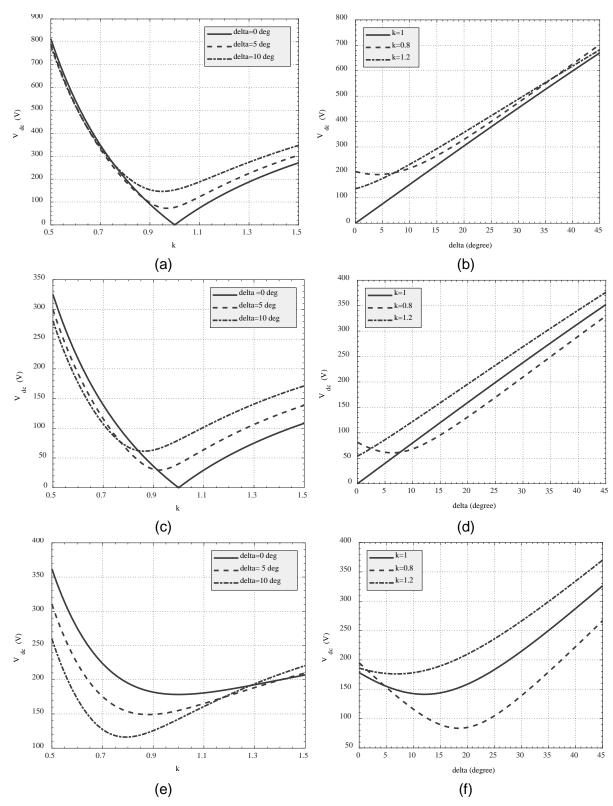

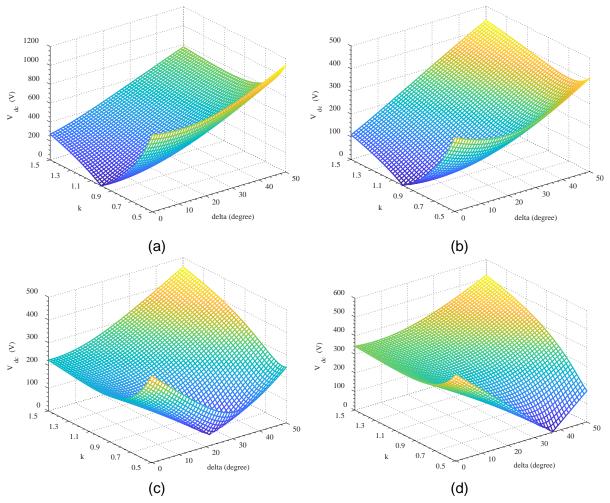

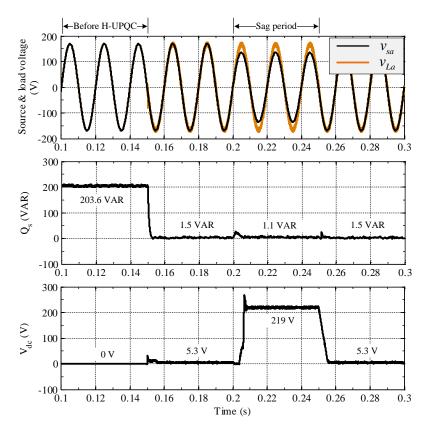

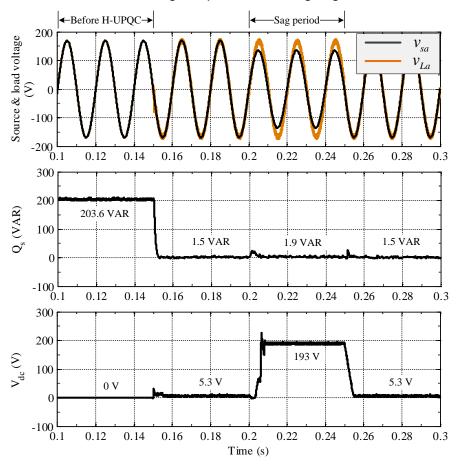

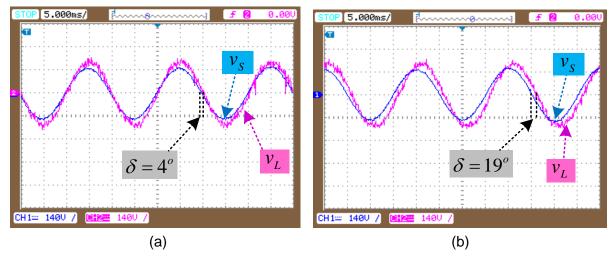

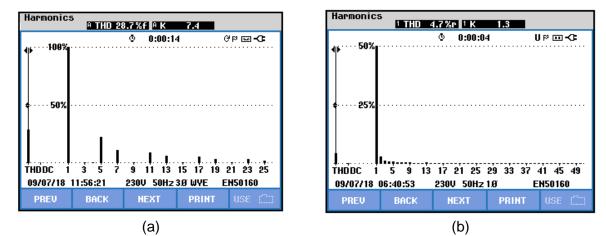

Fig. 4.28: Experimental results of minimum dc-link voltage requirement during voltage sag condition. (a) without application of PAC approach and (b) with proposed algorithm. ...... 187 Fig. 4.29: Experimental results of minimum dc-link voltage requirement during voltage swell condition. (a) without application of PAC approach and (b) with proposed algorithm. ...... 187 Fig. 4.30: Phase angle displacement between source voltage and load voltage obtained with the application of proposed algorithm during (a) voltage sag condition and (b) voltage swell Fig. 5.3: Placement of thyristor controlled impedance (TCZ) in the UPQC application. ..... 191 Fig. 5.6: Shunt converter VSI output voltage vs reactive loading current of conventional Fig. 5.7: Shunt converter VSI output voltage vs reactive loading current of PPF- hybrid Fig. 5.8: Shunt converter VSI output voltage vs reactive loading current of TCZ-PPF hybrid Fig. 5.9: Variation of dc-link voltage with lagging power factor of load with respect to sag/swell index (k) and load reactive power (Q) (a). with different load active power levels (P)Fig. 5.10: Variation of dc-link voltage with leading power factor of load with respect to sag/swell index (k) and load reactive power (Q) (a). at different load active power (P) levels Fig. 5.11: Variation of dc-link voltage with lagging power factor of load with respect to sag/swell index (k) and power angle ( $\delta$ ) for (a), (b) P = 500W, Q = 200VAR, (c), (d) Fig. 5.12: Variation of dc-link voltage with lagging power factor of load with respect to sag/swell index (k) and power angle ( $\delta$ ) for (a), P = 500W, Q = 200VAR, (b) P = 500W, Q = 500VAR, (c) P = 500W, Q = 800VAR, (d) P = 500W, Q = 1000VAR...... 202 Fig. 5.13: Flow chart to evaluate optimal dc-link voltage of TCZ-PPF based hybrid UPQC.203

| Fig. 5.16: Minimum dc-link voltage requirement during sag condition with 200VAR with PAC     |

|----------------------------------------------------------------------------------------------|

| control algorithm                                                                            |

| Fig. 5.17: Minimum dc-link voltage requirement during sag condition with 800VAR              |

| Fig. 5.18: Minimum dc-link voltage requirement during sag condition with 800VAR with PAC     |

| control algorithm                                                                            |

| Fig. 5.19: Experimental results of minimum dc-link voltage requirement during voltage sag    |

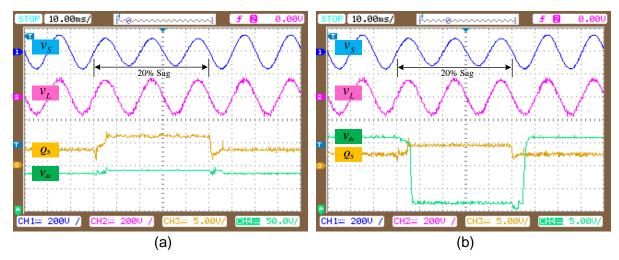

| condition. (a) without application of PAC approach and (b) with PAC algorithm                |

| Fig. 5.20: Experimental results of minimum dc-link voltage requirement during voltage swell  |

| condition. (a) without application of PAC approach and (b) with PAC algorithm209             |

| Fig. 5.21: Phase angle displacement between source voltage and load voltage obtained with    |

| the application of proposed algorithm during (a) voltage sag condition and (b) voltage swell |

| condition                                                                                    |

| Fig. 6.1: Structure of UPQC for 1P2W system [231]                                            |

| Fig. 6.2: Topology structures of reduced switch count for 1P2W system [231]212               |

| Fig. 6.3: Topology of nine switch UPQC of reduced switch count for 3P3W system [231]212      |

| Fig. 6.4: Ten switch topology of UPQC for 3P3W system [257]213                               |

| Fig. 6.5: Transformerless UPQC configuration for 3P4W system [264]                           |

| Fig. 6.6: Modular UPQC for 3P3W system (UPQC-MD) [256]214                                    |

| Fig. 6.7: Transformerless UPQC for 3P3W system [217]                                         |

| Fig. 6.8: Structure of UPQC for 3P4W system [230]215                                         |

| Fig. 6.9: Proposed transformer less series injection based UPQC (TLSI-UPQC) for 3P4W         |

| system                                                                                       |

| Fig. 6.10: Equivalent circuit of TLSI-UPQC                                                   |

| Fig. 6.11: Block diagram of control strategy of shunt converter                              |

| Fig. 6.12: PI+PR controller block diagram220                                                 |

| Fig. 6.13: Block diagram of control strategy of series converter                             |

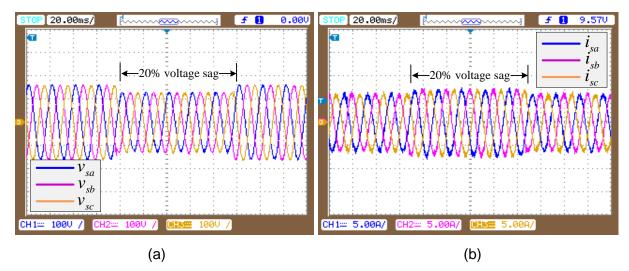

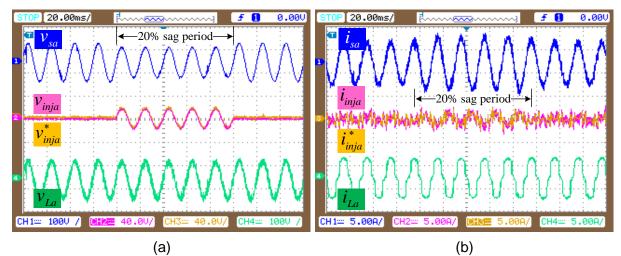

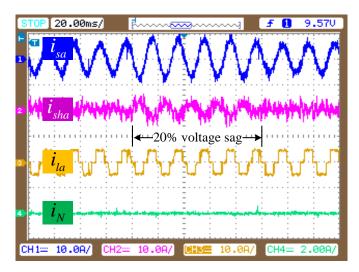

| Fig. 6.14: Simulation results of voltage profiles under voltage sag compensation             |

| Fig. 6.15: Experimental scope results of voltage profiles under voltage sag compensation for |

| phase-a along with dc-link capacitor voltage226                                              |

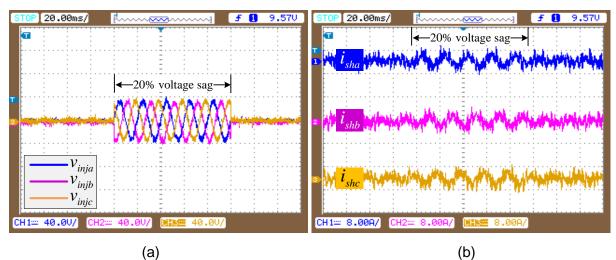

| Fig. 6.16: Simulation results of current profiles under voltage sag compensation226          |

| Fig. 6.17: Experimental scope results of current profiles under voltage sag compensation for |

| phase-a along with load neutral current                                                      |

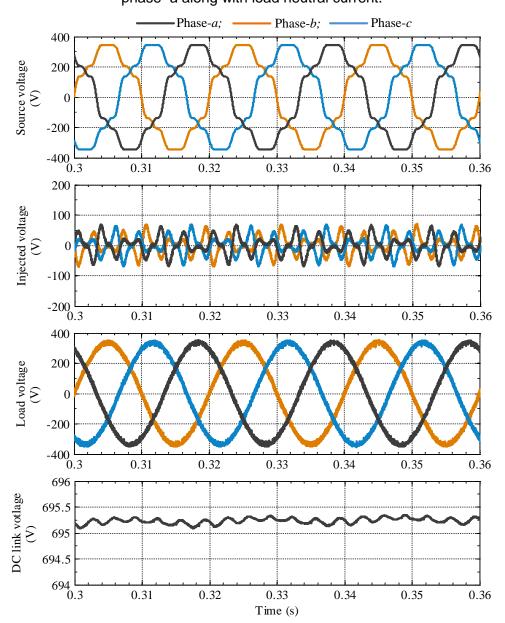

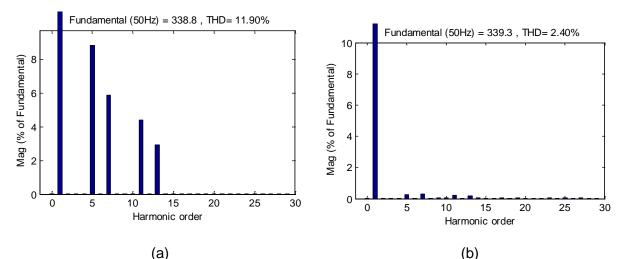

| Fig. 6.18: Simulation results of voltage profiles under distorted voltage compensation227    |

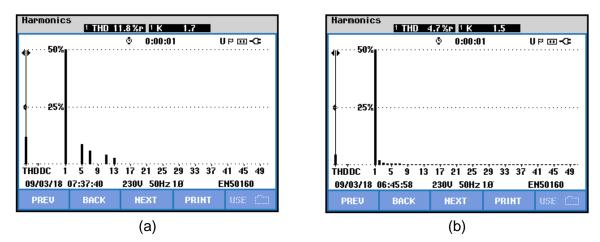

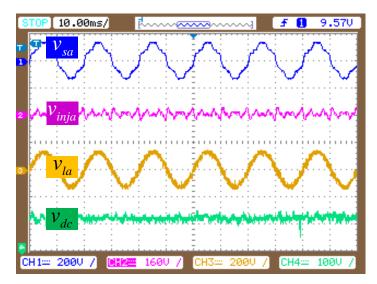

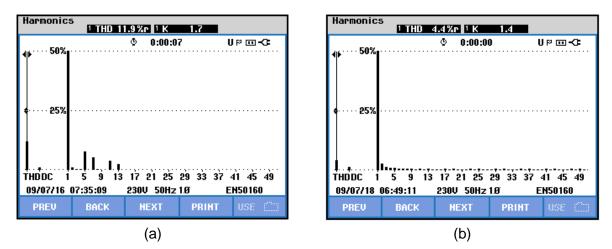

| Fig. 6.19: Harmonic spectrum of phase-a: (a) source voltage; (b) load voltage                |

| Fig. 6.20: Experimental scope results of voltage profiles under distorted source voltage     |

| compensation for phase-a along with dc-link capacitor voltage                                |

| Fig. 6.21: Harmonic spectrum of phase-a: (a) source voltage; (b) load voltage                |

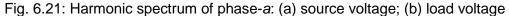

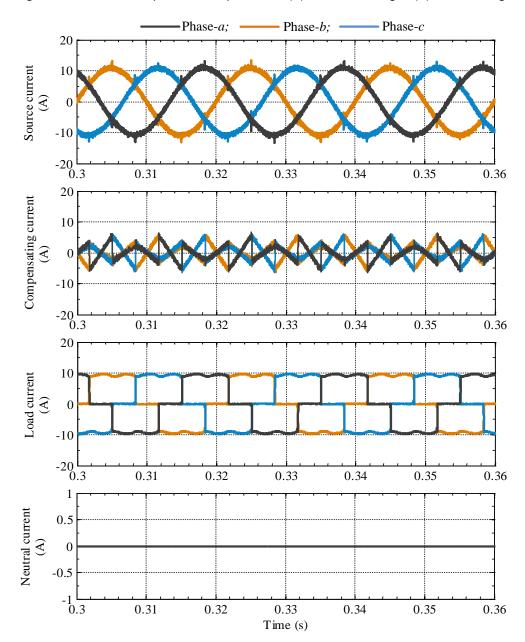

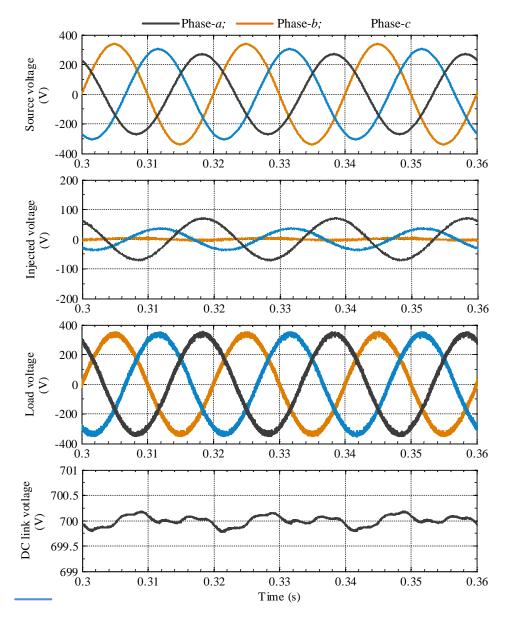

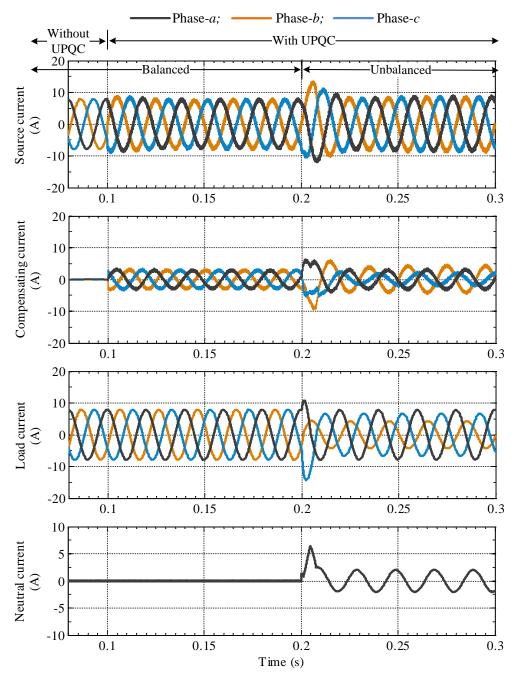

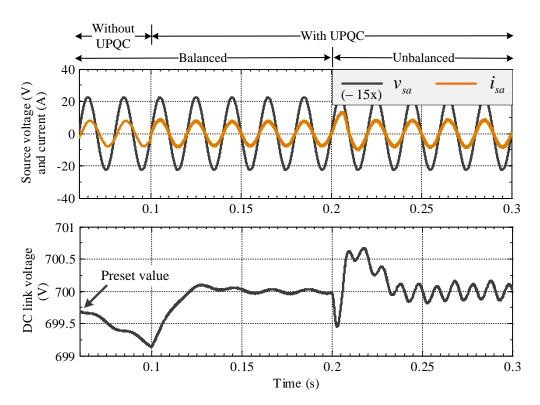

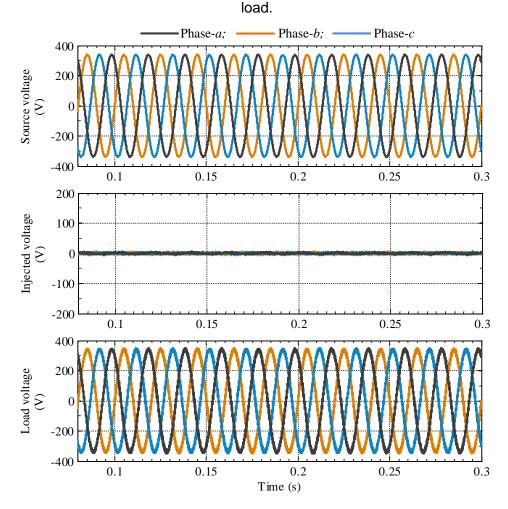

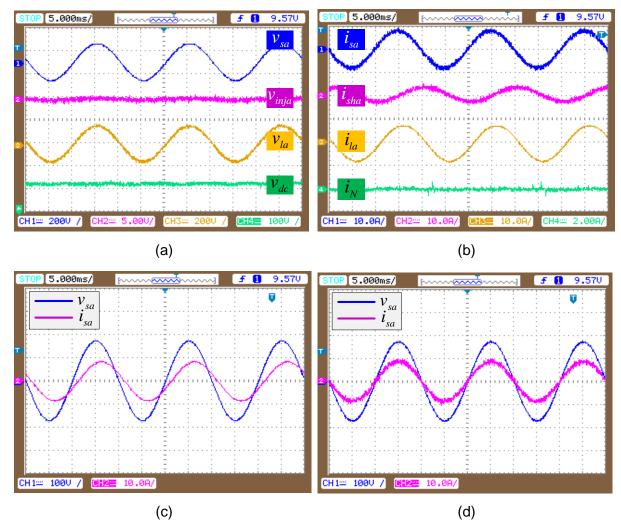

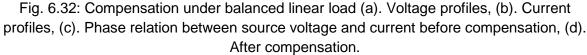

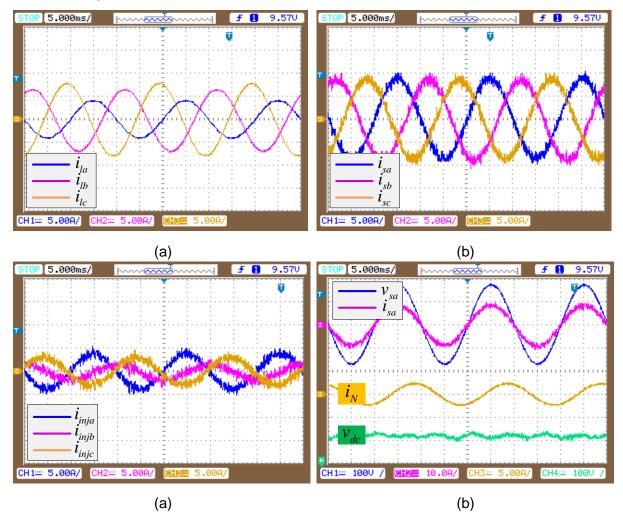

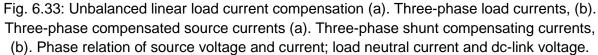

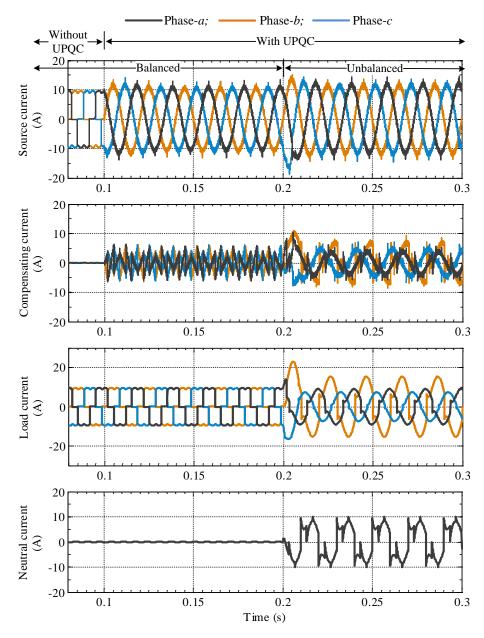

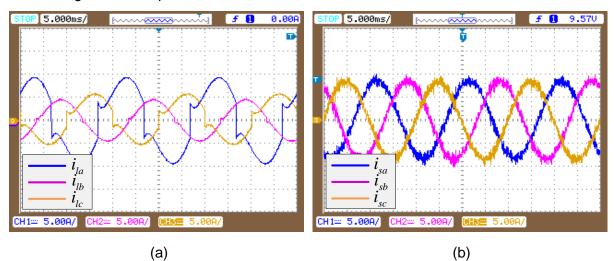

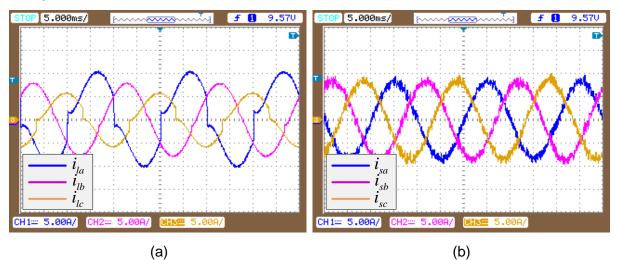

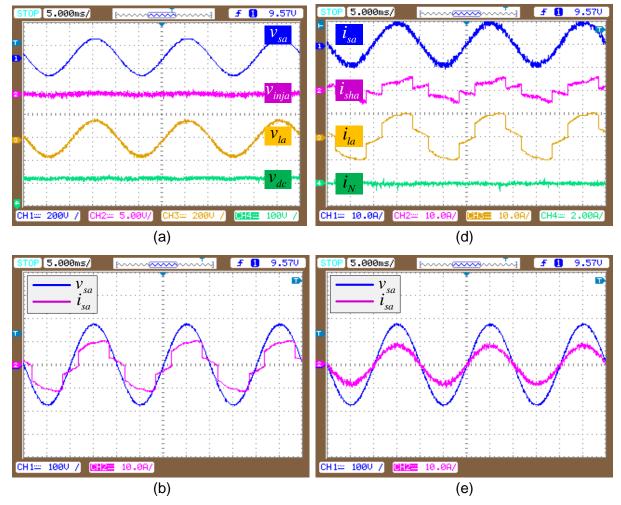

Fig. 6.22: Simulation results of current profiles by the shunt converter under distorted source Fig. 6.24: Experimental scope results of current profiles by the shunt converter under Fig. 6.26: Simulation results of voltage profiles under unbalanced source voltage Fig. 6.27: Unbalanced source voltage compensation (a). Three-phase supply voltages, (b). Fig. 6.28: Unbalanced source voltage compensation (a). Three-phase series injected Fig. 6.30: Simulation results showing reactive power compensation under unbalanced linear load......234 Fig. 6.32: Compensation under balanced linear load (a). Voltage profiles, (b). Current profiles, (c). Phase relation between source voltage and current before compensation, (d). Fig. 6.33: Unbalanced linear load current compensation (a). Three-phase load currents, (b). Three-phase compensated source currents (a). Three-phase shunt compensating currents, (b). Phase relation of source voltage and current; load neutral current and dc-link voltage.237 Fig. 6.35: Unbalanced load current compensation (a). Three-phase load currents, (b). Three-Fig. 6.36: Unbalanced nonlinear load current compensation (a). Three-phase load currents, Fig. 6.38: Compensation under balanced nonlinear load (a). Voltage profiles, (b). Current profiles, (c). Phase relation between source voltage and current before compensation, (d). Fig. 6.39: Compensation of source current under unbalanced linear and nonlinear load.... 243 Fig. 6.40: Unbalanced linear and nonlinear load current compensation (a). Three-phase load Fig. 6.41: Unbalanced linear and nonlinear load current compensation (a). Three-phase load Fig. 6.42: Compensation of source current under unbalanced linear and nonlinear load....244

| Table 1.1: Classification and characteristics of power quality problems [1]               |

|-------------------------------------------------------------------------------------------|

| Table 1.2: Power quality standards [1].    6                                              |

| Table 1.3: IEEE-519 current harmonic distortion limits [2].                               |

| Table 1.4: Harmonic voltage distortion limits in percent of nominal fundamental frequency |

| voltage [2]8                                                                              |

| Table 2.1: Selection of switching sequences for SVM in all sectors                        |

| Table 2.2: Three-level diode clamped multi-level inverter per phase switching states      |

| Table 2.3: Three-level switching states with vector classification [268]       56         |

| Table 2.4: System parameters under evaluation    67                                       |

| Table 2.5: THD Comparison between UPQC-2L and UPQC-3L with distorted source and           |

| non-linear load compensation80                                                            |

| Table 2.6: Comparison between UPQC-2L and UPQC-3L for sag compensation                    |

| Table 2.7: Comparison of phase-a peak fundamental value between UPQC-2L and UPQC-         |

| 3L for swell compensation                                                                 |

| Table 2.8: Comparison of phase-a peak fundamental value between UPQC-2L and UPQC-         |

| 3L for voltage unbalancing compensation                                                   |

| Table 2.9: Comparison of three-phase peak fundamental value and THDs between UPQC-2L      |

| and UPQC-3L for distorted unbalancing voltage compensation                                |

| Table 3.1: System parameters.    127                                                      |

| Table 3.2: THD Comparison between UPQC-2L and UPQC-3L with distorted source and           |

| non-linear load compensation                                                              |

| Table 3.3: THD Comparison between UPQC-2L and UPQC-3L with distorted unbalanced           |

| source voltage compensation144                                                            |

| Table 3.4: THD Comparison between UPQC-2L and UPQC-3L with voltage sag                    |

| compensation                                                                              |

| Table 3.5: THD Comparison between UPQC-2L and UPQC-3L with voltage swell                  |

| compensation                                                                              |

| Table 4.1: Design parameters of PPF.    171                                               |

| Table 4.2: The dc-link voltage variation with respect to phase angle $\delta$             |

| Table 4.3: The variation of VA loading with respect to phase angle $\delta$               |

| Table 4.4: Best possible dc-link voltage evaluate by the proposed algorithm               |

| Table 5.1: Design parameters of TCZ-PPF                                                   |

| Table 6.1: System parameters.   224                                                       |

| 3P3W      | Three-phase, Three-wire                           |

|-----------|---------------------------------------------------|

| 3P4W      | Three-phase, Four-wire                            |

| ac, AC    | Alternating Current                               |

| APF       | Active Power Filter                               |

| CSD       | Custom Power Device                               |

| CSI       | Current Source Inverter                           |

| dc, DC    | Direct Current                                    |

| DCMLI     | Diode Clamped Multilevel Inverter                 |

| DSO       | Digital Storage Oscilloscope                      |

| DSP       | Digital Signal Processor                          |

| D-STATCOM | Distribution Static Synchronous Compensator       |

| DVR       | Dynamic Voltage Restorer                          |

| EMI       | Electro Magnetic Interference                     |

| FACTS     | Flexible AC Transmission System                   |

| FCMLI     | Flying Capacitor Multilevel Inverter              |

| H-UPQC    | Hybrid UPQC                                       |

| IEC       | International Electrotechnical Commission         |

| IEEE      | Institute of Electrical & Electronics Engineers   |

| IGBT      | Insulated Gate Bipolar Transistor                 |

| KF        | Kalman Filter                                     |

| LPF       | Low Pass Filter                                   |

| LSPWM     | Level-shifted Pulsewidth Modulation               |

| MLI       | Multilevel Inverter                               |

| MOSFET    | Metal Oxide Semiconductor Field-effect Transistor |

| MPC       | Model Predictive Control                          |

| PAC       | Phase Angle Control                               |

| PCC       | Point of Common Coupling                          |

| pf, PF    | Power Factor                                      |

| PI        | Proportional and Integral                         |

| PPF       | Passive Power Filter                              |

| PR        | Proportional Resonant                             |

| PWM       | Pulsewidth Modulation                             |

| rms, RMS  | Root Mean Square                                  |

| SVM       | Space Vector Modulation                           |

| TCR       | Thyristor Controlled Reactor                      |

| TCZ       | Thyristor Controlled Impedance                    |

|           |                                                   |

| THD                    | Total Harmonic Distortion                                        |

|------------------------|------------------------------------------------------------------|

| TLSI-UPQC              | Transformer-Less Series Injection UPQC                           |

| UPQC                   | Unified Power Quality Conditioner                                |

| UPQC-2L                | Two-Level UPQC                                                   |

| UPQC-3L                | Three-Level UPQC                                                 |

| UPQC-D                 | 3P3W to 3P4W Distributed UPQC                                    |

| UPQC-DG                | Distributued Generator integrated with UPQC                      |

| UPQC-I                 | Interline UPQC                                                   |

| UPQC-L                 | Left shunt UPQC                                                  |

| UPQC-MC                | Multi-Converter UPQC                                             |

| UPQC-MD                | Modular UPQC                                                     |

| UPQC-ML                | Multi-Level UPQC                                                 |

| UPQC-P                 | UPQC mitigates sag by controlling active power                   |

| UPQC-Q                 | UPQC mitigates sag y controlling reactive power                  |

| UPQC-R                 | Right shunt UPQC                                                 |

| UPQC-S                 | UPQC mitigates sab by controlling both active and reactive power |

| $UPQC\text{-}VA_{min}$ | Minimum VA loading UPQC                                          |

| VSI                    | Voltage Source Inverter                                          |

| $v_{Sa}$ , $v_{Sb}$ and $v_{Sc}$       | Three-phase source voltages                           |

|----------------------------------------|-------------------------------------------------------|

| $i_{Sa}$ , $i_{Sb}$ and $i_{Sc}$       | Three-phase source currents                           |

| $i_{La}$ , $i_{Lb}$ and $i_{Lc}$       | Three-phase load currents                             |

| $i_{sh\_a}, i_{sh\_b}$ and $i_{sh\_c}$ | Three-phase shunt compensating currents               |

| т                                      | Number of levels in inverter                          |

| f <sub>cr</sub>                        | Carrier signal frequency                              |

| f <sub>m</sub>                         | Modulating signal frequency                           |

| m <sub>a</sub>                         | Amplitude modulation index                            |

| m <sub>f</sub>                         | Frequency modulation index                            |

| Ls                                     | Source inductance                                     |

| L <sub>sh</sub>                        | Coupling inductor of shunt converter                  |

| L <sub>ac</sub>                        | Commutation inductance                                |

| p, q                                   | Instantaneous real and reactive powers                |

| Rs                                     | Source resistance                                     |

| V <sub>dc</sub>                        | Reference dc-link voltage                             |

| $k_{ ho}, k_i$                         | Proportional and integral gains                       |

| İsn                                    | Source neutral current                                |

| İLn                                    | Load neutral current                                  |

| SUPQC                                  | VA loading of UPQC                                    |

| S <sub>H-UPQC</sub>                    | VA loading of hybrid UPQC                             |

| V <sub>dcl</sub>                       | Upper dc-link voltage of UPQC-3L                      |

| V <sub>dcu</sub>                       | Lower dc-link voltage of UPQC-3L                      |

| V <sub>t_abc</sub>                     | Three-phase terminal voltages                         |

| V <sub>inj_abc</sub>                   | Three-phase series injected voltages                  |

| Zs                                     | Source impedance                                      |

| Z <sub>PPF</sub>                       | Impedance of PPF                                      |

| δ                                      | Phase angle between terminal voltage and load voltage |

| Y                                      | Angle of series injected voltage wrt terminal voltage |

| ${oldsymbol{\Phi}}_L$                  | Load power factor angle                               |

|                                        |                                                       |

This chapter describes introduction to the research work. It will start with some background on foremost power quality problems in distribution systems. Then, the solutions to the problems will be discussed. The power quality problems are discussed in terms of voltage and current profile of various commonly used appliances and also the load profile of the department electrical supply system. After discussion about power quality problems, the detailed possible solutions are presented. The literature survey is conducted on custom power devices. The literature survey is extended to unified power quality conditioner in detail about various topology structures and control strategies as it is considered the research topic of this thesis. Next, scope of work, author's contribution and thesis outlines are explained.

The very inception of interconnected power networks lead to the use of alternating current (AC) circuits as a commonplace. In these power networks, the basic function of generators is to produce a clean sinusoidal voltage waveform, of constant frequency, at their terminals. However, a pure sinusoidal waveform with zero distortion is a hypothetical entity and not a practical one. The voltage waveform, even at the point of generation, contains a small amount of distortion, due to non-uniformity in the excitation magnetic field and discrete spatial distribution of coils around the generator stator slots. The distortion at the point of generation is usually very low, typically less than 1.0%. In past, majority of the loads in power distribution systems were of constant in nature, as regards to power, impedance, current or any of their combination. Such loads include incandescent lighting, heating, AC motors, etc., and are termed as linear loads. However, in recent years, the requirement for more efficient operation of electrical equipment and energy conditioning has led to the advancement in semiconductor technologies and introduction of new power electronic devices. This has significantly changed the nature of load composition because these power electronics based loads are nonlinear in nature. This nonlinearity results in non-sinusoidal load currents, which are periodic in nature and usually reflect Fourier series expansions. Non-sinusoidal periodic waves contain fundamental and higher order frequency components. These higher order frequency components are called harmonics. Harmonics can be defined as the undesirable components of a distorted periodic waveform whose frequencies are the integer multiples of the fundamental frequency [1]-[10].

The injected harmonics are responsible for the distortion of voltage and current wave shapes. A substantial amount of these harmonics are produced by high rating power converters. Other devices responsible for generation of harmonics are static var compensators, adjustable speed drives, power supplies, transformers, arc furnaces, personal computers, cyclo-converters, etc. In future, there may be many more new harmonic sources, such as fuel cells, battery storage devices, photovoltaic cells, etc. Non-sinusoidal currents generated by the nonlinear loads are propagated throughout the network, causing voltage drops across the impedance of transmission lines and transformers. Thus, the voltage at the

1

point of common coupling (PCC) is no longer sinusoidal, but periodic and also possesses Fourier series expansions. The quantum of voltage distortion depends on the line impedance and the magnitude of current. When several power users share a common power line, the voltage distortion produced due to harmonic current injection by one user can impact the quality of power supplied to others. Due to this, standards have been issued to limit the amount of harmonic currents fed into the source by an individual customer [6].

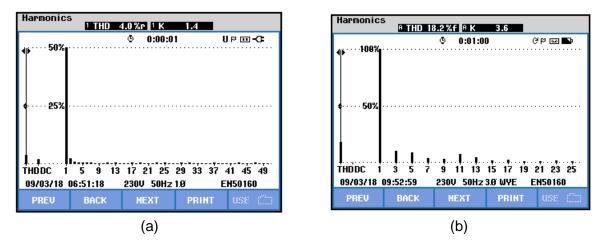

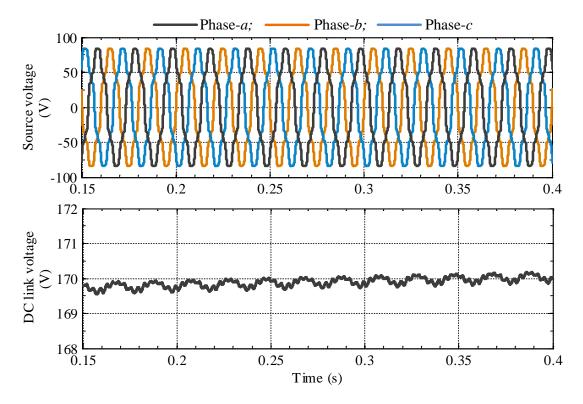

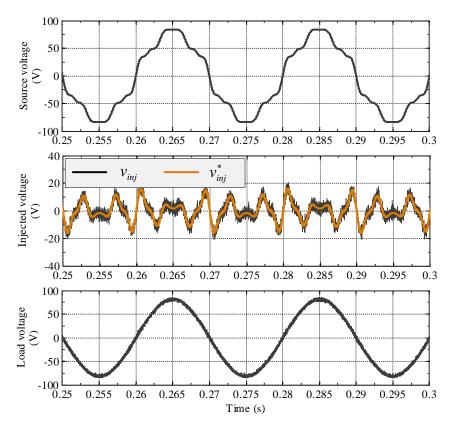

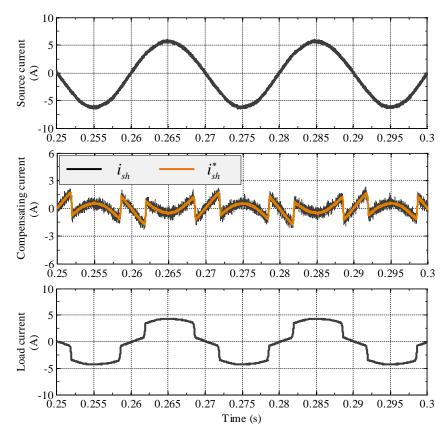

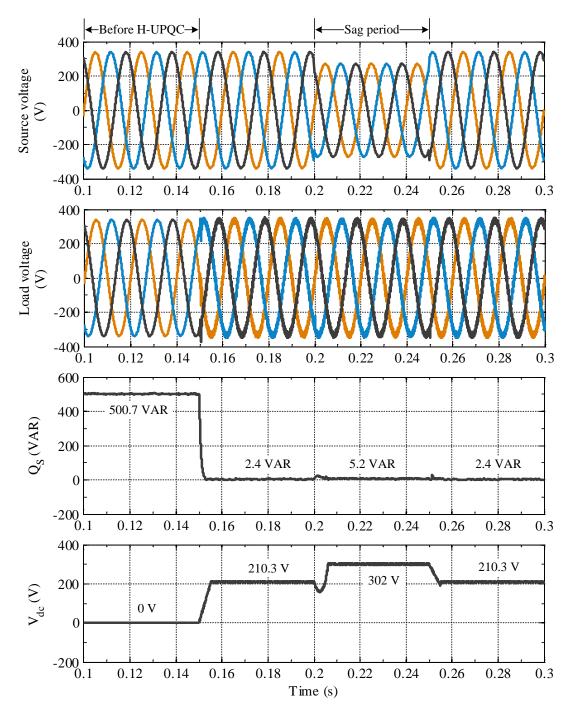

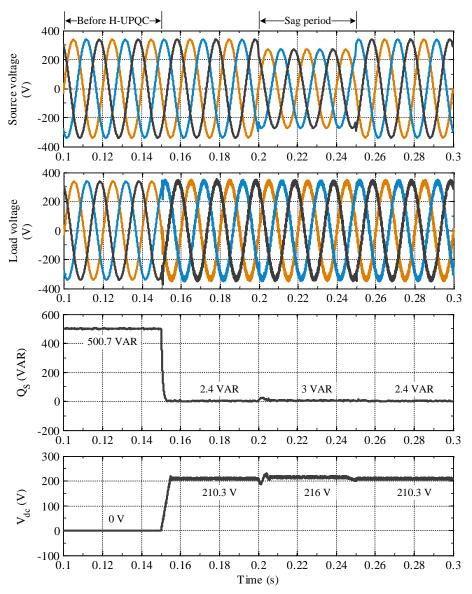

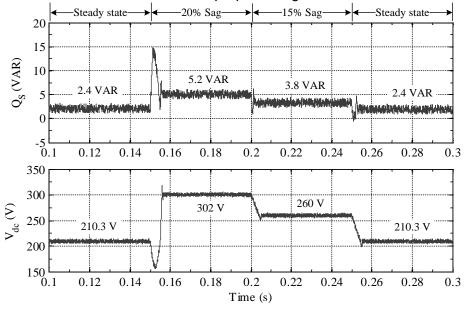

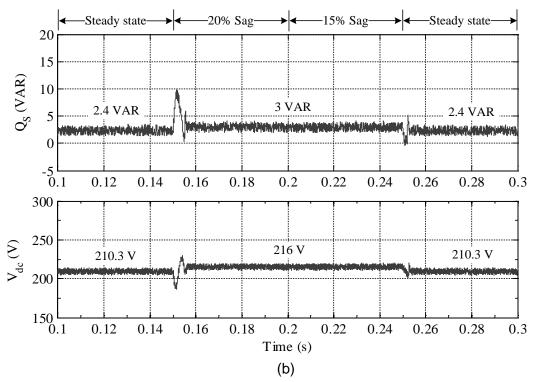

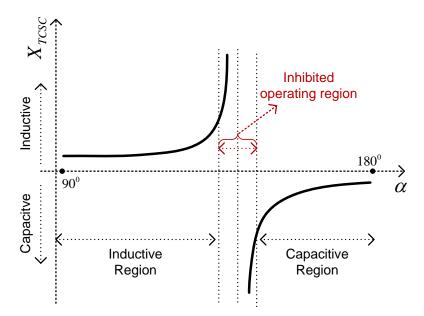

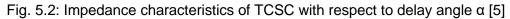

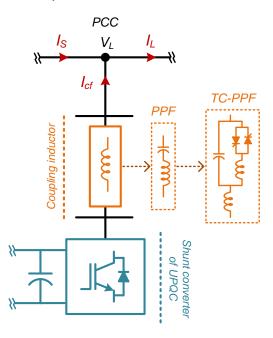

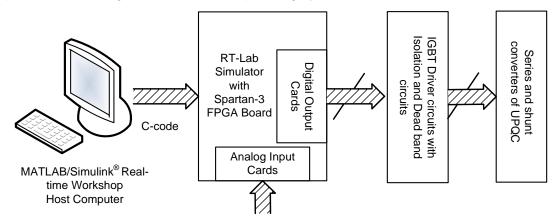

### 1.1 Electric Power Quality