# PERFORMANCE ANALYSIS OF UPS INVERTERS SYSTEM

Ph.D. THESIS

by

### SANTOSH KUMAR SINGH

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247 667 (INDIA) NOVEMBER, 2018

# PERFORMANCE ANALYSIS OF UPS INVERTERS SYSTEM

### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

### **DOCTOR OF PHILOSOPHY**

in

### **ELECTRICAL ENGINEERING**

by

### SANTOSH KUMAR SINGH

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247 667 (INDIA) NOVEMBER, 2018

## ©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2018 ALL RIGHTS RESERVED

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

### **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled "**PERFORMANCE ANALYSIS OF UPS INVERTERS SYSTEM**" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electrical Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from August, 2013 to November, 2018 under the supervision of Dr. Sumit Ghatak Choudhuri, Assistant Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other institution.

### SANTOSH KUMAR SINGH

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

(Sumit Ghatak Choudhuri) Supervisor

The Ph.D. Viva-Voce Examination of Santosh Kumar Singh, Research Scholar, has been held on March  $2^{nd}$ , 2019.

Chairperson, SRC

This is to certify that the student has made all the corrections in the thesis.

Signature of Supervisor Dated:

Head of the Department

### **Signature of External Examiner**

PS Inverters have been continuously growing during the past years due to power deficits, frequent power cuts, unreliable grid, digital dependency of day to day life, and most important, the demand of clean energy. Developments in power electronic devices, fast processors and advancements in utilisation techniques of renewable sources further catalyse the upsurge. Information Technology (IT) or Information Technology enabled Services (ITeS), such as, Banking, Financial Services and Insurance (BFSI), telecom, healthcare, education and manufacturing sectors heavily rely on UPS. Due to their criticality, at some instances, even a brief interruption is too hazardous and cannot be ignored. Therefore, under such situations, an added backup is utmost essential. Further, predicting future power requirements is almost next to impossible for anyone at the initial stages of planning. Therefore, reliability and power expansion of UPSs are among the major concerns for power supply designers. In addition, high performance, energy efficiency and robust design with low cost have been amongst prime pre-requisites from manufacturer as well as customer end.

This thesis investigates various control strategies for single-phase Pulse Width Modulated (PWM) voltage source inverters used in Uninterruptible Power Supplies (UPS) first for a unit inverter module and then for a parallel bi-module UPS inverter system. For the control of single inverter module, both single-loop and multi-loop control schemes have been examined. It has been observed that multi-loop approaches are better in terms of voltage regulation performance and robustness. However, voltage performance also depends on the compensator or controller utilised in realising the control strategy. Three commonly used integral controllers, namely; Proportional Integral (PI), Proportional Resonant (PR) and Synchronous Reference Frame Proportional Integral (SRF-PI) have been applied to obtain desired the voltage output. Conventionally, PI control suffers from large steady-state error and PR has fixed-point DSP implementation issues. On the other hand, SRF-PI can achieve excellent performance but the design and implementation complexities are high, particularly for the single-phase VSIs. These limitations have been moderated by implementing voltage-loop control in synchronous frame and current-loop in stationary frame of reference.

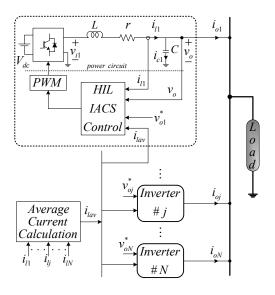

The presented research investigation further explores different control strategies on parallel inverter modules for enhancement in power rating of the UPS system. The focus has been on different Instantaneous Average Current Sharing (IACS) control schemes due to their better current sharing and expansion flexibilities. At first, using the structure of multi-loop inductor current feedback control for unit inverters, an Instantaneous Average Current Feed Forward (IACFF) based current sharing scheme has been proposed for multi-inverter UPS system. In this scheme, the instantaneous average current has been feed-forwarded to increase the impedance for the inter-modular circulating current.

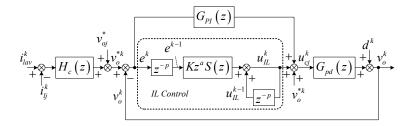

Along with the conventional PI and PR based controller based Instantaneous Average Current Sharing (IACS) control schemes, a non-linear and a periodic controller based current sharing control schemes have been attempted for multi-module UPS. An IACS scheme using non-linear controller based Hierarchical Fuzzy Logic (HFL) has been suggested for parallel connection of multi-module UPS inverters. Being a fuzzy based control scheme, the UPS system modelling needs not be precise and robustness of the control is high over wide variations in system parameters. In another IACS control scheme, a periodic controller based Hybrid Iterative Learning (HIL) has also been proposed for the multi-inverter system. Since signals are periodic in UPS application, the HIL has been realised by combining two controllers, i.e. Iterative Learning (IL) and PI control. The steady-state error of the stationary frame PI control can be successfully overcome by employing the IL based controller, whereas the poor transient dynamic of the later can be improved by the PI controller. Therefore, two controllers complement each other in overall performance efficacy of the HIL control. Further, the presented control uses an inductor current feedback to provide both damping to the inverter plant and current sharing control of the multi-inverter UPS system. Therefore, the HIL control reduces the requirement of one sensor per module in the multi-module UPS inverters system to achieve a good voltage regulation and proper current sharing, simultaneously.

A systematic design procedure and control analysis has been presented in due course for the respective control schemes. Simulation investigations and experimental implementations using two single-phase PWM VSIs prove the effectiveness of the proposed theoretical conceptions.

ii

For this magnificent opportunity of life, first of all my heartfelt thanking is to the Almighty Lord "Shiva".

I would like to express my sincere gratitude towards Dr. Sumit Ghatak Choudhuri, my supervisor, for his inspiring guidance and constant support during my doctoral research. His immense enthusiasm and encouragement made undertaking this study a pleasure. Apart from professional endeavours, his personal advices have always kept my motivation intact throughout this research tenure.

I would like to thank the precious support from the Head of the Department, Faculty members and staff of the Department of Electrical Engineering, IIT Roorkee, for providing laboratory, research facility and administrative helps, without which it would be impossible to conduct this research. I would also like to thank former Head of the Department, Prof. S. P Srivastava for the generous support for many troubles I brought to him. I also express my sincere gratitude towards my research committee members: Prof. S.P. Gupta (EED), Prof. S.P. Singh (EED), Dr. Mukesh Pathak (EED), Dr. B. Anand (ECED) and Chairman, Department Research Committee (DRC) for their valuable suggestions and cooperation.

I wish to convey my sincere thanks to Dr. Sandeep Madishetti (IIT D), Dr. Vashist Bist (IIT D), Dr. Chinmay Jain (IIT D) and Mr. Pradeep Chatterjee (Infineon Technologies) for their invaluable suggestions and support during hardware implementation. I am grateful to all my colleagues and friends in the institute for their generous support, encouragement and brain storming discussions. In particular, I would like to thank Dr. Sukanta Haldar, Dr. Yarlagadda Srinivasa Rao, Dr. Mithun Mondal, Haresh Sabhadia, Dr. Ankit Kumar Singh, Praveen Kumar, Saran Satsangi, and Shamik Sen for their professional and personal support during the stay at the IIT Roorkee.

Deep in my heart are special thanks to my wife Supriya Chauhan and daughter Mishika. Their love and affection has always accompanied me through bad and good moments of the tenure. Finally, I am obliged to my parents, Shri Rajnath Singh Chauhan and Smt. Asha Devi and brother, Dinesh Pratap Singh for their valuable support, patience and faith in me, which made all this possible.

### Santosh Kumar Singh

## CONTENTS

| ABSTRACT                                               | i   |

|--------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                       | iii |

| CONTENTS                                               | . v |

| LIST OF FIGURES                                        | xi  |

| LIST OF TABLESx                                        | ix  |

| LIST OF SYMBOLSx                                       | xi  |

| LIST OF ABBREVIATIONSxxv                               | 7ii |

| Chapter 1: Introduction                                | .1  |

| 1.1 UPS System Architecture                            | .2  |

| 1.1.1 Stand-By (Offline) UPS                           | . 3 |

| 1.1.2 Line Interactive UPS                             | .4  |

| 1.1.3 Double-Conversion (Online) UPS                   | .4  |

| 1.2 Modular UPS System                                 | . 5 |

| 1.2.1 Parallel UPS Inverter Configuration              | .6  |

| 1.2.2 Challenges Involved In Modular UPS Inverter      | .6  |

| 1.3 Research Objectives and Scope                      | . 8 |

| 1.4 Description of the Research Work                   | .9  |

| 1.5 Thesis Organization                                | 1   |

| Chapter 2: Literature Survey                           | 13  |

| 2.1 Introduction                                       | 3   |

| 2.2 Single-Phase UPS Inverter                          | 3   |

| 2.2.1 UPS Inverter Topologies                          | 3   |

| 2.2.2 Dynamic Modelling of UPS Inverter                | 4   |

| 2.3 Closed-Loop Control of Single-Phase UPS Inverter   | 6   |

| 2.3.1 Control Techniques for Single-Phase UPS Inverter | 17  |

| 2.3.1.1 Proportional Integral Controller                         | 17         |

|------------------------------------------------------------------|------------|

| 2.3.1.2 Proportional Resonant Controller                         | 19         |

| 2.3.1.3 Synchronous Reference Frame of Control                   | 22         |

| 2.3.1.4 Orthogonal Signal Generation Technique                   | 24         |

| 2.3.2 Alternate Control Options for Single-Phase UPS Inverters   | 25         |

| 2.3.2.1 Predictive Control                                       | 26         |

| 2.3.2.2 Non-Linear Control                                       |            |

| 2.3.2.3 Periodic Control                                         |            |

| 2.4 Multi-Modular UPS Inverters System                           | 32         |

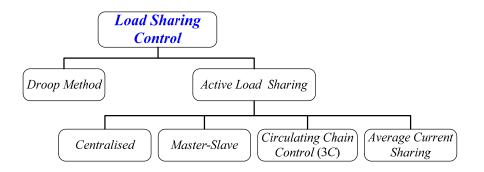

| 2.4.1 Droop Control Method                                       |            |

| 2.4.1.1 Power Flow Theory                                        |            |

| 2.4.1.2 Inductive Line Impedances, $Z_1 = \hat{i} X$             |            |

| 2.4.1.3 Droop Concept                                            | 35         |

| 2.4.1.4 Resistive Line Impedances, $Z_1 = R$                     |            |

| 2.4.2 Active Load Current Sharing Techniques                     |            |

| 2.4.2.1 Centralised Control                                      |            |

| 2.4.2.2 Master-Slave Control                                     | 39         |

| 2.4.2.3 Circular Chain Control (3C)                              | 40         |

| 2.4.2.4 Instantaneous Average Current Sharing Control            | 41         |

| 2.4.3 Review of Instantaneous Average Current Sharing Control    | 42         |

| 2.5 Summary                                                      | 44         |

| Chapter 3: Instantaneous Control Of Single-Phase UPS Inverter In | n Combined |

| Stationary And Synchronous Reference Frame                       | 45         |

| 3.1 Introduction                                                 | 45         |

| 3.2 Comparative Evaluation of Alternate Control Structures       | 46         |

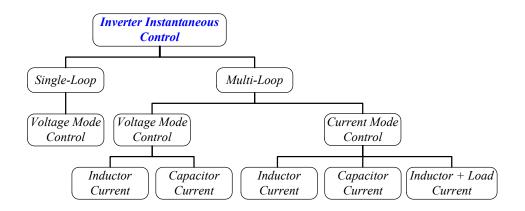

| 3.2.1 Classification of UPS Inverter Control Structures          | 46         |

| 3.2.2 Control Structures for UPS Inverters                       | 47         |

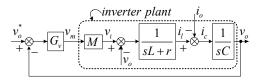

| 3.2.2.1 Single-loop Voltage Mode Control                                                    | 47             |

|---------------------------------------------------------------------------------------------|----------------|

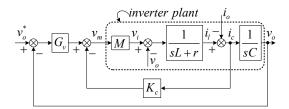

| 3.2.2.2 Multi-Loop Voltage Mode Control                                                     | 48             |

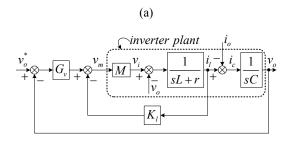

| 3.2.2.3 Multi-loop Current Mode Control                                                     | 49             |

| 3.2.3 Simulation Evaluation under Linear Load                                               | 53             |

| 3.2.4 Simulation Evaluation under Non-Linear Load                                           | 55             |

| 3.3 Synchronous Reference Frame Control of Single-Phase Inverter                            | 59             |

| 3.3.1 Orthogonal Signal Generation Technique                                                | 50             |

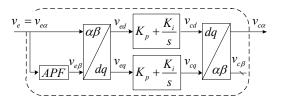

| 3.3.2 Combined <i>d-q</i> and $\alpha$ - $\beta$ Reference Frame Control Structure          | 50             |

| 3.3.3 Stationary $\alpha$ - $\beta$ frame equivalent of SRF-PI                              | 51             |

| 3.3.4 Controller Parameter Design                                                           | 53             |

| 3.3.4.1 Active Damping Coefficient, K <sub>c</sub>                                          | 54             |

| 3.3.4.2 Voltage Regulator                                                                   | 55             |

| 3.3.4.3 Effect of K <sub>i</sub> gain on the close-loop performance of integral controllers | 70             |

| 3.3.4.4 Effect of Feed-Forward Compensation                                                 | 73             |

| 3.3.4.5 Harmonic Impedance Compensation                                                     | 74             |

| 3.4 Results and Discussions                                                                 | 75             |

| 3.4.1 Simulation Evaluation                                                                 | 75             |

| 3.4.2 Experimental Results                                                                  | 79             |

| 3.5 Summary                                                                                 | 32             |

| Chapter 4: Instantaneous Average Current Feed-Forward Control For Equal Loa                 | ۱d             |

| Sharing In Parallel-Connected UPS Inverter System                                           | 85             |

| 4.1 Introduction                                                                            | 35             |

| 4.2 Modelling and Analysis of Circulating Current for UPS Inverters Connected in Parall     |                |

| 4.2.1 Open-Loop Inverter System                                                             | 35             |

| 4.2.2 Closed-Loop Inverter Control Topologies and Circulating Current Impedances 8          | 37             |

| 4.3 Development of Instantaneous Average Current Feed Forward (IACFF) Control9              | <del>)</del> 0 |

| 6.1 Introduction                                                                                                  | 129                  |

|-------------------------------------------------------------------------------------------------------------------|----------------------|

| Chapter 6: Hybrid Iterative Learning Based Instantaneous Average Current<br>Control For Multi-Inverter UPS System |                      |

| 5.7 Summary                                                                                                       |                      |

| 5.6.2 Experimental Results                                                                                        | 126                  |

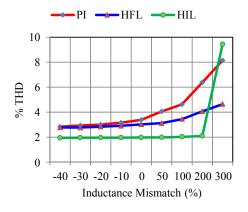

| 5.6.1.3 Effect of Parameters Variation                                                                            | 124                  |

| 5.6.1.2 Performance Comparison of PI and HFL Control                                                              | 122                  |

| 5.6.1.1 Comparison of Conventional FL and HFL                                                                     | 120                  |

| 5.6.1 Simulation Investigations                                                                                   | 120                  |

| 5.6 Results and Discussions                                                                                       | 120                  |

| 5.5 Hierarchical Fuzzy Logic Control Scheme                                                                       | 118                  |

| 5.4 Conventional Fuzzy Logic Control System                                                                       | 115                  |

| 5.3 System Configuration                                                                                          | 114                  |

| 5.2 Control Philosophy of Applied Instantaneous Average Current Sharing Scheme                                    | 112                  |

| 5.1 Introduction                                                                                                  | 111                  |

| Control For Multi-Inverter UPS System                                                                             | 111                  |

| Chapter 5: Hierarchical Fuzzy Logic Based Instantaneous Average Current                                           | Sharing              |

| 4.6 Summary                                                                                                       | 108                  |

| 4.5.2 Experimental Results                                                                                        | 106                  |

| 4.5.1 Simulation Investigations                                                                                   | 102                  |

| 4.5 Results and Discussions                                                                                       | 102                  |

| 4.4.5 Conflict between Voltage Regulation and Circulating Current Impedance (A                                    | Z <sub>cr</sub> )101 |

| 4.4.4 Effect of Control Parameters on Circulating Current Impedance, Z <sub>cr</sub>                              | 99                   |

| 4.4.3 Analysis of Output Impedance, Z <sub>cl</sub>                                                               | 97                   |

| 4.4.2 Outer Voltage Regulation Loop                                                                               | 95                   |

| 4.4.1 Inner Current Control Loop                                                                                  | 93                   |

| 4.4 Controller Parameter Design                                                                                   | 93                   |

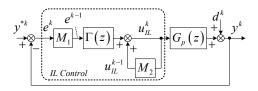

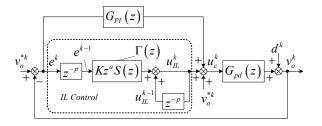

| 6.2 Principle of Iterative Learning Control                         | 130 |

|---------------------------------------------------------------------|-----|

| 6.2.1 P-type IL Control                                             | 131 |

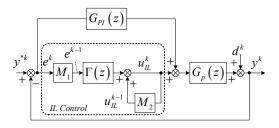

| 6.2.2 Hybrid Iterative Learning Control                             |     |

| 6.3 Proposed HIL Based IACS Control Scheme                          |     |

| 6.3.1 System Overview                                               |     |

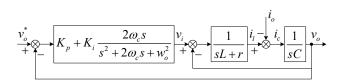

| 6.3.2 HIL Control of the Unit Inverter                              | 135 |

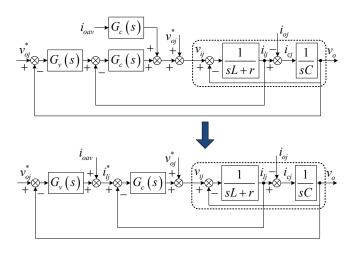

| 6.3.2.1 Modification of primitive inverter plant                    | 135 |

| 6.3.2.2 Proposed HIL Control for Unit Inverter                      | 136 |

| 6.3.3 HIL Based IACS Control of Multi-Inverter System               |     |

| 6.3.3.1 Voltage Regulation of the Multi-Inverter System             |     |

| 6.3.3.2 Current Sharing by Suppression of Circulating Current       | 140 |

| 6.4 Controller Design                                               | 141 |

| 6.4.1 Voltage Regulation loop                                       | 141 |

| 6.4.1.1 Active Damping of Resonant Peak                             | 141 |

| 6.4.1.2 Design of PI Controller                                     | 141 |

| 6.4.1.3 Design of Iterative Learning Controller with PI compensator | 142 |

| 6.4.2 Design of Current Sharing Control Loop                        | 145 |

| 6.5 Results and Discussions                                         | 145 |

| 6.5.1 Simulation Investigations on Unit Inverter                    | 145 |

| 6.5.2 Experimental Results of Unit Inverter system                  |     |

| 6.5.3 Simulation Investigations of Multi-Inverter System            | 152 |

| 6.5.4 Effect of Parameters Variation                                |     |

| 6.5.5 Experimental Results of multi-inverter system                 | 155 |

| 6.6 Summary                                                         | 156 |

| Chapter 7: Main Conclusions And Suggestions For Further work        | 159 |

| 7.1 General                                                         | 159 |

| 7.2 Main Conclusions                                                |     |

| 7.3 Suggestions for Further Work                        |     |

|---------------------------------------------------------|-----|

| BIBLIOGRAPHY                                            | 163 |

| APPENDIX-A: Stationary Frame Equivalent of SRF-PI       |     |

| APPENDIX-B: Derivation For Integral Gains               |     |

| B.1 PI Control                                          |     |

| B.2 PR Control                                          |     |

| B.3 SRF-PI Control                                      |     |

| APPENDIX-C: Experimental Set-UP                         |     |

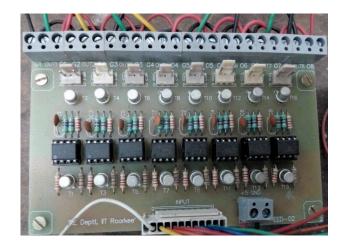

| C.1 Test Rig Structure                                  |     |

| C.2 Digital Signal Processor (DSP) Board                |     |

| C.3 Voltage and Current Sensing Circuit                 |     |

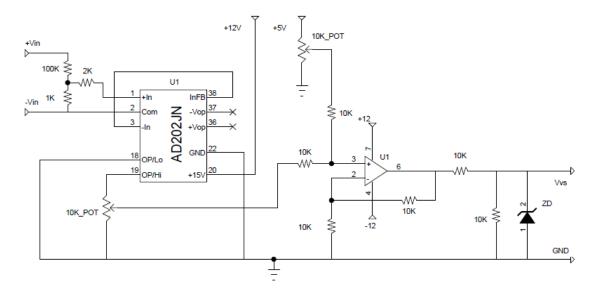

| C.3.1 Voltage Sensing Circuit                           |     |

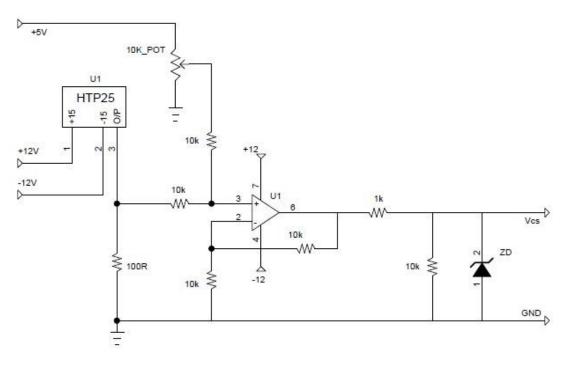

| C.3.2 Current Sensing Circuit                           |     |

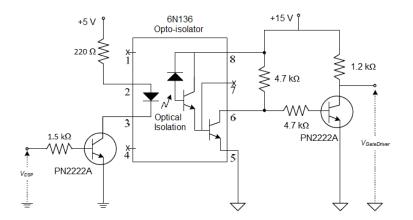

| C.4 Isolation and Amplification Circuit for PWM Signals |     |

| APPENDIX-D: Key Parameters                              |     |

| APPENDIX-E: PI Controller Disceretization               |     |

| LIST OF PUBLICATIONS                                    |     |

## **LIST OF FIGURES**

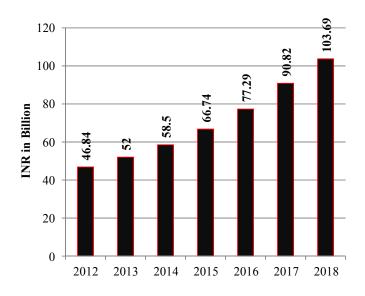

| Figure 1.1 India UPS market size in terms of value. <sup>[4]</sup>                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------|

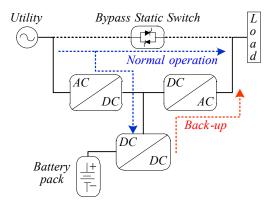

| Figure 1.2 Typical stand-by (Offline) topology of UPS                                                                                    |

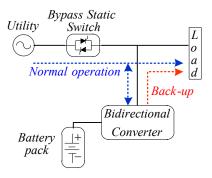

| Figure 1.3 Typical line-interactive topology of UPS                                                                                      |

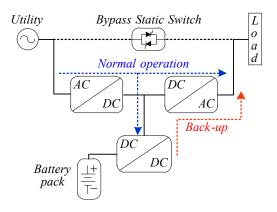

| Figure 1.4 Typical double conversion (Online) topology of UPS                                                                            |

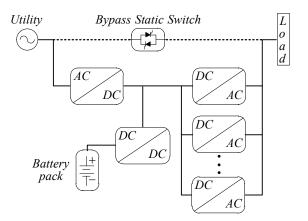

| Figure 1.5 Block diagram of a typical UPS system with several inverters in parallel                                                      |

| Figure 1.6 Block schematic of (a) UPS systems working in parallel and (b) UPS systems with dedicated power source is working in parallel |

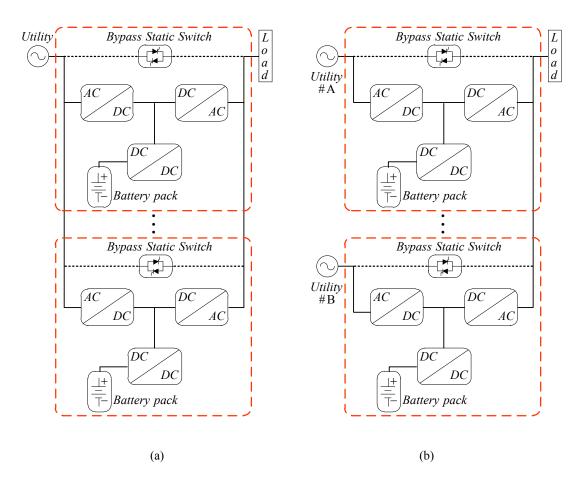

| Figure 1.7 Multi-Modular UPS inverters system                                                                                            |

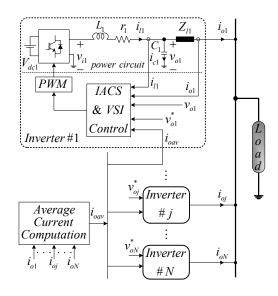

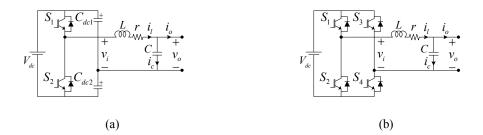

| Figure 2.1 Single-phase UPS inverter (a) Half-bridge and (b) Full-bridge topology14                                                      |

| Figure 2.2 Block schematic representation of single-phase voltage source inverter15                                                      |

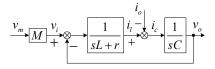

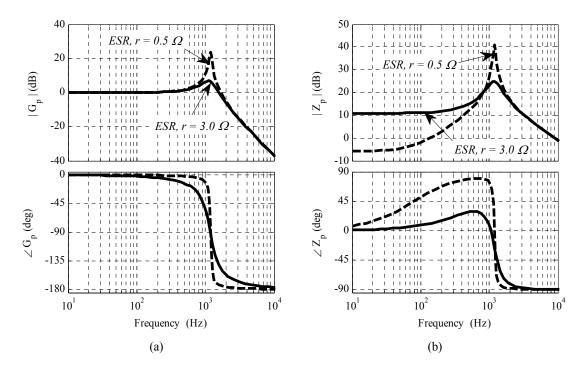

| Figure 2.3 Bode plots for inverter plant (a) Voltage gain and (b) Output impedance16                                                     |

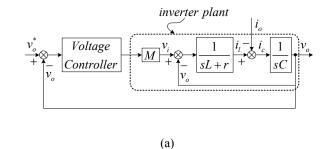

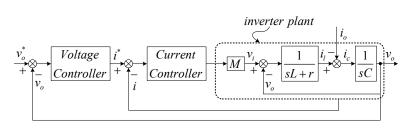

| Figure 2.4 Closed-loop instantaneous control of VSI (a) Single-loop and (b) Multiple-loop18                                              |

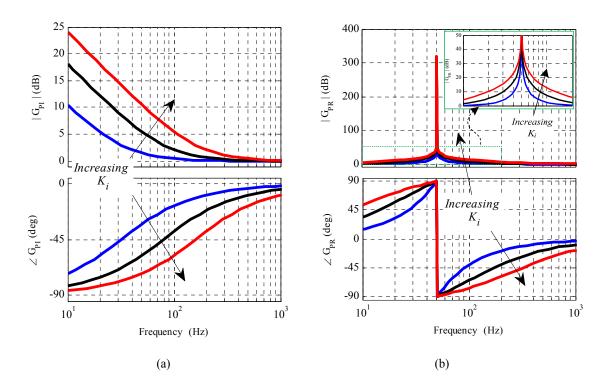

| Figure 2.5 Bode-plot for (a) PI controller, $G_{PI}$ and (b) PR controller, $G_{PR}$ where $K_p = 1$ ; $K_i = 200, 500$ and 1000.        |

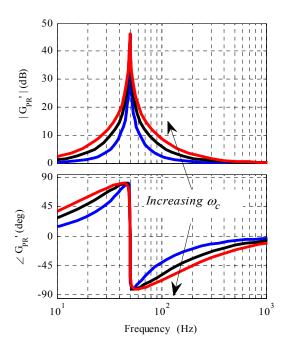

| Figure 2.6 Bode-plot for non-ideal PR controller with $\omega_c$ variations (2, 5 & 7), where $K_p = 1$ ;<br>$K_i = 200$                 |

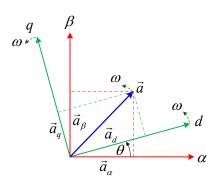

| Figure 2.7 Vector representation in stationary and synchronous reference frame                                                           |

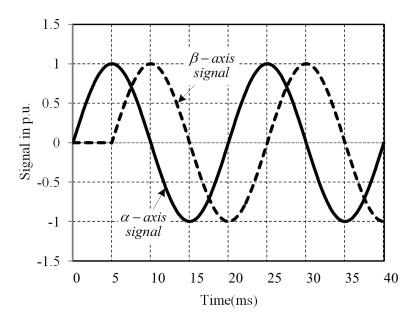

| Figure 2.8 Generation of virtual $\beta$ -axis orthogonal signal from $\alpha$ -axis signal                                              |

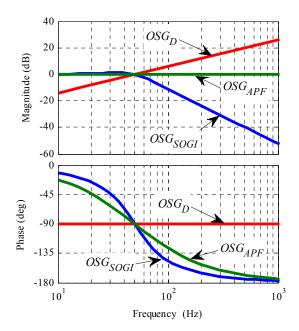

| Figure 2.9 Bode-plot for transfer characteristics of orthogonal signal generators25                                                      |

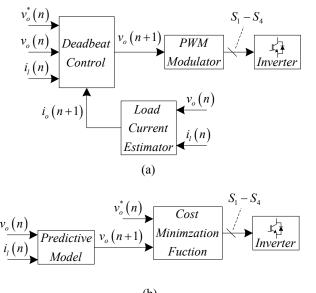

| Figure 2.10 Predictive control (a) Deadbeat control and (b) Model predictive control                                                     |

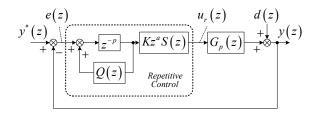

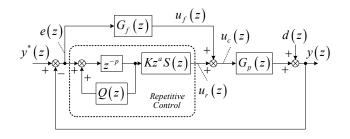

| Figure 2.11 Block schematic of a typical repetitive control system                                                                       |

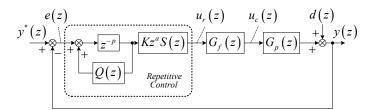

| Figure 2.12 Repetitive control using fast controller (a) Cascaded structure and (b) Parallel structure                                   |

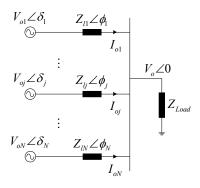

| Figure 2.13 Equivalent circuit of UPS inverters system connected in parallel to a common load                                            |

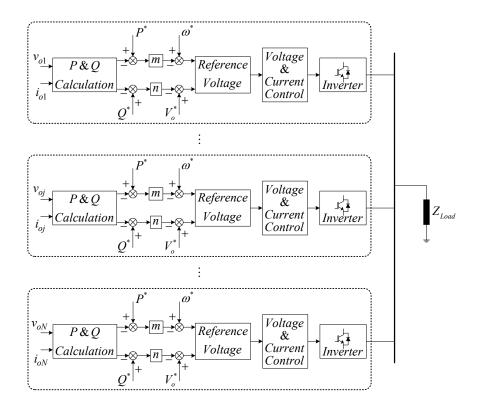

| Figure 2.14 Block schematic of droop control for parallel-connected inverters in an UPS system                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

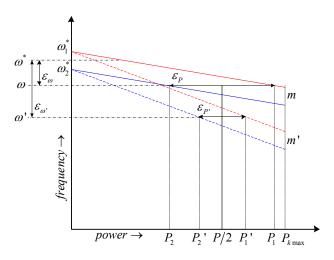

| Figure 2.15 Frequency versus active power of two inverters connected in parallel                                                                                                                                             |

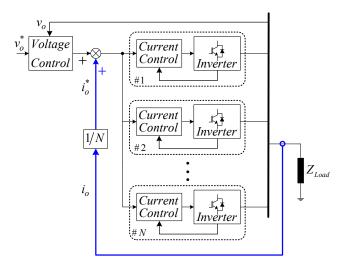

| Figure 2.16 Block schematic of centralised control strategy for parallel UPS inverters system.                                                                                                                               |

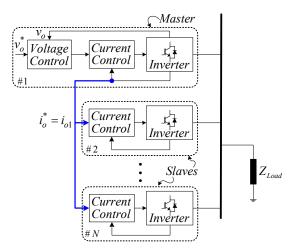

| Figure 2.17 Block schematic of Master-Slave (MS) control for parallel-connected UPS inverters system                                                                                                                         |

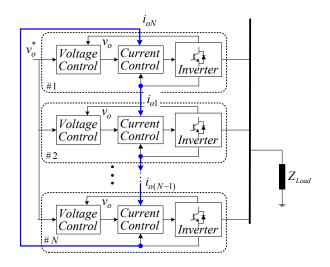

| Figure 2.18 Block schematic of Circular Chain Control (3C) for parallel-connected UPS inverters system                                                                                                                       |

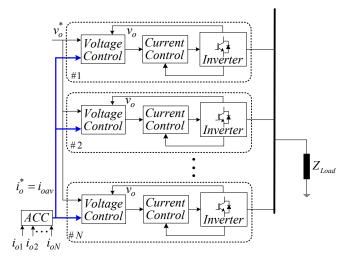

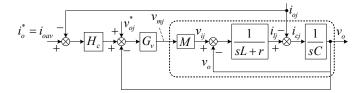

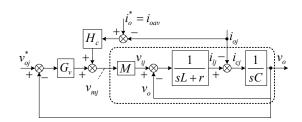

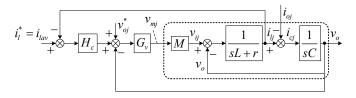

| Figure 2.19 Block schematic of Instantaneous Average Current Sharing (IACS) control for parallel-connected UPS inverters system                                                                                              |

| Figure 2.20 Control techniques for parallel operation of UPS inverters system                                                                                                                                                |

| Figure 2.21 Alternate control structures of IACS control for parallel-connected UPS inverters system                                                                                                                         |

| Figure 2.22 IACS control using inductor current for parallel-connected UPS inverters system.<br>                                                                                                                             |

| Figure 3.1 Categorisation of closed-loop inverter control                                                                                                                                                                    |

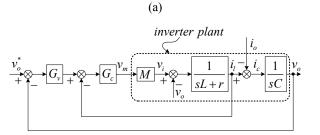

| Figure 3.2 Block schematic for single-loop voltage mode inverter control                                                                                                                                                     |

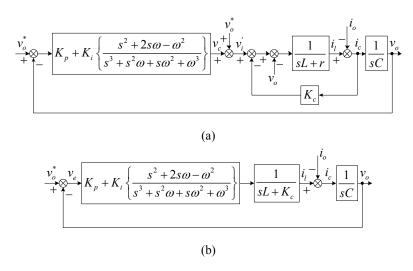

| Figure 3.3 Closed-loop inverter control strategy with (a) Voltage Mode Capacitor (VMC) and (b) Voltage Mode Inductor (VMI) current feedback                                                                                  |

| Figure 3.4 Closed-loop inverter control with (a) Current Mode Capacitor (CMC) & (b)<br>Current Mode Inductor (CMI) current feedbacks and (c) Current Mode Inductor current<br>feedback with Load (CMIL) current feed-forward |

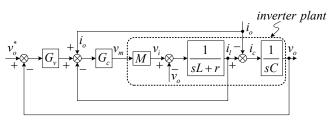

| Figure 3.5 Bode-plots for various control structures (a) Voltage gains and (b) Output impedances                                                                                                                             |

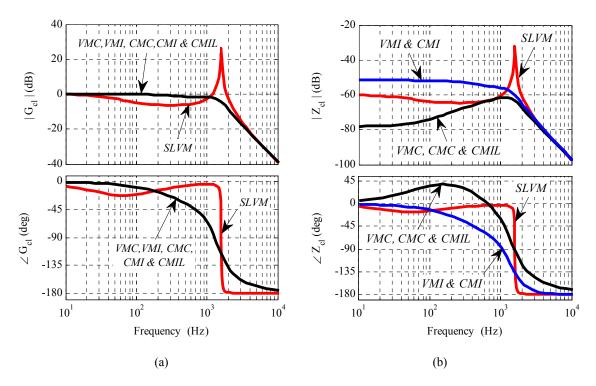

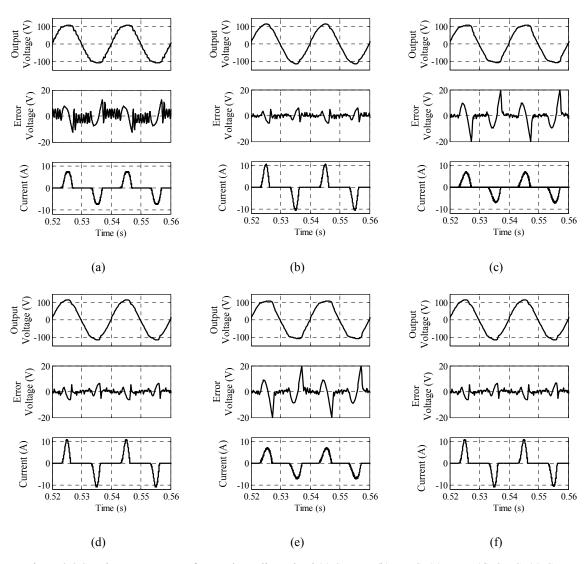

| Figure 3.6 Steady-state response for rated linear load (a) SLVM, (b) VMC, (c) VMI, (d) CMC, (e) CMI and (f) CMIL inverter control strategies                                                                                 |

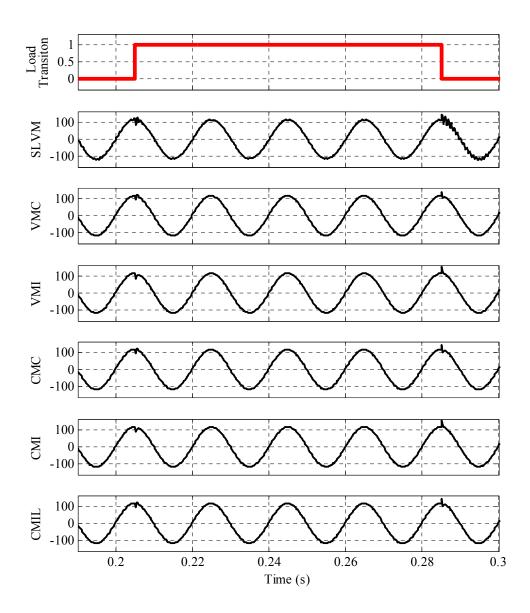

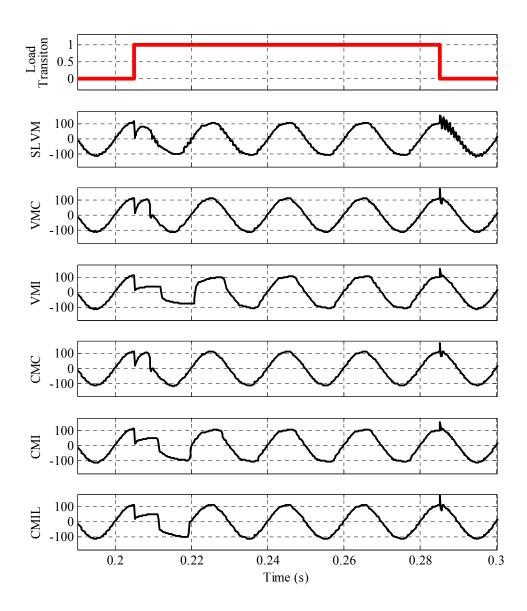

| Figure 3.7 Transient voltage (V) waveforms for step transitions of rated linear load with various control schemes                                                                                                            |

| Figure 3.8 Steady-state response for rated non-linear load (a) SLVM, (b) VMC, (c) VMI, (d)                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMC, (e) CMI and (f) CMIL inverter control strategies                                                                                                    |

| Figure 3.9 Transient voltage (V) waveforms for step transitions of rated non-linear load with various control schemes                                    |

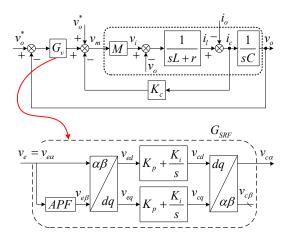

| Figure 3.10 Block schematic of single-phase SRF-PI control for UPS inverter60                                                                            |

| Figure 3.11 Block schematic (a) Equivalent stationary frame representation of SRF-PI inverter control and (b) Simplified model for voltage control-loop  |

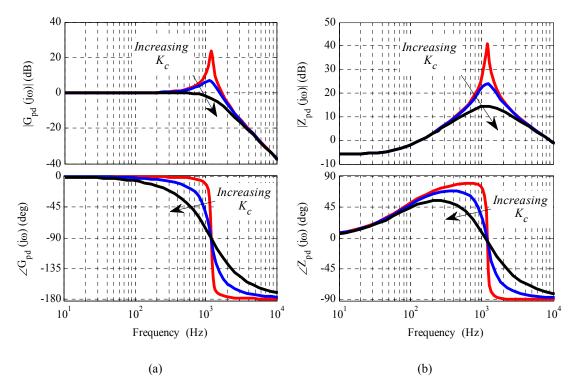

| Figure 3.12 Bode-plot of (a) Voltage gain and (b) Impedance for modified plant with active damping, where $K_c = 0$ , 3 and 10                           |

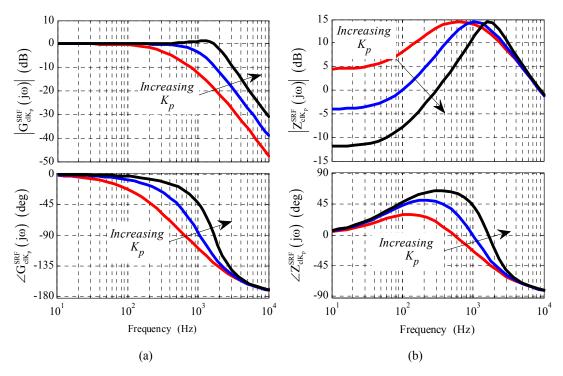

| Figure 3.13 Bode-plot (a) Voltage gain (b) Output impedance for proportional gain only, where variation of $K_p = 0.3$ , 0.8 and 2                       |

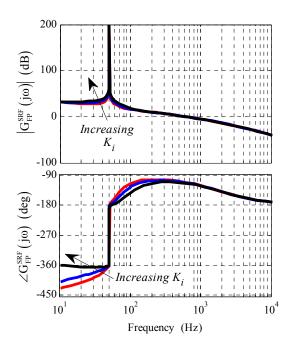

| Figure 3.14 Bode-plot for open-loop gain $G_{FP}^{SRF}(s)$ with SRF-PI controller, where $K_p = 0.8$ ; $K_i = 62, 125$ and 250                           |

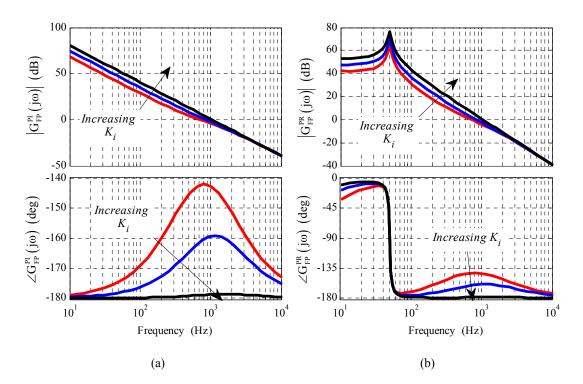

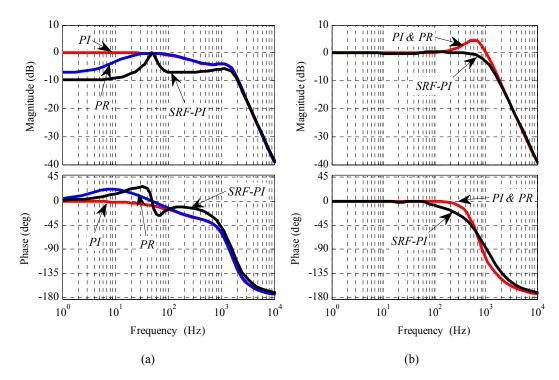

| Figure 3.15 (a) Bode-plot for open-loop gain (a) $G_{FP}^{PI}(s)$ with PI controller where $K_p = 0.8$ , $K_i$                                           |

| = 2000, 4000 and 8000; and (b) $G_{FP}^{PR}(s)$ with PR controller where $K_p = 0.8$ , $K_i = 100$ , 200 and                                             |

| 400                                                                                                                                                      |

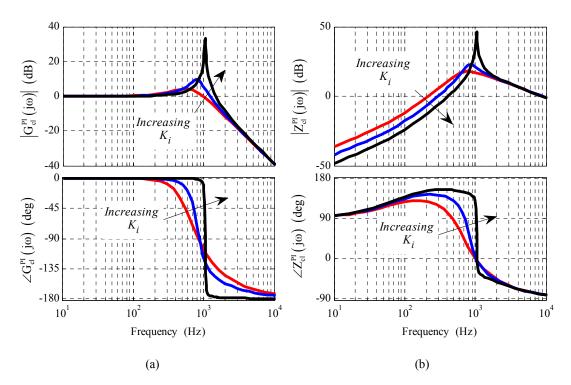

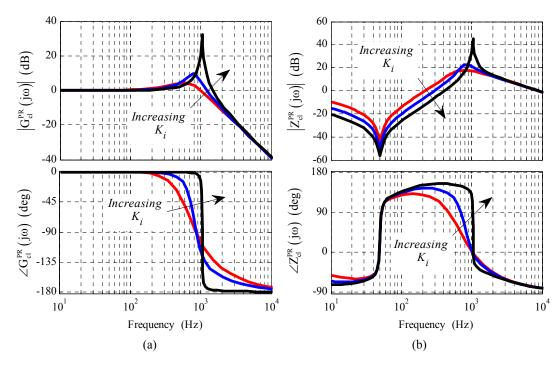

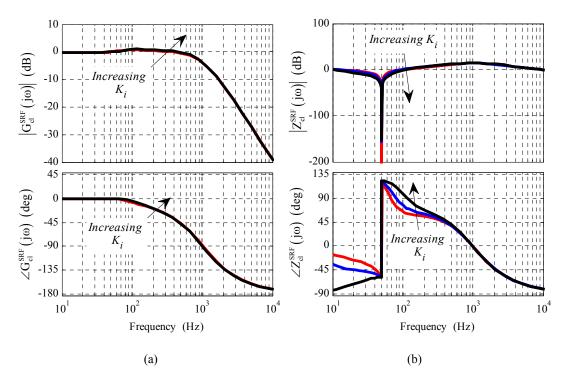

| Figure 3.16 Bode-plot for closed-loop (a) Voltage gain and (b) Output impedance with PI controllers, where $K_p = 0.8$ ; $K_i = 2000$ , 4000 and 8000    |

| Figure 3.17 Bode-plot for closed-loop (a) Voltage gain and (b) Output impedance using PR control, where $K_p = 0.8$ ; $K_i = 100$ , 200 and 400          |

| Figure 3.18 Bode-plot for closed-loop (a) Voltage gain and (b) Output impedance using SRF-PI controller, where $K_p = 0.8$ ; $K_i = 62$ , 125 and 250    |

| Figure 3.19 Bode-plot for closed-loop Voltage gain (a) without and (b) with voltage feed-forward                                                         |

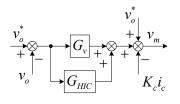

| Figure 3.20 (a) Voltage control with Harmonic Impedance Compensation (HIC) and (b)<br>Magnitude bode-plot of Output impedance for respective controllers |

| Figure 3.21 Simulated steady-state waveforms using PI voltage controller under rated (a)<br>Linear and (b) Non-linear load                               |

| Figure 3.22 Simulated steady-state waveforms using PR voltage controller under rated (a)<br>Linear and (b) Non-linear load                               |

| Figure 3.23 Simulated steady-state waveforms using SRF-PI voltage controller under rated (a) Linear and (b) Non-linear load                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

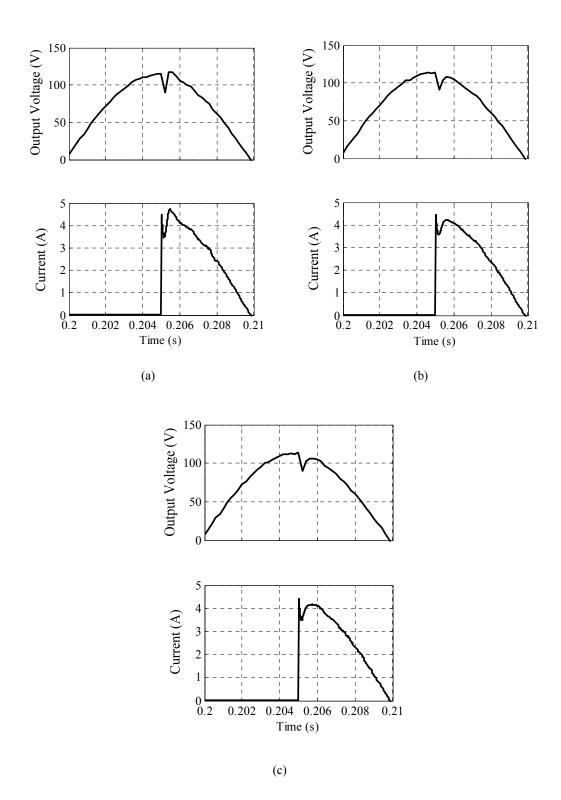

| Figure 3.24 Simulated transient response on step-load application from no-load to full-load using (a) PI, (b) PR and (c) SRF-PI voltage controller                                                          |

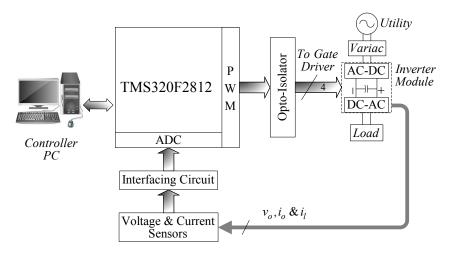

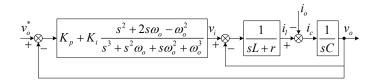

| Figure 3.25 Schematic of the TMS320F2812 DSP based Experimental Set-up                                                                                                                                      |

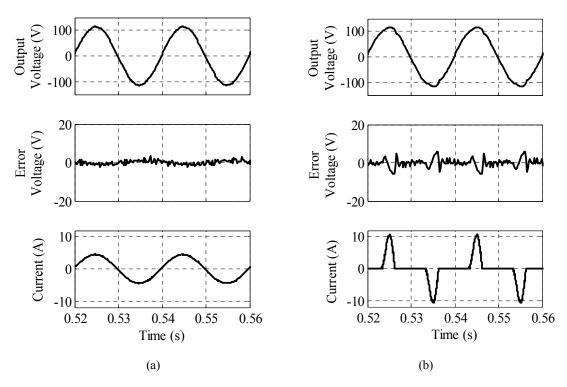

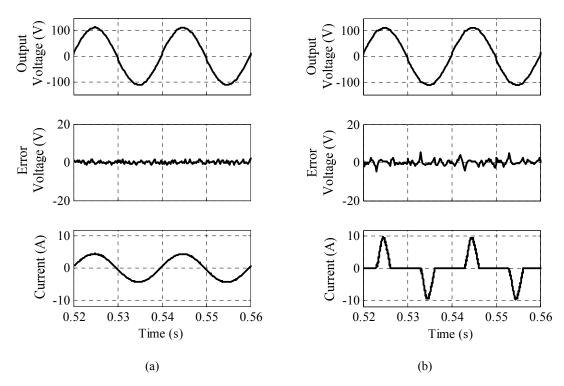

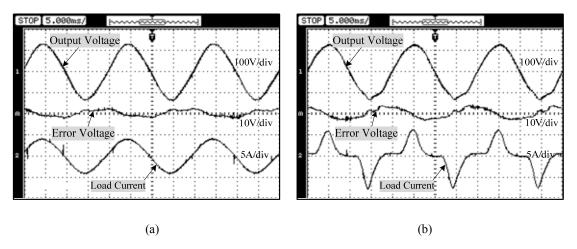

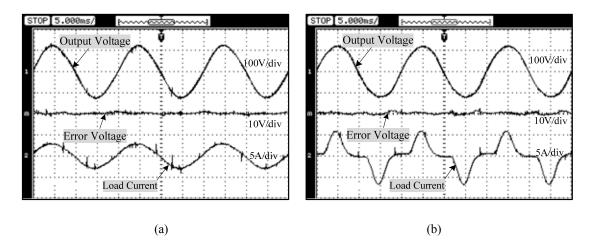

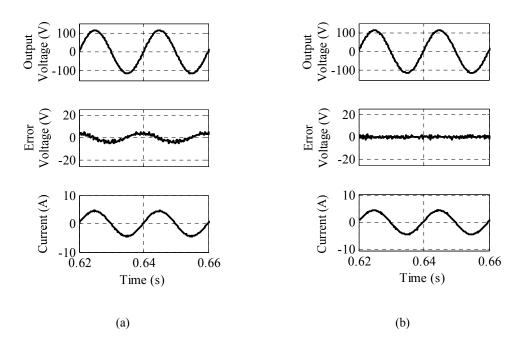

| Figure 3.26 Experimental steady-state waveforms with PI voltage controller under rated (a)<br>Linear and (b) Non-linear load                                                                                |

| Figure 3.27 Experimental steady-state waveforms with PR voltage controller under rated (a)<br>Linear and (b) Non-linear load                                                                                |

| Figure 3.28 Experimental steady-state waveforms with SRF-PI voltage controller under rated (a) Linear and (b) Non-linear load                                                                               |

| Figure 3.29 Experimental transient response on step-load application from no-load to full-load using (a) PI, (b) PR and (c) SRF-PI voltage controller                                                       |

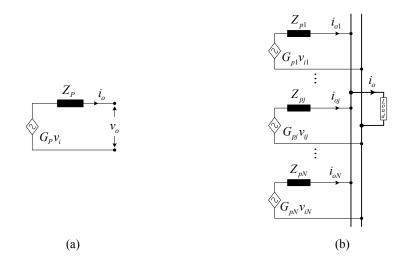

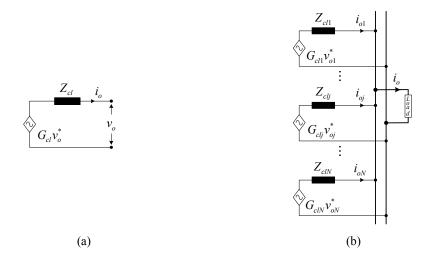

| Figure 4.1 Open-loop equivalent circuit of (a) Unit inverter and (b) 'N' inverter modules connected in parallel                                                                                             |

| Figure 4.2 Closed-loop equivalent circuit of (a) Unit inverter and (b) 'N' inverter modules connected in parallel                                                                                           |

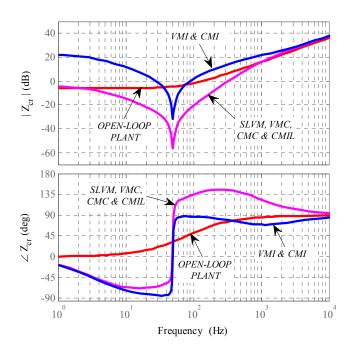

| Figure 4.3 Circulating current impedance for various control topologies                                                                                                                                     |

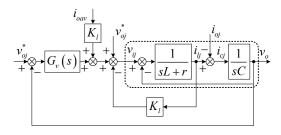

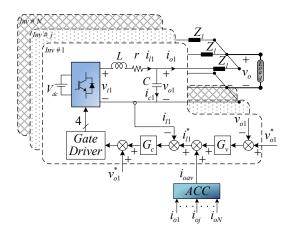

| Figure 4.4 Modified multi-loop inductor current feedback with IACFF control strategy (a) Voltage mode and (b) Current mode with its reduced model                                                           |

| Figure 4.5 Multi-modular UPS inverters system with proposed IACFF control                                                                                                                                   |

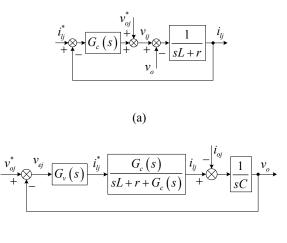

| Figure 4.6 Block schematic of an inverter module using IACFF control (a) Inner current control loop and (b) Outer voltage control loop                                                                      |

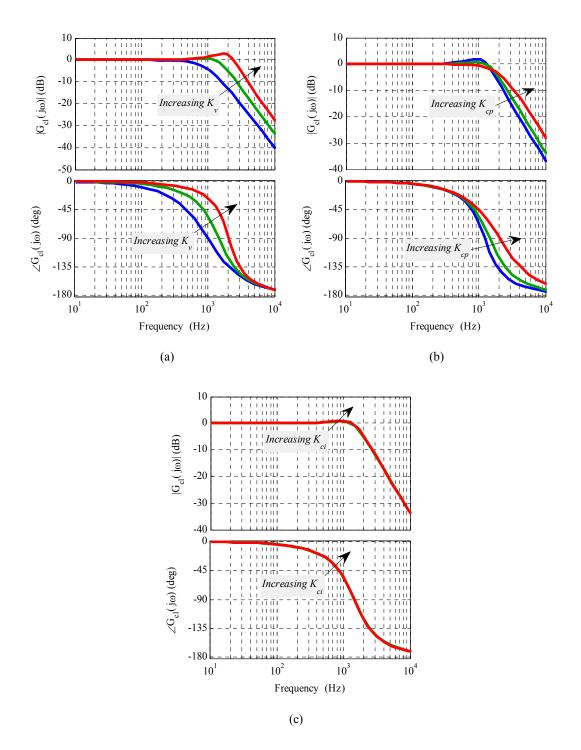

| Figure 4.7 Bode-plot depicting effect of controller parameter variations on close-loop voltage gain $G_{cl}$ (a) $K_v$ (0.07,0.15 and 0.3), (b) $K_{cp}$ (7,10 and 20) and (c) $K_{ci}$ (200,400 and 750)96 |

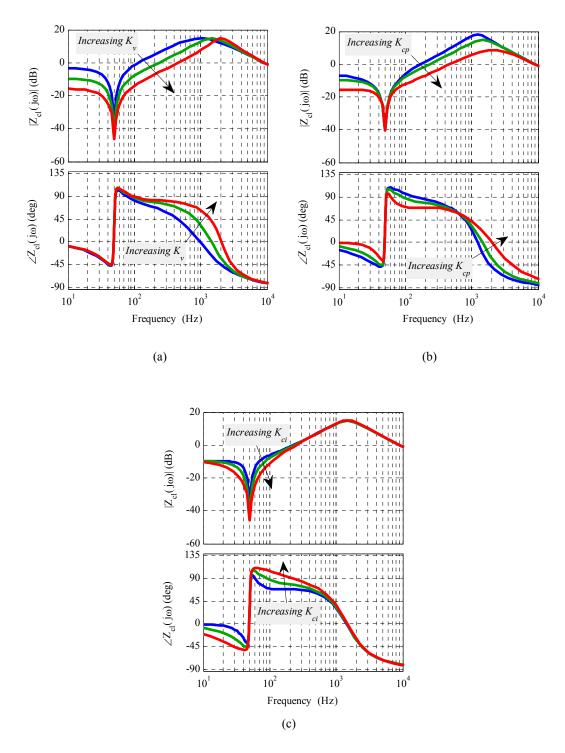

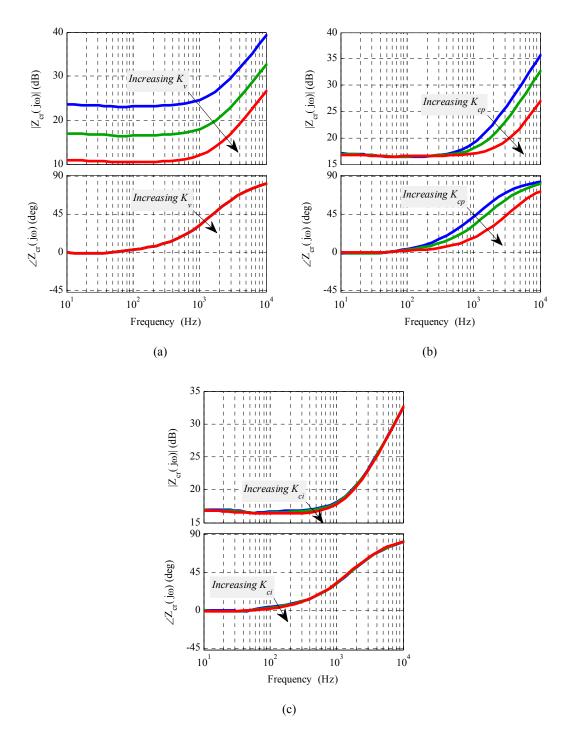

| Figure 4.8 Bode-plot showing effect of controller parameter variations on $Z_{cl}$ (a) $K_{\nu}$ (0.07,0.15 and 0.3), (b) $K_{cp}$ (7,10 and 20) and (c) $K_{ci}$ (200,400 and 750)                         |

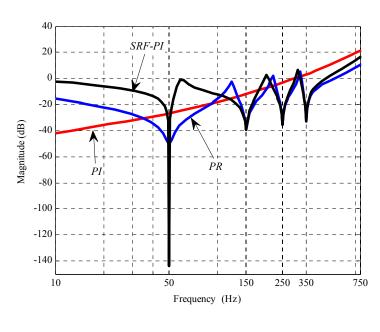

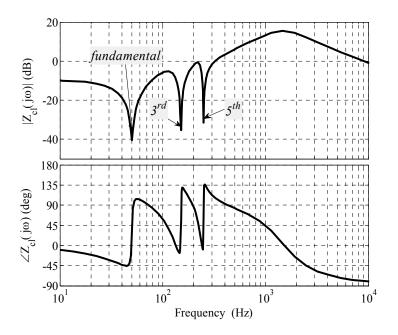

| Figure 4.9 Bode-plot for output impedance after incorporating 3 <sup>rd</sup> and 5 <sup>th</sup> harmonic compensation                                                                                     |

| Figure 4.10 Bode-plot showing effect of controller parameter variations on $Z_{cr}$ (a) $K_{\nu}$ (0.07,0.15 and 0.3), (b) $K_{cp}$ (7,10 and 20) and (c) $K_{ci}$ (200,400 and 750)                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

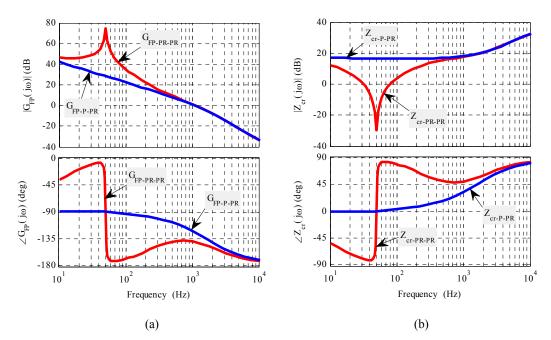

| Figure 4.11 Bode-plot (a) Forward path voltage gain $G_{FP}$ and (b) Circulating current impedance $Z_{cr}$                                                                                                                                                                                   |

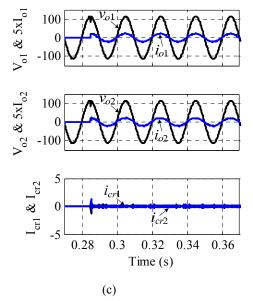

| Figure 4.12 Simulated waveforms under rated linear load for (a) PR-PR with no current sharing scheme, (b) PR-PR with IACFF control and (c) P-PR with IACFF control                                                                                                                            |

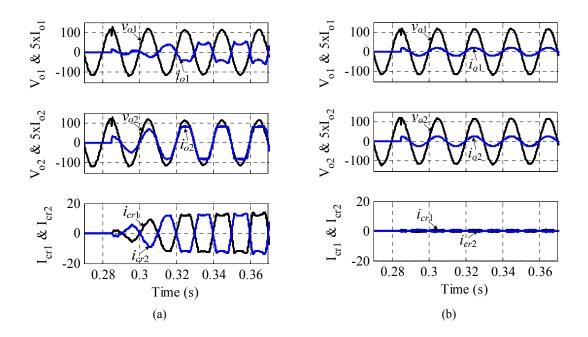

| Figure 4.13 Simulated waveforms under 5% reference voltage magnitude variation (80 and 84 V) for (a) PR-PR Control and (b) P-PR Control                                                                                                                                                       |

| Figure 4.14 Simulated waveforms under 5° reference voltage phase variation (0 and 5°) for (a) PR-PR control and (b) P-PR control                                                                                                                                                              |

| Figure 4.15 Simulated waveforms under 5% magnitude and 5° phase deviation simultaneously applied to reference voltages for (a) PR-PR control and (b) P-PR control105                                                                                                                          |

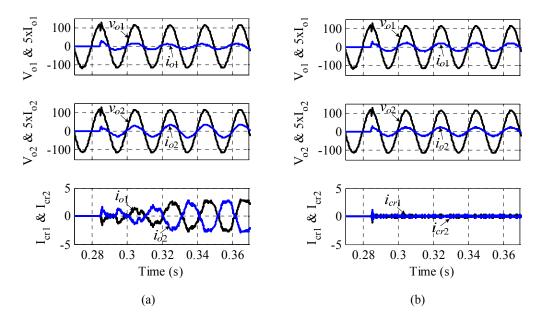

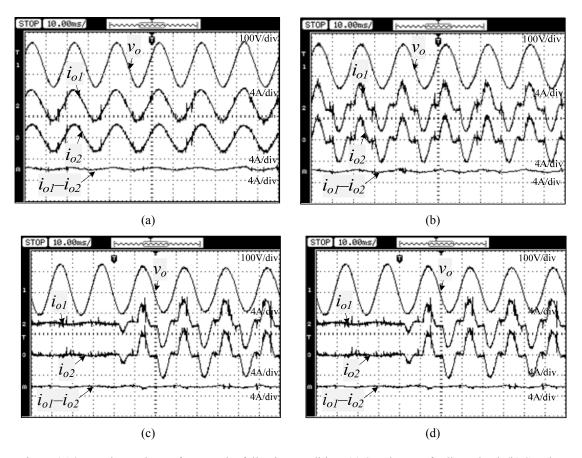

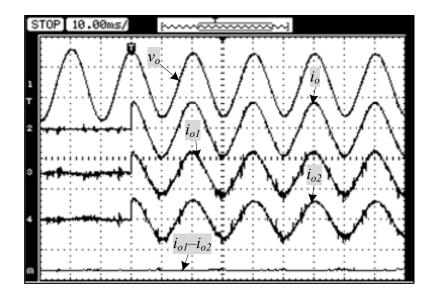

| Figure 4.16 Experimental waveforms under following condition: (a) Steady-state for linear load, (b) Steady-state for non-linear load, (c) Step-application of linear load and (d) Step-application of non-linear load                                                                         |

| Figure 4.17 Experimental waveforms for verifying controller robustness for the proposed IACFF Control: (a) 5% reference voltage magnitude variation (80 and 84 V), (b) 5° reference voltage phase variation (0 and 5°), (c) 5% magnitude and 5° phase variation of reference voltage on load. |

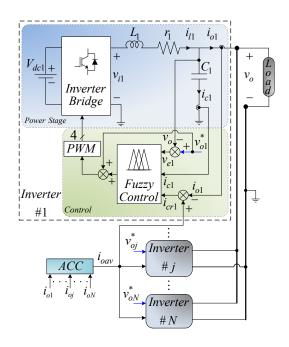

| Figure 5.1 Control block schematic showing IACS control applied to $j^{\text{th}}$ module of the <i>N</i> -modular UPS inverters system                                                                                                                                                       |

| Figure 5.2 Fuzzy logic IACS control for multi-inverter UPS system                                                                                                                                                                                                                             |

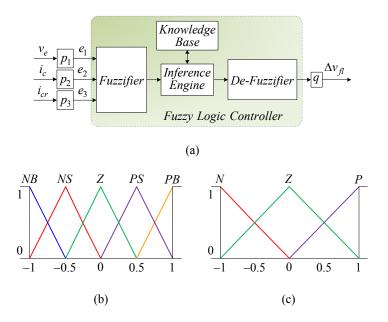

| Figure 5.3 (a) Block Schematic of multi-input FL controller and designated memberships, (b)<br>Five MFs for voltage error, capacitor current and FL output, and (c) Three MFs for circulating<br>current                                                                                      |

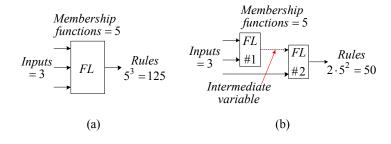

| Figure 5.4 Structure of (a) Conventional FL and (b) HFL control117                                                                                                                                                                                                                            |

| Figure 5.5 Proposed control structure with HFL                                                                                                                                                                                                                                                |

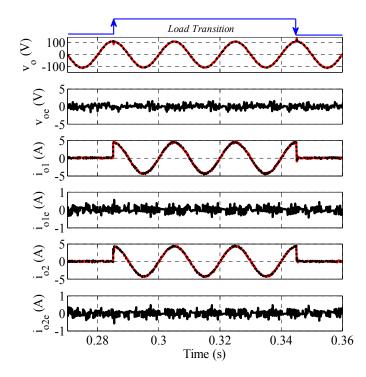

| Figure 5.6 Superimposed waveforms of inverter output voltage and output currents for HFL (solid black) and conventional FL (dotted red) control                                                                                                                                               |

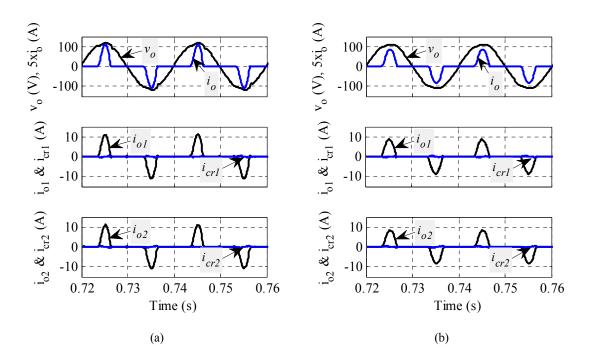

| Figure 5.7 Steady-state waveforms under rated linear load for (a) PI and (b) HFL control122                                                                                                                                                                                                   |

| Figure 5.8 Steady-state waveforms under rated non-linear load for (a) PI and (b) HFL control.                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.9 Transient waveforms on step load change from no-load to rated linear load for (a) PI and (b) HFL control                                                                                                                                     |

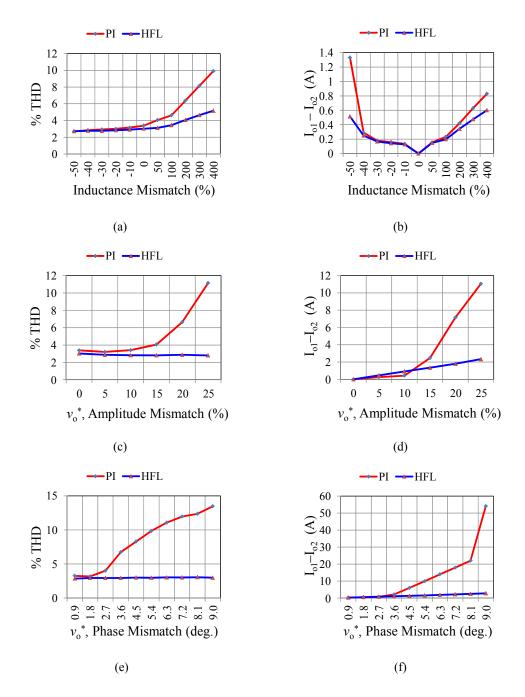

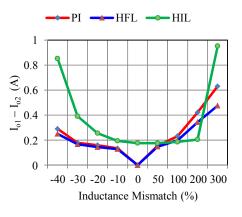

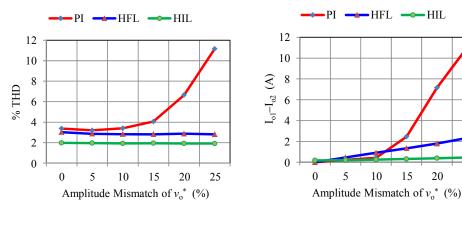

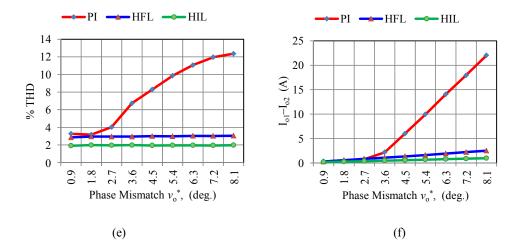

| Figure 5.10 HFL Influence of parameter mismatch; %THD of load voltage: (a), (c) and (e) ; and current difference $(I_{o1}-I_{o2})$ : (b), (d) and (f)125                                                                                                |

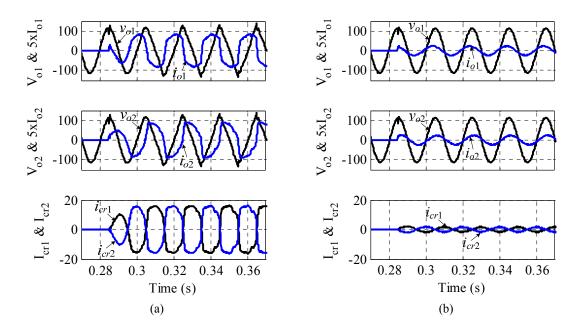

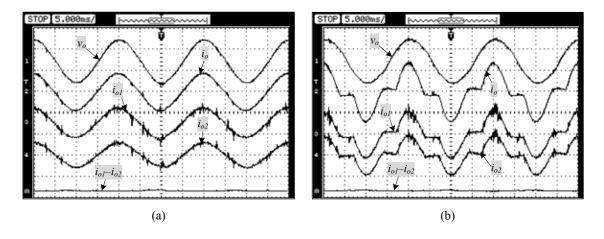

| Figure 5.11 Steady-state waveforms on 50% inductance deviation (1mH, 1.5mH), 10% reference amplitude difference(80V, 88V) and 2° reference phase difference (0°, 2°) under rated non-linear load for (a) PI and (b) HFL control                         |

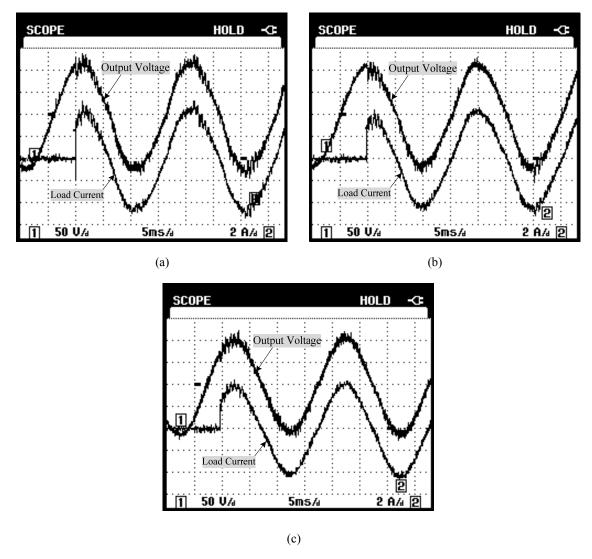

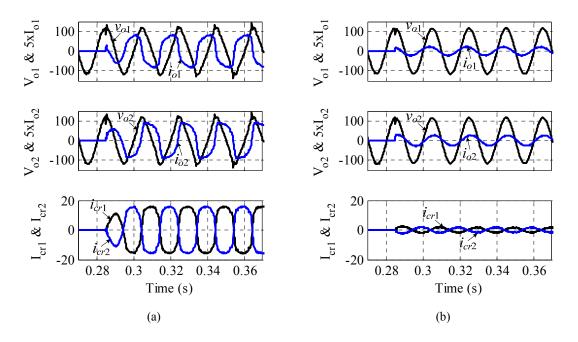

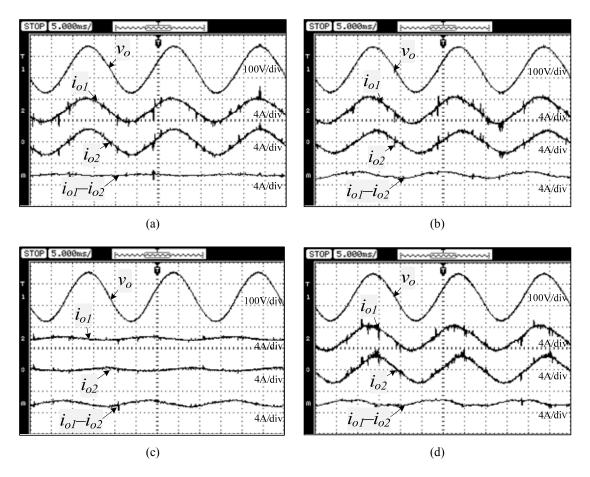

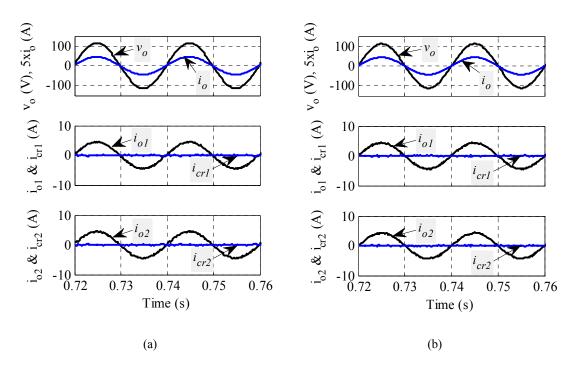

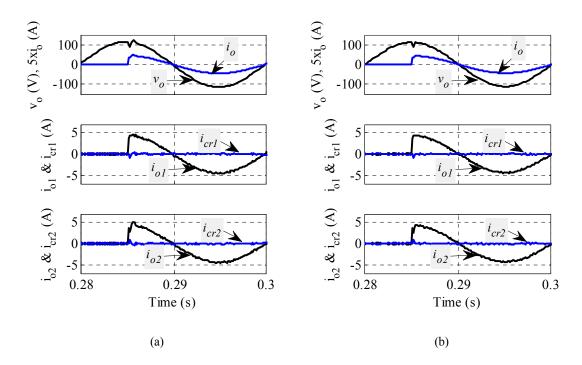

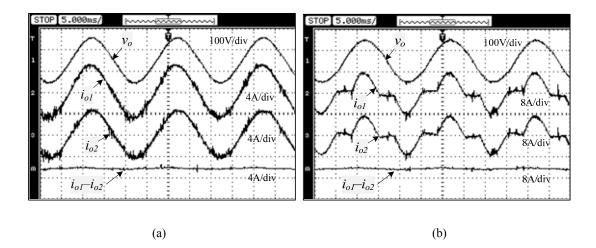

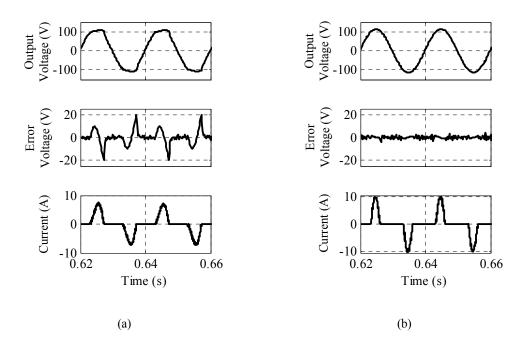

| Figure 5.12 Steady-state waveforms on rated load (a) Linear and (b) Non-linear                                                                                                                                                                          |

| Figure 5.13 Transient waveforms on step load change from no-load to rated load (a) Linear (b) Non-linear                                                                                                                                                |

| Figure 6.1 Block schematic representation of P-type IL control                                                                                                                                                                                          |

| Figure 6.2 Block structure of Hybrid IL (HIL) control                                                                                                                                                                                                   |

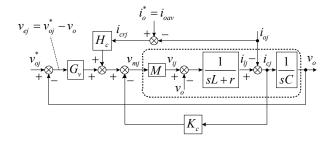

| Figure 6.3 HIL based IACS control starategy for parallel connected multi-inverter system. 133                                                                                                                                                           |

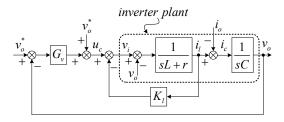

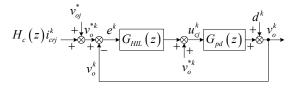

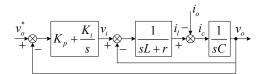

| Figure 6.4 Closed-loop voltage control for unit inverter system                                                                                                                                                                                         |

| Figure 6.5 HIL control for unit inverter UPS system                                                                                                                                                                                                     |

| Figure 6.6 HIL IACS control for multi-inverter UPS system                                                                                                                                                                                               |

| Figure 6.7 Simplified schematic of inner voltage control loop                                                                                                                                                                                           |

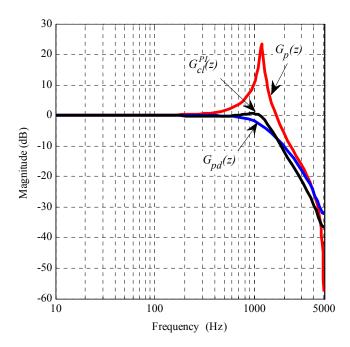

| Figure 6.8 Bode-plot for undamped plant $G_p(z)$ , modified damped plant $G_{pd}(z)$ , and PI tuned damped plant $G_{cl}^{PI}(z)$                                                                                                                       |

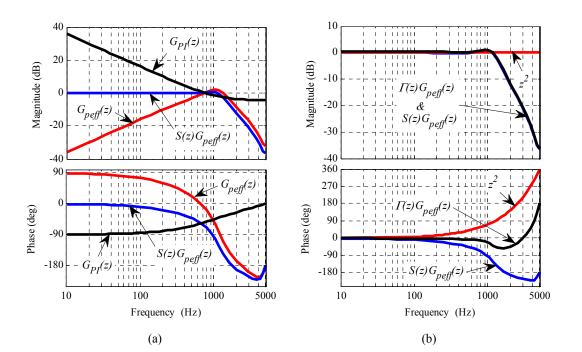

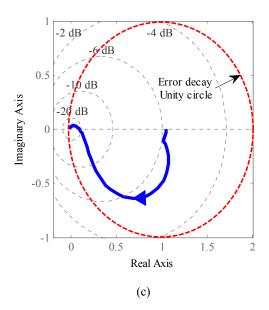

| Figure 6.9 Design of HIL control (a) Bode-plot for effective plant $G_{peff}(z)$ , $G_{Pl}(z)$ and $S(z)G_{peff}(z)$ , (b) Bode-plot for $z^2$ , $S(z)G_{peff}(z)$ and $\Gamma(z)G_{peff}(z)$ , and (c) Nyquist-plot of vector $\Gamma(z)G_{peff}(z)$ . |

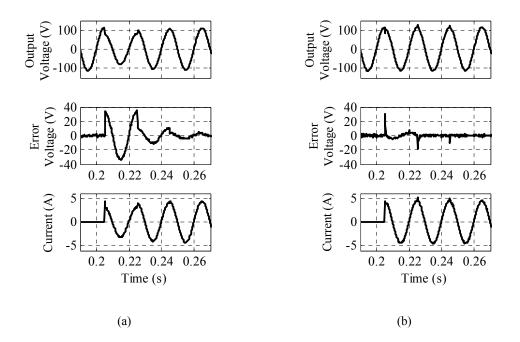

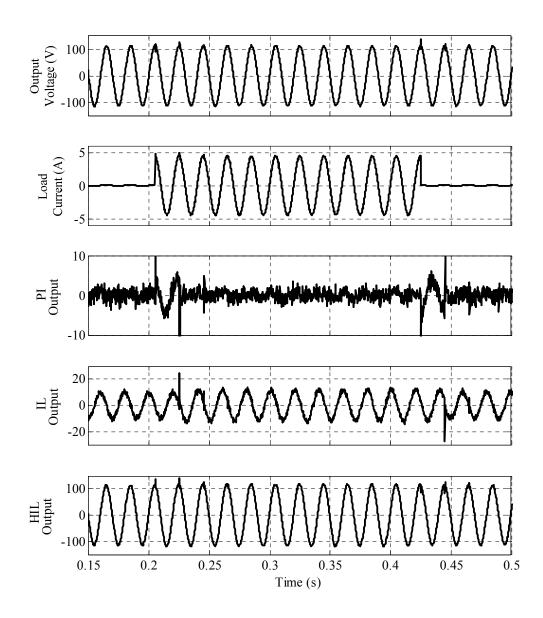

| Figure 6.10 Steady-state waveforms under rated linear load for (a) PI and (b) HIL control146                                                                                                                                                            |

| Figure 6.11 Steady-state waveforms under rated non-linear load for (a) PI and (b) HIL control                                                                                                                                                           |

| Figure 6.12 Transient response under rated linear load for (a) IL and (b) HIL control147                                                                                                                                                                |

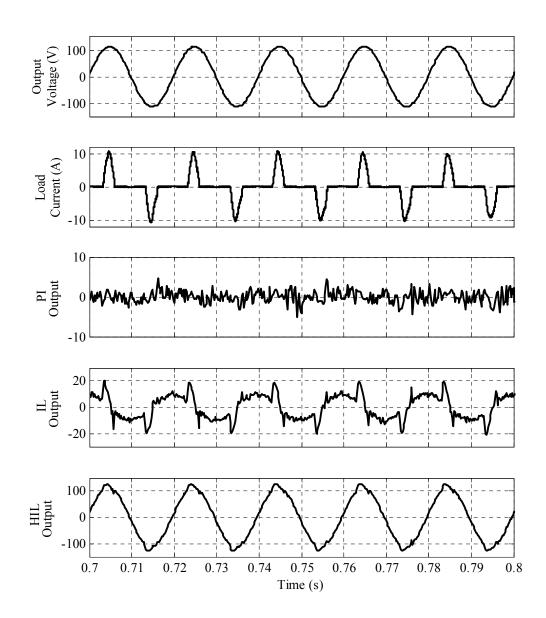

| Figure 6.13 Controller response in steady-state under non-linear load                                                                                                                                                                                   |

| Figure 6.14 Controller response during load transitions.                                                                                                                                                               | 149          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

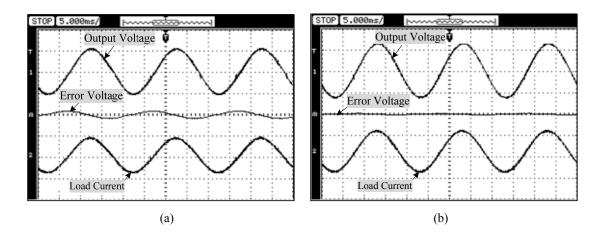

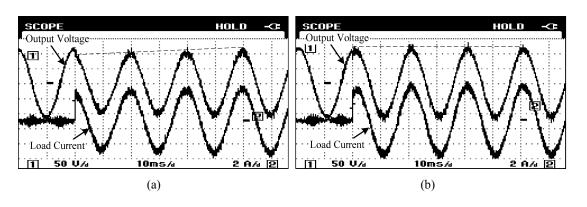

| Figure 6.15 Steady-state experimental waveforms under linear load for (a) PI and (b) control. <i>CH</i> -1: Output Voltage (100 V/div), <i>CH-m</i> : Tracking Error (10 V/div), and <i>CH</i> Load Current (5 A/div). | <i>H</i> -2: |

| Figure 6.16 Steady-state experimental waveforms under non-linear load for (a) PI (b) control. <i>CH</i> -1: Output Voltage (100 V/div), <i>CH-m</i> :Tracking Error (10 V/div), and <i>CH</i> Load Current (5 A/div).  | <i>H</i> -2: |

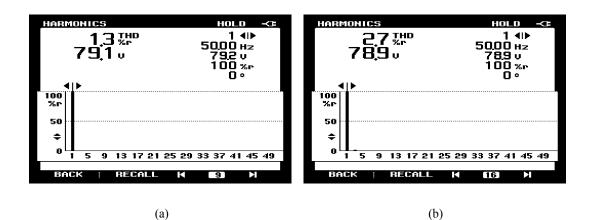

| Figure 6.17 Harmonic spectrum of load voltage using HIL control strategy under rated<br>Resistive load and (b) Rectifier load.                                                                                         | . ,          |

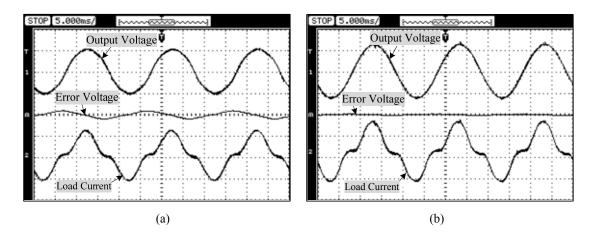

| Figure 6.18 Experimental results on step-load application under rated linear load using (a and (b) HIL control. <i>CH</i> -1: output voltage (50 V/div), and <i>CH</i> -2: load current (2 A/div)                      | ,            |

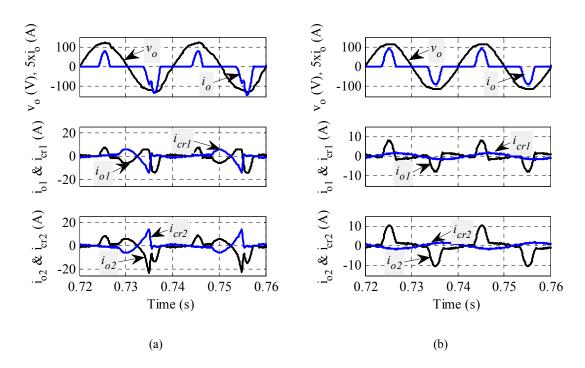

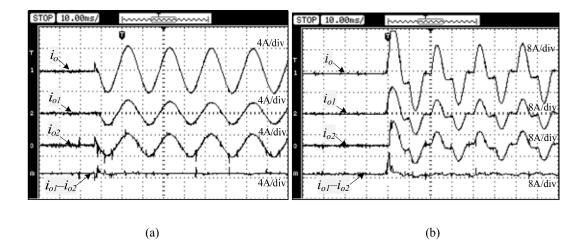

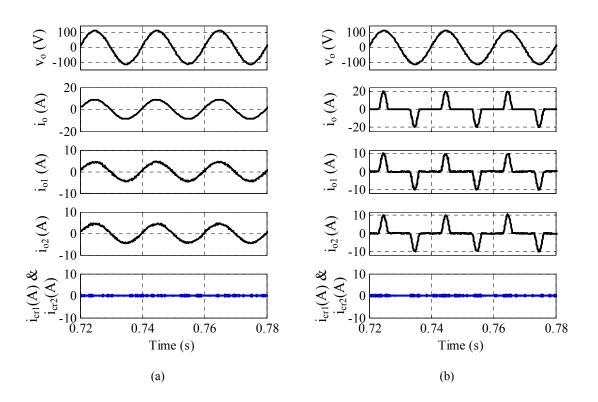

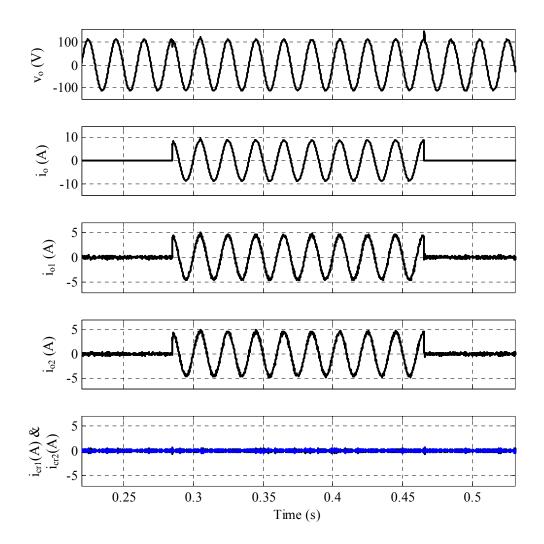

| Figure 6.19 Simulated steady-state response under rated (a) Linear and (b) Non-linear le                                                                                                                               |              |

| Figure 6.20 Transient response on step-load transition from no-load to rated load                                                                                                                                      | 153          |

| Figure 6.21 Influence of parameter and reference voltage mismatch on % THD of $I$ voltage and current difference (I <sub>01</sub> -I <sub>02</sub> ) (A)                                                               |              |

| Figure 6.22 Steady-state response on rated (a) Linear and (b) Non-linear load                                                                                                                                          | 156          |

| Figure 6.23 Transient response on step-load application from no-load to rated load                                                                                                                                     | 156          |

| Figure A.1 Block schematic representation of SRF-PI voltage controller in $\alpha$ - $\beta$ station frame.                                                                                                            | 2            |

| Figure B.1 Block schematic representation of inverter control using PI                                                                                                                                                 | 186          |

| Figure B.2 Block schematic representation of inverter control using practical PR.                                                                                                                                      | 187          |

| Figure B.3 Block schematic representation of inverter control using Staionary fr equivalent SRF-PI.                                                                                                                    |              |

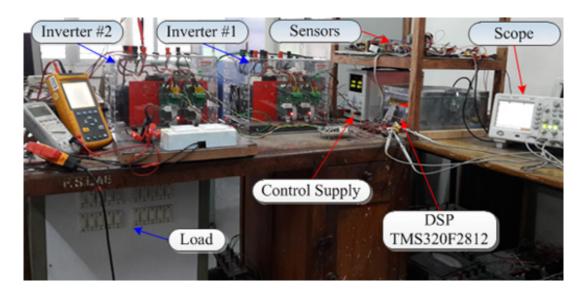

| Figure C.1 Photograph of the experimental set-up.                                                                                                                                                                      | 189          |

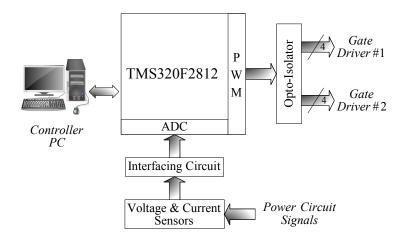

| Figure C.2 Contol architecture of the TMS320F2812 DSP based hardware implementat                                                                                                                                       |              |

| Figure C.3 TMS320F2812 DSP trainer kit                                                                                                                                                                                 |              |

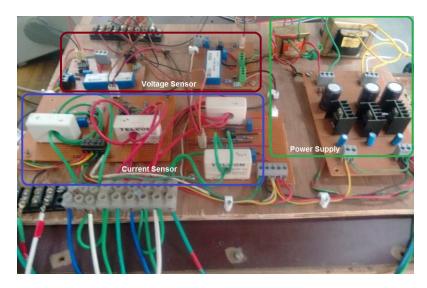

| Figure C.4 Photograph of voltage and current sensing circuit.                                                                                                                                                          | 191          |

## LIST OF TABLES

| Table 2.1 System parameters                                                         | 15  |

|-------------------------------------------------------------------------------------|-----|

| Table 2.2 Orthogonal signal generators                                              | 24  |

| Table 3.1 Controller parameters                                                     | 51  |

| Table 3.2 Transfer functions for various control strategies                         | 53  |

| Table 3.3 Steady-state performance on rated load                                    | 58  |

| Table 3.4 Transient performance on rated linear load                                | 58  |

| Table 3.5 Normalized performances under linear load considering CMIL as reference . | 58  |

| Table 3.6 Steady-state performance comparison                                       | 79  |

| Table 4.1 Transfer functions of various control topologies                          |     |

| Table 4.2 Simulation data for inverter currents under different conditions          | 106 |

| Table 5.1 Fuzzy rule base for conventional FL control.                              | 116 |

| Table 5.2 Fuzzy rule base for FL #1                                                 | 119 |

| Table 5.3 Fuzzy rule base for FL #2                                                 | 119 |

| Table 5.4 Performance comparison                                                    | 124 |

| Table 6.1 Performance comparison                                                    | 147 |

| Table B.1 Rouths's array for closed-loop inverter control using PI compensator      | 186 |

| Table B.2 Rouths's array for closed-loop inverter control using PR compensator      | 187 |

| Table B.3 Rouths's array for closed-loop inverter control using SRF-PI compensator  | 188 |

| Table D.1 Parameters for inverter modules                                           | 195 |

| Table D.2 Load parameters                                                           | 195 |

| Table D.3 Control parameter used in chapter 3                                       | 195 |

| Table D.4 Controller parameters used for Figure 4.3 in chapter 4                    | 195 |

| Table D.5 Control parameter used in chapter 4                                       | 196 |

| Table D.6 Control parameters used in chapter 6                                      | 196 |

## LIST OF SYMBOLS

| b                                  | System Order                                                         |

|------------------------------------|----------------------------------------------------------------------|

| $C_j$                              | Filter Capacitance of the $j^{th}$ Inverter                          |

| $D_{cl}$                           | Denominator of Closed-loop Gain $G_{cl}$                             |

| $D_{CM}$                           | Denominator of Current Mode Closed-loop Gain $G_{cl}^{CM}$           |

| $D_{VM}$                           | Denominator of Current Mode Closed-loop Gain $G_{cl}^{VM}$           |

| d                                  | Repetitive Disturbance                                               |

| $e_1, e_2, e_3$                    | Scaled Error of Fuzzy Logic                                          |

| $e_j$                              | Tracking Error of the $j^{\text{th}}$ Inverter                       |

| $e_{iss}$                          | Steady-State Current Error                                           |

| $e^k$                              | <i>k</i> <sup>th</sup> Cycle Error                                   |

| $e_{ss}$                           | Steady-State Error                                                   |

| $e_{vss}$                          | Steady-State Voltage Error                                           |

| f                                  | Number of Fuzzy inputs                                               |

| $f_{ m s}$                         | Sampling Frequency                                                   |

| g                                  | Fuzzy Subsets                                                        |

| $G_c$                              | Current Controller                                                   |

| $G_{cl}^{CM}$                      | Closed-loop Voltage Gain in Current Mode                             |

| $G_{cl}^{CMC}$                     | Closed-loop Voltage Gain for CM Capacitor Current Feedback           |

| $G_{cl}^{CMI}$                     | Closed-loop Voltage Gain for CM Inductor Current Feedback            |

| $G_{cl}^{CMIL}$                    | Closed-loop Voltage Gain for CM Inductor Plus Load Current Feedback  |

| $G_{cl}^{PI}$                      | Closed-loop Voltage Gain Using PI Controller                         |

| $G_{cl}^{PR}$                      | Closed-loop Voltage Gain Using PR Controller                         |

| $G_{cl}^{\scriptscriptstyle SLVM}$ | Closed-loop Voltage Gain for Single Loop Voltage Mode                |

| $G_{cl}^{\it SRF}$                 | Closed-loop Voltage Gain Using SRF-PI Controller                     |

| $G_{cl}^{\scriptscriptstyle V\!M}$ | Closed-loop Voltage Gain in Voltage Mode                             |

| $G_{cl}^{VMC}$                     | Closed-loop Voltage Gain for VM Capacitor Current Feedback           |

| $G_{cl}^{VMI}$                     | Closed-loop Voltage Gain for VM Inductor Current Feedback            |

| $G_{clK_p}^{SRF}$                  | Closed-loop Voltage Gain Using SRF-PI Controller with P-Control Only |

|                                    |                                                                      |

| $G_{DB}$                                               | Dead Beat Controller Transfer Function                        |

|--------------------------------------------------------|---------------------------------------------------------------|

| $G_{f}$                                                | Fast Controller Transfer Function                             |

| $G_{\scriptscriptstyle FP}^{\scriptscriptstyle PI}$    | Forward Path Gain with PI Controller                          |

| $G_{\scriptscriptstyle FP}^{\scriptscriptstyle P-PR}$  | Forward Path Gain with P-Voltage and PR-Current Controller    |

| $G_{\scriptscriptstyle FP}^{\scriptscriptstyle PR}$    | Forward Path Gain with PR Controller                          |

| $G_{\scriptscriptstyle FP}^{\scriptscriptstyle PR-PR}$ | Forward Path Gain with PR-Voltage and PR-Current Controller   |

| $G_{\scriptscriptstyle FP}^{\scriptscriptstyle SRF}$   | Forward Path Gain with SRF-PI Controller                      |

| $G_{HIC}$                                              | Harmonic Impedance Compensation Gain                          |

| $G_{in}$                                               | Inner-Loop Transfer Function                                  |

| $G_p$                                                  | Open-Loop Plant Transfer Function                             |

| $G_{pd}$                                               | Damped Plant Transfer Function                                |

| $G_{peff}$                                             | Effective Plant Transfer Function                             |

| $G_{PI}$                                               | PI Controller                                                 |

| $G_{PR}$                                               | PR Controller                                                 |

| $G_{PR}$                                               | Practical PR Controller                                       |

| $G_{SRF}$                                              | SRF-PI Controller                                             |

| $G_v$                                                  | Voltage Controller Gain                                       |

| h                                                      | Number of Control Variables                                   |

| $H_c$                                                  | Circulating Current Sharing Controller                        |

| î                                                      | imaginary operator                                            |

| <i>i</i> <sub>c</sub>                                  | Filter Capacitor Current                                      |

| <i>i</i> <sub>cr</sub>                                 | Circulating Current                                           |

| $i_l$                                                  | Filter Inductor Current                                       |

| $i_l^*$                                                | Reference Inductor Current                                    |

| <i>i</i> <sub>o</sub>                                  | Load Current                                                  |

| <i>i</i> <sub>ole</sub>                                | Current Difference Between FL and HFL Control for Inverter 1  |

| i <sub>o2e</sub>                                       | Current Difference Between FL and HFL Control for Inverter 2  |

| <i>i</i> <sub>oav</sub>                                | Average Load Current                                          |

| i <sub>oj</sub>                                        | Output Current of the <i>j</i> <sup>th</sup> Inverter         |

| $i_{oM}$                                               | Master Module Output Current                                  |

| k                                                      | Cycle Number                                                  |

| Κ                                                      | RC Constant or IL Gain                                        |

| $K_c$                                                  | Capacitor Current Active Damping Coefficient or Feedback Gain |

| $K_{ci}$                     | Current Controller Integral Gain                                        |

|------------------------------|-------------------------------------------------------------------------|

| $K_{cp}$                     | Current Controller Proportional Gain                                    |

| $K_i$                        | Integral Gain                                                           |

| $K_l$                        | Inductor Current Active Damping Coefficient or Feedback Gain            |

| $K_p$                        | Proportional Gain                                                       |

| $K_{v}$                      | Voltage Controller Proportional Gain                                    |

| l                            | Total Number of Fuzzy Rules                                             |

| $L_j$                        | Filter Inductance of the <i>j</i> <sup>th</sup> Inverter                |

| $m_j$                        | Active Power Droop Coefficient of the <i>j</i> <sup>th</sup> Inverter   |

| <i>n</i> <sub>j</sub>        | Reactive Power Droop Coefficient of the <i>j</i> <sup>th</sup> Inverter |

| n                            | Sampling Instant                                                        |

| N                            | Number of Parallel-Connected Modules                                    |

| р                            | Number of Samples in a Fundamental Cycle                                |

| $P_j$                        | Active power of the $j^{th}$ Inverter                                   |

| $p_1, p_2, p_3$              | Input Scaling Coefficients of FL                                        |

| q                            | Output Scaling Coefficients of FL                                       |

| Q(z)                         | Low Pass Filter                                                         |

| $Q_j$                        | Reactive Power of the $j^{th}$ Inverter                                 |

| R                            | Resistance                                                              |

| $r_j$                        | Equivalent Series Resistance of the <i>j</i> <sup>th</sup> Inverter     |

| S(z)                         | Loop Shaping Compensator                                                |

| $S_j$                        | Apparent Power of the <i>j</i> <sup>th</sup> Inverter                   |

| $T_s$                        | Sampling Time                                                           |

| $T_{d-q \to \alpha - \beta}$ | Inverse Park's Transformation Matrix                                    |

| $T_{\alpha-\beta \to d-q}$   | Park's Transformation Matrix                                            |

| <i>u</i> <sub>c</sub>        | Control Signal                                                          |

| $u_{IL}{}^k$                 | $k^{th}$ Cycle Control Signal of IL                                     |

| $V_{dc}$                     | DC Bus Voltage                                                          |

| $V_o^*$                      | Nominal Voltage Amplitude                                               |

| Ve                           | Voltage Tracking Error                                                  |

| $\mathcal{V}_i$              | Inverter Bridge Output                                                  |

| $v_m$                        | Modulating Voltage signal                                               |

| $v_o$                        | Output Voltage                                                          |

| $v_o^*$                      | Reference Output Voltage                                                |

|                              |                                                                         |

| $v_{oav}^{*}$                      | Average Reference Voltage                                                |

|------------------------------------|--------------------------------------------------------------------------|

| Voe                                | Voltage Difference Between FL and HFL                                    |

| $\mathcal{V}_{oj}$                 | Output Voltage of the $j^{th}$ Inverter                                  |

| $v_{lpha}$                         | $\alpha$ -Axis Voltage                                                   |

| $v_{eta}$                          | $\beta$ -Axis Voltage                                                    |

| x                                  | Control Variable                                                         |

| $x_h^*$                            | Reference Value of the $h^{th}$ Control Variable                         |

| $x_{im}$                           | Intermediate Variable                                                    |

| $x_h^{pre}$                        | Predicted Value of the <i>h</i> <sup>th</sup> Control Variable           |

| Х                                  | Reactance                                                                |

| У                                  | Output Variable                                                          |

| <i>y</i> *                         | Reference Command                                                        |

| $z^{a}$                            | Time Advancement Unit                                                    |

| $Z_{cl}^{CM}$                      | Closed-loop Output Impedance in Current Mode                             |

| $Z_{cl}^{CMC}$                     | Closed-loop Output Impedance for CM Capacitor Current Feedback           |

| $Z_{cl}^{CMI}$                     | Closed-loop Output Impedance for CM Inductor Current Feedback            |

| $Z_{cl}^{CMIL}$                    | Closed-loop Output Impedance for CM Inductor Plus Load Current Feedback  |

| $Z_{cl}^{PI}$                      | Close-loop Output Impedance with PI Controller                           |

| $Z_{cl}^{PR}$                      | Close-loop Output Impedance with PR Controller                           |

| $Z_{cl}^{SLVM}$                    | Closed-loop Output Impedance for Single Loop Voltage Mode                |

| $Z_{cl}^{SRF}$                     | Close-loop Output Impedance with SRF-PI Controller                       |

| $Z_{cl}^{\scriptscriptstyle V\!M}$ | Closed-loop Output Impedance in Voltage Mode                             |

| $Z_{cl}^{VMC}$                     | Closed-loop Voltage Gain for VM Capacitor Current Feedback               |

| $Z_{cl}^{VMI}$                     | Closed-loop Voltage Gain for VM Inductor Current Feedback                |

| $Z_{clK_p}^{SRF}$                  | Closed-loop Output Impedance Using SRF-PI Controller with P-Control Only |

| $Z_{cr}$                           | Circulating Current Impedance                                            |

| $Z_{cr}^{CM}$                      | Circulating Current Impedance in Current Mode                            |

| $Z_{cr}^{P-PR}$                    | Circulating Current Impedance with P-Voltage and PR-Current Controller   |

| $Z_{cr}^{PR-PR}$                   | Circulating Current Impedance with PR-Voltage and PR-Current Controller  |

|                                    |                                                                          |

| $Z_{cl}^{V\!M}$ | Circulating Current Impedance in Voltage Mode                             |

|-----------------|---------------------------------------------------------------------------|

| $Z_j$           | Output Impedance of the $j^{th}$ Inverter                                 |

| $Z_{lj}$        | Line Impedance of the <i>j</i> <sup>th</sup> Inverter                     |

| $Z_p$           | Open-Loop Plant Output Impedance                                          |

| $Z_{pd}$        | Damped Plant Output impedance                                             |

| $z^{-p}$        | Fundamental Cycle Delay                                                   |

| $\Gamma(z)$     | Learning Factor                                                           |

| $\mathcal{E}_P$ | Power Sharing Error                                                       |

| εω              | Deviation in Frequency                                                    |

| ζ               | Damping Ratio                                                             |

| $\phi$          | Line Impedance Angle                                                      |

| arphi           | Initial Phase of the System                                               |

| δ               | Phase Difference between Voltages                                         |

| heta            | Angle between $\alpha$ - $\beta$ Frame and $d$ - $q$ Frame in rad/s       |

| $\lambda_h$     | Weighting Factor of the $h^{th}$ Control Variable                         |

| ρ               | SMC constant                                                              |

| $\mu_i(x_i)$    | membership grade                                                          |

| ψ               | Sliding Surface or Function                                               |

| ω               | Frequency                                                                 |

| $\omega^{*}$    | Nominal Frequency                                                         |

| $\omega_{bi}$   | Bandwidth Frequency of Current Controller                                 |

| $\omega_c$      | Cut-off Frequency of PR Controller                                        |

| $\omega_n$      | Natural Frequency of a System                                             |

| $\omega_o$      | Fundamental Frequency                                                     |

| $\Delta v_{fl}$ | FL Controller Output                                                      |

| $\Delta E$      | Maximum Acceptable Amplitude Deviation                                    |

| $\Delta I_o$    | Current Difference between Inverter 1 &2 $(\Delta I_0 = I_{01} - I_{02})$ |

| $\Delta \omega$ | Maximum Acceptable Frequency Deviation                                    |

## LIST OF ABBREVIATIONS

| <b>3</b> C | Circular Chain Control                               |

|------------|------------------------------------------------------|

| AC         | Alternating Current                                  |

| ACC        | Average Current Computation                          |

| AD         | Active Damping                                       |

| ADC        | Analog to Digital Converter                          |

| ALCS       | Active Load Current Sharing                          |

| APF        | All Pass Filter                                      |

| CMC        | Current Mode Capacitor                               |

| CMF        | Cost Minimizing Function                             |

| CMI        | Current Mode Inductor                                |

| CMIL       | Current Mode Inductor Load                           |

| DC         | Direct Current                                       |

| DSP        | Digital Signal Processor / Digital Signal Processing |

| DTF        | Discrete Time Frame                                  |

| EDF        | Error Decay Factor                                   |

| ESR        | Equivalent Series Resistance                         |

| FL         | Fuzzy Logic                                          |

| HFL        | Hierarchical Fuzzy Logic                             |

| HIC        | Harmonic Impedance Compensation                      |

| HIL        | Hybrid Iterative Learning                            |

| IACFF      | Instantaneous Average Current Feed Forward           |

| IACS       | Instantaneous Average Current Sharing                |

| IEC        | International Electrotechnical Commission            |

| IGBT       | Insulated Gate Bipolar Transistor                    |

| IL         | Iterative Learning                                   |

| I-M        | Inter-Modular                                        |

| MF         | Membership Function                                  |

| MLCM       | Multi-Loop Current Mode                              |

| MLVM       | Multi-Loop Voltage Mode                              |

| M-M        | Multi-Modular                                        |

| MOSFET     | Metal Oxide Semiconductor Field Effect Transistor    |

| MPC    | Model Predictive Control                          |

|--------|---------------------------------------------------|

| MS     | Master Slave                                      |

| NB     | Negative Big                                      |

| NN     | Neural Networks                                   |

| NS     | Negative Small                                    |

| OSG    | Orthogonal Signal Generation                      |

| PB     | Positive Big                                      |

| PI     | Proportional Integral                             |

| PID    | Proportional Integral Derivative                  |

| PM     | Phase Margin                                      |

| PR     | Proportional Resonant                             |

| PS     | Positive Small                                    |

| PWM    | Pulse Width Modulated                             |

| RC     | Repetitive Control                                |

| RH     | Routh Hurwitz                                     |

| RMS    | Root Mean Square                                  |

| SLVM   | Single Loop Voltage Mode                          |

| SMC    | Sliding Mode Control                              |

| SOGI   | Second Order Generalised Integrator               |

| SPWM   | Sinusoidal Pulse Width Modulated                  |

| SRF    | Synchronous Reference Frame                       |

| SRF-PI | Synchronous Reference Frame Proportional Integral |

| THD    | Total Harmonic Distortion                         |

| UPS    | Uninterruptable Power Supply                      |

| VMC    | Voltage Mode Capacitor                            |

| VMI    | Voltage Mode Inductor                             |

| VSI    | Voltage Source Inverter                           |

| ZOH    | Zero Order Hold                                   |

# **CHAPTER 1: INTRODUCTION**

The influence of electrical and electronics devices in human being's modern life are emerging day by day. Usually, these devices receive energy from the utility grid. As the power grid is distributed in a wide area, in which generation and consumption have numerous interfaces, which eventually hampers its reliability. Developing nations like, India still face shortage of power due to gap between demand and supply of the electricity. Amidst government's supportive policy interventions and sector reforms, power deficit show a decreasing trend with average energy deficit reduced to 0.7 % and peak deficit to just 2 % [1]. However, these deficits only show the figures for those who are formally connected to the grid. The demand of unconnected users and informal consumers (usually included in line loss) remains unaccounted in these data. Further, power demand from rural India, mostly involved in agriculture sector, is either ignored or calculations are based on limited hours of supply. The true picture therefore can be captured by India's per capita electricity consumption, which is still on the lower side. With an energy consumption of just 818 units, India stands far behind China (4,292), European Union (5,368) and US (11,974) as per statistics in 2015 [2]. Therefore, Uninterruptable power supplies are prerequisite of power security and continuity for any developing economies, like India.