# THREE PHASE MULTIPOINT CLAMPED INVERTERS AND MODULATION STRATEGIES

Ph.D. THESIS

by

## NARENDRABABU A

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) DECEMBER, 2018

# THREE PHASE MULTIPOINT CLAMPED INVERTERS AND MODULATION STRATEGIES

### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

#### DOCTOR OF PHILOSOPHY

in

#### ELECTRICAL ENGINEERING

by

NARENDRABABU A

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) DECEMBER, 2018

©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2018 ALL RIGHTS RESERVED

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

# **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in this thesis entitled "THREE PHASE MULTIPOINT CLAMPED INVERTERS AND MODULATION STRATEGIES" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electrical Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from January, 2014 to December, 2018 under the supervision of Dr. Pramod Agarwal, Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

## (Narendrababu A)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

## (Pramod Agarwal) Supervisor

The Ph.D Viva-Voice examination of Mr. Narendrababu A, Research scholar, has been held on.....

## Chairman, SRC

## Signature of External Examiner

This is to certify that the student has made all the corrections in the thesis

| Signa  | ure of Supervisor |

|--------|-------------------|

| Date:_ |                   |

Head of the Department

In the recent years, the high penetration of various renewable and other nonconventional distributed generators with greater power capability has been an increasing interest. Sources like photovoltaic (PV) generators, fuel cells, wind-energy systems are widely being integrated into power system at distribution level. The main advantages of renewable sources are that they are inexhaustible and environmentally friendly in nature. However, due to uncertainty and uncontrollability of these sources, energy storage systems, power conversion and conditioning techniques are more challenging than ever for grid-connected systems or stand-alone systems. Power electronics, being the technology of efficient electric power conversion is an essential part for integration of various distributed generation systems (renewable energy and non-renewable energy systems) in power system.

Power converters such as DC-DC-AC and AC-DC-AC are typically required for integration of low voltage distributed generation sources into grid. Theoretically, a DC-DC boost converter followed by a conventional two-level voltage source inverters (VSI) can increase the voltage to desired level. However, the system imposes several limitations due to various factors and existing semiconductor technology. Since the RMS ac voltage output at the DC-AC input stage is always less than the DC link voltage, several PV arrays are connected in series to meet the required voltage level. A conventional two-level VSI does not allow the independent control of individual PV array in such cases.

Multilevel VSIs play the key role in aforementioned scenario by allowing direct connection of several low voltage PV arrays for their independent control and maximum utilization. Over the past few decades, multilevel power conversion technology has generated widespread interest both in the research community and in the industry, as they are becoming a viable technology for many applications. The multilevel topologies like Diode Clamped inverter (DCI), Cascaded H-bridge converter (CHI) and Flying Capacitor inverter (FCI) are considered as conventional multilevel VSIs. They are built with objective of using low voltage rating devices in medium and high voltage applications. However, these conventional multilevel VSI require more switching devices and associated components like driver circuits, power supplies, heatsinks, etc. Therefore, the conventional multilevel VSIs suffers from demerits like complexity, high cost and low reliability compared to two-level VSI counter parts.

Fortunately, with substantial improvement of conventional silicon devices and their packaging technologies, new wide band-gap materials reaching higher junction temperature and voltage blocking levels, are being evolved. As a result, voltage rating of the switching devices is no longer a core concern for opting multilevel VSI in various applications. Conversely,

achieving the functionality of multilevel VSIs (like minimum distortion) with minimum number of switching devices and associated components has become the key factor. This new approach has opened the door to researchers for developing new multilevel topologies aiming different objectives.

The research work starts with the literature survey of the multilevel inverter topologies with reduced device count. These topologies have their relative merits and demerits from the stand point of application requirement. No specific topology can be considered as suitable in all respects in most of the applications. Most of the newly proposed topologies in the literature are basically single-phase structures with "polarity-generation unit" and "level-generation unit". Some of the multilevel topologies need induvial "polarity-generation unit" and "level-generation unit", while some other can incorporate single "level-generation unit" for three-phase applications. Such inverters with separate "level-generation unit" must incorporate a greater number of DC-sources as the number of phases increases since they cannot be operated with single DC-link. On the other hand, topologies with common "level-generation unit", redundancy for generating phase voltage levels is limited and it further leads to unequal load sharing among the DC sources.

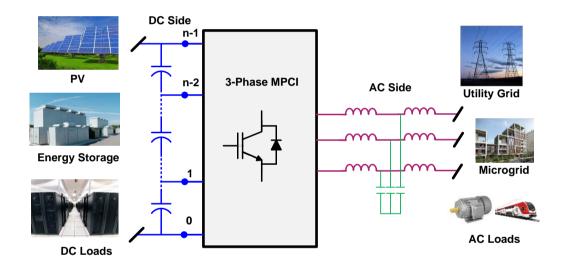

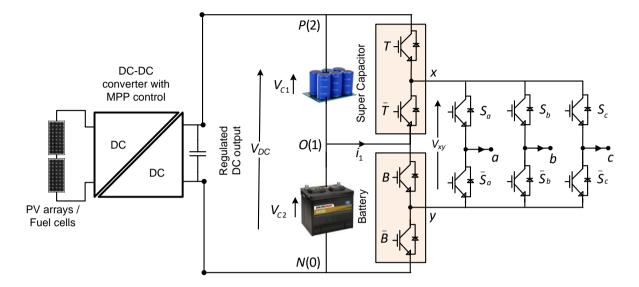

In present work, a detailed investigation is carried out on multipoint clamped inverter (MPCI) topologies, which are realized using single DC link for supplying more than one phase. The DC link of MPCI is formed by several low voltage DC sources like PV/Batteries or a frontend converter system. The output voltage levels of each phase are generated passively through number of clamping points in the common DC link of MPCI topology and hence, it is functionally equivalent to a single-pole multiple-throw switch ( $n \ge 3$  positions) (e.g., the diode-clamped topology). MPCI structure is also advantageous due to the requirement of least number of DC sources for multi-phase operation compared to other topologies. Furthermore, it can generate balanced phase voltages even under DC input source voltage variations, which are likely when using PV/Batteries. This thesis investigates the three-phase MPCI topologies and modulation strategies for the possible applications including renewable energy grid interface, energy storage system, electric drives and energy control centre for smart grid and micro-grids. The key challenges of the power conversion system are identified as power circuit complexity, modulation algorithms and power quality for MPCI topologies.

The modulation techniques for MPCIs are relatively complex compared to the two-level counter parts. The control techniques are generally classified as Carrier based modulation and space vector modulation (SVM). Carrier based modulation methods are very simple to implement. On the other hand, SVM provides the complete control over the modulation of the VSI. In this thesis, SVM is considered for detailed analysis. In SVM, there are number of ways to select the set of voltage vectors for synthesizing the reference vector. The selected voltage

vectors along with the switching sequence play key role for achieving various functionalities of the VSI like: Power loss reduction, power quality, capacitor voltage balancing etc. In the present work, the SVM strategies are classified as nearest three vector modulation (NTV) and nonnearest three voltage vector modulation (non-NTV). NTV modulations depending on the type voltage vectors selected. NTV strategies are very common as they produce better harmonic performance. However, depending on the MPCI topology, NTV strategies have several limitations. In such cases, non-NTV methods are essential even if they relatively increased harmonic distortion in the output voltage and current waveforms.

Three-level (3L) neutral point clamped inverter (NPCI) is the simplest example of MPCI. These are proven to be excellent tradeoff solution between performance and cost in high-voltage and high-power systems. The main advantages of 3L NPCI are reduced voltage ratings for the switches, good harmonic spectrum (making possible the use of smaller and less expensive filters), and good dynamic response. Even for low voltage applications, the NPCI and equivalent topologies like T-type NPCI are widely used as an alternative to two-level VSIs. In the present work, first 3L NPCI is presented thoroughly. NTV and non-NTV modulation strategies are implemented on 3L NPCI for elimination of low frequency neutral point (NP) voltage oscillations. A simplified implementation algorithm is developed for NTV and non-NTV modulation strategies. Therefore, coordinate transformation, trigonometric expressions and solutions of volt-second balance equations are not required in the proposed algorithms. Moreover, the unique feature the proposed modulation algorithm is that, they do not require independent voltage-second balance equations for NTV and non-NTV modulation strategies. Therefore, these algorithms can be easily modified for implementing the hybrid modulation methods without increasing the computational burden.

Further analysis is focused on reducing the complexity of MPCI topologies by minimizing power semiconductor device (PSD) count. In this context, first, a reduce device count 3L inverter termed as hybrid 2/3 level (2/3L) NPCI is presented based on the concept of non-NTV modulation. It can be formed by addition of two half bridge modules to a two-level inverter thereby uses only ten active switches. It can save two active switches and six clamping diodes compared to the conventional NPCI. However, as a result of reduction in switching combinations, the medium voltage vectors are absent in the SVD of hybrid 2/3 level inverter. The voltage vector selection is also no longer similar to conventional 3L NPCI. In order to address this issue, two types of voltage vector very closely. Effect of different switching state selections is studied in detail. A new virtual vector modulation to use both the small vectors for entire modulation index range is also proposed. Therefore, the modulation allows the interconnection of Z-source network to the hybrid 2/3L NPCI. Two new switching sequences for

iii

higher modulation range are analyzed to retain the same number of device commutations even with the insertion of shoot-through states.

It was observed that, in case of MPCI, if an attempt is made to reduce the number of active switches, it affects the number of available switching states (or voltage vectors) for synthesizing the reference voltage vector. Therefore, such devices are considered as reduced switching state (RSS) MPCI topologies. The position of available voltage vectors in SVD of a given RSS MPCI depends on i) total number of switching devices and ii) structure of the RSS MPCI topology. This effect is further explored by studying four and five level RSS MPCI topologies in detailed with different possible structures. Modulation techniques for such topologies are also investigated for synthesizing the reference vector using the available voltage vectors for achieving minimum distortion.

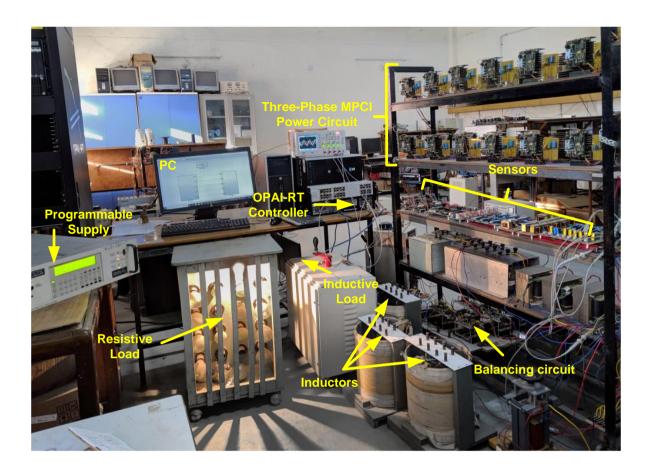

Computer simulation studies have been carried out in MATLAB/Simulink to verify the performance of various MPCI topologies and modulation strategies under different load conditions. The simulation study has been carried out for both steady-state and transient conditions. To validate the simulation studies of different topologies, downscaled hardware prototypes have been designed, developed and tested. The Real-Time Interface (RTI) of MATLAB and RT-Lab controller (OP 5600) are used to generate gate pulses for switching devices of the developed prototype. Different hardware components as required for the operation of the experimental set-up such as pulse amplification, isolation circuit, dead-band circuit, voltage and current sensor circuits have been developed and interfaced with the RT-Lab controller. As the experimental results are also performed and compared with experimental results. The experimental results have been found to be in good agreement with the simulation results. Although all the proposed schemes are experimentally tested and validated on downscaled laboratory prototypes, but the proposed topologies, SVM technique are general in nature and can be easily applied to high power applications.

iv

## ACKNOWLEDGEMENTS

With GOD's grace I have got this opportunity to thanks all those who have supported me all through this course of work. First and foremost, I would like to express my deepest sense of gratitude towards my supervisor Dr. Pramod Agarwal, Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee, for his patience, inspiring guidance, constant encouragement, moral support, and keen interest in minute details of the work. I am sincerely indebted to him for his pronounced individuality, humanistic and warm personal approach, and excellent facility provided to me in the laboratory to carry out this research.

I also express my sincere gratitude towards my research committee members Dr. Barjeev Tyagi, (Professor EED & Chairman SRC), Dr. B. Das, (Professor, EED) R.P. Saini, (Professor, Department of AHEC) for their invaluable direction, encouragement and support, and above all the noblest treatment extended by them during the course of my studies at IIT Roorkee.I heartily extend my gratitude to Head of the Department of Electrical Engineering, and all faculty members of the department for their help, moral support, and providing the excellent infrastructure, laboratory and computing facility for the research work.I acknowledge my sincere gratitude to the Ministry of Human Resources and Development (MHRD), Government of India for providing financial support during my doctoral research work.

I express my sincere thanks to all seniors especially to Dr. Sanjiv Kumar, Dr. Y Sreenivas Rao, Mr. Janardana Kotturu, Dr. Hari Krishna and Dr. Jagan Nayak supporting me during the whole period. I extend my sincere thanks to my colleagues Mr. Naveen Yalla, Mr. Sanjeev reddy, Mr. Siddhratha for sharing and supporting me during my research work.

I would also like to thank all the administrative &technical staff of the department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee for their cooperation and necessary facility provided to me to carry out this research work. My special thanks to Mr. Amir Ahmed, Mr. Gautam Singh and Mr. Rakesh Kumar, who helped me to prepare experimental setup of my research work.

I owe a debt of gratitude to my parents, Shri Bhaskar Babu and Smt. Vijaya, my brother Chaitanya Babu, for their endless support, encouragement, patience and care.

May all praise be to the Almighty, the most beneficent, and the most merciful.

(Narendrababu A)

# CONTENTS

| ABSTRACT                                                                  | i     |

|---------------------------------------------------------------------------|-------|

| ACKNOWLEDGEMENTS                                                          | v     |

| CONTENTS                                                                  | vii   |

| List of Figures                                                           | xiii  |

| List of Tables                                                            | xxvii |

| List of ACRONYMS                                                          | xxix  |

| List of SYMBOLS                                                           | xxxi  |

| Chapter 1: INTRODUCTION                                                   | 1     |

| 1.1 Overview                                                              | 1     |

| 1.2 Role of Power Electronic Systems (PES) in Modern Electric Grids       | 1     |

| 1.2.1 PES in Transmission System                                          | 2     |

| 1.2.2 PES in Distribution System                                          | 2     |

| 1.3 Research Background                                                   | 4     |

| 1.4 Multilevel VSI Systems                                                | 5     |

| 1.4.1 Diode Clamped Inverter (DCI)                                        | 6     |

| 1.4.2 Flying Capacitor Inverter (FCI)                                     | 7     |

| 1.4.3 Cascaded H-Bridge Inverter (CHBI)                                   | 8     |

| 1.5 Comparative Evaluation of Conventional MLIs                           | 9     |

| 1.5.1 Hybrid Multilevel Inverters:                                        | 10    |

| 1.6 New MLI Topologies with Reduce Device Count                           | 11    |

| 1.7 Three-Phase Multipoint Clamped Inverter (MPCI) Topologies with Reduce |       |

| 1.8 Scope of Work and Authors Contribution                                | 18    |

| 1.9 Organization of the Thesis                                            |       |

| Chapter 2: MODULATION STRATEGIES FOR MULTIPOINT CLAMPED INVERTERS       | 23 |

|-------------------------------------------------------------------------|----|

| 2.1 Introduction                                                        | 23 |

| 2.1.1 Principle of Voltage Source Converter Control:                    | 23 |

| 2.1.2 Modulation Control of Power Converters:                           | 24 |

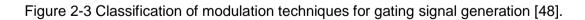

| 2.2 Classification of Switching Signals Generation Schemes for MLIs     | 25 |

| 2.2.1 Carrier Based PWM Strategies                                      | 25 |

| 2.2.2 Space Vector Modulation (SVM)                                     | 28 |

| 2.2.3 Other Methods                                                     | 29 |

| 2.3 SVM Strategies for MPCIs                                            | 30 |

| 2.3.1 Three Level (3L) NPCI Topology and Its Space Vector Diagram (SVD) | 30 |

| 2.3.2 NTV Strategy for 3L NPCI                                          | 32 |

| 2.3.3 Non-NTV Modulation for 3L NPCI                                    | 35 |

| 2.4 Performance Evaluation of 3L NPCI                                   | 39 |

| 2.5 Capacitor voltage balancing for Multilevel MPCI                     | 41 |

| 2.5.1 External Balancing Circuit                                        | 43 |

| 2.5.2 Converter/Inverter Back-to-Back Configuration                     | 44 |

| 2.5.3 Using Modulation Schemes                                          | 45 |

| 2.5.4 Other Emerging Methods                                            | 47 |

| 2.6 Conclusion                                                          | 47 |

| Chapter 3: SPACE VECTOR MODULATION ALGORITM FOR Three-level NPCI        | 49 |

| 3.1 Introduction                                                        | 49 |

| 3.2 Proposed Modulation Approach Based on 2L Equivalent SVD             | 50 |

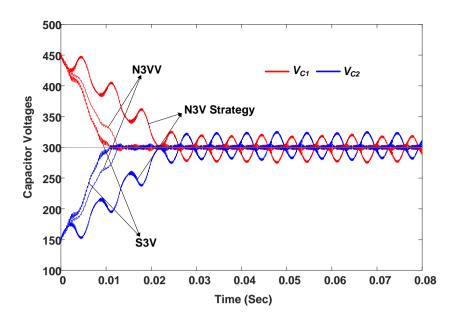

| 3.2.1 NTV Duty Ratio Expressions                                        | 52 |

| 3.2.2 NTVV Duty Ratio Expressions                                       | 56 |

| 3.2.3 STV Duty Ratio Expressions                                        | 58 |

| 3.3 Implementation of Proposed Modulation Algorithm                     | 59 |

| 3.3.1 2L SVD/MT Duty Ratios                                             | 60 |

| 3.3.2 Identification of Sub-Triangle Regions                            | 63 |

| 3.4 Voltage Imbalance Compensation                                      | 65 |

| 3.5 Extension SVM Algorithm for Higher Voltage Levels                  | 67  |

|------------------------------------------------------------------------|-----|

| 3.6 Performance Evaluation of Modulation Schemes                       | 68  |

| 3.6.1 Comparison of Modulation Schemes                                 | 69  |

| 3.6.2 Capacitor Voltage Unbalance Compensation:                        | 75  |

| 3.7 Conclusion                                                         | 76  |

| Chapter 4: HYBRID MODULATION STRATEGIES FOR 3L NPCI                    | 77  |

| 4.1 Introduction                                                       | 77  |

| 4.1.1 Combination of NTV And Non-NTV Modulations                       | 77  |

| 4.2 Elimination of Low Frequency NP Voltage Ripple                     | 80  |

| 4.2.1 Boundary Condition for NTV Modulation                            | 80  |

| 4.3 Proposed Hybrid Modulation Approach                                | 84  |

| 4.3.1 Duty Ratios Relations Between NTV and Non-NTV modulations        | 84  |

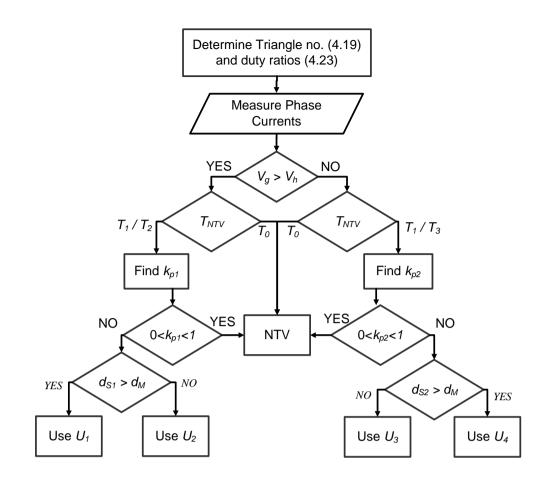

| 4.4 Implementation of Redistribution-Based Hybrid Modulation Algorithm | 88  |

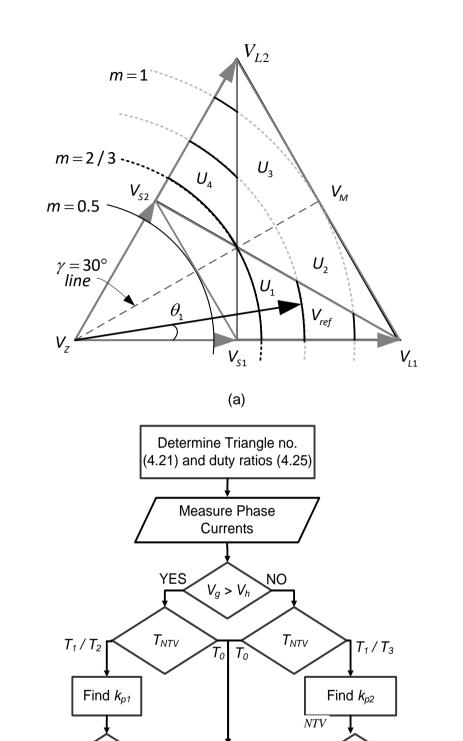

| 4.5 Hybrid NTV-SSTV Modulation Strategies                              | 92  |

| 4.6 Performance Evaluation of Hybrid Modulation Strategies             | 95  |

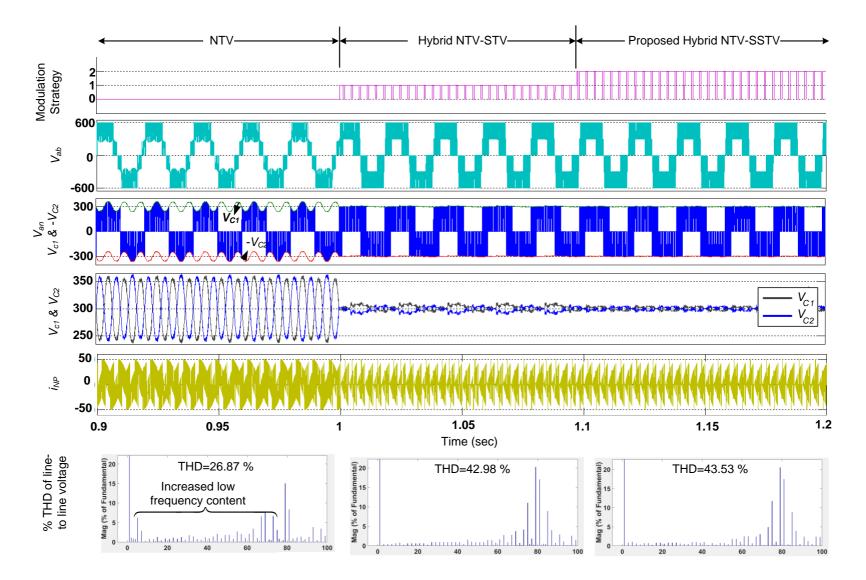

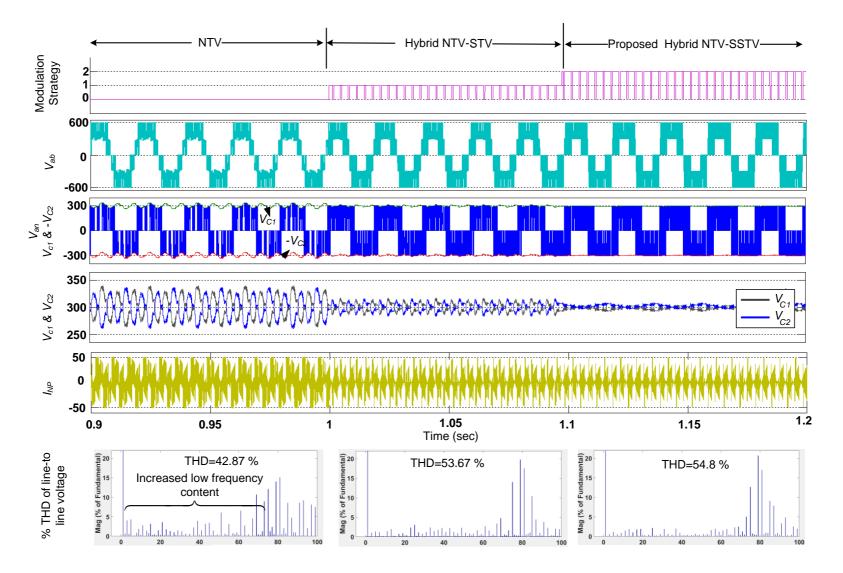

| 4.6.1 Comparison of Commutations and Power Losses                      | 100 |

| 4.6.2 Execution Time Comparison of Modulation Strategies               | 102 |

| 4.7 Conclusion                                                         | 103 |

| Chapter 5: HYBRID 2L/3L NPCI WITH SELF-CAPACITOR VOLTAGE BALANCING     | 105 |

| 5.1 Introduction                                                       | 105 |

| 5.1 Hybrid 2/3L NPCI                                                   | 106 |

| 5.1.1 Voltage Level Generation:                                        | 107 |

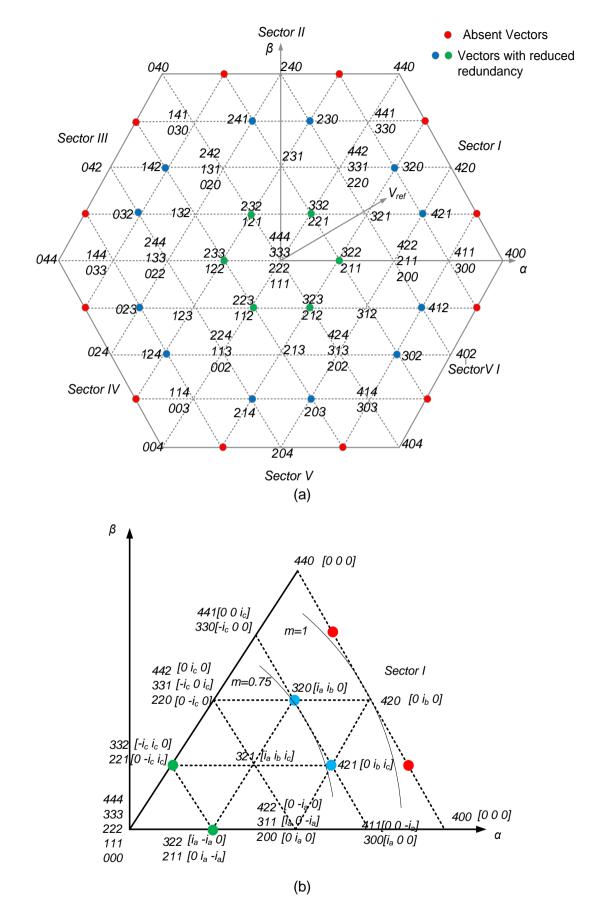

| 5.1.2 SVD of Hybrid 2/3L NPCI                                          | 109 |

| 5.2 Investigation of Modulation Methods for Hybrid 2/3L NPCI           | 109 |

| 5.2.1 Virtual Vector (VV) Based Modulation                             | 109 |

| 5.2.2 Selected Three-Vector (STV)-Based Modulation:                    | 112 |

| 5.3 Comparative Evaluation of Modulation methods for Hybrid 2/3L NPCI  | 115 |

| 5.4 Advanced Modulation Methods for Hybrid 2/3L NPCI                   | 120 |

| 5.5 Hybrid 2/3L Z-Source NPCI (Z-NPCI)                                 | 122 |

| 5.5.1 Circuit Description                                      | 122         |

|----------------------------------------------------------------|-------------|

| 5.5.2 Virtual Vector Modulation for Hybrid 2/3L ZVSI           | 123         |

| 5.5.3 Switching Sequence and Insertion of Shoot-Through States | 125         |

| 5.5.4 Modulation Algorithm for Hybrid 2/3L ZVSI                | 127         |

| 5.5.5 Performance Evaluation of Hybrid 2/3L ZNPCI              | 130         |

| 5.6 Hybrid 2/3L NPCI with Unequal DC Capacitor Voltages        | 133         |

| 5.6.1 Switching Sequence for DC Voltage Unbalance Compensation | 133         |

| 5.6.2 Performance Evaluation                                   | 135         |

| 5.7 Conclusion                                                 | 140         |

| Chapter 6: MULTILEVE MULTI-POINT CLAMPED INVERTERS WITH REDU   | JCED DEVICE |

| COUNT                                                          | 141         |

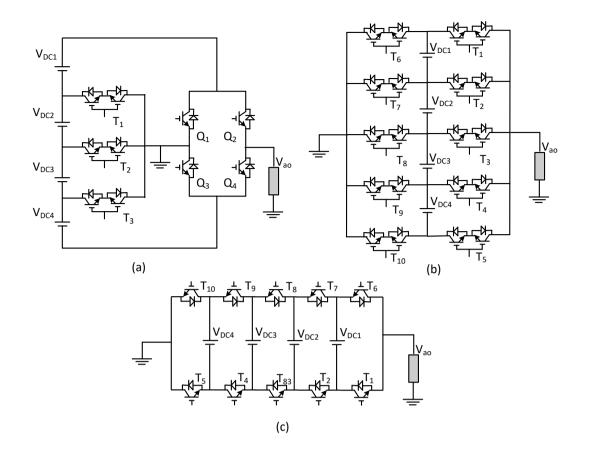

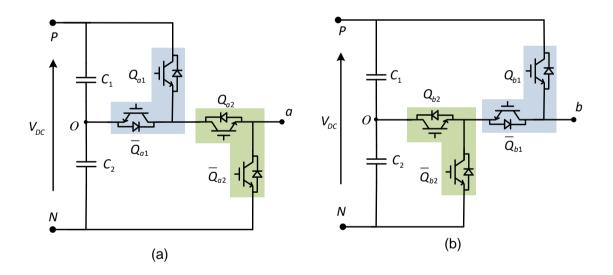

| 6.1 Introduction                                               | 141         |

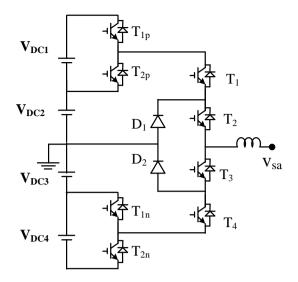

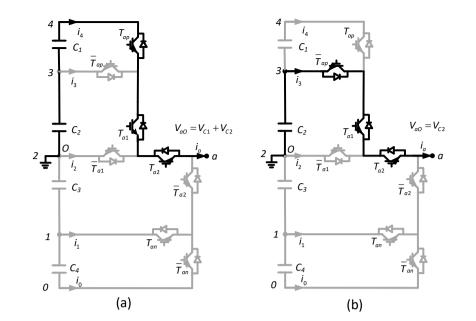

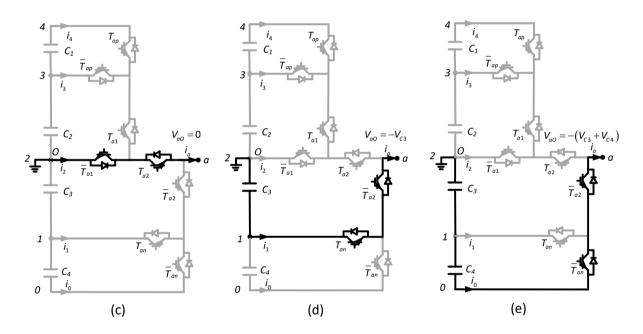

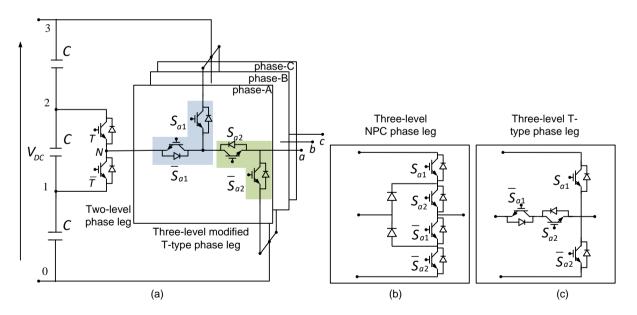

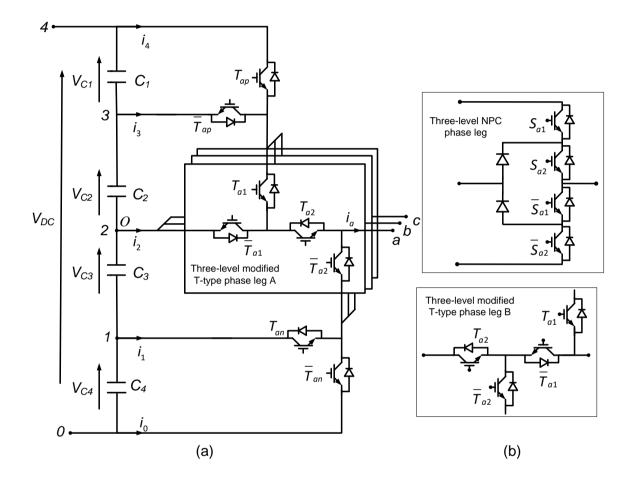

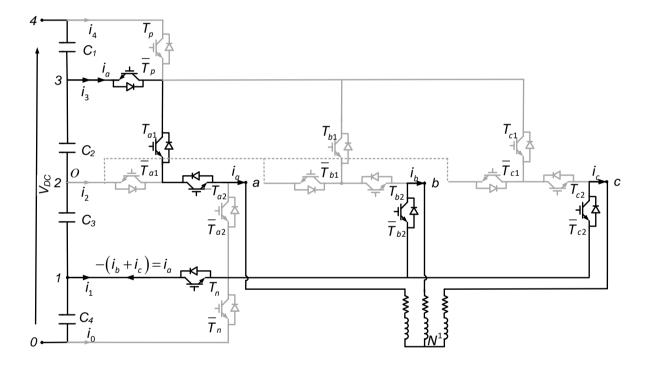

| 6.2 Modified T-Type 3L MPCI Topology                           | 142         |

| 6.2.1 Topology Synthesis                                       | 142         |

| 6.2.2 Circuit Description and Principle of Operation           | 143         |

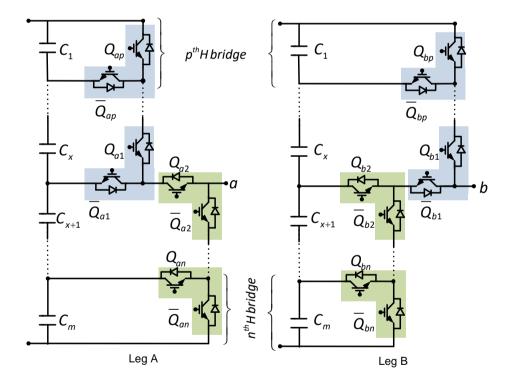

| 6.3 Extension to Higher Voltage Levels (Multilevel Operation)  | 144         |

| 6.4 Three-Phase 5L Modified T-Type MPCI                        | 145         |

| 6.4.1 Switching Signal Generation                              | 147         |

| 6.4.2 Comparison of Voltage Stress                             | 149         |

| 6.5 Reduced Switching State (RSS) MPCI Topologies              | 150         |

| 6.6 Four Level (4L) RSS MPCI                                   | 150         |

| 6.6.1 Virtual Vector (VV)-Based Modulation                     | 152         |

| 6.6.2 Proposed STV-Based Modulation                            | 153         |

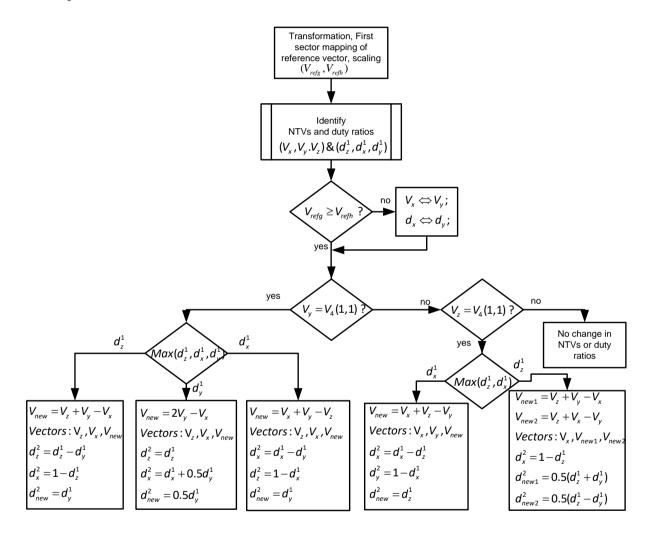

| 6.7 Modulation Algorithm for 4L RSS MPCI                       | 154         |

| 6.7.1 Voltage Vector Duty Ratio Expressions                    | 154         |

| 6.7.2 Implementation of Modulation Algorithm                   | 157         |

| 6.8 Performance Evaluation of 4L RSS MPCI                      | 159         |

| 6.8.1 Comparison of Modulation Schemes                         | 162         |

| 6.9 5L RSS MPCI with Common H-Bridge Cells                     |             |

| 6.9.1 Type-1 5L RSS MPCI                                                  | 162 |

|---------------------------------------------------------------------------|-----|

| 6.9.2 Type-2 5L RSS MPCI                                                  | 165 |

| 6.9.3 Modulation Strategy For 5L RSS MPCI Topologies                      | 168 |

| 6.10 Performance Evaluation of 5L RSS MPCI Topologies                     | 168 |

| 6.10.1 Comparative Analysis 5L RSS MPCI topologies                        | 172 |

| 6.10.2 Switch Rating in RSS MPCI Topolgoies                               | 173 |

| 6.11 Conclusion                                                           | 173 |

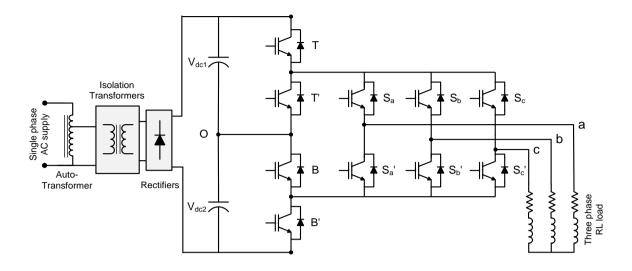

| Chapter 7: SYSTEM DEVELOPMENT AND EXPERIMENTATION                         | 175 |

| 7.1 Introduction                                                          | 175 |

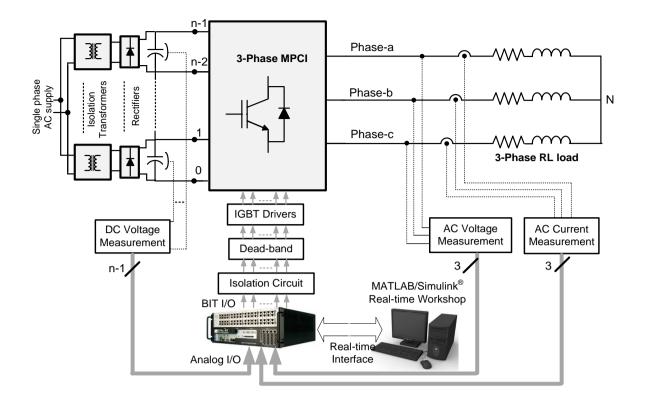

| 7.1.1 System Hardware                                                     | 176 |

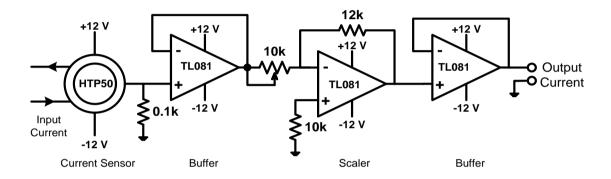

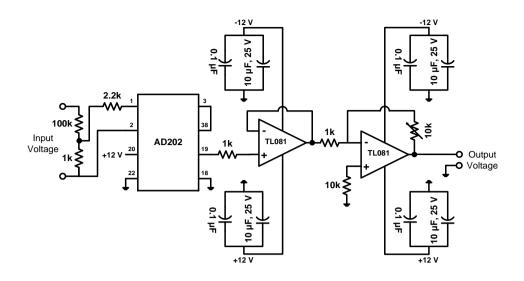

| 7.1.2 Measurement Circuits                                                | 176 |

| 7.1.3 Development of System Software                                      | 178 |

| 7.2 Control Hardware                                                      | 179 |

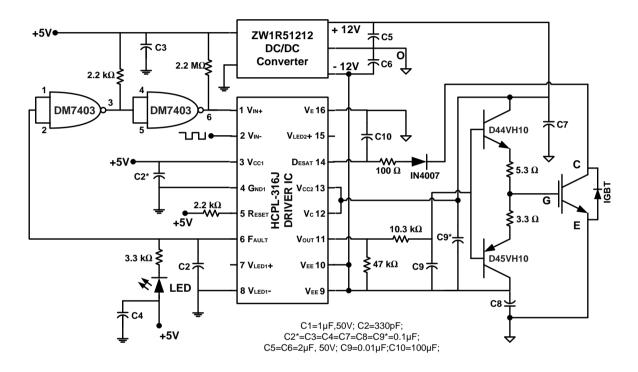

| 7.2.1 Isolation Circuit                                                   | 180 |

| 7.2.2 Dead-band Circuit                                                   | 180 |

| 7.2.3 IGBT Driver Circuits                                                | 181 |

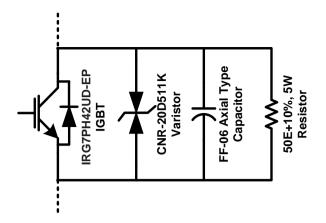

| 7.2.4 Snubber Circuit                                                     | 182 |

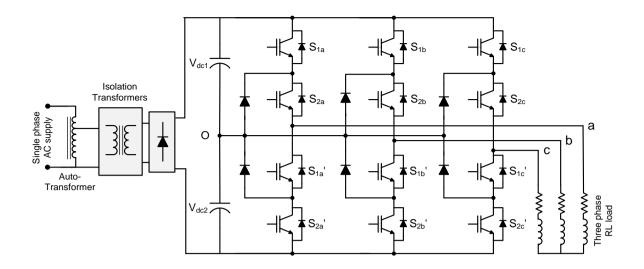

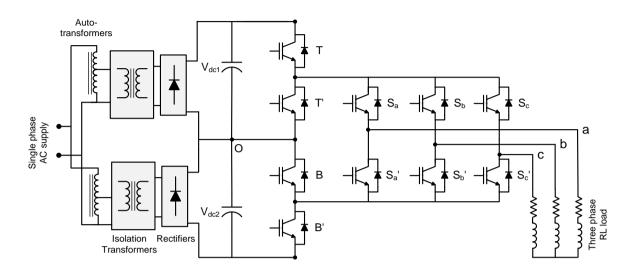

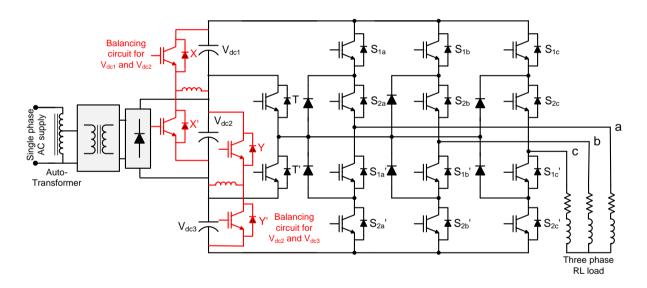

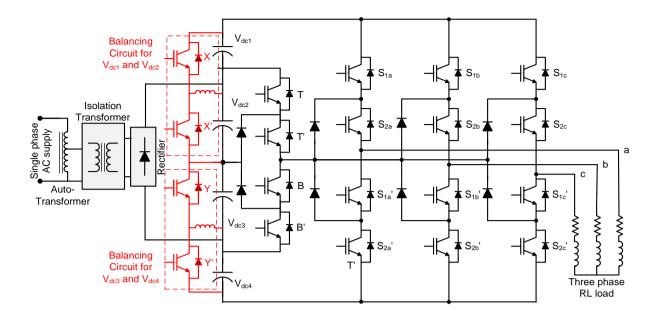

| 7.2.5 Power Circuit of Inverters                                          | 183 |

| 7.3 Performance Investigation of Three-Level NPCI                         | 183 |

| 7.3.1 Performance of 3L NPCI With SVM Based on Two-Level SVD:             | 184 |

| 7.3.2 Performance of 3L NPCI with Hybrid Modulation Methods:              | 197 |

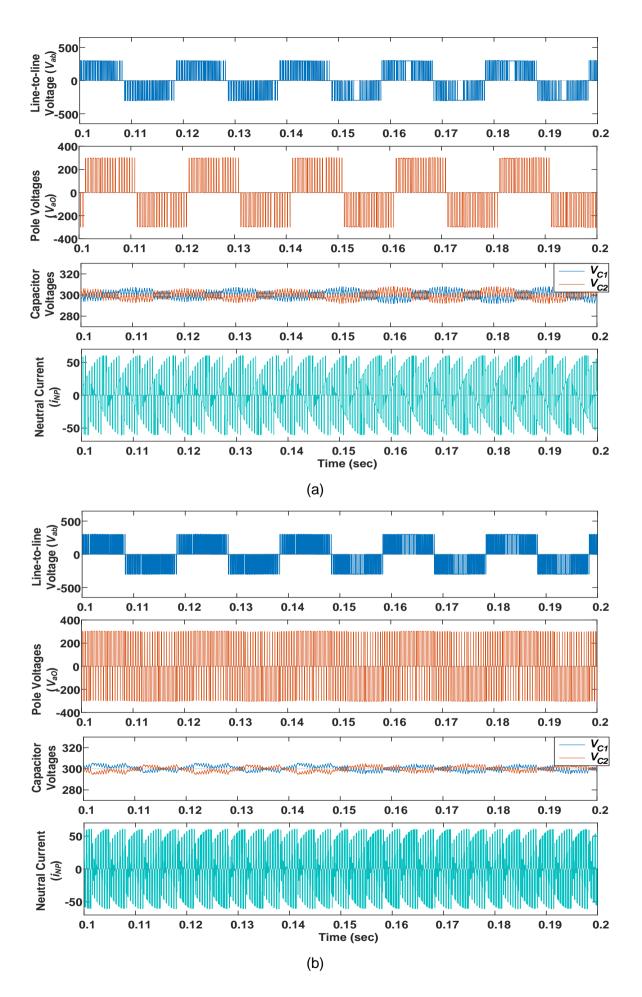

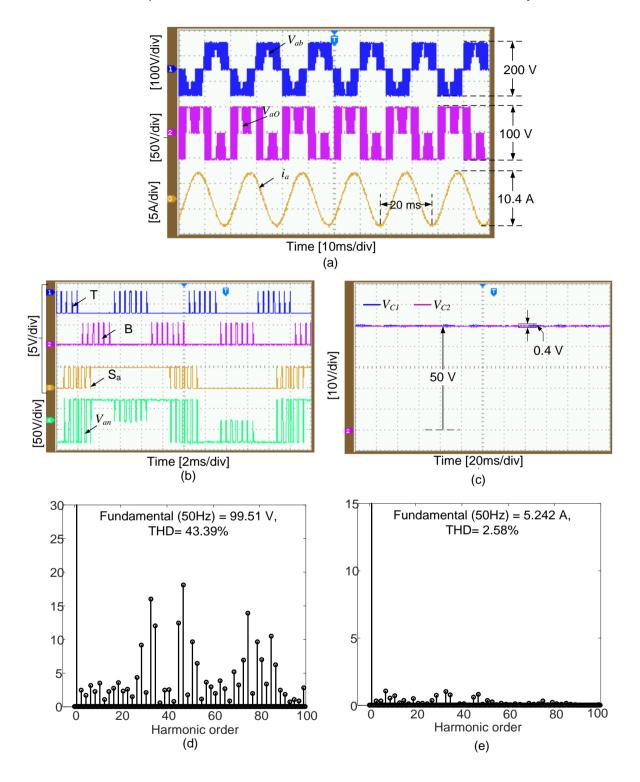

| 7.4 Performance Investigation Of Hybrid 2/3L NPCI                         | 205 |

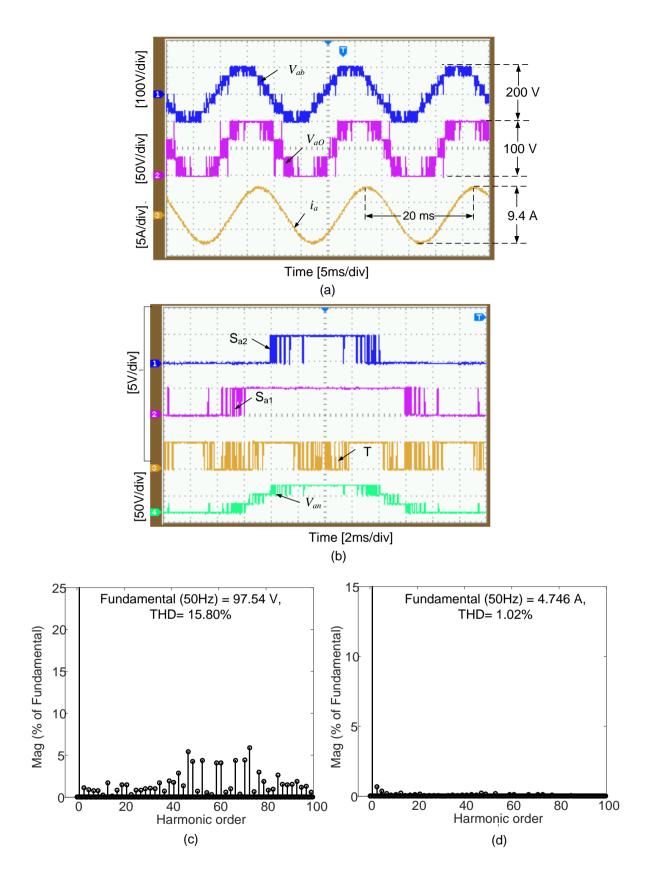

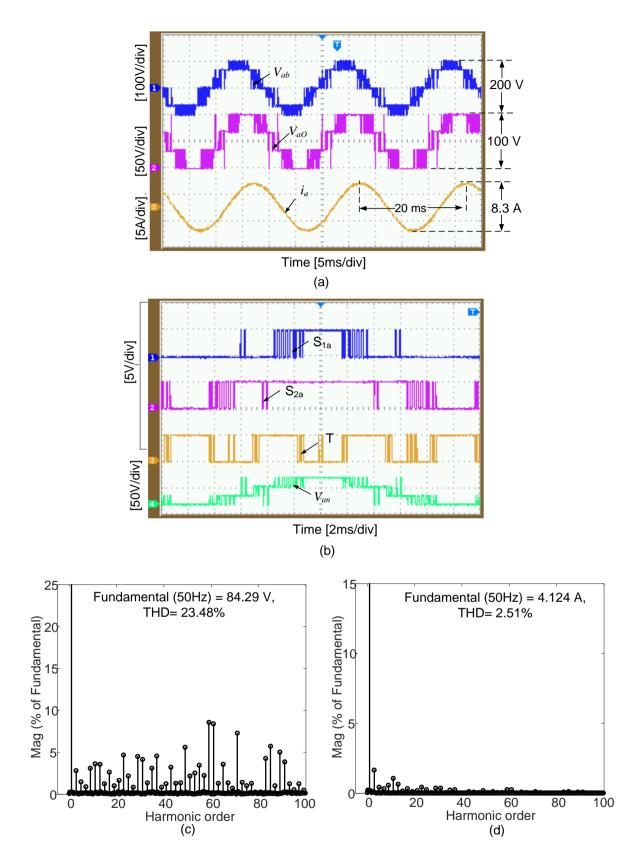

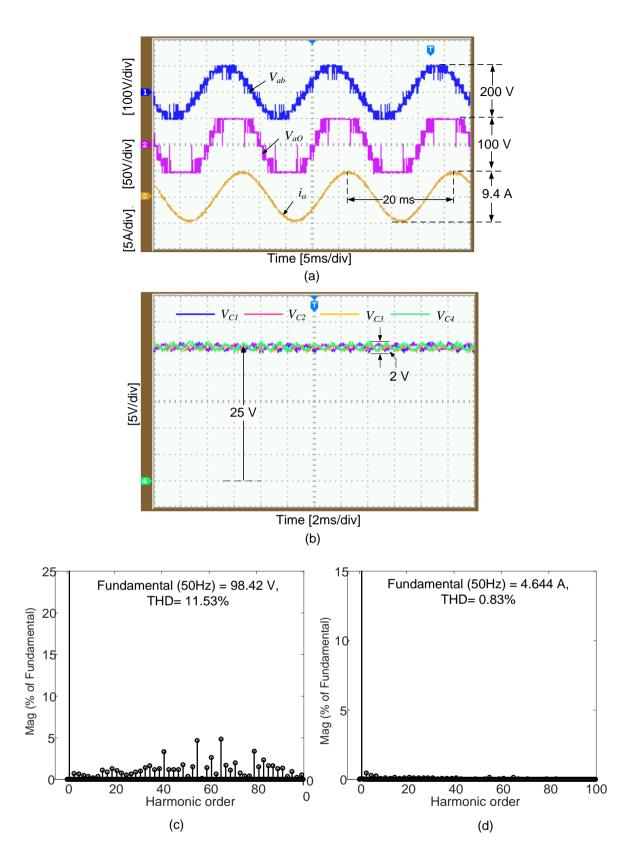

| 7.4.1 Performance of hybrid 2/3L NPCI with VV-based modulation:           | 205 |

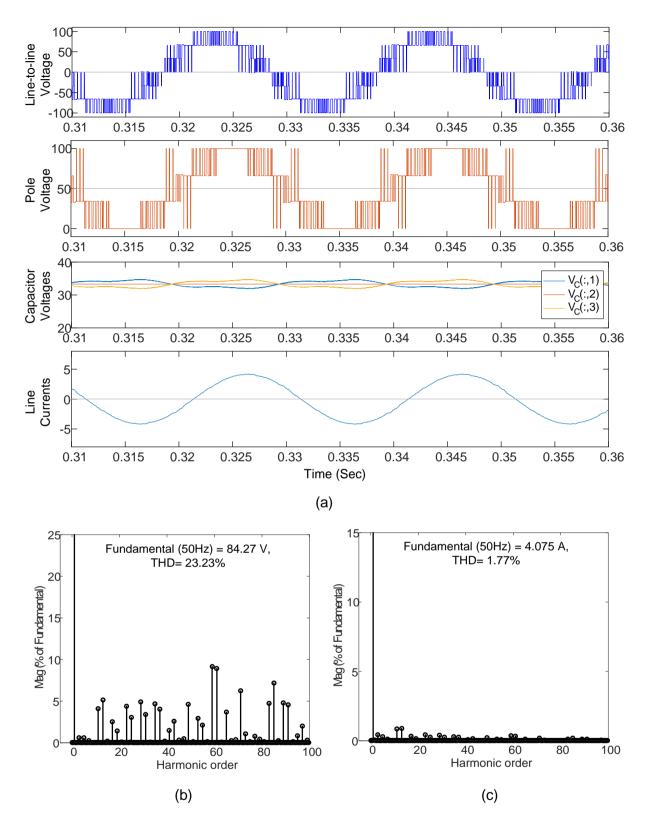

| 7.4.2 Performance of Hybrid 2/3L NPCI with STV-based Modulation:          | 210 |

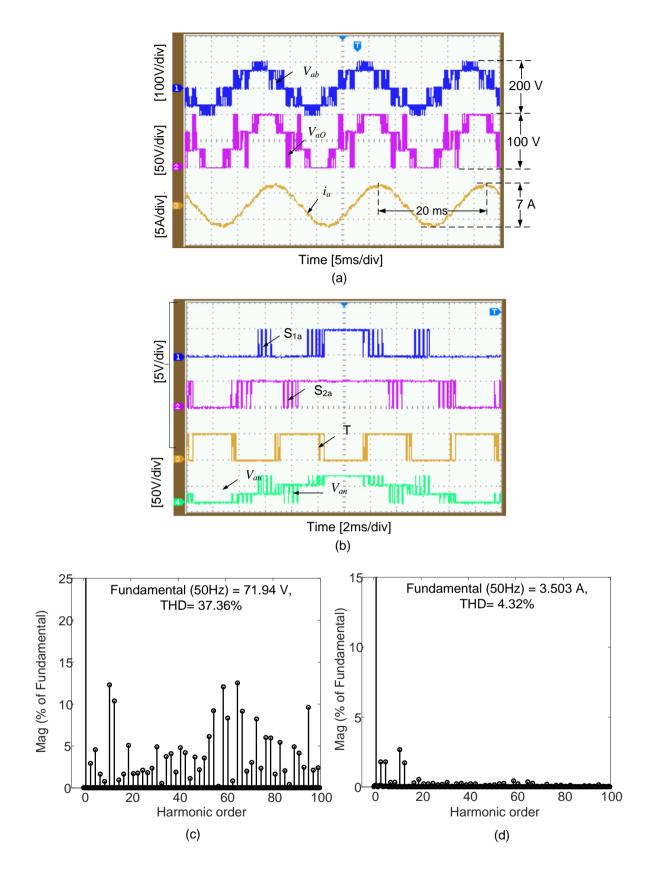

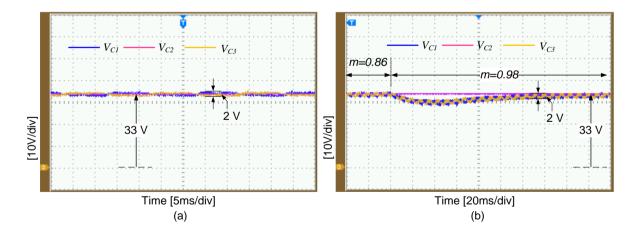

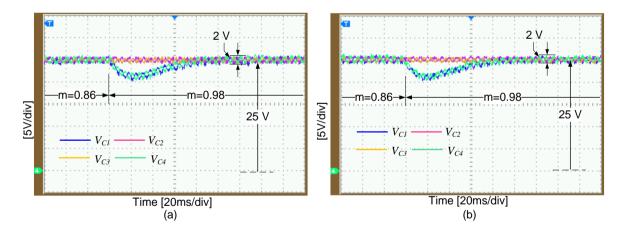

| 7.4.3 Performance of Hybrid 2/3L NPCI with Unequal DC Capacitor Voltages: | 216 |

| 7.5 Performance Investigation of 4L RSS MPCI                              | 224 |

| 7.5.1 Performance of 4L RSS MPCI with VV-based Method:                    | 224 |

| 7.5.2 Performance of 4L RSS MPCI with STV-based Method:                   | 231 |

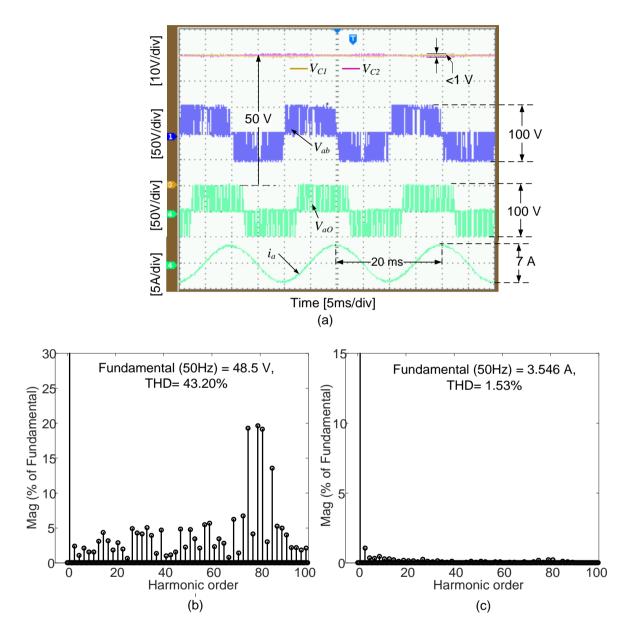

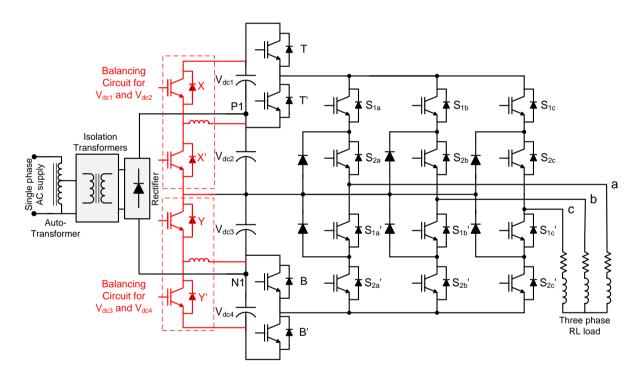

| 7.6 Performance Investigation of 5L RSS MPCI                              | 239 |

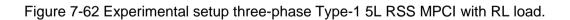

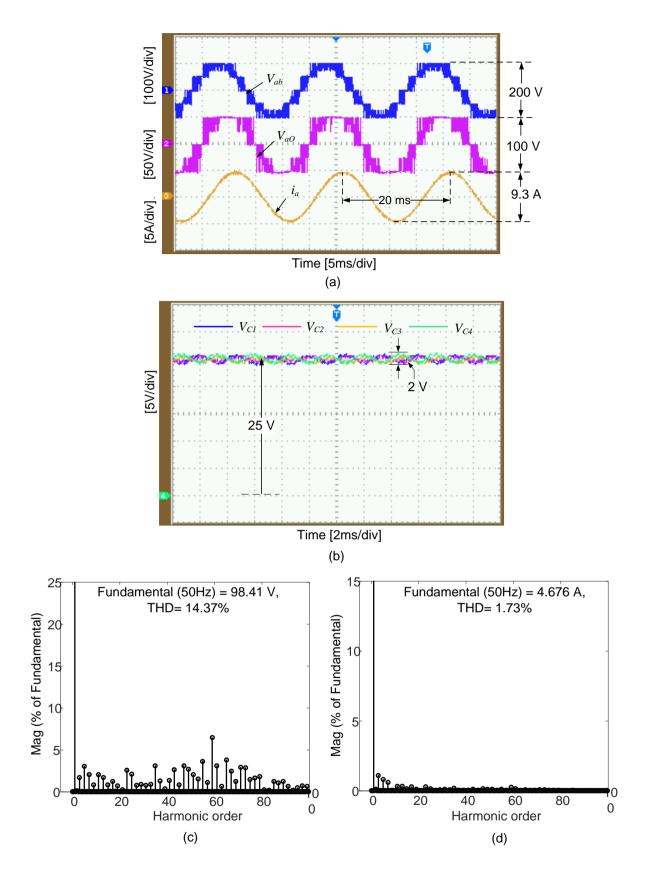

| 7.6.1 Performance of Type-1 5L RSS MPCI with VV-based Method: | 239 |

|---------------------------------------------------------------|-----|

| 7.6.2 Performance of Type-2 5L RSS MPCI with VV-based Method: | 245 |

| 7.7 Conclusion:                                               | 251 |

| Chapter 8: CONCLUSIONS AND FUTURE SCOPE                       | 253 |

| 8.1 Conclusions                                               | 253 |

| 8.2 Future Scope                                              | 255 |

| LIST OF PUBLICATIONS                                          | 257 |

| BIBLIOGRAPHY                                                  | 259 |

| APPENDIX                                                      | 275 |

|                                                               |     |

# LIST OF FIGURES

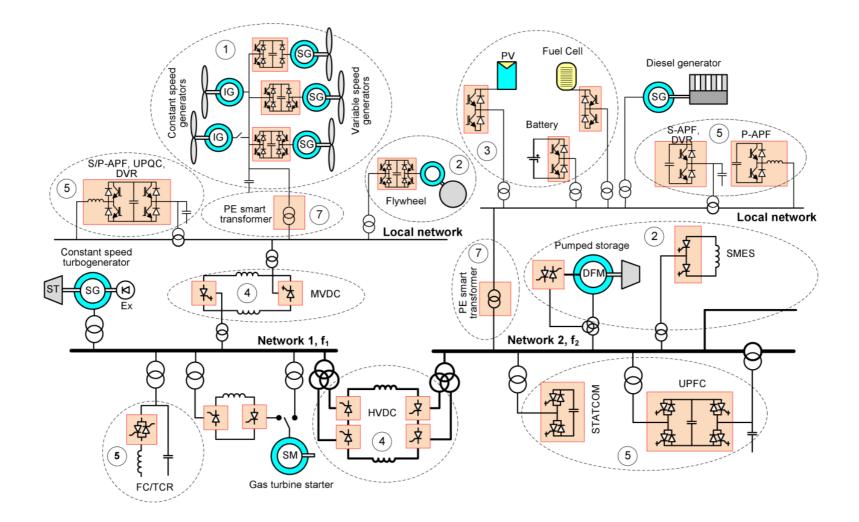

| Figure 1-1 Area of application of PE arrangements in electrical energy network: 1) wind                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| generators, 2) energy storage, 3) power supply systems from low-voltage sources, 4) network                                                                                                                                    |

| couplers, 5) devices for improvement of energy quality, 6) devices for control of energy delivery.                                                                                                                             |

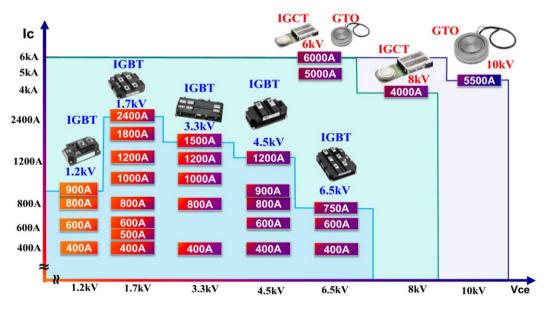

| Figure 1-2 Voltage and current rating of the semiconductor devices [3]                                                                                                                                                         |

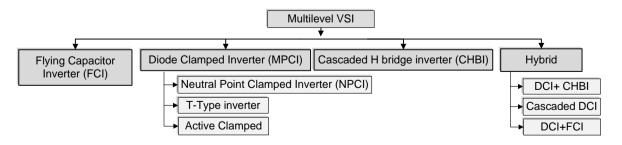

| Figure 1-3 Classification of Multilevel VSIs5                                                                                                                                                                                  |

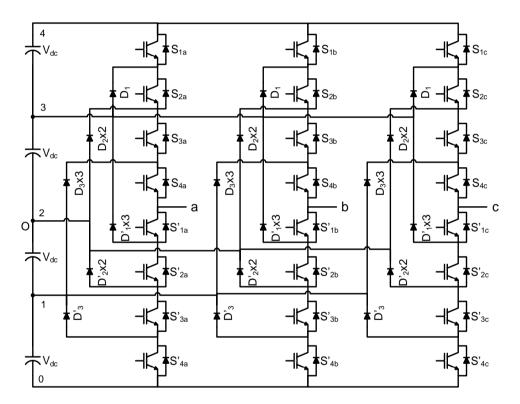

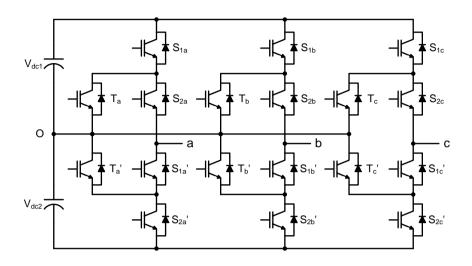

| Figure 1-4 A three-phase 5L DCI6                                                                                                                                                                                               |

| Figure 1-5 A three-phase 3L ANPCI7                                                                                                                                                                                             |

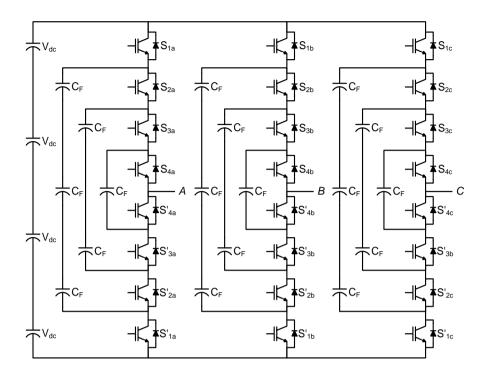

| Figure 1-6 A three-phase 5L FCI                                                                                                                                                                                                |

| Figure 1-7 A three-phase 5L CHBI topology9                                                                                                                                                                                     |

| Figure 1-8 A 5L Hybrid VSI proposed in [32] 11                                                                                                                                                                                 |

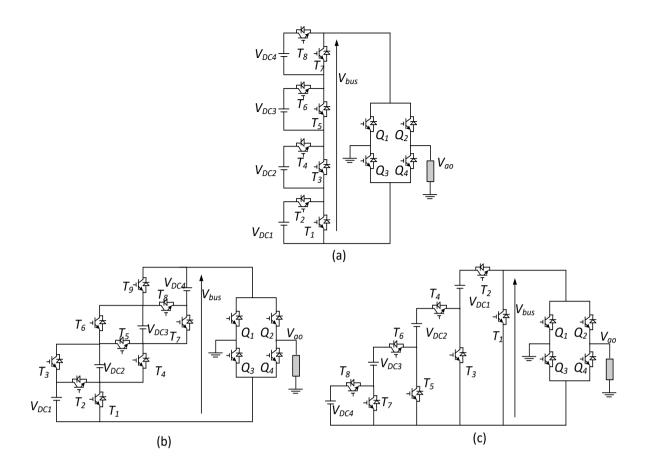

| Figure 1-9 Topologies with polarity generation unit which requires isolated DC-sources: (a) and (b) Topologies with phase voltage redundancy and (c) Topology without phase voltage redundancy                                 |

| Figure 1-10 Topologies with single high DC-link and dedicated polarity generation unit: (a)<br>Topologies with phase voltage redundancy; (b) Topology with phase voltage redundancy for<br>some voltage levels                 |

| Figure 1-11 Topologies without polarity generator unit: (a) and (b) Topologies with single high voltage DC-link; (c) Packed U-cell topologoy (Topology which requires isolated DC-sources)                                     |

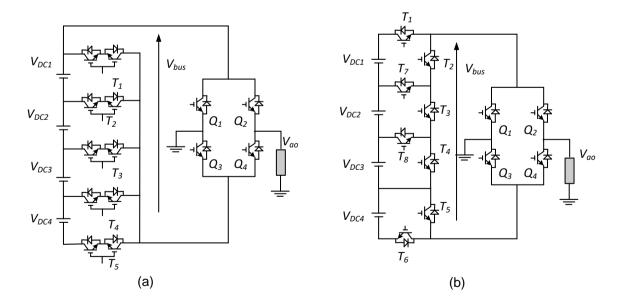

| Figure 1-12 A three-phase MPCI structure                                                                                                                                                                                       |

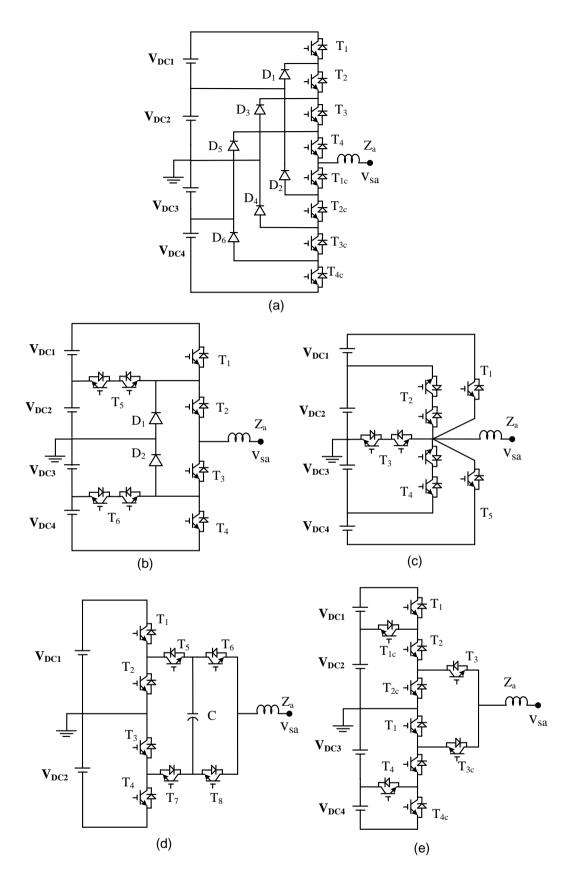

| Figure 1-13 Five-level (5L) MPCI topologies in the literature: (a) DCI, (b) Composite multilevel topology proposed in [38], (c) nested multilevel topology [39] (c) ANPC [40] and (d) ANPC for improved loss distribution [41] |

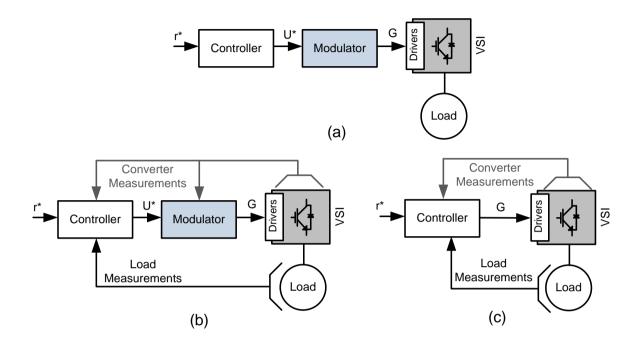

| Figure 2-1 Block diagrams of inverter with different controllers. (a) Open loop operation. (b) Closed-loop operation using a controller and a modulator. (c) Closed-loop operation using a controller with implicit modulator  |

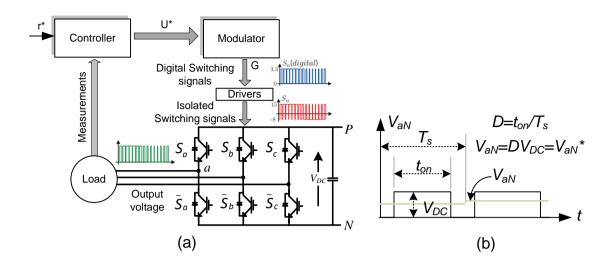

| Figure 2-2 (a) Typical structure of control and modulation method for VSI. (b) Switched waveform and average value of the phase voltage $V_{aN}$                                                                               |

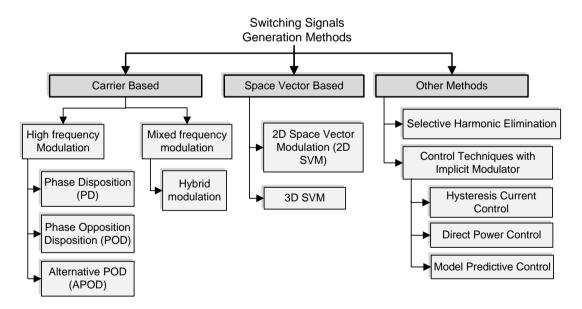

| Figure 2-3 Classification of modulation techniques for gating signal generation [48]                                                                                                                                           |

| Figure 2-4 PS-PWM for 7-level CHBI                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

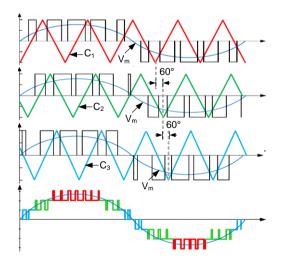

| Figure 2-5 LS-PWM methods for 5L VSI: (a) POD, (b) APOD and (C) PD                                                                                                                                                                                                                                                                                                                                                                 |

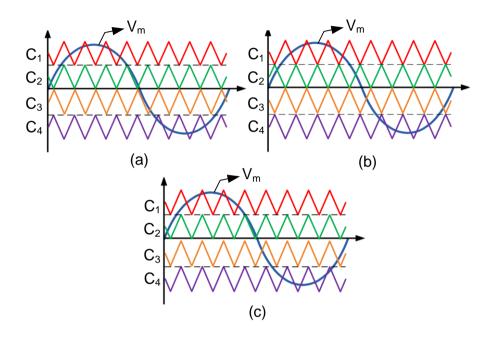

| Figure 2-6 Example of output voltages for hybrid carrier-based modulations                                                                                                                                                                                                                                                                                                                                                         |

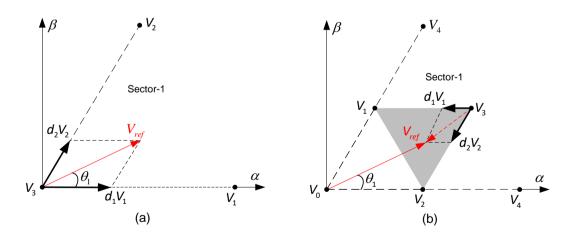

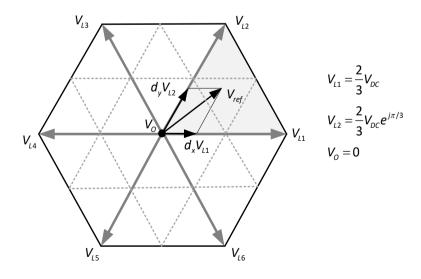

| Figure 2-7 Voltage-second balance princple for $V_{ref}$ in (a) 2L SVD and (b) 3L SVD                                                                                                                                                                                                                                                                                                                                              |

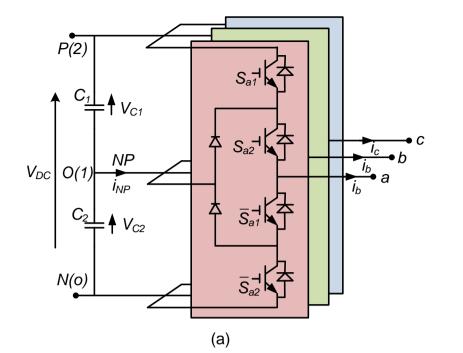

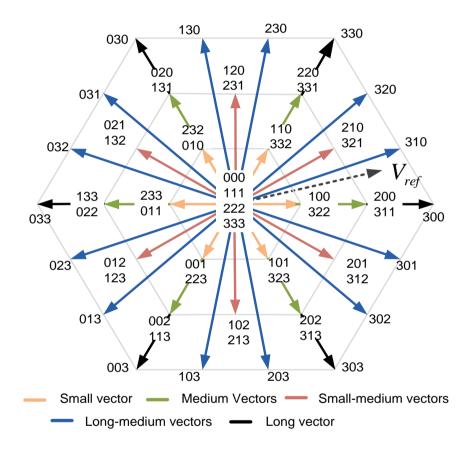

| Figure 2-8 Three-level (3L) NPCI (b) SVD of 3L NPCI                                                                                                                                                                                                                                                                                                                                                                                |

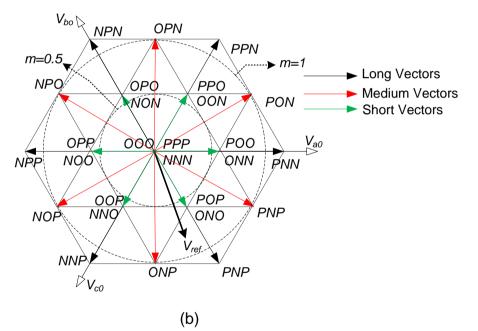

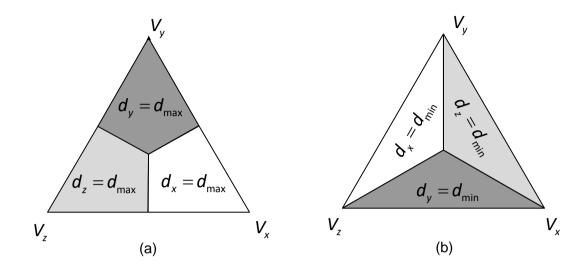

| Figure 2-9 Sector-1 of 3L NPCI SVD divided into NTV sub-triangle regions                                                                                                                                                                                                                                                                                                                                                           |

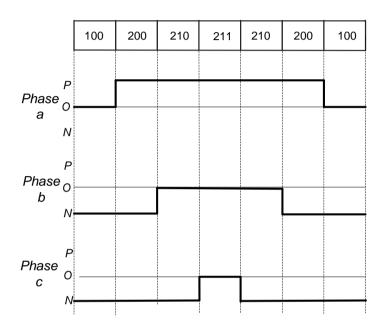

| Figure 2-10 Switching sequence for NTV modulation when $V_{ref}$ is located in $T_1$                                                                                                                                                                                                                                                                                                                                               |

| Figure 2-11 Sector 1 of 3L NPCI SVD divided into NTVV sub-triangle regions                                                                                                                                                                                                                                                                                                                                                         |

| Figure 2-12 Switching sequence for non-NTV modulation when $V_{ref}$ is located in $\Delta_2$                                                                                                                                                                                                                                                                                                                                      |

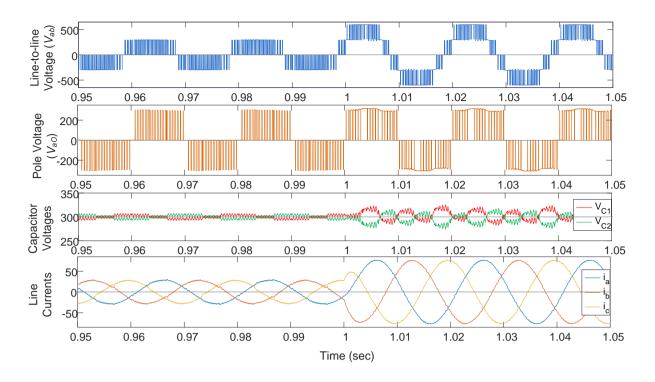

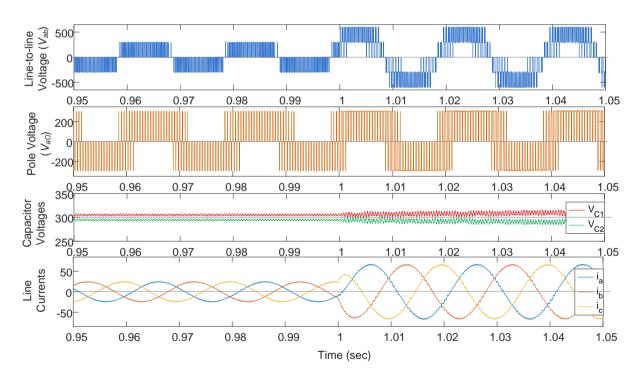

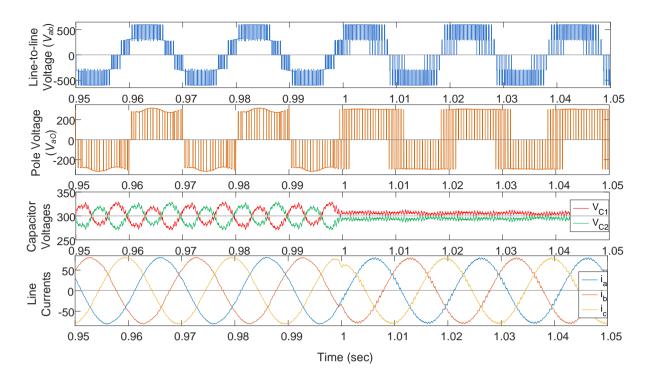

| Figure 2-13 NTV strategy simulation for m=0.35 (from t=0.95 to t=1 sec) and m=0.95 (after t=1 sec)                                                                                                                                                                                                                                                                                                                                 |

| Figure 2-14 NTVV strategy simulation for m=0.35 (from t=0.95 to t=1 sec) and m=0.95 (after t=1 sec)                                                                                                                                                                                                                                                                                                                                |

| Figure 2-15 Comparison of NTV (from t=0.95 to t=1 sec) and NTVV (after t=1sec) strategies at m=0.98 and RL load=4+j $\pi/2 \Omega$                                                                                                                                                                                                                                                                                                 |

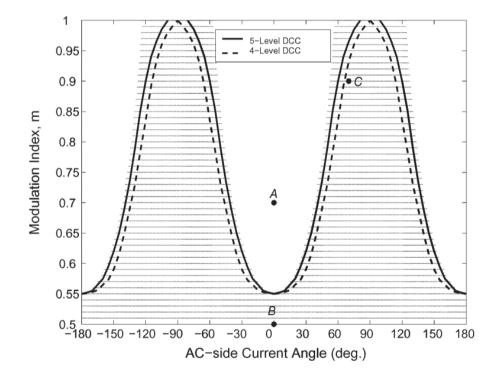

| Figure 2-16 Limits of voltage balance of the NTV-SVM-based balancing methods for a 4- and 5L passive front-end DCI [89]. (A) Operating point corresponding to $PF = 1$ and $m = 0$ .7 (unstable operation). (B) Operating point corresponding to $PF = 1$ and $m = 0$ .5 (stable, line to line voltage with 5 levels). (C) Operating point corresponding to $PF = 0.35$ and $m = 0.9$ (stable, line to line voltage with 9 levels) |

| Figure 2-17 External balancing circuits for DCI                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 2-18 AC/DC/AC MPCI converter system with self-capacitor voltage balancing                                                                                                                                                                                                                                                                                                                                                   |

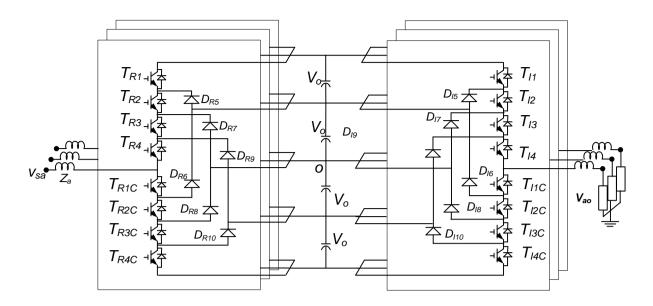

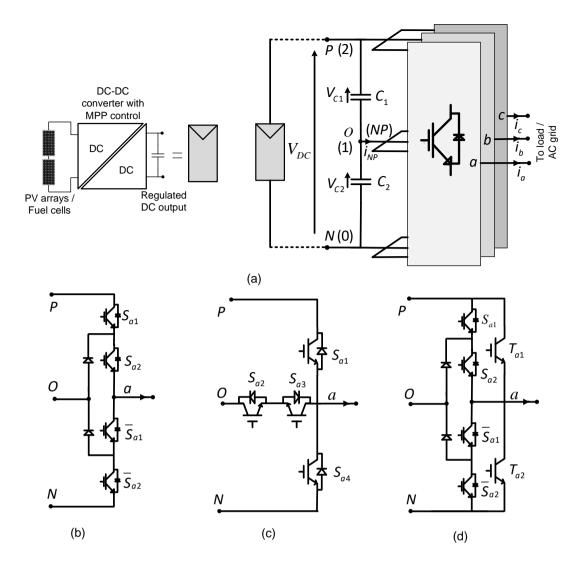

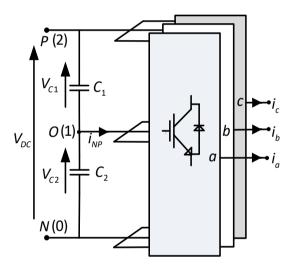

| Figure 3-1 (a) Circuit schematic of 3L NPCI, (b) 3L DCI leg, (c) T-type leg and (d) hybrid NPCI leg                                                                                                                                                                                                                                                                                                                                |

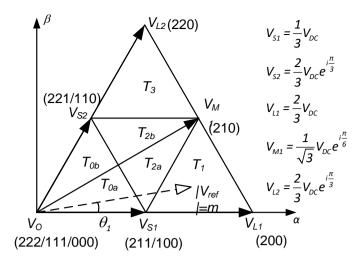

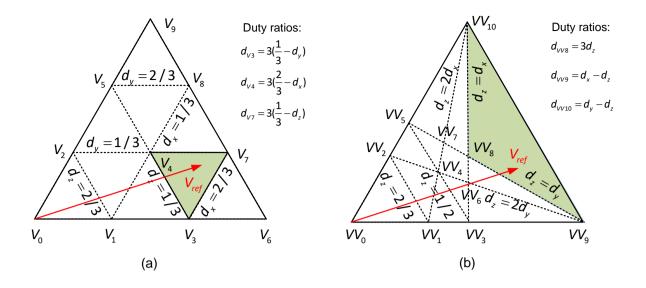

| Figure 3-2 Equivalent 2L SVD of 3L NPCI formed by the long vector and zero vector                                                                                                                                                                                                                                                                                                                                                  |

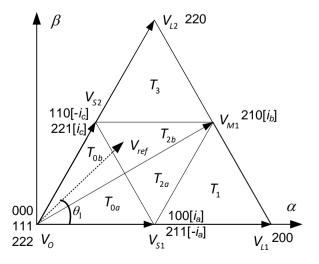

| Figure 3-3 First sector of 3L NPCI SVD divided into NTV sub-triangle regions                                                                                                                                                                                                                                                                                                                                                       |

| Figure 3-4 First sector of 3L NPCI SVD divided into NTVV sub-triangle regions                                                                                                                                                                                                                                                                                                                                                      |

| Figure 3-5 First sector of 3L NPCI SVD divided into STV sub-triangle regions                                                                                                                                                                                                                                                                                                                                                       |

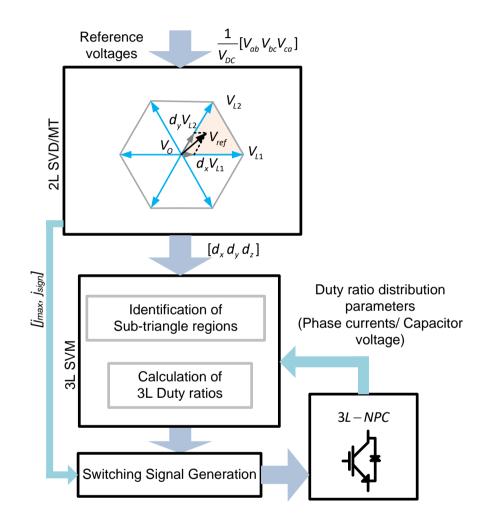

| Figure 3-6 Simplified block diagram of proposed modulation algorithm.                                                                                                                                                                                                                                                                                                                                                              |

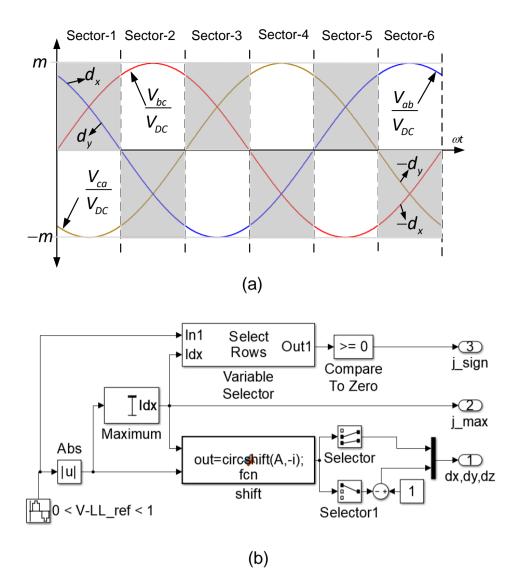

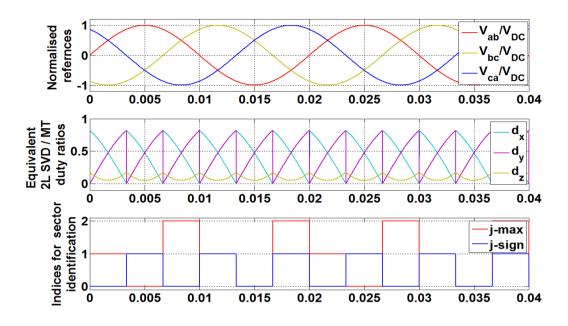

| Figure 3-7 Normalized three phase Line-to line voltages divided into sectors. (b) MATLAB Simulink model for 2L SVD duty ratios generation61                                                                                                                                                                                                                                                                                        |

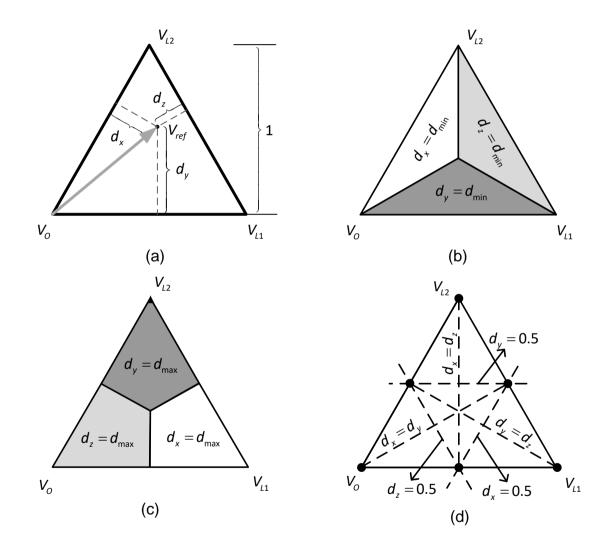

| Figure 3-8 Division of first sector of 3L SVD into various sub-triangle regions and the corresponding relations of MT duty ratios                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

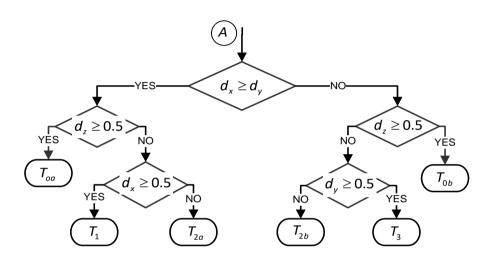

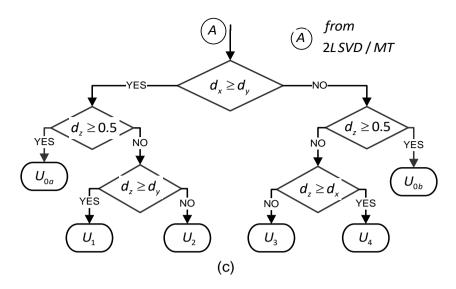

| Figure 3-9 Flow chart for identifying the sub-triangle regions from MT duty ratios. (a) NTV (b) NTVV and (c) STV                                                                                                                                                                                                                        |

| Figure 3-10 Block diagram of 3L NPCI65                                                                                                                                                                                                                                                                                                  |

| Figure 3-11 SVD of 4L MPCI and switching states67                                                                                                                                                                                                                                                                                       |

| Figure 3-12 Division of first sector of 4L SVD into various sub-triangle regions of (a) NTV modulation and (b) non-NTV modulation and the corresponding relations of MT duty ratios. 68                                                                                                                                                 |

| Figure 3-13 Equivalent 2L SVD / MT parameters for m=169                                                                                                                                                                                                                                                                                 |

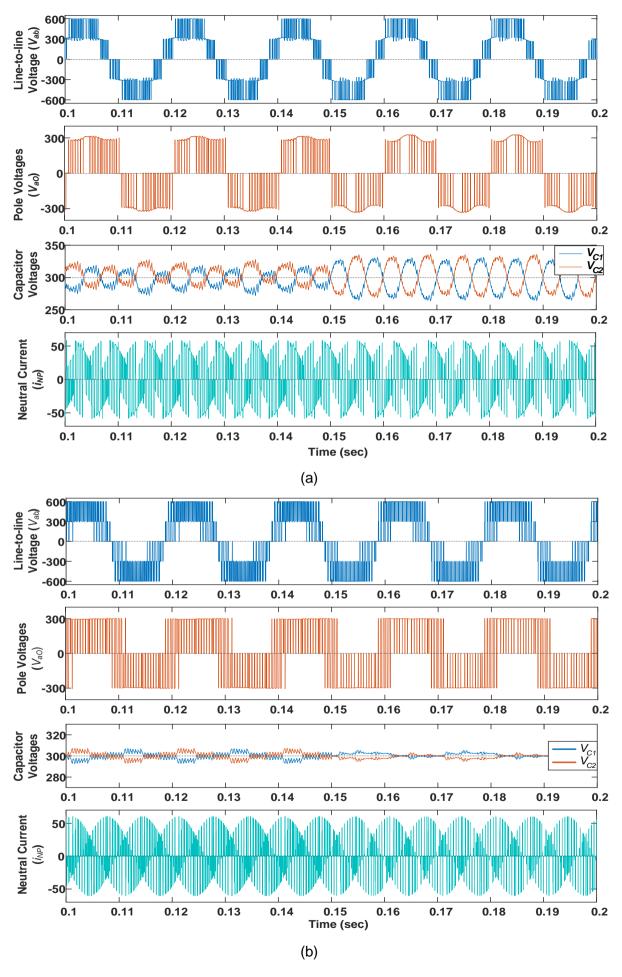

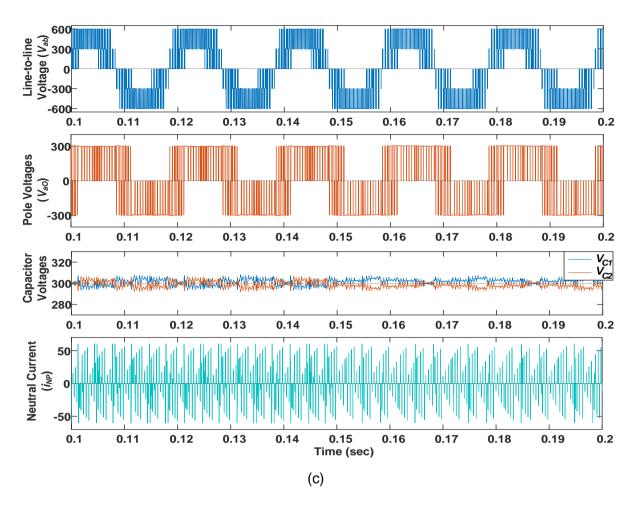

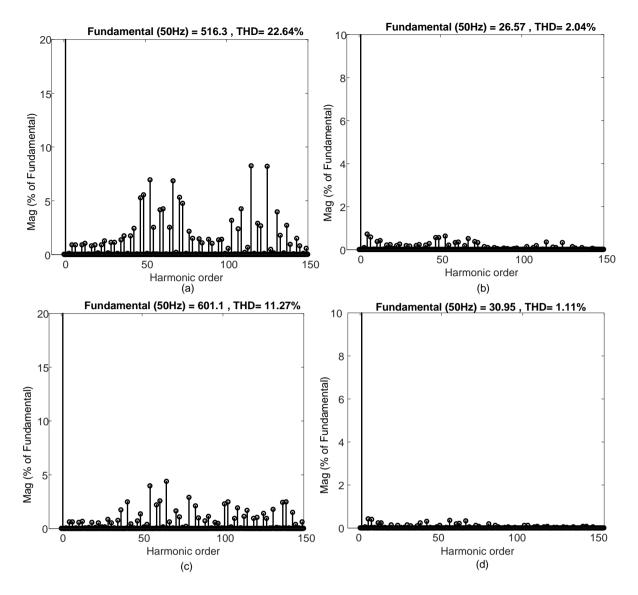

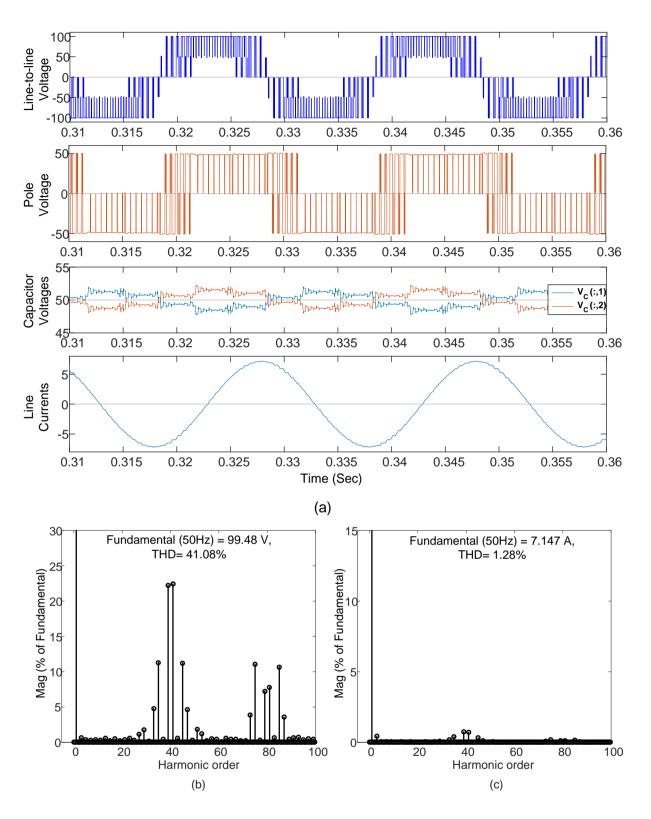

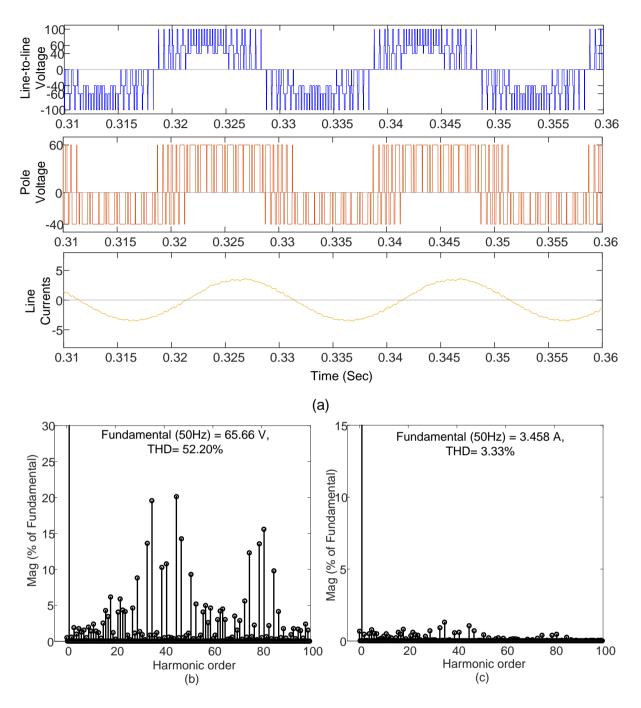

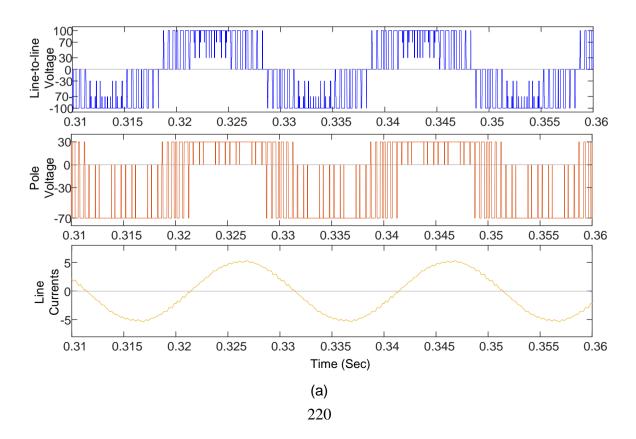

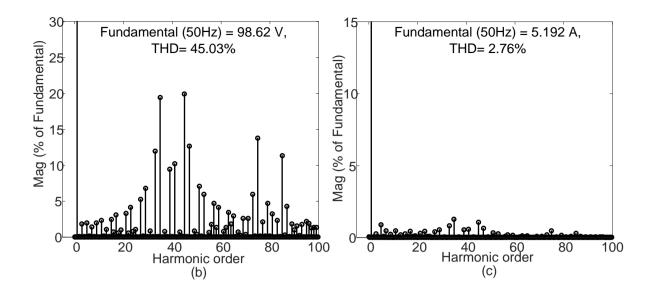

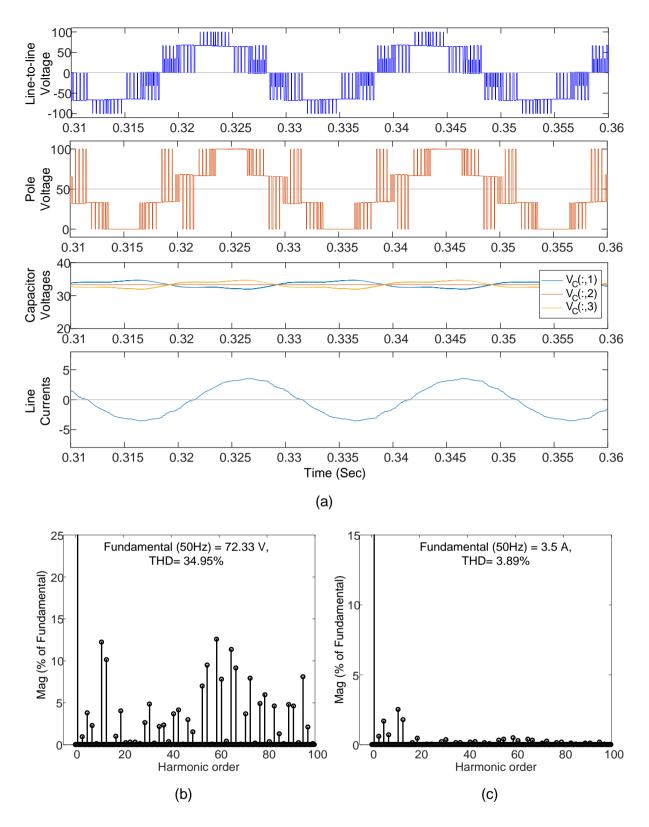

| Figure 3-14 Simulation results of NPCI with m=0.98 and and power factor 0.642 for (a) NTV, (b) NTVV and (c) STV                                                                                                                                                                                                                         |

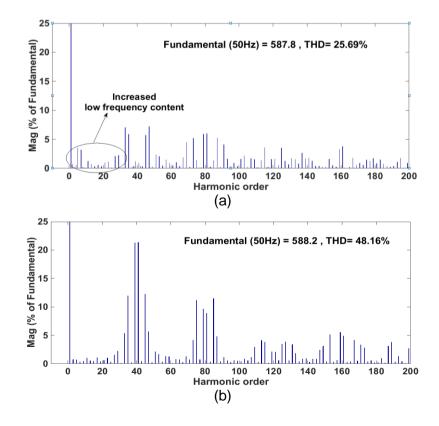

| Figure 3-15 Harmonic spectrum of line-to-line voltages for (a) NTV, (b) NTVV and (c) STV for the operating conditions shown in Figure 3-14 (Fundamental is 100 %)                                                                                                                                                                       |

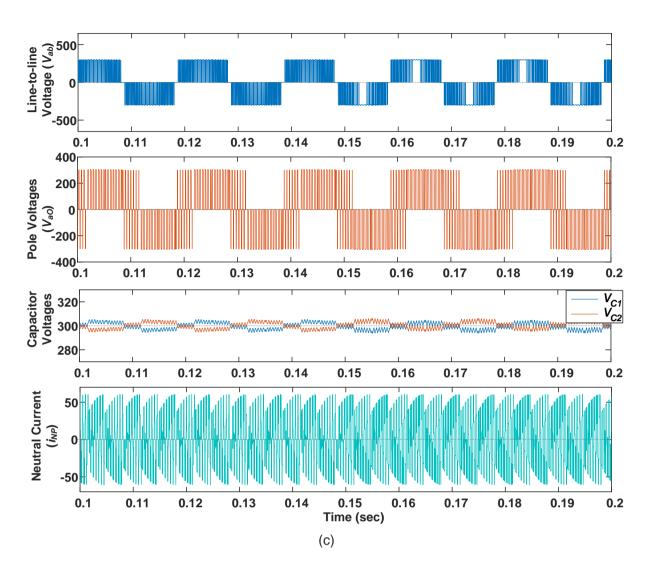

| Figure 3-16 Simulation results of NPCI with $m$ =0.5 and power factor 0.642 lagging for (a) NTV, (b) NTVV/STV using Sequence-1 and (c) NTVV/STV using Sequence-2                                                                                                                                                                        |

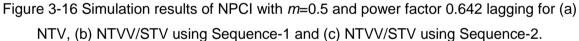

| Figure 3-17 Capacitor voltage balancing performance of NTV and non-NTV modulation methods for <i>m</i> =0.98 phase current=60A peak and power factor 0.642 lagging                                                                                                                                                                      |

| Figure 4-1 Sector-1 of 3L NPCI divided into NTV triangle regions                                                                                                                                                                                                                                                                        |

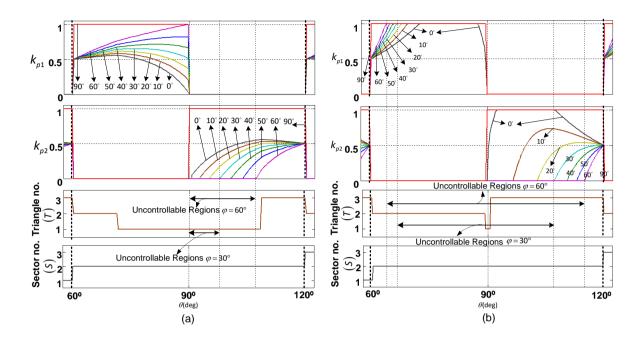

| Figure 4-2 Plot of $k_{p1}$ and $k_{p2}$ for different lagging power factor angles ( $\varphi$ ) when modulation index is (a) $m = 2/3$ and (b) $m = 0.98$                                                                                                                                                                              |

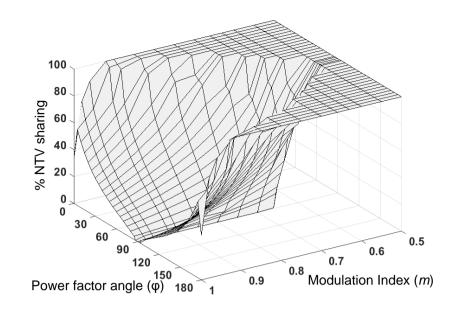

| Figure 4-3 Percentage duration of NTV operation in each fundamental cycle to eliminate NP voltage oscillations as a function of m and $\phi$ (lagging)                                                                                                                                                                                  |

| Figure 4-4 Sector-1 of 3L NPCI divided into (a) STV triangle regions and (b) NTVV triangle                                                                                                                                                                                                                                              |

| regions                                                                                                                                                                                                                                                                                                                                 |

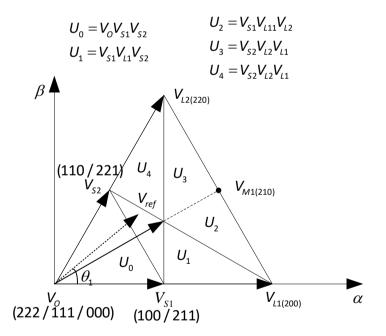

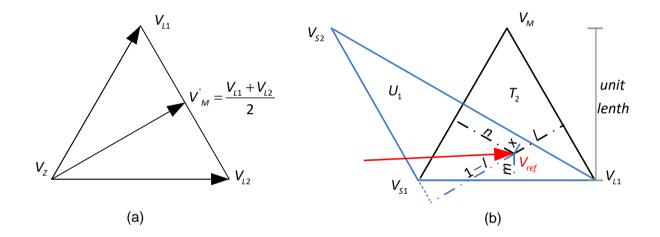

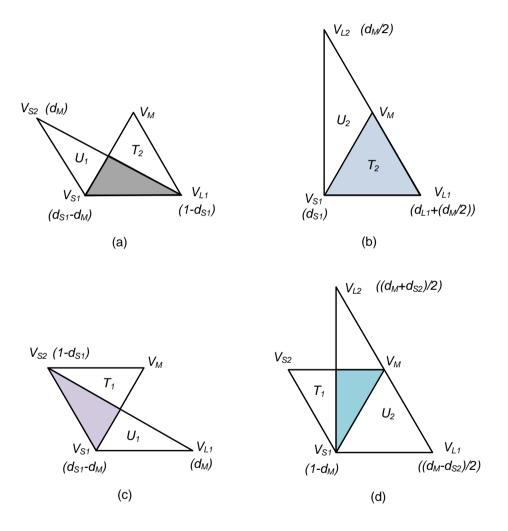

| Figure 4-5 Relation between NTV and non-NTV duty ratios: (a) Virtual medium vector $V_{M}$                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                         |

| Figure 4-5 Relation between NTV and non-NTV duty ratios: (a) Virtual medium vector $v'_{M}$ formed by two long vectors $v_{l_1}, v_{l_2}$ , (b) Duty ratio relations between NTV and STV triangles. 85 Figure 4-6 Distribution of NTV duty ratios to STV triangles for the region $0 \le \gamma \le 30^\circ$ (a) $T_2 \rightarrow U_1$ |

| Figure 4-5 Relation between NTV and non-NTV duty ratios: (a) Virtual medium vector $v'_{_{M}}$ formed by two long vectors $v_{_{L1}}, v_{_{L2}}$ , (b) Duty ratio relations between NTV and STV triangles. 85                                                                                                                           |

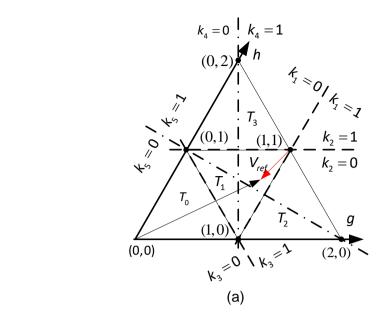

| Figure 4-8 First sector of space vector diagram 60° coordinate system. (a) Representation of variables in $g-h$ plane, (b) Transformation from $g-h$ plane to $g1-h1$ plane for $T_0, T_2, T_3$ and (c) Transformation from $g-h$ plane to $g1-h1$ plane for $T_1$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

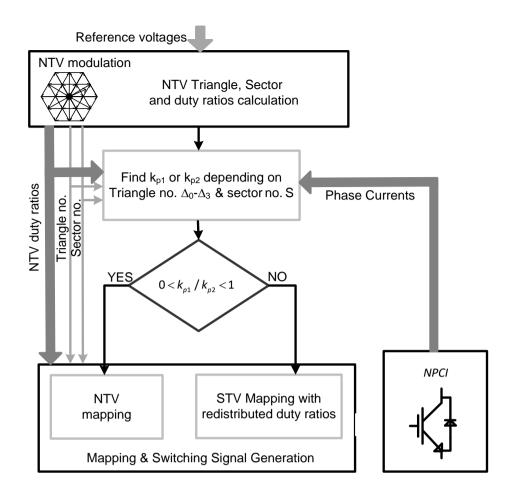

| Figure 4-9 Block diagram of the proposed hybrid modulation algorithm for NTV-STV92                                                                                                                                                                                 |

| Figure 4-10 (a)Sector-1 of SVD representing the trajectory $V_{ref}$ for different modulation indices.                                                                                                                                                             |

| (b) Simplified algorithm (hybrid NTV-SSTV modulation) by neglecting STV triangles $T_1$ and $T_4$ for $m \ge 2/3$                                                                                                                                                  |

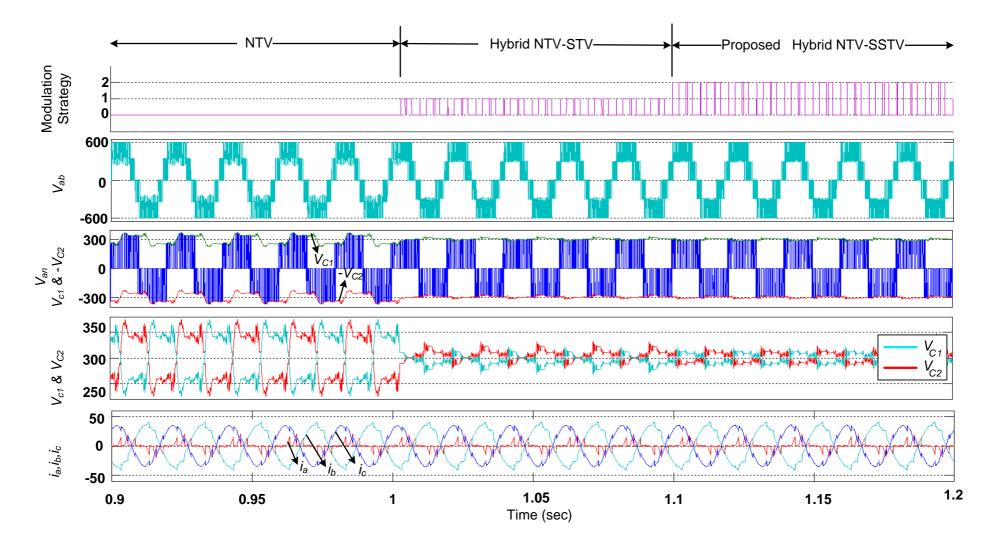

| Figure 4-11 Simulation waveforms at m=0.98 and power factor 0.5 lagging (NTV sharing=14.68 %)                                                                                                                                                                      |

| Figure 4-12 Simulation waveforms at m=0.83 and power factor 0.259 lagging (NTV sharing= 17.2 %)                                                                                                                                                                    |

| Figure 4-13 Simulation waveforms for a non-linear and un-balanced load                                                                                                                                                                                             |

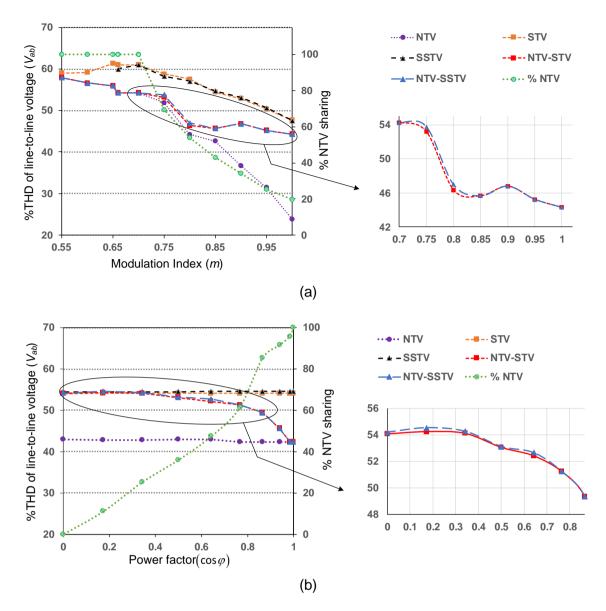

| Figure 4-14 Line to line voltage % THD for various modulation schemes: (a) with respect to the modulation index for power factor of 0.707 lagging. (b) with respect to power factor angle for m=0.83                                                               |

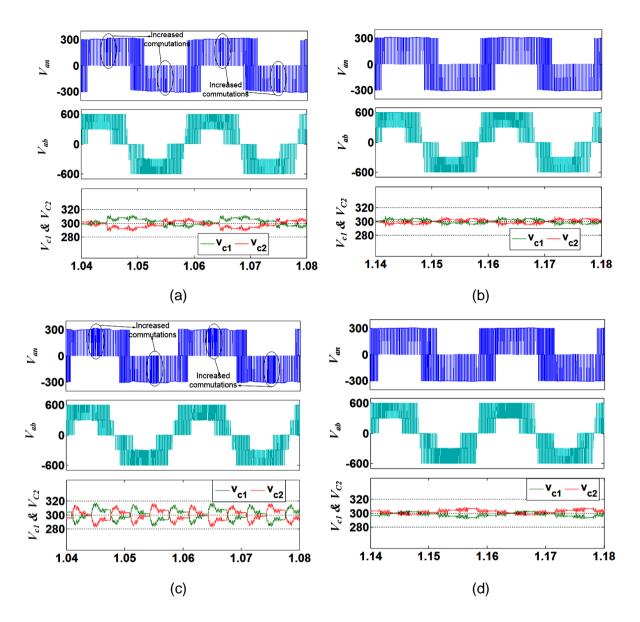

| Figure 4-15 Comparison of hybrid NTV-STV and hybrid NTV-SSTV modulations: (a) hybrid NTV-STV (b) NTV-SSTV modulation for m=0.98 and power factor 0.5 lagging and (c) Hybrid NTV-STV (d) Hybrid NTV-SSTV modulation for m=0.83 and power factor 0.259 lagging 101   |

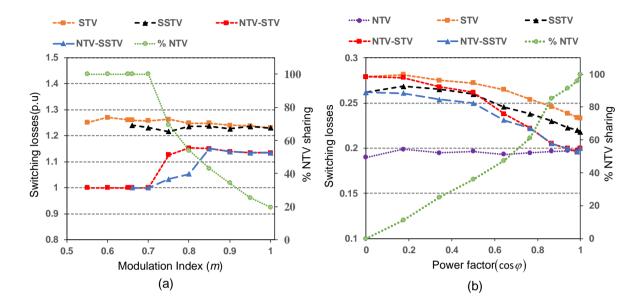

| Figure 4-16 Switching losses for various modulation schemes: (a) Variation of switching losses as a function of modulation index for power factor 0.707 lagging; (b) Variation of switching losses as a function of power factor angle for m=0.83                  |

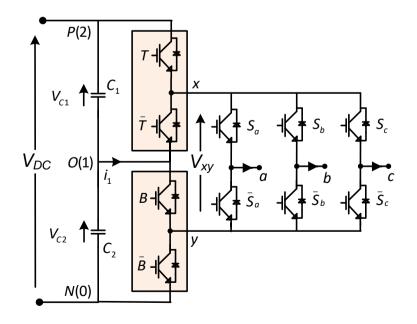

| Figure 5-1 Hybrid 2/3L NPCI topology 106                                                                                                                                                                                                                           |

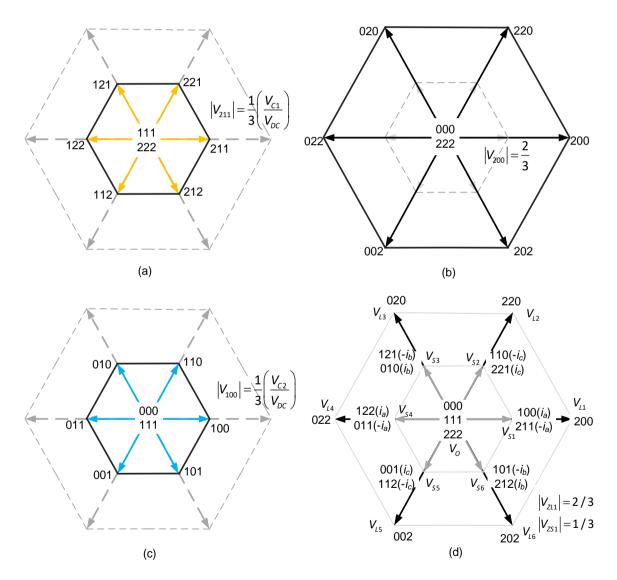

| Figure 5-2 Space vector diagram of hybrid 2/3L NPCI for (a) Mode-1, (b) Mode-2 and (c) Mode-3 and (d) Total SVD                                                                                                                                                    |

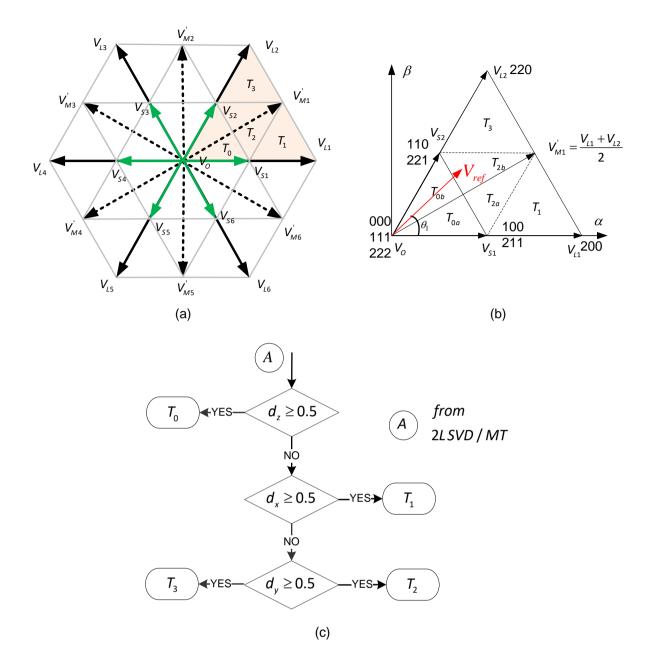

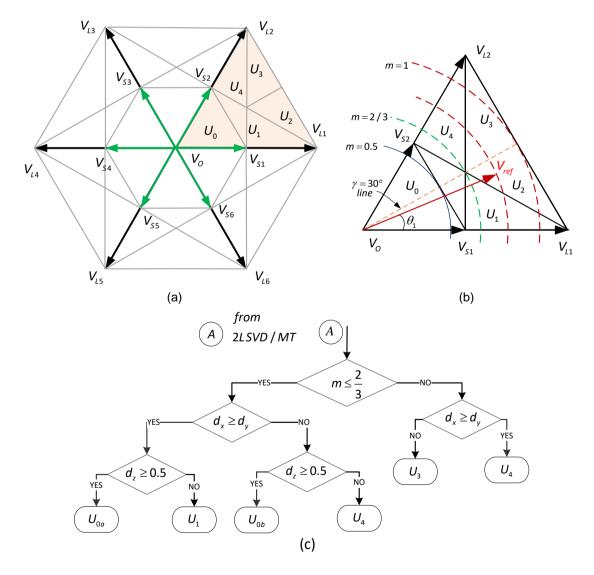

| Figure 5-3 (a) SVD of hybrid 2/3L NPCI with introduction of virtual medium vectors, (b) Sector-<br>1 of VV-based modulation and (c) flowchart for identification of sub-triangle regions                                                                           |

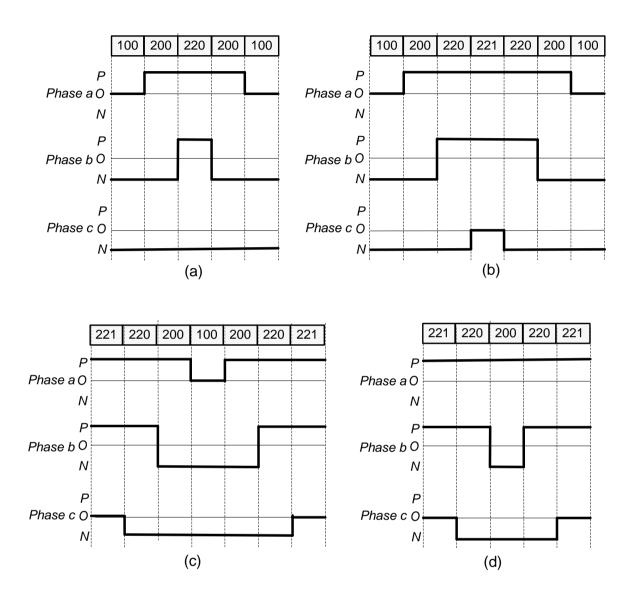

| Figure 5-4 Switching sequence for the VV-based modulation of hybrid 2/3L NPCI in sector-1 when $v_{ref}$ is located in sub-triangles (a) $T_1$ , (b) $T_{2a}$ , (c) $T_{2b}$ and (d) $T_3$ incorporating quarter wave symmetry.                                    |

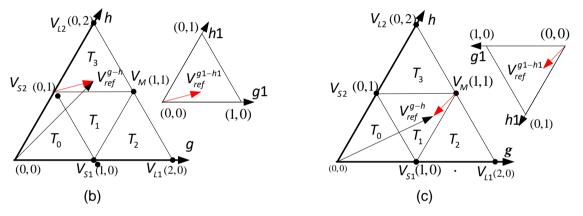

| Figure 5-5 SVD of hybrid 2/3L NPCI divided into various sub-triangle regions                                                                                                                                                                                       |

| Figure 5-6 Switching sequence for the STV-based modulation of hybrid 2/3L NPCI in sector-1 when $V_{ref}$ is located in sub-triangles (a) $U_1$ , (b) $U_2$ , (c) $U_3$ and (d) $U_4$                                                                              |

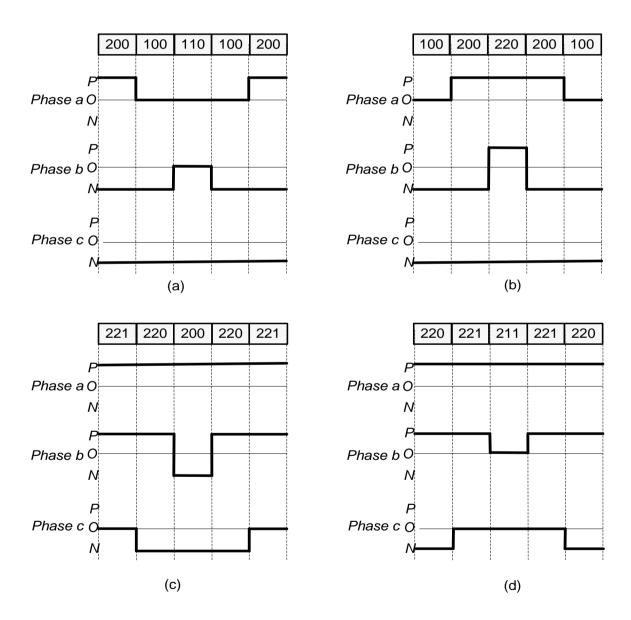

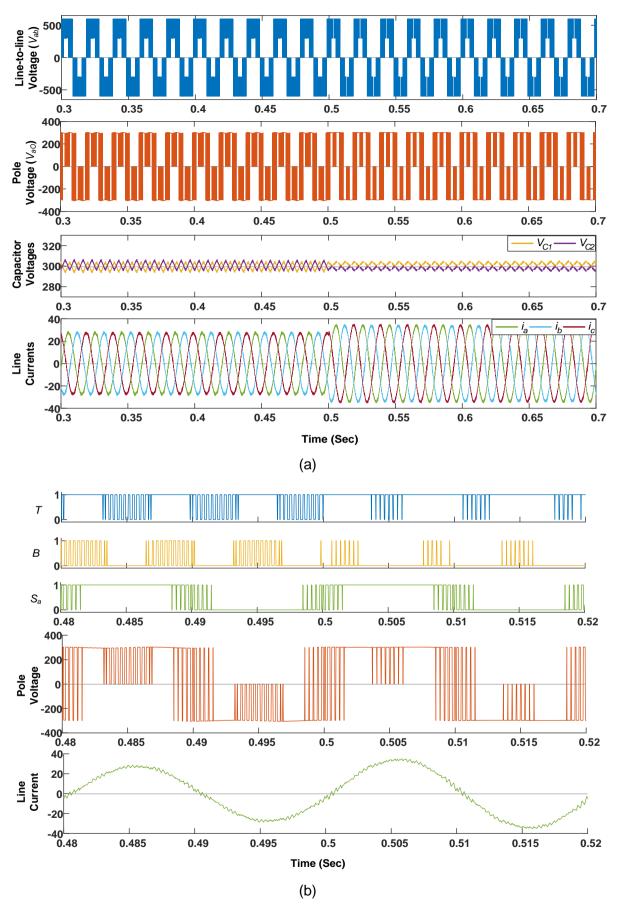

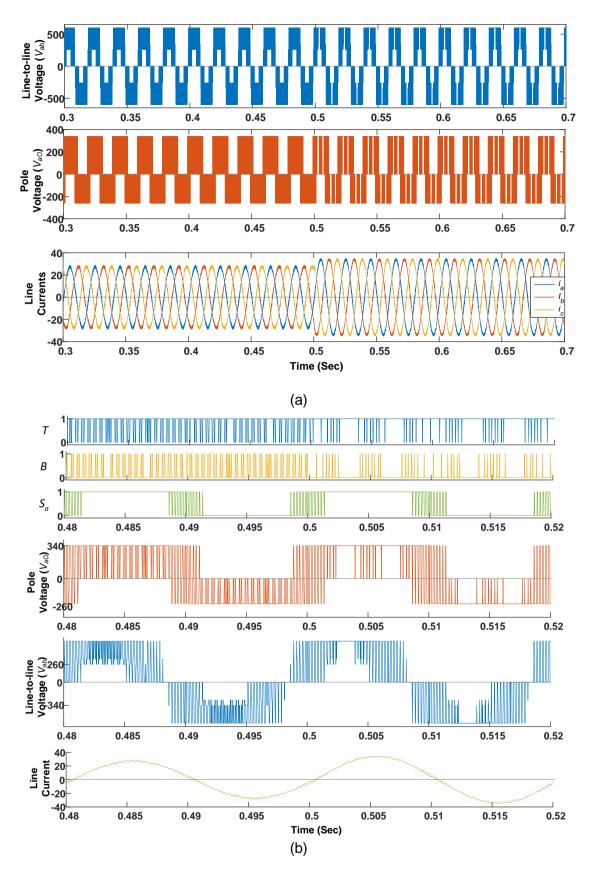

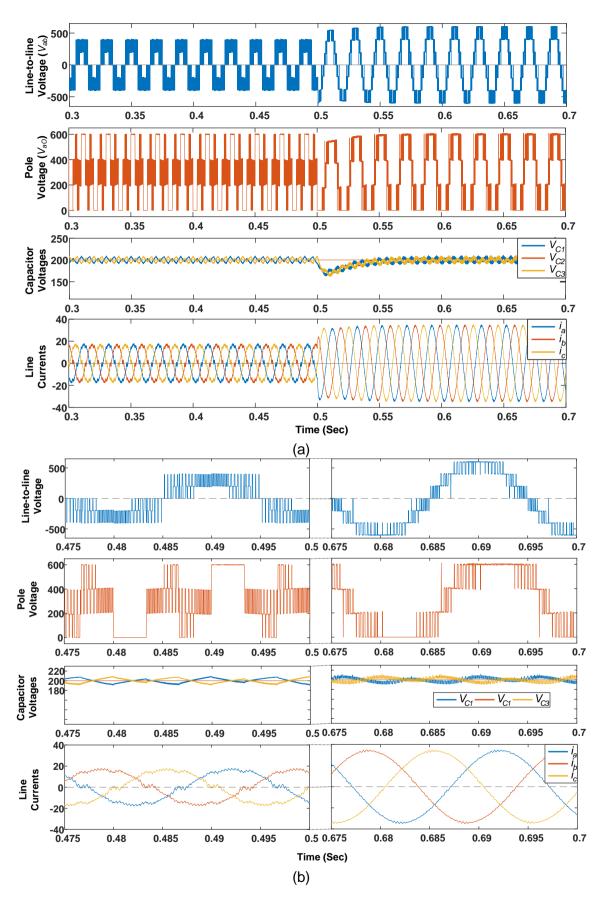

| Figure 5-7 (a) Simulation results of hybrid 2/3L NPCI with VV-based modulation; (b) Zoomed view and switching signals ( $m = 0.65$ for time $\le 0.5$ and $m = 0.75$ for time $> 0.5$ )                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

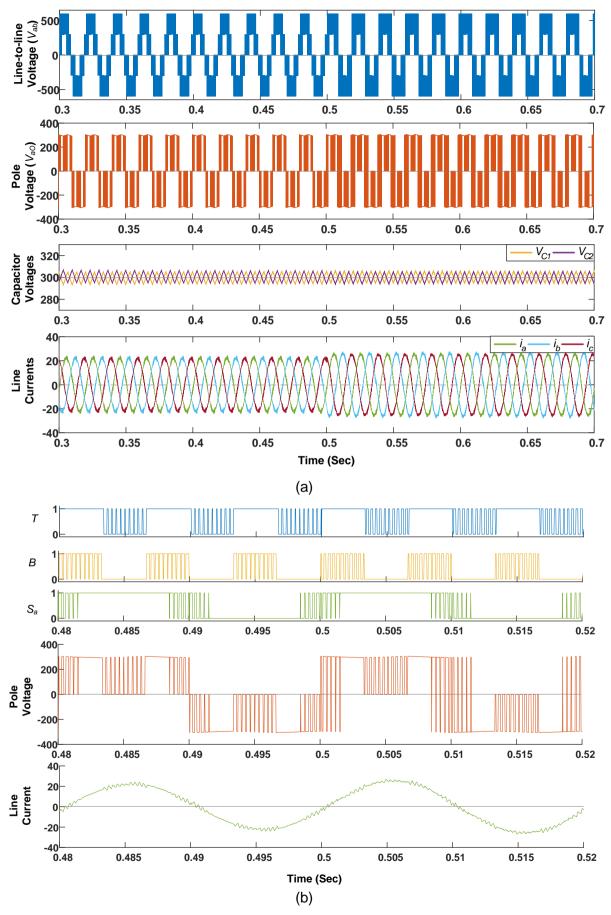

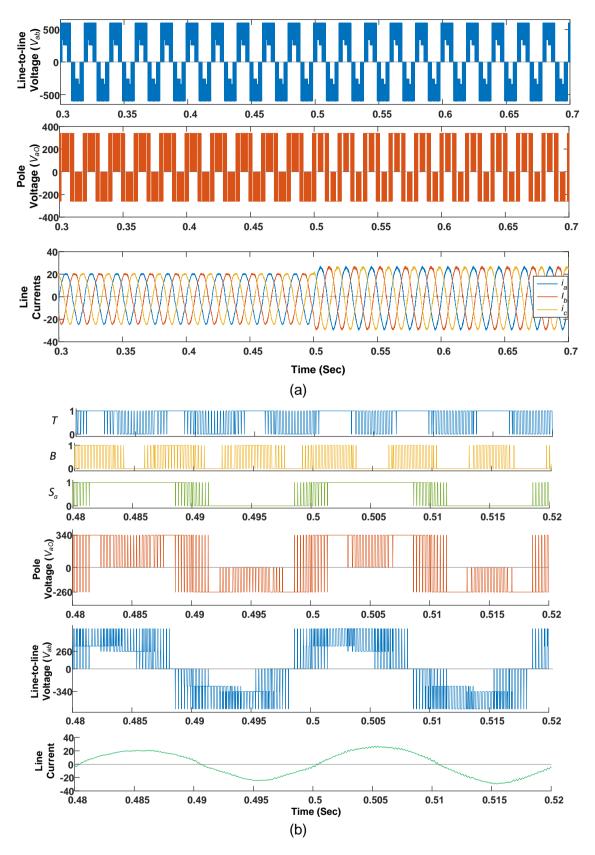

| Figure 5-8 (a) Simulation results of hybrid 2/3L NPCI VV-based modulation; (b) Zoomed view and switching signals ( $m=0.8$ for time $\le 0.5$ and $m=1$ for time $> 0.5$ )                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 5-9 (a) Simulation results of hybrid 2/3L NPCI with STV based modulation; (b) Zoomed view and switching signals ( $m = 0.65$ for time $\le 0.5$ and $m = 0.75$ for time $> 0.5$ )                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 5-10 (a) Simulation results of hybrid 2/3L NPCI with STV-based modulation; (b) Zoomed view and switching signals ( $m=0.8$ for time $\le 0.5$ and $m=1$ for time $>0.5$ )                                                                                                                                                                                                                                                                                                                                                                                                                               |

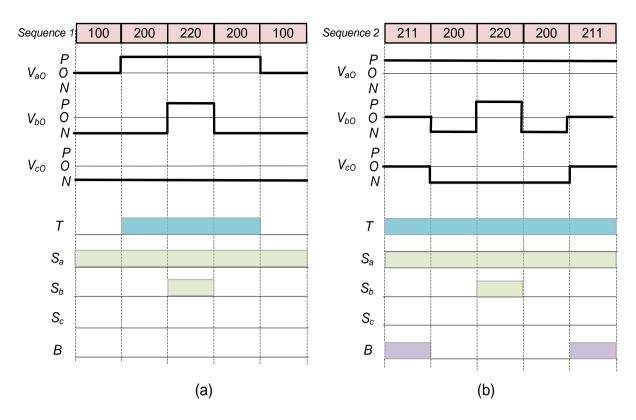

| Figure 5-11 Possible switching sequences for the STV modulation when $v_{ref}$ is located in $U_2$ and switching signals of the hybrid 2/3L NPCI; (a) Sequence-1 and (b) sequence-2                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 5-12 Possible switching sequences for the VV modulation when $V_{ref}$ is located in and switching signals of the hybrid 2/3L NPCI; (a) Sequence-1 and (b) sequence-2                                                                                                                                                                                                                                                                                                                                                                                                                                   |

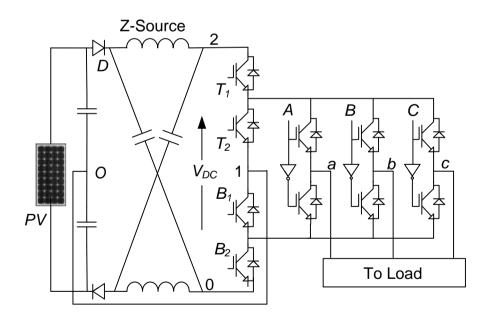

| Figure 5-13 Circuit of hybrid 2/3L ZNPCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

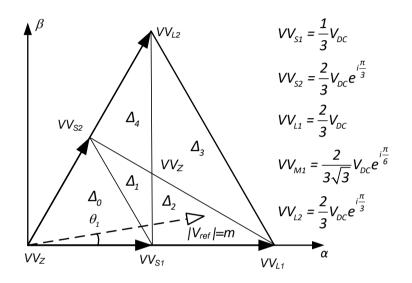

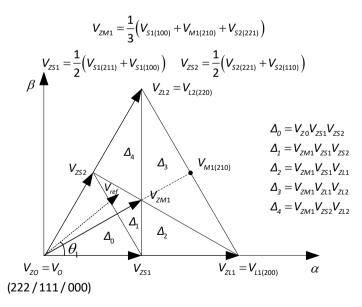

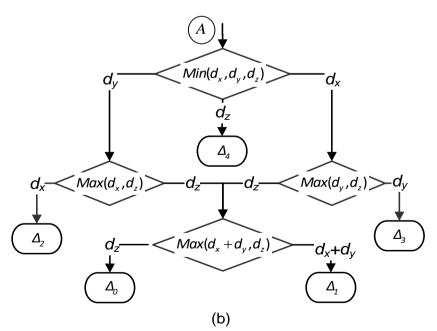

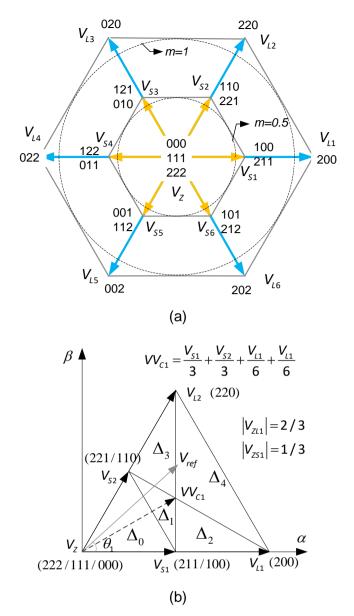

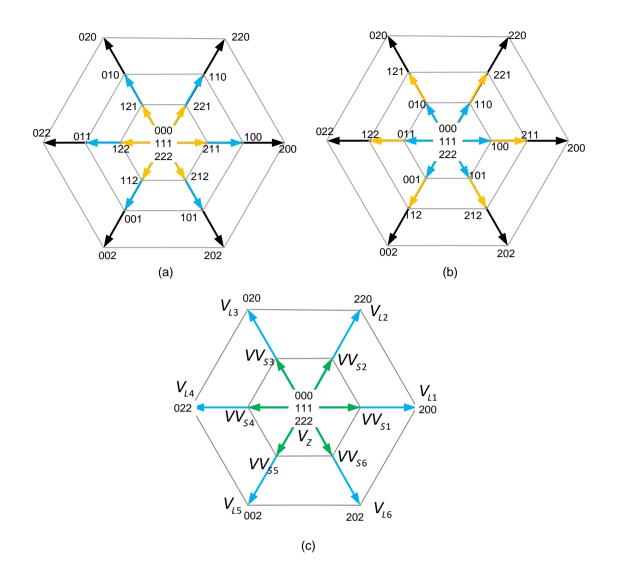

| regions. $(\Delta_0 = V_Z V_{S1} V_{S2}; \Delta_1 = V V_{C1} V_{S1} V_{S2}; \Delta_2 = V V_{C1} V_{S1} V_{L1}; \Delta_3 = V V_{C1} V_{L2} V_{S2}; \Delta_4 = V V_{C1} V_{L1} V_{L2})$                                                                                                                                                                                                                                                                                                                                                                                                                          |

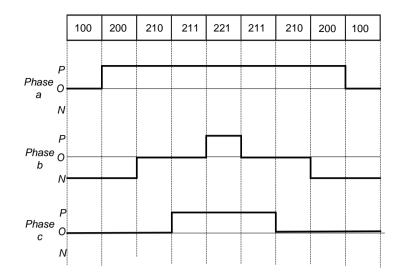

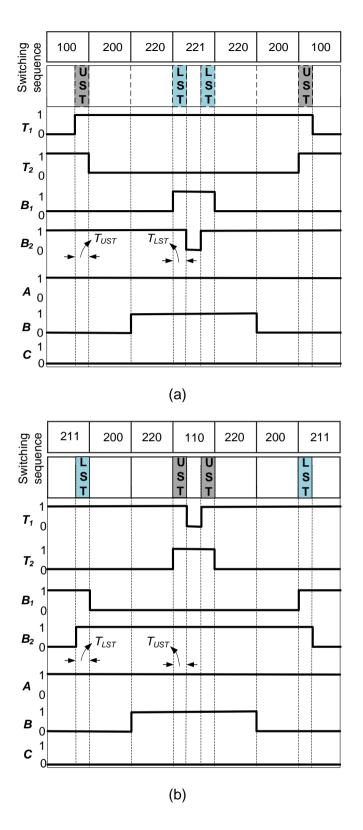

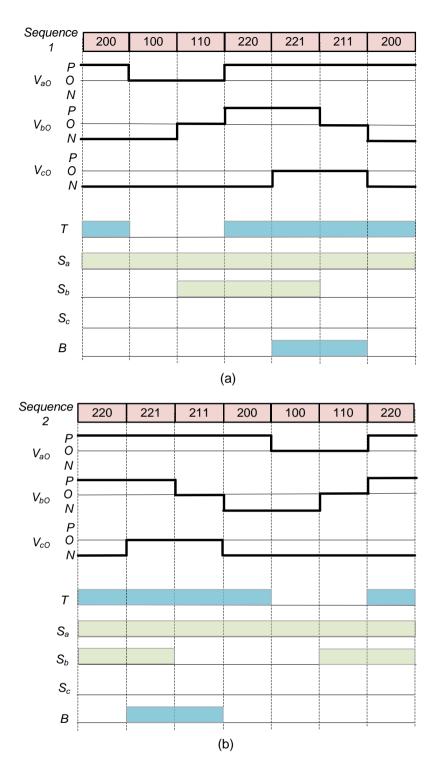

| Figure 5-15 Switching sequences for $0.5 < m \le 1$ : (a) SS1 and (b) SS2 (UST: Upper shoot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

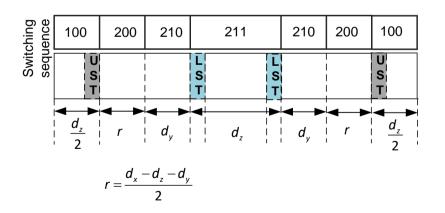

| Figure 5-15 Switching sequences for $0.5 < m \le 1$ : (a) SS1 and (b) SS2 (UST: Upper shoot through; LST: Lower shoot through)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| through; LST: Lower shoot through) 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

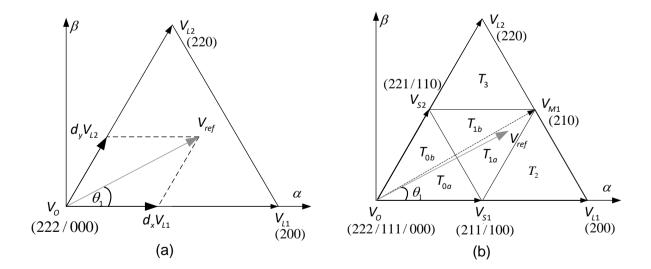

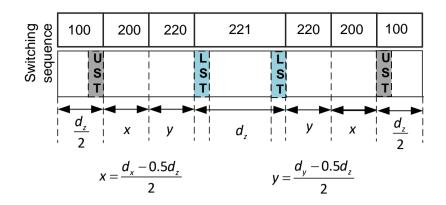

| through; LST: Lower shoot through). 126<br>Figure 5-16 Sector-1 of space vector diagram (SVD) of (a) equivalent 2L VSI and (b) 3L VSI.<br>127<br>Figure 5-17 Switching sequence for 3L NPCI VSI when $V_{ref}$ is located in $T_2$ using the<br>conventional SVM. 128                                                                                                                                                                                                                                                                                                                                          |

| through; LST: Lower shoot through)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| through; LST: Lower shoot through)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

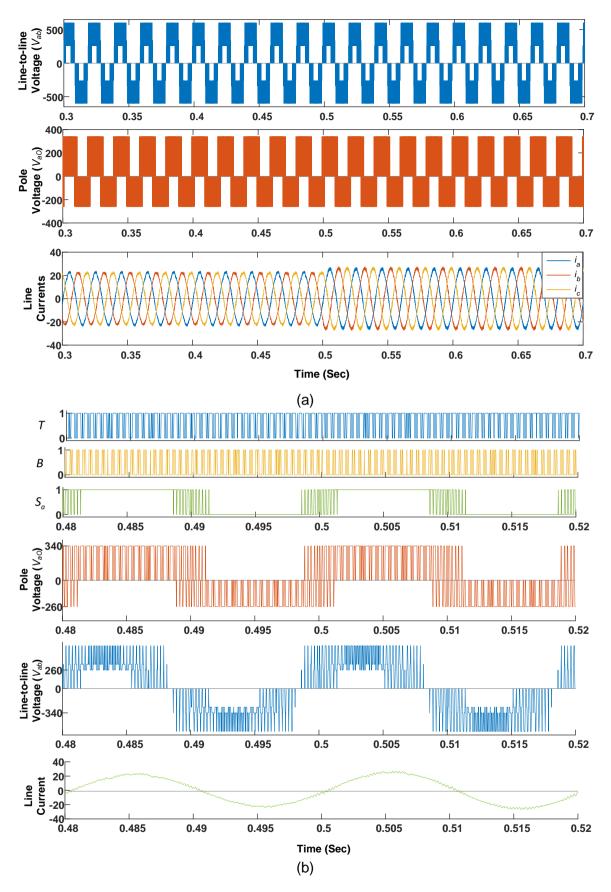

| through; LST: Lower shoot through). 126<br>Figure 5-16 Sector-1 of space vector diagram (SVD) of (a) equivalent 2L VSI and (b) 3L VSI.<br>127<br>Figure 5-17 Switching sequence for 3L NPCI VSI when $V_{ref}$ is located in $T_2$ using the<br>conventional SVM. 128<br>Figure 5-18 Switching sequence SS1 for hybrid 2/3L NPCI when $v_{ref}$ is located in $\Delta_4$ using the<br>proposed VV modulation. 129<br>Figure 5-19 Simulation results (a) without ST states and (b) Zoomed View along with the<br>switching signals for $m=0.65$ (from t=1.2 sec to t=1.25 sec) and $m=0.82$ (after t=1.25 sec). |

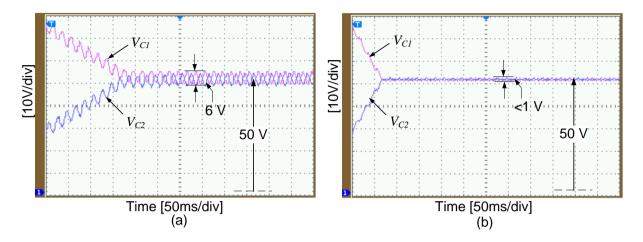

| Figure 5-22 SVD of the hybrid 2/3L NPCI for (a) $V_{c1} > V_{c2}$ , (b) $V_{c2} > V_{c2}$ and (c) when small vectors                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| are replaced with the virtual small vectors                                                                                                                                                                                           |

| Figure 5-23 switching sequences for DC voltage unbalance compensation                                                                                                                                                                 |

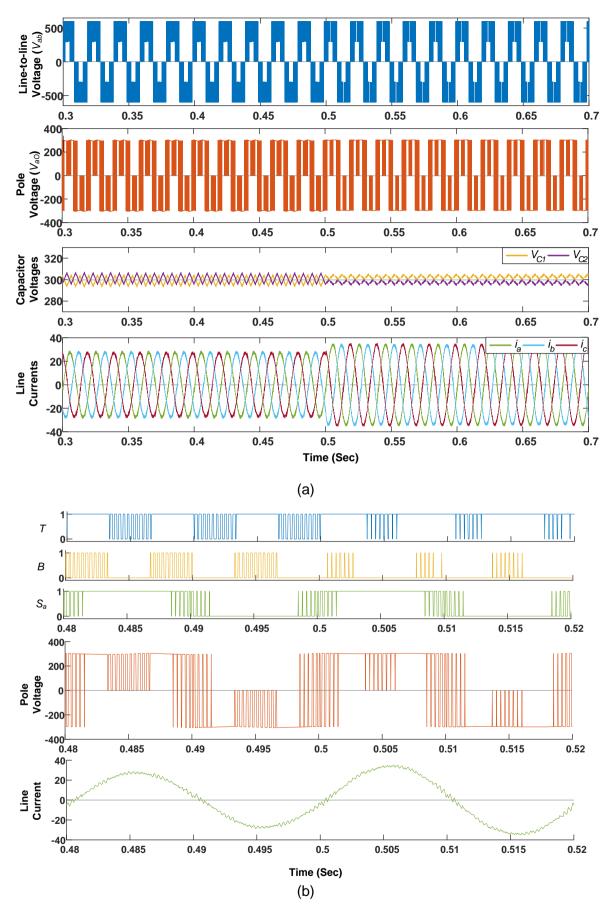

| Figure 5-24 Simulation results of hybrid 2/3L NPCI with unbalanced DC sources ( $m = 0.65$ from t=0.3 sec to t=0.5 sec and $m = 0.75$ after t=0.5); (b) Zoomed view of (a) and switching signals.                                     |

| Figure 5-25 Simulation results of hybrid 2/3L NPCI with unbalanced DC sources ( $m = 0.8$ from                                                                                                                                        |

| t=0.3 sec to t=0.5 sec and $m=1.0$ after t=0.5 sec); (b) Zoomed view (a) and switching signals.                                                                                                                                       |

|                                                                                                                                                                                                                                       |

| Figure 5-26 Simulation results of hybrid 2/3L NPCI with unbalanced DC sources using conventional VV-based modulation ( $m$ =0.65 from t=0.3 sec to t=0.5 sec and $m$ =0.8 after t=0.5 sec); (b) Zoomed view (a) and switching signals |

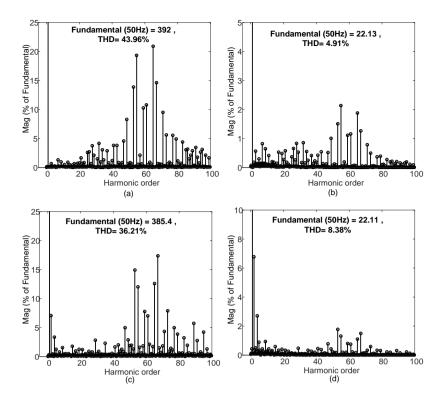

| Figure 5-27 THD Comparison of modulation methods for m=0.65: new VV-based modulation (a) Line-to-line voltage and (b) line current and conventional VV-based modulation (c) Line-to-line voltage and (d) line current                 |

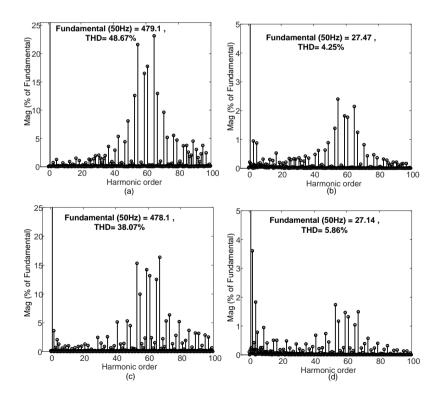

| Figure 5-28 THD Comparison of modulation methods for m=0.8: new VV-based modulation (a)<br>Line-to-line voltage and (b) line current and conventional VV-based modulation (c) Line-to-line<br>voltage and (d) line current            |

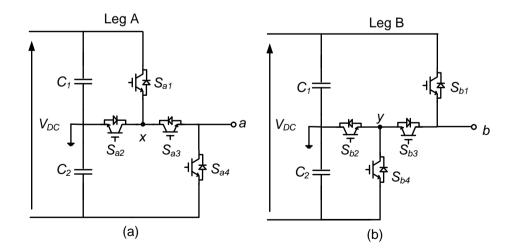

| Figure 6-1 T-type Inverter with (a) Common collector; (b) Common emitter configuration [43]                                                                                                                                           |

|                                                                                                                                                                                                                                       |

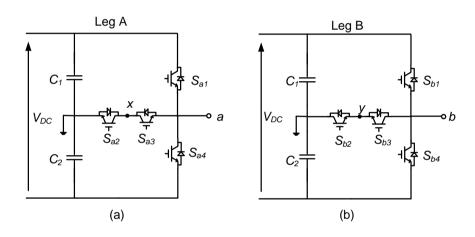

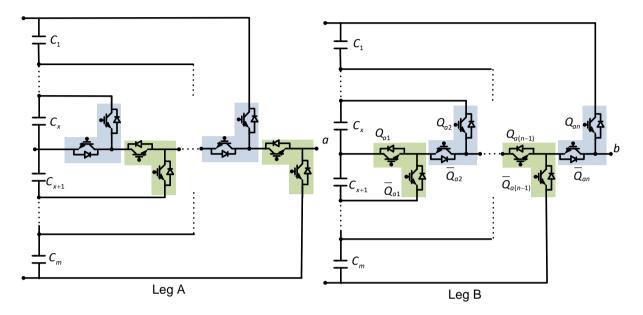

| Figure 6-2 Two modified 3L inverter legs142                                                                                                                                                                                           |

| Figure 6-3 Modified T-type three level legs: (a) leg A and (b) leg B                                                                                                                                                                  |

| Figure 6-4 Addition of half bridge cells at top and bottom to increase the voltage levels in leg A and leg B (Type-1)                                                                                                                 |

| Figure 6-5 Increasing the voltage levels by cascading the modified T-type legs at the output terminal (Type-2)                                                                                                                        |

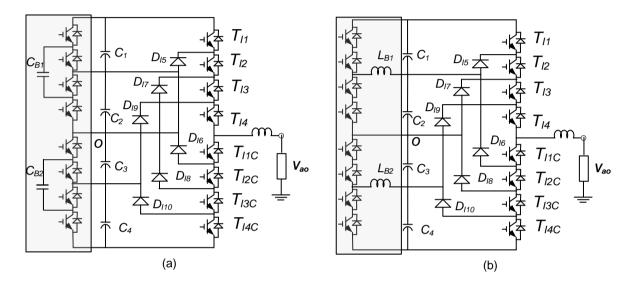

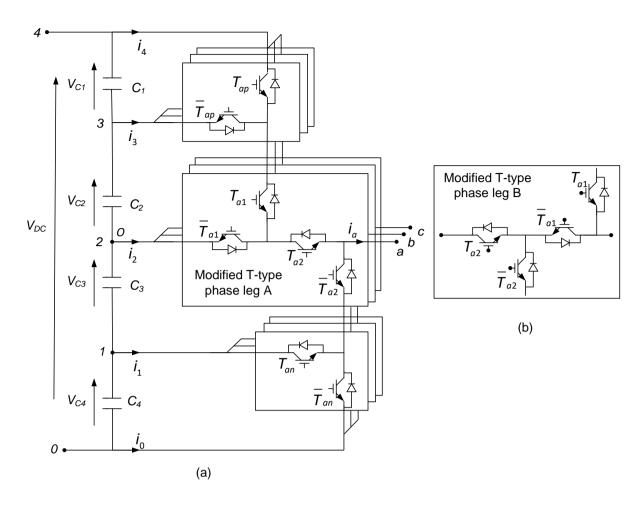

| Figure 6-6 Circuit diagram of (a) proposed 5L modified T-type MPCI with leg A which can be replaced with (b) Modified T-type phase leg B                                                                                              |

| Figure 6-7 Current paths output voltage levels of 5L modified T-type MPCI leg A 147                                                                                                                                                   |

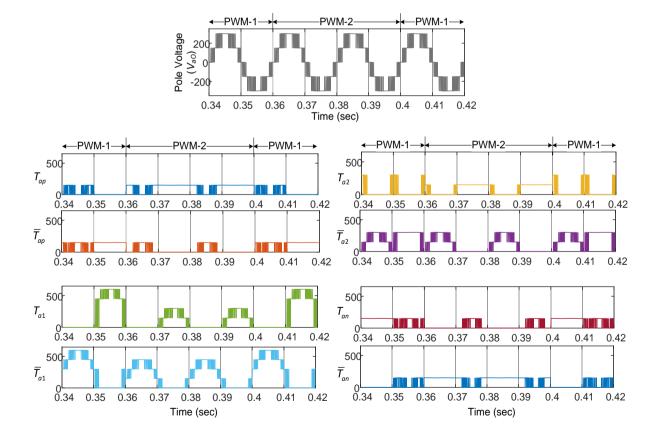

| Figure 6-8 Voltage stress across each switch with corresponding voltage levels by PWM-1 (0.34 to 0.36 sec. and 0.4 to 0.42 sec.) And PWM-2 (0.36 to 0.4 sec.)                                                                         |

| 10 0.30 Sec. and 0.4 to 0.42 Sec.) And F WM-2 (0.30 to 0.4 Sec.)                                                                                                                                                                      |

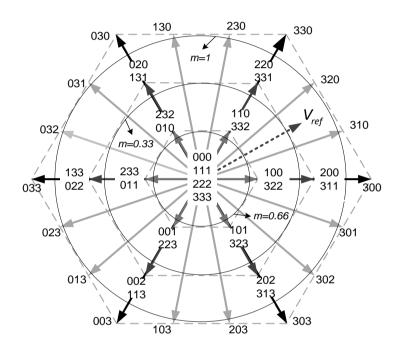

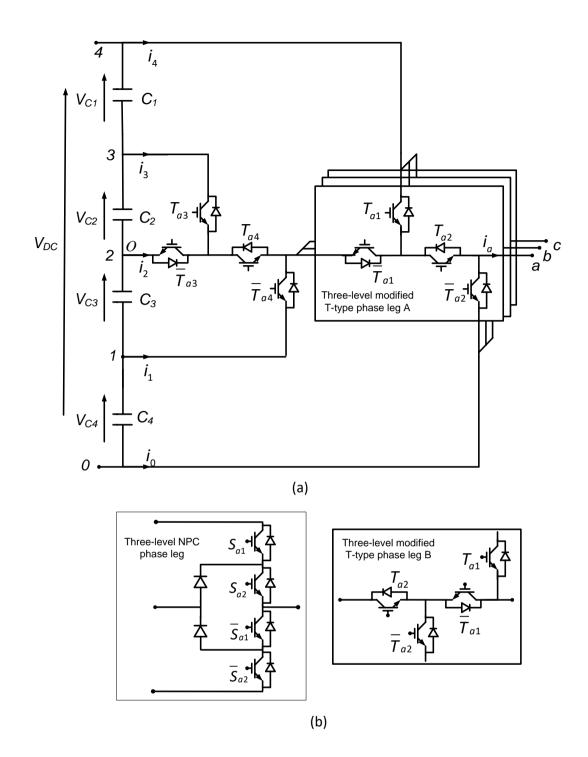

| Figure 6-10 Space vector diagram of 4L RSS MPCI151                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6-11 First sector of 4L RSS MPCI SVD divided into sub-triangle regions                                                                                                                   |

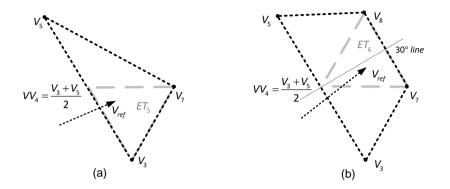

| Figure 6-12 Voltage vectors used for synthesising $V_{ref}$ when it is in (a) $ET_5$ and (b) $ET_6$ 153                                                                                         |

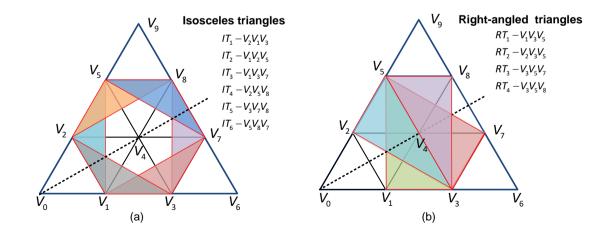

| Figure 6-13 First sector of 4L RSS MPCI SVD divided into (a) Isosceles triangle regions, (b) right angle triangle regions (RT) and sub-regions for $V_{ref}$ synthesis for proposed modulation. |

|                                                                                                                                                                                                 |

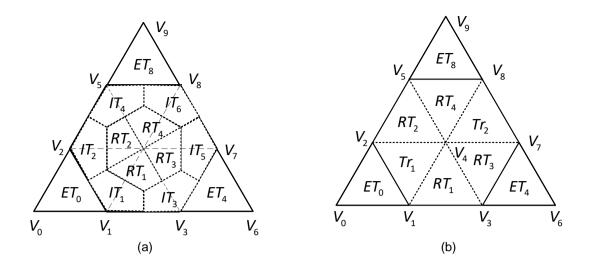

| Figure 6-14 Regions for selection of sub-triangle regions for (a) STV-based modulation and (b) VV-based modulation                                                                              |

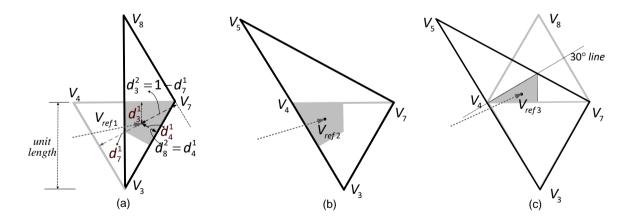

| Figure 6-15 Duty ratio relations between ET and IT regions (Where, in $d_p^q$ , subscript $p$ denotes                                                                                           |

| the vector number and super script $q$ denotes the type of modulation: $q=1$ for NTV modulation<br>and $q=2$ for proposed modulation.)                                                          |

| Figure 6-16 Proposed modulation algorithm for 4L RSS MPCI                                                                                                                                       |

| Figure 6-17 Relations of NTV sub-triangle regions with in the ET regions                                                                                                                        |

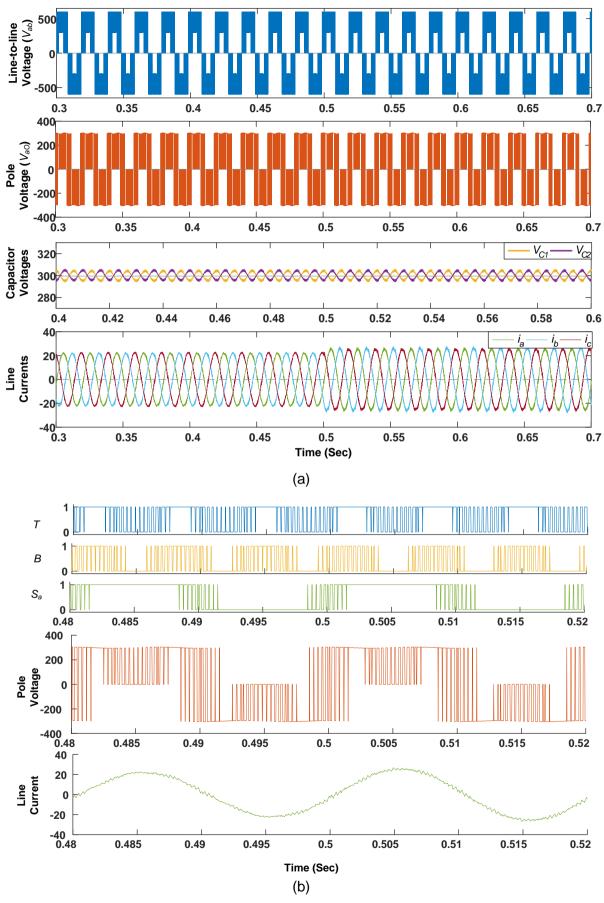

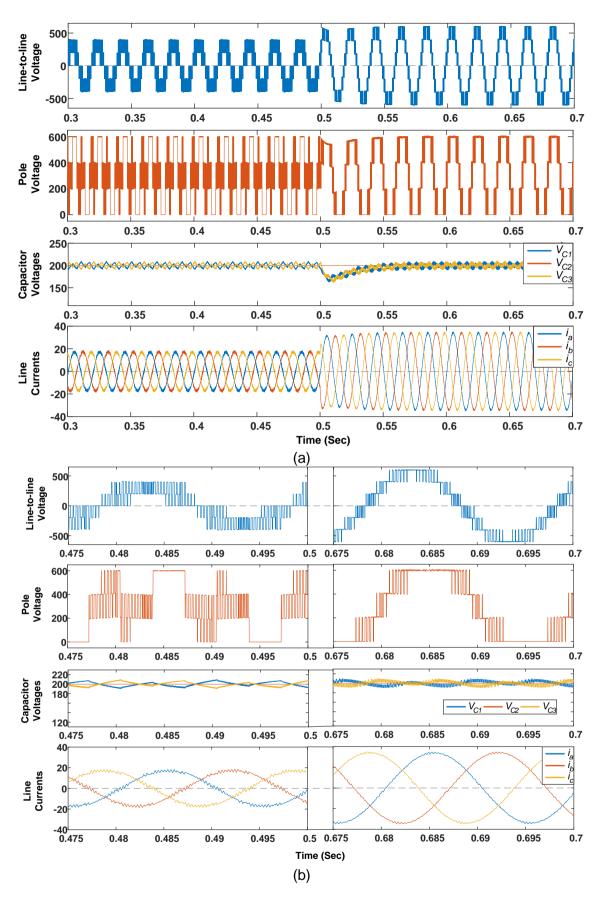

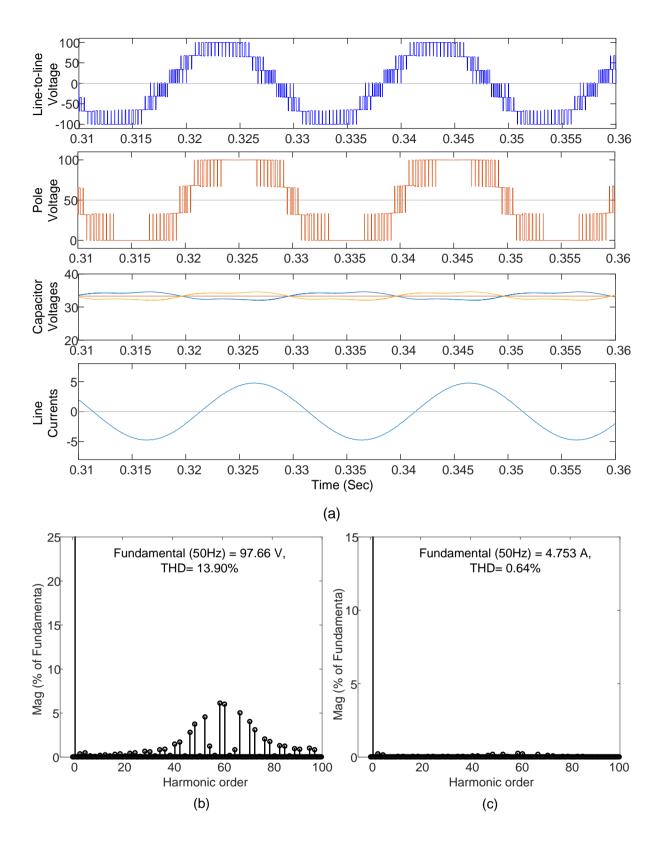

| Figure 6-18 Simulation results of 4L RSS MPCI with VV-based modulation for (a) m=0.75 (0.3 to 0.5 sec) and m=1(0.5 to 0.7 sec) and (b) Zoomed view of (a)                                       |

| Figure 6-19 Simulation results of 4L RSS MPCI with STV-based modulation for (a) m=0.75 (0.3 to 0.5 sec) and m=1(0.5 to 0.7 sec) and (b) Zoomed view of (a)                                      |

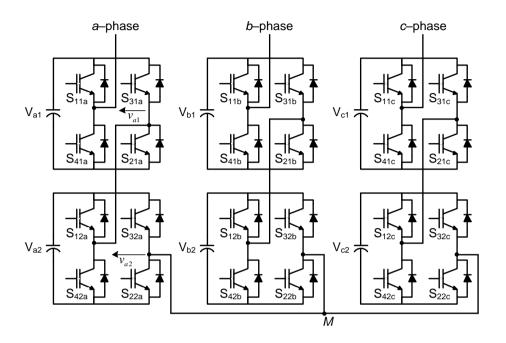

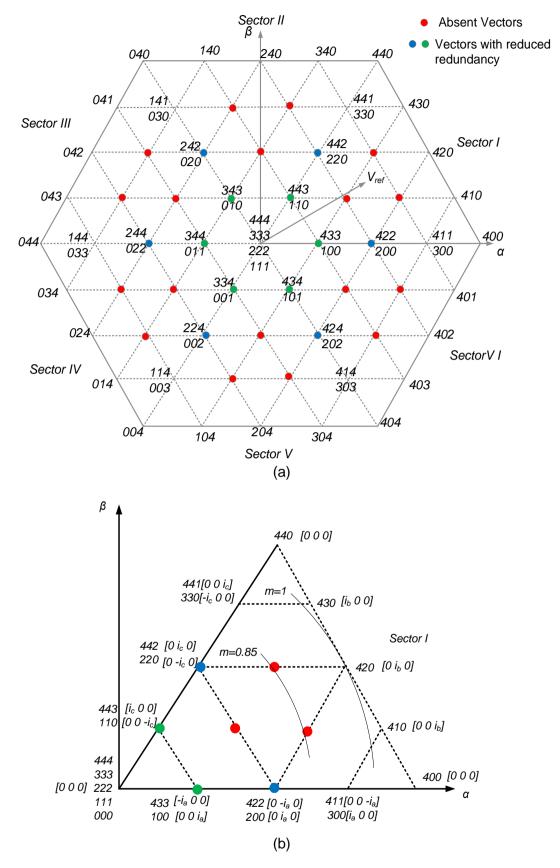

| Figure 6-20 Type-1 5L RSS MPCI formed by half bridge modules, (b) Other alternatives for modified T-Type leg                                                                                    |

| Figure 6-21 SVD of Type-1 5L RSS MPCI formed by half bridge modules: (a) Complete SVD and (b) Sector-1 of SVD                                                                                   |

| Figure 6-22 Type-1 5L RSS MPCI for switching state '311' 165                                                                                                                                    |

| Figure 6-23 A 5L RSS MPCI (Type-2) formed by half bridge modules, (b) Other alternatives for modified T-Type leg                                                                                |

| Figure 6-24 SVD of 5L RSS MPCI formed by half bridge modules: (a) Complete SVD and (b) Sector-1 of SVD                                                                                          |

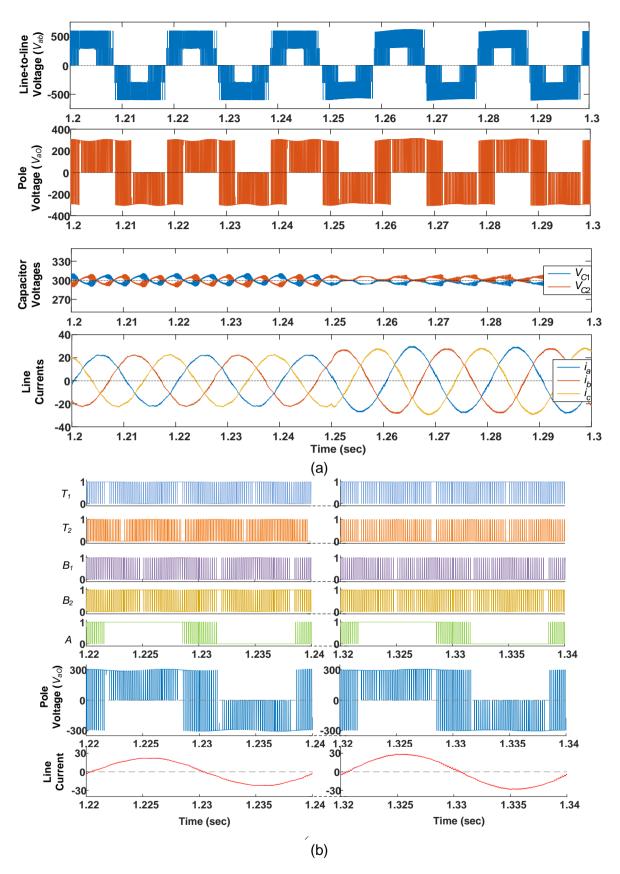

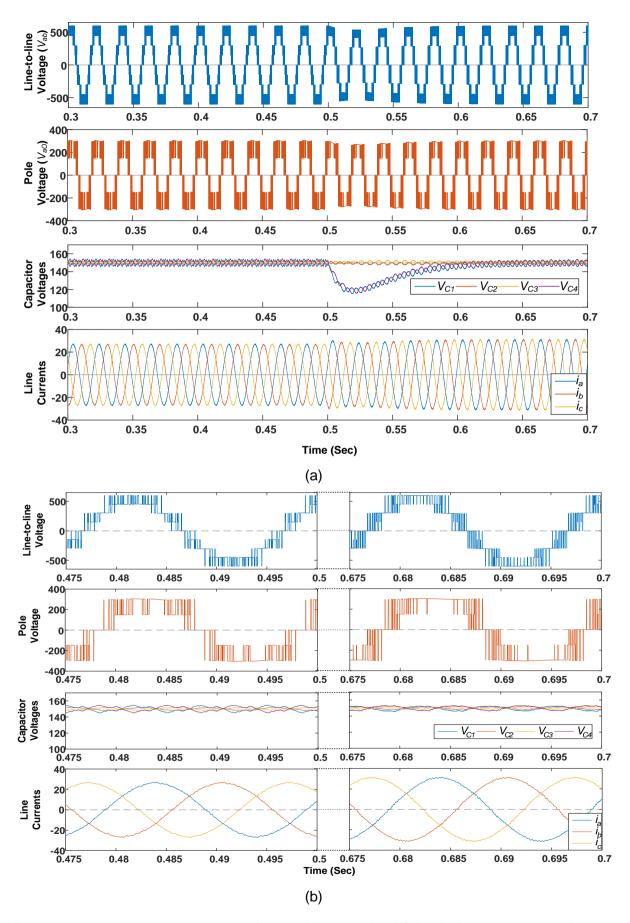

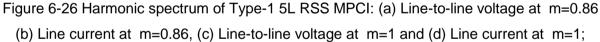

| Figure 6-25 Voltage and current waveforms of Type-1 5L RSS MPCI for change in modulation index: (a) m=0.86 up to t=0.5sec and m=1 from t=0.5 sec onwards and (b) Zoomed view of (a)             |

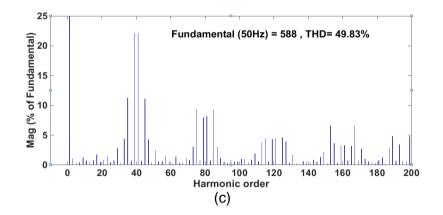

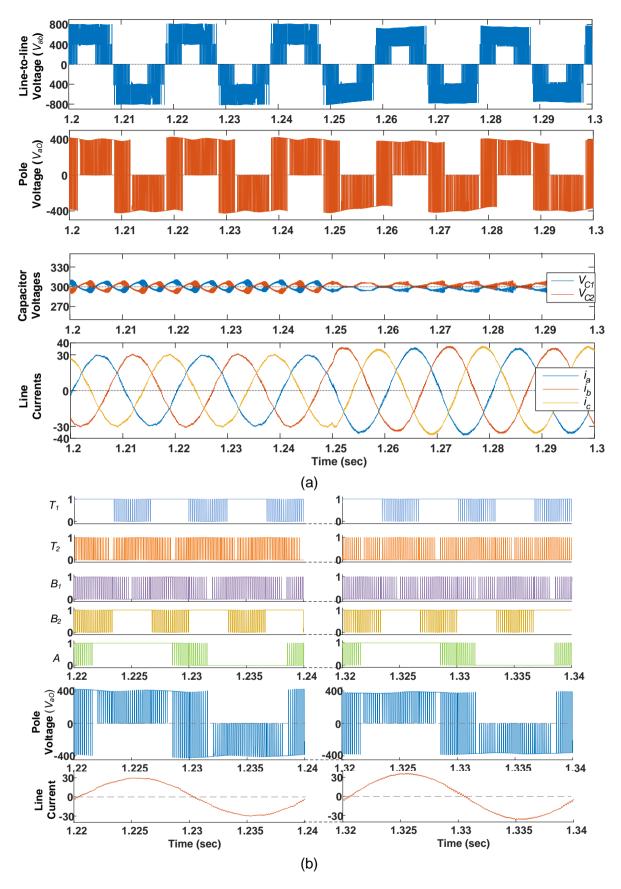

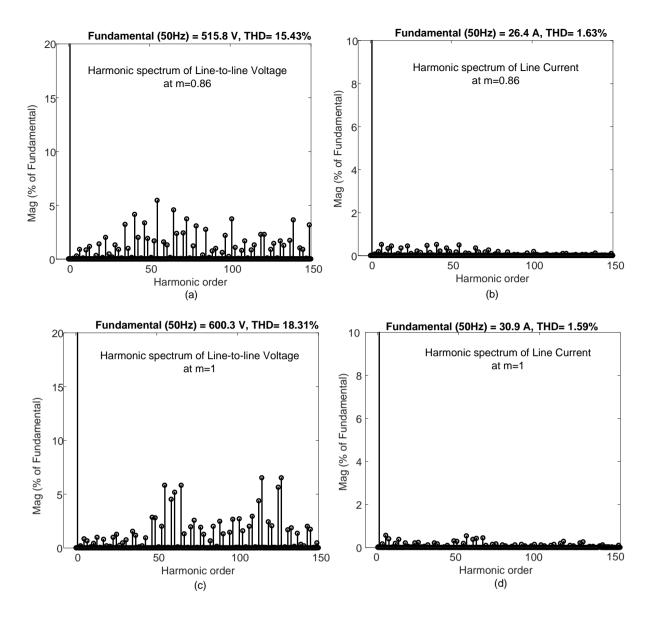

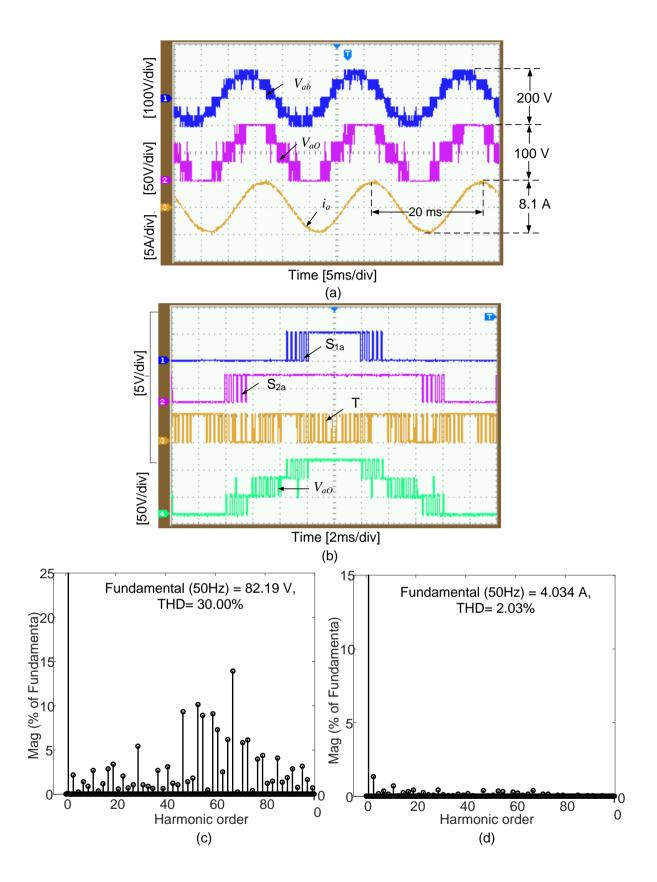

| Figure 6-26 Harmonic spectrum of Type-1 5L RSS MPCI: (a) Line-to-line voltage at m=0.86 (b)                                                                                                     |

Line current at m=0.86, (c) Line-to-line voltage at m=1 and (d) Line current at m=1; ...... 170

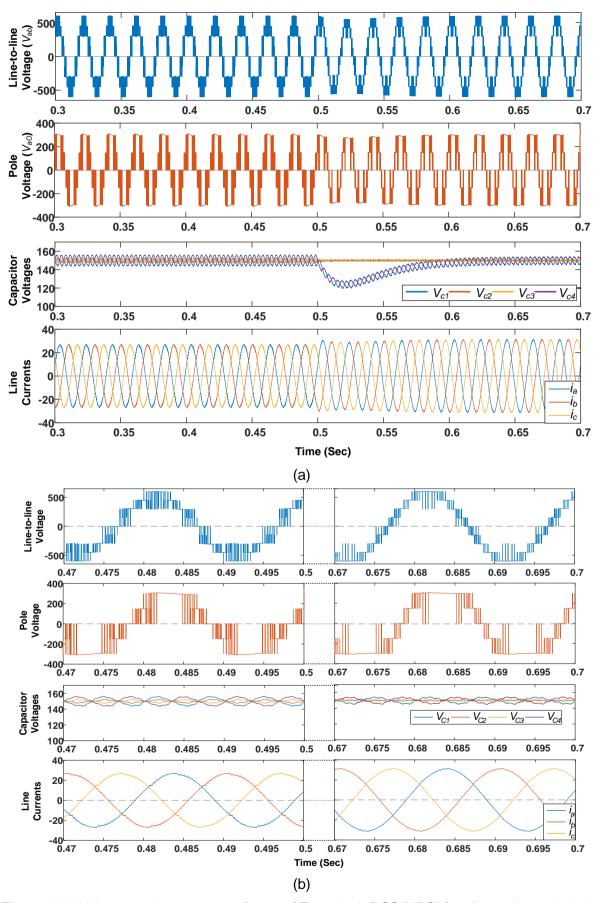

| Figure 6-28 Harmonic spectrum of Type-2 5L RSS MPCI: (a) Line-to-line voltage at m=0.86 (b) Line current at m=0.86, (c) Line-to-line voltage at m=1 and (d) Line current at m=1; 172                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

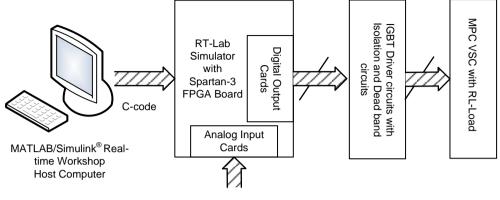

| Figure 7-1 Schematic diagram for hardware implementation of MPCI topologies                                                                                                                                                                                                                                                               |

| Figure 7-2 Current sensing circuit                                                                                                                                                                                                                                                                                                        |

| Figure 7-3 AC/DC voltage sensing circuit178                                                                                                                                                                                                                                                                                               |

| Figure 7-4 RT-Lab and MATLAB real-world interfacing179                                                                                                                                                                                                                                                                                    |

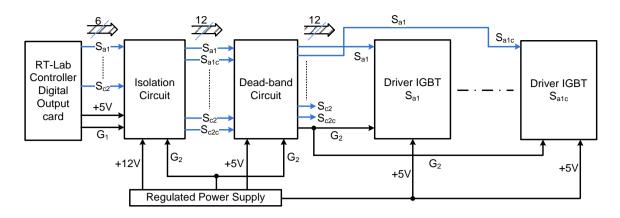

| Figure 7-5: Schematic diagram of interfacing firing pulses from RT-Lab controller board to switching devices                                                                                                                                                                                                                              |

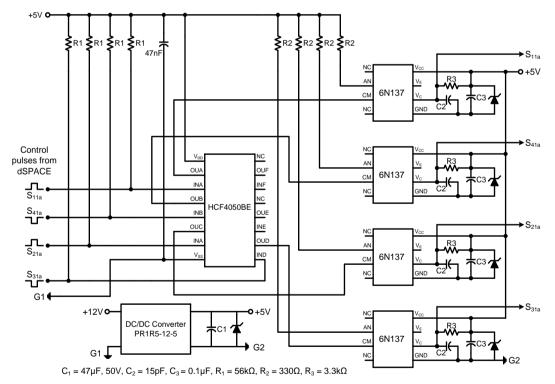

| Figure 7-6: Opto-isolation circuit for each switching device                                                                                                                                                                                                                                                                              |

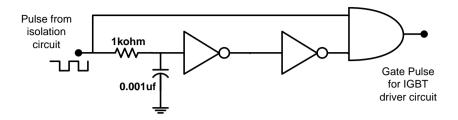

| Figure 7-7: Dead-band circuit for each switching device                                                                                                                                                                                                                                                                                   |

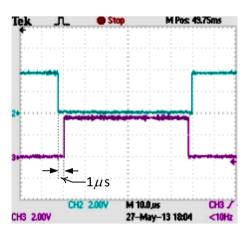

| Figure 7-8: Firing signals for the switches $S_1$ and $S'_1$ with dead-band circuit                                                                                                                                                                                                                                                       |

| Figure 7-9: IGBT driver circuit                                                                                                                                                                                                                                                                                                           |

| Figure 7-10: Snubber circuit used for switching device                                                                                                                                                                                                                                                                                    |

| Figure 7-11 Experimental Setup of three-phase 3L NPCI with RL load                                                                                                                                                                                                                                                                        |

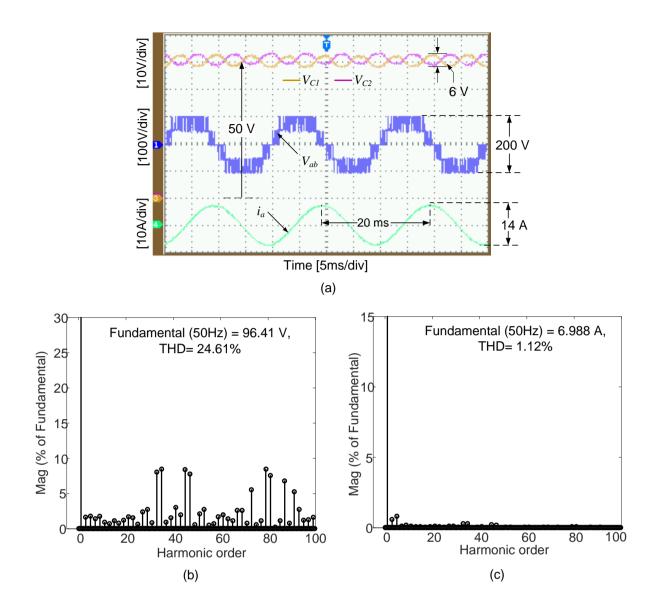

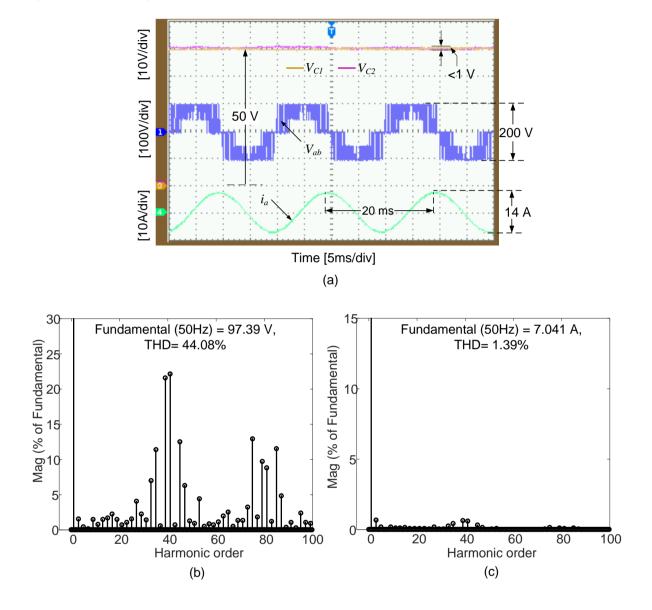

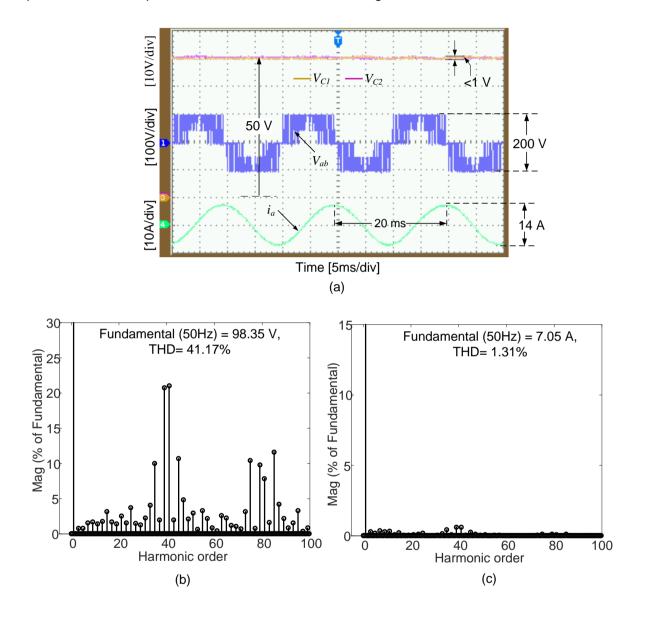

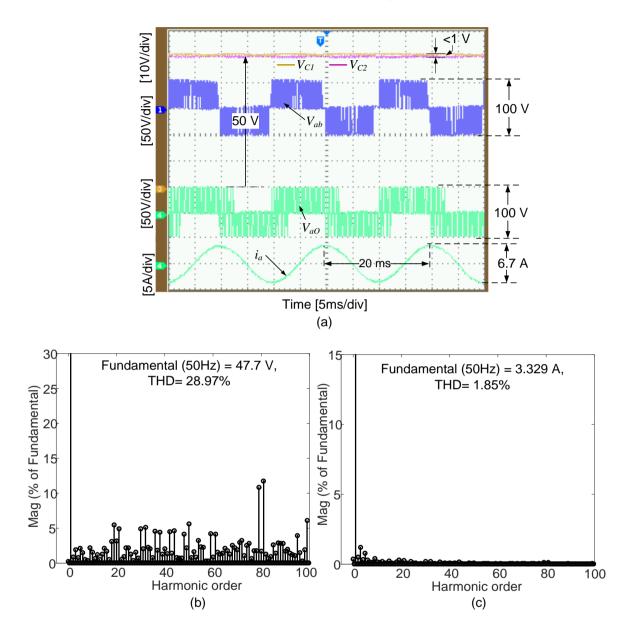

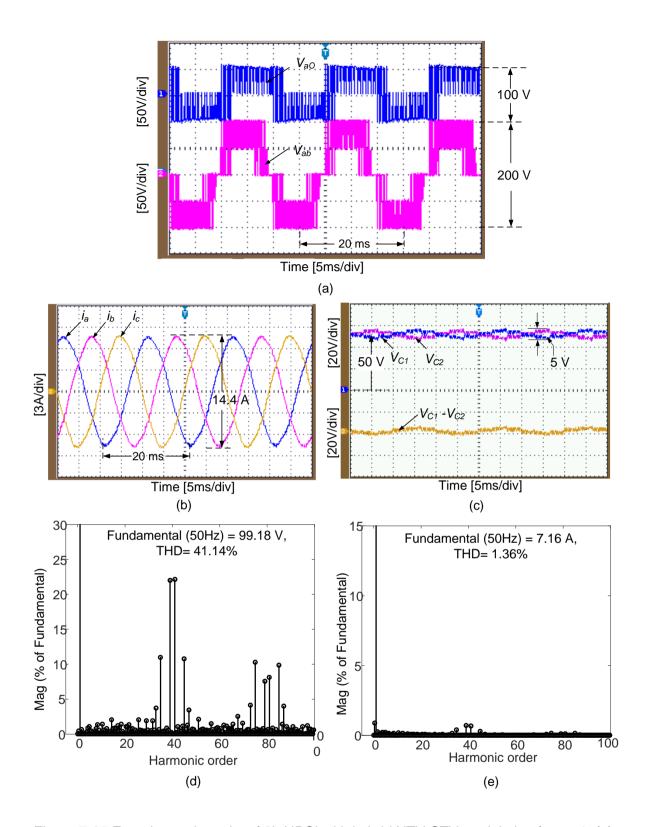

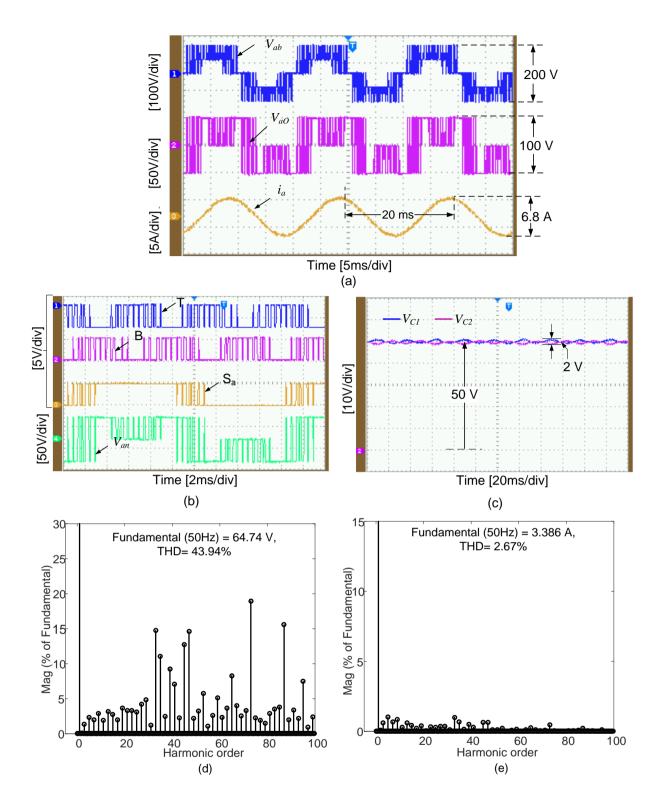

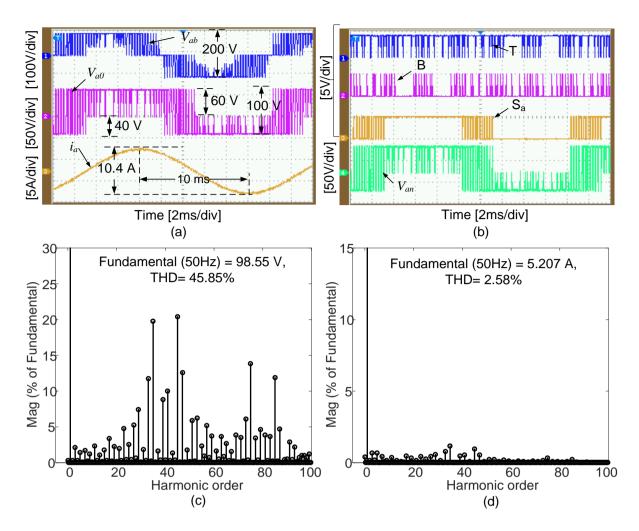

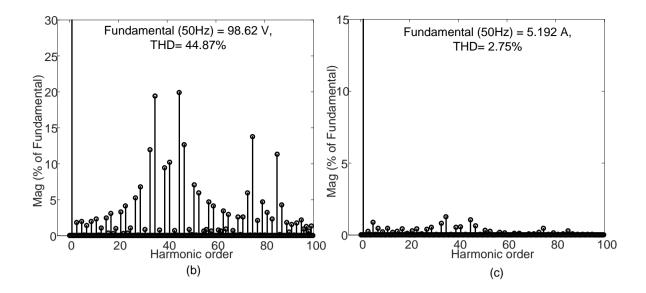

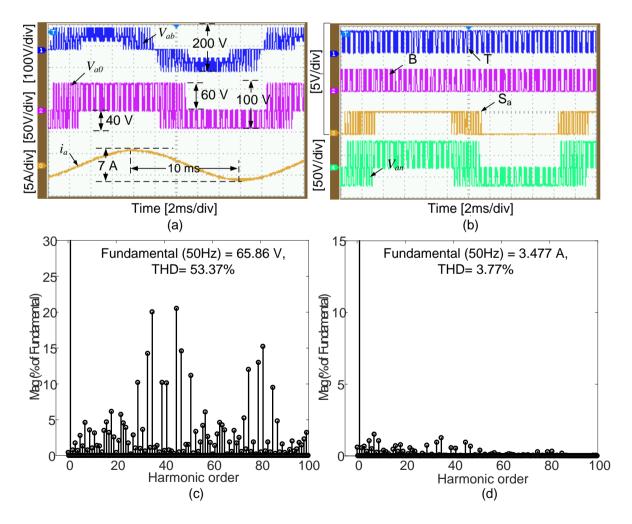

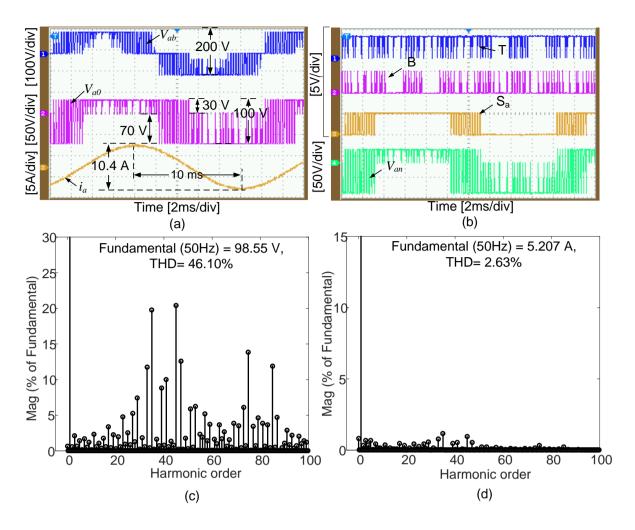

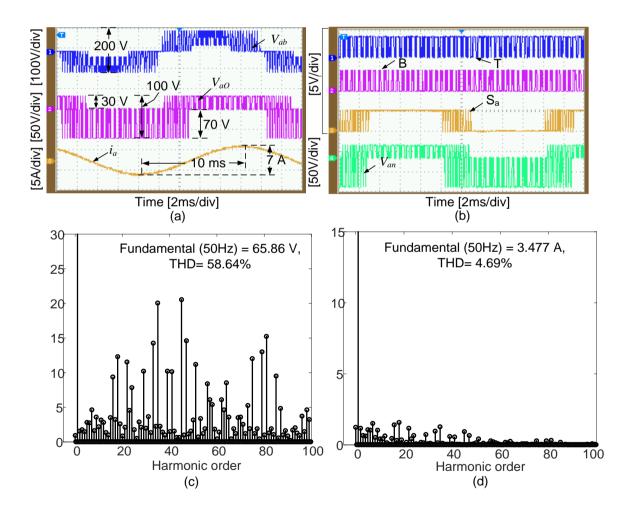

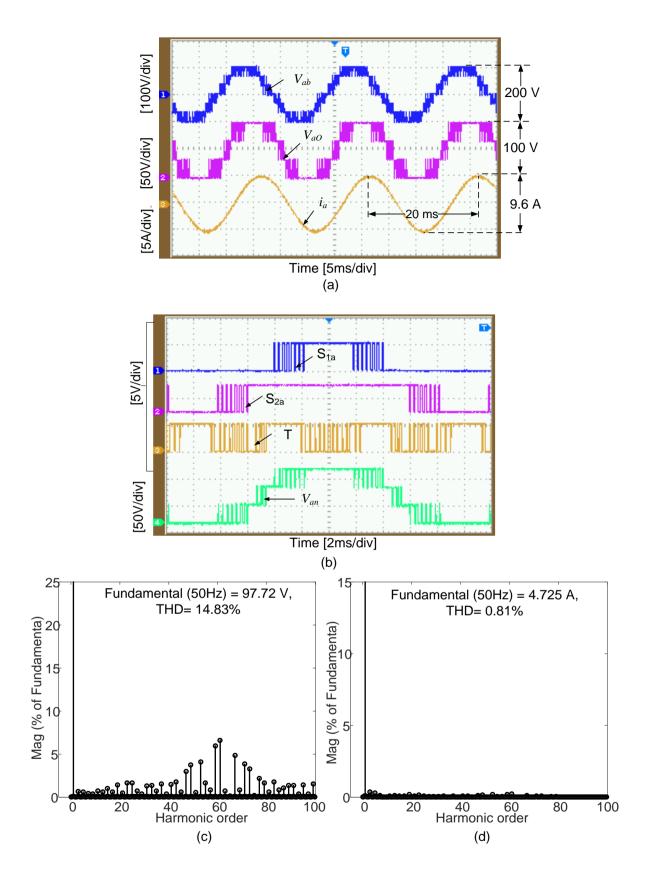

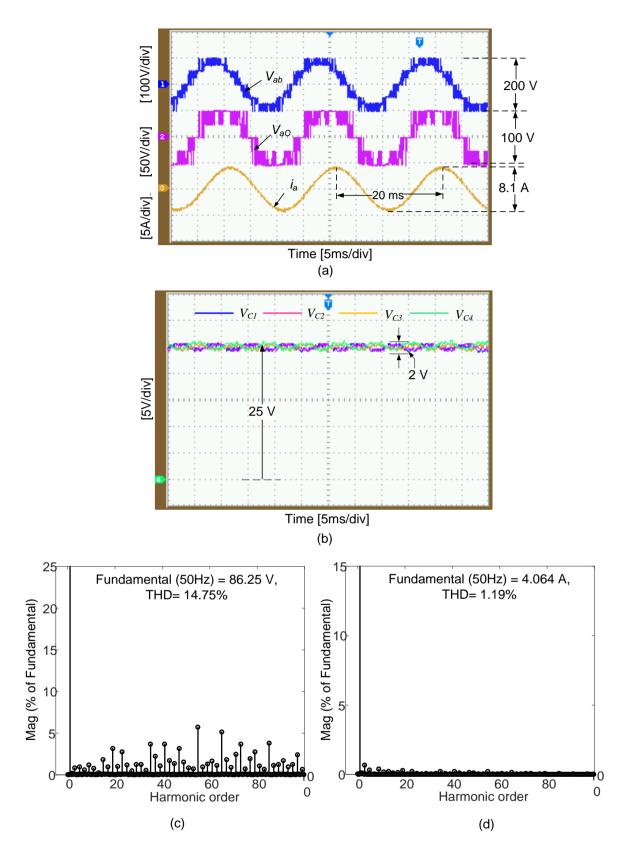

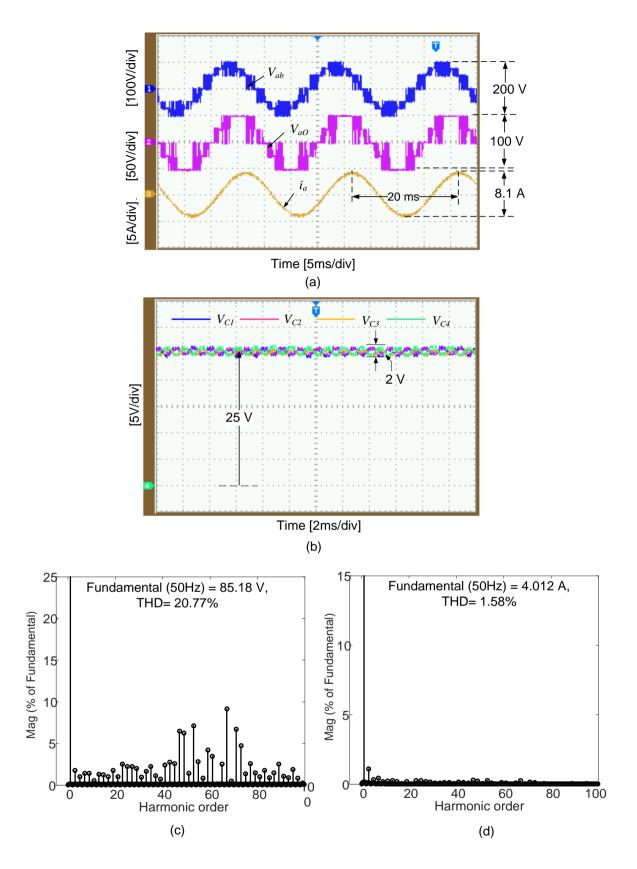

| Figure 7-12 Experimental results of 3L NPCI VSI at m=0.98, $C_1=C_2=1000\mu$ F, RL load=5 $\Omega/20$ mH for NTV modulation: (a) Voltage and current waveforms (top trace: capacitor voltages, middle trace: line-to-line voltage and bottom trace: Phase-a current); Harmonic spectrum of (b) Line to line voltage and (c) Line current  |

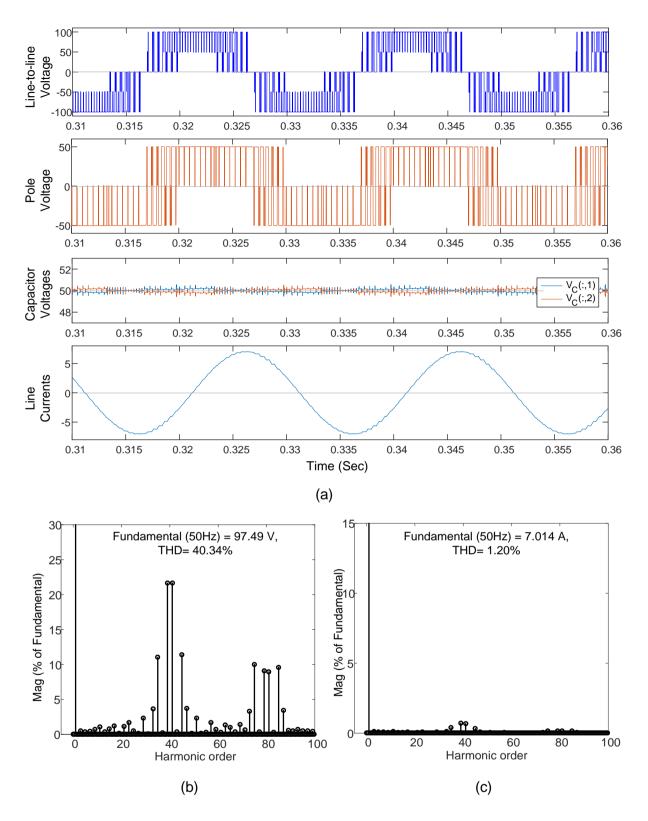

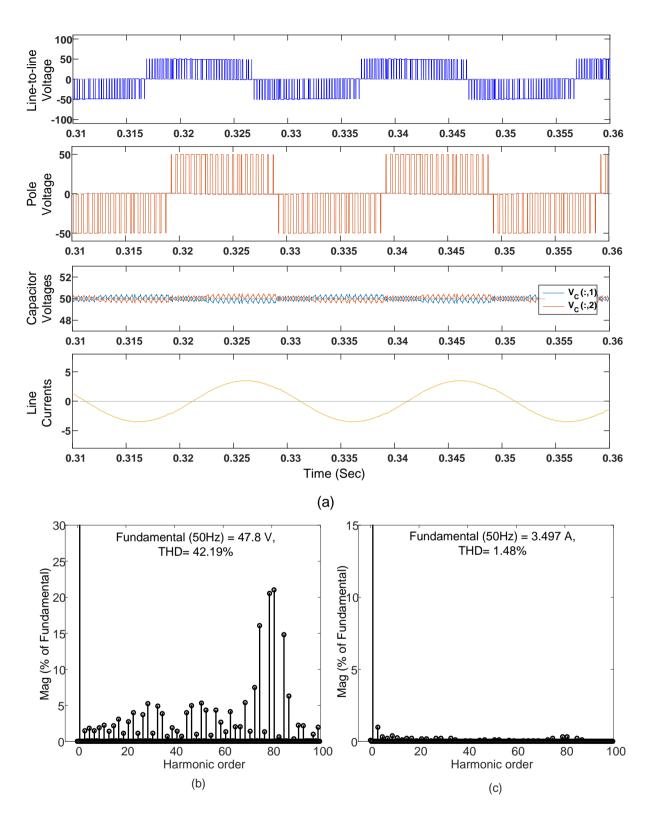

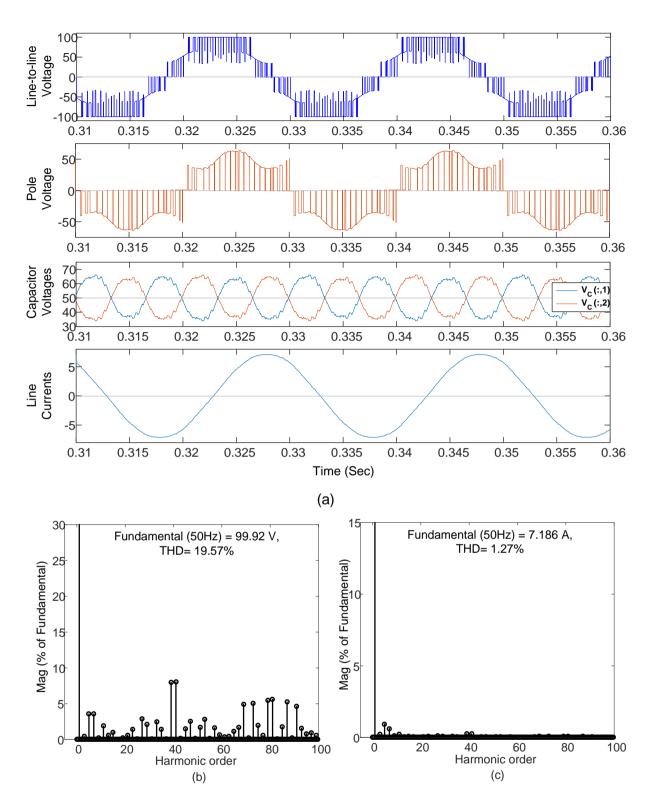

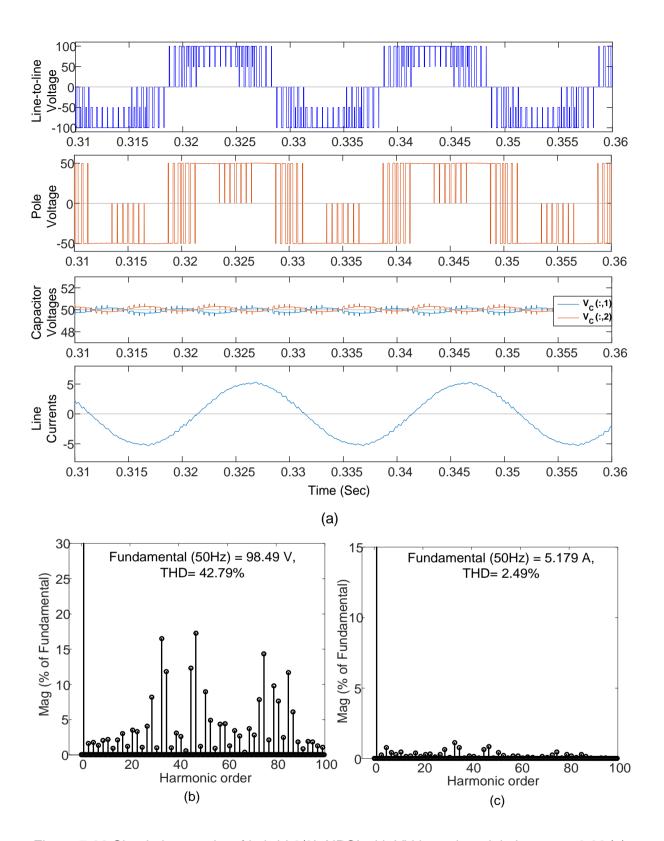

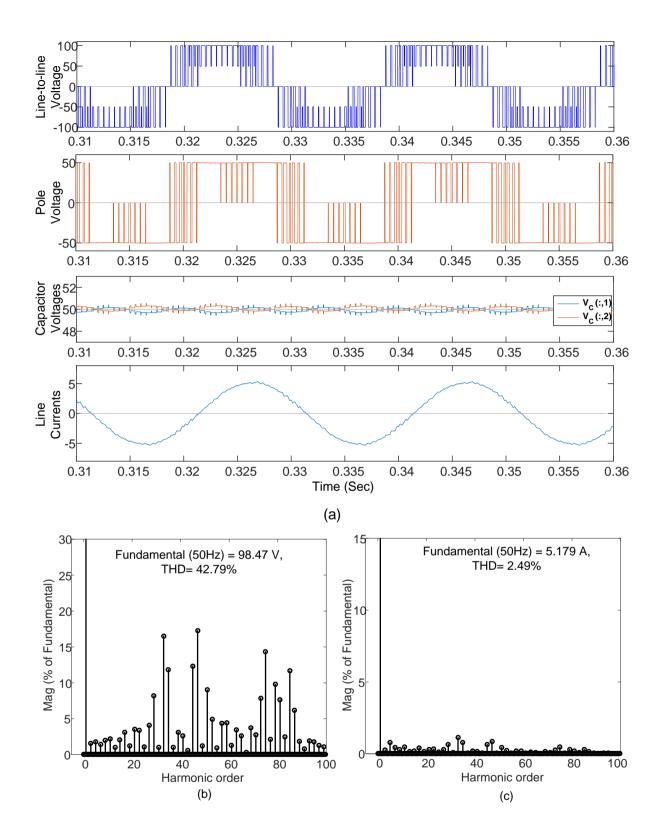

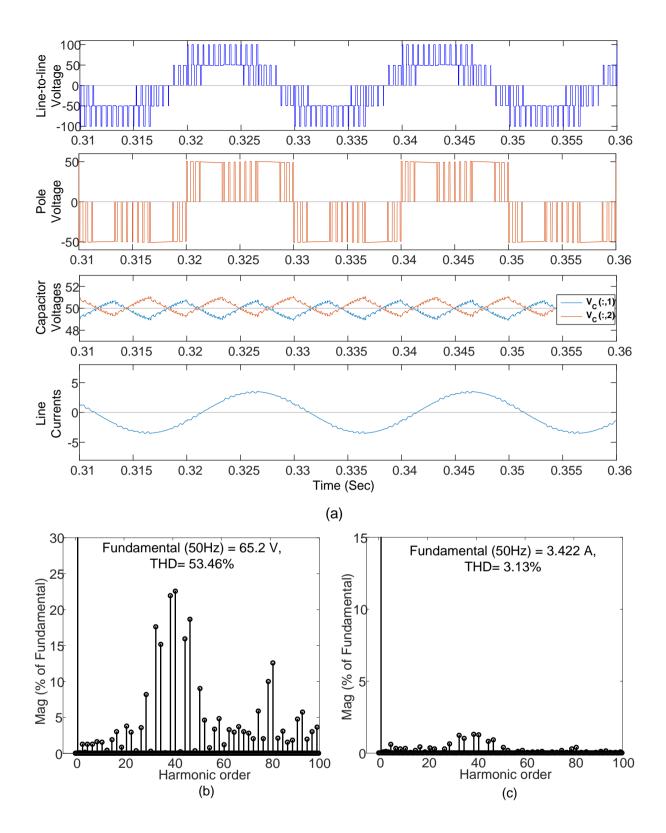

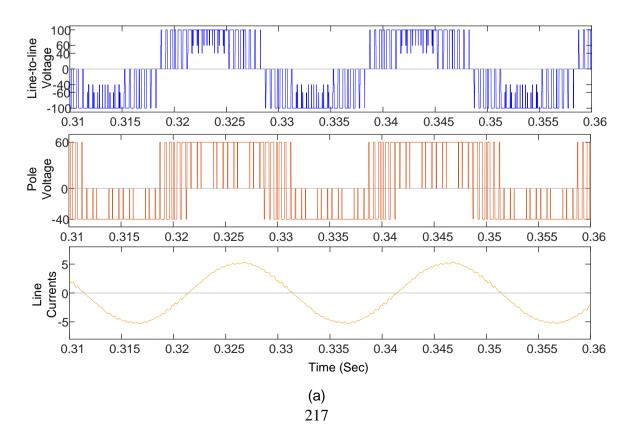

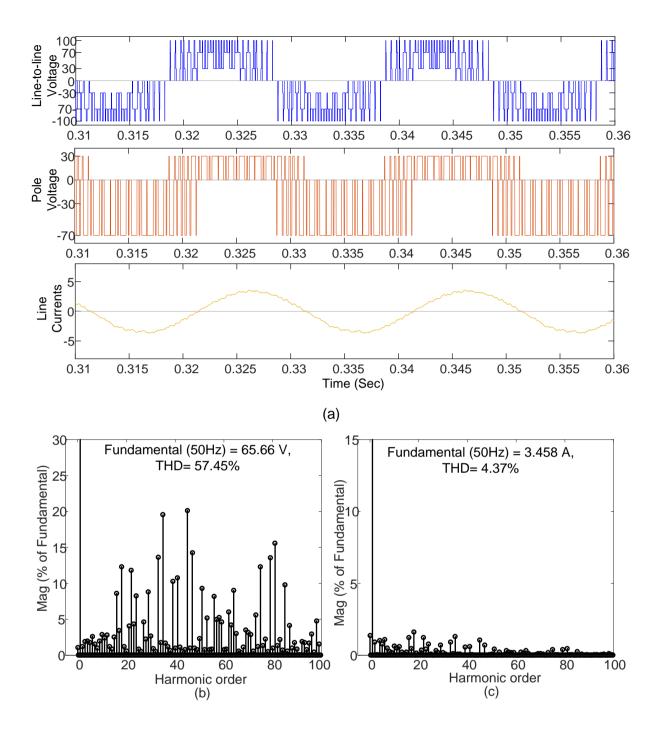

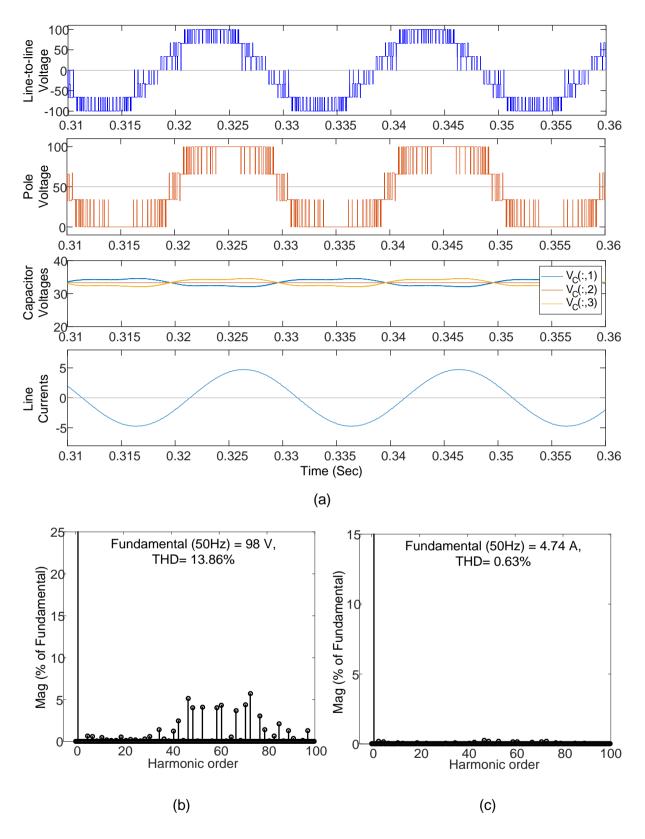

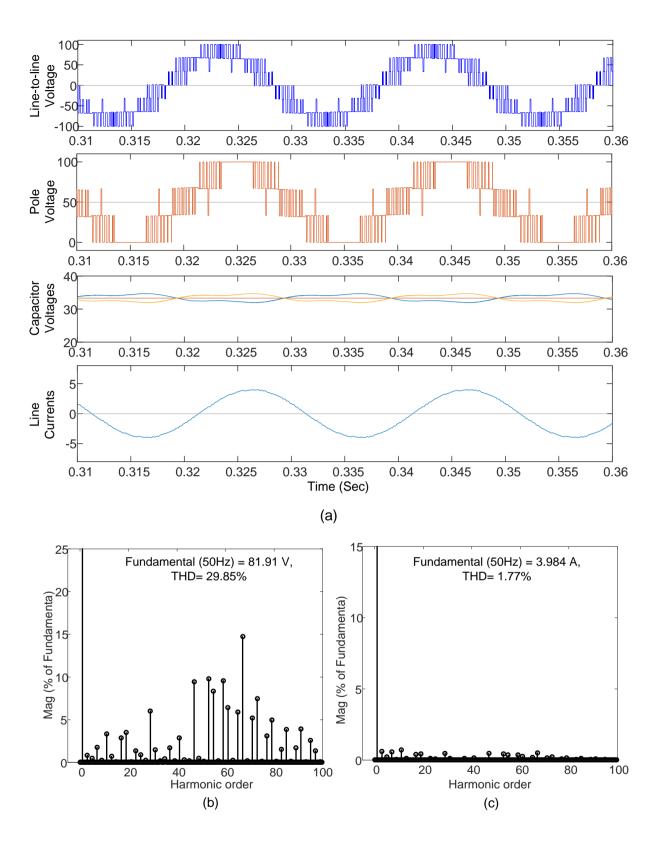

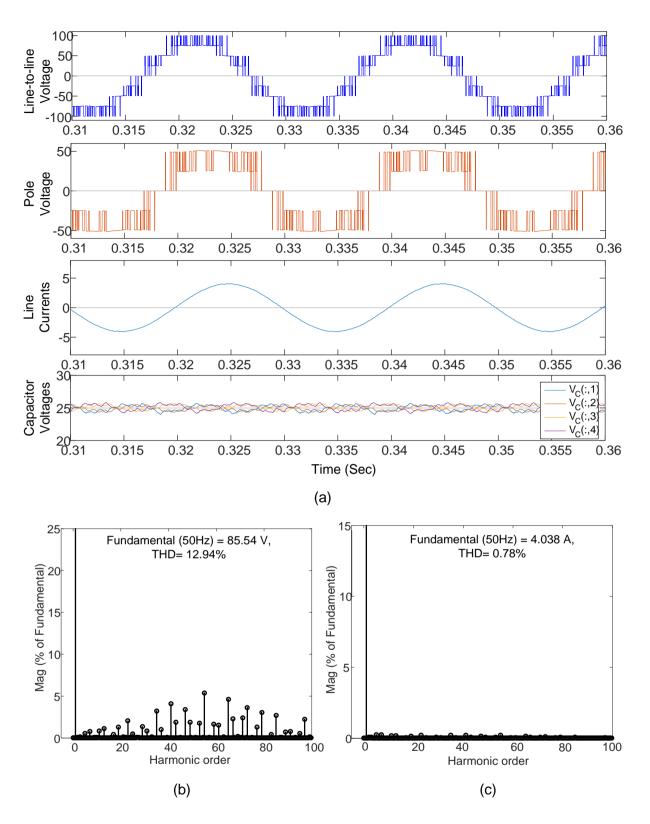

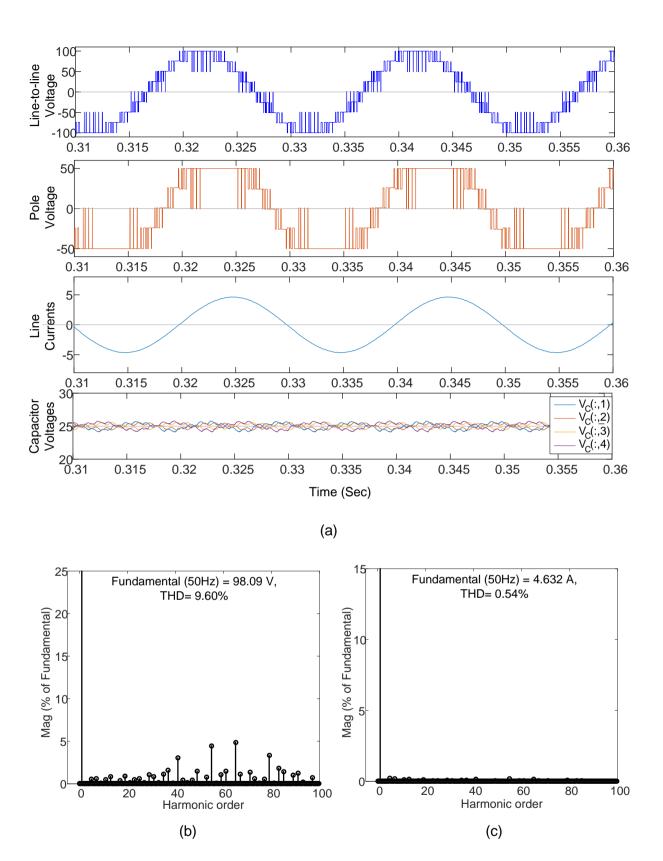

| Figure 7-13 Simulation Results at m=0.98, $C_1=C_2=1000\mu$ F, RL load=5 $\Omega/20$ mH with NTV modulation: (a) Voltage and current waveforms; Harmonic spectrum of (b) Line-to-line voltage and (c) Line current                                                                                                                        |

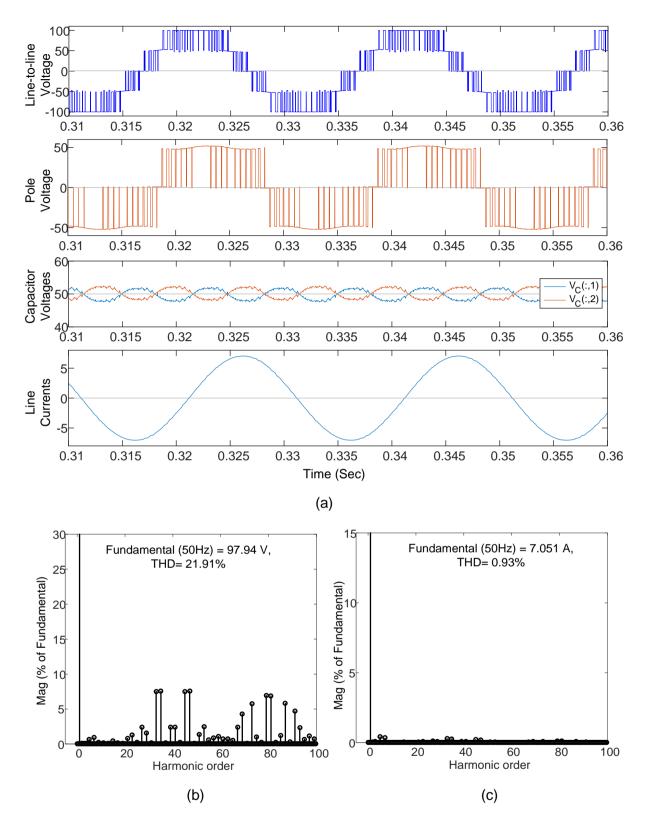

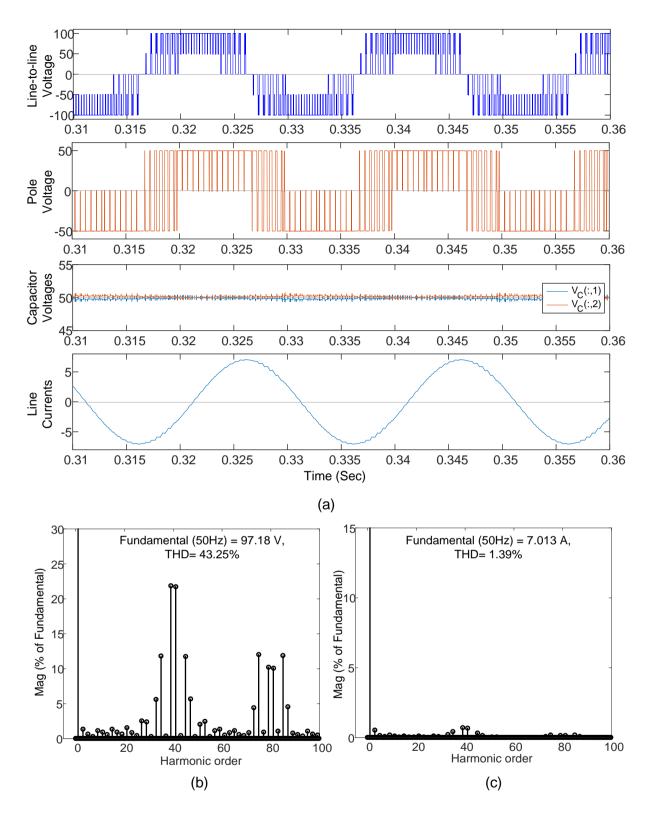

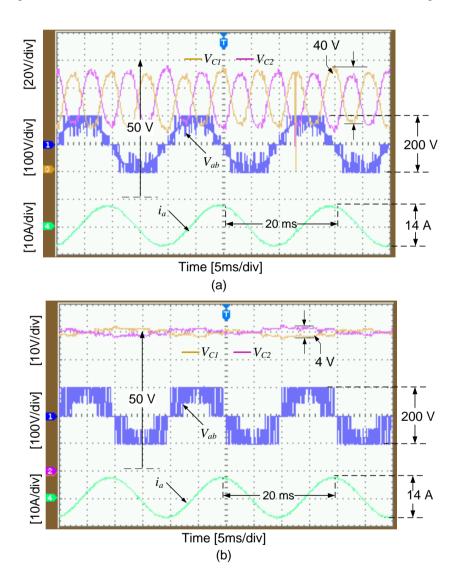

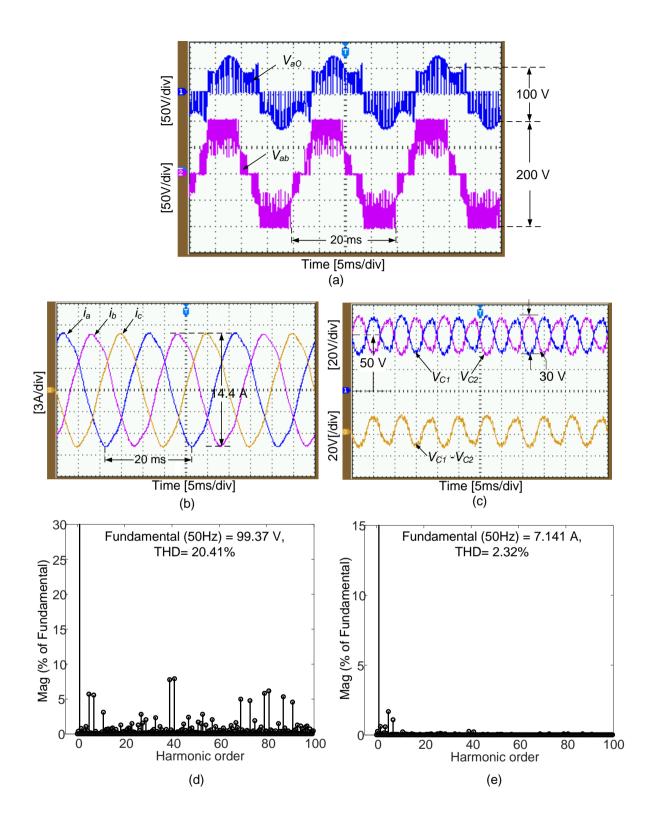

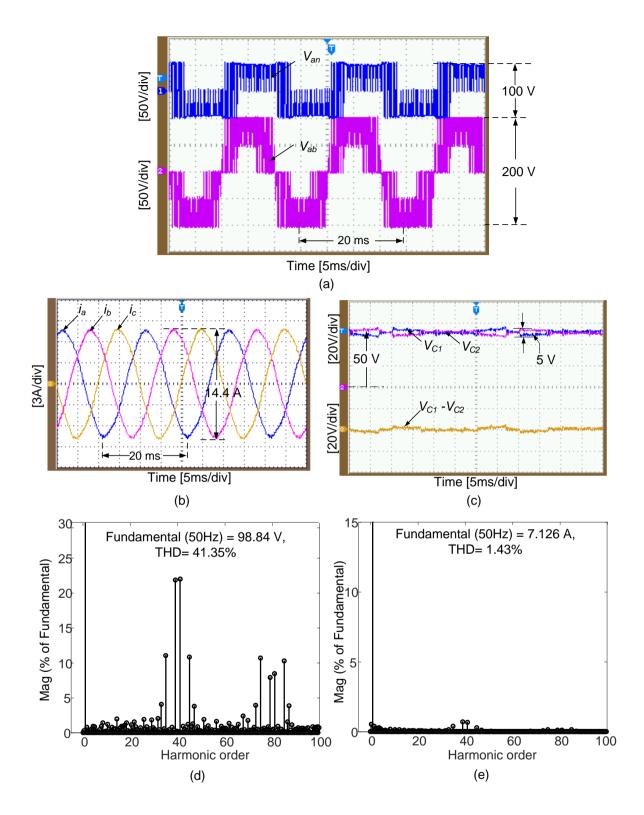

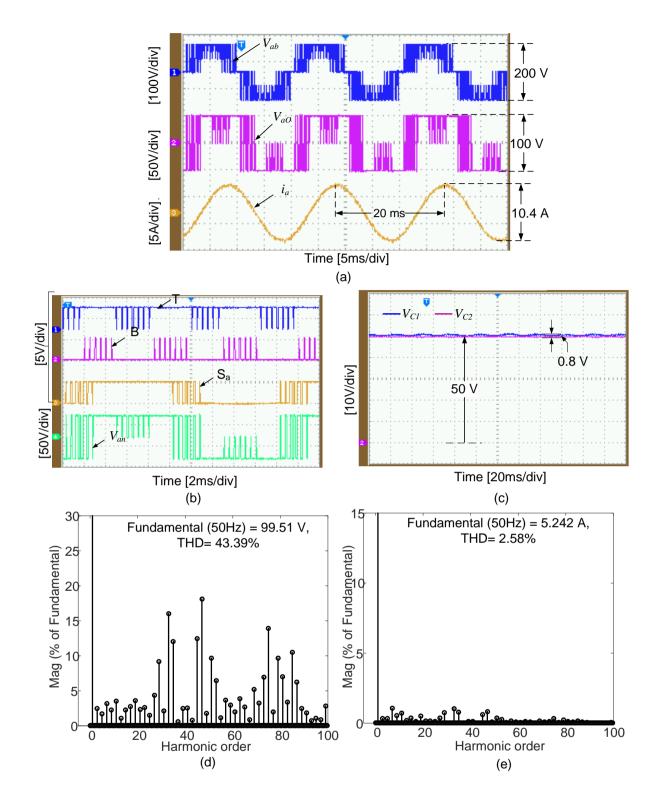

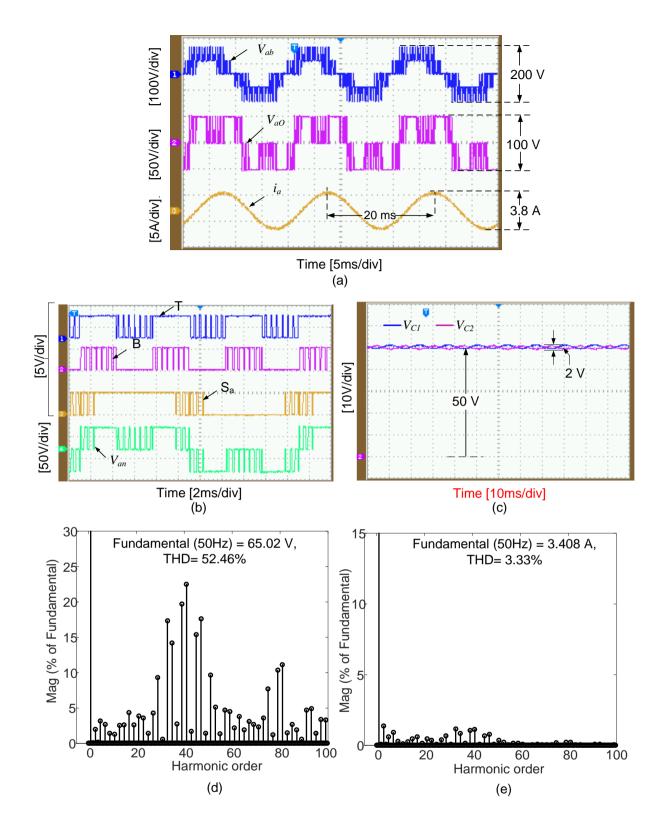

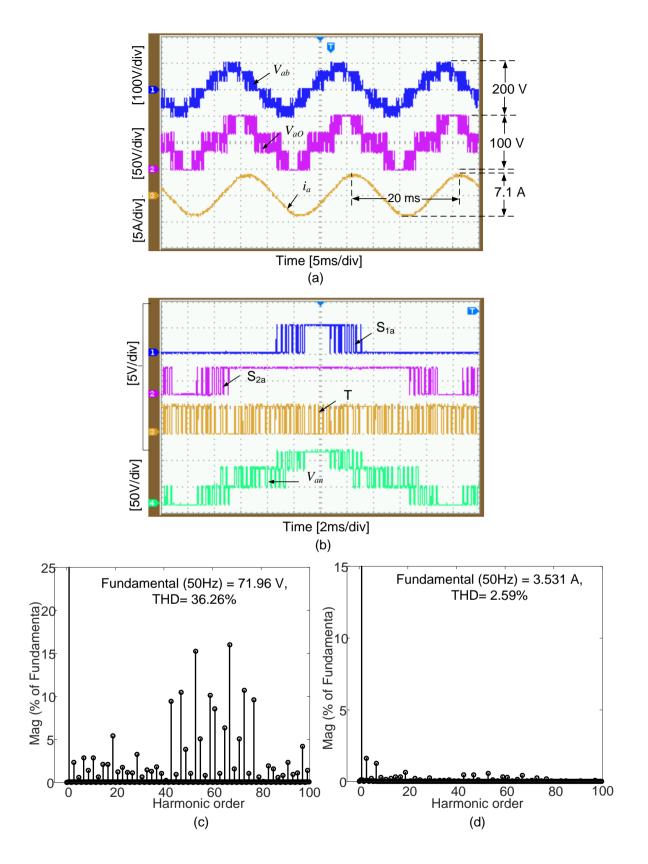

| Figure 7-14 Experimental results of 3L NPCI under m=0.98, $C_1=C_2=1000\mu$ F, RL load=5 $\Omega/20$ mH for NTVV modulation: (a) Voltage and current waveforms (top trace: capacitor voltages, middle trace: line-to-line voltage and bottom trace: Phase-a current); Harmonic spectrum of (b) Line to line voltage and (c) Line current. |

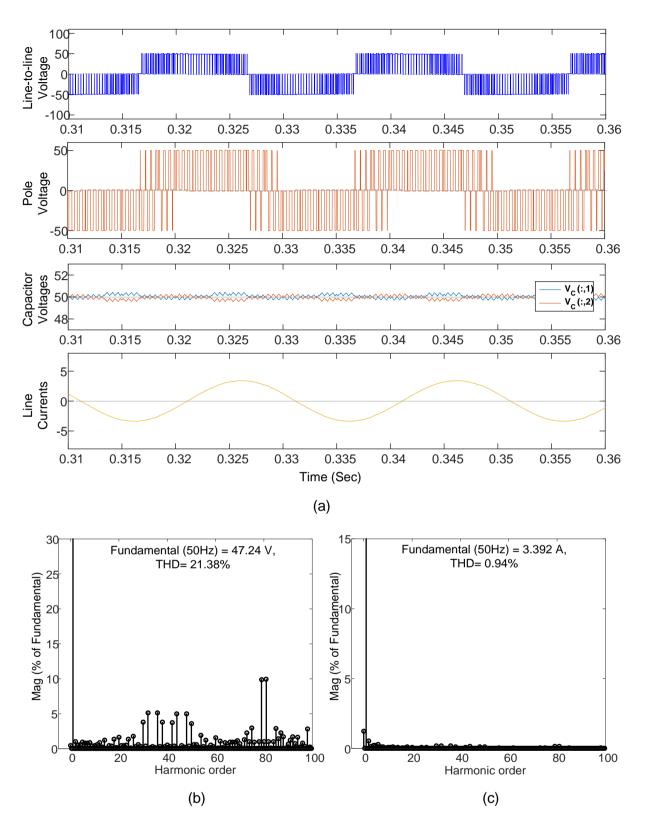

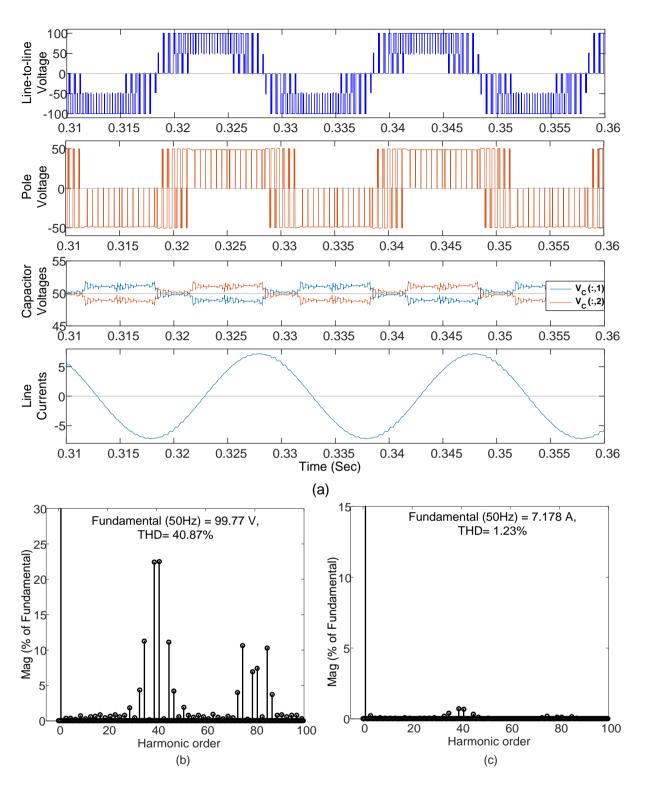

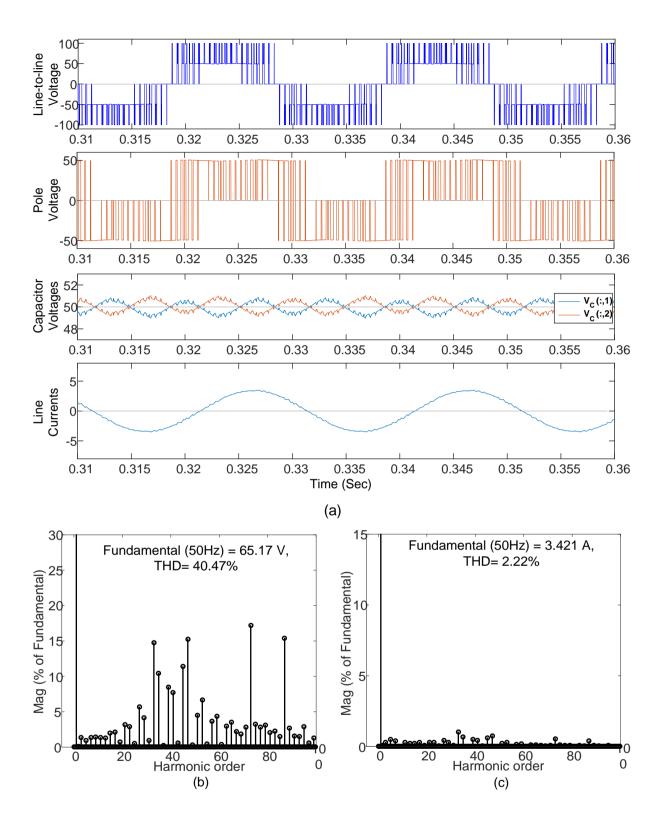

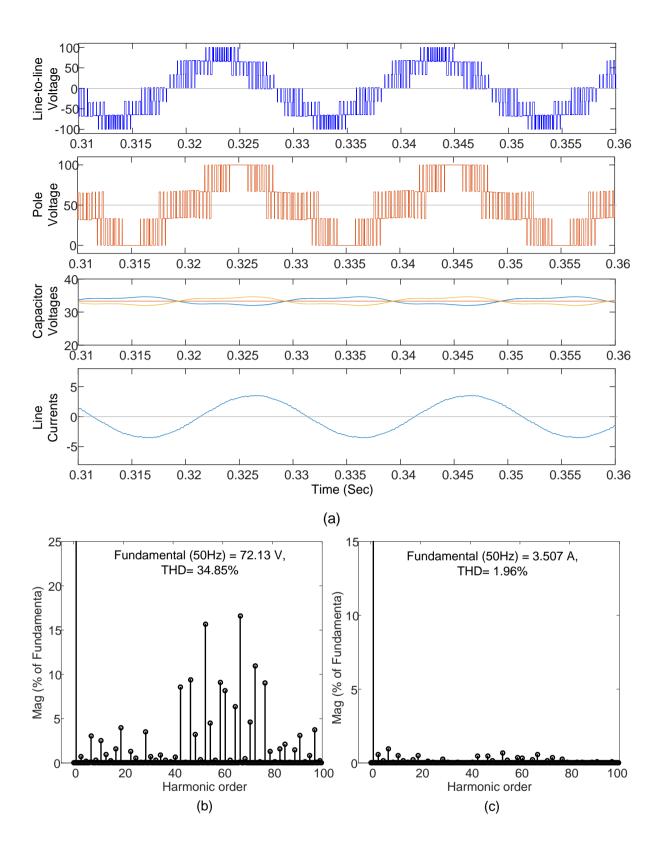

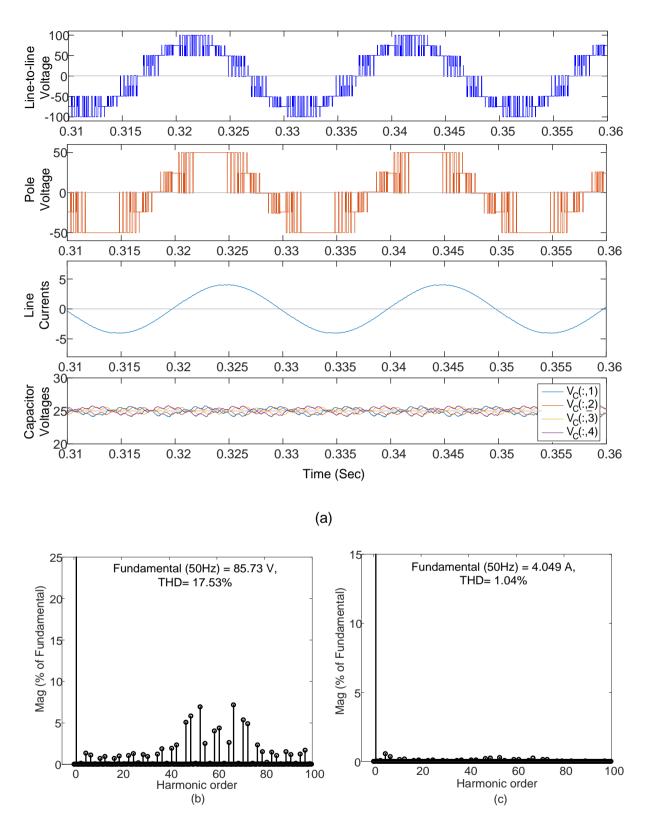

| Figure 7-15 Simulation Results at m=0.98, $C_1=C_2=1000\mu$ F, RL load=5 $\Omega/20$ mH for NTVV modulation: (a) Voltage and current waveforms; Harmonic spectrum of (b) Line-to-line voltage and (c) Line current                                                                                                                        |