# ANALYSIS AND CONTROL OF BIDIRECTIONAL DC-DC CONVERTERS

Ph.D. THESIS

by

# GURUSWAMY K P

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) DECEMBER, 2018

# ANALYSIS AND CONTROL OF BIDIRECTIONAL DC-DC CONVERTERS

## A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

## **DOCTOR OF PHILOSOPHY**

in

## **ELECTRICAL ENGINEERING**

by

**GURUSWAMY K P**

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) DECEMBER, 2018

# © INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2018 ALL RIGHTS RESERVED

# INDIAN INSTITUE OF TECHNOLOGY ROORKEE ROORKEE

# **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in this thesis entitled "ANALYSIS AND CONTROL OF BIDIRECTIONAL DC-DC CONVERTERS" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electrical Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from July, 2010 to December, 2018 under the supervision of Dr. S. P. SINGH, Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

## Signature of the Candidate

This is to certify that the above statement made by the candidate is correct to the best of my (our) knowledge.

### Signature of the Supervisor

The Ph.D Viva-voce Examination of Guruswamy K P, Research Scholar, has been held on ------

Chairman, SRC

### **Signature of External Examiner**

This is to certify that the student has made all the corrections in the thesis

Signature of the Supervisor Date:08/12/2018

Head of the Department

### ABSTRACT

This thesis introduces the design and implementation of 350W conventional bidirectional dc-dc converter with hard switching operation. A more accurate modeling of non-ideal elements of bidirectional dc-dc converter (BDDC) using state space averaging technique is presented. Steady state and small signal analytical expressions are derived individually for both boost and buck mode of BDDC in continuous conduction mode. Type III error amplifier for boost mode and PID controller for buck mode are designed to achieve the desired loop bandwidth of the converter system. Transient performance of the converter is simulated for both boost mode and buck mode to achieve precise regulation against the line and load abrupt change using MATLAB/SIMULINK software package. Hardware prototype of converter is then tested against the load variation. With the experimental measurement, the corresponding design has been verified. Results show that the model is accurate and offers a significant improvement in the computation. Ringing effect due to parasitic impedance across MOSFET switching device at 100 kHz is substantially reduced by proper selection of snubber circuit elements and sophisticated gate drive mechanism.

Analysis of three-phase interleaved bidirectional dc-dc converter (IBDDC) in continuous conduction mode using state space averaging method has been presented in this thesis. Analytical expression of small signal control to duty ratio has been derived for the three-phase IBDDC operates either in boost mode or in buck mode. Two or more identical converters are connected in parallel to reduce both input and output ripple currents, hence size of the capacitor decrease. Non-isolated three-phase IBDDC offers many advantages like equal current sharing capability among individual converter, increased output power, better utilization of switches, lower switching loss, increased efficiency, fast dynamic response, lower per phase ripple, reduced input and output ripple. The basic operation of three-phase IBDDC, steady state, small signal analysis, and voltage mode control of IBDDC are clearly described. Simulation of type 3 error amplifier and fuzzy logic controller based three-phase IBDDC is carried out in Simulink/SimPowerSystem and load dynamic performance is compared with the experimental results. I take this opportunity to express my sincere gratitude my august guide Dr. S. P. Singh, Professor, Electrical Engineering Department, Indian Institute of Technology, Roorkee, for their proficient and enthusiastic guidance, advice and encouragement, which were the constant source of inspiration for the completion of this research work.

Their painstaking support and exhaustive involvement in preparation of manuscript, conduction of the experimental investigations and simulation studies are gratefully acknowledged. I sincerely appreciate their pronounced individualities, humanistic and warm personal approach, which has given me strength to carry out this research work on steady and smooth course. I humbly acknowledge lifetime's gratitude to them.

My sincere thanks are also due to Prof. M. K. Vasantha, Prof. N.P. Padhy, Prof. K. S. Hariprasad, Prof. Vinay Pant and Prof. M.K. Pathak for their extending moral support and technical discussions as and when requiring during research work.

I acknowledge my sincere gratitude to the Quality Improvement Program (QIP) of MHRD Govt. of India. The research work is carried out under this scheme. I also acknowledge my appreciation to Coordinator, QIP Centre, Indian Institute of Technology, Roorkee, for their kind co-operation. I express my deep sense of gratitude to the Head, Electrical Engineering Department, Indian Institute of Technology, Roorkee, for providing the excellent laboratory and computing facilities of the department for the research work.

My hearty gratitude to the Vice-chancellor, Registrar Bangalore University, Bengaluru, and H.O.D (Electrical Engineering) U.V.C.E, Bengaluru (my parent Institution) for sponsoring me for Ph.D work. Special thanks are due to my colleagues for extending help during my stay at Roorkee.

I am thankful to the technical staff of computer controlled drives lab Shri Saadi Ram, and other staff member of workshop for their timely co-operation and needful help. Thanks are also due to all those who helped me directly and indirectly for the completion of the work.

I am lucky to get the helping hands from my wife Divya and loving son Jeevith. Even though they have missed me a lot during my research work, they waited patiently for the completion of the work. I appreciate them for the kind of support extended. No words can adequately express my gratitude to them.

(Guruswamy K P)

| ABSTRACT      |           | I   |

|---------------|-----------|-----|

| ACKNOWLED     | GEMENTS   | III |

| CONTENTS      |           | V   |

| LIST OF ABBR  | EVIATIONS | IX  |

| LIST OF SYMB  | BOLS      | XII |

| LIST OF FIGUI | RES       | XV  |

| LIST OF TABL  | ES        | XIX |

|               |           |     |

| CHA | APTER 1:   | INTRODUCTION AND LETRATURE REVIEW              | 1  |

|-----|------------|------------------------------------------------|----|

| 1.1 | Bidirectio | onal DC-DC Converter                           | 1  |

| 1.2 | Interleave | ed Bidirectional DC-DC Converter               | 3  |

| 1.3 | Interleave | ed Switching Scheme                            | 4  |

| 1.4 | Modelling  | g and Control of Bidirectional DC-DC Converter | 4  |

| 1.5 | LITERAT    | ΓURE REVIEW                                    | 5  |

|     | 1.5.1 No   | on-Isolated Bidirectional DC-DC Converter      | 6  |

|     | 1.5.2 Iso  | plated Bidirectional DC-DC Converter           | 12 |

|     | 1.5.3 Re   | esearch Gaps                                   | 18 |

|     | 1.5.4 Ol   | bjectives of Research Work                     | 19 |

| 1.6 | Organisat  | ion of Thesis                                  | 19 |

| 1.7 | Conclusio  | on                                             | 20 |

#

| 2.1 | Introd  | uction                                                   | 21 |

|-----|---------|----------------------------------------------------------|----|

| 2.2 | Stead   | y State Analysis of Bidirectional DC-DC Converter (BDDC) | 22 |

| 2.3 | Desig   | n of BDDC for Continuous Conduction Mode                 | 24 |

|     | 2.3.1   | Design of BDDC in Boost Mode for CCM                     | 25 |

|     | 2.3.2   | Design of BDDC in Buck Mode for CCM                      | 26 |

| 2.4 | State S | Space Averaged Model for BDDC                            | 28 |

|     | 2.4.1   | BDDC in Boost Mode                                       | 29 |

|     | 2.4.2   | BDDC in Buck Mode                                        | 32 |

| 2.5 | Desig   | n of Compensator/ Controller for BDDC                    | 35 |

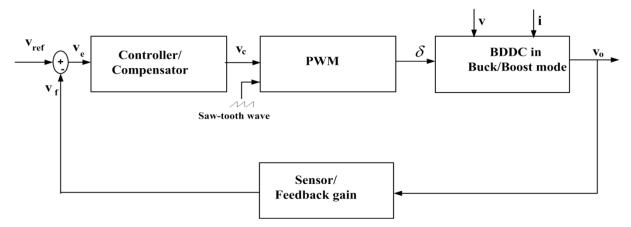

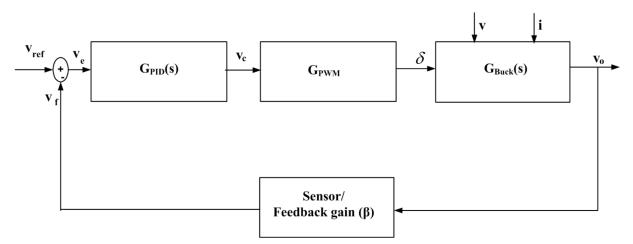

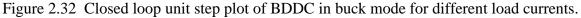

|     | 2.5.1   | Block Diagram of Closed Loop BDDC System                 | 35 |

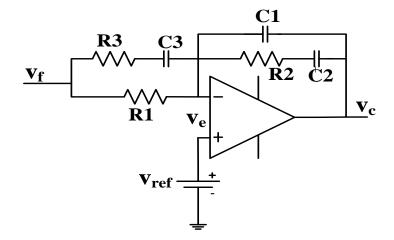

|     | 2.5.2   | Design Method of Compensation Network:                   | 37 |

|     |         |                                                          |    |

|             | 2.5.3  | Design of Type III Error Amplifier/Compensator for BDDC in Boost Mode  | 38 |

|-------------|--------|------------------------------------------------------------------------|----|

|             | 2.5.4  | Design of PID Controller for BDDC in Buck Mode                         | 44 |

| 2.6         | Simula | ation and Experimentatal results of BDDC                               | 51 |

|             | 2.6.1  | Simulation of Conventional BDDC                                        | 51 |

|             |        | 2.6.1.1 Simulation Results and Discussions                             | 51 |

|             | 2.6.2  | Experimental Setup of BDDC                                             | 52 |

|             |        | 2.6.2.1 Implementation of Digital Controller for Conventional BDDC     | 53 |

|             |        | 2.6.2.2 Experimental Results and Discussions                           | 60 |

| 2.7         | Conclu | usion                                                                  | 62 |

| СНА         | PTER   | 3: DESIGN, MODELLING, CONTROL, SIMULATION AND                          |    |

|             |        | ENTATION OF THREE-PHASE INTERLEAVED BIDIRECTIONAL DC                   |    |

| <b>3</b> .1 |        | E <b>RTER</b> uction                                                   |    |

| 3.2         |        | ple Operation of Three Phase Interleaved Bidirectional DC-DC Converter |    |

| 3.3         | -      | V State Analysis of Three-Phase IBDDC in Boost Mode                    |    |

| 3.4         | •      | 7 State Analysis of Three Phase IBDDC in Buck Mode                     |    |

| 3.5         | •      | n of Three-Phase IBDDC in CCM                                          |    |

| 5.5         | 3.5.1  | Design of Three-Phase IBDDC Inductor in Boost Mode                     |    |

|             | 3.5.2  | Design of Three-Phase IBDDC Output Capacitor in Boost Mode             |    |

|             | 3.5.3  | Design of Three-Phase IBDDC Output Capacitor in Buck Mode              |    |

| 3.6         |        | nic Analysis of Three-Phase IBDDC                                      |    |

|             | 3.6.1  | Three-Phase IBDDC in Boost Mode                                        |    |

|             | 3.6.2  | Three-Phase IBDDC in Buck Mode                                         |    |

| 3.7         |        | n of Compensator/ Controller for Three-Phase IBDDC                     | 84 |

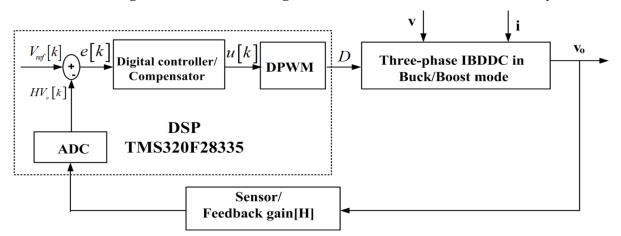

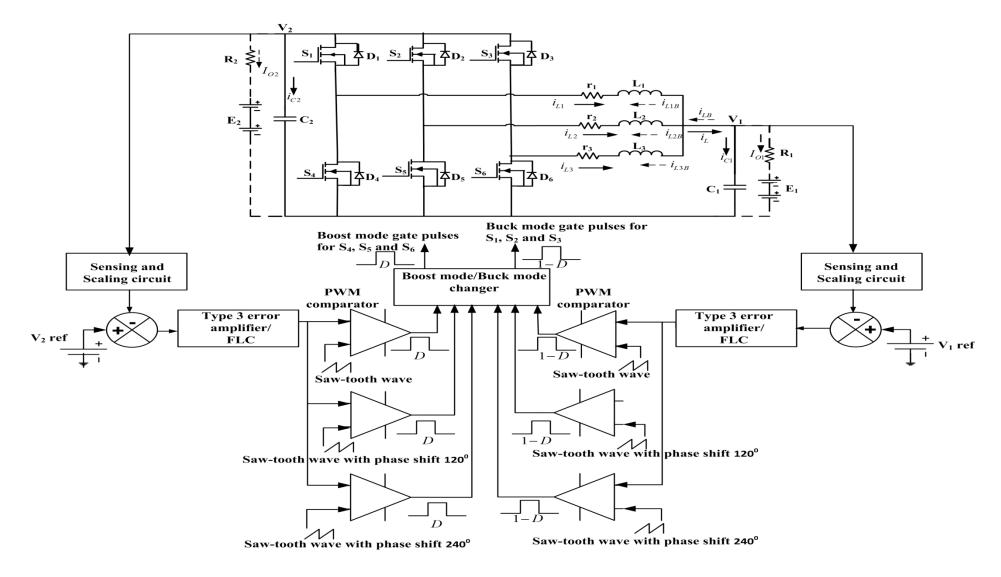

|             | 3.7.1  | Block Diagram of DSP Based Digital Control of Three-Phase IBDDC System | 84 |

|             | 3.7.2  | Design of Type III Error Amplifier for Three-Phase IBDDC in Boost Mode | 84 |

|             | 3.7.3  | Design of Type III Error Amplifier for Three-Phase IBDDC in Buck mode  | 91 |

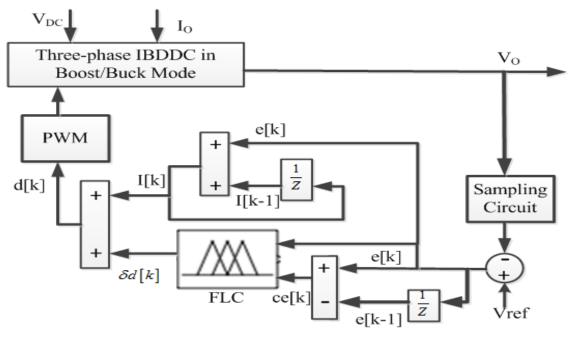

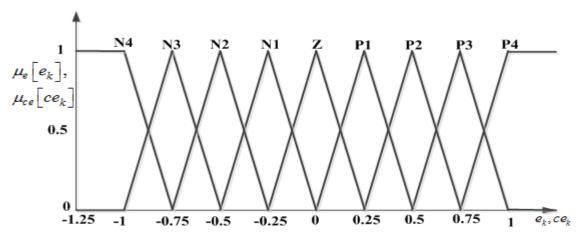

| 3.8         | Fuzzy  | Logic Controller for Three-Phase IBDDC                                 | 98 |

| 3.9         | Simula | ation and Experimental Results of IBDDC1                               | 01 |

|             | 3.9.1  | Simulation of Three-Phase IBDDC 1                                      | 01 |

|             |        | 3.9.1.1 Simulation Results and Discussions                             | 02 |

| 3.10        | Experi | imental Setup of IBDDC 1                                               | 03 |

|             | 3.10.1 | Implementation of Digital Controller 1                                 | 03 |

|             | 3.10.2 | Development of the Fuzzy Logic Controller on DSP 1                     | 03 |

|             | 3.10.3 | Experimental Results and Discussions 1                                 | 04 |

| 3.11 | 1 Conclusion |                              | 114 |

|------|--------------|------------------------------|-----|

| CH   | APTER 4:     | CONCLUSIONS AND FUTURE SCOPE |     |

| 4.1  | Conclusio    | ns                           | 117 |

| 4.2  | Future Sco   | ope                          |     |

| PUBLICATIONS FROM THE WORK |                                         |  |

|----------------------------|-----------------------------------------|--|

| BIBLIOGRAPHY               |                                         |  |

| APPENDIX-A                 |                                         |  |

|                            |                                         |  |

|                            |                                         |  |

|                            |                                         |  |

|                            |                                         |  |

| AFFENDIA-E                 | ••••••••••••••••••••••••••••••••••••••• |  |

# LIST OF ABBREVIATIONS

| Abbreviation | Description                               |

|--------------|-------------------------------------------|

| ADC          | Analog to Digital Converter               |

| BDDC         | Bidirectional DC-DC Converter             |

| ССМ          | Continuous Conduction Mode                |

| DAB          | Dual Active Bridge                        |

| DAC          | Digital to Analog Converter               |

| dB           | Decibel                                   |

| DCM          | Discontinuous Conduction Mode             |

| DPWM         | Digital Pulse Width Modulator             |

| DSO          | Digital Storage Oscilloscope              |

| DSP          | Digital Signal Processor                  |

| EA           | Error Amplifier                           |

| EMI          | Electro-Magnetic Interference             |

| ESR          | Equivalent Series Resistance              |

| IBDDC        | Interleaved Bidirectional DC-DC Converter |

| KCL          | Kirchhoff's Current Law                   |

| KVL          | Kirchhoff's Voltage Law                   |

| MOSFET       | Metal Oxide Field Effect Transistor       |

| PWM          | Pulse Width Modulator                     |

| SMPS         | Switch Mode Power Supply                  |

| SMPC         | Switch Mode Power Converter               |

| SSA          | State Space Averaging                     |

| UPS          | Uninterruptible Power Supply              |

|              |                                           |

# LIST OF SYMBOLS

| Symbols                            | Descriptions                                         |

|------------------------------------|------------------------------------------------------|

| $A_{_P}$                           | Area product                                         |

| I <sub>LB</sub>                    | Average inductor current in boost mode of BDDC       |

| $I_L$                              | Average inductor current in buck mode of BDDC        |

| I <sub>o1</sub>                    | Average load current for buck mode 3-Phase IBDDC     |

| I <sub>o2</sub>                    | Average load current for boost mode of 3-Phase IBDDC |

| $I_2$                              | Average load current in boost mode of BDDC           |

| $I_1$                              | Average load current in buck mode of BDDC            |

| $I_{D1}$                           | Average value of diode current in boost mode of BDDC |

| $I_{D2}$                           | Average value of diode current in buck mode of BDDC  |

| D1                                 | Boost mode diode of BDDC                             |

| $D_1, D_2, D_3$                    | Boost mode diodes of 3-Phase IBDDC                   |

| $\delta$                           | Boost mode duty ratio of BDDC                        |

| $\delta 1$                         | Buck mode duty ratio of BDDC                         |

| D                                  | Boost mode duty ratio in three-phase IBDDC           |

| $V_2$                              | Boost mode output voltage                            |

| $\Delta I_{\scriptscriptstyle LB}$ | Boost mode ripple current                            |

| $S_2$                              | Boost mode switch                                    |

| $S_4, S_5, S_6$                    | Boost mode switches of 3-Phase IBDDC                 |

| D2                                 | Buck mode diode of BDDC                              |

| $D_4, D_5, D_6$                    | Buck mode diodes of 3-Phase IBDDC                    |

| D                                  | Buck mode duty ratio of 3-phase IBDDC                |

| $V_1$                              | buck mode output voltage                             |

| $\Delta I_L$                       | Buck mode ripple current                             |

| S1                                 | Buck mode switch of BDDC                             |

| $S_1, S_2, S_3$                    | Buck mode switches of 3-Phase IBDDC                  |

| V <sub>c</sub>                     | Control voltage                                      |

| $K_c$                              | Crest factor                                         |

| $L_{\min}$                         | Critical value of inductance                         |

| $A_c$                              | Cross section area of core                           |

| $A_{\!\scriptscriptstyle W}$       | Cross section area of window                         |

| Symbols                                    | Descriptions                                         |

|--------------------------------------------|------------------------------------------------------|

| a                                          | Cross section area of wire gauge                     |

| $f_c$                                      | Crossover frequency                                  |

| J                                          | Current density                                      |

| $V_{\gamma 1}, V_{\gamma 2}, V_{\gamma 3}$ | Cut in voltage of $D_1, D_2, D_3$                    |

| $V_{\gamma4}, V_{\gamma5}, V_{\gamma6}$    | Cut in voltage of $D_4$ , $D_5$ , $D_6$              |

| d1,d2,d3,d4,d5,d6                          | Duration of 3phase IBDDC in boost mode               |

| $d_1^1, d_2^1, d_3^1, d_4^1, d_5^1, d_6^1$ | Duration of 3phase IBDDC in buck mode                |

| E                                          | Energy stored in inductor                            |

| v <sub>e</sub>                             | Error voltage                                        |

| R <sub>C1</sub>                            | ESR of C <sub>1</sub>                                |

| R <sub>C2</sub>                            | ESR of C <sub>2</sub>                                |

| v <sub>f</sub>                             | Feedback voltage                                     |

| V <sub>ref</sub>                           | Fixed reference voltage                              |

| R <sub>f1</sub>                            | Forward resistance of D <sub>1</sub>                 |

| $R_{f1}, R_{f2}, R_{f3}$                   | Forward resistance of $D_1, D_2, D_3$                |

| $R_{f4}$ , $R_{f5}$ , $R_{f6}$             | Forward resistance of $D_4, D_5, D_6$                |

| L                                          | Inductor                                             |

| $i_{L1B}, i_{L2B}, i_{L3B}$                | Inductor currents for boost mode of 3-Phase IBDDC    |

| $i_{L1}, i_{L2}, i_{L3}$                   | Inductor currents for buck mode of 3-Phase IBDDC     |

| $L_1, L_2, L_3$                            | Inductors of 3-Phase IBDDC                           |

| $E_1$                                      | Input voltage in boost mode of BDDC                  |

| $E_2$                                      | Input voltage in buck mode of BDDC                   |

| i <sub>LB</sub>                            | Instantaneous inductor current in boost mode of BDDC |

| iL                                         | Instantaneous inductor current in buck mode          |

| r                                          | Internal resistance of L                             |

| r1,r2,r3                                   | Internal resistance of $L_1, L_2$ and $L_3$          |

| R <sub>2</sub>                             | Load resistor in boost mode of BDDC                  |

| <b>R</b> <sub>1</sub>                      | Load resistor in buck mode of BDDC                   |

| D <sub>max</sub>                           | Maximum boost mode duty ratio                        |

| $B_{_m}$                                   | Maximum flux density                                 |

| R <sub>2max</sub>                          | Maximum load resistor in boost mode of BDDC          |

| $R_{1 \max}$                               | Maximum load resistor in buck mode of BDDC           |

|                                            |                                                      |

| Symbols                           | Descriptions                                              |

|-----------------------------------|-----------------------------------------------------------|

| $D_{ m lmin}$                     | Minimum buck mode duty ratio                              |

| $R_{2\min}$                       | Minimum load resistor in boost mode of BDDC               |

| $C_{2\min}$                       | Minimum output capacitor in boost mode of BDDC            |

| $C_{1\min}$                       | Minimum output capacitor in buck mode of BDDC             |

| М                                 | Mutual inductance                                         |

| n                                 | Number of phases                                          |

| Ν                                 | Number of turns                                           |

| d <sub>2</sub>                    | Off time duration of boost mode                           |

| $d_2^1$                           | Off time duration of buck mode                            |

| $R_{on1}, R_{on2}, R_{on3}$       | On state resistance of $S_1, S_2, S_3$                    |

| $R_{on4}, R_{on5}, R_{on6}$       | On state resistance of $S_4$ , $S_5$ , $S_6$              |

| R <sub>DS1</sub>                  | On state resistance of S <sub>1</sub>                     |

| R <sub>DS2</sub>                  | On state resistance of S <sub>2</sub>                     |

| d <sub>1</sub>                    | On time duration of boost mode                            |

| $d_1^{1}$                         | On time duration of buck mode                             |

| $\mathbf{f}_{\mathrm{s}}$         | Operating frequency                                       |

| i <sub>C2</sub>                   | Output capacitor current in boost mode of BDDC            |

| i <sub>C1</sub>                   | Output capacitor current in buck mode of BDDC             |

| $C_2$                             | Output capacitor in boost mode of BDDC                    |

| C <sub>1</sub>                    | Output capacitor in buck mode of BDDC                     |

| $V_{c1pp}$                        | Peak to peak voltage across C <sub>1</sub>                |

| V <sub>c2pp</sub>                 | Peak to peak voltage across C <sub>2</sub>                |

| $I_{m}$                           | Peak value of inductor current                            |

| I <sub>D1rms</sub>                | RMS value of diode current in boost mode of BDDC          |

| I <sub>D2rms</sub>                | RMS value of diode current in buck mode of BDDC           |

| I <sub>Lrms</sub>                 | RMS value of inductor current                             |

| I <sub>C2rms</sub>                | RMS value of output capacitor in boost mode of BDDC       |

| I <sub>C1rms</sub>                | RMS value of output capacitor in buck mode of BDDC        |

| T <sub>s</sub>                    | Switching period                                          |

| $V_{L1B}$ , $V_{L2B}$ , $V_{L3B}$ | Voltage across an inductors $L_1, L_2, L_3$ in boost mode |

| $v_{L1}$ , $v_{L2}$ , $v_{L3}$    | Voltage across an inductors $L_1, L_2, L_3$ in buck mode  |

| V <sub>C1</sub>                   | Voltage across C <sub>1</sub>                             |

| Symbols         | Descriptions                          |

|-----------------|---------------------------------------|

| V <sub>C2</sub> | Voltage across C <sub>2</sub>         |

| V <sub>LB</sub> | Voltage across inductor in boost mode |

| $v_L$           | Voltage across inductor in buck mode  |

| $K_{_W}$        | Window utilization factor             |

# LIST OF FIGURES

| Figure 1.1 Block diagram of hybrid distributed generation system.                             |

|-----------------------------------------------------------------------------------------------|

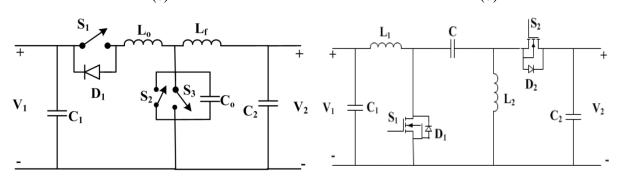

| Figure 1.2 Various topologies of non-isolated BDDC;10                                         |

| Figure 1.3 Various topologies of non-isolated interleaved BDDC;11                             |

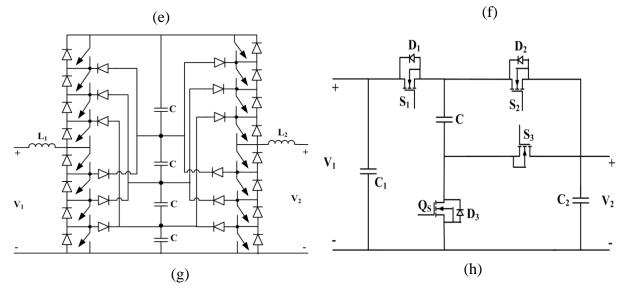

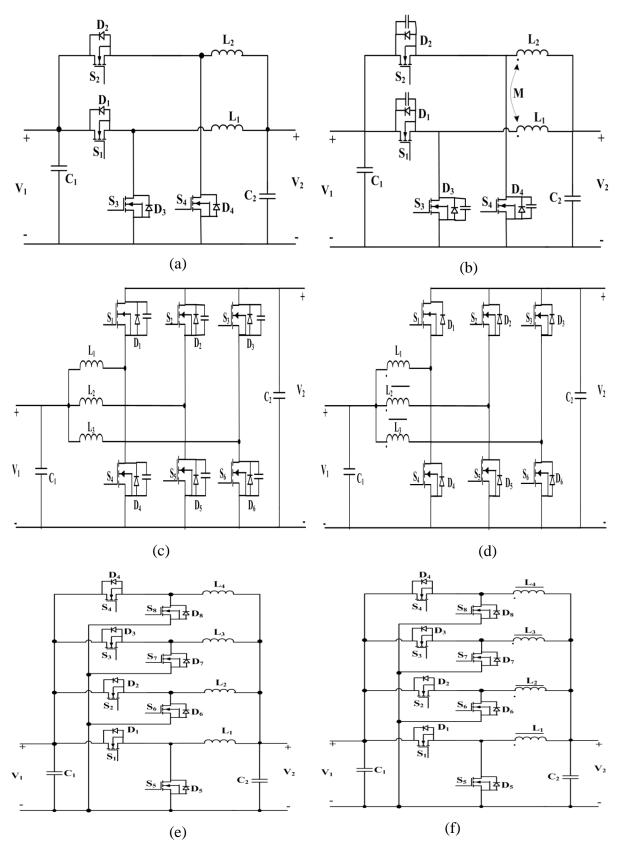

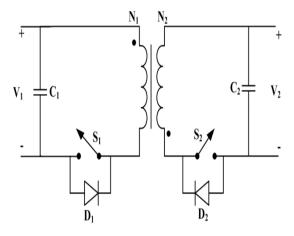

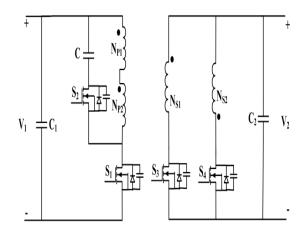

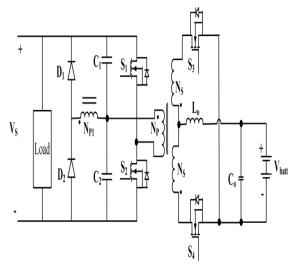

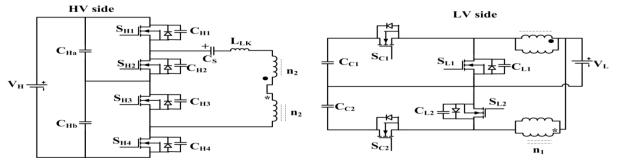

| Figure 1.4 Various topologies of isolated BDDC15                                              |

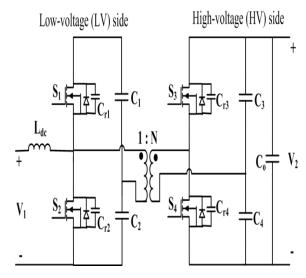

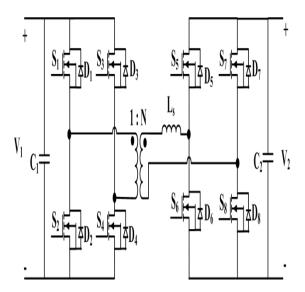

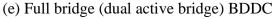

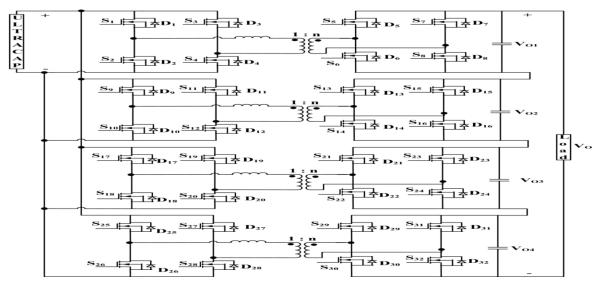

| Figure 1.5 Various topologies of isolated interleaved BDDC;16                                 |

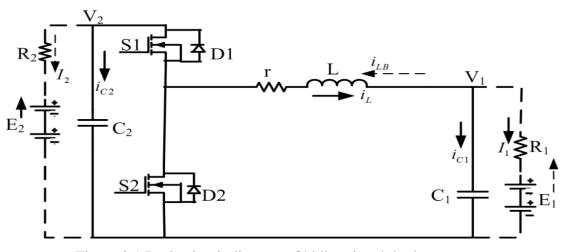

| Figure 2.1 Basic circuit diagram of bidirectional dc-dc converter22                           |

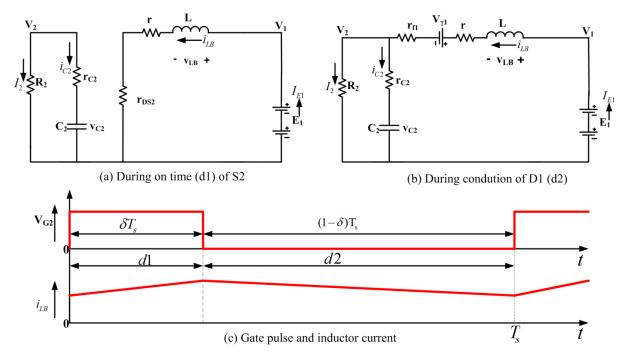

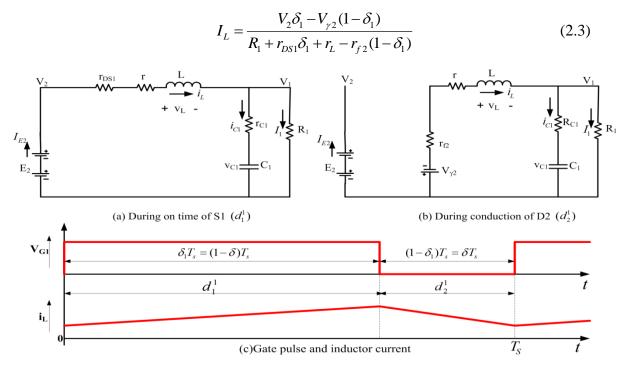

| Figure 2.2 Equivalent circuits and waveform of BDDC in boost mode                             |

| Figure 2.3 Equivalent circuits and waveform of BDDC in buck mode24                            |

| Figure 2.4 Bode plot of the state space averaged model of BDDC in boost mode                  |

| Figure 2.5 Unit step response plot of the state space averaged model of BDDC in boost mode.   |

|                                                                                               |

| Figure 2.6 Bode plot of the state space averaged model of BDDC in buck mode                   |

| Figure 2.7 Unit step plot response for the SSA model of BDDC in buck mode35                   |

| Figure 2.8 Block diagram of closed loop BDDC system                                           |

| Figure 2.9 Schematic diagram of type III error amplifier/compensator                          |

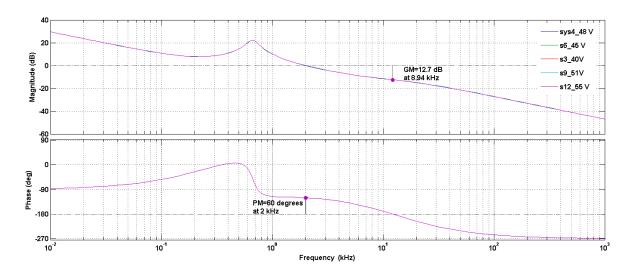

| Figure 2.10 Open loop bode for different input voltages of BDDC in boost mode                 |

| Figure 2.11 Open loop unit step plot for various input voltage of BDDC in boost mode39        |

| Figure 2.12 Open loop bode for different output load currents of BDDC in boost mode39         |

| Figure 2.13 Open loop unit step plot for different load current of BDDC in boost mode 39      |

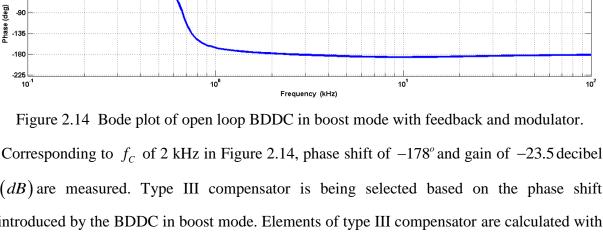

| Figure 2.14 Bode plot of open loop BDDC in boost mode with feedback and modulator40           |

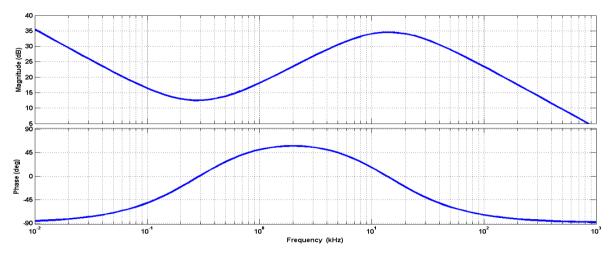

| Figure 2.15 Bode plot of type III compensator for BDDC in boost mode                          |

| Figure 2.16 Loop bode plot of BDDC in boost mode                                              |

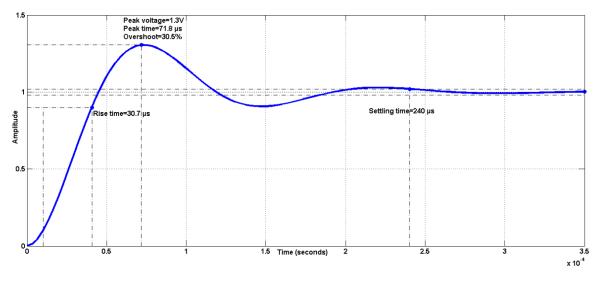

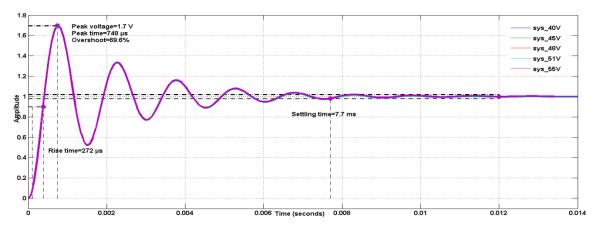

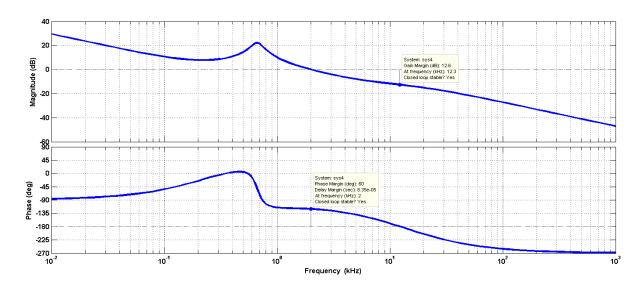

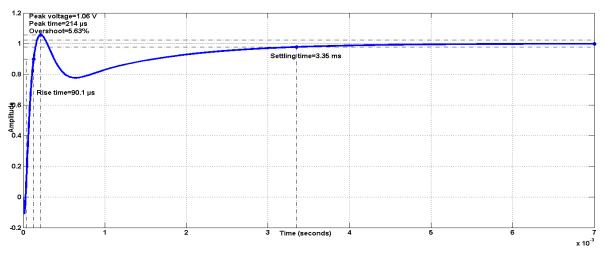

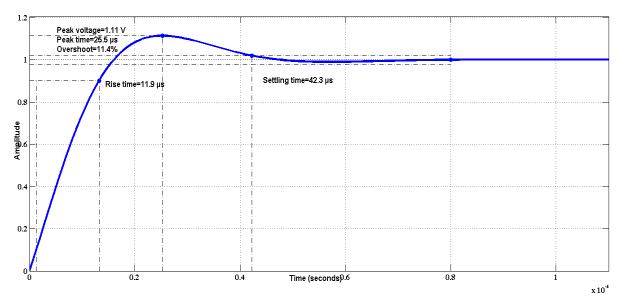

| Figure 2.17 Closed loop unit step response plot of BDDC in boost mode                         |

| Figure 2.18 Loop bode plot of BDDC in boost mode for different values of input voltage42      |

| Figure 2.19 Closed loop unit step plot of BDDC in boost mode for different input voltages. 42 |

| Figure 2.20 Loop bode plot of BDDC in boost mode for different values of load current43       |

| Figure 2.21 Closed loop unit step plot of BDDC in boost mode for different load currents43    |

| Figure 2.22 Block diagram of closed loop PID Controller for BDDC in buck mode                 |

| Figure 2.23 Open loop bode for different input voltages of BDDC in buck mode45                |

| Figure 2.24 Open loop unit step plot of different input voltages of BDDC in buck mode45       |

| Figure 2.25 Open loop bode plot for different output load currents of BDDC in buck mode.46    |

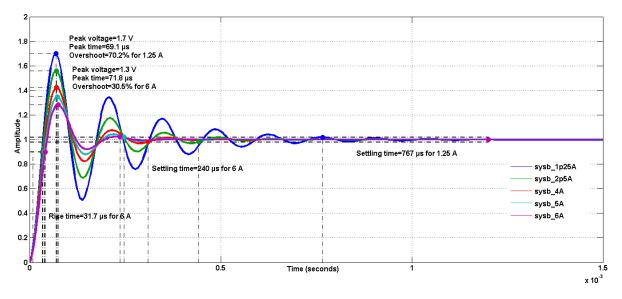

| Figure 2.26 Open loop unit step plots for different load currents of BDDC in buck mode 46     |

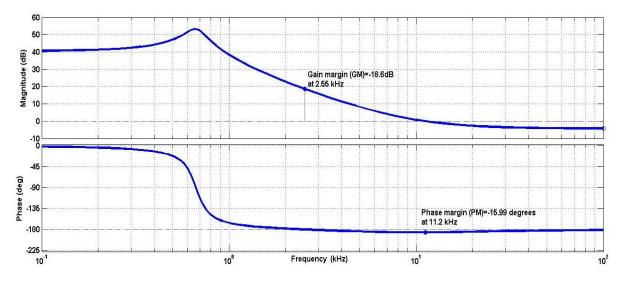

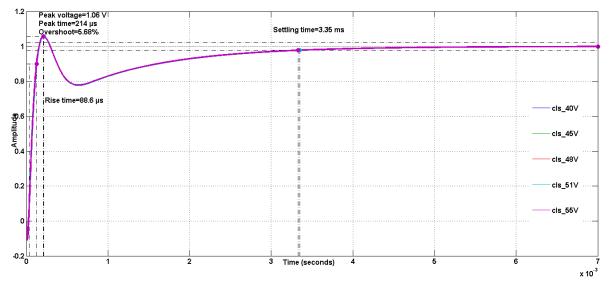

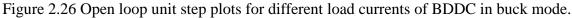

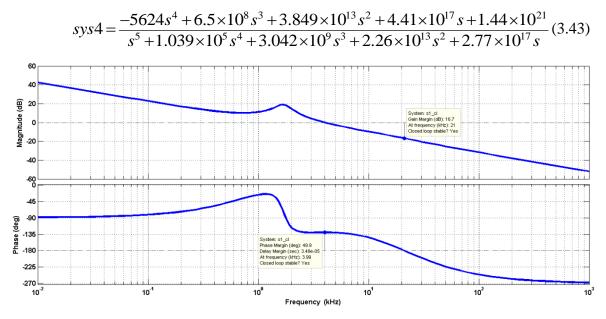

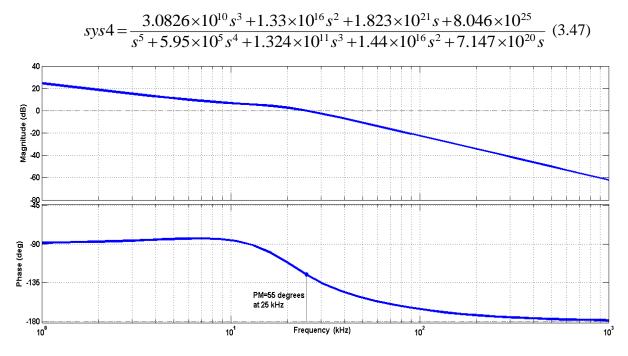

| Figure 2.27 Loop bode plot of BDDC in buck mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

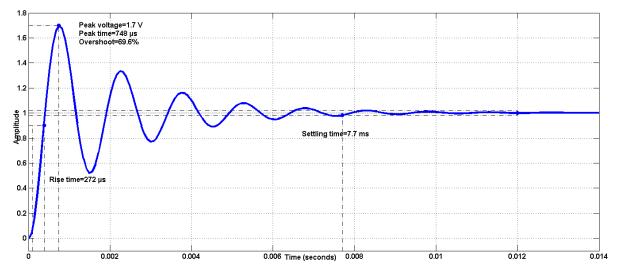

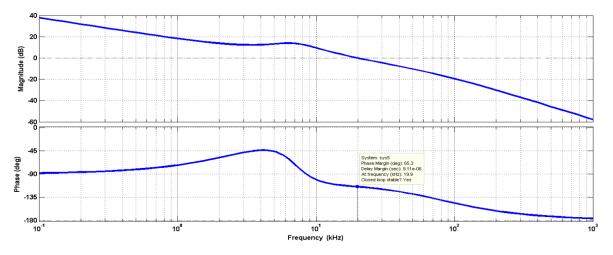

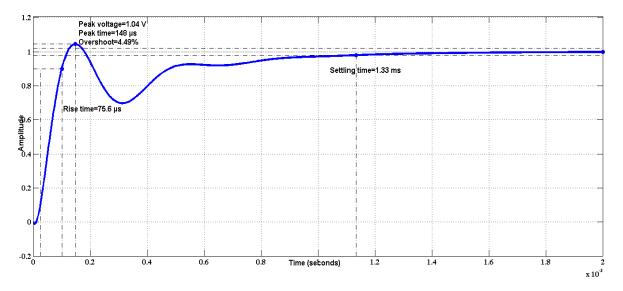

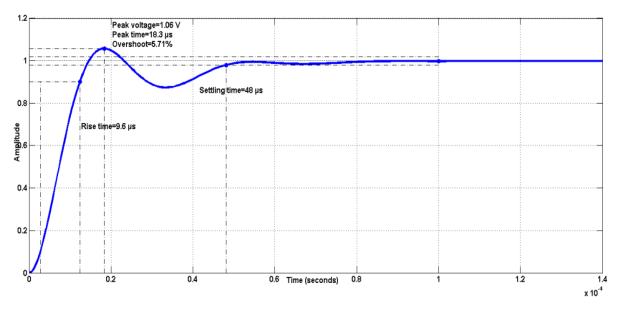

| Figure 2.28 Closed loop unit step response plot of BDDC in buck mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

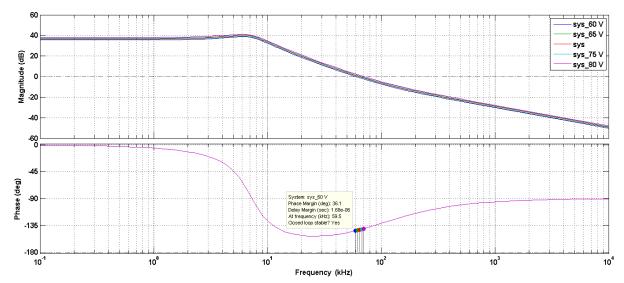

| Figure 2.29 Loop bode of BDDC in buck mode for different values of input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 2.30 Closed loop unit step plot of BDDC in buck mode for different input voltages 49                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

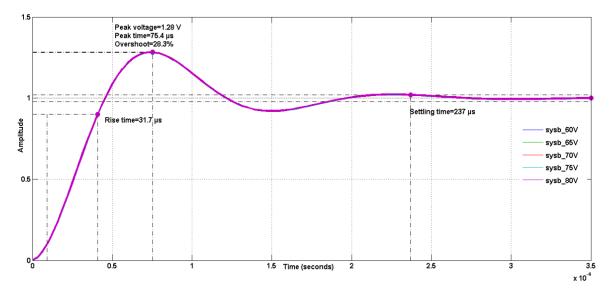

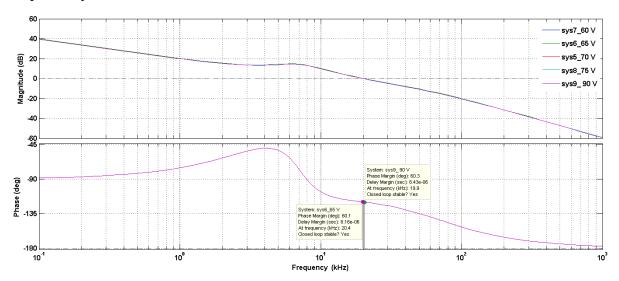

| Figure 2.31 Loop bode of BDDC in buck mode for different values of load current                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

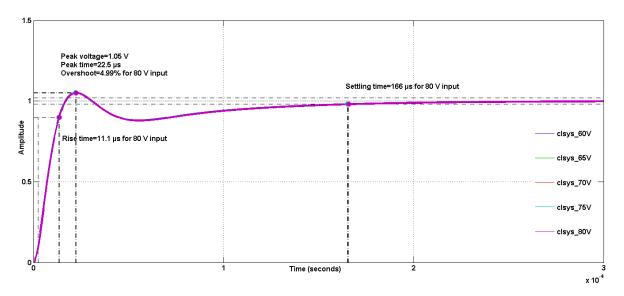

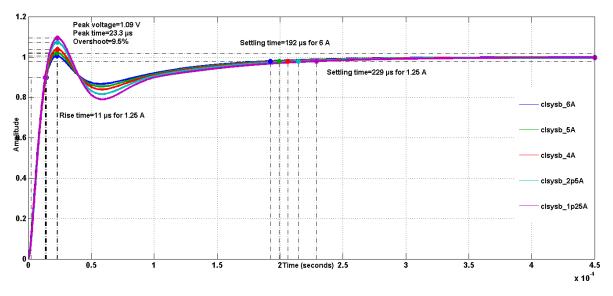

| Figure 2.32 Closed loop unit step plot of BDDC in buck mode for different load currents 50                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

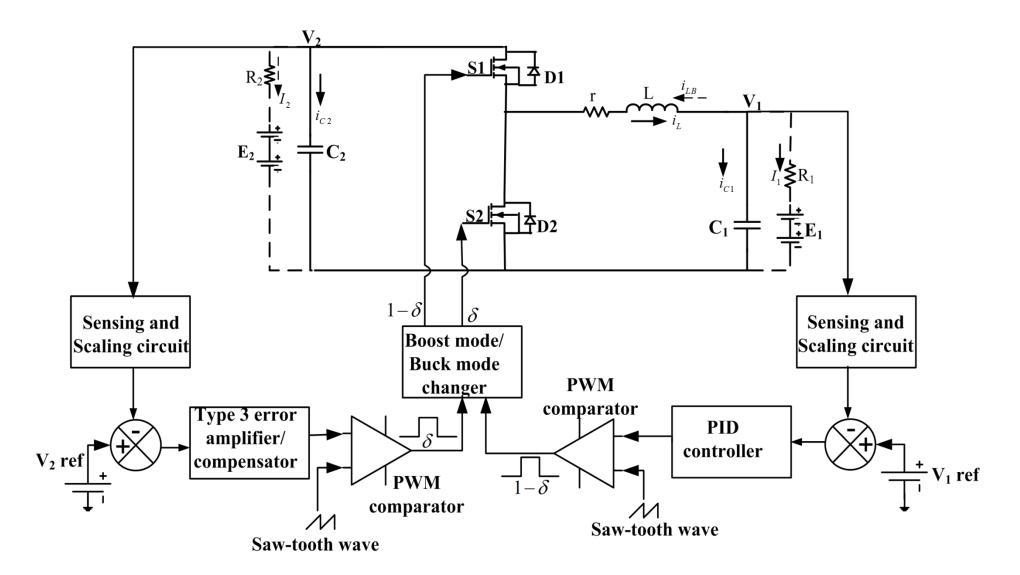

| Figure 2.33 Simulation circuit of BDDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 2.34 Simulation results of BDDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

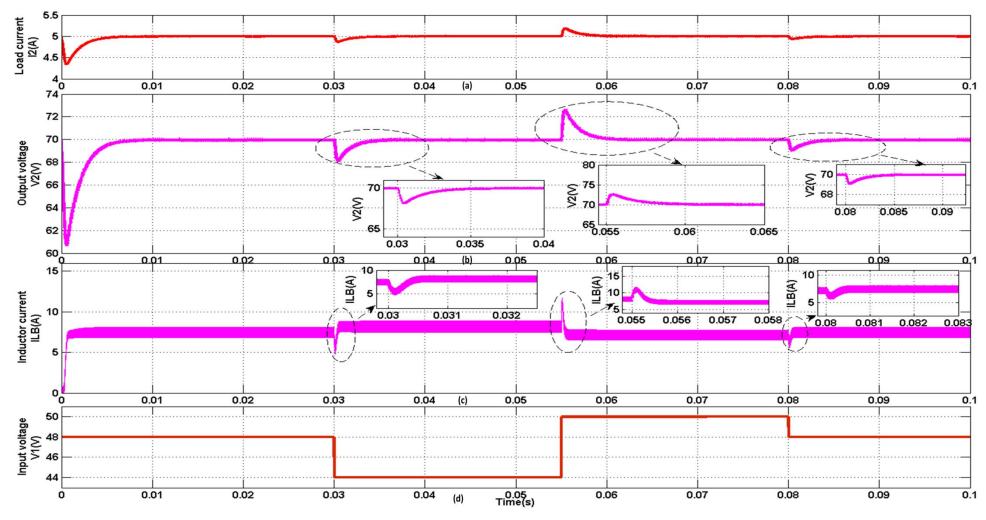

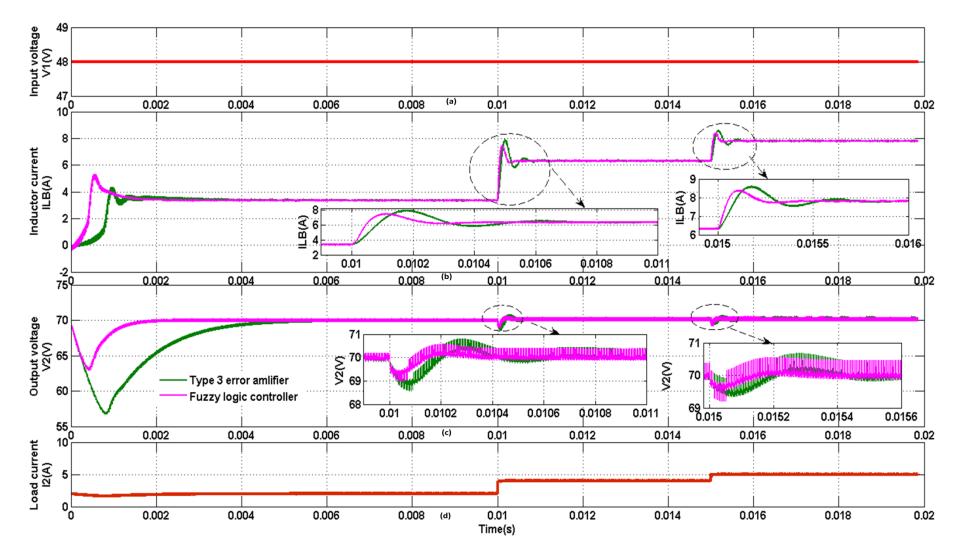

| Figure 2.35 Simulation results of BDDC in boost mode against input voltage variation 56                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 2.36 Simulation results of BDDC in boost mode against load current variation 57                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

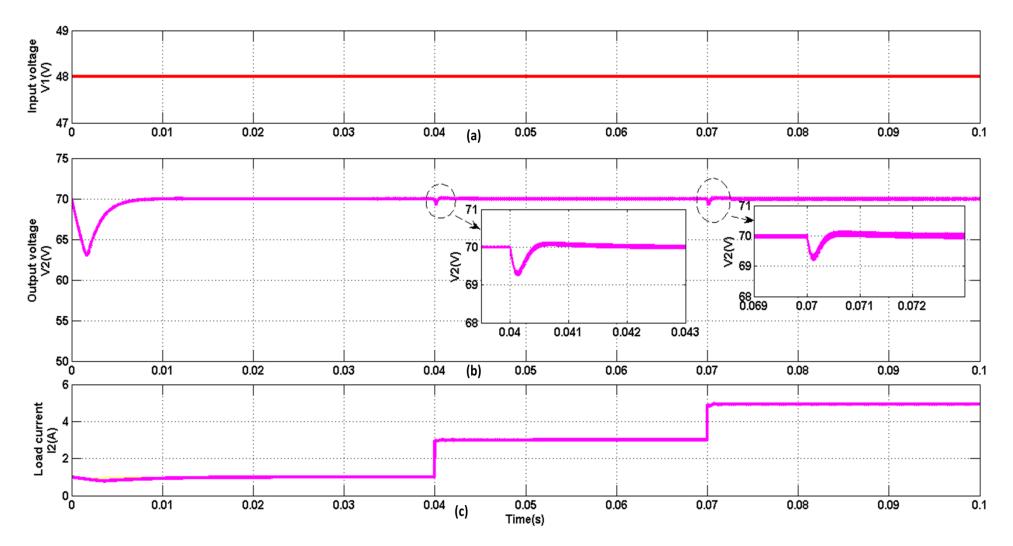

| Figure 2.37 Simulation results of BDDC in buck mode against input voltage variation 58                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 2.38 Simulation results of BDDC in buck mode against load current variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

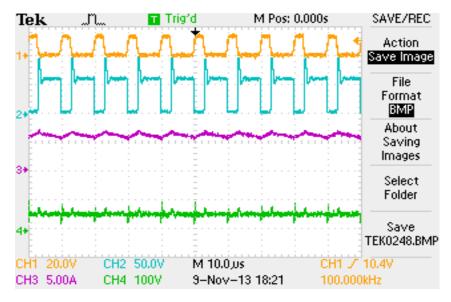

| Figure 2.39 Steady state waveforms of BDDC in boost mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 2.40 Steady state waveforms of BDDC in buck mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

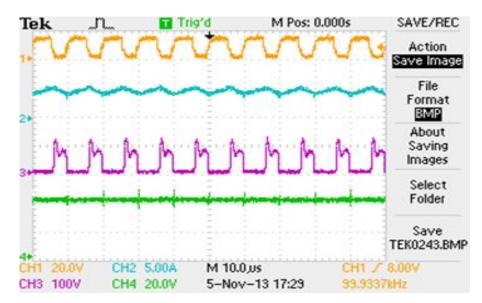

| Figure 2.41 Experimental results of BDDC in boost mode against load current $I_2$ variation                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| using type 3 EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 2.42 Experimental results of BDDC in buck mode against load current $I_1$ variation                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| using PID controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| using PID controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

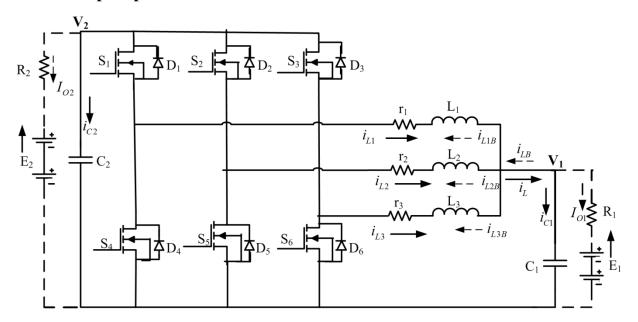

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

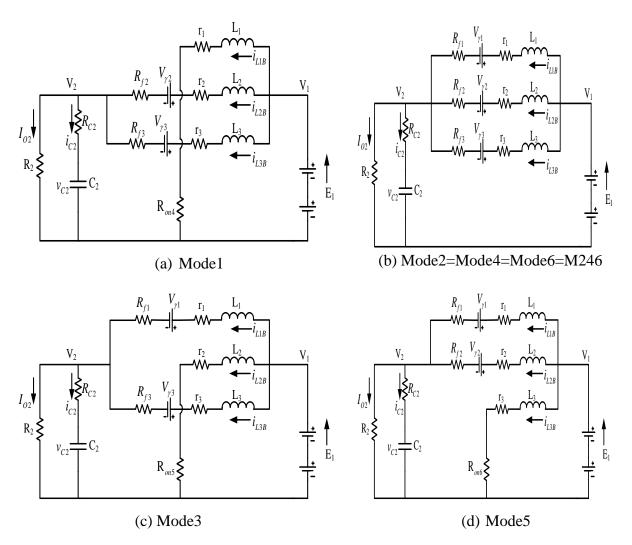

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66<br>Figure 3.2 Equivalent circuits of three-phase IBDDC in boost mode with different states 68                                                                                                                                                                                                                                                                                                                                                          |

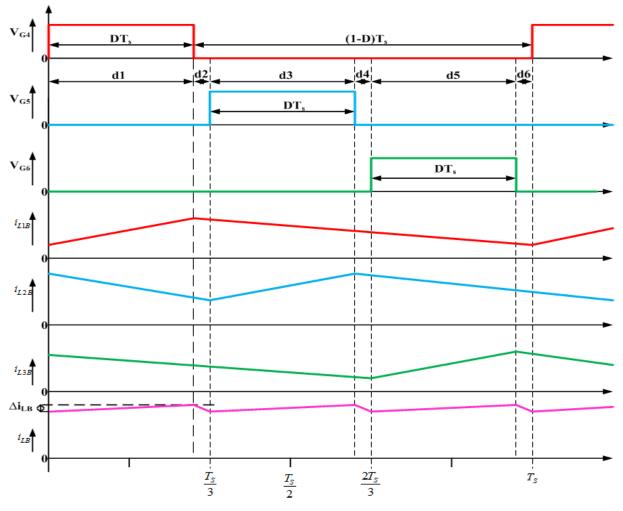

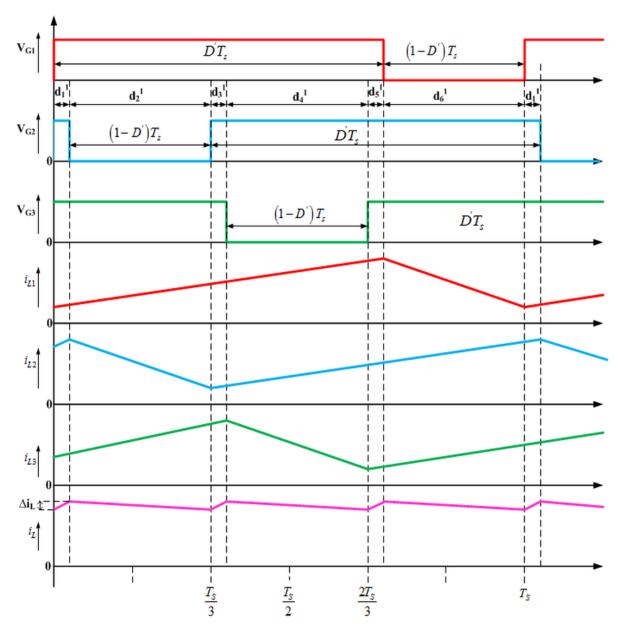

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66<br>Figure 3.2 Equivalent circuits of three-phase IBDDC in boost mode with different states 68<br>Figure 3.3 Three-phase IBDDC in boost mode operates in CCM with duty ratio D=0.32 69                                                                                                                                                                                                                                                                  |

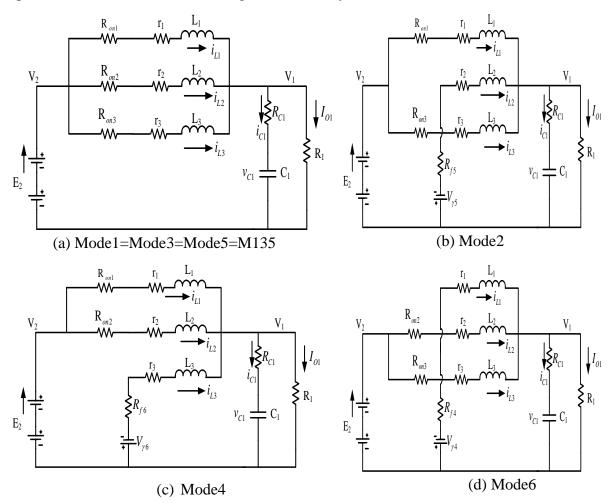

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66<br>Figure 3.2 Equivalent circuits of three-phase IBDDC in boost mode with different states 68<br>Figure 3.3 Three-phase IBDDC in boost mode operates in CCM with duty ratio D=0.32 69<br>Figure 3.4 Equivalent circuits of three-phase IBDDC in buck mode with different states 70                                                                                                                                                                     |

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66<br>Figure 3.2 Equivalent circuits of three-phase IBDDC in boost mode with different states 68<br>Figure 3.3 Three-phase IBDDC in boost mode operates in CCM with duty ratio D=0.32 69<br>Figure 3.4 Equivalent circuits of three-phase IBDDC in buck mode with different states 70<br>Figure 3.5 Three-phase IBDDC in buck mode operates in CCM with duty ratio $D' = 0.6872$                                                                          |

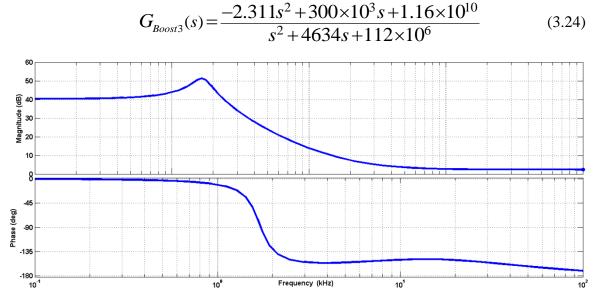

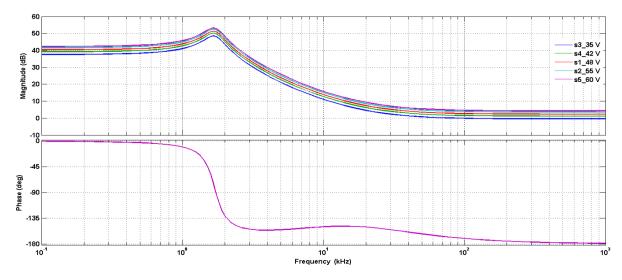

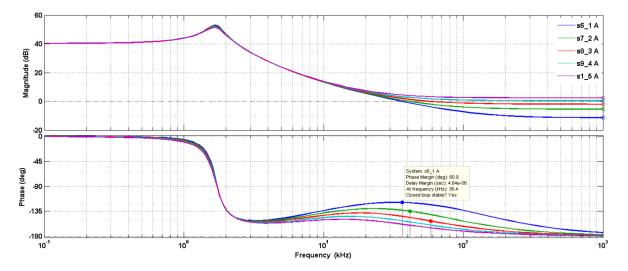

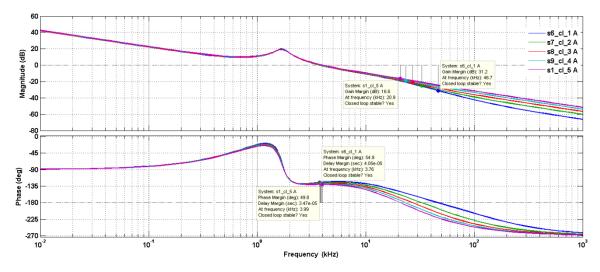

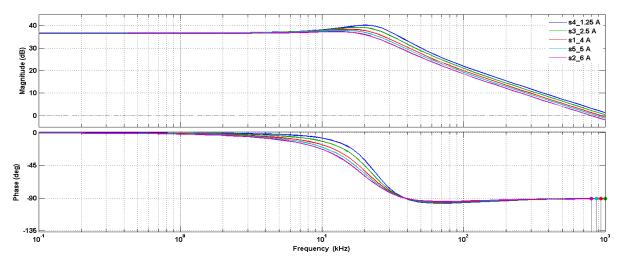

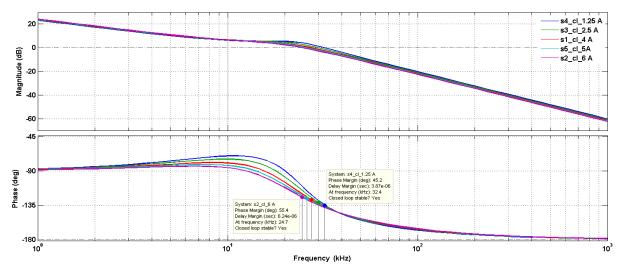

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66<br>Figure 3.2 Equivalent circuits of three-phase IBDDC in boost mode with different states 68<br>Figure 3.3 Three-phase IBDDC in boost mode operates in CCM with duty ratio D=0.32 69<br>Figure 3.4 Equivalent circuits of three-phase IBDDC in buck mode with different states 70<br>Figure 3.5 Three-phase IBDDC in buck mode operates in CCM with duty ratio $D' = 0.6872$<br>Figure 3.6 Open loop bode plot of three-phase IBDDC in boost mode     |

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66<br>Figure 3.2 Equivalent circuits of three-phase IBDDC in boost mode with different states 68<br>Figure 3.3 Three-phase IBDDC in boost mode operates in CCM with duty ratio D=0.32 69<br>Figure 3.4 Equivalent circuits of three-phase IBDDC in buck mode with different states 70<br>Figure 3.5 Three-phase IBDDC in buck mode operates in CCM with duty ratio $D' = 0.6872$<br>Figure 3.6 Open loop bode plot of three-phase IBDDC in boost mode     |

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66<br>Figure 3.2 Equivalent circuits of three-phase IBDDC in boost mode with different states 68<br>Figure 3.3 Three-phase IBDDC in boost mode operates in CCM with duty ratio D=0.32 69<br>Figure 3.4 Equivalent circuits of three-phase IBDDC in buck mode with different states 70<br>Figure 3.5 Three-phase IBDDC in buck mode operates in CCM with duty ratio $D' = 0.6872$<br>Figure 3.6 Open loop bode plot of three-phase IBDDC in boost mode     |

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66<br>Figure 3.2 Equivalent circuits of three-phase IBDDC in boost mode with different states 68<br>Figure 3.3 Three-phase IBDDC in boost mode operates in CCM with duty ratio D=0.32 69<br>Figure 3.4 Equivalent circuits of three-phase IBDDC in buck mode with different states 70<br>Figure 3.5 Three-phase IBDDC in buck mode operates in CCM with duty ratio $D' = 0.6872$<br>Figure 3.6 Open loop bode plot of three-phase IBDDC in boost mode     |

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66<br>Figure 3.2 Equivalent circuits of three-phase IBDDC in boost mode with different states 68<br>Figure 3.3 Three-phase IBDDC in boost mode operates in CCM with duty ratio $D=0.32$ 69<br>Figure 3.4 Equivalent circuits of three-phase IBDDC in buck mode with different states 70<br>Figure 3.5 Three-phase IBDDC in buck mode operates in CCM with duty ratio $D' = 0.6872$<br>Figure 3.6 Open loop bode plot of three-phase IBDDC in boost mode   |

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66<br>Figure 3.2 Equivalent circuits of three-phase IBDDC in boost mode with different states 68<br>Figure 3.3 Three-phase IBDDC in boost mode operates in CCM with duty ratio D= $0.32$ 69<br>Figure 3.4 Equivalent circuits of three-phase IBDDC in buck mode with different states 70<br>Figure 3.5 Three-phase IBDDC in buck mode operates in CCM with duty ratio $D' = 0.68$ 72<br>Figure 3.6 Open loop bode plot of three-phase IBDDC in boost mode |

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66<br>Figure 3.2 Equivalent circuits of three-phase IBDDC in boost mode with different states 68<br>Figure 3.3 Three-phase IBDDC in boost mode operates in CCM with duty ratio $D=0.32$ 69<br>Figure 3.4 Equivalent circuits of three-phase IBDDC in buck mode with different states 70<br>Figure 3.5 Three-phase IBDDC in buck mode operates in CCM with duty ratio $D' = 0.68$ 72<br>Figure 3.6 Open loop bode plot of three-phase IBDDC in boost mode  |

| Figure 3.1 Basic circuit diagram of three-phase interleaved bidirectional dc-dc converter 66<br>Figure 3.2 Equivalent circuits of three-phase IBDDC in boost mode with different states 68<br>Figure 3.3 Three-phase IBDDC in boost mode operates in CCM with duty ratio D=0.32 69<br>Figure 3.4 Equivalent circuits of three-phase IBDDC in buck mode with different states 70<br>Figure 3.5 Three-phase IBDDC in buck mode operates in CCM with duty ratio $D' = 0.6872$<br>Figure 3.6 Open loop bode plot of three-phase IBDDC in boost mode     |

| Figure 3.14 Open loop unit step plot of three-phase IBDDC in boost mode for different values   |

|------------------------------------------------------------------------------------------------|

| of load current                                                                                |

| Figure 3.15 Bode plot of three-phase IBDDC in boost mode with feedback and modulator. 87       |

| Figure 3.16 Bode plot of type III compensator for three-phase IBDDC in boost mode87            |

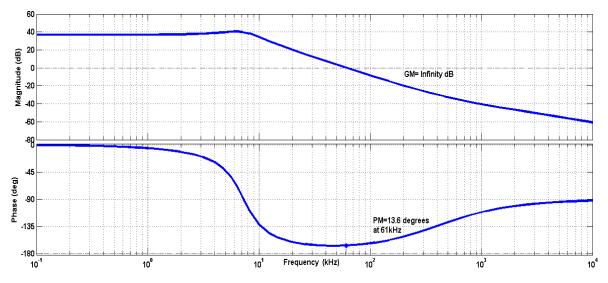

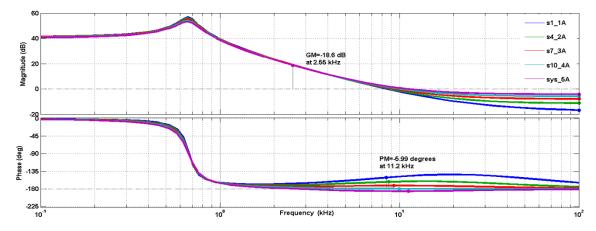

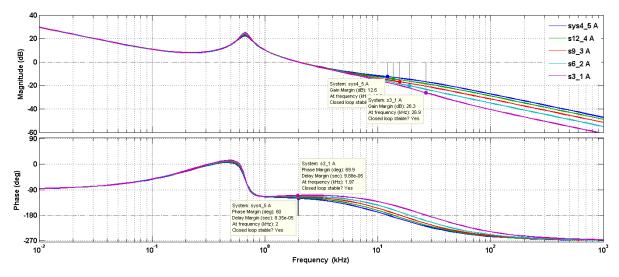

| Figure 3.17 Loop bode plot of three-phase IBDDC in boost mode                                  |

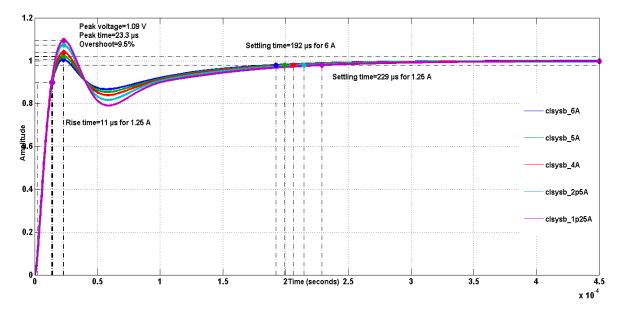

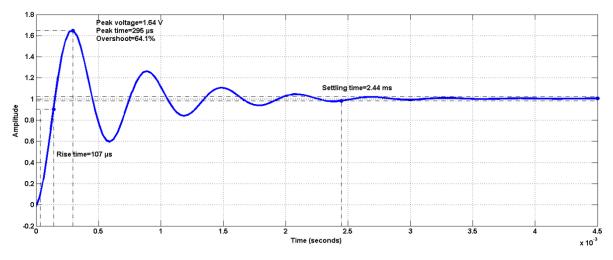

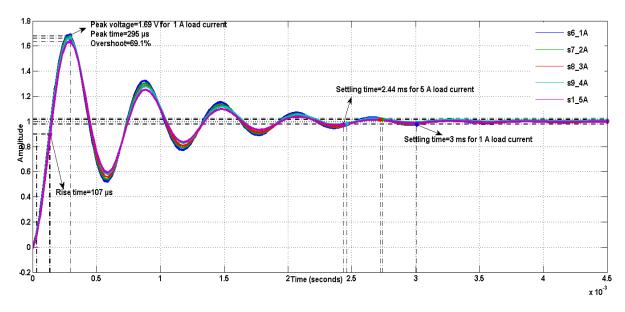

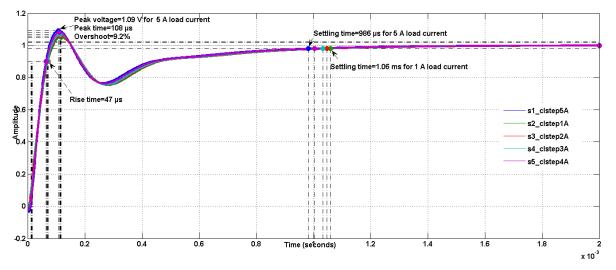

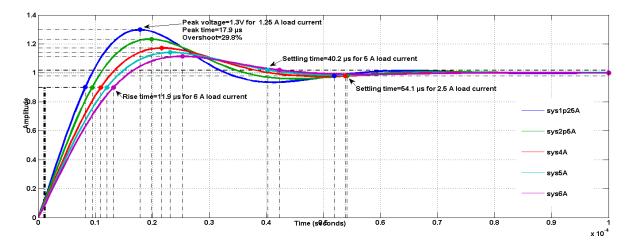

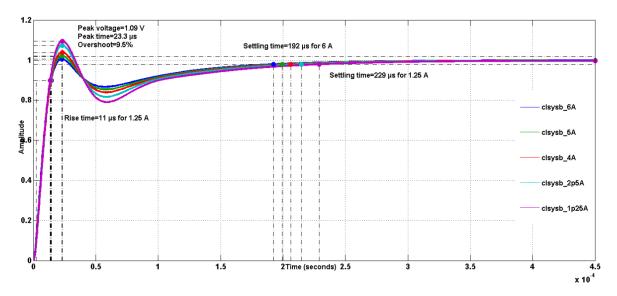

| Figure 3.18 Closed loop unit step response plot of three-phase IBDDC in boost mode88           |

| Figure 3.19 Loop bode plot of three-phase IBDDC in boost mode for different values of input    |

| voltage V <sub>1</sub> 89                                                                      |

| Figure 3.20 Closed loop unit step plot of three-phase IBDDC in boost mode for different        |

| values of input voltage                                                                        |

| Figure 3.21 Loop bode plot of three-phase IBDDC in boost mode for different values of load     |

| current I <sub>o2</sub> 90                                                                     |

| Figure 3.22 Closed loop unit step plot of three-phase IBDDC in boost mode for different load   |

| current I <sub>o2</sub> 90                                                                     |

| Figure 3.23 Open loop bode of different values of input voltage $V_2$ for three-phase IBDDC in |

| buck mode91                                                                                    |

| Figure 3.24 Open loop unit step plot of three-phase IBDDC in buck mode for different input     |

| voltages                                                                                       |

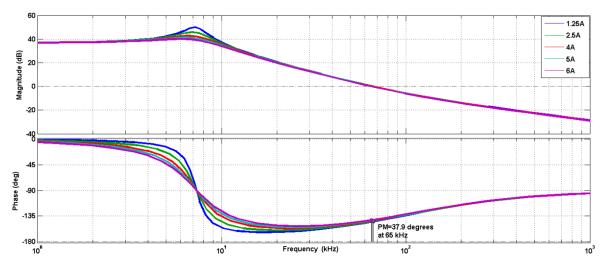

| Figure 3.25 Open loop bode of three-phase IBDDC in buck mode for different load currents.      |

|                                                                                                |

| Figure 3.26 Open loop unit step plot of three-phase IBDDC in buck mode for different load      |

| currents                                                                                       |

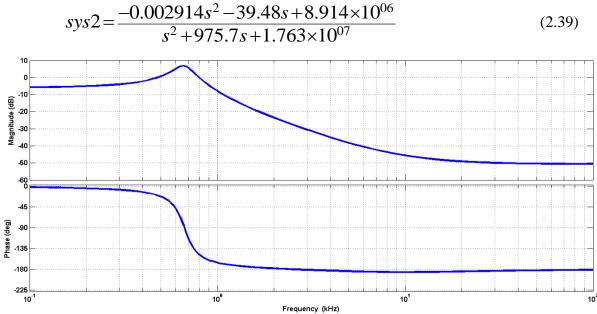

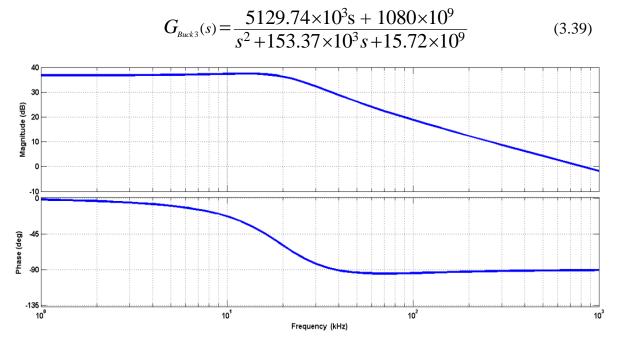

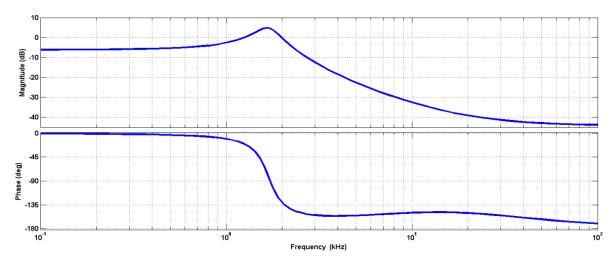

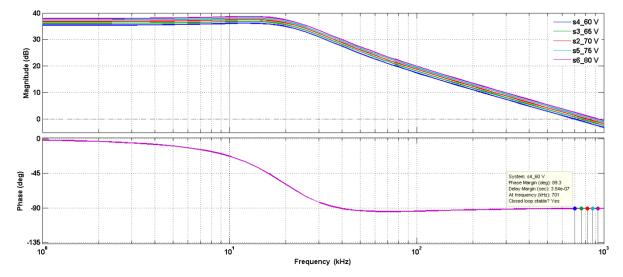

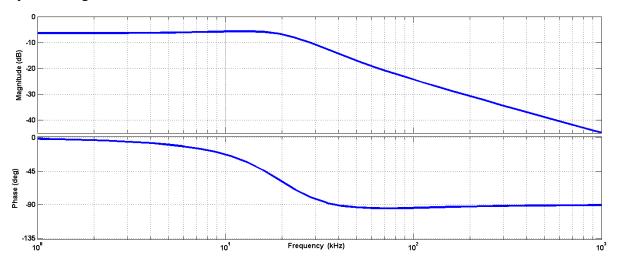

| Figure 3.27 Bode plot of three-phase IBDDC in buck mode with feedback and modulator93          |

| Figure 3.28 Bode plot of type III compensator for three-phase IBDDC in buck mode93             |

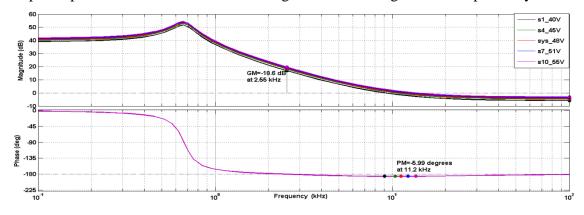

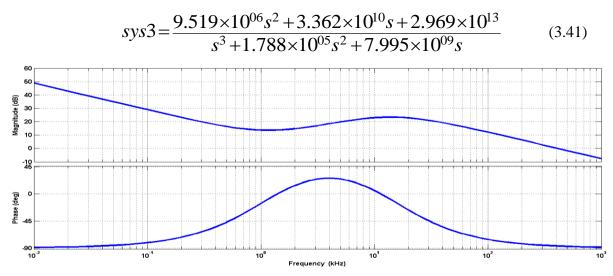

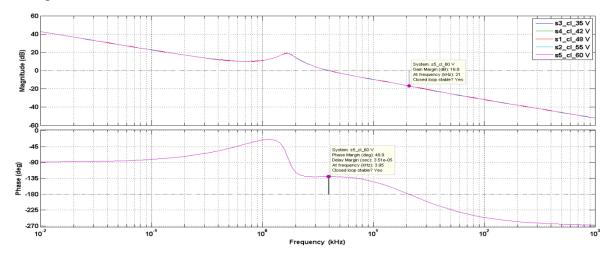

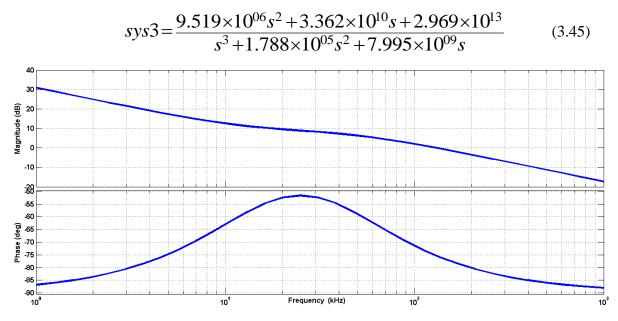

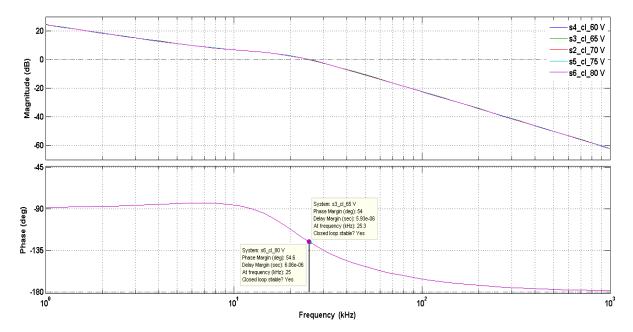

| Figure 3.29 Loop bode plot of three-phase IBDDC in buck mode                                   |

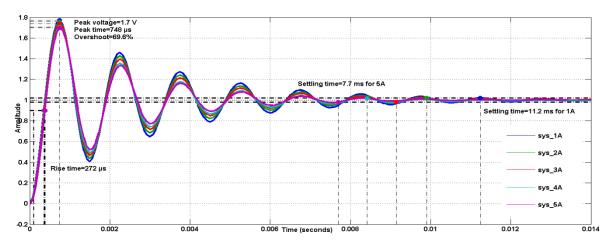

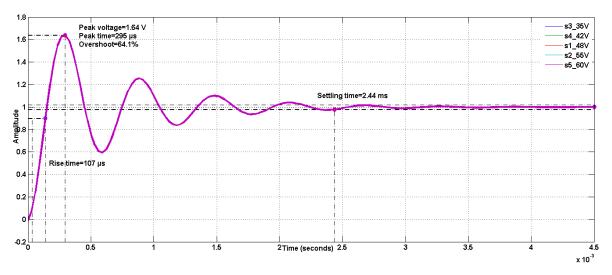

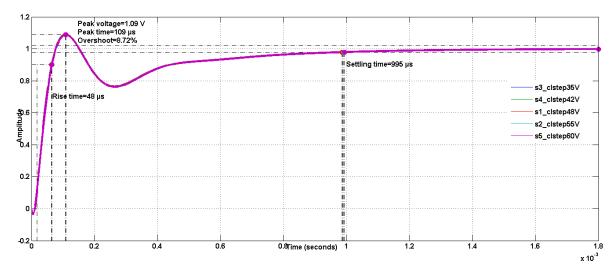

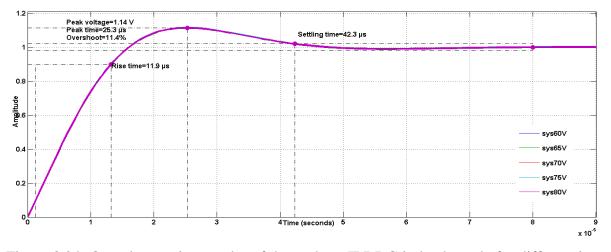

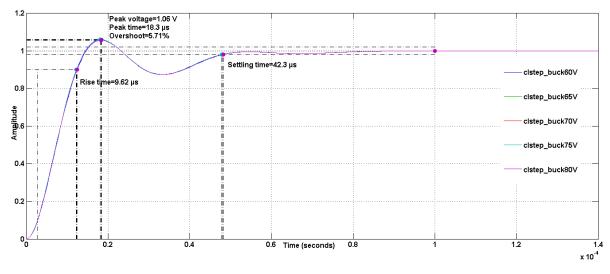

| Figure 3.30 Closed loop unit step response plot of three-phase IBDDC in buck mode95            |

| Figure 3.31 Loop bode plot of three-phase IBDDC in buck mode for different input voltages.     |

|                                                                                                |

| Figure 3.32 Closed loop unit step plot of three-phase IBDDC in buck mode for different         |

| input voltages                                                                                 |

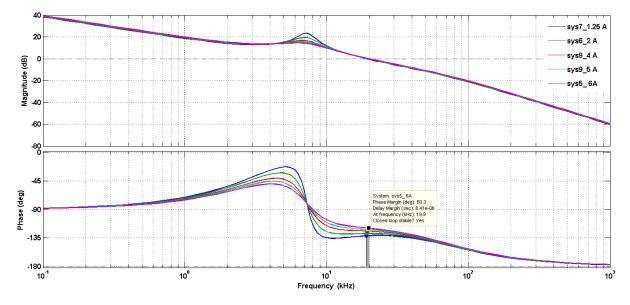

| Figure 3.33 Loop bode plot of three-phase IBDDC in buck mode for different values of load      |

| currents                                                                                       |

|                                                                                                |

| Figure 3.34 Closed loop unit step plot of three-phase IBDDC in buck mode for different load    |

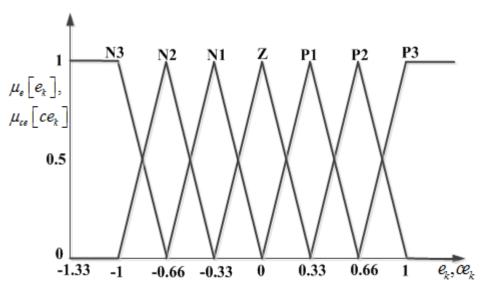

| Figure 3.35 Block diagram of FLC for three-phase IBDDC                                          |

|-------------------------------------------------------------------------------------------------|

| Figure 3.36 Membership function of $e_k$ and $ce_k$ for three-phase IBDDC in boost mode         |

| Figure 3.37 Membership function of $e_k$ and $ce_k$ for three-phase IBDDC in buck mode          |

| Figure 3.38 Simulation circuit of three-phase IBDDC                                             |

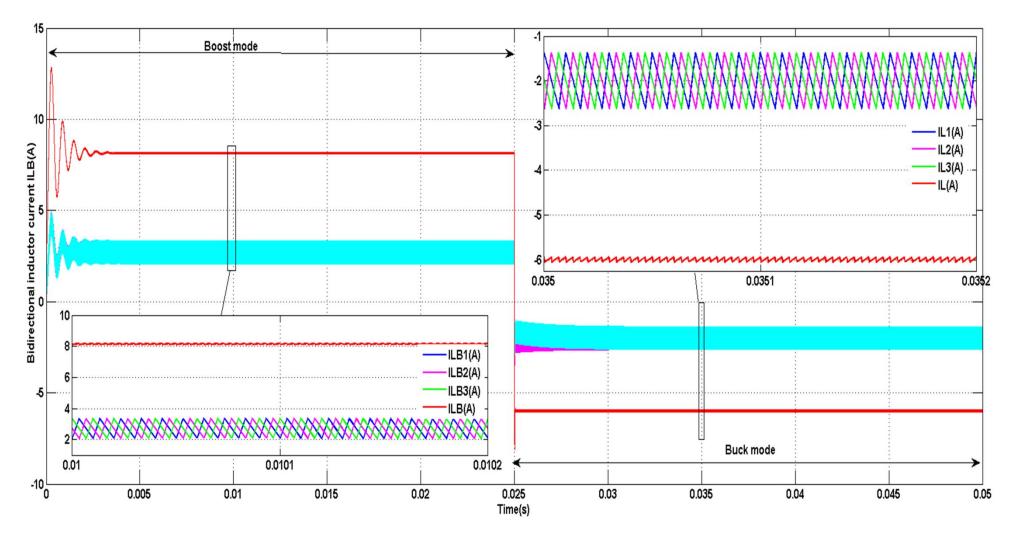

| Figure 3.39 Simulation results for bidirectional and individual inductor current of three-phase |

| IBDDC                                                                                           |

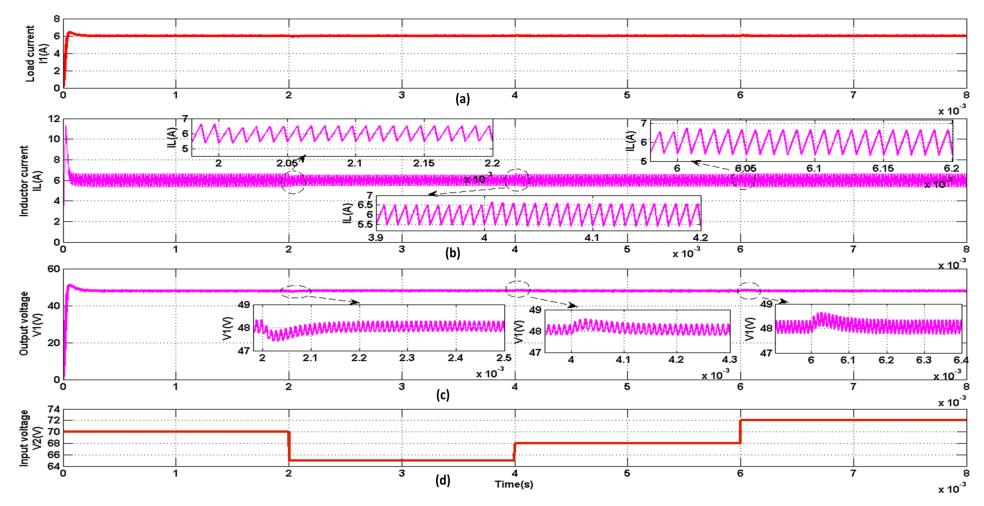

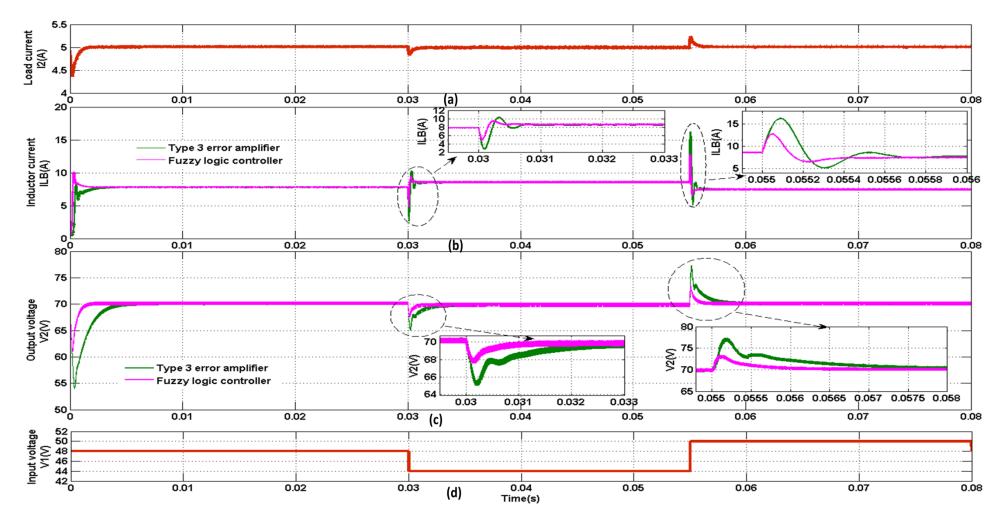

| Figure 3.40 Simulation results of three-phase IBDDC in boost mode against input voltage $V_1$   |

| variation                                                                                       |

| Figure 3.41 Simulation results of three-phase IBDDC in boost mode against load current          |

| variation                                                                                       |

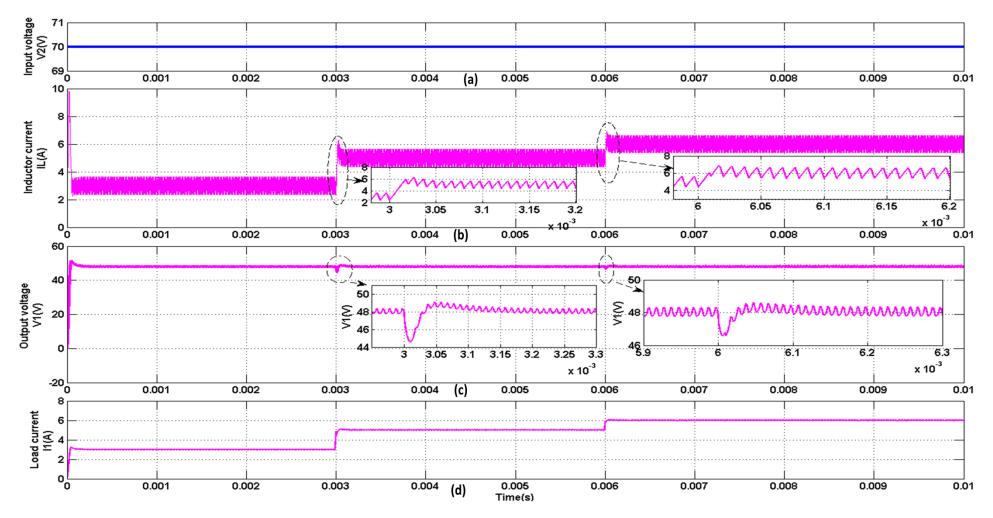

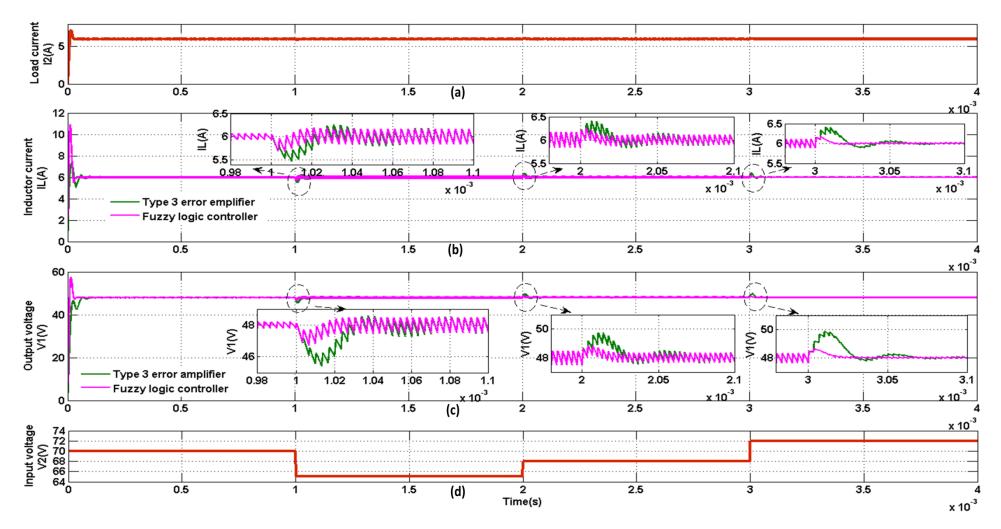

| Figure 3.42 Simulation results of three-phase IBDDC in buck mode against input voltage          |

| variation                                                                                       |

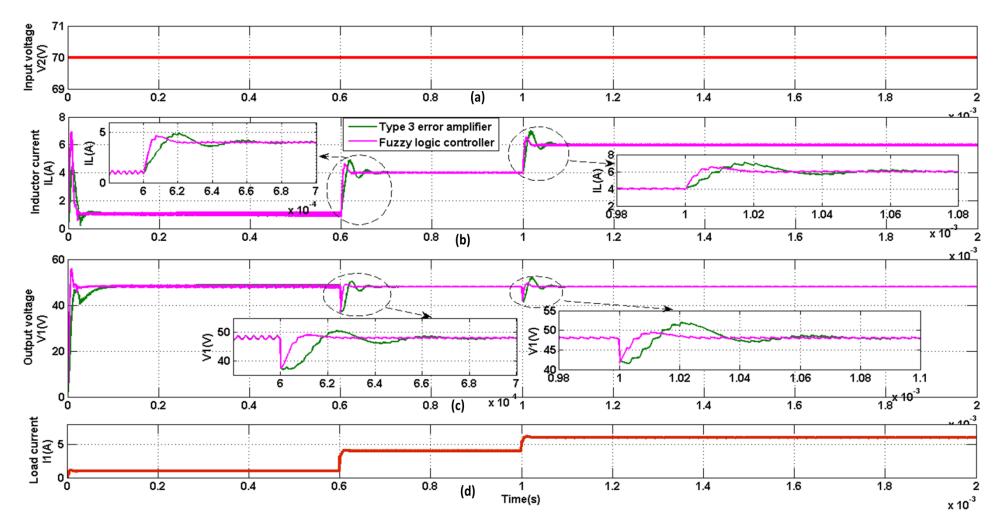

| Figure 3.43 Simulation results of three-phase IBDDC in buck mode against load current           |

| variation                                                                                       |

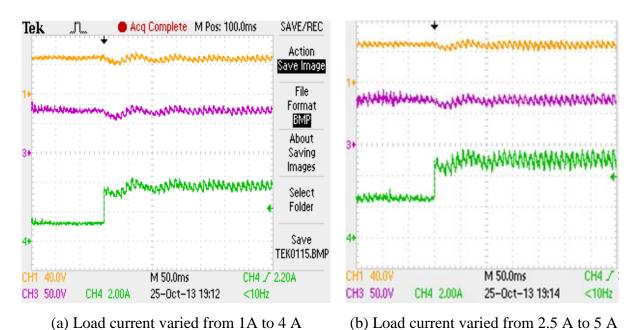

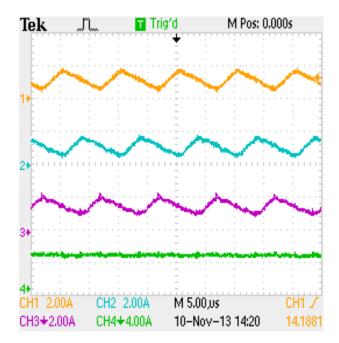

| Figure 3.44 Steady state inductor current waveforms of three-phase IBDDC in boost mode.         |

|                                                                                                 |

| Figure 3.45 Steady state inductor current waveforms of three-phase IBDDC in buck mode.111       |

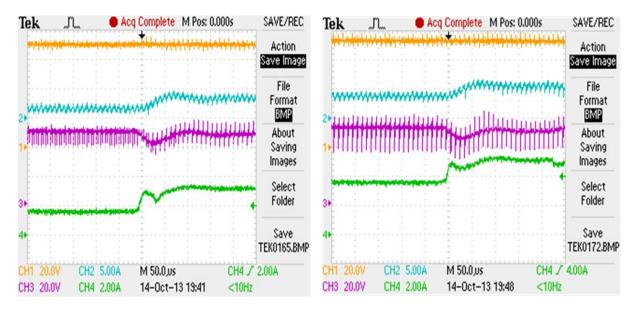

| Figure 3.46 Experimental results of three-phase IBDDC in boost mode using type III EA for       |

| different values of load current I <sub>o2</sub> 112                                            |

| Figure 3.47 Experimental results of three-phase IBDDC in boost mode using FLC for               |

| different values of load current I <sub>02</sub> 112                                            |

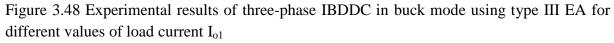

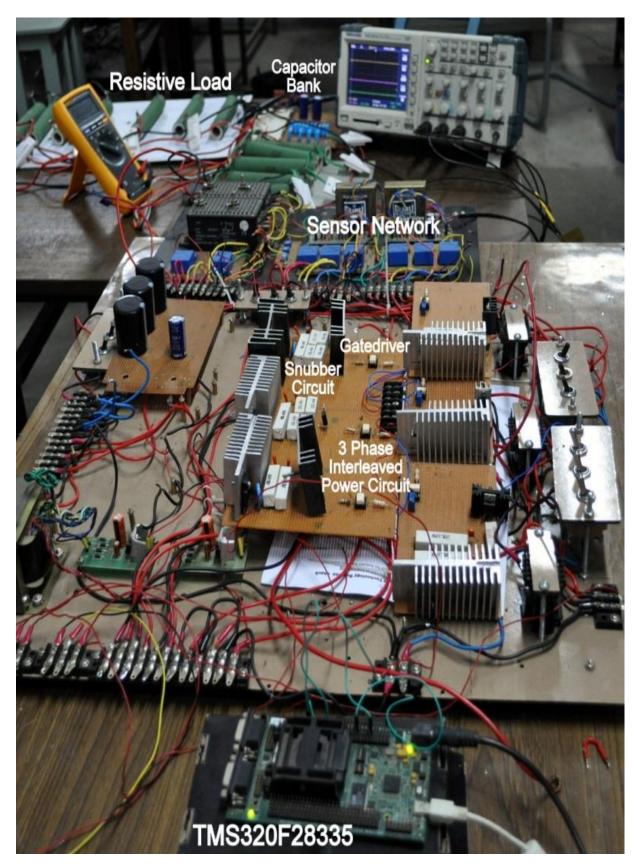

| Figure 3.48 Experimental results of three-phase IBDDC in buck mode using type III EA for        |

| different values of load current Io1 113                                                        |

| Figure 3.49 Experimental results of three-phase IBDDC in buck mode using FLC for different      |

| values of load current Io1 114                                                                  |

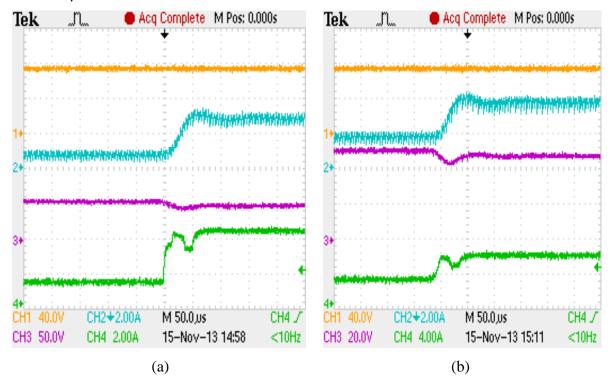

| Figure C.1 eZdspTMS320F28335 Hardware                                                           |

| Figure C.2 Block diagram of the basic configuration for the eZdspTMF28335139                    |

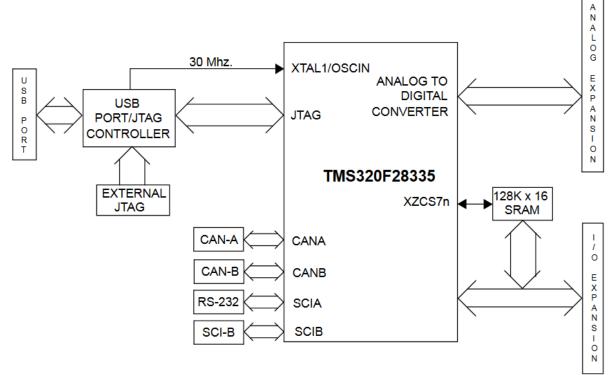

| Figure E.1 Photograph of hardware setup of BDDC and three-phase IBDDC143                        |

| Table 2.1 Specification of BDDC                                                        | 24    |

|----------------------------------------------------------------------------------------|-------|

| Table 2.2 Performance of type 3 error amplifier and PID controller on conventional BDE | OC 50 |

| Table 2.3 Specification and design parameters of conventional BDDC                     | 51    |

| Table 3.1 Specification of three-phase IBDDC in boost mode and buck mode               | 73    |

| Table 3.2 Performance of type 3 error amplifier on three-phase IBDDC.                  | 97    |

| Table 3.3 Rule base table of FLC for three-phase IBDDC in boost mode                   | 100   |

| Table 3.4 Rule base table of FLC for three-phase IBDDC in buck mode                    | 100   |

| Table 3.5 Specification and design parameters of three-phase IBDDC                     | 101   |

| Table C.1 Major components used for prototype of conventional BDDC                     | 137   |

| Table C.2 Major components used for prototype of three-phase IBDDC                     | 137   |

#### CHAPTER 1: INTRODUCTION AND LETRATURE REVIEW

[This chapter describes an overview of conventional bidirectional dc-dc converters, interleaved bidirectional dc-dc converters with switching scheme, modelling and control of bidirectional dc-dc converters. This chapter also presents a detailed literature review on non-isolated bidirectional dc-dc converter topologies, isolated bidirectional dc-dc converter topologies, modelling and control of bidirectional dc-dc converters. The scope of the research work has been highlighted and author's contributions are also presented in this chapter].

Switch mode power supply (SMPS) effectively regulates dc output voltage for a given unregulated dc input voltage. A SMPS offers many advantages like higher efficiency and power density compared to linear power supplies, which are operated in linear region with increased switching loss. SMPS consists of energy storage elements and solid-state devices. Energy storage elements include inductors and capacitors which are used for transfer of energy. Solid state elements include transistors and diodes, which are normally operated as switch. Topologies of SMPS are mainly buck derived or boost derived dc-dc converter.

Analog control technique is even good for the control of any topology of SMPS, but it changes the response of the system because of aging of components and temperature dependent characteristic. In order to overcome from the disadvantages of analog control technique, digital control technique is preferred because of higher immunity to temperature, flexibility by changing the software, advanced control techniques and shorter design cycle. Digital controllers like DSPs have maximum computational power capacity compared to microcontroller and hence advanced control algorithms can be easily implemented on digital signal processor (DSP).

### **1.1 Bidirectional DC-DC Converter**

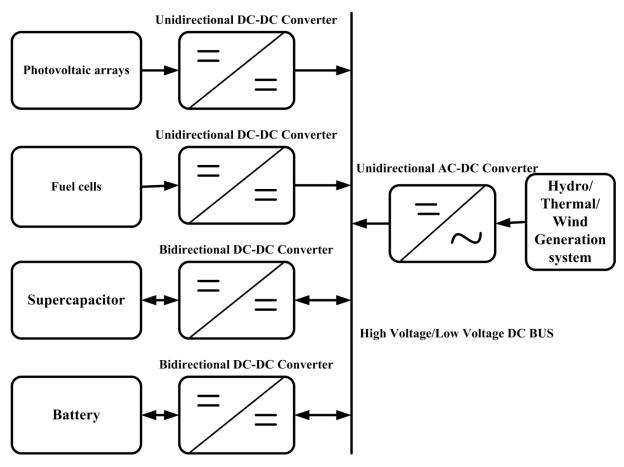

Bidirectional dc-dc converter (BDDC) is a switch mode power converter (SMPC) [1]. It is an essential candidate for many applications such as charging and discharging in uninterruptible power supplies (UPS) [2], renewable energy conversion system, electric vehicle system [3], aviation system and communication systems [4]. DC renewable energy sources like photovoltaic arrays and Fuel cells are providing variable output voltage and power. BDDC with proper control technique is essential to maintain desired constant voltage and power for driving different critical loads. A storage element is required as an energy buffer in all stand-alone systems to bridge the mismatch between available and required energy. Battery is generally the most popular energy storage element. The batteries are charged and often deep discharged and charged, which damages the battery and shortens its useful life. In addition, the environmental constraints are an important issue in the application. Ultra-capacitor has high power density, which allows the ultra-capacitor to supply more power over a short time. Conversely, the battery has a high energy density, which allows the battery to store maximum energy and supply it over a long period of time. Battery and supercapacitor are used as storage devices as well as input elements for the converter to meet the demand. Battery and supercapacitor will be charged and discharged through BDDC to maintain the DC bus voltage as constant [5]. The BDDC works as a mediator between the DC bus and the energy storage system, Hybrid distribution generation system with back up elements as depicted in Figure 1.1.

Figure 1.1 Block diagram of hybrid distributed generation system.

BDDC provides higher efficiency, power density and low cost. BDDC can also be used in two quadrant motor drive [6]. In medium power applications, a non-isolated BDDC is preferred. The total power and the direction flow of current are controlled by the suitable control algorithms. Therefore, the BDDC is very attractive for storage backup systems. The bidirectional converter works in two modes; one is forward buck mode to energy storage system and second one is reverse boost mode to supply the point of load. BDDC operating in continuous conduction mode (CCM) have lower conduction loss, and capacitor ripple current, and have better utilization of switching devices as compared to BDDC operating in discontinuous conduction mode (DCM).

Power sources with wide voltage variation in medium power applications [7], BDDC with transformer is not suitable because of large magnetizing currents, maximum copper losses occur on low voltage side and stored energy is being transformed from the large core.

MOSFET is used as a switching device in high frequency operation; by proper selection of snubber circuit [8], device turnoff loss can be minimized and with the proper selection of gate-drive circuit [9], turn on loss can be reduced and hence achieve increased efficiency.

### 1.2 Interleaved Bidirectional DC-DC Converter

Many parallel BDDC stages (phases) are used to build multi-phase interleaved bidirectional dc-dc converter topology [10] which can handle relatively high currents in medium and high power applications. The number of phases in interleaved bidirectional dc-dc converter (IBDDC) is related in terms of cost, efficiency, volume and complexity of control. The main advantage of this technique is to reduce the input and output filter size, device stress, alleviation of the effects of current ripple, reliability in a rugged environment, power density and hence achieve the higher efficiency [11]. Using interleaving technique, power stage of IBDDC is divided into smaller and several stages and hence reduces the size of each element. When IBDDC operates in CCM, it minimizes imbalance currents and eliminate current control loop. Interleaved converter share equal amount of load current in each converter [12, 13] and share the same output capacitor. Interleaved converters are used in central processing unit, switching audio amplifier, hybrid electric vehicles [14], power factor correction, renewable energy [15], fuel cell systems [16], and voltage regulator module for microprocessor. The ripple in the output voltage is very small, and requires a small capacitance.

Multi-phase IBDDC has  $N_{phase}$  inductors as compared to single phase BDDC, and increase the complexity. Multi-phase IBDDC operates in continuous conduction mode have better utilization of switching devices, lower conduction loss, and reduced electromagnetic interference. An interleaved converter operates in discontinuous conduction mode has reduction of inductor size, fast transient response, increased ripple current and parasitic ringing [17].

### 1.3 Interleaved Switching Scheme

Multi-phase IBDDC drive signals can be generated by comparing control signal with delayed saw-tooth waveforms, so the drive signals are uniformly distributed over the switching period by following relation

$$delay = \frac{T_{switch}}{N_{phase}}$$

(1.1)

where  $T_{switch}$  is the switching period and  $N_{phase}$  is the number of phases of IBDDC.

Filter capacitor design of multi-phase is easier because of  $N_{phase}$  times the current ripple frequency occurrence.

### 1.4 Modelling and Control of Bidirectional DC-DC Converter

The modelling and control issues of the bidirectional dc-dc converter play an important role to achieve the desired stability, high reliability and high efficiency. In order to obtain the dynamic characteristics of the switching converter circuit in addition to the static ones, a modelling method is imperative. Its transient response directly determines four of the most important characteristics of a power converter: the stability of the feedback loop, the rejection of input ripple and the compatibility with the input EMI filter.

BDDC is a highly nonlinear system because it contains controlled and uncontrolled switching devices. The output voltage of BDDC is to be highly regulated within a specified range for abrupt change in input voltage and load transients. Voltage mode and current mode control techniques are the two control methods for BDDC. In the voltage mode control technique, the BDDC's output voltage is being compared with a constant reference value to generate error signal. Duty cycle of the BDDC is automatically adjusted based on error signal to obtain desired output voltage which follows the reference value. In order to design the voltage mode controller for BDDC, frequency response method is being used. In order to apply linear control theory, nonlinearity should be averaged and linearized. Based on the signal model of the BDDC, the compensator can be easily designed and analog compensator can be implemented by using analog pulse width modulator (PWM) integrated circuits (ICs) along with the suitable values of resistors and capacitors to obtain desired transfer function. Digital compensator can be implemented on DSP using control algorithms. Current mode controller has two loops in which the first loop is the inner current loop and the second is the outer voltage loop. The duty cycle for BDDC can be obtained by comparing the inductor current with its reference value and then reference value for inductor current is generated by voltage loop.

State space averaging (SSA) method [18-20] is used to derive small signal averaged equations of pulse width modulated converter and it requires considerable matrix algebra for deriving various transfer function and step responses. The SSA method provides good intuitive insight into converter behaviour. The state space is canonical form for writing the differential equations which describe a system. Transfer function of BDDC in boost mode has zero in the right half s-plane and this system is called non minimum phase system. Right half plane (RHP) zero determines a phase lag in loop gain of the of the voltage mode controlled BDDC in boost mode forcing the maximum cross over frequency to be placed at most below RHP frequency. Stability analysis of feedback loop requires proper selection of compensator or controller. Feedback compensator can be designed by the K factor method [21] which defines with few algebraic equations and this scheme can be used to achieve desired cross over frequency and the phase margin.

Mathematical modelling of interleaved bidirectional dc-dc converter (IBDDC) is essential to design a proper linear controller, leads to maintain equal current in each phase of the converter. Optimal selection on the number of phases [22] in design of IBDDC results with the current ripple cancellation, high ripple frequency, and higher efficiency. For multiphase IBDDC, specific DSP as digital control is required to control the IBDDC [23].

Fuzzy logic has been effectively utilized in many field of knowledge to solve control and optimization problems [24]. Typically, the linguistic variables in a fuzzy logic control (FLC) are the state, state error, state error derivative, state error integral, etc. One of the key problems is to find the appropriate fuzzy control rules [25]. In general, membership sets and rule base are generated by trial and error tuning procedure [26].

### **1.5 LITERATURE REVIEW**

Based on the connection of BDDC with auxiliary energy storage element, BDDC can be classified into buck/boost type and buck-boost type. The buck type BDDC is to have auxiliary energy storage placed on the high voltage DC bus side, and the boost type BDDC is to have it placed on the low voltage side. In order to realize bidirectional power flow in BDDC, the switch unit should carry the current in both the directions. The switch unit consist of Power MOSFET in parallel with a antiparallel diode. Depending on the configuration of BDDC to meet different application requirements, BDDC can be majorly classified into two types, non-isolated BDDC and isolated BDDC.

### 1.5.1 Non-Isolated Bidirectional DC-DC Converter

Non-isolated BDDC topology comprising of a step up stage and step down stage connected in parallel [27]. The high frequency transformer based BDDC system provides isolation between the source and the load. But from the perspective of improving the efficiency, size, weight and cost, the transformer less type converter is attractive. Therefore, in high power and aerospace applications, where size or weight is the major interest, the transformer less BDDC topology is preferred.

Non-isolated bidirectional dc-dc converters are presented so far as follows

- 1. Bidirectional buck/boost type dc-dc converter [2].

- 2. Bidirectional buck-boost dc-dc converter [28].

- 3. Bidirectional Cuk/Cuk dc-dc converter [29].

- 4. Bidirectional Sepic/Zeta dc-dc converter [30].

- 5. Bidirectional quasi resonant dc-dc converter [31].

- 6. Bidirectional coupled inductor dc-dc converter [32].

- 7. Bidirectional multi-level dc-dc converter [33].

- 8. Bidirectional switched-capacitor dc-dc converter [34].

- 9. Multiphase interleaved bidirectional dc-dc converter [41, 42].

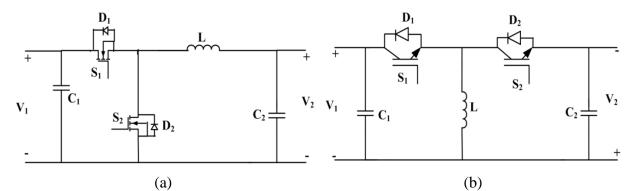

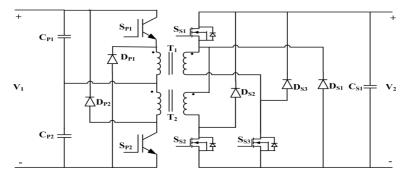

The bidirectional buck type and boost type dc-dc converter [2] shown in Figure 1.2(a) consists of step-up converter and which is connected in antiparallel with step-down converter. During the forward step-down operation,  $S_1$  conducts and the switch  $S_2$  is off while  $D_2$  is conducting. Similarly, during backward step-up operation,  $S_2$  conducts and  $S_1$  is off while  $D_1$  is conducting. It has simple circuit structure, equivalent series resistance (ESR) of both inductor and capacitor and the effect of switch limits the step up voltage gain [35]. By using BDDC power converter for charging and discharging of battery [36], a substantial weight saving is possible.

Bidirectional buck-boost dc-dc converter [28] shown in Figure 1.2(b) has additional switch in the conduction path. During the forward power flow mode,  $S_1$  conducts and the switch  $S_2$  is off while  $D_2$  is conducting. Similarly, during backward power flow mode,  $S_2$  conducts and  $S_1$  is off while  $D_1$  is conducting. The buck-boost type BDDC is more costly and less efficient than that of buck type or boost type BDDC and which cannot be operated in wide voltage conversion range.

Bidirectional Cuk/Cuk dc-dc converter [29] shown in Figure 1.2(c) is derived from the basic Cuk dc-dc converter. During the forward power flow mode,  $S_1$  conducts and the switch  $S_2$  is off while  $D_2$  is conducting. Similarly, during backward power flow mode,  $S_2$  conducts

and  $S_1$  is off while  $D_1$  is conducting. It offers low conversion efficiency because this converter consists of two power stage and this type of converter cannot offer wide voltage conversion range.

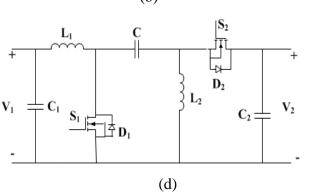

Bidirectional Sepic/Zeta dc-dc converter [30] shown in Figure 1.2(d) operates as Sepic converter during forward power flow and it operates as Zeta converter during reverse power flow. During the forward power flow mode,  $S_1$  conducts and the  $S_2$  is off while  $D_2$  is conducting. Similarly, during backward power flow mode,  $S_2$  conducts and  $S_1$  is off while  $D_1$  is conducting. It offers low conversion efficiency because this type of converter consists of two power stage and this converter cannot offer wide voltage conversion range.

Bidirectional quasi resonant dc-dc converter [31] is as shown in Figure 1.2(e). During forward power flow  $S_3$  is off, turning on  $S_1$  at zero current (ZC) and turn off  $S_2$  at zero voltage (ZV), then  $S_1$  is turned off at ZC and  $S_2$  is turned on at ZV, then this mode will ends at  $T_s$ when  $S_1$  is turned on at ZC and  $S_2$  is turned off at ZV. During reverse power flow  $S_2$  is off, turning on  $S_1$  at ZC and turn off  $S_3$  at ZV, then  $S_1$  is turned off at ZC and  $S_3$  is turned on at ZV, then this mode will ends at  $T_s$  when  $S_1$  is turned on at ZC and  $S_3$  is turned off at ZV. It provides load independent characteristics with unlimited load and dc conversion ratio range, increased efficiency and simple operation. This topology also provides the same DC conversion characteristics and small signal control to duty ratio transfer function is same as that of the conventional dc-dc converter.

Bidirectional coupled inductor dc-dc converter [32] is as shown in Figure 1.2(f). During the forward mode of operation,  $S_1$  conducts and the switch  $S_2$  is off while  $D_2$  is conducting. Similarly, during backward mode of operation,  $S_2$  conducts and  $S_1$  is off while  $D_1$  is conducting. Inductors  $L_1$  and  $L_2$  are coupled to achieve higher step-up and step-down gain and also provides the large voltage gain by adjusting the coupled inductor turns ratio. But configurations of the converter circuit are complicated.

Bidirectional multi-level dc-dc converter [33] shown in Figure 1.2(g) made up of two back to back connected diode clamped converter legs. This topology is symmetric. It allows the power in both forward and backward direction for any possible value of  $m = V_2 / V_1$ .

Bidirectional switched-capacitor dc-dc converter [34] is as shown in Figure 1.2(h). During forward power flow,  $S_1$  is turned on,  $Q_s$  is in saturation, rest of the switches are opened, and capacitor C is linearly charged from HV side through  $S_1$  and  $Q_s$  for duration  $T_s/2$ . When  $S_2$  and  $D_3$  are turned on, all other switches are open, C is disconnected from HV side and stored energy is supply to LV side through  $S_2$  and  $D_3$ . During backward power flow,  $D_2$  is turned on,  $Q_s$  is in saturation, rest of the switches are opened, and capacitor C will be charged

through  $D_2$  and  $Q_s$  for duration  $T_S/2$ . When  $S_2$  and  $S_3$  are turned on, all other switches are open; C is connected in series with LV side through  $D_1$  and  $S_3$  to supply energy to HV side. It provides the large voltage gain but more number of switches and capacitors are required [37]. Moreover, it requires complicated control circuit.

Multistage power converter consisting of many power converter stages (converter "phases") through inputs and outputs connected in parallel and their gating signal shifted by  $\frac{360^{0}}{N_{phase}}$  to make sure the uniform distribution over a switching period and this technique is also called as "interleaving" [38]. With multi-phase interleaved operation, net current ripple can be minimized and it also minimizes the size of passive components.

For the recent high power density BDDC, to improve its power density, multi-phase current sharing technology with minimized inductance has been used in high efficiency high power applications [39-41]. Multiphase BDDC offers the advantage of minimum current stress on the devices, fast dynamic response, low current/voltage ripple and improved efficiency.

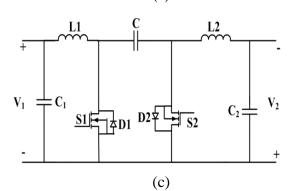

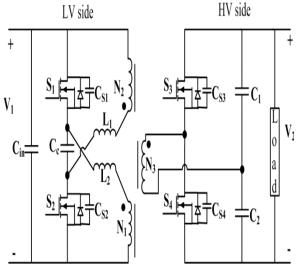

Two-phase interleaved bidirectional dc-dc converter [41, 42] is as shown in Figure 1.3(a) in which gate signals are interleaved with  $180^{\circ}$  phase difference. In case of buck mode, the PWM switches are S<sub>1</sub> and S<sub>2</sub>. Two PWM switches are operated by interleaved operation. Current flows via diode of two switches (S<sub>3</sub>,S<sub>4</sub>). By adjusting a duty ratio, two switches (S<sub>1</sub>,S<sub>2</sub>) are controlled. During buck mode operation, power is transferred from HV side to LV side. In case of boost mode, the PWM switches are S<sub>3</sub> and S<sub>4</sub>. Two PWM switches are operated by interleaved operation. Current flows via diode of two switches (S<sub>1</sub>, S<sub>2</sub>). By adjusting a duty ratio, two switches (S<sub>3</sub>, S<sub>4</sub>) are controlled. During boost mode operation, power is transferred from LV side to HV side. Under this two phases; inductance value, on state resistance of switching device, internal resistance of inductor are symmetric and actual duty ratio for each of the phase is equal. This type of converter provides the optimal DC link voltage, reduces the distortion of voltage and current, and can achieve higher power than the conventional single stage converter using small inductor.

Coupled inductor two-phase interleaved bidirectional dc-dc converter [43, 44] is as shown in Figure 1.3(b). The operation of this converter is same as the two-phase interleaved bidirectional dc-dc converter. A coupling inductance M between the two inductors ( $L_1$ ,  $L_2$ ) can represent the coupling effect. The two inductors can be directly coupled or inversely coupled, due to the different direction selection between two winding. The coupling inductance M is positive in direct coupling and negative in inverse coupling. This type of converter reduces the steady state current ripple, minimizes the conduction loss in MOSFET and improves the dynamic performance. Additionally, the coupling inductor core become simpler and increases the mechanical strength of the core.

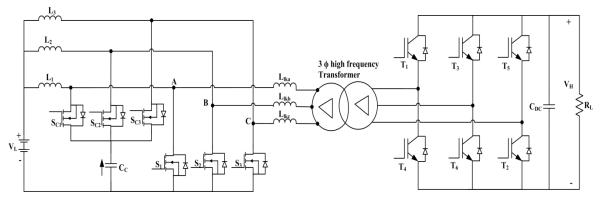

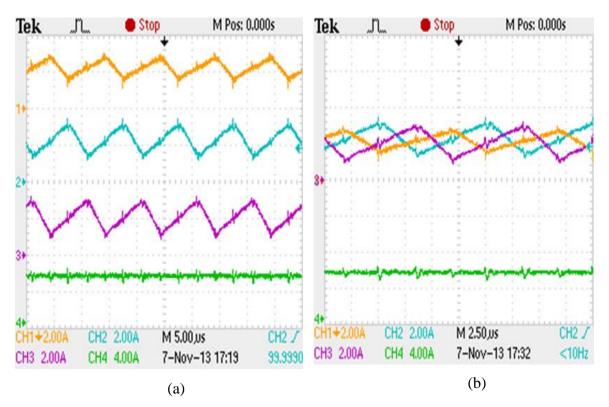

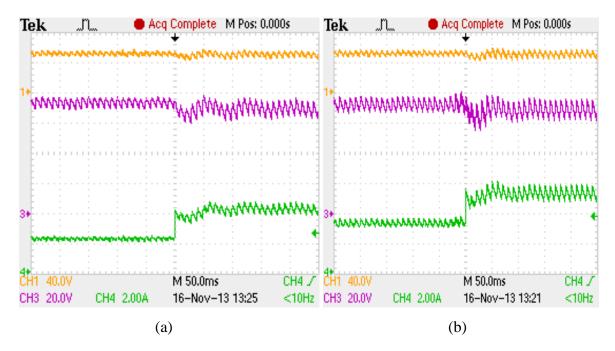

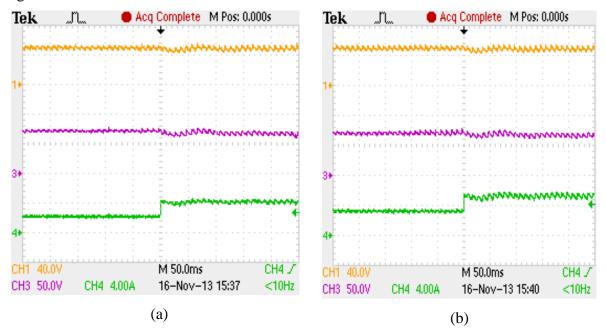

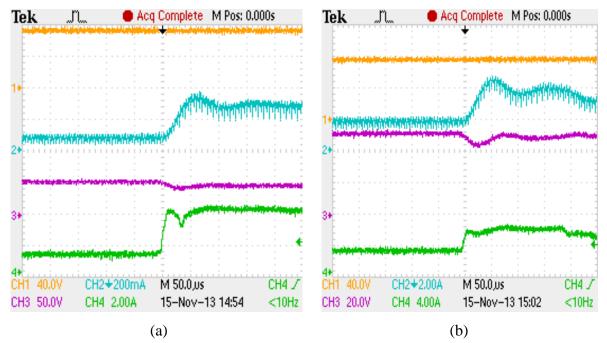

Three-phase interleaved bidirectional dc-dc converter [39, 40, 45] shown in Figure 1.3(c) consists of three independent inductors ( $L_1,L_2,L_3$ ) and each phase switches are interleaved with 120° phase difference. In case of boost mode, three PWM switches ( $S_4,S_5,S_6$ ) are operated by interleaved operation. Current flows via diode of three switches ( $S_1,S_2,S_3$ ). By adjusting a duty ratio, three switches ( $S_4,S_5,S_6$ ) are controlled. During boost mode operation, power is transferred from LV side to HV side. In case of buck mode, three PWM switches ( $S_1,S_2,S_3$ ) are operated by interleaved operation. Current flows via diode of three switches ( $S_4,S_5,S_6$ ). By adjusting a duty ratio, three switches ( $S_1,S_2,S_3$ ) are controlled. During buck mode operation, power is transferred from HV side to LV side. The ripple current in the total current will be minimized after interleaving and therefore relieves the current stress on both LV and HV side capacitors, and hence the converter uses small value film capacitors. The magnitude of the ripple in an output voltage becomes negligible.