# INVESTIGATIONS ON ENHANCED-BOOST Z-SOURCE INVERTERS

Ph.D. THESIS

by

VADTHYA JAGAN

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247 667 (INDIA) FEBRUARY, 2018

# INVESTIGATIONS ON ENHANCED-BOOST Z-SOURCE INVERTERS

#### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

#### DOCTOR OF PHILOSOPHY

in

#### **ELECTRICAL ENGINEERING**

by

VADTHYA JAGAN

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247 667 (INDIA) FEBRUARY, 2018

#### ©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2018 ALL RIGHTS RESERVED

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

### **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in this thesis entitled "**INVESTIGATIONS ON ENHANCED-BOOST Z-SOURCE INVERTERS**" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electrical Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from July, 2013 to February, 2018 under the supervision of Dr. Sharmili Das, Assistant Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

#### (VADTHYA JAGAN)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

(Sharmili Das) Supervisor

Date: \_\_\_\_\_

Increased demand of energy throughout the world, shortage of fossil fuels, and environmental problems caused by conventional power generation has led to an urgent search for renewable energy sources (RES) and harvest maximum energy from them. Renewable energy is energy that comes from natural resources such as sunlight, wind, tides, and geothermal heat, which are naturally replenished at a constant rate. These comprise of wind, biomass, geothermal, thermoelectric generation (TEG), solar photovoltaic (SPV), tidal, and wave energy systems. Renewable energy sources are clean, inexhaustible, and are thought to be "free" energy sources, such as solar and wind energies.

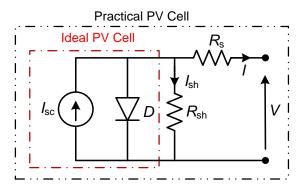

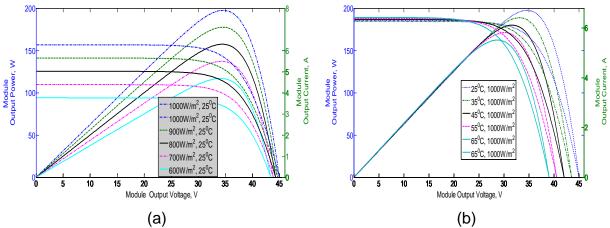

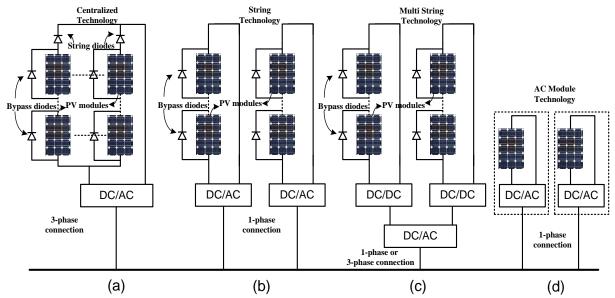

Among all these renewable energy sources, the photovoltaic energy is being widely utilized because of the ubiquity, abundance and sustainability of solar radiant energy. These photovoltaic cells or solar cells directly use the energy from the sun to generate electricity. But, the photovoltaic cell or module produces the peak (or maximum) power at a particular terminal voltage of the cell or module. Thus in order to extract this peak power from the module, a power conditioning circuit (also termed as power electronic interface) is needed. In addition, this power electronic interface is also need to feed extracted power from photovoltaic module to the grid or to the load at a required voltage level. To achieve this, generally traditional single-stage voltage source inverters (VSIs) were used as power electronic interface. But there are several limitations and disadvantages of single-stage inverters (VSIs) like: a) it is only a buck converter for DC-AC power conversion. b) The two semiconductor switches from the same arm or leg of the inverter bridge cannot be gated on simultaneously. Otherwise, a shoot-through will destroy the devices. c) Dead time must be employed, which will cause output voltage/current distortion. Therefore, usually DC-DC boost converter is cascaded in between the VSI bridge and supply terminals to boost the voltage to the required level. But, other drawbacks are remaining same. Reliability of these single-stage and two-stage power conversion topologies is less.

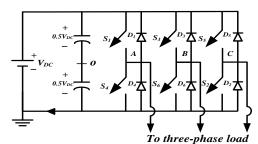

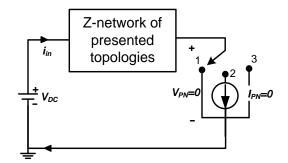

Therefore, in order to avoid the aforementioned drawbacks and limitations of both single-stage and two-stage power conversion systems, impedance (Z)-source inverter was proposed in 2002 with increased reliability. The Z-source inverter (ZSI) provides both buck and boost DC-AC inversion in a single-stage with high electromagnetic interference (EMI). First developed Z-source inverter (ZSI) has certain drawbacks like: a) it draws discontinuous input current from the supply, b)

i

more stress across the capacitors, c) huge inrush current at start-up condition, d) does not share common ground with source, and e) modulation index is limited by the shoot-through duty ratio which leads to poor utilization of the dc-link voltage and higher stress on the semiconductor switches. Except the last point, remaining all drawbacks can be eliminated by the quasi-Z-source inverters (qZSIs) with same boost factor. Many active impedance (Z)-source inverters (i.e., the impedance network consist of one active switch, two-diodes, and one capacitor) were proposed in the literature which produces the boot factor about same as that of the traditional ZSIs. But, the main drawbacks of these topologies are more stress across the capacitor and semiconductor switches. Generally, solar photovoltaic (SPV) module systems need high boost inverters to connect it to the grid/load. Therefore, to increase the boost factor, the switched-inductor Z-source inverter (SL-ZSI) was presented. But, the SL-ZSI has same drawbacks as the traditional ZSI. So, in order to avoid the drawbacks of SL-ZSI, the SL-qZSIs and Diode/Capacitor-Assisted qZSIs were proposed.

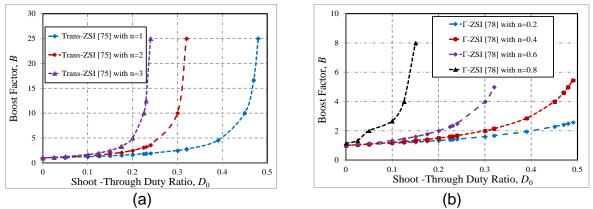

To further improve the boost factor, many magnetically coupled impedance source (MCIS) network topologies were proposed in the literature with less number of components (i.e., both passive and active) in the impedance network. The main disadvantages of coupled-inductor (MCIS) based topologies are; their leakage inductance must be low or they must be tightly coupled, otherwise a high voltage spike appears across the semiconductor switches and dc-link of the inverter bridge. Moreover, the stress across the elements of the impedance network and power switch is also increased. This can lead to use of high rating devices, which in turn increase the cost of the system.

Therefore, enhanced-boost Z-source inverter (EB-ZSI) with two switchedimpedance networks topology was proposed recently which provides high boost at low shoot-through duty ratio without any high spikes across the dc-link voltage and power switches. Moreover, the stress across the switches and the components are less. Even though the EB-ZSI topology uses more number of components in the impedance network (i.e., four inductors, four capacitors, and five diodes) when compare to existing topologies, the stresses across those devices (capacitors, diodes, and switches) is less. Therefore, lower rating devices can be used which results in low cost. The EB-ZSI also has similar drawbacks to that of the traditional ZSI/ SL-ZSI. In order to modulate and to control the all existing Z-source inverters,

ii

many modulation techniques were presented in the literature. But for simplicity most of the impedance source networks were analyzed using simple boost method of control.

In this thesis, improved enhanced-boost Z-source inverters are presented which provides high voltage boost in a single-stage at low shoot-through duty ratio and at high modulation index with high reliability, and shares common ground with the source and inverter bridge. Moreover, these presented topologies reduce the starting inrush current problem and capacitor stress. The expressions for inductance and capacitance design are derived. All the inductors, capacitors, switches and diodes with lower ratings can be used owing to the lower voltage stresses so that the cost is largely decreased. Throughout this thesis, the analysis of these presented topologies is carried out using simple boost control (SBC) technique due to its simple structure.

Firstly, the analysis and derivations of different voltage stresses of One switched-inductor 'Z-source' / 'Improved Z'-source inverter is presented. Then, the voltage-lift type of 'Z-source' / 'Improved Z'-source inverter which is derived from one switched-inductor Z-source inverter (One SL-ZSI) is proposed to get high voltage boost with same number of elements in the impedance network just by replacing the middle diode of SL-cell with voltage-lift capacitor. Then, the two configurations of enhanced-boost guasi Z-source inverters (EB-gZSIs) are proposed in this thesis which provides similar voltage boost compare to EB-ZSI using same number of passive components, and draws continuous input current from the input supply which improves the lifespan of passive components. In addition to this, the stress across the capacitors is also reduced. To reduce the capacitor stress of EB-ZSI further, improved topology of EB-ZSI is proposed in this thesis which is named as enhancedboost series Z-source inverter (EB-SZSI). Therefore, lower rating capacitors can be used to reduce the cost of the system. Another enhanced-boost quasi Z-source inverter is proposed in this thesis which is named as four different configurations of enhanced-boost quasi Z-source inverters which reduces the capacitor stresses further. Except the discrete input current, the other advantages of EB-qZSIs are remained. All these presented topologies are compared with existing Z-network topologies. For the same input voltage and boost factor, the proposed topologies provides less stress across the capacitors, diodes, and semiconductor switches in comparison with existing topologies. Moreover, the proposed topologies require low

shoot-through duty ratio and high modulation index to obtain the same voltage boost. Even though these proposed topologies uses more number of components in the impedance network, the stresses across those devices (capacitors, diodes, and switches) is less which results in low cost and less weight.

The thesis is organized into eight chapters. In **Chapter 1**, a brief introduction of traditional inverters for solar photovoltaic systems such as single-stage and two-stage conversion systems has been given. The drawbacks of traditional single-stage inverter and two-stage inverter topology and the need of impedance (Z)-source inverter (ZSI) topology are discussed. The major contributions of the thesis and the organization of the thesis are also detailed.

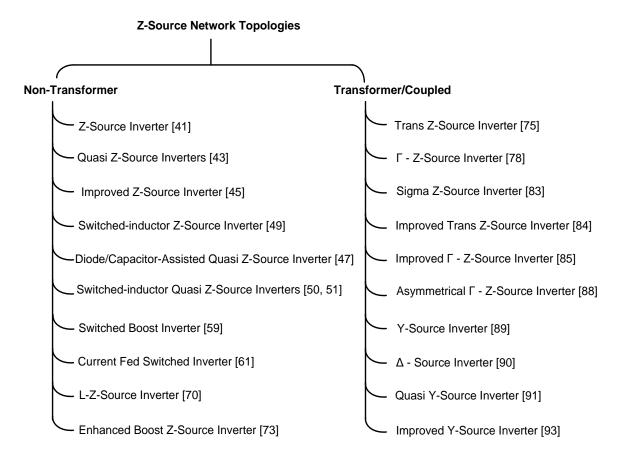

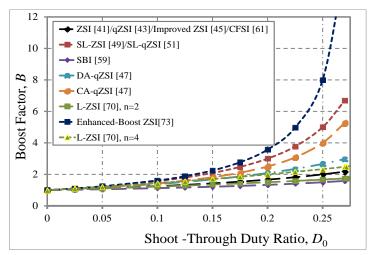

**Chapter 2** starts with state-of-art of different impedance (Z)-network inverter topologies including conventional Z-source inverter are provided. All these impedance (Z)-source network topologies are broadly classified into coupled-based and non-coupled based inverter topologies and are discussed briefly. Among the non-coupled based topologies available in the literature, the enhanced-boost Z-source inverter (EB-ZSI) with two-switched impedance network topology provides very high boost factor at low shoot-though duty ratio and high modulation index and provides better quality output waveforms. The boost factor of the existing inverter topologies is provided for gain comparison. Some of the magnetically coupled impedance source (MCIS) networks are also addressed, which gives high boost factor at low shoot-through duty ratio with less number of components and the drawback of MCIS networks are also highlighted.

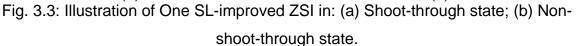

In **Chapter 3**, the circuit development of the one switched-inductor Z-source inverter (one SL-ZSI) from a conventional Z-source inverter is presented. The operating principle, steady-state operation and boost factor derivation of one SL- is explained. The comparison and advantages of one switched-inductor improved Z-source inverter over one SL-ZSI is described in detail. The steady-state operation of one switched-inductor improved Z-source inverter is also validated in experiments.

**Chapter 4** presents the voltage-lift concept of Z-source/improved Z-source inverters which is derived from one switched-inductor Z-source inverter. Steady-state operation, derivation of boost factor and voltage gain, and performance comparison of voltage-lift ZSI/improved ZSI is described. The advantages and comparison of both the topologies is discussed in detail. The simulation and experimental results is also given to validate the theoretical analysis.

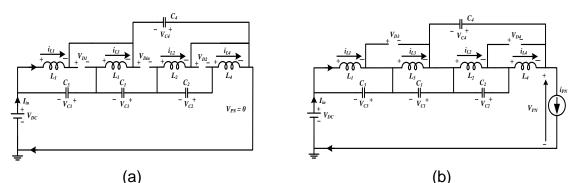

In **Chapter 5**, the circuit development of the enhanced-boost quasi Z-source inverters (EB-qZSIs) with two switched-impedance network is discussed in detail. The steady-state and principle of operation of EB-qZSIs is explained and the mathematical equation for capacitors and voltage gain is established. The performance comparison of the proposed and existing topologies is also described. The advantages and drawbacks of the proposed EB-qZSIs and other Z-network topologies are described. The steady-state operation of the enhanced-boost quasi Z-source inverters is validated in simulations and experiments to verify the theoretical analysis.

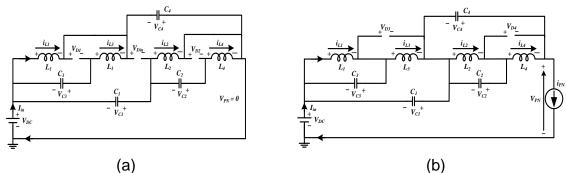

In **Chapter 6**, high boost switched-impedance Z-source inverter, named enhanced-boost series Z-source inverter with two switched impedance network is studied in details. The theoretical analysis of the switched-impedance network series ZSI is validated in simulations and experiments. The detailed performance of the series switched-impedance Z-source inverter is compared in its class to uncover its operational advantages.

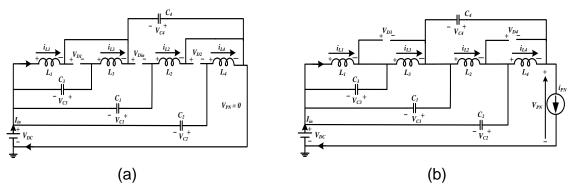

**Chapter 7** describes another enhanced-boost quasi Z-source inverter, named as four different configurations of enhanced-boost quasi Z-source inverters. In this chapter, four configurations of EB-qZSIs topologies are presented. All these topologies provide same boost factor or voltage gain but with different capacitor stresses. The detail steady-state analysis, design of impedance networks and comparison with other EB-ZSIs are presented. Simulation and experimental tests are conducted in order to validate the theoretical expressions.

The general conclusions of the presented work and possible future research have been summarized in **Chapter 8**.

The completion of this thesis work has become possible with the support, inspiration, and continuous encouragement of several individuals.

I am grateful to Indian Institute of Technology (**IIT**) Roorkee for offering me with full scholarship to carry out doctoral research in the Department of Electrical Engineering.

I would like to express my special and sincere thanks to my supervisor, Dr. Sharmili Das. Being her student is my great honor. I deeply respect her not only for her broad knowledge, but the attitude for perfection and the spirits of helping others. I really appreciate her trust and support for me to work on research freely. Without her kind support and encouragement, I would never reach this far.

I am grateful to my student research committee (SRC) members: Prof. S.P. Gupta, Emeritus Professor, Prof. S.P. Srivastava, and Prof. R.P. Saini for their insights, suggestions and kind supports for my research work. I have gained so much learning from their wonderful classes and valuable advisories in my research.

Special thanks to Prof. Pramod Agarwal for teaching me Power Electronics and setting a role model as a life-long engineer and educator.

I express my thankfulness to the faculty and staff members of the Electrical Engineering Department, IIT Roorkee for their continuous encouragement and suggestions.

I acknowledge my sincere gratitude to the Ministry of Human Resources Development (MHRD), Government of India for its financial support to carry out this research.

I would like thank Mr. Mohan Singh and Mr. Rishab Verma for their cooperation, suggestion and support in office related works.

I would also like to thank the laboratory technicians Mr. Ameer Ahmed and his technicians for all their help and co-operation in lending tools and ordering electrical and electronic components.

My special thanks to all my colleagues in the Power Quality Laboratory and all my other friends at IIT Roorkee.

I express my heartfelt thanks to the International Journal Reviewers for giving their valuable comments on the published papers in different international journals, which helps to carry the research work in a right direction. I also thank to the International/ National Conference Organizers for intensely reviewing the published papers.

I am thankful to my previous colleagues Dr. N. Venkata Ramana Naik, Dr. Kishore Kumar Pedapenki, and Dr. Suresh Dhanavath for helping me familiarize myself with the laboratory and their experience with research during my research. I would also like to thank my classmates Mr. Janardhana Rao Kotturu, Mr. Srinivasarao Yarlagadda, and Dr. Sukanta Halder for their technical discussions, suggestions and help with use of tools and equipment within the laboratory.

I want to thank many of you who have helped with many good discussions and gave me so many pleasant times: Dr. Om Hari Gupta, Mr. Vishwanatha Siddhartha, Mr. Santosh Kumar Singh, Dr. Mithun Mondal, Dr. Hari Krishna Muda, Mr. Ankit Kumar Singh, Mr. Raveendhra Dogga, Mr. Pannala Sanjeev Reddy, Mr. Sudharsana Rao Potturi, Mr. Maneesh Kumar, Mr. Gaurav Shukla, Mr. Naveen Yella, Dr. Arun Balodi, Mr. Nenavath Ramesh, and Mr. Anil K. Naik.

My special thanks goes to my best buddies group (Dr. Mahesh Aeidapu, Ms. Swati Bhardwaj, Ms. Meenu Rani Banait, Mr. Madhukar Kurakula, Ms. Suneha Gupta, Mr. Hari Krishna Kuruva, Mr. Varuganti Gopal, Mr. Raja Sekhar Sankuri, Ms. Sushnigdha Mahesh Gangireddy, and Ms. Amandeep Kaur) with whom I have worked at Sharda University, Greater Noida, India and also to Nagaraju Pulipati (DE, BHEL), Narayana Naik Nenavath with whom I have worked at Nalla Malla Reddy Engineering College, Hyderabad, Telangana State, India. They encouraged me to go for research and helped me a lot. I cannot forget those wonderful days.

I express my deep sense of gratitude and reverence to my beloved father Sri. Vadthya Somla Naik, Mother Smt. Jeeja Bai, my brothers Mr. Vadthya Nama Naik and Vadthya Bhasker Naik and my sisters Ms. Jabli Bai, Ms. Jagni Bai, and Ms. Bujji Bai for their unconditional love, unwavering support and financial support in critical times and encouraged me all the time, no matter what difficulties I encountered. You have made countless sacrifices to provide the best opportunities for me, and I will never be able to adequately express my gratitude. They have made me the person I am today. My special thanks go to my elder brother, Vadthya Nama Naik, for constantly looking out for me and encouraging me. I would like to express my greatest admiration to all my family members and relatives for their positive encouragement that they showered on me throughout this research work. Without my family's sacrifice and support, this research work would not have been possible.

It is a great pleasure for me to acknowledge and express my appreciation to all my well-wishers for their understanding, relentless supports, and encouragement during my research work. Last but not the least; I wish to express my sincere thanks to all those who helped me directly or indirectly at various stages of this work.

Finally, my thanks go to my lovely children's, Vadthya Dakshika Bai and Vadthya Tejas Naik, and I wish, when they will grow up, you will read this acknowledgement and will find that I have dedicated my work to them.

Finally and most importantly, I would like to thank my wife Vadthya Bhavika Bai (Kavitha) for her sacrifice, support and unconditional care. Without her years of encouragement and continuous support, I would not have reached this point.

May all praise be to the Almighty, the most beneficent, and the most merciful.

Thanks to all of you.

(Vadthya Jagan)

This Thesis is dedicated:

TO MY PARENTS VADTHYA SOMLA NAIK AND JEEJA BAI TO MY BROTHERS VADTHYA NAMA NAIK AND VADTHYA BHASKAR NAIK TO MY SISTERS JABLI BAI, JAGNI BAI AND BUJJI BAI TO MY CHILDRENS VADTHYA DAKSHIKA BAI AND VADTHYA TEJAS NAIK TO MY WIFE VADTHYA BHAVIKA BAI (KAVITHA)

| ABS  | TRACT    |            |                                                              | I     |  |

|------|----------|------------|--------------------------------------------------------------|-------|--|

| ACK  | NOWL     | EDGEME     | NTS                                                          | VII   |  |

| CON  | CONTENTS |            |                                                              |       |  |

| LIST | OF FIG   | GURES      |                                                              | .XVII |  |

| LIST | OF TA    | BLES       |                                                              | XXIII |  |

| LIST | OF AC    | RONYMS     | 3                                                            | XXV   |  |

| LIST | OF SY    | MBOLS.     |                                                              | XXVII |  |

|      |          |            |                                                              | _     |  |

| -    | PTER 1   |            | RODUCTION                                                    |       |  |

| 1.1  |          |            |                                                              |       |  |

| 1.2  |          |            | aic Inverter Topologies                                      |       |  |

|      | 1.2.1    |            | age DC- AC Power Conversion                                  |       |  |

|      |          |            | Limitations and Drawbacks of the Single-stage Conversion     |       |  |

|      | 1.2.2    |            | ge Power Conversion                                          |       |  |

|      |          |            | Drawbacks of Two-stage Converter                             |       |  |

|      | 1.2.3    | -          | tage Impedance (Z)-Source Network DC-AC Power Conversion     |       |  |

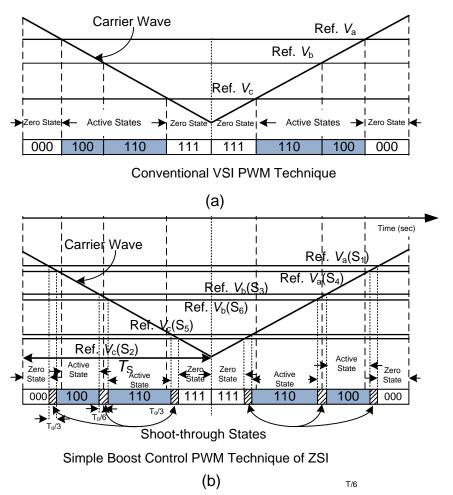

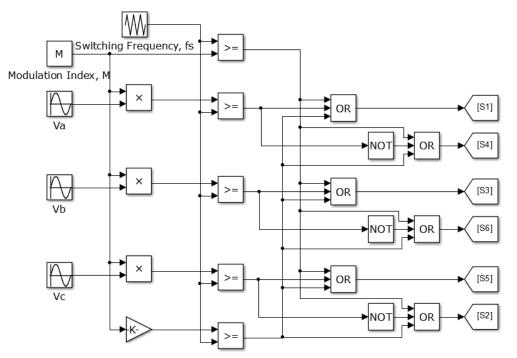

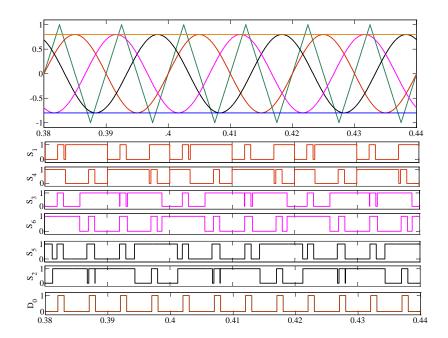

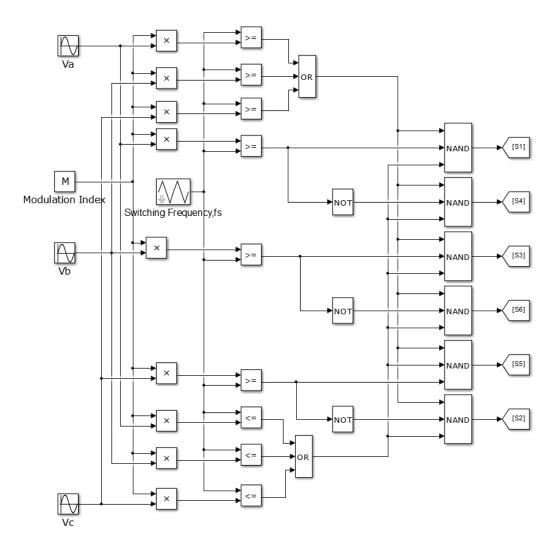

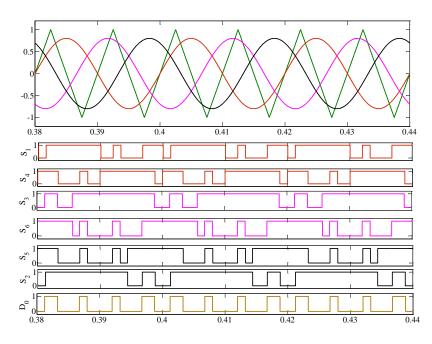

|      |          |            | Modulations Techniques of the Three-phase Impedance (Z) - Ne |       |  |

|      | Inver    | •          | ogies                                                        |       |  |

|      |          |            | Advantages of Z-source Inverter                              |       |  |

|      |          |            | Limitations of the Traditional Z-source Inverter             |       |  |

| 1.3  |          | •          | oost Impedance Source Network Inverter Topologies            |       |  |

| 1.4  |          |            | esis and Author's Contribution                               |       |  |

| 1.5  | Organi   | ization of | the Thesis                                                   | 16    |  |

| CHA  | PTER 2   | 2: ST/     | ATE-OF-ART OF Z-SOURCE INVERTER TOPOLOGIES                   | 19    |  |

| 2.1  | Introdu  | uction     |                                                              | 19    |  |

| 2.2  | Review   | v of Z-So  | urce Network Topologies                                      | 20    |  |

| 2.3  | Non-co   | oupled ba  | sed Z-Source Network Topologies                              | 21    |  |

|      | 2.3.1    | Convent    | ional "Z"/ "Quasi-Z" - Source Inverters                      | 21    |  |

|      | 2.3.2    | Switched   | d-Inductor "Z"/ "Quasi-Z"- Source Inverters                  | 23    |  |

|      | 2.3.3    | Diode/ C   | apacitor-Assisted Quasi Z-Source Inverters                   | 24    |  |

|      | 2.3.4    | Active In  | npedance (Z)-Source Inverters                                | 24    |  |

|      | 2.3.5    | L - Z-So   | urce Inverter                                                | 25    |  |

|      | 2.3.6    | Enhance    | ed-Boost Z-Source Inverter                                   | 26    |  |

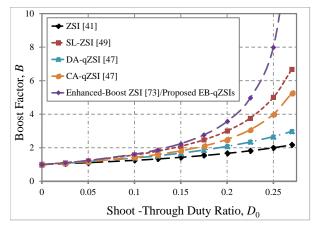

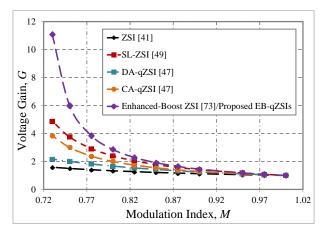

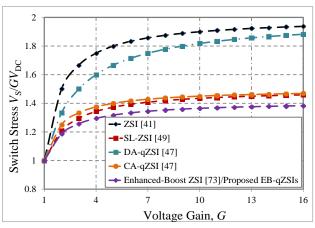

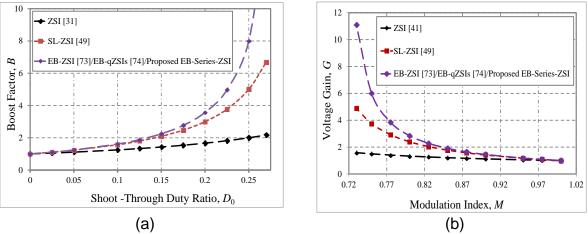

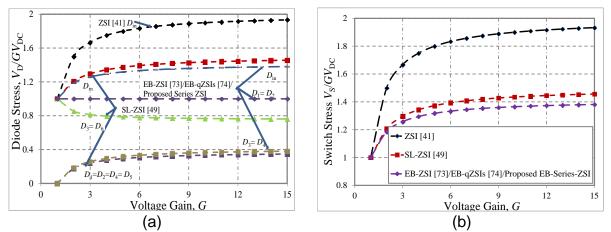

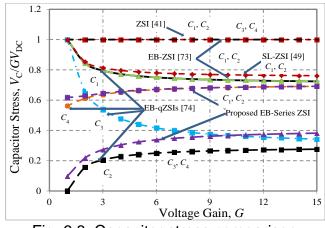

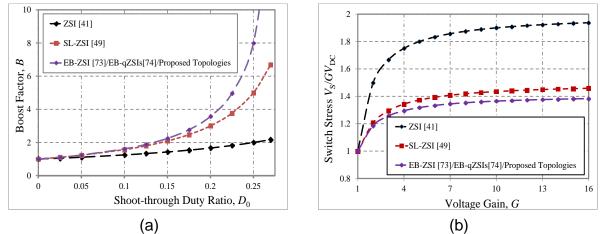

| 2.4  | Boost    | Factor an  | d Switch Stress Comparison of Different Existing Topologies  | 26    |  |

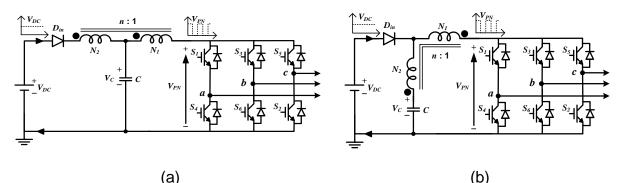

| 2.5  | Magne    | tically Co | upled based Z-Source Network Topologies                      | 28    |  |

|      | 2.5.1    | Two-win    | ding Magnetically Coupled Impedance Source (MCIS) Networks   | 29    |  |

|     |         | 2.5.1.1 With Less Number of Components                                | 29   |

|-----|---------|-----------------------------------------------------------------------|------|

|     |         | 2.5.1.2 With More Number of Components                                | 30   |

|     | 2.5.2   | Three-winding Magnetically Coupled Impedance Source (MCIS) Networks   | 31   |

|     |         | 2.5.2.1 With Less Number of Components                                | 31   |

|     |         | 2.5.2.2 With More Number of Components                                | 33   |

|     | 2.5.3   | Active Magnetically Coupled Impedance Source (MCIS) Networks          | 34   |

|     | 2.5.4   | Effect of Leakage Inductances on Magnetically Coupled Impedance So    | urce |

|     | (MCIS   | i) Networks                                                           | 37   |

| 2.6 | Ideal C | Characteristics of High Boost Impedance (Z)-Source Network Topologies | 37   |

| 2.7 | Conclu  | usion                                                                 | 38   |

| СНА | PTER 3  | 3: ONE SWITCHED-INDUCTOR Z-NETWORK TOPOLOGIES                         | 39   |

| 3.1 | Introdu | uction                                                                |      |

| 3.2 |         | t Diagrams and Explanation of the Proposed Topologies                 |      |

|     | 3.2.1   | One Switched-Inductor Z-Source Inverter                               |      |

|     | 3.2.2   | One Switched-Inductor Improved Z-Source Network Inverter with Redu    |      |

|     | Capac   | citor Stress                                                          | 41   |

|     | 3.2.3   | Advantages of One SL- Improved ZSI                                    | 42   |

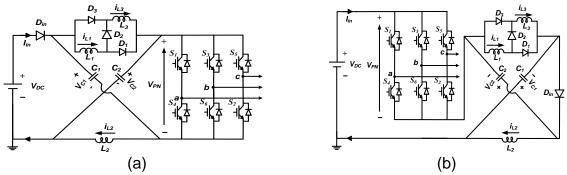

| 3.3 | Princip | ole of Operation and Analysis of One SL-IZSI                          | 42   |

|     | 3.3.1   | Shoot-Through State                                                   | 43   |

|     | 3.3.2   | Non-Shoot-Through State                                               | 43   |

|     | 3.3.3   | Boost Factor and Inductor Currents Derivation                         | 44   |

| 3.4 | Suppre  | ession of Inrush Current at Start-up Condition                        | 46   |

| 3.5 | Z-Netv  | work Parameter Design                                                 | 46   |

|     | 3.5.1   | Design of Inductors                                                   | 46   |

|     | 3.5.2   | Design of Capacitors                                                  | 47   |

| 3.6 | Extens  | sion of the One SL-improved ZSI                                       | 47   |

| 3.7 | Perfor  | mance Comparison of Proposed Inverters with Other Topologies          | 48   |

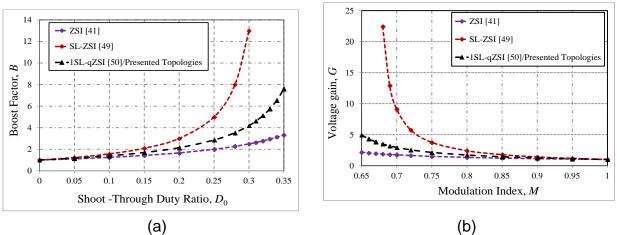

|     | 3.7.1   | Boost Factor and Voltage Gain Comparison                              | 49   |

|     | 3.7.2   | Voltage Stress Comparisons                                            | 49   |

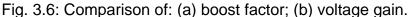

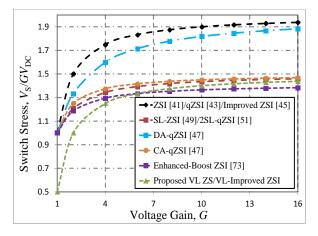

|     |         | 3.7.2.1 Switch Stress versus Voltage Gain                             | 49   |

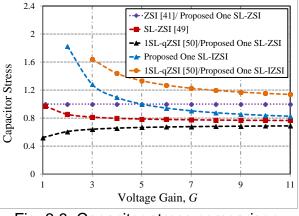

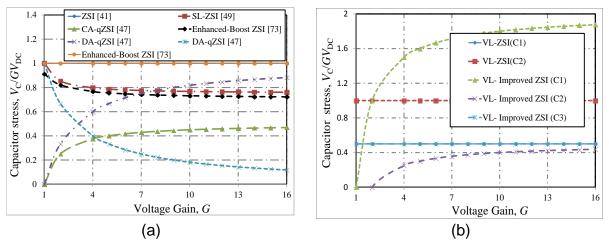

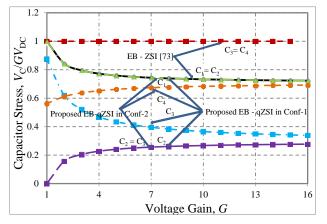

|     |         | 3.7.2.2 Capacitor Stress versus Voltage Gain                          | 50   |

|     | 3.7.3   | Component Count                                                       | 50   |

|     | 3.7.4   | Nature of Input Current                                               | 51   |

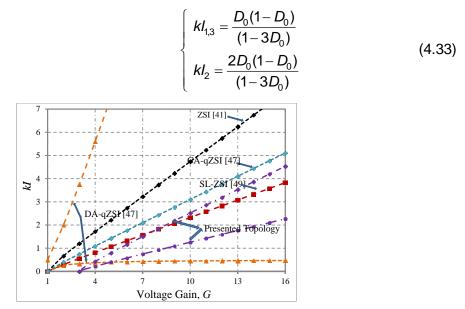

|     | 3.7.5   | Average DC-link Current and Inductor Current Expressions              | 51   |

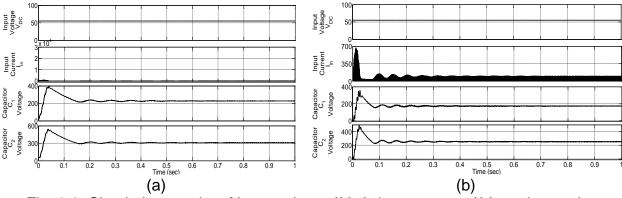

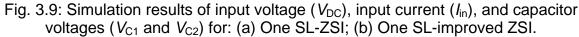

| 3.8  | Discus     | ssion on S | Simulation Results                                              | 52        |

|------|------------|------------|-----------------------------------------------------------------|-----------|

| 3.9  | Conclusion |            |                                                                 |           |

| СНА  | PTER 4     | 4: VO      | LTAGE-LIFT Z-SOURCE/ IMPROVED Z-SOURCE INVERTER                 | ₹S57      |

| 4.1  | Introd     | uction     |                                                                 | 57        |

| 4.2  | Deriva     | tion of Vo | oltage-lift Concept from One Switched-Inductor Z-Source / Impr  | oved Z-   |

| Sour | ce Inve    | rters and  | their Circuit Diagrams                                          | 59        |

| 4.3  | Propo      | sed Volta  | ge-lift ZSI and Voltage-lift Improved-ZSI                       | 60        |

|      | 4.3.1      | Steady-s   | state Operation and Boost Factor Derivation of Voltage-lift     | Z-Source  |

|      | Inverte    | er         |                                                                 | 60        |

|      |            | 4.3.1.1    | Shoot-Through State                                             | 61        |

|      |            | 4.3.1.2    | Non-Shoot-Through State                                         | 61        |

|      | 4.3.2      | Steady-s   | state Operation and Boost Factor Derivation of Voltage-lift Imp | proved Z- |

|      | Sourc      | e Inverter |                                                                 | 63        |

|      |            | 4.3.2.1    | Shoot-Through State                                             |           |

|      |            | 4.3.2.2    | Non-Shoot-Through State                                         | 63        |

|      | 4.3.3      | -          | ion of Voltage Gain and Switch Stress                           |           |

| 4.4  |            |            | Inrush Current at Startup Condition                             |           |

| 4.5  | -          | -          | pedance Network Parameters                                      |           |

| 4.6  |            |            | omparison of the Voltage-Lift Impedance Network Inverter Topo   | -         |

|      | 4.6.1      |            | actor and Voltage Gain Comparison                               |           |

|      | 4.6.2      | 0          | Stress Comparison                                               |           |

|      |            | 4.6.2.1    |                                                                 |           |

|      |            |            | Capacitor Stress versus Voltage Gain                            |           |

|      | 4.6.3      |            | nalysis and Comparisons                                         |           |

|      |            | 4.6.3.1    | Inductor Current Ripple Analysis                                |           |

|      |            |            | Capacitor Voltage Ripple Analysis                               |           |

|      | 4.6.4      | •          | ent Count Comparison                                            |           |

| 4 7  | 4.6.5      |            | DC-link Current and Inductor Current                            |           |

| 4.7  |            |            | ults and Discussion                                             |           |

| 4.8  |            |            | alidation and Discussion                                        |           |

| 4.9  |            |            |                                                                 |           |

|      | PTER       |            | HANCED-BOOST QUASI-Z-SOURCE INVERTERS                           |           |

| 5.1  |            |            |                                                                 |           |

| 5.2  |            | •          | s and Explanations of the Enhanced-Boost Quasi Z-Source Inv     |           |

| 5.3  |            | •          | perations and its Derivations                                   |           |

|      | 5.3.1      |            | g Principle for Configuration-1                                 |           |

|      |            | 5.3.1.1    | Shoot-Through State                                             | 82        |

|      |         | 5.3.1.2    | Non-Shoot-Through State                                           | 83    |

|------|---------|------------|-------------------------------------------------------------------|-------|

|      |         | 5.3.1.3    | Derivation of Boost Factor and Voltage Gain                       | 84    |

|      | 5.3.2   | Operatin   | g Principle for Configuration-2                                   | 85    |

|      |         | 5.3.2.1    | Shoot-Through State                                               | 85    |

|      |         | 5.3.2.2    | Non-Shoot-Through State                                           | 86    |

|      |         | 5.3.2.3    | Derivation of Boost Factor and Voltage Gain                       | 86    |

| 5.4  | Suppre  | ession of  | Inrush Current at Start-up Condition                              | 88    |

| 5.5  | Design  | ing of Im  | pedance Network Parameters and their Expressions                  | 88    |

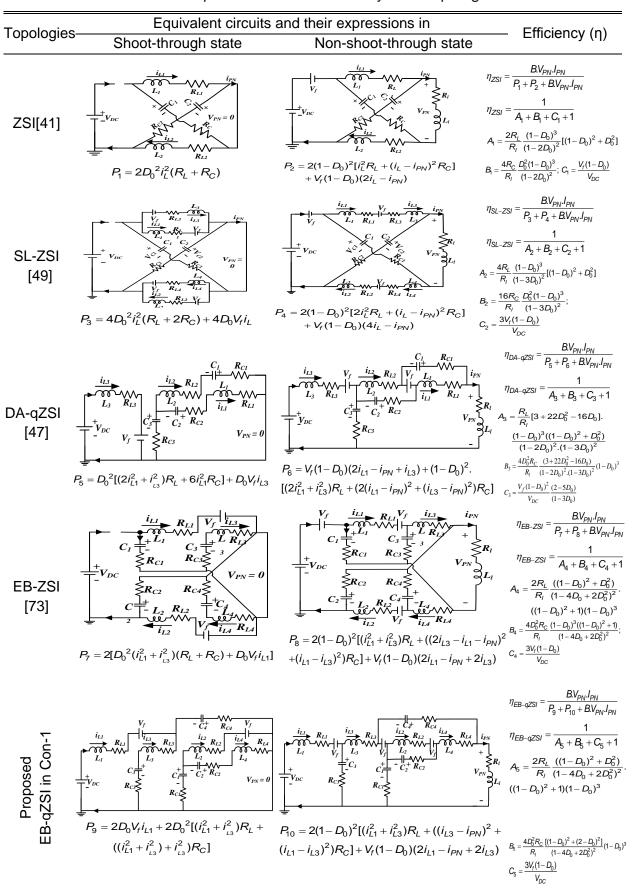

| 5.6  | Perforr | nance Co   | omparison of the Enhanced-Boost Quasi-ZSIs with other Topologie   | s.89  |

|      | 5.6.1   | Boost Fa   | actor and Voltage Gain Comparisons                                | 89    |

|      | 5.6.2   | Voltage \$ | Stress Comparisons                                                | 91    |

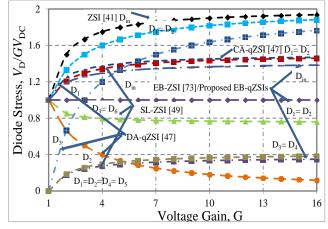

|      |         | 5.6.2.1    | Switch Stress versus Voltage Gain                                 | 92    |

|      |         | 5.6.2.2    | Capacitor Stress versus Voltage Gain                              | 92    |

|      |         | 5.6.2.3    | Diode Stress versus Voltage Gain                                  | 93    |

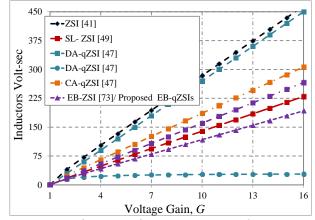

|      | 5.6.3   | Flux (vol  | t-sec) Comparison of the Inductors                                | 93    |

|      | 5.6.4   | Average    | DC-link Current and Inductor Currents                             | 93    |

|      | 5.6.5   | Compon     | ent Count                                                         | 94    |

|      | 5.6.6   | Nature o   | f Input Current                                                   | 94    |

|      | 5.6.7   | Input Cu   | rrent Ripple                                                      | 94    |

|      | 5.6.8   | Inductan   | ce and Capacitance Values                                         | 95    |

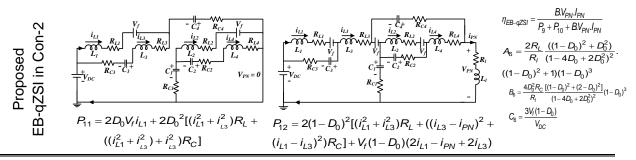

|      | 5.6.9   | Impedan    | ce Network Power Loss Analysis                                    | 97    |

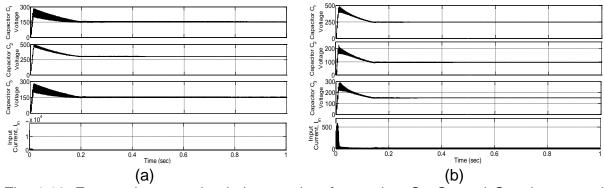

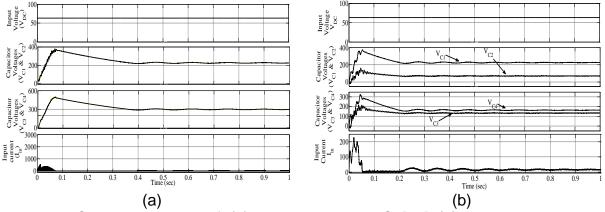

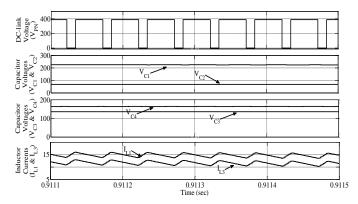

| 5.7  | Simula  | tion Resu  | Ilts and Discussions                                              | 98    |

| 5.8  | Experii | mental Va  | alidation and Discussions                                         | . 101 |

| 5.9  | Conclu  | sion       |                                                                   | . 105 |

| СНА  | PTER 6  | : ENI      | HANCED-BOOST SERIES-Z-SOURCE INVERTER                             | . 107 |

| 6.1  |         |            |                                                                   |       |

| 6.2  |         |            | iples and Circuit Analysis of the Proposed Enhanced-Boost Series- |       |

| Торо | -       | •          | · · ·                                                             |       |

| •    | 0,      |            | n Principle and Boost Factor Derivation of the Proposed Enhar     |       |

|      |         | •          | SI                                                                |       |

|      |         | 6.2.1.1    | Shoot-through State                                               | . 109 |

|      |         | 6.2.1.2    | Non-shoot-through State                                           |       |

|      |         | 6.2.1.3    | Boost Factor Derivation                                           |       |

|      | 6.2.2   | Suppres    | sion of Huge Inrush Current at Start-up Condition                 | . 113 |

|      | 6.2.3   | Impedan    | ce Network Design                                                 | . 113 |

| 6.3 | State- | Space Analysis of the Proposed Topology 11                                    | 4              |

|-----|--------|-------------------------------------------------------------------------------|----------------|

| 6.4 | Perfor | rmance Comparison of Enhanced-Boost Series-ZSI with other Topologies 11       | 17             |

|     | 6.4.1  | Boost Factor and Voltage Gain Comparisons11                                   | 17             |

|     | 6.4.2  | Voltage Stress Comparisons 11                                                 | 17             |

|     |        | 6.4.2.1 Diode Stress versus Voltage Gain11                                    | 8              |

|     |        | 6.4.2.2 Switch Stress versus Voltage Gain 11                                  | 8              |

|     |        | 6.4.2.3 Capacitor Stress versus Voltage Gain 11                               | 19             |

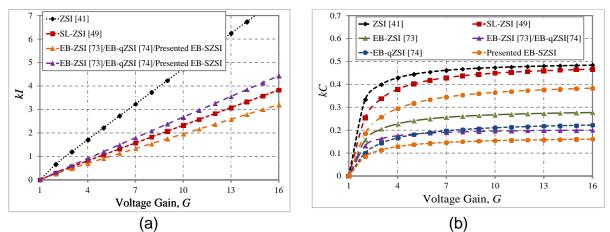

|     | 6.4.3  | Ripple Analysis and Comparison 11                                             | 9              |

|     | 6.4.4  | Topology Characteristics 12                                                   | 20             |

|     |        | 6.4.4.1 Input Current Nature 12                                               | 21             |

|     |        | 6.4.4.2 Common Ground Sharing and Start-up Current Suppression 12             | 21             |

|     |        | 6.4.4.3 Component Count 12                                                    | 21             |

|     | 6.4.5  | Comparison of Current Stresses12                                              | 21             |

|     | 6.4.6  | Inductor Currents and Average dc-link Current12                               | 22             |

| 6.5 | Powe   | r Loss Analysis and Expression for Efficiency Evaluation                      | 22             |

| 6.6 | Simula | ation Results and Discussions12                                               | 23             |

| 6.7 | Exper  | imental Validation and Discussions12                                          | 25             |

| 6.8 | Concl  | usion 12                                                                      | 28             |

| СНА | PTER   | 7: FOUR DIFFERENT CONFIGURATIONS OF ENHANCED-BOOST                            |                |

| QUA |        | OURCE INVERTERS12                                                             |                |

| 7.1 | Introd | uction12                                                                      | 29             |

| 7.2 |        | ations of Different Configurations of Enhanced-Boost Quasi Z-Source Inverters |                |

|     |        |                                                                               |                |

|     | 7.2.1  |                                                                               |                |

|     |        | gurations of EB-qZSIs                                                         |                |

| 7.3 |        | t Configurations and Operating Principles of the Proposed Topologies          |                |

|     | 7.3.1  | Configuration-1                                                               |                |

|     |        | 7.3.1.1 Shoot-Through State                                                   |                |

|     |        | 7.3.1.2 Non-Shoot-Through State                                               |                |

|     |        | 7.3.1.3 Derivation of Boost Factor Expression                                 |                |

|     | 7.3.2  | Configuration-2                                                               |                |

|     |        | 7.3.2.1 Shoot-Through State                                                   | 35             |

|     |        |                                                                               |                |

|     |        | 7.3.2.2 Non-Shoot-Through State                                               |                |

|     | 7.3.3  | Configuration-3 13                                                            | 36             |

|     | 7.3.3  | Configuration-3                                                               | 36<br>37       |

|     | 7.3.3  | Configuration-3 13                                                            | 36<br>37<br>37 |

|      |        | 7.3.4.1     | Shoot-Through State                        | 138 |

|------|--------|-------------|--------------------------------------------|-----|

|      |        | 7.3.4.2     | Non-Shoot-Through State                    | 138 |

| 7.4  | Z-Netv | vork Para   | meter Design                               | 140 |

|      | 7.4.1  | Inductors   | s Design                                   | 140 |

|      | 7.4.2  | Capacito    | ors Design                                 | 140 |

| 7.5  | Compa  | arison of t | he Proposed Topologies                     | 142 |

|      | 7.5.1  | Boost Fa    | actor and Switch Stress Comparison         | 142 |

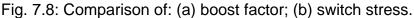

|      | 7.5.2  | Compari     | son of Capacitor Stresses                  | 143 |

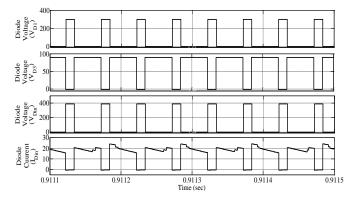

| 7.6  | Discus | sion on S   | imulation and Experimental Results         | 144 |

|      | 7.6.1  | Simulatio   | on Results                                 | 144 |

|      | 7.6.2  | Experim     | ental Results                              | 146 |

| 7.7  | Conclu | usion       |                                            | 148 |

| CHA  | PTER 8 | 3: CO       | NCLUSIONS AND FUTURE SCOPE OF THE RESEARCH | 149 |

| 8.1  | Conclu | usions      |                                            | 149 |

| 8.2  | Scope  | of the Fu   | ture Work                                  | 150 |

|      |        |             |                                            |     |

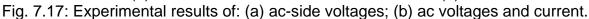

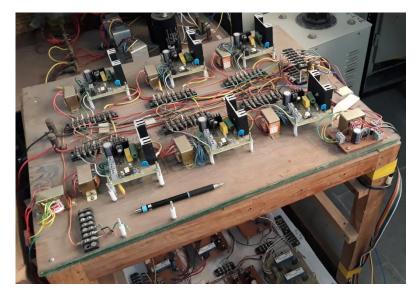

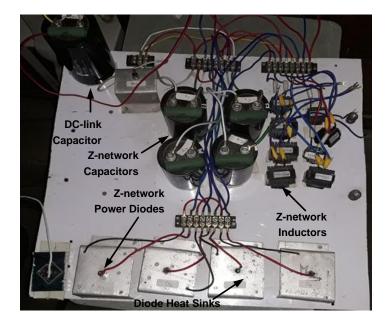

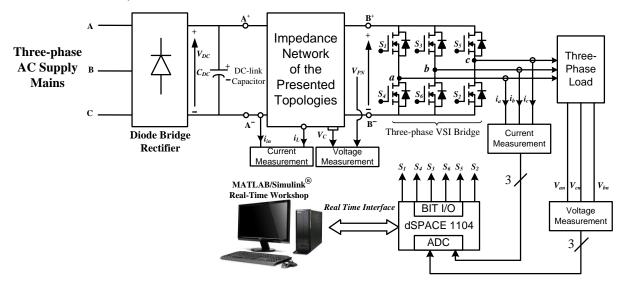

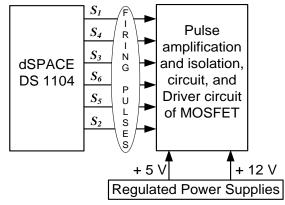

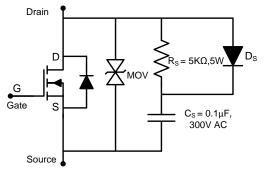

| EXPE | ERIME  | NTAL SE     | TUP PHOTOGRAPHS                            | 153 |

| PUB  | LICATI | ONS FRC     | OM THE WORK                                | 155 |

| BIBL | IOGRA  | PHY         |                                            | 157 |

| BIBLIOGRAPHY |     |

|--------------|-----|

| APPENDIX – A | 173 |

| APPENDIX – B |     |

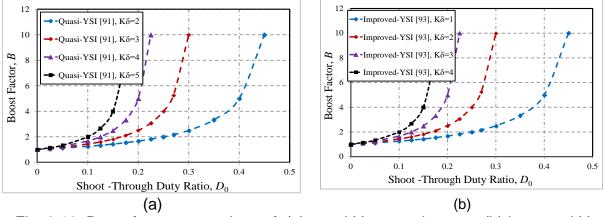

| Fig. 2.18: Boost factor comparison of: (a) quasi-Y-source inverter; (b) improved-Y-source                               |

|-------------------------------------------------------------------------------------------------------------------------|

| inverter                                                                                                                |

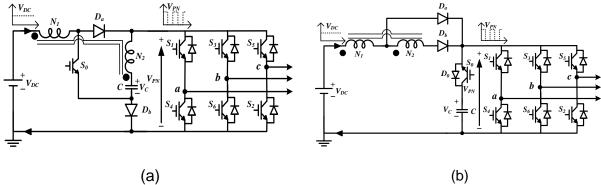

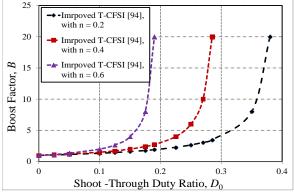

| Fig. 2.19: Illustration of coupled-inductor: (a) high boost switched inverter;                                          |

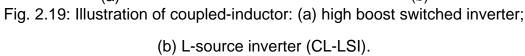

| Fig. 2.20: Comparisons of boost factor for Improved Trans-CFSI                                                          |

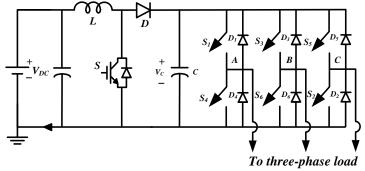

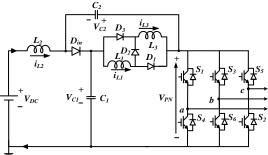

| Fig. 3.1: Illustration of one switched-inductor quasi Z-source inverter                                                 |

| Fig. 3.2: Configuration of the presented topologies: (a) One SL-ZSI; (b) One SL-improved                                |

| ZSI                                                                                                                     |

| Fig. 3.3: Illustration of One SL-improved ZSI in: (a) Shoot-through state; (b) Non-shoot-                               |

| through state42                                                                                                         |

| Fig. 3.4: Circuit diagram for inrush current of One SL-ZSI during starting condition                                    |

| Fig. 3.5: Configuration of the extended One SL-improved ZSI                                                             |

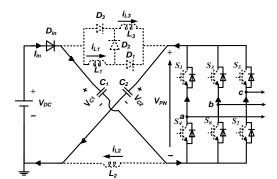

| Fig. 3.6: Comparison of: (a) boost factor; (b) voltage gain                                                             |

| Fig. 3.7: Switch stress comparison                                                                                      |

| Fig. 3.8: Capacitor stress comparison                                                                                   |

| Fig. 3.9: Simulation results of input voltage ( $V_{DC}$ ), input current ( $I_{in}$ ), and capacitor voltages          |

| ( $V_{C1}$ and $V_{C2}$ ) for: (a) One SL-ZSI; (b) One SL-improved ZSI                                                  |

| Fig. 3.10: Simulation results of input current ( $I_{in}$ ) in steady-state condition for: (a) One SL-ZSI;              |

| (b) One SL-improved ZSI53                                                                                               |

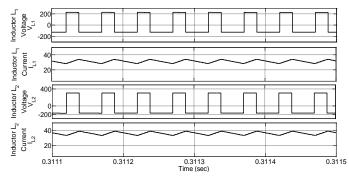

| Fig. 3.11: From top to bottom; Simulation results of inductor $L_1$ voltage ( $V_{L1}$ ), inductor $L_1$                |

| current ( $I_{L1}$ ), inductor $L_2$ voltage ( $V_{L2}$ ), and inductor current ( $I_{L2}$ ) respectively               |

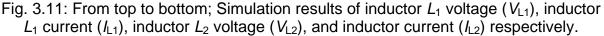

| Fig. 3.12: From top to bottom; Simulation results of peak dc-link voltage ( $V_{PN}$ ), diode voltage                   |

| (V <sub>Din</sub> ), and diode current (I <sub>Din</sub> )54                                                            |

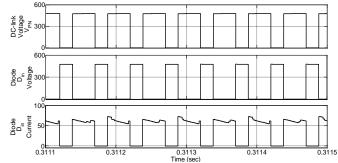

| Fig. 3.13: From top to bottom; Simulation results of diode voltage ( $V_{D1}$ ), diode current ( $I_{D1}$ ),            |

| diode voltage ( $V_{D1}$ ), and diode current ( $I_{D1}$ )                                                              |

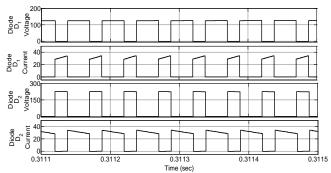

| Fig. 3.14: Simulation results of line voltage ( $V_{ab}$ ), phase voltage ( $V_{an}$ ), and phase currents ( $I_{an}$ , |

| <i>I</i> <sub>bn</sub> , and <i>I</i> <sub>cn</sub> )54                                                                 |

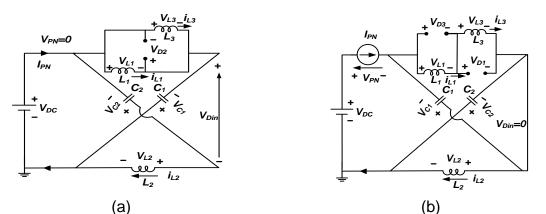

| Fig. 4.1: Illustration of: (a) One SL-ZSI; (b) One SL-improved ZSI                                                      |

| Fig. 4.2: Configuration of proposed VL-impedance network topologies: (a) Voltage-lift ZSI; (b)                          |

| Voltage-lift improved ZSI59                                                                                             |

| Fig. 4.3: Circuit diagram of voltage-lift type-ZSI in : (a) shoot-through; (b) non-shoot-through                        |

| states                                                                                                                  |

| Fig. 4.4: Circuit diagram of voltage-lift type improved-ZSI in: (a) shoot-through state; (b) non-                       |

| shoot-through state63                                                                                                   |

| Fig. 4.5: Inrush current equivalent circuit at starting condition                                                       |

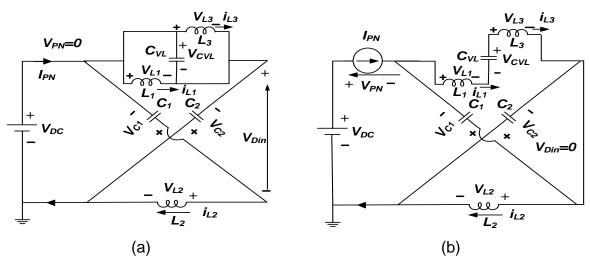

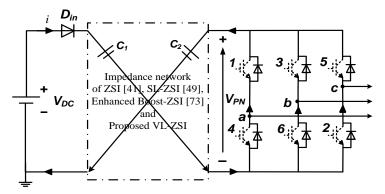

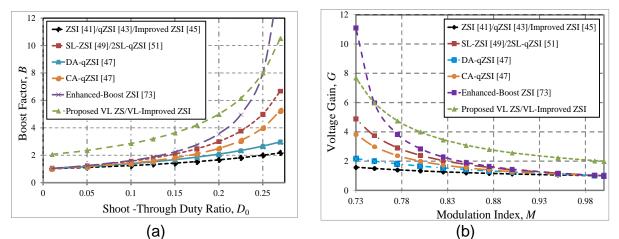

| Fig. 4.6: Comparison of proposed VL-ZS/Improved ZSI topologies: (a) boost factor versus                                 |

| duty ratio; (b) voltage gain versus modulation index67                                                                  |

| Fig. 4.7: Comparison of switch stress versus voltage gain for different topologies                                      |

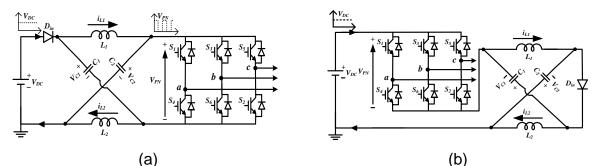

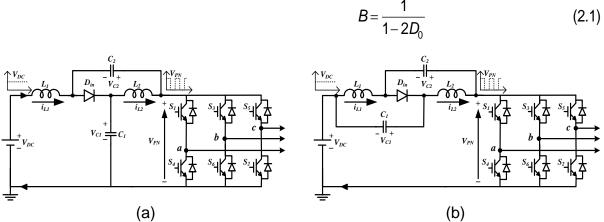

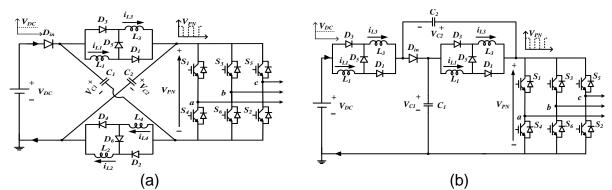

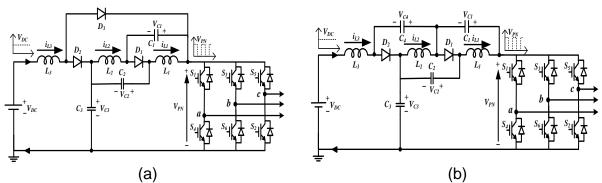

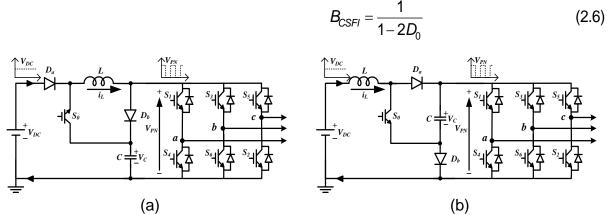

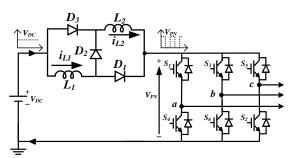

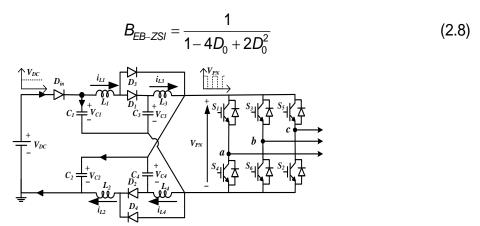

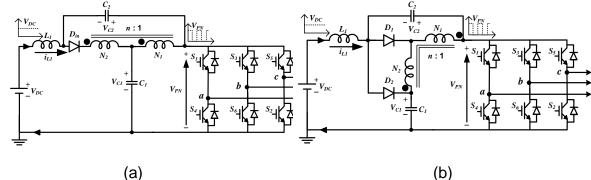

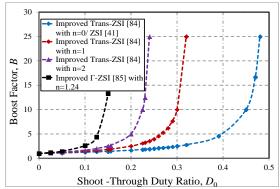

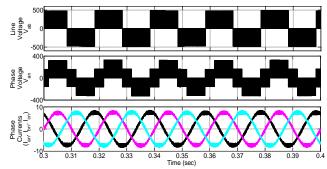

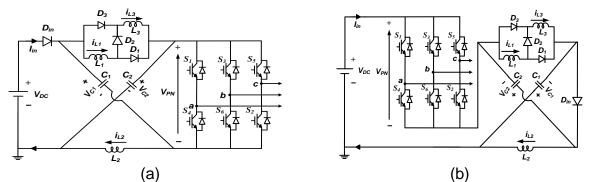

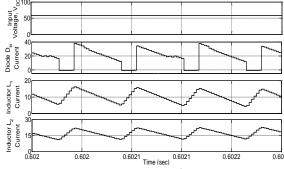

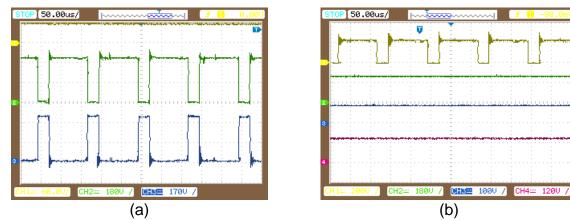

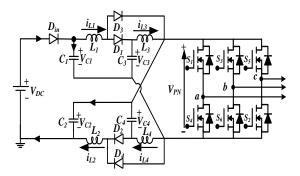

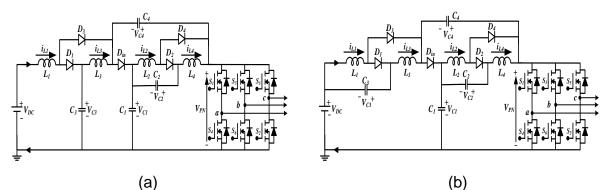

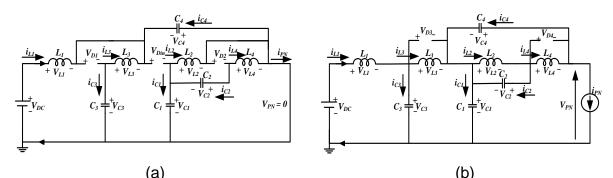

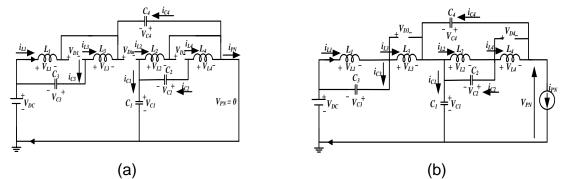

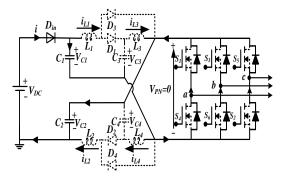

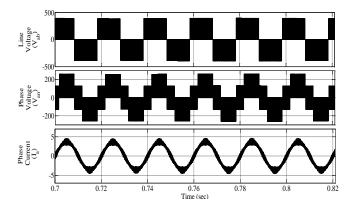

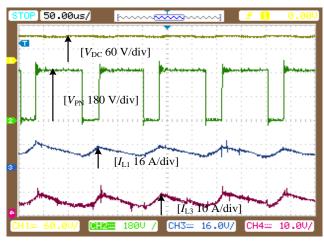

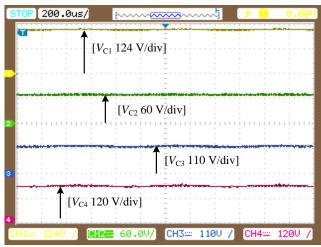

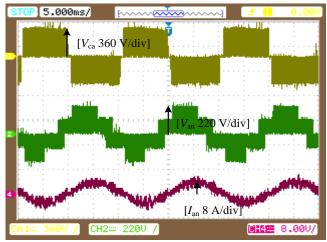

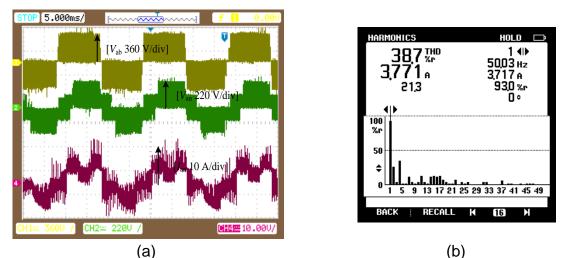

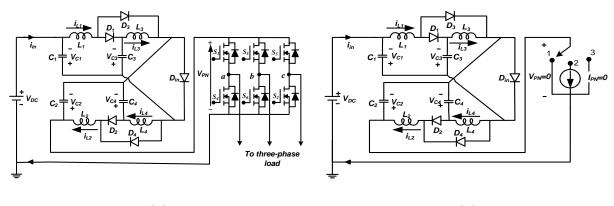

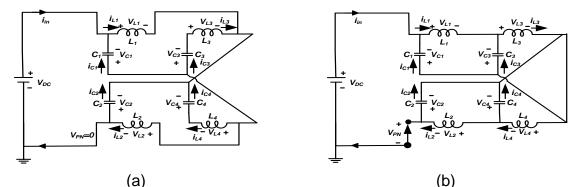

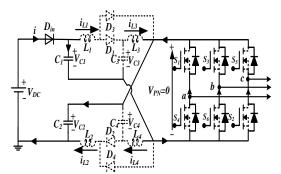

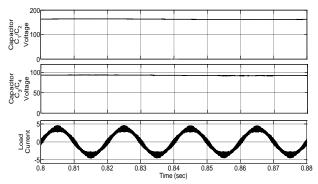

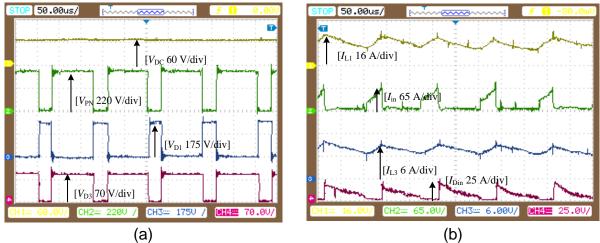

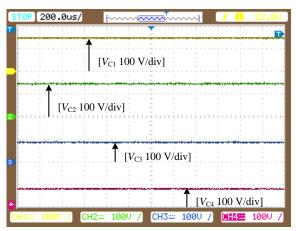

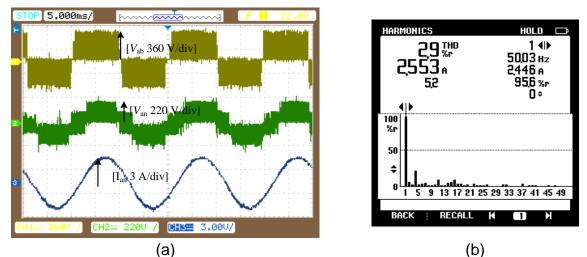

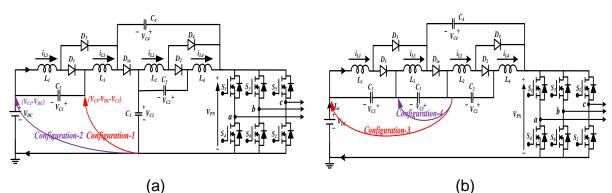

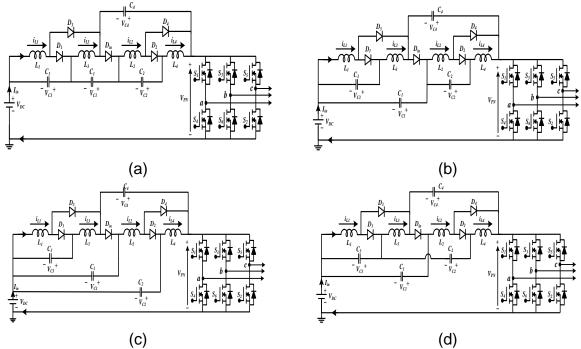

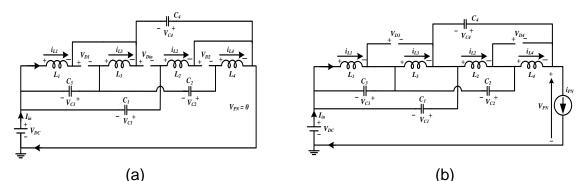

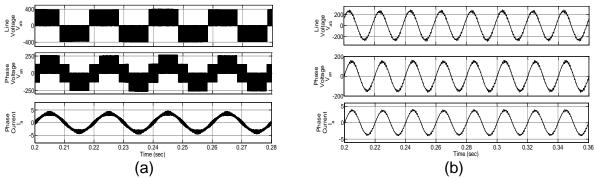

Fig. 4.8: Comparison of capacitor stress of: (a) conventional impedance network inverters; Fig. 4.10: From to bottom, simulation results of capacitor  $C_1$ ,  $C_2$ , and  $C_3$  voltages and input Fig. 4.11: From to bottom, simulation results of input voltage, diode D<sub>in</sub> current, and inductor Fig. 4.12: From to bottom, simulation results of dc-link voltage, diode  $D_1$ ,  $D_{in}$  and  $D_2$  voltages Fig. 4.13: Simulation results of ac-side voltages and current of both proposed VL-ZS/ VL-Fig. 4.14: From top to bottom, Experimental results of VL-ZSI: (a) input, dc-link, and diode Din Fig. 4.15: From top to bottom, Experimental results of VL-improved ZSI: (a) input dc, peak Fig. 4.16: From top to bottom, Experimental results of diode  $D_{in}$  current, input current  $I_{in}$ , and Fig. 5.1: Enhanced-boost Z-source inverter with two switched Z-impedance source network. Fig. 5.2: Continuous input current enhanced-boost quasi ZSIs with two-switched impedance networks for: (a) configuration-1; (b) configuration-2......81 Fig. 5.3: Equivalent circuits of the proposed continuous input current configuration-1 Fig. 5.4: Equivalent circuits of the proposed continuous input current configuration-2 Fig. 5.5: Equivalent circuit for inrush current at starting condition of enhanced-boost ZSI with Fig. 5.6: Boost factor comparison of different Z-source inverters with proposed inverter Fig. 5.7: Voltage gain comparison of different Z-source inverters with proposed inverter Fig. 5.9: Capacitor voltage stress comparison of enhanced-boost ZSI and proposed Fig. 5.10: Diode stress comparison of different existing topologies and the proposed

| Fig. 5.11: Flux (volt-sec) comparison of the inductors                                                            |

|-------------------------------------------------------------------------------------------------------------------|

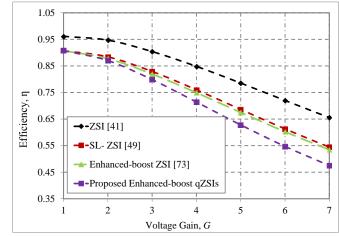

| Fig. 5.12: Efficiency comparison of different Z-network topologies                                                |

| Fig. 5.13: Simulation results of: (a) enhanced-boost ZSI [73]; (b) proposed enhanced-boost                        |

| qZSI with $M = 0.75888$ and $D_0 = 0.24112$                                                                       |

| Fig. 5.14: From top to bottom: Simulation results of dc-link voltage ( $V_{PN}$ ), capacitor voltages             |

| ( $V_{C1}$ , $V_{C2}$ , $V_{C3}$ , and $V_{C4}$ respectively), and inductor currents ( $I_{L1}$ and $I_{L3}$ )100 |

| Fig. 5.15: From top to bottom: Simulation results of diode voltages ( $V_{D1}$ , $V_{D3}$ , and $V_{Din}$ ) and   |

| diode <i>D</i> <sub>in</sub> current in steady state condition                                                    |

| Fig. 5.16: From top to bottom: Simulation results of line voltage ( $V_{ab}$ ), phase-voltage ( $V_{an}$ ) and    |

| load current without filter                                                                                       |

| Fig. 5.17: Photograph of experimental setup                                                                       |

| Fig. 5.18: From top to bottom: Experimental results of input voltage, dc-link voltage, and                        |

| inductor ( $L_1$ , $L_3$ ) currents respectively                                                                  |

| Fig. 5.19: From top to bottom: Experimental results of capacitor $C_1$ , $C_2$ , $C_3$ , and $C_4$ voltages       |

| respectively102                                                                                                   |

| Fig. 5.20: From top to bottom: Experimental results of line-voltage, phase-voltage, and                           |

| phase-current respectively102                                                                                     |

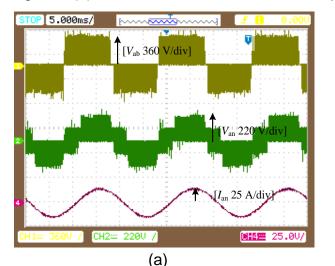

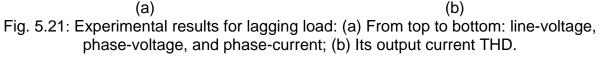

| Fig. 5.21: Experimental results for lagging load: (a) From top to bottom: line-voltage, phase-                    |

| voltage, and phase-current; (b) Its output current THD                                                            |

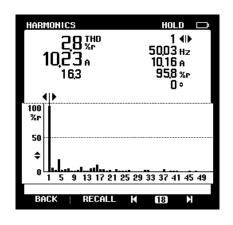

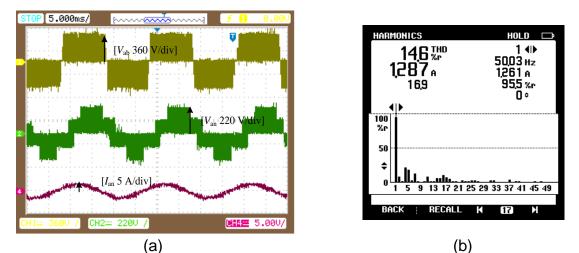

| Fig. 5.22: Experimental results for leading load: (a) From top to bottom: line-voltage, phase-                    |

| voltage, and phase-current; (b) Its output current THD                                                            |

| Fig. 5.23: Experimental results for non-linear load: (a) From top to bottom: line-voltage,                        |

| phase-voltage, and phase-current; (b) Its output current THD                                                      |

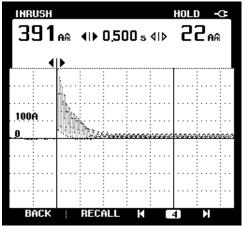

| Fig. 5.24: Inrush current of the proposed enhanced-boost qZSI                                                     |

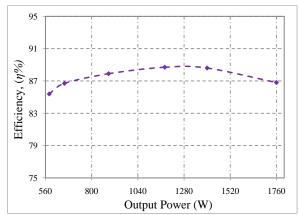

| Fig. 5.25: Efficiency versus output power plot of the EB-qZSI at 110 Vrms output voltage and                      |

| at $V_{\rm DC} = 60$ V, $D_0 = 0.24112$                                                                           |

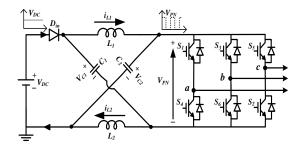

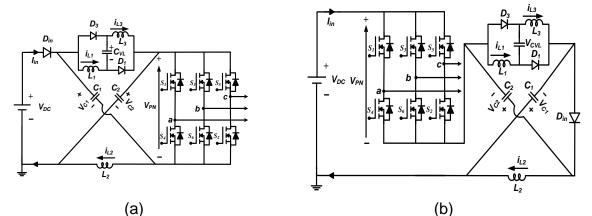

| Fig. 6.1: Illustration of: (a) the proposed enhanced-boost series-ZSI; (b) Its simplified circuit.                |

|                                                                                                                   |

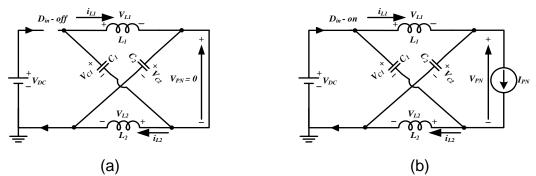

| Fig. 6.2: Proposed series-ZSI equivalent circuits: (a) shoot-through state; (b) non-shoot-                        |

| through state                                                                                                     |

| Fig. 6.3: Inrush current equivalent circuit of enhanced boost-ZSI                                                 |

| Fig. 6.4: Simplified diagram of the proposed network115                                                           |

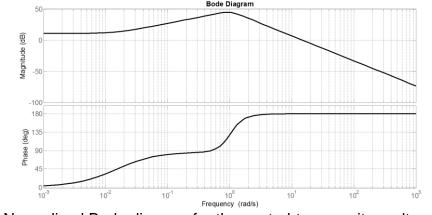

| Fig. 6.5: Normalized Bode diagram for the control-to-capacitor-voltage transfer function 116                      |

| Fig. 6.6: Comparison of: (a) boost factor; (b) voltage gain                                                       |

| Fig. 6.7: Comparison of the proposed series-ZSI with the existing topologies: (a) voltage gain                    |

| <i>G</i> versus diode stress; (b) voltage gain <i>G</i> versus switch stress $V_{\rm S}$                          |

| Fig. 6.8: Capacitor stress comparison                                                                             |

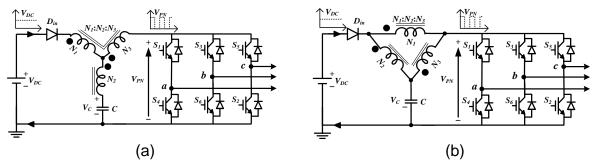

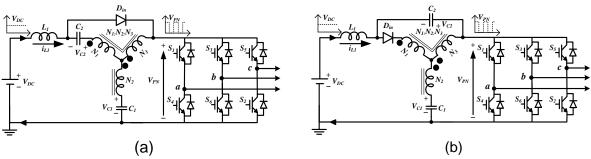

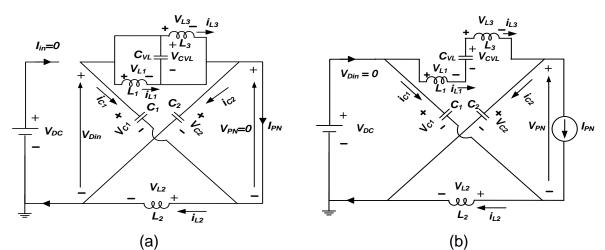

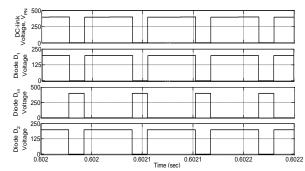

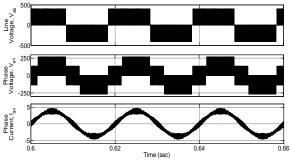

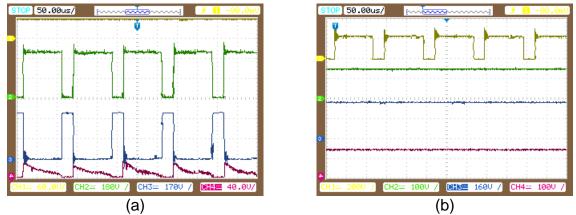

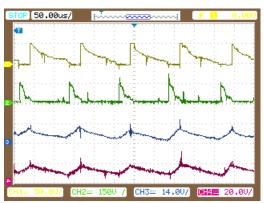

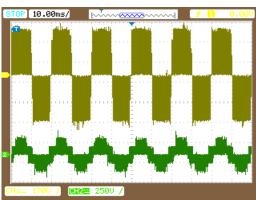

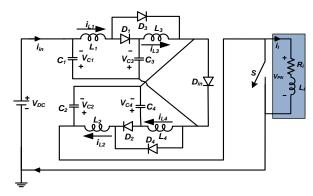

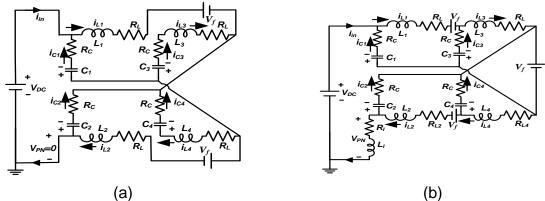

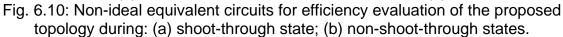

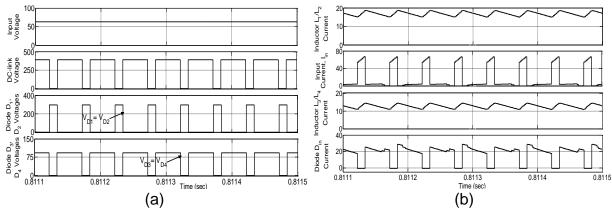

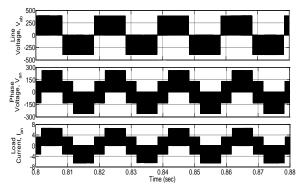

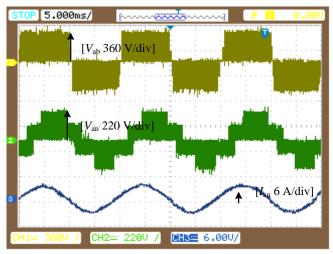

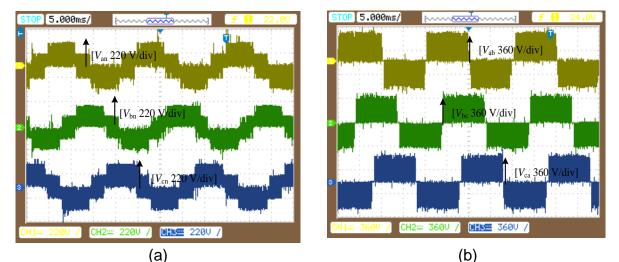

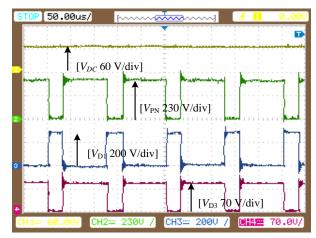

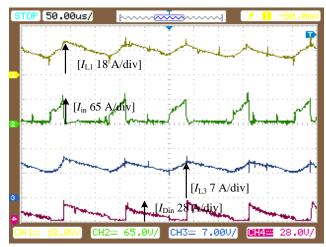

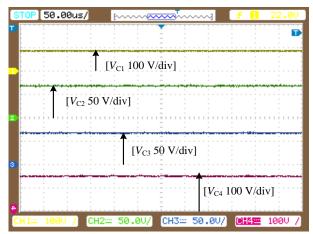

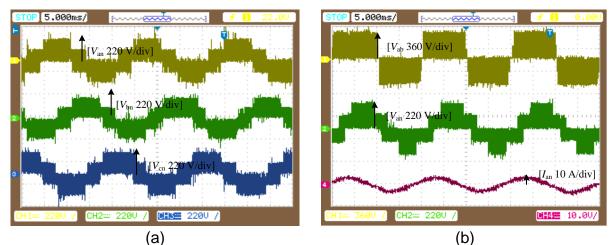

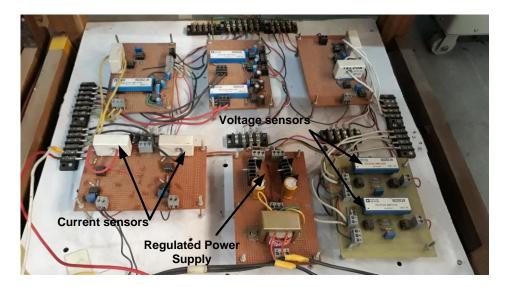

Fig. 6.9: Comparison of ripples: (a) kl versus voltage gain; (b) kC versus voltage gain..... 120 Fig. 6.10: Non-ideal equivalent circuits for efficiency evaluation of the proposed topology Fig. 6.11: From top to bottom; Simulation results of: (a) input, dc-link, diode  $D_1/D_2$ , and diode  $D_3/D_4$  voltages; (b) inductor  $L_1$ , input  $I_{in}$ , inductor  $L_3$ , and diode  $D_{in}$  currents respectively. .. 124 Fig. 6.12: From top to bottom: Simulation results of line voltage, phase voltage and phase Fig. 6.13: Simulation results of capacitor voltages and load current for resistive-inductive Fig. 6.14: Experimental results: From top to bottom; (a) input, dc-link, diode  $D_1$ , and diode  $D_3$ Fig. 6.15: Experimental results, From top to bottom: line voltage  $V_{ab}$ , phase voltage  $V_{an}$ , and Fig. 6.16: From top to bottom, experimental results of: (a) three-phase voltages ( $V_{ab}$ ,  $V_{bc}$ , and Fig. 6.18: Experimental results: (a) ac-side voltages and load current; (b) output current THD Fig. 7.1: Derivation of different configurations of EB-qZSIs from continuous input current EBqZSI: (a) derivation of configuration-1 and configuration-2; (b) derivation of configuration-3 and configuration-4......130 Fig. 7.2: Different configurations of proposed EB-qZSIs for: (a) configuration-1; (b) Fig. 7.4: Equivalent circuits of configuration-1 in: (a) shoot-through state; (b) non-shoot-Fig. 7.5: Equivalent circuits of configuration-2 in: (a) shoot-through state; (b) non-shoot-Fig. 7.6: Equivalent circuits of configuration-3 in: (a) shoot-through state; (b) non-shoot-Fig. 7.7: Equivalent circuits of configuration-4 in: (a) shoot-through state; (b) non-shoot-Fig. 7.9: Capacitor stress comparison of proposed topologies: (a) capacitor  $C_1$  stress comparison; (b) capacitor  $C_2$  stress comparison; (c) capacitor  $C_3$  stress comparison; and (d)

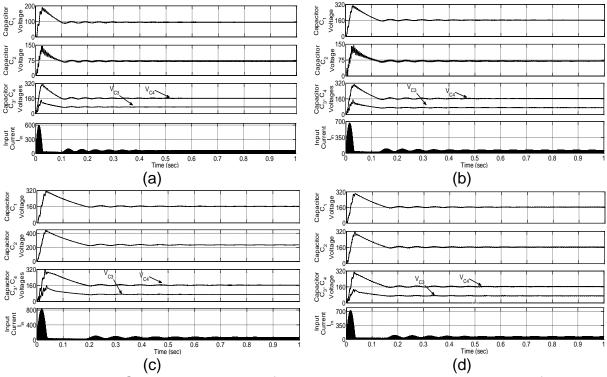

| current for: (a)                                                | Fig. 7.10: Simulations results of capacitor voltages and input                 |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------|

| iguration-4144                                                  | configuration-1; (b) configuration-2; (c) configuration-3; (d) co              |

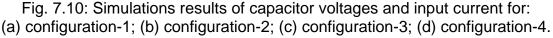

| uge $V_{\text{DC}}$ , diode $D_1$ , $D_3$ , and $D_{\text{in}}$ | Fig. 7.11: From top to bottom, simulation results of input vo                  |

|                                                                 | voltages                                                                       |

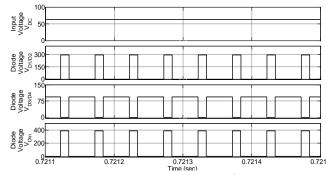

| Itage, inductor $L_1$ , $L_3$ currents,                         | Fig. 7.12: From top to bottom, simulation results of dc-link                   |

|                                                                 | diode <i>D</i> <sub>in</sub> current and dc-link currents                      |

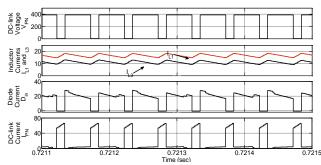

| ages and currents: (a) without                                  | Fig. 7.13: From top to bottom, simulation results of ac-side v                 |

|                                                                 | <i>LC</i> filter; (b) with <i>LC</i> filter                                    |

| jes147                                                          | Fig. 7.14: Experimental results of input, dc-link and diode vol                |

| ents147                                                         | Fig. 7.15: Experimental results of inductor, input and diode cu                |

| voltages (from top to bottom).                                  | Fig. 7.16: Experimental results of capacitor $C_1$ , $C_2$ , $C_3$ , and $C_3$ |

|                                                                 |                                                                                |

| oltages and current 148                                         | Fig. 7.17: Experimental results of: (a) ac-side voltages; (b) ac               |

|                                                                 |                                                                                |

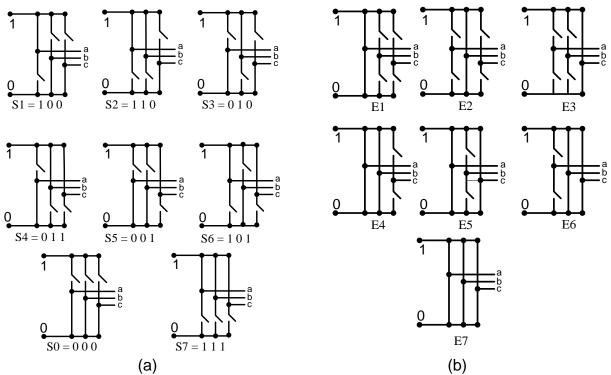

| Table. 1.1: Switching states and their corresponding output voltages of three-phase-Z-source   |

|------------------------------------------------------------------------------------------------|

| inverter ( $!s_x$ represents complement of $s_x$ , where x =1, 3, or 5)                        |

| Table 2.1: Comparison of different non-coupled based inverter topologies                       |

| Table 2.2: Comparison of different coupled inductor based inverter topologies         36       |

| Table 3.1: Performance comparison of the proposed topologies with existing topologies 48       |

| Table 3.2: Common ground, start-up current, number of elements, and nature of input current    |

| comparison                                                                                     |

| Table 3.3: Components and parameters used for the simulation         52                        |

| Table 4.1: Comparison of component count, nature of input current, inrush current, and         |

| common ground for different topologies                                                         |

| Table 4.2: Boost factor, voltage stress, input currents, average DC-link current, and inductor |

| current comparison with the same voltage gain and duty ratio $D_0$                             |

| Table 4.3: Components and parameters specifications used for hardware set-up                   |

| Table 5.1: Comparison of the voltage stress, boost factor, current stress, DC-link voltage,    |

| and input current ripple of the proposed inverter with conventional topologies                 |

| Table 5.2: Input current nature and components (both passive and active) count comparison      |

| of the proposed inverter with conventional inverter topologies                                 |

| Table 5.3: Comparison of inductances and capacitances and their values for the boost factor,   |

| <i>B</i> = 6.6                                                                                 |

| Table 5.4: Expression for the efficiency of all topologies.    96                              |

| Table 5.5: Components and parameters used for the simulation and hardware.         98          |

| Table 6.1: Comparison of voltage stress in the same duty ratio and voltage gain                |

| Table 6.2: Comparison of topology characteristics                                              |

| Table 6.3: Current stress comparisons with same dc-link current and load.         122          |

| Table 7.1: Parameter comparison of proposed topologies with same input voltage and shoot-      |

| through duty ratio 141                                                                         |

| Table 7.2: Comparison of proposed topologies with other Z-networks                             |

| Table 7.3: Parameters for hardware setup    146                                                |

| ac, AC | Alternating Current                               |

|--------|---------------------------------------------------|

| dc, DC | Direct Current                                    |

| VSI    | Voltage Source Inverter                           |

| CSI    | Current Source Inverter                           |

| EMI    | Electro Magnetic Interference                     |

| MPP    | Maximum Power Point                               |

| MOSFET | Metal Oxide Semiconductor Field-Effect Transistor |

| ZSI    | Z-Source Inverter/ Impedance-Source Inverter      |

| qZSI   | Quasi Z-Source Inverter                           |

| SPV    | Solar Photovoltaic                                |

| TEG    | Thermo Electric Generation                        |

| FC     | Fuel Cell                                         |

| HEV    | Hybrid Electric Vehicles                          |

| UPS    | Uninterruptible Power Supplies                    |

| MPPT   | Maximum Power Point Tracking                      |

| ASD    | Adjustable Speed Drive                            |

| PWM    | Pulse Width Modulation                            |

| SVM    | Space Vector Modulation                           |

| DA     | Diode-Assisted                                    |

| CA     | Capacitor-Assisted                                |

| EB     | Enhanced-Boost                                    |

| IEEE   | Institute of Electrical & Electronics Engineers   |

| DSO    | Digital Storage Oscilloscope                      |

| pf, PF | Power Factor                                      |

| THD    | Total Harmonic Distortion                         |

| LCCT   | Inductor-Capacitor-Capacitor-Transformer          |

| SL     | Switched-Inductor                                 |

| VL     | Voltage-Lift                                      |

| SI     | Switched-Impedance                                |

| MCIS   | Magnetically Coupled Impedance Source             |

| CL-LSI | Coupled-Inductor L-Source Inverter                |

| SBI    | Switched Boost Inverter                           |

| CFSI   | Current Fed Switched Inverter                     |

| L-ZSI  | Inductor Z-Source Inverter                        |

|        |                                                   |

| SSI      | Split Source Inverter             |  |

|----------|-----------------------------------|--|

| ΔSI      | ·                                 |  |

|          | $\Delta$ -Source Inverter         |  |

| YSI      | Y-Source Inverter                 |  |

| SZSI     | Series Z-Source Inverter          |  |

| IZSI     | Improved Z-Source Inverter        |  |

| DE-ZSI   | Developed Embedded-ZSI            |  |

| IGBT     | Insulated Gate Bipolar Transistor |  |

| MLI      | Multilevel Inverter               |  |

| SBC      | Simple Boost Control              |  |

| MBC      | Maximum Boost Control             |  |

| MCB      | Maximum Constant Boost            |  |

| rms, RMS | Root Mean Square                  |  |

| DCM      | Discontinuous Conduction Mode     |  |

| ССМ      | Continuous Conduction Mode        |  |

| KVL      | Kirchhoff's Voltage Law           |  |

| KCL      | Kirchhoff's Current Law           |  |

| RTW      | Real-Time Workshop                |  |

| MOV      | Metal-Oxide Varistor              |  |

| RTI      | Real-Time Interface               |  |

| TDE      | Total Development Environment     |  |

| ADC      | Analog-to-Digital Converter       |  |

| DAC      | Digital-to-Analog Converter       |  |

| PCI      | Peripheral Component Interconnect |  |

| DSP      | Digital Signal Processor          |  |

| FPGA     | Field Programmable Gate Array     |  |

| $F_{\rm S}$ Switching frequency $M$ Modulation index $G$ Voltage gain $B$ Boost factor $\Gamma$ Gamma $\Delta$ Delta $T$ Transformer $\Sigma$ Sigma $V_{DC}$ Input dc-voltage $V_{PN}$ Peak-dc link voltage $V_{an}$ Peak-phase voltage $v_{an}$ Three-phase line voltages $i_{an}$ , $i_{bn}$ and $i_{cn}$ Three-phase currents $C_1, C_2, C_3$ and $C_4$ Z-source network capacitors $I_1, L_2, I_3$ and $L_4$ Z-source network diodes $D_{ln}$ Input diode $K_0$ Number of shoot-through states $f_m$ Gapacitor voltages $m_1$ Frequency modulation index $m_1$ Zapacitor voltages $I_{11}, I_{12}, I_{13}$ and $I_{L4}$ Average inductor currents $V_{D1}, V_{D2}, V_{D3}$ and $V_{C4}$ Diade voltages $V_{D1}, V_{D2}, V_{D3}$ and $V_{C4}$ Diade voltages $V_{D1}, V_{D2}, V_{D3}$ and $V_{C4}$ Diade voltages $V_{D1}, V_{D2}, V_{D3}$ and $V_{C4}$ Diode voltages $V_{D1}, V_{D2}, V_{D3}$ and $V_{C4}$ Signal control for switch S $T_S$ Switching time period $T_0$ Shoot-through period $V_{D1}$ Voltage-lift capacitor $V_S$ Switch stress $I_{PN}$ Switch stress $I_{PN}$ Average D-link Current                                                                                                                                                                                                                         | $D_0$                                                 | Shoot-through duty ratio         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------|

| GVoltage gainBBoost factor $F$ Gamma $\Delta$ Delta $T$ Transformer $\Sigma$ Sigma $V_{DC}$ Input dc-voltage $V_{PN}$ Peak-dc link voltage $V_{an}$ Peak-phase voltage $v_{an}$ Three-phase line voltages $i_{ani}, i_{bn}$ and $i_{cn}$ Three-phase currents $C_1, C_2, C_3$ and $C_4$ Z-source network capacitors $L_1, L_2, L_3$ and $L_4$ Z-source network diodes $D_n$ Input diode $K_0$ Number of shoot-through states $f_m$ Garrier signal frequency $f_r$ Carrier signal frequency $m_t$ Frequency modulation index $V_{D1}, V_{D2}, V_{D3}$ and $V_{D4}$ Diode voltages $V_{D1}, V_{D2}, V_{D3}$ and $V_{D4}$ Switching time period $T_{S}$ Switching time period $V_{D1}, V_{D2}, V_{D3}$ <td< td=""><td>Fs</td><td>Switching frequency</td></td<> | Fs                                                    | Switching frequency              |

| BBoost factorFGamma $\Delta$ DeltaTTransformer $\Sigma$ Sigma $V_{DC}$ Input dc-voltage $V_{PN}$ Peak-dc link voltage $V_{an}$ Peak-phase voltage $V_{an}$ Peak-phase unrents $Input dc.$ Input dc-voltage $V_{an}$ Peak-phase unrents $C_1, C_2, C_3$ and $V_{ca}$ Three-phase currents $I_1, L_2, L_3$ and $L_4$ Z-source network capacitors $L_1, L_2, L_3$ and $L_4$ Z-source network diodes $D_n$ Input diode $K_0$ Number of shoot-through states $f_m$ Modulating signal frequency $f_{cr}$ Carrier signal frequency $m_f$ Frequency modulation index $W_{C1}, V_{C2}, V_{C3}$ and $V_{C4}$ Capacitor voltages $I_{L1}, I_{L2}, I_{L3}$ and $I_{L4}$ Average inductor currents $V_{D1}, V_{D2}, V_{D3}$ and $V_{D4}$ Diode voltages $I_{D1}, V_{D2}, V_{D3}$ and $V_{D4}$ Diode voltages $I_n$ Input diode voltage $I_n$ Input current $S_0$ Gate signal control for switch $S$ $T_S$ Switching time period $T_0$ Shoot-through period $V_{VL}$ Voltage-lift capacitor $V_S$ Switch stress                                                                                                                                                                                                                                                                                                                                     | Μ                                                     | Modulation index                 |

| $\Gamma$ Gamma $\Delta$ Delta $T$ Transformer $\Sigma$ Sigma $V_{DC}$ Input dc-voltage $V_{PN}$ Peak-dc link voltage $V_{an}$ Peak-phase voltage $v_{an}$ Peak-phase unrents $t_{an}, t_{bn}$ and $t_{cn}$ Three-phase line voltages $i_{an}, t_{bn}$ and $i_{cn}$ Three-phase currents $C_1, C_2, C_3$ and $C_4$ Z-source network capacitors $L_1, L_2, L_3$ and $L_4$ Z-source network diodes $D_{in}$ Input diode $K_0$ Number of shoot-through states $f_m$ Modulating signal frequency $f_{cr}$ Carrier signal frequency $m_f$ Frequency modulation index $V_{C1}, V_{C2}, V_{C3}$ and $V_{C4}$ Capacitor voltages $I_{L1}, I_{L2}, I_{L3}$ and $I_{L4}$ Average inductor currents $V_{Din}, V_{D2}, V_{D3}$ and $V_{D4}$ Diode voltages $I_{Din}$ Input diode voltages $V_{Din}$ Input diode voltage $I_n$ Switching time period $T_0$ Shoot-through period $V_{VL}$ Voltage-lift capacitor $V_S$ Switch stress                                                                                                                                                                                                                                                                                                                                                                                                                 | G                                                     | Voltage gain                     |

| $\Delta$ Delta $T$ Transformer $\Sigma$ Sigma $V_{DC}$ Input dc-voltage $V_{PN}$ Peak-dc link voltage $V_{an}$ Peak-phase voltage $V_{an}$ Peak-phase voltage $V_{an}$ Peak-phase unrents $I_{n}, I_{bn}$ and $I_{cn}$ Three-phase currents $C_1, C_2, C_3$ and $C_4$ Z-source network capacitors $L_1, L_2, L_3$ and $L_4$ Z-source network diodes $D_n$ Input diode $K_0$ Number of shoot-through states $f_m$ Modulating signal frequency $f_cr$ Carrier signal frequency $m_f$ Frequency modulation index $W_{C1}, V_{C2}, V_{C3}$ and $V_{C4}$ Capacitor voltages $V_{D1}, V_{D2}, V_{D3}$ and $V_{D4}$ Diode voltages $V_{Din}$ Input diode $N_{D1}, V_{D2}, V_{D3}$ and $V_{D4}$ Diode voltage $I_n$ Input diode voltage $I_n$ Switching time period $T_s$ Switching time period $V_{S}$ Switch stress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | В                                                     | Boost factor                     |

| TTransformer $\Sigma$ Sigma $V_{DC}$ Input dc-voltage $V_{PN}$ Peak-dc link voltage $V_{an}$ Peak-phase voltage $v_{ab}, v_{bc}$ and $v_{ca}$ Three-phase line voltages $i_{an, ibn}$ and $i_{cn}$ Three-phase currents $C_1, C_2, C_3$ and $C_4$ Z-source network capacitors $l_1, L_2, L_3$ and $L_4$ Z-source network diodes $D_{in}$ Input diode $K_0$ Number of shoot-through states $f_m$ Modulating signal frequency $f_{cr}$ Carrier signal frequency $m_i$ Average inductor currents $N_{c1}, V_{c2}, V_{c3}$ and $V_{c4}$ Qapacitor voltages $V_{c1}, V_{c2}, V_{c3}$ and $V_{c4}$ Diode voltages $V_{Din}$ Input diode voltages $V_{Din}$ Input diode voltage $I_n$ Source network of since for switch $S$ $T_s$ Switching time period $T_s$ Switching time period $V_{c1}, V_{c2}, V_{c3}$ and $V_{c4}$ Switching time period $V_{Din}$ Input diode voltage $V_{an}$ Switching time period $T_s$ Switching time period $T_s$ Switching time period $V_{c1}$ Switch stress                                                                                                                                                                                                                                                                                                                                                 | Г                                                     | Gamma                            |

| $\Sigma$ Sigma $\Sigma$ Sigma $V_{DC}$ Input dc-voltage $V_{PN}$ Peak-dc link voltage $V_{an}$ Peak-phase voltage $V_{an}$ Peak-phase line voltages $i_{an}$ , $i_{bn}$ and $i_{cn}$ Three-phase currents $C_1, C_2, C_3$ and $C_4$ Z-source network capacitors $L_1, L_2, L_3$ and $L_4$ Z-source network diodes $D_{1n}$ Input diode $K_0$ Number of shoot-through states $f_m$ Modulating signal frequency $f_{cr}$ Carrier signal frequency $m_1$ Frequency modulation index $M_{21}, V_{22}, V_{C3}$ and $V_{c4}$ Capacitor voltages $I_{L1}, I_{L2}, I_{L3}$ and $I_{L4}$ Average inductor currents $V_{D1}, V_{D2}, V_{D3}$ and $V_{D4}$ Diode voltages $I_{D1}, V_{D2}, V_{D3}$ and $V_{D4}$ Diode voltages $I_{D1}$ Input diode voltage $I_{D1}$ Switching time period $T_0$ Shoot-through period $V_{S}$ Switch stress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Δ                                                     | Delta                            |

| $V_{DC}$ Input dc-voltage $V_{PN}$ Peak-dc link voltage $V_{an}$ Peak-phase voltage $V_{ab}$ , $V_{bc}$ and $v_{ca}$ Three-phase line voltages $i_{an}$ , $i_{bn}$ and $i_{cn}$ Three-phase currents $C_1, C_2, C_3$ and $C_4$ Z-source network capacitors $L_1, L_2, L_3$ and $L_4$ Z-source network inductors $D_1, D_2, D_3$ and $D_4$ Z-source network diodes $D_m$ Input diode $K_0$ Number of shoot-through states $f_m$ Gatrier signal frequency $f_cr$ Carrier signal frequency $m_f$ Frequency modulation index $m_a$ Amplitude modulation index $V_{D1}, V_{D2}, V_{D3}$ and $V_{D4}$ Diode voltages $V_{D1}, V_{D2}, V_{D3}$ and $V_{D4}$ Diode voltages $V_{D1}, V_{D2}, V_{D3}$ and $V_{D4}$ Diode voltage $I_n$ Input diode voltage $I_n$ Switching time period $T_0$ Shoot-through period $V_V_K$ Switch stress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Т                                                     | Transformer                      |

| $V_{PN}$ Peak-dc link voltage $V_{an}$ Peak-phase voltage $V_{ab}, V_{bc}$ and $v_{ca}$ Three-phase line voltages $i_{an}, i_{bn}$ and $i_{cn}$ Three-phase currents $C_1, C_2, C_3$ and $C_4$ Z-source network capacitors $L_1, L_2, L_3$ and $L_4$ Z-source network inductors $D_1, D_2, D_3$ and $D_4$ Z-source network diodes $D_{in}$ Input diode $K_0$ Number of shoot-through states $f_m$ Modulating signal frequency $f_{cr}$ Carrier signal frequency $m_f$ Frequency modulation index $m_a$ Amplitude modulation index $V_{C1}, V_{C2}, V_{C3}$ and $V_{C4}$ Capacitor voltages $V_{Din}$ Input diode voltage $V_{Din}$ Input diode voltage $I_n$ Switching time period $T_0$ Shoot-through period $V_{VL}$ Voltage-lift capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Σ                                                     | Sigma                            |