# POWER QUALITY IMPROVEMENT USING MODULAR D-STATCOM

Ph.D. THESIS

by

#### YARLAGADDA SRINIVASA RAO

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) MARCH, 2018

## POWER QUALITY IMPROVEMENT USING MODULAR D-STATCOM

#### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

#### **DOCTOR OF PHILOSOPHY**

in

#### **ELECTRICAL ENGINEERING**

by

#### YARLAGADDA SRINIVASA RAO

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) MARCH, 2018

#### ©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2018 ALL RIGHTS RESERVED

## INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

### **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in this thesis entitled "**POWER QUALITY IMPROVEMENT USING MODULAR D-STATCOM''** in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electrical Engineering of Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from January, 2013 to March, 2018 under the supervision of Dr. M.K Pathak, Associate Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

#### (YARLAGADDA SRINIVASA RAO)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

(M. K Pathak) Supervisor

Dated: \_\_\_\_\_

#### ABSTRACT

In present scenario, majority of loads such as motor drives, fans, pumps, and power electronic converters put reactive power burden on the distribution systems. Excessive reactive power demand results into low power factor, poor voltage regulation and increases feeder losses and reduces the active power flow capability of the distribution system. Moreover, situation worsens in the presence of non-linear loads and raises power quality issues on distribution system. The primary source that draw non-linear currents from the distribution systems are power electronic devices. The operation of non-linear loads on distribution systems draw harmonics currents, which may interrupt the normal operation of other electrical equipment connected to the network. With ever-increasing penetration of power electronic devices, the power quality equipped with sophisticated microprocessor-based controllers which are quite sensitive to deviations of the voltage from its ideal waveform. In recent years, with the advent of sophisticated electrical and electronic equipment, the electric power quality (PQ) has become an issue of concern and extensive research is being carried out to improve the power quality.

In the early days, synchronous condenser and mechanically switched capacitors and inductors have been used for reactive power compensation. However, due to their slow response and mechanical wear and tear, use of these devices is limited for the applications where fast compensation is not needed. With the advent of the first generation of Flexible AC Transmission System (FACTS) devices, thyristor-controlled static var compensators (SVCs) schemes made significant advances in reactive power compensation as these devices are fast in operation and smooth control of reactive power compensation can be obtained with these devices. Despite the attractive theoretical simplicity of the SVC schemes, their penetration has been hindered by a number of disadvantages such as large size of capacitor and inductor banks, dependency of the reactive power compensation on operating voltage. With the remarkable progress of gate commutated semiconductor devices, attention has been focused on second generation FACTS devices which are based on self-commutated inverters. Among them, Static Synchronous Compensation and voltage regulation in transmission systems.

Harmonic regulations or guidelines such as IEEE 519-1992 and IEC 61000 have become acceptable standards and are being applied to limit the current and voltage harmonics levels. To

meet these requirements, harmonics must be mitigated by using harmonic filters. Active and passive filters are used either together to form hybrid filters or separately to mitigate harmonics.

Conventional power quality mitigation equipment can respond only to a particular power quality problem, and this fact has attracted the attention of power engineers to develop dynamic and adjustable solutions to power quality problems. One modern and very promising group of solutions that deals with load current and/or supply voltage imperfections is the Custom Power Devices (CPDs). CPDs rectify most of the distribution system problems and many of the existing compensation devices are being replaced by CPDs, thereby reducing the cost. The family of CPDs includes distribution static synchronous compensator (D-STATCOM), dynamic voltage restorer (DVR) and unified power quality conditioners (UPQC) which are used for compensating the power quality problems in the current and/or voltage waveforms. Among these members, D-STATCOM is a shunt-connected device, which takes care of the power quality problems in the current waveform. In this thesis, an attempt has been made to develop a robust computer-controlled D-STATCOM for power quality improvement in single phase and 3P3W distribution systems.

It is well known that high performance and cost-effective inverter is a prerequisite for the realization of a D-STATCOM. These inverters can be broadly categorised into two classes, namely, voltage source inverter (VSI) and current source inverter (CSI). A critical comparison of the performance of VSI and CSI when used as a power circuit of D-STATCOM is beyond the scope of this thesis. However, in the present work, VSI has been considered as a power circuit for D-STATCOM as it has higher market penetration and a more noticeable development on VSI has taken place over the last decade, in comparison to CSI topologies. The high harmonic content of the output voltage makes basic six-pulse (two-level) VSI impractical for direct use in high-power, medium-voltage applications. Instead of using filters and connecting several switching devices in series to achieve the required voltage level, several alternative possible solutions are reported in the literature and can be broadly categorized into two groups: multipulse and multilevel inverters. The first one requires complex phase-shifting transformers and therefore, its application is limited to high-power, high-voltage systems. The second approach, multilevel inverters, uses the concept of addition of multiple small voltage levels for achieving the required voltage level with the help of additional switching devices and few components like diodes or capacitors. This approach does not require complex phase shifting transformers and hence these topologies are best suited for medium-power applications. The common multilevel inverters (MLI) topologies are the diode-clamped (DCMLI), flying capacitor (FCMLI), and cascaded multilevel inverters (CMLI) or modular multilevel cascade inverters (MMCI).

The selection of individual inverter topologies for D-STATCOM applications depends on their performance, cost, size, and implementation issues. DCMLI topology seems to be the most suited for D-STATCOM applications. But, the large number of power components and voltage unbalance problem at higher levels limits the DCMLI for low power rating applications. On the other hand, FCMLI has a natural voltage balancing operation and modular structure, but its application as a D-STATCOM is limited due to the requirement of large number of capacitors and their pre-charging. On the other hand, MMCI is one of the next generation multilevel inverters intended for high or medium-voltage power conversion without the requirement of line-frequency transformers. The MMCI is based on cascade connection of multiple single-phase H-bridge cell (SDBC) are characterized by the cascade connection of multiple single-phase H-bridge cells per leg.

The least component requirement, low cost, modular structure, easy expansion to any number of levels, high fault tolerance and absence of complex input transformer and non-initialization of the capacitor voltages make SSBC and SDBC best suited for D-STATCOM applications. Both SSBC and SDBC can reach higher output voltages and power levels (13.8 kV, 30 MVA) with readily available medium-voltage semiconductor devices. The SSBC and SDBC inverters have found input transformerless applications such as STATCOM, Battery Energy Storage System (BESS), and DVR. In this work, the application of MMCI has been extended to D-STATCOM, intended for direct installation on a medium-voltage distribution system for reactive power compensation and harmonic compensation. Towards this goal, the SSBC based inverter configuration has been chosen over SDBC as the number of converter-cells required for SDBC is  $1.732 (=\sqrt{3})$  times that required for SSBC.

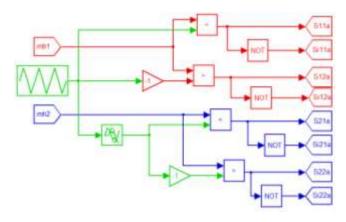

In order to control the output voltage of the inverter of D-STATCOM to act as a controllable current source, a suitable modulation technique is be required for the SSBC inverter. Although a large number of different modulation schemes for multilevel inverters have been proposed in the literature, for industrial application, carrier based PWM schemes are still preferred because of their proven technology, simplicity and ease of implementation.

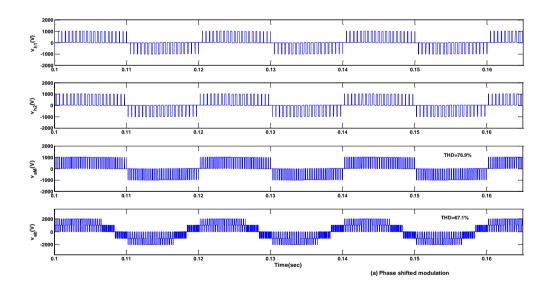

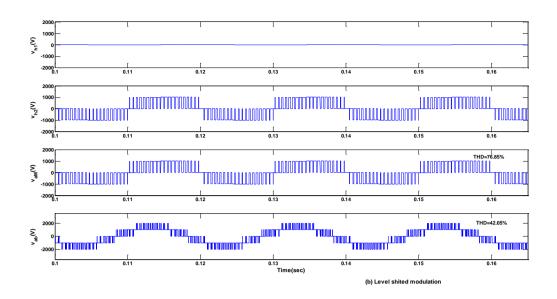

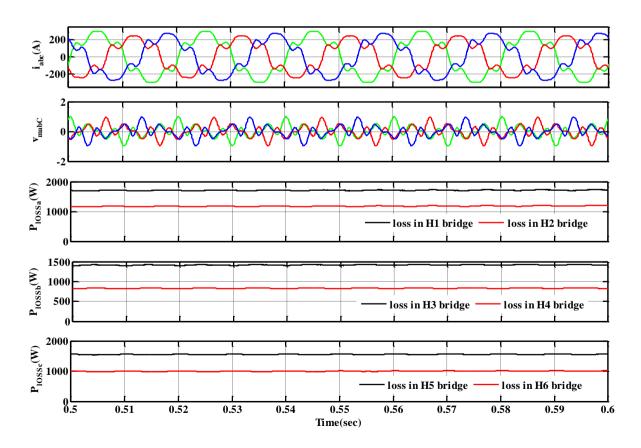

The carrier-based modulation schemes for multilevel inverters can be generally classified into two categories: phase-shifted PWM (PSPWM) and level-shifted PWM (LSPWM) techniques. The LSPWM technique produces the better harmonic performance when compared with the PSPWM technique, but it avoids the current harmonic cancellation at the input side of the phaseshifting transformer. Nevertheless, because of the unequal device conduction periods of the LSPWM technique, it has penetrated smaller market even in those applications where transformer is not required at the input side, such as FACTS and CPDs, electric vehicle applications. The unequal device conduction periods affect the charging and discharging of the dc bus capacitors and cause non-uniform power and heat distribution in the inverter. The PSPWM distribute the switching and conduction losses evenly if the H-bridges characteristics are ideal. However if the devices characteristics are uneven or the SSBC inverter is supplying the unbalanced currents in PSPWM, the capacitor voltages deviate from the reference voltage. To prove this statement, a five level inverter the losses in a H-bridge are modeled in MATLAB from the data sheet of device characteristics to observe uneven losses among the H-bridges when supplying the unbalanced current or with different devices. In the present work, the control algorithms for capacitor voltage balancing are extended to single phase and three phase SSBC inverter with PSPWM modulation.

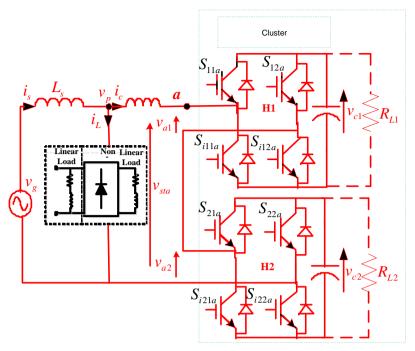

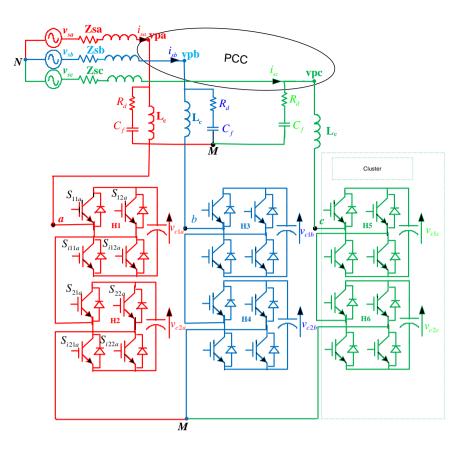

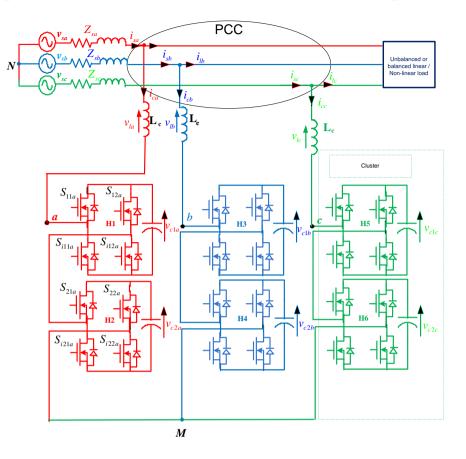

Towards the goal of achieving harmonic elimination and reactive power compensation with D-STATCOM, a 2.2-kV industrial three-phase, three-wire (3P3W) distribution system has been considered. For a 2.2-kV system, generally the inverter is equipped with a transformer for galvanic isolation and voltage matching between the industrial/utility distribution system voltage and the inverter voltage. However, weight and size of the transformer is more than 50% of the inverter. To alleviate this problem, the focus of this research is to design a SSBC based D-STATCOM without any line frequency transformer. The cascade number (N, i.e. the number of cascaded voltage source H-bridge inverters in each phase) is one of the most important design parameters for designing a transformerless PWM D-STATCOM. The value of N depends on the blocking voltage of the switching devices, cost, size and performance of the inverter. In the present work, IGBT has been used as the switching device and further, a cascade number of N equal to 2 has been chosen, considering percentage total harmonic distortion (%THD), the dc voltage requirement and the voltage rating of IGBT. This allows the use of 1.7-kV IGBTs, which are available readily at a reasonable cost. For this D-STATCOM, a suitable value of reference dc voltage for each H-bridge cell has been chosen. Ratings of various components of D-STATCOM such as DC capacitors for each H-bridge cell and inductance of coupling reactors have been designed and carefully selected.

For a single phase D-STATCOM the pq theory is used for load harmonic current extraction but if supply voltage is distorted, then a proper Reference current generated for D-STATCOM is not possible. The modified single phase pq theory with PLL is used to generate a proper reference current for D-STATCOM. The performance of modified and original pq theory is compared for different harmonic and reactive power loads. The unequal power losses arising because of asymmetries in device characteristics and the consequent deviation of capacitor voltages is investigated with an improved modulating signal method (IMS) and is compared to active voltage superposition (AVS) method.

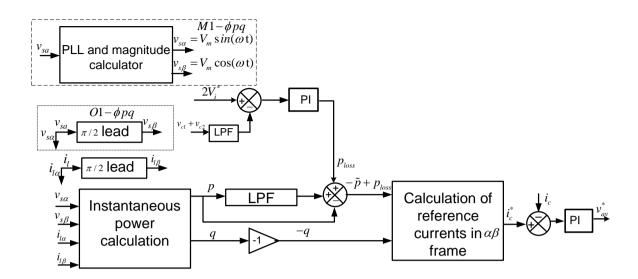

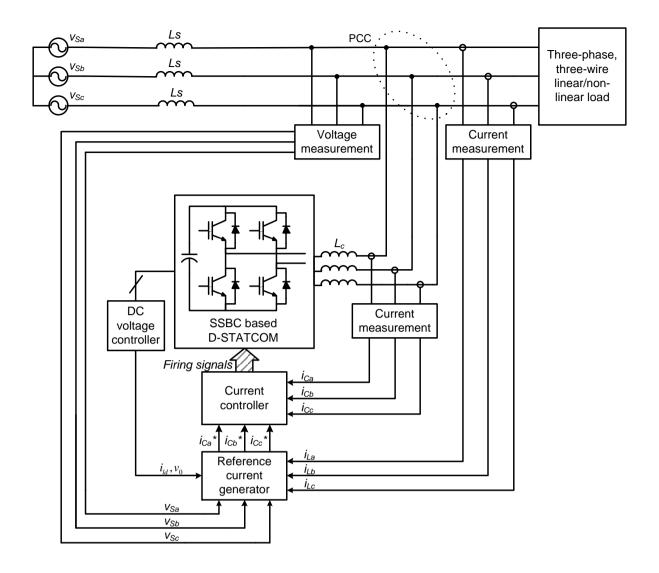

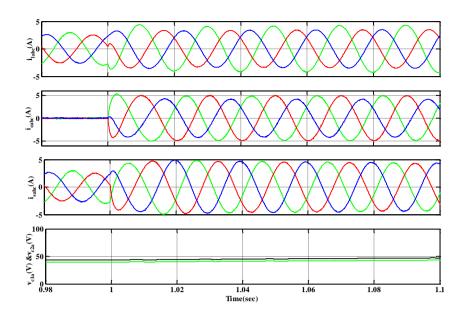

The performance of three-phase D-STATCOM largely depends on the control algorithm used for its implementation. The control algorithm considered in this work aims to eliminate harmonics, compensate reactive power as well as control and balance all the dc capacitor voltages of the SSBC in steady-state and in transient conditions. The load harmonic currents have been derived by using the measured voltages at point of common coupling (PCC), load currents, and the dc bus voltages of the H-bridge cells of the SSBC using Synchronous reference frame (SRP) theory. The performance of two current controllers namely PI and PI with resonant controller is investigated for different types of non-linear loads. In order to control the voltages of the floating dc capacitors of the 5-level SSBC based D-STATCOM while absorbing the unbalanced currents, the dc voltage balancing control has been divided into two control parts: (a) cluster voltage balancing control and (b) individual voltage balancing control. The former calculates the zero sequence voltage for balancing the three cluster voltages of the inverter and the later modifies the individual modulating signal for floating dc capacitors to follow their corresponding reference values. The capacitor voltage balancing method is investigated for unity power factor (UPF) and zero voltage regulation (ZVR) modes.

Computer simulation studies under different load conditions have been carried out to verify the performance of the 3P3W D-STATCOM for harmonic elimination and reactive power compensation. The simulation study of the entire system has been carried out in MATLAB/Simulink environment. Extensive simulation studies have been carried out to investigate the performance of the D-STATCOM current controllers PI and PI with resonant. The simulation studies have been performed for both steady-state and transient conditions with different non-linear and reactive loads. Further, performance of the D-STATCOM has been investigated with unity power factor and zero voltage regulation mode, the capacitor voltage balancing among the individual dc capacitors of the D-STATCOM.

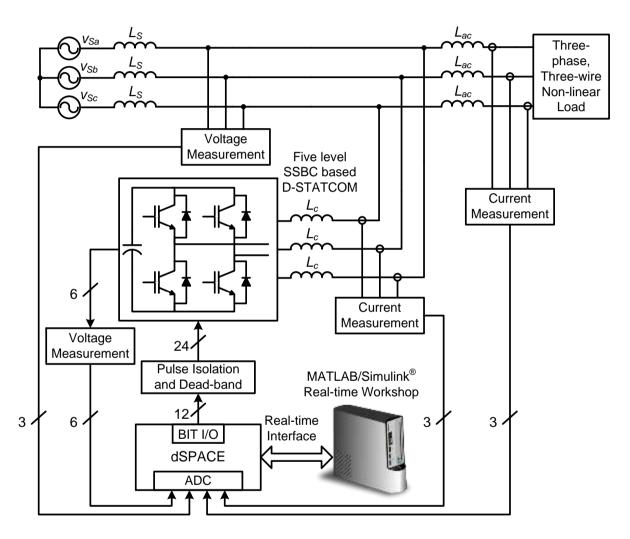

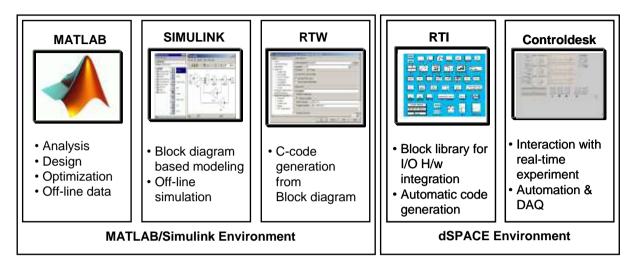

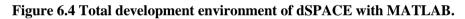

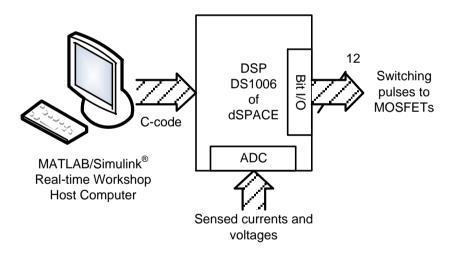

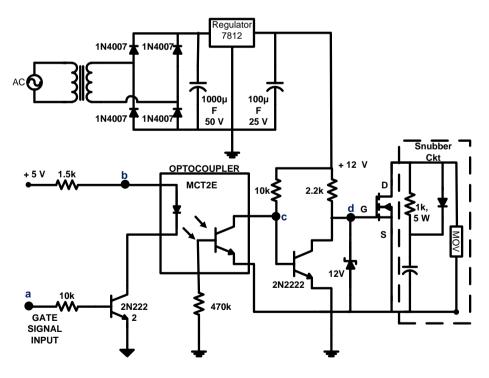

In order to further verify the simulation studies of a single phase and a three-phase downscaled SSBC based inverter has been designed, constructed, and tested to verify the viability and effectiveness of the control theories, current controllers and capacitor voltage balancing methods. For hardware implementation, the power circuit of D-STATCOM is made with MOSFETs (IRFP460) as switching devices. Different hardware components as required for the operation of the experimental set-up such as pulse amplification, isolation circuit, dead-band

circuit, voltage and current sensor circuits, and non-linear/reactive loads have been designed and developed. By using the Real-Time Workshop (RTW) of MATLAB and Real-Time Interface (RTI) feature of dSPACE-DS1006, the Simulink models of the various controllers of the prototypes have been implemented. The generated firing pulses have been given to the corresponding semiconductor devices of each H-bridge of the inverter through isolation, delay, and pulse amplification circuits in real-time.

The developed prototype SSBC based D-STATCOM is used to verify the viability and effectiveness of the Current controllers for harmonic elimination and reactive compensation. In D-STATCOM implementation, each H-bridge cell is equipped with a galvanically isolated and floating dc capacitor without any power source or circuit. The SRF based controller of the D-STATCOM has been implemented in dSPACE. An uncontrolled rectifier with *RL* elements on DC side have been used as a nonlinear load.

After compensation with D-STATCOM, the source currents have been observed to be sinusoidal and their corresponding THDs being within the limits of IEEE–519–1992 recommended value of 5%. The source displacement and power factors have been found to be close to unity. The switching response and the dynamic performance of D-STATCOM for a step change in the load have been studied and in both cases, a smooth control of source current has been achieved. The regulation of capacitor voltages has been ensured by the DC voltage regulator. A smooth control of dc voltages ensures the effectiveness of the DC voltage controller. Further, the experimental results of the capacitor voltage balancing dynamics of the H-bridge cells with zero sequence voltage injection and individual capacitor voltage balancing have been studied. The experimental results have been found to be in good agreement with the simulation results.

With GOD's grace I have got this opportunity to thanks all those who have supported me all through this course of work. First and foremost, I would like to express my deepest sense of gratitude towards my supervisor Dr. Mukesh Pathak, Associate Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee for his patience, inspiring guidance, constant encouragement, moral support, and keen interest in minute details of the work. I am sincerely indebted to him for his pronounced individuality, humanistic and warm personal approach, and excellent facility provided to me in the laboratory to carry out this research.

I also express my sincere gratitude towards my research committee members Dr. S.P.Singh (Professor EED & Chairman SRC), Dr. Pramod Agarwal, (Professor, EED) Dr. N.P Pathak, (Professor, Department of ECE) for their invaluable direction, encouragement and support, and above all the noblest treatment extended by them during the course of my studies at IIT Roorkee.

I heartily extend my gratitude to Head of the Department of Electrical Engineering, and all faculty members of the department for their help, moral support, and providing the excellent infrastructure, laboratory and computing facility for the research work.

I acknowledge my sincere gratitude to the Ministry of Human Resources and Development (MHRD), Government of India for providing financial support during my doctoral research work.

I express my sincere thanks to all seniors especially to Dr. D Sreenivas Rao, Dr. Jai ram, Dr. Giri babu, Dr. Aurobinda Panda, Dr. D. Suresh, Dr. P Kishore, and Dr. Ramana naik supporting me during the whole period. I extend my sincere thanks to my colleagues Mr. Janardana Kotturu, Mr. Vadtiya Jagan, Mr. Santosh Kumar, Mr. Narendra babu, Mr. sanjeev reddy, Mr. Y Naveen, Mr. Siddhratha for sharing and supporting me during my research work.

I would also like to thank all the administrative &technical staff of the department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee for their cooperation and necessary facility provided to me to carry out this research work. My special thanks to Mr. Amir Ahmed, Mr. Gautam Singh and Mr. Rakesh Kumar, who helped me to prepare experimental setup of my research work.

I owe a debt of gratitude to my parents, Shri Rama subbarao and Smt. Sathyavathi, my brother Rama Krishna, for their endless support, encouragement, patience and care.

I sincerely acknowledge the ethical support from my Father-in-law Shri Kishore babu and Mother-in-law Smt. Naryanamma.

No words can adequately express my deepest gratitude and love to my wife Smt. Soujanya for her unconditional support, encouragement, love and inspiration and always being there for good and bad times.

May all praise be to the Almighty, the most beneficent, and the most merciful.

(Yarlagadda Srinivasa Rao)

## CONTENTS

| ABSTRACT                                                      | i     |

|---------------------------------------------------------------|-------|

| ACKNOWLEDGEMENTS                                              | vii   |

| CONTENTS                                                      | ix    |

| LIST OF FIGURES                                               | XV    |

| LIST OF TABLES                                                | xxiii |

| LIST OF SYMBOLS                                               | XXV   |

| LIST OF ABBREVIATIONS                                         | xxvii |

| Chapter 1: INTRODUCTION                                       | 1     |

| 1.1 Overview                                                  | 1     |

| 1.2 Reactive Power Burden                                     | 1     |

| 1.2.1 Sources of Reactive Power                               | 3     |

| 1.2.2 Problems due to High Reactive Power                     | 3     |

| 1.3 Harmonic Distortion                                       | 3     |

| 1.3.1 Effects of Harmonics                                    | 5     |

| 1.3.2 Harmonic Standards                                      | 6     |

| 1.4 Solutions to Power Quality Problem in Distribution System | 6     |

| 1.4.1 Reactive Power Compensators                             | 7     |

| 1.4.1.1 Thyristor Controlled Static Var Compensators (SVC)    | 7     |

| 1.4.1.2 VAR Generators Employing Static Inverters             | 9     |

| 1.4.2 Harmonic Compensation                                   | 12    |

| 1.4.2.1 Passive Power Filters                                 | 13    |

| 1.4.2.2 Active Power Filters                                  | 14    |

| 1.4.2.3 Hybrid Power Filters                                  | 15    |

| 1.5 Power Quality Improvement using D-STATCOM                 | 16    |

| 1.6 Distribution Static Synchronous Compensator (D-STATCOM)   | 17    |

|   | 1.6.1 STATCOM in Transmission and Distribution Systems            | 17 |

|---|-------------------------------------------------------------------|----|

|   | 1.6.2 Basic Compensation Principle of D-STATCOM                   | 18 |

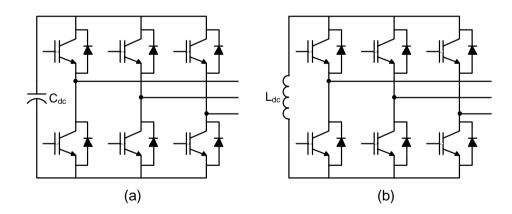

|   | 1.7 Configurations of D-STATCOM                                   | 19 |

|   | 1.7.1 Power Circuit Based Classification                          | 19 |

|   | 1.7.2 Supply System Based Classification                          | 21 |

|   | 1.7.2.1 Single-phase D-STATCOMs                                   | 21 |

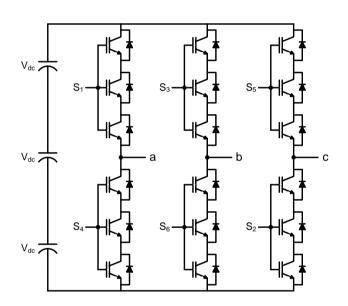

|   | 1.7.2.2 Three-phase, Three-wire D-STATCOMs                        | 21 |

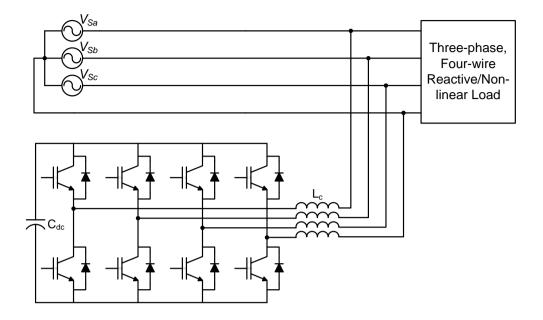

|   | 1.7.2.3 Three-phase, Four-wire D-STATCOMs                         | 22 |

|   | 1.8 D-STATCOM Controller                                          | 24 |

|   | 1.9 Scope of Work and Author's Contribution                       | 25 |

|   | 1.10 Organization of the Thesis                                   | 26 |

| ( | Chapter 2: PWM INVERTERS FOR D-STATCOM                            | 29 |

|   | 2.1 Introduction                                                  | 29 |

|   | 2.2 Two-level VSI for High-power, Medium-voltage                  | 30 |

|   | 2.3 VSI Topologies for High power, Medium voltage applications    | 30 |

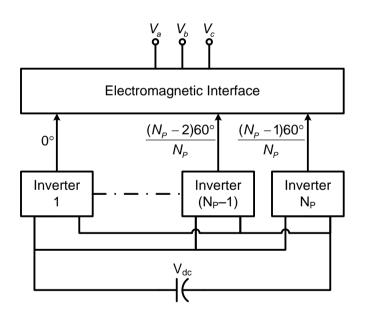

|   | 2.3.1 Multipulse inverters                                        | 31 |

|   | 2.3.2 Multilevel inverters                                        | 32 |

|   | 2.4 Multilevel inverter topologies                                | 32 |

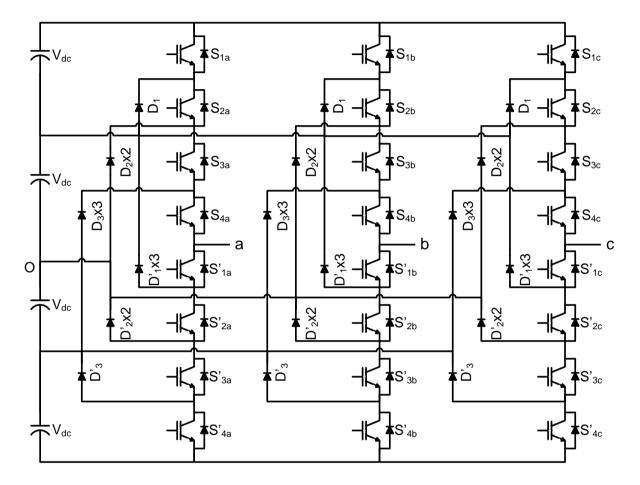

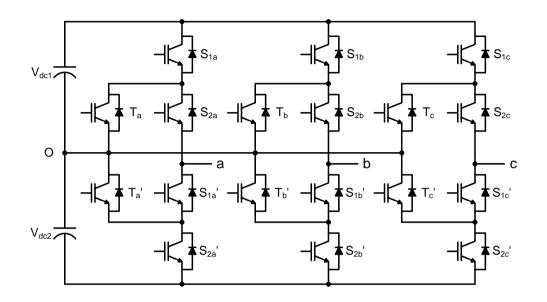

|   | 2.4.1 Diode Clamped Multilevel inverter (DCMLI)                   | 33 |

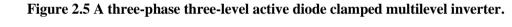

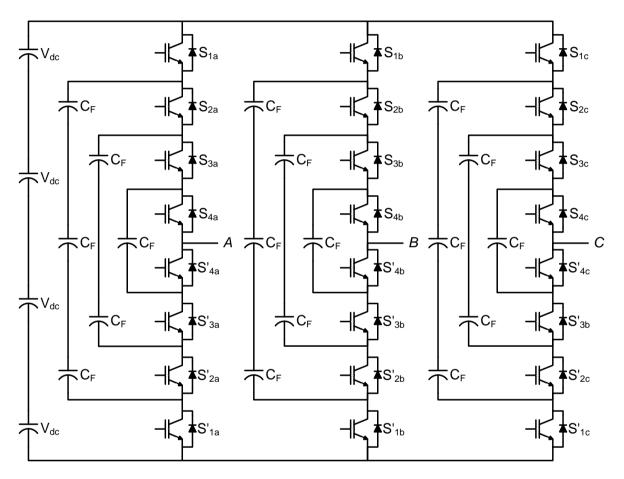

|   | 2.4.2 Flying Capacitor Mulitlevel inverter (FCMLI)                | 35 |

|   | 2.4.3 Cascaded Multilevel inverters (CMLI)                        | 36 |

|   | 2.5 Comparative evaluation of multilevel converters for D-STATCOM | 41 |

|   | 2.6 Carrier based PWM schemes                                     | 43 |

|   | 2.6.1 Phase shifted pulse width modulation (PSPWM)                | 44 |

|   | 2.6.2 Level shifted pulse width modulation (LSPWM)                | 45 |

|   | 2.7 Comparison of carrier based PWM Schemes                       | 47 |

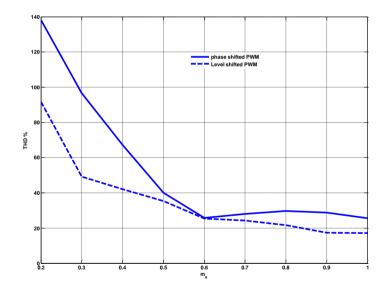

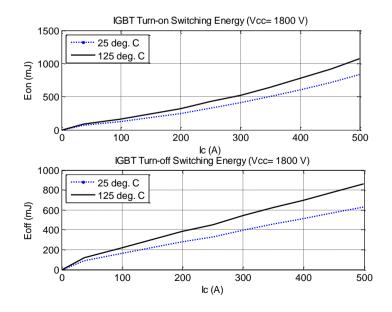

|   | 2.8 Scheme for calculating switching and conduction losses        | 49 |

| 2.8.1.1 Conduction loss:                                               |    |

|------------------------------------------------------------------------|----|

| 2.8.1.2 Turn-on/off switching loss and Diode Reverse recovery loss:    | 52 |

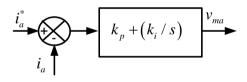

| 2.9 Power loss calculation in five level SSBC inverter                 | 53 |

| 2.10 Conclusion                                                        | 56 |

| Chapter 3: CASCADED H-BRIDGE BASED SINGLE PHASE D-STATCOM              | 57 |

| 3.1 Introduction                                                       | 57 |

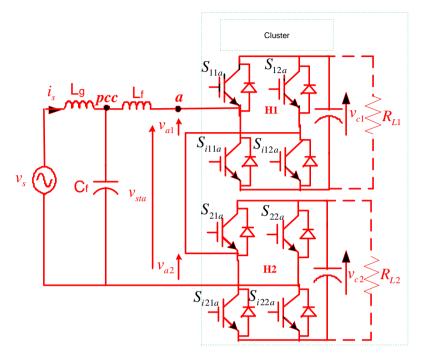

| 3.2 System configuration and pulse width modulation                    | 58 |

| 3.3 Design of 1-phase 1.2 KV 100 KVA five level CHB based D-STATCOM    | 60 |

| 3.3.1 Selection of interface inductor and DC capacitance               | 60 |

| 3.3.1.1 Selection of DC Capacitors                                     | 60 |

| 3.3.1.2 Selection of Coupling Inductor                                 | 61 |

| 3.4 Control scheme for load compensation                               | 62 |

| 3.5 Simulation results of single phase D-STATCOM for load compensation | 66 |

| 3.5.1 Linear RL load                                                   | 67 |

| 3.5.2 Uncontrolled rectifier load                                      | 69 |

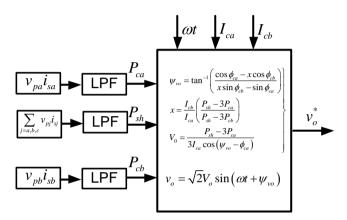

| 3.5.3 Comparison of performance of D-STACOM with load                  | 71 |

| 3.6 Reactive Power Compensation Control scheme for D-STATCOM           | 72 |

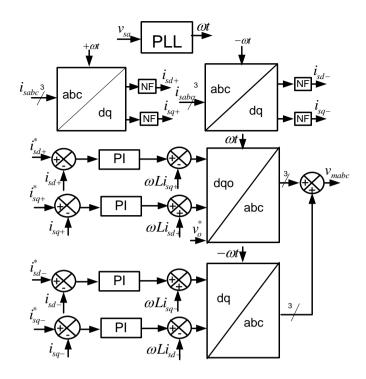

| 3.7 DC capacitor voltage balancing                                     | 73 |

| 3.8 Simulation results                                                 | 76 |

| 3.8.1 Performance of D-STATCOM with average modulating signal:         | 76 |

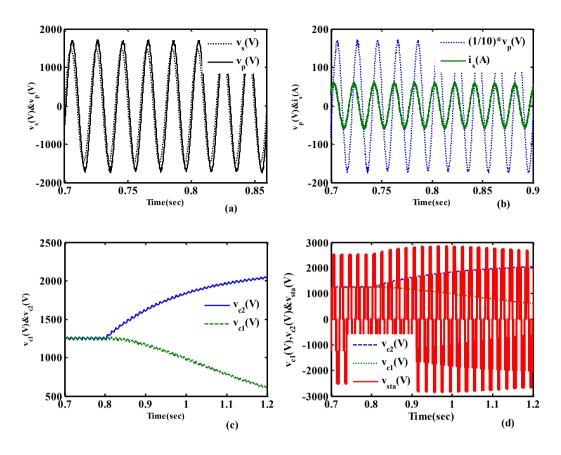

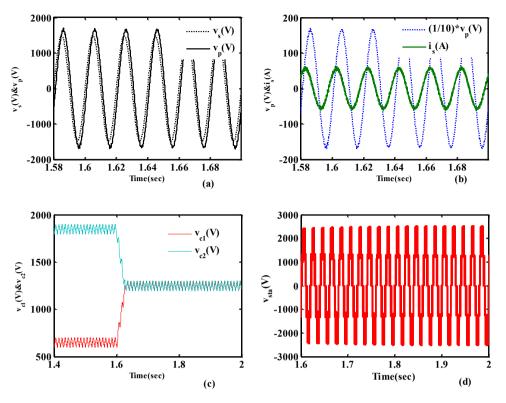

| 3.8.2 Performance with improved modulating signal (IMS):               | 77 |

| 3.8.3 Performance with Active voltage superposition (AVS):             | 78 |

| 3.8.4 Comparison of IMS and AVS methods:                               | 79 |

| 3.9 Conclusion                                                         | 80 |

| Chapter 4: CASCADED H-BRIDGE BASED THREE PHASE D-STATCOM               | 81 |

| 4.1 Introduction                                                       | 81 |

| 4.2 Control of D-STATCOM                                               | 81 |

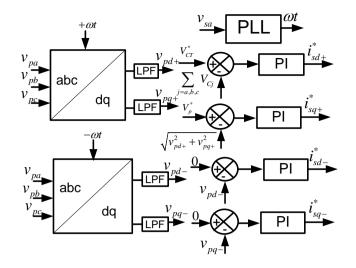

| 4.2.1 Reference current generator                                                     | .82 |

|---------------------------------------------------------------------------------------|-----|

| 4.2.1.1 Implementation of SRF theory                                                  | .83 |

| 4.2.1.2 Compensation for D-STATCOM losses                                             | .85 |

| 4.2.1.3 Calculation of reference D-STATCOM currents                                   | .86 |

| 4.3 Design of 2.2 KV 1 MVA Transformer less D-STATCOM for three phase-three w system. |     |

| 4.3.1 Selection of interface inductor and DC capacitance                              | .88 |

| 4.3.1.1 Selection of DC capacitors                                                    | .89 |

| 4.3.1.2 Selection of coupling inductor                                                | .90 |

| 4.3.2 Modelling of modular SSBC D-STATCOM                                             | .91 |

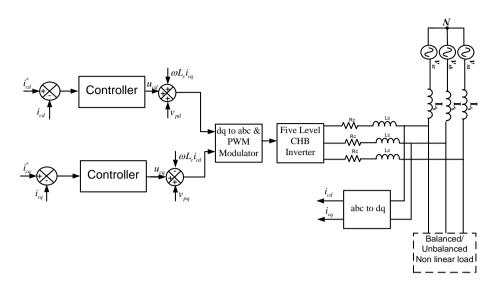

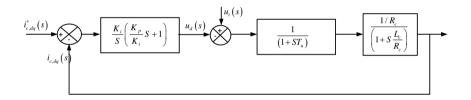

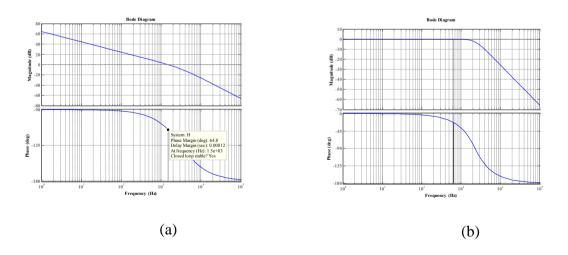

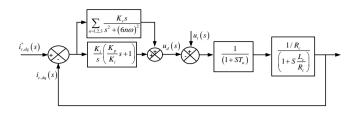

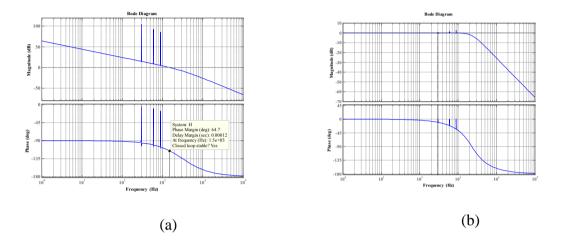

| 4.3.3 PI current controller                                                           | .92 |

| 4.3.4 PI with resonant current controller                                             | .94 |

| 4.3.5 DC voltage regulation                                                           | .96 |

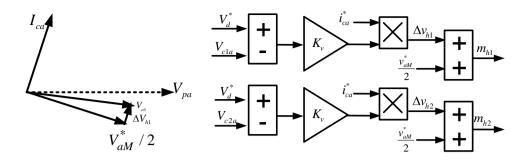

| 4.3.5.1 Individual DC capacitor voltage balancing                                     | .96 |

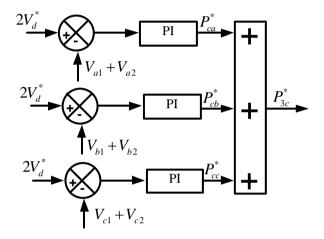

| 4.3.5.2 Cluster voltage balancing                                                     | .97 |

| 4.4 Simulation Results                                                                | .98 |

| 4.4.1 D-STATCOM Current controller performance with Non-linear load                   | .98 |

| 4.4.1.1 Uncontrolled rectifier with RL load                                           | .99 |

| 4.4.1.2 Uncontrolled rectifier with RC load1                                          | .03 |

| 4.4.1.3 Controlled rectifier with RL load1                                            | .06 |

| 4.4.1.4 Controlled rectifier with RC load1                                            | .09 |

| 4.4.1.5 Comparison of current controllers1                                            | 12  |

| 4.4.2 Performance of D-STATCOM under unbalanced linear load1                          | 12  |

| 4.4.2.1 Load balancing and Zero voltage regulation mode (ZVR)1                        | 13  |

| 4.4.2.2 Load balancing in unity power factor mode1                                    | 16  |

| 4.5 Conclusion1                                                                       | 17  |

| Chapter 5: D-STATCOM OPERATION IN VOLTAGE CONTROL MODE1                               | 19  |

| 5.1 Introduction                                                            | 119 |

|-----------------------------------------------------------------------------|-----|

| 5.2 Voltage control mode for single phase D-STATCOM                         | 120 |

| 5.2.1 Simulation results in voltage control mode for single phase D-STATCOM | 122 |

| 5.2.1.1 Performance of D-STATCOM with average modulating signal             | 122 |

| 5.2.1.2 Performance with improved modulating signal (IMS)                   | 123 |

| 5.3 Voltage control mode for three-phase D-STATCOM                          | 124 |

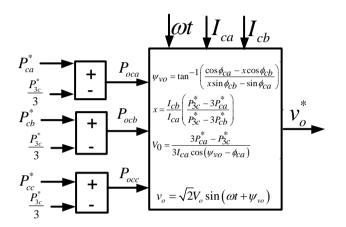

| 5.3.1 Generation of reference D-STATCOM currents                            | 125 |

| 5.3.2 Calculation of zero sequence voltage                                  | 126 |

| 5.3.3 Double Synchronous Reference Frame Current Controller (DSRF)          | 127 |

| 5.3.4 PCC voltage and current controller                                    | 128 |

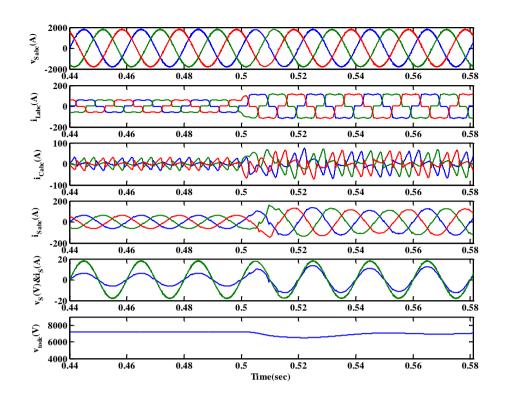

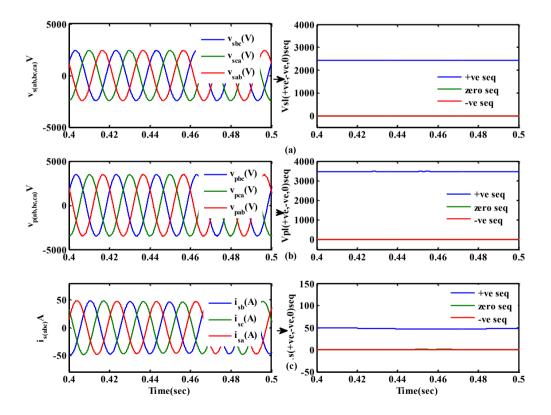

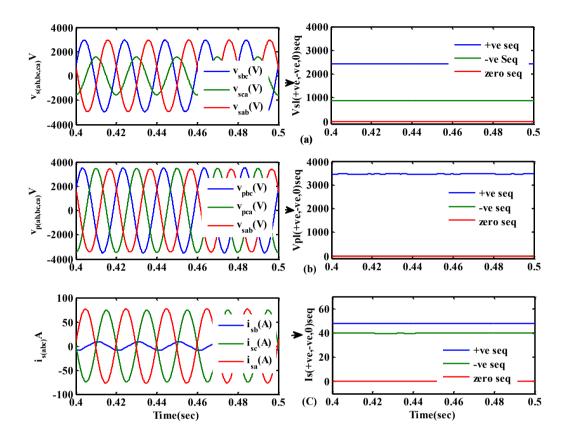

| 5.3.5 Simulation results                                                    | 134 |

| 5.4 Conclusion                                                              | 137 |

| Chapter 6: SYSTEM DEVELOPMENT AND EXPERIMENTATION                           | 139 |

| 6.1 Introduction                                                            | 139 |

| 6.2 Development of System Hardware                                          | 140 |

| 6.2.1 Development of Power Circuit                                          | 141 |

| 6.2.2 Measurement Circuits                                                  | 141 |

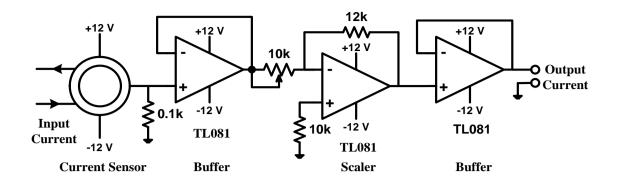

| 6.2.2.1 Sensing of AC Current                                               | 141 |

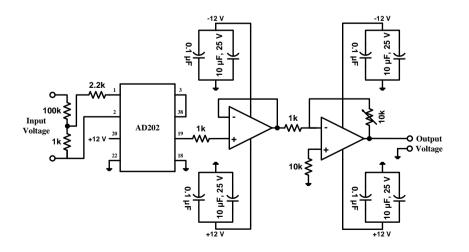

| 6.2.2.2 Sensing of Voltage                                                  | 142 |

| 6.2.3 Development of System Software                                        | 143 |

| 6.2.4 Development of Control Hardware                                       | 145 |

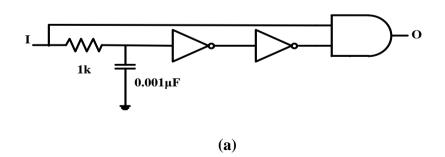

| 6.2.4.1 Dead-band Circuit                                                   | 146 |

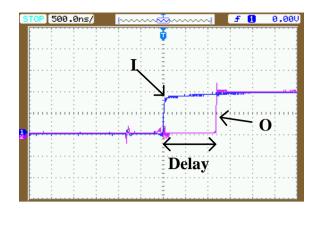

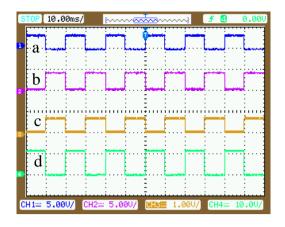

| 6.2.4.2 MOSFET Driver Circuit                                               | 147 |

| 6.3 Experimental validation of single phase D-STATCOM                       | 148 |

| 6.3.1 Performance of single phase D-STATCOM for load compensation           | 149 |

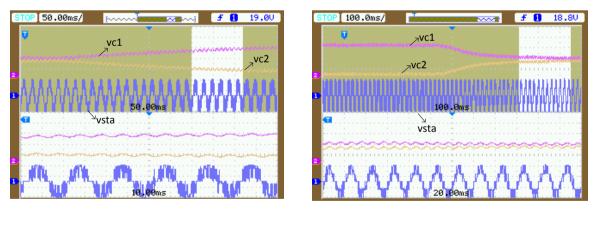

| 6.3.2 Performance of improved modulating signal method                      | 154 |

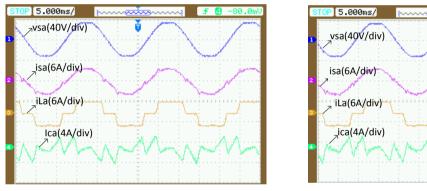

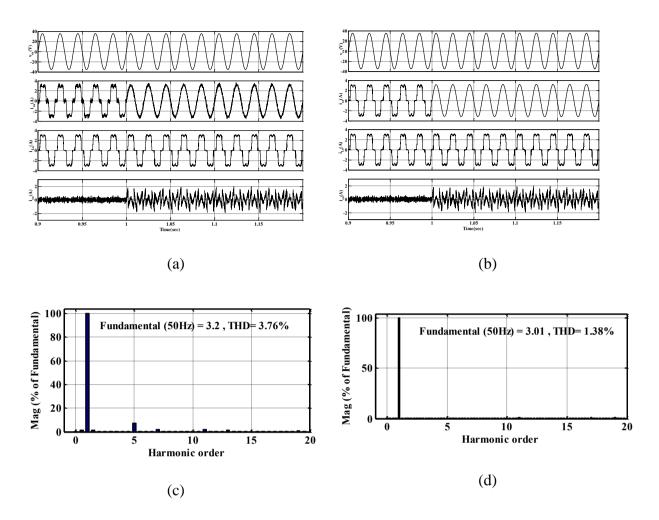

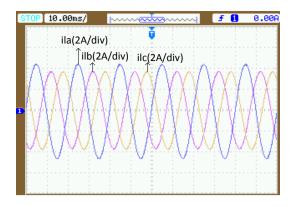

| 6.4 Three-phase modular D-STATCOM current controller performance            | 157 |

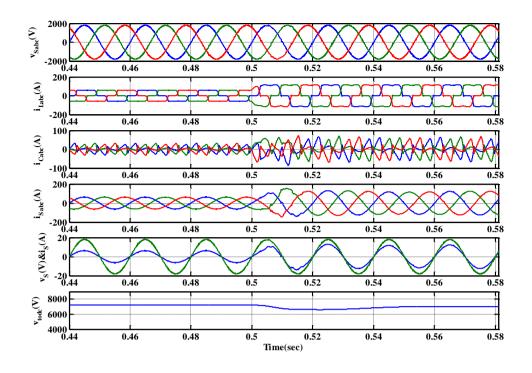

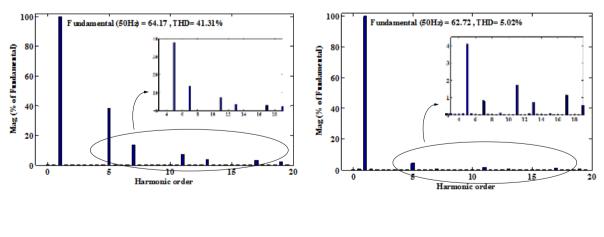

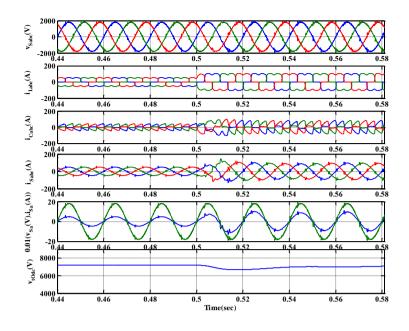

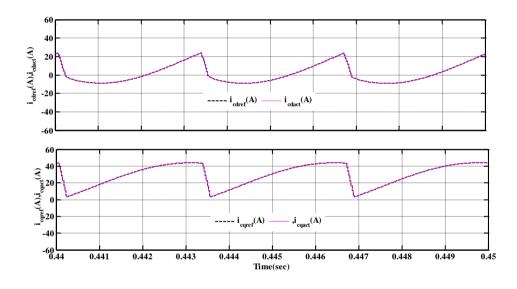

| 6.5 Experimental verification of UPF and ZVR modes of D-STATCOM | 160 |

|-----------------------------------------------------------------|-----|

| 6.6 Conclusion                                                  | 165 |

| Chapter 7: CONCLUSIONS AND FUTURE SCOPE                         | 167 |

| 7.1 Conclusions                                                 | 167 |

| 7.2 Future Scope                                                | 168 |

| BIBLIOGRAPHY                                                    | 171 |

| PHOTOGRAPH OF THE EXPERIMENTAL SETUP                            |     |

| LIST OF PUBLICATIONS                                            | 185 |

## LIST OF FIGURES

| Figure 1.1 A small power system model2                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Performance of a phase-controlled rectifier: (a) Source current of phase-a; (b) Harmonic spectrum of phase-a                                                                        |

| Figure 1.3 Performance of phase controlled rectifier: (a) Variation of source power factor and displacement factor with firing angle; (b) Variation of %THD of load current with firing angle. |

| Figure 1.4 Static var compensators: (a) Thyristor-switched shunt capacitors; (2) Thyristor controlled shunt reactor; (c) Combination of both                                                   |

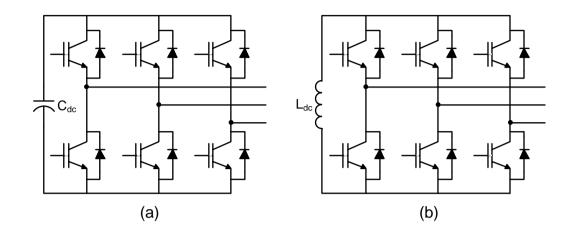

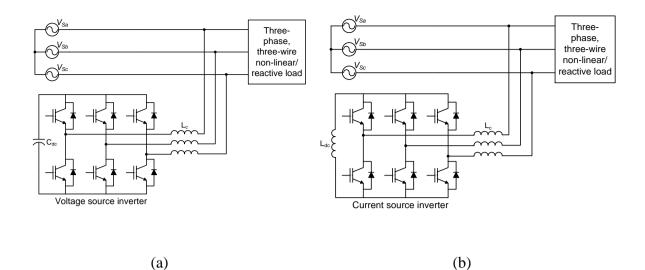

| Figure 1.5 Topologies of inverters (a) Voltage source inverter; (b) Current source inverter 10                                                                                                 |

| Figure 1.6 Schematic diagram of a VSI based STATCOM10                                                                                                                                          |

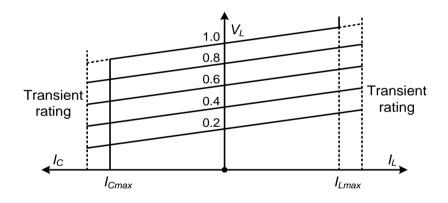

| Figure 1.7 V–I characteristics of a STATCOM11                                                                                                                                                  |

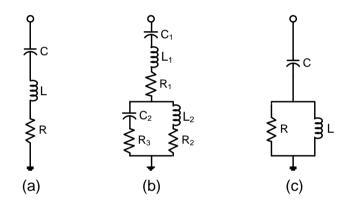

| Figure 1.8 Shunt passive filters: (a) Single-tuned; (b) Double-tuned; (c) Second-order high-pass damped                                                                                        |

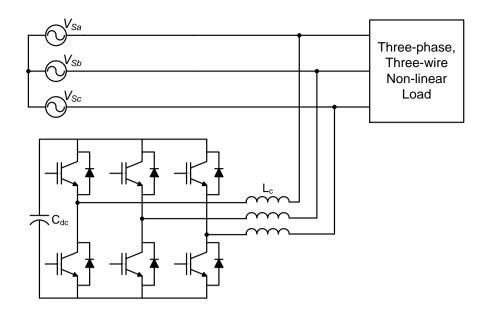

| Figure 1.9 A voltage source inverter based shunt active power filter15                                                                                                                         |

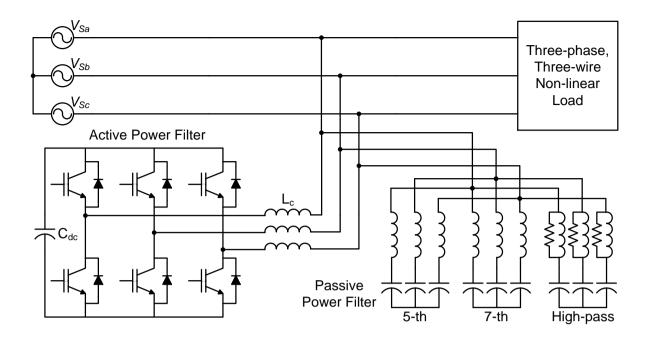

| Figure 1.10 A hybrid power filter16                                                                                                                                                            |

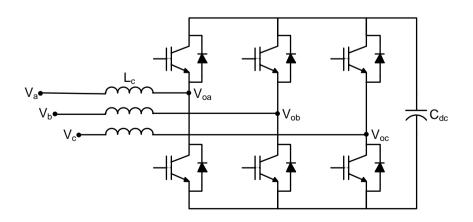

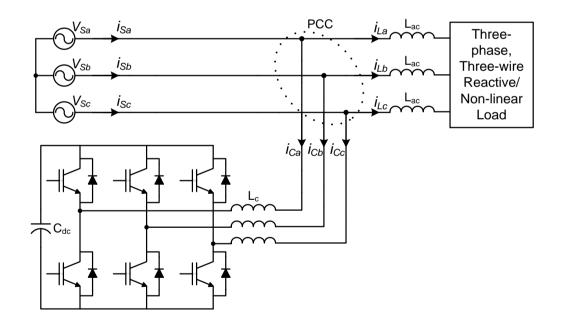

| Figure 1.11 A D-STATCOM connected to the 3P3W distribution system for harmonic elimination and reactive power compensation                                                                     |

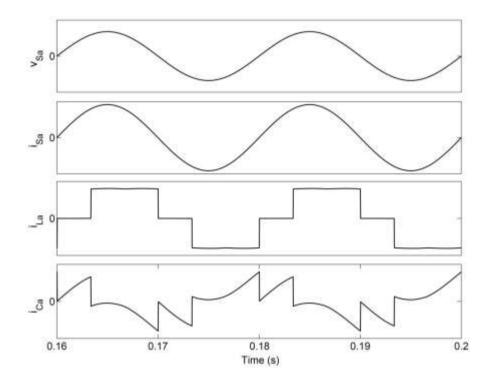

| Figure 1.12 Basic compensation principle of D-STATCOM: phase-a waveforms of source voltage, source current after compensation, load current and D-STATCOM current                              |

| Figure 1.13 (a) Voltage source inverter based D-STATCOM; (b) Current source inverter based D-STATCOM                                                                                           |

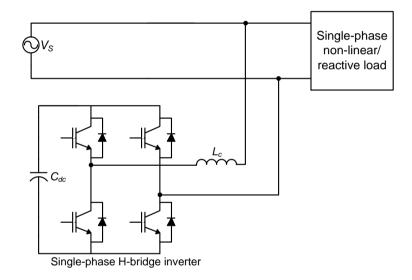

| Figure 1.14 D-STATCOM for two-wire systems                                                                                                                                                     |

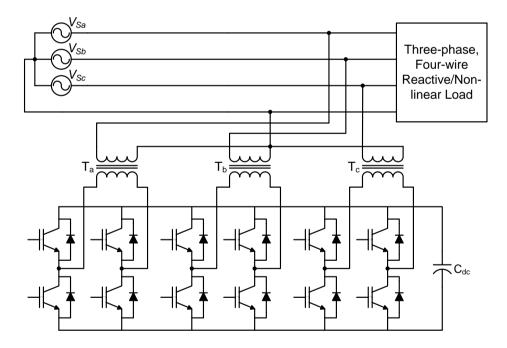

| Figure 1.15 The three H-bridge D-STATCOM topology                                                                                                                                              |

| Figure 1.16 The three H-bridge D-STATCOM topology                                                                                                                                              |

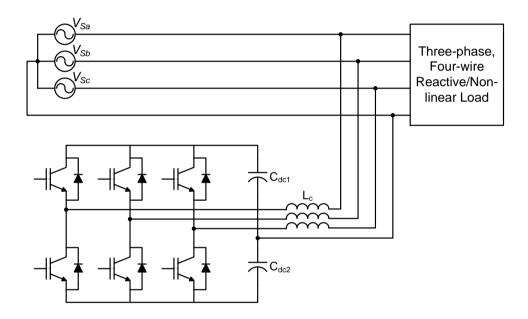

| Figure 1.17 The 3P4W four-leg topology24                                                                                                                                                       |

| Figure 2.1 Topologies of inverters (a) Voltage source inverter (b) Current source inverter29                                                                                                   |

| Figure 2.2 Two-level high-power VSI power circuit                                                                      |

|------------------------------------------------------------------------------------------------------------------------|

| Figure 2.3 General structure of multipulse inverter                                                                    |

| Figure 2.4 A three-phase five-level diode clamped multilevel inverter                                                  |

| Figure 2.5 A three-phase three-level active diode clamped multilevel inverter                                          |

| Figure 2.6 A three-phase five-level flying-capacitor multilevel inverter                                               |

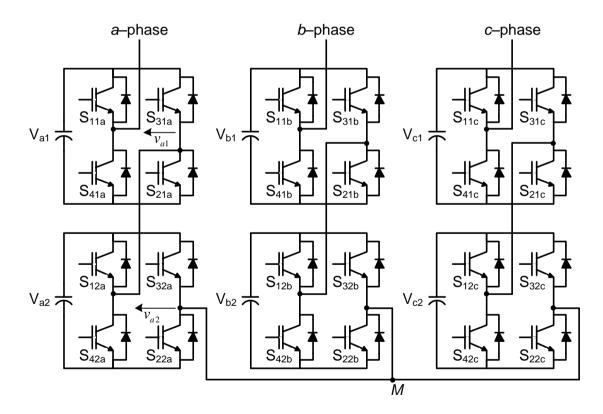

| Figure 2.7 A three-phase five-level SSBC based modular multilevel inverter topology                                    |

| Figure 2.8 A three-phase five-level SDBC based modular multilevel inverter topology                                    |

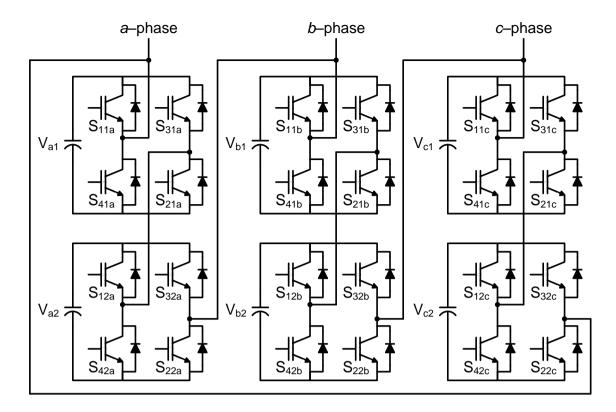

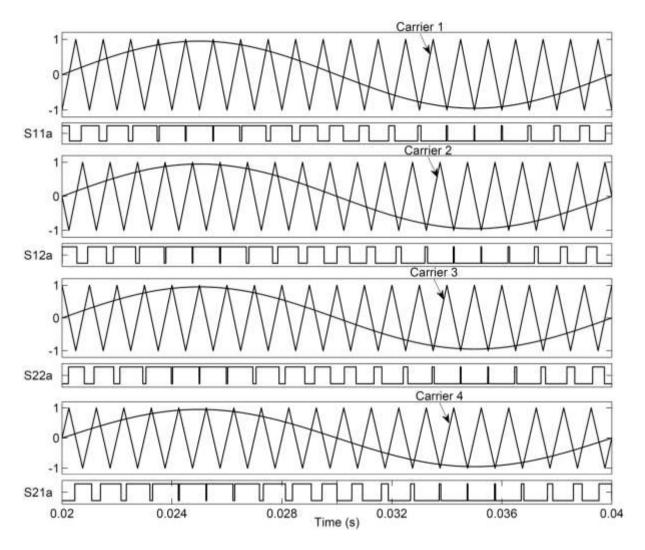

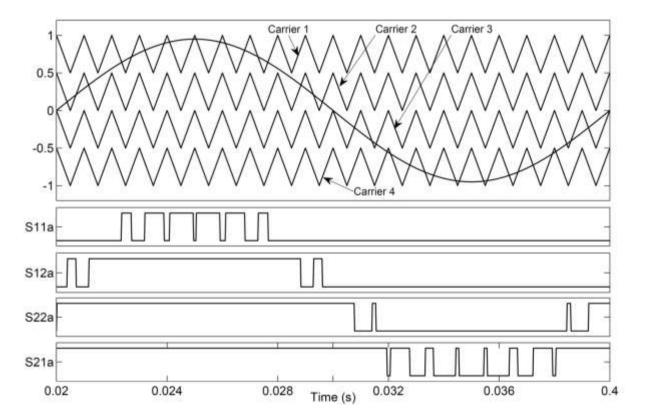

| Figure 2.9 PSPWM technique for a five-level SSBC based multilevel inverter                                             |

| Figure 2.10 LSPWM technique for a five-level SSBC based multilevel inverter                                            |

| Figure 2.11 Output voltage waveforms of the five level inverter operating at a low modulation                          |

| index (a) phase siftwed PWM (b) level shifted PWM48                                                                    |

| Figure 2.12 Line voltage THD produced by five level SSBC inverter with phase and level shifted modulation schemes      |

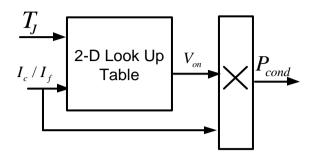

| Figure 2.13 Procedure to caliculate the losses in a switch                                                             |

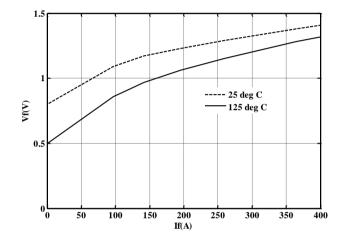

| Figure 2.14 Calculation of conduction loss of IGBT/Diode                                                               |

| Figure 2.15 Diode on state charecteristics                                                                             |

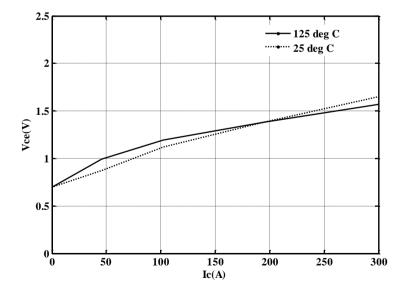

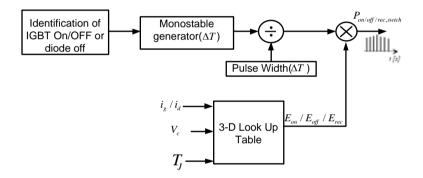

| Figure 2.16 IGBT on-state Characteristics                                                                              |

| Figure 2.17 Calculation of switching loss                                                                              |

| Figure 2.18 Energy loss during turn on and turn off of IGBT switch                                                     |

| Figure 2.19 Energy recovery loss of diode                                                                              |

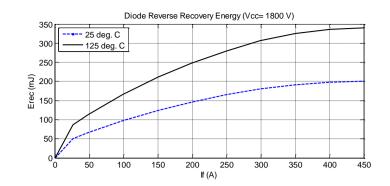

| Figure 2.20 Current controller for phase-a                                                                             |

| Figure 2.21 Perormance of SSBC inverter with reference unbalanced currents and at the same                             |

| device charecteristics                                                                                                 |

| Figure 2.22 Perormance of SSBC inverter with reference unbalanced currents and at the different device charecteristics |

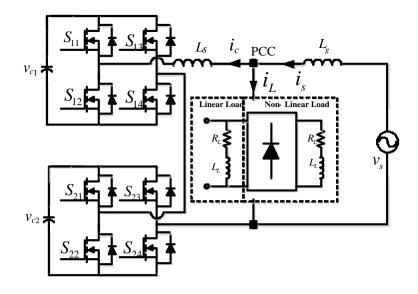

| Figure 3.1 Circuit configuration of single phase cascaded H-bridge D-STATCOM59                                         |

| Figure 3.2 Phase shift pulse width modulation                                                                          |

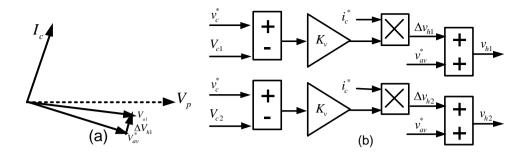

| Figure 3.3 Block diagram of single phase D-STATCOM for harmonic and reactive power compensation                               |

|-------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.4 Phasor diagram for active voltage superposition for H1-bridge (b) implementation of AVS method                     |

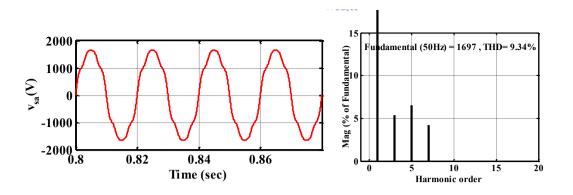

| Figure 3.5 Source voltage waveform and its THD67                                                                              |

| Figure 3.6 Linear load current waveform and its THD67                                                                         |

| Figure 3.7 Performance of D-STATCOM for linear load using original pq theory68                                                |

| Figure 3.8 Performance of D-STATCOM for linear load using modified pq theory69                                                |

| Figure 3.9 Non-linear load current waform and its THD70                                                                       |

| Figure 3.10 Performance of D-STATCOM for nonlinear load using original pq theory70                                            |

| Figure 3.11 Performance of D-STATCOM for non-linear load using modified pq theory71                                           |

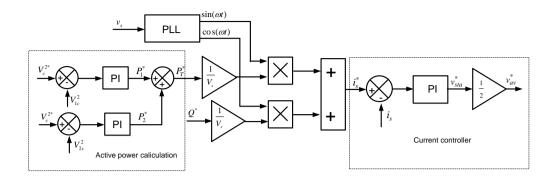

| Figure 3.12 Active power calculation and Current controller73                                                                 |

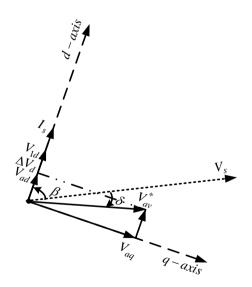

| Figure 3.13 Phasor diagram with the average modulating signal73                                                               |

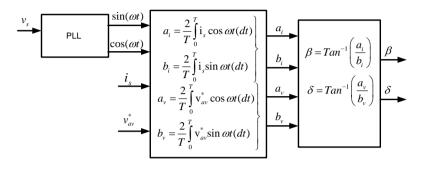

| Figure 3.14 Calculation of phase angle of source current and average modulating signal74                                      |

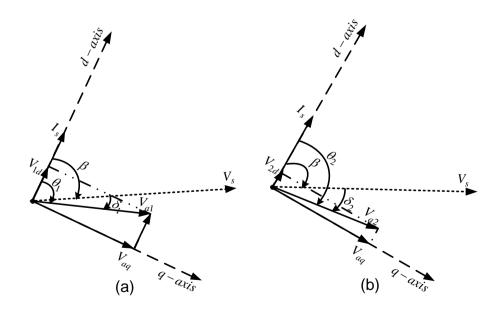

| Figure 3.15 Phasor diagram for modulating the signal for (a) H1-bridge (b) H2-bridge75                                        |

| Figure 3.16 Response of D-STATCOM with the average modulating signal77                                                        |

| Figure 3.17 Response of D-STATCOM with the average and improved modulating signals78                                          |

| Figure 3.18 Response of D-STATCOM with active voltage superposition                                                           |

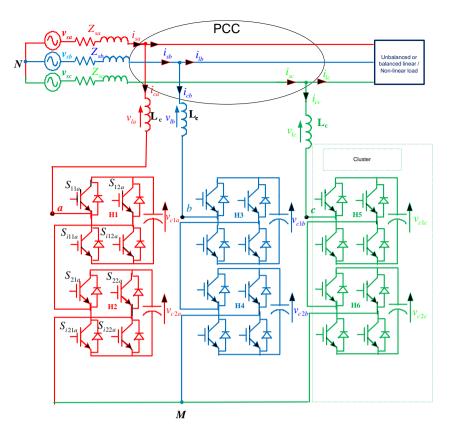

| Figure 4.1 Schematic diagram of the 3P3W system with shunt connected D-STATCOM83                                              |

| Figure 4.2 A five level SSBC based D-STATCOM                                                                                  |

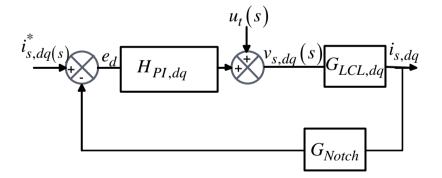

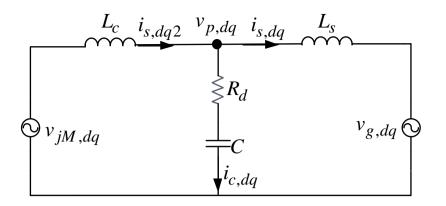

| Figure 4.3 Modelling of current controlled D-STATCOM92                                                                        |

| Figure 4.4 Block diagram representation for PI control                                                                        |

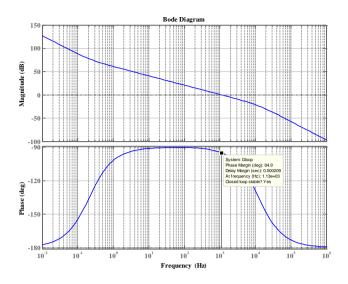

| Figure 4.5 Bode plot of the (a) open loop (b) closed loop transfer function with PI controller.93                             |

| Figure 4.6 Block diagram representation for PI and Resonant current control                                                   |

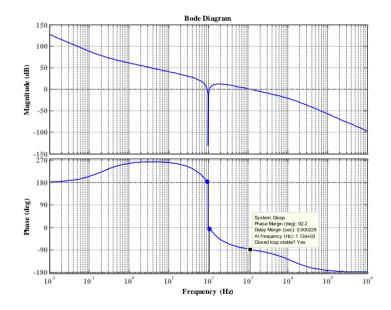

| Figure 4.7 Bode plot of the (a) open loop (b) closed loop transfer function with PI and Resonant current controller           |

| Figure 4.8 Phasor diagram for active voltage superposition for H1-bridge (b) Individual DC capacitor voltage balancing method |

| Figure 4.9 Calculation of Compensator powers.                                                                                                                       | 97  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.10 Calculation of zero sequence voltage                                                                                                                    | 98  |

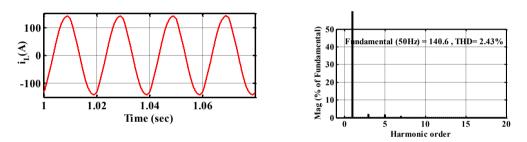

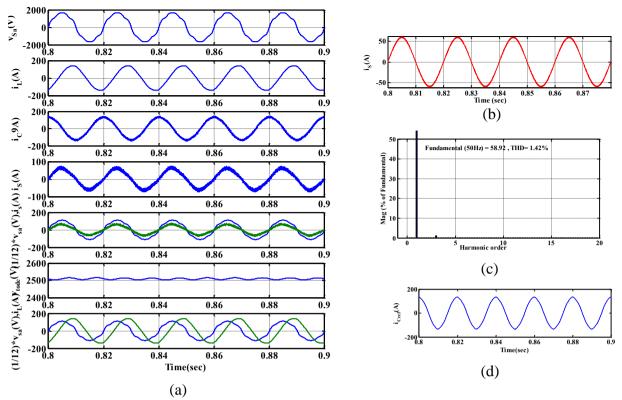

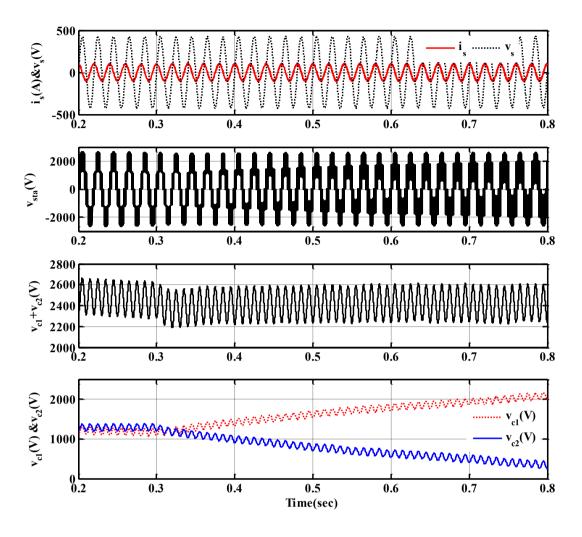

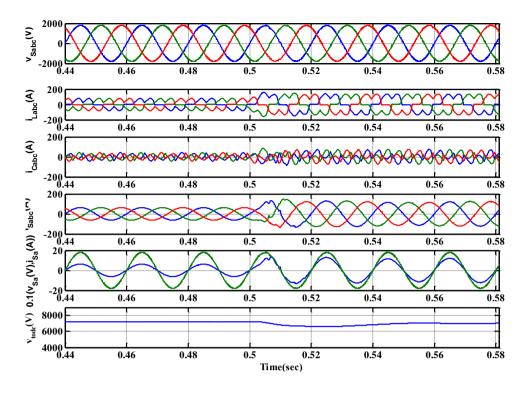

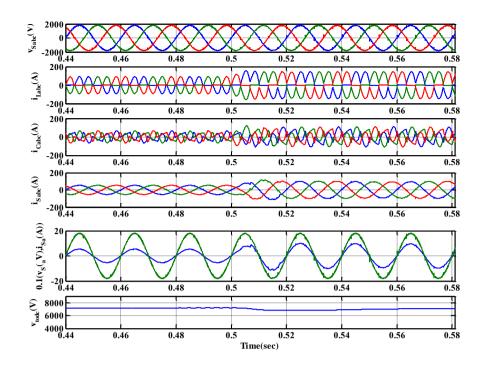

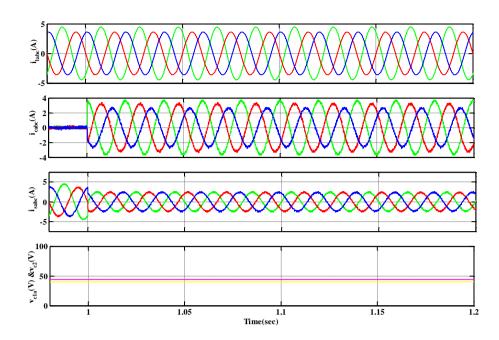

| Figure 4.11 Performance of D-STATCOM for an RL load on the dc side of an uncont<br>rectifier with PI current controller.                                            |     |

| Figure 4.12 Performance of D-STATCOM for an RL load on the dc side of an uncont<br>rectifier with PI and resonant current controller.                               |     |

| Figure 4.13 Performance of D-STATCOM for an RC load on the dc side of an uncont rectifier with PI current controller.                                               |     |

| Figure 4.14 Performance of D-STATCOM for an RC load on the dc side of an uncont<br>rectifier with PI and resonant current controller                                |     |

| Figure 4.15 Performance of D-STATCOM for an RL load on the dc side of a controlled re operating at a firing angle of $30^0$ with PI current controller.             |     |

| Figure 4.16 Performance of D-STATCOM for an RL load on the dc side of a controlled re operating at a firing angle of $30^0$ with PI and resonant current controller |     |

| Figure 4.17 Performance of D-STATCOM for an RC load on the dc side of a controlled re operating at a firing angle of $30^0$ with PI current controller              |     |

| Figure 4.18 Performance of D-STATCOM for an RC load on the dc side of a controlled re operating at a firing angle of $30^0$ with PI and resonant current controller |     |

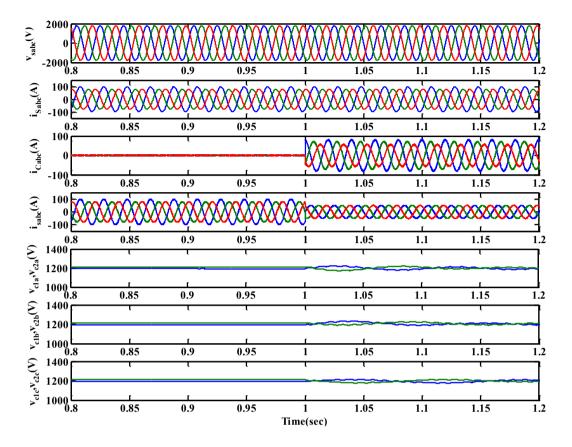

| Figure 4.19 Response of D-STATCOM under ZVR mode of operation                                                                                                       | 114 |

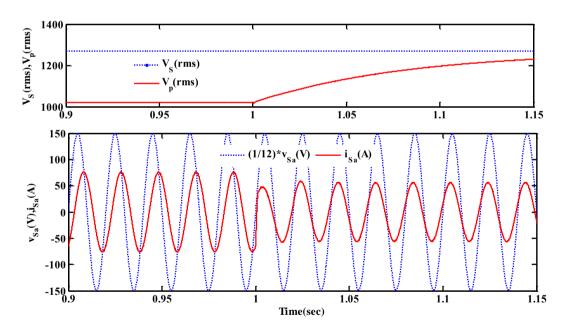

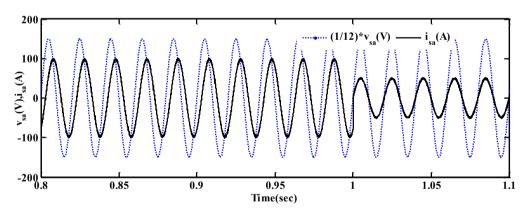

| Figure 4.20 Source phase voltage and phase current under ZVR mode                                                                                                   | 114 |

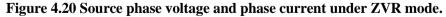

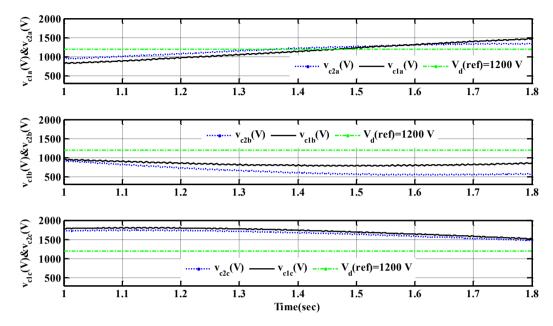

| Figure 4.21 DC Capacitor voltages without injection of zero sequence voltage                                                                                        | 115 |

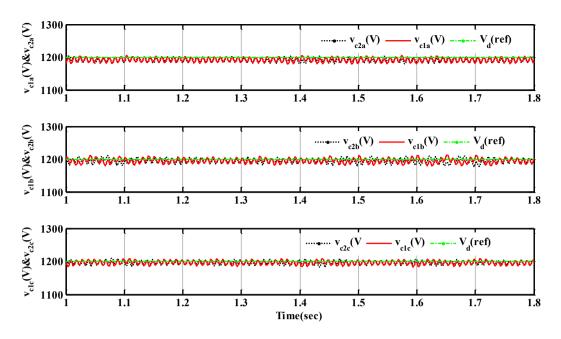

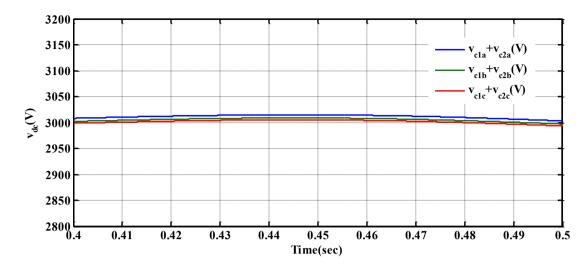

| Figure 4.22 DC Capacitor voltages with injection of zero sequence voltage                                                                                           | 115 |

| Figure 4.23 DC Capacitor voltages after the injection of zero sequence voltage and indivoltage balancing method.                                                    |     |

| Figure 4.24 Performance of D-STATCOM under UPF mode                                                                                                                 | 117 |

| Figure 4.25 Source phase voltage and phase current under UPF mode                                                                                                   | 117 |

| Figure 5.1 Single phase CHB based D-STACOM.                                                                                                                         | 120 |

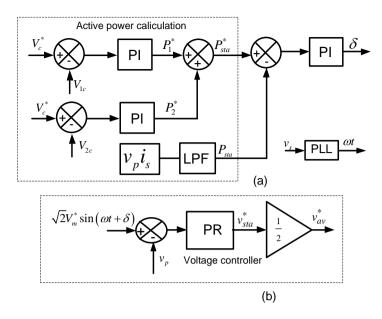

| Figure 5.2 (a) Active power calculation and (b) voltage controller                                                                                                  | 121 |

| Figure 5.3 Response of D-STATCOM with the average modulating signal                                                                                                 | 123 |

| Figure 5.4 Response of D-STATCOM with the improved modulating signals                                                                                                     | 4 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 5.5 SSBC based D-STATCOM                                                                                                                                           | 5 |

| Figure 5.6 Generation of reference currents for D-STATCOM                                                                                                                 | 6 |

| Figure 5.7 Calculation of zero sequence voltage                                                                                                                           | 7 |

| Figure 5.8 Dual current controller for D-STATCOM12                                                                                                                        | 8 |

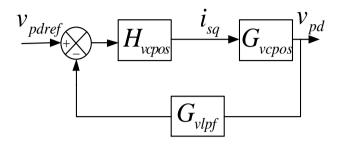

| Figure 5.9 PCC voltage control loop13                                                                                                                                     | 0 |

| Figure 5.10 Bode plot of voltage controller loop gain                                                                                                                     | 2 |

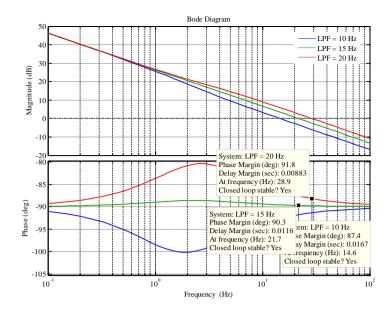

| Figure 5.11 : Closed loop current control                                                                                                                                 | 2 |

| Figure 5.12 : Single phase equivalent circuit diagram                                                                                                                     | 3 |

| Figure 5.13 Bode plot of loop gain of current controller excluding the notch filter                                                                                       | 4 |

| Figure 5.14 Bode plot of loop gain of current controller after the inclusion of notch filter13                                                                            | 4 |

| Figure 5.15 (a) Source line voltage and its sequence components (b) PCC line voltage and it sequence components (c) Source current and its sequence components            |   |

| Figure 5.16 (a) unbalanced Source line voltage and its sequence components (b) PCC lin voltage and its sequence components (c) Source current and its sequence components |   |

| Figure 5.17 DC capacitor voltages after injection of zero sequence voltage                                                                                                | 7 |

| Figure 6.1 Schematic diagram for hardware implementation of SSBC based D-STATCOM.14                                                                                       | 0 |

| Figure 6.2 Current sensing circuit14                                                                                                                                      | 2 |

| Figure 6.3 AC/DC voltage sensing circuit                                                                                                                                  | 2 |

| Figure 6.4 Total development environment of dSPACE with MATLAB14                                                                                                          | 4 |

| Figure 6.5 DSP (dSPACE-DS1006) circuit board interfacing                                                                                                                  | 5 |

| Figure 6.6 Schematic diagram of interfacing firing pulses from dSPACE controller board t switching devices                                                                |   |

| Figure 6.7(a) Dead-band circuit (b) Input-output waveform14                                                                                                               | 7 |

| Figure 6.8 (a) MOSFET driver circuit (b) Waveform at points a (channel 1), b (channel 2), (channel 3) and d (channel 4)                                                   |   |

| Figure 6.9 Schematic of experimental prototype for Single phase D-STATCOM14                                                                                               | 9 |

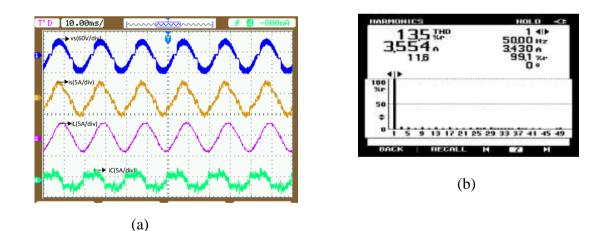

| Figure 6.10 Experimental Performance of single phase D-STATCOM for linear load compensation with orginal 1-phase pq theory                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.11 Simulation result of single phase D-STATCOM for linear load compensation with original 1-phase pq theory                                                   |

| Figure 6.12 Experimental Performance of single phase D-STATCOM for linear load compensation with modified 1-phase pq theory                                            |

| Figure 6.13 Simulation result of single phase D-STATCOM for linear load compensation with modified 1-phase pq theory                                                   |

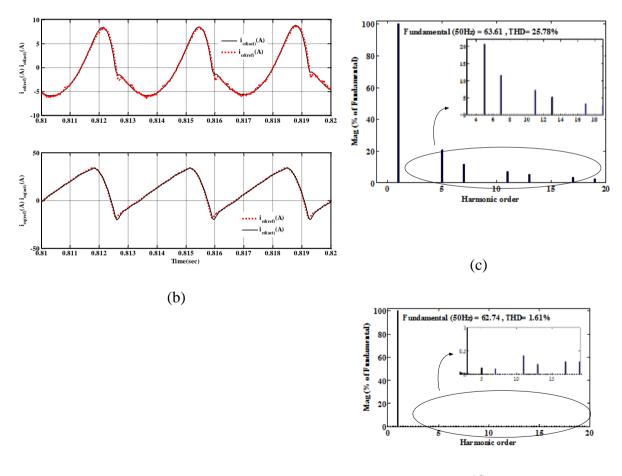

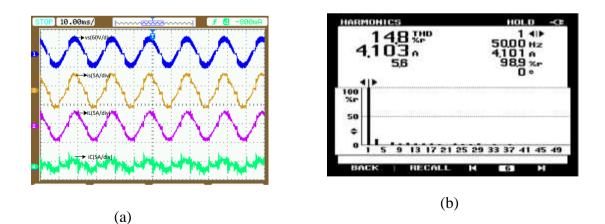

| Figure 6.14 Experimental Performance of single phase D-STATCOM for non-linear load compensation with original 1-phase pq theory                                        |

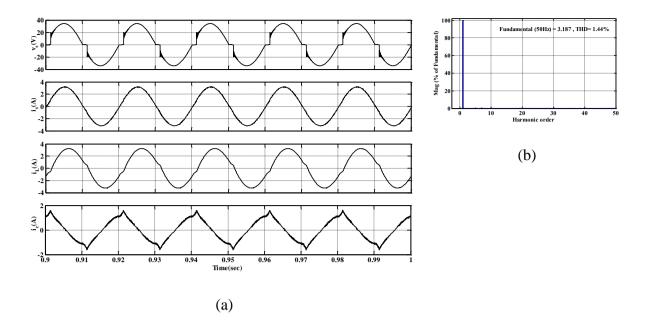

| Figure 6.15 Simulation result of single phase D-STATCOM for non-linear load compensation with original 1-phase pq theory                                               |

| Figure 6.16 Experimental Performance of single phase D-STATCOM for non-linear load compensation with modified 1-phase pq theory                                        |

| Figure 6.17 Simulation result of single phase D-STATCOM for non-linear load compensation with modified 1-phase pq theory                                               |

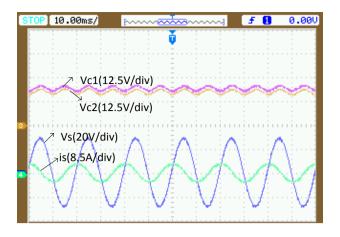

| Figure 6.18 Simulation result of the performance of improved modulating signal method155                                                                               |

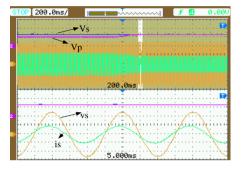

| Figure 6.19 Performance of single phase D-STATCOM with improved modulating signal method                                                                               |

| Figure 6.20 Schematic of experimental prototype for SSBC based D-STATCOM157                                                                                            |

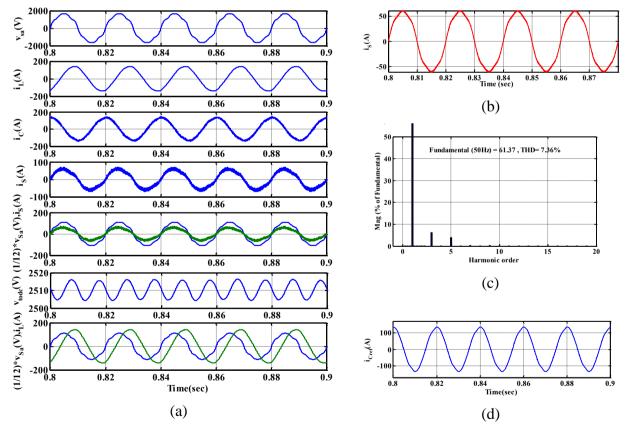

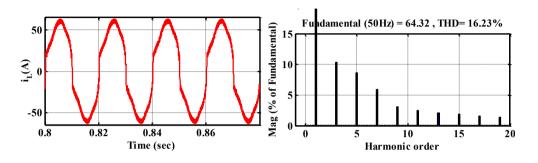

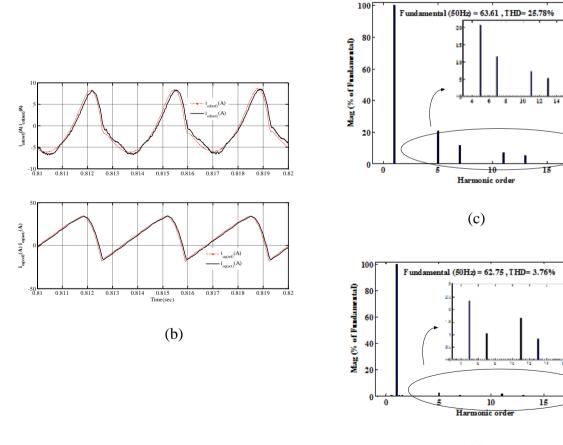

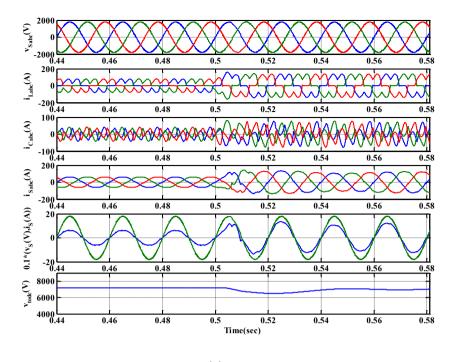

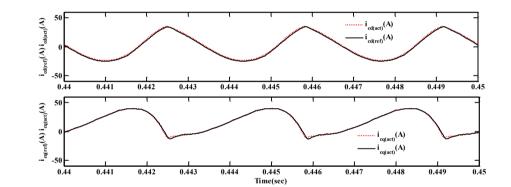

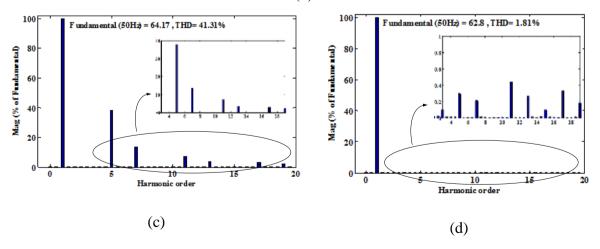

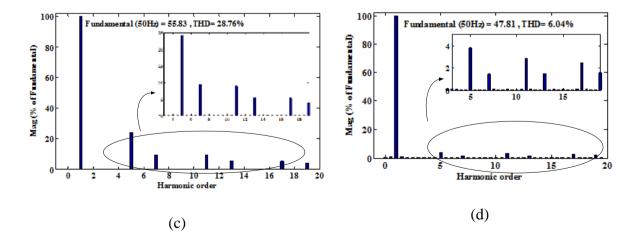

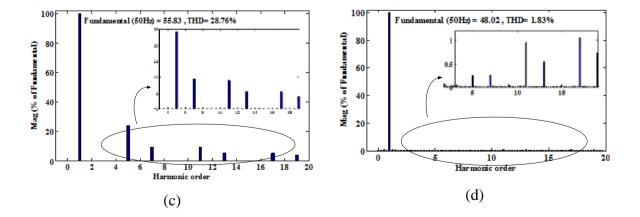

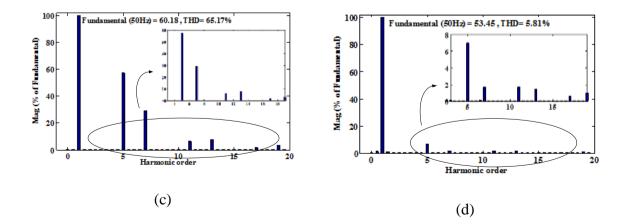

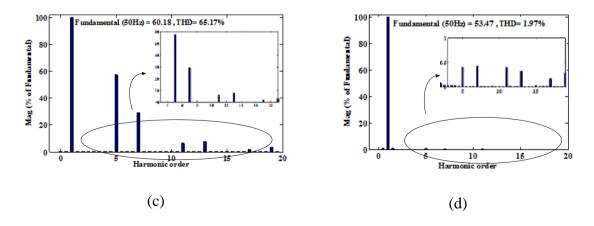

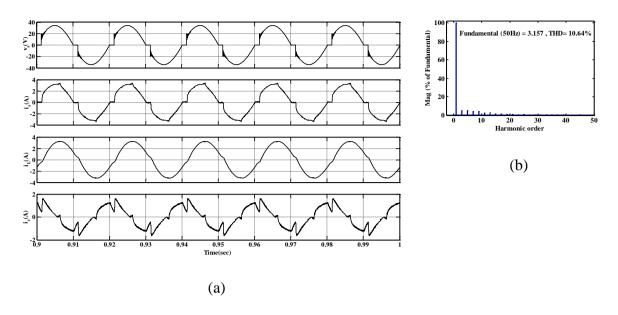

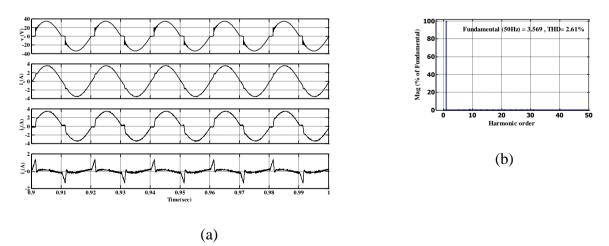

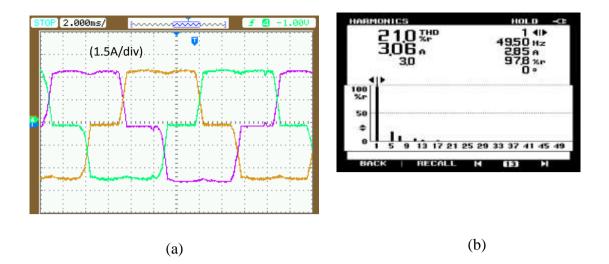

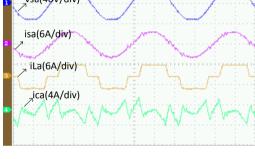

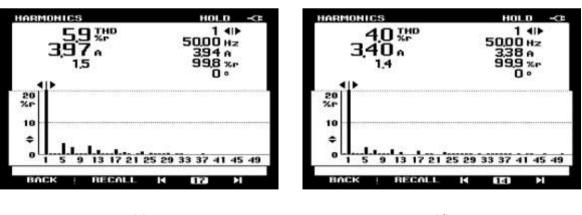

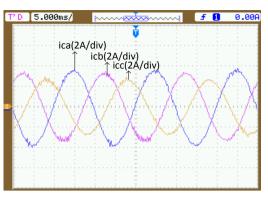

| Figure 6.21Performance of uncontrolled rectifier with RL-load on its dc side: (a) Three-phase load currents; (b) Harmonic spectrum of phase–a load current             |

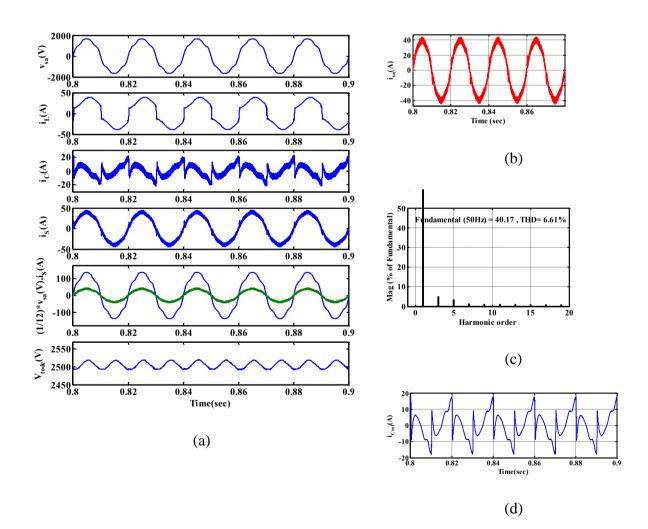

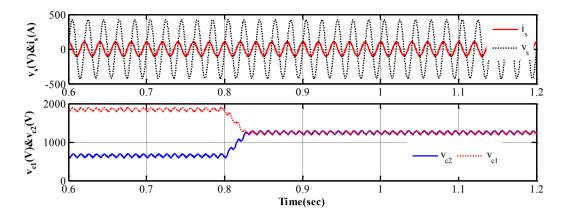

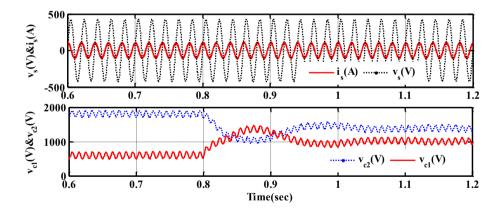

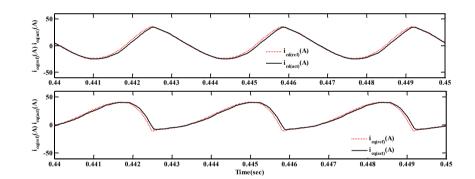

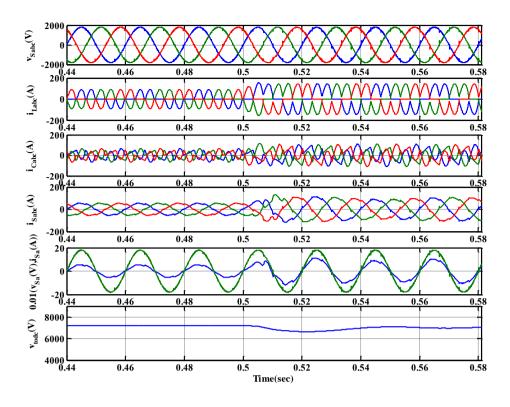

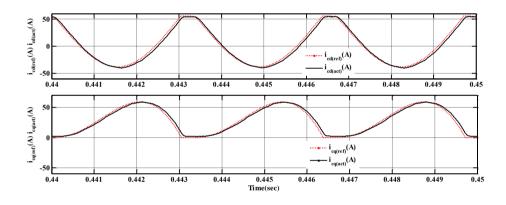

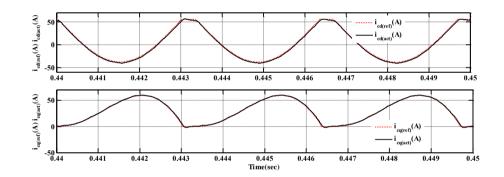

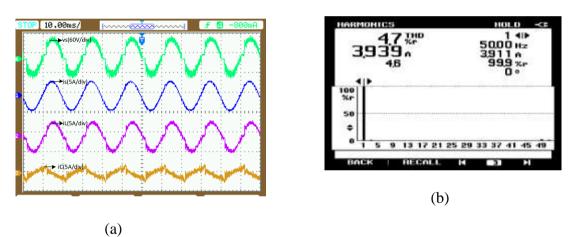

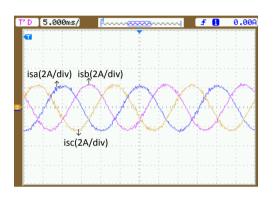

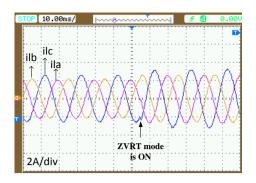

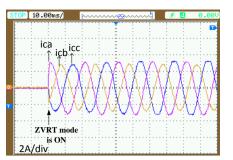

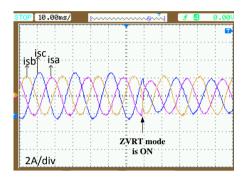

| Figure 6.22 Experimental results of 3P3W D-STATCOM for an RL-load on the dc side of an uncontrolled rectifier with PI and PI with resonant current controller          |

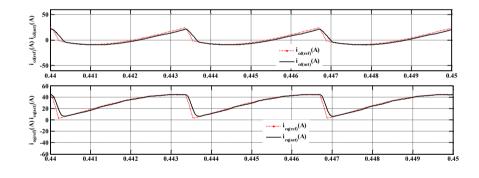

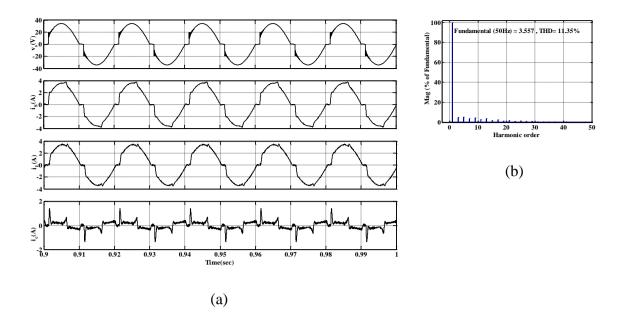

| Figure 6.23 Dounscaled simulation results of 3P3W D-STATCOM for an RL-load on the dc side of an uncontrolled rectifier with PI and PI with resonant current controller |

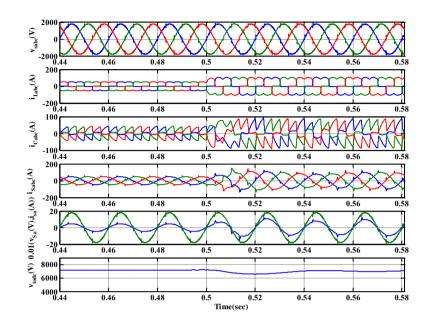

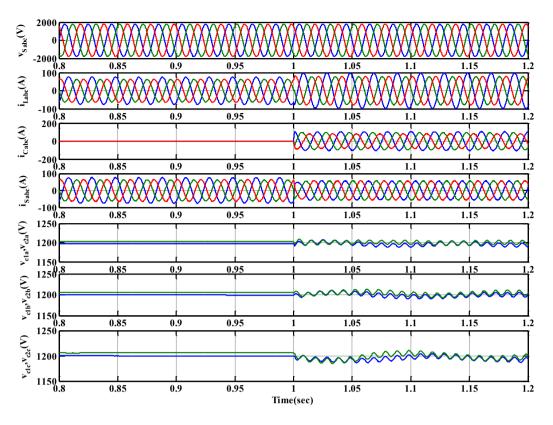

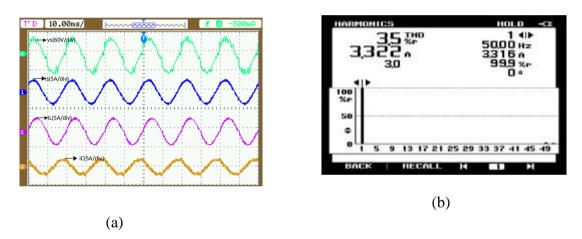

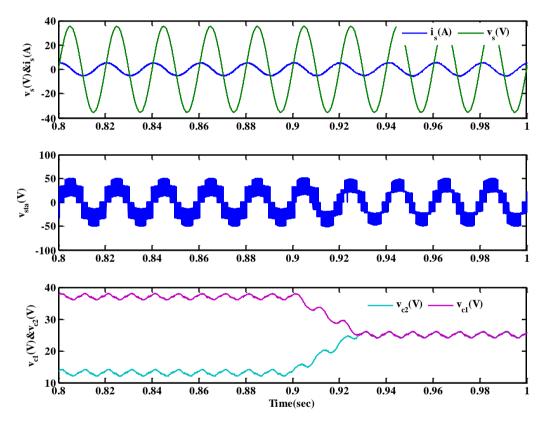

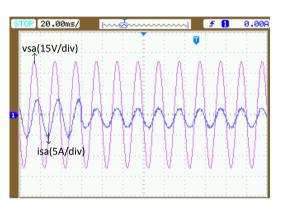

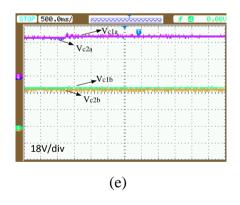

| Figure 6.24 Performance of D-STATCOM under UPF mode with individual voltage balancing and zero sequence voltage injection                                              |

| Figure 6.25 Simulation result of D-STATCOM for UPF mode163                                                                                                             |

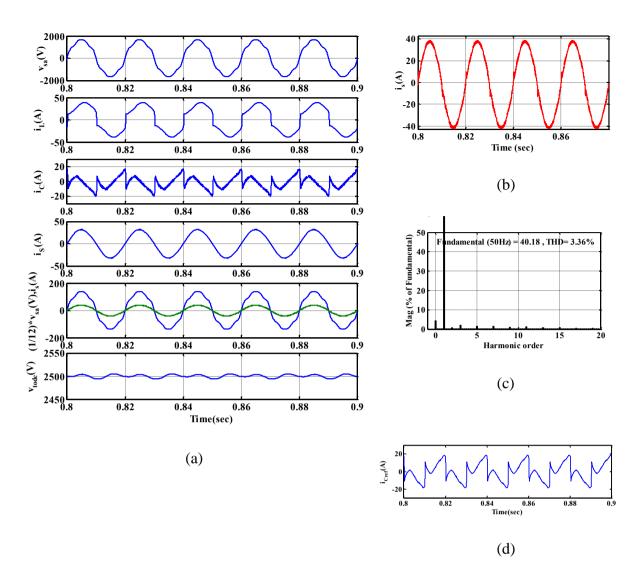

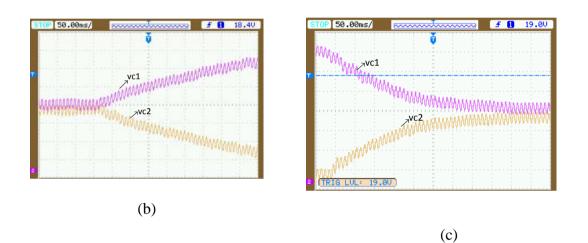

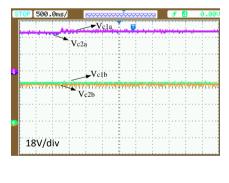

| Figure 6.26 Performance of D-STATCOM under ZVR mode with individual vo  | oltage balancing |

|-------------------------------------------------------------------------|------------------|

| and zero sequence voltage injection                                     | 164              |

| Figure 6.27 Simulation result of D-STATCOM under ZVR mode of operation. | 165              |

## LIST OF TABLES

| Table 1-1: Comparison of basic types of shunt var compensators.    12                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2-1 Voltage levels and their corresponding switch states for a five-level SSBC or SDBC      based inverter.      39                      |

| Table 2-2 Comparison of power component requirements per phase-leg among multilevel      inverter topologies.                                  |

| Table 2-3 Comparison of multilevel inverter topologies based on implementation factors41                                                       |

| Table 2-4 Comparison of SSBC and SDBC topologies.    42                                                                                        |

| Table 2-5 comparision between the phase and level shifted PWM schemes.    49                                                                   |

| Table 2-6 Simulation parameters for power loss calculation.    54                                                                              |

| Table 3-1 System parameters for simulation study    66                                                                                         |

| Table 3-2 THD comparison for different control theories.    71                                                                                 |

| Table 3-3 Comparison of IMS and AVS methods.    79                                                                                             |

| Table 4-1 closed loop gain and phase for PI controller at harmonic order                                                                       |

| Table 4-2 closed loop gain and phase for PI and resonant controller at harmonic order95                                                        |

| Table 4-3 System parameters for simulation study for current controller performance                                                            |

| Table 4-4 Comparison of two current controller with different non-linear loads                                                                 |

| Table 4-5 System parameters for simulation study.    113                                                                                       |

| Table 5-1 System parameters for the simulation study.    135                                                                                   |

| Table 6-1 Prameters used for experimental validation for Single phase D-STATCOM                                                                |

| Table 6-2 Source current THD(%) in simulation and experimentation with orginal and modified         single phase control theories.         154 |

| Table 6-3 Parameters used for the experimental validation of 3P3W D-STATCOM158                                                                 |

| Table 6-4 Source current THD(%) in simulation and experimentation with PI and PI with      resonant controller.      160                       |

| Table 6-5 System parameters for Experimental study.    161                                                                                     |

## LIST OF SYMBOLS

| $v_{Sa}$ , $v_{Sb}$ and $v_{Sc}$ | Three-phase source voltages                 |

|----------------------------------|---------------------------------------------|

| $i_{Sa}$ , $i_{Sb}$ and $i_{Sc}$ | Three-phase source currents                 |

| $i_{La}$ , $i_{Lb}$ and $i_{Lc}$ | Three-phase load currents                   |

| $i_{Ca}$ , $i_{Cb}$ and $i_{Cc}$ | Three-phase D-STATCOM currents              |

| т                                | Number of levels in inverter                |

| Ν                                | Cascade number                              |

| $f_{cr}$                         | Carrier signal frequency                    |

| $f_m$                            | Modulating signal frequency                 |

| $m_a$                            | Amplitude modulation index                  |

| $m_f$                            | Frequency modulation index                  |

| $L_s$                            | Source inductance                           |

| $L_C$                            | Coupling inductor of D-STATCOM              |

| $L_{f}$                          | Coupling inductor of single-phase APF       |

| Lac                              | Commutation inductance                      |

| <i>p</i> , <i>q</i>              | Instantaneous real and reactive powers      |

| V <sub>ref,c</sub>               | Cluster reference voltage                   |

| V <sub>ref,i</sub>               | Reference dc voltage for each H-bridge cell |

| $k_p, k_i$                       | Proportional and integral gains             |

## LIST OF ABBREVIATIONS

| 3P3W      | Three-phase, Three-wire                           |

|-----------|---------------------------------------------------|

| 3P4W      | Three-phase, Four-wire                            |

| ac, AC    | Alternating Current                               |

| APF       | Active Power Filter                               |

| ASD       | Adjustable Speed Drive                            |

| CHB       | Cascaded H-bridge                                 |

| CSD       | Custom Power Device                               |

| CSI       | Current Source Inverter                           |

| dc, DC    | Direct Current                                    |

| DCMLI     | Diode Clamped Multilevel Inverter                 |

| DPF       | Displacement Power Factor                         |

| DSO       | Digital Storage Oscilloscope                      |

| DSP       | Digital Signal Processor                          |

| D-STATCOM | Distribution Static Synchronous Compensator       |

| EMI       | Electro Magnetic Interference                     |

| FACTS     | Flexible AC Transmission System                   |

| FCMLI     | Flying Capacitor Multilevel Inverter              |

| GTO       | Gate Turn-off Thyristor                           |

| HVDC      | High Voltage Direct Current                       |

| IEC       | International Electrotechnical Commission         |

| IEEE      | Institute of Electrical & Electronics Engineers   |

| IGBT      | Insulated Gate Bipolar Transistor                 |

| LSPWM     | Level-shifted Pulsewidth Modulation               |

| MLI       | Multilevel Inverter                               |

| MOSFET    | Metal Oxide Semiconductor Field-effect Transistor |

| PCC       | Point of Common Coupling                          |

| pf, PF    | Power Factor                                      |

| PI        | Proportional and Integral                         |

| PSPWM     | Phase-shifted Pulsewidth Modulation               |

| PWM       | Pulsewidth Modulation                             |

| rms, RMS  | Root Mean Square                                  |

| SMPS      | Switch Mode Power Supply                          |

| STATCOM   | Static Synchronous Compensator                    |

|           |                                                   |

| SVC | Static var Compensator       |

|-----|------------------------------|

| TCR | Thyristor Controlled Reactor |

| THD | Total Harmonic Distortion    |

| SRF | Synchronous Reference Frame  |

| ZVR | Zero voltage regulation      |

| UPF | Unity power factor           |

# **CHAPTER 1: INTRODUCTION**

[This chapter describes introduction to the research work. It starts with brief background on foremost power quality problems in distribution systems. Then, the various solutions to the problem have been discussed, through which D-STATCOM is selected. Finally, scope of work, author's contribution, and thesis outlines are explained.]

## **1.1 Overview**

Traditionally, the role of the alternating current (ac) distribution system is to provide a link between the generation and transmission system to industrial, commercial, and residential load centres. The distribution system has always been susceptible to problems due to reactive power and unbalance from the very beginning [1]–[3]. But, with rapid development of semiconductor device technology in last three decades, the present day power distribution systems are also suffering from severe power quality problems[4].

The voltage and current variations in terms deviation from ideal sinusoidal waveform including frequency and amplitude variations from base values beyond the permissible levels, which are caused by the various possible situations are considered under power quality issues. Some of the causes of power quality problems are listed out as follows:

- Energization of large capacitor banks and transformers.

- Operation of reactive, non-linear and unbalanced loads.

- Failure of equipment, e.g. transformers and cables.

- Inexperience operation of distribution substations and plants.

- Lightning.

- Switching or start-up of large loads such as motors.

The above power system disturbances leads to power quality problems to the both utility and customers. Among them, reactive power, non-linear and unbalanced loads are considered to be most significant causes of power quality problems in modern distribution systems.

The low power factor, higher harmonic currents, poor voltage regulation and excess neutral currents are caused by the operation of non-linear and unbalanced loads on power distribution systems. The increased reactive power, harmonics and unbalance cause increase in line losses, and voltage distortion in the power system. For completeness, the aforementioned problems are briefly discussed below.

## **1.2 Reactive Power Burden**

Reactive power burden on distribution systems is due to the operation of loads that draw high reactive power from the system. Reactive power is a concept used by engineers to describe the background energy movement in an ac system arising from the production of electric and magnetic fields. These fields store energy which is exchanged through each ac cycle. Devices which store energy by virtue of a magnetic field produced by a flow of current are said to absorb reactive power; while those which store energy by virtue of electric fields are said to generate reactive power. Volt-ampere reactive (VAR) is a unit used to measure reactive power in an ac system.

Reactive power (var) is required to maintain the voltage to deliver active power (watt) through transmission lines and distribution feeders. Motor loads and other loads require reactive power for their successful operation. When enough reactive power is not available, the voltage sags and it is not possible to push the real power demanded by the loads through the lines.

For better understating, a simple power system model indicating the coupling between source and load[5], [6] is shown in Figure 1.1.

#### Figure 1.1 A small power system model.

In general the flow of active and reactive powers in a power system is governed by the following equations.

The transmitted active power (P) is given by,

$$P = \frac{V_{\rm S}V_{\rm L}}{X}\sin\delta \tag{1.1}$$

For small value of  $\delta$ , the reactive power (Q) transferred to the load is given as,

$$Q = \frac{V_{\rm S}(V_{\rm S} - V_{\rm L})}{X} \tag{1.2}$$

The load voltage  $(V_L)$  is given by,

$$V_L = V_S - \frac{QX}{V_S} \tag{1.3}$$

Eq. (1.1) shows that the active power flow depends on the amplitudes of source voltage and load voltage and it flows from the leading voltage bus to lagging voltage bus. On the other hand, the reactive power depends mainly on the difference of voltage amplitudes across a feeder and it flows from higher voltage side to lower voltage side as given by eq. (1.2). It can be observed

from eq. (1.3) that to keep the  $V_L$  fixed for a given value of  $V_S$ , the drop  $\left(\frac{QX}{V_S}\right)$  must remain

constant. In this expression the only variable quantity is Q, which must be locally adjusted to keep  $V_L$  fixed. In other words, let Q be the value of reactive power which keeps  $V_L$  to be a specified value, and any deviation in Q at load end must be locally adjusted. If Q is made zero (i.e. the load reactive power is supplied locally), the source and load voltages will be the same. The local generation of reactive power can be accomplished by any of the reactive power in electric power system.

#### **1.2.1 Sources of Reactive Power**

The major sources that draw reactive power from distribution systems are[7]:

- 1. Phase-controlled rectifiers

- 2. Motors

- 3. Transformers, tap-changing transformers

- 4. Choke inductors.

#### **1.2.2 Problems due to High Reactive Power**

The high reactive power burden leads to the underutilisation of power system capacity due to:

- Increased losses in the transmission and distribution systems.

- Overrated equipment within the ac system: due to larger current drawn for a given real power demand, and low efficiency owing to more losses.

- Low power factor and poor voltage regulation.

# **1.3 Harmonic Distortion**

Harmonic distortion is caused by the operation of non-linear loads in the power system. Nonlinear loads change the sinusoidal nature of the ac power current, thereby resulting in the flow of harmonic currents in the power system that can cause interference with communication circuits and other types of electrical and electronic equipments[4], [8], [9]. Harmonics are basically the additional frequency components present in the mains voltage or current which are integral multiples of the mains (fundamental) frequency. Interharmonics are a special category of harmonics which are non-integer multiples of the fundamental frequency. Sub-harmonics are special category of interharmonics, which have frequency values less than the fundamental frequency. Most equipments only produce odd harmonics but some devices have a fluctuating power consumption over a duration of half cycle period or less, which may generate even, interharmonic, or sub-harmonics currents. The harmonic distortion of each device depends on its consumption of active power, background voltage distortion and source impedance.

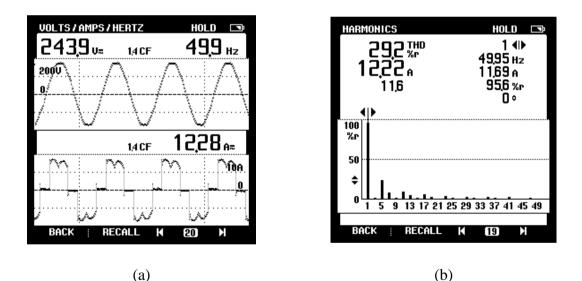

Phase controlled rectifiers are major source for harmonics and reactive power burden. They have a wide range of applications, from small rectifiers to large High Voltage Direct Current (HVDC) transmission systems. They are used for electro-chemical process, motor drives[10], traction equipment, controlled power supplies, and many other applications. The phase-a current drawn by a three phase-controlled rectifier is shown in Figure 1.2(a). The corresponding harmonic spectrum of source current is shown in Figure 1.2(b). From Figure 1.2(b) it is observed that the source current contains large amount of low order harmonics with an observed THD of 29.2%.

Figure 1.2 Performance of a phase-controlled rectifier: (a) Source current of phase-a; (b) Harmonic spectrum of phase-a.

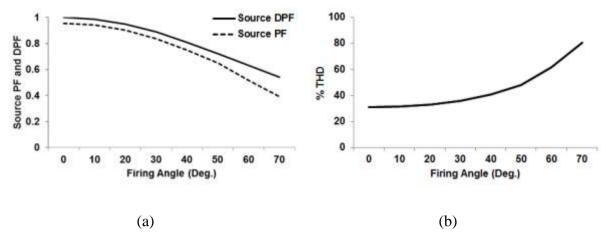

The phase-controlled rectifiers have following distinct features: a) they draw significant fundamental reactive power, whose magnitude depends on the firing angle of the rectifier, b) They draw currents with sharp rising and falling edges with high harmonic content. Source power factor, displacement factor and %THD of the load current of the phase controlled rectifier as a function of firing angle are plotted in Figure 1.3(a) and (b). From Figure 1.3 it is observed that the reactive power demand and %THD of the load current increases with the increase in firing angle of the rectifier.

Figure 1.3 Performance of phase controlled rectifier: (a) Variation of source power factor and displacement factor with firing angle; (b) Variation of %THD of load current with firing angle.

#### **1.3.1 Effects of Harmonics**

Harmonics can lead to mal-operation of power system components. Some of the ways that harmonics may affect equipments negatively are listed below[8]:

- Communication interference: Magnetic (or electrostatic) coupling between electrical power circuits and communication circuits can cause communication interference. Current flowing in the power circuit produces a magnetic (or electrostatic) field which, in turn, induces a current (or voltage) in the nearby conductors of the communication circuit. The amount of interference depends upon the magnitude of the induced current (or voltage), frequency, and the magnetic (or electrostatic) coupling. Other types of communication interference are:

- Induced line noise

- Interference with power line carrier systems

- Relay malfunctions.

- 2. Heating: Harmonic currents can cause excessive losses in motors, capacitors and transformers connected to the system. This in turn, may cause excessive heat in the winding, thus leading to the failure of insulation and danger of fire hazard.

- 3. Malfunction of solid-state devices: Harmonics can cause solid-state devices to malfunction if the equipment is sensitive to zero crossings or operates in response to the peak values of utility voltage. The typical malfunctions are:

- Errors in measurement equipment

- Nuisance tripping of relays and breakers

- Unstable operation of zero-voltage crossing firing circuit

- Interference with motor controllers.

- 4. Damage to capacitors: The presence of capacitors, such as those used for power factor correction, can result in local system resonances, which, in turn, can lead to excessive currents and possible subsequent damage to the capacitors.

- 5. Malfunction of utility Meters: May record measurements incorrectly, result in higher billings to consumers.

- Failure of sophisticated electronic equipments: Failure of sophisticated electronic equipments such as computers, remote monitoring systems, air conditioning systems and premature failure of switched-mode power supplies (SMPS) and uninterrupted power supplies (UPSs).

- 7. Flickering of lights: Due to the operation of arcing devices such as arc furnaces, arc welders, and discharge type lightning with magnetic ballasts, flickering of light may take place.

#### **1.3.2 Harmonic Standards**

There are various organizations on national and international levels working closely with engineers, equipment manufactures, and research organizations to come up with standards governing guide lines, recommended practices, and harmonic limits. The primary objective of the standards is to provide a common ground for all involved parties to work together to ensure compatibility between the end-user equipments and the system equipments. The most commonly used harmonic standards are IEEE–519–1992[11], International Electrotechnical Commission standard IEC–61000[12], South African standard NRS–048, and European standard EN–50160.

IEEE–519–1992 standard limits the amount of current harmonics injected by a user at the Point of Common Coupling (PCC). For example, the IEEE–519–1992 standard recommends a limit of 5% Total Harmonic Distortion (THD) in the current at the PCC in a weak system. The THD in the current is the ratio of the rms value of its distortion components to the rms value of its fundamental-frequency component. It is given as,

$$\% THD = \frac{\sqrt{\left(\sum_{h=2}^{\infty} l_h^2\right)}}{l_1} \times 100\%$$

(1.4)

Where,  $l_h = \text{rms}$  value of the current at harmonic order *h*, and  $I_I = \text{rms}$  value of the fundamental-frequency current component.

#### **1.4 Solutions to Power Quality Problem in Distribution System**

Poor quality power affects electricity customers in many ways. The lack of quality power can cause loss of production, damage of equipment or appliances or can even be detrimental to

human health. Therefore, it is very important to maintain high standard of power quality. Utilities and researchers all over the world have for decades worked on the improvement of power quality. There are sets of conventional solutions to the power quality problems, which have existed for a long time. However these conventional solutions use passive elements and do not always respond correctly as power system conditions change. The ever increased power capabilities, ease of control, and reduced costs of modern semiconductor devices have made power electronic converters affordable for many applications. New flexible solutions to many power quality problems have become possible with the help of these power electronic converters.

#### **1.4.1 Reactive Power Compensators**

Reactive power compensators or VAR compensators are used to control and/or regulate the terminal voltage in transmission/distribution system and to provide power factor correction[7], [13]. Two types of compensation problems are normally encountered in practical applications. The first is the load compensation where the requirements are usually to reduce or cancel the reactive power demand of large, and fluctuating industrial loads, such as electric arc furnaces, rolling mills, phase-controlled rectifiers. The second type of compensation is related to the voltage support of transmission/distribution lines.

In general, var compensators are classified depending on the technology used in their implementation[14]. They are broadly classified as rotating and static var compensators. The first one uses electro-mechanical power device like synchronous machine[6] and the later one uses power electronic technologies to accomplish the task. Again, there are two approaches for the realization of power electronics based var compensators[15], the one that employs thyristor-switched capacitors and reactors with tap-changing transformers, and the other approach uses static inverter circuits. A brief description of the most commonly used shunt compensators are presented below.

#### 1.4.1.1 Thyristor Controlled Static Var Compensators (SVC)

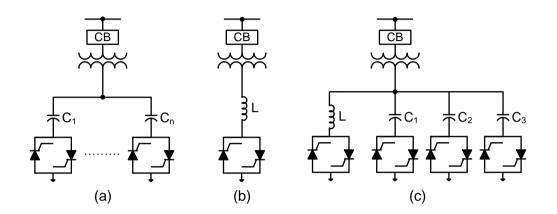

Advances in high power semiconductor and sophisticated electronic control technologies have made the development of thyristor-controlled static var compensators (SVCs) possible. These compensators were originally developed[16] for arc furnace compensation in the early 1970s, and a few years later they were adopted for transmission and distribution systems[17]. SVC is essentially a variable impedance type var compensator. Two basic schemes of SVC are available in the literature. The first one controls the leading vars by synchronously switching capacitor banks to the lines; the second one achieves the control of lagging vars with a thyristor-controlled variable inductor. They are named as, thyristor switched capacitors (TSC) and thyristor controlled reactors (TCR), respectively.

# (a) Thyristor Switched Capacitors (TSC)

The basic idea of thyristor switched shunt capacitors is to split up a capacitor bank into appropriate number of capacitor steps and switch these steps on and off individually using antiparallel thyristors as switching elements. Figure 1.4(a) shows the basic scheme.