### ANALYSIS AND MODELLING OF SPACER BASED GATE-ALL-AROUND RECONFIGURABLE DEVICE

Ph.D. THESIS

by

### **ABHISHEK BHATTACHARJEE**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-247 667, INDIA MARCH, 2018

### ANALYSIS AND MODELLING OF SPACER BASED GATE-ALL-AROUND RECONFIGURABLE DEVICE

### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

### **DOCTOR OF PHILOSOPHY**

in

### ELECTRONICS AND COMMUNICATION ENGINEERING

by

#### **ABHISHEK BHATTACHARJEE**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-247 667, INDIA MARCH, 2018

### ©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2018 ALL RIGHTS RESERVED

### INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

### **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled "ANALYSIS AND MODELLING OF SPACER BASED GATE-ALL-AROUND RECONFIGURABLE DEVICE" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electronics and Communication Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from July, 2014 to March, 2018 under the supervision of Dr. Sudeb Dasgupta, Associate Professor, Department of Electronics and Communication Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institution.

### (ABHISHEK BHATTACHARJEE)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

(Sudeb Dasgupta) Supervisor

### Date: 12<sup>th</sup> March 2018

The Ph. D Viva-Voce Examination of Mr. Abhishek Bhattacharjee, Research Scholar, has been held on 14<sup>th</sup> August 2018.

#### Chairman, SRC

Signature of External Examiner

This is to certify that the student has made all the corrections in the thesis.

#### Signature of Supervisor

Head of the Department

Date: 14<sup>th</sup> August 2018

### ABSTRACT

As the scaling limit is gradually reaching its ultimatum, the devices with multiple functionalities such as TFET, multi gate FiNFET, Silicon nanowire FET are been thoroughly investigated. Silicon nanowire-field-effect transistors (SiNWFETs) are among those devices which can replace the planar as well as fin-shaped field-effect transistors (FinFETs). One of the major drawbacks of the conventional CMOS technology is the inability to reconfigure it. To deal with this problem nanoscale technology with flexible configurability has recently gained a lot of attention in the device research community.

An axial silicon nanowire transistor which can be programmed dynamically as n- or p-FET by externally tuning the applied gate voltage forms the modern day reconfigurable field effect transistor (RFET). This device mainly exploits the interesting and unique properties of metal-silicide Schottky junctions to tune the polarity of charge carriers. In a RFET apart from the three electrodes which are common in any field effect transistor, a fourth one acts as an external electric signal to select the desired FET characteristics.

This new technology also provides a lot of advantages in terms of fabrication ease using the traditional bottom-up approach. The channel is almost doping free which leads to lesser short channel effects (SCE's) and the S/D contacts are also metallic which aids its possibility to become a lean technology in upcoming days. Enhanced electrical performance in terms of extremely low gate leakage makes it highly desirable for future low power digital applications. Noteworthy maturity in complex logic and circuit implementation with fewer numbers of transistors than usual has also been recently portrayed using this novel platform.

Unlike any other field effect transistor dependent on band to band tunneling (BTBT) for its on-current generation like tunnel field effect transistor (TFET), RFETs too suffer from various challenges and one of them is lower current drive and higher subthreshold swing (S/S) as compared to other planar devices. In view of these drawbacks, modification to the existing RFET architecture leading to a new device concept is necessary.

The objective of this thesis is many folds, firstly, to design for the first time a source/drain (S/D) spacer based *underlap* ambipolar silicon nanowire field-effect transistor device structure which shows enhanced electrical performance over the existing ambipolar topologies. The main reason behind these improvements is the ability of S/D spacers to

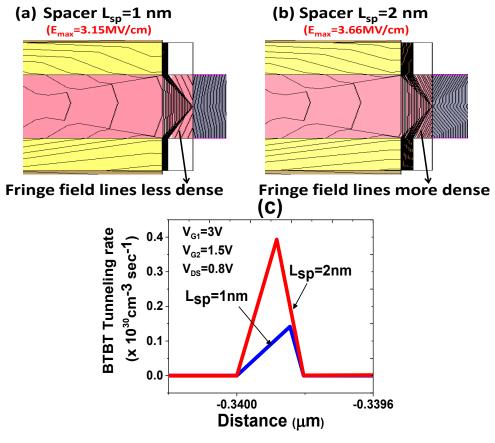

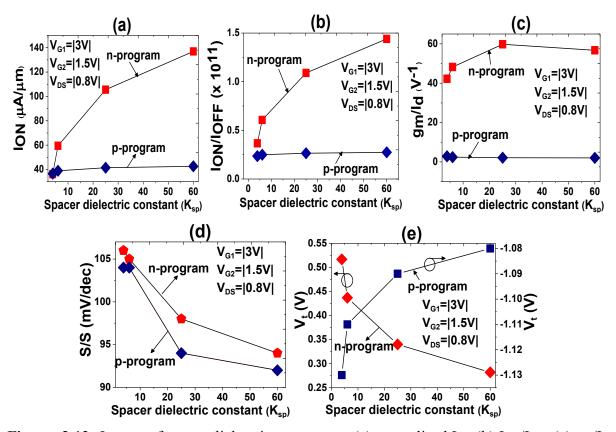

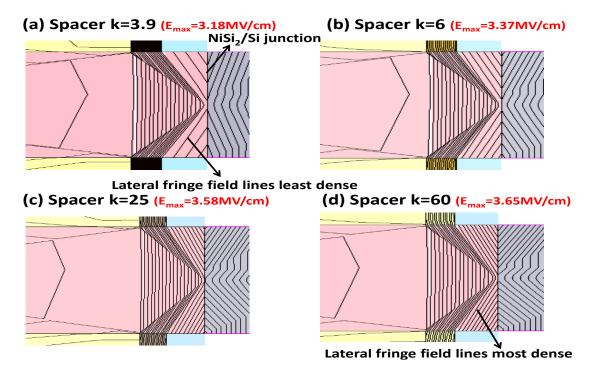

terminate the fringe field lines in to the Schottky contact more nicely which increases the junction electric field and hence the BTBT rate is boosted. The next aim is optimization of various device aspects like spacer material type and length of spacer  $(L_{sp})$ , gate dielectric and its thickness ( $t_{ox}$ ) and inters gate distance ( $d_{G1G2}$ ) using rigorous coupled 3-D Technology Computer Aided Design (TCAD) numerical device simulations. A systematic investigation of the impact of these critical design parameters on the vital device performance parameters, such as ON current, on to off current ratio, Subthreshold swing (S/S), threshold voltage, and transconductance generation factor was done. It was observed that higher spacer lengths, gate and spacer dielectric constants improves the device performance mainly because of better electrostatic coupling between metal gates and Schottky junctions and also due to increase in density of fringe field lines near the metal/semiconductor interface. To acquire a deeper understanding of various physical details behind spacer based performance enhancements over the conventional *non-underlap* RFET architecture through device level optimizations, the impact of variation in the gate channel underlap ( $L_{GCU}$ ) and spacer channel underlap region ( $L_{SCU}$ ) on the device behaviour was also studied. The main aim of shifting to a high- $\kappa$ gate dielectric is to lower the equivalent oxide thickness (EOT) without making a trade off with the gate leakage. So, the role of gate oxide EOT and scaling properties of the proposed device was also investigated.

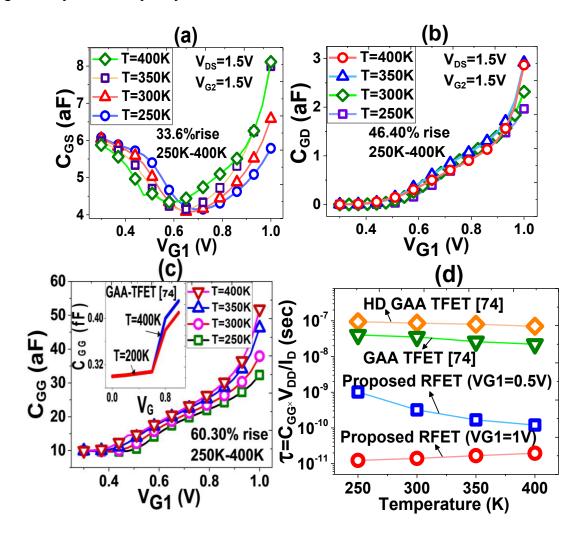

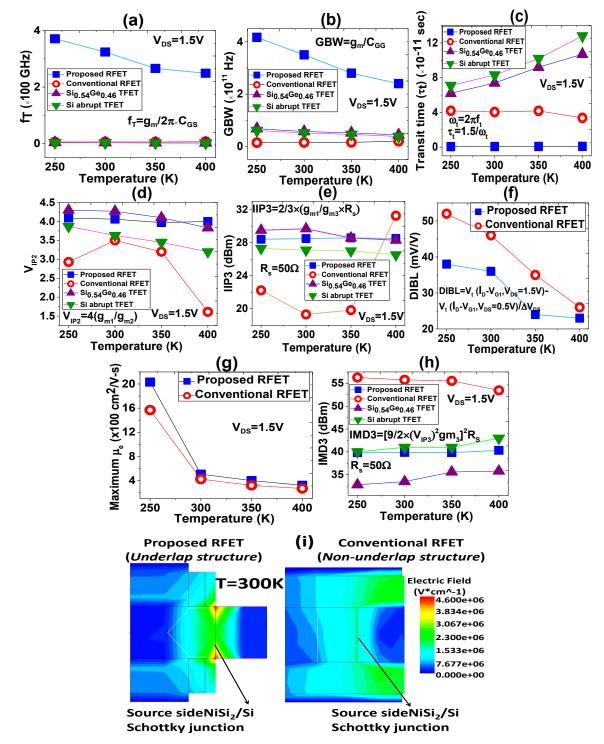

Since the subthreshold drain current of a RFET depends upon thermionic emission which is itself a temperature dependent phenomenon, the work was further extended to study the temperature dependence of the digital/analog parameters and RF figure of merits of the spacer based RFET and compare the same with the existing RFET topology and other devices which depend on band to band tunneling (BTBT) for their on current generation. Having a better thermal stability over TFET and sufficiently lesser V<sub>th</sub> roll-off, the proposed device portrays orders of magnitude reduction in parasitic gate capacitances and intrinsic delay as compared to gate-all-around (GAA) and heterogeneous gate dielectric gate all around (HD GAA) TFET devices over the considered range of temperature, thus ensuring higher switching speed for digital applications. It is found to have a comparatively better analog performance than SiGe and full silicon TFETs with increased values of  $g_m$ ,  $g_m/I_d$  and  $A_v$  in the considered range of temperature mainly because of BTBT dependent drive current and superior gate control over the silicon channel. Temperature variation of various

important RF parameters like higher order transconductance coefficients, cut-off frequency ( $f_T$ ), gain bandwidth product (GBW), transit time ( $\tau_t$ ), device figures of merits (FOMs) VIP2, the third-order intercept point (IIP3) and the third-order intermodulation distortion (IMD3) was shown and the results were also compared with conventional RFET, Si abrupt TFET and SiGe TFET. For most of these metrics, the proposed device shows superior RF performance as compared to its counterparts. The device FOMs were also found to be less sensitive to temperature variations making it more suitable for applications where temperature fluctuation is a major concern.

Finally, a physics based compact model was developed for surface potential and drain current for a dual gate (DG) source/drain (S/D) spacer based silicon nanowire reconfigurable field effect transistor. The models were derived by dividing the active portion of the device into several regions based on positioning of the gates, spacers and the metalsilicide Schottky junctions. A charge density expression was first developed and the 2-D Poisson's equation was self consistently solved for various sub-regions of the device. By using the charge density expression, a single-piece-approximation of the long channel surface potential was developed. Then it was added to the potential distribution at the Schottky junctions which is then solved by using a quasi-2D approach. The drain current was modeled by first finding the barrier height required for the carriers to overcome the maximum potential barrier induced in the silicon channel by the control gate near the source end of the device which was then used to find out the current through the Schottky barriers. This was equated based on the principle of current continuity with the drift diffusion current in the channel obtained by using the earlier derived charged density expression to generate a final drain current expression. The accuracy of the derived results was tested using 3-D numerical TCAD simulations. This work was lastly concluded by developing a Verilog-A model of the device under consideration for investigating the spacer induced performance improvements over the conventional *non-underlap* RFET with respect to delay reduction mainly in logic applications.

First of all I would like to thank almighty God for giving me enough dedication and strength to finally complete this work.

I would like to express my sincere obligation to my supervisor Dr. S. Dasgupta for continuously supporting me during my Ph.D work and related research with his diligence and enormous knowledge. I thank him from the core of my heart for all his suggestions and positive motivation during tough times that made this work possible. Besides gaining from his amicable and positive disposition, I have learned immensely from his noteworthy competence and professionalism. Dr. Dasgupta has always helped to clarify my doubts with exciting discussions we had during the entire Ph.D tenure. For my entire life, I will remain obliged to him for the experience that I have acquired while working with him.

I am indebted to Prof. Debashis Ghosh, Head, ECE dept., Prof. Dharmendra Singh Chairman SRC, Dr. Nagendra Prasad Pathak, Dr. A. Patnaik, Chairman DRC, Dr. Bulusu Anand, Internal Expert and Prof. Ghanshyam Das Verma, External Expert, Department of Physics, for being members of my Student Research Committee (SRC), and for providing their valuable time for carefully scrutinizing this research work and providing their highly important suggestions. I am also grateful to all the faculty members of Microelectronics and VLSI (MEV) Group including Dr. S. Manhas, Dr. A. Datta, Dr. B. P. Das, Dr. B. K. Kaushik and Dr. Brijesh Kumar for helping me at various stages of my work.

My heartfelt thanks to Mr. Naveen Kanwar of VLSI lab, and other non-teaching staffs of ECE Department for providing me support. I would like to candidly thank my colleagues Inder, Sandeep, Narendra, Priyamvada, Poorvi, Savitesh, Ruchi, Arvind, Mandeep, Govinda, Upendra, Om for their kind abutment and technical discussions from time to time. I would also pay my commendations to fellow group mates, Prabhat, Lalit, Saurabh, Amit, Swati, Sonal, Navjeet, Aditya for helping me in various stages of my research. I have been highly affluent to interact with my Ph.D. seniors and would like to pay my honest gratitude to P. K. Pal, S. Verma, G. Kaushal, A. Nandi, Menka and M. Majumdar for helping me a lot during the preliminary stages of my work. The current research work is financed by the Institute Fellowship from Ministry of Human Resource Development, Government of India. Their support is admiringly acknowledged.

Finally, I would like to acknowledge my parents, Mr. Ajoy Nrisingha Bhattacharjee and Mrs. Supriya Bhattacharjee for their generous love and continuous support and sacrifices made in making me what I am today. Without their assistance and enduring support my success in my life would never have been possible. I also thank my aunts Mrs. Gita Bhattacharjee, Mrs. Gayatri Bhattacharjee, Ms. Bijoya Bhattacharjee, Mrs. Tapati Bhattacharjee, my uncles Mr. Arindam Bhattacharjee, Mr. Debabrata Kumar Bandyopadhyay, Mr. Subimal Chakraborty, Mr. Swapan Chakraborty and my beloved cousins Mr. Debarijit Bandyppadhyay, Mr. Sourav Chakraborty, Ms. Soumalika Chakraborty and Ms. Alangkrita Bhattacharjee for their mental support, help and love throughout my life. Last but not the least I am highly gratified to my grandfather late Mr. Ajit Kumar Bhattacharjee who supported me in my studies.

Date:

(Abhishek Bhattacharjee)

То

my beloved parents and all my cousins

# **TABLE OF CONTENTS**

|   | Abs  | tract   |                                          | i     |

|---|------|---------|------------------------------------------|-------|

|   | Ack  | nowled  | dgement                                  | iv    |

|   | Tab  | le of C | ontents                                  | vii   |

|   | List | of Fig  | ures                                     | xii   |

|   | List | of Tab  | bles                                     | xviii |

|   | List | of Abl  | breviations                              | xix   |

|   | List | of Syn  | nbols                                    | xxii  |

| 1 | Intr | oducti  | ion                                      | 1     |

|   | 1.1  | Intro   | duction                                  | 1     |

|   | 1.2  | Motiv   | vation behind the Research               | 2     |

|   |      | 1.2.1   | Moore's Law and MOS transistors          | 2     |

|   |      | 1.2.2   | Scaling techniques and Short Channel     | 3     |

|   |      |         | Effects                                  |       |

|   |      | 1.2.3   | Introduction to Gate All Around (GAA)    | 5     |

|   |      |         | Devices                                  |       |

|   | 1.3  | Silico  | on Nanowires as Future Nanoscale Devices | 6     |

|   |      | 1.3.1   | Importance of Nanowire Based Devices     | 6     |

|   |      | 1.3.2   | Quest for a Universal CMOS Switch        | 7     |

|   | 1.4  | Probl   | em Statement                             | 8     |

|   | 1.5  | Objec   | ctives of the Thesis                     | 9     |

|   | 1.6  | Outli   | ne of the Work                           | 10    |

|   | 1.7 | Thesis Organization                                                                                  | 10 |

|---|-----|------------------------------------------------------------------------------------------------------|----|

| 2 |     | onfigurable Field Effect Transistor-Device Physics,<br>llenges and Applications: A Literature Review | 13 |

|   | 2.1 | Introduction                                                                                         | 13 |

|   | 2.2 | Nanowire FET Classification                                                                          | 13 |

|   |     | 2.2.1 Properties and Applications of SiNWFETs                                                        | 14 |

|   | 2.3 | Tunneling Based FETs                                                                                 | 14 |

|   |     | 2.3.1 Theory of Tunneling                                                                            | 14 |

|   |     | 2.3.2 Brief History of Planar and GAA Tunneling                                                      | 15 |

|   |     | Transistors                                                                                          |    |

|   | 2.4 | Concept of Ambipolarity in SiNWFETs                                                                  | 16 |

|   |     | 2.4.1 Device structure                                                                               | 16 |

|   |     | 2.4.2 Fabrication of Ambipolar SINWFETs                                                              | 18 |

|   |     | 2.4.3 Associated physics and modes of operation                                                      | 19 |

|   |     | 2.4.4 Dual Threshold behaviour and its advantages                                                    | 24 |

|   |     | 2.4.5 Suitability in Complex Logic Architectures                                                     | 25 |

|   |     | 2.4.6 Advantages of RFETs over other Classical and Non-                                              | 27 |

|   |     | Classical Devices                                                                                    |    |

|   | 2.5 | Technical Gaps                                                                                       | 28 |

| 3 |     | rce/Drain (S/D) Spacer Based Dual Gate (DG) RFET and<br>Optimization                                 | 30 |

|   | 3.1 | Introduction                                                                                         | 30 |

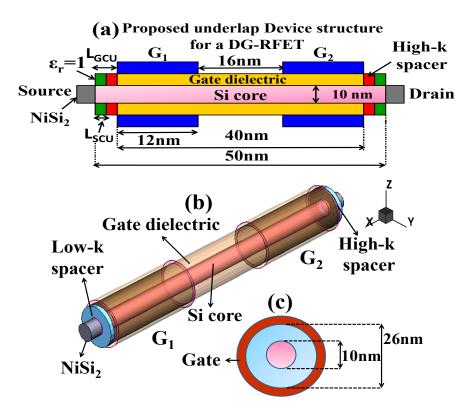

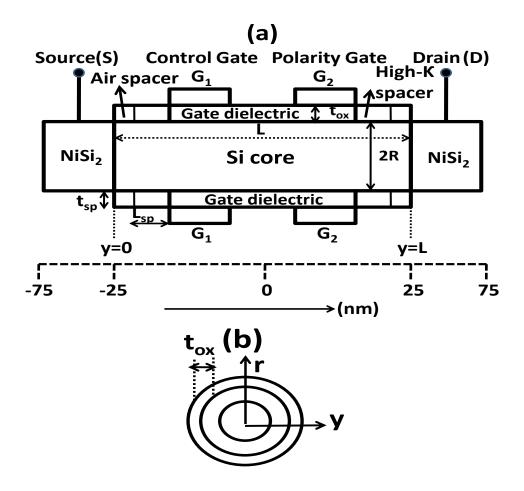

|   | 3.2 | Proposed S/D Spacer DG RFET, Operation and Simulation Framework                                      | 32 |

|     | 3.2.1  | Proposed Device Structure and Simulation                                               | 32 |

|-----|--------|----------------------------------------------------------------------------------------|----|

|     |        | Methodology                                                                            | 32 |

|     | 3.2.2  | Working Principle                                                                      | 34 |

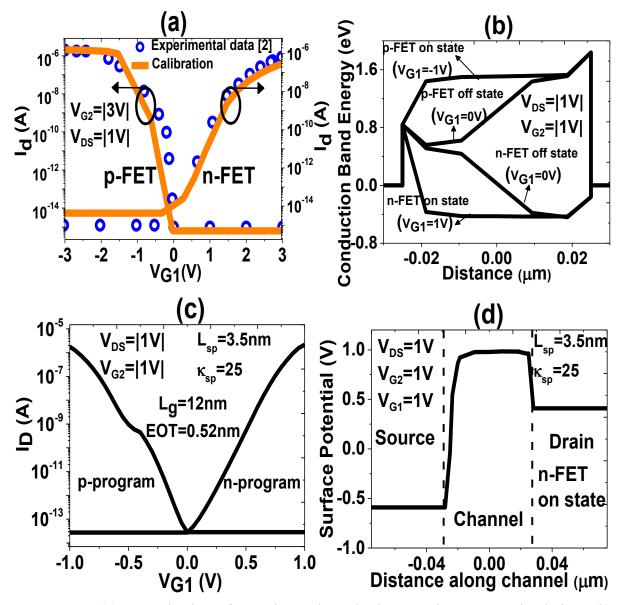

| 3.3 | Simul  | ation Calibration and Spacer Induced Performance                                       | 35 |

|     | Enhar  | ncements                                                                               |    |

|     | 3.3.1  | Calibration with Experimental Data                                                     | 35 |

|     | 3.3.2  | Physical Explanations behind the Performance                                           | 36 |

|     |        | Improvements                                                                           |    |

| 3.4 | Paran  | neter Optimization for the Proposed Device                                             | 42 |

|     | 3.4.1  | Spacer Length (L <sub>sp</sub> ) Optimization                                          | 42 |

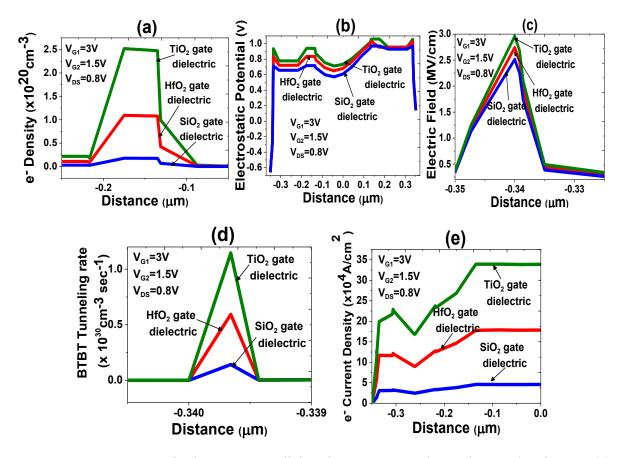

|     | 3.4.2  | Optimization of Gate Dielectric Constant                                               | 45 |

|     | 3.4.3  | Optimization of Spacer Dielectric Constant ( $\kappa_{sp}$ )                           | 46 |

|     | 3.4.4  | Optimization of Gate Dielectric Thickness (tox)                                        | 48 |

|     | 3.4.5  | Inter gate Distance (d <sub>G1G2</sub> ) Scaling Performance                           | 49 |

| 3.5 | Sumn   | 5                                                                                      | 52 |

| -   |        | Gate/Spacer Channel Underlap, Gate Oxide EOT<br>g on the Device performance of DG-RFET | 53 |

| 4.1 | Introd | luction                                                                                | 53 |

| 4.2 | Under  | rlap RFET Device and High-κ Spacer Optimization                                        | 54 |

| 4.3 | Impac  | et of Variation of the Gate-Channel Underlap $(L_{GCU})$                               | 56 |

|     | 4.3.1  | Varying Spacer Channel Underlap (L <sub>SCU</sub> )                                    | 56 |

|     | 4.3.2  | Fixed Spacer Channel Underlap (L <sub>SCU</sub> )                                      | 60 |

| 4.4 | Influe | ence of Gate Oxide EOT on the Device performance                                       | 63 |

|     | 4.4.1  | Fixed EOT                                                                              | 63 |

4

|   |     | 4.4.2 Varying EOT                                                                                | 66  |

|---|-----|--------------------------------------------------------------------------------------------------|-----|

|   | 4.5 | Impact of Scaling Nanowire Length, Gate Length,                                                  | 68  |

|   |     | Nanowire Diameter, $L_{GCU}$ and $L_{SCU}$                                                       |     |

|   | 4.6 | Summary                                                                                          | 70  |

| 5 |     | nperature Dependence of the DC, Analog and RF<br>formance of the S/D Spacer Based DG-RFET        | 72  |

|   | 5.1 | Introduction                                                                                     | 72  |

|   | 5.2 | Impact of Temperature on DC Characteristics                                                      | 74  |

|   | 5.3 | Temperature Influence on the Analog Performance                                                  | 79  |

|   | 5.4 | Effect of Temperature on Capacitive Behavior                                                     | 81  |

|   | 5.5 | Temperature Dependence of the RF Characteristics                                                 | 83  |

|   | 5.6 | Summary                                                                                          | 86  |

| 6 |     | deling of S/D Spacer Based DG-RFET and its Verilog-A<br>del Development for Digital Applications | 87  |

|   | 6.1 | Introduction                                                                                     | 87  |

|   | 6.2 | Model Development                                                                                | 92  |

|   |     | 6.2.1 Surface Potential Model                                                                    | 92  |

|   |     | 6.2.2 Drain Current Model                                                                        | 97  |

|   | 6.3 | Model Validation                                                                                 | 100 |

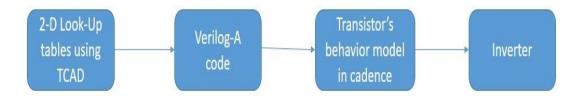

|   | 6.4 | Verilog-A Model Development                                                                      | 105 |

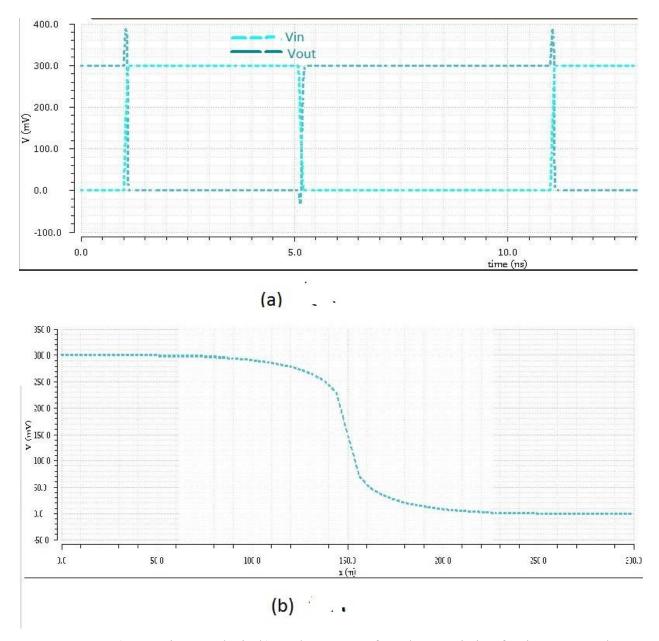

|   |     | 6.4.1 Inverter simulation in cadence                                                             | 107 |

|   | 6.5 | Summary                                                                                          | 110 |

| 7      | Con                  | clusions and Future Scope        | 112 |

|--------|----------------------|----------------------------------|-----|

|        | 7.1                  | Conclusions                      | 112 |

|        | 7.2                  | Major Contributions of this Work | 113 |

|        | 7.3                  | Future Scope                     | 115 |

| Refer  | ences                |                                  | 117 |

| List o | List of Publications |                                  | 132 |

# **LIST OF FIGURES**

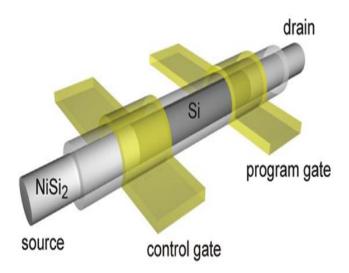

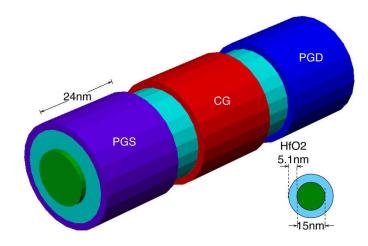

| 2.1  | Dual gate ambipolar SiNWFET [2].                                                | 17 |

|------|---------------------------------------------------------------------------------|----|

| 2.2  | Tri gate ambipolar SiNWFET [46].                                                | 17 |

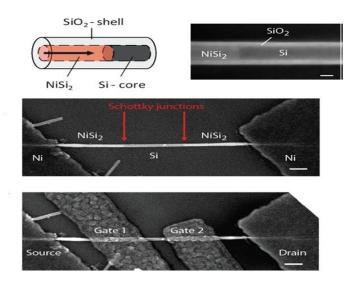

| 2.3  | SEM images showing fabricated dual gate SiNWFETs [2].                           | 18 |

| 2.4  | SEM images showing fabricated tri gate SiNWFETs [46].                           | 19 |

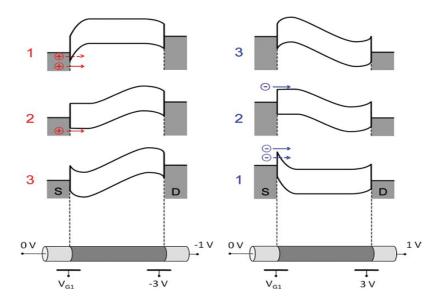

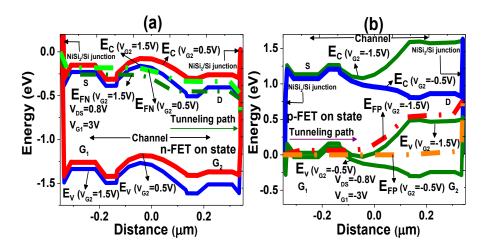

| 2.5  | Band bending at different biases applied during p-FET and n-FET                 | 20 |

|      | operation [2].                                                                  |    |

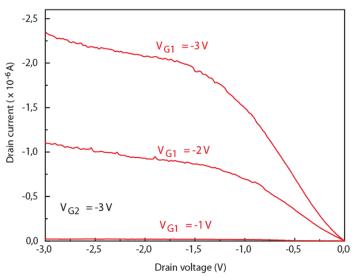

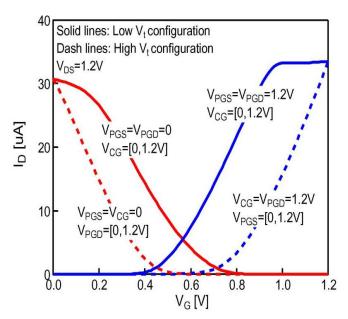

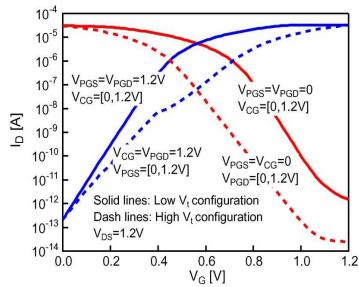

| 2.6  | Ambipolar behaviour in dual gate SiNWFET [2].                                   | 21 |

| 2.7  | Output characteristic during p-FET operation [2].                               | 21 |

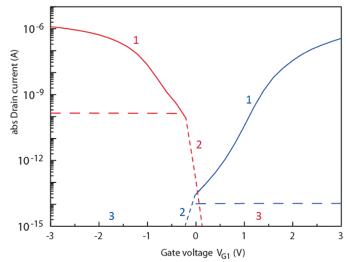

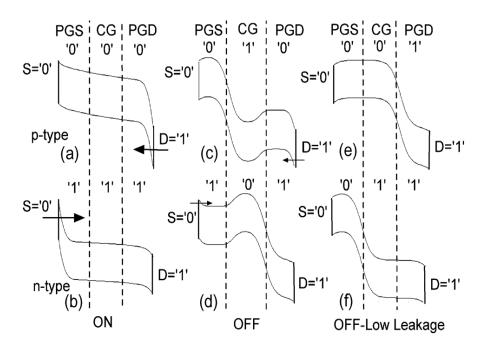

| 2.8  | Various modes of operation and their corresponding band edge shifts [46].       | 22 |

| 2.9  | $I_d$ - $V_g$ of the triple gate ambipolar FET showing the dual threshold [46]. | 23 |

| 2.10 | Transfer characteristic of TIG SINWFET in log scale [46].                       | 24 |

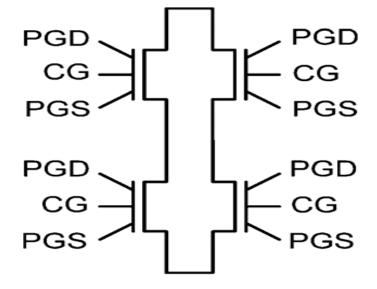

| 2.11 | Uncommitted Logic Gate Pattern [46].                                            | 25 |

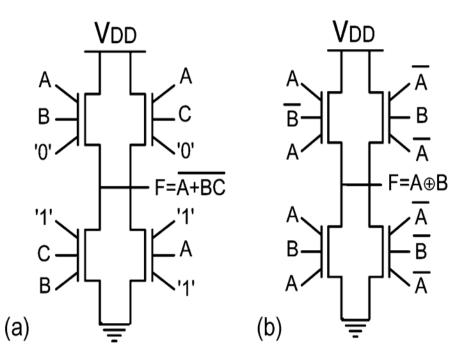

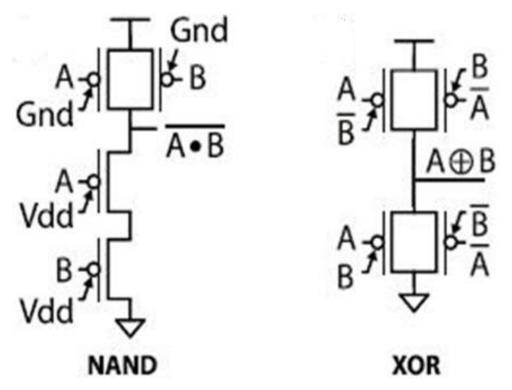

| 2.12 | AOI and XOR Gates using pattern proposed by Zhang et. al [46].                  | 25 |

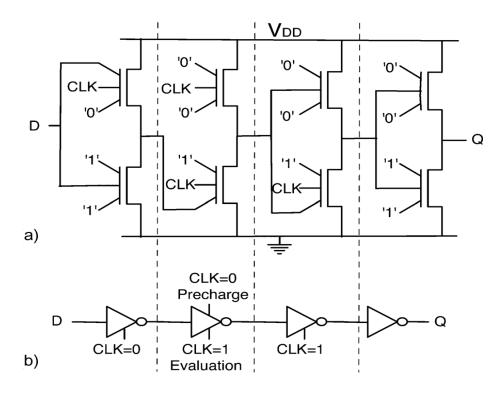

| 2.13 | TSPC DFF and equivalent Gate level circuit proposed by Zhang et. al.            | 26 |

|      | [46].                                                                           |    |

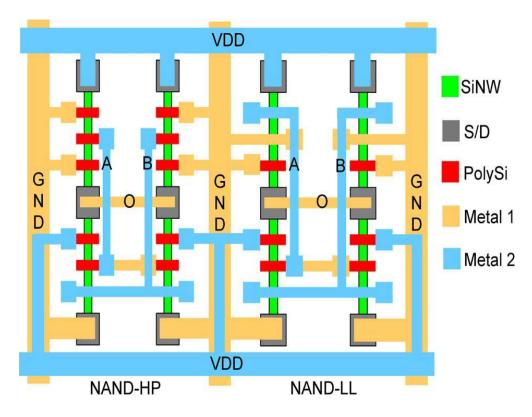

| 2.14 | NAND gate connection technique [46].                                            | 27 |

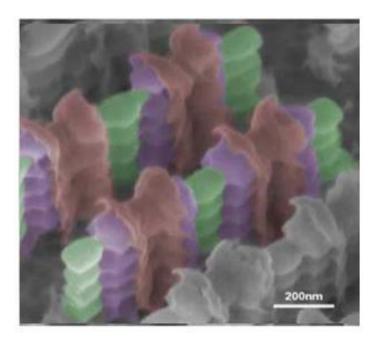

| 2.15 | Implementation of complex architectures with reduced number of gates [48].      | 28 |

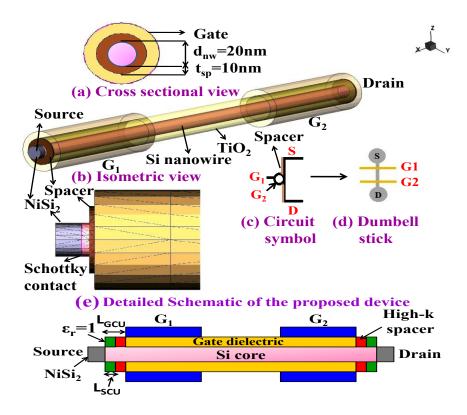

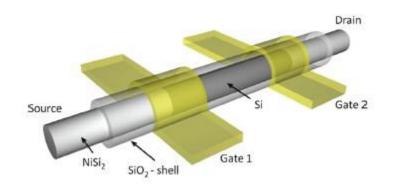

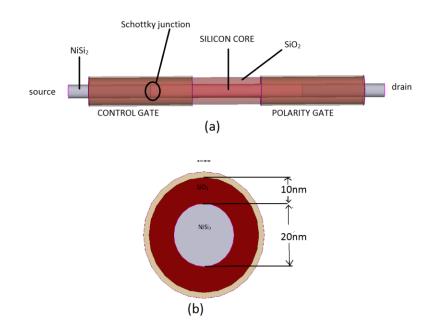

| 3.1  | (a) Cross sectional view (b) Isometric view showing the position of S/D         | 33 |

|      | spacers and mid-gap metal gates along with zoomed view from one side to         |    |

|      | illustrate the position of Schottky contact (c) Circuit symbol (d) Dumbell-     |    |

|      | stick diagram (e) Detailed Schematic of the proposed device.                    |    |

| 3.2  | Band diagrams of the device in lateral direction for various gate voltages      | 34 |

|      | for (a) n-FET on state (b) p-FET on state.                                      |    |

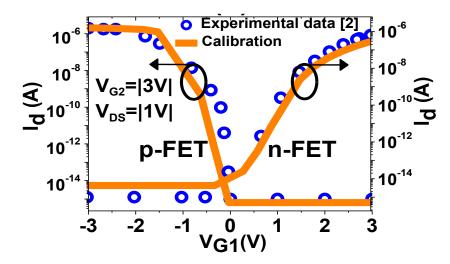

| 3.3  | Experimental device with length 680nm and gate length 200nm [2]                 | 35 |

| 3.4  | Calibration of $I_D$ - $V_{G1}$ characteristics with experimental device [2].   | 36 |

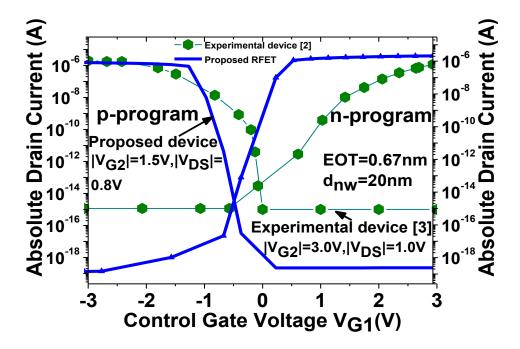

| 3.5  | Comparison of typical simulated I <sub>D</sub> -V <sub>G1</sub> characteristics (lines) of proposed | 37 |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | device with that of experimental device [2] (dotted).                                               |    |

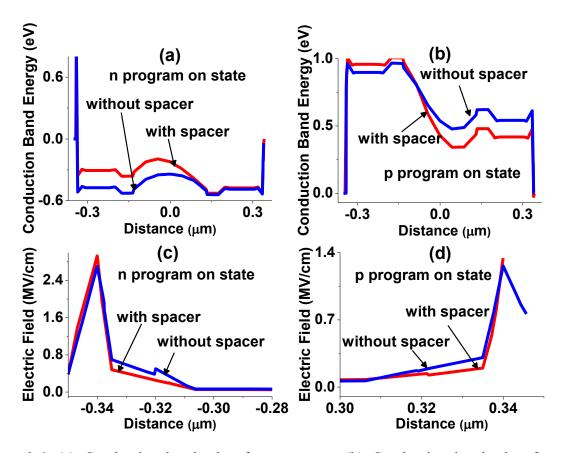

| 3.6  | (a) Conduction band edge for n-program (b) Conduction band edge for p-                              | 38 |

|      | program (c) Electric field variation for n-program (source side) (d) Electric                       |    |

|      | field variation for p-program (drain side) in ON state for proposed device                          |    |

|      | along the lateral direction (with and without HfO <sub>2</sub> spacer).                             |    |

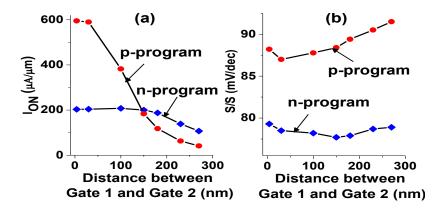

| 3.7  | (a) $I_{ON}$ versus inter-gate distance (d <sub>G1G2</sub> ) for n (p-FET) (b) S/S versus inter-    | 40 |

|      | gate distance (d <sub>G1G2</sub> ) for n (p-FET).                                                   |    |

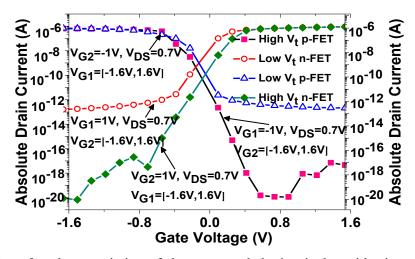

| 3.8  | Transfer characteristics of the proposed device in logarithmic scale                                | 41 |

|      | illustrating the dual Vt property.                                                                  |    |

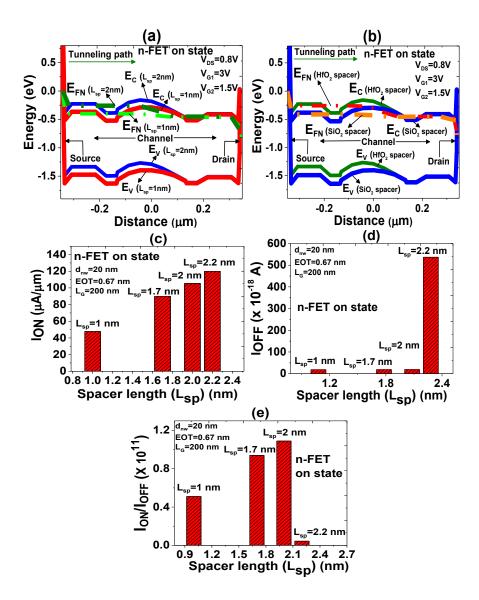

| 3.9  | Impact of variation in (a) spacer length $(L_{sp})$ and (b) spacer material on                      | 42 |

| •••  | lateral band diagram of the device (c) $I_{ON}$ vs spacer length ( $L_{sp}$ ) (d) $I_{OFF}$ vs      |    |

|      | spacer length ( $L_{sp}$ ) (e) $I_{ON}/I_{OFF}$ vs spacer length ( $L_{sp}$ ) for n-FET on state.   |    |

|      |                                                                                                     |    |

| 3.10 | Fringe field coupling through the spacer for (a) $L_{sp}=1nm$ (b) $L_{sp}=2nm$ (c)                  | 44 |

|      | BTBT rate comparison for $L_{sp}=1$ nm and 2nm.                                                     |    |

| 3.11 | Impact of $TiO_2$ as gate dielectric as compared to $SiO_2$ and $HfO_2$ on (a)                      | 45 |

|      | electrostatic potential (b) electric field (c) electron density (d) BTBT rate                       |    |

|      | (e) electron current density.                                                                       |    |

| 3.12 | Impact of spacer dielectric constant on (a) normalized $I_{ON}$ (b) $I_{ON}/I_{OFF}$ (c)            | 47 |

|      | $g_m/I_d$ (d) S/S (e) V <sub>t</sub> for n and p-FET on state.                                      |    |

| 3.13 | Fringe field coupling through the spacer at source end for the four cases                           | 48 |

|      | shown in Fig. 6 with varying spacer dielectric constant.                                            |    |

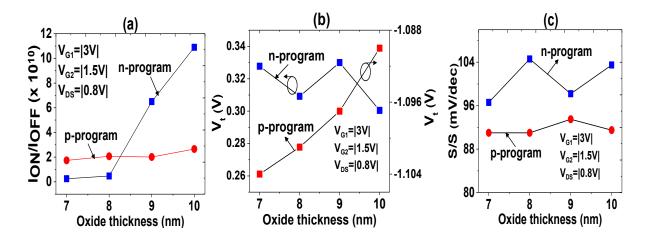

| 3.14 | Impact of $t_{ox}$ scaling on (a) $I_{ON}/I_{OFF}$ (b) $V_t$ (c) S/S for n and p-program on         | 49 |

|      | state.                                                                                              |    |

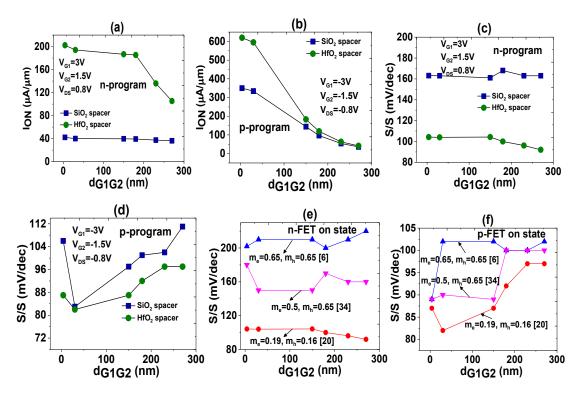

| 3.15 | Impact of $d_{G1G2}$ scaling on (a) $I_{ON}$ for n-FET (b) $I_{ON}$ for n-FET (c) S/S for           | 50 |

|      | n-FET (d) S/S for p-FET for $SiO_2$ (blue lines) and $HfO_2$ (green lines)                          |    |

|      | spacer material. (e) S/S vs $d_{G1G2}$ with varying $m_n$ , $m_p$ [56, 47, 69] for n-FET            |    |

|      | (f) S/S vs $d_{G1G2}$ with varying $m_n$ , $m_p$ for p-FET. Note the biasing                        |    |

|      | arrangements in all the cases are for on-state of the respective program.                           |    |

|      |                                                                                                     |    |

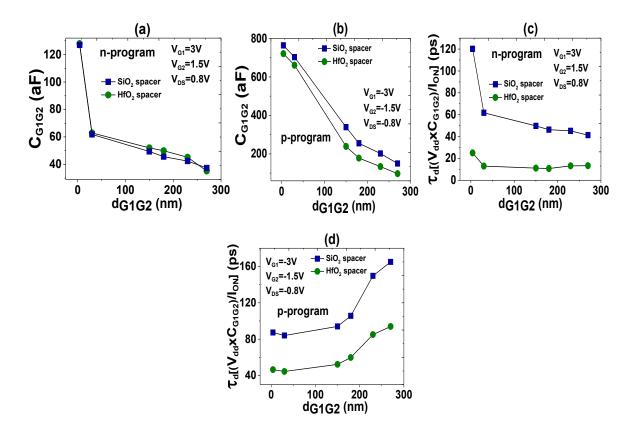

- 3.16 Impact of d<sub>G1G2</sub> scaling on (a) I<sub>ON</sub> for n-FET (b) I<sub>ON</sub> for n-FET (c) S/S for 51 n-FET (d) S/S for p-FET for SiO<sub>2</sub> (blue lines) and HfO<sub>2</sub> (green lines) spacer material. Note the biasing arrangements in all the cases are for on-state of the respective program.

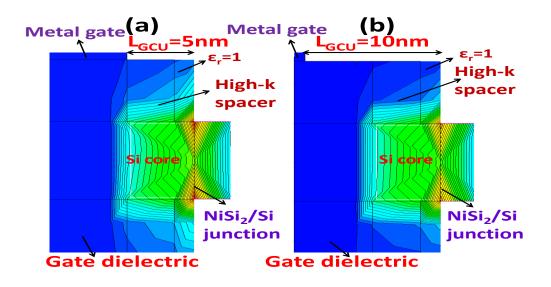

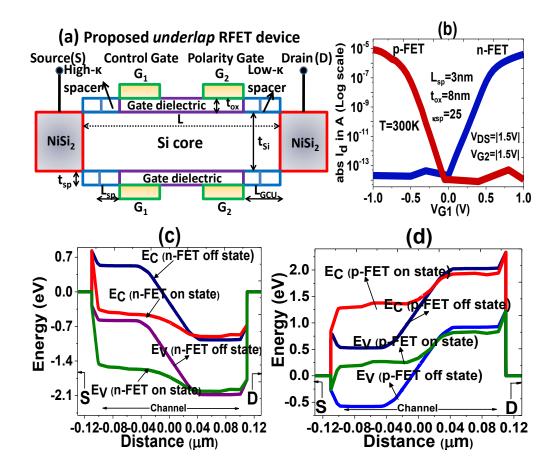

- **4.1** (a) Schematic representation (b) 3-D isometric view (c) Cross-sectional 54 view of the target RFET.

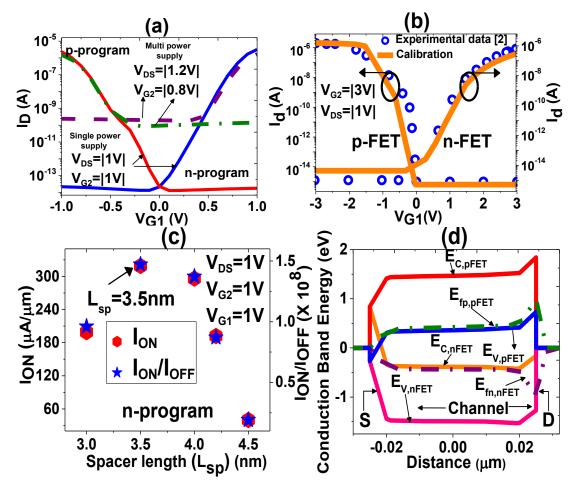

- 4.2 (a) Transfer characteristics comparison for single and multi stage power 55 supply for both n and p-programs (b) Calibration of BTBT model against experimental data [2] (c) Optimization of high-κ spacer length (d) Simulated energy band diagrams for n- and p-program on-state of the proposed RFET.

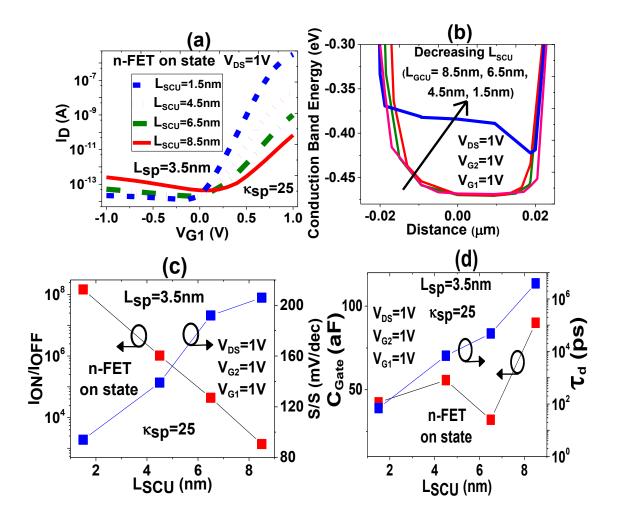

- 4.3 (a) Transfer characteristics (b) Simulated energy band diagrams (c) I<sub>ON</sub>/I<sub>OFF</sub> ratio and S/S (d) Total gate capacitance and intrinsic gate delay for n- program on-state of the proposed RFET at V<sub>G1</sub>=1V, V<sub>G2</sub>=1V and V<sub>DS</sub>=1V for varying spacer-channel underlap (L<sub>SCU</sub>).

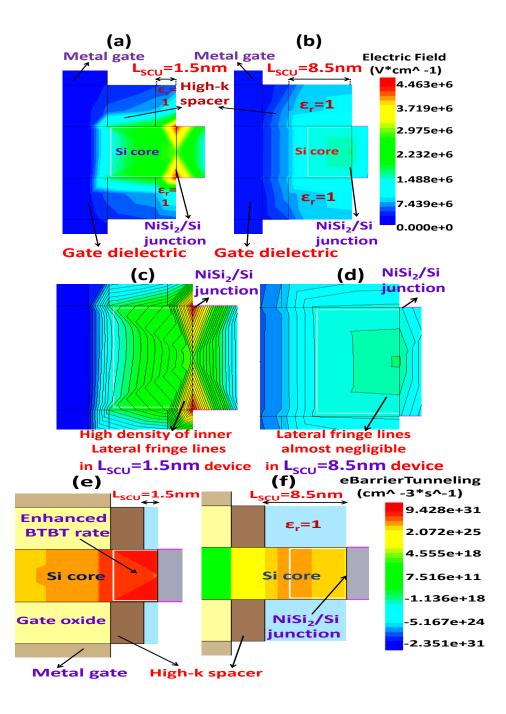

- **4.4** (a) Electric field contour for  $L_{SCU}=1.5$ nm (b) Electric field contour for  $L_{SCU}=8.5$ nm (c) Magnified electric field plot showing the lateral fringe field coupling through the spacer for  $L_{SCU}=1.5$ nm (d) ) Magnified electric field plot showing the lateral fringe field coupling through the spacer for  $L_{SCU}=8.5$ nm (e) BTBT contour for  $L_{SCU}=1.5$ nm (f) BTBT contour for  $L_{SCU}=8.5$ nm at source end for n-program on-state of the proposed RFET at  $V_{G1}=1V$ ,  $V_{G2}=1V$  and  $V_{DS}=1V$  for varying spacer-channel underlap ( $L_{SCU}$ ).

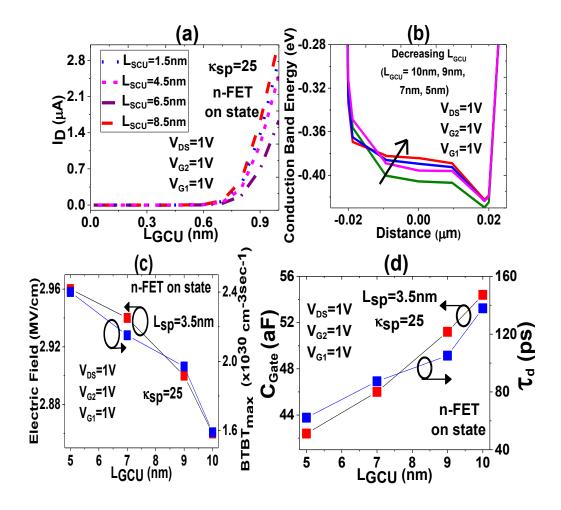

- 4.5 (a) I<sub>ON</sub> and V<sub>t</sub> (b) Simulated energy band diagrams (c) Electric field and BTBT rate (d) Total gate capacitance and intrinsic gate delay for n-program on-state of the proposed RFET at V<sub>G1</sub>=1V, V<sub>G2</sub>=1V and V<sub>DS</sub>=1V for varying gate-channel underlap (L<sub>GCU</sub>) at fixed spacer-channel underlap (L<sub>SCU</sub>).

- **4.6** (a) Fringe field contour plot showing the lateral fringe field coupling 62 through the spacer for  $L_{GCU}=5$ nm device (b) ) Fringe field contour plot showing the lateral fringe field coupling through the spacer for  $L_{GCU}=5$ nm

- xiv

58

57

61

device at source end for n-program on-state of the proposed RFET at  $V_{G1}=1V$ ,  $V_{G2}=1V$  and  $V_{DS}=1V$  for varying gate-channel underlap ( $L_{GCU}$ ).

63

65

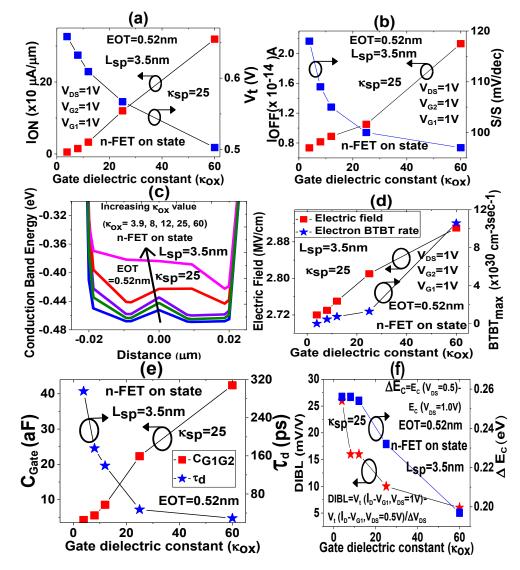

- 4.7 (a) Normalized I<sub>ON</sub> and V<sub>t</sub> (b) I<sub>OFF</sub> and S/S (c) Simulated energy band diagram (d) Electric field and electron BTBT rate (e)Total gate capacitance and intrinsic gate delay (f) DIBL as a function of of gate dielectric constant ( $\kappa_{ox}$ ) gate dielectric constant ( $\kappa_{ox}$ ) for varying  $\kappa_{ox}$  and a fixed V<sub>DS</sub> for n-FET on-state of the proposed device for a fixed EOT of 0.52 nm.

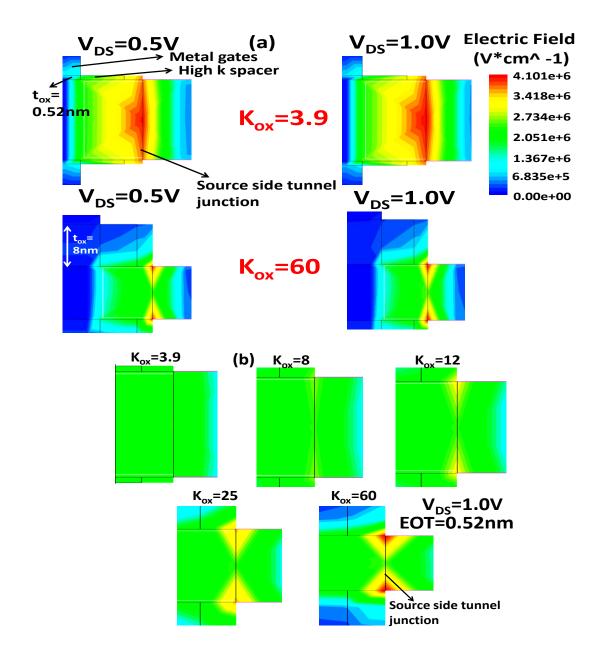

- **4.8** (a) Electric field contours for varying  $\kappa_{ox}$  and a varying  $V_{DS}$  (b) Electric field contours for varying  $\kappa_{ox}$  and a fixed  $V_{DS}$  for n-FET on-state of the proposed device for a fixed EOT of 0.52nm.

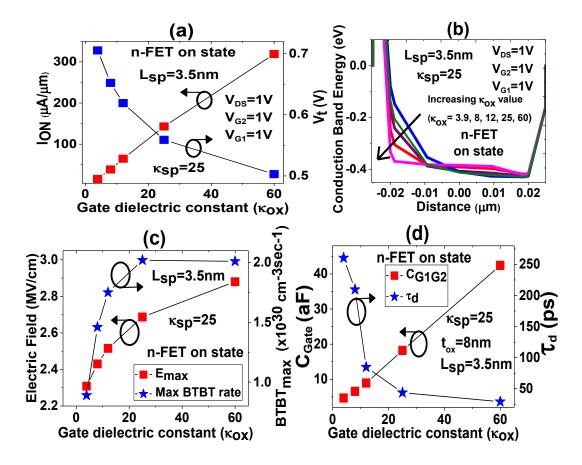

- 4.9 (a) Normalized I<sub>ON</sub> and V<sub>t</sub> (b) Simulated energy band diagrams (c) Electric

68 field and max<sup>m</sup> BTBT rate (d) Total gate capacitance and intrinsic gate

delay as a function of gate dielectric constant (κ<sub>ox</sub>) at fixed t<sub>ox</sub> for n-FET

on-state of the proposed device at V<sub>DS</sub>=1V, V<sub>G2</sub>=1V and V<sub>G1</sub>=1V.

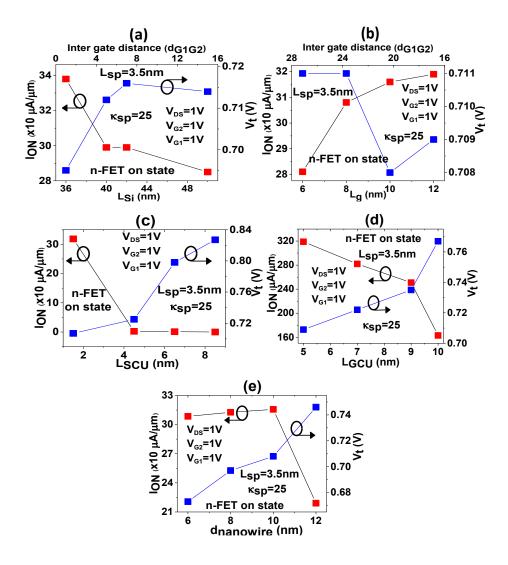

- **4.10** (a) Normalized I<sub>ON</sub> and V<sub>t</sub> as a function of silicon nanowire length (L<sub>Si</sub>) (b) 69 Normalized I<sub>ON</sub> and V<sub>t</sub> as a function of gate length (L<sub>g</sub>) (c) Normalized I<sub>ON</sub> and V<sub>t</sub> as a function of L<sub>SCU</sub> (d) Normalized I<sub>ON</sub> and V<sub>t</sub> as a function of L<sub>GCU</sub> (e) Normalized I<sub>ON</sub> and V<sub>t</sub> as a function of nanowire diameter (d<sub>nanowire</sub>) for n-FET on-state of the proposed device at V<sub>DS</sub>=1V, V<sub>G2</sub>=1V and V<sub>G1</sub>=1V.

- 5.1 (a) Schematic representation of the proposed device (b) Transfer

75 characteristics for both n and p-programs (c) Energy band diagrams for nFET on and off states (c) Energy band diagrams for p-FET on and off states

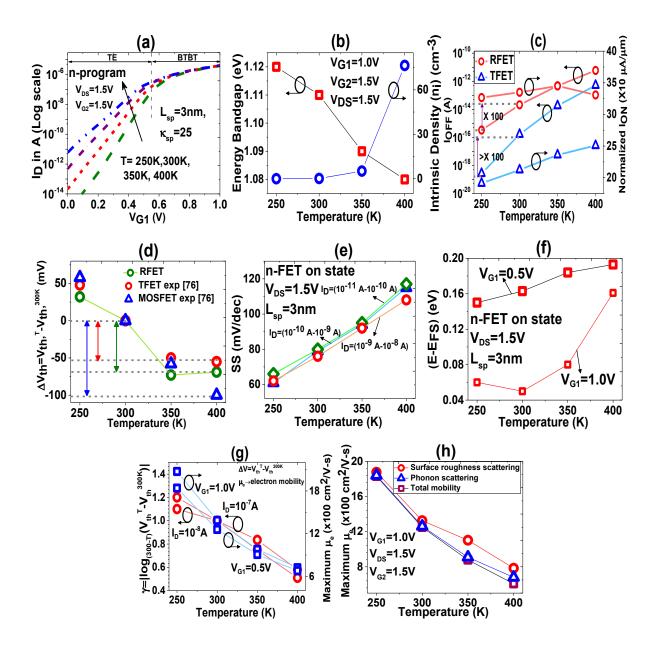

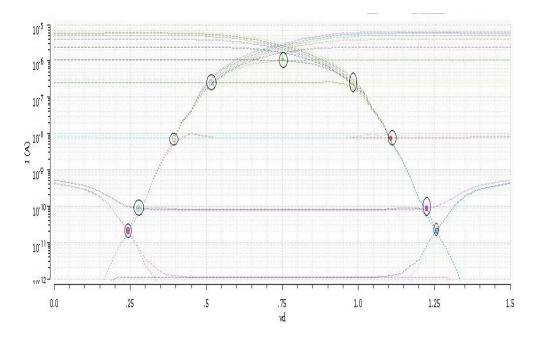

- **5.2** Variation of (a)  $I_D$  (log scale) vs.  $V_{G1}$  (b) Energy bandgap and intrinsic 76 density (c)  $I_{OFF}$  and normalized  $I_{ON}$  (d)  $\Delta V_{th}(e)$  S/S (f) E-E<sub>FS</sub> (g)  $\gamma$  and maximum mobility (h) Maximum mobility contribution due to phonon and surface roughness scattering for n-FET on state at  $V_{DS}$ =1.5V with temperature.

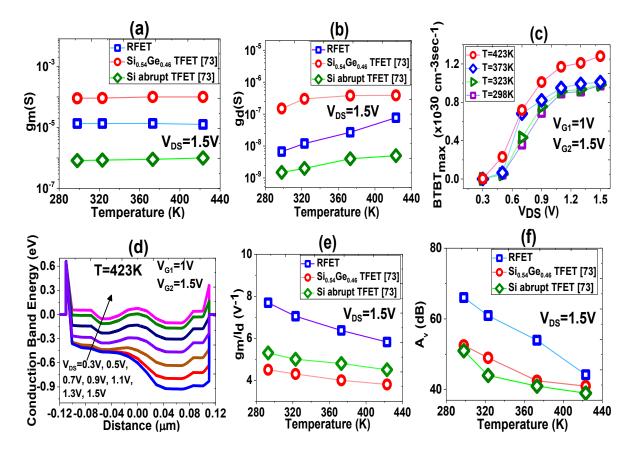

- 5.3 Variation of (a) Transconductance  $(g_m)$  (b) Output Conductance  $(g_d)$  (c) 80

BTBT max (d) Conduction band energy (e) Transconductance generation factor  $(g_m/I_d)$  (f) Intrinsic voltage gain  $(A_v)$  for the proposed RFET, experimental Si<sub>0.54</sub>Ge<sub>0.46</sub> TFET [73] and Si abrupt TFET [73] for n-FET on state at V<sub>DS</sub>=1.5V with temperature.

5.4 Variation of (a) Gate to source capacitance (C<sub>GS</sub>) with V<sub>G1</sub> for varying temperature (b) Gate to drain capacitance (C<sub>GD</sub>) with V<sub>G1</sub> for varying temperature (c) Total gate capacitance (C<sub>GG</sub>) with V<sub>G1</sub> for varying temperature (d) Intrinsic delay for proposed RFET (n-FET on state), HDD FFET [74] and GAA TFET [74] with temperature.

81

5.5 Variation of (a) Cut-off frequency (f<sub>T</sub>) (b) Gain bandwidth product (GBW)

84 (c) Transit time (τ<sub>t</sub>) (d) V<sub>IP2</sub> (e) IIP3 (f) IMD3 (g) DIBL (h) Maximum mobility (i) Electric Field contour with temperature for the proposed RFET (n-FET on state), conventional RFET described in [61], with similar device dimensions, Si<sub>0.54</sub>Ge<sub>0.46</sub> TFET [73] and Si abrupt TFET [73].

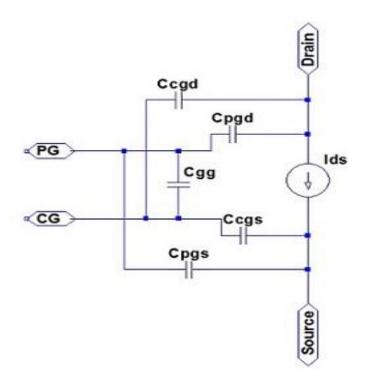

# 6.1 (a) Schematic representation (drawn not to scale) (b) Cross sectional view 89 of the target S/D spacer based RFET.

- 6.2 (a) Reproduction of experimental results in [13] using TCAD simulations 91

(b) Simulated conduction band profiles for n-FET and p-FET on and offstates (c) Transfer characteristics at V<sub>G2</sub>=|1V|, V<sub>DS</sub>=|1V| (d) Surface potential for n-type device at V<sub>G1</sub>=1V, V<sub>G2</sub>=1V, V<sub>DS</sub>=1V of the proposed RFET.

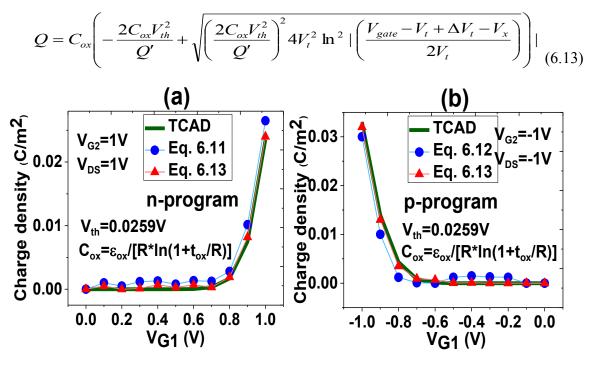

- **6.3** (a) Carrier density for n-program (b) Carrier density for p-program. 95

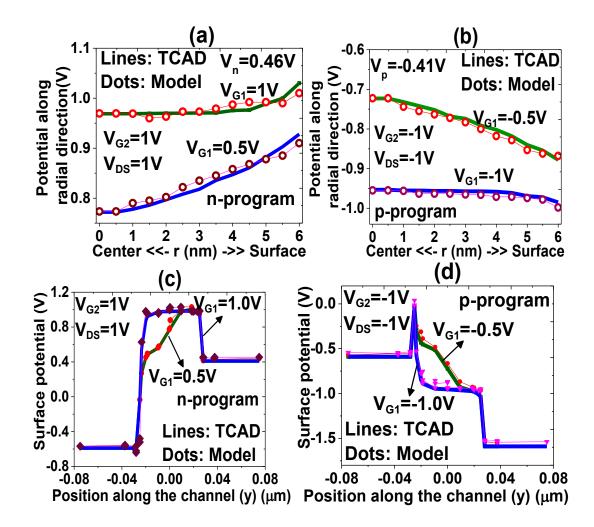

- 6.4 The predicted (a) Potential along radial direction for n-program (taking 101 cutline at y=L) (b) Potential along radial direction for p-program (taking cutline at y=L) (c) Surface potential for n-program (d) Surface potential for p-program (lines: TCAD simulation, dots: model).

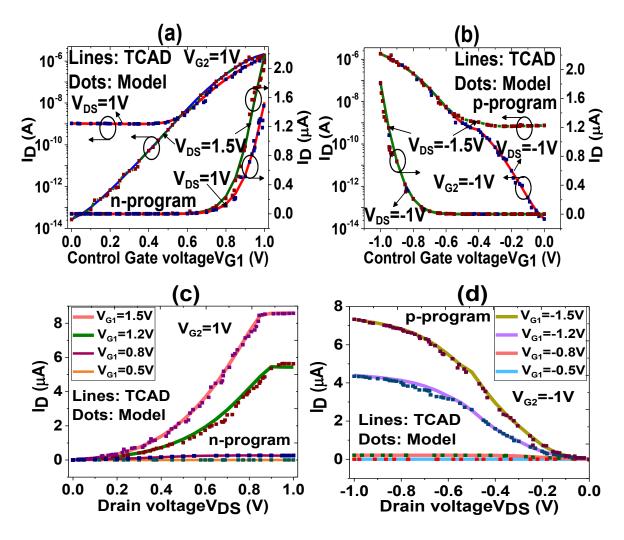

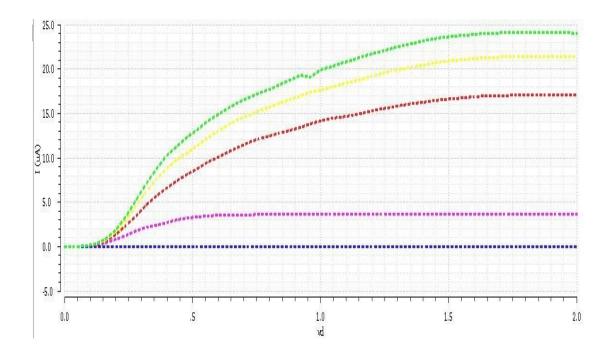

- 6.5 (a) Drain characteristics for varying  $V_{CG}$  at a fixed  $V_{PG}$  for n program (b) 102

Drain characteristics for varying  $V_{CG}$  at a fixed  $V_{PG}$  for p-program (c) Drain characteristics for varying  $V_{DS}$  at a fixed  $V_{CG}$  for n program (d) Drain characteristics for varying  $V_{DS}$  at a fixed  $V_{CG}$  for p program (lines: TCAD simulation, dots: model).

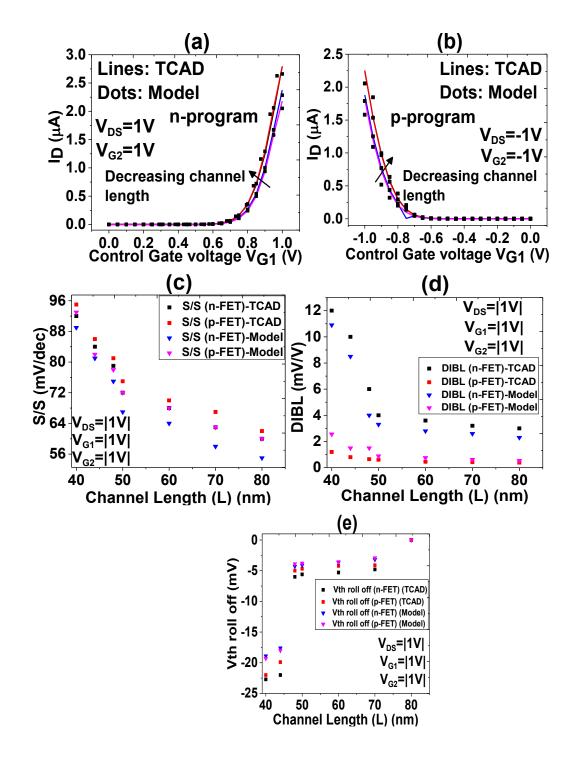

6.6 (a) Variation of I<sub>d</sub> vs.V<sub>G1</sub> for n-FET for various channel lengths (Lines-104 TCAD, Dots-Model) (b) Variation of I<sub>d</sub> vs.V<sub>G1</sub> for p-FET for various channel lengths (Lines-TCAD, Dots-Model) (c) Variation of S/S with channel length for both n- and p-FET (Lines-TCAD, Dots-Model) (d) Variation of DIBL with channel length for both n- and p-FET (Lines-TCAD, Dots-Model) (e) Variation of V<sub>th</sub> roll off with channel length for both n- and p-FET (Lines-TCAD, Dots-Model).

| <b>6.7</b> a) 3-D isometric view of dual-gate SiNWFET b) Cross-sectional view. | 10: | 5 |

|--------------------------------------------------------------------------------|-----|---|

|--------------------------------------------------------------------------------|-----|---|

106

Verliog-A model of the device.

6.8

| 6.9  | Complete flow from data extraction to making an inverter.                   | 107 |

|------|-----------------------------------------------------------------------------|-----|

| 6.10 | a) Transient analysis b) Voltage Transfer Characteristics for inverter made | 108 |

|      | using TFET.                                                                 |     |

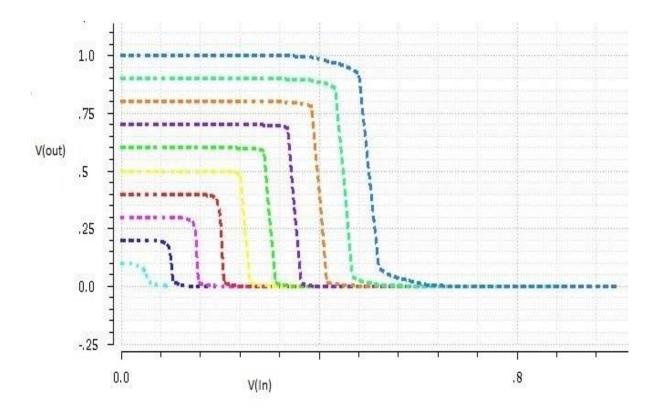

| 6.11 | Family of curves for n FET and its mirror image (here p FET).               | 109 |

- **6.12** I<sub>d</sub>-V<sub>d</sub> characteristics of p-programmed transistor (mirrored about x and y 109 axis).

- **6.13** Voltage Transfer Characteristics of inverter obtained using pFET 110 characteristics for various V<sub>DD</sub>.

# LIST OF TABLES

| 3.1 | Device performance with and without spacer                                                                                                                      | 39 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Variation in device performance with spacer material                                                                                                            | 40 |

| 3.3 | Performance comparison of dual gate RGFET [2], TIG SiNWFET [55] and proposed device                                                                             | 41 |

| 3.4 | Variation in electron velocity with spacer attributes                                                                                                           | 44 |

| 3.5 | Performance comparison of various RFETs proposed in literature with our proposed device                                                                         | 50 |

| 5.1 | Performance Analog Performance Comparison with Temperature Variation for Proposed RFET, Si <sub>0.54</sub> Ge <sub>0.46</sub> TFET [73] and Si abrupt TFET [73] | 80 |

# LIST OF ABBREAVATIONS

| DG      | Double Gate                                         |

|---------|-----------------------------------------------------|

| SBH     | Schottky Barrier Height                             |

| DIBL    | Drain Induced Barrier Lowering                      |

| FIBL    | Fringe Induced Barrier lowering                     |

| eV      | Electron Volt                                       |

| VLSI    | Very Large Scale Integration                        |

| EOT     | Equivalent Oxide Thickness                          |

| CMOS    | Complementary Metal Oxide Semiconductor             |

| SiNWFET | Silicon Nanowire Field Effect Transistor            |

| FOM     | Figure Of Merit                                     |

| TCAD    | Technology Computer Aided Design                    |

| SS      | Subthreshold Slope                                  |

| RFET    | Reconfigurable Field Effect Transistor              |

| RF      | Radio Frequency                                     |

| ITRS    | International Technology Roadmap for Semiconductors |

| Si      | Silicon                                             |

| S/D     | Source/Drain                                        |

| GAA     | Gate-All-Around                                     |

| TFET    | Tunnel Field Effect Transistor                      |

| SiGe    | Silicon germanium                                   |

| TIG     | Three Independent Gate                              |

| SOC     | System-On-Chip                                      |

| 0-D     | Zero Dimensional                                    |

| 1-D      | One Dimensional                               |

|----------|-----------------------------------------------|

| 2-D      | Two Dimensional                               |

| 3-D      | Three Dimensional                             |

| CNT      | Carbon Nano Tube                              |

| BJT      | Bipolar Junction Transistor                   |

| NW       | Nano Wire                                     |

| BTBT     | Band to Band Tunneling                        |

| FET      | Field Effect Transistor                       |

| SBFET    | Schottky Barrier FET                          |

| WKB      | Wentzel-Kramers-Brillouin                     |

| SRH      | Shockley-Read-Hall                            |

| IC       | Integrated Circuit                            |

| SCE      | Short Channel Effect                          |

| SOI      | Silicon On Insulator                          |

| eDensity | Electron Density                              |

| hDensity | Hole Density                                  |

| HEMT     | High Electron Mobility Transistor             |

| NMOS     | n-Channel MOSFET                              |

| PMOS     | p-Channel MOSFET                              |

| FinFET   | Fin Field Effect Transistor                   |

| TAT      | Trap Assisted Tunneling                       |

| HD GAA   | Heterogeneous gate dielectric gate all around |

| VTC      | Voltage Transfer Characteristics              |

| NMH      | High level noise margin                       |

| NML      | Low level noise margin                        |

| GBW      | Gain bandwidth product                        |

|          |                                               |

- IMD3 Third order intermodulation

- IIP3 Third-order intercept point

- K Kelvin

# LIST OF SYMBOLS

| $V_{DD}$           | Drain Voltage                   |

|--------------------|---------------------------------|

| $V_{DS}$           | Drain to Source Voltage         |

| HfO <sub>2</sub>   | Hafnium dioxide                 |

| SiO <sub>2</sub>   | Silicon dioxide                 |

| t                  | time                            |

| Т                  | Temperature                     |

| E <sub>r</sub>     | Relative dielectric constant    |

| З                  | Permittivity                    |

| $\mathcal{E}_{OX}$ | Permittivity of Oxide           |

| $N_A$              | Acceptor concentration          |

| $N_D$              | Donor concentration             |

| $L_{sp}$           | Spacer length                   |

| $t_{sp}$           | Spacer width                    |

| V <sub>bi</sub>    | Built in Potential              |

| $t_{ox}$           | Oxide thickness                 |

| q                  | Electronic charge               |

| $n_i$              | Intrinsic carrier concentration |

| $I_{ON}$           | ON state current                |

| I <sub>OFF</sub>   | OFF state leakage current       |

| $f_T$              | Cut off frequency               |

| $g_m$              | Transconductance                |

| $g_d$              | Output Conductance              |

| $A_{v}$            | Intrinsic voltage gain          |

|                    |                                 |

| $d_{G1G2}$     | Inter gate separation                       |

|----------------|---------------------------------------------|

| τ <sub>d</sub> | Intrinsic delay                             |

| $g_{m2}$       | Second order transconductance coefficient   |

| $	au_t$        | Transit time                                |

| $V_{FB}$       | Flatband voltage                            |

| $C_{GS}$       | Gate to source capacitance                  |

| $C_{GD}$       | Gate to drain capacitance                   |

| $\Psi(x, y)$   | Potential distribution along x, y direction |

| $TiO_2$        | Titanium dioxide                            |

| $E_{FN}$       | Electron quasi fermi energy level           |

| $E_{FP}$       | Hole quasi fermi energy level               |

| Vn             | Electron quasi fermi potential              |

| $V_p$          | Hole quasi fermi potential                  |

|                |                                             |

## **Chapter 1**

### Introduction

### **1.1 Introduction**

Since the past forty years, due to continuous scaling in gate length, gate oxide thickness and supply voltage, the transistor performance has seen a lot of potential improvement [1-4]. The more a device is down scaled, the higher is its packing density, the higher its circuit speed, and lower its power dissipation. However, as CMOS dimensions have started to approach the sub nanometer regime (<100 nm), we observe a change in the device performance. To maintain the rate of improvement in device performance with continued down scaling, modifications to device designs and fabrication techniques are required. Advanced MOSFET structures like ultra thin-body (UTB) FET, Dual-gate FET, FinFET, TriGate FET and Gate All Around (GAA) FET offer the opportunity to continue scaling beyond the bulk because they provide reduced short channel effects (SCE's), a sharper subthreshold slope (S/S) and better carrier transport as channel doping is reduced. Silicon Nanowire Field Effect Transistor (SiNWFET) is a promising candidate [1] for future CMOS device for further scaling. The Gate All around structure enhances the Gate length scalability because the electrostatic control is improved. Moreover threshold voltage variations due to random dopant fluctuations are minimized because it enables the use of an undoped channel [2].

Over the past few decades of dominance of CMOS devices in electronic applications, combining n- and p-FET to reduce power dissipation and silicon area, recently a demonstrable concept was provided for universal transistor which can be configured as n-FET/p-FET by application of appropriate potentials in an axial nanowire heterostructure [Metal-Insulator-Metal (M-i-M)] with independent Schottky junctions. This latest modification in SiNWFET technology is to provoke the concept of ambipolarity in these devices i.e. tuning the polarity allowing the device to act as an n-FET or a p-FET by mere application of voltage with the help of two or three metal gates. The concept to make ambipolar devices using Si is thought to be a modification to next generation FinFET as well as GAAFET and their physics is very much similar to Tunnel Field Effect Transistors

(TFETs). With the help of one control gate and another polarity gate it is possible to make one type of carrier (either e<sup>-</sup>'s or holes) to tunnel from Drain to Source end and block the flow of other type of carrier. FinFETs have successfully shown that short channel effects (SCEs) can be minimized to a great extent due to better electrostatic control. To acquire a more superior gate control, Silicon NanoWire FETs (SiNWFETs) having gate-all-around structures have proven to be an ideal replacements to FinFETs. The Schottky metallic contacts at the source and drain junctions creates Schottky junctions that can be tuned electrically to invoke the reconfigurable behaviour. The logic architectures that are impossible to implement with CMOS intrinsically can be developed using ambipolar DG in a compact form.

For reduction of the overall leakage power dissipation of circuits in current CMOS technology, multi threshold voltage (multi- $V_t$ ) design is used widely. In the critical paths low- $V_t$  devices are used so that the timing constrains are met, while in the slack paths, high- $V_t$  devices with low-leakage are used. However, to implement the multi- $V_t$  circuits additional technological steps are required to create devices with multiple threshold voltages, which affects the regularity in layout and also increases the process costs compared to single- $V_t$  circuits. Ambipolar SiNWFETs having dual  $V_t$  are expected to deliver better performance with smaller consumption of leakage power as compared to low standby power FinFET's.

This chapter introduces the work carried out in this thesis. Section 1.2 describes the background and motivation behind the research topic. Section 1.3 presents a brief discussion on the importance and expectations with SiNWFETs. The major problems with the GAA devices at the current technology node are highlighted in section 1.4. Section 1.5 presents the objectives of this thesis. In section 1.6 the main focus and outline of the work is presented. Finally, the chapter wise organization of the thesis in a compact form is provided in section 1.7.

### **1.2 Motivation behind the Research**

#### 1.2.1 Moore's Law and MOS transistors

After the invention of Bipolar junction transistor (BJT) in 1948 by William Shockley, Walter Houser Brattain and John Bardeen researchers across the globe were looking to overcome various shortcomings of this device such as low thermal stability, higher noise, low switching frequency, complex base control resulting in the requirement of skillful handling, predominant radiation affect etc. In search for other alternatives, the initial research on present day MOS transistors was started many years ago. In 1965 an observation was made by Intel co-founder Gordon Moore which is also known as Moore's law [3]. It states that after every two years the number of transistors in a dense integrated circuit will get doubled. This law remained unchanged over the next thirty years after this famous observation. It may be noted that at the time of Gordon Moore, the number of transistors in a particular integrated circuit were not more than 32 but now a day's almost 20 billion transistors are integrated on a single chip which clearly shows how important his observation was thus leading to the scaling of transistors. At present the general consensus that has been accepted by the microelectronics industry is that the number of transistors per chip gets doubled every 18 months. There are several implications of Moore's law on the semiconductors over the last several decades. The number of logic transistors in a chip defines its functionality. In the same chip, if more and more components are integrated, then the functionality per chip increases which reduces the delay of data flow and also increases the overall density of transistors per chip area. The next most important implication of Moore's law is the reduction in the cost of manufacturing per function in an integrated circuit along with increasing the functionality per chip. The third implication of this law is improving the speed of a particular microprocessor which is also known as performance factor. The density of transistors in a logic circuit is inversely proportional to the total chip area and directly proportional its overall speed and performance.

### 1.2.2 Scaling techniques and Short Channel Effects

The initial constant field scaling law for MOS transistors was propped by Robert. H. Dennard [4] in one of his research papers in which gate length of 10  $\mu$ m was demonstrated. After that an approximate reduction of 15% in gate length of MOSFET is registered every year and currently we have reached 22nm in 2014. By downscaling the MOSFET dimensions, using the constant field scaling theory deteriorate the electrical performance of the transistor. This is due to various SCE's which influence the output characteristics of the device and degrades its performance. There is another type of scaling mechanism known as the constant voltage scaling. In this approach the supply voltage of the transistor is kept

constant. This results in an increase in the electric field which in turn introduces hot carrier effects (HCEs) in the device. The constant voltage scaling is largely adopted in the industry because the rate of reduction in channel length of the MOS transistors with every technology generation [5] is not same as that of the supply voltage scaling ( $V_{DD}$ ). Moreover, constant field scaling yields the largest reduction in the power-delay product of a single transistor and the disadvantage of constant voltage scaling is that the electric field increases as the minimum feature length is reduced. Though there are a lot of potential improvements in a transistor's performance with continuous downscaling [6-11] in feature size such as increase in operating speed and packing density along with reduction in power dissipation but as we have entered into the sub nanometer regime (<100nm) various other unwanted problems are causing serious hindrance in maintaining the improvement rate. Such problems are collectively called SCEs [12-14]. It consists of a group of phenomenon like V<sub>th</sub>-roll off, drain-induced-barrier-lowering (DIBL), punch through, channel length modulation, impact ionization etc. Threshold voltage roll off refers to the fact that in short channel devices where the distance between source and drain is nearly equal to the depletion region width of the MOSFET in vertical direction, a part of the charge which is supposed to be controlled by the gate is actually shared between source and the drain. As a result, the gate voltage required to create a particular level of inversion decreases due to a reduction in effective charge being masked by the gate. It may cause serious problems for circuit designers because there is variation in V<sub>th</sub> due to process variations and with every technology node new techniques are needed to be found out for adequate control of threshold voltage. Another short channel effect known as drain-induced-barrier-lowering (DIBL) occurs when the height of the potential barrier between channel and source gets lowered at higher drain biases resulting in an enhanced drain current and as a result of which threshold voltage (V<sub>th</sub>) gets lowered. When the drain voltage is increased, the depletion layer width at the drain side may increase and the channel may actually become pinched-off (finished) at the drain side. This may reduce the overall channel length and increase the drain current and is termed as channel length modulation or CLM. This results in a decrease in the effective channel length. At a very high drain to source voltage, especially in small channel devices with low-doped substrates the depletion region under the drain and source can actually merge into a single depletion layer and under this conditions the field beneath the gate becomes a strong function

of drain to source voltage V<sub>DS</sub>. This may led into an uncontrolled drain current which is undesirable and may decrease the output conductance. Other unwanted effect which occurs especially in n-channel MOSFET is impact ionization. This may lead into increase of subthreshold current at larger drain voltages. Apart from the above mentioned short-channeleffects due to thinning of gate oxide following the constant field scaling approach the gate oxide tunneling current also increases exponentially and poses serious threats to further scaling of the device [13] as it becomes comparable to the drain current (I<sub>ON</sub>) at an oxide thickness of about 1nm. One of the main aim of technology scaling is to lower the dynamic power dissipation but at the same time since  $V_{DD}$  is scaled down and is approaching  $V_{th}$ , the static or standby power increases as the transistor size becomes small. For an enhanced higher circuit operation, higher on-current is desirable. Higher drive current is important in view of reduction of delay time in a circuit which depends upon the charging time of next stage capacitance and since the intrinsic delay determines the maximum frequency of operation of any logic circuit, it is one of the most important factors for circuit designers. On the other hand, in the operation of CMOS we find that when there is a change in the input logic state, the total load capacitance of next stage gets changed. Under steady state condition, only one of either NMOS or PMOS is in on-state and the other one remains off. So, under steady state conditions the only current which flows is the off state leakage current and thus for the reduction of total steady state or waiting power consumption, curtailment of off state leakage is very important.

#### 1.2.3 Introduction to Gate All Around (GAA) Devices

After the invention of MOSFET revolutionized the computer industry, the researchers were now focussing on developing new device structures which could further enhance the device performance. An idea was proposed to increase the number of gates to form multi gate transistors to enhance the electrostatic controllability of the channel as compared to single gate bulk SOI MOSFET thus reducing SCE and increase on current. It was found that a double gate (DG) MOSFET scaling can be done more aggressively and short cannel effects are further suppressed because of better effective gate control. Quite a number of double gate FET structures were proposed in the research community out of which the fin shaped field effect transistor or FiNFET emerged as the most popular one [15]. The speciality of this

structure is that the channel region consists of a vertical fin around which the gate is wrapped from the three sides. A few more GAA device structures such as tri gate and omega shaped gated FETs were also proposed. In comparison to tri gate structure an effective fourth gate extends into the substrate from one of the sides in the omega shaped one which makes it better in terms of device performance as the gate control is further improved. But the ultimate scaling options for a MOS transistor were actually provided by semiconductor nanowires which are cylindrical two dimensional crystal structures with few nanometres of diameter. Since the gate actually wraps the channel from all sides, a complete GAA structure was actually possible with this in contrary to all the above mentioned device architectures and the best performance in terms of short channel effects was also achieved with them.

### **1.3 Silicon Nanowires as Future Nanoscale Devices**

#### **1.3.1 Importance of Nanowire Based Devices**

Silicon nanowires are quasi one dimensional nanostructures having diameter less than 100nm. Over the last few years silicon nanowires have received considerable attention as chemical as well as biological sensors, photovoltaic as well as nanoelectronics devices [16-26]. Though planar and tri gate device proved their usefulness in various fields of technological applications with silicon as well as other materials [27-45], the small diameter of nanowires has proved to be highly advantageous as it results in a high surface to volume ratio which is an important requirement in sensor based applications because with even a very small input signal the nanowire potential can be effectively controlled. Moreover, their superior sensitivity in chemical surface processes also lies in the fact that one or more of their physical dimensions is always less than the charge screening length or the Debye length. When it comes to applications like photovoltaic solar cells, these nanowire structures are found to be more efficient than Li-ion batteries to collect the incoming solar radiation. In comparison to III-V semiconductors, the quantum confinement of carriers is visible only at large diameters; it is predicted to be substantial only at diameters below 3nm in silicon nanowires. For this reason the behaviour of silicon nanowires are often referred to as quasi 1-D. This quasi 1-D behaviour of silicon nanowires proves to be essential in devices in various ways. With nanowires having diameter below 10nm, the band structure also gets modified in a quiet interesting manner. It is observed that there is an increase in band gap for smaller

diameters and at sufficiently small diameters a direct band gap can be obtained. When it comes to field effect devices, silicon nanowire field effect transistors (SiNWFETs) have achieved the class of most important devices to investigate and optimize the electronic properties of nanowires. An optimum geometric gate coupling can be provided to the active area of the device because the gate is completely wrapped around the nanowire [21-24]. The best scaling performance can be achieved if the silicon thickness is quiet small to allow a full depletion at lower gate voltages. The fact that silicon nanowire field effect transistors is proposed and also studied nowadays by a lot of researchers across the globe lies in many of their superior features which make them a perfect candidate to become the building blocks for future nanoelectronics [23-25]. Some of these features are discussed here. They can be produced in huge quantities with electronic properties that are reproducible which is highly essential for very-large-scale-integrated (VLSI) systems. Moreover, they provide the ease of processing and ability for integration with conventional fabrication techniques which include the conventional bottom up approach to synthesize ultra thin nanowires with well controlled channel width which is not possible with the conventional lithography techniques. It is easier to maintain the electrical integrity of nanowire based electronics even if the gate length is scaled aggressively because their diameters can be controlled well below 10nm which is becoming increasingly difficult to achieve in conventional MOSFETs. Apart from the superior gate control, they are also able to provide radial and axial heterostructures which can reduce scattering and result in higher carrier mobility. By keeping the silicon film thickness same as that of the gate length subthreshold swing less than 75mV/dec and DIBL less than 50mV/V can be achieved using these GAA structures. But, reliability issues such as self heating effect (SHE) can affect the performance of these devices. It arises mainly due to difficulty in evacuating the generated heat due to electron phonon scattering in these structures. Furthermore, surface roughness and spatial confinement can further increase the self heating phenomenon. But through improved fabrication techniques and reduced variability most of the reliability issues can be controlled up to a great extent.

#### 1.3.2 Quest for a Universal CMOS Switch

The computer industry has relied upon n-type and p-type transistors for the implementation of computing circuits over the last four decades. The alternative switching of

n and p FETs is because of the different polarity of the charge carriers. Due to aggressive scaling of the dimensions of transistors, it is becoming increasingly difficult to accurately control the doping distribution in modern 3-D structures. To achieve the energy efficient CMOS operation, it is mandatory that the performance of the n and p-transistors have to be comparable. This means that they must have almost equal on-currents, threshold voltages and inverse subthreshold slopes. The larger channel width requirement in silicon to align oncurrents is due to the significantly lower hole mobility compared to that of electrons. For modern 3-D CMOS devices, it is quite difficult to adjust the channel width freely without affecting the device electrostatics. To double the number of p-channels connected in parallel is one possible solution to adjust the current in such cases. The reconfigurable technology can provide solutions to both these problems [46-51], i.e. the difficulty to control the dopant distribution and dissimilar sizing of p and n FETs and hence can reduce the intricacy to build CMOS logic circuits. The channel is kept intrinsic in these devices to allow n and p conduction from the same channel and to avoid impact of doping. After the successful demonstration of field programmable FPGA in 1984, reprogrammable nanowire FPGA matrices have been developed in 2003 and programmable circuits for nano-processors in 2011 by Lieber et. al. [52]. Finally, Schottky barrier engineering technique is adopted to selectively inject electrons and holes into the intrinsic channel from the source and drain electrodes to form the so called reconfigurable FET (RFET) which are discussed later.

#### **1.4 Problem Statement**

In light of the existing literature survey, the major problems we have encountered with the various GAA devices at the current technology node are listed below:

- i) Since, separate n- and p-transistors are required the layout area is basically large.

- ii) The fabrication process is relatively complex and costly.

- iii) Increased short channel effects due to scaling.

- The drive current is degraded due to various scattering mechanisms which are resulted from heavy doping in the channel region.

#### **1.5 Objectives of the Thesis**

The objectives of this thesis are enumerated below.

- (a) To design for the first time a source/drain (S/D) spacer based *underlap* ambipolar silicon nanowire field-effect transistor device structure and optimize various device aspects like spacer material type and length of spacer length ( $L_{sp}$ ), gate dielectric and its thickness ( $t_{ins}$ ) and inter gate distance ( $d_{G1G2}$ ) using rigorous coupled 3-D Technology Computer Aided Design (TCAD) numerical device simulations. A systematic investigation of the impact of these critical design parameters on the vital device performance parameters, such as  $I_{ON}$ ,  $I_{ON}/I_{OFF}$ , Subthreshold swing (S/S),  $V_t$ , and  $g_m/I_d$  is proposed to be undertaken.

- (b) To acquire a deeper understanding of various physical details behind spacer based performance enhancements over the conventional *non-underlap* RFET architecture through device level optimizations, the impact of variation in the *gate channel underlap* (L<sub>GCU</sub>) and *spacer channel underlap* region (L<sub>SCU</sub>) on the device behaviour is also studied. So, the role of gate oxide EOT and scaling properties of the proposed device is also investigated.

- (c) Since the subthreshold drain current of a RFET depends upon thermionic emission which is itself a temperature dependent phenomenon, it is proposed to further extend the study as the temperature dependence of the digital/analog parameters and RF figure of merits of a spacer based RFET. The same are proposed to be compared with the existing RFET topology and other devices which depend on band to band tunneling (BTBT) for their on current generation. Having a better thermal stability over TFET and sufficiently lesser V<sub>th</sub> roll-off, the proposed device portrays orders of magnitude reduction in parasitic gate capacitances and intrinsic delay as compared to GAA and HD GAA TFET devices over the considered range of temperature, thus enduring higher switching speed for digital applications. The device is proposed to be more stable under temperature variations.

- (d) To develop a physics based compact model is developed for surface potential and drain current for a dual gate (DG) source/drain (S/D) spacer based silicon nanowire reconfigurable field effect transistor. The models are derived by dividing the active

portion of the device into several regions based on positioning of the gates, spacers and the metal-silicide Schottky junctions. A charge density expression is first developed and the 2-D Poisson's equation is self consistently solved for various sub-regions of the device, to model the drain current and surface potential. The accuracy of the derived results is tested using 3-D numerical TCAD simulations. This work is concluded by investigating the spacer induced performance improvements over the conventional *non-underlap* RFET with respect to delay reduction mainly in logic and digital circuit applications.

#### **1.6 Outline of the Work**

The focus of the thesis is to propose a novel ambipolar FET architecture in which many of the limitations of the current *non-underlap* RFET is overcome. This is done by bringing into focus the *underlap* RFET device using the source/drain spacer technology. The inherent device physics behind the spacer induced performance enhancements and the effects of variation in various device attributes on the behaviour of the proposed RFET are discussed in details. Looking at the fact that the device on current is partially dependent on thermionic emission, the temperature dependence of the DC, analog and RF performance of the device is also illustrated. Finally, a charge based compact analytical model of the device under consideration is developed and in addition it is also shown that how S/D spacers can be useful in delay reduction in case of few digital circuit applications. In total the thesis has seven chapters. At the beginning of each chapter there is a brief introduction along with the motivation about the concerned problem. In addition, the simulation methodology, results and analysis are discussed in a comprehendible way.

#### **1.7 Thesis Organization**

**Chapter 1** introduces the entire thesis. It provides the motivation and outline behind this research and the agenda for choosing the objectives of the work. Problem statement, objectives of the thesis and the thesis organization is presented in this chapter.

Chapter 2 provides a comprehensive literature review on RFET devices and work done by various research groups across the world so far. Starting from the basic single gate ambipolar transistor, we gradually move into dual and triple gate RFET architectures. The device physics, advantages and the technological challenges are also discussed.

**Chapter 3** introduces the new device concept in details. For the very first time the effect of source/drain spacer oxide on the performance of a dual gate ambipolar silicon nanowire field effect transistor are portrayed using extensive 3-D TCAD simulations. We show discusses the impact of various physical attributes of the device under consideration such as spacer length, spacer material, gate oxide material along with its thickness and inter gate distance on vital performance parameters of the device such as  $I_{ON}$ ,  $I_{ON}/I_{OFF}$ , Subthreshold swing (*S/S*),  $V_t$  and  $g_m/I_d$  along with their optimization for achieving best device performance.

**Chapter 4** discusses the appropriate designing of the gate/spacer channel underlap region to maximize the  $I_{ON}$  and  $I_{ON}/I_{OFF}$  ratio and the inherent device physics behind the performance enhancements is also illustrated in details. It further elucidates the role of gate oxide equivalent oxide thickness (EOT) on the performance of the proposed RFET along with which the scaling properties of this device are also reported.

**Chapter 5** illustrates the temperature dependence of the digital/analog parameters and RF figure of merits (FOMs) of the proposed RFET and compares the same with the existing RFET topology and other devices which depend on band-to-band tunneling (BTBT) for their on-current generation. Since the on-current of a RFET depends on thermionic emission phenomenon as well which is itself temperature dependent, it is highly interesting to study the temperature dependence of the device characteristics for this unique nanotransistor because though the impact of temperature on the device performance for tunnel field effect transistor (TFET) has been reported earlier by various groups, such an investigation has not yet been presented so far in case of an RFET.

**Chapter 6** begins with the development of a physics based compact model for surface potential and drain current for the device under consideration which can be used can be used to study the behavior of ambipolar FETs having S/D spacers for varying device dimensions and also can be utilized for the future design of memory devices and circuits using spacer based RFETS. The model includes the effects of drain voltage, nanowire radius, temperature and Schottky barrier height. The accuracy of the derived results is tested using 3-D numerical

TCAD simulations. The chapter ends with the illustration of how the spacer technology can be useful in digital logic applications.

The conclusions of the thesis are drawn based on the obtained results in **Chapter 7**. The thesis ends with future scopes related to this work and a complete bibliography.

# **Chapter 2**

# **Reconfigurable Field Effect Transistor-Device Physics, Challenges and Applications: A Literature Review**

#### 2.1 Introduction

As the state of art CMOS technology is reaching its scaling limits, sub threshold leakage is becoming a big threat at the current 22nm node technology. Various methods have been tried in the past to resolve this problem. Use of high- $\kappa$  gate dielectrics is one of such methods [53]. Moreover, multi  $V_t$  design has gained immense popularity in designing modern complex logic architectures. Nearly, five decade old research in CMOS based IC's portrays the use of combination of n- and p-FET devices [5-30]. But, exact control of doping are required in these devices and changing their electrical characteristics is very tough. Among the futuristic devices, CNT FETs and various tunneling based transistors has gained immense attention from various device researchers In recent years [54-84], one such class of device is the reconfigurable Gate All Around (GAA) SiNWFET which is of immense interest because of their negligible random dopant fluctuation, lower series resistance, excellent electrostatic integrity, low thermal budget and higher on to off current ratio at a given supply voltage. Moreover the ease of fabrication with the conventional bottom up approach has made them as one of the potential competitors for future CMOS logic technologies. Recent research by Zhang et. al. [46], have shown that ambipolar SiNWFET can be immensely useful in the design of complex logic architectures. This chapter presents a detailed study on this current topic of research i.e Ambipolar SiNWFETs, history of development, their operation, method of fabrication and their application from digital logic design point of view. After an extensive literature survey, the chapter ends with outlining the current technical gaps.

#### 2.2 Nanowire FET Classification

Depending on the materials by which they are made, nanowire can be broadly classified as semiconductor nanowires, metallic nanowires and molecular nanowires. They can also be categorized as metal nitride, metal carbide and metal oxide nanowires [21]. Among the various types of nanowire Si/SiO<sub>2</sub> based nanowires having a stable semiconductor/oxide interface have gained immense popularity. Examples of elemental

nanowires include Ge, B, In, Sn nanowires whereas metal oxide nanowires include  $SnO_2$ , GeO<sub>2</sub>, SiO<sub>2</sub> nanowires. Further, metal carbide and metal nitride nanowires consists of BC, SiC and BN, AlN nanowires respectively.

#### 2.2.1 Properties and Applications of SiNWFETs

Nanowires can also be defined as structures with certain length and thickness or diameter limited to tens of nanometer or even less. In nanowires with diameter less than 15nm mobility of electrons is found to behave in a different manner mainly due to quantum confinement as compared to its bulk counterpart. Kotlyar et. al. [85] had shown that as wire size reduces, phonon-limited electron mobility decreases. Jin et. al. [86] stated that there is an enhancement in total electron mobility at high transverse field due to volume inversion. When the material size is smaller than de Broglie wavelength, electrons and holes are confined spatially leading to the formation of electric dipoles. Moreover, in all materials discrete electronic energy levels are formed. The energy separation between adjacent levels increases with decreasing dimension. The electron Density of States (DOS) depends largely on the dimensions of structures in nanoscale. For bulk systems, there is a square-root dependence of energy, discrete features are seen in zero dimensional (0D) quantum dots, in one dimensional (1D) quantum wires spikes are observed and for two dimensional (2D) quantum well structures the behaviour is more like a staircase. V. K. Arora [87] described that ballistic transport mechanism is an important phenomenon that takes place in nanowires. It generally takes place if device length is smaller than the mean-free path of electrons. With respect to ballistic transport is that there is neither any elastic scattering nor energy dissipation in the process of conduction. Impurities and defects should be there for scattering to take place. The transmission coefficients will be reduced when elastic scattering takes place.

#### **2.3 Tunneling Based FETs**

#### 2.3.1 Theory of Tunneling