## DEVICE-CIRCUIT INTERACTIONS IN TUNNEL FET: AN ANALOG DESIGN PERSPECTIVE

Ph.D. THESIS

CENTRE OF NANOTECHNOLOGY INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE - 247667, INDIA OCTOBER, 2018

## DEVICE-CIRCUIT INTERACTIONS IN TUNNEL FET: AN ANALOG DESIGN PERSPECTIVE

#### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

#### DOCTOR OF PHILOSOPHY

in

NANOTECHNOLOGY

by

**ABHISHEK ACHARYA**

CENTRE OF NANOTECHNOLOGY INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247 667 (INDIA) OCTOBER, 2018

## INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

## **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled "DEVICE-CIRCUIT INTERACTIONS IN TUNNEL FET: AN ANALOG DESIGN PERSPECTIVE" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Centre of Nanotechnology of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from January, 2015 to October, 2018 under the supervision of Dr. Anand Bulusu, Associate Professor, Department of Electronics and Communication Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

#### (ABHISHEK ACHARYA)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

Date: 09/04/2019

#### Supervisor

The Ph. D. Viva-Voce Examination of <u>Abhishek Acharya</u>, Research Scholar, has been held on <u>09/04/2019</u>.

Chairperson, SRC

Signature of External Examiner

This is to certify that the student has made all the corrections in the thesis.

Signature of Supervisor Dated: <u>09/04/2019</u>

Head of the Department

#### ABSTRACT

The static-power constrained applications have promoted the research on the steep slope transistor based analog/digital circuits. The prime objective is to overcome the problem of the MOSFET's ever-increasing leakage current while maintaining the performance. Therefore, the transistors with a steep subthreshold swing (SS) are being extensively investigated by the device research community. Among the emerging transistors, Tunnel FET (TFET) is one of the most promising by virtue of its ultra-low leakage current and MOSFET compatible fabrication processes. There are two kinds of TFETs, point and line TFET which are differentiated as per the direction of tunneling with respect to the gate. The steep slope of these devices makes them suitable for the sensing and other low power applications. However, the biasing schemes and the impact of device design parameters on the analog circuit performance have not been discussed in depth for TFETs. Bearing the above facts in mind, the biasing strategies and the small signal model for TFET need to be examined in detail. In addition, the drain current saturation voltage ( $V_{DSAT}$ ) and the body bias saturation voltage ( $V_{BSAT}$ ) are extremely important from the perspective of analog design.

We investigated for the first time, a method to extract  $V_{\text{DSAT}}$  for the point and line TFETs. The saturation in output characteristics of a point TFET is attained when the difference in the conduction band energy of the channel and drain is a few  $K_{\text{B}}T$ . As the drain voltage ( $V_{\text{DS}}$ ) increases, the device initially enters in a *soft* saturation state and subsequently into *deep* saturation. The onset of *soft* and *deep* saturation happens for a constant difference in the gatedrain bias ( $V_{\text{GD}}$ ). We have also validated our results with the published experimental data. A *soft* saturation state in L-TFET is attained when the electron density in the epitaxial layer over the source saturates with the drain bias ( $V_{\text{DS}}$ ) and the conduction band energy gets pinned. In addition, at the onset of *deep* saturation, the electron density in the epitaxial layer over the channel drops below its doping level and the conduction band energy becomes invariant of any further increase in  $V_{\text{DS}}$ . The transconductance and output resistance abruptly increases when the device enters in the *soft* saturation regime and attains a maximum in the *deep* saturation. The difference  $V_{\text{GD}}$  is found to be a constant at the onset of saturation and remains independent of the gate-source overlap length ( $L_{\text{OV}}$ ). A shift in  $V_{\text{DSAT}}$  and  $V_{\text{GD}}$  is also observed with a change in the thickness and doping of the epitaxial layer. Further, a nominal change of ~ 5% in the voltage gain of a common source amplifier is observed when the *n*-device is either biased in *soft* or *deep* saturation regime, without any trade-off in the bandwidth. The proposed method is suitable for the analog design as  $V_{\text{DSAT}}$  varies linearly with  $V_{\text{GS}}$ .

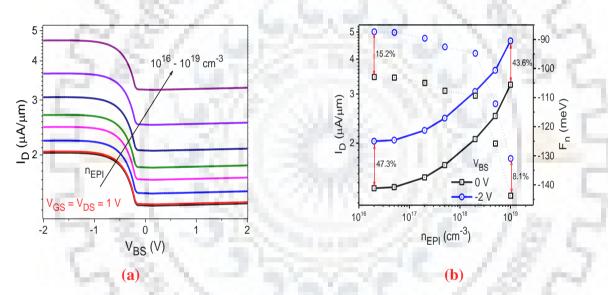

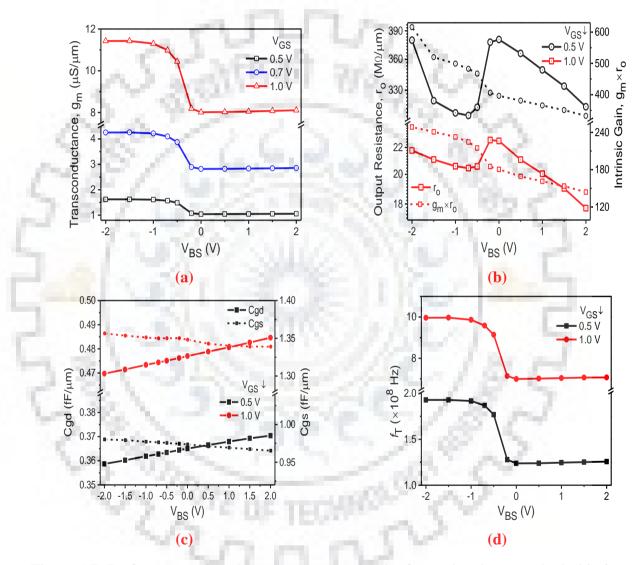

The impact of body bias ( $V_{BS}$ ) and gate-source overlap on the device-circuit analog performance of the epitaxial layer based L-TFETs is reported for the first time. The occupancy probability within the valence band of the source determines the modulation of  $I_D$  with  $V_{BS}$ . An increase of 40-60 % in  $I_D$  with the reverse  $V_{BS}$  is observed, while the forward  $V_{BS}$  does not significantly alter the drain current. The reverse  $V_{BS}$  at which  $I_D$  attains the maximum value is defined as  $V_{BSAT}$ , which changes almost linearly with  $V_{GS}$ . We also proposed a mathematical model to determine  $V_{BSAT}$ , bsed on the electrostastics of the gate-source overlap region.  $V_{BSAT}$ increases with the gate-source overlap length ( $L_{OV}$ ) and decreases with the thickness of epitaxial layer. The intrinsic gain and unity gain cut-off frequency increase with the reverse  $V_{BS}$ and remain nearly constant with the forward  $V_{BS}$ .

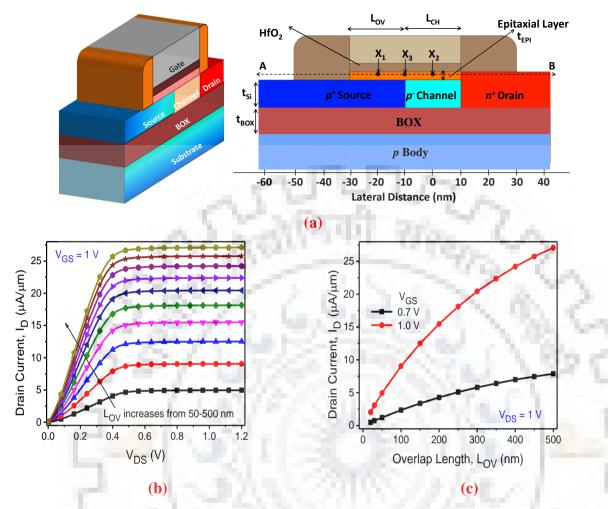

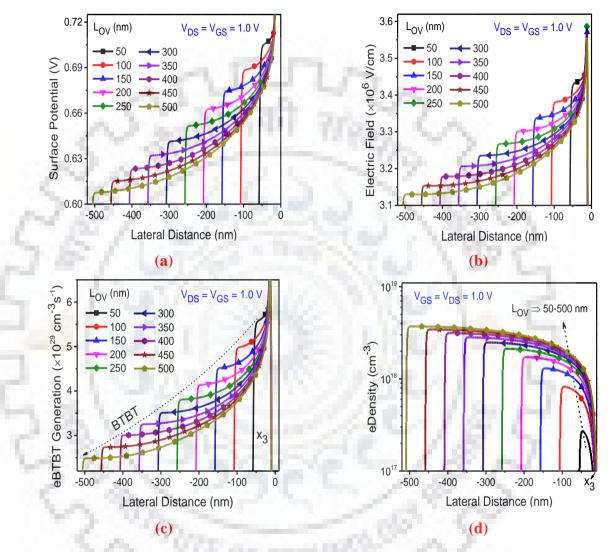

In general, the device width is being used to improve the drive capability in circuit design. We investigated that an increase in the gate-source overlap can also substantially enhance the analog performance of L-TFETs. Thus, we propose  $L_{OV}$  variation-aware small signal model for L-TFETs based analog circuit design. This model can be used for appropriate sizing of the transistor for a target amplifier performance. The drain current initially increases linearly with  $L_{OV}$ , and then exhibits a non-linear behavior. This is due to reduced effect of the lateral electric field at the far end of the gate-source overlap region. It is observed than an increase of 2.5× in  $L_{OV}$  results in ~2.33× increase in the voltage gain without any significant penalty in the bandwidth. Therefore,  $L_{OV}$  can be used as an important design parameter in the analog circuit design, as it does not significantly change the output resistance and the gate-drain capacitance of the device.

#### ACKNOWLEDGMENTS

#### वक्रतुण्ड महाकाय सूर्यकोटि समप्रभ । निर्विघ्नं कुरु मे देव सर्वकार्येषु सर्वदा ॥

I have been very blessed to pursue my PhD studies under the esteemed guidance of **Dr. Anand Bulusu**, Associate Professor, Department of Electronics and Communication Engineering, IIT Roorkee, Roorkee. With his continuous guidance and encouragement, I could be motivated to explore a heterogeneous array of topics in the device/circuit engineering. I am extremely thankful to him for the meticulous care with which he examined my work and a multitude of other reasons, which made it possible for this thesis to take its present shape.

I deeply value the insights and advice received from the faculty members of Microelectronics & VLSI Group, IIT Roorkee on a wide variety of topics. My conversations with them and their students have been a fantastic learning experience for me. I'd also like to thank the members of my Student Research Committee for sparing their precious time to carefully review my progress and providing critical suggestions to improve the work. I sincerely thank Naveen Sir for his support in dealing with the workstations, tools, licenses, and internet related issues.

I am also thankful to my parent organization *Government Engineering College Bikaner* for sponsoring me for this noble cause and *Quality Improvement Programme Centre*, *IIT Roorkee* for providing all the necessary logistic arrangement, during this tenure. Special thanks to my fellow colleague, brother, and good friends Alok Acharya and Ajay Choudhary. It was always cool hanging out with you guys in the mother tongue.

I have been fortunate to be part of a lab filled with fellow students who have been great teachers (and co-learners), colleagues, and friends. I have learned much from and enjoyed to know all of my labmates over the years, including Navjeet, Shashank, Neeraj, Lalit, Deepak, Rahul, Inder, Govinda, Shivam Sir, Arvind Sir, Om Sir, and Bhattacharjee. My graduate experience would be unimaginable without the deep discussions and time frittered away in their company. Prabhat Dubey has been a constant sounding board and debate partner on just about every topic imaginable. Abhishek Solanki was an able and willing helper during his free time in our lab. Outside of our group, I have similarly benefited and drawn inspiration from continual discussions with many other fellow students. Out of so many educational and entertaining

conversation partners, I've benefited in particular from knowing, and talking the ears off of Vikas, Anant, Sanjay, Gyanendra, and Amit. I've spent a lot of time with them and the memories that bring smile on my face. The never ending tea sessions with them at different corners of the campus were magical to vaporize my fatigues. There are no words to describe my gratitude towards my fellow colleagues Kunal, Jyoti, Rahul and Lomash for their unconditional encouragement and inspiration. There all are pillar of support guiding through the thick and thin of time.

Most or all of the materials presented in Chapters 3, 4, 5, and 6 have been either published or communicated in assorted IEEE journals and conferences; they are reproduced here with the minor modifications in accord with the author rights agreements for the respective publications.

Thanking my family is both essential and inadequate in the face of all the experiences we've been through together. There are no words to describe gratitude towards my family members for their unconditional love, trust, inspiration, and encouragement. I would like to express my great appreciation to my late grandfather, late father, mother, wife and my lovely daughter, for their patience and sacrifice to my selfish dream.

I know that all things work together for the good of those who love God. May my life and work be in accord with His will and glorify His name.

(Abhishek Acharya)

## Contents

Ĺ

| AcknowledgementiiiTable of ContentsviiList of FiguresxiList of Tablesxv1Introduction11.1 Fundamental Limitation of CMOS: Tunnel FETs11.2 Working Principle of Tunnel FETs41.3 Motivation71.4 Objectives71.5 Outline of Work in this Report82Literature Survey112.1 Initial work on Tunnel Device112.2.1 Quench of Steep Slope and High Drive Current122.2.2 Current Fabrication Status of TFET142.3 Tunnel FET Device Physics and Modeling152.3.1 Device Physics152.3.2 Device Modeling162.4 Tunnel FET for Analog and Digital Circuits172.5 Technical Gaps193VDSAT Extraction Method for Tunnel FETs and its Implication to Analog21Design3.1 Introduction21                                                                                        |        | Abstract                                                                      | i   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------|-----|

| List of FiguresxiList of Tablesxv1Introduction11.1 Fundamental Limitation of CMOS: Tunnel FETs11.2 Working Principle of Tunnel FETs41.3 Motivation71.4 Objectives71.5 Outline of Work in this Report82Literature Survey112.1 Initial work on Tunnel Device112.2 The Promise and Status of Tunneling FETs112.3.1 Quench of Steep Slope and High Drive Current122.4.2 Current Fabrication Status of TFET142.3 Tunnel FET Device Physics and Modeling152.3.2 Device Modeling162.4 Tunnel FET for Analog and Digital Circuits172.5 Technical Gaps193V <sub>DSAT</sub> Extraction Method for Tunnel FETs and its Implication to Analog21Design11                                                                                                          |        | Acknowledgement                                                               | iii |

| List of Tablesxv1Introduction11.1Fundamental Limitation of CMOS: Tunnel FETs11.2Working Principle of Tunnel FETs41.3Motivation71.4Objectives71.5Outline of Work in this Report82Literature Survey112.1Initial work on Tunnel Device112.2The Promise and Status of Tunneling FETs112.2.1Quench of Steep Slope and High Drive Current122.2.2Current Fabrication Status of TFET142.3Tunnel FET Device Physics and Modeling152.3.1Device Physics152.3.2Device Modeling162.4Tunnel FET for Analog and Digital Circuits172.5Technical Gaps193VDSAT Extraction Method for Tunnel FETs and its Implication to Analog21DesignDesign14                                                                                                                         |        | Table of Contents                                                             | vii |

| 1Introduction11.1Fundamental Limitation of CMOS: Tunnel FETs11.2Working Principle of Tunnel FETs41.3Motivation71.4Objectives71.5Outline of Work in this Report82Literature Survey112.1Initial work on Tunnel Device112.2The Promise and Status of Tunneling FETs112.2.1Quench of Steep Slope and High Drive Current122.2.2Current Fabrication Status of TFET142.3Tunnel FET Device Physics and Modeling152.3.1Device Physics152.3.2Device Physics152.3.2Device Modeling162.4Tunnel FET for Analog and Digital Circuits172.5Technical Gaps193VDSAT Extraction Method for Tunnel FETs and its Implication to Analog21DesignDesign14                                                                                                                    |        | List of Figures                                                               | xi  |

| 1.1 Fundamental Limitation of CMOS: Tunnel FETs11.2 Working Principle of Tunnel FETs41.3 Motivation71.4 Objectives71.5 Outline of Work in this Report82 Literature Survey112.1 Initial work on Tunnel Device112.2 The Promise and Status of Tunneling FETs112.1 Quench of Steep Slope and High Drive Current122.2.2 Current Fabrication Status of TFET142.3 Tunnel FET Device Physics and Modeling152.3.1 Device Physics152.3.2 Device Modeling162.4 Tunnel FET for Analog and Digital Circuits172.5 Technical Gaps193 VDSAT Extraction Method for Tunnel FETs and its Implication to Analog21Design14                                                                                                                                               |        | List of Tables                                                                | XV  |

| 1.1 Fundamental Limitation of CMOS: Tunnel FETs11.2 Working Principle of Tunnel FETs41.3 Motivation71.4 Objectives71.5 Outline of Work in this Report82 Literature Survey112.1 Initial work on Tunnel Device112.2 The Promise and Status of Tunneling FETs112.1 Quench of Steep Slope and High Drive Current122.2.2 Current Fabrication Status of TFET142.3 Tunnel FET Device Physics and Modeling152.3.1 Device Physics152.3.2 Device Modeling162.4 Tunnel FET for Analog and Digital Circuits172.5 Technical Gaps193 VDSAT Extraction Method for Tunnel FETs and its Implication to Analog21Design14                                                                                                                                               | 1      |                                                                               |     |

| 1.2Working Principle of Tunnel FETs41.3Motivation71.4Objectives71.5Outline of Work in this Report82Literature Survey112.1Initial work on Tunnel Device112.2The Promise and Status of Tunneling FETs112.1Quench of Steep Slope and High Drive Current122.2.2Current Fabrication Status of TFET142.3Tunnel FET Device Physics and Modeling152.3.1Device Physics152.3.2Device Modeling162.4Tunnel FET for Analog and Digital Circuits172.5Technical Gaps193VDSAT Extraction Method for Tunnel FETs and its Implication to Analog<br>Design21                                                                                                                                                                                                            | 1      | Introduction                                                                  | 1   |

| 1.3 Motivation       7         1.4 Objectives       7         1.5 Outline of Work in this Report       8         2 Literature Survey       11         2.1 Initial work on Tunnel Device       11         2.2 The Promise and Status of Tunneling FETs       11         2.2.1 Quench of Steep Slope and High Drive Current       12         2.2.2 Current Fabrication Status of TFET       14         2.3 Tunnel FET Device Physics and Modeling       15         2.3.1 Device Physics       15         2.3.2 Device Modeling       16         2.4 Tunnel FET for Analog and Digital Circuits       17         2.5 Technical Gaps       19         3       V <sub>DSAT</sub> Extraction Method for Tunnel FETs and its Implication to Analog       21 | $\sim$ | 1.1 Fundamental Limitation of CMOS: Tunnel FETs                               | 1   |

| 1.4 Objectives71.5 Outline of Work in this Report82 Literature Survey112.1 Initial work on Tunnel Device112.2 The Promise and Status of Tunneling FETs112.1 Quench of Steep Slope and High Drive Current122.2.2 Current Fabrication Status of TFET142.3 Tunnel FET Device Physics and Modeling152.3.1 Device Physics152.3.2 Device Modeling162.4 Tunnel FET for Analog and Digital Circuits172.5 Technical Gaps193 V <sub>DSAT</sub> Extraction Method for Tunnel FETs and its Implication to Analog21Design21                                                                                                                                                                                                                                       | ×.     | 1.2 Working Principle of Tunnel FETs                                          | 4   |

| 1.5 Outline of Work in this Report82 Literature Survey112.1 Initial work on Tunnel Device112.2 The Promise and Status of Tunneling FETs112.2.1 Quench of Steep Slope and High Drive Current122.2.2 Current Fabrication Status of TFET142.3 Tunnel FET Device Physics and Modeling152.3.1 Device Physics152.3.2 Device Modeling162.4 Tunnel FET for Analog and Digital Circuits172.5 Technical Gaps193 VDSAT Extraction Method for Tunnel FETs and its Implication to Analog21Design14                                                                                                                                                                                                                                                                |        | 1.3 Motivation                                                                | 7   |

| 1.5 Outline of Work in this Report82 Literature Survey112.1 Initial work on Tunnel Device112.2 The Promise and Status of Tunneling FETs112.2.1 Quench of Steep Slope and High Drive Current122.2.2 Current Fabrication Status of TFET142.3 Tunnel FET Device Physics and Modeling152.3.1 Device Physics152.3.2 Device Modeling162.4 Tunnel FET for Analog and Digital Circuits172.5 Technical Gaps193 VDSAT Extraction Method for Tunnel FETs and its Implication to Analog21Design14                                                                                                                                                                                                                                                                |        | 1.4 Objectives                                                                | 7   |

| 2.1 Initial work on Tunnel Device112.2 The Promise and Status of Tunneling FETs112.2.1 Quench of Steep Slope and High Drive Current122.2.2 Current Fabrication Status of TFET142.3 Tunnel FET Device Physics and Modeling152.3.1 Device Physics152.3.2 Device Modeling162.4 Tunnel FET for Analog and Digital Circuits172.5 Technical Gaps19VDSAT Extraction Method for Tunnel FETs and its Implication to Analog21                                                                                                                                                                                                                                                                                                                                  |        | 1.5 Outline of Work in this Report                                            | 8   |

| 2.1 Initial work on Tunnel Device112.2 The Promise and Status of Tunneling FETs112.2.1 Quench of Steep Slope and High Drive Current122.2.2 Current Fabrication Status of TFET142.3 Tunnel FET Device Physics and Modeling152.3.1 Device Physics152.3.2 Device Modeling162.4 Tunnel FET for Analog and Digital Circuits172.5 Technical Gaps19VDSAT Extraction Method for Tunnel FETs and its Implication to Analog21                                                                                                                                                                                                                                                                                                                                  | 1      |                                                                               |     |

| 2.2 The Promise and Status of Tunneling FETs112.2.1 Quench of Steep Slope and High Drive Current122.2.2 Current Fabrication Status of TFET142.3 Tunnel FET Device Physics and Modeling152.3.1 Device Physics152.3.2 Device Modeling162.4 Tunnel FET for Analog and Digital Circuits172.5 Technical Gaps19VDSAT Extraction Method for Tunnel FETs and its Implication to Analog21Design                                                                                                                                                                                                                                                                                                                                                               | 2      | Literature Survey                                                             | 11  |

| 2.2.1 Quench of Steep Slope and High Drive Current122.2.2 Current Fabrication Status of TFET142.3 Tunnel FET Device Physics and Modeling152.3.1 Device Physics152.3.2 Device Modeling162.4 Tunnel FET for Analog and Digital Circuits172.5 Technical Gaps19V <sub>DSAT</sub> Extraction Method for Tunnel FETs and its Implication to Analog21Design                                                                                                                                                                                                                                                                                                                                                                                                 |        | 2.1 Initial work on Tunnel Device                                             | 11  |

| 2.2.2 Current Fabrication Status of TFET142.3 Tunnel FET Device Physics and Modeling152.3.1 Device Physics152.3.2 Device Modeling162.4 Tunnel FET for Analog and Digital Circuits172.5 Technical Gaps19VDSAT Extraction Method for Tunnel FETs and its Implication to Analog21Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C.,    | 2.2 The Promise and Status of Tunneling FETs                                  | 11  |

| 2.3 Tunnel FET Device Physics and Modeling       15         2.3.1 Device Physics       15         2.3.2 Device Modeling       16         2.4 Tunnel FET for Analog and Digital Circuits       17         2.5 Technical Gaps       19         3       V <sub>DSAT</sub> Extraction Method for Tunnel FETs and its Implication to Analog       21         Design       21                                                                                                                                                                                                                                                                                                                                                                              | 5      | 2.2.1 Quench of Steep Slope and High Drive Current                            | 12  |

| 2.3.1 Device Physics       15         2.3.2 Device Modeling       16         2.4 Tunnel FET for Analog and Digital Circuits       17         2.5 Technical Gaps       19         3       V <sub>DSAT</sub> Extraction Method for Tunnel FETs and its Implication to Analog       21         Design       21                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19     |                                                                               | 14  |

| 2.3.1 Device Physics       15         2.3.2 Device Modeling       16         2.4 Tunnel FET for Analog and Digital Circuits       17         2.5 Technical Gaps       19         3       V <sub>DSAT</sub> Extraction Method for Tunnel FETs and its Implication to Analog       21         Design       21                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | 2.3 Tunnel FET Device Physics and Modeling                                    | 15  |

| 2.3.2 Device Modeling       16         2.4 Tunnel FET for Analog and Digital Circuits       17         2.5 Technical Gaps       19         3 V <sub>DSAT</sub> Extraction Method for Tunnel FETs and its Implication to Analog       21         Design       21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        | 2.3.1 Device Physics                                                          | 15  |

| <ul> <li>2.5 Technical Gaps</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | 2.3.2 Device Modeling                                                         | 16  |

| 3 <i>V</i> <sub>DSAT</sub> Extraction Method for Tunnel FETs and its Implication to Analog 21<br>Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | 2.4 Tunnel FET for Analog and Digital Circuits                                | 17  |

| Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | 2.5 Technical Gaps                                                            | 19  |

| Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                                                               |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3      | $V_{ m DSAT}$ Extraction Method for Tunnel FETs and its Implication to Analog | 21  |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | Design                                                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        | 3.1 Introduction                                                              | 21  |

|                                                           | Device Structure And Simulation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22                                                                                                                                 |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 3.3                                                       | Proposed V <sub>DSAT</sub> Extraction Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24                                                                                                                                 |

|                                                           | 3.3.1 Definition of Soft and <i>Deep</i> Saturation in Tunnel FET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24                                                                                                                                 |

|                                                           | 3.3.2 A Novel Technique to Extract $V_{\text{DSAT}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26                                                                                                                                 |

| 3.4                                                       | Impact of Device Design Parameters on $V_{\text{DSAT}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29                                                                                                                                 |

|                                                           | 3.4.1 Impact of short channel length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29                                                                                                                                 |

|                                                           | 3.4.2 Impact of gate-drain underlap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30                                                                                                                                 |

|                                                           | 3.4.3 Impact of source/drain doping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                                                                                 |

|                                                           | 3.4.4 Impact of nanowire diameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32                                                                                                                                 |

|                                                           | 3.4.5 Impact of hetero/homo-junctions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32                                                                                                                                 |

| 3.5                                                       | Implications of Proposed $V_{\text{DSAT}}$ Extraction Technique to Analog Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33                                                                                                                                 |

|                                                           | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 33                                                                                                                                 |

| 3.6                                                       | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35                                                                                                                                 |

|                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                    |

| Dra                                                       | in Current Saturation in Line Tunneling based TFETs: An Analog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37                                                                                                                                 |

| dogi                                                      | ign Perspective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                    |

| uesi                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                    |

| 4.1                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37                                                                                                                                 |

| 4.1                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37<br>39                                                                                                                           |

| 4.1<br>4.2                                                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                    |

| 4.1<br>4.2                                                | Introduction Device Structure and Simulation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                    |

| 4.1<br>4.2                                                | Introduction       Introduction         Device Structure and Simulation Framework       Insights of the Output Current Saturation and Proposed V <sub>DSAT</sub> Extract                                                                                                                                                                                                                                                                                                                                                                          | 39                                                                                                                                 |

| 4.1<br>4.2                                                | Introduction       Introduction         Device Structure and Simulation Framework       Insights of the Output Current Saturation and Proposed V <sub>DSAT</sub> Extract         Method       Instruct                                                                                                                                                                                                                                                                                                                                            | 39<br>39                                                                                                                           |

| <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | Introduction          Device Structure and Simulation Framework          Insights of the Output Current Saturation and Proposed V <sub>DSAT</sub> Extract         Method          4.3.1       Output current saturation mechanism                                                                                                                                                                                                                                                                                                                 | 39<br>39<br>40                                                                                                                     |

| <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | Introduction          Device Structure and Simulation Framework          Insights of the Output Current Saturation and Proposed V <sub>DSAT</sub> Extract         Method          4.3.1       Output current saturation mechanism         4.3.2       Proposed V <sub>DSAT</sub> extraction technique for L-TFET                                                                                                                                                                                                                                  | <ol> <li>39</li> <li>39</li> <li>40</li> <li>42</li> </ol>                                                                         |

| <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | Introduction          Device Structure and Simulation Framework          Insights of the Output Current Saturation and Proposed V <sub>DSAT</sub> Extract         Method          4.3.1       Output current saturation mechanism         4.3.2       Proposed V <sub>DSAT</sub> extraction technique for L-TFET         Impact of L-TFET Structural Variation on V <sub>DSAT</sub>                                                                                                                                                               | <ol> <li>39</li> <li>39</li> <li>40</li> <li>42</li> <li>44</li> </ol>                                                             |

| <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | Introduction       Introduction         Device Structure and Simulation Framework       Device Structure and Simulation Framework         Insights of the Output Current Saturation and Proposed V <sub>DSAT</sub> Extract         Method       4.3.1         Output current saturation mechanism       4.3.2         Proposed V <sub>DSAT</sub> extraction technique for L-TFET       1.1         Impact of L-TFET Structural Variation on V <sub>DSAT</sub> 4.4.1         Impact of the gate source overlap length (L <sub>OV</sub> )       1.1 | <ul> <li>39</li> <li>39</li> <li>40</li> <li>42</li> <li>44</li> <li>44</li> </ul>                                                 |

| <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul> | IntroductionDevice Structure and Simulation FrameworkInsights of the Output Current Saturation and Proposed $V_{DSAT}$ ExtractMethod4.3.1Output current saturation mechanism4.3.2Proposed $V_{DSAT}$ extraction technique for L-TFETImpact of L-TFET Structural Variation on $V_{DSAT}$ 4.4.1Impact of the gate source overlap length ( $L_{OV}$ )4.4.2Impact of the epitaxial layer doping ( $n_{EPI}$ )4.4.3Impact of epitaxial layer thickness ( $t_{EPI}$ )                                                                                   | <ol> <li>39</li> <li>39</li> <li>40</li> <li>42</li> <li>44</li> <li>44</li> <li>46</li> </ol>                                     |

| <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul> | Introduction          Device Structure and Simulation Framework          Insights of the Output Current Saturation and Proposed V <sub>DSAT</sub> Extract         Method                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>39</li> <li>39</li> <li>40</li> <li>42</li> <li>44</li> <li>44</li> <li>46</li> <li>47</li> </ul>                         |

| <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul> | Introduction       Device Structure and Simulation Framework         Insights of the Output Current Saturation and Proposed V <sub>DSAT</sub> Extract         Method                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li>39</li> <li>39</li> <li>40</li> <li>42</li> <li>44</li> <li>44</li> <li>46</li> <li>47</li> <li>48</li> </ul>             |

| <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul> | IntroductionDevice Structure and Simulation FrameworkInsights of the Output Current Saturation and Proposed $V_{DSAT}$ ExtractMethod4.3.1Output current saturation mechanism4.3.2Proposed $V_{DSAT}$ extraction technique for L-TFETImpact of L-TFET Structural Variation on $V_{DSAT}$ 4.4.1Impact of the gate source overlap length $(L_{OV})$ 4.4.2Impact of the epitaxial layer doping $(n_{EPI})$ 4.4.3Impact of Proposed Method to Analog Design4.5.1Analog parameters in the <i>soft/deep</i> saturation regime                            | <ul> <li>39</li> <li>39</li> <li>40</li> <li>42</li> <li>44</li> <li>44</li> <li>46</li> <li>47</li> <li>48</li> <li>48</li> </ul> |

4

|     |     | 4.6.1 Influence of $L_{OV}$ , $n_{EPI}$ and $t_{EPI}$ on the analog parameters | 51 |

|-----|-----|--------------------------------------------------------------------------------|----|

|     |     | 4.6.2 Impact of $L_{OV}$ , $n_{EPI}$ and $t_{EPI}$ on Common Source Amplifier  | 54 |

|     | 4.7 | Conclusion                                                                     | 55 |

|     |     |                                                                                |    |

| 5   | Imp | pact of Body Bias in Line TFETs and its Implications to Analog Design          | 57 |

|     | 5.1 | Introduction                                                                   | 57 |

|     | 5.2 | Device Structure and Simulation Framework                                      | 58 |

|     | 5.3 | Impact of Body Bias on Line TFETs                                              | 60 |

|     |     | 5.3.1 Reverse body bias                                                        | 60 |

| 100 |     | 5.3.2 Forward body bias                                                        | 65 |

|     | 22  | 5.3.3 Impact of body bias on $V_{\text{DSAT}}$                                 | 65 |

| 100 | 5.4 | Impact of Device Design Parameters on $V_{BSAT}$                               | 65 |

| 5.  | 85  | 5.4.1 Gate-source overlap length                                               | 66 |

|     |     | 5.4.2 Thickness of epitaxial layer                                             | 67 |

|     |     | 5.4.3 Doping of epitaxial layer                                                | 68 |

|     | 5.5 | Impact of Body Biasing on Analog Performance                                   | 68 |

| -   | 5.6 | Conclusion                                                                     | 70 |

| 2   |     |                                                                                |    |

| 6   | Imp | pact of Gate-Source Overlap Length on Small Signal Parameters of Line          | 71 |

| 1   | TF  |                                                                                |    |

| 100 | 6.1 | Introduction                                                                   | 71 |

| 1   | 6.2 | Device Design and Simulation Framework                                         | 73 |

|     | 6.3 | Dependence of $I_D$ on $L_{OV}$ : Physical Insights                            | 73 |

|     | 25  | 6.3.1 Why $I_D$ increases sub-linearly with $L_{OV}$                           | 74 |

|     |     | 6.3.2 Semi-empirical Model for $I_D$ - $L_{OV}$ characteristics                | 77 |

|     |     | 6.3.3 Impact of device geometry on $I_{\rm D}$ - $L_{\rm OV}$ characteristics  | 79 |

|     | 6.4 | Dependence of Small Signal Parameters on Lov                                   | 79 |

|     | 6.5 | Impact of Lov on the Analog Circuit Design                                     | 82 |

|     | 6.6 | Conclusion                                                                     | 83 |

|     |     |                                                                                |    |

7 Conclusions and Future Scope

85

| 7.1 | Conclusions  | 85 |

|-----|--------------|----|

| 7.2 | Future Scope | 87 |

## References

List of Publications

# **List of Figures**

| 1.1 | (a) Transfer characteristics of MOSFET indicating an exponential increase in the                                           |    |

|-----|----------------------------------------------------------------------------------------------------------------------------|----|

|     | leakage current with lowering of the threshold voltage ( $V_{\rm TH}$ ). (b) Trends of the                                 |    |

|     | dynamic and static CMOS power                                                                                              | 2  |

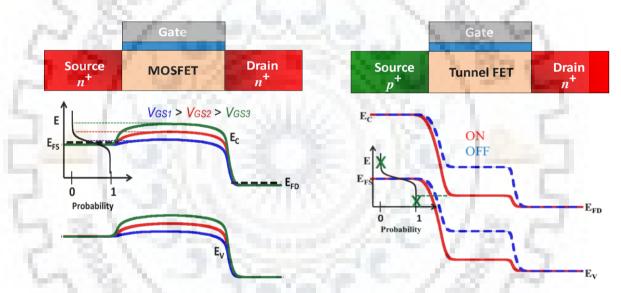

| 1.2 | Comparison of working mechanism between MOSFET and TFET                                                                    | 5  |

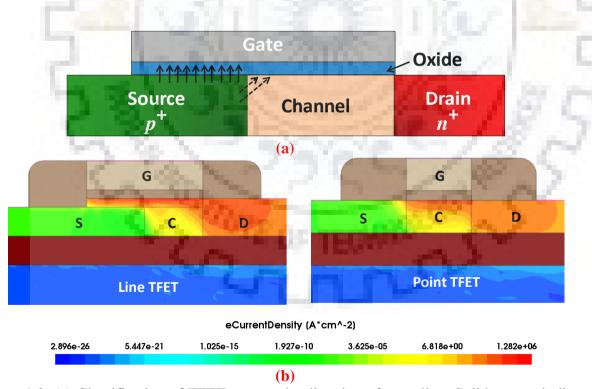

| 1.3 | Classification of TFET Devices as per the direction of tunneling. Solid arrows                                             |    |

|     | indicate the Line tunneling and dashed arrows indicate the Point tunneling. (b)                                            |    |

|     | Current Density in the Line and Point TFET devices obtained through our                                                    |    |

| 100 | numerical TCAD simulation two devices                                                                                      | 6  |

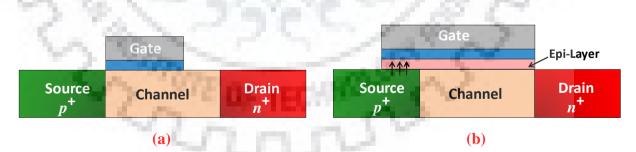

| 2.1 | Tunnel FET structures (a) gate-drain underlap (b) epitaxial layer based TFET with                                          |    |

|     | increased cross-section area of BTBT                                                                                       | 13 |

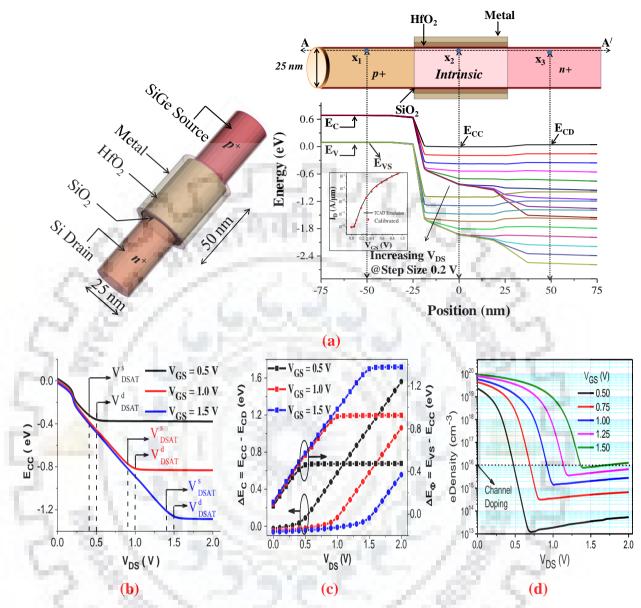

| 3.1 | (a) 3-D View and 2-D schematic of the target device and its simulated energy band                                          |    |

|     | diagram for $V_{GS} = 1$ V and $V_{DS}$ varying from 0 - 1.6 V. Inset shows the calibration                                |    |

| -   | of $I_D$ - $V_{GS}$ characteristics. The variation in (b) $E_{CC}$ (c) $\Delta E_C$ and $\Delta E_{\varphi}$ with $V_{DS}$ | 23 |

| 3.2 | Variation in (a) drain current (b) gate capacitance (c) output resistance and intrinsic                                    |    |

|     | gain (d) output conductance with $V_{DS}$ . Here, empty and solid circle indicate <i>soft</i> and                          |    |

| 2   | deep V <sub>DSAT</sub> points respectively.                                                                                | 26 |

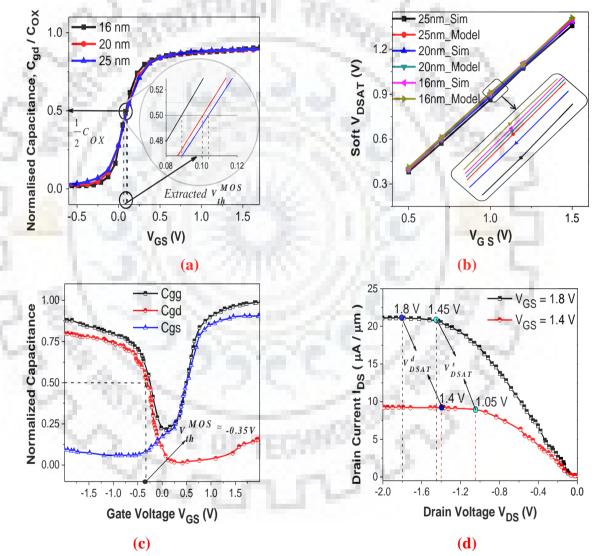

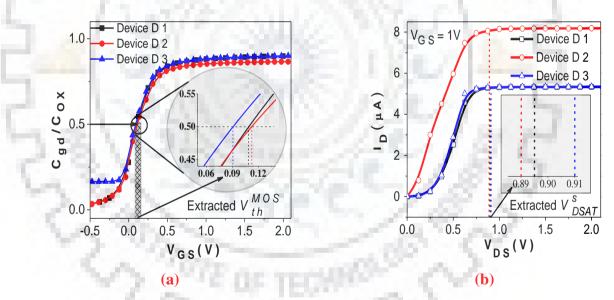

| 3.3 | Extraction of $V_{th}^{MOS}$ from $C_{gd}$ - $V_{GS}$ curve for $V_{DS} = 0$ V. Inset shows $V_{th}^{MOS}$ for             |    |

| 126 | different NWTFET diameters. (b) Validation of the proposed method with the (b)                                             |    |

|     | Numerical TCAD simulations and experimentally measured (c) $C-V_{GS}$ (d) $I_D-V_{DS}$                                     |    |

|     | curve of a p-type device show a good match between the proposed and the                                                    |    |

|     | experimental data                                                                                                          | 27 |

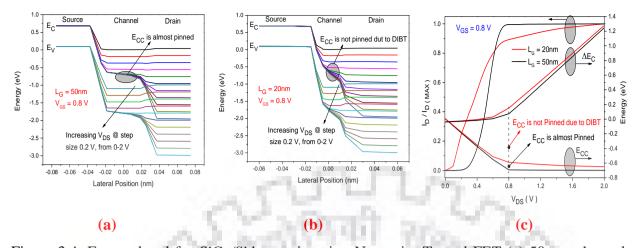

| 3.4 | Energy band for SiGe/Si hetero junction Nanowire Tunnel FET (a) 50 nm channel                                              |    |

|     | length (b) 20 nm channel length. (c) Imperfect saturation results in short channel                                         |    |

|     | TFETs due to pronounced effect of DIBT                                                                                     | 30 |

| 3.5 | (a) Variation in gate-drain capacitance with $V_{\rm GS}$ for $V_{\rm DS}=0$ V. The dotted line                            |    |

|     | shows extracted values of $V_{\rm th}^{\rm MOS}$ for device D1, D2 and D3. (b) $I_{\rm D}$ - $V_{\rm DS}$                  |    |

|     | characteristics show the value of <i>soft</i> and <i>deep</i> $V_{\text{DSAT}}$ .                                          | 31 |

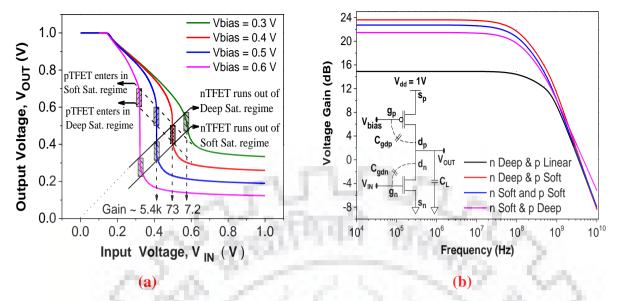

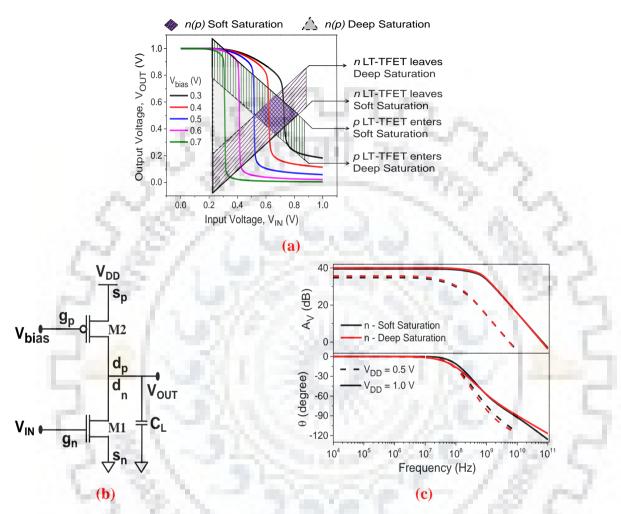

| 3.6  | (a) VTC for different values of $V_{bias}$ . Shaded areas on VTC show the boundaries for                                       |     |

|------|--------------------------------------------------------------------------------------------------------------------------------|-----|

|      | the <i>soft</i> and <i>deep</i> saturation regimes for $n(p)$ device. (b) Frequency response of a                              |     |

|      | CS amplifier for a fixed $V_{bias}$ (0.4 V).                                                                                   | 34  |

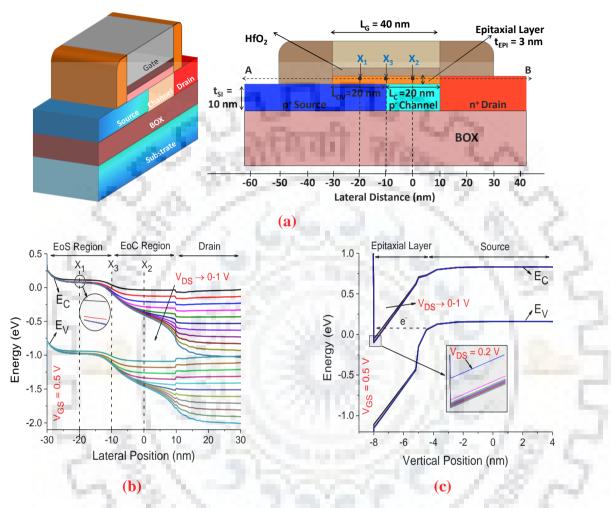

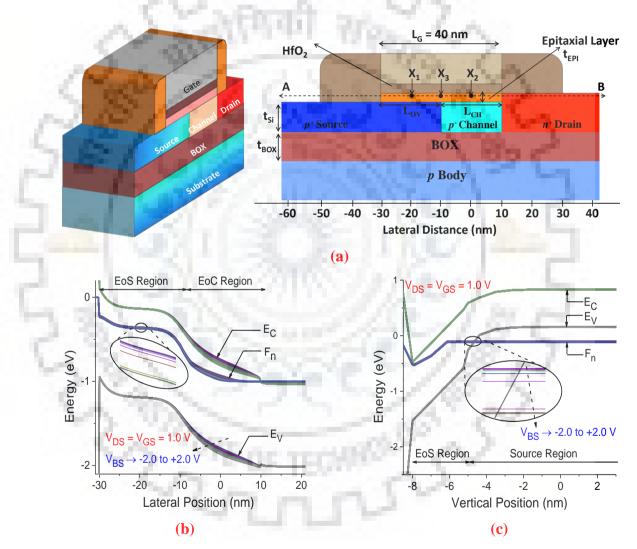

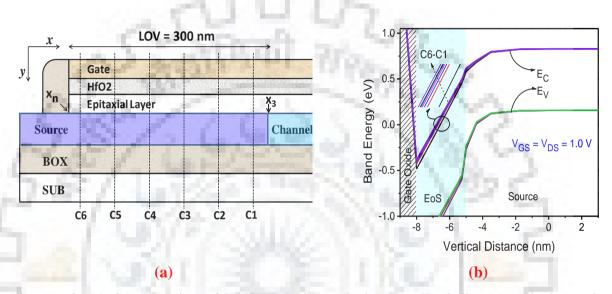

| 4.1  | (a) 3-D view and 2-D schematic of target device. (b) Lateral energy bands across                                               |     |

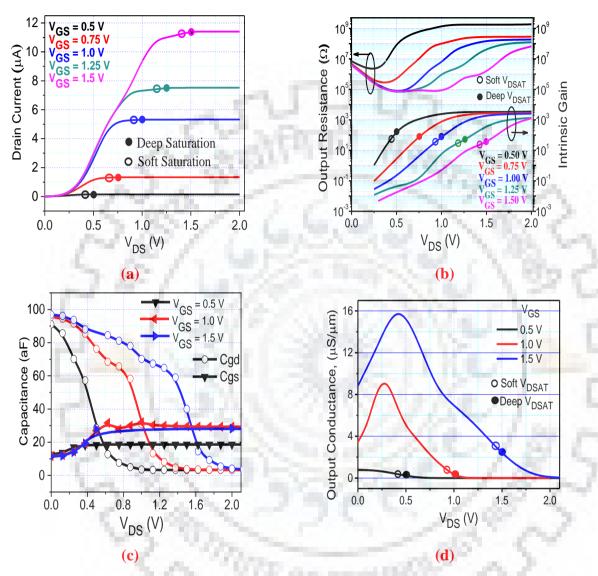

|      | AB. (c) Vertical energy bands across EoS region show the tunneling at point $x_1$                                              | 40  |

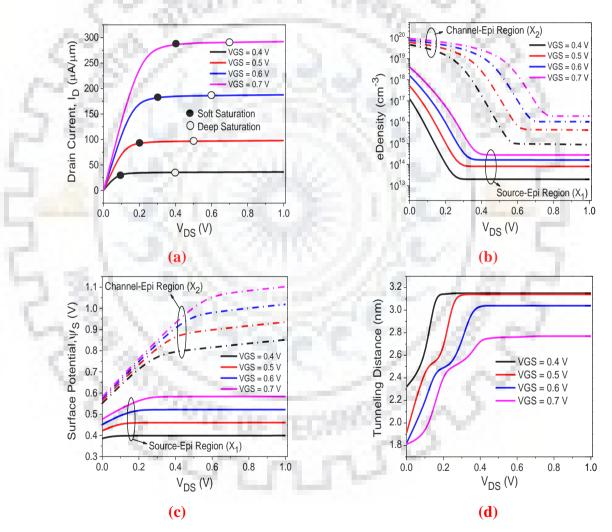

| 4.2  | (a) $I_{\rm D}$ - $V_{\rm DS}$ characteristics showing near perfect saturation in L-TFETs. Soft and deep                       |     |

|      | saturation voltages are marked for different $V_{GS}$ (b) Electron density and (c) Surface                                     |     |

|      | potential in the epitaxial region at points $x_1$ and $x_2$ . (d) Tunneling distance is                                        |     |

|      | extracted from TCAD simulations.                                                                                               | 41  |

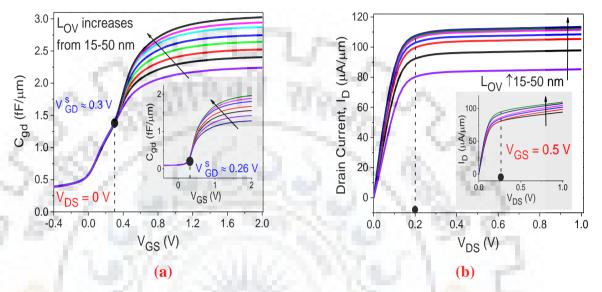

| 4.3  | (a) Extraction of $V_{GD}^s$ from $C_{gd}$ - $V_{GS}$ curve at $V_{DS} = 0$ V. Inset shows $C_{gd}$ - $V_{GS}$ curve           |     |

|      | for the device having non-gated ( $L_{\rm G} = L_{\rm OV}$ ) intrinsic region. (b) The output                                  |     |

|      | characteristics show that the value of $V_{DSAT}^{s,d}$ is invariant of the overlap lengths $L_{OV}$ .                         | ς.  |

|      | Device without gate-channel overlap [Inset of (b)].                                                                            | 43  |

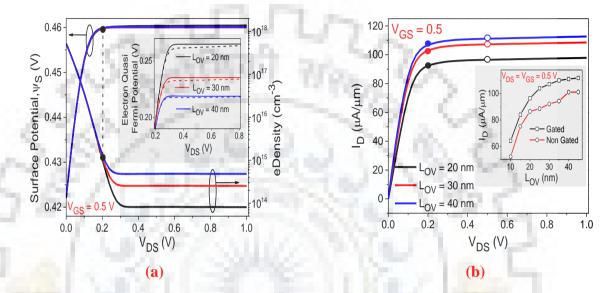

| 4.4  | (a) Trends of surface potential and electron density (at point $x_1$ ). Inset shows the                                        |     |

|      | electron quasi-Fermi potential for gated non-gated devices at point $x_1$ . (b) $I_D-V_{DS}$                                   | r.  |

|      | characteristics exhibit a similar onset of saturation voltage for different $L_{OV}$ . Inset                                   |     |

|      | of shows the saturation of $I_D$ with increasing $L_{OV}$ for gated and non-gated devices.                                     | 45  |

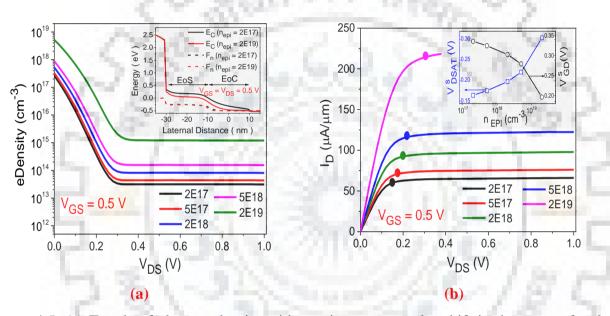

| 4.5  | (a) Trends of electron density with varying $n_{\text{EPI}}$ . Inset shows that the difference $E_{\text{C}}$ -                |     |

|      | $F_{\rm n}$ reduces with increasing $n_{\rm EPI}$ . (b) Output characteristics are marked with soft                            |     |

|      | saturation voltage. Increase in $V_{DSAT}^s$ with the increasing value of $n_{EPI}$ [Inset]                                    | 46  |

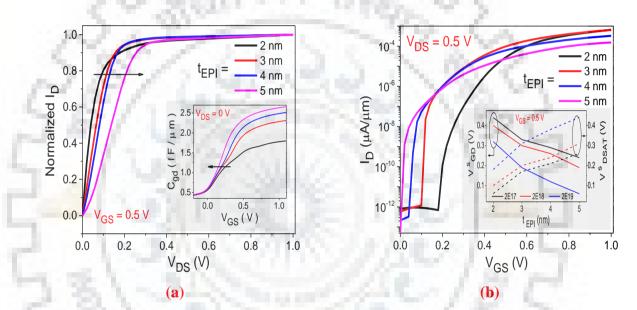

| 4.6  | (a) Normalized $I_{\rm D}$ - $V_{\rm DS}$ curves show the delayed saturation with increasing $t_{\rm EPI}$ . $V_{GD}^{S}$      | ÷., |

|      | increases with decreasing $t_{\rm EPI}$ [Inset of (a)]. (b) $I_{\rm D}$ - $V_{\rm GS}$ for different values of $t_{\rm EPI}$ . |     |

|      | Inset shows the trends of $V_{GD}^s$ and $V_{DSAT}^s$ with change in $n_{\text{EPI}}$ and $t_{\text{EPI}}$                     | 47  |

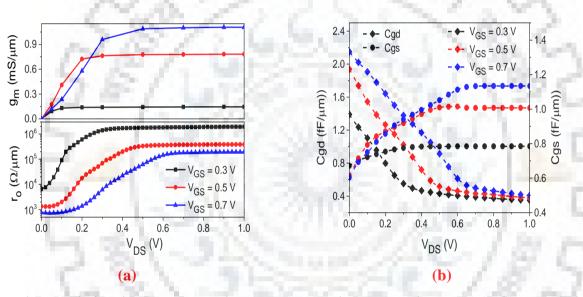

| 4.7  | Variation in (a) transconductance and output resistance (b) gate capacitances with                                             |     |

|      | the gate and drain bias for the target device.                                                                                 | 48  |

| 4.8  | (a) VTC of the L-TFETs based CS amplifier. (b) Schematic of the current source                                                 |     |

|      | load CS Amplifier. (c) The voltage gain (phase) v/s frequency plot of CS amplifier.                                            | 50  |

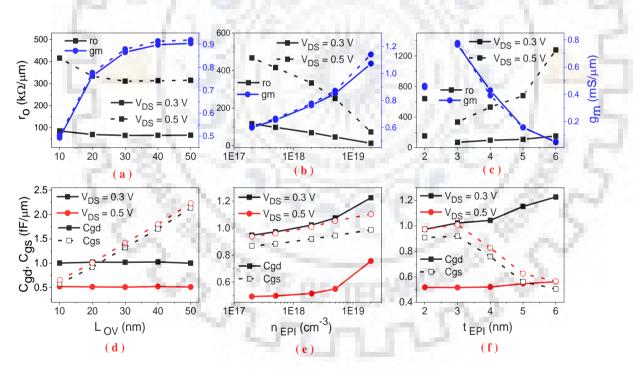

| 4.9  | Variation in transconductance and output resistance with (a) $L_{\rm OV}$ (b) $n_{\rm EPI}$ (c) $t_{\rm EPI}$                  |     |

|      | Variation in gate capacitances capacitance with (d) $L_{OV}$ (e) $n_{EPI}$ (f) $t_{EPI}$                                       | 52  |

| 4.10 | (a) Frequency response of the CS amplifier with varying device design parameters                                               |     |

|      | (a) $L_{OV}$ . (b) $n_{EPI}$ . (c) $t_{EPI}$                                                                                   | 54  |

| 5.1 | (a) 3-D vie and 2-D schematic of target device. (b) Lateral energy bands across line                                            |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------|----|

|     | AB. (c) Vertical energy bands across EoS region show the tunneling at point $x_1$                                               | 59 |

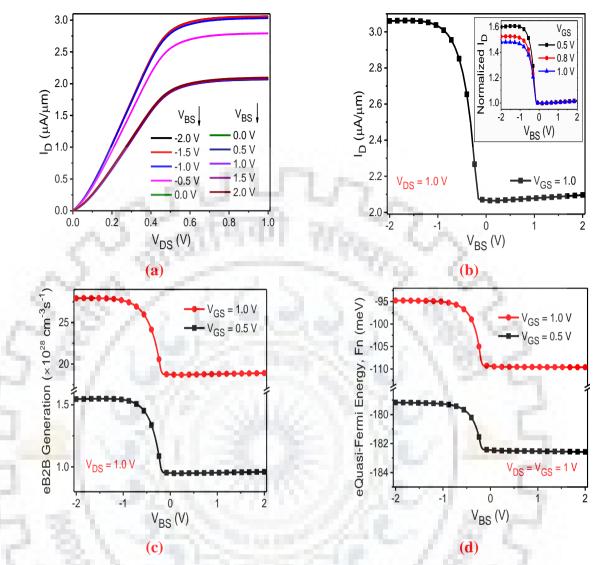

| 5.2 | (a) Output characteristics of the target device. (b) Saturation in $I_D$ is observed with                                       |    |

|     | reverse body bias, while, $I_D$ does not significantly changes with forward body bias.                                          |    |

|     | Normalized values of $I_{\rm D}$ show the modulation efficiency for different $V_{\rm GS}$ [Inset of                            |    |

|     | (b)]. Trends of (c) Electron band-to band generation rate at point $x_1$ (d) Electron                                           |    |

|     | quasi-Fermi energy with $V_{BS}$ for different $V_{GS}$ at EoS/source junction along the line                                   |    |

|     | $x_1$ for different gate biases                                                                                                 | 61 |

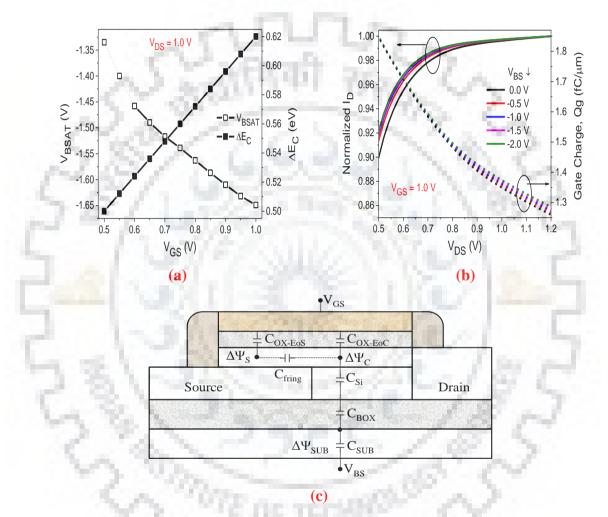

| 5.3 | (a) The variation of $V_{\text{BSAT}}$ and $\Delta E_{\text{C}}$ with the gate bias. (b) A small shift in the $V_{\text{DSAT}}$ |    |

|     | due to $V_{\rm BS}$ is observed. (c) Gauss law is applied from body to gate terminal to                                         |    |

| 1   | obtain the potential balance equation for L-TFET device                                                                         | 63 |

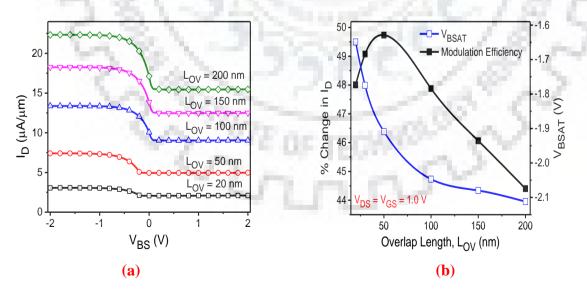

| 5.4 | (a) $I_{\rm D}$ - $V_{\rm BS}$ characteristics for the different values of $L_{\rm OV}$ . (b) Modulation of $I_{\rm D}$ by      |    |

| 5.  | $V_{\rm BS}$ is almost independent of $L_{\rm OV}$ , and the magnitude of $V_{\rm BSAT}$ increases with $L_{\rm OV}$ .          | 66 |

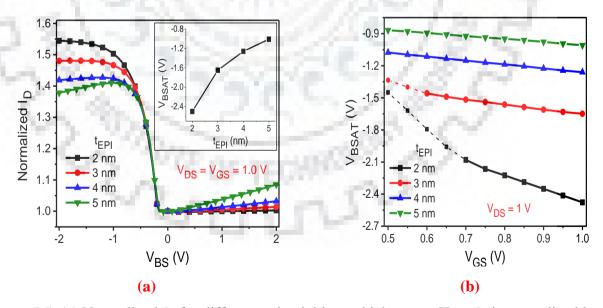

| 5.5 | (a) Normalized $I_{\rm D}$ for different epitaxial layer thicknesses. Inset shows the variation                                 |    |

|     | of $V_{BSAT}$ with $t_{EPI}$ . (b) Linear dependence of $V_{BSAT}$ on $V_{GS}$ is justified by the                              |    |

|     | simulations and the model presented in Eq. (5)                                                                                  | 67 |

| 5.6 | (a) Drain current for different values of $n_{\text{EPI}}$ . (b) Comparison of percentage change                                |    |

| ÷., | in $I_D$ and $F_n$ for different values of $n_{EPI}$ with and without reverse $V_{BS}$ .                                        | 68 |

| 5.7 | Performance of analog parameters under the forward and reverse body biasing at                                                  |    |

| e.  | $V_{\rm DS} = 1.0$ V (a) transconductance (b) output resistance and intrinsic gain (c) gate                                     |    |

| 10  | capacitances (d) Unity gain cut-off frequency.                                                                                  | 69 |

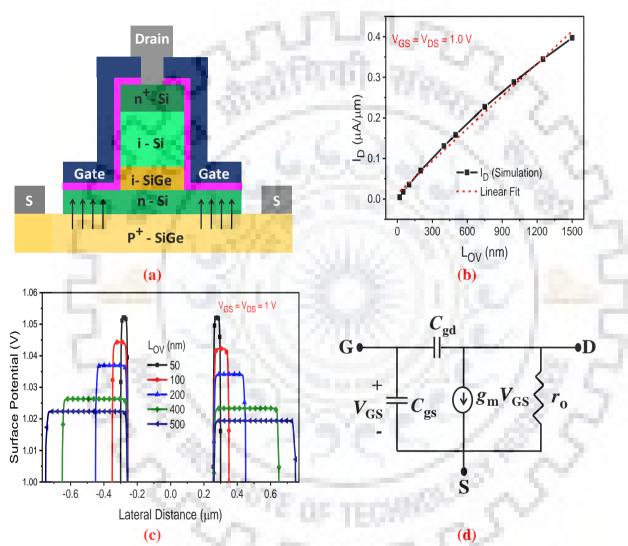

| 6.1 | (a) 3-D view and 2-D schematic of the target device. (b) The variation in drain                                                 |    |

|     | current with increasing $L_{OV}$ . (c) Non-linear trend of $I_D$ with $L_{OV}$ extracted from (b)                               | 74 |

| 6.2 | (a) Potential profile along the line AB within EoS region [Fig. 6.1(a)]. (b)                                                    |    |

|     | Magnitude of the electric field at the source-EoS junction. (c) Variation in the                                                |    |

|     | electron band-to-band generation and (d) electron density along the line AB                                                     | 75 |

| 6.3 | (a) Cross section of L-TFET underneath the gate. (b) Band energies for cut planes                                               |    |

|     | C1-C6 are plotted to find the tunneling distance                                                                                | 77 |

| 6.4 | (a) 2D schematic of pillar based line tunneling device with vertical process flow.                                              |    |

|     | (b) Drain current changes almost linearly with $L_{OV}$ . (c) Potential profile underneath                                      |    |

|     | the gate at the EoS region. (d) Small signal model for L-TFET                                                                   | 78 |

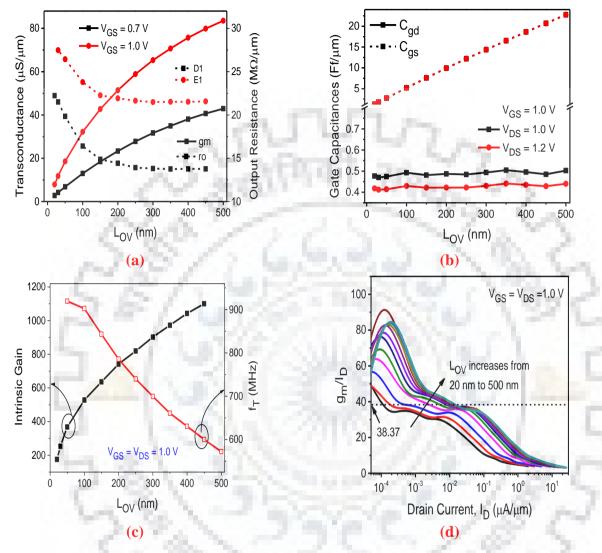

- 6.5 Performance of analog parameters with gate-source overlap lengths (a) Transconductance and output resistance (b) Gate capacitances (c) Intrinsic gain and unity gain cutoff frequency. (d) Variation in  $g_m/I_D$  with drain current ..... 80 82

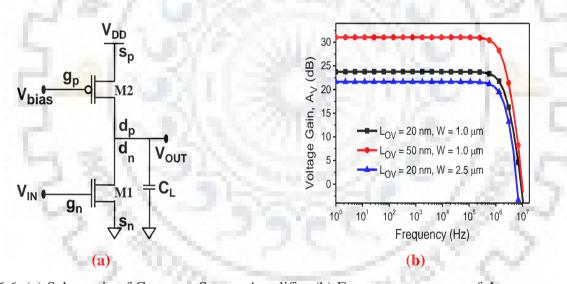

- 6.6 (a) Schematic of a CS Amplifier (b) Frequency response of the CS amplifier. ....

# **List of Tables**

| 3.1 | Comparison of the Proposed Technique with the Existing Work.                        | 29 |

|-----|-------------------------------------------------------------------------------------|----|

| 3.2 | Extracted value of $V_{th}^{MOS}$ and $V_{DSAT}^{s}$ at $V_{GS} = 0.5$ V for NWTFET | 32 |

| 4.1 | Comparison of Intrinsic Gain and Unity-Gain Cutoff Frequency (GHz) for              |    |

|     | Different Values of $L_{OV}$ , $n_{EPI}$ and $t_{EPI}$ at $V_{GS} = 0.5$ V          | 53 |

# Chapter 1 Introduction

The modern semiconductor devices have established a new dimension in the handheld consumer and healthcare electronics such as tablet PC, smartphones, and sensors. This requires an electronic device that consumes less power with a minimum supply voltage and OFF-state leakage current ( $I_{OFF}$ ) [1]. The reduction in power dissipation turns out to be essential as CMOS technologies grow. This demands for a new transistor based switch which works at the lower operating voltages and maintains a reduced level of the leakage current. In this manner, the opportunities and challenges emerge from the quantum mechanical transport. A novel tunnel transistor can essentially operate at significantly lower voltages than MOSFETs by employing band-to-band tunneling as the main conduction mechanism with the small subthreshold slopes (SS) [2].

### **1.1 Fundamental Limitation of CMOS: Tunnel FETs**

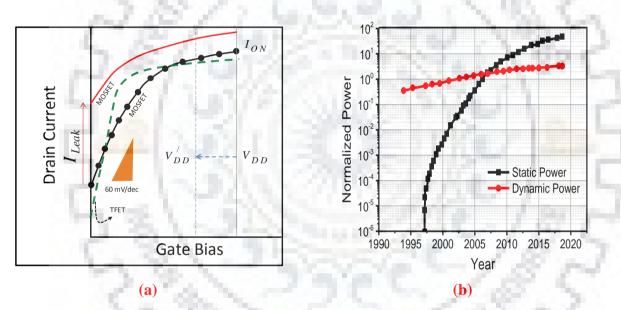

A reduction in the power consumption of MOSFETs is primarily because of the lowering of the supply voltage. However, keeping this trend by employing the CMOS technology scaling, gives diminishing results due to an increase in the OFF-state leakage current. Consequently, the total power consumption also increases. The MOSFET devices suffer from a fundamental limitation of the lower bound o subthreshold slope and thus also the OFF-state leakage current. The complementary MOSFETs are not suitable for the circuit operation below 0.5 V supply voltage because of their SS limitation, which is not possible to scale below 60 mV/decade at the room temperature, as shown in Fig. 1.1(a) [3]. As per the scale length theory of MOSFETs, the threshold voltage can be reduced by the same scale as of the supply voltage [4]. This results in a net increase in the gate overdrive voltage and  $I_{OFF}$ . Beyond 65 nm technology node, the leakage is very high and static power dominates, as shown in Fig. 1.1(b) [5]. Therefore, the fundamental bottleneck with the MOSFET based technologies is the non-scalability of SS. In conventional MOSFETs, the lower bound of 60 mV/decade is because the subthreshold current

is driven by the 'Boltzmann tail' of the source carrier population, with the energies greater than the top of the barrier in the channel. In addition, this 'Boltzmann tail' becomes more significant because of the drain induced barrier lowering (DIBL), which is a major challenge for the short channel MOSFETs of the present era.

At the room temperature,  $SS = \frac{dV_{GS}}{d\log_{10}I_D} = \frac{2.3\text{mK}_B\text{T}}{\text{q}}$ , and  $m = 1 + \frac{C_{\text{DEP}}}{C_{\text{OX}}}$  indicates the voltage drop across the channel effectively. Here, *m*, *K*<sub>B</sub>, *T*, *C*<sub>DEP</sub> and *C*<sub>OX</sub> are the mass of electron, the temperature, Boltzmann's constant, depletion and oxide capacitance respectively. This fundamental limitation necessitates a very small supply voltage for operating the MOSFET devices. In addition, the voltage scaling also hampers by the increased variability of the scaled devices owing to the random dopant fluctuations [6].

Figure 1.1: (a) Transfer characteristics of MOSFET indicating an exponential increase in the leakage current with a decrease in the threshold voltage ( $V_{TH}$ ) due to the technology scaling. (b) Trends of the dynamic and static CMOS power show that static power consumption has become a serious problem [5].

To prevail over these fundamental constraints, a new carrier injection mechanism must be employed instead of the drift and diffusion of carriers. This has initiated the research in socalled "steep slope" transistors which can have SS < 60 mV/decade. Therefore it is possible to achieve a good  $I_{ON}/I_{OFF}$  ratio at the lower voltages. Many such devices have been proposed to achieve the steep slopes [6], [137] as follows: