# PERFORMANCE INVESTIGATIONS OF LOW VOLTAGE HIGH CURRENT POWER SUPPLY

#### A THESIS

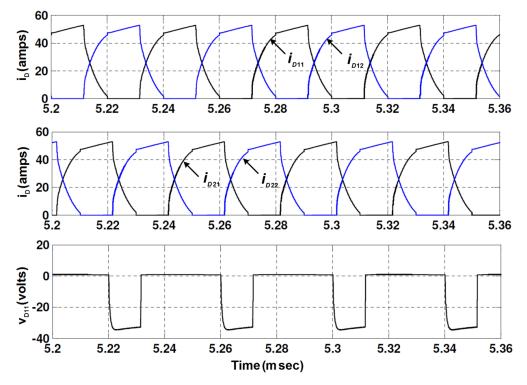

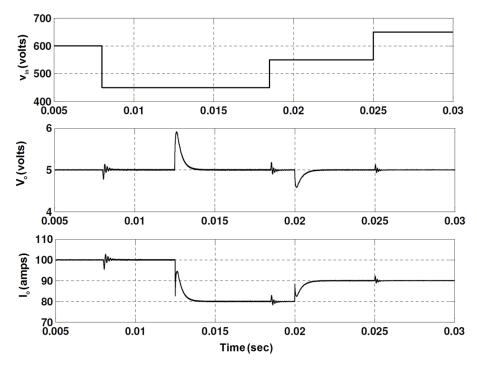

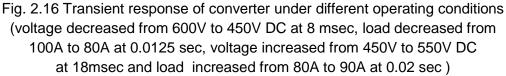

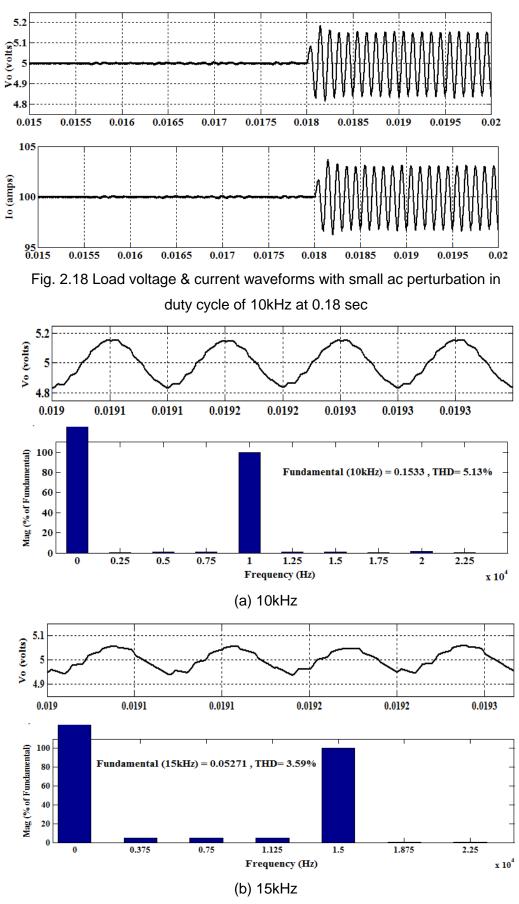

# Submitted in partial fulfilment of the requirements for the award of the degree

of

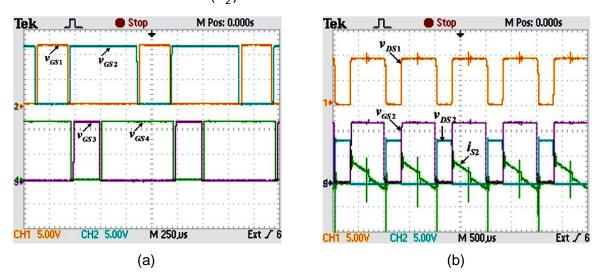

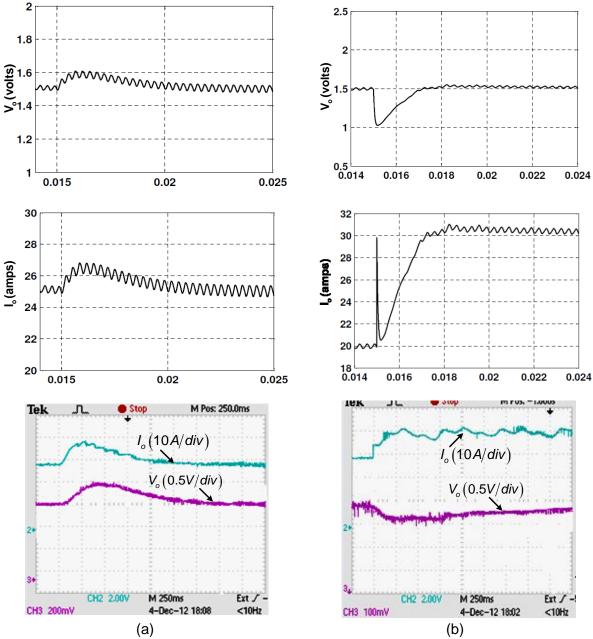

#### DOCTOR OF PHILOSOPHY

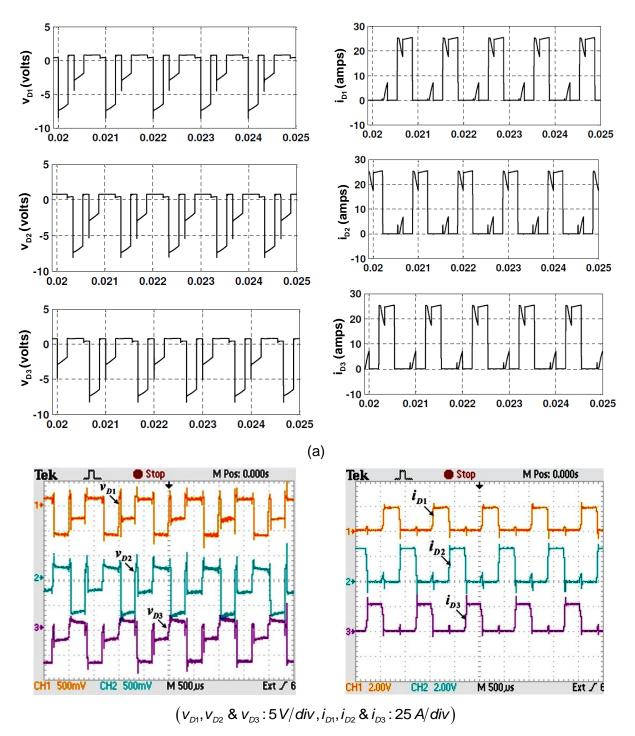

in

#### ELECTRICAL ENGINEERING

by

## **RAKESH MAURYA**

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) DECEMBER, 2013

# ©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE- 2013 ALL RIGHTS RESERVED

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

# **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in this thesis entitled **"PERFORMANCE INVESTIGATIONS OF LOW VOLTAGE HIGH CURRENT POWER SUPPLY"** in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electrical Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from July, 2010 to December, 2013 under the supervision of Dr. S. P. Srivastava, Professor and Dr. Pramod Agarwal, Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

#### (RAKESH MAURYA)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

(Pramod Agarwal) Supervisor (S. P. Srivastava) Supervisor

Date: \_\_\_\_\_

The Ph.D. Viva-Voce Examination of **Mr. RAKESH MAURYA**, Research Scholar, has been held on .....

Signature of Supervisors Chairman, SRC Signature of External Examiner

Head of the Department/ Chairman, ODC

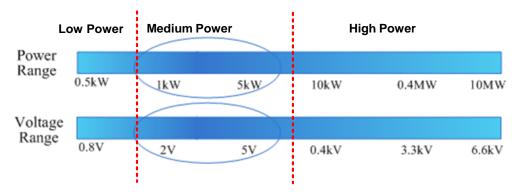

As bulk of electrical power is extensively utilized in the form of A.C., but contemporary, DC power has also gained significant importance due to wide applications of electronic devices. Some of the industrial processes where controlled DC is required are electroplating, electrolysis, anodizing, and metal refining, electronic welding, plasma torch applications, battery charging, electrical traction, telecommunication and computer industry. There are several applications which require high power at reduced DC voltage power because high voltage cannot be applied due to the system requirements. These applications include telecommunication, computer server system, electrochemical processes, DC arc furnaces, Large Hadran Collider (LHC), and nuclear fusion research of magnetic confinement etc. The power supply installed in aforesaid applications is named as Low Voltage High Current (LVHC) power supply.

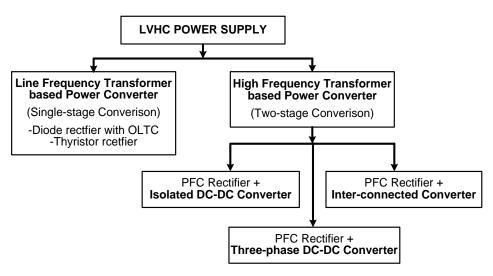

In light of the variety of the aforementioned applications, several power converters are reported in literature which could be employed for low, medium and high power applications. Keeping in view of high power applications at low output voltage, the use of transformer is essential for voltage scaling, electrical isolation and safety. Based on electrical isolation, the existing topologies are broadly classified in two groups namely line frequency transformer based converter and high frequency transformer based converter. These groups of power converters are normally compared from the viewpoint of size and weight, location of transformer and DC-DC converter in order to search for suitable power circuit for providing high current at low output voltage.

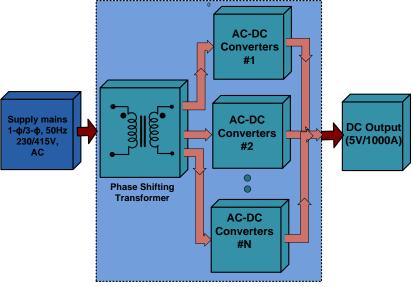

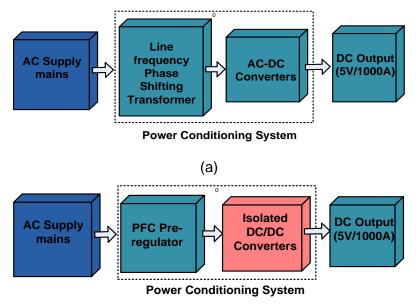

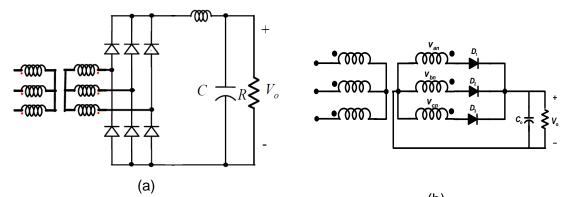

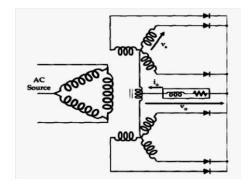

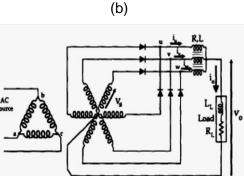

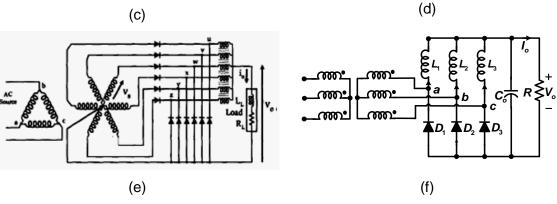

The majority of high-power rectifier manufacturers around the world inevitably use line frequency transformer based power converter due to low cost and well-established technique. Invariably, these converters consist of a power conditioning system which comprises of phase shift transformers and multiple AC-DC converters that transfers power to load in single-stage conversion. The phase shifting transformer is essential to provide desired phase shift in input voltages of converters and is achieved by different connections of three-phase and single phase transformers. Additionally, phase shifting transformer provides electrical isolation and reduction in voltage to achieve high current at low voltage. Although such multipulse converters help in achieving reduction in DC voltage ripples and harmonics in input current simultaneously, but they are quite bulky and more weight due to line frequency operation. Further, the efficiency of such system is low to deliver same power at reduced voltage.

To comply harmonics regulation set by IEEE Standard 519-1992, the line frequency transformer based converter requires additional filters at the input which further increases size, weight and cost.

i

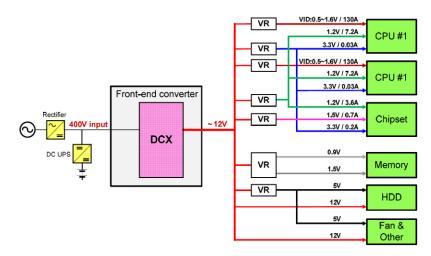

In light of the above limitations, the high frequency transformer based power converters are selected in which power conditioning system consists of two stages namely AC –DC and DC-DC power conversion. The most common practice for AC-DC conversion is to use 1-phase/3-phase diode bridge rectifier followed by a large capacitor to obtain ripple free DC voltage. As a result, the line current becomes non-sinusoidal and has several undesired effects on both the utility and consumer sides such as losses and overheating in transformer, shunt capacitors, power cables, reduced power factor and distortion of the line voltage due to the line impedance drop. Hence, PFC pre-regulator are used to ensure power quality issues at utility sides. The output DC voltage obtained by PFC pre-regulator from  $1-\phi$ , 230 V, 50Hz /  $3-\phi$ , 415 V, 50 Hz AC power supply varies from 400-1000V DC.

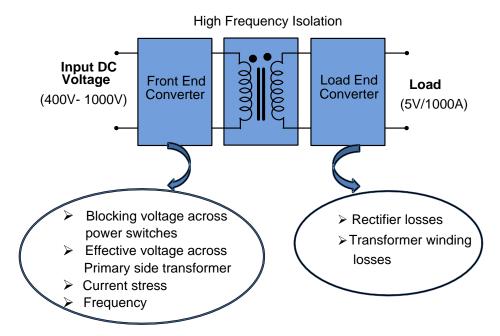

In order to meet demand of large current at low output voltage, the survey of power converter topologies for the second stage of power conversion (DC-DC) is extremely important. Keeping in view the requirement of low output voltage from high input DC voltage, high conduction losses, and controller design, the performance of the following DC-DC converters are evaluated.

- Isolated DC-DC Converter

- Inter-Connected Converter

- Three-phase DC-DC Converter

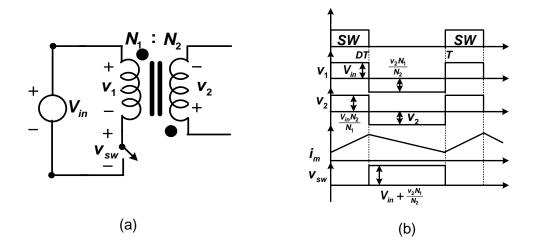

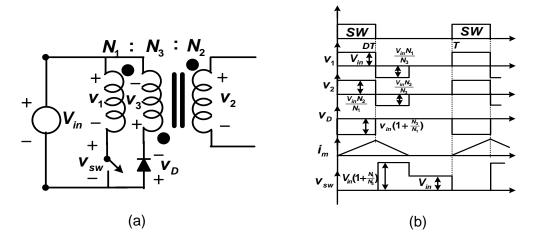

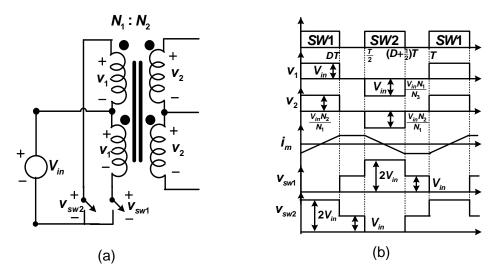

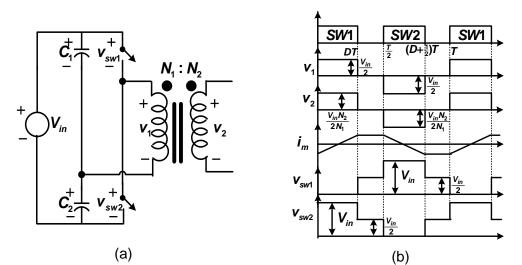

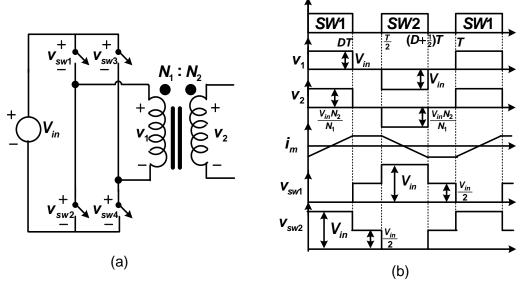

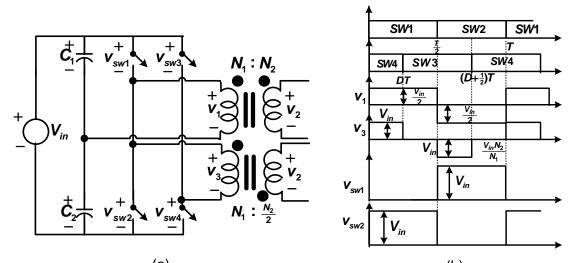

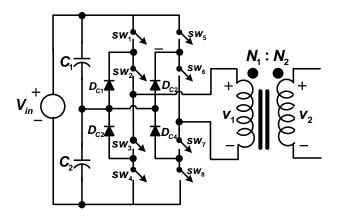

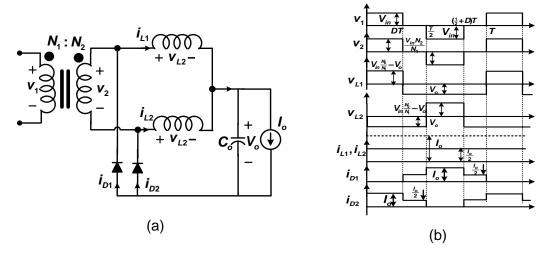

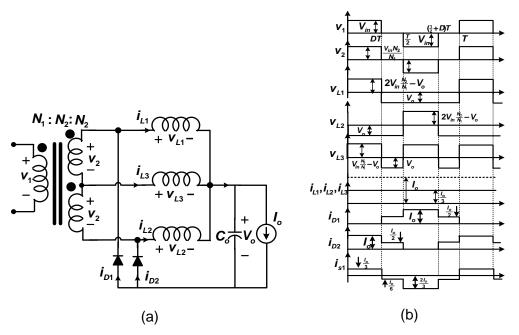

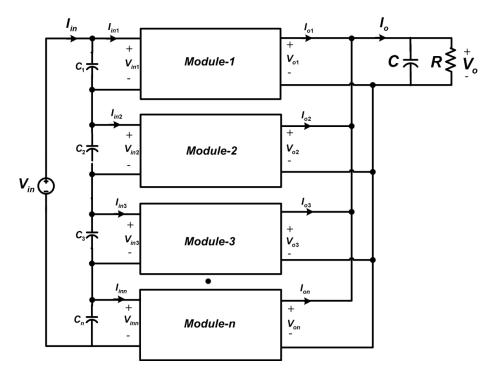

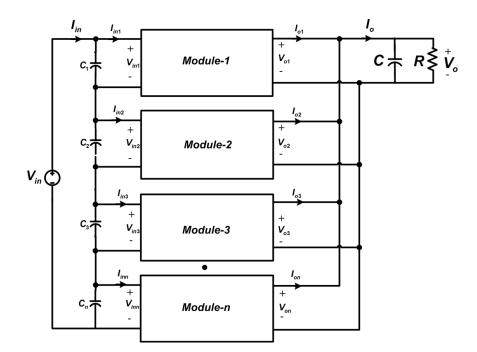

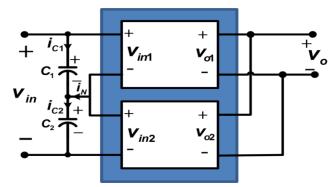

Isolated DC-DC converters in its basic forms i.e. forward, fly-back, push-pull, half and full bridge for the second stage of implementation face the problem of high voltage stress on the switching devices of front end converter and it has become a major concern in designing converter. Conventionally, in order to reduce voltage/current stress, each power devices are replaced by two or more series/parallel connected switches respectively. In practice, the devices are not identical but have forward dropping characteristics within a narrow band. In addition, the parasitic elements significantly influence the unequal voltage and current sharing by the switching devices. Alternatively, the modular approach for designing LVHC DC-DC converter be adopted in which low rating DC-DC converter modules are integrated in series or parallel, both at input side as well as output side to achieve desired input and output specifications. Among four possible inter-connections namely input-parallel-output-parallel (IPOP), input-parallel-output-series (IPOS), input-series-output-parallel (ISOP), and inputseries-output-series (ISOS), the ISOP connection is preferred for low voltage high current applications due to better voltage stress at front end converter and current stresses at load end converter, increase power processing capability, improved reliability because of more even distribution of stresses, ease of expansion and repair.

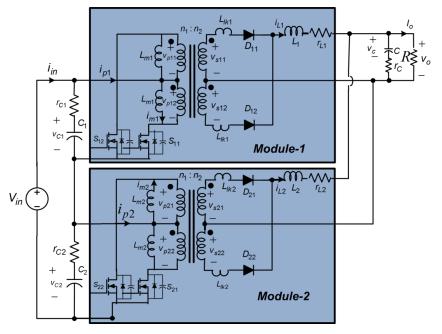

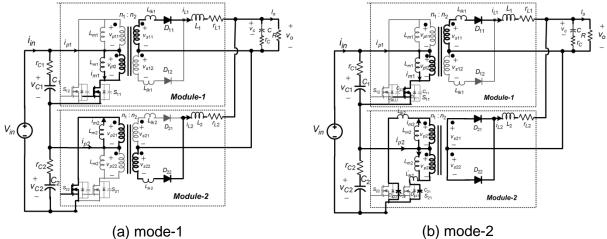

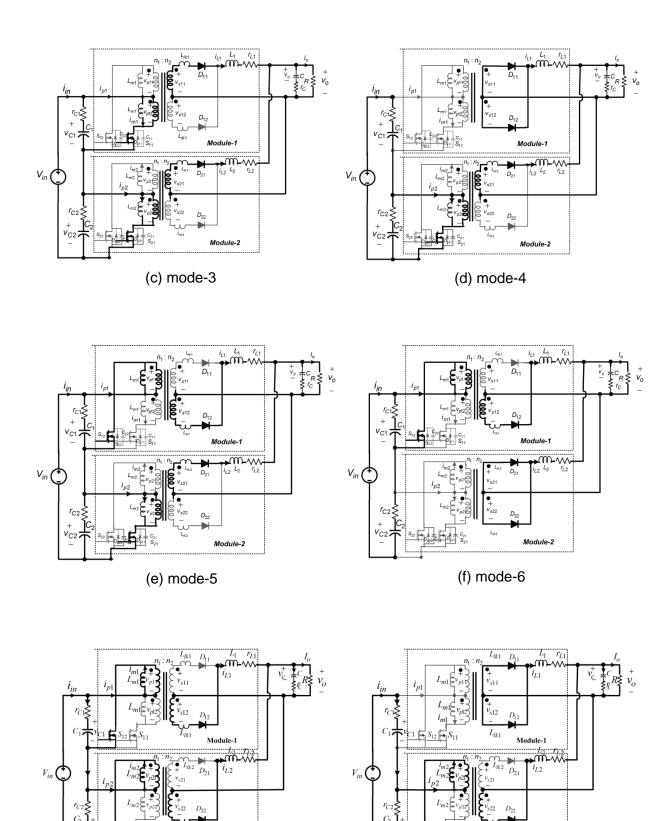

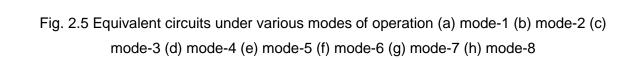

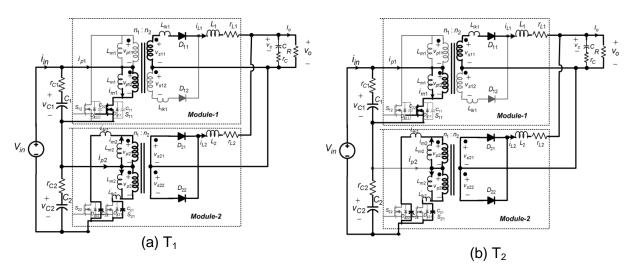

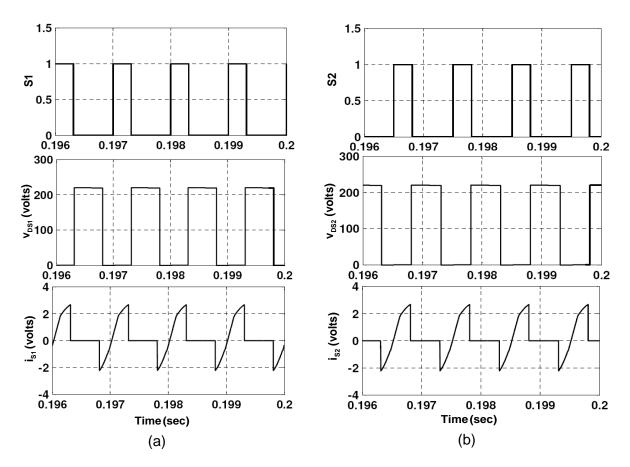

Keeping this in mind, the performance of two identical modules of push-pull converters is investigated. The effect of parasitic elements such as effective series resistance of

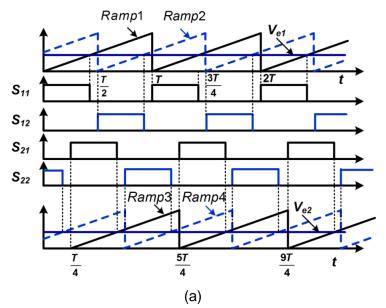

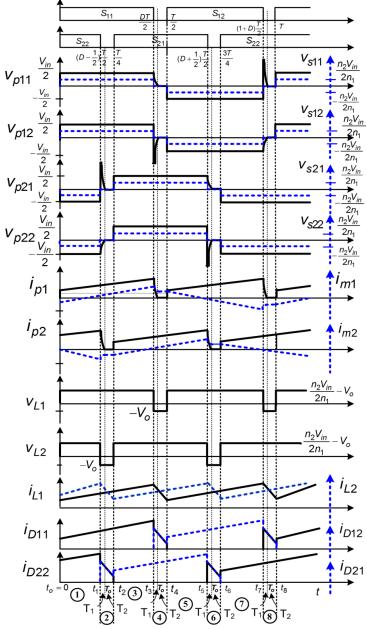

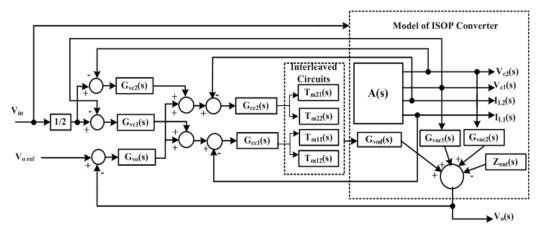

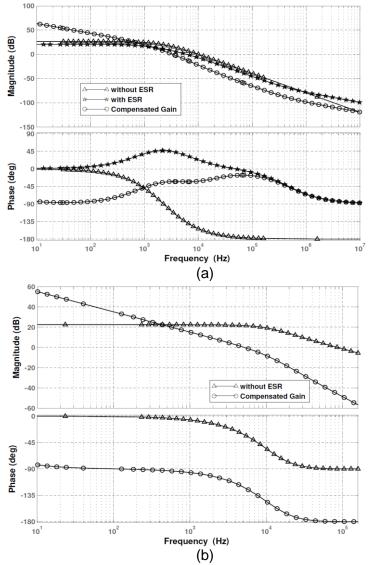

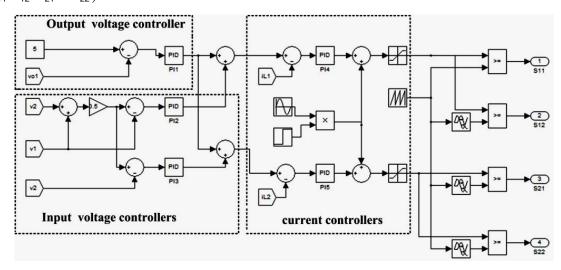

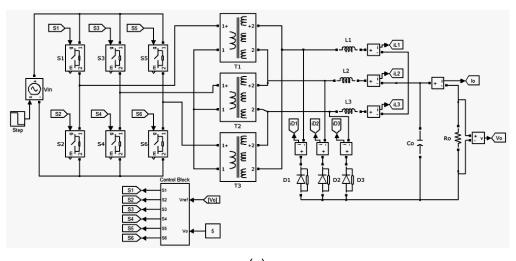

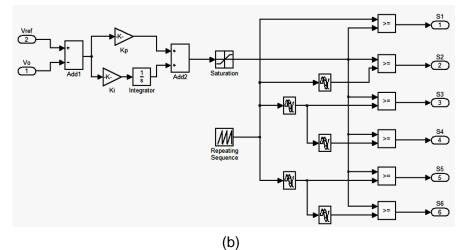

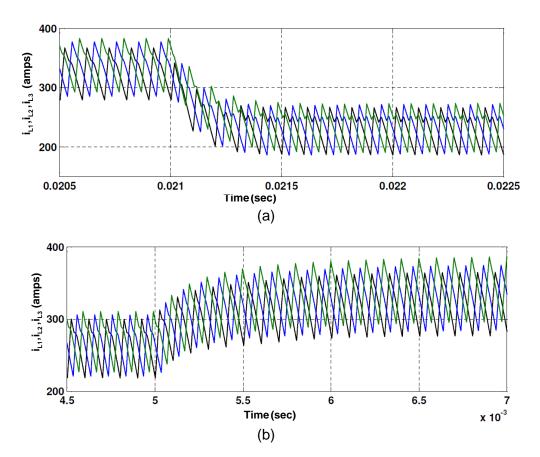

capacitors and output inductors, leakage and magnetizing reactances of transformers and with inter-connected in series at input side and in parallel at output side are included. The converter modules of same rating cannot be identical i.e. any mismatch in circuit parameters leads to unequal sharing of power by individual converter modules i.e. the module which supplies more power suffers more stress and the probability of its failure increases. In order to share equal power by two push-pull converters, three controllers namely common output voltage controller, inner current controller and input voltage controller are employed. A stable feedback system is designed to regulate the output voltage. A systematic development of a small-signal linear dynamic model of proposed converter is carried out using State-Space Averaging (SSA) technique. The transfer functions of different control blocks of converter are obtained. Furthermore, stability analysis of control loops is carried out to ensure closed loop operation. The Simulink model of proposed converter is developed using MATLAB/ SimPowerSystem<sup>™</sup> and the simulation results are presented. For high power applications, a large number of small rating modules are connected in ISOP connection and to ensure equal power sharing, several controllers are to be employed. Therefore, on account of more number of components, controllers, system reliability decreases and furthermore design of controllers becomes complex.

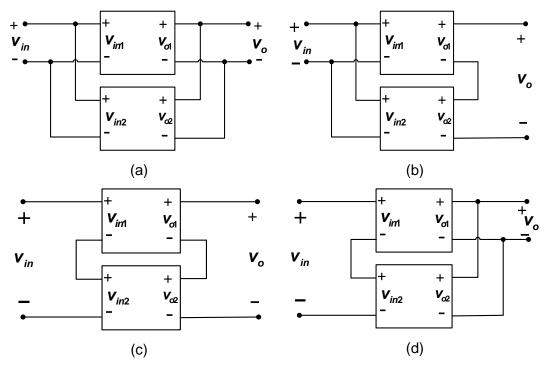

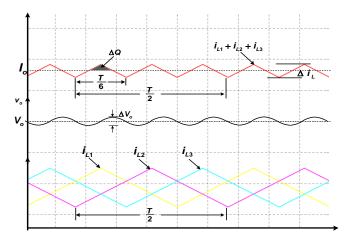

A three-phase DC-DC converter is proposed as an alternative for high power applications. It has several advantages over the single-phase DC-DC converter such as ease of power device (MOSFETs) selection due to reduced current rating, reduction of size and weight of passive components due to increased effective switching frequency by a factor of 3 compared to single-phase DC-DC converter and reduction in transformer size due to better transformer core utilization.

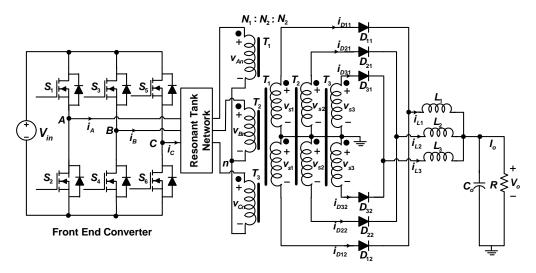

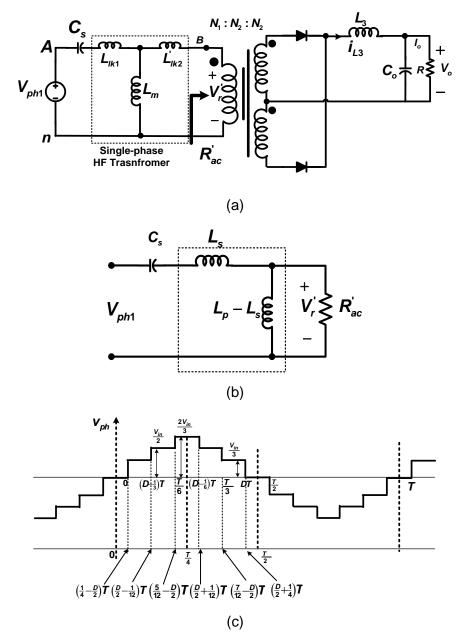

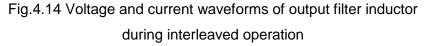

This work presents mathematical modelling, analysis, design, simulation and experimental results of three-phase, high frequency isolation transformer based DC-DC converters suitable for low voltage and high current applications. A high-frequency isolated three-phase LLC resonant DC-DC converter with centre-tapped secondary windings of trasnformer is proposed which consists of three units of single-phase half bridge LLC DC-DC converter and operated in interleaved manner to feed high power load. The proposed topology with interleaved control technique increases the effective frequency of operation without increase in switching frequency of switches and hence reduces the size and weight of passive components. However, operation with higher frequency leads to increase in switching losses and EMI problems. The performance of proposed topology is further improved by implementation of Zero Voltage Switching (ZVS) making use of snubber capacitance, leakage and magnetizing inductances of transformer (LLC resonant tank) and hence reduced switching losses in front end converter, and better current sharing at load end converter can be achieved. The mathematical modeling of LLC resonant tank network is

iii

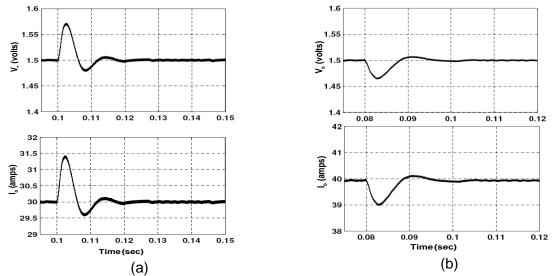

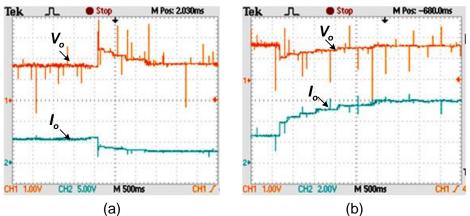

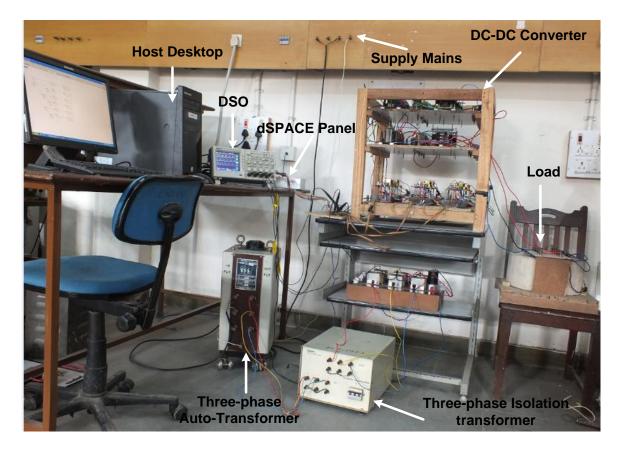

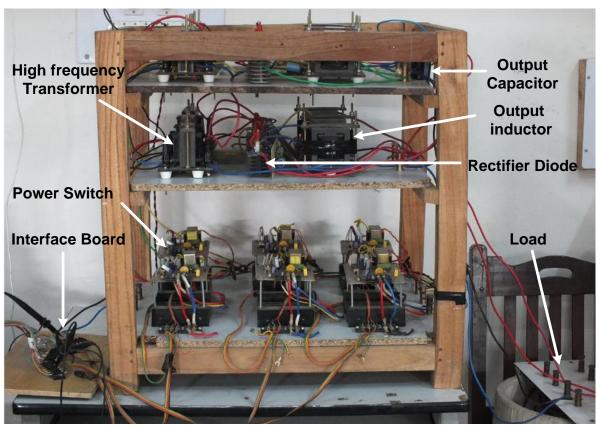

developed and its design curves are plotted against variation of normalized frequency for different values of load. Based on the design curves, the Simulink model of converter is developed using MATLAB/SimPowerSystems<sup>™</sup> and simulation study is carried out to investigate its performances for low voltage high current applications. To validate simulation results, a prototype model of 75W, 1.5V/50A is built and its performance is investigated under various operating conditions.

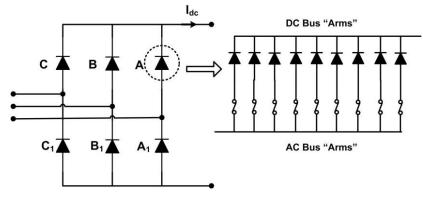

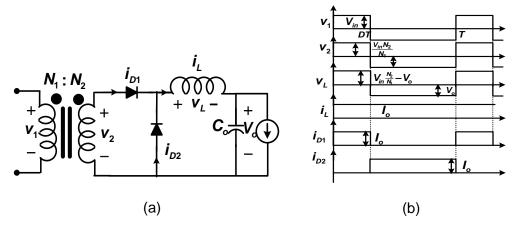

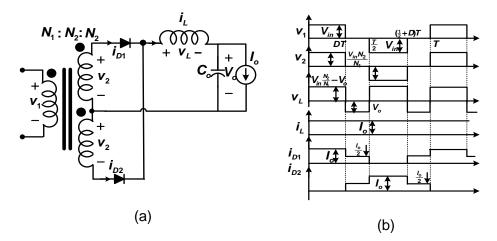

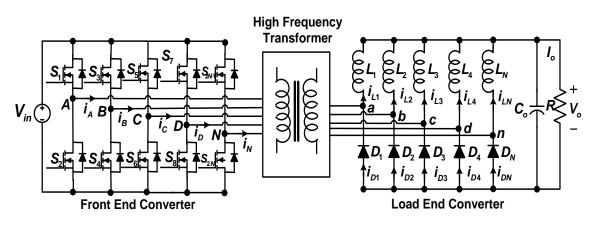

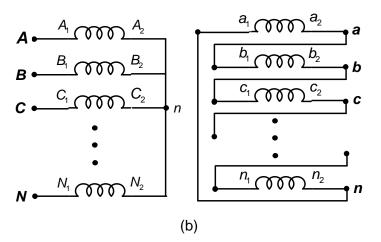

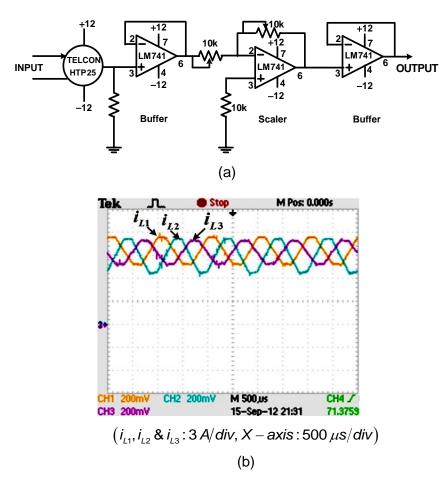

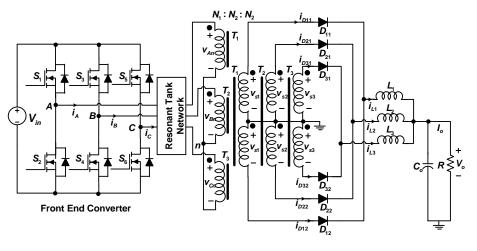

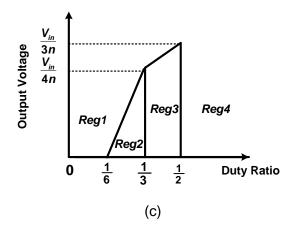

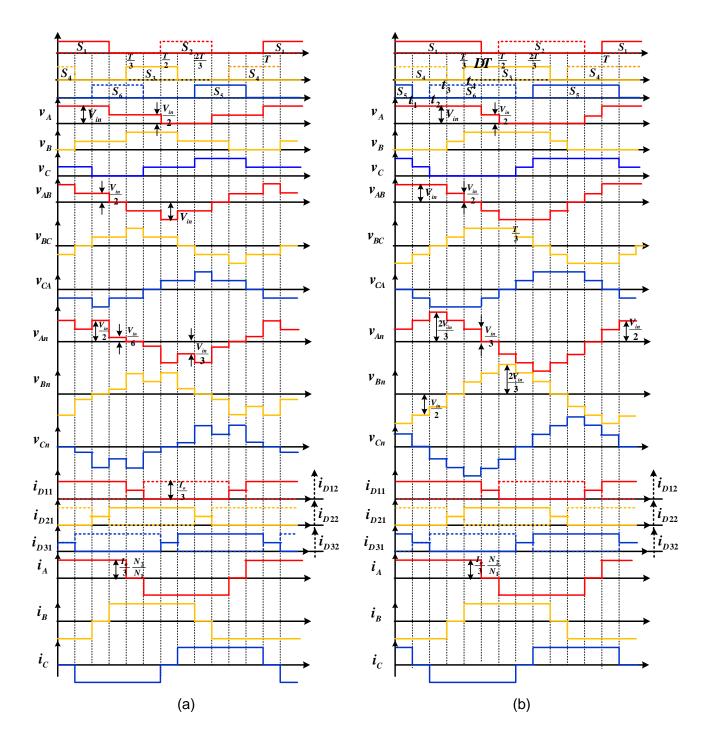

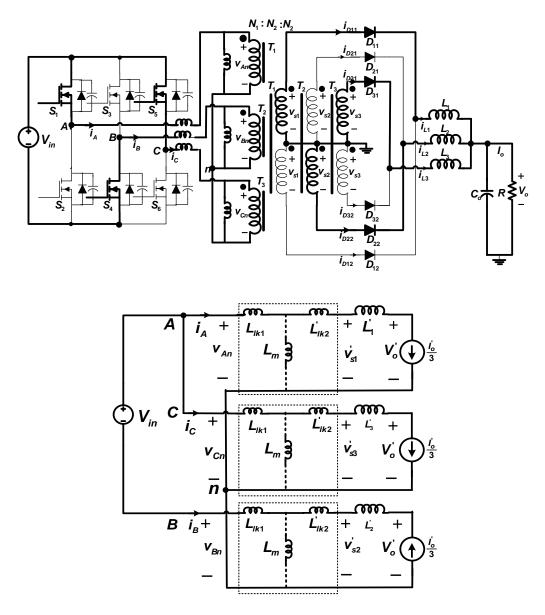

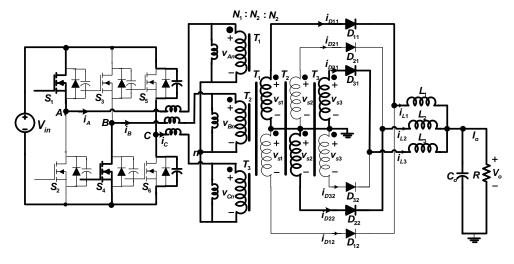

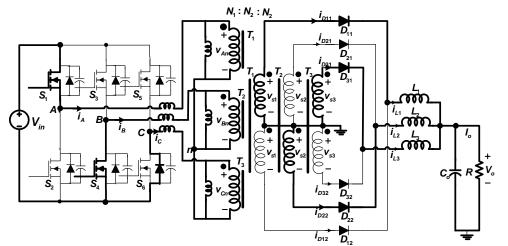

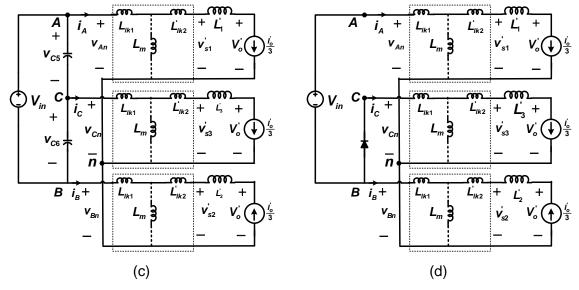

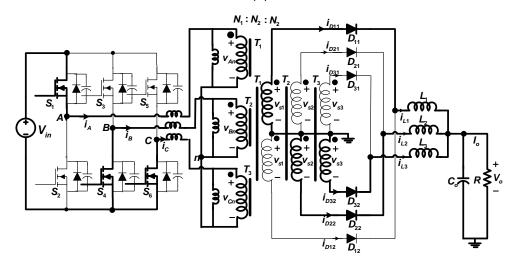

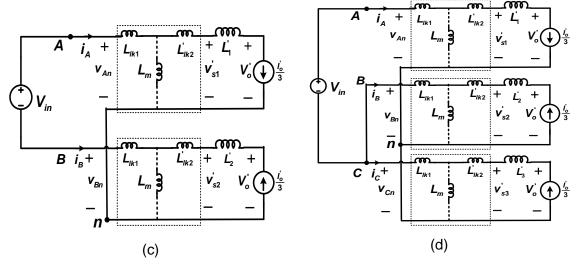

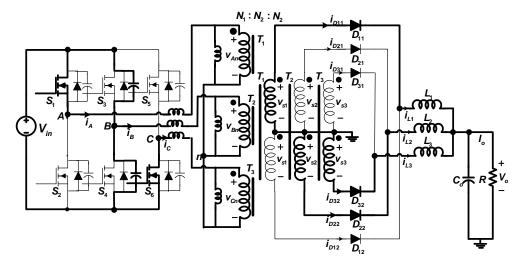

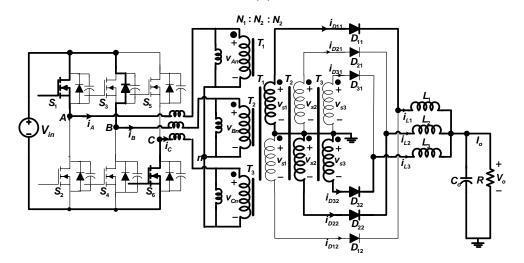

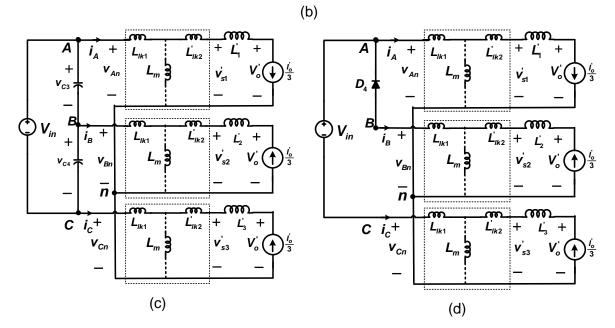

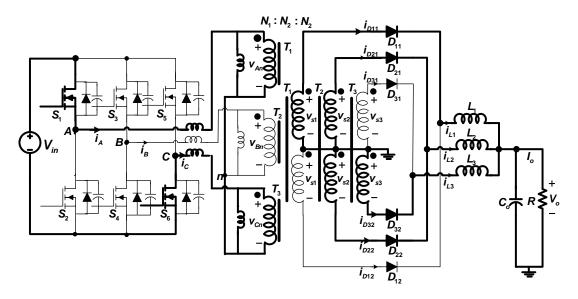

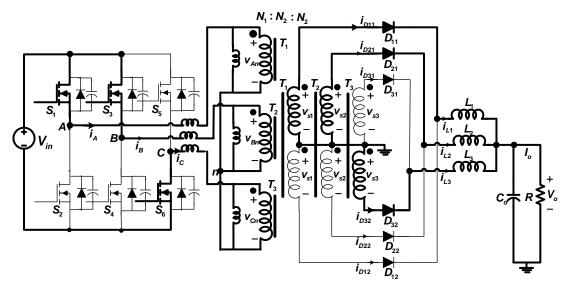

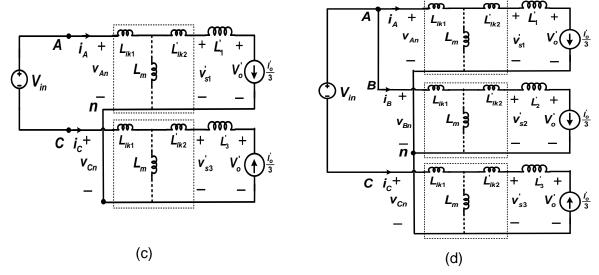

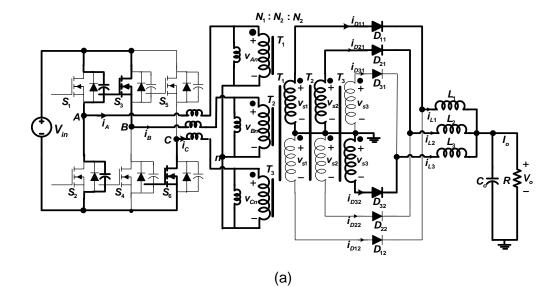

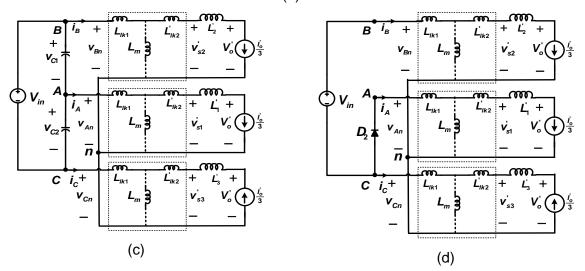

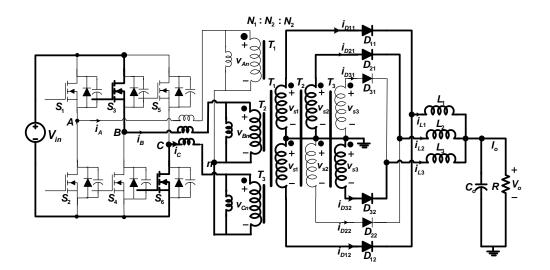

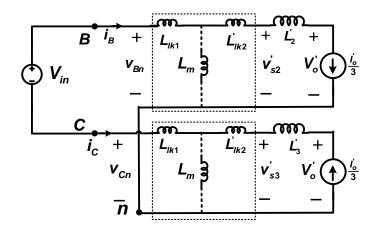

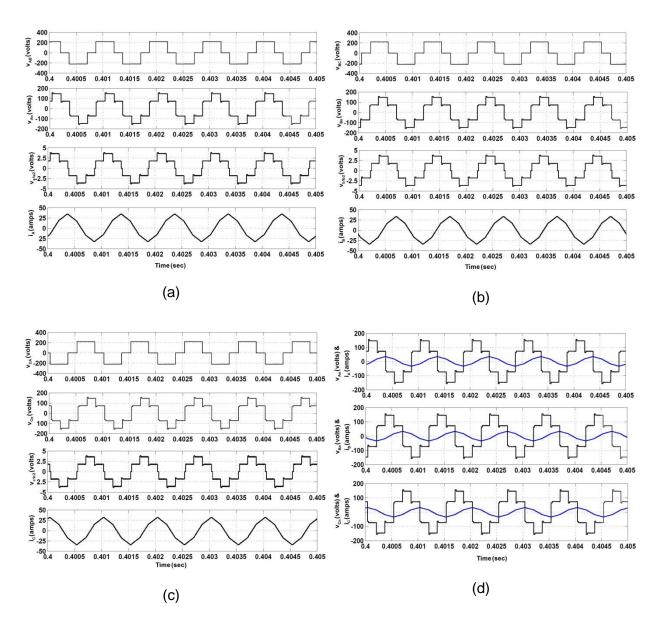

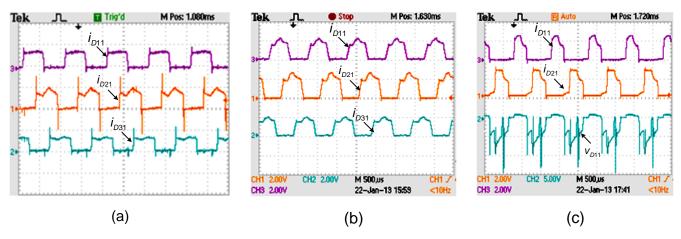

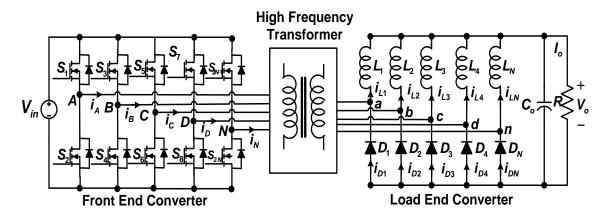

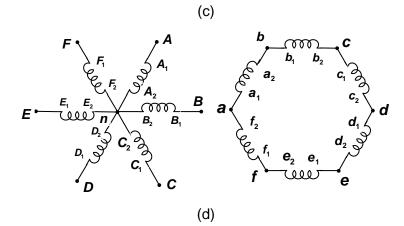

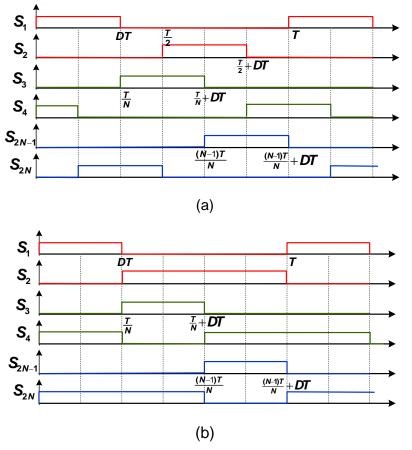

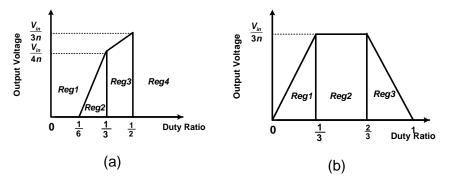

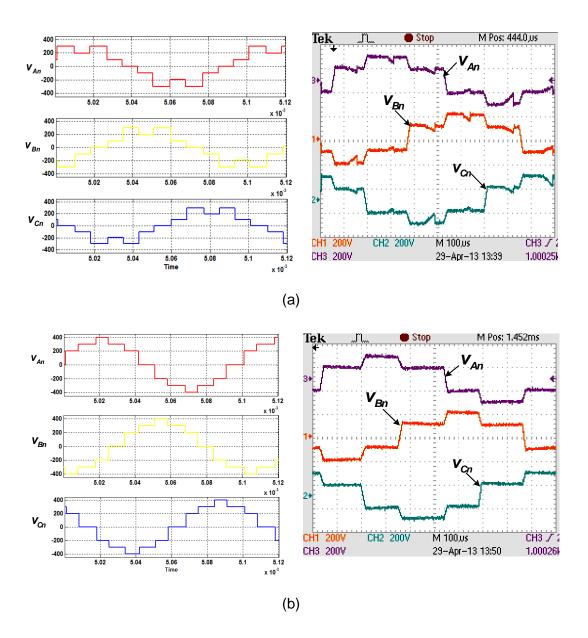

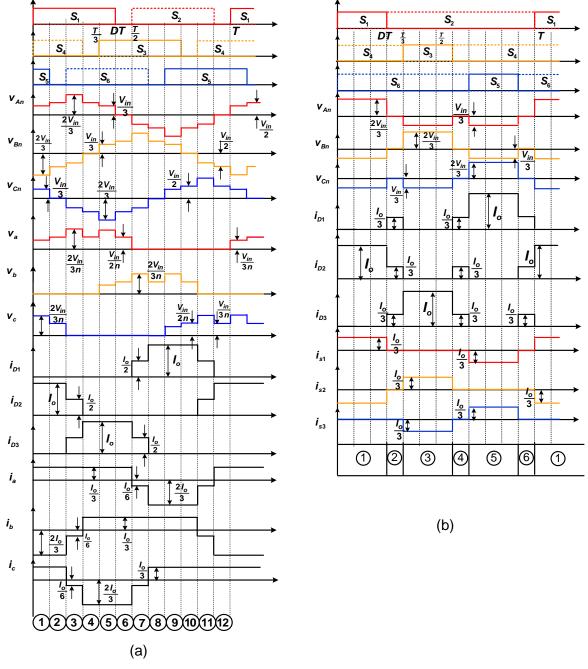

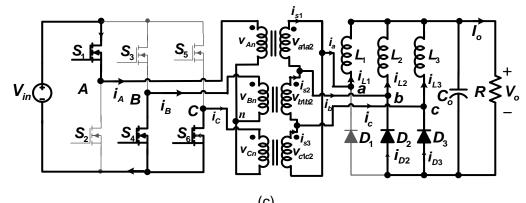

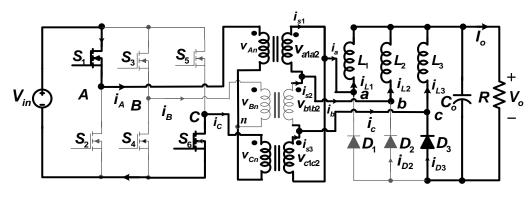

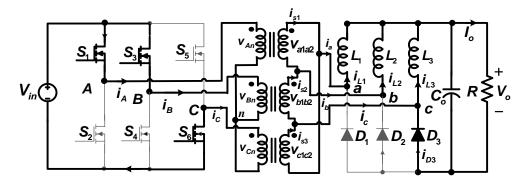

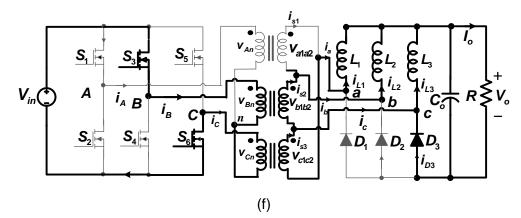

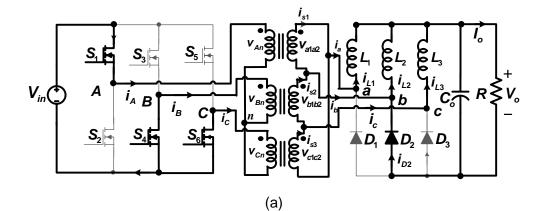

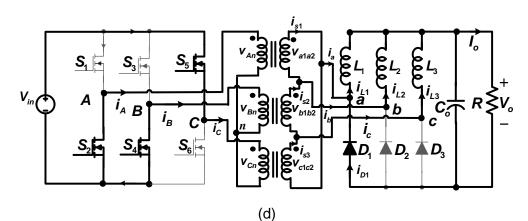

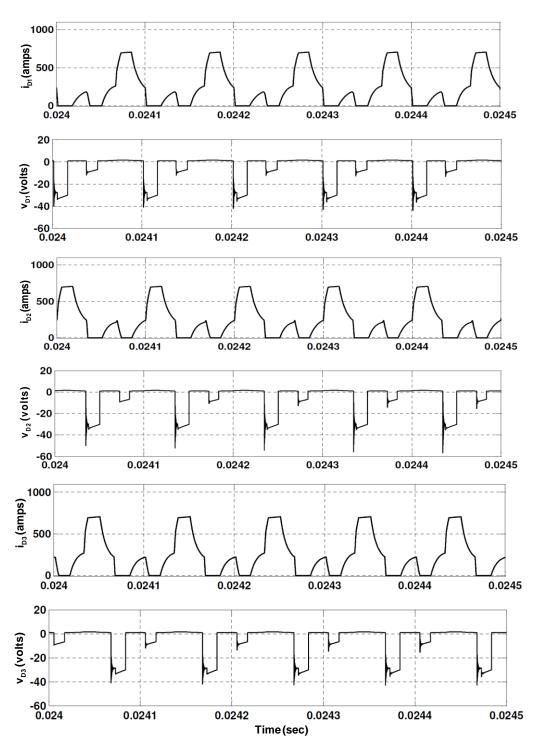

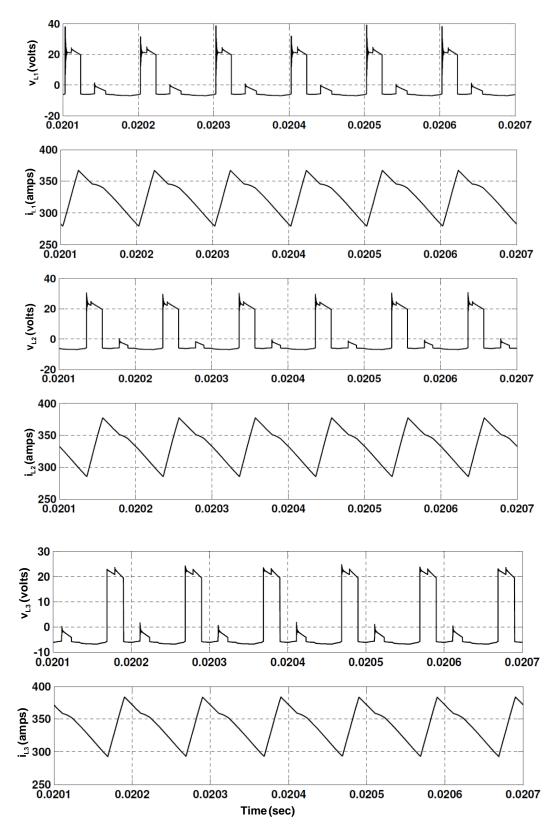

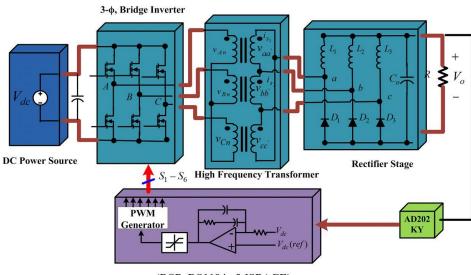

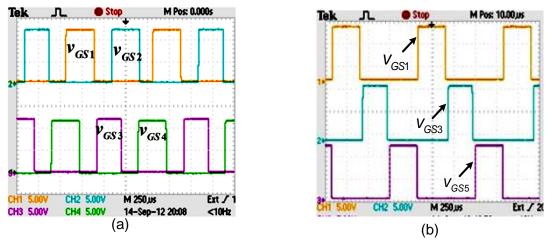

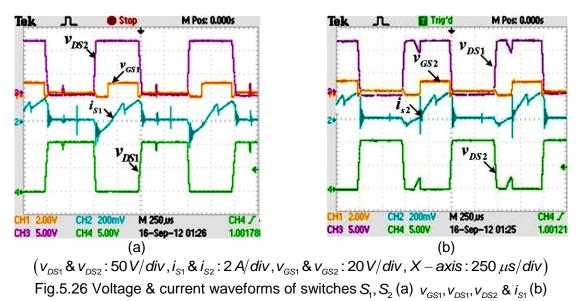

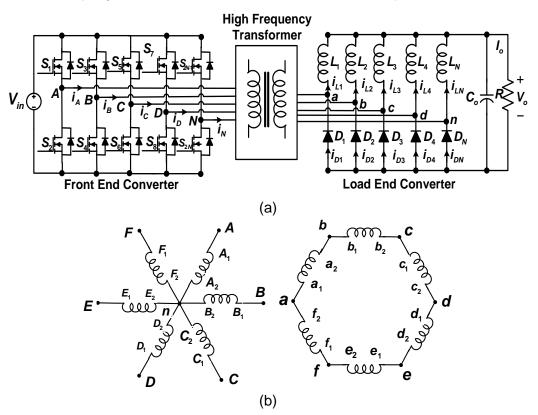

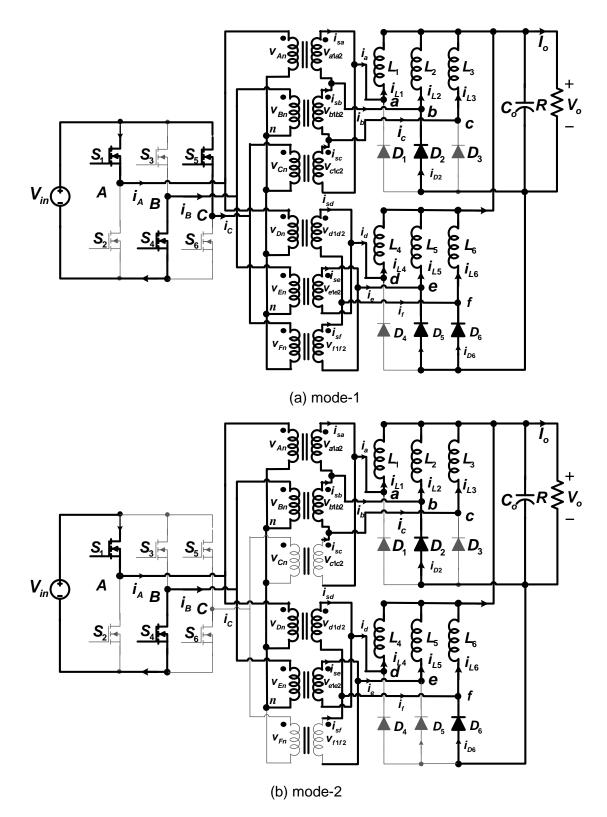

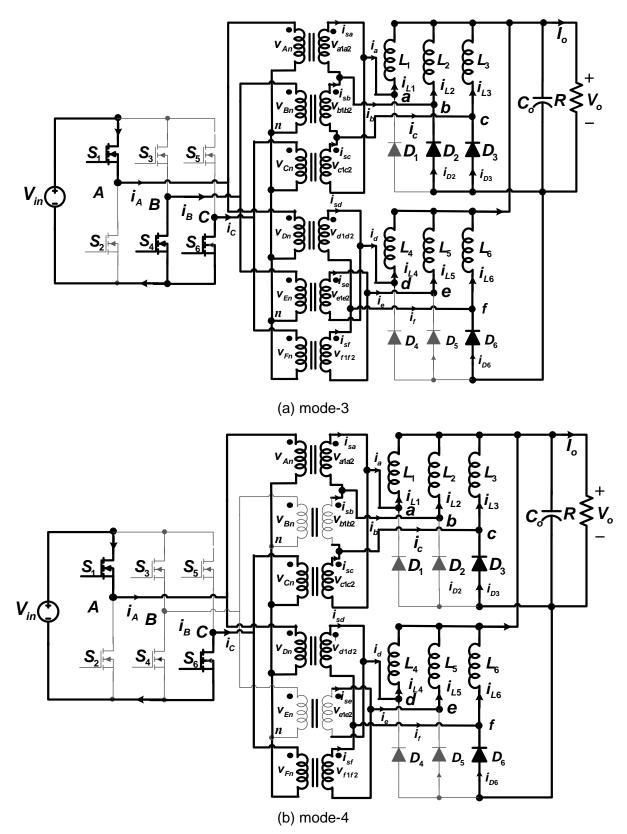

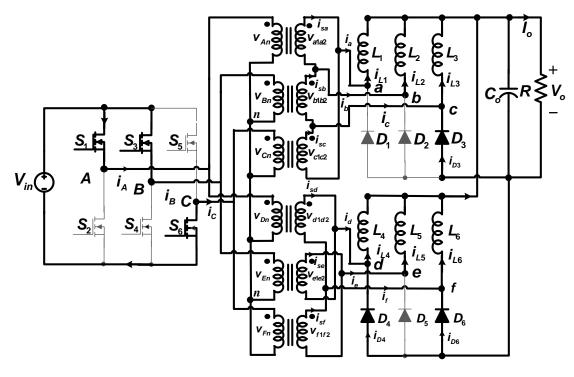

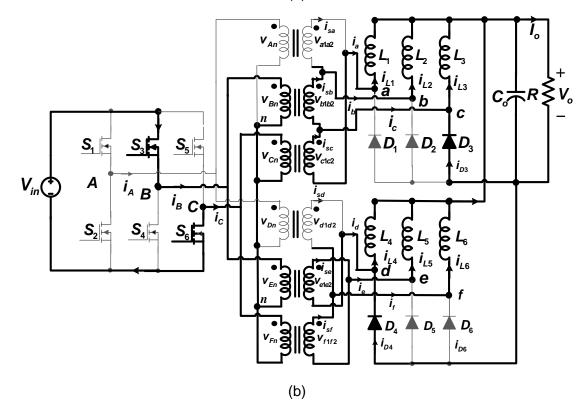

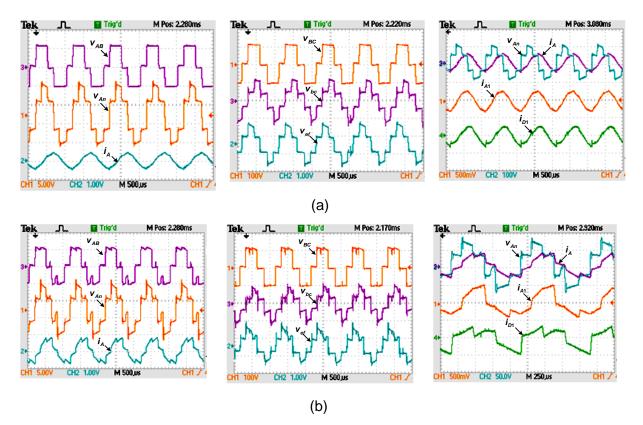

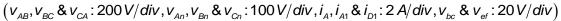

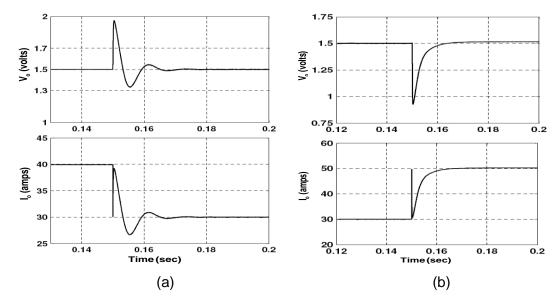

For high-current applications, the rectifier configuration of current-doubler converter is preferred over the centre-tapped converter for a number of reasons. First, in the currentdoubler converter the inductor currents and the transformer secondary current are lower than the corresponding currents in the centre-tapped converter. As a result, the current-doubler converter exhibits lower conduction losses than the centre-tapped converter. Second, the current-doubler converter minimizes the number of high-current interconnections that further simplify the secondary layout and reduces the layout-related loss. On the basis of secondary side load sharing, transformer design and thermal heat dissipation, the three-phase high frequency isolated DC-DC converter with three-phase rectification is proposed. It consists of three main parts: front end converter, high frequency transformer and load end converter. The front end converter comprises of N legs and each leg consists of two power switches. The midpoints of each leg are connected to one end of the primary winding of single-phase high frequency transformers and other ends of the primary winding of transformers are connected at one point. The load end converter of three-phase rectification is similar to threephase full diode bridge in which upper diodes are replaced by inductors. The performance of proposed converter is investigated under symmetrical and asymmetrical phase shifted PWM control methods with fixed frequency operation. The steady state operation of the converter is discussed in detailed using operating waveforms and its equivalent circuits during different modes. A Simulink model of proposed converter is developed using MATLAB/ SimPowerSystems<sup>™</sup> and its simulation results are presented under various operating conditions. To validate the simulation results of proposed topology, a scaled prototype model is developed and experimentally tested under different operating conditions. The comparative evaluation of proposed converter under symmetrical and asymmetrical control method is carried out with respect to various parameters such as duty cycle control, voltage gain, transformer secondary winding current, voltage and current of rectifier diodes, thermal stress and ZVS and ZCS implementation. It is concluded that under symmetrical control method, all the power switches conduct uniformly unlike to asymmetrical control and hence uniform heat distribution is achieved with symmetrical control. Implementation of asymmetrical control technique requires dead band circuits as compared to symmetrical control. Furthermore, reduction in secondary side losses can be done by employing self driven synchronous rectifier replacing rectifier power diodes.

iv

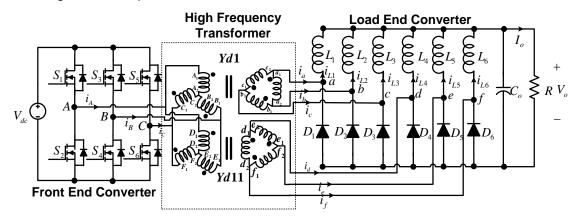

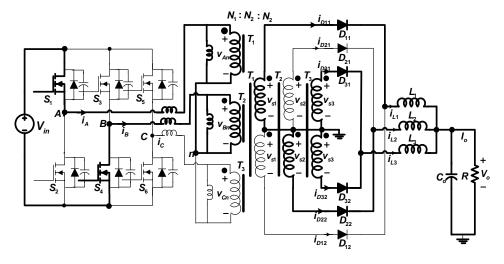

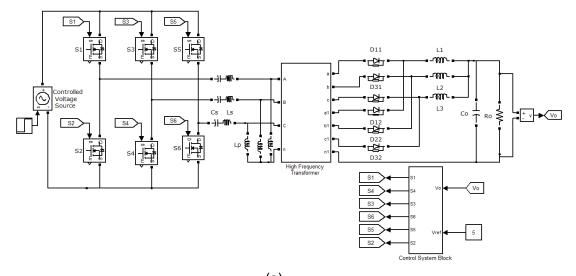

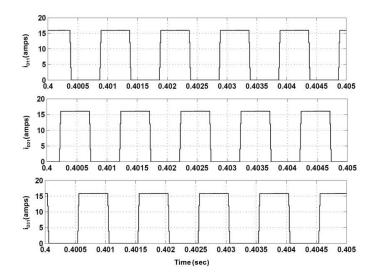

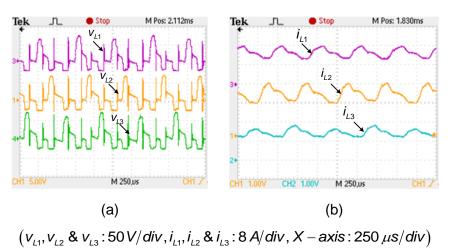

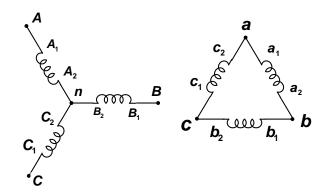

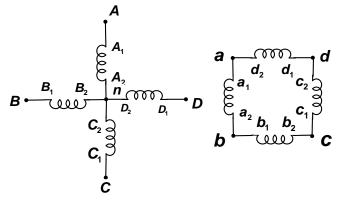

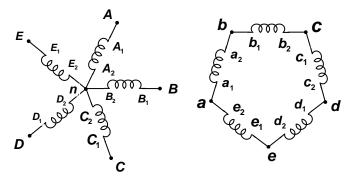

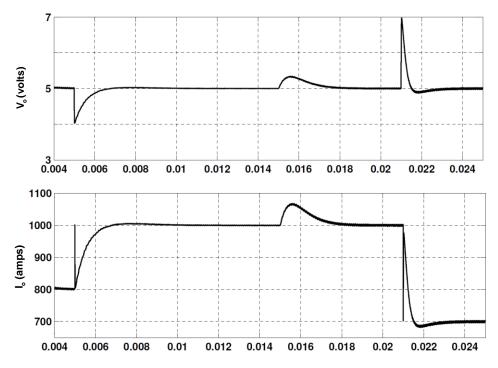

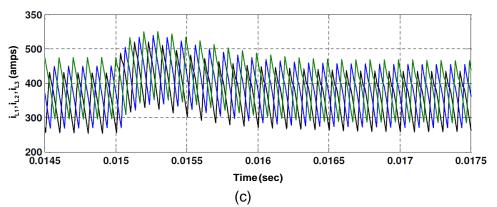

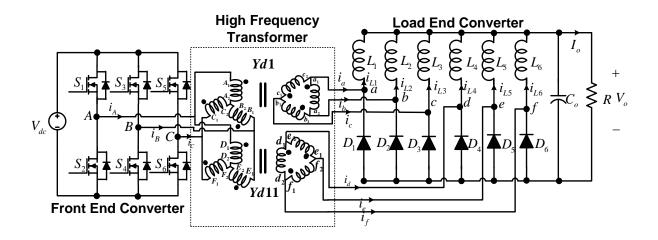

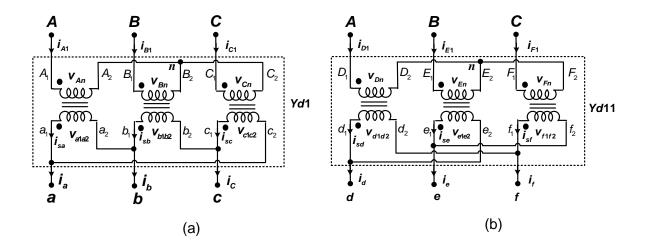

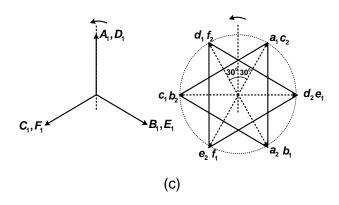

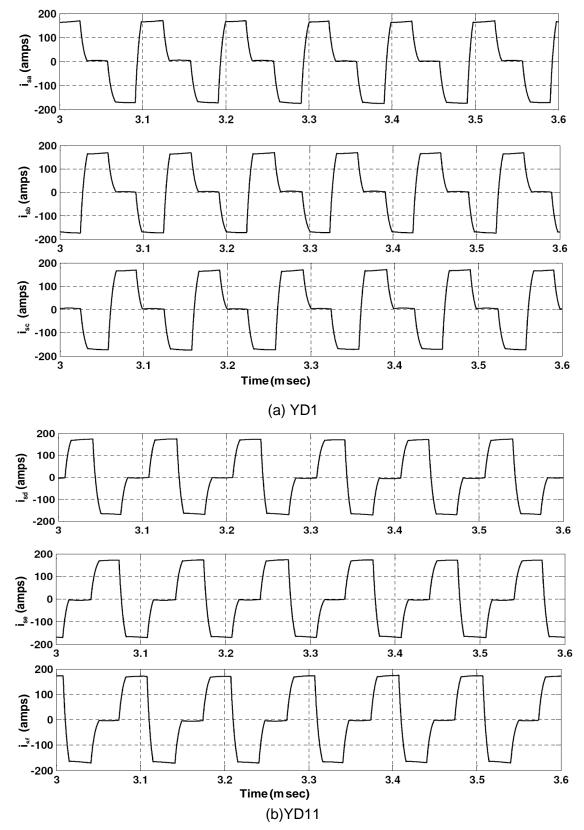

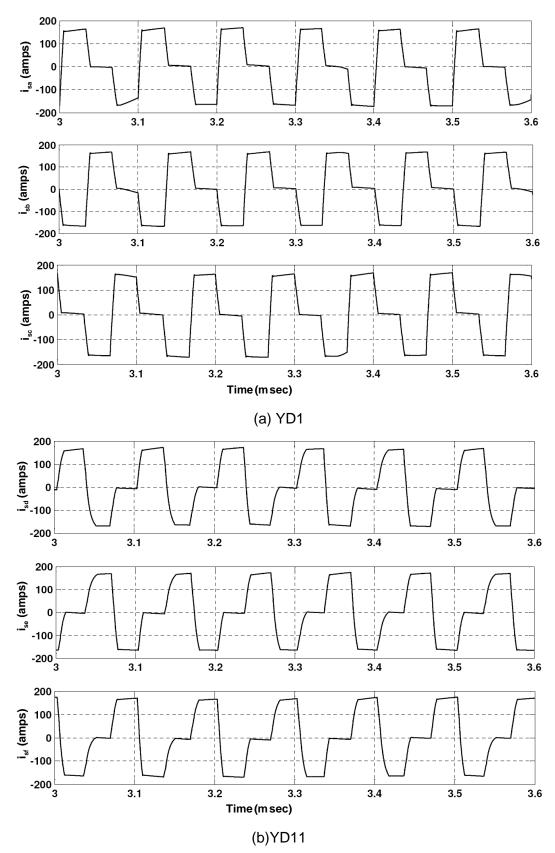

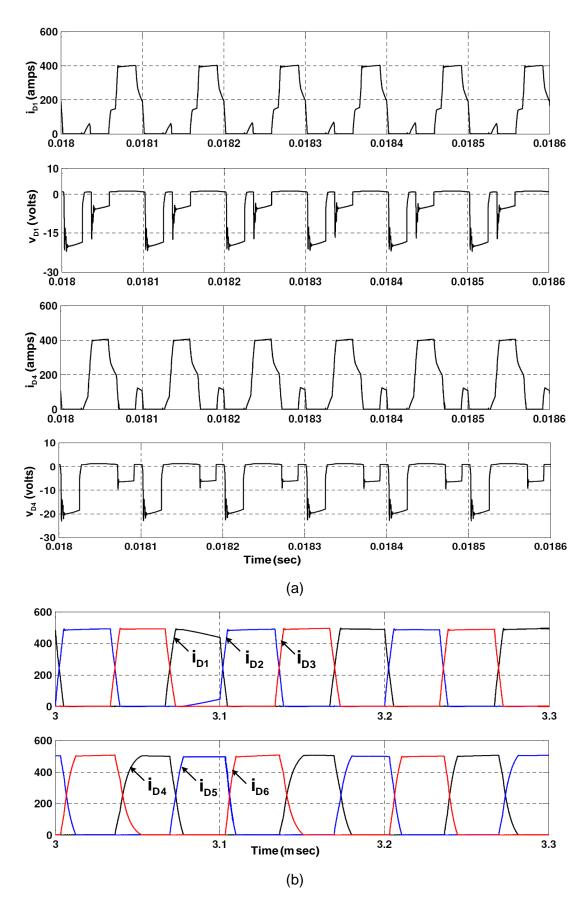

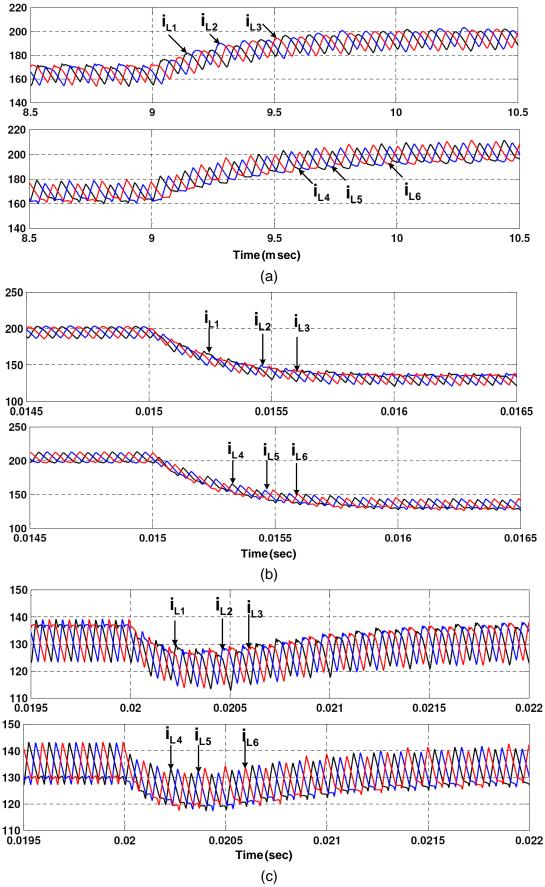

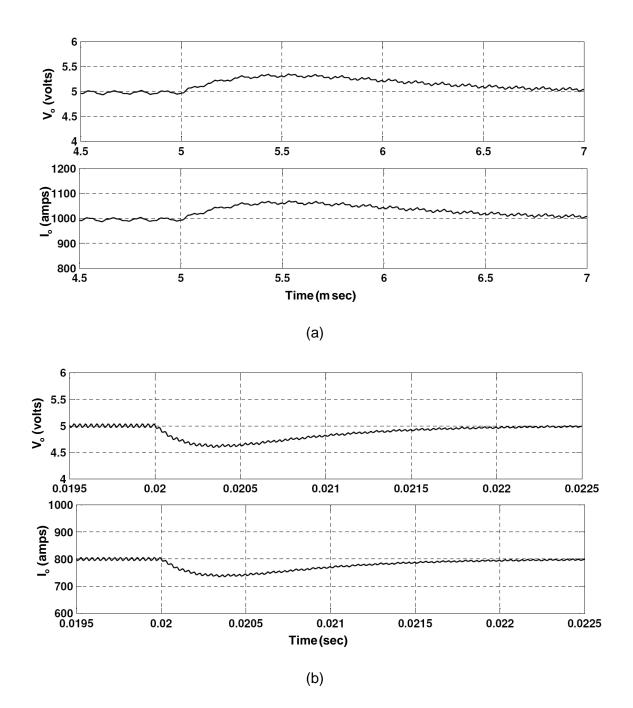

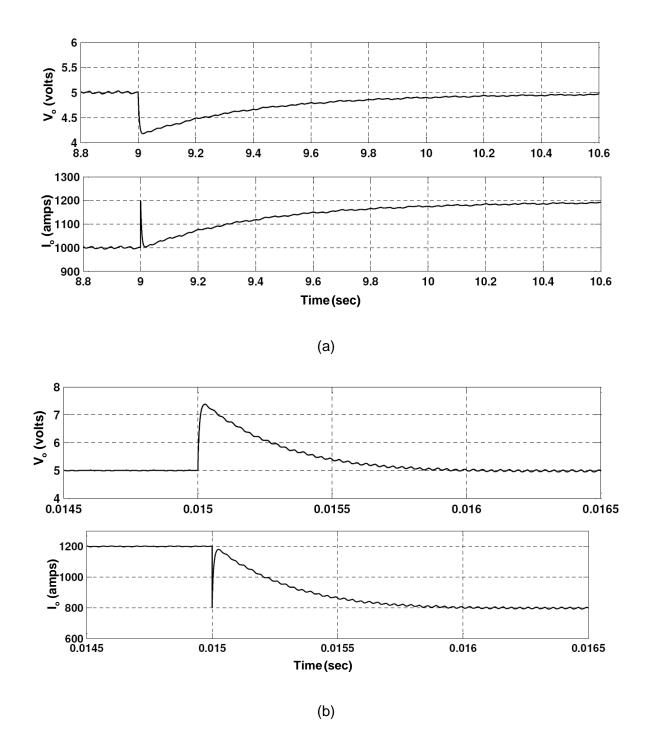

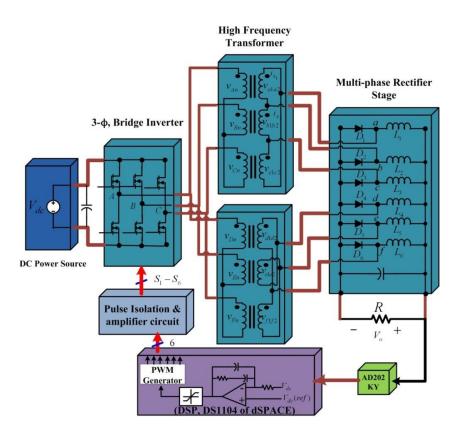

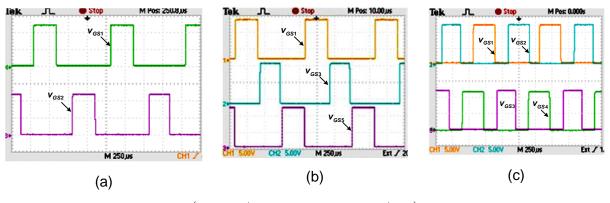

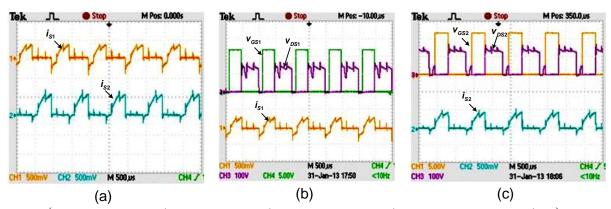

Many industrial applications such as welding, plasma cutting, and surface hardening require large DC current at low voltage. In such applications, the rating of power supply varies from several kilowatts to hundreds of kilowatts. The power supply employs in such applications particularly in arc welding process is expected to operate from open-circuit (no-load) to short-circuit (when the electrode sticks to the workpiece for a short span of time) quickly and also the transients occur during the striking of the arc, rapid arc length changes and metal transfer across the arc. The power supply must respond to these changes rapidly. In the present work, a multi-phase high frequency isolated DC-DC converter is proposed which is well suited for aforementioned applications. The proposed converter comprises of front end converter, two units of three-phase high frequency transformers and multi-phase rectifier stage at load end converter. In proposed topology, one three-phase transformer is configured in Yd1 and other transformer is configured in Yd11 to provide phase shift for interleaved operation. The performance of proposed converter has been investigated under symmetrical and asymmetrical phase shifted PWM control methods with fixed frequency operation. In comparison with conventional welding machine employed in many industries, the size and weight, efficiency and dynamic response of proposed converter is improved significantly. The simulation and experimental results are obtained under different operating conditions and presented.

I take this opportunity to express my sincere gratitude towards my supervisiors Dr. Satya Prakash Srivastava & Dr. Pramod Agarwal, Professors, Departmnent of Electrical Engineering, Indian Insitute of Technology Roorkee (IITR) for their guidance, valuable suggestions, patience, continuous encouragement and constant source of inspiration throughout the course of this study. It is my valued oppurtunuity to learn the rigorous attitude towards study and research.

I also express my sincere gratitude towards my research committee members namely, Prof.S.P. Gupta (EED), Prof. A.K. Saxena (E&C), Prof.S.P. Singh (EED) and my supervisiors for their valuable suggestions and cooperation during period of research.

My special thanks to Prof. Satya Pal Gupta, Deputy Director, IITR for inspiring me towards teaching and research. I also express my sincere gratitude to Prof. Pramod Agarwal, Professor & Head, Electrical Engineering Department of this institute for their help, moral support, and providing the excellent infrastructure, laboratory and computing facilities for the research work.

I acknowledge my sincere gratitude to All India Council for Technical Education, Government of India for providing financial support during my Ph.D work. The research work has been carried out under Quality Improvement Programme (QIP) scheme of AICTE.

I am thankful to the technical and office staffs of Electrical Engineering Department, especially Mr. Gautam Singh, Mr. Rakesh Saini, Mr. Ameer Ahmad, Mr. Rishabh Verma and Mr. Mohan Singh for their cooperation and needful help in the fabrication and assembly of the experimental set-up.

It has been a great pleasure to work in the Power Quality and Conditioning lab, not only because of the talented colleagues but also the friendly environments. I would like to thanks all those who have directly or indirectly provided support and encouragement in this endeavour. In particular, I would like to thank Dr. Madhukar Waware, Dr. Subhash Dubey, Dr. Subhash Joshi, Dr. Nitin Gupta, Mr. Seenivasarao D, Mr. Jayram, Mr.Aurobind Panda, Mr. Jignesh Makwana, Mr. Ambarish Mishra, Ms. Vasundhara Mahajan, Mr. Sanjiv Kumar Mr. Anubhav Agarwal, Mr. Sukant Haldar, Mr. Vikas Kumar, and Mr. Sandeep Sharma.

I wish to thank the Director and faculty of electrical engineering department of Sardar Vallbhbhai National Institute of Technology, Surat, Gujarat (India) for the cooperation they have extended to me while working at Roorkee.

Finally, I wish to express my deepest gratitude to my parents, Archana (my wife), Istuti and Aastha (daughtors) for their endless, support, encouragement and patience during study of course.

(Rakesh Maurya)

| ACKNOWLEDGEMENTS       VI         CONTENTS       VII         LIST OF FIGURES       XI         LIST OF TABLES       XX         LIST OF SYMBOLS       XXI         CHAPTER 1:       INTRODUCTION       1         1.1       Introduction       1         1.2       Applications of Low Voltage High Current Power Supply       2         1.2.1       Low Power Applications       3         1.2.2       Medium Power Applications       3         1.2.3       High Power Applications       4         1.3       Literature Review       6         1.3.1       Topologies of DC-DC Power Converters       9         1.3.2       Pulse Width Modulation Control       22         1.4       Scope of Work and Motivation       25         1.5       Proposed Topology for Low Voltage High Current Power Converters       26         1.6       Author's Contribution       29         1.7       Organization of the Thesis       31         CHAPTER 2:       INTER-CONNECTED MULTIPLE DC-DC CONVERTER       33         2.1       Introduction       33 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIST OF FIGURES       XI         LIST OF TABLES       XX         LIST OF SYMBOLS       XXI         CHAPTER 1:       INTRODUCTION       1         1.1       Introduction       1         1.2       Applications of Low Voltage High Current Power Supply       2         1.2.1       Low Power Applications       3         1.2.2       Medium Power Applications       3         1.2.3       High Power Applications       4         1.3       Literature Review       6         1.3.1       Topologies of DC-DC Power Converters       9         1.3.2       Pulse Width Modulation Control       22         1.4       Scope of Work and Motivation       25         1.5       Proposed Topology for Low Voltage High Current Power Converters       26         1.6       Author's Contribution       29         1.7       Organization of the Thesis       31         CHAPTER 2:       INTER-CONNECTED MULTIPLE DC-DC CONVERTER       33         2.1       Introduction       33                                                              |

| LIST OF TABLES.       XX         LIST OF SYMBOLS       XXI         CHAPTER 1:       INTRODUCTION       1         1.1       Introduction       1         1.2       Applications of Low Voltage High Current Power Supply       2         1.2.1       Low Power Applications       3         1.2.2       Medium Power Applications       3         1.2.3       High Power Applications       4         1.3       Literature Review       6         1.3.1       Topologies of DC-DC Power Converters       9         1.3.2       Pulse Width Modulation Control       22         1.4       Scope of Work and Motivation       25         1.5       Proposed Topology for Low Voltage High Current Power Converters       26         1.6       Author's Contribution       29         1.7       Organization of the Thesis       31         CHAPTER 2:       INTER-CONNECTED MULTIPLE DC-DC CONVERTER       33                                                                                                                                      |

| LIST OF SYMBOLS       XXI         CHAPTER 1:       INTRODUCTION       1         1.1       Introduction       1         1.2       Applications of Low Voltage High Current Power Supply       2         1.2.1       Low Power Applications       3         1.2.2       Medium Power Applications       3         1.2.3       High Power Applications       3         1.2.3       Literature Review       6         1.3.1       Topologies of DC-DC Power Converters       9         1.3.2       Pulse Width Modulation Control       22         1.4       Scope of Work and Motivation       25         1.5       Proposed Topology for Low Voltage High Current Power Converters       26         1.6       Author's Contribution       29         1.7       Organization of the Thesis       31         CHAPTER 2:       INTER-CONNECTED MULTIPLE DC-DC CONVERTER       33         2.1       Introduction       33                                                                                                                             |

| CHAPTER 1:       INTRODUCTION       1         1.1       Introduction       1         1.2       Applications of Low Voltage High Current Power Supply       2         1.2.1       Low Power Applications       3         1.2.2       Medium Power Applications       3         1.2.3       High Power Applications       4         1.3       Literature Review       6         1.3.1       Topologies of DC-DC Power Converters       9         1.3.2       Pulse Width Modulation Control       22         1.4       Scope of Work and Motivation       25         1.5       Proposed Topology for Low Voltage High Current Power Converters       26         1.6       Author's Contribution       29         1.7       Organization of the Thesis       31         CHAPTER 2:       INTER-CONNECTED MULTIPLE DC-DC CONVERTER       33         2.1       Introduction       33                                                                                                                                                                 |

| 1.1       Introduction       1         1.2       Applications of Low Voltage High Current Power Supply       2         1.2.1       Low Power Applications       3         1.2.2       Medium Power Applications       3         1.2.3       High Power Applications       3         1.2.3       High Power Applications       4         1.3       Literature Review       6         1.3.1       Topologies of DC-DC Power Converters       9         1.3.2       Pulse Width Modulation Control       22         1.4       Scope of Work and Motivation       25         1.5       Proposed Topology for Low Voltage High Current Power Converters       26         1.6       Author's Contribution       29         1.7       Organization of the Thesis       31         CHAPTER 2:       INTER-CONNECTED MULTIPLE DC-DC CONVERTER       33         2.1       Introduction       33                                                                                                                                                           |

| 1.1       Introduction       1         1.2       Applications of Low Voltage High Current Power Supply       2         1.2.1       Low Power Applications       3         1.2.2       Medium Power Applications       3         1.2.3       High Power Applications       3         1.2.3       High Power Applications       4         1.3       Literature Review       6         1.3.1       Topologies of DC-DC Power Converters       9         1.3.2       Pulse Width Modulation Control       22         1.4       Scope of Work and Motivation       25         1.5       Proposed Topology for Low Voltage High Current Power Converters       26         1.6       Author's Contribution       29         1.7       Organization of the Thesis       31         CHAPTER 2:       INTER-CONNECTED MULTIPLE DC-DC CONVERTER       33         2.1       Introduction       33                                                                                                                                                           |

| 1.2       Applications of Low Voltage High Current Power Supply       2         1.2.1       Low Power Applications       3         1.2.2       Medium Power Applications       3         1.2.3       High Power Applications       4         1.3       Literature Review       6         1.3.1       Topologies of DC-DC Power Converters       9         1.3.2       Pulse Width Modulation Control       22         1.4       Scope of Work and Motivation       25         1.5       Proposed Topology for Low Voltage High Current Power Converters       26         1.6       Author's Contribution       29         1.7       Organization of the Thesis       31         CHAPTER 2:       INTER-CONNECTED MULTIPLE DC-DC CONVERTER       33         2.1       Introduction       33                                                                                                                                                                                                                                                      |

| 1.2.1       Low Power Applications       3         1.2.2       Medium Power Applications       3         1.2.3       High Power Applications       4         1.3       Literature Review       6         1.3.1       Topologies of DC-DC Power Converters       9         1.3.2       Pulse Width Modulation Control       22         1.4       Scope of Work and Motivation       25         1.5       Proposed Topology for Low Voltage High Current Power Converters       26         1.6       Author's Contribution       29         1.7       Organization of the Thesis       31         CHAPTER 2: INTER-CONNECTED MULTIPLE DC-DC CONVERTER         33       2.1       Introduction       33                                                                                                                                                                                                                                                                                                                                            |

| 1.2.2       Medium Power Applications       3         1.2.3       High Power Applications       4         1.3       Literature Review       6         1.3.1       Topologies of DC-DC Power Converters       9         1.3.2       Pulse Width Modulation Control       22         1.4       Scope of Work and Motivation       25         1.5       Proposed Topology for Low Voltage High Current Power Converters       26         1.6       Author's Contribution       29         1.7       Organization of the Thesis       31         CHAPTER 2:       INTER-CONNECTED MULTIPLE DC-DC CONVERTER       33         2.1       Introduction       33                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.2.3 High Power Applications.       4         1.3 Literature Review.       6         1.3.1 Topologies of DC-DC Power Converters.       9         1.3.2 Pulse Width Modulation Control       22         1.4 Scope of Work and Motivation       25         1.5 Proposed Topology for Low Voltage High Current Power Converters       26         1.6 Author's Contribution       29         1.7 Organization of the Thesis       31         CHAPTER 2: INTER-CONNECTED MULTIPLE DC-DC CONVERTER         33       2.1 Introduction       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.3       Literature Review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.3.1 Topologies of DC-DC Power Converters91.3.2 Pulse Width Modulation Control221.4 Scope of Work and Motivation251.5 Proposed Topology for Low Voltage High Current Power Converters261.6 Author's Contribution291.7 Organization of the Thesis31CHAPTER 2: INTER-CONNECTED MULTIPLE DC-DC CONVERTER332.1 Introduction33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.3.2Pulse Width Modulation Control221.4Scope of Work and Motivation251.5Proposed Topology for Low Voltage High Current Power Converters261.6Author's Contribution291.7Organization of the Thesis31CHAPTER 2: INTER-CONNECTED MULTIPLE DC-DC CONVERTER332.1Introduction33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.4Scope of Work and Motivation251.5Proposed Topology for Low Voltage High Current Power Converters261.6Author's Contribution291.7Organization of the Thesis31CHAPTER 2: INTER-CONNECTED MULTIPLE DC-DC CONVERTER332.1Introduction33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.5       Proposed Topology for Low Voltage High Current Power Converters       26         1.6       Author's Contribution       29         1.7       Organization of the Thesis       31         CHAPTER 2: INTER-CONNECTED MULTIPLE DC-DC CONVERTER         33       2.1       Introduction       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.6       Author's Contribution       29         1.7       Organization of the Thesis       31         CHAPTER 2: INTER-CONNECTED MULTIPLE DC-DC CONVERTER         33       2.1       Introduction       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.7 Organization of the Thesis       31         CHAPTER 2:       INTER-CONNECTED MULTIPLE DC-DC CONVERTER       33         2.1       Introduction       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CHAPTER 2: INTER-CONNECTED MULTIPLE DC-DC CONVERTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2 System Configuration and Control Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2.1 Power Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.2.2 Control Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.3 Operation, Modeling and Analysis of the Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.4 Design of Power Circuit Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.4.1 Input voltage divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.4.2 Output Filter Inductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.4.3 Output Filter Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.5 Dynamic Modelling of Converter with State-Space Averaging (SSA) Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.6 System Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.7 Simulation Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.8 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| СНА               | PTER 3                                                                    | B: DEVELOPMENT OF SYSTEM HARDWARE                                          | 61  |

|-------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|

| 3.1               | Introdu                                                                   | uction                                                                     | 61  |

| 3.2               | Develo                                                                    | opment of power circuit                                                    | 62  |

|                   | 3.2.1                                                                     | Design of Front End Converter                                              | 62  |

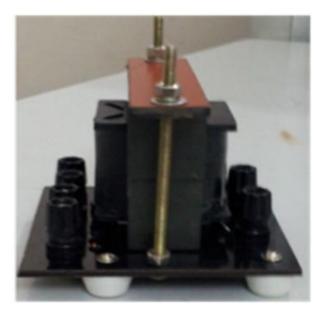

|                   | 3.2.2                                                                     | Design of High Frequency Transformer                                       | 62  |

| 3.3               | Develo                                                                    | ppment of Control Circuit                                                  | 66  |

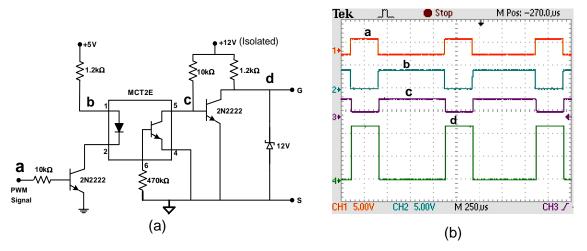

|                   | 3.3.1                                                                     | MOSFET Driver Circuits                                                     | 66  |

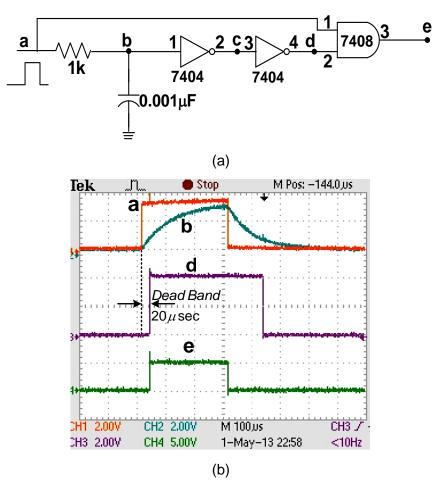

|                   | 3.3.2                                                                     | Dead-Band Circuit                                                          | 67  |

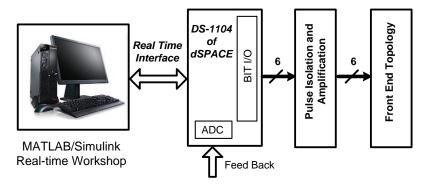

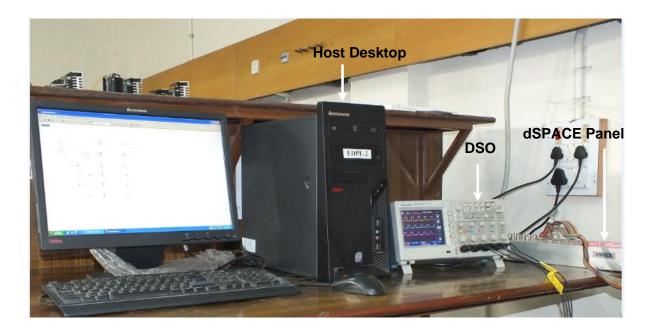

|                   | 3.3.3                                                                     | DS1104 DSP (dSPACE) hardware board                                         | 67  |

| 3.4               | Measu                                                                     | rements of System Parameters                                               | 69  |

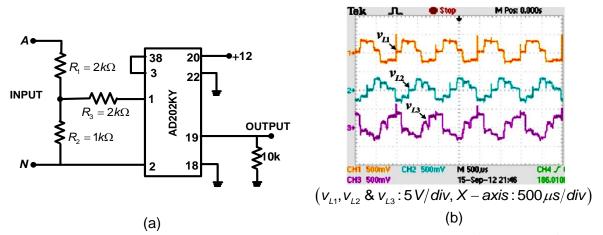

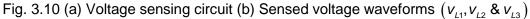

|                   | 3.4.1                                                                     | Voltage Sensing                                                            | 69  |

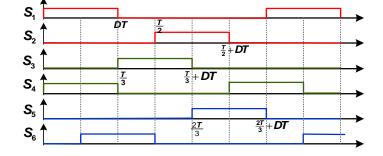

|                   | 3.4.2                                                                     | Current Sensing                                                            | 71  |

| 3.5               | Conclu                                                                    | usion                                                                      | 71  |

| •••••             |                                                                           | I: THREE-PHASE LLC RESONANT DC-DC POWER CONVERTER<br>RE-TAPPED TRANSFORMER | 73  |

| 4.1               |                                                                           |                                                                            |     |

| 4.2               |                                                                           | n Configuration and Control Scheme                                         |     |

|                   | •                                                                         | Power Circuit                                                              |     |

|                   |                                                                           | Control Strategy                                                           |     |

| 4.3               |                                                                           | tion, Modeling and Analysis of the Converter                               |     |

|                   | 4.3.1                                                                     | Operation of Converter                                                     |     |

|                   | 4.3.2                                                                     | Modeling of LLC Resonant Tank                                              |     |

|                   | 4.3.3                                                                     | Converter Design                                                           |     |

| 4.4               | Simula                                                                    | ation Studies                                                              | 100 |

|                   | 4.4.1                                                                     | Simulation Results & Discussion                                            | 102 |

| 4.5               | Experi                                                                    | mental Validation                                                          | 110 |

|                   | 4.5.1                                                                     | A Prototype Model of Proposed Converter                                    | 110 |

|                   | 4.5.2                                                                     | Experimental Results and Discussions                                       | 110 |

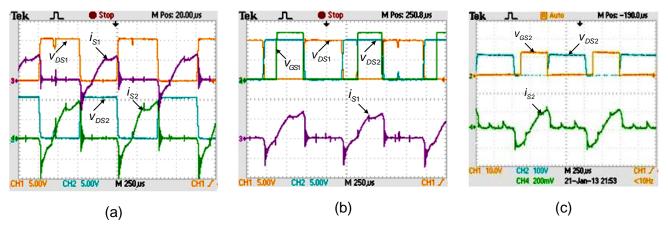

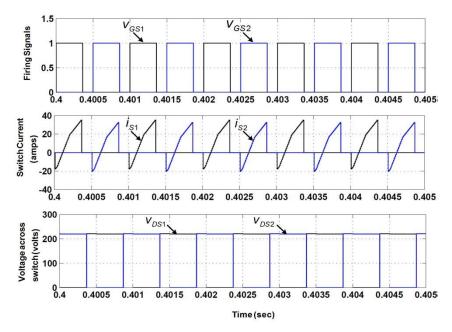

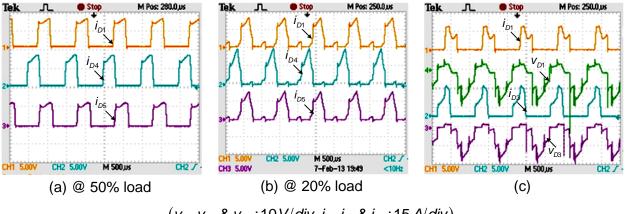

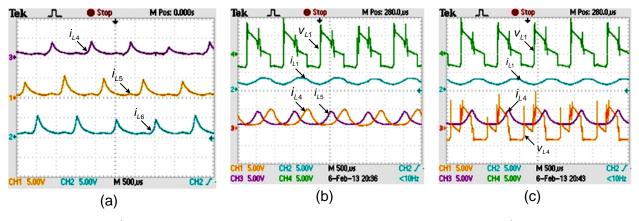

|                   |                                                                           | (a) Steady State Performance                                               | 111 |

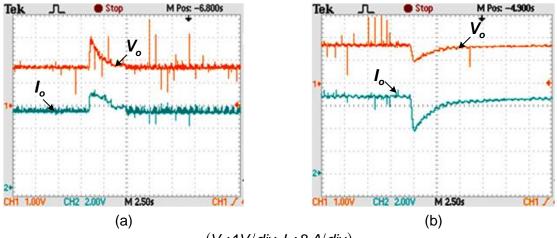

|                   |                                                                           | (b) Transient Performance                                                  | 116 |

| 4.6               | Conclu                                                                    | usion                                                                      | 119 |

|                   |                                                                           |                                                                            | 101 |

| <b>ТНК</b><br>5.1 |                                                                           | ASE RECTIFICATION                                                          |     |

| 5.1<br>5.2        |                                                                           |                                                                            |     |

| 0.2               | System Configuration and Control Scheme         5.2.1       Power Circuit |                                                                            |     |

|                   | 5.2.1                                                                     | Control Strategy                                                           |     |

|                   | 0.2.2                                                                     |                                                                            |     |

| 5.3                                                                                      |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                 | 125                                                                                                          |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

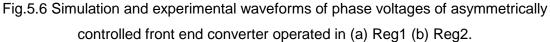

|                                                                                          | 5.3.1                                                                                                                | Operation of Converter under Symmetrical Control Method                                                                                                                                                                                                                                                                                                                         | 129                                                                                                          |

|                                                                                          | 5.3.2                                                                                                                | Operation of Converter under Asymmetrical Control Method                                                                                                                                                                                                                                                                                                                        | 133                                                                                                          |

| 5.4                                                                                      | Desig                                                                                                                | n of Output Filter Inductor                                                                                                                                                                                                                                                                                                                                                     | 135                                                                                                          |

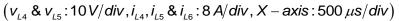

| 5.5                                                                                      | Simul                                                                                                                | ation Studies                                                                                                                                                                                                                                                                                                                                                                   | 137                                                                                                          |

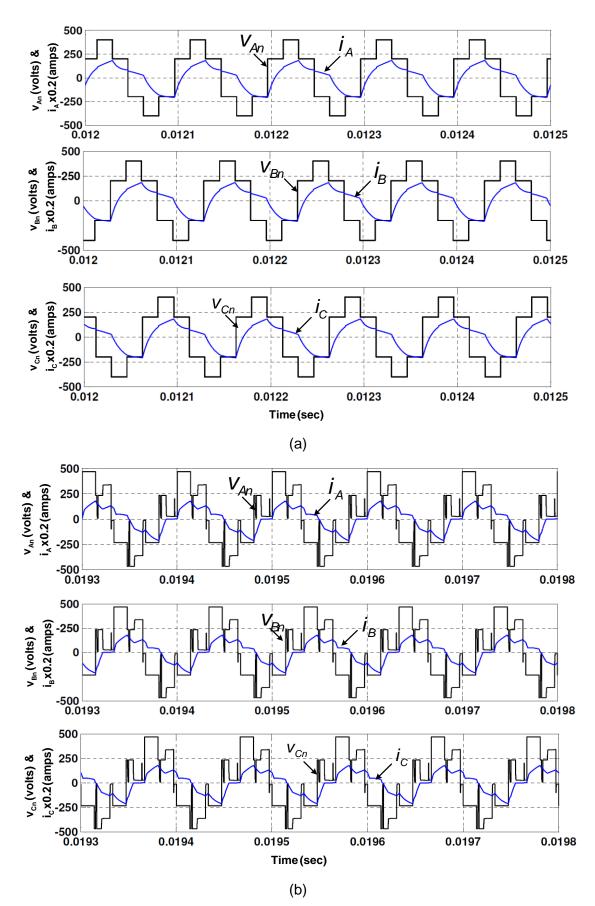

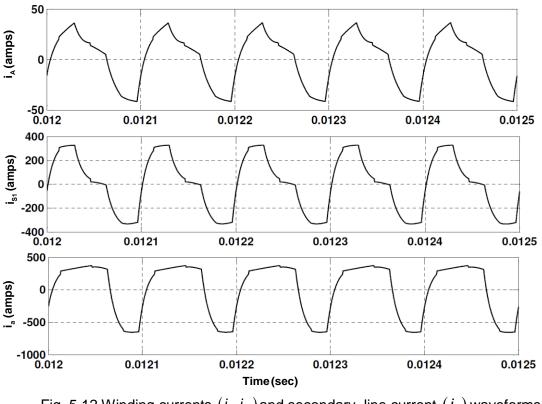

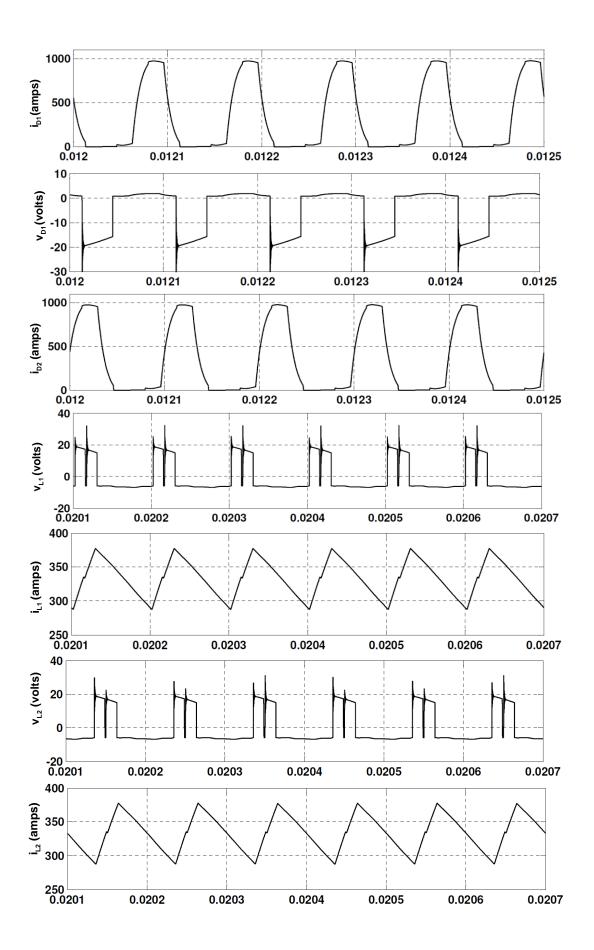

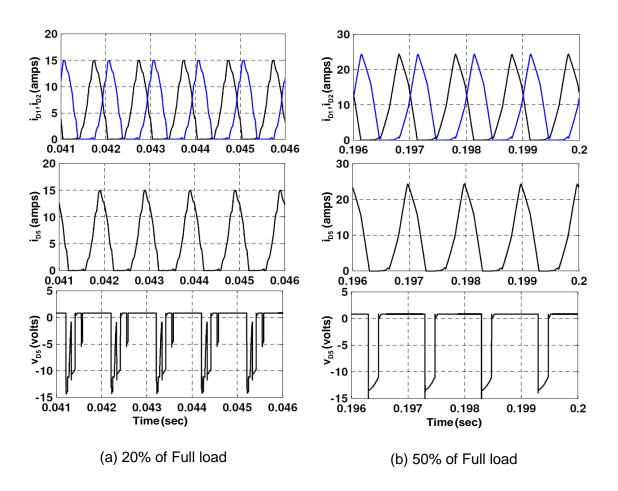

|                                                                                          | 5.5.1                                                                                                                | Simulation Results and Discussions                                                                                                                                                                                                                                                                                                                                              | 139                                                                                                          |

|                                                                                          |                                                                                                                      | (a) Performance with Symmetrical Control Method                                                                                                                                                                                                                                                                                                                                 | 139                                                                                                          |

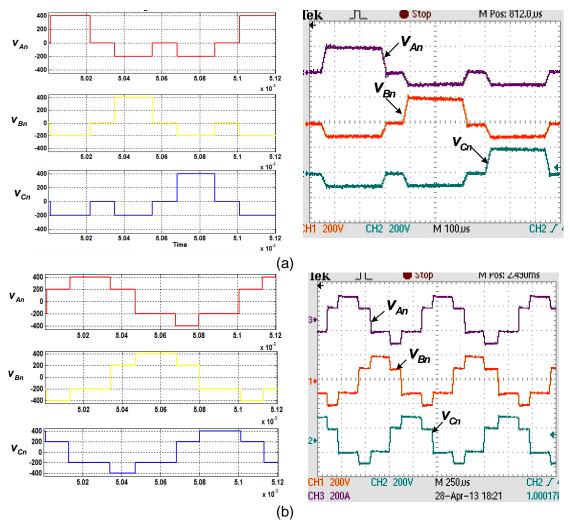

|                                                                                          |                                                                                                                      | (b) Performance with Asymmetrical Control Method                                                                                                                                                                                                                                                                                                                                | 145                                                                                                          |

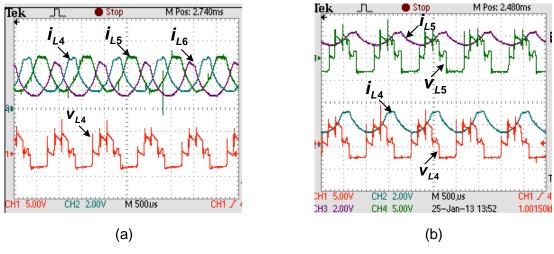

| 5.6                                                                                      | Exper                                                                                                                | imental Validation                                                                                                                                                                                                                                                                                                                                                              | 154                                                                                                          |

|                                                                                          | 5.6.1                                                                                                                | A Prototype Model                                                                                                                                                                                                                                                                                                                                                               | 154                                                                                                          |

|                                                                                          | 5.6.2                                                                                                                | Experimental Results and Discussions                                                                                                                                                                                                                                                                                                                                            | 154                                                                                                          |

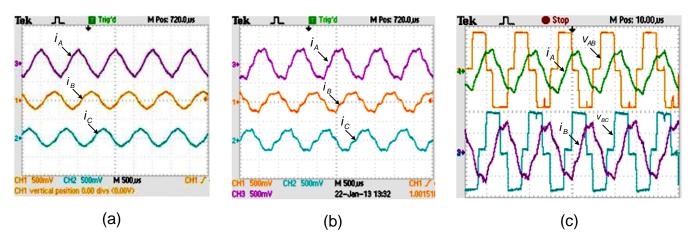

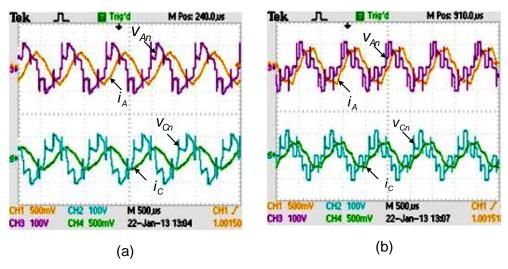

|                                                                                          |                                                                                                                      | (a) Steady-State Performance of Converter with Symmetrical Control                                                                                                                                                                                                                                                                                                              | 154                                                                                                          |

|                                                                                          |                                                                                                                      | (b) Steady-State Performance of Converter with Asymmetrical Control.                                                                                                                                                                                                                                                                                                            | 159                                                                                                          |

|                                                                                          |                                                                                                                      | (c) Trasient Performance of Converter                                                                                                                                                                                                                                                                                                                                           | 162                                                                                                          |

| 5.7                                                                                      | Perfo                                                                                                                | mance Comparison                                                                                                                                                                                                                                                                                                                                                                | 163                                                                                                          |

| 5.8                                                                                      | Concl                                                                                                                | usion                                                                                                                                                                                                                                                                                                                                                                           | 164                                                                                                          |

| СНА                                                                                      | PTER                                                                                                                 | 6: THREE-PHASE HIGH FREQUENCY ISOLATED DC-DC                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |

| <b>U</b> 11/                                                                             |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |

|                                                                                          |                                                                                                                      | ER WITH MULTI-PHASE RECTIFICATION                                                                                                                                                                                                                                                                                                                                               | 167                                                                                                          |

|                                                                                          | IVERT                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |

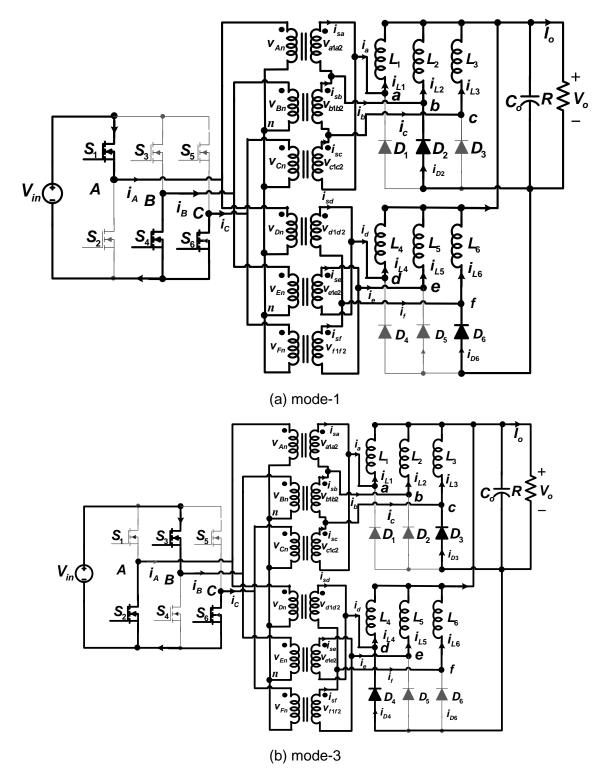

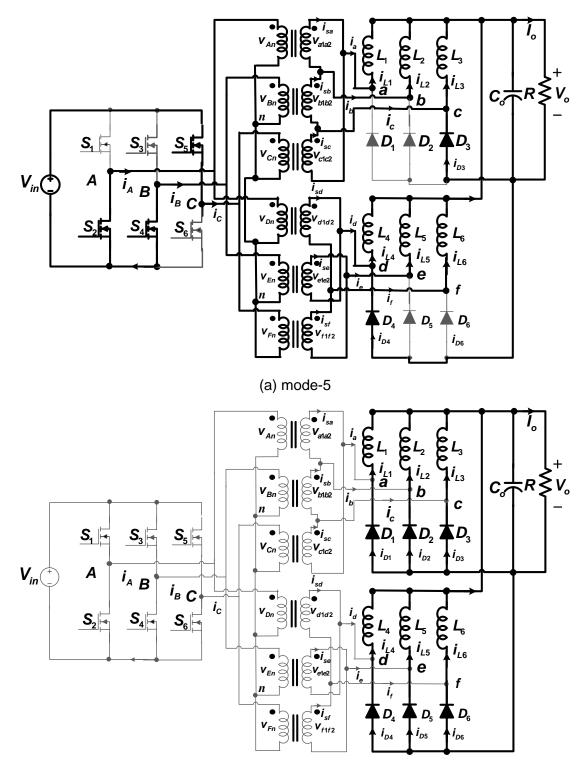

| CON                                                                                      | IVERTE<br>Introd                                                                                                     | ER WITH MULTI-PHASE RECTIFICATION<br>uction<br>m Configuration and Control Scheme                                                                                                                                                                                                                                                                                               | 167<br>169                                                                                                   |

| <b>CON</b><br>6.1                                                                        | IVERTE<br>Introd                                                                                                     | ER WITH MULTI-PHASE RECTIFICATION                                                                                                                                                                                                                                                                                                                                               | 167<br>169                                                                                                   |

| <b>CON</b><br>6.1                                                                        | IVERTE<br>Introd<br>Syste                                                                                            | ER WITH MULTI-PHASE RECTIFICATION<br>uction<br>m Configuration and Control Scheme                                                                                                                                                                                                                                                                                               | 167<br>169<br>169                                                                                            |

| <b>CON</b><br>6.1                                                                        | IVERTI<br>Introd<br>Syste<br>6.2.1                                                                                   | ER WITH MULTI-PHASE RECTIFICATION<br>uction<br>m Configuration and Control Scheme<br>Power Circuit                                                                                                                                                                                                                                                                              | 167<br>169<br>169<br>171                                                                                     |

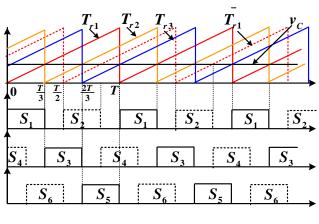

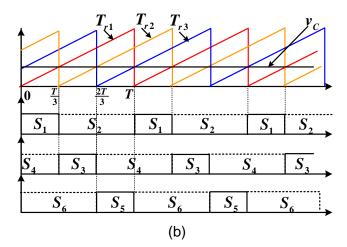

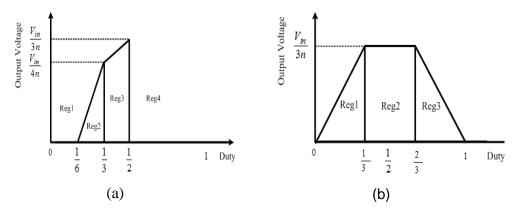

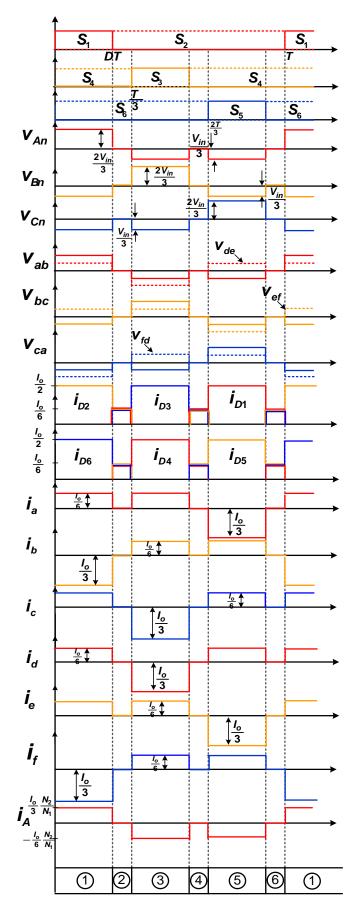

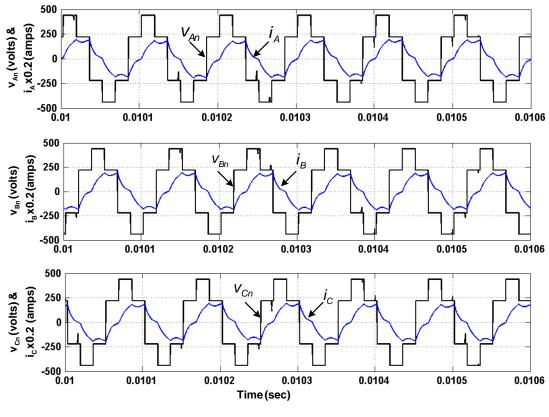

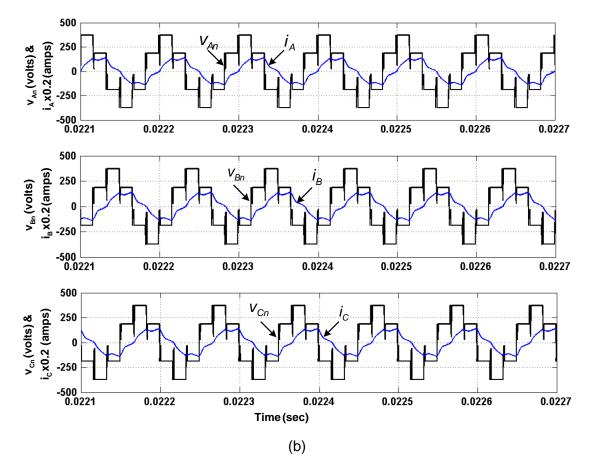

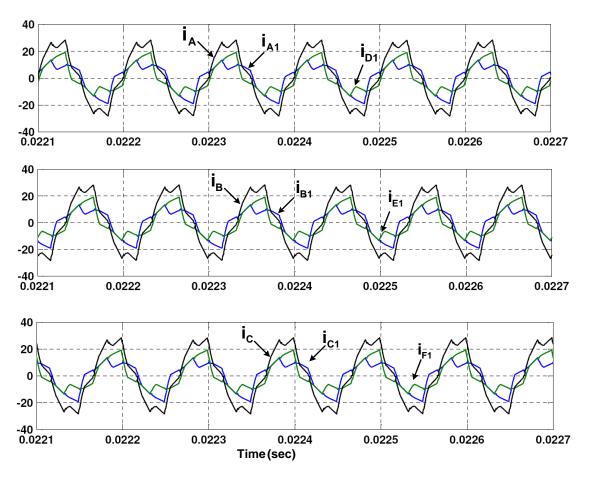

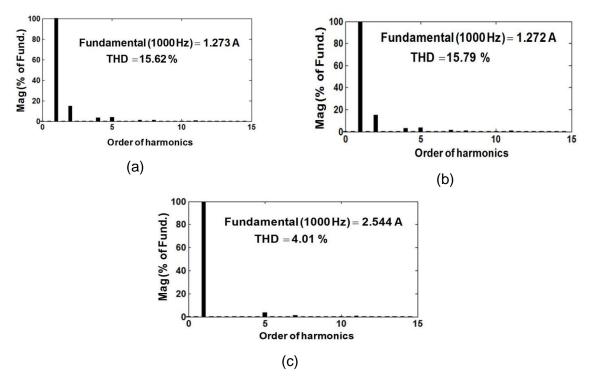

| <b>CON</b><br>6.1                                                                        | IVERTE<br>Introd<br>Syste<br>6.2.1<br>6.2.2<br>6.2.3                                                                 | ER WITH MULTI-PHASE RECTIFICATION<br>uction<br>m Configuration and Control Scheme<br>Power Circuit<br>Transformer winding currents and voltages                                                                                                                                                                                                                                 | 167<br>169<br>169<br>171<br>172                                                                              |

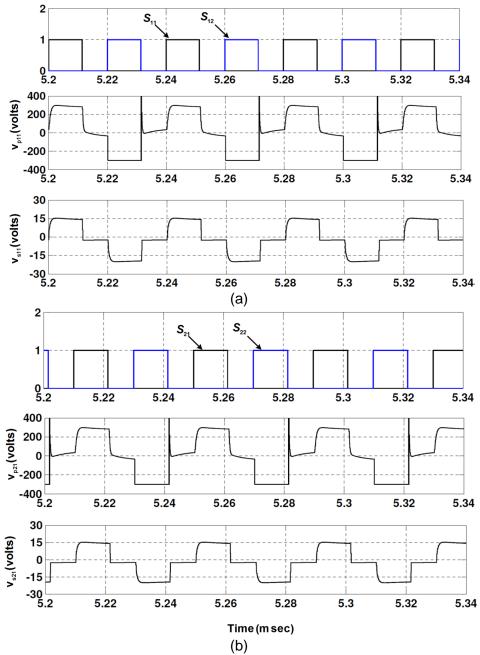

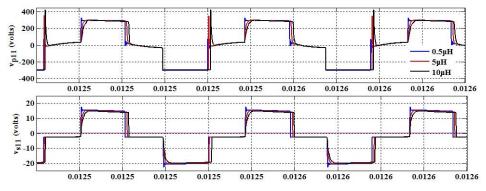

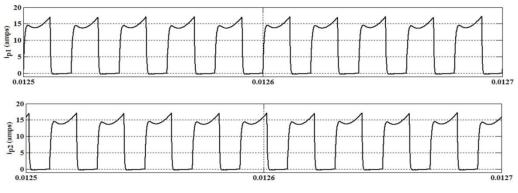

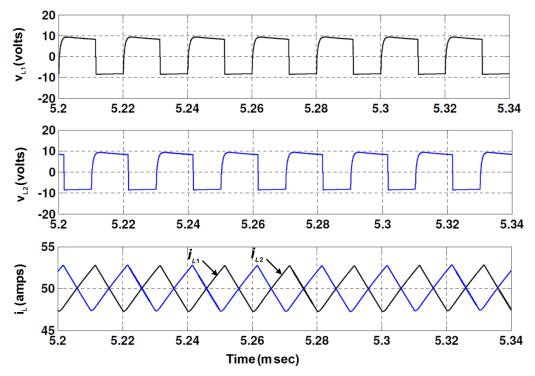

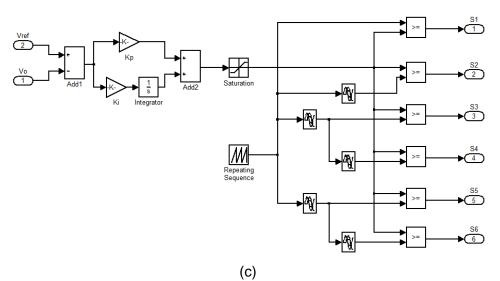

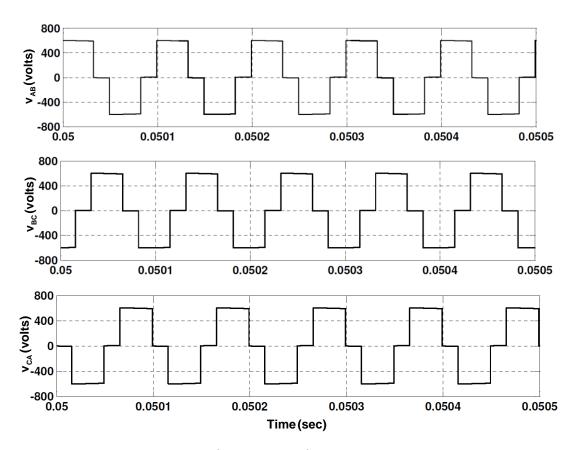

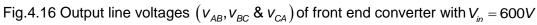

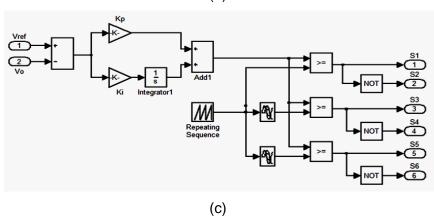

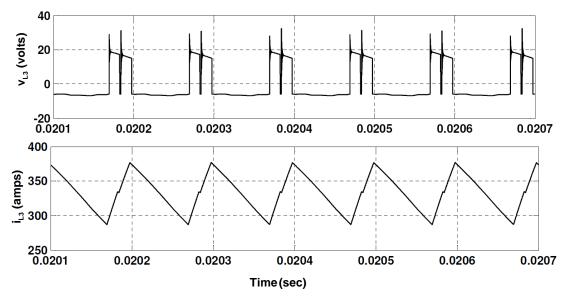

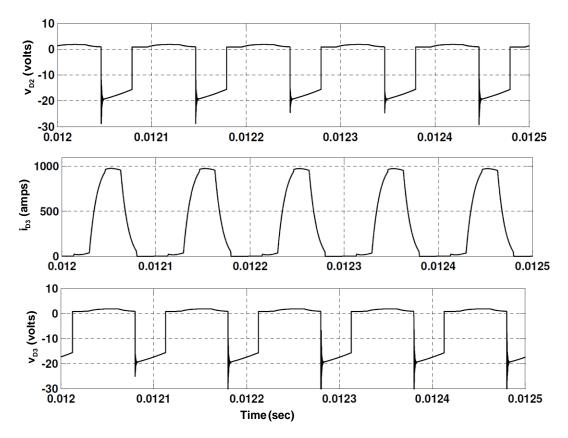

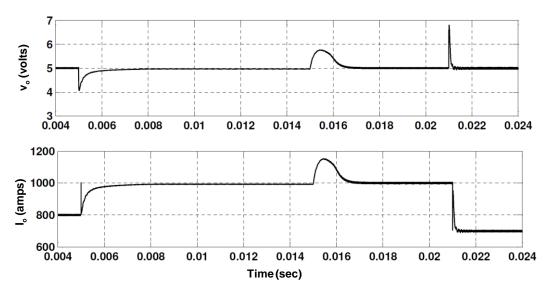

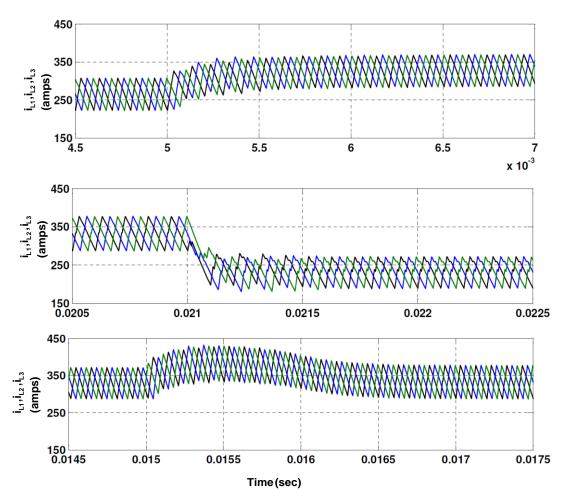

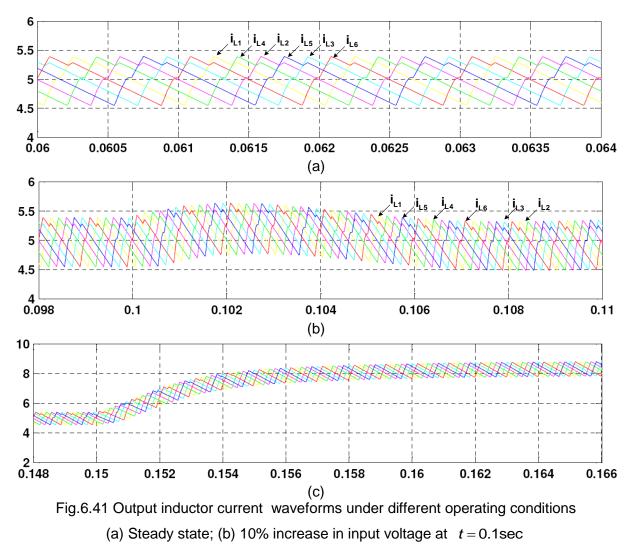

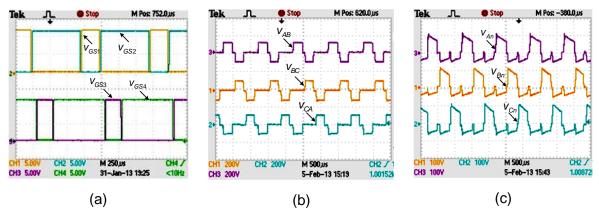

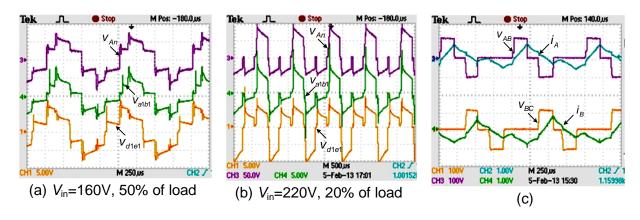

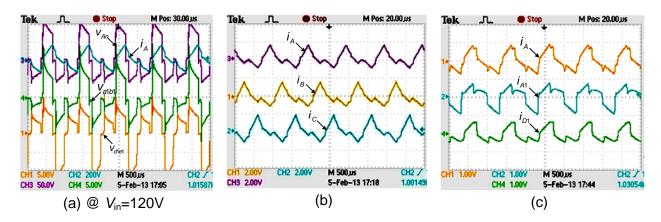

| <b>CON</b><br>6.1<br>6.2                                                                 | IVERTE<br>Introd<br>Syste<br>6.2.1<br>6.2.2<br>6.2.3                                                                 | ER WITH MULTI-PHASE RECTIFICATION<br>uction<br>m Configuration and Control Scheme<br>Power Circuit<br>Transformer winding currents and voltages<br>Control Strategy                                                                                                                                                                                                             | 167<br>169<br>169<br>171<br>172<br>176                                                                       |