# TIMING MODELS FOR EFFICIENT CHARACTERIZATION OF NANOSCALE VLSI SINGLE STAGE STANDARD CELLS

Ph.D THESIS

by

BALJIT KAUR

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247667, INDIA SEPTEMBER, 2014

# TIMING MODELS FOR EFFICIENT CHARACTERIZATION OF NANOSCALE VLSI SINGLE STAGE STANDARD CELLS

### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

#### DOCTOR OF PHILOSOPHY

in

### ELECTRONICS AND COMMUNICATION ENGINEERING

by

BALJIT KAUR

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247667, INDIA SEPTEMBER, 2014

©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2014 ALL RIGHTS RESERVED

### INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the thesis entitled "TIMING MODELS FOR EFFICIENT CHARACTERIZATION OF NANOSCALE VLSI SIN-GLE STAGE STANDARD CELLS" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electronics and Communication Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from December, 2009 to September, 2014 under the supervision of **Dr. Anand Bulusu**, Associate Professor and **Dr. Sanjeev Manhas**, Associate Professor, Department of Electronics and Communication Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

### (BALJIT KAUR)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

(Anand Bulusu) Supervisor (Sanjeev Manhas) Supervisor

Date:

#### ABSTRACT

In nanometer range VLSI technologies, semi-custom chip design approach using predesigned and pre-characterized standard cells is popular because of increasing complexity. For efficient circuit design, these standard cells are pre-characterized for delay, transition times, terminal capacitances, power dissipation, noise and area using SPICE simulations. The traditional Non Linear Delay Models (NLDM) based Lookup Table (LUT) approach for standard cell characterization and Static Timing Analysis (STA) is facing serious challenges in nanometer technologies, because it does not account for the nature of input and output terminal voltage transitions. Because of voltage dependent values of effective capacitances of device and interconnects, it becomes important to consider the nature of output transition. To overcome these limitations, researchers introduced Current Source Modeling (CSM), in which for a given value of load capacitance, the value of output voltage and equivalent circuit parameters of the standard cell are given as a function of input voltage. This increases the complexity of the model and the amount of data to be stored for standard cell characterization.

To solve these issues, vendors found the models as a middle path (between NLDM and CSM), known as vendor CSM formats. These vendor CSM formats are Effective CSM (ECSM) and Composite CSM (CCSM). For a given input transition time  $(T_R)$  and load capacitance  $(C_l = C_{eff})$  values, ECSM stores the times at which the output voltage waveform crosses certain predefined threshold points, whereas CCSM stores the output current values at specified voltage level points. Both the vendor models are equivalent and one can be derived from the other. Vendor CSMs use Lookup Table (LUT) based format for representing characterization data. The major issue with ECSM characterization is that it requires re-characterization of standard cells with variation in cell size, layout dependent parameters, temperature, supply voltage and device model updates. This recharacterization is highly time consuming. Therefore, there is a need for a model which is more efficient in standard cell characterization, thus saving time and effort. In this thesis, we undertake a detailed study of existing timing/delay models of CMOS inverter and NAND gate standard cells. We find that these delay models are unsuitable for use in standard cell characterization, because the region of validity in  ${\cal T}_R$  ,  ${\cal C}_l$  space is not clear. Apart from this cell size, layout dependent parameters, power supply voltage and temperature variations are also not inputs to such models. In addition, it is seen that the intermediate node voltage transition of the series stack nMOS devices of a NAND gate, which plays an important role in sub-nanometer technology nodes, has not been considered appropriately in earlier models. We show that considering these issues in standard cell characterization, the re-characterization effort would increase significantly.

For an efficient ECSM characterization, we developed the timing models for CMOS inverter and 2-input NAND gate (therefore, for 2-input NOR gate also), to reduce the re-characterization effort. All the multistage combinational cells can be derived from these basic cells. Firstly, we propose the analytical timing models relating all the Threshold

Crossing Points (TCPs) of output transition with  $T_R$ ,  $C_l$  values, for CMOS inverter and 2-input NAND gate. We then identify the region of validity of the model in  $T_R$ ,  $C_l$  space used in characterization LUTs. It makes the timing models useable in reducing the HSPICE simulations in ECSM library characterization. Further, we identify the relationships of model coefficients with cell size, process induced mechanical stress, temperature and supply voltage variation. Our NAND gate timing models are robust because of an appropriate and detailed consideration of voltage transition at the intermediate node of the series stack of nMOS devices. For this, we consider the input to intermediate node capacitive coupling effect, parasitic capacitances at the intermediate node and the regions of operation of the two nMOS devices placed in series stack. We present the timing models for 2-input NAND gate, considering the following two cases : 1) When upper nMOS transistor in the series stack switches; and 2) When lower nMOS transistor in the series stack switches. In this thesis, we show that the use of these models in standard cell characterization reduces the number of SPICE simulations by 50% and 67% for CMOS inverter and 2-input NAND gate, respectively. We also show that our timing models remain valid with PVT variations. This would help in reducing the re-characterization effort significantly (nearly 85% reduction in SPICE simulations) for standard cell libraries. Further, we present an analytical overshoot timing model for CMOS inverter and NAND gate for accurate timing analysis. For NAND gate overshoot modeling, we see that an inclusion of intermediate node voltage transition with appropriate assumptions lead to accurate estimation (max. error is 2.5% with respect to HSPICE simulations) of overshoot timing values for Case 1 and 2, respectively.

### ACKNOWLEDGEMENT

Completion of this doctoral dissertation was possible with the support of several people. I would like to express my sincere gratitude to all of them. First and foremost, I would like to express my deepest gratitude to my supervisors Dr. Anand Bulusu and Dr. Sanjeev Manhas for their inspiration, encouragement and moral support in the successful completion of this work.

I am also thankful to Dr. A.K. Saxena, Dr. Sudeb Dasgupta, Dr. B.K. Kaushik of Microelectronics and VLSI (MEV) Group for their valuable guidance, scholarly inputs and consistent encouragement I received throughout my research work. I am grateful to Prof. M.V. Kartikeyan, Head of the department, for the academic support and the facilities provided to carry out the research work. I express my gratitude to the board of research studies and the members of my Student Research Committee (SRC) Prof. Dharmendra Dingh, Chairman (DRC), and Prof. R. Nath, Department of Physics, for the support at various phases of the programme and sparing their precious time in spite of all their busy schedule for carefully examining my research work and providing valuable suggestions. I gratefully acknowledge the funding sources that made my Ph.D. work possible. I was funded by the Ministry of Human Resource Development, Government of India for 4 years and 3 months. I would like to thank research scholars Manoj Kumar Majumder, Asutosh Nandi, Menka, Pankaj Kumar Pal, V. Ramesh Kumar, Shivam Verma, Om Prakash, Savitesh Sharma and Ruchi, of my lab for helping me with technical discussions. I admire the support of my colleagues Satish Maheshwaram, Archana Pandey and Arvind Kumar Sharma, and thank them for their concern and good wishes. My sincere thanks to my Ph.D. seniors of Microelectronics and VLSI group Dr. S. S. Rathod, Dr. R. Vaddi, Dr. Jitendra Kanungo, Dr. Naushad Alam and Dr. Gaurav Kaushal, for their support and encouragement throughout my work. I sincerely appreciate the lab staffs, Mr. Naveen Kanwar and Mr. Dinesh Sharma , for their help and support during the research work. I would like to thank my friends Nitasha Bansal, Deepti Chaudhary, Deepika Agarwal, Surabhi Singh, Mamta Saxena, Sujata Parida and Divya Madhuri for their support during my Ph.D.

In particular, I am profoundly indebted to my guide Dr. Anand Bulusu, a person with an amicable and positive disposition. I consider it as a great opportunity to do my doctoral programme under his guidance and to learn from his research expertise. He has always been responsible and supportive throughout all the highs and lows during the journey of my Ph.D. He has been a tremendous mentor for me. Words are not enough to express my gratitude to him. Last but not the least, I am deeply indebted to my parents for their unconditional love, sacrificial giving and support to me. Without their teachings and blessings, I could not have come to this stage of life. I owe a lot to my whole family who encouraged and helped me at every stage of my personal and academic life, and longed to see this achievement come true. Above all, I owe it all to Almighty God for granting me the wisdom, health and strength to undertake this research task and enabling me to its completion.

Date:

Place:

(Baljit Kaur)

## Contents

| 1        | Int                  | roduction                                                                                 | 1        |

|----------|----------------------|-------------------------------------------------------------------------------------------|----------|

|          | 1.1                  | Motivation                                                                                | 1        |

|          | 1.2                  | Previous Work                                                                             | 3        |

|          | 1.3                  | Problem Definition                                                                        | 6        |

|          | 1.4                  | Contributions                                                                             | 6        |

|          | 1.5                  | Thesis Organization                                                                       | 7        |

| <b>2</b> | Lit                  | cerature Review                                                                           | 9        |

|          | 2.1                  | Overview                                                                                  | 9        |

|          | 2.2                  | Introduction                                                                              | 9        |

|          | 2.3                  | Literature survey on existing delay models                                                | 9        |

|          |                      | 2.3.1 CSM based standard cell timing analysis                                             | 13       |

|          |                      | 2.3.2 Overshoot timing Model for CMOS inverter and 2-input NAND gate                      | 15       |

|          | 2.4                  | Technical Gaps                                                                            | 16       |

| 3        | $\operatorname{Tin}$ | 0 0                                                                                       | 17       |

|          | 3.1                  | Overview                                                                                  | 17       |

|          | 3.2                  | Simulation Setup                                                                          | 17       |

|          | 3.3                  | Timing model for CMOS inverter standard cell                                              | 18       |

|          |                      | 3.3.1 Derivation of the model in Region I                                                 | 18       |

|          |                      | $3.3.1.1$ Verification of the model $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 22       |

|          |                      | 3.3.2 Derivation of the model in Region II                                                | 23       |

|          |                      | $3.3.2.1$ Verification of the model $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 25       |

|          | 3.4                  | Efficient ECSM Characterization                                                           | 25       |

|          | 3.5                  | Impact of technology scaling on timing models                                             | 28       |

|          | 3.6                  | Summary                                                                                   | 29       |

| 4        |                      | cient ECSM Characterization of CMOS Inverter Standard Cell Con-                           |          |

|          |                      | ering PVT Variations                                                                      | 31       |

|          |                      | Overview                                                                                  | 31       |

|          | 4.2                  | Simulation Setup                                                                          | 31       |

|          | 4.3                  | TCP models considering stress variability for CMOS inverter standard cell                 | 32       |

|          |                      | 4.3.1 Impact of stress induced variability in Region I                                    | 34       |

|          |                      | 4.3.2 Impact of stress induced variability in Region II                                   | 35       |

|          |                      | 4.3.3 Efficient stress aware ECSM characterization                                        | 36       |

|          | 4.4                  | TCP models considering temperature variability for CMOS inverter standard cell            | 36       |

|          |                      |                                                                                           |          |

|          |                      |                                                                                           | 37       |

|          |                      | <ul><li>4.4.2 Impact of temperature variability in Region II</li></ul>                    | 38<br>39 |

|          |                      | 4.4.5 Emolent temperature variation aware EOSW characterization                           | 59       |

|   | 4.5 | TCP models considering supply voltage variability for CMOS inverter stan-<br>dard cell              | 40              |

|---|-----|-----------------------------------------------------------------------------------------------------|-----------------|

|   |     |                                                                                                     | 40              |

|   |     |                                                                                                     | 41              |

|   |     |                                                                                                     | 42              |

|   | 4.6 |                                                                                                     | 42<br>43        |

| - |     | U U U U U U U U U U U U U U U U U U U                                                               | 10              |

| 5 |     | ning model for 2-input NAND gate standard cell considering PVT ation                                | 45              |

|   | 5.1 | Overview                                                                                            | 45              |

|   | 5.2 | Simulation Setup                                                                                    | 45              |

|   | 5.3 | Timing model for 2-input NAND gate standard cell                                                    | 46              |

|   | 5.4 | Case 1: Derivation and Validation of $t_{TCP}$ model $\ldots \ldots \ldots \ldots \ldots$           | 46              |

|   |     | 5.4.1 Derivation of the model in Region I $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 47              |

|   |     | 5.4.2 Derivation of the model in Region II $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$       | 51              |

|   |     | 5.4.3 Efficient ECSM Characterization                                                               | 52              |

|   | 5.5 | Case 1: Variation aware TCP models                                                                  | 53              |

|   |     | 5.5.1 TCP models considering stress variability                                                     | 55              |

|   |     | 5.5.1.1 Impact of stress induced variability in Region I $\ldots$ .                                 | 55              |

|   |     | 5.5.1.2 Impact of stress induced variability in Region II $\ldots$                                  | 56              |

|   |     | 5.5.1.3 Efficient stress aware ECSM characterization                                                | 57              |

|   |     | 5.5.2 TCP models considering temperature variability                                                | 58              |

|   |     | 5.5.2.1 Impact of temperature variability in Region I $\ldots$ .                                    | 58              |

|   |     |                                                                                                     | 59              |

|   |     | 5.5.2.3 Efficient temperature variation aware ECSM characterization                                 | 60              |

|   |     | 5.5.3 TCP models considering Supply Voltage Variability                                             | 60              |

|   |     | 5.5.3.1 Impact of supply voltage variability in Region I $\ldots$ .                                 | 61              |

|   |     | 5.5.3.2 Impact of supply voltage variability in Region II                                           | 61              |

|   |     | 5.5.3.3 Efficient supply voltage variation aware ECSM characteri-                                   | 61              |

|   | 5.6 |                                                                                                     | 61              |

|   | 0.0 | 101                                                                                                 | 02<br>63        |

|   |     | -                                                                                                   | 67              |

|   |     | 0                                                                                                   | 70              |

|   | 5.7 |                                                                                                     | 70<br>72        |

|   | 0.7 |                                                                                                     | 72<br>72        |

|   |     | 0                                                                                                   | $\frac{12}{72}$ |

|   |     |                                                                                                     | 72<br>73        |

|   |     |                                                                                                     | 73<br>74        |

|   |     |                                                                                                     | 74<br>74        |

|   |     |                                                                                                     | 74<br>75        |

|   |     |                                                                                                     | 75<br>75        |

|   |     |                                                                                                     | 75<br>76        |

|   |     | 1                                                                                                   | 76              |

|   |     |                                                                                                     | 70<br>76        |

|   |     |                                                                                                     | 70<br>77        |

|   |     | 5.7.3.3 Efficient supply voltage variation aware ECSM characteri-                                   | 11              |

|   |     |                                                                                                     | 77              |

|   | 5.8 |                                                                                                     | 77              |

|   |     | J                                                                                                   |                 |

| 6  | Ove   | rshoot Timing Model for CMOS Inverter and NAND Gate Standard |     |

|----|-------|--------------------------------------------------------------|-----|

|    | Cell  | s                                                            | 81  |

|    | 6.1   | Overview                                                     | 81  |

|    | 6.2   | Simulation Setup                                             | 82  |

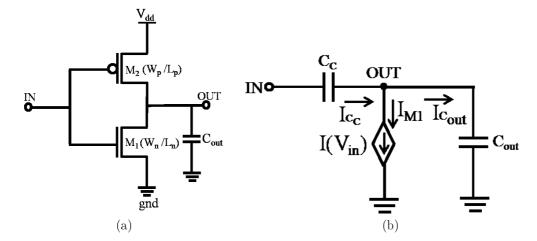

|    | 6.3   | Our approach towards CMOS inverter overshoot modeling        | 83  |

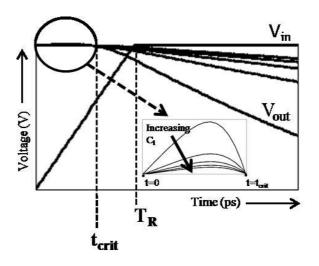

|    |       | 6.3.1 Model for Overshoot Time $t_{crit}$                    | 84  |

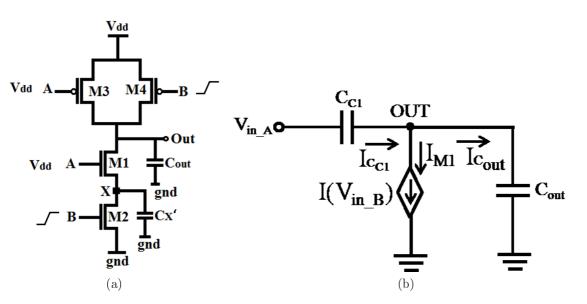

|    | 6.4   | NAND gate overshoot modeling                                 | 86  |

|    |       | 6.4.1 NAND gate overshoot modeling for Case 1                | 86  |

|    |       | 6.4.2 NAND gate overshoot modeling for Case 2                | 88  |

|    |       | 6.4.2.1 Proposed Model for $t_{Xa}$                          | 89  |

|    |       | 6.4.2.2 Proposed Model for $t_{crit}$                        | 90  |

|    | 6.5   | Summary                                                      | 93  |

| 7  | Con   | clusion and Future Scope                                     | 95  |

|    | 7.1   | Conclusions                                                  | 95  |

|    | 7.2   | Scope for Future Research                                    | 97  |

| Bi | bliog | graphy                                                       | 101 |

# List of Figures

| 1.1<br>1.2<br>1.3                          | Variation of cell delay with input transition time and output capacitance [1].<br>ECSM characterization overview                                                                                                                                                                                                                                                                            | 2<br>3<br>3                                                                                                                        |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 2.1                                        | Response of the NAND gate for fixed input transition time; $V_{out}$ : 1 represents the O/P voltage when the upper nMOS transistor is replaced by an equivalent resistor and $V_{out}$ : 2 represents the O/P voltage for the realistic case where the upper nMOS of 2-input NAND gate is not replaced (For $V_{out:1}$ , we obtain the equivalent resistance value from the linear current |                                                                                                                                    |

| 2.2                                        | equation (1) of [2])                                                                                                                                                                                                                                                                                                                                                                        | 12                                                                                                                                 |

| 2.3                                        | conventional 2-input NAND gate                                                                                                                                                                                                                                                                                                                                                              | 12                                                                                                                                 |

| 2.4<br>2.5                                 | load                                                                                                                                                                                                                                                                                                                                                                                        | 13<br>14<br>14                                                                                                                     |

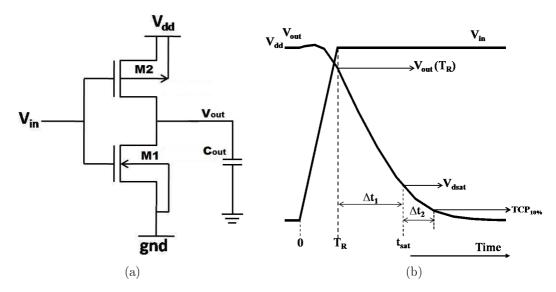

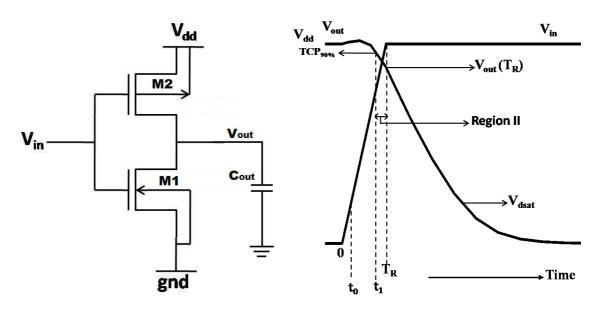

| $3.1 \\ 3.2$                               | CMOS inverter with input and output waveform                                                                                                                                                                                                                                                                                                                                                | 18                                                                                                                                 |

| $\begin{array}{c} 3.11\\ 3.12 \end{array}$ | Region I                                                                                                                                                                                                                                                                                                                                                                                    | <ol> <li>19</li> <li>22</li> <li>22</li> <li>23</li> <li>24</li> <li>25</li> <li>25</li> <li>28</li> <li>28</li> <li>29</li> </ol> |

| 4 1                                        | nology node                                                                                                                                                                                                                                                                                                                                                                                 | 29                                                                                                                                 |

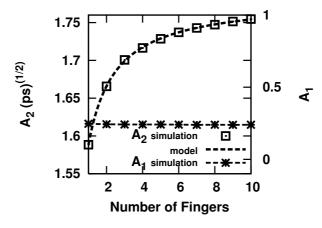

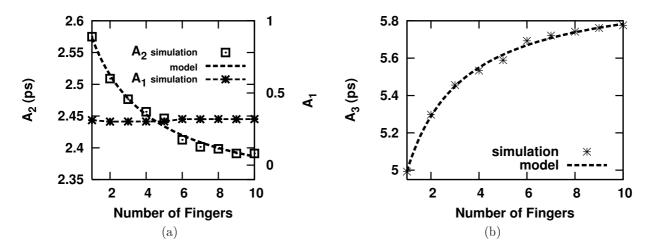

| $4.1 \\ 4.2$                               | $K_1$ , $K_2$ and $K_3$ as a function of $NF$ (which also represents to channel stress).<br>$A_1$ and $A_2$ as a function of $NF$ .                                                                                                                                                                                                                                                         | $\frac{35}{35}$                                                                                                                    |

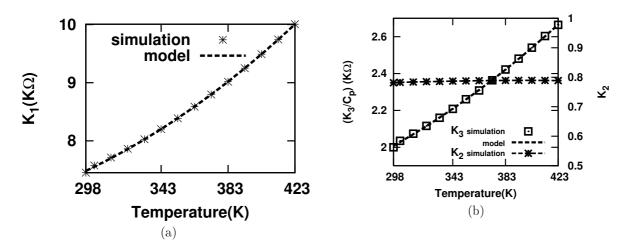

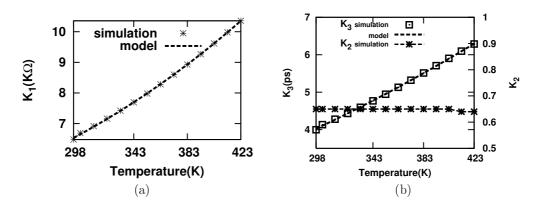

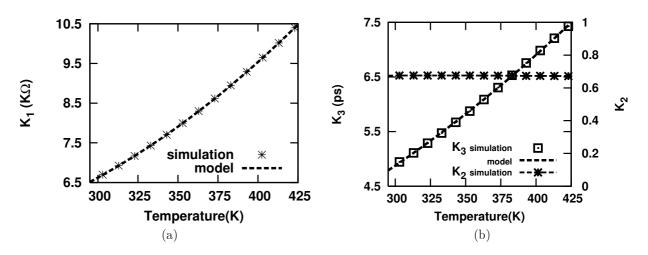

| 4.3                                        | Variation of $K_1$ , $K_2$ and $K_3$ with temperature                                                                                                                                                                                                                                                                                                                                       | 38                                                                                                                                 |

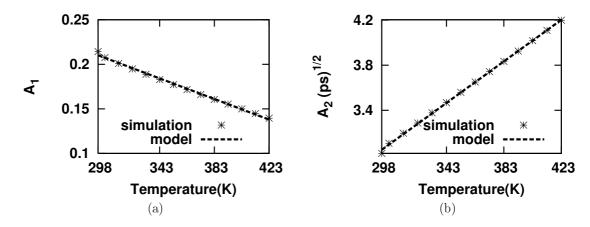

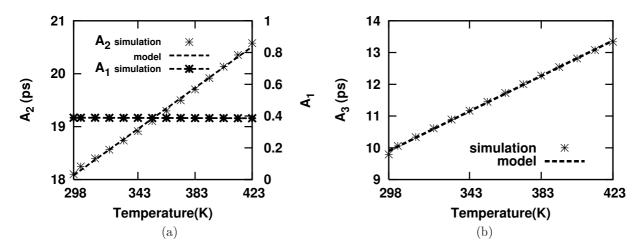

| 4.4  | Variation of $A_1$ and $A_2$ with temperature.                                             | 39 |

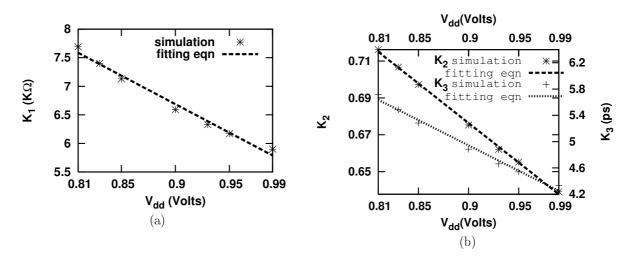

|------|--------------------------------------------------------------------------------------------|----|

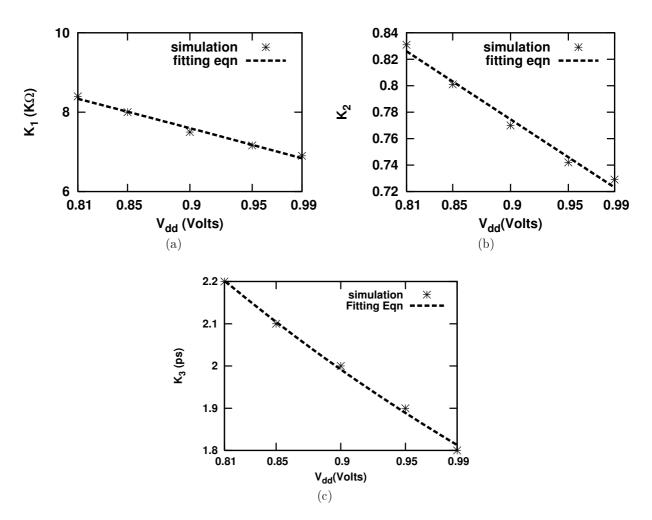

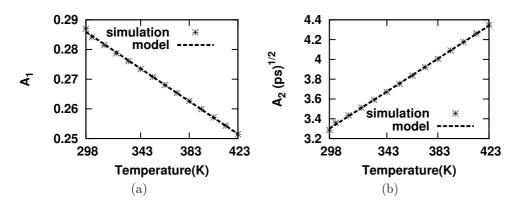

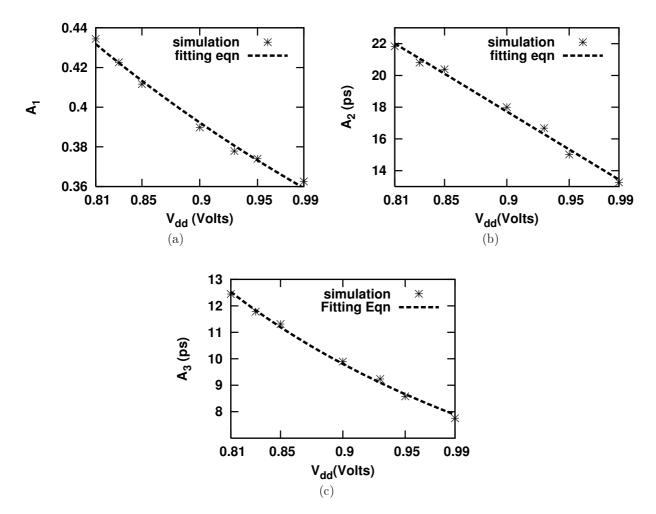

| 4.5  | Variation of $K_1$ , $K_2$ and $K_3$ with supply voltage                                   | 41 |

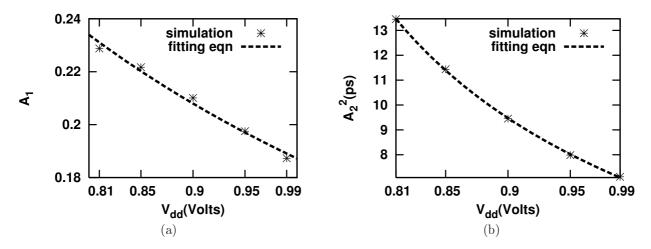

| 4.6  | Variation of $A_1$ and $A_2$ with supply voltage                                           | 42 |

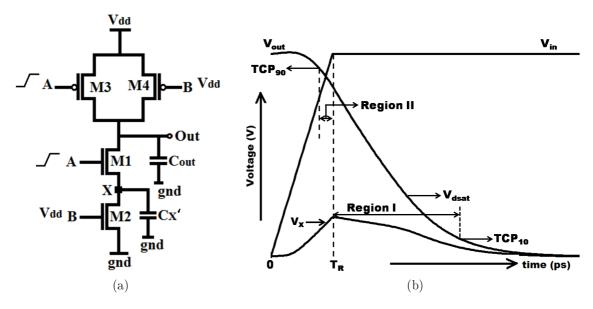

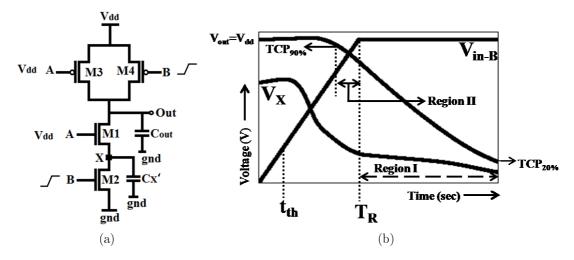

| 5.1  | Case 1: (a) 2-input NAND gate schematic (b) its I/O waveform.                              | 47 |

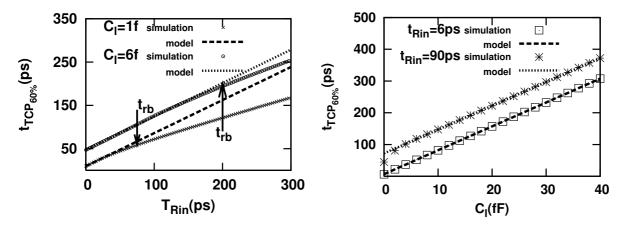

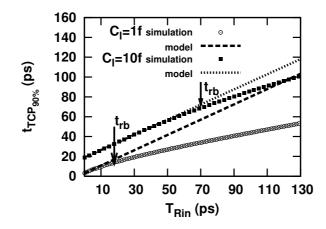

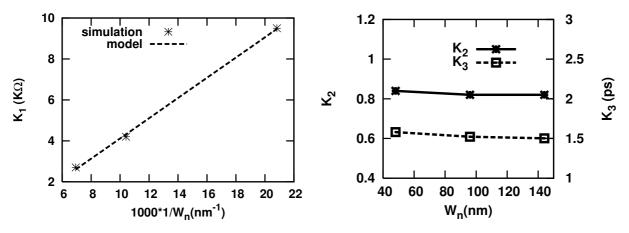

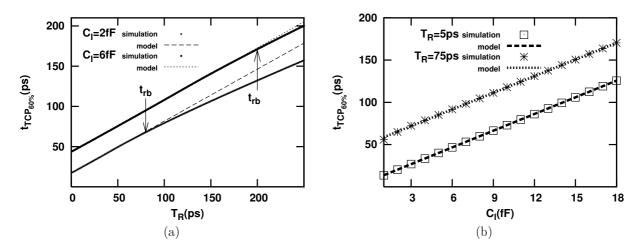

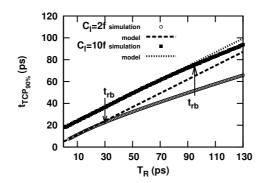

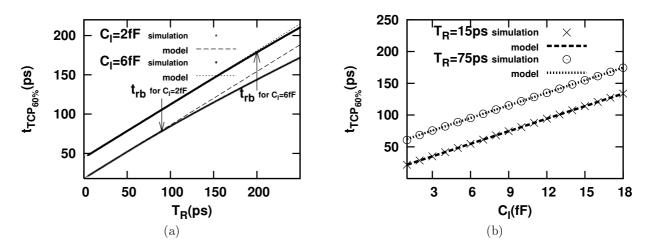

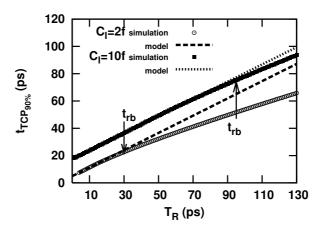

| 5.2  | Case 1: Variation of $t_{TCP60\%}$ with respect to $T_R$ and $C_l$ values                  | 50 |

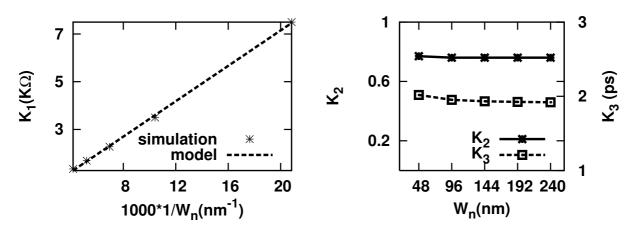

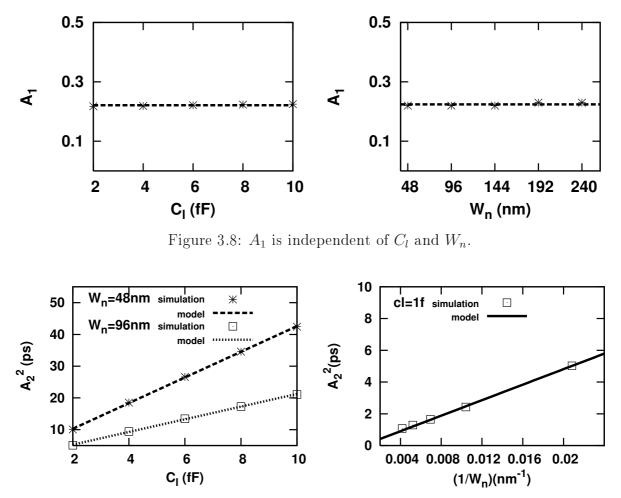

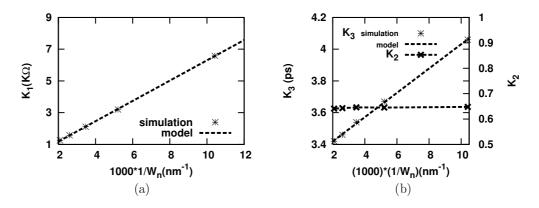

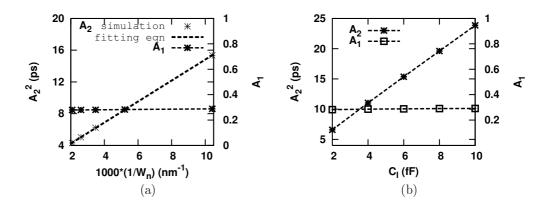

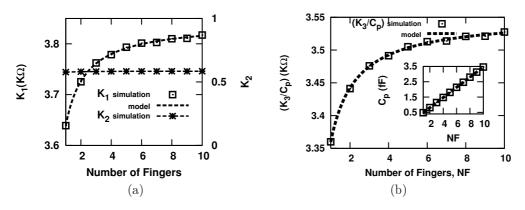

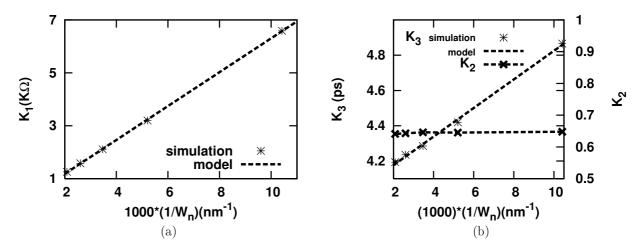

| 5.3  | Case 1: Variation of $K_1$ , $K_2$ and $K_3$ with cell size $(W_n)$ .                      | 51 |

| 5.4  | Case 1: Variation of $t_{TCP90\%}$ with respect to $T_R$ .                                 | 52 |

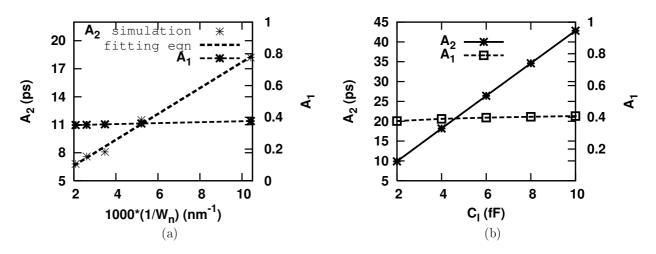

| 5.5  | Case 1: Variation of $A_1$ and $A_2$ with cell size $(W_n)$ and load capacitance $(C_l)$ . | 53 |

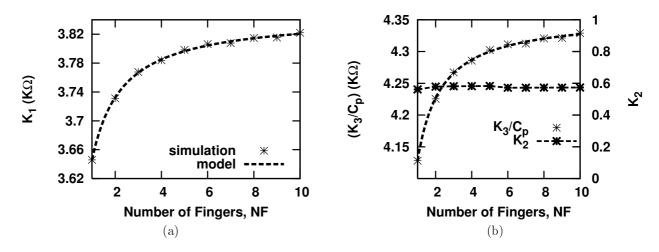

| 5.6  | Case 1: $K_1$ , $K_2$ and $K_3$ as a function of $NF$ .                                    | 56 |

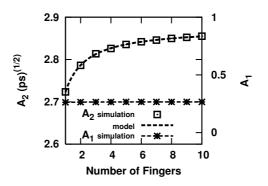

| 5.7  | Case 1: $A_1$ and $A_2$ as a function of $NF$                                              | 57 |

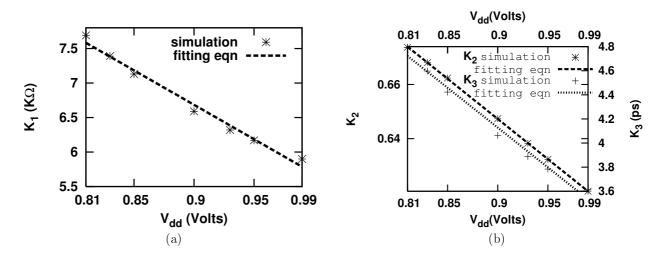

| 5.8  | Case 1: Variation of $K_1$ , $K_2$ and $K_3$ with temperature.                             | 59 |

| 5.9  | Case 1: Variation of $A_1$ and $A_2$ with temperature                                      | 60 |

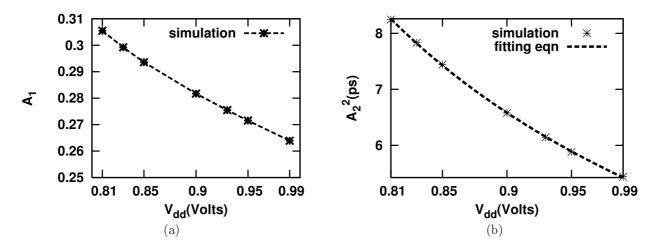

| 5.10 | Case 1: Variation of $K_1$ , $K_2$ and $K_3$ with supply voltage                           | 61 |

| 5.11 |                                                                                            | 62 |

| 5.12 |                                                                                            | 63 |

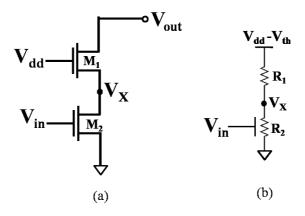

| 5.13 | (a) Pull Down part of 2-input NAND gate (b) Its equivalent circuit looking                 |    |

|      | at node 'X' when $M_1$ operates in saturation region and $M_2$ operates in linear          |    |

|      | region.                                                                                    | 65 |

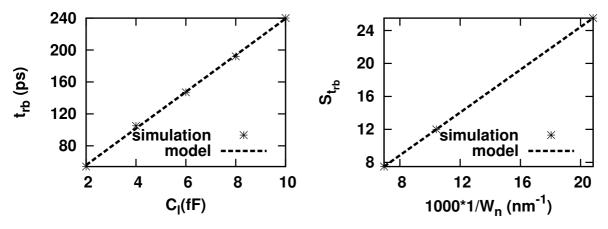

|      | Case 2: Variation of $t_{TCP60\%}$ with respect to $T_R$ and $C_l$ values                  | 67 |

|      | Case 2: Variation of $K_1$ , $K_2$ and $K_3$ with cell size $(W_n)$                        | 67 |

|      | Case 2: Variation of $t_{TCP90\%}$ with respect to $T_R$ .                                 | 69 |

|      | Case 2: Variation of $A_1$ and $A_2$ with cell size $(W_n)$ and load capacitance $(C_l)$ . | 69 |

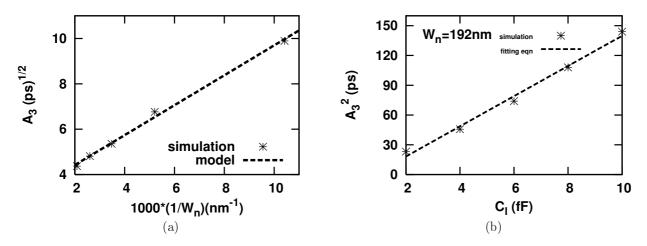

|      | Case 2: Variation of $A_3$ with cell size $(W_n)$ and load capacitance $(C_l)$ .           | 70 |

| 5.19 | Case 2: $K_1$ , $K_2$ and $K_3$ as a function of $NF$ (which also represents to channel    | -0 |

| ۳.00 | stress)                                                                                    | 73 |

|      | Case 2: $A_1$ , $A_2$ and $A_3$ as a function of $NF$                                      | 74 |

|      | Case 2: Variation of $K_1$ , $K_2$ and $K_3$ with temperature.                             | 75 |

|      | Case 2: Variation of $A_1$ , $A_2$ and $A_3$ with temperature                              | 76 |

|      | Case 2: Variation of $K_1$ , $K_2$ and $K_3$ with supply voltage                           | 77 |

| 0.24 | Case 2: Variation of $A_1$ , $A_2$ and $A_3$ with supply voltage                           | 78 |

| 6.1  | (a) CMOS inverter schematic (b) its equivalent circuit during overshoot pe-                |    |

|      | riod                                                                                       | 82 |

| 6.2  | (a) 2-input NAND gate Schematic (b) its equivalent circuit during overshoot                |    |

|      | period                                                                                     | 82 |

| 6.3  | $\rm I/O$ waveform of standard cell CMOS inverter.                                         | 83 |

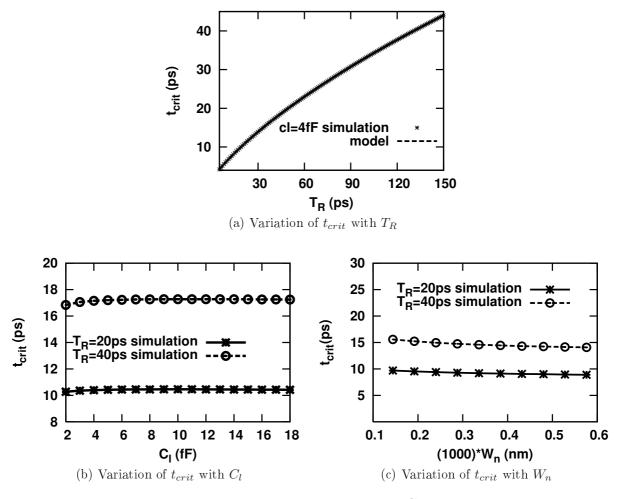

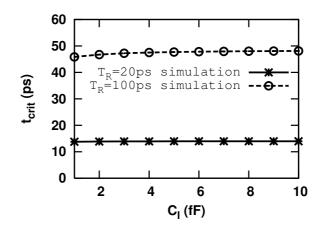

| 6.4  | Variation of $t_{crit}$ with $T_R$ , $C_l$ and $W_n$ .                                     | 85 |

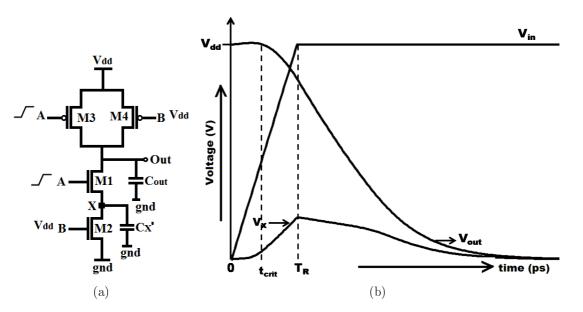

| 6.5  | Case 1: (a) NAND gate schematic (b) its I/O waveform                                       | 86 |

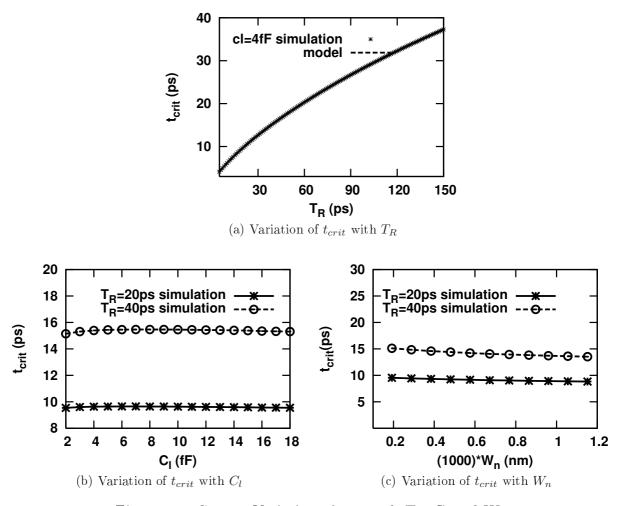

| 6.6  | Case 1: Variation of $t_{crit}$ with $T_R$ , $C_l$ and $W_n$ .                             | 87 |

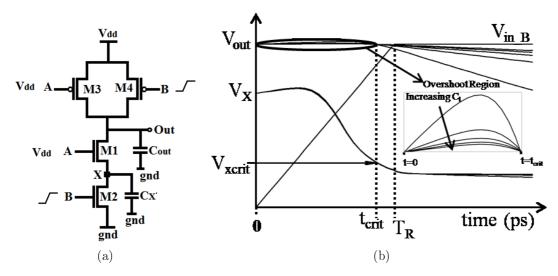

| 6.7  | Case 2: NAND gate schematic and its I/O waveform                                           | 88 |

| 6.8  | Case 2: $t_{crit}$ is independent of $C_l$                                                 | 89 |

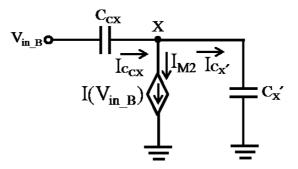

| 6.9  | Case 2: NAND gate equivalent circuit at node 'X'                                           | 89 |

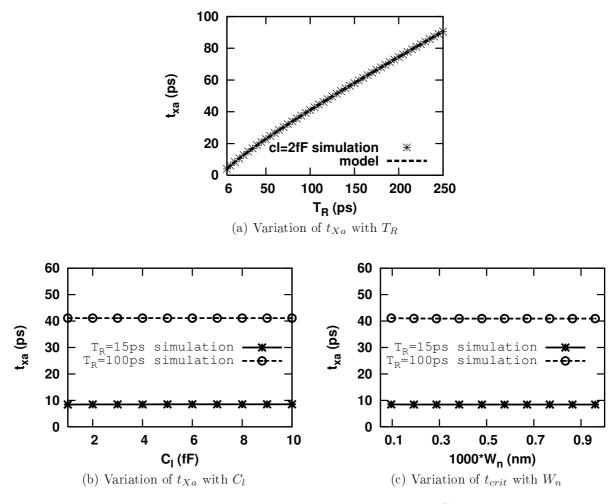

| 6.10 | Case 2: Variation of $t_{Xa}$ with $T_R$ , $C_l$ and $W_n$ .                               | 91 |

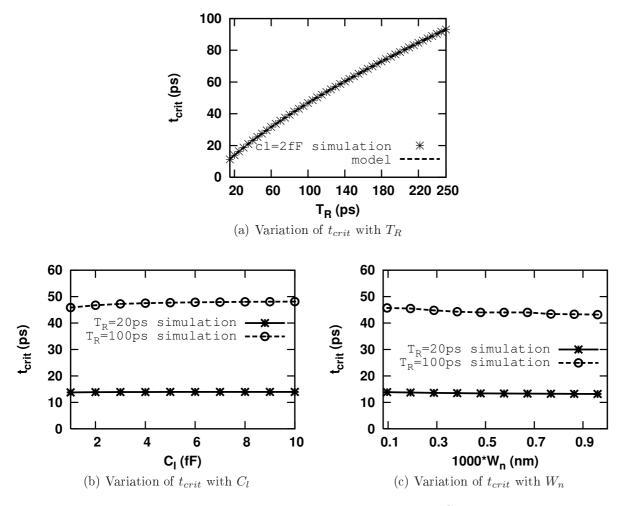

| 6.11 | Case 2: Variation of $t_{crit}$ with $T_R$ , $C_l$ and $W_n$ .                             | 92 |

## List of Tables

| $3.1 \\ 3.2$ | LUT of $TCP_{60\%}$ for minimum size CMOS inverter using our Region I model.<br>LUT of $TCP_{60\%}$ for minimum size CMOS inverter obtained using HSPICE | 26 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 0.2          | simulations.                                                                                                                                             | 26 |

| 3.3          | Percentage error in proposed model's LUT with respect to fully HSPICE                                                                                    | 20 |

| 0.0          | generated ECSM LUT of $TCP_{60\%}$ for CMOS inverter. Entries shown by '×'                                                                               |    |

|              | correspond to the values obtained from HSPICE simulations (not through                                                                                   |    |

|              | our models).                                                                                                                                             | 26 |

| 3.4          | LUT of $TCP_{90\%}$ for minimum size CMOS inverter using our Region II model.                                                                            | 27 |

| 3.5          | LUT of $TCP_{90\%}$ for minimum size CMOS inverter obtained using HSPICE                                                                                 |    |

|              | simulations.                                                                                                                                             | 27 |

| 3.6          | Percentage error in proposed model's LUT with respect to fully HSPICE                                                                                    |    |

|              | generated ECSM LUT of $TCP_{90\%}$ for CMOS inverter. Entries shown by '×'                                                                               |    |

|              | correspond to the values obtained from HSPICE simulations (not through                                                                                   |    |

|              | our models).                                                                                                                                             | 27 |

| 3.7          | Percentage saving in HSPICE simulation for ECSM characterization using                                                                                   | 20 |

|              | our models.                                                                                                                                              | 28 |

| 5.1          | Case 1: LUT of $TCP_{60\%}$ for 2-input CMOS NAND gate using our model.                                                                                  | 54 |

| 5.2          | Case 1: ECSM LUT of $TCP_{60\%}$ for 2-input CMOS NAND gate obtained                                                                                     |    |

|              | using HSPICE simulations.                                                                                                                                | 54 |

| 5.3          | Case 1: Percentage error in proposed model's LUT with respect to fully                                                                                   |    |

|              | HSPICE generated ECSM LUT of $TCP_{60\%}$ for 2-input CMOS NAND gate.                                                                                    | 54 |

| 5.4          | Case 2: LUT of $TCP_{60\%}$ for 2-input CMOS NAND gate using our model.                                                                                  | 71 |

| 5.5          | Case 2: ECSM LUT of $TCP_{60\%}$ for 2-input CMOS NAND gate obtained                                                                                     |    |

|              | using HSPICE simulations.                                                                                                                                | 71 |

| 5.6          | Case 2: Percentage error in proposed model's LUT with respect to fully                                                                                   |    |

|              | HSPICE generated ECSM LUT of $TCP_{60\%}$ for 2-input CMOS NAND gate.                                                                                    | 71 |

## Abbreviations and Symbols

| CCSM               | Composite Current Source Model                                                                   |

|--------------------|--------------------------------------------------------------------------------------------------|

| CSM                | Current Source Model                                                                             |

| DELVT0             | Threshold Voltage Shift                                                                          |

| ECSM               | Effective Current Source Model                                                                   |

| LUT                | Lookup Table                                                                                     |

| MFGSs              | Multi-Fingered Gate Structures                                                                   |

| MULU0              | Mobility Multiplier                                                                              |

|                    |                                                                                                  |

| NF                 | Number of Fingers                                                                                |

| NF<br>NLDM         | Number of Fingers<br>Non-Linear Delay Model                                                      |

|                    |                                                                                                  |

| NLDM               | Non-Linear Delay Model                                                                           |

| NLDM<br>PTM        | Non-Linear Delay Model<br>Predictive Technology device Model                                     |

| NLDM<br>PTM<br>PVT | Non-Linear Delay Model<br>Predictive Technology device Model<br>Process, Voltage and Temperature |

### Chapter 1

### Introduction

### 1.1 Motivation

Due to aggressive technology scaling, the number of logic gates in VLSI chips continue to grow fast. A semi-custom design with pre-designed and pre-characterized standard cell library is essential in this scenario. In this regard, it is prerequisite to characterize basic standard cells, such as inverter, NAND, NOR, latch, flip-flop etc. The objective of cell characterization is to design a high quality model that accurately and efficiently predicts the cell behavior of a standard cell library. Digital design tools use these characterization models for different purposes. Generally, the characterization of standard cells is for parameters related to timing, area and power [5].

In nanometer range technologies, digital design tools need to account for several complex phenomena such as short channel effects, input to output coupling capacitance, interconnect coupling, power supply noise and process variations, etc. Because of the smaller delays and transition times of nanometer range technology standard cells, a minor variation due to these effects influences timing parameters significantly [6]. This increases the need for re-characterization of standard cell library at different process, voltage and temperature corners. Therefore, designing high performance VLSI standard cell library and its characterization has become more challenging than ever in deep sub-micron era. The following two methods are used to measure delays and thus eliminate timing violations in a data path :

1. Circuit simulations using SPICE can be used to estimate the delay of a circuit accurately. However, SPICE simulations need large CPU times to process an entire circuit having large number of transistors. SPICE takes few seconds to process individual transistors in a circuit, so the processing of an entire circuit takes large time [7].

2. An alternative method to measure delay is Static Timing Analysis (STA) method. STA makes use of the simple gate delay models to find the delay of the entire data path, hence takes lesser time [8].

In order to find the delay of an entire combinational circuit using STA, we must determine the delay of its logic gates. This delay is expressed as a function of the load

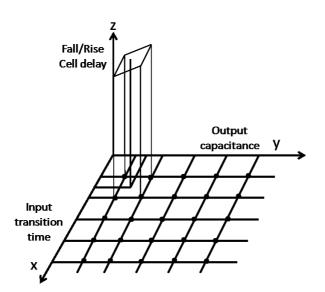

Figure 1.1: Variation of cell delay with input transition time and output capacitance [1].

capacitance  $(C_l)$  and input transition time  $(T_R)$  of logic gates. These gate delay models are classified as:

- 1. Analytical Delay Models: The delay of a logic gate is found from the output voltage transition of logic gate across the load capacitance. They make use of the current equation of the MOSFET. The accuracy of these models depends on accuracy of the current equation. Alpha power law delay model is a typical example [9].

- 2. Empirical Delay Models: These models are based on the curve fitting on the simulation data obtained using SPICE. Scalable polynomial delay model is a typical example [10].

- 3. Look Up Table (LUT) Method: Here we have representation of the delay variation with  $T_R$  and  $C_l$  values. Having known  $T_R$  and  $C_l$  values, we can pick the delay of that particular gate from the table. A typical example is Synopsys ".lib" format Non-Linear Delay Model (NLDM) representation [5, 1], shown in Fig. 1.1.

Conventionally, NLDM based standard cell library characterization was used in STA. In this, delay is a non-linear function of  $C_l$  and  $T_R$  and it is expressed in an LUT with respect to several values of  $C_l$  and  $T_R$ . However, NLDM doesn't capture the nature of terminal voltage transition and variation of capacitance with terminal voltage [11, 12]. To address these issues, recently Current Source Model (CSM) has become important in the standard cell characterization and STA [13]. CSMs ideally support arbitrary input waveforms and output loads since their model parameters are waveform and load independent[14]-[17]. However, vendor CSMs presently impose some more constraints; they provide CSM data for a set of  $T_R$  and effective load capacitance  $C_{eff}$ . Two popular vendor CSMs are known as Effective CSM (ECSM) and Composite CSM (CCSM). For a given set of values of  $T_R$

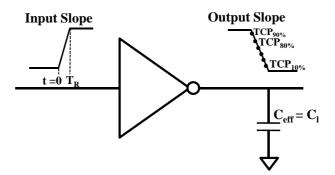

Figure 1.2: ECSM characterization overview.

and  $C_{eff}$ , ECSM stores the time at which the output voltage waveform crosses certain predefined  $\alpha$ % Threshold Crossing Points (TCPs) (shown in Fig.1.2) while CCSM stores the output current values at different threshold crossing points [13]. Both the vendor models are equivalent and one can be derived from the other. In ECSM, LUT of threshold crossing points for several values of  $C_l$  and  $T_R$  is used.

|                 | Input Transition Time (T <sub>R</sub> ) |                 |  |   |                 |

|-----------------|-----------------------------------------|-----------------|--|---|-----------------|

| C <sub>1</sub>  | T <sub>R1</sub>                         | T <sub>R2</sub> |  | • | T <sub>Rn</sub> |

| C <sub>n</sub>  | <b>V</b> <sub>11</sub>                  | V <sub>21</sub> |  |   | V <sub>n1</sub> |

| C <sub>12</sub> | V <sub>12</sub>                         | V <sub>22</sub> |  |   | V <sub>n2</sub> |

| •               |                                         |                 |  |   |                 |

| •               |                                         |                 |  |   |                 |

| C <sub>In</sub> | V <sub>1n</sub>                         | V <sub>2n</sub> |  |   | V <sub>nn</sub> |

Figure 1.3: An LUT of ECSM vectors. For each set of  $C_l$  and  $T_R$ , the characterization data is represented as vector V consisting of time of TCPs.

An LUT used for STA is a two dimensional table (shown in Fig.1.3), in which parameter to be characterized is stored for various  $C_l$  and  $T_R$  values. To minimize the storage, values of parameter to be extracted is stored for limited set of  $C_l$  and  $T_R$  and linear interpolation is used to obtain delay or time of a TCP for other values of  $C_l$ ,  $T_R$ . ECSM characterization is a computationally tedious task. In addition, Process, Voltage and Temperature (PVT) variations and frequent device model updates require a lot of re-characterization. In this work, we address the problem of reducing the number of SPICE simulation in ECSM library characterization. We consider the input to output coupling capacitance effect for CMOS inverter and NAND gate to accurately measure the timing values for ECSM characterization.

### 1.2 Previous Work

Several delay models have been proposed to characterize the behavior of CMOS logic

gates. Some commonly used delay models are discussed here.

The lumped RC delay model is proposed by Ousterhout [18]. In this model, the delay is computed by lumping all of the resistances and capacitances together through a stage. All of the resistances are summed separately, as are all the capacitances, and the product gives the delay through the stage as

$$delay = \left(\sum R\right) \left(\sum C\right) \tag{1.1}$$

The drawback of this model includes overestimation of delay due to lumping of resistance and capacitance values. It does not take into account the influence of input waveform on delay since it is limited to the step input waveform only. Later on, Hedenstierna and Jeppson [19] presented an analytical delay model for CMOS inverter, derived using Shockley's model [20]. The model included the input waveform slope effect. Although it is quite simple to use, but the model proved to be unsuccessful for short channel devices [9]. It does not consider the short channel effects dominating at sub-65nm technology nodes. Sakurai *et al.* [9] proposed an alpha power law model. This model is an extension of Shockley's model considering the velocity saturation effect in short channel devices. The model remains valid for the fast input ramp where input slope crosses one-third of the output slope [21]. In [21], authors reported that the  $\alpha$ -power law model is not valid for slow input ramps and presented an analytical delay model for both fast and slow input rise time.

In 1998, Sutherland *et al.* [22] presented a logical effort method to measure the delay efficiently. This model enables us to find the least delay of the circuit. It finds that how many stages would then be required and what should be size of the transistors in the gates to get the least delay. The method is quite useful for optimizing the circuit speed. The author presented the delay of a logic gate as

$$d = f + p \tag{1.2}$$

Where, f represents the effort delay proportional to the gate's output load and p represents the parasitic delay. The parasitic delay is fixed for a logic gate and independent of cell size and load capacitance it drives. The model is very simple to use but it neglects the input transition time effects and secondary effects like velocity saturation, body effect etc. Traditional method (empirical model) to characterize delay is to use an equation of the form  $k_1C_l + k_2$ , where  $k_1$  is the input transition slope and  $k_2$  is the intrinsic delay. In [10], researchers working with Synopsys presented the Scalable Polynomial Delay Model (SPDM) to characterize the cell delay. The model uses a product of polynomials to fit the delay data. For example, to characterize the delay for two parameters  $C_l$  and  $T_R$ , a product of  $m^{th}$  order polynomial in  $C_l$  with an  $n^{th}$  order polynomial in  $T_R$  may be used in the following form:

$$delay = (a_0 + a_1C_l + \dots + a_mC_l^m)(b_0 + b_1T_R + s\dots + b_nT_R^n)$$

(1.3)

To overcome this complexity, people in industry are now making use of LUTs to obtain

the delay of a logic gate. LUTs with delays tabulated for several values of  $T_R$  and  $C_l$  values are today used in STA. These LUTs are popular due to limitations of analytical and polynomial delay models as discussed above. LUT used for STA is a 2-D table, where the standard cell delay is characterized with several  $T_R$  and  $C_l$  values. There are several problems with the existing LUTs, for example  $T_R$  and  $C_l$  values are selected in an ad-hoc manner, need of re-characterization due to PVT variations, accuracy of the delay values obtained depends on the size of the LUT.

All the aforementioned delay models measure only the propagation delay. These models do not consider the PVT variations and input to output coupling capacitance which are very important at nanometer range technologies. To address the variation in delay values in presence of PVT variations, several delay models are reported [23]-[45]. However, they did not derive the model coefficients considering PVT variation with physical reasoning for the same. While considering process variations, they considered the change in process parameters such as oxide thickness, threshold voltage, doping concentration, gate length, etc. However, they didn't consider the effect of mechanical induced stress as a function of Number of Fingers (NF) on the timing values while the stress engineering is widely being incorporated at nanometer range technologies to enhance the device performance. In this work, we show the dependence of timing values on cell size, load capacitance, input slew, process (mechanical induced stress as a function of NF), voltage and temperature variations. Beside this, we also investigated the importance of overshoot modeling in accurate timing analysis. We found that there are very few researchers who worked on overshoot timing models [46, 47, 48, 49]. In [49], authors show that the conventional delay models [9, 21, 50, 51, which ignore overshoot effect face serious issues of accuracy at these technology nodes. Huang et al. [49] proposed an analytical overshoot model at nanometer technology node. This work gives an overshoot time  $(t_{ov})$  expression according to which  $t_{ov}$  is a function of the logic gates capacitance  $C_l$ . The authors assumed that a linearly time varying current discharges (charges)  $C_l$ . This model has been verified for only large values of input transition time  $T_R$  and  $C_l$ . The minimum value of  $C_l$  used in [49] are typically fanout 100. They also assume that  $t_{ov}$  varies with  $C_l$  which is not validated by the simulation results shown in their reported research work.

- 1. Therefore, the delay models which can be used in nanometer range technologies are either inaccurate or fully empirical and cumbersome to use.

- 2. They neither consider PVT variations through physical reasoning nor the important second order phenomenon such as overshoot due to gate to drain coupling capacitance  $(C_{gd})$ .

- 3. They are not amenable to be used easily in standard cell characterization for STA.

### **1.3** Problem Definition

The aim of this thesis is to propose the timing models to reduce the computational effort in characterization of single stage standard cells at nanometer range technologies. Such a work can easily be extended to multistage standard cells. In order to accomplish this, following approach have been taken:

- Derivation of timing models and their region of validity as a function of  $T_R$  and  $C_l$  for standard cell CMOS inverter

- Verification of the model coefficients' behavior with cell size and technology node for standard cell CMOS inverter

- Derivation of timing models and their region of validity with PVT variability for standard cell CMOS inverter

- Derivation of timing models and their region of validity as a function of  $T_R$  and  $C_l$  for 2-input CMOS NAND gate

- Verification of the model coefficients' behavior with cell size for NAND gate

- Derivation of timing models and their region of validity with PVT variability for NAND gate

- CMOS inverter and NAND gate overshoot modeling

### 1.4 Contributions

The objective of this thesis is to develop an accurate timing model for ECSM characterization of all the TCPs of output voltage at nanometer range technologies. For this, we first develop a timing model for CMOS inverter at 32nm technology node. The model is formulated based on current equations considering velocity saturation. All the factors which affects delay, namely: cell size,  $T_R$  and  $C_l$  are considered in the model. The proposed model matches with the HSPICE simulated results closely for all the TCPs. The model remains valid with the technology scaling.

At nanometer technology node, there is a need for library re-characterization due to onchip PVT variations. To improve the performance, it is important to accurately measure the timing values in circuits while considering voltage, temperature and process induced variability. We derive relationships of the coefficients of our ECSM timing models with PVT variation. For voltage variability, we consider  $\pm 10\%$  variation in nominal supply voltage. For temperature variability, we vary the temperature range from 298K to 423K. For stress variability, we consider the variation in device channel mechanical stress as a function of NF in inverter layout. This is because, often the size of inverter cell is increased by increasing NF, therefore the consequent variation in channel mechanical stress is important. Stress induced in the channel of pMOS (nMOS) using various sources like Compressive/Tensile Etch Stop Liner (c/t-ESL), embedded SiGe (eSiGe) and Stress Memorization Technique (SMT) [52] has been considered in this work.

We derive the timing models for 2-input CMOS NAND gate, considering single input switching and also derive their region of validity in  $T_R$ ,  $C_l$  space. We observe that the improper consideration of intermediate node voltage transition leads to significant percentage error in delay/timing values (we later discuss this in detail). Based on this observation, we consider the intermediate node voltage transition for accurate timing analysis. Further, we determine the relationships of the model coefficients with the cell size, power supply voltage, carrier mobility, threshold voltage and temperature. We also consider layout dependent effects due to mechanical stress in deriving these relationships.

Next, we propose an analytical overshoot timing model for very wide range of  $T_R$  values for CMOS inverter and 2-input NAND gate. For NAND gate standard cell, it becomes important to consider the intermediate node voltage transition in accurate timing analysis. Therefore, we first model the behavior of intermediate node voltage for large values of  $T_R$ . Later on, we derive the relationships of overshoot time with cell size,  $T_R$  and  $C_l$  values. We find that the proposed model is independent of cell size and  $C_l$  values.

The proposed model reduces the number of HSPICE simulations in ECSM characterization of CMOS inverter and NAND gate standard cell by nearly 50% and 67%, respectively. The need to re-characterize the timing models with PVT variation, has thus been reduced.

### 1.5 Thesis Organization

This thesis is organized into 7 chapters as follows:

**Chapter 1:** In this chapter, an introduction to the standard cell characterization and challenges it faces due to the need for more accurate cell characterization are presented.

**Chapter 2:** This chapter provides a detailed literature review on propagation delay models, overshoot timing models, along with the need of an efficient timing model. Technical gaps in the existing literature on timing models and digital circuit performance are discussed. The chapter is concluded with a brief summary of technical gaps to be addressed in the thesis.

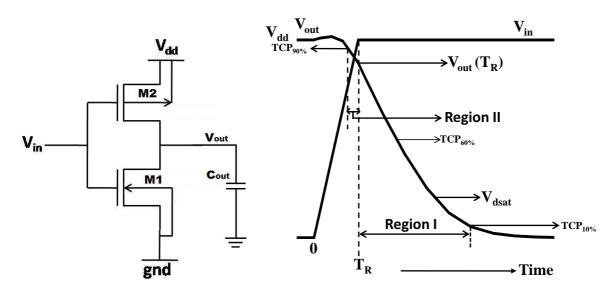

**Chapter 3:** This chapter focuses on modeling of timing values of threshold crossing points  $(t_{TCP}s)$  as a function of  $T_R$  and  $C_l$  for a minimum sized CMOS inverter. Further, the region of validity of the model in  $T_R$ ,  $C_l$  space is derived. The relationship between cell size and model coefficient is also derived. We also analyzed, the impact of technology scaling on these model coefficients. The results depict that the proposed model is in good agreement with HSPICE simulations with a maximum error of 2.5%. The contribution of these models in reducing the number of HSPICE simulations in ECSM characterization of the inverter standard cell is nearly half. **Chapter 4:** In this chapter, we consider the impact of process parameters (mechanical induced stress as a function of Number of Fingers (NF)), supply voltage and temperature variations on the proposed  $(t_{TCP})$  models. We derive the relationships of model's coefficients and their region of validity with the process, supply voltage and temperature variations in  $T_R$ ,  $C_l$  space. Therefore, the models considering PVT variation helps in reducing the re-characterization effort in standard cell library characterization. In this chapter, we demonstrate that the inclusion of PVT variation in our  $t_{TCP}$  models reduces the number of HSPICE simulations by about half.

**Chapter 5:** This chapter focuses on modeling of  $t_{TCPS}$  as a function of  $T_R$  and  $C_l$  for 2-input CMOS NAND gate. The NAND gate ECSM characterization done for the following two cases.

- Case 1: When the upper nMOS transistor in series-stack switches

- Case 2: When the lower nMOS transistor in series-stack switches

The region of validity of the  $t_{TCP}$  models in both the cases of 2-input NAND gate is derived. The relationship between cell size and model coefficient is also derived. Further, the impact of PVT variation on the model coefficient's is observed. The results depict that the proposed models are in good agreement with HSPICE simulations with a maximum error of 3%.

**Chapter 6:** This chapter focuses on overshoot timing model for CMOS inverter and 2-input NAND gate. For NAND gate, the boundary conditions are identified based on operating regions of the nMOS series-stack transistors. The relationship between cell size and model coefficient is also derived. The results depict that the overshoot time is independent of  $C_l$  and proportional to  $T_R$ . The proposed model gives a highly accurate estimation of delay values at nanometer range technologies.

**Chapter 7:** Finally, a summary of the presented research work along with the major conclusions of the work and future scope are presented in this chapter.

### Chapter 2

### Literature Review

### 2.1 Overview

This chapter starts with the study of existing delay models of CMOS inverter and NAND gate standard cell. There are several delay/timing models used in digital system design, some are briefly mentioned in the previous chapter. Further, we discuss the technical gaps present in the existing models. We also discuss the reason for their unsuitability in standard cell characterization.

### 2.2 Introduction

Semi-custom design approach at sub nanometer technologies requires efficient computeraided design tools. Designers need to consider several aspects of the chip design such as timing, area and power. In this regard, designers need an accurate and efficient timing model in order to adequately optimize the standard cell based designs. For this an accurate and efficient method for characterizing standard cells is required. In this context, we discuss the limitations of the existing delay models in the following section.

### 2.3 Literature survey on existing delay models

As we discussed in previous section, down scaling and high performance circuits demand accurate timing analysis at sub-nanometer regime. At such technology nodes, a minor variation due to several factors like short channel effects, input to output coupling capacitance, power supply noise and process variations, etc. influences timing parameters significantly [6]. Standard cell or logic gate timing characterization must therefore account for all these parameters. Therefore, designing accurate and high performance circuits has become more challenging than ever in deep sub-micron era, in semi-custom domain. This section presents a brief description of past researcher's timing models for CMOS combinational logic gates.

The first delay model for CMOS inverter was introduced by Burns [53]. The model presented the differential equation based closed-form expression for the output waveform of CMOS inverter using a step input. Burns also derived a closed-form expressions for the

rise and fall time of CMOS inverter. Later on, the lumped RC delay model was proposed by Ousterhout [54]. In this model, the delay is computed by lumping all of the resistances and capacitances together through a stage. But, this model gives an overestimation of the delay due to lumped resistances and capacitances. And the major drawback of this model is that it doesn't deal with the shape of input waveform. To improve the delay analysis, Hedenstierna and Jeppson [19] presented an analytical delay model derived using Shockley's model [20], that includes the input waveform slope effect. Since, the Shockley's model is quite simple and has been used by many researchers. However, the model is not suitable for short channel devices as it does not consider the second order effects.

In [55], Jeppson presented an improved semi-empirical delay model by considering gateto-drain coupling capacitance. Soon, Nabavi *et. al* [56] presented an empirical model for computing the inverter delay. In [56], authors discussed the transient behavior for the two extreme cases i.e. very fast and very slow input transition times. For slow inputs, authors assumed that the negligible current flows through the load, whereas for fast inputs, the change in output voltage is negligibly small during the input transition. Hence, they ignored the effect of the output load on the delay for the extremely slow and fast inputs. All the models described above have a limitation that they ignored velocity saturation effect which is prominent at nanometer range technology nodes.

In [9], Sakurai et. al presented the " $\alpha$ - power law delay model" considering the velocity saturation effect for short channel devices. To derive this model authors neglected the short circuit current and gate-to-drain coupling capacitance. And, the model remains valid for fast input ramps only. Using the  $\alpha$ -power law model, Embabi et. al [57] presented the delay model considering the short-circuit current into account. But, the model assumed the output voltage and the currents through the transistors to be piecewise linear. For slow input ramps, Dutta et. al [21] presented a delay model for CMOS inverter, which is an extension of Sakurai's delay model. Soon, Choi et. al [58] presented a delay model for CMOS logic gates to overcome the disadvantage of RC delay model. The model considered the MOSFET as a resistor or current source depending on the input and output voltage of the inverter. For NAND/NOR gate, authors assumed that N number of transistors in the series stack can be modeled as a single transistor. This assumption leads to significant error in the delay values. In [22], Sutherland et al. presented the method of "logical effort" which enables us to choose the topology and also tells us which topology is better for the circuit, how many stages would then be required to get the least delay and what should be size of the transistors in the gates. The method is quite simple and accurate if the input slope effect is ignored. Since, input transition time is one of the important parameters in the standard cell characterization which can not be ignored.

Traditional method (empirical models) to characterize delay is to use an equation of the form  $k_1C_l + k_2$ , where  $k_1$  is the input transition slope and  $k_2$  is the intrinsic delay. Soon, Synopsys [10], presented the Scalable Polynomial Delay Model (SPDM) to characterize the cell delay. The model uses a product of polynomials to fit the delay data. For example, to characterize the delay for two parameters  $C_l$  and  $T_R$ , a product of  $m^{th}$  order polynomial in  $C_l$  with an  $n^{th}$  order polynomial in  $T_R$  may be used in the following form:

$$delay = (a_0 + a_1C_l + \ldots + a_mC_l^m)(b_0 + b_1T_R + s \ldots + b_nT_R^n)$$

(2.1)

Which is a purely empirical expression and has to be extracted for each variation in any parameter affecting circuits. To avoid such complex expressions, industry people are now using LUTs to represent the delay of a logic gate. LUTs with delays tabulated for several values of  $T_R$  and  $C_l$  values are today used in STA. These LUTs are popular due to limitations of analytical and polynomial delay models as discussed above. LUT used for STA is a 2-D table, where the standard cell delay is characterized with several  $T_R$  and  $C_l$ values. Delays for the  $T_R$  and  $C_l$  values which are not listed in the LUTs are obtained using linear interpolation between the nearest two  $T_R$  and  $C_l$  values. There are several problem with the existing LUTs, for example  $T_R$  and  $C_l$  values are selected in an ad-ho c manner, need of re-characterization due to PVT variations, accuracy of the delay values obtained depends on the size of the LUT.

In [59], authors proposed a linear timing model to characterize delay and power dissipation of cells. The 50% delay is used to characterize the linear delay parameters. In [60], Patel presented a method to characterize the cell delay and capacitance parameters. However, these models are inconsistent when a cell drives different type of cell. In [61], authors proposed an LUT based approach to simplify the characterization of complicated cells. The method is particularly useful for the cases when the internal structure of standard cell is known. Further, in [62], Cirit used an LUT based approach to characterize the cells, where a cell being characterized is considered as a black box. It gave us the flexibility to consider any standard cell for characterization whose internal structure is not known. The model uses interpolation method to compute the delay values for those  $T_R$  and  $C_l$  values which are not given in the LUT. It requires software to perform mathematical analysis, thus makes the cell characterization process slow.

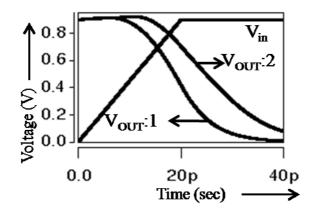

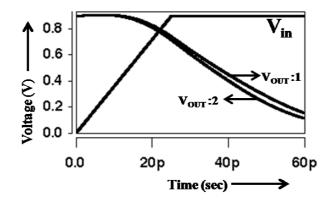

There are several delay models [63]-[73], proposed for CMOS inverter, and very few for the NAND gate standard cell. Recently, Gummalla *et al.* [2] presented an analytical timing model for 2-input NAND gate. The authors used Elmore delay model to consider the intermediate node voltage transition of the series stack for the switching of lower nMOS transistor in the series stack of the NAND gate, which may lead to significant error. This is because the upper nMOS transistor in the series stack operates in the saturation region for the  $C_l$  and  $T_R$  values typically found in circuits (explained in detail in Chapter 5). However, since they use Elmore delay model, they assumed it to be operating in linear region which results in a gross underestimation of delay values (as shown in Fig. 2.1).

Figure 2.1: Response of the NAND gate for fixed input transition time;  $V_{out}$ : 1 represents the O/P voltage when the upper nMOS transistor is replaced by an equivalent resistor and  $V_{out}$ : 2 represents the O/P voltage for the realistic case where the upper nMOS of 2-input NAND gate is not replaced (For  $V_{out:1}$ , we obtain the equivalent resistance value from the linear current equation (1) of [2]).

Figure 2.2: Response of the NAND gate for fixed input transition time;  $V_{out}$ : 1 represents the O/P voltage when the pull down part is replaced with the half width single nMOS transistor and  $V_{out}$ : 2 represents the O/P voltage for the conventional 2-input NAND gate.

When upper nMOS transistor in the series stack switches, Gummalla did not consider the effect of intermediate node of the series stack of nMOS transistors and replaced the series stack of nMOS transistors with the half width single nMOS transistor. We observe that this assumption leads to an overestimation of delay values as shown in Fig. 2.2.

Due to simplicity and accuracy, NLDM based on LUT approach is used widely for standard cell characterization by Synopsys. At sub-nanometer technologies, there are limitations of the NLDM in cell characterization which makes it less accurate. These limitations are the inaccurate shape of input waveform, undesirable value of nonlinear capacitance, etc [55]. Therefore, in modern CMOS technology, it becomes increasingly important to model the complex input waveforms, nonlinear capacitance and process variations [74]. In this scenario, the conventional standard cell characterization approach isn't found as an efficient technique to address problems. This conventional technique is useful to model the signal transitions as saturated ramps with known arrival and transition times. Therefore, researchers have introduced an alternative modeling technique known as Current Source Modeling (CSM) which becomes increasingly important for use in standard cell characterization and static timing analysis (STA).

### 2.3.1 CSM based standard cell timing analysis

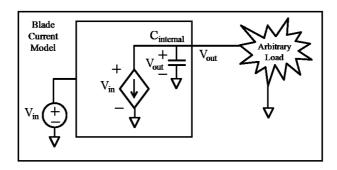

CSMs ideally support arbitrary input waveforms and output loads since their model parameters are waveform and load independent [75]. A current-based gate model includes a 2-D lookup table  $I_0(V_i, V_0)$  which gives gate output current for a pair of gate input and output voltages, and voltage-controlled capacitor at the gate output. The CSM model proposed by Tutuianu *et al.* [76] is similar to [77, 78]. Croix *et al.* [14], proposed a CSM model which is independent of input waveform and output load as shown in Fig. 2.3. This "Blade" model consists of a voltage-controlled current source, an internal capacitance (Cinternal), and a time shift of the output waveform. The model is essentially a  $V_i - V_o$  based (input voltage, output voltage) current source with transient effects modeled by a linear capacitance at the output. A linear capacitance to model the active input load is assumed because the capacitances have a linear relationship with respect to device dimension for a given technology.

Figure 2.3: The Blade model consists of a voltage-controlled current source with a constant internal capacitance and input waveform time shift driving an arbitrary load.

It was the first CSM of a logic cell in which a pre-characterized current source is utilized to capture the non-linear behavior of the cell with respect to the input and output voltage values. The single output capacitance does not capture non-linearity. The miller effect between input and output nodes was ignored in this model. The ignorance of miller capacitance resulted in an under-estimation of delay. Keller et. al. [15], presented a CSM for the purpose of crosstalk noise analysis. The authors used a pre-characterized current source for the noise analysis. The parasitic components, namely the output and miller capacitances are assumed to be constant regardless of input and output voltage values. In practice, these capacitive effects can vary by orders of magnitude depending on cell input and output voltage values [79, 80].

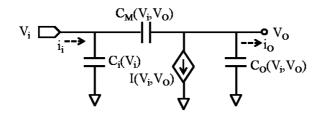

In [16], Li and Acar has resolved this weakness by introducing a non-linear output capacitance model. Soon, Fatemi et.al. [3] used non-linear input, output and miller capacitances along with an output current source for the delay analysis, these all are function of the input and output voltages as shown in Fig. 2.4.

Figure 2.4: Current-based circuit model of a logic cell proposed by [3].

In [81], Kashyap *et. al.* presented a CSM in which input and output pins as well as several chosen internal pins of the cell are modeled with a voltage dependent current source and a non-linear capacitance. Veetil *et. al.* [82], investigated the importance of various modeling decisions on the accuracy and complexity of CSMs. The authors reported the bi-cubic spline based DC current source model for accurate and efficient timing analysis. For transient analysis, authors assumed that a cell can be replaced with simple parasitic capacitance model and a time shift parameter. These models require the precharacterization of standard cells. Its very time consuming and cumbersome, as each parameter is dependent on input and output voltages.

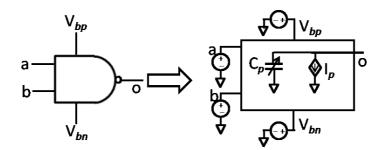

Figure 2.5: Example of a CSM: the output port is modeled as a nonlinear voltage controlled current source, dependent on all input port voltages, in parallel with a nonlinear capacitance [4]).

In 2010, Gupta *et al.* [4] developed a new approach to capture compactly the body bias effects within a mainstream CSM framework (shown in Fig. 2.5). The model is based on Blade model (given in [14]) except that the output port is replaced by a nonlinear voltage controlled current source,  $I_p$ , in parallel with a nonlinear capacitance,  $C_p$ . The mathematical framework for this new approach consists of two key steps. First approach is made by adapting an existing scheme to enable the compact storage of look-up tables for the sensitivities of CSM components to body bias, over the range of allowable values of the body bias. Second approach is on the basis of development of a novel waveform sensitivity model for evaluating the impact of applied body bias that provides accurate waveforms at the output of the cell under any body bias with minimal computation. Challenges of CSM [83] :

1. Each parameter of the cell is dependent on input and output node voltages which results in much larger libraries. Hence, library size has increased due to the development of CSM. 2. The complexity of the models has increased significantly over the NLDM models used for standard cell characterization.

EDA tool vendors found a middle path to solve these issues, known as vendor CSM formats. Two available CSM vendor formats are ECSM [84] and CCSM [85]. For a given input slew and load capacitance  $(C_l=C_{eff})$  values, ECSM stores the times at which the output voltage waveform crosses certain predefined threshold points whereas CCSM stores the output current values at specified voltage level points. Both the vendor models are equivalent and one can be derived from the other. Vendor CSMs use LUT based format for representing characterization data. It overcomes the problems of the voltage-based models which is not compatible with the arbitrary shapes of voltage waveforms and falls short when dealing with crosstalk-induced noisy waveforms. ECSMs have recently received increased attention with major EDA vendors for supporting the noise model or power droop model [77, 78].

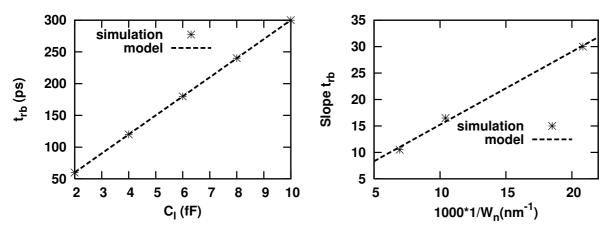

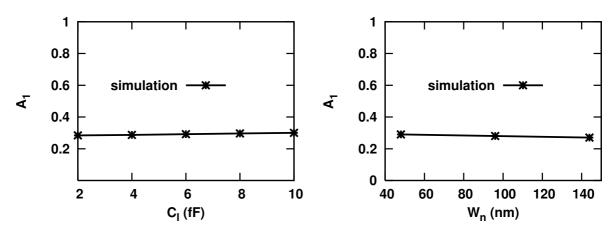

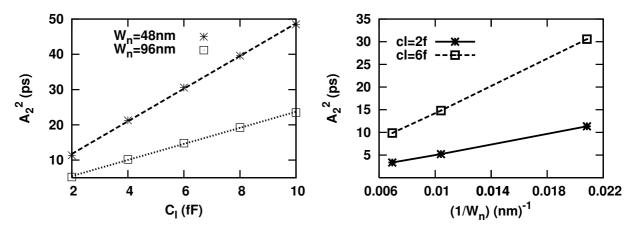

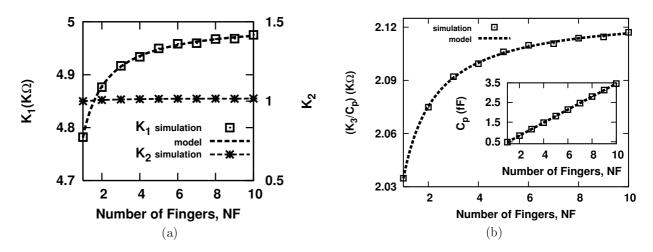

# 2.3.2 Overshoot timing Model for CMOS inverter and 2-input NAND gate