### MODELING OF CROSSTALK EFFECTS IN CMOS GATE DRIVEN ON-CHIP INTERCONNECTS USING FDTD TECHNIQUE

Ph.D. THESIS

by

### RAMESH KUMAR VOBULAPURAM

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247667 (INDIA) NOVEMBER, 2015

### MODELING OF CROSSTALK EFFECTS IN CMOS GATE DRIVEN ON-CHIP INTERCONNECTS USING FDTD TECHNIQUE

A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

#### **DOCTOR OF PHILOSOPHY**

in

### ELECTRONICS AND COMMUNICATION ENGINEERING

by

RAMESH KUMAR VOBULAPURAM

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247667 (INDIA) NOVEMBER, 2015

©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE- 2015 ALL RIGHTS RESERVED

### INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

### **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled **"MODELING OF CROSSTALK EFFECTS IN CMOS GATE DRIVEN ON-CHIP INTERCONNECTS USING FDTD TECHNIQUE"** in partial fulfillment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electronics and Communication Engineering of the Indian Institute of Technology Roorkee is an authentic record of my own work carried out during a period from December, 2011 to November, 2015 under the supervision of Dr. B. K. Kaushik, Associate Professor and Dr. A. Patnaik, Associate Professor, Department of Electronics and Communication Engineering, Indian Institute of Technology Roorkee.

The matter presented in the thesis has not been submitted by me for the award of any other degree of this or any other Institute.

### (Ramesh Kumar Vobulapuram)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

### (B. K. Kaushik) Supervisor

### (A. Patnaik) Supervisor

The Ph.D. Viva-Voce Examination of Ramesh Kumar Vobulapuram, Research Scholar has been held on March 2, 2016.

### Chairman, SRC

**External Examiner**

This is to certify that the student has made all the corrections in the thesis.

Signature of Supervisors

Dated: 2<sup>nd</sup> March 2016

Head of the Department

### ABSTRACT

Advancement in very large scale integration (VLSI) technology offers gigascale integrated circuits in a system on-chip. In these circuits, interconnects play a key role in determining circuit performance, such as time delay and power consumption. At high operating frequencies, the closely packed interconnects produce transient crosstalk. The crosstalk noise strongly influences the signal propagation delay and causes the logic or functional failure.

Over the years, several mathematical models have been proposed for the analysis of CMOS gate driven coupled on-chip interconnects. However, most of these crosstalk noise models approximately considered the non-linear CMOS driver as a linear resistor. This approximation is not valid for on-chip interconnects because during the input and output transition states the transistor operates in cutoff, linear and saturation regions. The transistor operating time in the saturation region is about 50% during the transition period. Thus, assuming that the transistor operates in the linear region leads to severe errors in the performance estimation of the driver-interconnect-load system. Therefore, it is necessary to develop an accurate model that appropriately considers the non-linear effects of CMOS driver and accurately measures the crosstalk induced performance parameters of on-chip interconnects.

This thesis presents an accurate and time efficient model of CMOS gate driven coupled on-chip interconnects for crosstalk induced performance analysis. The proposed model successfully incorporates the non-linear effects of CMOS driver. The model is developed using the finite-difference time-domain (FDTD) technique for coupled on-chip interconnects, whereas, the CMOS driver is modeled by either *n*-th power law or modified alpha power law model. The model is validated by comparing the results with HSPICE simulations. It is observed that the results of the proposed model closely matches with that of HSPICE simulations. Encouragingly, the FDTD model is highly time efficient than the HSPICE.

The conventional copper interconnect suffers from low reliability with down scaling of interconnect dimensions. The reliability of Cu reduces due to the electromigration induced problems such as hillock and void formations. Moreover, with highly scaled dimensions the resistivity of Cu increases due to electron-surface scattering and grain-boundary scattering. Therefore, researchers are forced to find an alternative material for on-chip interconnects. Carbon nanotubes (CNTs) have been proposed as a promising interconnect material. A portion of this thesis is focused towards the modeling of multi-walled CNT (MWCNT) interconnects. An accurate FDTD model is presented while incorporating the quantum effects of nanowire and non-linear effects of CMOS driver. To reduce the computational effort required for analyzing the CMOS driver, a simplified but accurate model is employed, named as, modified alpha power law model. The crosstalk noise is comprehensively analyzed by examining both functional and dynamic crosstalk effects.

Graphene nanoribbon (GNR), a strip of ultra-thin width graphene layer, has also been considered aggressively by the researchers as a potential alternative material for realizing on-chip interconnects. Most of the physical and electrical properties of GNRs are similar to that of CNTs; however, the major advantage of GNRs over CNTs is that both transistor and interconnect can be fabricated on the same graphene layer, thus avoiding the metal-graphene contact problems. This thesis presents an accurate model for the analysis of multi-layer GNR (MLGNR) interconnects. In a more realistic manner, the model incorporates the width dependent mean free path that helps in accurately estimating the crosstalk induced performance in comparison to the conventional models.

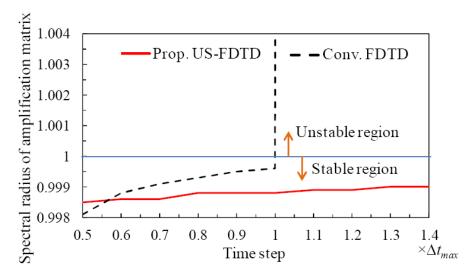

The stability of the FDTD technique is constrained by the Courant-Friedrichs-Lewy (CFL) stability condition. Hence, beyond the CFL condition, the FDTD technique is unstable and within it, the technique is inefficient. The efficiency improvements in FDTD technique can be addressed, if the CFL stability condition is removed. To improve the efficiency of FDTD technique, an unconditionally stable FDTD (US-FDTD) technique is presented for the analysis of on-chip interconnects. It is observed that the stability of the proposed model is not constrained by the CFL condition and is therefore unconditionally stable. The accuracy of the proposed model is validated against the conventional FDTD model. It is observed that the US-FDTD model is highly time efficient while being as accurate as the conventional FDTD. Moreover, a comparative analysis of crosstalk induced performance is presented among Cu, MWCNT and MLGNR interconnects. It is observed that the MLGNR and MWCNT interconnects outperform the Cu interconnect.

### ACKNOWLEDGEMENTS

I take this opportunity to truly thank my advisors, Dr. B. K. Kaushik and Dr. A. Patnaik, for their continuing guidance, support and encouragement during my Ph.D. study. Their enthusiasm and expertise in the area of interconnect modeling helped me better understand the overall perspectives and subtle facets of this work. Their rigorous attitude toward science and research motivated me throughout the work of this thesis. I humbly acknowledge a lifetime deep gratitude to them.

I feel lucky to have had the opportunity to work with very bright and helpful research faculty members in Microelectronics and VLSI group. I am also very much thankful to Prof. M. V. Kartikeyan, HOD, ECE Department for providing me an excellent learning environment and all support. I owe a lot of thanks to Prof. A. K. Saxena, Dr. S. Dasgupta, Dr. A. Bulusu, Dr. S. Manhas, Dr. A. Datta, Dr. B. Kumar and Dr. B. P. Das for enriching me with their unrestrained help. I am grateful to Chairman (DRC/SRC) for sparing his precious time regardless of all busy schedules to carefully examine my research work and providing valuable suggestions.

My friends and colleagues in IIT Roorkee made the journey towards this thesis a pleasant and memorable one. I am thankful to my colleagues Pankaj, Manoj, Girish, Govinda, Shivam, Naushad, Arvind, Omprakash, Satish, Baljit, and Jittendra for constructive technical discussions at various stages of preparation that made it possible to complete in time. I am very much thankful to the anonymous editors and reviewers of various peer-reviewed journals for analyzing the manuscripts critically and in-depth that helped me to substantially improve the quality of work. I am also thankful to the M. Tech students Shailesh Mittal, Arsalan Alam, Murthy, Trishankar and Nitanshu for their unrestrained help in successful completion of my research work. I sincerely appreciate Mr. Naveen Kanwar, lab staff for his support during the research work. The present is sponsored by the Institute Fellowship from Ministry of Human Resource Development, Govt. of India. This support is gratefully acknowledged. No person can be successful without the love and support of his family. I humbly and respectfully acknowledge the love, blessings, and sacrifices of my parents Mrs. Suneetha and Mr. Balaiah and my brother Suresh. I compliment most warmly my loving and caring wife, Divya Madhuri, who had to endure and share the pain and the pleasures of my arduous professional life. I must thank my daughter, Geetika, who missed me sometimes from dawn to dusk for not being available to play with.

Lastly and mostly, I cannot find the right words to thank our Lord who is always beside me, wakes me up every time when I am in dark, heals me when I mess up and stands me up when I am down. Lord, I am always with you even unto the end of the world.

This thesis is dedicated to my parents and my loving family.

Dated: 2<sup>nd</sup> March 2016

(V. Ramesh Kumar)

# **TABLE OF CONTENTS**

|               |                                                      | Page<br>No. |

|---------------|------------------------------------------------------|-------------|

| Copyright     |                                                      |             |

| Candidateøs   | Declaration                                          |             |

| Abstract      |                                                      | i           |

| Acknowledg    | ement                                                | iii         |

| Table of Cor  | ntents                                               | v           |

| List of Figur | es                                                   | ix          |

| List of Table | S                                                    | xiii        |

| List of Symb  | ools                                                 | XV          |

| List of Abbre | eviations                                            | xvii        |

| Chapter 1:    | Introduction                                         |             |

| 1.1           | Introduction                                         | 1           |

| 1.2           | Evolution of Interconnect Materials                  | 2           |

|               | 1.2.1 Carbon Nanotubes (CNTs)                        | 3           |

|               | 1.2.2 Graphene Nanoribbons (GNRs)                    | 4           |

| 1.3           | Modeling of On-chip Interconnects                    | 5           |

| 1.4           | Problem Definition                                   | 7           |

| 1.5           | Outline of the Work                                  | 8           |

| Chapter 2:    | Review of Cu, MWCNT and MLGNR Interconnect<br>Models |             |

| 2.1           | Interconnect Modeling Approaches                     | 11          |

|               | 2.1.1 Lumped Model with CMOS Driver                  | 11          |

|               | 2.1.2 Distributed Model with Resistive Driver        | 12          |

|               | 2.1.3 Distributed Model with CMOS Driver             | 13          |

| 2.2        | Carbon Nanotubes                                                                                                                                                  | 14                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|            | 2.2.1 Basic Structure of CNTs                                                                                                                                     | 15                   |

|            | 2.2.2 Semiconducting and Metallic CNTs                                                                                                                            | 18                   |

|            | 2.2.3 Properties and Characteristics of CNTs                                                                                                                      | 21                   |

|            | 2.2.4 Conductivity Comparison                                                                                                                                     | 23                   |

|            | 2.2.5 MWCNT Interconnect Modeling                                                                                                                                 | 25                   |

|            | 2.2.6 MWCNT Performance Analysis                                                                                                                                  | 29                   |

| 2.3        | Graphene Nanoribbons                                                                                                                                              | 31                   |

|            | 2.3.1 Basic Structure of GNRs                                                                                                                                     | 31                   |

|            | 2.3.2 Semiconducting and Metallic GNRs                                                                                                                            | 33                   |

|            | 2.3.3 Properties and Characteristics of GNRs                                                                                                                      | 34                   |

|            | 2.3.4 Conductivity Comparison                                                                                                                                     | 36                   |

|            | 2.3.5 MLGNR Interconnect Modeling                                                                                                                                 | 37                   |

|            | 2.3.6 MLGNR Performance Analysis                                                                                                                                  | 40                   |

| 2.4        | Technical Gaps                                                                                                                                                    | 41                   |

| Chapter 3: | FDTD Model for Crosstalk Analysis of CMOS Gate-<br>Driven Coupled Copper Interconnects                                                                            |                      |

|            | ······································                                                                                                                            |                      |

| 3.1        | Introduction                                                                                                                                                      | 45                   |

| 3.1<br>3.2 |                                                                                                                                                                   | 45<br>46             |

|            | Introduction                                                                                                                                                      |                      |

| 3.2        | Introduction<br>Motivation                                                                                                                                        | 46                   |

| 3.2        | Introduction<br>Motivation<br>FDTD Model of CMOS Gate-Driven Cu Interconnects                                                                                     | 46<br>49             |

| 3.2        | Introduction<br>Motivation<br>FDTD Model of CMOS Gate-Driven Cu Interconnects<br>3.3.1 FDTD Model of Interconnects                                                | 46<br>49<br>50       |

| 3.2<br>3.3 | Introduction<br>Motivation<br>FDTD Model of CMOS Gate-Driven Cu Interconnects<br>3.3.1 FDTD Model of Interconnects<br>3.3.2 Incorporation of Boundary Constraints | 46<br>49<br>50<br>52 |

| empre n    | Carbon Nanotube (MWCNT) Interconnects                                                   |    |

|------------|-----------------------------------------------------------------------------------------|----|

| 4.1        | Introduction                                                                            | 65 |

| 4.2        | Equivalent Single Conductor Model of the MWCNT<br>Interconnect                          | 67 |

|            | 4.2.1 Resistance                                                                        | 69 |

|            | 4.2.2 Inductance                                                                        | 70 |

|            | 4.2.3 Capacitance                                                                       | 71 |

| 4.3        | FDTD Model of MWCNT Interconnect                                                        | 72 |

|            | 4.3.1 The MWCNT Interconnect Line                                                       | 72 |

|            | 4.3.2 Boundary Condition at Near-end Terminal                                           | 74 |

|            | 4.3.3 Boundary Condition at Far-end Terminal                                            | 76 |

| 4.4        | Validation of the Model                                                                 | 76 |

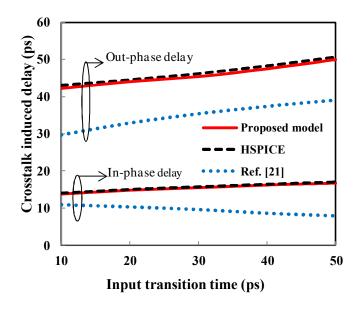

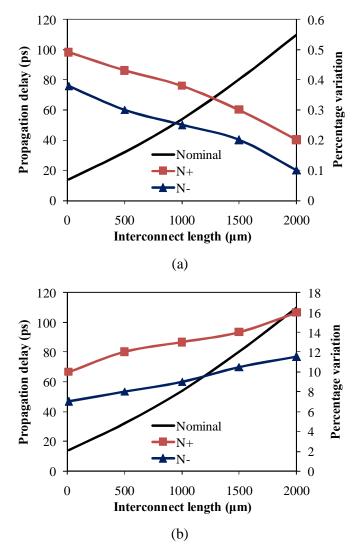

| 4.5        | Sensitivity Analysis                                                                    | 80 |

|            | 4.5.1 Sensitivity analysis for number of conducting channels                            | 80 |

|            | 4.5.2 Sensitivity analysis for contact resistance                                       | 81 |

|            | 4.5.3 Sensitivity analysis for PVT variations                                           | 82 |

| 4.6        | Summary                                                                                 | 83 |

| Chapter 5: | Crosstalk Modeling with Width Dependent MFP in MLGNR Interconnects Using FDTD Technique |    |

| 5.1        | Introduction                                                                            | 85 |

| 5.2        | Equivalent Single Conductor Model of the MLGNR Interconnect                             | 86 |

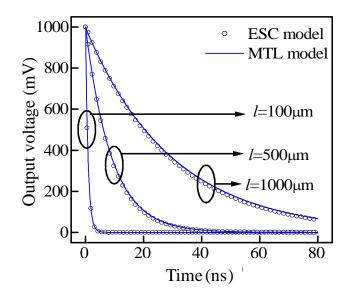

|            | 5.2.1 Transient Analysis of MTL and ESC Models                                          | 89 |

| 5.3        | FDTD Model of the MLGNR Interconnect                                                    | 90 |

| 5.4        | Results and Discussion                                                                  | 94 |

|            | 5.4.1 Analysis of Mean Free Path, Resistance and<br>Propagation Delay with Rough Edges  | 94 |

# Chapter 4: FDTD Model for Crosstalk Analysis of Multiwall

|               | 5.4.2 Crosstalk Induced Delay                                                 | 96  |

|---------------|-------------------------------------------------------------------------------|-----|

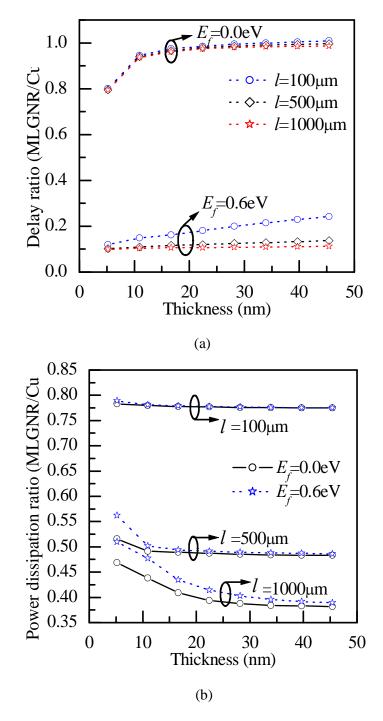

|               | 5.4.3 Performance Comparison between Cu and MLGNR Interconnects               | 98  |

| 5.5           | Summary                                                                       | 100 |

| Chapter 6:    | An Efficient US-FDTD Model for Crosstalk<br>Analysis of On-chip Interconnects |     |

| 6.1           | Introduction                                                                  | 101 |

| 6.2           | Development of Proposed US-FDTD Model                                         | 102 |

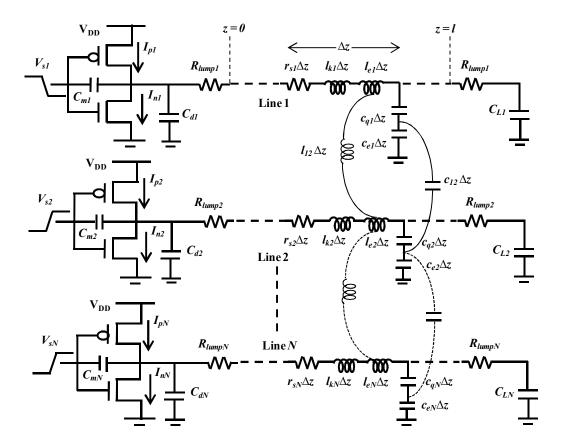

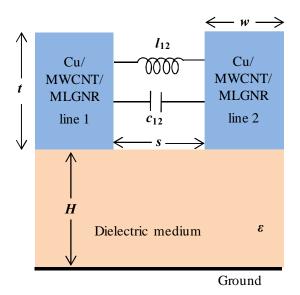

|               | 6.2.1 Modeling of Coupled On-chip Interconnects                               | 103 |

|               | 6.2.2 Modeling of CMOS Driver                                                 | 105 |

|               | 6.2.3 Modeling of Driver-Interconnect-Load                                    | 106 |

|               | 6.2.4 Stability Analysis                                                      | 110 |

| 6.3           | Simulation Setup and Results                                                  | 111 |

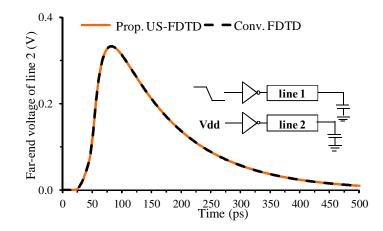

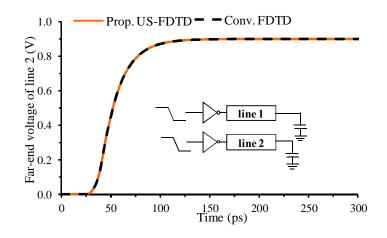

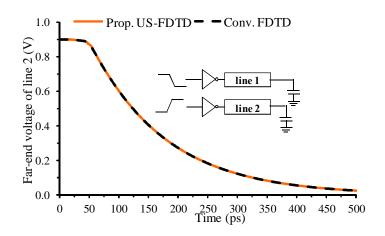

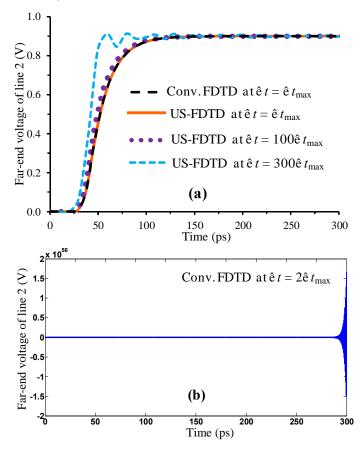

|               | 6.3.1 Transient Analysis                                                      | 112 |

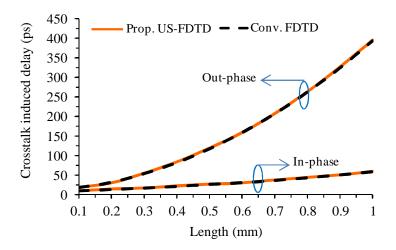

|               | 6.3.2 Crosstalk Induced Noise Peak, Width and Delay<br>Analysis               | 112 |

|               | 6.3.3 Unconditional Stability of the Proposed Model                           | 115 |

|               | 6.3.4 Efficiency of the Proposed Model                                        | 116 |

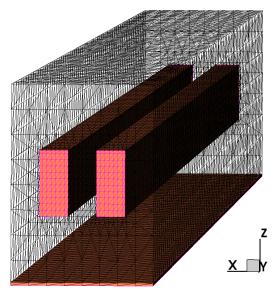

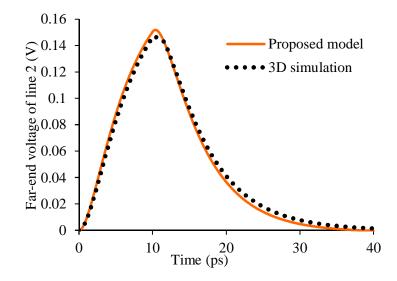

|               | 6.3.5 Comparison with 3D Simulations                                          | 116 |

| 6.4           | Performance Comparison of Cu, MWCNT and MLGNR<br>Interconnects                | 118 |

| 6.5           | Summary                                                                       | 119 |

| Chapter 7:    | <b>Conclusions and Future Scope</b>                                           |     |

| 7.1           | Conclusions                                                                   | 121 |

| 7.2           | Future Work                                                                   | 123 |

| References    |                                                                               | 125 |

| List of Publi | cations                                                                       | 139 |

# **LIST OF FIGURES**

| Figure<br>No. | Caption                                                                                                                                                                                                                                               | Page<br>No. |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

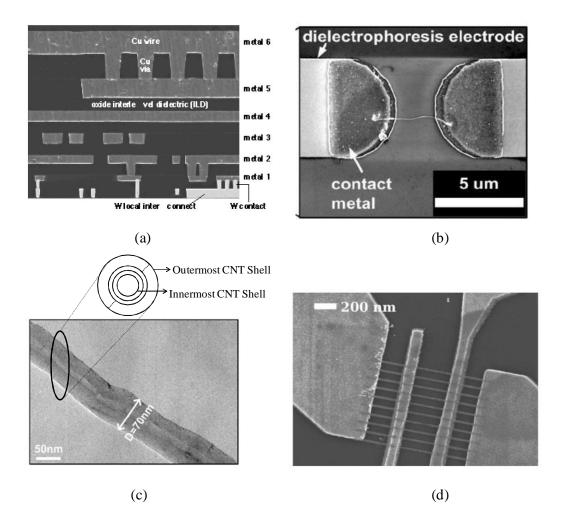

| Figure 1.1    | (a) Cross-sectional view of Cu interconnect architecture with 6 levels, (b) fabricated structure of an MWCNT between two metal contacts, (c) close-up view of MWCNT, consisting of 80 shells (d) fabricated structure of MLGNR, consists of 10 layers | 5           |

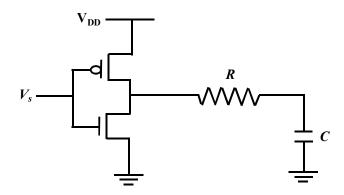

| Figure 2.1    | A CMOS gate driven RC load                                                                                                                                                                                                                            | 12          |

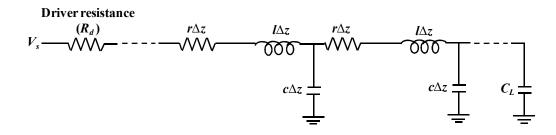

| Figure 2.2    | A distributed <i>RLC</i> interconnect line driven by a resistive driver                                                                                                                                                                               | 13          |

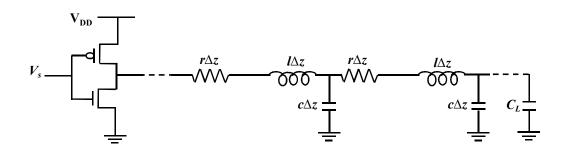

| Figure 2.3    | A CMOS gate driven distributed RLC interconnect line                                                                                                                                                                                                  | 14          |

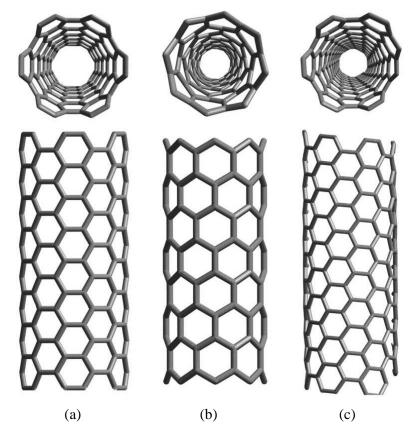

| Figure 2.4    | Sketches of three different SWCNT structures (a) armchair nanotube, (b) zigzag nanotube and (c) chiral nanotube                                                                                                                                       | 15          |

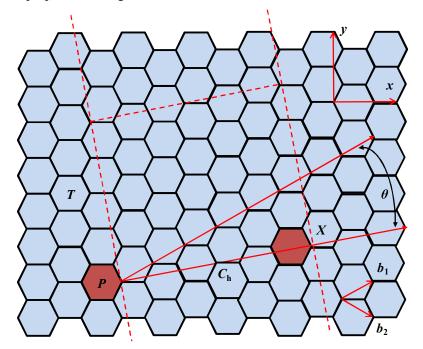

| Figure 2.5    | Sketch representing the procedure to obtain an CNT, starting from a graphene sheet                                                                                                                                                                    | 17          |

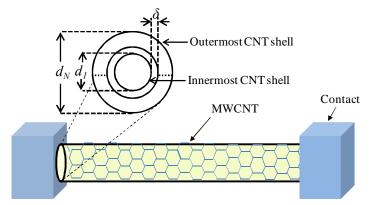

| Figure 2.6    | The structure of MWCNT placed between the two contacts                                                                                                                                                                                                | 18          |

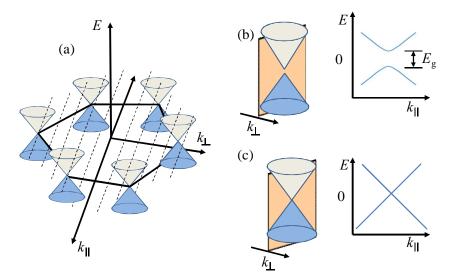

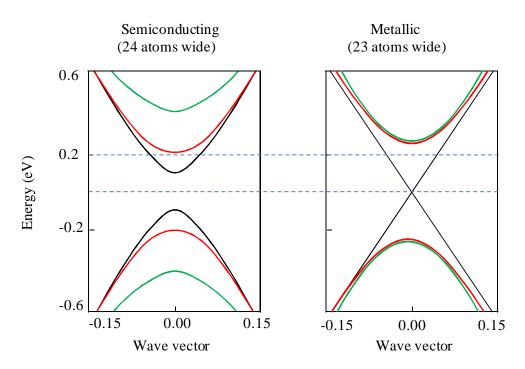

| Figure 2.7    | Band structures of CNT shell                                                                                                                                                                                                                          | 19          |

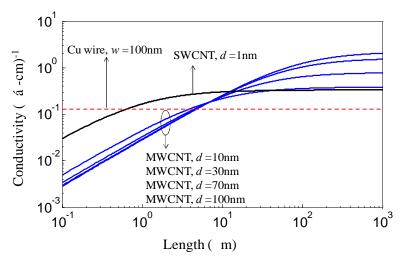

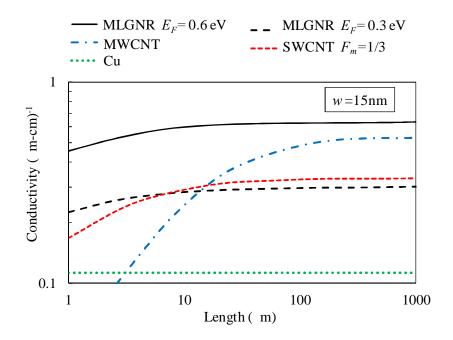

| Figure 2.8    | The conductivity comparison among Cu, SWCNT and MWCNT                                                                                                                                                                                                 | 24          |

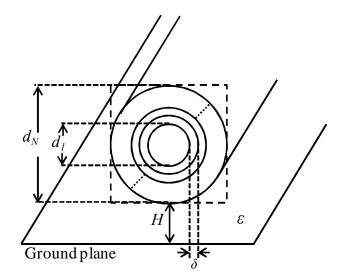

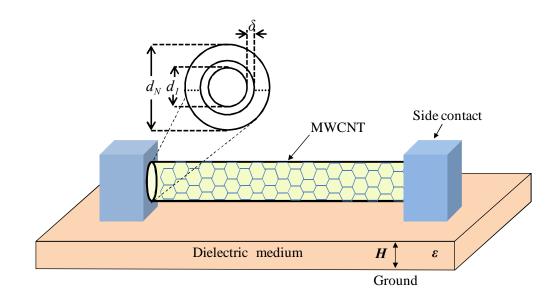

| Figure 2.9    | Geometry of an MWCNT with $N$ shells above a ground plane                                                                                                                                                                                             | 26          |

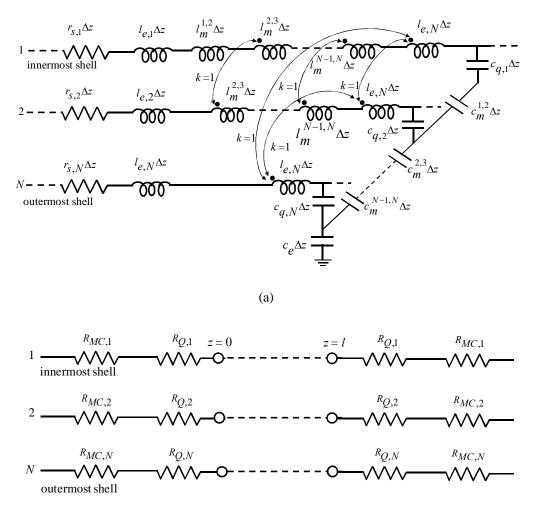

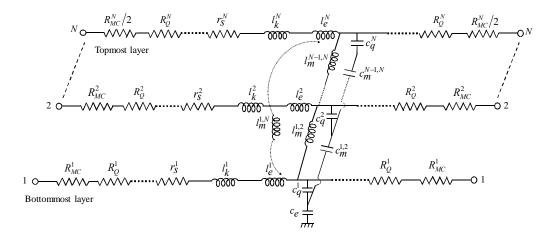

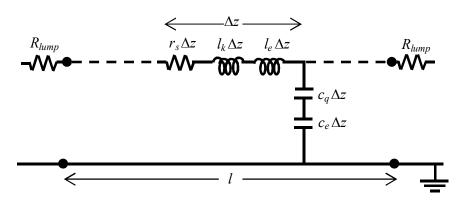

| Figure 2.10   | Multiconductor transmission line model of MWCNT (a) section of infinitesimal length $\hat{e}z$ , where $k = 1$ represents perfect magnetic coupling (b) nanotube of length <i>l</i> including terminal resistance                                     | 27          |

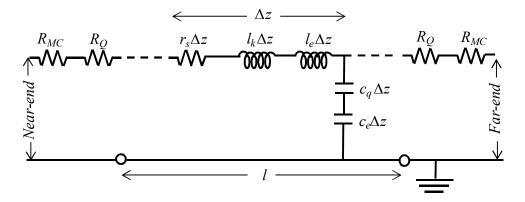

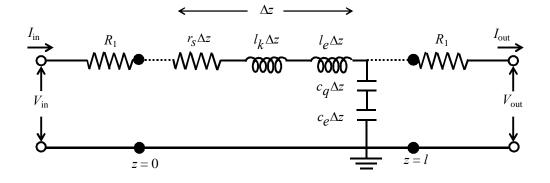

| Figure 2.11   | Equivalent single conductor model of MWCNT                                                                                                                                                                                                            | 28          |

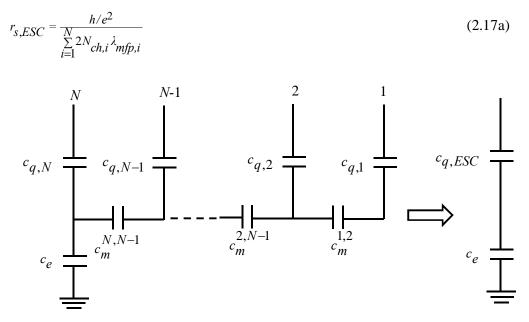

| Figure 2.12   | Per unit length capacitance network of the MWCNT                                                                                                                                                                                                      | 29          |

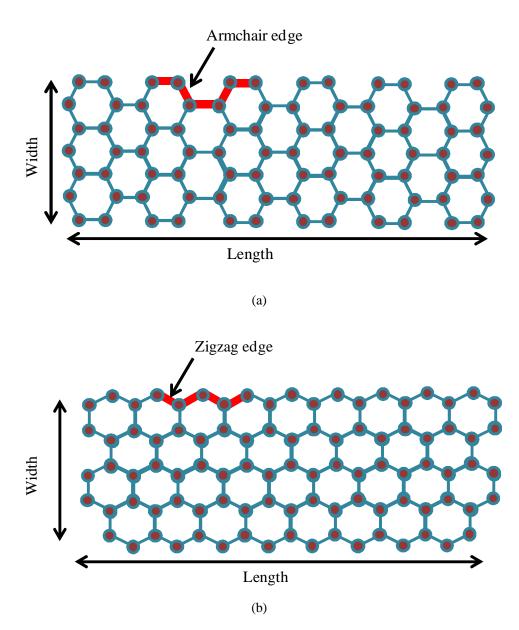

| Figure 2.13   | Structure of GNR (a) armchair and (b) zigzag                                                                                                                                                                                                          | 32          |

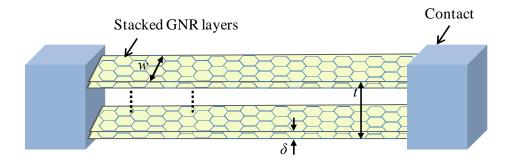

| Figure 2.14   | The geometric structure of an MLGNR interconnect                                                                                                                                                                                                      | 32          |

| Figure 2.15   | Band structures of (a) semiconducting and (b) metallic armchair GNRs whose widths are 6.02 nm (24 atoms wide) and 5.78 nm (23 atoms wide), respectively [103]                                                                                         | 34          |

| Figure 2.16   | Conductivity comparison among Cu, SWCNT bundle, MWCNT and MLGNR interconnects                                                                                                                                                                         | 36          |

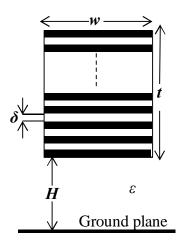

| Figure 2.17 | Geometry of MLGNR above ground plane                                                                                                | 37 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.18 | Equivalent RLC model of MLGNR interconnect                                                                                          | 37 |

| Figure 2.19 | Equivalent single conductor (ESC) model of MLGNR interconnect                                                                       | 39 |

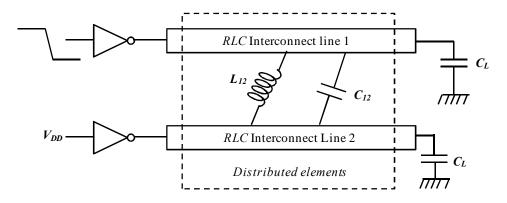

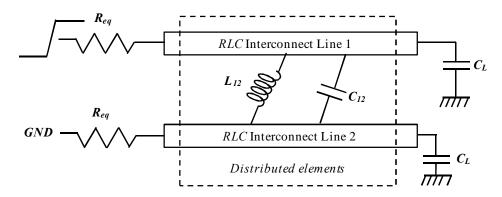

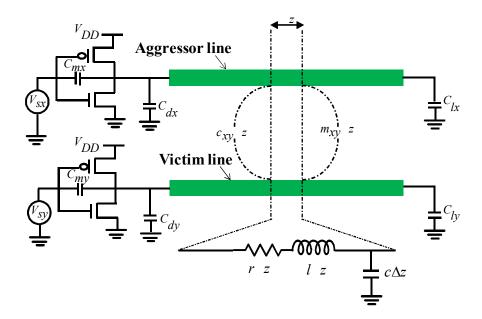

| Figure 3.1  | Coupled-two interconnects driven by CMOS inverter                                                                                   | 47 |

| Figure 3.2  | Coupled-two interconnects driven by resistive driver                                                                                | 48 |

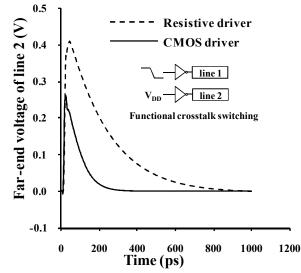

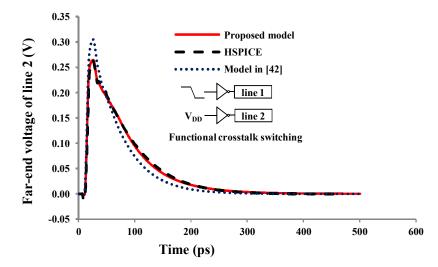

| Figure 3.3  | Transient response comparison during the functional crosstalk                                                                       | 48 |

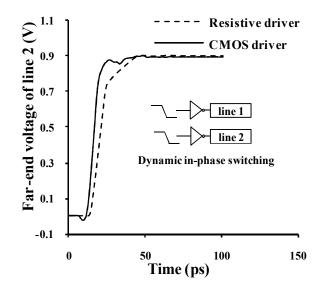

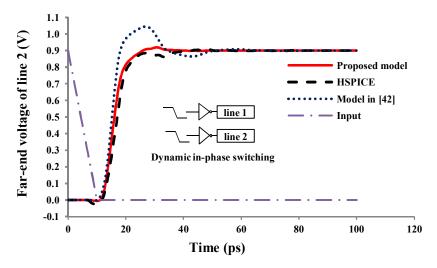

| Figure 3.4  | Transient response comparison during the dynamic in-phase crosstalk                                                                 | 49 |

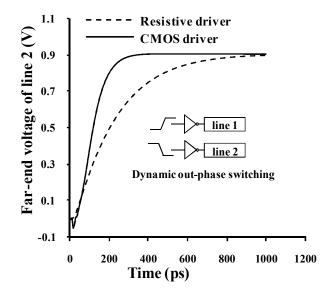

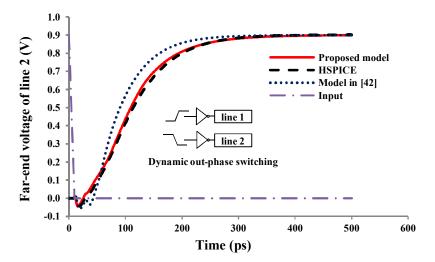

| Figure 3.5  | Transient response comparison during the dynamic out-phase crosstalk switching                                                      | 49 |

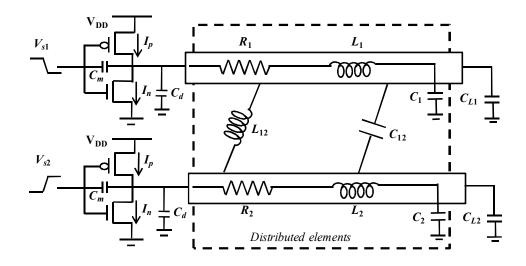

| Figure 3.6  | Coupled-two interconnect lines driven by CMOS inverter                                                                              | 50 |

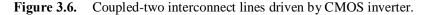

| Figure 3.7  | The relation between spatial and time discretization to achieve second order accuracy                                               | 51 |

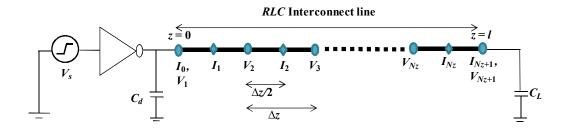

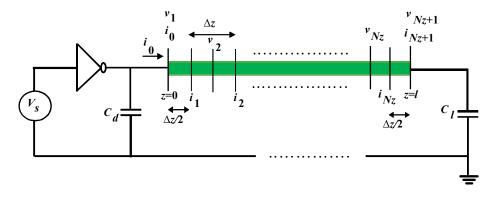

| Figure 3.8  | Illustration of space discretization of line for FDTD implementation                                                                | 52 |

| Figure 3.9  | Transient response of quiescent line 2 during the functional crosstalk switching                                                    | 57 |

| Figure 3.10 | Transient response of line 2 during the dynamic in-phase crosstalk switching                                                        | 57 |

| Figure 3.11 | Transient response of line 2 during the dynamic out-phase crosstalk switching                                                       | 57 |

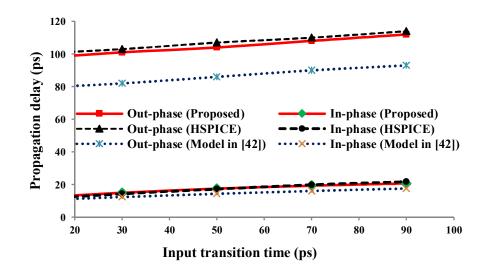

| Figure 3.12 | Variation of propagation delay with respect to transition time                                                                      | 59 |

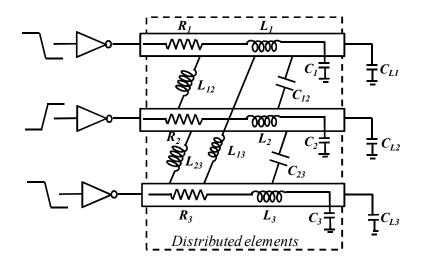

| Figure 3.13 | Coupled-three interconnect lines driven by CMOS inverter                                                                            | 61 |

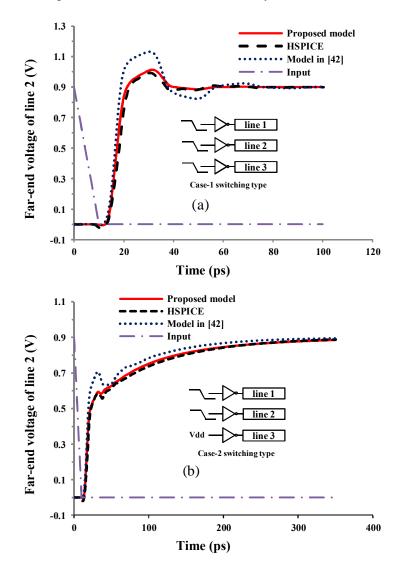

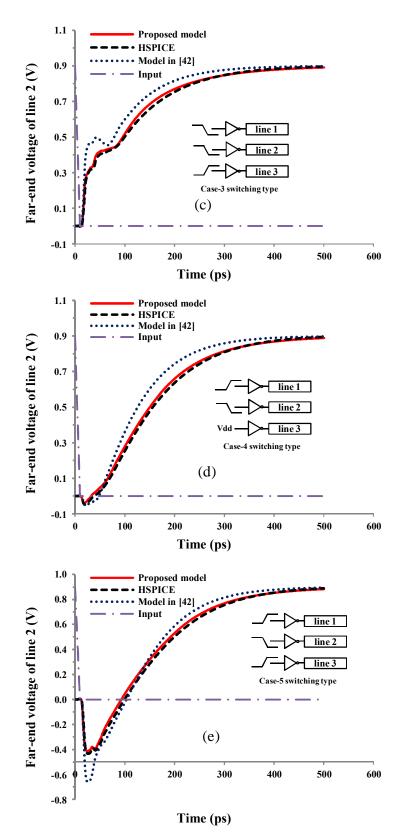

| Figure 3.14 | Transient response comparison on victim line 2 (a) case-1, (b) case-2, (c) case-3, (d) case-4, and (e) case-5 input switching modes | 62 |

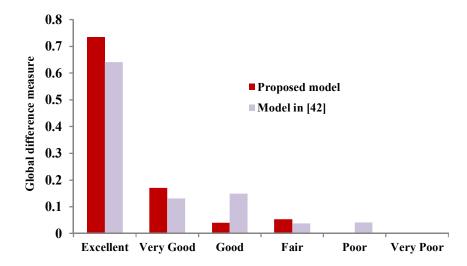

| Figure 3.15 | Histogram form the datasets of Figure 3.14(a) using FSV tool                                                                        | 63 |

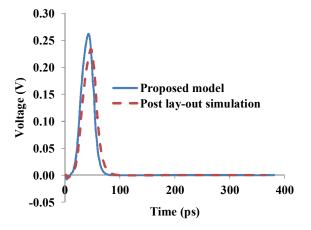

| Figure 3.16 | Transient response comparison between proposed model and post lay-out simulations.                                                  | 64 |

| Figure 4.1  | Geometry of an MWCNT interconnect above the ground plane                                                                            | 68 |

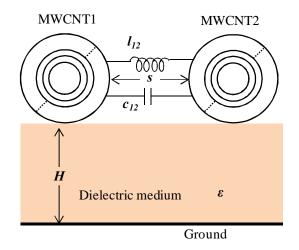

| Figure 4.2  | Cross-sectional view and coupling parasitics between MWCNTs                                                                         | 68 |

| Figure 4.3  | Electrical equivalent model of an MWCNT interconnect                                                                                                                                                   | 68 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.4  | A single CNT shell above a ground plane                                                                                                                                                                | 70 |

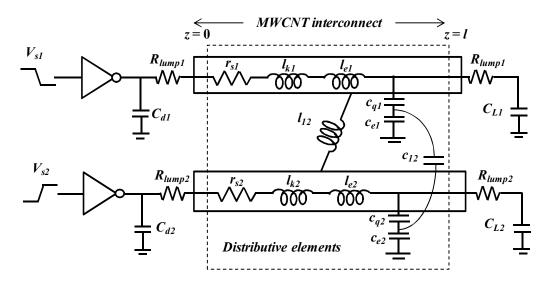

| Figure 4.5  | Coupled MWCNT interconnect lines                                                                                                                                                                       | 73 |

| Figure 4.6  | Illustration of space discretization of line for FDTD implementation                                                                                                                                   | 74 |

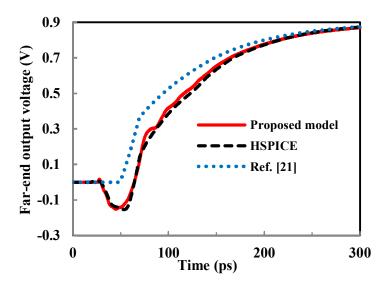

| Figure 4.7  | Transient response at the far-end terminal of the victim line when<br>the aggressor and victim lines are switched out-of-phase                                                                         | 77 |

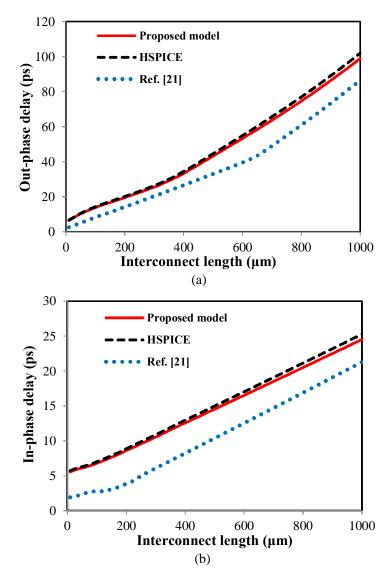

| Figure 4.8  | Crosstalk induced delay comparison (a) out-phase delay and (b) in-phase phase delay with the variation of interconnect length                                                                          | 78 |

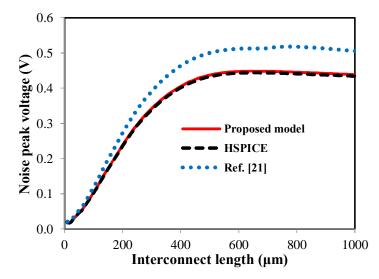

| Figure 4.9  | Noise peak voltage comparison of victim line 2 with the variation of interconnect length                                                                                                               | 79 |

| Figure 4.10 | Crosstalk induced delay comparison on victim line 2 with the variation of input transition time                                                                                                        | 79 |

| Figure 4.11 | Propagation delay with different interconnect lengths for process<br>induced variations on (a) device threshold and (b) interconnect<br>thickness                                                      | 83 |

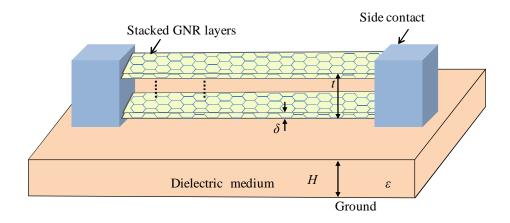

| Figure 5.1  | The geometric structure of MLGNR                                                                                                                                                                       | 88 |

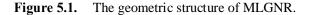

| Figure 5.2  | Equivalent single conductor model of an MLGNR interconnect                                                                                                                                             | 88 |

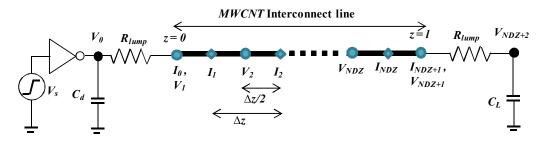

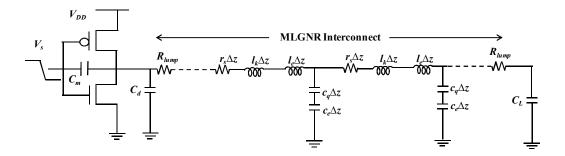

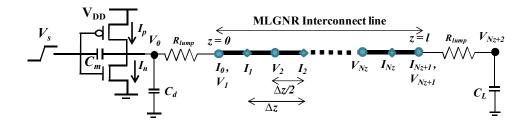

| Figure 5.3  | Driver-interconnect-load (DIL) structure, wherein $R_{lump}$ is placed<br>at near-end and far-end terminals of the interconnect line due to<br>the effect of quantum and imperfect contact resistances | 90 |

| Figure 5.4  | Transient waveforms of the output voltages of MLGNR ( $N_{layer} = 20$ ) interconnect                                                                                                                  | 90 |

| Figure 5.5  | Illustration of space discretization of line for FDTD implementation                                                                                                                                   | 91 |

| Figure 5.6  | Coupled MWCNT interconnect lines driven by CMOS inverter                                                                                                                                               | 91 |

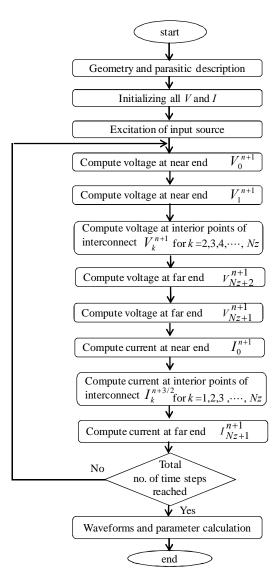

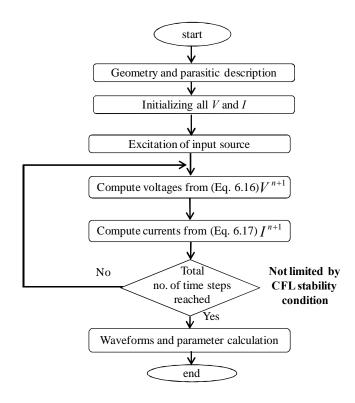

| Figure 5.7  | Flowchart for evaluation of voltage and current using the proposed FDTD technique                                                                                                                      | 93 |

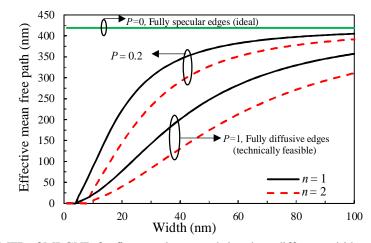

| Figure 5.8  | MFP of MLGNR for first two lowest sub-bands at different widths                                                                                                                                        | 95 |

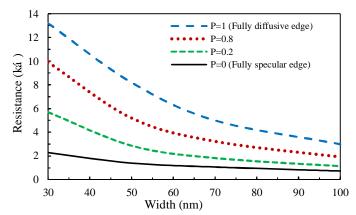

| Figure 5.9  | Resistance of MLGNR for different interconnect widths                                                                                                                                                  | 95 |

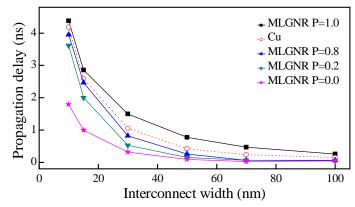

| Figure 5.10 | Propagation delay of MLGNR and Cu at $t = 56.9$ nm and $l = 100$ m                                                                                                                                     | 95 |

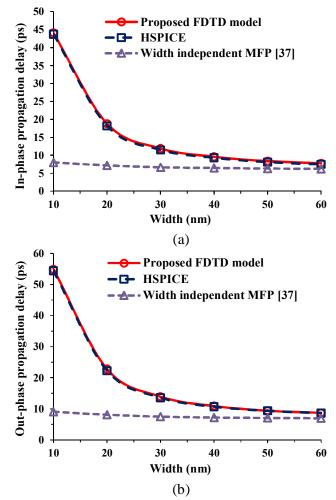

| Figure 5.11 | Crosstalk-induced propagation delay performance with change in interconnect width under (a) in-phase switching, and (b) out-phase switching                                                                | 96  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

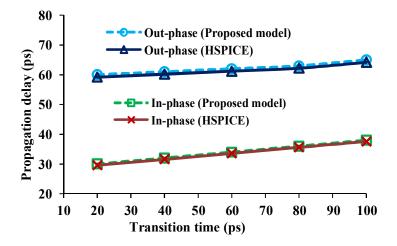

| Figure 5.12 | Variation of propagation delay with respect to input transition time                                                                                                                                       | 97  |

| Figure 5.13 | MLGNR to Cu (a) delay and (b) power dissipation ratio at different interconnect thicknesses                                                                                                                | 99  |

| Figure 6.1  | Schematic view of coupled interconnects driven by CMOS drivers                                                                                                                                             | 103 |

| Figure 6.2  | Representation of space discretization of an interconnect line for<br>unconditionally stable FDTD technique                                                                                                | 104 |

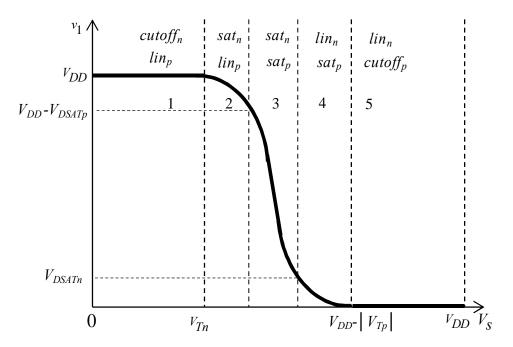

| Figure 6.3  | The five regions of operation of a CMOS inverter                                                                                                                                                           | 105 |

| Figure 6.4  | Flowchart for evaluation of voltage and current using the proposed US-FDTD technique                                                                                                                       | 109 |

| Figure 6.5  | Comparison of spectral radius of amplification matrix between proposed US-FDTD and conventional FDTD model.                                                                                                | 111 |

| Figure 6.6  | Transient response comparison during the functional crosstalk                                                                                                                                              | 113 |

| Figure 6.7  | Transient response comparison during the dynamic in-phase crosstalk                                                                                                                                        | 113 |

| Figure 6.8  | Transient response comparison during the dynamic out-phase crosstalk                                                                                                                                       | 113 |

| Figure 6.9  | Comparison of crosstalk induced propagation delay between proposed US-FDTD model and conventional FDTD model                                                                                               | 114 |

| Figure 6.10 | Dynamic in-phase crosstalk analysis at different time steps (a) stable output of conventional FDTD and proposed US-FDTD and (b) unstable output of conventional FDTD due to the violation of CFL condition | 115 |

| Figure 6.11 | Structure of two coupled interconnects                                                                                                                                                                     | 117 |

| Figure 6.12 | Transient response comparison between the proposed US-FDTD model and 3D simulations at the far-end terminal of line 2 during the functional crosstalk switching                                            | 117 |

| Figure 6.13 | Structure of two coupled interconnects                                                                                                                                                                     | 118 |

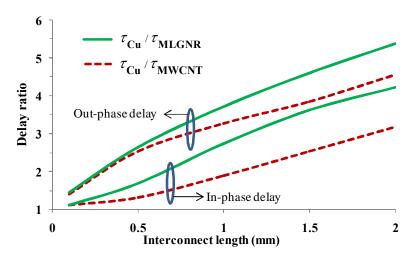

| Figure 6.14 | Performance delay comparison among Cu, MWCNT and MLGNR interconnects                                                                                                                                       | 118 |

### LIST OF TABLES

| Table<br>No. | Title                                                                                                               | Page<br>No. |

|--------------|---------------------------------------------------------------------------------------------------------------------|-------------|

| Table 3.1    | Interconnect parasitics                                                                                             | 48          |

| Table 3.2    | Model parameters for 32 nm node                                                                                     | 54          |

| Table 3.3    | Computational error involved in peak noise voltage                                                                  | 58          |

| Table 3.4    | Computational error involved in peak voltage timing                                                                 | 58          |

| Table 3.5    | Computational error involved for propagation delay on victim line2                                                  | 63          |

| Table 4.1    | CPU runtime comparison between proposed model and HSPICE with 1000 time segments                                    | 80          |

| Table 4.2    | Variation between (4.2a) and (4.2b) on parasitics and crosstalk induced performance parameters                      | 81          |

| Table 4.3    | Variation of performance parameters due to change in $R_{MC}$                                                       | 81          |

| Table 5.1    | Fitting parameters $(a_0-a_6)$ for calculating the $N_{ch}$ of $E_F > 0$                                            | 87          |

| Table 5.2    | Fitting parameters ( $b_0$ - $b_3$ ) for calculating the $N_{ch}$ of $E_F = 0$                                      | 87          |

| Table 5.3    | Percentage reduction in propagation delay and power dissipation<br>for doped MLGNR with respect to Cu interconnects | 100         |

| Table 6.1    | Model parameters for 32 nm node                                                                                     | 106         |

| Table 6.2    | $E_1$ and $E_2$ for different regions of operation                                                                  | 108         |

| Table 6.3    | Noise peak voltage and noise width comparison between proposed US-FDTD and conventional FDTD simulations            | 114         |

| Table 6.4    | Comparison of computational efforts                                                                                 | 116         |

# LIST OF SYMBOLS

| Capacitance                                                                                  |

|----------------------------------------------------------------------------------------------|

| Driver capacitance                                                                           |

| Load capacitance                                                                             |

| Coupling capacitance between the interconnects                                               |

| Electrostatic capacitance                                                                    |

| Quantum capacitance                                                                          |

| Innermost shell diameter of MWCNT                                                            |

| Diameter of $i^{th}$ shell in MWCNT                                                          |

| Outermost shell diameter of MWCNT                                                            |

| Fermi energy level                                                                           |

| Energy gap                                                                                   |

| The lowest (or highest) energy level of the $i^{\text{th}}$ -conduction (or valence) subband |

| Energy gap between the subbands                                                              |

| Electron charge                                                                              |

| Metallic to semiconducting ratio                                                             |

| Distance between the interconnect and the ground plane                                       |

| Planckøs constant                                                                            |

| Drain saturation current                                                                     |

| Boltzmann constant                                                                           |

|                                                                                              |

| NMOS current                                                                                 |

| NMOS current PMOS current                                                                    |

|                                                                                              |

| PMOS current                                                                                 |

| PMOS current<br>Inductance                                                                   |

| PMOS current<br>Inductance<br>Magnetic inductance                                            |

|                                                                                              |

| N <sub>ch,i</sub>     | Number of conducting channels of $i^{th}$ shell/layer |

|-----------------------|-------------------------------------------------------|

| $N_C$                 | Number of carbon atoms across the GNR width           |

| Р                     | Backscattering probability                            |

| R                     | Resistance                                            |

| $R_{eq}$              | Driver resistance                                     |

| R <sub>lump</sub>     | Lumped resistance                                     |

| $R_{MC}$              | Contact resistance                                    |

| $R_Q$                 | Quantum resistance                                    |

| <i>r</i> <sub>s</sub> | Scattering resistance                                 |

| Т                     | Temperature                                           |

| t                     | Interconnect thickness                                |

| $V_{DD}$              | Supply voltage                                        |

| V <sub>DSAT</sub>     | Drain saturation voltage                              |

| $V_S$                 | Input voltage                                         |

| $\mathcal{V}_F$       | Fermi velocity                                        |

| W                     | Interconnect width                                    |

| τ                     | Time delay                                            |

| σ                     | Drain conductance parameter                           |

| $\delta$              | Inter-shell/inter-layer distance                      |

| $\lambda_{mfp}$       | Mean free path                                        |

| $\lambda_d$           | Mean free path due to defects                         |

| $\lambda_n$           | Mean free path due to edge roughness                  |

| $\lambda_{eff}$       | Effective mean free path                              |

| heta                  | Chirality angle                                       |

| З                     | Permittivity                                          |

| μ                     | Permeability                                          |

| $\Delta t$            | Time step size                                        |

| $\Delta z$            | Space step size                                       |

# LIST OF ABBREVIATIONS

| ac     | Armchair                                                    |

|--------|-------------------------------------------------------------|

| ADI    | Alternating Direction Implicit                              |

| CFL    | Courant-Friedrichs-Lewy                                     |

| CMOS   | Complementary Metal Oxide Semiconductor                     |

| CN     | Crank-Nicolson                                              |

| CNT    | Carbon Nano Tube                                            |

| DIL    | Driver Interconnect Load                                    |

| ESC    | Equivalent Single Conductor                                 |

| FDTD   | Finite-Difference Time-Domain                               |

| FET    | Field Effect Transistor                                     |

| FSV    | Feature Selective Validation                                |

| GDM    | Global Difference Measure                                   |

| GNR    | Graphene Nano Ribbon                                        |

| HSPICE | Hewlett Simulation Program with Integrated Circuit Emphasis |

| IC     | Integrated Circuit                                          |

| ITRS   | International Technology Roadmap for Semiconductors         |

| LER    | Line Edge Roughness                                         |

| MFP    | Mean Free Path                                              |

| MLGNR  | Multi Layer Graphene Nano Ribbon                            |

| MNA    | Modified Nodal Analysis                                     |

| MOS    | Metal Oxide Semiconductor                                   |

| MTL    | Multi-conductor Transmission Line                           |

| MWCNT  | Multi Walled Carbon Nano Tube                               |

| p.u.l. | Per Unit Length                                             |

| RC      | Resistance Capacitance                        |

|---------|-----------------------------------------------|

| RLC     | Resistance Inductance Capacitance             |

| RLCG    | Resistance Inductance Capacitance Conductance |

| SLGNR   | Single Layer Graphene Nano Ribbon             |

| SWCNT   | Single Walled Carbon Nano Tube                |

| TB      | Tight Binding                                 |

| TEM     | Transverse Electro-Magnetic                   |

| US-FDTD | Unconditionally Stable FDTD                   |

| VLSI    | Very Large Scale Integration                  |

| ZZ      | Zigzag                                        |

| 1D      | One Dimensional                               |

| 2D      | Two Dimensional                               |

| 3D      | Three Dimensional                             |

# **Chapter 1**

### Introduction

### **1.1 Introduction**

Advancement of technology in the nanometer regime considers high speed and high density very large scale integration (VLSI) circuits. It is desirable to use multilayer interconnections in three or more levels to achieve higher packing densities and smaller footprint [1, 2]. Based on the length and cross-sectional dimensions, the on-chip interconnects can be broadly characterized into three categories: local, intermediate and global interconnects. Local interconnects consist of very thin lines, used to connect gates and transistors in a functional block. Intermediate interconnects are wider and longer than local interconnects, provide low resistance signal paths in a functional block. The global interconnects provide long distance communication between the functional blocks and have a large cross-sectional area to minimize the resistance [3]. The global interconnects are placed at the higher level of the chip and can be as long as 1-2 cm in current high-performance integrated circuits [1].

In early days, the operating speed of an integrated circuit was limited by the speed of a logic gate. Interconnects between the gates were considered as ideal conductors, where the signal propagates instantaneously. Therefore, the interconnects had little effect on circuit operation. However, after the introduction of submicron semiconductor devices, the ideal behavior of interconnects no longer remains adequate. In fact, the performance of the chip is primarily determined by the interconnect line rather than the device [4].

At high operating frequencies, the closely packed interconnects produce transient crosstalk [5-7]. The undesired effect created on one line due to a signal transmitted on another line is defined as crosstalk. The crosstalk noise strongly influences the signal propagation delay and causes the circuit malfunction or functional failure. Based on the switching transitions in the coupled lines, crosstalk can be broadly classified into functional and dynamic crosstalks. When the victim line is quiescent, a voltage spike appearing on it due to switching in an adjacent line is referred as the functional crosstalk. Dynamic crosstalk appears when the adjacent lines are simultaneously switching either in-phase or out-phase. A change in logic value and propagation delay can be experienced under functional and dynamic crosstalks, respectively. Moreover, the crosstalk noise causes signal overshoot, undershoot and ringing effects. Therefore, accurate estimation of performance parameters, under the effect of crosstalk, gained importance for the design of high performance on-chip interconnects.

#### **1.2 Evolution of Interconnect Materials**

Aluminium had been used for a long time to form interconnect lines because of its compatibility with silicon. However, as device dimensions scale down the reliability decreases due to increasing current density that may lead to electromigration induced problems [2]. In 1997, IBM announced plans to replace aluminium with copper, a metal with lower resistivity than aluminum [2]. Copper provides high current density  $(10^7 \text{ A/cm}^2)$  leading to the electromigration effect being less significant [8]. Later on, it was realized that even Cu was not able to fulŁll the demands of high-speed interconnects due to the following reasons:

- i) The reliability decreases with down scaling of interconnect dimensions due to increase in current density.

- ii) The resistivity increases at lower dimensions, due to grain-boundary scattering and surface scattering.

- iii) The resistivity increases rapidly due to Joule heating.

- iv) The conductivity reduces at high operating frequencies, due to the skin effect.

Therefore, the copper interconnect material is unable to meet the requirements of future technology needs. The widening gap between the requirements of future onchip interconnect material and the presently used copper material has compelled researchers and designers to look out for novel material solutions. Graphene based nano interconnects have been proposed as a promising solution for the future on-chip interconnects [9-15]. Encouragingly, graphene nano interconnects demonstrate longer mean free paths in the order of several micrometers, higher current densities in excess of 10<sup>9</sup> A/cm<sup>2</sup>, and higher thermal stability than copper. These properties create lots of interest among researchers to use these materials as VLSI interconnects [16, 17]. Graphene nano interconnects can be classified into carbon nanotubes (CNTs) and graphene nanoribbons (GNRs).

#### **1.2.1 Carbon Nanotubes (CNTs)**

Carbon nanotubes are single layer of graphene sheets rolled up into cylinders with diameters ranging from 1 nm to 5 nm. The electron transport in metallic CNTs is ballistic that results in movement of electrons without scattering along the nanotube axis and enables a long mean free path in the range of micrometers [18-22]. Contrastingly, the mean free path of electrons in Cu is limited to a few nanometers. Due to the large mean free path and small diameter, the electrons do not scatter as often in CNTs that results in low resistance. This low resistance ensures that the energy dissipated in CNTs is incredibly small. Thus, the problem of dissipated power density can be properly addressed. Moreover, the 1D structure of CNT offers many electrical properties, such as

- i) High quality CNTs have long mean free path (MFP) ranging from 1-5  $\mu$ m that results in ballistic transport phenomenon.

- ii) The strong sigma bonds are useful for high mechanical strength and pi bonds are useful for high conductivity.

- iii) Higher electron mobility (~  $10^5 \text{ cm}^2/(\text{V}\cdot\text{s})$ ) in comparison to Cu (~  $10^3 \text{ cm}^2/(\text{V}\cdot\text{s})$ ) that results in high drift velocity.

- iv) Larger current densities  $(10^9 \text{ A/cm}^2)$  in comparison to Cu  $(10^7 \text{ A/cm}^2)$  that results in lower electromigration effect.

Depending on the number of concentrically rolled up graphene sheets, CNTs are categorized as single-walled CNTs (SWCNTs) and multi-walled CNTs (MWCNTs) [23, 24]. SWCNT is a single-layer sheet of graphite rolled up into a cylinder. The primary drawback of SWCNT bundle is the non-controllability of its chirality. The metallic and semiconducting properties of CNTs are primarily dependent on their chirality. Statistically, one-third of the CNTs in a bundle are considered to be conducting (*i.e.*, metallic) while the remaining behaves as semiconductors. Morris [25] observed that the SWCNTs with random chiralities do not show any advantage over the conventional interconnect materials. This problem can

be rectified by using MWCNTs that consist of multiple layers of graphene sheets arranged in co-axial configuration with the diameters ranging from 2 nm to several tens of nanometers. Due to the large diameters, the MWCNT shells are conductive even if they are of semiconducting chirality because the energy gap is inversely proportional to the shell diameter. For a semiconducting CNT having a diameter greater than 20 nm, the gap between the conduction band and the Fermi level is observed to be smaller than 0.0258 eV, which can be smeared by the environmental temperature [26].

#### **1.2.2 Graphene Nanoribbons (GNRs)**

Graphene nanoribbon, a strip of ultra-thin width graphene layer, has also been considered aggressively by the researchers as a potential alternative material for realizing on-chip interconnects [27, 28]. Most of the physical and electrical properties of GNRs are similar to that of CNTs, however, the major advantage of GNRs over CNTs is that both transistors and interconnects can be fabricated on the same graphene layer [29]. Therefore, one of the manufacturing difficulties regarding the formation of metal-nanotube contact can be avoided. Depending on the number of stacked graphene sheets, GNRs are classified as single-layer GNRs (SLGNRs) and multi-layer GNRs (MLGNRs). Due to the lower resistivity and easy fabrication process, the MLGNRs are often preferred over SLGNRs as interconnect material. However, the MLGNRs fabricated till date have displayed some level of edge roughness [30, 31]. The electron scattering at the rough edges, reduces the mean free path (MFP) that substantially lowers the conductance of the MLGNRs. This fundamental challenge limits the performance of MLGNR interconnects. The SEM images of Cu, MWCNT and MLGNR interconnects are shown in Figure 1.1. Figure 1.1 (a) shows the Cu interconnect structure with different interconnect levels. The MWCNT structure with 80-CNT shells is shown in Figure 1.1 (b) and the close-up view is shown in Figure 1.1 (c). The MLGNR interconnect structure with 10-GNR layers is shown in Figure 1.1 (d).

**Figure 1.1.** (a) Cross-sectional view of Cu interconnect architecture with 6 levels [6], (b) fabricated structure of an MWCNT between two metal contacts, (c) close-up view of MWCNT, consisting of 80 shells [19] and (d) fabricated structure of MLGNR, consists of 10 layers [27].

### **1.3 Modeling of On-chip Interconnects**

Historically, interconnects were modeled as a lumped capacitor [1]. With the advancement of technology, the cross-sectional area of interconnects were scaled down, due to which the line resistance became significant and therefore, the interconnect line was represented as lumped resistance-capacitance (RC) [32]. However, later these interconnect parasitic elements were not treated as lumped elements. To improve the accuracy, a distributed RC model was considered [33]. Currently, the parasitic inductance has started to play an important role in an on-chip interconnect performance due to the adoption of low resistive interconnect materials, and high operating switching frequencies. Therefore, the on-chip interconnects must

be treated as distributed *RLC* lines or as transmission lines to estimate the performance accurately [34]. Agarwal *et al.* [4] proposed a model considering the transmission line effects of coupled on-chip interconnects driven by a linear resistor. Kaushik *et al.* extended this model to a non-linear complementary metal-oxide semiconductor (CMOS) driver using alpha-power law model and analyzed functional crosstalk effects in [35] and dynamic crosstalk effects in [36]. The models reported in [4], [35] and [36] are based on even-odd modes and hence limited to purely two coupled interconnect lines. Furthermore, the transient analysis was carried out for lossless lines, which is impractical.

The modeling of distributed *RLC* lines along with non-linear CMOS driver suffers from frequency/time domain conversion problem. This problem arises because the transmission lines were traditionally solved in the frequency domain by using the partial differential equations, whereas the CMOS driver is modeled in the time domain. Therefore, to avoid this conversion problem, most of the researchers [4, 5], [37] replace the non-linear CMOS driver by the linear resistive driver that severely affects the accuracy of the model. In the present research work, to avoid the conversion problem, finite-difference time-domain (FDTD) technique is used to solve the transmission line equations in the time domain. Using the FDTD method, the voltage and current values can be correctly estimated at any particular point on the interconnect line. Moreover, the FDTD model can be extended to n coupled interconnect lines with low computational cost.

In past, FDTD techniques were used to analyze the transmission lines, which are excited and terminated by resistive driver and resistive load, respectively [38-40]. Including the frequency dependent losses, Orlandi *et al.* [41] proposed the FDTD model for the analysis of multiconductor transmission lines terminated in arbitrary loads using the state-variable formulation. However, the models proposed in [38-40] analyses the transmission lines with resistive drivers and hence not valid for the accurate study of on-chip interconnects performance, which are actually excited and terminated by the CMOS inverters. Based on the FDTD technique, Li *et al.* [42] proposed a model for the transient analysis of CMOS gate-driven distributed *RLC* interconnects. Coupled interconnects were analyzed at global interconnect length using 180 nm technology node where the non-linear CMOS drivers were modeled by

the alpha power law model. This model is not accurate under the conditions when the technology is scaled down beyond 180 nm, due to the ignorance of the finite drain conductance parameter. Therefore, it is necessary to develop an accurate model that appropriately considers the non-linear effects of CMOS drivers and accurately measures the crosstalk induced performance parameters of on-chip interconnects. This thesis presents an accurate and time efficient model of CMOS gate driven coupled interconnects for crosstalk induced performance analysis. The model is developed using the FDTD technique for coupled on-chip interconnects, whereas the CMOS driver is modeled by either *n*-th power law or modified alpha power law model by considering the finite drain conductance parameter. The model is validated by comparing the results with HSPICE simulations.

#### **1.4 Problem Definition**

Over the years, several mathematical models have been proposed for the analysis of CMOS gate driven coupled interconnect lines [4-7], [21], [37]. However, most of these crosstalk noise models consider the non-linear CMOS driver as a linear resistor. In actual practice, this approximation is not valid, since during the signal transition states the MOSFET operates in cutoff, linear and saturation regions. The MOSFET operating time in the saturation region is about 50% during the transition period. Thus, assumption of the non-linear transistor as a linear resistor leads to severe errors in the performance estimation of on-chip interconnects. The aim of this research work is to incorporate the non-linear effects of CMOS driver in the modeling of different on-chip interconnects. The time/frequency domain conversion problem is addressed by analyzing the interconnect lines in time domain using the FDTD technique. The entire work is divided into four parts:

- i) FDTD modeling of CMOS gate driven Cu interconnects for comprehensive crosstalk analysis, including functional and dynamic crosstalk effects.

- Development of a numerical model for the crosstalk induced performance analysis of MWCNT interconnects by incorporating the quantum effects of a nanowire.

- iii) Accurate crosstalk noise modeling of MLGNR interconnects by including the width dependent MFP.

iv) Development of a novel unconditionally stable FDTD model to increase the efficiency of the conventional FDTD model.

### **1.5 Outline of the Work**

The thesis consists of seven chapters. A brief discussion of each chapter is presented below:

**Chapter 1** introduces the challenges associated with the modeling of on-chip interconnects. This chapter also introduces the evolution of graphene interconnect materials and the challenges associated with them. The motivation for taking the specific problem for the purpose of the present research work is demonstrated. Furthermore, it presents the outline of the complete thesis work.

**Chapter 2** reviews the Cu based on-chip interconnect modeling. The structures, properties and characteristics of graphene based on-chip interconnects are discussed. Depending on the physical configuration, equivalent electrical models of MWCNT and MLGNR interconnect lines are also introduced. An extensive review on performance analysis of on-chip interconnects is presented. This chapter brings forward various technical gaps based on vast literature review.

**Chapter 3** deals with the modeling of Cu based on-chip interconnects. The model considers the non-linear effects of CMOS driver as well as the transmission line effects of interconnect line. The CMOS driver is represented by the *n*-th power law model and the coupled-multiple interconnect lines are modeled by the FDTD technique. The model is validated by the industry standard HSPICE simulator. It is observed that the results of the proposed model closely matches with that of HSPICE simulations. Encouragingly, the proposed model is highly time efficient than the HSPICE.

**Chapter 4** introduces an equivalent single conductor (ESC) model of MWCNT interconnects. Based on the ESC model, this chapter presents an accurate FDTD model of MWCNT while incorporating the quantum effects of nanowire and non-linear effects of CMOS driver. To reduce the computational effort required for analyzing the CMOS driver, a simplified but accurate model is employed named as modified alpha power law model.

**Chapter 5** analyzes the performance of coupled MLGNR interconnects using the FDTD technique. In a more realistic manner, the proposed model incorporates the width dependent MFP parameter of the MLGNR while taking into account the edge roughness. This helps in accurate estimation of the crosstalk induced performance in comparison to the conventional models. The crosstalk noise is comprehensively analyzed by examining both functional and dynamic crosstalk effects.

**Chapter 6** introduces a novel unconditionally stable FDTD (US-FDTD) model for the performance analysis of on-chip interconnects. It is observed that the stability of the proposed US-FDTD model is not constrained by the CFL condition and is therefore unconditionally stable. The accuracy of the proposed model is validated against the conventional FDTD model. It is observed that the US-FDTD model is as accurate as the conventional FDTD model while being highly time efficient. Moreover, the performance of Cu interconnect is compared with MWCNT and MLGNR interconnects under the influence of crosstalk.

**Chapter 7** concludes the thesis. Conclusions are made based on the obtained results. The future scope of the work is also presented in this chapter.

The thesis ends with a complete list of references along with the list of publications based on the research work carried out.

# Chapter 2

### **Review of Cu, MWCNT and MLGNR Interconnect Models**

### 2.1 Interconnect Modeling Approaches

In the early days of VLSI design, the crosstalk induced signal integrity effects were negligible because of relatively low integration density and slow operating speed. However, with the introduction of technology scaling of below 0.25 m, there were many significant changes in the structure and electrical characteristics [43, 44]. The interconnect lines started to be a dominating factor for chip performance and robustness. The line parasitic elements have a major impact on the electrical behavior of the interconnect model. These models vary from simple to very complex depending upon the effects that are being studied and the required accuracy. There are three different types of approaches available in literature for modeling Cu based on-chip interconnects.

#### 2.1.1 Lumped Model with CMOS Driver

This approach focuses on the CMOS gate modeling while the interconnect line is approximately considered as a lumped circuit. Alpha-power law model [45] has been widely used for representation of short-channel transistor that includes the velocity saturation effects. Based on the alpha-power law model, delay formulas were developed for CMOS gate driven lumped capacitance modeled interconnect line [46, 47]. Bisdounis et al. [48] extended the model to include the influences of short-circuit current and gate-to-drain coupling capacitance. With the resistive component of interconnect becoming comparable to the gate output impedance, the line resistance Rof interconnect line needs to be considered. Considering the line resistance, the modeling of CMOS gate driven resistor-capacitor (RC) line was presented in [49-51]. The representation of CMOS gate driven lumped RC load is shown in Figure 2.1. Alder and Friedman [52] derived the delay equations for repeater insertion of a CMOS buffer design with RC interconnects. They developed a closed form expression for the timing analysis of CMOS gate driven RC load. They also derived an expression for the short-circuit power dissipation of the driver-interconnect-load system. However, all these approaches [45-52], lumped the total wire resistance of

each segment into one single R and similarly combined the global capacitance into a single capacitor C. This lumped RC model is inaccurate for long interconnect wires, which are more adequately represented by a distributed RC model. Moreover, due to high operating frequencies and wider interconnect dimensions, interconnects exhibit inductance effects and should be included in the delay and crosstalk noise models. Hence, the analytical models that considered only RC were no longer accurate [45-52].

Figure 2.1. A CMOS gate driven *RC* load.

#### 2.1.2 Distributed Model with Resistive Driver

In the distributed model with resistive driver, the driver-interconnect-load system is analyzed by simplifying the CMOS gate driver as a resistive driver [53]. Using the linear driver approximation, Elmore delay model was initially developed for *RC* lines [54] and then extended to *RLC* lines [55, 56]. The distributed *RLC* line with linear driver is shown in Figure 2.2, where  $R_d$  and  $C_L$  represent driver resistance and load capacitance, respectively; *r*, *l* and *c* represent per-unit-length line resistance, inductance and capacitance, respectively. Considering the nonlinearity of the driver, Bai *et al.* [57] improved the linear driver model by calculating the effective resistance. Davis and Meindl proposed closed-form delay expressions for the analysis of distributed *RLC* lines by considering the single transmission line effects in [58] and a crosstalk noise model of coupled transmission lines in [59].

Based on even-odd mode technique, the crosstalk noise model was developed by Agarwal *et al.* [4] for coupled-two lossless lines and then modified for low-loss lines to analyze crosstalk induced noise peak voltage. They investigated that at high operating frequencies, inductive coupling effects are significant and should be included for accurate crosstalk-noise analysis. Using the coupled transmission line theory, the authors developed a crosstalk noise model that is useful to guide noise-aware physical design optimizations. A closed form analytical transient response model was derived for resistance/capacitance loads by solving semi-finite transmission line equations [60]. However, all these models [4], [53-60] consider the non-linear CMOS driver as a linear driver that limits the accuracy of the models.

Figure 2.2. A distributed *RLC* interconnect line driven by a resistive driver.

#### 2.1.3 Distributed Model with CMOS Driver

The distributed model with CMOS driver approach co-simulates the nonlinear CMOS gate and the distributed interconnect. The CMOS gate driven distributed *RLC* interconnect line is shown in Figure 2.3. Based on the even-odd modes, Kaushik et al. proposed a simple analytical model for functional crosstalk analysis in [61] and dynamic crosstalk analysis in [36] of CMOS gate-driven two coupled interconnect lines. The model was developed based on the alpha power law model of MOS transistors and transmission line theory of interconnects. There the authors have observed that the non-linear effects of the CMOS inverter should be incorporated in a valid crosstalk noise modeling. Moreover, it was noticed that the use of resistive driver model presented a pessimistic view on the performance analysis of on-chip interconnects. However, these models [36], [61] were based on the even-odd modes and hence limited to two coupled interconnect lines. Later on, Li et al. [42] proposed an FDTD method for the transient analysis of CMOS-gate driven lossy transmission lines including frequency dependent losses and observed the effect of functional crosstalk. However, the model ignored the finite drain conductance parameter in the modeling of CMOS driver and hence not useful for nano-scaled devices.

Figure 2.3. A CMOS gate driven distributed *RLC* interconnect line.

## 2.2 Carbon Nanotubes

Until mid-1980øs, diamond and graphite were the only two known forms of carbon allotropes. In 1985, Kroto *et al.* [62] were able to synthesize new allotrope of carbon,  $C_{60}$ . They used a high pulse of laser light to vaporize a sample of graphite. The vaporized graphite was sent to a mass spectrometer with the help of helium gas. The mass spectrometer detected the presence of  $C_{60}$ , a molecule consisting of 60 carbon atoms. The  $C_{60}$  had the shape of a soccer ball with 12 pentagon faces and 20 hexagonal faces. The easy synthesis of  $C_{60}$  led the group to propose the existence of another allotrope of carbon named as õbuckyballö due to its soccer ball shaped structure. The shape of the new allotrope of carbon did not end at the soccer shaped structures and long cylindrical tube like structures were also reported, which are known as carbon nanotubes (CNTs).

CNTs have fascinated the research world due to their extraordinary physical, electrical and chemical properties. Many of the properties defy the conventional trends and scientists are still discovering the unique properties and constantly making efforts to understand and explain the phenomenon for such distinctive behavior. One of the remarkable physical properties of CNT is its ability to scale down its thickness to a single atomic layer. Another interesting physical property observed in CNTs is when two slightly different structured CNTs are joined together; the resultant junction formed can be used as an electronic device. The properties of the device formed are dependent on the type of CNTs used for their formation.

## 2.2.1 Basic Structure of CNTs

A single-walled carbon nanotube can be assumed as a structure formed when a single graphene sheet is rolled into a cylindrical shape (Figure 2.4). Depending on the shape of the circumference, CNTs can be classified as armchair (ac), zigzag (zz) or chiral CNTs as shown in Figures 2.4 (a), (b), and (c), respectively. The terms zigzag and armchair are inspired from the pattern in which the carbon atoms are arranged at the edge of the nanotube cross-section. Graphene consists of  $sp^2$ -hybridized atoms of carbon that are arranged in a hexagonal pattern. The hexagonal carbon rings should join coherently when placed in contact to adjacent carbon atoms. Accordingly, in an SWCNT tube, all the carbon atoms (except at the edges) form hexagonal rings and are therefore equally spaced from one another. Xu *et al.* [63] reported the fabrication of vertically grown CNT bundles with an average diameter of 50 m and a pitch of 110 m.

**Figure 2.4.** Sketches of three different SWCNT structures (a) armchair nanotube, (b) zigzag nanotube and (c) chiral nanotube [64].