## SIMULATION AND MODELLING OF MULTIGATE MOSFETS FOR ANALOG APPLICATIONS

Ph.D. THESIS

by ASHUTOSH NANDI

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247667 (INDIA) APRIL, 2015

## SIMULATION AND MODELLING OF MULTIGATE MOSFETS FOR ANALOG APPLICATIONS

#### A THESIS

# Submitted in partial fulfilment of the requirements for the award of the degree of

#### DOCTOR OF PHILOSOPHY

in

#### ELECTRONICS AND COMMUNICATION ENGINEERING

by ASHUTOSH NANDI

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247667 (INDIA) APRIL, 2015

©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2015 ALL RIGHTS RESERVED

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

#### **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled "SIMULATION AND MODELLING OF MULTIGATE MOSFETS FOR ANALOG APPLICATIONS" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electronics and Communication Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from July, 2010 to April, 2015 under the supervision of **Dr. S. Dasgupta**, Associate Professor and **Dr. A. K. Saxena**, Professor, Department of Electronics and Communication Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

#### (ASHUTOSH NANDI)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

(A. K. Saxena) Supervisor (S. Dasgupta) Supervisor

Date:

The Ph. D. Viva-Voce Examination of **Mr. ASHUTOSH NANDI**, Research Scholar, has been held on.....

Signature of Supervisors

Signature of External Examiner

#### ABSTRACT

Complementary metal oxide semiconductor (CMOS) integrated circuits (ICs) have seen overwhelming growth in electronic industry with gadgets for entertainment, communication, computing, signal processing and other applications. Low power consumption, reduced area, increased speed and lower production cost per chip etc., are some advantages of CMOS technology that have opened the door for integration of millions of transistors on a single chip. It is also believed that, with technology scaling, the trend of rapid improvements in performance of CMOS ICs will continue in near future. Advancement in CMOS technology in modern times has further ensured not only higher packing density but also improved performance in digital, analog and mixed signal circuit design.

However, as the number of transistors that are integrated per chip is increased, the problems of leakage currents, thermal management, reliability etc. have also been pronounced. These problems are posing great threat to circuit designer in recent years, because of increasing use of battery operated portable electronic gadgets in various spectrum of life. Starting from micro environmental sensors and radio frequency identification to personal digital assistants like laptops, cell phones, cameras etc., the demand for ultra low power consumption and prolonged battery life is increasing day by day. Therefore, single gate bulk CMOS devices scaled below 100nm gate length are practically losing its credibility with pronounced increase in short channel effects (SCEs) that degrades the battery run time in these portable devices. Multi-gate (MG) MOSFETs such as double gate (DG), triple gate (TG) and gate all around (GAA) MOSFETs etc., on the other hand, posses good properties like, near ideal subthreshold slope, improved threshold voltage roll-off and drain induced barrier lowering (DIBL).

More importantly, due to better channel control, the channel region of MG MOSFETs can be left undoped or lightly doped. This leads to enhanced carrier mobility and lower random doping fluctuation (RDF) effects that are some added advantages of MG MOSFETs.

Digital/analog circuits design with MOSFETs operating in subthreshold and weak/moderate inversion regime have gained wide interest these days due to their suitability for battery operated portable applications requiring ultra low power consumption, high gain with low/moderate frequency of operation. One of the major concerns for circuit design at this operation regime of device is its increased sensitivity to process, voltage and temperature variations. In addition, gate length scaling in nano-meter regime worsens various short channel effects (SCEs) that are posing serious threats to both digital and analog performance of the device. Considerable attention has been given for analyzing super threshold circuit behavior with progressive technology scaling, but no such attention has been given to subthreshold or weak/moderate inversion circuits, particularly using MG MOSFETs with circuit co-design techniques.

Volume inversion in MG MOSFET is one of the important properties in this regard that has to be used effectively for performance improvement. The volume inverted carriers are confined at the center of the channel rather than at Si-SiO<sub>2</sub> interface. This results in (i) Higher current due to great increase in number of minority carriers (ii) Reduction in surface scattering and interface defects (iii) Higher carrier mobility due to use of thick volume inversion as compared to narrow surface inversion and (iv) Higher transconductance. Secondly, for channel thickness between 5nm to 20nm, the volume inversion mobility of minority carriers are improved substantially at low temperature than at room temperature. These special features enhance the current drive, transconductance, subthreshold slope and speed of the device. Secondly, use of high-k gate dielectric material is beneficial in expanding design space due to possible use of thicker gate dielectric that can reduce the gate tunneling leakage while the device dimensions are scaled down in nano-meter regime. Nevertheless, fringe induced barrier lowering (FIBL) is fast becoming a major concern that can worsen SCEs, enhances off current and introduces threshold voltage roll-off because of loss of gate electrostatic control over the channel region. Third, Fin type FET (FinFET) has almost all advantages of MG MOSFETs in addition to lesser design related issues because of its self aligned gates. Providing sufficient underlap to the FinFET can enhance the digital performance because of variation in effective gate length in strong and weak inversion regime of operation of device. The analog performance of this kind of underlap FinFET is enhanced at subthreshold/weak inversion regime due to higher effective gate length. Nevertheless, introducing high-k spacer dielectric in underlap section of FinFET can enhance the digital performance because of gate fringe induced barrier lowering (GFIBL) effect. Dual-k spacer based underlap FinFET is another option for suppressing direct source to drain tunneling (DSDT) and short channel effects due to effective increase in gate fringing fields near gate edges of device via inner high-k spacer dielectric.

This issue is addressed as first part of the work with detailed analysis of the impact of dual-*k* spacer on analog and short channel performance of device. The length of inner high-*k* spacer dielectric is optimized in terms of these performances. Suitable fin thickness is selected to account for the volume inversion effect too. From the study, we conclude that dual-*k* spacer formation in underlap FinFET is an attractive option in controlling DSDT, SCEs and improving analog figures of merit (FOM). The transconductance and output conductance improves in all extension lengths

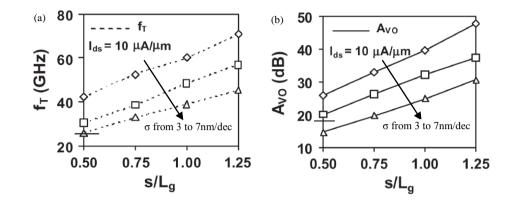

irrespective of doping gradient. Use of optimized inner high-k spacer length can compensate the increase in capacitance by transconductance improvement which can produce almost the same cutoff and maximum oscillation frequency as compared to low-k FinFET, in addition to a large increase in intrinsic gain. Transconductance-tocurrent ratio and early voltage are also observed to improve by formation of dual-k spacer in underlap FinFET. More so, pronounced effect of barrier modulation result in improved frequencies ( $f_T$  and  $f_{max}$ ) and intrinsic gain as the devices are scaled in nanometer regime. In the second part of the work, detailed analysis of the effect of variations on crucial device parameters like gate oxide thickness  $(T_{ox})$ , fin width  $(W_{fin})$ , lateral straggle  $(X_i)$  of source drain doping profile etc., are carried out to formulate a guideline for dual-k spacer underlap FinFET design in analog domain. The process induced variations in these parameters are becoming more prominent with shrinking device dimensions causing negative impact on the inter device variability and, in turn, degrading the mismatch parameter. More so, the effect of alternative inner high-k spacer dielectric materials on analog performance of the device is studied in detail. It is shown that, for an optimum aspect ratio (fin height/fin width), the FOM of dual-k N/P-FinFETs are considerably higher and posses lesser variation to fin width, oxide thickness and S/D lateral straggle which, in turn, can improve the lithographic limitations at process level. Subsequently, the work has been extended to study the effect of spatial variations in critical transistor attributes,  $T_{ox}$  and  $X_i$  of underlap FinFET, on single stage operational transconductance amplifier (OTA) performance. It is observed that, improved and variation less threshold voltage and mobility of dual-k FinFET are crucial in improving analog FOM like  $A_{DM}$ ,  $A_{CM}$  and CMRR of the OTA.

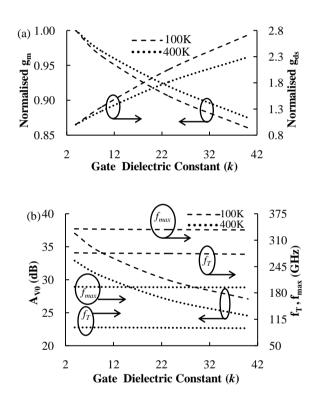

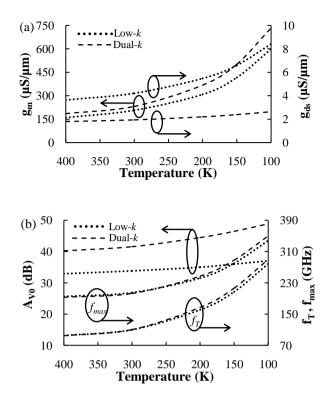

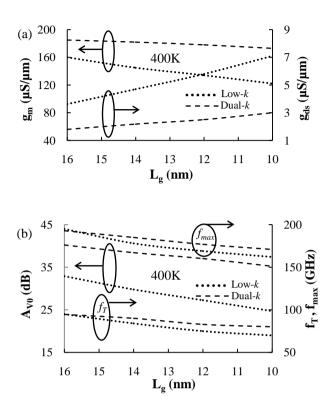

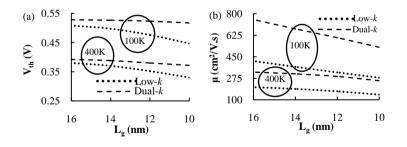

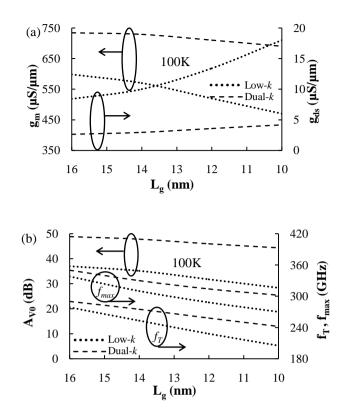

The analog performance of the device can be enhanced at low temperature environment because of improved threshold voltage due to increase in fermi potential and improved carrier mobility due to volume inversion, subband splitting, reduced phonon scattering and enhanced velocity overshoot effect at liquid nitrogen range ( $\geq$ 77K). Therefore, in third part of our work, extensive study of low temperature operation of underlap FinFET is carried out. It is shown that, as the temperature is lowered to 100K, the percentage improvements in analog FOM of dual-*k* FinFET are enhanced further because of improvement in mobility and threshold voltage. Secondly, scaling down the gate length of dual-*k* FinFET to 10nm seems feasible at 100K temperature range, which can target  $A_{V0}$ ,  $f_T$  and  $f_{max}$  of ~44dB, 242GHz and 302GHz respectively.

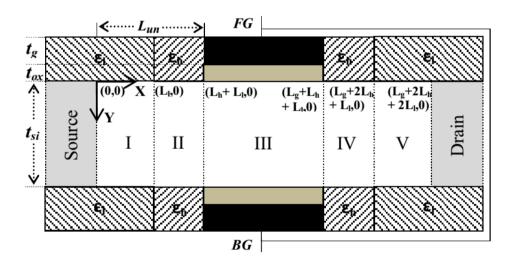

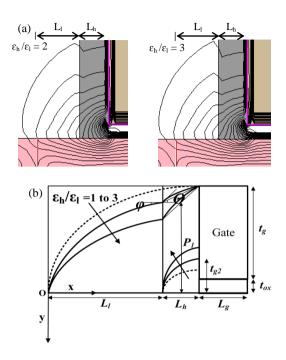

Fourth part of the work deals with development of analytical models for double gate underlap FinFET. The change in electric field line path between two different dielectric interfaces ( $\varepsilon_h$  and  $\varepsilon_l$ ) of underlap section and its effect, is the part that have been modeled for the first time. Each underlap section has been divided into two parts low-*k* and high-*k* section. Modelling of inner high-*k* section is carried out by conformal mapping technique where as modeling of outer low-*k* section has been carried out by solving continuity equations in two different (low-*k*/high-*k*) dielectric interface and considering change in effective gate heights for the elliptical field lines at dielectric interface. It is shown that, the proposed model captures well the effect of inner high-*k* spacer on change in electric field lines at dielectric interface and its subsequent effect on potential profile of dual-*k* spacer based underlap FinFET. Furthermore, the model matches well with TCAD sentaurus device simulation results with variation in crucial device dimensions such as, gate oxide thickness, inner high-*k* spacer length and its dielectric constant. With lightly doped channel, the source/drain dopant species can intrude into the channel region when rapid thermal processing step following the high temperature annealing is performed to activate the dopant species. Therefore, final part of our work deals with generation of compact model for DG MOSFET that considers the effect of lateral straggle of source/drain gaussian profile. It has been observed that, increase in lateral straggle of source/drain gaussian profile facilitates propagation of lateral electric field which, in turn, lowers the threshold voltage and effective channel length of the device. These two effects will alter the current drive and change crucial parameters like transconductance, output conductance and, in turn, intrinsic gain of the device. Finally conclusions are drawn based on the findings of the research. Future scope of the work is also enumerated.

#### ACKNOWLEDGEMENTS

The author expresses his sincere regards and gratitude to Dr. A. K. Saxena and Dr. S. Dasgupta, for their inspiration in successful completion of the present work. With their wide experience, sharp and incisive intellect, maestro ability combined with astute research methodology and deep insight of subject have unerringly steered the work on smooth and steady course. They have taught very basic things I used to ignore at every stage of my Ph.D. I learned a lot from them. They spared lot of time for my research, giving very valuable inputs and took great pains to see me through. I sincerely appreciate their pronounced individualities, humanistic and warm personal approach which have given me the strength and will to carry this research work. I humbly acknowledge a lifetime deep gratitude to my supervisors.

I am thankful to Dr. Sanjeev Manhas, Dr. Anand Bulusu and Dr. Brajesh Kaushik, Microelectronics and VLSI (MEV) Group, ECE, IIT Roorkee for providing guidance and having very fruitful personal discussions at various stages of my work. I am also grateful to Dr. M. V. Kartikeyan, Professor and Head, ECE, Dr. R. Mitra, DRC Ex-Chairman, Dr. D. Singh, DRC Chairman, Dr. A. Bulusu, Associate Professor, ECE, Dr. Vipul Rastogi, Associate Professor, Department of Physics for being members of my Student Research Committee (SRC) and sparing their precious time in spite of all their busy schedule for carefully examining the work and providing valuable suggestions. I am thankful to the editors of various peerreviewed journals for providing timely reviews of the manuscripts submitted. I am very grateful to the anonymous reviewers who have helped me improve the quality of my work by giving critical comments and suggestions. I sincerely thank Mr. Naveen Kanwar, Mr. Dinesh Sharma and many other ECE Department non-teaching staff for their constant help during the research work. I would like to sincerely thank Dr. R. Vaddi, Dr. M. K. Panda, Dr. J. Kanungo, Dr. G. Kaushal, Dr. N. Alam, Mr. O. P. Acharya, Dr. B. Kaur, Mr. S. Maheshwaram, Dr. M. Majumder, Mr. P. Pal, Mrs. Maneka, Ms. A. Pandey, Mr. Ramesh, Mr. A. K. Sharma and M. Tech. friends for having many technical discussions and all support throughout my work without which it is extremely difficult to complete my work in time.

Last, but certainly not the least; I am deeply indebted to the unconditional love and support given by my parents, sisters and my wife Rajashree. Without their selfless support and encouragement, I could not have come to this stage of life. They relieved me of all the family responsibilities to pursue a higher cause. Their ever well-wishing nature inspired my commitment and ushered a fresh life into my efforts. I offer my heartfelt gratitude to the Supreme Godhead for giving me the right inspiration at right time, blessing me with all good fortune and making me contact the right people in my life in making me move towards the goal of life.

This thesis is dedicated to my parents and family.

Date:

Place:

(Ashutosh Nandi)

# **TABLE OF CONTENTS**

|                         | Page No |

|-------------------------|---------|

| Copyright               |         |

| Candidate's Declaration |         |

| Abstract                | i       |

| Acknowledgement         | vii     |

| Contents                | ix      |

| List of Figures         | xiii    |

| List of Tables          | xvii    |

| List of Symbols         | xix     |

| List of Abbreviations   | XXV     |

## **CHAPTER 1:** Introduction

| 1.1 | Introd | uction                                | 1  |

|-----|--------|---------------------------------------|----|

| 1.2 | Backg  | ground and Motivation                 | 3  |

|     | 1.2.1  | Multigate Advantages                  | 4  |

|     | 1.2.2  | Analog Performance                    | 8  |

|     | 1.2.3  | Design Issues in Multigate Device     | 10 |

|     | 1.2.4  | Compact Mathematical Model Generation | 12 |

| 1.3 | Proble | em Description                        | 14 |

| 1.4 | Thesis | s Organization                        | 16 |

#### **CHAPTER 2:** Literature Review

2.1 Introduction

19

| 2.2 | Survey of Underlap FinFETs                                     | 20 |

|-----|----------------------------------------------------------------|----|

| 2.3 | Process Parameter Related Design Issues                        | 27 |

| 2.4 | Low Temperature Operation and Scaling Issue                    | 32 |

| 2.5 | Analytical Modeling                                            | 35 |

| 2.6 | Mathematical Modeling Considering S/D Lateral Gaussian Profile | 40 |

| 2.7 | Technical gaps                                                 | 45 |

#### CHAPTER 3: Impact of Dual-k Spacer Formation on Analog Performance of Underlap FinFET

| 3.1 | Introduction                            | 49 |

|-----|-----------------------------------------|----|

| 3.2 | Device Structure and Simulation Setup   | 52 |

| 3.3 | Underlap Advantages                     | 55 |

| 3.4 | Effect of Dual- <i>k</i> on Performance | 56 |

| 3.5 | Inner High-k Spacer Length Optimisation | 59 |

| 3.6 | Analog Performance Comparison           | 60 |

| 3.7 | Short Channel Effects Study             | 63 |

| 3.8 | Summary                                 | 64 |

#### CHAPTER 4: Design and Analysis of Analog Performance of Underlap FinFET and its circuit performance study

| 4.1 | Introdu | ction                                        | 67 |

|-----|---------|----------------------------------------------|----|

| 4.2 | Dual-k  | underlap FinFET Device Physics Study         | 71 |

| 4.3 | Design  | and Analysis                                 | 74 |

|     | 4.3.1   | Performance Variation with Aspect Ratio (AR) | 74 |

|     | 4.3.2   | Performance Variation with Fin Width         | 76 |

|     | 4.3.3   | Performance Variation with Oxide Thickness   | 78 |

|     | 4.3.4   | Performance Variation with Lateral Straggle  | 80 |

|     | 4.3.5  | Selecting Alternate High-k Material as Inner Spacer | 81 |

|-----|--------|-----------------------------------------------------|----|

| 4.4 | Circui | t Performance Study of Single stage OTA             | 82 |

|     | 4.4.1  | Spatial Variations in Transistors M1 and M2         | 86 |

|     | 4.4.2  | Spatial Variations in Transistors M1 and M2         | 88 |

|     | 4.4.3  | Gate Length Scaling                                 | 91 |

| 4.5 | Summ   | nary                                                | 92 |

## CHAPTER 5: Enhancing Low Temperature Analog Performance of Underlap FinFET

| 5.1 | Introduction                                    | 95  |

|-----|-------------------------------------------------|-----|

| 5.2 | Simulation Setup                                | 98  |

| 5.3 | Variation of Gate Dielectric Constant           | 99  |

| 5.4 | Analysis of Dual-k Spacer Based Underlap FinFET | 101 |

| 5.5 | Gate Length Scaling Issues                      | 104 |

| 5.6 | Summary                                         | 107 |

## CHAPTER 6: Analytical Modelling of Dual-k Spacer Based Double Gate (DG) Underlap FinFET

| 6.1 | Introduction                | 109 |

|-----|-----------------------------|-----|

| 6.2 | Elliptic Field Line Model   | 113 |

| 6.3 | Potential Model             | 115 |

|     | 6.3.1 Boundary Conditions   | 118 |

| 6.4 | Threshold Voltage Model     | 121 |

| 6.5 | Drain Current Model         | 122 |

| 6.6 | Analog Parameter Extraction | 124 |

| 6.7 | Summary                     | 125 |

## CHAPTER 7: Analytical Modelling of DG MOSFET Considering Source/Drain Lateral Gussian Doping Profile

| 7.1 | Introduction                | 127 |

|-----|-----------------------------|-----|

| 7.2 | Surface Potential Model     | 131 |

| 7.3 | Threshold Voltage Model     | 134 |

| 7.4 | Drain Current Model         | 136 |

| 7.5 | Analog Parameter Extraction | 137 |

| 7.6 | Summary                     | 139 |

## **CHAPTER 8:** Conclusions and Further Scope

| 8.1 | Conclusions               | 141 |

|-----|---------------------------|-----|

| 8.2 | Scope for Future Research | 143 |

| APPENDIX: PHYSICAL CONSTANTS AND DEVICE PARAMETERS | 145 |

|----------------------------------------------------|-----|

| BIBLIOGRAPHY                                       | 147 |

| LIST OF PUBLICATIONS                               | 163 |

# LIST OF FIGURES

| Figure No. | Caption                                                                                                                                                         | Page No. |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Fig. 1.1   | Schematic of FinFET                                                                                                                                             | 6        |

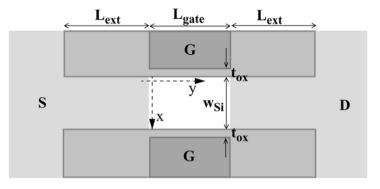

| Fig. 1.2   | Top Cross-sectional view of FinFET                                                                                                                              | 7        |

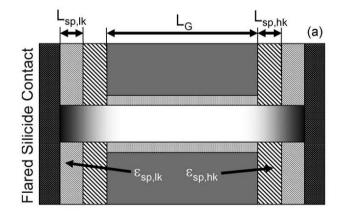

| Fig. 2.1   | Cross section of dual- <i>k</i> spacer based dopant segregated schottky (DSS) MOSFET                                                                            | 26       |

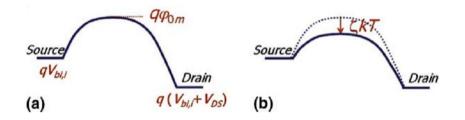

| Fig. 2.2   | Conduction band energy along the channel of the device<br>(a) with low gate dielectric material (b) with high gate<br>dielectric material of same EOT           | 34       |

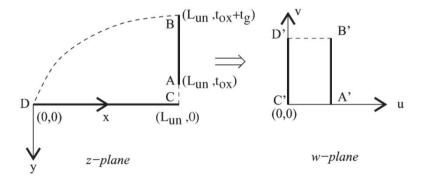

| Fig. 2.3   | Conformal mapping technique. The left gate edge AB<br>and Si-SiO <sub>2</sub> interface CD of <i>z</i> -plane is converted to AB'<br>and CD' in <i>w</i> -plane | 37       |

| Fig. 2.4   | Variation of (a) cutoff frequency $(f_T)$ and (b) intrinsic<br>gain $(A_{V0})$ with ratio of underlap spacer length to gate<br>length $(s/L_g)$                 | 41       |

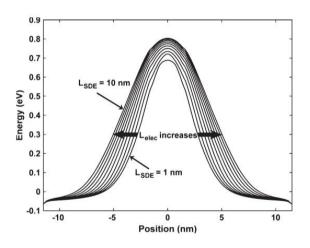

| Fig. 3.1   | OFF-state conduction band profile of dopant segregated<br>schottky MOSFET for different source/drain extension<br>length ( $L_{SDE}$ )                          | 50       |

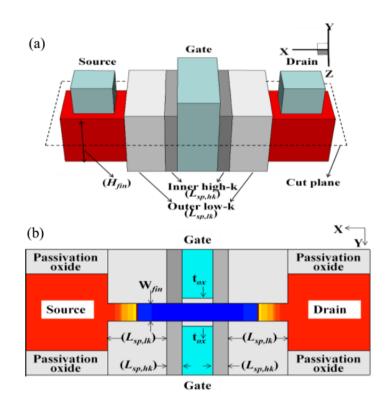

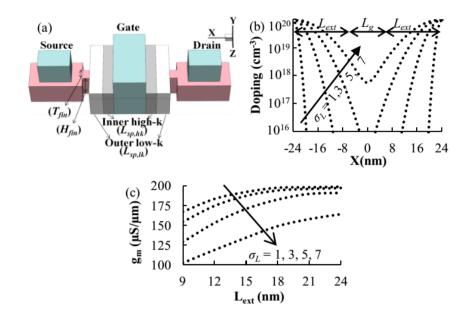

| Fig. 3.2   | (a) 3-D Schematic of underlap FinFET (b) 2-D view along cut plane                                                                                               | 52       |

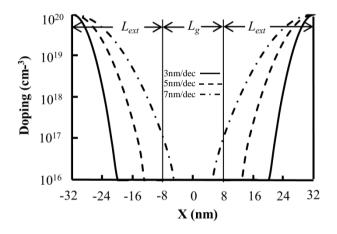

| Fig. 3.3   | Lateral S/D doping profile ( $N_{sd}$ ) along the center of the channel showing various doping gradients ( $\sigma$ )                                           | 53       |

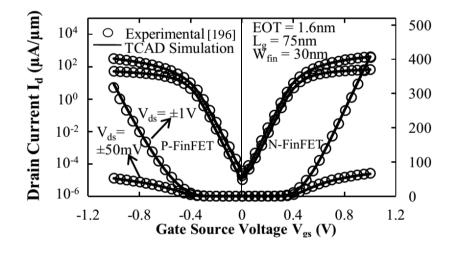

| Fig. 3.4   | Simulated and Experimental $I_{ds}$ - $V_{gs}$ characteristics of N/P<br>FinFETs at low (50 mV) and high (1V) drain biases                                      | 54       |

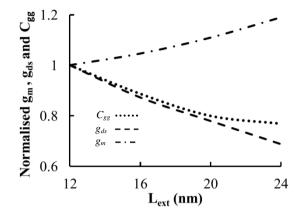

| Fig. 3.5   | Variation of normalized $g_m$ , $g_{ds}$ and $C_{gg}$ with extension length                                                                                     | 56       |

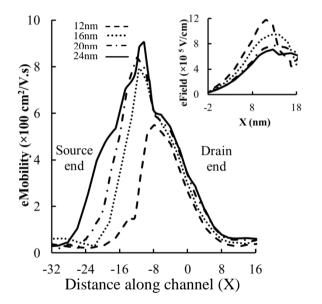

| Fig. 3.6   | Electron mobility and electric field at center of channel<br>extracted at $10\mu A/\mu m$ for various $L_{ext}$ based conventional<br>underlap FinFET           | 56       |

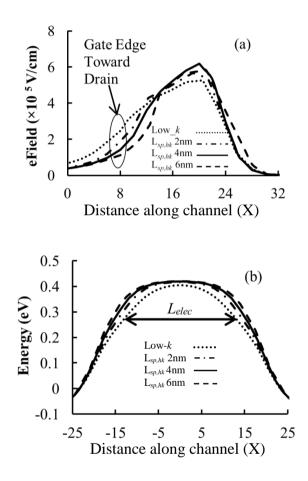

| Fig. 3.7   | (a) Lateral electric field at the center of the body (b) OFF-state<br>lateral conduction band profile at the center of the body                                 | 58       |

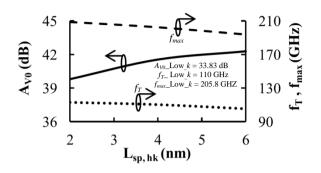

| Fig. 3.8   | Variation of $A_{V0}$ , $f_T$ and $f_{max}$ extracted at 10 $\mu$ A/ $\mu$ m drain<br>current with different inner spacer length $L_{sp,hk}$                    | 60       |

| Fig. 3.9   | Fig. 3.9. (a) Variation of $g_m$ and $g_{ds}$ (b) Variation of $C_{gg}$ and $C_{gd}$ with extension length ( $L_{ext}$ ).                                       | 61       |

| Figure No. | Caption                                                                                                                                                                                                                                                    | Page No. |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

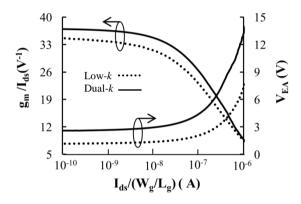

| Fig. 3.10  | Variation of $g_m/I_{ds}$ ratio and $V_{EA}$ with normalized drain current $I_{ds}/(W_g/L_g)$                                                                                                                                                              | 62       |

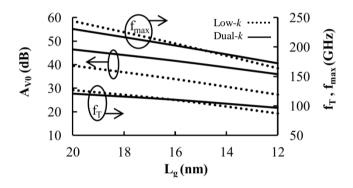

| Fig. 3.11  | Variation of $f_T$ , $f_{max}$ ) and $A_{V0}$ with gate length ( $L_g$ )                                                                                                                                                                                   | 63       |

| Fig. 4.1   | (a) 3-D Schematic of dual- <i>k</i> underlap FinFET. (b) Variation of lateral source/drain doping profile N(x) for various lateral straggle ( $\sigma_L$ ) values along the center of the channel (c) $g_m$ variation with $L_{ext}$                       | 72       |

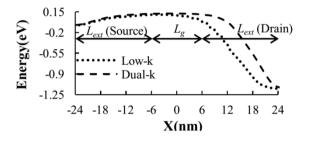

| Fig. 4.2   | Variation of conduction band energy as a function of X for low- <i>k</i> and dual- <i>k</i> FinFET                                                                                                                                                         | 73       |

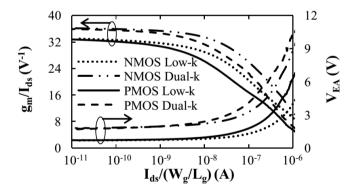

| Fig. 4.3   | Variation of $g_{m'}/I_{ds}$ ratio and $V_{EA}$ with respect to normalised<br>drain current $I_{ds'}(W_g/L_g)$                                                                                                                                             | 73       |

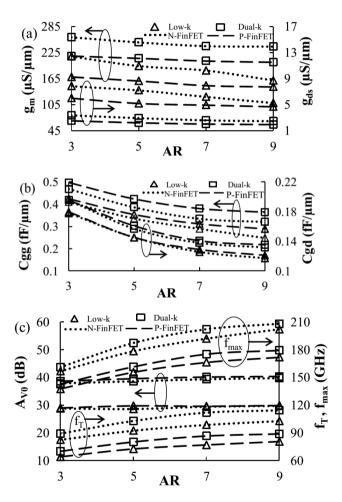

| Fig. 4.4   | Variation of (a) $g_m$ and $g_{ds}$ (b) $C_{gg}$ and $C_{gd}$ (c) $A_{v0}$ , $f_T$ and $f_{max}$ of N/P-FinFETs with aspect ratio ( <i>AR</i> )                                                                                                            | 75       |

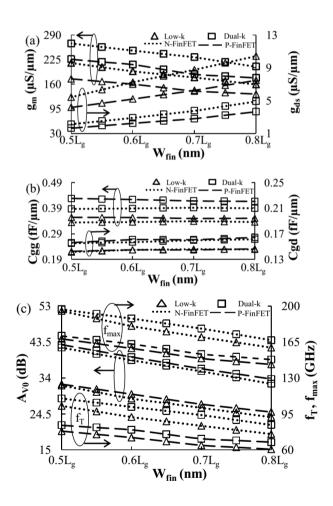

| Fig. 4.5   | Variation of (a) $g_m$ and $g_{ds}$ (b) $C_{gg}$ and $C_{gd}$ (c) $A_{v0}$ , $f_T$ and $f_{max}$ of N/P-FinFETs with fin width ( $W_{fin}$ )                                                                                                               | 77       |

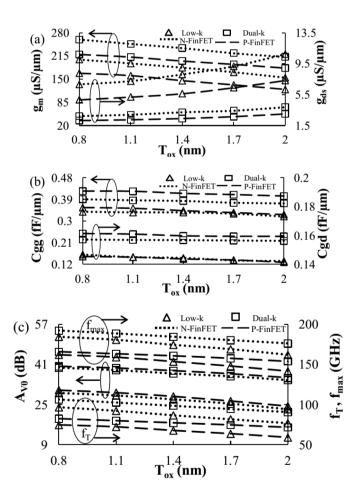

| Fig. 4.6   | Variation of (a) $g_m$ and $g_{ds}$ (b) $C_{gg}$ and $C_{gd}$ (c) $A_{v0}$ , $f_T$ and $f_{max}$ of N/P-FinFETs with oxide thickness ( $T_{ox}$ )                                                                                                          | 78       |

| Fig. 4.7   | Variation of (a) $g_m$ and $g_{ds}$ (b) $C_{gg}$ and $C_{gd}$ (c) $A_{v0}$ , $f_T$ and $f_{max}$ of N/P-FinFETs with lateral straggle ( $\sigma_L$ ) of S/D profile                                                                                        | 80       |

| Fig. 4.8   | Variation of (a) $A_{\nu 0}$ (b) $f_T$ and $f_{max}$ of dual- <i>k</i> N-FinFETs with spacer dielectric constant ( <i>k</i> )                                                                                                                              | 82       |

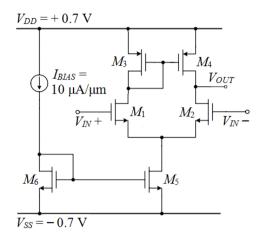

| Fig. 4.9   | 3-D Schematic of single stage OTA circuit                                                                                                                                                                                                                  | 83       |

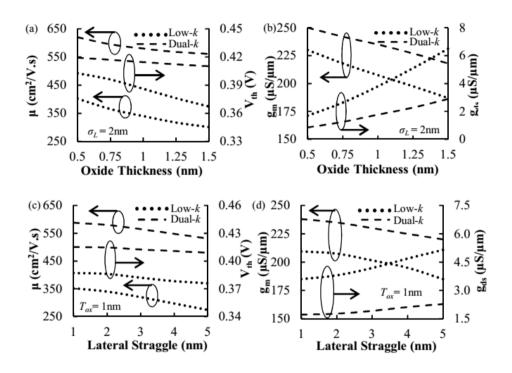

| Fig. 4.10  | Variation of (a) mobility and $V_{th}$ (b) $g_m$ and $g_{ds}$ of N-<br>FinFET with $T_{ox}$ (c) mobility and $V_{th}$ (d) $g_m$ and $g_{ds}$ of N-<br>FinFET with $\sigma_L$ of S/D profile                                                                | 84       |

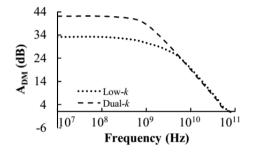

| Fig. 4.11  | Gain vs. frequency variation of single stage OTA circuit                                                                                                                                                                                                   | 85       |

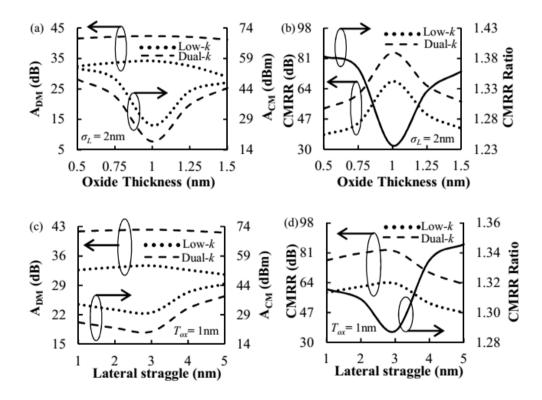

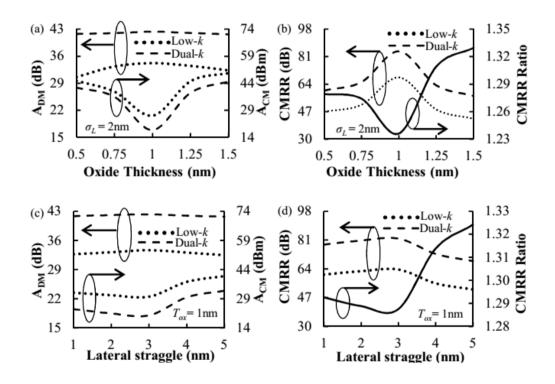

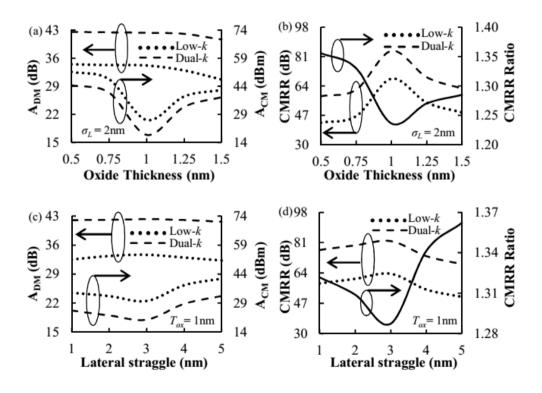

| Fig. 4.12  | Variation of (a) $A_{DM}$ , $A_{CM}$ (b) CMRR and CMRR Ratio of<br>OTA with $\pm$ 0.5nm variation in $T_{ox}$ of M1. Variation of (c)<br>$A_{DM}$ , $A_{CM}$ (d) CMRR and CMRR ratio of OTA with $\pm$ 2nm<br>variation in $\sigma_L$ of S/D profile of M1 | 86       |

| Fig. 4.13  | Variation of (a) $A_{DM}$ , $A_{CM}$ (b) CMRR and CMRR Ratio of<br>OTA with $\pm$ 0.5nm variation in $T_{ox}$ of M2. Variation of (c)<br>$A_{DM}$ , $A_{CM}$ (d) CMRR and CMRR ratio of OTA with $\pm$ 2nm<br>variation in $\sigma_L$ of S/D profile of M2 | 88       |

| Figure No. | Caption                                                                                                                                                                                                                                                    | Page No. |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

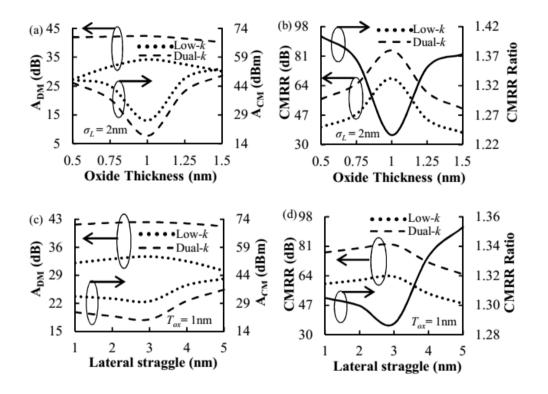

| Fig. 4.14  | Variation of (a) $A_{DM}$ , $A_{CM}$ (b) CMRR and CMRR Ratio of<br>OTA with $\pm$ 0.5nm variation in $T_{ox}$ of M3. Variation of (c)<br>$A_{DM}$ , $A_{CM}$ (d) CMRR and CMRR ratio of OTA with $\pm$ 2nm<br>variation in $\sigma_L$ of S/D profile of M3 | 89       |

| Fig. 4.15  | Variation of (a) $A_{DM}$ , $A_{CM}$ (b) CMRR and CMRR Ratio of<br>OTA with $\pm$ 0.5nm variation in $T_{ox}$ of M4. Variation of (c)<br>$A_{DM}$ , $A_{CM}$ (d) CMRR and CMRR ratio of OTA with $\pm$ 2nm<br>variation in $\sigma_L$ of S/D profile of M4 | 90       |

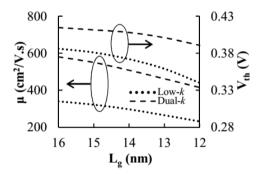

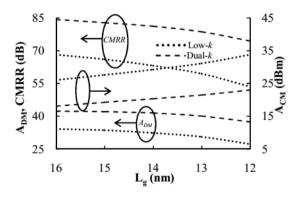

| Fig. 4.16  | Variation of (a) threshold voltage (b) mobility with gate length                                                                                                                                                                                           | 91       |

| Fig. 4.17  | Variation of $A_{DM}$ , $A_{CM}$ and CMRR of OTA with gate length scaling                                                                                                                                                                                  | 91       |

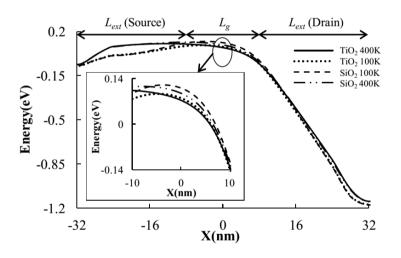

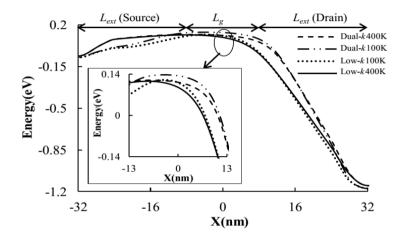

| Fig. 5.1   | Variation of conduction band energy as a function of lateral<br>direction (X) for various gate dielectric based underlap<br>FinFETs                                                                                                                        | 99       |

| Fig. 5.2   | Variation of (a) Normalised $g_m$ and $g_{ds}$ (b) $A_{V0}$ , $f_T$ and $f_{max}$ of<br>conventional underlap N-FinFET with gate dielectric constant<br>( <i>k</i> )                                                                                       | 100      |

| Fig. 5.3   | Variation of conduction band energy as a function of lateral direction (X) for low- <i>k</i> and dual- <i>k</i> spacer based underlap FinFET                                                                                                               | 102      |

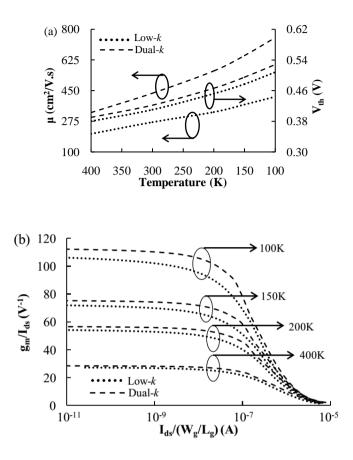

| Fig. 5.4   | Variation of (a) mobility and threshold voltage with<br>temperature (b) $g_m/I_{ds}$ ratio with respect to normalised<br>drain current $I_{ds}/(W_g/L_g)$                                                                                                  | 103      |

| Fig. 5.5   | Variation of (a) $g_m$ and $g_{ds}$ (b) $A_{V0}$ , $f_T$ and $f_{max}$ of N-FinFET with temperature                                                                                                                                                        | 104      |

| Fig. 5.6   | Variation of (a) $g_m$ and $g_{ds}$ (b) $A_{v0}$ , $f_T$ and $f_{max}$ of N-FinFET<br>with gate length ( $L_g$ ) at 400K                                                                                                                                   | 105      |

| Fig. 5.7   | Variation of (a) threshold voltage (b) mobility with gate length                                                                                                                                                                                           | 105      |

| Fig. 5.8   | Variation of (a) $g_m$ and $g_{ds}$ (b) $A_{v0}$ , $f_T$ and $f_{max}$ of N-<br>FinFET with gate length ( $L_g$ ) at 100K                                                                                                                                  | 106      |

| Fig. 6.1   | Schematic of dual-k spacer based DG underlap FinFET                                                                                                                                                                                                        | 110      |

| Fig. 6.2   | (a) TCAD Simulated electric field lines through $\varepsilon_h - \varepsilon_l$ interface<br>(b) Electric field line mapping of dual- <i>k</i> spacer based DG<br>underlap FinFET                                                                          | 114      |

| Figure No. | Caption                                                                                                           | Page No. |

|------------|-------------------------------------------------------------------------------------------------------------------|----------|

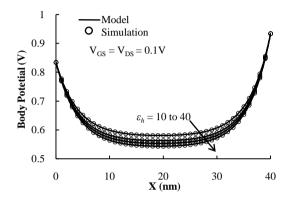

| Fig. 6.3   | Body potential ( $y = t_{si}/2$ ) variation along the channel for<br>different inner high- <i>k</i> spacer values | 121      |

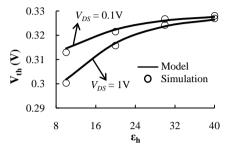

| Fig. 6.4   | Variation of $V_{th}$ with $\varepsilon_h$ for high and low $V_{DS}$                                              | 122      |

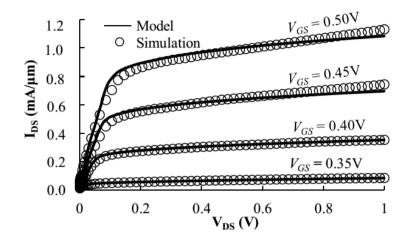

| Fig. 6.5   | $I_{DS}$ - $V_{ds}$ characteristics of DG underlap FinFET                                                         | 124      |

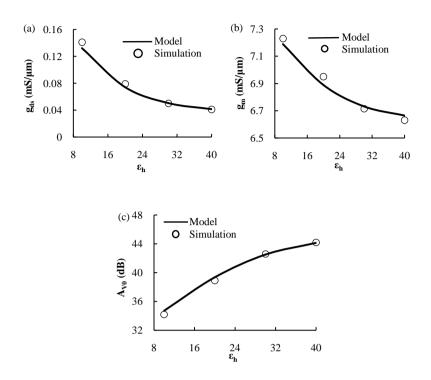

| Fig. 6.6   | Variation of (a) $g_{ds}$ (b) $g_m$ (c) $A_{v0}$ with $\varepsilon_h$                                             | 125      |

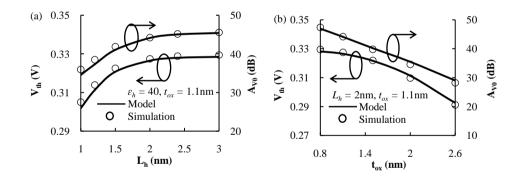

| Fig. 6.7   | Variation of $V_{th}$ and $A_{v0}$ with (a) $L_h$ (b) $t_{ox}$                                                    | 125      |

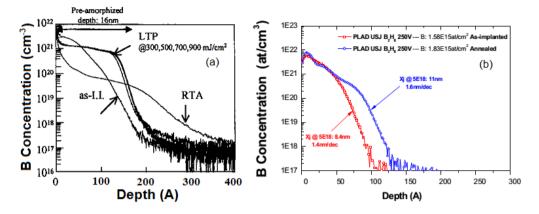

| Fig. 7.1   | SIMS profile showing dopant distribution (a) Shima et al. (b)<br>Gelpey et al.                                    | 128      |

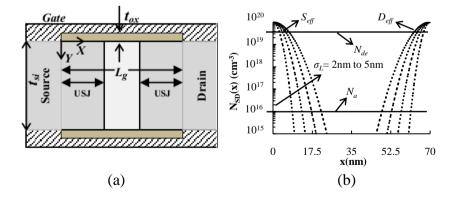

| Fig. 7.2   | (a) Schematic of DG-MOSFET (b) S/D Doping profile                                                                 | 128      |

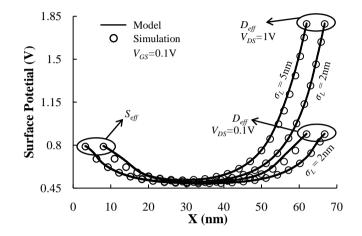

| Fig. 7.3   | Surface potential variation along the channel                                                                     | 134      |

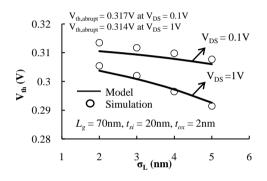

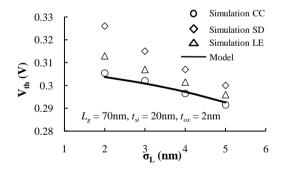

| Fig. 7.4   | Variation of threshold voltage with $\sigma_L$ for high and low $V_{DS}$                                          | 135      |

| Fig. 7.5   | Threshold voltage comparison with several extracted methods                                                       | 135      |

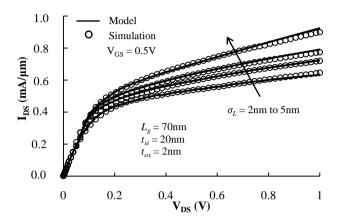

| Fig. 7.6   | $I_{DS}$ - $V_{DS}$ characteristics of DG MOSFET for various $\sigma_L$ value                                     | 137      |

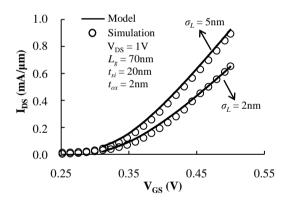

| Fig. 7.7   | $I_{DS}$ - $V_{GS}$ characteristics of DG MOSFET for various $\sigma_L$ value                                     | 137      |

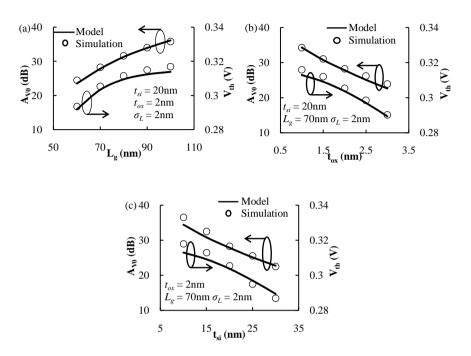

| Fig. 7.8   | Variation of (a) $g_{ds}$ (b) $g_m$ (c) $A_{v0}$ with lateral straggle                                            | 138      |

| Fig. 7.9   | Variation of $V_{th}$ and $A_{v0}$ with (a) $L_g$ (b) $t_{ox}$ (c) $t_{si}$                                       | 139      |

# LIST OF TABLES

| Table No. | Title                                                                                                          | Page No. |

|-----------|----------------------------------------------------------------------------------------------------------------|----------|

| Table 3.1 | Simulated Values of $A_{V0}$ , $F_T$ and $F_{max}$ with Variation in<br>Doping Gradients and Extension Lengths | 60       |

| Table 3.2 | DIBL and Subthreshold Slope (SS) of N and P Channel<br>FinFETs                                                 | 64       |

| Table 4.1 | Device Specifications                                                                                          | 83       |

| Table 4.2 | Maximum Variations in Analog FOM of OTA Designed at $L_g = 12$ nm                                              | 92       |

# LIST OF SYMBOLS

| e <sub>h</sub>            | Eccentricity of High-k Dielectric                    |

|---------------------------|------------------------------------------------------|

| e <sub>1</sub>            | Eccentricity of Low-k Dielectric                     |

| $\mathbf{f}_{\text{max}}$ | Maximum Oscillation Frequency                        |

| $\mathbf{f}_{\mathrm{T}}$ | Cutoff Frequency                                     |

| g <sub>ds</sub>           | Output Conductance                                   |

| g <sub>m</sub>            | Transconductance                                     |

| $g_m\!/I_{ds}$            | Transconductance-to-current Ratio                    |

| k                         | Boltzmann's Constant                                 |

| l <sub>d</sub>            | Channel Length Modulation Factor                     |

| n <sub>i</sub>            | Intrinsic Carrier Density of Semiconductor           |

| n <sub>i,eff</sub>        | Effective Intrinsic Carrier Density of Semiconductor |

| q                         | Electronic Charge                                    |

| s <sub>D</sub>            | Spin Degeneracy Factor                               |

| t                         | Time                                                 |

| v <sub>t</sub>            | Thermal Voltage                                      |

| х                         | Channel Length Direction                             |

| У                         | Body Thickness Direction                             |

| $Al_2O_3$                 | Silicon Oxide                                        |

| A <sub>CM</sub>           | Common Mode Gain                                     |

| A <sub>DM</sub>           | Differential Mode Gain                               |

| $A_{V0}$                  | Intrinsic DC Gain                                    |

| $C_d$                     | Depletion Capacitance per Unit Area                  |

| $\mathbf{C}_{gg}$         | Total Gate Oxide Capacitance per Unit Area           |

| $\mathbf{C}_{gd}$         | Gate to Drain Capacitance per Unit Area              |

| C <sub>if</sub>           | Inner Fringe Capacitance per Unit Area               |

| C <sub>of</sub>             | Outer Fringe Capacitance per Unit Area     |

|-----------------------------|--------------------------------------------|

| Cox                         | Gate Oxide Capacitance per Unit Area       |

| C <sub>si</sub>             | Silicon Body Capacitance per Unit Area     |

| $D_{\text{eff}}$            | Effective Drain End                        |

| E <sub>eff</sub>            | Effective Electric Field                   |

| E(e <sub>x</sub> )          | Elliptical Integral                        |

| $\mathrm{E}_{\mathrm{g}}$   | Silicon Band Gap Energy                    |

| $E_{g,eff}$                 | Effective Band-gap Energy                  |

| Ei                          | Ionization Energy                          |

| E <sub>i0</sub>             | Ionization Energy of Undoped Silicon       |

| Ex                          | X Directional Electric Field               |

| $E_y$                       | Y Directional Electric Field               |

| Ez                          | Z Directional Electric Field               |

| E <sub>C</sub>              | Critical Electric Field                    |

| E <sub>D</sub>              | Donor Level Energy                         |

| E <sub>F</sub>              | Fermi Level Energy                         |

| $H_{\mathrm{fin}}$          | Fin Height                                 |

| HfO <sub>2</sub>            | Hafnium Oxide                              |

| $I_{D,lin}$                 | Linear Drain Current                       |

| I <sub>D,sat</sub>          | Total Saturation Drain Current             |

| $\mathbf{I}_{\mathrm{off}}$ | 'off' State Leakage Current                |

| Ion                         | 'on' State Driving Current                 |

| $I_{sub}$                   | Sub-threshold Leakage Current              |

| I <sub>CBO</sub>            | Gate Lekage Current                        |

| Larch                       | Elliptical Arc Length of High-k Dielectric |

| L <sub>arcl</sub>           | Elliptical Arc Length of Low-k Dielectric  |

| LaAlO <sub>3</sub>          | Lanthanum Aluminate                        |

| L <sub>eff</sub>               | Effective Channel Length                                |

|--------------------------------|---------------------------------------------------------|

| Lelec                          | Electrical Length                                       |

| L <sub>ext</sub>               | Spacer Extension Length                                 |

| Lg                             | Channel Length                                          |

| L <sub>sp,lk</sub>             | Low-k Spacer Extension Length                           |

| L <sub>sp,hk</sub>             | High-k Spacer Extension Length                          |

| L <sub>un</sub>                | Channel Underlap Length                                 |

| N <sub>a</sub>                 | Channel Acceptor Doping Concentration                   |

| $N_a$                          | Ionized Acceptor Concentration                          |

| N <sub>d</sub>                 | Channel Donor Doping Concentration                      |

| $N^+_{d}$                      | Ionized Donor Concentration                             |

| N <sub>de</sub>                | Degenrated Doping Concentration                         |

| NdGaO <sub>3</sub>             | Neodymium Gallate                                       |

| N <sub>SD</sub> (p)            | Peak Doing Concentration of Source/Drain Doping Profile |

| $N^+_{SD}(x)$                  | Ionized Source/Drain Donor Doping Concentration         |

| N <sub>SD</sub> (x)            | Lateral Source/Drain Doping Profile                     |

| Q <sub>b</sub>                 | Bulk Charge                                             |

| Q <sub>DEP</sub>               | Depletion Charge                                        |

| Q <sub>INV</sub>               | Inversion Charge                                        |

| $\mathbf{S}_{eff}$             | Effective Source End                                    |

| Si <sub>3</sub> N <sub>4</sub> | Silicon Nitride                                         |

| SiO <sub>2</sub>               | Silicon Dioxide                                         |

| SS                             | Sub-threshold Slope Factor                              |

| Т                              | Temperature                                             |

| Tg                             | Gate Height                                             |

| TiO <sub>2</sub>               | Titanium Dioxide                                        |

| T <sub>ox</sub>                | Gate Oxide Thickness                                    |

| T <sub>si</sub>                   | Channel Thickness of Multigate Device     |

|-----------------------------------|-------------------------------------------|

| V <sub>bi</sub>                   | Built in Potential                        |

| V <sub>dd</sub>                   | Supply Voltage                            |

| $V_{fb}$                          | Flat- Band Voltage                        |

| $V_{th}$                          | Threshold Voltage                         |

| V <sub>DS</sub>                   | Drain to Source Voltage                   |

| V <sub>DS,sat</sub>               | Drain to Source Saturation Voltage        |

| V <sub>EA</sub>                   | Early Voltage                             |

| V <sub>GS</sub>                   | Gate to Source Voltage                    |

| W                                 | Channel Width                             |

| $W_{\mathrm{fin}}$                | Fin Thickness                             |

| $\Delta E_{g}$                    | Change in Band-gap Energy                 |

| $\Delta I_D$                      | Shift in Drain Current                    |

| $\Delta V_{th}$                   | Shift in Threshold Voltage                |

| ε <sub>h</sub>                    | Permittivity of High-k Dielectric         |

| ε <sub>l</sub>                    | Permittivity of Low-k Dielectric          |

| ε <sub>ox</sub>                   | Permittivity of Silicon Dioxide           |

| ε <sub>si</sub>                   | Permittivity of Silicon                   |

| φ                                 | Fermi Potential                           |

| λ                                 | Natural Length                            |

| $\lambda_a$                       | Velocity Overshoot Effect Factor          |

| μ                                 | Channel Carrier Mobility                  |

| $\mu_n$                           | Electron Mobility                         |

| $\Psi(\mathbf{x},\mathbf{y})$     | 2D Potential along x, y Directions        |

| $\Psi_{b}\left(x ight)$           | Body Potential along x Direction          |

| $\Psi_{\mathrm{f}}\left(x\right)$ | Front Surface Potential along x Direction |

- $\Psi_{tsi}(x)$  Back Surface Potential along x Direction

- σ Doping Gradient of Source/Drain Doping Profile

- $\sigma_L$  Lateral Straggle of Source/Drain Doping Profile

# LIST OF ABBREVIATIONS

| ACF       | Auto Correlation Function                       |

|-----------|-------------------------------------------------|

| AR        | Aspect Ratio                                    |

| BG        | Back Gate                                       |

| BJT       | Bipolar Junction Transistor                     |

| BOX       | Buried Oxide                                    |

| BTBT      | Band-to-Band Tunneling                          |

| CMOS      | Complementary Metal Oxide Semiconductor         |

| CMRR      | Common Mode Rejection Ratio                     |

| DG        | Double Gate                                     |

| DG-FinFET | Double Gate Fin Field Effect Transistor         |

| DG MOSFET | Double gate Metal Oxide Field Effect Transistor |

| DIBL      | Drain Induced Barrier Lowering                  |

| DMDG      | Dual Metal Double Gate                          |

| DRAM      | Dynamic Random Access Memory                    |

| DSDT      | Direct Source to Drain Tunneling                |

| DSS       | Dopant Segregated Schottky                      |

| EDGE      | Enhance Data rate for GSM Evolution             |

| EI        | Electrostatic Integrity                         |

| EOT       | Equivalent Oxide Thickness                      |

| FD        | Fully Depleted                                  |

| FET       | Field Effect Transistor                         |

| FG        | Front Gate                                      |

| FIBL      | Fringe Induced Barrier Lowering                 |

| FinFET    | Fin Field Effect Transistor                     |

| FOM       | Figures of Merit                                |

| FSB        | First Sub-Band                                      |

|------------|-----------------------------------------------------|

| GAA        | Gate-All-Around                                     |

| GAA MOSFET | Gate-All-Around MOSFET                              |

| GFIBL      | Gate Fringe Induced Barrier Lowering                |

| GIDL       | Gate Induced Drain Leakage                          |

| GSM        | Global System for Mobile                            |

| HDD        | Highly Doped Drain                                  |

| IC         | Integrated Circuit                                  |

| ITRS       | International Technology Roadmap for Semiconductors |

| LER        | Line Edge Roughness                                 |

| LNA        | Low Noise Apmlifier                                 |

| LSI        | Large Scale Integration                             |

| LWR        | Line width Roughness                                |

| MLDA       | Modified Local Density Approximation                |

| MOS        | Metal Oxide Semiconductor                           |

| MOSFET     | Metal Oxide Semiconductor Field Effect Transistor   |

| MUG        | Masson's Unilateral Gain                            |

| N-FinFET   | n-Channel FinFET                                    |

| NMOS       | n-Channel MOSFET                                    |

| OPAMP      | Operational Amplifier                               |

| OTA        | Operational Transconductance Amplifier              |

| OTV        | Oxide Thickness Variation                           |

| PAI        | Pre Amorphization Implant                           |

| PD-SOI     | Partially Depleted Silicon-on-Insulator             |

| P-FinFET   | p-Channel FinFET                                    |

| PMOS       | p-Channel MOSFET                                    |

| PPM        | Parts per Million                                   |

|            |                                                     |

| RIE        | Reactive Ion Etching             |

|------------|----------------------------------|

| RTP        | Rapid Thermal Processing         |

| SCE        | Short Channel Effect             |

| S/D        | Source/Drain                     |

| SG         | Single Gate                      |

| SG-SOI     | Single Gate Silicon-on-Insulator |

| SIMS       | Secondary Ion Mass Spectrometry  |

| SoC        | System-on-Chip                   |

| SOI        | Silicon on Insulator             |

| SOI MOSFET | Silicon on Insulator MOSFET      |

| SNWT       | Silicon Nano Wire Transistor     |

| SRAM       | Static Random Access Memory      |

| SRH        | Shockley–Read–Hall               |

| TCAD       | Technology Computer Aided Design |

| TED        | Transient Enhance Diffusion      |

| TFET       | Tunnel Field Effect Transistor   |

| TG         | Tripple Gate                     |

| TG MOSFET  | Tripple Gate MOSFET              |

| USJ        | Ultra Shallow Junction           |

| VLSI       | Very Large Scale Integration     |

|            |                                  |

#### xxviii

# **Chapter 1**

## Introduction

### **1.1 Introduction:**

Moore's law proposed at least twofold increase in number of devices on a single chip every two years since the invention of complementary metal oxide semiconductor (CMOS) [1]. This increase in number of transistors per chip combined with decreasing average cost of production has lead to possible high speed and complex designs [2]. Present day electronic gadgets are so small and so economical that billions of basic functions can be performed by a hand held system. Since early 1990's, academia and researchers from various semiconductor companies have teamed up for accurate prediction of the future of semiconductor industries. Their initiatives resulted in a well organized body "International Technology Roadmap for Semiconductors (ITRS)" [3]. ITRS issues a yearly basis report, which serve as a benchmark for various semiconductor industries and academic institutions around the world. ITRS has predicted that in the near future, the semiconductor devices will achieve the gate length down to 20nm and below, in order to target low power and high performance device operation. Complementary metal oxide semiconductor (CMOS) technology has played a major role in down-scaling the device dimensions, so that realization of compact high performance digital/analog circuits becomes a reality. But when the device dimensions are scaled to this extent, several mulfunctions in device operation start to crop up [4-5]. Therefore, reliability of CMOS technology has become one of the major bottlenecks in the evolution of next generation systems.

Stojadinovic et al. [6] have emphasized the failure physics of integrated circuits and their influence on device reliability. The work is further elaborated in [7], which systematizes different failure modes in integrated circuits. Important tests are enumerated for enhancing

different failure modes and a relationship between failure modes and respective tests for their detection is discussed. This, in turn, raises the instabilities and reliability issues in CMOS integrated circuits. Stress induced instabilities in CMOS can be introduced due to positive gate bias affecting gate dielectric and surface state charges in CMOS transistors [8]. This leads to development of various methods to separate and calculate gate dielectric and surface state charges for effective analysis of instabilities in CMOS integrated circuits [9]. There will be phenomenal influence of these gate oxide charges and interface trap charges on threshold voltage and gain factor of CMOS transistors leading to introduction of fluctuation mechanism in semiconductor devices [10]. Presence of small signal noise in semiconductor devices enhances the fluctuation mechanism further. Therefore, proper guidelines need to be developed for effective small signal noise modelling techniques while opting for numerical simulation of semiconductor devices considering different kinds of fluctuation mechanisms [11]. Subsequently, various authors have reviewed large signal operation of semiconductor devices by physics based numerical simulation in presence of noise that led to evolution of various techniques to measure frequency conversion and noise under this large signal operation [12-13]. Secondly, random doping fluctuations in channel region of device are one of the important causes of variability in nano-scale device. Masoero et al. [14] have evaluated the statistical current fluctuation property, induced by this kind of random doping fluctuations. A linear perturbation theory is adopted to determine the total current fluctuations. Subsequently, a surface potential model that considers this random doping fluctuations effect in device channel had been developed where green's function formulation of external device parameters is used for an efficient circuit level sensitivity analysis [15]. Therefore, when the technology is scaled to nano-meter regime, several device level sensitivity issues are required to be addressed to avoid possible malfunction in device that can possibly hamper circuit operation [4-5].

Some of these major sensitive issues that affect the performance of nano-scale MOSFET are:

- $\succ$   $V_{th}$  roll-off

- Gate Oxide and Interface Trap Charges

- Drain Induced Barrier Lowering (DIBL)

- Increased Subthreshold Source/Drain (S/D) leakage

- Gate Induced Drain Leakage (GIDL)

- Gate direct tunneling and hot carrier effect

- Random Dopant fluctuation

- Controlling junction and depletion depths

- Quantum mechanical tunneling of charge carriers from source to drain and from drain to body of MOSFET

- Control of density and location of dopant atoms in channel and source/drain region of MOSFET to provide a high on/off current ratio

- Interconnect resistance and capacitance

Power consumption and hot carrier effects can be reduced by reducing supply voltage  $V_{DD}$  but at the cost of performance degradation. The performance can be improved by lowering threshold voltage; however source/drain leakage is increased with reduction in threshold voltage. Oxide thickness reduction is an approach to reduce DIBL and enhance adequate channel control by gate electrode. However, reducing oxide thickness increases the gate leakage [16]. Therefore, it is quite a challenge to design nano-scale MOSFET that can address all the instability issues in addition to performance improvement.

#### **1.2 Background and Motivation:**

The motivation behind this research work is to provide alternative device design to engineers that can address most of the scaling issues as well as performance improvement at compact low power environment in order to satisfy overwhelming demand of present day battery operated

portable devices. Noticeable applications of such devices are in the field of cellular phones, biomedical instruments, wireless sensor networks, ambient intelligent systems and others [17-19]. Elementary digital/analog circuits such as CMOS logic gates, reference circuits, SRAM cells, current mirrors, operational amplifiers are basic building blocks of these battery operated portable gadgets. The semiconductor devices that are used to realize these digital/analog circuits demand low power, high gain and low/moderate frequency of operation. Subthreshold/weak inversion regime of operation of semiconductor devices achieves this target [3], [20-22]. More so, subthreshold operation of MOSFET has performance advantages such as better linearity and output impedance in addition to low power consumption and better tolerance to temperature variation. These additional features of the device are most suited while designing signal conditioning circuitry required for environmental sensors [23]. Short channel effects (SCEs) are of serious concern in nano-scaled devices affecting both digital and analog performance. Increasing off state leakage current is another major concern due to pronounced increase in source to drain lateral electric field that deteriorates the gate electrostatic integrity (EI). Analog operation of device is another key performance area that is affected most by this loss of EI. Therefore, better short channel effect (SCE) immunity and increased gate electrostatic control are of paramount importance in order to pursue scaling at nano-scale regime without deteriorating the performance.

#### 1.2.1 Multigate advantages:

With better channel control and reduced short channel effects, the multi-gate MOSFET is considered to be the successor to planner MOSFET [24-25]. Various multigate MOSFETs are reported recently that have superior scalability because of better short channel immunity and performance improvement. Few examples are, source engineered double gate vertical strained SiGe MOSFET [26] for better  $I_{on}/I_{off}$  ratio, gate work function engineered full depleted silicon-on-insulator (FDSOI) MOSFET [27-28], single halo dual material double gate (DMDG)

MOSFET [29-31] for better analog performance, tunneling source MOSFET [32-34] for better SCE and intrinsic gain, novel bottom spacer based FinFET [35] for better power delay and self heating performance etc. Among the multigate family, FinFET is emerging as a promising candidate that can be a suitable alternative to conventional single gate (SG) technologies [36-40]. Larger gate area of FinFET increases drive current of the device while sub-threshold leakage is minimized through reduced channel doping [41]. Further, it has sharper subthreshold slope, which allows better switching in the device. Also, the threshold voltage is controlled without the use of heavy channel doping in fin. Therefore, the effects of random doping fluctuations (RDF) are eliminated [42]. This lightly doped fin reduces the mobility degradation phenomenon due to scattering and can reduce the drain to body band-to-band (BTBT) leakage currents. Secondly, single lithography and etch step in fabrication is an attractive feature of FinFET due to its self aligned gates [43-45]. More so, FinFET is becoming a popular device of choice among mutigate FET that can address scaling and process variation challenges which are generally present in the SG technologies [46]. Fig. 1.1 shows the schematic of a FinFET. The gate wraps over the thin silicon fin type channel resulting in a quasi-planar symmetrical FinFET structure. All three gates, front and back and top are made up of same material and have same work function. The top and front gate insulators are marked as  $T_{ox1}$  and  $T_{ox2}$  whereas,  $T_{ox3}$  is adjacent to back gate. Various definitions of geometrical parameters of the device shown in the figure are as follows,  $L_g$ : effective channel length of FinFET estimated by the metallurgical junction,  $H_{fin}$ : height of Si fin defined as the distance between top gate (TG) and buried oxide,  $T_{fin}$ : thickness of Si fin defined by the distance between front gate (FG) and back gate (BG) oxides, W: geometrical channel width defined as [47]:  $W = 2H_{fin} + T_{fin}$ .

The main features of FinFET are:

(a) An ultra-thin silicon fin type channel for suppressing short channel effects

(b) Single lithography and etch step in fabrication is possible due to its self aligned gates

(c) Raised source/drain structure for reducing parasitic resistance

(d) Gate last process compatible with low temperature and high-k gate dielectrics

Fig. 1.1. Schematic of FinFET.

Integration of high-*k* dielectric material is an added advantage. It is reported that, titanium oxide (TiO<sub>2</sub>) can be used as alternative storage dielectrics for DRAM applications [48-49] due to its high permittivity and excellent step coverage. TiO<sub>2</sub> based MOS capacitors are preferable because only schottky emission effect dominates the current conduction mechanism at low electric field [50]. Similarly, due to larger bandgap and thermodynamic compatibility to interface with silicon, hafnium oxide (HfO<sub>2</sub>) can be used as gate material in reducing ever increasing tunneling current and reliability issues while oxide thickness are scaled down in nano meter regime [51]. Manoj et al. [52] have studied the impact of high-*k* gate dielectric material on FinFET short channel effects and its digital circuit performance. Nevertheless, the short channel effects worsen with increasing dielectric constant of gate dielectrics. Various approaches such as gate work function engineering, fin width scaling and doping adjustment in

fin are studied in order to deduce an optimum dielectric constant value so that an acceptable subthreshold leakage current can be targeted [52].

Fig. 1.2. Top cross-sectional view of FinFET [53].

Considerable attention has been paid on underlap FinFET because of its variable gate length in strong and weak inversion [53-54]. As shown in **Fig. 1.2**, the source and drain ends are at considerable distance from the gate edges. This distance is termed as extension length ( $L_{ext}$ ) of the device. At strong inversion underlap extension portion is fully inverted with high electron concentration providing effective channel length  $L_{eff} \approx L_g$ . At subthreshold/weak inversion regime of operation, on the other hand, low electron concentration allows the source and drain extension lengths ( $L_{ext_s}/L_{ext_s}$ ) to add to the actual channel length resulting in effective gate length  $L_{eff} \approx L_{ext_s}+L_g+L_{ext_s}$ . Therefore, in addition to suppressing short channel effects (SCEs) and reducing off current, it also serves in providing higher on current. Some of the striking features of underlap FinFET are as follows [53-57]:

- (a) Increase in effective channel length in off state to control SCE.

- (b) High  $I_{on}/I_{off}$  ratio.

- (c) Reduction of gate edge direct tunnel leakage

- (c) Reduction of gate sidewall fringe capacitance

- (d) GIDL is reduced due to undoped body

(e) Intrinsically doped channel region avoids random dopant effects and improves carrier mobility

As per aforementioned properties, underlap FinFET operating at subthreshold/weak inversion, has the potential to suppress short channel effects and, in turn, can enhance the performance.

#### **1.2.2 Analog performance:**

The analog figures of merit (FOM) such as transconductance  $(g_m)$ , output conductance  $(g_{ds})$ , early voltage  $(V_{EA} = I_{ds}/g_{ds})$ , transconductance-to-current ratio  $(g_m/I_{ds})$ , intrinsic dc gain  $(A_{V0} = g_m/g_{ds})$  and cutoff frequency  $(f_T = g_m/2\Pi C_{gg})$  are affected by short channel effects and, in turn, depend upon the effectiveness of gate electrostatic integrity (*EI*) over channel region [58-59]. With scaling down of gate length, it is reported that for a fixed gate and drain overdrive voltages, both unity gain cut-off frequency  $(f_T)$  and non-quasi-static transition frequency  $(f_{NQS})$ increase monotonically as  $1/L^2_{eff}$  [60]. However, aggressive scaling of supply voltages can result in turnaround of both  $f_{NQS}$  and  $f_T$  beyond 100nm regime. This kind of performance degradation at scaled gate lengths can be attributed to lower mobility at reduced gate overdrive voltages [60].

A halo implanted MOSFET has been reported to enhance the analog FOM of bulk MOSFETs in subthreshold region of operation [61]. The authors further show that adopting dual material single gate structure for conventional MOSFET can enhance the analog FOM too at subthreshold regime of operation of device. 70% improvement in intrinsic voltage gain is observed as compared to the gain of single material based MOSFET [22]. Subsequently, it is shown that single halo dual material double gate (DMDG) MOSFET has superior scalability because of better short channel immunity and improved analog performance [29]. Higher electron mobility and velocity at surface of the device are crucial parameters of DMDG MOSFET that accounts for better performance and noise immunity [30]. The advantage of DMDG structure over channel engineered devices is further studied in detail [31]. FinFET is emerging as a popular choice because of reduced SCE and superior RF performance. Sengupta et al. [62] have reported that the drive current and peak cut-off frequency of n-FinFET improves with higher implantation energy and reduced channel implantation dose. Subsequently, high frequency noise parameters in FinFETs have been studied and different models are deduced for extraction of minimum noise figure, equivalent noise resistance and optimum source admittance [63].

With an increase in both source and drain extension lengths ( $L_{ext}$ ) of underlap FinFET the analog FOM are reported to improve further [20-21]. Similarly, a drain extended FinFET has been proposed for high voltage and high speed (or RF) applications. The device shows a better on resistance vs break down voltage tradeoff [64]. More so, downscaling of FinFET is beneficial to analog performance by improving gate electrostatic control although losses due to series parasitic increase [65]. However, quantum mechanical effects are of serious concern in multigate devices when silicon fin thickness is scaled to 5nm or below [66-67]. This would affect both digital and analog performance.

Furthermore, use of high-*k* dielectric in underlap section of FinFET can enhance the fringing field coupling. This effect is known as gate fringe induced barrier lowering (GFIBL) capability of high-*k* spacer that enhances the digital performance at strong inversion regime of operation of device [68]. Increasing  $L_{ext}$  length will increase the undoped/low-doped portion of  $L_{ext}$  near to gate edge of underlap FinFET. Therefore, restricting high-*k* dielectric to the gate side wall only, can enhance the gate sidewall fringing fields and, in turn, can raise the barrier to conduction at weak/moderate inversion regime of operation. Vega et al. [69-70] has reported that this kind of dual-*k* spacer based underlap FinFET can improve the gate electrostatic integrity (*EI*  $\alpha$  1/ $L_{elec}$ ) and, in turn, can control direct source to drain tunneling (DSDT) and short channel effects. Virani et al. [71-72] has also analyzed the implications of dual-*k* spacer in improving performance of Tunnel FET with underlap.

FinFET has the potential to shift the influence of drain potential away from the gate edge toward drain and, in turn, can enhance the analog performance of the device.

#### **1.2.3 Design Issues in Multigate Devices:**

Harish et al. [73] have proposed a methodology for modeling the process variation effects on delay performance of digital circuits. The variations in implant dose and energy, processing techniques such as oxidation and high temperature annealing etc. are categorized under extrinsic variations to device. Whereas, variations such as, random dopant fluctuation in channel, gate dielectric thickness and its permittivity, interface and oxide charges etc. are categorized under intrinsic variations of device dimensions. It is reported that this kind of severe process related variations in deep sub-micrometer regime cannot be adequately produced by deterministic circuit design approach. Therefore, it becomes imperative to adopt statistical circuit design approach that can account any number of process related variability issues [73].

Dadgour et al. [74] have modeled the threshold voltage fluctuation effect due to work function variability in emerging devices like FDSOI MOSFET, FinFET etc. The source of variability is identified as defects in grain orientations of metal. TiN and WN materials show lower  $V_{th}$  fluctuations. Furthermore, FinFET is less affected by work function variations due to its larger gate area. Nevertheless, few VLSI circuits can show degraded performance and reliability issue due to  $V_{th}$  fluctuation [75]. Subsequently, an accurate physical model has been developed that considers the effect of the work function variation for ultra short channel MOSFETs [76]. More so, the model has the advantages of capturing work function variation effects of 3-D device by using 2-D device simulation. This results in a significant lower simulation time as compared to the simulation time of 3-D device. Quantum mechanical effect and width quantization are two important properties that need to be accounted for characterization of FinFET even in subthreshold regime. In addition, work function variation results in quantum mechanical confinement. Therefore, a reliable design framework has to be targeted that considers the width

quantization effect [77-78]. Secondly, sources of variability such as random doping fluctuation in source/drain extension regions, line edge and line width roughness (LER/LWR) etc., need to be studied in detail for characterization and optimization of CMOS in nano-meter regime [79-80]. These studies are crucial considering their effect on threshold voltage and on current of the device [81-83].

Better electrostatic control over channel is of paramount importance for performance improvement at nano-scale regime. Tall and narrow fin formation, oxide thickness reduction and doping profile control are crucial aspects of device design that can target better EI [84-86]. However, unique manufacturing challenge while incorporating tall and narrow fins (high aspect ratio), and process induced variations in the fins and oxide thickness are pronounced with shrinking device dimensions [87-93]. Similarly, formation of ultra shallow junction (USJ) for controlling doping profile is governed by defect formation and junction leakage in addition to associated manufacturing challenge and cost effectiveness [94-100]. These important manufacturing factors are causing negative impact on the inter device variability and, in turn, degrade the mismatch parameter in nano-scale devices. Furthermore, the mismatch in critical device attributes can limit the accuracy of digital as well as analog circuits. For comparators and operational amplifiers, the mismatch has serious implications on offsets. For analog to digital converter it can affect the bit accuracy, whereas power supply noise and common mode rejection ratio of differential amplifier are two important parameters that are affected by this mismatch [101]. This culminates in designing FinFET with excellent *EI* so that the performance is less immune to parametric variations and inter-device variability considering the aforementioned process challenges.

Low temperature operation of field effect transistors (FETs), on the other hand, have some excellent properties like: improved switching speed due to increase in saturation velocity and carrier mobility, improved reliability, reduced thermal noise, higher packing density, lower

power dissipation etc. [102-106]. Secondly, high transconductance and velocity overshoot effects in NMOS devices are added incentive when the device is cooled to liquid nitrogen temperature [107]. More so, the volume inversion property of multigate device is enhanced at low temperature than at room temperatures results in substantial improvement in mobility of minority carriers [108]. Therefore, further scaling down of device dimensions in low temperature environment is possible because of improved subthreshold slope, lower leakage current, improved gate electrostatic integrity and, in turn, enhanced analog performance [107-114].

#### **1.2.4 Compact Mathematical Model Generation:**

Simple compact mathematical models of MOS transistors are needed for high speed computation of device characteristics that can be used in computer-aided circuit simulators in order to design and optimize the performance of integrated circuits containing millions of transistors on single silicon chip [115]. Surface potential model approach of channel region of MOS device is one of the simple, compact and accurate mathematical analysis that is widely accepted by researchers [116-118]. In addition, the equations derived from these surface potential models are continuous in all three operation regions of device. Therefore, the current can be accurately determined using these models which are often needed for VLSI circuit simulation [119-120]. Several authors have proposed analytical models of threshold voltage, DIBL, subthreshold slope and subthreshold current using the surface potential model approach [121-124]. Therefore, this kind of approach is familiar in device characterization of most of the present day MOSFETs starting from bulk MOSFET to FDSOI MOSFET, DG MOSFET, triple gate (TG) MOSFET and gate all around (GAA) MOSFET etc. Furthermore, the mathematical computation is easier while solving wide range of poisson equations governing 2-D, 3-D and cylindrical co-ordinate systems. In addition, inclusion of short channel and narrow width effects are also possible while deducing models for short channel MOSFETs.

For underlap FinFET, on the other hand, the gate fringing field effects in underlap region cannot be captured by adopting the conventional double gate MOSFET model approach. The electric flux continuity expressions of underlap regions will be different, as the effective oxide thickness between gate side wall and Si-SiO<sub>2</sub> interface is not constant due to fringing fields. Conformal mapping technique has been used by Bansal et al. [125] to model the gate fringing field of DG underlap FinFET. As the underlap surfaces are not equipotential surfaces, the fringing field can be solved self-consistently with the surface potential using Poisson equation in order to generate a compact analytical model [125-127]. Subsequently, modelling of threshold voltage of the device can be carried out by equating the electron concentration at minimum potential point in the channel region with the channel doping concentration that satisfies the inversion condition. Using the threshold voltage model, the drain current in linear and saturation region of DG MOSFET can be deduced by following the approach as suggested by Suzuki et al. [128]. In addition, effects like impact ionization and parasitic BJT effects have to be included while modeling conduction current considering high lateral electric filed in saturation region of operation of device [129]. More importantly, the non local effects such as channel length modulation [130], velocity overshoot effect [131] and drain induced barrier lowering (DIBL) [132] are also required to be included in current model as the device dimensions are scaled down to nano-meter regime [133].

Second aspect of model formulation should capture the effect of heavily doped source/drain (S/D) region on channel region of device. Heavily doped S/D region is usually preferred to control the device parasitics in order to avoid performance deterioration [44]. However, when rapid thermal processing step following the high temperature annealing is performed to activate the dopant species of both channel and S/D region, the heavily doped S/D dopant species can easily intrude into the lightly doped channel region. This effect will enhance the lateral spread of S/D electric field and, in turn, will deteriorate short channel effects (SCEs) and performance