## DESIGN AND ANALYSIS OF VERTICAL NANOWIRE CMOS DEVICES AND CIRCUITS

**Ph.D THESIS**

by

## MAHESHWARAM SATISH

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE - 247667, INDIA DECEMBER, 2014

## DESIGN AND ANALYSIS OF VERTICAL NANOWIRE CMOS DEVICES AND CIRCUITS

#### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

#### **DOCTOR OF PHILOSOPHY**

in

### ELECTRONICS AND COMMUNICATION ENGINEERING

by

## MAHESHWARAM SATISH

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247 667 (INDIA) DECEMBER, 2014

## ©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE- 2014 ALL RIGHTS RESERVED

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE <u>CANDIDATE'S DECLARATION</u>

I hereby certify that the work which is being presented in the thesis entitled "DESIGN AND ANALYSIS OF VERTICAL NANOWIRE CMOS DEVICES AND CIRCUITS" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electronics and Communication Engineering of the Indian Institute of Technology Roorkee is an authentic record of my own work carried out during a period from July, 2010 to December, 2014 under the supervision of Dr. S. Manhas, Associate Professor and Dr. B. Anand, Associate Professor, Department of Electronics and Communication Engineering, Indian Institute of Technology Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

## (MAHESHWARAM SATISH)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

(S. Manhas) Supervisor (B. Anand) Supervisor

Date:\_\_\_\_\_

## ABSTRACT

The continued CMOS scaling has led to the need for introduction of 3-D transistors such as multigate FETs for technology nodes at 22 nm and below replacing planar MOSFETs (Metal Oxide Semiconductor Field Effect Transistors). Of these novel devices, the nanowire (NW) devices have minimum short channel effects (SCE) and allow thicker gate insulator thereby reducing the leakage currents in the device. Further, in NW device family, the Vertical Nanowire FETs (VNWFET) have additional strong advantage of occupying least silicon area due to vertical pillar structure and possibility of stacking devices vertically. This has driven numerous researchers to work on vertical nanowire devices and its circuits. Although there have been studies reporting device level fabrication results for VNW FETs, but due to fabrication challenges and large cost involved in developing technologies, accurate VNW CMOS circuit performance evaluation has not been well demonstrated and thoroughly investigated. The use of TCAD in VNW CMOS development is of high importance, as TCAD can help to reduce design cycles as well as provide critical insight into VNW CMOS behavior and key performance factors. At extremely scaled dimensions, the device and layout parasitics also start to dominate and are of high importance in evaluating circuit performance. The vertical device architecture has several issues like: newer/different kind of parasitic components such as contact overlapping nanowire tip, increased parasitic due to cylindrical structure and asymmetry due to differences in top/bottom electrodes contacts. Thus, the impact of parasitic and electrode asymmetry on device and circuit performance with scaling are important design issues. In this thesis, we investigate the performance of VNW CMOS and its design issues using well calibrated 3D TCAD simulations at 15 nm technology node as test vehicle. The important results are compared with corresponding FinFET/planar devices and circuits.

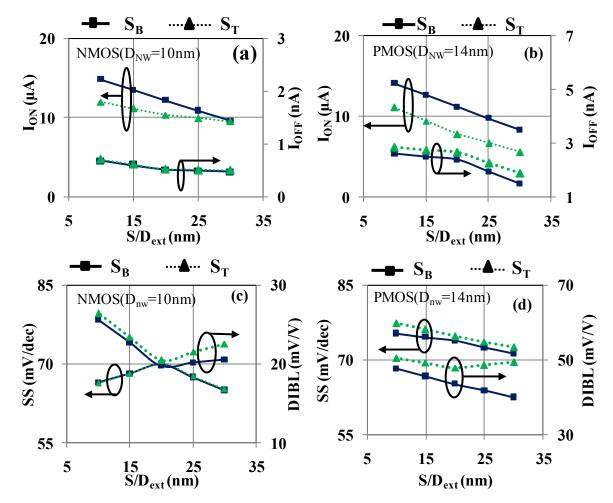

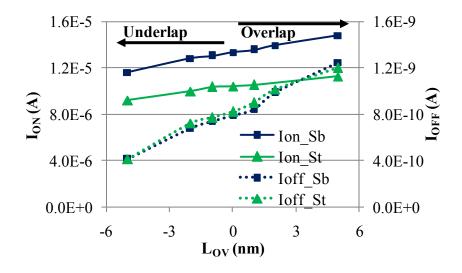

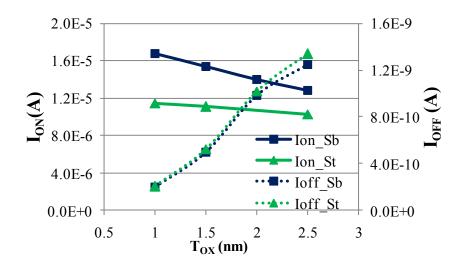

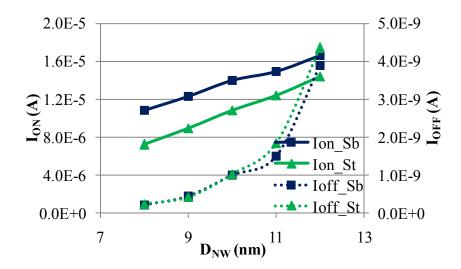

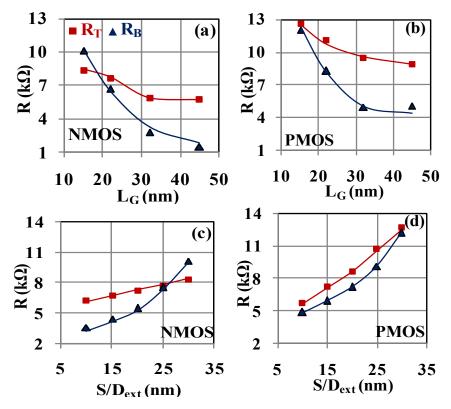

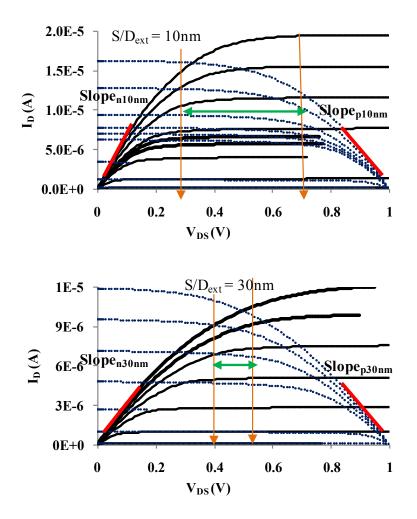

Using well-calibrated process and device parameters the scaling performance of VNWFET device is performed with respect to channel length ( $L_G$ ), S/D extension length (S/D<sub>ext</sub>), gate overlap/underlap length ( $L_{OV}$ ), gate dielectric thickness ( $T_{OX}$ ) and nanowire diameter ( $D_{NW}$ ). The  $L_G$  scaling study shows that the VNWFET devices can be easily scaled down to 15 nm with a thicker dielectric of 2 nm as opposed to less than 1 nm dielectric thickness required in planar MOSFETs. From, the S/D<sub>ext</sub> scaling and S/D asymmetry we find that device drive current can be increased by decreasing S/D<sub>ext</sub> and source as the bottom electrode has better performance. The optimum device structure parameters for 15 nm node are:  $L_{OV} = 2$  nm,  $T_{OX} = 2$  nm and  $D_{NW}$  (NMOS/PMOS) = 10/15 nm. Also, it is shown that n<sup>th</sup> power law can be used to

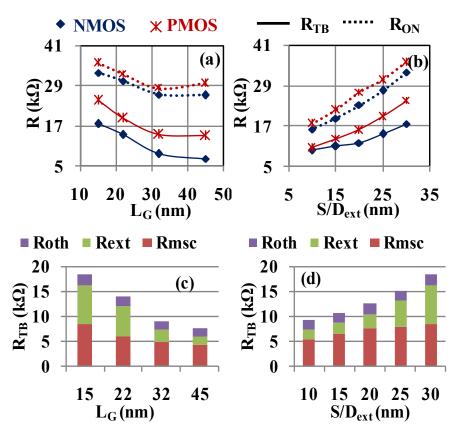

obtain device I-V characteristics matching to TCAD simulation results. Next, we develop models for parasitic series resistance and capacitance components which match well with simulation results. It is observed that gate to bottom electrode capacitance is a major contributor to device parasitic capacitance, while the contact and extension resistance are major contributors to device parasitic resistance. Further, the device performance with respect to  $L_G$ ,  $S/D_{ext}$  and S/D asymmetry is explained with the help of modeled parasitic components. These parasitic models are later used in analyzing CMOS circuit performance.

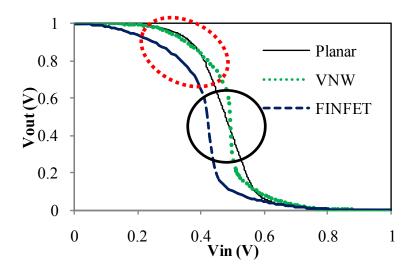

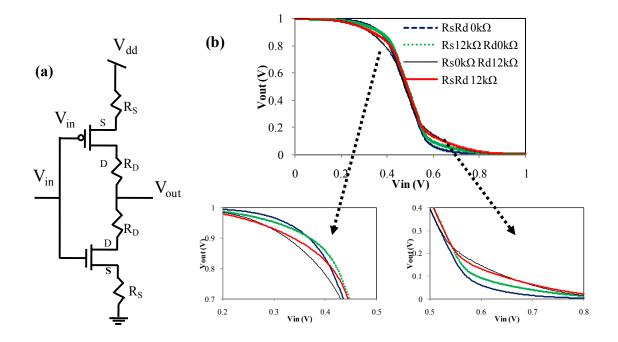

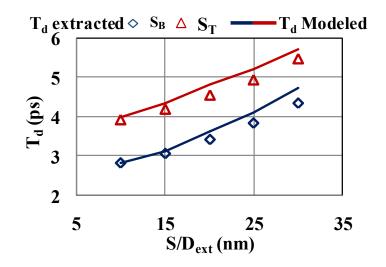

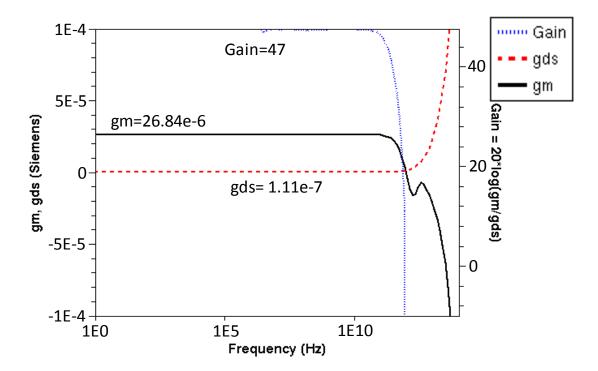

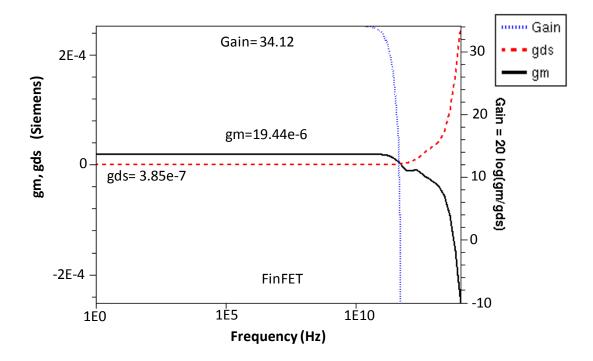

Finally, we study detailed digital and analog circuit performance of VNWFET CMOS. It is observed that due to better SCE, the VNWFET CMOS inverter voltage transfer characteristics (VTC) have sharper transition than planar MOSFET. Also, we note a gradient around the noise margin (NM) extraction point which is attributed to larger series resistance that can be minimized by reducing S/Dext. The CMOS inverter's dynamic performance is carried with respect to L<sub>G</sub> scaling and compared to reported FinFET and planar MOSFET inverters. It is found that VNWFET has the better delay, area and power performance when compared to planar or FinFET. The device S/D asymmetry leading to various possible CMOS layouts for a given circuit are investigated, we report new layout rule guidelines for VNWFET based circuit design. Further, it is shown that VNWFET based inverter delay can be improved by reducing S/D<sub>ext</sub> and by using device with source as bottom electrode provides best circuit performance. The CMOS inverter delay is modeled using the effective current method, which uses the parasitic capacitance model for delay prediction, and the delay model results match well with simulation results. This also explains the circuit performance with respect to S/Dext scaling and S/D asymmetry. Lastly, analog performance of VNWFET device is done and the intrinsic frequency response is compared to an equivalent FinFET. It is found that VNWFET has better gain, 3dB bandwidth and unity gain bandwidth (f<sub>T</sub>). Further, the impact of S/D<sub>ext</sub> length on common source (CS) amplifier is performed and it is seen that with lower source extension length the amplifier has better performance in terms of gain, 3dB bandwidth and  $f_T$ .

The overall results obtained in this study demonstrate that VNW CMOS has very high potential for use in CMOS based digital/analog circuits and offers best overall performance for CMOS technology nodes below 22 nm when compared to planar or FinFET. The study of digital/analog circuit design in this thesis highlight new circuit design methodologies and circuit layout rules, which addresses device asymmetry and parasitics. The parasitic models proposed through this work can be used to develop a compact SPICE model for VNWFET, with which circuit design and performance analysis on various standard cells, analog building blocks, SRAM cell and reliability study can be easily performed.

I cannot stop myself from writing a very long acknowledgement as I have to cover almost 6 and 1//2 years of my stay at Indian Institute of Technology, Roorkee, which includes 2 years of M.Tech.

First of all, I would like to thank Dr. Sanjeev Manhas who guided me during M.Tech dissertation and is the real motivation for me to choose Ph.D as my next step in career. I would like to thank my M.Tech batch mates Parag, Nema, Sandeep, Ankit, Atul bhai, NVSS, Sravan, and Vivek ji for the support and encouragement given to me when I was in dilemma regarding choosing Ph.D as my career. All of them along with Dr. Manhas believed that I can do justice to what I have started as my M.Tech dissertation and give it completeness through Ph.D. At this point I would like to thank my parents and sisters for allowing me to enroll for Ph.D program and relieving me from various family responsibilities to pursue research.

Now that I am submitting my thesis, I express my heartfelt gratitude to Dr. Sanjeev Manhas, and Dr. Anand Bulusu, Associate Professors in Department of Electronics and Communication Engineering at Indian Institute of Technology Roorkee, for their valuable guidance, support, encouragement and immense help. I consider myself extremely fortunate for getting the opportunity to learn and work under their able supervision. Working under their guidance will always remain a cherished experience in my memory and I will adore it throughout my life. I would like to thank Dr. Manhas's family, as I have taken a lot of his personal time for my thesis related discussions.

My sincere thanks to the faculty of Microelectronics and VLSI Technology group Department of Electronics and Communication Engineering at Indian Institute of Technology Roorkee, for the technical knowhow and analytical abilities they have imbibed, which have helped me in dealing with the problems I encountered during the thesis. I am thankful to my student research committee which has given critical suggestions and reviewed my progress time to time.

I take this opportunity to thank the lab supervisors Naveen ji and Dinesh ji for their support in providing and maintenance of lab facilities whether it is faster license procurement, high end workstation procurement and networking/internet related issues.

I would also like to remember my seniors and juniors with whom I have spent a lot of time at IITR and memories that bring smile on my face. I am really indebted to Manju mam, Puru sir, Kola, Baljit mam, Anju, and Shivam who have taken care of my appetite with their version of

rasam, sambhar, curries, soya chaap, rotis, and pulao respectively. I am thankful to god for introducing me to Santu, Ron dada, Gaurav bro, Gaurav Kapil, Venu and Ashok who gave constant support, motivation, help even though they were from different departments or groups and spent a lot of time on trips, daily badminton matches and weekend parties. I would like to sincerely thank senior research scholars of Microelectronics and VLSI group Jiten sir, Naushad sir, Rathod sir, Vaddi sir, Gaurav sir and Nandi who have given a lot of their time to clarify my research doubts. I am happy to have known industrious M.Tech juniors Jitano, Swati, Siva, Deepika, Gaurav Bharadwaj, Arvind, Ravisankar, Sarvesh, Raghav, Asheesh, Prateek, Bipin, and Sai with whom I had very long discussions. A special mention of time spent with Durga, Akhil, Sandeep, Sidhu and Sashank on trips to Rohtang pass, Vaishno devi temple and Surkanda devi temple.

I want to thank Dr. Bulusu for giving the opportunity to mentor his Ph.D student Archana. I am really proud to have mentored such hard working and sincere learner. I would like to thank Archana as she made me to learn a lot of new things in order to clarify her doubts. I want to thank Dr. Manhas once again, for giving the opportunity to mentor his students Sakshi (summer intern from NIT Hamirpur), Mohit (M.Tech) and Omdot (Ph.D). I have spent a lot of time with them working on compact modeling of MOSFET devices. I consider these four as my torch bearers, and wish them to take my work to the next level successfully. I wish each one of my juniors a very bright future and a healthy life.

My acknowledgement is incomplete without mentioning thanks to Ministry of Human Resource Development, Govt. of India, who have provided fellowship during my Ph.D.

Finally, I want to thank నాన్న శైపైలం గారు, అమ్మ స్త్రవేని గారు and అక్కలు సునిత, కల్పన, and ఉష for their love and support, without which I wouldn't have made it this far in my career. I thank god gifted sisters Veenakka, Swa, Meena, Sampada, Reppika, Kanchu, Havi, Sona, 'Su'dha/ma, Soumya, and friends Rohit, Chandu, Kishore, Puneet, Manasa, Chaitu, Chan, Swe, Pal and Saja, whom I met at different junctures during my life time for their unending support and motivation during my higher education at IITR. I am happy to have them as part of my life as I can talk to them any time and on anything. I am thankful to Bachan and Suru (trekking guides) for showing me the beauty of nature during my trek to Devkhira, in the valley of Harki-dun and for allowing me to lead the group during trek of Devban's snowy peaks. I will end with a mention of regular visitors Parag, Nema, Mona, Baba, and Gullu who forced me to take time out for myself.

> Maheshwaram Satish Ph. D. (MEV)

# CONTENTS

| ABSTF  | RACT                                   | i    |

|--------|----------------------------------------|------|

| ACKN   | OWLEDGEMENT                            | iii  |

| CONT   | ENTS                                   | V    |

| LIST C | OF FIGURES                             | ix   |

| LIST C | DF TABLES                              | xiii |

| ABBRI  | EVIATIONS AND SYMBOLS                  | XV   |

| 1 CI   | HAPTER                                 | 1    |

| INTRO  | DUCTION                                | 1    |

| 1.1    | Introduction                           | 1    |

| 1.2    | Motivation                             | 4    |

| 1.3    | Objectives                             | 5    |

| 1.4    | Thesis Organization                    | 5    |

| 2 CI   | HAPTER                                 | 9    |

| LITER  | ATURE SURVEY                           | 9    |

| 2.1    | Scaling Theory                         | 9    |

| 2.2    | Device Fabrication                     | 11   |

| 2.3    | NW Circuit Performance                 | 14   |

| 2.4    | NW Modeling                            | 15   |

| 2.5    | Vertical NW Circuit Performance        | 16   |

| 2.6    | VNWFET Other Applications              | 16   |

| 2.7    | Technical Gaps                         | 17   |

| 3 CI   | HAPTER                                 | 19   |

| TCAD   | CALIBRATION                            | 19   |

| 3.1    | Technology Computer Aided Design: TCAD | 19   |

| 3.     | 1.1 Process Simulation                 | 20   |

|        |                                        |      |

| 3.1   | .2 Device Simulation                                                 | 21 |

|-------|----------------------------------------------------------------------|----|

| 3.2   | Calibrated Simulation Setup                                          | 23 |

| 3.3   | Device and Simulation Details                                        | 27 |

| 4 CH  | IAPTER                                                               | 29 |

| DEVIC | E SCALING PERFORMANCE                                                | 29 |

| 4.1   | Scaling of Channel Length: L <sub>G</sub>                            | 30 |

| 4.2   | Scaling of Extension Length: S/Dext                                  | 31 |

| 4.3   | Scaling of Gate Overlap/Underlap Length: Lov                         | 32 |

| 4.4   | Scaling of Gate Dielectric: T <sub>OX</sub>                          | 33 |

| 4.5   | Scaling of Nanowire Diameter: D <sub>NW</sub>                        | 34 |

| 4.6   | n <sup>th</sup> Power Law Modeling                                   | 34 |

| 4.7   | Summary                                                              | 37 |

| 5 CH  | IAPTER                                                               | 39 |

| PARAS | ITIC MODELING                                                        | 39 |

| 5.1   | Capacitance Modeling                                                 | 39 |

| 5.2   | Series Resistance Modeling                                           | 46 |

| 5.3   | Summary                                                              | 53 |

| 6 CH  | IAPTER                                                               | 55 |

| CIRCU | IT PERFORMANCE                                                       | 55 |

| 6.1   | Digital Performance                                                  | 55 |

| 6.1   | .1 VNW CMOS Inverter Voltage Transfer Characteristics (VTC) Analysis | 55 |

| 6.1   | .2 Benchmarking of Inverter Transient Response                       | 60 |

| 6.1   | .3 VNW CMOS Inverter Delay Analysis                                  | 61 |

| 6.1   | .4 VNW CMOS Inverter Delay Modeling                                  | 65 |

| 6.2   | Analog Performance                                                   | 67 |

| 6.3   | Summary                                                              | 72 |

| 7 CH  | IAPTER                                                               | 75 |

| CONCL | USION & FUTURE SCOPE                                                 | 75 |

| 7.1    | Conclusion   | 75  |

|--------|--------------|-----|

| 7.2    | Future Scope | 78  |

| BIBLIC | OGRAPHY      | 81  |

| PUBLI  | CATIONS      | 99  |

| APPEN  | NDIX A       |     |

| APPEN  | IDIX B       | 107 |

| APPEN  | IDIX C       | 113 |

## **LIST OF FIGURES**

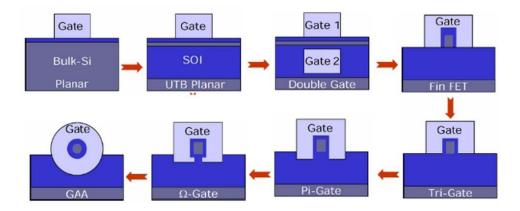

| Figure 1.1 Evolution of device structure from single-gated to GAA NWFET [25]2                                                    |

|----------------------------------------------------------------------------------------------------------------------------------|

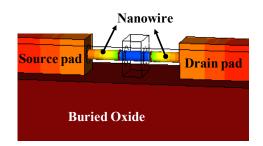

| Figure 1.2 3D device structure of lateral nanowire supported by source/drain pads at its ends                                    |

| [55]                                                                                                                             |

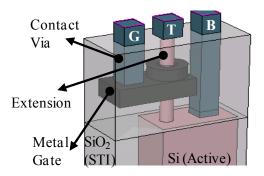

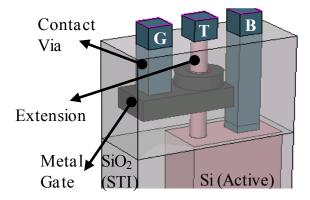

| Figure 1.3 3D isometric view of Vertical Nanowire device [57]3                                                                   |

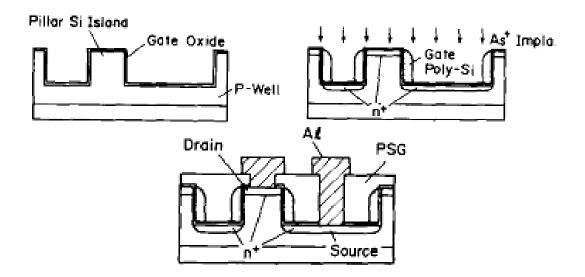

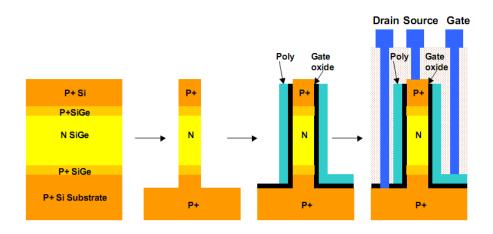

| Figure 2.1 Fabrication flow of SGT [76]12                                                                                        |

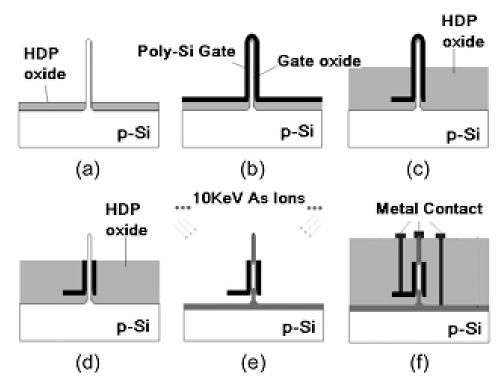

| Figure 2.2 Process flow of vertical MOSFET [77]12                                                                                |

| Figure 2.3 Process flow for pillar and transistor formation [78]                                                                 |

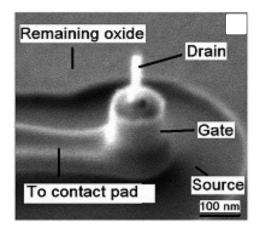

| Figure 2.4 SEM image of vertical NWFET [78]14                                                                                    |

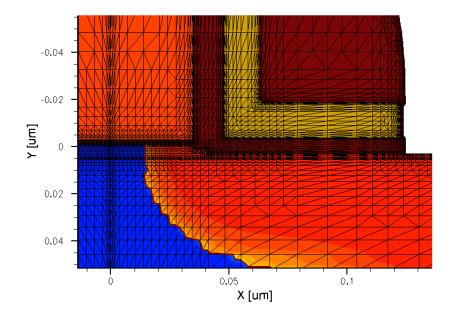

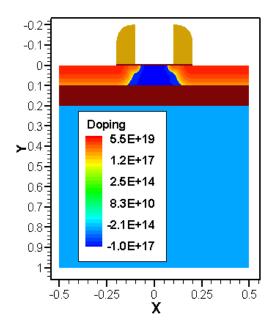

| Figure 3.1 Finite element grid magnified at gate-drain corner of an NMOSFET [66]20                                               |

| Figure 3.2 2D SOI MOSFET obtained using structure editor [66]21                                                                  |

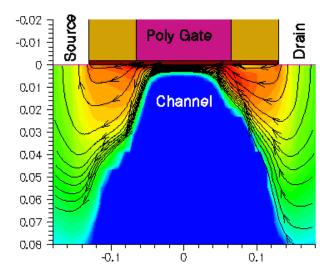

| Figure 3.3 Current flow lines in a 0.13- $\mu$ m NMOSFET at V <sub>gs</sub> = 1.5 V and V <sub>ds</sub> = 3.0 V; shading         |

| represents current density [66]                                                                                                  |

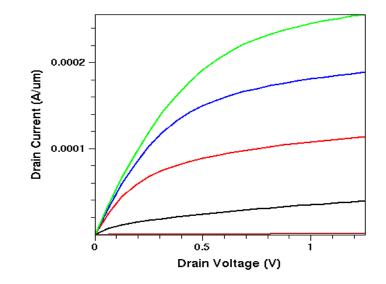

| Figure 3.4 Drain current as function of drain voltage for a 50-nm NMOSFET at $V_{gs} = 0.25, 0.5,$                               |

| 0.75, 1.0, and 1.25 V [66]23                                                                                                     |

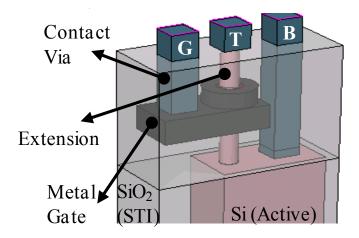

| Figure 3.5 3D isometric view of Vertical nanowire device [127]                                                                   |

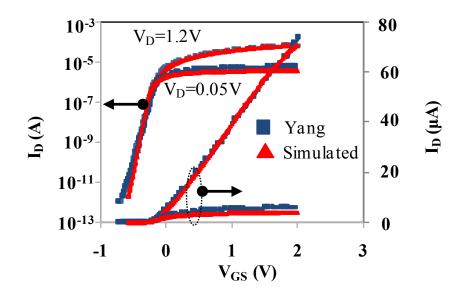

| Figure 3.6 $I_{D}\text{-}V_{GS}$ characteristics of VNWFET device with reported dimensions is found to                           |

| match well with experimentally reported data [57]25                                                                              |

| Figure 3.7 $I_{D}\text{-}V_{GS}$ characteristics of rectangular nanowire device with reported dimensions is                      |

| found to match well with experimentally reported data [135]26                                                                    |

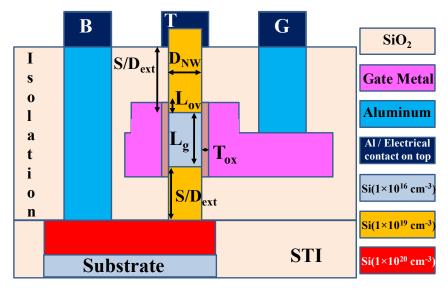

| Figure 4.1 Vertical Nanowire FET structure highlighting important physical dimensions29                                          |

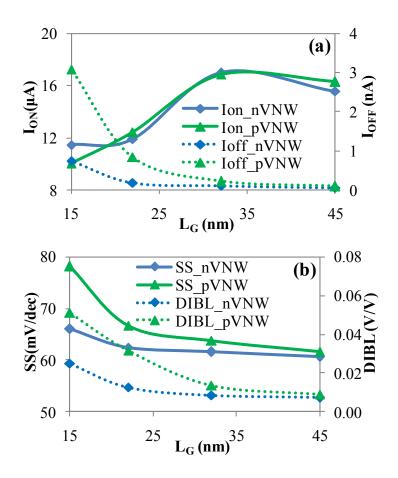

| Figure 4.2 (a) $I_{ON}$ ( $V_{GS} = V_{DS} = V_{DD}$ ) and $I_{OFF}$ ( $V_{GS} = 0V$ , $V_{DS} = V_{DD}$ ) of NMOS and PMOS      |

| VNW FET versus $L_{G}.$ (b) SS and DIBL of NMOS and PMOS VNWFET versus $L_{G}$ showing                                           |

| marginal presence of SCE when $L_G$ is scaled down to 15 nm                                                                      |

| Figure 4.3 $I_{ON}$ ( $V_{GS} = V_{DS} = 0.8$ V) and $I_{OFF}$ ( $V_{GS} = 0V$ , $V_{DS} = 0.8$ V) of (a) n ( $D_{NW} = 10$ nm), |

| (b) p ( $D_{NW}$ = 14 nm) VNW FET drive showing excellent scaling performance with S/ $D_{ext}$ down                             |

| to 10nm. SS and DIBL of (c) NMOS and (d) PMOS VNWFET showing marginal presence of                                                |

| SCE when S/D <sub>ext</sub> =10 nm                                                                                               |

| Figure 4.4 $I_{ON}$ , $I_{OFF}$ variation with respect to gate overlap/underlap length32                                         |

| Figure 4.5 I <sub>ON</sub> , I <sub>OFF</sub> variation with respect to gate dielectric thickness                                |

| Figure 4.6 I <sub>ON</sub> , I <sub>OFF</sub> variation with respect to nanowire diameter variation                              |

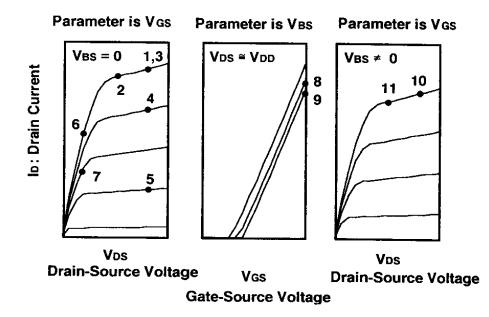

| Figure 4.7 Selected points for model parameter extraction of n <sup>th</sup> power law [67]35                                    |

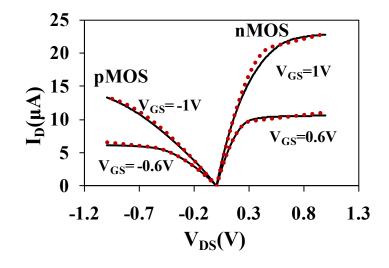

| Figure 4.8 I-V characteristics of NMOS and PMOS VNWFET (L <sub>G</sub> =45nm, S/D <sub>ext</sub> =30nm,                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Diameter=15nm) obtained from simulation (solid lines) and obtained from n <sup>th</sup> power law model                                 |

| (dotted lines) [57]                                                                                                                     |

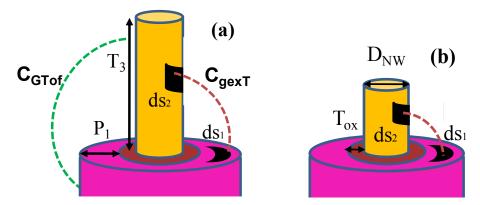

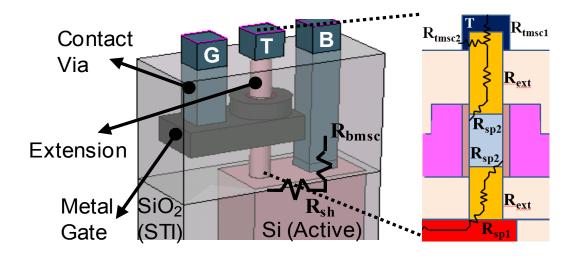

| Figure 5.1 VNW FET 3-D isometric view                                                                                                   |

|                                                                                                                                         |

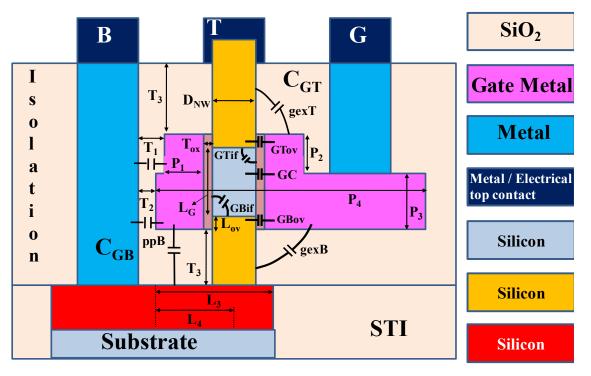

| Figure 5.2 VNWFET 2-D view marked with parasitic capacitance components                                                                 |

| Figure 5.3 <i>GTof</i> and <i>gexT</i> components are identified for (a) Extension length > gate thickness                              |

| (b) Extension Length < gate thickness [139]                                                                                             |

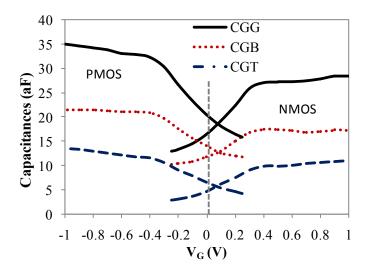

| Figure 5.4 Inter electrode capacitances versus $V_G$ for NMOS and PMOS VNWFET ( $L_G=15$ nm,                                            |

| $S/D_{ext} = 30 \text{ nm and } D_{NW} = 10/15 \text{ nm}$                                                                              |

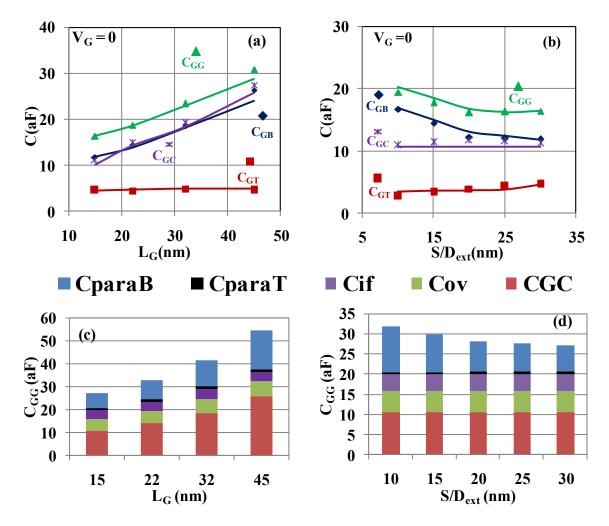

| Figure 5.5 NMOS ( $D_{NW}$ =10nm) simulated (symbol) and modeled (line) parasitic off state                                             |

| capacitances versus (a) $L_G(S/D_{ext}=30\text{nm})$ and (b) $S/D_{ex}(L_G=15\text{nm})$ and individual components                      |

| contributing to $C_{GG}$ versus (c) $L_G$ and (d) $S/D_{ext}$                                                                           |

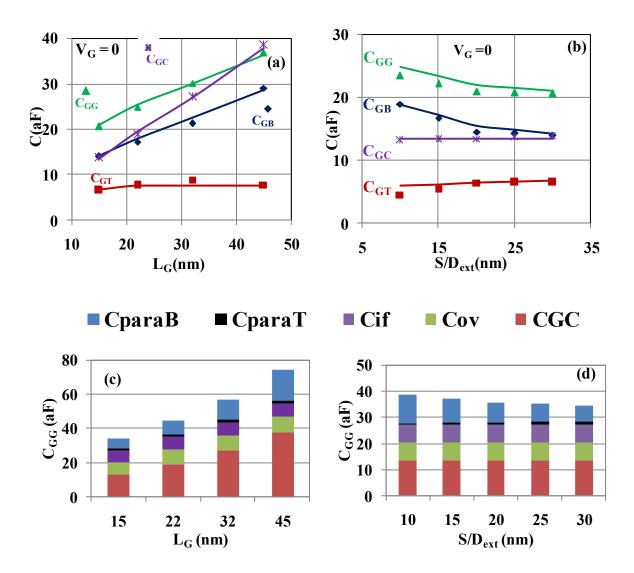

| Figure 5.6 PMOS ( $D_{NW}$ =14/15nm) simulated (symbol) and modeled (line) parasitic off state                                          |

| capacitances versus (a) $L_G$ (S/D <sub>ext</sub> =30nm) and (b) S/D <sub>ex</sub> ( $L_G$ =15nm) and individual components             |

| contributing to $C_{GG}$ versus (c) $L_G$ and (d) $S/D_{ext}$                                                                           |

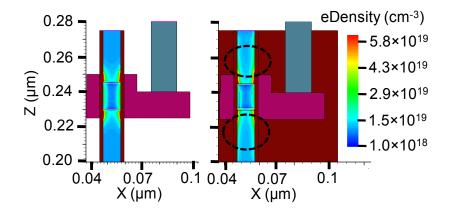

| Figure 5.7 VNW FET 3-D isometric view with individual resistance components identified46                                                |

| Figure 5.8 Electron (e) density profile in the device cross section through nanowire centre                                             |

|                                                                                                                                         |

| shown at $V_G = V_{DD}$ and $V_D = 0.05$ V to highlight the impact of isolation oxide                                                   |

| shown at $V_G = V_{DD}$ and $V_D = 0.05$ V to highlight the impact of isolation oxide                                                   |

|                                                                                                                                         |

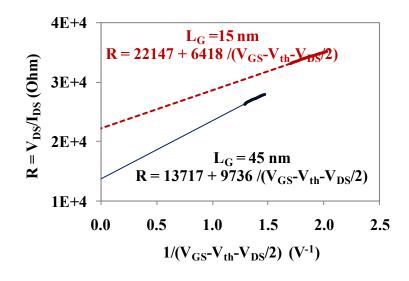

| Figure 5.9 $R_{TB}$ extraction methodology shown for NMOS VNW for $L_G$ = 45 nm and 15 nm,                                              |

| Figure 5.9 $R_{TB}$ extraction methodology shown for NMOS VNW for $L_G = 45$ nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm                 |

| Figure 5.9 $R_{TB}$ extraction methodology shown for NMOS VNW for $L_G = 45$ nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm                 |

| Figure 5.9 $R_{TB}$ extraction methodology shown for NMOS VNW for $L_G = 45$ nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm                 |

| Figure 5.9 $R_{TB}$ extraction methodology shown for NMOS VNW for $L_G = 45$ nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm                 |

| Figure 5.9 R <sub>TB</sub> extraction methodology shown for NMOS VNW for L <sub>G</sub> = 45 nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm |

| Figure 5.9 $R_{TB}$ extraction methodology shown for NMOS VNW for $L_G = 45$ nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm                 |

| Figure 5.9 $R_{TB}$ extraction methodology shown for NMOS VNW for $L_G = 45$ nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm                 |

| Figure 5.9 $R_{TB}$ extraction methodology shown for NMOS VNW for $L_G = 45$ nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm                 |

| Figure 5.9 $R_{TB}$ extraction methodology shown for NMOS VNW for $L_G = 45$ nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm                 |

| Figure 5.9 $R_{TB}$ extraction methodology shown for NMOS VNW for $L_G = 45$ nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm                 |

| Figure 5.9 R <sub>TB</sub> extraction methodology shown for NMOS VNW for L <sub>G</sub> = 45 nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm |

| Figure 5.9 R <sub>TB</sub> extraction methodology shown for NMOS VNW for L <sub>G</sub> = 45 nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm |

| Figure 5.9 R <sub>TB</sub> extraction methodology shown for NMOS VNW for L <sub>G</sub> = 45 nm and 15 nm,<br>S/D <sub>ext</sub> = 30nm |

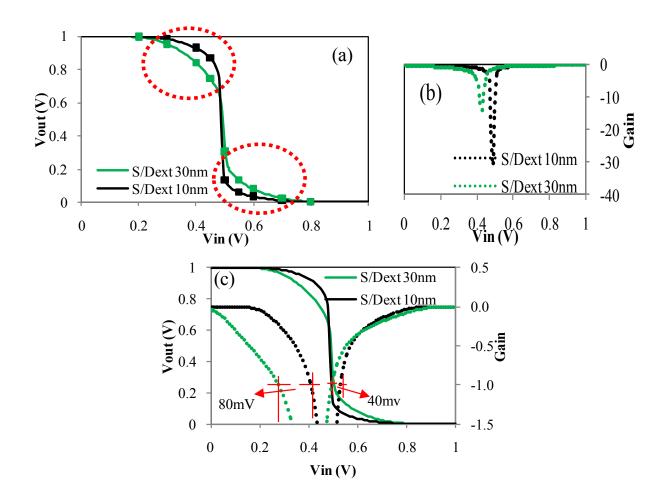

| Figure 6.4 VNW NMOS, PMOS I <sub>D</sub> -V <sub>DS</sub> characteristics with $S/D_{ext} = 10/30$ nm resistance58<br>Figure 6.5 (a) VNW VTC simulated (lines) and VTC generated using I <sub>D</sub> -V <sub>DS</sub> characteristics (symbols) for L <sub>G</sub> =45nm, $S/D_{ext} = 30/10$ nm. (b) Gain of inverter for varying $S/D_{ext}$ . (c) NM extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10/15nm (NMOS/PMOS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

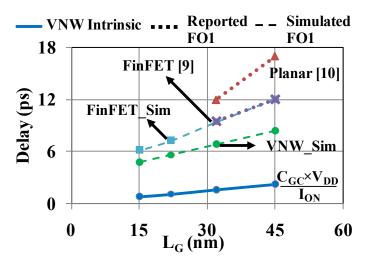

| Figure 6.7 Benchmarking of VNW, simulated FinFET, experimentally reported FinFET and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| planar CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

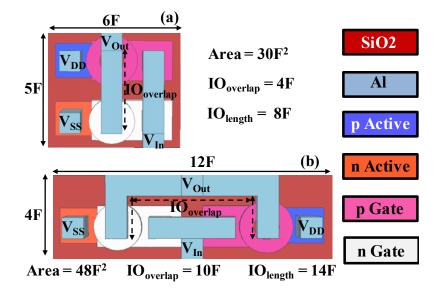

| Figure 6.8 Topview of S <sub>B</sub> inverter (a) L1 layout. (b) L2 layout. F is minimum feature size (15 nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

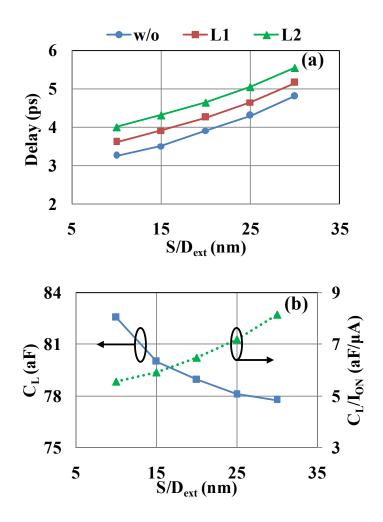

| Figure 6.9 (a) Delay versus S/D <sub>ext.</sub> (b) Load capacitance ( $C_L$ ) and circuit speed metric ( $C_L/I_{ON}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| versus S/D <sub>ext</sub> for S <sub>B</sub> VNW CMOS $L_G = 15 \text{ nm}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

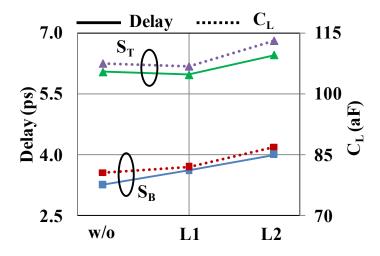

| Figure 6.10 Impact of S/D asymmetry on delay performance and extracted C <sub>L</sub> of different layouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

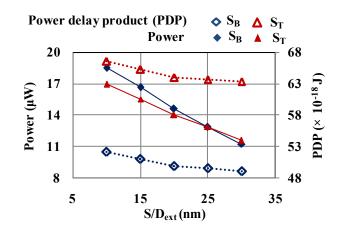

| Figure 6.11 Delay and power variation with $S/D_{ext}$ for $S_B$ and $S_T$ inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 6.12 Power and power delay product (PDP) variation with S/D <sub>ext</sub> for S <sub>B</sub> and S <sub>T</sub> inverters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 6.13 Schematic diagram of two stage inverter chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

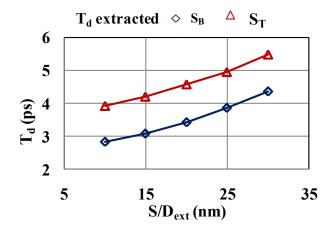

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS ( $L_G$ =15nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS ( $L_G$ =15nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS ( $L_G$ =15nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS ( $L_G$ =15nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS ( $L_G$ =15nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS ( $L_G$ =15nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

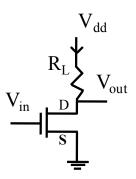

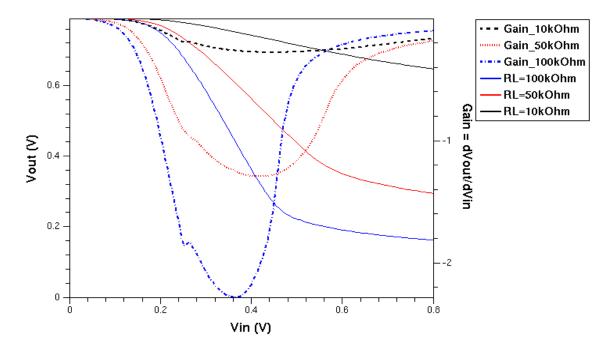

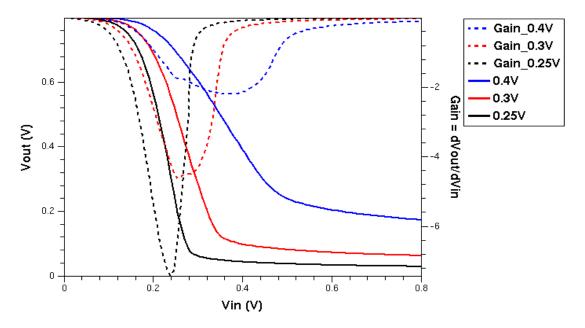

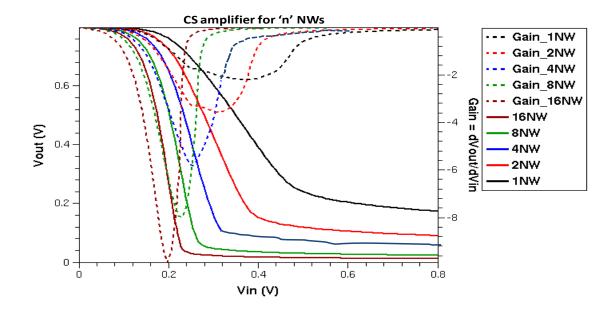

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS( $L_G$ =15nm).66Figure 6.15 CS amplifier circuit topology.67Figure 6.16 CS amplifier $V_{out}$ , gain versus $V_{in}$ for various $R_L$ . VNW device $L_G$ =15nm, $S/D_{ext}$ =20nm.68Figure 6.17 Impact of bias voltage on CS amplifier performance. VNW device $L_G$ =15nm, $S/D_{ext}$ =20nm.68Figure 6.18 Impact of multiple nanowires in VNW on CS amplifier performance. VNW device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS( $L_G$ =15nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS( $L_G$ =15nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS( $L_G$ =15nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS( $L_G$ =15nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS( $L_G$ =15nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 6.14 Delay ( $T_d$ ) extracted-modeled and power versus $S/D_{ext}$ for $S_B$ and $S_T$ VNW CMOS( $L_G$ =15nm).66Figure 6.15 CS amplifier circuit topology.67Figure 6.16 CS amplifier V <sub>out</sub> , gain versus V <sub>in</sub> for various R <sub>L</sub> . VNW device L <sub>G</sub> =15nm, S/D <sub>ext</sub> =20nm.68Figure 6.17 Impact of bias voltage on CS amplifier performance. VNW device L <sub>G</sub> =15nm,S/D <sub>ext</sub> = 20nm.68Figure 6.18 Impact of multiple nanowires in VNW on CS amplifier performance. VNW deviceL <sub>G</sub> =15nm, S/D <sub>ext</sub> = 20nm.69Figure 6.19 Frequency response of intrinsic VNW device (L <sub>G</sub> =15nm, S/D <sub>ext</sub> =20nm, Dia=10nm)biased at V <sub>D</sub> = 0.8V and V <sub>G</sub> = 0.4V.70Figure 6.20 Frequency response of intrinsic FinFET device (L <sub>G</sub> =16nm, S/D <sub>ext</sub> =20nm,W <sub>fin</sub> =10nm, H <sub>fin</sub> =30nm) biased at V <sub>D</sub> = 0.8V and V <sub>G</sub> = 0.4V.70 |

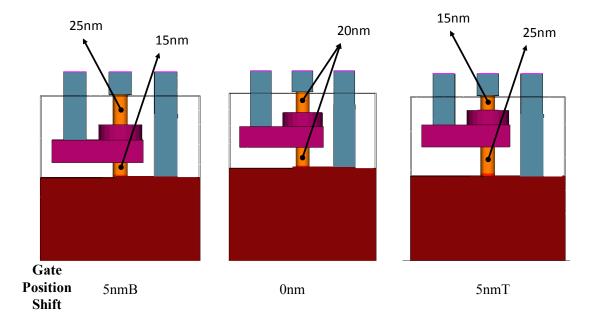

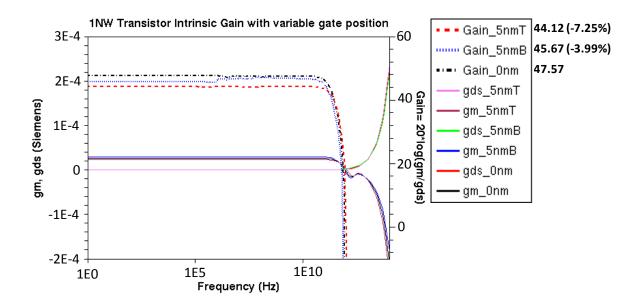

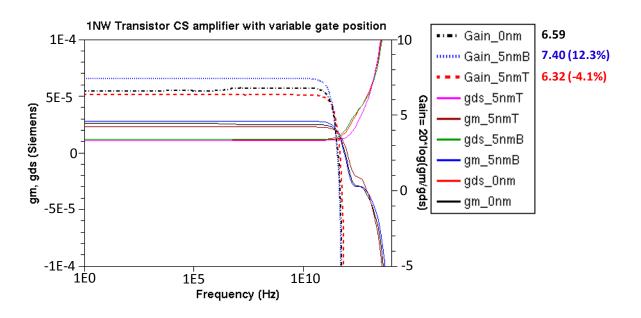

| Figure 6.22 Intrinsic gain of VNW device with variation in gate position71             |

|----------------------------------------------------------------------------------------|

| Figure 6.23 CS amplifier gain of VNW with variation in gate position72                 |

| Figure A.1 3D device structure of a VNWFET with typical dimensions and coarse meshing. |

| The isolation oxide is made translucent to see the nanowire and gate regions           |

| Table 2.1 Natural scale length and minimum channel length of different devices       | 11           |

|--------------------------------------------------------------------------------------|--------------|

| Table 3.1 Device structural parameters used in the thesis.                           | 27           |

| Table 4.1 Extracted n <sup>th</sup> power model parameters for various VNWFET device |              |

| Table 5.1 Parameters used in standard capacitance components.                        | 40           |

| Table 5.2 Parameters used in standard resistance components                          | 47           |

| Table 6.1 Performance comparison of planar, FINFET and VNW inverters for 45          | nm channel   |

| length                                                                               | 60           |

| Table 6.2 Performance of VNW device with increase in number of nanowires an          | nd change in |

| S/D <sub>ext</sub>                                                                   | 69           |

|                                                                                      |              |

# **ABBREVIATIONS AND SYMBOLS**

| C <sub>GB</sub>           | Gate to Bottom electrode capacitance                |

|---------------------------|-----------------------------------------------------|

| C <sub>GG</sub>           | Total gate parasitic capacitance                    |

| C <sub>GT</sub>           | Gate to Top electrode capacitance                   |

| $C_{load}$                | Total output node capacitance                       |

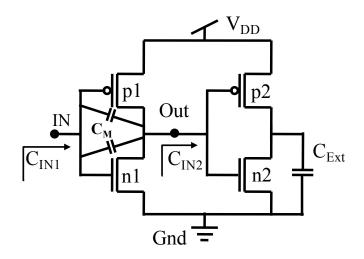

| C <sub>M</sub>            | Miller capacitance                                  |

| CMOS                      | Complementary MOS                                   |

| CS                        | Common Source                                       |

| CVD                       | Chemical Vapor Deposition                           |

| DG                        | Double Gate                                         |

| DIBL                      | Drain Induced Barrier Lowering                      |

| D <sub>NW</sub>           | Nanowire diameter                                   |

| F                         | Minimum feature size                                |

| FPGA                      | Field Programmable Gate Array                       |

| $\mathbf{f}_{\mathrm{T}}$ | Unity gain bandwidth                                |

| GAA                       | Gate-all-around                                     |

| <b>g</b> ds               | Output conductance                                  |

| g <sub>m</sub>            | Transconductance                                    |

| HBT                       | Heterojunction Bipolar Transistor                   |

| HDP                       | High Density Plasma                                 |

| HEMT                      | High Electron Mobility Transistor                   |

| IC                        | Integrated Circuits                                 |

| ITRS                      | International Technology Roadmap for Semiconductors |

| L <sub>G</sub>            | Channel Length                                      |

| L <sub>OV</sub>           | Gate-Overlap/Underlap length                        |

| MG                        | Multi-Gate                                          |

| MOSFET                    | Metal Oxide Semiconductor Field Effect Transistor   |

| NM                        | Noise Margin                                        |

| NW                        | Nanowire                                            |

| R <sub>B</sub>            | Bottom electrode series resistance                  |

| RO                        | Ring Oscillator                                     |

| R <sub>T</sub>            | Top electrode series resistance                     |

|                           |                                                     |

| R <sub>TB</sub>        | Total series resistance                               |

|------------------------|-------------------------------------------------------|

| S/D                    | Source/Drain                                          |

| S/D <sub>ext</sub>     | Source/Drain extension length                         |

| S <sub>B</sub>         | Source as Bottom electrode and drain as top electrode |

| SCE                    | Short Channel Effects                                 |

| SEM                    | Scanning Electron Microscopy                          |

| SGT                    | Surrounding Gate Transistor                           |

| SOI                    | Silicon on Insulator                                  |

| SS                     | Subthreshold Slope                                    |

| S <sub>T</sub>         | Source as Top electrode and drain as bottom electrode |

| STI                    | Shallow Trench Isolation                              |

| TCAD                   | Technology Computer Aided Design                      |

| T <sub>OX</sub>        | Gate dielectric thickness                             |

| $T_{\text{pHL}}$       | High to Low delay                                     |

| $T_{pLH}$              | Low to High delay                                     |

| VLS                    | Vapor –Liquid-Solid                                   |

| VNWFET                 | Vertical Nanowire FET                                 |

| VTC                    | Voltage Transfer Characteristics                      |

| θ                      | Mobility degradation parameter                        |

| λ                      | Natural scale length                                  |

| $\lambda_{\text{CLM}}$ | Channel Length Modulation coefficient                 |

## **INTRODUCTION**

## **1.1 Introduction**

Moore's law [1] has been followed for more than 40 years while scaling down the device dimension of planar/bulk metal oxide semiconductor field effect transistor (MOSFET). To address the scaling related issues, new process technologies such as: lightly doped drain, lateral non-uniformity in channel doping, junctionless device, strained silicon, high-k dielectrics and metal gates have been introduced in complementary metal oxide semiconductor (CMOS) device architecture [2]-[9]. These improvements in fabrication processes have kept the technology in pace with international technology roadmap for semiconductors (ITRS) guidelines for future technology requirements [10]. However, for deca-nanometer and beyond technology nodes, the conventional MOSFET suffers severely from short channel effects (SCE) [2]. Thus the novel devices with multiple gates or 3D structures (Double Gate FET [11]–[13], Fin-FET [14]-[16], and Nanowire (NW) Gate-all-around (GAA) FET) are researched as potential replacements [2], [17]-[21]. These multiple gate devices have better scalability and electrostatic control over channel [22]-[26]. Recently, Intel corp. has reported introduction of 22 nm FinFET (3D transistor) [27]–[30] in their microprocessors named Ivy Bridge, released in 2013 [31], also Taiwan Semiconductor Manufacturing Corporation has released its production details of 28 nm and below technology node planar MOSFET [32]. Other firms like IBM, Samsung are also planning to implement FinFET below 20 nm technology node. Further for sub-50 nm nodes NWFET has been reported by industrial researchers [33]. This underlies the importance and potential of the 3D/multigate or novel devices to extend existing MOSFET scaling limits.

The evolution of MOSFET from single gate through multi-gate to gate all around (GAA) structure having improvement in electrostatic control is shown in Figure 1.1 [25]. In Figure 1.1, double gate FET has the following salient features 1) better SCE control when compared to single gate planar FET due of presence of two gates, 2) tight electrostatic coupling of the gate with the channel due to thin silicon film. These features provide the advantage of: 1) reduction in SCE, resulting in allowable channel length to be much shorter when compared to planar FET, 2) near ideal value of sub-threshold slope SS ( $\sim 60 \text{ mV/dec}$  when compared to > 80

mV/dec for planar FET), which allows gate overdrive to be large for the same off- state current and the same power supply and 3) better carrier transport is observed with reduced channel doping [2].

Among the important 3D or non-planar structure family, the FinFET is considered to be the first member. It is named so, as the silicon channel is etched into the wafer surface like a fin [2]. The fabrication of the FinFET device begins with the formation of a fin obtained by patterning and etching on an SOI/bulk substrate using a hard mask, which is retained throughout the fabrication process. The other derivative devices such as tri-gate, Pi-gate,  $\Omega$ -gate are similarly produced. It is reported that the drive current of FinFET devices rival those of best conventional planar devices [34]–[40]. Despite the non-planar/unconventional device structure and topology, the presence of more than a single gate leads to increase in electrostatic coupling of gate and channel, thus the minimum gate length achieved is among the shortest [2], [41]–[46].

Due to multiple gates in GAA structure, this device architecture is the most effective for better electrostatic control of the channel charge and is resistant to SCEs [25]. One major problem with scaling of planar CMOS is the requirement to shrink gate oxide thickness, which causes increase in tunneling leakages. It is observed that, NW GAA FET can be scaled without proportionally reducing the gate dielectric thickness [47]. Thus, the NW GAA FET is the best device for deca-nanometer dimensions [48].

Figure 1.1 Evolution of device structure from single-gated to GAA NWFET [25].

Nanowires can be obtained by two different fabrication approaches namely: the bottom–up approach and the top–down approach [25]. The bottom up approach is a non-lithographic method in which vapor-liquid-solid (VLS) mechanism is employed using a suitable catalyst and chemical vapor deposition process to produce nanowires. However, these nanowires are

randomly distributed and additional processing steps are necessary to assemble them into functional devices. The top-down approach is a CMOS compatible process and is lithographically used to define the orientation and location of nanowire with respect to wafer surface, thus resulting in two types of devices: 1) vertical pillar nanowires and 2) lateral nanowires [25], [49]–[54].

Between the two types based on orientation of nanowire with respect to surface, the lateral nanowire type follows process steps similar to FinFET. But it employs an additional step after the Si fin formation, which is to convert the rectangular fin to a cylindrical wire structure. It is achieved by first etching away a part of the buried oxide or etching the dummy layer (introduced so that the fin can be released in air) and then oxidizing the fin. This is followed by an oxide etching to release the nanowire which is supported at its ends by the source/drain pads as shown in Figure 1.2.

Figure 1.2 3D device structure of lateral nanowire supported by source/drain pads at its ends [55].

Vertical nanowire structure shown in Figure 1.3 follow different process steps than used for lateral nanowire device. The first step involves formation of vertical pillar structure by selective deep etching of silicon with hard mask resist dots [56]. In this device structure substrate acts as source, the nanowire tip acts as drain and channel in between them. Also source and drain electrodes can be interchanged. The gate around the nanowire channel is obtained by special processing steps, which will be presented in detail in next chapter.

Figure 1.3 3D isometric view of Vertical Nanowire device [57].

In this thesis, the studies on design and analysis of vertical silicon nanowire gate all around FET (NW GAAFET) devices and circuits are presented. The device structure used is a modified version of VNW structure reported by Yang et al. [56].

#### **1.2 Motivation**

Among the different 3D device structures discussed in the previous section, the vertical NW GAA FET has the best SCEs performance due to multiple gate structure and also occupies the least silicon wafer area owing to its vertical architecture. Thus, ultra dense integrated circuits (IC) for high performance applications can be obtained using these devices.

Further, the VNW GAA FET devices can be fabricated in vias, which is a step towards reconfigurable logic which can be widely used in field programmable gate arrays (FPGA) and can also be used to introduce logic functions in interconnects [58]. This improves performance in terms of area, delay and power. Furthermore, the VNWs also have good potential to realize high sensitivity chemical [59] or bio sensors [60]–[63], gas sensors [64] and solar cells [65].

From the extensive literature survey presented in chapter 2, we find that the vertical nanowire device performance with respect to various device dimensions is necessary for optimization. The impact of device asymmetry and different layouts arising thereby are not yet studied. Also, the impact of parasitic on device and circuit performance needs to be quantified in terms of various parasitic components, which can be estimated by developing appropriate models.

Thus, the literature gaps/issues and the advantages of VNW GAA FET listed above have motivated us in carrying out detailed device and circuit analysis in this work. The work has been extensively carried using 3D TCAD simulator i.e., Sentaurus (version 2009.10), which is the state of the art virtual fabrication and characterization software package supplied by Synopsys Inc. [66].

The work presented in this thesis addresses optimization of VNW device and presents various circuit design issues when working with VNW devices. This can be used by device and circuit engineers in industry to take a leap forward in developing low power memory applications, digital logic and analog circuit design.

## 1.3 Objectives

In this thesis, work has been carried out on device and circuit performance of vertical nanowire (VNW) silicon MOSFET compatible with CMOS technology. The study has the following objectives:

1. Thorough analysis of vertical nanowire device in terms of performance parameters ( $I_{ON}/I_{OFF}$  ratio, SS, drain induced barrier lowering - DIBL) at sub 45nm channel lengths, where the series source/drain resistance and parasitic capacitances are expected to affect the device performance significantly.

2. To evaluate device performance and process variation, the impact of device parameters such as channel length, wire diameter, source/drain asymmetry and S/D extension region length  $(S/D_{ext})$  on device characteristics.

3. A comprehensive parasitic model for resistance and capacitance, which can take into account the device asymmetry and cylindrical structure is developed for VNW device. Further, the device I-V modeling is realized with n<sup>th</sup> power law [67].

4. Finally, thorough circuit analysis is carried out, in order to demonstrate the better circuit performance potential of VNW devices. Firstly, performance of digital circuits [68], [69] with the help of CMOS inverter is investigated considering some of the device scaling parameters & the impact of source/drain asymmetry, and different layouts arising thereby. Secondly, the n<sup>th</sup> power law and parasitic capacitance models are used to analyze the delay trends. Finally, analog performance [70] of VNW device is analyzed using common-source (CS) amplifier to complete the study. We highlight the better performance of VNW CMOS by comparing and benchmarking the results with reported FinFET/planar technologies.

## **1.4 Thesis Organization**

This thesis is organized into different chapters as below:

*Chapter 1:* In this chapter, introduction is presented with brief highlights of technological advancements in the field of MOSFET devices to date. Further, the motivation arising out of technical gaps/issues and advantages of using VNW devices are presented. Finally the various objectives addressed through this thesis are pointed out along with thesis organization details.

*Chapter 2:* This chapter provides detailed literature review of MOSFET device evolution along with the need and advantages of VNW device. The technical gaps in the existing literature on VNW device performance, device modeling, digital and analog circuit performance are discussed. The chapter is concludes with a brief summary of technical gaps to be addressed in the thesis.

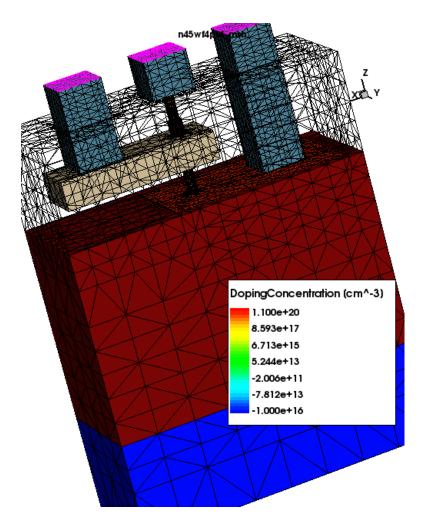

*Chapter 3:* In this chapter, TCAD details of implemented VNW MOS structures, simulation models and related tools are discussed. A well calibrated TCAD simulation setup is established. This is carried out by creating an equivalent structure of reported device [56] and [52] to match the I-V characteristics at low and high  $V_{DS}$ . This also includes selection of appropriate physical models for carrier transport, velocity saturation, contact resistance, surface and bulk scatterings, along with quantization effects. Finally, the complete details of device and important model parameters, which are used in simulations carried in this thesis work is presented. This is followed by details of simulation setup such as DC sweep parameters, AC parameters for device analysis and transient parameters for circuit analysis.

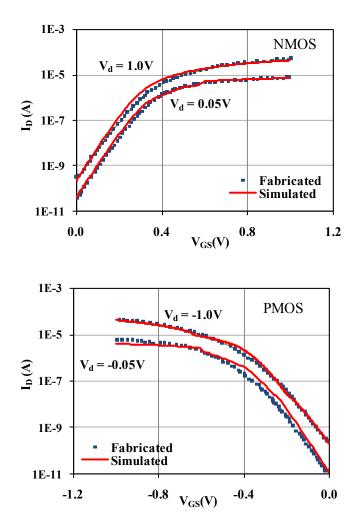

*Chapter 4:* This chapter deals with the VNW device performance in terms of  $I_{ON}$ ,  $I_{OFF}$ ,  $I_{ON}/I_{OFF}$  ratio, SS, DIBL with channel length scaling from 45 to 15nm, for both NMOS and PMOS. Important results, such as  $I_{ON}/I_{OFF} > 10^4$ , SS ~ 60 – 70 mV/dec and DIBL < 30 mV, highlight greater control of short channel effects due to surrounding gate architecture. For 15nm channel length devices, performance is analysed in terms of wire diameter variations, source/drain asymmetry and S/D<sub>ext</sub> length. This study highlights importance of achieving matched drive currents for NMOS and PMOS, which differ by a non integral factor (~ 1.4) with the help of single nanowire devices, as opposed to multi nanowire/fins required in lateral novel devices. Finally, the device I-V characteristics are modeled with nth power law, which will be employed later in circuit delay prediction. The chapter concludes with highlights of the important device performance parameters found.

*Chapter 5:* This chapter focuses on modeling of parasitic resistance and capacitance present in VNW devices. In these models, the inherent device asymmetry and device structural topology such as the cylindrical gate, rectangular vias, gate extension and contact pad overlapping the tip of nanowire are considered. Further, the impact of device scaling on these parasitic components is thoroughly investigated, and emphasis is given on the major parasitic contributors. The results depicts that nearly 50% of the total series resistance is contributed by the metal semiconductor contacts and the total parasitic capacitance is nearly 1.5 to 2 times the channel

capacitance. This chapter ends with the highlights of the important aspects of parasitic modeling and its importance in compact modeling.

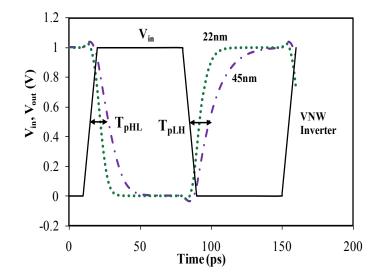

*Chapter 6:* This chapter discusses the circuit performance of VNW devices in detail. The digital circuit performance is carried out with CMOS inverter circuit with device scaling and is benchmarked with existing literature for FinFET and planar CMOS inverters. The results show better performance of VNW based circuits and justify its usefulness in low power applications. For 15nm VNW devices, complete performance analysis of CMOS inverter is presented with respect to S/D extension length, S/D asymmetry and impact of different layouts arising thereby. The results show ~65% better delay performance by devices with drain at top as compared to devices with drain at bottom. Moreover, detailed insight into static characteristics of VNW CMOS inverter and the use of S/D<sub>ext</sub> as tuning parameter to obtain required gain and noise margin is presented provided.

Further, analog performance of 15nm VNW device are analysed for intrinsic device and common-source amplifier in terms of performance metrics such as gain, 3dB bandwidth and unity gain bandwidth ( $f_T$ ), and are compared with FinFET technologies at same node. It is observed that VNW devices have nearly 40% higher gain and 66% higher  $f_T$  when compared to equivalent FinFET device. In a VNW device the impact of extension length and number of nanowires over gain of intrinsic device and CS amplifier is studied. Also, the position of gate can be used to obtain VNW based amplifier with required gain and  $f_T$ . The chapter ends with a summary of important circuit performance metrics and guidelines.

*Chapter 7:* This chapter concludes the present study and results obtained. Further, recommended research directions for future investigations are also discussed.

## LITERATURE SURVEY

In the previous chapter, introduction to the thesis is presented with an emphasis on VNWFET. In this chapter the VNWFET literature is discussed, and research gaps which are investigated in this thesis are identified. The scaling theory of MOSFETs and best scaling performance of NWFETs are briefly described. It is followed by discussion on different fabrication approaches reported in literature for VNWFET. The various silicon data related to NWFET are presented from literature with comparison to state of the art FinFET and planar devices. Further, we briefly highlight different models proposed for NWFET current-voltage and capacitance-voltage characteristics. We then present various circuit performance metrics reported in literature for VNWFET. The warious as CMOS, tunnel FET, SONOS memory, etc. Finally, the chapter is concluded by identifying research gaps to be addressed through this thesis.

## 2.1 Scaling Theory

C.P. Auth *et al.*, [71] have presented the scaling theory of GAA MOSFET considering cylindrical form of Poisson's equation, assuming a parabolic potential in radial direction. They have compared scaling theory of cylindrical MOSFET with the double gate (DG) MOSFET [72], and observed nearly 40% improvement in minimum effective channel length for cylindrical MOSFET. The scaling theory of cylindrical MOSFET as proposed by Auth *et al.*, is as follows:

A parabolic solution is assumed for the potential,  $\Phi(r,z)$ , in cylindrical co-ordinates as:

$$\emptyset(\mathbf{r}, \mathbf{z}) = c_0(\mathbf{z}) + c_1(\mathbf{z})\mathbf{r} + c_2(\mathbf{z})\mathbf{r}^2$$

(2.1)

to find the solution of Poisson's equation in cylindrical co-ordinates represented as

$$\frac{1}{r}\frac{\partial}{\partial r}\left(r\frac{\partial}{\partial r}\phi(r,z)\right) + \frac{\partial^2}{\partial z^2}\phi(r,z) = \frac{qN_a}{\varepsilon_{si}}$$

(2.2)

where N<sub>a</sub> is the uniform channel doping.

The following three boundary conditions are necessary to obtain a solution:

1) The center potential ( $\Phi_c$ ) is independent of radius term and varies as a function of z

$$\phi(0, z) = \phi_{c}(z) = c_{0}(z)$$

(2.3)

2) Due to cylindrical geometry the electric field in the center of the nanowire is zero

$$\frac{d}{dr}\phi(r,z)|_{r=0} = 0 = c_1(z)$$

(2.4)

3) Using the gate potential ( $\Phi_{gs}$ ) and surface potential ( $\Phi_s$ ), the electric potential at Si/SiO<sub>2</sub> interface is given as

$$\frac{d}{dr}\phi(r,z)\big|_{r=\frac{t_{si}}{2}} = \frac{\varepsilon_{ox}}{\varepsilon_{si}}\left(\left(\phi_{gs} - \phi_{s}(z)\right) / \left(\frac{t_{si}}{2}\ln\left(1 + \frac{2t_{ox}}{t_{si}}\right)\right)\right) = t_{si}c_{2}(z)$$

(2.5)

The solution of potential after eliminating surface potential is given by

$$\phi(r,z) = \phi_c(z) - \left( \left( 2\varepsilon_{ox} r^2 \left( \phi_c(z) - \phi_{gs} \right) \right) / \left( \varepsilon_{si} t_{si}^2 \ln \left( 1 + \frac{2t_{ox}}{t_{si}} \right) + \frac{\varepsilon_{ox} t_{si}^2}{2} \right) \right)$$

(2.6)

Using the above potential, solution of the Poisson's equation at the nanowire centre r = 0 is given by

$$\frac{\partial^2}{\partial z^2} \phi_c(z) - \left(\phi_c(z) - \phi_{gs}\right) / \lambda^2 = q N_a / \varepsilon_{si}$$

(2.7)