### PERFORMANCE INVESTIGATION OF PV BASED 3-LEVEL INVERTER USING 2-LEVEL INVERTERS

#### A DISSERTATION

Submitted in partial fulfillment of the requirements for the award of the degree

of

#### MASTER OF TECHNOLOGY

in

#### ELECTRICAL ENGINEERING

(With specialization in Electric Drives and Power Electronics)

By

#### ASHISH SRIVASTAVA

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE - 247 667 (INDIA) June 2016

### Candidate's Declaration

I hereby declare that this thesis report entitled **PERFORMANCE INVES-TIGATION OF PV BASED 3-LEVEL INVERTER USING 2-LEVEL INVERTERS**, submitted to the Department of Electrical Engineering, Indian Institute of Technology, Roorkee, India, in partial fulfillment of the requirements for the award of the Degree of Master of Technology in Electrical Engineering with specialization in Electric Drives and Power Electronics is an authentic record of the work carried out by me during the period June 2015 through May 2016, under the supervision of **Prof. S. P. SINGH, Department of Electrical Engineering, Indian Institute of Technology, Roorkee.** The matter presented in this thesis report has not been submitted by me for the award of any other degree of this institute or any other institutes.

Date:

Place: Roorkee

Ashish Srivastava Enrolment No:14527004

### Certificate

This is to certify that the above statement made by the candidate is true to the best of my knowledge and belief.

#### Prof. S. P. SINGH

Professor Department of Electrical Engineering Indian Institute of Technology Roorkee

i

### Abstract

This Thesis presents a photovoltaic supply system fed multilevel inverter for pump load with common mode voltage elimination, the cascaded MLI topology is needed only 12 switches and no extra clamping devices required unlike others MLIs, which make it unique and suitable modulation technique provide the reliable single stage conversion with PV system. The modulation technique used is for tracking maximum power point and also to converts dc from PV to ac for a resistive load, inductive load and for a pump load. The unique solution to eliminate common mode voltage is also discussed, in the proposed method to eliminate common mode voltage series voltage is injected through 4-winding transformer which makes the common mode to zero. The voltage THD from the proposed method is less as compared to conventional method of common mode votage elimination. The sinusoidal level shift PWM method and space vector pulse width modulation method are used to generate the switching pulses for the MLI while modulation index for switching of MLI is controlled by incremental conductance or perturbation and observation algorithm. The proposed topology is compared with three well known basic MLI topologies on the basis of component used. As compared to generally used two stage conversion techniques this single stage system is having higher efficiency, reliability and reduced cost. The complete system is developed and tested on MATLAB/ Simulink, the hardware prototype is also developed and tested.

### Acknowledgements

I would like to express my deep sense of gratitude and sincere thanks to my guide **Prof. S. P. SINGH**, Department of Electrical Engineering, Indian Institute of Technology Roorkee, for his valuable guidance and support. I am highly indebted to him for his encouragement and constructive criticism throughout the course of this project work. Inspite of his hectic schedule, He was always there for clarifying my doubts and reviewed my dissertation progress in a constructive manner. Without his help, this thesis would not have been possible. I also very Thank full to **Prof. PRAMOD AGARWAL**, **Asst. Prof. AVIK BHATTACHARYA** and **Ass t. Prof. ANUBRATA DEY** for giving me valuable guidance, i would like to thank all faculty members of Electrical Engineering Department for their help and encouragement to complete this report.

I would like to record my sincere gratitude for the blessings of my parents for their encouragement and moral suport during the course of this study. Also I would like to thank Ajay K Maurya, Ravindra Dogga and Ankit, Research Scholars, Department of Electrical Engineering and for all those who in any manner directly or indirectly, put a helping hand in every bit of completion of this Project.

Ashish Srivastava

## Contents

| Ca | andic                          | late's Declaration                                                                                                                                                                                                                                                                                                                                                            | i                                                                                   |

|----|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Al | ostra                          | ict                                                                                                                                                                                                                                                                                                                                                                           | ii                                                                                  |

| A  | cknov                          | wledgements                                                                                                                                                                                                                                                                                                                                                                   | iii                                                                                 |

| Li | st of                          | Figures                                                                                                                                                                                                                                                                                                                                                                       | vii                                                                                 |

| Li | st of                          | Tables                                                                                                                                                                                                                                                                                                                                                                        | x                                                                                   |

| Ał | obre                           | viations                                                                                                                                                                                                                                                                                                                                                                      | xi                                                                                  |

| 1  | $1.1 \\ 1.2 \\ 1.3 \\ 1.4$     | ProductionRSEARCH MOTIVATIONLITERATURE SURVEYOBJECTIVE OF DISSERTATION WORKORGANISATION OF REPORTORGANISATION OF REPORTONOULTAIC MODULES AND ARRAYMODELING OF PV PANELSCURRENT-VOLTAGE AND POWER- VOLTAGE CURVESPHOTOVOLTAIC POWER GENERATING SYSTEMMAXIMUM POWER POINT TRACKING TECHNIQUES2.5.1Perturbation and Observation (P&O)2.5.2Incremental Conductance (IC)CONCLUSION | 1<br>2<br>3<br>10<br>10<br>10<br>11<br>11<br>12<br>13<br>15<br>16<br>17<br>19<br>21 |

| 3  | <b>Mu</b><br>3.1<br>3.2<br>3.3 | Iti-Level Inverter TopologiesINTRODUCTIONADVANTAGES AND DISADVANTAGES OF MLIMULTILEVEL POWER CONVERTER TOPOLOGIES                                                                                                                                                                                                                                                             | <ul> <li>23</li> <li>23</li> <li>24</li> <li>25</li> </ul>                          |

|   | 3.4<br>3.5<br>3.6<br>3.7 | NEUTRAL POINT CLAMPED (NPC) MLI                                      | 26<br>28<br>30<br>31<br>34 |

|---|--------------------------|----------------------------------------------------------------------|----------------------------|

|   | 3.8                      | CONCLUSION                                                           | 38                         |

| 4 | Moo                      | dulation Strategies                                                  | 39                         |

|   | 4.1                      | INTRODUCTION                                                         | 39                         |

|   | 4.2                      | MULTILEVEL CONVERTER PWM STRATEGIES                                  | 40                         |

|   | 4.3                      | SINUSOIDAL PULSE WIDTH MODULATION (SPWM)                             | 41                         |

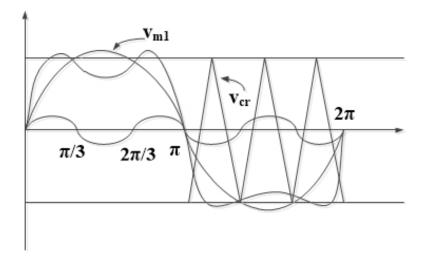

|   | 4.4                      | THIRD HARMONIC INJECTION PWM                                         | 42                         |

|   | 4.5                      | SPACE VECTOR PULSE WIDTH MODULATION                                  | 43                         |

|   |                          | 4.5.1 Space Vectors                                                  | 44                         |

|   |                          | 4.5.2 classification, magnitude and switching state of space vectors | 45                         |

|   |                          | 4.5.3 Dwell Time Calculation                                         | 48                         |

|   |                          | 4.5.4 Identification of Triangle                                     | 49                         |

|   | 4.6                      | PERFORMANCE EVALUATION                                               | 53                         |

|   | 4.7                      | COMMON MODE VOLTAGE                                                  | 54                         |

|   | 4.8                      | COMMON MODE VOLTAGE ELIMINATION METHOD                               | 56                         |

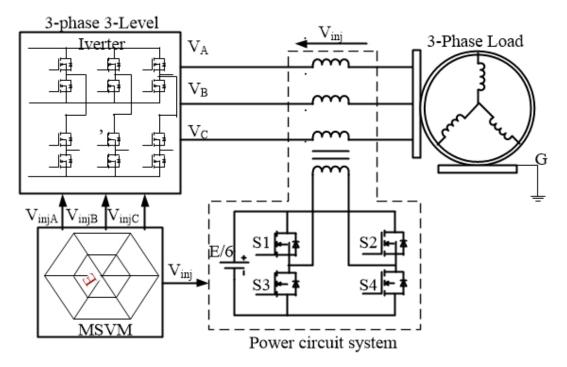

|   | 4.9                      | PPROPOSED CMV ELIMINATION METHOD                                     | 57                         |

|   | 4.10                     | CONCLUSION                                                           | 60                         |

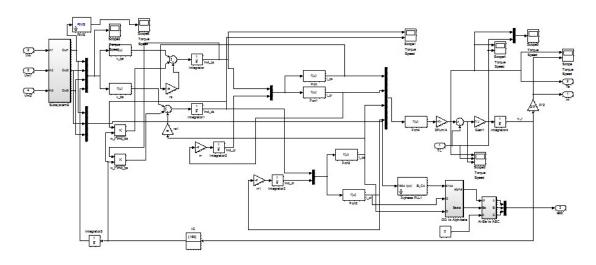

| 5 | Оре                      | eration and Modeling of Proposed System                              | 61                         |

|   | 5.1                      | INTRODUCTION & OPERATION OF PROPOSED SYSTEM                          | 61                         |

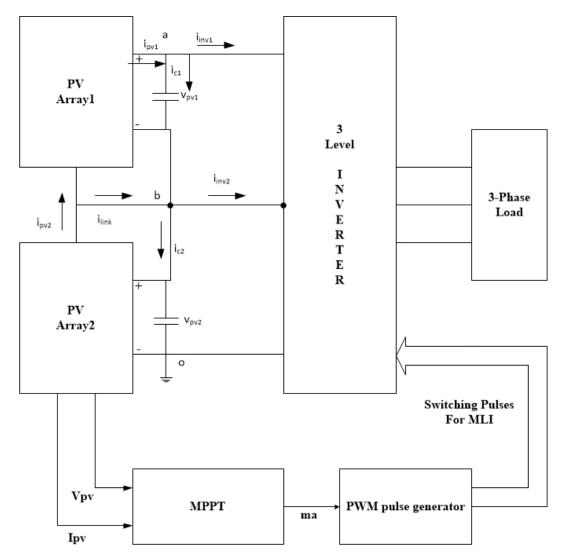

|   | 5.2                      | PV SOURCE MODEL                                                      | 64                         |

|   | 5.3                      | THREE-LEVEL CASCADED-INVERTER MODEL                                  | 64                         |

|   | 5.4                      | PUMP LOAD                                                            | 66                         |

|   | 5.5                      | INDUCTION MOTOR MODELING                                             | 67                         |

|   | 5.6                      | V/f CONTROL                                                          |                            |

|   | 5.7                      | CONCLUSION                                                           | 72                         |

| 6 | Per                      | formance Evaluation using MATLAB/Simulink                            | 73                         |

|   | 6.1                      | PHOTOVOLTAIC MODULE                                                  | 73                         |

|   | 6.2                      | SVPWM TECHNIQUE                                                      | 74                         |

|   | 6.3                      | CONVENTIONAL COMMON MODE VOLTAGE ELIMINATION                         |                            |

|   |                          | METHOD                                                               | 76                         |

|   | 6.4                      | ACMV ELIMINATION METHOD                                              | 79                         |

|   | 6.5                      | PUMP LOAD WITH SPWM                                                  | 82                         |

|   | 6.6                      | CONCLUSION                                                           | 87                         |

| 7 | Har                      | dware Implementation                                                 | 88                         |

|   | 7.1                      | DESIGN OF HARDWARE COMPONENTS                                        | 89                         |

v

| 7.1.1 MOSFET Driver Circuit        | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.1.2 Snubber Circuit and varistor | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

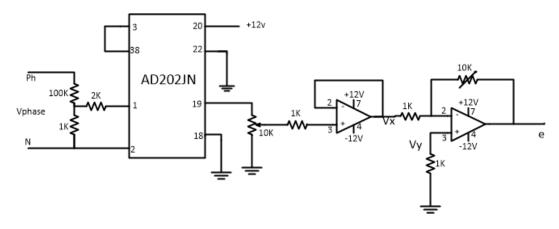

| 7.1.3 Voltage Sensing Circuit      | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

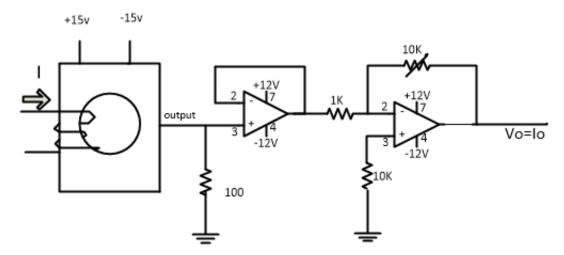

| 7.1.4 Current Sensing Circuit      | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

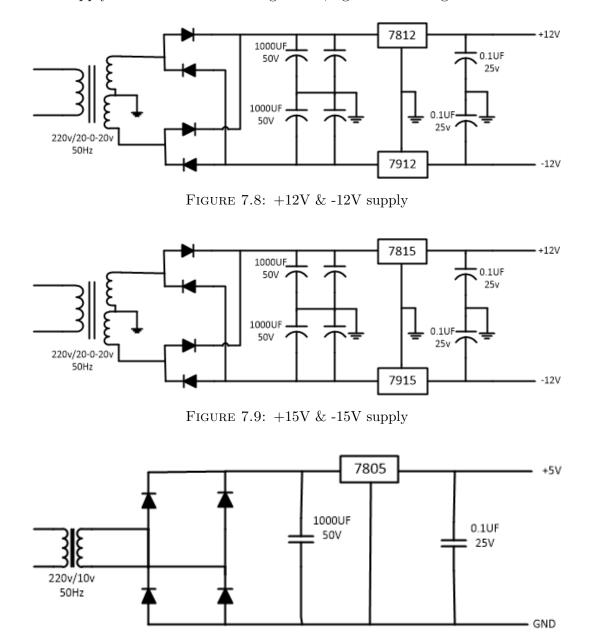

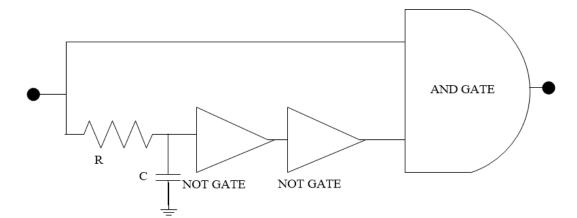

|                                    | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                    | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| onclusion & Future Scope           | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| cations                            | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ences                              | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ndix A                             | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                    | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                    | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ndix B                             | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                    | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                    | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ndix C                             | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

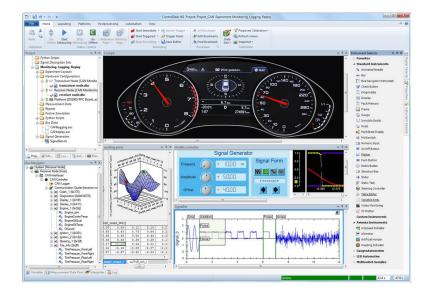

| dSPACE CONTROLDESK                 | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                    | 7.1.2       Snubber Circuit and varistor         7.1.3       Voltage Sensing Circuit         7.1.4       Current Sensing Circuit         7.1.5       Power Supplies         7.1.6       Dead Band         HARDWARE RESULTS       CONCLUSION         conclusion & Future Scope         cations         ences         ndix A         SIMULATION MODEL OF SVPWM BASED THREE LEVEL         CASCADED INVERTER FOR RL-LOAD         MATHEMATICAL MODEL OF THE THREE PHASE INDUC-         TION MOTOR WITH PUMP LOAD         matix B         INDUCTION MOTOR PARAMETERS FOR PUMP LOAD         SPECIFICATION OF ONE SOALR PV MODULE         MATLAB Code for MPPT P&O |

# List of Figures

| 2.1  | PV cell, modules and array                                              | 12 |

|------|-------------------------------------------------------------------------|----|

| 2.2  | Single diode model of PV cell                                           | 12 |

| 2.3  | I-V Curve of a typical silicon PV cell                                  | 14 |

| 2.4  | P-V characteristic of the PV cell                                       | 14 |

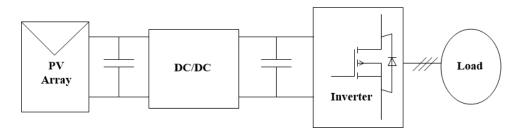

| 2.5  | Two stage topology                                                      | 15 |

| 2.6  | Single stage topology                                                   | 15 |

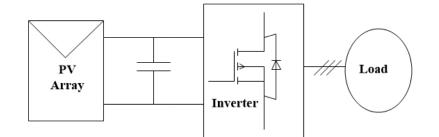

| 2.7  | Current v/s voltage and power v/s voltage characteristics at various    |    |

|      | solar irradiations                                                      | 17 |

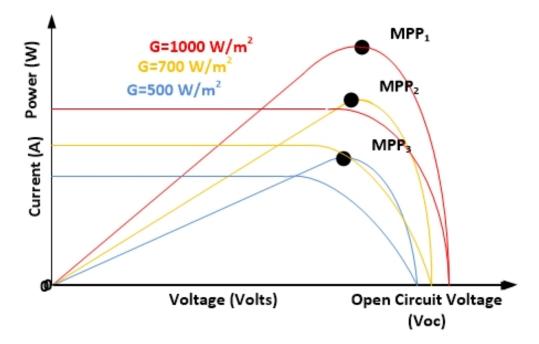

| 2.8  | Flow chart of Perturbation and observation method                       | 18 |

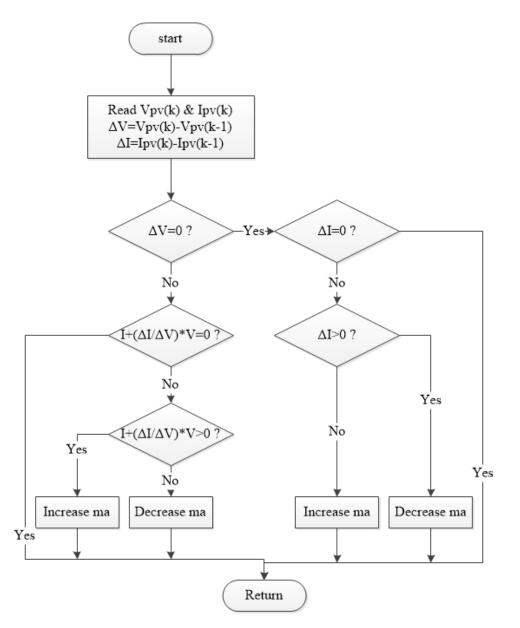

| 2.9  | Flow chart of Incremental conductance method                            | 20 |

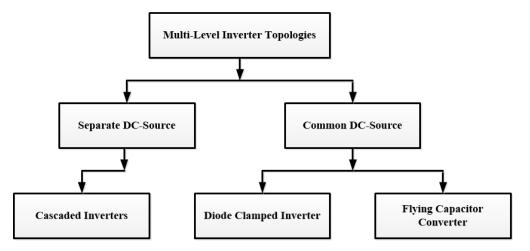

| 3.1  | classifications of Multi-level converters                               | 25 |

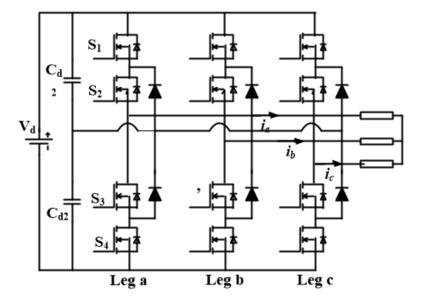

| 3.2  | Three level NPC Inverter                                                | 26 |

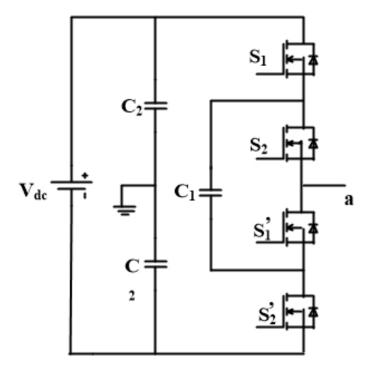

| 3.3  | One phase leg of three level Capacitor Inverter                         | 29 |

| 3.4  | Cascaded H-bridge topology with two cells                               | 30 |

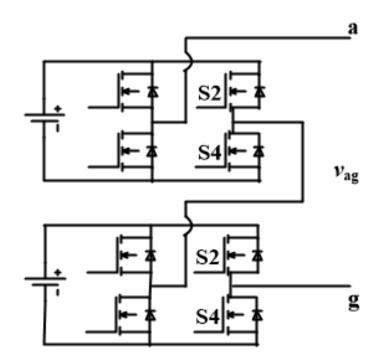

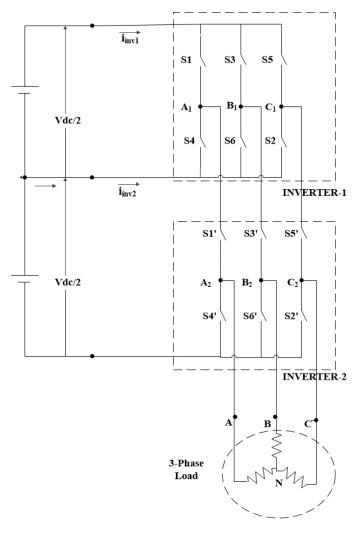

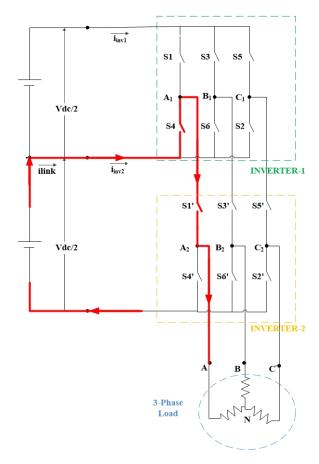

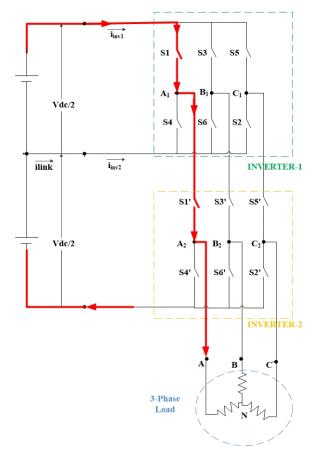

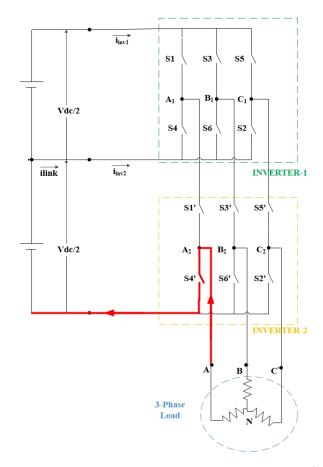

| 3.5  | The circuit configuration of cascaded three-level inverter              | 32 |

| 3.6  | switching states for Vdc/2 Pole voltage $(V_{A20})$                     | 33 |

| 3.7  | switching states for Vdc Pole voltage $(V_{A20})$                       | 34 |

| 3.8  | switching states for Zero Pole voltage $(V_{A20})$                      | 35 |

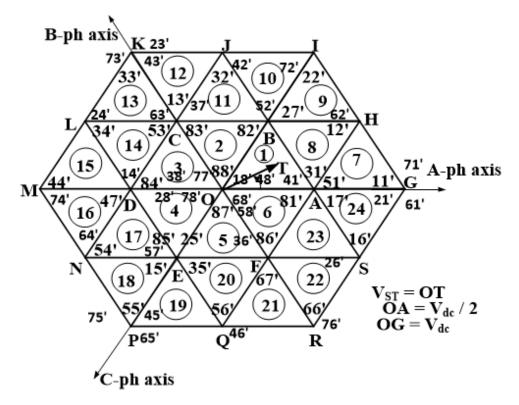

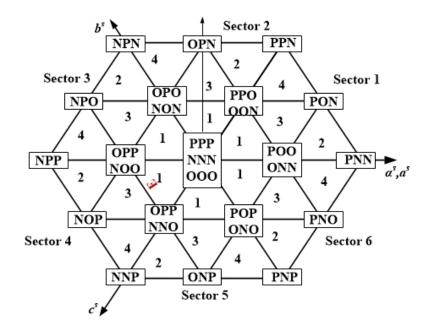

| 3.9  | Space vector locations and combinations in the novel cascaded inverter  | 36 |

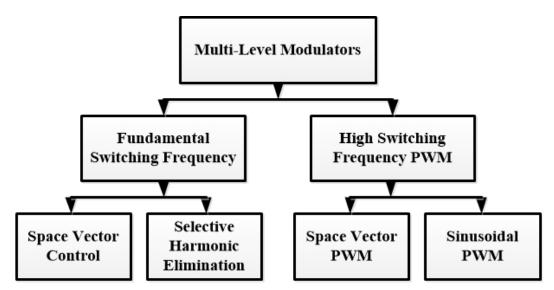

| 4.1  | Classification of PWM multilevel converter modulation strategies .      | 40 |

| 4.2  | Modulating wave VmA with third harmonic injection                       | 42 |

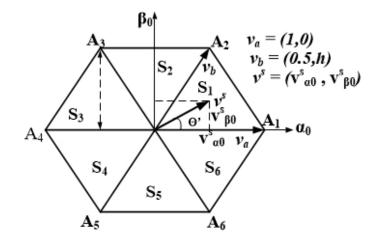

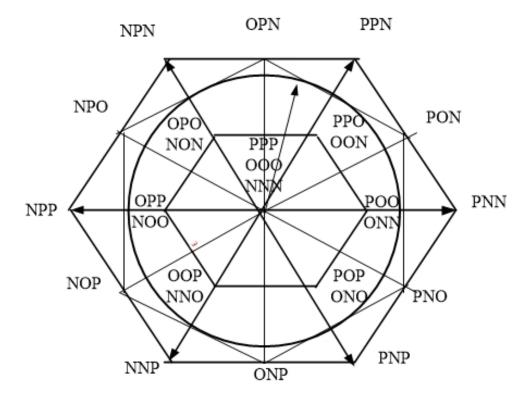

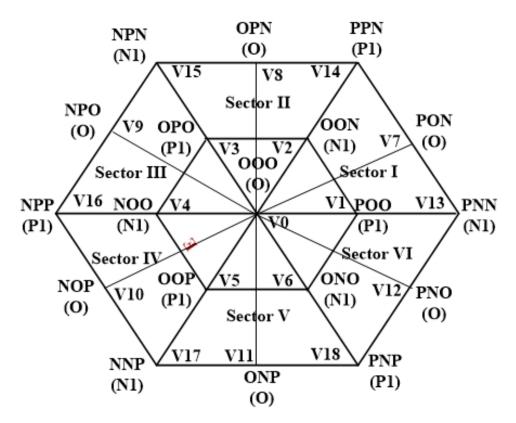

| 4.3  | Space-vector diagram showing switching states for three-level inverter  | 45 |

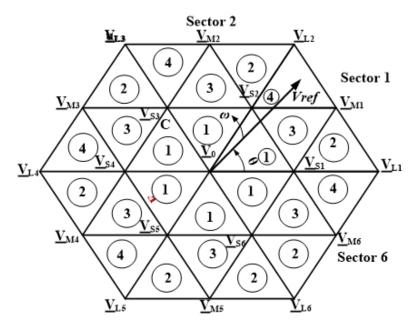

| 4.4  | Space vector with sector and region definition for three-level inverter | 45 |

| 4.5  | Space vector placement and regions in sector 1                          | 46 |

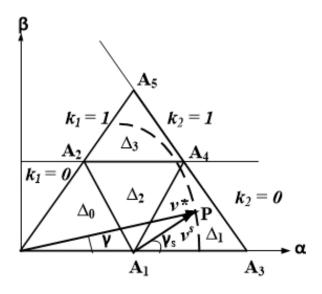

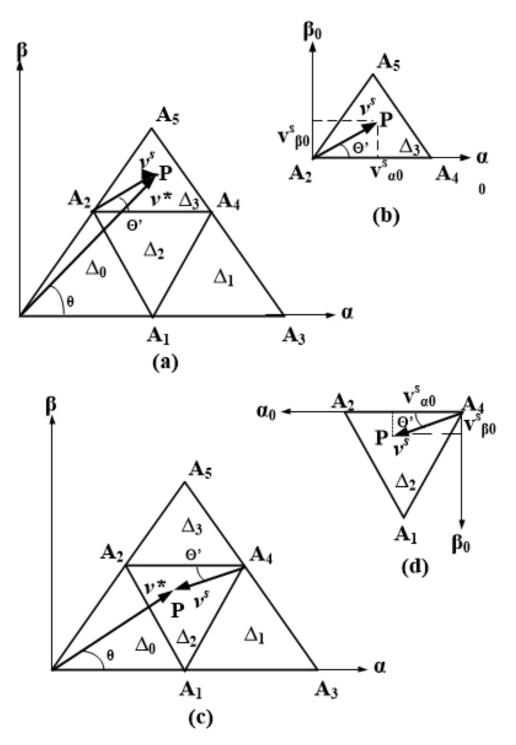

| 4.6  | Co-ordinate systems with reference to point $A_0$ (a) and point $A_4$   |    |

|      | (b) and type 1 and type 2 triangular regions                            | 50 |

| 4.7  | Space vector diagram for two-level inverter                             | 52 |

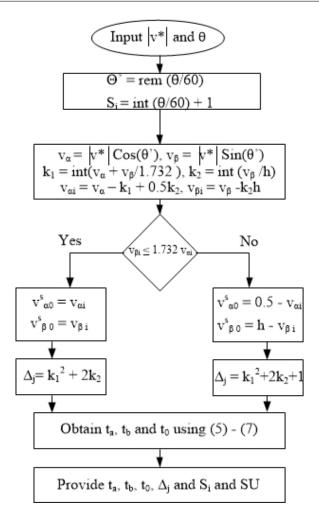

| 4.8  | Flowchart of Three-level SVPWM algorithm for linear under-modulation    | n  |

|      | mode                                                                    | 53 |

| 4.9  | Flowchart of main routine: overall SVPWM process                        | 54 |

| 4.10 | Flowchart of Routine-1: sub-routine to calculate the on-times and       |    |

|      | triangular number for the circular track                                | 55 |

| 4.11 | Flowchart of Routine-2: sub-routine to calculate the on-times and triangular number for the hexagonal track | 56         |

|------|-------------------------------------------------------------------------------------------------------------|------------|

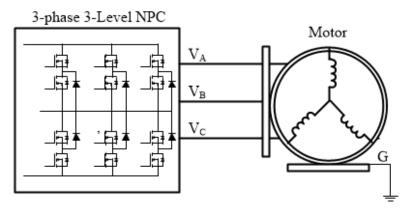

| 1 19 | Three-level inverter driving IM                                                                             | $50 \\ 56$ |

|      | Space vector hexagon diagram of 3-level inverter                                                            | 50<br>57   |

|      | Block diagram of proposed method of eliminating CMV                                                         | 59         |

|      | The modified SV diagram for proposed method                                                                 | 59<br>59   |

| 4.10 | The modified SV diagram for proposed method                                                                 | 99         |

| 5.1  | Square outline of single stage PV controlled centrifugal pump                                               | 62         |

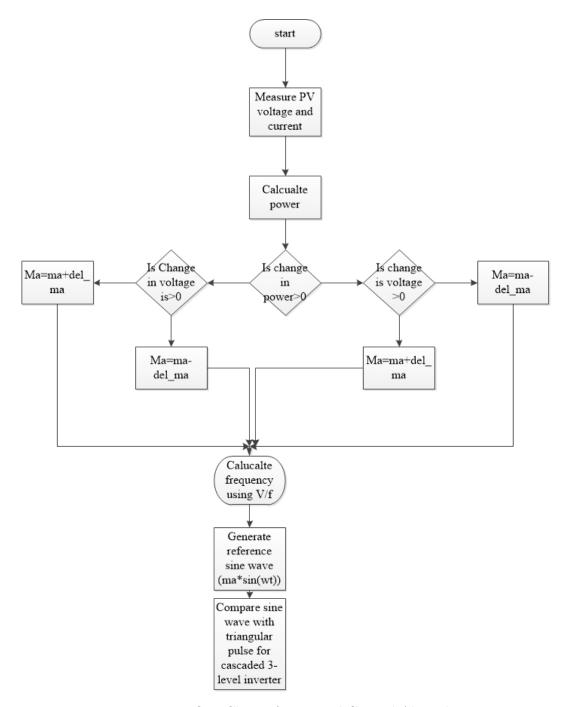

| 5.2  | flow Chart of Proposed Control Algorithm                                                                    | 63         |

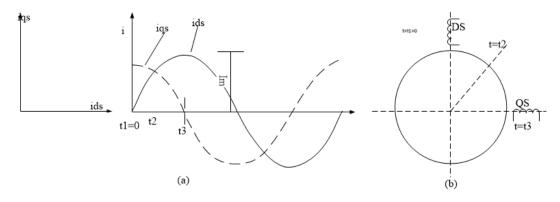

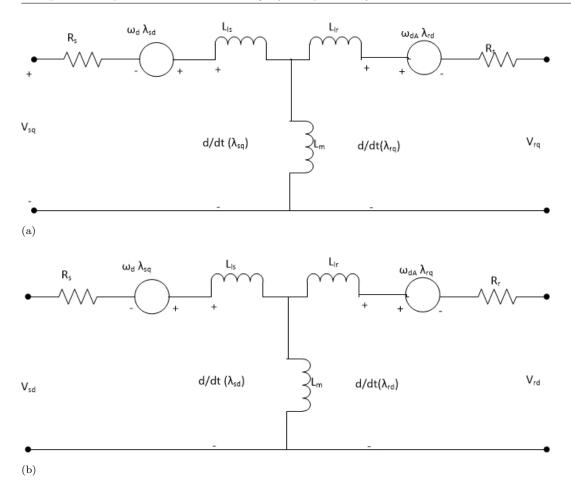

| 5.3  | (a) Distribution of currents in the two stator coils. (b) The orien-                                        |            |

|      | tation of stator mmf at the instant considered                                                              | 68         |

| 5.4  | (a) and (b) Equivalent circuit of induction machine in d-q frame                                            | 69         |

| 0.1  |                                                                                                             |            |

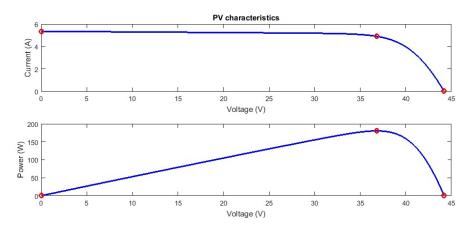

| 6.1  | V-I and PV curves                                                                                           | 74         |

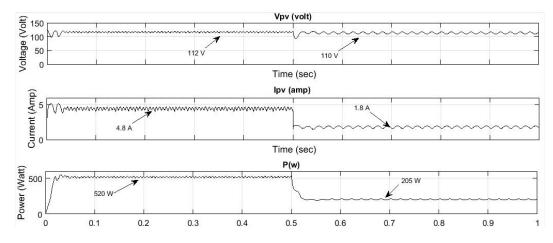

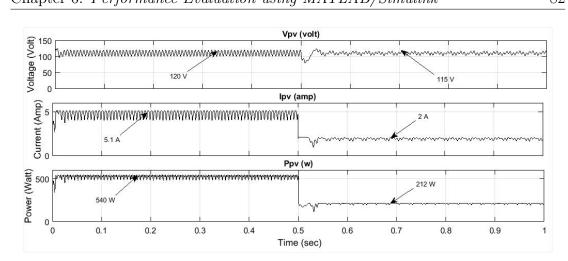

| 6.2  | Voltage, current and power characteristic of PV module                                                      | 75         |

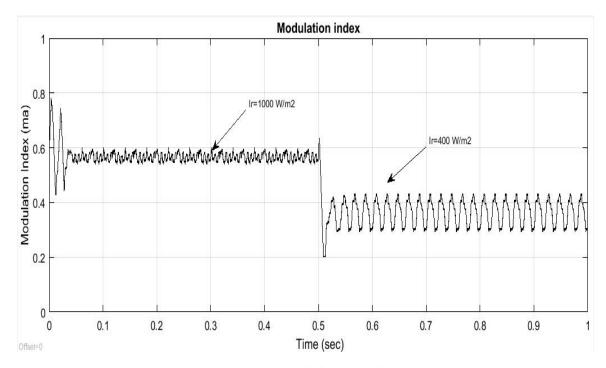

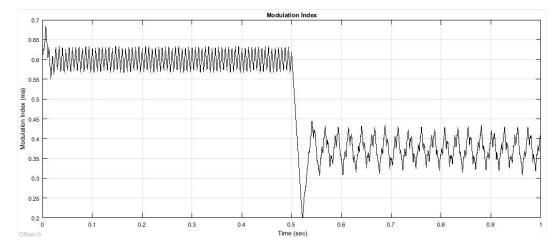

| 6.3  | Modulation index                                                                                            | 75         |

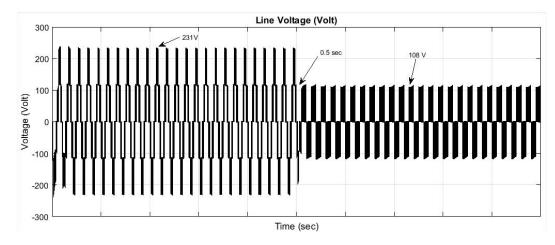

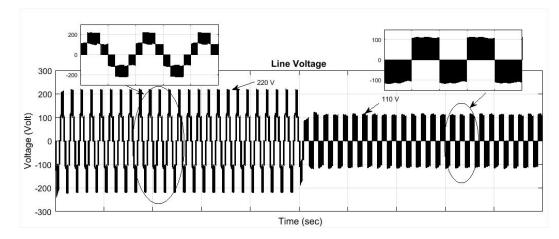

| 6.4  | Inverter output line voltage Vab                                                                            | 76         |

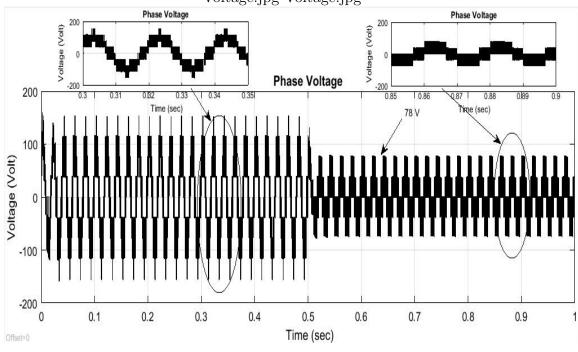

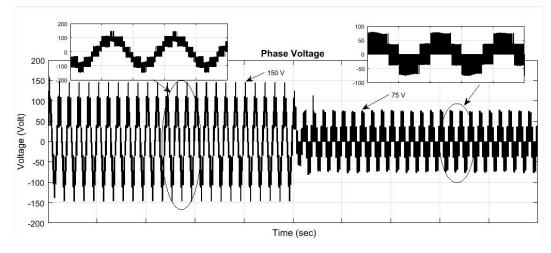

| 6.5  | Inverter output phase voltage Van.                                                                          | 76         |

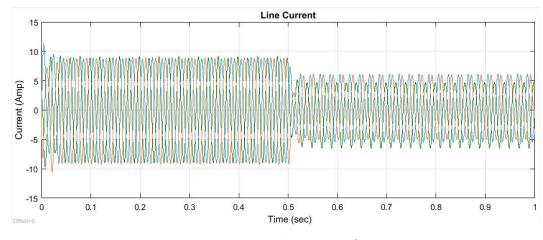

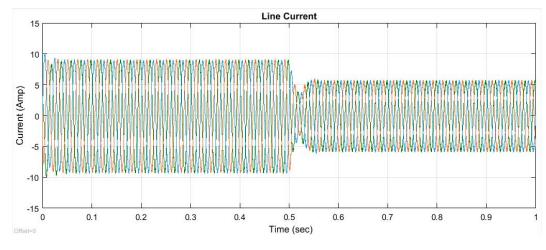

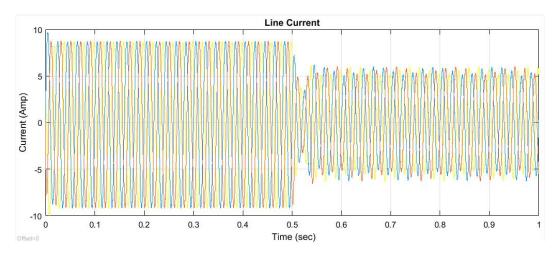

| 6.6  | Three phase Line Current.                                                                                   | 77         |

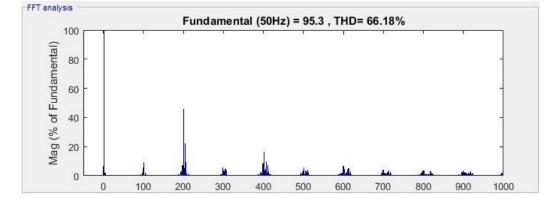

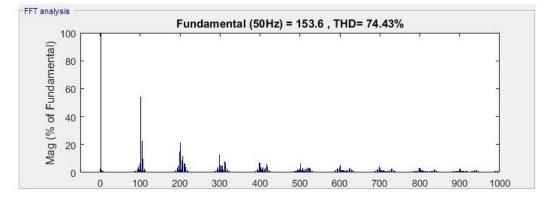

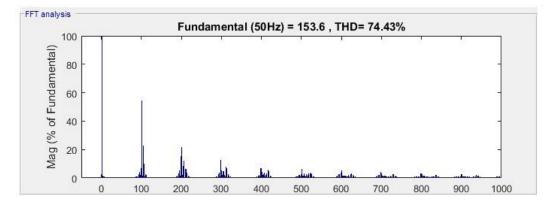

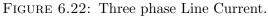

| 6.7  | FFT analysis for 0.6 modulation index                                                                       | 77         |

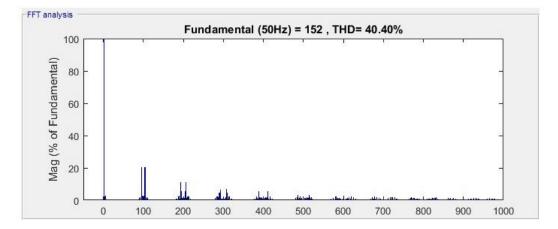

| 6.8  | FFT analysis for 0.4 modulation index                                                                       | 77         |

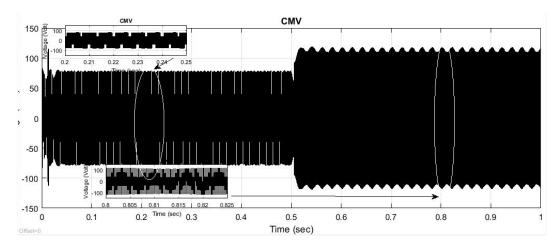

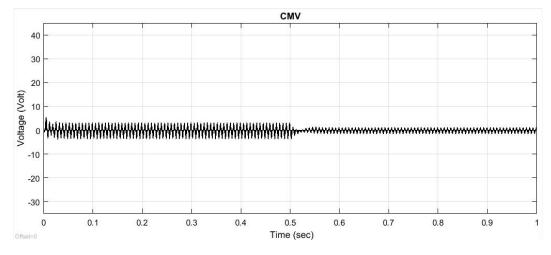

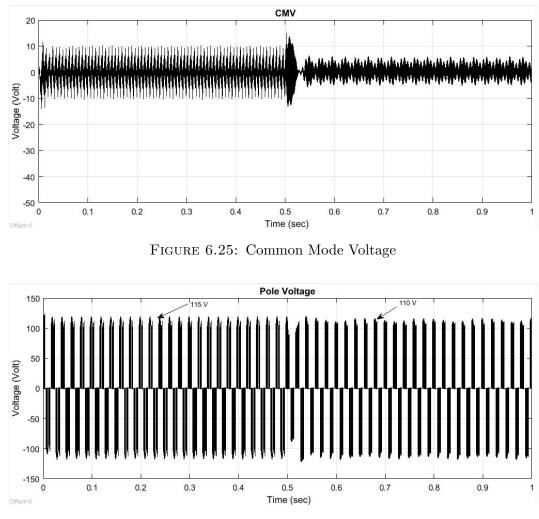

| 6.9  | Common Mode Voltage                                                                                         | 78         |

| 6.10 |                                                                                                             | 78         |

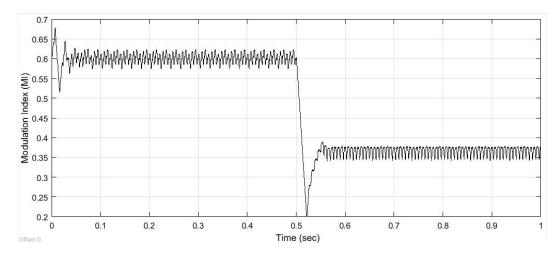

|      | Modulation index                                                                                            | 79         |

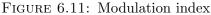

| 6.12 | Inverter output line voltage Vab                                                                            | 79         |

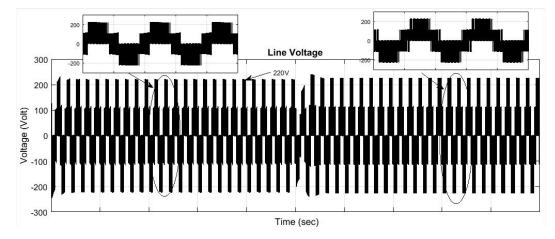

|      | Inverter output phase voltage Van.                                                                          | 79         |

| 6.14 | Three phase Line Current.                                                                                   | 80         |

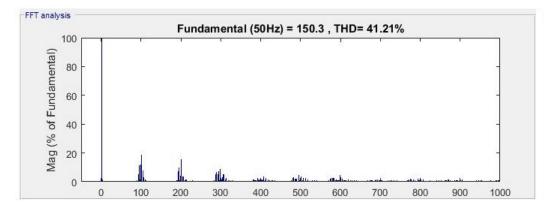

| 6.15 | FFT analysis for 0.6 modulation index                                                                       | 80         |

| 6.16 | FFT analysis for 0.37 modulation index                                                                      | 80         |

| 6.17 | Common Mode Voltage                                                                                         | 81         |

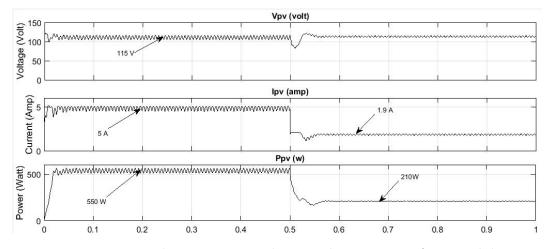

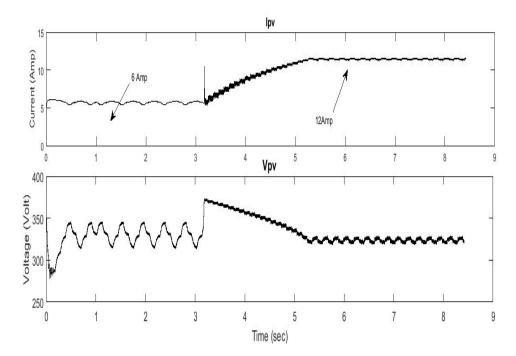

| 6.18 | Voltage, current and power characteristic of PV module                                                      | 82         |

| 6.19 | Modulation index                                                                                            | 82         |

| 6.20 | Inverter output line voltage Vab                                                                            | 82         |

| 6.21 | Inverter output phase voltage Van.                                                                          | 83         |

| 6.22 | Three phase Line Current.                                                                                   | 83         |

| 6.23 | FFT analysis for 0.6 modulation index                                                                       | 83         |

| 6.24 | FFT analysis for 0.37 modulation index                                                                      | 84         |

| 6.25 | Common Mode Voltage                                                                                         | 84         |

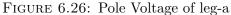

| 6.26 | Pole Voltage of leg-a                                                                                       | 84         |

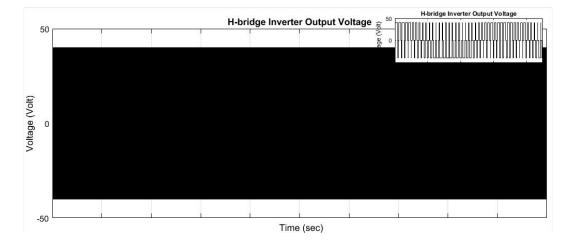

|      | H-bridge Inverter Output Voltage                                                                            | 85         |

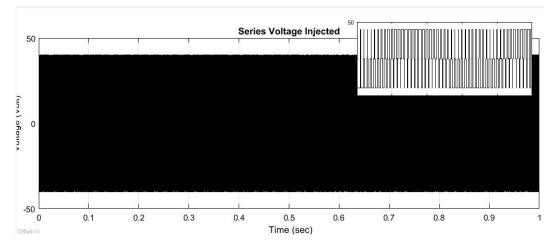

|      | Voltage injected in series of phase-a                                                                       | 85         |

|      | Characteristics of PV Array used for Pump Load                                                              | 85         |

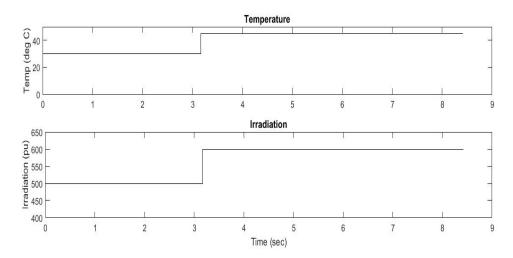

|      | Variation of Irradiation and Temperature                                                                    | 86         |

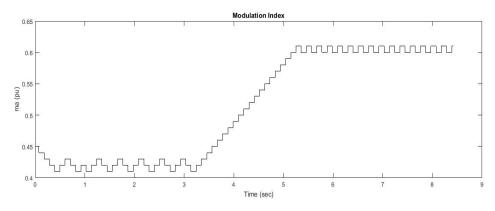

| 6.31 | Modualtion Index                                                                                                                           |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|

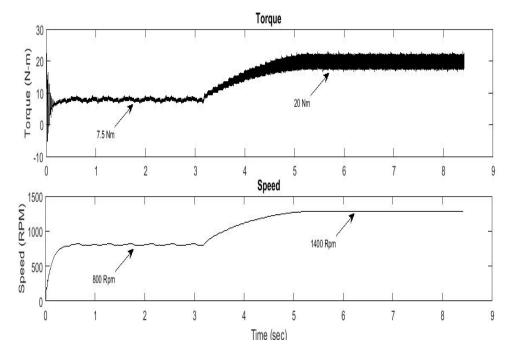

| 6.32 | Speed and Torque Variation                                                                                                                 |

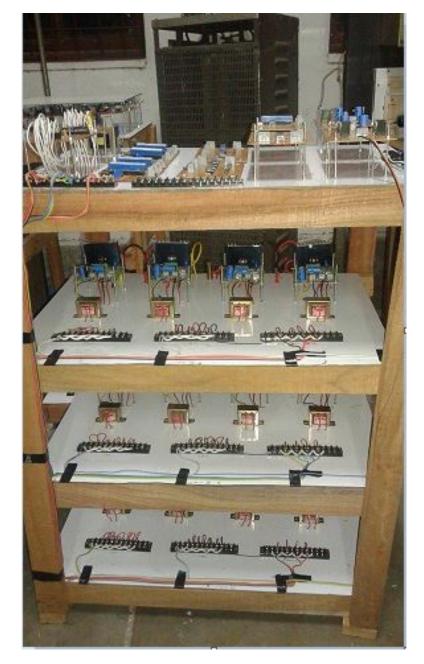

| 7.1  | Cascaded Three-level Inverter                                                                                                              |

| 7.2  | H-bridge Converter                                                                                                                         |

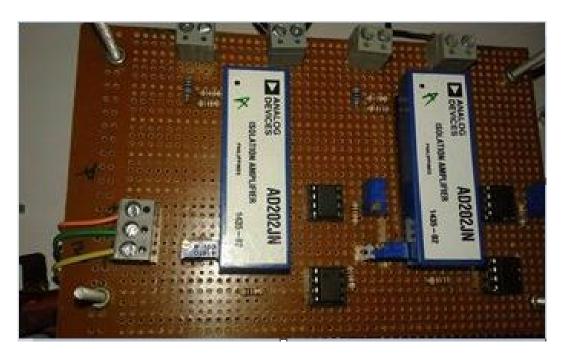

| 7.3  | Volgage Sensor                                                                                                                             |

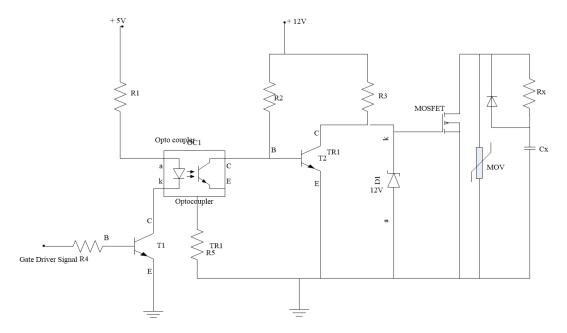

| 7.4  | MOSFET driver circuit                                                                                                                      |

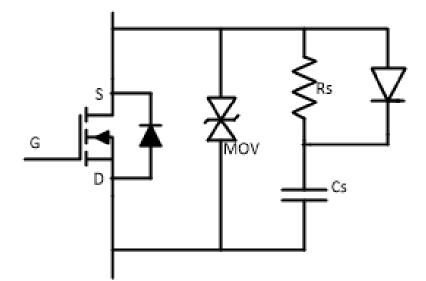

| 7.5  | Snubber circuit for MOSFET protection                                                                                                      |

| 7.6  | Voltage sensing circuit                                                                                                                    |

| 7.7  | current sensor circuit                                                                                                                     |

| 7.8  | $+12V \& -12V $ supply $\dots \dots \dots$ |

| 7.9  | +15V & -15V  supply                                                                                                                        |

| 7.10 | $+5V$ supply $\ldots \ldots 94$                               |

| 7.11 | Dead band circuit                                                                                                                          |

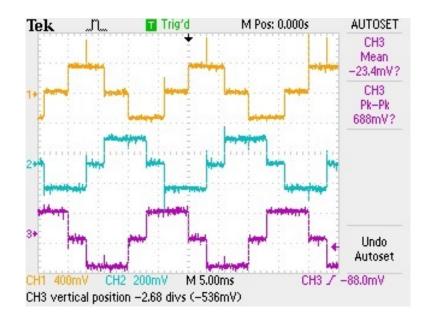

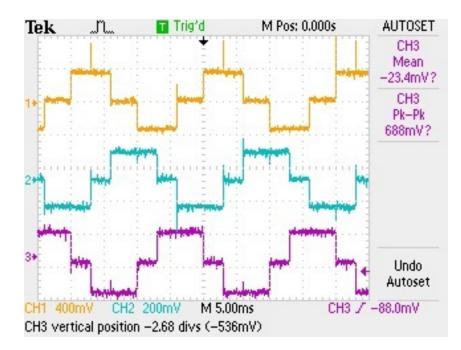

| 7.12 | Pole Voltage of Leg-a                                                                                                                      |

| 7.13 | Gate Pulse of one switch                                                                                                                   |

| 7.14 | Phase voltage                                                                                                                              |

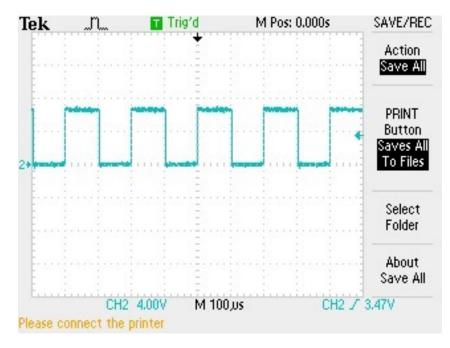

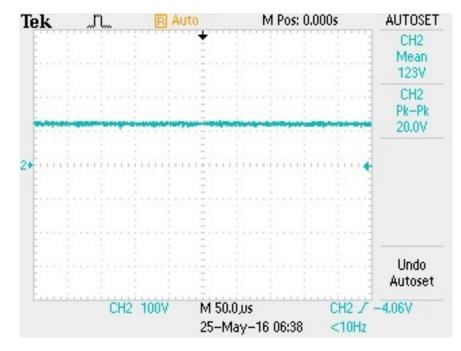

| 7.15 | Voltage across DC link capacitor                                                                                                           |

| 7.16 | Voltage across DC link capacitor                                                                                                           |

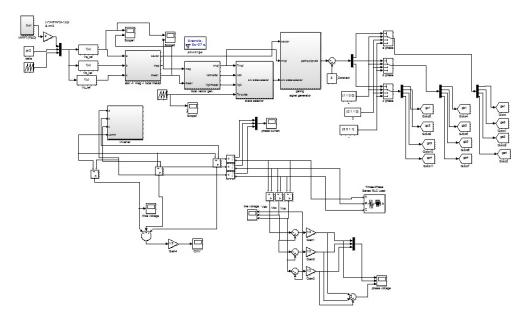

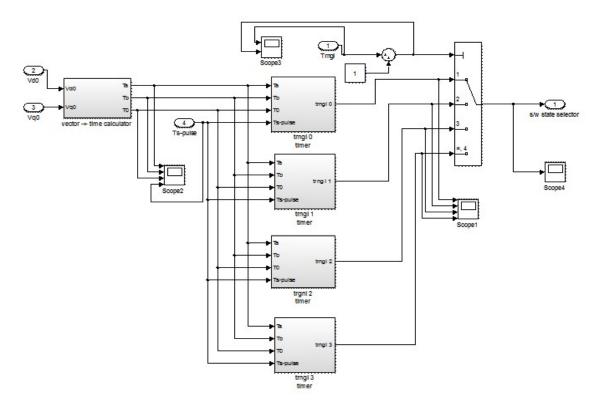

| A.1  | SVPWM complete MATLAB/Simulink diagram                                                                                                     |

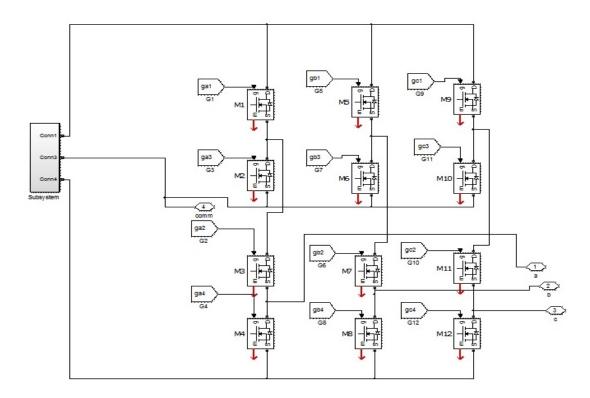

| A.2  | Cascaded inverter                                                                                                                          |

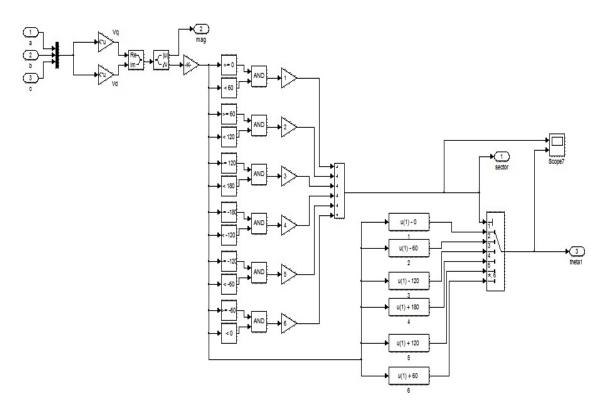

| A.3  | Sector Generation block                                                                                                                    |

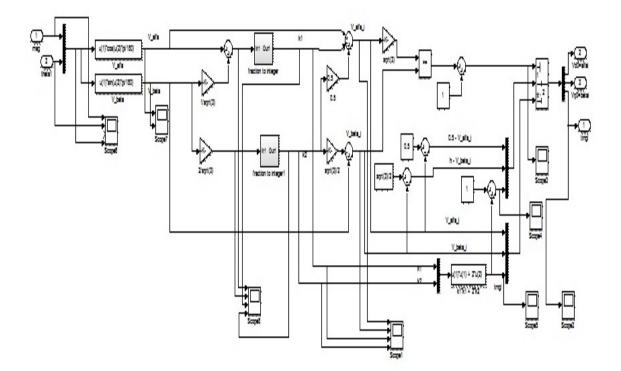

| A.4  | Local Vector generator block                                                                                                               |

| A.5  | Sector Selector block                                                                                                                      |

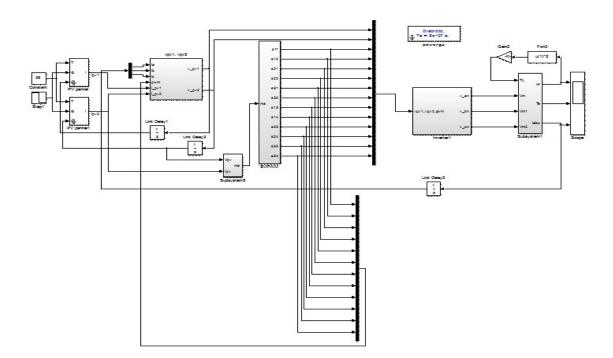

| A.6  | MATLAB/Simulink block diagram of PV connected Cascaded Inverter fed Pump load                                                              |

| A.7  |                                                                                                                                            |

|      | Induction motor model                                                                                                                      |

| C.1  | Main window of dSPACE ControlDesk                                                                                                          |

# List of Tables

| 2.1 | Comparative study of MPPT Techniques [21]                      | 22 |

|-----|----------------------------------------------------------------|----|

| 3.1 | Definition of Switching State                                  | 27 |

| 3.2 | Component count of diode clamped multilevel inverters          | 27 |

| 3.3 | Definition of Switching State                                  | 34 |

| 3.4 | Inverter states for individual inverters                       | 36 |

| 4.1 | classification, magnitude and switching state of space vectors | 47 |

| 4.2 | Three-level cascaded inverter switching states (single-leg)    | 48 |

| 4.3 | CMV generated by switching states of 3-level inverter          | 58 |

| 4.4 | Swtiching sequence of bridge inverter to eliminate CMV         | 60 |

## Abbreviations

| AC                     | Alternating Current                                                                                                                                         |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| $\mathbf{C}\mathbf{M}$ | $\mathbf{C}\mathbf{o}\mathbf{m}\mathbf{m}\mathbf{o}\mathbf{d}\mathbf{e}$                                                                                    |  |  |

| $\mathbf{CMV}$         | $\mathbf{C} \mathbf{o} \mathbf{m} \mathbf{m} \mathbf{o} \mathbf{d} \mathbf{e} \mathbf{V} \mathbf{o} \mathbf{l} \mathbf{t} \mathbf{a} \mathbf{g} \mathbf{e}$ |  |  |

| DCMLI                  | Diode Clamped Multi Level Inverter                                                                                                                          |  |  |

| DC                     | Direct Current                                                                                                                                              |  |  |

| DSP                    | $\mathbf{D}$ igital $\mathbf{S}$ ignal $\mathbf{P}$ rocessing                                                                                               |  |  |

| EMC                    | Electro Magnetic Compatibility                                                                                                                              |  |  |

| EMI                    | Electro Magnetic Interference                                                                                                                               |  |  |

| FCMLI                  | Flying Capactior Multi Level Inverter                                                                                                                       |  |  |

| IC                     | Incremental Conductance                                                                                                                                     |  |  |

| KCL                    | Kirchoffs Current Law                                                                                                                                       |  |  |

| MPPT                   | $\mathbf{M}$ aximum $\mathbf{P}$ ower $\mathbf{P}$ oint $\mathbf{T}$ racking                                                                                |  |  |

| MLI                    | $\mathbf{M}$ ulti Level Inverter                                                                                                                            |  |  |

| MPP                    | $\mathbf{M}$ aximum $\mathbf{P}$ ower $\mathbf{P}$ oint                                                                                                     |  |  |

| MI                     | $\mathbf{M} \mathbf{odulation} \ \mathbf{I} \mathbf{n} \mathbf{dex}$                                                                                        |  |  |

| $\mathbf{MV}$          | $\mathbf{M}\mathbf{e}\mathbf{d}\mathbf{i}\mathbf{u}\mathbf{m}\ \mathbf{V}\mathbf{o}\mathbf{l}\mathbf{t}\mathbf{a}\mathbf{g}\mathbf{e}$                      |  |  |

| NPC                    | Neutral Point Clamped                                                                                                                                       |  |  |

| $\mathbf{PV}$          | Photo Voltaic                                                                                                                                               |  |  |

| P& 0                   | $\mathbf{P} erturbation \ \& and \ \mathbf{O} bservation$                                                                                                   |  |  |

| PSO                    | $\mathbf{P} \text{article } \mathbf{S} \text{warm } \mathbf{O} \text{aptimization}$                                                                         |  |  |

| PWM                    | $\mathbf{P}\text{ulse}~\mathbf{W}\text{idth}~\mathbf{M}\text{odulation}$                                                                                    |  |  |

| RID                    | ${\bf R} igion \ {\bf I} dentification \ {\bf F} actor$                                                                                                     |  |  |

| SPWM                   | sine Pulse Width Modulation                                                                                                                                 |  |  |

|                        | :                                                                                                                                                           |  |  |

| SVPWM          | $\mathbf{S} \text{pace Vector Pulse Width Modulation}$                                                                             |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SHEPWM         | $\mathbf{S} elective \ \mathbf{H} armonics \ \mathbf{E} limination \ \mathbf{P} ulse \ \mathbf{W} idth \ \mathbf{M} odulation$     |  |  |  |

| $\mathbf{SVM}$ | Space Vector Modualtion                                                                                                            |  |  |  |

| THD            | Total Harmonic Distortion                                                                                                          |  |  |  |

| VHDL           | <b>V</b> HSIC <b>H</b> ardware <b>D</b> escriptive Language                                                                        |  |  |  |

| VHSIC          | $\mathbf{V}\mathrm{ery}\ \mathbf{H}\mathrm{igh}\ \mathbf{S}\mathrm{peed}\ \mathbf{I}\mathrm{ntegrated}\ \mathbf{C}\mathrm{ircuit}$ |  |  |  |

### Chapter 1

### Introduction

The world energy demand is rapidly increasing, a large amount of energy requiremnet is full fill by the fossil fuel which have the adverse effect on environment and create health hazard. The fossil fuel will be vanished sooner or later so we have to move on sustainable energy resources. The solar energy is freely available through out the world. The Pv based power supply system have some challanges due to its non linear characteristics and the generated power is depends on atmoshpheric conditions like variation in irradiation and temperature. Most of the home appliance is worked on AC supply, therefore inverter is necessary and inverter topology is plays a key role for the conversion of DC voltage into Ac voltage. Traditionally two stage inverters are required to track the maximum power and to convert DC voltage into AC voltage.

Electric motors provide driving power for a large part of modern prime movers. induction motors are the most widely used in industries as they are simple, reliable rugged, compact in size and cheap. Induction motor can also be used in aggressive or volatile environment since there are no problem of spark and corrosion in contrast to the commutation problem in DC motors. A wide range of speed control of IM requires variable frequency and variable voltage supply which necessitates complex control of inverters. However, the advantages of IM override the issue of complex control. In order to improve output waveform quality in two-level VSIs, the general trend is to use high frequency PWM techniques which may cause problems like higher switching losses, higher common-mode voltages, high dv/dt, more EMI problems etc. Therefor research efforts are being made for new solutions like MLI to minimize the waveform distortion with limited switching frequencies.

#### 1.1 RSEARCH MOTIVATION

This thesis gives the detail analysis of the system to be proposed. the PV array model with novel cascaded 3-level inverter control the induction motor for a pump load application with help of V/f control and MPPT schemes. India is the country where 70% of population live in rural area whose primary occupation is agriculture even though we have become self sufficient in food grains and technology has reached to help the formers, but many villages in India is not have electricity supply by today. Solar photo-voltaic base motor pump set is aimed that , helping such former groups who can not have electricity and can not afford costly technology.

Many researcher have worked on DC-motor based water pumping system but the size and cost of DC-motor is 2 to 3 times the cost of induction motor of the same rating. The induction motor is robust than the DC-motor. The maintenance required by DC-motor is also very high as compared to induction motor. In the proposed model the three phase induction motor is fed by the PV source through a 3-level inverter. Lots of the literature is available on the inverter topology. The multi-level inverter (MLI) gives better response than the normal two-level inverters. The output voltage THD and the rating of the switches used in the inverter is decreases depending upon the level of inverter, the low THD also reduces the size of the filter. Out of the basic MLI topologies available., H-bridge and cascaded inverters are most preferable for non renewable energy resources. The reason behind this is the interconnection of two different rating sources is simple and both the sources can supply a single load through a single inverter. Among all the basic MLI configuration present the cascaded inverter proposed by K. Gopakumar & V.T. Somasekhar in literature [4] is used for investigation. It has many advantages compared to conventional multi-level inverters.

To further improve the performance and efficiency of PV fed induction motor pumping system through cascaded multi-level inverter, the selection of modulation strategy plays an important role. the V/f control is the oldest and very popular method to control 3-phase induction motor(IM) due to its simplicity. but the digital implementation V/f method is not easy also the DC-source utilization by V/f is 15% less than the space vector modulation (SVM) technique. Hence many researchers now focused on space vector based modulation techniques. The space vector modulation is simple to implement digitally. Space vector modulation gives better utilization of DC-source than the V/f control, this is also very important factor when working with low-power, low-voltage photo-voltaic source.

Further investigation on the inverter shows that the common mode voltage (CMV) developed across the motor, which may cause the damage of the induction motor due to heavy ground current flow. The problem of CM can be eliminated when working with MLI topology. Therefore a cascaded MLI topology with SPWM and SVPWM is tested for induction motor based pump load system. The proper selection of switching sequence in space vector based MLI, the common mode voltage can be fully eliminated.

#### **1.2 LITERATURE SURVEY**

This section presents a review of research works that have already been done so far in the field of PV based water pumping system and MLI topologies. The literature review is presented in five sections. First, solar photovoltaic modules connected in possible array configurations under normal/partial shaded conditions with MPPT are discussed. Followed by, various existing MLI are briefed, based on its topological and design, modulation schemes and common mode mode voltage in the subsequent sections.

• Bum-Seok Suh et.a.l[1] in this paper author discussed about the GTO based novel MLI inverter topology with the advantage and drawback of using MLI for medium and high voltage. Also explain the problem with the conventional MLI topology available and its solution.

- jih sheng lai et.al.[2] in this paper presented a basic three types of MLI topology and compare their features, and investigate the performance of all three MLIs with their applications.

- Jose Rodriguez et.al.[3] discussed about the basic diode clamped, flying capacitor and multi-cell MLI topology. Main focus on the emerging topology with their control and modulation strategy like SPWM, selective harmonic eliminations, SVPWM etc. given. Author also gives the detail analysis of the present and future application of such basic and new MLI topologies.

- V.T Somasekhar and K. Gopakumar [4] in this paper a novel three-level cascaded inverter is presented. The advantage of this topology is its simplicity and control as compared to the DCMLI. The topology given in this paper have many advantages like isolated DC-sources of magnitude half of used in DCMLI, higher efficiency and low cost etc.

- R. S Kanchan, K. Gopakuamr et.al.[5] in this paper discussed about the CMV appeared due to high switching in MLIs. Author gives the solution to eliminate the CMV by using two cascaded three level inverter topology for open end winding induction motor drive. The modulation technique used is SVPWM. The switching of inverters are done in the way that, the MLIs are connected at both ends of the motor winding generate same CMV and cancel each other.

- Jianye Rao & Youngdong Li [6] in this paper presented the novel hybrid cascaded MLI topology. In this scheme two MLIs are used, the H-bridge inverter is working as a main inverter and the DCMLI is working as a conditioning inverter. Both the inverter together drive the motor. The DC source is connected across the main inverter only while, the conditioning inverter requires only ultra capacitors. This ultra capacitors reduces the consumption of DC batteries by supplying the reactive power of the motor under steady state condition and it stored the charge during the braking operation. The proposed topology is applied and tested in electric vehicle by the author.

- Nasrudin Abdul Rahim and Jeyraj Selvaraj [7] in this paper single-phase multi-string 5-level photo-voltaic inverter is presented. The grid connected

PV system is presented, the PV feeds the power to grid, to supply the common load. The novel sine-PWM method gives the better control and low THD for the proposed 1- $\phi$  5-level inverter, the overall system is operated at near unity power factor.

- Liu Miao and Hong Feng [8] in this paper a dual buck half bridge 3-level inverter is proposed. The proposed topology have high reliability, high efficiency, less losses and no shoot through problem.

- Sujitha.N and RAmani.K [9] in this paper application of MLI in hybrid vehicle is discussed. The main advantage of a novel MLI inverter topology with low THD and high efficiency with better utilization of DC-source. The proposed topology required a traditional three-phase inverter connected in series. The control pulses for the inverter is generated by selective harmonic elimination PWM scheme.

- Subhadeep Bhattacharya et.al.[10] in this paper described about the modular multilevel inverter (MMLI), MMLI is applied to the low voltage and medium power electric vehicle. Main work is done on the comparison of MMLI topology with conventional 2-level inverter topology for electric vehicle application. The topology of MMLI explained is based on half bridge inverter. the review on different operating mode is also given in the paper.

- Mohammad Farhadi Kangarlu et.al.[11] in this paper discussed about the new cascaded MLI topology. The new topology is tested in both symmetrical and asymmetrical condition, and compared with the conventional cascaded H-bridge inverter topology. The proposed topology proved better than the conventional cascaded H-bridge topology with respect to the number of switches used and the output voltage resolution while in both the inverters the voltage stress across the switches are equal. The proposed inverter topology also control the charge balance of the capacitors without any extra effort. The comparative study given in the paper stated that the proposed topology of cascaded MLI required less number of switches compared to other Asymmetrical inverter configuration.

- Ramulu Chhinthamalla, Sachin jain et.al.[12] in this paper presented a single stage 3-φ, 3-level inverter with simple sinusoidal PWM scheme is used to control the motor pump system, the V/f scheme applied allows the motor to work on the maximum power provided by the PV array. The proposed model required a two PV array and only one MPPT circuitry to control the switching of inverter to supply the pump load with maximum power under variable irradiation condition.

- Zuhair Alaas and Caisheng Wang [13] In this paper presented a new topology of isolated MLI. The major advantage of proposed MLI is the requirement of less number of switches as compared to conventional MLI. It also required only one DC-source and cascaded to high frequency transformer. The application of the proposed topology is suitable for high voltage and high power system, like integrated battery storage system and unconventional energy sources to grid. A simple phase shifted PWM scheme is applied to control the six switches inverter for harmonic reduction.

- Hossein Sepahvand et.al.[14] in this paper discusses about the general Hbridge MLI topology. Author suggested a alternative option of replace the DC sources required by each H-bridge cell by a capacitor. In the proposed system only one H-bride cell is feeds by a DC-source and rest of all H-bridge cells are connected to capacitors, this reduces the overall cost of the system. A simple phase shift PWM scheme is used to control the MLI. The proposed system has a wide range of voltage regulation.

- Mariusz Malinowski and K. Gopakumar [15] in this paper a detail survey of different MLI topologies is presented. author also discussed the advanced and regenerative MLI topologies with the proper application. The future development and suggestions are also discussed.

- G. M. Dousoky et.al.[16] in this paper presented the dual mode controlled maximum power point tracker for grid connected photo-voltaic system. the proposed MPPt technique controls both load angle and modulation index of the inverter, and worked in two control modes; active and reactive power

mode. The proposed single stage grid connected system gives good dynamic and steady state response with flexible active and reactive power control.

- Trishan Esram and Patrick L. Chapman [17] in this paper a detailed review on various MPPT techniques are presented. The 19 MPPT techniques are discussed with the various implementations.

- Kenji Kobayashi et.al.[18] in this paper a novel two stage MPPT technique is discussed. The proposed technique maximize the output power of the PV-array and track the real maximum power point under uniform or non uniform solar irradiation condition. The proposed technique is tested for both the insolation conditions.

- S. Ozdemir et.al.[19] in this paper a PV based variable speed drive for 3-φ induction motor to stimulate a ventilation system is proposed. A variable stepped incremental conductance (IC) and constant voltage MPPT techniques are applied to track the maximum power point during the operation. Both the MPPT techniques are used in a single system to generate the voltage & frequency reference for the V/f controlled 3-φ 3-level inverter based induction motor pump drive.

- Auttawut Waiprib et.al.[20] in this paper a V/f controlled 3-φ solar water pumping system is discussed. The micro-controller is used to gnerate the control signal for the proposed solar water pump in system. Also discussed the various complexity of applying the SPWM for 3-φ inverter drive. The maximum power point technique applied in the software to ensure the system at max power point.

- A. Darwish et.al.[21] in this paper a novel approach to convert DC in to AC is discussed. A modified cuk converter is used for the conversion of DC into AC current with the reduced size of energy storing element like inductors and capacitors. The reduced size energy storage elements also reduces the size and cost of the proposed inverter topology. The cuk converter perform both boost and buck operation depending upon the duty ratio. The comparison with the conventional VSI and CSI proved the proposed topology better with respect to the voltage and current drop at the output side and the efficiency.

The proposed cuk based inverter is most suitable for the PV application in which a continuous average input current is needed to track maximum power point throughout the operation.

- s. jai and v. Agarwal [22] in this paper various MPPT techniques are reviewed and compare on the basis of various factors. for 1-φ, single stage grid connected PV applications. for the study purpose author considered a buck-boost converter topology operating in discontinuous current mode for single stage grid connected system. The main focus on the comparison of various MPPT techniques. The MPPT techniques are compared on the basis of energy extracted from PV source during transient and steady state condition, time taken to reach maximum power point, oscillation at operating point etc. A new terminology "Energy tracking factor" is also introduced and defined. At the end concluded that all the MPPT techniques have their advantages and drawbacks. The novel B-technique and ripple correlation method of MPPT have overall good features compared to rest of the MPPT technique discussed.

- Sachin jain and Vivek Agarwal [23] in this paper a novel fast MPPT algorithm is presented. The proposed MPPT algorithm gives teh significantly improved efficiency during the tracking as compared to conventional algorithm. The proposed technique is most suitable and fast changing environment conditions, and easy to implement in any ast controller like DSP or FPGA.

- Ch. Ramulu, Sachin jain et.al.[24] in this paper a single stage open end winding induction motor based water pumping is discussed. The detail analysis and modeling of the proposed system is presented. The proposed single stage system takes care about the CMV and the maximum power point tracking with V/f control throughout the application.

- M.S. Taha and K. Suresh [25] in this paper a 1-HP submersible solar water pumping system is introduced and discussed in detail. To track the maximum power point the speed of the motor is taken as variable using V/f

control which allow to track MPP under varying insolation conditions. A simple P&O MPPT is used for the purpose.

- A. K. guta and A. M. Khambadkone [33] in this paper explain the new method to implement the multilevel SVPWM. The generalized method is discussed which can be applied to any level for DCMLI. The modes of operation will vary from linear modulation region to overmodulation region very smoothly. The method discussed is very good for digital implementation for any level of MLI.

- Haorn Zhang et.al. [35] in this paper discussed about the conventional method to eliminate CMV using SVPWM for three level DCMLI. Also discussed the method to eliminate the CMV using SPWM with some modifications.

- Sachin Jain et.al. [40] in this paper a single stage topology for solar water pumping system with open end winding induction motor is discussed. teh sample averaged zero sequence elimination (SAZE) PWM method is employed with V/f control to control the motor operation under varying solar irradiation. The MPPT is used to generate the reference signal (ie. modulation index, ma) for V/f block.

- Manoj R Reddy and J. Chelladurai [41] in this paper discussed about the PV fed grid connected MLI with SVPWM control. The DCMLI is used as 3-level for the analysis of single stage and two stage converter. The operation of MLI in over-modulation range is also discussed.

- h. Alawieh et.al. [42] in this paper discussed about the common mode voltage generated by VSI across the motor windings. Also discussed some advanced method (ACME) to reduce common mode voltage based on modified-SVPWM, which is better than conventional method with respect to output voltage THD.

#### **1.3 OBJECTIVE OF DISSERTATION WORK**

The objectives of this dissertation work include:

- 1. Propose a single stage Pv based water pumping system of rating 1-HP.

- 2. Study on MLI topology and modulation schemes.

- 3. Propose a novel scheme to eliminate a CMV elimination without reducing the out put voltage THD and level.

- 4. Simulate the proposed system with SPWM, SVPWM With and without common mode elimination schemes.

- 5. Implement the proposed scheme on FPGA.

- 6. Evaluate the performance of the proposed scheme.

#### 1.4 ORGANISATION OF REPORT

This report is organized as follows: **Chapter2** describe about the modeling of Photovoltaic system and Maximum power point tracking techniques. In **Chapter3** study of conventional MLI topology and Multi-level inverter topology used in the proposed work is discussed. In the **Chapter4** the conventional modulation techniques like SPWM and SVPWM with CMV elimination for three-level inverter is discussed. The operation and mathematical modeling of proposed system is given in **Chapter5**. In **Chapter6** the simulation of the proposed system in MAT-LAB/Simulink environment is discussed. The development of hardware prototype and and results of the proposed system is given in **Chapter7**.

### Chapter 2

# Photovoltaic Energy Conversion System

There are two methods are available to utilize the solar energy, solar heating and electrical power generation. This chapter is focused on photovoltaic based supply system and its utilization.

### 2.1 PHOTOVOLTAIC MODULES AND ARRAY

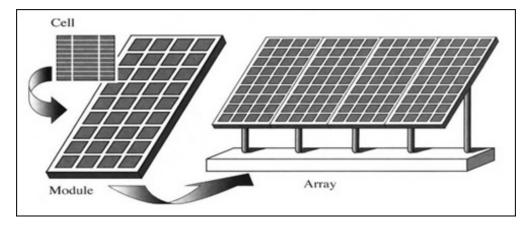

Soalr photovoltaic panels are used photoelectric effect to directly convert sunlight into electrical energy. Sunlight contains photons and when these photons strike on pv panel it gives the sufficient energy to electrons to move from valance band to conduction band therefore current starts flowing. now a days mono crystalline silicon and amorphous silicon materials are the most commonly used to design PV panels. The PV panes have robust structure and no movable parts so it requires less maintenance as comparison to the other form of energy sources. Series and parallel connections of PV cells is known as PV modules and the series and parallel connections of such modules are known as pv array as shown in figure 2.1. PV modules are generally available in between 60W and 200W. to increase the voltage modules are connected in series and parallel connections of these modules increases the current rating of pv array.

FIGURE 2.1: PV cell, modules and array

#### 2.2 MODELING OF PV PANELS

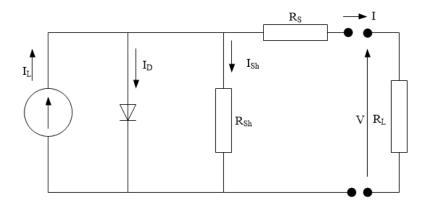

The single diode model [24, 26] is used to develop the characteristics of solar photovoltaic as shown in Fig.2. For the analysis of the system the mathematical model of photovoltaic cell is developed with the help of equations (1) to (5) given below:

FIGURE 2.2: Single diode model of PV cell

Short-circuits current of photovoltaic is presented by  $I_{PV}(orI_L)$ ,  $I_D$  represents the diode current, Rs and Rp represents the photovoltaic cell series and parallel resistances respectively. The output current of the PV cell is given by equation (2.1)

$$I = I_{PV} - I_D - I_{sh} \tag{2.1}$$

$$I = I_{PV} - I_0[exp(\frac{q(V + IR_s)}{AK_BT}) - 1] - \frac{V + IR_{sh}}{R_{sh}}$$

(2.2)

$$I = I_{PV} - I_D - I_{sh} \tag{2.3}$$

$$I_0 = I_{RS} \left(\frac{T_c}{T_{Ref}}\right)^3 exp[qE_B \left(\frac{1}{T_{Ref}} - \frac{1}{T_C}\right)/K_B A]$$

(2.4)

Where,  $I_{RS}$ =Reverse saturation current, q= Electron Charge 1.6 × 10<sup>-19</sup> (C),  $K_B = Boltzmann Constant 1.38 \times 10^{-32} (j/K)$ , A= p-n junction quality or ideality factor. Reverse saturation current ( $I_{RS}$ ) used in equation (2.4) is represented as:

$$I_{RS} = \frac{I_{SC}}{exp(qV_{oc}/N_sKAT_C) - 1}$$

(2.5)

Where,  $V_{OC}$  =open circuit voltage of the cell,  $N_S$  = Number of series connected cells per string.

$$I_L = N_P I_{PV} - N_P I_S [exp(\frac{qV}{N_s K T_C A}) - 1]$$

(2.6)

Where, V= Output Voltage of PV cell (V),  $I_S$  = diode saturation current of PV cell,  $N_P$ = Number of Parallel connected cells in strings.

## 2.3 CURRENT-VOLTAGE AND POWER- VOLT-AGE CURVES

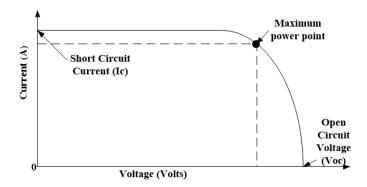

The current vs. voltage (I-V) curve generally shows the electrical behavior of the PV cell. The figure 2.3 shows the I-V characteristic of typical PV cell. The curve

shows that the variation of current and voltage when cell resistance varies from zero to infinity. The curve is flat in the initial region and falls off towards zero after the threshold voltage. This makes the PV cell differ than the ideal current source. The shows the three main points, the point at which current is zero is called short-circuit current and the point at which voltage is zero is known as open circuit voltage, this is the voltage measured with output terminal open. In between Isc and Voc the curve has a knee point known as maximum power point.

FIGURE 2.3: I-V Curve of a typical silicon PV cell

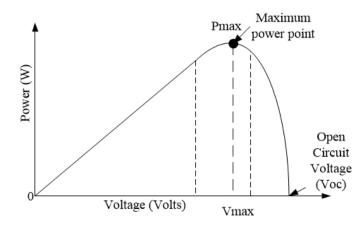

The power vs voltage curve of pv module is known as power curve. The power generated by the panel is the product voltage and current output. The PV cell does not produce any power at zero voltage or zero current, and maximum power is produced at the knee point of I-V curve as shown in the figure 2.4. In the electrical analysis of the PV circuit it is modeled approximately as a constant current source.

FIGURE 2.4: P-V characteristic of the PV cell

The following standard test conditions are established internationally in order to measure the photovoltaic cells output power. The level of solar irradiance is 1000

$W/m^2$ , with the reference air mass of 1.5 solar spectral irradiance distributions and cell or module junction temperature of 25<sup>o</sup>C.

## 2.4 PHOTOVOLTAIC POWER GENERATING SYSTEM

The PV voltage generation system can be classified as stand-alone and grid connected system. The topologies used for such generation is further classified as single stage and two-stage systems. In two-stage there is a intermediate DC to DC converter, which works on the MPP developed by the PV array. In comparison to this the single stage works without the intermediate DC to DC converter stage and the inverter works directly on MPP of PV array. The second topology gives higher efficiency because of the elimination of the DC to DC converter but there is a need of a more complex control schemes.

FIGURE 2.5: Two stage topology

FIGURE 2.6: Single stage topology

## 2.5 MAXIMUM POWER POINT TRACKING TECHNIQUES

The non linear IV and PV characteristic of photovoltaic array is already discussed and the characteristics are shown in figure 2.3 and figure 2.4 respectively. From the above discussion it is concluded that the solar PV output voltage voltage and current is depends on environmental conditions such as irradiation and temperature [27]. To extract maximum power from solar photovoltaic under varying atmospheric conditions an appropriate MPPT technique is required according the system requirement.

The essential component of PV system (grid connected or stand-alone) is an MPPT. Now a day a number of MPPT techniques have been developed few of them are adaptive perturbation and observation, adaptive fuzzy, estimated perturb and perturb, generatic algorithm, neural network and ant-colony based MPPT, etc. The MPPT techniques are compared on the basis of circuitry used, complexity of algorithm, difficulty in hardware implementation. Table 2.1 gives the summary of comparative study of various MPPT techniques available.

Table (2.1) shows the comparison chart of 26 MPPT techniques, comparison is based on control strategy applied, control variable used, Type of circuitry, Complexity in application, suitable application of technique and the converter used with the specific MPPT technique,

Where, IndC= Indirect Control, Samp= Sampling method, Mod= Modulation method, Digi= Digital, Ana= Analog and A-z represents MPPT techniques given below:

A. Curve fitting technique, B. Fractional short circuit current (FSCI) technique, C. Fractional open circuit voltage (FOCV) technique, D. Look up table technique, E. One cycle control (OCC) technique, F. Differentiation technique, G. Feedback voltage or current technique, H. Feedback of power variation with voltage technique, I. Feedback of power variation with current technique, J. Perturbation and observation (P&O) or hill climbing technique K. Incremental conductance (Inc-Cond) technique, L. Forced oscillation technique, M. Ripple correlation control (RCC) technique, N. Current sweep technique, O. Estimated perturb-perturb (EPP) technique, P. Parasitic capacitance technique, Q. Load current/load voltage maximization technique, R. DC link capacitor droop control technique, S. Linearization based MPPT technique, T. Intelligence MPPT technique, U. Sliding mode based MPPT technique, V. Gauss-Newton technique, W. Steepest-Descent technique, X. Analytic based MPPT technique, Y. Hybrid MPPT (HMPPT) techniques, Z. MPPT techniques for mismatched conditions.

The basic and generally used MPPT techniques are:

- Perturb and Observe (P&O) Method

- Incremental Conductance (IC) Method

FIGURE 2.7: Current v/s voltage and power v/s voltage characteristics at various solar irradiations

#### 2.5.1 Perturbation and Observation (P&O)