# DESIGN AND SIMULATION OF CASCADED H BRIDGE MULTILEVEL INVERTER USING GRID CONNECTED PV SYSTEM

A DISSERTATION

Submitted in the partial fulfillment of the Requirements for the award of the degree

of

## MASTER OF TECHNOLOGY

in

## **ELECTRICAL ENGINEERING**

(With Specialization in Electric Drives & Power Electronics)

by

## NEHA TAK

(Enrollment No - 14527014)

## DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247667

MAY-2016

#### **CANDIDATE'S DECLARATION**

I hereby certify that work being presented in the Dissertation titled "Design and Simulation of Cascaded H bridge Multilevel Inverter using Grid connected PV system" is in partial fulfillment of the requirement for the award of Master of Technology in Electrical Engineering with specialization in "Electric Drives and Power Electronics and submitted to the Department of Electrical Engineering, Indian Institute of Technology Roorkee. This is an authentic record work carried out under the supervision and guidance of Dr. S.P.Singh, Professor, Electrical Engineering, IIT Roorkee, Uttrakhand, India.

The matter presented in this Dissertation has not been submitted by me for the award of any other degree.

24<sup>th</sup> May, 2016

Roorkee.

Neha Tak Enrollment No.14527014

#### CERTIFICATE

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

Dr. S.P.Singh Professor Department of Electrical Engineering, IIT Roorkee Roorkee – 247667, India

#### ACKNOWLEDGEMENT

I am extremely grateful to my project supervisor **Mr. S.P. Singh**, who guided me at every stage of preparation of this Thesis. His support, encouragement, valuable ideas and many excellent comments have been crucial for accomplishing this thesis work. I am truly thankful for his guidance and many interesting analytical discussions.

I also express my sincere thanks to Head of Dept. Mr. S.P. Srivastava, Department of Electrical Engineering, for his invaluable support and encouragement throughout the report.

I am also deeply grateful to Mr. Dogga Raveendhra, PhD Scholar for his valuable instructions. I greatly appreciate their time and input to this dissertation.

A special thank to my family members for their great support, encouragement and kind understanding.

I am also thankful to my colleagues and friends for their support.

I wish to thank all Electrical Engineering department staff for their kind co-operation throughout the report work.

Finally, I am grateful to Almighty God who made me capable to do what I did.

(NEHA TAK)

#### ABSTRACT

The continuous increase in power demands and need for a cleaner environment makes decentralized renewable energy production, like solar and wind, more and more interesting. Decentralized energy production using solar energy could be a solution for balancing the continuously-increasing power demands. This continuously increasing consumption overloads the distribution grids as well as the power stations, therefore having a negative impact on power availability, security and quality. One of the solutions for overcoming this is the grid-connected photovoltaic (PV) system.

With the extraordinary market growth in grid-connected PV systems, there is increasing interests in grid-connected PV inverters. Focus has been placed on inexpensive, high-efficiency, and innovative inverter solutions, leading to a high diversity within the inverters and new system configurations. This report chooses cascaded multilevel inverter topologies for grid connected PV systems to reduce the cost and improve the efficiency.

First, a single-phase cascaded H-bridge multilevel PV inverter is discussed. To maximize the solar energy extraction of each PV string, an individual maximum power point tracking (MPPT) control scheme is applied, which allows independent control of each dc-link voltage. A generalized non active power theory is applied to generate the reactive current reference. Within the inverter's capability, the local consumption of reactive power is provided to realize power factor correction. Then, the modular cascaded H-bridge multilevel inverter is connected to a three-phase utility system and nine PV panels. Individual MPPT control is also applied to realize better utilization of PV modules. Also, mismatches between PV panels may introduce unbalanced power supplied to the three-phase grid-connected system. Thus, a modulation compensation scheme is applied to balance the three-phase grid current by injecting a zero sequence voltage.

A modular cascaded multilevel inverter prototype has been built and tested in both the single phase and three-phase PV system. Simulation and experimental results are presented to validate the proposed control schemes. The targets of reducing the cost and improving the overall efficiency of the PV inverters can be achieved by applying the cascaded PV inverters and the proposed control schemes.

## TABLE OF CONTENTS

| Certificate                                           |      |

|-------------------------------------------------------|------|

| Acknowledgement                                       |      |

| Abstract                                              |      |

| Table of Contents                                     | iv   |

| Figure index                                          | viii |

| Table index                                           | xii  |

| 1. Introduction                                       | 01   |

| 1.1 Objectives                                        | 03   |

| 1.2 Organization of report                            | 04   |

| 2. Literature Review                                  | 06   |

| 2.1 Overview of Grid connected PV system              | 06   |

| 2.2 Topologies of Grid-Connected PV Inverter          | 10   |

| 2.2.1 Single Stage Inverter                           | 11   |

| 2.2.2 Dual Stage Inverter with Single DC/DC Converter | 12   |

| 2.3 Comparison of various methods                     | 13   |

| 2.4 Conclusion                                        |      |

| 3. Photo voltaic system                               |      |

| 3.1 Stand alone PV system                             |      |

| 3.1.1 Consumer applications                           | 17   |

| 3.1.2 Solar home system                               | 17   |

| 3.1.3 Residential system                              | 17   |

| 3.1.4 Hybrid system                                   | 18   |

| 3.2 Grid connected PV system                          | 19   |

| 3.3 Solar PV modeling                                 | 20   |

| 3.4 Equivalent circuit of solar cell                  | 21   |

| 3.4.1 Solar cell method                               | 21   |

| 3.4.2 Solar cell method with ohmic losses             | 22   |

| 3.5 Conclusion                                        | 23   |

| 4. Power conditioning devices of photo voltaic system |      |

| 4.1 DC/DC converters                                  |      |

| 4.1.1 DC analysis of PWM boost converter                       | 26 |

|----------------------------------------------------------------|----|

| 4.2 Maximum power point trackers                               | 31 |

| 4.2.1 MPPT control                                             | 33 |

| 4.3 PV inverters                                               | 36 |

| 4.3.1 Conventional inverters (VSI and CSI)                     | 37 |

| 4.3.1.1 Standard VSI                                           | 38 |

| 4.3.1.2 Standard CSI                                           | 38 |

| 4.3.2 Multi level converters                                   | 39 |

| 4.3.2.1 Cascaded H Bridge Multilevel Inverter                  | 41 |

| 4.3.2.1.1 Control techniques for CHMLI                         | 42 |

| 4.4 Classification of SPWM techniques                          | 43 |

| 4.5 Conclusion                                                 | 45 |

| 5. Control of Single-Phase Cascaded H-Bridge Multilevel        |    |

| Inverter for Grid-Connected Photovoltaic Systems               | 46 |

| 5.1 Topology Description                                       | 46 |

| 5.2 PV panel mismatches                                        | 51 |

| 5.3 Control Scheme                                             | 51 |

| 5.3.1 Individual MPPT Control                                  | 51 |

| 5.4 Conclusion                                                 | 53 |

| 6. Control of Three-Phase modular Cascaded H-Bridge Multilevel |    |

| Inverter for Grid-Connected Photovoltaic Systems               | 54 |

| 6.1 System Description                                         | 54 |

| 6.2 Control Scheme                                             | 55 |

| 6.2.1 Individual MPPT Control                                  | 57 |

| 6.3 Discussion of control Scheme                               | 58 |

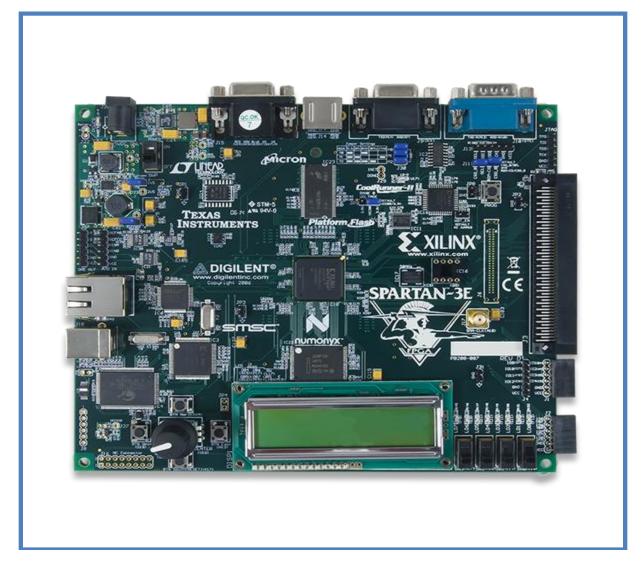

| 7. FPGA based Design Procedure                                 | 59 |

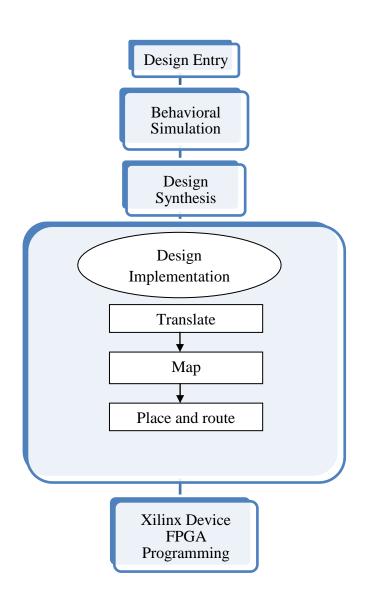

| 7.1 FPGA design flow                                           | 59 |

| 7.2 FPGA basics                                                | 60 |

| 7.2.1 Design entry                                             | 60 |

| 7.2.2 Behavioral simulation                                    | 60 |

| 7.2.3 Design synthesis                                     | 60 |

|------------------------------------------------------------|----|

| 7.2.4 Design implementation                                | 60 |

| 7.2.5 Xilinx Device (FPGA) Programming                     | 61 |

| 7.2.6 Configuring Target Device                            | 62 |

| 7.3 Conclusion                                             | 62 |

| 8. Simulation Result                                       | 63 |

| 8.1Solar PV module                                         | 63 |

| 8.2 Boost converter Results                                | 66 |

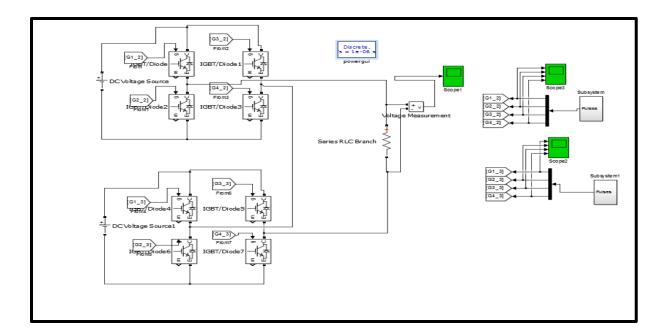

| 8.3 5- level H- Bridge Multilevel Inverter                 | 67 |

| 8.3.1 Open loop simulation of H bridge multilevel Inverter | 68 |

| 8.3.2 Closed loop simulation of 1-phase H Bridge Inverter  | 70 |

| 8.4 3- Phase H- Bridge Multilevel Inverter                 | 79 |

| 8.4.1 Open loop simulation of 3- phase                     | 79 |

| H-Bridge multilevel Inverter                               |    |

| 8.4.2 Closed loop simulation of 3- phase                   | 84 |

| H-Bridge multilevel Inverter                               |    |

| 8.5 Conclusion                                             | 89 |

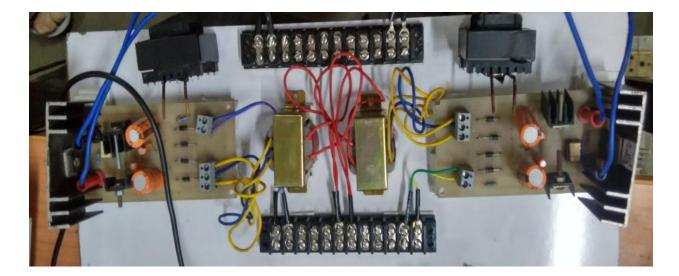

| 9. System Hardware Development                             | 90 |

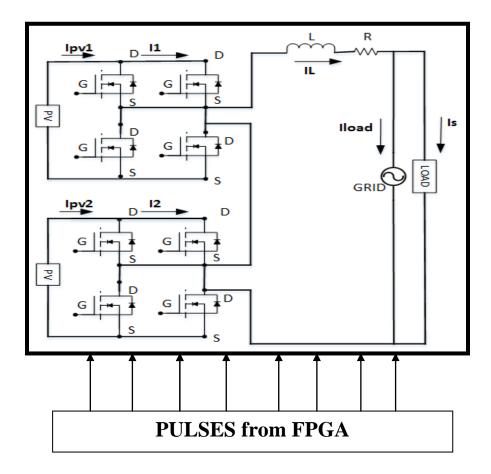

| 9.1 Development of system hardware                         | 90 |

| 9.2 Power Circuit development                              | 90 |

| 9.2.1 Power Circuit                                        | 90 |

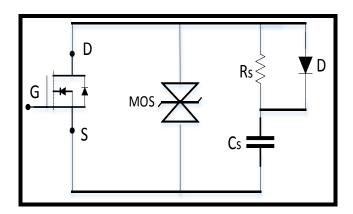

| 9.2.2 Snubber Circuit                                      | 91 |

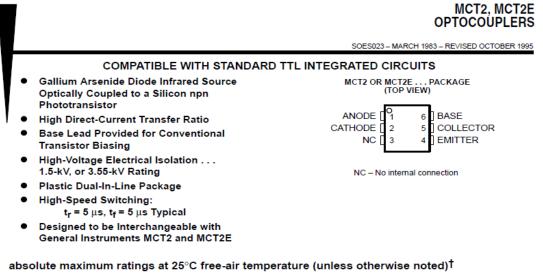

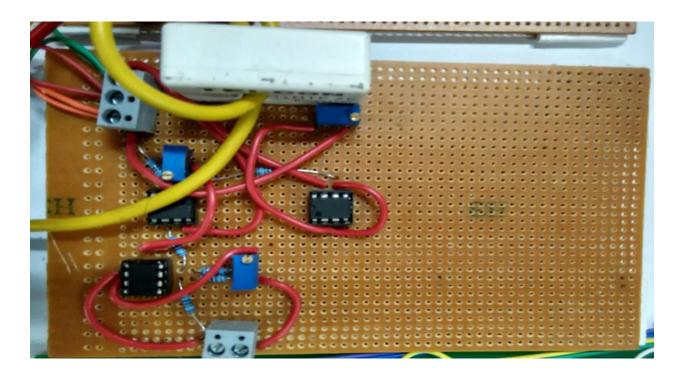

| 9.3 Pulse amplification and Isolation Circuit              | 93 |

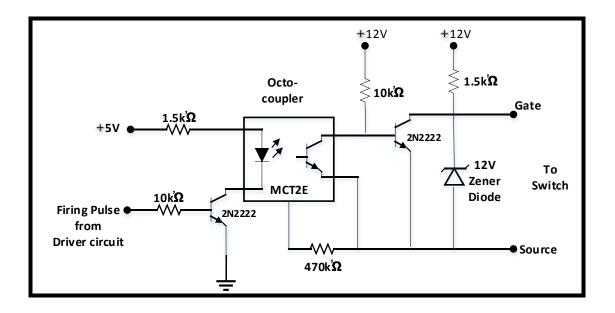

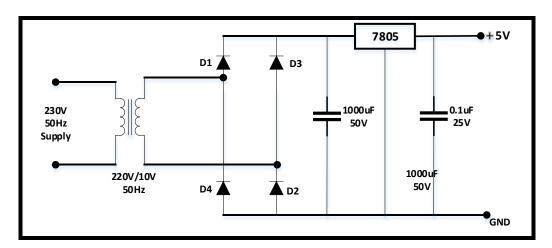

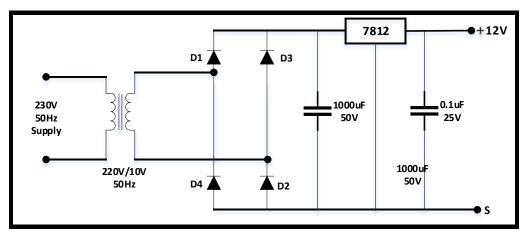

| 9.4 Regulated Power supply                                 | 94 |

| 9.5 Measurement of system parameters                       | 95 |

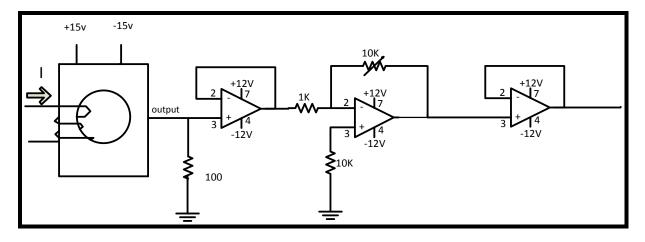

| 9.5.1 AC Current Sensing                                   | 95 |

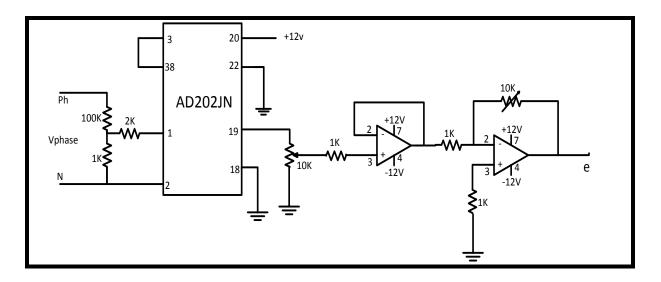

| 9.5.2 AC voltage sensing                                   | 96 |

| 9.6 Hardware Results                                       | 97 |

| 9.7 Conclusion                                             | 98 |

| 10. Conclusion and Future Scope                            | 99 |

| BIBLIOGRAPHY                | 100 |

|-----------------------------|-----|

| Research Paper Communicated | 107 |

| Appendix A                  |     |

| Appendix B                  |     |

Appendix C

Appendix D

## **FIGURE INDEX**

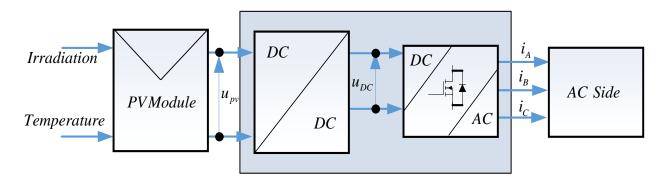

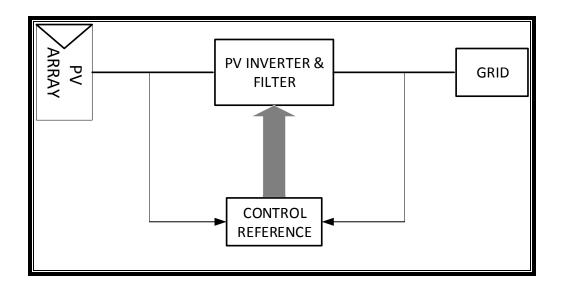

| Figure 1.1 | Block Diagram of Solar System using Inverter          | 03 |

|------------|-------------------------------------------------------|----|

| Figure 2.1 | Configuration of PV systems                           | 07 |

| Figure 2.2 | Three cases of multiple and single stage inverter     | 11 |

| Figure 2.3 | Power electronic Systems                              | 12 |

| Figure 2.4 | Two stage topology                                    | 13 |

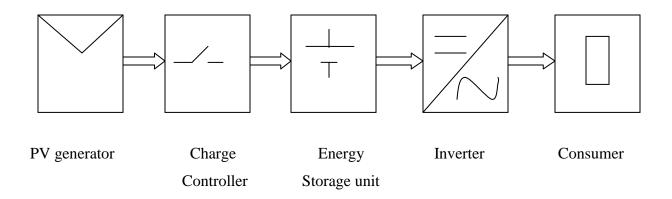

| Figure 3.1 | Schematic diagram of a standalone system              | 16 |

| Figure 3.2 | Block diagram of PV power supply for a small          | 17 |

|            | consumer product                                      |    |

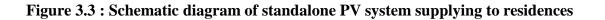

| Figure 3.3 | Schematic diagram of a standalone PV system           | 18 |

|            | Supplying to residences                               |    |

| Figure 3.4 | Schematic diagram of a hybrid system                  | 18 |

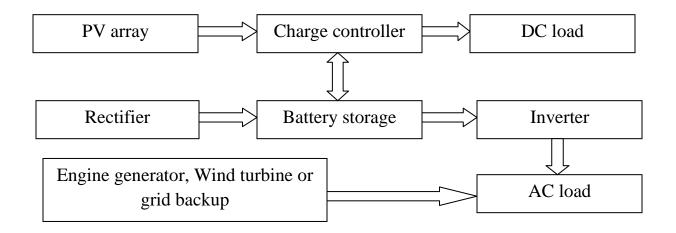

| Figure 3.5 | Schematic diagram of a grid connected PV system       | 19 |

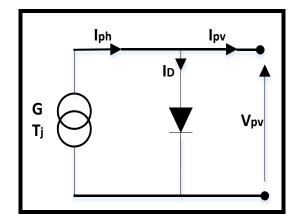

| Figure 3.6 | Simplified equivalent circuit of ideal solar cell     | 21 |

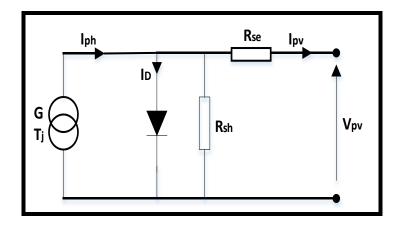

| Figure 3.7 | Simplified equivalent circuit of practical solar cell | 23 |

| Figure 4.1 | Boost converter circuits                              | 27 |

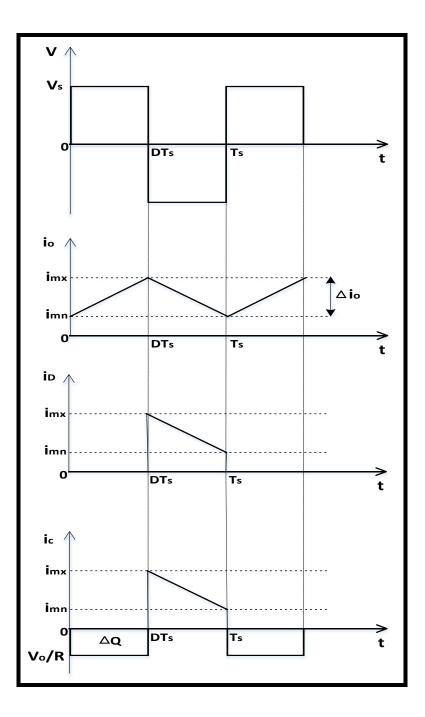

| Figure 4.2 | Boost converter waveforms                             | 30 |

| Figure 4.3 | PV and IV characteristics under different irradiance  | 32 |

| Figure 4.4 | MPPT with PWM control loop                            | 33 |

| Figure 4.5 | Change in power with respect to voltage at            | 34 |

|            | different positions                                   |    |

| Figure 4.6 | Flowchart of incremental conductance method           | 35 |

| Figure 4.7 | Inverter topologies by waveform                       | 37 |

| Figure 4.8  | Circuit of VSI                                               | 38 |

|-------------|--------------------------------------------------------------|----|

| Figure 4.9  | Circuit of CSI                                               | 39 |

| Figure 4.10 | Classification of converters                                 | 40 |

| Figure 4.11 | Single phase H Bridge multilevel inverter                    | 42 |

| Figure 4.12 | Classification of SPWM techniques                            | 44 |

| Figure 5.1  | Topology for Grid connection                                 | 47 |

| Figure 5.2  | Output voltage of Inverter and ripple current waveform       | 49 |

| Figure 5.3  | Relation between modulation index and the ripple current     | 50 |

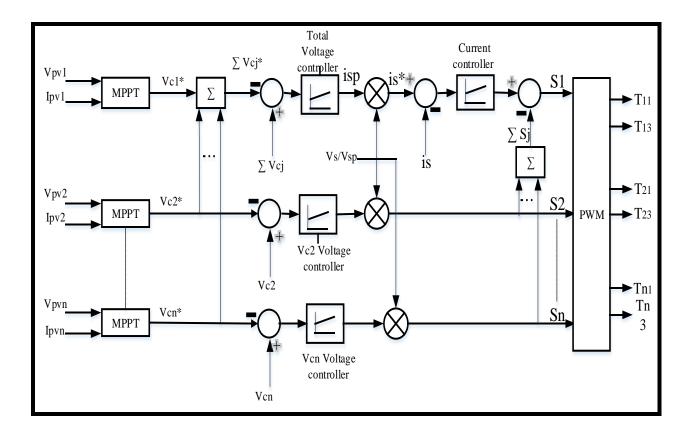

| Figure 5.4  | Control strategy                                             | 52 |

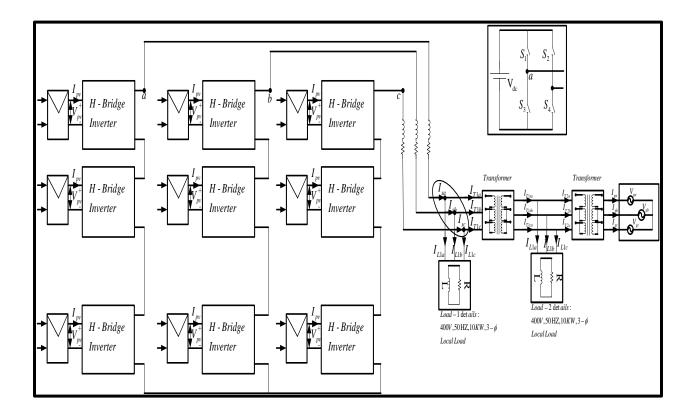

| Figure 6.1  | Topology of the three phase grid connected system            | 55 |

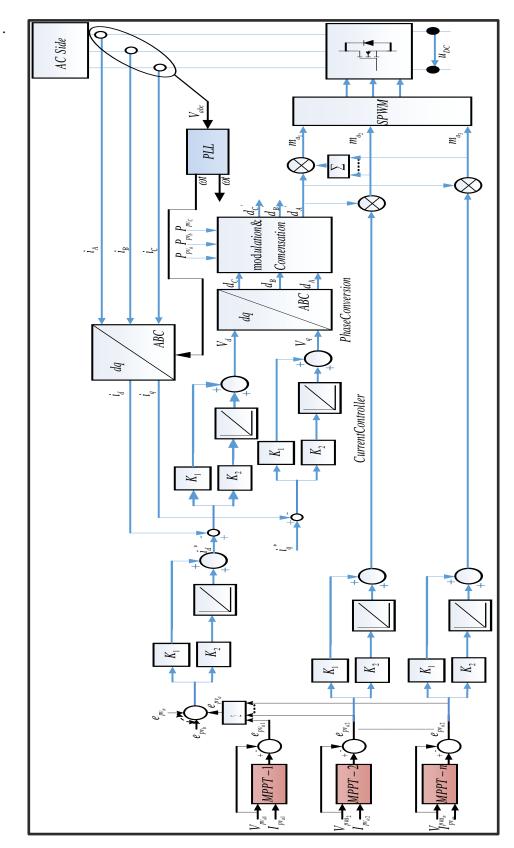

| Figure 6.2  | Control scheme for three phase H bridge multilevel inverter  | 56 |

| Figure 7.1  | FPGA design flow                                             | 59 |

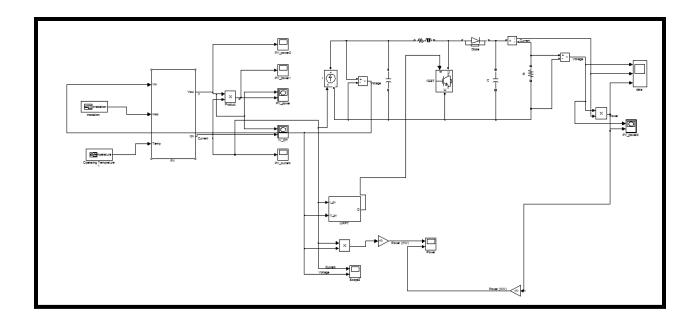

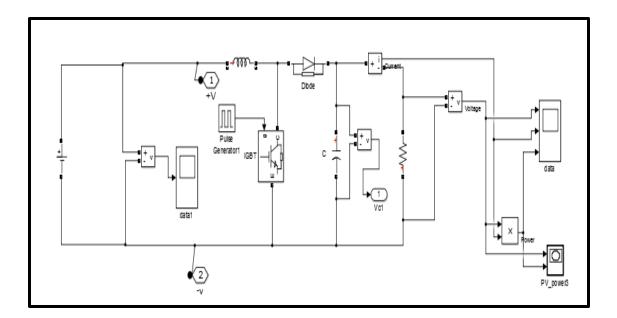

| Figure 8.1  | Simulink model of solar PV cell                              | 62 |

| Figure 8.2  | Temperature variations at input side solar PV module         | 63 |

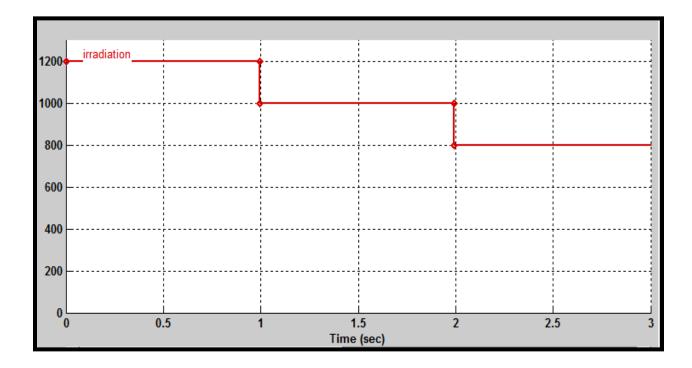

| Figure 8.3  | Irradiation variations at input side solar PV module         | 63 |

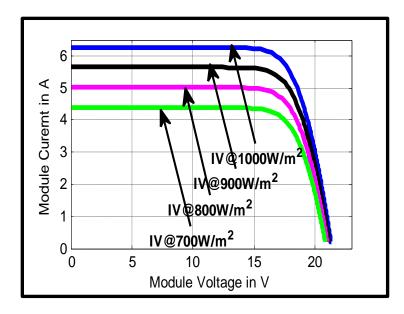

| Figure 8.4  | IV characteristics under different irradiation               | 64 |

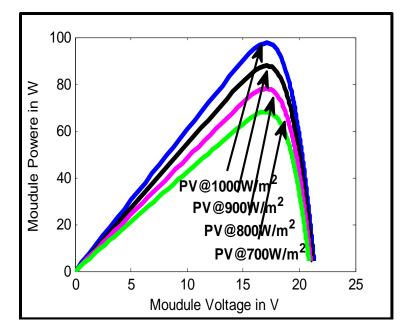

| Figure 8.5  | PV characteristics under different irradiation               | 65 |

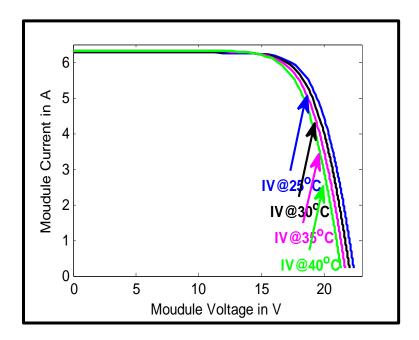

| Figure 8.6  | IV characteristics under different Temperature               | 65 |

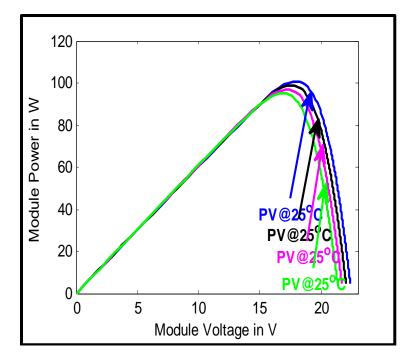

| Figure 8.7  | PV characteristics under different Temperature               | 66 |

| Figure 8.8  | Model of Boost converter                                     | 67 |

| Figure 8.9  | Simulink model of 5- level H Bridge Inverter                 | 68 |

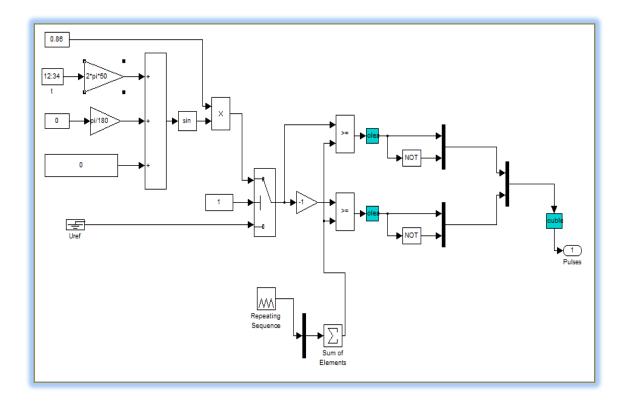

| Figure 8.10 | Control Scheme of 5- level H Bridge Inverter                 | 68 |

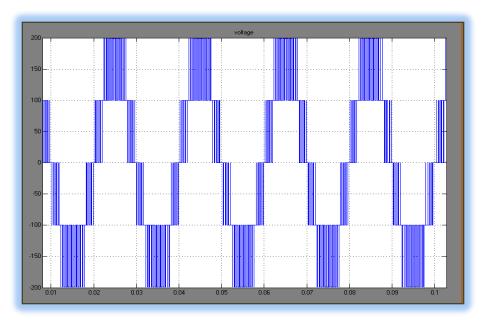

| Figure 8.11 | Simulation of output Voltage of 5- level H Bridge Inverter   | 69 |

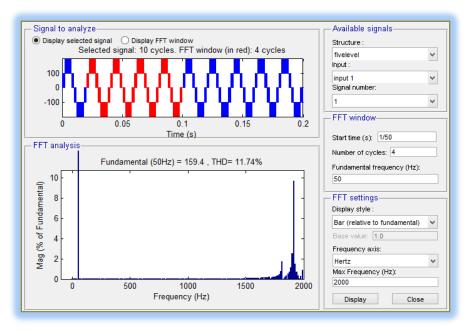

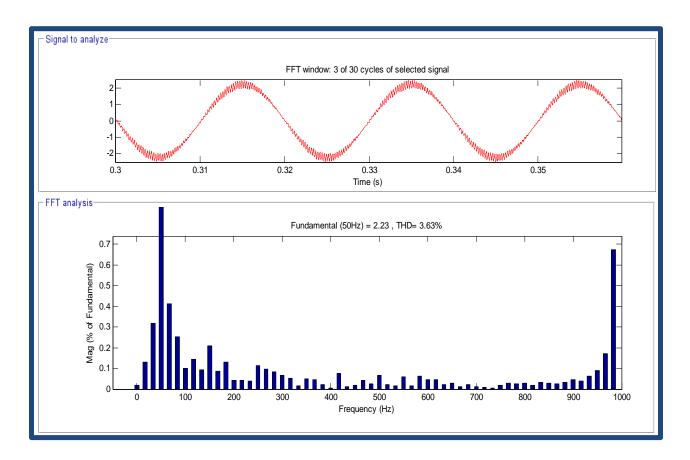

| Figure 8.12 | THD Analysis of output Voltage of 5- level H Bridge Inverter | 69 |

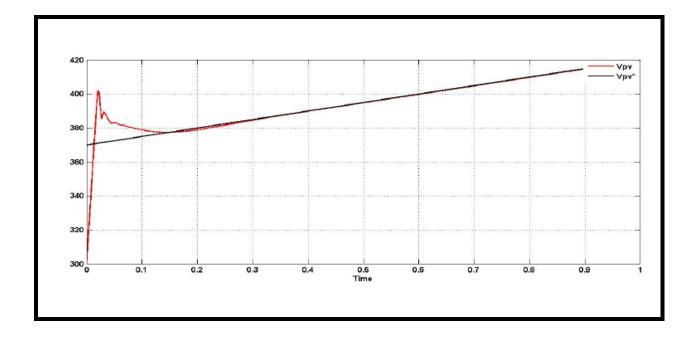

| Figure 8.13 | Tracking Response of Proposed Controller for<br>Boost Converter for Ramp Input | 72 |

|-------------|--------------------------------------------------------------------------------|----|

| Figure 8.14 | Tracking Response of Proposed Controller for                                   | 72 |

|             | Boost Converter for Ramp Input                                                 |    |

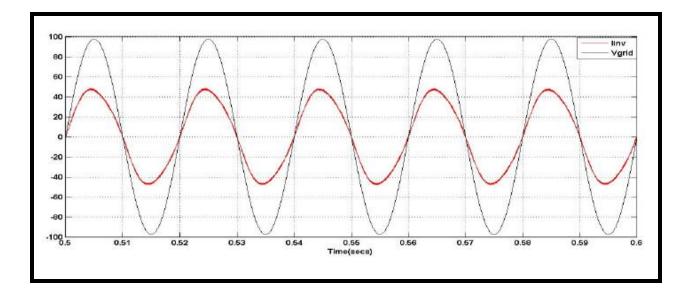

| Figure 8.15 | Scale Grid voltage and Supplied Current by VSI                                 | 73 |

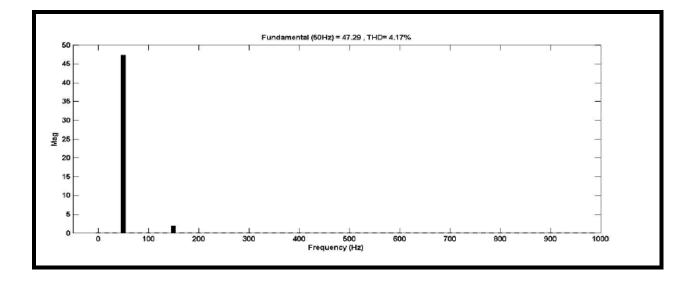

| Figure 8.16 | Frequency Spectrum of Inverter Output Current                                  | 73 |

| Figure 8.17 | Tracking Response of Proposed Controller for Boost Converter                   | 74 |

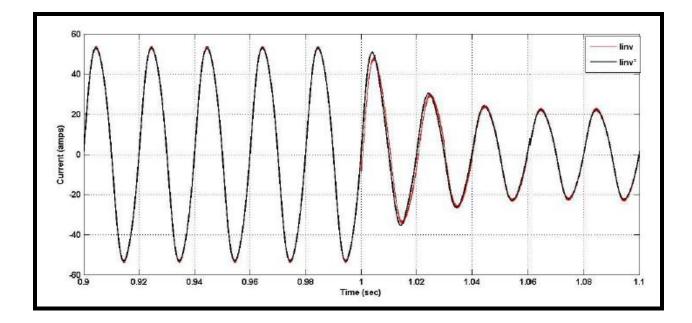

| Figure 8.18 | Tracking Response of Proposed Nonlinear Controller                             | 75 |

| Figure 8.19 | Magnified Tracking Response of Proposed Nonlinear Controller                   | 75 |

| Figure 8.20 | Tracking Response of Conventional PI Controller                                | 76 |

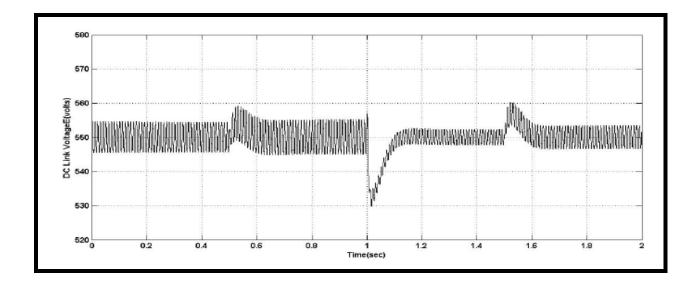

| Figure 8.21 | DC link Voltage                                                                | 76 |

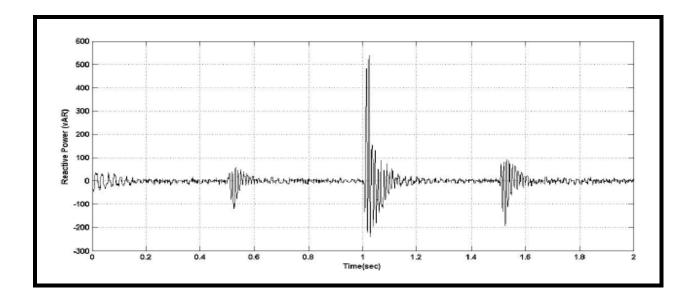

| Figure 8.22 | Reactive Power Supplied By VSI                                                 | 77 |

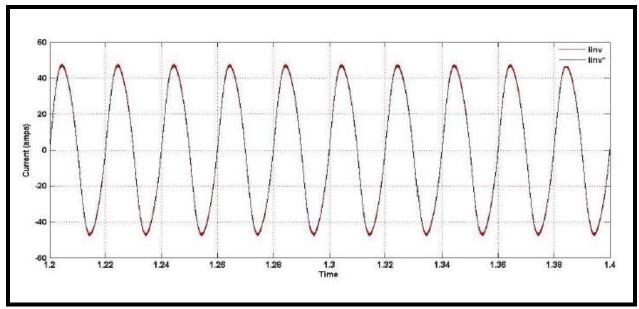

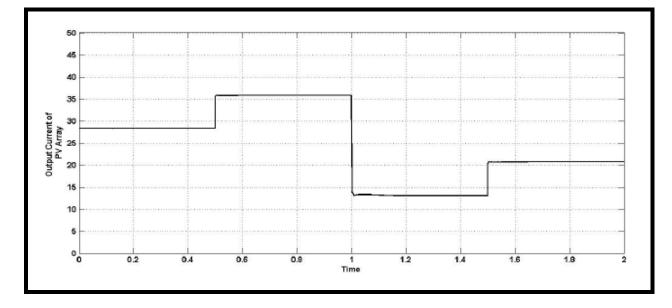

| Figure 8.23 | Output Current of PV Array                                                     | 77 |

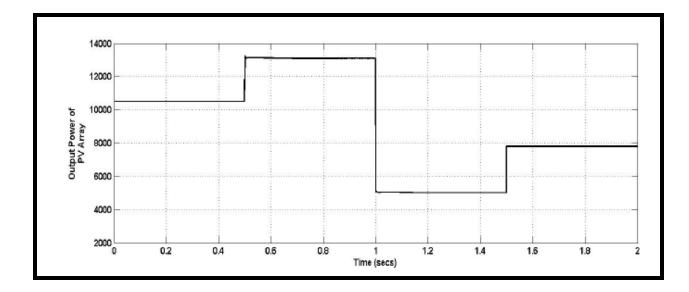

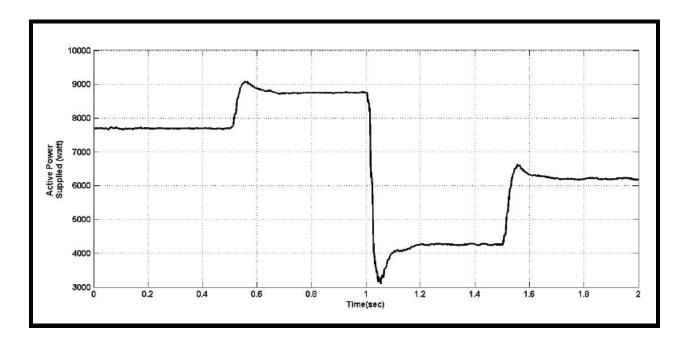

| Figure 8.24 | Output Power of PV Array                                                       | 78 |

| Figure 8.25 | Active Power Supplied by VSI                                                   | 78 |

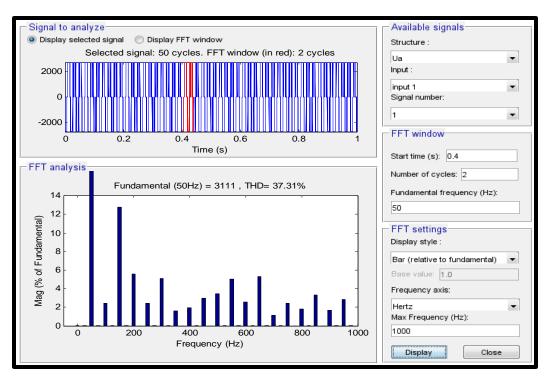

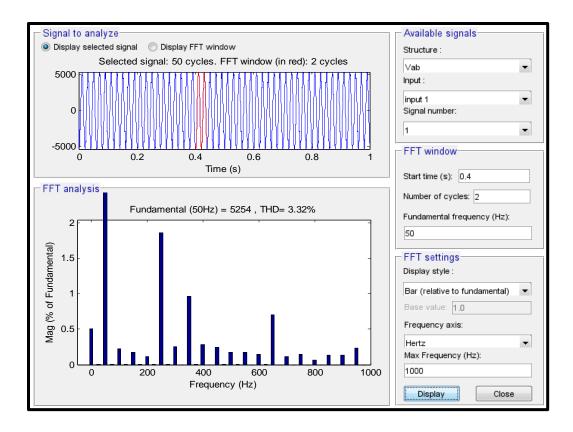

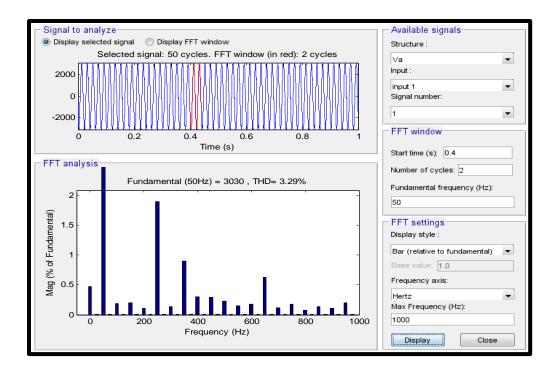

| Figure 8.26 | THD analysis of phase voltage at CHMLI Terminal                                | 80 |

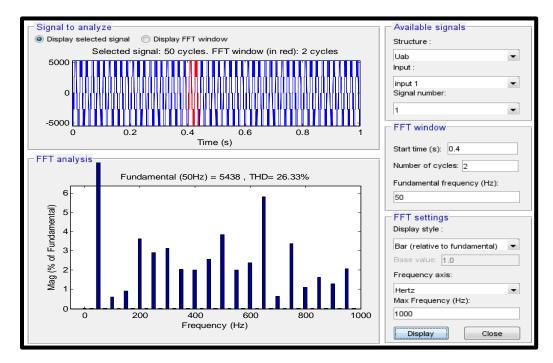

| Figure 8.27 | THD analysis of line to line voltage at CHMLI terminals                        | 80 |

| Figure 8.28 | THD analysis of line to line voltage load terminals                            | 81 |

| Figure 8.29 | THD analysis of phase voltage at load terminals                                | 81 |

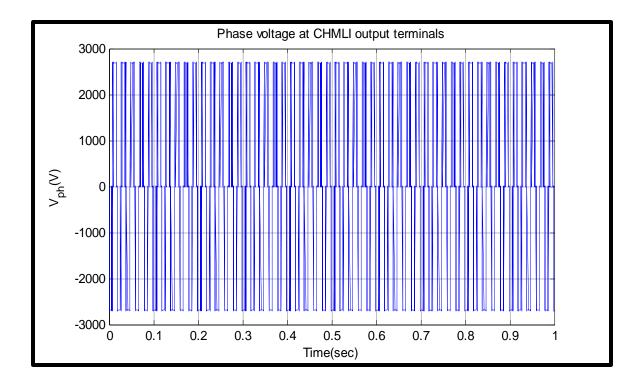

| Figure 8.30 | Phase voltage at CHMLI output terminals                                        | 82 |

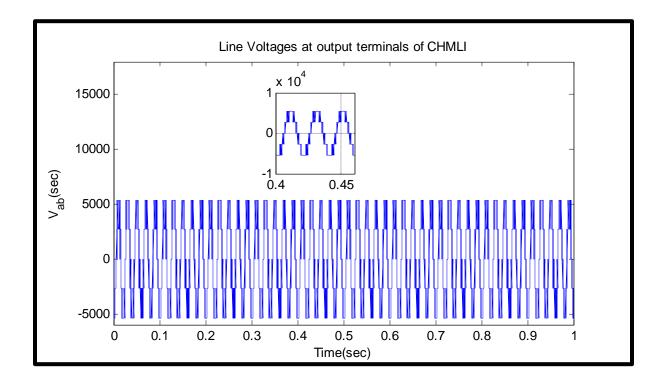

| Figure 8.31 | line to line voltage at CHMLI terminals                                        | 82 |

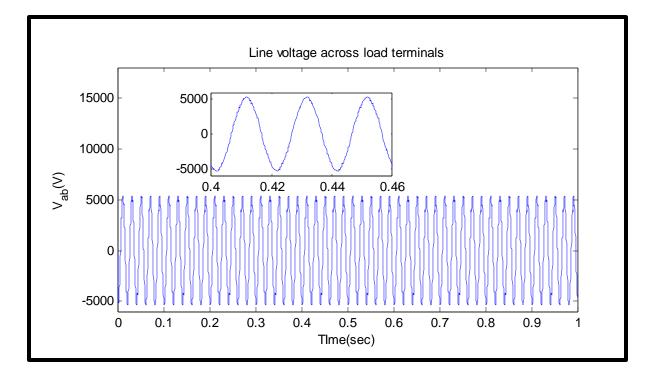

| Figure 8.32 | line to line voltage across load terminals                                     | 83 |

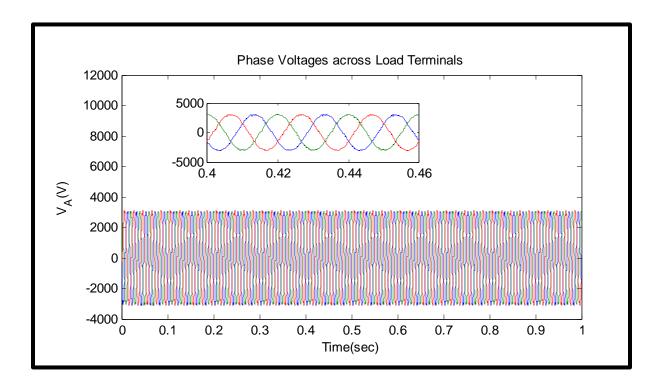

| Figure 8.33 | Phase voltage across load terminals                                            | 83 |

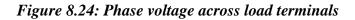

| Figure 8.34 | Phase current across load terminal                                             | 84 |

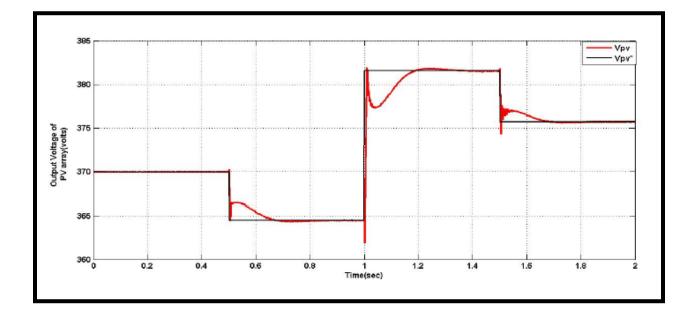

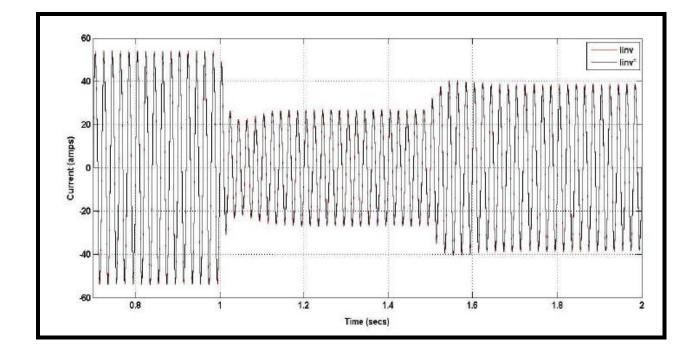

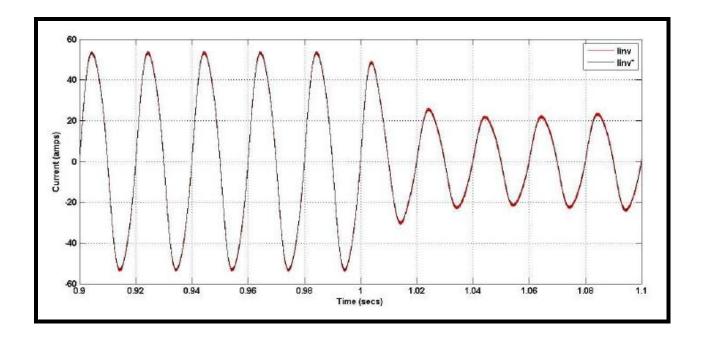

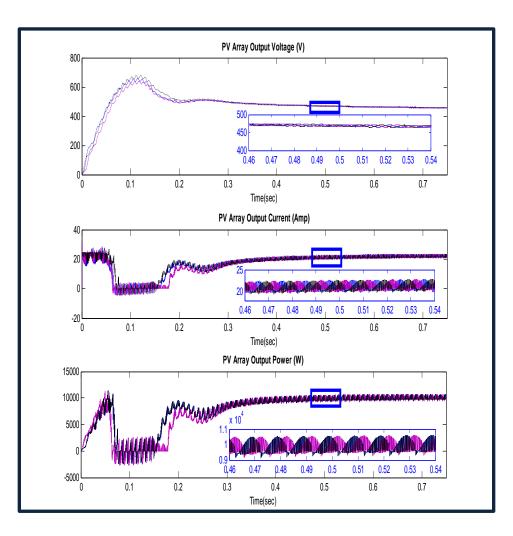

| Figure 8.35 | String output (a) voltage (b) current and (c) power                            | 85 |

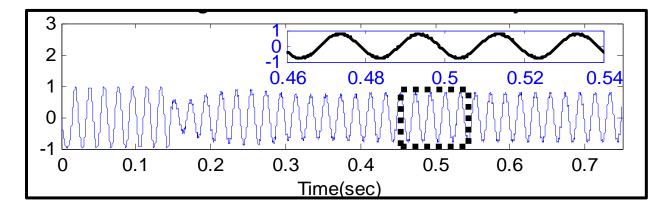

| Figure 8.36 | Modulating wave                                                                | 86 |

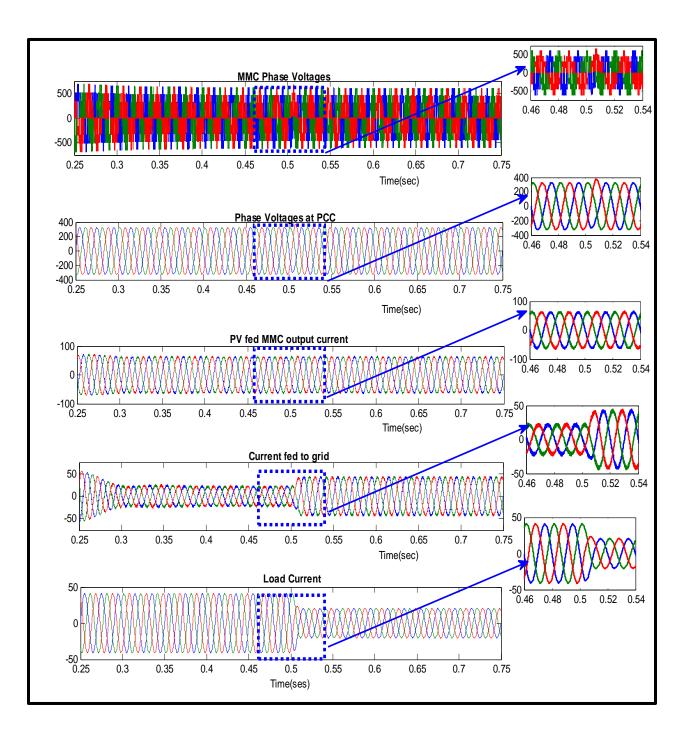

| Figure 8.37 | Parameters after inversion                              | 87 |

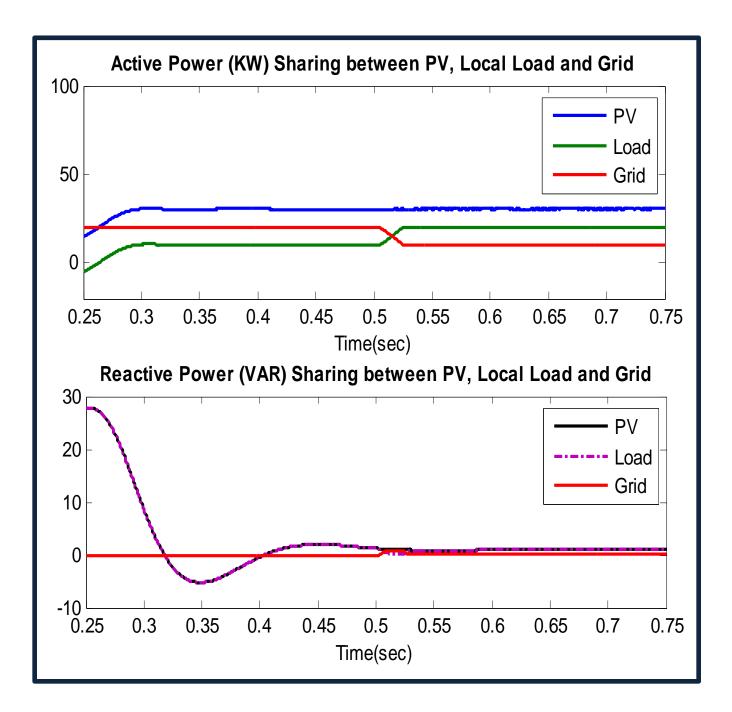

|-------------|---------------------------------------------------------|----|

| Figure 8.38 | Active Power and Reactive Power sharing between         | 88 |

|             | PV, Local Load and Grid                                 |    |

| Figure 9.1  | Power circuit of Voltage source converter               | 90 |

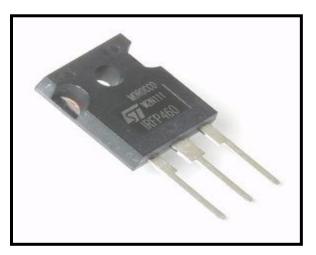

| Figure 9.2  | MOSFET IRFP 460                                         | 91 |

| Figure 9.3  | Snubber circuit for MOSFET protection                   | 92 |

| Figure 9.4  | Pulse amplification and regulation circuit              | 93 |

| Figure 9.5  | Connection Diagram for +5v and +12v regulated supply    | 94 |

| Figure 9.6  | AC current sensor circuit                               | 96 |

| Figure 9.7  | AC voltage sensing circuit                              | 96 |

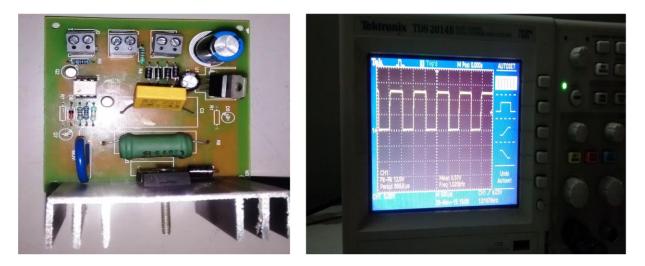

| Figure 9.8  | Hardware setup of 5-level H bridge inverter (open loop) | 97 |

| Figure 9.9  | Driver circuit and its output pulses                    | 97 |

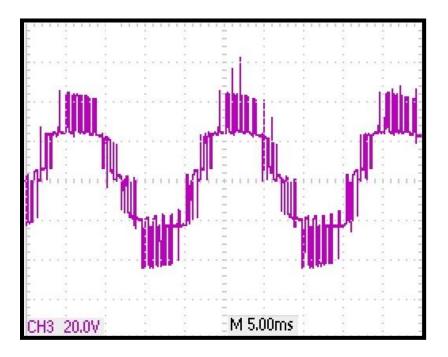

| Figure 9.10 | Output Line voltage of 5-level H bridge Inverter        | 97 |

## TABLE INDEX

| Table 8.1: Datasheet value of solar PV module             | 66 |

|-----------------------------------------------------------|----|

| Table 8.2: Voltage THD level of 5-level H bridge inverter | 70 |

| Table 8.3: Datasheet parameters of PV-MF165EB3 module     | 70 |

| Table 8.3: Simulation Parameters of System                | 71 |

## Chapter 1

#### INTRODUCTION

The primary energy used in generating electricity is about 40 percent. Out of this, the energy used for domestic purpose that is in homes and offices is nearly 70 percent which is nothing just in the form of electricity.

In all over the world the new installations of plants are becoming complicated because less availability of sites for generation, transmission and distribution. In the U.S.A., people have not been got permission since 1978 to establish nuclear power plant. The main causes for that are safety concerns, expenses during the construction as well as local opposition. If existing power plants are not relicensed at the expiration of 40 years and no nuclear power plants are built then the net power output will decrease. This decline must be replaced by other means. As gas prices are increasing day by day that means dependence will increase on coal for base load power generation. The U.S.A. has high reserves of coal but that are not fully acceptable to the public due to lack of clean coal burning technologies.

Renewable energy technologies (Wind, solar, hydro, biomass, geothermal, tidal and ocean) are an alternative to the nuclear and fossil fuel power. It is very difficult to set up hydro electric projects on large scale due to competing use of land and water. To get the relicense of existing hydro power plants, it is required to remove some of dams to protect wild life habitats. In the next decades renewable energy sources will become the only reliable energy supply due to less dependence over fossil and unclear fuels. Particularly, wind and solar photovoltaic energy conversion systems are the fastest growing renewable energy sources.

Both the solar and wind power are highly modular. The above are better in terms of economy as installations are done in stages. Even the PV is more modular than wind. It can be designed for any capacity, as the price of solar array depends directly upon peak generating capacity and indirectly upon area that is in square foot. The modularity of the wind and photo voltaic system is more important for small grids. In case of wind power plant the requirement of number and size of wind turbine is high. Without the loss of economy number of tower can be added to the existing system. Apart from that in case of existing conventional power plant expansion is neither economical not free from risk.

It is more preferable to install a new PV or wind power plant to fulfill demand in compare to laying new transmission line. In case of long overload line the voltage drop is high, so this problem can be overcome by local renewable power plant that is generation near the load. In China and India the demand is increasing day by day but apart from that these two countries rapidly growing in the field of electrical power.

Solar energy technologies are less expensive and efficient. This is an attractive solution because it is more cleaner and environment friendly than fossil fuels, coal and nuclear. Researchers are working in the field of photovoltaic to make solar energy more efficient. To make this topology more productive number of avenues exists. For example, one branch is dealing with the materials used in solar cells whereas other is finding methods to manufacture high quality silicon at lower manufacturing costs. This is the fact that energy efficiency of the solar panels affected by the high quality semiconductor material. A PV system is a combination of solar panels, battery system, DC/AC conversion circuits and other power conditioning devices.

The dissertation report I am presenting in this body of work concentrates more on the electronic means of enhancing energy efficiency in a PV system as well as converts the variable DC from sun into AC to fed AC loads. This branch of power electronics is generally called power conditioning and in the present case is used to describe the management of electrical energy to effectively charge batteries, to draw maximum power from the solar panels or provide a high quality AC output.

In case if the PV system is not constructed properly then the power output of solar panels will dissipate power as heat in the system components. In order to prevent the waste of useful electrical energy, it is necessary to develop modern methods to manage electrical power. It is advisable to increase energy efficiency as solar energy systems are more expensive in compare to other energy sources. It is beneficial to enhance the power output of renewable energy sources as they are clean energy sources, such as solar energy and they don't create pollution like traditional ones. In addition to enhance efficiency, power conditioning is also used to facilitate energy storage. For example, to provide a desired current to charge batteries it may require power conditioning circuitry. The current supplied by the PV array to the battery can be control by a DC/DC converter.

To draw maximum power from solar panels, maximum power point trackers are used. DC- DC converters are used to design circuitry for the above one. In case if load is directly connected to the solar panels and MPPT is absent then great part of electrical power may be dissipated in the form of heat. To get maximum power despite variations in light intensity and to get maximum energy efficiency, MPPTs are connected between the solar panels and load. Solar panels supply DC voltage but load side AC is required to power electronic devices. The circuitry which is used to convert the DC voltage into AC voltage is called inverter. The AC voltage can be transferred into the grid only when its frequency is 50 Hz. Hence DC voltage is converted into a 50Hz waveform with proper amplitude. The following diagram explains the use of inverter and DC/DC converter.

#### SOLAR PANEL

Figure 1.1:Block diagram of solar system using inverter

#### **1.1 Objectives**

PV inverter is the heart of PV system. The output of inverter contains umber of harmonics, hence to reduce the size of filter and the electromagnetic interference, the T.H.D. of output waveform should be as low as possible. Due to advantages of multilevel inverters over three level PWM inverters, it has become point of attraction for manufacturers and researchers.

In this report to reduce to improve the efficiency and to reduce the cost cascaded inverter topologies are used and to harvest more solar energy MPPT control is developed.

Firstly, the converters are connected in series under cascaded inverter topology to reach high power as well as voltage level. With the help of this topology the voltage stress on the semiconductor switches can be reduced. Thus, this is helpful to reduce the cost of PV inverters as low voltage rating MOSFETs are used and even it can be applied to large PV system. The low cost, reliability, robustness, efficiency and modularity of multilevel inverter attract the people towards this.

The better utilization of Photo voltaic module can be done without any sacrifice. Due to the above mentioned benefit cascaded H Bridge MLI can extensively be used in medium as well as large grid connected PV system. The power quality may be affected by the impact and higher penetration of PV system.

#### **1.2 Organization of dissertation**

**Chapter 2-** This chapter is of literature review. In this chapter grid connected PV inverter topologies as well as various PV system configurations are summarized and discussed.

**Chapter 3-** This chapter gives basic idea about PV systems, different types of PV systems and their applications. It also presents the topic of Matlab modeling of PV module under varying irradiance and temperature conditions.

**Chapter 4-** This chapter explains in detail about power conditioning system for solar PV system and the role of power conditioning elements in PV systems. It also presents the use of DC-DC converter. In addition to these controlling of boost converter is also discussed. Other than that this chapter explains in detail about the need of maximum power point trackers in power conditioning system.

**Chapter 5-** This chapter presents the single phase cascaded H bridge multilevel inverter for grid connected PV system. A control scheme is proposed and design calculation is given.

**Chapter 6-** This chapter gives idea of three phase cascaded H bridge multilevel inverter for grid connected PV system. Other than that a control scheme is proposed which gives individual MPPT control as well as to avoid the problem of shading modulation compensation is used.

Chapter 7- This chapter gives the brief idea of design procedure on FPGA.

**Chapter 8-** This chapter includes the simulation of solar PV module, DC-DC boost converter and single phase & three phase 3-level inverter and total PV system on MATLAB and on Xilinx System generator also.

**Chapter 9-** In this chapter mainly presented the way of implementation of hardware. The results from hardware are also presented in this chapter.

**Chapter 10-** This chapter gives conclusions of dissertation work followed by scope for future work in this area.

Chapter 2

#### LITERATURE REVIEW

In distribution generation systems photo voltaic systems connected to the grid play an important role. The essential element of grid connected photo voltaic system is a PV inverter which is used to convert DC power into the AC power. This AC power is further fed to the grid. To make solar power more attractive cost per inverter is important. Therefore, new system configurations are used to get high efficiency and inexpensive and innovative inverter solution. This chapter presents a literature review of present nature of the grid connected photo voltaic inverters.

To increase the PV installations, photo voltaic inverters should have following characteristics:

- Small size and weight

- High efficiency

- High reliability

- Low cost

- Be safe for human interaction

#### 2.1 Overview of grid connected Photo Voltaic system

Solar electric energy demand growth is mostly in grid connected applications [1]. To increase the solar energy extraction, a maximum power point tracking (MPPT) control scheme is used which continuously tune the system. It increases the overall efficiency of the system.

Five inverter structures can be used for different configurations of PV system [2-7]:

- Central Inverters

- String Inverters

- Multistring Inverters

- AC module Inverters

- Cascaded Inverters

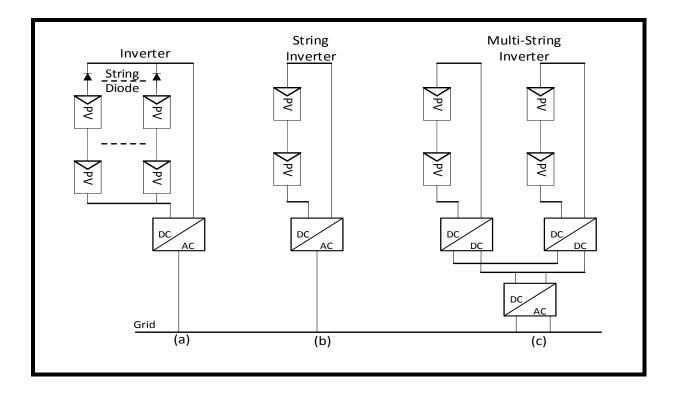

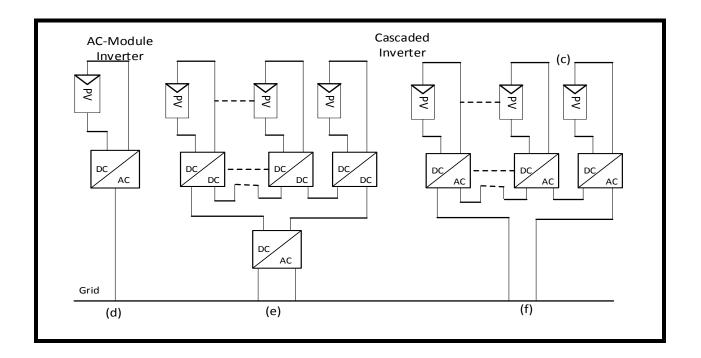

(a) Central inverter. (b) String inverter. (c) Multi-string inverter. (d) AC-module inverter.

(e) Cascaded DC/DC converter. (f) Cascaded DC/AC inverter.

Figure 2.1: Configurations of PV systems.

The Photo voltaic system configurations are shown in figure 2.1. One PV module output is very low, so to get a sufficiently high voltage PV modules are connected in series. Along with this it also avoid further amplification. The strings are also connected in parallel through string diodes to reach higher system power level.

#### (a) Central inverter

Central inverters are mainly used in medium and large scale PV applications. Its power ranging starts from 10 kW. Its voltage is high enough to avoid the use of boost converters and transformers. Several inverters are shunted for high power applications [8-10].

Advantages:

- Low cost

- Simplicity

- High inverter efficiency

#### Disadvantages:

- Power loss due to common MPPT

- Power loss due to mismatches

- Losses in the string diodes

- Requirement of high voltage DC cables between PV panels and Inverter

#### (b) String Inverter

String inverters mainly used in small domestic applications. Its power ranging starts from 0.5 kW to 1 kW. It is the reduced version of centralized inverter with one string connected to an inverter useful for MPPT.

#### Advantages:

- No string diodes needed

- Individual MPPT for each string

- Very flexible configuration

- High system reliability

- Low cost due to mass production

• Different space orientation for each group

#### (c) Multistring Inverter

As shown in figure 2.1(c) multi string inverter is further development of string inverters. Each PV module is followed by DC-DC converter [11-12] and then connected to a common DC-AC inverter. It is an intermediate solution between string inverters and AC module inverters. With the help of DC-DC converter further enlargement of PV plant is possible.

Advantages:

- Flexible

- High efficiency of power extraction

- PV string is individually controlled

- Reduced power loss

#### (d) AC module inverter

It is a complex topology and mainly used in small scale residential applications. In this case inverter is connected to only one photo voltaic panel there is no chances of mismatching between PV modules [13-15].

Advantages:

- No mismatches losses

- Less risk of fire and arc in DC wiring

- Flexible design

- Independent function of each module unit

#### Disadvantages:

- Low overall efficiency

- Requirement of high voltage amplification

- Price per watt is high

- Complex circuit topologies

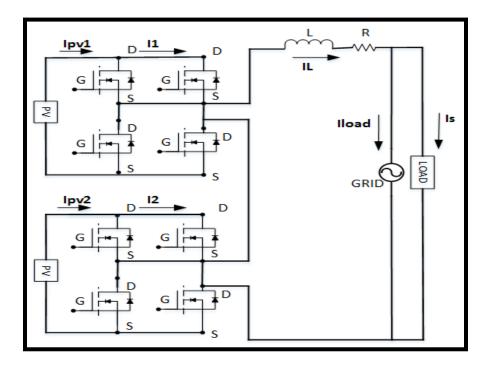

#### (e) Cascaded inverter

When several converters are connected in series to get high output voltage is known as cascaded inverter. This module is a combination of AC module inverter and string inverter [16-18]. Each PV module contains its DC-DC converter and again these modules along with their converters are connected in series, which further gives High DC voltage.

#### Advantages:

- Individual module MPPT

- Cheaper and efficient than AC module inverter

- Better utilization per PV module

- Redundancy of system

- No requirement of per string DC bus and inverter

- Controls grid current and reactive power compensation

## 2.2 Topologies of grid connected PV inverter

Grid connected photo voltaic inverter topologies can be divided as follows:

- The number of power conversion stages

- With or without transformer

- The use of decoupling capacitors

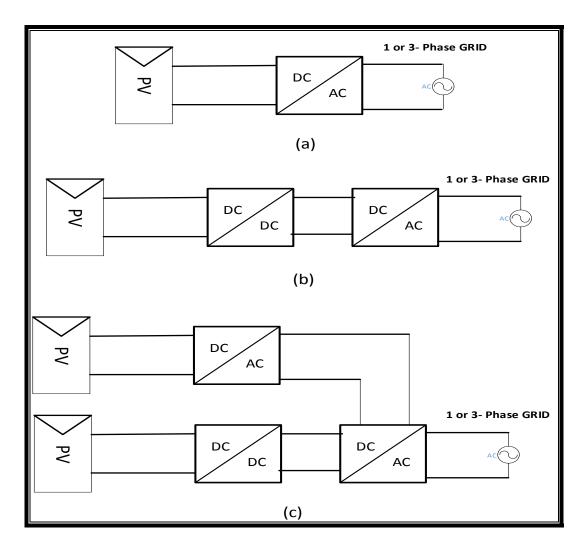

Further it can be categorized on the basis of power processing stages. These stages are as shown in below figure 2.2. These stages are:

- Single stage inverter

- Dual stage inverter with single DC-DC converter

- Dual stage inverter with multiple DC-DC converter

(a) Single stage inverter (b) Dual stage inverter with single DC-DC converter(c) Dual stage inverter with multiple DC-DC converter

Figure 2.2: Three cases of multiple and single stage inverter

#### 2.2.1 Single stage inverter

The configuration of single stage inverter is shown in figure 2.3. Full bridge inverter is mainly used in single phase system. The main advantage of single phase inerter is that it does not required additional devices hence; there is no high cost, conduction losses and sluggish transient response like two stage inverter.

Figure 2.3: Power electronic system

Advantages:

- High efficiency

- Low price

- Easy implementation

Disadvantages:

• Due to shading effect on PV panels it can affect the efficiency of the system.

#### 2.2.2 Two stage inverter

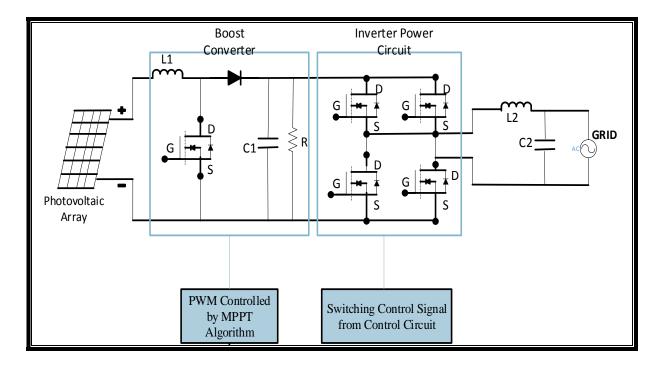

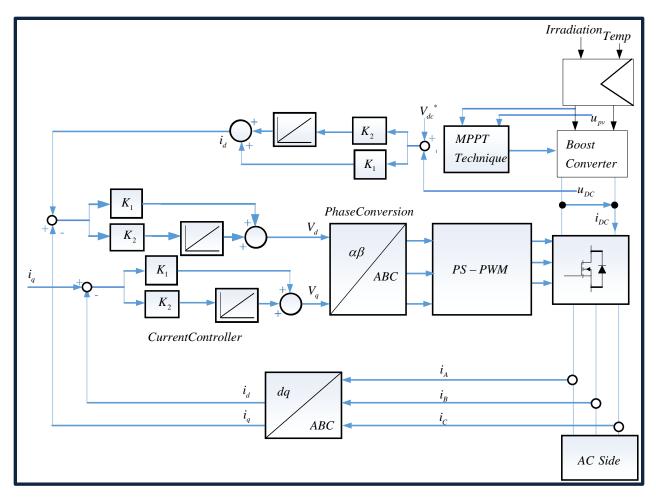

Dual stage inverter is a combination of DC-DC converter and Inverter circuit. The dual stage topology is shown in the figure 2.4. In this topology the DC-DC converter is working as a boost converter which performs MPPT as well as voltage amplification and inverter is playing an important role to control grid current.

At first stage boost converter is used to provide fixed DC voltage and at the second stage voltage source inverter is used in the single or three phase system. This topology removes the requirement of transformer at load side. Hence this is cost effective technique which also increases the efficiency of the system.

Figure 2.4: Two stage topology

#### 2.3 Comparison of various methods

A PV inverter is the heart of grid/load connected PV system and it is used to convert DC power from the solar panels into AC power fed to the grid. There are three type of multilevel inverter topologies which are basically used now days. These are Neutral point clamped (NPC), Cascaded H Bridge (CHB), Flying Capacitor (FC).

The cascaded H Bridge has many features which make it superior than others like its modularity and simple layout. It does not required extra clamping diodes or capacitors like remaining two. It also allow transformer less connection which make it modular in nature [19].

The CHB-MLI like other multilevel inverter topologies, gives staircase AC output waveform with less THD in compare to 2-level inverters. Using multicarrier techniques [20-21] the above thing can be carried out either at fundamental frequency or at higher switching frequency.

Modular Cascaded multilevel topology improves efficiency and flexibility of PV system. In Cascaded multilevel inverter several single phase inverters are connected in series and each PV panel is connected to its own DC/AC inverter. This topology is favorable for medium and large grid connected PV system as it gives [22-23] high power and high voltage from the combination

of no. of modules. Grid/load connected PV system generally uses 2 stages [24-25] to feed solar power into the grid. The first stage is of boost converter which is used to boost the PV voltage and track the maximum solar power. The second stage is DC/AC inverter which is particularly used for inversion of power.

The CHB consists of several DC links connected to PV strings individually and with independent MPPT [26] which is its major advantage but in case of three phases the problem of PV mismatches may occur. It leads to unbalanced supply power leading to unbalanced current. Above problem can be sort out with the help of various compensation techniques [27]. Most of the research is going on in the field of single phase solution [28-32] because there is a great drawback of CHB-MLI that is power imbalance. One of the solutions proposed in the literature [33]. In this method to make unbalanced current the neutral of reference voltage is shifted. This is also known as feed forward compensation.

In past [34], the balancing achieved through a redundancy based strategy but afterwards it uses simple PI controller combinations. This solves the problem related to stability. The grid current should be in phase with grid voltage to maintain stability. This requirement can be fulfilled by using a PLL [35] which used "Virtual flux" based synchronization. All of these papers [36-37] assumed that the dc sources are equal and do not vary with time. In [38-39] analytical solutions have been derived for the condition of unequal dc sources. But all the above techniques used are time consuming. Therefore to store the results in a look up table and to calculate the solution of switching angle offline an alternate approach [40-41] has been determined. Even then, the solution could be missing for some operating point.

To resolve this problem, the ANN [42] replaced the look up table. It is faster than others and real time control can be easily established. In CHB-MLI large numbers of inverters are required to reduce the harmonics. Apart from that a complex DC voltage regulation method has to be used to control the output voltage of STATCOM [43]. A new type of method [44] is proposed to solve the above problem of current harmonics which occurs due to ripple voltage.

#### **2.4 Conclusion**

A literature review on PV inverters which are connected to grid has been discussed. Other than that grid-connected PV inverter topologies are also discussed. The inverter topologies can be divided on the basis of power processing stages and these are single stage and dual stage inverters. Many topologies related to single as well as dual stage inverter have been reviewed. Comparison have done between different topologies to get better results.

## PHOTO VOLTAIC SYSTEM

A PV solar cell or module converts solar energy into electrical energy. Solar cell is the basic part of solar panel and a solar PV module is formed if many cells are connected in parallel and series. PV systems are combination of solar arrays, power conditioning devices and load [45].

#### Photo voltaic system applications:-

- 1. Stand alone PV systems

- Consumer applications

- Simple house systems

- Residential systems

- Hybrid systems

- 2. Grid connected PV system

- Decentralized grid connected systems

- Centralized grid connected systems

## 3.1 Stand alone PV systems

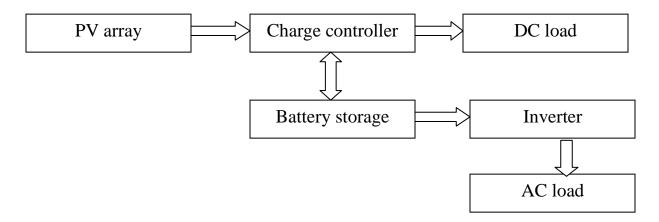

The areas which have no access to an electric grid normally used stand alone PV systems. In standalone systems the energy produced from PV module being stored in batteries. These systems are also known as isolated systems.

Figure 3.1: Schematic diagram of a standalone PV system

#### **3.1.1** Consumer applications

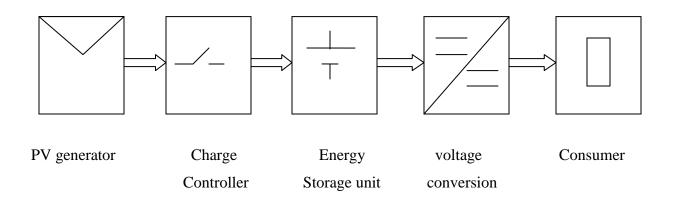

The first consumer application was solar calculators. As no storage require the above one is an ideal application. The other products which are available with solar power are watches, battery chargers etc. All the products consist of small PV modules, DC-DC converter, energy storage unit and a charge controller.

#### Figure 3.2: Block diagram of PV power supply for a small consumer product

#### **3.1.2 Solar home system**

A solar home system consists of the solar generator, led battery and charge controller and DC appliances as a load. For the appliances support structures are also needed which are sockets, cables and module.

The benefits of solar home system compared to traditional energy sources used for lightening are as follows:-

- Improvement in illumination quality

- No health risk that is smoke and smell

- No risk of fire hazard

- Long lifetime

- Less expensive than traditional one

#### 3.1.3 Residential system

Stand alone systems supply electric power to buildings. PV is very economic alternative to a diesel engine when there is no connection to the grid. For residential system AC power is

required. Therefore, it also consists of inverter to convert DC into AC. Stand alone PV systems which supply electrical energy to buildings must also have storage battery as radiation intensity changes with season and weather conditions. The schematic diagram of standalone PV system supplying to residences is given below:-

#### 3.1.4 Hybrid systems

Figure 3.4 : Schematic diagram of a hybrid system

When more than one electricity generators are employed then the system is known as hybrid system. The other type of generators can be renewable that is wind or conventional such as diesel engine or the utility grid. The schematic diagram of hybrid system is shown in figure 3.4.

#### 3.2 Grid connected PV system

As technology is increasing people are attracting towards grid connected photo voltaic system. In this the utility power that is power from the grid is automatically provided at night as well during the day when demand exceeds the solar power generation. That means during the day the electricity generated from PV system can be immediately fed to the respective loads or it can be sold to the electricity supply companies.

For grid connected photo voltaic system battery storage is not required. A schematic diagram of grid connected PV system is shown in figure 3.5 [46].

#### Figure 3.5: Schematic diagram of a grid connected PV system

Grid connected photo voltaic systems can be further divided as follows:-

#### • Decentralized Grid connected PV system

Mainly used for small power range and rooftop installations.

#### • Centralized Grid connected PV system

These systems have an installed power up to MW range and mainly used for medium and large grid connected photo voltaic system.

#### 3.3 Solar PV modeling

PV cell is a semiconductor device which is mainly used to convert light energy into electrical energy. The output of solar PV cell that is solar energy not remains constant all the time, as it depends upon season, weather and day – night effect. The power extracted from photo voltaic system is function of voltage as well as current. The external conditions like temperature and solar irradiance affect the power output. The current-voltage (I-V) curve and the power – voltage (P-V) curve are non linear in nature even under presence of uniform solar irradiance and absence of partial shading.

Due to non linear characteristics of PV cell it is necessary to track a point which gives maximum power. As solar radiation increases, the current and power output of PV module increases. Other than that as cell temperature increases, voltage and power output of PV module decreases. Multiple maximum power points may exist on the PV curve due to effect of shading on some cells. Shading can occur due to clouds in the sky, nearby buildings and birds landing on panels. Due to complex nature of solar PV module it is advantageous to simulate a model under different illumination conditions.

A PV module generates very small power. The maximum power can be extracted under particular voltage condition due to non linear characteristics of PV cell. So the main task of a MPPT in a PV system is to continuously tune the system. It gives maximum power from the solar array and does not get affected by weather or load conditions.

A PV cell generates a voltage around 0.5 to 0.8 volts which further depend upon the semiconductor. Therefore, it is necessary to connect the PV cell either in series or in parallel to get higher output.

To design the PV system it is important that the modeling of PV module should be reliable and accurate. The modeling of solar PV cells can be done by below mentioned two methods:-

- Mathematical based modeling

- Electronic component based modeling

Mathematical based model of solar cell can be developed with the help of software, MATLAB. Mathematical based model is good to obtained desired output. It also considers the effect of solar irradiance, ambient temperature and load voltage.

#### 3.4 Equivalent circuit of solar cell

The operation of the p-n junction solar PV cell can be explained by diode equation. The p-n junction is fabricated over a layer of semiconductor. The illumination comes from sun light is nothing but the photons. Solar cell absorbed these photons only when its energy is greater than semiconductor band gap energy. When valence electrons lose their existence from the atoms then, the generation of electron hole pair takes place. Due to the internal electric fields of the p-n junction current starts to flow in the circuit.

#### 3.4.1 Solar cell model

**IDEAL MODEL:** - Ideal solar cell consists of a current source and a diode which are connected in series. The photon current which is produced by current source is directly proportional to the solar irradiance G. Short circuit current and open circuit voltage are two key parameters which are used to characterize photo voltaic cell. The value of short circuit current and open circuit voltage is provided by the data sheet.

The simplified circuit of solar cell without considering losses is shown in figure 3.6.

Figure 3.1: Simplified equivalent circuit of ideal solar cell

From Kirchhoff's law, we have-

$$I_{pv} = I_p - I_d \tag{3.1}$$

Where

$$I_{d} = I_{o} \begin{bmatrix} q \checkmark_{pv} \\ e^{\frac{AKT_{j}}{KT_{j}}} - 1 \end{bmatrix}$$

(3.2)

Thus

$$I_{pv} = I_p - I_0 \begin{bmatrix} q \langle q_{pv} \rangle \\ e^{AKT_j} \\ -1 \end{bmatrix}$$

(3.3)

Where,

$I_{pv}$  is the current through PV cell.

$V_{pv}$  is the voltage across PV cell

$I_p$  is the photon current that is equal to short circuit current

$I_o$  is the reverse saturation current of diode

q is electron charge  $(1.6*10^{-9} \text{ C})$

K is boltzman constant (1.381 \*  $10^{-23}$  J/K)

$I_d$  is current shunted through the intrinsic diode

A is diode intrinsic factor

$T_i$  is junction temperature of panels (Kelvin)

#### 3.4.2 Solar cell model with ohmic losses

**Practical Model:** - Figure 3.6 shows the practical circuit for PV cell. This circuit consists of photo current source, a diode, a series resistor and a parallel resistor. This model takes account of ohmic losses and the material resistivity due to levels of contact.

Figure 3.7: Simplified equivalent circuit of practical solar cell [51]

The PV cell output current can be defined as a function of the output voltage of the PV cell as follows:-

$$I_{pv} = I_{p} - I_{o} \left[ \left[ e^{\frac{q \left( \left( pv - R_{s} I_{pv} \right) \right)}{AKT_{j}}} - 1 \right] - \frac{\left( \left( \left( pv \right) + R_{s} I_{pv} \right) \right)}{R_{sh}} \right]$$

(3.4)

Where,

$R_s$  is parasitic series resistance

$R_{sh}$  is parasitic shunt conductance

The photon current  $I_p$  is proportional to the sun irradiance and to the cell temperature, which is given by,

$$I_{p} = I_{sc} \left[ -\alpha \left( -T_{ref} \right) \right] = \frac{G}{G_{o}}$$

$$(3.5)$$

Where,  $\alpha = 0.0012 * I_{sc}$ , which is the temperature coefficient of short circuit current

G is solar irradiance level (kW/m<sup>2</sup>)

$G_{\rm o}$  is solar irradiance under normal operating conditions, 1000  $kW/m^2$

#### **3.5 Conclusion**

In this chapter various application of PV system has been discussed like in standalone and grid connected system as well as PV modeling has been explained with theoretical and practical methods.

# POWER CONDITIONING DEVICES OF PHOTO VOLTAIC SYSTEM

A photo voltaic system is the combination of solar panels and power conditioning devices. The branch of power electronics which is called power conditioning is very important from view point of management of electrical energy. It helps to draw maximum power from solar panels and also provides a high quality AC output.

To manage electrical power in PV system it is necessary to find modern and sophisticated methods. In absence of power conditioning devices power generated by solar panels will be wastefully dissipated as heat in the system components.

To enhance the efficiency of PV system electronics play very vital role. Along with that to increase the solar generated electricity appropriate electrical techniques can be implemented for grid connected PV system.

It is necessary to maximize the energy efficiency as solar energy systems are more expensive in compare to other energy sources. Power conditioning devices are also used for energy storage. Some power conditioning devices which are used to increase the efficiency of PV system are as follows:-

- 1. DC/DC converters

- 2. Maximum power point trackers

- 3. Inverters

## 4.1 DC/DC converters

DC/DC converters used in number of circuits for example battery chargers and maximum power point trackers. With the help of DC/DC converter, the output voltage and current of solar panel can be adjusted to any value. In modern power electronics DC/DC converters are more preferable than linear power regulator [47].

Linear regulators provide high quality DC voltage but it energy efficiency is poor. Linear regulator keeps constant output voltage and functions as a variable voltage divider. It is highly inefficient circuit as it dissipates heat in the resistive elements.

Maximum power efficiency is a main goal in solar PV system that's why DC/DC converters are preferred. Linear regulators provide an output voltage, less than input. Whereas DC/DC converters are flexible as they can step up as well as step down the input voltage.

DC/DC converters must be able to maintain controllable or constant output voltage. By proper switching topology the above goal can be achieved despite variations in the input voltage. The operations of switches must be controllable and periodic to achieve a stable average output voltage. In DC/DC converters mainly two energy storage elements are used that is inductor and capacitor. Other than that transistor is always used as a switching element and with the help of control circuit proper and periodic switching of transistor can be achieved. Transistors types which are mainly used for switching are BJT (bipolar junction transistor) and FET (Field effect transistor).

MOSFET is best suited for switching circuit as it dissipates very little power in on and off states and with the help of this switching circuit can achieve high power efficiency. In the ON state, due to low resistance very small voltage drop will takes place across switching device whereas in the OFF state very little current will flow that is nothing just the leakage current.

It is advantageous to operate switching regulators at high frequencies. High frequency of switching device decides the size of other components which further decides the cost. Due to high frequency of switching regulators, components used such as capacitor, inductor and transformer can be of smaller size.

Output voltage of PV system, power transfer and battery charging can be optimized with the help of DC/DC converter. DC/DC converter converts constant output voltage and current of solar panel into variable one. This conversion can takes place in between various places. For example:-

- Between a battery and inverter

- Between a solar panel and an inverter

- Between a battery and an inverter

It is usually seen at the output of solar panels and its ability is used for maximum power point trackers.

For safety benefits, transformers can be used along with DC/DC converter, as transformer provides electrical isolation. Transformer is generally used at the input side of DC/DC converter in series with switching element.

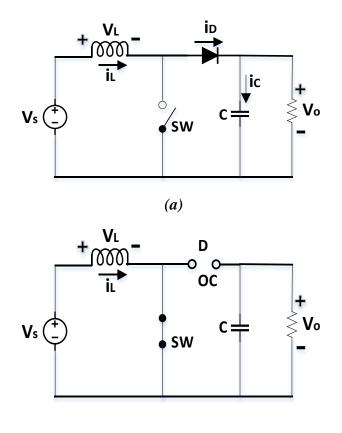

#### 4.1.1 DC analysis of PWM boost converter

The circuit of boost converter is shown in figure 4.1.For steady state operation its output voltage  $V_o$  is always higher than input voltage  $V_i$ . This converter circuit boosts the output of solar panel to higher level. It consists of a power MOSFET, a diode  $D_1$ , an inductor L, filter capacitor C and a load resistor  $R_L$ . The switch is turned ON and OFF at switching frequency with the ON duty ratio.

The switching frequency is given by,

$$f = \frac{1}{T} \tag{4.1}$$

And the ON duty ratio is given by,

$$D = \frac{t_{OII}}{T} \tag{4.2}$$

Where  $t_{ON}$  is the time interval when the switch S is remains on.

The boost converter can operate in two modes which depend upon the waveform of inductor current. The two modes are as follows:-

- Continuous conduction mode

- Discontinuous conduction mode

Continuous conduction mode is considered for the project. Figure 4.2 shows the equivalent circuit of boost converter for continuous conduction mode when the switch is ON and diode remains reverse biased. Whereas figure 4.3 depicts when the switch S is OFF and diode is forward biased.

Assumptions for analysis of boost converter:-

1. The switch is closed for DT time and it will remain open for (1-D)T.

- 2. All components are ideal.

- 3. The value of the capacitor is high and output voltage remains constant.

- 4. The inductor current always remains positive.

**(b)**

(c)

Figure 4.1: Boost converter (a) Main circuit (b) Equivalent circuit for switch closed (c) Equivalent circuit for switch open [48]

#### Analysis for the switch closed:-

When the switch is ON, the diode will remain open circuit. The current will flow through inductor and voltage source. The voltage across inductor is given by,

$$V_L = V_S = L \frac{dI_L}{dt} \tag{4.3}$$

Or

$\frac{dIL}{dt} = \frac{VS}{L}$

When the switch is closed the current increases linearly as the rate of change of current is constant. Change in inductor current for switch closed is given by-

$$(\Delta i_L)Closed = \frac{V_S DT}{L}$$

(4.4)

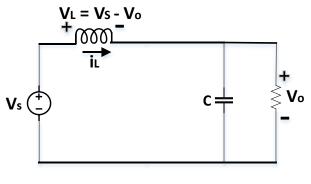

#### Analysis for the switch open:- [48]

When the switch is open, the diode become forward biased as the inductor current cannot decrease instantaneously and it provides path for inductor current.

$$V_{L} = V_{S} - V_{O} = L \frac{dI_{L}}{dt}$$

Or

$$\frac{dI_L}{dt} = \frac{V_S - V_O}{L} \tag{4.5}$$

When the switch is open the current increases linearly as the rate of change of current is constant. Change in inductor current for switch open is given by-

$$(\Delta i_L)Open = \frac{\Psi_S - VO(1-D)T}{L}$$

(4.6)

For steady state operation, the net change in inductor current will remain zero and it is given by,

$$\Lambda I_L$$

closed +  $(\Delta I_L)_{open} = 0$

By solving equation 4.4 and 4.6,

$$V_O = \frac{V_S}{1 - D} \tag{4.7}$$

By the above equation it can be concluded that boost converter produces an output voltage which is always greater than or equal to input voltage.

For design perspective values of inductor and capacitor is very important. It can be calculated by the formula given below:-

$$L = \frac{V_S DT}{\Delta i_L} = \frac{V_S D}{\Delta i_L f}$$

(4.8)

$$C = \frac{D}{R\left(\frac{\Delta VO}{VO}\right)f} \tag{4.9}$$

Figure 4.2 : Boost converter waveform (a) Inductor voltage (b) Inductor current (c) diode current (d) capacitor current

Hence, DC/DC converter plays an important role for grid connected photo voltaic system. It also reduces the requirement of transformers in the circuit which further reduces the cost, losses and complexity in the circuit.

#### 4.2 Maximum Power point trackers

The characteristics of PV cell is non linear in nature hence, under particular voltage condition only maximum power can be extracted. In photo voltaic array maximum power point tracking algorithm is used to get maximum output power. Perturb & observe and incremental conductance are some direct control techniques which have less complexity and easy to implement.

The output of PV module is generally low so, MPPT continuously tune the system to draw maximum power from PV array as well as it does not get affected by the weather condition and load variation.

MPPT play very important role to improve the efficiency of solar panel. According to maximum power point theorem by adjusting load impedance equal to source impedance output power can be maximized. To get maximum output voltage MPPT helps to find the duty cycle. If output voltage increases then output power also increases.

Due to the variation in temperature and illumination level of solar cell, the maximum power point can vary frequently. So, to avoid the above condition a dynamic system inserted between solar panel and the load [49]. That system is known as maximum power point tracker.

MPPT is used to vary the duty ratio of the DC –DC converter and also vary the current and voltage at its input which can be finding out by voltage and current sensors. It is considered that power efficiency of DC-DC converter is very high that means all the power present in input is transferred to load without much variation [50].

To find maximum power point MPPT uses an iterative process. In this type of operation to calculate the power at its input, in this type of operation variation of duty ratio takes place in one direction. Due to the variation if the increase in power occurs then it results into further increment of duty ratio in the same direction. Apart from that the duty ratio is adjusted in reverse direction, if the power at the input deceases [50].

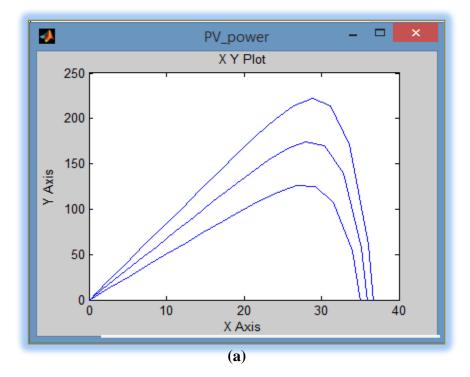

Figure 4.3 shows the I-V and P-V characteristics of PV cell. These graphs show that at irradiation or illumination increases the graph shifted upwards. The top one is at irradiation 1200  $kW/m^2$ , middle one at 1000  $kW/m^2$  and last one at 800  $kW/m^2$ .

(**b**)

Figure 4. 1: (a) PV (b) IV characteristics under different irradiance

The maximum power point is located at knee of the I-V curve and it is indicated at voltage MPP and current MPP. Power delivered to the load changes only when if there are any changes in current and voltage supplied from PV array.

#### 4.2.2 MPPT operation

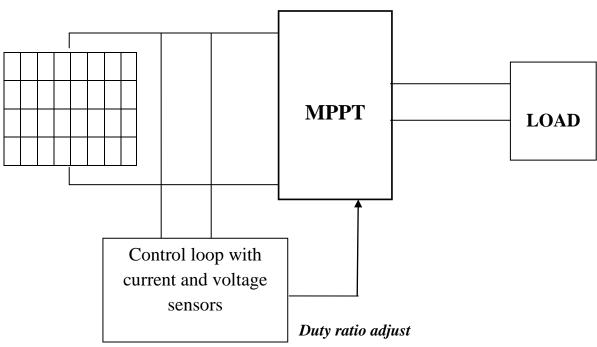

As mentioned earlier, MPPT is nothing just a DC/DC converter which is used to vary duty ratio in order to get maximum power output at load. This is due to the fact that any change in duty ratio will further change the current drawn from MPPT and this leads to do changes in operation on I-V curve of MPPT. The current which is drawn by the MPPT is proportion to duty ratio  $(t_{on} / T)$ .

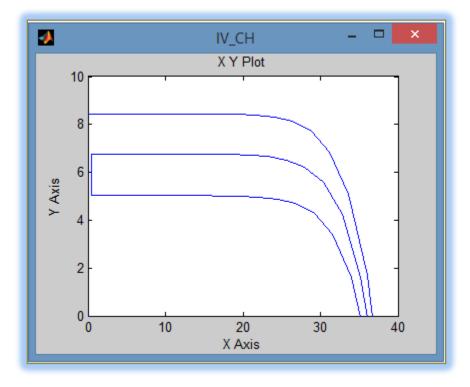

The number of voltage and current sensors depending upon the configuration can be employed in a PWM feedback loop to find the power present at the input of MPPT and the input of MPPT is nothing but the PV current and PV voltage. To maximize the power at input, PWM control loop vary the duty ratio. A block diagram of MPPT is shown in figure 4.4.

SOLAR PANEL

Figure 4.4:MPPT with PWM control loop

There are number of ways to control MPPT for example P & O and incremental conductance. The voltage and current sensors which are part of PWM feedback loop take care of power at the input of MPPT that whether it is increased or decreased. If there is an increase in power the MPPT will either increases or decreases the duty ratio in same direction. Once a decrease in power occurs, the system will set the duty ratio in opposite direction.

P&O is direct control method which is less complex and easy to implement but it has some drawbacks that is slow response and it gives transient nearby MPPT.

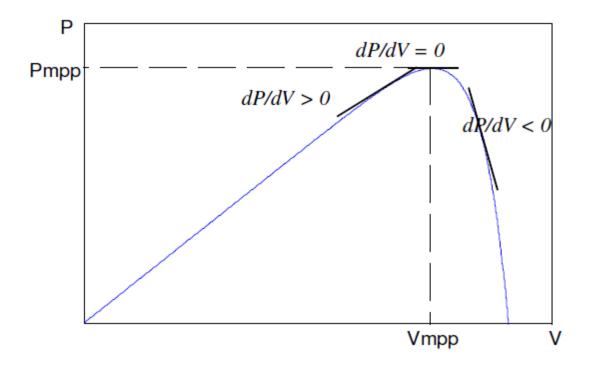

#### Figure 4.5: Change in power with respect to voltage at different positions [58]

Another method for MPPT is incremental conductance method. This method is based on the fact that at the MPP slope of the PV panel power curve is zero. According to d(VI)/dv = 0, the result is,

$$\frac{\Delta I}{\Delta V} = \frac{-I}{V}, \text{ At Maximum power point}$$

$$\frac{\Delta I}{\Delta V} > \frac{-I}{V}, \text{ At left of Maximum power point}$$

$$\frac{\Delta I}{\Delta V} < \frac{-I}{V}$$

, At right of Maximum power point

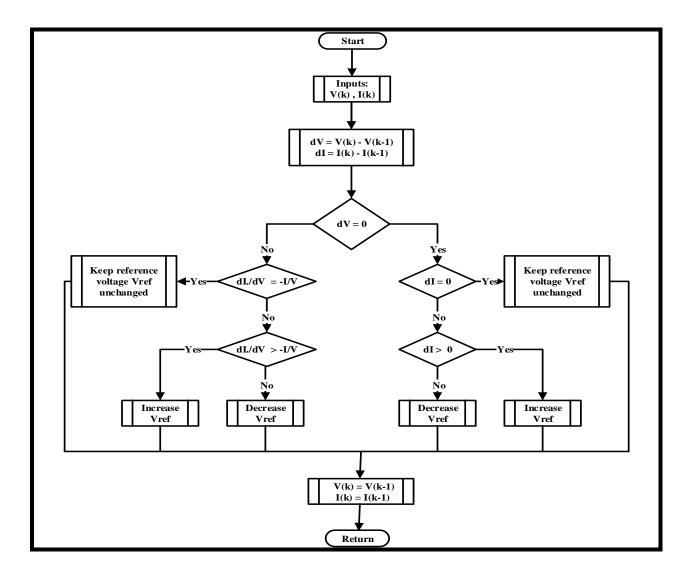

The working of incremental conductance method is explained by a flowchart which is shown in figure 4.6.

The PV panel should operate at particular voltage which is given by  $V_r$ . The speed of MPP tracking can be finding out by increment size. Fast tracking can be achieved with bigger increments. There is a possibility that system can oscillate around MPP.

Figure 4.6 Flowchart of incremental conductance method

For grid connected system MPPT is best alternative but it can be used for standalone system in conjunction with battery chargers. Some power loss can take place in DC/DC converter but MPPT enhance the system efficiency [58].

#### **4.3 PV Inverters**

There are number of inverter topologies which can be classified on the basis of their output waveform. These topologies are:-

- Square wave Inverter

- Quasi square wave Inverter

- Multilevel Inverter

- High frequency sine wave Inverter

Square and quasi square wave inverters are not at all recommendable due to its poor quality waveform. Apart from that multilevel inverter and sine wave inverter are considered in most of the applications. The output of these inverters varies due to its switching frequency.

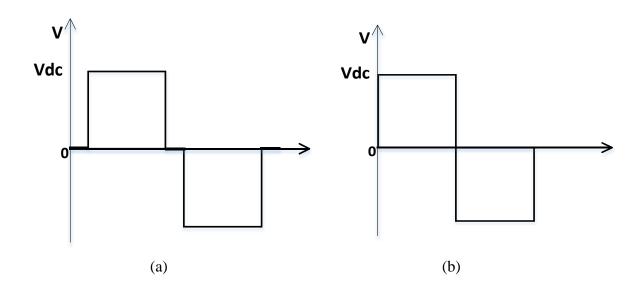

Multilevel inverter gives good quality waveform. Its switching frequency is low and its output is staircase in nature. This method is quit efficient and robust. Sine wave inverter works on high switching frequency that's why its output is pure sinusoidal. These inverters are compact and its cost is low. Waveforms of different inverter topologies are shown in figure 4.7.

#### Figure 4.7 Inverter topologies by waveform

(a) Quasi Square wave inverter (b) square wave inverter(c) multilevel inverter

#### 4.3.1 Conventional inverters (VSI and CSI)

To get single stage DC/AC conversion Current source inverter (CSI) and voltage source inverter (VSI) are mainly used. VSI and CSI have some shortcomings like large voltage variation that's why it's not preferable for photo voltaic system.

VSI is a step down inverter, hence to avoid over modulation it is preferred that DC link voltage should be higher than the peak line to line grid voltage. The CSI is a step up inverter. So in this also to avoid over modulation, the dc link voltage should be 0.866 of the peak line to line grid voltage.

For VSI, if line to line supply voltage is 415  $V_{rms}$ , then the DC link voltage i.e. the output of DC/DC converter around the maximum power point should be 587 volt. In contrast, for CSI at no load the DC link voltage should be less than 508 volt. As compare to VSI, CSI require less modulation depth. The main reason behind this is that at full power its operation takes place at higher current [52].

#### **4.3.1.1 Standard Voltage source inverter**

In VSI the inverter is fed from the DC voltage source or PV source and to get smooth DC link voltage large capacitor is connected in parallel to it. An inductive filter is used in source side or AC side to absorb the rapid change in voltage and to reduce the ripples in current waveform [52].

Figure 4.8 Voltage source inverter

#### 4.3.1.2 Standard current source inverter

In CSI large DC link inductor is connected in series with the DC voltage source. On source side or AC side capacitor filter is used to absorb the change in current as well as to smooth the grid ripple voltage [52]. Due to switching current ripples generated at AC side hence, AC inductors are used to overcome this problem.

Figure 4.9 Current source inverter

#### 4.3.2 Multilevel converters

The main concept of multilevel inverter is to achieve high power. In multilevel inverter to get staircase output voltage waveform, several lower voltage DC sources are connected in series with power semiconductor devices. To generate DC voltage renewable energy source, batteries and capacitors can be used. By proper commutation of semiconductor switches, it is possible to achieve high voltage with less T.H.D. at output. Mainly one or more DC sources are used in most dominant multilevel inverters [53].

For high power applications multilevel inverter is the best choice. Multilevel inverters are not that much appealing as high frequency sine wave inverters. Low frequency inverters have efficiency and robustness but the high frequency inverters are compact and less expensive.

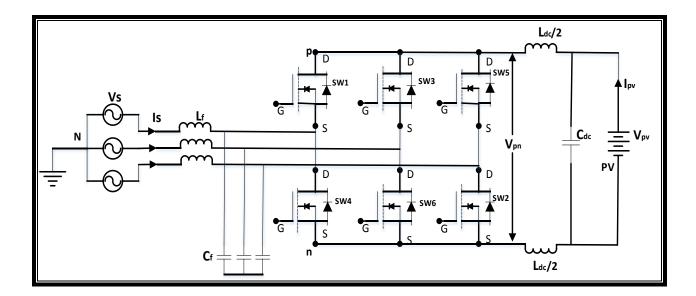

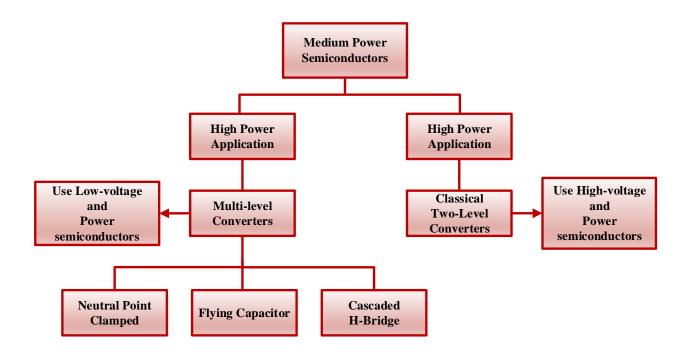

Figure 4.10 represents the comparison of two level converter and multilevel power converters.

The maximum power limit of three phase converter depends upon the maximum voltage and current of a switching component. There is an inverse relation between powers and switching frequency that means it the power of the switch is high then the switching frequency will be low.

Figure 4.10 Classification of converter

To overcome the above problem switches can be connected in parallel or in series. But there is a problem in series connection as in this case it is difficult to synchronize the commutation of switches.

In series connection if one of the switches will turn off then entire voltage of circuit will come across remaining switches so there is a chance of blow up of switches. Instead parallel connection is less complicated due to the positive coefficient property of MOSFETs and IGBTs.

#### Advantages of multilevel converters

- Due to greater number of levels of output voltage power quality of waveform increases and its total harmonic distortion decreases. So, filter size can be reduced at AC side which further decreases the losses as well as cost.

- Generate better output waveforms with lower dv/dt.

- These converters do not require transformers and can be directly connected to high voltage source, which reduces the complexity and cost.

#### **Disadvantages of multilevel converters**

- Increases complexity in the circuit as it requires large number of semiconductor switches.

- To create the DC voltage step capacitor banks are required.

The most common multilevel inverter topologies are [53]:-

- Diode clamped( neutral point clamped)

- Flying capacitor ( Capacitor clamped)

- Cascaded H Bridge

All types of multilevel inverters can produce same output voltage but main difference occurs due to control complexity, average voltage/current, number of switches and their topology.

Among these three different topologies, Cascaded H Bridge multilevel inverter is used in this project due to its several advantages.

#### 4.3.2.1 Cascaded H Bridge multilevel inverter

Cascaded H bridge multilevel inverter mainly used in medium and high power applications. This method use independent DC sources and each connected with individual bridge. A circuit with 2 DC voltage source is shown in figure 4.11 [55].

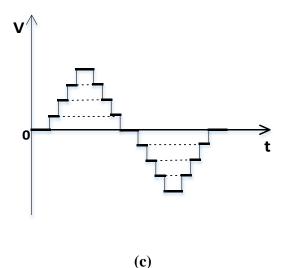

The output of each H bridge is given by  $0,+V_{dc}$ ,  $-V_{dc}$ . The combination of individual bridge voltage gives the total instantaneous output voltage. Thus for five level inverter the output  $v_o$  is given by  $+2 V_{dc}$ ,  $+V_{dc}$ ,  $0, -V_{dc}$ ,  $-2 V_{dc}$ .

Each H Bridge operates with different switching scheme and this is used to control harmonics as well as amplitude.

Figure 4.11 Single phase five level H Bridge multilevel inverter

#### **Characteristics of Multilevel inverter**

- The number of separate DC sources attached to each bridge decides the number of output levels of multilevel inverter.

- The relation is m= 2p+1, here p is the number of DC sources and m is the output levels of multilevel inverter.

- No even harmonics present.

- It gives staircase output or which is quarter symmetric in nature. The above condition is necessary to generate sine like wave.

- In this topology power can be easily scaled as it consists of series of power conversion cells.

#### 4.3.2.1.1 Control techniques for CHMLI

Control techniques for the CHMLI can be classifies into the three main categories:-

1. Selective harmonic elimination technique (SHE)

- 2. Pulse width modulation technique (PWM)

- 3. Optimized harmonic stepped waveform technique (OHSW)

Among all control techniques, in project the main focus is given to PWM techniques.

#### Pulse width modulation technique (PWM)

To control the AC output of inverter the best known technique is PWM. To achieve the low frequency output this technique varies the duty cycle of the switches at a higher frequency. Some unwanted harmonic components present in the train of pulses and it should be minimized in order to get desired output voltage and current.

The PWM technique can further classify as follows [54]:-

- (a) Open loop control techniques

- i. Sinusoidal PWM techniques

- ii. Space vector PWM techniques

- iii. Sigma delta PWM techniques

- (b) Closed loop control techniques

- i. Hysteresis current controller technique

- ii. Linear current controller technique

- iii. Dead band current controller technique

- iv. Optimized current controller technique

Among all above discussed categories SPWM is one of the best and easy techniques to control the CHBMLI on FPGA.

# 4.4 Classification of SPWM technique

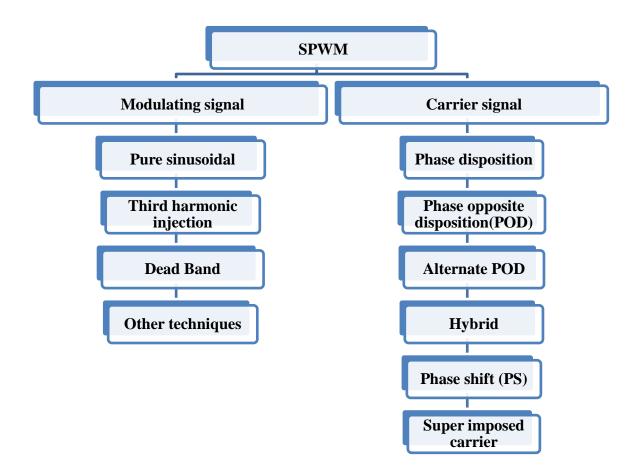

The classification of SPWM technique is based upon carrier signal and modulating signal as shown in figure 4.12.

Figure 4.12 Classification of SPWM technique

Hence there are number of techniques which can be used to generate staircase output. In this project Phase disposition technique is considered.

#### **Advantages of CHBMLI**

- This topology does not require diode or capacitors for clamping,

- This inverter gives the output waveform which is quite near to sinusoidal and even filters are not required.

- Cost effective

- High efficiency

#### **Disadvantages of CHBMLI**

- Need separate DC source with each leg

- NO common DC bus

#### **Application of CHBMLI**

- Motor drives

- Active filters

- Electric vehicle drives

- DC power source utilization

- Power factor compensators

- Back to back frequency link systems

- Interfacing with renewable energy resources

# **4.5** Conclusion

In this chapter all power conditioning devices are discussed. In this chapter many MPPT algorithms are discussed and mainly incremental conductance is reviewed. Other than that type of multilevel inverters and mainly the significance of CHBMLI is discussed.

# SINGLE-PHASE CASCADED H-BRIDGE MULTILEVEL INVERTER FOR GRID CONNECTED PHOTOVOLTAIC SYSTEMS [56]

In case of cascaded H Bridge MLI an individual DC source is required for each H Bridge and this combination gives high voltage as well as high power. Due to this feature we can use this method in large grid connected photovoltaic system [57]. Along with this individual and independent control can be achieved by applying separate DC source to each inverter. Henceforth MPPT i.e. Maximum power point tracking is possible and with the help of this we can get the maximum energy from the combination of PV panels. The low cost, reliability, robustness, efficiency and modularity of multilevel inverter attract the people toward this.

The multilevel inverter topology for the Photovoltaic system is discussed in this chapter. To avoid the panel mismatches issue individual MPPT control is required. To achieve the above mention phenomenon as well as for reactive power control one control scheme is proposed in this chapter.

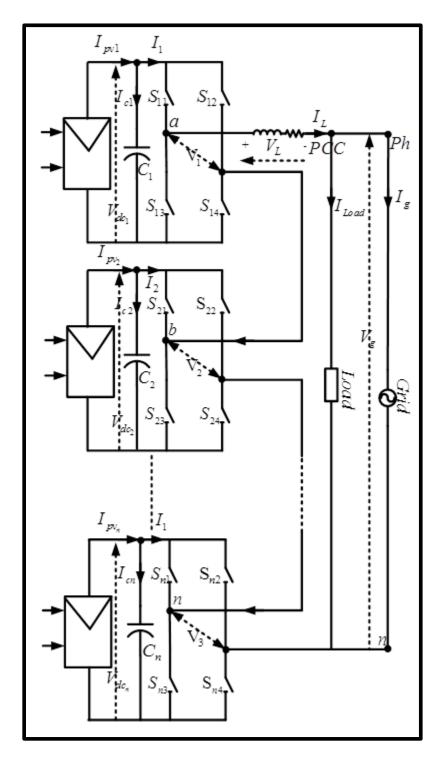

#### 5.1 Topology Description

The structure of cascaded multilevel inverter consists of N H-bridge inverter converters which are connected in series. Each inverter consists of DC link voltage to generate modulated output voltage. Each DC link is fed by a short string of PV panels. The sum of each individual output voltage is used to find total output voltage. With the help of different combinations of the switches, each inverter is able to produce three output voltages that are 0,  $+V_{dc}$  and  $-V_{dc}$ . The number of voltage levels of the phase voltage is given by,

$$M_{ph} = 2N+1$$

Where N is the number of inverters

Due to this high quality and (2N+1) levels output voltage waveform, harmonic reduces in the generated current as well as reduces the size of output filter. It also reduces the voltage stress on the semiconductor switches.

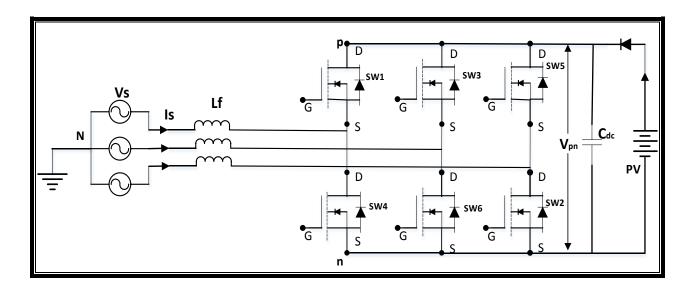

Figure 2.1 Topology for grid connection

As shown in figure 5.1 an L filter is connected between inverter and grid/load to reduce switching harmonics in output current .A local load is connected in parallel to the grid and both of them receives PV power according to the loading or operating conditions.

The output voltage is given by,

$$V_{pj} = (A_{j1} - A_{j3}) \cdot V_{cj} = Q_j V_{cj}$$

$$j = 1, 2, \dots, N$$

(5.1)

$V_{cj}$  is DC link voltage of the j<sup>th</sup> inverter. Here  $A_{yy}$  represents the switching state as in figure 5.2. It shows two discrete values that is '1' to show turn on and '0' to show turn off conditions.

To get linear model, the continuous switching function replaced the discrete switching function in (1) that is  $S_j \in [-1, 1]$ . The dynamic behavior of the grid connected PV system is given by,

$$\frac{di_o}{dt} = \frac{1}{L} \left( \sum_{j=1} S_j V_j - V_s - Ri_o \right)$$

(5.2)

$$\frac{dV_{j}}{dt} = \frac{1}{C_{j}} (i_{p_{j}} - S_{j} i_{o})$$

(5.3)

$$i_o = i_l + i_g \tag{5.4}$$

Where  $i_0$  is the output current of the cascaded H- bridge multilevel inverter, L and R the decoupling inductance and resistance,  $i_1$  is the load current and  $i_g$  is the grid current.

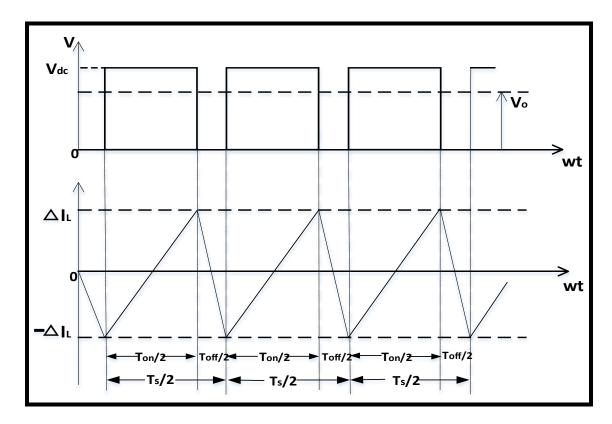

To select the value of inductor L,  $\Delta i_L$  that is inductor ripple current is to be calculated. If we assume that the fundamental current is zero for inductor L and SPWM (Sinusoidal pulse width modulation) is applied then the ripple current is given by,

$$2\Delta i_l = \frac{V_{dc} - V_{av}}{L} \cdot \frac{d_{1on}}{2} \cdot \frac{1}{f_s}$$

(5.5)

Where,  $d_{1on}$  is given by the on period of one cycle and  $f_s$  is the frequency of switch. When  $\hat{\omega}t$  lie between 0 and  $\pi$ , we will get,

$$V_{av} \bigoplus t = m V_{dc} \sin \omega t \tag{5.6}$$

$$d_{1on} \Phi t = m \sin \omega t \tag{5.7}$$

Where m is the modulation index.

From equation (5.5),(5.6) and (5.7) the ripple current  $\Delta i_L$  can be expressed as,

$$\Delta i_L = \frac{V_{dc}}{4f_s L} \left( -m\sin\omega t \right) \sin\omega t \tag{5.8}$$

The waveforms of inverter output voltage and ripple current is shown in the below figure 5.2.

Figure 5.2 Output voltage of Inverter and ripple current  $\Delta i_L$  waveforms.[58]

The maximum ripple current is given by,

$$\Delta i_{L \max} = \frac{V_{dc}}{4f_s L} \tag{5.9}$$

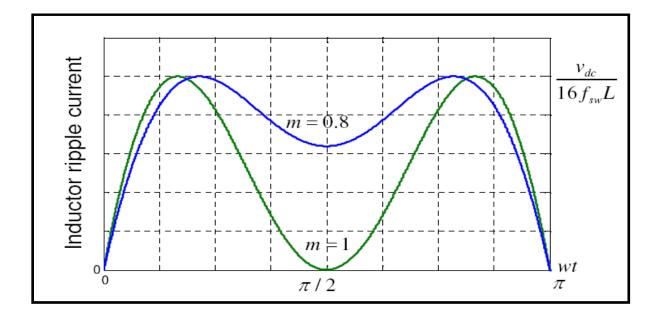

With the help of this we can select value of inductor L and the relation between the modulation index and ripple current is given by fig. 5.3.

Figure 5.3 Relation between modulation index and the ripple current [58]

To reduce the cost of manufacturing modular design is used in this report. According to this, value of C for individual H bridge inverter will remain same and is given by,

$$C = \frac{P_T}{2n\omega_g V_{dc} V_{rip}}$$

(5.10)

Where the total rated power of CHMLI is  $P_T$ ,  $V_{dc}$  is the average voltage across capacitor and  $V_{rip}$  is voltage ripple amplitude.

The input of the inverter is PV cell followed by boost converter. Hence  $V_{dc}$  is the output of boost converter which is further input of One H Bridge module and it is maximum power point voltage. The ripples should be low at PV module terminals otherwise it gives high fluctuations. The voltage ripple [59] amplitude should be as low as possible that is below 6% of maximum power point voltage. This is to be done to achieve a utilization ratio of 99%.

# $\textbf{Utilization ratio} = \frac{Average \ generated \ power}{Theoritical \ MPP \ power}$

# **5.2 PV Panel mismatches**