# PERFORMANCE ANALYSIS OF UPQC UNDER DIFFERENT OPERATING CONDITIONS

# **A DISSERTATION**

Submitted in partial fulfilment of the requirements for the award of the degree of INTEGRATED DUAL DEGREE in ELECTRICAL ENGINEERING (With Specialization in Power Electronics)

By

SUBHASH SAHNI

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE- 247667 (INDIA) MAY, 2016

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

# **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in this thesis entitled **PERFRORMANCE ANALYSIS OF UPQC UNDER DIFFERENT OPERATING CONDITIONS**, in partial fulfilment of the requirements for the award of Integrated Dual Degree and submitted to the Department of Electrical Engineering of Indian Institute of Technology Roorkee, is an authentic record of my own work carried out during the period from May 2015 to May 2016 under supervision of Prof. Pramod Agarwal, Department of Electrical Engineering, Indian Institute of Technology Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

(SUBHASH SAHNI)

This is to certify that the above statement made by the student is correct to the best of my knowledge.

# (PRAMOD AGARWAL)

Professor

Department of Electrical Engineering

Indian Institute of Technology, Roorkee

| Date: |  |  |  |

|-------|--|--|--|

|       |  |  |  |

### ABSTRACT

The problem of power quality is highly pressing in this era. The rise in the use of new generation loads based on microprocessors and power electronic equipment has increased concerns about quality of supplied power. The study of different power quality phenomena including frequency variation, overvoltage, under voltage, voltage sag, voltage swell, transient, waveform distortions and voltage fluctuation along with poor power factor at point of common coupling (PCC) was done in order to have a thorough understanding of these events. To improve the power quality at PCC, passive filters along with several power electronics based devices (active filters) such as Dynamic voltage regulator (DVR), dynamic static compensator (DSTATCOM), unified power quality controller (UPQC) are used. Unified power quality conditioner (UPQC) is the most effective device to improve the power quality at PCC. UPQC is the integration of shunt and series active filters that compensate for almost all kind of voltage and current problems in the power system.

This thesis includes study of power quality issues and use of UPQC to mitigate voltage and current harmonics. UPQC is analysed for three phase three wires system with two control strategies to generate reference generation. The whole system was simulated in MATLAB/Simulink environment. A prototype of UPQC for three phase three wires system is developed for the validation of the simulation results. Thus, the proposed control strategy can be used to operate UPQC and eliminate variations in voltage at PCC thereby preventing mal-operation of sensitive loads.

# **ACKNOWLEDGEMENT**

I express my deep sense of gratitude and indebtedness to my supervisor Dr. Pramod Agarwal, Professor, EED, IIT Roorkee for providing me an opportunity to work on this innovative dissertation topic involving real industrial application and guiding me throughout the course of this study. His keen interest and constant encouragement gave me the confidence to complete my work. I wish to extend my sincere thanks for his excellent guidance and suggestions. Despite his busy schedule, he used to review my dissertation progress, give his valuable suggestion and feedback. His dedication towards work and self-belief will always inspire me, and I hope to imbibe these qualities myself.

Secondly I would also like to thank my parents and sister for their sacrifices, and moral support throughout the course of this work. I would like to pay regards to them for being a motivator throughout my life. Their unconditional support made this work possible and I would like to dedicate this work to them.

\_\_\_\_\_

| ABSTRACTi                                           |

|-----------------------------------------------------|

| ACKNOWLEDGEMENT ii                                  |

| CONTENTSiii                                         |

| LIST OF FIGURES vi                                  |

| LIST OF ACRONYMx                                    |

| CHAPTER 1: INTRODUCTION1                            |

| 1.1 Introduction to Power Quality                   |

| 1.1.1 Sources of Disturbances                       |

| 1.1.2 Effect of Disturbances                        |

| 1.1.3 Importance of Power Quality                   |

| 1.1.4 Power Quality Issues                          |

| 1.2 Literature Review                               |

| 1.2.1 Passive Filters                               |

| 1.2.2 Active Filters                                |

| 1.2.3 Hybrid Active Filters                         |

| 1.2.4 Signal Conditioning 11                        |

| 1.2.5 Calculation of Reference Signals              |

| 1.2.6 Switching Pulse Generation                    |

| 1.3 Organization of Dissertation                    |

| CHAPTER 2: UNIFIED POWER QUALITY CONDITIONER        |

| 2.1 Classification of UPQC                          |

| 2.1.1 Converter Based Classification                |

| 2.1.2 Supply System Based Configuration             |

| 2.1.3 Classification of UPQC Based on Configuration |

| CHAPTER 3: CONTROL STRATEGIES FOR UPQC 18           |

| 3.1 Signal Conditioning                                                                                                                              | 18 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 Reference Generation Techniques                                                                                                                  | 18 |

| <ul><li>3.2.1 Frequency Domain Approach for Reference Signal Generation</li><li>3.2.2 Time Domain Approach for Reference Signal Generation</li></ul> |    |

| 3.3 Gating Pulse Generation Techniques                                                                                                               | 24 |

| 3.3.1 Hysteresis Control                                                                                                                             | 24 |

| 3.3.2 Triangular Carrier Wave Control                                                                                                                | 25 |

| CHAPTER 4: ANALYSIS OF UNIFIED POWER QUALITY CONDITIONER                                                                                             | 25 |

| 4.1 Simulations and Results in Three Phase Three Wire System                                                                                         | 25 |

| 4.2 Load and Source Configuration                                                                                                                    | 27 |

| 4.3 Simulation Results Using UVT Techniques for Reference Generation                                                                                 | 28 |

| 4.3.1 Shunt Filter in action                                                                                                                         | 28 |

| 4.3.1.1 Simulation results with load being Rectifier with R-L on DC side                                                                             | 28 |

| 4.3.1.2 Simulation results with additional R-L load along with Rectifier with R-L oDC side                                                           |    |

| 4.3.2 Series Filter in action                                                                                                                        | 32 |

| 4.3.2.1 Simulation results with load being Rectifier with R-L on DC side                                                                             | 32 |

| 4.3.2.2 Simulation results with additional R-L load along with Rectifier with R-L oDC side                                                           |    |

| 4.3.3 Both Shunt and Series Filter in action                                                                                                         | 36 |

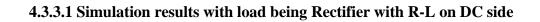

| 4.3.3.1 Simulation results with load being Rectifier with R-L on DC side                                                                             | 36 |

| 4.3.3.2 Simulation results with additional R-L load along with Rectifier with R-L oDC side                                                           |    |

| 4.4 Simulation Results Using p-q theory for Reference Generation                                                                                     | 40 |

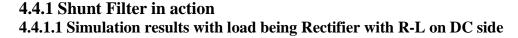

| 4.4.1 Shunt Filter in action                                                                                                                         | 40 |

| 4.4.1.1 Simulation results with load being Rectifier with R-L on DC side                                                                             | 40 |

| 4.4.1.2 Simulation results with additional R-L load along with Rectifier with R-L oDC side                                                           |    |

| 4.4.2 Series Filter in action                                                                                                                        | 44 |

| 4.4.2.1 Simulation results with load being Rectifier with R-L on DC side                                                                             | 44 |

| 4.4.2.2 Simulation results with additional R-L load along with Rectifier with R-L oDC side                                                           |    |

| 4.4.3 Both Shunt and Series Filter in action                                                | 48          |

|---------------------------------------------------------------------------------------------|-------------|

| 4.4.3.1 Simulation results with load being Rectifier with R-L on DC side                    |             |

|                                                                                             |             |

| 4.4.3.2 Simulation results with additional R-L load along with Rectifier with R-L o DC side |             |

| 4.5 Simulation Results with Voltage Unbalance                                               | 52          |

| 4.5.1 Shunt Filter in action                                                                | 52          |

| 4.5.2 Series Filter in action                                                               | 54          |

| 4.5.3 Both Shunt and Series Filter in action                                                | 55          |

| 4.6 Simulation Results with Load Unbalance                                                  | 57          |

| 4.6.1 Shunt Filter in action                                                                | 58          |

| 4.6.2 Series Filter in action                                                               | 59          |

| 4.6.3 Both Shunt and Series Filter in action                                                | 61          |

| CHAPTER 5 : HARDWARE PROTOTYPE DEVELOPMENT                                                  | 64          |

| 5.1 Active Power Filter Circuit Development                                                 | 65          |

| 5.2 Diode bridge rectifier as Non-Linear Load                                               | 66          |

| 5.3 Gate Driver Circuit for MOSFET                                                          | 67          |

| 5.4 Development of Snubber Circuit and Varistor                                             | 68          |

| 5.5 Development of Voltage Sensing Circuit                                                  | 69          |

| 5.6 Development of Current Sensing Circuit                                                  | 70          |

| 5.7 Development of Dead Band Circuit                                                        | 71          |

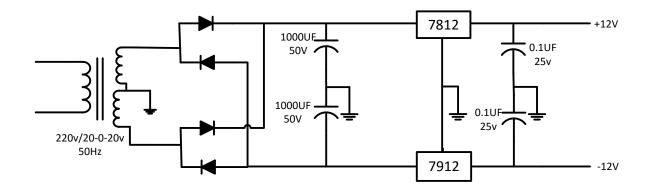

| 5.8 Development of Power Supply Circuits                                                    | 71          |

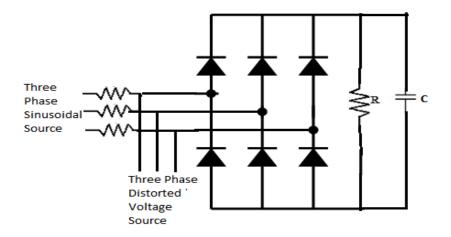

| 5.9 Harmonic Voltage Source                                                                 | 72          |

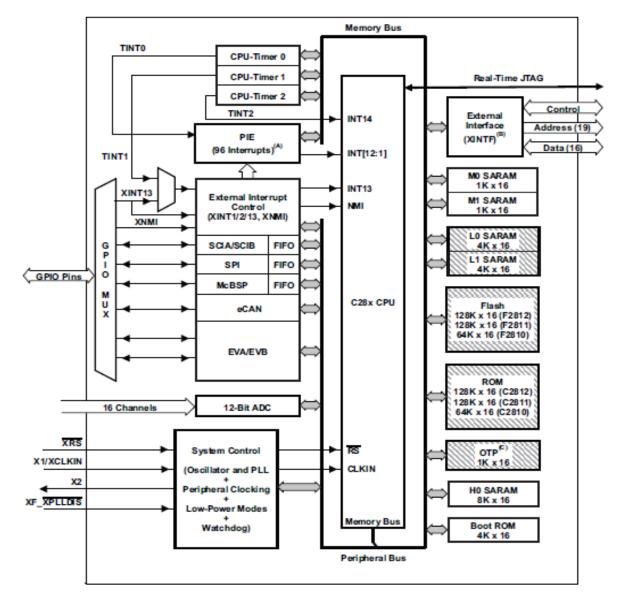

| 5.10 TMS320F2812 DSP Kit                                                                    | 73          |

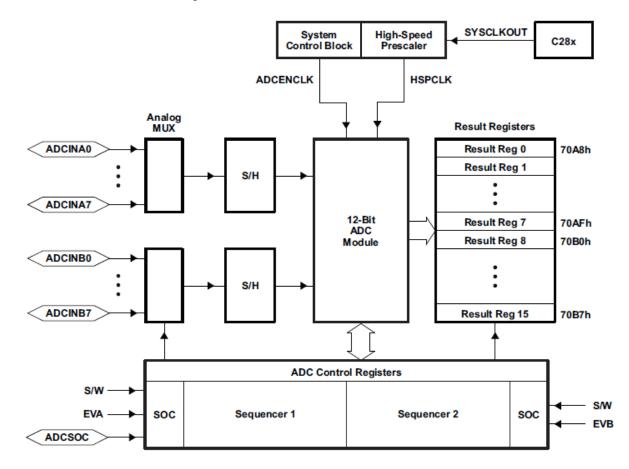

| 5.10.1 ADC Unit                                                                             | 74          |

| 5.10.2 Event Manager Module                                                                 | 75          |

| 5.11Verification of Individual Hardware Components                                          | 76          |

| CHAPTER 6: CONCLUSION                                                                       | . <b>79</b> |

| 6.1 Conclusion                                                                              | 79          |

| 6.2 Future Work Load                                                                        | 79          |

| PHOTOGRAPHS OF THE HARDWARE PROTOTYPE                                                       | 80          |

| REFERENCES                                                                                  | 82          |

# LIST OF FIGURES

| Figure 1.1 Input current of adjustable speed drive (ASD) in continuous conduction mode [9]    | 1    |

|-----------------------------------------------------------------------------------------------|------|

| Figure 1.2 Voltage sag [2]                                                                    | 2    |

| Figure 1.3 Voltage Swell [2]                                                                  | 2    |

| Figure 1.4 Current impulsive transient due to lightening stroke [2]                           | 3    |

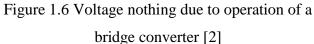

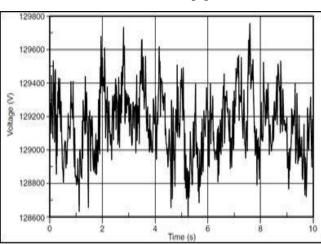

| Figure 1.5 Oscillatory transient current waveforms [2]                                        | 3    |

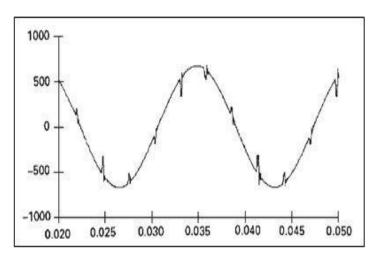

| Figure 1.6 Voltage nothing due to operation of a bridge converter [2]                         | 3    |

| Figure 1.7 Voltage fluctuations due to operation of an arc furnace [2]                        |      |

| Figure 1.8 System Configuration of Shunt Active Filter [3]                                    | 7    |

| Figure 1.9 System Configuration of Series Active Filter [3]                                   |      |

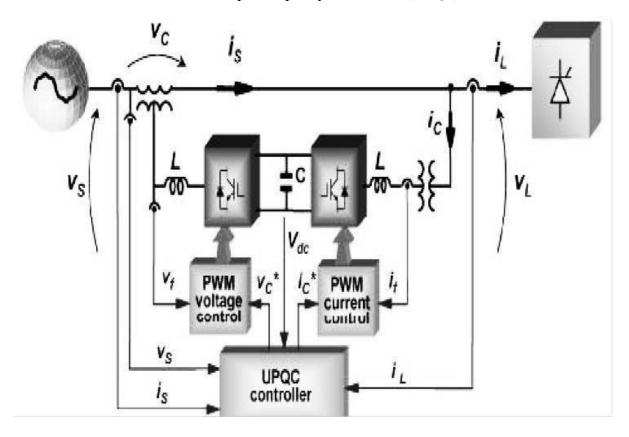

| Figure 1.10 Basic configuration of UPQC [3]                                                   | 8    |

| Figure 1.11 Basic Schematics of shunt active and shunt passive filters in shunt with load [1] | 9    |

| Figure 1.12 Basic Schematics of Series active and shunt passive filter [4]                    | . 10 |

| Figure 2.1 VSI Based UPQC [6]                                                                 | . 13 |

| Figure 2.2 CSI Based UPQC [6]                                                                 | . 13 |

| Figure 2.3 Two H-Bridge Configuration [6]                                                     | . 14 |

| Figure 2.4 Three Leg Configuration [6]                                                        |      |

| Figure 2.5 Tow Half Bridge configuration [6]                                                  | . 14 |

| Figure 2.6 3P3W UPQC [6]                                                                      | . 14 |

| Figure 2.7 3P4W Four leg Shunt configuration of UPQC [7]                                      | . 14 |

| Figure 2.8 3P4W split capacitor type UPQC [7]                                                 | . 14 |

| Figure 2.9 3P4W three H-bridge configuration of UPQC [7]                                      | . 15 |

| Figure 2.10 Basic configuration of UPQC-R [6]                                                 | . 15 |

| Figure 2.11 Basic configuration of UPQC-L [6]                                                 | . 15 |

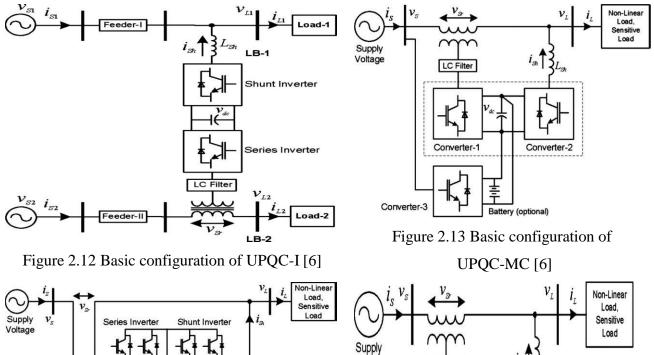

| Figure 2.12 Basic configuration of UPQC-I [6]                                                 | . 16 |

| Figure 2.13 Basic configuration of UPQC-MC [6]                                                | . 16 |

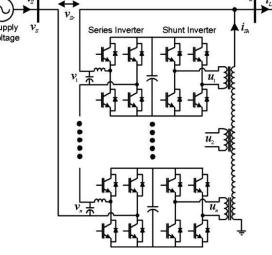

| Figure 2.14 Basic configuration of UPQC-MD [6]                                                |      |

| Figure 2.15 Basic configuration of UPQC-ML [6]                                                | . 16 |

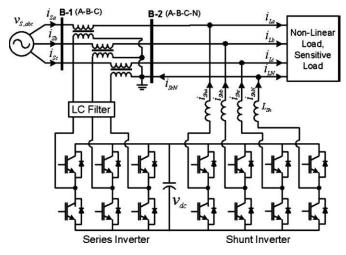

| Figure 2.16 Basic configuration of UPQC-D [6]                                                 | . 16 |

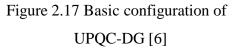

| Figure 2.17 Basic configuration of UPQC-DG [6]                                                | . 16 |

| Figure 3.1 Extraction of unit vector templates and reference 3-phase load voltages            | . 18 |

| Figure 3.2 Reference current signal generation for shunt APF                                  | . 19 |

| Figure 3.3 Switching pulse generation for fourth leg of shunt filter inverter                 | . 19 |

| Figure 3.4 Schematic representation of synthesizing shunt inverter reference current based on | p-   |

| q method                                                                                      | . 21 |

| Figure 3.5 Hysteresis band limiting signals into its limits                                   |      |

| Figure 3.6 Hysteresis Current Control                                                         |      |

| Figure 3.7 Triangular wave control for generating firing pulses for inverters                 | . 24 |

| Figure 4.1 Simulink model of UPQC with unit vector templates control techniques for referen  | ce   |

|----------------------------------------------------------------------------------------------|------|

| generation                                                                                   | . 25 |

| Figure 4.2 Simulink model of UPQC with instantaneous power calculation control technique for | or   |

| reference generation                                                                         | . 26 |

| Figure 4.3 Connected load (Circuit breaker is Switched ON at t= 0.8s)                        | . 27 |

| Figure 4.4 Harmonic content of phase A of source voltage                                     | . 27 |

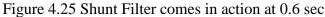

| Figure 4.5 Shunt Filter comes in action at 0.6 sec                                           | . 28 |

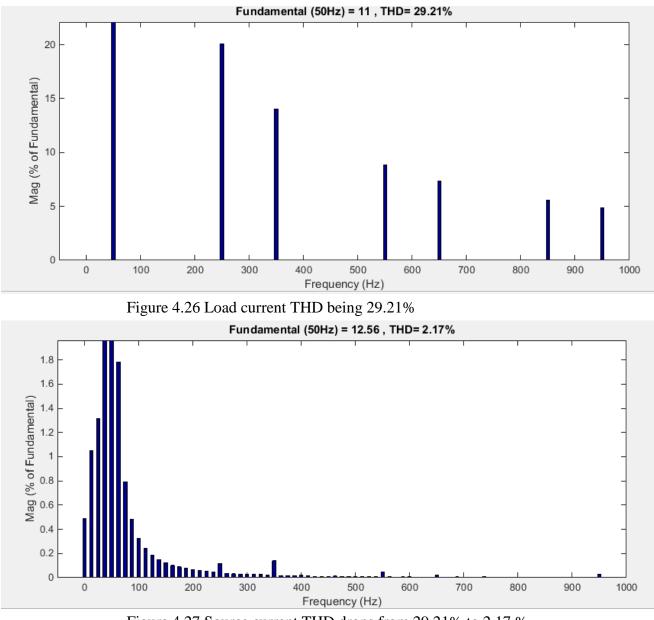

| Figure 4.6 Load current THD being 29.21%                                                     |      |

| Figure 4.7 Source current THD drops from 29.21% to 0.84%                                     | . 29 |

| Figure 4.8 Shunt Filter responding to load change at 0.8 seconds                             |      |

| Figure 4.9 Source current THD drops from 0.84% to 0.52 %                                     |      |

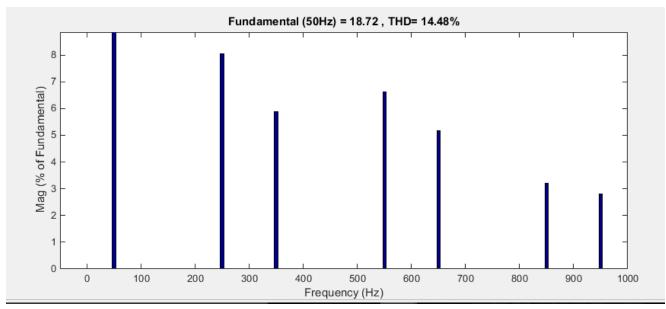

| Figure 4.10 Load current THD decreases to 14.48%                                             |      |

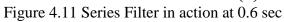

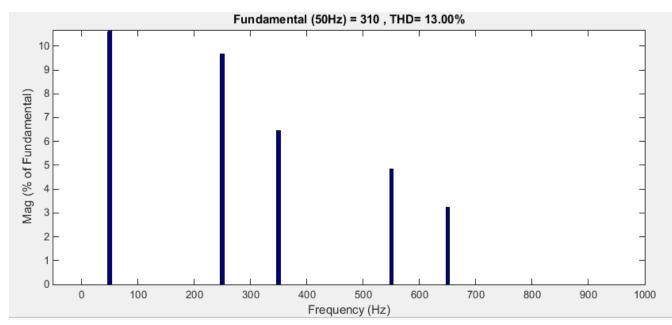

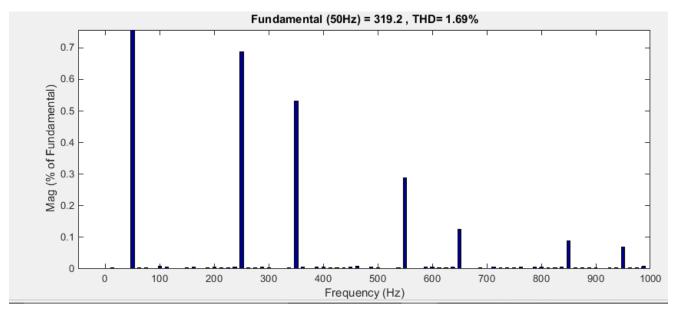

| Figure 4.11 Series Filter comes in action at 0.6 sec                                         | . 32 |

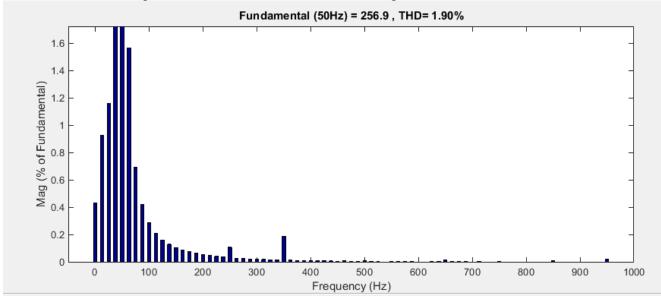

| Figure 4.12 Source voltage THD being 13%                                                     | . 33 |

| Figure 4.13 Load Voltage THD drops from 13% to 1.69%                                         | . 33 |

| Figure 4.14 Series Filter responding to load change at 0.8s                                  | . 34 |

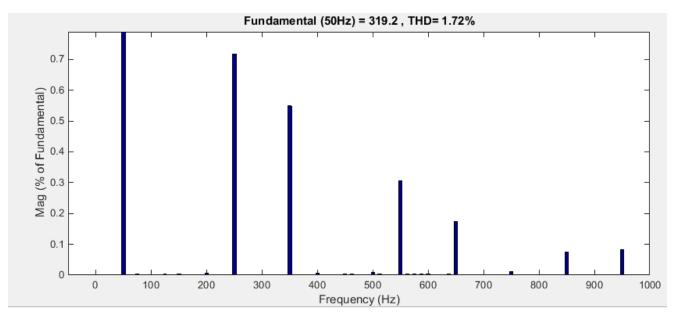

| Figure 4.15 Load Voltage THD after load change remains almost same at 1.72%                  |      |

| Figure 4.16 UPQC comes in action at 0.6 sec                                                  | . 36 |

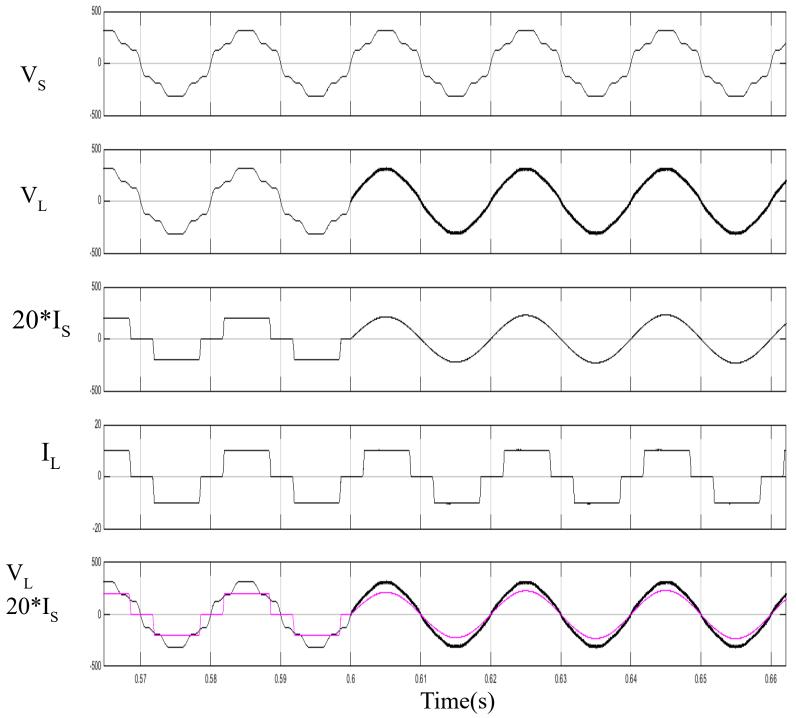

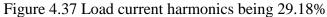

| Figure 4.17 Load Current Harmonics being 29.18%                                              | . 37 |

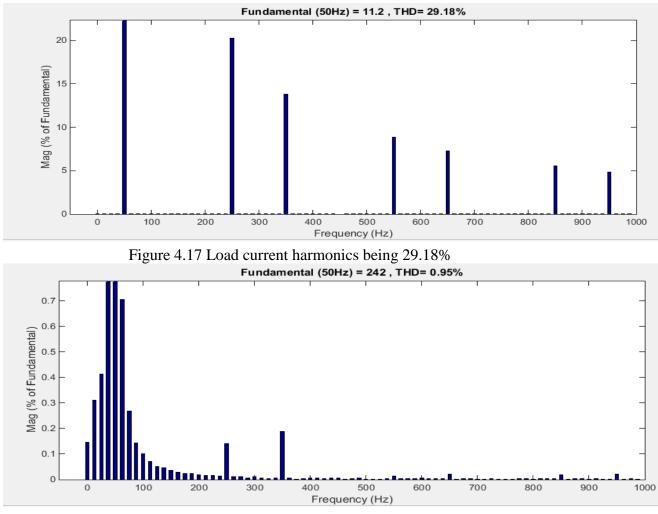

| Figure 4.18 Source Current Harmonics drop from 29.18% to 0.95% due to shunt filtering        | . 37 |

| Figure 4.19 Source voltage harmonics being 13%                                               | . 37 |

| Figure 4.20 Load voltage THD falls from 13% to 3.34%                                         | . 38 |

| Figure 4.21 UPQC in action after load change at 0.8 seconds                                  | . 38 |

| Figure 4.22 Load current harmonics being 16.71% after load change                            | . 39 |

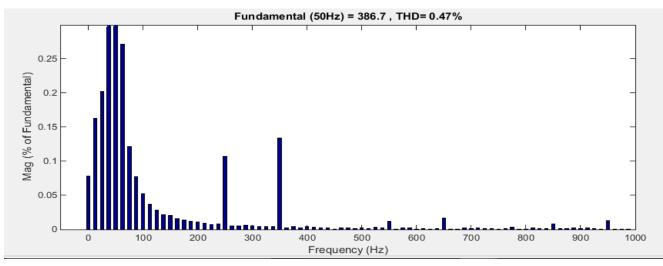

| Figure 4.23 Source current harmonics drop from 16.71% to 0.47 % due to shunt filtering       | . 39 |

| Figure 4.24 Load voltage THD after load changes remains almost same at 3.36%                 | . 39 |

| Figure 4.25 Shunt Filter comes in action at 0.6 sec                                          | . 40 |

| Figure 4.26 Load current THD being 29.21%                                                    | . 41 |

| Figure 4.27 Source current THD drops from 29.21% to 2.17 %                                   | . 41 |

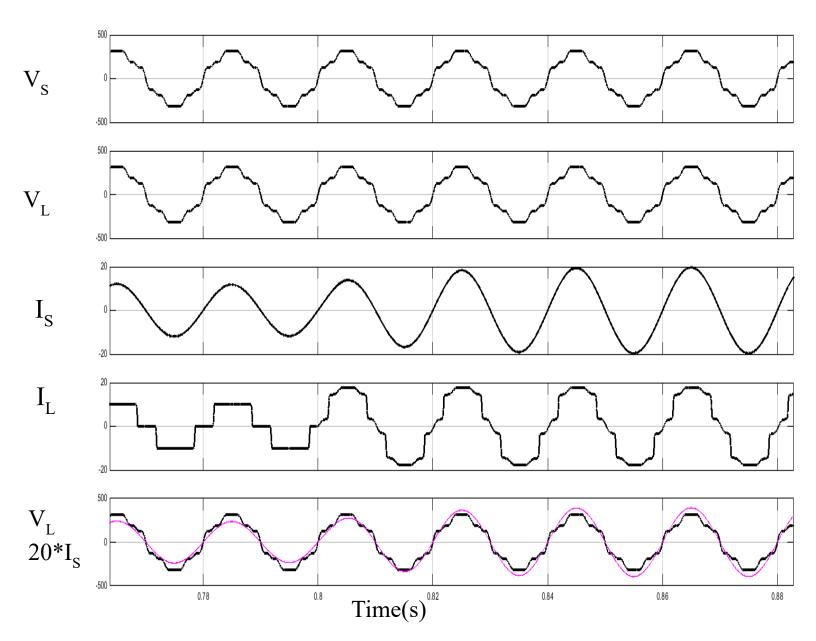

| Figure 4.28 Shunt Filter responding to load change at 0.8 seconds                            | . 42 |

| Figure 4.29 Load current THD decreases to 14.48%                                             | . 43 |

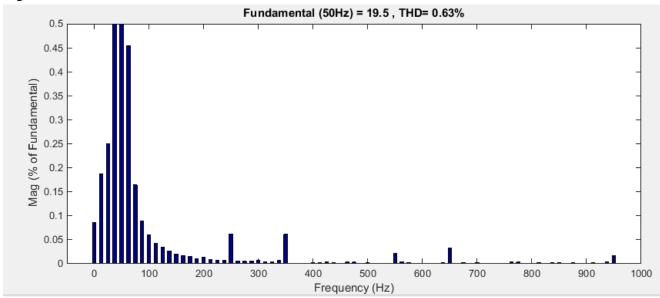

| Figure 4.30 Source current THD drops from 2.17 % to 0.63%                                    | . 43 |

| Figure 4.31 Series Filter in action at 0.6 sec                                               | . 44 |

| Figure 4.32 Source voltage THD being 13%                                                     | . 45 |

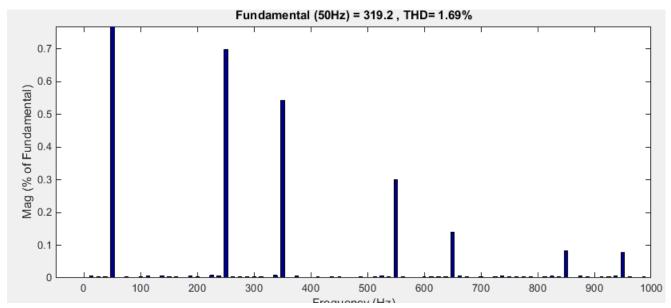

| Figure 4.33 Load voltage THD drops from 13% to 1.69%                                         | . 45 |

| Figure 4.34 Series Filter responding to load change at 0.8 seconds                           | . 46 |

| Figure 4.35 Load voltage THD after load changes remains almost same at 1.72                  | . 47 |

| Figure 4.36 UPQC comes in action at 0.6 sec                                                  | . 48 |

| Figure 4.37 Load current harmonics being 29.18 %                                             | . 49 |

| Figure 4.38 Source current harmonics drop from 29.18% to 1.90 % due to shunt filtering       | . 49 |

| Figure 4.39 Source voltage harmonics being 29.18%                                      | . 49 |

|----------------------------------------------------------------------------------------|------|

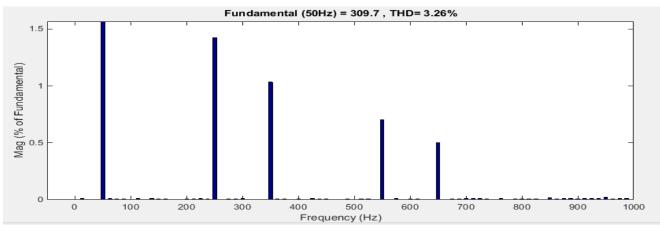

| Figure 4.40 Load voltage THD falls from 13% to 3.26%                                   | . 50 |

| Figure 4.41 UPQC in action after load change at 0.8 seconds                            | . 50 |

| Figure 4.42 Load current harmonics being 16.71% after load change                      | . 51 |

| Figure 4.43 Source current harmonics drop from 16.71% to 0.58 % due to shunt filtering | . 51 |

| Figure 4.44 Load voltage THD after load changes remains almost same at 3.33%           | . 51 |

| Figure 4.45 Voltage Unbalance                                                          | . 52 |

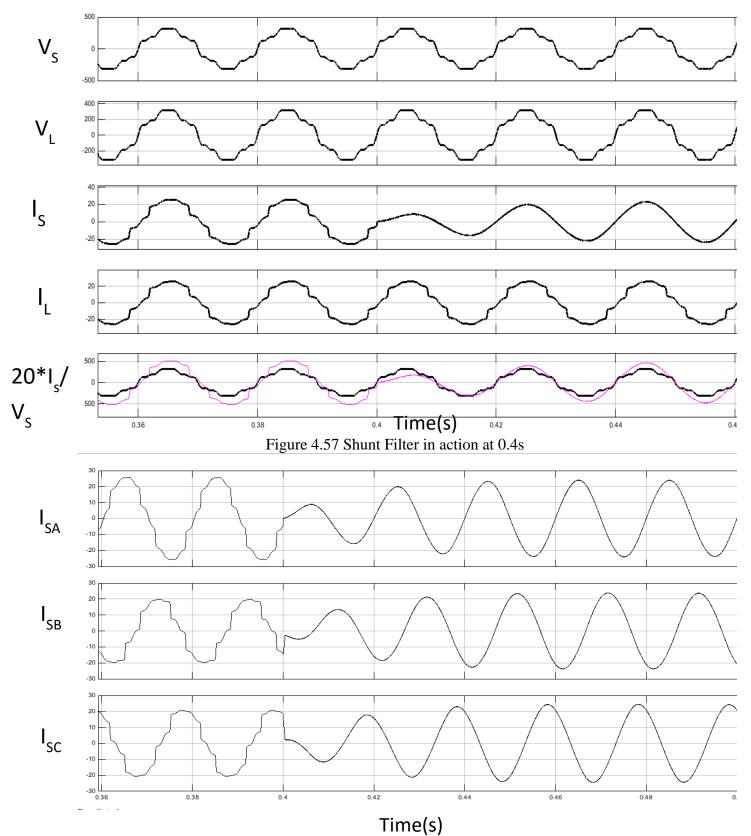

| Figure 4.46 Shunt Filter in action at 0.4s                                             | . 52 |

| Figure 4.47 Three phase currents before and after compensation                         | . 53 |

| Figure 4.48 Load & source currents THD & peak value                                    | . 53 |

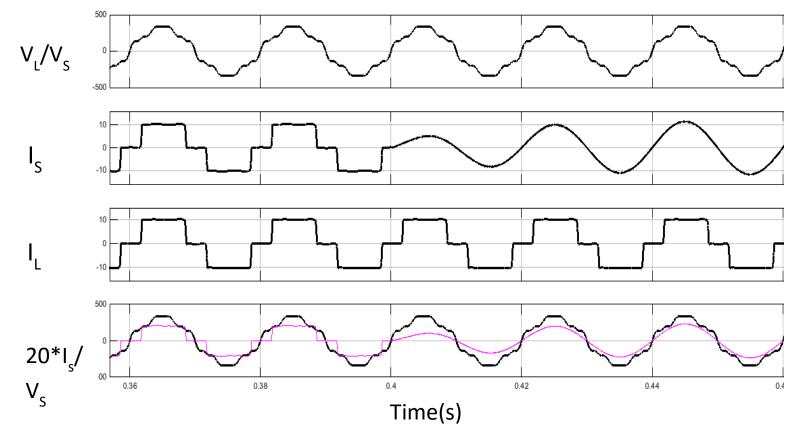

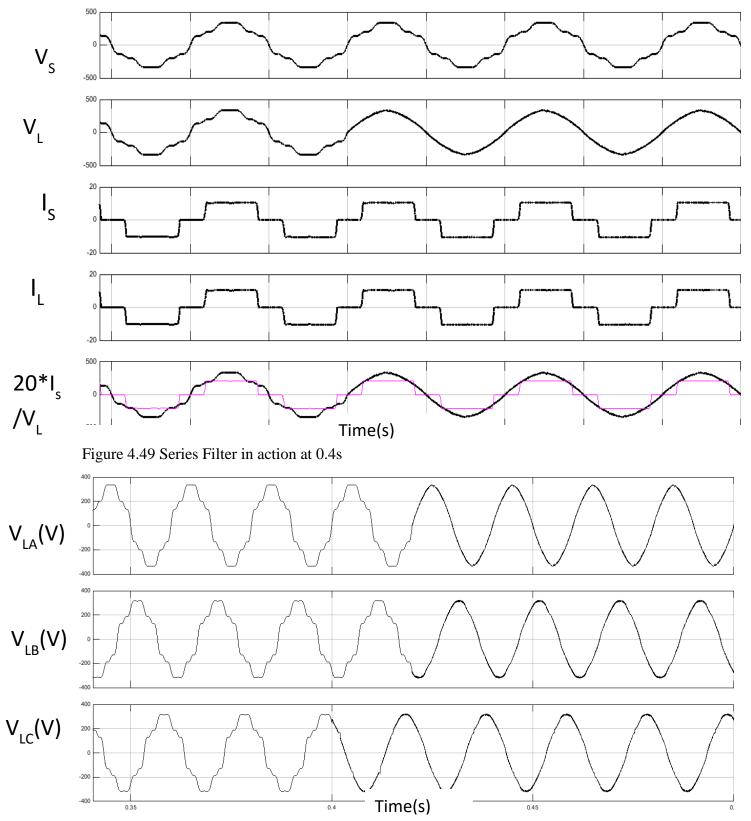

| Figure 4.49 Series Filter in action at 0.4 s                                           |      |

| Figure 4.50 Three phase voltages before and after compensation                         | . 54 |

| Figure 4.51 Load Voltage & Current THD & peak value                                    | . 55 |

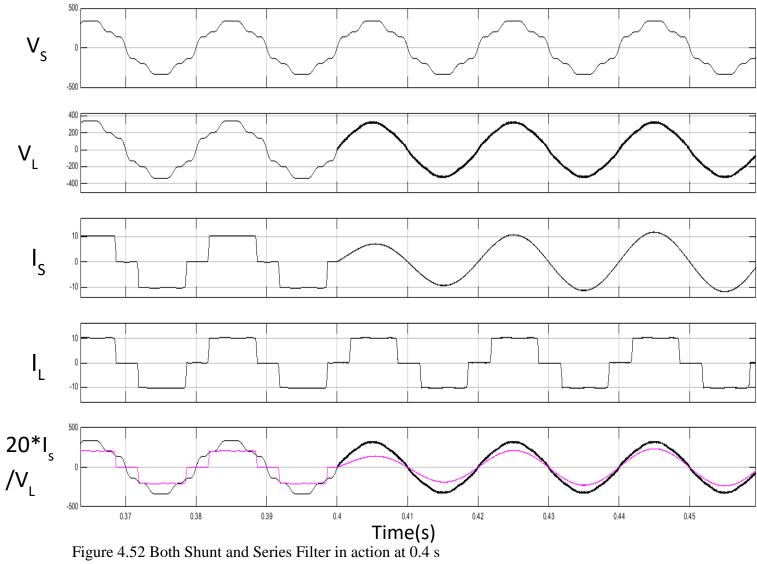

| Figure 4.52 Both Shunt & Series Filter in action at 0.4s                               | . 55 |

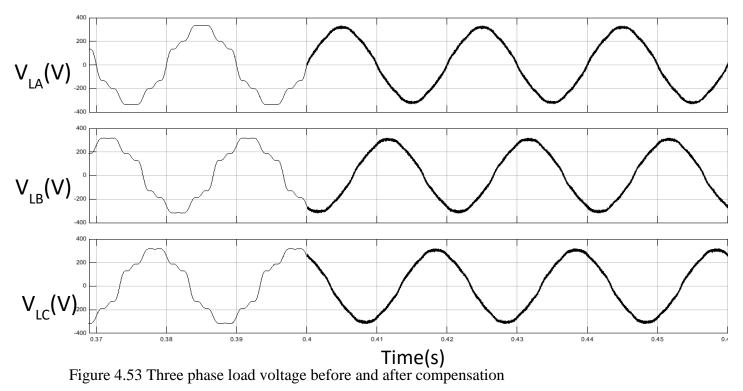

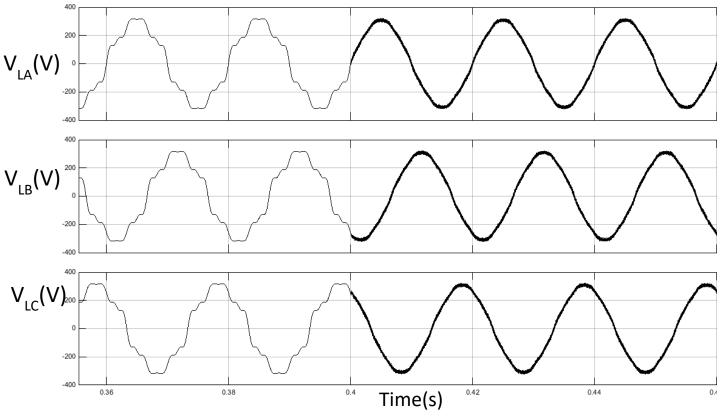

| Figure 4.53 Three phase load voltage before & after compensation                       | . 56 |

| Figure 4.54 Three phase source current before & after compensation                     | . 56 |

| Figure 4.55 Load Voltage & Source Currents THD & peak values                           | . 57 |

| Figure 4.56 Load Unbalance                                                             | . 57 |

| Figure 4.57 Shunt Filter in action at 0.4s                                             | . 58 |

| Figure 4.58 Three phase currents before and after compensation                         |      |

| Figure 4.59 Load & source currents THD & peak value                                    |      |

| Figure 4.60 Series Filter in action at 0.4 s                                           | . 59 |

| Figure 4.61 Three phase voltages before and after compensation                         |      |

| Figure 4.62 Load Voltage & Current THD & peak value                                    |      |

| Figure 4.63 Both Shunt & Series Filter in action at 0.4s                               | . 61 |

| Figure 4.64 Three phase load voltage before & after compensation                       |      |

| Figure 4.65 Three phase source current before & after compensation                     |      |

| Figure 4.66 Load Voltage & Source Currents THD & peak values                           | . 63 |

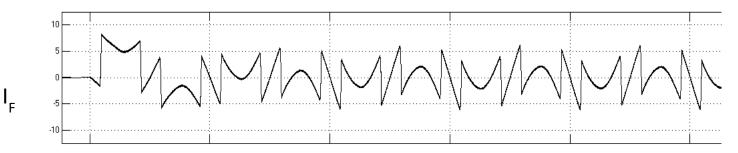

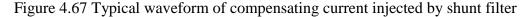

| Figure 4.67 Typical waveform of compensating current injected by shunt filter          | . 63 |

| Figure 4.68 Typical waveform of compensating voltage injected by series filter         | . 63 |

| Figure 4.69 Typical waveform of DC link capacitor voltage                              |      |

| Figure 5.1 One line block diagram of developed system                                  | . 64 |

| Figure 5.2 Power circuit connections of UPQC                                           | . 66 |

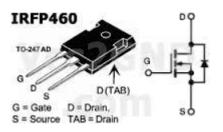

| Figure 5.3 MOSFET IRFP 460                                                             | . 66 |

| Figure 5.4 Schematic diagram of Non-Linear load connected from PCC                     | . 67 |

| Figure 5.5 Schematic diagram of MOSFET IRFP-460 driver circuit                         | . 68 |

| Figure 5.6 Schematic diagrams of protection circuits of MOSFET                         | . 69 |

| Figure 5.7 Schematic diagram of voltage sensing circuit using AD202JN                  | . 69 |

| Figure 5.8 Schematic diagram of current sensing circuit using HTP 25                   | . 70 |

| Figure 5.9 Dead band circuits for a leg                                                |      |

| Figure 5.10 Schematic diagram of +5V power supply                                      | . 71 |

| Figure 5.11 Schematic diagram of ±12V power supply                                  | 72        |

|-------------------------------------------------------------------------------------|-----------|

| Figure 5.12 Block schematics of harmonic voltage source                             | 72        |

| Figure 5.13 Functional overview of TMS320F2812 DSP Kit                              | 73        |

| Figure 5.14 ADC Architecture                                                        | 74        |

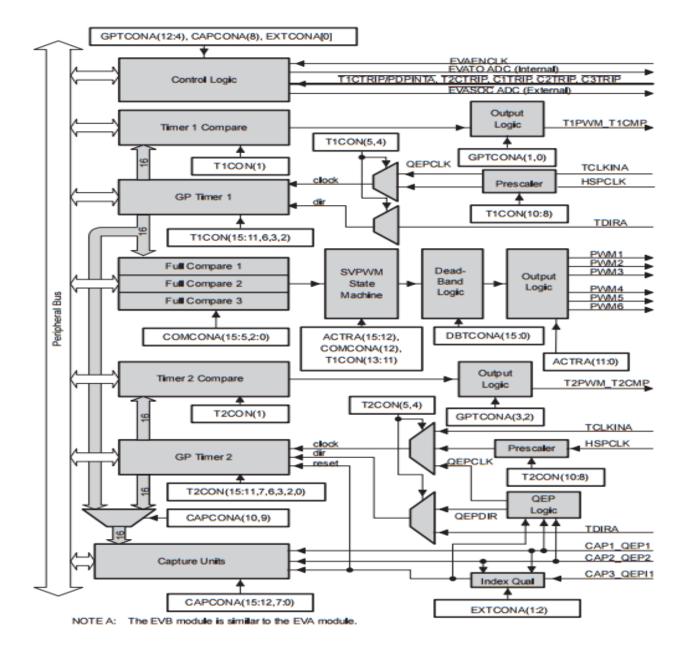

| Figure 5.15 Functional details of Event Manager Module                              | 75        |

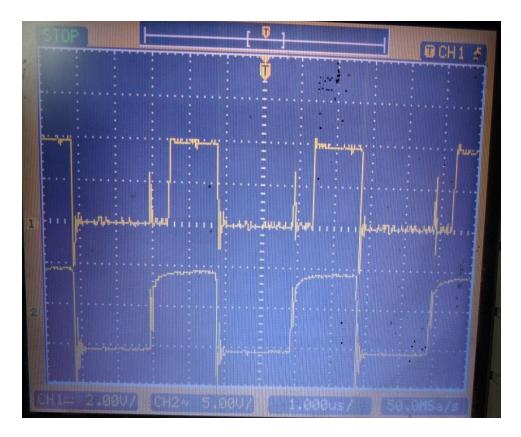

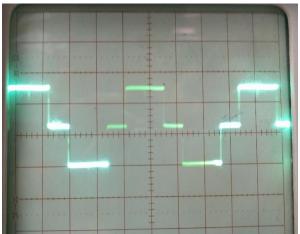

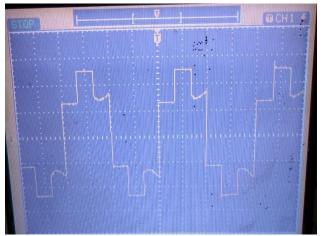

| Figure 5.16 Deadband circuit input and output waveforms                             | 76        |

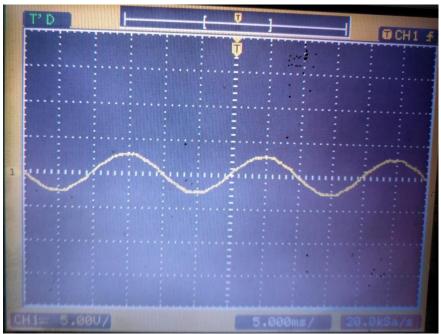

| Figure 5.17 Typical Current sensor output waveform                                  | 77        |

| Figure 5.18 Typical Voltage sensor output waveform                                  | 77        |

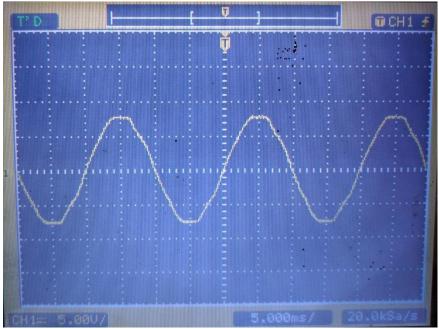

| Figure 5.19 Line to line voltage waveform obtained through power scope. Scale Y: 5V | X: 5ms 78 |

| Figure 5.20 Phase current waveform Scale Y: 0.5V X: 5ms                             | 78        |

# LIST OF ACRONYM

| 3P3W      | Three-phase, Three-wire                           |

|-----------|---------------------------------------------------|

| ac, AC    | Alternating Current                               |

| dc, DC    | Direct Current                                    |

| DSO       | Digital Storage Oscilloscope                      |

| D-STATCOM | Distribution Static Synchronous Compensator       |

| DVR       | Dynamic Voltage Restorer                          |

| FACTS     | FLEXIBLE ac Transmission System                   |

| IEEE      | Institute of Electrical and Electronics Engineers |

| IEC       | International Electro technical Commission        |

| MOSFET    | Metal Oxide Semiconductor Field-effect Transistor |

| PCC       | Point of Common Coupling                          |

| Pf, PF    | Power Factor                                      |

| PI        | Proportional and Integral                         |

| PWM       | Pulse Width Modulation                            |

| RMS       | Root Mean Square                                  |

| THD       | Total Harmonic Distortion                         |

| UPQC      | Unified Power Quality Conditioner                 |

|           |                                                   |

# **CHAPTER 1: INTRODUCTION**

# **1.1 Introduction to Power Quality**

Power quality determines the fitness of electrical power to consumer devices. A utility defines power quality as reliability. A manufacturer of load equipment defines power quality as those characteristics of the power supply that enable the equipment to work properly. Any power problem manifested in voltage, current, or frequency deviations that results in failure or disoperation of customer equipment is known as Power Quality Issues [1]. Utility is responsible for making sinusoidal voltage at point of common coupling (PCC) and the consumer is responsible for injecting current harmonics within limits.

# 1.1.1 Sources of Disturbances

Due to presence of non-linear loads such as power electronics converters, transformers, rotating machines, arching devices, fluorescent lighting, FACTS devices etc. non-sinusoidal current is drawn from the supply. Along with presence of inductive loads in most of the applications input power factor is poor. Also voltage shape is dependent on shape of pole shoes of alternator that is not exactly sinusoidal. Shape of voltage also deteriorates due to voltage drop by non-sinusoidal current.

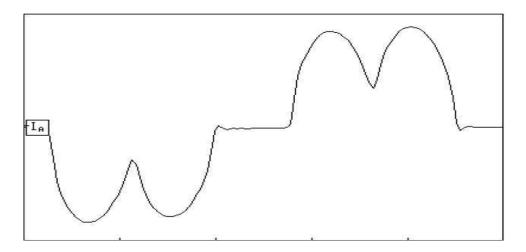

Figure 1.1 Input current of adjustable speed drive (ASD) in continuous mode of conduction [9]

### 1.1.2 Effect of Disturbances

Now a days power system is interconnected in nature. Due to interconnected system voltage variation and waveform distortions are the most influencing power quality issues. Due to these disturbances series and parallel resonance may occur in the system. Also losses in transmission lines, cables, transformers, rotating machines etc. increase. Due to different frequency components present in the system relays and other protective equipment may malfunction and this may also deteriorate the quality communication line due to interference.

# 1.1.3 Importance of Power Quality

We are concern about good power quality due to following reasons-

- i) There is steep rise in use of power electronics and microcontroller based devices which are sensitive to power quality variations.

- ii) For improving the efficiency of power system power factor correction is a prime concern.

- iii) Users are more concern about voltage sag, swell, fluctuations etc.

- iv) For utility reliability is considered as power quality. In interconnected system there are chances for propagation of fault thus good power quality is important.

## **1.1.4 Power Quality Issues**

- **A. Power Frequency Variations** Nominal frequency is either 50 Hz or 60 Hz. Deviation in frequency from its nominal value is known as power frequency variation. It is a major problem in standalone power system. But in interconnected system it is not a major concern.

- **B. Voltage Variations** Depending on time of occurrence of disturbances voltage disturbances are classified into long-duration voltage variations, short-duration voltage variations, voltage unbalance, voltage transient and voltage fluctuations.

- i) *Long-duration Voltage Variations* If the duration of voltage disturbance is more than 1 minute then the disturbance is known as long term voltage variation. This is further categorized into three categories; undervoltage, overvoltage and sustain interruption. An increase in R.M.S. voltage greater than 110% at nominal frequency for a period more than one minute is known

as overvoltage. Decrease in R.M.S. voltage less than 90% at nominal frequency for a period more than one minute is known as undervoltage. Sustain interruption is unavailability of power for more than 1 minute.

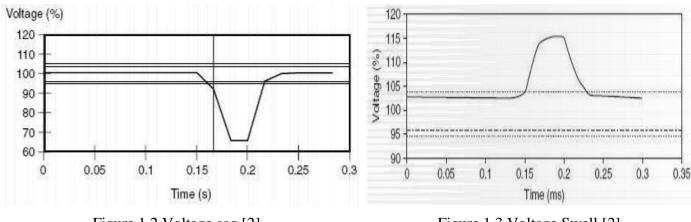

- ii) Short-duration Voltage Variation- If the duration of voltage disturbance is more than 1 minute then the disturbance is known as long term voltage variation. This is classified into voltage sag, swell and interruption. Based on the time duration these are further divided into three categories- instantaneous (0.5 cycles- 30 cycles), momentary (30 cycles- 3 seconds) and temporary (3 seconds- 1 minute). Decrease in R.M.S. voltage in range 10% to 90% at nominal power frequency for less than 1 minute is known as voltage sag. Increases in R.M.S. voltage in range 110% to 180% at nominal power frequency for less than 1 minute is known as voltage swell. Interruption is reduction in R.M.S. value of voltage less than 10% at nominal power frequency for less than 1 minute.

- iii) Voltage Unbalance- If three voltage magnitudes are not equal or they are not 120° apart, the system is said to have unbalance voltages.

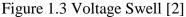

- iv) Voltage Transient- Transients are undesirable and momentary in nature. These are of two types- impulsive and oscillatory. Impulsive transient is characterized by rise and fall time while oscillatory transients are characterized by frequency spectrum.

Figure 1.2 Voltage sag [2]

Figure 1.4 Current impulsive transient due to lightening stroke [2]

Figure 1.7 Voltage fluctuations due to operation of an arc furnace [2]

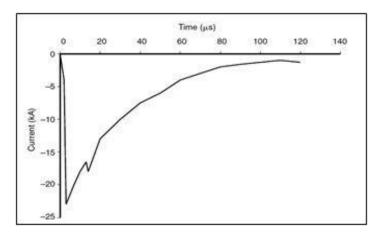

- v) *Voltage Fluctuation* Systemic variation in voltage envelope with R.M.S. value of voltage is in between 90% to 110% of nominal value of voltage is known as voltage fluctuation. This causes lightening flicker that is responsible for psychological effect on human brains.

- **C. Waveform Distortion** Steady-state deviation from an ideal sine waveform of power frequency is known as waveform distortion. Some types of waveform distortions are listed down.

- i) *DC Offset* Due to use of half wave converters etc. there is presence of DC components in AC system known as DC offset. Due to presence of DC

4

components in the system transformer core may get saturated or may not work properly.

- ii) *Harmonics* Sinusoidal voltages or currents with frequencies as integer multiple of fundamental frequency are harmonics.

- iii) *Interharmonics* Frequency components that are not integer multiple of the fundamental frequency are known as interharmonics.

- iv) *Notching* Due to commutation of valves present in power electronic devices a periodic voltage disturbance is caused that is called notching.

- v) Noise- Unwanted electrical signals with broadband harmonic spectrum lower than 200 kHz that gets superimposed on voltage or current in power or communication system is known as noise.

### **1.2 Literature Review**

Voltage sag, swell and flicker are the main power quality issues that utility must take care of. Current drawn by a load depends on equipment and users. For working equipment properly it must draw the current it needs. Most of the power electronics converters used for adjustable speed devices, mobile chargers draws non-linear current due to non-linear property of valves. Also magnetization curve of electrical machines or transformers etc. are non-linear in nature. Arching devices draws fluctuating current results in voltage flicker. Due to non-linear current and presence of transmission line impedances voltage at point of common coupling (PCC) may also get distorted.

Most of power electronics devices and microcontroller based devices are highly sensitive to voltage waveform at the PCC. Due to steep rise in the field of digital electronics and power electronics devices a good power quality is an important concern. To maintain the nominal value of undistorted voltage at PCC is generally performed by utility. But user must not inject any current harmonics in the power system as well as for highly sensitive load if supply voltage is distorted then user must remove distortion before using that voltage for highly sensitive load. If the load is itself producing voltage harmonics then user must filter it before connecting it to PCC. To improve power quality several traditional and power electronic based devices are used such as saturated reactor, synchronous condenser, shunt capacitors, series capacitors, Static Var Compensator (SVC), passive filters and several converter based methods like DSTATCOM, series active filter, unified power quality conditioner (UPQC) etc. The most effective way to improve power quality at PCC is to use filters. Filters are most effective when connected near the load. Broadly filters are divided into three categories-

- Passive filters

- Active filters

- Hybrid filters

#### **1.2.1 Passive Filters**

Passive elements i.e. resistance, inductance and capacitance are combined to make passive filters. Some important types of passive filters are listed below-

- i) Series Passive Filters

- ii) Shunt Passive Filters

- iii) Low Pass Filters

- iv) Damped Passive Filters etc.

Passive filters can be implemented for high power rating and is very robust in nature. Due to use of only passive elements it is economical. Along with harmonic mitigation it also compensates for reactive power.

Tuned frequency of passive filters can't be tuned easily thus it is not suitable for changing system conditions. Also due to presence of capacitor there are chances of resonance in the system. Single tuned filter can be tuned to one frequency thus for compensating multiple harmonic components we need several passive filters.

# **1.2.2 Active Filters**

To overcome the drawbacks of passive filters active compensation approach been introduced by researchers. Active power filter (APF) provides dynamic compensation for eliminating harmonics, unbalance, sag, swell, and flicker along with reactive power compensation. Active filters are classified into two categories- Shunt and series active filters.

# 1.2.2.1 Shunt Active Filters

Shunt active filter or dynamic static compensator (DSTATCOM) are the most effective device for compensating all types of current related problems like harmonic current elimination, reactive power compensation and balancing unbalanced currents. It is used on load side.

Figure 1.8 System Configuration of Shunt Active Filter [3]

### 1.2.2.2 Series Active Filters

Series active filter or dynamic voltage restorer (DVR) are the most effective device for compensating all types of voltage related problems like harmonic voltage elimination, voltage sag, swell compensation, voltage flicker compensation and balancing unbalanced voltages.

Figure 1.9 System Configuration of Series Active Filter [3]

Both shunt and series active filters are combined together with common DC link to make the most effective device for mitigating almost all current and voltage related power quality issues and the device is known as unified power quality conditioner (UPQC).

Figure 1.10 Basic configuration of UPQC [3]

Shunt active filters have fine response to changes in a system. Two converters are sufficient to mitigate almost all voltage and current related problems. For some loads rating of converters goes as high as 80% of load rating and thus it becomes expensive for such applications as power electronics converters are expensive that passive filters.

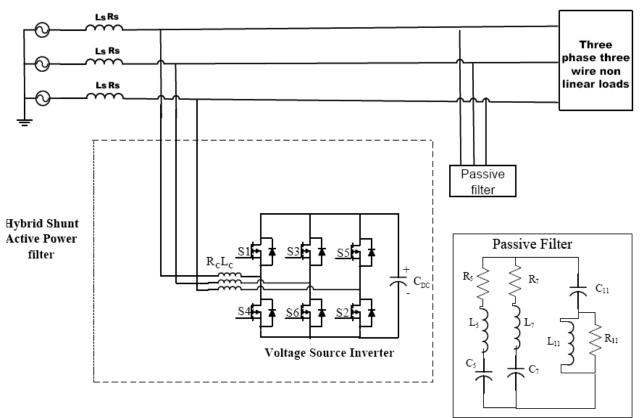

### **1.2.3 Hybrid Active Filters**

Both active filters and passive filters are combined to give a cost effective solution with comparable filtering characteristic known as hybrid active filters. Some important topologies of hybrid active filters are explained belowi) *Shunt active and shunt passive filters in shunt with load-* For reducing the size of inverter of shunt active filter some harmonics components having large magnitude are filtered by shunt passive filter. Thus rating hence cost of shunt active filter decreases.

Figure 1.11 Basic Schematics of shunt active and shunt passive filters in shunt with load [1]

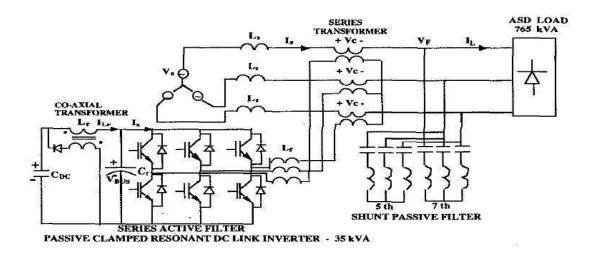

ii) Series active and shunt passive filter with shunt passive filter at the load end- Series active filter provides very low impedance to the fundamental component and very high impedance to frequencies above fundamental frequencies. Thus it acts as a barrier for harmonics and avoids harmonic currents from entering into source. All harmonic components are forced to flow through shunt passive filter connected at the load end even if it is not tuned for all the harmonics.

Figure 1.12 Basic Schematics of Series active and shunt passive filter [4]

After this very brief introduction about power quality problems, sources of disturbances, effect of disturbances, filters for mitigating power quality problems this thesis is focused on UPQC topologies and control strategies. Two control strategies for generation of current and voltage references for shunt and series part of UPQC are-

- i) Unit vector template (UVT) based reference generation technique and

- ii) Instantaneous power theory (p-q theory) based reference generation technique.

For proper working of UPQC control strategy can be classified into three parts-

- Signal Conditioning

- Calculation of reference signals

- switching pulse generation

# **1.2.4 Signal Conditioning**

For hardware implementation of UPQC different voltages and currents need to be sensed. In case of unit vector template based reference generation technique source and load voltages, DC link voltage along with source currents must be sensed. In case of instantaneous power theory based reference generation technique source voltages and series filter injected voltages on the secondary side of insertion transformer, DC link voltage along with load and shunt filter currents must be sensed. Voltage is sensed by using isolation amplifier type voltage sensor. Current is sensed using Hall Effect current sensors.

#### **1.2.5 Calculation of Reference Signals**

For generating reference signals two techniques are used in this dissertation work. One is unit vector based reference generation technique and the second one is p-q theory based reference generation techniques.

#### **1.2.6 Switching Pulse Generation**

Each of shunt and series part has one two level three phase inverters. Firing pulses for shunt inverter is generated by comparing reference current by actual current signals. Firing pulses for series inverter is generated by comparing reference current by actual current signals.

# 1.3 Organization of Dissertation

The thesis consists of seven chapters as written below-

Chapter 1 includes the overview about power quality, filters and dissertation work.

Chapter 2 includes overview and different topologies of UPQC.

*Chapter 3* includes detailed analysis of control strategies used for reference generation in both 3 phase 3 wire system (3P4W) and 3 phase 4 wire system (3P4W).

*Chapter 4* includes simulation results of UPQC by using UVT based reference generation and p-q theory based reference generation for 3P3W system in MATLAB/Simulink environment.

Chapter 5 includes hardware system development.

*Chapter 6* includes the conclusion of the dissertation work.

# **CHAPTER 2: UNIFIED POWER QUALITY CONDITIONER**

D-SSTATCOM is the most affective device to mitigate current related problems like current harmonics mitigation, reactive power compensation and balancing unbalanced currents. DVR is the most effective device to mitigate almost all voltage related problems such as voltage harmonic, sag/ swell, flicker compensation as well as balancing unbalanced voltage at PCC. Both D-STATCOM and DVR are connected back to back with a common self-supporting DC bus to make a universal device to solve almost all voltage and current related power quality problems is known as unified power quality conditioner (UPQC). UPQC is manly used in distribution system near to the point of common coupling from which point non-linear loads are connected.

Backup storage devices used in UPQC are [5]-

- i) DC storage capacitor

- ii) Batteries

- iii) Super Capacitors

- iv) Flywheels and

- v) Superconducting coils.

DC capacitor is most versatile in used as it is economical. As capacitor cannot store much energy for increasing ride time we sometimes may use batteries as a storage system. However response time of batteries is slower than capacitor. For comparable energy densities to batteries and faster response time then batteries we use super capacitors. However response time of super capacitors is less than DC storage capacitors. Flywheels are generally not in use as stored energy cannot be extracted fully. Superconducting coils are most cost attractive for short ride time high power applications.

# 2.1 Classification of UPQC

UPQC can be classified on the basis of types of converters used, supply system where it is to be installed and configuration of UPQC.

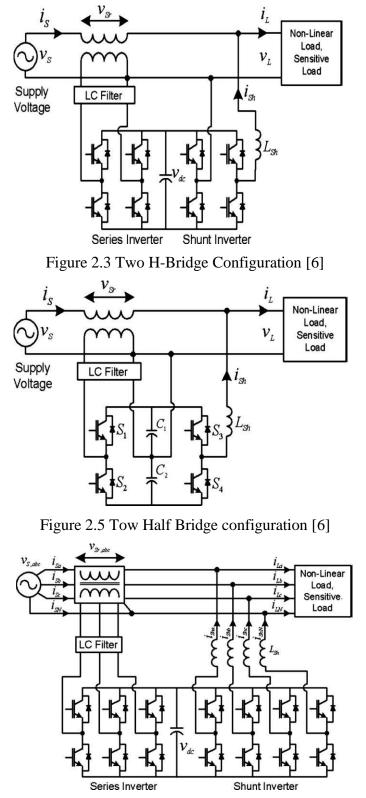

#### 2.1.1 Converter Based Classification

- i) Voltage Source Converter (VSI)

- ii) Current Source Converter (CSI)

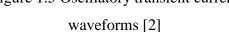

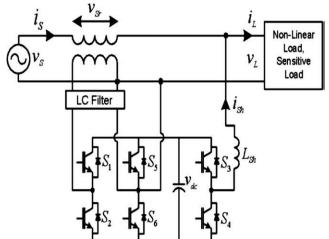

Both VSI and CSI inverters can be used for both series and shunt inverters. Figure 7 and 8 shows basic schematics of UPQC based on VSI and CSI respectively. Voltage source inverters are widely used as to maintain DC link constant current in case of CSI we need large inductances and it is difficult to do so.

Figure 2.1 VSI Based UPQC [6]

# 2.1.2 Supply System Based Configuration

- i) Single phase UPQC- Three topologies are used in single phase UPQC as listed below-

- Full bridge (8 switches) a)

- b) 3-Leg topology (6 switches)

- c) Half Bridge (total 4 switches)

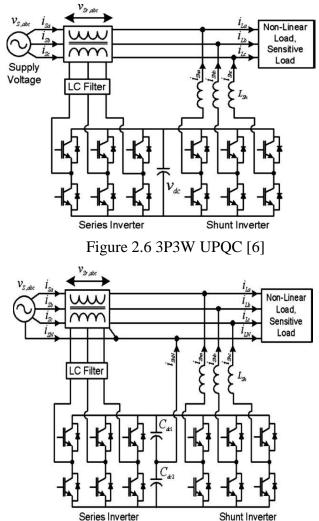

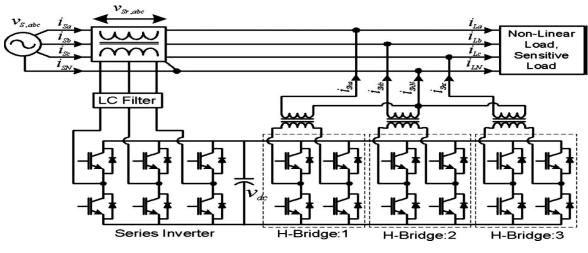

- ii) Three phase UPQC- In three phase there are either 3 wire distribution system or 4 wire distribution system.

- Three wire  $\geq$

- $\geq$ Four Wire- Three topologies are used listed below

- a) Four-Leg

- b) Split Capacitor

- Three-H Bridge c)

Figure 2.7 3P4W Four leg Shunt configuration of UPQC [7]

Figure 2.4 Three Leg Configuration [6]

Figure 2.8 3P4W split capacitor type UPQC [7]

Figure 2.9 3P4W three H-bridge configuration of UPQC [7]

# 2.1.3 Classification of UPQC Based on Configuration

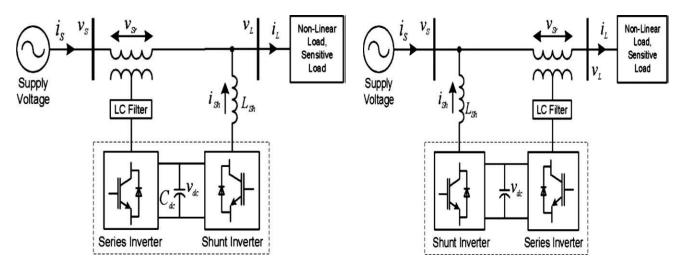

- i) Right Shunt UPQC (UPQC-R)

- ii) Left Shunt UPQC (UPQC-L)

- iii) Interline UPQC (UPQC-I)

- iv) Multi-converter UPQC

- v) Modular UPQC (UPQC-MD)

- vi) Multilevel UPQC (UPQC-ML)

- vii) Distributed UPQC (UPQC-D)

- viii) Distributed Generator Integrated UPQC (UPQC-DG)

Figure 2.10 Basic configuration of UPQC-R [6]

Figure 2.11 Basic configuration of UPQC-L [6]

Voltage

LC Filter

Series Inverter

Figure 2.14 Basic configuration of UPQC-MD [6]

Figure 2.16 Basic configuration of UPQC-D [6]

Figure 2.15 Basic configuration of

Shunt Inverter

V

1<sub>Sh</sub>

UPQC-ML [6]

## <u>CHAPTER 3: CONTROL STRATEGIES FOR UPQC</u>

The performance of UPQC is depends on upon its control algorithm. For designing controller for UPQC we need to sense voltages and currents according to the control strategies we are using for reference current and voltage generation techniques. Firing pulses for valves are generated by comparing reference signal to the actual signal. Thus control strategies of UPQC are implemented in three stages-

# 3.1 Signal Conditioning

For real hardware implementation of controller of UPQC voltages and currents need to be sensed by either isolation amplifier type or Hall Effect type sensors.

# 3.2 Reference Generation Techniques

For generating firing pulses for valves reference current and voltage signals need to compare with actual current and voltage signals. For generation of reference signals several techniques are used in both frequency domain and time domain approaches.

# 3.2.1 Frequency Domain Approach for Reference Signal Generation

Frequency domain approach is based on Fourier or Fast Fourier Analysis of distorted voltages or currents. For doing Fourier analysis we need to integrate a signal for at least one cycle thus response time of frequency domain approach for reference signal generations are not preferred in case of UPQC.

#### 3.2.2 Time Domain Approach for Reference Signal Generation

Time domain approach is based on instantaneous calculation of reference current and voltage signals from sensed polluted current and voltage signals. Being instantaneous in nature time domain approach is fast than frequency domain approach.

Two time domain approach for reference signal generation are studied and simulated in MATLAB/ Simulink environment. Both control techniques are explained below-

- i) Unit vector template (UVT) based reference generation techniques

- ii) Instantaneous power (p-q) based reference generation techniques

## 3.2.2.1 UVT based reference generation techniques [8]

#### A. For three phase three wire system

In this techniques unit vector templates are extracted from input supply voltage by using phase locked loop. The templates are balanced with unity magnitude. For current generation by shunt inverter and voltage generation by series inverter based on unit vector templates generated by the use of PLL (phase locked loops) is used.

Required peak value of fundamental input voltage magnitude is multiplied by unit vector templates calculated by using phase locked loop block for generating reference voltage required on the load side. We can directly compare the reference load voltage and actual load voltage by using hysteresis voltage controller to generate the firing pulses for shunt inverter.

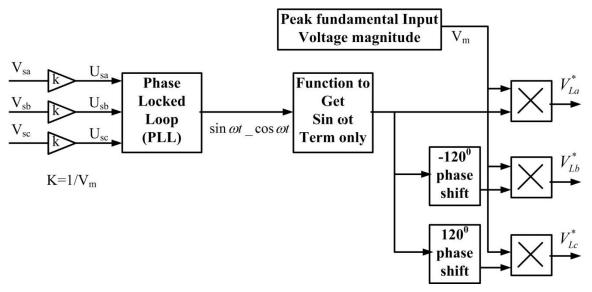

Figure 3.1 Extraction of unit vector templates and reference 3-phase load voltages

$U_{a} = \sin (\omega t)$  $U_{b} = \sin (\omega t - 2^{*}\pi/3)$  $U_{c} = \sin (\omega t - 4^{*}\pi/3)$

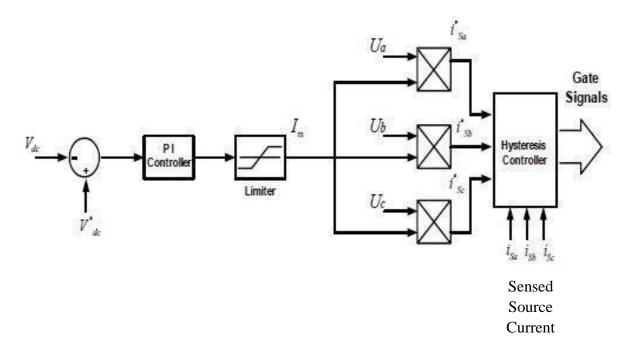

By comparing DC link voltage with fixed reference voltage and passing it through a PI controller and a limiter we get the required peak magnitude of sinusoidal source current to be drawn from the source. Reference source current is thus generated by multiplying the output of limiter block by unit vector templates as shown in the below figure.

Figure 3.2 Reference current signal generation for shunt APF

# B. Three phase four wire system

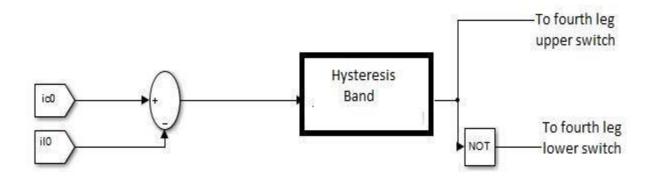

The control strategy of generating firing pulses for three legs of series and shunt inverters are same as in case of three phase three wire system. For generating firing pulses for fourth leg we feed the difference of load neutral current and current through fourth leg in a hysteresis controller. Pulses for upper and lower switches are complementary of each other.

Figure 3.3 Switching pulse generation for fourth leg of shunt filter inverter

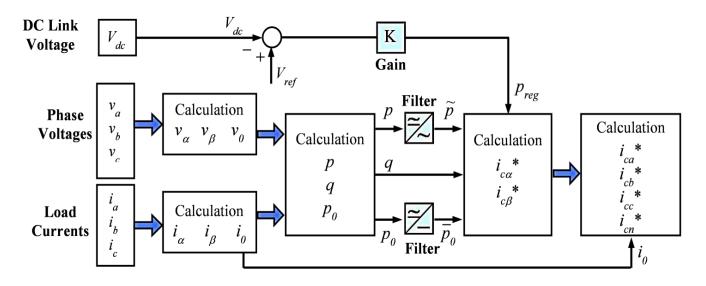

# 3.2.2.2 p-q theory based reference generation techniques [3]

# A. <u>Three phase three wire system</u>

The Instantaneous Reactive Power Compensation was first introduced by H. Akagi in 1984. In a three phase three wire system zero sequence component of voltage and current are not present. This approach takes the use of Clarke's transformation.

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ 0 & \sqrt{3}/2 & -\sqrt{3}/2 \end{bmatrix} \begin{bmatrix} v_{a} \\ v_{b} \\ v_{c} \end{bmatrix}$$

$$\begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ 0 & \sqrt{3}/2 & -\sqrt{3}/2 \end{bmatrix} \begin{bmatrix} i_{a} \\ i_{b} \\ i_{c} \end{bmatrix}$$

$$\begin{bmatrix} p \\ q \end{bmatrix} = \begin{bmatrix} v_{\alpha} & v_{\beta} \\ -v_{\beta} & v_{\alpha} \end{bmatrix} \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix}$$

According the instantaneous reactive power theory, p and q are decomposed into instantaneous real and imaginary powers, respectively,

$$p = \overline{p} + \widetilde{p} \quad q = \overline{q} + \widetilde{q}$$

Where  $\overline{p}$  and  $\overline{q}$  are the dc components to the fundamental current,  $\widetilde{p}$  and  $\widetilde{q}$  are the ac

So, the reference current signal can be achieved, in order to have fundamental active power component only, i.e., unity power factor, and harmonic compensation, as:

$$\begin{bmatrix} i_{a}^{*} \\ i_{b}^{*} \\ i_{c}^{*} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & 0 \\ -1/2 & \sqrt{3}/2 \\ -1/2 & -\sqrt{3}/2 \end{bmatrix} \begin{bmatrix} v_{\alpha} & v_{\beta} \\ -v_{\beta} & v_{\alpha} \end{bmatrix}^{-1} \begin{bmatrix} \overline{p} \\ q \end{bmatrix}$$

Figure 3.4 Schematic representation of synthesizing shunt inverter reference current based on p-q method

The p-q method based generation of compensating current as shown in Figure 2.12, guarantees that the instantaneous active power delivered by the source equal to the active load power demand.

Due to use of positive sequence detector series inverter control becomes very easy. As we want voltage at PCC as positive sequence components of source voltage.

| VLa      |     | $v'_a$ |

|----------|-----|--------|

| VLb      | (E) | vb     |

| $V_{Lc}$ |     | $v_c'$ |

Thus reference voltage generated by series inverter vca\*, vcb\* and vcc\* are given by

| $v_{Ca}^*$      | $\begin{bmatrix} v'_a \end{bmatrix}$ | VSa             |

|-----------------|--------------------------------------|-----------------|

| $v_{Cb}^* =$    | $v_b'$ –                             | v <sub>sb</sub> |

| V <sub>Cc</sub> | $v_c'$                               | VSc_            |

# B. Three phase four wire system

In case of three phase four wire system instantaneous power theory is modified to compensate for neutral current by fourth leg of shunt active filter inverter. Series filter reference generation is the same as in p-q theory for three phase three wire system. But shunt filter reference generation techniques is modified as follows-

Three phase active power

$$p = \mathbf{e}_{\alpha\beta0} \cdot \mathbf{i}_{\alpha\beta0} = v_{\alpha}i_{\alpha} + v_{\beta}i_{\beta} + v_{0}i_{0}$$

Three phase reactive power

$$\mathbf{q} = \mathbf{e}_{\alpha\beta0} \times \mathbf{i}_{\alpha\beta0} = \begin{bmatrix} q_{\alpha} \\ q_{\beta} \\ q_{0} \end{bmatrix} = \begin{bmatrix} v_{\beta} & v_{0} \\ i_{\beta} & i_{0} \end{bmatrix}$$

$$\begin{bmatrix} v_{0} & v_{\alpha} \\ i_{0} & i_{\alpha} \end{bmatrix}$$

$$\begin{bmatrix} v_{\alpha} & v_{\beta} \\ i_{\alpha} & i_{\beta} \end{bmatrix}$$

Power matrix is given by

$$\begin{bmatrix} p \\ q_{\alpha} \\ q_{\beta} \\ q_{0} \end{bmatrix} = \begin{bmatrix} v_{\alpha} & v_{\beta} & v_{0} \\ 0 & -v_{0} & v_{\beta} \\ v_{0} & 0 & -v_{\alpha} \\ -v_{\beta} & v_{\alpha} & 0 \end{bmatrix} \begin{bmatrix} i_{\alpha} \\ i_{\beta} \\ i_{0} \end{bmatrix}$$

Thus currents can be calculated by

$$\begin{bmatrix} i_{\alpha} \\ i_{\beta} \\ i_{0} \end{bmatrix} = \frac{1}{v_{\alpha\beta0}^{2}} \begin{bmatrix} v_{\alpha} & 0 & v_{0} & -v_{\beta} \\ v_{\beta} & -v_{0} & 0 & v_{\alpha} \\ v_{0} & v_{\beta} & -v_{\alpha} & 0 \end{bmatrix} \begin{bmatrix} p \\ q_{\alpha} \\ q_{\beta} \\ q_{0} \end{bmatrix}$$

where

$$v_{\alpha\beta0}^2 = v_{\alpha}^2 + v_{\beta}^2 + v_0^2$$

For shunt filter we want it to provide harmonic load current as well as reactive power required by the load. Thus in above equation we p= power loss in

| $q_{\alpha}$ |     | $q_{\alpha}$ |

|--------------|-----|--------------|

| $q_{\beta}$  | = - | $q_{\beta}$  |

| $q_0$        |     | 90           |

DC link- fluctuating part of real load power and then current reference in  $\alpha\beta0$  frame for shunt active filter can be generated by putting the appropriate power to be compensated in the current calculation as shown above. Then by using inverse Clarke's transformation we get ica\*, icb\* and icc\*.

# 3.3 Gating Pulse Generation Techniques

Several techniques are contrived for generation of gating pulses of valves of shunt and series inverters. Two techniques are discussed below-

- i) Hysteresis control

- ii) Triangular carrier wave control

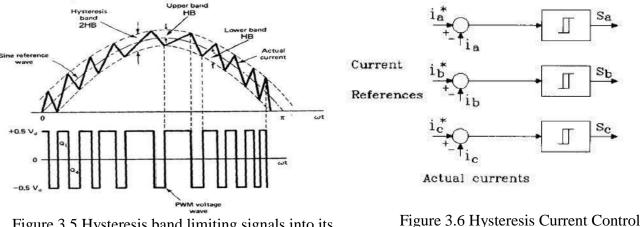

# 3.3.1 Hysteresis Control

This control technique for generating firing pulses for shunt and series inverters is the most robust control and is widely used. For generating firing pulses for shunt inverter reference currents and actual currents are compared and the error is fed to a Schmitt trigger where gating pulses are generated when error goes beyond the limit of hysteresis band or tolerance band such that error comes within limit of hysteresis band.

Figure 3.5 Hysteresis band limiting signals into its limits

# Advantages-

- i) It is very simple to implement

- ii) It is highly robust

- iii) It has good stability

- iv) It gives good dynamic response

Disadvantages-

i) It produces varying firing.

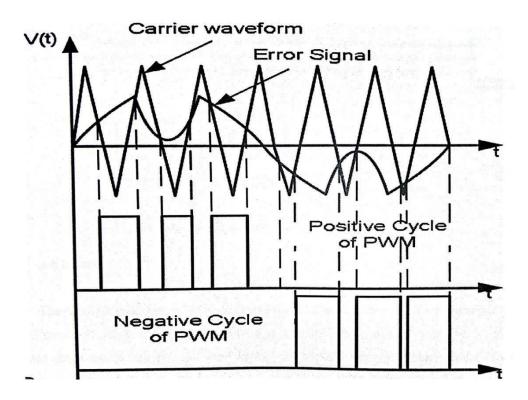

# 3.3.2 Triangular Carrier Wave Control

In this control method, error between reference and actual signals are compared with a high frequency triangular wave to generate pulses using a comparator. Since both shunt and series inverters have to feed mainly non-sinusoidal components of currents and voltages respectively implementation of triangular carrier wave control is difficult. The advantage here that we get fixed switching frequency that is equal to frequency of carrier wave.

Figure 3.7 Triangular wave control for generating firing pulses for inverters

## **CHAPTER 4: ANALYSIS OF UNIFIED POWER QUALITY CONDITIONER**

#### 4.1 Simulations and Results in Three Phase Three Wire System

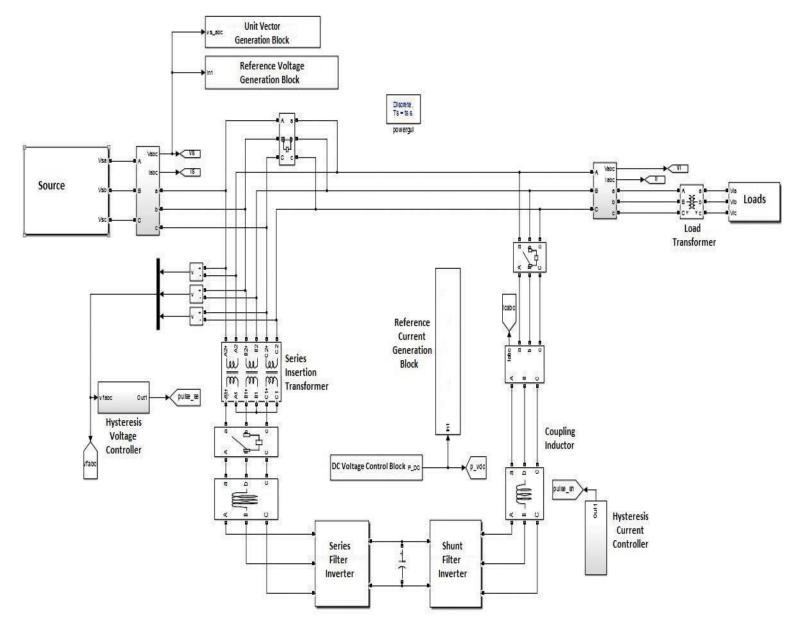

### A. <u>Unit Vector Template Based Reference Generation Technique</u>

Figure 4.1 Simulink model of UPQC with unit vector templates control techniques for reference generation

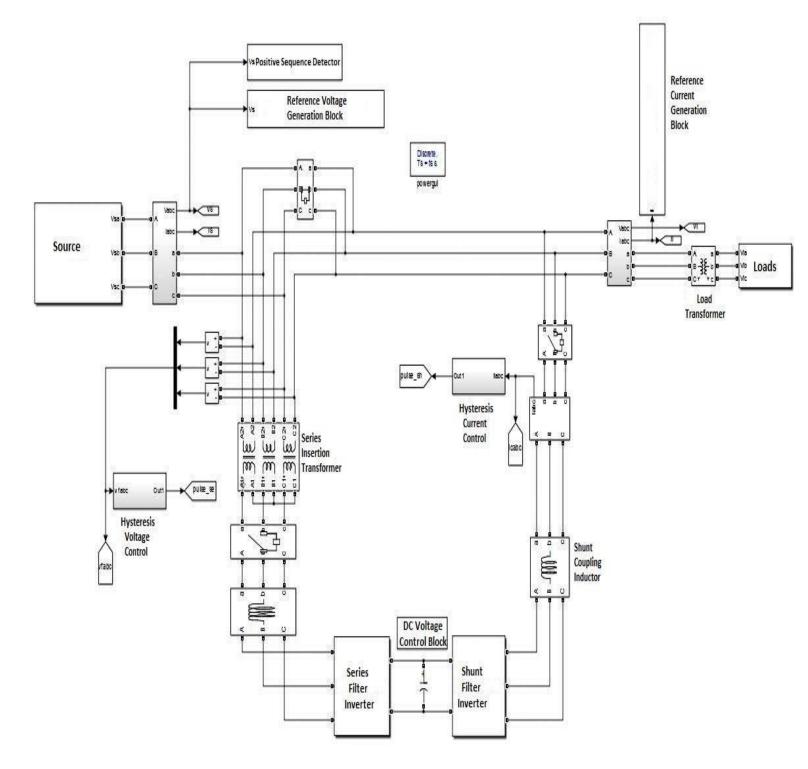

### B. Instantaneous Power Theory Based Reference Generation

Figure 4.2 Simulink model of UPQC with instantaneous power calculation control technique for reference generation

#### 4.2 Load and Source Configuration

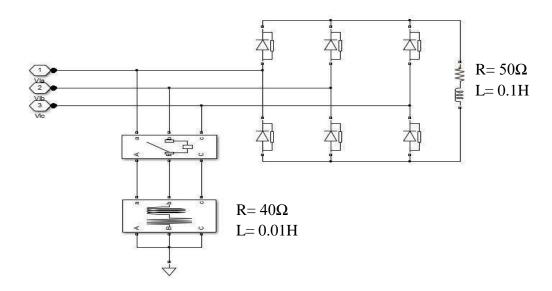

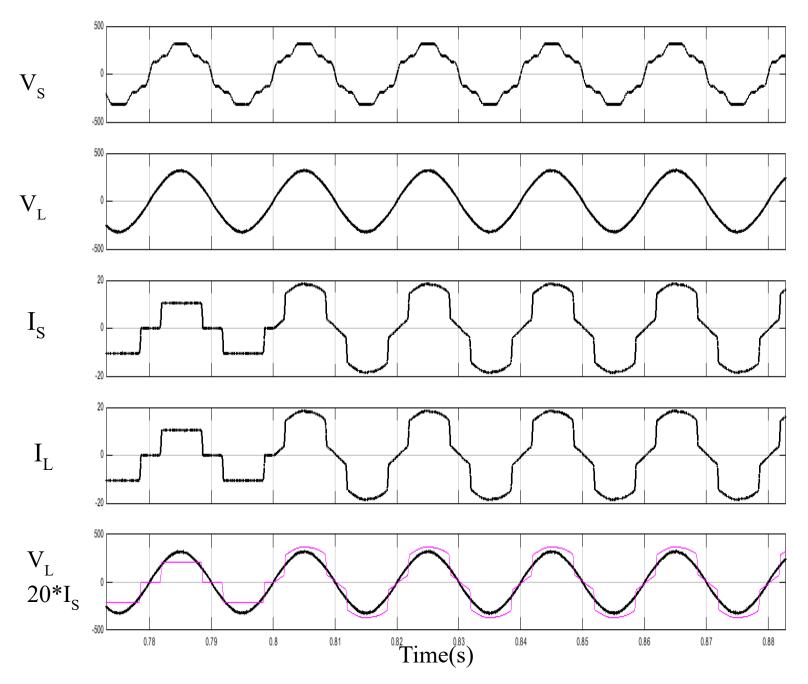

Balanced loads are fed by balanced but distorted source. At t=0.6s shunt active filter is switched ON by using the breaker. Also at t=0.6s series active filter is switched ON by using another breaker and the breaker across series insertion transformer is opened at the same time. Run time for simulation is 1.2 seconds. Before 0.8s load is only a rectifier load having R-L load connected on DC side. At t= 0.8s the load circuit breaker is closed and load consists of two parts one diode bridge rectifier feeding R-L load and another is three phase balanced R-L load connected in star.

Figure 4.3 Connected load (Circuit breaker is Switched ON at t=0.8s)

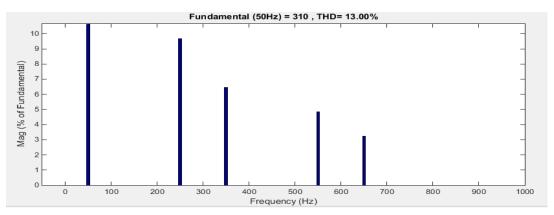

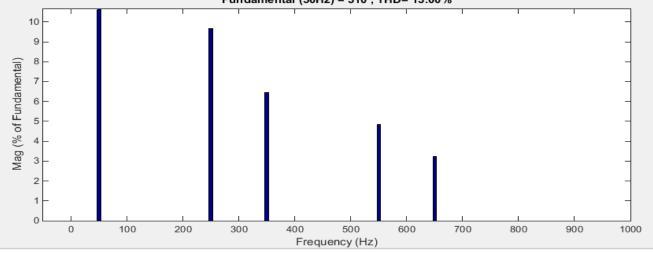

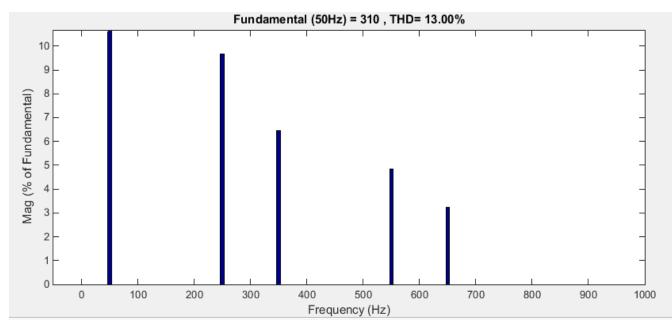

Source is balanced and distorted has peak of fundamental 310 V. It contains 5th, 7th, 11th and 13th order harmonics in phase with fundamental having peak magnitude of 30V, 20V, 15V and 10V respectively. Source voltage has 13% THD with dominating 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup> and 13<sup>th</sup> order harmonics. Peak value of fundamental of source voltage is 310V. Figure 4.5 shows the harmonic contents of source voltage up to 2000 Hz. Phase B and phase C has same harmonic spectrum as the source is balanced.

Figure 4.4 Harmonic content of phase A of source voltage

#### 4.3 Simulation Results Using UVT Techniques for Reference Generation

Simulation is performed in a manner to ascertain the performance analysis of the individual components of a UPQC i.e. Shunt active filter and series active filter. Thus with the same load configuration as shown above the analysis is performed where first of all system functions without any filter, next the shunt component is turned ON and is allowed to filter out harmonic currents which is followed by a load variation and it is seen how well the system responds to changing load.

Similar procedure is repeated for series active filter whereby no filtering period is followed by bringing series active filter into the system and allowed to compensate harmonic voltages. Again load is varied to observe systems capability to adjust to such real life changes. In case of operating the series filter a voltage source is used instead of DC link capacitor since real power gets drawn from the series filter while compensating for voltage harmonics.

In the final analysis both the shunt and series parts are brought into picture and are both turned ON at the same instant and allowed to compensate for both voltage and current harmonics. Next load variation is performed to ascertain system's dynamic response.

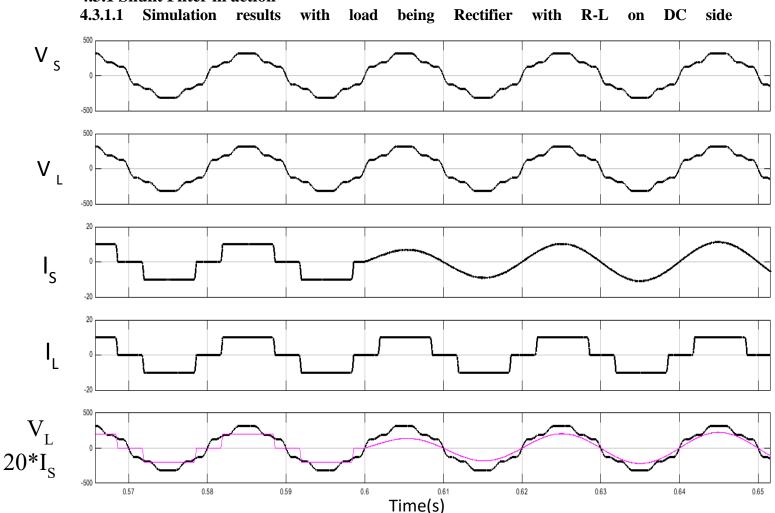

4.3.1 Shunt Filter in action

Figure 4.5 Shunt Filter comes in action at 0.6 sec

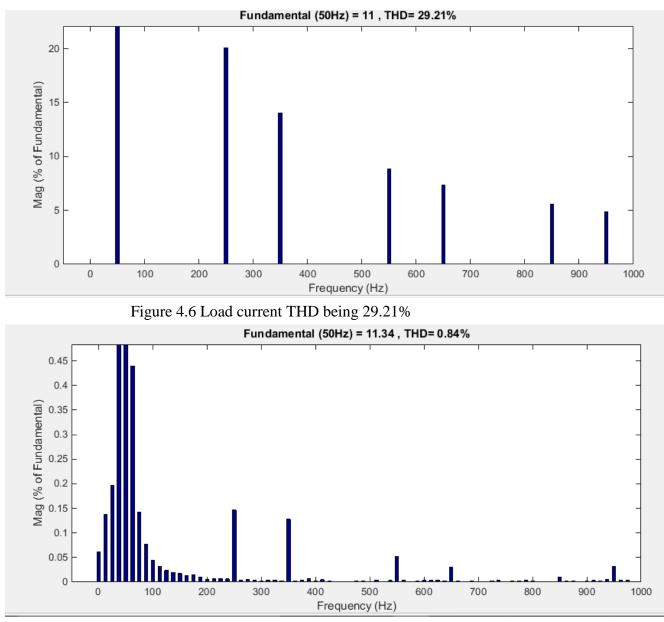

Figure 4.7 Source current THD drops from 29.21% to 0.84 %

We observe that Shunt filter after coming into action reduces current harmonics to a negligible amount and that the current being drawn from the supply is almost sinusoidal. This happens because the shunt filter injects equal and opposite harmonic currents to cancel them or supplies harmonic currents to the load such that supply side just provides sinusoidal currents.

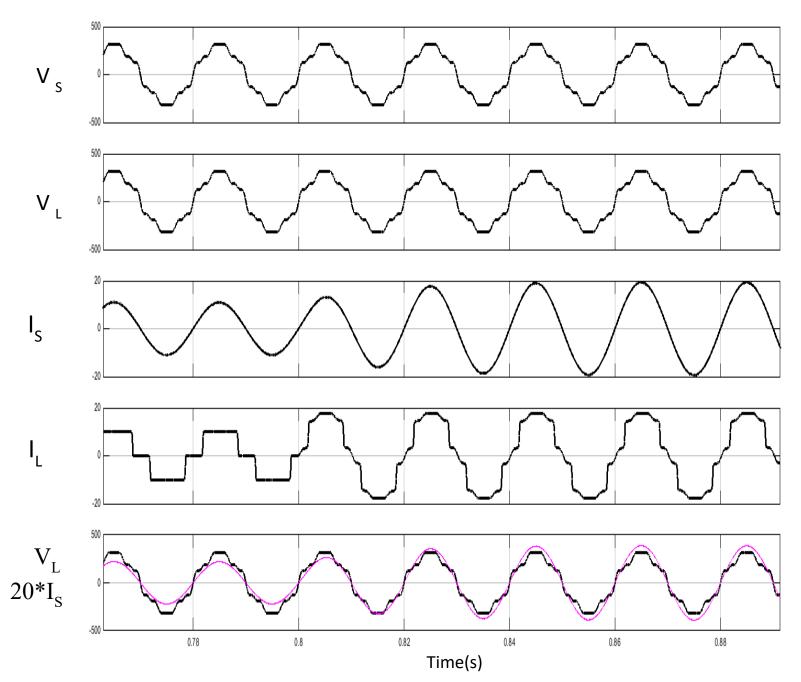

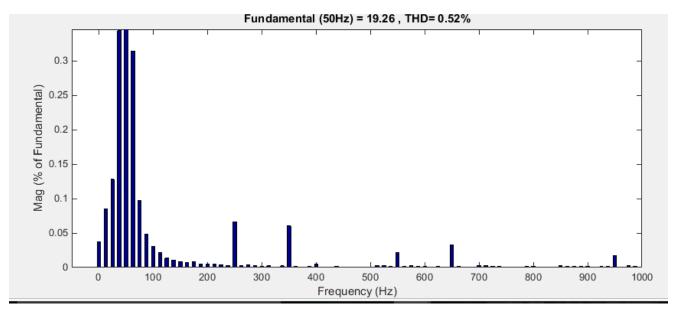

#### 4.3.1.2 Simulation results with additional R-L load along with Rectifier with R-L on DC side

Once the shunt filter comes into action after a delay of 0.2 seconds i.e. at 0.8 seconds an additional load is added to observe dynamic response of shunt filter.

Figure 4.8 Shunt Filter responding to load change at 0.8 seconds

Figure 4.9 Source current THD drops from 0.84% to 0.52 %

Figure 4.10 Load current THD decreases to 14.48%

Since after the addition of new load the net THD of load current drops down to 14.48% hence shunt filter does even a better job. Also the response of shunt filter is in pace with sudden load change.

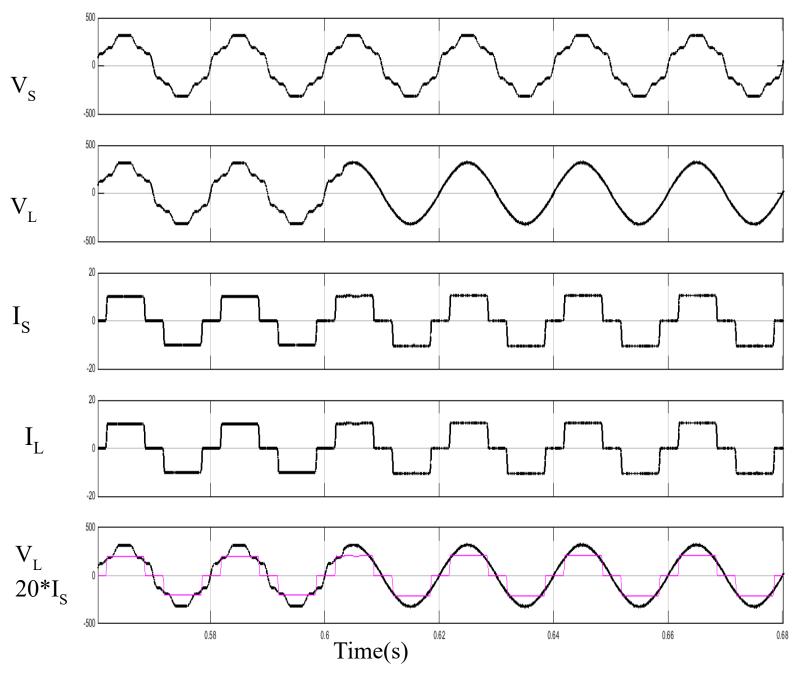

## 4.3.2 Series Filter in action

## 4.3.2.1 Simulation results with load being Rectifier with R-L on DC side

Figure 4.12 Source voltage THD being 13%

Figure 4.13 Load voltage THD drops from 13% to 1.69%

### 4.3.2.2 Simulation results with additional R-L load along with Rectifier with R-L on DC side

Once the series filter comes into action after a delay of 0.2 seconds i.e. at 0.8 seconds an additional load is added to observe dynamic response of series filter.

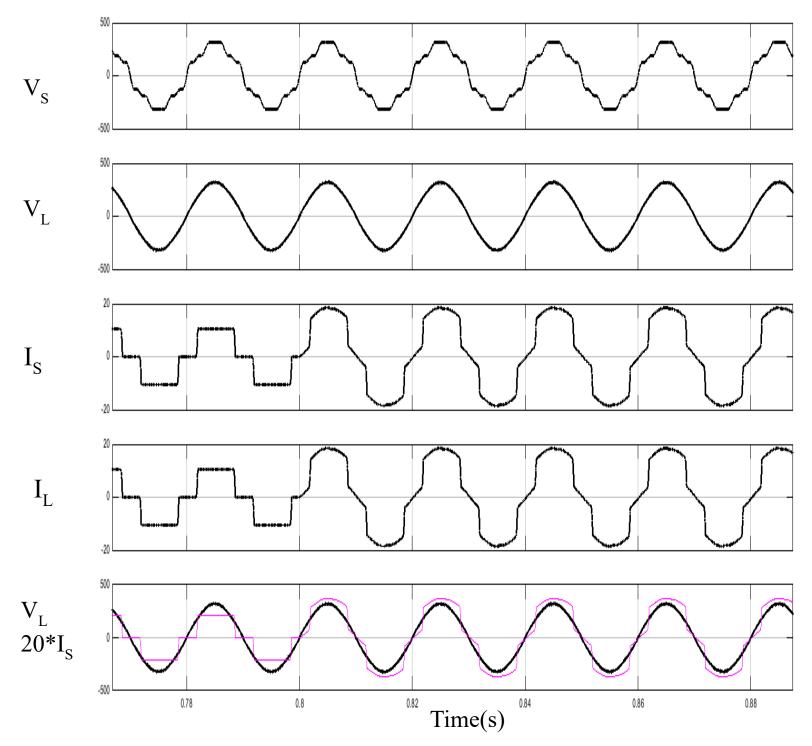

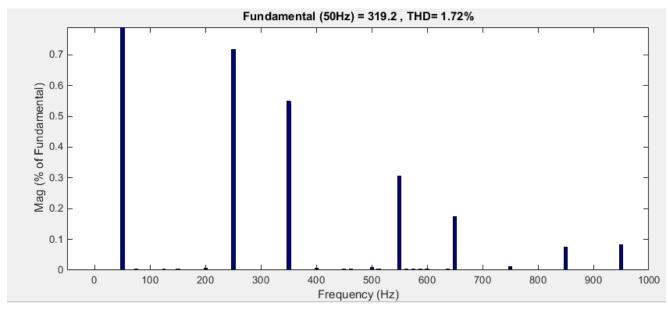

Figure 4.14 Series Filter responding to load change at 0.8 seconds

Figure 4.15 Load voltage THD after load changes remains almost same at 1.72%

## 4.3.3 Both Shunt and Series Filter in action

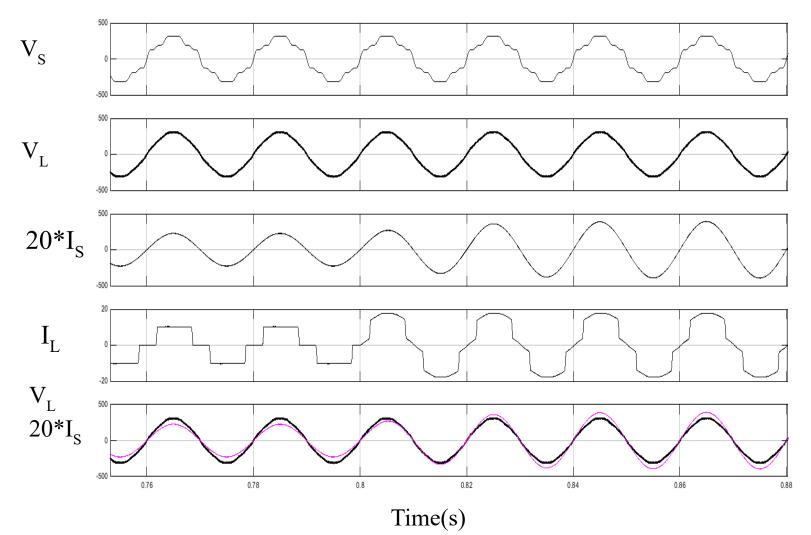

Figure 4.16 UPQC comes in action at 0.6 sec

Figure 4.18 Source current harmonics drop from 29.18% to 0.95 % due to shunt filtering Fundamental (50Hz) = 310, THD= 13.00%

Figure 4.19 Source voltage harmonics being 13%

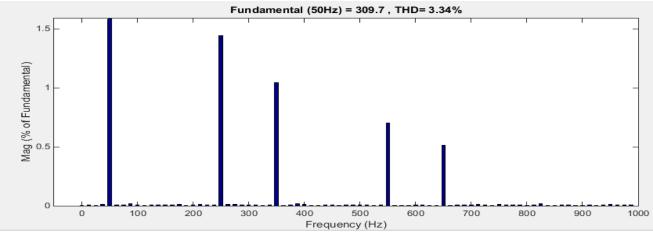

Figure 4.20 Load voltage THD falls from 13% to 3.34%

4.3.3.2 Simulation results of UPQC with additional R-L load along with Rectifier with R-L on DC side

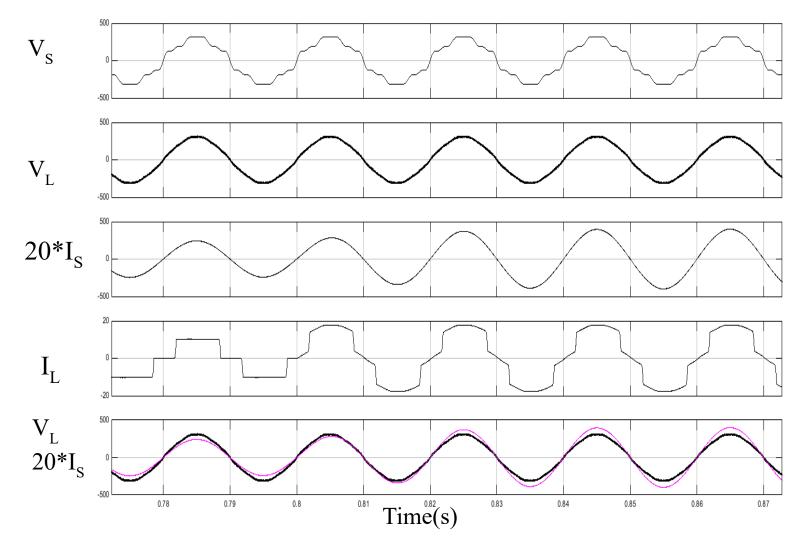

Figure 4.21 UPQC in action after load change at 0.8 seconds

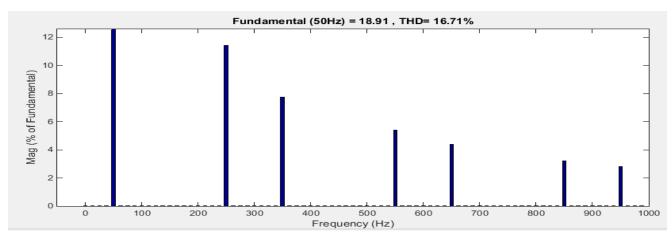

Figure 4.22 Load current harmonics being 16.71% after load change

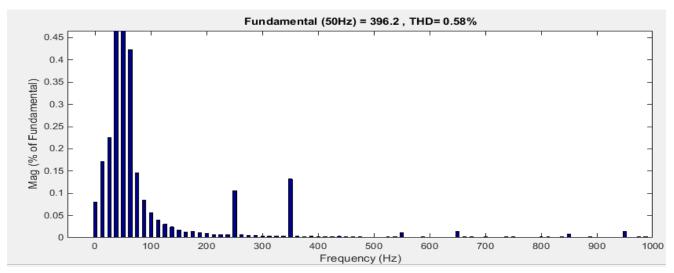

Figure 4.23 Source current harmonics drop from 16.71% to 0.47 % due to shunt filtering

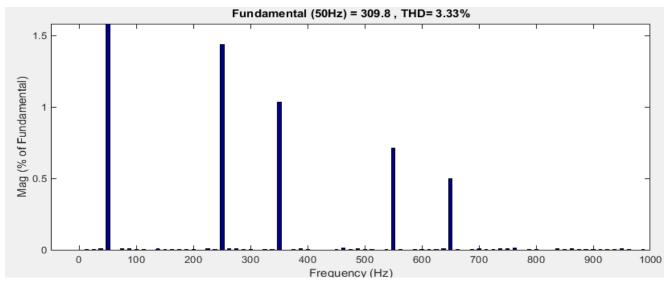

Fundamental (50Hz) = 309.7 , THD= 3.36%

Figure 4.24 Load voltage THD after load changes remains almost same at 3.36%

#### 4.4 Simulation Results using p-q theory based Techniques for Reference Generation

Simulation is performed in a manner to ascertain the performance analysis of the individual components of a UPQC i.e. Shunt active filter and series active filter. Thus with the same load configuration as shown above the analysis is performed where first of all functions without any filter, next the shunt component is turned ON and is allowed to filter out harmonic currents which is followed by a load variation and it is seen how well the system responds to changing load.

Similar procedure is repeated for series active filter whereby no filtering period is followed by bringing series active filter into the system and allowed to compensate harmonic voltages. Again load is varied to observe systems capability to adjust to such real life changes. In case of operating the series filter a voltage source is used instead of DC link capacitor since real power gets drawn from the series filter while compensating for voltage harmonics.

In the final analysis both the shunt and series parts are brought into picture and are both turned ON at the same instant and allowed to compensate for both voltage and current harmonics. Next load variation is performed to ascertain system's dynamic response.

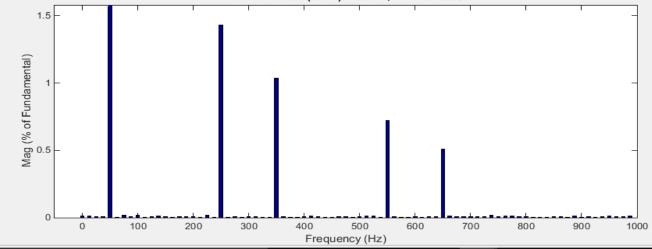

Figure 4.27 Source current THD drops from 29.21% to 2.17 %

We observe that Shunt filter after coming into action reduces current harmonics to a negligible amount and that the current being drawn from the supply is almost sinusoidal.

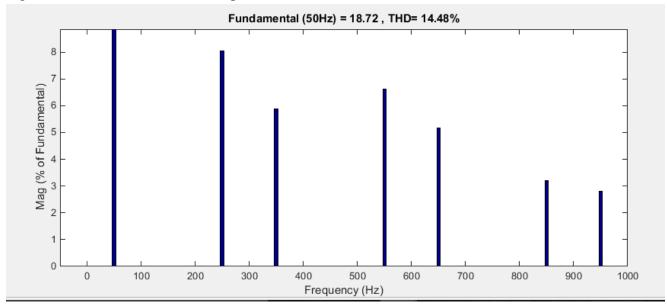

### 4.4.1.2 Simulation results with additional R-L load along with Rectifier with R-L on DC side

Once the shunt filter comes into action after a delay of 0.2 seconds i.e. at 0.8 seconds an additional load is added to observe dynamic response of shunt filter.

Figure 4.28 Shunt Filter responding to load change at 0.8 seconds

Figure 4.29 Load current THD decreases to 14.48%

Figure 4.30 Source current THD drops from 2.17 % to 0.63%

Since after the addition of new load the net THD of load current drops down to 14.48% hence shunt filter does even a better job.

#### 4.4.2 Series Filter in action

### 4.4.2.1 Simulation results with load being Rectifier with R-L on DC side

Figure 4.31 Series Filter in action at 0.6 sec

Figure 4.32 Source voltage THD being 13%

Figure 4.33 Load voltage THD drops from 13% to 1.69%

### 4.4.2.2 Simulation results with additional R-L load along with Rectifier with R-L on DC side

Once the series filter comes into action after a delay of 0.2 seconds i.e. at 0.8 seconds an additional load is added to observe dynamic response of series filter.

Figure 4.34 Series Filter responding to load change at 0.8 seconds

Figure 4.35 Load voltage THD after load changes remains almost same at 1.72%

### 4.4.3 Both Shunt and Series Filter in action

### 4.4.3.1 Simulation results with load being Rectifier with R-L on DC side

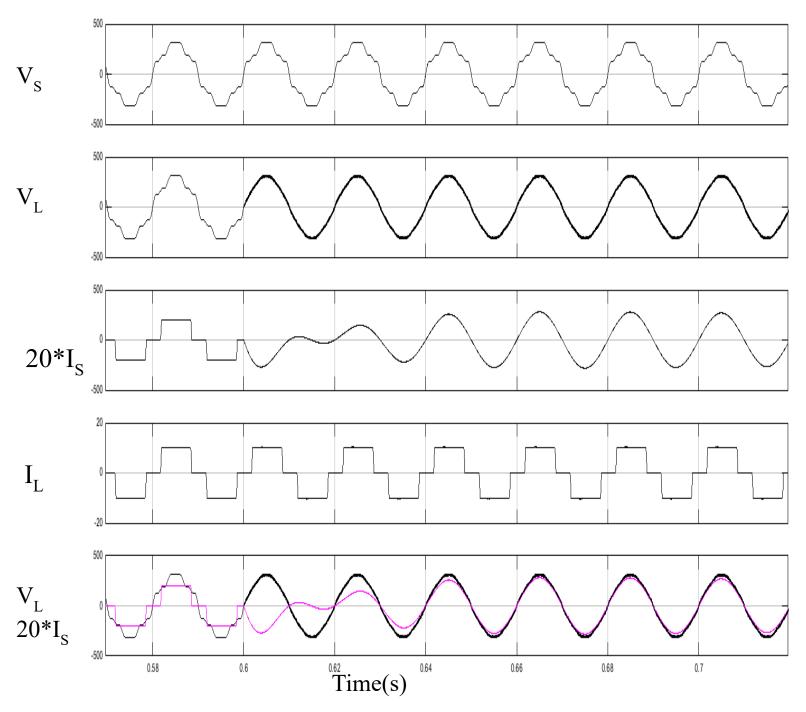

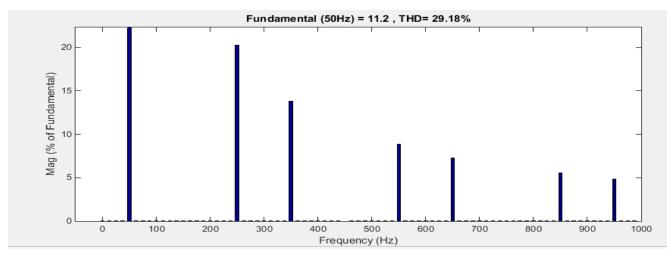

Figure 4.36 UPQC comes in action at 0.6 sec

Figure 4.38 Source current harmonics drop from 29.18% to 1.90 % due to shunt filtering

Figure 4.39 Source voltage harmonics being 29.18%

Figure 4.40 Load voltage THD falls from 13% to 3.26%

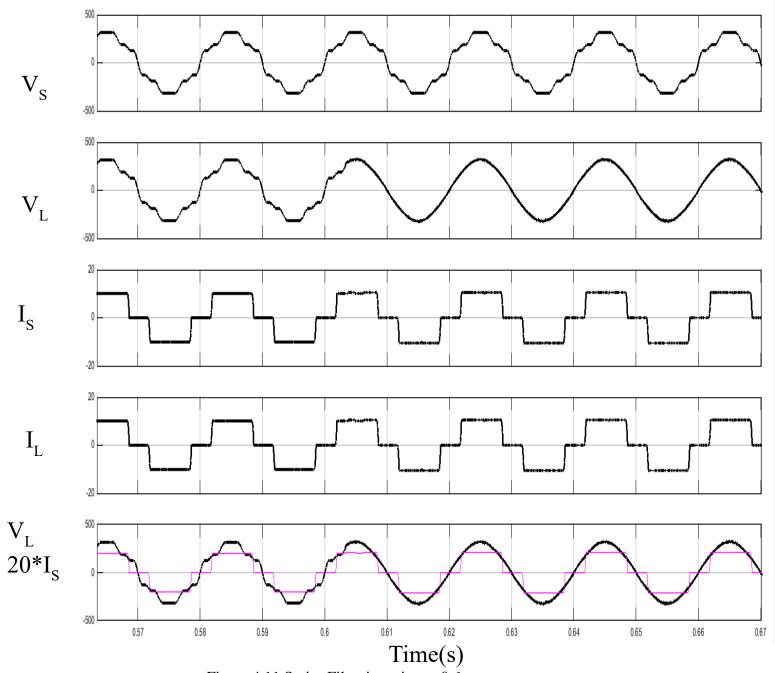

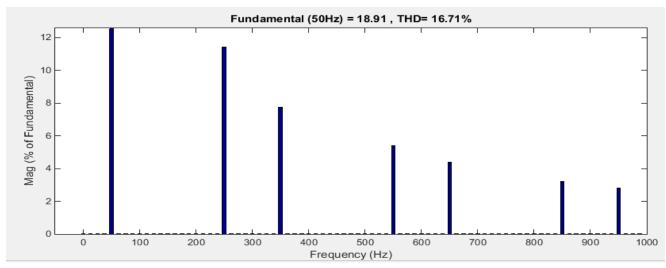

4.4.3.2 Simulation results of UPQC with additional R-L load along with Rectifier with R-L on DC side

Figure 4.41 UPQC in action after load change at 0.8 seconds

Figure 4.42 Load current harmonics being 16.71% after load change

Figure 4.43 Source current harmonics drop from 16.71% to 0.58 % due to shunt filtering

Figure 4.44 Load voltage THD after load changes remains almost same at 3.33%

#### 4.5 Simulation Results with Voltage Unbalance

Voltage unbalance is introduced in Phase A of the 3P-3W system by increasing the fundamental positive sequence component to 330V while remaining phases are at 310V. This causes THD content of A phase to be different from remaining phases as shown in Figure below.

|                 | V <sub>SA</sub> (V) | V <sub>SB</sub> (V) | V <sub>sc</sub> (V) |

|-----------------|---------------------|---------------------|---------------------|

| V <sub>1</sub>  | 330                 | 310                 | 310                 |

| $V_5$           | 30                  | 30                  | 30                  |

| V <sub>7</sub>  | 20                  | 20                  | 20                  |

| V <sub>11</sub> | 15                  | 15                  | 15                  |

| V <sub>13</sub> | 10                  | 10                  | 10                  |

| THD             | 12.22%              | 13%                 | 13%                 |

Figure 4.45 Voltage Unbalance **4.5.1 Shunt Filter in action**

Figure 4.46 Shunt Filter in action at 0.4s

Time(s)

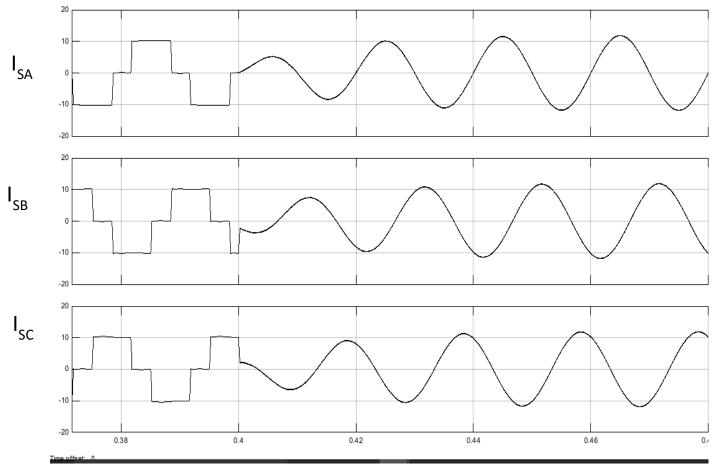

Figure 4.47 Three phase currents before and after compensation

|                 | THD % | I <sub>1</sub> |                 | THD % | I <sub>1</sub> |

|-----------------|-------|----------------|-----------------|-------|----------------|

| ILA             | 28.33 | 11.42          | I <sub>SA</sub> | 0.71  | 11.08          |

| I <sub>LB</sub> | 29.86 | 11.12          | I <sub>SB</sub> | 0.71  | 11.09          |

| I <sub>LC</sub> | 29.45 | 11.12          | I <sub>SC</sub> | 0.72  | 11.09          |

Figure 4.48 Load and Source current THD and peak values

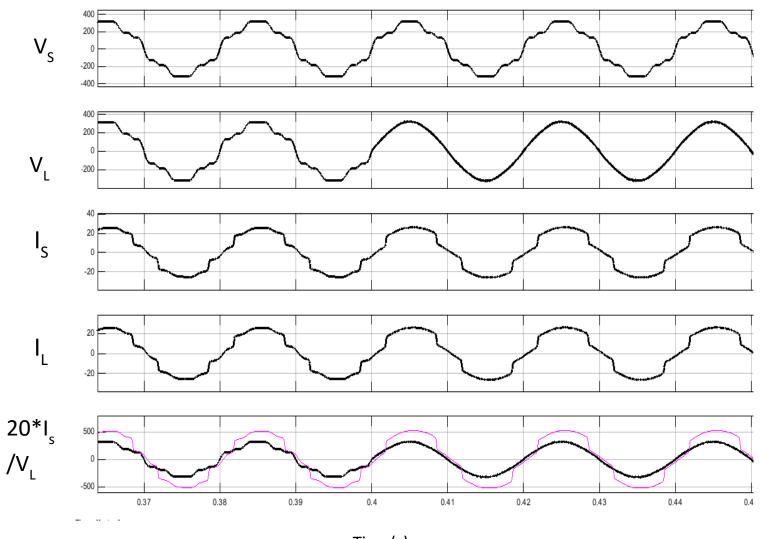

## 4.5.2 Series Filter in action

Figure 4.50 Three phase voltages before and after compensation

|                 | THD % | I <sub>1</sub> |                 | THD % | Volts |

|-----------------|-------|----------------|-----------------|-------|-------|

| ILA             | 29    | 11.54          | $V_{LA}$        | 2.15  | 325.4 |

| I <sub>LB</sub> | 28.76 | 11.57          | $V_{LB}$        | 2.78  | 316.4 |

| I <sub>LC</sub> | 29.11 | 11.51          | V <sub>LC</sub> | 2.80  | 316.1 |

Figure 4.51 Load voltage and currents THD and peak values

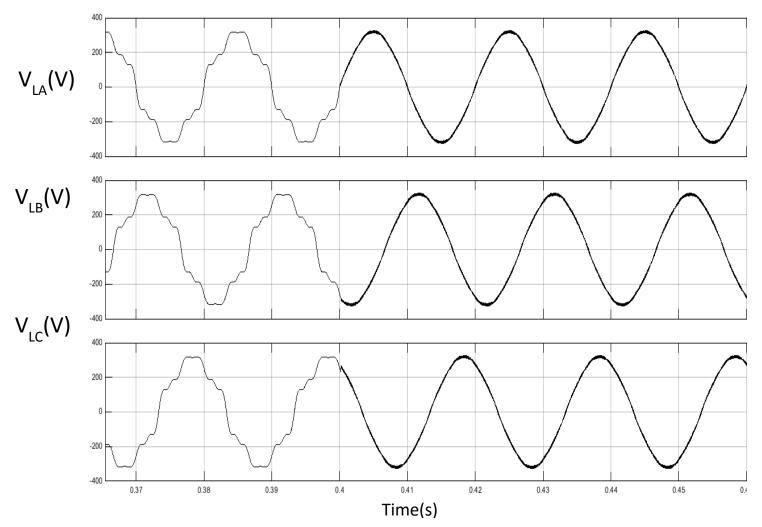

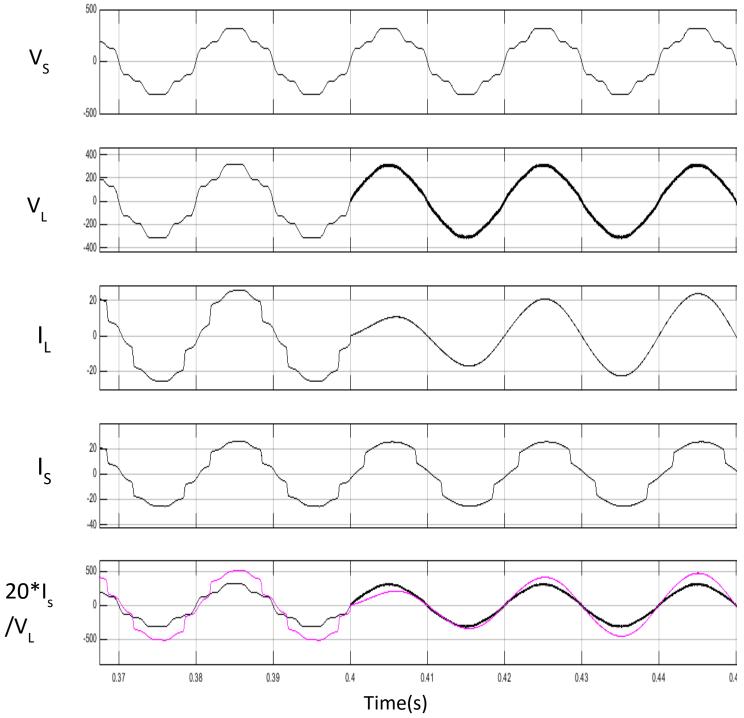

# 4.5.3 Both Shunt and Series Filter in action

Figure 4.54 Three phase source before and after compensation

|                 | THD % | Volts |                 | THD % | I <sub>1</sub> |

|-----------------|-------|-------|-----------------|-------|----------------|

| V <sub>LA</sub> | 3.37  | 318.6 | I <sub>SA</sub> | 0.60  | 11.21          |

| V <sub>LB</sub> | 3.56  | 307.6 | I <sub>SB</sub> | 0.63  | 11.23          |

| V <sub>LC</sub> | 3.61  | 307.5 | I <sub>SC</sub> | 0.64  | 11.21          |

Figure 4.55 Load voltage and source current THD and peak values

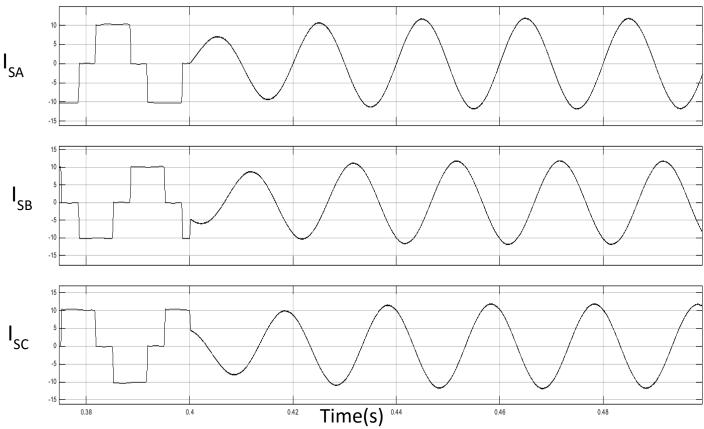

### 4.6 Simulation Results with Load Unbalance

Load unbalance is introduced in Phase A of the 3P-3W system by increasing the load in A phase while that in other two phases are less and equal.

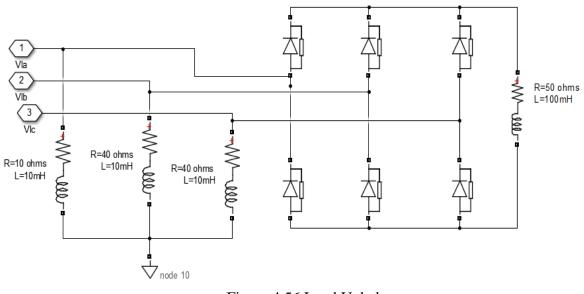

Figure 4.56 Load Unbalance

## 4.6.1 Shunt Filter in action

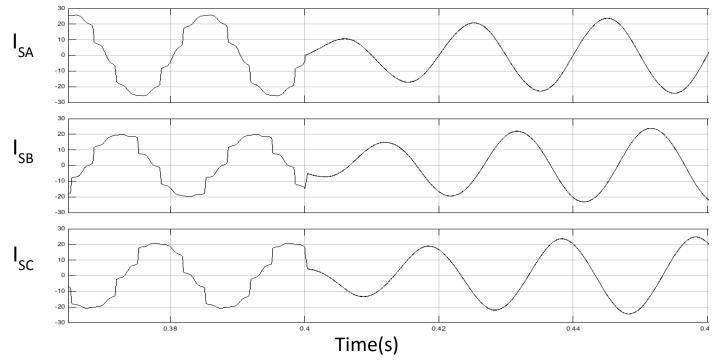

Figure 4.58 Three phase currents before and after compensation

|                 | THD % | I <sub>1</sub> |                 | THD % | I <sub>1</sub> |

|-----------------|-------|----------------|-----------------|-------|----------------|

| ILA             | 9.55  | 26.25          | I <sub>SA</sub> | 1.03  | 22.39          |

| I <sub>LB</sub> | 12.93 | 20.32          | I <sub>SB</sub> | 0.94  | 22.26          |

| I <sub>LC</sub> | 12.58 | 21.39          | I <sub>SC</sub> | 0.94  | 22.61          |

Figure 4.59 Load and Source current THD and peak values

Figure 4.60 Series Filter in action at 0.4s Time(s)

Figure 4.61 Three phase voltages before and after compensation

|                 | THD % | Volts |                 | THD % | I <sub>1</sub> |

|-----------------|-------|-------|-----------------|-------|----------------|

| V <sub>LA</sub> | 1.73  | 319.1 | $I_{LA}$        | 11.87 | 27.26          |

| $V_{LB}$        | 1.72  | 319.2 | I <sub>LB</sub> | 15.50 | 21.16          |

| V <sub>LC</sub> | 1.74  | 319.2 | ILC             | 14.73 | 22.24          |

Figure 4.62 Load voltage and currents THD and peak values

# 4.6.3 Both Shunt and Series Filter in action

Figure 4.63 Both Shunt and Series Filter in action at 0.4 s

Figure 4.64 Three phase load voltage before and after compensation

Figure 4.65 Three phase source before and after compensation

|                 | THD % | Volts |                 | THD % | I <sub>1</sub> |

|-----------------|-------|-------|-----------------|-------|----------------|

| $V_{LA}$        | 3.36  | 309.7 | I <sub>SA</sub> | 0.96  | 22.89          |

| $V_{LB}$        | 3.38  | 309.7 | I <sub>SB</sub> | 0.95  | 22.77          |

| V <sub>LC</sub> | 3.38  | 309.7 | I <sub>SC</sub> | 0.96  | 23.1           |

Figure 4.66 Load voltage and source current THD and peak values

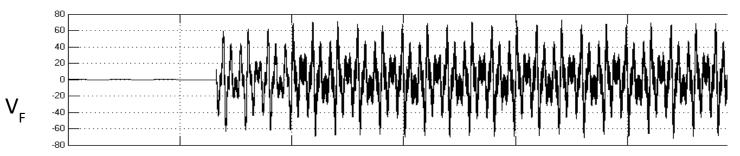

Figure 4.68 Typical waveform of compensating voltage injected by series filter

Figure 4.69 Typical waveform of DC link capacitor voltage stabilizing once UPQC is in action

It can be concluded from the simulation models using UVT based technique and p-q theory that the UVT theory has better dynamic response and is able to compensate for the harmonics faster than p-q theory based model. Both models perform extremely well to compensate for voltage and current harmonics even when discretely used as Shunt and Series filters.

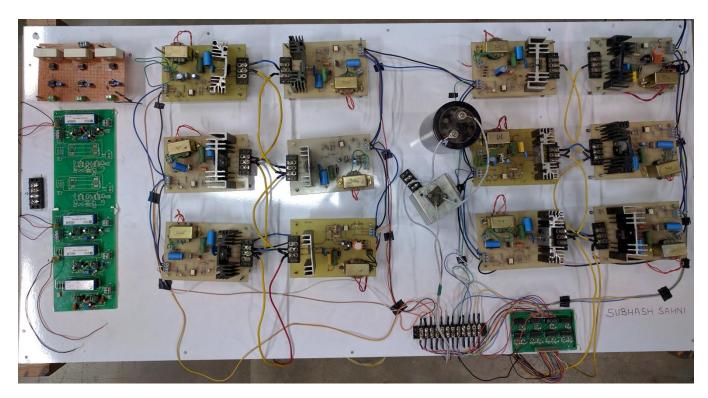

### CHAPTER 5: HARDWARE PROTOTYPE DEVELOPMENT

In this chapter we will discuss about details of hardware involved in implementation of a 3 phase 3 wire UPQC.

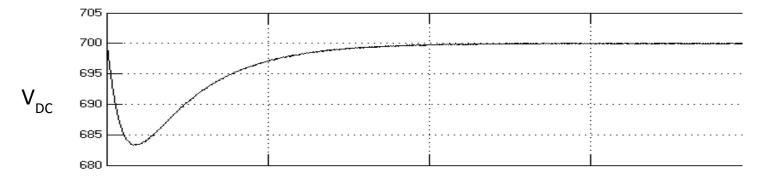

Figure 5.1 One line block diagram of UPQC hardware setup

A laboratory prototype of UPQC is implemented for verification of simulation results. A diode bridge rectifier with R-L load on dc side is used to prototype typical non-linear loads. For drawing reactive power three phase balanced R-L loads are connected through switches. A voltage source inverter (VSI) in current control mode is used as shunt active filter and VSI in voltage control mode as series active power filter. The converter switches are controlled to control the source current and the voltage across the insertion transformers such that the source current and the voltage at the point of common coupling become purely sinusoidal. Thus these two voltage source inverters have been used for filtering voltage and current harmonics. Control of shunt and series active filters is achieved by incorporating TMS320F2812 DSP Kit. This DSP Kit is used for interfacing sensor inputs and output gating pulses. For the purpose of generating firing pulses for the inverters following signals are sensed-

- i. Source voltage

- ii. Voltage at Point of common coupling.

- iii. DC link voltage

- iv. Source current

The hardware prototype development requires following circuits-

- i. Active Power Filter circuit development

- ii. Diode bridge rectifier as non-linear load

- iii. Gate driver circuit for MOSFET

- iv. Snubber circuit of MOSFET

- v. Voltage sensor circuit

- vi. Current sensor circuit

- vii. Dead band circuit

- viii. Power supply

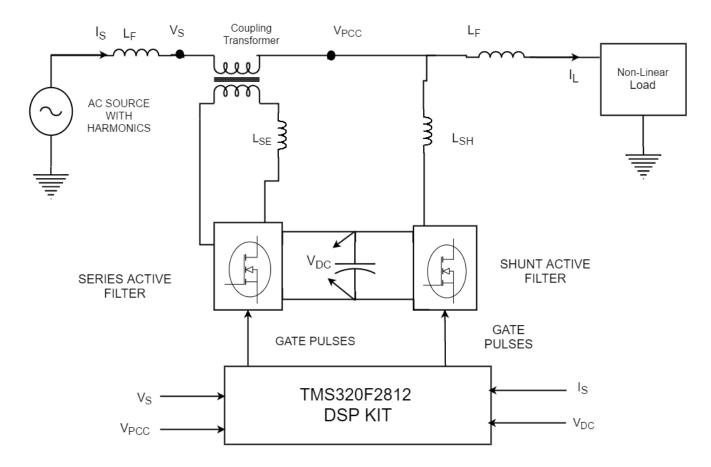

#### **5.1 Active Power Filter Circuit Development**

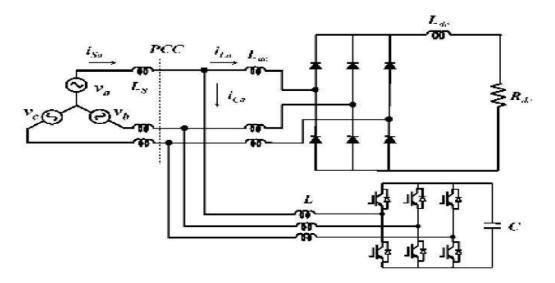

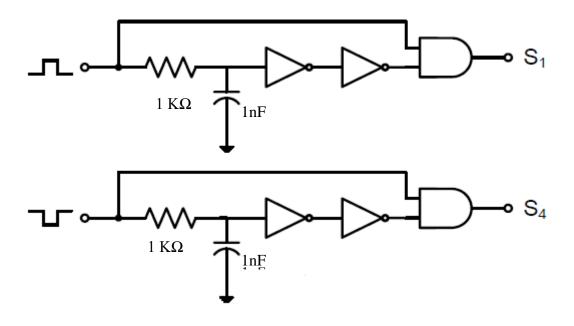

Power circuit of 3P3W UPQC comprises two three phase VSI connected in a back to back fashion to a common DC link capacitor.

Each inverter is implemented using 6 switches and hence complete implementation involves twelve MOSFET's. This is clearly indicated in the figure below showing the switches labelled S1 to S6. AC sides of shunt inverter is connected to PCC using coupling inductor and that of series inverter using a coupling transformer. Power MOSFET IRFP 460 is incorporated to implement the switch owing to its low cost and capability to operate at high switching frequency. For MOSFET's protection against high rate of change of current and voltage, snubber circuits and metal oxide varistors are used. MOSFETs are mounted with metallic heat sinks for thermal protection.

Figure 5.2 Power circuit connections of UPQC

Figure 5.3 MOSFET IRFP 460

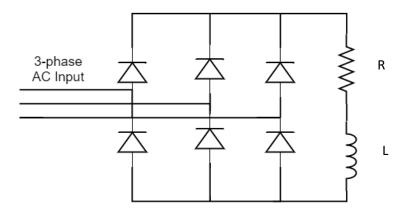

## 5.2 Diode bridge rectifier as Non-Linear Load

A 6-pulse diode bridge rectifier feeding to highly inductive load is used for drawing non- linear currents from the supply. This load behaves as a current sink on the Dc side and drawing reactive power from the supply.

Figure 5.4 Schematic diagram of Non-Linear load connected from PCC

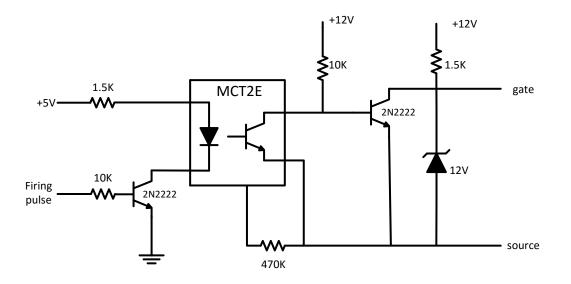

#### **5.3 Gate Driver Circuit for MOSFET**

Details of MOSFET gate driver circuit diagram as shown in figure 5.5. The requirement of a gate driver circuit arises because high frequency turn on and turn off of the MOSFET requires charging and discharging of its gate-source capacitance  $C_{GS}$  at a very fast rate which requires a source of high current and similarly a large current sink. Also in order to separate the signal ground from source of the MOSFET an opto-coupler IC is required else all the sources of switches will get shorted. Thus MCT2E opto-coupler IC is used for this function. Now the functioning of the complete circuit is explained. When the digital high is applied at base of input transistor, it turns ON and current flows through LED of opto-coupler. The photo transistor turns ON and thus base of output transistor is pulled down which causes it to remain in cutoff state making VGS 12V. Separate power supply of 12V is generated for each driver circuit to ensure isolation of grounds. Whenever input pulse is low, input transistor is OFF making photo transistor to also conduct no current. Hence output transistor's base is pulled up and so it conducts ensuring VGS of close to zero value

Figure 5.5 Schematic diagram of MOSFET IRFP-460 driver circuit

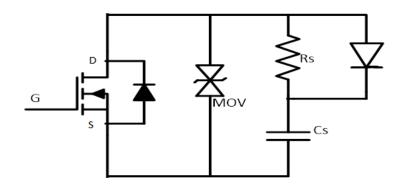

### 5.4 Development of Snubber Circuit and Varistor

Figure 5.6 shows schematics diagram of protection circuit of MOSFET. Protection circuit includes snubber circuit and metal oxide varistor (MOV). MOV is used to protect the switch from over voltages. It is also known as voltage dependent resistor (VDR) and has non-linear and non-ohmic current-voltage characteristic.

The charge and discharge snubber circuit is used for protection of MOSFET from high voltage and current transients. Rating of snubber resistance is 5K, 5W, snubber capacitance of  $0.1\mu$ F with rated voltage of 300V AC is used.

Figure 5.6 Schematic diagrams of protection circuits of MOSFET

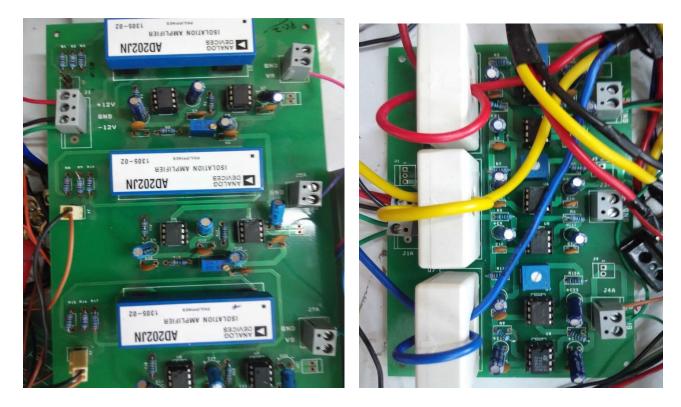

## 5.5 Development of Voltage Sensing Circuit

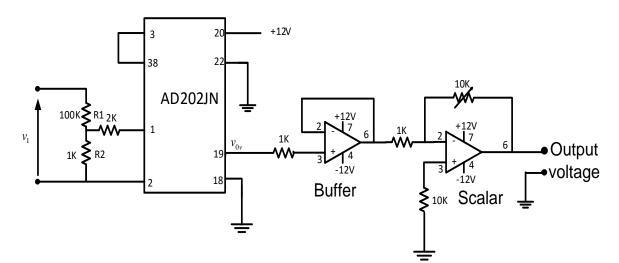

AD202JN is used for the purpose of sensing voltages. For UPQC if UVT reference generation technique is used then seven voltages need to be sensed- three phase source voltages, three phase load voltages and DC link voltage. AD202JN is an isolation amplifier having dual in line (DIP) packaging. AD202JN has good accuracy and wide bandwidth. It consumes less power and is having small size.

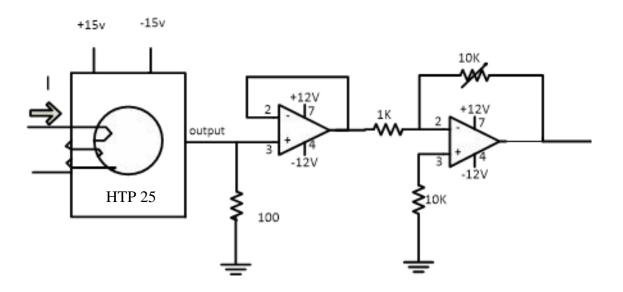

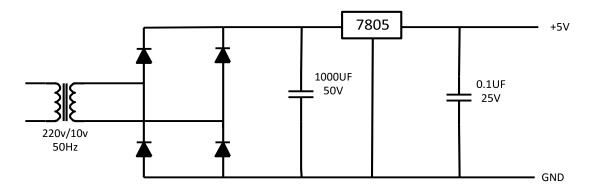

Figure 5.7 Schematic diagram of voltage sensing circuit using AD202JN isolation amplifier