# MODELING AND CONTROL OF DC-DC CONVERTERS

Ph.D. THESIS

by

MAN MOHAN GARG

## DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA)

**JANUARY**, 2016

# MODELING AND CONTROL OF DC-DC CONVERTERS

### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree of DOCTOR OF PHILOSOPHY in

ELECTRICAL ENGINEERING

by

### MAN MOHAN GARG

## DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA)

**JANUARY**, 2016

© INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE- 2016 ALL RIGHTS RESERVED

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

## **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in this thesis entitled "**MODELING AND CONTROL OF DC-DC CONVERTERS**" in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electrical Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from July 2011 to January 2016 under the supervision of Dr. Yogesh Vijay Hote, Assistant Professor and Dr. Mukesh Kumar Pathak, Associate Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee, India.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

### (MAN MOHAN GARG)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

(Yogesh Vijay Hote) Supervisor (Mukesh Kumar Pathak) Supervisor

Date: \_\_\_\_\_

The switch mode DC-DC converters are widely used in modern electronic systems as power supply because of their merits in terms of efficiency, compactness, light-weight, and reliability. They have many applications such as computer power supplies, aerospace instruments, medical instruments, telecommunication equipment, *etc.* The main feature of any DC-DC converter is to provide the stable desired DC output voltage irrespective of variations in the operating conditions such as input voltage, load current and reference output voltage (set point voltage). Normally, the input voltage to DC-DC converters is unregulated and the load current or set point voltage may also vary depending upon application requirements. Therefore, an accurate and reliable operation of DC-DC converters is essential under these circumstances. This has motivated to carry out this research work on the design, analysis, modeling, and control of the DC-DC converters.

This thesis moves around the three important aspects of the DC-DC converters namely design, modeling and control. The DC-DC converters have many non-isolated topologies like buck converter, boost converter, buck-boost converter, Cuk converter, Zeta converter, SEPIC converter, *etc.* In this thesis, two DC-DC converters, namely buck converter and Cuk converter have been considered for the research on above-mentioned aspects. The non-idealities of these converter elements are taken into consideration. These non-idealities are present in form of equivalent series resistances (ESRs) of the inductors and capacitors, the diode forward voltage drop and the on-resistances of the switch and diode.

In the first part of the thesis, the different design issues of the non-ideal DC-DC buck and Cuk converters are considered. The expressions of duty cycle, inductors, and capacitors are improved involving the non-ideal parameters of the converters. A detailed analysis of the output voltage ripple is carried out and importance of capacitor equivalent series resistance (ESR) is analyzed. A formula for maximum permissible ESR for specified output voltage ripple is proposed. The theoretical studies are validated via simulation and experimental results.

The second main aim of this thesis is to develop a mathematical model including all non-ideal elements, such that the developed model will be a close-replica of the practical converter in terms of dynamic and steady-state behaviour. The state-space averaging technique, averaged switch model technique and energy factor approach are used to develop the more accurate models of the non-ideal buck and Cuk converter. Further, the mathematical models in ideal and non-ideal case are compared. It is found that the models with non-idealities have much improved closeness to the practical converter as compared to the ideal counterpart.

i

In the final part, the performance of DC-DC buck and Cuk converters are improved using various controllers, namely the PI controller based on the stability boundary locus approach, PI-lead controller, two-loop controller, sliding mode controller. The algorithms for tuning the parameters of these controllers are proposed. The PI controller is also designed based on the reduced-order model of Cuk converter. The model-order reduction technique is used to obtain the reduced second-order model of the fourth-order Cuk converter. The hardware prototypes of DC-DC buck converters are developed and these control techniques are implemented on the prototypes. Extensive experimental and simulation studies are carried out for both types of converters. The comparative analysis of these control techniques is presented.

The completion of this research work has become possible with the support, inspiration and encouragement of several individuals. I would like to take this opportunity to express my sincere gratitude to all of them. First, I would like to express my sincere gratitude to my supervisors Dr. Yogesh Vijay Hote, Assistant Professor and Dr. Mukesh Kumar Pathak, Associate Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee (IITR), India for their continuous support, enthusiastic guidance, valuable suggestions and motivation during the research work.

I also express my sincere gratitude towards my research committee members: Prof. G.N. Pillai, Prof. S.P. Yadav and Dr. Barjeev Tyagi for giving their valuable suggestions during the several meetings held for my research work.

I am also very thankful to the Head and all faculty members of Electrical Engineering Department, IIT Roorkee for their help, moral support, and providing the excellent laboratory facilities during this research work at IITR. I acknowledge my sincere gratitude to the Ministry of Human Resources Development (MHRD), Government of India for providing the fellowship to carry out this research work.

I am thankful to technical and office staff of the department especially Mr. Gautam Singh, Mr. Rakesh Saini, Mr. Amir Ahmad, Mr. Mohan Singh, Mr. Rishabh Verma, Mr. Narendra ji, Mr. Agrawal ji, Mr. Sanjay for their cooperation and help in my experimental work and other official work related to this research.

I would also like to take this opportunity to express my special gratitude to my graduation (B.E.) professors: Dr. Akhil Ranjan Garg, Dr. Jayashri Vajpai and Mr. M.G.Soni sir at M.B.M. Engineering College, Jodhpur. They inspired me to take higher education since my graduation days at M.B.M. and motivated me morally during my entire research work at IITR. I am also thankful to my uncle Mr. M.L.Gupta, Lecturer, commerce college, Kota for his inspiration and motivation during the work.

It has been a delight for me to work among my colleagues at the Power Quality Conditioning Laboratory. I am also thankful to all my friends. The list is very long but some of them I would like to mention are Dr. Aurbindo Panda, Mr. Om Hari Gupta, Mr. Sanjeev Saxena, Mr. S. Krishnama Raju, Dr. Neeraj Gupta, Mr. Srinivasarao, Mr. Janardhana Rao, Mr. Sukanta, Mr. Anubhav.

Finally, I wish to express my hearty gratitude to my all-family members specially my parents, my parent-in-law, my siblings, my school friends for their patience, endless moral support, and encouragement. My lovely thanks to my chaste wife Annu and little son Nimai who joined me in the mid of this research journey. I am very debtful to all merciful Lord who gave me blessing and wisdom to carry out this Ph.D research work.

(Man Mohan Garg)

| ABS                             | TRACT  |                                                                                                  | I    |

|---------------------------------|--------|--------------------------------------------------------------------------------------------------|------|

| ACK                             | NOWL   | EDGEMENTS                                                                                        | III  |

| CON                             | TENTS  |                                                                                                  | V    |

| LIST                            | OF FIC | GURES                                                                                            | IX   |

| LIST                            | OF TA  | BLES                                                                                             | XVII |

| LIST                            | OF AC  | RONYMS                                                                                           | XIX  |

| LIST                            | OF SY  | MBOLS                                                                                            | XXI  |

| ~                               | PTER 1 |                                                                                                  |      |

| <b>Спа</b><br>1.1               |        | I: INTRODUCTION                                                                                  |      |

| 1.1                             |        | uction to DC-DC Converters                                                                       |      |

| 1.3                             |        | ition to the Research Work                                                                       |      |

| 1.4                             |        | oution of the Author and Thesis Organization                                                     |      |

|                                 |        |                                                                                                  |      |

| -                               | PTER 2 |                                                                                                  | -    |

| 2.1                             |        |                                                                                                  |      |

| 2.2                             | -      | sis of Non-ideal DC-DC Buck Converter                                                            |      |

|                                 | 2.2.1  | When the switch is on (time interval $0 < t \le DT$ )                                            |      |

|                                 | 2.2.2  | When the switch is off (time interval $DT < t \le T$ )                                           |      |

|                                 | 2.2.3  | Steady-state analysis                                                                            |      |

|                                 |        | 8.1 Expression for output voltage                                                                |      |

|                                 |        | 8.2 Improved expression of duty cycle                                                            |      |

|                                 | 2.2.4  | Inductor current ripple and inductor design                                                      |      |

|                                 | 2.2.5  | Output voltage ripple and capacitor design                                                       |      |

|                                 |        | 5.1 Analysis of output voltage ripple                                                            |      |

| 2.2.5.2 Output capacitor design |        |                                                                                                  |      |

|                                 | 2.2.5  | 5.3 Derivation of maximum permissible ESR ( <i>r<sub>c,max</sub></i> )<br>Results and discussion |      |

| 2.3                             |        | sis of Non-ideal DC-DC Cuk Converter                                                             |      |

| 2.3                             | 2.3.1  | When the switch is on (time interval $0 < t \le DT$ )                                            |      |

|                                 | 2.3.1  | When the switch is off (time interval $DT < t \le T$ )                                           |      |

|                                 | 2.3.2  | Steady-state analysis                                                                            |      |

|                                 |        | 3.1 Expression for output voltage                                                                |      |

|                                 |        | <ul> <li>2.2 Improved expression of duty cycle</li> </ul>                                        |      |

|                                 | 2.3.3  | Inductor current ripple and inductor design                                                      |      |

|                                 | -      | $.1$ Inductor $L_1$                                                                              |      |

|                                 |        | $.2$ Inductor $L_2$                                                                              |      |

|                                 | 2.0.4  |                                                                                                  |      |

|     | 2.3.5 Capacitor design                                                | 41  |

|-----|-----------------------------------------------------------------------|-----|

|     | 2.3.5.1 Capacitor $C_1$                                               | 41  |

|     | 2.3.5.2 Capacitor <i>C</i> <sub>2</sub>                               | 43  |

|     | 2.3.6 Results and discussion                                          | 47  |

| 2.4 | Conclusion                                                            | 52  |

| СНА | APTER 3: MODELING OF NON-IDEAL DC-DC CONVERTERS                       | 53  |

| 3.1 | Introduction                                                          | 53  |

| 3.2 | State-space Averaging (SSA) Modeling Technique                        | 53  |

|     | 3.2.1 Generalized state-space averaging modeling technique            | 54  |

|     | 3.2.1.1 Computation of resolvent matrix $(sI - A)^{-1}$               | 58  |

|     | 3.2.1.2 Generalized Leverrier's Algorithm                             | 59  |

|     | 3.2.2 Modeling of non-ideal DC-DC buck converter                      | 59  |

|     | 3.2.3 Modeling of non-ideal DC-DC Cuk converter                       | 67  |

| 3.3 | Averaged Switch Model Technique                                       | 77  |

|     | 3.3.1 Modeling of non-ideal DC-DC buck converter                      | 78  |

|     | 3.3.2 Modeling of non-ideal DC-DC Cuk converter                       | 85  |

| 3.4 | Comparison of Ideal and Non-ideal DC-DC Buck and Cuk Converter Models | 94  |

|     | 3.4.1 Buck converter                                                  | 94  |

|     | 3.4.1.1 Steady-state model                                            | 96  |

|     | 3.4.1.2 Input voltage to output voltage transfer function             | 96  |

|     | 3.4.1.3 Load current to output voltage transfer function              | 98  |

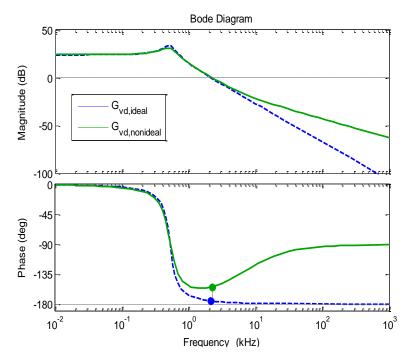

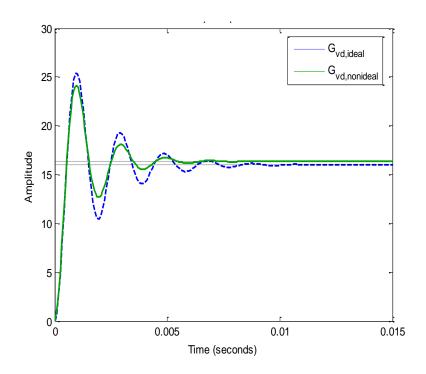

|     | 3.4.1.4 Duty cycle to output voltage transfer function                | 99  |

|     | 3.4.2 Cuk converter                                                   | 100 |

|     | 3.4.2.1 Steady-state model                                            | 103 |

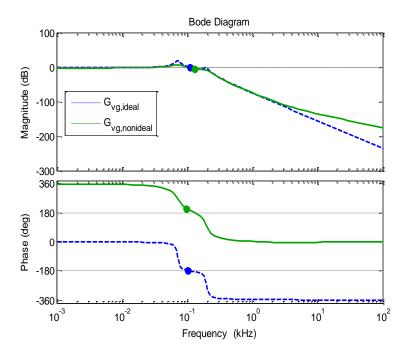

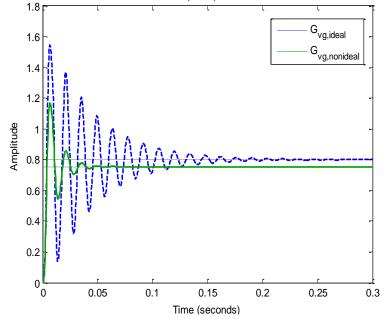

|     | 3.4.2.2 Input voltage to output voltage transfer function             | 103 |

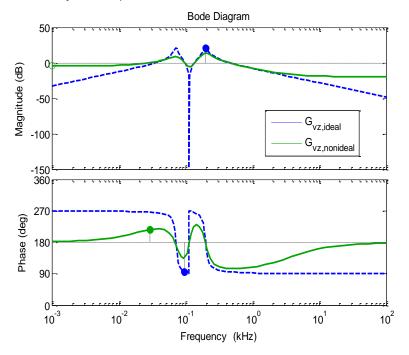

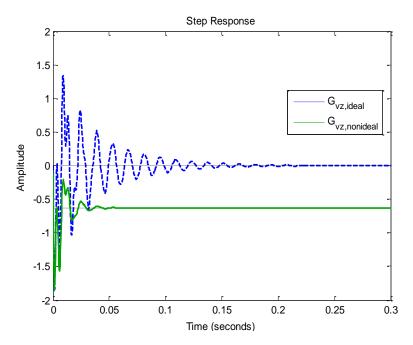

|     | 3.4.2.3 Load current to output voltage transfer function              | 105 |

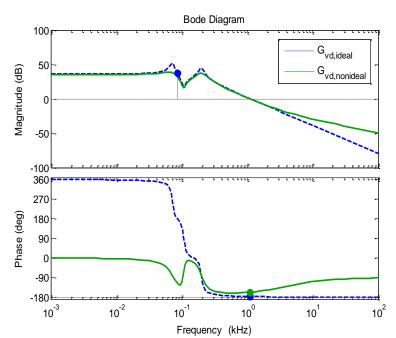

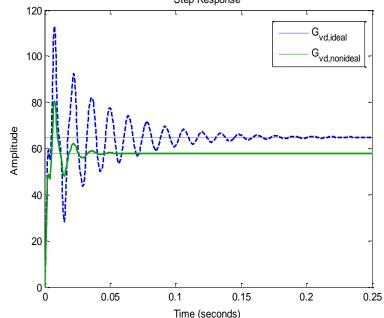

|     | 3.4.2.4 Duty cycle to output voltage transfer function                | 106 |

| 3.5 | Modeling using Energy Factor Approach                                 | 107 |

|     | 3.5.1 Energy factor and its associated parameters                     | 108 |

|     | 3.5.1.1 Time constant ( $\tau$ )                                      | 109 |

|     | 3.5.1.2 Damping time constant ( $\tau_d$ )                            | 109 |

|     | 3.5.1.3 Transfer function of DC-DC converter                          | 109 |

|     | 3.5.2 Simplified analysis                                             | 110 |

|     | 3.5.3 Non-ideal buck converter                                        | 111 |

|     | 3.5.4 Non-ideal Cuk converter                                         | 112 |

|     | 3.5.5 Simulation results                                              | 114 |

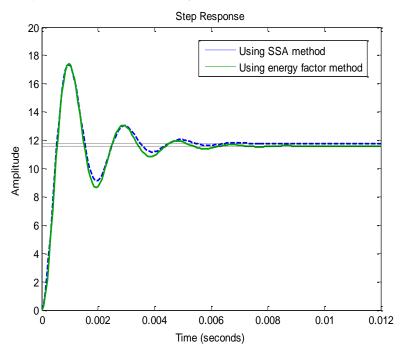

|     | 3.5.5.1 Buck converter                                                | 114 |

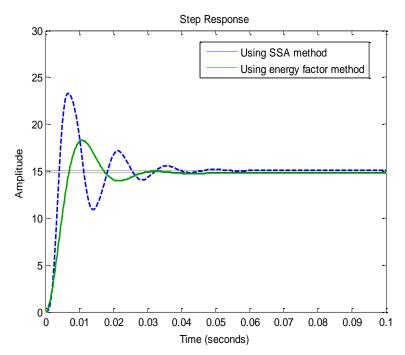

|     | 3.5.5.2 Cuk converter                                                               | 116  |

|-----|-------------------------------------------------------------------------------------|------|

| 3.6 | Conclusion                                                                          | 118  |

| СНА | PTER 4: CONTROL OF DC-DC CONVERTERS                                                 | 119  |

| 4.1 | Introduction                                                                        | 119  |

| 4.2 | Control of DC-DC Buck Converter                                                     | 122  |

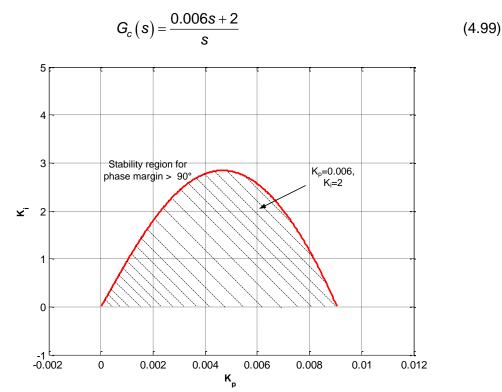

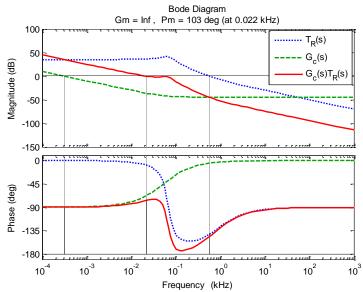

|     | 4.2.1 PI controller design                                                          | 122  |

|     | 4.2.1.1 Algorithm for tuning PI controller using stability boundary locus approach. | 123  |

|     | 4.2.1.2 PI controller design for DC-DC buck converter                               | 125  |

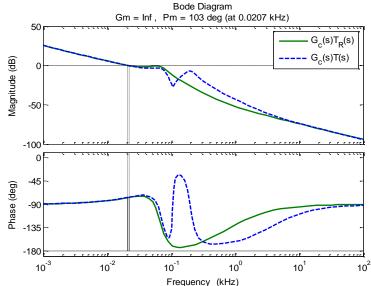

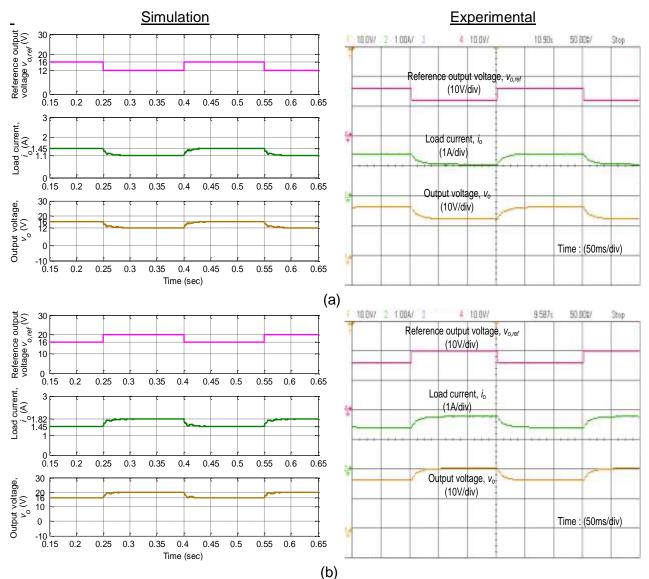

|     | 4.2.1.3 Results and discussion                                                      | 128  |

|     | 4.2.2 PI-lead controller design                                                     | 133  |

|     | 4.2.2.1 Algorithm for tuning of PI-lead controller parameters                       | 135  |

|     | 4.2.2.2 PI-lead controller design for buck converter                                | 137  |

|     | 4.2.2.3 Results and discussion                                                      | 151  |

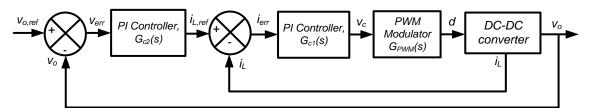

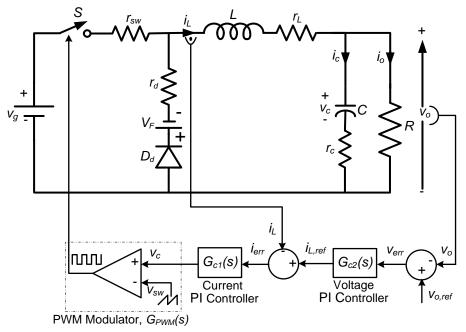

|     | 4.2.3 Two-loop PI controller design                                                 | 157  |

|     | 4.2.3.1 Proposed PI controller algorithm for specified phase margin and             | gain |

|     | crossover frequency                                                                 | 158  |

|     | 4.2.3.2 Two-loop control scheme for DC-DC buck converter                            |      |

|     | 4.2.3.3 Results and discussion                                                      |      |

|     | 4.2.4 Performance comparison of different control techniques for buck converter     |      |

| 4.3 | Control of DC-DC Cuk Converter                                                      |      |

|     | 4.3.1 PI controller design                                                          |      |

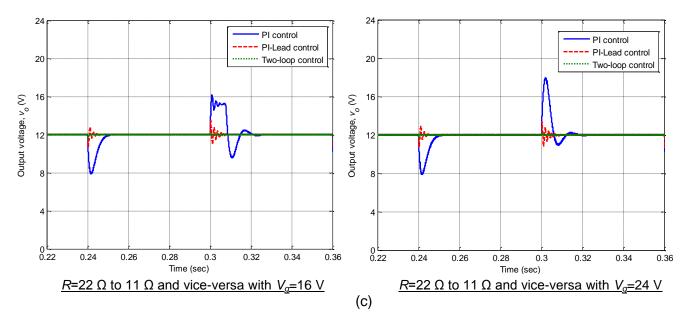

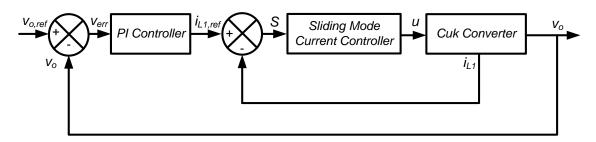

|     | 4.3.1.1 Description of the control scheme                                           |      |

|     | 4.3.1.2 Results and discussion                                                      |      |

|     | 4.3.2 PI controller design using reduced second-order model                         |      |

|     | 4.3.2.1 Truncation method for model-order reduction                                 |      |

|     | 4.3.2.2 Description of control scheme                                               |      |

|     | 4.3.2.3 Results and discussion                                                      |      |

|     | 4.3.3 PI-lead controller design                                                     |      |

|     | 4.3.3.1 Description of control scheme         4.3.3.2 Results and discussion        |      |

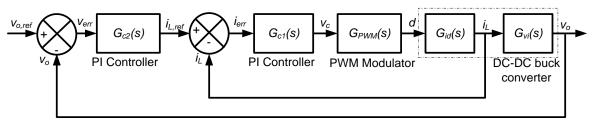

|     | 4.3.4 Two-loop PI controller design                                                 |      |

|     | 4.3.4.1 Inner current control loop (ICCL) design                                    |      |

|     | 4.3.4.2 Outer voltage control loop (OVCL) design                                    |      |

|     | 4.3.4.3 Results and discussion                                                      |      |

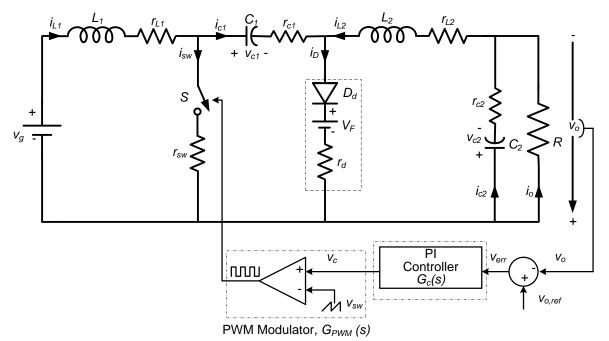

|     | 4.3.5 Performance comparison of different control techniques for Cuk converter      |      |

|     | 4.3.5.1 Performance comparison of reduced model and original model base             |      |

|     | controllers for DC-DC Cuk converter                                                 |      |

|                            | 4.3.5.2 Performance comparison of PI, PI-lead and two-loop PI controllers for I | C-  |

|----------------------------|---------------------------------------------------------------------------------|-----|

|                            | DC Cuk converter                                                                | 211 |

| 4.4                        | Conclusion                                                                      | 213 |

| СНА                        | PTER 5: SLIDING MODE CONTROL OF CUK CONVERTER                                   | 215 |

| 5.1                        | Introduction                                                                    | 215 |

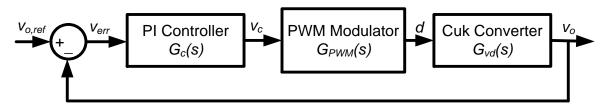

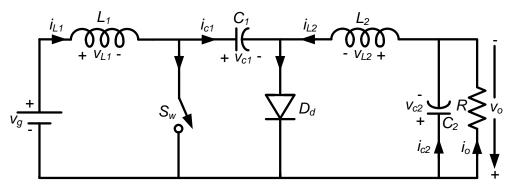

| 5.2                        | Cuk converter                                                                   | 216 |

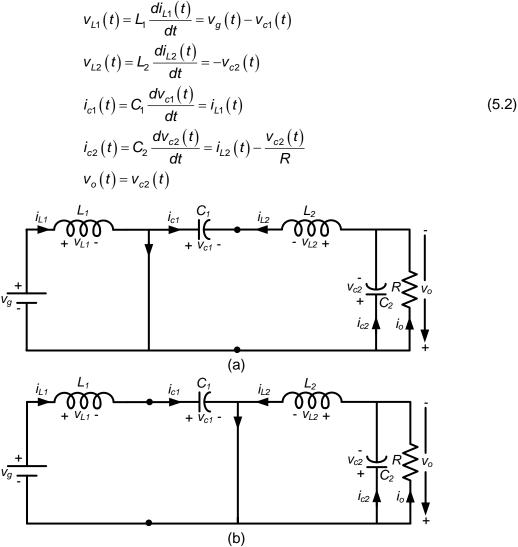

|                            | 5.2.1 Dynamic equations of DC-DC Cuk converter                                  | 216 |

|                            | 5.2.2 State-space representation                                                | 218 |

| 5.3                        | Design of sliding mode control for Cuk converter                                | 218 |

|                            | 5.3.1 Sliding surface                                                           | 219 |

|                            | 5.3.2 Equivalent control                                                        | 220 |

|                            | 5.3.3 Hitting and existence conditions                                          | 220 |

| 5.4                        | Stability analysis of closed-loop dynamics                                      | 222 |

|                            | 5.4.1 Ideal sliding dynamics                                                    | 222 |

|                            | 5.4.2 Equilibrium point                                                         | 222 |

|                            | 5.4.3 Small-signal analysis                                                     | 223 |

|                            | 5.4.3.1 Transfer function for step variation in reference voltage               | 226 |

|                            | 5.4.3.2 Transfer function for step variation in input voltage                   | 227 |

|                            | 5.4.3.3 Transfer function for step variation in load resistance                 | 228 |

|                            | 5.4.4 Selection of parameters of SM based PI controller                         | 228 |

|                            | 5.4.4.1 Existing method using Routh-Hurwitz stability criterion                 | 229 |

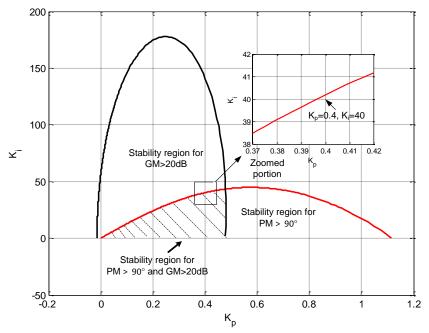

|                            | 5.4.4.2 Proposed method using the stability boundary locus method               | 229 |

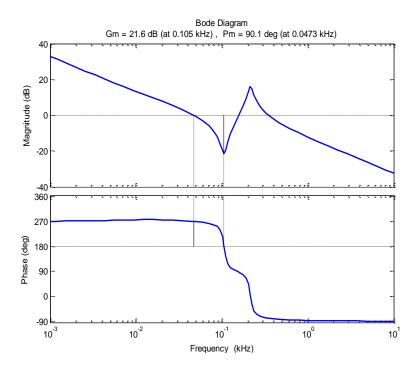

| 5.5                        | Design example                                                                  | 230 |

| 5.6                        | Results and discussion                                                          | 232 |

| 5.7                        | Performance comparison of two-loop PI control and sliding mode control of Cuk   |     |

| conv                       | erter2                                                                          | 237 |

| 5.8                        | Conclusion                                                                      | 238 |

| СНА                        | PTER 6: CONCLUSION AND FUTURE SCOPE                                             | 239 |

| 6.1                        | Conclusion                                                                      | 239 |

| 6.2                        | Future scope                                                                    | 241 |

|                            |                                                                                 |     |

| APPENDIX – A               |                                                                                 |     |

| APPENDIX – B               |                                                                                 |     |

| PUBLICATIONS FROM THE WORK |                                                                                 |     |

| BIBL                       | IOGRAPHY                                                                        | 261 |

| Fig. 1.1. Basic DC-DC converter topologies (a) Buck (b) Boost (c) Buck-boost                                           |

|------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2. DC-DC Cuk converter topology                                                                                 |

| Fig. 2.1.(a) Basic circuit of a non-ideal DC-DC buck converter (b) equivalent circuit when the                         |

| switch is on (c) equivalent circuit when the switch is off (d) associated waveforms                                    |

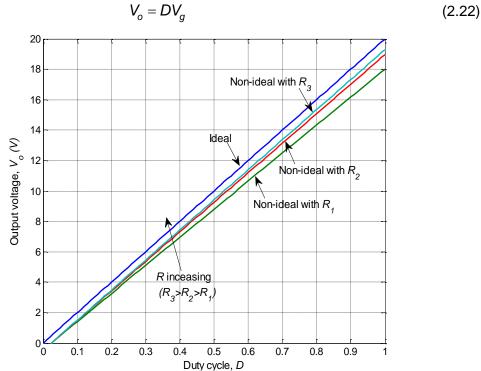

| Fig. 2.2. Output voltage variation with duty cycle at various $R$ and constant $V_g$                                   |

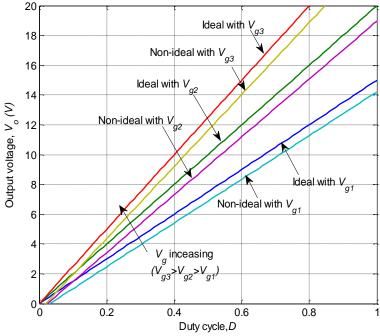

| Fig. 2.3. Output voltage variation with duty cycle at various $V_g$ and constant $R$                                   |

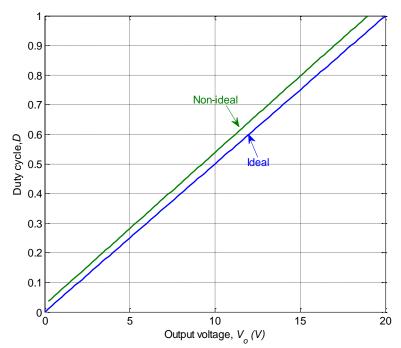

| Fig. 2.4. Variation in duty cycle with desired output voltage                                                          |

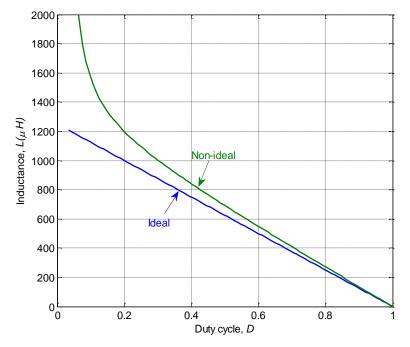

| Fig. 2.5. Inductance variation with duty cycle for ideal and non-ideal buck converter                                  |

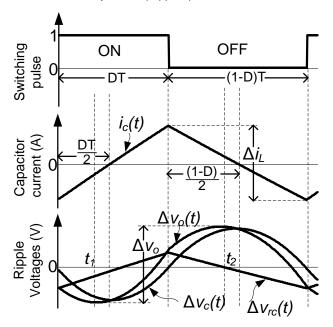

| Fig. 2.6. Capacitor current and voltage ripple waveforms                                                               |

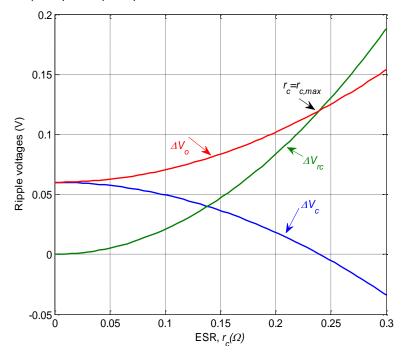

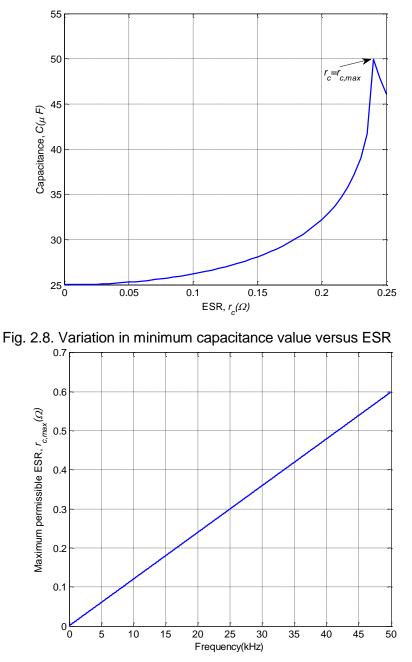

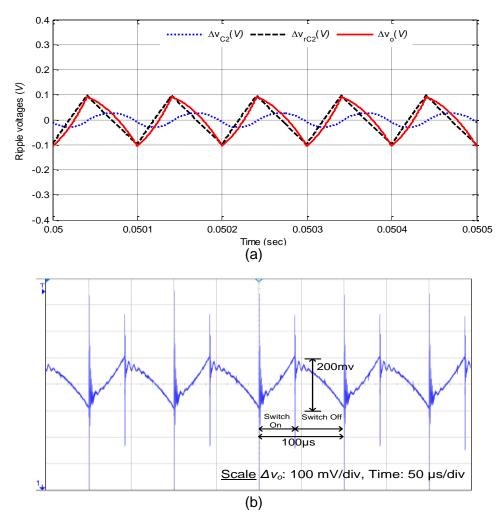

| Fig. 2.7. Variations in different voltage ripple with capacitor ESR                                                    |

| Fig. 2.8. Variation in minimum capacitance value versus ESR25                                                          |

| Fig. 2.9. Maximum permissible ESR ( <i>r<sub>c,max</sub></i> ) versus frequency25                                      |

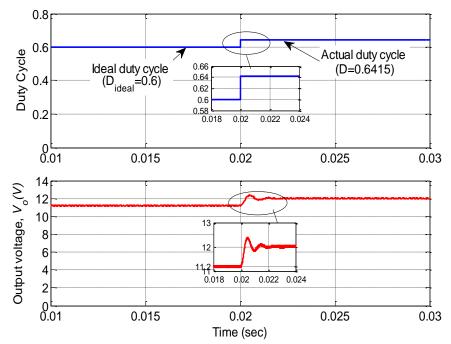

| Fig. 2.10. Simulated output voltage response with ideal and improved duty cycles                                       |

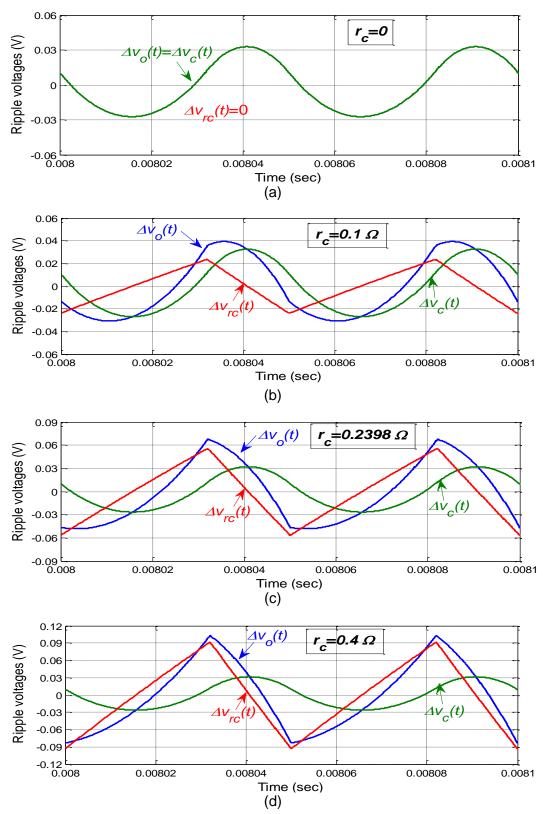

| Fig. 2.11. Simulated voltage ripple waveforms for different ESR values (a) $r_c$ =0 (b) $r_c$ =0.1 $\Omega$            |

| $(r_c < r_{c,max})$ (c) $r_c = 0.2398 \Omega (r_c = r_{c,max})$ (d) $r_c = 0.4 \Omega (r_c > r_{c,max})$               |

| Fig. 2.12. Experimental results of output voltage response with ideal duty cycle (0.6 )and                             |

| improved duty cycle (0.642)                                                                                            |

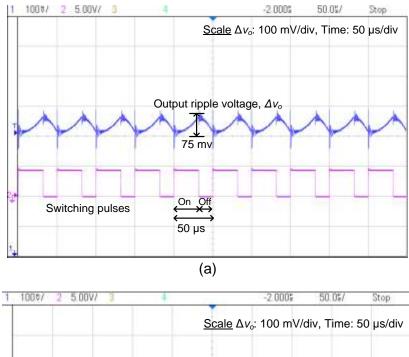

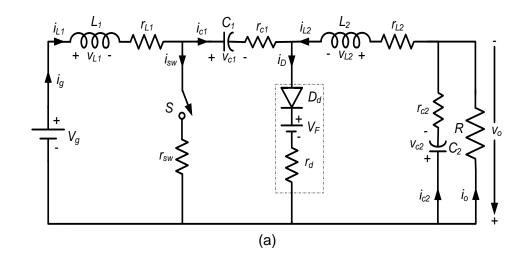

| Fig. 2.13. Experimental results for output voltage ripple with (a) $r_c$ =0.1 $\Omega$ ( $r_c$ < $r_{c,max}$ ) and (b) |

| <i>r</i> <sub>c</sub> =0.4 Ω ( <i>r</i> <sub>c</sub> > <i>r</i> <sub>c,max</sub> )                                     |

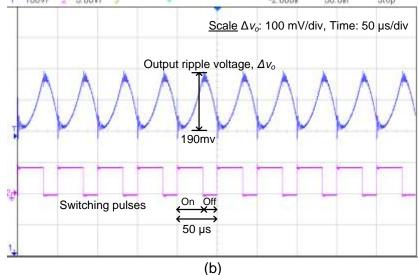

| Fig. 2.14. Experimental results of output voltage ripple variation with frequency with (a) $r_c=0.1$                   |

| Ω (b) $r_c$ =0.35 Ω (c) $r_c$ =0.5 Ω                                                                                   |

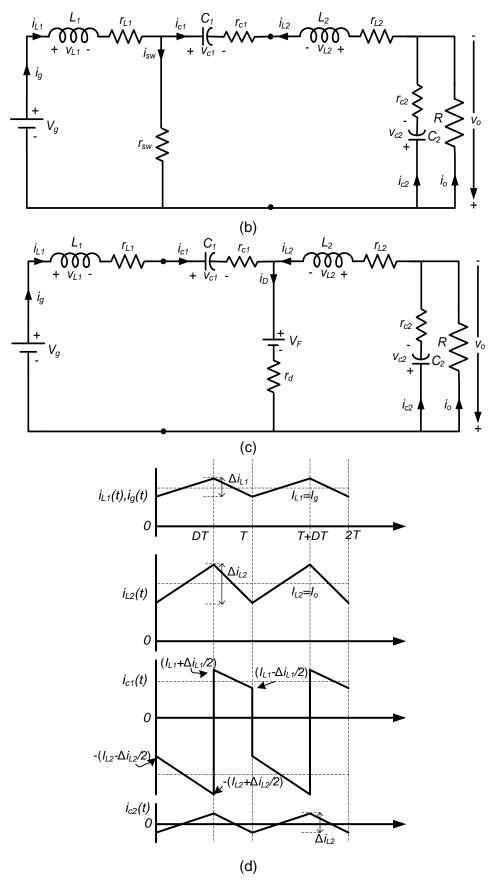

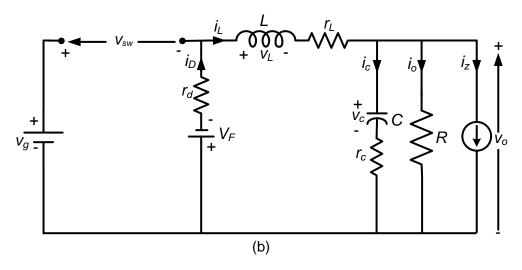

| Fig. 2.15. (a) Basic circuit of a non-ideal DC-DC Cuk converter (b) equivalent circuit when the                        |

| switch is on (c) equivalent circuit when the switch is off (d) associated waveforms                                    |

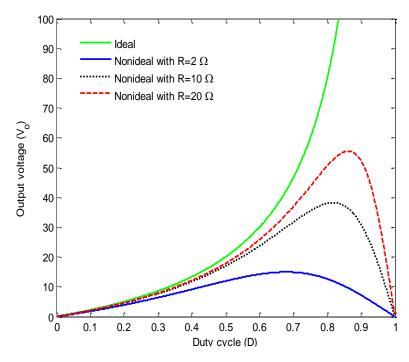

| Fig. 2.16. Output voltage of DC-DC Cuk converter as a function of duty cycle                                           |

| Fig. 2.17. Duty cycle variation as a function of (a) input voltage (b) load resistance                                 |

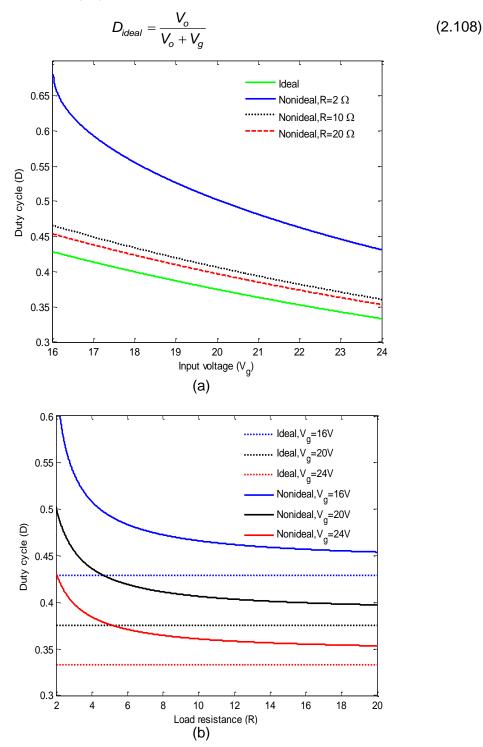

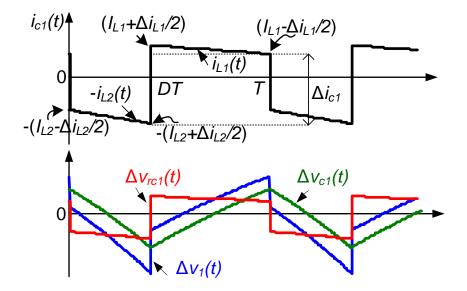

| Fig. 2.18. Current and ripple voltage waveforms associated with capacitor $C_1$                                        |

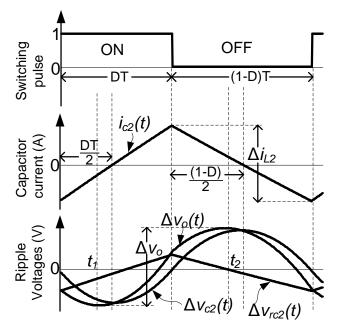

| Fig. 2.19. Current and ripple voltage waveforms associated with capacitor $C_2$ 43                                     |

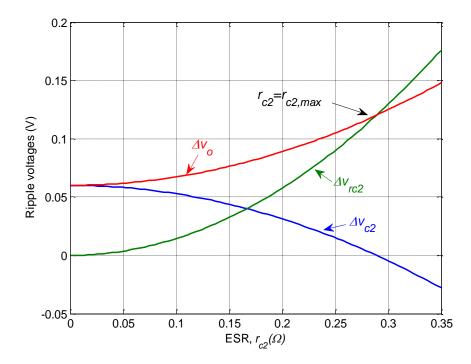

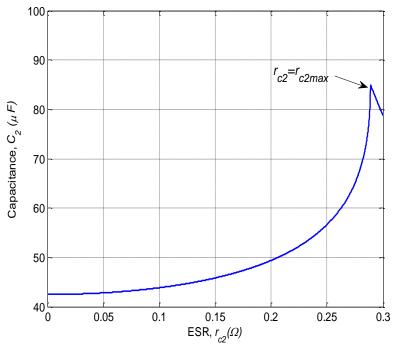

| Fig. 2.20. Ripple voltage variations with ESR for DC-DC Cuk converter                                                  |

| Fig. 2.21. Variations in minimum required value of capacitor $C_2$ with ESR                                            |

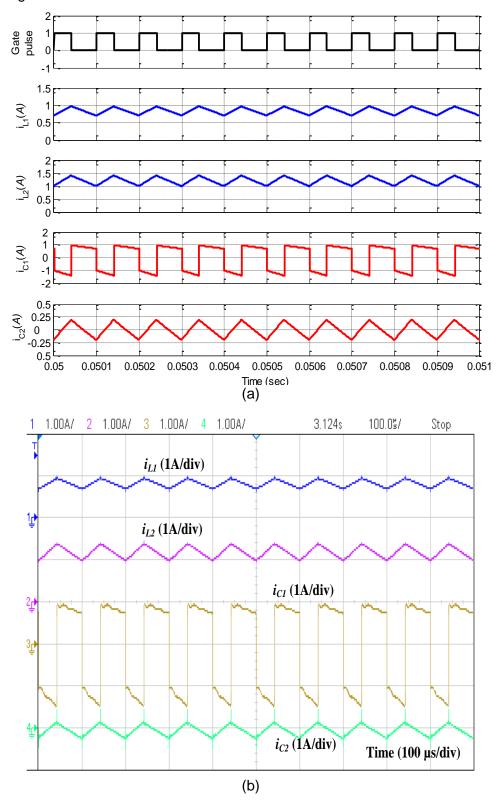

| Fig. 2.22. Inductor current and capacitor current waveforms of Cuk converter (a) Simulation                            |

| (b) Experimental                                                                                                       |

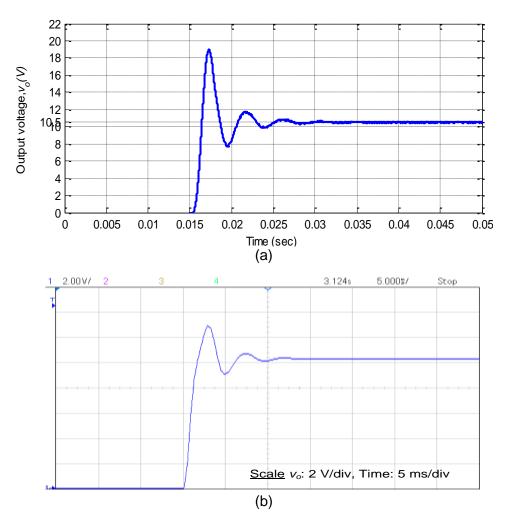

| Fig. 2.23. Output voltage response of Cuk converter with ideal duty cycle $D=0.375$                                    |

| (a) Simulation (b) Experimental50                                                                                      |

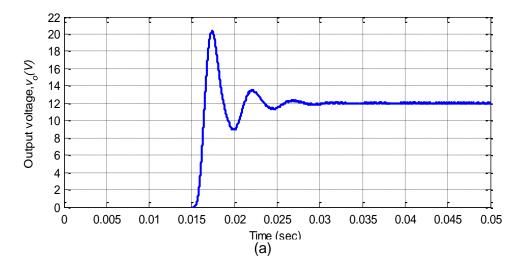

| Fig. 2.24. Output voltage response of Cuk converter with improved duty cycle $D=0.406$                                 |

| (a) Simulation (b) Experimental51                                                                                      |

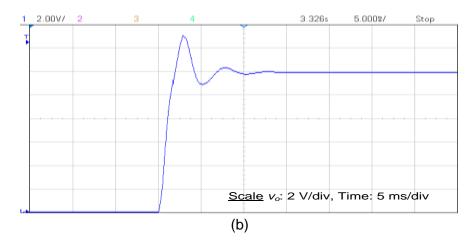

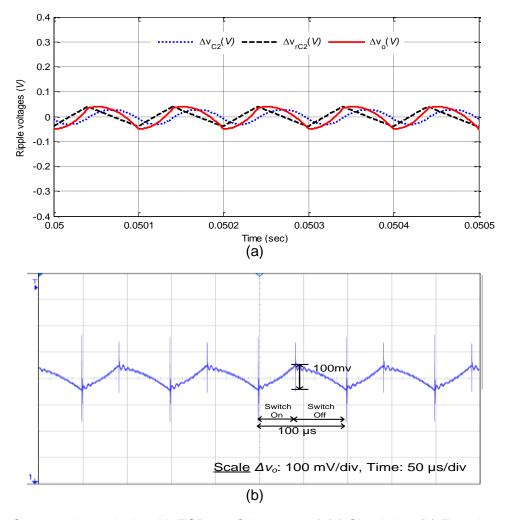

| Fig. 2.25. Output voltage ripple with ESR 0.2 $\Omega$ ( $r_{c2} < r_{c2,max}$ ) (a) Simulation (b) Experimental |

|------------------------------------------------------------------------------------------------------------------|

| Fig. 2.26. Output voltage ripple with ESR 0.5 $\Omega$ ( $r_{c2} > r_{c2,max}$ ) (a) Simulation (b) Experimental |

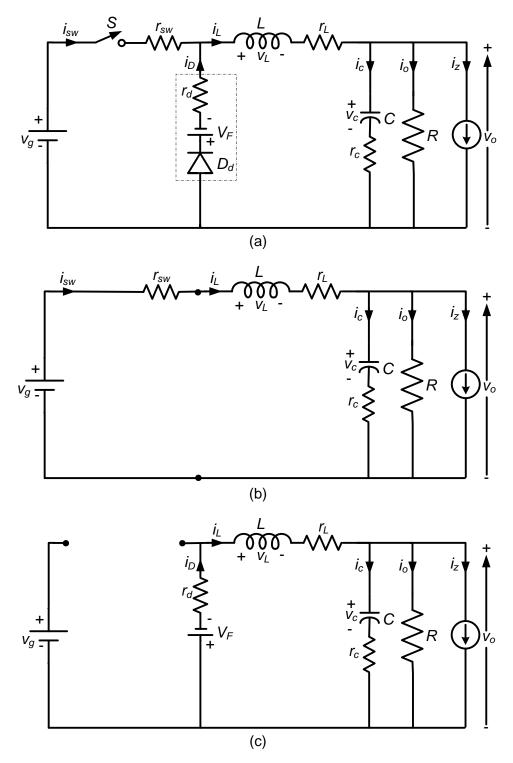

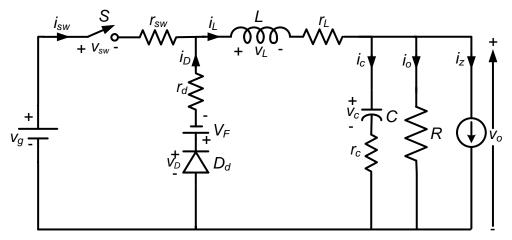

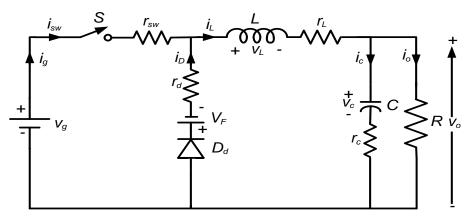

| Fig. 3.1. (a) Circuit diagram of non-ideal DC-DC buck converter (b) equivalent circuit during                    |

| switch-on (c) equivalent circuit during switch off                                                               |

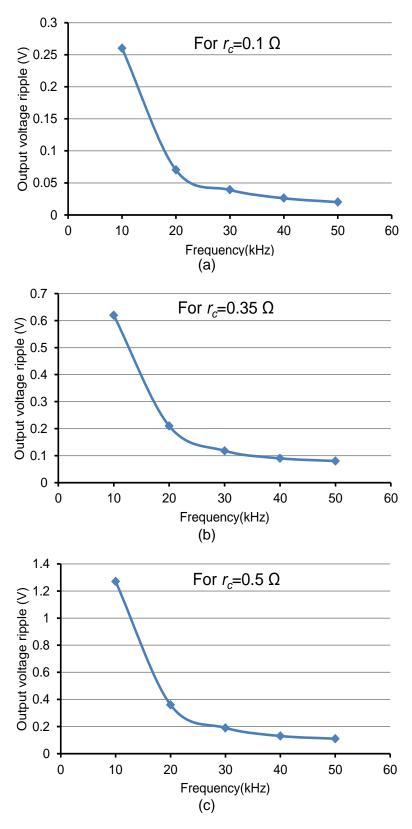

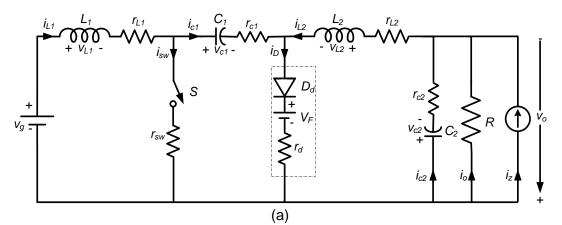

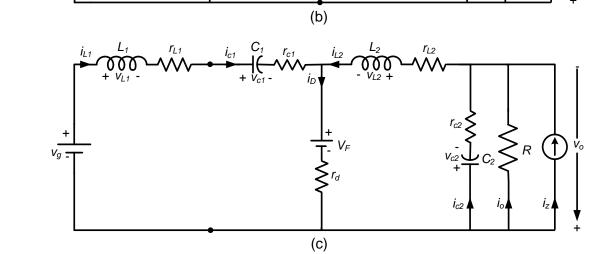

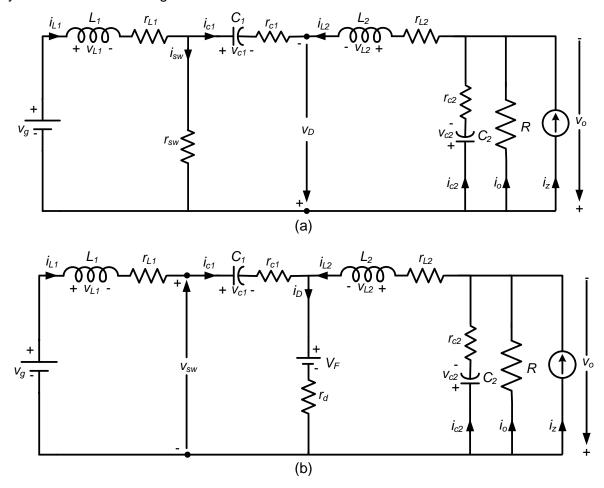

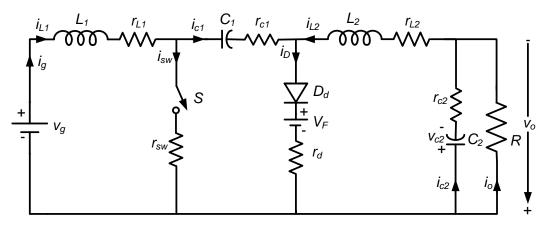

| Fig. 3.2.(a) Circuit diagram of non-ideal DC-DC Cuk converter (b) equivalent circuit during                      |

| switch-on (c) equivalent circuit during switch off                                                               |

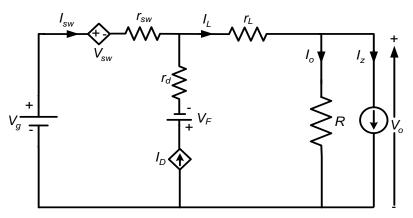

| Fig. 3.3. Basic circuit of non-ideal DC-DC buck converter                                                        |

| Fig. 3.4. Equivalent circuit diagram of non-ideal buck converter during (a) switch-on (b) switch-off             |

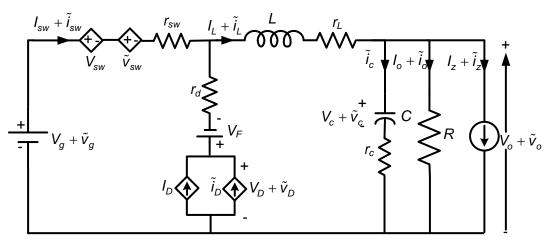

| Fig. 3.5. Linearized large-signal averaged switch model of non-ideal buck converter                              |

| Fig. 3.6. Steady-state model of non-ideal DC-DC buck converter                                                   |

| Fig. 3.7. Linearized small-signal model of non-ideal DC-DC buck converter                                        |

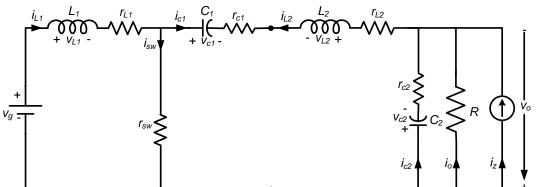

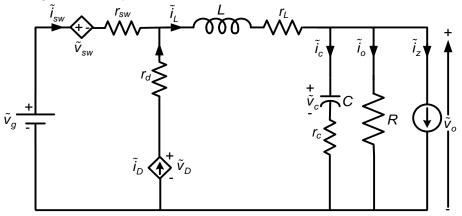

| Fig. 3.8. Circuit diagram of non-ideal DC-DC Cuk converter                                                       |

| Fig. 3.9. Equivalent circuit diagram of non-ideal Cuk converter during (a) switch-on (b)                         |

| switch-off                                                                                                       |

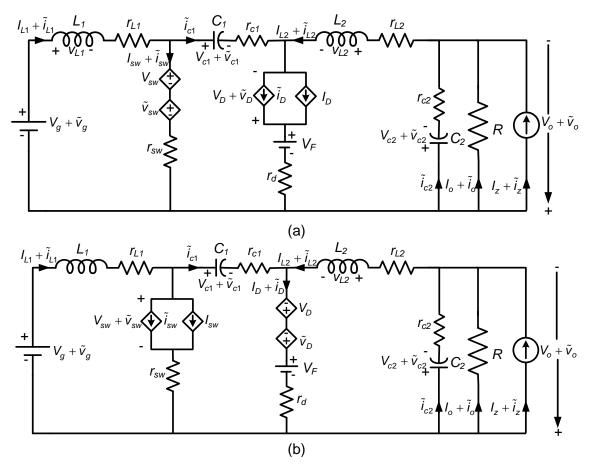

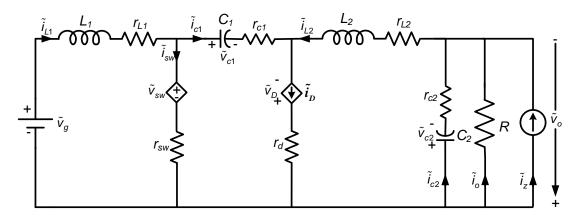

| Fig. 3.10. Linearized large-signal averaged switch model of non-ideal Cuk converter                              |

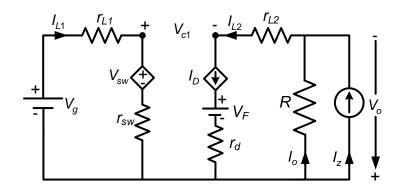

| Fig. 3.11. Steady-state model of non-ideal DC-DC Cuk converter                                                   |

| Fig. 3.12. Linearized small-signal model of non-ideal DC-DC Cuk converter                                        |

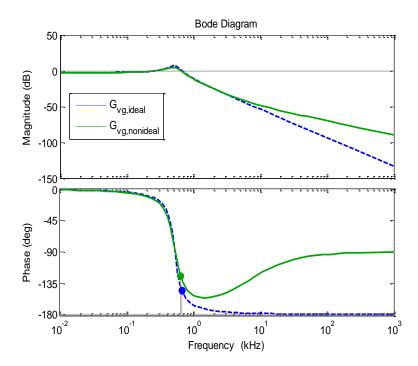

| Fig. 3.13. Comparison of Bode plots of $G_{vg}(s)$ for ideal and non-ideal buck converter                        |

| Fig. 3.14. Comparison of step responses of $G_{vg}(s)$ for ideal and non-ideal buck converter97                  |

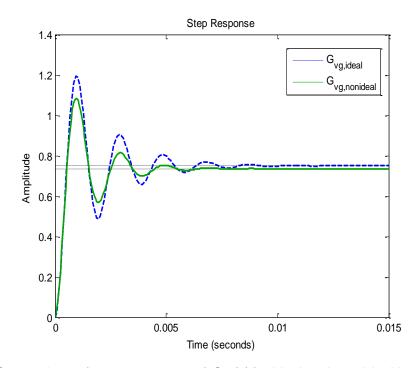

| Fig. 3.15. Comparison of Bode plots of $G_{vz}(s)$ for ideal and non-ideal buck converter                        |

| Fig. 3.16. Comparison of step responses of $G_{vz}(s)$ for ideal and non-ideal buck converter98                  |

| Fig. 3.17. Comparison of Bode plots of $G_{vd}(s)$ for ideal and non-ideal buck converter                        |

| Fig. 3.18. Comparison of step responses of $G_{vd}(s)$ for ideal and non-ideal buck converter. 100               |

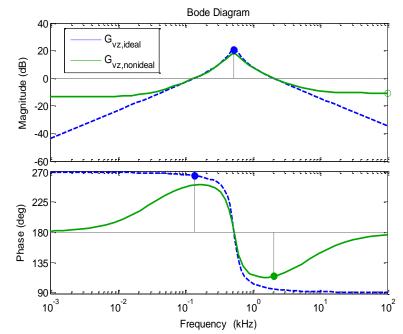

| Fig. 3.19. Comparison of Bode plots of $G_{vg}(s)$ for ideal and non-ideal Cuk converter                         |

| Fig. 3.20. Comparison of step responses of $G_{vg}(s)$ for ideal and non-ideal Cuk converter 104                 |

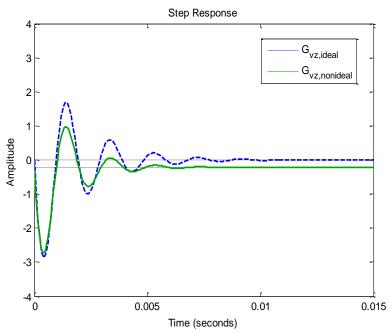

| Fig. 3.21. Comparison of Bode plots of $G_{vz}(s)$ for ideal and non-ideal Cuk converter                         |

| Fig. 3.22. Comparison of step responses of $G_{vz}(s)$ for ideal and non-ideal Cuk converter 106                 |

| Fig. 3.23. Comparison of Bode plots of $G_{vd}(s)$ for ideal and non-ideal Cuk converter                         |

| Fig. 3.24. Comparison of step responses of $G_{v\sigma}(s)$ for ideal and non-ideal Cuk converter 107            |

| Fig. 3.25. Non-ideal DC-DC buck converter                                                                        |

| Fig. 3.26. Non-ideal DC-DC Cuk converter                                                                         |

| Fig. 3.27. Comparison of output voltage step responses of non-ideal buck converter 115                           |

| Fig. 3.28. Comparison of output voltage step responses of non-ideal Cuk converter 117                            |

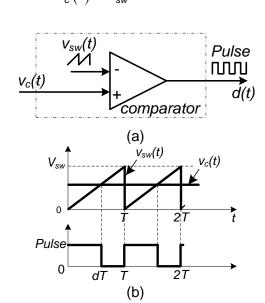

| Fig. 4.1. (a) Pulse width modulator circuit (b) corresponding waveforms                                          |

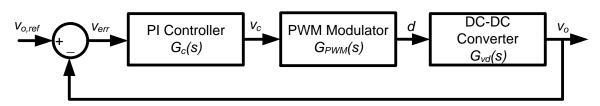

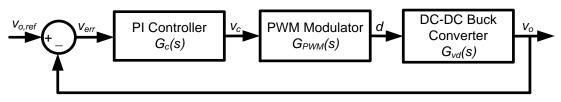

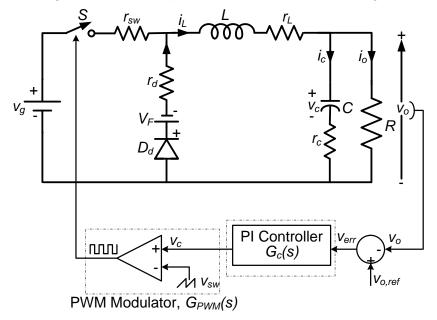

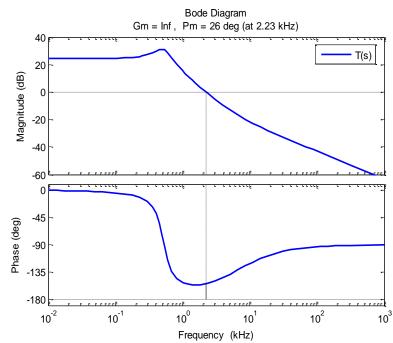

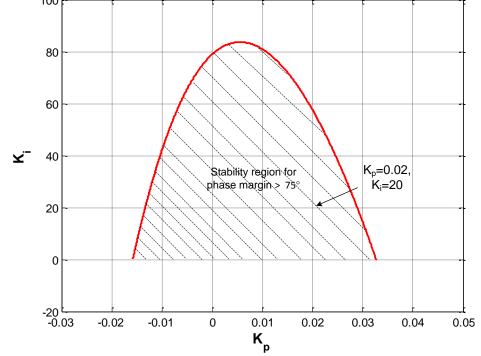

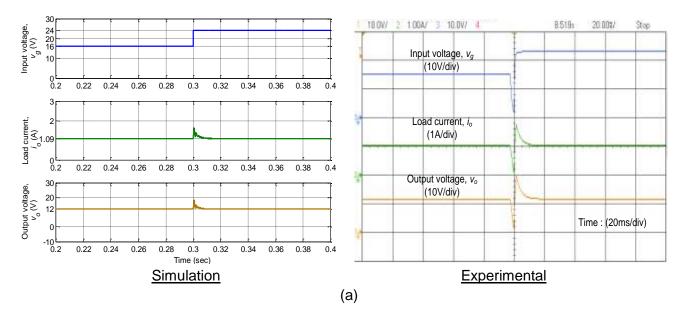

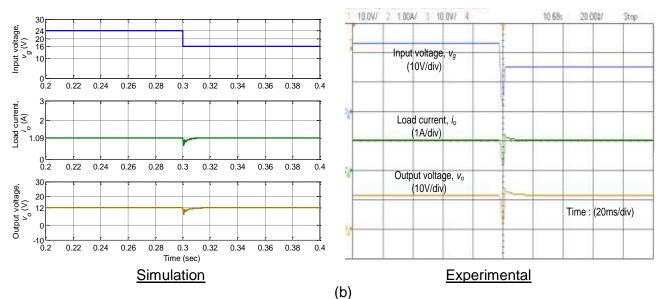

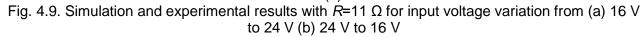

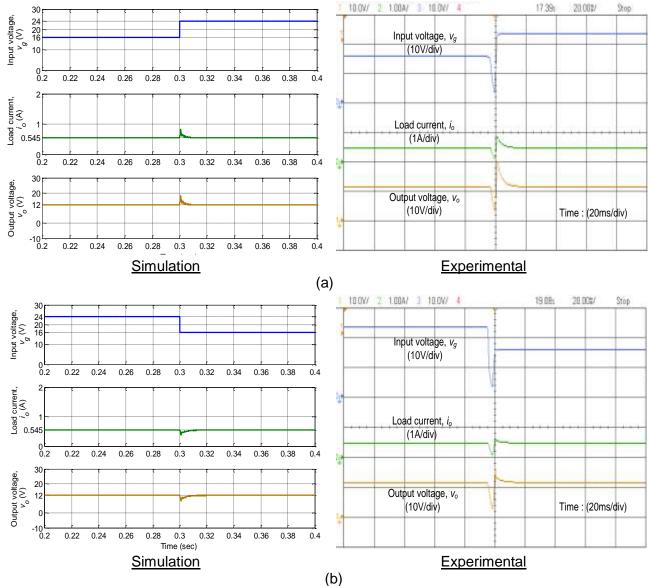

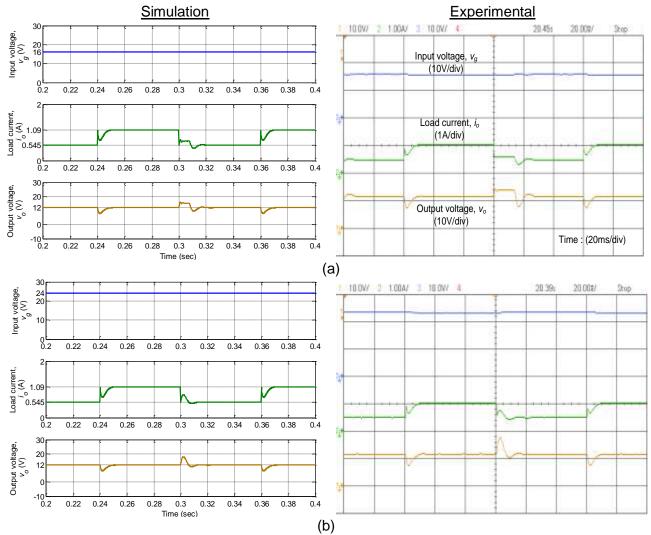

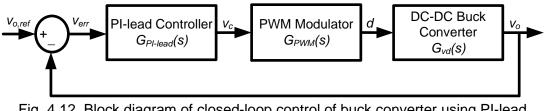

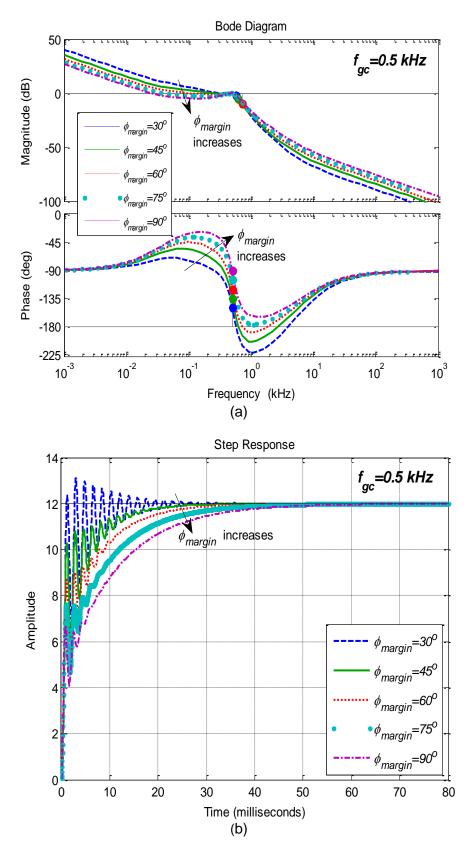

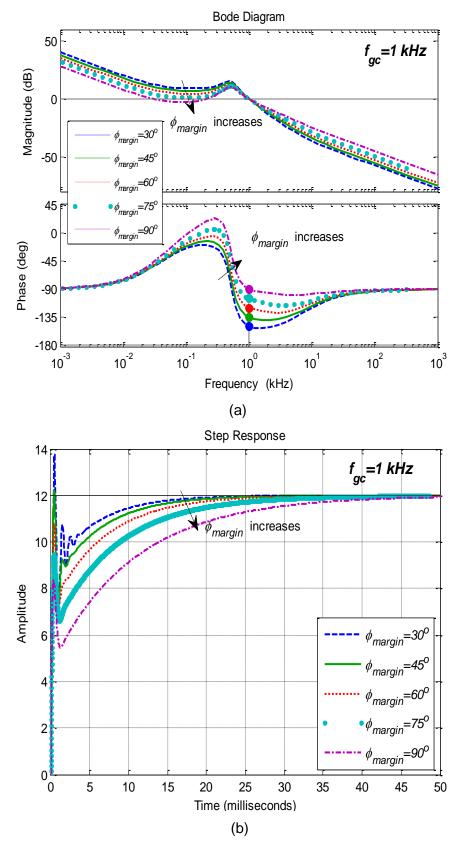

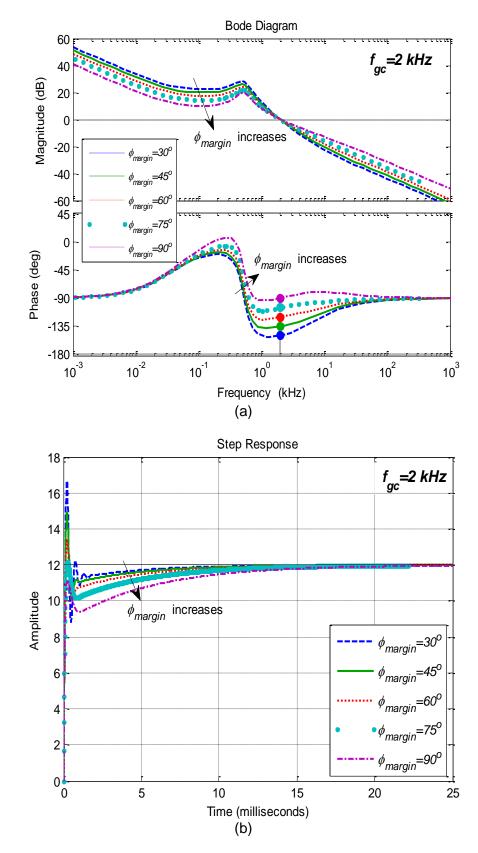

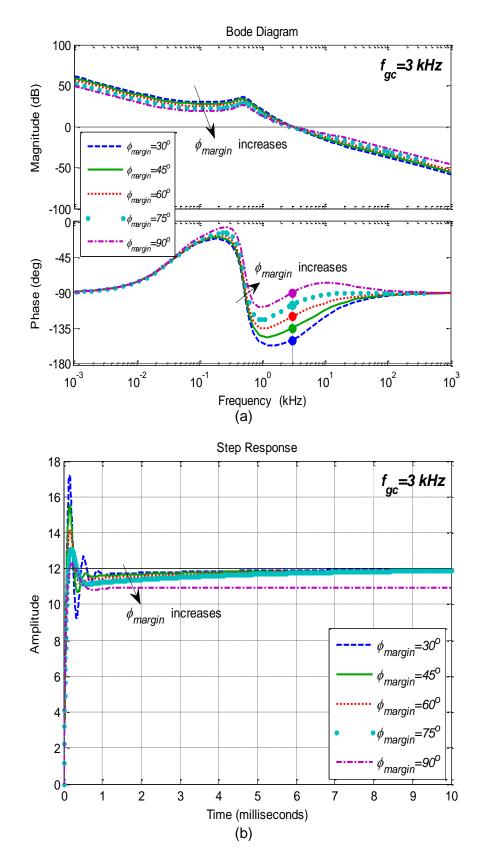

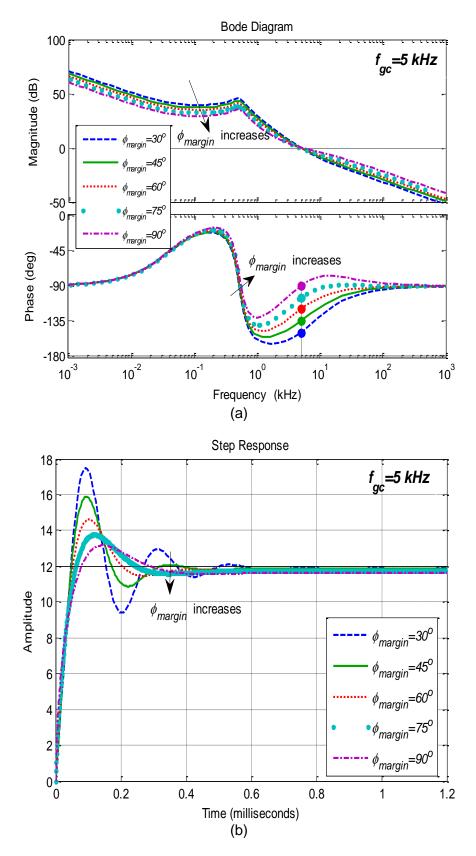

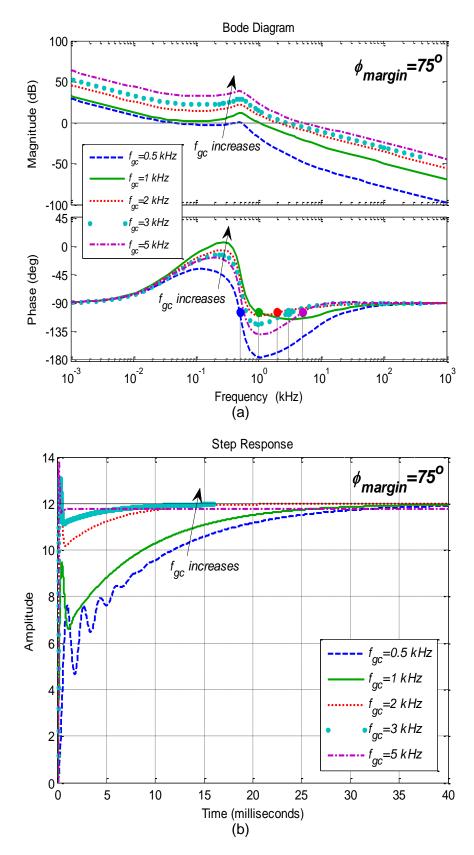

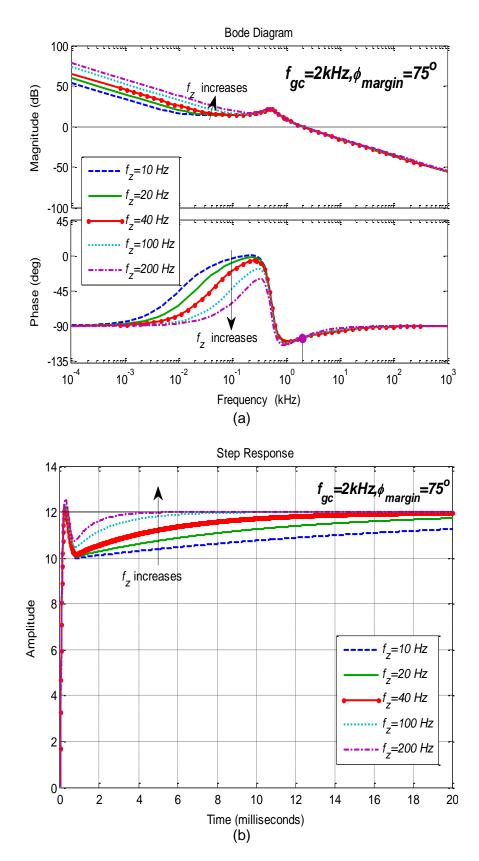

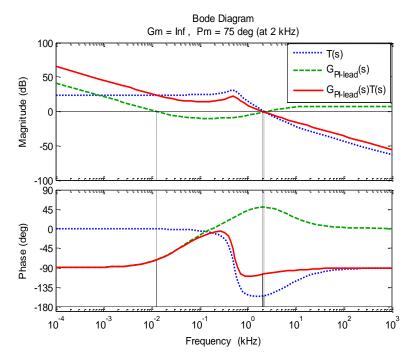

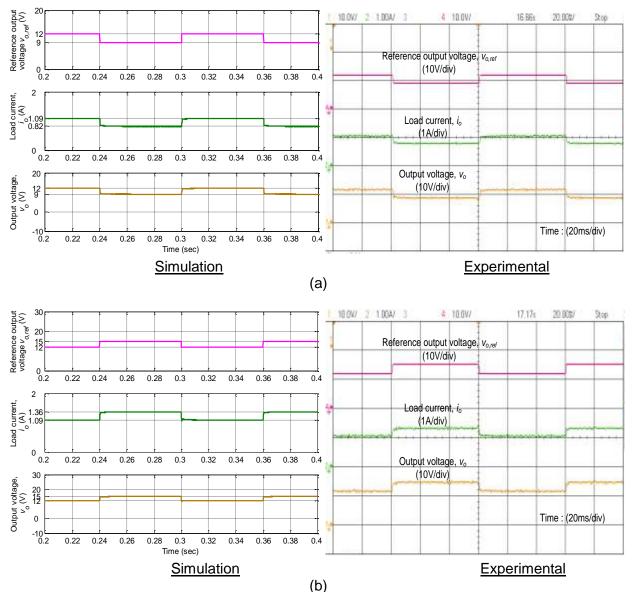

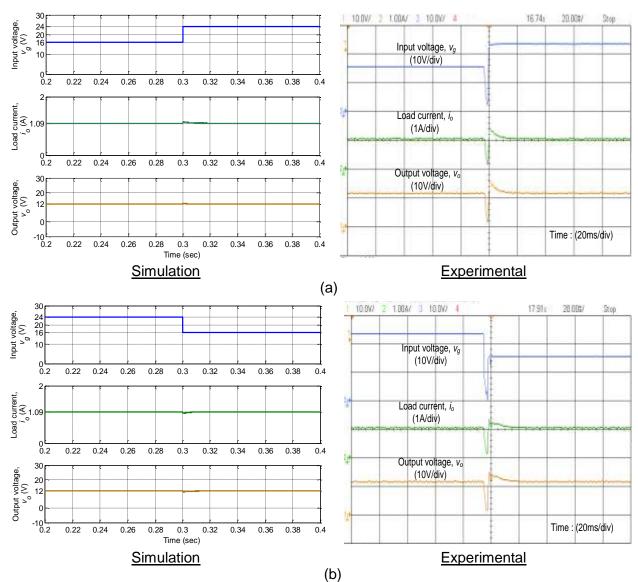

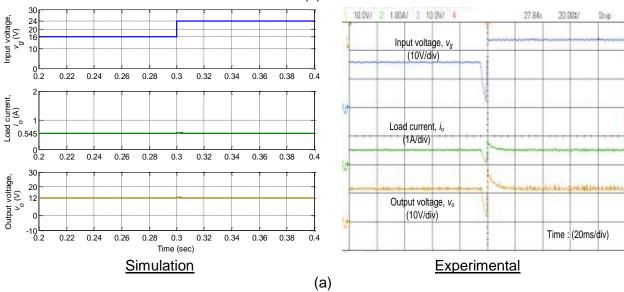

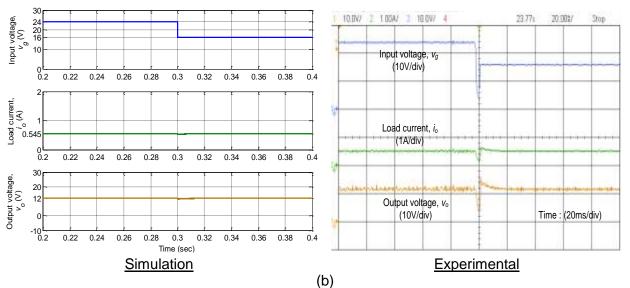

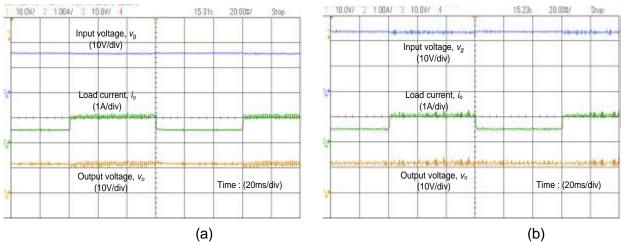

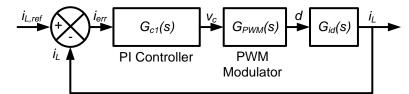

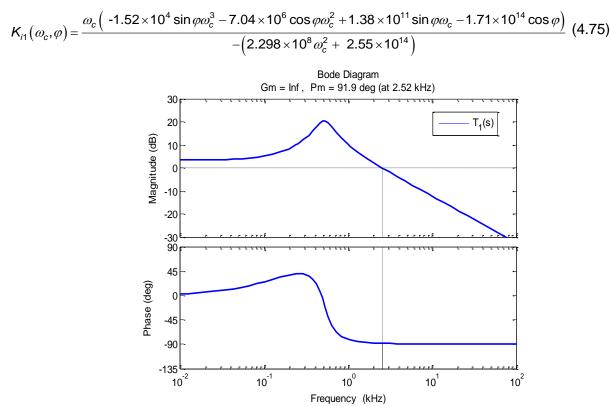

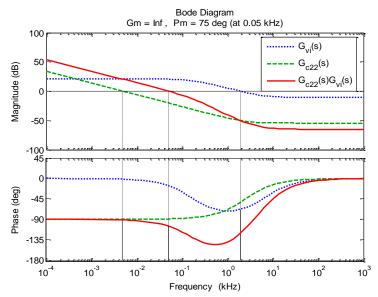

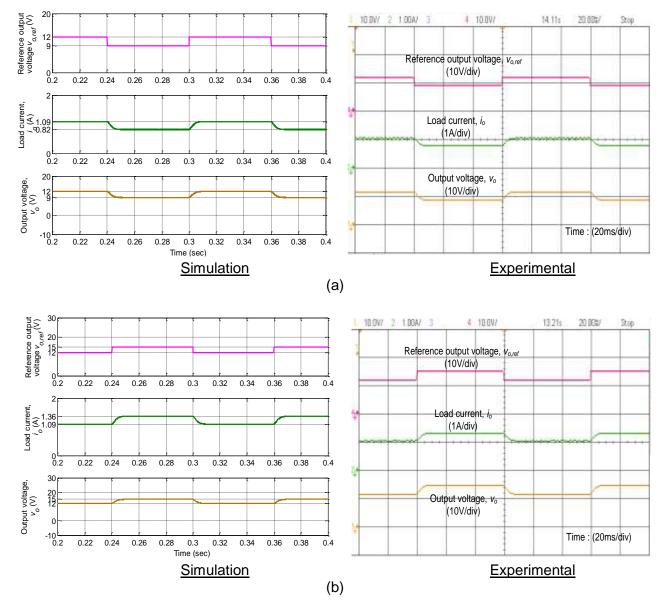

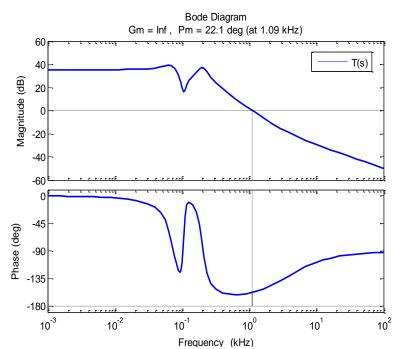

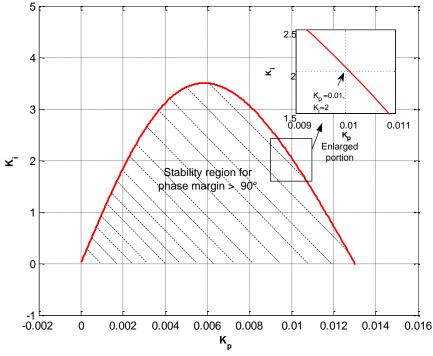

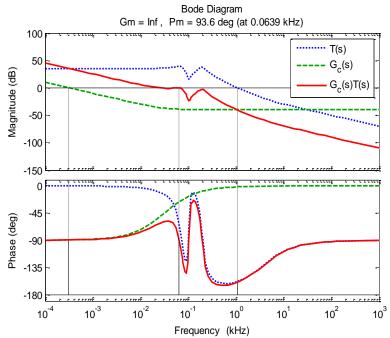

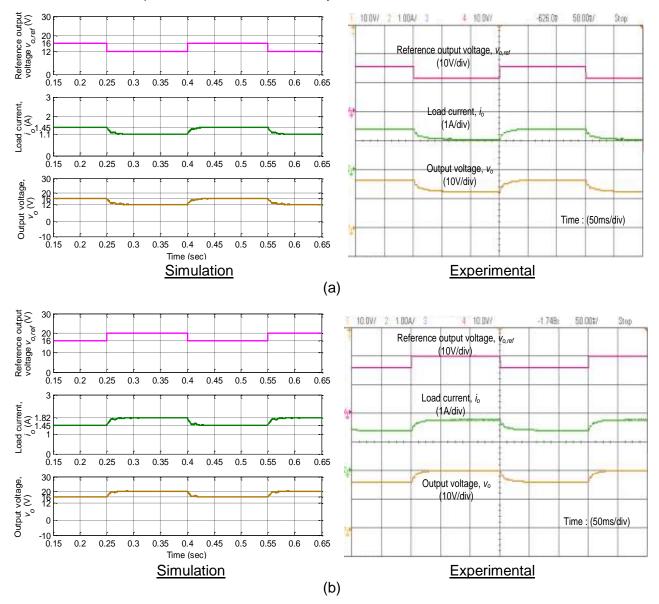

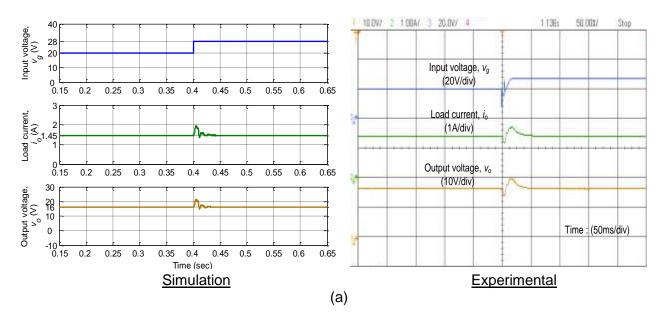

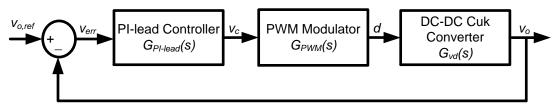

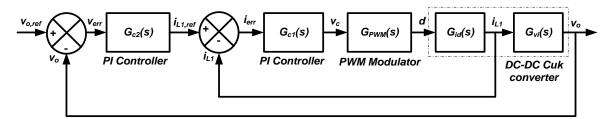

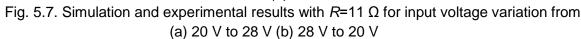

Fig. 4.3. Block diagram of closed-loop control of buck converter using PI controller ........ 125 Fig. 4.8. Simulation and experimental results for reference output voltage variation from (a) Fig. 4.9. Simulation and experimental results with  $R=11 \Omega$  for input voltage variation from (a) Fig. 4.10. Simulation and experimental results with  $R=22 \Omega$  for input voltage variation from Fig. 4.11. Simulation and experimental results for variation in load resistance from 22  $\Omega$  to 11 Fig. 4.12. Block diagram of closed-loop control of buck converter using PI-lead controller. 138 Fig. 4.13. Compensated DC-DC buck converter responses with different phase margin at  $f_{ac}$ = Fig. 4.14. Compensated DC-DC buck converter responses with different phase margin at  $f_{qc}$ = Fig. 4.15. Compensated DC-DC buck converter responses with different phase margin at  $f_{\alpha c}$ = Fig. 4.16. Compensated DC-DC buck converter responses with different phase margin at  $f_{\alpha c}$ = Fig. 4.17. Compensated DC-DC buck converter responses with different phase margin at  $f_{\alpha c}$ = Fig. 4.18. Compensated DC-DC buck converter responses with  $\varphi_{margin}$ =75° at different gain Fig. 4.19. Compensated DC-DC buck converter responses at different values of  $f_z$  with Fig. 4.21. Simulation and experimental results for reference output voltage variation from (a) Fig. 4.22. Simulation and experimental results with  $R=11 \Omega$  for input voltage variation from Fig. 4.23. Simulation and experimental results with  $R=22 \Omega$  for input voltage variation from

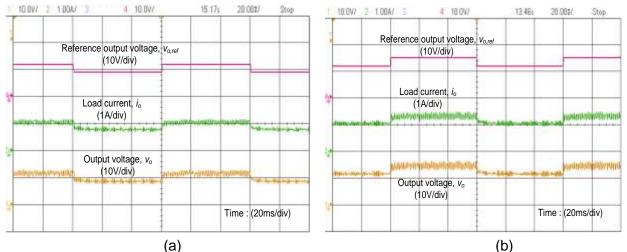

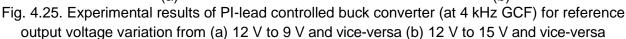

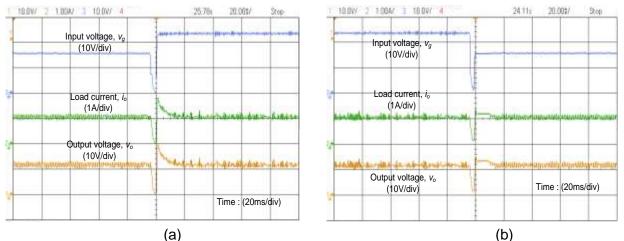

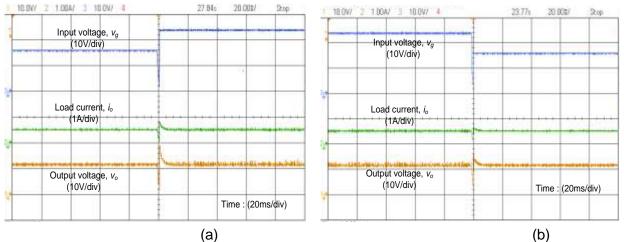

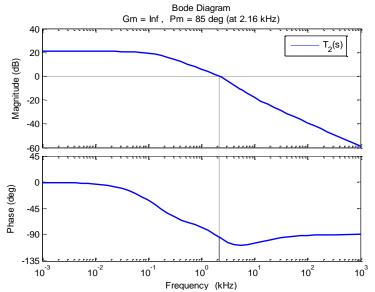

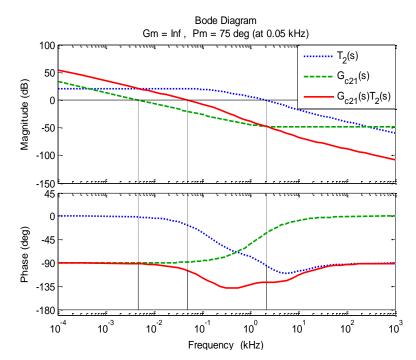

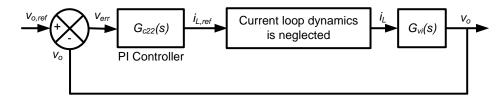

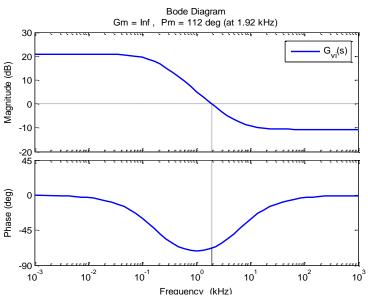

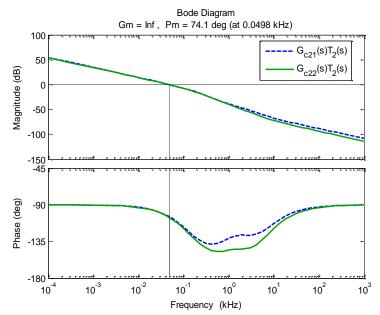

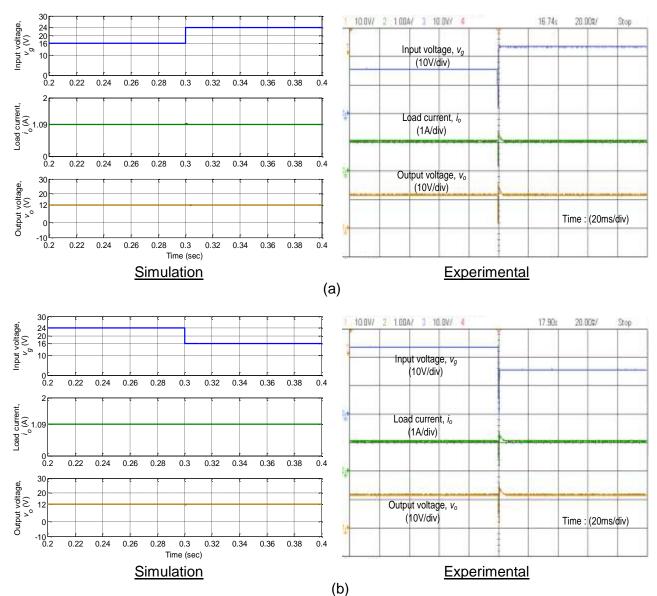

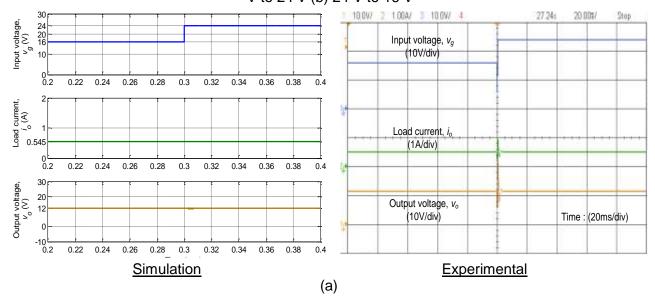

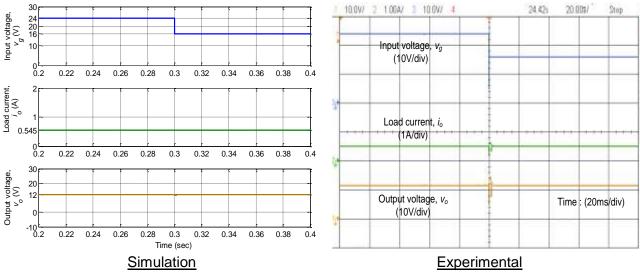

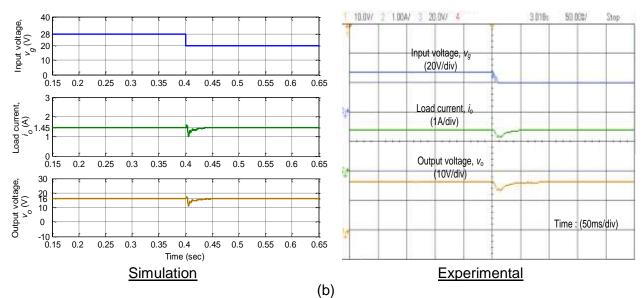

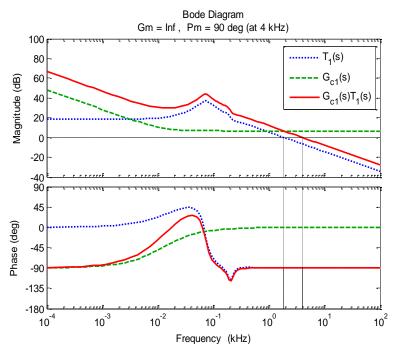

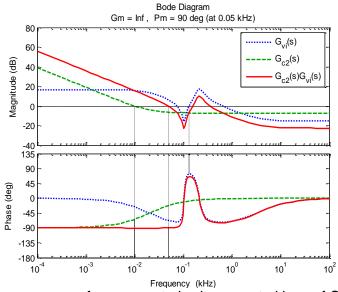

Fig. 4.24. Simulation and experimental results for variation in load resistance from 22 Ω to 11 Fig. 4.25. Experimental results of PI-lead controlled buck converter (at 4 kHz GCF) for reference output voltage variation from (a) 12 V to 9 V and vice-versa (b) 12 V to 15 V and Fig. 4.26. Experimental results of PI-lead controlled buck converter (at 4 kHz GCF) for load Fig. 4.27. Experimental results of PI-lead controlled buck converter (at 4 kHz GCF) for load resistance 22  $\Omega$  and Input voltage variation from (a) 16 V to 24 V (b) 24 V to 16 V......156 Fig. 4.28. Experimental results of PI-lead controlled buck converter (at 4 kHz GCF) for load resistance variation from 22  $\Omega$  to 11  $\Omega$  and vice-versa at input voltage (a)  $V_q$ =16 V (b)  $V_q$ =24 V......157 Fig. 4.29. Block diagram of closed two-loop PI control scheme for a DC-DC converter..... 158 Fig. 4.30. Complete block diagram of closed two-loop controlled DC-DC buck converter...160 Fig. 4.31. Detailed schematic for closed two-loop PI control of DC-DC buck converter ..... 160 Fig. 4.33. Frequency response of uncompensated current control loop of buck converter . 162 Fig. 4.34. Frequency response of compensated current control loop of buck converter ..... 163 Fig. 4.36. Frequency response of uncompensated voltage control loop of buck converter. 164 Fig. 4.37. Frequency response of compensated voltage control loop of buck converter ..... 165 Fig. 4.38. Block diagram of outer voltage control loop of DC-DC buck converter when inner current loop dynamics is neglected ......165 Fig. 4.39. Frequency response of uncompensated voltage control loop of buck converter when inner current loop dynamics is neglected......166 Fig. 4.40. Frequency response of compensated voltage control loop of buck converter when inner current loop dynamics is neglected ......166 Fig. 4.41. Comparison of frequency responses of compensated voltage control loop of buck Fig. 4.42. Simulation and experimental results for reference output voltage variation from (a) Fig. 4.43. Simulation and experimental results with  $R=11 \Omega$  for input voltage variation from Fig. 4.44. Simulation and experimental results with  $R=22 \Omega$  for input voltage variation from Fig. 4.45. Simulation and experimental results for variation in load resistance from 22 Ω to 11

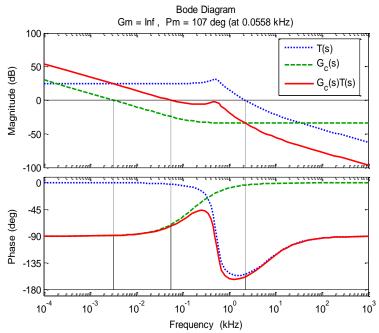

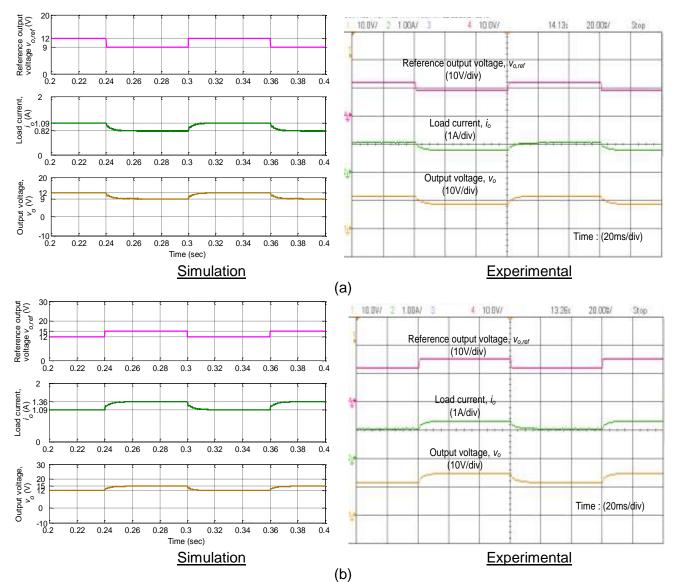

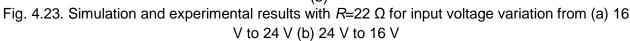

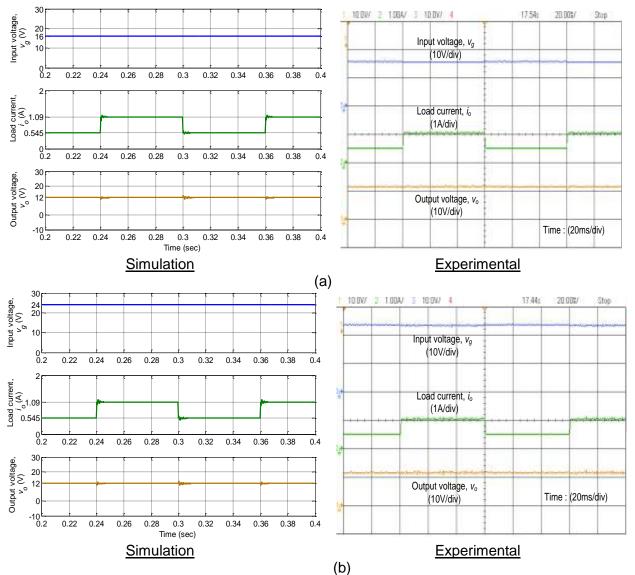

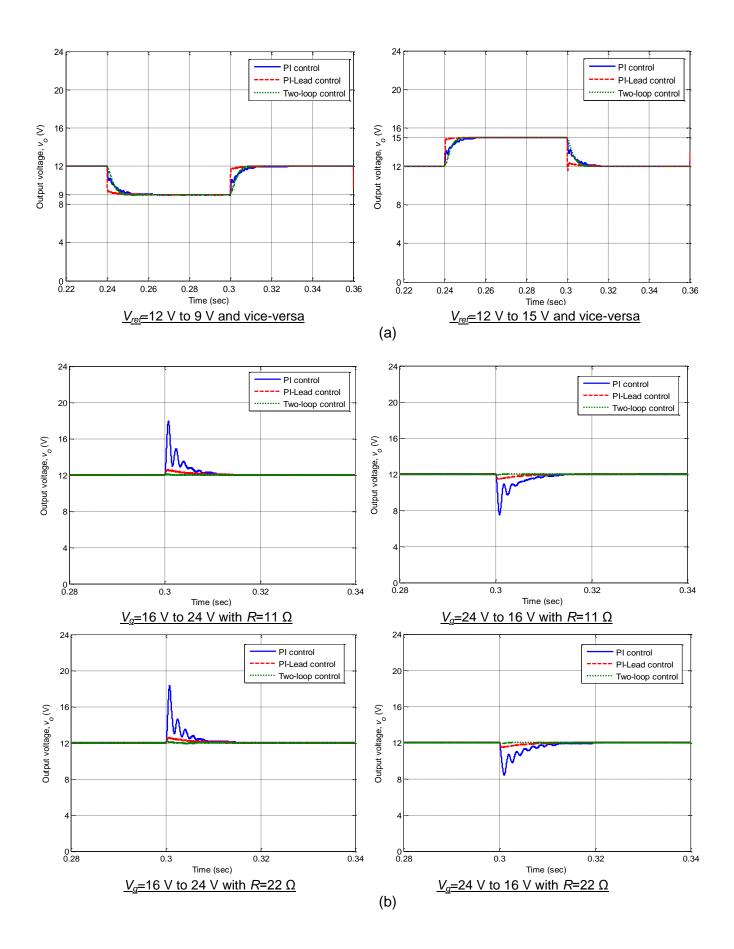

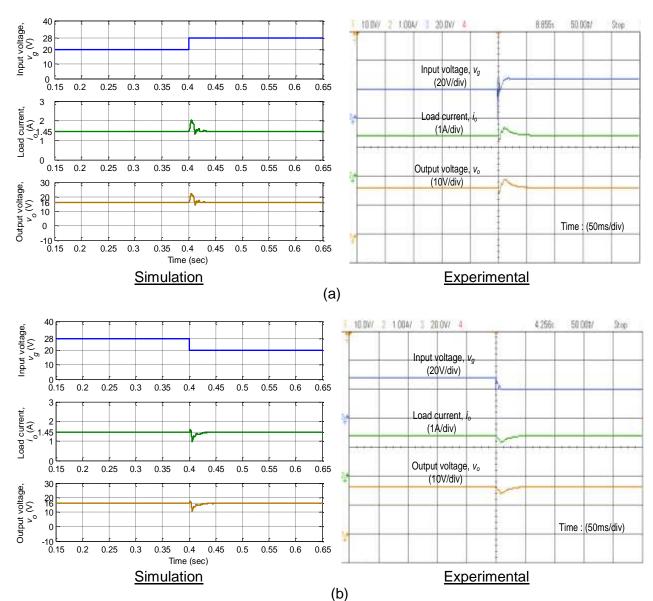

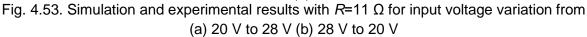

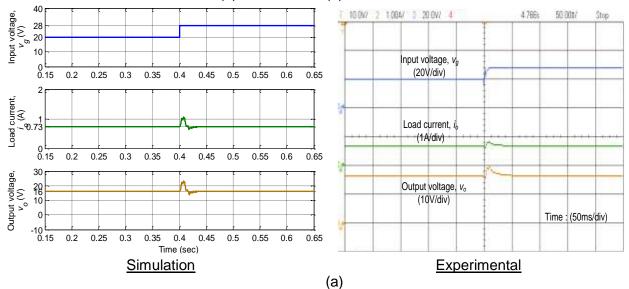

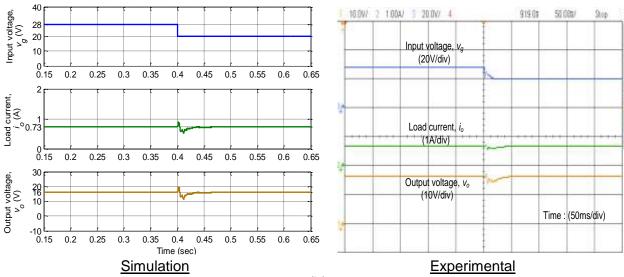

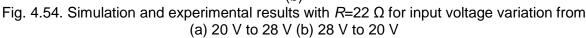

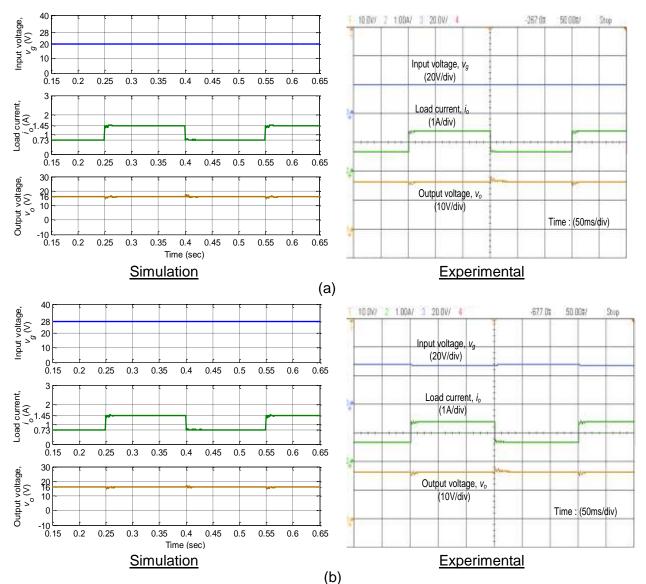

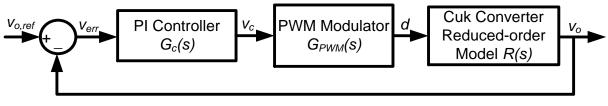

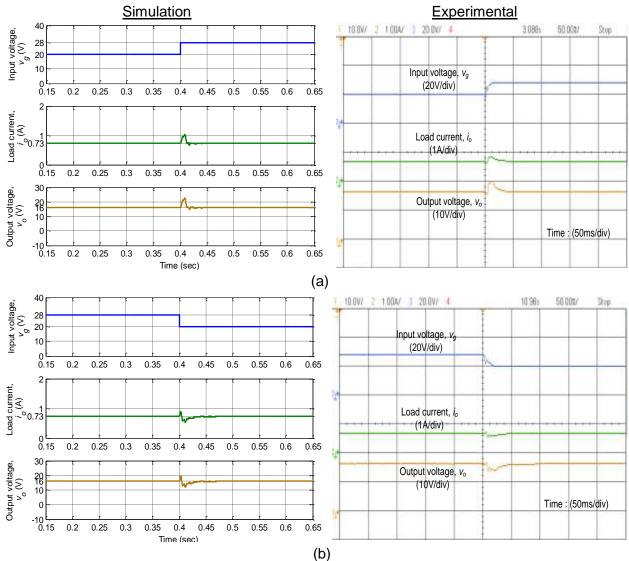

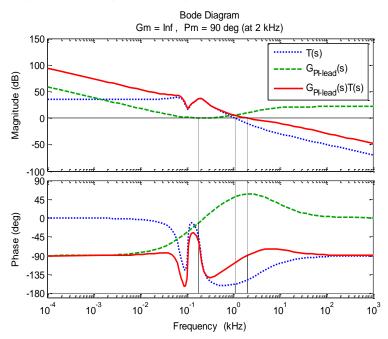

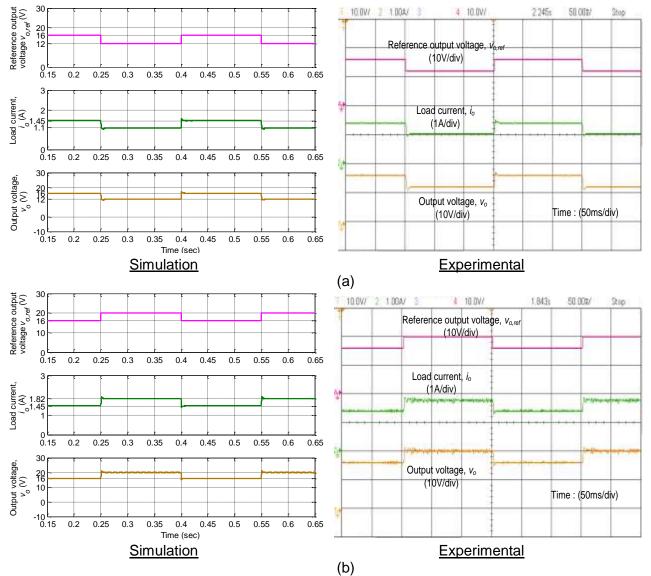

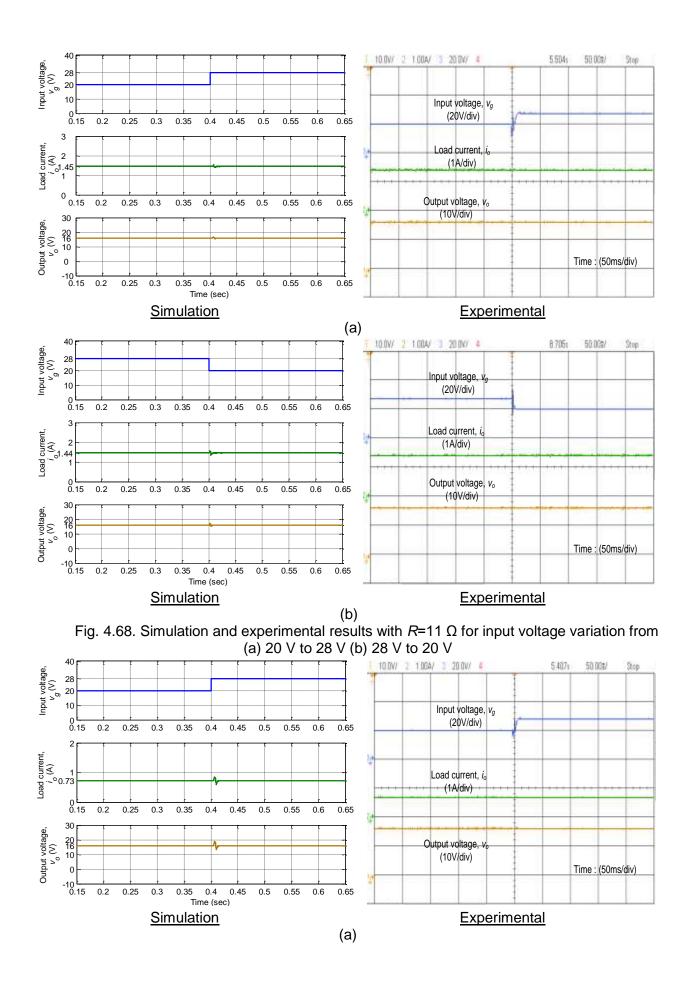

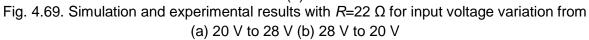

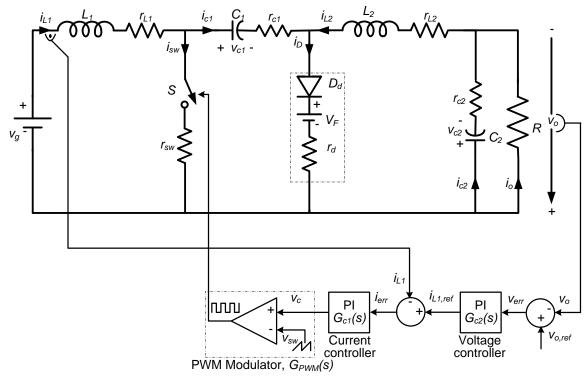

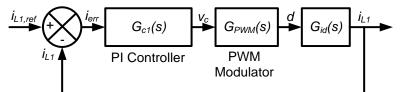

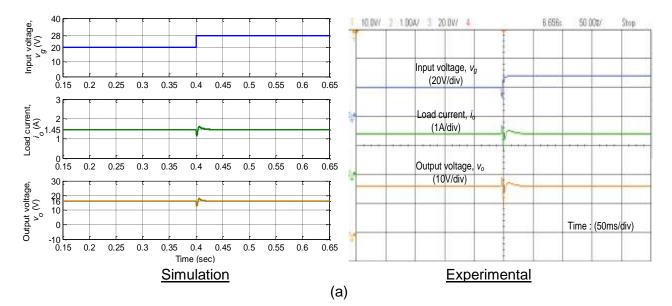

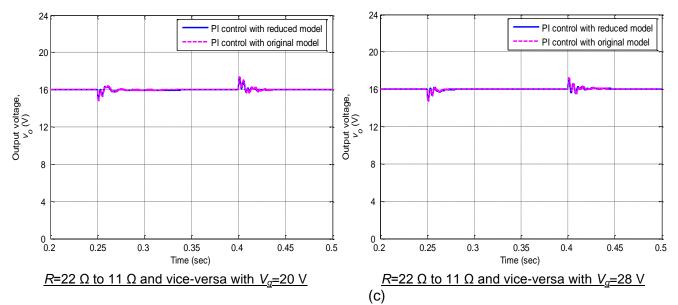

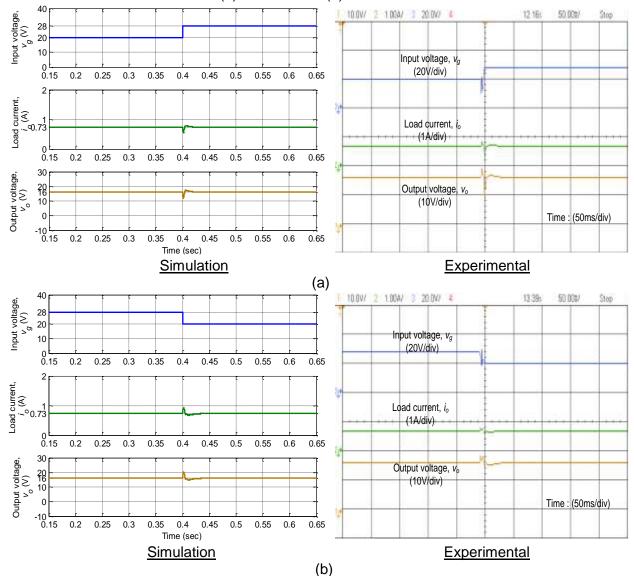

Fig. 4.52. Simulation and experimental results for reference output voltage variation from (a) Fig. 4.53. Simulation and experimental results with  $R=11 \Omega$  for input voltage variation from Fig. 4.54. Simulation and experimental results with  $R=22 \Omega$  for input voltage variation from Fig. 4.55. Simulation and experimental results for variation in load resistance from 22  $\Omega$  to 11 Fig. 4.56. Block diagram of closed-loop PI control of DC-DC Cuk converter using reduced Fig. 4.57. Frequency responses of uncompensated DC-DC Cuk converter with original and Fig. 4.58. Stability boundary locus for reduced second-order model of Cuk converter ...... 185 Fig. 4.59. Frequency response of PI controlled Cuk converter with reduced-order model.. 186 Fig. 4.60. Comparison of frequency responses of PI compensated Cuk converter with Fig. 4.61. Simulation and experimental results for reference output voltage variation from Fig. 4.62. Simulation and experimental results with  $R=11 \Omega$  for input voltage variation from Fig. 4.63. Simulation and experimental results with  $R=22 \Omega$  for input voltage variation from Fig. 4.64. Simulation and experimental results for variation in load resistance from 22  $\Omega$  to 11 Fig. 4.67. Simulation and experimental results for reference output voltage variation from (a) Fig. 4.68. Simulation and experimental results with  $R=11 \Omega$  for input voltage variation from

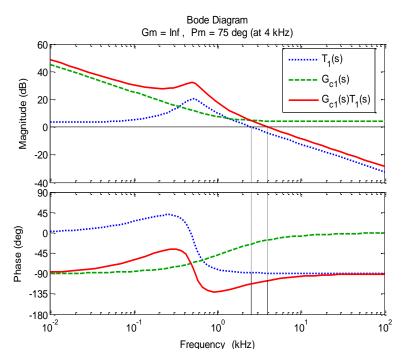

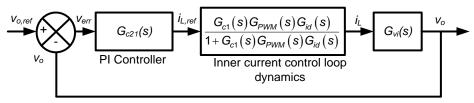

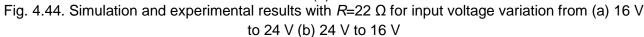

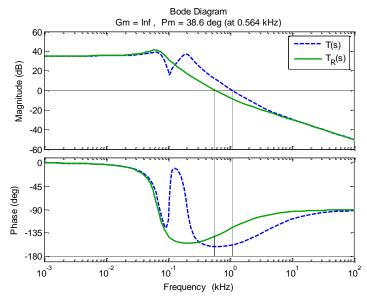

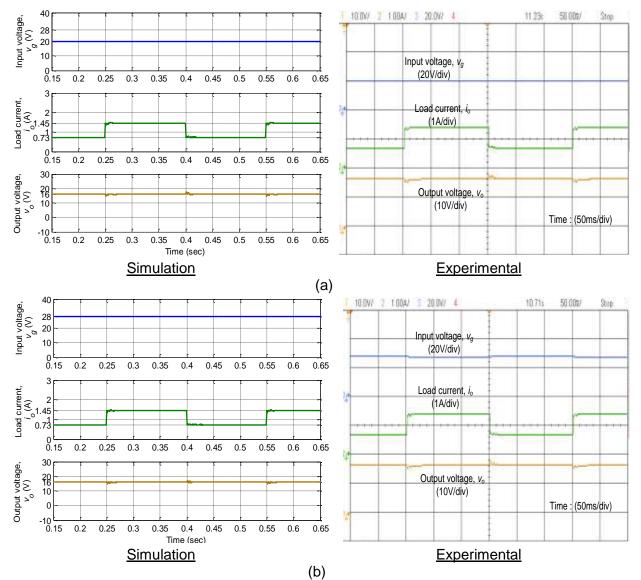

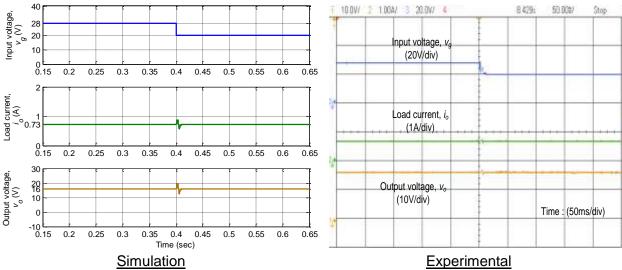

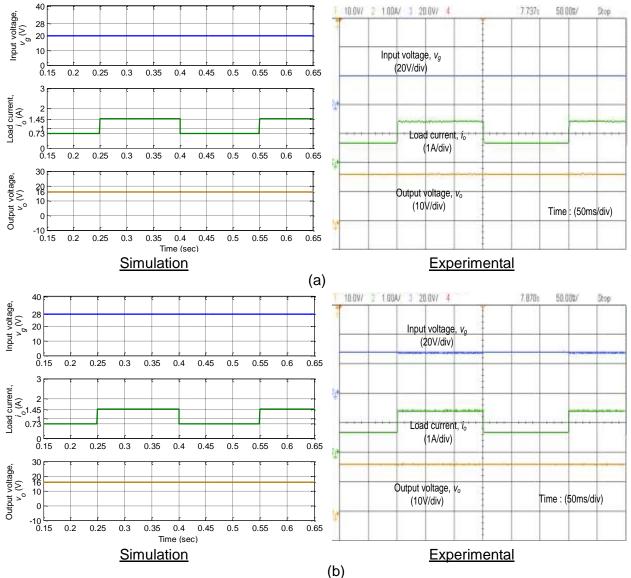

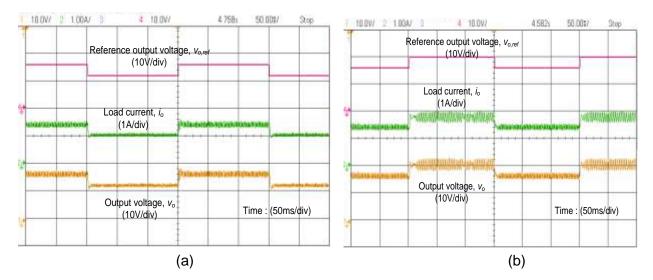

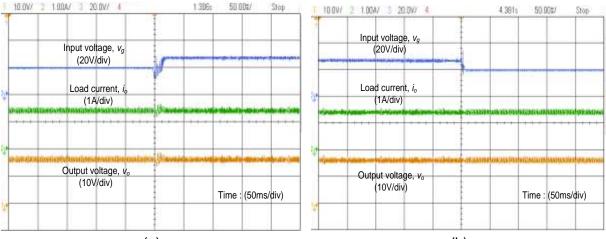

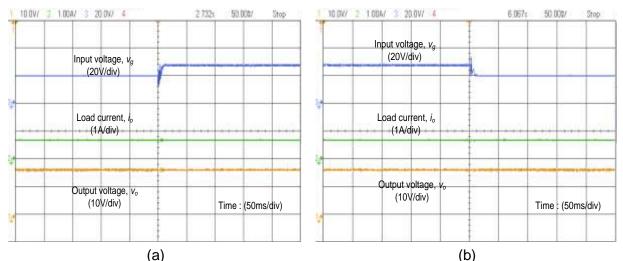

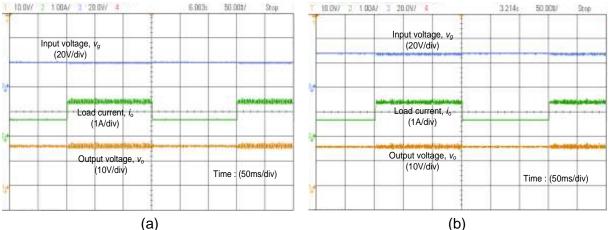

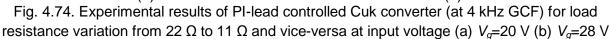

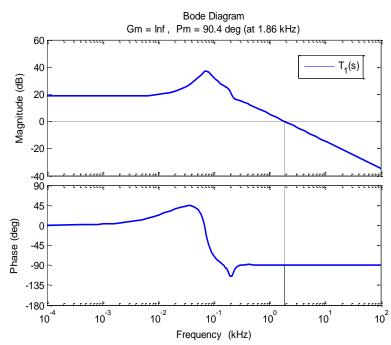

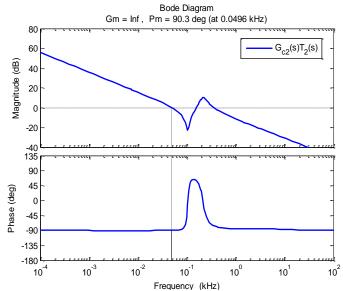

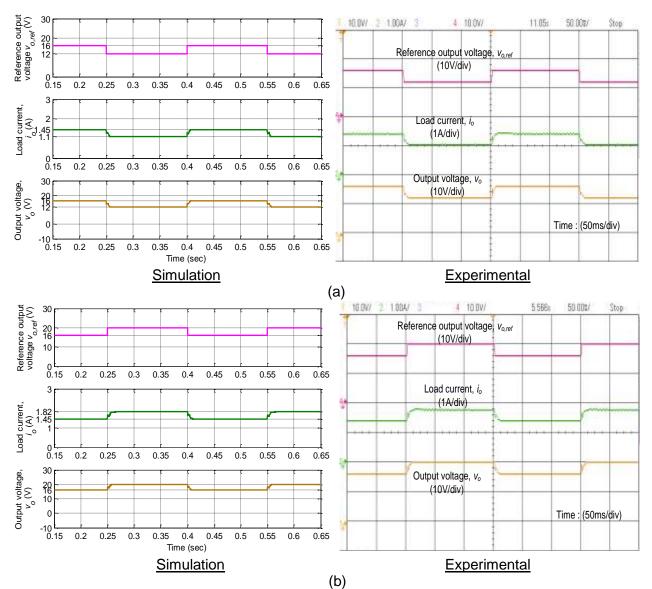

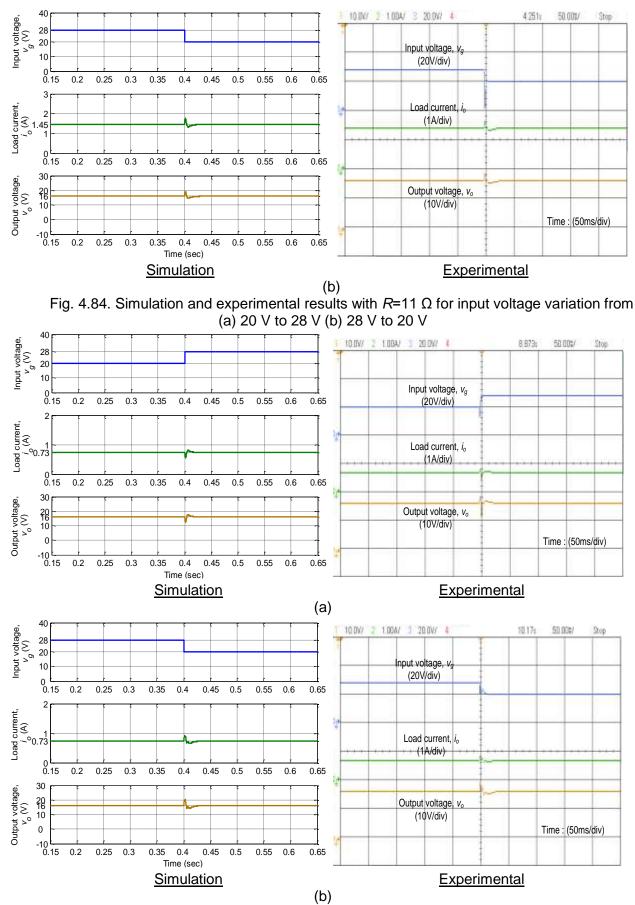

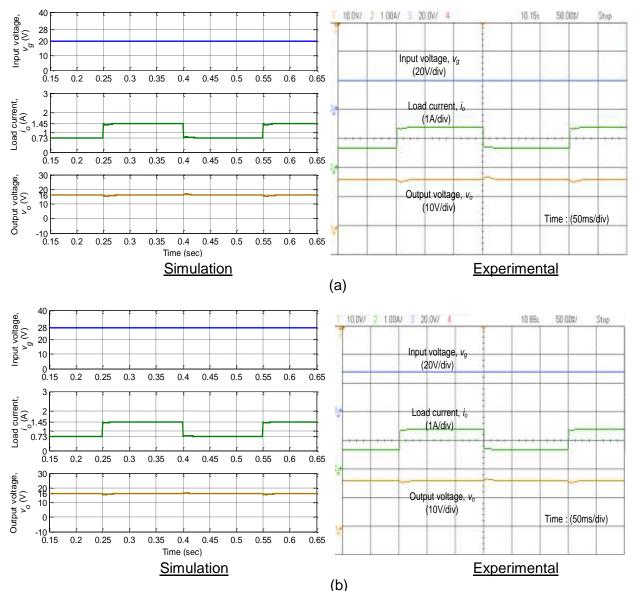

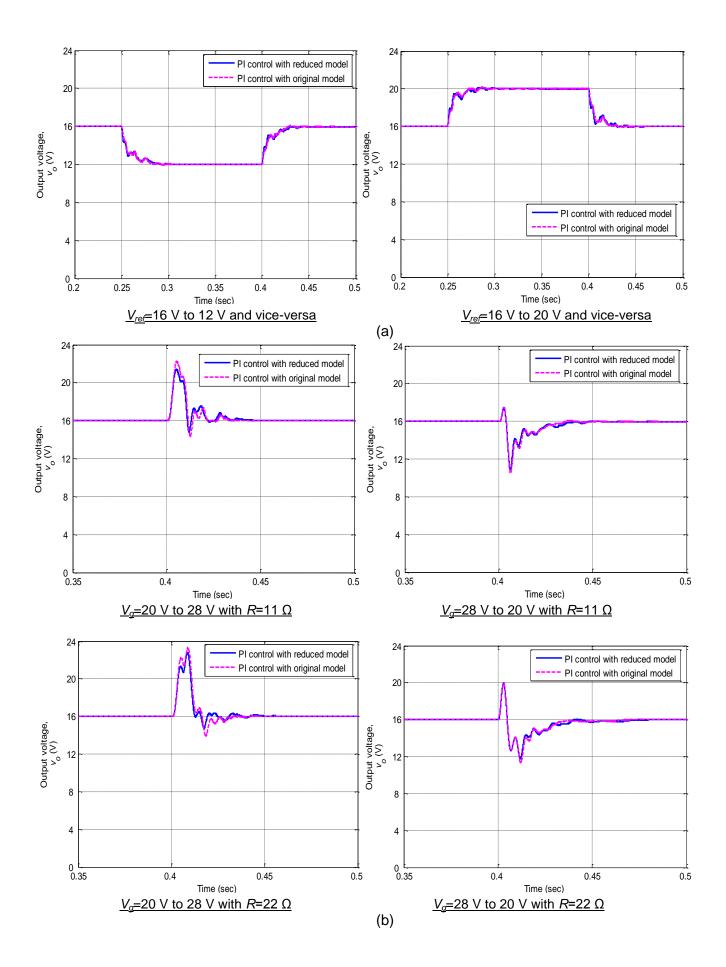

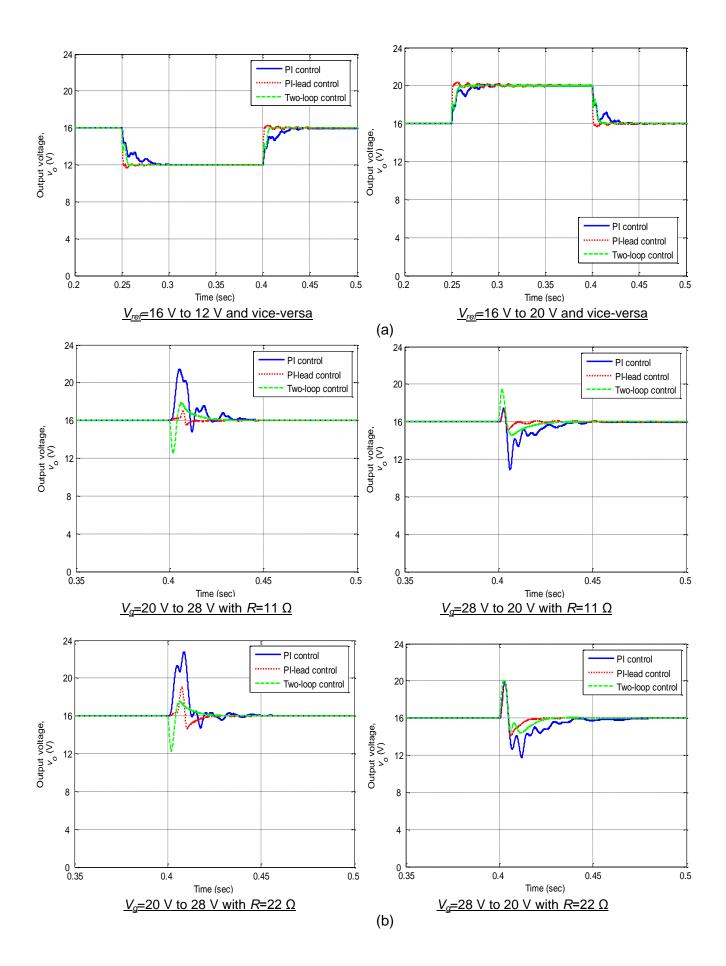

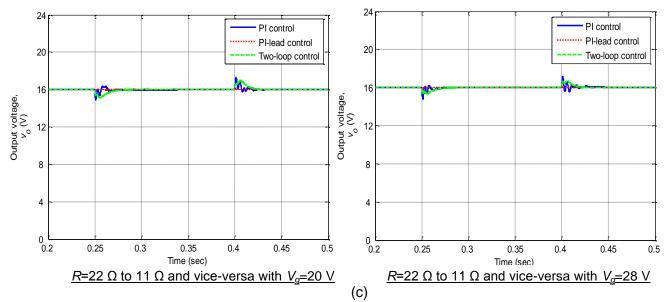

Fig. 4.69. Simulation and experimental results with  $R=22 \Omega$  for input voltage variation from Fig. 4.70. Simulation and experimental results for variation in load resistance from 22  $\Omega$  to 11 Fig. 4.71. Experimental results of PI-lead controlled Cuk converter (at 4 kHz GCF) for reference output voltage variation from (a) 16 V to 12 V and vice-versa (b) 16 V to 20 V and Fig. 4.72. Experimental results of PI-lead controlled Cuk converter (at 4 kHz GCF) for load Fig. 4.73. Experimental results of PI-lead controlled Cuk converter (at 4 kHz GCF) for load Fig. 4.74. Experimental results of PI-lead controlled Cuk converter (at 4 kHz GCF) for load resistance variation from 22  $\Omega$  to 11  $\Omega$  and vice-versa at input voltage (a) V<sub>g</sub>=20 V (b) V<sub>g</sub>=28 Fig. 4.75. Complete block diagram for closed two-loop PI control of DC-DC Cuk converter Fig. 4.76. Detailed schematic for closed two-loop PI control of DC-DC Cuk converter ...... 199 Fig. 4.78. Frequency response of uncompensated current control loop of Cuk converter .. 201 Fig. 4.79. Frequency response of compensated current control loop of Cuk converter ......202 Fig. 4.80. Block diagram of outer voltage control loop of Cuk converter (a) with current Fig. 4.81. Frequency response of compensated voltage control loop of Cuk converter without Fig. 4.82. Frequency response of compensated voltage control loop of Cuk converter with inner current loop dynamics and PI controller G<sub>c2</sub>(s)......204 Fig. 4.83. Simulation and experimental results for reference output voltage variation from (a) Fig. 4.84. Simulation and experimental results with  $R=11 \Omega$  for input voltage variation from Fig. 4.85. Simulation and experimental results with  $R=22 \Omega$  for input voltage variation from Fig. 4.86. Simulation and experimental results for variation in load resistance from 22  $\Omega$  to 11 Fig. 4.87. Perfpremance comparison of reduced and original model based PI controllers for

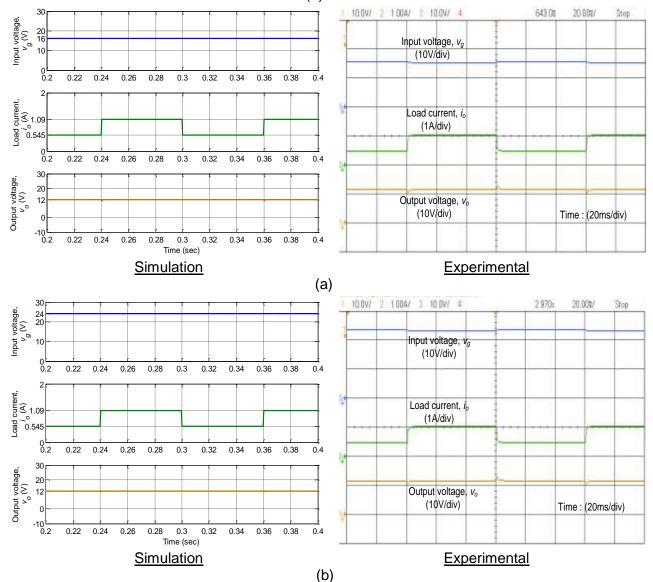

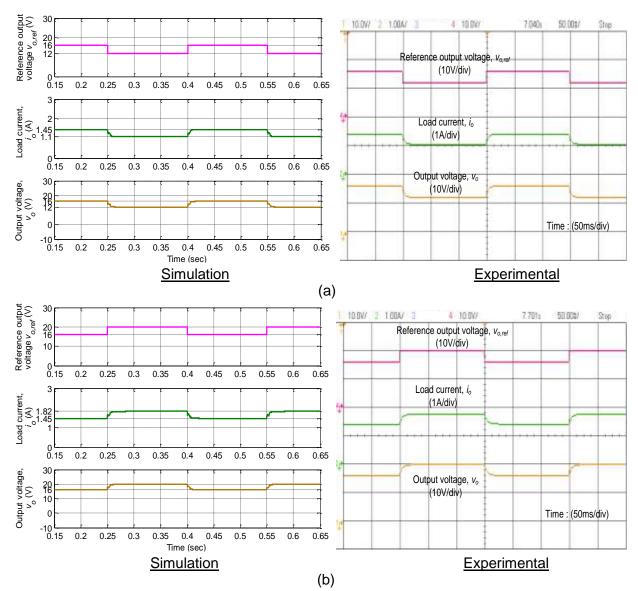

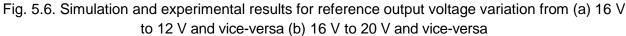

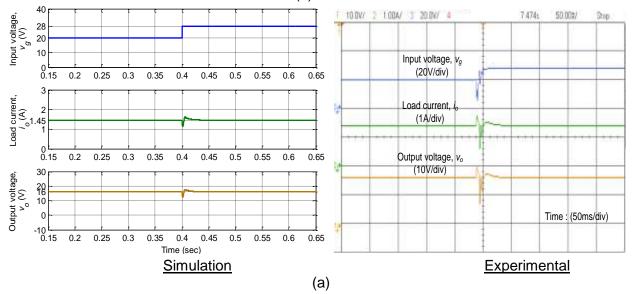

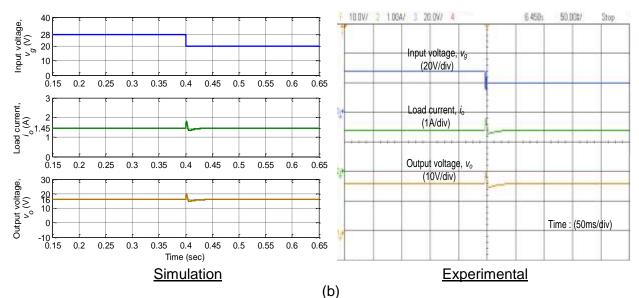

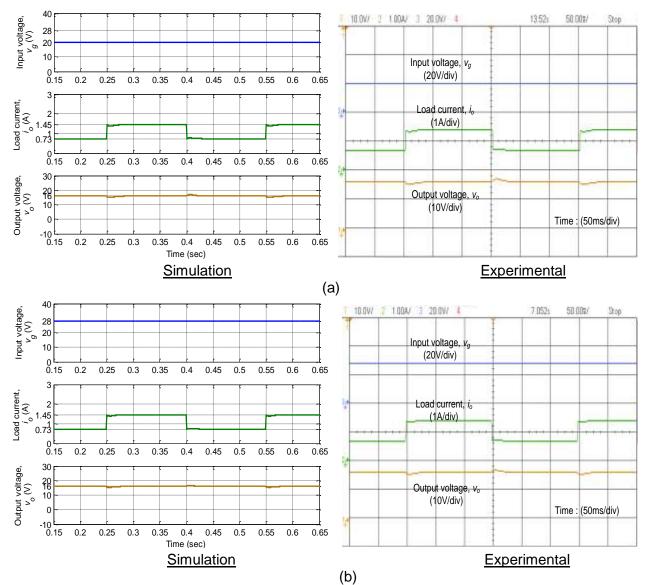

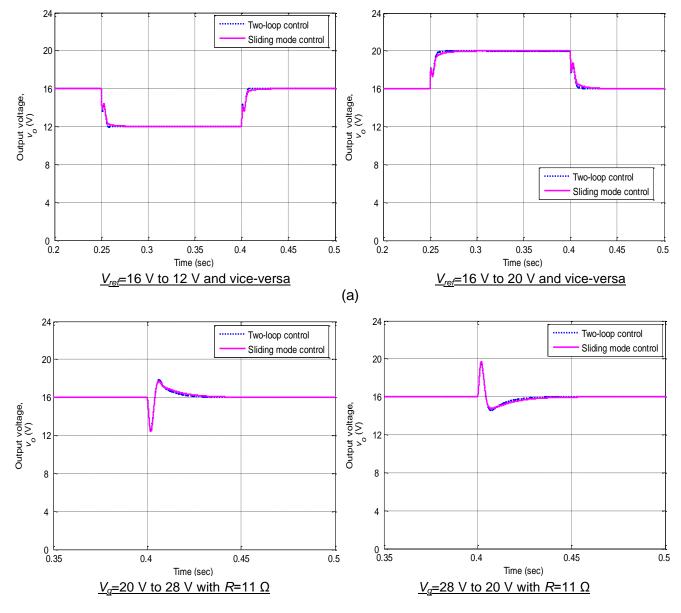

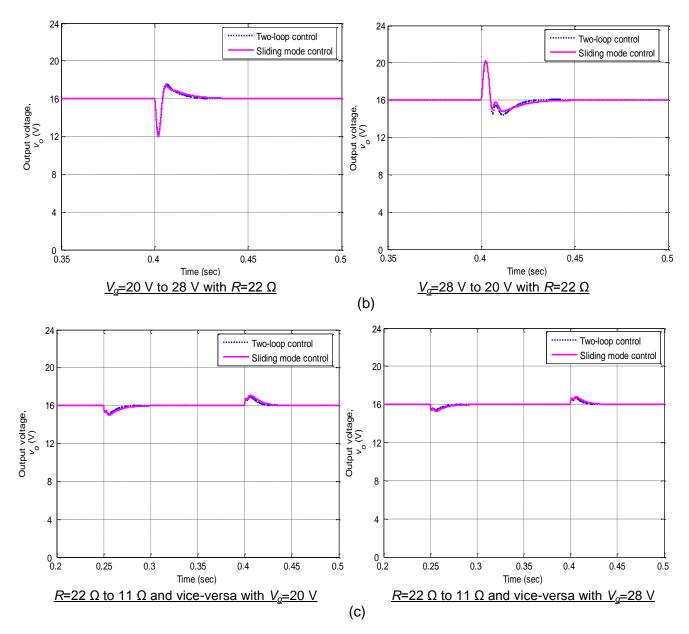

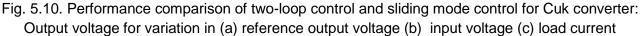

Fig. 4.88. Performance comparison of PI, PI-lead and two-loop PI controllers for Cuk Fig. 5.2. Equivalent circuit of the Cuk converter (a) during switch-on (b) during switch-off. 217 Fig. 5.5. Bode plot of sliding mode controlled Cuk converter with  $K_p = 0.4$  and K = 40 ...... 232 Fig. 5.6. Simulation and experimental results for reference output voltage variation from (a) Fig. 5.7. Simulation and experimental results with  $R=11 \Omega$  for input voltage variation from Fig. 5.8. Simulation and experimental results with  $R=22 \Omega$  for input voltage variation from (a) Fig. 5.9. Simulation and experimental results for variation in load resistance from 22  $\Omega$  to 11 Fig. 5.10. Performance comparison of two-loop control and sliding mode control for Cuk converter: Output voltage for variation in (a) reference output voltage (b) input voltage (c) Fig. A.1. Various steady-state current waveforms for DC-DC buck converter (not to scale)243 Fig. A.2. Various steady-state current waveforms for DC-DC Cuk converter (not to scale) 245

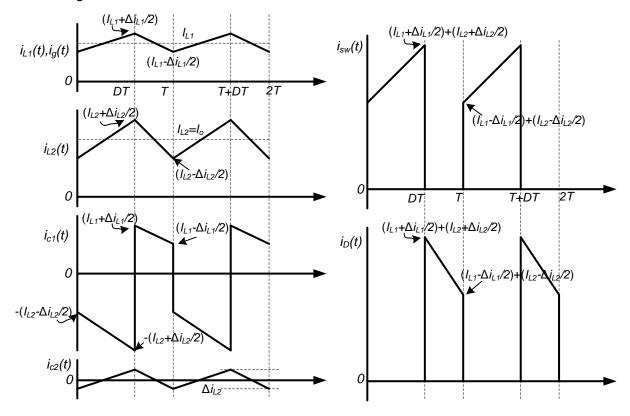

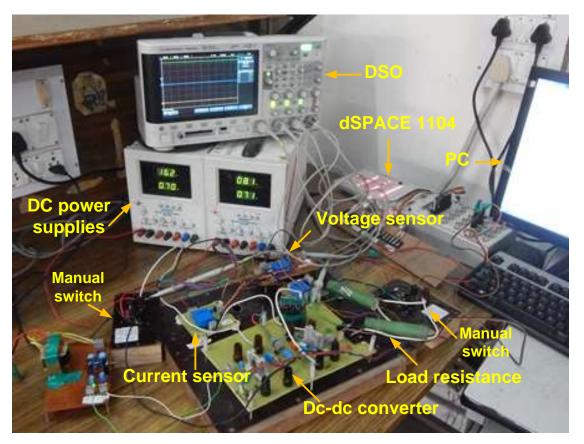

| Fig. B.1. Generalized block diagram representation of experimental setup                   | 250      |

|--------------------------------------------------------------------------------------------|----------|

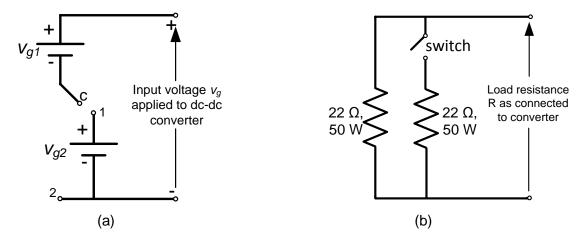

| Fig. B.2. Laboratory experimental setup                                                    | 250      |

| Fig. B.3. Connection diagram for step variation of (a) input voltage (b) load resistance . | 252      |

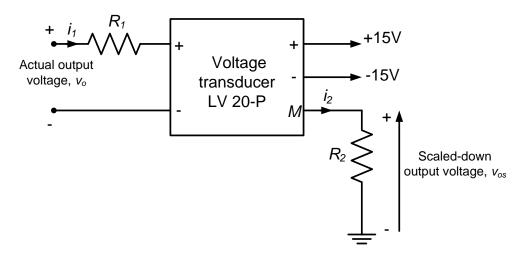

| Fig. B.4. Connection diagram of voltage sensor circuit                                     | 253      |

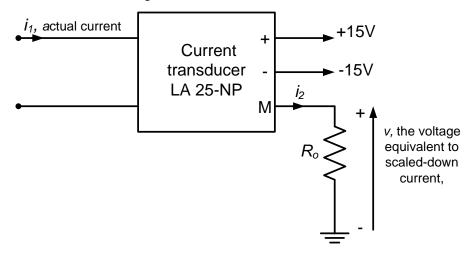

| Fig. B.5. Connection diagram of current sensor circuit                                     | 254      |

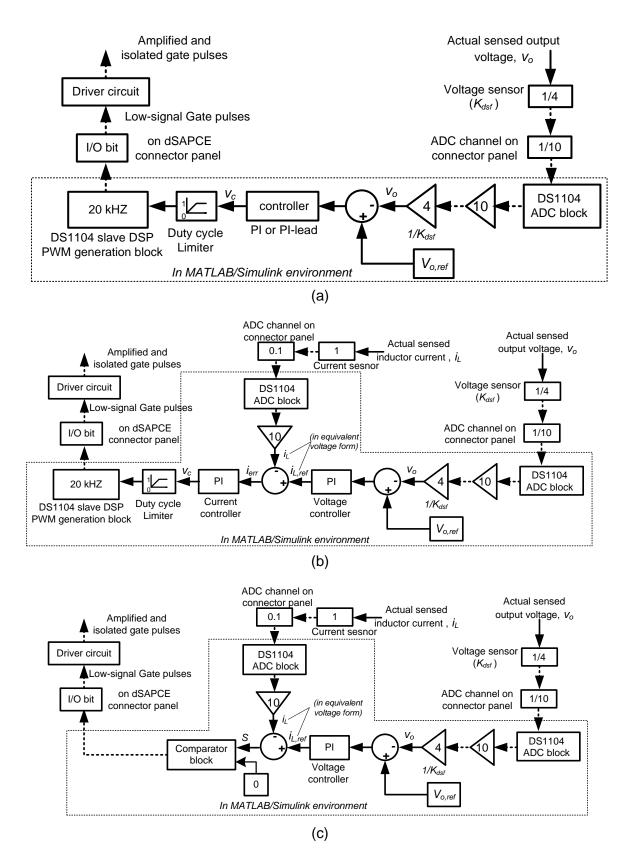

| Fig. B.6. Implementation of the different control techniques using dSPACE DS1104 con       | ntroller |

| system (a) PI or PI-lead control (b) Two-loop PI control (c) Sliding mode control          | 256      |

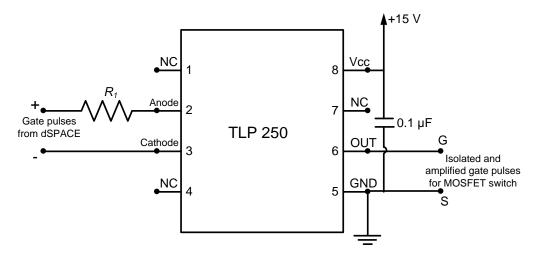

| Fig. B.7. MOSFET driver circuit                                                            | 257      |

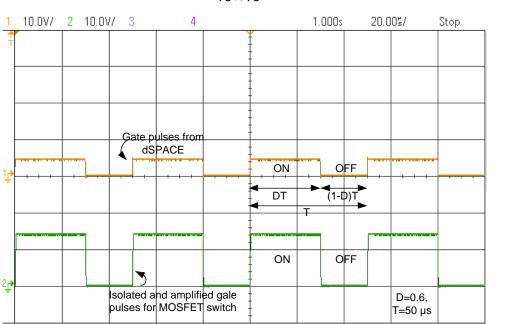

| Fig. B.8. Input and output switching gate pulses from the MOSFET driver circuit            | 258      |

| Table 2.1. Non-ideal DC-DC buck converter specifications                                             |

|------------------------------------------------------------------------------------------------------|

| Table 2.2. Non-ideal DC-DC Cuk converter specifications                                              |

| Table 3.1. Parameter values of non-ideal buck converter                                              |

| Table 3.2. Comparison of steady-state parameters of ideal and non-ideal buck converter 96            |

| Table 3.3. Parameter values of non-ideal Cuk converter103                                            |

| Table 3.4. Comparison of steady-state parameters of ideal and non-ideal Cuk converter 103            |

| Table 3.5. Comparison of time constants $\tau$ and damping time constant $\tau_d$ for buck converter |

|                                                                                                      |

| Table 3.6. Comparison of time constants $\tau$ and damping time constant $\tau_d$ for Cuk converter  |

|                                                                                                      |

| Table 4.1. DC-DC buck converter specifications 126                                                   |

| Table 4.2. Performance indices of compensated buck converter for $f_z$ =40 Hz and $f_{gc}$ =0.5 kHz  |

|                                                                                                      |

| Table 4.3. Performance indices of compensated buck converter for $f_z$ =40 Hz and $f_{gc}$ =1 kHz    |

|                                                                                                      |

| Table 4.4. Performance indices of compensated buck converter for $f_z$ =40 Hz and $f_{gc}$ =2 kHz    |

|                                                                                                      |

| Table 4.5. Performance indices of compensated buck converter for $f_z$ =40 Hz and $f_{gc}$ =3 kHz    |

|                                                                                                      |

| Table 4.6. Performance indices of compensated buck converter for $f_z$ =40 Hz and $f_{gc}$ =5 kHz    |

|                                                                                                      |

| Table 4.7. Performance indices of compensated buck converter for $f_z$ =40 Hz and PM=75°147          |

| Table 4.8. Performance indices of compensated buck converter for PM=75° and $f_{gc}$ =2 kHz          |

|                                                                                                      |

| Table 4.9. DC-DC Cuk converter specifications    175                                                 |

| Table 4.10. Comparison of frequency domain parameters for uncompensated DC-DC Cuk                    |

| converter with original and reduced second-order model 184                                           |

| Table 4.11. Comparison of frequency domain parameters for PI compensated DC-DC Cuk                   |

| converter with original and reduced second-order model 186                                           |

## LIST OF ACRONYMS

| dc, DC   | Direct Current                                    |

|----------|---------------------------------------------------|

| ac, AC   | Alternating Current                               |

| DSO      | Digital Storage Oscilloscope                      |

| DSP      | Digital Signal Processor                          |

| MOSFET   | Metal Oxide Semiconductor Field-effect Transistor |

| pf, PF   | Power Factor                                      |

| PI       | Proportional and Integral                         |

| PID      | Proportional-Derivative-Integral                  |

| rms, RMS | Root Mean Square                                  |

| SMPS     | Switch Mode Power Supply                          |

| SSA      | State-Space Averaging                             |

| SSE      | Steady-State Error                                |

| PWM      | Pulse Width Modulation                            |

| GM       | Gain Margin                                       |

| GCF      | Gain Crossover Frequency                          |

| PM       | Phase Margin                                      |

| ESR      | Equivalent Series Resistance                      |

| OVR      | Output Voltage Ripple                             |

| CCM      | Continuous Conduction Mode                        |

| DCM      | Discontinuous Conduction Mode                     |

|          |                                                   |

## LIST OF SYMBOLS

| $V_g(t)$                           | instantaneous input voltage     |

|------------------------------------|---------------------------------|

| $V_L(t), V_{L1}(t), V_{L2}(t)$     | instantaneous inductor voltage  |

| $V_{c}(t), V_{c1}(t), V_{c2}(t)$   | instantaneous capacitor voltage |

| $V_o(t)$                           | instantaneous output voltage    |

| $I_g(t)$                           | instantaneous input current     |

| i <sub>sw</sub> (t)                | instantaneous switch current    |

| <i>i<sub>D</sub>(t)</i>            | instantaneous diode current     |

| $i_{L}(t), i_{L1}(t), i_{L2}(t),$  | instantaneous inductor current  |

| $i_{c}(t), i_{c1}(t), i_{c2}(t)$   | instantaneous capacitor current |

| <i>i</i> <sub>o</sub> ( <i>t</i> ) | instantaneous output current    |

| $K_{p}, K_{i}$                     | Proportional and integral gains |

| L, L <sub>1</sub> , L <sub>2</sub> | Inductor                        |

| C, C <sub>1</sub> , C <sub>2</sub> | Capacitor                       |

| R                                  | Load resistance                 |

| D                                  | Duty cycle                      |

| D'                                 | 1- <i>D</i>                     |

| r <sub>d</sub>                     | Diode forward resistance        |

| r <sub>sw</sub>                    | Switch on-resistance            |

| r <sub>x</sub>                     | $Dr_{sw}$ + $D'r_d$             |

| $r_{L,} r_{L1,} r_{L2}$            | ESR of Inductor                 |

| $r_{c,} r_{c1,} r_{c2}$            | ESR of capacitor                |

| V <sub>F</sub>                     | Diode forward voltage drop      |

|                                    |                                 |

[This chapter describes the introduction of the thesis. The basic overview of power electronic converter and classifications of DC-DC converters are presented. The motivation of the work and thesis outlines is discussed.]

#### 1.1 Overview

In the modern world, electric power has become a necessity for domestic appliances as well for industrial applications. There are various applications, which require the electric power in different forms like AC (Alternative current) or DC (direct current), constant or variable voltage, fixed or variable frequency, *etc.* Generally, at the consumer end, the electrical power is supplied in AC form with fixed voltage magnitude and fixed frequency (50 or 60 Hz). Therefore, to meet the demands of the different consumers, various types of power electronic converters have been developed. They convert one form of electrical power into another required form. Broadly, the power electronic converters can be classified into four types [1]–[3]:

1. AC-DC converters: These power electronic circuits convert AC voltage into a fixed or variable DC voltage. For example, diode rectifiers convert AC voltage into fixed DC voltage, whereas phase controlled rectifiers convert AC voltage into variable DC voltage.

2. DC-AC converters: They are also known as inverters. The input voltage to this converter is DC, which is converted into AC voltage of desired magnitude and frequency by varying the conduction period of the switches.

3. AC-AC converters: They convert fixed frequency and fixed magnitude AC voltage into variable magnitude AC voltage with same or variable frequency. For example, AC voltage regulators convert fixed AC voltage into variable AC voltage with the same frequency, whereas cyclo-converters give variable AC output voltage with variable frequency.

4. DC-DC converters: These converters transform electrical power of fixed DC voltage into variable DC voltage by controlling the conduction time of the switching devices.

In this thesis, the research work related to DC-DC converters have been carried out and discussed in the subsequent sections and chapters.

### 1.2 Introduction to DC-DC Converters

Modern electronic systems require high quality, compact, light-weight, reliable and efficient power supplies. For conventional low-power applications, the linear voltage regulators have generally been used. These linear regulators work on the principle of voltage divider circuit. The linear regulator can provide the output voltage only lower than the input voltage. Moreover, their energy conversion efficiency and power density are also low [1], [2], [4]. This makes them unsuitable for high power applications. For higher power applications, switching mode DC-DC converters are used. The switching mode DC-DC converters use the

power semiconductor switches, which either operate in saturation or cut off region [1]. Since the power loss is very small in these switches during the operation, the switching mode DC-DC converters can achieve higher energy conversion efficiency. Further, the modern semiconductor devices can operate at high frequencies leading to overall compact size due to reduction in the inductor and capacitor values [5], [6]. The switching mode DC-DC converters are now extensively used in the variety of industrial as well domestic applications owing to the advantages of controllable output voltage, compact size, light-weight and higher conversion efficiency [7]. Some of these applications include computer power supplies, aerospace instruments, fuel cells, medical instruments, power factor correction schemes, battery chargers, variable speed dc motor drives, telecommunication equipments, electrical vehicles, military instruments, chemical refineries, *etc* [8]–[21].

It is desirable to have minimum losses in the DC-DC converters while converting one level of DC voltage to another level. Therefore, to reduce the power losses, only inductors and capacitors are used in DC-DC converters (because ideally they have no losses). These passive components along with the semiconductor switches are assembled in different ways to obtain various topologies, each one having different properties [3], [22], [23]. In the literature, there are several classifications of DC-DC converters topologies based on the different criterion. However, the important DC-DC converters can be classified as follows:

*Non-isolated DC-DC converters:* In these converters, the load and input voltage source are not isolated electrically. There are several such topologies available in literature. The important topologies are: Buck converter, Boost converter, Buck-boost converter, Cuk converter, Zeta converter, SEPIC converter, *etc*.

*Isolated DC-DC converters:* In these DC-DC converters, the electrical isolation is provided between the input voltage source and load by means of a high frequency isolation transformer. The basic configurations are forward converter, flyback converter, push-pull converter, half bridge converter, full bridge converter, *etc*.

Further, several classifications are possible based on numbers of output (single output or multiple output), inductor current flow (continuous conduction mode (CCM) or discontinuous conduction mode (DCM)), magnitude of output voltage (buck, boost, buck-boost), *etc.* In continuous conduction mode (CCM), the inductor current is always positive during the entire switching period, whereas in discontinuous conduction mode (DCM), the inductor current becomes zero for a certain portion of switching period.

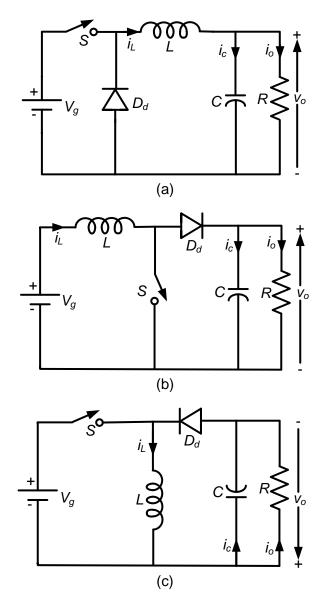

Based on the output voltage magnitude, a DC-DC switching converter can broadly be classified into the three categories: buck, boost and buck-boost. The basic topologies are shown in Fig. 1.1.

Fig. 1.1. Basic DC-DC converter topologies (a) Buck (b) Boost (c) Buck-boost

Fig. 1.2. DC-DC Cuk converter topology

The buck converter has an output voltage lower than the input voltage. It gives a continuous output current and lesser output voltage ripple requiring low value of capacitance. However, the input current is discontinuous (pulsed) in this topology, which requires the input filter. The boost converter provides an output voltage greater than the input voltage. The

input current is continuous, which eliminates the need of input filter. However, the output current is discontinuous (pulsed) in this topology and therefore, requires high value capacitance to reduce the output voltage ripple. The buck-boost converter gives an output voltage, which can be lower, equal or higher than the input voltage. The input current and output current both are discontinuous. The polarity of output voltage is opposite of the input voltage. These three basic topologies of DC-DC converters have simple configurations involving only one semiconductor switch, one diode, one inductor and one filter capacitor. These converters are second-order systems.

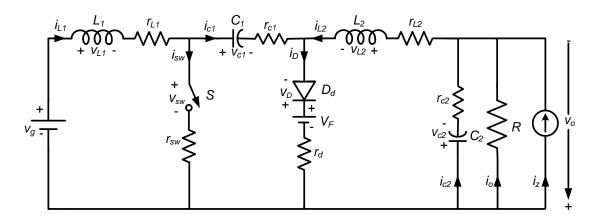

The advantages of these three converters can be combined in a single DC-DC converter arising a new topology named as Cuk converter [24],[25]. The circuit configuration of Cuk converter is shown in Fig. 1.2. This DC-DC converter provides continuous inductor current and continuous output current. The output voltage can be lower, equal or higher than the input voltage. Similar to buck-boost converter, the output voltage polarity is reverse of the input voltage. This converter involves two inductors and two capacitors. Therefore, it is a fourth-order system.

However, there are two other topologies similar to Cuk converter, which provides the output voltage with the same polarity as the input voltage. The topologies are DC-DC Zeta and SEPIC converters [26]–[28]. However, the Zeta converter suffers from discontinuous (pulsed) input current similar to buck converter and SEPIC converter suffers from discontinuous (pulsed) output current similar to boost converter. The Zeta and SEPIC converters are also fourth-order systems.

#### **1.3 Motivation to the Research Work**

In the previous section, it was discussed that there are several DC-DC converter topologies utilized in various applications. To meet the user requirements, it is necessary to decide the proper ratings of the different components of the particular DC-DC converter topology [29]–[40]. There are several factors, which decide the rating of the various passive elements and semiconductor devices used in the design of DC-DC converters [41], [42]. These factors are DC input voltage, DC output voltage, input current ripple, output voltage ripple, output power and switching frequency, *etc.* For an ideal DC-DC converter, the inductor current ripple, the high value of inductance is required [43]. However, the inductance value can be reduced by increasing the converter switching frequency. In practice, an inductance has small resistance, which causes some power losses in DC-DC converters. Therefore, inductor with low resistance is always preferred. The ferrite core inductors are normally used in the DC-DC converters operating at high switching frequencies. However, in the research papers and textbooks, the design equations of the inductors and capacitors do not involve the effect of all the non-idealities present in the elements. Similarly, the design of

capacitor is also an important issue for DC-DC converters. The capacitor value depends on the specified voltage ripple and switching frequency. However, the equivalent series resistance (ESR) of capacitor directly affects the output voltage ripple. The voltage ripple increases with the ESR. The various techniques has been reported in literature for output voltage ripple estimation and reduction [44]–[52]. Therefore, a proper analysis of ESR effect on the output voltage ripple on DC-DC converter is necessary, which is carried out in this thesis.

In addition to the design issues, the modeling of the switching converters has always been a topic of wide interest for power electronics engineers [1], [2], [25], [53]–[61]. In order to achieve the desired performance of a controller for DC-DC converters, an accurate model of DC-DC converter is required. In the last few decades, several techniques have been developed in literature to obtain the mathematical model of DC-DC converters such as state space averaging (SSA) method [58], [62]–[65], averaged switch model [66]–[68], energy factor approach [69], [70], transformer equivalent modeling method [3],[71], current injected equivalent circuit (CIEC) approach [72], [73], switching flow graph (SFG) technique [74], [75], bond graph technique [76], *etc.* These techniques are useful for modeling of DC-DC converter dynamics. It is observed in the literature that the converter models are generally obtained by neglecting the converter non-idealities. However, incorporation of non-idealities is an important aspect for getting more accurate mathematical models.

Further, the development of simple and efficient control algorithms for these converters is an interesting aspect for control engineers and researchers devoted in this area. A suitable controller is required to achieve the output voltage regulation of DC-DC converters in the presence of input voltage disturbances, load variations or set point (reference output voltage) variations and parameter variations. Especially, the controller design requires special attention as the order of DC-DC converters increases (due to increase in energy storage elements such as inductors and capacitors). The main objective of the controller design for DC-DC converters is to generate the switching pulses for the semiconductor devices with a duty cycle such that the DC output voltage is equal to the reference voltage. This output voltage regulation should be maintained despite variations in any operating conditions (such as load current, input voltage). This can be achieved by varying the duty cycle of the semiconductor switching device (hence the switch-on time) keeping the switching frequency constant. For this purpose, pulse-width modulation (PWM) technique is generally used. Therefore, the control problem is to monitor this duty cycle continuously so that the proper switching pulses are generated. The voltage mode control and current mode control are generally used for DC-DC converters in conjunction with suitable controller. In literature, many control design techniques are discussed, e.g. PI/PID controller, lag compensator, lead compensator, lag-lead compensator, pole-placement technique, fuzzy controller, genetic

5

algorithm based controller, sliding mode controller, H-infinity controller, *etc* [77]–[105]. All these control techniques have their own advantages and disadvantages depending upon the applications. However, there is always a scope to improve these techniques for better performance of the DC-DC converters. Further, the Cuk converter is a fourth-order system and therefore, the several model-order reduction techniques available in the literature can be used to obtain its reduced-order model [106]–[109]. The reduced-order model can be used to design the controller for the original system with less computational efforts.

In summary, for any DC-DC converter, one first needs to design its parameters for specified user requirements. Then, carry out its mathematical modeling and finally, design a suitable controller to regulate the output voltage under various working conditions. Therefore, in this thesis, the research work is carried out on these three aspects of DC-DC converters, which are as follows:

- 1. Design of DC-DC converters

- 2. Mathematical modeling of DC-DC converters

- 3. Control design techniques for DC-DC converters

As discussed earlier, there are several DC-DC converter topologies, but in this thesis, these three aspects are discussed detail for non-ideal DC-DC buck converter and Cuk converter.

#### **1.4** Contribution of the Author and Thesis Organization

Although lot of research work have been carried out in the field of design, modeling and control of DC-DC converters. In this thesis an attempt has been made to contribute further in these three aspects of the DC-DC converters. In the literature, it is found that the effect of all the non-idealities has not been considered while designing the converter parameters and modeling the DC-DC converters. These non-idealities are present in the form of equivalent series resistances (ESRs) of inductors and capacitors, parasitic resistances of the diode and MOSFET during conduction and the forward voltage drop of the diode. In this thesis, the effect of all the non-idealities has been incorporated. The detailed contribution of the author has been reported in the subsequent chapters of the thesis. This thesis has five more chapters in addition to this introduction chapter. The brief descriptions of the author's contribution in each chapter are outlined as follows:

In Chapter 2, the improved expressions of the duty cycle are derived for the non-ideal DC-DC buck converter and Cuk converter. The effect of the non-idealities is included. Based on the improved expression, the design equations for inductor and capacitor calculations are also modified for these two converters. The improved expressions show that the duty cycle also depends on load resistances and non-idealities along with the input voltage. Further, with the detailed analysis of the capacitor voltage ripple, a formula for the maximum

allowable value of the capacitor ESR is developed for non-ideal buck converter and Cuk converter. This expression gives the maximum value of ESR for specified output voltage ripple and inductor current ripple at a particular frequency. For the Cuk converter, the design formula for input capacitor is also modified to incorporate the effect of its ESR. The theoretical studies are then validated by both simulation and experimental results.

Chapter 3 presents a detailed mathematical modeling of non-ideal DC-DC buck and Cuk converter based on state-space averaging technique, averaged switch model technique and energy factor approach. The parasitic resistances and diode voltage drop are included in the improved mathematical model of these converters. In the state-space averaging technique, the Leverrier's algorithm is used to derive the various transfer functions of the non-ideal converter. The comparisons of mathematical models in the case of ideal converter and non-ideal converter are presented, which shows that the mathematical modeling of the non-ideal converter gives more information of the physical converter, which are not revealed if the converter is assumed ideal.

In Chapter 4, the different classical control techniques are discussed which are based on the transfer function model of non-ideal DC-DC buck and Cuk converter. In this chapter, a PI controller has been designed for the buck and Cuk converter using the stability boundary locus approach based on the specified phase margin. It is seen that the PI controller is useful to eliminate the steady-state error in output voltage, but the transient response is not very good. Therefore, a PI-lead control technique has been presented. An algorithm has been proposed to tune the parameters of this PI-lead controller based on desired phase margin and gain crossover frequency. This algorithm provides the analytical formulae, which give the phase margin and gain crossover frequency exactly as specified. The PI-lead controller results in improved transient response. However, this controller contributes noise in output voltage for higher bandwidth. To improve the output voltage response of DC-DC converters further, a two-loop control scheme has been reported in this chapter. This control scheme has one inner current PI controller and one outer voltage PI controller. An algorithm is proposed for tuning the parameters of these two PI controllers based upon the desired phase margin and gain crossover frequency specifications. The beauty of the proposed algorithm is that the designed controller simultaneously satisfies the desired phase margin and crossover frequency requirements. As the Cuk converter is a fourth-order system, therefore, its reduced second-order model has also been obtained by means of model-order reduction techniques. Then, the PI controller is design based on reduced second-order model. It requires less computational effort for controller design in comparison to original fourth-order model. The controller thus obtained is implemented on actual fourth-order Cuk converter and shows good performance almost similar to the PI controller designed with original model.

All the control techniques are validated on the hardware prototypes of DC-DC buck and Cuk converters under various operating conditions and show the close agreement with MATLAB simulation results.

Chapter 5 describes the sliding mode control of DC-DC Cuk converter. The various transfer functions are obtained to analyse the closed-loop dynamics of sliding mode controlled Cuk converter. A simplified technique is suggested to tune the parameters of the controller. The simulation and experimental results are presented to validate the performance of the designed controller.

Finally, the conclusion of this complete work and possible future scope are summarized in chapter 6.

The appendixes and important references used in this entire work are given at the end of this thesis.

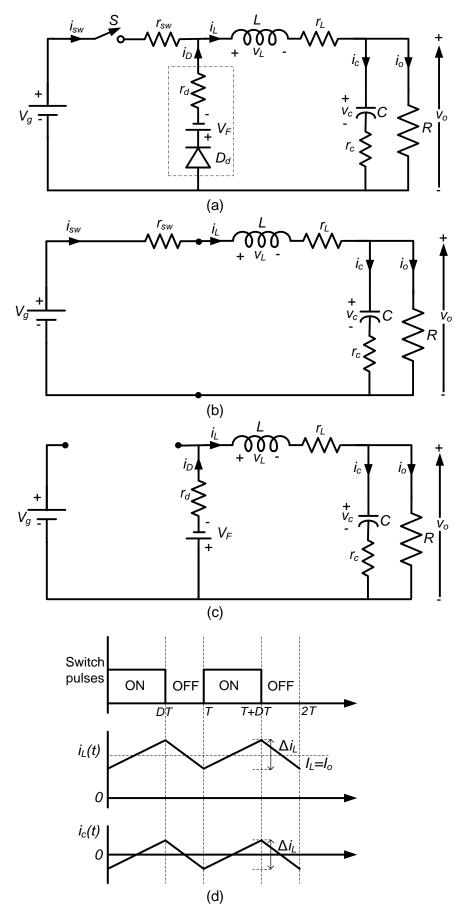

[In this chapter, various design issues related to non-ideal DC-DC Buck and Cuk converters have been covered in detail. The effects of all the non-idealities present in the converter elements are included.]

#### 2.1 Introduction

DC-DC converters are widely used as power supply in various applications. Some applications like aerospace, military, chemical refineries and mines require tightly regulated, optimally designed and compact power supplies. For such applications, the optimum design of inductance and capacitance for DC-DC converters is required [110]–[113]. In most of the research papers and text-books, the analysis and design have been carried out by assuming the converter's elements to be ideal [1]–[3], [48], [114]. However, the elements of the DC-DC converters are not ideal in practice and have many non-idealities [115]–[117]. These non-idealities are present in the form of equivalent series resistances (ESRs) of inductors and capacitors, parasitic resistances of the MOSFET and diode during conduction and the forward voltage drop of diode. These non-idealities affect the performance and parameter design of DC-DC converter, which is not acceptable for an accurate and well-designed power supply. For example, the expressions of duty cycle for an ideal buck and Cuk converter operating in continuous conduction mode (CCM) are given as:

For buck converter,

$$D_{ideal} = \frac{V_o}{V_g}$$

(2.1)

For Cuk converter,

$$D_{ideal} = \frac{V_o}{V_o + V_c}$$

(2.2)

Where,  $V_{\alpha}$  is the input voltage and  $V_{\alpha}$  is the output voltage.

The above expressions are derived by assuming that all the elements in buck and Cuk converter are ideal [2], [3]. Therefore, in practical (lossy) buck and Cuk converter, these ideal duty cycle expressions do not provide the desired output voltage  $V_o$  for given input voltage  $V_g$ . This is because of the voltage drops (or power losses) occurring across the non-ideal components. To compensate these voltage drops or power losses, the actual duty cycle should be greater than the ideal duty cycle given by (2.1) and (2.2). Similarly, the proper design of the converter parameters is essential for achieving the desired performance. This requires in-depth analysis of converter circuit and its operation. In this chapter, a detailed analysis of non-ideal DC-DC buck converter and Cuk converter are carried out to obtain the improved design equations for inductor and capacitors.

Similarly, the capacitor design and correct estimation of output voltage ripple (OVR) are important issues for DC-DC converters, especially in high performance applications [49], [118], [119]. The equivalent series resistance (ESR) of the output capacitor plays an

important role in the design of capacitor for specified output voltage ripple. The low ESR capacitor results in lesser output voltage ripple. On the other hand, large ESR increases the output voltage ripple, hence requiring the higher value of capacitance. Moreover, ESR may also affect the stability and increase the power loss in converters [46], [120]–[122]. Therefore, the arbitrary value of ESR is not advisable for a precisely designed DC-DC converter. The ESR of a capacitor is a parasitic parameter that cannot be avoided by a capacitor manufacturer. However, from a power supply designer's point of view, a capacitance with low ESR is always preferable [50]. In literature, no analytical solution is available to determine the upper limit of ESR, which can be used without exceeding the specified output voltage ripple at a particular switching frequency. In this chapter, with detailed analysis of capacitor voltage ripple, a formula for the maximum allowable value of the capacitor ESR is developed for non-ideal buck converter and Cuk converter.

In the following sections, all these design issues are investigated for non-ideal DC-DC buck and Cuk converters.

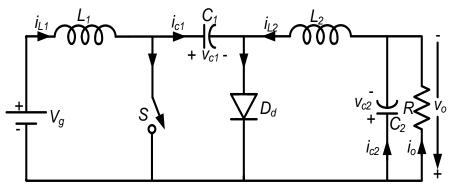

#### 2.2 Analysis of Non-ideal DC-DC Buck Converter

The basic circuit of a non-ideal DC-DC buck converter is shown in Fig. 2.1(a). It consists of a power MOSFET switch *S*, diode  $D_{d_1}$  inductor *L*, capacitor *C* and load resistance *R* [1], [3]. For accurate analysis and design of the converter parameters, the non-idealities have been included in this circuit. These non-ideal elements are represented as equivalent series resistance (ESR) of inductor  $r_L$ , ESR of capacitor  $r_c$ , switch on-resistance  $r_{swn}$ , diode forward resistance  $r_d$  and diode forward voltage drop  $V_{F}$ . The values of these parasitic resistances are very small in comparison to load resistance *R*. The buck converter can operate in continuous conduction mode (CCM) and discontinuous conduction mode (DCM). However, in this thesis, the converter is assumed to operate in a continuous current conduction mode (CCM) with static duty cycle *D* and switching frequency  $f_s$  (or switching period *T*). The duty cycle *D* is the ratio of time duration for which switch is on ( $t_{on}$ ) to the total switching period (*T*). Mathematically,

$$D = \frac{t_{on}}{t_{on} + t_{off}} = \frac{t_{on}}{T} = t_{on}f_{s}$$

(2.3)

Where,  $t_{on}$  is the time interval for which the switch is on and  $t_{off}$  is the time interval for which the switch is off.

From (2.3), we get

Switch-on time

$$t_{op} = DT$$

(2.4)

Switch-off time  $t_{off} = (1 - D)T = D'T$  (2.5) Where D'=1-D

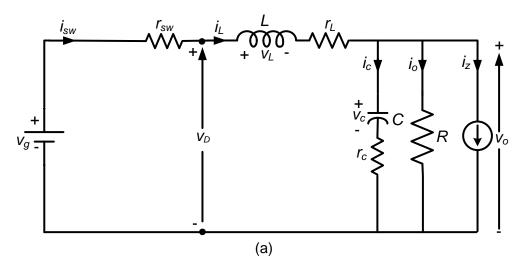

Fig. 2.1.(a) Basic circuit of a non-ideal DC-DC buck converter (b) equivalent circuit when the switch is on (c) equivalent circuit when the switch is off (d) associated waveforms

In continuous current conduction mode, the buck converter has two circuit states (a) when MOSFET switch conducts and diode remains off (b) when MOSFET switch remains off and diode conducts. The analysis of non-ideal buck converter in these two states is discussed in detail as follows:

### 2.2.1 When the switch is on (time interval $0 < t \le DT$ )

The corresponding equivalent circuit of a non-ideal DC-DC buck converter is shown in Fig. 2.1(b) for the time interval  $0 < t \le DT$ . In this duration, the MOSFET switch S is conducting and diode  $D_d$  is off. The switch is represented by its on-resistance  $r_{sw}$  and diode is represented as an open circuit. The switch current ( $i_{sw}$ ) is equal to inductor current ( $i_L$ ) and the diode current ( $i_D$ ) is zero. The input power source supplies the power for inductor energy storage and load resistance. In this mode, the capacitor is discharged initially by the load resistance and then charged by the input current. The corresponding important waveforms are given in Fig. 2.1(d).

Using the Kirchhoff's voltage and current law (KVL and KCL), the voltage across inductor *L*, the current through capacitor *C* and the output voltage are given as:

$$v_{L,on}(t) = L \frac{di_{L}(t)}{dt} = v_{g}(t) - (r_{L} + r_{sw})i_{L}(t) - v_{o}(t)$$

(2.6)

$$i_{c,on}(t) = i_L(t) - \frac{v_o(t)}{R}$$

(2.7)

$$\mathbf{v}_{o,on}\left(t\right) = \mathbf{v}_{c}\left(t\right) + r_{c}i_{c}\left(t\right)$$

(2.8)

### 2.2.2 When the switch is off (time interval $DT < t \le T$ )

The corresponding equivalent circuit of a non-ideal DC-DC buck converter is shown in Fig. 2.1(c) for time interval  $DT < t \le T$ . In this duration, the MOSFET switch *S* is off and diode  $D_d$  is conducting. The diode is represented by its on-resistance  $r_d$  and switch is represented as an open circuit. The diode current  $(i_D)$  is equal to inductor current  $(i_L)$  and the switch current  $(i_{sw})$  is zero. In this mode, the load is disconnected from the input power source. The energy stored in the inductor is used to feed the power to load resistance. The capacitor is charged initially by inductor energy and then discharged by load current. The corresponding important waveforms are given in Fig. 2.1 (d).

Using the Kirchhoff's voltage and current law (KVL and KCL), the voltage across inductor L, the current through capacitor C and the output voltage are given as:

$$v_{L,off}(t) = L \frac{di_{L}(t)}{dt} = -(r_{L} + r_{d})i_{L}(t) - V_{F} - v_{o}(t)$$

(2.9)

$$i_{c,off}(t) = i_L(t) - \frac{v_o(t)}{R}$$

(2.10)

$$\boldsymbol{v}_{o,off}\left(t\right) = \boldsymbol{v}_{c}\left(t\right) + \boldsymbol{r}_{c}\boldsymbol{i}_{c}\left(t\right)$$

(2.11)

### 2.2.3 Steady-state analysis

For steady-state analysis, the average value Z of a current and voltage variable z(t) can be given as [3]:

$$Z = \frac{1}{T} \int_{0}^{T} z(t) dt = \frac{1}{T} \int_{0}^{DT} z_{on}(t) dt + \frac{1}{T} \int_{DT}^{T} z_{off}(t) dt$$

(2.12)

Where,  $z_{on}(t)$  and  $z_{off}(t)$  represent the variable z(t) during switch on and switch off, respectively.

According to the principle of inductor volt-second balance, in steady-state, the average inductor voltage must be equal to zero *i.e.*,