## PERFORMANCE ENHANCEMENT OF MULTILEVEL INVERTER FOR INDUCTION MOTOR DRIVE

Ph.D. THESIS

by

SANJIV KUMAR

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) JULY, 2016

## PERFORMANCE ENHANCEMENT OF MULTILEVEL INVERTER FOR INDUCTION MOTOR DRIVE

#### A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree

of

#### DOCTOR OF PHILOSOPHY

in

#### ELECTRICAL ENGINEERING

by

#### SANJIV KUMAR

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) JULY, 2016

©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2016 ALL RIGHTS RESERVED

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

## **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in this thesis entitled **"PERFORMANCE ENHANCEMENT OF MULTILEVEL INVERTER FOR INDUCTION MOTOR DRIVE ",** in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electrical Engineering of the Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from July, 2012 to July, 2016 under the supervision of Dr. Pramod Agarwal, Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

(Sanjiv Kumar)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

(Pramod Agarwal) Supervisor

Dated: \_\_\_\_\_

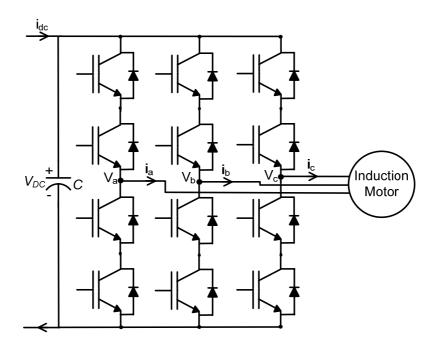

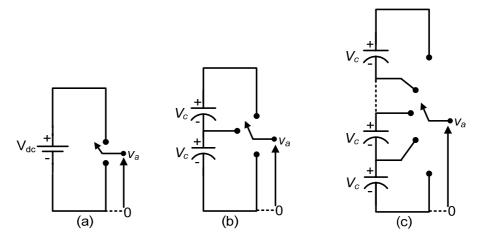

Conversion from electrical energy to mechanical energy is an important process in modern industrial civilization and it is done by means of electrical machines. About half of the electrical energy generated in a developed country is ultimately consumed by electric motors, of which 90% are induction motors as they are simple, rugged and cheap. The rapid development of power electronic devices and converter technologies in the last few decades has made possible to develop energy efficient adjustable speed induction motor drives. The conventional two-level voltage source inverters (VSIs) are widely used in induction motor drive applications due to the simple structure, control, reliability as well as cheaper parts. In recent years, industries have begun to use high power equipment, which now are at megawatt levels. In high power and high performance drive applications, two-level VSIs suffers from problems like high dv/dt, higher switching loss, poor power quality, higher common-mode voltages and electromagnetic interference (EMI). Adjustable speed drives in megawatt range are usually connected to medium-voltage network due to restriction on current rating at low-voltage, therefore to connect the conventional two-level VSI with medium-voltage network several switching devices are to be connected in series. All the series connected switching devices should have accurate static and dynamic voltage sharing circuit which is not practically possible.

Multilevel inverter (MLI) approach, on the other hand offers low dv/dt stress, good power quality, low switching loss, high voltage capability and good electro-magnetic compatibility (EMC) even at high power applications. Use of several levels of DC-voltage enables MLI to achieve better quality output voltages at low switching frequency. MLI topologies require more device count, but they are modular in structure and compact in size as they require reduced size output filter and transformer or none of them. Due to above features multilevel inverters emerge as an attractive solution for high power and high performance medium-voltage induction motor drives.

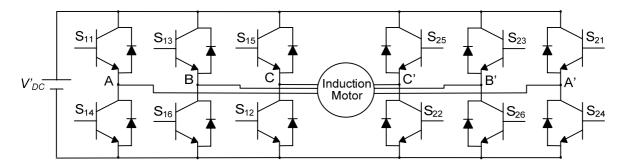

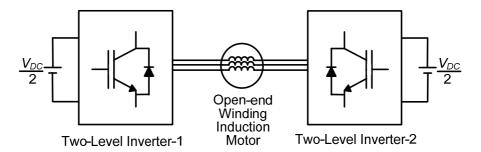

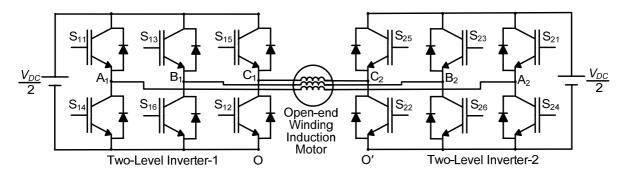

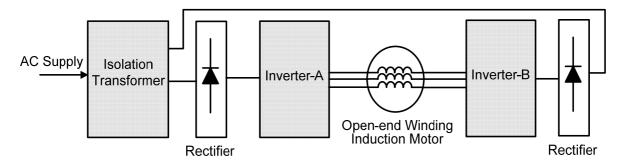

Induction motors used in electric drives are either delta or star connected with three terminals and the motors are fed using two-level VSIs. In open-end winding induction motor, this delta or star connection is opened and the motor now has six terminals. The performance equivalent to 3-level inverter can be obtained by feeding these six terminals of open-end winding induction motor from both sides using two three-phase two-level VSI. There are certain advantages of the open-end winding method, such as common-mode voltage reduction and increase in the voltage transfer ratio. The multilevel inverter topologies proposed in the thesis uses this dual inverter fed open-end winding configuration for the induction motor.

The present work is carried out to improve the performance of MLI for induction motor drive with simplified modelling, control and implementation. Problems associated with

i

conventional two-level voltage source PWM (Pulse Width Modulation) inverter fed induction motor drives are addressed first. Their possible solutions and recent trends are discussed. Different MLIs topologies along with their features, technical challenges, applications, historical developments and research gaps are discussed. A comprehensive literature survey on MLI including various MLI topologies, diverse modulation and control schemes for induction motor are given in detail. MLI for induction motor drive is designed, developed and investigated.

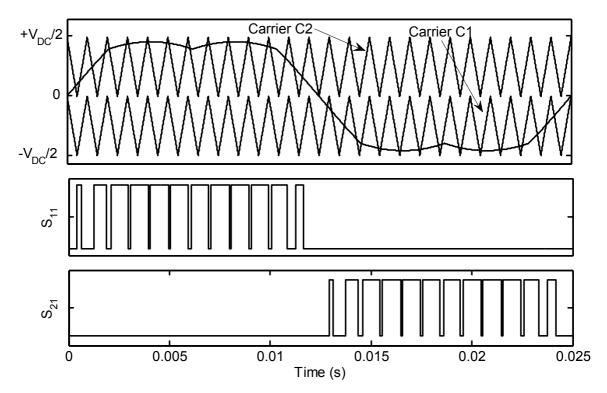

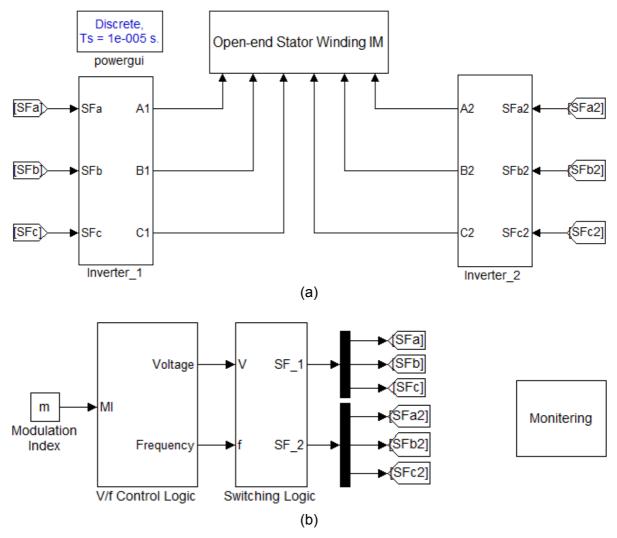

In the literature, it has been shown that an open-end winding induction motor drive fed with two-level VSI inverters produce phase voltage waveforms and voltage space vector locations similar to a conventional 3-level inverter. This dual two-level (D2L) configuration is taken as the first investigative object. A mathematical model of the squirrel cage open-end stator winding induction motor in stationary reference is developed along with switching function based D2L inverter model. The carrier based space vector pulse width modulation (SVPWM) scheme is used to generate the control pulses for switching devices. To investigate the performance of SVPWM based D2L inverter scheme for open-end induction motor drive under steady-state and dynamic conditions simulation study is carried out in MATLAB/Simulink environment. The developed motor model is operated in constant *V/f* mode under no-load condition covering the entire range of modulation. Various simulation results are obtained and analyzed for performance evaluation.

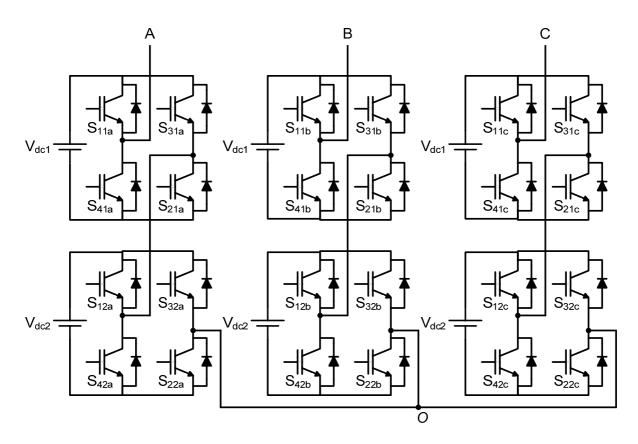

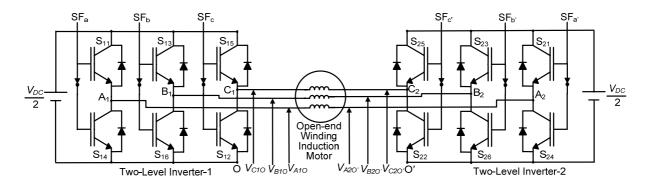

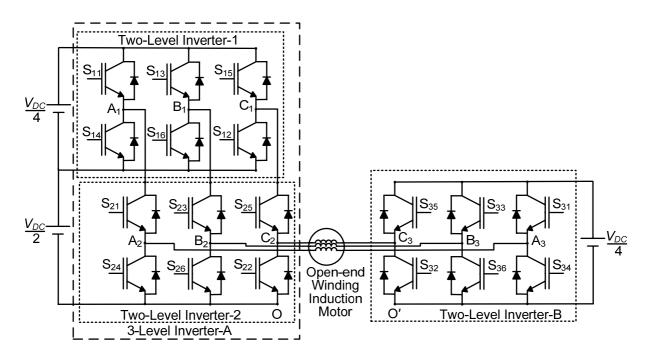

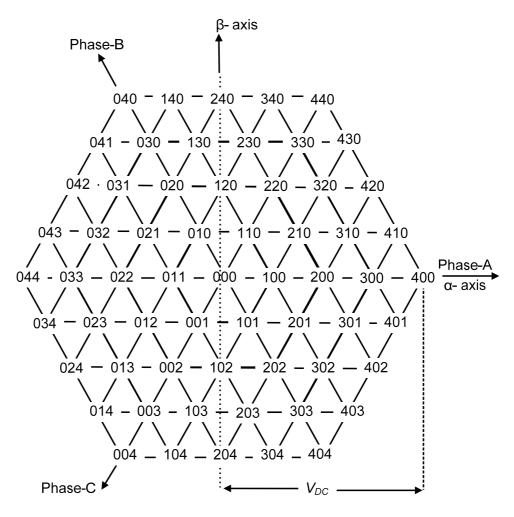

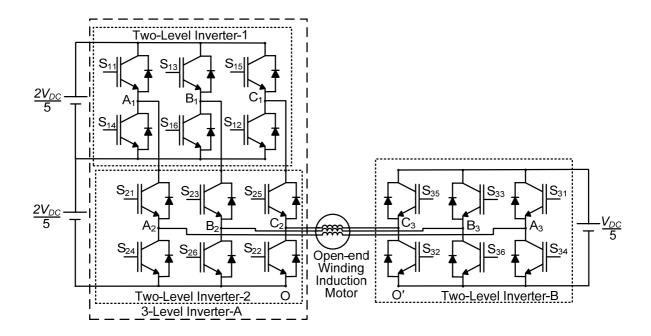

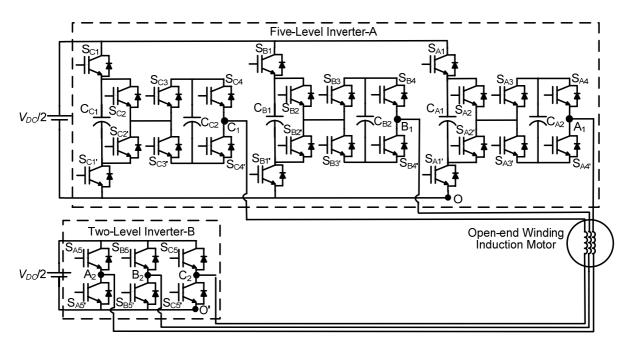

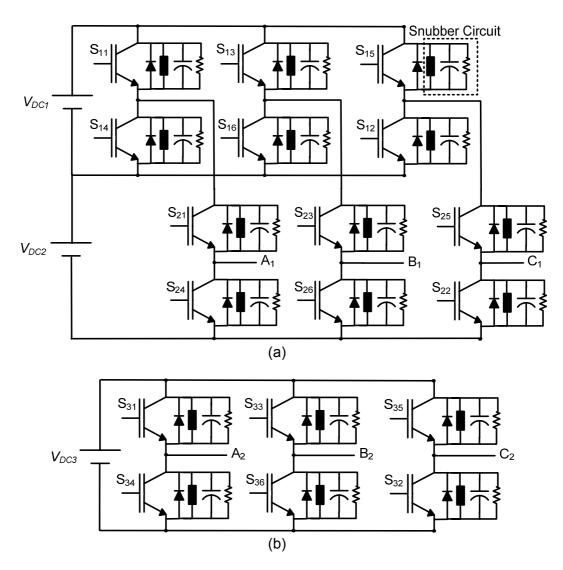

A 5-level inverter configuration based on conventional 2-level inverters is selected as a second investigative object. The open-end winding induction motor is fed by 3-level inverter from one end and the other end is fed by two-level inverter. The combined effect of these two inverters generates five levels as  $-V_{DC}/4$ , 0,  $+V_{DC}/4$ ,  $+V_{DC}/2$  and  $+3V_{DC}/4$ , where  $V_{DC}$  is the equivalent DC link voltage of the conventional two-level inverter fed induction motor drive. The 3-level inverter is realized by cascading two conventional two-level inverters. All three conventional two-level inverters are powered by isolated DC sources. This scheme uses asymmetrical DC link voltages to generate five levels in phase voltage of induction motor. A total of 512 space vector combinations are possible with this configuration which are distributed over 61 space vector locations. It has been shown that the same 5-level inverter circuit can produce six levels as  $-V_{DC}/5$ , 0,  $+V_{DC}/5$ ,  $+2V_{DC}/5$ ,  $+3V_{DC}/5$  and  $+4V_{DC}/5$  by selecting a proper ratio of DC link voltages of individual two-level inverters. A switching function based mathematical model is developed and simulated with MATLAB/Simulink. The 5-level inverter performance is evaluated in MATLAB by running a 1.5 kW open-end winding induction motor model at no-load in V/f control mode. In the simulation results, it is found that the adopted scheme generates the voltage levels similar to conventional 5-level inverters.

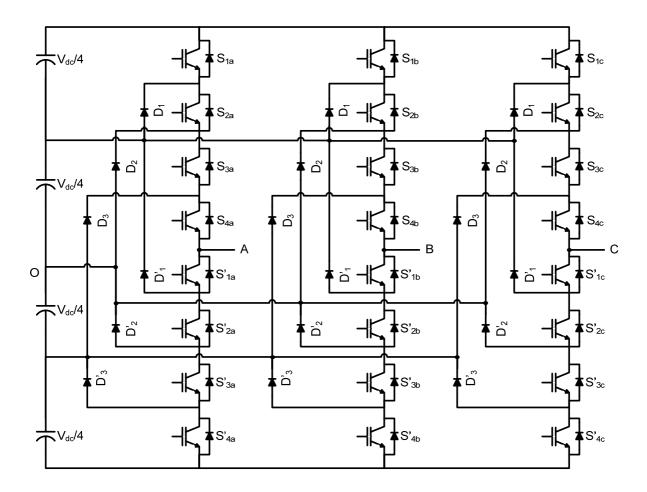

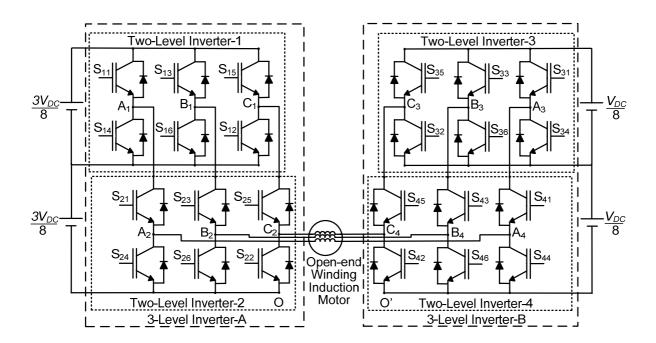

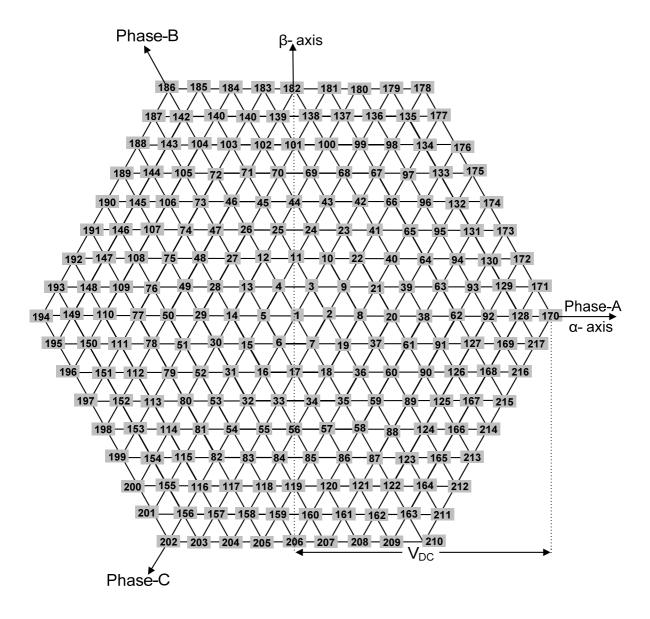

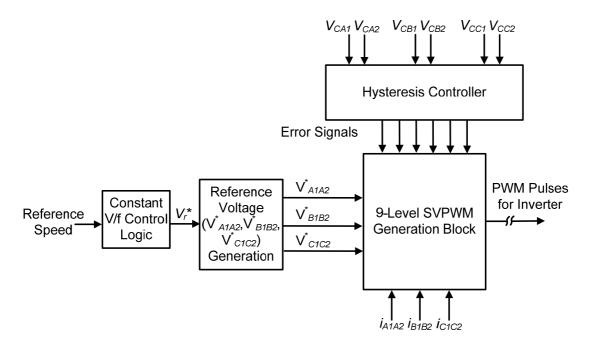

To generate high resolution voltage space vectors with reduced number of components for an open-end winding induction motor, a 9-level inverter scheme is proposed. The 9-level inverter operation is realized by feeding both ends of the open-end winding by two 3-level inverters with asymmetrical DC link voltage. These 3-level inverters are realized by cascading two 2-level inverters. The total DC link voltage  $V_{DC}$  is divided into two 3-level inverters in the ratio of  $3V_{DC}/4$  and  $V_{DC}/4$ . The proposed topology completely eliminates the requirement of clamping diodes and DC-link capacitors which are needed in the neutral point clamped (NPC) inverter. It also eliminates eighty four capacitors of rating  $V_{DC}/8$  which are required in case of 9-level FC inverter topology. Compared to the conventional cascade Hbridge topology, the proposed inverter requires less number of power supplies. The flow of triplen harmonic current through the switches and motor windings is not possible in the proposed scheme due to use of four isolated DC supply. A modified level shifted triangular carrier based SVPWM technique is used for the proposed drive system. The proposed PWM scheme is capable of ensuring a smooth changeover from the mode of two-level inversion to the 3-level, then 3-level to 4-level, then from 4-level to 5-level and so on up to 9-level inversion and vice versa. This feature reduces the switching losses at lower speed range. A switching function based mathematical model of the proposed drive system is developed and validated by detailed analytical results in MATLAB/Simulink environment.

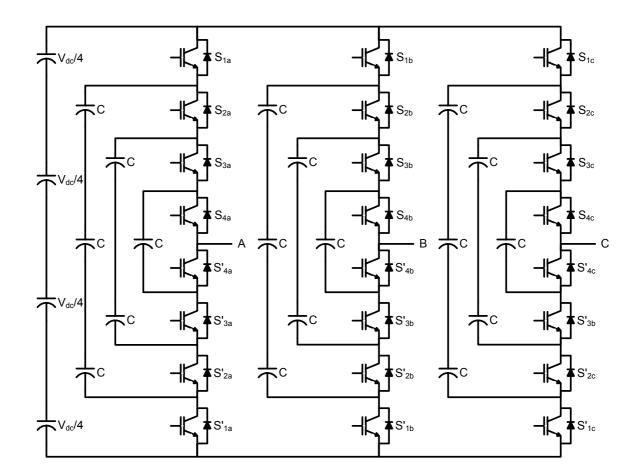

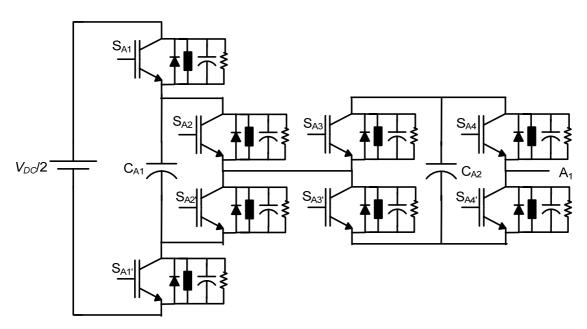

A hybrid 9-level inverter is another configuration proposed in the thesis to reduce the requirement of four isolated DC sources of two different voltage rating into two isolated DC sources of the same voltage rating. The proposed topology is realized by feeding one end of the open-end winding induction motor by 5-level hybrid inverter and the other end by conventional two-level inverter. The three phase hybrid 5-level inverter is realized by cascading a 3-level flying capacitor (FC) inverter with capacitor fed H-bridge in each phase. The capacitor voltages are maintained at desired voltage level for the entire modulation range and also during transient operation by making use of redundant switching states available for generating different voltage levels. The proposed topology is capable of operating as 5-level inverter at full load in case of failure of H-bridge by simply bypass the faulty H-bridge; this feature enhances the reliability drive of the system. The proposed topology is compared with conventional topology in terms of the number of components used. The proposed inverter requires thirty IGBTs whereas the conventional topologies NPC, FC and CHB topology based 9-level inverters require forty eight IGBTs. As compared to asymmetrical cascade H-bridge (ACHB) topology which requires six isolated DC supply of two different voltages rating the proposed topology needs only two isolated DC supplies of the same rating. The proposed topology requires only six capacitors out of which three are of voltage rating  $V_{DC}/4$  and three are of voltage rating  $V_{DC}/8$  on the other hand, conventional 9level FC inverter requires eighty four capacitors of voltage rating  $V_{DC}/8$ . The conventional

iii

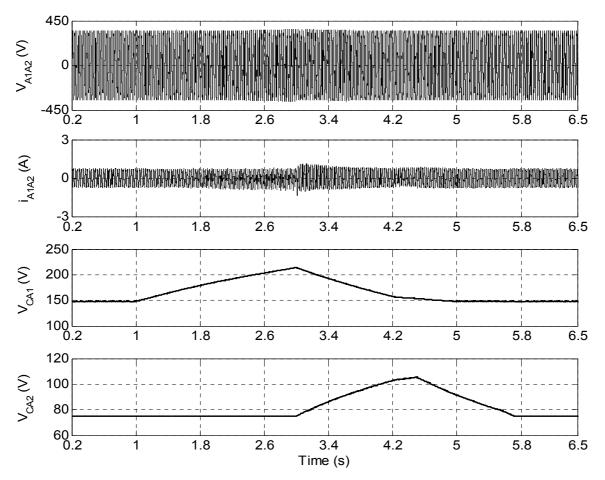

NPC 9-level inverter requires 168 clamping diodes and eight capacitors of voltage rating  $V_{DC}/8$ ; this requirement is completely eliminated in the proposed hybrid 9-level inverter. In the proposed inverter semiconductor switching devices which operated at a higher DC voltage switch less, hence low switching frequency rating devices can be used. As both sides inverters are fed by isolated DC supply so zero sequence currents are inherently prevented because there is no path available to flow of these currents. In the proposed hybrid 9-level inverter switching devices which operate at higher voltage level switch less as compared to the switching devices which operate at lower voltage level in the entire range of linear modulation, this feature can lead to use of low switching state based mathematical model is developed to realize 9-level inversion operation. The space vector location and available switching redundancy at different locations are discussed. The capacitors voltage balancing algorithm and performance of the drive is evaluated during steady state and transient state in MATLAB/Simulink environment by operating an open-end winding induction motor at no-load in constant *V/f* mode and results are presented.

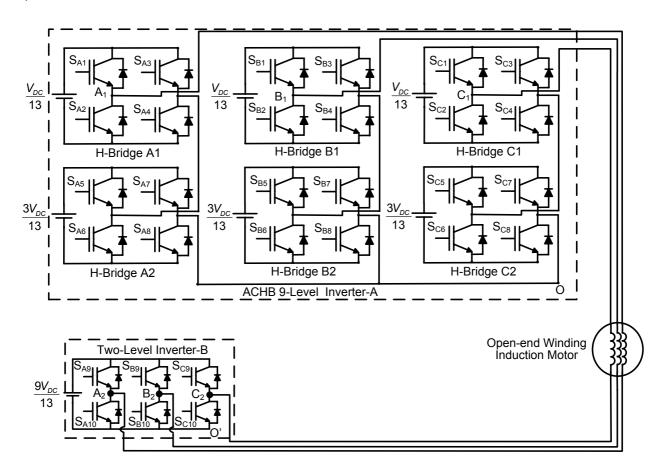

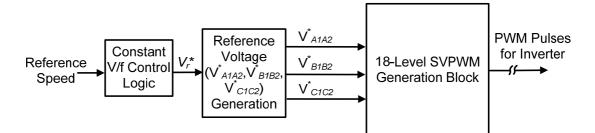

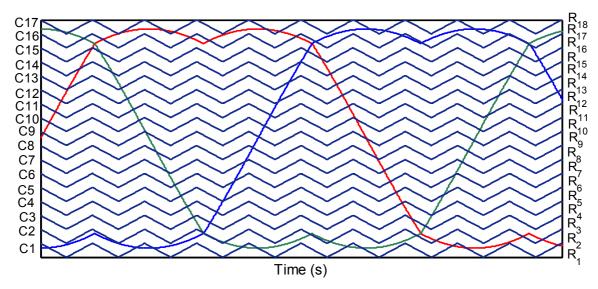

The third topology proposed in the present work is an eighteen-level inverter topology for open-end winding induction motor drive. In the proposed topology one end of the openend IM is fed by conventional two-level inverter, while the other end is connected to a ninelevel asymmetrical cascade H-bridge (ACHB) inverter. The proposed topology is capable of generating eighteen levels as  $-V_{DC}$ ,  $-12V_{DC}/13$ ,  $-11V_{DC}/13$   $-10V_{DC}/13$ ,  $-9V_{DC}/13$ ,  $-8V_{DC}/13$ ,  $-7V_{DC}/13$ ,  $-6V_{DC}/13$ ,  $-5V_{DC}/13$ ,  $-4V_{DC}/13$ ,  $-3V_{DC}/13$ ,  $-2V_{DC}/13$ ,  $-V_{DC}/13$ , 0,  $+V_{DC}/13$ ,  $+2V_{DC}/13$ ,  $+3V_{DC}/13$  and  $+4V_{DC}/13$ . The proposed topology requires less number of components as compared to conventional multilevel inverter (MLI) topology. An interesting feature of the proposed topology is that, it can operate in nine-level mode by connecting the motor winding in star in case of failure of the two-level inverter. Similarly, if the fault occurs in ACHB inverter the proposed inverter can operate in two-level mode. Thus, the reliability of the system is improved. Exhaustive simulation study is carried out to evaluate the performance of proposed inverter for the entire modulation range and results are presented.

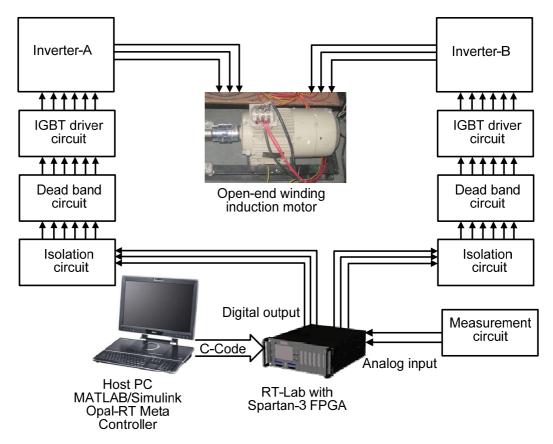

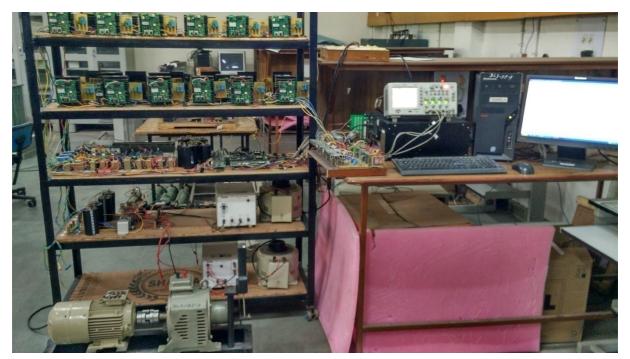

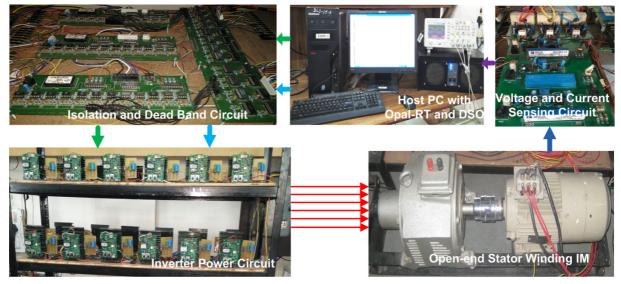

In this thesis extensive simulation study is carried out on D2L inverter, 5-level inverter, 9-level inverter, hybrid 9-level inverter and 18-level inverter for an induction motor with openend windings. In order to validate the simulation results, downscaled prototypes of following topologies are developed in the laboratory and experimentation is carried out:

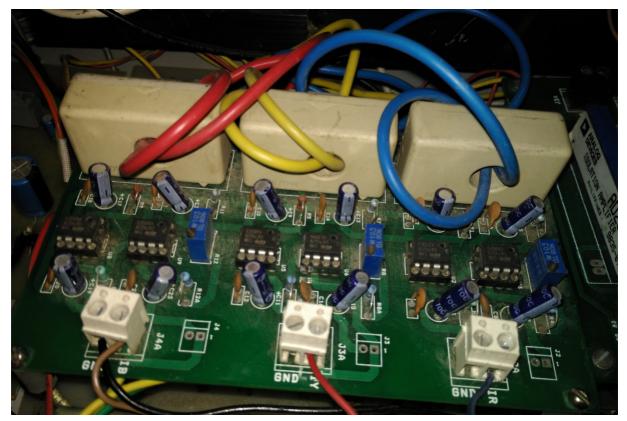

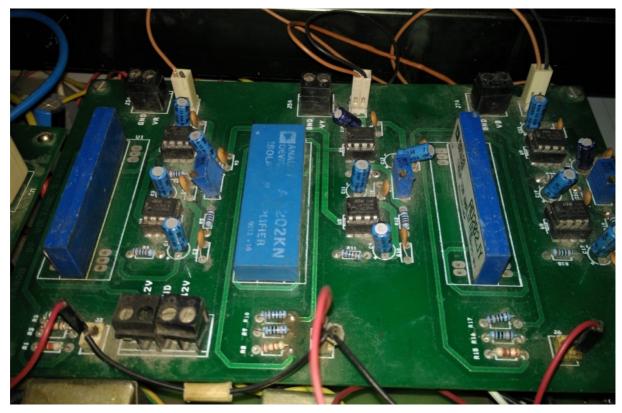

Topology-1: 5-Level Inverter for open-end IMD Topology-2: 9-Level Inverter for open-end IMD Topology-3: Hybrid 9-Level Inverter for open-end IMD The system hardware of these prototypes is developed in three stages:

- Implementation of power circuit

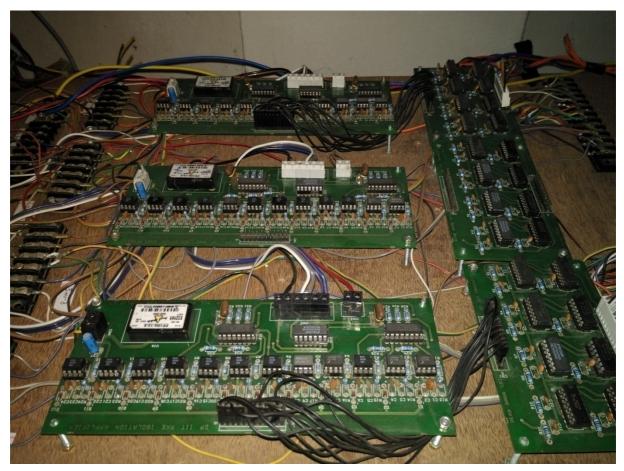

- Implementation of control circuit

- Measurement of system parameters

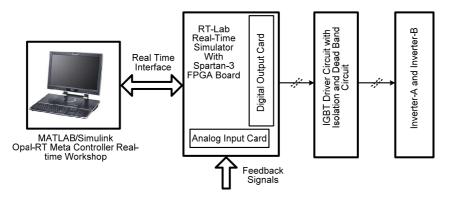

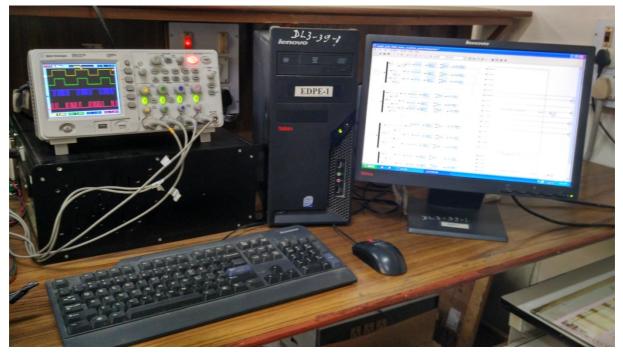

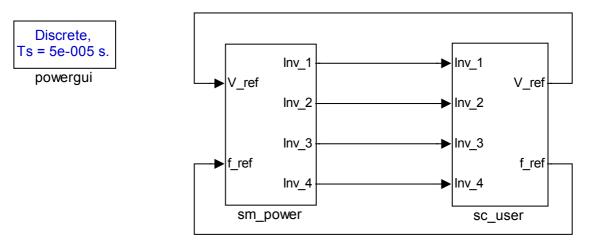

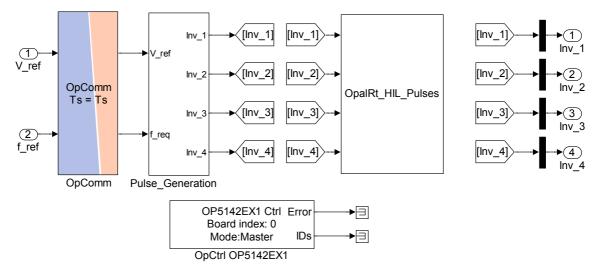

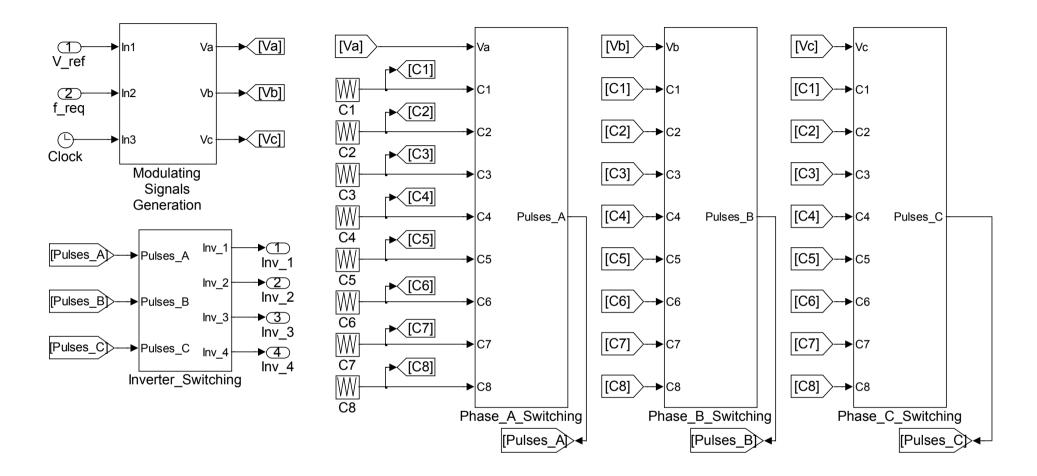

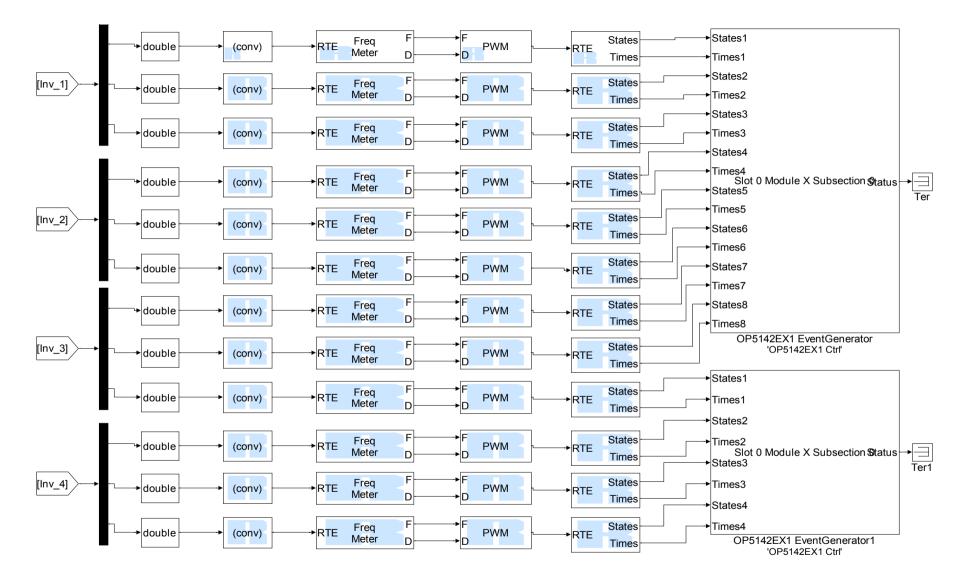

The inverter circuits of all three topologies are developed using IGBTs (IRG4PH40KD). RT-Lab from Opal-RT Technologies is used as real-time hardware-in-loop controller to generate gate pulses for IGBTs in real-time. The different hardware circuits which are required for the proper operation of experimental setup such as driver circuit, isolation and dead-band circuits, voltage and current sensor circuits are designed, developed and interfaced with RT-Lab real time controller.

In simulation studies of aforementioned topologies, the total DC link voltage ( $V_{DC}$ ) of 600V was selected, but due to the practical constraints total DC-link voltage of 200V is used for experimental investigations. An open-end winding induction motor of 1.5kW, 415V, 50Hz, 4pole is used as load and operated at no-load with constant *V/f* control. As the experimentation is carried out at reduced voltage, for validating the experimental results, the simulation study at reduced voltage is also carried out. The experimental and simulation results are matching to each other.

The multilevel inverter topologies presented in this thesis are particularly suitable for high power drive applications such as an electric vehicle, traction, etc. Although all the proposed schemes are experimentally tested and validated on downscaled laboratory prototypes, but the proposed topologies, SVPWM technique and *V/f* control scheme are general in nature and can be easily applied to high power applications induction motor drive.

With GOD's grace I have got this opportunity to thanks all those who have supported me all through this course of work. First and foremost, I would like to express my sincere gratitude to my supervisor Dr. Pramod Agarwal, Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, for his guidance, valuable suggestions, patience, continuous encouragement and constant source of inspiration throughout the course of this study. I am sincerely indebted to him for his pronounced individuality, humanistic and warm personal approach, and excellent facilities provided to me in the laboratory to carry out this research work smoothly.

I heartily extend my gratitude to Dr. S. P. Srivastava, Professor & Head, Department of Electrical Engineering, Indian Institute of Technology, Roorkee, for providing excellent laboratory and computing facilities of the Department for the research work.

I would like to acknowledge my research committee members Dr. B. Das (Professor EED & Chairman SRC), Dr. S. P. Gupta (Professor EED) and Dr. R. C. Mittal (Professor Mathematics Department), for their time to time critical examination of my research work and for their constructive recommendations.

My heartfelt thanks to Dr. K. Gopakumar (Professor, CEDT, IISc Bangalore), Dr. Bhim Singh (Professor, EED, IITD), Mr. Mooteri K. Vasantha (Emeritus Professor, EED, IITR), and Dr. Shailendra Jain (Professor, EED, NIT Bhopal), for their valuable suggestions during the work.

I acknowledge my sincere gratitude to All India Council for Technical Education, Government of India for providing financial support during my Ph.D. work. The research work has been carried out under Quality Improvement Programme (QIP) scheme of AICTE.

I will never forget my friends Dr. Aurobind Panda, Dr. Rakesh Maurya, Dr. Lal Bahadur Prasad, Dr. Vasundhara Mahajan, Mr. Sukant Haldar, and Mr. Anubhav Agarwal for kept me motivated by their caring words and wholehearted supports during the research work. I will always thankful to my good friends Mr. Pannala Sanjeev and Mr. Ravindra Kumar for their help and moral support.

I would also like to thank all the administrative & technical staff of the Department of Electrical Engineering, Indian Institute of Technology Roorkee, for their cooperation and necessary facilities provided to me to carry out this research work. My special thanks to Mr. Ameer Ahmad, Mr. Gautam Singh and Mr. Rakesh Kumar, who helped me to prepare experimental setup of my research work.

My sincere thanks are also due to Director Harcourt Butler Technological Institute (HBTI), Kanpur (India) and all faculty members of Electrical Engineering Department of HBTI, Kanpur (India), for the cooperation they have extended to me while working at IIT Roorkee.

"God could not be everywhere so he created mothers! With her blessing there's always a good day after, one know everything will turn out fine". With these words, I sincerely acknowledge the blessing of my mother Smt. Sheela Saxena for her encouragement and moral support rendered to me throughout my life.

No words can adequately express my deepest gratitude and love to my wife Smt. Jyoti Saxena for her unconditional support, encouragement, love and inspiration and always being there for me during good and bad times. I once again thanks to my wife and mother for shouldering all family responsibilities with a smiling face. I am thankful to my loving son Manas who always provided entertainment and a grand welcome to me at home with his big cheerful smile after long working hours in the lab. I am indebted to my son, as he has missed me lot during my work.

I sincerely acknowledge the ethical support from my Father-in-law Shri. Rakesh Prakesh Srivastava and Mother-in-law Smt. Suman Srivastava. I would like to thank whole in-law's family for their constant love and encouragement.

Last but not the least I would like to thank to Almighty 'GOD' for giving me health, strength and perseverance to complete this study.

#### (SANJIV KUMAR)

| ABSTRACT         | I    |

|------------------|------|

| ACKNOWLEDGEMENTS | VII  |

| CONTENTS         | IX   |

| LIST OF FIGURES  | XIII |

| LIST OF TABLES   | XXXI |

| LIST OF ACRONYMS |      |

| LIST OF SYMBOLS  | XXXV |

|                  |      |

| CHA | PTER 1  | : INT     | RODUCTION AND LITERATURE REVIEW                             | 1  |

|-----|---------|-----------|-------------------------------------------------------------|----|

| 1.1 | Overvi  | ew        |                                                             | 1  |

| 1.2 | Inverte | r Topolog | gies for Induction Motor Drives                             | 2  |

|     | 1.2.1   | Convent   | ional Two-Level Inverter                                    | 2  |

|     | 1.2.2   | Multileve | el Inverter                                                 | 4  |

| 1.3 | Literat | ure Revie | W                                                           | 6  |

|     | 1.3.1   | Multileve | el Inverter Topologies                                      | 6  |

|     |         | 1.3.1.1   | Diode Clamped Multilevel Inverter (DCMLI)                   | 7  |

|     |         | 1.3.1.2   | Flying Capacitor Multilevel Inverter (FCMLI)                | 9  |

|     |         | 1.3.1.3   | Cascade H-Bridge Multilevel Inverter (CHBMLI)               | 10 |

|     |         | 1.3.1.4   | Multilevel Inversion Using Split-phase Induction Motor      | 11 |

|     |         | 1.3.1.5   | Multilevel Inversion Using Open-end Winding Induction Motor | 12 |

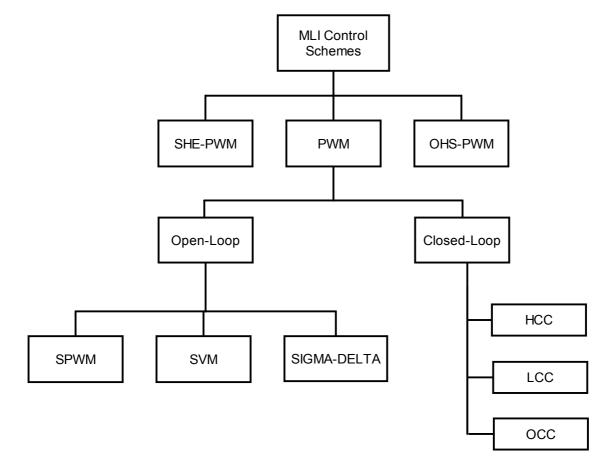

|     | 1.3.2   | Modulati  | on Techniques for Multilevel Inverters                      | 14 |

|     |         | 1.3.2.1   | Selective Harmonic Elimination PWM (SHE-PWM)                | 15 |

|     |         | 1.3.2.2   | Sinusoidal PWM (SPWM)                                       | 15 |

|     |         | 1.3.2.3   | Space Vector PWM (SVPWM)                                    | 18 |

|     |         | 1.3.2.4   | Sigma Delta Modulation (SDM)                                | 19 |

|     |         | 1.3.2.5   | Hysteresis Current Control (HCC) Modulation                 | 20 |

|     | 1.3.3   | Applicati | ons of Multilevel Inverters                                 | 21 |

|     | 1.3.4   | Induction | n Motor Speed Control Methods                               | 24 |

| 1.4 | Scope   | of Work a | and Author's Contribution                                   | 25 |

| 1.5 | Organi  | zation of | the Thesis                                                  | 28 |

| СНА | PTER 2  | ווח יי    | AL TWO-LEVEL INVERTER FOR INDUCTION MOTOR DRIVE             | 31 |

| 2.1 |         |           |                                                             |    |

| 2.1 |         |           | ration and Switching Logic                                  |    |

| 2.2 | -       | -         |                                                             |    |

|     | ۲.۷.۱   | Fower C   | ircuit                                                      | SI |

|     | 2.2.2   | Switching Logic                                                   | 32  |

|-----|---------|-------------------------------------------------------------------|-----|

| 2.3 | Control | Scheme                                                            | 33  |

| 2.4 | Mathen  | natical Modelling of Dual Two-Level (D2L) Inverter fed IMD        | 34  |

|     | 2.4.1   | Model of D2L Inverter                                             | 34  |

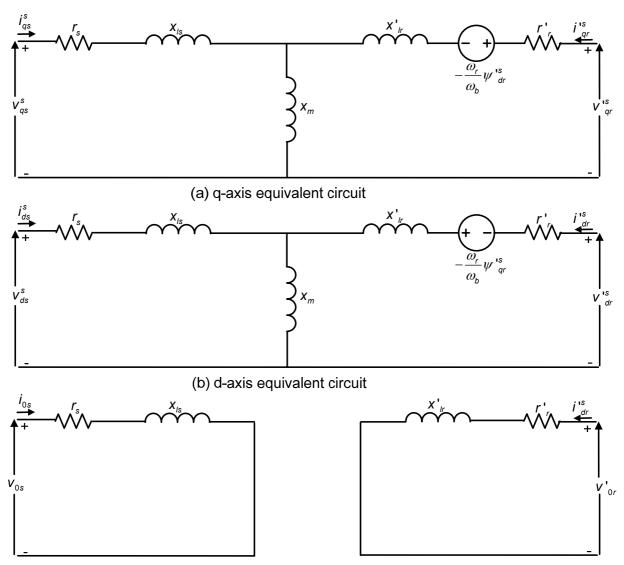

|     | 2.4.2   | Mathematical Modelling of Open-end Stator Winding Induction Motor | 37  |

| 2.5 | Simulat | tion Studies                                                      | 40  |

|     | 2.5.1   | Simulation Results and Discussion                                 | 43  |

| 2.6 | Conclu  | sion                                                              | 52  |

| СНА | PTER 3  | : FIVE-LEVEL INVERTER FOR INDUCTION MOTOR DRIVE                   | 53  |

| 3.1 | Introdu | ction                                                             |     |

| 3.2 |         | Inverter Scheme for Induction Motor Drive                         |     |

| •   |         | Power Circuit                                                     |     |

|     |         | Switching Logic                                                   |     |

|     |         | Analysis of Voltage Space Vectors                                 |     |

|     |         | Selection of DC Link Voltage Ratio                                |     |

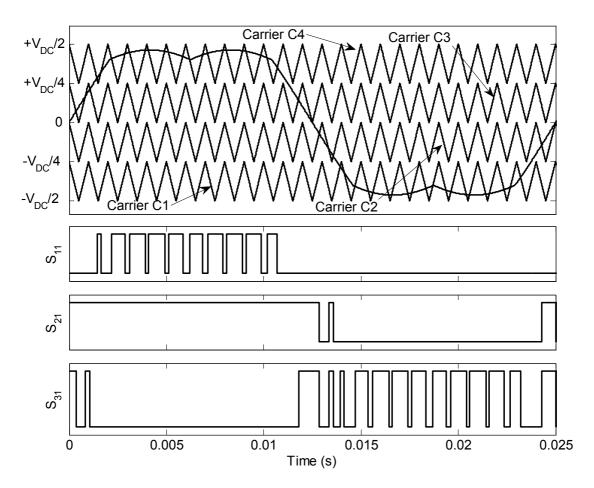

| 3.3 | Control | Scheme                                                            | 59  |

| 3.4 | Mathen  | natical Modelling of 5-level Inverter Scheme                      | 61  |

| 3.5 | Simulat | tion Results and Discussion                                       | 62  |

| 3.6 | Perforn | nance Comparison                                                  | 73  |

| 3.7 | Conclu  | sion                                                              | 73  |

| СНА | PTER 4  | : NINE-LEVEL INVERTER FOR INDUCTION MOTOR DRIVE                   | 75  |

| 4.1 |         | ction                                                             |     |

| 4.2 |         | Inverter Scheme for Induction Motor Drive                         |     |

|     |         | Power Circuit                                                     |     |

|     |         | 4.2.1.1 Comparison between Proposed Inverter and Conventional MLI |     |

|     |         | Switching Logic                                                   |     |

|     |         | Analysis of Voltage Space Vectors                                 |     |

|     | 4.2.4   | Effect of common-mode voltage                                     | 81  |

|     | 4.2.5   | Selection of DC Link Voltage Ratio                                | 81  |

| 4.3 | Modifie | d SVPWM technique for the proposed nine-level inverter            | 82  |

| 4.4 | Mathen  | natical Modelling of Proposed 9-Level Inverter                    | 86  |

|     | 4.4.1   | Mathematical Model of 9-Level Inverter                            | 87  |

| 4.5 | Simulat | tion Results and Discussion                                       | 89  |

| 4.6 | Perform | nance Comparison                                                  | 110 |

| 4.7 | Caral   | sion                                                              | 111 |

| СНА | PTER   | 5: HY       | BRID NINE-LEVEL INVERTER FOR INDUCTION MOTOR DRIV            | /E113 |

|-----|--------|-------------|--------------------------------------------------------------|-------|

| 5.1 | Introd | uction      |                                                              | 113   |

| 5.2 | Hybric | 9-Level I   | nverter Scheme for Induction Motor Drive                     | 114   |

|     | 5.2.1  | Power C     | ircuit                                                       | 114   |

|     |        | 5.2.1.1     | Salient Features of Proposed Inverter Topology               | 115   |

|     | 5.2.2  | Generati    | on of Different Levels and Capacitor Voltage Balancing Logic | 116   |

|     | 5.2.3  | Control S   | Strategy and Capacitor Design                                | 127   |

|     | 5.2.4  | Analysis    | of Voltage Space Vectors                                     | 129   |

| 5.3 | Mathe  | matical M   | odelling of Hybrid 9-Level Inverter                          | 132   |

| 5.4 | Simula | ation Resu  | ults and Discussion                                          | 133   |

| 5.5 | Perfor | mance Co    | omparison                                                    | 161   |

| 5.6 | Concl  | usion       |                                                              | 163   |

| СНА | PTER   | 6: EIG      | HTEEN-LEVEL INVERTER FOR INDUCTION MOTOR DRIVE.              | 165   |

| 6.1 | Introd | uction      |                                                              | 165   |

| 6.2 | 18-Le  | vel Inverte | er Scheme for Induction Motor Drive                          | 166   |

|     | 6.2.1  | Power C     | ircuit                                                       | 166   |

|     | 6.2.2  | Salient F   | eatures of Proposed Inverter Topology                        | 168   |

| 6.3 | Contro | ol Strategy | / and PWM Generation                                         | 169   |

| 6.4 | Mathe  | matical M   | odelling of Proposed 18-Level Inverter                       | 172   |

| 6.5 | Simula | ation Resu  | ults and Discussion                                          | 173   |

| 6.6 | Perfor | mance Co    | omparison                                                    | 185   |

| 6.7 | Concl  | usion       |                                                              | 186   |

| СНА | PTER   | 7: SYS      | STEM DEVELOPMENT AND EXPERIMENTATION                         | 187   |

| 7.1 | Introd | uction      |                                                              | 187   |

| 7.2 | Hardw  | are Imple   | mentation                                                    | 188   |

|     | 7.2.1  | Power C     | ircuit Implementation                                        | 188   |

|     |        | 7.2.1.1     | Topology-1: 5-Level Inverter Scheme                          | 189   |

|     |        | 7.2.1.2     | Topology-2: 9-Level Inverter Scheme                          | 190   |

|     |        | 7.2.1.3     | Topology-3: Hybrid 9-Level Inverter Scheme                   | 190   |

|     | 7.2.2  | Control (   | Circuit Implementation                                       | 190   |

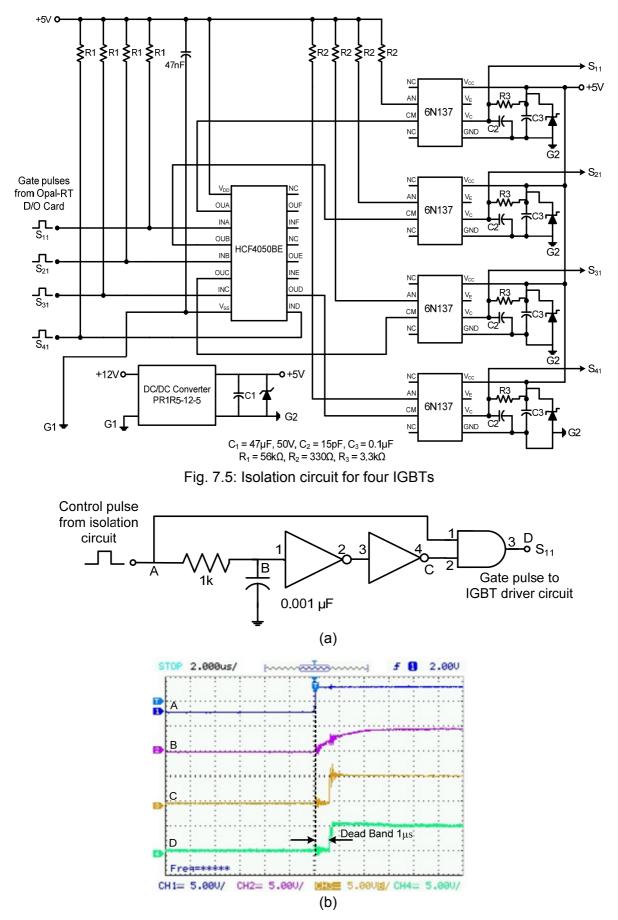

|     |        | 7.2.2.1     | Isolation Circuit                                            | 191   |

|     |        | 7.2.2.2     | Dead-Band Circuit                                            | 191   |

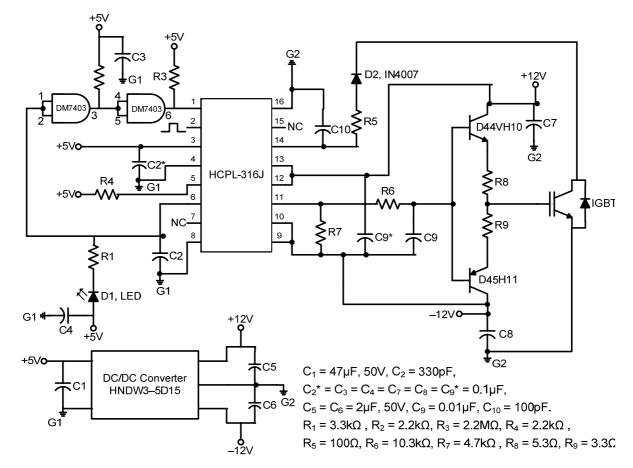

|     |        | 7.2.2.3     | IGBT Driver Circuit                                          | 193   |

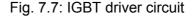

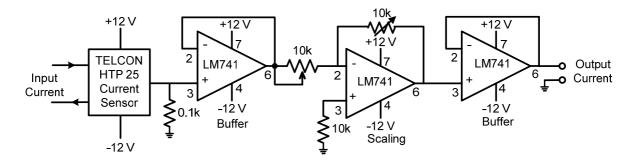

|     | 7.2.3  | Measure     | ment of System Parameter                                     | 194   |

|     |        | 7.2.3.1     | Measurement of Voltage                                       | 194   |

|     |        | 7.2.3.2     | Measurement of Current                                       | 195   |

|      | 7.2.4  | System Software                                    | 196 |

|------|--------|----------------------------------------------------|-----|

| 7.3  | Exper  | mental Validation                                  | 196 |

|      | 7.3.1  | Experimental Validation of 5-level Inverter        | 197 |

|      | 7.3.2  | Experimental Validation of 9-level Inverter        | 210 |

|      | 7.3.3  | Experimental Validation of Hybrid 9-level Inverter |     |

| 7.4  | Concl  | usion                                              |     |

| СНА  |        | 3: CONCLUSION AND FUTURE SCOPE OF RESEARCH         | 255 |

| 8.1  | Concl  | usion                                              |     |

| 8.2  | Future | Scope of Research                                  | 258 |

| PUB  |        | ONS FROM THE WORK                                  | 259 |

| РНС  | TOGR   | APHS OF THE EXPERIMENTAL SET-UP                    | 261 |

| BIBI | logra  | \PHY                                               | 267 |

| APP  | ENDIX  | – A                                                | 283 |

| APP  |        | – В                                                | 285 |

### LIST OF FIGURES

| Fig. 1.1: Power circuit of conventional two-level MV VSI drive                                                    | 3   |

|-------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 1.2: One phase leg of an inverter with (a) two levels; (b) three levels; (c) n levels                        | 5   |

| Fig. 1.3: Three-phase five-level diode clamped inverter                                                           | 8   |

| Fig. 1.4: Three-phase five-level flying capacitor inverter                                                        | 9   |

| Fig. 1.5: Three-phase five-level cascade H-bridge inverter 1                                                      | 0   |

| Fig. 1.6: Split phase induction motor drive 1                                                                     | 2   |

| Fig. 1.7: Schematic of power circuit for open-end winding based three-level inverter 1                            | 3   |

| Fig. 1.8: Classification of multilevel modulation techniques 1                                                    | 4   |

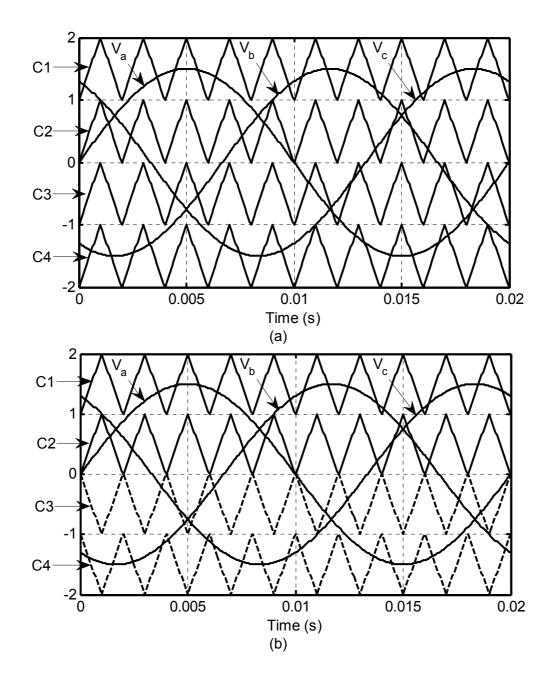

| Fig. 1.9: Carrier arrangements for five-level inverter; (a) PD, (b) POD, (c) APOD, (d)PS 1                        | 7   |

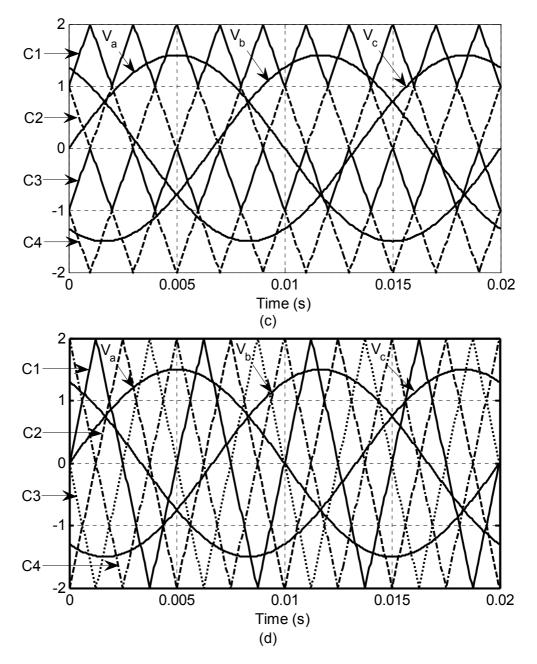

| Fig. 1.10: Block diagrams of delta modulation: (a) Simple delta modulator, (b) Sigma-del                          | ta  |

| modulator                                                                                                         | 20  |

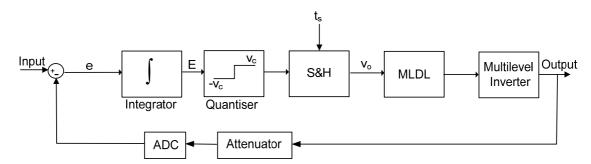

| Fig. 1.11: Block diagram of sigma delta modulation control of a multilevel inverter                               | 20  |

| Fig. 2.1 :Dual two-level (D2L) inverter scheme for open-end winding induction motor drive 3                       | 32  |

| Fig. 2.2: Switching signals for the devices of phase-A of three-level D2L inverter usin                           | ıg  |

| LSPWM technique                                                                                                   | 3   |

| Fig. 2.3: Diagrammatic representation of switching functions and inverter pole voltages for                       | or  |

| D2L inverter                                                                                                      | \$5 |

| Fig. 2.4: Equivalent circuit of an induction motor in stationary reference frame                                  | 9   |

| Fig. 2.5: Simulink model of D2L inverter scheme (a) Power circuit (b) Control circuit an                          | ١d  |

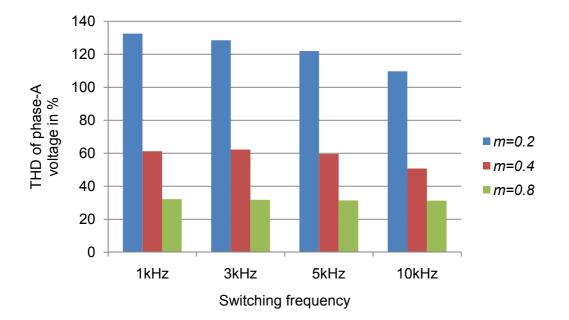

| monitoring 4                                                                                                      | 1   |

| Fig. 2.6: Graph between THD of motor phase-A voltage and switching frequency for different                        | nt  |

| value of modulation index 4                                                                                       | 2   |

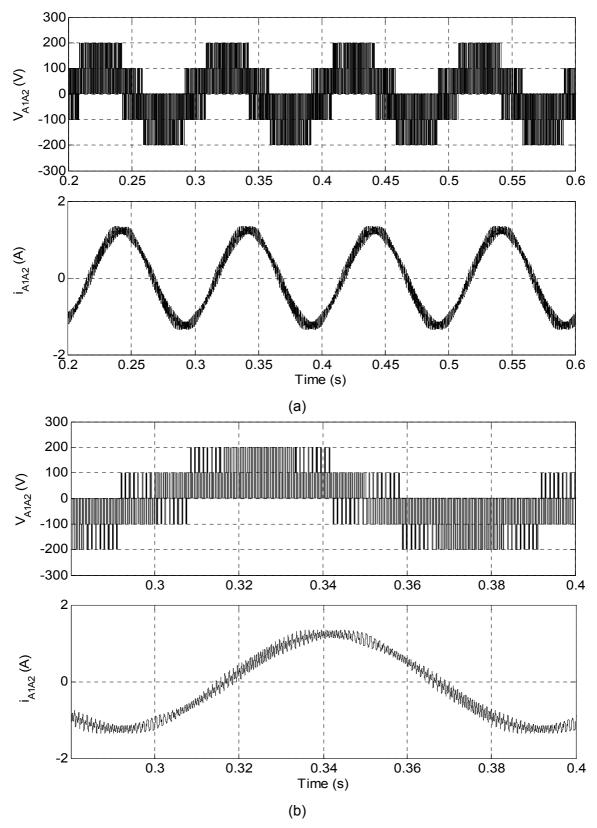

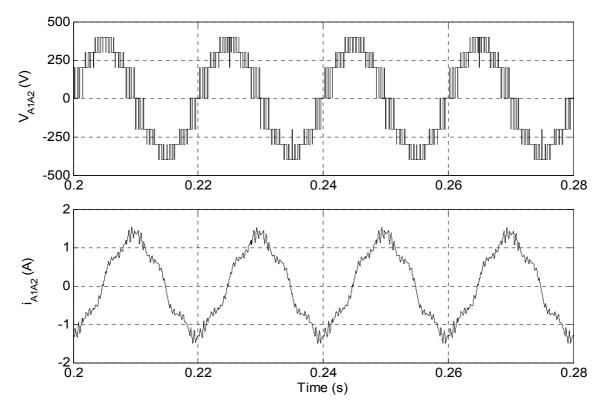

| Fig. 2.7: (a) Motor phase-A, voltage ( $V_{A1A2}$ ) and current ( $i_{A1A2}$ ) at m=0.2; $f_m^*$ =10Hz for        | or  |

| SVPWM based D2L inverter for open-end IM drive at no load (b) zoom view of waveform                               | າຣ  |

| shown in (a)                                                                                                      | 4   |

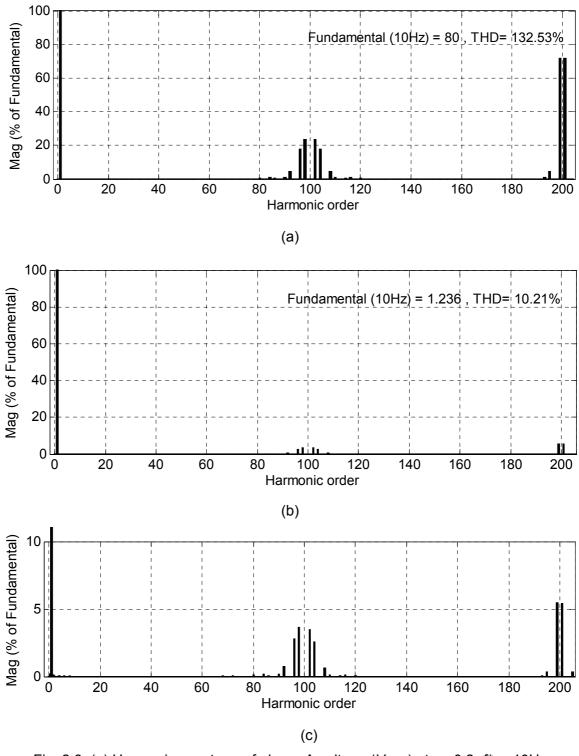

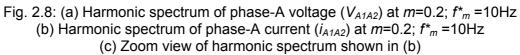

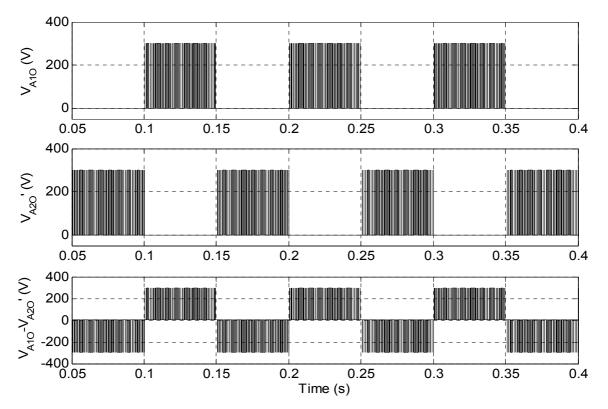

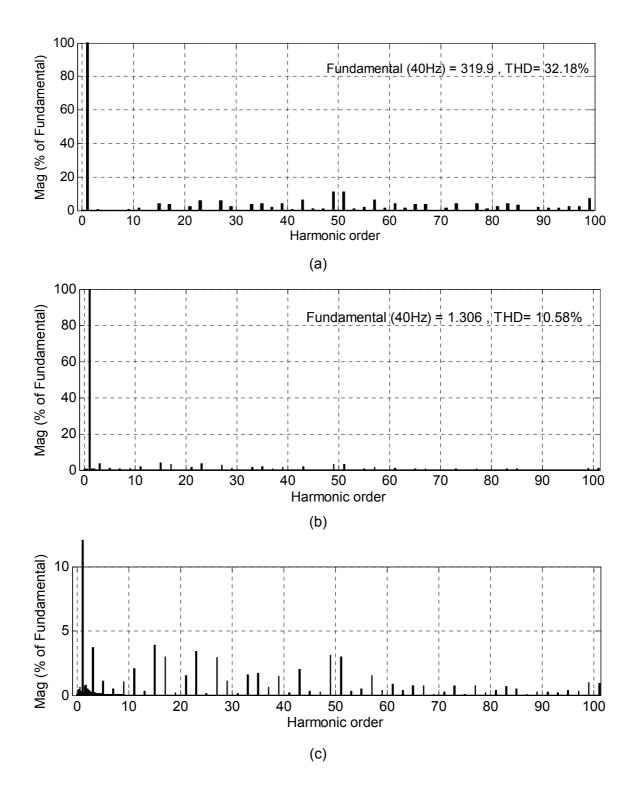

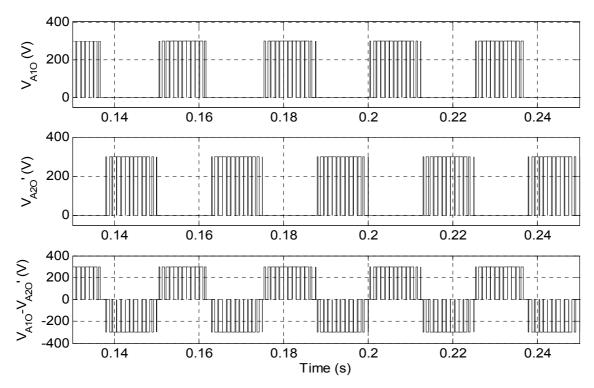

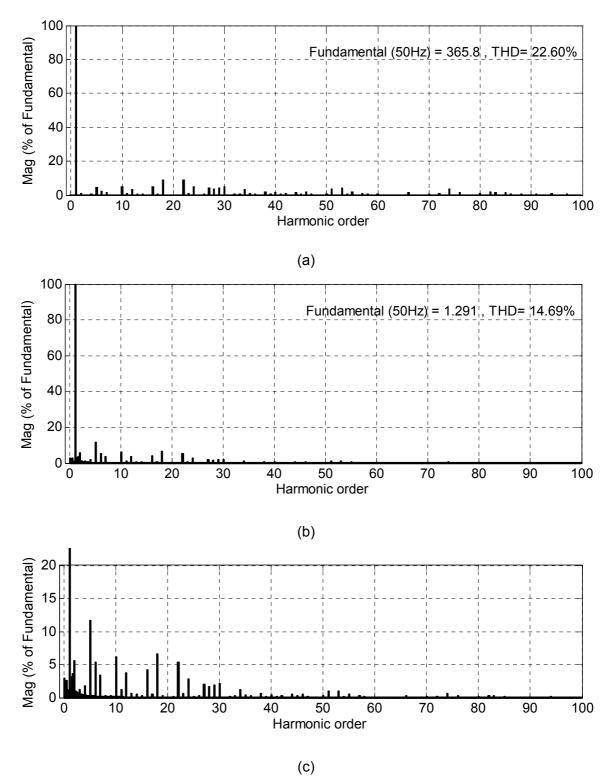

| Fig. 2.8: (a) Harmonic spectrum of phase-A voltage ( $V_{A1A2}$ ) at $m=0.2$ ; $f_m^*=10$ Hz (b) Harmon           | ic  |

| spectrum of phase-A current ( $i_{A1A2}$ ) at m=0.2; $f_m^*$ =10Hz (c) Zoom view of harmonic spectru              | m   |

| shown in (b)                                                                                                      | 5   |

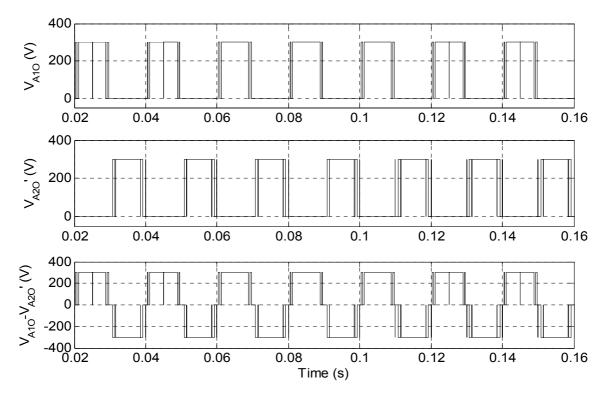

| Fig. 2.9: Top trace; Inverter-1 pole voltage ( $V_{A10}$ ), Middle trace; Inverter-2 pole voltage 4               | 6   |

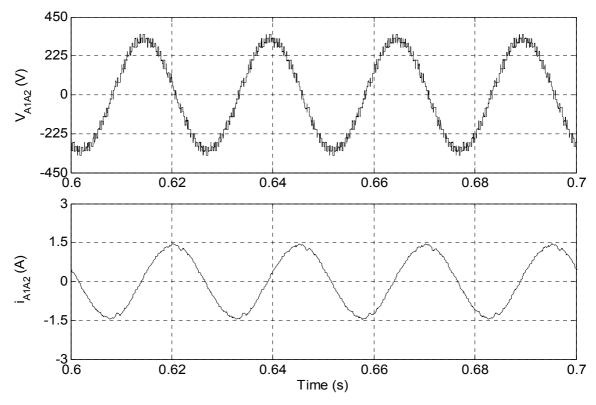

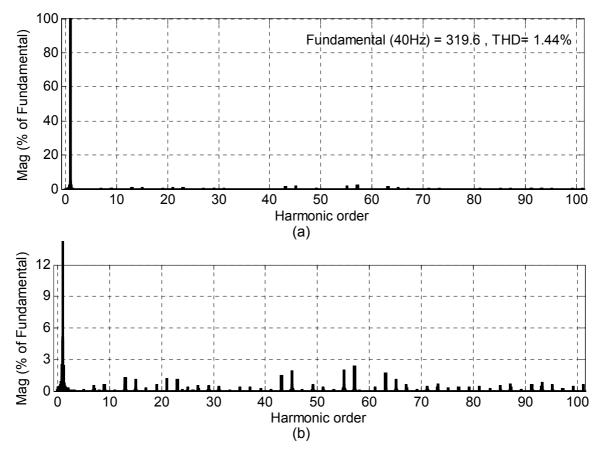

| Fig. 2.10: Motor phase-A, voltage ( $V_{A1A2}$ ) and current ( $i_{A1A2}$ ) at $m$ =0.8; $f_m^*$ =40Hz for SVPWM4 | 6   |

| Fig. 2.11: (a) Harmonic spectrum of phase-A voltage ( $V_{A1A2}$ ) at $m$ =0.8; $f_m^*$ =40Hz (b) Harmon          | ic  |

| spectrum of phase-A current ( $i_{A1A2}$ ) at m=0.8; $f_m^*$ =40Hz (c) Zoom view of harmonic spectru              | m   |

| shown in (b)                                                                                                      | 7   |

| Fig. 2.12: Top trace; Inverter-1 pole voltage ( $V_{A1O}$ ), Middle trace; Inverter-2 pole voltage 4              | 8   |

| Fig. 2.13 : Motor phase-A, voltage ( $V_{A1A2}$ ) and current ( $i_{A1A2}$ ) at $m=1$ ; $f_m^*=50$ Hz for SVPWM4  | 8   |

| Fig. 2.14: (a) Harmonic spectrum of phase-A voltage ( $V_{A1A2}$ ) at $m=1.0$ ; $f_m^*=50$ Hz (b) Harmonic                   |

|------------------------------------------------------------------------------------------------------------------------------|

| spectrum of phase-A current ( $i_{A1A2}$ ) at $m=1.0$ ; $f_m^*=50$ Hz (c) Zoom view of harmonic spectrum                     |

| shown in (b)                                                                                                                 |

| Fig. 2.15: Top trace; Inverter-1 pole voltage ( $V_{A10}$ ), Middle trace; Inverter-2 pole voltage 50                        |

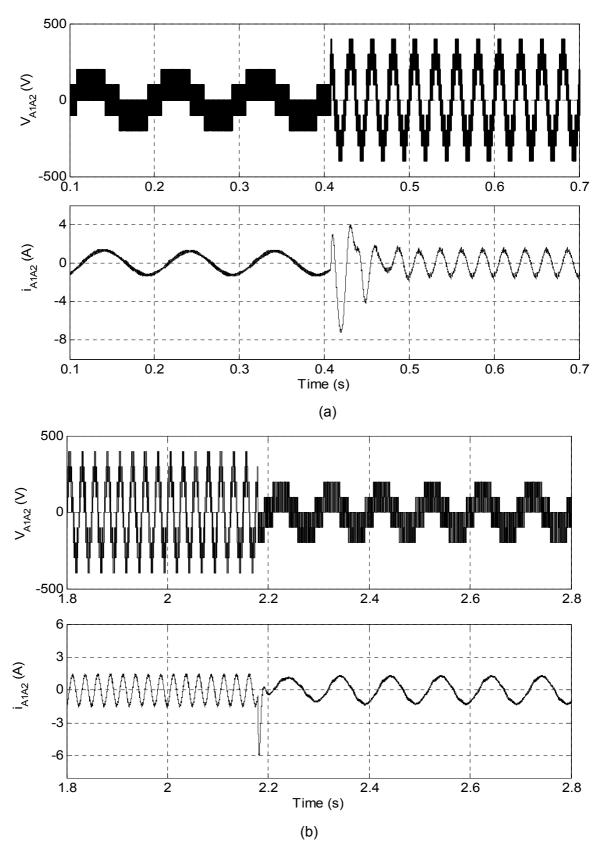

| Fig. 2.16: (a) Motor phase-A, voltage $V_{A1A2}$ (upper trace) and current $i_{A1A2}$ (lower trace)                          |

| waveforms under sudden change in modulation index from 0.2 to 0.8 (b) Motor phase-A,                                         |

| voltage $V_{A1A2}$ (upper trace) and current $i_{A1A2}$ (lower trace) waveforms under sudden change                          |

| in modulation index from 0.8 to 0.2                                                                                          |

| Fig. 3.1: Power circuit of 5-level inverter scheme for open-end winding induction motor drive 54                             |

| Fig. 3.2: Equivalent voltage space vector $V_s$ in $\alpha$ - $\beta$ plane                                                  |

| Fig. 3.3: Voltage space vectors distribution for 5-level inverter                                                            |

| Fig. 3.4: Power circuit of 6-level inverter scheme for open-end winding induction motor drive 59                             |

| Fig. 3.5: Switching signals for the devices of phase–A of 5-level inverter using LSPWM                                       |

| technique                                                                                                                    |

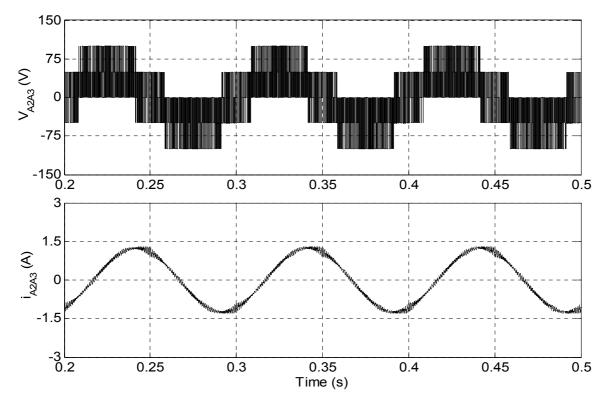

| Fig. 3.6: Motor phase-A, voltage $V_{A2A3}$ (upper trace) and current $i_{A2A3}$ (lower trace) of 5-level                    |

| inverter fed open-end IM drive at no load ( $m$ =0.2; $f_m^*$ =10Hz)                                                         |

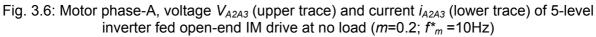

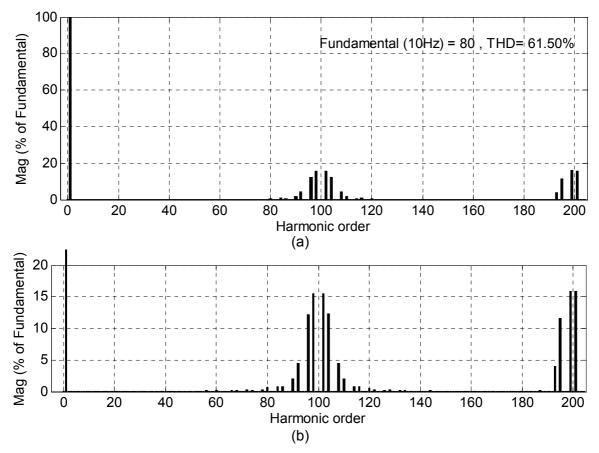

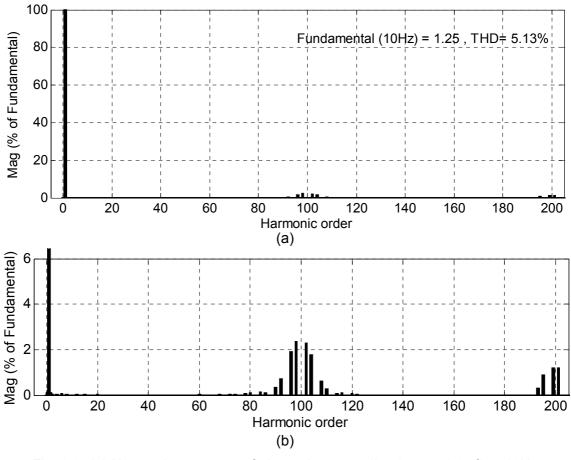

| Fig. 3.7: (a) Harmonic spectrum of phase-A voltage ( $V_{A2A3}$ ) at $m=0.2$ ; $f_m^*=10$ Hz (b) Zoom                        |

| view of harmonic spectrum shown in (a)                                                                                       |

| Fig. 3.8: (a) Harmonic spectrum of phase-A current ( $i_{A2A3}$ ) at $m=0.2$ ; $f_m^*=10$ Hz (b) Zoom view                   |

| of harmonic spectrum shown in (a)                                                                                            |

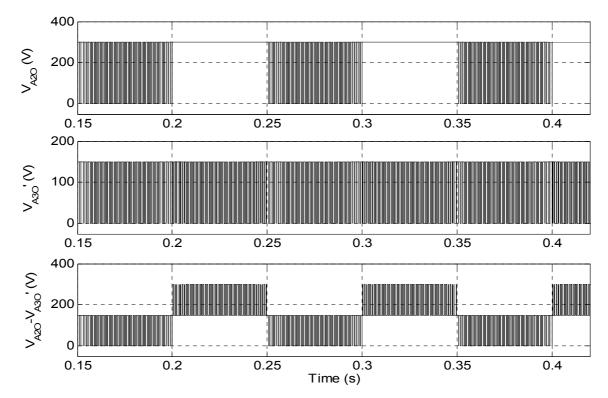

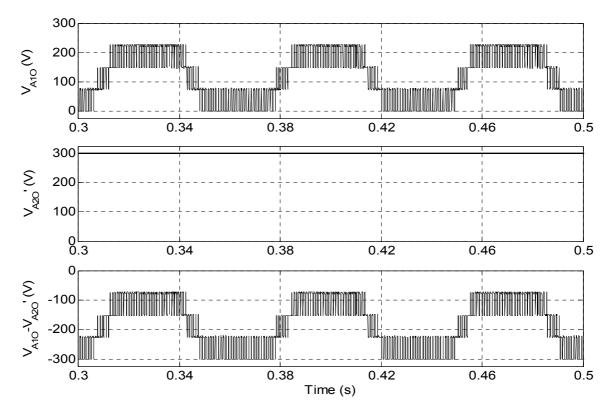

| Fig. 3.9: Top trace; 3-level inverter-A pole voltage ( $V_{A2O}$ ), Middle trace; Two-level inverter-B                       |

| pole voltage ( $V_{A30}$ ), Bottom trace; Difference of 3-level inverter-A and two-level inverter-B                          |

| pole voltages ( $V_{A20}$ - $V_{A30}$ ) at m=0.2; $f_m^*$ =10Hz                                                              |

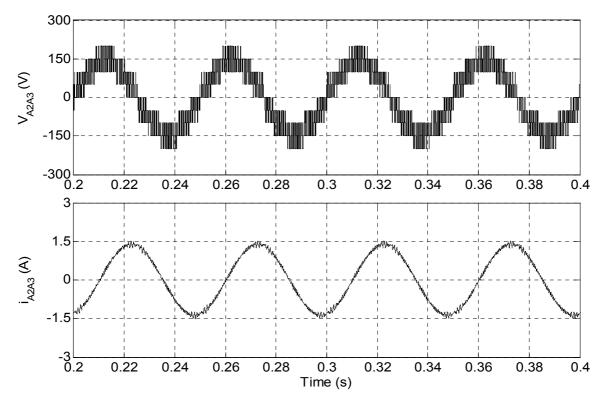

| Fig. 3.10: Motor phase-A, voltage $V_{A2A3}$ (upper trace) and current $i_{A2A3}$ (lower trace) of 5-level                   |

| inverter fed open-end IM drive at no load ( $m$ =0.4; $f_m^*$ =20Hz)                                                         |

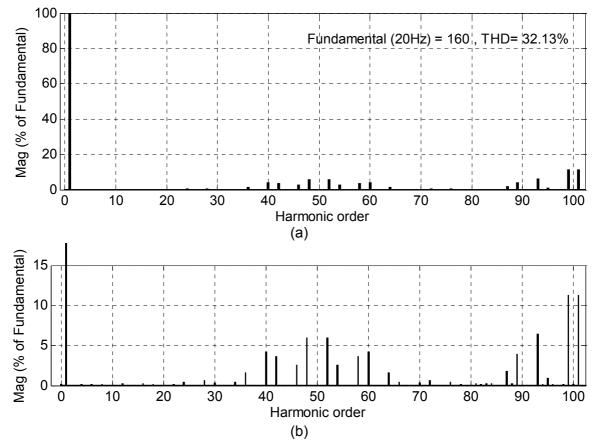

| Fig. 3.11: (a) Harmonic spectrum of phase-A voltage ( $V_{A2A3}$ ) at m=0.4; $f_m^*$ =20Hz (b) Zoom                          |

| view of harmonic spectrum shown in (a)66                                                                                     |

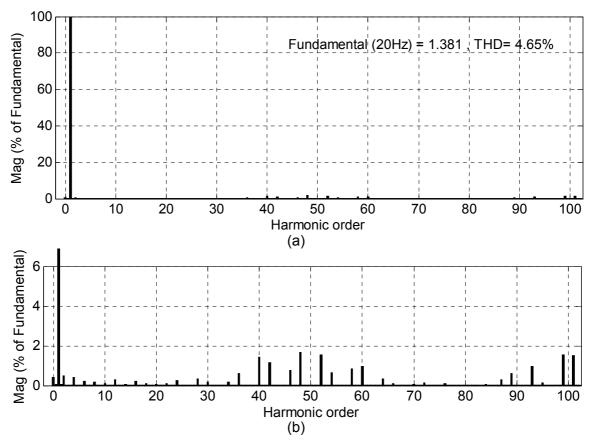

| Fig. 3.12: (a) Harmonic spectrum of phase-A current ( $i_{A2A3}$ ) at m=0.4; $f_m^*$ =20Hz (b) Zoom                          |

| view of harmonic spectrum shown in (a)67                                                                                     |

| Fig. 3.13: Top trace; 3-level inverter-A pole voltage ( $V_{A2O}$ ), Middle trace; Two-level inverter-B                      |

| pole voltage ( $V_{A3O}$ ), Bottom trace; Difference of 3-level inverter-A and two-level inverter-B                          |

| pole voltages ( <i>V</i> <sub>A2O</sub> - <i>V</i> <sub>A3O</sub> ) at <i>m</i> =0.4; <i>f</i> * <sub><i>m</i></sub> =20Hz67 |

| Fig. 3.14: Motor phase-A, voltage $V_{A2A3}$ (upper trace) and current $i_{A2A3}$ (lower trace) of 5-level                   |

| inverter fed open-end IM drive at no load ( $m$ =0.6; $f_m^*$ =30Hz)68                                                       |

| Fig. 3.15: (a) Harmonic spectrum of phase-A voltage ( $V_{A2A3}$ ) at m=0.6; $f_m^*$ =30Hz (b) Zoom                          |

| view of harmonic spectrum shown in (a)                                                                                       |

|                                                                                                                              |

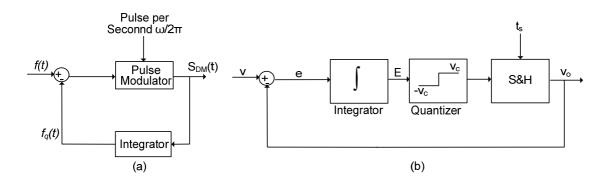

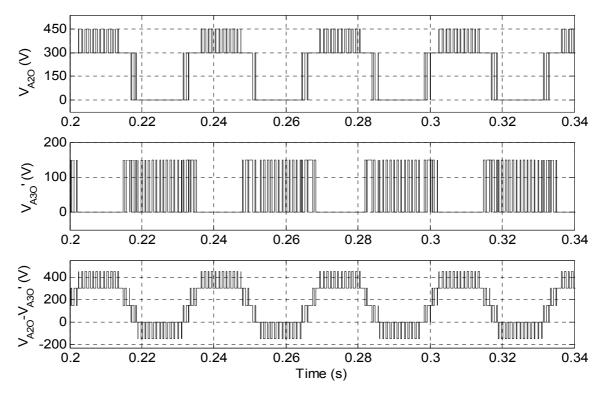

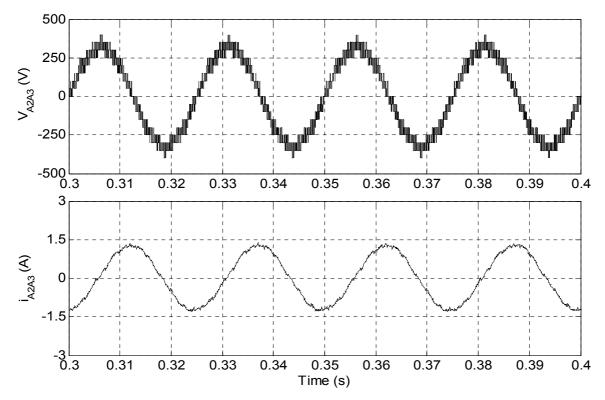

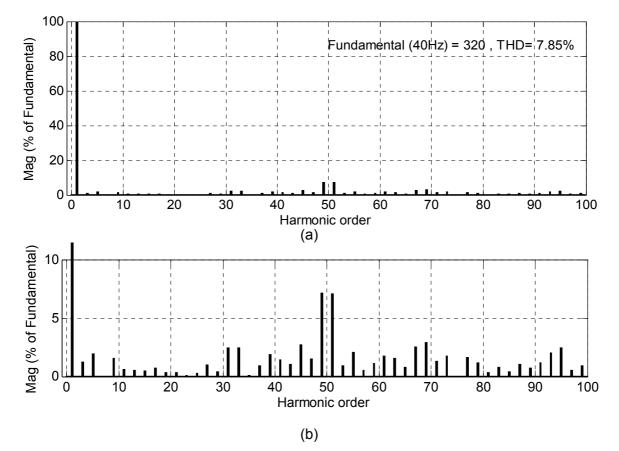

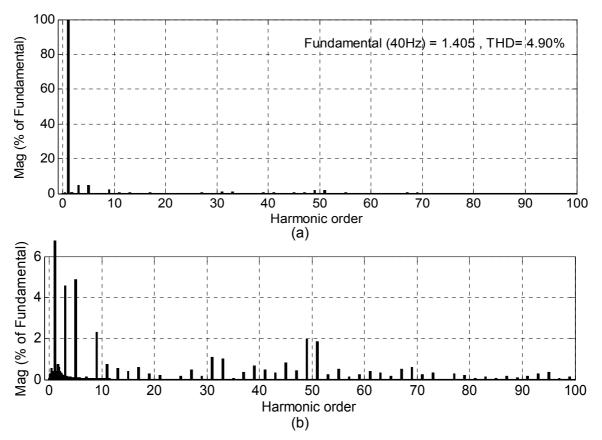

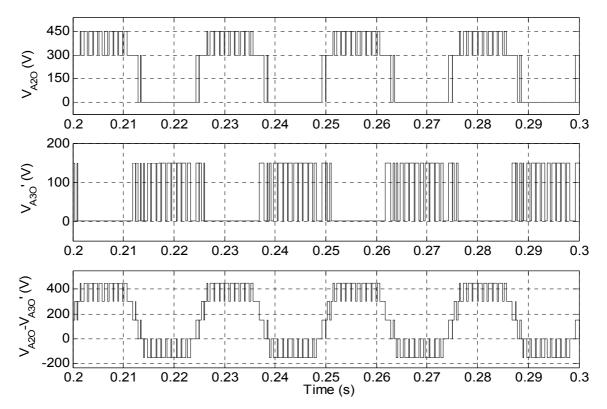

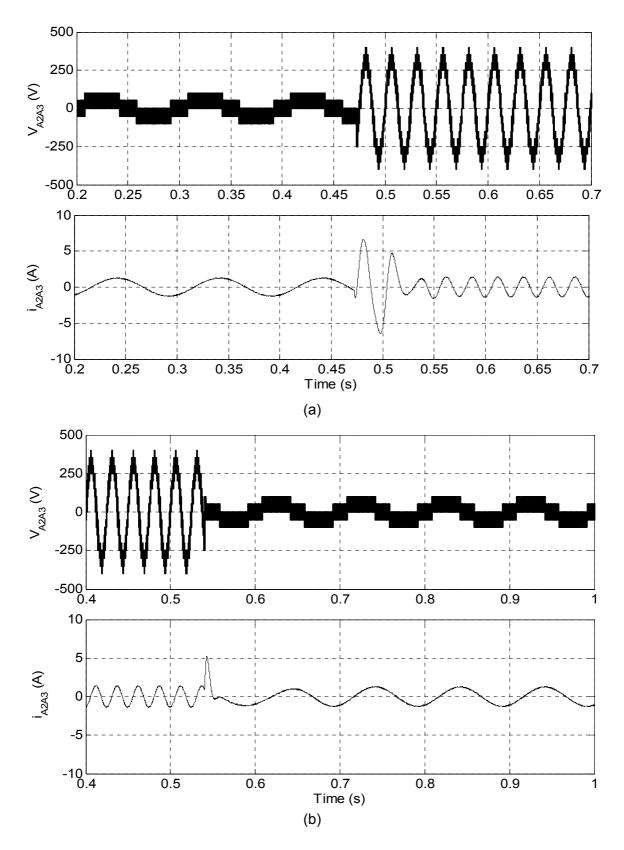

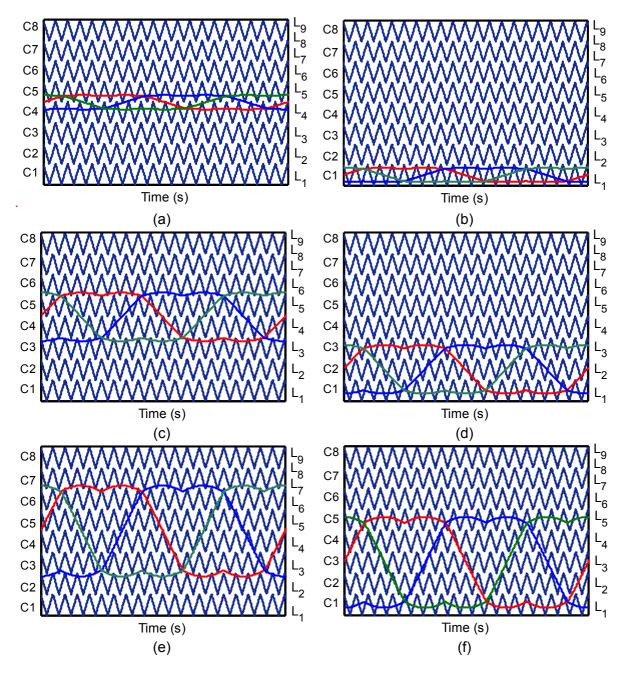

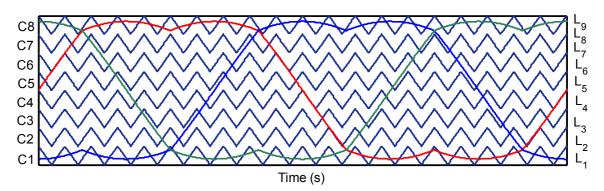

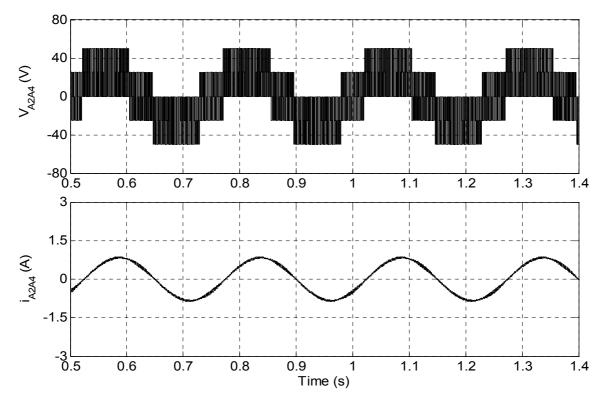

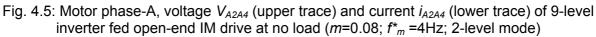

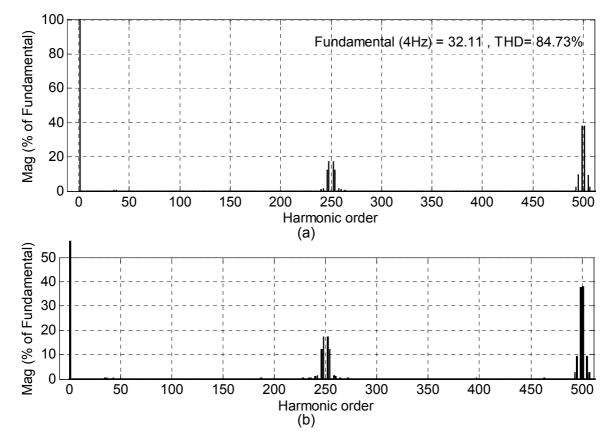

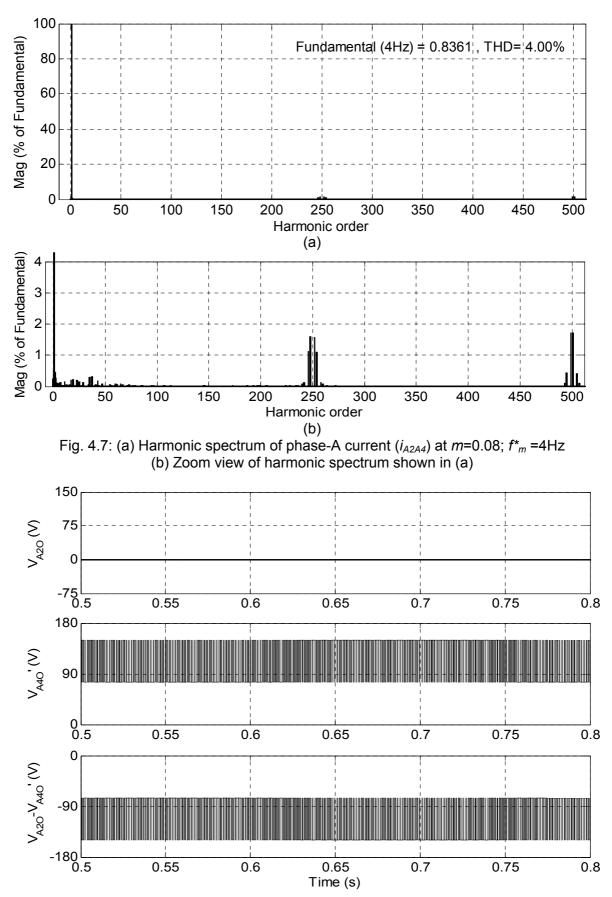

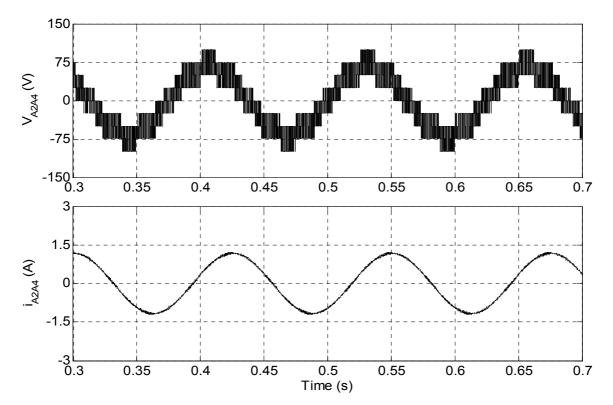

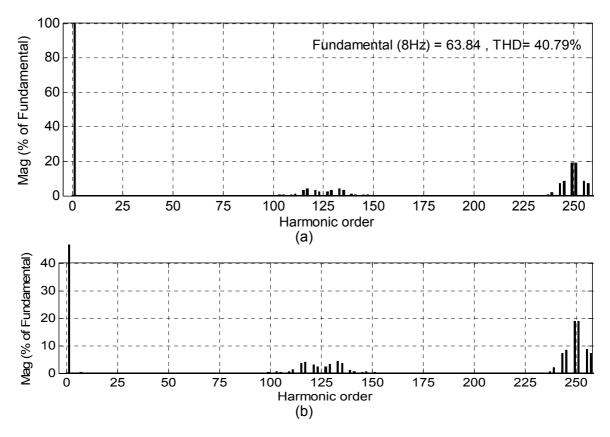

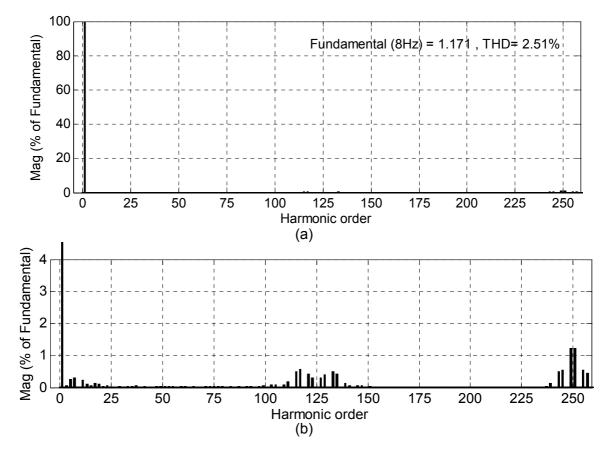

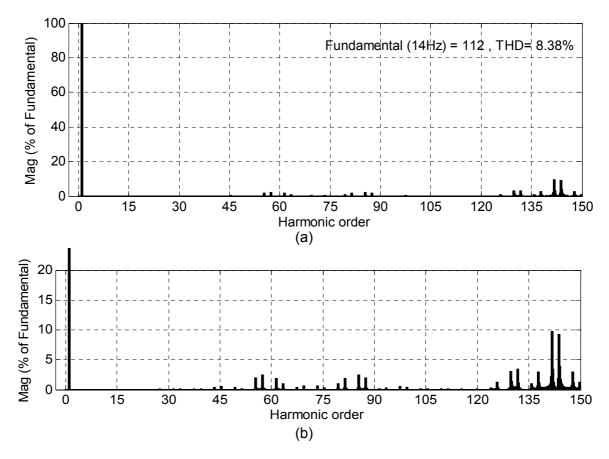

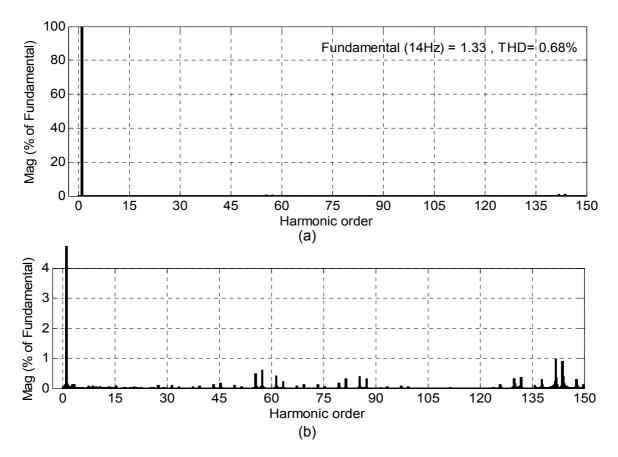

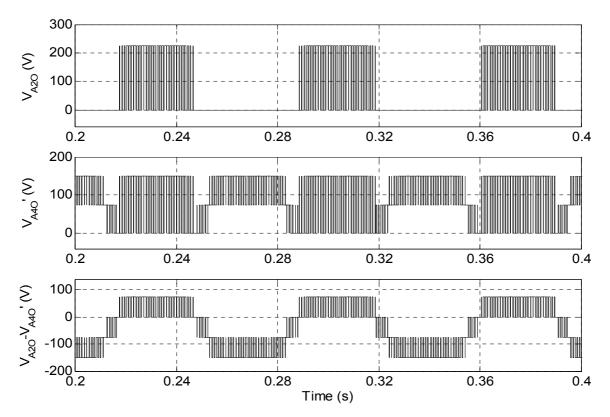

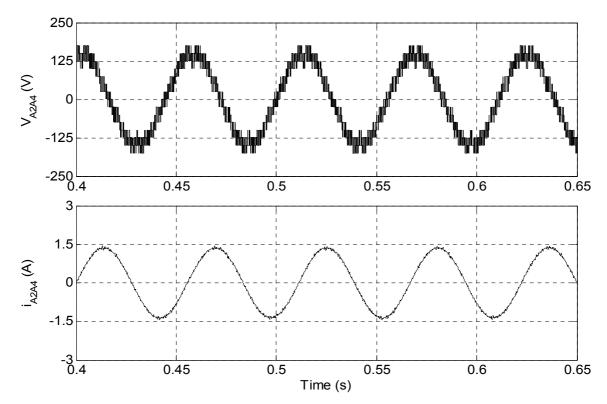

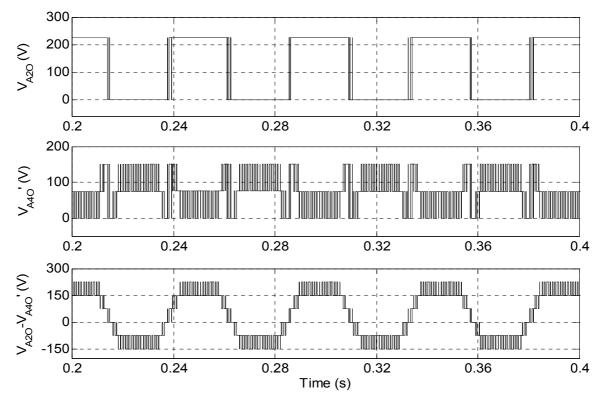

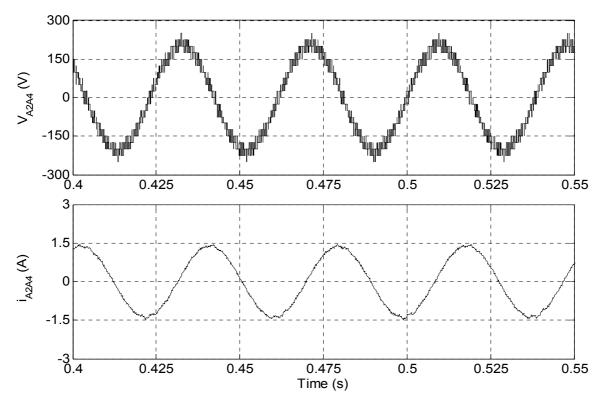

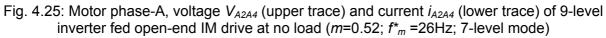

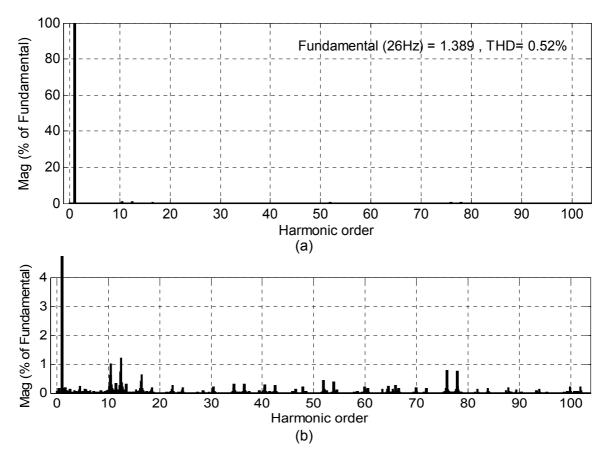

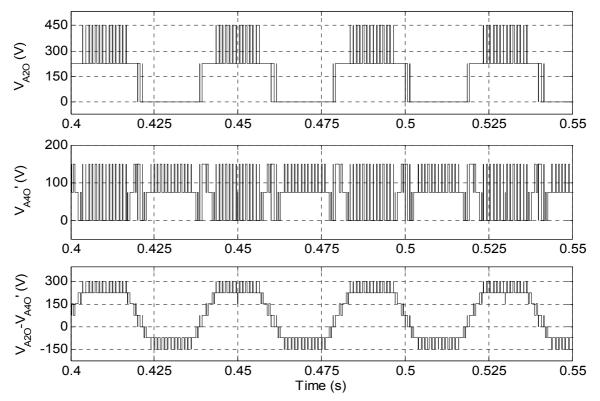

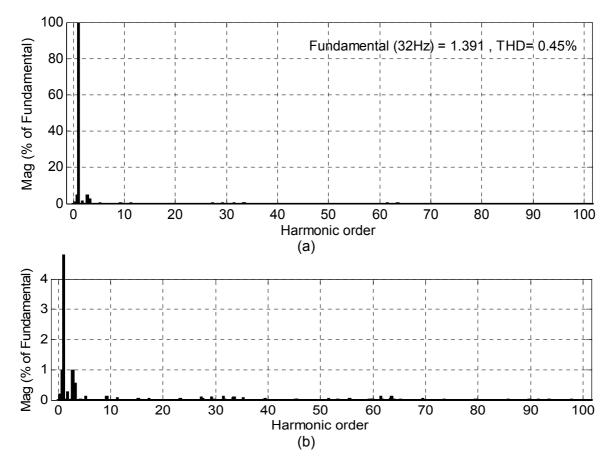

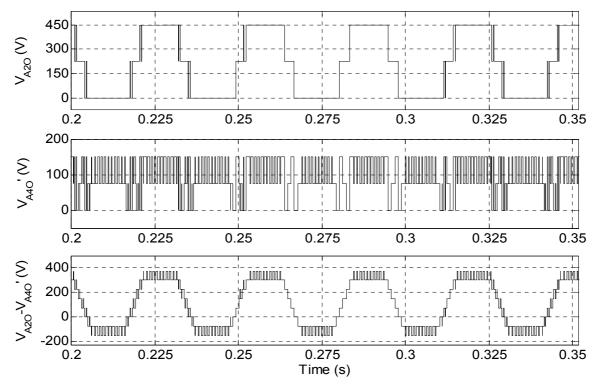

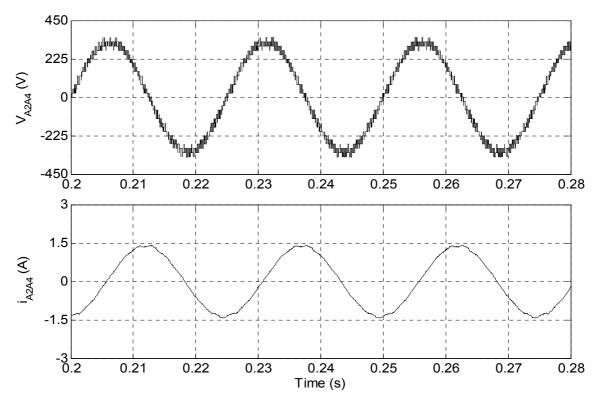

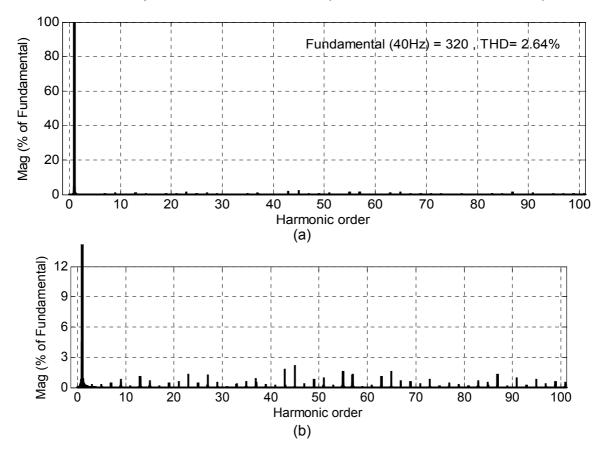

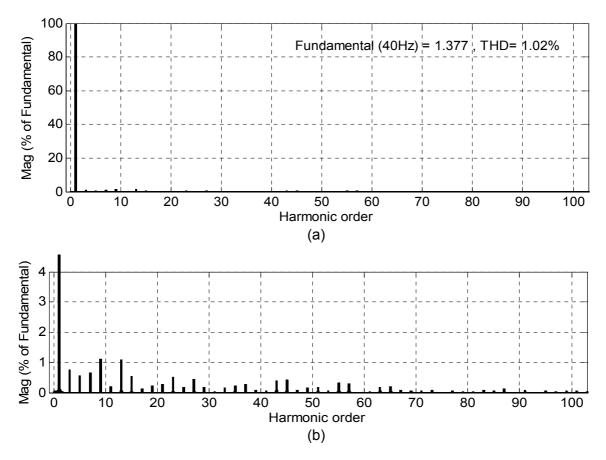

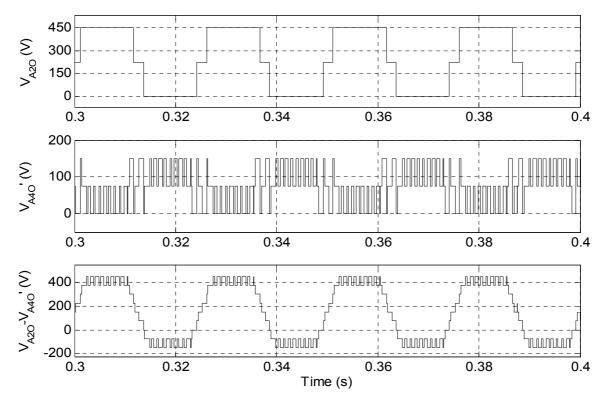

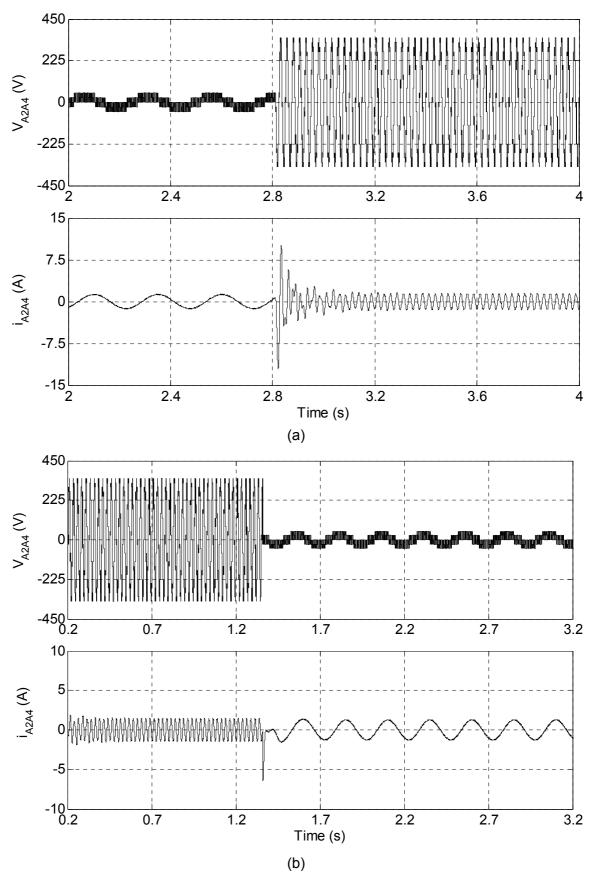

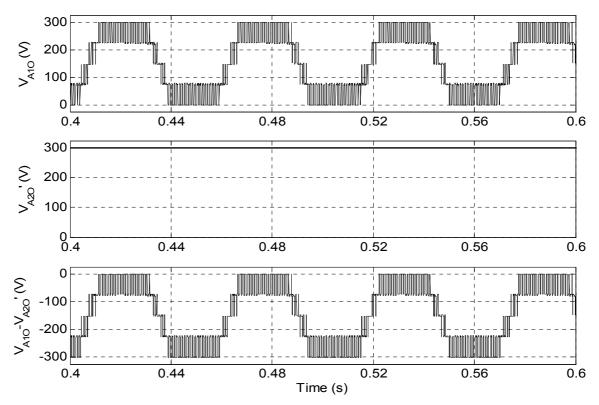

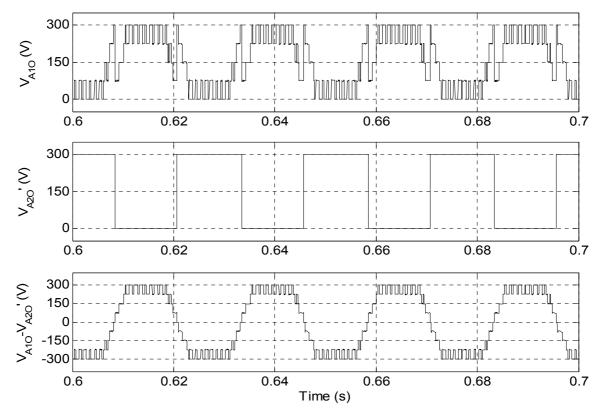

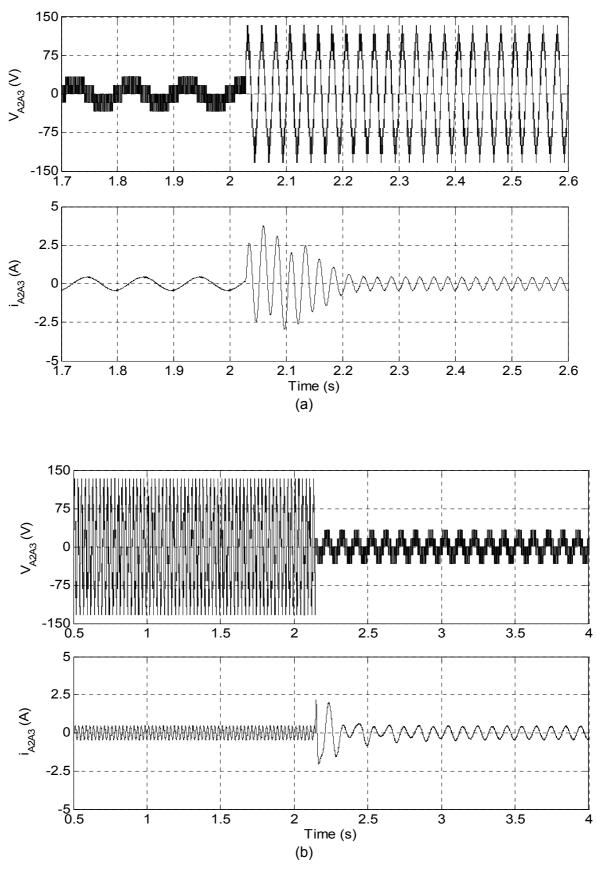

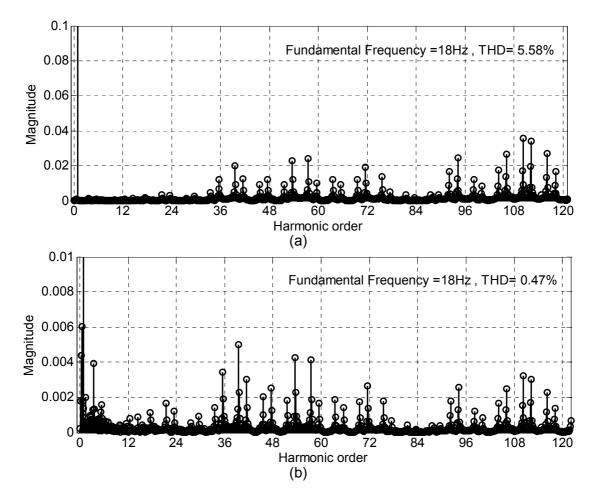

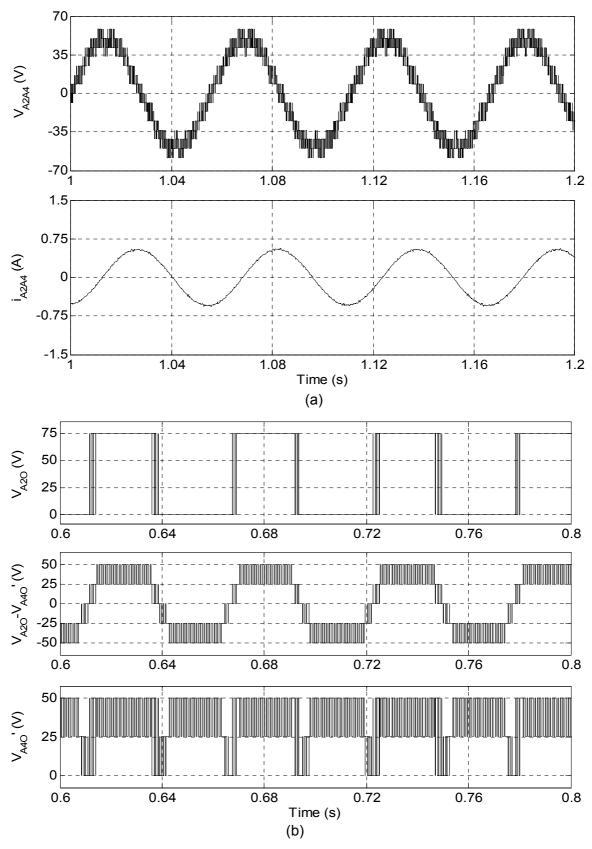

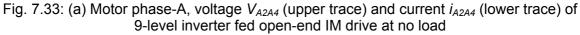

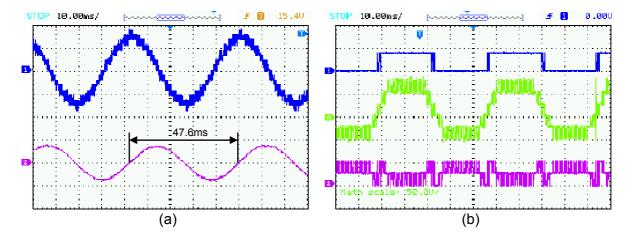

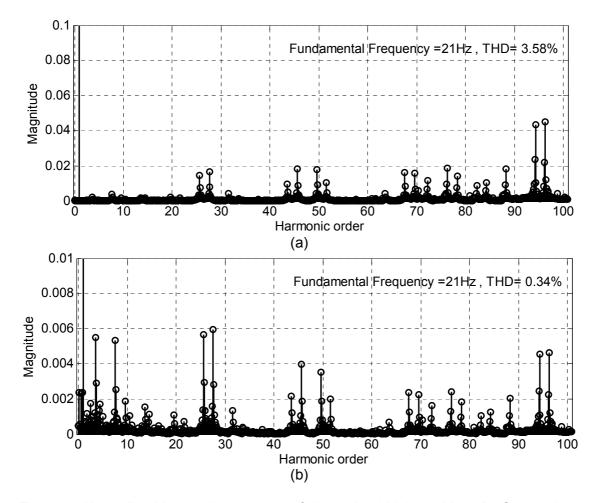

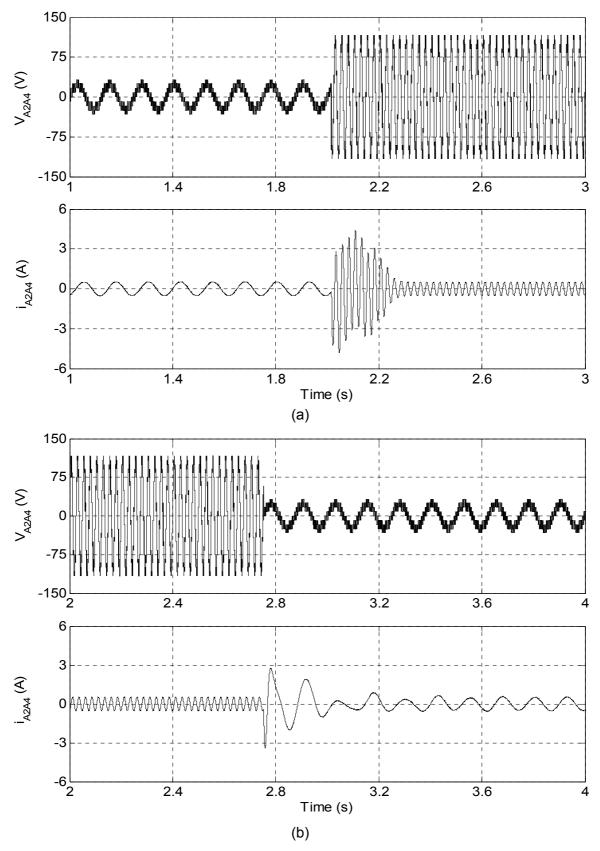

Fig. 3.16: (a) Harmonic spectrum of phase-A current ( $i_{A2A3}$ ) at m=0.6;  $f_m^*$  =30Hz (b) Zoom Fig. 3.17: Top trace; 3-level inverter-A pole voltage ( $V_{A2O}$ ), Middle trace; Two-level inverter-B pole voltage ( $V_{A3O}$ ), Bottom trace; Difference of 3-level inverter-A and two-level inverter-B Fig. 3.18: Motor phase-A, voltage  $V_{A2A3}$  (upper trace) and current  $i_{A2A3}$  (lower trace) of 5-level inverter fed open-end IM drive at no load (m=0.8;  $f_m^*=40$ Hz).....70 Fig. 3.19: (a) Harmonic spectrum of phase-A voltage ( $V_{A2A3}$ ) at m=0.8;  $f_m^*$  =40Hz (b) Zoom view of harmonic spectrum shown in (a) ......70 Fig. 3.20: (a) Harmonic spectrum of phase-A current ( $i_{A2A3}$ ) at m=0.8;  $f_m^*=40$ Hz (b) Zoom view of harmonic spectrum shown in (a) ......71 Fig. 3.21: Top trace; 3-level inverter-A pole voltage ( $V_{A2O}$ ), Middle trace; Two-level inverter-B pole voltage ( $V_{A3O'}$ ), Bottom trace; Difference of 3-level inverter-A and two-level inverter-B Fig. 3.22: (a) Motor phase-A voltage  $V_{A2A3}$  (upper trace) and current  $i_{A2A3}$  (lower trace) waveforms under sudden change in operation from two-level to 5-level at no-load (b) Motor phase-A voltage  $V_{A2A3}$  (upper trace) and current  $i_{A2A3}$  (lower trace) waveforms Fig. 4.3: (a) Reference waves during two-level operation in conventional SVPWM (b) Reference waves during two-level operation in modified SVPWM (c) Reference waves during 4-level operation in conventional SVPWM (d) Reference waves during 4-level operation in modified SVPWM (e) Reference waves during 6-level operation in conventional Fig. 4.4: Reference waves during 9-level operation in conventional and modified SVPWM . 85 Fig. 4.5: Motor phase-A, voltage  $V_{A2A4}$  (upper trace) and current  $i_{A2A4}$  (lower trace) of 9-level Fig. 4.6: (a) Harmonic spectrum of phase-A voltage ( $V_{A2A4}$ ) at m=0.08;  $f_m^*$  =4Hz (b) Zoom Fig. 4.7: (a) Harmonic spectrum of phase-A current ( $i_{A2A4}$ ) at m=0.08;  $f_m^*=4Hz$  (b) Zoom view Fig. 4.8 :Top trace; Inverter-A pole voltage ( $V_{A20}$ ), Middle trace; Inverter-B pole voltage  $(V_{A4O'})$ , Bottom trace; Difference of Inverter-A and Inverter-B pole voltages  $(V_{A2O} - V_{A4O'})$  at Fig. 4.9: Motor phase-A, voltage  $V_{A2A4}$  (upper trace) and current  $i_{A2A4}$  (lower trace) of 9-level

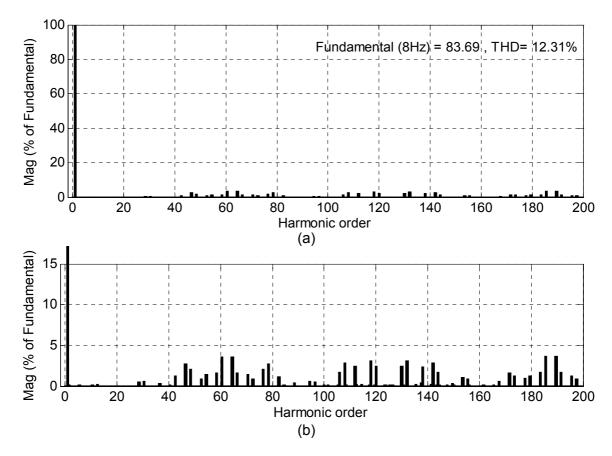

| Fig. 4.10: (a) Harmonic spectrum of phase-A voltage ( $V_{A2A4}$ ) at m=0.16; $f_m^*$ =8Hz (b) Zoom          |

|--------------------------------------------------------------------------------------------------------------|

| view of harmonic spectrum shown in (a)93                                                                     |

| Fig. 4.11: (a) Harmonic spectrum of phase-A current ( $i_{A2A4}$ ) at m=0.16; $f_m^*$ =8Hz (b) Zoom          |

| view of harmonic spectrum shown in (a)93                                                                     |

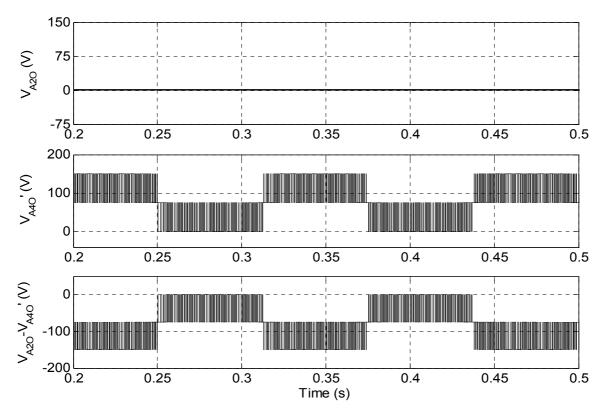

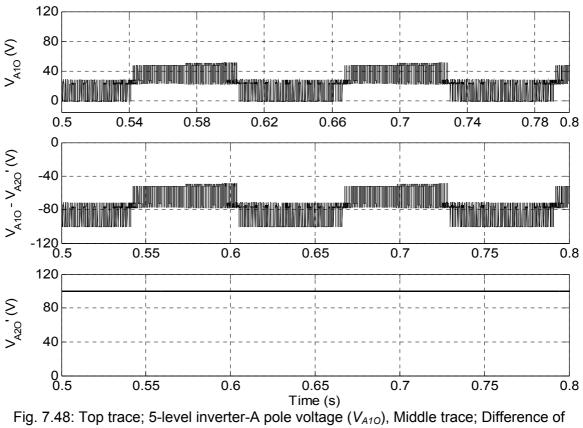

| Fig. 4.12 :Top trace; Inverter-A pole voltage ( $V_{A2O}$ ), Middle trace; Inverter-B pole voltage           |

| $(V_{A4O'})$ , Bottom trace; Difference of Inverter-A and Inverter-B pole voltages $(V_{A2O} - V_{A4O'})$ at |

| <i>m</i> =0.16; <i>f</i> * <sub><i>m</i></sub> =8Hz (3-level mode)94                                         |

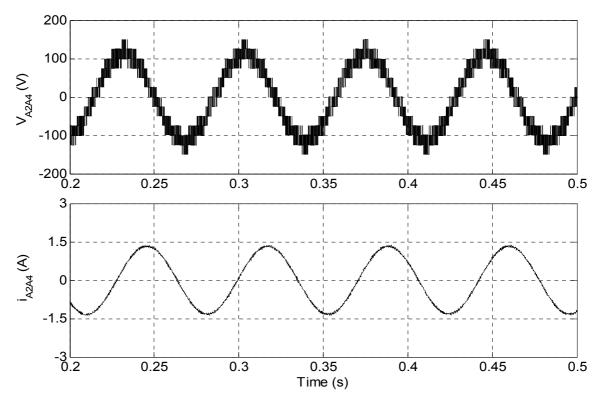

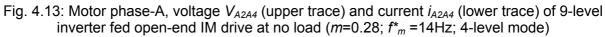

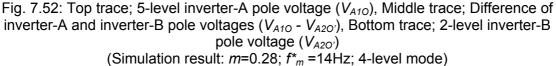

| Fig. 4.13: Motor phase-A, voltage $V_{A2A4}$ (upper trace) and current $i_{A2A4}$ (lower trace) of 9-level   |

| inverter fed open-end IM drive at no load ( $m$ =0.28; $f_m^*$ =14Hz; 4-level mode)                          |

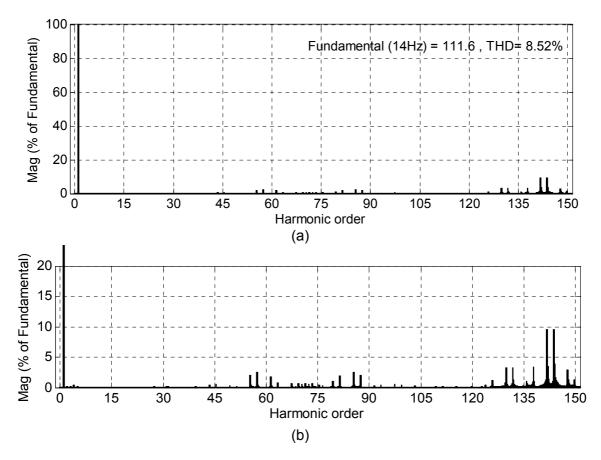

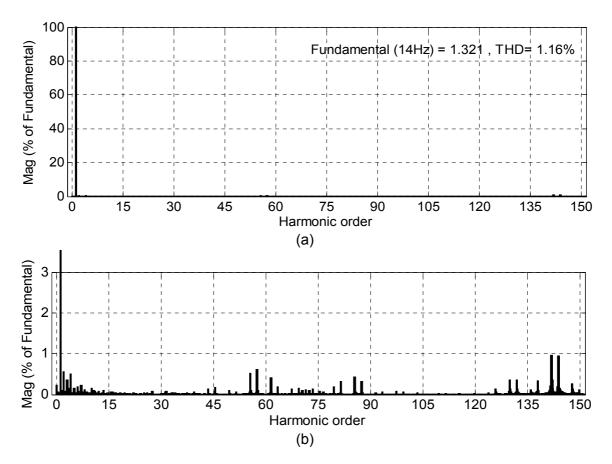

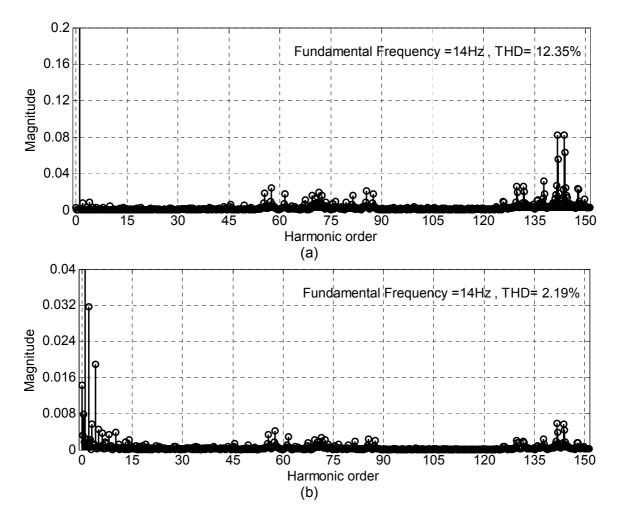

| Fig. 4.14: (a) Harmonic spectrum of phase-A voltage ( $V_{A2A4}$ ) at m=0.28; $f_m^*$ =14Hz (b) Zoom         |

| view of harmonic spectrum shown in (a)95                                                                     |

| Fig. 4.15: (a) Harmonic spectrum of phase-A current ( $i_{A2A4}$ ) at m=0.28; $f_m^*$ =14Hz (b) Zoom         |

| view of harmonic spectrum shown in (a)96                                                                     |

| Fig. 4.16 :Top trace; Inverter-A pole voltage ( $V_{A2O}$ ), Middle trace; Inverter-B pole voltage           |

| $(V_{A4O'})$ , Bottom trace; Difference of Inverter-A and Inverter-B pole voltages $(V_{A2O} - V_{A4O'})$ at |

| <i>m</i> =0.28; <i>f</i> * <sub><i>m</i></sub> =14Hz (4-level mode)96                                        |

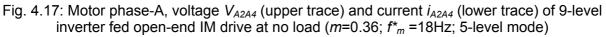

| Fig. 4.17: Motor phase-A, voltage $V_{A2A4}$ (upper trace) and current $i_{A2A4}$ (lower trace) of 9-level   |

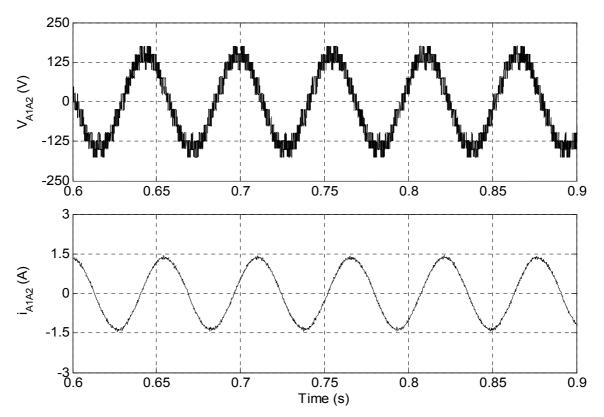

| inverter fed open-end IM drive at no load ( $m$ =0.36; $f_m^*$ =18Hz; 5-level mode)                          |

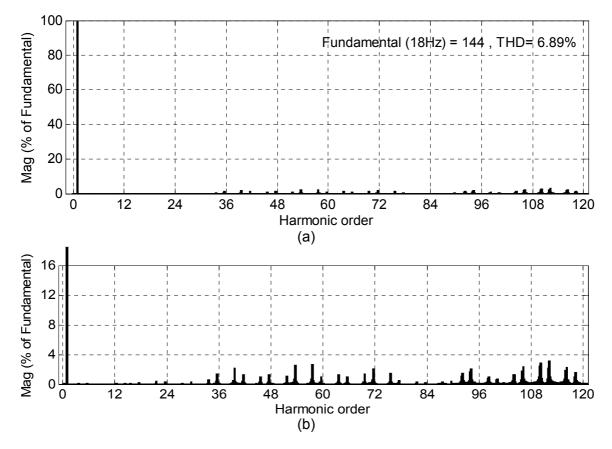

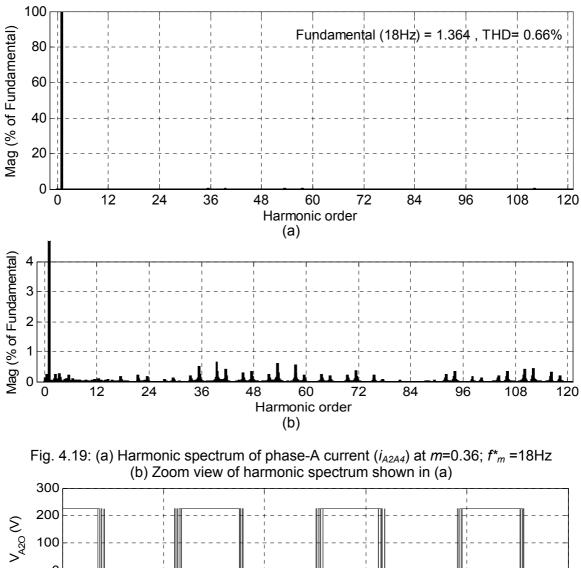

| Fig. 4.18: (a) Harmonic spectrum of phase-A voltage ( $V_{A2A4}$ ) at m=0.36; $f_m^*$ =18Hz (b) Zoom         |

| view of harmonic spectrum shown in (a)98                                                                     |

| Fig. 4.19: (a) Harmonic spectrum of phase-A current ( $i_{A2A4}$ ) at $m=0.36$ ; $f_m^*=18$ Hz (b) Zoom      |

| view of harmonic spectrum shown in (a)99                                                                     |

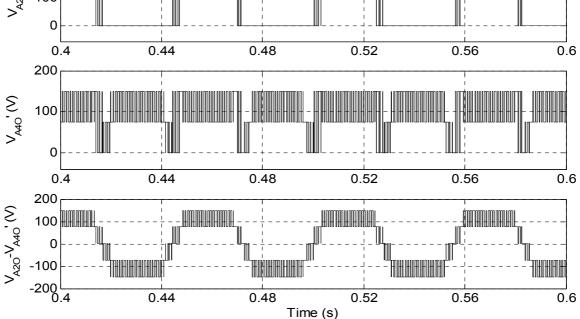

| Fig. 4.20 :Top trace; Inverter-A pole voltage ( $V_{A2O}$ ), Middle trace; Inverter-B pole voltage           |

| $(V_{A4O'})$ , Bottom trace; Difference of Inverter-A and Inverter-B pole voltages $(V_{A2O} - V_{A4O'})$ at |

| $m$ =0.36; $f_m^*$ =18Hz (5-level mode)                                                                      |

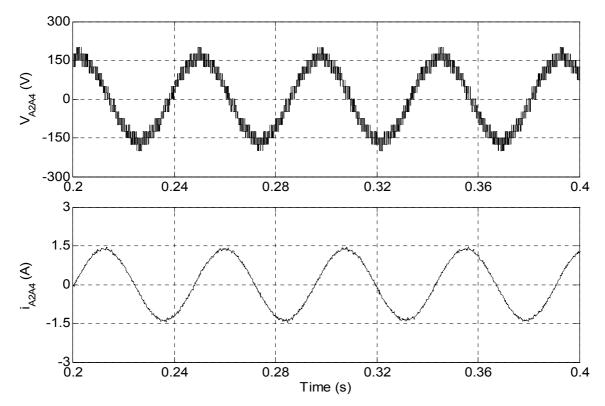

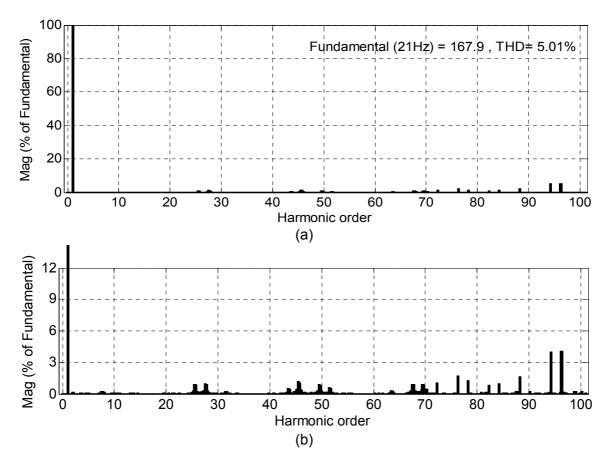

| Fig. 4.21: Motor phase-A, voltage $V_{A2A4}$ (upper trace) and current $i_{A2A4}$ (lower trace) of 9-level   |

| inverter fed open-end IM drive at no load ( $m$ =0.42; $f_m^*$ =21Hz; 6-level mode)                          |

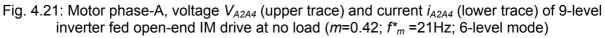

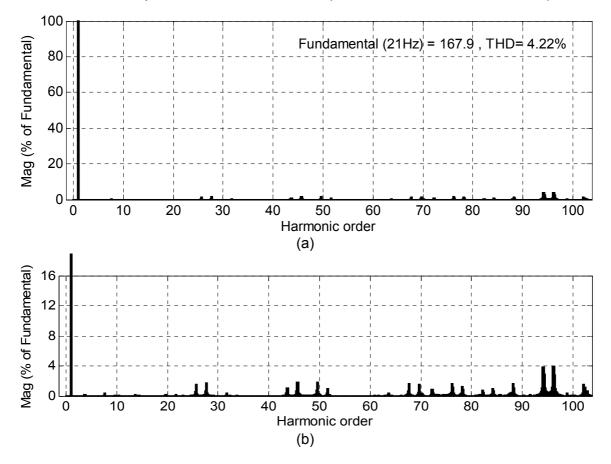

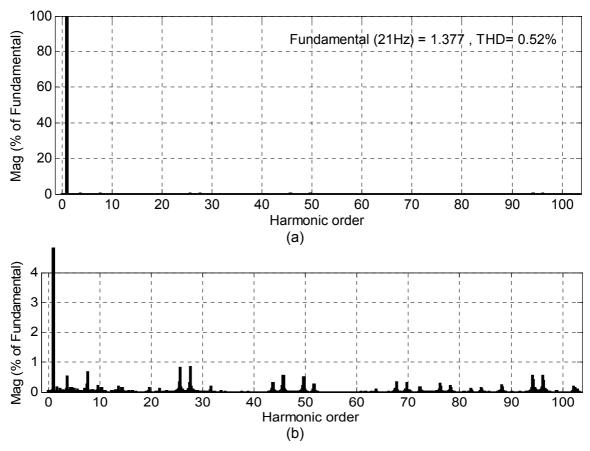

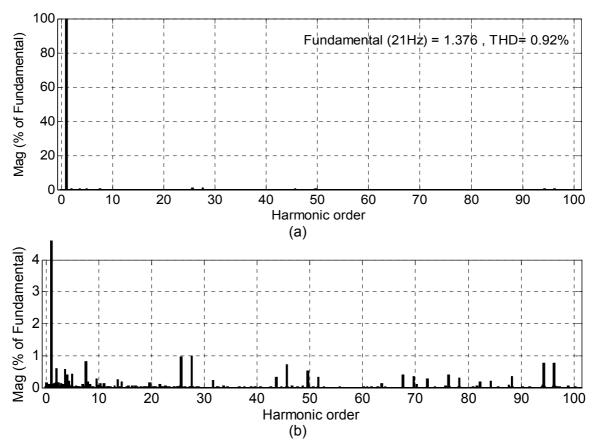

| Fig. 4.22: (a) Harmonic spectrum of phase-A voltage ( $V_{A2A4}$ ) at m=0.42; $f_m^*$ =21Hz (b) Zoom         |

| view of harmonic spectrum shown in (a)100                                                                    |

| Fig. 4.23: (a) Harmonic spectrum of phase-A current ( $i_{A2A4}$ ) at $m=0.42$ ; $f_m^*=21$ Hz (b) Zoom      |

| view of harmonic spectrum shown in (a)101                                                                    |

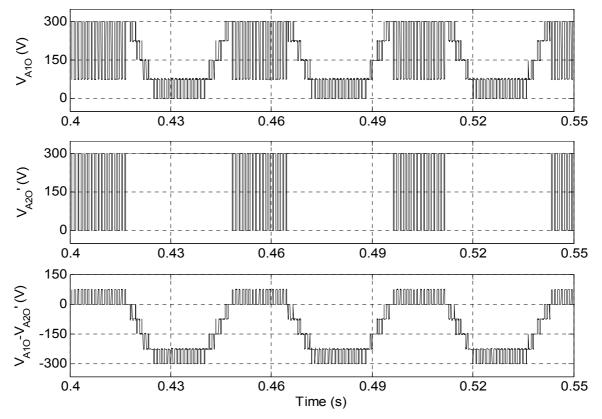

| Fig. 4.24 :Top trace; Inverter-A pole voltage ( $V_{A2O}$ ), Middle trace; Inverter-B pole voltage           |

| $(V_{A4O'})$ , Bottom trace; Difference of Inverter-A and Inverter-B pole voltages $(V_{A2O} - V_{A4O'})$ at |

| <i>m</i> =0.42; <i>f</i> * <sub><i>m</i></sub> =21Hz (6-level mode)                                          |

| Fig. 4.25: Motor phase-A, voltage $V_{A2A4}$ (upper trace) and current $i_{A2A4}$ (lower trace) of 9-level   |

|                                                                                                              |

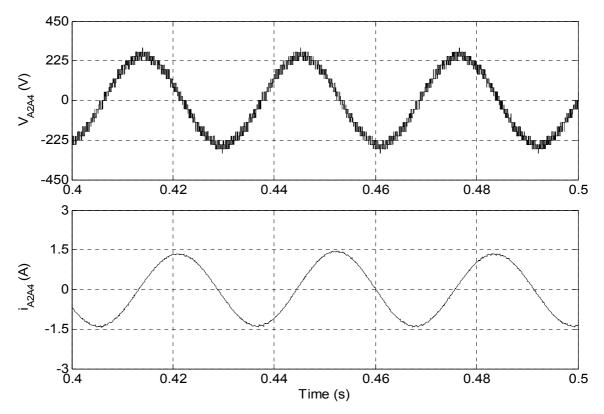

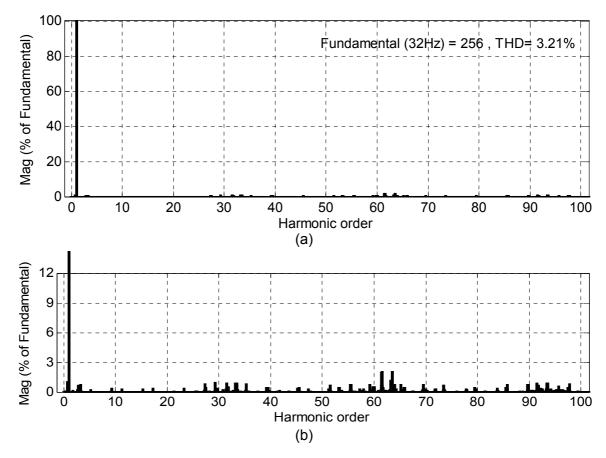

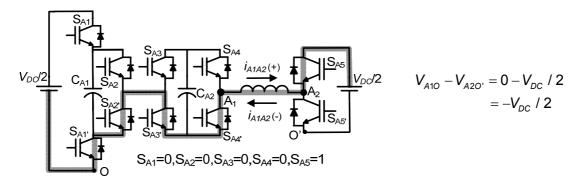

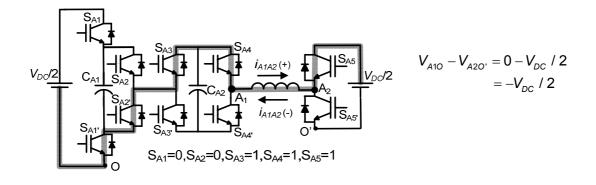

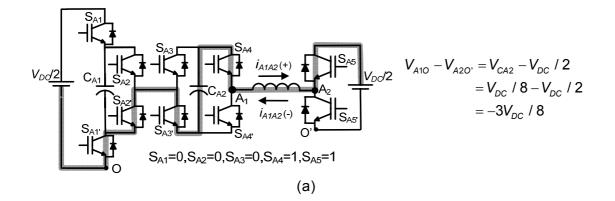

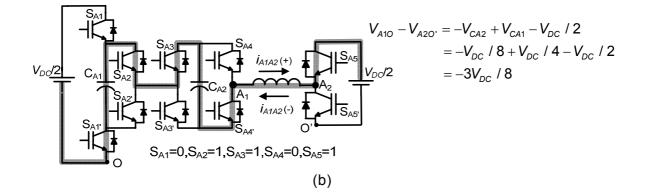

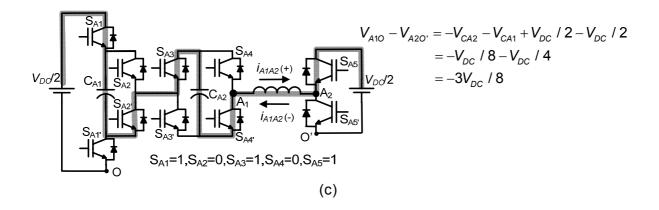

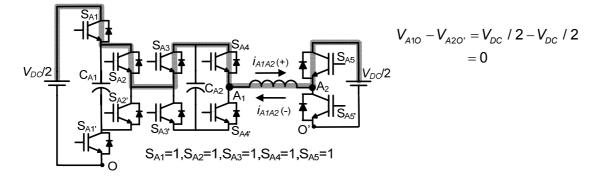

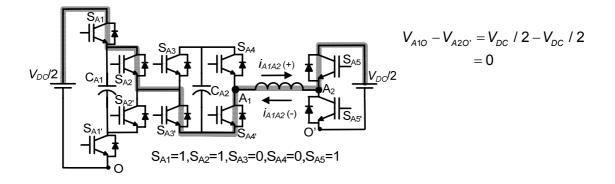

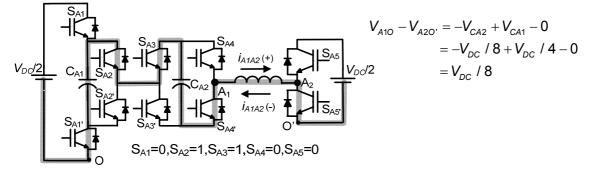

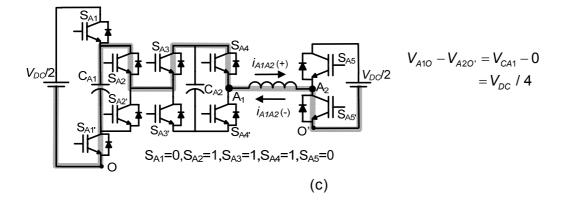

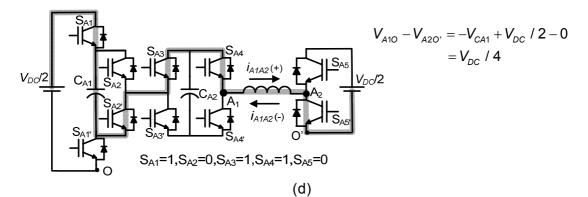

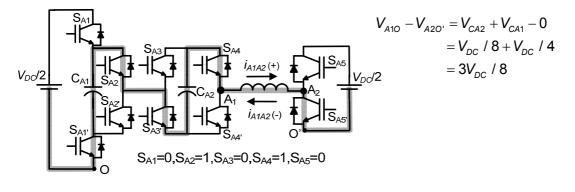

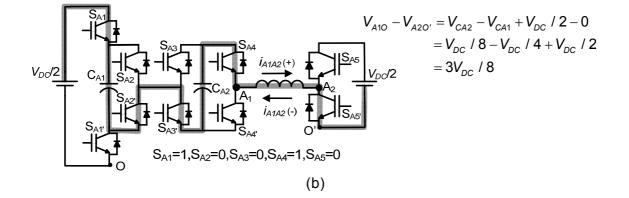

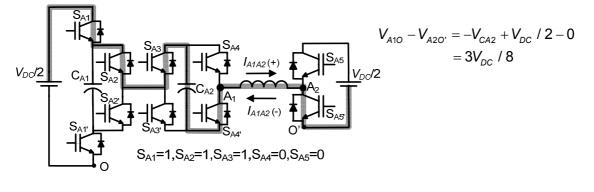

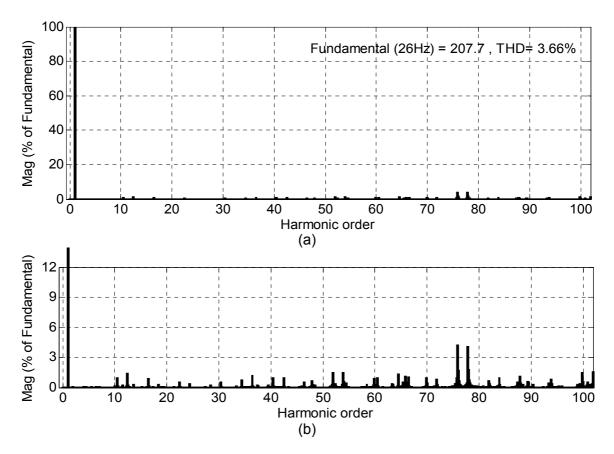

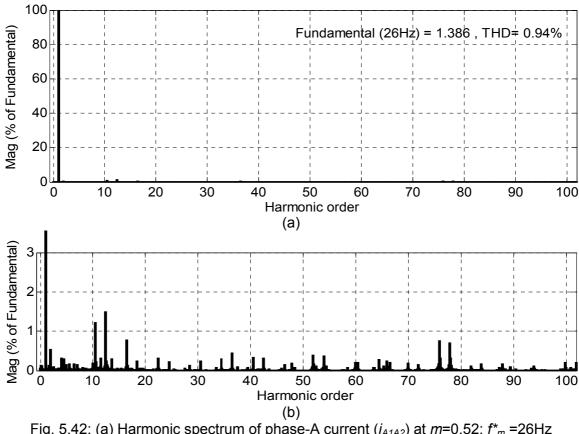

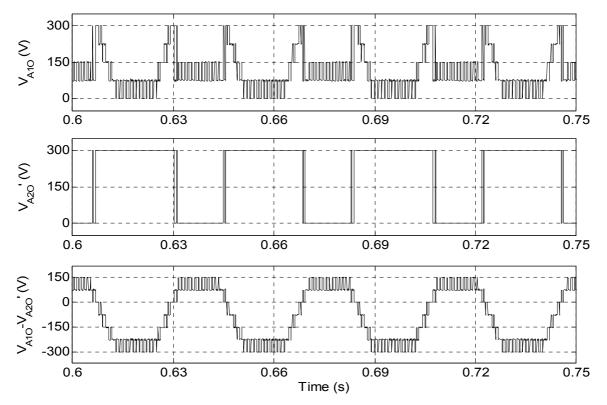

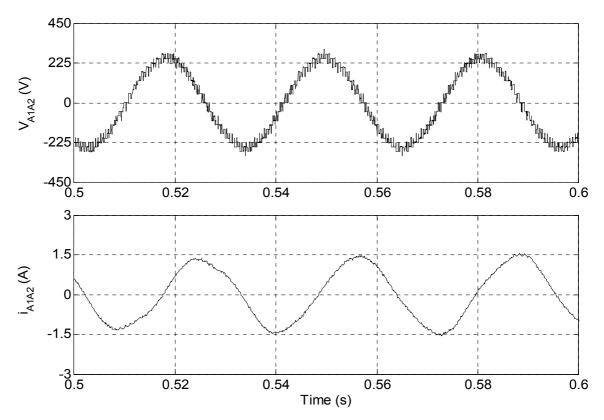

Fig. 4.26: (a) Harmonic spectrum of phase-A voltage ( $V_{A2A4}$ ) at m=0.52;  $f_m^*$  =26Hz (b) Zoom view of harmonic spectrum shown in (a) ...... 102 Fig. 4.27: (a) Harmonic spectrum of phase-A current ( $i_{A2A4}$ ) at m=0.52;  $f_m^*$  =26Hz (b) Zoom view of harmonic spectrum shown in (a) ..... 103 Fig. 4.28 :Top trace; Inverter-A pole voltage ( $V_{A2O}$ ), Middle trace; Inverter-B pole voltage  $(V_{A40'})$ , Bottom trace; Difference of Inverter-A and Inverter-B pole voltages  $(V_{A20} - V_{A40'})$  at Fig. 4.29: Motor phase-A, voltage  $V_{A2A4}$  (upper trace) and current  $i_{A2A4}$  (lower trace) of 9-level Fig. 4.30: (a) Harmonic spectrum of phase-A voltage ( $V_{A2A4}$ ) at m=0.64;  $f_m^*=32$ Hz (b) Zoom Fig. 4.31: (a) Harmonic spectrum of phase-A current ( $i_{A2A4}$ ) at m=0.64;  $f_m^*=32$ Hz (b) Zoom Fig. 4.32 :Top trace; Inverter-A pole voltage ( $V_{A2O}$ ), Middle trace; Inverter-B pole voltage  $(V_{A4O'})$ , Bottom trace; Difference of Inverter-A and Inverter-B pole voltages  $(V_{A2O} - V_{A4O'})$  at Fig. 4.33: Motor phase-A, voltage  $V_{A2A4}$  (upper trace) and current  $i_{A2A4}$  (lower trace) of 9-level Fig. 4.34: (a) Harmonic spectrum of phase-A voltage ( $V_{A2A4}$ ) at m=0.8;  $f_m^*$  =40Hz (b) Zoom view of harmonic spectrum shown in (a) ..... 107 Fig. 4.35: (a) Harmonic spectrum of phase-A current ( $i_{A2A4}$ ) at m=0.8;  $f_m^*=40$ Hz (b) Zoom view of harmonic spectrum shown in (a) ..... 108 Fig. 4.36 :Top trace; Inverter-A pole voltage (VA2O), Middle trace; Inverter-B pole voltage  $(V_{A40'})$ , Bottom trace; Difference of Inverter-A and Inverter-B pole voltages  $(V_{A20} - V_{A40'})$  at Fig. 4.37: (a) Motor phase-A voltage  $V_{A2A4}$  (upper trace) and current  $i_{A2A4}$  (lower trace) waveforms under sudden change in operation from two-level to 9-level at no-load (b) Motor phase-A voltage  $V_{A2A4}$  (upper trace) and current  $i_{A2A4}$  (lower trace) waveforms Fig. 5.2: Methods of generating voltage level  $-V_{DC}/2$  (L<sub>1</sub>) in phase-A and current path (a) For switching state  $S_{A1}=0$ ,  $S_{A2}=0$ ,  $S_{A3}=0$ ,  $S_{A4}=0$ ,  $S_{A5}=1$  (b) For switching state  $S_{A1}=0$ ,  $S_{A2}=0$ , Fig. 5.3: Methods of generating voltage level  $-3V_{DC}/8$  (L<sub>2</sub>) in phase-A and current path (a) For switching state  $S_{A1}=0$ ,  $S_{A2}=0$ ,  $S_{A3}=0$ ,  $S_{A4}=1$ ,  $S_{A5}=1$  (b) For switching state  $S_{A1}=0$ ,  $S_{A2}=1$ , S<sub>A3</sub>=1, S<sub>A4</sub>=0, S<sub>A5</sub>=1 (c) For switching state S<sub>A1</sub>=1, S<sub>A2</sub>=0, S<sub>A3</sub>=1, S<sub>A4</sub>=0, S<sub>A5</sub>=1 ...... 120

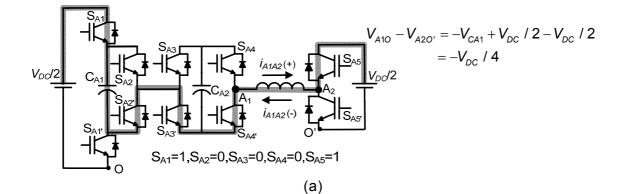

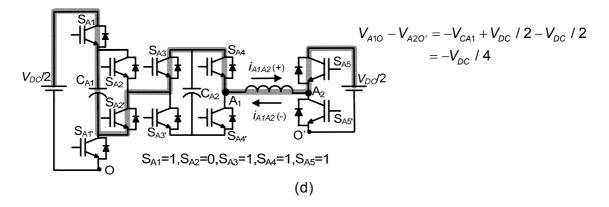

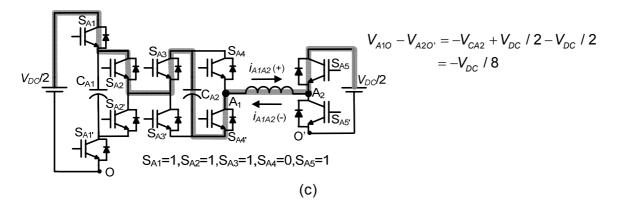

| Fig. 5.4: Methods of generating voltage level $-V_{DC}/4$ (L <sub>3</sub> ) in phase-A and current path (a) For switching state S <sub>A1</sub> =1, S <sub>A2</sub> =0, S <sub>A3</sub> =0, S <sub>A4</sub> =0, S <sub>A5</sub> =1 (b) For switching state S <sub>A1</sub> =0, S <sub>A2</sub> =1, |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $S_{A3}=0$ , $S_{A4}=0$ , $S_{A5}=1$ (c) For switching state $S_{A1}=0$ , $S_{A2}=1$ , $S_{A3}=1$ , $S_{A4}=1$ , $S_{A5}=1$ (d) For                                                                                                                                                                |

| switching state $S_{A1}=1$ , $S_{A2}=0$ , $S_{A3}=1$ , $S_{A4}=1$ , $S_{A5}=1$                                                                                                                                                                                                                     |

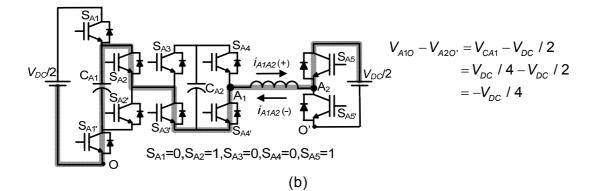

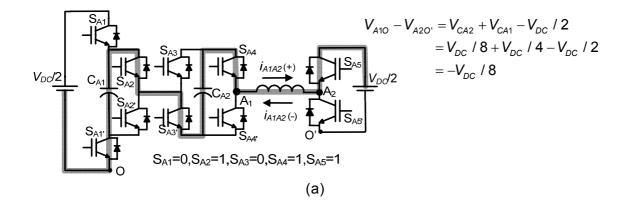

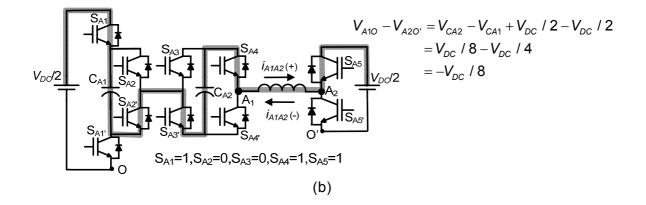

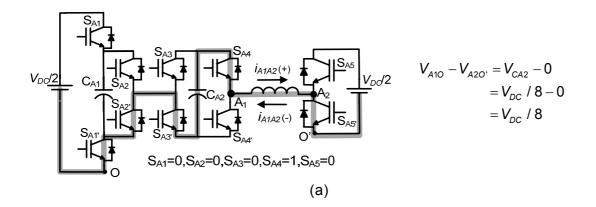

| Fig. 5.5: Methods of generating voltage level $-V_{DC}/8$ (L4) in phase-A and current path (a) For                                                                                                                                                                                                 |

| switching state $S_{A1}=0$ , $S_{A2}=1$ , $S_{A3}=0$ , $S_{A4}=1$ , $S_{A5}=1$ (b) For switching state $S_{A1}=1$ , $S_{A2}=0$ ,                                                                                                                                                                   |

| $S_{A3}=0$ , $S_{A4}=1$ , $S_{A5}=1$ (c) For switching state $S_{A1}=1$ , $S_{A2}=1$ , $S_{A3}=1$ , $S_{A4}=0$ , $S_{A5}=1$                                                                                                                                                                        |

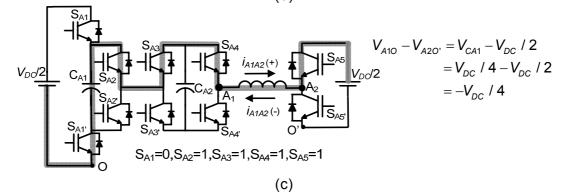

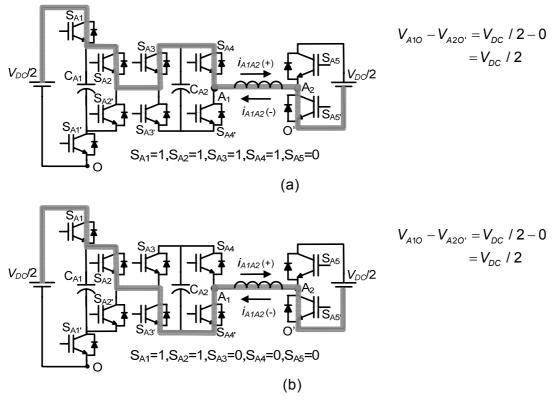

| Fig. 5.6: Methods of generating voltage level 0 ( $L_5$ ) in phase-A and current path (a) For                                                                                                                                                                                                      |

| switching state $S_{A1}=1$ , $S_{A2}=1$ , $S_{A3}=1$ , $S_{A4}=1$ , $S_{A5}=1$ (b) For switching state $S_{A1}=1$ , $S_{A2}=1$ ,                                                                                                                                                                   |

| S <sub>A3</sub> =0, S <sub>A4</sub> =0, S <sub>A5</sub> =1                                                                                                                                                                                                                                         |

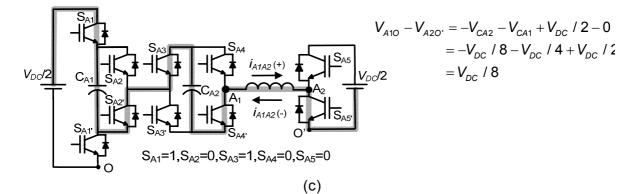

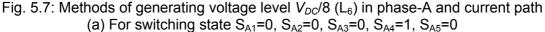

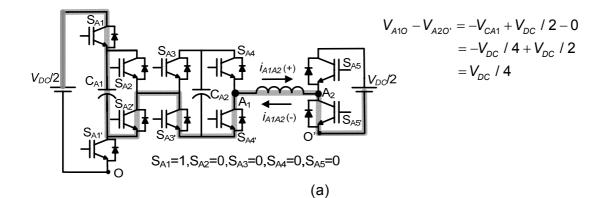

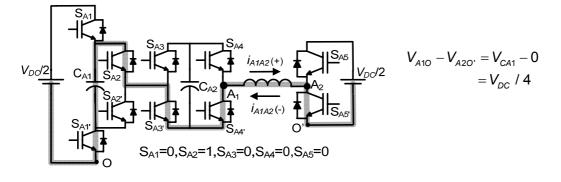

| Fig. 5.7: Methods of generating voltage level $V_{DC}/8$ (L <sub>6</sub> ) in phase-A and current path (a) For                                                                                                                                                                                     |

| switching state $S_{A1}=0$ , $S_{A2}=0$ , $S_{A3}=0$ , $S_{A4}=1$ , $S_{A5}=0$ (b) For switching state $S_{A1}=0$ , $S_{A2}=1$ ,                                                                                                                                                                   |

| $S_{A3}=1$ , $S_{A4}=0$ , $S_{A5}=0$ (c) For switching state $S_{A1}=1$ , $S_{A2}=0$ , $S_{A3}=1$ , $S_{A4}=0$ , $S_{A5}=0$                                                                                                                                                                        |

| Fig. 5.8: Methods of generating voltage level $V_{DC}/4$ (L <sub>7</sub> ) in phase-A and current path (a) For                                                                                                                                                                                     |

| switching state $S_{A1}=1$ , $S_{A2}=0$ , $S_{A3}=0$ , $S_{A4}=0$ , $S_{A5}=0$ (b) For switching state $S_{A1}=0$ , $S_{A2}=1$ ,                                                                                                                                                                   |

| $S_{A3}=0$ , $S_{A4}=0$ , $S_{A5}=0$ (c) For switching state $S_{A1}=0$ , $S_{A2}=1$ , $S_{A3}=1$ , $S_{A4}=1$ , $S_{A5}=0$ (d) For                                                                                                                                                                |

| switching state $S_{A1}=1$ , $S_{A2}=0$ , $S_{A3}=1$ , $S_{A4}=1$ , $S_{A5}=0$                                                                                                                                                                                                                     |

| Fig. 5.9: Methods of generating voltage level $3V_{DC}/8$ (L8) in phase-A and current path (a) For                                                                                                                                                                                                 |

| switching state $S_{A1}=0$ , $S_{A2}=1$ , $S_{A3}=0$ , $S_{A4}=1$ , $S_{A5}=0$ (b) For switching state $S_{A1}=1$ , $S_{A2}=0$ ,                                                                                                                                                                   |

| $S_{A3}=0$ , $S_{A4}=1$ , $S_{A5}=0$ (c) For switching state $S_{A1}=1$ , $S_{A2}=1$ , $S_{A3}=1$ , $S_{A4}=0$ , $S_{A5}=0$                                                                                                                                                                        |

| Fig. 5.10: Methods of generating voltage level $V_{DC}/2$ (L <sub>9</sub> ) in phase-A and current path (a) For                                                                                                                                                                                    |

| switching state $S_{A1}=1$ , $S_{A2}=1$ , $S_{A3}=1$ , $S_{A4}=1$ , $S_{A5}=0$ (b) For switching state $S_{A1}=1$ , $S_{A2}=1$ ,                                                                                                                                                                   |

| S <sub>A3</sub> =0, S <sub>A4</sub> =0, S <sub>A5</sub> =0                                                                                                                                                                                                                                         |

| Fig. 5.11: Block diagram of control logic 128                                                                                                                                                                                                                                                      |

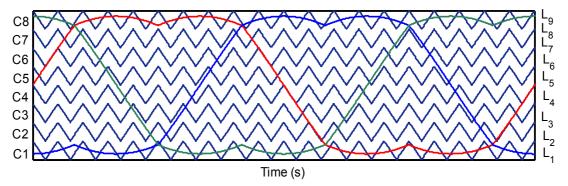

| Fig. 5.12: Modulating signals with eight level shifted triangular carriers                                                                                                                                                                                                                         |

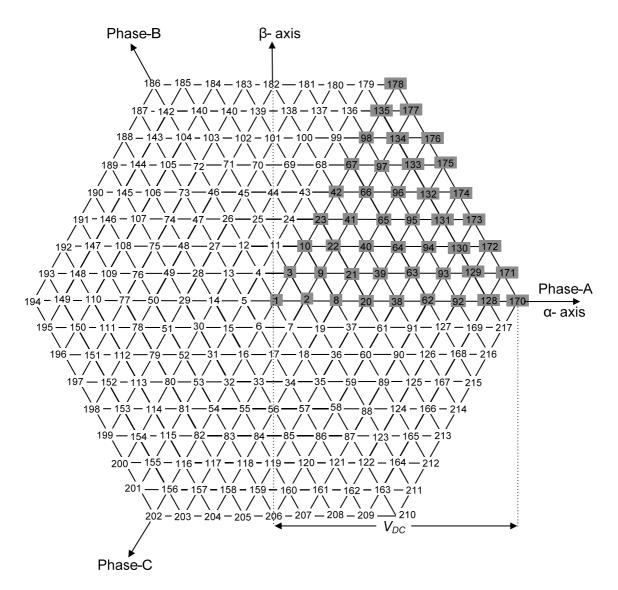

| Fig. 5.13: Locations of voltage space-phasors for 9-level inverter                                                                                                                                                                                                                                 |

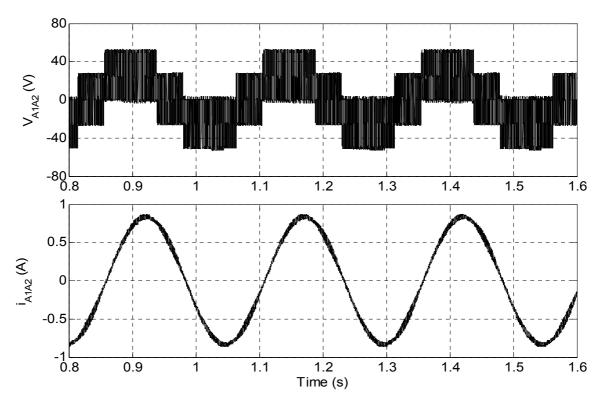

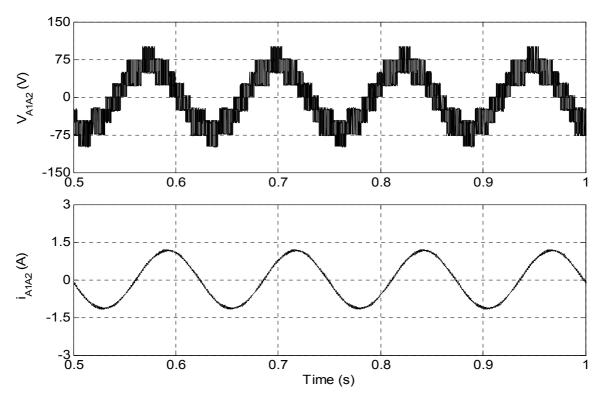

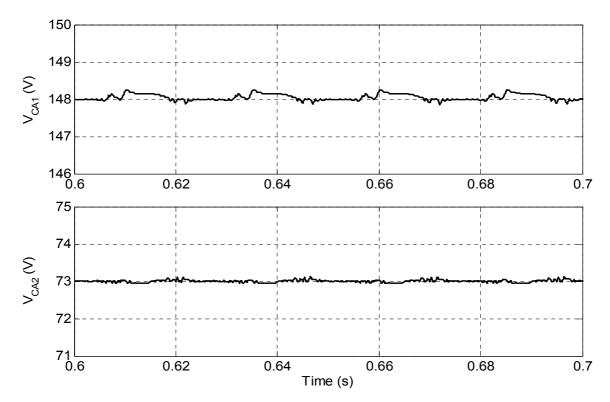

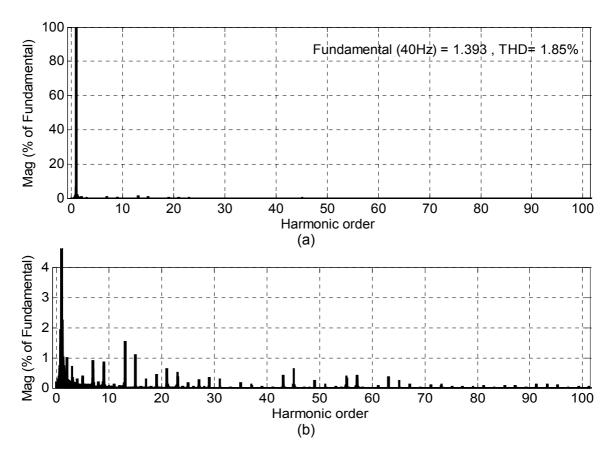

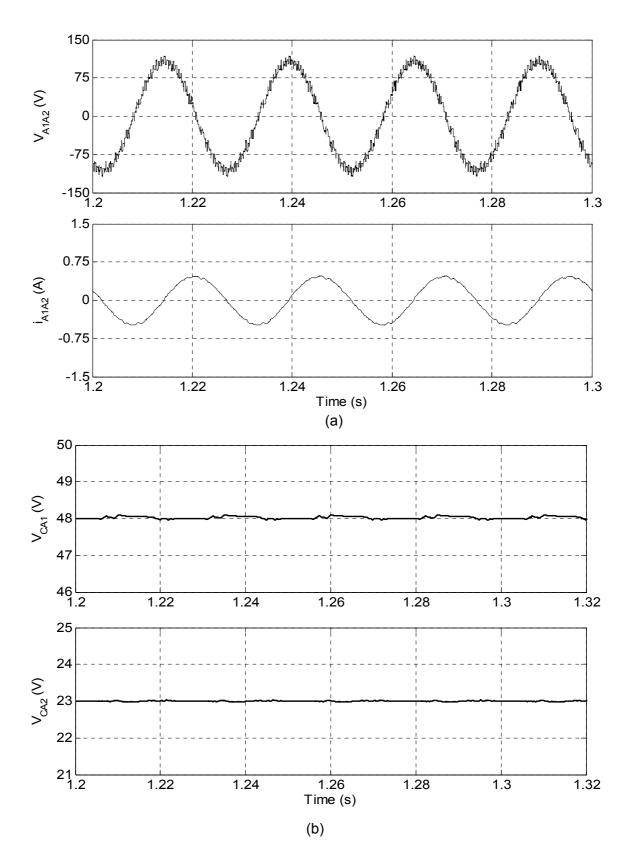

| Fig. 5.14: Motor phase-A, voltage $V_{A1A2}$ (upper trace) and current $i_{A1A2}$ (lower trace) of hybrid                                                                                                                                                                                          |

| 9-level inverter fed open-end IM drive at no load ( $m$ =0.08; $f_m^*$ =4Hz; 2-level mode)                                                                                                                                                                                                         |

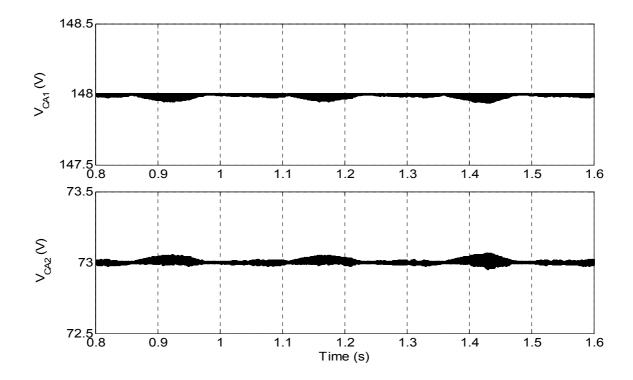

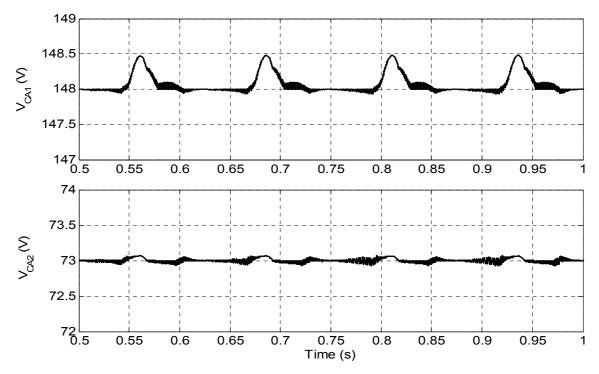

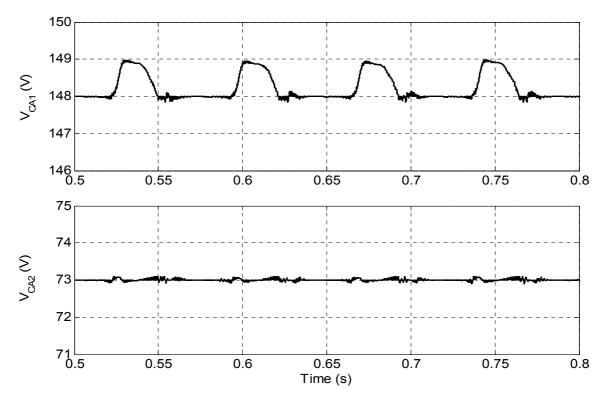

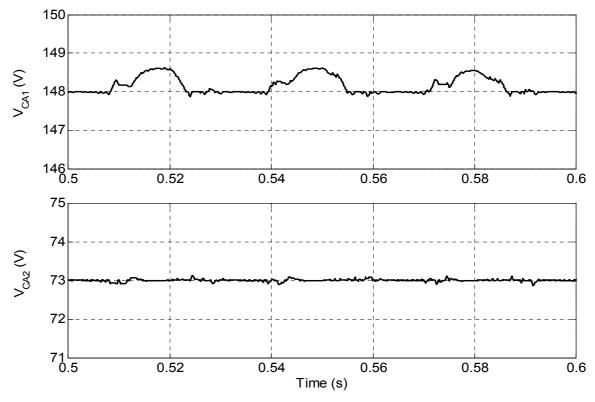

| Fig. 5.15: Capacitors voltages $V_{CA1}$ (upper trace) and $V_{CA2}$ (lower trace) in 2-level mode 135                                                                                                                                                                                             |

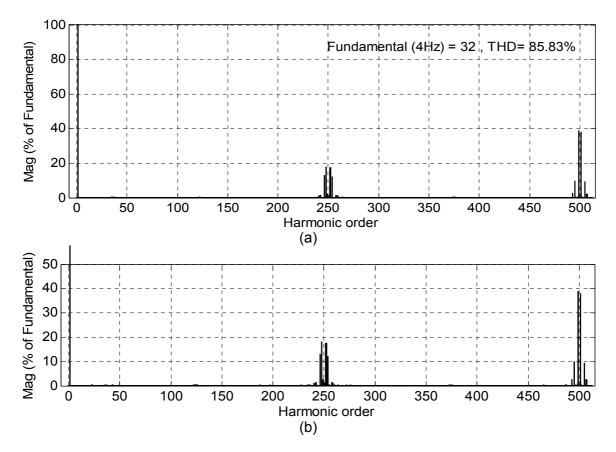

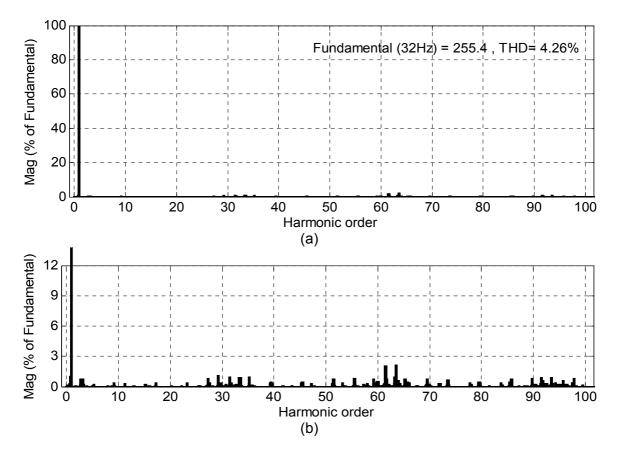

| Fig. 5.16: (a) Harmonic spectrum of phase-A voltage ( $V_{A1A2}$ ) at $m=0.08$ ; $f_m^*=4$ Hz                                                                                                                                                                                                      |

| (b) Zoom view of harmonic spectrum shown in (a)136                                                                                                                                                                                                                                                 |

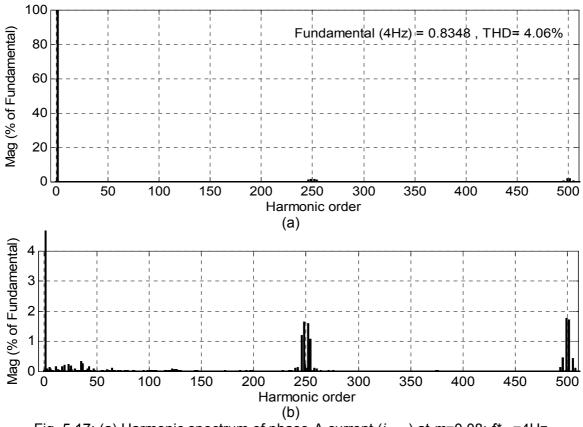

| Fig. 5.17: (a) Harmonic spectrum of phase-A current ( $i_{A1A2}$ ) at $m=0.08$ ; $f_m^*=4Hz$                                                                                                                                                                                                       |

| (b) Zoom view of harmonic spectrum shown in (a)136                                                                                                                                                                                                                                                 |

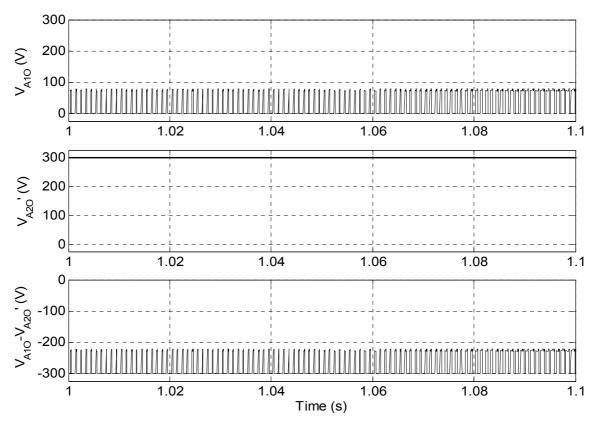

| Fig. 5.18: Top trace; Inverter-A pole voltage ( $V_{A10}$ ), Middle trace; Inverter-B pole voltage                                                                                                                                                                                                 |

| $(V_{A2O'})$ , Bottom trace; Difference of Inverter-A and -B pole voltages $(V_{A1O} - V_{A2O'})$ at m=0.08;                                                                                                                                                                                       |

| <i>f</i> <sup>*</sup> <sub><i>m</i></sub> =4Hz (2-level mode)                                                                                                                                                                                                                                      |

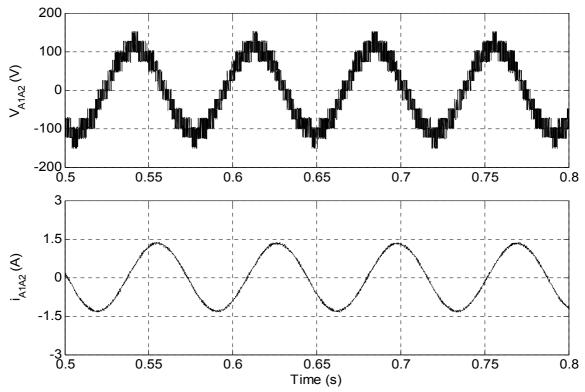

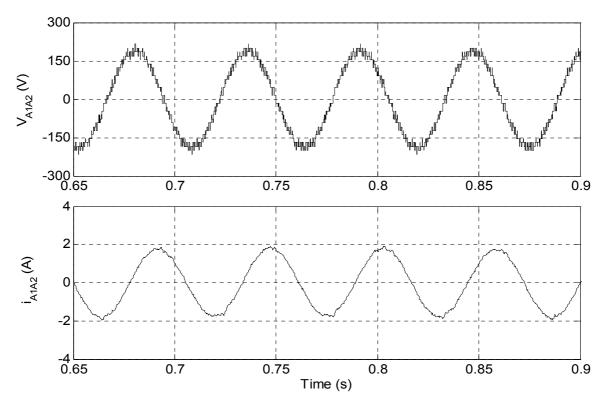

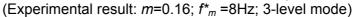

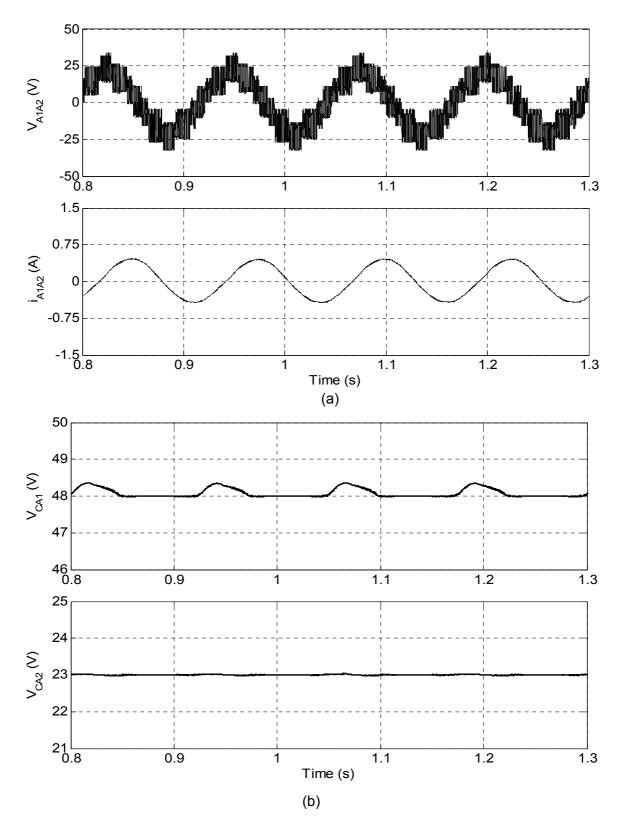

| Fig. 5.19: Motor phase-A, voltage $V_{A1A2}$ (upper trace) and current $i_{A1A2}$ (lower trace) of hybrid<br>9-level inverter fed open-end IM drive at no load ( <i>m</i> =0.16; $f_m^*$ =8Hz; 3-level mode) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

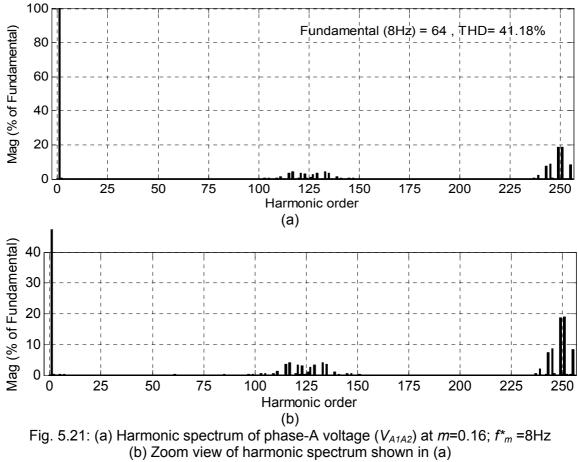

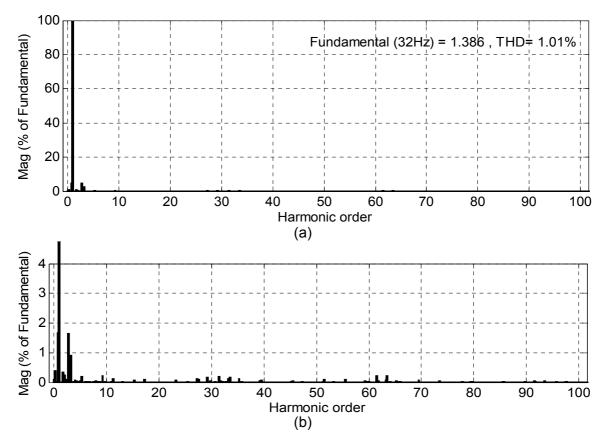

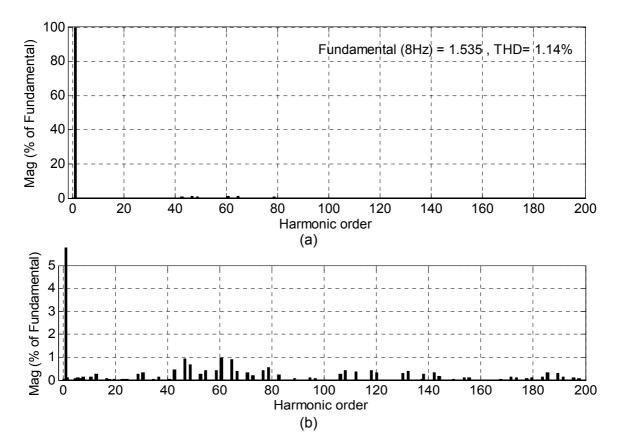

| Fig. 5.21: (a) Harmonic spectrum of phase-A voltage ( $V_{A1A2}$ ) at $m=0.16$ ; $f_m^*=8$ Hz (b) Zoom                                                                                                       |

| view of harmonic spectrum shown in (a)                                                                                                                                                                       |

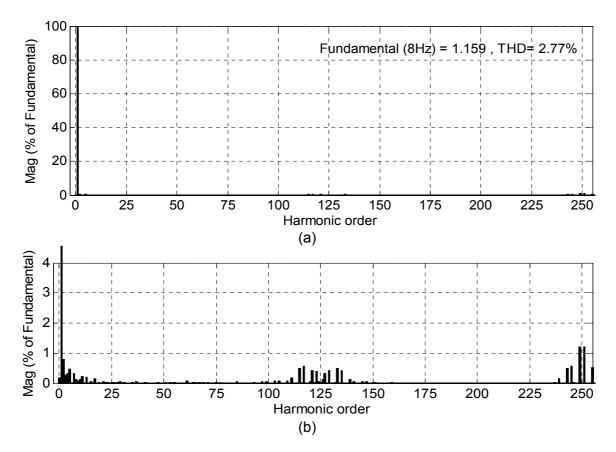

| Fig. 5.22: (a) Harmonic spectrum of phase-A current ( $i_{A1A2}$ ) at m=0.16; $f_m^*$ =8Hz (b) Zoom                                                                                                          |

| view of harmonic spectrum shown in (a)                                                                                                                                                                       |

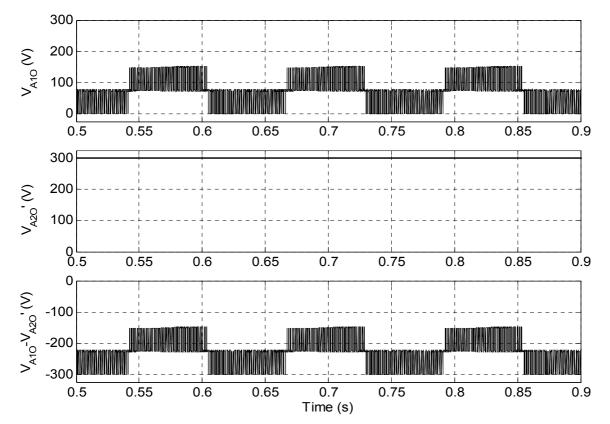

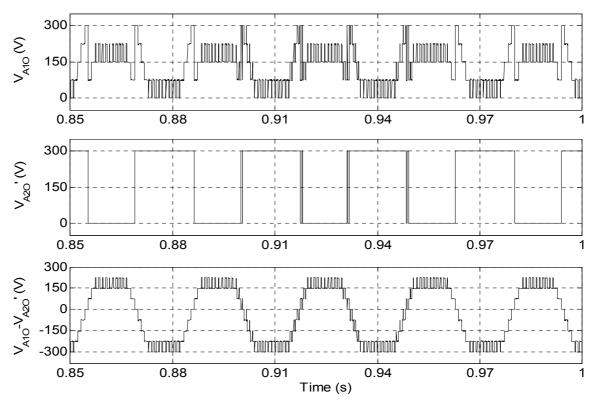

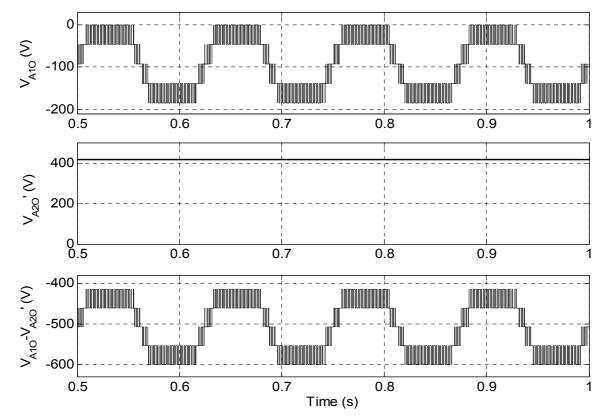

| Fig. 5.23: Top trace; Inverter-A pole voltage ( $V_{A1O}$ ), Middle trace; Inverter-B pole voltage                                                                                                           |

| $(V_{A2O'})$ , Bottom trace; Difference of Inverter-A and -B pole voltages $(V_{A1O} - V_{A2O'})$ at m=0.16;                                                                                                 |

| <i>f</i> * <sub><i>m</i></sub> =8Hz (3-level mode)                                                                                                                                                           |

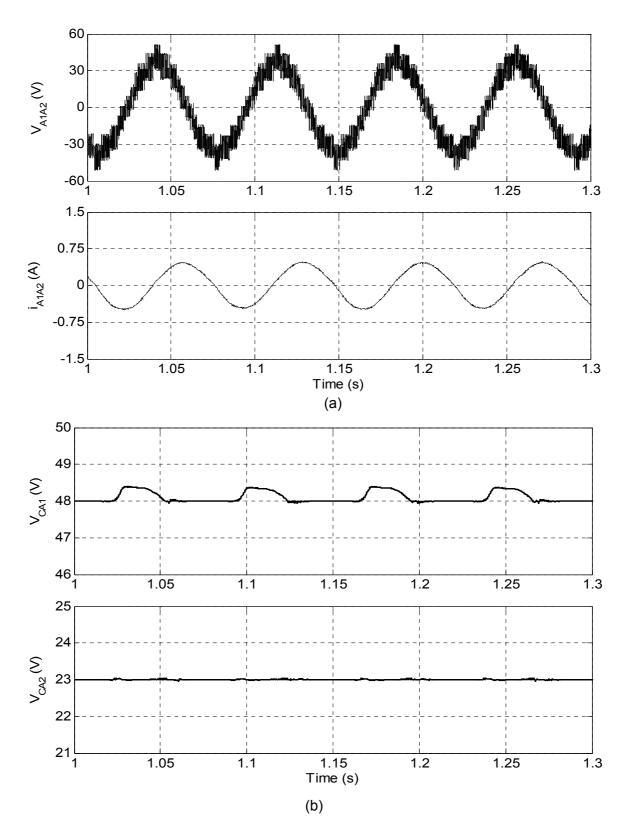

| Fig. 5.24: Motor phase-A, voltage $V_{A1A2}$ (upper trace) and current $i_{A2A4}$ (lower trace) of hybrid                                                                                                    |

| 9-level inverter fed open-end IM drive at no load ( $m$ =0.28; $f_m^*$ =14Hz; 4-level mode)                                                                                                                  |

| Fig. 5.25: Capacitors voltages $V_{CA1}$ (upper trace) and $V_{CA2}$ (lower trace) in 4-level mode 142                                                                                                       |

| Fig. 5.26: (a) Harmonic spectrum of phase-A voltage ( $V_{A1A2}$ ) at m=0.28; $f_m^*$ =14Hz (b) Zoom                                                                                                         |

| view of harmonic spectrum shown in (a) 142                                                                                                                                                                   |

| Fig. 5.27: (a) Harmonic spectrum of phase-A current ( $i_{A1A2}$ ) at $m$ =0.28; $f_m^*$ =14Hz (b) Zoom                                                                                                      |

| view of harmonic spectrum shown in (a)                                                                                                                                                                       |

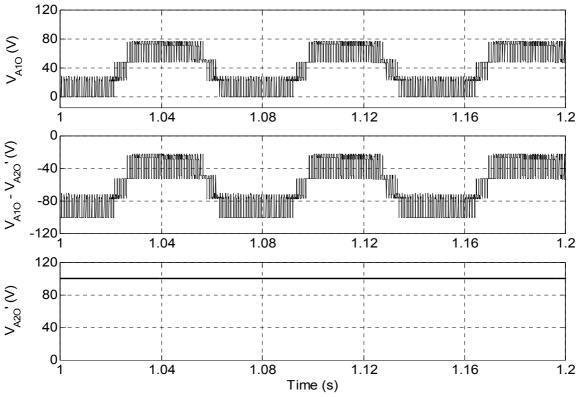

| Fig. 5.28 :Top trace; Inverter-A pole voltage ( $V_{A2O}$ ), Middle trace; Inverter-B pole voltage                                                                                                           |

| $(V_{A4O'})$ , Bottom trace; Difference of Inverter-A and -B pole voltages $(V_{A2O} - V_{A4O'})$ at <i>m</i> =0.28;                                                                                         |

| $f_m^* = 14$ Hz (4-level mode)                                                                                                                                                                               |

| Fig. 5.29: Motor phase-A, voltage $V_{A1A2}$ (upper trace) and current $i_{A2A2}$ (lower trace) of hybrid                                                                                                    |

| 9-level inverter fed open-end IM drive at no load ( $m$ =0.36; $f_m^*$ =18Hz; 5-level mode)                                                                                                                  |

| Fig. 5.30: Capacitors voltages $V_{CA1}$ (upper trace) and $V_{CA2}$ (lower trace) in 5-level mode 145                                                                                                       |

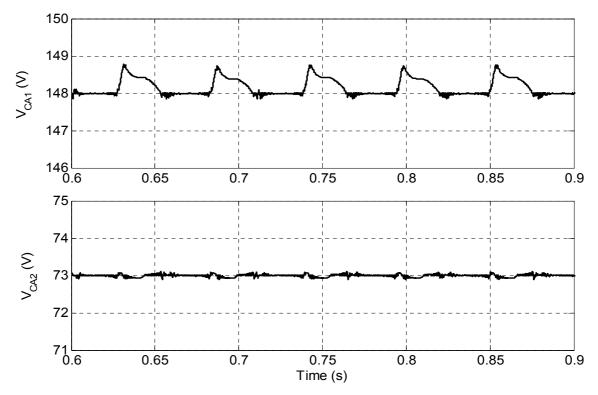

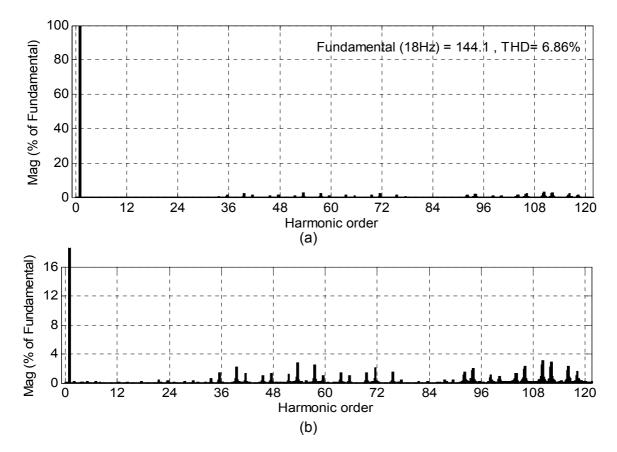

| Fig. 5.31: (a) Harmonic spectrum of phase-A voltage ( $V_{A1A2}$ ) at m=0.36; $f_m^*$ =18Hz (b) Zoom                                                                                                         |

| view of harmonic spectrum shown in (a) 146                                                                                                                                                                   |

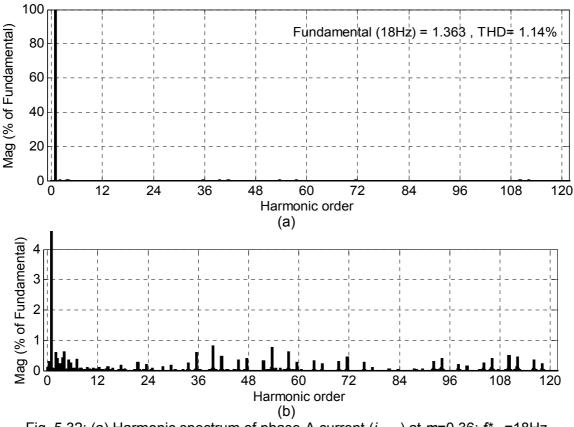

| Fig. 5.32: (a) Harmonic spectrum of phase-A current ( $i_{A1A2}$ ) at $m$ =0.36; $f_m^*$ =18Hz (b) Zoom                                                                                                      |

| view of harmonic spectrum shown in (a) 146                                                                                                                                                                   |

| Fig. 5.33 :Top trace; Inverter-A pole voltage ( $V_{A10}$ ), Middle trace; Inverter-B pole voltage                                                                                                           |

| $(V_{A2O'})$ , Bottom trace; Difference of Inverter-A and -B pole voltages $(V_{A1O} - V_{A2O'})$ at $m=0.36$ ;                                                                                              |

| <i>f</i> * <sub><i>m</i></sub> =18Hz (5-level mode)                                                                                                                                                          |

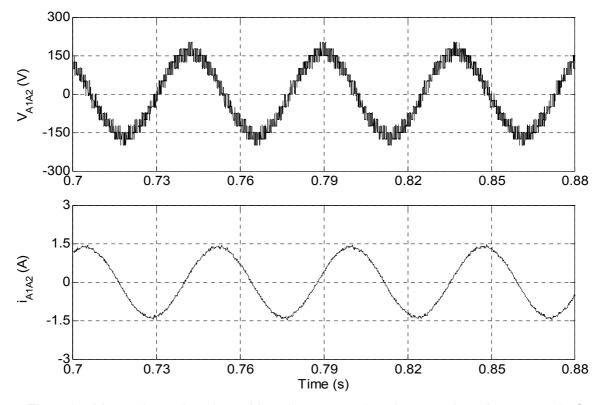

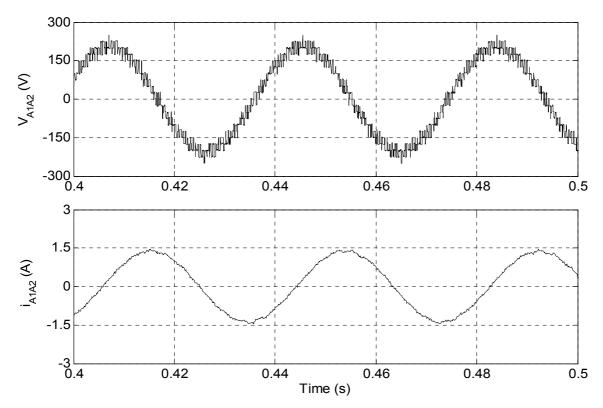

| Fig. 5.34: Motor phase-A, voltage $V_{A1A2}$ (upper trace) and current $i_{A1A2}$ (lower trace) of hybrid                                                                                                    |

| 9-level inverter fed open-end IM drive at no load ( $m$ =0.42; $f_m^*$ =21Hz; 6-level mode)                                                                                                                  |

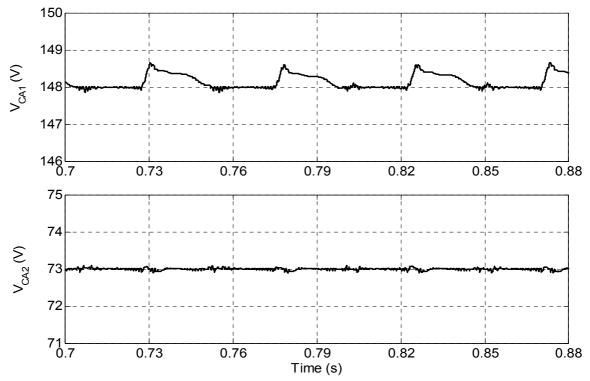

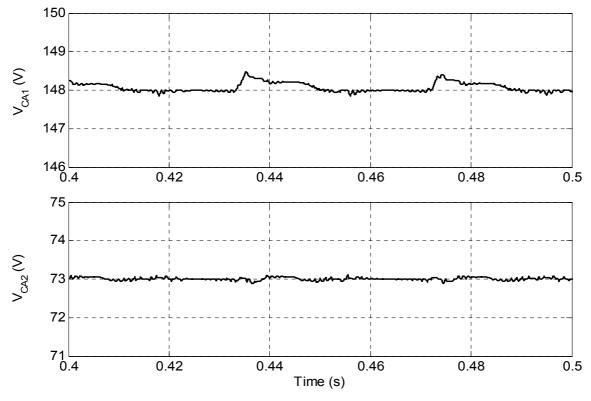

| Fig. 5.35: Capacitors voltages $V_{CA1}$ (upper trace) and $V_{CA2}$ (lower trace) in 6-level mode 148                                                                                                       |

| Fig. 5.36: (a) Harmonic spectrum of phase-A voltage ( $V_{A1A2}$ ) at $m=0.42$ ; $f_m^*=21$ Hz (b) Zoom                                                                                                      |

| view of harmonic spectrum shown in (a)                                                                                                                                                                       |

| Fig. 5.37: (a) Harmonic spectrum of phase-A current ( $i_{A1A2}$ ) at $m$ =0.42; $f_m^*$ =21Hz (b) Zoom                                                                                                      |

| view of harmonic spectrum shown in (a) 149                                                                                                                                                                   |

| Fig. 5.56: Effect of disabling the capacitor voltage balancing algorithm                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 6.1: Power circuit of 18-level inverter for induction motor drive                                                                              |

| Fig. 6.2: Schematic block diagram of V/f control scheme                                                                                             |

| Fig. 6.3: Modulating signals with eight level shifted triangular carriers                                                                           |

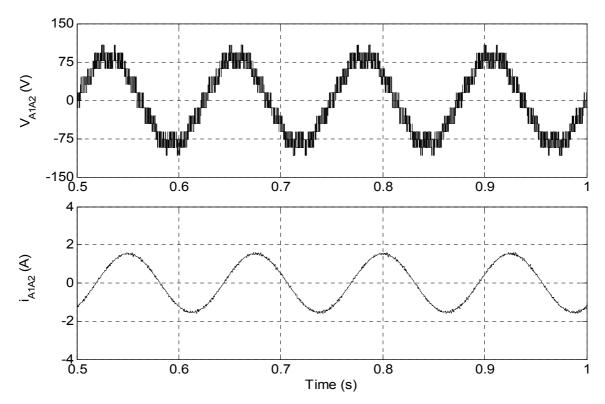

| Fig. 6.4: Motor phase-A, voltage $V_{A1A2}$ (upper trace) and current $i_{A2A2}$ (lower trace) of 18-level                                          |

| inverter fed open-end IM drive at no load ( $m$ =0.16; $f_m^*$ =8Hz; 5-level mode)                                                                  |

| Fig. 6.5: (a) Harmonic spectrum of phase-A voltage ( $V_{A1A2}$ ) at $m$ =0.16; $f_m^*$ =8Hz (b) Zoom                                               |

| view of harmonic spectrum shown in (a)                                                                                                              |

| Fig. 6.6: (a) Harmonic spectrum of phase-A current ( $i_{A1A2}$ ) at <i>m</i> =0.16; <i>f</i> * <sub><i>m</i></sub> =8Hz (b) Zoom view              |

| of harmonic spectrum shown in (a)                                                                                                                   |

|                                                                                                                                                     |

| Fig. 6.7 :Top trace; Inverter-A pole voltage ( $V_{A10}$ ), Middle trace; Inverter-B pole voltage                                                   |

| $(V_{A2O'})$ , Bottom trace; Difference of Inverter-A and -B pole voltages $(V_{A1O} - V_{A2O'})$ at <i>m</i> =0.16;<br>$f_m^*$ =8Hz (5-level mode) |

|                                                                                                                                                     |

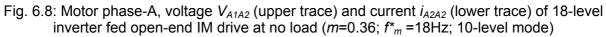

| Fig. 6.8: Motor phase-A, voltage $V_{A1A2}$ (upper trace) and current $i_{A2A2}$ (lower trace) of 18-level                                          |

| inverter fed open-end IM drive at no load ( $m$ =0.36; $f_m^*$ =18Hz; 10-level mode)                                                                |

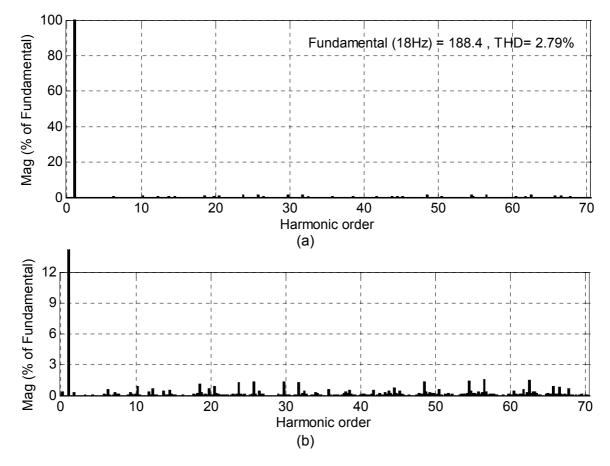

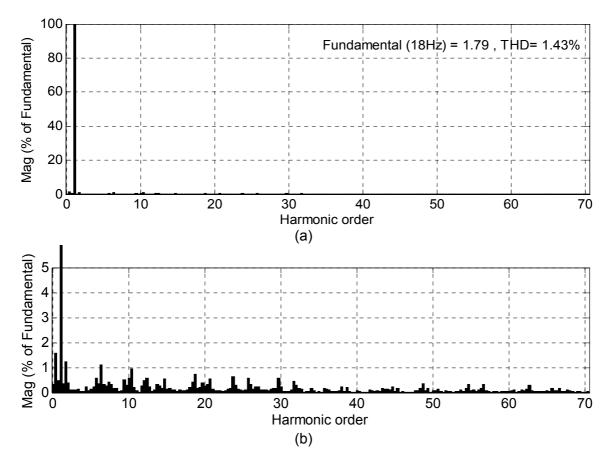

| Fig. 6.9: (a) Harmonic spectrum of phase-A voltage ( $V_{A1A2}$ ) at $m$ =0.36; $f_m^*$ =18Hz (b) Zoom                                              |

| view of harmonic spectrum shown in (a)                                                                                                              |

| Fig. 6.10: (a) Harmonic spectrum of phase-A current ( $i_{A1A2}$ ) at $m$ =0.36; $f_m^*$ =18Hz (b) Zoom                                             |

| view of harmonic spectrum shown in (a)                                                                                                              |

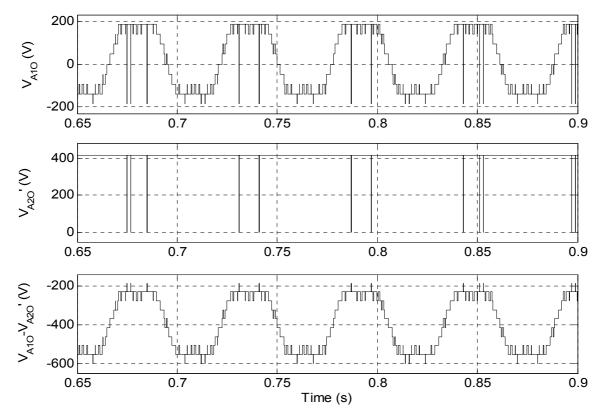

| Fig. 6.11 :Top trace; Inverter-A pole voltage ( $V_{A1O}$ ), Middle trace; Inverter-B pole voltage                                                  |

| $(V_{A2O'})$ , Bottom trace; Difference of Inverter-A and -B pole voltages $(V_{A1O} - V_{A2O'})$ at $m=0.36$ ;                                     |

| <i>f</i> * <sub><i>m</i></sub> =18Hz (10-level mode)                                                                                                |

| Fig. 6.12: Motor phase-A, voltage $V_{A1A2}$ (upper trace) and current $i_{A2A2}$ (lower trace) of 18-                                              |

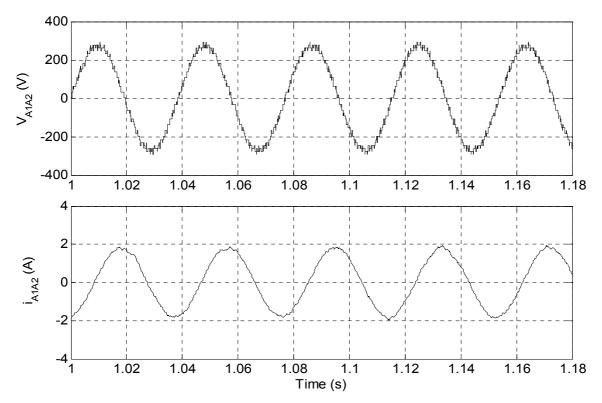

| level inverter fed open-end IM drive at no load ( $m$ =0.52; $f_m^*$ =26Hz; 13-level mode)                                                          |

| Fig. 6.13: (a) Harmonic spectrum of phase-A voltage ( $V_{A1A2}$ ) at m=0.52; $f_m^*$ =26Hz (b) Zoom                                                |

| view of harmonic spectrum shown in (a)                                                                                                              |

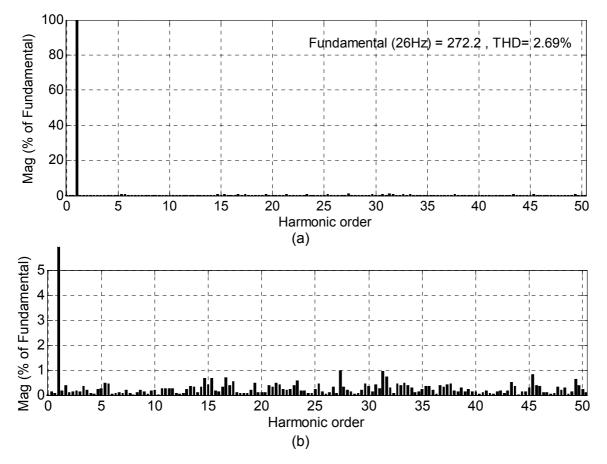

| Fig. 6.14: (a) Harmonic spectrum of phase-A current ( $i_{A1A2}$ ) at $m$ =0.52; $f_m^*$ =26Hz (b) Zoom                                             |

| view of harmonic spectrum shown in (a)                                                                                                              |

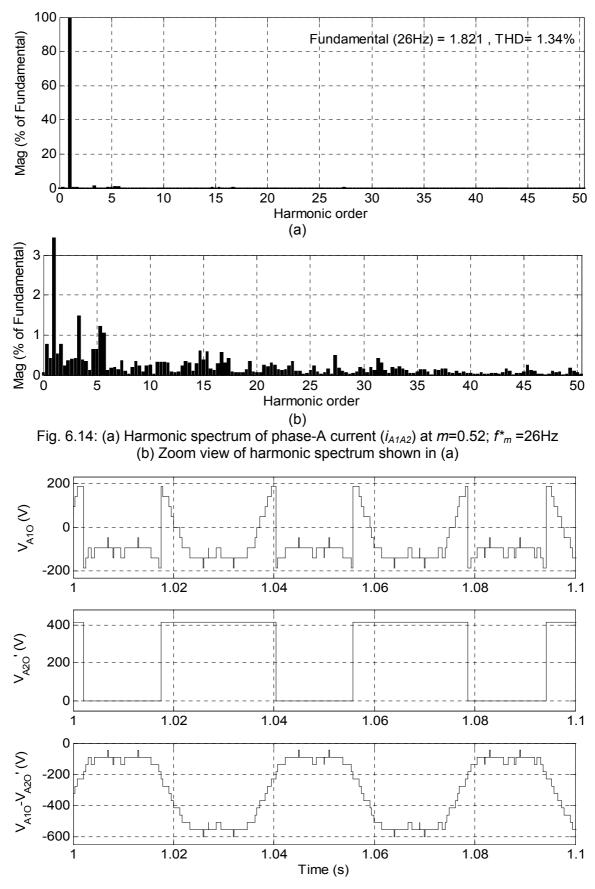

| Fig. 6.15 :Top trace; Inverter-A pole voltage ( $V_{A10}$ ), Middle trace; Inverter-B pole voltage                                                  |

| $(V_{A2O'})$ , Bottom trace; Difference of Inverter-A and -B pole voltages $(V_{A1O} - V_{A2O'})$ at <i>m</i> =0.52;                                |

| <i>f</i> * <sub><i>m</i></sub> =26Hz (13-level mode)                                                                                                |

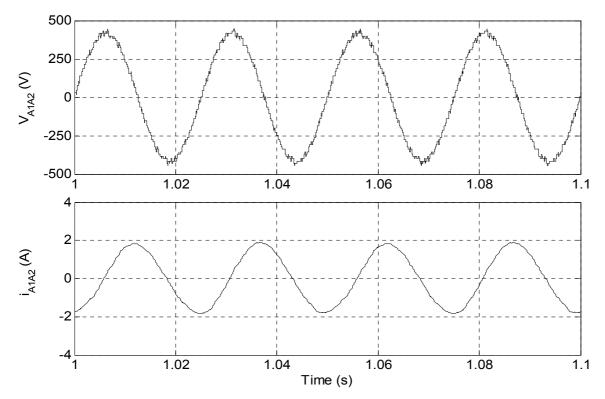

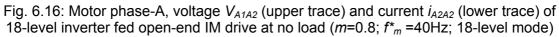

| Fig. 6.16: Motor phase-A, voltage $V_{A1A2}$ (upper trace) and current $i_{A2A2}$ (lower trace) of                                                  |

| 18-level inverter fed open-end IM drive at no load ( $m=0.8$ ; $f_m^*=40$ Hz; 18-level mode) 182                                                    |

| Fig. 6.17: (a) Harmonic spectrum of phase-A voltage ( $V_{A1A2}$ ) at m=0.8; $f_m^*$ =40Hz (b) Zoom                                                 |

| view of harmonic spectrum shown in (a)                                                                                                              |

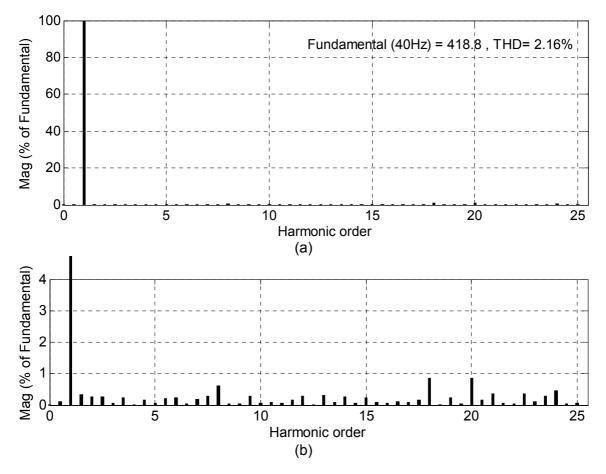

| Fig. 6.18: (a) Harmonic spectrum of phase-A current ( $i_{A1A2}$ ) at m=0.8; $f_m^*$ =40Hz (b) Zoom                                                 |

| view of harmonic spectrum shown in (a) 183                                                                                                          |

|                                                                                                                                                     |

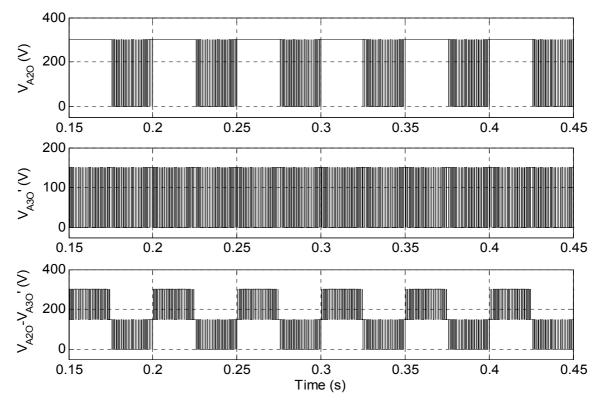

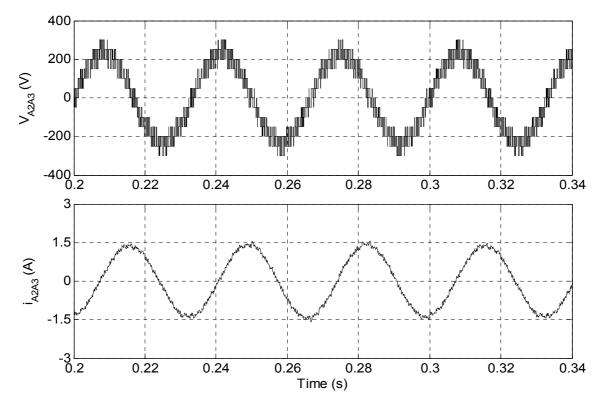

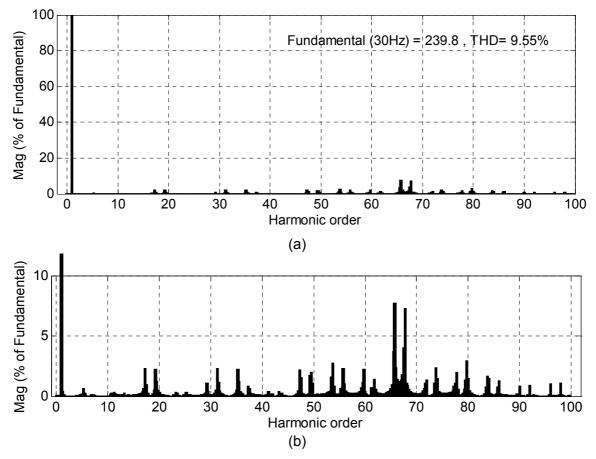

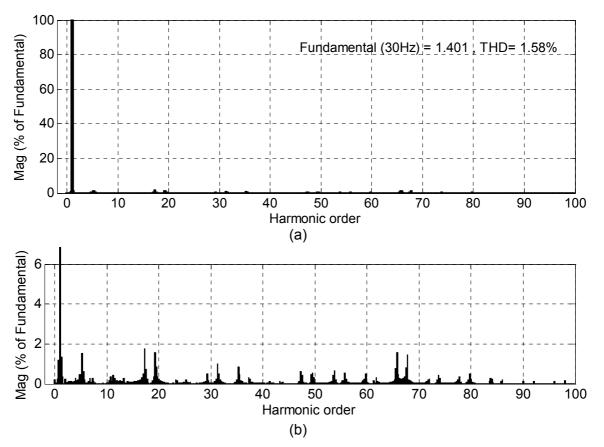

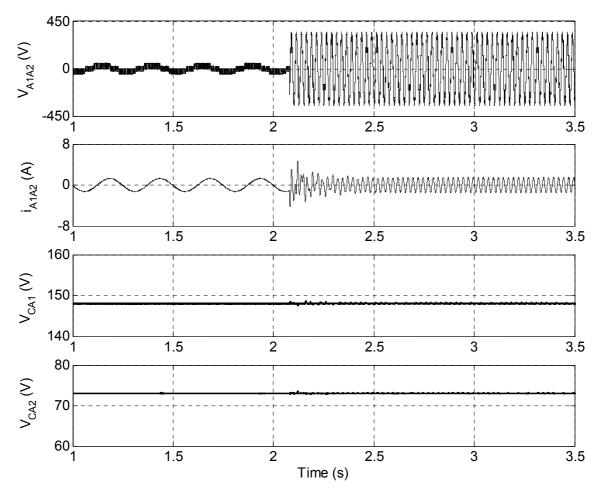

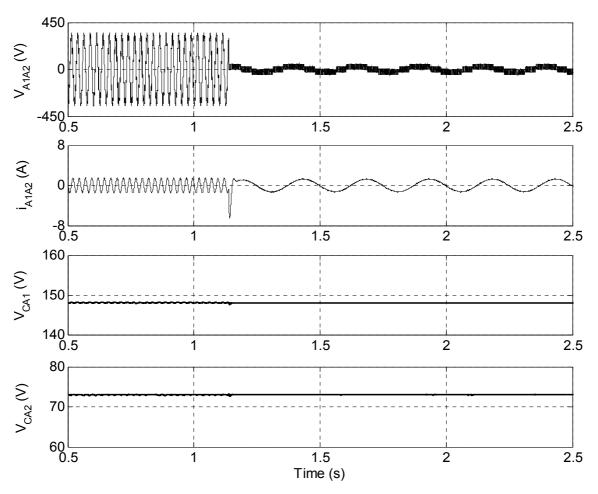

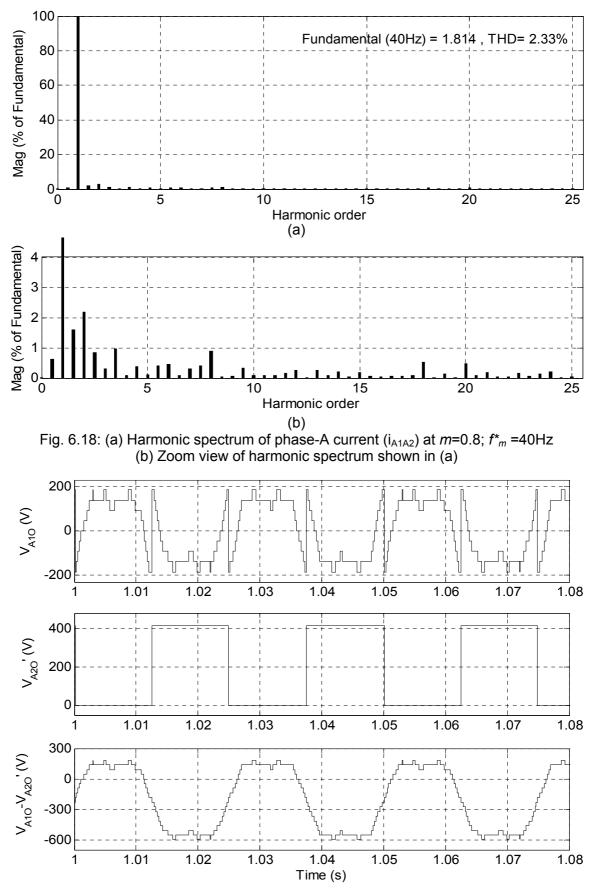

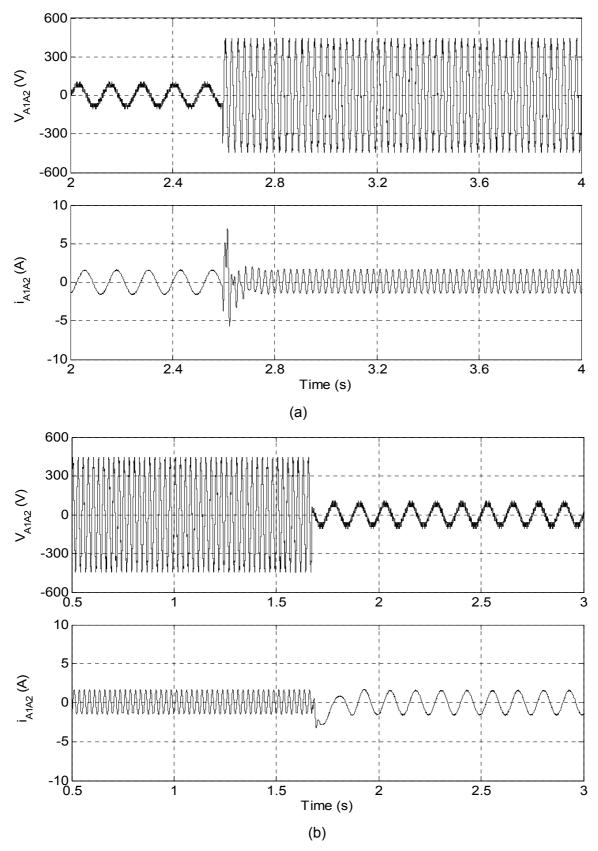

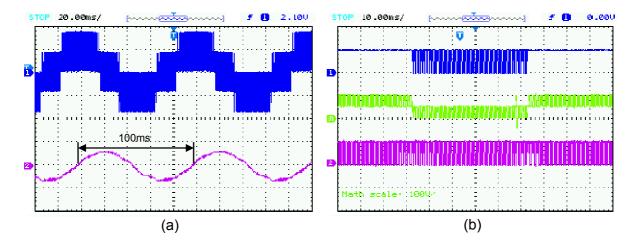

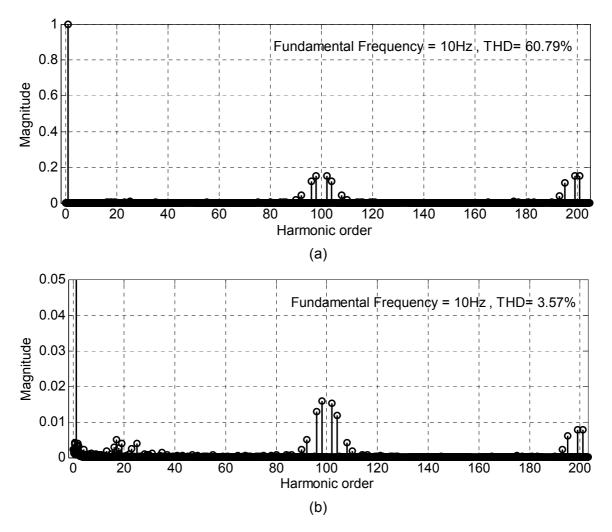

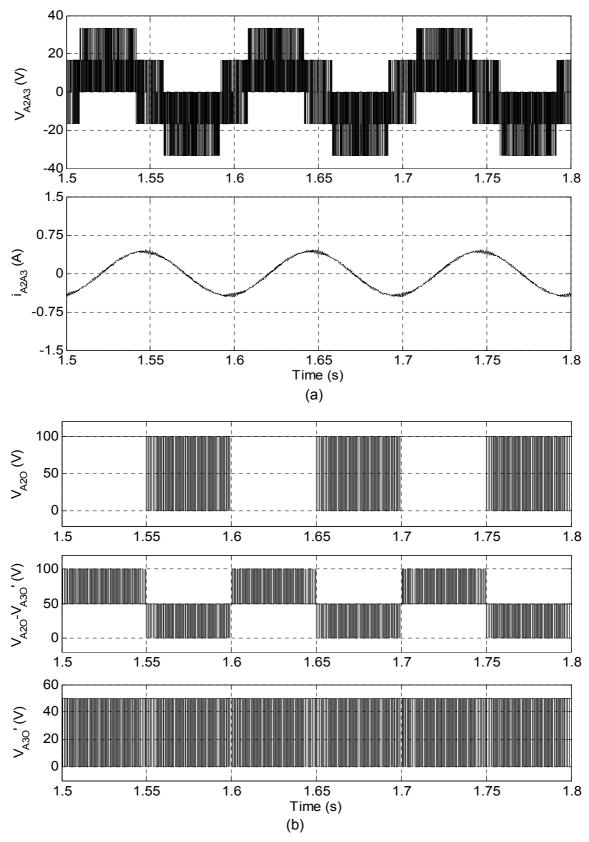

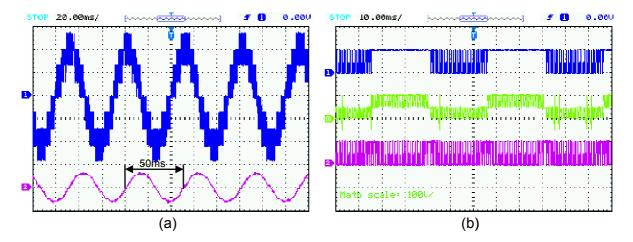

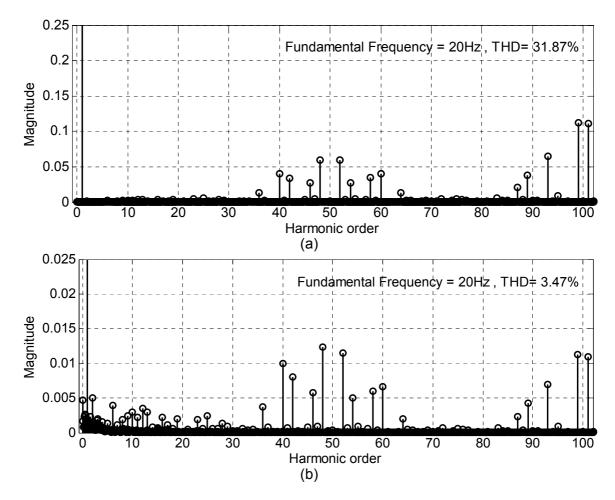

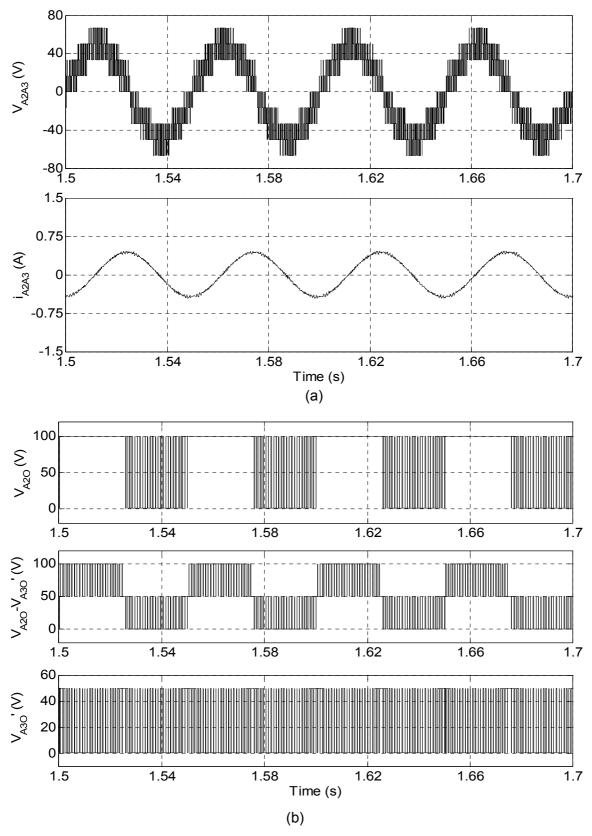

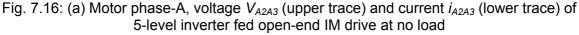

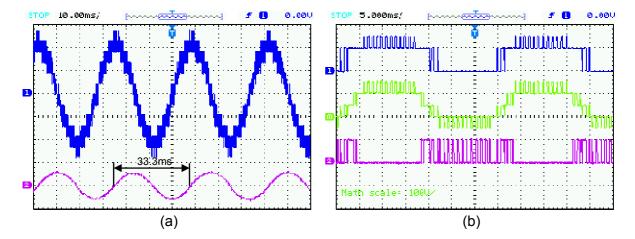

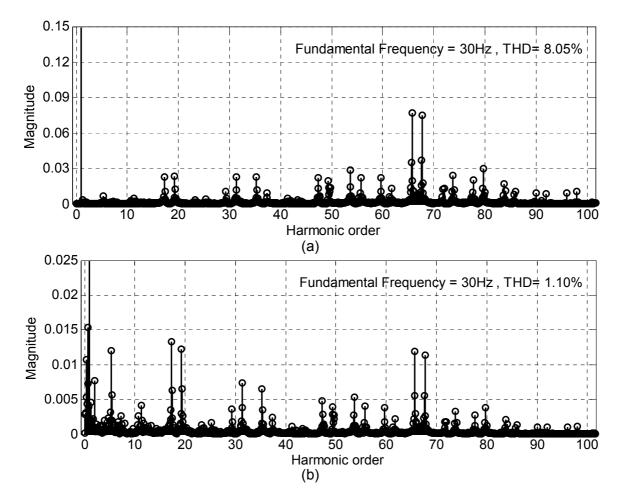

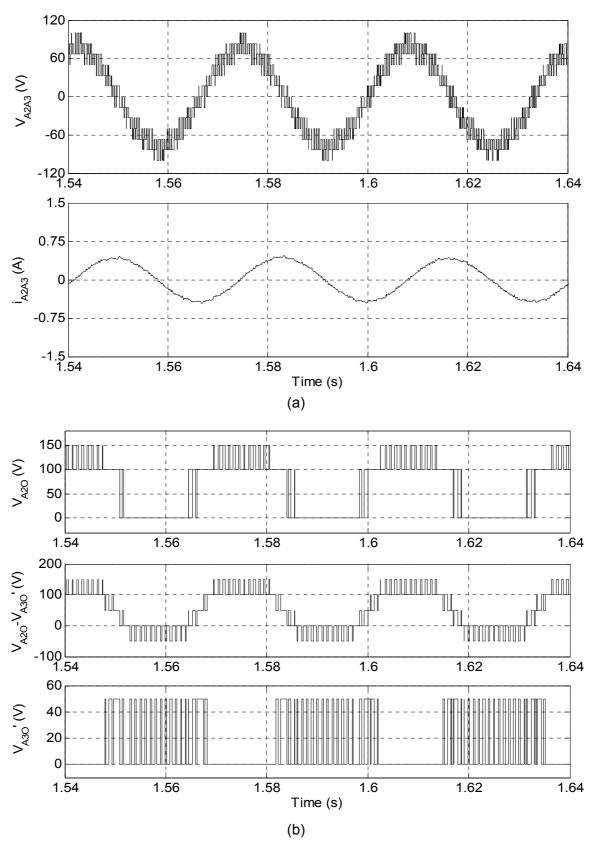

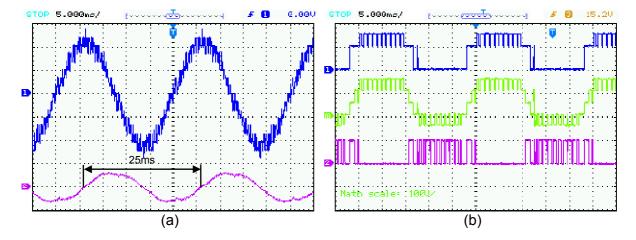

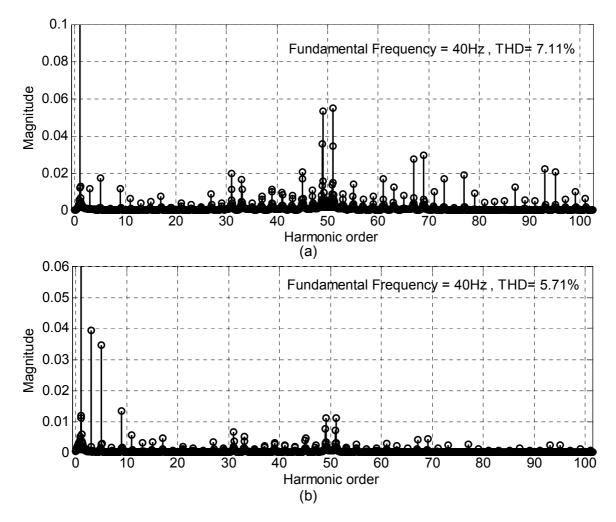

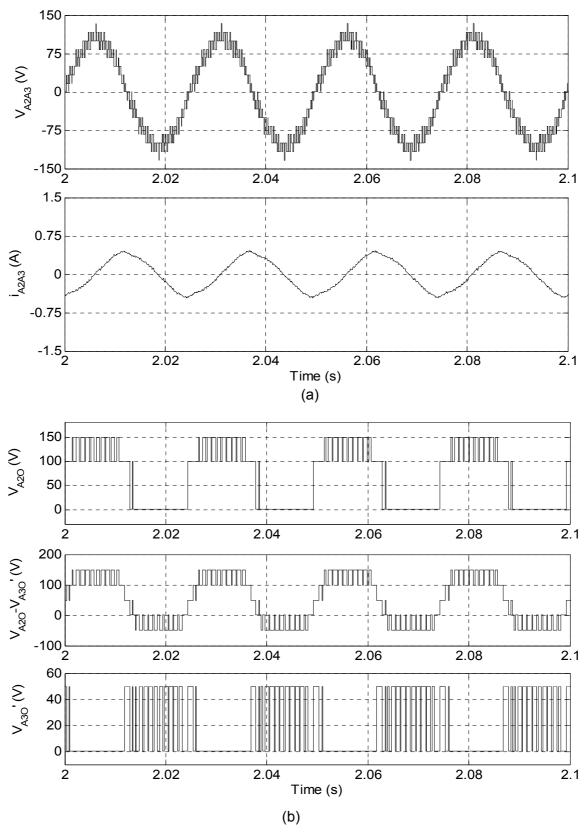

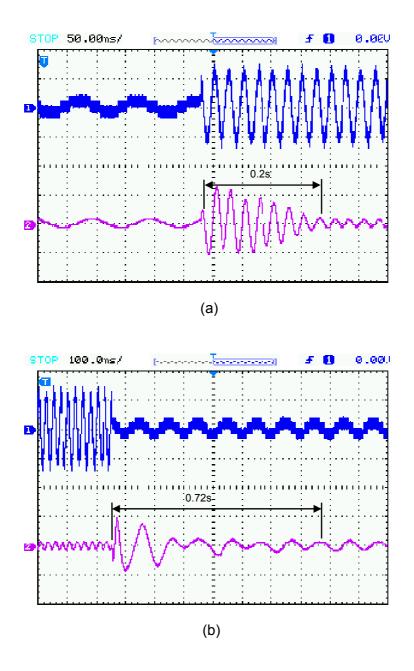

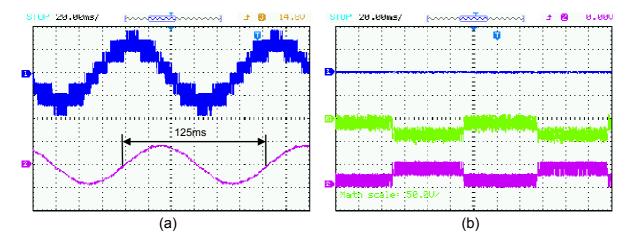

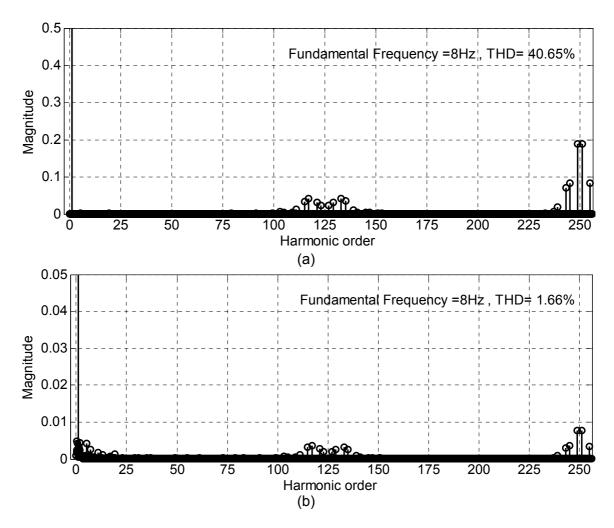

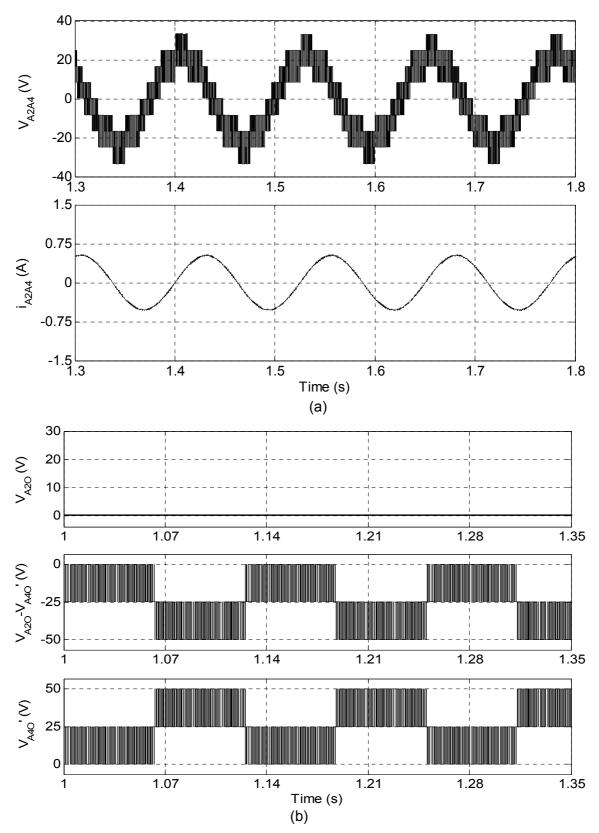

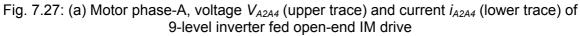

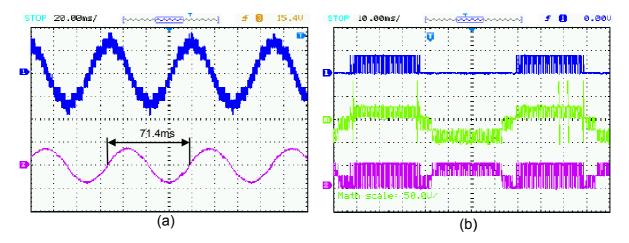

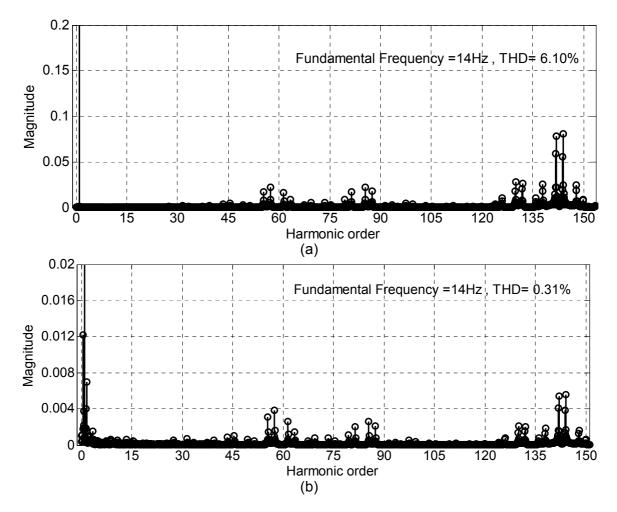

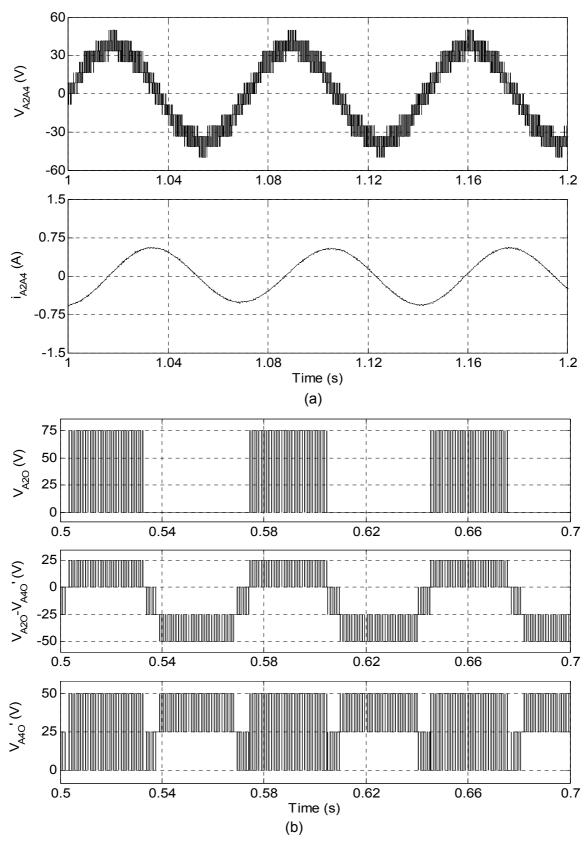

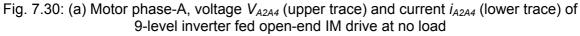

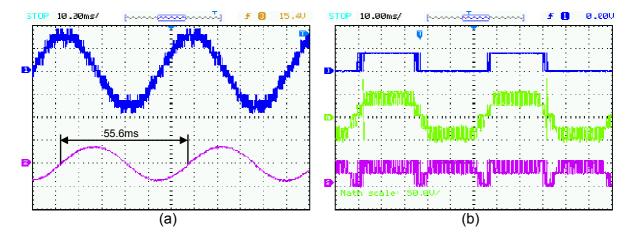

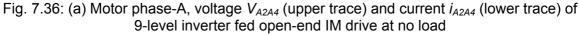

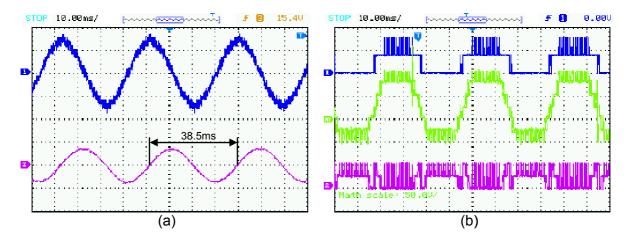

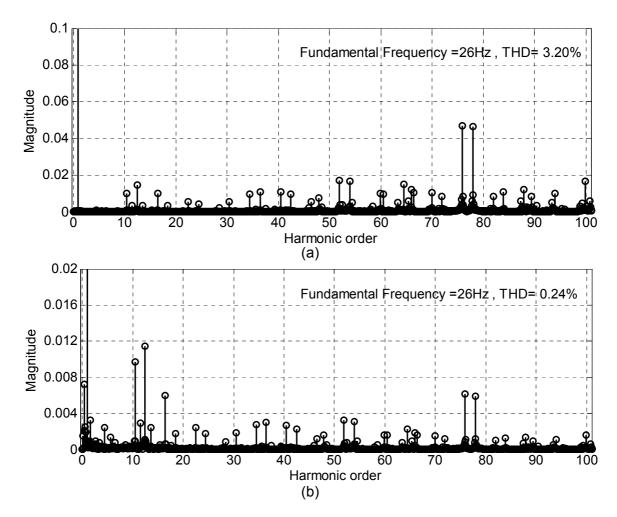

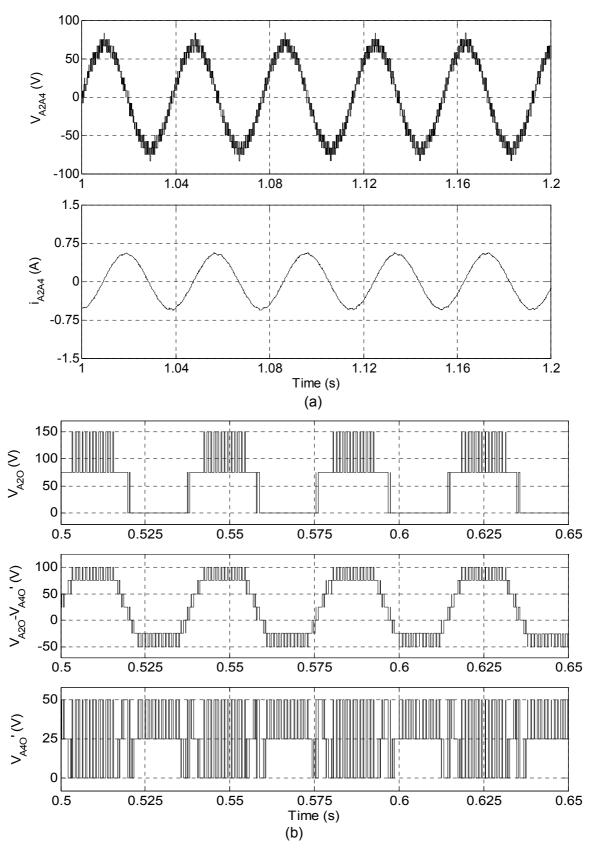

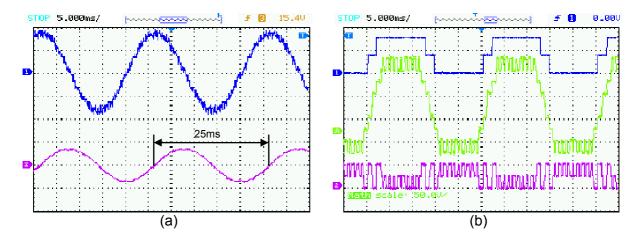

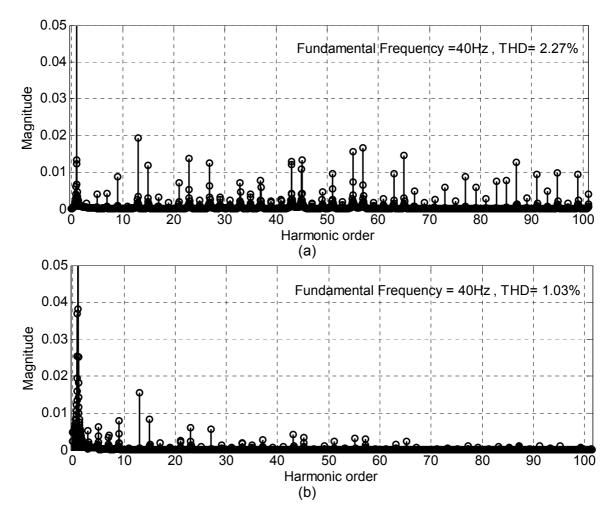

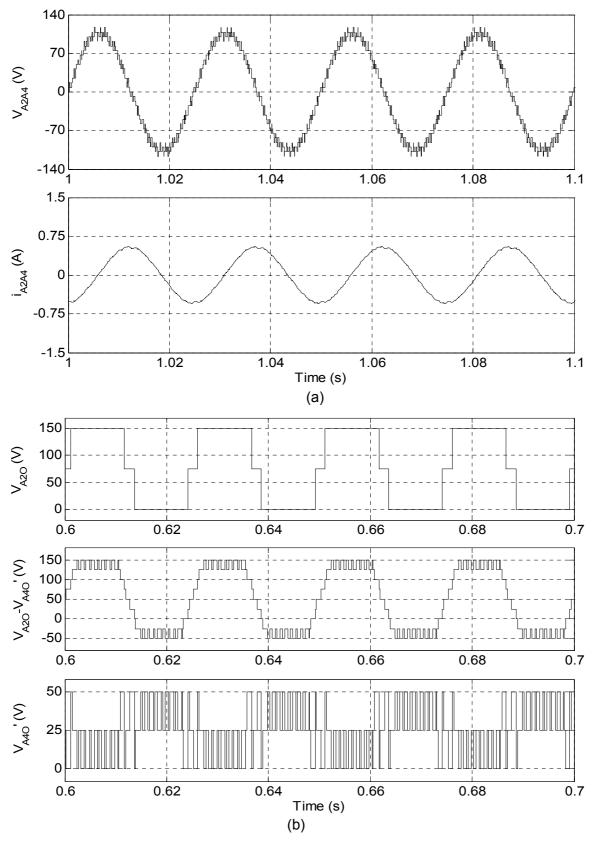

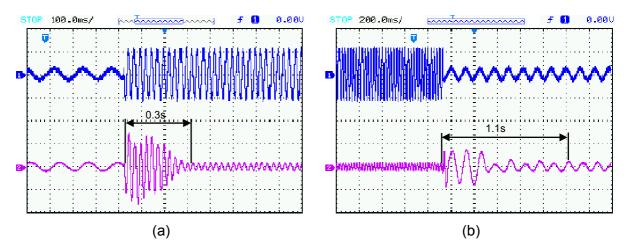

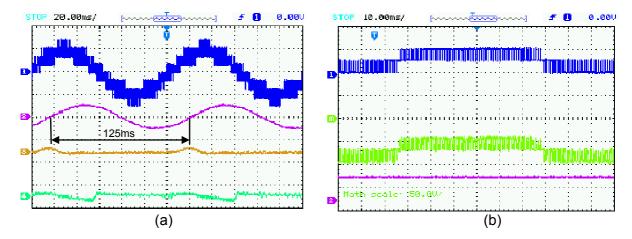

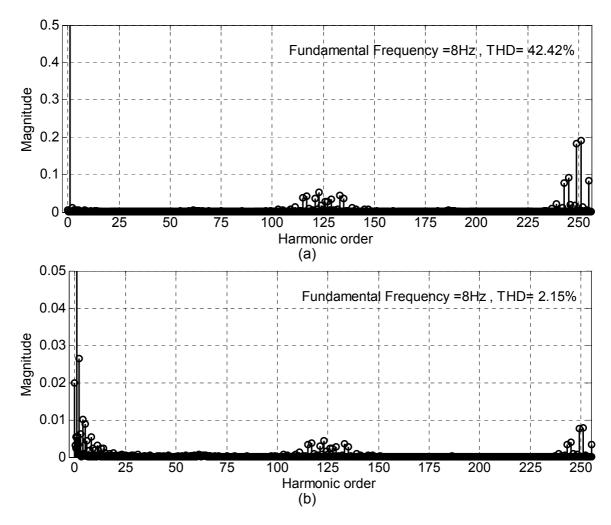

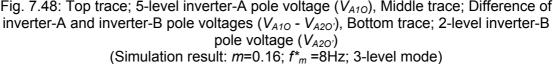

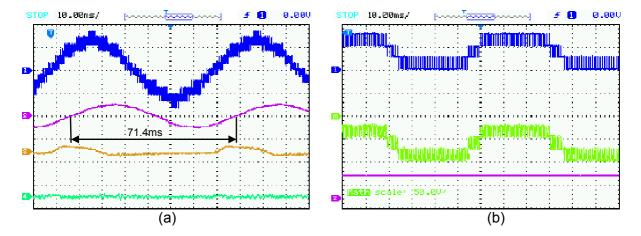

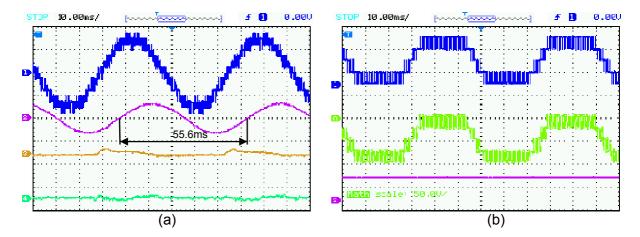

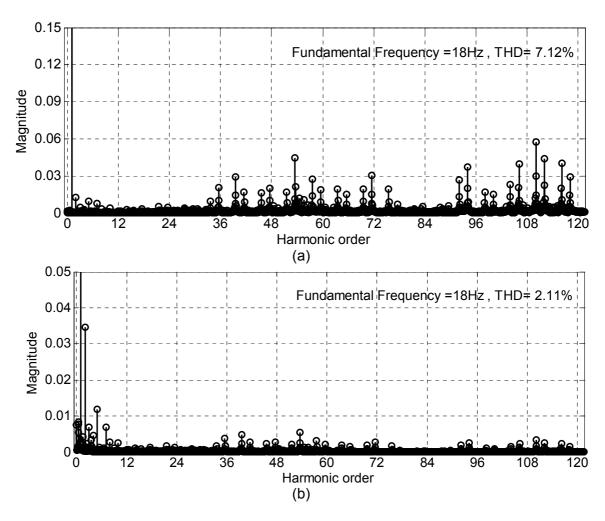

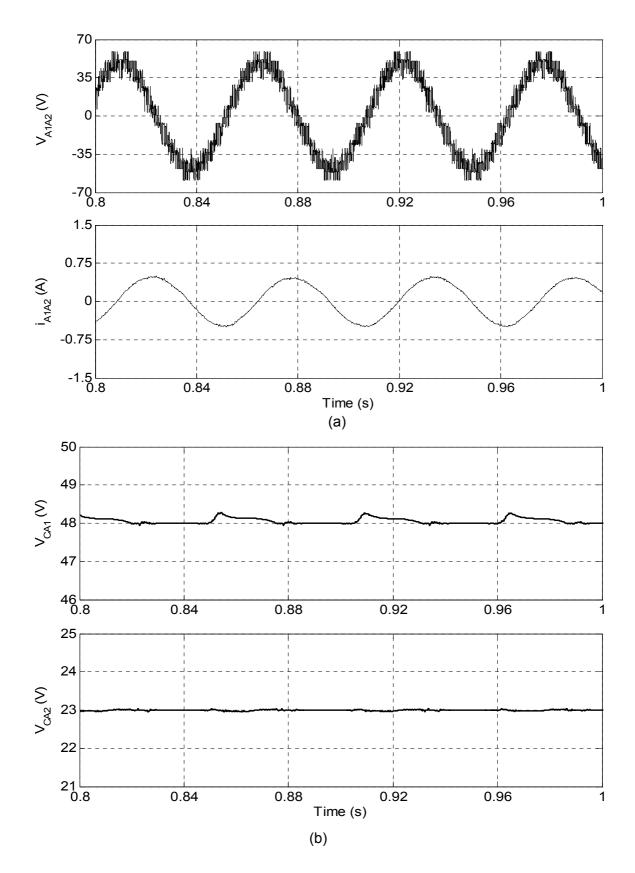

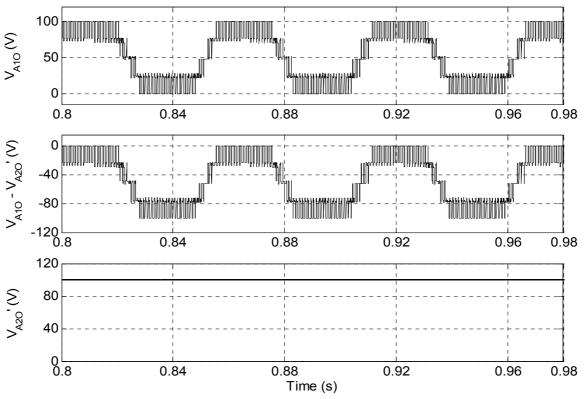

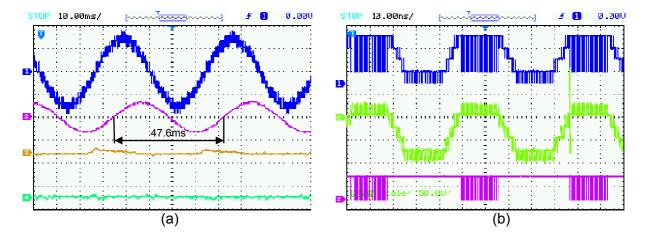

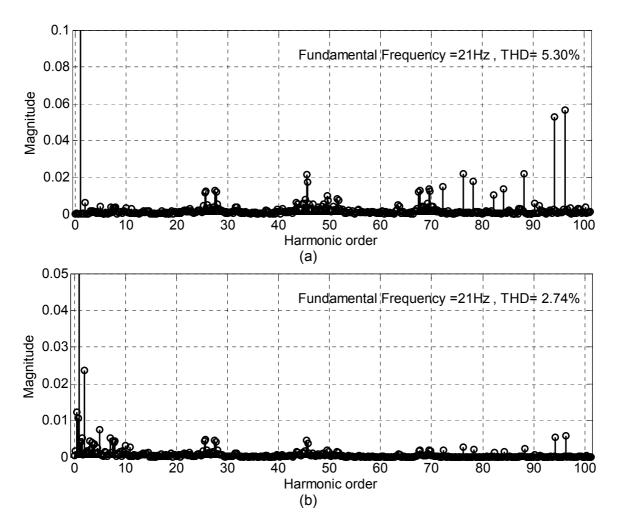

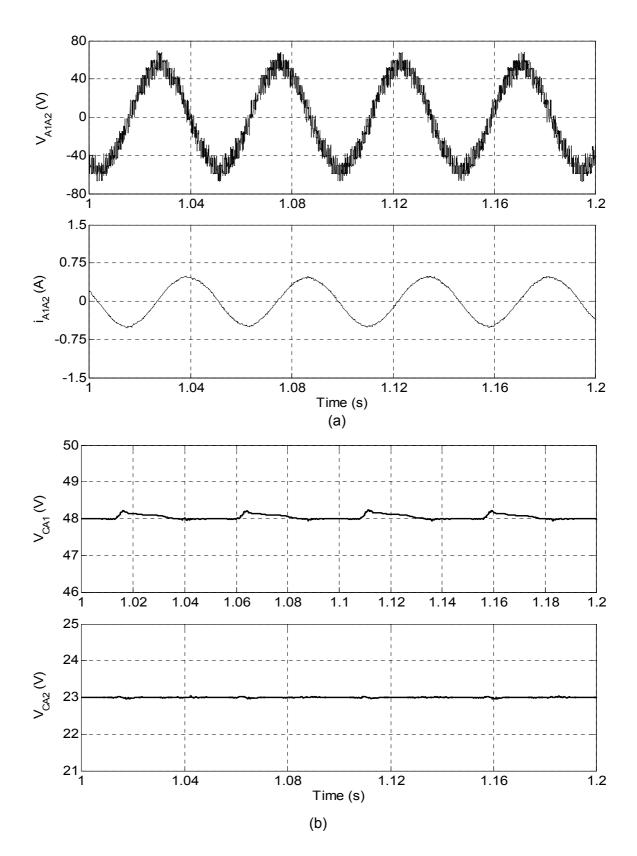

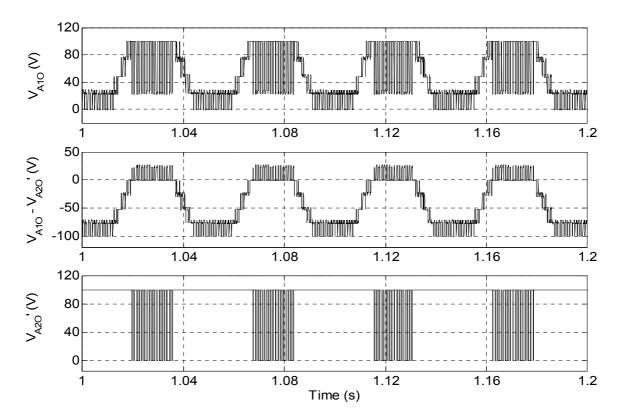

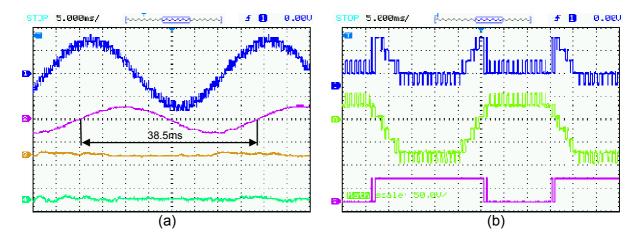

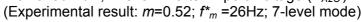

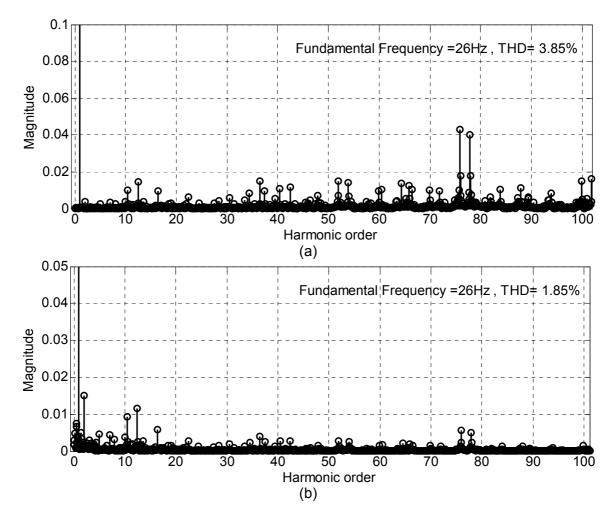

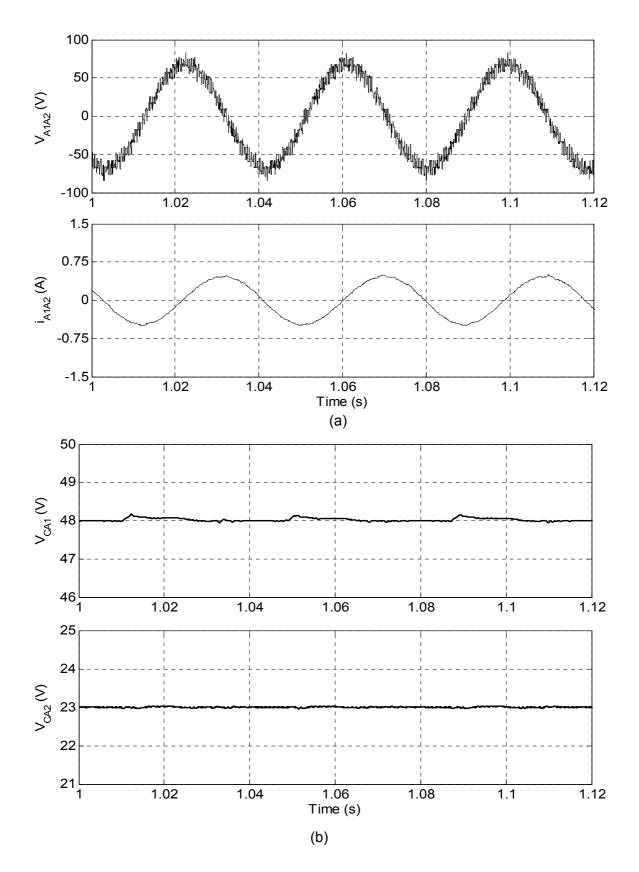

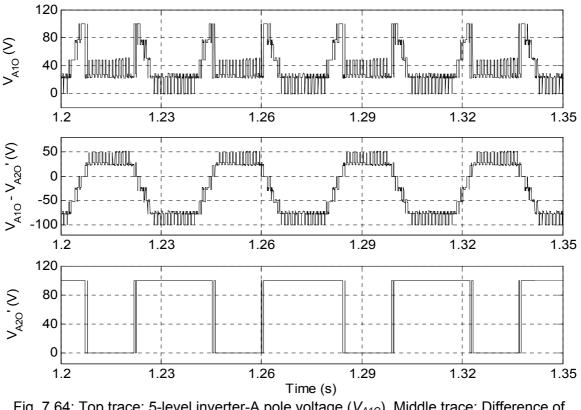

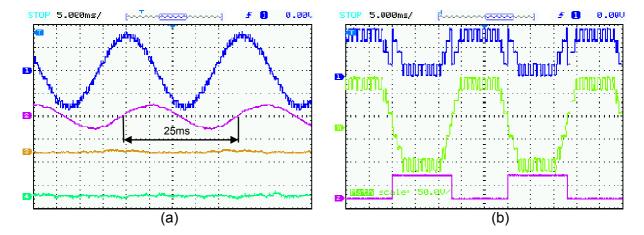

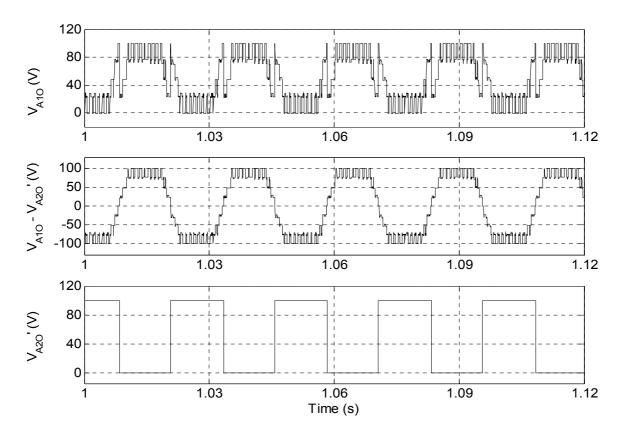

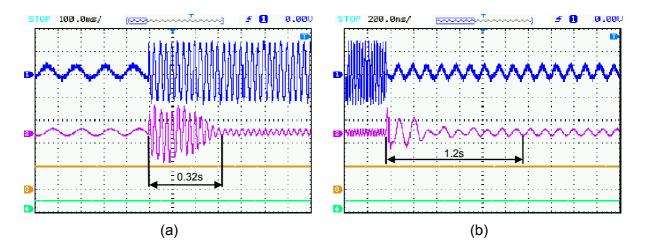

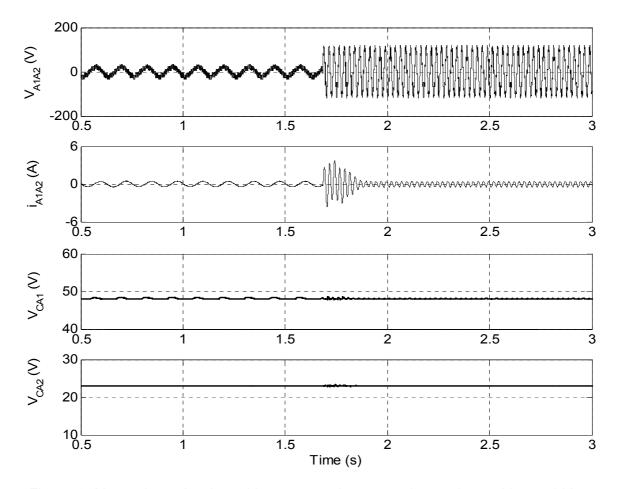

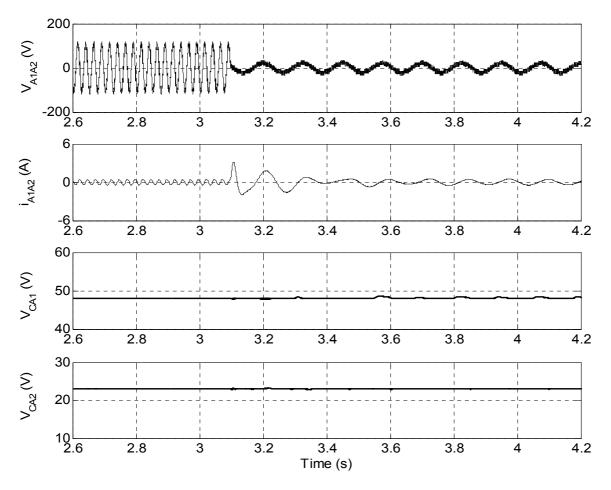

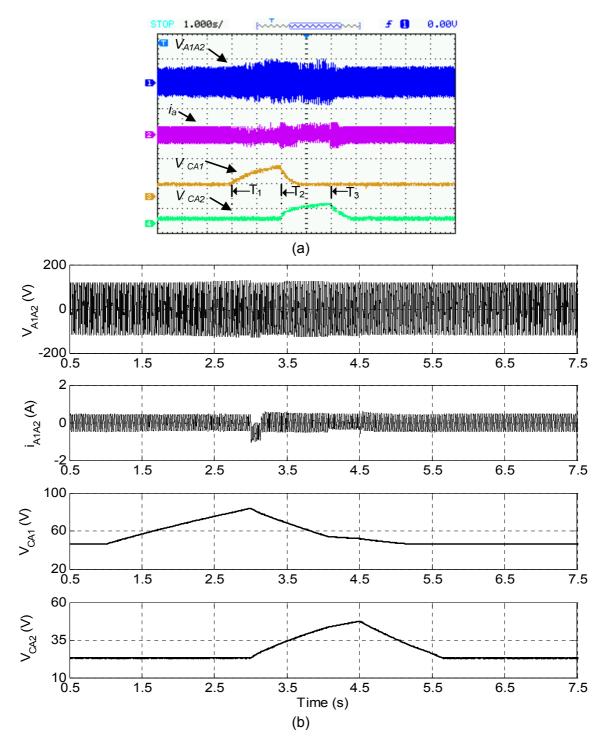

Fig. 6.19 :Top trace; Inverter-A pole voltage ( $V_{A10}$ ), Middle trace; Inverter-B pole voltage  $(V_{A2O'})$ , Bottom trace; Difference of Inverter-A and -B pole voltages  $(V_{A1O} - V_{A2O'})$  at m=0.8; Fig. 6.20: (a) Motor phase-A voltage  $V_{A1A2}$  (upper trace) and current  $i_{A1A2}$  (lower trace) waveforms under sudden change in modulation index from 0.16 (5-level mode) to 0.8 (18-level mode) at no-load (b) Motor phase-A voltage  $V_{A1A2}$  (upper trace) and current  $i_{A1A2}$ (lower trace) waveforms under sudden change in modulation index from 0.8 (18-level mode) Fig. 7.2: (a) Power circuit of 3-Level inverter-A; (b) Power circuit of two-level inverter-B .... 189 Fig. 7.10: Interfacing of RT-Lab with MATLAB and real-world plant (Inverter-A and B) ..... 196 Fig. 7.11: (a) Motor phase-A, voltage  $V_{A2A3}$  (upper trace Y-axis: 20V/div) and current  $i_{A2A3}$ (lower trace Y-axis: 1A/div) of 5-level inverter fed open-end IM drive at no load (b) Top trace Y-axis: 100V/div; 3-level inverter-A pole voltage ( $V_{A2O}$ ), Middle trace Y-axis: 100V/div; Difference of 3-level inverter-A and two-level inverter-B pole voltages ( $V_{A20} - V_{A30'}$ ), Bottom trace Y-axis: 50V/div; Two-level inverter-B pole voltage ( $V_{A3O'}$ ) (Experimental result: Fig. 7.12: Normalized harmonic spectrum of phase-A (a) Voltage  $V_{A2A3}$  (b) Current  $i_{A2A3}$ Fig. 7.13: (a) Motor phase-A, voltage  $V_{A2A3}$  (upper trace) and current  $i_{A2A3}$  (lower trace) of 5level inverter fed open-end IM drive at no load (b) Top trace; 3-level inverter-A pole voltage  $(V_{A2O})$ , Middle trace; Difference of 3-level inverter-A and two-level inverter-B pole voltages  $(V_{A2O} - V_{A3O'})$ , Bottom trace; Two-level inverter-B pole voltage  $(V_{A3O'})$  (Simulation result: *m*=0.2; *f*\*<sub>*m*</sub> =10Hz)......200 Fig. 7.14: (a) Motor phase-A, voltage  $V_{A2A3}$  (upper trace Y-axis: 25V/div) and current  $i_{A2A3}$ (lower trace Y-axis: 1A/div) of 5-level inverter fed open-end IM drive at no load (b) Top trace Y-axis: 100V/div; 3-level inverter-A pole voltage ( $V_{A2O}$ ), Middle trace Y-axis: 100V/div; Difference of 3-level inverter-A and two-level inverter-B pole voltages ( $V_{A20} - V_{A30}$ ), Bottom trace Y-axis: 50V/div; Two-level inverter-B pole voltage ( $V_{A30'}$ ) (Experimental result: