## MLI BASED ACTIVE POWER FILTER FOR POWER QUALITY IMPROVEMENT

A THESIS

Submitted in partial fulfilment of the requirements for the award of the degree of

#### DOCTOR OF PHILOSOPHY

in

ELECTRICAL ENGINEERING

by

### **DHANAVATH SURESH**

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247667 (INDIA) JUNE, 2015

## ©INDIAN INSTITUTE OF TECHNOLOGY ROORKEE, ROORKEE-2015 ALL RIGHTS RESERVED

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

## **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in this thesis entitled "**MLI BASED ACTIVE POWER FILTER FOR POWER QUALITY IMPROVEMENT"** in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy and submitted in the Department of Electrical Engineering of the Indian Institute of Technology Roorkee is an authentic record of my own work carried out during a period from December, 2010 to June, 2015 under the supervision of Prof. S. P. Singh, Professors, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

## (DHANAVATH SURESH)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

(S.P. Singh) Supervisor

Date: \_\_\_\_\_

Electrical power system is designed to operate at 50 or 60Hz. However, the nonlinear loads connected to the power system generate harmonic currents. The power system harmonics are not new phenomenon. Concern over harmonic distortions has flowed during the history of electrical power systems.

Conventionally, the saturated iron in transformers, induction machines, electric arc furnaces, welding equipment and fluorescent lamps, etc. have been responsible for the generation of harmonics in electric power systems. Most of these equipments also cause the flow of reactive component of current in the system. In recent years, many power electronic converter utilizing switching devices are being widely used in domestic, commercial and industrial applications, ranging from few watts to megawatts. However, these converters suffer from the drawbacks of harmonic generation and reactive power flow from the source and offer highly nonlinear characteristics. The generation of harmonics and reactive power flow in the power systems has given rise to 'Electric Power Quality problems'. These power quality problems are reflected in the system in the form of reduced efficiency of equipment, deteriorated performance of electrical machines, interference with nearby communications networks, neutral burning, mal-operation of relays, blowing of fuses and so on. Thus there is a growing concerned of power quality with proliferation of ac/dc converters in adjustable-speed drives, power supplies, SMPS, DC motor drives, and so on.

Harmonic regulation or standard guide lines such as IEEE-519-1992, IEC 1000-4-7, AS 2279 and IEC 6100, etc. are currently used to keep current and voltage harmonics level within the standard limits. In addition, the equipment designed based on these standards can improve the performance of power system.

To meet these requirements, passive filters, active filters and their combination have been used with two level inverters in order to improve power quality. Conventionally, passive filters have been used for the power quality improvement. Though passive compensations is a simple approach, but they have several drawbacks such as inability to provide dynamic compensation, bulky size, cost, resonance problem, separate filters for each harmonics, etc. and this fact has attracted the attention of power engineers to develop dynamic and adjustable solutions to power quality problems. One modern and very promising group of solutions that deals with load current and/or supply voltage imperfections is active power filter (APF). It is well known that high performance and cost-effective inverter is a prerequisite for the realization of an APF. These inverters can be broadly categorised into two classes, namely, voltage source inverter (VSI) and current source inverter (CSI). A critical comparison of the performance of VSI and CSI when used as a power circuit of APF is beyond the scope of this report. However, in the present work, VSI has been considered as a power circuit for APF as it has higher market penetration and a more noticeable development on VSI has

i

taken place over the last decade, in comparison to CSI topologies. The high harmonic content of the output voltage makes basic six-pulse (two-level) VSI impractical for direct use in high-power, medium-voltage applications. Instead of using filters and connecting several switching devices in series to achieve the required voltage level, several alternative possible solutions are reported in the literature and can be broadly categorized into two groups: multipulse and multilevel inverters. The first one requires bulky phase-shifting transformers and therefore, its application is limited to high-power, high-voltage systems. The second approach, multilevel inverters, uses the concept of addition of multiple small voltage levels for achieving the required voltage level with the help of additional switching devices and few components like diodes or capacitors. This approach does not require bulky phase shifting transformers and hence these topologies are best suited for medium-power applications. The common multilevel inverters (MLI) topologies are the diode-clamped (DCMLI), flying capacitor (FCMLI), and cascaded H-bridge multilevel inverters (CHBMLI).

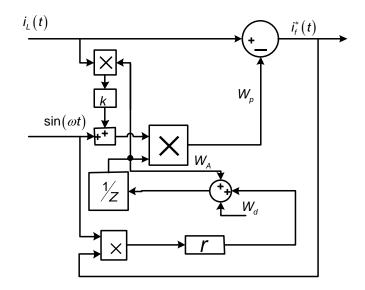

The performance of APF depends on the control strategy used for its implementation. The control algorithm proposed in this work aims to eliminate harmonics, compensate reactive power as well as control and balance the dc capacitor voltages of the APFs in steady-state and in transient conditions. The load harmonic currents have been derived by using the measured voltages at point of common coupling (PCC), load currents, and the dc bus voltages of the capacitors of the APF using proposed control strategies based on adaptive neural network such as least mean square (LMS), anti-Hebbian and anti-Hebbian based on TLS (Total least square). The controlling performance of the APF depends on the controller design. However it is difficult to develop the mathematical model of APF with multilevel inverters under parametric varying conditions. Therefore, there is great tendency to use unconventional controllers (intelligent controller) namely type-2 fuzzy logic controller. The type-2 fuzzy logic controller (T2FLC) is one of the intelligent controllers which handles the uncertainty in a better way and has been used in many of the application. The T2FLC, which is a highly nonlinear dynamic controller and does not require the mathematical model of system, not only has a strong adaptive and learning ability but also has a good processing and nonlinear mapping capabilities with large time delay and uncertain conditions. These characteristics result in meeting the control requirement of three level active power filter for three phase three wire system.

A computer simulation study under different load condition has been carried out to verify the performance of the three level DCMLI APF for harmonic elimination and reactive power compensation. The simulation study of the entire system has been carried out in MATLAB/Simulink environment. Various performance indices such as THD, power factor, active and reactive powers have been investigated. From these studies it has been observed that the adaptive control schemes with proposed controllers can compensates the reactive

ii

power of the load and makes the harmonic currents to be less and within the limits imposed by IEEE–519–1992.

The selection of individual inverter topologies for APF applications depends on their performance, cost, size, and implementation issues. DCMLI topology appears to be the most suited for APF applications. But, the large number of power components and voltage unbalance problem at higher levels limits the DCMLI for low power rating applications. On the other hand, Cascaded H-bridge multilevel inverter (CHBMLI) is one of the next generation multilevel inverters intended for high or medium-voltage power conversion without the requirement of line-frequency transformers. The CHBMLI is based on cascade connection of multiple single-phase H-bridge converter cells or chopper cells per leg. The least, low cost, modular structure, easy expansion to any number of levels, high fault tolerance component requirement and absence of bulky complex input transformer and without requirement of pre-charging circuit for the capacitor voltages make CHBMLI best suited for APF applications.

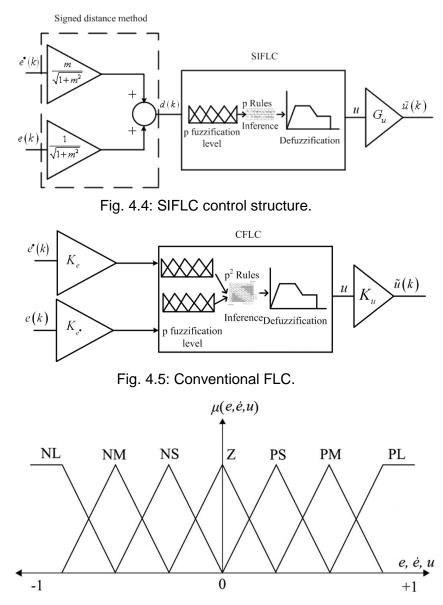

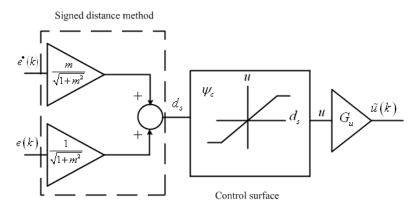

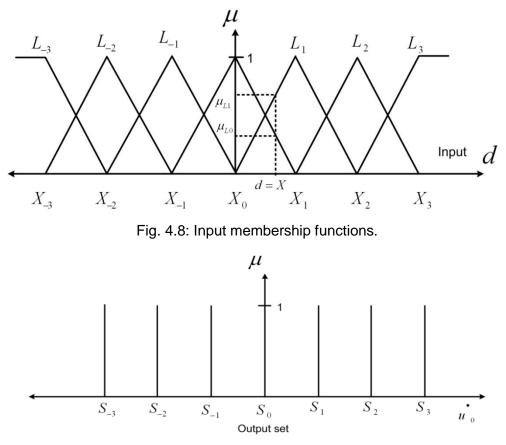

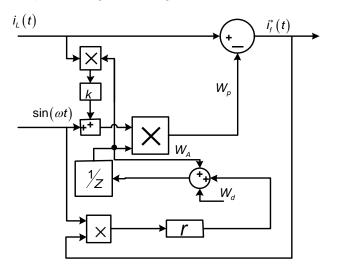

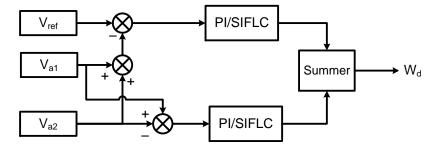

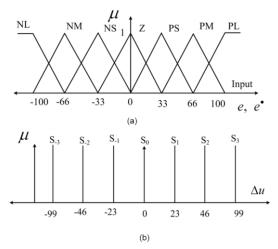

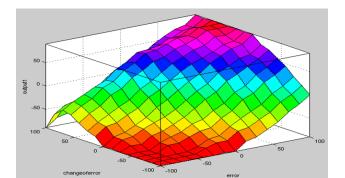

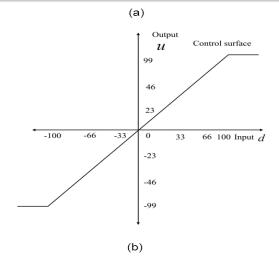

The fuzzy logic controller is promising solution for five levels CHBMLI based APF. Because, they provide a high degree of robustness and immunity to external disturbances. Furthermore, they can be configured to be self-learning and adaptive. However, they require substantial computational power, due to the complex decision-making processes. For example, conventional FLC involves fuzzification, rule-base storage, inference mechanism, and defuzzification operations. For better accuracy in control, a larger set of rules is required, which results in longer computational time. However, this may not be practical because there are many implementation aspects that must be addressed, namely, sampling time and dc voltage excursion. Apart from these constraints, it is known fact that FLC requires simpler mathematics and offers a higher degree of freedom in tuning its control parameters compared to other nonlinear controllers. Most conventional FLCs use the error and the change of error as fuzzy input variables regardless of the complexity of controlled plants. These conventional FLCs came from the concepts of linear PD and PI control schemes. Such FLCs are suitable for simple lower order plants. However, in case of complex large order plants, such as multilevel inverter, all of the states are required to implement state feedback-based FLCs. Then, the design of an FLC is very difficult due to an increased number of fuzzy control rules as well as tuning parameters. Therefore, it is necessary to design an FLC that has a simple control structure and is computationally efficient compared to the conventional FLC. In the presents work, the simplified approach to design a fuzzy logic controller, known as a single-input fuzzy logic controller (SIFLC). The simplification converts two input fuzzy logic controllers to a single input known as signed distance. In this method, the SIFLC control surface can be approximated by a simple piecewise linear (PWL) function, which results in a significant simplification of the design and parameter tuning. The individual dc voltage regulation of CHBMLI based APF with anti-Hebbian based on total least square using SIFLC and PI controller has been carried out for balancing the voltages of the floating dc capacitors to their corresponding reference values.

Computer simulation studies under different load conditions have been carried out to verify the performance of an APF for harmonic elimination and reactive power compensation. The simulation study of the entire system has been carried out in MATLAB/Simulink environment. The PI and SIFLC have been used to regulate the dc voltage of APF. Extensive simulation studies have been carried out to investigate the performance of the three phase three wire APF in normal voltage condition. The simulation studies have been performed for both steady-state and transient conditions with different non-linear loads. The capacitor voltage balance behaviour has been observed among the individual dc capacitors of the APF. Various performance indices such as THD, power factor, active and reactive power have been investigated. From these studies it has been observed that the PI and SIFLC with the anti-Hebbian based on total least square algorithm completely compensates the reactive power of the load and makes the harmonic currents to be less and within the limits imposed by IEEE–519–1992.

The three-phase, four-wire distribution systems have been widely applied to deliver electric power to three-phase four wire loads. The asymmetrical distribution of larger number of single-phase loads, ranging from few watts to MWs results in voltage and current unbalance in the three phase four wire (3P4W) electrical distribution system. They are responsible for excessive neutral current. The problems associated with the excessive neutral current are: overloading of distribution feeders and transformers, ground voltage fluctuation, flat-topping of voltage waveform and wiring failure etc. Therefore, these excess neutral currents must be compensated for the reliable operation of the 3P4W electrical distribution system.

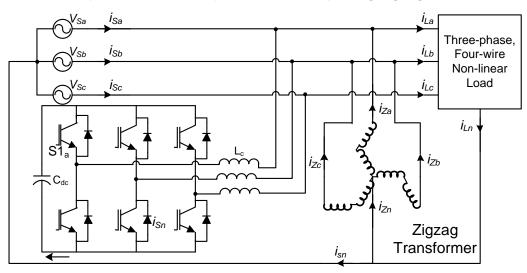

In recent years, a number of APF schemes have been reported for simultaneous compensation of reactive power, source current harmonics and neutral current in 3P4W electrical distribution systems. They are: (1) split capacitor (2) three H-bridge topology and (3) four-leg topology. However, these schemes were complicated in control and require large volt-ampere rating inverter. Different transformer topologies such as zigzag, star-delta, Scott-connected and star/hexagon-connected have also been used in recent years to attenuate the neutral current on the utility sides due to the advantages of low cost, high reliability and simplified circuit connection. Among these, zigzag transformer based approach requires least kVA inverter rating. However, these configurations also have a low impedance path for zero-sequence voltage of the unbalanced utility, which will further cause a significant neutral current. Further, their attenuation characteristics are dependent on their locations, impedances of the transformers and utility voltage conditions. A reduced rating hybrid

iv

topology comprising of a zigzag-delta transformer, a 3P3W active power filter (APF) and a single-phase APF had been demonstrated for the compensation of source neutral current and phase current harmonics, but, in this topology power factor and displacement factor are not improved. Also, the fundamental-frequency phase currents were also not made balanced. Single-phase powers APF can be combined with the zig-zag/ zero sequence transformers to advance the performance of the neutral current attenuation have been proposed in the literature. However, these schemes suffer from source phase current harmonics and unbalance. To address the above limitations, in the present work, two reduced rating hybrid 3P4W APF have been proposed. The proposed topologies of hybrid 3P4W active power filter comprises of three phase three wire APF, zero sequence transformer, ac power capacitor and single phase APF.

- 1. A 3P4W active power filter comprises of 3P3W APF, zero sequence transformer and single-phase APF.

- 2. A 3P4W hybrid active power filter comprises of ac power capacitors, 3P3W APF zero sequence transformer and single-phase APF.

To show the effectiveness of the proposed topologies, extensive simulation studies have been carried out in MATLAB/Simulink<sup>®</sup> environment. The performances of the proposed schemes have been studied for reactive power compensation, harmonic elimination and neutral current attenuation under various loading and utility voltage conditions. From these studies it is observed that the proposed control schemes completely compensates the reactive power of the load and makes the harmonic currents to be reduced below the limits imposed by IEEE–519–1992. Further, it also attenuates the source neutral current to a very large extent.

In order to further verify the simulation studies, a three-phase downscaled three level DCMLI and five level CHBMLI based APF has been designed, constructed, and tested to verify the viability and effectiveness of the control scheme with intelligent controller techniques. For this purpose, the following prototypes have been developed.

- 1. Three-level DCMLI based APF for three phase three wire system (LMS, anti-Hebbian and anti-Hebbian based on TLS with PI/type-2 fuzzy logic controller)

- Five level CHBMLI based APF for three phase three wire system(PI and SIFLC with anti-Hebbian based on TLS algorithm)

- A 3P4W APF comprising of a zero sequence transformer, CHBMLI based 3P3W APF and series connected single-phase APF (anti-Hebbian based on TLS algorithm with SIFLC).

- Another 3P4W hybrid APF comprising of a zero sequence transformer, 3P3W APF, AC capacitors and series connected single-phase APF (anti-Hebbian based on TLS algorithm with SIFLC).

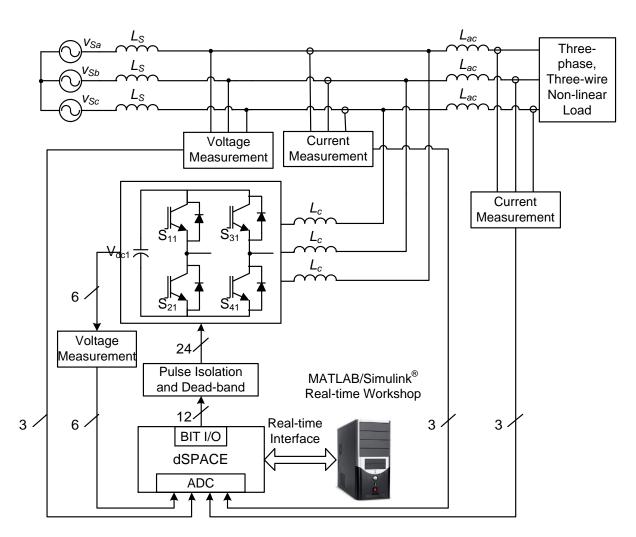

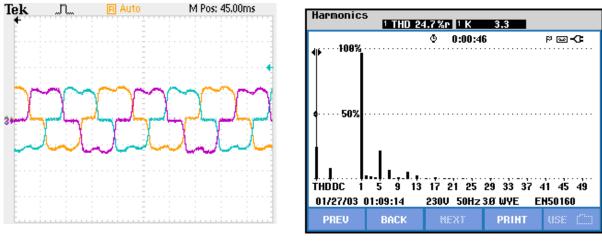

For hardware implementation, the IGBTs (IRG4PH40KD) have been used as the switching devices. Different hardware components as required for the operation of the experimental set-up such as pulse amplification, isolation circuit, dead-band circuit, voltage and current sensor circuits, and non-linear loads have been designed and developed. By using the Real-Time Workshop (RTW) of MATLAB and Real-Time Interface (RTI) feature of dSPACE-DS1104, the Simulink models of the various controllers of the prototypes have been implemented. The generated firing pulses have been given to the corresponding semiconductor devices of APF through isolation, delay, and pulse amplification circuits in real-time. An uncontrolled six pulse rectifiers with *RL* elements on their DC sides have been observed to be sinusoidal and their corresponding THDs have also been observed to be well within the limits of IEEE–519–1992 recommended value of 5%. The switching in response and the dynamic performance of APF for a step change in the load has been studied. A smooth control of dc voltages ensures the effectiveness of the DC voltage controllers.

Initially, the simulation and experimentation of three level DCMLI based APF with PI and T2FLC with different adaptive neural network algorithm such as LMS, anti-Hebbian and Anti-Hebbian based on TLS has been carried out to study the performance of three level DCMLI APF for three phase three wire system. From the performance characteristics, it is found that the T2FLC with anti-Hebbian based on TLS adaptive algorithm is better for three level DCMLI APF. However, the T2FLC is very complex to implement with higher level inverter due to the association of length process such as fuzzification, rule base, inference and defuzzification. For this purpose, single input fuzzy logic controller is derived using Conventional FLC. The performance of five level CHBMLI based APF with SIFLC as well as PI controller is also studied with anti-Hebbian based on TLS algorithm. It found that the performance characteristics of CHBMLI based APF with the SIFLC is superior than PI controller. Therefore, for three phase three wire APF, the single input fuzzy logic controller is recommended if number of level in three phase APF is more than three.

Finally, simulation of two 3P4W APF comprising three phase APF, zero sequence transformer, ac capacitors and single phase APF is carried out to study performance characteristics. The single input fuzzy logic controller integrated with anti-Hebbian based TLS algorithm is used for controlling three phase APF. The single phase APF control is implemented using PI controller. The simulated performance characteristics of 3P4W are also experimentally validated.

vi

Honestly, acknowledging contribution and support that was extended to me generously and thanklessly, is one of the most difficult, but inevitable, task. But, I would like to pen down some of them through this opportunity. This research work is an outcome of true moral support from individuals/group members directly or indirectly involved with me during my research work at Indian Institute of Technology, Roorkee.

I, from the bottom of my heart, want to express sincere acknowledgment with warm regards and gratitude to my thesis supervisor Dr. S.P. Singh, Professor, Department of Electrical engineering, Indian Institute of Technology, Roorkee for his proficient and enthusiastic guidance, constructive criticism, encouragement and immense support throughout the research work for Ph.D. He has been constant source of inspiration for the completion of this research work. I am sincerely indebted to him for his pronounced individualities, humanistic and warm personal approach, and excellent facilities provided to me in the laboratory to carry out this research work smoothly.

I would like to acknowledge my research committee members Dr. Pramod Agarwal (Prof., Dean Academics & Chairman SRC), Dr. M.K. Pathak (Associate Prof. EED), Prof. R.C. Mittal for their time to time critical examination of my research work and made constructive recommendations.

I heartily extend my gratitude to Dr. S.P. Srivasthava, Professor & Head, Department of Electrical Engineering, Indian Institute of Technology Roorkee for his humanistic, encouraging and warm personal approach and for the necessary facilities provided to me to carry out my research work.

I am also thankful to the whole administrative and technical staff. My special thanks to Mr. Shadiram and Mr. S.L. Yadav of computer controlled drives laboratory, Department of Electrical Engineering for their substantial technical assistance and cooperation during my experimental work.

My sincere thanks to the family members of my supervisor Dr. S.P. Singh, who have rendered immense support to them so that they would able to devote enough of their precious time for this work.

I thankfully acknowledge the precious financial support provided by Ministry of Human Resources and Development (MHRD), without which it would be difficult to carry out the work at this stage. The other financial support provided by Dean Alumni Affairs, Indian Institute of Technology, Roorkee is sincerely and honestly acknowledged.

My heartfelt thanks to Dr. Nitin Gupta, Geetanjali Mehta, Aurobinda panda Dr. Giribabu, Dr. Jayaram Nakka, Dr. Srinivas rao Dharmavarapu, N.V.Ramana Naik, Srinivas rao yarlagadda, Janardhan, Srinivasulu Bathala, Anil Naik, Narendra Babu, Naveen Yalla, Jagan, Raveendhra Dogga, Sanjeev saxena, Ajay Maurya and Sukanth haldar.

"God could not be everywhere so he created mothers! With her blessing there's always a good day after, one know everything will turn out fine". With these words, I sincerely acknowledge the blessing of my mother Smt. Shanti for her encouragement and moral support rendered to me throughout my life and also thankful to my brothers Ramu and Laxman for their constant encouragement.

No words can adequately express my deepest gratitude and love to my wife Smt. Prameela and who not only endured, without any protest, the loneliness, while I did this research work, rather she also provided unconditional support, encouragement, love and inspiration and always being there for me during good and bad times. I once again thanks to my wife and mother for shouldering all family responsibilities with a smiling face. I am also thankful to my sweet daughters Sarayu and Shanvi for bringing lot of joy into my life.

I sincerely acknowledge the ethical support from my father-in-law Dhasarath and mother-in-law Rajini for the sign of love and affection towards me. I would like to thank whole in law's family for their constant love and encouragement.

I also sincerely acknowledge the ethical support from my uncle S. Bodiya Naik and aunty Dwali for the sign of love and affection towards me. I would like to thank whole family of my uncle for their constant love and encouragement.

I, with my wet eyes, acknowledge the two person who's carying and loving eyes are looking from the sky and giving me blessing for completing this research work, my grandfather late D. Bhadriya, my father late Sh. D. Badya, and my father-in-law late M. Happa.

Last but not the least I would like to thank to almighty `GOD' for giving me strength and perseverance.

(DHANAVATH SURESH)

| ABS  | TRACT  |             |                                                      | I    |

|------|--------|-------------|------------------------------------------------------|------|

| ACK  | NOWLE  | EDGEME      | NTS                                                  | VII  |

| CON  | TENTS  |             |                                                      | IX   |

| LIST | OF FIG | URES        |                                                      | ΧΙΧ  |

| LIST | OF TA  | BLES        |                                                      | хіх  |

| LIST | OF AC  | RONYMS      | 5                                                    | . XX |

| LIST | OF SY  | MBOLS.      |                                                      | XXI  |

|      |        |             |                                                      |      |

| -    | PTER 1 |             | RODUCTION                                            |      |

| 1.1  |        |             |                                                      |      |

| 1.2  |        |             | pances                                               |      |

|      | 1.2.1  |             | harmonics (and / or) voltage                         |      |

|      |        | 1.2.1.1     | Sources of harmonics and their effects               |      |

|      |        | 1.2.1.2     | Harmonic distortion rate                             |      |

|      |        | 1.2.1.3     | The power factor                                     |      |

|      | 1.2.2  |             | ce in the three-phase voltage system                 |      |

|      |        | 1.2.2.1     | Consequences of unbalanced three-phase system        | 5    |

| 1.3  | Neutra | l currents  | effects                                              | 6    |

| 1.4  | Compe  | ensation s  | solutions                                            | 6    |

|      | 1.4.1  | Passive     | filters                                              | 7    |

|      | 1.4.2  | Active po   | ower filters                                         | 7    |

|      |        | 1.4.2.1     | Shunt active power filter                            | 8    |

| 1.5  | Config | urations o  | of active power filter                               | 8    |

|      | 1.5.1  | Power C     | ircuit Based Classification                          | 9    |

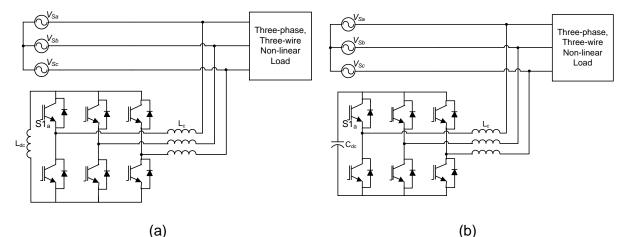

|      |        | 1.5.1.1     | Diode-Clamped Multilevel inverter                    | 10   |

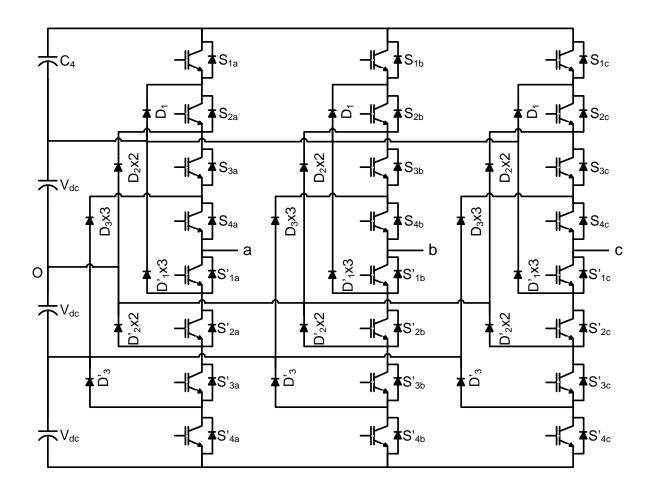

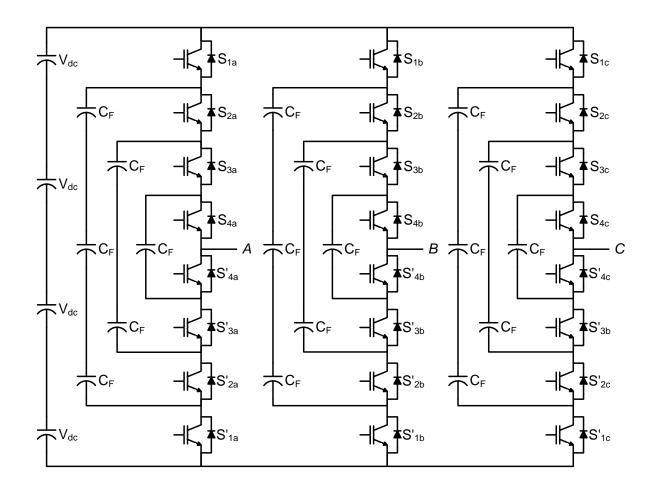

|      |        | 1.5.1.2     | Flying-Capacitor Multilevel Inverter                 | 11   |

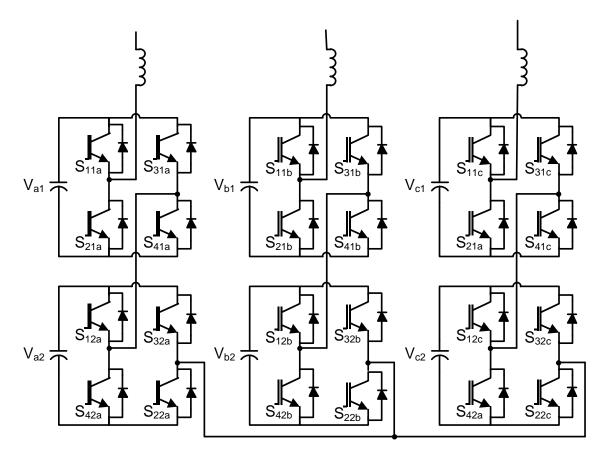

|      |        | 1.5.1.3     | Cascaded-Multilevel Inverter                         | 12   |

| 1.6  | Compa  | arison of I | Nultilevel converters for active power filter        | 14   |

| 1.7  | Supply | y System    | Based Classification of active power filters         | 15   |

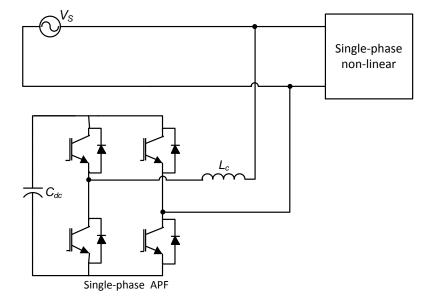

|      |        | 1.7.1.1     | Single-phase active power filter                     | 15   |

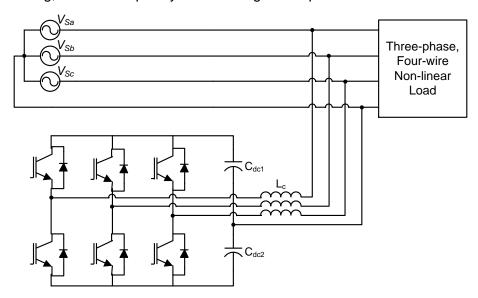

|      |        | 1.7.1.2     | Three-phase, Three-wire active power filter          | 15   |

|      |        | 1.7.1.3     | Three-phase, Four-wire active power filter           | 15   |

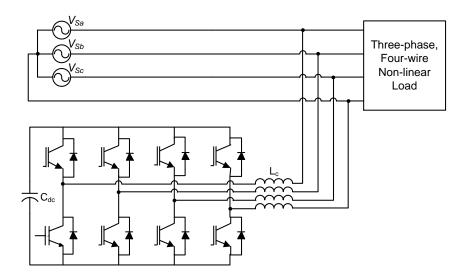

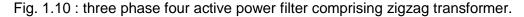

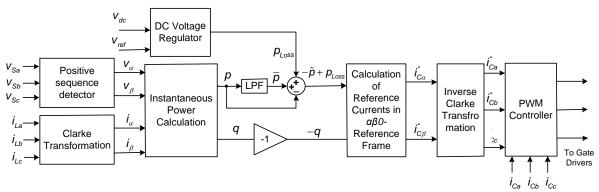

| 1.8  | Three  | phase fou   | ur active power filter comprising zigzag transformer | 17   |

| 1.9  | APF C  | ontroller.  |                                                      | 17   |

|      | 1.9.1  | Harmoni     | cs detection                                         | 18   |

|      | 1.9.2  | Frequen     | cy domain technique                                  | 18   |

|       | 1.9.3             | Time do          | main technique                                                | 19     |

|-------|-------------------|------------------|---------------------------------------------------------------|--------|

|       | 1.9.4             | Wavelet          | transform based algorithm                                     | 21     |

|       | 1.9.5             | Artificial       | Neural Network (ANN) algorithm                                | 21     |

|       | 1.9.6             | Generat          | tion of Gating Signal to Control Switches                     | 28     |

| 1.10  | Scop              | be of Wor        | k and Author's Contribution                                   | 28     |

| 1.11  | Orga              | anization        | of the Thesis                                                 | 31     |

| СНА   | PTER              | 2: EX            | PERIMENTAL SYSTEM DEVELOPMENT                                 | 33     |

| 2.1   | Introd            | uction           |                                                               |        |

| 2.2   | Syster            | m Hardwa         | are                                                           | 34     |

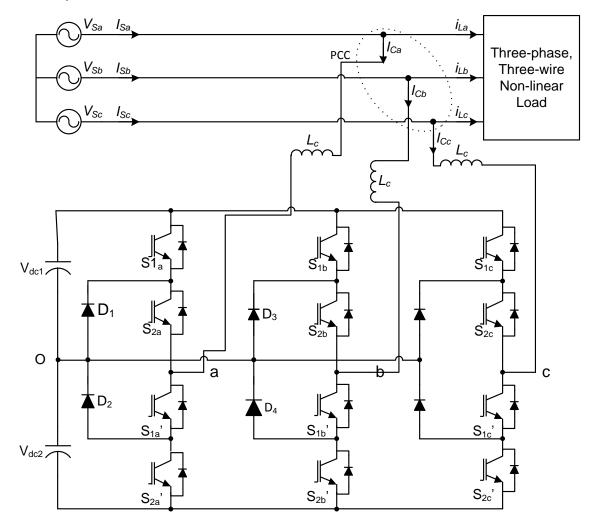

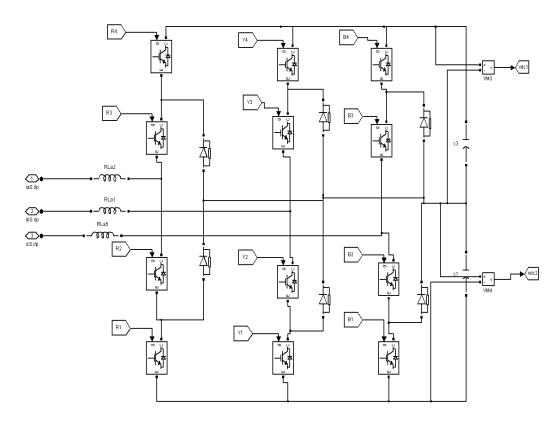

|       | 2.2.1             | Power c          | ircuit of inverters extended to use as active power filter    | 34     |

|       |                   | 2.2.1.1          | Performance of three-phase three-level diode clamped          | based  |

|       |                   | inverte          | er.35                                                         |        |

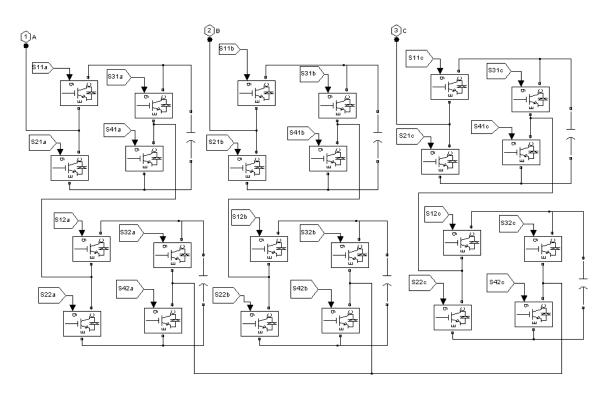

|       |                   | 2.2.1.2          | Performance of three-phase five-level cascaded H-bridge inver | ter 38 |

|       | 2.2.2             | Measure          | ement Circuits                                                |        |

|       |                   | 2.2.2.1          | Sensing of AC Current                                         | 40     |

|       |                   | 2.2.2.2          | Sensing of Voltage                                            | 40     |

|       | 2.2.3             | System           | Software                                                      | 41     |

|       | 2.2.4             | Control          | Hardware                                                      | 44     |

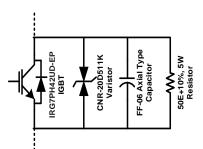

|       |                   | 2.2.4.1          | Dead-band Circuit                                             | 45     |

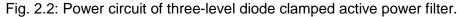

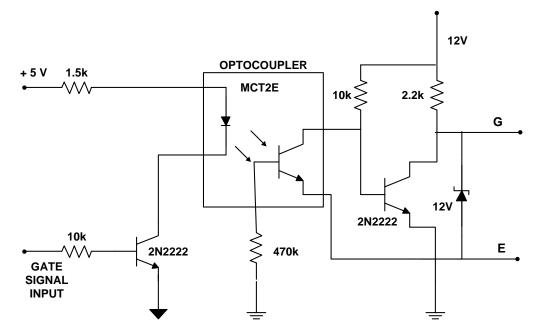

|       |                   | 2.2.4.2          | IGBT Driver and isolation circuit with MCT2E                  | 45     |

|       | 2.2.5             | Compar           | ison with Simulation Results                                  | 46     |

| 2.3   | Concl             | usion            |                                                               | 48     |

| ••••• | PTER :<br>VER FIL | 3: AD<br>_TER 49 | APTIVE CONTROL OF THREE LEVEL DIODE CLAMPED ACT               | ΓIVE   |

| 3.1   | Introd            | uction           |                                                               | 49     |

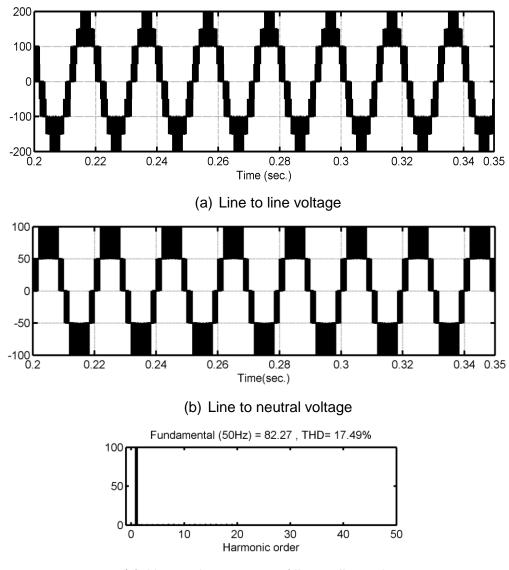

| 3.2   | Power             | r circuit of     | DCMLI based active power filter                               | 49     |

|       | 3.2.1             | Design o         | of passive parameter for the active power filter              | 50     |

|       |                   | 3.2.1.1          | Selection of DC side Capacitors                               | 51     |

|       |                   | 3.2.1.2          | Selection of interfacing Inductor                             | 51     |

| 3.3   | Refere            | ence curre       | ent generation                                                | 52     |

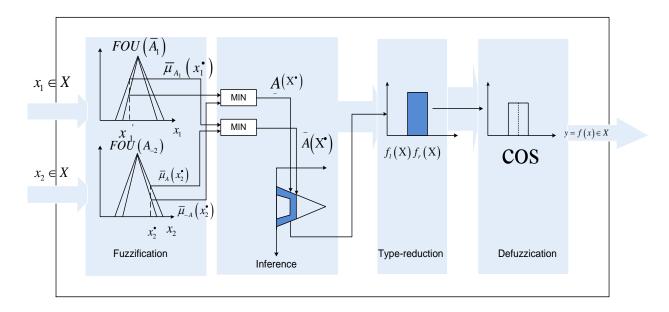

|       | 3.3.1             | Type-2 f         | fuzzy logic controller (T2FLC)                                | 56     |

|       |                   | 3.3.1.1          | Fuzzifier                                                     | 57     |

|       |                   | 3.3.1.2          | Rule base                                                     | 57     |

|       |                   | 3.3.1.3          | Rule inference                                                | 57     |

|       |                   | 3.3.1.4          | Type reducer                                                  | 58     |

|       |                   | 3.3.1.5          | Defuzzifier                                                   | 58     |

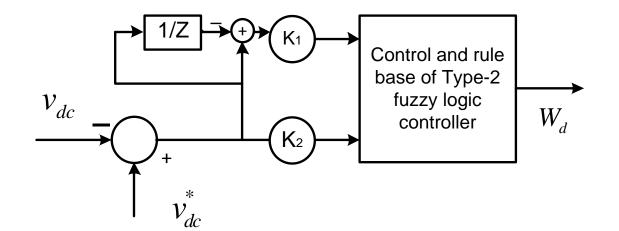

|       |                   | 3.3.1.6          | DC voltage regulation                                         | 58     |

|             | 3.3.2  | Control scheme based on LMS algorithm integrated with PI/T2FLC          | 60     |

|-------------|--------|-------------------------------------------------------------------------|--------|

|             |        | 3.3.2.1 Simulations results                                             | 60     |

|             | 3.3.3  | Control scheme based on anti-Hebbian Algorithm                          | 63     |

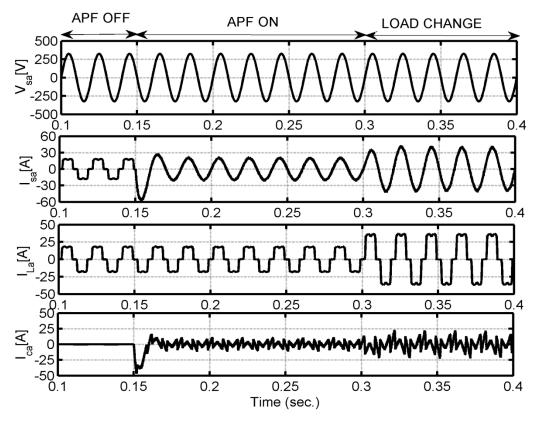

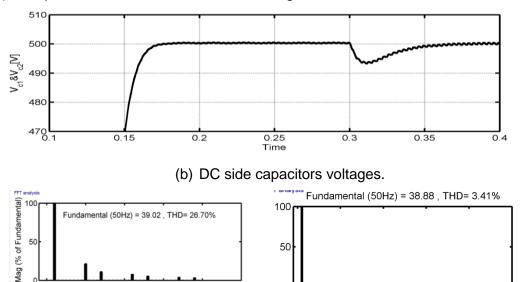

|             |        | 3.3.3.1 Simulations results                                             | 63     |

|             | 3.3.4  | Anti-Hebbian based on total least square algorithm                      | 66     |

|             |        | 3.3.4.1 Simulation results                                              | 66     |

| 3.4         | Exper  | imental validation                                                      | 69     |

|             | 3.4.1  | Control scheme based on LMS algorithm integrated with T2FLC             | 69     |

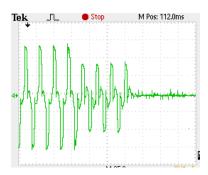

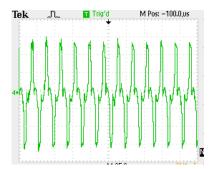

|             |        | 3.4.1.1 Transient performance of the active power filter                | 71     |

|             |        | 3.4.1.2 DC capacitor voltage regulation                                 | 71     |

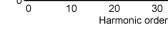

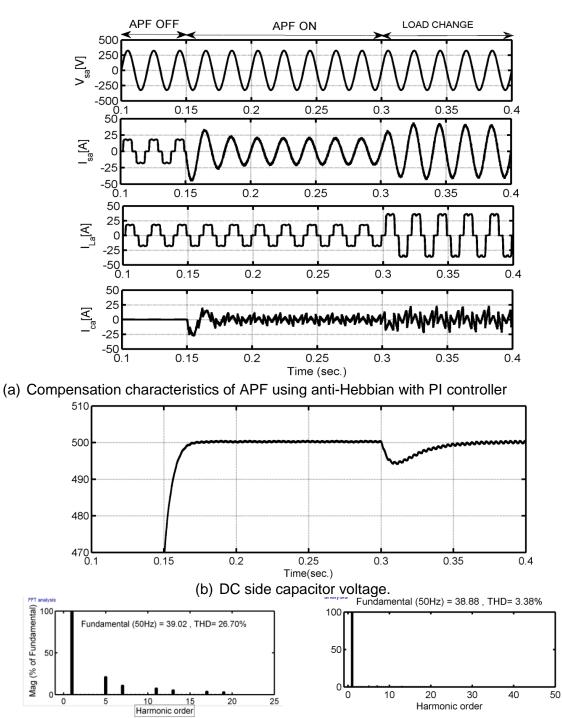

|             | 3.4.2  | Control scheme based on anti-Hebbian algorithm integrated with PI/T2FLC | C72    |

|             |        | 3.4.2.1 Transient performance of the active power filter                | 73     |

|             |        | 3.4.2.2 DC voltage regulation                                           | 74     |

|             |        | 3.4.2.3 Anti-Hebbian algorithm based on total least square (TLS) integ  | grated |

|             | with   | PI/T2FLC 75                                                             |        |

|             |        | 3.4.2.4 Transient performance of the active power filter                | 76     |

|             |        | 3.4.2.5 DC voltage regulation                                           | 77     |

| 3.5         | Comp   | arison of control strategies integrated with PI/T2FLC                   | 78     |

| 3.6         | Concl  | usion                                                                   | 83     |

| CHA<br>FILT |        | 4: ADAPTIVE CONTROL FIVE LEVEL CHBMLI BASED ACTIVE POW                  |        |

| 4.1         |        | uction                                                                  |        |

| 4.2         |        | n of passive component of active power filter                           |        |

|             | -      | Design of capacitor                                                     |        |

|             | 4.2.2  | Interfacing inductor                                                    |        |

| 4.3         |        | e input fuzzy logic controller                                          |        |

|             | 4.3.1  | Design of Signed distance SIFLC                                         |        |

|             | 4.3.2  | Comparison of CFLC and SIFLC                                            |        |

|             | 4.3.3  | Stability analysis of single input fuzzy logic controller               |        |

|             | 4.3.4  | Control surface of SIFLC                                                |        |

| 4.4         | Refere | ence current generation using anti-Hebbian based on TLS algorithm       | 97     |

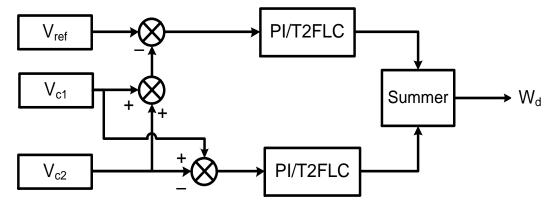

|             | 4.4.1  | Voltage regulation of dc side capacitors                                | 99     |

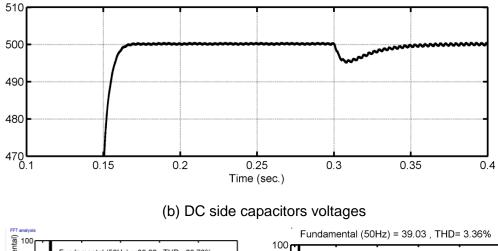

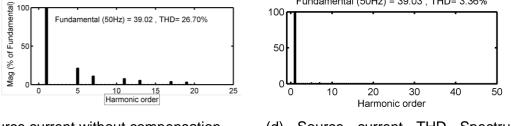

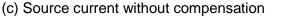

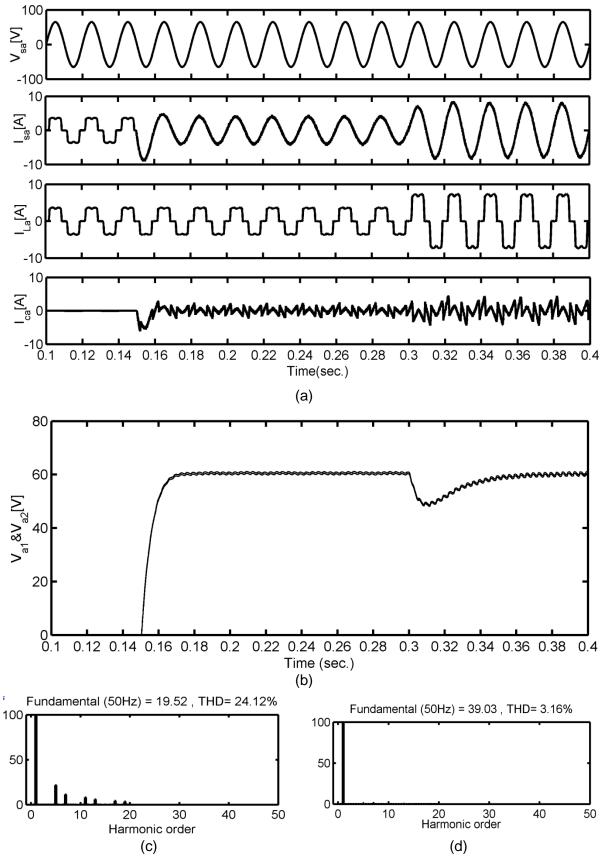

| 4.5         | Simula | ation results                                                           | 100    |

| 4.6         | Exper  | imental validation                                                      | 104    |

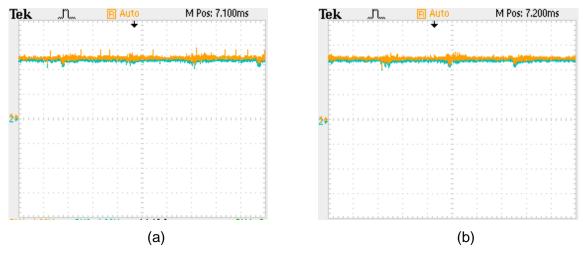

|             |        | 4.6.1.1 Transient Performance of active power filter                    | 106    |

| 4.7         | DC ca  | apacitors voltage regulation                                            | 107    |

|             |        | 4.7.1.1 DC voltage regulation during Transient Conditions               | 108    |

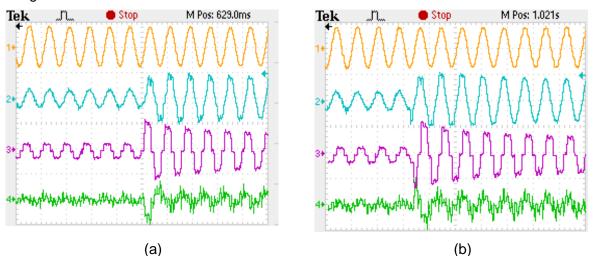

|               | 4.7.2        | Comparison with Simulation Results                                       | 109 |

|---------------|--------------|--------------------------------------------------------------------------|-----|

| 4.8           | Conclu       | usion                                                                    | 113 |

| CHAI<br>FILTI | PTER 5<br>ER | 5: THREE PHASE FOUR WIRE REDUCED RATINGACTIVE POWER                      | 115 |

| 5.1           | Introdu      | uction                                                                   | 115 |

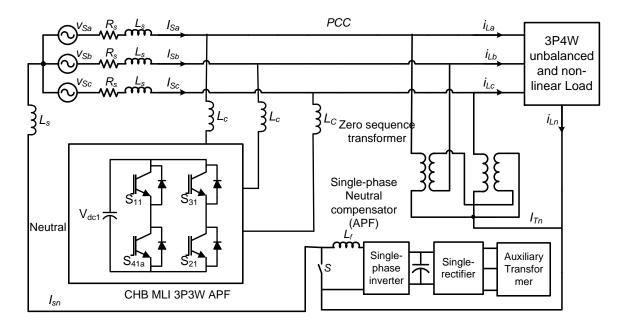

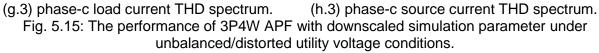

| 5.2           | Reduc        | ed rating 3P4W active power filter                                       | 116 |

| 5.3           | Refere       | ence current generation for 3P3W APF                                     | 118 |

|               | 5.3.1        | Neutral current attenuation under unbalanced/distorted voltage condition | 119 |

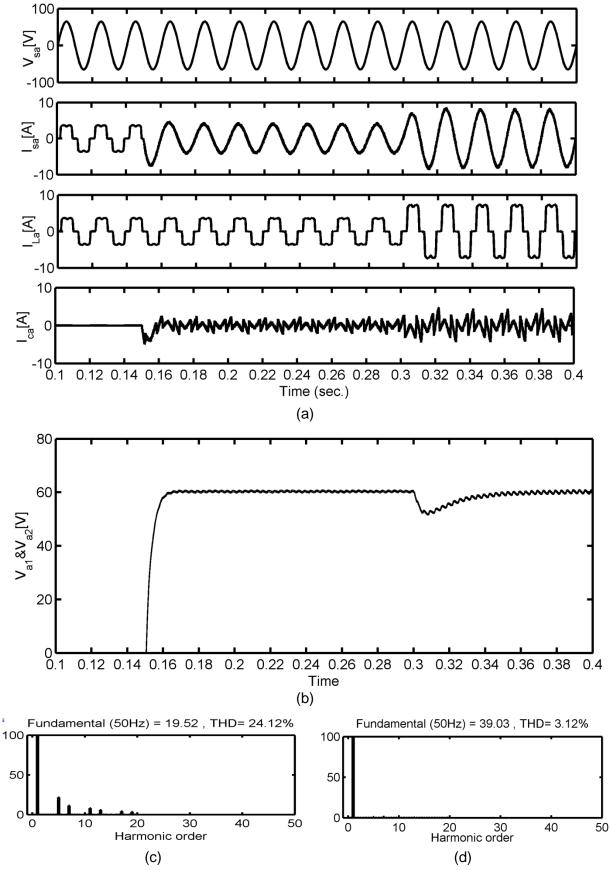

| 5.4           | Simula       | ation result                                                             | 121 |

|               | 5.4.1        | Ideal utility voltage                                                    | 122 |

|               | 5.4.2        | Unbalance utility voltage condition                                      | 123 |

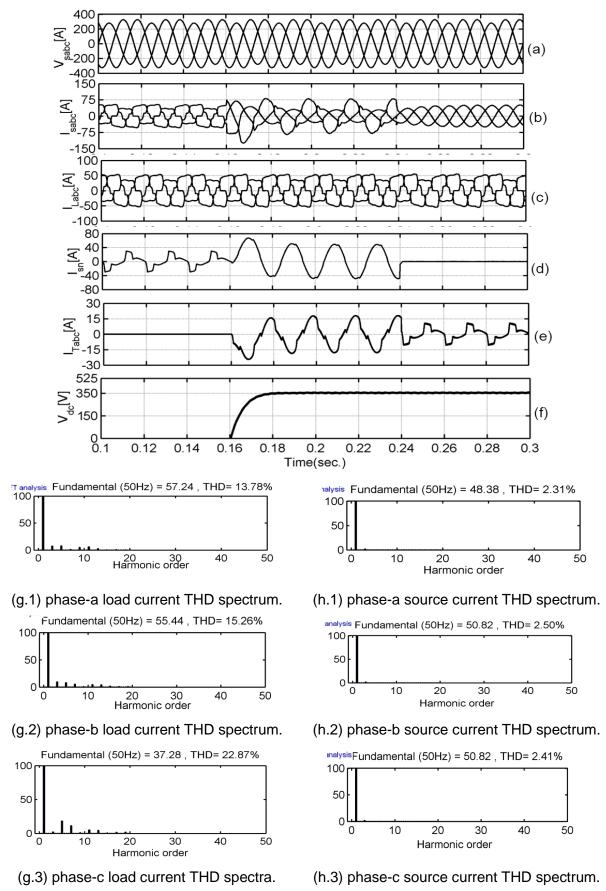

|               | 5.4.3        | Single phase load condition with ideal utility voltage                   | 125 |

|               | 5.4.4        | Distorted voltage conditions                                             | 127 |

|               | 5.4.5        | Comparison of 3P4W APF configurations                                    | 128 |

| 5.5           | Experi       | mental validation                                                        | 129 |

|               | 5.5.1        | Balance utility voltage                                                  | 129 |

|               | 5.5.2        | Unbalance utility voltage                                                | 131 |

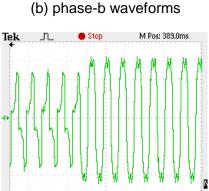

|               | 5.5.3        | Transients performance of the 3P4W APF                                   | 133 |

| 5.6           | Compa        | arison with Simulation Results                                           | 134 |

| 5.7           | Conclu       | usion                                                                    | 138 |

| CHA           | PTER 6       | <b>HYBRID 3P4W APF FOR SUPPRESSING HARMONICS AND NEUT</b>                | RAL |

| CUR           |              | N 3P4W DISTRIBUTION SYSTEM                                               |     |

| 6.1           | Introdu      | uction                                                                   | 139 |

| 6.2           | Config       | uration of the 3P4W APF                                                  | 140 |

| 6.3           | Neutra       | al current attenuation under unbalanced/distorted voltage condition      |     |

|               | 6.3.1        | Control of 3P3W APF                                                      |     |

|               | 6.3.2        | DC voltage regulation                                                    | 143 |

|               | 6.3.3        | Control of single phase neutral compensator                              | 143 |

| 6.4           | Modell       | ling and simulation results                                              | 143 |

|               | 6.4.1        | Simulation results                                                       | 144 |

|               |              | 6.4.1.1 Under ideal utility condition                                    | 144 |

|               |              | 6.4.1.2 Unbalance utility voltage                                        | 146 |

|               |              | 6.4.1.3 Distorted voltage condition                                      | 148 |

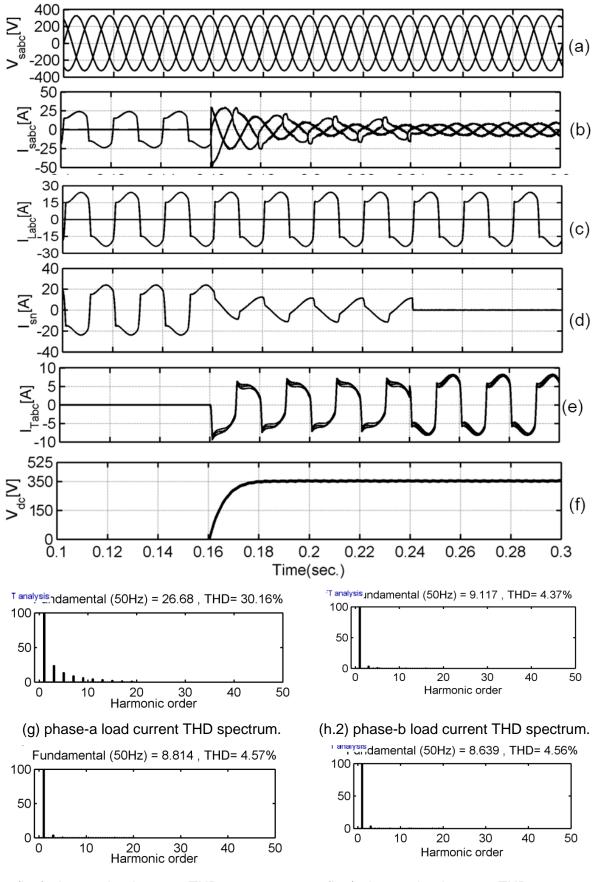

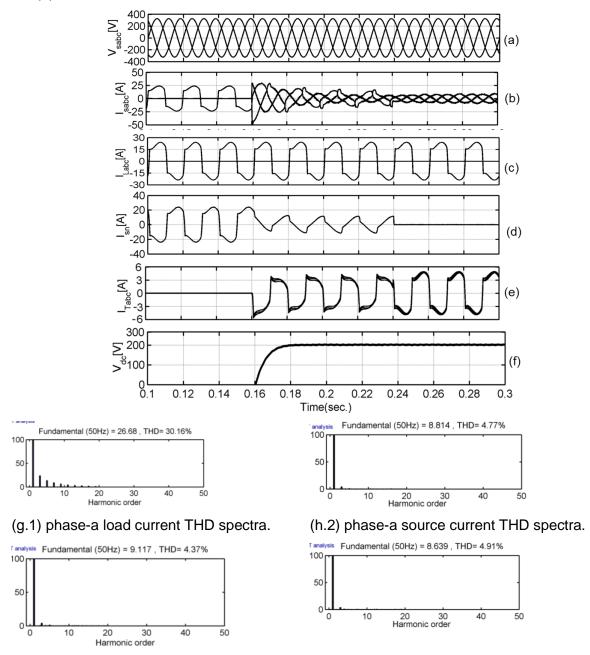

|               |              | 6.4.1.4 Single phase load condition                                      | 149 |

|               | 6.4.2        | Volt-ampere rating of 3P4W APF                                           | 150 |

|               |              | 6.4.2.1 Volt-ampere rating of the Single-phase active power filter       | 151 |

|               |              | 6.4.2.2 Volt-ampere rating of the three phase three wire APF             | 151 |

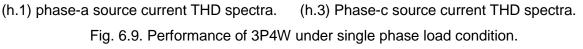

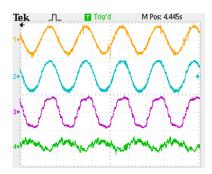

|      | 6.4.3  | Experimental validation                | 151 |

|------|--------|----------------------------------------|-----|

|      | 6.4.4  | Balance utility voltage/distorted      | 152 |

|      | 6.4.5  | Unbalance utility voltage/distorted.   | 154 |

|      | 6.4.6  | Transients performance of the 3P4W APF | 156 |

| 6.5  | Compa  | arison with Simulation Results         | 157 |

| 6.6  | Conclu | ision                                  | 161 |

| СНА  | PTER 7 | CONCLUSION                             | 162 |

| 7.1  | Future | scope                                  | 164 |

| PUBI |        | ONS FROM THE WORK                      | 165 |

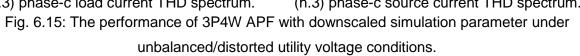

| PHO  | TOGRA  | APHS OF THE EXPERIMENTAL SETUP         | 167 |

| BIBL | IOGRA  | РНҮ                                    | 169 |

| APP  |        | – A                                    | 186 |

| APPI |        | – B                                    | 187 |

### **LIST OF FIGURES**

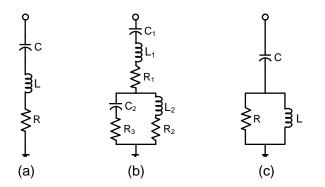

| Fig. 1.1: Shunt passive filters: (a) Single-tuned; (b) Double-tuned; (c) Second-order hi   | gh-              |

|--------------------------------------------------------------------------------------------|------------------|

| pass damped                                                                                | 7                |

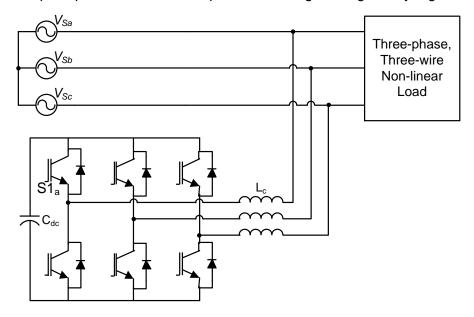

| Fig. 1.2: Shunt active power filter.                                                       | 8                |

| Fig. 1.3: (a) Current source inverter based APF; (b) Voltage source inverter based APF     | 9                |

| Fig. 1.4: Diode clamped multilevel inverter                                                | .11              |

| Fig. 1.5: Flying capacitor multilevel inverter                                             | . 12             |

| Fig.1.7: APF for two-wire systems                                                          | . 15             |

| Fig. 1.8: The 3P4W split capacitor.                                                        | . 16             |

| Fig. 1.9: The 3P4W four-leg topology                                                       | . 17             |

| Fig. 1.10 : three phase four active power filter comprising zigzag transformer             | . 17             |

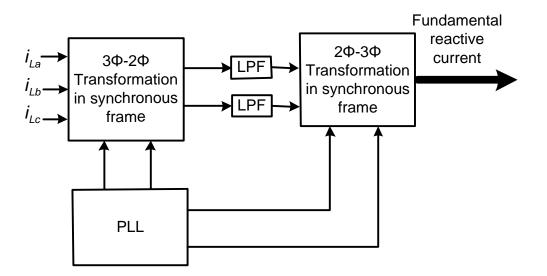

| Fig. 1.12: synchronous reference frame based algorithm                                     | . 20             |

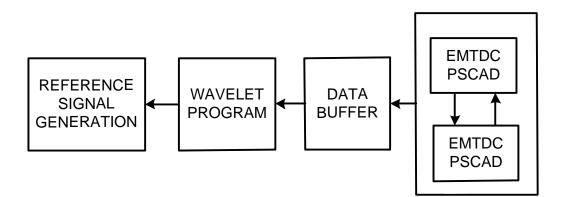

| Fig. 1.13: Block diagram of interface process of wavelet                                   | .21              |

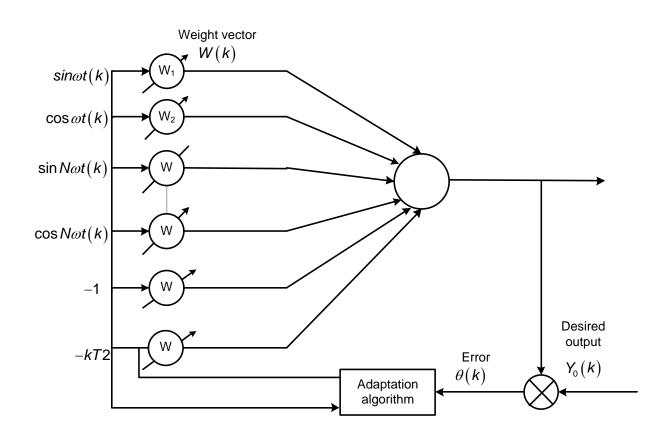

| Fig. 1.14: ADALINE based harmonics estimator                                               | . 22             |

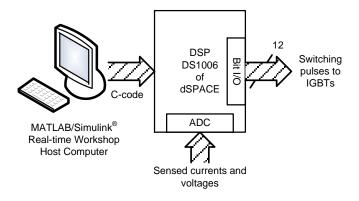

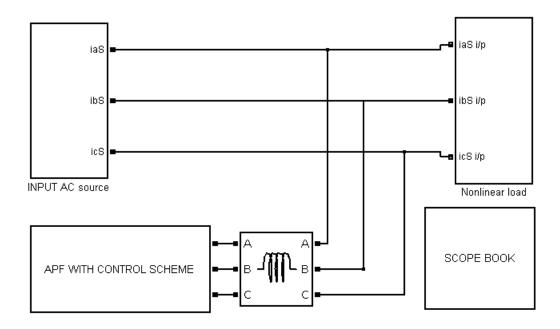

| Fig. 2.1: Schematic diagram for hardware implementation of active power filter             | . 34             |

| Fig. 2.2: Power circuit of three-level diode clamped active power filter                   | . 35             |

| Fig. 2.3: Snubber circuit connected across every switching device of inverter circuits     | . 36             |

| Fig. 2.4: Firing signals of inverter's phase leg-a with different modulation techniques (m | ι <sub>a</sub> = |

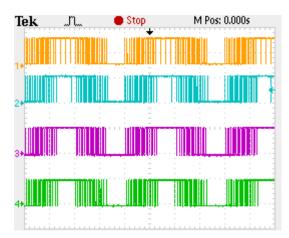

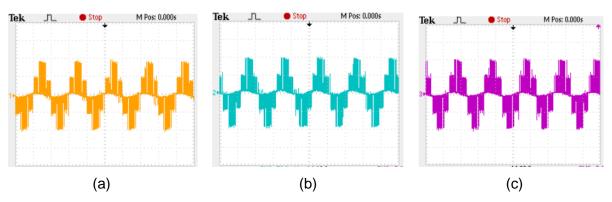

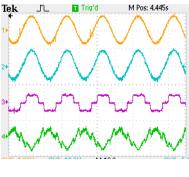

| 0.95, $f_m$ = 50 Hz and $m_f$ = 30) with basic LSPWM                                       | . 37             |

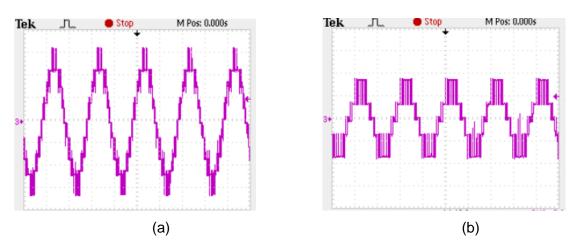

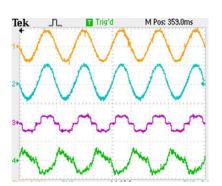

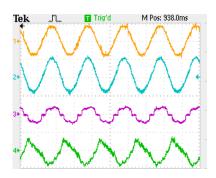

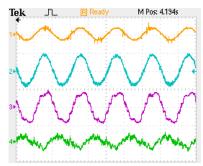

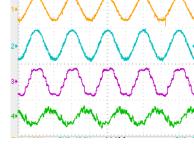

| Fig. 2.5: Experimental waveforms of a three-level diode clamped inverter                   | . 37             |

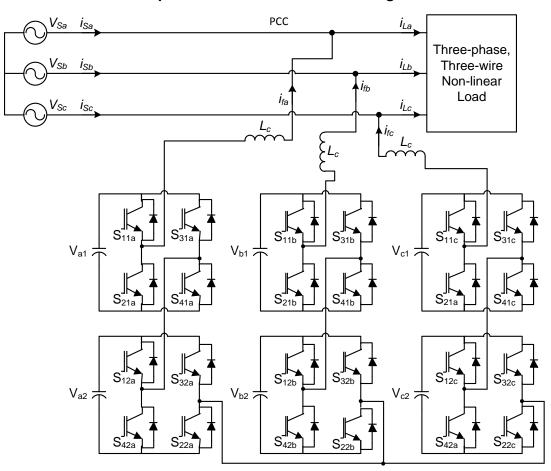

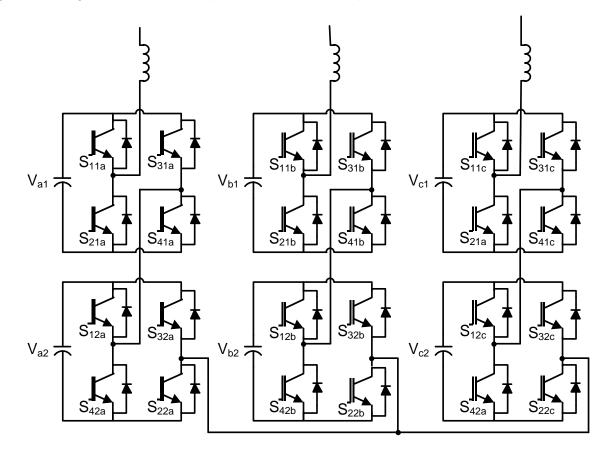

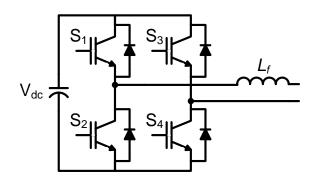

| Fig. 2.6: Power circuit of five-level cascaded H-bridge active power filter                | . 38             |

| Fig. 2.7: Firing signals of inverter's phase leg-a with different modulation techniques (m | ) <sub>a</sub> = |

| 0.95, $f_m$ = 50 Hz and $m_f$ = 30) with Level Shifted PWM                                 | . 39             |

| Fig. 2.8: Experimental waveforms of a five-level cascaded H-bridge inverter                | . 39             |

| Fig. 2.9: AC current sensing circuit                                                       | . 40             |

| Fig. 2.10: AC/DC voltage sensing circuit.                                                  | . 41             |

| Fig. 2.11: Total development environment of dSPACE with MATLAB/Simulink                    | . 42             |

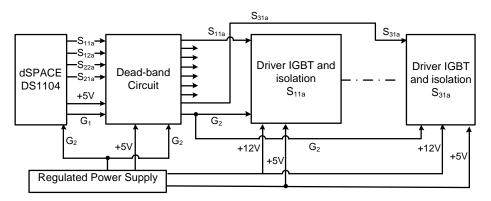

| Fig. 2.12: DSP (dSPACE-DS1104) circuit board interfacing                                   | .44              |

| Fig. 2.13: Schematic diagram of interfacing firing pulses from dSPACE controller board     | l to             |

| switching devices                                                                          | .44              |

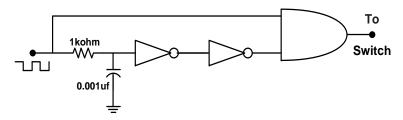

| Fig. 2.14: Dead-band circuit for each switching device                                     | . 45             |

| Fig. 2.15: Firing signals for the switches $S_1$ and $S'_1$ with dead-band circuit.        | . 45             |

| Fig. 2.16: IGBT driver circuit and isolation circuit                                       | . 46             |

| Fig. 2.17: simulated waveforms of a three-level diode clamped inverter                     | . 46             |

| Fig. 2.18: simulated waveforms of a five-level cascaded H-bridge inverter                  | . 47             |

| Fig. 3.1. Power circuit of three level active power filter                                 | . 50             |

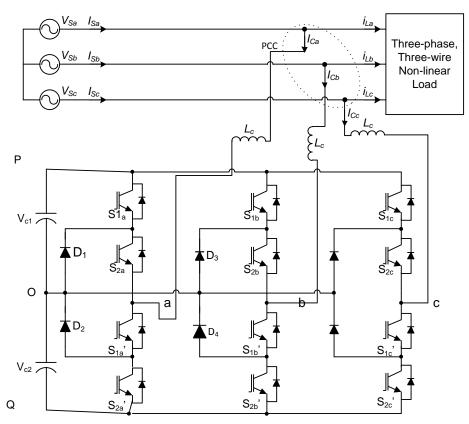

| Fig. 3.2: Reference current generation using LMS algorithm for phase-a                     | .54              |

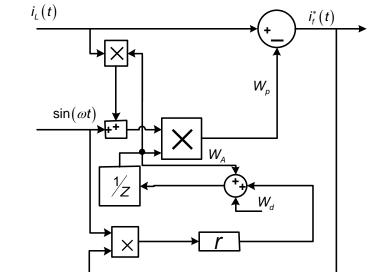

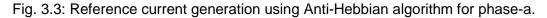

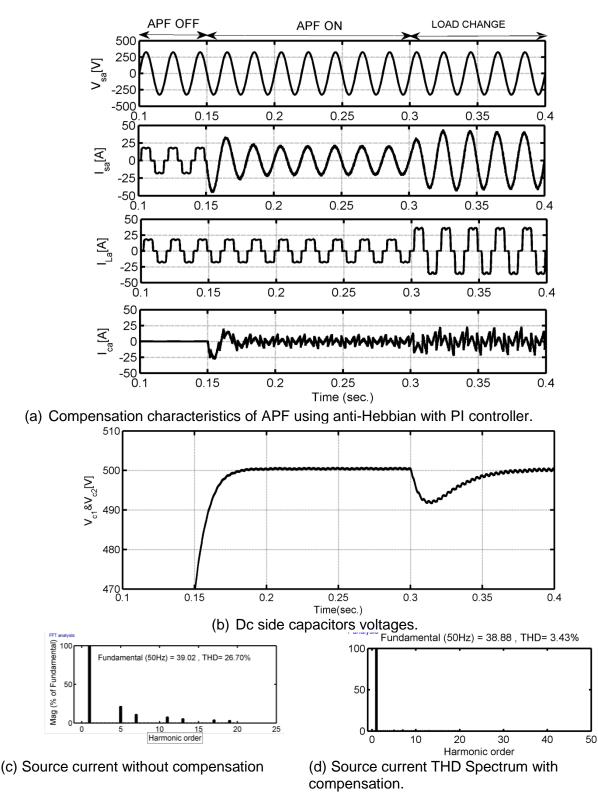

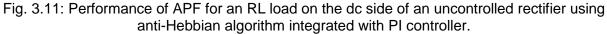

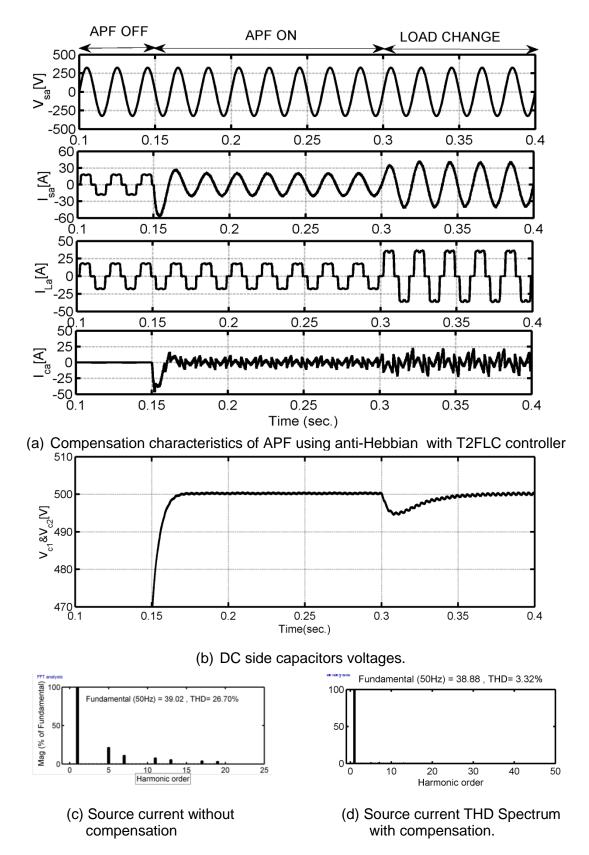

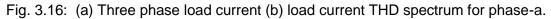

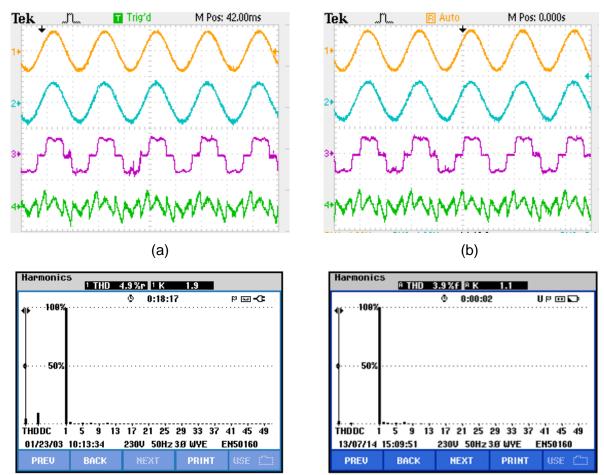

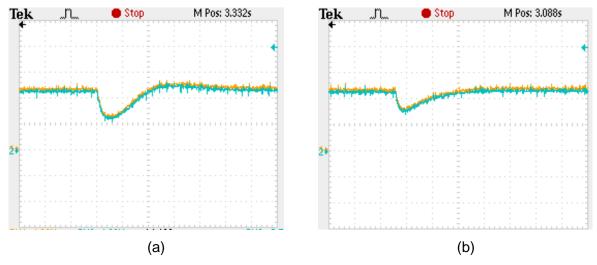

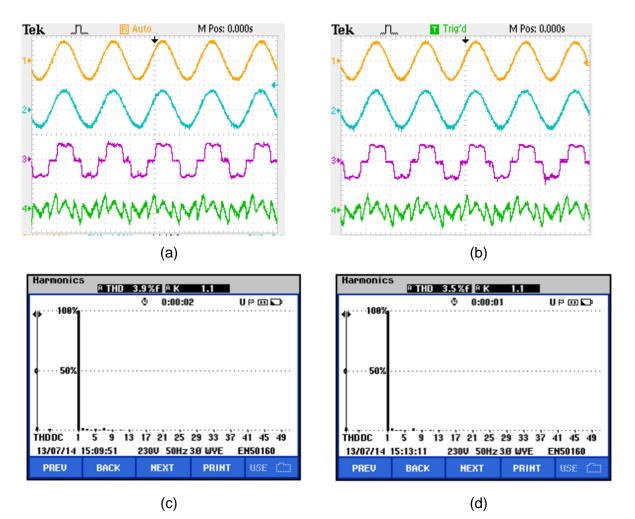

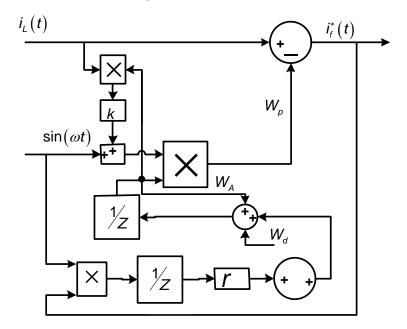

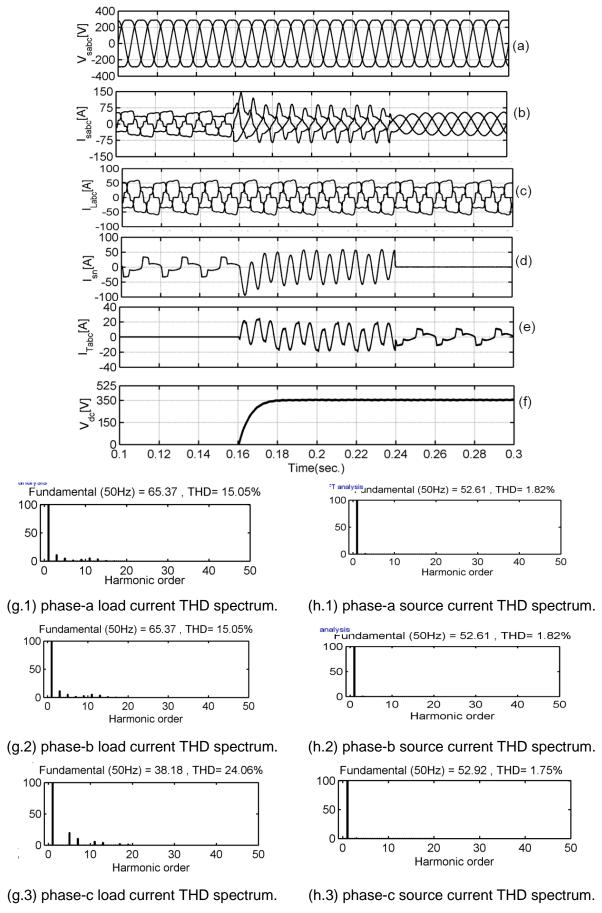

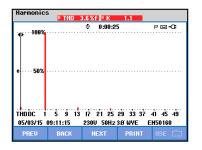

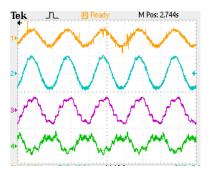

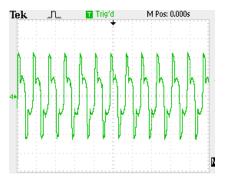

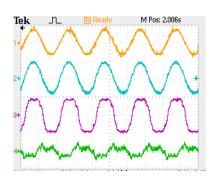

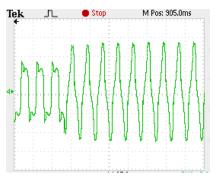

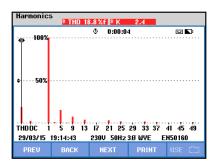

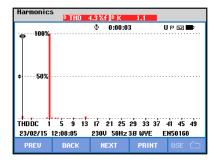

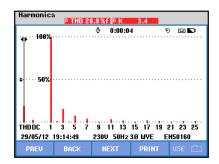

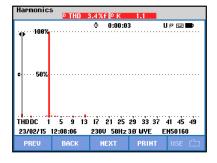

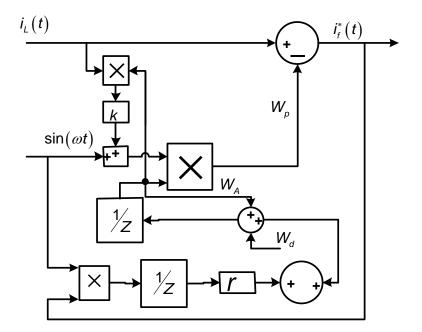

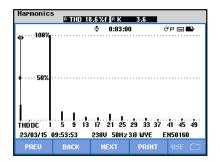

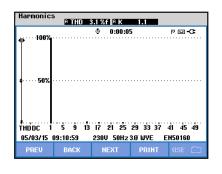

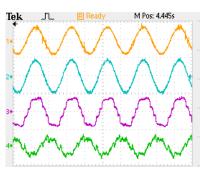

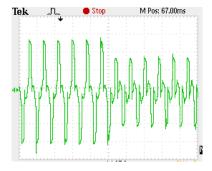

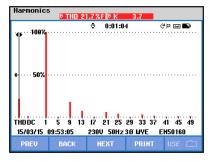

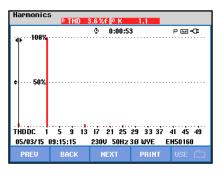

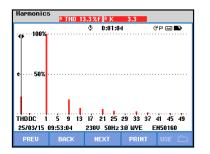

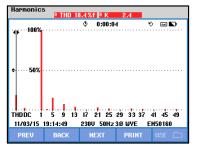

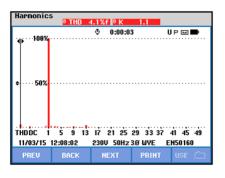

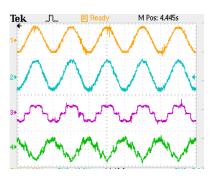

Fig. 3.3: Reference current generation using Anti-Hebbian algorithm for phase-a......55 Fig. 3.4: Reference current generation using anti-Hebbian based on TLS algorithm for phase-Fig. 3.6: Block diagram of type-2 fuzzy logic controller......57 Fig. 3.8 dc voltage regulation loop. .....60 Fig. 3.9: Performance of APF for an RL load on the dc side of an uncontrolled rectifier using anti-Hebbian algorithm integrated with PI controller. ......61 Fig. 3.10: Performance of APF for RL load on the dc side of an uncontrolled rectifier using anti-Hebbian algorithm integrated with T2FLC-controller. .....63 Fig. 3.11: Performance of APF for an RL load on the dc side of an uncontrolled rectifier using anti-Hebbian algorithm integrated with PI controller......64 Fig. 3.12: Performance of APF for an RL load on the dc side of an uncontrolled rectifier using Fig. 3.13: Performance of APF for an RL load on the dc side of an uncontrolled rectifier using Fig. 3.14: Performance of APF for an RL load on the dc side of an uncontrolled rectifier using Fig. 3.17: Experimental results of 3P3W APF for an RL-load on the dc side of a phaseuncontrolled rectifier with PI controller and T2FLC......70 Fig. 3.18: Experimental results of 3P3W APF for RL-load: (a) LMS integrated with PI controller (b) LMS integrated with T2FLC.....71 Fig. 3.19: (a) dc capacitors voltages PI controller (b) dc capacitors voltages with T2FLC. ...72 Fig. 3.20: (a) DC capacitors voltages PI controller (b) dc capacitors voltages with T2FLC...72 Fig. 3.21: Experimental results of 3P3W APF for an RL-load on the dc side of a phaseuncontrolled rectifier with PI controller and T2FLC......73 Fig. 3.22: Experimental results of 3P3W APF for RL-load: (a) anti-Hebbian integrated with PI controller (b) anti-Hebbian integrated with T2FLC.....74 Fig. 3.23: (a) dc capacitors voltages PI controller (b) dc capacitors voltages with T2FLC...75 Fig. 3.24: (a) dc capacitors voltages PI controller (b) dc capacitors voltages with T2FLC...75 Fig. 3.25: Experimental results of 3P3W APF for an RL-load on the dc side of a phaseuncontrolled rectifier with PI controller and T2FLC......76

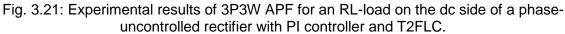

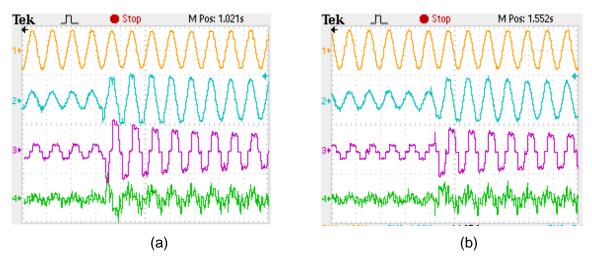

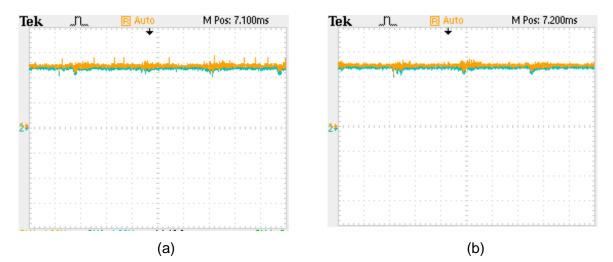

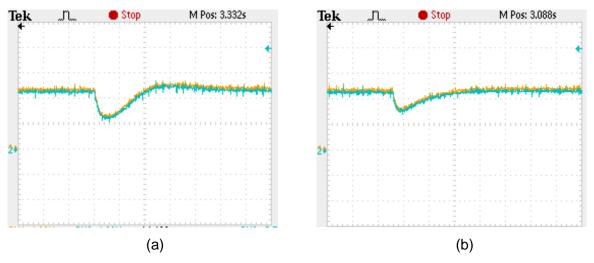

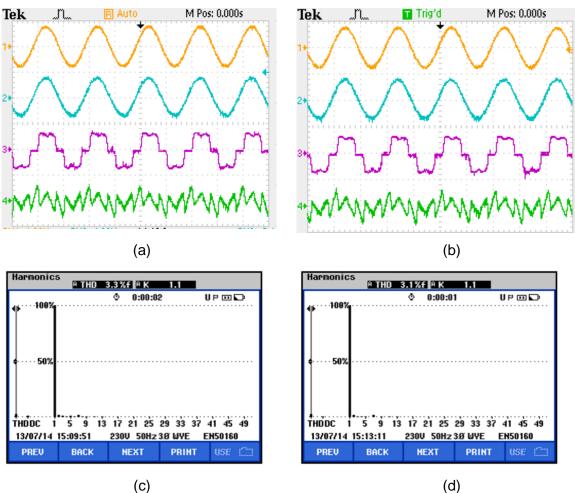

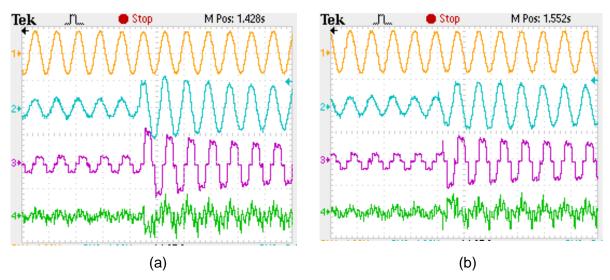

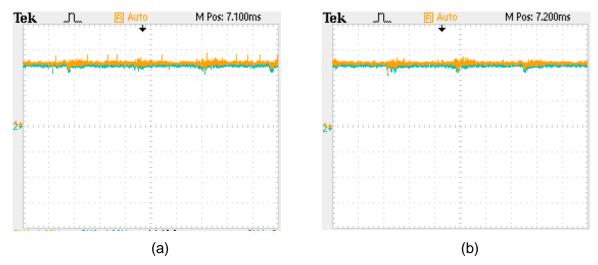

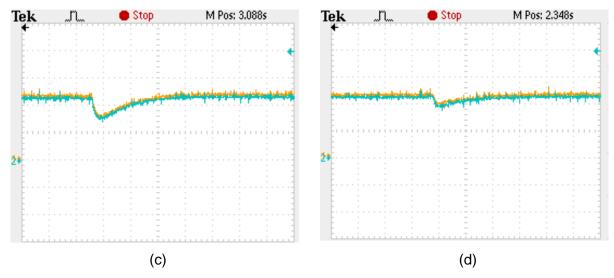

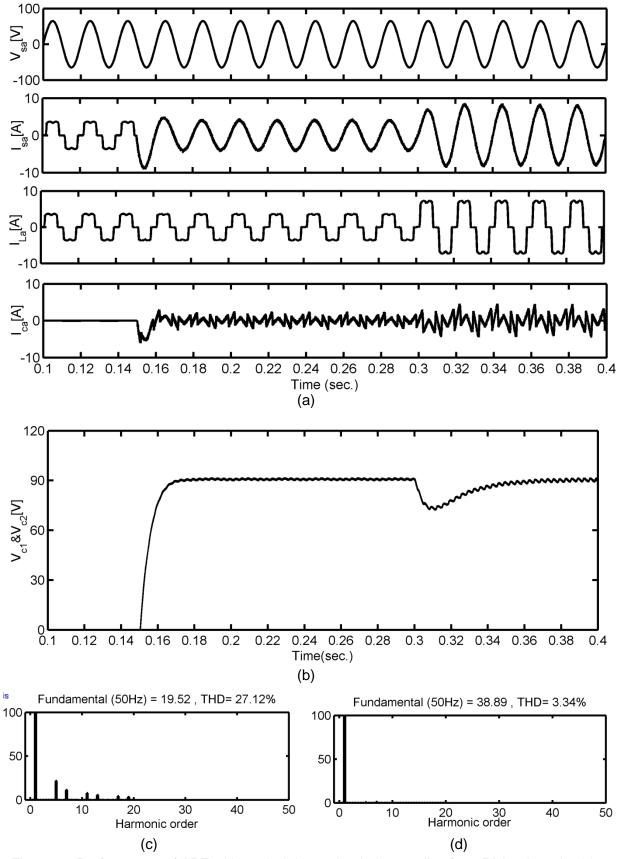

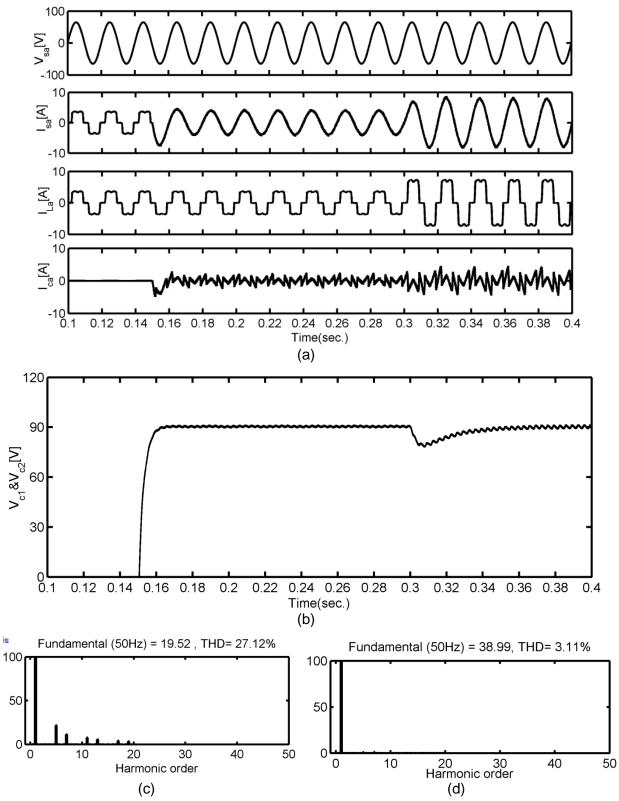

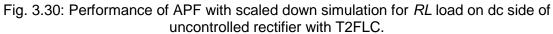

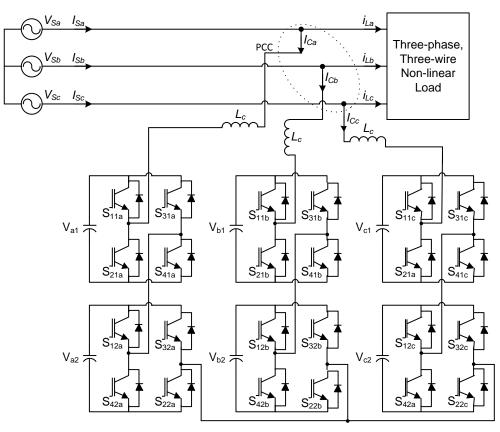

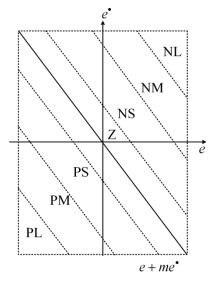

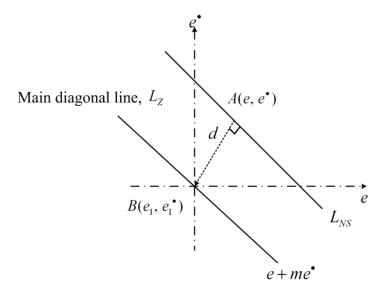

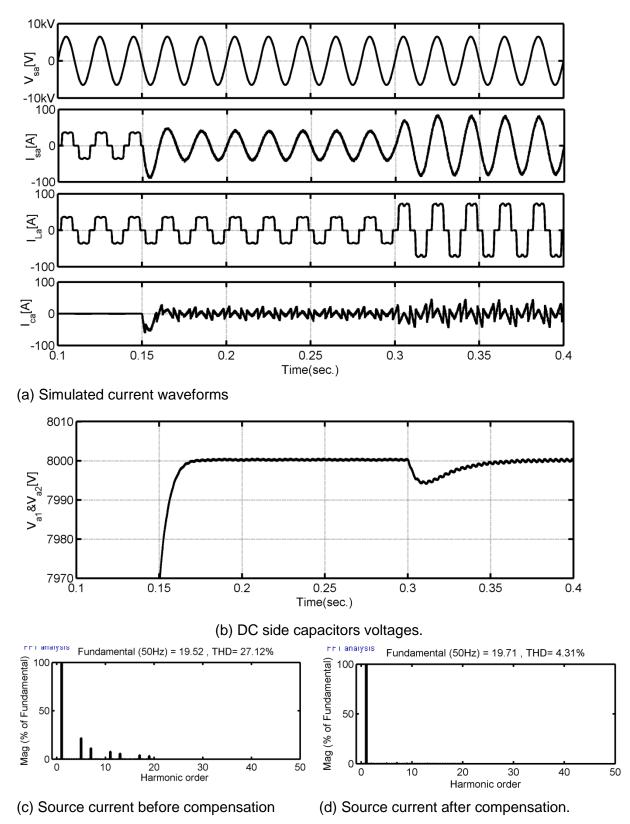

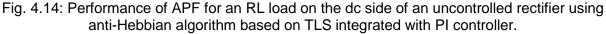

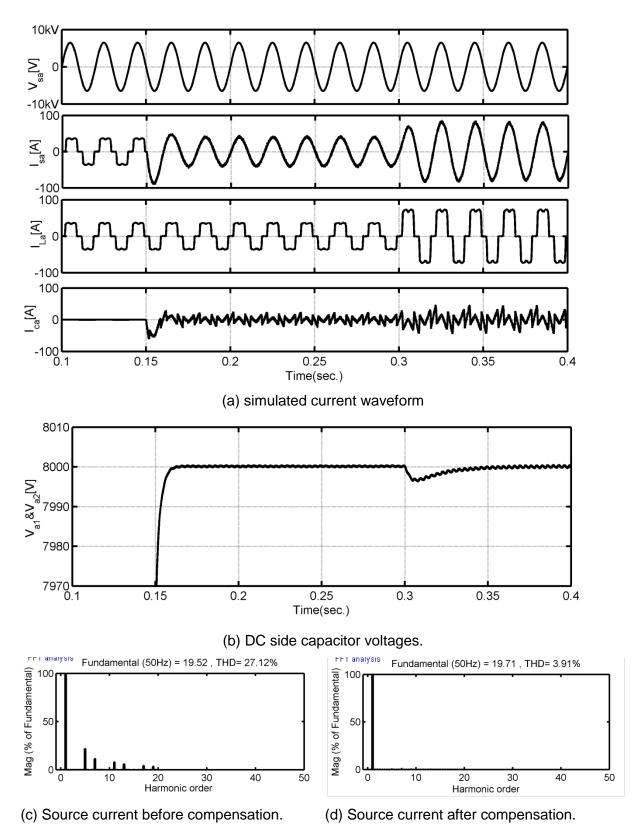

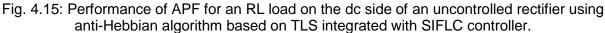

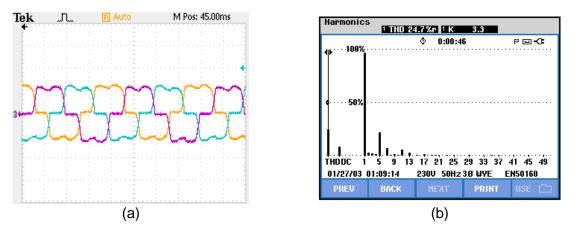

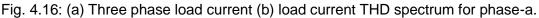

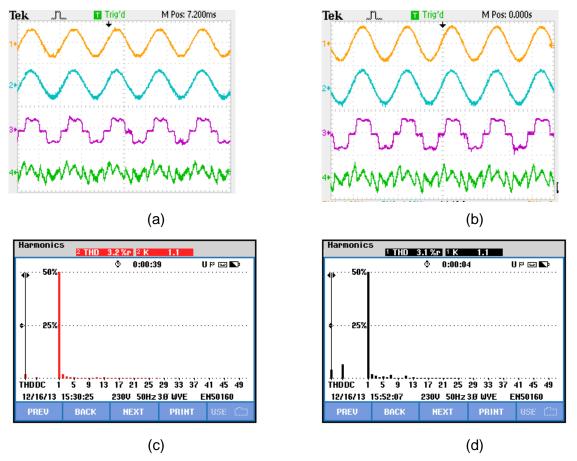

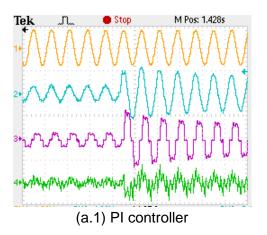

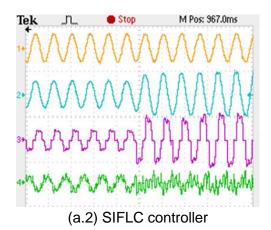

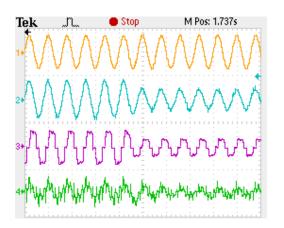

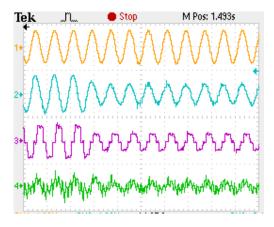

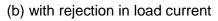

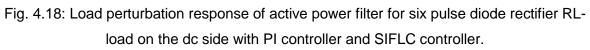

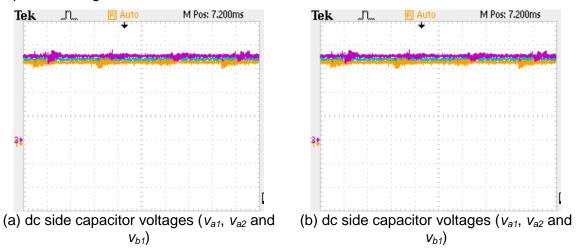

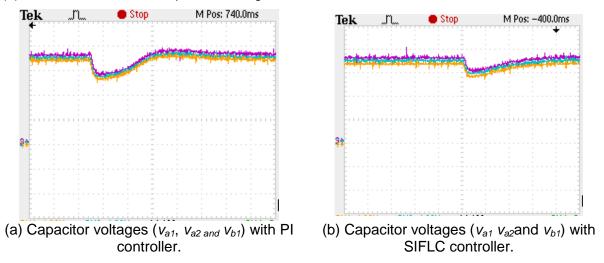

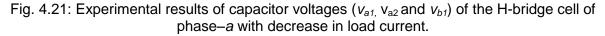

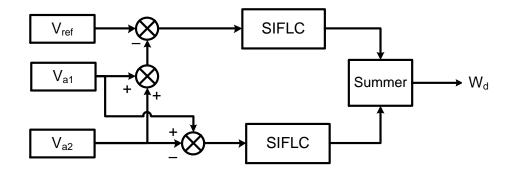

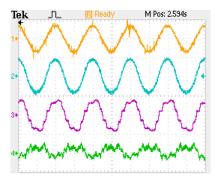

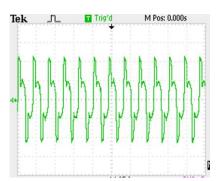

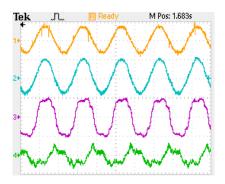

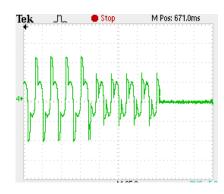

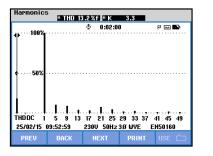

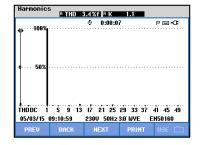

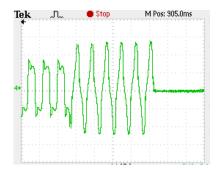

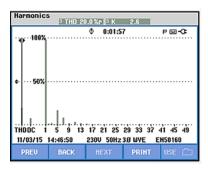

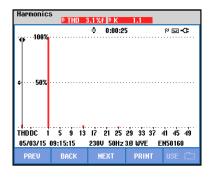

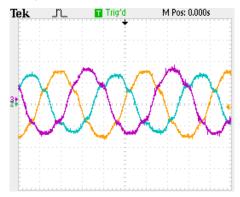

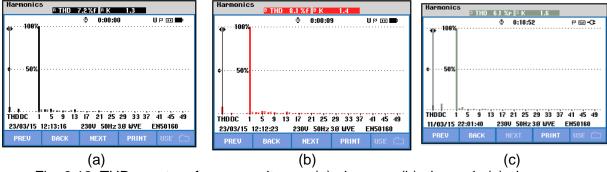

Fig. 3.26: Experimental results of 3P3W APF for RL-load: (a) anti-Hebbian based on TLS algorithm integrated with PI controller (b) anti-Hebbian integrated based on TLS with T2FLC Fig. 3.27: a) dc capacitors voltages PI controller (b) dc capacitors voltages with T2FLC.....78 Fig. 3.28: c) dc capacitors voltages PI controller (d) dc capacitors voltages with T2FLC.....78 Fig. 3.29: Performance of APF with scaled down simulation studies for RL load on dc side dc side of uncontrolled rectifier with anti-Hebbian based on TLS integrated with T2FLC.....80 Fig. 3.30: Performance of APF with scaled down simulation for RL load on dc side of uncontrolled rectifier with T2FLC......81 Fig. 4.7: SIFLC with the PWL control surface......95 Fig. 4.12: Membership functions (a) error and change of error for inputs and (b) output. .. 100 Fig. 4.13: (a) Conventional FLC Control surface. (b) Equivalent PWL (SIFLC) control surface corresponding to MFs in Fig. 4.12.....101 Fig. 4.14: Performance of APF for an RL load on the dc side of an uncontrolled rectifier using Fig. 4.15: Performance of APF for an RL load on the dc side of an uncontrolled rectifier using Fig. 4.17: Experimental results of 3P3W APF for an RL-load on the dc side of a phaseuncontrolled rectifier with PI controller and SIFLC......105 Fig. 4.18: Load perturbation response of active power filter for six pulse diode rectifier RL-Fig. 4.19: Experimental results of capacitor voltages of the H-bridge cells for a five-level CHB Fig. 4.21: Experimental results of capacitor voltages ( $v_{a1}$ ,  $v_{a2}$  and  $v_{b1}$ ) of the H-bridge cell of

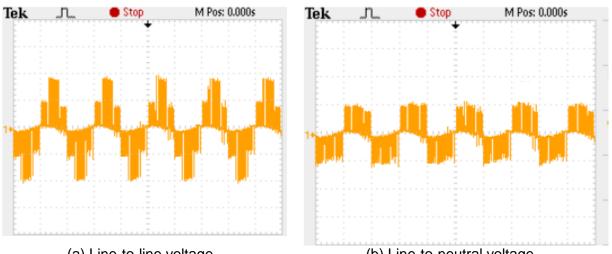

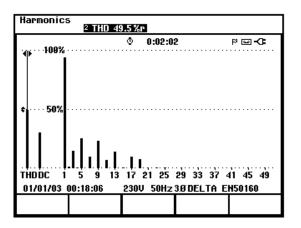

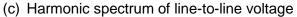

| Fig. 4.22: voltage waveforms: (a) line to line voltage (b) line neutral voltage109           |

|----------------------------------------------------------------------------------------------|

| Fig. 4.23: Performance of APF with scaled down simulation studies for a RL element at its do |

| side of an uncontrolled rectifier with PI controller111                                      |

| Fig. 4.24: Performance of APF with scaled down simulation studies for a RL load on dc side   |

| of an uncontrolled rectifier with SIFLC controller112                                        |

| Fig. 5.1: Configuration of the three phase four wire active power filter (3P4W APF) 117      |

| Fig. 5.2: Five level CHBMLI based APF117                                                     |

| Fig. 5.3 . Single phase active power filter                                                  |

| Fig. 5.4: Reference current generation for phase-a using anti-Hebbian learning rule 118      |

| Fig. 5.5: dc voltage regulation using SIFLC controller for phase-a                           |

| Fig. 5.6: Zero-sequence equivalent circuit of the 3P4W distribution system                   |

| Fig. 5.7: Control block diagram for single phase active power filter                         |

| Fig. 5.8: Performances of 3P4W active power filter under balance utility voltage 122         |

| Fig. 5.9. Performance of 3P4W APF under unbalance utility condition                          |

| Fig. 5.10. Performance of 3P4WAPF under single phase load                                    |

| Fig. 5.11. Performance of 3P4W APF under distorted utility condition                         |

| Fig. 5.12. Experimental waveform of 3P4W APF for balance utility voltage                     |

| Fig. 5.13. Experimental waveform of 3P4W APF for unbalance utility voltage                   |

| Fig. 5.14: Experimental waveform under transient condition                                   |

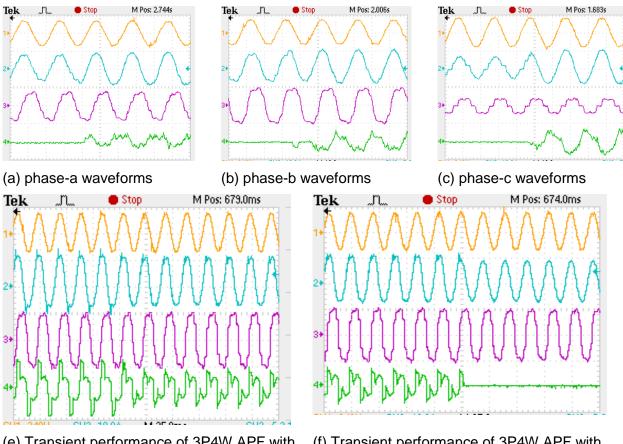

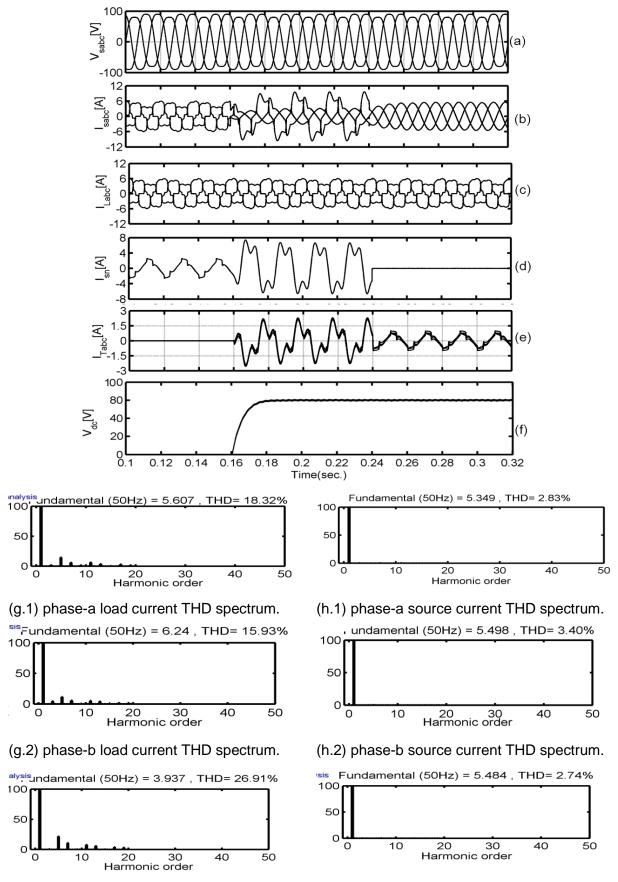

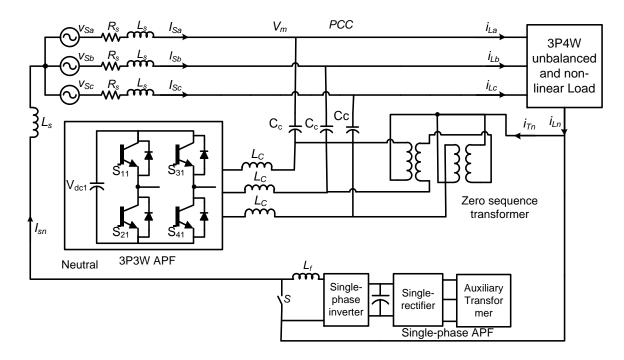

| Fig. 5.15: The performance of 3P4W APF with downscaled simulation parameter under            |

| unbalanced/distorted utility voltage conditions                                              |

| Fig. 6.1 A reduced rating hybrid APF for 3P4W distribution systems using transformer, 3P3W   |

| APF and single-phase APF141                                                                  |

| Fig. 6.2: Zero-sequence equivalent circuit142                                                |

| Fig. 6.3: reference current generation using anti-Hebbian based on total least square        |

| algorithm for phase-a143                                                                     |

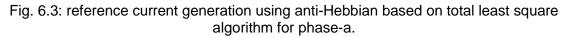

| Fig. 6.4: dc voltage regulation using SIFLC controller for phase-a                           |

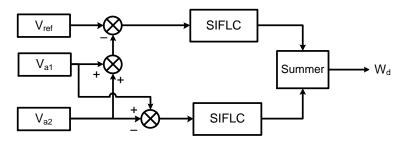

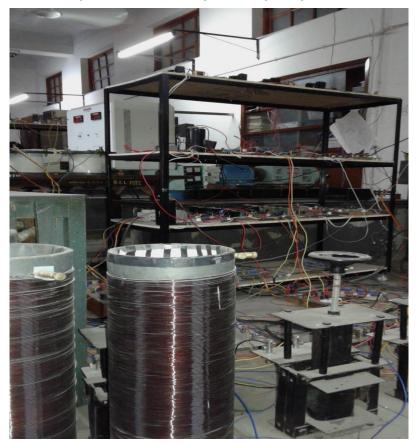

| Fig. 6.5: MATLAB/Simulink model of the proposed system                                       |

| Fig. 6.6. Performance characteristics of 3P4W APF under balance voltage condition 145        |

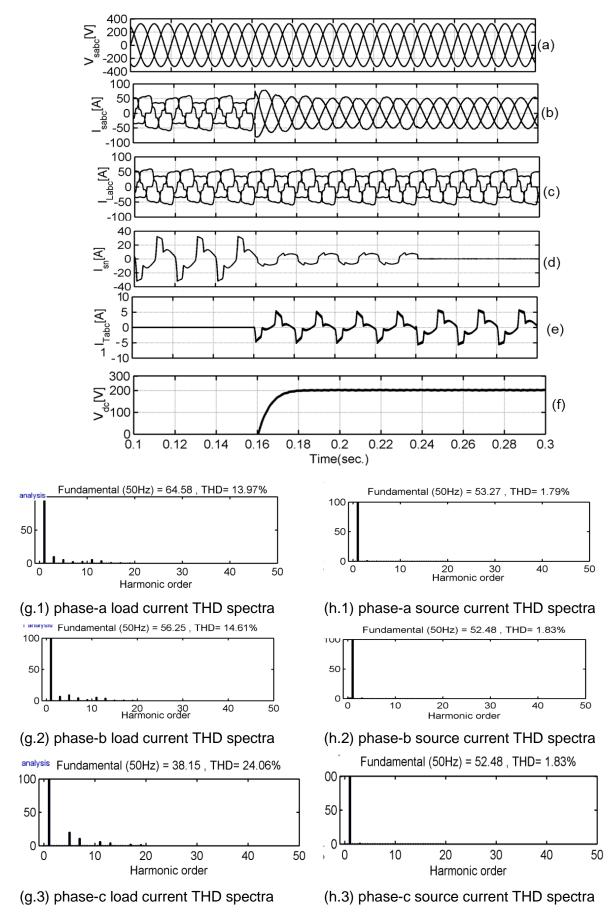

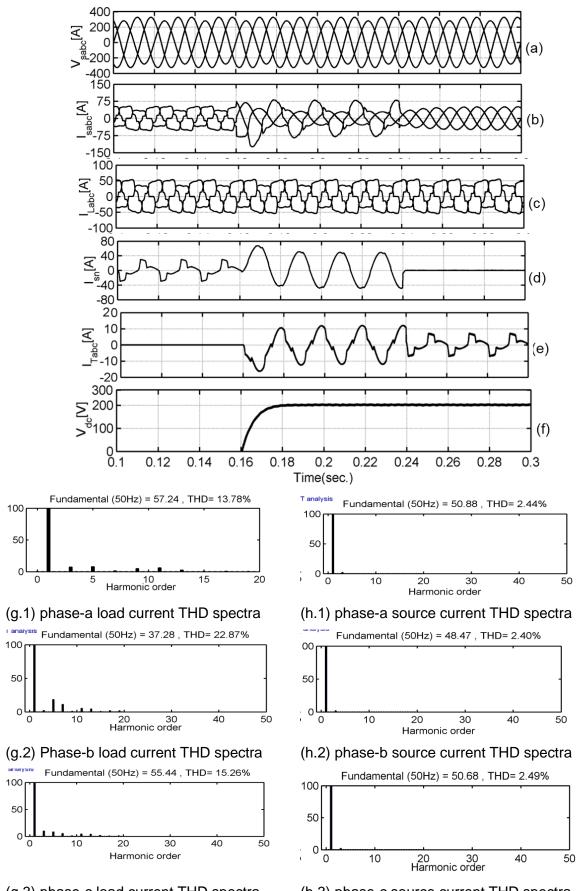

| Fig. 6.7. Performance of 3P4W APF under unbalanced utility voltage condition                 |

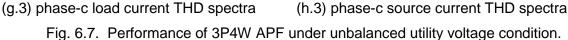

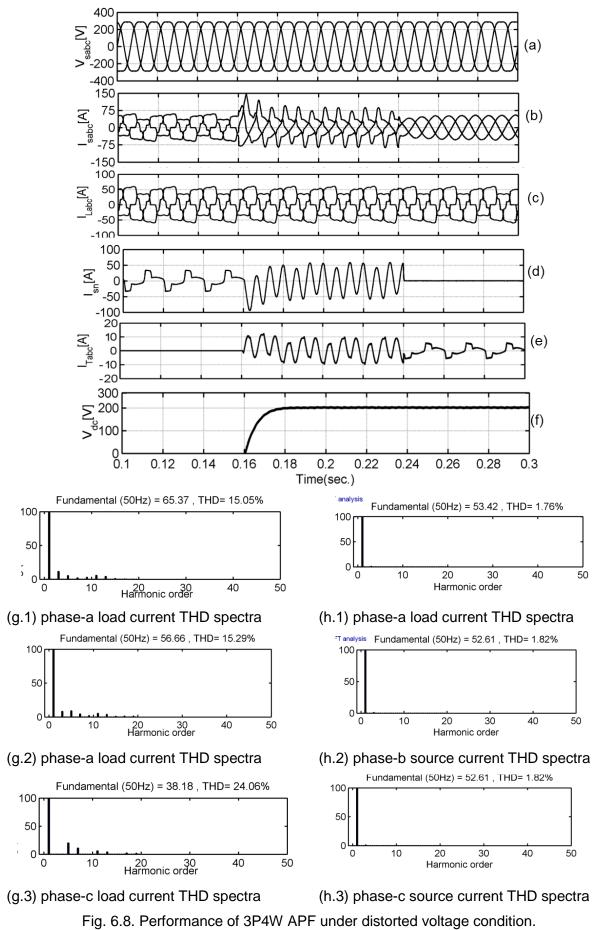

| Fig. 6.8. Performance of 3P4W APF under distorted voltage condition                          |

| Fig. 6.9. Performance of 3P4W under single phase load condition                              |

| Fig. 6.10: Experimental waveform of 3P4W APF for balance utility voltage153                  |

| Fig. 6.11: Unbalanced/distorted three-phase source voltages154                               |

| Fig. 6.12: THD spectra of source voltages: (a) phase-a; (b) phase-b; (c) phase-c             |

| Fig. 6.13: Experimental waveform of 3P4W APF for unbalance utility voltage155                |

| Fig. 6.14: Experimental waveform under transient condition                                   |

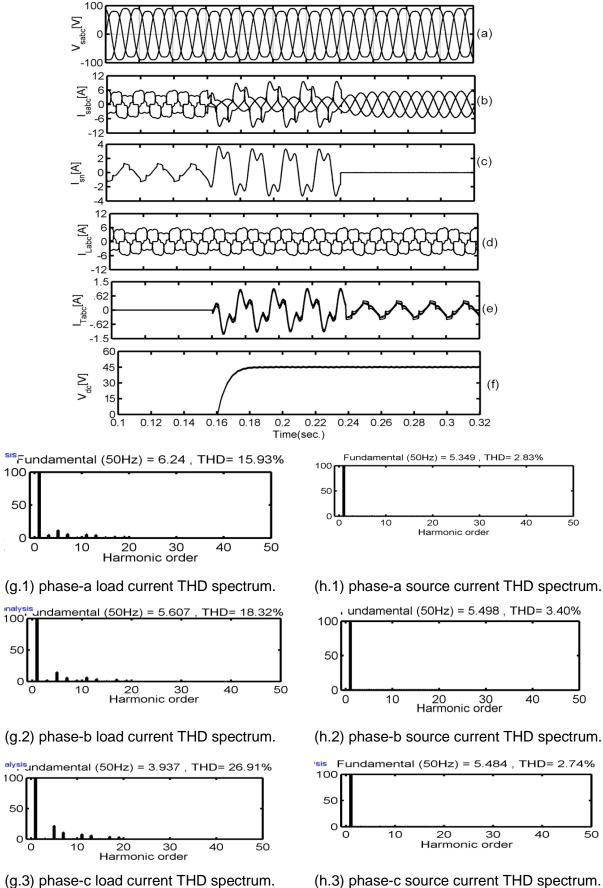

| Fig. 6.15: The performance of 3P4W APF with     | n downscaled simulation parameter under |

|-------------------------------------------------|-----------------------------------------|

| unbalanced/distorted utility voltage conditions |                                         |

## LIST OF TABLES

| Table 2.1: Parameters used for the experimental validation of diode clamped and H-bridge       |

|------------------------------------------------------------------------------------------------|

| inverter topologies                                                                            |

| Table 3.1: Rule matrix for voltage regulation                                                  |

| Table 3.2: The parameters used in the simulation studies                                       |

| Table 3.3: Comparison of experimental and simulation results with anti-Hebbian based on        |

| TLS algorithm with different controllers                                                       |

| Table 3.4: Comparison of experimental and simulation results with LMS algorithm with           |

| different controllers                                                                          |

| Table 3.5: Comparison of experimental and simulation results with anti-Hebbian algorithm       |

| with different controllers                                                                     |

| Table 4.1: Parameters used in the simulation study                                             |

| Table 4.2: Interfacing inductor                                                                |

| Table 4.3: FLC rule table with Teoplitz structure                                              |

| Table 4.4: Reduced rule Table91                                                                |

| Table 4.5: Rule Table with Teoplitz structure for dc voltage regulation (conventional FLC rule |

| base)                                                                                          |

| Table 4.6: Reduced SIFLC rule table                                                            |

| Table 4.7: The parameters used in the simulation studies                                       |

| Table 4.9: Comparison of experimental and simulation results with different controller with    |

| anti-Hebbian based on TLS control algorithm                                                    |

| Table 5.1: The parameter used for simulation study                                             |

| Table 5.2: Comparison of three-phase four-wire active power filters compensation               |

| characteristics                                                                                |

| Table 5.3: The parameters used in the downscaled simulation studies                            |

| Table 5.4: Comparison of experimental and downscaled simulation results under normal           |

| utility voltage conditions with 3P4W APF137                                                    |

| Table 5.5: Comparison of experimental and downloaded simulation results under                  |

| unbalanced/distorted utility voltage conditions 3P4W APF137                                    |

| Table 6.1: The parameters used in the downscaled simulation studies                            |

| Table 6.2: Comparison of experimental and downscaled simulation results under normal           |

| utility voltage conditions with 3P4W APF158                                                    |

| Table 6.3: Comparison of experimental and downloaded simulation results under                  |

| unbalanced/distorted utility voltage conditions 3P4W APF159                                    |

| 3P3W     | Three-phase, Three-wire                           |

|----------|---------------------------------------------------|

| 3P4W     | Three-phase, Four-wire                            |

| ac, AC   | Alternating Current                               |

| APF      | Active Power Filter                               |

| ASD      | Adjustable Speed Drive                            |

| СНВ      | Cascaded H-bridge                                 |

| CSD      | Custom Power Device                               |

| CSI      | Current Source Inverter                           |

| CHBMLI   | Cascaded H-bridge multilevel inverter             |

| dc, DC   | Direct Current                                    |

| DCMLI    | Diode Clamped Multilevel Inverter                 |

| DPF      | Displacement Power Factor                         |

| DSO      | Digital Storage Oscilloscope                      |

| DSP      | Digital Signal Processor                          |

| EMI      | Electro Magnetic Interference                     |

| FCMLI    | Flying Capacitor Multilevel Inverter              |

| GTO      | Gate Turn-off Thyristor                           |

| HVDC     | High Voltage Direct Current                       |

| IEC      | International Electrotechnical Commission         |

| IEEE     | Institute of Electrical & Electronics Engineers   |

| IGBT     | Insulated Gate Bipolar Transistor                 |

| LMS      | Least mean square                                 |

| LSPWM    | Level-shifted Pulse width Modulation              |

| MLI      | Multilevel Inverter                               |

| MOSFET   | Metal Oxide Semiconductor Field-effect Transistor |

| PCC      | Point of Common Coupling                          |

| PF       | Power Factor                                      |

| PI       | Proportional and Integral                         |

| PWM      | Pulse width Modulation                            |

| rms, RMS | Root Mean Square                                  |

| SMPS     | Switch Mode Power Supply                          |

| SIFLC    | Single input fuzzy logic controller               |

| THD      | Total Harmonic Distortion                         |

| TLS      | Total least square                                |

| T2LC     | Type-2 fuzzy logic controller                     |

|          |                                                   |

| $v_{Sa}$ , $v_{Sb}$ and $v_{Sc}$ | Three-phase source voltages                             |

|----------------------------------|---------------------------------------------------------|

| $i_{Sa}$ , $i_{Sb}$ and $i_{Sc}$ | Three-phase source currents                             |

| $i_{La}$ , $i_{Lb}$ and $i_{Lc}$ | Three-phase load currents                               |

| $i_{Ca}$ , $i_{Cb}$ and $i_{Cc}$ | Three-phase APF currents                                |

| т                                | Number of levels in inverter                            |

| Ν                                | Cascade number                                          |

| f <sub>cr</sub>                  | Carrier signal frequency                                |

| f <sub>m</sub>                   | Modulating signal frequency                             |

| m <sub>a</sub>                   | Amplitude modulation index                              |

| <i>m</i> <sub>f</sub>            | Frequency modulation index                              |

| Ls                               | Source inductance                                       |

| L <sub>C</sub>                   | Interfacing inductor of APF                             |

| L <sub>f</sub>                   | Coupling inductor of single-phase APF                   |

| L <sub>ac</sub>                  | Commutation inductance                                  |

| <i>p</i> , <i>q</i>              | Instantaneous real and reactive powers                  |

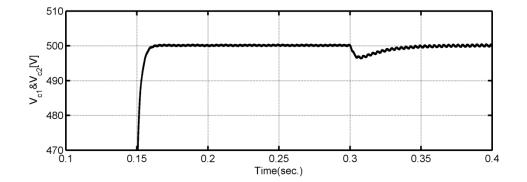

| $V_{c1} \& V_{c2}$               | reference voltage of each capacitor of DCMLI            |

| $V_{a1\&}V_{a2}$                 | Reference dc voltage for each H-bridge cell for phase-a |

| $k_{p}, k_{i}$                   | Proportional and integral gains                         |

| i <sub>Sn</sub>                  | Source neutral current                                  |

| i <sub>Ln</sub>                  | Load neutral current                                    |

| r                                | Learning factor                                         |

|                                  |                                                         |

This chapter describes introduction to the research work. It will start with some background on foremost power quality problems in distribution systems. Then, the solutions to the problems will be discussed through which APF will be selected. Next, harmonics detection, scope of work, author's contribution and thesis outlines are explained.

#### 1.1 Overview

From very inception of the interconnected power networks, use of alternating current (AC) circuits has been a commonplace. In these power networks, the basic function of generators is to produce a clean sinusoidal voltage waveform, of constant frequency, at their terminals. However, a pure sinusoidal waveform with zero distortion is a hypothetical entity and not a practical one. The voltage waveform, even at the point of generation, contains a small amount of distortion, due to non-uniformity in the excitation magnetic field and discrete spatial distribution of coils around the generator stator slots. The distortion at the point of generation is usually very low, typically less than 1.0%. In past, majority of the loads in power distribution systems were of constant in nature, as regards to power, impedance, current or any of their combination. Such loads include incandescent lighting, heating, AC motors, etc., and are termed as linear loads. However, in recent years, the requirement for more efficient operation of electrical equipment and energy conditioning has led to the advancement in semiconductor technologies and introduction of new power electronic devices. This has significantly changed the nature of load composition because these power electronics based loads are nonlinear in nature. This nonlinearity results in non-sinusoidal load currents, which are periodic in nature and usually reflect Fourier series expansions. Non-sinusoidal periodic waves contain fundamental and higher order frequency components. These higher order frequency components are called harmonics. Harmonics can be defined as the undesirable components of a distorted periodic waveform whose frequencies are the integer multiples of the fundamental frequency [1-10]

The injected harmonics are responsible for the distortion of voltage and current wave shapes. A substantial amount of these harmonics are produced by high rating power converters. Other devices responsible for generation of harmonics are static var compensators, adjustable speed drives, power supplies, transformers, arc furnaces, personal computers, cyclo-converters, etc. In future, there may be many more new harmonic sources, such as fuel cells, battery storage devices, photovoltaic cells, etc. Non-sinusoidal currents generated by the nonlinear loads are propagated throughout the network, causing voltage drops across the impedance of transmission lines and transformers. Thus, the voltage at the point of common coupling (PCC) is no longer sinusoidal, but periodic and also possesses Fourier series expansions. The quantum of voltage distortion depends on the line impedance and the magnitude of current. When several power users share a common power line, the

1

voltage distortion produced due to harmonic current injection by one user can impact the quality of power supplied to others. Due to this, standards have been issued to limit the amount of harmonic currents fed into the source by an individual customer [6].

Harmonics are responsible for increased system losses, equipment heating and reduction in useful life, mal-operation of protective devices, failure of reactive power compensating capacitors, interference with protection, control and communication circuits as well as customer loads and amplification of harmonics by means of parallel resonance between the supply system reactance and power factor improvement capacitors [7-50].

#### 1.2 Electrical disturbances

The quality of electric power is closely related to the quality of the voltage wave which is characterized by the following parameters [7]

- Perfectly sinusoidal waveform; no distortion , spikes , dips

- Balance and perfect symmetry of the amplitude and phase phases

- RMS within allowable limits

- Frequency stability.

- Power factor within tolerable limits

Disturbances are all internal and external phenomena to the network with a power to amend a transitional or permanent in amplitude and / or shape of the electrical parameters of the network (current, voltage, frequency). These disturbances can be classified according to two criteria: the length of time or the method of allocation is to say, their effects on electrical parameters

According to the first classification, there are two basic categories:

- Periodic disturbances (which last for a given duration), as the case of harmonic distortion, voltage drops due to reactive power flows in the network, and imbalances :

- Aperiodic disturbances: or mainly in all fugitives' phenomena often very difficult to predict as transient voltage dips or surges.

According to their assignment modes, there are three main families:

- Disturbances on the amplitude or the RMS values ,

- Unbalanced three-phase systems,

- harmonic distortion

#### 1.2.1 Current harmonics (and / or) voltage

#### 1.2.1.1 Sources of harmonics and their effects

The proliferation of electrical equipment using static converters has led in recent years a significant increase in the level of harmonic pollution of power systems. These electrical equipment are considered as non- linear loads emitting harmonic currents whose frequencies are integer multiples of the fundamental frequency, or sometimes to any of the frequencies (the most significant harmonics being harmonics 5, 7, 11 and 13). The passage of these harmonic currents through the impedances of the electrical network may cause harmonic voltages at the connection points and then pollute users powered by the same electric network.

The presence of harmonics of current or voltage leads to adverse effects on the distribution network, such as

- The heating of the conductors, cables, capacitors and machinery due to additional copper and iron losses,

- The interference with telecommunication networks , caused by the electromagnetic coupling between the electrical network and the telecommunication networks which can induce in these significant noises,

- Dysfunction of some electrical equipment, such as control and regulating devices,

- In the presence of harmonics, voltage and current can change sign several times during a half - period. Therefore, sensitive equipment at the zero crossing these electrical quantities are disrupted,

- The resonance frequencies of the circuits formed by the inductances of the transformer and cable capacities are usually quite high, but they may coincide with the frequency of a harmonic; in this case, there will be a significant amplification of voltage/current, which can destroy the equipment connected to the network,

- The degradation of the accuracy of measuring devices,

- Induced disturbances on the communication lines, electromagnetic radiation in particular.

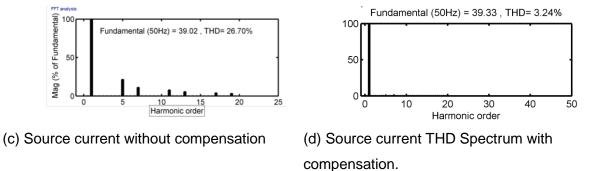

#### 1.2.1.2 Harmonic distortion rate

Different criteria are defined to characterize this type of disturbance. THD (the rate Harmonic distortion) and power factor are most used to quantify respectively harmonic disturbances and reactive power consumption. THD represents the ratio of the RMS value of the harmonics to the RMS value of the fundamental. THD is defined by the relation

$$THD = \sqrt{\frac{\sum_{n=1}^{\infty} X_h^2}{X_1^2}} X100$$

(1.1)

Along With  $X_1$  the effective value of the current (voltage) fundamental and  $X_h$  effective values different harmonics of the current (voltage). In general, harmonics included in a power grid is lower than 2500 Hz, which corresponds to the range of low interference frequencies

within the meaning of standardization. Higher frequency harmonics are strongly attenuated by the skin effect and the presence of the rows of inductors. In addition, the apparatus generating harmonics have, mostly, lower emission spectrum at 2500 Hz, why the field of study of harmonics is usually from 100 to 2500 Hz, that is to say rows 2-50

TDD is the ratio of the RMS value of the harmonics to the maximum value of current drawn by the load. It is defined by the relation

$$TDD = \sqrt{\frac{\sum_{h=2}^{\infty} I_h^2}{I_L^2} \times 100\%}$$

(1.2)

#### 1.2.1.3 The power factor

For a sine wave power factor is given by the ratio between the power active P and the apparent power S. the generators, transformers, transmission lines and control and measurement devices are designed for the maximum rated voltage and current. A low value of power factor results in misuse of these equipment. In the case where there are harmonics, power factor is degraded additional power called the deforming power (S) given by relation (1.3) is added:

$$S = 3V_1 \sqrt{\sum_{h=2}^{50} I_h^2}$$

(1.3)

The power factor (*pf*) becomes

$$PF = \frac{P}{\sqrt{P^2 + Q^2 + S^2}}$$

(1.4)

To limit the influence of a pollution load on the various loads connected to network standards on power quality have been developed. The main standard is IEEE 519: 1992 [Recommended Practices and Requirements for Harmonic Control in Power Systems] it determines the procedure to control the harmonics present on the grid and it also imposes the recommended limits of harmonic pollution generated by customers and total harmonic distortion on the network. This standard limits harmonic distortion (THD) of current networks < 69kV to 5% It is customary to say that in the industrial plants, whose harmonic voltage THD is less than 5% does not produce a significant effect. Between 5% and 7% are beginning to see effects, and to more than 10% the effects are almost certain

| $V_n < 69 kV$                    |        |          |          |          |       |        |

|----------------------------------|--------|----------|----------|----------|-------|--------|

| I <sub>sc</sub> /I <sub>cn</sub> | H<11   | 11<=h<17 | 17<=h<23 | 23<=h<35 | 35<=h | TDD4.0 |

| <20                              | 4.0    | 2.0      | 1.5      | 0.6      | 0.3   | 5.0    |

| 20-50                            | 7.0    | 3.5      | 2.5      | 1.0      | 0.5   | 8.0    |

| 50-100                           | 10.0   | 4.5      | 4.0      | 1.5      | 0.7   | 12.0   |

| 100-1000                         | 12.0   | 0        | 5.0      | 2.0      | 1.0   | 15.0   |

| $69kV \ll Vn$                    | <161kV | •        |          |          | •     |        |

| < 20                             | 2.0    | 1.0      | 0.75     | 0.3      | 0.15  | 2.5    |

| 20-50                            | 3.5    | 1.75     | 1.25     | 0.5      | 0.25  | 4.0    |

| 50-100                           | 5.0    | 2.25     | 2.0      | 1.25     | 0.35  | 6.0    |

| 100-1000                         | 6.0    | 2.75     | 2.5      | 1.0      | 0.5   | 7.5    |

| > 1000                           | 7.5    | 3.5      | 3.0      | 1.25     | 0.7   | 10     |

Table 1.1 IEEE limits of harmonic current emissions (IEEE 519 :1992)[8]

Where  $I_{sc}$  is the short - circuit current  $I_{ch}$  is the nominal load current, the rated voltage  $V_n$  and TDD is the total demand distortion (current distortion from the maximum demand).

| Connection point to           | Individual Harmonic | THD V <sub>n</sub> (%) |  |  |

|-------------------------------|---------------------|------------------------|--|--|

| the voltage $(V_n)$           | Distortion          |                        |  |  |

| $V_n < =69kV$                 | 3.0                 | 5.0                    |  |  |

|                               |                     |                        |  |  |

| 69kV < V <sub>n</sub> <=161kV | 1.5                 | 2.5                    |  |  |

|                               |                     |                        |  |  |

Table 1.2 IEEE limits for harmonic voltage distortion (IEEE 519: 1992)

#### 1.2.2 Imbalance in the three-phase voltage system

It is said that there is imbalance in a network, when recording steady, asymmetries of amplitudes and phase shifts of the phase voltages. This type of disturbance is caused mainly by impedance mismatches lines of the network, and also by short circuits single-phase or two-phase. This imbalance is manifested by disturbances in rotating machines, overheating, etc.

#### 1.2.2.1 Consequences of unbalanced three-phase system

The imbalance of a three-phase system can cause malfunction of the low voltage devices connected

- Malfunction of a single-phase device powered by a low voltage (incandescent lamp that provides poor lighting)

- Destruction of a single-phase device powered by a voltage too high, it can be destroyed (break-down of a filament lamp overvoltage).

Regarding power electronics devices, mainly the rectifier bridges, and the operation in the presence of imbalance leads to the appearance of components non-characteristic harmonics, including multiple harmonics of third. The appearance of these harmonic currents can cause problems such as generating an anti-resonant when filtering order of the harmonic 5. In addition to the classic effects of harmonics, the frequency characteristics cannot lead, in some cases, the blocking of the order. The consequence of the negative sequence on rotating machinery is the creation of a field rotating in opposite direction to the direction of rotation, from which a braking torque and parasitic losses which cause additional heating of the machine. Regarding the effect of unbalance zero sequence, it must be reported overheating risk neutral conductor in a distribution network, when the size is too small diameter, may cause rupture of the wire or fire.

#### **1.3 Neutral currents effects**

In case of a three-phase four-wire (3P4W) system with balanced nonlinear loads, fundamental and harmonics (including triplen harmonics) are present in the phase currents. Summing these currents at the neutral point, the fundamental and non-triplen harmonic components are found to be zero [12-15]. However, the triplen harmonic components in neutral are three times the triplen harmonic phase currents, because they coincide in phase and time. Triplen become an important issue for grounded wye system, as they are added in the neutral and produce a substantial neutral current. The current may exceed the rating of the neutral conductors, resulting in the overheating of power system equipments. The excessive neutral current may cause other adverse effects, such as overloading of power feeders, overloading of distribution transformers, voltage distortion and common mode noise

#### **1.4 Compensation solutions**

Two types of solutions are possible, the first is to use less static converters, while the second is the implementation of a harmonic filtering components. The first class of solutions focuses on the design and the second is to offset current or voltage harmonics. Two groups remediation solutions to compensate for any disturbances can be distinguished

- Traditional passive filter most commonly used

- modern solutions (active power filters) that are designed to overcome the limitations of passive filters

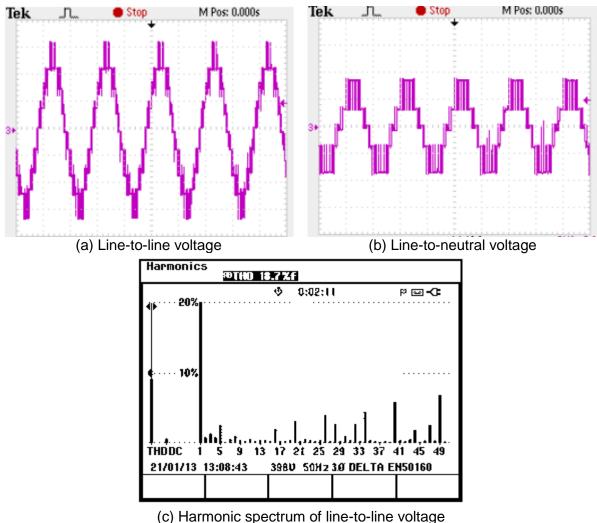

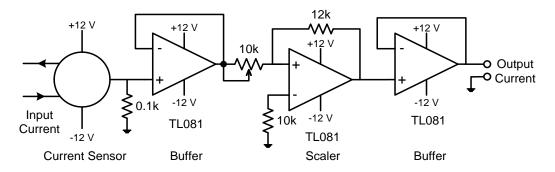

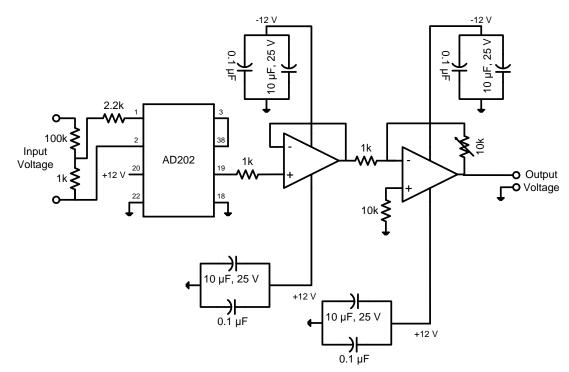

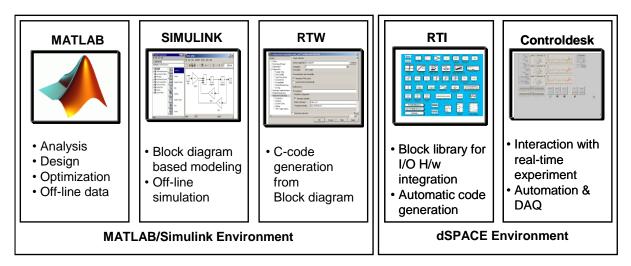

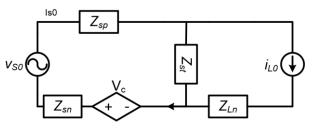

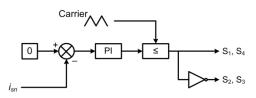

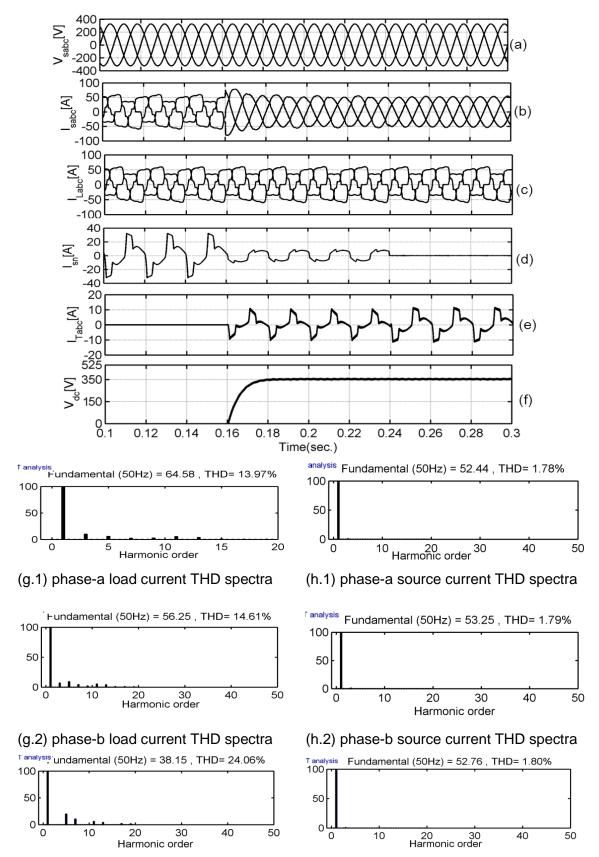

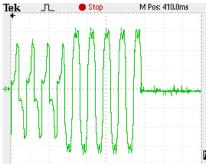

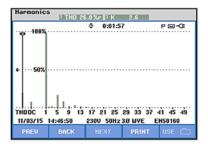

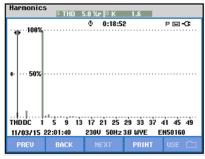

#### 1.4.1 Passive filters