# DESIGN AND IMPLEMENTATION OF DC-DC BI-DIRECTIONAL BUCK AND BOOST CONVERTER

### **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree

of

INTEGRATED DUAL DEGREE

in

ELECTRICAL ENGINEERING (With Specialization in Power Electronics)

By

#

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE = 247 667 (INDIA) JUNE, 2012

# ID.NO. MT/193/SP/56.

### CANDIDATE'S DECLARATION

I hereby declare that the work that is being presented in this dissertation entitled "Design and Implementation of DC-DC Bi-directional Buck and Boost Converter" in partial fulfillment of the requirement for the award of the degree of Integrated Dual Degree in Electrical Engineering with specialization in "Power Electronics" submitted to the Department of Electrical Engineering, Indian Institute of Technology, Roorkee, INDIA is an authentic record of my own work carried under the guidance of Dr. S.P. SINGH, Professor, Department of Electrical Engineering, Indian Institute of Technology, Roorkee.

The matter embodied in this dissertation has not been submitted for the award of any other degree or diploma.

Date: 15/06/2012 Place: Roorkee

P. S. A.

### CERTIFICATE

This is to certify that the above statement made by the candidate is true to the best of my knowledge.

Date: 15/6/12

Place: Roorkee

Dr. S.P. SINGH Professor Department of Electrical Engineering Indian Institute of Technology Roorkee Roorkee - 247667, INDIA.

### ACKNOWLEDGEMENT

I wish to acknowledge my deep sense of gratitude and indebtedness to my respected guide **Dr. S.P.SINGH**, Professor of Electrical Engineering Department, Indian Institute of Technology Roorkee for his intuitive and meticulous guidance and perpetual inspiration in completion of this dissertation work. I want to express my profound gratitude for his co-operation in scrutinizing the manuscript and his valuable suggestions throughout the work. I feel privileged to work under him during the course of work. His encouraging support and thorough involvement in the formulation of the research work and preparation of manuscript are gratefully acknowledged.

I convey my gratitude to EPE faculty for helping me to widen my knowledge through discussions at the time of seminar and project presentations.

I express my sincere thanks to all the research scholars of our department for helping me in revealing my doubts as when necessary.

I would like to mention my Special thanks to my parents for their endless support and encouragement and for always believing, and helping me to believe, that I can succeed at anything.

Date: 15 06 2012

Place : Roorkee

### SUMANTH PALA

Enrollment No: 071606

# ABSTRACT

Switch Mode Power Supplies (SMPS) are very important components in present day electronics and have continued to thrive and grow over the past 25 years. Electronic switch-mode DC to DC converters convert one DC voltage level to another, by storing the input energy temporarily and then releasing that energy to the output at a different voltage. The storage may be in either magnetic field storage components (inductors, transformers) or electric field storage components (capacitors). This conversion method is more power efficient (often 75% to 98%) than linear voltage regulation (which dissipates unwanted power as heat).

Most DC to DC converters are designed to transfer power in only one direction, from the input to the output. However, all switching regulator topologies can be made bi-directional by replacing all diodes with independently controlled active rectification. A bi-directional converter can transfer power in either direction, which is useful in applications requiring regenerative braking etc.

This project deals with the bi-directional buck and boost converter, their basic functioning and their stability under closed loop. It discusses clearly about how to design, implement the analog controller and digital controller for bi-directional buck and boost converter. It also discuss about non-linear controller design i.e. fuzzy controller for the boost converter. Designing of the controller is verified with the help of MATLAB simulation.

# LIST OF FIGURES

| Fig1.1           | Schematic linear voltage regulator                                                                        | 2  |

|------------------|-----------------------------------------------------------------------------------------------------------|----|

| Fig1.2           | Schematic SMPS                                                                                            | 3  |

| Fig 1.3          | Basic structure of an IBDC                                                                                | 10 |

| Fig 1.4          | Basic structure of an energy storage device connected to an ac grid through a line frequency transformer. | 11 |

| Fig 2.1          | Buck Converter Circuit                                                                                    | 13 |

| Fig 2.2          | Boost Converter Circuit                                                                                   | 15 |

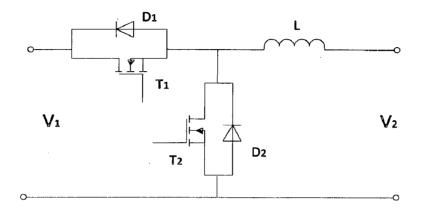

| Fig 2.3          | Bi-directional buck and boost converter $(V_1 > V_2)$                                                     | 16 |

| Fig 2.4          | Buck operation of bi-directional converter                                                                | 17 |

| Fig 2.5          | Boost operation of bi-directional converter                                                               | 17 |

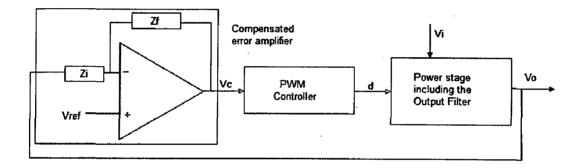

| Fig 3.1          | Voltage-mode control                                                                                      | 19 |

| Fig 3.2          | Type I Compensation                                                                                       | 21 |

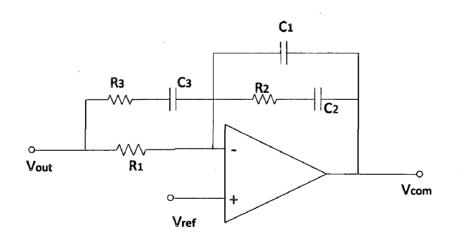

| Fig 3.3          | Type II Compensation                                                                                      | 22 |

| Fig 3.4          | Type III Compensation                                                                                     | 22 |

| Fi <b>g 4</b> .1 | Buck Converter Circuit                                                                                    | 26 |

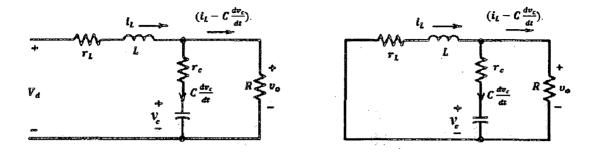

| Fig 4.2          | Buck Converter (a) switch on; (b) switch off                                                              | 27 |

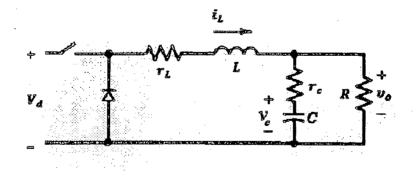

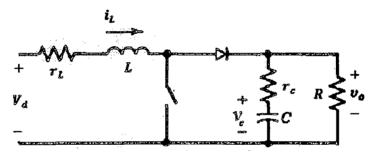

| Fig 4.3          | Boost Converter Circuit                                                                                   | 29 |

| Fig 4.4          | Boost Converter (a) switch on; (b) switch off                                                             | 29 |

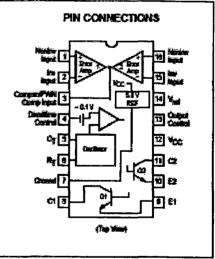

| Fig 4.5          | Pulse-width modulator                                                                                     | 33 |

| Fig 4.6          | Type 3 compensation                                                                                       | 35 |

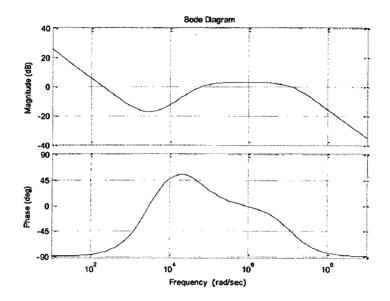

| Fig 4.7          | Behavior of Type 3 compensation                                                                           | 35 |

iv

| Fig 4.8  | Feedback Control System                                                      | 37 |

|----------|------------------------------------------------------------------------------|----|

| Fig 4.9  | Linearized Feedback Control System                                           | 38 |

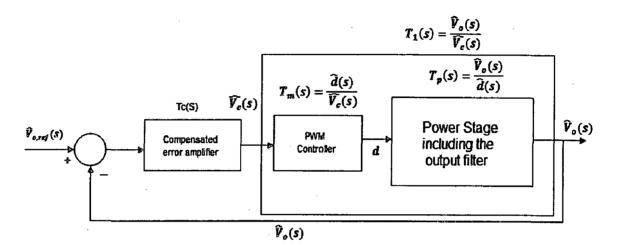

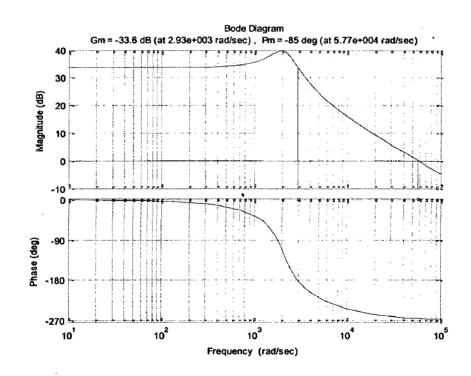

| Fig 4.10 | Bode plot of buck converter                                                  | 39 |

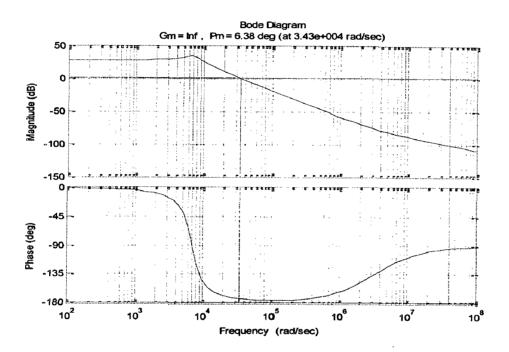

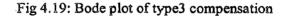

| Fig 4.11 | Bode plot of type3 compensation                                              | 40 |

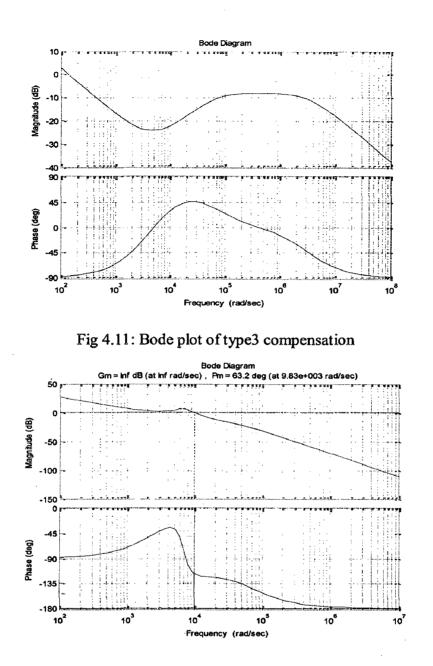

| Fig 4.12 | Bode plot of compensated open loop buck converter                            | 40 |

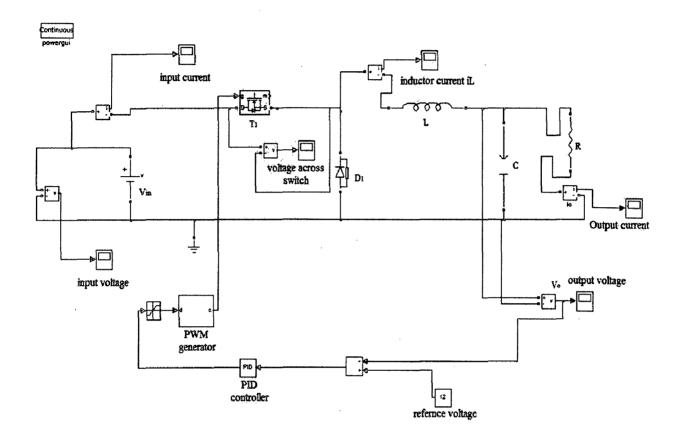

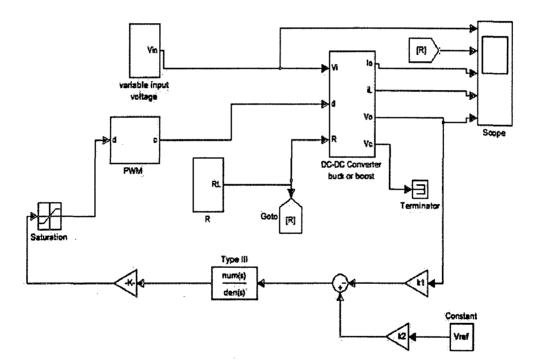

| Fig 4.13 | MATLAB simulation of buck converter                                          | 41 |

| Fig 4.14 | Simulation response of buck converter                                        | 42 |

| Fig 4.15 | Simulation response of buck converter under steady state(enlarged view)      | 43 |

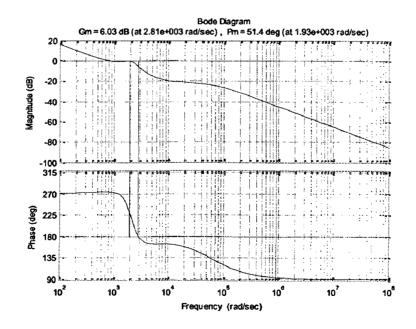

| Fig 4.16 | Closed loop Simulink model for buck converter                                | 44 |

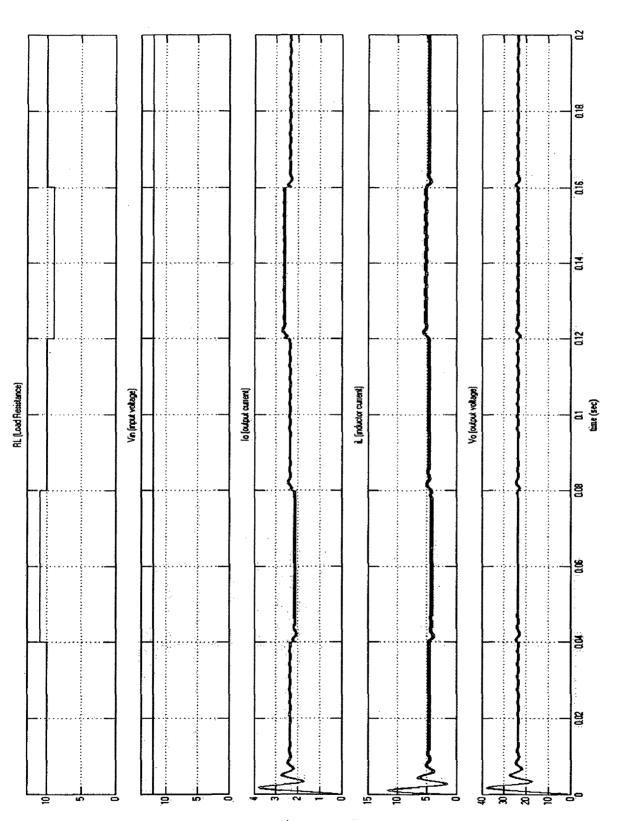

| Fig 4.17 | Closed loop response of Buck converter ( $V_{in}$ and $R_L$ variation)       | 45 |

| Fig 4.18 | Bode plot of boost converter                                                 | 46 |

| Fig 4.19 | Bode plot of type3 compensation                                              | 47 |

| Fig 4.20 | Bode plot of compensated open loop boost converter                           | 47 |

| Fig 4.21 | MATLAB simulation of boost converter                                         | 48 |

| Fig 4.22 | Simulation response of boost converter                                       | 49 |

| Fig 4.23 | Simulation response of boost converter under steady state (enlarged view)    | 50 |

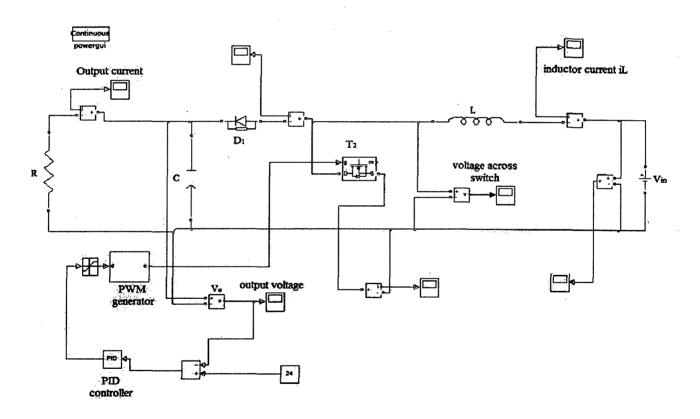

| Fig 4.24 | Closed loop Simulink model for boost converter                               | 51 |

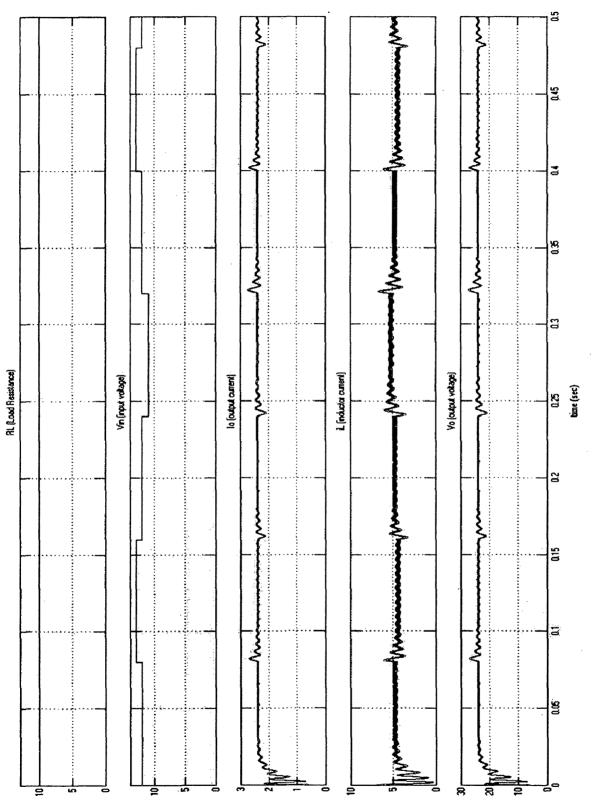

| Fig 4.25 | Closed loop response of Boost converter ( $V_{in}$ and $R_L$ variation)      | 52 |

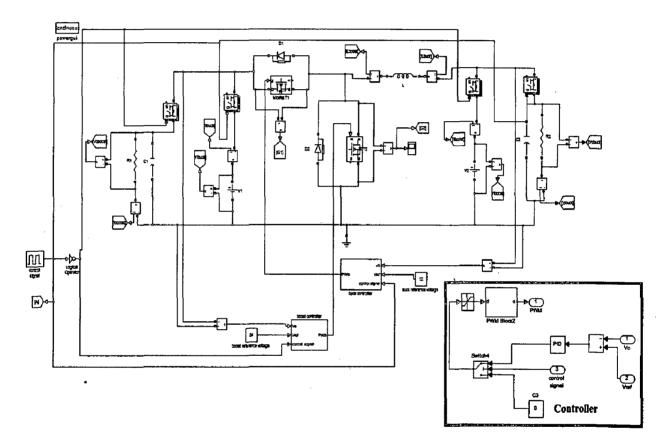

| Fig 4.26 | Simulink model of bi-directional buck and boost converter with control logic | 54 |

| Fig 4.27 | Operation of bi-directional buck and boost converter                         | 55 |

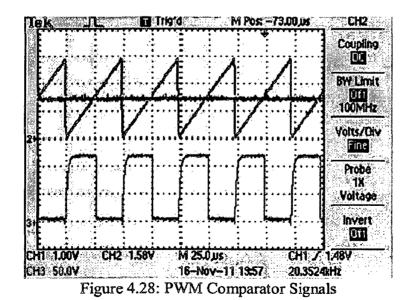

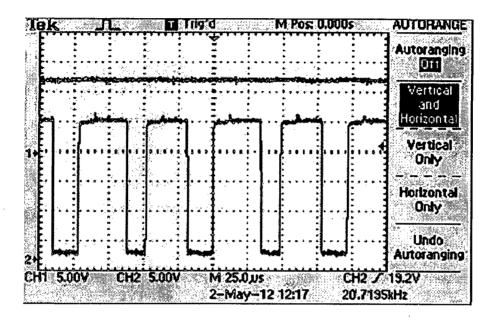

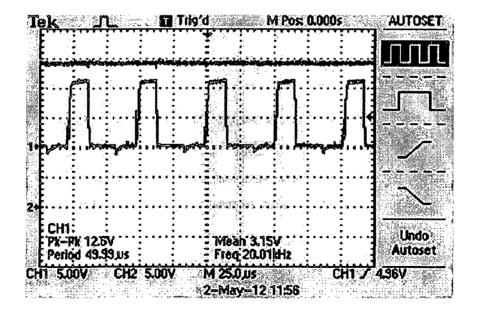

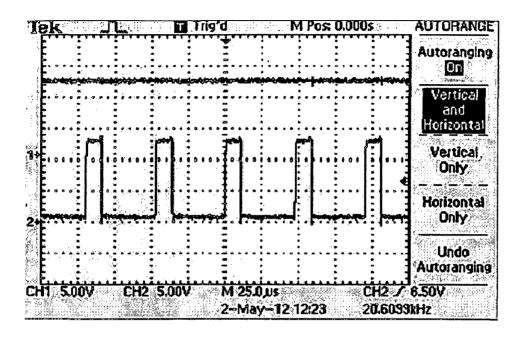

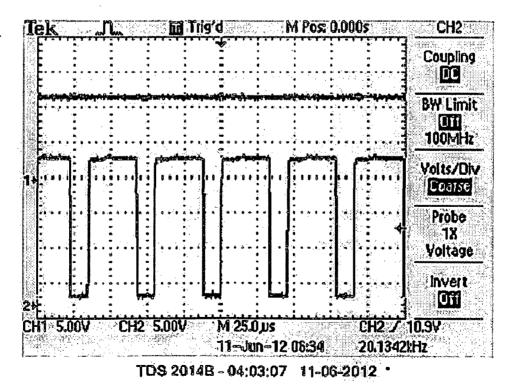

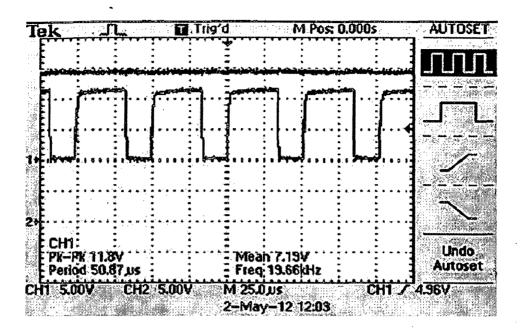

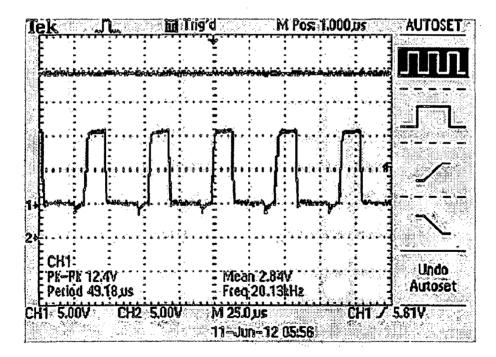

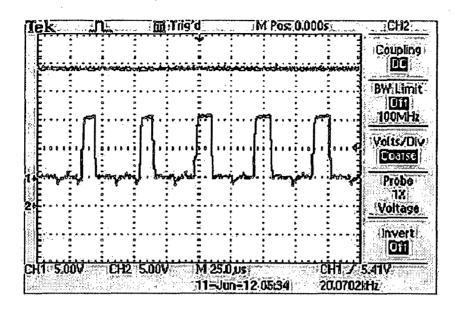

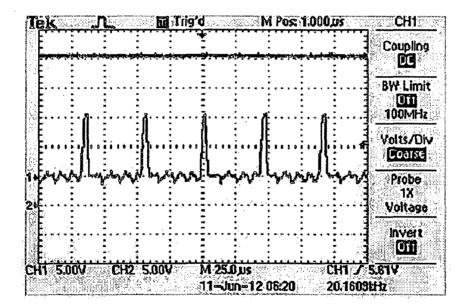

| Fig 4.28 | PWM Comparator Signals                                                       | 56 |

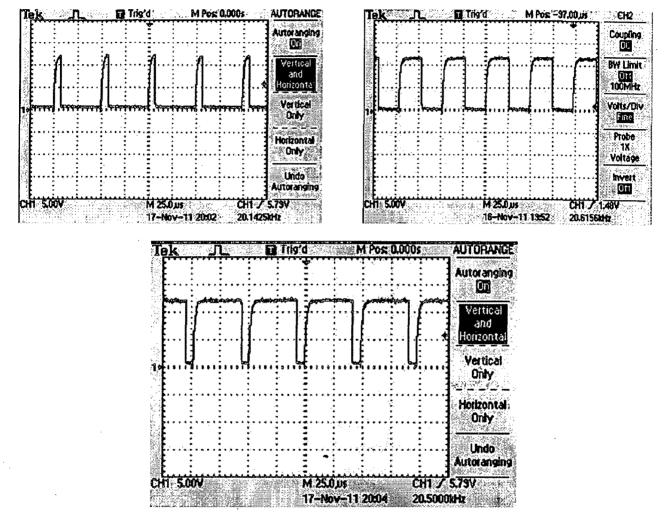

| Fig 4.29 | PWM (10%,50%,90%)                                                            | 57 |

. . .

| Fig 4.30 | Buck converter (24V-12V)                                             | 58 |

|----------|----------------------------------------------------------------------|----|

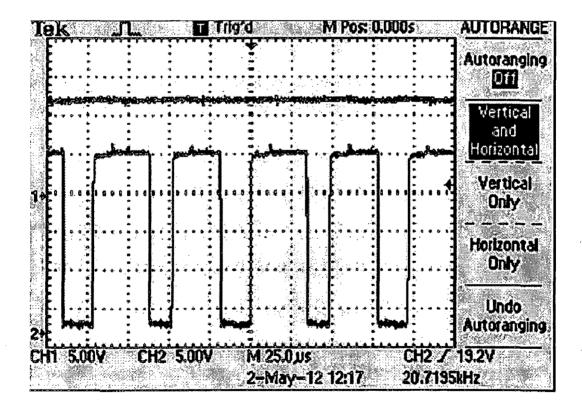

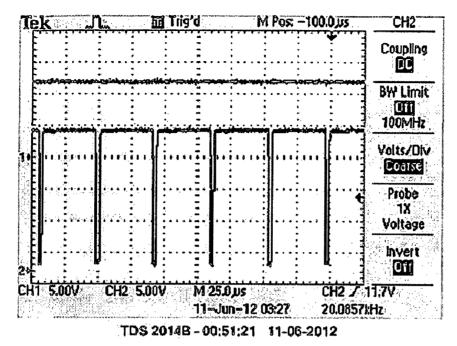

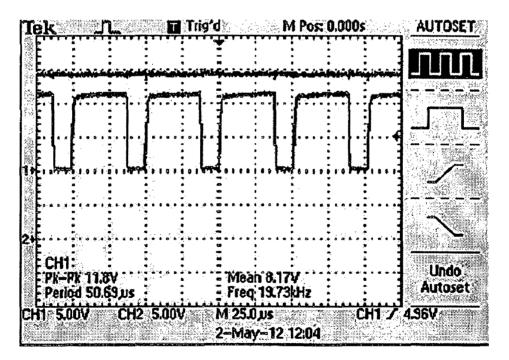

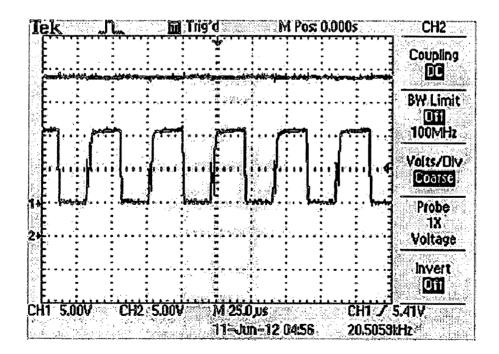

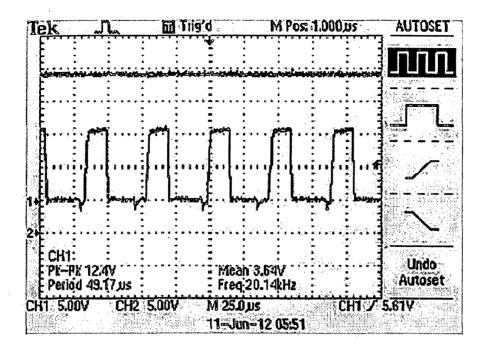

| Fig 4.31 | Buck converter gate pulses and output voltage (24V to 12V)           | 59 |

| Fig 4.32 | Boost converter (12V-24V)                                            | 60 |

| Fig 4.33 | Boost converter gate pulses and output voltage (12V to 24V)          | 60 |

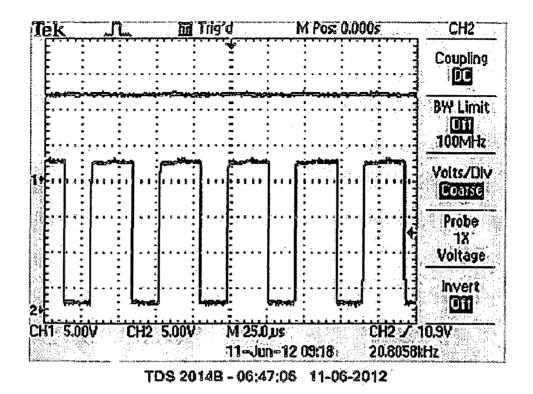

| Fig 4.34 | Bi-directional buck and boost converter $(V_1 > V_2)$                | 61 |

| Fig 4.35 | Bi-directional buck and boost converter $(V_1 > V_2)$                | 62 |

| Fig 4.36 | BDC in buck mode, gate pulses and output voltage (24V to 12V)        | 63 |

| Fig 4.37 | BDC in buck mode, gate pulses and output voltage at $V_{in}$ =19V    | 64 |

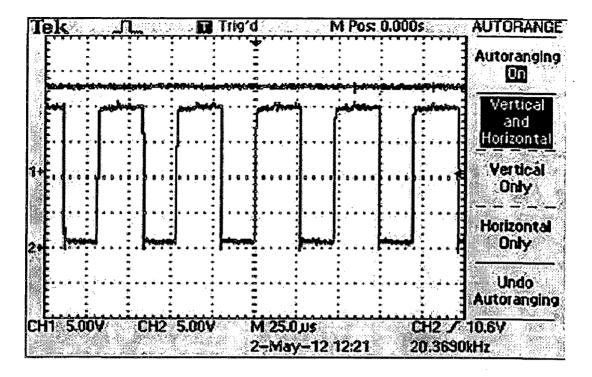

| Fig 4.38 | BDC in buck mode, gate pulses and output voltage at $V_{in}$ =15V    | 64 |

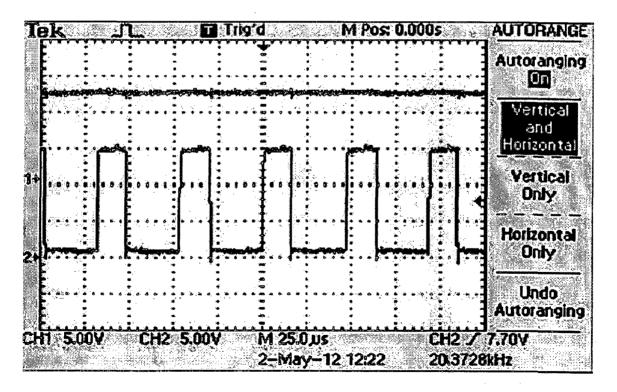

| Fig 4.39 | BDC in buck mode, gate pulses and output voltage at $V_{in}$ =13V    | 65 |

| Fig 4.40 | BDC in buck mode, gate pulses and output voltage at $R_L=14$ ohms    | 66 |

| Fig 4.41 | BDC in buck mode, gate pulses and output voltage at $R_L$ =65 ohms   | 66 |

| Fig 4.42 | BDC in buck mode, gate pulses and output voltage at $R_L$ =95 ohms   | 67 |

| Fig 4.43 | BDC in buck mode, gate pulses and output voltage at $R_L$ =150 ohms  | 67 |

| Fig 4.44 | BDC in buck mode, gate pulses and output voltage at $R_L$ =250 ohms  | 68 |

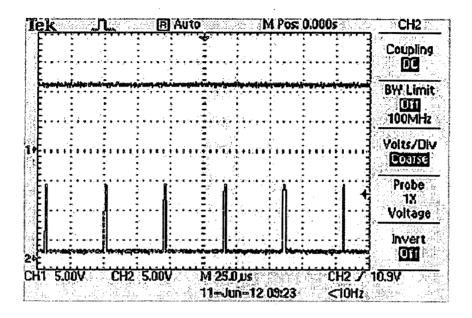

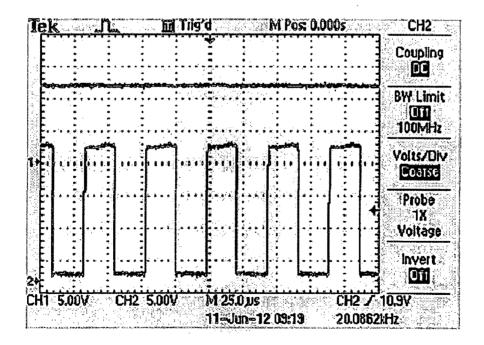

| Fig 4.45 | BDC in boost mode, gate pulses and output voltage at $V_{in}$ =22V   | 69 |

| Fig 4.46 | BDC in boost mode, gate pulses and output voltage at $V_{in}$ =17V   | 70 |

| Fig 4.47 | BDC in boost mode, gate pulses and output (12V to 24V)               | 70 |

| Fig 4.48 | BDC in boost mode, gate pulses and output voltage at $V_{in}$ =8.5V  | 71 |

| Fig 4.49 | BDC in boost mode, gate pulses and output voltage at $V_{in}$ =6.5V  | 71 |

| Fig 4.50 | BDC in boost mode, gate pulses and output voltage at $R_L=110$ ohms  | 72 |

| Fig 4.51 | BDC in boost mode, gate pulses and output voltage at $R_L$ =200 ohms | 73 |

| Fig 4:52 | BDC in boost mode, gate pulses and output voltage at $R_L$ =450 ohms | 73 |

|          | vi                                                                   |    |

| Fig 4.53 | BDC in boost mode, gate pulses and output voltage at $R_L$ =550 ohms                              | 74 |

|----------|---------------------------------------------------------------------------------------------------|----|

| Fig 4.54 | BDC in boost mode, gate pulses and output voltage at $R_L=1.5k$ ohms                              | 74 |

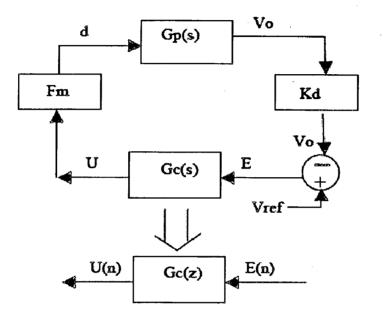

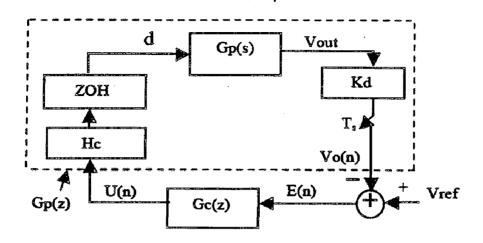

| Fig 5.1  | DC-DC Converter Control Loop Block Diagram in s-domain                                            | 77 |

| Fig 5.2  | DC-DC Converter Digital Control Loop Block Diagram                                                | 78 |

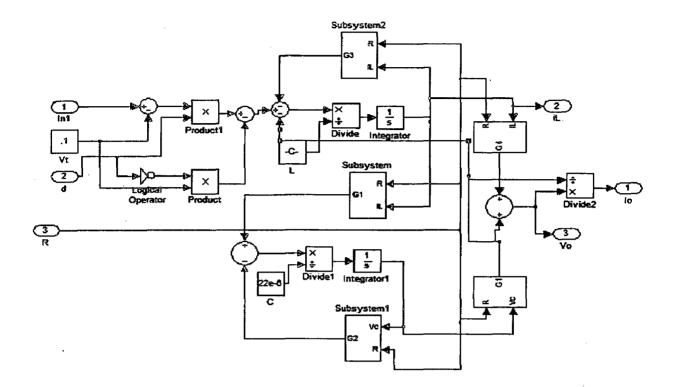

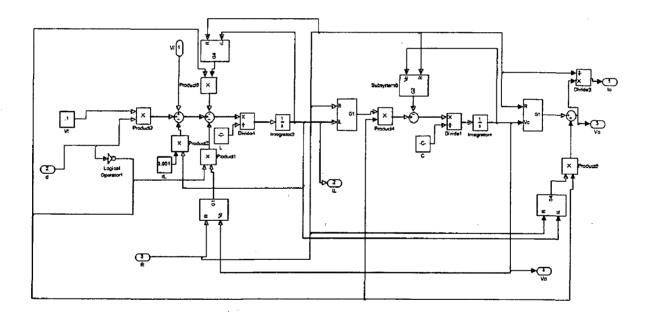

| Fig 5.3  | Simulink Model of Buck converter (Power stage using state-space)                                  | 79 |

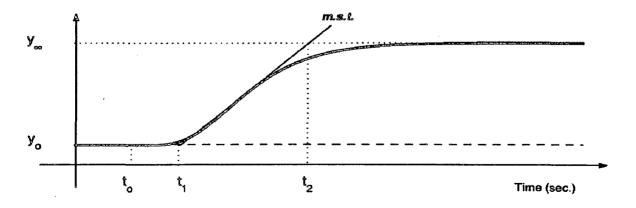

| Fig 5.4  | Process Reaction Curve Method                                                                     | 80 |

| Fig 5.5  | Step response of open loop buck converter                                                         | 82 |

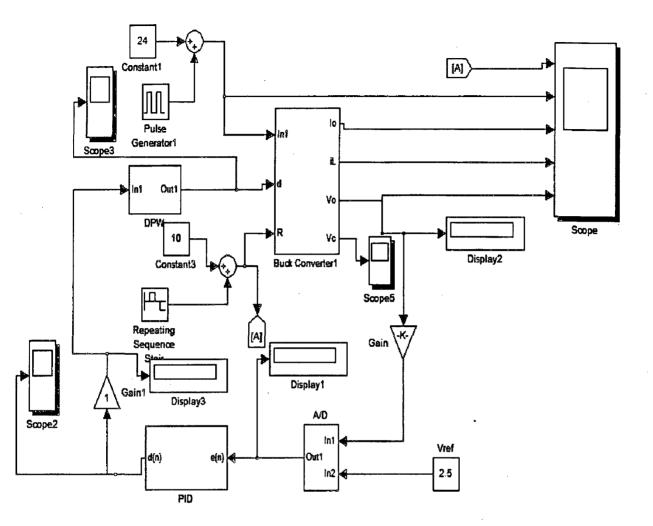

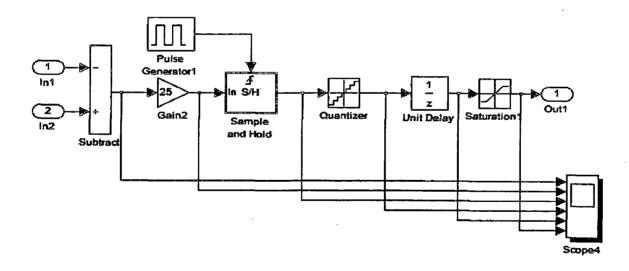

| Fig 5.6  | MATLAB simulation of buck converter using PID(digitally)                                          | 83 |

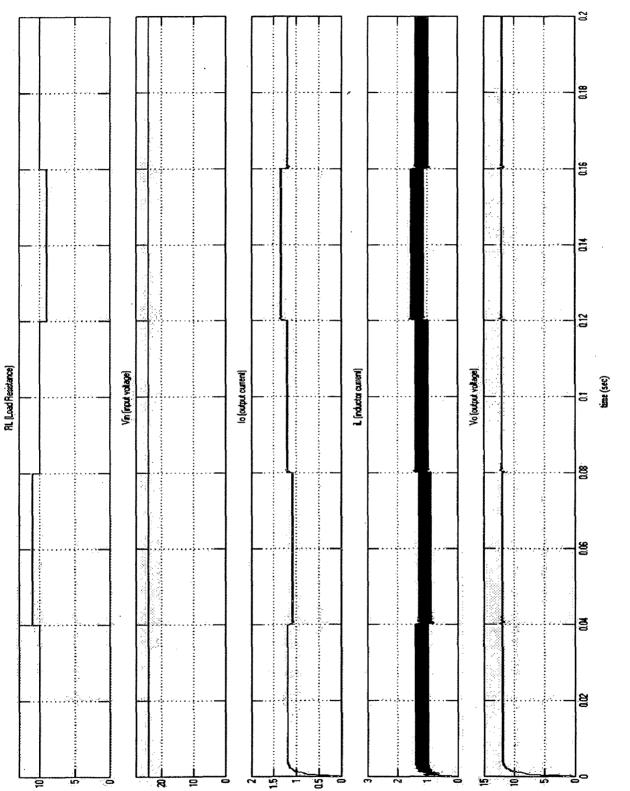

| Fig 5.7  | Simulation response of buck converter using PID(digital) with variation in load                   | 84 |

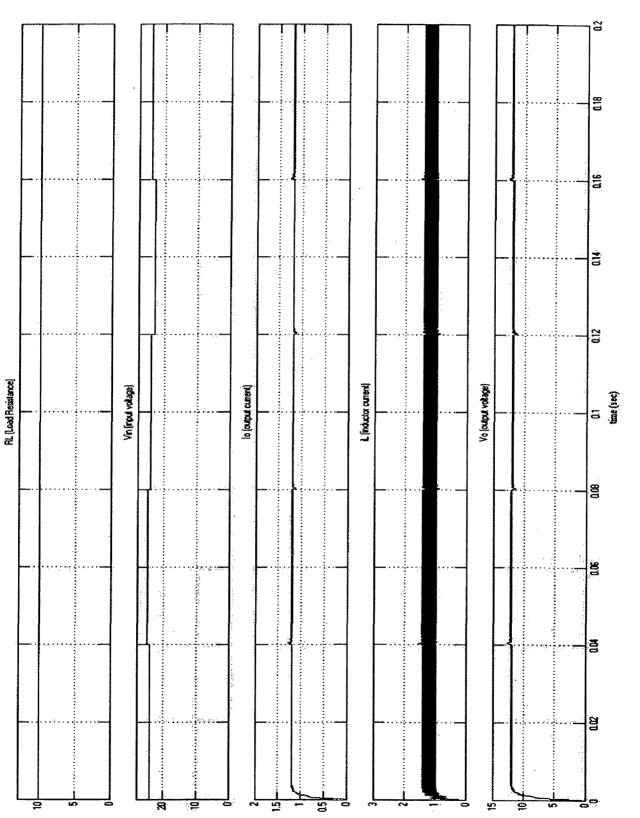

| Fig 5.8  | Simulation response of buck converter using PID (digital) with variation in $V_{\text{in}}$       | 85 |

| Fig 5.9  | Simulink Model of Boost converter (Power stage using state-space)                                 | 86 |

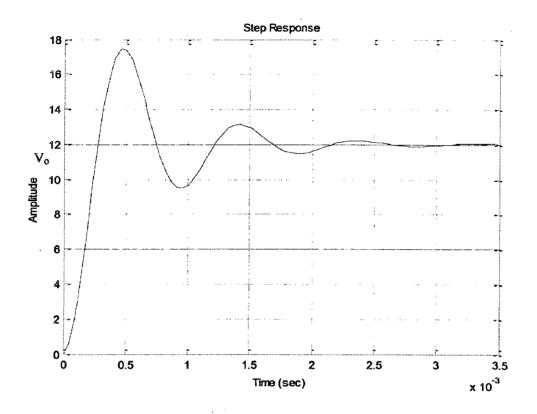

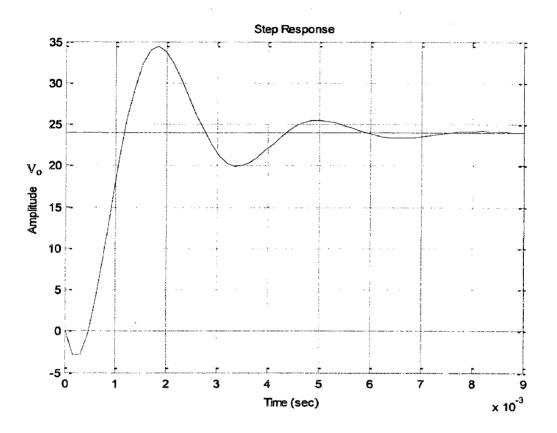

| Fig 5.10 | Step response of open loop boost converter                                                        | 87 |

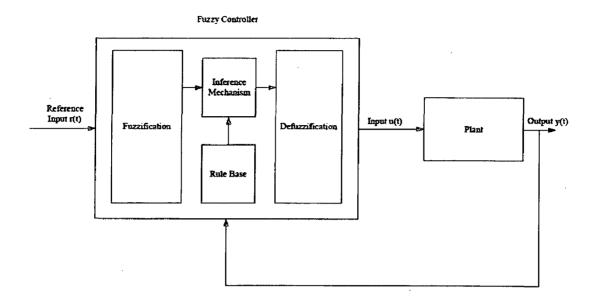

| Fig 5.11 | Block diagram of fuzzy control system                                                             | 89 |

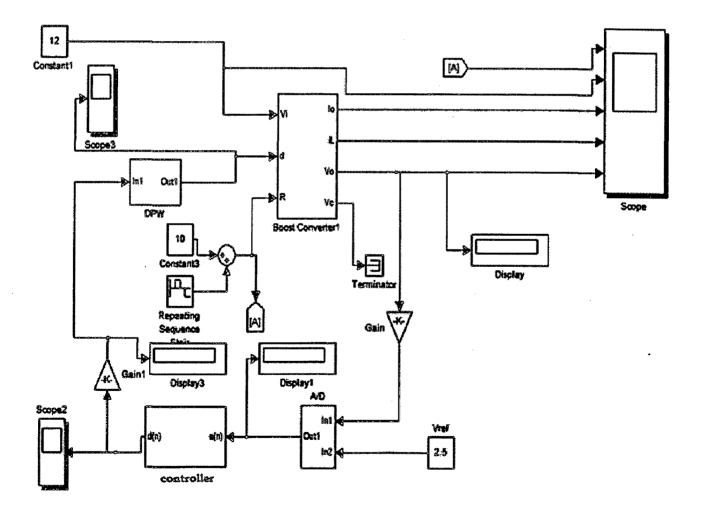

| Fig 5.12 | MATLAB simulation of boost converter using type III (discretized) or fuzzy controller             | 90 |

| Fig 5.13 | Simulation response of boost converter using Type III (digital) with variation in $V_{\text{in}}$ | 91 |

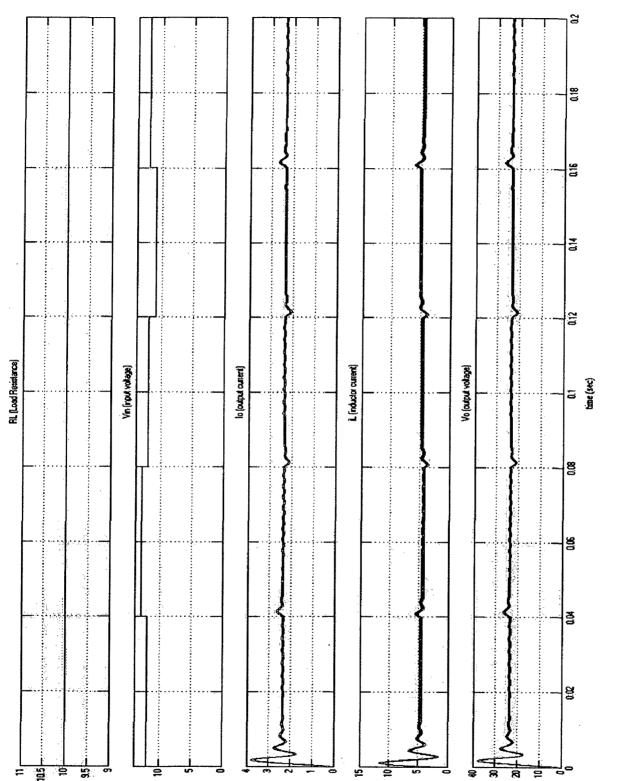

| Fig 5.14 | Simulation response of boost converter using Type III (digital) with variation in R               | 92 |

| Fig 5.15 | Simulation response of boost converter using FUZZY controller with variation in $\mathbb{R}$      | 94 |

| Fig 5.16 | Simulation response of boost converter using FUZZY controller with variation in $V_{\text{in}}$   | 95 |

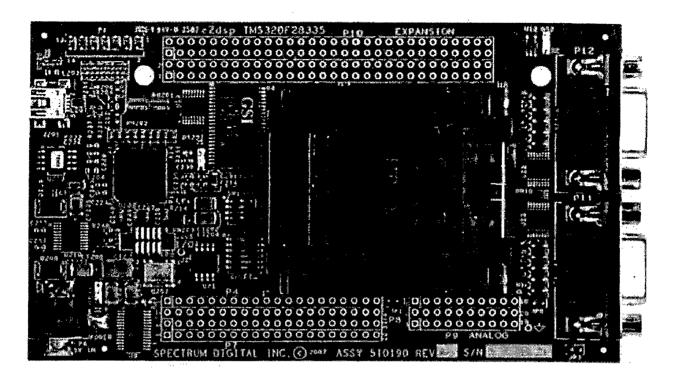

| Fig 5.17 | The pictorial view of eZdsp F28335 kit                                                            | 98 |

vii

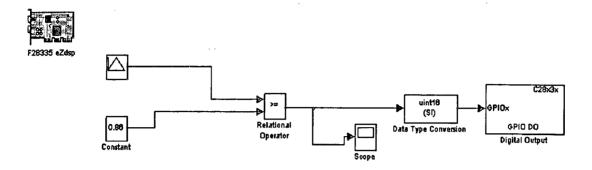

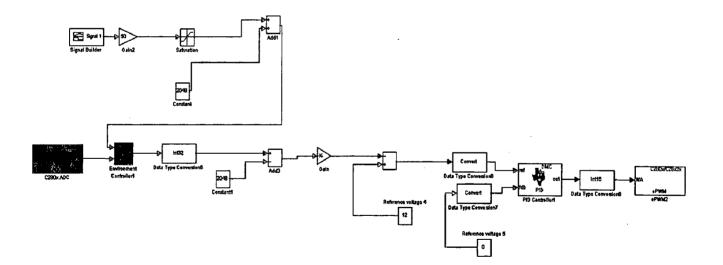

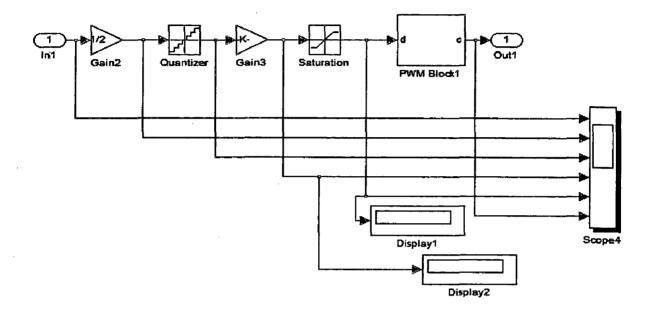

| Fig.5.18 | Simulink model for PWMs in DSP                                                           | 100 |

|----------|------------------------------------------------------------------------------------------|-----|

| Fig.5.19 | Simulink model of closed loop for DSP                                                    | 100 |

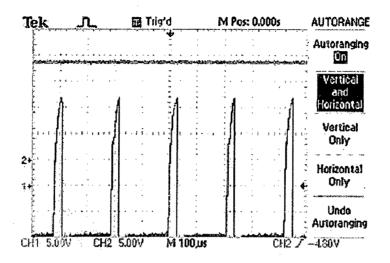

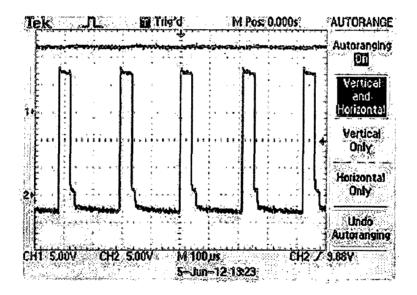

| Fig.5.20 | BDC in boost mode using DSP (12V to 24V)                                                 | 101 |

| Fig.5.21 | BDC in buck mode using DSP (24V to 12V)                                                  | 101 |

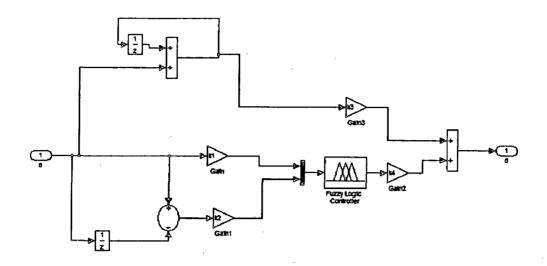

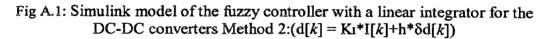

| Fig A.1  | Simulink model of the fuzzy controller with a linear integrator for the DC-DC converters | 117 |

| Fig A.2  | Simulink model of the PID controller                                                     | 117 |

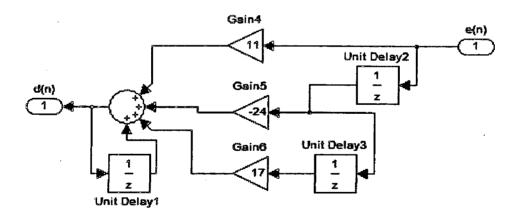

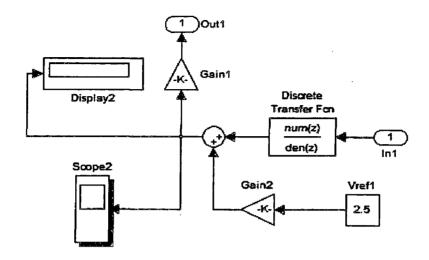

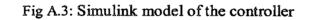

| Fig A.3  | Simulink model of the controller                                                         | 118 |

| Fig A.4  | Simulink model of the A/D converter                                                      | 118 |

| Fig A.5  | Simulink model of the DPWM                                                               | 119 |

.

# LIST OF TABLES

| fable no. |                                                             | Page no. |  |

|-----------|-------------------------------------------------------------|----------|--|

| 5.1       | Calculation of PID parameters                               | 81       |  |

| 5.2       | Rule base                                                   | 89       |  |

| A.1       | Power circuit specifications                                | 114      |  |

| A.2       | Parameters of type III compensation                         | 114      |  |

| A.3       | Power circuit specifications for hardware implementation    | 115      |  |

| A.4       | Parameters of the converter for the input voltage variation | 115      |  |

| A.5       | Parameters of the converter for the load variation          | 115      |  |

# LIST OF SYMBOLS

V<sub>in</sub>, V<sub>i</sub>, V<sub>d</sub> Input voltage R Resistance R<sub>L</sub> Load resistance iL Inductor current I, Output current I<sub>in</sub> Input current Output voltage V, ESR value of the inductor rL ESR value of the capacitor rc С Capacitor L Inductor D, d Duty cycle or duty ratio  $F_{sw}, f_{sw}$ Switching frequency Cross over frequency  $\mathbf{f}_{co}$ Voltage across a switch  $V_{sw}$

# CONTENTS

| Title                                       | Page No |

|---------------------------------------------|---------|

| CANDIDATE'S DECLARATION                     | i       |

| ACKNOWLEDGEMENT                             | ii      |

| ABSTRACT                                    | iii     |

| LIST OF FIGURES                             | iv      |

| LIST OF TABLES                              | ix      |

| LIST OF SYMBOLS                             | x       |

|                                             |         |

| CHAPTER-I                                   |         |

| INTRODUCTION                                | 1       |

| 1.1 Introduction to SMPS                    | 1       |

| 1.2 Linear regulated power supply           | · 1     |

| 1.3 Switched Mode Power Supply (SMPS)       | 2       |

| 1.4 SMPS versus linear power supply         | 3       |

| 1.5 Literature Review                       | 4       |

| 1.5.1 Bi-directional dc-dc converters (BDC) | 8       |

| 1.5.2 Non-isolated BDC                      | 9       |

| 1.5.3 Isolated BDC (IBDC)                   | 9       |

| 1.5.4 Applications                          | 10      |

| 1.6 Recent Advancements                     | 11      |

| 1.7 Objectives of Thesis Work               | 12      |

| •                                           |         |

| CHAPTER - II                                |         |

| DC-DC CONVERTERS                            | 13      |

| 2.1 Introduction                            | 13      |

| 2.2 Buck Converter                          | 13      |

| 2.2.1 Theory of Operation                   | 14      |

| 2.2.2 Continuous Mode                                                                                     | 14   |

|-----------------------------------------------------------------------------------------------------------|------|

| 2.2.3 Discontinuous Mode                                                                                  | 14   |

| 2.3 Boost Converter                                                                                       | 14   |

| 2.3.1 Theory of Operation                                                                                 | 15   |

| 2.3.2 Continuous Conduction Mode (CCM)                                                                    | 15   |

| 2.3.3 Discontinuous Conduction Mode (DCM)                                                                 | 15   |

| 2.4 Bi-directional DC-DC buck & boost converter                                                           | 16   |

| 2.4.1 Theory of Operation                                                                                 | 16   |

| 2.4.2 Buck operation                                                                                      | 16   |

| 2.4.3 Boost operation                                                                                     | 17   |

| CHAPTER-III                                                                                               |      |

| CONTROL TECHNIQUES                                                                                        | 18   |

| <ul><li>3.1 Introduction to closed loop control</li><li>3.2 Control requirements and techniques</li></ul> |      |

|                                                                                                           |      |

| 3.4 Compensator (error amplifier)                                                                         | 21   |

| 3.4.1 Type I Compensation                                                                                 | 21   |

| 3.4.2 Type II Compensation                                                                                | 21   |

| 3.4.3 Type III Compensation                                                                               | 22   |

| CHAPTER-IV                                                                                                |      |

| Design and Implementation of Bi-directional Buck and Boost Converter Using<br>Analog Controller           | 23   |

| 4.1 State-Variable Description for Each Circuit State                                                     | 23   |

| 4.1.1 Averaging the State-Variable Description Using the Duty Ratio d                                     | 24   |

| 4.1.2 Introducing Small ac Perturbations and Separation into ac and do                                    | 24   |

| Components                                                                                                |      |

| 4.1.3 Transformation of the ac Equations in to s-Domain to Solve for the                                  | e 26 |

-

Transfer Function

| 4.2 Buck Converter Operation                                                | 26 |

|-----------------------------------------------------------------------------|----|

| 4.3 Boost Converter Operation                                               |    |

| 4.4 Pulse Width Modulator                                                   |    |

| 4.5 Compensator                                                             | 34 |

| 4.5.1 Type III Compensation                                                 | 34 |

| 4.6 Feedback Control System                                                 | 37 |

| 4.7 Simulation Results                                                      |    |

| 4.7.1 Stability analysis of Buck Converter                                  | 39 |

| 4.7.2 Simulation of a closed loop Buck Converter                            | 41 |

| 4.7.3 Closed loop Simulink model of Buck Converter with type III controller | 44 |

| 4.7.4 Stability analysis of Boost converter                                 | 46 |

| 4.7.5 Simulation of a closed loop boost converter                           | 48 |

| 4.7.6 Closed loop Simulink model of Boost Converter with Type III           | 51 |

| controller                                                                  |    |

| 4.7.7 Bi-directional buck and boost converter                               | 53 |

| 4.8 Hardware & results                                                      | 56 |

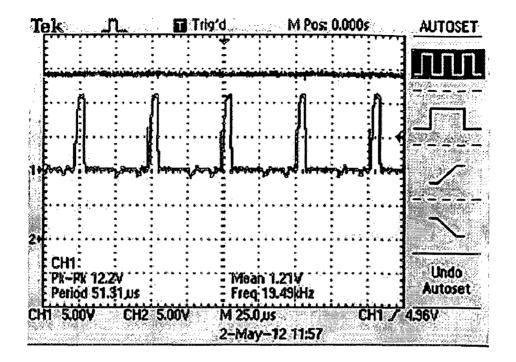

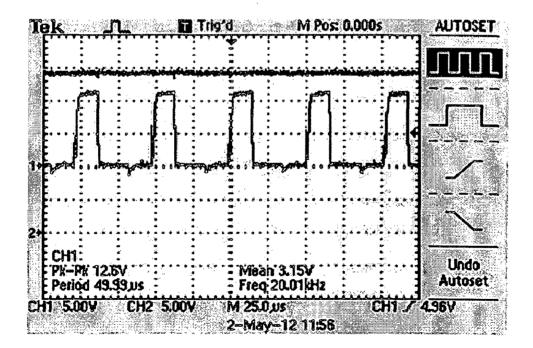

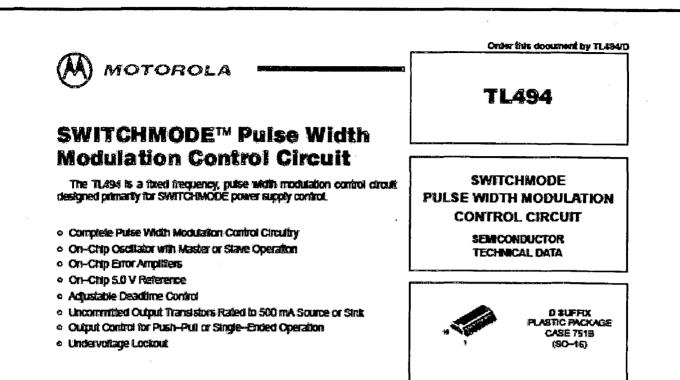

| 4.8.1 PWM Controller                                                        | 56 |

| 4.8.2 PWM Generation                                                        | 56 |

| 4.8.3 Buck Converter (using TL494)                                          | 58 |

| 4.8.4 Boost Converter (using TL494)                                         | 59 |

| 4.8.5 Bi-directional Buck and Boost Converter                               | 61 |

| (A) BDC in Buck Mode operation                                              | 62 |

| (i) Input Voltage (V <sub>in</sub> ) Variation                              | 63 |

| (ii) Load (R <sub>L</sub> ) Variation                                       | 65 |

| (B) BDC in Boost Mode operation                                             | 68 |

| (i) Input Voltage(V <sub>in</sub> ) Variation                               | 69 |

| (ii) Load (R <sub>L</sub> ) Variation                                       | 72 |

| 4.9 Conclusion                                                              | 75 |

,

| CHAPTER-V                                                                                        |     |

|--------------------------------------------------------------------------------------------------|-----|

| Design and Implementation of Bi-directional Buck and Boost Converter Using<br>Digital Controller | 76  |

| 5.1 Introduction                                                                                 | 76  |

| 5.1.1 Design by Emulation                                                                        | 76  |

| 5.1.2 Direct Digital Design                                                                      | 77  |

| 5.2 Design And MATLAB Simulation                                                                 | 78  |

| 5.2.1 Buck Converter                                                                             | 78  |

| 5.2.2 Design of PID Controller                                                                   | 79  |

| 5.2.3 Discrete PID Controller                                                                    | 79  |

| 5.2.4 Closed loop Simulink model of buck converter                                               | 82  |

| 5.3 Boost Converter                                                                              | 86  |

| 5.3.1 Design of PID Controller                                                                   | 86  |

| 5.3.2 Fuzzy Controller                                                                           | 88  |

| 5.3.3 Closed loop Simulink model of boost converter                                              | 90  |

| 5.4 Hardware Implementation                                                                      | 96  |

| 5.4.1 Digital Signal Processor                                                                   | 96  |

| A. Overview of Digital Signal controllers                                                        | 96  |

| B. Specifications of 28335eZdsp                                                                  | 97  |

| C. Key Features of the F28335 eZdsp                                                              | 97  |

| 5.4.2 Implementation                                                                             | 99  |

| 5.4.3 Hardware Results                                                                           | 101 |

| 5.5 Conclusion                                                                                   | 102 |

|                                                                                                  |     |

| CHAPTER-VI                                                                                       |     |

| CONCLUSION AND FUTURE SCOPE                                                                      | 103 |

| 6.1 Conclusion                                                                                   | 103 |

| 6.2 Pros and Cons of the Digital Control                                                         | 104 |

| 6.2.1 Pros of Digital Control                                                                    | 104 |

| 6.2.2 Cons of Digital Control                                                                    | 106 |

xiv

| 6.3 Future Scope     | 107 |

|----------------------|-----|

| BIBLIOGRAPHY         | 108 |

| LIST OF PUBLICATIONS | 113 |

| APPENDIX             | 114 |

# **CHAPTER-I**

# INTRODUCTION

[This chapter gives basic insight about SMPS, bi-directional dc-dc converters. It also presents literature review on bi-directional dc-dc converters, their recent advancements and applications.]

### **1.1 Introduction to SMPS**

In day to day life many applications need well-regulated dc supply for their proper operation. In majority of the cases the required voltages are of magnitudes varying between -24 to +24 volts. Some equipment may need multiple output power supplies. For example, in a Personal Computer one may need 3.3 volt,  $\pm 5$  volt and  $\pm 12$  volt power supplies. The digital ICs may need 3.3volt supply and the hard disk driver or the floppy driver may need  $\pm 5$  and  $\pm 12$  volts supplies. The individual output voltages from the multiple output power supply may have different current ratings and different voltage regulation requirements. The input connection to these power supplies is often taken from the standard utility power plug point (ac voltage of 115V / 60Hz or 230V / 50Hz). It may not be unusual, though, to have a power supply working from any other voltage level which could be of either ac or dc type.

There are two broad categories of power supplies: Linear regulated power supply and switched mode power supply (SMPS). In some cases one may use a combination of switched mode and linear power supplies to gain some desired advantages of both the types.

### 1.2 Linear regulated power supply

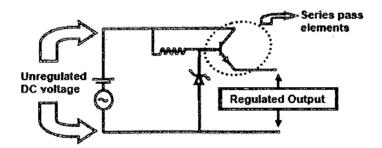

Fig. 1.1 shows the basic block for a linear power supply operating from an unregulated dc input. This kind of unregulated dc voltage is most often derived from the utility ac source. The utility ac voltage is first stepped down using a utility frequency transformer, and then it is rectified using diode rectifier and filtered by placing a capacitor across the rectifier output. The voltage across the capacitor is still fairly unregulated and is load dependent. The ripple in the capacitor voltage is not only dependent on the capacitance magnitude but also depends on load and supply

1

voltage variations. The unregulated capacitor voltage becomes the input to the linear type power supply circuit. The filter capacitor size is chosen to optimize the overall cost and volume. However, unless the capacitor is sufficiently large the capacitor voltage may have unacceptably large ripple. The magnitude of voltage-ripple across the input capacitor increases with increase in load connected at the output.

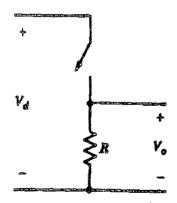

The end user of the power supply will like to have a regulated output voltage (with voltage ripple within some specified range) while the load and supply voltage fluctuations remain within the allowable limit. To achieve the unregulated dc voltage is fed to a voltage regulator circuit. The circuit in Fig.1.1 shows, schematically, a linear regulator circuit where a transistor is placed in between the unregulated dc voltage and the desired regulated dc output. Efficiency of linear voltage regulator circuits will be quite low when supply voltage is on the higher side of the nominal voltage.

Fig 1.1: Schematic linear voltage regulator

### 1.3 Switched Mode Power Supply (SMPS)

Like a linear power supply, the switched mode power supply too converts the available unregulated ac or dc input voltage to a regulated dc output voltage. However in case of SMPS with input supply drawn from the ac mains, the input voltage is first rectified and filtered using a capacitor at the rectifier output. The unregulated dc voltage across the capacitor is then fed to a high frequency dc-to-dc converter. Most of the dc-to-dc converters used in SMPS circuits have an intermediate high frequency ac conversion stage to facilitate the use of a high frequency transformer for voltage scaling and isolation. In contrast, in linear power supplies with input voltage drawn from ac mains, the mains voltage is first stepped down (and isolated) to the desired magnitude using a mains frequency transformer, followed by rectification and filtering. The high frequency transformer used in a SMPS circuit is much smaller in size and weight compared to the low frequency transformer of the linear power supply circuit.

The 'Switched Mode Power Supply' owes its name to the dc-to-dc switching converter for conversion from unregulated dc input voltage to regulated dc output voltage. The switch employed is turned 'ON' and 'OFF' (referred as switching) at a high frequency. During 'ON' mode the switch is in saturation mode with negligible voltage drop across the collector and emitter terminals of the switch whereas in 'OFF' mode the switch is in cut-off mode with negligible current through the collector and emitter terminals. On the contrary the voltage-regulating switch, in a linear regulator circuit, always remains in the active region.

A high switching frequency (of the order of 100 KHz) and a fast control over the duty ratio results in application of the desired mean voltage along with ripple voltage of a very high frequency to the output side, consisting of a low pass filter circuit followed by the load. The high frequency ripple in voltage is effectively filtered using small values of filter capacitors and inductors.

Fig 1.2: Schematic SMPS

### 1.4 SMPS versus linear power supply

As discussed above, in a linear regulator circuit the excess voltage from the unregulated dc input supply drops across a series element (and hence there is power loss in proportion to this voltage drop) whereas in switched mode circuit the unregulated portion of the voltage is removed by modulating the switch duty ratio. The switching losses in modern switches (like: MOSFETs) are much less compared to the loss in the linear element.

In most of the switched mode power supplies it is possible to insert a high frequency transformer to isolate the output and to scale the output voltage magnitude. In linear power supply the isolation and voltage-scaling transformer can be put only across the low frequency utility supply. The low frequency transformer is very heavy and bulky in comparison to the high frequency transformer of similar VA rating. Similarly the output voltage filtering circuit, in case of low frequency ripples is much bulkier than if the ripple is of high frequency. The switched mode circuit produces ripple of high frequency that can be filtered easily using smaller volume of filtering elements.

Linear power supply though more bulky and less efficient has some advantages too when compared with the switched mode power supply. Generally the control of the linear power supply circuit is much simpler than that of SMPS circuit. Since there is no high frequency switching, the switching related electro-magnetic interference (EMI) is practically absent in linear power supplies but is of some concern in SMPS circuits. Also, as far as output voltage regulation is concerned the linear power supplies are superior to SMPS. One can more easily meet tighter specifications on output voltage ripples by using linear power supplies.

### **1.5 Literature Review**

Switch mode power supplies were already developed in the beginning of the 1920s. the first switching power supplies used mercury-arc rectifiers and grid controlled mercury arc tubes. However, these mercury arc supplies had limited commercialization due to some problems found in the switching devices used. They were namely poor efficiency, high cost, questionable reliability and high maintenance [16].

During the late 1960s, these problems were overcome when the semiconductor industry developed a variety of high performance switching devices. The discovery of these switching devices became significant to power supplies and had a great impact on its industry. Their superior performance characteristics had allowed them to break markets that had been

unattainable for mercury arc. Nonetheless, it was only until the 1970s that SMPS had been widely used [5].

The first switched-mode power supply was patented in 1976. In the following year, Apple Computer became the first computer manufacturer to use a SMPS in a production unit. The use of this type of power supply allowed the Apple II to be lighter and more compact than other competing computers.

Prior to the development of the switched-mode power supply, most personal computers used linear regulators. These earlier power units produced a set, unvaried amount of voltage. In order to keep this output constant, linear supplies typically used simple resistors. This generated a significant amount of heat, and wasted voltage during the regulation process.

In 1986, Lab.gruppen achieved an industry breakthrough with development of the Regulated Switch Mode Power Supply, or R.SMPS. The concept of a switch mode power supply was well known at the time, but difficult engineering challenges had prevented successful implementation in high-power audio amplifiers. Lab.gruppen's Kenneth Andersson had devised an innovative solution, though the components required to make it work were not yet available. As soon as Siemens introduced its first high voltage MOSFET devices, Andersson's design was quickly implemented in the revolutionary SS 1300.

D. R. Northcott, S. Filizadeh, A. R. Chevrefils [17] presented a process for the design and development of a bidirectional buck-boost dc/dc converter for use as a generator controller in a series hybrid electric vehicle is presented. The converter allows a single permanent magnet dc (PMDC) electric machine to be used for both engine starting and generating modes. The power electronics and the control system methodology are studied. A control system is developed for which the parameters are selected and optimized using nonlinear simplex simulation based optimization. The converter and optimized control system are tested under a simulated scenario to verify acceptable functionality and performance.

Wei Li, Géza Joós, and Chad Abbey [18] have proposed a parallel structure of bidirectional buck/boost converters and its power-tracking control scheme for wind ESS applications. The converter performance is studied and compared to the single-unit topologies. The proposed

converter has smooth currents and fast dynamics which allow reduction of converter switching frequency and dc filtering capacitor. Other advantages of this topology include reduction of switching losses, improved reliability and flexibility.

Chin Chang, Zytec Corporation, [19] describes the dynamic behavior of the Buck converter for voltage mode control. For the current mode control case, an unstructured multiplicative uncertainty model is used to capture the family of perturbed small signal dynamics of the Buck converter. The powerful Kharitonov's theorem and the LQG/LTR technique are suitable for the design of robust controllers for DC-DC converters even it is more challenge for Boost and Fly back converters.

RD.Middlebrook And Slobodan Cuk [20] developed a method for modeling switching-converter power stages, whose starting point is the unified state-space representation of the switched networks and whose end result is either a complete state-space description or its equivalent small-signal low-frequency linear circuit model. The new canonical circuit model predicts that, in general, switching action introduces both zero and poles into the duty ratio to output transfer function in addition to those from the effective filter network.

Jian-ming HU, Yuan-rui CHEN, Zi-juan [21] discuss about high power bidirectional flow capability, with wide input voltage range, and output voltage of energy storage devices such as super capacitors or batteries vary with the change in load. Then the selection and design of aforementioned converter is proposed.

H. Li, Fang Z. Peng [22] presented a new zero-voltage-switching (ZVS) bidirectional dc-dc converter. Compared to the traditional bidirectional dc-dc converters for the similar applications, the new topology has the advantages of simple circuit topology with no total device rating (TDR) penalty, soft-switching implementation without additional devices, high efficiency and simple control. These advantages make the new converter promising for medium and high power applications especially for auxiliary power supply in fuel cell vehicles and power generation where the high power density, low cost, lightweight and high reliability power converters are required.

Mikkel C. W. Høyerby, Michael A. E. Andersen [26] describes the derivation of a practical solution to designing a medium-power non-isolated DC/DC power converter with very low

output ripple voltage and very high output voltage slew-rate capability. A simple and effective analog control scheme for the converter is developed, along with an accurate linear model.

Duan and Jin from University of British Columbia [27] made a thorough evaluation of different digital control design approaches and the performance of the approaches is compared in terms of both the bandwidth and the phase margin of the control loop, as well as the output transient response subject to line and load step change. Best digital design approach for power converter applications is identified based on the comparison results.

Giuseppe Capponi, Patrizia Livreri, Giuseppe Di Blasi, Filippo Marino [30] presents a new linear model for the Sigma-Delta modulator, based on modeling the nonlinear quantizer with a linear factor. The use of a 1-bit Sigma-Delta modulator in dc/dc power converter systems permits to implement a complete digital control.

J. Carwardine, F. Lenkszus [32] review current trends in the use of advanced technology such as embedded DSP controllers, and the application of real-time algorithms to the regulation and control of power supplies for accelerators and other large scale physics applications.

P R Holme and C D Manning [33] presented a method for the digital control of high frequency pwm converters. Digital current mode control and its advantages are discussed. Slope compensation is not required to stabilise the converter at duty ratios above 0.5. A modular architecture is put forward for practical circuit implementation.

R. M. Button, P. E. Kascak, R. Lebron-Velilla [38] discuss the digital control technologies that have been developed to greatly reduce the input filter requirements for paralleled, modular DC-DC converters. The use of phase shift technique reduced the filter size required for commercial DC-DC converters.

Dragon Maksimovic, and Regan Zane [42] presented an exact small-signal discrete-time model for digitally controlled pulse width modulated (PWM) dc-dc converters operating in constant frequency continuous conduction mode (CCM) with a single effective A/D sampling instant per switching period. The model, which is based on well-known approaches to discrete-time modeling and the standard -transform, takes into account sampling, modulator effects and delays in the control loop, and is well suited for direct digital design of digital compensators.

7

N. Rajarajeswari and K. Thanushkodi [43] introduces a novel Bi-directional DC-DC converter with artificial neural network controller (ANN).Bidirectional power flow is obtained by the same power components and provides a simple, efficient, and galvanically isolated converter. In the presence of DC mains the converter operates as buck converter and charges the battery. When the DC main fails, the converter operates as boost converter and the battery feeds the load.

N. Rajarajeswari and K. Thanushkodi [44] introduces a Bi-directional DC-DC converter with adaptive fuzzy logic controller. The power switches are controlled by Pulse Width Modulation technique and the pulses are generated by the application of fuzzy logic with an adoption algorithm.

### **1.5.1 Bi-directional dc-dc converters (BDC)**

Bidirectional dc-dc converters (BDC) have recently received a lot of attention due to the increasing need to systems with the capability of bidirectional energy transfer between two dc buses. Apart from traditional application in dc motor drives, new applications of BDC include energy storage in renewable energy systems, fuel cell energy systems, hybrid electric vehicles (HEV) and uninterruptible power supplies (UPS). The fluctuation nature of most renewable energy resources, like wind and solar, makes them unsuitable for standalone operation as the sole source of power. A common solution to overcome this problem is to use an energy storage device besides the renewable energy resource to compensate for these fluctuations and maintain a smooth and continuous power flow to the load. As the most common and economical energy storage devices in medium-power range are batteries and super-capacitors, a dc-dc converter is always required to allow energy exchange between storage device and the rest of system. Such a converter must have bidirectional power flow capability with flexible control in all operating modes.

In HEV applications, BDCs are required to link different dc voltage buses and transfer energy between them. For example, a BDC is used to exchange energy between main batteries (200-300V) and the drive motor with 500V dc link. High efficiency, lightweight, compact size and high reliability are some important requirements for the BDC used in such an application.

BDCs also have applications in line-interactive UPS which do not use double conversion technology and thus can achieve higher efficiency. In a line-interactive UPS, the UPS output

terminals are connected to the grid and therefore energy can be fed back to the inverter dc bus and charge the batteries via a BDC during normal mode. In backup mode, the battery feeds the inverter dc bus again via BDC but in reverse power flow direction.

BDCs can be classified into non-isolated and isolated types. Non-isolated BDCs (NBDC) are simpler than isolated BDCs (IBDC) and can achieve better efficiency. However, galvanic isolation is required in many applications and mandated by different standards. The complexity of IBDCs stems from the fact that an AC link must be present in their structure in order to enable power transfer via a magnetically isolating media, i.e. a transformer. In this chapter, first some NBDC structures are briefly discussed. As isolation and/or voltage matching is required in many applications, more attention in this chapter is paid on the description of different IBDC configurations. It should be stated that in order to improve the efficiency, almost all recently proposed medium-power IBDC configurations have exploited the benefits of soft-switching or resonant techniques to increase the switching frequency and achieve lower size and weight.

### **1.5.2 Non-isolated BDC**

Basic dc-dc converters such as buck and boost converters (and their derivatives) do not have bidirectional power flow capability. This limitation is due to the presence of diodes in their structure which prevents reverse current flow. In general, a unidirectional dc-dc converter can be turned into a bidirectional converter by replacing the diodes with a controllable switch in; its structure. As compared to high-frequency transformer-isolated bidirectional dc-dc converters, non-isolated bi-directional dc-dc converters generally have advantages of simple structure, high efficiency, low cost, high reliability, etc. These BDC are used in high power applications i.e is around 30kW if isolation is already taken care [46].

### 1.5.3 Isolated BDC (IBDC)

Galvanic isolation between multi-source systems is a requirement mandated by many standards. Personnel safety, noise reduction and correct operation of protection systems are the main reasons behind galvanic isolation.

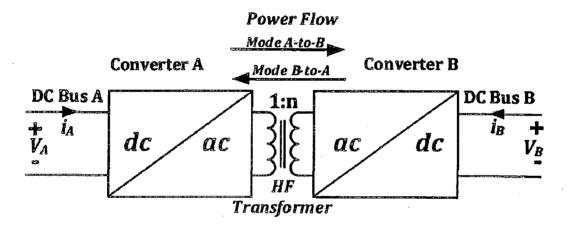

Most of the Medium-power IBDCs have a structure similar to Fig.1.3 generally rated at rated at 1-5 kW. This structure consists of two high-frequency switching dc-ac converters and a high-

frequency transformer which is primarily used to maintain galvanic isolation between two sources. This transformer is also essential for voltage matching in case of large voltage ratio between two sources. The transformer calls for ac quantities at its terminals and thus a dc-ac converter is employed on each side. As energy transfer in either direction is required for the system, each dc-ac converter must also have bidirectional energy transfer capability. With the same token, the dc buses in this structure must also be able to either generate or absorb energy. Galvanic isolation by a transformer provides a measure of safety, and the design of this transformer introduces many choices. These BDC are preferred for high power applications i.e is around 35kW.

Fig 1.3: Basic structure of an IBDC

### **1.5.4 Applications**

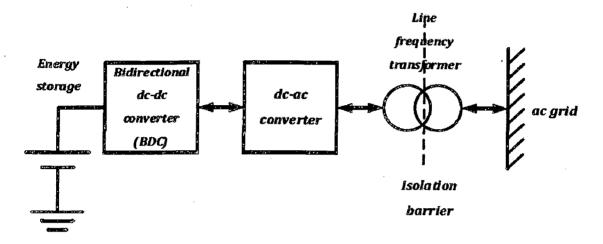

Minimizing greenhouse gas effects by reducing CO2 and other emissions is one of the most challenging issues that human is presently facing. As electricity generation is one of the major causes of the pollution, finding alternative clean electricity generation methods is thus becoming attractive. In this regard, renewable energy resources such as wind and solar energy are among the most important substitutes for traditional fuel-based energy production. However, the intermittent nature of most renewable sources does not allow having a reliable and continuous source of energy when these resources are used alone. The fluctuating energy produced by these sources may also cause adverse effects on the power quality of the grid that these resources are connected to. By using energy storage devices, these fluctuations can be absorbed to deliver smooth power to consumers and at the same time maximize the energy output of renewable resources. This reduces the output required from conventional power stations which directly reduces CO2 emissions. The dc-dc converter shown in this system is of non-isolated type, e.g. the converter shown in Fig.1.4.

Fig 1.4: Basic structure of an energy storage device connected to an ac grid through a line frequency transformer.

Besides smoothing the energy output of renewable resources, energy storage systems have other technical applications in the utility grid including grid stabilization, frequency and voltage support, power quality and reliability enhancement and load shifting.

### **1.6 Recent advancements**

- Bi-directional DC-DC converter with artificial neural network controller (ANN). In the presence of DC mains the converter operates as buck converter and charges the battery. When the DC main fails, the converter operates as boost converter and the battery feeds the load. In both the modes the PWM pulses are generated by application of ANN controller.

- Bi-directional DC-DC converter with adaptive fuzzy logic controller. The power switches are controlled by Pulse Width Modulation technique and the pulses are generated by the application of fuzzy logic with an adoption algorithm.

- DSP or FPGA controlled Bi-directional buck and boost converter. In both the modes the power switches are controlled by PWM technique and the PWM pulses are

generated by DSP or FPGA. By using this digital processor we can implement neural network controller (ANN), Adaptive fuzzy logic controller.

### 1.7 Objectives of Thesis Work

My current area of working is to design implementation of Bi-directional buck and boost converter using both analog controller and digital controller. Analog controller is designed using the available analog ICs; the digital controller is designed with the use of DSP or FPGA

The methodology to achieve the objectives is as follows

- 1. Design the power circuit for the both buck and boost converters based on the requirements.

- 2. Design the compensation or controller using type 3 for analog controller and digital controllers are designed using PID, fuzzy, direct & In-direct digital design approach.

- 3. Modelling of the converter with complete closed loop control using Simulink in MATLAB.

- 4. Hardware is implemented of the bi-directional converter using analog controller with IC's and for digital implementation DSP or FPGA is used.

# **CHAPTER - II**

# **DC-DC CONVERTERS**

[Presented in this chapter are the basic operations of different non-isolated dc-dc converters like buck converter, boost converter, bi-directional buck and boost converter.]

### 2.1 Introduction

Switch-mode DC-DC converters are used to convert the unregulated DC input to a controlled DC output at a desired voltage level. Switch-mode DC-DC converters include buck converters, boost converters, Cuk converters and full-bridge converters, etc. Among these converters, the buck converter and the boost converter are the basic topologies. Both the buck-boost and Cuk converters are combinations of the two basic topologies. The full-bridge converter is derived from the buck converter. There are usually two modes of operation for DC-DC converters: continuous and discontinuous. The current flowing through the inductor never falls to zero during the time the switch is turned off. Only operation in the continuous mode is considered in this dissertation.

### 2.2 Buck Converter

A buck converter is a step-down DC to DC converter. This converter takes an input voltage source and step it down to a lower voltage. Switch-based regulators move energy from input to

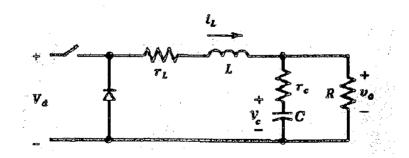

Fig 2.1: Buck Converter Circuit

output in discrete packets via two or more switches. An inductor is used as the energy storage element that transfers energy from the input to the output of the power supply circuit.

### 2.2.1 Theory of Operation

During the interval when the switch is on, the diode in Fig.2.1 becomes reverse biased and the input provides energy to the load as well as to the inductor. During the interval when switch is off, the inductor current flows through the diode, transferring some of its stored energy to the load. The output voltage is controlled by varying the duty cycle. During steady state, the ratio of output voltage over input voltage is (D), which is given by

$$\frac{V_{out}}{V_{in}} = D \tag{2.1}$$

### 2.2.2 Continuous Mode

A buck converter operates in continuous mode if the current through the inductor  $(I_L)$  never falls to zero during the commutation cycle.

$$L > \frac{V_{out}}{2I_{out}f} \tag{2.2}$$

### 2.2.3 Discontinuous Mode

A buck converter operates in discontinuous mode if the current through the inductor  $(I_L)$  falls to zero during the commutation cycle.

### 2.3 Boost Converter

A boost converter (step-up converter) is a power converter with an output DC voltage greater than its input DC voltage. It is a class of switching-mode power supply (SMPS) containing at least two semiconductor switches (a diode and a transistor) and at least one energy storage element. Filters made of capacitors (sometimes in combination with inductors) are normally added to the output of the converter to reduce output voltage ripple.

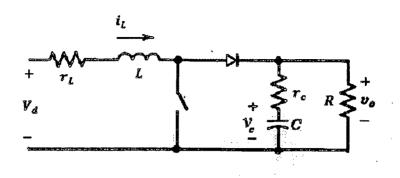

Fig 2.2: Boost Converter Circuit

### 2.3.1 Theory of Operation

When the switch is on, the diode is reversed biased, thus isolating the output stage. The input supplies energy to the inductor. When the switch is off, the output stage receives energy from the inductor as well as from the input. The output voltage is controlled by varying the duty cycle. During steady state, the ratio of output voltage over input voltage is (1-D), which is given by

$$\frac{v_{in}}{v_{out}} = 1 - D \tag{2.3}$$

### 2.3.2 Continuous Conduction Mode (CCM):

In continuous conduction mode inductor current is continuous. The continuous conduction mode depends up on value of inductor. If the value of inductor is greater than that of critical inductance value then we say that converter under continuous conduction mode.

$$L > \frac{DT(1-D)^2 R}{2}$$

(2.4)

### 2.3.3 Discontinuous Conduction Mode (DCM):

In this mode of operation inductor current is discontinuous. If the inductance value is less than critical inductance then it is in discontinuous conduction mode.

### 2.4 Bi-directional DC-DC buck & boost converter

A converter which can transfer power in two directions i.e. take or give power is called bidirectional converter. Now we will discuss about the basic structure and function of the bidirectional buck & boost converter.

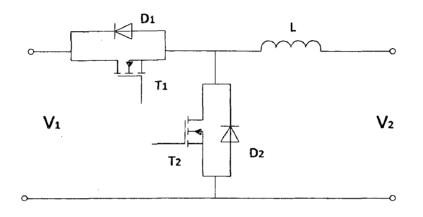

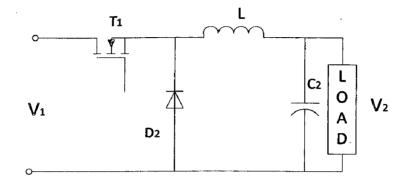

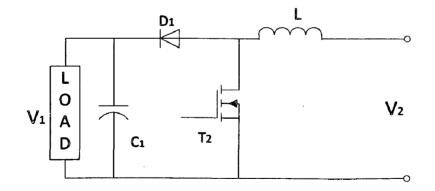

Fig 2.3: Bi-directional buck and boost converter  $(V_1 > V_2)$ .

A bidirectional buck and boost converter is shown in Figure 2. In this circuit, both switches are composed of a transistor and an antiparallel diode. They can conduct current in both directions, but can support the voltage in only one direction. In other words, the switches are bidirectional for the current and unidirectional for the voltage. These are two-quadrant switches, which permit energy flow in both directions, from left to right, and vice versa.

### 2.4.1 Theory of Operation

This converter behaves as a two types of dc-dc converter. It depends on the direction of operation. In one direction, it behaves as buck converter and in other direction it behaves as boost converter.

### 2.4.2 Buck operation:

If a dc voltage source  $V_1$  is connected in parallel with the capacitor  $C_1$  and a load is connected in parallel with the capacitor  $C_2$ , the buck converter is obtained. In this case, the energy flows from left to right. The MOSFET (T<sub>1</sub>) channel is used as a controllable switch and its antiparallel diode

$D_1$  is permanently OFF, whereas the diode  $D_2$  is used as a passive (naturally commutated) switch. The channel of the MOSFET (T<sub>2</sub>) can be held permanently OFF or can be turned on by a driver, when the diode  $D_2$  is ON. This buck operation is shown in the below Fig.2.4.

Fig 2.4: Buck operation of bi-directional converter

### 2.4.3 Boost operation

If a dc voltage source  $V_2$  is connected in parallel with the capacitor  $C_2$  and a load is connected in parallel with the capacitor  $C_1$ , the boost converter is obtained. In this case, the energy flows from right to left. The MOSFET (T<sub>2</sub>) channel is used as a controllable switch and its antiparallel diode  $D_2$  is permanently OFF, whereas the diode  $D_1$  is used as a passive (naturally commutated) switch. The channel of the MOSFET (T<sub>1</sub>) can be held permanently OFF or can be turned on by a driver, when the diode  $D_1$  is ON. This boost operation is shown in the below Fig.2.5

Fig 2.5: Boost operation of bi-directional converter.

# **CHAPTER-III**

# **CONTROL TECHNIQUES**

[Presented in this chapter are the control techniques, stability criteria, types of compensation for DC-DC converters for closed loop control.]

### **3.1 Introduction to closed loop control**

The buck & boost converters can be controlled in two ways, known as:

- 1. Constant-frequency operation or pulse-width modulation control

- 2. Variable-frequency operation or control by frequency modulation

With pulse-width modulation control, the regulation of output voltage is achieved by varying the duty cycle of the switch, keeping the frequency of operation constant. Duty cycle refers to the ratio of the period for which the power semiconductor is kept ON to the cycle period. Usually control by pulse width modulation is the preferred method since constant frequency operation leads to optimization of LC filter and the ripple content in output voltage can be controlled within the set limits. On the other hand, if the load on the converter is below a certain level, voltage regulation of output becomes a problem and in such a case, control by frequency modulation is to be preferred. When control by frequency modulation is to be achieved, the ON period of the power semiconductor switch is kept constant and the frequency of operation is varied to effect voltage regulation. Design of LC filter is not easy in such a case.

### **3.2 Control requirements and techniques**

A power supply should be designed to [4]:

- 1. Have good line regulation, such that output remains constant, if the input voltage varies.

- 2. Have good load regulation, such that the output remains constant, if the load changes.

- 3. Have good transient response to system disturbances, such a sudden changes to the input voltage, or to the load.

- 4. Remain stable under all operating conditions.

The above requirements are met by designing a feedback control system, which will control the duty ratio, of the transistor to keep the output all the times.

The output voltage of a switch mode power supply is kept constant with the help of closed loop control. The value of the output voltage (actual value) is compared with a reference voltage (nominal voltage). The difference between actual and nominal value controls the duty cycle of the transistor drive. The function of the control loop is to regulate the variation of the mains and of the change of the output current. This is called line regulation and load regulation.

There are two different methods of regulation:

- Voltage-mode

- Current-mode control.

The voltage-mode control is the "traditional" method of regulation.

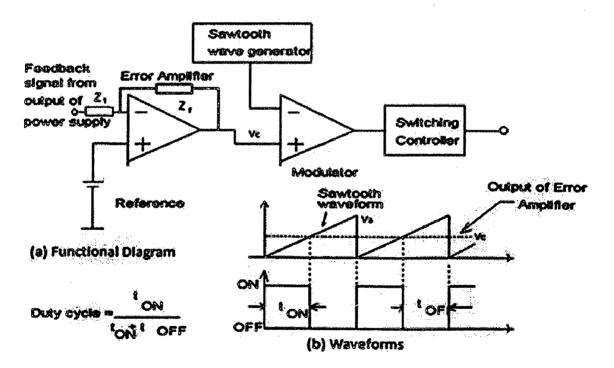

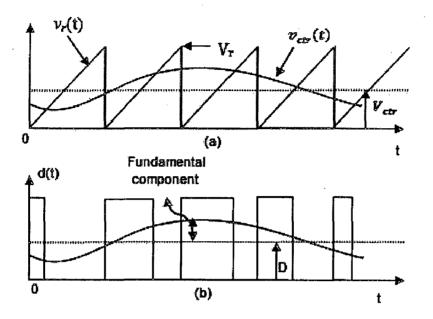

Fig 3.1: Voltage-mode control

The simplified functional diagram of a typical pulse-width modulator is shown in Fig, whereas the waveforms in Fig explain the operation. The pulse-width modulator circuit consists of a saw-tooth generator, an error amplifier, and a comparator. The error amplifier compares the reference

voltage and the feedback signal. The feedback signal is obtained using a voltage divider network across the output of the SMPS circuit.

The output of the error amplifier is compared with the saw-tooth waveform and when this voltage is greater than the output of saw tooth generator, the output of the comparator would be at logic '1'. When the output of comparator is at logic '1', the switch in the SMPS circuit can be kept in the ON state. When the comparator is at logic '0', the switch in the SMPS circuit can be kept in the OFF state. If the output voltage tends to be greater than the ref voltage, the output voltage of the error amplifier would fall and the duration for which the output of comparator remains at logic '1' would decrease.

$$D=(t_{on}/T)=V_o/V_s$$

Thus the duty cycle of the switch reduces and the output of the SMPS would fall. Thus it can be seen that the negative feedback control maintains the output at the desired value.

### 3.3 Stability Criteria

It is the desire of all designers of power supplies, whether they are switching or not, for accurate and tight regulation of the output voltage. To accomplish regulation we need to add a feedback loop. The feedback loop can cause an otherwise stable system to become unstable. Even though the transfer function of the original converter might not contain any right hand poles but after feedback it is possible that right hand poles may be introduced.

There are three important points to be followed for the system to be stable. They are:

- The first criterion was that the total phase shift at the crossover frequency (frequency where total open-loop gain is unity or 0 dB) should be short of 360° by the "phase margin," which is usually taken as at least 45°.

- The second criterion for a stable circuit is that to prevent rapid changes of phase shift with frequency characteristic of a circuit with a - 2 gain slope, the slope of the open-loop gain-frequency curve of the entire circuit (arithmetic sum in decibels of all the gain elements involved) as it passes through crossover frequency should be - 1 gain slope.

- The third criterion for a stable loop is to provide the desired phase margin, which will be set at 45° herein. To satisfy all three criteria, it is necessary to know how to calculate gains and phase shifts of all the elements.

We have to design the error amplifier (compensator) satisfying the above stability criteria for the analog controller.

#### **3.4 Compensator (error amplifier)**

There are three types of compensation or error amplifier for the stabilizing the analog circuit based on the requirement. They are Type I, Type II & Type III. In most cases, a Type II or Type III compensated network will properly compensate the system [6].

#### **3.4.1 Type I Compensation**

Dominant pole compensations, or single pole compensation, are referred to as a Type I Compensation. This type of compensation is used for converter topologies that exhibit a minimal phase shift prior to the anticipated gain crossover point. This compensation yields, though, a relatively poor transient response time because the gain crossover frequency occurs at a low frequency. Its load regulation is very good, though, since its DC gain is very high.

Fig.3.2: Type I Compensation

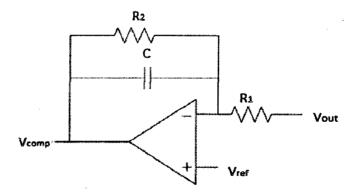

#### 3.4.2 Type II Compensation:

The Type II network helps to shape the profile of the gain with respect to frequency and also gives a 90° boost to the phase. This boost is necessary to counteract the effects of the resonant output filter at the double pole.

Fig 3.3: Type II Compensation

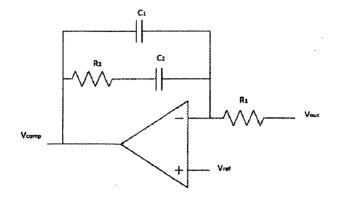

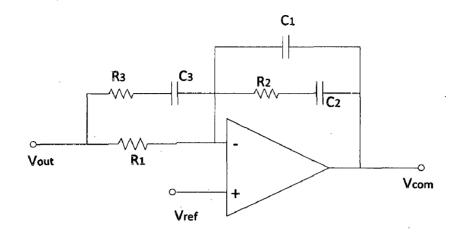

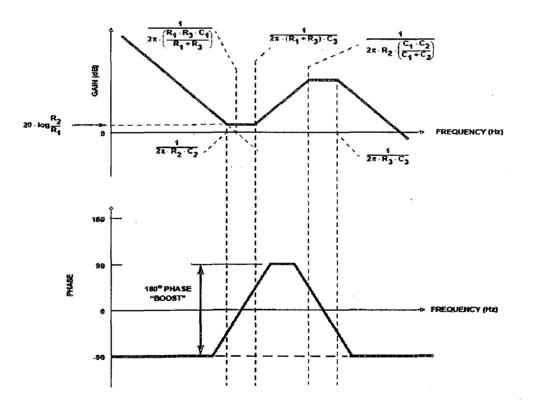

#### **3.4.3 Type III Compensation:**

Type III network shapes the profile of the gain with respect to frequency in a similar fashion to the Type II network, but utilizes two zeroes to give a phase boost of 180°. This boost is necessary to counteract the effects of an under damped resonance of the output filter at the double pole. The Type III compensation circuit has two poles, with two zeros and a pole at its origin providing an integration function for better DC accuracy. Optimal selection of the compensation circuit depends on the power-stage frequency response [11].

Fig 3.4: Type III Compensation

# **CHAPTER-IV**

# Design and Implementation of Bi-directional Buck and Boost Converter Using Analog Controller

[Presented in this chapter is the control design for DC-DC converters using linear control methods. An accurate model is essential to design linear controllers. Small signal models for buck and boost converters were obtained using the standard state-space averaging techniques. Modeling and implementation of buck, boost and bi-directional buck/boost converter are also discussed.]

#### 4.1 State-Variable Description for Each Circuit State

In a converter operating in a continuous-conduction mode, there are two circuit states: one state corresponds to when the switch is on and the other to when the switch is off. A third circuit state exists during the discontinuous interval, which is not considered in the following analysis because of the assumption of a continuous conduction mode of operation.

During each circuit state, the linear circuit is described by means of the state variable vector  $\mathbf{x}$  consisting of the inductor current and the capacitor voltage. In the circuit description, the parasitic elements such as the resistance of the filter inductor and the equivalent series resistance (ESR) of the filter capacitor should also be included. Here V<sub>d</sub> is the input voltage. A lowercase letter is used to represent a variable, which includes its steady-state dc value plus a small ac perturbation, for example,

$$v_o = V_o + \hat{v}_o \tag{4.1}$$

Therefore, during each circuit state, we can write the following state equations:

$$\dot{\mathbf{x}} = A_1 \mathbf{x} + B_1 v_d \qquad \text{during } d. T_S$$

$$\dot{\mathbf{x}} = A_2 \mathbf{x} + B_2 v_d \qquad \text{during } (1 - d). T_S \qquad (4.2)$$

and

where A1 and A2 are state matrices and B1 and B2 are vectors.

The output  $v_0$  in all converters can be described in terms of their state variables alone as

$v_0 = C_1 x$  during  $d. T_S$

and

$$v_0 = C_2 x$$

during  $(1 - d) T_S$  (4.3)

where C1 and C2 are transposed vector s

#### 4.1.1 Averaging the State-Variable Description Using the Duty Ratio d

To produce an average description of the circuit over a switching period, the equations corresponding to the two foregoing states are time weighted and averaged, resulting in the following equations:

$$\dot{x} = (dA_1 + d'A_2)x + (dB_1 + d'B_2)v_d$$

$$v_o = (dC_1 + d'C_2)x \qquad (4.4)$$

# 4.1.2 Introducing Small ac Perturbations and Separation into ac and dc Components

Small ac perturbations, represented by "~", are introduced in the dc steady-state quantities (which are represented by the upper case letters). Therefore,

$$x = X + \hat{x}(t)$$

$$v_o = V_o + \hat{v_o}(t)$$

$$d = D + \hat{d}(t)$$

(4.5)

In general,  $v_d = V_d + \widehat{v_d}(t)$ . However, in view of our goal to obtain the transfer function between voltage  $\widehat{v_o}$  and the duty ratio  $\hat{d}$ , the perturbation  $\widehat{v_d}$  is assumed to be zero in the input voltage to simplify our analysis. Therefore

$$v_d = V_d$$

Using Eq. 4.5 in Eq 4.4 and recognizing that in steady state,

$$\hat{x} = AX + BV_d + A\hat{x} + \{(A_1 - A_2)X + (B_1 - B_2)V_d\}\hat{d}$$

+terms containing products of  $\hat{x}$  and  $\hat{d}$  (to be neglected) (4.6)

Where

$$A = A_1 D + A_2 (1 - D)$$

And

$$B = B_1 D + B_2 (1 - D) \tag{4.7}$$

The steady-state equation can be obtained from Eq.8.6 by setting all the perturbation terms and their derivatives to zero. Therefore, the steady-state equation is

$$AX + BV_{d} = 0$$

$$Bate - \frac{2.3}{8} / \frac{1.2}{1.2}$$

$$Bate - \frac{2.3}{8} / \frac{1.2}{1.2}$$

$$AX + (A_{1} - A_{2})X + (B_{1} - B_{2})V_{d} + \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$Bate - \frac{2.3}{8} / \frac{1.2}{1.2}$$

$$AX + (A_{1} - A_{2})X + (B_{1} - B_{2})V_{d} + \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$AX + BV_{d} = 0$$

$$Bate - \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$Bate - \frac{1.2}{1.2}$$

$$AX + (A_{1} - A_{2})X + (B_{1} - B_{2})V_{d} + \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$AX + BV_{d} = 0$$

$$Bate - \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$AX + BV_{d} = 0$$

$$Bate - \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$Bate - \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$AX + BV_{d} = 0$$

$$Bate - \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$AX + BV_{d} = 0$$

$$Bate - \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$AX + BV_{d} = 0$$

$$Bate - \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$AX + BV_{d} = 0$$

$$Bate - \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$AX + BV_{d} = 0$$

$$Bate - \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$AX + BV_{d} = 0$$

$$AX + BV_{d} = 0$$

$$Bate - \frac{1.2}{1.2}$$

$$AX + BV_{d} = 0$$

$$A$$

and therefore in Eq. 4.6

Similarly, using Eqs.4.5 in Eq.4.4 results in

$$V_o + \widehat{v_o} = C\widehat{x} + CX + \{(C_1 - C_2)X\}\widehat{d}$$

Where

$$C = C_1 D + C_2 (1 - D) \tag{4.10}$$

In Eq. 4.10, the steady-state output voltage is given as

$$V_o = CX \tag{4.11}$$

and therefore,

$$\widehat{v_o} = C\widehat{x} + \{(C_1 - C_2)X\}\widehat{d}$$

(4.12)

Using Eqs.4.8 and 4.11, the steady-state dc voltage transfer function is

$$\frac{v_0}{v_d} = -CA^{-1}B \tag{4.13}$$

# 4.1.3 Transformation of the ac Equations in to s-Domain to Solve for the Transfer Function.

Equations 4.9 and 4.12 consist of the ac perturbations. Using Laplace transformation in Eq4.9,

$$s\hat{x}(s) = A\hat{x}(s) + \{(A_1 - A_2)X + (B_1 - B_2)V_d\}\hat{d}(s)$$

$$\hat{x}(s) = [sI - A]^{-1}\{(A_1 - A_2)X + (B_1 - B_2)V_d\}\hat{d}(s)$$

(4.14)

Where I is a unity matrix. Using a Laplace transformation in Eq.4.12 and expressing in terms  $\hat{x}(s)$  in terms of d(s) from Eq.4.14 results in the desired transfer function Tp(s) of the power stages:

$$T_p(s) = \frac{\hat{v_0}(s)}{\hat{d}(s)} = C[sI - A]^{-1} \{ (A_1 - A_2)X + (B_1 - B_2)V_d \} + (C_1 - C_2)X$$

(4.15)

#### **4.2 Buck Converter Operation**

Linearizing the power stage and the output filter of the Buck Converter given in Figure 4.1. The two switches are represented by diodes.

Fig 4.1: Buck Converter Circuit[1]

$r_L$  is inductor resistance,  $r_c$  is the equivalent series resistance of the capacitor, and R is the load resistance.

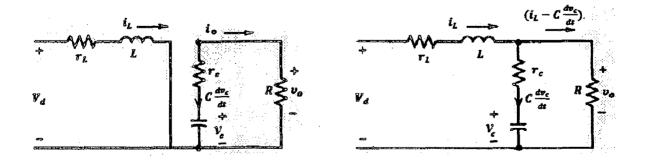

Fig 4.2: Buck Converter (a) switch on; (b) switch off [1]

$V_d = 0$

From Figure 4.2 the following equations can be derived

When switch is closed or ON

$$V_{d} = r_{L}i_{L} + L\frac{di_{L}}{dt} + R(i_{L} - C\frac{dv_{c}}{dt})$$

(4.16)

$$R\left(i_L - C\frac{dv_c}{dt}\right) = r_c C\frac{dv_c}{dt} + v_c \tag{4.17}$$

Using 4.16&4.17

$$\frac{dv_c}{dt} = \frac{Ri_L}{C(R+r_c)} - \frac{v_c}{C(R+r_c)}$$

(4.18)

When switch is open or OFF

$$0 = r_L i_L + L \frac{di_L}{dt} + R(i_L - C \frac{dv_c}{dt})$$

(4.19)

$$R\left(i_L - C\frac{dv_c}{dt}\right) = r_c C\frac{dv_c}{dt} + v_c \tag{4.20}$$

When we consider ON condition

Sub Eq.4.21 in Eq.4.16 we get

$$\frac{di_L}{dt} = \frac{v_d}{L} - \left(\frac{r_L r_c + Rr_L + r_c R}{L(R + r_c)}\right) i_L - \left(\frac{R}{R + r_c}\right) \frac{v_c}{L}$$

(4.21)

27

Using eq.4.21 & eq.4.18 we can get matrices A<sub>1</sub>, B<sub>1</sub>, C<sub>1</sub>, D<sub>1</sub> when switch is ON.

$$\begin{bmatrix} \frac{di_L}{dt} \\ \frac{dv_c}{dt} \end{bmatrix} = \begin{bmatrix} -\left(\frac{r_L r_c + R r_L + r_c R}{L(R+r_c)}\right) & -\left(\frac{R}{R+r_c}\right)\frac{1}{L} \\ \frac{R}{C(R+r_c)} & -\frac{1}{C(R+r_c)} \end{bmatrix} \begin{bmatrix} i_L \\ v_c \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} V_d$$

(4.22)

$$V_o = \begin{bmatrix} \frac{Rr_c}{(R+r_c)} & \frac{R}{(R+r_c)} \end{bmatrix} \begin{bmatrix} i_L \\ v_c \end{bmatrix}$$

(4.23)

When switch is open or OFF  $V_d = 0$ , So  $A_1 = A_2$ ,  $B_2 = \begin{bmatrix} 0 \\ 0 \end{bmatrix}$ ,  $C_1 = C_2$ . In all practical circuits  $R \gg (r_c + r_L)$ , now we get the final simplified matrices as.

$$A_{1} = A_{2} = \begin{bmatrix} -\left(\frac{r_{L}+r_{c}}{L}\right) & -\frac{1}{L} \\ \frac{1}{c} & -\frac{1}{cR} \end{bmatrix}$$

(4.24)

$$B_1 = \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix}, B_2 = 0 \tag{4.25}$$

$$C_1 = C_2 = [r_c \quad 1] \tag{4.26}$$

According to the state-space average methods the averaged matrices are

$$A = DA_{1} + D'A_{2}$$

$$B = DB_{1} + D'B_{2}$$

$$C = DC_{1} + D'C_{2}$$

$$E = DE_{1} + D'E_{2}$$

(4.27)

Whereas D'=1-D. Here A=A<sub>1</sub>, C=C<sub>1</sub>,  $B = B_1 D = \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} D$ .

the steady-state dc voltage transfer function is

$$\frac{v_o}{v_d} = -CA^{-1}B = D \tag{4.28}$$

$$T_p(s) = \frac{\widehat{v_o(s)}}{\widehat{d(s)}} = C[sI - A]^{-1} \{ (A_1 - A_2)X + (B_1 - B_2)V_d \} + (C_1 - C_2)X$$

$$=> C[sI - A]^{-1}B_1V_d$$

$$T_{p}(s) = \frac{\widehat{v_{o}(s)}}{d(s)} = V_{d} \frac{1 + sr_{c}C}{LC\{s^{2} + s\left[\frac{1}{LR} + \frac{(r_{c} + r_{L})}{L}\right] + \frac{1}{LC}\}}$$

(4.26)

#### 4.3 Boost Converter Operation

Linearizing the power stage and the output filter of the Boost Converter given in Figure 4.3. The complete diagram of the boost converter is given.

Fig 4.3: Boost Converter Circuit

$r_L$  is inductor resistance,  $r_c$  is the equivalent series resistance of the capacitor, and R is the load resistance.

Fig 4.4: Boost Converter (a) switch on; (b) switch off [1]

From Figure 4.4 the following equations can be derived

When switch is closed or ON

$$V_d = r_L i_L + L \frac{di_L}{dt} \tag{4.30}$$

$$V_o = r_c C \frac{dv_c}{dt} + v_c \tag{4.31}$$

$$V_o = -RC \frac{dv_c}{dt} \tag{4.32}$$

Sub Eq.4.32 in Eq.4.31 we get

$$\frac{dv_c}{dt} = -\frac{v_c}{(RC+r_cC)} \tag{4.33}$$

$$\frac{di_L}{dt} = \frac{V_d}{L} - \frac{r_L}{L} i_L \tag{4.34}$$

Using eq.4.33 & eq.4.34 we can get matrices  $A_1$ ,  $B_1$ ,  $C_1$ ,  $D_1$  when switch is ON.

$$\begin{bmatrix} \frac{di_L}{dt} \\ \frac{dv_c}{dt} \end{bmatrix} = \begin{bmatrix} -\frac{r_L}{L} & 0 \\ 0 & -\frac{1}{C(R+r_c)} \end{bmatrix} \begin{bmatrix} i_L \\ v_c \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} V_d$$

(4.35)

$$V_o = \begin{bmatrix} 0 & \frac{R}{(R+r_c)} \end{bmatrix} \begin{bmatrix} i_L \\ v_c \end{bmatrix}$$

(4.36)

When switch is open or OFF

$$V_{d} = r_{L}i_{L} + L\frac{di_{L}}{dt} + R(i_{L} - C\frac{dv_{c}}{dt})$$

(4.37)

$$R\left(i_L - C\frac{dv_c}{dt}\right) = r_c C\frac{dv_c}{dt} + v_c \tag{4.38}$$

$$\frac{dv_c}{dt} = \frac{Ri_L}{C(R+r_c)} - \frac{v_c}{C(R+r_c)}$$

(4.39)

Sub Eq.4.39 in Eq.4.37 we get

$$\frac{di_L}{dt} = \frac{v_d}{L} - \left(\frac{r_L r_c + Rr_L + r_c R}{L(R + r_c)}\right) i_L - \left(\frac{R}{R + r_c}\right) \frac{v_c}{L}$$

(4.40)

Using eq.4.39 & eq.4.40 we can get matrices  $A_2$ ,  $B_2$ ,  $C_2$ ,  $D_2$  when switch is OFF.

$$\begin{bmatrix} \frac{di_L}{dt} \\ \frac{dv_c}{dt} \end{bmatrix} = \begin{bmatrix} -\left(\frac{r_L r_c + Rr_L + r_c R}{L(R+r_c)}\right) & -\left(\frac{R}{R+r_c}\right)\frac{1}{L} \\ \frac{R}{C(R+r_c)} & -\frac{1}{C(R+r_c)} \end{bmatrix} \begin{bmatrix} i_L \\ v_c \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} V_d$$

(4.41)

$$V_o = \begin{bmatrix} \frac{Rr_c}{(R+r_c)} & \frac{R}{(R+r_c)} \end{bmatrix} \begin{bmatrix} i_L \\ v_C \end{bmatrix}$$

(4.42)

In all practical circuits  $R \gg (r_c + r_L)$ , now we get the final simplified matrices as.

$$A_{1} = \begin{bmatrix} -\frac{r_{L}}{L} & 0\\ 0 & -\frac{1}{CR} \end{bmatrix}$$

$$B_{1} = \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix}$$

$$C_1 = \begin{bmatrix} 0 & 1 \end{bmatrix}$$

$$A_{2} = \begin{bmatrix} -\left(\frac{r_{L}+r_{c}}{L}\right) & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{CR} \end{bmatrix}$$

$$B_{2} = \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix}$$

$$C_{2} = \begin{bmatrix} r_{c} & 1 \end{bmatrix}$$

(4.43)

According to the state-space average methods the averaged matrices are

$$A = DA_{1} + D'A_{2}$$

$$B = DB_{1} + D'B_{2}$$

$$C = DC_{1} + D'C_{2}$$

$$E = DE_{1} + D'E_{2}$$

(4.44)

Whereas D'=1-D.

the steady-state dc voltage transfer function is

$$\frac{v_o}{v_d} = -CA^{-1}B = \frac{1}{(1-D)}$$

(4.45)

$$T_p(s) = \frac{\widehat{v_o(s)}}{d(s)} = C[sI - A]^{-1} \{ (A_1 - A_2)X + (B_1 - B_2)V_d \} + (C_1 - C_2)X$$

On solving we get[6]

$$T_p(s) = \frac{\hat{v_o}(s)}{d(s)} = V_d \frac{(R+r_c)(sCr_c+1)\{-(sL+r_L)(R+r_c)+D'^2R^2\}}{P(s)\{D'R(D'R+r_c)+r_L(R+r_c)\}} RV_d$$

(4.46)

Where,

$$P(s) = s^{2}LC(R + r_{c})^{2} + s\{L(R + r_{c}) + r_{L}C(R + r_{c})^{2} + D'Rr_{c}C(R + r_{c})\} + r_{L}(R + r_{c}) + D'R(D'R + r_{c})$$

#### 4.4 Pulse Width Modulator