# PC BASED PROTECTIVE RELAYING FOR TRANSFORMERS

#### A DISSERTATION

submitted in partial fulfilment of the requirements for the award of the degree

of

#### MASTER OF ENGINEERING

in

#### ELECTRICAL ENGINEERING

(With Specialization in Power System Engineering)

## DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247 667 (INDIA)

MARCH, 1999

# **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the Dissertation entitled. "PC BASED PROTECTIVE RELAYING FOR TRANSFORMERS" in fulfilment of the requirement for the award of the Master Degree and Submitted in the Department of Electrical Engg, University of Roorkee, Roorkee is an authentic record of own work carried and during a period from Sep. 1998 to March, 1999, under the supervision of Sri Bharat Gupta, Assistant Professor, Department of Electrical Engineering, University of Roorkee, Roorkee.

The Matter presented in this Disseration has not been submitted by me for the award of any other degree of this or any other university.

Date: 31.03.99

Ajay Kumar

Ajay Kuman

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

Sri Bharat Gupta Supervisor

# **ACKNOWLEDGEMENTS**

I express my foremost and deepest gratitude to Sri Bharat Gupta, Asst. Prof. Electrical Engineering Department in Electrical Engineering Department, University of Roorkee, Roorkee, for his invaluable guidance, support and encouragement throughout this work. I consider myself extremely fortunate for having got the opportunity to learn and work under his able Supervision and guidance over the entire period of my association with him.

Thanks are also due to my all friends who gave their direct or indirect Support in completing my M E Disseration.

I am highly indebted to my Father and family members for providing moral support and encouragement during the course of this study.

The help rendered by Power system Lab, staff of the Electrical Engg. Department particularly Sr. Jai Pal Singh and N.P.S. Singh are also grateful acknowledged.

Last, but not the least, my deepest gratitude is to the Almighty whose Divine light provided me guidance, inspiration and strength to complete this work.

ay Kumar

ABSTRACT

The present work aims at development of a percentage biased harmonic restrained differential protection using PC for a single phase power transformer.

The protective Scheme, differential protection of power transformers consists in converting the primary and secondary line currents to a common base using appropriately connected CTs of Suitable ratios and comparing these currents. During normal operating conditions, the difference between these currents is small, resulting from normal magnetizing current and small CT errors. This difference during external faults can be quite large because of a difference in the dynamic behaviours of CTs on the two sides of the transformer. On the contrary, during a winding (internal) fault, the difference current may not be very large. If only a small portion of the winding is short circuited.

In the protective Scheme followed here the presence of large second harmonic in the operating current, which is the difference between primary and secondary current, has been chosen to indicate the presence of magnetizing inrush condition. During over excitation condition it has been observed that third and fifth harmonics predominate. Here fifth harmonic has been chosen to indicate the condition of over excitation. Whenever second harmonic or fifth harmonic content of the operating current is greater than a fixed percentage of fundamental of the operating current the relay is restrained from issuing trip signal to the circuit breaker.

In this scheme fitter out second and fifth harmonic are filtered out with the hardware filter. These harmonic fed to the computer through ADDA 14 Card for taking decision to either issue trip signal or issue magnetizing condition or over excitation condition depending upon the magnitude of harmonic.

# **CONTENTS**

## CANDIDATE'S DECLARATION ACKNOWLEDGEMENTS ABSTRACT

|   |                                           |                                                | PAGE NO. |

|---|-------------------------------------------|------------------------------------------------|----------|

| 1 |                                           | Introduction                                   |          |

| 2 | Differential Protection fundamental       |                                                | 11       |

|   | 2.1                                       | Protection of transformer                      | 11       |

|   | ·· <sup>-</sup> 2.2                       | The differential principle                     | 11       |

|   | 2.3                                       | Factors affecting differential protection      | 18       |

|   | 2.4                                       | Transformer differential relay characteristics | 23       |

|   | 2.5                                       | Harmonic restraint                             | 26       |

|   | 2.6                                       | Methods of minimizing inrush current           | 28       |

| 3 | Harmonic analysis                         |                                                | 31       |

|   | 3.1                                       | Hardware filtering                             | 31       |

|   | 3.2                                       | Digital storage oscilloscope                   | 31       |

|   | 3.3                                       | Wave form processor                            | 33       |

| 4 | Hardware development                      |                                                | 34       |

|   | 4.1                                       | Design requirements                            | 34       |

|   | 4.2                                       | Design of relay hardware                       | 34       |

|   | 4.3                                       | Circuit details                                | 40       |

|   | 4.4                                       | Working operation                              | 40       |

| 5 | Soft                                      | ware implementation and flow chart             | 42       |

| 6 | <b>Results and scope for further work</b> |                                                |          |

|   | References                                |                                                |          |

|   | App                                       | endix                                          | · ·      |

|   |                                           |                                                |          |

## **INTRODUCTION**

Transformers are everywhere in all parts of the power system, between all voltage levels, and existing in many different sizes, types and connections. Usually, circuit breakers or other disconnection means are available at or near the winding terminals of the transformer banks. However, economics sometimes omission of a breaker. Thus transformer banks can be directly to a bus, line or generator. The latter is the unit generator arrangement.

Reliable operation of power transformers has became more important with the advent of EHV and UHV transmission. The abnormalities occurring in power transformers can be split up into two categories, the first covering winding short circuits where high speed tripping is essential while the second covers the core, tank and cooling systems faults and externally imposed abnormalities such as overloads where delayed tripping is sufficient.

High reliability relays for transmission line protection that can operate in a quarter cycle (Sms) or less have already been developed using travelling wave phenomenon. The same is not true for generators and transformers which can be grouped together, because both require unit protection Schemes.

#### **TYPES OF FAULTS:**

The varied characteristics of the power transformer have tended to become more complicated in recent years. It is thus worthwhile to review the different types of faults generally encountered by a transformer.

#### 1. Through Faults :

These can be subdivided into overload conditions and external Short Circuit conditions, the transformer must be disconnected when such faults occur only after allowing a predetermined time during which other protective gear should have operated. A sustained overload condition can be detected by thermal relays which give an alarm so that the situation can be attended to or the supply disconnected, if necessary. For the external short-circuit (bus-bar short circuit on the main Supply network) time graded over current relays or fuses are usually employed. Proper co-ordination of this backup transformer protection should be made with the primary protection of the associated power supply network. The primary protective scheme associated with transformer itself however should be made so that the protective gear does not operate under such conditions.

#### 2. Internal faults :

The primary protection of a power transformer is intended for

conditions which arise as a result of faults inside the protected zone. Internal faults are very serious and there is always the risk of fire, these internal faults can be classified into two groups.

#### Group (a) :

Electrical faults which cause immediate serious damage but are generally detectable by unbalance of current or voltage such as:

- (i) Phase-earth fault or phase-phase fault on the H.V and L.V external terminals.

- (ii) Phase-earth faults or phase-phase fault on H.V and L.V windings.

- (iii) Short-circuit between turns of H.V and L.V windings.

- (iv) Earth fault on a tertiary winding or short circuit between turns of a tertiary winding.

#### Group (b) :

So-called 'incipient' faults which are initially minor faults causing slowly developing damage. These are not detectable at the winding terminals by unbalance, they include:

(i) A poor electrical connection of conductors or a core fault (due to break down of the insulation of lamination, bolts or damping rings) which cause limited arcing under the oil.

- (ii) Coolant failure which will cause a rise of temperature even for full load operation.

- (iii) Related to (ii) is the possibility of low oil content or clogged oil flow, which can readily cause local hot-spots on windings.

- (iv) Regulator faults and bad load-sharing between transformers in parallel, which can cause overheating due to circulating currents.

Generally, for groups (a) it is important that the faulted equipment should be isolated as quickly as possible after the fault has occurred, not only to limit the damage to the equipment but also to minimize the length of time that the system voltage is depressed. A prolonged period of low voltage may result in loss of synchronism between rotating machines and, if this occurs the excessive current drawn by an out of step machine may well cause other relays to operate and initiate sequential and false tripping.

The fault of group (b) though not serious in their incipient stage may cause major faults in the course of time, and should thus be cleared as soon as possible.

Differential protection, where applicable, provides the best overall protection for both phase and ground faults, except in ungrounded systems or where the fault current is limited by high-impedance grounding. In these latter low-ground-fault current systems, differential provides only phase-fault protection.

Generally, differential protection is applied to transformer banks of 1 MVA and above. The key is the importance of the transformer in the system, so differential protection may be desirable for smaller units in some cases.

#### LITERATURE SURVEY:

Percentage differential relays for the protection of transformers were reported as early as 1931, by R.E Cordray Harmonic restraint to prevent false tripping due to magnetizing inrush current was introduced soon after by Kennedy et. al., [13] in 1938. A relay incorporating these features and with a claimed tripping time of around 20 ms after the occurrence of a fault was reported by hayword in 1941. Following this, several other schemes using analog components were added to the literature on this Subject, until Rockfeller came out with his landmark paper in 1969, discussing the use of digital computer for: amongst various other things; transformer protection. This was followed by another paper in 1972 by Sykes et.al. [3]. Proposing a concrete scheme which could be implemented digitally giving simulation results to evaluate its performance. This scheme used harmonic restraint to avoid tripping due to the magnetizing inrush current and used analog response filters to separate harmonics.

This resulted in slow operating and carried with it all the drawbacks of the analog filters mimicked by it. In 1975 Einvall et. al.[5] enlarged

upon the established harmonic restraint differential relay of concepts to provide a new static multiple-winding transformer differential relay. The resulting design included simplification of the frequency selective circuits and new techniques for rapidly determining the harmonic content of the applied currents. The relay was shown to have improved sensitivity and to be responsive to internal transformer winding faults in less than two cycles and to the more severe type of fault in less than one cycle. Full security against inrush currents and over excitation as well as to external faults was achieved.

Later attempts used digital filtering techniques as they emerged for various purposes like digital signal processing, image processing etc. In 1976 Malik et.al.[2] proposed the use of Fourier techniques for filtering response. In 1982 Thrope et.al. [14] presented an algorition for digital protection of a three phase three-winding power transformer. Simple recursive expression were given for the harmonics using a sampling rate of 12 times a cycle. The algorithm was successfully tested on data obtained from a model transformer.

In 1990 Verma et. al. [6] reported the development of a comprehensive relaying scheme for power transformer protection wherein one 8-bit microprocessor performs all high speed relaying functions and another similar processor provides all time-lag relaying function. The high speed

relaying functions include inrush-restrained biased differential and restricted earth-fault protection while the time-lag relaying includes over current backup, overfluxing, overload, tank leakage and stand by earth fault protection. The relay logic is based on current wave-shape rather than harmonic analysis.

A paper in 1991 by Benmouyal [7] reports the design of a differential and V/f relay for step-up transformers. The instantaneous values of the quantities sought are acquired at a rate of 12 samples per cycle and are processed by means of discrete fourier transform algorithm to obtain fundamental frequency phasors. An adaptive sampling rate generator combined with full cycle discrete fourier transform has been used to provide a sampling rate that will follow the speed of alternators such that whatever speed reached by the machines the number of samples per cycle would be 12. In 1992 Sidhu et.al. [15] described the design, implementation and testing of microprocessor base relays for protecting single phase and three phase power transformers. The relays do not use harmonic components of the differential currents to block operation during magnetizing inrush. Instead they used a non-linear model of the transformer to verify the health of the transformer. The non-linear model used electromagnetic equations of a transformers. These are differential equations which express voltage as functions of current, mutual flux

linkages and other transformer parameters. These equation are valid during magnetizing inruch, normal operating conditions and external faults. However, during faults in the transformers protection zone, these equations do not valid hold. The algorithm used this feature for detecting internal faults.

Measurement of transformer inrush currents offer important data for a power system operation and protection. In 1993 Lin et.al. [17] proposed a simple method to simulated the magnetizing inrush currents using real time measurements. The proposed methods formulates a simplified model to represent the inrush current under different loading conditions. A digital simulation method was proposed using a PC-AT microcomputer. Transformer operating condition including transformer loading power factors, switching - on angles and remnant flux are also included. The simulation results were found to be in agreement with experimental results.

In 1995. Verma, proposed an adaptive digital differential protection scheme for transformer, implementable on a microprocessor, for differential protection of a transformer. The transformer is continuously monitored to decide its condition and operating tap. In the event of an abnormal operation, the fundamental frequency and harmonic components of the differential current are used to identify the nature of abnormality

and accordingly an indication is given and trip decision is taken. The value of percentage bias to detect internal faults is chosen dynamically taking into account the actual CT mismatch for the operating tap along with the CT errors. The relay Scheme has been evaluated through simulation. On internal faults it is found to have better sensitivity and faster operation than a similar fixed-bias scheme. It does not operate on external fault, magnetizing inrush and over excitation conditions. In 1995 Verma proposed an intelligent digital differential relay for transformer protection, which is based on the continuous monitoring of the tap change position and correcting the CT Secondary currents to obtain the true time currents using a precalculated correction factor. Only a small fixed bias is provided to take care of CT errors under in dynamic conditions and the relay errors. In order to avoid tripping on magnetizing inrush and overexcitation conditions, second-cum fifth harmonic restraint is used. The proposed relay has the same sensitivity at all tap settings and clear low-level internal faults, some of which would remain uncleared by a fixed bias relay. The filter and relay algorithms have been designed for minimizing the calculations to facilitate their real-time implementation on a microprocessor.

In this dissertation work, first the differential current is filtered through hardware filter by restraining the fundamental component. Then

່ 9

processing is done inside the computer and accordingly trip signal in issued depending upon magnitude of second and fifth harmonic component. If percentage of second and fifth harmonic is less than specified percentage and the differential current greater than the restrained current, a trip signal is issued to isolate the faulted transformer otherwise alarm signal indicating magnetizing inrush condition and overexcitation condition and relay is restrained from operating during external fault.

The present work is organised into six chapters, including the present one. In chapter 2 basic principle of protection has been discussed. It has been pointed out as to why the percentage basis feature is important and fundamentals of harmonic restraint feature has been introduced.

In Chapter - 3, harmonic analysis has been discussed.

In chapter-4 hardwar requirements of protective Scheme have been laid down. Design parameters of current sensors meant for sum & difference of the signal have been given and Analog to digital card: ADDA-14has been discussed. Circuit details and working operation has also been discussed.

Chapter-5 describes the implementation of the proposes protection scheme and flowcharts have been given.

Finally in chapter 6 results have been discussed.

#### **CHAPTER 2**

#### **DIFFERTIAL PROTECTION FUNDAMENTALS**

#### 2.1 PROTECTION OF TRANSFORMERS:

Differential protection is the most common type of protection used for internal phase-phase and phase-earth faults of transformers. A transformer differential relay compares the currents in the windings of the transformer through the medium of current transformers who ratios are such as to make their secondary current normally equal except for the care magnetizing currents of the transformer which are relatively small. The polarity of the current transformer (CT) is such as to make the current circulate normally without going through the relay, during load conditions and external faults, i.e. the relay coil receives the vector sum of the derived currents which is normally zero. Any fault within the transformer disturbs the balance and the relay operates.

#### 2.2 THE DIFFERENTIAL PRINCIPLE

"A differential relay responds to vector difference between two or more similar electrical quantities."

Following aspects of Differential protection are

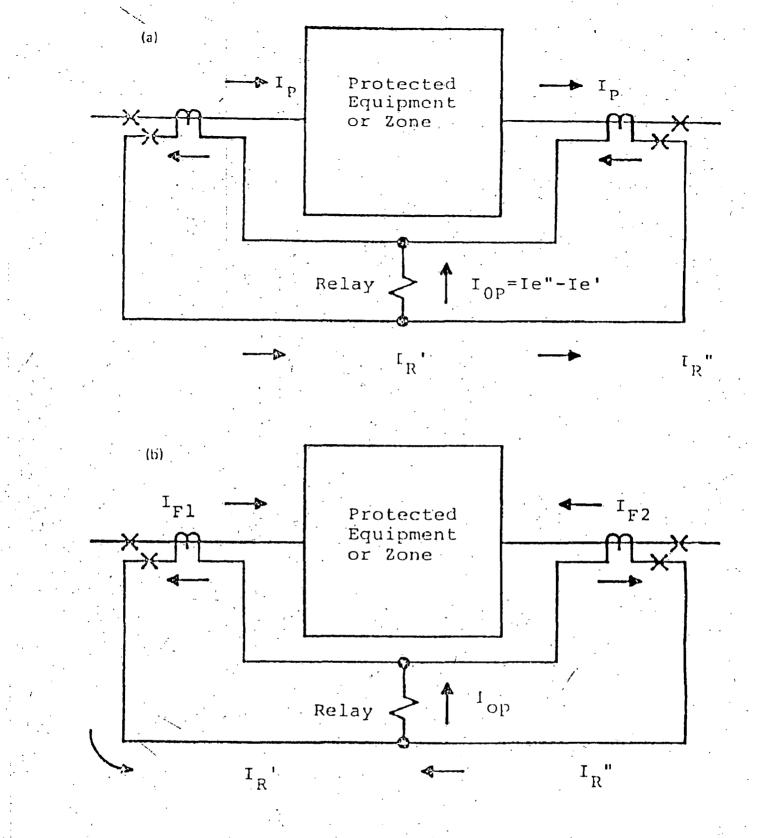

FIG. 2.1 BASIC CURRENT DIFFERENTIAL SCHEME ILLUSTRATED FOR TH PROTECTION OF A ZONE WITH TWO CIRCUITS (a) NORMA CONDITIONS,  $I_{op} = I_R'' - I_R' = I_e'' - I_e'$  (b) INTERNAL FAULT;  $= I_{op} = I_R' + I_R''$

1) The differential relay has at least two actuating quantities say  $I_{1}$ ,

The two or more actuating quantities should be similar.

The relay responds to the vector difference between the two i.e.

to  $I_1 - I_2$ , which includes magnitude and/or phase angle difference.

Differential protection is generally unit protection. The protected zone is exactly determined by location of CT's. The vector difference is achieved by suitable connections of current transformer or voltage transformer secondaries.

This fundamental technique is illustrated in Fig 2.1 and for simplicity only two circuits to the protection zone are shown. Multiple circuits may exist but the principle is the some. The Sum of the currents flowing in essentially equals the sum of the currents flowing out during normal operation.

For normal operation and all external faults ( the through condition ), the Secondary in fig 2.1 (a) in the protective relay is the difference in the exciting currents of the differential connected current transformers. Per unit current of the distribution is shown.  $I_p$  is the primary current in the lines entering or leaving the protected area.  $I_r$ ' and  $I_r$ " is the secondary ampere currents and is equal to primary current

divided by the current transformer ratio minus the secondary exciting current. Even with exactly the same ratio and type of current transformer the relay current  $I_{op}$  will be small but never zero. This is be case of the losses within the protected area and small difference between the same type of CTs. This assumes that no current transformer significantly saturates for the maximum symmetrical ac through currents. With different CTs and ratio, larger differences will exist which must be minimized and /or the pick-up of the relay set not to operate on any through fault condition.

For internal faults, fig 2.1b shows that the differential relay operating current essentially is the sum of the input current feeding the fault. This is the total fault current on a secondary ampere basis. Except for very light internal faults, good discrimination is available to detect problems (faults) within the differential zone.

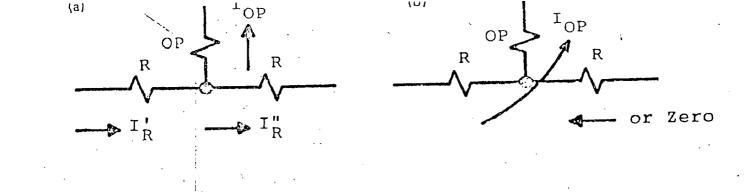

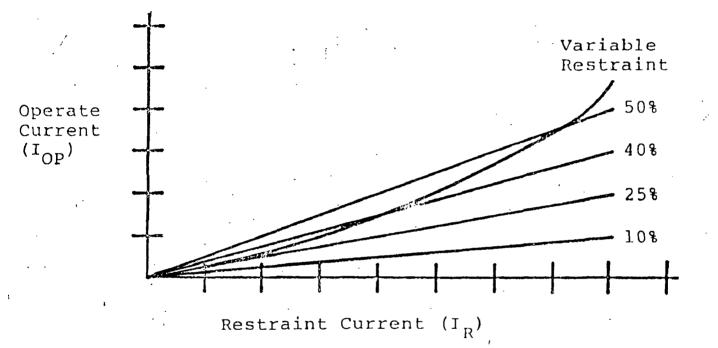

To provide high sensitivity to light internal faults with security (high restraint) for internal faults, most differential relays are of the percentage differential type. Fig. 2.2 is a solemnified schematic of this type of relay for two circuits, as shown in fig 2.1. The secondaries of the CTs are connected to restraint windings (R). and operating winding (OP). Current in operating winding tends to operate the relay. Differential relay may be of either fixed or variable percentage and

FIG. 2.2 PERCENTAGE DIFFERENTIAL RELAY : (a) EXTERNAL FAULTS (b) INTERNAL FAULTS

FIG. 2.3 TYPICAL THROUGH CURRENT CHARACTERISTICS OF VARIOUS DIFFERENTIAL TYPE RELAYS.

typical characteristics are illustrated in Fig. 2.3. The ordinate is the current  $(I_{op})$  required to operate the relay. Fixed percentage relays exist between 10 and 50% and may or may to not have taps to change the percentage.

Thus with a 50% characteristic and internal or through current of 10 A would require a difference or operating current of 5A or more for the relay to operate. With 10%, and 10A through current, 1A or more difference current would produce relay operation.

The variable percentage type do not have percentage taps. At low through currents is low since at these levels the current transformer performance is usually quite good. At high through-fault currents, where the CT performance may not be as good, a high percentage characteristic is provided. This gives increased sensitivity with higher security.

It is important to recognize that characteristics such as those shown in Fig, 2.3 apply only for external faults or through current flow. Differential relays are quite sensitive to internal faults where the currents in the restraint windings are in opposite directions or one restraint current is zero as in fig 2.2. These relays are calibrated with current through one restraint and the operating winding with no current through the other restraint (s). Typical pickup currents for differential relays are of the order of 0.14 to 3.0 A, depending on the type tap and application.

·16

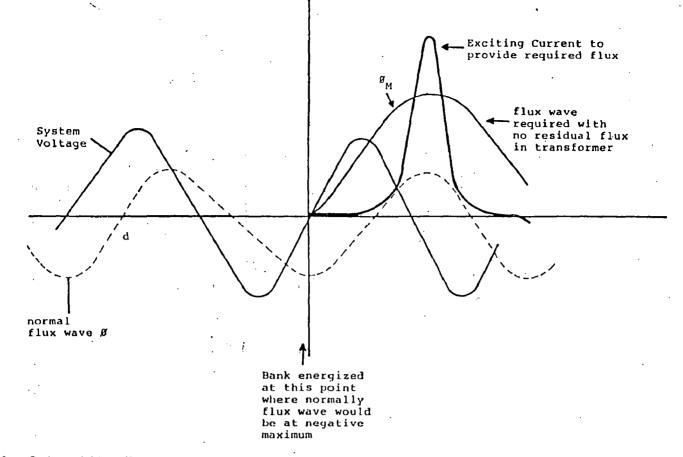

FIG. 2.4 MAGNETIZING INRUSH CURRENT PHENOMENON (NO RESIDUAL FL INITIALLY IN TRANSFORMER)

2.3 FACTORS AFFECTING DIFFERENTIAL PROTECTION:

1. Magnetizing inrush current.

- 2. Different voltage levels and hence the current transformers are of different types, ratios, and performance characteristics.

- 3. Phase shifts in wye-delta connected banks.

4. Transformer taps for voltage control.

5. Phase shift and/or voltage taps in regulating transformers.

#### **MAGNETIZING INRUSH:**

When system voltage is applied to a transformer at a time when normal steady-state flux should be at a different value from that existing in the transformer, a current transient occurs, known as magnetizing inrush current. This phenomenon is illustrated in Fig 2.4 for a transformer with no residual flux. In the figure the transformer is energized when the system voltage is zero. With the highly reactive circuit involved, the flux  $\phi$  should be or very near negative maximum but the transformer has no flux. Thus the flux must start at zero and reach a value of  $2\phi$  in the first cycle period.

To provide this flux, requires a large exciting current Transformers are normally operated near saturation for best efficiency, so value of flux greater than normal result in severe saturation and a large exciting

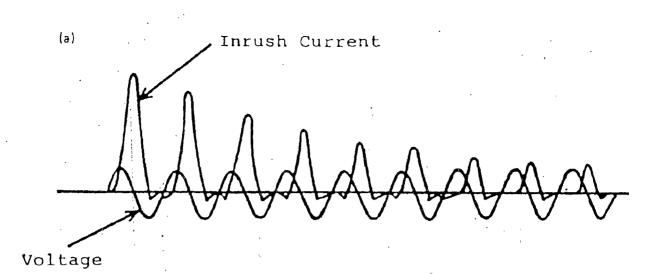

FIG. 2.5 TYPICAL MAGNETIZING INRUSH CURRENT TO TRANSFORMERS (a) A - PHASE CURRENT TO WYE - CONNECTED WINDINGS (b) A - PHASE CURRENT TO DELTA CONNECTED WINDINGS.

#### current.

If a transformer has been energized previously, there is a high possibility that upon deenergization some flux  $\phi R$ , was left in the iron. This could be positive or negative. If positive then earlier energization results in a  $2\phi + \phi R$ , higher maximum magnetizing inrush current. If negative then the maximum required flux would be  $2\phi - \phi R$  with less inrush current.

This is a random phenomenon. If the transformer had been encrgized at or near maximum positive voltage, the flux requirement at that time is zero. Thus normal exciting current flow with negligible or no transient inrush. Normal exciting current for power transformers are of the order of 2 to 5% of full-load current.

The maximum initial magnetizing current may be as high as 8 to 30 times full-load current. Resistance in the supply circuit and transformer and the stray losses in the transformer reduce the peaks of the inrush current so that eventually it decays to the normal exciting current value. The time constant varies from around 10 cycles to as long as 1 minute in very high inductive circuits.

The factors involved in the inrush, in addition to the time point of energization with relation to the flux requirements, are the size of the transformer, the size and nature of the power system source, the type

of iron in the transformer, prior history, and the L/R ratio of the transformer and system.

In a three-phase circuit in the inrush will always occur in one or two and generally all three phases with the voltages 120<sup>o</sup> apart, although it may or may not be maximum or zero in one of the phases.

#### **RECOVERY MAGNETIZING INRUSH:**

During a fault or momentary dip in voltage, an inrush may occur when the voltage returns to normal. This is called the recovery inrush. The worst case is a solid three-phase external fault near the transformer bank. During the fault the voltage is reduced and nearly to zero on the bank; then when the fault is cleared, the voltage suddenly returns to essentially normal value. This may produce a magnetizing inrush, but it maximum will not be as high as the initial since the transformer is partially energized.

#### SYMPATHETIC MAGNETIZING INRUSH:

A magnetizing inrush can occur in an encrgized transformer when a nearby transformer is encrgized. A common case is paralleling a second transformer bank with a bank already in operation. The dc component of the inrush current can also saturate the energized

transformers, resulting in an apparent inrush current. This transient current, when added to the inrush current of the bank being energized, provides an offset symmetrical total current that is very low in harmonics. This would be the current flowing in the supply circuit to both transformer banks.

LARGE INRUSH CURRENTS IN POWER TRANSFORMERS: WITH LOW-LOSS STEEL CORES :

There is a tendency in transformer design towards the use of cold rolled steels for cores in which the hysteresis loss per cycle is much smaller than with hot rolled steels. Allowing the some core losses, the normal working flux density in cold-rolled steels can be made higher than in the earlier types. The attainment of the these advantages have been accompanied by an increases of the initial transient magnetizing current.

#### **CURRENT TRANSFORMER CHARACTERISTICS :**

Unless saturation is avoided the difference in C.T. characteristics due to different ratios being required in circuits of different voltage may cause appreciable difference in the respective secondary currents whenever through faults occur even through these currents are of equal value at normal load. This is particularly troublesome when different

types of current transformers are used, as is frequently the case in transformer protection.

Unequal length of current transformer secondary leads my well cause a difference in V.A. burden between the two sets of CTs, this generally tends to give a ratio error between the two sets of current transformers.

#### **RATIO CHANGE AS A RESULT OF CHANGE OF TAPPING:**

Nearly all large modern power transformers are equipped with on load ratio change gear. As the transformer ratio is changed, the ratio between the primary side and secondary side current transformers can be made to match at one point only of the tap-changing range. At other points an unbalance current will flow in the differential relay, the effect of which requires biased relays for its control.

#### 2.4 TRANSFORMER DIFFERENTIAL RELAY CHARACTERISTICS:

The basic principles of differential relays and protection were outlines in above paragraphs. For applications to transformers the differential relays are less sensitive and with typical percentage characteristics between 20% and 60%. This provides accommodation for the different CT ratios, types and characteristics, different primary

current energization levels, and for transformers taps where they exist. To avoid desired operation on the magnetizing inrush current the relays may (1) be designed with reduced sensitivity to the transient inrush current, (2) use the harmonics of the inrush current to prevent operation, or (3) desensitize operation momentarily during the energization time.

For smaller transformer banks, particularly in the lower-voltage sub-transmission and distribution systems, the electromechanical induction disk transformer differential relays with typically 50% characteristics and operating time about 0.08 to 0.10 s (four to five cycle in a 50 Hz system) are used with good immunity to inrush. Generally in these areas the inrush is not too server and there is sufficient resistance in the system to damp the transient rapidly. Also, the induction disk unit does not operate on dc. The advantage is the relative simple rugged design and low cost. However, it is not possible to assure that the relay will never operate on inrush , although experience can show it to be quite immune. Someone has observed that this type of relay "has long and enviable record" of good performance, which account for its continued use.

For larger banks, banks in the higher-voltage and/or where it is important to assure no operation on inrush, harmonic restrained

differential relays should be used. For faults the harmonics are of very low values, so the "handle" of harmonics provides are an effective means to distinguish the inrush current from fault currents. The second harmonic, which is a major component in the inruch wave, is used to restain or prevent relay operation. In some designs it is used alone, in other in combination with the other harmonics.

Momentary desensitizing or disconnecting differential relays is not recommended, as it limits protection. It is used occasionally to solve a problem until a more satisfactory solution can be effected. A slip contact on the breaker control switch can insert a resistor in the operation coil circuit to desensitize the relay or momentarily short the operating coil while break is being closed. A high-set instantaneous trip unit can be used to operate for a heavy current internal fault occuring on energization.

#### 2.5 HARMONIC RESTRAINTS :

By for the most common technique used for preventing false trips during energization is the use of a 'harmonic restraint' relay. The fact that an inrush current is richer in harmonics than a fault current is key to the design of a harmonic restraint function.

The harmonic content of the inrush current depends upon many

factors; residual magnetization of the core and instant of switching are two of the more important factors. There are other phenomena which also contribute to the harmonic to the hamronics and their effect on the behaviour of the harmonic restraint function must also be considered. Three major sources of harmonics are as follows:-

(i) Magnetizing inrush due to non-linearities of transformer core.

(ii) Saturation of current transformers.

(iii) Over excitation of the transformers due to a dynamic over voltage condition.

The harmonic restraint function should be so designed that it restraints during the magnetizing inrush and over excitation conditions, while during an internal faults the harmonics generated by a saturated CT should not restrain the differential relay.

The inrush to a three-phase transformer is more complex than just the sum of three individual transformer inrushes. In particular, a delta connection either of the main transformers or of the CTs will result in a less favourable ratio of 2nd harmonic current to fundamental in at least one of the phases. This is because wye-delta transformers cause different relative phase shifts to three-phase 'single-phase and the harmonics currents. Since these are all complexities stemming from the three-phase environment, it is logical to resolve them with a threephase analysis. The energizing inrush depends significantly upon the residual magnetization in the transformer core.

The harmonic restraint feature may result in the failure of the relay to operate on a heavy internal fault if considerable harmonics are present. These harmonics may be present in the fault current itself due to an are and produce harmonic. Also if a fault exists at the time a transformer is energized, harmonics in the nagnetizing current may prevent it from tripping. For this purpose it is customary to provide an instantiations over current relay in the differential circuit which is set above the maximum inrush current but will operate within one cycle on internal faults. In this way fast tripping is assured for all internal faults.

#### 2.6 Methods of Minimising Inrush Current

Although no commercial means have become available for the suppression of magnetising currents in a transformer, the following methods have been proposed.

a) Resistance Energisation

A series resistance is inserted is the energising circuit by the first step of a two step switch and it is proportioned so that, when the first

contact closes, only about one half of the circuit voltage will be impressed on the transformer. Since the voltage is raised in steps, the transient flux swing can be arranged so as not to exceed the steady state normal value. This method requires a very large value of series resistance and it is capable of reducing the switching surges, it but it fails to cater for the suitation of inrush currents accompanying the recovery voltage, e.g. after an external fault close to the transformer has been cleared.

## b) Capacitance for reducing residual magnetism -

A capacitance is connected in parallel with the transformer so that, when the transformer is disconnected from the supply, the damped oscillation in the turned circuit so formed eventually eliminates any residual magnetism. This method has not very effective in reducing the peak value of magnetising inrushes.

This may be due to the fact that modern transformers using improved silicon steel and normally working nearly at saturation flux density may in some cases, retain considerable residual magnetism after deenergisation. When re-energised, these transformers will tend to draw inrush currents which in early cycles, may cover the period of nearly a complete voltage cycle. This type of inrush current will contain a high percentage of d.c. component but less second harmonic component; thus any relay which depended for its restraint relay on the second harmonic component of transformer magnetising inrush current would encounter difficulties. Since the inrush current exists only on the source side of the transformer, the inrush current will appear in the differential circuit and operate the relay. The amplitudes of harmonics, compared with the fundamental (100%) are as follows :

1) The d.c. component varies between 40% and 60%.

2) The second harmonic between 30% and 70%.

3) The third harmonic between 10% and 30%.

The other harmonic are progressively less.

# <u>Chapter-3</u> Harmonic Analysis

## 3.1 Hardware Filtering -

Large second harmonic content of operating current is indication of magnetising inrush condition while fifth harmonic content is indication of over excitation conditions, due to these harnomic content maloperation of relays takes place which operate relay for through fault. We use analog filters to obtain trip and restraint signals with different harmonic content. After filtering harmonics means block the fundamental component and pass all higher frequencies component then to perform the relaying function based on the harmonic content of the signal.

Harmonic spectrums have also been obtained experimentally with the help of FFT analyser facility of the storage oscilloscope. The waveforms of transformer primary and secondary current are recorded in each case and their hardware FFT specturms are obtained and printed through the integral plotter of the oscilloscope.

## 3.2 Digital Storage Oscilloscope

The Gould 1604 digital storage oscilloscopes have been designed to provide a versatile range of instruments for use in a wide range of applications.

The 1604 can operate in storage or non-storage made as required and includes all the features expected of an advanced modern oscilloscope at the same time retaining user friendliness. For the first time user obtaining a trace is especially simple just connect the signal and press the auto setup button. The 1604 does the rest. Having obtained a trace, three readily accessible cursors make it easy to take automatic time and voltage measurements directly from the display. The innovative use of five position paddle controls instead of dials makes precise control of the instrument possible, the digital read out on the display constantly showing the current status where appropriate.

More advanced features of the 1604 include a comprehensive system of many controlled functions.

Another many controlled feature of the 1604 is it memory. Two complete traces can be stored for future use, and four complete front panel control setups. With the optional battery backup facility. These can be retained even when the 1604 is switched off.

The 1604 comes complete with serial-channel and four-parallel channel analogue outputs for use with external plotters as standard. Optional extras include GPIB (IEEE 485) & RS 423 input/output ports for enternal control by a host computer, and Gould waveform processors to provide enchanced measurement and trace processing.

## 3.3 Wave form processor type 260 :

The 260 waveform processor adds a range of function to the 1604 series which increases the power of the instrument in terms of both capture and post storage analysis and measurement functions. The waveform processor can perform fourier transform on any trace captured by the 1604.

Pressing 'FFT Menu' ('F' followed by FFT) displays the options associated with the FFT.

Window : Rectangular Hanning ... 1 Points : 1024 512 256 Cursor ... 2 Result To:

CH1 CH2 CH3 CH4 REF 1 REF2....3 Horiz Scale: Linear Log....4 Vert Scale : Linear Log......5 Hz measurement : Harmonic Rel.....6

"Fourier Transform MENU"

The number of points analysed by the FFT is selected from this menu. With 1024, 512 or 256 points the FFT will use every point, every 2nd point and every 4th point of the source trace respectively. The FFT will calculate the frequency specturm faster when using the smaller number of points.

## <u>CHAPTER - 4</u>

## HARDWARE DEVELOPMENT

4.1 DESIGN REQUIREMENTS:-

1.

3.

4.

The following design requirements for the relay were identified. The relay should be suitable for use on any transformers irrespective of their capacity and voltage ratings.

2. Provisions should be made to isolate and protect the relay hardware for power system transients,

The hardware should be modular permitting replacement of a faulty module in the event of a failure.

The relay should include a man-machine interface (MMI) for modifying the software and for changing relay setting.

## 4.2 DESIGN OF RELAY HARDWARE:-

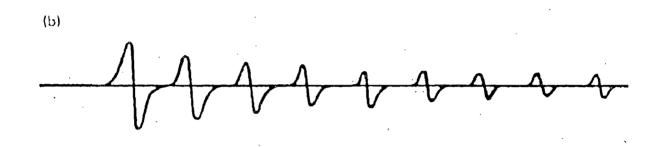

The relay hardware was designed keeping in mind the requirements out lined in the previous section. As shown in fig 4 through two current sensor primary and secondary sides current of three phase transformer were sensed then these currents are converted into voltage by use of suitable resistance. After conversion the resulting voltage is fed into ADDA-14 card for storing data in PC.

As shown in figure 4. hardware filter has been designed which blocks

· 34

fundamental component and passes all higher harmonics. This filtered wave from is then recorded on the computer through ADDA-14 card. After calculating harmonic percentage, final decision has been taken depending upon the magnitude of harmonic percentage, either to operate the relay or indicate magnetizing inrush or overexcitation conditions.

#### Specification :

#### 1. Main Transformer -

Rating - 1 KVA

- 220 V.

Primary to secondary turns ratio - 2:1

2. Current sensor -

Two sets of current sensor

1. Primary current rating - 50 A

primary to secondary turns ratio - 1: 1000

3. Filter -

IC- 741. OP- APM.

C = 1 u F

R= 3.18 K

## THE ANALOG TO DIGITAL CONVERTER :

For analog to digital conversion the data card VPC - ADDA 14 was used. The various features of this card are as follows:

#### **1.)** SPECIFICATIONS :

- a) 14 bit resolution

- b) 16 input channels

- c) input voltage 0 to 4.5 for unipolar and -4.5 V to +4.5 V for bipolar.

- d) Conversion time less than 4.2 usec

- e) relative accuracy  $\pm 1/2$  LSB.

## 2.) **DESCRIPTION**:

ADDA-14 is a high precision data converter card having 16 channels of analog to digital converter and two channels of digital to analog converter. The card uses three number of high resolution 14 bit DAC 7614 chip which is a 14 bit digital to analog converter. The first chip is used for A/D conversion using successive approximation technique. In this part of A/D conversion a chip 4051 is used for multiplexing the 16 channels i.e. to select one out of 16 channels at a time.

The channel number is software selectable. A jumper J1 is used for selecting unipolar or biopolar input. If a jumper is placed at J1 the card accepts bipolar input otherwise it accept only unipolar input.

# 3.) PORT ADDRESS OF THE CARD

The port address of the card is selectable by jumpers J4 and J5. The card address can either be 0x170 to 0x17f or 0x1fo to 0x1ff. The addresses is expressed in decimal would be from 368 to 383 or 496 to 511. The address can be selected as follows:

| Jamaper J4 | Jumper J5 CA |  | RD ADDRESS |  |

|------------|--------------|--|------------|--|

| ON         | OFF          |  | 368 TO 383 |  |

| OFF        | ON           |  | 496 TO 511 |  |

# ON - JUMPER IS PLACED

## OFF- JUMPER IS NOT PLACED

The basic address of the port would be either 368 or 496.

The remaining address would be as follows:

| PORT =     | 368 Or 496                                   |

|------------|----------------------------------------------|

| PORT + 0 = | Out put data (0 to 15) to select A/D channel |

| PORT + 1 = | Out put 00 to clear A/D data                 |

| PORT + 2 = | Read A/D low 8 bit data                      |

| PORT + 3 = | Read A/D high 6 bit data                     |

| PORT + 4 = | Output at 1st D/A low 8 bit data             |

| PORT + 5 = | Output at 1st D/A high 6 bit data            |

PORT + 6 = Output at 2nd D/A low 8 bit data

PORT + 7 = Output at 2nd D/A high 6 bit data

PORT + 8 = Loop back 8 times to start A/D high 7 bit conversion

PORT +12 = Loop back 8 times to start A/D low 7 bit conversion.

#### 4.) CONVERSION PROCESS FOR A/D :

- a) Output channel number to PORT 0 + 0

- b) Initialize A/D register

- c) Start conversion by looping back individually exactly 8 times in PORT

+ 8 and PORT + 12.

- d) Read data in PORT + 2 for low 8 bit and PORT + 3 for high 6 bit.

#### CARD ADDRESS - h 170

Channel utilised - channel no - 0, 1, 2

### 5) CONNECTOR DETAILS:

A 25 pm D type connector is provided for interfacing the card with the analog signals.

| PIN NO. | SIGNAL      | PIN NO. | SIGNAL      |

|---------|-------------|---------|-------------|

| 1       | + 12V       | 14      | -12 V       |

| 2       | 2nd D/A out | 15      | 1st D/A out |

| •    | :    |     | •    |

|------|------|-----|------|

| 3    | GND  | 16  | CH6  |

| 4    | CH7  | 17  | CH4  |

| 5    | CH5  | 18  | CH2  |

| 6    | СНЗ  | 19  | CHO  |

| 7 ·  | CH1  | 20  | CH15 |

| 8    | CH14 | 21  | CH13 |

| 9    | CH12 | 22  | CH11 |

| 10   | CH10 | 23  | CH9  |

| 11 · | CH8  | 24. | GND  |

| 12   | GND  | 25  | -5V  |

| 13   | +5V  |     |      |

|      |      |     |      |

### (6). 8255. Input Output Card :

The 8255 I/o card is a programmable Input - Output interface card for IBM -PC /AT/XT or their compatiables. The card contains 48 fully programmable Input - Output lines, 3 independently programmable 16-bit counters, each with a count rate up to 2 MHz. The hardware address is selectable between 01 Boh and 01Bfh and also between 01foh and 01ffh.

Port address -PORT = h1B0 For 8255 - 2. PORT 2-A = PORT + 8 + 0 PORT 2-B = PORT + 8 + 1 PORT 2 - C = PORT + 8 + 2 PORT 2 - CW = PORT + 8 + 3

#### 4.3 Circuit Details -

Two current sensors are used in primary and secondary sides of transformer for current sensing. Amplifiers uses IC-324OP-AMP are used for signal amplification.

IC-741OP-AMP is used for filterout of 50 Hz and other higher frequencies to pass.

The amplified signals are converted into digital using ADDA-14 and recording in PC.

The diagram of develop circuit of PC based Protective relaying for transformers are shown in fig 4.

## 4.4 Working Operation -

The circuit for PC based protecting relaying for single phase transformers is shown in fig 4. Primary and secondary current have been sensed through current sensors of turns ratio 1:1000. Then resistance is

Fig. 4. Circuit Diagram of PC Based Differential Protection for Transformers

connected through secondary of each current sensor and current is converted into proportionate voltage these voltages are amplified through IC-324. They are then fed to ADC card ADDA-14 and recorded in PC. The fundamental component of primary current filtered out through IC 741 op-amp. and harmonics contents are amplified through IC-324 and then fed to ADDA-14. This is done in order to detect magnetisation inrush condition. In this way recording of signals takes place. The recorded signals are then processed in PC for operating current, restraining current and harmonic percentage when operating current is greater than restraining current and harmonic percentage is greater than 40%, relay is restrained from operation. But if harmonic percentage is less than 40%, relay operate and indicate internal fault. This trip signal generate at PORT-A of 8255-2 I/O and LED glows.

## Chapter-5

## Software Implementation And Flow Chart

## **Input Requirement and Notations :**

Relaying Scheme needs 3 input signals for its operation : two signals for primary and secondary currents and one for harmonic current.

The notations used for various quantities are as follows:

Channel number : i

Primary Current : I [o] = a

Secondary current : I [1] = b

Harmonic Current : I [2] = c

ith sample of primary current : I [o] [i]

ith sample of Secondary current : I[1] [i]

Inside the computer the samples of all 3 input signals are stored in 3x16 data array. The three signals are read via channels 0, 1, 2 and stored in data array.

The value of percentage bias taken here is 0.4 i.e. 40%. The turn ratio of current sensor is 1:1000 and a suitable value of resitance connected across the current sensor for conversion purpose (to convert the current signal into a proportional voltage signal). This converted voltage is within the range of ADDA-14. To eliminate the effect of harmonics and noise in currents, the different frequency components are extracted using hardware filters and used in the relay operation logic. The relay operates if the following conditions are satisfied.

$I_d > I_O$ and  $I_d > BI_t$

where  $I_d$  and  $I_t$  are the fundamental frequency components of differential and through currents, respectively; and Io and B are pick up current and fractional bias.

Then calculate the harmonic restraint factor.

# HRF = (harmonic restraint Component + Fifth harmonic component) Fundamental frequency component

. .

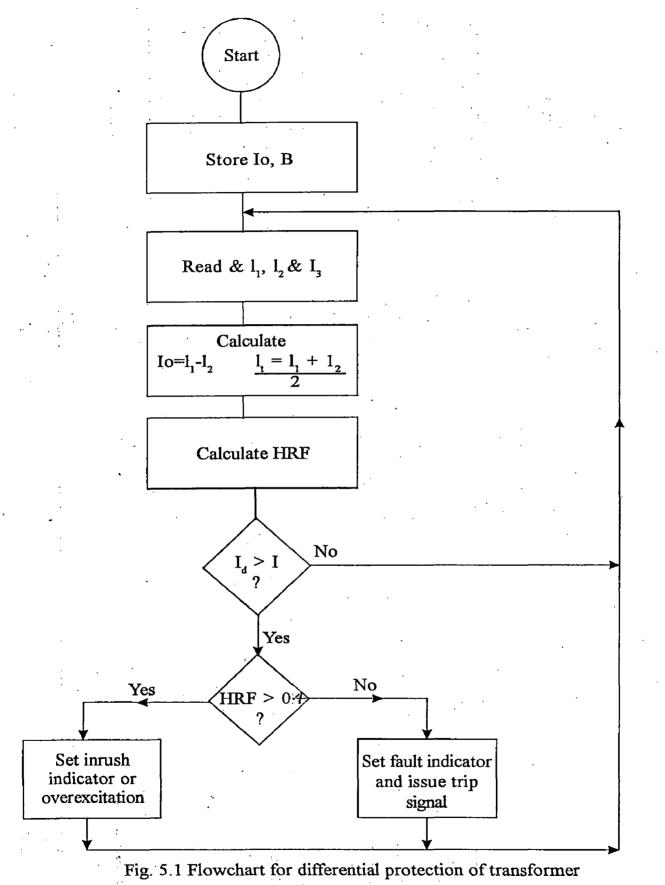

#### Flow Chart :-

A flow chart of the relaying scheme has been shown in Fig. 5.1.

The value of pick up current  $I_0$ , bias B are prestored in memory. In the second block, the value of primary. Secondary and filtered harmonic current are read via channel no. 0, 1, 2 respectively of ADC card ADDA-14.

Then calculate the difference, sum current and harmonic restraint factor. If the operating current (difference current) is greater than the restraining current (Sum current) and HRF is greater than 0.4 then set inrush indicator.

But if HRF is less than 0.4 then set fault indicator and issue trip signal otherwise read next sample.

**CHAPTER-6**

## **RESULTS AND SCOPE FOR FURTHER WORK**

The author has carried out simulated test for differential protection of transformer with the help of function generators

1) First of all given fundamental component to the PC through the ADC and harmonics ,40% of fundamental component. Then the observed that relay yielded a blocking signal and indicated magnetising inrush condition.

2) Under no internal fault codition, the differance is zero as  $I_1$  and  $I_2$  are of same magnitude and cancel each other, relay indicated no operation. 3) Under internal fault condition the relay operation indicated (Primary current ( $I_1$ ) is greater than secondary current with second harmonic percentage less than 40%)

Actual experimentation could not be carried out because of nonavailability of three phase transformer).

## Scope for further work

The relay logic was found to be working satisfactorily under all the cases. Most of the relaying function have been achieved through hardware, the software requirement is extremely simple.

The present work can be carried through software only without need of hardware filter by digital filtering and simulate the actual normal and abnormal condition.

The research has been going in this field for taking into acount tap changing error and CT ratio error.

#### REFERENCES

- 1. Verma, H.K., Maheshwari, R.P. "Intelligent digital differential relay for transformer protection" Research paper Oct, 1995 pp 158-163.

- Verma, H.K., Maheshwari, R.P., "Adaptive digital differential protection of transformer improvement over the fixed bias scheme" Research paper. Sept. 1995, pp 218-221

- 3. Maheshwari, R.P., Verma, H.K. ""Adaptive digital differential relay of parabolic characteristic for transformer protection" Dec. 1995 pp- 459-472

- 4. Maheshwari, R.P., Venna, H.K. ""Adaptive digital differential relay with overexcitation and inrush restraint" Sept 1996 pp 175-184

- 5. Warrington, A.R., Vaan, C. "Protective relays- Their theory and parctice", Vol.

1, 1968, Champan and Hall London pp 390-405

- Warrington, A.R., Vaan, C. "Protective relays- Their theory and paretice", Vol.

2, 1968, Champan and Hall London pp 207-213

- 7. Ravindranath, B., Chander, M. "Power System protection and switchgear" Willey Eastern Limited.

- 8. Sunil, S. Rao " Switchgear and protection"

- 9. Wadhwa, C.L. " Electrical Power System" Wiley Easter Limited, pp 413-419

- 10 Power system Protection Principles and Component peter peregrium Ltd. pp 259-264

- IEEE Recommended practise for protection and coordination of Industrial and Commercial Power System. The Institute of Electrical and Electrics Engineers, Inc., pp-169-176

#### **APPENDIX**

```

# include <stdio.h>

# include <math.h>

# include <dos.h>

int PORT = 0 \times 170;

int a 8255 base add = 0 \times 1b0;

int IL, IH, IT[3], k,i,t,j;

float T[3];

void main()

```

```

{

```

{

```

outport b ( a_8255 base add + 11, 0x e4);

for (k=0; k<16; k++)

for(i = 0; i < 3; i + +)

{

outportb(PORT + 1, 0);

outportb(PORT + 0, i);

for (j = 0; j < 8; j + +)

{

inportb (PORT +12);

}

IL = inportb (PORT +2);

for (j = 0; j < 8; j ++)

{

inportb (PORT + 8);

}

IH = inportb (PORT + 3);

IH = (IH \& 0x3f);

IT [i] = IH + IL;

T [i] = (IH-8090)/1685.0;

a = T [0];

b = T [1];

c = T[2];

}

```

Printf ("n a = % fc=%f", a,b,c); b=%f getch(); /\* Program for implementing protective scheme \*/ Id = a-b;Is = (a + b)/2;Ih = (c/a) \* 100;Printf (" Ih = % f'', Id, Is,Is = %fId = %fIh); if (Id > Is){ if (Ih > 0.4){ outportb (  $a_8255$  base add + 8,0); printf("INRUSH condition") } else outportb (  $a_8255$  base add + 8,1); } else

printf("no fault" );