# **IMPLEMENTATION OF DSP PROCESSOR ON FPGA**

### **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree of

MASTER OF TECHNOLOGY

in

### ELECTRICAL ENGINEERING

(With Specialization in System Engineering and Operations Research)

By T.RAVI KUMAR

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE - 247 667 (INDIA) JUNE, 2008

# CANDIDATE'S DECLARATION

I hereby declare that the work which is being presented in this dissertation entitled, "IMPLEMENTATION OF DSP PROCESSOR ON FPGA" submitted in the partial fulfillment of the requirements for the award of the degree "Master of Technology" with specialization in System Engineering and Operations Research, to the Department of Electrical Engineering, IIT Roorkee, Roorkee is an authentic record of my own work carried out during the period from August 2007 to June 2008 under the supervision of Dr. Indra Gupta, Associate.Professor, Department of Electrical Engineering, IIT Roorkee.

The matters embodied in this report have not been submitted by me for the award of any other degree or diploma.

Date: 30 June 2008 Place: Roorkee

This is to certify that above statement made by candidates is correct to the best of my knowledge.

Date: 30 June 2008 Place: Roorkee

(**Dr. Indra Gupta**) Associate Professor, Electrical Engineering Department, Indian Institute of Technology Roorkee.

# ACKNOWLEDGEMENTS

I would like to express my sincere appreciation to my supervisor, **Dr. Indra Gupta**, Associate Professor, Department of Electrical Engineering, for the patience and guidance throughout the entire duration of my thesis. Continuous monitoring and time management was an inspiring force for me to complete the work. Without her supervision, this thesis would never have been a success. Working under her guidance has been a great experience which has given me a deep insight in the area of technical research. Her painstaking support and involvement in preparation of manuscript, theoretical analysis and simulation studies are gratefully acknowledged. I humbly acknowledge a lifetime's gratitude to her and hope for a continued interaction even in the future.

I consider myself extremely lucky and privileged to learn about Micro Processors subject from **Prof. M. K. Vasantha**. It is because of him, that I started developing interest in Digital electronics and Computer architecture. His way of teaching, presentation in the classroom, the discipline he has inculcated in us, will be what I would like to follow throughout my life. His constant encouragement and willingness to listen to and help with my academic queries are some of the things I benefited with.

I also thank **Dr. H.O Gupta**, **Dr. Surendra Kumar**, **Dr. Rajendra Prasad**, **Dr. G.N. Pillai** and **Dr. Barjeev Tyagi** for extending moral support and technical discussions as and when required during the work.

I would like to take this opportunity to express my deep sense of gratitude to my family for their support and encouragement they have provided me over the years.

I would also like to thank my friends and lab assistants who have offered me their unrelenting assistance throughout the course.

Date: 30 June 2008

T.Ravi Kumar

Place: Roorkee.

### Abstract

Microprocessors built specifically for digital signal processing are DSP processors. DSP chips are high-speed, dedicated microprocessors that have been optimized to perform Arithmetic operations on the huge amounts of data required by spectral analysis and signal processing algorithms.

DSP Processors are the computational engines on which DSP applications are built. General purpose DSP processors provides an effective way to design and implement DSP algorithms for real-world applications. DSP is one of the core technologies in rapidly growing applications like communications and audio processing. DSP systems have progressed remarkably in the past decades, especially within the last few years. The estimated growth of DSP processors in the last 6 years is over 40%. The variety of DSP capable processors for various applications also increased with the rising popularity of DSP processors.

The present work is a structured approach to design and implementation of an embedded DSP processor core. The work focuses on the design of the 16bit DSP Processor described by the VHDL language and optimized by forcing timing constraints. The proposed DSP Processor is implemented and tested through simulation results and the results of the processor are validated.

The designs are coded with VHDL, synthesized and configured into Spartan-2 XC2S200-5Q208 FPGA, from Xilinx family. The ISE 7.1 synthesis tool is used in this project for synthesis and implementation.

# CONTENTS

|                                                                           | Page no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DECLARATION                                                               | I.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GEMENT                                                                    | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2                                                                         | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -                                                                         | IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RES                                                                       | VI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Introduction                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.1 General Introduction                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.1.1 A Brief History of FPGAs                                            | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.1.2 What can FPGAs be used for                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.2 Objectives of the dissertation                                        | 5,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.3 Organization of Thesis                                                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DSP Processors                                                            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1 Introduction to DSP Processors                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1.1 DSP Environment                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1.2 Applications                                                        | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1.3 DSP Architecture                                                    | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.2. General Architecture of DSP Processors                               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.2.1 Data Path                                                           | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.2.2 Control unit                                                        | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.2.3 Memory                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Developed Processor: Instruction Set Architecture<br>and Addressing Modes | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.1 Introduction                                                          | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.2 Instruction Format                                                    | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.3 Addressing Modes                                                      | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.4 Instruction Types                                                     | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                           | GEMENT<br>RES<br>Introduction<br>1.1 General Introduction<br>1.1.1 A Brief History of FPGAs<br>1.1.2 What can FPGAs be used for<br>1.2 Objectives of the dissertation<br>1.3 Organization of Thesis<br>DSP Processors<br>2.1 Introduction to DSP Processors<br>2.1.1 DSP Environment<br>2.1.2 Applications<br>2.1.3 DSP Architecture<br>2.2. General Architecture of DSP Processors<br>2.2.1 Data Path<br>2.2.2 Control unit<br>2.2.3 Memory<br>Developed Processor: Instruction Set Architecture<br>and Addressing Modes<br>3.1 Introduction<br>3.2 Instruction Format<br>3.3 Addressing Modes |

|            | 3.4.1 R-type instructions                              | 15 |

|------------|--------------------------------------------------------|----|

|            | 3.4.2 I-type instructions                              | 15 |

|            | 3.4.3 J-type instructions                              | 16 |

|            | 3.5 Instruction Set                                    | 17 |

|            | 3.5.1 Data transfer instructions                       | 18 |

|            | 3.5.2 Arithmetic instructions                          | 19 |

|            | 3.5.3 Logical instructions                             | 19 |

|            | 3.5.4 T register, P register and Multiply instructions | 20 |

|            | 3.5.5 Shift instructions                               | 20 |

|            | 3.5.6 Branching instructions                           | 21 |

| CHAPTER 4: | Design Architecture of Proposed DSP Processor          | 22 |

|            | 4.1 Introduction                                       | 22 |

|            | 4.2 Architecture Overview                              | 22 |

|            | 4.3 Data Path (DP)                                     | 25 |

|            | 4.3.1 Arithmetic and Logic Unit (ALU)                  | 25 |

|            | 4.3.2 Comparator                                       | 26 |

|            | 4.3.3.Multiplier                                       | 27 |

|            | 4.3.3.1 Array-Based Multiplication                     | 30 |

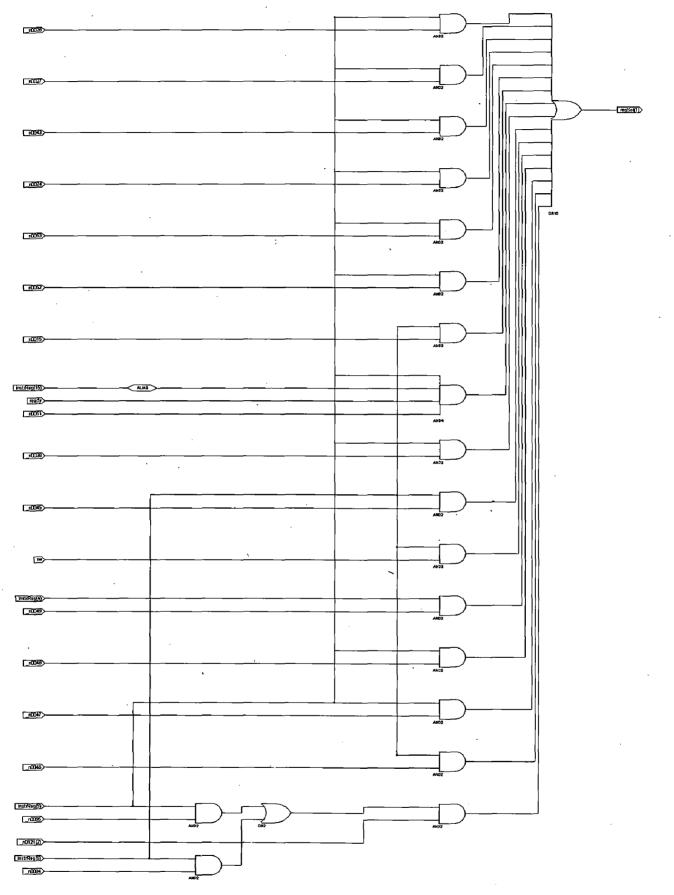

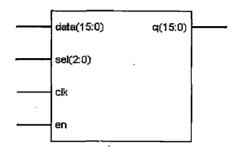

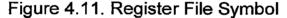

|            | 4.3.4 Register File                                    | 33 |

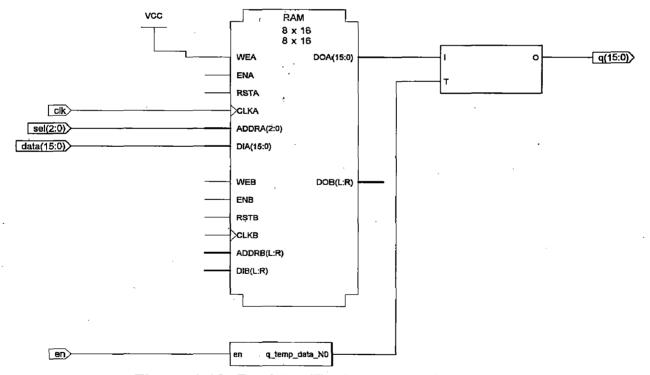

|            | 4.3.5 Multiplexer                                      | 34 |

|            | 4.3.6 Shifters                                         | 35 |

|            | 4.3.7 Reg                                              | 37 |

|            | 4.3.8 Trireg                                           | 37 |

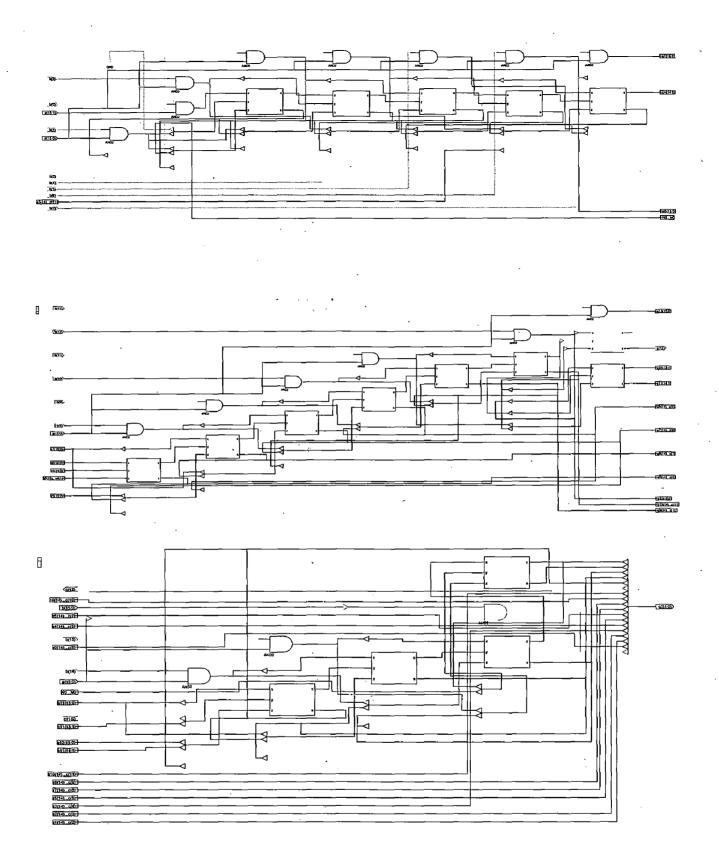

| 4.         | 4 Controller                                           | 38 |

| 4.         | 5 CPU                                                  | 41 |

| CHAPTER 5: | Simulation Results                                     | 43 |

| CHAPTER 6: | Conclusion and Future Scope                            | 50 |

| REFERENCES |                                                        | 52 |

| APPENDIX A |                                                        | 54 |

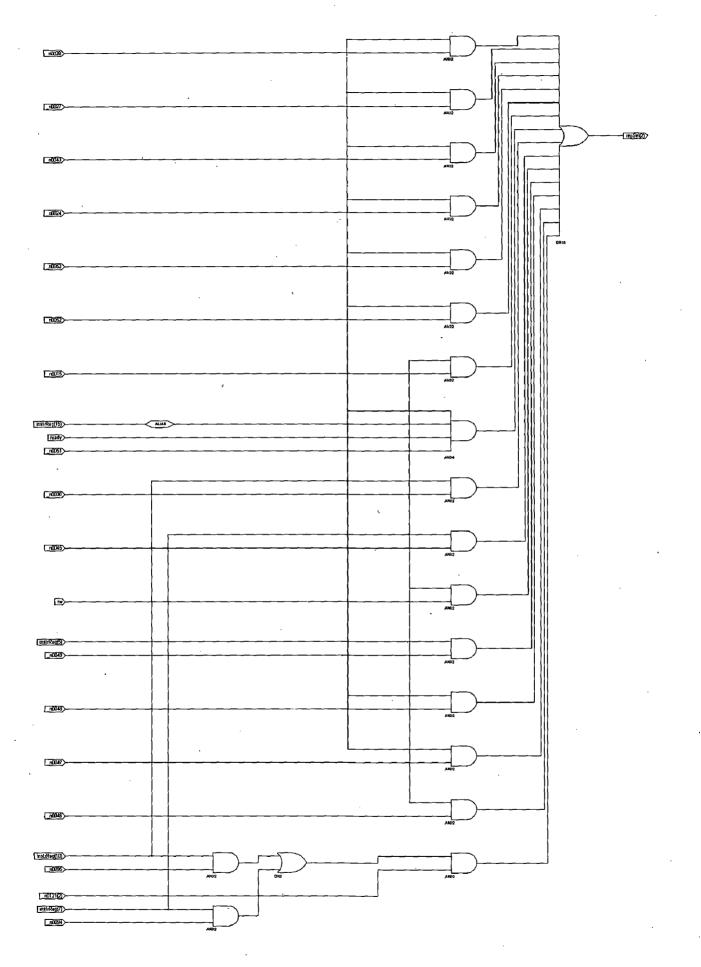

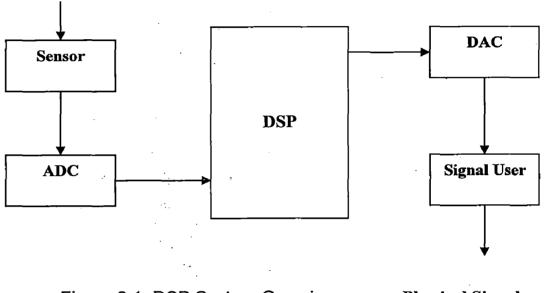

| APPENDIX B | ·                                                      | 59 |

| APPENDIX C |                                                        | 62 |

, '

.

.

v

# List of Figures

|                                                             | Page No. |

|-------------------------------------------------------------|----------|

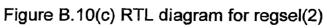

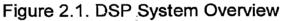

| Figure 2.1. DSP System Overview                             | 8        |

| Figure 2.2. Von Neumann Architecture                        | 9        |

| Figure 2.3. Harvard Architecture                            | 9        |

| Figure 2.4 General Architecture of DSP Processor            | 10       |

| Figure 3.1. Instruction format                              | 13       |

| Figure 3.2 Fields in the R-type instruction                 | 15       |

| Figure 3.3 Data path for an R-type instruction              | 15       |

| Figure 3.4 Fields in an I-type instructions                 | 16       |

| Figure 3.5. Data path for an I-type instruction             | 16       |

| Figure 3.6 Instruction fields for Jump instruction          | 16       |

| Figure 3.7 Data path for Jump instruction                   | 17       |

| Figure 4.1. Internal Architecture of designed DSP Processor | 23       |

| Figure 4.2 ALU                                              | 25       |

| Figure 4.3. Symbol of Comparator                            | 26       |

| Figure 4.4. Architecture of comparator                      | 27       |

| Figure 4.5. Multiplier Block diagram                        | 28       |

| Figure 4.6 A 16-bit Array Multiplication                    | 29       |

| Figure 4.7. Full Adder symbol                               | 30       |

| Figure 4.8. Full adder RTL diagram                          | 30       |

| Figure 4.9. A16 Bit Array Multiplier                        | 31       |

| Figure 4.10. Multiplier Internal Architecture               | 32       |

| Figure 4.11. Register File Symbol                            | 33   |

|--------------------------------------------------------------|------|

| Figure 4.12. Register File internal architecture             | 33   |

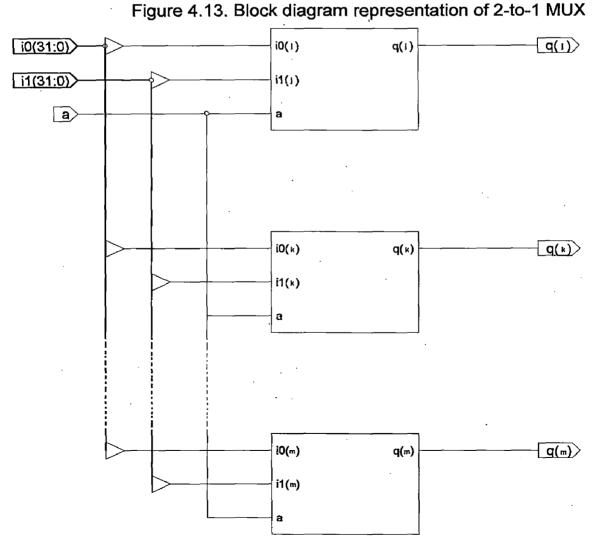

| Figure 4.13. Block diagram representation of 2-to-1 MUX      | 34   |

| Figure 4.14. Multiplexer                                     | 34   |

| Figure 4.15. Block diagram of Barrel Shifter                 | 35   |

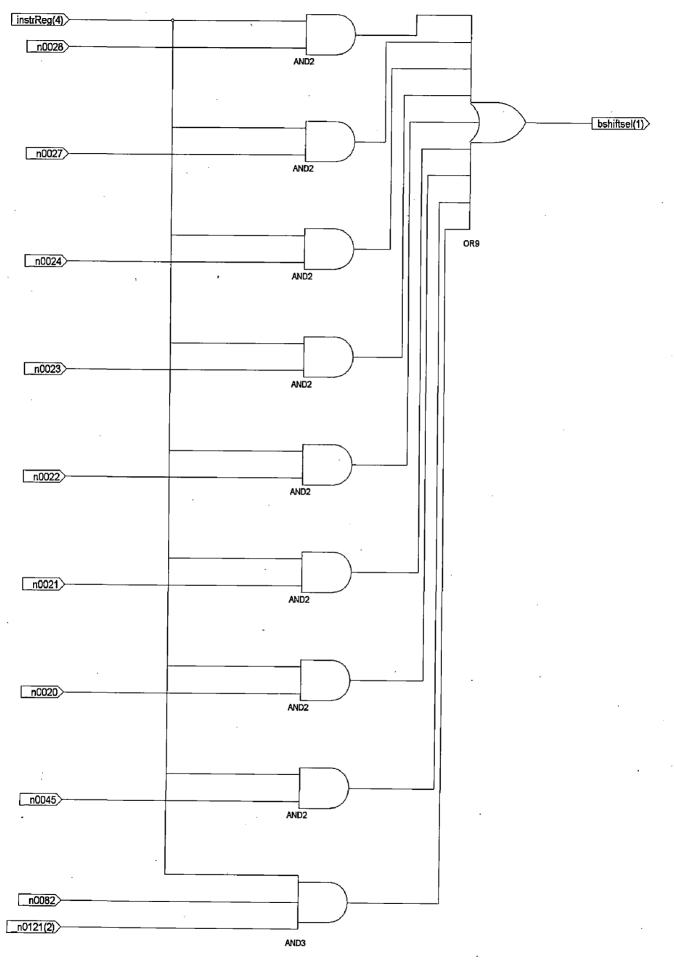

| Figure 4.16 RTL Diagram of Barrel Shifter                    | 36   |

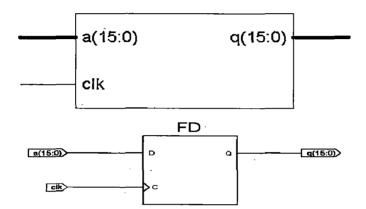

| Figure 4.17. Register Symbol and RTL diagram                 | 37   |

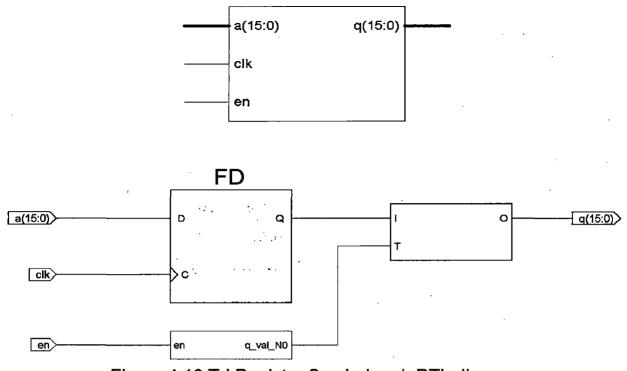

| Figure 4.18 Tri Register Symbol and RTL diagram              | . 38 |

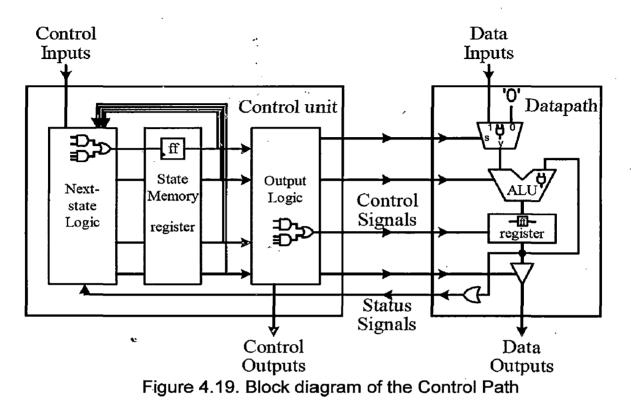

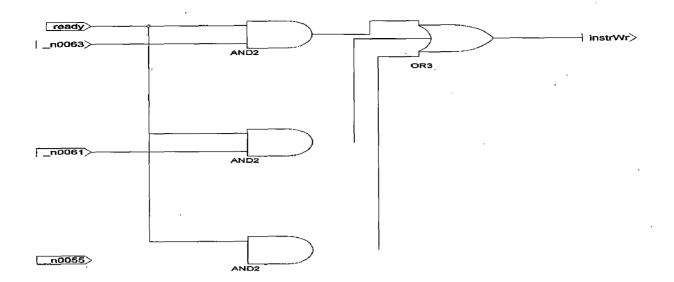

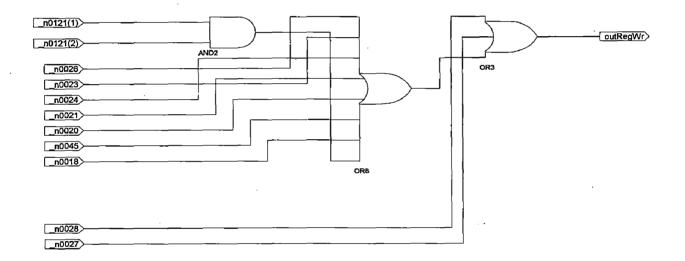

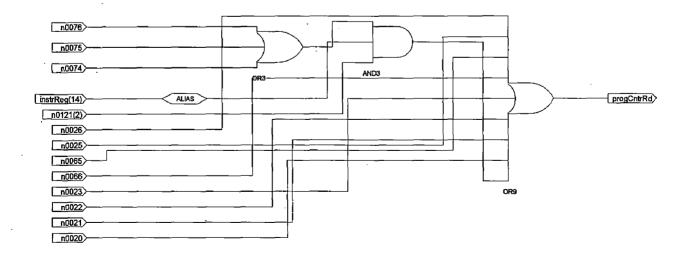

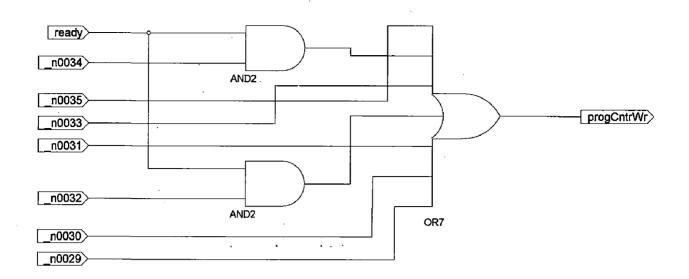

| Figure 4.19. Block diagram of the Control Path               | 39   |

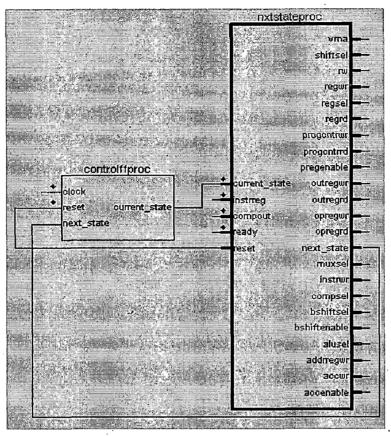

| Figure 4.20. Controller Block diagram                        | 40   |

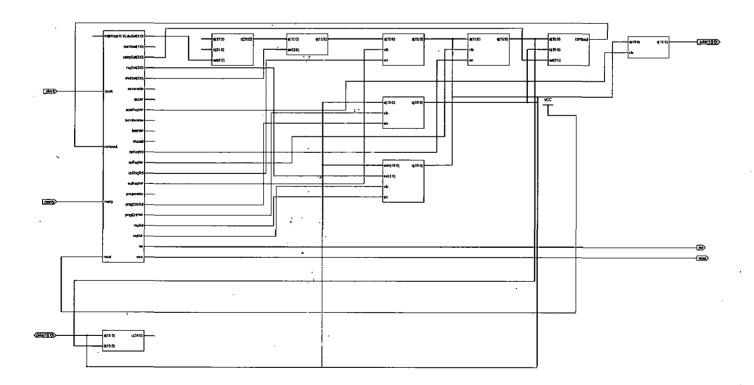

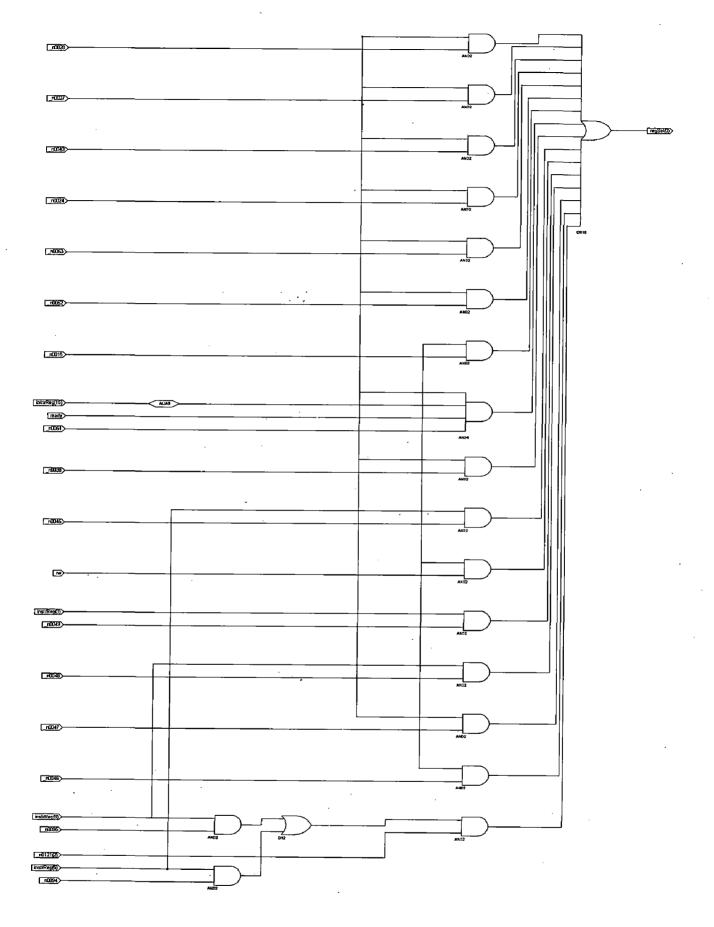

| Figure 4.21 RTL Diagram of CPU                               | 41   |

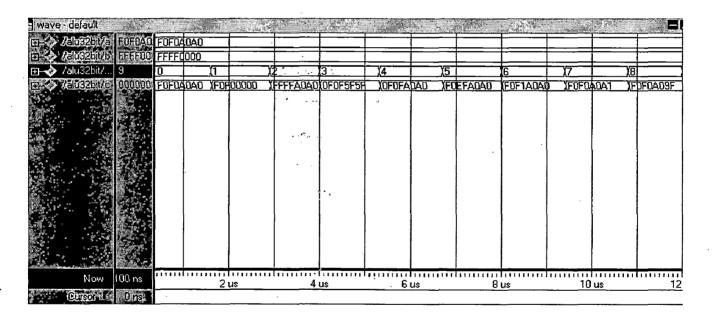

| Figure 5.1 Simulation Result of ALU                          | 43   |

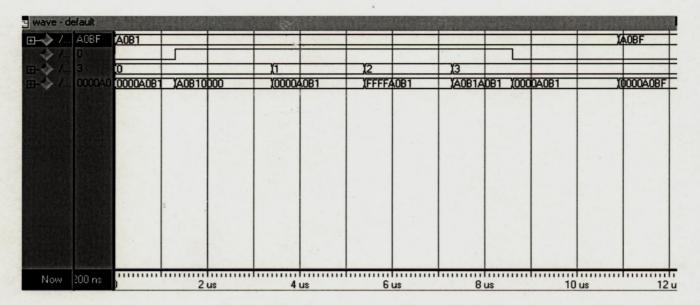

| Figure 5.2 Simulation Result of B Shifter                    | 44   |

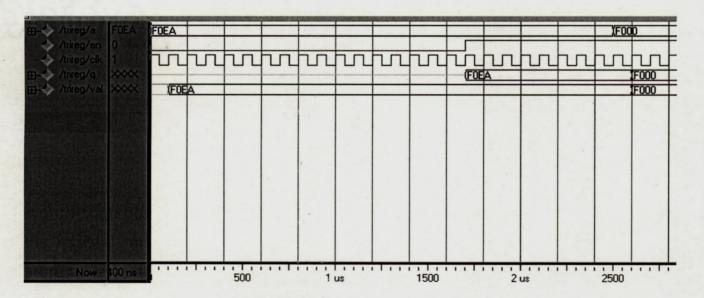

| Figure 5.3 Simulation Result of Tri Register                 | 44   |

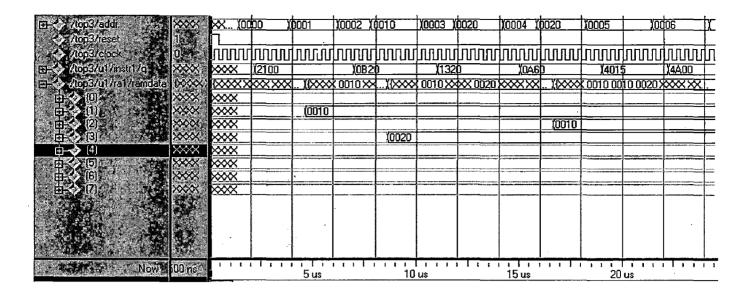

| Figure 5.4 Simulation Result of Register Array               | 45   |

| Figure 5.5 Simulation Result of Control Unit                 | 45   |

| Figure 5.6 Simulation Result of 16 bit Array Multiplier      | 46   |

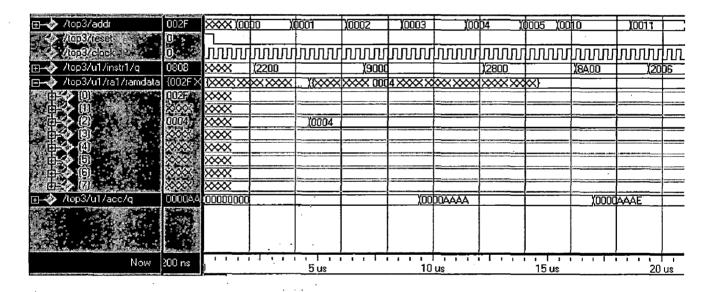

| Figure 5.7(a) Simulation report of DSP Processor for case 1  | 47   |

| Figure 5.7 (b) Simulation report of DSP Processor for case 2 | 48   |

| Figure 5.7 (c) Simulation report of DSP Processor for case 3 | 48   |

| Figure 5.7 (d) Simulation report of DSP Processor for case 4 | 49   |

## Chapter 1

# Introduction

### **1.1 General Introduction**

A signal is an impulse or a fluctuating electric quantity, such as voltage, current, or electric field strength, whose variations represent coded information. Electrical signals are normally either discrete in time and amplitude or continuous in time and amplitude. Digital signals are a sequence of quantized values making them discrete in time and amplitude. The digital signal [5,18] amplitude is represented by limited number of predefined values unlike continuous values where it is samples continuously. To convert the continuous signal into a digital signal an Analog to Digital Converter (ADC) can be used. Once the signals are processed it needs to be converted back into the continuous domain for which a Digital to Analog Converter (DAC) is used. The ADC works by sampling the signal at fixed points and the DAC works by interpolation.

DSP stands for Digital Signal Processing. In practice DSP mean processing of digital signals using electronic circuits or computers such as DSP Processors or Application Specific Integrated Circuit (ASIC). Processing signals mean applying algorithms based on arithmetic computations. Arithmetic could be any arithmetic operations like addition, subtraction, and so on. DSP is the processing of analog signals in the digital domain [18]. Real-world signals, such as voltages, pressures, seismic vibrations, visual images, sound waves and temperatures, are converted to their digital equivalents at discrete time intervals for processing by the CPU of a digital computer. DSP is the mathematics, algorithms and the techniques used to manipulate these signals after they have been converted into a digital form. The world of science and engineering is filled with signals: images from remote space probes, voltages generated by the heart and brain, radar and sonar echoes, seismic vibrations, and countless other applications. DSP is the science of using computers to understand these types of data. This includes a wide variety of goals: filtering, speech recognition, image enhancement, data compression, neural networks, and much more. DSP is one

of the most powerful technologies that will shape science and engineering in the twenty-first century.

DSP is useful in almost any application that requires the high-speed processing of a large amount of numerical data. The data can be anything from position and velocity information for a closed loop control system, to twodimensional video images, to digitized audio and vibration signals.

The roots of DSP are in the 1960s and 1970s when digital computers first became available. Computers were expensive during this era, and DSP was limited to only a few critical applications. Pioneering efforts were made in four key areas: radar & sonar, where national security was at risk; oil exploration, where large amounts of money could be made; space exploration, where the data are irreplaceable; and medical imaging, where lives could be saved. The personal computer revolution of the 1980s and 1990s caused DSP to exploded with new applications. Rather than being motivated by military and government needs, DSP was suddenly driven by the commercial marketplace. Anyone who thought they could make money in the rapidly expanding field was suddenly a DSP vender. DSP reached the public in such products as: mobile telephones, compact disc players, and electronic voice mail.

DSP Processors are micro processors designed to perform DSP. Digital Signal Processing is one of core technology on the most rapidly growing areas such as wireless communication, industrial control, audio and video applications. With the rise in DSP processor applications there has been a huge increase in the DSP Processors in the industry since the 1980's.

If an application to be controlled or analyzed requires that time-critical functions be completed within a given time interval, then a system can be called a real-time system [16] if it will completely execute the necessary functions within the given time interval for all cases. More specifically, real time implies real time within the constraints of the system of interest. A real time DSP is a system which has to process and output data samples at the same frequency the input samples arrive.

2

والمراجع والمراجع والمراجع

Most DSP Processors are meant to handle high performance, repetitive, numerical task like the famous multiply and accumulate. Second important feature in DSP Processors is the ability to handle several memory accesses in the same instruction cycle like fetching instructions while fetching operands or storing the result of previous computations to memory. Third feature is the ability to generate address using the address generation circuitry in parallel with the other instructions though initially the address generation has to configured and set. The DSP Processor has a loop counter implemented within so that there is no necessary for the programmer to expand the instruction cycle to implement a for loop. To facilitate low cost, high performance most DSP processors incorporate serial and parallel I/O interfaces, specialized I/O handling mechanisms like Direct Memory Access (DMA) or interrupt handler. This will allow data transfers to proceed with none or little intervention [16].

### 1.1.1 A Brief history of FPGAs

The FPGAs first arrived in the mid–1980s, they were largely used to implement glue logic medium complexity state machines, and relatively limited data process- ing tasks. During the early 1990s, as the size and sophistication of FPGAs started to increase, their big markets at that time were in the telecommunications and networking arenas, both of which involved processing large blocks of data and pushing that data around. Later, toward the end of 1990s, the use of FPGAs in consumer, automotive, and industrial applications underwent a humongous growth spurt [6].

FPGAs are often used to prototype ASIC designs or to provide a hardware platform on which the verification of the physical implementation of new algorithms was done. However, their low development cost and short time-tomarket mean that they are increasingly finding their way into final products.By the early–2000s, high–performance FPGAs containing millions of gates has become available. Some of these devices feature embedded microprocessor cores, high speed–input/output (I/O) interfaces, and the like ones. The end result is that today FPGAs can be used to implement just about anything, including communications devices and software-defined radios, radar, image, and other DSP applications [5].

#### 1.1.2 What can FPGAs be used for?

Mainly FPGAs are currently into four major market segments: Application Specific Integrated Circuit (ASIC) and custom silicon, DSP, embedded microcontroller applications, and physical layer communication chips. Furthermore, FPGAs have created a new market in their own right: Reconfigurable Computing (RC).

- ASIC and custom silicon: Today FPGAs are increasingly being used to implement a variety of designs that could previously have been realized using only ASICs and custom silicon.

- Digital Signal Processing: High speed DSP has traditionally been implemented using specially tailored microprocessors called Digital Signal Processors. However, the FPGAs available today can contain embedded multipliers, dedicated arithmetic routing, and large amounts of on-chip RAM, all of which facilitate DSP operations. When these features are coupled with the massive parallelism provided by FPGAs, the result is to outperform the fastest DSP chip by a factor of 500 or more.

- Embedded microcontrollers: Small control functions have traditionally been handled by special-purpose embedded processors called microcontrollers. These low-cost devices contain on-chip program and instruction memories, timers, and I/O peripherals wrapped around a processor core. FPGA prices are falling, however, and even the smallest devices now have more than enough capability to implement a soft processor core combined with a selection of custom I/O functions. The end result is that FPGAs are becoming increasingly attractive for embedded control applications.

- Physical layer communications: FPGAs are used to implement the glue logic that interfaces between physical layer communication chips and high-level net- working protocol layers. As high-end FPGAs can contain multiple high-speed transceivers mean that communications and networking functions can be consolidated into a single device.

- Reconfigurable Computing: This refers to exploiting the inherent parallelism and reconfigurability provided by FPGAs to "hardware

accelerate" software algorithms. Various companies are currently building huge FPGA-based re- configurable computing engines for tasks ranging from hardware simulation to cryptography analysis.

### **1.2** Objectives of the Dissertation:

An attempt has been made to develop a simple 16-bit DSP Processor on FPGA. The instruction size, data path size as well as the operand size is of 16-bits.

The objectives of the dissertation are mentioned briefly:

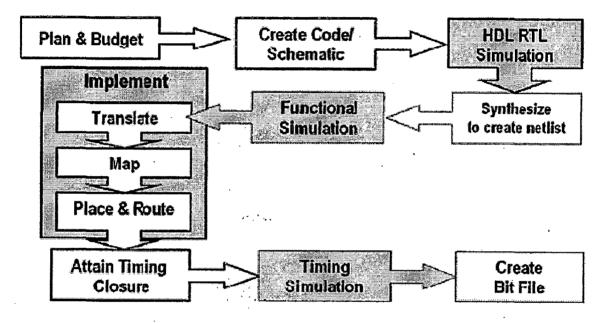

- The individual blocks of the DSP Processor are implemented using VHDL (VHSIC Hardware Descriptive Language). These can be implemented using any HDL, there are two main languages namely Verilog and VHDL, In this dissertation, VDHL is used for the implementation. The algorithms implemented are then simulated and tested for suitability for synthesis. If these are not suitable for synthesis, the coding has to be done again. Care should be taken so that the HDL coding is done using the structural design method.

- The VHDL programs simulated are then synthesized on an suitable FPGA kit. In this work the Spartan 2, XC2S200 FPGA development kit is used. After the synthesis, the bit-streams are loaded onto the FPGA. This completes the implementation of DSP Processor on FPGA.

### **1.3 Organization of Thesis:**

- Chapter 1 includes a brief introduction about Digital Signal Processing and Field Programming Gate Arrays. The various applications of DSP and FPGA is discussed along with the evolution and the applications in various fields.

- Chapter 2 explains about general DSP Processors and its environment, their architecture, applications.

- Chapter 3 explains about Instruction set architecture and addressing modes of the proposed processor.

- Chapter 4 gives an insight to the Processor design flow that has been followed in this thesis work. It is the main chapter that gives an idea about how exactly the Processor design was carried out.

- > Chapter 5 summarizes the various results and discussions.

- Chapter 6 gives the Conclusions and Scope for Future work. This includes the concluding remarks and the other developments expected in the same field.

- The Appendix A and B explain about the various softwares and hardware kit details utilized for this dissertation. The softwares and the FPGA development kit are listed. Detailed explanation about each of them is included for a better understanding. As the market is on the rise, there are more and more new FPGA development kits coming into the market. It is going on in a such a pace that every month, a new FPGA development kit is being released by some or the other VLSI company.

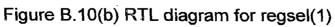

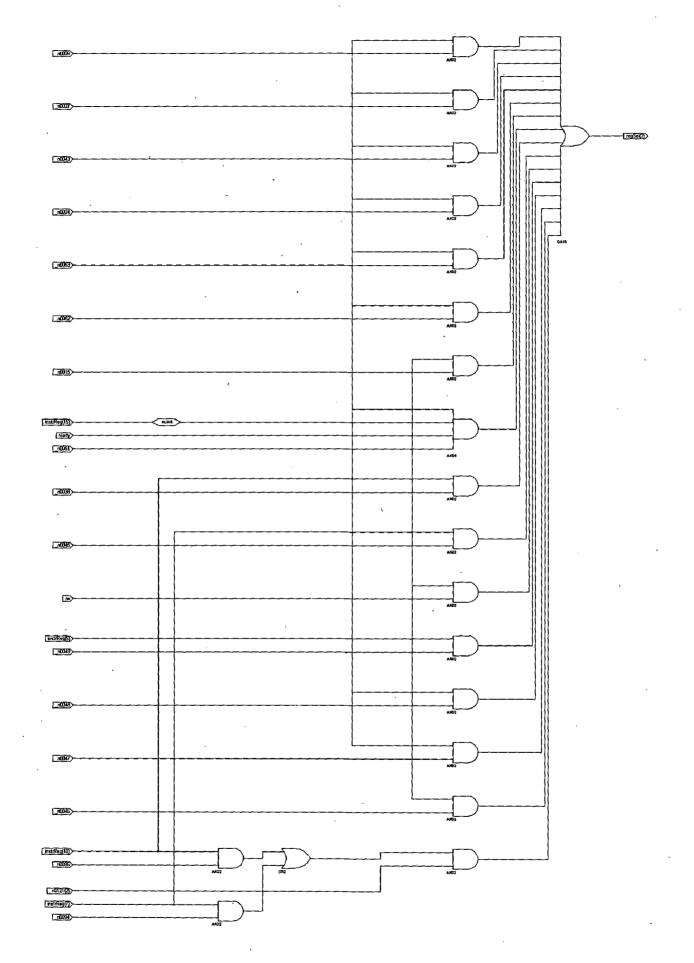

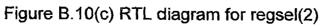

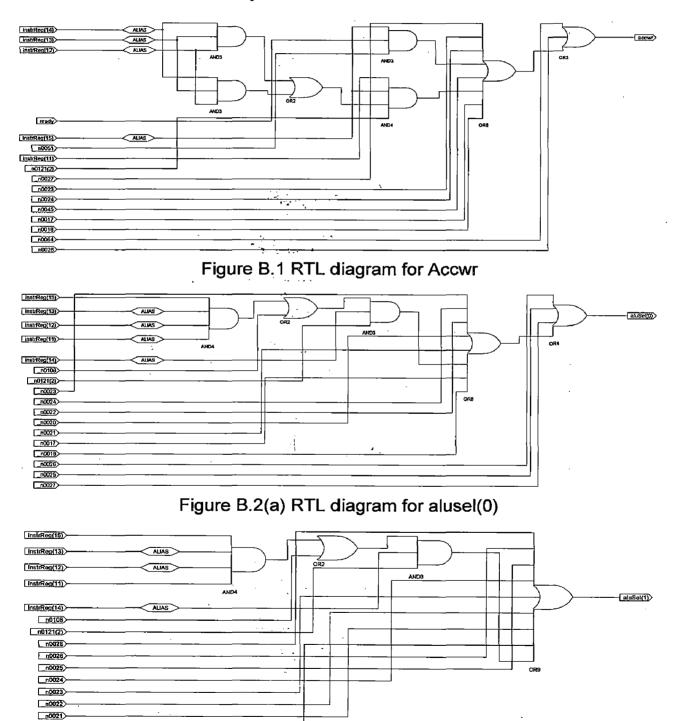

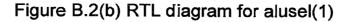

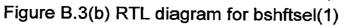

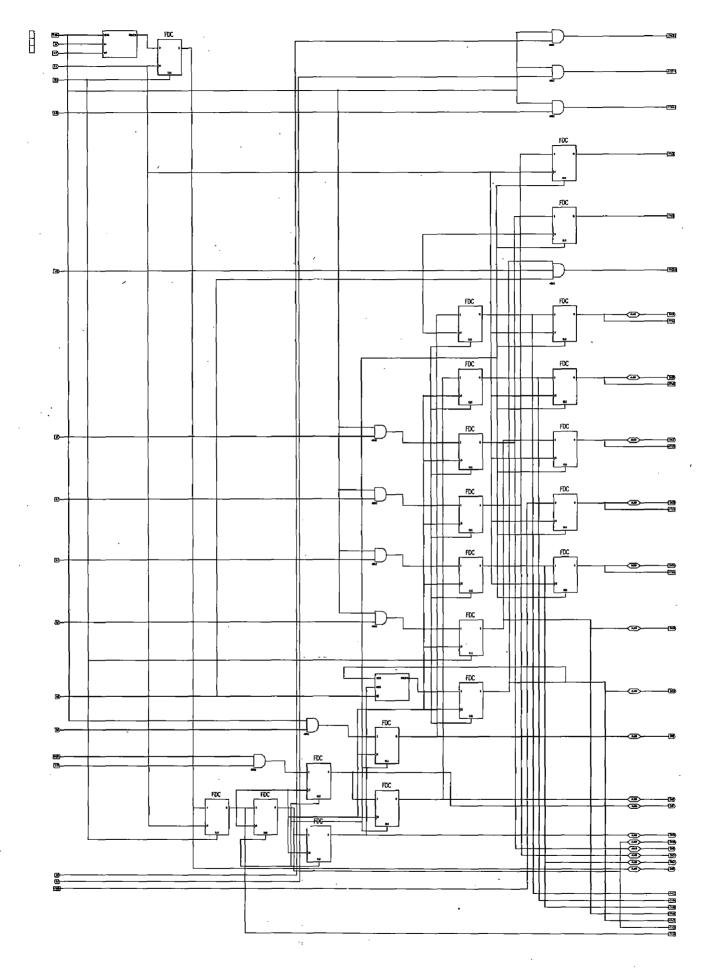

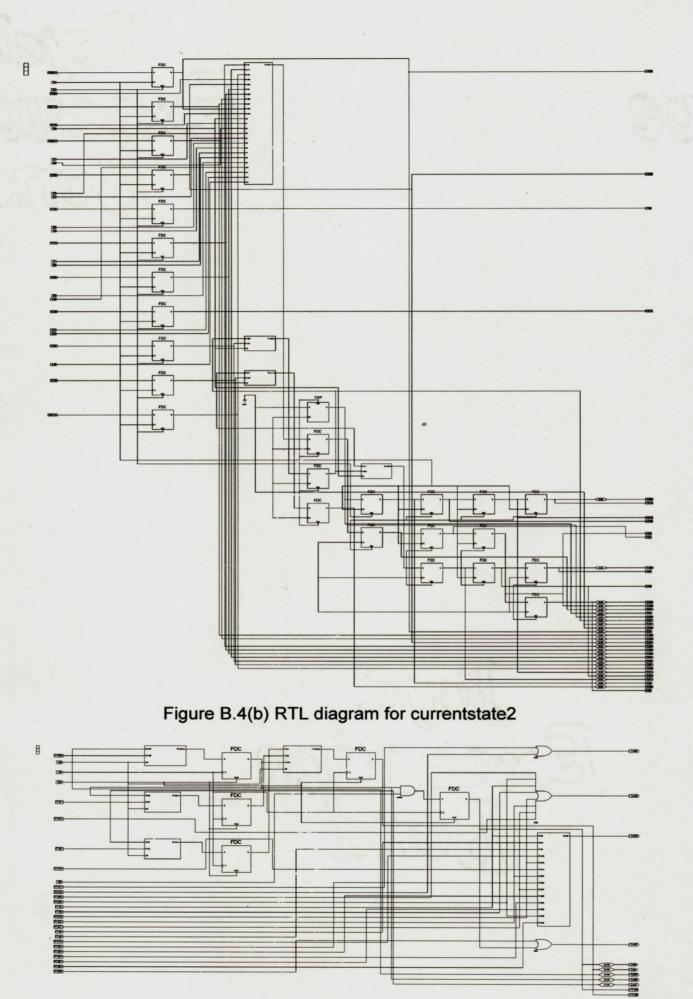

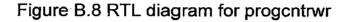

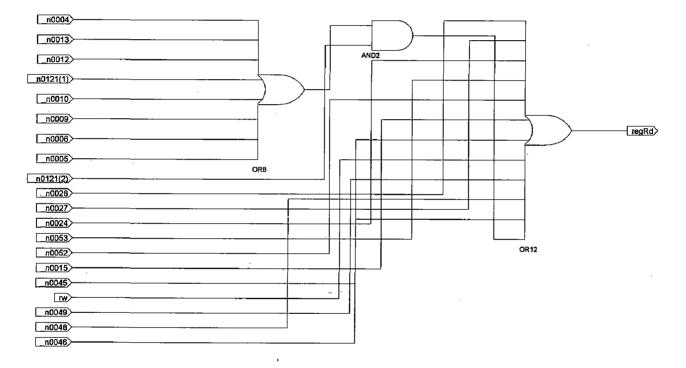

- > Appendix C gives the RTL Diagrams of the processor.

# **Chapter 2**

### **DSP Processors**

### 2.1 INTRODUCTION TO DSP PROCESSORS

#### 2.1.1 DSP Environment

The Digital Signal Processing (DSP) Processor is designed specially for processing digital signals. DSP has a wide range of applications such as RADAR, Audio, SONAR, Telephony, Process Control, Digital Television, and Facsimile. There are a wide range of applications they have some common features like they have a lot of math involved, deal with signals from real world and require response in certain time [17,18].

The main advantages of using digital systems are repeatability, versatility and simplicity.

- Repeatability is when they can be easily duplicated; responses do not drift away with temperature and do not depend on strict component tolerances.

- Versatility is when systems can be reprogrammed for other applications or can be ported to other hardware like board level product. And finally

- Simplicity means some things are easier in digital systems than in analogue systems.

Most DSP applications deal with analogue signals which have to be converted to digital signals for processing as in Figure 2-1. During this conversion some information is lost due to uncertainty in timing, limits on duration of measurement or inaccuracies in measurement. The effects are called Quantization Errors. The continuous analogue signal has to be held before it can be sampled and measured so that value is not changing during the measurement. Then once it has been measured the signal will be converted to digital value for processing. The sampling results in a discrete set of digital numbers that were measured in equal intervals of time. The sampling takes places after the hold. So the Analog to Digital Converter (ADC) has to be fast

enough to sample the signal before the next signal value is taken in by the hold circuit. In short the ADC will have all the time to perform the conversion as long as the signal is held. A fast sampling needs to be done so that the rapid changes in the incoming signals are not lost. If not some higher frequencies can be interpreted as low frequencies [5,22].

#### **Physical Signal**

**Physical Signal**

#### 2.1.2 Applications :

Applications of DSP are RADAR, Audio, SONAR, Telephony, Process Control, Digital Television, and Facsimile. DSP Processors have a wide range of applications from consumer electronics to Radar. There is no specific DSP Processor that will match all the applications. It is the designer choice to first evaluate the constraints in hand like power consumption, area, speed, performance, integration and other metrics in hand. In terms of money volume the biggest applications of DSP are in portable digital audio players commonly know as mp3 now days, mobile phones and disk drives where DSP is used for servo control. In these applications the integration and cost are paramount. For portable productions the battery consumption is very important and hence the focus is on power consumption.

### 2.1.3 DSP Architecture

All DSPs consist of several fundamental modules: a digital signal processing core to perform mathematical operations, memory to store data and program instructions. As a stored-program machine, the processor must be told what to do every clock cycle. Typically, a DSP fetches an instruction and some data from memory, operates on these, and then returns the manipulated data to storage. The way this is conducted is not the same for all processors. Two different architectures can be identified: Von Neumann and Harvard (see Figure 2.2 and 2.3).

The DSP application, in addition to the memory and peripheral configuration, usually governs the type of architecture employed [5,16].

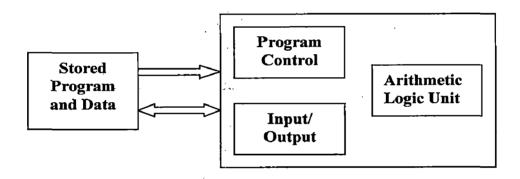

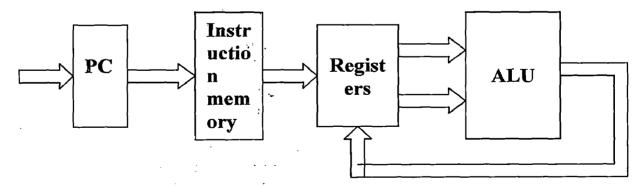

Figure 2.2. Von Neumann Architecture

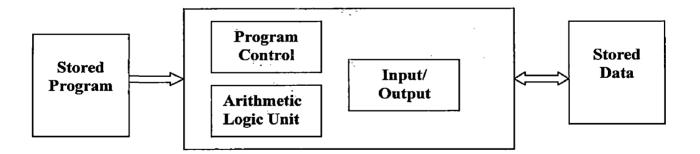

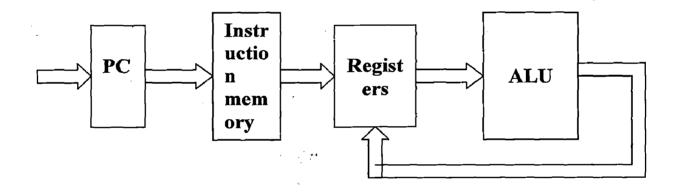

Figure 2.3. Harvard Architecture

Von Neumann architecture has set the standard for computer development over the past 40 years. Essentially, the architecture is very simple. Both program and data can reside in the same memory-mapped space. This architecture forms a basis for more general-purpose processing needs.

Harvard architecture separates the program and data memory spaces. Having two buses to serve each address space ensures that data and program access occurs in parallel, increasing processing speed.

### 2.2. General Architecture of DSP Processors

A DSP Processor is a programmable digital system intended to solve computational problems in a large variety of applications. A general purpose processor consists of a data path and a control unit tightly linked with a memory.

10 10

A - MAR MARTIN

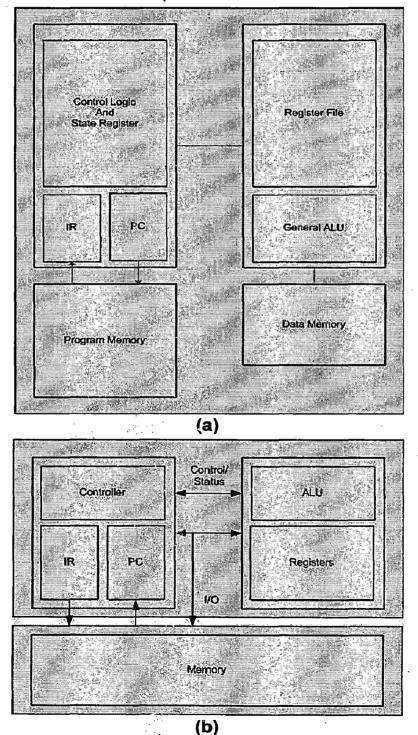

All general DSP Processors Core is composed of the Data Path, Control Path and Program Path. The Memory Subsystem is located out of the processor core. Figure 2.3 (a) and (b) shows the general architecture of DSP Processor in both Harvard and Von Neumann fashion.

A basic DSP processor supports RISC and CISC instructions. The RISC uses the general registers for operands and writes them back to the Register File (RF). The CISC used the memory subsystem to compute vector elements like in the case of convolution. The CISC reads from the memory and write them to the Accumulator and to the registers.

The memory bus is distributed to the memory and DSP core DP components MAC and RF. However, there could be more components that can be connected to the memory bus. This depends on the choice of the instruction set which specifies all the operands required to perform a certain instruction. If there are instructions that ALU performs by fetching operands from the memory subsystem then the memory bus would also be connected to the ALU and so on. The Control Path generates the control signals for all components in the core, keeps track of the Program Counter and has a stack to service subroutines.

#### 2.2.1 Data Path :

The datapath is the second main part of a processor. The datapath is responsible for the manipulation of data. The datapath consists of the circuitry for transforming data from and for storing temporary data. It includes (1) functional units such as adders, shifters, multipliers, ALUs, and comparators, (2) registers and other memory elements for the temporary storage of data, and (3) buses and multiplexers for the transfer of data between the different components in the datapath. External data can be entered into the datapath through the data input lines. Results from the computation are provided through the data output lines.

Processors are typically distinguished by their size, i.e. the bit width of the datapaths components. Common processor sizes include, 4-bit, 8-bit, 16-bit, 32-bit and 64-bit.

#### 2.2.2 Control Unit :

Even though the datapath is capable of performing all the operations of the processor, it cannot, however, do it on its own. In order for the datapath to execute the operations automatically and correctly, the appropriate control signals must be asserted at the right time. In a processor, these control signals are generated by the control unit.

The control unit, also known as the controller, controls the operations of the datapath, and therefore, the operations of the entire processor. The controller is a finite state machine (FSM) because it is a machine that executes by going from one state to another, and the fact that there are only a finite number of states for the machine to go to.

The control unit consists of circuitry for retrieving program instructions and for moving data to, from and through the datapath according to those instructions. For each instruction the controller typically sequences through several stages, such as fetching the instruction from memory, decoding it, fetching operands, executing the instruction in the datapath, and storing the results. Each stage may consists of one or more clock cycles. A clock cycle is usually the longest time required for data to travel from one register to another.

#### 2.2.3 Memory:

The registers server a processor's short-term storage requirements, memory server the processor's medium and long-term information-storage requirements, i.e. the storage information as either program or data. Program information consists of the sequence of instruction that cause the processor to carry out the desired system functionality. Data information requests the values being input, output and transformed by the program.

### **Chapter 3**

# Developed Processor: Instruction Set Architecture and Addressing Modes

#### **3.1. Introduction :**

The operation of the processor is determined by the instructions it executes, referred to as machine instructions. The collection of the different instructions that the processor executes is referred to as the instruction set. Each instruction is represented by sequence of bits. The instruction is divided into fields, corresponding to the constituent elements of the instruction [13,14,19].

The decision regarding the instruction format and addressing modes of a processor is the most important stage in the design. This decision will lead to the structure of the data path and the control unit. In the present work a 16 bit instruction format is adopted for the implementation of the proposed processor, where the operands and opcodes are of 16 bits. The instructions are of variable length. The instruction format is explained in detail in next few pages.

### **3.2 Instruction Format :**

An instruction format must include an opcode and implicitly, zero or more operands. The format must, explicitly or implicitly, indicate addressing mode for each operand. The various fields of the instruction format are explained below.

| Opcode | RD     | RS     | SHAMT  | SE    | IAmode | I/Dcontrol |

|--------|--------|--------|--------|-------|--------|------------|

| 5 bits | 3 bits | 3 bits | 2 bits | 1 bit | 1 bit  | 1 bit      |

|  | Immediate Data |  |

|--|----------------|--|

|  |                |  |

|  |                |  |

|  |                |  |

(2 Bytes/none)

#### Figure 3.1. Instruction format

The meaning of each of the fields is given as

- Opcode: Specifies the operation to be performed. It is the basic operation of the instruction.

- RD: The destination register operand, it gets the result of the operation.

- RS: Source register

- SHAMT: Shift amount

- SE: Shift enable bit

- IAmode: Indirect Addressing mode control bit

- I/D control: Increment/decrement after the operation when IAmode bit is 1.

#### **3.3. Addressing modes:**

The way of representing the operand in the instruction is known as the addressing mode. The proposed DSP Processor's instruction set provides the following addressing modes.

- Register addressing modes: The register will be identified in the instruction and the content of the register will be the operand. The address field that references registers is of 3 bits, thus 8 general purpose registers can be referenced. This addressing mode includes the data transfer instructions, i.e. the register to register data transfer instructions as well as the arithmetic instructions.

- Immediate addressing: It is the simplest form of the addressing, in which the operand is actually present in the instruction. This mode uses constants as operands to set the initial values of variables.

- Direct addressing mode: In this the operand is at the memory location whose address is specified in the instruction.

- Indirect addressing mode: In this the operand is at the memory location whose address is present in the register and the register is specified in the instruction.

### 3.4. Instruction types:

The instruction set is classified depending on the operands, broadly under the following categories.

- R-type instructions

- I-type instructions

- J-type instructions

### **3.4.1 R-type instructions:**

The format for the R-type instruction is given in the figure.

| Opcode | RD     | RS     | SHAMT  | SE    | Ignored | Ignored |

|--------|--------|--------|--------|-------|---------|---------|

| 5 bits | 3 bits | 3 bits | 2 bits | 1 bit | 1 bit   | 1 bit   |

Figure 3.2 Fields in the R-type instruction

The operation which has to be performed on two registers is decided by the Opcode field. The resultant value of the operation will go to the destination register which is provided in the field named RD. The data path for the R-type instructions is shown below.

Figure 3.3 Data path for an R-type instruction

#### **3.4.2 I-type instructions:**

The instruction format of I-type instructions is shown in figure. Since the immediate data present in the instruction itself, this instruction needs another

word to contain the immediate data (either data or address). Some of the fields in the instruction are ignored.

| Opcode | RD     | XXXXXXXX |

|--------|--------|----------|

| 5 bits | 3 bits | 8 bits   |

| Immediate Data or Address |  |

|---------------------------|--|

| 16 bits                   |  |

Figure 3.4 Fields in an I-type instructions

This group includes instructions with immediate operand, which is of 16 bits in length. The data path for immediate data instructions is shown in figure.

Figure 3.5. Data path for an I-type instruction

### **3.4.3 J-type instruction:**

| Opcode | XXXXXXXXXXX |

|--------|-------------|

| 1      |             |

| 5 bits | 11 bits     |

| Target Address |  |

|----------------|--|

| 16 bits        |  |

| •              |  |

### Figure 3.6 Instruction fields for Jump instruction

These instructions require 16-bit address field to specify the target of the jump. The instruction format is shown in figure. The target address is of 16-bits. So, the target can be any location within a range of 2<sup>15</sup> locations.

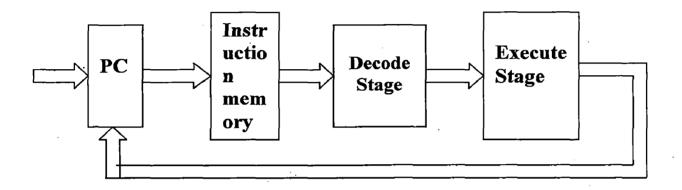

The data path for the Jump instruction is shown in the figure 3.7. The necessary control signals are decoded in the decode stage and depending on these controls the next address for PC is decided.

Figure 3.7 Data path for Jump instruction

### 3.5. Instruction set:

The total instruction set for the proposed DSP Processor consists of both single word and double word instructions. These instructions are classified into the following, as per the operation they perform as follows

- Data transfer instructions

- Arithmetic instructions

- Logical instructions

- T register, P register and multiply instructions

- Shift instructions

- Branching instructions

#### 3.5.1 Data transfer instructions:

### MVI R, IMMDATA

The immediate data of 16 bits is loaded into the register specified as R. The opcode for the instruction is of the format

| OPCODE | R VALUE | XXXXXXXX | IMMDATA |

|--------|---------|----------|---------|

| 5 Bits | 3 Bits  | 8 Bits   | 16 Bits |

### MOV Rd, Rs

The data in Rs is copied to Rd. The opcode for the instruction is of the format

| OPCODE | <b>R VALUE</b> | <b>R VALUE</b> | XXXXX  |

|--------|----------------|----------------|--------|

| 5 Bits | 3 Bits         | 3 Bits         | 5 Bits |

### MOV Rd, (Rs)

The data in the address specified by the register Rs is copied in to Rd. The opcode for the instruction is of the format

| OPCODE | R VALUE | <b>R VALUE</b> | XXX    | 1     | I/D   |

|--------|---------|----------------|--------|-------|-------|

| 5 Bits | 3 Bits  | 3 Bits         | 3 Bits | 1 Bit | 1 Bit |

From the above format IAmode field '1' indicates the indirect addressing mode and I/D field indicates either the auto decrement or increment in Rs value.

### LDAI IMMDATA

The accumulator is loaded with the IMMDATA. Accumulator is the implicit operand. The opcode for the instruction is of the format

| OPCODE XXXXXXXXXX |        | IMMDATA |

|-------------------|--------|---------|

| 5 Bits            | 8 Bits | 16 Bits |

### STORE (Rd), Rs

The data in register Rs is copied in to the address specified in the register Rd. The opcode for the instruction is of the format

| OPCODE | <b>R VALUE</b> | R VALUE | XXX    | 1     | I/D   |

|--------|----------------|---------|--------|-------|-------|

| 5 Bits | 3 Bits         | 3 Bits  | 3 Bits | 1 Bit | 1 Bit |

#### 3.5.2 Arithmetic instructions:

#### INC/DEC R

The data in register R is either incremented or decremented as per the operation and the result is stored in the same register.

| OPCODE | R VALUE | XXXXXXXXX |

|--------|---------|-----------|

| 5 Bits | 3 Bits  | 8 Bits    |

#### ADD/SUB Rs

The data in the register Rs is operated with the accumulator as per the instruction and the result is stored in the accumulator. The instruction format is shown below.

| OPCODE | XXX    | R VALUE | XXXXX  |

|--------|--------|---------|--------|

| 5 Bits | 3 Bits | 3 Bits  | 8 Bits |

# 3.5.3 Logical instructions: ORA/ANA/XRA Rs

The value of Rs is operated as per the logical operation with the contents of accumulator and the result is stored in the accumulator. The instruction format is shown below.

| OPCODE | R VALUE | XXX    | xxxxxxx |

|--------|---------|--------|---------|

| 5 Bits | 3 Bits  | 3 Bits | 8 Bits  |

#### ORA/ANA/XRA IMMDATA

The content of accumulator and immediate data are operated according to the logical operation specified and the result is stored in the accumulator. The instruction format is shown below

| OPCODE | XXXXXXXXXXXX | IMMDATA |

|--------|--------------|---------|

| 5 Bits | 11 Bits      | 16 Bits |

#### 3.5.4 T register, P register and multiply instructions:

#### LT IMMDATA

The T register is loaded with the sign extended form of the IMMDATA. The IMMDATA is sign extended to 16 bits and is loaded into T register. The opcode for the instruction is of the format

| OPCODE | IMMDATA |  |

|--------|---------|--|

| 5 Bits | 11 Bits |  |

#### MPY R

The contents of the register R are multiplied with the contents of implicit operand T register and the result is placed in the P register. The instruction format is shown below

| OPCODE | XXX    | R VALUE | XXXXX  |

|--------|--------|---------|--------|

| 5 Bits | 3 Bits | 3 Bits  | 5 Bits |

#### 3.5.5 Shift instructions

### SHL/R Rd, Rs, SHAMT

The shift instruction shifts the data present in the register Rs by number of bits specified in the field SHAMT and stores the result in register Rd. The instruction format is shown below

| OPCODE | <b>R VALUE</b> | <b>R VALUE</b> | SHAMT  | SE    | XX     |

|--------|----------------|----------------|--------|-------|--------|

| 5 Bits | 3 Bits         | 3 Bits         | 2 Bits | 1 Bit | 2 Bits |

## **3.5.6 Branching instructions**

### JMP IMMDATA

The jump instruction always branches to the target address that is specified in the instruction itself. The instruction format is shown below

| OPCODE | XXXXXXXXXXXX | IMMDATA |  |

|--------|--------------|---------|--|

| 5 Bits | 11 Bits      | 16 Bits |  |

# Chapter 4

# **Design Architecture of DSP Processor**

#### **4.1 Introduction**

The circuit for the DSP Processor can be divided into two parts: the datapath and the control unit. The datapath is responsible for the actual execution of all operations performed by the DSP Processor. The control unit, also known as the controller, provides all control signals to the programPath and dataPath.

Every digital logic circuit, regardless of whether it is part of the control unit or the datapath, is categorized as either a combinational circuit or a sequential circuit. A combinational circuit is one where the output of the circuit is dependent only on the current inputs to the circuit. A sequential circuit, on the other hand, is dependent not only on the current inputs but also on all the previous inputs. Since sequential circuits are dependent on the history, they must therefore contain memory elements for remembering the history, whereas, combinational circuits do not have memory elements [10,14,19].

This chapter describes the various modules of the Processor Data Path, their design considerations and architecture. This chapter also describes about the ControlPath which is the most complicated and tricky in designing a Processor.

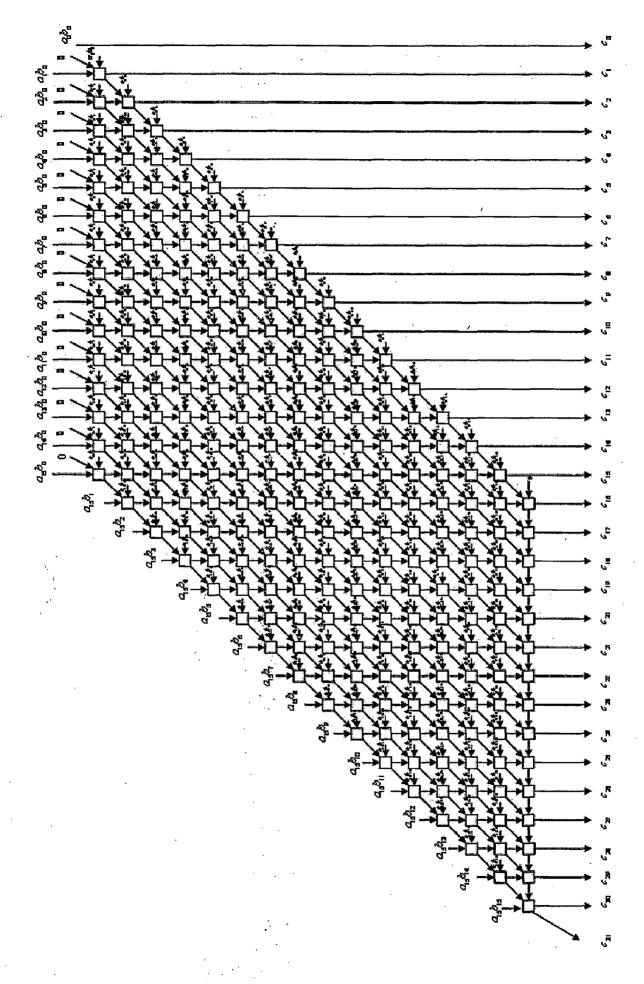

#### **4.2 Architecture Overview**

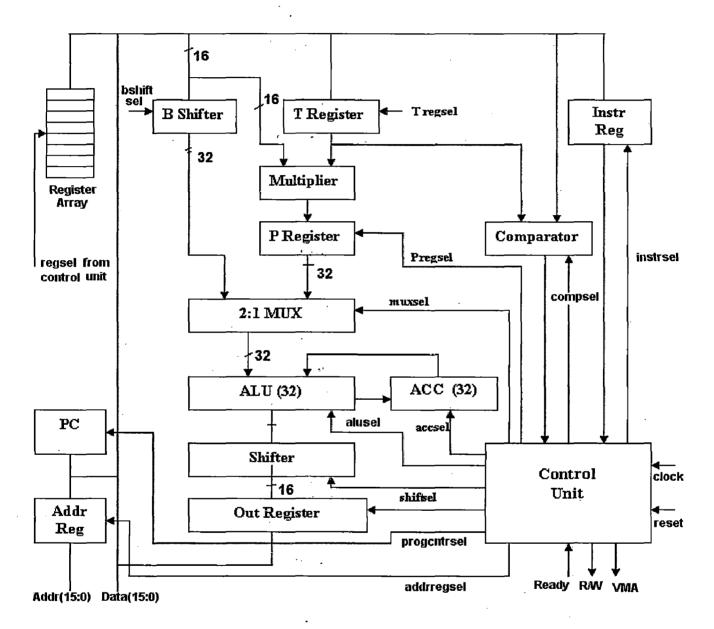

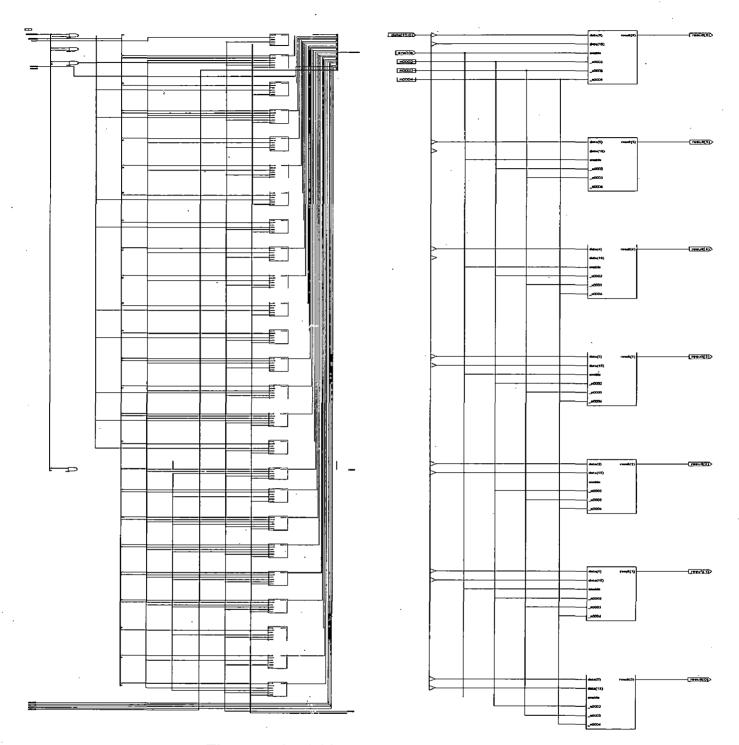

The architecture of the designed 16-bit DSP Processor is split into 3 main modules: controller, dataBus, and programBus. The controller consists of a finite state machine with states for instruction fetch and decode based on the 16-bit instruction set. The controller outputs control signals to every submodule in the dataBus and programBus. The program Bus module consists of a 16-bit bus called programBus (actually, Instruction Register), which contains each fetched

instructions from the Program ROM. The data Bus module consists of a 16-bit bus called dataBus, which has complete data information. The dataBus also contains an ALU, multiplier, accumulator, barrel shifter, and muxes [2,3,15]. The DSP Processor supports three addressing modes: direct, register-indirect, and immediate modes. The internal datapath architecture is shown in Figure 4.1.

Figure 4.1. Internal Architecture of designed DSP Processor

The proposed processor's DataPath houses all the arithmetic hardware, a 32-bit ALU, 32-bit accumulator, and 16x16-bit multiplier with 32-bit product. It also contains a 144x16-bit data RAM. Two shifters are also used in the architecture. The 0 to 16 bit barrel shifter with 16-bit data bus input outputs a 32-bit value to the ALU. The second shifter takes the output of the accumulator and shifts 0, 1,

or 4-bits and outputs 16-bits to the dataBus. The register array (RF) used for indirect addressing and for storage of operands is also located within the dataPath. All these functional units inside the datapath (ALU, accumulator, shifter, multiplier, etc.) and the registers are connected together with multiplexers and buses to form one unit, the datapath. The 16-bit dataBus, which holds data to and from the data RAM and accumulator.

The controller provides all control signals to the programPath and dataPath. They include all the select lines for multiplexers, ALU and other functional units having multiple operations, all the read/write enable signals for registers and register files, address lines for register files, and enable signals for tri-state buffers. The operation of the datapath is determined by which control signals are asserted and at what time.

During startup and reset, an initialization state followed by two wait states set up the CPU. This allows initialization values to propagate through the logic. The decode state determines which instruction is on the programBus. Direct/indirect addressing functionality are also detected within this state. When an instruction execution is complete, the state machine will always return to the fetch/decode state.

The number of states per instruction varies from four to six states depending on the complexity of the instruction. The controller outputs mux controls, ALU functions, register reads/writes and other control signals to the DSP hardware depending on the current instruction. The program counter (PC) is enabled during the second to last instruction state. It takes two state cycles for the next instruction to stabilize on the programBus.

In return, the datapath needs to supply status signals back to the control unit in order for it to operate correctly. These status signals are usually from the output of comparators. The comparator tests for a given logical condition between two values. These values can be obtained either from memory elements, directly from the output of functional units, or hardwired as constants. These status signals provide input information for the control unit to determine what operation to perform next. For example, in a conditional loop situation, the status signal will tell the control unit whether to repeat or exit the loop.

### 4.3 Data Path (DP)

The datapath performs all the functional operations of a processor, and the processor is for solving problems, therefore the datapath must be able to perform all the operations required to solve the given problem.

Datapath design is also referred to as the register-transfer level (RTL) design. The register-transfer level design tells how data is transferred from one register to another or back to the same register. If the same data is written back to a register without any modifications, then nothing has been accomplished. So before writing the data to a register, the data passes through one or more functional units and gets modified.

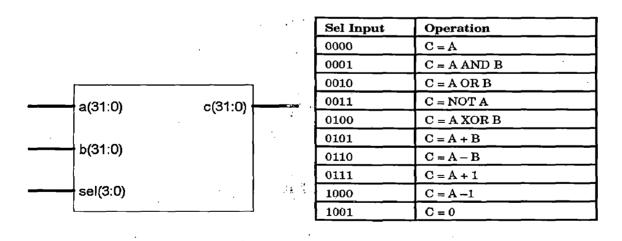

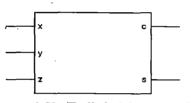

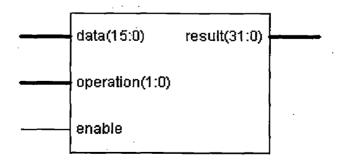

#### 4.3.1 Arithmetic and Logic Unit (ALU)

As the name describes, the ALU does all the logic and arithmetic computations. This entity performs a number of arithmetic or logical operations on one or more input busses. A symbol for the ALU is shown in Figure 4.2. All of the other elements of the processor bring data into the ALU [7,9,10,19] for it to process and then take the results back out.

. . .

ŝą

#### Figure 4.2 ALU

The proposed 16 bit DSP processor contains two 32-bit input ports and one 32-bit output port feeding the accumulator. ALU and accumulator for arithmetic operations. The ALU is a general purpose arithmetic unit; operations

performed with the 16-bit words taken from memory, the 16-bit words derived form immediate instructions, or the 32-bit result taken from the product register of the multiplier. In addition to the normal arithmetic instructions, the ALU perform Boolean operations, providing a bit manipulation ability required of a high speed controller.

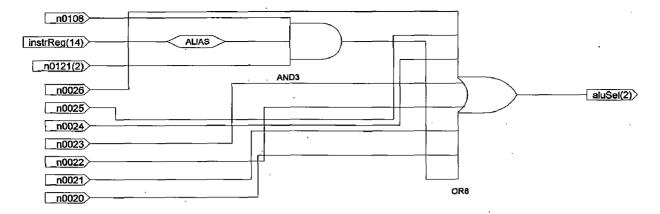

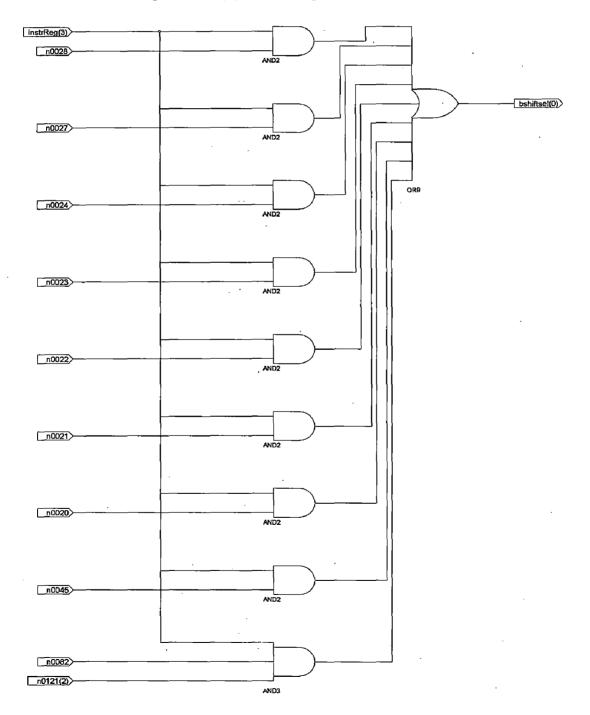

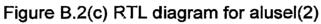

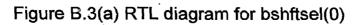

Inputs **a** and **b** are the two input busses upon which the ALU operations are performed. Output bus **c** returns the result of the ALU operation. Both the inputs **a** and **b** and output **c** are of 32-bits. Input **sel** determines which operation is to be performed as specified by the table 4.1. The input **sel** is of 4-bits.

The control unit provides **sel(3:0)** signals that control the operation of the ALU and the movement of the data into and out of the ALU. The ALU can perform a number of arithmetic operations, such as add and subtract, and some logical operations, such as AND, OR, and XOR.

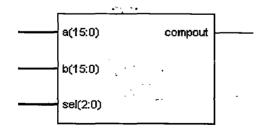

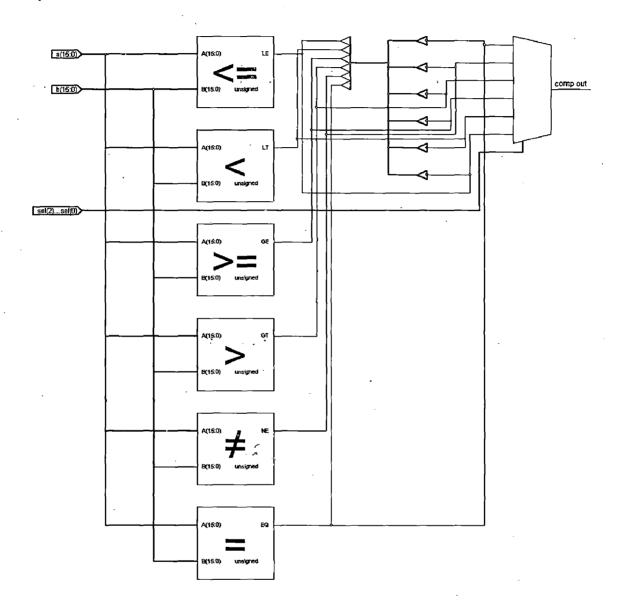

#### 4.3.2 Comparator

This entity compares two values and returns either a '1' or '0' to the control unit as the status signals, depending on the type of comparison requested and the values being compared. Based on this status signal the controller determine what operation to perform next. A symbol showing the ports of the comparator is shown in Figure 4.3. The comparison type is determined by the value on input port **sel(2:0)**.

Figure 4.3. Symbol of Comparator

To compare if inputs **a** and **b** are equal, apply the value **eq** to port **sel**. If ports **a** and **b** have the same value, port **compout** returns **'1'**. If the values are not equal, **'0'** is returned. All operations work on two input values and return a

single bit result. This bit is used to control the flow of operation within the processor while executing instructions. If the condition tested is true, a '1' value is assigned; otherwise, a '0' is assigned. Figure 4.4 shows the internal architecture of comparator.

Figure 4.4. Architecture of comparator

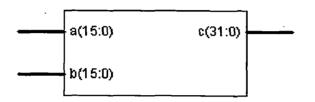

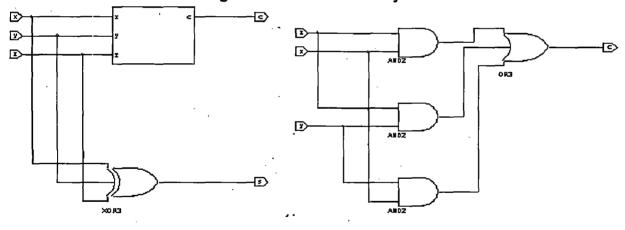

**4.3.3 Multiplier**: Multiplication is one of the basic and critical operations in the computations. Efficient implementations of multipliers are required in many applications. In this present work a 16-bit array multiplier [4,5] is designed, whose block diagram is shown in figure 4.5. The multiplier performs a 16 x 16 bit multiplication with a 32-bit result in a single machine cycle. The multiplier consists of three elements:

- The T Register,

- The P Register,

- The multiplier array

The 16-bit T register temporarily stores the multiplicand; the P register stores the 32-bit product. The multiplier values either come from the data memory or are derived from instruction word. The on-chip multiplier allows the device to perform fundamental DSP operations such as convolution, correlation, and filtering.

Figure 4.5. Multiplier Block diagram

There are 3 methods for performing the multiplication.

**1. Serial/Parallel multiplication**: In this one operand is used in parallel and the second operand is used bitwise, i.e. serial.

**2. Serial/Serial multiplication**: if both operands are used serial, the scheme is called a serial/serial multiplier. Such a multiplier only needs one full adder, but the latency of serial/serial multipliers is high, because the state machine needs about N x N cycles.

**3.Parallel/Parallel or Array multiplication**: In this approach both operands are used in parallel. It improves the speed of the operation with increased complexity. This arrangement is viable if the time required to complete the carry and sum calculations are same. For modern FPGA the carry computation is performed faster than the sum calculation and a different architecture is more efficient for FPGAs. The approach for this array multiplier is shown in figure 4.6.

This is a direct array form of "pencil and paper" method and must therefore produce a valid product. In this work, the array multiplier for unsigned numbers is proposed. The proposed scheme is applicable for VLSI and FPGA application. For VLSI implementations of multipliers, array-based multipliers are well known and often used.

1

1

ſ

|                   |                 |         |         |          |          | •                    |          |                    |        |          |             |            |              |                   |           |                     | S                               |

|-------------------|-----------------|---------|---------|----------|----------|----------------------|----------|--------------------|--------|----------|-------------|------------|--------------|-------------------|-----------|---------------------|---------------------------------|

|                   | _               | -17'    |         |          |          | •                    |          |                    |        |          |             |            |              |                   |           |                     |                                 |

| å                 | ລິ              | -f:     |         |          |          |                      |          |                    |        |          |             |            |              |                   |           |                     | บั                              |

| a,                | ค้              | g:      | \$      |          |          |                      |          |                    |        |          |             |            |              |                   |           |                     | ថ                               |

| aı                | p <sub>2</sub>  | ę.      | 4       | ୍ଷ       |          | . • .                |          | 7                  |        |          |             |            |              |                   |           |                     | ຮ                               |

| a<br>3            | р <sup>3</sup>  | \$      | \$      | 4        | 3        | ,                    |          |                    |        |          |             |            |              |                   |           |                     | J                               |

| a4                | 4               | ş       | \$      | 5        | ş        | ş                    |          |                    |        |          |             |            |              |                   |           |                     | 5                               |

| a5                | p5              | \$      | \$      | 5.       | 5        | - Q,                 | ş        |                    |        |          |             |            |              |                   |           |                     | പ്                              |

| ag                | മ്              | Ť       | Ť       | 45       | ş        | रू<br>ब              | ¥        | \$                 |        |          |             |            |              |                   |           |                     | 5                               |

| a,                | ä               | \$      | 4       | ş        | 53       | \$                   | ş        | 4                  | ş      |          |             |            |              |                   |           |                     | ້ບ                              |

| ő                 | ĝ               | Ť       | ş       | Ŧ        | ş        | а<br>Т               | ş        | ş                  | ¥      | Ŧ        |             |            |              |                   |           |                     | S                               |

| 9<br>9<br>9       | 6q              | ą.      | Ť       | 5        | ş        | \$                   | *        | ş                  | ¥      | æ        | \$          |            |              |                   |           |                     | c <sub>to</sub>                 |

| ,<br>,            |                 | 5       | \$      | 4        | ş        | 4                    | ş        | 3                  | \$     | ş        | ÷           | ÷,         |              |                   |           |                     | c <sub>t</sub>                  |

| a11               | p44             | ц.      | 4       | Ŧ        | р.<br>Р  | 셯                    | 3        | \$                 | ¥;     | ş        | 4           | Ę          | \$           |                   |           |                     | 6 <sub>13</sub> (               |

| <sup>3</sup> 12   | Ę12             | ş       | ,<br>S  | \$       | 4        | र्ष्ट<br>च           | ş        | 4                  | *      | 4        | ŝ           | à.         | ų,           | Ś                 |           |                     | 6 <sup>13</sup> 5               |

| 9<br>13           | р <b>1</b> 3    | 5       | *       | 7        | ÷.       | 4                    | ÷.       | **                 | *      | şş       | 4           | A          | 2            | ÷,                | i i       |                     | *15                             |

| a<br>14           | b <sub>14</sub> | ,<br>;  | ÷.      | \$       | 45       | 4                    | े.<br>इ  | *                  | 3      | *        | 4           | च<br>सं    | 3            | *                 | , .<br>   | 4                   |                                 |

| a <sub>15</sub> a | 1<br>2<br>2     | ې<br>چې | 4       | *        | ş        | 4.9                  | ÷        | 4                  | ÷      | ž        | *           | ÷,         | य<br>सं<br>म | بر                | •<br>***  | 4<br>십 <sup>8</sup> | c <sub>le</sub> c <sub>l±</sub> |

|                   | ľ               |         | म्यून्य |          |          |                      |          |                    |        |          |             |            |              |                   |           |                     | l                               |

| >                 | < 1             |         | พ้      | 4.8<br>5 |          | 4<br>8<br>9          | **       | 4.9                | 3      | \$       | 4.4         | ÷.         | 4            | <b>*</b> **       | Ţ.        | 4                   | 614                             |

|                   |                 |         |         | Ч°р      | 5        | 4                    | र्थ<br>व | 8<br>5             | 1      | \$       | 4           | 4¥,        | 4            | 1                 | r.<br>F   | ð                   | C <sub>18</sub>                 |

|                   |                 |         |         |          | 9.0<br>9 | с. р.                |          | ς,                 | 4      | 4        | 4           | 4          | 3            | 2                 | 4         | ę.                  | en<br>S                         |

|                   |                 |         |         |          |          | म् <sup>म</sup><br>न | 4        | <b>4</b> .9        | 2      | \$       | 47          | \$         | *            | 4                 | र्थ<br>ब  | 4                   | ъ.                              |

|                   |                 |         |         |          |          |                      | ţŗ÷      | ٨.                 | 4,9    | ब<br>*   | 47          | भू<br>म    | 4            | ş                 | 2         | સં                  | รี                              |

|                   |                 |         |         |          |          |                      |          | पुं <sup>3</sup> व | 4.5    | Ş        | Ş           | Ş          | ÷            | 4                 | 4         | ¥2                  |                                 |

|                   |                 |         |         |          |          |                      |          |                    | ቑ፝፝፞፝፝ | र्ष<br>म |             | न्द्र<br>क | 4.<br>1      | ĨĘ <sup>®</sup> R |           | сţ.                 | -<br>2<br>5                     |

|                   |                 |         |         |          |          |                      |          |                    |        | ę.<br>P  | 3           |            | 47<br>7      | 4.4               | ş         | \$                  | ្មី                             |

|                   |                 |         |         |          |          |                      |          |                    |        |          | م<br>م<br>م | 42 ·       | ŝ            | с.<br>У.          | ۲۰۱۶      |                     | - <sup>2</sup> 5                |