# DESIGN AND IMPLEMENTATION OF SOFTWARE DEFINED RADIO SYSTEM ON FPGA FOR MEDICAL SIGNALS

### **A DISSERTATION**

# Submitted in partial fulfillment of the requirements for the award of the degree

of

### MASTER OF TECHNOLOGY

in

### **ELECTRICAL ENGINEERING**

(With Specialization in Measurement and Instrumentation)

By

PALLE SHAILAJA

### DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE - 247 667 (INDIA) JUNE, 2008

1.D. NO.-M. 7444, 2008-09, VK

INDIAN INSTITUTE OF TECHNOLOGY ROORKEE

### **Student declaration**

I hereby declare that the work that is being presented in this dissertation report entitled "Design and implementation of Software Defined Radio system for medical signals" submitted in fulfillment of the requirements for the award of the degree of Master of Technology in Electrical Engineering with specialization in Measurement & Instrumentation, submitted in the Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee, is an authentic record of my own work carried out, under the guidance of Dr.Vinod Kumar, Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee.

I have not submitted the matter embodied in this project report any other degree.

Date: 30-06-08

Place: Roorkee

shailaja

(PALLE SHAILAJA)

#### CERTIFICATE

This is to certify that the above statement made by the candidate is true to the best of my knowledge.

i

Prof. Dr. Vinod Kumai

Professor,

Department of Electrical Engineering,

Indian Institute of Technology Roorkee,

Roorkee – 247667.

India

## Acknowledgements

First and foremost, my sincere regards to my supervisor Dr. Vinod Kumar, Professor, Department of Electrical Engineering, for his encouragement, valuable suggestions, amiable, amicable and caring nature. His guidance was helpful throughout this dissertation work.

Thanks are due to Prof. H. K. Verma, Group Leader (M&I) and Prof. Vinod Kumar (Chairman, DRC), for their moral support and advice.

I thank Prof. S. P. Gupta, Head of the Department, Dr. R.S.Anand, Assoc. Professor, Department of Electrical Engineering for their support.

I would also like to thank the Department of Electrical Engineering at the Indian Institute of Technology, Roorkee for giving me the opportunity to do a Master's degree in this honorable institution.

I am extremely grateful to my parents, friends, and well-wishers for their candid help, suggestions and persistent encouragement given to me at different stages of my work.

Shaila 9 (PALLE SHAILAJA)

### Abstract

The fourth generation of wireless communications will demand the use of software radio technology as the basic architecture to support multi-standard and multi-mode radio designs. The aim of this thesis is to design and implement a baseband section of software defined radio based wireless communication system for transmission of medical signals, which requires multi communication links. Software defined radio is a feasible solution for reconfigurable radios, which can perform different functions at different times on the same hardware. The baseband section of a wireless communication system is first simulated and then implemented in hardware. Baseband processing of medical signals involves functions such as forward error correction, modulation and digital up conversion on transmitter side and digital down conversion, demodulation and viterbi decoding on receiver side. System involving all these functions is developed. Digital Up/Down conversion is present in intermediate frequency section of Software defined radio. The performance of the baseband transmitter is analyzed using constellation and eye diagrams for different modulation techniques i.e QPSK, QAM techniques and different signal-to-noise ratios, while considering an additive white Gaussian noise channel. The performance of the receiver is analyzed by comparing the input and output waveforms by transmitting EEG and EMG signals. The performance of the system in is also analyzed by implementing the system in hardware using Xilinx Spartan 3E field programmable gate array. A comparison of the simulation results with the results obtained from implementing the system on Spartan 3E hardware is presented and discussed. It is shown that the simulation results and experimental results are similar.

# Table of Contents

| Stude   | nt declarationi                                      |

|---------|------------------------------------------------------|

| Ackno   | owledgementsii                                       |

| Abstr   | actiii                                               |

| Table   | of Contentsvi                                        |

| List o  | f Figuresvii                                         |

| List of | f Tablesxi                                           |

| Abbre   | eviationsxii                                         |

| Chapt   | er 1 Introduction1                                   |

| 1.1     | Introduction1                                        |

| 1.2     | Communications in medical field2                     |

|         | 1.2.1 Networks used in transmission of medical data  |

|         | 1.2.2 Transmission technologies for medical signals4 |

| 1.3     | Software defined radio for medical signals           |

| 1.4     | Motivation                                           |

| 1.5     | Statement of problem                                 |

| 1.6     | Outline of thesis                                    |

| 1.7     | Summary                                              |

# **Table of Contents**

| Stude   | nt declarationi                                      |

|---------|------------------------------------------------------|

| Ackno   | owledgementsii                                       |

| Abstra  | actiii                                               |

| Table   | of Contentsvi                                        |

| List of | f Figuresvii                                         |

| List of | f Tablesxi                                           |

| Abbre   | viationsxii                                          |

| Chapt   | er 1 Introduction1                                   |

| 1.1     | Introduction1                                        |

| 1.2     | Communications in medical field2                     |

| . •     | 1.2.1 Networks used in transmission of medical data  |

|         | 1.2.2 Transmission technologies for medical signals4 |

| 1.3     | Software defined radio for medical signals           |

| 1.4     | Motivation                                           |

| 1.5     | Statement of problem10                               |

| 1.6     | Outline of thesis                                    |

| 1.7     | Summary                                              |

| Chapter 2 Fundamentals of Software Defined Radio13                   |

|----------------------------------------------------------------------|

| 2.1 Introduction                                                     |

| 2.2 Definition of Software defined radio15                           |

| 2.3 Software defined radio concepts                                  |

| 2.3.1 Conventional Versus Software Defined Radio19                   |

| 2.3.2 Characteristics of Software Defined Radio                      |

| 2.3.3 Advantages and Disadvantages of Software Defined Radio22       |

| 2.4 Software Defined Radio Implementation Platform                   |

| 2.5 Technical Challenges                                             |

| 2.6 Summary                                                          |

|                                                                      |

| Chapter 3 Framework for SDR based design                             |

| 3.1 Introduction                                                     |

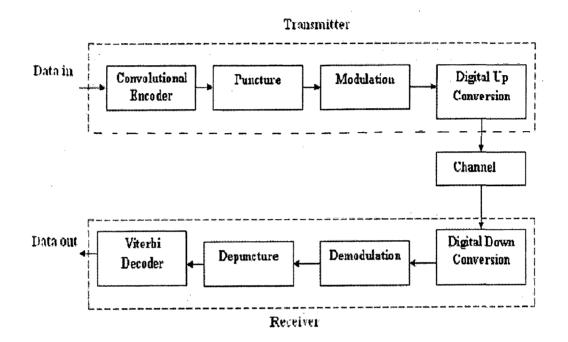

| 3.2 Communication System Model for transmission of medical signals28 |

| 3.2.1 Radio Frequency Section                                        |

| 3.2.2 Intermediate Frequency Section                                 |

| 3.2.3. Baseband Section                                              |

| 3.3 Softwares used                                                   |

| 3.3.1 Hardware Descriptive Language                                  |

| 3.3.2 MATLAB                                                         |

| 3.3.3 Xilinx System Generator                                        |

| 3.3.4 Xilinx ISE 9.2i                                                |

| 3.3.5 Drivers for FPGA development kits                              |

| 3.4 XUP Spartan 3E FPGA development kit                              |

| 3.5 Design Process for Reprogrammable Computing                      |

| 3.5.1 Simulation with SIMULINK and System Generator                  |

| Conte | ents |

|-------|------|

|-------|------|

|     | 3.5.2 | HDL Co-Simulation      | .40 |

|-----|-------|------------------------|-----|

|     | 3.5.3 | Hardware Co-Simulation | 41  |

| 3.6 | Sumn  | nary                   | .42 |

| Chapte | er 4 System model                       | .43 |

|--------|-----------------------------------------|-----|

| 4.1    | Introduction                            | .43 |

| 4.2    | OSI Seven-Layer                         | .43 |

| 4.3    | System Model                            | .44 |

| 4.4    | Forward Error Correction                | .45 |

|        | 4.4.1. Convolutional Encoder            | .46 |

|        | 4.4.2 Puncturing Coding                 | .47 |

|        | 4.4.3. Depuncturing coding              | .49 |

|        | 4.4.4 Viterbi decoding                  | .50 |

| 4.5    | Modulation/Demodulation                 | 51  |

|        | 4.5.1. QPSK modulation                  | 52  |

|        | 4.5.2 16-QAM modulation                 | .55 |

|        | 4.5.3. Demodulation                     | .56 |

|        | 4.5.3.1 Costas loop                     | 57  |

| 4.6    | Up/Down Conversion                      | .59 |

|        | 4.6.1. Frequency Converter Fundamentals | .60 |

|        | 4.6.2 Sample rate conversion filters    | .62 |

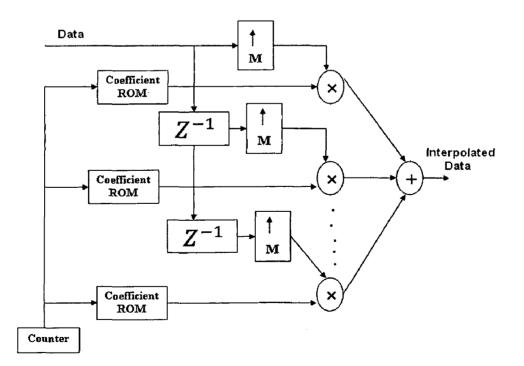

|        | 4.6.3. Polyphase filter                 | .63 |

| 4.7    | Summary                                 | 64  |

| Chapte | r 5 Simulation and | l implementation results | 65 |

|--------|--------------------|--------------------------|----|

| 5.1    | Introduction       | •••••••••••••••••••••    |    |

| 5.2 | System Model for transmission of medical signals65        |

|-----|-----------------------------------------------------------|

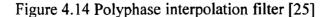

| 5.3 | 16-QAM Transmitter Model                                  |

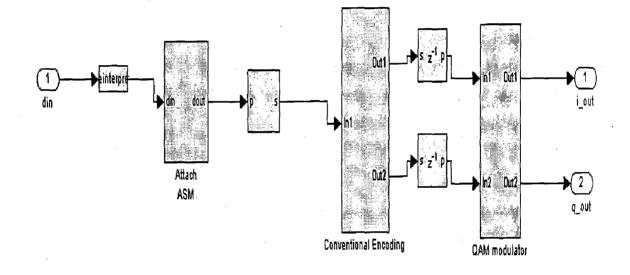

| 5.4 | QAM Receiver Model                                        |

| 5.5 | QPSK transmitter                                          |

| 5.6 | QPSK receiver                                             |

| 5.7 | Simulation Results                                        |

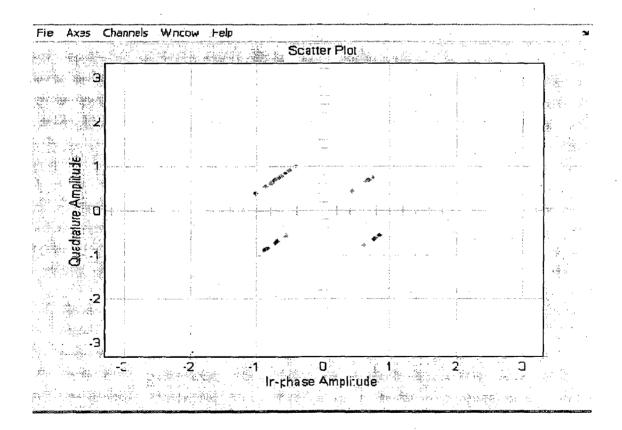

|     | 5.7.1 Constellation Diagrams71                            |

|     | 5.7.2 Eye Diagrams                                        |

|     | 5.7.3 Results for sample rate conversion of EMG signals75 |

|     | 5.7.4 Results from QAM system for ECG signal              |

|     | 5.7.5 Output Waveform of medical signals                  |

| 5.8 | FPGA Implementation of system                             |

| 5.9 | Summary                                                   |

| Chapter | 6 Conclusions and future work | 87 |

|---------|-------------------------------|----|

| 6.1     | Conclusions                   | 87 |

| 6.2     | Future work                   |    |

| EFERENCES |

|-----------|

|-----------|

| APPENDIX A | )) | 2 |

|------------|----|---|

|------------|----|---|

| APPENDIX B | 94 |

|------------|----|

|            |    |

# **List of Figures**

| Figure 2.1  | Model of software defined radio system19                      |

|-------------|---------------------------------------------------------------|

| Figure 2.2  | Hardware implementation platforms for SDR23                   |

| Figure 3.1  | Functional block diagram of a wireless communication system28 |

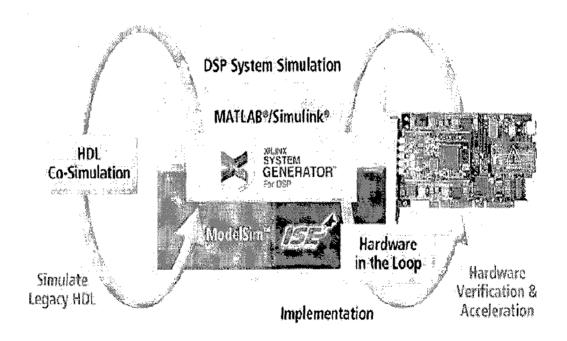

| Figure 3.2  | Design process for reconfigurable computing32                 |

| Figure 3.3  | XUP Spartan 3E FPGA development kit                           |

| Figure 3.4  | Illustration of test-bed implementation process               |

| Figure 3.5  | System Generator dialog box40                                 |

| Figure 4.1  | Software definable baseband communication system'45           |

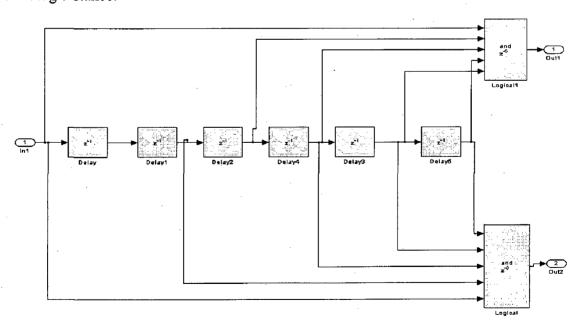

| Figura 4.2  | Conventional encoder                                          |

| Figure 4.3  | Example of puncturing rate 1/2 encoder                        |

| Figure 4.4  | Example of depuncturing rate 2/3 encoded data                 |

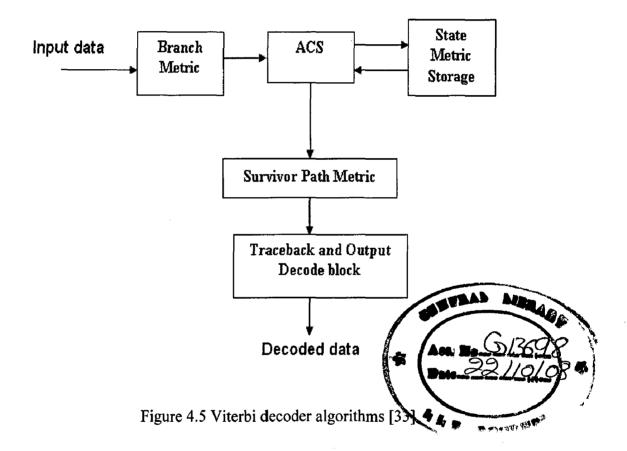

| Figure 4.5  | Viterbi decoder algorithm                                     |

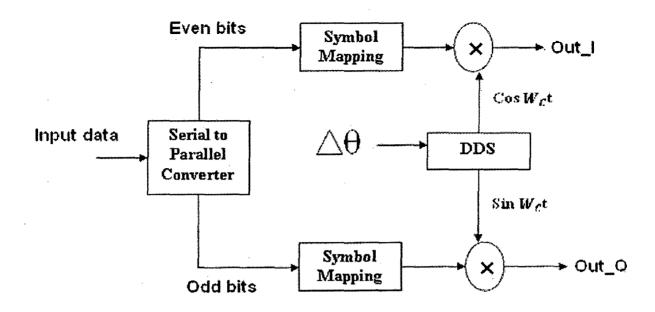

| Figure 4.6  | QPSK modulator schematic diagram53                            |

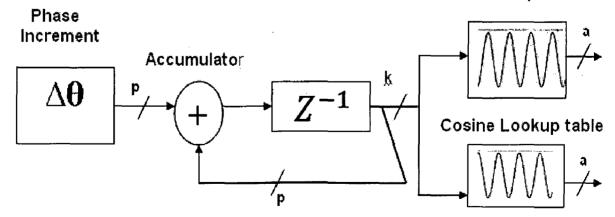

| Figura 4.7  | Direct Digital Synthesizer                                    |

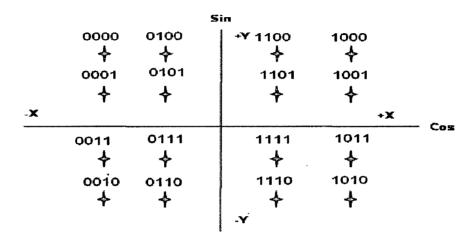

| Figure 4.8  | Symbol mapping for QAM modulator57                            |

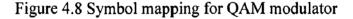

| Figure 4.9  | Demodulator schematic diagram59                               |

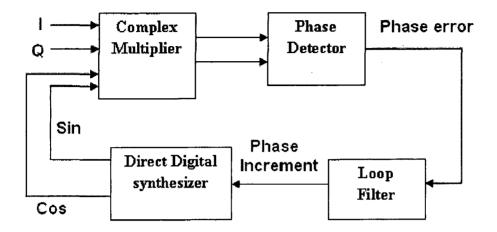

| Figure 4.10 | Carrier recovery schematic diagram60                          |

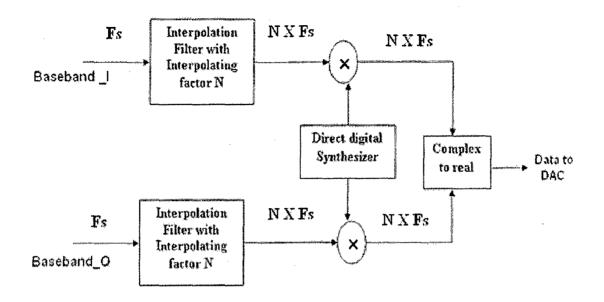

| Figure 4.11 | Digital up conversion                                         |

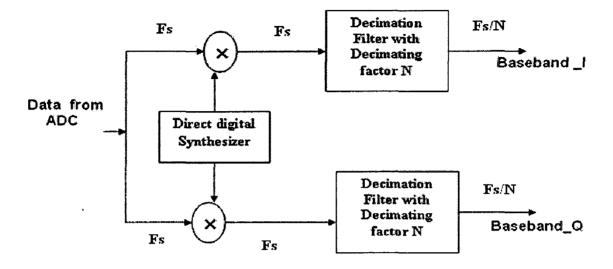

| Figura 4.12 | Digital down conversion61                                     |

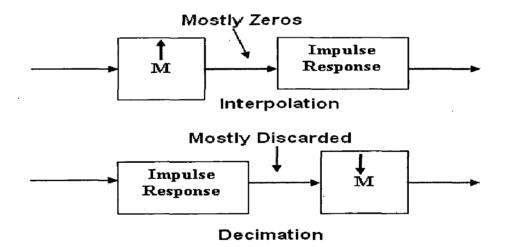

| Figure 4.13 | Sample rate conversion filter structure                       |

| Figure 4.14 | Polyphase interpolation filter                                |

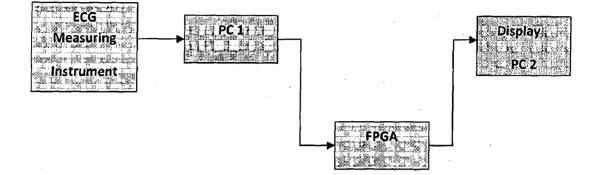

| Figura 5.25 | Experimental set up of system82                                    |

|-------------|--------------------------------------------------------------------|

| Figure 5.26 | Command window showing the progress of implementation tools83      |

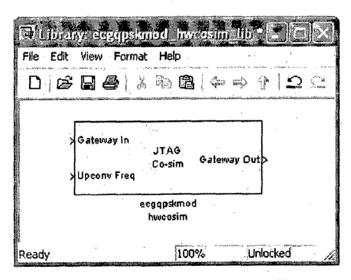

| Figure 5.27 | Hardware co-simulation library84                                   |

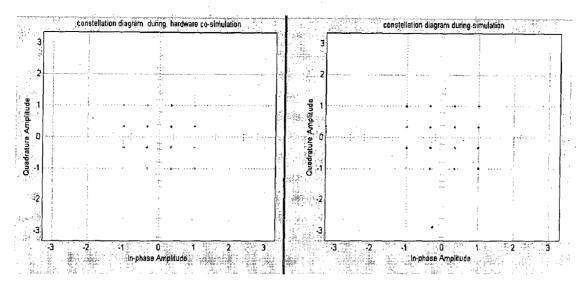

| Figure 5.28 | Constellation diagram for hardware co-simulation and simulation85  |

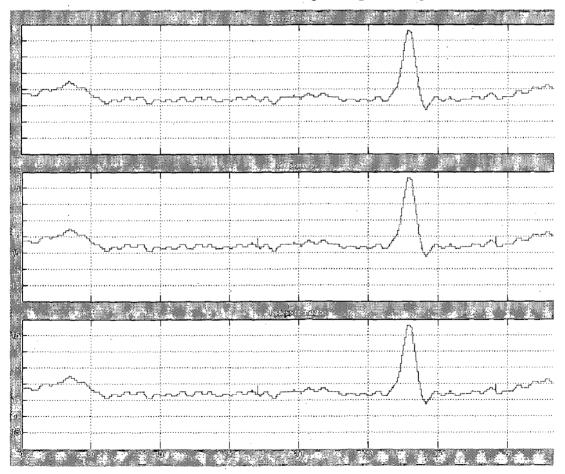

| Figura 5.29 | ECG input and output signals of system in hardware co-simulation85 |

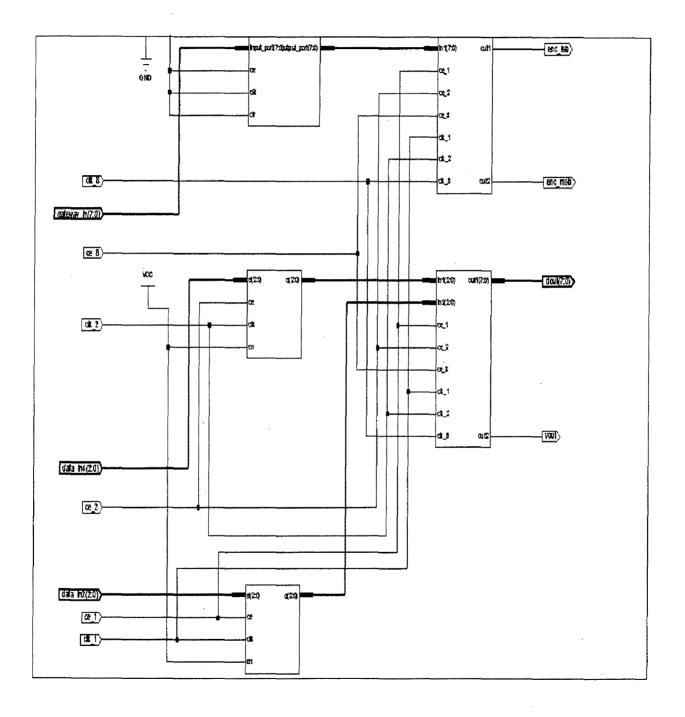

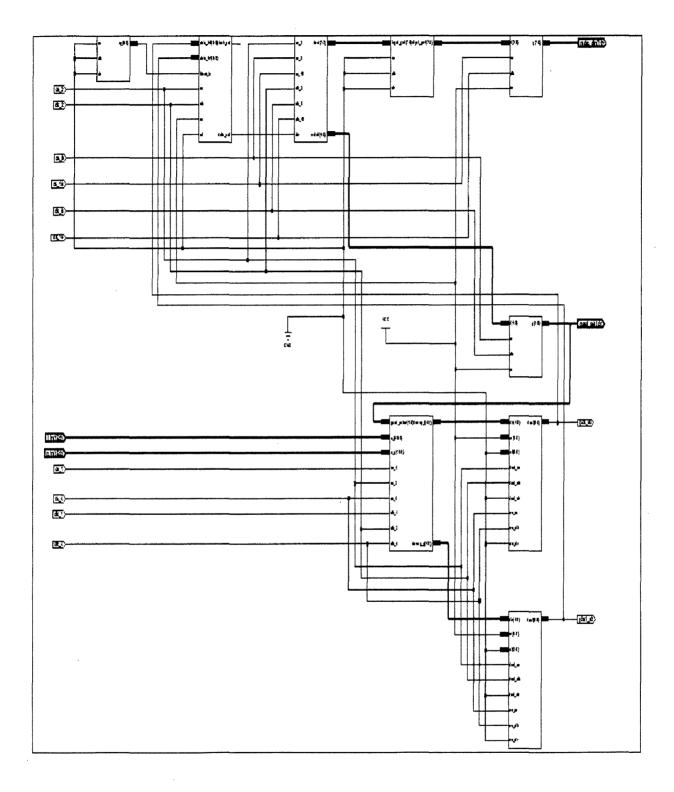

| Figure A.1  | RTL simulation of QAM transmitter84                                |

| Figure A.2  | RTL simulation of QAM receiver85                                   |

# **List of Figures**

| Figure 2.1  | Model of software defined radio system19                      |

|-------------|---------------------------------------------------------------|

| Figure 2.2  | Hardware implementation platforms for SDR23                   |

| Figure 3.1  | Functional block diagram of a wireless communication system28 |

| Figure 3.2  | Design process for reconfigurable computing32                 |

| Figure 3.3  | XUP Spartan 3E FPGA development kit                           |

| Figure 3.4  | Illustration of test-bed implementation process               |

| Figure 3.5  | System Generator dialog box40                                 |

| Figure 4.1  | Software definable baseband communication system'45           |

| Figura 4.2  | Conventional encoder                                          |

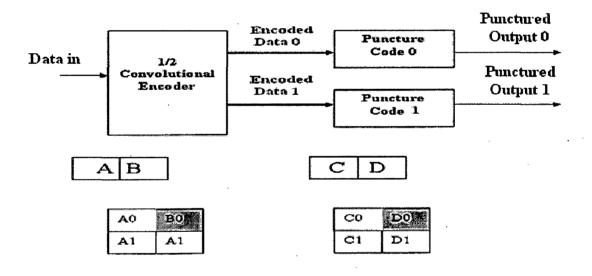

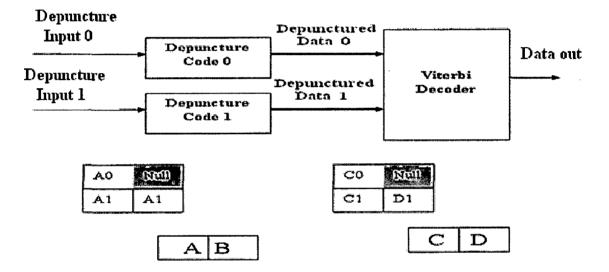

| Figure 4.3  | Example of puncturing rate 1/2 encoder48                      |

| Figure 4.4  | Example of depuncturing rate 2/3 encoded data49               |

| Figure 4.5  | Viterbi decoder algorithm                                     |

| Figure 4.6  | QPSK modulator schematic diagram53                            |

| Figura 4.7  | Direct Digital Synthesizer55                                  |

| Figure 4.8  | Symbol mapping for QAM modulator57                            |

| Figure 4.9  | Demodulator schematic diagram59                               |

| Figure 4.10 | Carrier recovery schematic diagram60                          |

| Figure 4.11 | Digital up conversion61                                       |

| Figura 4.12 | Digital down conversion61                                     |

| Figure 4.13 | Sample rate conversion filter structure                       |

| Figure 4.14 | Polyphase interpolation filter63                              |

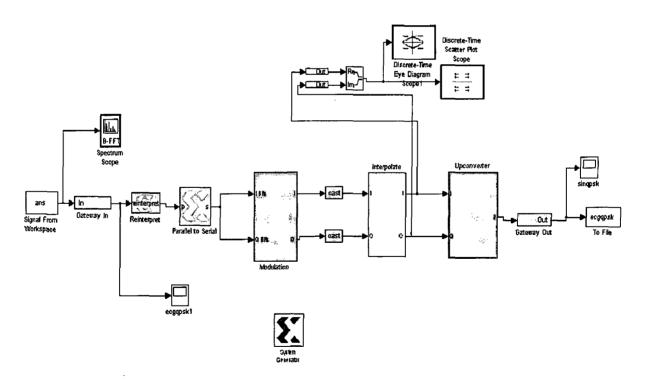

| Figure 5.1  | Simulation model of QAM transmitter                              | 66 |

|-------------|------------------------------------------------------------------|----|

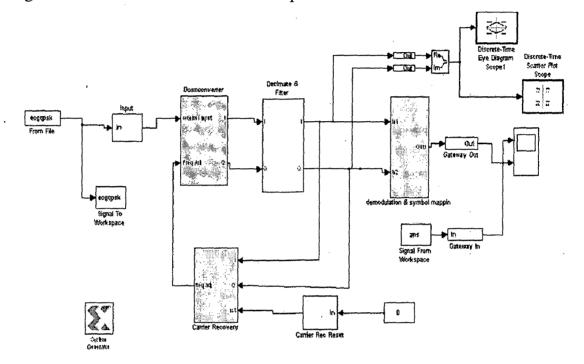

| Figure 5.2  | QAM receiver system                                              | 67 |

| Figura 5.3  | QPSK transmitter model                                           | 69 |

| Figure 5.4  | QPSK receiver system                                             | 70 |

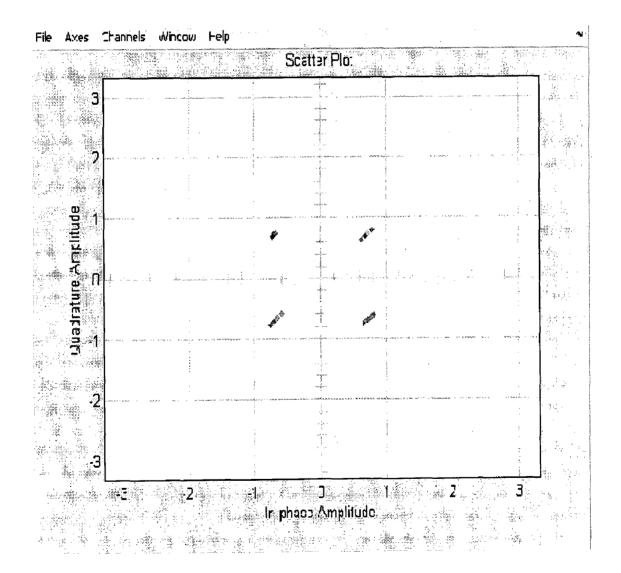

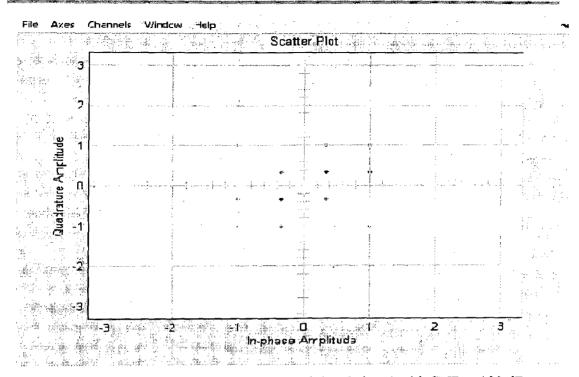

| Figure 5.5  | Constellation diagram for QPSK signal with SNR = 15 dB           | 71 |

| Figure 5.6  | Constellation diagram for QPSK signal with SNR = 25 dB           | 72 |

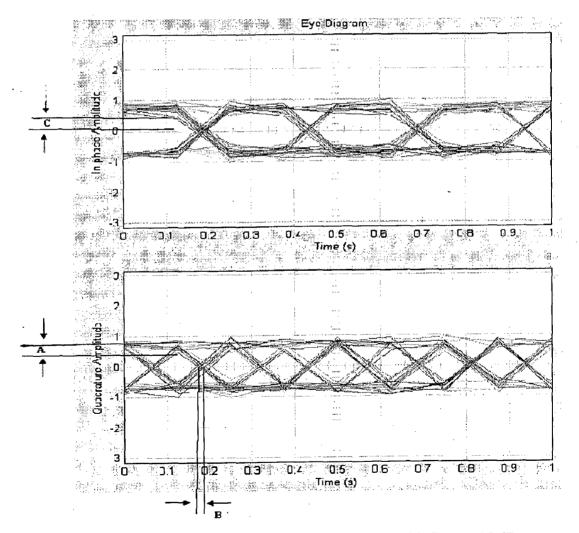

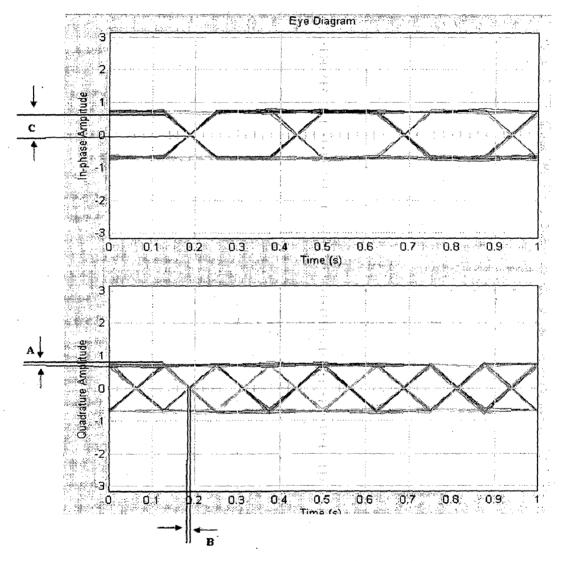

| Figura 5.7  | Eye diagram for QPSK modulated signal with $SNR = 15 \text{ dB}$ | 73 |

| Figure 5.8  | Eye diagram for QPSK modulated signal with SNR = 25 dB           | 74 |

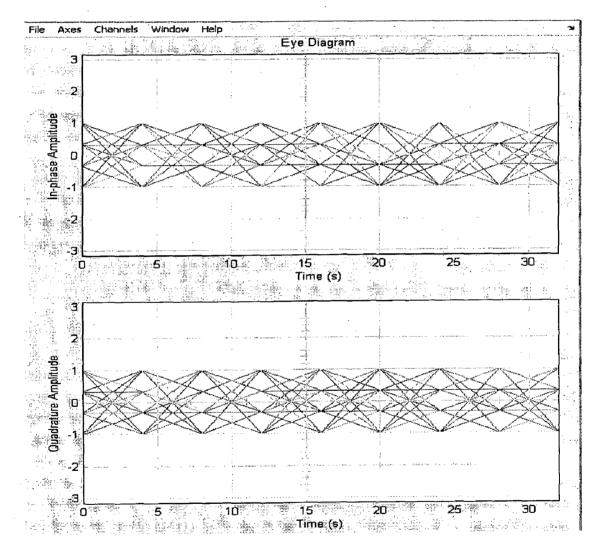

| Figure 5.9  | Eye diagram for QAM modulated signal with SNR = 100 dB           | 75 |

| Figure 5.10 | Constellation diagram for QPSK signal with SNR = 25 dB           | 76 |

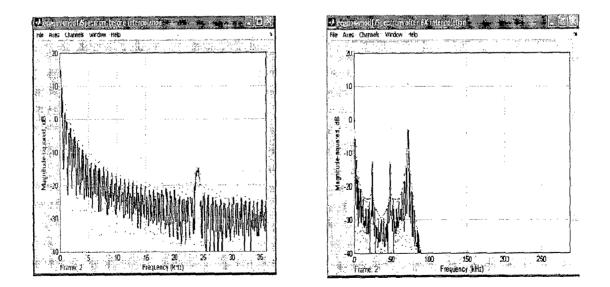

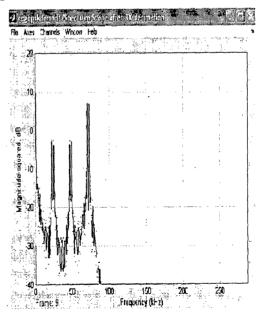

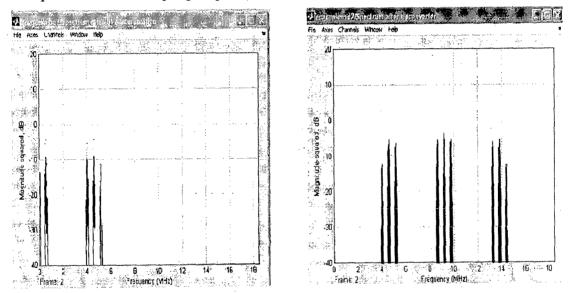

| Figure 5.11 | Spectrum before interpolation                                    | 76 |

| Figure 5.12 | Spectrum after 8X interpolation                                  | 76 |

| Figure 5.13 | Spectrum after 64X interploation                                 | 77 |

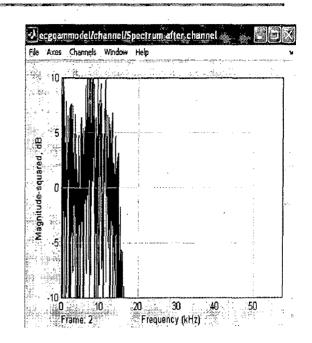

| Figure 5.14 | Spectrum after upconversion                                      | 77 |

| Figura 5.15 | Spectrum after downconversion                                    | 77 |

| Figure 5.16 | Spectrum after 8X Decimation                                     | 77 |

| Figure 5.17 | Spectrum after 64X Decimation                                    | 78 |

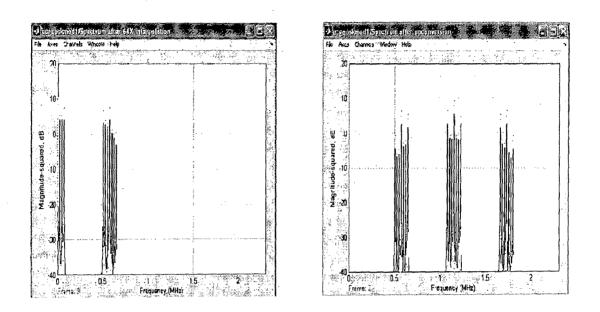

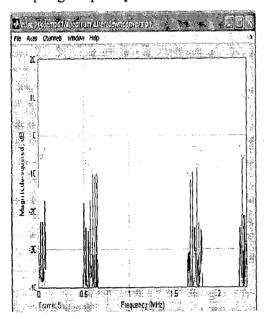

| Figure 5.18 | Spectrum after 512 X interpolation                               | 78 |

| Figure 5.19 | Spectrum after Upconversion                                      | 78 |

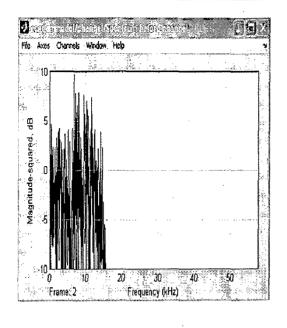

| Figure 5.20 | Spectrum before channel for QAM system                           | 79 |

| Figure 5.21 | Spectrum after channel for QAM system                            | 79 |

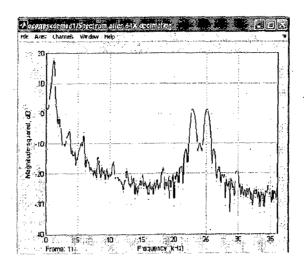

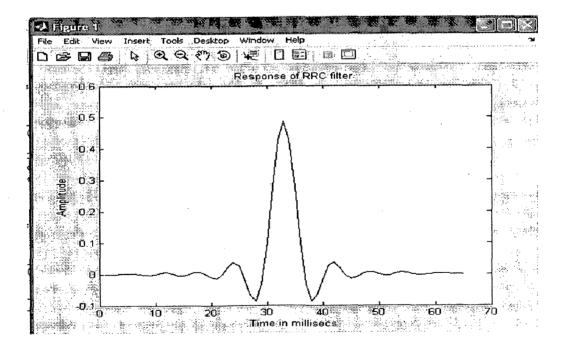

| Figure 5.22 | Response of RRC filter with roll of factor 0.3                   | 79 |

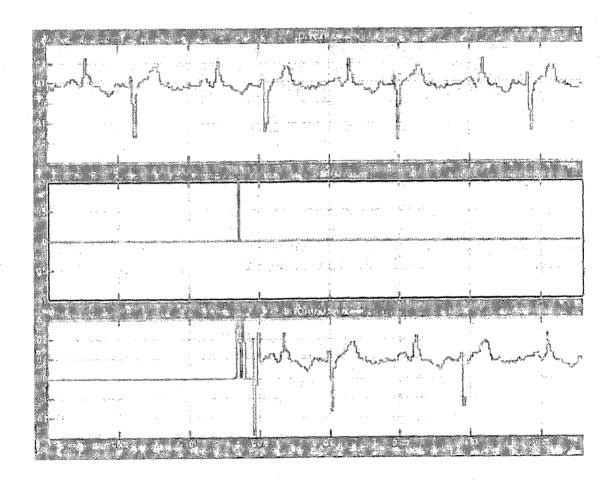

| Figure 5.23 | ECG Input and output waveforms of the QAM system                 | 80 |

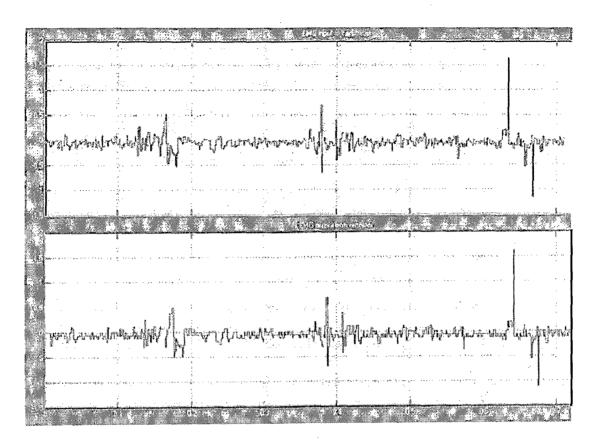

| Figure 5.24 | EMG Input and output waveforms of the QPSK system                | 81 |

| Figura 5.25 | Experimental set up of system                                      |

|-------------|--------------------------------------------------------------------|

| Figure 5.26 | Command window showing the progress of implementation tools83      |

| Figure 5.27 | Hardware co-simulation library84                                   |

| Figure 5.28 | Constellation diagram for hardware co-simulation and simulation85  |

| Figura 5.29 | ECG input and output signals of system in hardware co-simulation85 |

| Figure A.1  | RTL simulation of QAM transmitter84                                |

| Figure A.2  | RTL simulation of OAM receiver85                                   |

# List of Tables

| Table 2.1 | Difference between conventional and software defined radios | 8              |

|-----------|-------------------------------------------------------------|----------------|

| Table 2.2 | Advantages of Software Defined Radio                        | 22             |

| Table 4.1 | Parameters of conventional encoder4                         | 17             |

| Table 4.2 | Four symbols mapping definitions for QPSK                   | 53             |

| Table 5.1 | Parameters used for implementation                          | 70             |

| Table B.1 | Device utilization for QAM transmitter                      | <b>)</b> 6     |

| Table B.2 | Device utilization for QPSK transmitter9                    | 97             |

| Table B.3 | Device utilization for QPSK receiver                        | <del>)</del> 8 |

# Abbreviations

| AWGN | Additive White Gaussian Noise      |  |

|------|------------------------------------|--|

| CDMA | Code Division Multiple Access      |  |

| DA   | Distributed Arithmetic             |  |

| DSP  | Digital Signal Processing          |  |

| ECG  | Electro Cardio Gram                |  |

| EEG  | ElectroEncephaloGram               |  |

| EMG  | ElectroMyeloGram                   |  |

| EDK  | Embedded Design Kit                |  |

| FIR  | Finite duration Impulse Response   |  |

| FPGA | Field Programmable Gate Array      |  |

| GPP  | General Purpose Processor          |  |

| GSM  | Global System for Mobile           |  |

| GUI  | Graphical User Interface           |  |

| HDL  | Hardware Descriptive Language      |  |

| HR   | Hardware Radio                     |  |

| IC   | Integrated Circuit                 |  |

| IF   | Intermediate Frequency             |  |

| IP   | Intellectual Property              |  |

| IS   | Interim Standard                   |  |

| ISE  | Integrated Software Environment    |  |

| ISDR | Ideal Software Defined Radio       |  |

| JHDL | Java Hardware Descriptive Language |  |

- JTAG Joint Test Action Group

- LCM Least Common Multiple

- LO Local Oscillator

- MAC Multiply and Accumulate

- **NCO** Numerically controlled oscillator

- PC Personal Computer

- PCS Personal Communication Services

- PN Pseudorandom Noise

- **PSD** Power Spectral Density

- **QPSK** Quadrature Phase Shift Keying

- **QAM** Quadrature Amplitude Modulation

- **RF** Radio Frequency

- **RTL** Register Transfer Logic

- SCR Software Controlled Radio

- SDR Software Defined Radio

- SNR Signal-to-Noise Ratio

- TACSTotal Access Communication System

- USR Ultimate Software Radio

- VHSIC Very High Speed Integrated Circuit

- VHDL VHSIC Hardware Description Language

- VLSI Very Large Scale Integration

- WI-FI Wireless-Fidelity

- WLAN Wireless Local Area Network

- XST Xilinx Synthesis Technology

- **XUP** Xilinx University Programme

### CHAPTER I INTRODUCTION

#### **1.1 Introduction**

Wireless communication networks have become more popular in the past two decades since the advent of cellular communications. The rapid growth in cellular communications has proved that wireless communication is viable for voice and data services. Traditional wireless devices are designed to deliver a single communication service using a particular standard [1]. With the steady increase of new wireless services and standards, single purpose devices with dedicated hardware resources can no longer meet the user's needs. It is also expensive to upgrade and maintain a wireless system each time a new standard comes into existence.

A feasible solution to make communication systems more flexible and user friendly can be achieved through the software defined radio (SDR) concept. Software defined radio refers to the class of reprogrammable or reconfigurable radios in which the same piece of hardware can perform different functions at different times [4]. Software defined radio is an emerging technology, for multi-service, multi-standard, multi-band, reconfigurable radio systems, which are reprogrammable by software.

A working definition of a software defined radio is a radio that is considerably defined in software and whose physical layer behavior can be significantly altered through changes to its software. Thus, the same piece of hardware can be used to realize different applications by modifying the software.

Software defined radio has generated tremendous interest in the wireless communication industry because of the wide-ranging economic and deployment benefits it offers [5]. Programmable hardware modules are increasingly being used in communication systems design at different functional levels.

Software defined radio (SDR) technology can be used to take advantage of programmable hardware modules to build open system architecture based on software. In this case, a variety of transceiver functions such as automatic gain control, frequency translation, filtering, modulation and demodulation can be integrated on a single hardware platform.

This could result in maximizing the number of radio functions for a particular application. Software defined radio offers the flexibility and upgradeability necessary to satisfy these requirements [5].

#### **1.2 Communications in medical field**

Transmission of medical data i.e. telemedicine has become increasingly possible due to influence of ongoing technical advances in multimedia, imaging, computers and information systems, as well as in telecommunications. A more advanced approach emerged in the 1960s, when the National Aeronautics and Space Administration first used radio signals to beam orbiting astronaut's physiological data back to Earth. Today, with the advent of high-speed broadband communications, telemedicine is becoming a part of everyday medical practice. Some people suffering from congestive heart failure equip their homes with remote monitoring systems that periodically transmit vital data, such as heart rate and weight, for expert evaluation and some hospitals teleconference on same high-speed networks.

Ambulances, Rural Health Centers (RHC) or other remote health location such as Ships navigating in wide seas and Continuous transmission of physiologic monitoring data from a passenger on a commercial airliner are common examples where transmission of medical data is required. In order to support the above different growing application fields, the integrated system had developed, which consists of a base unit and a telemedicine (mobile) unit. It can be used when handling emergency cases in ambulances, RHC or ships by using a mobile telemedicine unit at the

emergency site and a base unit at the hospital-expert's site, and enables home telemonitoring, by installing the telemedicine unit at the patient's home while the base unit remains at the physician's office or hospital. The system allows the transmission of vital biosignals (3–12 lead ECG, SPO2, NIBP, IBP and Temp) and still images of the patient [6]. The transmission is performed through GSM mobile telecommunication network, through satellite links (where GSM is not available) or through Plain Old Telephony Systems (POTS) where available.

#### 1.2.1 Networks used in transmission of medical data

#### (a) Local Area Network (LAN)

A LAN is used to connect digital devices such as personal computers and mainframe computers over a localized area such as a building or campus of a hospital, university or factory. LANs are normally installed and maintained by the organization and are essentially a small private computer network. Distances are small, 1-2 kilometers at the most, and this allows high data transmission rates. LANs are used to share information throughout an organization. In a hospital they are often used to access a Patient Master Index, medical record tracking, appointment booking systems and pathology test results. Any organization with two or more computers will generally have those networked [2].

#### (b) Wide Area Networks (WAN)

A wide area network is a network which covers a greater geographic area than a LAN. Generally, the dispersed sites are linked by lines leased from the telephone companies. Because of the distance involved, WANs have lower transmission rates than a LAN. In health a typical WAN would connect the LANs from all the hospitals in a city or region.

#### (c) Public Switched Telephone Network (PSTN)

This is the analogue telephone network which is the largest network in existence. It can be used to carry voice and, by using a modem, data as well. It

consists of a large number of carriers whose networks are interconnected. Telecommunications companies are continually developing and offering an expanding range of value-added communication services beyond the basic telephone service. For district hospitals ISDN (integrated services digital network) services are the most relevant additional service. An ISDN connection is required for video-conferencing and also for high bandwidth access to the Internet.

(d) Private Automatic Branch Exchange (PABX)

Many organizations have a PABX to automatically switch calls between telephone extensions in an organization and to and from the public telephone network.

**1.2.2** Transmission technologies for medical signals

The technologies involved in the transmission and receiving of the medical information (i.e. running the network) [2],

(a) Wires and cabling

Digital signals are sent as streams of electrical impulses. The existing telephone networks are generally built around copper wires and co-axial cables. The amount of information which can be carried (bandwidth) depends on the type of cable or wire. Most computer networks within LAN are connected with co-axial cable. Here, the quality of the connection and the potential bandwidth of the connection to the exchange fall rapidly with distance.

(b) Fibre optic cable

Fibre optic cable is very fine glass fibres which carry digital signals as pulses of light. Fibre optic cable has revolutionized telecommunications because it is able to carry enormous volumes of information. It is also not subject to electrical interference. The initial roll-out and maintenance is expensive.

**Electrical Department**, **IIT Roorkee**

#### (c) Satellite technology

Satellites are able to receive radio signals from earth and then retransmit them back. The device which does this is a satellite transponder. Most communications satellites are in geostationary orbit above the equator. The equipment required for transmitting a signal to a satellite in geostationary orbit and the equipment required to receive the signal from the satellite is expensive. Numbers of repeaters are required for covering large distances. For this reason, satellite technology is often used to broadcast signals.

#### (d) Radio-based technologies

This uses radio waves to send information through the air. The fixed equipment required is a transmitter and a receiver. Radiotelephony has been used in health care since it was first introduced commercially in the 1950s, but it was not until the introduction of hand-held transceivers and nation-wide cellular network coverage in the last decade. Radio frequencies are regulated in each country with frequency bands being reserved for various purposes. It may be used for radio broadcast or point-to-point telephony as in the mobile phone network. Its range varies with frequency and the power of the transmitter. Their advantages are mobility, reliability and not being reliant on wires and cabling.

#### 1.3 Software defined radio for medical signals

The communication of medical data can occur among patients, specialists, clinics and hospitals. In medical application, there are two communication modes. One is point to point mode. It means the communication is going on between two users; the other is multipoint to multipoint mode. It means the communication is going on among many users' i.e. patients, specialists and medical centers.

The point to point mode is not enough to meet the actual requirements for applications. Because an application is usually asked to provide the following functions:

Electrical Department, IIT Roorkee

(1) The patient's data need to be sent to one or more specialists, a database, and the display terminal at the same time.

(2) A specialist needs to send information to the others in the same working group as well as to receive information from other specialists in a medical conference.

Therefore, a multipoint to multipoint communication mode is required for the communication of data. They have different communication mode and rates.

Internet can support various physical connections and provide multiple logical channels [3]. The communication may be difficult to manage. Firstly, each patient or specialist need to setup a connection with other specialists related to the same work. Secondly, each patient need to send the same data packages to many specialist and respond to the information sending backward. It is a complex process. The communication rate could be very low, for example, the telephone line has the rate of 9600-14400 bps.

Multipoint communication can be provided by using Wireless communications which provides higher bandwidth and data rates. for example, protocols such as IEEE 802.11 and its siblings. IEEE 802.11 allows for use of either the RF or IR mediums. When using RF, IEEE 802.11 uses the Frequency Hopping Spread Spectrum (FHSS) wideband system and has bandwidth limitation of 3 Mbps. IEEE 802.11b uses the Direct Sequence Spread Spectrum (DSSS) wideband system and can reach speeds up to 11Mbps.Bluetooth is a low cost, low power short range radio link for wireless connectivity between sensors and mobile devices and access points.

To meet these requirements communication system, software defined radio is required which provides different rates and modes at different times, and able to receive data packages and deliver them according to the request asked by users.

System with multi communication links is to provide patient monitoring during the prehospital transport and to offer health services, for people who live in underserved areas [6]. Therefore, medical information transmission becomes very

Electrical Department, IIT Roorkee

crucial, since there is no transmission link stability guarantee. Selection of the communication links which includes VHF radio, internet, GSM/CDMA mobile phones, and GPRS depends on the availability of the local communication infrastructure.

The SDR system will exploit the advantage of wireless technology and combine it with other communication technologies such as VHF radio to meet different locals and geographic requirements.SDR system is reprogrammed to provide required transmission link at any time.

As mentioned above, the system for medical data communication consists of two main units, namely a Mobile Telemedicine unit that is placed in an ambulance, and a Base unit or Hospital unit. The Mobile Telemedicine unit is responsible for collecting medical information that includes biosignals and image from the patient and display the critical signals, e.g. ECG signal, blood pressure (BP) and fetal heart rate (FHR). The unit must also be able to write and to record the data, and support the data transaction with variety of communication links. Furthermore, the unit should be able to transmit the patient's biosignals to the base unit automatically. To support the functions, the mobile telemedicine unit is provided with processing unit and communication manager module.

Communication manager module is makes use of Software defined radio. It is a modem array that comprises of mixture a number of GSM, CDMA, radio, GPRS, and satellite (optional) modems i.e. system is bandwidth independent. The SDR system is reconfigured to select a most suitable communication link to transmit the data.

While advances in implantable RF transceiver chips is facilitating in-body medical communications, rapid developments in ultralow-power wireless body sensors is resulting in on-body communications[9]. Thus, creating a platform for body area network or BAN to wirelessly connect in/on-body medical sensors with monitoring tools and provide patient health data in real time.

To implement such a medical healthcare

#### Electrical Department, IIT Roorkee

service, advanced medical info-communication technology uses mobile communication systems based on advances in ultra wideband (UWB), softwaredefined radio (SDR), and multiple-input, multiple-output (MIMO) technologies. Software defined radio system provides multichannel system, can continuously monitor multiple health signs, such as heart rate, body temperature, pulse rate and respiration and transfer that data to a base station where a medical record is kept.

From above applications, it implied that SDR is used in telemedicine to support multi standard, multi data rates and wider bandwidth.

#### 1.4 Motivation

Consider a typical communication system scenario where the user would like to have access to information through different wireless networks (e.g., wireless local area network (WLAN), Bluetooth, etc.), or a mobile phone user may be traveling between two regions around the globe, where the wireless technologies or standards are different. To utilize the services offered by the broad range of technology alternatives around the world, the user has to carry different devices due to incompatibility of systems and standards.

The practical solution to overcome this problem is to use a single device that can adapt to different technologies [5]. This could be possible using software defined radio, since it represents a radio that uses a reprogrammable hardware to create a generic hardware base. On top of the generic hardware platform, flexible software architecture is embedded.

The software allows for multiple protocols, fast upgrades, and complete reconfigurations of radio features and functions. Some of the attractive features of SDR are as

(1)Performance: The functionality of conventional radio architectures is usually determined primarily by hardware with minimal configurability through software. The

Electrical Department, IIT Roorkee

#### Introduction

hardware consists of the amplifiers, filters, mixers and oscillators dedicated to a particular mode of transmission. The software is confined to functions such as controlling the interface with the network, and error correction. Since the hardware dominates the design, upgrading a conventional radio design essentially means completely abandoning the old design and starting over again, resulting in a waste of time and resources. Software defined radio solves this problem by implementing radio functionalities as software modules running on generic hardware platforms. Since the radio functionalities are defined in software, when a new technology is introduced, it can be easily implemented by dynamic selection of parameters for its functional modules, i.e., reprogramming the software. Software defined radio systems can provide only fixed parameters with limited performance [5].

(2) Flexibility: The inflexibility of conventional radio systems limits the ability to get the right information to the right users at the right time. Conventional radio systems do not provide the wave form agility necessary to achieve this objective. With software defined radio, modulation waveforms and multiple air interface standards are possible. Thus, SDR platforms can serve a range of applications including analog cellular , digital cellular , personal communications services (PCS), wideband systems, spread spectrum, navigation waveforms (e.g., global positioning system) , emergency radio , public safety , and other radio systems[10]. Depending on the waveform, architecture, and implementation, a single software radio platform has the flexibility or potential to support a broad range of communication service.

(3) **Compatibility**: The concept of seamless global coverage requires that the radio support two distinct features. (a) Global roaming or seamless coverage across geographical regions (b) -interfacing with different systems and standards to provide seamless services at a fixed location. Existing technologies for voice ,video, and data use different packet structures, data types, and signal processing techniques. Integrated services can be obtained with either a single device capable of delivering various services or with a radio that can communicate with devices providing

Electrical Department, IIT Roorkee

complementary services. The supporting technologies and networks that the radio might have to use can vary with the physical location of the user. To successfully communicate with different systems, the radio has to communicate and decode the signals from devices using different air interfaces [5].

(4) **Cost**: Every time a new technology evolves, it results in the migration of functions from an older design to the new design. Implementing a new design involves manufacturing and testing. The cost of this process increases since upgrading to a newer design is not always possible in conventional systems. Software based radio can reduce the cost of manufacturing and testing, while providing a quick and easy way to upgrade the product to take advantage of newer signal processing techniques and new service applications [11].

#### **1.5 Statement of Problem**

The analysis presented in this thesis has many attractive features and several contributions to the current state of knowledge. The general and specific contributions of this research include the following:

(1) The development of a framework for the design and implementation of baseband section of software defined radio based communication systems.

(2) The analysis of a sample implementation of software defined radio based wireless communication system with coding (i.e., convolution encoding), viterbi decoding, puncturing and depuncturing, modulation and demodulation, Digital Up Conversion and Digital down conversion.

(3) The comparison of the performance of different modulation and demodulation techniques in a SDR implementation environment. The modulation techniques considered are quadrature phase shift keying (QPSK) and Quadrature Amplitude Modulation.

(4) Initiation of the development of a testbed for the design and implementation of SDR based wireless communication system.

(5) Presentation of results based on the simulation and actual experimentation.

(6) Evaluation of the performance of the SDR system in terms of signal-to-noise ratio in an additive white Guassian noise (AWGN) channel.

(7) Evaluation of the performance for the simulation of an SDR system and its implementation on the Xilinx Spartan 3E field programmable gate array (FPGA) platform [8]. The results obtained during simulation and experiments are compared.

#### **1.6 Outline of Thesis**

In this thesis, the fundamentals of software defined radio are first presented in Chapter II, which includes the general background information and various definitions for SDR. The presentation includes the difference between the SDR and conventional radio, characteristics and advantages of SDR, possible design issues, and the platform choices for implementing SDR based wireless communication systems.

In Chapter III, Various softwares and hardware kits utilized for this dissertation are explained. The framework for the implementation of a wireless communication system in SDR is presented. This includes a brief introduction of wireless communication systems, with a block diagram of the end-to-end communication system architecture, and the methodology of implementation.

SDR system model is explained in Chapter IV. Different baseband functions like encoding/decoding techniques, modulation/demodulation methods and frequency translation techniques are explained in this chapter.

An illustrative baseband communication system implementation, simulation and Electrical Department, IIT Roorkee 11

results are presented and discussed in Chapter V. Results of the simulation including constellation diagrams, eye diagrams, output waveforms, for different modulation techniques are presented and analyzed. The system is implemented on the Xilinx Spartan 2E FPGA platform [8]. The results of the implementation are compared with the simulation results.

Chapter VI summarizes the content of the thesis. Also, possible extensions of the thesis are discussed.

#### 1.7 Summary

This chapter gives brief description about Software defined radio based wireless communication system. It explains the statement of problem and how whole thesis organized.

#### **CHAPTER II**

#### FUNDAMENTALS OF SOFTWARE DEFINED RADIO

#### **2.1 Introduction**

Cellular communication systems have undergone tremendous growth since the early 1980's. As a result, mobile communication has become a major worldwide business. Because of this rapid growth, many analog and digital communication standards such as total access communication system (TACS), global system for mobile (GSM), digital cellular system-1800 (DCS-1800), interim standard-95 (IS-95), code division multiple access 2000 (CDMA2000), have been developed [7]. In fact, many competing standards have been introduced. The proliferation of standards is not only difficult for manufacturers but also for consumers. Manufacturers have to develop a new device for each technology or standard. This results in extra development costs and divided markets. It is also bad for consumers because users cannot use their mobile communication systems everywhere [10].

New generation wireless systems [1, 4] are being designed to provide a wide variety of multimedia services and to seamlessly switch between different wireless standards, such as wireless LAN and wideband CDMA. Each of these standards require different physical layer algorithms to be implemented. Also, algorithmic parameters such as the coding rate and constraint length for decoding need to be configured based on the channel environment. The wide range of configuration parameters and flexibility in the choice of algorithms to be implemented motivates the need for a software defined radio (SDR) solution.

Efforts to define a unique worldwide standard to overcome the above problems often results in a new standard [13]. A unique common worldwide standard has its own advantages, but the industrial competition between different manufacturers

introduces many difficulties. Therefore, software defined radio (SDR) concept is considered by many as an emerging technology that offers potential pragmatic solutions. For example, a software implementation of the user terminal will be able to dynamically adapt to the radio environment in which it is located [14]. Software defined radio concepts can be viewed as a means to make users, service providers, and equipment manufacturers more independent of standards.

Software radio also describes radio functionalities defined by software. The possibility to define the typical functionalities of a radio interface by software will be an excellent opportunity to improve system performance. Currently the radio functionalities in communication systems are usually implemented by dedicated hardware. The presence of software defining the radio interface implies the use of digital signal processors (DSPs) replacing dedicated hardware to execute in real time, the necessary radio functions [15]. To completely realize a digital programmable transceiver, it is necessary for the digital signal processors and the programmable logic such as field programmable gate arrays (FPGAs) to have a high processing power. Although advances have been made in digital signal processing since the 1980's, the processing power of DSPs and FPGAs is still not enough to realize fully functional software defined radios. The required processing power is expected to become available in the near future.

It is expected that multiple radio access standards and systems will coexist in the same environment beyond 3G. The superior reconfigurability and reprogrammability of software defined radio (SDR) had made itself become the most promising technology to realize such a flexible radio system The future wireless environment is expected to consist of multiple radio access standards that provide users different level of mobility and bandwidth.

In this chapter, the definitions and meanings of the software defined radio are presented. The difference between SDR and conventional radio is highlighted, as well as the characteristics, advantages and disadvantages. Then, different hardware platforms available to implement SDR are discussed. The design issue in implementing SDR is highlighted.

#### 2.2 Definition of Software Defined Radio

Because of the many features of SDR, there are many definitions available. The level of reconfigurability required to define a radio function in software is still not clear. A radio that includes a microprocessor or digital signal processor does not necessarily qualify as a software radio. However, a radio that defines in software its functions such as modulation, error correction, and encryption processes, exhibits some control over the RF hardware, and can be reprogrammed, qualifies as software defined radio [5]. The degree of configurability is largely determined by a complex interaction between a number of common issues in radio design, including system engineering, antenna form factors, RF electronics, baseband processing, speed and reconfigurability of the hardware and power supply management [5]. The FCC has proposed to define SDR as a radio that includes a transmitter in which the operating parameters of the transmitter, including the frequency range, modulation type, and maximum radiated or conducted output power can be altered by making a change in software without any hardware.

One definition of SDR is provided by the SDR forum [16], is that SDR is the radio that accepts fully programmable traffic and control information and supports a broad range of frequencies, air interfaces, and application software. The SDR forum discriminates between different levels of flexibility in a radio. These are:

Hardware Radio (HR): In a HR, system attributes cannot be changed since the functionality of the hardware radio is fixed. However, this radio can use internal software as long as it cannot be changed externally.

Software Controlled Radio (SCR): This is the radio in which only the control functions are implemented in software. For example, the transmitted power level of a

radio can be controlled by software, while all other functions are fixed in hardware. Current radio designs often fall under this category.

**Software Defined Radio (SDR)**: These are radios that provide software control of almost every radio function, including modulation, multiplexing, amplification, superheterodyne mixers, multiple access and other transmitter and receiver processes. The software should have the capability to add new air interfaces without reloading the entire set of software.

Ideal Software Defined Radio (ISDR): This radio has the same functionality as the SDR, but it does not have an analog front-end (amplification, mixers, etc.), thereby unable to eliminate analog noise and distortions. The analog front-end contains an antenna, analog-to-digital converters (ADCs) and digital-to-analog converters (DACs), directly attached to it.

Ultimate Software Radio (USR): The USR is an ideal, flexible, small, lightweight, low-power radio which is fully programmable. Please note that, software radios use digital techniques, but software controlled digital radios are generally not software radios [2]. The difference between software controlled digital radios and software radios is the total programmability of software defined radio. This programmability includes programmable radio frequency bands, channel access modes, and modulation.

It is obvious that unique definition for the software radio concept may not be possible. The most common definitions are summed up below and quoted from [4], [16]]:

(1) "Flexible transceiver architecture, controlled and programmable by software."

(2) "Signal processing able to replace, as much as possible, radio functionalities."

(3) "A system with air interface downloadability. That is, it is possible to Dynamically reconfigure radio equipment by downloadable software, at every level of the protocol stack."

(4) "Software realization of terminals."

(5) "A transceiver with frequency band and radio channel bandwidth, modulation and coding scheme, radio resource and mobility management protocols, and user applications."

It appears that in SDR, the parameters of interest can be adapted and changed by the network operator, service provider, and end users. A software defined radio system can operate in multi-service environments. This means that the system is able to offer services of any already standardized systems or future ones, on any radio frequency band. The system is not constrained to a particular standard. For that reason the software radio system is very flexible. The compatibility of a software radio system with any defined mobile radio standard is guaranteed by its reconfigurability, which is achieved by DSP processors. These processors implement in real time radio interface and upper layer protocols.

A software defined radio not only transmits and receives signals but it does more in an advanced application [17]. Before transmission, SDR can distinguish the available transmission channel, select suitable channel modulation, direct the transmit beam in the direction of interest, check for proper power level and then transmit the signal. Similarly, on the receive path, apart from just receiving the signal, SDR can characterize the energy distribution in the desired channel and adjacent channels, provide adaptive equalization, null interference, approximate the dynamic properties of the desired signal, decode the channel modulation using appropriate schemes, correct errors through forward error correction (FEC), and hence help in obtaining the desired signal with less bit error rate (BER).

#### 2.3 Software Defined Radio Concepts

In this section, the difference between conventional radio and software defined radio is presented. Also, the characteristics of SDR, its advantages and disadvantages are discussed.

#### 2.3.1 Conventional Versus Software Defined Radio

To compare the functionalities of the conventional radio and SDR, we provide a tabulation of their functions in Table 2.1.

| Conventional Radios                                                                                                          | Software Defined Radios                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Radio functionalities are primarily defined in hardware with minimum configurability in software.                            | Radio functionalities are defined in software.                                                                                                             |

| Since the design is dominated by<br>hardware upgrading the design is not<br>possible.                                        | Software based architecture allows for easy<br>upgrade of the design without abandoning<br>the older design                                                |

| The user has to use different mobile<br>devices due to incompatibility of<br>standards                                       | Global mobility can be achieved by<br>downloading the appropriate air interface<br>thus overcoming the incompatibility of<br>standards.                    |

| Multi-function radios design<br>including separate silicon for each<br>system decreases the efficiency and<br>becomes bulky. | Reprogrammability makes SDR to be efficient and compact                                                                                                    |

| Results in waste of silicon area since<br>each system has to be implemented<br>separately                                    | Silicon area is conserved by using the same<br>chip to perform a function and changing the<br>configurations during runtime to perform<br>another function |

Table 2.1 Difference between conventional and software defined radios [17]

Finally, software radio supports incremental service enhancements through a wide range of software tools. These tools assist in analyzing the radio environment, defining the required enhancements, prototyping incremental enhancements via the software, testing the enhancements in the radio environment, and finally delivering service enhancements via software and/or hardware [17].

#### 2.3.2 Characteristics of Software Defined Radio

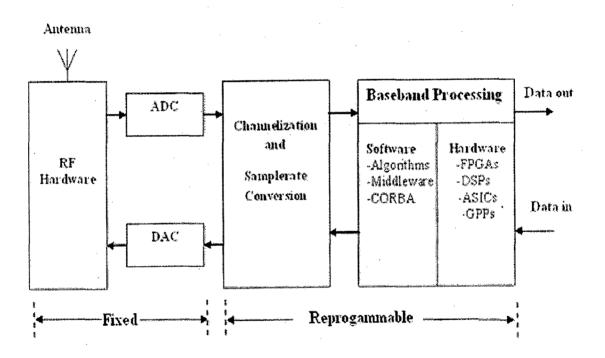

Consider a system model of a software defined radio shown in Figure 2.1. The receiver implemented with a smart antenna that provides a gain versus direction Electrical Department, IIT Roorkee 18

characteristic to minimize interference, multipath and noise. The smart antenna provides similar benefits for the transmitter. Digitization of the signal is carried out as close as possible to the antenna in the receiver using the analog-to-digital converter. Similarly, the signal is converted to the analog domain as late as possible in the transmitter using digital-to-analog converter. The digitization of the signal is mostly done in the intermediate frequency (IF) range. Software defined radio uses analog-to-digital converter to digitize the signal in the IF range, thus overcoming the problems like carrier offset and imaging involved in digitizing the signal using superheterodyne method commonly used in conventional radios.

Figure 2.1 Model of software defined radio processes [5].

Channelization and sample rate conversion on the transmit path is used to interface the digital hardware to the digital-to-analog converter and to interface ADC to the processing hardware on the receive path. Baseband processing is performed in software using digital signal processors (DSPs), field programmable gate arrays (FPGAs), application specific integrated circuits (ASICs), or general purpose processors (GPPs). The algorithm used to modulate or demodulate signal may use a

Electrical Department, IIT Roorkee

variety of software methodologies, such as middleware, e.g., common object request broker architecture (CORBA) [5].

# 2.3.3 Advantages and Disadvantages of Software Defined Radio

According to its operational area an SDR can be

(i) A multiband system which is supporting more than one frequency band used by a wireless standard (e.g., GSM 900, GSM 1800, GSM 1900),

(ii) A multistandard system that is supporting more than one standard. Multistandard systems can work within one standard family (e.g., UTRA-FDD, UTRA-TDD for UMTS) or across different networks (e.g., DECT, GSM, UMTS, WLAN),

(iii) A multiservice system which provides different services (e.g., telephony, data, video streaming),

(iv) A multichannel system that supports two or more independent transmission and reception channels at the same time.

Following are the advantages of SDR technology:

**Reconfigurability:** SDR allows co-existence of multiple software Module implementing different standards on the same system allowing dynamic configuration of the system by just selecting the appropriate software module to run. This dynamic configuration is possible both in handsets as well as infrastructure equipment. The wireless network infrastructure can reconfigure itself to subscriber's handset type or the subscriber's handset can reconfigure itself to network type.

**Ubiquitous Connectivity :** SDR enables implementation of air interface standards as software modules and multiple instances of such modules that implement different standards can co-exist in infrastructure equipment and handsets. This helps in realizing global roaming facility. If the terminal is incompatible with the network technology in a particular region, an appropriate software module needs to be installed onto the handset (possibly over-the-air) resulting in seamless network access across various geographies.

Electrical Department, IIT Roorkee

**Interoperability:** SDR facilitates implementation of open architecture radio systems. End-users can seamlessly use innovative third-party applications on their handsets as in a PC system. This enhances the appeal and utility of the handsets.

**Easy upgradeability to new communication standards.** Signal generation and analysis are largely performed by routines programmed into the Hardware. When new standards emerge, it's easy to create new programs for the new functions and distribute them to the owners of existing instruments via firmware upgrades.

**Improved throughput due to faster frequency switching and signal analysis** Wide bandwidth A/D converters and fast DSP devices can process large FFTs very efficiently. For example, a DSP-based analyzer can provide measurement times several orders of magnitude faster than traditional spectrum analyzers, under conditions of wide spans and narrow resolution bandwidths. Direct digital synthesis provides significantly faster frequency switching than traditional approaches allow. Fast frequency switching will improve the throughput of both signal generators and signal analyzers.

Faster time to market for test instruments. Test equipment manufacturers can leverage the capability of leading-edge, commercially available signal processing devices and achieve instrument-level performance from them. This reduces the amount of development required for test instruments dramatically. Also, the basic digital design can be shared across a range of instruments, further reducing development costs

With SDR, the same piece of hardware will be configured to perform different functions. The reconfigurability of the platform will ensure hardware reusability. System reprogrammability allows hardware reuse until a new generation of hardware platforms is available. This will provide cost and time savings. Manufacturers will not be limited to reduced hardware platform set. As a consequence, mass production will allow lowered costs [5].

Electrical Department, IIT Roorkee

Another advantage of SDR would be the possibility to improve the software in successive steps, and the correction of software errors and bugs discovered during the operation.

In addition, SDR can enhance the interoperability of different systems in many applications such as the military, law enforcement, or search and rescue teams. Incompatibility of radio systems that has always hindered the seamless operation of the military, the law enforcement agencies and many rescue teams, will be eliminated.

With the increase of channel data rates through multiplexing and spectrum spreading, SDR could be used in cellular networks, GSM based PCS network, and future generation systems network. A new approach to wireless base station design using SDR has the potential of offering significant benefits such as reduced size, complexity, and power consumption. More importantly, SDR can support a variety of air interface standards, modulation schemes and protocols, simultaneously. Some commercial telephone service providers have begun expressing interest in the SDR economic benefits in long term [10]. More highlights on the benefits of SDR are given in Section 1.2.

While SDRs offer benefits as outlined above, there are drawbacks in the design and implementation of SDR. Those include:

(1) The difficulty of designing software for various target systems or standards.

(2) The difficulty of designing air interfaces to digital signals and algorithms for different standards.

(2) The problem of poor dynamic range in some communication systems design

SDR technology may not be suitable for all kinds of radio equipment due to higher power consumption, higher processing power (MIPS) requirement and higher

initial cost.

| Interoperability        | Supports of multiple standards through multimode, multiband radio capabilites                             |

|-------------------------|-----------------------------------------------------------------------------------------------------------|

| Flexibility             | Efficient shift of technology and resources                                                               |

| Adaptability            | Faster migration towards new standards and<br>technologies through programmability and<br>reconfiguration |

| Sustainability          | Increased utilization through generic hardware platforms                                                  |

| Reduced Ownership Costs | Less infrastructure ,less maintenance ,easier<br>deployment                                               |

Table 2.2 Advantages of Software Defined Radio

# 2.4 Software Defined Radio Implementation Platforms

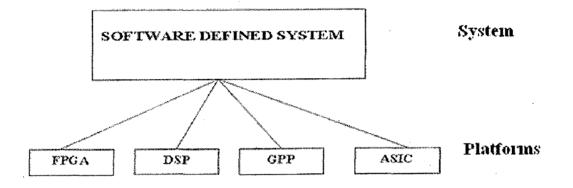

As indicated above, the global trend in the communication industry is to replace hardware by software, because of software flexibility. Real time software defined radio design can be implemented using a variety of digital hardware namely (a) field programmable gate arrays, (b) digital signal processors, (c) application specific integrated circuits and (d) general purpose processors. The different implementation platforms are shown in Figure 2.2. All the four platforms shown in Figure 2.2 possess a level of reprogrammability or reconfigurability (i.e., the ability to modify the hardware or software) [25]. The DSP platform is essentially a microprocessor based system optimized for digital signal processing applications [5], [17]. DSPs can be programmed repeatedly with a high level language such as C, MATLAB [5]. Modifications and upgrades to the design are made through these high level languages, thus reducing the design times for each iteration. The flexibility offered by the digital signal processor comes at the cost of efficiency. When there are several

computations to be performed, parallel executions of these computations will slow down the rate at which data is processed and this leads to the use of more than one DSP. This solution is limited since synchronizing several DSPs is difficult.

A field programmable gate array is a general purpose integrated circuit that is programmed by the designer rather than the device manufacturer. A unique feature of FPGA is that it can be reprogrammed, even after it has been deployed into a system. Field programmable gate array is programmed by downloading a configuration program (bitstream) into the static on-chip random access memory [11]. This is

Figure 2.2: Hardware implementation platforms for SDR

similar to the object code of a microprocessor, in which the bitstream is the product of compilation tools that translate the high level abstractions produced by a designer into equivalent but low level executable code [18].

Field programmable gate arrays were designed for multilevel circuits to handle complex circuits on a single chip. Since they are reprogrammable, their configurations can be easily changed to upgrade systems or correct system bugs, making it ideal for prototyping. Field programmable gate arrays are now used in various configurations, as in multimode systems, and are very useful in meeting the needs of a software defined radio implementation [18].

Application specific integrated circuits (ASICs) implement the system circuitry in fixed hardware, resulting in the most optimized implementation of the circuit in

terms of speed and power consumption. However, ASIC design requires sophisticated circuit design and layout software tools [5]. Also, as the name implies, their use are for specific application and not subject to modification at a later date. A general purpose processor is similar to DSP as a hardware platform in the design of software defined radio. Like DSP, it offers flexibility and ease of design. Radio functionalities can be implemented in high level languages such as C and C++. Designers can use the familiar approaches of object oriented programming anddebugging to develop real time software radio systems. This increases productivity significantly and reduces system development time [19].

Digital signal processor is the most generalized type of hardware that can be programmed to perform various functions, while ASIC is the most specialized and can be used only in specific application. Field programmable gate arrays offers a compromise in flexibility between ASIC and DSP platforms. In general, these hardware components constitute design spaces that trade flexibility, processing speed, and power consumption among other things. There should be a tradeoff between the maximum flexibility and high power consumption of DSP platforms to minimum flexibility and less power consumption of ASICs compared to FPGAs, which have good hardware optimization. Recently, FPGAs have become increasingly popular due to their ability to reduce design and development cycle time. Furthermore, latest FPGAs come with intellectual property (IP) cores, which are used for specific applications [11].

There are other advantages of using FPGAs instead of DSPs for signal processing in commercial telecommunication systems. The power consumption is lower; the size is smaller, quicker to use and the costs are much lower in comparison to DSPs. Since the chip can be reused after fixing the bugs or upgrading a system, they are ideal for prototyping and testing the circuit design. Since FPGAs are reprogrammable, one chip can be configured to perform more than one function and the configurations can be changed during run time [11].

## Electrical Department, IIT Roorkee

## **2.5 Technical Challenges**

This section discusses the technical issues, which have to be solved before software radio can be commercially available. The important technical issues involved in the development of a software radio system are as follows:

(1)In transceivers, the border between analog and digital domain should be moved closer, as much as possible, towards the RF. This requires ADC and DAC wideband converters placed as near as possible to the antenna. The border between the analog and digital domain is not reduced to a extent software defined radio. Much research has been carried out in the wideband transceiver realization [16]. The primary goal of this transceiver was to extend the digital domain at the IF stage and keeping the RF stage analog [14].

(2) The process of replacement of dedicated hardware in communication systems with DSPs or FPGAs should be further developed. In other words, we need to define the radio functionalities as much as possible in software. This opens the way to two possible horizons: software implementation of baseband functions, such as coding, modulation, equalization and pulse shaping; and reprogrammability of the system to guarantee multi-standard operation. Though DSP technology has been used in implementing the baseband processing in base stations, it is not possible to categorize it as SDR since not all baseband functionalities are implemented in DSPs. Also, the software is limited and preloaded; therefore the system is constrained to a specific radio interface and cannot be reconfigured [14]. Hence, implementing communication functions in software presents a major challenge in practical systems.

(3) Analog-to-digital and digital-to-analog conversions for the ideal software defined radio are difficult to achieve. In practice, the selection requires trading power consumption, dynamic range and bandwidth. Current conversion technology is limited and is often the weak link in the overall system design. There are post digitization techniques based on multirate digital signal processing that can be used to improve the flexibility of the digitization process [5], [20].

#### Electrical Department, IIT Roorkee

(4) Power management is also a major challenge. For example, sleep modes of DSPs or other hardware save power but introduce a probability that the radio will be asleep during a paging message. A possible solution is a structured timing of paging messages, which reduces the probability of a miss, and further conserves battery life [21], [22].

(5)The clock generation and distribution is another challenge in SDR design. Every standard such as GSM or IS-95 has its own clock rate. Using one reference oscillator per standard may increase parts count, increase complexity, and therefore cost. A single master clock may use the least common multiple (LCM) of the required clocks, but this leads to a high clock rate, which is power inefficient. A possible solution is to use normalize standards to avoid clock rates with large LCMs [17].

(6) Receiver complexity is typically four or more times the transmitter complexity [5]. Thus, the receiver architecture has a first order impact on handset cost. The challenge is to develop a simple receiver. With the current technology, the support of many standards leads to complex and power inefficient solutions. Application specific integrated circuits are power efficient but inflexible. Field programmable gate arrays could be a possible solution. Hybrids of platform implementation could be utilized. The ideal radio frequency stage for SDR should incorporate flexibility in selection of power gain, bandwidth, dynamic range, etc. Achieving strict flexibility is impractical and trade-offs must be made [5].

## 2.6 Summary

The fundamentals of SDR are presented in this chapter. It also dealt with definition and concepts of SDR. The difference between the conventional radio and SDR, characteristics, advantages and disadvantages were also presented. The choices of hardware available for real time implementation and technical challenges involved in implementation were discussed.

# CHAPTER III FRAMEWORK FOR SDR BASED DESIGN

# **3.1 Introduction**

Signal processing systems for transmission of medical signals will have to operate in rapidly changing environments. To suitably adapt to the varying requirements, control strategies targeted at selecting and tuning the signal processing algorithms need to be developed

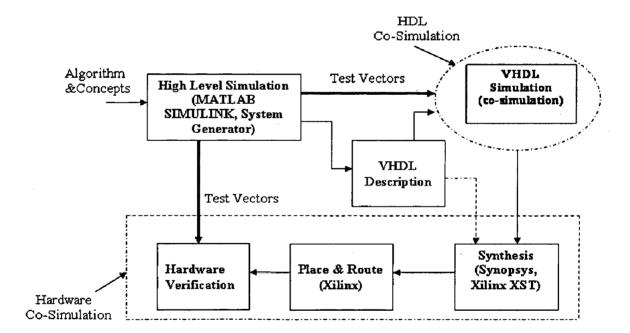

In this chapter, a conventional wireless communication system model used in telemedicine is briefly reviewed. Raw medical data cann't be transmitted as in its natural form as there is provision for noise addition. The operations performed on data to transmit through the channel are explained. This is followed by explanation of softwares used. The softwares were utilized for the simulation, verification and for the validation purposes. The hardware here means the FPGA development kit, on which the developed design is implemented [16]. In this thesis, FPGA development kits are utilized which were provided as a part of the Xilinx University Program (XUP). The XUP Spartan 3E FPGA development kits are used. Finally, steps involved in implementing the design on a reconfigurable computing platform are presented. In this thesis, only the baseband section of a communication system is modeled and simulated.

# 3.2 Wireless Communication System Model for transmission of medical signals.

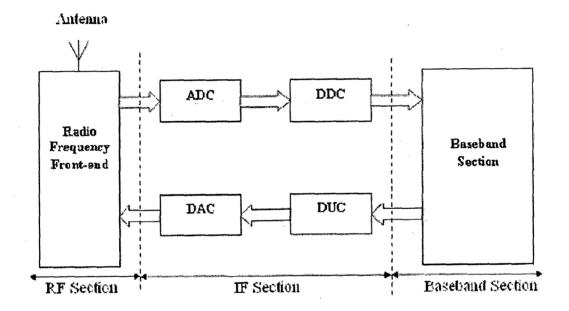

The generic wireless communication system consists of a transmitter, channel and a receiver. The functional block diagram of the digital transceiver is shown in Figure 3.1 [5].

## **3.2.1 Radio Frequency Section**

The radio frequency (RF) section is responsible for transmitting and receiving the RF signal and converting the RF signal into an intermediate frequency (IF) signal. The RF section consists of antennas and analog hardware modules. The RF front-end is designed in such a way to reduce interference, multipath and noise. The RF frontend on the receive side performs RF amplification and down conversion from RF to IF. On the transmit side, the RF section performs analog up conversion and RF power amplification.

Figure 3.1: Functional block diagram of a wireless communication system [5].

## **3.2.2 Intermediate Frequency Section**

The ADC/DAC performs analog-to-digital conversion on the receive path, and digital to analog conversion on the transmit path. These blocks interface between the analog and digital sections of the radio system. Usually, the above conversion takes place in the IF stage. Digitizing the signal with an ADC eliminates the last stage in the

conventional model, where problems such as carrier offset and imaging are encountered.

As the names imply, the digital down converter (DDC) and digital up converter (DUC) perform digital down conversion on the receive path and digital up conversion on the transmit path, respectively[19]. Digital filtering and sample rate conversion are often needed to interface the output of the ADC to the processing hardware at the receiver. The same happens in the reverse direction in the transmitter, where digital filtering and sample rate conversion are necessary to interface the digital hardware to the DAC that converts the modulated waveform to an analog waveform.

## 3.2.3 Baseband Section

The baseband section performs operations, such as error correction, equalization, frequency hopping, modulation, demodulation, spreading, despreading and timing recovery. Forward error correction is a method of obtaining error control in data transmission in which the transmitter sends redundant data and the receiver recognizes only the portion of the data that contains no apparent errors. Equalization is done to counteract the inter symbol interference in the channel. Frequency hopping and spreading is used to minimize unauthorized interception or jamming of the communication system by repeated switching of frequencies during radio transmission using a specified algorithm. In a wireless communication system, many modulation techniques such as MPSK, QPSK, DPSK, etc., are used. The DDC, DUC and the baseband processing requires large computing power and these modules are generally implemented using DSPs, FPGAs, and ASICs Details of the specific blocks that were implemented in this thesis are provided in Chapter IV.

## 3.3 Softwares used

The following softwares were used in this thesis.