# MODELLING AND SIMULATION OF DC/DC CONVERTER

**A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree

# of MASTER OF TECHNOLOGY

in

# ELECTRICAL ENGINEERING

(With Specialization in Power Apparatus and Electric Drive)

Ву

SUDHA BANSAL

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE -247 667 (INDIA) JUNE, 2006

#### **CANDIDATE'S DECLARATION**

I hereby declare that the work that is being presented in this dissertation report entitled "MODELLING AND SIMULATION OF DC/DC CONVERTER" submitted in partial fulfillment of the requirements for the award of the degree of MASTER OF TECHNOLOGY in ELECTRICAL ENGINEERING with specialization in POWER APPARATUS AND ELECTRIC DRIVE, submitted in the Department of Electrical Engineering, Indian Institute of Technology, Roorkee, is an authentic record of my own work carried out under the guidance of Dr. Pramod Agrawal, Professor, Department of Electrical engineering, IIT Roorkee, and Dr. S.P. Gupta, Professor & Head, Department of Electrical engineering.

The matter embodied in this dissertation report has not been submitted by me for the award of any other degree or diploma.

Date: 305,01 Place: Roorkee

(SUDHA BANSAL)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

(DR. PRAMOD AGRAWAL) Professor, Department of Electrical Engineering, IIT Roorkee,

S.P. CAPE-

(**DR. S.P. GUPTA**) Professor & Head, Department of Electrical Engineering IIT Roorkee I wish to express my deep sense of gratitude and sincere thanks to my guides **Dr. Pramod Agrawal**, Professor, Department of Electrical engineering, IIT Roorkee, and **Dr. S.P. Gupta**, Professor & Head, Department of Electrical engineering, IIT Roorkee, for being helpful and a great source of inspiration. Their keen interest and constant encouragement gave me the confidence to complete my work. I wish to extend my sincere thanks for excellent guidance and suggestions for the successful completion of my dissertation work.

I am thankful to all of my classmates in PAED group for their constant support for successful completion of my work. I gratefully acknowledge my special thanks to Mr. Abdul Hamid Bhat, Ph.D, Research scholar for his valuable guidance and to my friends and family members for their inspirational impetus and moral support during the course of this work.

I also express sincere thanks to all staff members of Drives Lab and Electrical workshop for their help in completion of this work.

(Sudha Bansal)

#### ABSTRACT

The SMPS are used for many applications where regulated DC is required e.g. office equipment, spacecraft power systems, laptop computers, cordless phone etc. because of its high efficiency and high energy density. Though linear power supply can serve the purpose. The disadvantage with linear power supply is their bulkiness and poor efficiency. They <u>can not</u> work at high frequency. Earlier AC to DC conversion was achieved using Motor-Generator (MG) sets, Mercury-arc rectifiers, Cascade converter, Rotary Converters, thyratrons. The disadvantages of these are bulkiness and its poor regulation.

To overcome these limitations switch mode power supply are in use. Full bridge dc/dc converter topology is extensively applied in medium to high power conversion. In a power level up to 3 kW, the full bridge converter now employs MOSFET switches. High efficiency, high power density, high reliability and low EMI are some of the most desirable features in these applications, particularly for computer and telecom systems. To achieve these features, soft switching techniques are normally employed. Various types of soft switching topology are reviewed in the literature review. However, the conventional soft switching full bridge converter topologies would either lose the soft switching at some operating conditions, or become rather complex in design and implementation for a few-kilo watts applications.

In this dissertation a novel zero voltage switching dc/dc full bridge converter topology is presented and analyzed. The proposed topology employs phaseshift at the rectifier section and does not employ any passive component. However, the advantage of the proposed topology is significant: it achieves soft switching independent of line and load conditions.

Experimental and simulation results of a prototype 200 W 100-110 Vdc to 50 Vdc converter operating at 10 KHz verify the analysis and design.

CONTENTS

|                  |                                                       | Page No. |

|------------------|-------------------------------------------------------|----------|

| Candidate's D    | leclaration                                           | i        |

| Acknowledge      | ment                                                  | ii       |

| Abstract         |                                                       | iii      |

| Contents         | · · · ·                                               | iv       |

| List of Figure   | S .                                                   | vi       |

| CHAPTER 1        | INTRODUCTION                                          |          |

| 1.1              | General                                               | 1        |

| 1.2              | Switch Mode Power Supplies                            | 2        |

| 1.3              | Soft-switching Technique                              | 5        |

| 1.4              | Organisation of this Thesis                           | 6        |

| CHAPTER 2        | LITERATURE REVIEW                                     | 8        |

| CHAPTER 3        | <b>CONTROL TECHNIQUES FOR DC – DC CONVERTER</b>       | RS .     |

| 3.1              | Voltage Mode Control                                  | 18       |

| 3.2              | Current Mode Control                                  | 19       |

| 3.3              | Peak Current Mode Control                             | 20       |

| 3.4              | Average Current Mode Control                          | 21       |

| 3.5              | Sensorless Current Mode Control                       | 22       |

| <b>CHAPTER 4</b> | ZVS FULL BRIDGE PHASE SHIFTED DC-DC CON               | VERTERS  |

| 4.1              | Introduction                                          | 25       |

| 4.2              | ZVS Primary Phase Shifted Full Bridge Topology        |          |

|                  | 4.2.1 General Description                             | 25       |

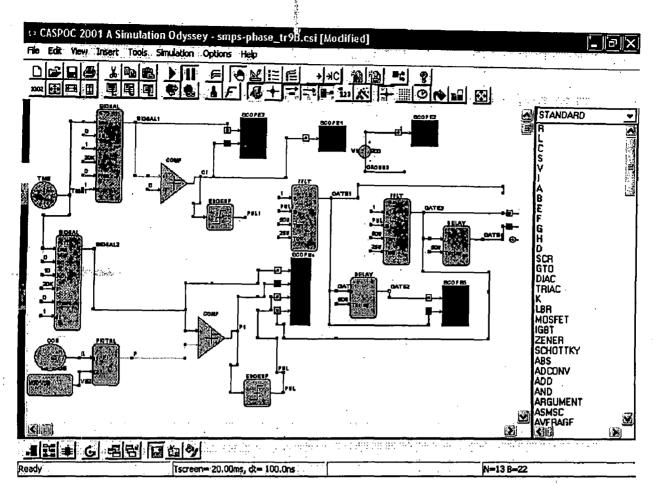

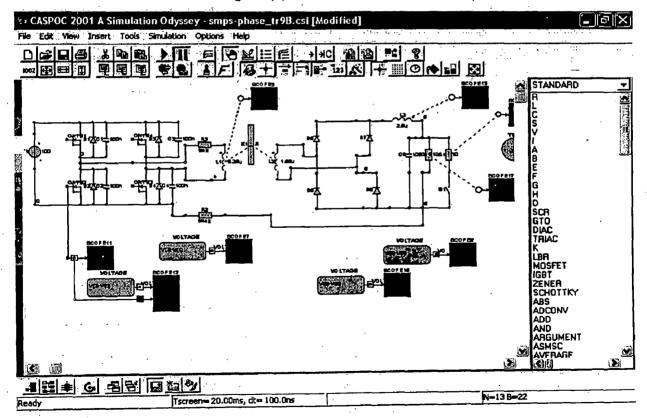

|                  | 4.1.2 CASPOC Simulation                               | 28       |

|                  | 4.1.3 Advantages and Disadvantages                    | 31       |

| 4.3              | ZVS Full Bridge with Secondary Phase Shifted Topology | . 51     |

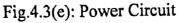

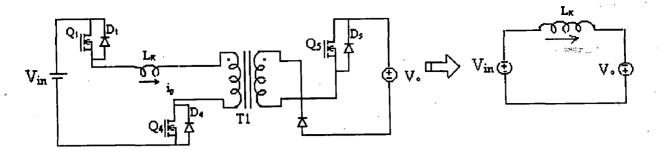

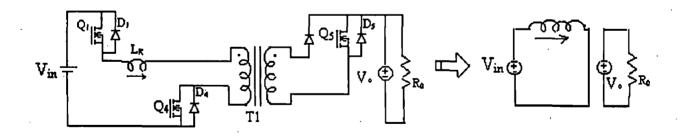

|                  | 4.3.1 Circuit Description                             | 32       |

|                  | 4.3.2 CASPOC Simulation                               | 33       |

|                  | 4.3.3 Advantages and Disadvantages                    | 35       |

| CHAPTER 5        | MODELING OF ZVS DC/DC CONVERTER                       |          |

| 5.1              | Modeling of Unregulated Rectifier                     | 37       |

| Operation of the High Frequency Inverter and Phase-shifted |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| secondary active Rectifier                                 | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

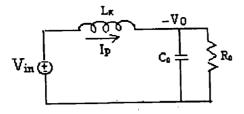

| Modes of operation and the equivalent circuits             | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| State space equations                                      | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.4.1 Modeling of PI Controller                            | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.4.2 Averaged state space equations                       | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.4.3 DC and AC models                                     | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.4.4 Small signal model                                   | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.4.5 Transfer Function                                    | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

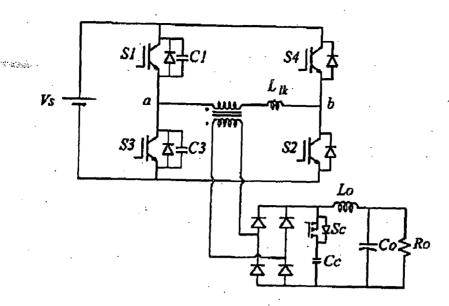

| Control loop                                               | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DESIGN OF ZVS DC-DC CONVERTER                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $T_{d}$ switching dead time                                | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Selection of the Magnetizing Inductance                    | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Selection of filter Capacitor                              | - 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Selection of the Diode                                     | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Active switch selection                                    | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SIMULATION OF ZVS DC-DC CONVERTERS                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Simulation of Full-Bridge ZVS Primary Phase-Shifted DC/DC  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Converter                                                  | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Simulation of Full-Bridge ZVS Secondary Phase-Shifted      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DC/DC Converter                                            | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HARDWARE DESIGN                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

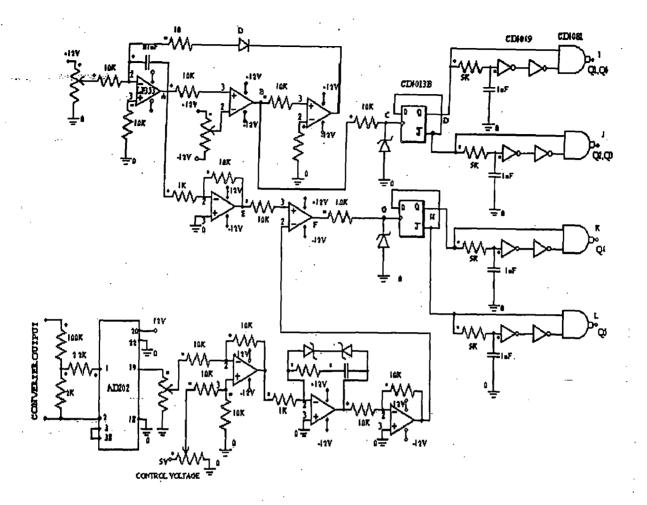

| Control Circuit                                            | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Philosophy of Phase Shift Control and closed loop control  | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

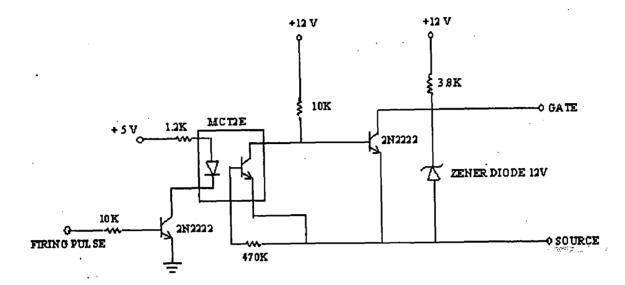

| Firing Pulse Amplification and isolation Circuit           | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

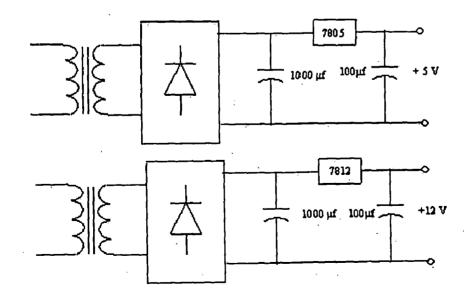

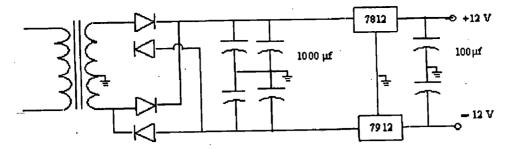

| Power Supplies                                             | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

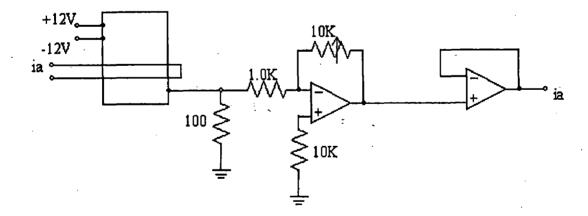

| Current Sensor Circuit                                     | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

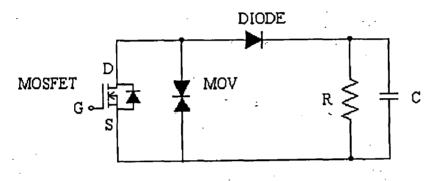

| Protection pf MOSFETs                                      | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Transformer Design                                         | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PERFORMANCE INVESTIGATION OF DC-DC CONVERTERS              | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CONCLUSIONS                                                | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| REFRENCES                                                  | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Appendix-I                                                 | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                            | secondary active Rectifier<br>Modes of operation and the equivalent circuits<br>State space equations<br>5.4.1 Modeling of PI Controller<br>5.4.2 Averaged state space equations<br>5.4.3 DC and AC models<br>5.4.4 Small signal model<br>5.4.4 Small signal model<br>5.4.5 Transfer Function<br>Control loop<br>DESIGN OF ZVS DC-DC CONVERTER<br>T <sub>a</sub> switching dead time<br>Selection of the Magnetizing Inductance<br>Selection of the Magnetizing Inductance<br>Selection of the Diode<br>Active switch selection<br>Simulation of Full-Bridge ZVS Primary Phase-Shifted DC/DC<br>Converter<br>Simulation of Full-Bridge ZVS Secondary Phase-Shifted DC/DC<br>Converter<br>HARDWARE DESIGN<br>Control Circuit<br>Philosophy of Phase Shift Control and closed loop control<br>Firing Pulse Amplification and isolation Circuit<br>Power Supplies<br>Current Sensor Circuit<br>Protection pf MOSFETS<br>Transformer Design<br>PERFORMANCE INVESTIGATION OF DC-DC CONVERTERS<br>FRENCES |

• ••

•

-

-

v

# LIST OF FIGURES

| Fig.1.1 Block Diagram of an SMPS                                                                            |

|-------------------------------------------------------------------------------------------------------------|

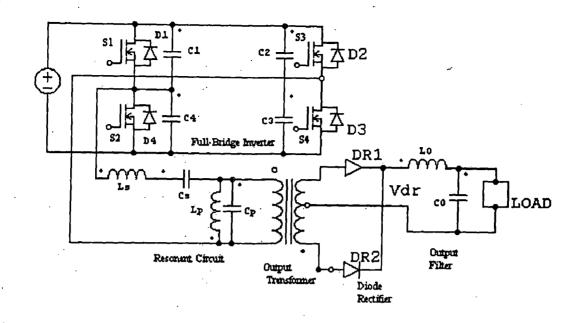

| Fig.2.1 Optimum ZVS Full-Bridge DC/DC Converter with PWM Phase-Shift Control9                               |

| Fig.2.2 Constant Frequency Resonant DC/DC Converters with Zero Switching Losses.13                          |

| Fig.2.3 Single-Stage ZVS PWM Full-Bridge Converter                                                          |

| Fig.2.4 A Novel Single-Phase Soft-Switched Rectifier with Unity Power Factor and<br>Minimal Component Count |

| Fig.2.5 Full Bridge Zero Voltage Switched Phase Shift DC-DC Converter with Improved<br>Efficiency           |

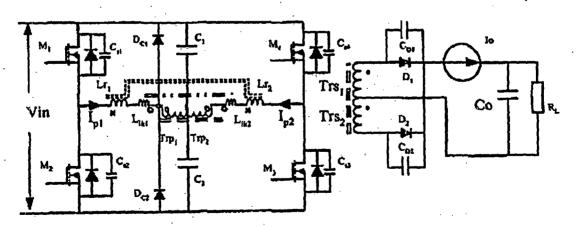

| Fig.2.6 An improved high efficiency Full Bridge ZVS DC-DC converter15                                       |

| Fig.2.7 Zero-Voltage and Zero-Current-Switching Full Bridge PWM Converter17                                 |

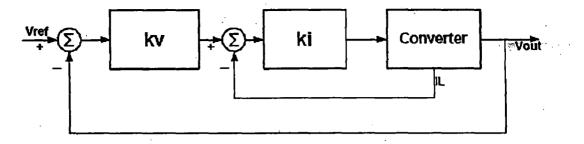

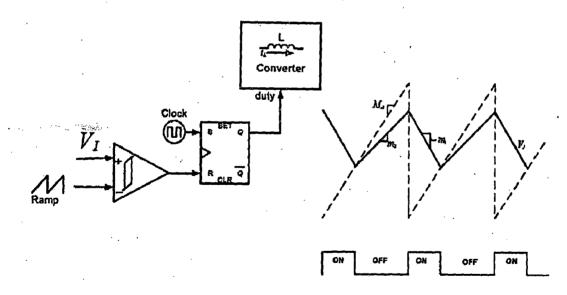

| Fig.3.1 Voltage Mode Control                                                                                |

| Fig.3.2 Current Mode control                                                                                |

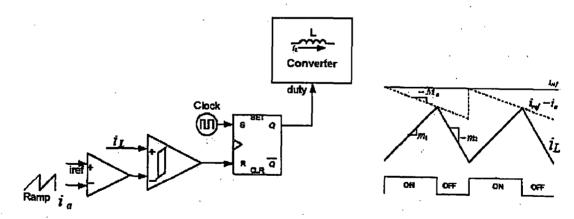

| Fig.3.3 Peak current mode control20                                                                         |

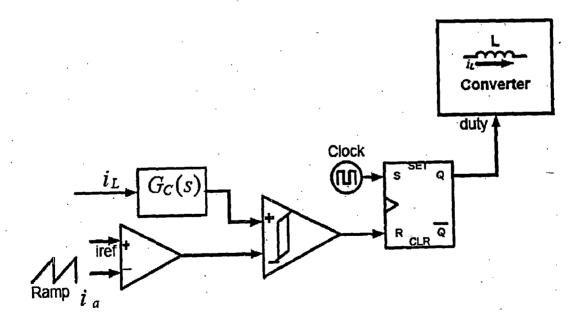

| Fig.3.4 Average Current Mode Control (ACM)                                                                  |

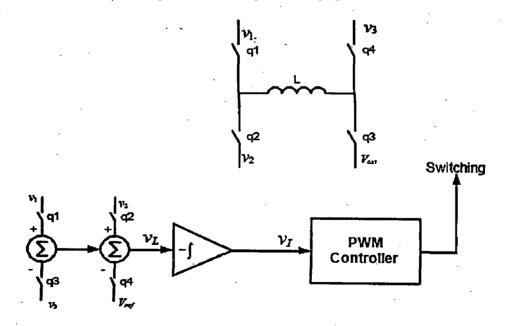

| Fig.3.5 General SCM Process                                                                                 |

| Fig.3.6 Sensorless Current Mode Control                                                                     |

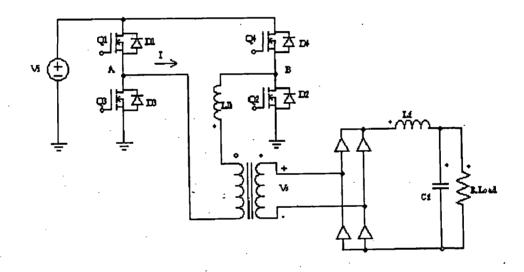

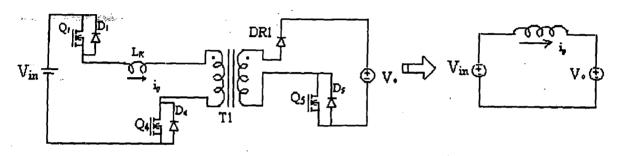

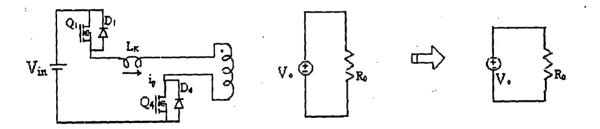

| Fig.4.1 Full-bridge primary phase-shifted ZVS dc/dc converter                                               |

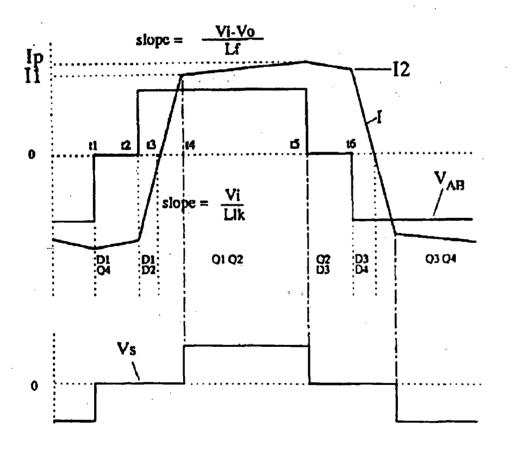

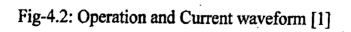

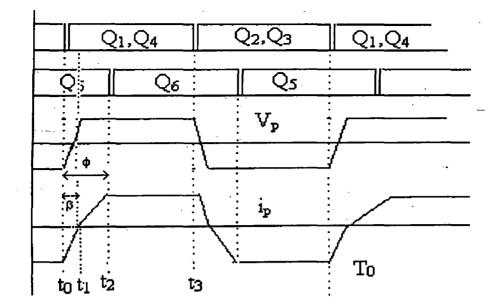

| Fig.4.2 Operation and Current waveform                                                                      |

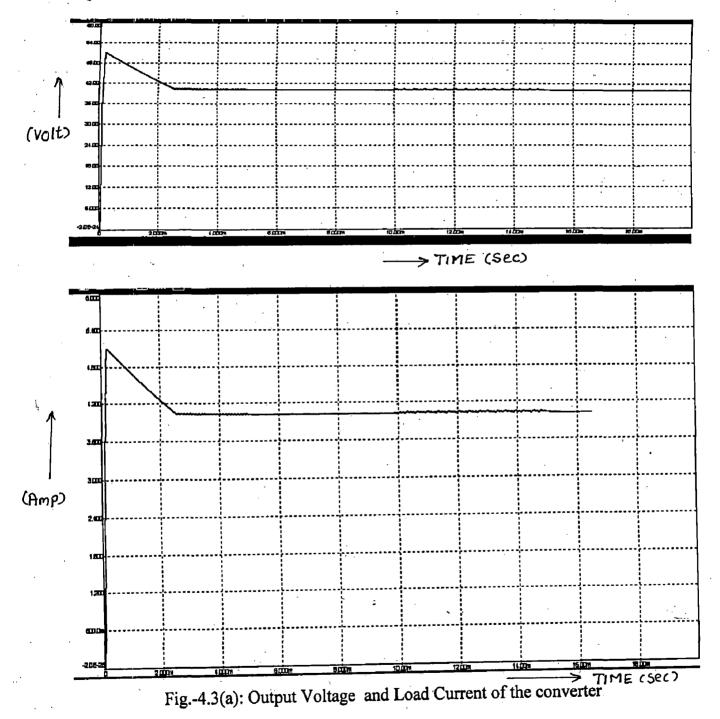

| Fig.4.3(a) Output Voltage and Load Current of the converter                                                 |

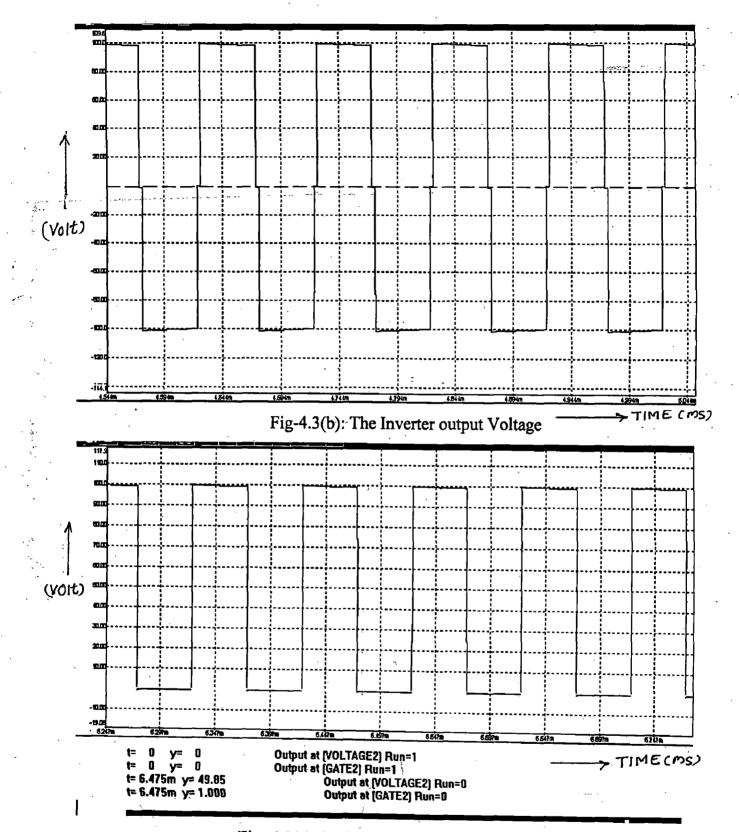

| Fig.4.3(b) The Inverter output Voltage                                                                      |

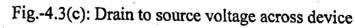

| Fig.4.3(c) Drain to source voltage across device                                                            |

| Fig.4.3(d) Control Circuit                                                                                  |

| Fig.4.3(e) Power Circuit                                                                                    |

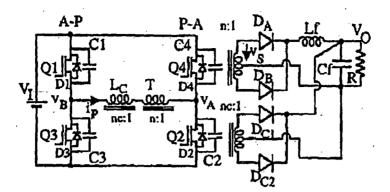

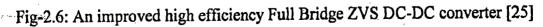

| Fig.4.4 Novel ZVS Full Bridge DC/DC Converter32                                                             |

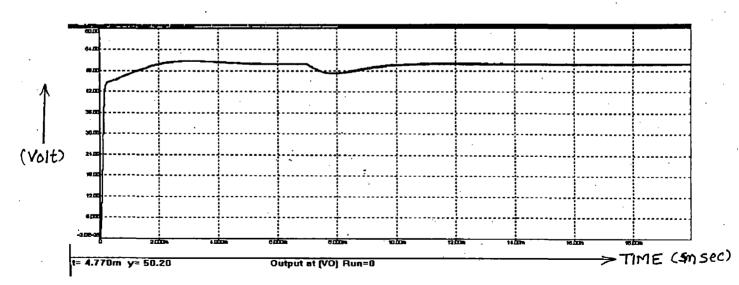

| Fig.4.5(a) Output voltage with step change at 5msec                                                         |

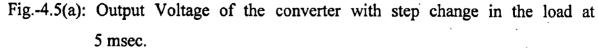

| Fig. 4.5(b) Load Current with step change in the load at 5 msec                                             |

| Fig. 4.5 (c) Step up change in Load at 5msec34                                                              |

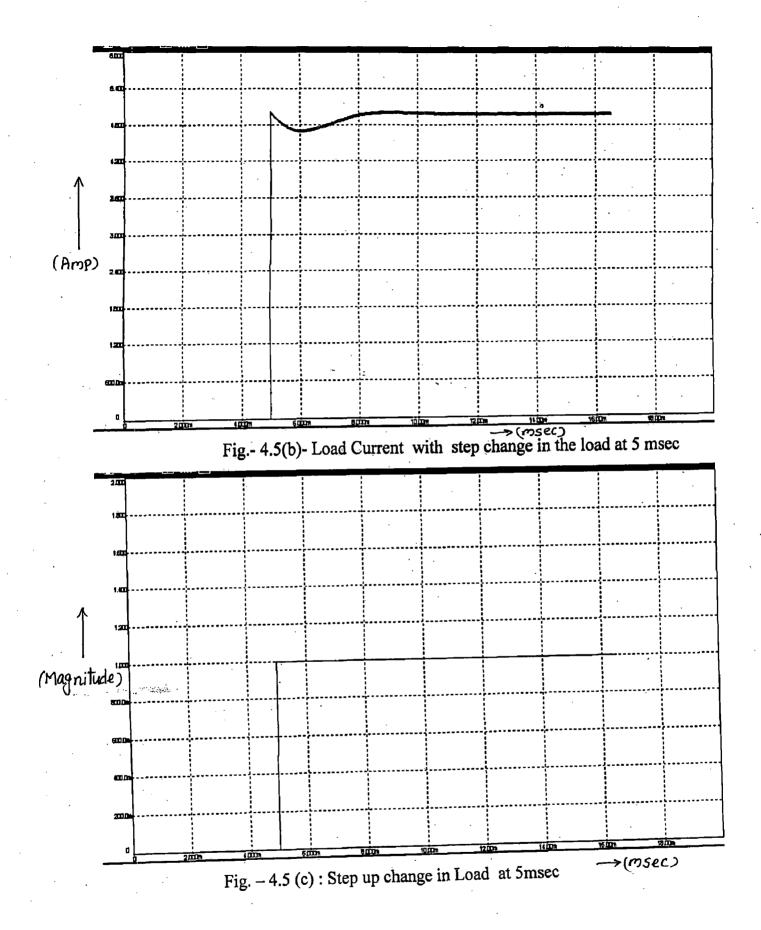

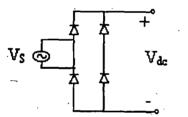

| Fig-4.5(d): Inverter output voltage                                                                         |

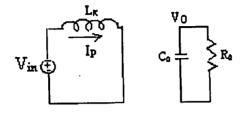

| Fig.5.1 Full- Bridge Diode Rectifier                                                                        |

| Fig. 5.2(a) Mode 1, (b) Mode 2, (c) Mode 3 & (d) DCM Mode340                                                |

| Fig.5.3 Operation Waveform45                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig.5.4 Equivalent circuits in three different modes each switching cycle                                                                                                   |

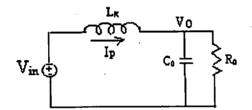

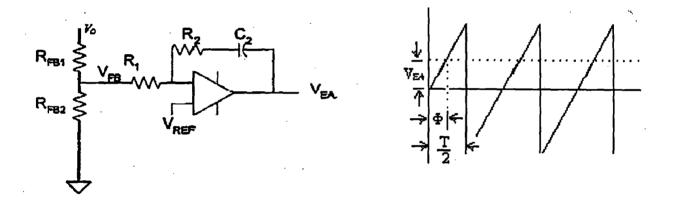

| Fig.5.5 PI Controller and the output of the comparator                                                                                                                      |

| Fig. 5.6 Closed Loop of the Converter                                                                                                                                       |

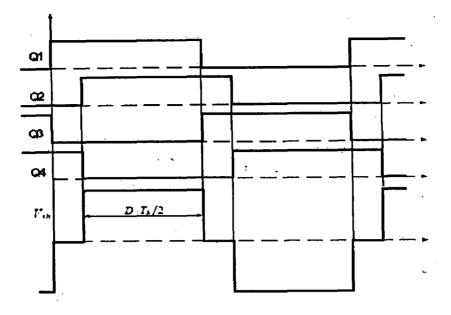

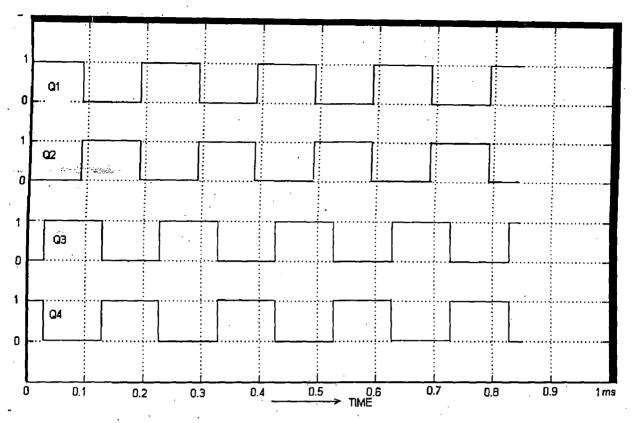

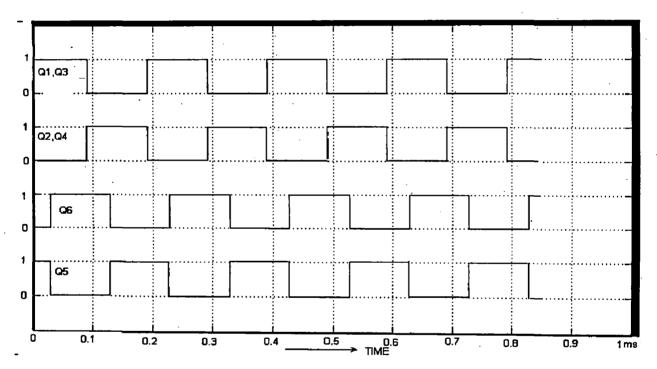

| Fig.7.1 Phase – shifted gate pulses                                                                                                                                         |

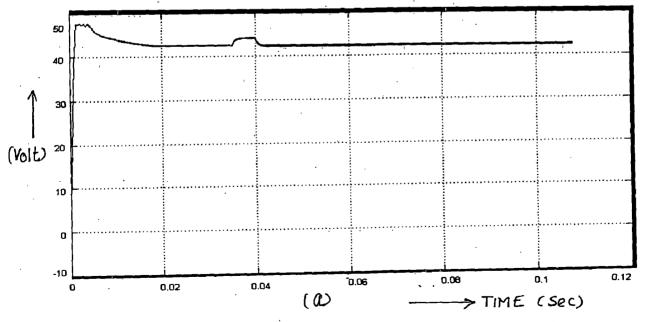

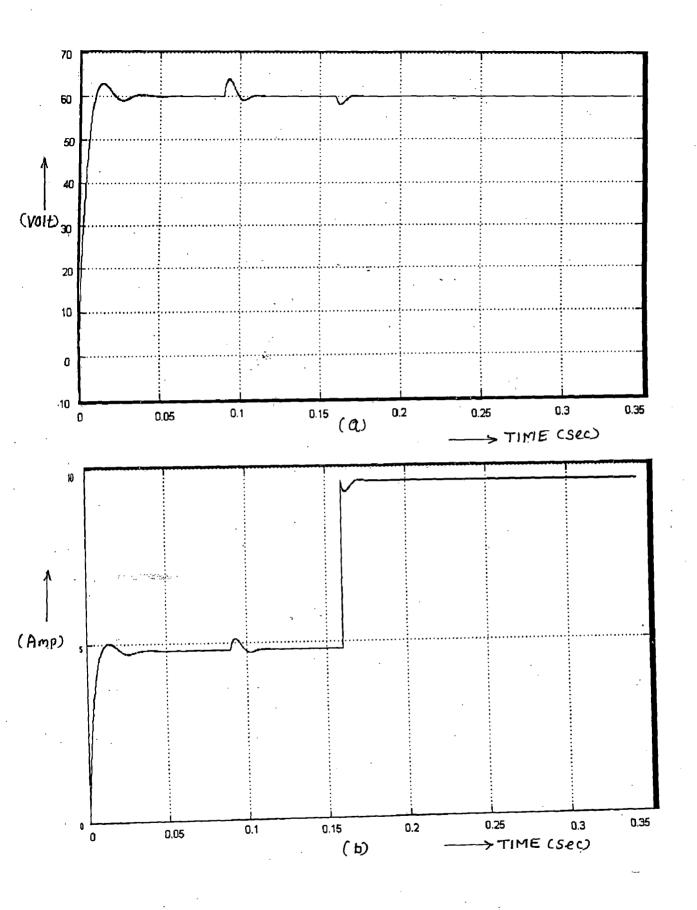

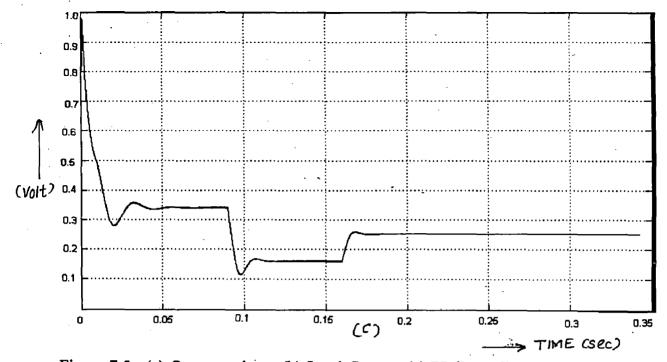

| Fig.7.2 a) Output Voltage Waveform b) Load Current c) PI Controller Output with change in Load at 0.04 sec                                                                  |

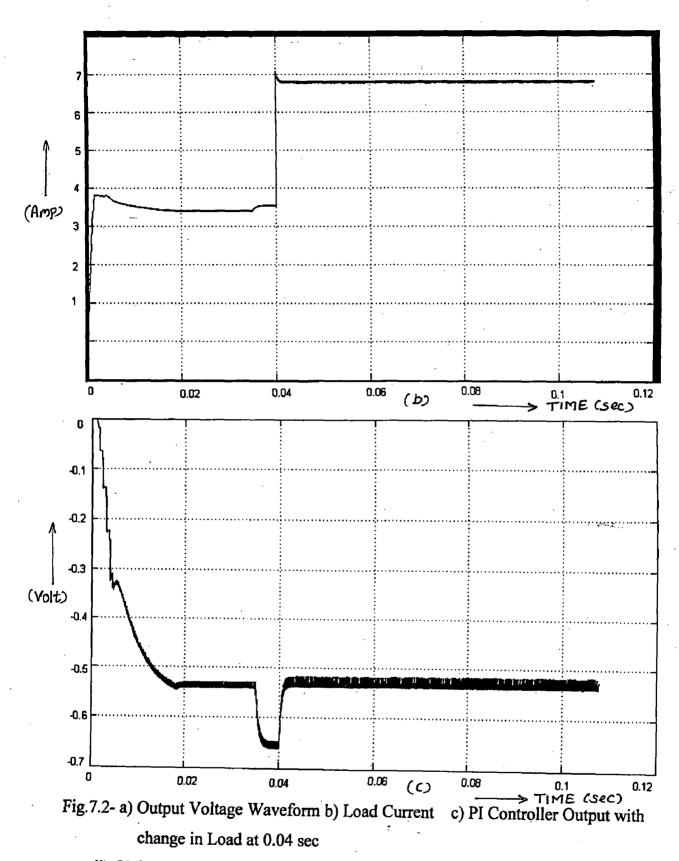

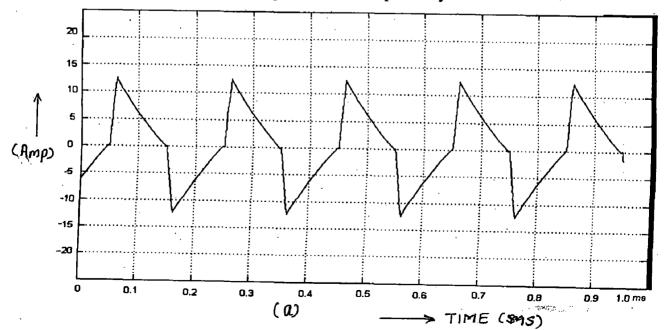

| Fig.7.3: Inverter Voltage & Current waveform                                                                                                                                |

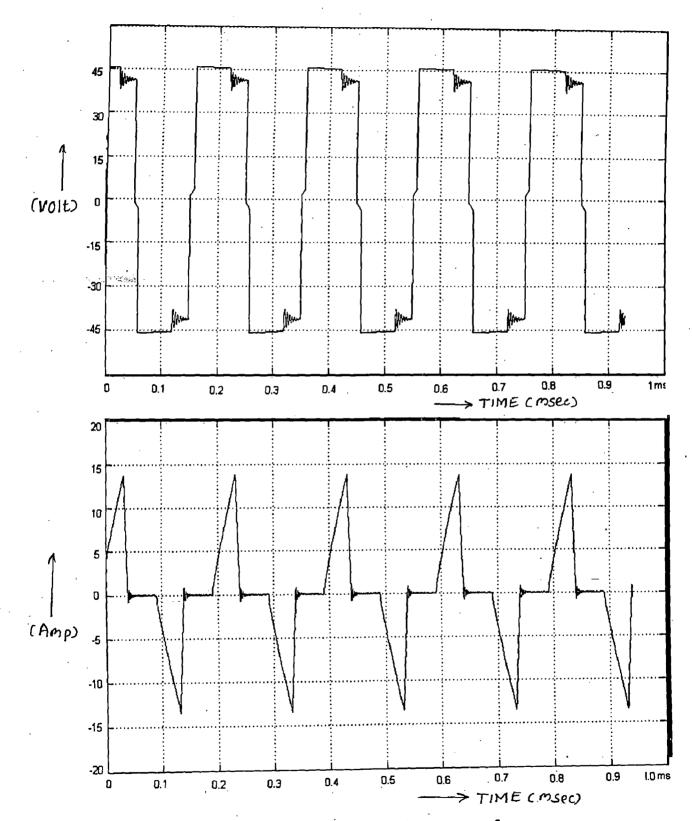

| Fig.7.4: Gate pulses for the Switches                                                                                                                                       |

| Fig.7.5: (a) Output voltage (b) Load Current (c) PI Controller output variation. with step up change in input voltage at 0.1 sec and with step up change in load at 0.2 sec |

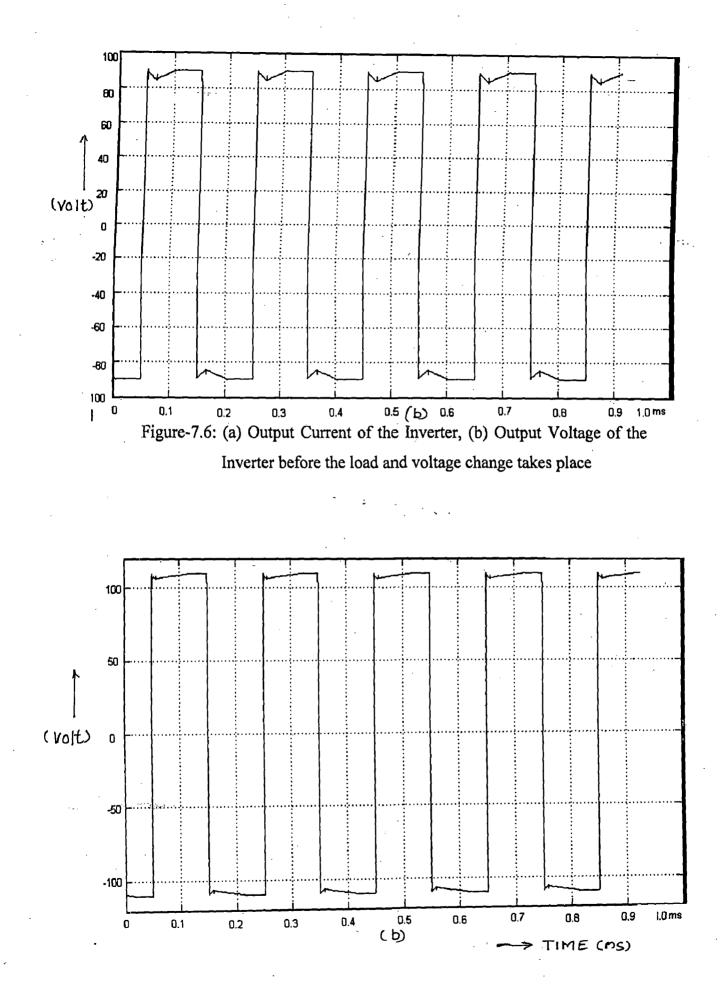

| Fig-7.6: (a) Output Current of the Inverter, (b) Output Voltage of the Inverter before the change takes place                                                               |

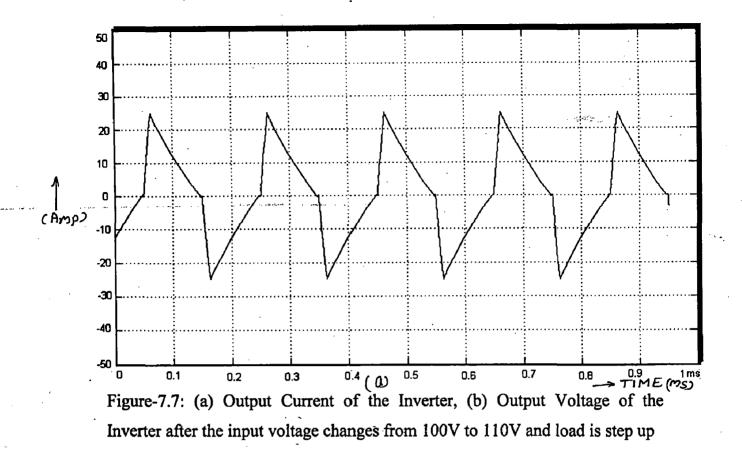

| Fig-7.7:(a)Output Current of the Inverter, (b) Output Voltage of the Inverter after the input voltage changes from 100V to 110V and load is step up68                       |

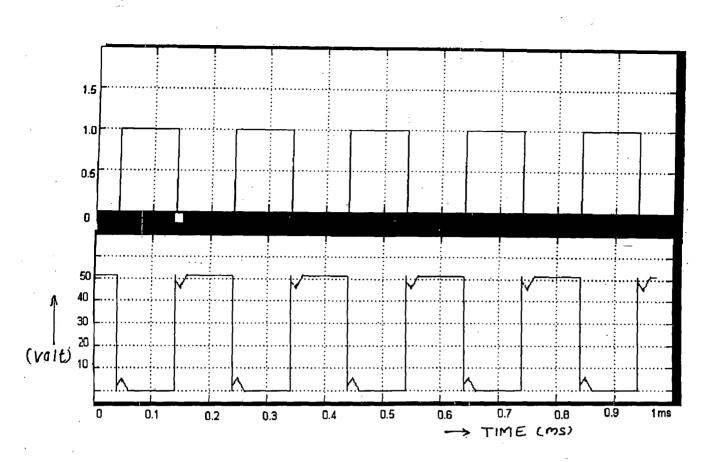

| Fig.7.8: Gate pulse and Voltage across Drain to Source of the Switch                                                                                                        |

| Fig-7.8: Gate pulse and Voltage across Drain to Source of the Switch                                                                                                        |

| Fig.8.1 Control Circuit for Single phase inverter & rectifier71                                                                                                             |

| Fig.8.2 Generation of Phase shifted Square Waves for DC/DC converter73                                                                                                      |

| Fig.8.3 Firing Pulse Amplification and isolation Circuit74                                                                                                                  |

| Fig.8.4 DC Power supplies (a) +5 V supply (b) +12 V supply (c) +12 V supply76                                                                                               |

| Fig.8.5 Hall effect current measurement circuit                                                                                                                             |

| Fig.8.6 Snubber circuit77                                                                                                                                                   |

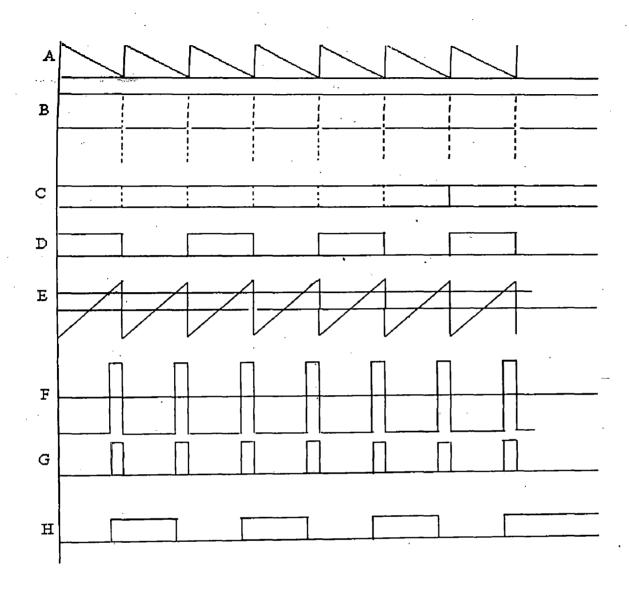

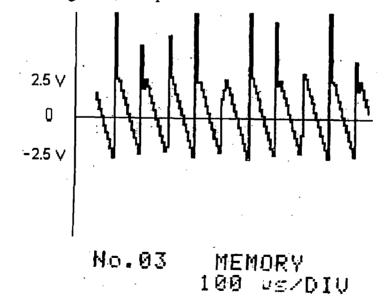

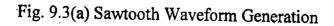

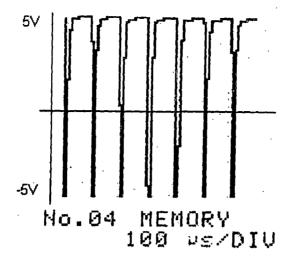

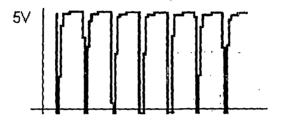

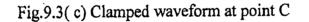

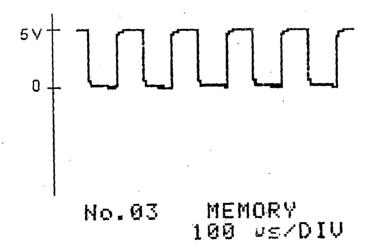

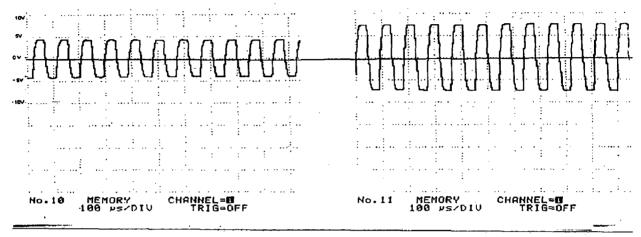

| Fig. 9.3(a) Sawtooth Waveform Generation (b) Waveform at point B(c) Clamped waveform (d) Square wave (e) Phase-shifted pulse waveform                                       |

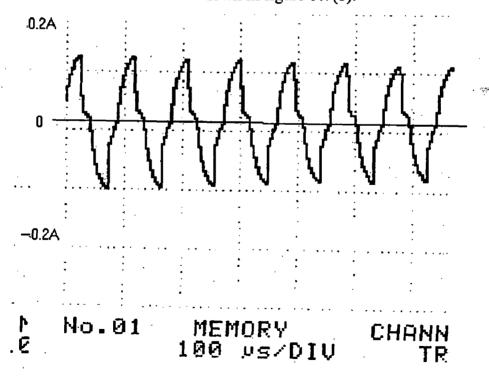

| Fig.9.4(a) Transformer Primary and Secondary Voltage(b) Primary Current                                                                                                     |

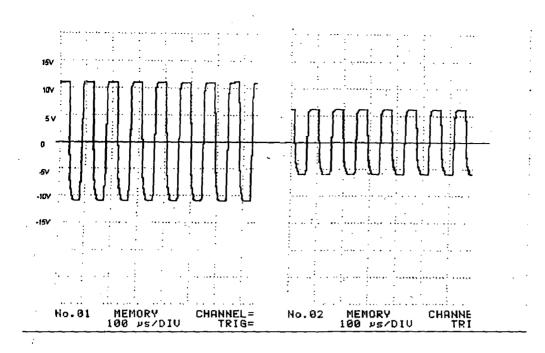

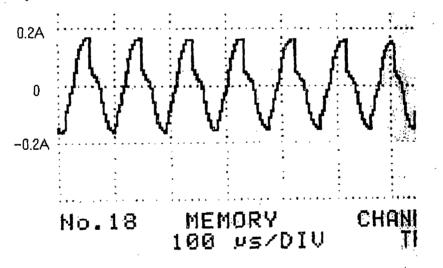

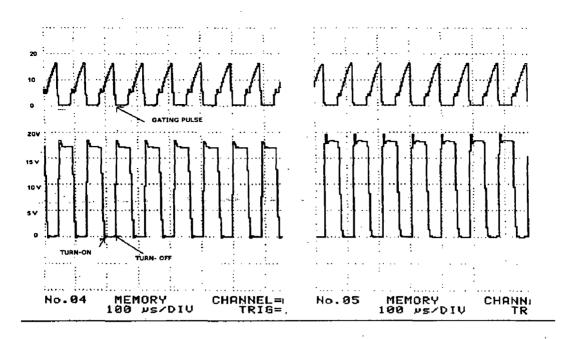

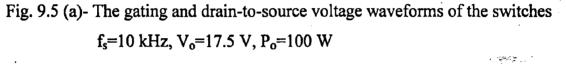

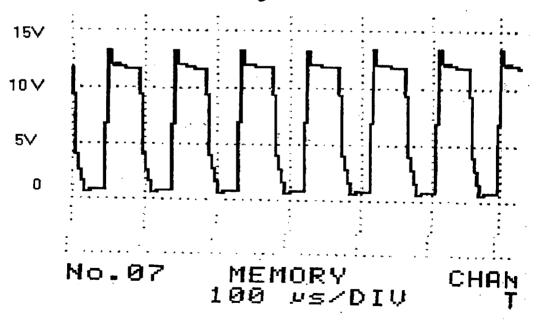

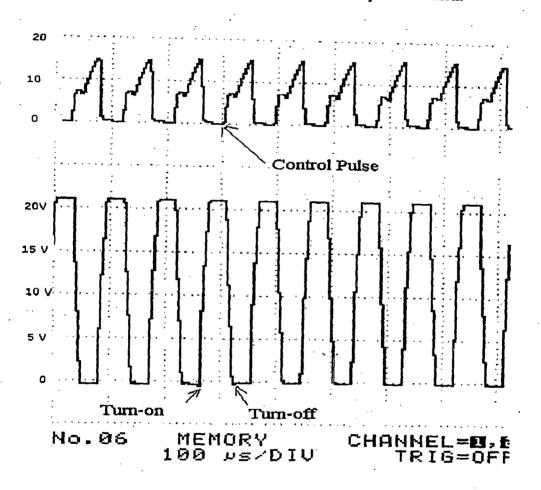

| Fig. 9.5(a) The gating and drain-to-source voltage waveforms of the switches (b) Voltage across the Diode                                                                   |

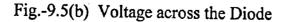

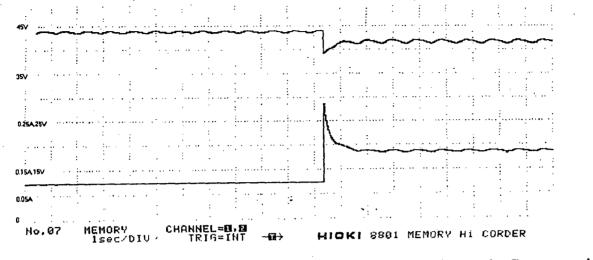

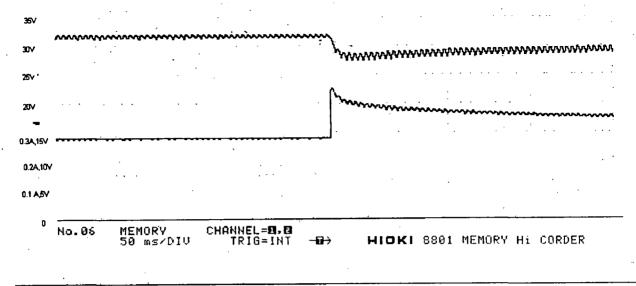

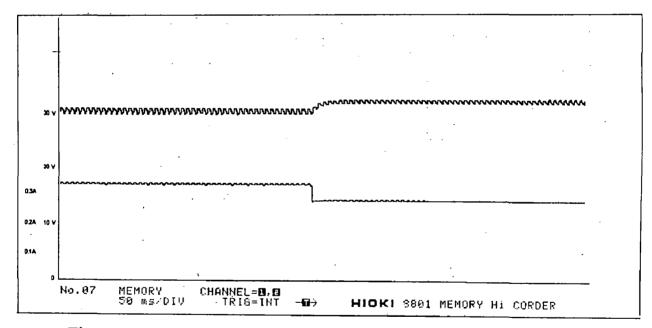

| Fig.9.6(a):- Transient response of Output Voltage and Load Current with step increase in the load from 50% to 100%.(b) with step decrease in the load                       |

| Fig9.7- Transformer Secondary and Primary Voltage (b) Primary Current                                                                                                       |

| Fig9.9: Control pulse and Drain to Source Voltage91                                                                                                                         |

| Fig9.10: The output voltage and load current dynamics (a) with the step up increase in the load (b) ) with the step up decrease in the load                                 |

vii

#### **CHAPTER-1**

#### **1.1 GENERAL**

The DC supply is widely used in automotive, aerospace, communication systems, marine industry, medical and military applications. It is also used in various equipments including power supplies for office equipment, spacecraft power systems, laptop computers, cordless phone, portable personal equipment i.e. MPEG player, personal computers and telecommunications equipment, as well as dc motor drives and also in specialised high-power applications such as battery charging, plating and welding.

Many Industrial applications require variable DC power. Some of these are:

i) Steel mills, paper and textiles mills employing DC motor drives.

ii) AC- fed traction system using DC traction motors.

- iii) Electro-chemical and electro-metallurgical processes.

- iv) Magnet power supplies.

- v) Reactor controls.

vi) Portable hand- tool drives.

For these applications earlier AC to DC conversion was achieved using Motor-Generator (MG) sets, Mercury-arc rectifiers, Cascade converter, Rotary Converters, thyratrons.

A Cascade Converter is a type of motor-generator which consists of an induction motor driving a dynamo through a shaft. In addition, the rotor of the induction motor is electrically connected to the armature of the dynamo. When the machine is running, half the power is transmitted mechanically through the shaft while the other half is transmitted electrically. The advantage of this arrangement is that the machine can be smaller than a conventional motor-generator of the same power. The rotary converter can be thought of as motor- generator where the two machines share a single rotating armature and set of field coils. In this two commutators one at each end of the armature are used. The advantage of rotary converter over the discrete motor-generator set is that the rotary converter avoids converting all of the power flow into the mechanical energy and then back into electrical energy, some of the electrical energy instead flows directly

from input to output, allowing the rotary converter to be much smaller and lighter than amotore- generator set of an equivalent power -handling capability. Mercury arc rectifiers were used until the 1960s for the production of high voltage direct current. applications included power supply for streetcars and electric railways, variable-voltage power supplies for large radio transmitters, and static inverters. Small mercury arc rectifiers were used in the power supplies for vacuum tube (valve) electronic equipment such as power amplifiers and transmitters.

Since 1960 mercury arc rectifiers were increasingly replaced by silicon rectifiers. Conventionally such rectifiers have been being made using a diode bridge rectifier the input to which is given through a three phase autotransformer which in turn is controlled by a stepper motor or a servomotor to get a controlled output. Linear power supplies also used to regulate the output by generating a higher voltage than needed at the output, then reducing it by converting some of the electrical power to heat. This loss is a necessary part of the operation of the circuit, and cannot be eliminated by improving the design.

Such systems are simple in configuration but they are quite bulky. The power factor of the system is poor and the total harmonic distortion is also high, efficiency is poor. The system is slow in response due to the mechanical movement of the motor used to control the applied input voltage. Linear power supplies use a mainstransformer operating at the mains frequency of 50/60 Hz (if they are isolating types), and line-frequency smoothing filters. These components are larger and heavier.

# **1.2 SWITCH MODE POWER SUPPLY**

Today in the quest for the ultimate in user comfort, the tendency to reduce the physical size and weight of the battery of portable personal equipment. The switching-mode power supply offers a better solution in this case. It provides the power supply function through low loss components such as capacitors, inductors, and transformers and the use of switches that are in one of two states, on or off. The advantage is that the switch dissipates very little power in either of these two states and power conversion can be accomplished with minimal power loss, which equates to high efficiency. Switched power supplies are more efficient, lighter in weight , having

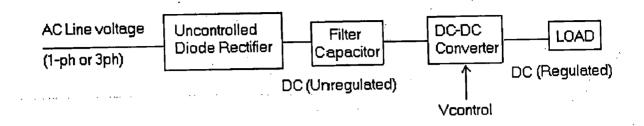

excellent closed loop operation, no mechanical wear and tear and they tend to have an efficiency of 80% or more. Block Diagram of an SMPS is shown in figure-1.1.

Figure-1.1 : Block Diagram of an SMPS

The main controlling block of the switching-mode power supply is DC-DC converters. Switched-mode power supplies can be classified according to the circuit isolation in the two categories:

> Non-isolating converters (i.e. Buck, Boost, Buckboost, Cuk converters).

> Isolating converters (i.e. Flyback, Forward converters).

Isolating forward converters are mainly two switch forward, and halfbridge converters, full-bridge, type. Among these possibilities for the power level under consideration (1 kW), half-bridge converter and full bridge converter provide the best combination of simple structure, low device stress and soft switching capability. Isolating full-bridge forward converter uses transformer for isolation purpose, which has certain advantages over non-isolating converters. These are:

- o to obtain dc isolation between the converter input and output

- when a large step-up or step-down conversion ratio is required, the use of a transformer can allow better converter optimization. By proper choice of the transformer turns ratio, the voltage or current stresses imposed on the transistors and diodes can be minimized, leading to improved efficiency and lower cost.

• The ability to set the turns ratio also removes the  $V_{in}$  vs.  $V_o$  and polarity restrictions that apply to the basic topologies. Also, multiple outputs at various voltages are easily obtained with multiple secondary windings.

3.

• since transformer size and weight vary inversely with frequency, thus high frequencies lead to dramatic reductions in transformer size.

Disadvantages are:

- o additional cost, size and weight,

- o losses in the core and windings,

- potential core saturation (especially in push-pull circuits, core\_reset in single-ended circuits, and voltage spikes and losses due to transformer leakage reactance).

Full-bridge dc/dc converters are extensively used in medium to high power level applications. For most of these applications, particularly those for the computer and telecommunication systems, the most desirable features of the converter are high efficiency, high power density, high reliability and low Electro-Magnetic Interference (EMI). The standard full bridge topology operates in hard switching, and the hard switching converter is unable to achieve high efficiency and high power density for the following reasons:

➤ in order to achieve high power density, the switching frequency is normally increased, because at increased frequencies, the converter can employ smaller sized power magnetics and capacitors, both of which are the largest devices of a power converter.

However, as the switching frequency increases, the switching losses associated with the turning on and off of switches will become excessive. These losses greatly reduce the converter's overall efficiency, and high power density is not achievable due to the resultant high cooling requirements. Switching loss imposes an upper limit on the switching frequencies of practical converters. Several mechanisms lead to switching loss. During the switching transitions, the transistor voltage and current are simultaneously large. In consequence, the transistor experiences high instantaneous power loss. This can lead to significant average power loss, even though the switching transitions are short in duration. The diode reverse recovery process induces substantial additional energy loss in the transistor during the transistor turn-on transition. The energy stored in the semiconductor output capacitances is dissipated during the transistor turn-on transition. Energy stored in transformer leakage inductances and other stray inductances

is usually dissipated by the transistor during the turn-off transition. The total switching loss is equal to the sum of the energy losses that arise via these mechanisms, multiplied by the switching frequency. Switching loss causes the converter efficiency to decrease as the switching frequency is increased.

## **1.3 SOFT SWITCHING TECHNIQUES**

To solve these problems, soft switching techniques are normally used. Basically there are two types of the soft switching techniques: Zero Voltage Switching (ZVS) and Zero Current Switching (ZCS). Either of the techniques can greatly reduce and even completely eliminate the switching losses in the converter. However, it is well understood that ZVS is more advantageous for a MOSFET switch topology than the ZCS. High power level full bridge converters usually use IGBT switches, due to IGBT's low conduction losses and higher power capability. However, IGBT is not as fast as MOSFET, and its switching frequency can not be increased beyond 50 kHz even if softly switched. Contrary to IGBT, MOSFET is a resistive device when it is turned on, and the conduction losses are higher as compared to IGBT at high power levels. However, MOSFET is a faster device and is able to operate up to a few MHz.

Isolated converter topologies provide advantages in applications requiring large voltage conversion ratios. Hence an isolated topology is favored for converter optimization through the incorporation of a small high-frequency transformer. Transformer isolation can reduce switch and diode device stresses and allows multiple windings or taps to be used to for multiple converter outputs. The full-bridge is a popular design for both buck and boost applications and has become a basis for numerous resonant zero voltage and zero current switching (ZVS, ZCS) schemes. Often in high power applications a phase shift modulation (PSM) switching scheme is used to achieve ZVS and/or ZCS transitions through the interaction of converter parasitic energy storage. The main limitations of phase-shift ZVS/ZCS topologies are:

- High circulating current

- Soft switching is not achieved for wide load range

#### **1.4 ORGANISATION OF THIS THESIS**

CHAPTER 2: This chapter is a review of the various publications in this field has been discussed briefly.

**CHAPTER 3:** This chapter focuses on the various principle of control strategy i.e. voltage mode control, current mode control, peak current mode control, hysteresis current control etc. The comparative advantages and disadvantages of each strategy are discussed.

**CHAPTER 4:** In this chapter, the topology of ZVS PWM for the full-bridge Phaseshifted secondary dc/dc converter has been selected and the reasons for selecting the topology have been mentioned. The comparison with ZVS PWM for the full-bridge Phase-shifted Primary dc/dc converter topology in which phase shift is given at the inverter section is also discussed. The advantages of using phase-shifted strategy at the secondary side are described.

**CHAPTER 5**: This chapter discusses the detailed circuit operation of the ZVS PWM for the Full-bridge Phase-shifted secondary dc/dc converter topology and the circuit equation at the various interval are given. Equivalent circuit in different mode is drawn and the state space equation are derived. Then small signal model is obtained for the system by which overall transfer function of the whole system is found.

**CHAPTER 6 :** This chapter calculates the various parameters which is required in deciding the component selection for hardware development. The selection of switches, diodes, Transformer parameters on the basis of design specification is done.

**CHAPTER 7 :** This chapter includes the simulation of Full-Bridge ZVS Phase-shifted DC/DC converters . The converter's performance is tested in the case

- when step up change in the input voltage occurs at 0.1 sec.

- when the load is step up changed at 0.2 sec.

The voltage across the devices is recorded in order to see whether ZVS is achieved.

**CHAPTER 8 :** This chapter consists of hardware development of control circuit for single-phase inverter and phase-shifted gating control circuit for the synchronous rectifier section. These pulses obtained from the control circuits are amplified through Firing Pulse Amplification & Isolation Circuit. The +5 V, +12 V, -12V power supply for the dc

biasing of different IC's are developed. Current sensor circuit for the measurement of current is fabricated.

**CHAPTER 9 :** In this chapter the experimental results for the developed prototype recorded are presented. The waveform of firing pulses to MOSFETs, voltage across transformer primary and secondary ,current in the transformer primary, the voltage across the switches and the output voltage have been described.

**CHAPTER 10 :** Conclusions of the thesis work are drawn in this chapter followed by suggestions for future work

In this chapter, the need for a DC supply has been emphasized. The various industrial approaches for the generation of DC supply and its regulation and their limitations have been discussed. The use of switch mode power supply to overcome those limitations has also been presented. Block diagram of switch mode power supply and various types of it has been discussed. The benefits and limitations of use of high frequency in the switch mode power supply with the stress upon using soft-switching in overcoming the limitations and reducing the size and weight of power supply has been detailed. In the next chapter the limitations occur in the conventional converters will be discussed and the methods to improve soft-switching at various load conditions are being discussed.

#### LITERATURE REVIEW

The problems faced in the conventional Full bridge ZVS PWM dc/dc converters are discussed in this chapter and suggestion of remedial measures by researchers to overcome these problems are reviewed. Each of them has suggested one or the other modification in the conventional circuit so as to get improvement in the results. Full bridge ZVS PWM dc/dc converters are some of the simplest power electronic circuits. They are widely used in the power supply equipment for most electronic instruments and also in specialized high-power applications such as battery charging, plating and welding etc. Various topologies are used to make such dc/dc converters. Each topology has got its own advantages and disadvantages and the real choice depends on the application. In this chapter, a brief overview of the various topologies used for Full bridge Phase- shifted ZVS PWM dc/dc converters is presented.

Full Bridge Zero Voltage Switched Phase Shift DC-DC Converter is preferred due to its remarkable features [1] -[4]. It combines the advantages of quasiresonant converters in what concerns the turn on switching losses, and also the advantages of classical PWM converters related to conduction losses and operating frequency. These benefits can be summarized as follows:

- zero voltage switching for all the bridge transistors;

- reduction of the conduction losses when compared with Quasi Resonant converters;

- reduction of the electromagnetic noise;

- utilization of the devices' output capacitances and transformer leakage inductance; and

- fixed frequency operation.

However, there are some drawbacks:

- 1. High circulating currents;

- 2. loss of duty cycle and

#### 3. ZVS is lost for light loads.

These problems are due to the fact that to assure ZVS in a wide range of load and input voltage, it is necessary to have sufficient stored energy in the leakage inductor. Especially at light loads, the energy stored in the leakage inductor of the transformer is not sufficient to achieve ZVS. Therefore, there is a need of adding a commutating inductor in series with the primary winding of the transformer. As it is known the size of this inductor increases with the ranges of variation of the input voltage and of the load, where ZVS is to be maintained. A large commutating inductor enables ZVS in a wide range of load and input voltage but also causes higher circulating energy, which increases the conduction losses. A large commutating inductor is also responsible for a larger loss of duty cycle because the primary current transitions, in order to change its polarity, are slower. So, there must be a design compromise considering the specifications of input voltage and load ranges and the effective duty cycle and efficiency.

To solve these problems some different solutions have been proposed:

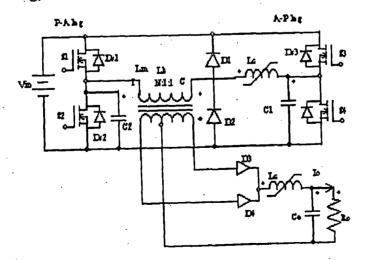

Richard Redl in [5]-[6] uses a primary commutating inductor with one terminal connected to the passive to active leg midpoint, and the other connected to the input voltage source via two clamping diodes shown in Fig-2.1. With this process, zero voltage switching is achieved in a wide range of load current for the bridge transistors. However, the clamping diodes, that provide a continuous current in the P-A leg, suffer from hard switching, with the consequent commutating losses.

#### Advantages

- i) Reduce the voltage stress due to ringing and overshoot across the rectifier diodes.

- ii) The extension of soft switching toward light load

- iii) An optimal winding configuration of the power transformer (There is no need to build in a large leakage inductance in the transformer)

- A New Family of Full-Bridge ZVS Converters is proposed in [7]-[8]. The ZVS of primary switches is achieved by employing two magnetic components whose volt-second products change in the opposite directions with a change of phase shift between the two bridge legs. One magnetic component is a transformer while the other magnetic component is either a coupled inductor or a single-winding inductor. In this the energy available for ZVS increases as the input voltage increases, which is the desirable direction of change since more energy is required to achieve ZVS at higher input voltages.

#### Advantages :

- The stored energy is independent of load.

- Ideally, the auxiliary circuit needs to provide very little energy, if any, at full load because the full-load current stores enough energy in converter's inductive components to achieve a complete ZVS for all switches. As the load current decreases, the auxiliary circuit needs to provide progressively more ZVS energy, with the maximum energy required at no load.

- zero-voltage-switching (ZVS) of all bridge switches over a wide range of input voltage

#### Disadvantage

- duty cycle loss and circulating current

- voltage unbalance of the transformer at starting up.

- > A comparative study of a class of full bridge zero-voltage-switched PWM converters is discussed in [7]. Four different topologies are compared-

- a) linear resonant inductor is employed to achieve ZVS, in this approach ZVS is achieved for a narrow range and also secondary parasitic ringing is very large.

- b) It is observed that by employing saturable inductor and reducing the leakage inductance of the transformer ZVS range can be extended to a wide range, circulating energy is reduced and ringing in the secondary side is small.

- c) ZVS range can be extended to no-load if magnetizing inductor is used; also secondary parasitic oscillations are greatly reduced because of the very small leakage inductance.

Disadvantage:

i) deliberately increased magnetizing energy circulates in the primary, resulting in an increased conduction loss.

d) In this approach, Instead of using the energy stored in the magnetizing inductance to achieve ZVS, the saturable reactors can be arranged to utilize the energy of the output filter inductor to obtain ZVS. It causes circulating energy very small, hence efficiency is higher. Secondary parasitic ringing is virtually eliminated because of the use of a very small leakage inductance and because of the damping effect of the saturable reactors.

The converter topology presented [10] here employs an asymmetrical auxiliary circuit consisting of four drain-to-source snubber capacitors, each connected across one switch, a capacitor voltage divider, and two auxiliary inductors. With this auxiliary circuit, the full bridge converter can achieve ZVS independent of line and load conditions.

In terms of power transfer from the input to load, the power circuit operates in exactly the same way as does a conventional phase-shift full bridge converter, and the auxiliary circuit hardly interferes with this power transfer. However, the auxiliary circuit does have significant influences on the switching

transients of the switches: it removes the switching losses from all the switches, at both turn-on and turn-off.

- In reference [11-[13] define the limitations of the FB-ZVS-PWM converter and use a saturable reactor in series with the primary winding or with the secondary rectifier diodes. This process enables a wider range of operation under ZVS without a significant increase in conduction losses. However, it is always a problem to eliminate energy excess when saturation occurs.

- ➢ Novel soft-commutation DC-DC power converter with high-frequency transformer secondary side phase-shifted PWM active rectifier [14], can achieve ZVS for non-controlled active power switches on the primary side of the transformer and ZCS for PS-PWM active switches on the secondary side of the transformer under wide load variations as well as a wide PS-PWM regulation range. The switching power losses and conduction power losses of the active devices of the proposed DC-DC converter can be considerably reduced, because it blocks circulating current.

- Two distinct resonant dc/dc converter topologies, which exhibit near zero switching losses is presented in [15] shown in Fig-2.2. The difference between two topologies is the connection of auxiliary circuit in series or in parallel. Connection of an inductor and a capacitor in the series branch makes it well suited for low input voltage, low output voltage, and high output current. While parallel-connected topology is favorable for high voltage, high power system with ultra low ripples requirements.

- Fig-2.2 : Constant Frequency Resonant DC/DC Converters With Zero Switching Losses [15]

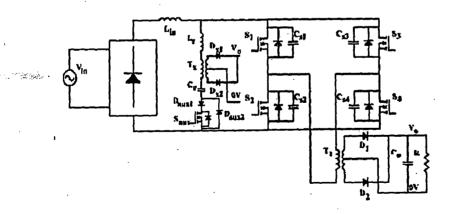

- A single-stage converter with an auxiliary circuit that allows its main power circuit switches to operate with ZVS is given in [16]. The features of this converter include soft switching all switches, fixed frequency operation, and PFC with a continuous input current. The auxiliary circuit shown in Fig-2.3, is simple, requires only one active switch, and operates with a ZCS turn-on and a ZVS turnoff.

Fig-2.3: Single-Stage ZVS PWM Full-Bridge Converter [16]

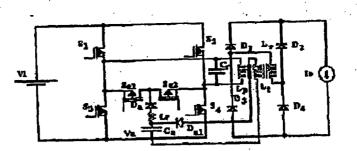

[17] is based on the principle of the self-resonance, that is: an auxiliary voltage source feeds the resonant circuit, charging the capacitor, which provides the condition for the zero voltage switching (ZVS) of the main switches.

Fig-2.4: A Novel Single-Phase Soft-Switched Rectifier with Unity Power Factor and Minimal Component Count [17]

- A novel, single-phase soft-switched boost ac-dc rectifier [18]-[19] that operates with power-factor correction are discussed. The rectifier is a modified boost voltage-doubler converter well suited for low-line-input applications. It operates with fewer conduction losses and half the switch voltage stresses found in a standard boost converter. Soft switching in the converter is achieved using a zerocurrent-switching quasi-resonant technique.

- ➢ By replacing the linear resonant inductor with a nonlinear inductor. The inductance value of which decreases with the increasing of the load current and hence achieve zero-voltage switching for a wide load range [20].

- A soft-switching converter topology [21], which employs a small saturable reactor, can achieve soft- switching in a wide load range from no load to full load without substantial reduction for the output voltage and no substantial increase in current stresses. Since saturable reactor acts as a magnetic switch, blocks the load current during the switching transition interval.

- '1 kW/250 kHz Full Bridge Zero Voltage Switched Phase Shift DC-DC Converter with Improved Efficiency' is proposed in [22]. In this a two-windings inductor is used. The inductor primary winding is connected in series with the transformer primary and its secondary is connected to the output capacitor by two rectifier diodes is shown in Fig-2.5. This process enables the recovering of the excess of energy directly to the load and in an increase in the effective duty cycle, which

permits to increase the converter performance. Stress analysis of switches is presented in [23].

Fig-2.5: Full Bridge Zero Voltage Switched Phase Shift DC-DC Converter with Improved Efficiency [22]

- Liviu Mihalache, proposed a new PWM technique [24] to ensure uniform losses among all four devices. The basic idea is to make one leg behave as the "leading leg" in one period and as a "lagging leg" in the next period, thus the average losses over two periods are equal for all four devices, for this it utilizes a different gating method.

- In [25] leakage inductance is increased to achieve ZVS with wide input voltage range and load range but it causes voltage ringing across rectifier diodes, which is reduced by adding two clamp diodes in the primary side of the transformer.

- With the inclusion of a LCC auxiliary circuit [26], primary current will become reinforced during the passive-to active transition, thus increasing the available energy to achieve ZVS and minimizing the problems of duty cycle.

- It utilizes the magnetizing inductance of the transformer to achieve zero voltage turn-on of the primary switches [27]. By employing saturable inductor(s) on the secondary-side, soft turn-off of the output rectifier(s) is obtained with a minimum circulating energy flowing through the converter.

- ➢ In [28] a New Start-up Schemes for Isolated Full-Bridge Boost Converters is proposed The purpose of using a start-up circuit for a boost-type converter is to establish an initial output voltage before the converter operates in the normal boost mode. The initial output voltage should not be lower than the input voltage (reflected).