## SIMULATION AND EXPERIMENTAL VALIDATION OF MULTI PULSE AC/DC CONVERTER FOR MEDIUM VOLTAGE ASD:

#### **A DISSERTATION**

# Submitted in partial fulfillment of the requirements for the award of the degree

of

MASTER OF TECHNOLOGY

In

#### ELECTRICAL ENGINEERING

#### (With Specialization in Power Apparatus and Electric Drives)

8y

A SALANA A SALA

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA)

JUNE, 2006

### SANJIV KUMAR

I here by declare that the work which has being presented in the Dissertation Thesis entitled "Simulation And Experimental Validation Of Multi Pulse AC/DC Converter For Medium Voltage ASDs" in partial fulfillment of the requirements for the award of the degree of Master of Technology in Electrical Engineering with specialization in Power Apparatus and Electric Drives, submitted in the Department of Electrical Engineering, Indian Institute of Technology, Roorkee, INDIA – 247667. This is an authentic record of my own work carried out in the period of last two semesters from August 2005 to June 2006, under the supervision of Shri Y. P. Singh, Assistant Professor, Department of Electrical Engineering, Indian Institute of Technology, Roorkee, INDIA – 247667.

The matter embodied in this Dissertation Thesis has not been submitted by me for the award of any other degree or diploma.

Date: 27/06/06 Place: Roorkee

This is to certify that the above statements made by the candidate are correct to the best of my knowledge.

(Shri. Y. P. Singh) Assistant Professor, Electrical Engineering Dept, Indian Institute of Technology, Roorkee

### Acknowledgements

I take this opportunity to express my sincere gratitude to Shri. Y. P. Singh, Assistant Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, for his whole heartedness and high dedication with which he involved in this work. I am grateful for hours he spent in discussing and explaining even the minute details of the work in spite of his hectic schedule of work in the department. He listened patiently and authoritatively as he guided me and made his valuable suggestions.

I am grateful to all my teachers of the PAED group for their suggestions and constant encouragement. I am also grateful to all Research Scholars of the PAED group for their suggestions and constant encouragement.

Special sincere heartfelt gratitude to my mother, whose sincere prayer, best wishes, concern, support, unflinching encouragement and thoughtfulness has been a constant source of strength for me during the entire work.

Timely assistance and help from the laboratory staff of Drives Lab, Stores, and Workshop is sincerely acknowledged. Grateful acknowledgements also to my friends and other well wishers whose timely help has gone a long way in this work.

(Sanjiv Kumar) M.Tech (Elect.) PAED

Date: 27/06/06 Place: Roovkee

### Abstract

In this dissertation work a 24-Pulse Buck-Boost AC/DC Converter is discussed. The objective of presented dissertation work is to simulate 24-pulse buck-boost AC/DC converter in MATLAB, and to validate experimentally the voltage regulation and power quality of the converter from utility side.

In the proposed scheme, phase shifted transformer is used in which secondary (that supply the power cells i.e. cascade single phase VSI modules in each phase of the A.C. motor) are wound to obtain small phase angle between them. The phase angle differs by multiples of 20° for 2.4 KV drives; multiples of 15° for 3.3 KV drives & by multiples of 12° for 4.6 KV drive. They cancel most of the harmonic currents drawn by individual power cell so that primary current are nearly sinusoidal & confirm to or approaches to IEEE power quality standards 519 -1992.

The proposed scheme also take care of unbalancing in secondaries winding voltage of phase shifted transformer or fluctuation in supply voltage. Developed converter maintains constant DC voltage of all the modules for entire range of supply voltage. Harmonic spectrum of input current, power factor of supply side also tested.

A simulation model is developed in MATLAB for different topologies and also for proposed scheme to compare the results and to obtain the performance comparison. Simulation results are also verified with experimental results and these are found satisfactory.

# List of Figures

| Figure No.       | <b>Figure Description</b>                                                     | Page<br>No |

|------------------|-------------------------------------------------------------------------------|------------|

| Fig 1.1          | Harmonic Source Current Type                                                  | 2          |

| Fig 1.2          | Harmonic Voltage and Current Waveform                                         | 3          |

| Fig 1.3<br>a & b | Harmonic Source Voltage Type                                                  | 3          |

| Fig 1.4          | Harmonic Voltage and Current Waveform                                         | 3          |

| Fig 2.1          | Basic Structure                                                               | 15         |

| Fig 2.2          | 6-Pulse Rectifier                                                             | 17         |

| Fig 2.3          | $\Delta$ -Y Isolated Transformer 12-Pulse converter                           | · 17       |

| Fig 2.4          | 12-Pulse Phase Control AC/DC Converters With $\Delta$ -Y Isolated Transformer | . 18       |

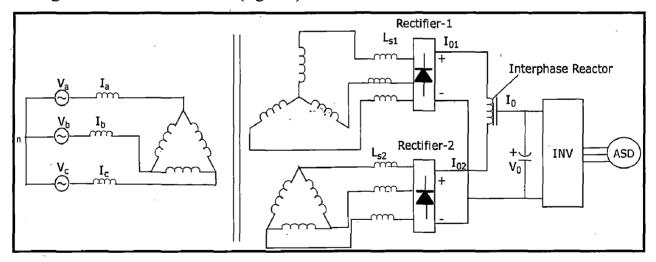

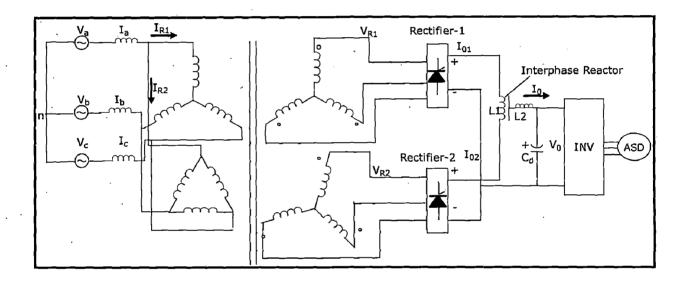

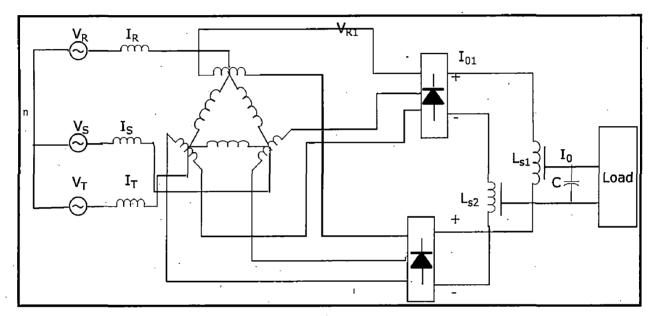

| Fig 2.5          | 12-Pulse Phase Control AC/DC Converters<br>With Autotransformer               | 19         |

| Fig 2.6          | 18-Pulse Converter                                                            | 20         |

| Fig 2.7          | Circuit Diagram of 24-Pulse System                                            | 21         |

| Fig 2.8          | Circuit Diagram of 24-Pulse Extended Delta Converter                          | 21         |

| Fig 2.9          | 24- Pulse Converter                                                           | 22         |

| Fig 2.10         | 36-Pulse Self-Commutated Voltage-Source Converter                             | 23         |

| Fig 3.1          | Single-Phase Cascaded ASD                                                     | 24         |

| Fig 3.2          | Winding Diagram of Phase Shifting Transformer                                 | 26         |

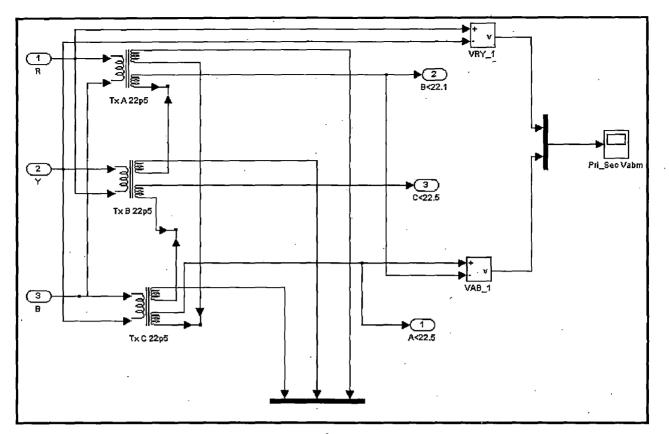

| Fig 3.3          | Connection Diagram for +22.5 ° Phase Shift                                    | 27         |

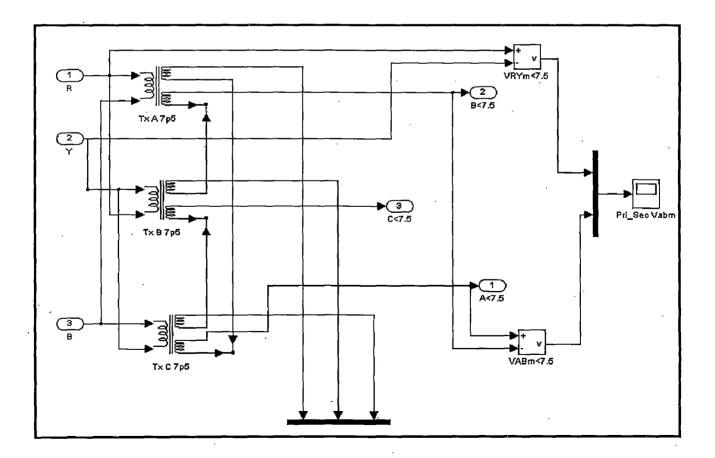

| Fig 3.4          | Connection diagram of +7.5 ° Phase Shift                                      | 27         |

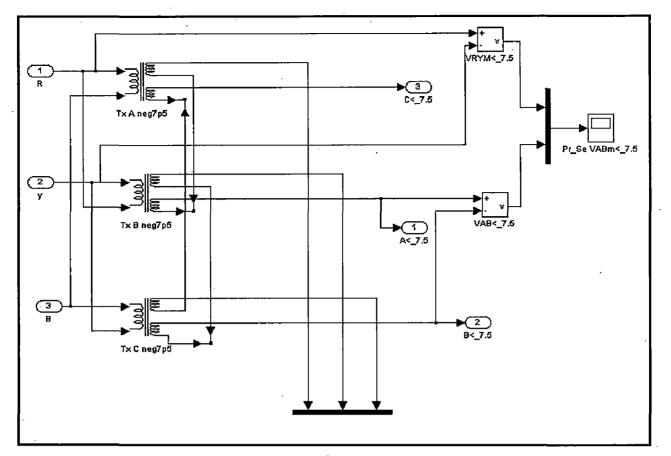

| Fig 3.5          | Connection Diagram for -7.5 ° Phase Shift                                     | 28         |

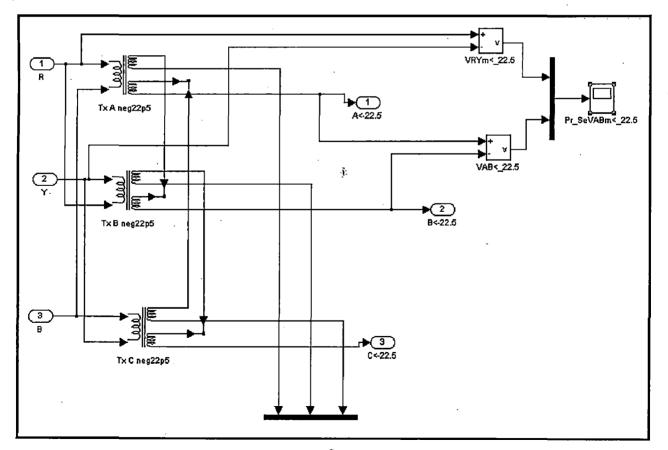

| Fig 3.6          | Connection diagram for -22.5 ° Phase Shift                                    | 29         |

| Fig 3.7 a        | 3-Phase Rectifier                                                             | 29         |

| Fig 3.7 b        | Complete Rectifier System                                                     | 30         |

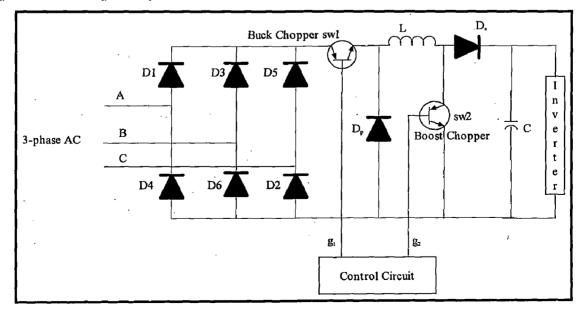

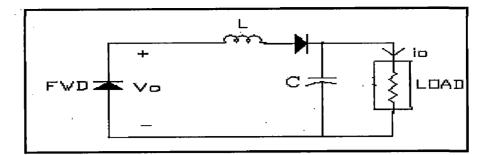

| Fig 3.8          | Buck-Boost Chopper Rectifier                                                  | 30         |

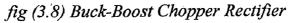

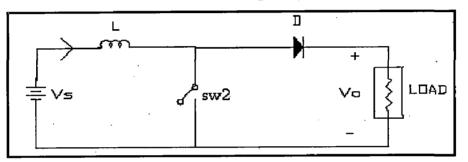

| Fig 3.9          | General circuit for Buck Chopper                                              | 31         |

| Fig 3.10 a       | Equivalent Circuit of Buck Chopper During TON Period                          | 32         |

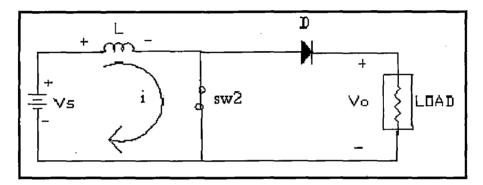

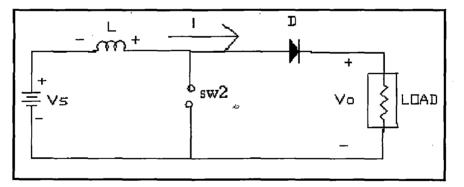

| Fig 3.10 b       | Equivalent Circuit of Buck Chopper During TOFF Period                         | 33         |

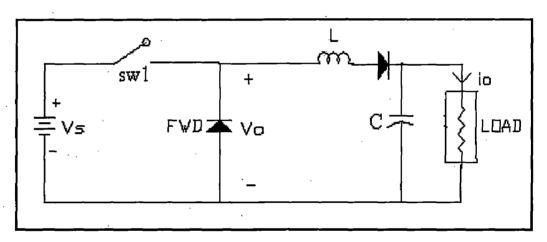

| Fig 3.11         | General Circuit For Boost Chopper                                             | 33         |

| Fig 3.12 a       | Equivalent Circuit of Boost Chopper During T <sub>ON</sub> Period             | 34         |

| Fig 3.12 b       | Equivalent Circuit of Boost Chopper During T <sub>OFF</sub> Period            | 34         |

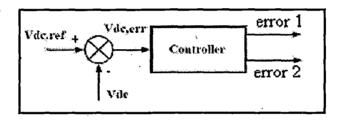

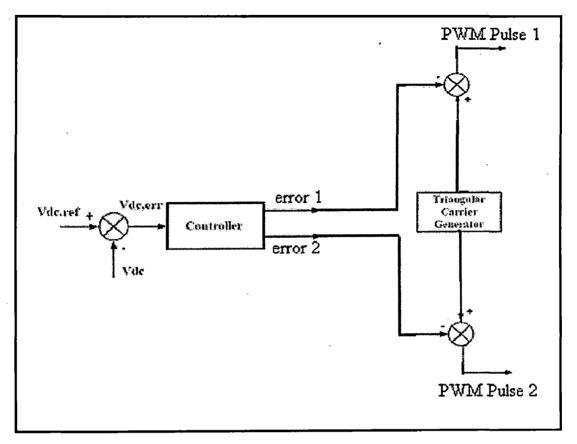

| Fig 3.13         | Block Diagram of Error Estimator Block                                        | 37         |

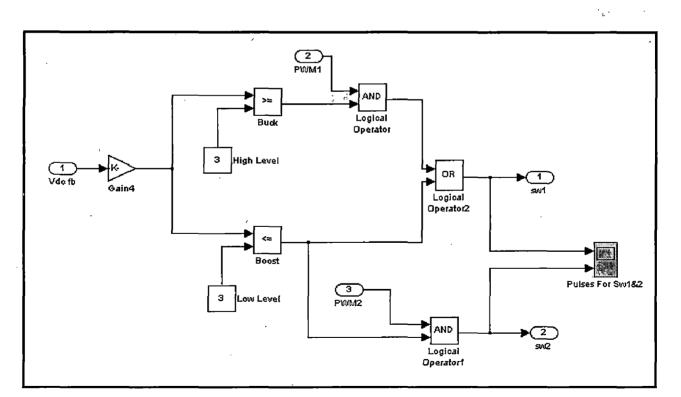

| Fig 3.14         | Block Diagram of PWM Pulse Generation                                         | 38         |

i

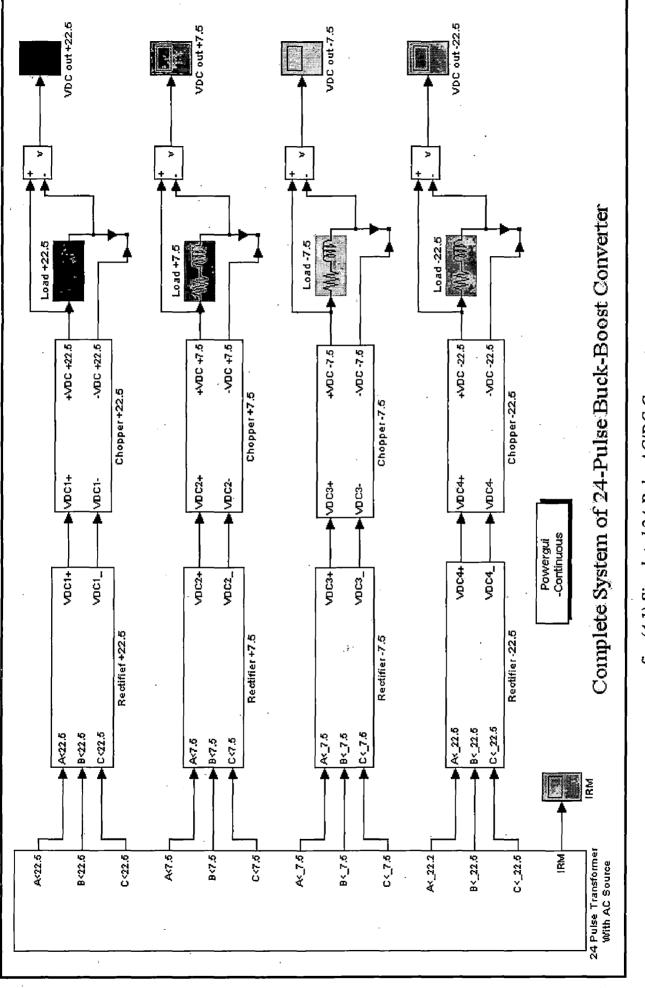

| Fig 4.1           | Simulated 24-Pulse AC/DC Converter                                        | 40              |

|-------------------|---------------------------------------------------------------------------|-----------------|

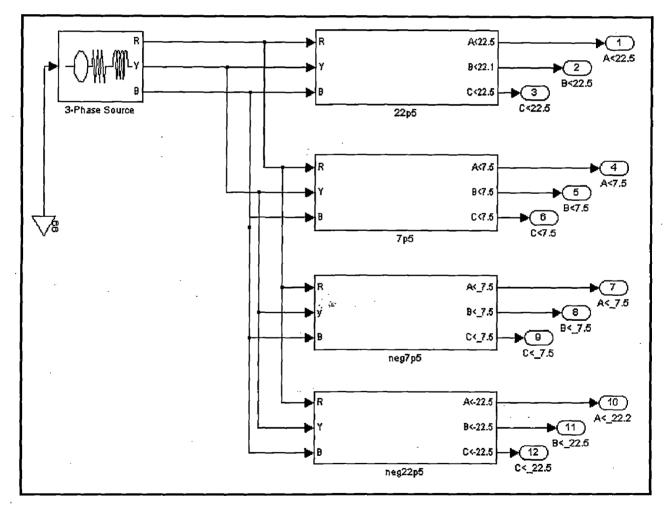

| Fig 4.2           | Simulated 24-Pulse Transformer                                            | 41              |

| Fig 4.3 a         | Simulated +22.5 <sup>0</sup> Phase Shifted Secondaries                    | 42              |

| Fig 4.3 b         | Simulated +7.5 <sup>0</sup> Phase Shifted Secondaries                     | 42              |

| Fig 4.3 c         | Simulated -7.5 <sup>0</sup> Phase Shifted Secondaries                     | 43              |

| Fig 4.3 d         | Simulated -22.5 <sup>0</sup> Phase Shifted Secondaries                    | 43              |

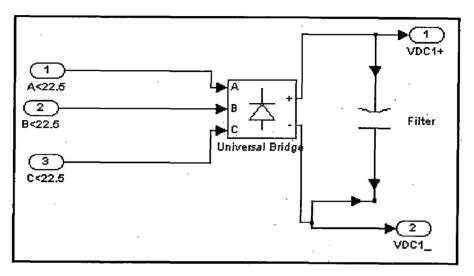

| Fig 4.4           | Simulated Rectifier Module                                                | <sup>.</sup> 44 |

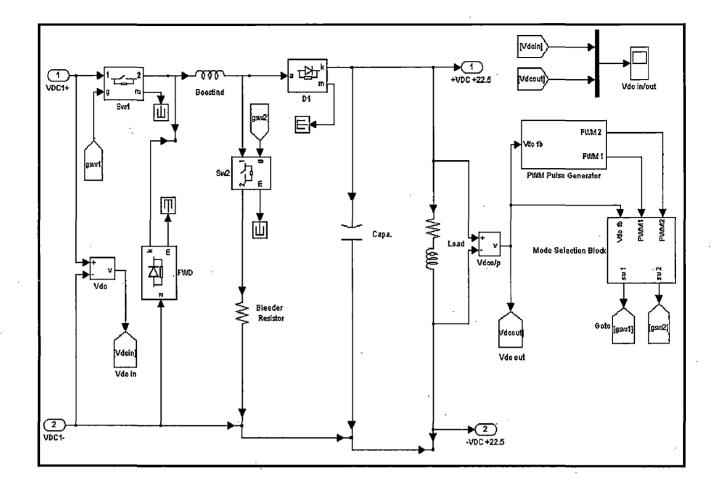

| Fig 4.5           | Simulated Buck-Boost Chopper                                              | 45              |

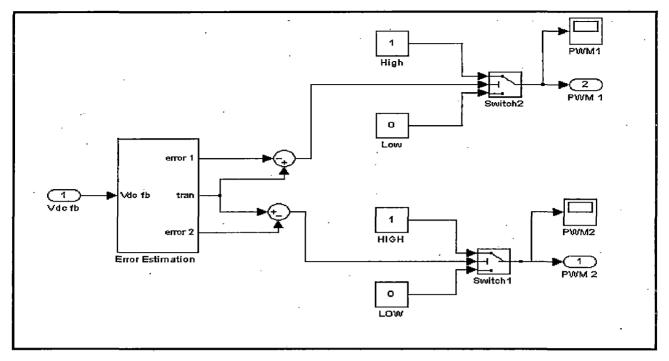

| Fig 4.6           | Simulated PWM Pulse Generator Block                                       | 46              |

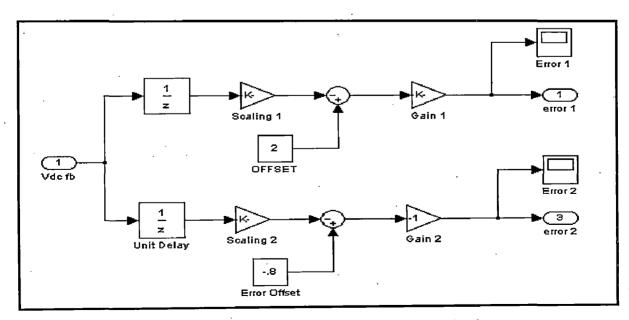

| Fig 4.7 a         | Simulated Error Estimation Block                                          | 46              |

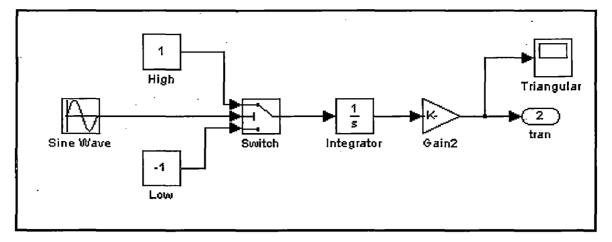

| Fig 4.7 b         | Simulated Triangular Wave Generator Block                                 | 47              |

| Fig 4.8           | Simulated Mode Selection Block                                            | 47              |

| Fig 5.1           | Simulated 6-Pulse Converter                                               | 48              |

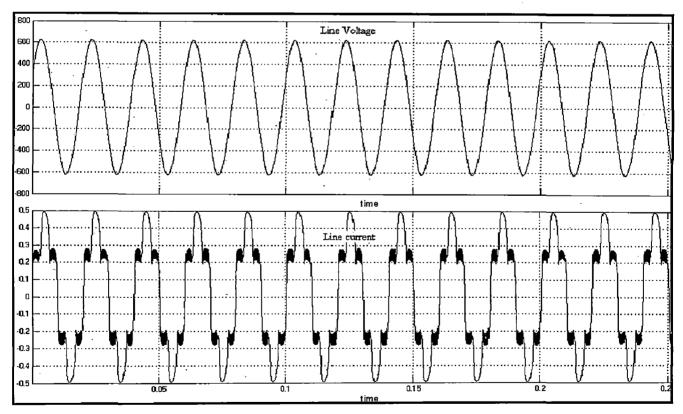

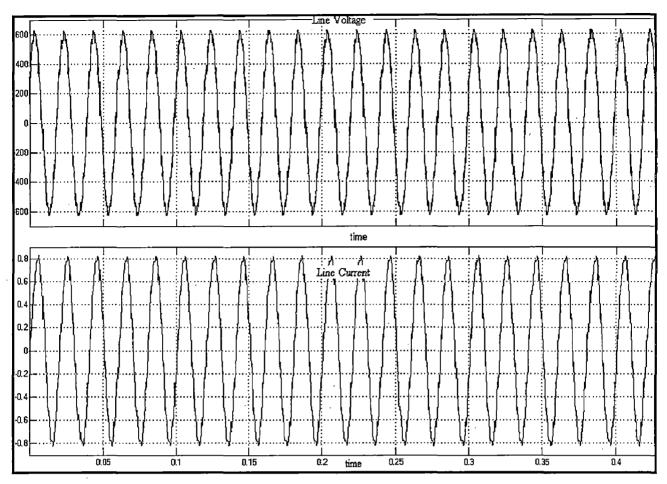

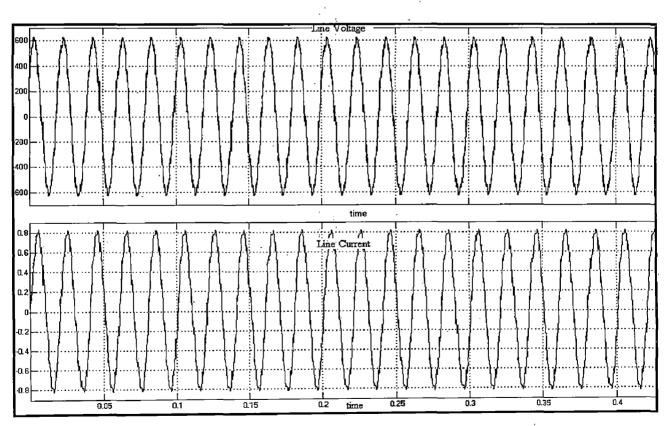

| Fig 5.2           | Input Line Voltage and Current Waveform for                               | 49              |

| a<br>Fig 5.2<br>b | Resistive Load<br>Input Line Voltage and Current Waveform<br>for R-L Load | 49              |

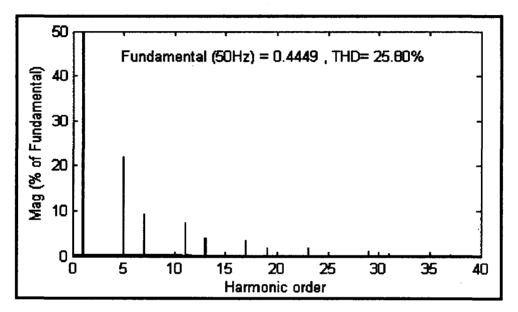

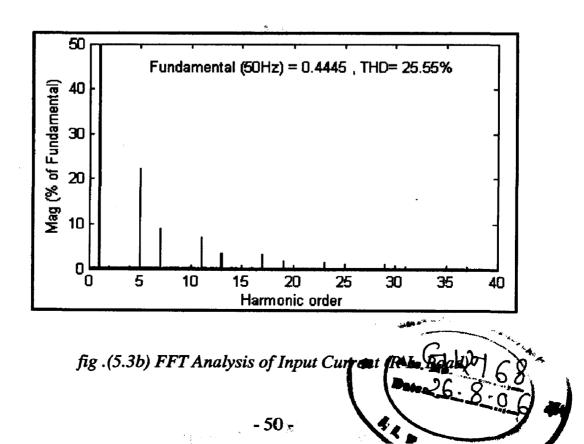

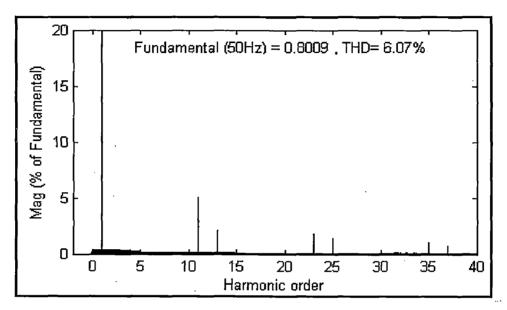

| Fig 5.3 a         | FFT Analysis of Input Current (Resistive Load)                            | <b>50</b> -     |

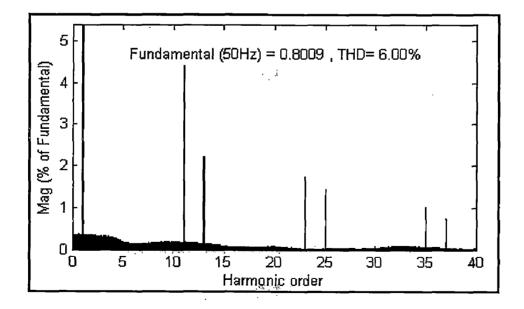

| Fig 5.3 b         | FFT Analysis of Input Current (R-L Load)                                  | 50              |

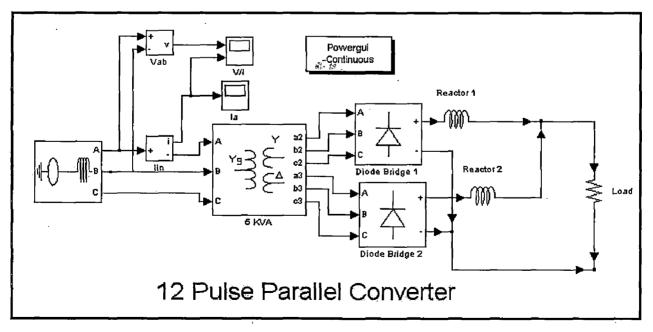

| Fig 5.4           | Simulated 12-Pulse Parallel Converter                                     | 52              |

| Fig 5.5<br>a      | Input Line Voltage and Current Waveform for Resistive Load                | 53              |

| Fig 5.5           | Input Line Voltage and Current Waveform for                               | 53              |

| b<br>Fig 5.6 a    | R-L Load<br>FFT Analysis of Input Current (Resistive Load)                | 54              |

| Fig 5.6 b         | FFT Analysis of Input Current (R-L Load)                                  | 54              |

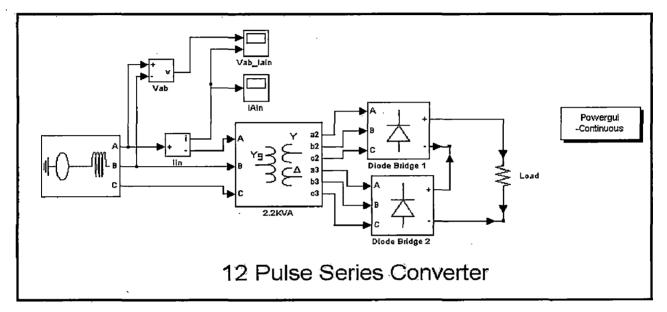

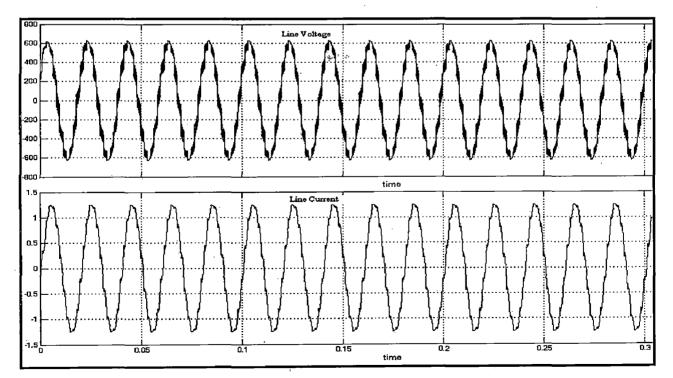

| Fig 5.7           | Simulated 12-Pulse Series Converter                                       | 56              |

| Fig 5.8           | Input Line Voltage and Current Waveform for R-L Load                      | 56              |

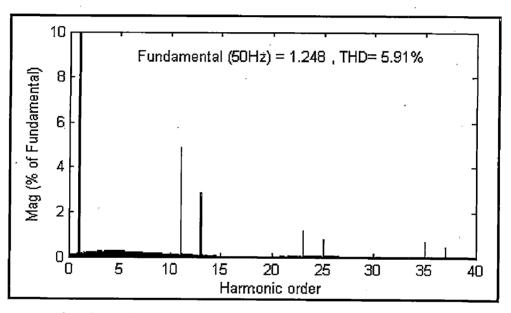

| Fig 5.9 a         | FFT Analysis of Input Current (R-L Load)                                  | 57              |

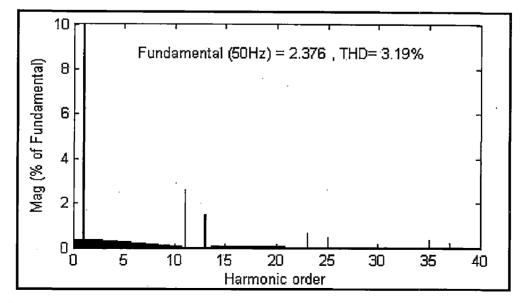

| Fig 5.9<br>b      | FFT Analysis of Input Current<br>(50% of previous R-L Load)               | 57              |

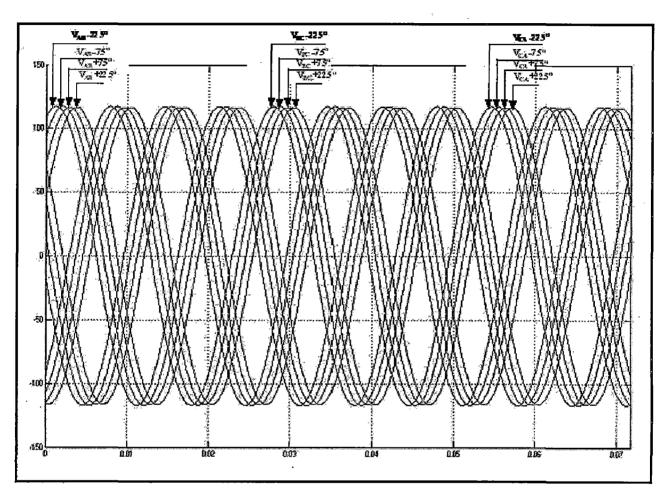

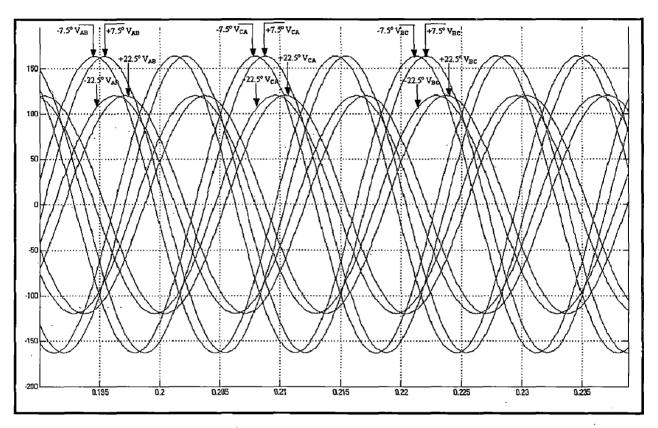

| Fig 5.10          | Phase Shifted Line to Line voltages of all Secondaries                    | 59              |

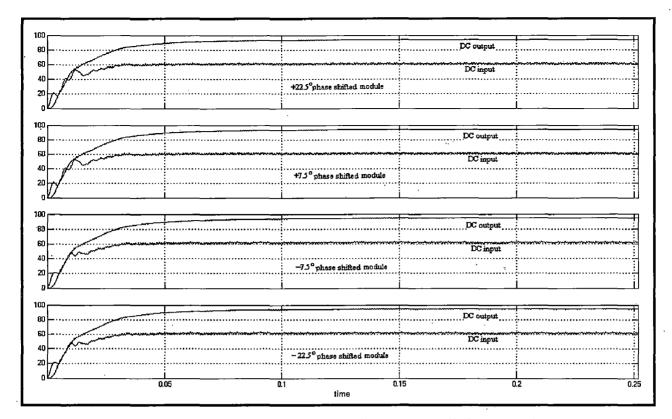

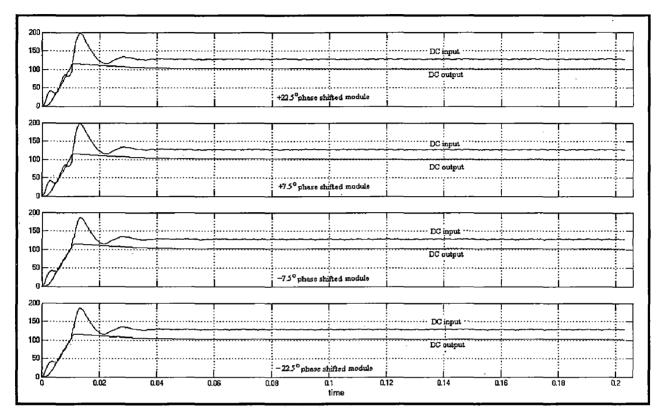

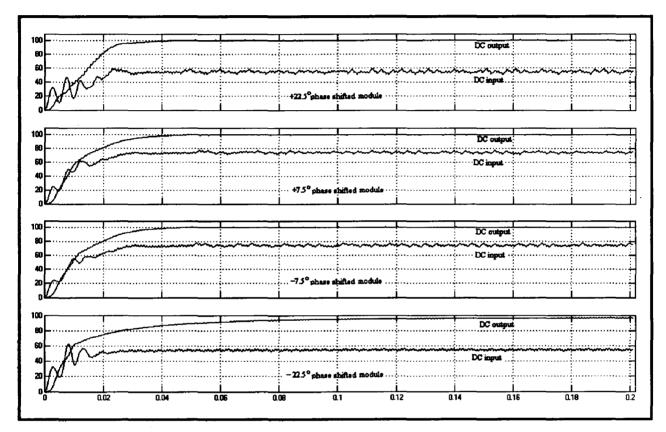

| Fig 5.11          | Waveforms of DC input and output of all the four choppers                 | 60              |

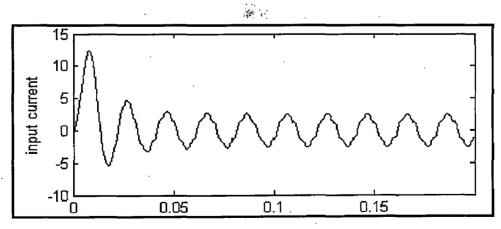

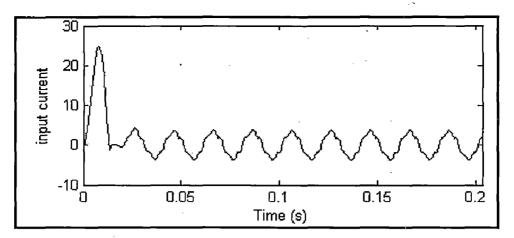

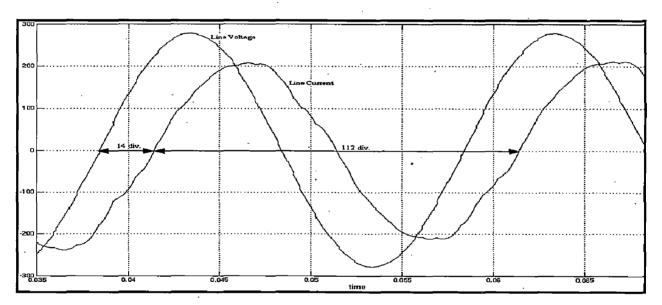

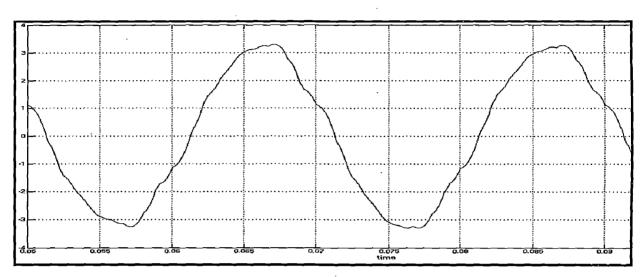

| Fig 5.12          | Input Current Waveform in Boost Mode                                      | 60              |

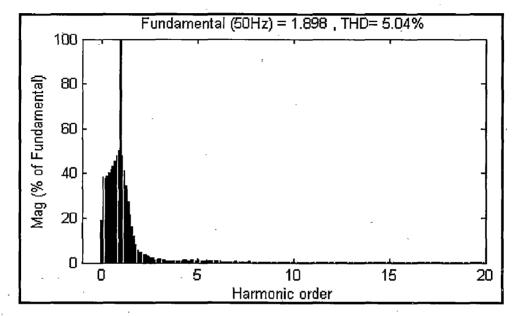

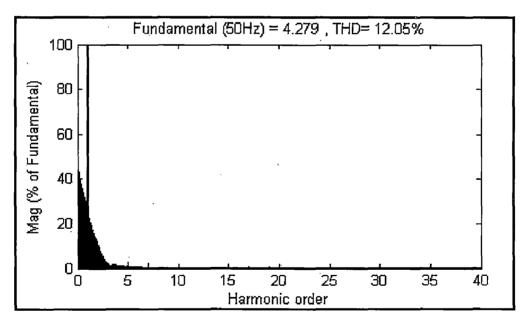

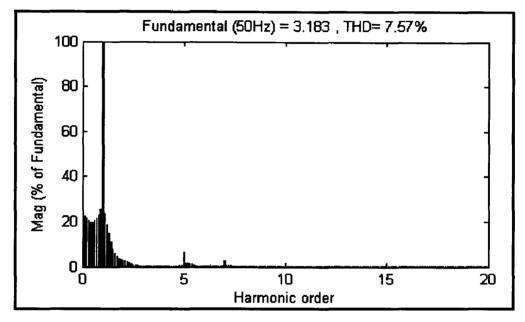

| Fig 5.13          | FFT Analysis of Input Current                                             | 61              |

ii

| Fig 5.14     | Waveforms of DC input and output of all the four choppers                      | 62         |

|--------------|--------------------------------------------------------------------------------|------------|

| Fig 5.15     | Input Current Waveform in Buck Mode                                            | 63         |

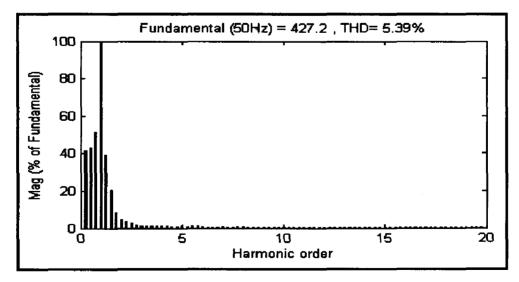

| Fig 5.16     | FFT Analysis of Input Current                                                  | 63         |

| Fig 5.17     | Phase Shifted Line to Line voltages of all Secondaries                         | 65         |

| Fig 5.18     | Waveforms of DC input and output of all the four choppers                      | 66         |

| Fig 5.19a    | Input Current Waveform in Boost Mode at 1 kHz                                  | 67         |

| Fig 5.19b    | Input Voltage and Current Waveform in Boost Mode at 10                         | 67         |

|              | kHz                                                                            |            |

| Fig 5.20a    | FFT Analysis of Input Current (1 kHz)                                          | 68         |

| Fig 5.20a    | FFT Analysis of Input Current (10 kHz)                                         | 68         |

| Fig 5.21     | Waveforms of DC input and output of all the four choppers                      | 70         |

| Fig 5.22a    | Input Current Waveform in Buck Mode at 1 kHz                                   | 71         |

| Fig 5.22b    | Input Voltage and Current Waveform in Buck Mode at 10 kHz                      | <b>7</b> 1 |

| Fig 5.23a    | FFT Analysis of Input Current (1 kHz)                                          | 72         |

| Fig 5.23b    | FFT Analysis of Input Current (10 kHz)                                         | 72         |

| Fig 5.24     | Input Current Waveform of Uncontrolled Converter                               | 74         |

| Fig 5.25     | FFT Analysis of Input Current                                                  | 74         |

| Fig 6.1      | Block Diagram of Developed 24-pulse Converter                                  | 76         |

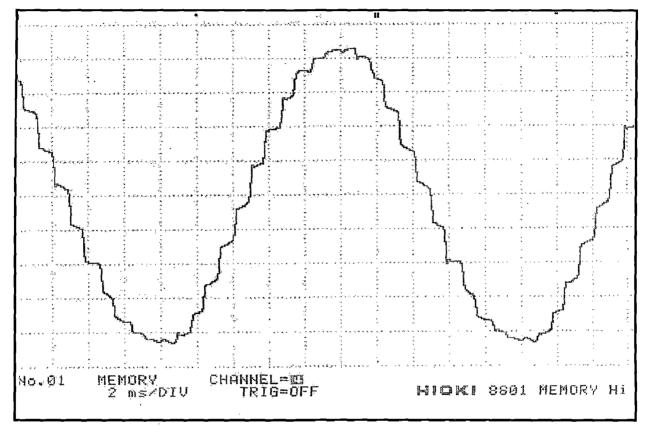

| Fig 6.2      | Recorded Input Line Current Waveform of 24-Pulse<br>Converter                  | 79         |

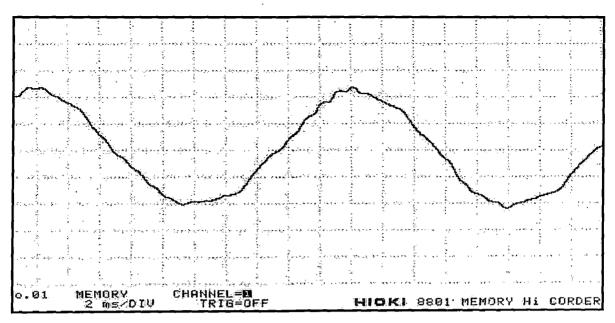

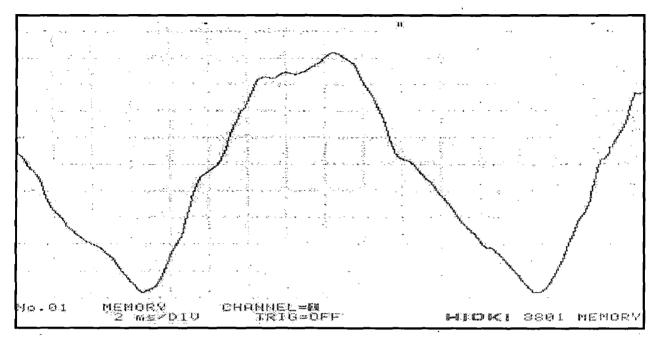

| Fig 6.3      | Output Waveform of All The Four Secondaries Winding At<br>The Scale of 2ms/div | 81         |

| Fig 6.3<br>b | Output Waveform of All The Four Secondaries Winding At<br>The Scale of 1ms/div | 82         |

| Fig 6.4 a    | DC Output Waveform of -/+ 7.5° Phase Shifted Module                            | 84         |

| Fig 6.4 b    | DC Output Waveform of -/+ 22.5° Phase Shifted Module                           | 84         |

| Fig 6.5      | Block Diagram of single unit of Buck-Boost Converter                           | 86         |

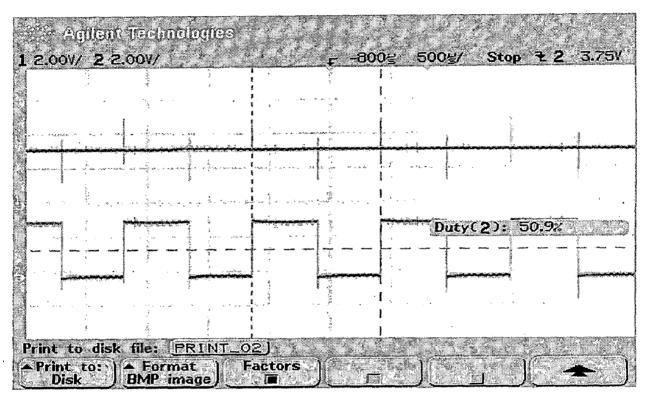

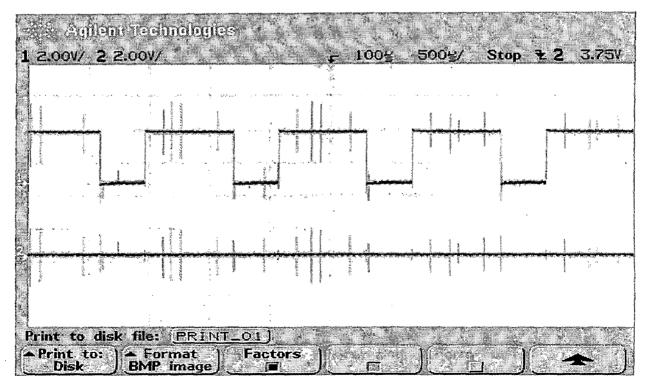

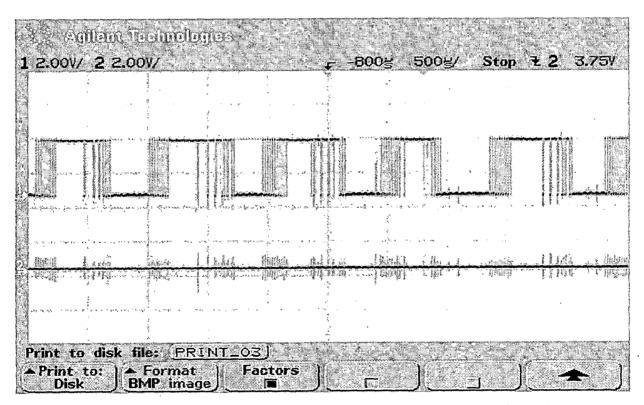

| Fig 6.6 a    | Gating Pulses when Converter Operated in Boost Mode                            | 87         |

| Fig 6.6 b    | Gating Pulses when Converter Operated in Buck Mode                             | 87         |

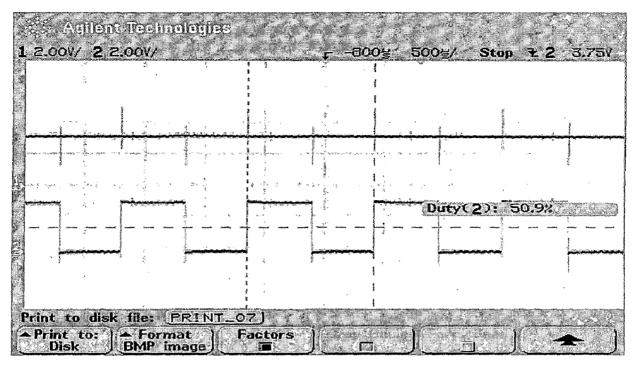

| Fig 6.7 a    | Gating Pulses when Converter Operated in Boost Mode                            | 89         |

| Fig 6.7 b    | Gating Pulses when Converter Operated in Buck Mode                             | 89         |

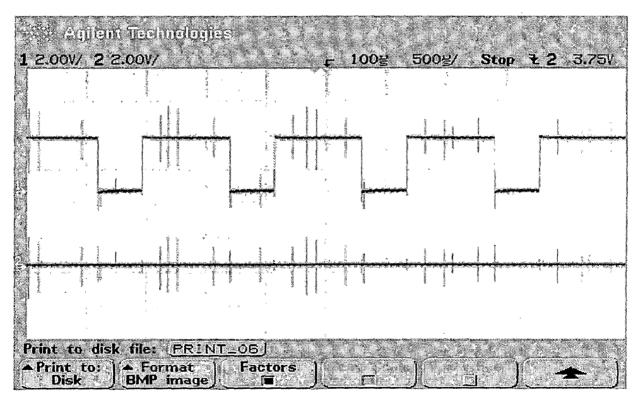

| Fig 6.8 a    | Gating Pulses when Converter Operated in Boost Mode                            | 91         |

|              |                                                                                |            |

## iii

N-

|                    | r                                                     |      |

|--------------------|-------------------------------------------------------|------|

| Fig 6.8 b          | Gating Pulses when Converter Operated in Buck Mode    | 91   |

| Fig 6.9 a          | Gating Pulses when Converter Operated in Boost Mode   | 93   |

| Fig 6.9 b          | Gating Pulses when Converter Operated in Buck Mode    | 93   |

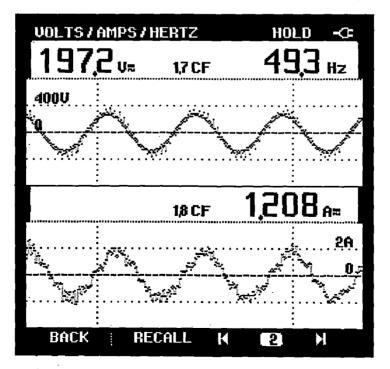

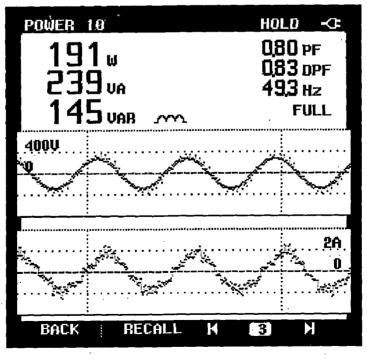

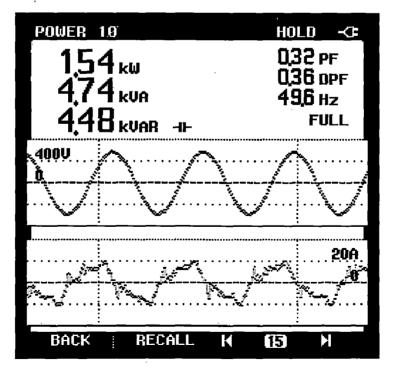

| Fig 6.10           | Converter Input Voltage & Current                     | 94   |

| Fig 6.11           | Expended View of Converter Input Current              | 95   |

| Fig 6.12           | Input Side Power Factor                               | 95   |

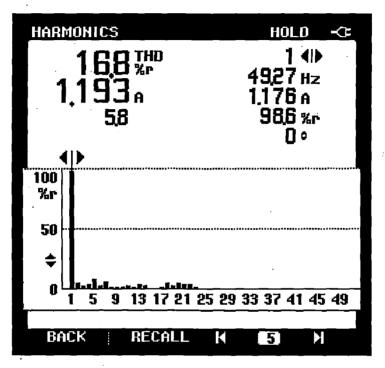

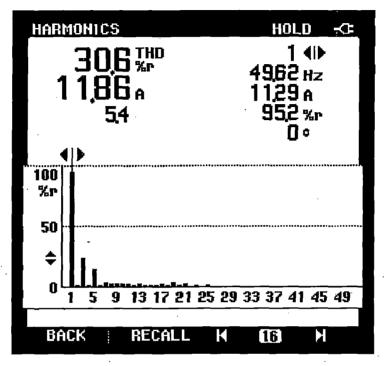

| Fig 6.13           | Harmonic Spectrum of Input Current                    | 96   |

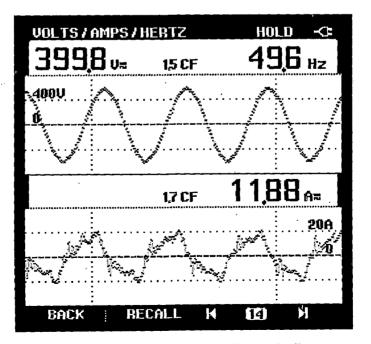

| Fig 6.14           | Converter Input Voltage & Current                     | 97   |

| Fig 6.15           | Expended View of Converter Input Current              | 98   |

| Fig 6.16           | Input Side Power Factor                               | 98   |

| Fig 6.17           | Harmonic Spectrum of Input Current                    | , 99 |

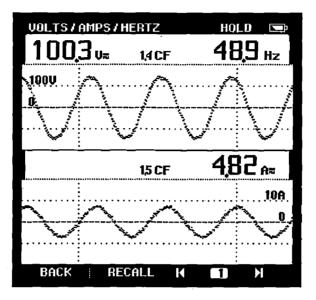

| Fig 6.18           | Input Current and Voltage                             | 100  |

| Fig 6.19           | Input Side Power Factor                               | 100  |

| Fig 6.20           | Harmonic Spectrum of Input Current                    | 101  |

| Fig 6.21 a         | +12V D.C. Supply                                      | 102  |

| Fig 6.21 b         | -12V D.C. Supply                                      | 103  |

| Fig 6.21 c         | +5V D.C. Supply                                       | 103  |

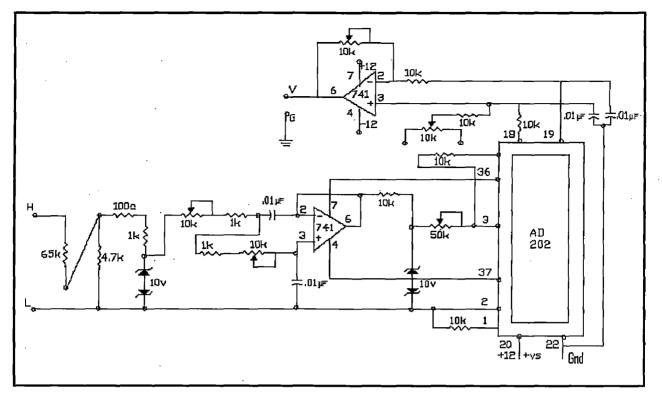

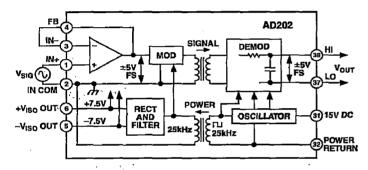

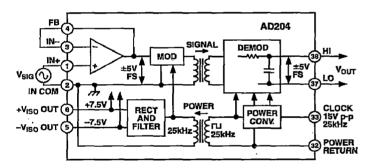

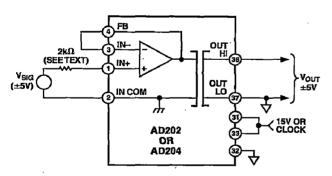

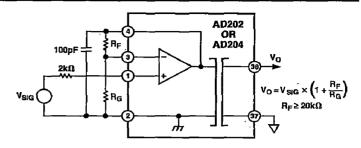

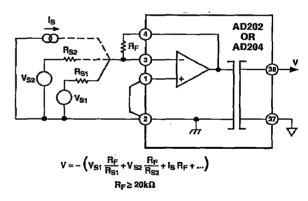

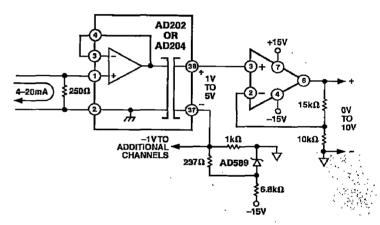

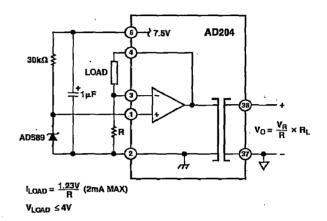

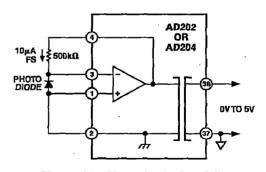

| Fig 6.22           | AD 202 Based Voltage Sensing Circuit                  | 104  |

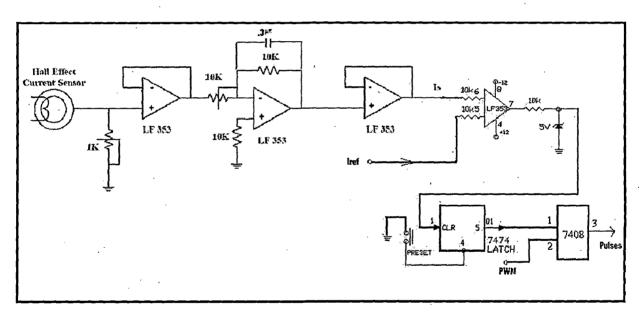

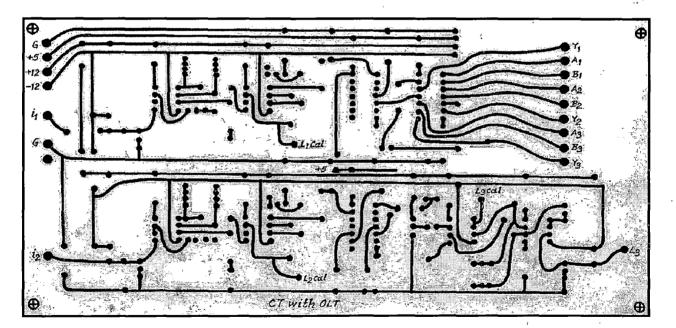

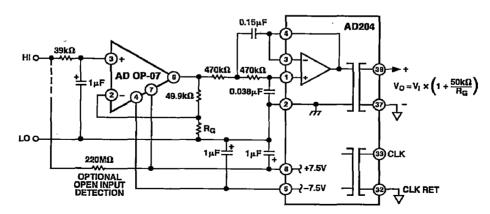

| Fig 6.23           | Current Sensing Circuit With OLT                      | 105  |

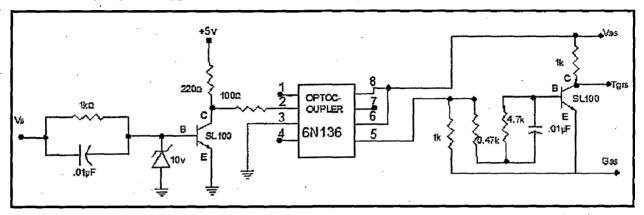

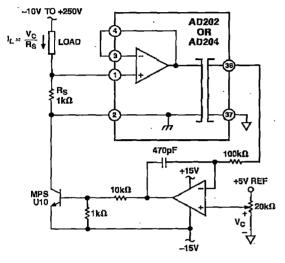

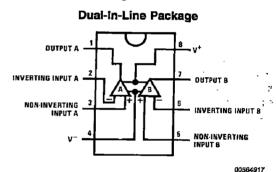

| Fig 6.24           | Gate Driver Circuit                                   | 107  |

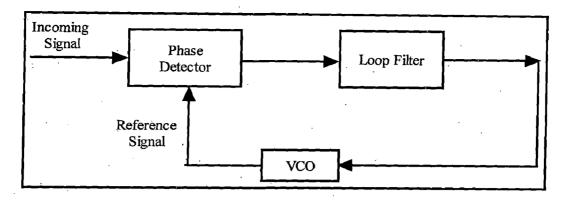

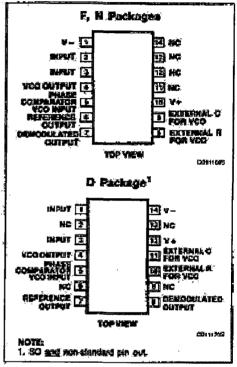

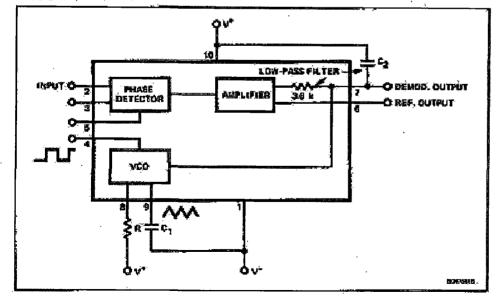

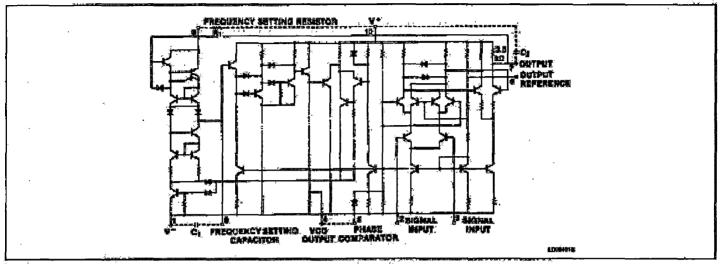

| Fig 6.25           | Block Diagram of PLL Circuit                          | 109  |

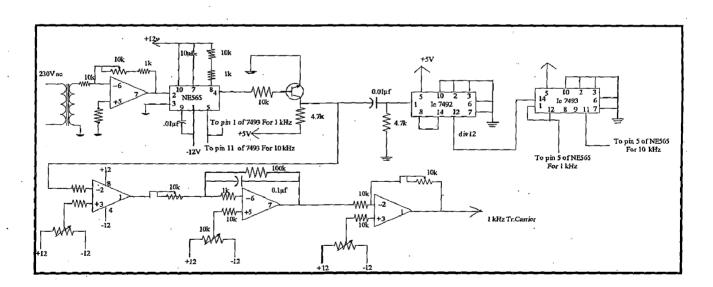

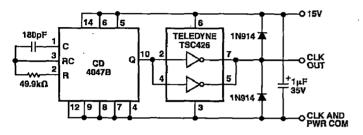

| Fig 6.26           | PLL Based Triangular Carrier Generator                | 109  |

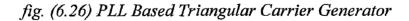

| Fig 6.27           | Generated Triangular Carrier for all the Four Modules | 110  |

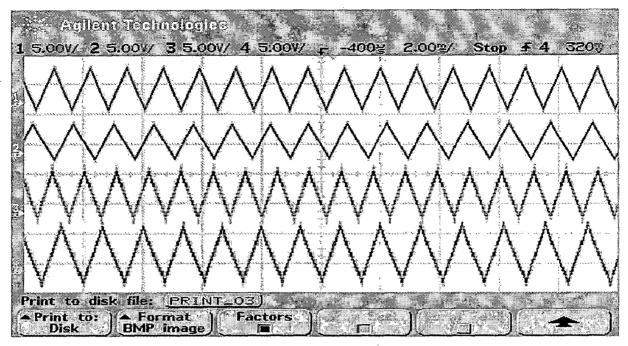

| Fig 6.28           | Synchronization With Supply Frequency for Module 1&2  | 110  |

| a<br>Fig 6.28<br>b | Synchronization With Supply Frequency for Module 3&4  | 111  |

| Fig 6.29 a         | Programmable Controller for SW1                       | 112  |

| Fig 6.29 b         | Programmable Controller for SW2                       | 113  |

| Fig 6.30           | Generated PWM Signal for All The Four Module          | 113  |

| Fig 6.31           | Mode Selection Circuit                                | 114  |

·

# List of Tables

| Table<br>No.            | Table Description                                                                                                                     | Page<br>No. |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Table 2.1               | Harmonic Spectrum of 36-Pulse Converter                                                                                               | 23          |

| Table 3.1               | Number of Pulse and Phase Shift                                                                                                       | 25          |

| Table 3.2               | Logic State of Sw1 and Sw2                                                                                                            | 37          |

| Table 4.1               | Switching State                                                                                                                       | 44          |

| Table 5.1               | Harmonic Currents Represents in % of Fundamental Component by FFT Analysis of Rectifier Input Current                                 | 51          |

| Table 5.2               | Harmonic Currents Represents in % of Fundamental<br>Component by FFT Analysis of 12-Pulse Rectifier Input<br>Current                  | 55          |

| Table 5.3               | Harmonic Currents Represents in % of Fundamental<br>Component by FFT Analysis of 12-Pulse Series Connected<br>Rectifier Input Current | 58          |

| Table 5.4               | Harmonic Currents Represents in % of Fundamental Component                                                                            | 61          |

| Table 5.5               | Harmonic Currents Represents in % of Fundamental Component                                                                            | 64          |

| Table 5.6               | Harmonic Currents Represents in % of Fundamental<br>Component                                                                         | 69          |

| Table 5.7               | Harmonic Currents Represents in % of Fundamental Component                                                                            | 73          |

| Table 5.8               | Harmonic Currents Represents in % of Fundamental Component                                                                            | 75          |

| Table 6.1               | Calculation of Transformer Input Voltage from Motor Terminal Voltage                                                                  | 78          |

| Table 6.2               | Transformer Primary and Phase Shifted Secondary<br>Winding Voltages                                                                   | 80          |

| Table 6.3               | Transformer Primary and Secondary Winding Voltages for all Phases                                                                     | 80          |

| Table 6.4               | DC Output Voltage of All Four Rectifier module                                                                                        | 83          |

| Table 6.5               | Experimental Reading of +22.5° Module                                                                                                 | 86          |

| Table 6.6               | Experimental Reading of +7.5° Module                                                                                                  | 88          |

| Table 6.7               | Experimental Reading of -7.5° Module                                                                                                  | 90          |

| Table 6.8               | Experimental Reading of -22.5° Module                                                                                                 | 92          |

| Table 6.9<br>Table 6.10 | Maximum Boost Voltages of All Modules<br>Maximum Buck Voltages of All Modules                                                         | 94<br>97    |

v

# Nomenclature

| THD    | Total Harmonic Distortion                        |

|--------|--------------------------------------------------|

| IEEE   | Institute of Electrical ad Electronics Engineers |

| MV     | Medium Voltage                                   |

| IEC    | International Electro Technical Commission       |

| PWM    | Pulse width Modulation                           |

| AC     | Alternating Current                              |

| DC     | Direct Current                                   |

| MV-ASD | Medium Voltage – Adjustable Speed Drive          |

| MWPST  | Multi-Winding Phase Shifting Transformer         |

| IC     | Integrated Chip                                  |

| KHz    | Kilo-Hertz                                       |

| IPQC   | Improved Power Quality AC-DC Converter           |

| IGBT   | Insulated Gate Bi-polar Transistor               |

| GTO    | Gate Turn Off Transistor                         |

| VFD    | Variable Frequency Drive                         |

| ASD    | Adjustable Speed Drive                           |

| VSI    | Voltage Source Inverter                          |

| CSI    | Current Source Inverter                          |

| SCR    | Silicon Controlled Rectifier                     |

| FFT    | Fast Fourier Transform                           |

| LH VFD | Low Harmonic Variable Frequency Drive            |

| SC     | Single Phase Cascade                             |

| Candidate's Declaration                             |    |

|-----------------------------------------------------|----|

| Acknowledgement                                     |    |

| Abstract                                            |    |

| List of Figures                                     | i  |

| List of Tables                                      | v  |

| Nomenclature                                        | vi |

| Chapter 1                                           | ·  |

| Introduction, Literature Survey and Overview        |    |

| 1.1 Introduction                                    | 1  |

| 1.2 Harmonics                                       | 2  |

| 1.2.1 Source of Harmonics                           | 2  |

| 1.2.2 Effects of Harmonics                          | 4  |

| 1.2.3 Power Quality Concepts Related to Harmonics   | 5  |

| 1.2.4 Harmonic standards                            | 5  |

| 1.2.4.1 IEEE 519-1981                               | 5  |

| 1.2.4.2 IEEE 519-1992                               | 6  |

| 1.2.5 Remedial Measures                             | 7  |

| 1.2.6 Emerging Solution                             | 8  |

| 1.3 Literature Survey                               | 9  |

| 1.4 Organization of Thesis                          | 13 |

| Chapter 2                                           |    |

| Multi-Pulse AC/DC Converters                        |    |

| 2.1 Introduction                                    | 15 |

| 2.2 Multi-pulse Topologies                          | 16 |

| 2.2.1 6-Pulse Converter                             | 16 |

| 2.2.2 12-Pulse Converter                            | 17 |

| 2.2.2.1 Δ-Y Isolated Transformer 12-Pulse converter | 17 |

| 2.2.2.2 Auto Transformer 12-Pulse converter         | 19 |

| 2.2.3 18-Pulse Converter                            | 20 |

| 2.2.4 24-Pulse Converter                            | 20 |

| 2.2.4.1 24-Pulse Auto Transformer Converter         | 21 |

| 2.2.4.2 24-Pulse Isolated Transformer Converter     | 21   |

|-----------------------------------------------------|------|

| 2.2.5 Improved 12-Pulse Converter                   | . 22 |

| Chapter 3                                           |      |

| 24 Pulse AC/DC Buck-Boost Converter                 | • •  |

| 3.1 Introduction                                    | 24   |

| 3.2 Design of 24-Pulse Converter                    | . 25 |

| 3.2.1 Multi-Winding Transformer                     | 25   |

| 3.2.1.1 Connection for +22.5° Phase Shifted Winding | 26   |

| 3.2.1.2 Connection for +7.5° Phase Shifted Winding  | 27   |

| 3.2.1.3 Connection for -7.5° Phase Shifted Winding  | 28   |

| 3.2.1.4 Connection for Getting -22.5° Phase Shift   | 28   |

| 3.2.2 Rectifier Modules                             | . 29 |

| 3.2.3 Chopper Circuit                               | 30   |

| 3.2.3.1 Buck Chopper                                | 31   |

| 3.2.3.2 Boost Chopper                               | 33   |

| 3.2.3.3 Filter Circuit                              | 35   |

| 3.2.3.4 Designing Principle of Inductor             | 35   |

| 3.2.4 Control Circuit                               | 37   |

| 3.2.4.1 Error estimation Circuit                    | 37   |

| 3.2.4.2 Pulse Generation Circuit                    | 37   |

| Chapter 4                                           |      |

| Simulation Study                                    |      |

| 4.1 Introduction                                    | 39   |

| 4.2 24-Pulses Transformer                           | 41   |

| 4.3 Rectifier Modules                               | 44   |

| 4.4 Buck-Boost Converter                            | 44   |

| 4.4.1 PWM Pulse Generator                           | 45   |

| 4.4.2 Mode Selection Block                          | 47   |

| Chapter 5                                           |      |

| Simulation Results                                  |      |

| 5.1 Introduction                                    | 48   |

| 5.2 6-Pulse Converter                               | 48   |

| 5.3 12-Pulse Converter                              | 52   |

· · ·

| 5.3.1 12-Pulse Parallel Converter              | 5   |

|------------------------------------------------|-----|

| 5.3.2 12-Pulse Series Converter                | 5   |

| 5.4 24-Pulses Converter                        | 5   |

| 5.4.1 Simulation Results of Buck-Boost Chopper | 5   |

| 5.4.1.1 Chopper Operating in Boost Mode        | 5   |

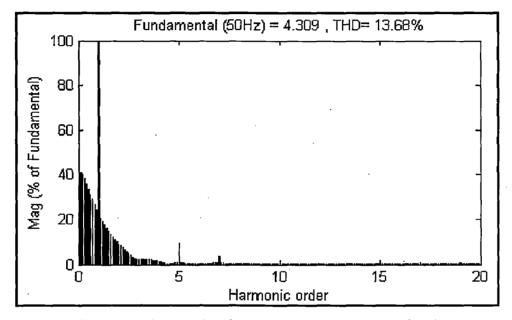

| 5.4.1.2 THD of Input Line Current              | . 6 |

| 5.4.1.3 Chopper Operating in Buck Mode         | 6   |

| 5.4.1.4 THD of Input Line Current              | 6   |

| 5.5 24-Pulses Unbalance Converter              | . 6 |

| 5.5.1 Unbalance Buck-Boost Chopper             | 6   |

| 5.5.1.1 Chopper Operating in Boost Mode        | . 6 |

| 5.5.1.2 THD of Input Line Current              | 6   |

| 5.5.1.3 Chopper Operating in Buck Mode         | 7   |

| 5.5.1.4 THD of Input Line Current              | 7   |

| 5.6 Uncontrolled 24-Pulse Converter            | 7   |

| 5.6.1 THD of Input Line Current                | 7   |

| Chapter 6                                      |     |

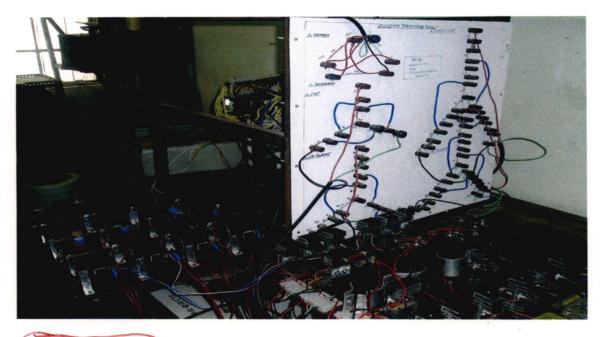

| System Development and Experimentation         |     |

| 6.1 Introduction                               | . 7 |

| 6.2 Power Circuit                              | 7   |

| 6.2.1 Selection of Transformer Voltage Rating  | 7   |

| 6.2.1.1 Analysis of Input Line Currents        | 7   |

| 6.2.1.2 Testing of Secondaries Voltages        | 8   |

| 6.2.1.3 Recorded Phase-Shifted Waveforms       | . 8 |

| 6.2.2 3-Phase Rectifier Module                 | 8   |

| 6.2.3 Buck-Boost Chopper                       | 8   |

| 6.2.3.1 Closed Loop Operation                  | 8   |

| 6.2.3.2 Experimental Result of +22.5° Module   | . 8 |

| 6.2.3.3 Experimental Result of +7.5° Module    | 8   |

| 6.2.3.4 Experimental Result of -7.5° Module    | 9   |

| 6.2.3.5 Experimental Result of -22.5° Module   | 9   |

| 6.2.4 Boost Operation of All Modules           | 9   |

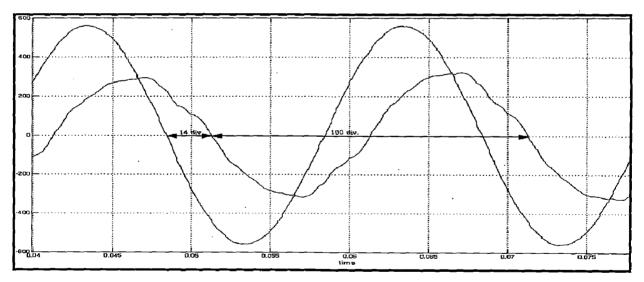

| 6.2.4.1 Input Current in Boost Mode            | 9   |

ē

| 6.2.4.2 Input Power Factor             | 95   |

|----------------------------------------|------|

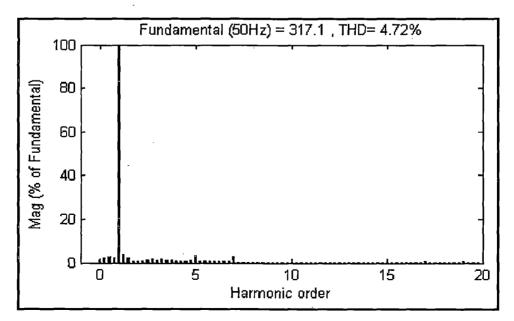

| 6.2.4.3 THD of Input Current           | 96   |

| 6.2.5 Buck Operation of All Modules    | . 97 |

| 6.2.5.1 Input Current in Buck Mode     | 97   |

| 6.2.5.2 Input Power Factor             | 98   |

| 6.2.5.3 THD of Input Current           | 99   |

| 6.2.6 Uncontrolled Operation           | 100  |

| 6.2.6.1 Input Power Factor             | 100  |

| 6.2.6.2 THD of Input Current           | 101  |

| 6.3 Control Circuits                   | 102  |

| 6.3.1 Power Supply Circuits            | 102  |

| 6.3.2 Voltage Sensing Circuit          | 103  |

| 6.3.2.1 Operating Principal            | 104  |

| 6.3.3 Current Sensing Circuit with OLT | 105  |

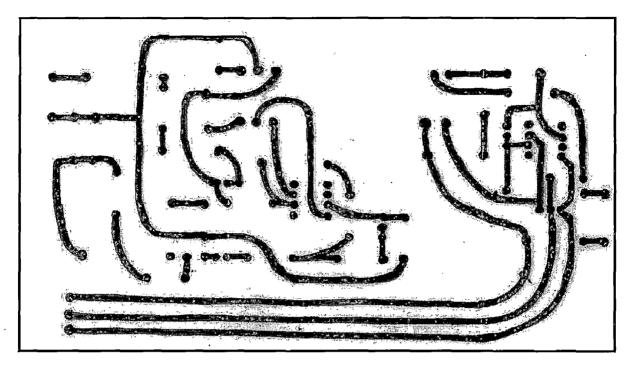

| 6.3.4 Gate Driver Circuit              | 107  |

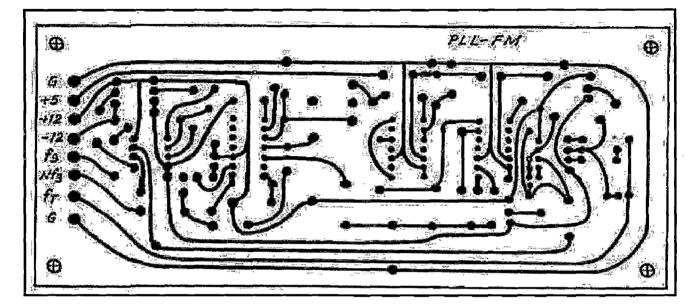

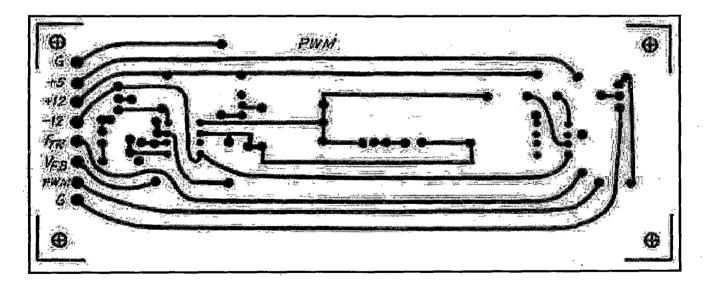

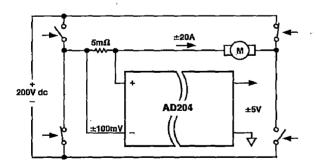

| 6.3.5 Triangular Carrier Generator     | 108  |

| 6.3.5.1 Operating Principal            | 108  |

| 6.3.5.2 Circuit Diagram                | 109  |

| 6.3.6 Programmable Controller Circuit  | 112  |

| 6.3.7 Mode Selection Circuit           | 114  |

| Chapter 7                              |      |

| Conclusion and Future Scope            | 115  |

| References                             | 117  |

| Appendix - A Simulation Parameter      |      |

| Appendix - B PCB Layouts               |      |

| Appendix - C Sample of Data Sheets     |      |

|                                        |      |

Appendix - D List of used IC's, Power Switches, Diode etc.

.

### Introduction, Literature Survey and Overview

Chapter 1

#### 1.1 Introduction:

THREE-PHASE ac-dc conversion of electric power is widely employed in adjustable-speeds drive (ASDs), uninterruptible power supplies (UPSs), HVDC systems, and utility interfaces with nonconventional energy sources such as solar photovoltaic systems (PVs), etc., battery energy storage systems (BESSs), in process technology such as electroplating, welding units, etc., battery charging for electric vehicles, and power supplies for telecommunication systems [1] traditionally, ac-dc converters, which are also known as rectifiers, are developed using diodes and thyristors to provide controlled and uncontrolled unidirectional and bi-directional dc power. They have the problems of poor power quality in terms of injected current harmonics, resultant voltage distortion and poor power factor at input ac mains and slowly varying rippled dc output at load end, low efficiency, and large size of ac and dc filters. In view of their increased applications, a new breed of rectifiers has been developed using new solid-state self-commutating devices such as MOSFETs, insulated gate bipolar transistors (IGBTs).

In recent years, the harmonics in the power system are serious due to the widely applications of the electronic equipments in which the AC/DC converter are usually used. Therefore, it is an important topic to reduce harmonic components in the AC/DC converter [2]. The harmonic problems can be solved by using the active filters which are usually operated at high switching frequency and are not suitable for high power applications. The power factor and harmonic components of the utility input line current can be improved by the poly-pulse AC/DC converter.

In high-power applications, ac-dc converters based on the concept of multi-pulse, namely, 12, 18, 24, 30, 36, 48 pulses are used to reduce the harmonics in ac supply currents as well as the power factor of the input supply. These are named as multi-pulse converters [1]. They use either a diode bridge or thyristor bridge and a special arrangement of magnetic coupling through transformers and tapped inductors. One of the important reasons for such an extensive development in ac-dc converters is due to self-commutating devices. At low power rating, MOSFETs are used with unsurpassed performance because of their high switching rate with negligible losses. At medium power rating, an IGBT is considered an ideal device for such converters

-1-

with PWM technology. At a higher power rating, a GTO is normally used with selfcommutating and reverse voltage-blocking capabilities at only a few kilohertz switching frequency.

**1.2** <u>Harmonics</u>: Variable frequency drives all generate line currents at multiples of the AC line frequency-harmonics of 50 Hz. In three-phase drives they are generally a series of currents at harmonics 5, 7, 11, 13, 17, 19 and higher odd multiples of the 50 Hz fundamental frequency. The series is given by  $6*n\pm1$  where n takes on all integer values. The magnitude of these harmonics depends on several factors.

#### 1.2.1 Source of Harmonics:

These sources are briefly classified in to two as current-source nonlinear loads and voltage-source nonlinear loads [3].

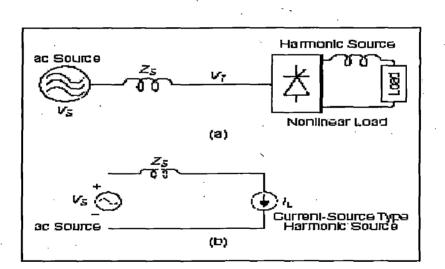

Thyristor converters are a common and typical source of harmonic currents. Thyristor rectifier with a sufficient dc inductance produces a dc current. This is shown in figure (1.1a) below.

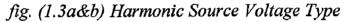

#### fig. (1.1a&b) Harmonic Source Current Type

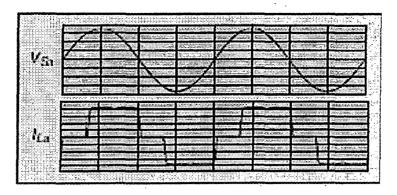

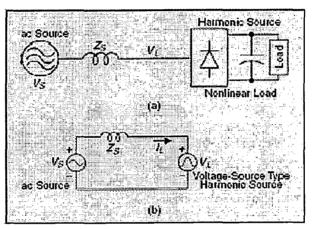

The current waveform distortion i.e., the generation of harmonics results from the switching operation. A typical waveform is shown in figure (1.2). Because the harmonic current contents and characteristics are less dependent on the ac-side, this nonlinear load behaves like a current source non-linear load and represented as current source as shown in figure (1.1b). Therefore it is called a current source. Similarly, diode rectifiers with a sufficient dc inductance, a highly inductive load with silicon-controlled rectifier (SCR) ac power control, etc., are current-source nonlinear loads.

- 2 -

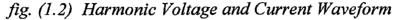

Another common type of harmonic source is a diode rectifier with smoothing dc capacitors as shown in figure (1.3a).

Current and voltage waveforms are shown in figure (1.4). Although the current is highly distorted, its harmonic amplitude is greatly affected by the ac side impedance and source voltage unbalance, whereas the rectifier voltage, such as the voltage at the rectifier input terminal are less dependent on ac side impedance. Therefore, the diode rectifiers behave like a voltage source, rather than a current source. Figure 3(b) shows the equivalent circuit of the diode rectifier system where the diode rectifier behaves like a voltage source, rather than a current source.

fig. (1.4) Harmonic Voltage and Current Waveform

وريد به ترجع

- The current source SCR drives, generally used in the higher ratings, have harmonic amplitudes which are equal to the reciprocal of the harmonic order. Thus, 20% of 5th, 14% of 7th, 9% of 11th and so on. Total current distortion can reach about 30%, PWM or "diode front end" drives can have very high 5<sup>th</sup> and 7<sup>th</sup> harmonic distortion, reaching levels of 60% and 30% respectively, but their higher frequency harmonics are much lower than those for the SCR drives.

- A second factor is the source reactance. In general, increasing the reactance on the load side of a distribution transformer will have a favorable effect on harmonic amplitudes.

#### 1.2.2 Effects of Harmonics: [17]

There are several common problem areas caused by harmonics:-

- 1) Problems caused by harmonic voltages:

- Voltage distortion in induction motors

- Zero-crossing noise

2) Problems caused by harmonic currents

- Overloading of neutrals

- Overheating of transformers

- Nuisance tripping of circuit breakers

- Over-stressing of power factor correction capacitors

- Skin effect

- These harmonic currents flow into the utility supply lines. Since the supply is generally characterized by transformer and distribution circuit reactance, the harmonic currents will cause harmonic voltage drops and consequent distortion of the line voltage. The results may be interference to electric clocks, data communications, telephone circuits, digital controls and a host of other effects in connected customer facilities.

- They can also overheat transformers and supply apparatus.

Finally, harmonics can flow into power factor capacitors and actually be magnified by resonances with the supply reactance. The result is blown fuses or failure of capacitor.

#### 1.2.3 Power Quality Concepts Related to Harmonics:

The impact of harmonics on power system components such as transformers and relays, and on consumers such as transformers, induction machines, and electronic devices can be described as a function of the below listed parameters. One most know how to calculate the harmonics in the system. The system voltages and currents can be shown in form of equations.

Harmonic Voltage is given by:

$$v(t) = V_o + \sqrt{2} \sum_{k=1,2,3,\dots}^{k \max} V_{krms} \cos(kwt + \alpha_k)$$

Harmonic Current is given by:

$$i(t) = i_o + \sqrt{2} \sum_{k=1,2,3,...}^{k \max} I_{krms} \cos(kwt + \alpha_k)$$

Total harmonic distortion of voltage is given by:

$$THDv = \frac{\sqrt{\sum_{k=2}^{k \max} V_h^2}}{V_1}$$

Total harmonic distortion of current is given by:

$$\text{THD}_{I} = \frac{\sqrt{\sum_{k=2}^{k \max} \text{Ih}^2}}{\text{I}_{1}}$$

#### 1.2.4 Harmonic standards: [17]

**1.2.4.1 IEEE 519-1981**: A task force of industry engineers formed IEEE 519-1981, IEEE Guide for Harmonic Control and Reactive Compensation of Static Power Converters. This specification defined the allowable levels of voltage distortion on distribution feeders and served as a procurement document for new equipment. Unfortunately, the voltage distortion is very much a function of the short circuit capability of the source, and the filters used to obtain compliance with the specification had to be designed for each application. Still, this specification did much to get voltage distortion under control and it served as a valuable standard for mitigation of harmonic effects.

5 -

**1.2.4.2 IEEE 519-1992:** The problem arose in the implementation of IEEE 519-1981 that a number of customers on a distribution feeder could individually meet the distortion but, in the aggregate, exceed allowable limits. The specification was then revised to become IEEE 519-1992, and places severe restrictions on allowable levels of current harmonics from variable frequency drives. Filtering is not usually practical, and new technologies must be employed. It is suggested that conformance to IEEE 519-1992 should be a part of any new drive procurement document unless the drive is a small part of a large plant load. IEEE Recommended Practices and Requirements for Harmonic Control in Electrical Power Systems, a document which now places limits on harmonic currents which a customer is allowed to source into the utility lines. The effects of this new standard are to introduce a whole new ball game for harmonic control. IEEE 519-1992 allows a graduated series of harmonic current levels depending on the source short circuit ratio.

Some other standards are:-

- EN 50 006," The limitation of disturbances in electricity supply networks caused by domestic and similar appliances equipped with electronic devices," European standard prepared by CENELEC.

- IEC Norm 555-3, prepared by the International Electrical commission.

- West German Standards VDE 0838 for household appliances, VDE 0160 for converters, and VDE 0712 for fluorescent lamp ballasts.

- 6 -

**1.2.5** <u>Remedial Measures</u>: some basic techniques for removal of harmonics are as follows:-

- Install input/output filters to reduce harmonic distortion and improve power factor. This option was initially considered for existing wells, but the maintenance of each filter, coupled with the additional limitation imposed by the filters to the VFD power output and the substantial investment to install them in all wells, proved this a non-viable solution.

- Install twelve pulse VFDs. This topology was not a viable solution either, since while offering an input harmonic distortion lower than the Six Pulse CSI VFD, it had the same harmonics problem in the output.

- Install standard single level PWM Drives. This again was not implemented because even though PWM drives have a harmonic distortion lower than Six Pulse CSI VFDs, they have shown to cause detrimental effects to the ESP motor and cable insulation. These problems are associated with the rapid switching and dv/dt stresses.

- Utilize existing alternatives of Medium Voltage VFDs with low harmonic distortion (input/output) and without the rapid switching and dv/dt stress problems.

- <sup>2</sup> ... ir.

#### 1.2.6 Emerging Solution:

Recent trained is to use higher pulse number drives. Drives are now manufactured with 24-pulse rectification at 2400V and 30-pulse rectification at 4160V. Medium-Voltage Adjustable Speed drives used modularity concept in which the single-phase cascaded voltage-source inverter that uses series connection of insulated gate bipolar transistor (IGBT) modules with isolated dc buses. The concept of using cascaded inverters is further extended to a new modular motor-modular inverter system where the motor winding connections are reconnected into several three-phase groups, either six-lead or 12-lead connection according to the voltage level, each powered by a standard IGBT inverter module [12,20]. These types of drives are known as multi-pulse drives. THD of these types of drives meets the IEEE-519 and power factor of input supply also gets improve. These drives uses phase shifted multi winding transformer which may have unbalancing in secondaries winding voltages, in this dissertation a concept to nullify the winding unbalance effect employing buck-boost converter is used along with rectifier system to maintain constant DC link voltage.

The developed converter is also suitable for that system which is powered by week link where voltage fluctuation is around +/-20%. The developed converter maintains constant DC link voltage even in case supply voltage varies +/-30%.

#### 1.3 Literature Survey:

Multi-Pulse AC/DC converters are gaining popularity in many industries such as aerospace, petroleum, marine, air conditioning etc. Many authors have discussed about multi-pulse converters their uses advantages and disadvantages. The significant contributions in this field are discussed in this section.

Bhim Singh, Brij N. Singh, Ambrish Chandra, Kamal Al-Haddad, Ashish Pandey and Dwarka P. Kothari, Y Shakweh, P Aufleger [1],[26] presents an exhaustive review of three-phase improved power quality ac-dc converters (IPQCs) configurations, control strategies, selection of components, comparative factors, recent trends, their suitability, and selection for specific applications. The main aim of this paper is presenting a state of the art on the IPQC technology of three-phase ac-dc converters.

Richard H. Osman [2] compares the performance characteristics of five commonly used types of medium voltage motor drives. All of them have a DC link. Two of the drives are voltage fed types, the neutral point clamped inverter using GTO.s or IGBT.s, and the series-cell inverter using IGBT.s. The other three are current-fed designs, the filter-commutated drive using series thyristors in the inverter, the current-fed inverter with series GTO.s and auxiliary capacitors, and the load commutated inverter. Input characteristics of power factor and harmonics will be compared particularly with regard to IEEE-519 compliance. Output characteristics of waveform quality and common mode voltage also studied.

In this paper Fang Zheng Peng [3] describes the applications of active power filters and different topologies. How these filter helps to improve harmonic spectrum of input line current are studied. Various developed active filter are compared and tabulated in the proper manner. Application issues of these active power filters have been discussed elaborately

J.Ghaisari and A.Bakhshai [4] a PWM switching technique, which can be implemented on a multi-pulse converter system. It is also verified in this paper that proposed PWM switching technique preserves advantage of multi-pulse converter. Voltage control through PWM is linear, fast and straightforward. Thus PWM mode of operation is more useful in transient state.

D. Rendusara, K.J. Slater ,B.S. Lee, P. Enjeti [5] and others describes auto transformer connected 12-pulse and 24-pulse rectifier schemes as cost effective

- 9 -

methods for reducing line current harmonics in PWM drive systems. Design considerations for these rectifiers are also explained and performances of 12/24 pulse rectifier systems are also discussed.

Peter W. Hammond [6] describes a new approach to medium voltage variable frequency static AC drives which offers improvements in power quality and harmonic current injection in the power lines. The power factor of this new type of drive is high, motor voltage, current voltage waveforms are improved and also that torque pulsations are reduced.

Tsomg-Juu Liang, Jim-Fuh Chen, Ching- Lung Chu,Kuen-Jyh Chen [7] and Toshihko Tanaka, Naotsugu Koshio, Hirofumi Akagi [15] given idea about the unbalanced current in the 12-pulse phase control AC/DC converters in this paper. The 12-pulse star-delta type AC/DC converter will keep a balanced voltage with 30° phase shifted at the low coupling coefficient condition. But an unbalanced current will be obtained in the 12-pulse autotransformer phase shift AC/DC converter at the low coupling coefficient condition. The theoretical phasor analysis of the unbalanced current was presented and a feedback controller was designed to overcome this problem.

Sewan Choi, Bang Sup Lee and Prasad N. Enjeti [8] [19] proposes two new passive 24-pulse diode rectifier systems for utility interface of pulse-width modulated (PWM) ac motor drives. The first approach employs an extended delta transformer arrangement, which results in near equal leakage inductance in series with each diode rectifier bridge. This promotes equal current sharing and improved performance. The proposed system exhibits clean power characteristics with fifth, seventh, eleventh, thirteenth, seventeenth, and nineteenth harmonics eliminated from the utility line currents. The second scheme is a reduced volt-ampere approach employing autotransformers to obtain 24-pulse operation. Detailed analysis and simulations verify the proposed concept, and experimental results from a 208-V 10-kVA rectifier system are provided.

In this paper Y.H. Liu, J. Arrillaga and N.R. Watson [9] proposed multilevel voltage-sourced converter is based on the reinjection of DC voltage pulses at six times the fundamental frequency. Substantial reduction in the capacitor size at the cost of extra components required is achived. It is shown that the resulting voltage and current

harmonics are well within the present standards without the assistance of pulse width modulation and theoretical waveforms are verified by computer simulation.

Bang Sup Lee, Prasad N. Enjeti and Ira J. Pitel [10] propose a 24-pulse diode rectifier system suitable for utility interface of PWM ac motor drive systems with low kVA components. Functioning of autotransformer and two zero sequence blocking transformers (ZSBT) in the dc link and a tapped interphase reactor is studied. Results produce near equal leakage inductance in series with each diode rectifier bridge ensuring equal current sharing and performance improvements. How the conventional 12-pulse converter can be converted in to 24-pulse operation from an input current stand point with use of specially tapped interphase reactor and two additional diodes is also discussed.

Ekrem Cengelci, Prasad N. Enjeti and JamesW. Gray [11],[24] discussed the modular motor-modular inverter concept for a medium-voltage adjustable-speed drive (MV-ASD) system. It is shown that standard MV motor winding connections can be reconnected into several three-phase groups, each powered by a separate three-phase pulse width modulation inverter, resulting in a high-performance MV-ASD system.

R. Teodorescu, F. Blaabjerg, J.K. Pedersen, E.Cengelci and P. Enjeti [12] discussed the Single-phase Cascaded (SC) VSI, triphase cascaded (TC) VSI that uses three IGBT triphase inverter modules along with an output transformer to obtain a 3 p.u. multilevel output voltage. The system yields a high-quality multistep voltage with up to 4 levels and low dv/dt, balanced operation of the inverter modules that supply each a third of the motor kVA. A staggered space vector modulation (SSVM) technique applicable to triphase cascaded VSI topologies is also demonstrated.

Mohamed C. Ghanem, Kamal Al-Haddad and Gilles Roy [13] presents a detailed theoretical analysis and experimental results of a novel means of obtaining sinusoidal input current and unity power factor (UPF) via a cascade buck-boost converter. Gating signals are generated by comparison of stored value in EPROM and instantaneous value of output voltage and current. Complete theoretical analysis, simulation results and experimental data on a 500 W converter are presented.

Vanice Scaini, P. Eng. [14] describe the availability of larger power switching devices that brought the development of larger power electronic circuits in recent years. One such circuit which is dc to dc converter, known as a DC chopper is explained and the benefits of DC choppers are also explained.

$(\bar{Q})$

In this paper Someshwar C. Gupta [16] has given an idea of phase-locked loop (PLL). Apart from discussing the various analyses, design it is also discussed how this PLL circuit helps in synchronization.

Keith H. Sucker and Rafael A. Lastra, Carlos A.Loza and Albert Roc [17][18] discussed the various harmonic issues in case of variable frequency drives. Cause and effect of these harmonics are also studied. Author also suggested the remedial measures for these harmonics. Authors also suggested an alternative to conventional VFD technologies and the test of this drive is the subject of this paper. This Medium Voltage Low Harmonic Variable Frequency Drive (LH VFD) offers improvements in power factor, system efficiency and a reduction in harmonics effects as compared to traditional approaches.

Remus Teodorescu, Frede Blaabjerg, John. K. Pedersen, Ekrem Cengelci and Prasad N. Enjeti [20] describe the modularity concept applied to medium-voltage adjustable speed drives. This concept is applied to three-phase cascaded voltagesource inverter along with an output transformer to obtain a 3-pu multilevel output voltage. The system yields in high-quality multi step voltage up to four levels having low dv/dt. Both computer simulation results and experimental results are also demonstrated.

Sewan Choi, Prasad N. Enjeti and Ira J. Pitel [21] describes the polyphase transformer arrangements with reduced KVA capacities for harmonic current reduction in high power diode rectifier-type utility interface system, based on the concept of an autotransformer. The advantages of these systems are also explained.

A. Sapin, P. Allenbach, J.J. Simond [22] describes the modeling of multiwinding transformers. Two application examples of multi-winding phase shifting transformers (18 and 24 pulse) are also described in this paper.

G. Gonzalez, Microwave Transistor Amplifiers: Analysis and Design [23] describe the design consideration of inductor. Design procedure for air core inductor and toroidal core are also studied.

Leon M. Tolbert and Fang Z. Peng [25] describe two different multilevel topologies which can be used to make a converter for electric drives. Simulation and experimental results are also discussed and verified.

Richard Dickinson & Shaun Milano [27] describes the current sensing techniques using Hall Effect type sensors and also explains the advantages and disadvantages of these type of current sensor circuit.

#### 1.4 Organization of Thesis:

#### **Chapter 1: Introduction, Literature Survey and Overview**

This gives brief introduction about the causes of harmonic, how does it affect the system, different disadvantages of harmonics. As it is need to reduce the harmonics due to different disadvantages traditional solutions are discussed to become familiar with the basic principles of compensation. The emerging topologies to improve the performance are discussed. Different harmonic standards that are dealt with in common are listed following with literature study. The objective of the dissertation work presented here is also indicated.

#### Chapter2: Multi-Pulse AC/DC Converters

Basic introduction of Multi-Pulse AC/DC converter is given in this chapter. Various topologies of Multi-Pulse AC/DC converter are also given along with their circuit diagram. Harmonic spectrum of various topologies is also discussed in this chapter.

#### Chapter 3: 24-Pulse AC/DC Buck-Boost Converter

The drive system where we use 24-Pulse converter is discussed in this chapter. Winding configuration of 24- pulse transformer, 3-phase diode rectifier along with Buck-Boost chopper circuit is also discussed. How to generate firing pulses in Buck and Boost mode is studied along with the mode selection logic.

#### **Chapter 4: Simulation Study**

Simulation models are developed using MATLAB Simulink. A 24-Pulse AC/DC Buck-Boost converter is developed. Error estimation block for close loop operation, pulse generation block, buck-boost chopper circuit, phase shifted transformer are simulated in this chapter and detail design of simulation is given in this chapter.

#### **Chapter 5: Simulation Results**

In this chapter simulation result of 6-Pulse, 12-Pulse and 24-Pulse are discussed. Voltage and Current wave form of input current of 6-Pulse, 12-Pulse are shown. Harmonic spectrum using FFT analysis is presented and various harmonic components are tabulated. 24-pulse Buck-Boost converter output voltage waveform for buck and boost mode is presented. Harmonic spectrum of converter input line current using FFT analysis is also presented and various harmonic components are tabulated. Performance of converter with change in load is also studied.

#### **Chapter 6: System Development and Experimentation**

The second part of the thesis is the experimental validation of simulated system. The hardware circuits which are developed are presented and recorded results are displayed. The fabrication of control circuit and power circuit is briefly discussed. The organization of control circuit fabrication is briefly presented. Closed loop results which are recorded are presented and FFT analysis is carried out. Tabulation of harmonic contents is done for different topologies to clearly specify the improvement achieved which is proved by using simulation model.

#### Chapter 7: Conclusion and Future Scope

Conclusion is drawn from the simulation and experimental work done, and presented in this chapter. Future scope for improvements in the same field to improve the performance and to handle the problems associated are briefly studied and presented to carry out in upcoming projects.

#### 2.1 <u>Introduction</u>:

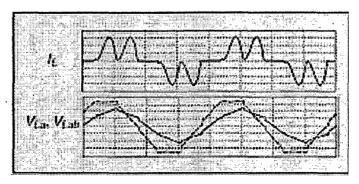

In Multi-pulse converter, quasi-square output voltage of N element six-pulse converter are combine through an electromagnetic interface electro-magnetically to produce a nearly sinusoidal output waveform [4,26]. The basic structure is shown in figure (2.1).

#### fig. (2.1) Basic Structure

The reduction in output distortion that is achieved by increasing the number of six-pulse unit, N, comes about through harmonics cancellation. Each unit produces a quasi-square-wave time shifted from that required for the final output. The phase-shift transformers align the fundamental component in the output voltage of multi-pulse converter. This provides the best utilization of the DC side voltage among the other power converter. The frequency of harmonics in the output of a 6N-pulse converter are ( $6N*k\pm1$ ) f, where f is the fundamental frequency, N is the number of converter modules, and k=1, 2, 3, an integer. The Multi-Pulse configuration consists of several six-pulse converter units in either series or parallel on the DC side and phase shift in each unit is obtained by the special type of phase shifting transformer.

Pulse numbers as high as 48 are used in industrial drives system; however pulse numbers higher than 24 requires complicated and costly transformer and circuitry. But these are gaining popularity in market due to their additional features and the latest techniques in construction of multi-winding phase shifting transformers [5,6] have reduced their constructional complexity and cost is reduced significantly as well. The recent developments in auto-transformers allow us to make multi-winding phase shifting transformers (MW-PST's) of higher voltage and current ratings on same three phase cores. These transformers are used to feed rectifier modules which may be single phase or three phase and other buck boost switch arrangements. The PWM inverter modules are used in the rectified outputs and the whole circuit is used as a motor drive system. The harmonics are reduced as numbers of pulses are increased and the input current is nearly sinusoidal. These multi pulse converters are most popularly used in marine, aerospace and many other industrial applications where the size and power ratings are major considerations.

#### 2.2 Multi-pulse Topologies:

According to number of pulses multi-pulse converter can be characterized in to following :

- a) 6-Pulse Converter

- b) 12-Pulse Converter

- c) 18-Pulse converter

- d) 24-Pulse Converter

- e) Improve 12-Pulse converter

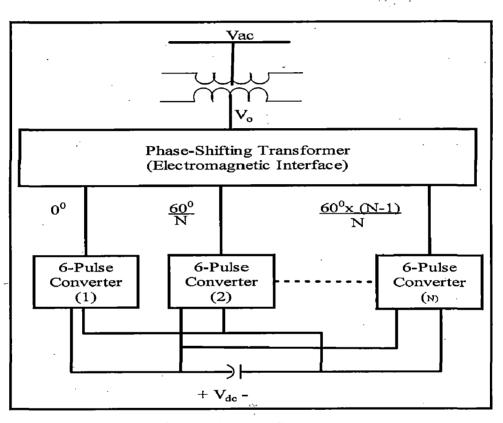

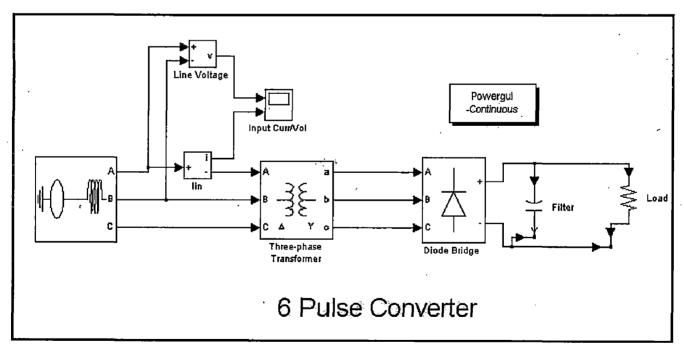

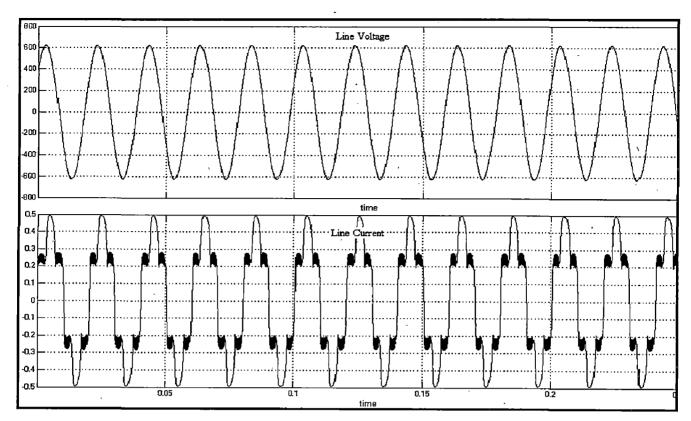

#### 2.2.1 6-Pulse Converter:

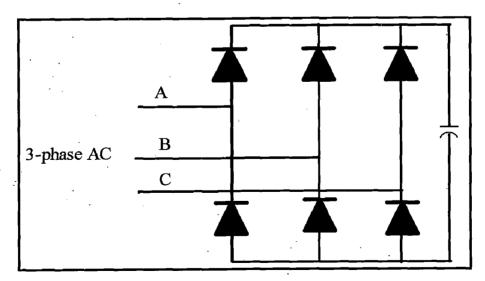

This is the simplest converter as shown in figure 2.2. A diode bridge rectifier unit fed from the delta-star transformer. This is the cheapest converter. It has the poorest harmonic performance. The input current spectrum has 20% fifth and 12% seventh harmonics. The rapid commutation rate results in significant harmonic components out to the 35<sup>th</sup>.

fig (2.2) 6-Pulse Rectifier

#### 2.2.2 <u>12-Pulse Converter</u> :[7]

12-Pulse converter is divided into following two category on the basis of transformer used

a)  $\Delta$ -Y Isolated Transformer 12-Pulse converter

b) Auto Transformer 12-Pulse converter

#### 2.2.2.1 Δ-Y Isolated Transformer 12-Pulse converter :

The conventional  $\Delta$ -Y Isolated Transformer 12-Pulse converter is shown in figure (2.3). The 12-pulse converter requires two six-pulse converters connected through isolation transformers (fig. 2.3).

#### fig. 2.3 △-Y Isolated Transformer 12-Pulse converter

An interphase transformer (IPT) is required to ensure independent operation of the two three-phase diode bridge rectifiers. The operation of the conventional 12pulse converter results in the absence of the fifth and seventh harmonics in the input utility line current. However, the total harmonic distortion (THD) of input line currents are still high and do not qualify as clean power [8]. The power factor and

1 Present Bartister

न निरोधसंग्रह

harmonic components of the utility input line current can be improved by shifting the input voltages 30° in the  $\Delta$ -Y connected AC/DC converter as well as in the autotransformer phase-shifted AC/DC converter. But the output voltages of these AC/DC converters are not controllable. The output voltage of the 12-pulse AC/DC converter can be controlled by using the thyristors instead of diodes. The 12-pulse phase control AC/DC converters with  $\Delta$  -Y isolated transformer is shown in figure (2.4) [7]. A very important point is that although only half of the harmonic spectrum is present in the 12-pulse case compared to the 6 pulse, those components of the 12 pulse spectrum are about equal to the 6-pulse values. Due to the rapid commutation rates, the high order harmonics are quite significant. For the current-fed cases, the total current harmonic distortion at the converter input is about 15% for 12-pulse.

fig.(2.4) 12-Pulse Phase Control AC/DC Converters With  $\Delta$  -Y Isolated Transformer

#### 2.2.2.2 <u>Auto Transformer 12-Pulse converter</u> :

The conventional Auto Transformer 12-Pulse converter shown in figure (2.5). The power factor and harmonic components of the utility input line current can be improved by autotransformer phase-shifted AC/DC converter. But the output voltages of this AC/DC converters are not controllable. The output voltage of the 12-pulse AC/DC converter can be controlled by using the thyristors instead of diodes. The 12-pulse phase control AC/DC converters with autotransformer connected is shown in figure (2.5) [7,21].

• 18

- 19 -

#### 2.2.3 <u>18-Pulse Converter</u> :

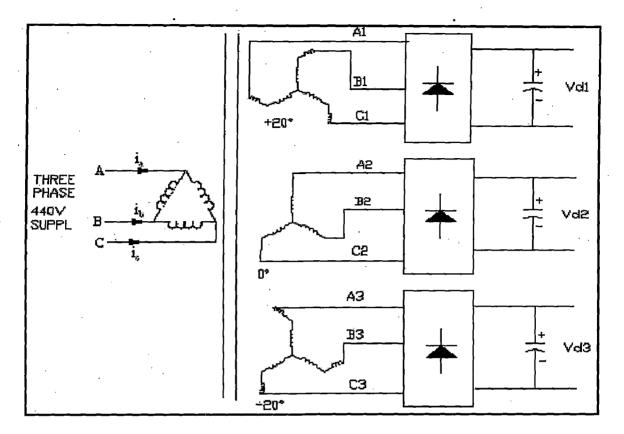

#### fig.(2.6) 18-Pulse Converter

Figure (2.6) shows the schematic diagram of 18-pulse rectifier with a three phase delta-star multi winding phase shifting transformer. The secondary windings voltages are displaced with respect to each other by  $20^{\circ}$  and are phase displaced by  $+20^{\circ}$ ,  $0^{\circ}$ ,  $-20^{\circ}$  with respect to primary. The current waveform of this rectifier shows that the input current is 18 stepped and is approaching more towards sinusoidal. The harmonics are further reduced in this type of multi-pulse converter. This type of rectifier system is gaining more and more popularity due to the fact that certain order harmonics which it reduces to minimum.

#### 2.2.4 24-Pulse Converter :[8]

24-pulse converter can be divided in to following two categories on the basis of transformer used:

- a) Non-Isolated type converter

- b) Isolated type converter

#### 2.2.4.1 24-Pulse Auto Transformer Converter:

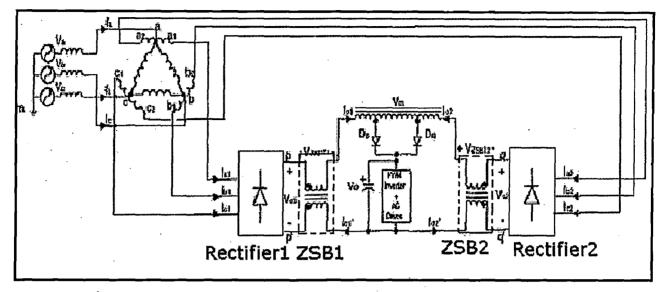

Figure (2.7) shows the 24-pulse system with auto transformer [10, 19]. This approach employs a polyphase autotransformer to provide 30° phase-shifted voltages to rectifier bridges I and 11.

fig. (2.7) Circuit Diagram of 24-Pulse System

The kVA rating of each ZSBT is 3.7% and the interphase reactor is 1.65% of the total output power for the 24-pulse system.

#### 2.2.4.2 24-Pulse Isolated Transformer Converter :

24-pulse system by using isolated transformer can be made by two way first is identical to the conventional 12-pulse isolated system, with some modification in transformer configuration and the two diodes connected to a specially tapped interphase transformer as shown in figure (2.8).

fig. (2.8) Circuit Diagram of 24-Pulse Extended Delta Converter

× - 21 -

The secondary windings of the input transformer are configured in extended delta and generate balanced sets of three-phase voltages with 30° phase shift for the diode rectifiers. The extended delta arrangement provides equal leakage reactance in series with rectifiers I and II.

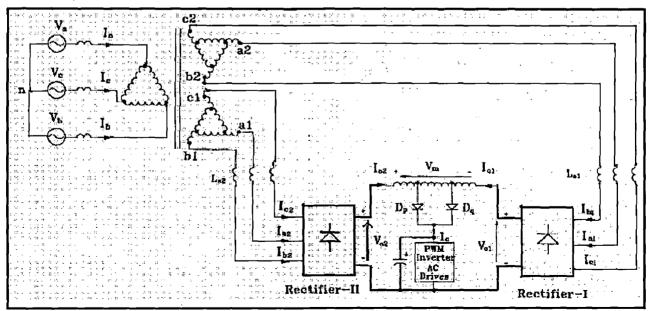

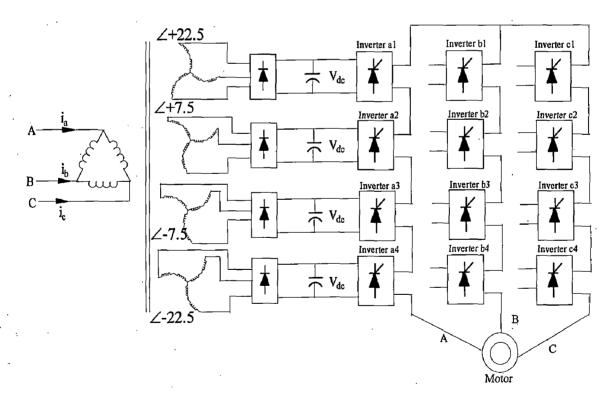

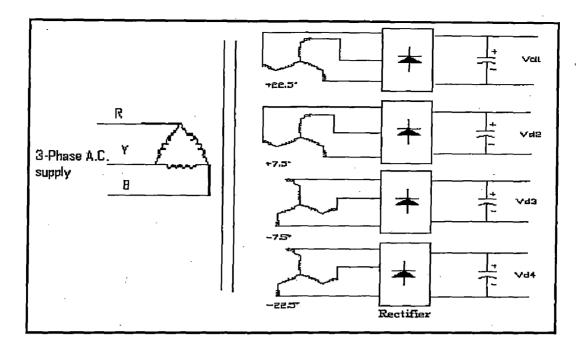

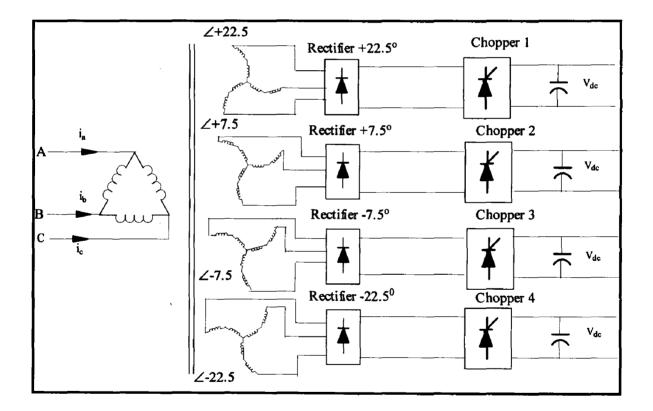

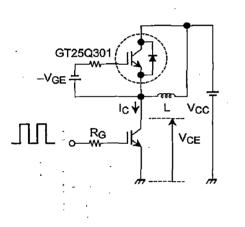

The second way of making 24-pulse converter is by using 24-pulse transformer, where primary is connected in delta and 4-phase shifted secondaries are connected to rectifier module [11]. Each secondary is phase shifted by 15° with each other, and with respect to secondary these are phase shifted by +22.5°, +7.5°, -7.5°, -22.5°. Rectifier module is connected to Buck/Boost chopper which control the D.C out put voltage of converter. This controlled D.C output will be fed to PWM Inverter circuit and output of inverter circuit goes to modular motor. The complete approach is shown below in figure (2.9).

fig. (2.9) 24-Pulse Converter

#### 2.2.5 Improved 12-Pulse Converter :[9]

The multi-pulse and most multilevel arrangements use fundamental frequency modulation because each switch in the converter turns on and off only once per cycle to reduce the switching losses. A ripple reinjection concept has been developed for line-commutated converters which are used to increase the pulse number of the conventional converter units and thus reduce harmonic distortion. Using a similar concept, we can developed a new scheme based on the reinjection of direct voltage pulses at six times the fundamental frequency to reduce the harmonic content produced by voltage-source converters. An improve 12-pulse converter is shown in figure (2.10).

fig (2.10) 36-Pulse Self-Commutated Voltage-Source Converter

The improve harmonic performance is shown in Table-2.1

| <b>m</b> 11 | -            | 1 |

|-------------|--------------|---|

| Tabl        | <u>e.</u> /  | 1 |

| 1 4171      | <u>v</u> -2. |   |

| Harmonic<br>Order  | 11    | 13    | 23    | 25    | 35    | 37    |

|--------------------|-------|-------|-------|-------|-------|-------|

| %THD of<br>Voltage | 0.387 | 0.444 | 0.251 | 0.170 | 2.86  | 2.70  |

| %THD of<br>Current | 0.352 | 0.341 | 0.109 | 0.068 | 0.816 | 0.731 |

Table-(2.1) Harmonic Spectrum of 36-Pulse Converter

### 3.1 <u>Introduction</u>:

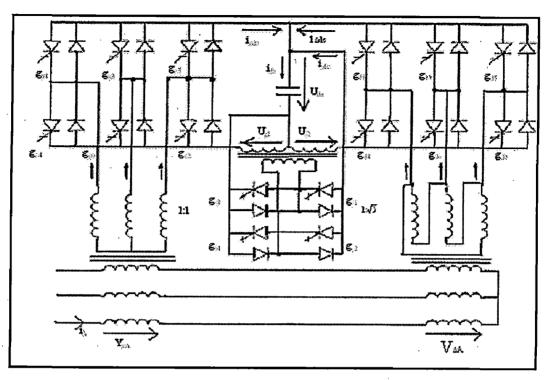

In modularity concept of Medium-Voltage Adjustable Speed drives, the Single-phase Cascaded (SC) VSI that uses series connection of IGBT based inverter modules with isolated dc-buses for each inverter [12]. The system yields a high-quality multi step voltage with up to 4 levels and low dv/dt, balanced operation of the inverter modules that supply each a fourth of the motor kVA. This modular structure leads to important advantages such as lower cost per kW due to the cheaper IGBT technology, power scalability, built-in redundancy and easy maintenance. Fault tolerance can be achieved by bypassing the fault modules [20,24]. The main drawbacks are high dc-link capacitive energy storage requirement especially in constant torque applications and a special expensive transformer with 24 pulses/l2 windings for ASD, required to provide the isolated dc- buses. The complete drive system is shown in figure (3.1).

#### fig. (3.1) Single-Phase Cascaded ASD

So to provide constant DC link voltage for each inverter module this converter is implemented and other objective is to reduce DC link capacitor value, as well as input line current harmonics.

## 3.2 Design of 24-Pulse Converter :

In this dissertation a 24-Pulse converter is implemented to provide D.C. link voltage to all four inverter module of a single leg. The complete system can be divided in to following three parts

- a) Multi-Winding Transformer

- b) Rectifier Modules

- c) Chopper Circuit

- d) Control Circuit

#### 3.2.1 Multi-Winding Transformer :

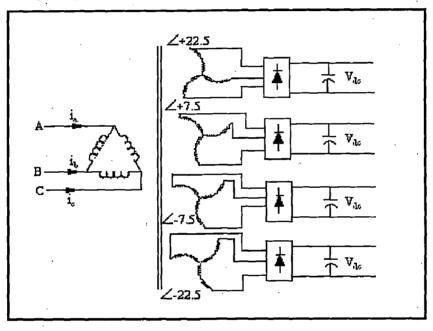

A multi-winding transformer is used in system to developed four secondary, which are used to feed AC supply to four rectifier module [22]. The transformer has four three phase secondary windings each winding voltage is phase shifted from each other by an angle of  $15^{0}$ . The criterion for deciding the phase angle is as follows.

360/pulse number = phase shift in degree

Table 3.1 represents the pulse number and the respective phase shift on the basis of this criterion.

| Pulse  | Phase | Phase Shifting Angles     |

|--------|-------|---------------------------|

| Number | shift | r hase shirting Angles    |

| 12     | 30    | 0°,30°                    |

| . 18   | 20    | 20°,0°,-20°               |

| 24     | 15    | +22.5°,+7.5°,+7.5°,+22.5° |

| 30     | 12    | 24°,12°,0°,-12°,24°       |

| m 11            | n. | 1 \ |

|-----------------|----|-----|

| Table-          | 4  | 11  |

| $1 a 0 10^{-1}$ | 1  |     |

#### Table (3.1) Number of Pulse and Phase Shift

Transformer is used to convert three-phase AC power to phase shifted four 3-phase AC power module. it helps in providing reduced harmonics on the AC side and minimizing ripple on the DC side of an AC to DC rectifier.

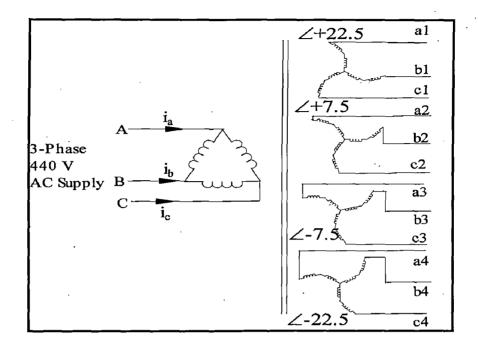

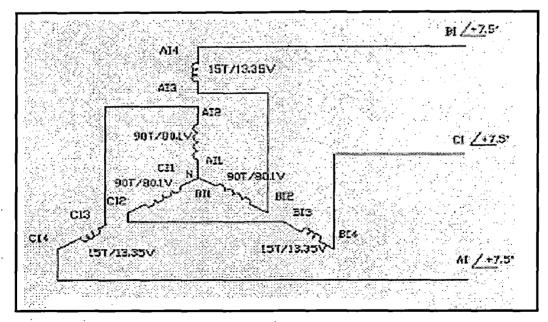

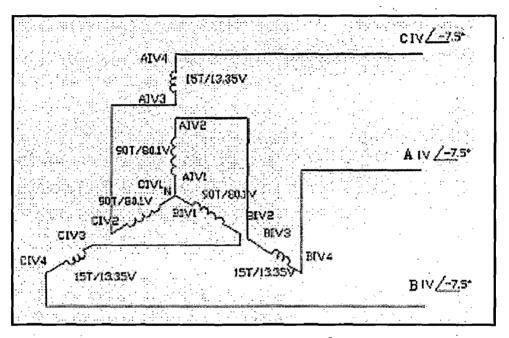

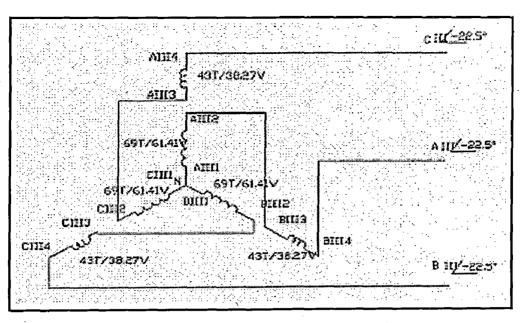

These AC phases are phase-shifted by each other by  $15^{\circ}$  and with respect to primary these are phase shifted by an angle of  $+22.5^{\circ}$ ,  $+7.5^{\circ}$ ,  $-7.5^{\circ}$  and  $-22.5^{\circ}$  respectively. It is designed in such a way that all line to line three phase output voltage will be equal in magnitude and phase shifted from the input voltage by these angles and these are phase shifted from each other by an angle of  $15^{\circ}$ . Figure (3.2)

shows the winding diagram for phase shifting transformer. First winding is phase shifted  $+22.5^{\circ}$ , second  $+7.5^{\circ}$  phase shifted third  $-7.5^{\circ}$  phase shifted and fourth is  $-22.5^{\circ}$  phase shifted. All the windings are phase shifted from each other by an angle of  $15^{\circ}$ .

fig (3.2) Winding Diagram of Phase Shifting Transformer

From figure (3.2) it is clear that secondaries of transformer are connected in such a way that they give required phase shift i.e.  $+22.5^{\circ}$ ,  $+7.5^{\circ}$ ,  $-7.5^{\circ}$  and  $-22.5^{\circ}$ .

# 3.2.1.1 Connection for +22.5° Phase Shifted Winding :

Figure (3.3) shows the connection diagram for  $+22.5^{\circ}$  phase shift. To get  $+22.5^{\circ}$  phase shift some number of turns of one phase is added with some number of turns of other phase to get the desired phase shift . For  $+22.5^{\circ}$  phase shift for the desired voltage in A phase, 69 turns of phase A are added with 43 turns of phase C . Similarly in phase B 69 turns of phase B are added with 43 turns of phase A and in phase C 69 turns of phase C are added with 43 turns of phase B.

|                              | alia<br>E                 | 431/382       | 71         |      | 신 11일 - 11일 : 12일 : 12일<br>- 12일 : 12<br>- 12일 : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12[ : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] : 12] |

|------------------------------|---------------------------|---------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

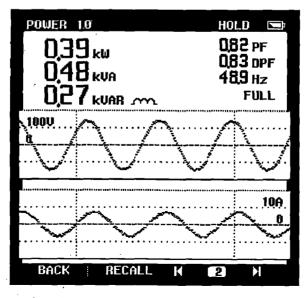

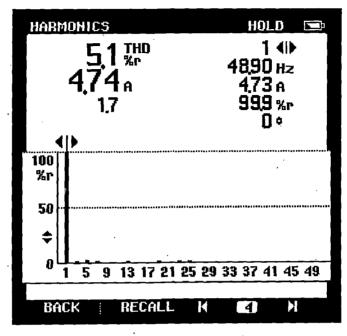

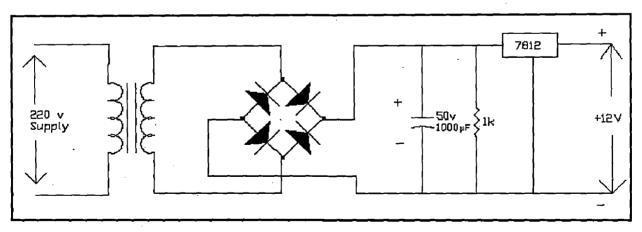

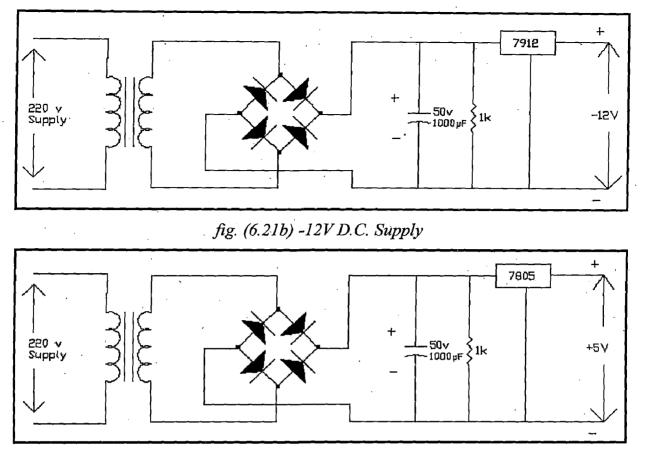

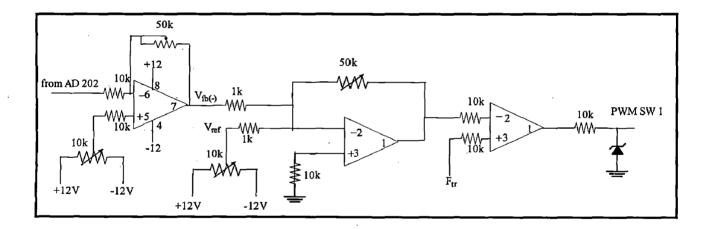

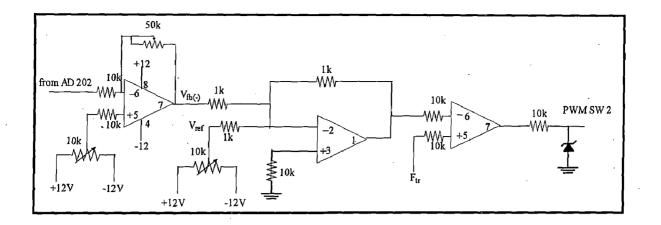

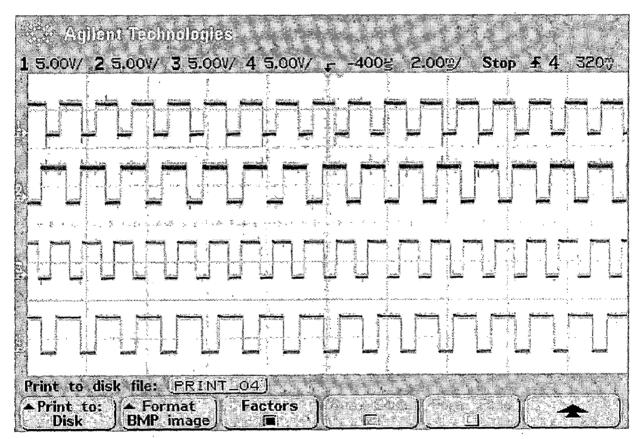

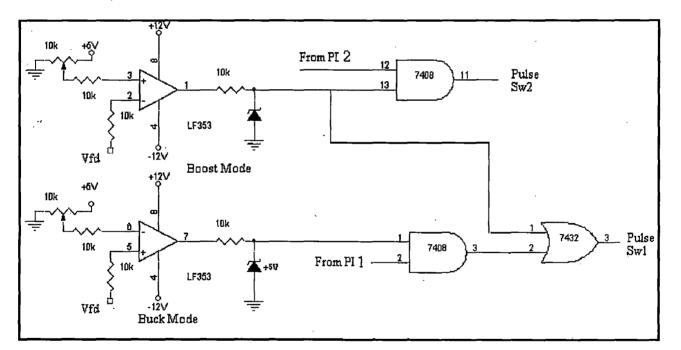

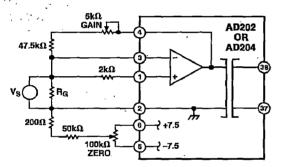

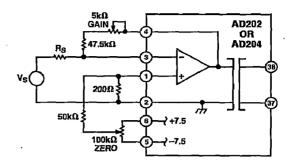

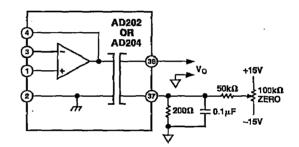

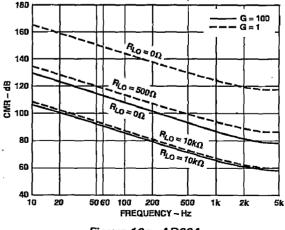

|                              | EII4                      |               | 1          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |