## MODELING AND SIMULATION OF THREE PHASE POWER FACTOR CORRECTED ACTIVE RECTIFIER WITH REDUCED SWITCH COUNT

**A DISSERTATION**

# Submitted in pertial fulfillment of the requirements for the award of the degree of

MASTER OF TECHNOLOGY

in

#### ELECTRICAL ENGINEERING

(With Specialization in Power Apparatus and Electric Drives)

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA)

**JUNE, 2006**

# IDNO. MT-341/2006-36/RKTVVS-PA

#### **CANDIDATE'S DECLARATION**

I hereby declare that the work that is being presented in this dissertation report entitled "MODELING AND SIMULATION OF THREE PHASE POWER FACTOR CORRECTED ACTIVE RECTIFIER WITH REDUCED SWITCH COUNT" submitted in partial fulfillment of the requirements for the award of the degree of Master Of Technology with specialization in Power Apparatus and Electric Drives, to the Department Of Electrical Engineering, Indian Institute Of Technology, Roorkee, is an authentic record of my own work carried out, under the guidance of Dr. Pramod Agrawal, Professor, Department of Electrical Engineering.

The matter embodied in this dissertation report has not been submitted by me for the Award of any other degree or diploma.

Date: 29/06/06 Place: Roorkee

(RAVI KUMAR T V V S)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

(DR. PRAMOD AGRAWAL)

Professor,

Department of Electrical Engineering, Indian Institute of Technology, ROORKEE – 247 667,

INDIA.

### ACKNOWLEDGEMENT

I wish to express my deep sense of gratitude and sincere thanks to **Dr. Pramod Agarwal**, Professor, Department of Electrical Engineering, IIT Roorkee for his whole heartedness and high dedication with which he was involved in this work. I am grateful for the hours he spent in discussing and explaining even the minute details of the work in spite of the hectic schedule of work in the department. The huge quantum of knowledge I had gained during his inspiring guidance would be immensely beneficial for my future endeavors.

I am also thankful to all my friends for their continuous support and enthusiastic help.

Date: **30-06-2006.** Place: **ROORKEE.**

(RAVI KUMAR T V V S)

#### ABSTRACT

The AC–DC converters, also known as rectifiers, are conventionally developed using diodes and thyristors to provide controlled and uncontrolled unidirectional and bidirectional dc power. However, these rectifiers can pollute the AC supply with significant levels of low frequency harmonics, pulsating input current (electromagnetic interference (EMI)), and excessive VAR. With tough regulations and severe economic restraints, the design of a three-phase switching mode rectifier which draws nearly sinusoidal three-phase input currents with unity power factor is very important from the point of view of energy saving and also to satisfy harmonic standards such as IEEE 519 or IEC 1000-3-2.

In response to these problems, a significant amount of research has been devoted to the area of pulse width modulation (PWM) rectifiers (i.e., switching-mode interfaces). Current research has been focusing recently on decreasing the number of power semiconductor switches to simplify the circuit and increase its reliability.

In the present work, a four switch three-phase active rectifier(reduced switch topology) is considered. Detailed power circuit analysis for the undertaken topology is presented. The design considerations are detailed. Four high performance control strategies(reduced hysteresis, space vector modulation, direct power modulation, Fuzzy space vector modulation) are discussed and verified and compared through simulations. The application of the considered four switch three phase topology to the improvement of power quality is investigated. The considered rectifier can also be used for harmonic current filtering. The feasibility is tested through simulation. A reduced switch count series filter is presented and verified. Finally experimental prototype of the considered four switch three phase rectifier is constructed and tested for reduced hysteresis control scheme.

i

## LIST OF FIGURES

| FIG NO         | FIGURE DESCRIPTION                                  | PAGE NO |

|----------------|-----------------------------------------------------|---------|

| Fig 1.1        | Single switch unidirectional boost converter        | 7       |

| Fig 1.2        | VSI bridge based bidirectional boost converter      | 8       |

| Fig 1.3        | Single switch unidirectional buck converter         | 8       |

| Fig 1.4        | IGBT based Bidirectional buck converter             | 8       |

| Fig 1.5        | SEPIC-derived unidirectional buck-boost converter   | 8       |

| Fig 1.6        | Matrix based bidirectional buck-boost converter     | 8       |

| Fig 1.7        | Five-level flying capacitor bidirectional converter | 9       |

| Fig 1.8        | 48-pulse bidirectional converter                    | 9       |

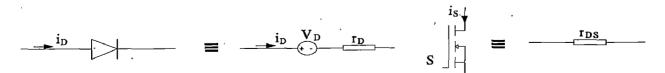

| Fig 1.9        | Static models of on state switching devices         | 9       |

| Fig 1.10       | Novel power electronics bidirectional interface     | 11      |

| Fig 1.11       | Three phase four switch step-up/down rectifier      | 15      |

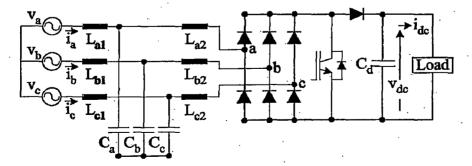

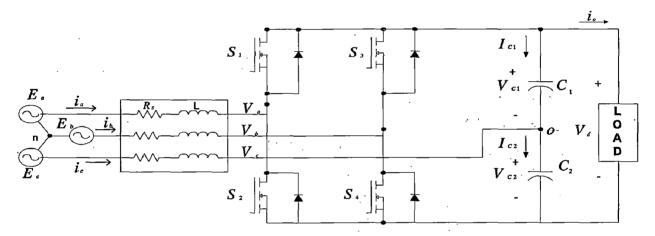

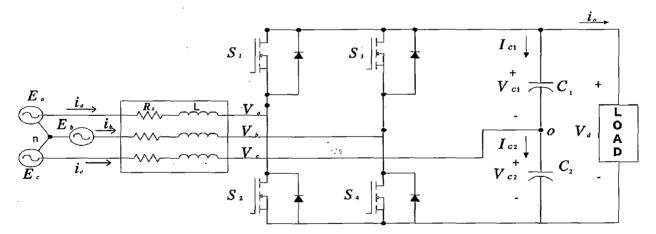

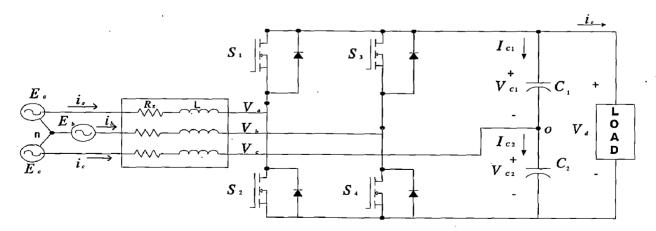

| <b>Fig 2.1</b> | Reversible four switch three phase active rectifier | 18      |

| Fig 2.2        | Space vector diagram                                | 21      |

| Fig 2.3        | Accurate simulation model of four switch three      | 27      |

|                | phase active rectifier                              |         |

| Fig 3.1        | General control block diagram                       | 29      |

| Fig 3.2        | Block diagram of hysteresis control                 | 31      |

| Fig 3.3        | Complete block diagram of closed form pwm           | 32      |

|                | duty cycle control                                  |         |

| Fig 3.4        | Gating signal of reversible four switch rectifier   | 32      |

| Fig 3.5        | Waveforms of ideal three phase input current        | 32      |

| Fig 3.6        | Equivalent circuits for section a and b of fig 3.5  | 33      |

| Fig 3.7        | Equivalent circuits for section a and b of fig 3.5  | 33      |

| Fig 3.8        | Control block diagram of reduced hysteresis control | 36      |

| Fig 3.9        | Space Vector Diagram for SVM                        | 37      |

| Fig 3.10       | Complete block diagram of the SVM scheme            | 39      |

| Fig 3.11       | Complete block diagram of the DPM scheme            | 42      |

| Fig 4.1 | Blocks of a fuzzy controller                               | 44 |

|---------|------------------------------------------------------------|----|

| Fig 4.2 | General step response                                      | 45 |

| Fig 4.3 | Graphical construction of the control signal in a fuzzy    | 47 |

|         | Pd ntroller (generated in the matlab fuzzy logic toolbox). |    |

| Fig 4.4 | One input, one output rule base with                       | 48 |

|         | non-singleton output sets.                                 |    |

| Fig 4.5 | Block diagram of fuzzy SVM control                         | 51 |

| Fig 4.6 | Fuzzy variable membership functions                        | 52 |

|         | Fuzzy control surface                                      |    |

| Fig 5.1 | Configuration of Shunt Active Power Filter                 | 56 |

| Fig 5.2 | Conventional Six Switch Topology                           | 56 |

| Fig 5.3 | Four switch Three Phase Active Rectifier acting            | 56 |

|         | as a Active power filter                                   |    |

| Fig 5.4 | Non linear load current, desired source current            | 57 |

|         | Harmonic content in load current                           |    |

| Fig 5.5 | Source current estimation                                  | 60 |

| Fig 5.6 | Reduced hysteresis control of four switch three            | 60 |

|         | phase rectifier applied to active filtering                |    |

| Fig 5.7 | Configuration of series active power filter                | 61 |

| Fig 5.8 | Series active power filter using vsi bridge                | 61 |

| Fig 5.9 | Series active power filter using four switch               | 62 |

|         | three-phase toplogy                                        |    |

| Fig 6.1 | A-phase source voltage and current(reduced hysteresis)     | 66 |

| Fig 6.2 | DC output voltage(reduced hysteresis)                      | 66 |

| Fig 6.3 | Three Phase source currents(reduced hysteresis)            | 66 |

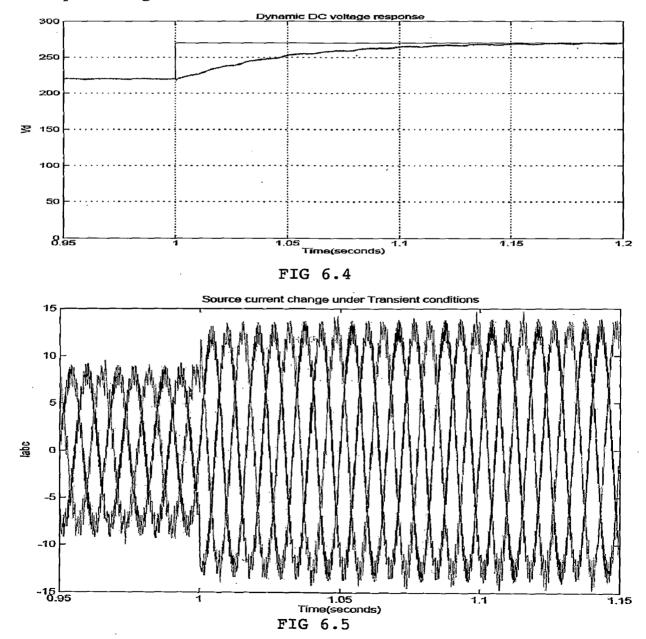

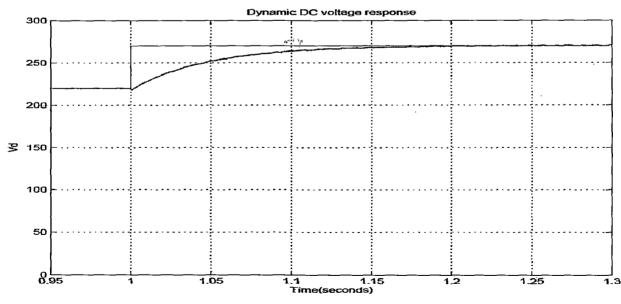

| Fig 6.4 | Dynamic DC Voltage response(reduced hysteresis)            | 67 |

| Fig 6.5 | Source current change under transient conditions           | 67 |

|         | (reduced hysteresis)                                       |    |

| Fig 6.6 | Regenerative capability(reduced hysteresis)                | 68 |

| Fig 6.7 | Hysteresis switching frequency(reduced hysteresis)         | 68 |

٠.,

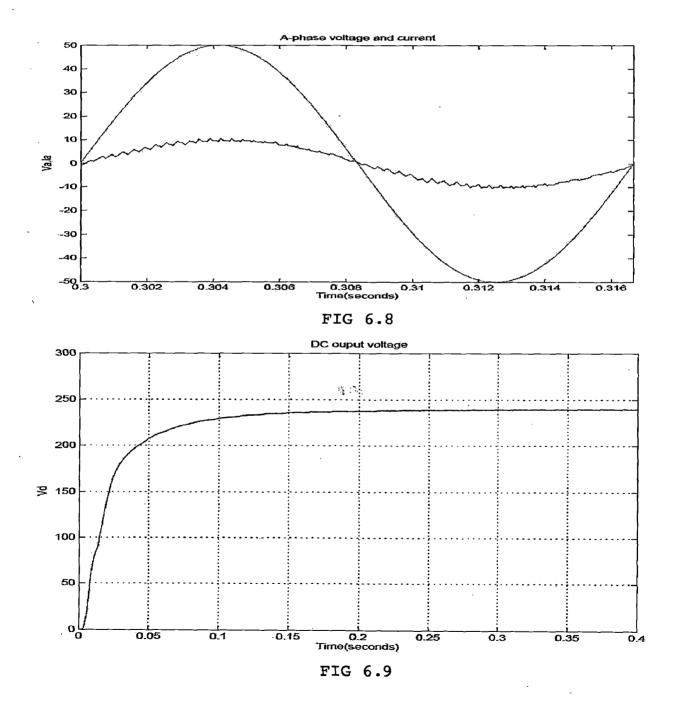

| Fig 6.8  | A-phase source voltage and current(SVM)               | 69 |

|----------|-------------------------------------------------------|----|

| Fig 6.9  | DC output voltage(SVM)                                | 69 |

| Fig 6.10 | Three Phase source currents(SVM)                      | 70 |

| Fig 6.11 | Input current space vector                            | 70 |

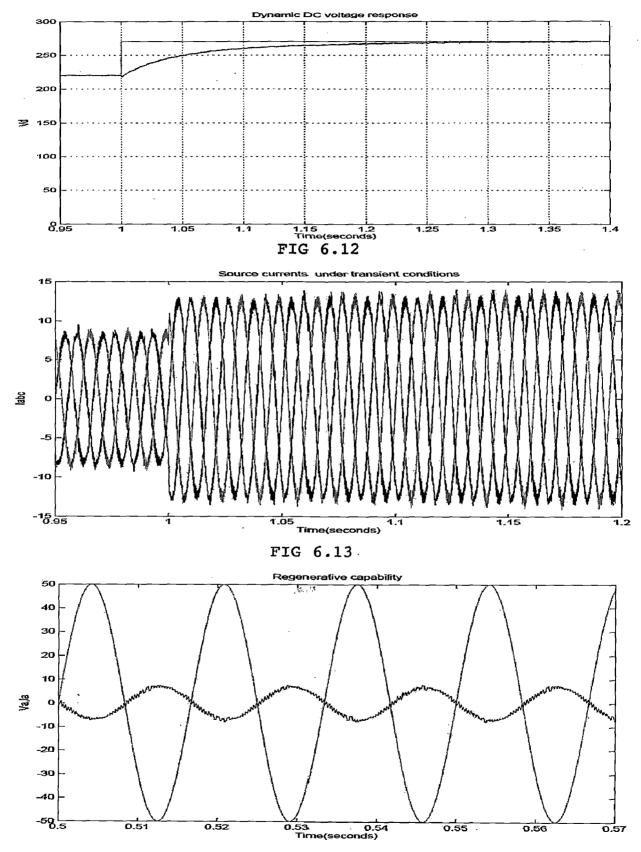

| Fig 6.12 | Dynamic DC Voltage response(SVM)                      | 71 |

| Fig 6.13 | Source current change under transient conditions(SVM) | 71 |

| Fig 6.14 | Regenerative capability(SVM)                          | 71 |

| Fig 6.15 | A-phase source voltage and current(DPM)               | 72 |

| Fig 6.16 | Active and Reactive Powers                            | 72 |

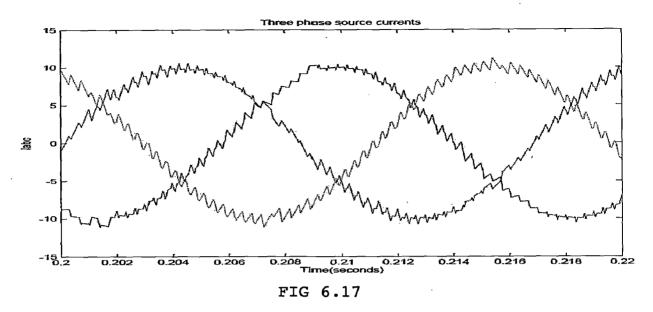

| Fig 6.17 | Three Phase source currents(DPM)                      | 73 |

| Fig 6.18 | Dynamic DC Voltage response(DPM)                      | 73 |

| Fig 6.19 | Source current change under transient conditions(DPM) | 74 |

| Fig 6.20 | Regenerative capability(DPM)                          | 74 |

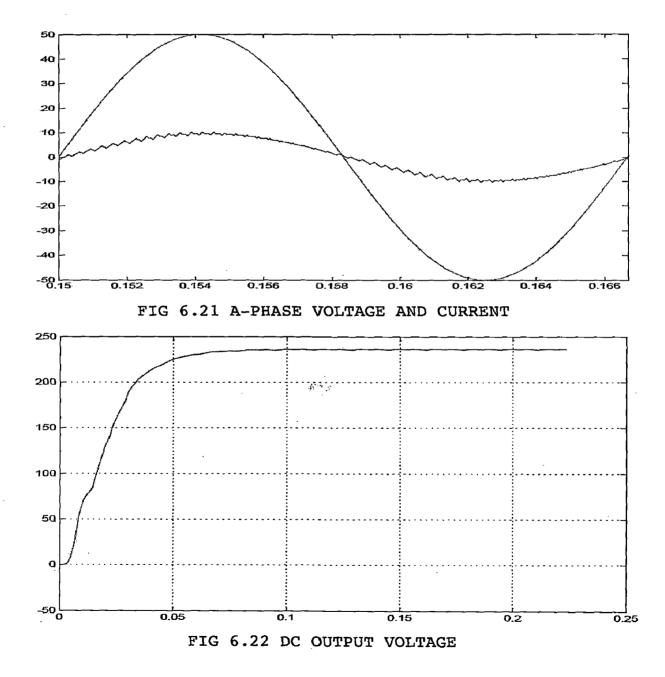

| Fig 6.21 | A-phase source voltage and current(Fuzzy SVM)         | 75 |

| Fig 6.22 | DC output voltage(Fuzzy SVM)                          | 75 |

| Fig 6.23 | Three Phase source currents(Fuzzy SVM)                | 76 |

| Fig 6.24 | Dynamic DC Voltage response(Fuzzy SVM)                | 76 |

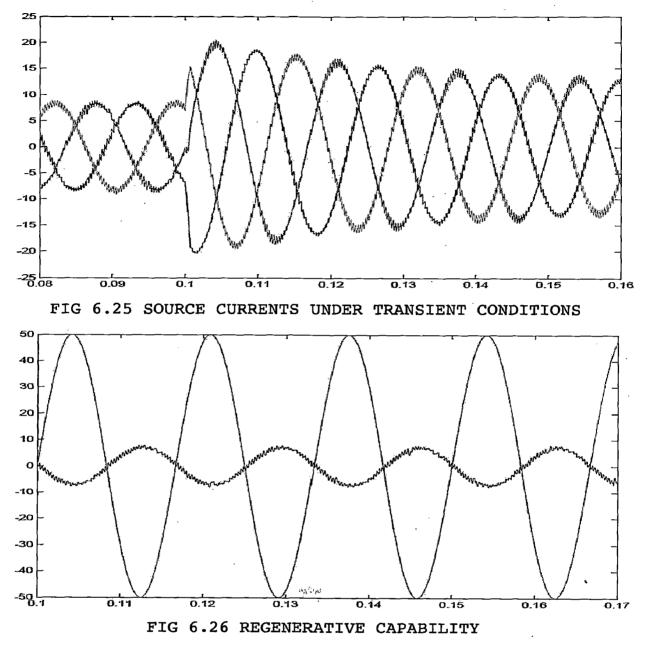

| Fig 6.25 | Source current change under                           |    |

|          | transient conditions(Fuzzy SVM)                       | 77 |

| Fig 6.26 | Regenerative capability(SVM)                          | 77 |

| Fig 6.27 | Three phase currents for different controls           | 78 |

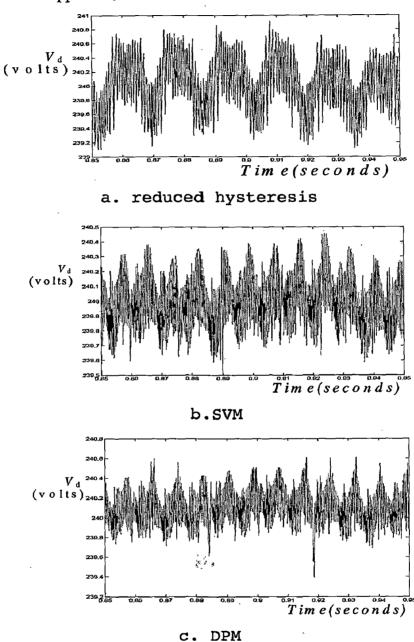

| Fig 6.28 | V <sub>d</sub> Ripple for different controls          | 79 |

| Fig 6.29 | Dynamic response improvements using Fuzzy SVM         | 80 |

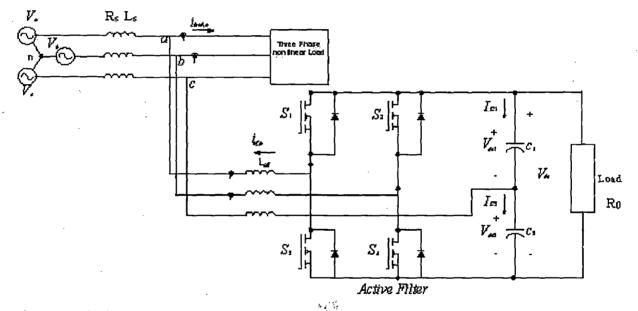

| Fig 6.30 | Four switch three phase active rectifier              |    |

|          | acting as a active power filter                       | 81 |

| Fig 6.31 | A-phase source voltage                                | 82 |

| Fig 6.32 | A-phase non linear load current                       | 82 |

| Fig 6.33 | A-phase source current with compensation              | 82 |

| Fig 6.34 | A-phase current drawn by active filter                | 82 |

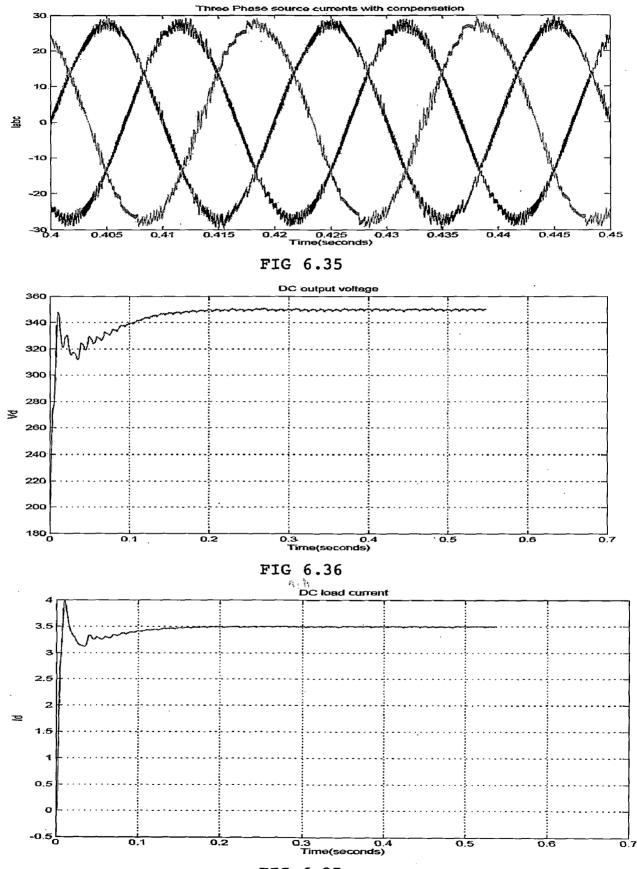

| Fig 6.35 | Three phase source currents with compensation         | 83 |

| Fig 6.36 | DC output voltage                                    | 83  |   |

|----------|------------------------------------------------------|-----|---|

| Fig 6.37 | DC load current                                      | 83  |   |

| Fig 6.38 | FFT Analysis of three phase line                     |     |   |

|          | currents with compensation                           | 84  |   |

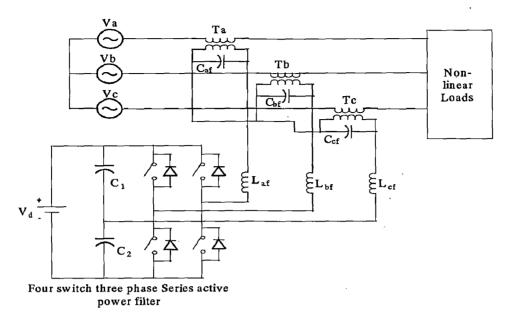

| Fig 6.39 | Four switch three-phase series active power filter   | 85  |   |

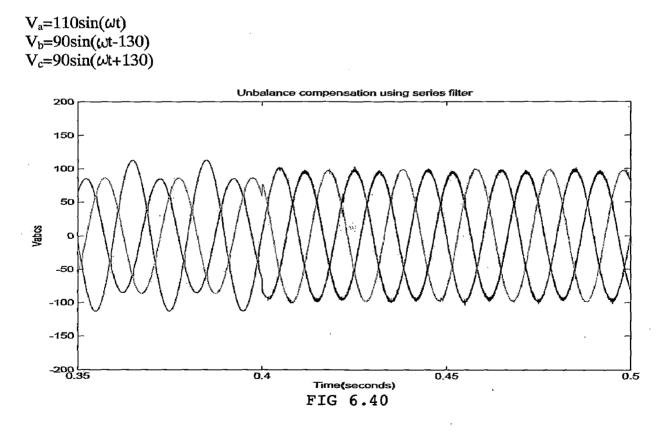

| Fig 6.40 | Unbalance compensation using series filter           | 85  |   |

| Fig 6.41 | Harmonic Voltage compensation for A-phase            | 86  |   |

| Fig 6.42 | A-phase injected Voltage                             | 86  |   |

| Fig 6.43 | Harmonic Voltage compensation for B-phase            | 86  |   |

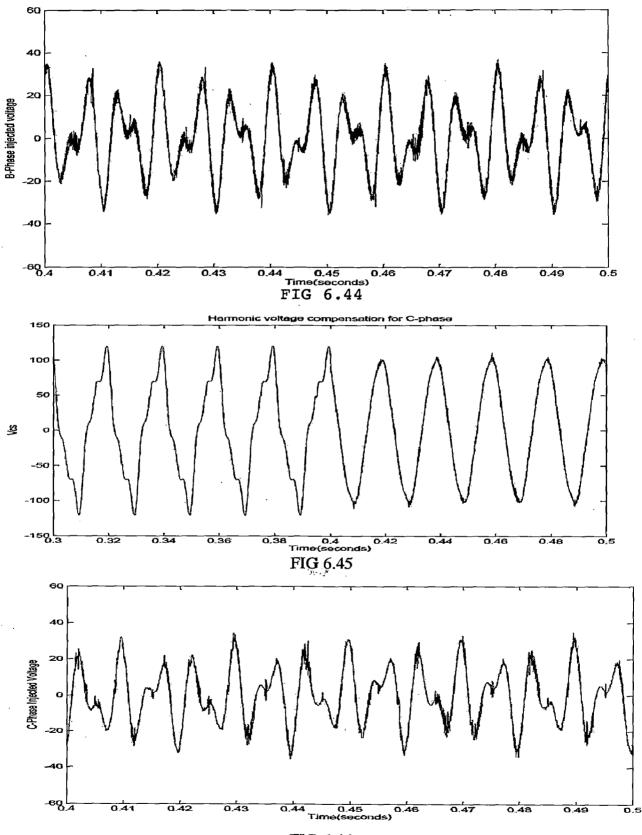

| Fig 6.44 | B-phase injected Voltage                             | 87  |   |

| Fig 6.45 | Harmonic Voltage compensation for C-phase            | 87  |   |

| Fig 6.46 | C-phase injected Voltage                             | 87  |   |

| Fig 6.47 | FFT Analysis of three phase line                     |     |   |

|          | Voltages after compensation                          | 88  |   |

| Fig 7.1  | Four switch three phase active rectifier             | 89  |   |

| Fig 7.2  | Pulse amplification and isolation circuit            | 90  |   |

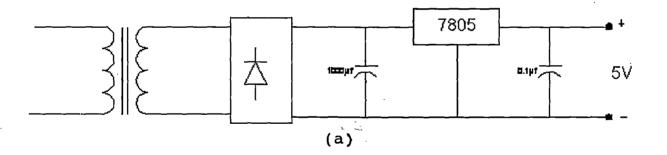

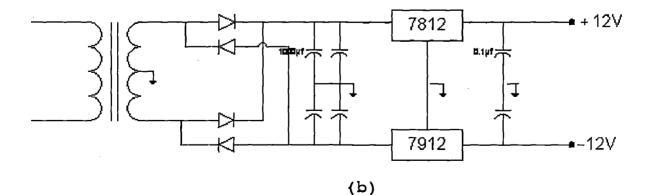

| Fig 7.3  | Power supplies                                       | 91  |   |

| Fig 7.4  | Snubber circuit                                      | 92  |   |

| Fig 7.5  | Hall effect current sensor                           | 93  |   |

| Fig 7.6  | DC Link Voltage sensing                              | 94  |   |

| Fig 7.7  | PI Controller                                        | 95  |   |

| Fig 7.8  | PI controller with analog multiplication using AD633 | 96  |   |

| Fig 7.9  | Hysteresis current controller                        | 96  |   |

| Fig 7.10 | Delay Circuit                                        | 97  |   |

| Fig 8.1  | Labaratory experimental setup                        | 98  |   |

| Fig 8.2  | DC output voltage                                    | 99  | · |

| Fig 8.3  | Source A-phase voltage and current                   | 99  |   |

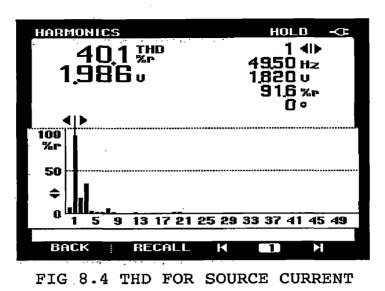

| Fig 8.4  | Thd for source current                               | 100 |   |

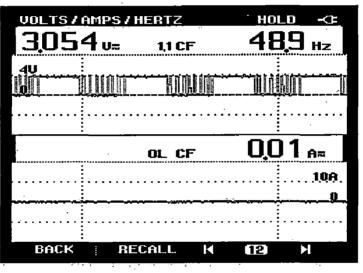

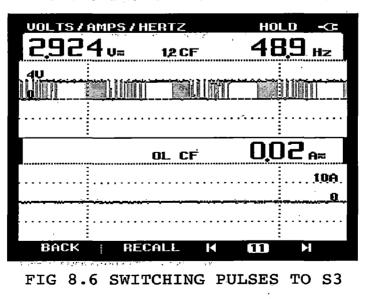

| Fig 8.5  | Switching pulses for S1                              | 100 |   |

| Fig 8.6  | Switching pulses for S3                              | 100 |   |

.

The second s **v** .

•

## LIST OF TABLES

| TABLE NO  | TABLE DESCRIPTION                                                                       | PAGE NO |

|-----------|-----------------------------------------------------------------------------------------|---------|

| TABLE 1.1 | IEC-1000-3-2 class A harmonic current limits                                            | 2       |

| TABLE 1.2 | IEC-1000-3-2 class B and class C harmonic current limits                                | 3       |

| TABLE 1.3 | IEC-1000-3-2 D harmonic current limits                                                  | 3       |

| TABLE 2.1 | Switching modes of the rectifier                                                        | 20      |

| TABLE 2.2 | Rectifier input vectors in d-q plane                                                    | 21      |

| TABLE 3.1 | $\boldsymbol{V}_k$ , $\boldsymbol{i}_k$ and the conducting switches for four conducting |         |

|           | paths                                                                                   | 35      |

| TABLE 3.2 | Switching states (S1, S2, S3, AND S4) as a function of                                  |         |

|           | the section number and the polarities of . ia, . ib.                                    | 35      |

| TABLE 3.3 | Space vectors for different combinations                                                | 37      |

| TABLE 3.4 | Quadrant selection                                                                      | 38      |

| TABLE 3.5 | Duty ratio calculation                                                                  | 39      |

| TABLE 4.1 | Rule base of the adopted Fuzzy controller                                               | 52      |

| TABLE 6.1 | Thd comparison for different control strategies                                         | 78      |

|           |                                                                                         |         |

## NOMENCLATURE

| PWM  | Pulse width Modulation                           |

|------|--------------------------------------------------|

| THD  | Total Harmonic Distortion                        |

| IEEE | Institute of Electrical ad Electronics Engineers |

| EMI  | Electromagnetic Interference                     |

| IEC  | International Electro technical Commission       |

| PFC  | Power Factor correction                          |

| KHz  | Kilo-Hertz                                       |

| IGBT | Insulated Gate Bi-polar Transistor               |

| PI   | Proportional Integral                            |

| VSI  | Voltage source inverter                          |

| MOV  | Metal Oxide Varistor                             |

| SVM  | Space Vector Modulation                          |

| DPM  | Direct Power Modulation                          |

| FFT  | Fast Fourier Transform                           |

| AC   | Alternating Current                              |

| DC   | Direct Current                                   |

| IC   | Integrated Chip                                  |

|      |                                                  |

## CONTENTS

| (  | CANDIDATE'S DECLARATION                            |     |

|----|----------------------------------------------------|-----|

| -  | ACKNOWLEDGEMENT                                    |     |

|    | ABSTRACT                                           | i   |

| L  | LIST OF FIGURES                                    | ii  |

| Ł  | LIST OF TABLES                                     | vi  |

| 1  | NOMENCLATURE                                       | vii |

| 1. | INTRODUCTION                                       | 1   |

|    | 1.1 NEED FOR POWER FACTOR CORRECTION               | 01  |

|    | 1.1.1 Introduction                                 |     |

|    | 1.1.2 Standards regulating line current harmonics  |     |

|    | 1.1.3 Power factor                                 |     |

|    | 1.2 CONVENTIONAL PFC RECTIFIERS: STATE OF ART      | 06  |

|    | 1.3 REDUCED SWITCH COUNT PFC RECTIFIERS            | 09  |

|    | 1.3.1 Advantages                                   |     |

|    | 1.3.2 Limitations                                  |     |

|    | 1.4 LITERATURE SURVEY                              | 11  |

|    | 1.5 STATEMENT OF PROBLEM                           | 15  |

| 19 | 1.6 ORGANIZATION OF THESIS                         | 16  |

| 2. | FOUR SWITCH THREE PHASE ACTIVE RECTIFIER: ANALYSIS | 18  |

|    | MODELING AND DESIGN                                |     |

|    | 2.1 POWER CIRCUIT DESCRIPTION                      | 18  |

|    | 2.2 POWER CIRCUIT ANALYSIS                         | .18 |

|    | 2.3 DESIGN OF FOUR SWITCH THREE PHASE RECTIER      | 22  |

|    | 2.3.1 Critical Inductance Condition                |     |

|    | 2.3.2 Capacitor Design                             |     |

|    | 2.3.3 Operating Range of the Interface             |     |

|    | 2.4 COMPARISION WITH SIX SWITCH TOPOLOGY           | 24  |

|    | 2.4.1 DC bus Voltage                                                                                                                       |          |

|----|--------------------------------------------------------------------------------------------------------------------------------------------|----------|

|    | 2.4.2 Three phase Inductor                                                                                                                 |          |

|    | 2.4.3 DC bus Capacitor                                                                                                                     |          |

|    | 2.4.4 Switching Losses                                                                                                                     |          |

|    | 2.5 ACCURATE SIMULATION MODEL                                                                                                              | 25       |

|    | 2.6 CONCLUSIONS                                                                                                                            | 28       |

| 3. | CONTROL STRATEGIES                                                                                                                         | 29       |

|    | 3.1 INTRODUCTION                                                                                                                           | 29       |

|    | 3.2 TRADITIONAL CONTROL SCHEMES                                                                                                            | 30       |

|    | 3.2.1 Hysteresis control                                                                                                                   |          |

|    | 3.2.2 Closed form PWM duty cycle control                                                                                                   |          |

|    | 3.3 HIGH PERFORMANCE CONTROL SCHEMES                                                                                                       | 34       |

|    | 3.3.1 Reduced Hysteresis control                                                                                                           |          |

|    | 3.3.2 Space Vector Modulated control                                                                                                       |          |

|    | 3.3.3 Direct Power Modulated control                                                                                                       |          |

| 4. | FUZZY CONTROL OF FOUR SWITCH THREE PHASE ACTIVE                                                                                            | 43       |

|    | RECTIFIER                                                                                                                                  |          |

|    | 4.1 INTRODUCTION                                                                                                                           | 43       |

|    |                                                                                                                                            | 40       |

|    | 4.2 STRUCTURE OF A FUZZY CONTROLLER                                                                                                        | 40<br>44 |

|    |                                                                                                                                            |          |

|    | 4.2 STRUCTURE OF A FUZZY CONTROLLER                                                                                                        |          |

|    | 4.2 STRUCTURE OF A FUZZY CONTROLLER<br>4.2.1 Preprocessing                                                                                 |          |

|    | 4.2 STRUCTURE OF A FUZZY CONTROLLER<br>4.2.1 Preprocessing<br>4.2.2 Fuzzification                                                          |          |

|    | <ul> <li>4.2 STRUCTURE OF A FUZZY CONTROLLER</li> <li>4.2.1 Preprocessing</li> <li>4.2.2 Fuzzification</li> <li>4.2.3 Rule Base</li> </ul> |          |

.

.

|   | 5. | APPLICATION OF FOUR SWITCH THREE-PHASE TOPOLOGY     | 53  |

|---|----|-----------------------------------------------------|-----|

|   |    | TO POWER QUALITY IMPROVEMENT                        | · . |

|   | ·  | 5.1 POWER QUALITY ISSUES: AN INTRODUCTION           | 53  |

|   |    | 5.2 A FOUR SWITCH THREE-PHASE ACTIVE RECTIFIER WITH |     |

|   |    | THE FUNCTION OF A SHUNT ACTIVE POWER FILTER         | 55  |

|   |    | 5.2.1 Compensation Principle                        |     |

|   |    | 5.2.2 The Control Scheme                            |     |

|   |    | 5.3 A SERIES ACTIVE POWER FILTER BASED ON A FOUR    |     |

|   |    | SWITCH THREE-PHASE TOPOLOGY                         | 61  |

|   |    | 5.3.1 Basic Compensation Principle                  |     |

|   |    | 5.3.2 The Control Scheme                            |     |

|   | _  |                                                     |     |

|   | 6. | SIMULATION RESULTS                                  | 65  |

|   |    | 6.1 REDUCED HYSTERESIS CONTROL                      | 65  |

| ` |    | 6.2 SPACE VECTOR MODULATED CONTROL                  | 69  |

|   |    | 6.3 DIRECT POWER MODULATED CONTROL                  | 72  |

|   |    | 6.4 FUZZY SPACE VECTOR MODULATED CONTROL            | 75  |

|   |    | 6.5 COMPARISION OF CONTROL SCHEMES                  | 78  |

|   |    | 6.6 A FOUR SWITCH THREE-PHASE ACTIVE RECTIFIER WITH |     |

|   |    | THE FUNCTION OF AN ACTIVE POWER FILTER              | 81  |

|   |    | 6.7 A SERIES ACTIVE POWER FILTER BASED ON A FOUR    | ·   |

|   |    | SWITCH THREE-PHASE TOPOLOGY                         | 84  |

|   | 7. | SYSTEM DEVELOPMENT                                  | 00  |

|   | 7. |                                                     | 89  |

|   |    | 7.1 POWER CIRCUIT                                   | 89  |

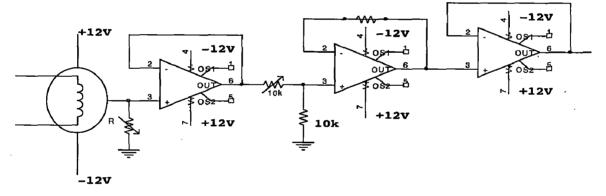

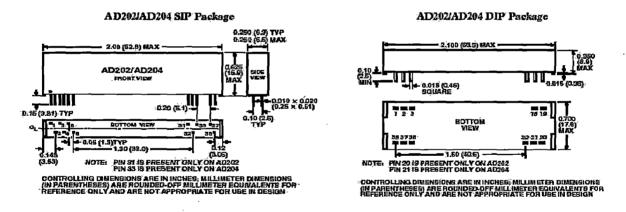

|   |    | 7.2 PULSE AMPLIFICATION AND ISOLATION CIRCUIT       | 90  |

|   |    | 7.3 POWER SUPPLIES                                  | 91  |

| · |    | 7.4 PROTECTION OF MOSFETS                           | 92  |

|   |    | 7.5 CURRENT SENSING CIRCUIT                         | 92  |

|   |    | 7.6 VOLTAGE SENSING CIRCUIT                         | 93  |

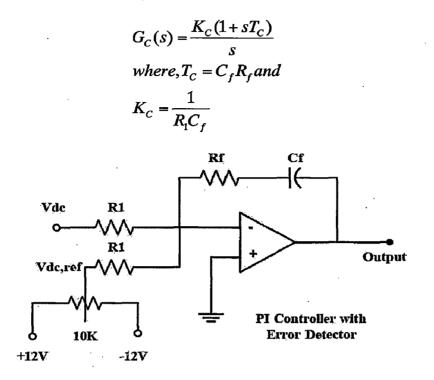

|   |    | 7.7 PI CONTROLLER                                   | 94  |

|   |    |                                                     |     |

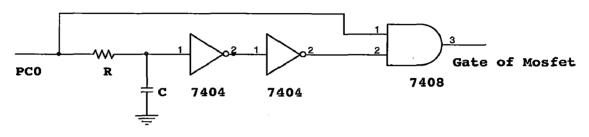

|       | 7.8 HYSTERESIS CURRENT CONTROLLER | 95  |

|-------|-----------------------------------|-----|

|       | 7.9 DELAY CIRCUIT                 | 97  |

| 8.    | EXPERIMENTAL RESULTS              | 98  |

| 9.    | CONCLUSIONS AND FUTURE SCOPE      | 101 |

| REFEF | RENCES                            | 103 |

| APPER | NDIX                              | 105 |

•

.

.

Class A includes: balanced three-phase equipment; household appliances, excluding equipment identified as Class D, tools, excluding portable tools, dimmers for incandescent lamps; and audio equipment. Equipment not specified in one of the other three classes should be considered as Class A equipment. The limits for Class A are presented in Table 1.1.

Class B equipment includes: portable tools; and nonprofessional arc welding equipment. The limits for this class are those shown in Table 1.2 multiplied by a factor of 1.5.

| Harmonic order | Maximum permissible harmonic current<br>Expressed as a percentage of the input |

|----------------|--------------------------------------------------------------------------------|

|                | Current at the fundamental frequency                                           |

| <b>'n'</b>     | %                                                                              |

| 2              | 2                                                                              |

| 3              | 30.PF *                                                                        |

| 5              | 10                                                                             |

| 7              | 7                                                                              |

| 9              | 5                                                                              |

| 11. n. 39      | 3                                                                              |

| PF             | * is the circuit power factor                                                  |

| TABLE 1 |  | 2 |

|---------|--|---|

|---------|--|---|

Class C includes lighting equipment. For an active input power greater than 25W, the harmonic currents should not exceed the limits resented in Table 1.2 the harmonic limits for Class D are presented in Table 1.3. They are defined in both power related and absolute terms. These includes personal computers, personal computer monitors, and television receivers, equipment having active input power less than or equal to 600W.

| TABLE | 1 |  | 3 |

|-------|---|--|---|

|-------|---|--|---|

| Harmonic order | Maximum permissible  | Maximum permissible |

|----------------|----------------------|---------------------|

|                | Harmonic current per | Harmonic current    |

|                | Watt                 |                     |

| 'n'            | 'Ma/W'               | 'A'                 |

| 3              | 3.4                  | 2.30                |

| 5              | 1.9                  | 1.14                |

| 7              | 1.0                  | 0.77                |

| 9              | 0.5                  | 0.44                |

| 11             | 0.35                 | 0.33                |

| 13. n. 39      | 3.85. n              | As in Class A       |

3

المنتر لويتي والمنافرة والمنافرة

- It causes poor voltage regulation at the load.

- As the load voltage decreases due to poor voltage regulation the power transfer capacity is adversely affected

- The investment in system facilities per KW of load supplied increases with decrease in supply power factor

Improving the power factor brings three benefits:

- Power distribution costs for the electric company are reduced, making the power company much happier. A side benefit is to reduce the tendency of the current peaks to "flatten" the tops of the input voltage sinusoidal waveform.

- More power can be drawn from a line of a given current rating, allowing more powerful equipment to be connected without having to re-wire a building, saving time and money.

- Various governmental and quasi-governmental agencies are passing laws requiring improved power factors on certain types of equipment, especially those which draw a lot of power. These laws make it illegal to sell certain types of equipment without testing and certification of a minimum power factor. To continue to sell medium-to high power supplies in the future, power supply manufacturers will have to deal with power factor correction.

Because of the severity of problems due to low power factor, some options such as passive filters, active filters, and hybrid filters, to be used along with traditional Thyristor/Diode rectifiers have been extensively developed, especially in large rating and already existing installations. However, these filters are quite costly, bulky, and have reasonable losses, which reduce overall efficiency of the complete system. Even in some cases the rating of converter used in active filters is almost close to the rating of the load. Under such circumstances, it is considered better option to use such converters as an inherent part of the system of AC-DC conversion, which provides reduced size, high efficiency, and well controlled and regulated DC to provide comfortable and flexible operation of the system.

As det

. .

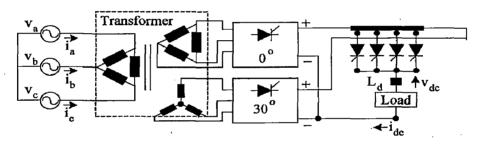

transformers and tapped inductors. Therefore, the last category is multipulse converters with unidirectional and bidirectional power flow.

One of the important reasons for such an extensive development in ac-dc converters is due to self-commutating devices. At low power rating, MOSFETs are used with unsurpassed performance because of their high switching rate with negligible losses. At medium power rating, an IGBT is considered an ideal device for such converters with PWM technology. At a higher power rating, a GTO is normally used with selfcommutating and reverse voltage-blocking capabilities at only a few kilohertz switching frequency. Another breakthrough in PFCs has been because of fast response Hall-effect voltage and current sensors, and isolation amplifiers normally required for the feedback used in the control of these ac-dc converters result in a high level of dynamic and steadystate performance. Many manufacturers, such as ABB, LEM, HEME, Analog Devices, and others are offering the sensors at competitively low prices. A major boost to the technology of PFCs has also been due to the revolution in microelectronics. Because of the heavy volume requirement, a number of manufacturers have developed dedicated ICs for cost-effective and compact control of these converters. Moreover, high-speed microcontrollers and digital signal processors (DSPs) are available at reasonable cost. Many processors have been developed to give direct PWM outputs with fast software normally used in some of these algorithms such as space-vector control (SVC), converters, which reduce hardware drastically. With these processors it is now possible to implement new and improved control algorithms to provide fast dynamic performance of PFCs. Starting with proportional-integral (PI) controllers, sliding-mode, fuzzy logic, and neural network- based controllers have been employed for the control of these converters. Some of the popular topologies are presented in Fig. 1.1 through Fig. 1.8.

7

Sec. Ash

FIG 1.7 FIVE-LEVEL FLYING CAPACITOR BIDIRECTIONAL CONVERTER

FIG 1.8 48-PULSE BIDIRECTIONAL CONVERTER

#### **1.3 REDUCED SWITCH COUNT PFC RECTIFIERS**

The PFC stage performs an additional power processing operation, and therefore it has a negative impact on the overall efficiency of the power supply.

Conduction losses are caused by the current flowing through a non-ideal switching device in the on state, which determines a certain voltage drop on the device. A static model of the switching device is useful for estimating the conduction losses. Static models are presented in Fig. 1.9, for on-state diode and MOSFET.

FIG 1.9 STATIC MODELS OF ON STATE SWITCHING DEVICES

9

م الم الم الم الم الم

• Greater switching frequencies required for same performance.

#### **1.4 LITERATURE SURVEY**

Maoh chin Jiang[2] proposed a novel three-phase bidirectional interface(shown in Fig.1.10) using only four power semiconductor switches to simplify the hardware circuit. The circuit is analyzed and design considerations are elaborated. An accurate simulation model is proposed for convenient simulation using common PC software tools. A critical inductance condition is derived for successful current tracking. The capacity to generate maximum active power is also estimated. A systematic design method for the feedback controller is presented to find the parameters of the controller.

FIG 1.10 NOVEL POWER ELECTRONICS BIDIRECTIONAL INTERFACE

J.J.Shieh, C.-T, Pan Z.-J.Cuey[3], proposed a reversible three-phase switching mode rectifier consisting of a four-active-switch and without current sensor. To achieve controllable power factor, clean sinusoidal input current, adjustable DC output voltage, and bidirectional power flow capability, a closed-form pulse width modulation (PWM) duty cycle function is derived. The popularly used state space averaging technique is extended for modeling the reversible three-phase four-active switch rectifier. The space vector representation technique is then used to simplify the modeling process without sacrificing accuracy and valid frequency range. Both steady-state and small signal analyses are made. Guidelines for determining the LC parameters and the PI controller gains are described.

Sar. Balance

adaptive SVM algorithm with the advantage of improving the response of the dc-link filter and the output quality of the inverter becoming high.

Toshihiko Noguchi, Hiroaki Tomiki, Seiji Kondo, and Isao Takahashi[8] proposed a novel control strategy of a pulse width modulation (PWM) converter with no power-source voltage sensors. The strategy has two main features to improve a total power factor and efficiency, taking harmonic components into account without detecting the voltage waveforms. One feature is a direct instantaneous power control technique for the converter, which has been developed to control the instantaneous active and reactive power directly by selecting the optimum switching state of the converter. The other feature is an estimation technique of the power-source voltages, which can be performed by calculating the active and reactive power for each switching state of the converter from the line currents.

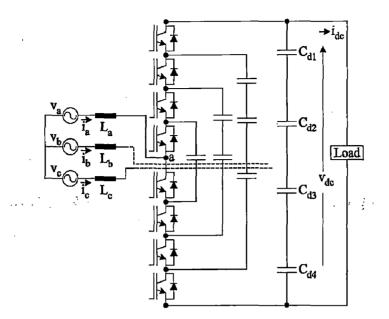

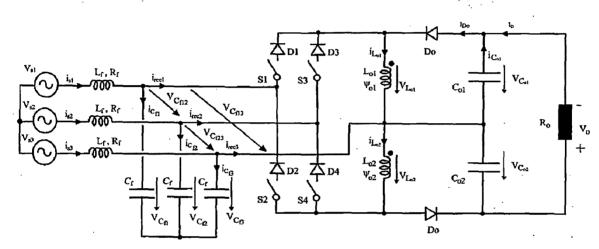

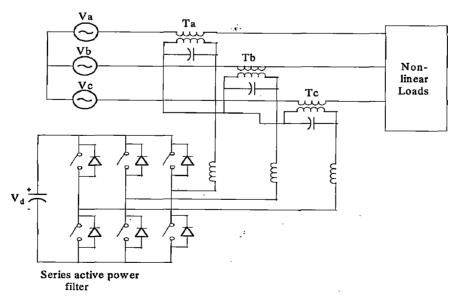

Kevork Haddad and Geza Joos[9] proposed a low cost three-phase active filter based on a PWM voltage structure with a reduced number of switches. Operation, cost, rating, and practical issues are considered and compared with the conventional six switch PWM-VSI. The paper also investigates the unbalance in the voltages of the two capacitors and discusses a new control scheme to eliminate the voltage difference.

Geza Joos Su Chen and Kevork Haddad[10] presented an active filter with reduced numbers of power switches and current sensors. The power circuit is a four-switch voltage source topology with a self controlled dc bus. Two power switches are eliminated, the third phase being connected to the capacitor center tap. Harmonic compensation is achieved by forcing the line current to be sinusoidal and no harmonic current extraction is therefore required. The proposed the algorithm is robust and there are no spikes in the line current. The active filter operates effectively in the presence of unbalanced and distorted ac mains.

S.K Jain, Pramod Agarwal and H.O Gupta[11] proposed a Fuzzy logic controlled shunt active power filter for power quality improvement. The compensation process is based on

13

only one reverse blocking power semiconductor conducts at any time. A sliding mode control of the 3-phase input currents using a space vector *a*. current modulator, capable of fast and robust current control, is also proposed. Using this control method, the converter presents high power factor and draws near sinusoidal input currents. A Proportional Integral (PI) controller is adopted to regulate the output voltage of the converter. This external voltage controller modulates the amplitudes of the current references, which are sinusoidal.

FIG 1.11 THREE PHASE FOUR SWITCH STEP-UP/DOWN RECTIFIER

#### **1.5 STATEMENT OF PROBLEM**

A particular reduced switch count topology shown in Fig. 1.10 is considered.

A three phase power factor corrected Active rectifier which draws unity power factor sinusoidal currents and which develops the desired output DC voltage with only four active switches is to be modeled, simulated and experimentally verified.

In the present work, detailed power circuit analysis was done for the undertaken topology. The design considerations and the applicability range of the rectifier were detailed. Four control strategies(reduced hysteresis, space vector modulation, direct power modulation, Fuzzy space vector modulation) were proposed and verified and compared through simulations. The application of the considered four switch three phase topology to the improvement of power quality was investigated. It is proposed that the considered rectifier can also be used for harmonic current filtering. The feasibility is

VIC HALLER & STAR

are briefly stated followed by the introduction of Shunt and series active power filters as viable power conditioners for mitigating power quality problems. Low cost three-phase active filters based on a PWM voltage structure with a reduced number of switches are proposed.

**Chapter 6:** Simulation models are developed using MATLAB/SIMULINK. Elaborate simulation study was done to check the validity of the control strategies proposed in chapter 3. The three control strategies were compared and It is found that the performance of Space vector modulated technique and direct power modulated technique are far superior than the reduced hysteresis scheme. SIMULINK models are also developed for the proposed fuzzy controlled active rectifier, reduced switch shunt active filter and reduced switch count series filter and their validity is verified.

**Chapter 7:** The second part of the thesis is the experimental validation of simulated system or proposed scheme. The hardware circuits which are developed are presented. The fabrication of control circuit and power circuit is briefly discussed.

**Chapter 8:** The recorded experimental results are displayed in this chapter.

**Chapter 9:** Conclusion is drawn from the work done and presented. Future scope for improvements in the same field to improve the performance is presented to carry out in upcoming projects.

17

Sec. 1. A.

#### **CHAPTER-2**

#### FOUR SWITCH THREE PHASE ACTIVE RECTIFIER: ANALYSIS, MODELING AND DESIGN

#### 2.1 POWER CIRCUIT DESCRIPTION

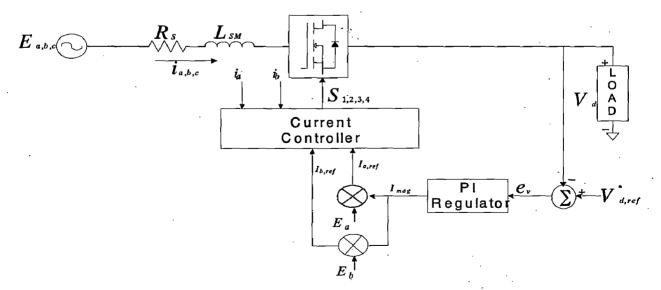

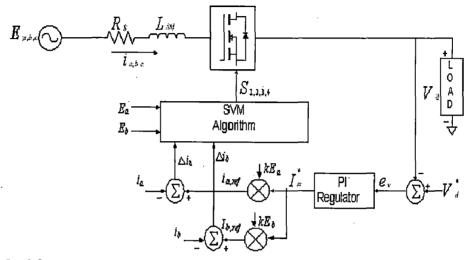

The main circuit of the proposed reversible four switch three-phase switching mode rectifier (SMR) with sinusoidal input current and regulated DC output voltage is shown in Fig 2.1. Fig 2.1 shows that the proposed rectifier consists of four switches together with two output Capacitors in series (C1 = C2) and a three-phase boost-type coupling inductor to decrease the volume, weight and size of the SMR. In order to reduce the total harmonic distortion of the input line current, a filter inductor is used on the ac side. The dc load is assumed to have resistance  $r_0$ , The power circuit is rather simple which renders the rectifier more reliable and more efficient. Because the three-phase system is balanced, it is only necessary to control two phases: the current in the third phase is controlled automatically.

#### 2.2 POWER CIRCUIT ANALYSIS

Kevork Haddad and Geza Joos[9] presented the power circuit analysis for Four switch Three-phase topology. For analysis, the following assumptions are made:

(i) the dc bus voltage  $V_{c1}$ ,  $V_{c2}$ , are pure dc and balanced

$$(V_{c1} + V_{c2} - V_d/2).$$

(ii) the converter switching elements are ideal.

| Sa | Sb | mode k | S <sub>wa</sub> (k) | S <sub>wb</sub> (k) | Swc(k) |

|----|----|--------|---------------------|---------------------|--------|

| Õ  | 0  | 1      | -1/3                | -1/3                | 2/3    |

| 1  | 0  | 2      | 1                   | -1                  | 0      |

| 1  | 1  | 3      | 1/3                 | 1/3                 | 2/3    |

| 0  | 1  | 4      | -1                  | 1                   | 0      |

and k represents the switching modes of the rectifier as given in Table 2.1.

Further, from Fig 2.1 one can derive

$$V_{an} = E_a + L \frac{di_a}{dt} \tag{9}$$

$$V_{,bn} = E_b + L \frac{di_b}{dt} \tag{10}$$

$$V_{,cn} = E_{c} + L \frac{di_{c}}{dt}$$

(11)

To facilitate the analysis, the phase variables are transformed into d-q plane. The transformation is defined as:

$\mathbf{I}_{\text{ref}} = \begin{bmatrix} i_d \\ i_q \\ i_q \end{bmatrix} = \mathbf{T} \begin{bmatrix} i^*_a \\ i^*_b \\ i^*_c \end{bmatrix} \text{ and } \mathbf{I} = \begin{bmatrix} i_d \\ i_q \end{bmatrix} = \mathbf{T} \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix}$ (12)

where

$$T = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ & & \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix}$$

(13)

$$\mathbf{V}_{\mathbf{a}}(k) = \mathbf{E} + L \frac{d}{dt} \mathbf{I}$$

(14)

$$\mathbf{E} = \begin{bmatrix} E_d \\ E_q \end{bmatrix} = \mathbf{T} \begin{bmatrix} E_a \\ E_b \\ E_c \end{bmatrix} \text{ and }$$

where

$$V_{d} > V_{d,\min} = 2\sqrt{3} \left( \hat{E} + L \left| \frac{di^{*}}{dt} \right|_{\max} \right)$$

(17)

where  $\hat{E}$  is the peak phase voltage of the supply.

#### 2.3 DESIGN OF FOUR SWITCH THREE PHASE RECTIFIER

From Fig. 2.1, one can see that the design of the power stage mainly involves determining the values of L and C =  $C_1 = C_2$ . Hence, in this section the critical condition of the inductance value needed for successful current tracking of the reference current command is derived (Ref[2]) and an analytic design method is presented to find the value of the output capacitor. For simplicity, the series resistance  $R_s$  of inductance L is neglected and it is assumed that  $V_{cl} = V_{c2} = V_d/2$ .

#### **2.3.1.** Critical Inductance Condition

From the above geometrical interpretation, one can find that the critical condition occurs only when the circle is tangent to the parallelogram. Hence, one has the following inequality:

$$(wL)^{2} < \frac{\left(\frac{V_{d}^{2}}{12} - E_{m}^{2}\right)}{I_{m}^{2}}$$

(18)

where  $V_d$  is the output dc voltage,  $E_m$  and  $I_m$ , are the peak source phase voltage and peak source line current, respectively. For design purposes, the inductance value should be based on the worst case. This is obtained by setting the output power equal to the input power so that  $I_m$  can be expressed in terms of  $E_m$  and  $P_{om}$ . This allows us to arrange the above equation in the following form

$$L < \frac{3E_m}{2wP_{om}} \sqrt{\frac{V_d^2}{12} - E_m^2}$$

(19)

where  $P_{om}$  is the maximum output power.

#### 2.3.2. Capacitor Design

The average storage energy of the capacitor can be stated as

$$I_m = \frac{E_m}{wL} \left(\frac{K}{2} - \sin\theta\right) \tag{29}$$

where  $K = V_d/E_m$ , is the normalized capacitor dc voltage parameter. The maximum active power is

$$P_m = \frac{3E_m^2}{2wL} \left(\frac{K}{2} - \sin\theta\right) \cos\theta \tag{30}$$

The normalized value of the maximum active power is

$$P_{mn} = \frac{P_m}{\frac{3E_m^2}{2wL}} = (\frac{K}{2} - \sin\theta)\cos\theta$$

(31)

#### 2.4 COMPARISON WITH SIX SWITCH TOPOLOGY

The reduced switch count inverter and the conventional three phase inverter each impose different type of stress on the active and the passive components.

#### 2.4.1. Dc Bus Voltage

For three phase inverter the condition to track the reference current is given by [15]:

$$V_d > V_{d,\min} = 2\sqrt{3} \left( \hat{E} + L \left| \frac{di^*}{dt} \right|_{\max} \right)$$

(32)

Comparing (17) and (32) we obtain

$$\frac{(V_d)_{FourSwitch}}{(V_d)_{SixSwitch}} = 2$$

(33)

Equation (33) shows that the proposed topology requires switches with blocking capability twice as high when compared to the six switch topology.

#### 2.4.2. Three Phase Inductor

The peak to peak ripple,  $\Delta I$ , generated by the six switch topology is expressed by [16]:

$$\Delta i = \frac{\left(V_d\right)_{SixSwitch}}{6L f_{sw}} \tag{34}$$

Where  $f_{sw}$  is the switching frequency.

It can be shown that the worst case peak to peak ripple for the reduced switch count topology is given by

and  $S_b$ ) in Fig 2.1. For convenient simulation using common software tools available for PC's, one can define the currents  $i_1$ ,  $i_2$  and  $i_3$  and voltages  $V_{an}$ ,  $V_{bn}$ ,  $V_{cn}$  as shown in Fig. 2.1 as well as the following switching functions:

$S_a(t) = +1$  if  $S_a^+$  is off and  $S_a^-$  is on.

= -1 if  $S_a^+$  is on and  $S_a^-$  is off.

$S_b(t) = +1$  if  $S_b^+$  is off and  $S_b^-$  is on.

= -1 if  $S_b^+$  is on and  $S_b^-$  is off.

From Fig.2.1 it is quite straight forward to find the following state equations and the output equations

$$\frac{d}{dt} \begin{bmatrix} v_{c1} \\ v_{c2} \\ i_{a} \\ i_{b} \end{bmatrix} = \begin{bmatrix} \frac{1}{R_{0}C} & -\frac{1}{R_{0}C} & a_{13} & a_{14} \\ -\frac{1}{R_{0}C} & -\frac{1}{R_{0}C} & a_{23} & a_{24} \\ a_{31} & a_{32} & -\frac{r}{L} & 0 \\ a_{43} & a_{42} & 0 & -\frac{r}{L} \end{bmatrix} \begin{bmatrix} v_{c1} \\ v_{c2} \\ i_{a} \\ i_{b} \end{bmatrix} \\

+ \begin{bmatrix} 0 & 0 \\ 0 & 0 \\ \frac{1}{L} & 0 \\ 0 & \frac{1}{L} \end{bmatrix} \begin{bmatrix} v_{a} \\ v_{b} \end{bmatrix} \\

\frac{V_{an}}{V_{an}} \\ V_{an} \end{bmatrix} = \frac{1}{6} \begin{bmatrix} 1+2S_{a}(t)-S_{b}(t) & -1+2S_{a}(t)-S_{b}(t) \\ 1-S_{a}(t)+2S_{b}(t) & -1-S_{a}(t)+2S_{b}(t) \\ -2-S_{a}(t)-S_{b}(t) & 2-S_{a}(t)-S_{b}(t) \end{bmatrix} \begin{bmatrix} V_{c1} \\ V_{c2} \end{bmatrix} \\

\begin{bmatrix} i_{1} \\ i_{2} \\ i_{3} \end{bmatrix} = \frac{1}{2} \begin{bmatrix} 1+S_{a}(t) & 1+S_{b}(t) \\ -2 & -2 \\ 1-S_{a}(t) & 1-S_{b}(t) \end{bmatrix} \begin{bmatrix} i_{a} \\ i_{b} \end{bmatrix}$$

where

$a_{13} = \frac{1}{2C} [S_a(t) + 1]$

#### **2.6 CONCLUSIONS**

- A minimum DC output voltage condition for successful current tracking for a given boost inductor value is derived (eqn.17).

- A critical Inductance condition for successful current tracking is derived (eqn.18) for a given maximum output power.

- A design criteria for capacitance value is derived (eqn.26) in terms of ΔP<sub>max</sub>, the maximum expected variation of the output power, and T<sub>r</sub> is the response time of the voltage control loop.

- Comparisons were made between six switch topology and four switch case in terms of capacitor values, inductor values and switching losses.

- An accurate simulation model for convenient simulation using common PC software tools is given.

#### **CHAPTER-3**

#### **CONTROL STRATEGIES**

This chapter mainly focuses on the control techniques of Four switch Three-Phase active rectifier. The traditional controls (Hysteresis,Closed form PWM duty cycle control) are briefly discussed. Three High performance control strategies Reduced hysteresis control, Space vector modulated control, Direct Power modulated control of the reduced switch Interface are then presented. The basic theory and implementation of the control strategies are explained.

#### **3.1 INTRODUCTION**

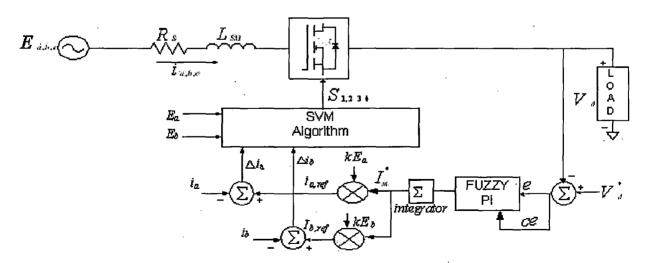

Fig 3.1 shows the general control block diagram of the four switch three phase active rectifier. The PI controller controls the sum of capacitor voltage, the overall dc link voltage. For unity power factor operation the controller output  $I_{mag}$  is multiplied by the ac main phase voltage templates to generate the input current references. Because the input references are in phase with the input phase voltages, the PI controller output is, in effect, the magnitude of power component of current, the required power by the capacitors to maintain the dc link voltage constant. Reactive current components can be added to the current references to control input power factor.

#### FIG 3.1 GENERAL CONTROL BLOCK DIAGRAM

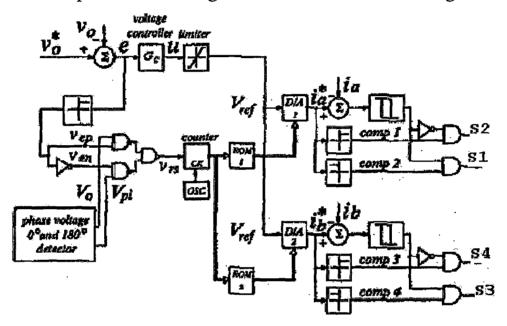

are then forced to follow the respective reference current signals by two hysteretic current controllers. As far as the rectifier objective is concerned, it is the output dc voltage which has to be controlled. Hence, the second loop is the voltage control loop. By comparing the output voltage signal  $V_0$  with the reference signal  $V_0^*$ ; one can obtain the error signal. A voltage controller, such as the simple proportional-integral (PI) controller  $G_C$  in Fig 3.2, is used to shape the system dynamic response characteristics. Naturally, in a practical implementation, a limiter must be imposed to obtain a reasonable output. This output is then used in the current loop to control the magnitude of the current-command signals.

FIG 3.2 BLOCK DIAGRAM OF HYSTERESIS CONTROL

#### 3.2.2 Closed-form PWM duty cycle Control

A closed form PWM duty cycle control law is derived. The input line current is forced to be sinusoidal by following the derived equations. Also, by closed-loop implementation,  $I_m^*$  can be controlled automatically and indirectly without using any current sensor. Fig. 3.3 shows the schematic diagram of the control function.

#### Derivation of closed form PWM duty cycle control law

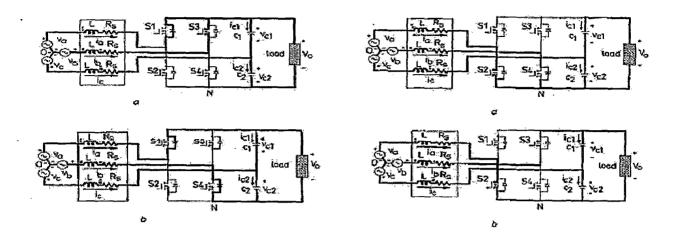

A typical gating signal and ideal three-phase input current waveforms are shown in Figs 3.4 and 3.5, respectively. Figs 3.6 and 3.7 show the resulting equivalent circuit during time intervals A and B in Fig. 3.5 for one switching cycle  $t_0$  - $t_4$ .

31

FIG 3.6 EQUIVALENT CIRCUITS FOR SECTION A AND B OF FIG 3.5 FIG 3.7 Г

I

$$\begin{bmatrix} L+2L_{m} & 0 & 0 & 0 & 0 \\ 0 & L+2L_{m} & 0 & 0 & 0 \\ 0 & 0 & L+2L_{m} & 0 & 0 \\ 0 & 0 & 0 & C & 0 \\ 0 & 0 & 0 & 0 & C \end{bmatrix} \stackrel{i}{d} \frac{d}{dt} \begin{bmatrix} i_{a} \\ i_{b} \\ i_{c} \\ v_{e1} \\ v_{e2} \end{bmatrix}$$

$$= \begin{bmatrix} -R_{s} & 0 & 0 & -d_{a} - d_{a} \\ 0 & -R_{s} & 0 & -d_{b} - d_{b} \\ 0 & 0 & -R_{s} & 0 & 1 \\ d_{a} & d_{b} & 0 & -\frac{1}{R} - \frac{1}{R} \end{bmatrix} \begin{bmatrix} i_{a} \\ i_{b} \\ i_{c} \\ v_{c2} \end{bmatrix}$$

$$+ \begin{bmatrix} v_{a} \\ v_{b} \\ v_{v} \\ 0 \\ 0 \end{bmatrix} - \begin{bmatrix} 1 \\ 1 \\ 1 \\ 0 \\ 0 \end{bmatrix} \underbrace{v_{N0}}$$

Where  $d_{a}$ , and  $d_{b}$  are duty ratios of switch S1, and S3, respectively. Assuming that the three-phase source is balanced, i.e.

$i_a + i_b + i_c = 0$  $v_a + v_b + v_c = 0$

r

; **; ; ;**

decrease. The maximum ripple of ic could happen under this condition. In other conducting path (say 2), ia increases and ib decreases. Therefore, ic could increase or decrease. However,  $|i_c|$  must be smaller than the maximum of  $|i_a|$  and  $|i_b|$ . Originally, it needs four control inputs (two for determining the section number and two for indicating the polarities of . i<sub>a</sub> and . i<sub>b</sub>) to choose from 16 combinations of switching states, as shown in Table 3.2, where "1" represents turned-on, "0" represents turned-off, and "x" means "do not care." When the state of a switch is "do not care," the current is actually carried by its paralleled reverse diode. However, the switch can still be turned on without affecting the circuit operations. If we replace "x" in Table 3.2 with "1," the dimension of the lookup table can be greatly reduced. For example, in case ia and ib are to be increased, we can always select the switching state as (0 1 0 1). There is no need to detect the section number. Therefore, only two control inputs are required to choose from four switching states. Fig. 3.8 shows the schematic diagram of the proposed system, in which  $d_a$  and  $d_b$  are the outputs of the hysteresis comparators. For example, if both  $i_a$  and  $i_b$  are to be decreased, then  $(d_a d_b)$  will be (0 0). Thus, S2 and S4 should be turned on according to Table 3.2. The current commands iaref and ibref are sinusoidal and in phase with the respective source voltages. Their magnitudes are determined by the feedback dc output voltage V<sub>d</sub>.

|            |               |                    | IADLL           | 5.1            |                 |                 |                                         |

|------------|---------------|--------------------|-----------------|----------------|-----------------|-----------------|-----------------------------------------|

| Conducting | Conducting    | Va                 | V <sub>b</sub>  | V <sub>c</sub> |                 |                 | Δic                                     |

| Path       | Switches      | _                  | · · ·           |                | Δi <sub>a</sub> | Δi <sub>b</sub> | (                                       |

| 1          | S2(D2),S4(D4) | -V <sub>d</sub> /3 | $-V_d/3$        | $2V_d/3$       | +               | +               | -                                       |

| 2          | S2(D2),S3(D3) | -V <sub>d</sub>    | Vd              | 0              | +               | -               | $ . i_c < max\{ . i_a ,  . i_b \}$      |

| 3          | S1(D1),S4(D4) | V <sub>d</sub>     | -V <sub>d</sub> | 0              | -               | +               | $i_{c} < max\{  , i_{a} ,  , i_{b}  \}$ |

| 4          | S1(D1),S3(D3) | $V_d/3$            | $V_d/3$         | $-2V_{d}/3$    | -               | _               | +                                       |

TABLE 3.1

TABLE 3.2

| Section/ $Ai_a$ , $Ai_b$ | ++                     | +-               | -+                                  |                                     |

|--------------------------|------------------------|------------------|-------------------------------------|-------------------------------------|

| $I(E_a > 0, E_b < 0)$    | (0 10 x)               | (0 1 1 0)        | $(\mathbf{x} \ 0 \ 0 \ \mathbf{x})$ | (x 0 1 0)                           |

| $II(E_a > 0, E_b > 0)$   | (0101)                 | $(0 1 \times 0)$ | (x 0 0 1)                           | $(\mathbf{x} \ 0 \ \mathbf{x} \ 0)$ |

| $III(E_a < 0, E_b > 0)$  | $(0 \times 0 1)$       | $(0 \times x 0)$ | (1001)                              | $(10 \times 0)$                     |

| $IV(E_a < 0, E_b < 0)$   | $(0 \times 0 \times )$ | $(0 \ge 1 \ 0)$  | (100 x)                             |                                     |

| $2\pi$ period            | (0101)                 | (0 1 1 0)        | (1001)                              | (1010)                              |

35

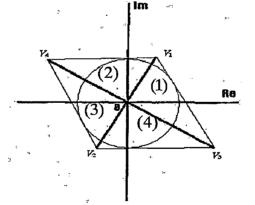

increase in switching frequency. If surplus modulation time is shared between,  $(V_3, V_4)$  then  $V_c$  has more ripple and hence  $i_c$  ripple increases causing increased voltage imbalance across two capacitors.

| SPACE VECTORS FOR DIFFERENT COMBINATIONS |                               |                  |                  |                  |                                                    |

|------------------------------------------|-------------------------------|------------------|------------------|------------------|----------------------------------------------------|

|                                          | Active<br>switches            | Va               | Vb               | V <sub>c</sub>   | Space<br>Vector<br>(V)                             |

| 11<br>(C <sub>1</sub> )                  | S <sub>1</sub> S <sub>3</sub> | $\frac{V_d}{6}$  | $\frac{V_d}{6}$  | $\frac{-V_d}{3}$ | $\frac{\frac{V_d}{6}(1+j\sqrt{3})}{(V_1)}$         |

| 00<br>(C <sub>2</sub> )                  | S <sub>2</sub> S <sub>4</sub> | $\frac{-V_d}{6}$ | $\frac{-V_d}{6}$ | $\frac{V_d}{3}$  | $\frac{-V_d}{6}^{(1+j\sqrt{3})}$                   |

| 10<br>(C <sub>3</sub> )                  | S <sub>1</sub> S <sub>4</sub> | $\frac{V_d}{2}$  | $\frac{-V_d}{2}$ | 0                | $\frac{\frac{V_d}{6}}{(3\cdot\mathbf{j}\sqrt{3})}$ |

| 01<br>(C4)                               | S <sub>2</sub> S <sub>3</sub> | $\frac{-V_d}{2}$ | $\frac{V_d}{2}$  | 0                | $-\frac{V_d}{6}(3-\sqrt{3})$ $(V_4)$               |

| TABLE 3.3 |         |     |           |              |

|-----------|---------|-----|-----------|--------------|

| SPACE     | VECTORS | FOR | DIFFERENT | COMBINATIONS |

FIG 3.9 SPACE VECTOR DIAGRAM

Hence  $(V_1, V_2)$  combination is preferred. If  $V_{a,ref}$ ,  $V_{b,ref}$ ,  $V_{c,ref}$  are the desired rectifier input phase voltages to be synthesized, It can be written in space vector notation as

$$V_{ref} = (V_{d,ref} + jV_{q,ref}) = V_{a,ref} + V_{b,ref} e^{j2\pi/3} + V_{c,ref} e^{-j2\pi/3}$$

(A)

The quadrant in which the desired  $V_{ref}$  lies can be obtained using Table 3.4.

3.

- b. Using eqn. (A) calculate  $V_{d,ref}$ ,  $V_{q,ref}$ , From Table 3.4, the quadrant in which  $V_{ref}$  is present can be found.

- c. The duty ratios  $d_1$ ,  $d_2$ ,  $d_3$ ,  $d_4$  for which the switching states,  $V_1$ ,  $V_2$ ,  $V_3$ ,  $V_4$  are applied is calculated from Table 3.5.

FIG 3.10 COMPLETE BLOCK DIAGRAM OF THE SVM SCHEME

| DUTY      | RATIO CALCULATION                                                                                                                                                     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Quadrants | Duty ratios                                                                                                                                                           |

| 2,3       | $d_{1} = \frac{1}{2} + \frac{V_{a,ref} - V_{c,ref}}{V_{d}}$ $d_{2} = \frac{1}{2} + \frac{V_{c,ref} - V_{b,ref}}{V_{d}}$ $d_{4} = \frac{V_{b,ref} - V_{a,ref}}{V_{d}}$ |

| 1,4       | $d_{1} = \frac{1}{2} + \frac{V_{b,ref} - V_{c,ref}}{V_{d}}$ $d_{2} = \frac{1}{2} + \frac{V_{c,ref} - V_{a,ref}}{V_{d}}$ $d_{3} = \frac{V_{a,ref} - V_{b,ref}}{V_{d}}$ |

TABLE 3.5 DUTY RATIO CALCULATION b. The following equations are to be solved to obtain  $d_1, d_2, d_3$ .

$p_{ref} = p_1 d_1 + p_2 d_2 + p_3 d_3$  $q_{ref} = q_1 d_1 + q_2 d_2 + q_3 d_3$  $d_1 + d_2 + d_3 = 1$

where  $p_{ref}$ ,  $q_{ref}$  are reference instantaneous active and reactive powers.

c. If  $d_1>0$ ,  $d_2>0$  and  $d_3>0$ , then the duty ratios for which switching states  $C_1, C_2, C_3$  are to be applied are obtained. Else replace  $p_3, q_3d_3$  by  $p_4, q_4, d_4$  respectively, in the above equations and solve them to obtain  $d_1, d_2, d_4$ . The obtained duty ratios are the duty ratios for which  $C_1, C_2, C_4$  are to be applied with in a sampling period.

The complete control block diagram for DPM bidirectional interface is shown in Fig 3.11 The active power reference( $p_{ref}$ ) is set by dc-link voltage controller while the reactive power reference( $q_{ref}$ ) is set to zero for unity power factor.

Suppose instantaneous active and reactive powers that would have developed if  $C_1$  were to be applied for the entire sampling period is to be calculated, the currents at the end of the sampling period are obtained from Table 3.3 as

$$i_{a,n+1} = i_{a,n} + \frac{\Delta T}{L} (E_a - \frac{V_d}{6})$$

$$i_{b,n+1} = i_{b,n} + \frac{\Delta T}{L} (E_b - \frac{V_d}{6})$$

where  $(n+1)^{th}$  instant is the instant at the end of sampling period and n<sup>th</sup> instant is the present instant. The instantaneous active and reactive powers at  $(n+1)^{th}$  instant  $p_{1,n+1}, q_{1,n+1}$  are obtained from

$$p_{1,n+1} = E_{a,n+1}i_{a,n+1} + E_{b,n+1}i_{b,n+1} + E_{c,n+1}i_{c,n+1}$$

$$q_{1,n+1} = \frac{1}{\sqrt{3}} \left[ (E_{b,n+1} - E_{c,n+1})i_{a,n+1} + (E_{c,n+1} - E_{a,n+1})i_{b,n+1} + (E_{a,n+1} - E_{b,n+1})i_{c,n+1} \right]$$

where  $E_{a,n+1}$ ,  $E_{b,n+1}$ ,  $E_{c,n+1}$  are the input phase voltages at  $(n+1)^{\text{th}}$  instant. For balanced three phase system

$$E_{c,n+1} = -(E_{a,n+1} + E_{b,n+1})$$

$$i_{c,n+1} = -(i_{a,n+1} + i_{b,n+1})$$

Hence sensing two phase voltages  $(E_a, E_b)$  and two line currents  $(i_a, i_b)$  is enough. The

159

#### **CHAPTER-4**

#### FUZZY CONTROL OF FOUR SWITCH THREE PHASE ACTIVE RECTIFIER

This chapter mainly focuses on the application of fuzzy controller to the DC output voltage control loop. The use of fuzzy controller improves the dynamic response of the rectifier. The theoretical aspects and design procedures of fuzzy controllers are briefly discussed followed by the definition of membership functions and Rule base used in the adopted fuzzy controller.

#### **4.1 INTRODUCTION**

Since the introduction of the theory of fuzzy sets by L. A. Zadeh in 1965, and the industrial application of the first fuzzy controller by E.H. Mamadani in 1974, fuzzy systems have obtained a major role in engineering systems and consumer's products in 1980s and 1990s. New applications are presented continuously. A reason for this significant role is that fuzzy computing provides a flexible and powerful alternative to contract controllers, supervisory blocks, computing units and compensation systems in different application areas. With fuzzy sets very nonlinear control actions can be formed easily. The transparency of fuzzy rules and the locality of parameters are helpful in the design and maintenances of the systems. Therefore, preliminary results can be obtained within a short development period. However, fuzzy control does have some weaknesses. One is that fuzzy control is still lacking generally accepted theoretical design tools. Although preliminary results are easily obtained, further improvements need a lot of labor especially when the number of inputs increases, the maintenances of the multi-dimensional rule base is time consuming.

Due to continuously developing automation systems and more demanding Control performance requirements, conventional control methods are not always adequate. On the other hand, practical control problems are usually imprecise. The input output relations of the system may be uncertain and they can be changed by unknown external disturbances. New schemes are needed to solve such problems. One such an approach is to utilize fuzzy control. universe is U=(-5, -4, ..., 0, ..., 4, 5). The quantiser rounds to 5 to fit it to the nearest level. Quantisation is a means to reduce data, but if the quantisation is too coarse the controller may oscillate around the reference or even become unstable. When the input to the controller is error, the control strategy is a static mapping between input and control signal. A dynamic controller would have additional inputs, for example derivatives, integrals, or previous values of measurements backwards in time. These are created in the preprocessor thus making the controller multi-dimensional, which requires many rules and makes it more difficult to design. The preprocessor then passes the data on to the controller.

### 4.2.2 Fuzzification

ナ

The first block inside the controller is fuzzification, which converts each piece of input data to degrees of membership by a lookup in one or several membership functions. The fuzzification block thus matches the input data with the conditions of the rules to determine how well the condition of each rule matches that particular input instance. There is a degree of membership for each linguistic term that applies to that input variable

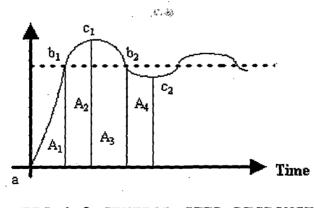

**4.2.3 Rule base** The rule base is to do with the fuzzy inference rules. The step response of the system can be roughly divided into four areas  $A_I \sim A_4$  and two sets of points: cross-over  $\{b_1, b_2\}$  and peak-valley  $\{c_1, c_2\}$  as shown in Fig.4.2. The system equilibrium point is the origin of the phase plane

FIG 4.2 GENERAL, STEP RESPONSE

a) The sign of rules: The sign of the rule base can be determined by following meta-rules

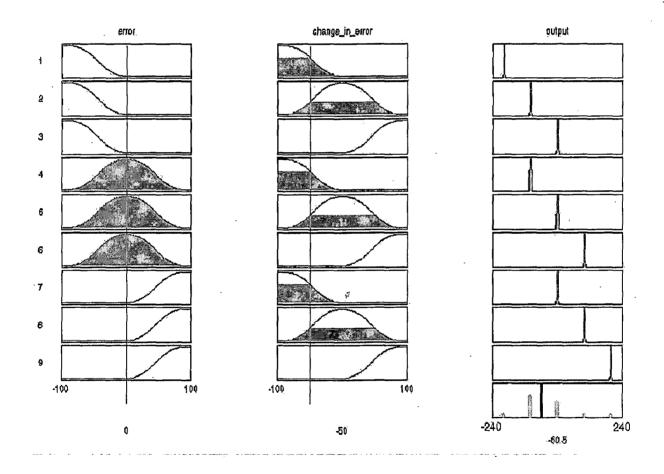

Activation: The activation of a rule is the deduction of the conclusion, possibly reduced by its firing strength. Thickened lines in the third column indicate the firing strength of each rule. Only the thickened part of the singletons are activated, and **min** or product (\*) is used as the activation operator. It makes no difference in this case, since the output membership functions are singletons, but in the general case of s-,. - and z- functions in the third column, the multiplication scales the membership curves, thus preserving the initial shape, rather than clipping them as the **min** operation does. Both methods work well in general, although the multiplication results in a slightly smoother control signal. In Fig. 4.3, only rules four and five are active.

FIG 4.3 GRAPHICAL CONSTRUCTION OF THE CONTROL SIGNAL IN A FUZZY PD CONTROLLER (GENERATED IN THE MATLAB FUZZY LOGIC TOOLBOX).

The alphas are the firing strengths from the k rules and s1 ... sn are the output singletons. Since this can be computed as a vector product, this type of inference is relatively fast in a matrix oriented language. There could actually have been several conclusion sets. An example of a one-input two- outputs rule is "If  $e_a$  is **a** then  $o_1$  is **x** and  $o_2$  is **y**'. The inference engine can treat two (or several) columns on the conclusion side in parallel by applying the firing strength to both conclusion sets. In practice, one would often implement this situation as two rules rather than one, that is, "If  $e_a$  is **a** then  $o_1$  is **x**", "If ea is **a** then  $o_2$  is **y**".

#### **4.2.5 Defuzzification**

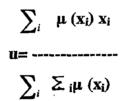

The resulting fuzzy set (Fig. 4.3, bottom right; Fig. 4.4, extreme right) must be converted to a number that can be sent to the process as a control signal. This operation is called defuzzification, and in Fig. 4.4 the x-coordinate marked by a white, vertical dividing line becomes the control signal. The resulting fuzzy set is thus defuzzified into a crisp control signal. There are several defuzzification methods.

Centre of gravity (COG): The crisp output value u (white line in Fig. 4.4) is the abscissa under the centre of gravity of the fuzzy set,

Here  $x_i$  is a running point in a discrete universe, and  $\mu(x_i)$ , is its membership value in the membership function. The expression can be interpreted as the weighted average of the elements in the support set. For the continuous case, replace the summations by integrals. It is a much used method although its computational complexity is relatively high. This method is also called centroid of area.

Centre of gravity method for singleton (COGS): If the membership functions of the conclusions are singletons (Fig.4.3), the output value is

March Mar

## 4.3 FUZZY CONTROL OF FOUR SWITCH PFC RECTIFIER

Fig 4.5 shows the schematic control block diagram of Four switch three phase active rectifier with fuzzy output control. In order to implement the control algorithm in closed loop, the DC side capacitor voltage is sensed and then compared with a reference value. The obtained error  $e(=V_d^*-V_d)$  and change of error signal ce(n)=e(n)-e(n-1) at the n<sup>th</sup> sampling instant are used as input to fuzzy processing. The output of fuzzy controller is integrated in discrete time to get the amplitude of current reference  $I_m^*$ . This current  $I_m^*$  takes care of the active power demand of the load and losses in the system. For unity power factor operation  $I_m^*$  is multiplied by input phase voltage templates to get reference instantaneous currents ( $i_{a,ref}$ ,  $i_{b,ref}$ ). Then the reduced hysteresis control or SVM or DPM algorithm discussed in previous chapter can be applied to make the actual current track the references.

The adopted Fuzzy controller has the following characteristics

- a. seven sets for each input and output

- b. Triangular membership functions for simplicity

- c. Fuzzification using continuous universe of discourse

- d. Implication using mamdani's min operator

- e. Defuzzification using centre of gravity method

FIG 4.5 BLOCK DIAGRAM OF FUZZY SVM CONTROL

# APPLICATION OF FOUR SWITCH THREE-PHASE TOPOLOGY TO POWER QUALITY IMPROVEMENT

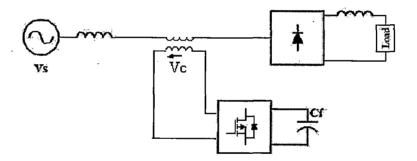

The main focus of this chapter is to investigate application of four switch threephase topology for power quality improvement. The causes of power quality problems are briefly stated followed by the introduction of Shunt and series active power filters as viable power conditioners for mitigating power quality problems. The four-switch three phase topology discussed in the previous chapters can be extended to filter harmonic line currents. The control scheme for such rectifier acting as shunt filter is discussed. A Low cost three-phase series active filter to compensate source voltage unbalances and harmonics is also discussed along with its control strategy.

## **5.1 POWER QUALITY ISSUES: AN INTRODUCTION**

Power quality phenomena include all possible situations in which the waveform of the supply voltage (voltage quality) or load current (current quality) deviate from the sinusoidal waveform at rated frequency with amplitude corresponding to the rated rms value for all three phases of a three-phase system. The wide range of power quality disturbances covers sudden, short duration deviations, e.g. impulsive and oscillatory transients, voltage dips (or sags), short interruptions, as well as steady-state deviations, such as harmonics and flicker. One can also distinguish, based on the cause, between disturbances related to the quality of the supply voltage and those related to the quality of the current taken by the load.

To the first class belong, among others, voltage unbalances, harmonics and interruptions, mostly caused by faults in the power system. The voltage imbalance is usually due to the unbalanced consumption of single-phase loads connected to the distribution network or due to the unbalanced emf of the network itself. The voltage harmonics are mainly caused by nonlinear loads which inject current harmonics through supply impedance or by voltage harmonics present in the mains emf. These disturbances may cause tripping of "sensitive" electronic equipment with disastrous consequences in industrial plants, where tripping of critical equipment can bear the stoppage of the whole

# 5.2 A FOUR SWITCH THREE-PHASE ACTIVE RECTIFIER WITH THE FUNCTION OF A SHUNTACTIVE POWER FILTER

A number of topologies have been proposed in the literature for shunt active power filters based on voltage source structures. The most common is the conventional six-switch structure, as in Fig. 5.2. However, these filters become costly at increased power levels. The growing interest in low cost active filters has led researchers to investigate hybrid active filters. By combining passive and active filters, the rating of the active filter is reduced, hence the cost. This section present a cost effective reduced switch count PWM rectifier based active filter Fig. 5.3. Most of the compensation schemes for active filters are based on sensing harmonics and reactive volt-ampere requirements of the nonlinear load, and require complex control. Duke and Round [17] have proposed a scheme in which the required compensating current is determined using a simple synthetic sinusoid generation technique by sensing the load current. This scheme is further modified by sensing line currents only, which is simple and easy to implement. The three phase currents/voltages are detected using only two current/voltage sensors. The DC capacitor voltage is regulated to estimate the reference current template. Fig. 5.3 shows the configuration of a four switch three phase active rectifier with active line current filtering capability. The main advantages of the proposed active filter are:

(i) reduced number of switches and lower cost

(ii) lower overall converter and switch ratings and higher efficiency

(iii) increased reliability

(iv) simple power structure

(v) reduced number of current sensors.

A PWM rectifier is used here for active power filtering purpose. The active power filter and PWM rectifier have basically the same circuit configuration and can operate based on the same control principle. Therefore, a power converter capable of both the active filter operation and PWM rectifier operation at the same time can be designed. Such a converter operates as a PWM rectifier to supply DC power to its own load and, at the same time, operates as an active filter to supply to the AC line a compensating current equal to the harmonic current produced by the nonlinear load connected to the same AC line.

and the second second

#### **5.2.1 Compensation Principle**

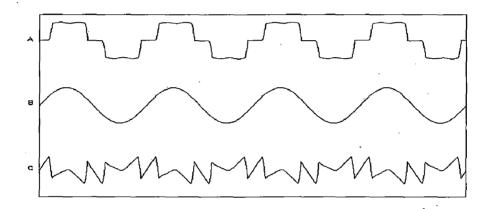

The active filter is controlled to draw/supply a compensating current  $i_{af}$  from/to the utility, so that it cancels current harmonics on the AC side, and makes the source current in phase with the source voltage. Fig. 5.4 shows the different waveforms. Curve 'A' shows the load current waveform and curve 'B' shows the desired source current. Curve 'C' shows the compensating current injected by the active power filter containing all the harmonics, to make the source current sinusoidal.

Fig 5.4:A NON LINEAR LOAD CURRENT B DESIRED SOURCE CURRENT C HARMONIC CONTENT IN LOAD CURRENT

### **5.2.2 The Control Scheme**

Ref [18, 19] proposed a indirect estimation for harmonic and reactive power compensation. This technique has brought a revolution in the control technique. It can be easily implemented using simple and less analog circuits. The voltage and current sensors can also be reduced making the control circuitry simple.

Role of DC link capacitors serves important role in this technique. They maintain a DC voltage with small ripples in steady state and serves as an energy storage element to supply real power difference between load and source during transients. In steady state the real power supplied by the source should be equal to the real power demand of the load plus some small power to compensate the losses in the active filter. Thus DC link voltage can be maintained at a reference value. However, when the load condition changes the real power balance between the mains and the load will be disturbed. This

1.1914 - 1

From (4), the real (fundamental) power drawn by the load is

$$p_{f}(t) = V_{m}I_{1}\sin^{2}\omega t * \cos \phi_{1} = v_{s}(t)*i_{s}(t)$$

(6)

From (6), the source current supplied by the source, after compensation is

$$i_s(t) = p_f(t) / v_s(t) = I_1 \cos \phi_1 \sin t = I_{sm} \sin \omega t$$

where  $I_{sm} = I_1 \cos \phi_1$ .

There are also some switching losses in the PWM converter, and hence utility must supply a small overhead for capacitor leakage and converter switching losses in addition to the real power of the load. The total peak current supplied by the source is therefore

$$I_{sp} = I_{sm} + I_{sl} \tag{7}$$

If the active filter provides the total reactive and harmonic power, then  $i_s(t)$  will be in phase with the utility voltage and purely sinusoidal. At this time, the active filter must provide the following compensation current:

$$I_{af}(t) = i_{load}(t) - i_s(t)$$

hence for accurate and instantaneous compensation of reactive and harmonic power it is necessary to estimate  $i_s(t)$ , i.e. the fundamental component of the load current as the reference current.

The peak value of reference current  $I_{sp}$  can be estimated by controlling the DC capacitor voltage. Ideal compensation requires the main current to be sinusoidal and in phase with the source voltage, irrespective of the load current nature. The desired source currents after compensation can be given as

$$i_{sa}^{*} = I_{sp} \sin \omega t$$

$$i_{sb}^{*} = I_{sp} \sin (\omega t - 120^{0})$$