# COMPARISON OF CONFIGURATIONS OF CONVERTER FOR UPFC

### **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree of

MASTER OF TECHNOLOGY

## ELECTRICAL ENGINEERING

(With Specialization in Power System Engineering)

By

EGA AJITH KUMAR

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA)

**JUNE, 2006**

ID. NO. MT-346/2006-41/EAK-BO-VP

## INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE – 247 667 (INDIA)

## **CANDIDATE'S DECLARATION**

I hereby declare that the work presented in this dissertation entitled "Comparison of configurations of converter for UPFC" is submitted in partial fulfillment of the requirement for the award of the degree of Master of Technology with specialization in Power Systems Engineering in the Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out from July 2005 to June 2006 under the esteemed guidance of Dr. B.Das, Associate professor & Dr. Vinay pant, Assistant professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee.

I have not submitted the matter embodied in this report for the award of any other degree or diploma.

**30<sup>th</sup>** Date: June, 2006 Place: Roorkee

## **CERTIFICATE**

This is to certify that the above statement made by the candidate is true to the best of my knowledge and belief.

(**Dr. Vinay pant**) Assistant Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee – 247667, India.

(Dr. B.Das) Associate Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee – 247667, India.

## ACKNOWLEDGEMENTS

This is consummated and symbolized not only my efforts but also guidance and vital inputs of my supervisor at crucial junctures in the course of this undertaking to whom I would like to express my gratitude.

I wish to express my deep sense of gratitude and sincere thanks to my loving guides **Dr. B.Das** and **Dr. Vinay Pant**, Electrical Engineering Department, IIT Roorkee, for being helpful and a great source of inspiration. Their keen Interest and constant encouragement gave me the confidence to complete my work. I wish to extend my sincere thanks from the soul of my heart, for their excellent guidance and suggestions for the successful completion of my project work.

I would like to express my sincere thanks to **Dr. R.N. Patel** Electrical Engineering Department, IIT Roorkee, for being helpful timely, suggestions towards the successful completion of this work.

I wish to express my thanks to all my friends, especially Miss. *Swathi*. *Y* for her kind support and help during my entire work of thesis.

I am also thankful to *Ankur. somvanshi, Avinash wadhvani* and all my friends for their continuous support and help during different stages of thesis work especially during my documentation work.

Last but not least, I'm highly indebted to my parents and family members whose sincere prayers, best wishes, moral support have a constant source of assurance, guidance, and inspiration for me.

#### (Ega Ajith Kumar)

# CONTENTS

| <b>Sl.</b> No. | Title                                                   | age No. |

|----------------|---------------------------------------------------------|---------|

|                | Candidate's Declaration                                 |         |

|                | Acknowledgements                                        | i       |

|                | List of Figures                                         | v       |

|                | List of Tables                                          | vii     |

|                | Abstract                                                | viii    |

| 1. Intro       | oduction                                                | 1       |

|                | 1.1 FACTS in power systems                              | 2       |

|                | 1.1.1 Controllable parameters for FACTS                 | 2       |

|                | 1.1.2 Types of FACTS Controllers                        | 3       |

|                | a. Series Controller                                    | -3      |

|                | b. Shunt Controller                                     | - 4     |

|                | c. Combined series-shunt Controller                     | 5       |

|                | d. Combined series-series Controller                    | 6       |

| • • •          | 1.1.3 Advantages of FACTS Controllers                   | 6       |

|                | 1.2 Unified Power Flow Controller (UPFC)                | 9       |

|                | 1.2.1 Basic operating principle                         | 10      |

|                | 1.2.2 Transmission line controllable capabilities       | 11      |

|                | 1.2.3 Basic control structure of UPFC                   | 12      |

|                | 1.2.4 Different configurations of UPFC & literature rev | view 14 |

|                | 1.2.5 Relevant review of literature                     | 14      |

|                | 1.3 Outline of the Thesis                               | 17      |

|                | 1.3.1 Description of Test System and its results        | 18      |

| • • •          | 1.4 Conclusions                                         | 20      |

| 2. | UPFC using Basic 2-level VSC                                                            | 21       |

|----|-----------------------------------------------------------------------------------------|----------|

|    | 2.1 Introduction                                                                        | 21       |

|    | 2.2 Shunt Inverter switching scheme                                                     | 22       |

|    | 2.2.1 Hysterisis Current Control                                                        | 23       |

|    | 2.3 Series Inverter switching scheme                                                    | 25       |

|    | 2.3.1 Sinusoidal Pulse Width Modulation                                                 | 25       |

|    | 2.4 Control structure                                                                   | 27       |

|    | 2.5 Simulation results                                                                  | 28       |

|    | 2.5.1 Case (i)                                                                          | 28       |

|    | 2.5.2 Case (ii)                                                                         | 33       |

|    | 2.6 Conclusion                                                                          | 36       |

| 3. | UPFC using on 3-level Half-Bridge Diode-Clamped<br>Multi Level Inverter (DC MLI) Module | 37       |

|    | Multi Level Inverter (DC MLI) Module                                                    | 37       |

|    | 3.1 Introduction                                                                        | 37       |

| `  | 3.1.1 Multilevel inverters<br>3.2 Basic Operating principle DC MLI                      | 37<br>39 |

|    | 3.2.1 Advantages                                                                        | 43       |

|    | 3.2.2 Disadvantages                                                                     | 43       |

|    | 3.3 Structure of UPFC                                                                   | 43       |

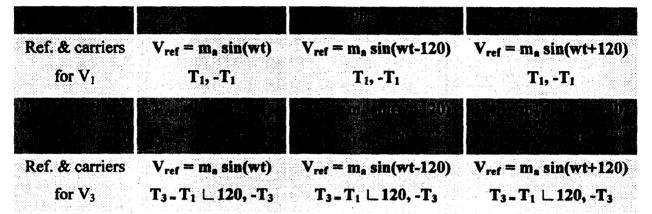

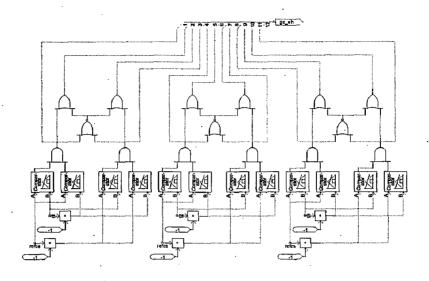

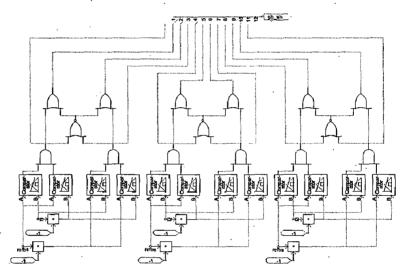

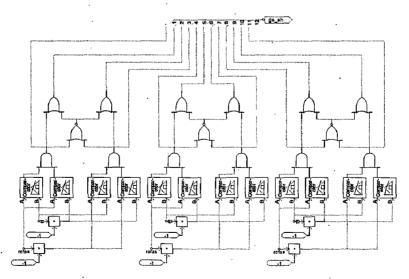

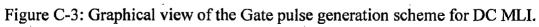

|    | 3.3.1 Gate Pulses Generation                                                            | 46       |

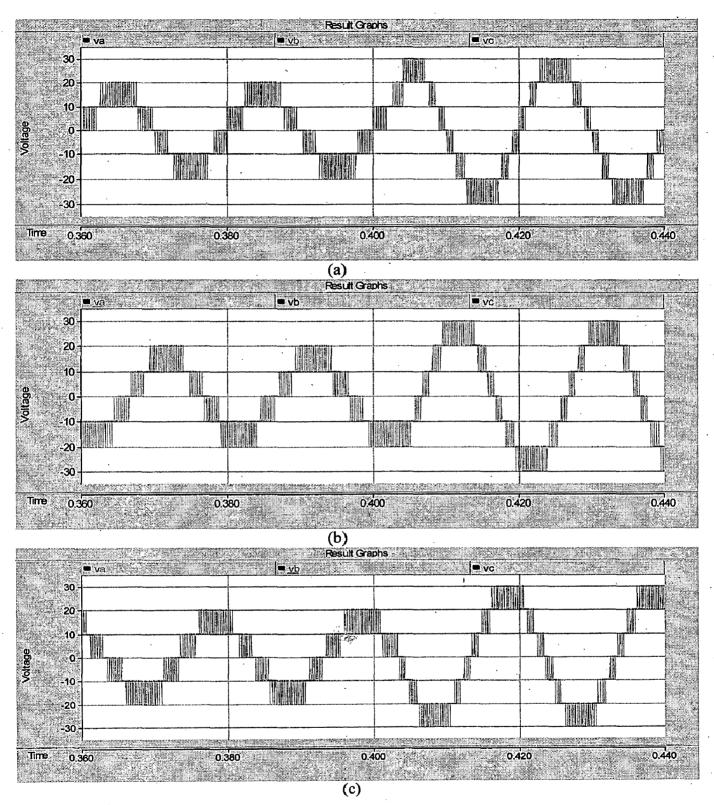

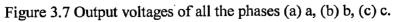

|    | 3.4 Simulation results standalone Inverter                                              | 48       |

|    | 3.5 Control principles & structure                                                      | 51       |

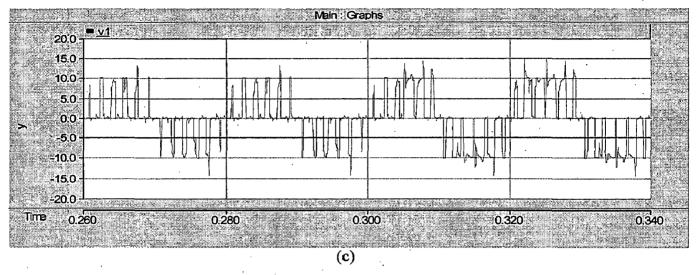

|    | 3.5.1 Control of the shunt inverter                                                     | 51       |

|    | 3.5.2 Control of the series inverter                                                    | 52       |

|    | 3.6 Detailed Simulation studies and Results                                             | 54       |

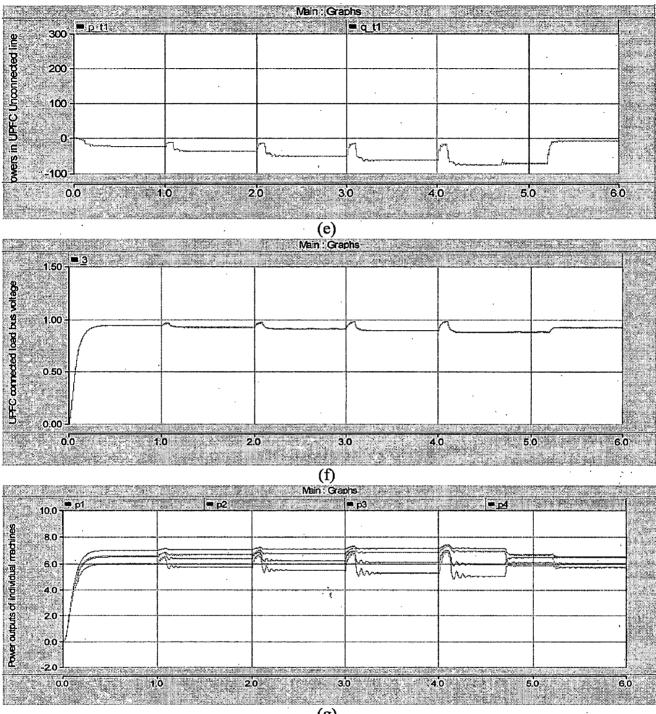

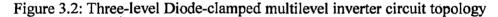

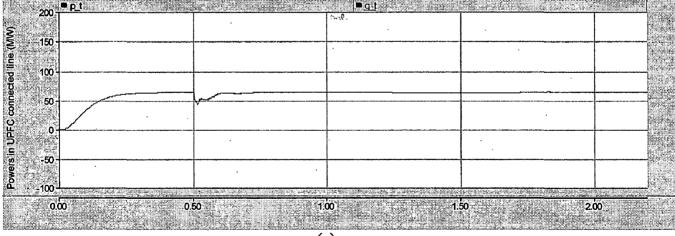

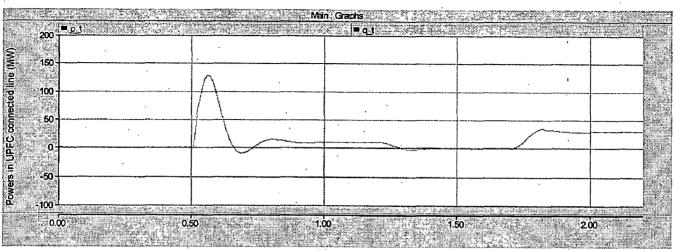

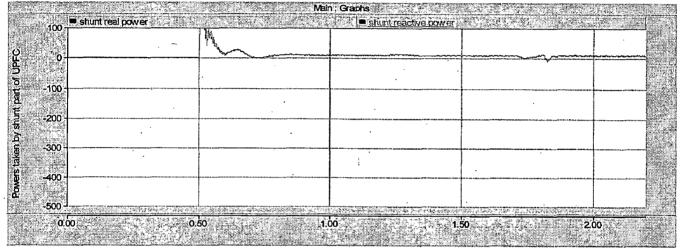

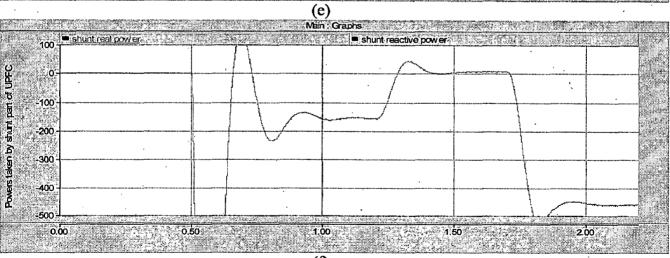

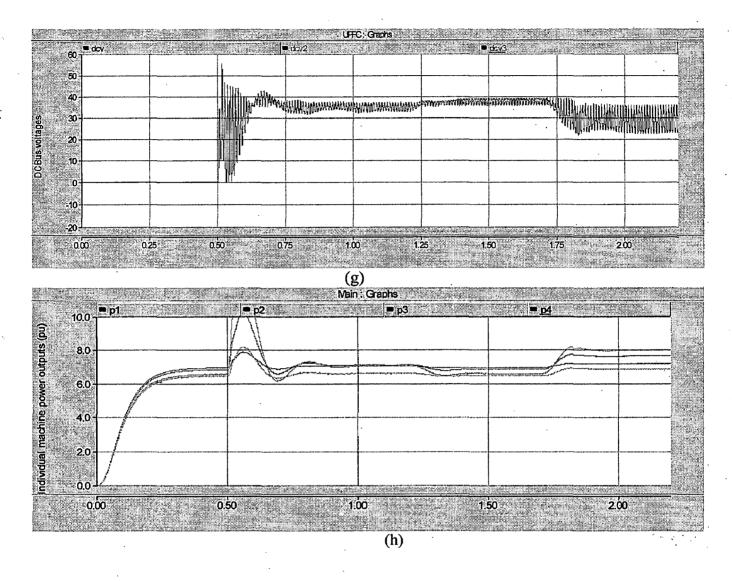

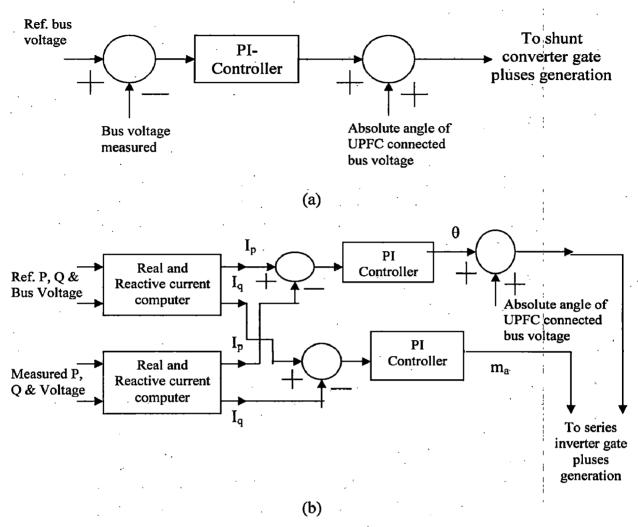

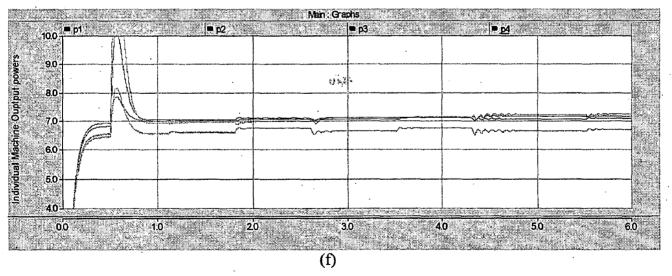

3.6 Detailed Simulation studies and Results543.6.1 Control of bus voltage543.6.2 UPFC as controlling the powers in open loop573.6.3 UPFC as controlling the powers in closed loop62

65

3.7 Conclusion

iii

| 4.  | H-B     | ridge inverter module based UPFC.                                          | 66       |

|-----|---------|----------------------------------------------------------------------------|----------|

|     |         | 4.1 Introduction                                                           | 66       |

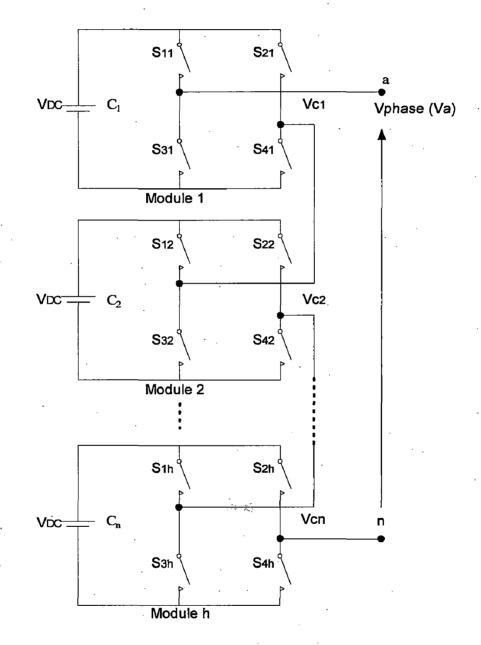

|     | · · · . | 4.2 Basic Operating principle of cascaded H-Bridge MLI<br>4.2.1 Advantages | 66<br>70 |

|     |         | 4.2.2 Disadvantages                                                        | 70       |

|     |         | 4.3 Structure of UPFC                                                      | 70       |

|     |         | 4.3.1 Gate Pulses Generation                                               | 74       |

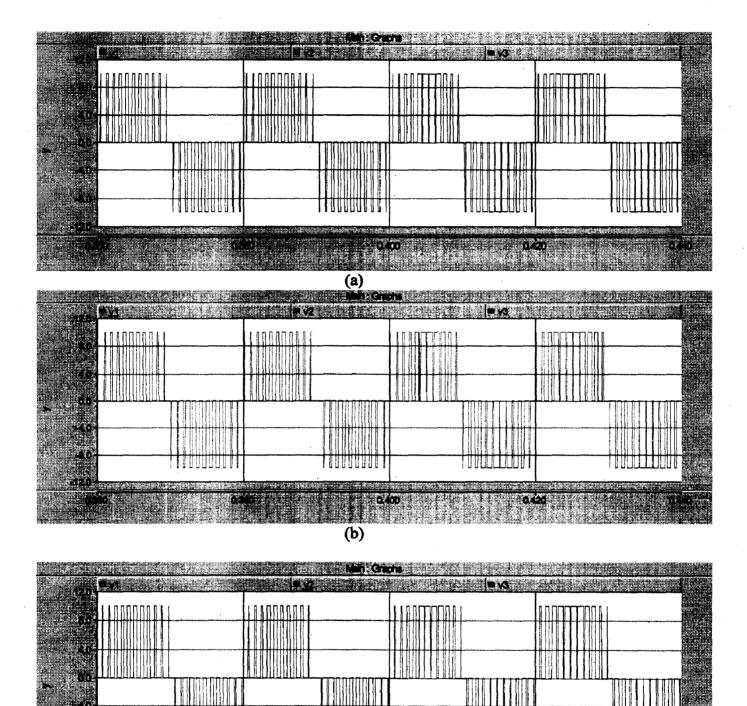

|     |         | 4.4 Inverter standalone simulations                                        | 76       |

|     |         | 4.5 Control Schemes for UPFC                                               | 76       |

|     |         | 4.6 Detailed Simulation studies and Results                                | 81       |

|     |         | 4.6.1 Control of bus voltage                                               | 81       |

|     |         | 4.7.2 UPFC as controlling the powers in open loop                          | 84       |

|     |         | 4.7.3 UPFC as controlling the powers in closed loop                        | 91       |

| 5.  | Con     | parisons & Conclusions                                                     | 95       |

|     |         | 5.1 Comparison of different configurations considered                      | 95       |

|     |         | 5.1.1 Switching frequency and harmonic content                             | 95       |

|     |         | 5.1.2 Comparison on the basis of DC voltage                                | 96       |

|     |         | 5.1.3 Discussion on Rating of the Valve.                                   | 99       |

| -   |         | 5.1.4 Based on physical structure                                          | 100      |

|     |         | 5.2 Conclusions                                                            | 101      |

|     |         | 5.3 Future scope of work                                                   | 102      |

| 6.  | Refe    | erences                                                                    | 103      |

| Apr | endic   | es                                                                         |          |

|     | Α       | Test system                                                                | 107      |

|     | В       | UPFC using basic 2 level VSC                                               | 110      |

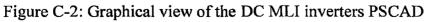

|     | C       | <b>UPFC using 3 level DC MLI modules</b>                                   | 112      |

|     | D       | H bridge inverter module based UPFC                                        | 115      |

### iv

# List of Figures

| Figure | Description                                                    |      |

|--------|----------------------------------------------------------------|------|

| No.    |                                                                | No.  |

| 1.1    | Series Controller                                              | 4    |

| 1.2    | Shunt Controller                                               | 5    |

| 1.3    | Combined series-series controller                              | 5    |

| 1.4    | Combined series-shunt controller                               | 6    |

| 1.5    | Conceptual representation of the UPFC in a power system        | 9    |

| 1.6    | Phasor diagram illustrating the conventional transmission      | 11   |

|        | capabilities of the UPFC                                       |      |

| 1.7    | Basic UPFC control structure                                   | . 13 |

| 1.8    | Single line diagram of the UPFC connected system               | 19   |

| 2.1    | Schematic diagram of a UPFC using 2-level VSCs.                | 21   |

| 2.2    | Simple hysterisis current control scheme                       | 23   |

| 2.3    | Generation of pulses for HCC control                           | 24   |

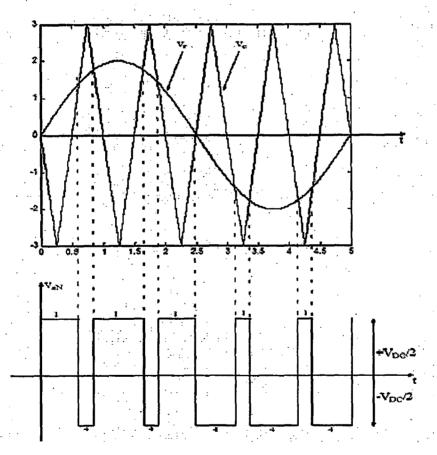

| 2.4    | Illustrating the SPWM                                          | 26   |

| 2.5    | Generation of gate pulses for SPWM                             | 27   |

| 2.6    | Block diagram of control system                                | 28   |

| 2.7    | Simulation results of UPFC in open-loop control for case (i)   | 32   |

| 2.8    | Simulation results of UPFC in open-loop control for case (ii)  | 35   |

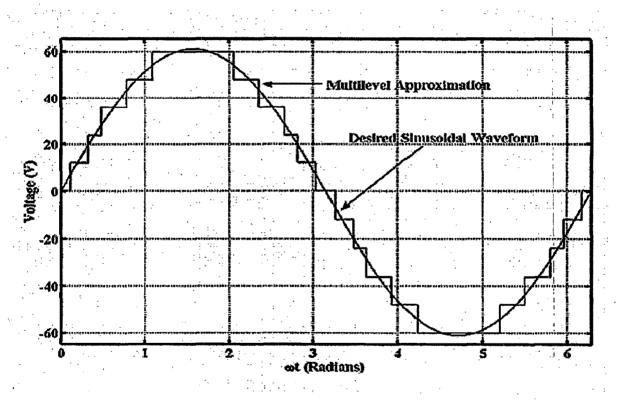

| 3.1    | Output of a Multi level inverter                               | 38   |

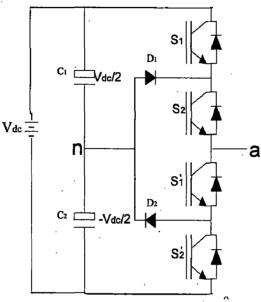

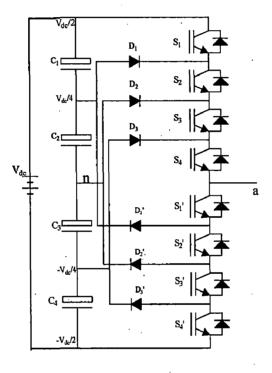

| 3.2    | Three-level Diode-clamped multilevel inverter circuit topology | · 40 |

| 3.3    | Five-level Diode-clamped multilevel inverter circuit topology  | 41   |

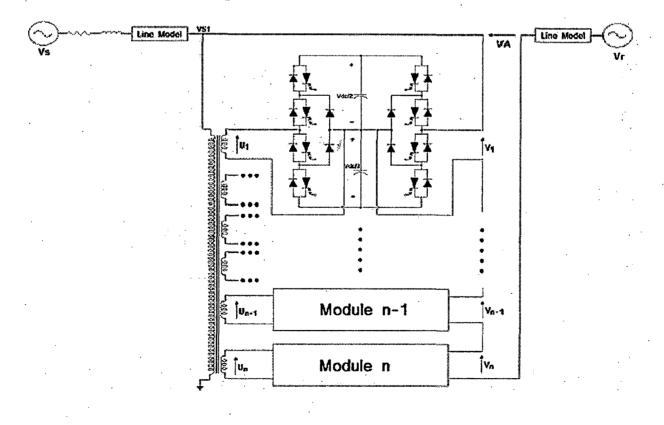

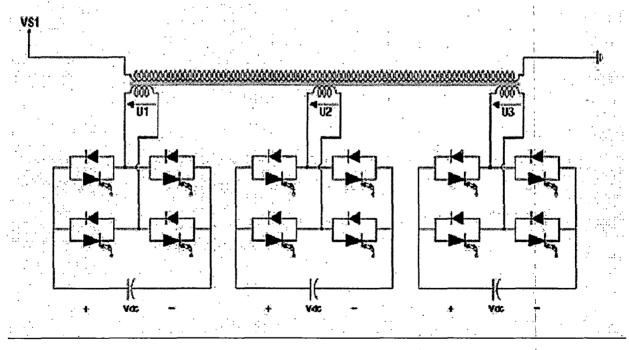

| 3.4    | Configuration of UPFC using 3-level DC MLI                     | 43   |

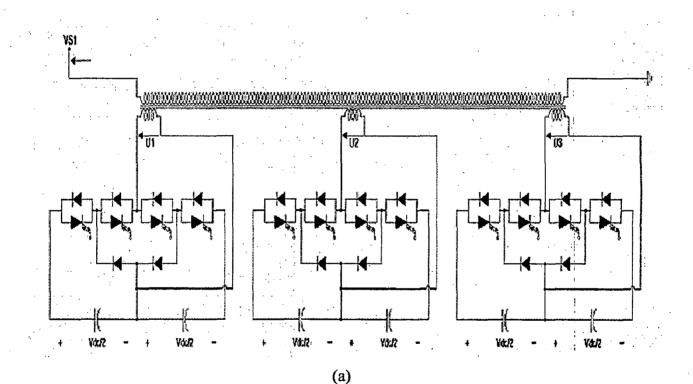

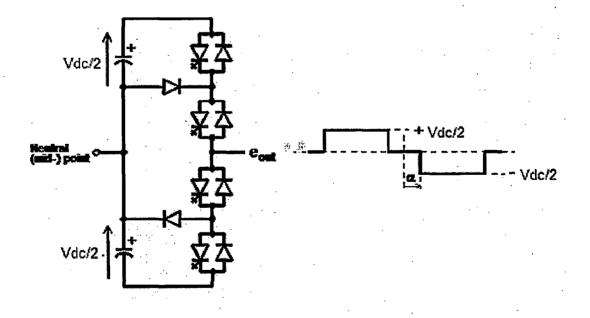

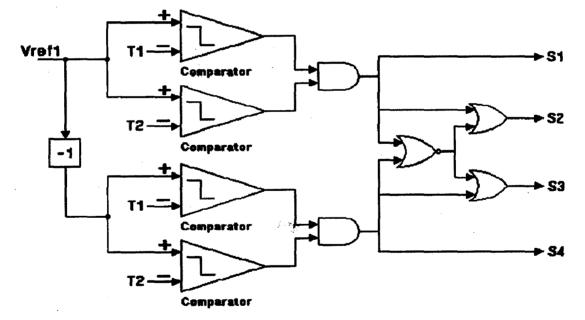

| 3.5    | Inverter structure and switching pattern                       | 45   |

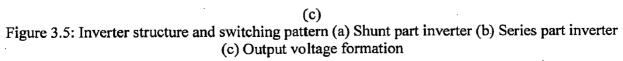

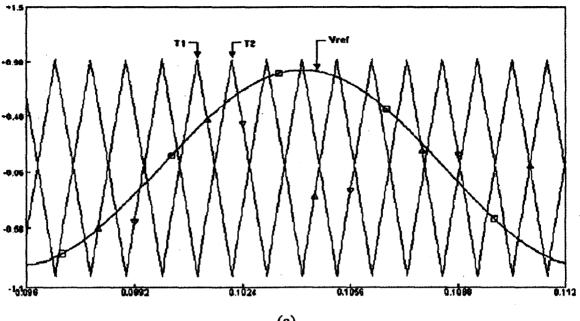

| 3.6    | Principle of gate pulse generation                             | 47   |

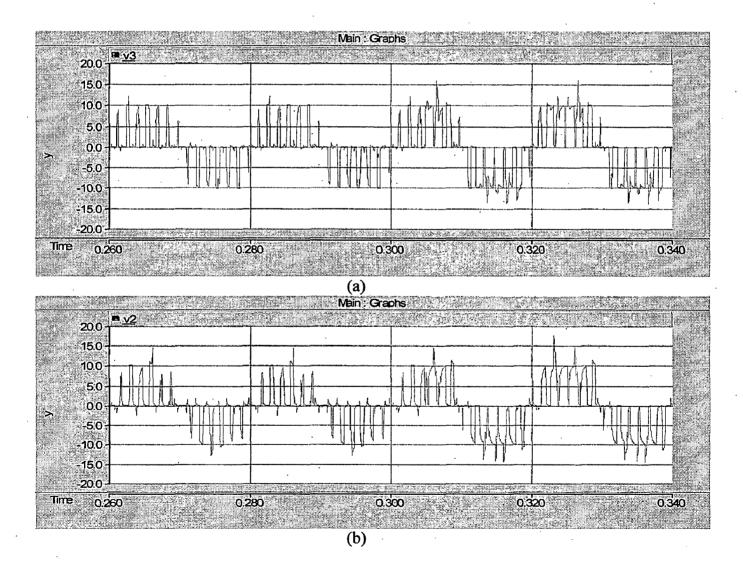

| 3.7    | Output voltages of all the phases-a, b, c                      | 49   |

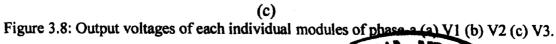

| 3.8    | Output voltages of each individual modules of phase-a          | 50   |

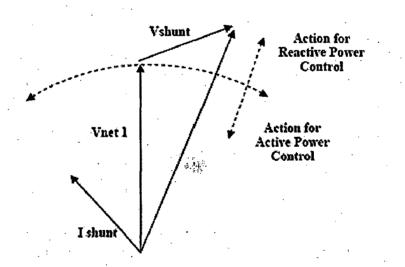

| 3.9    | Principle of control of the shunt inverter of the UPFC         | 51   |

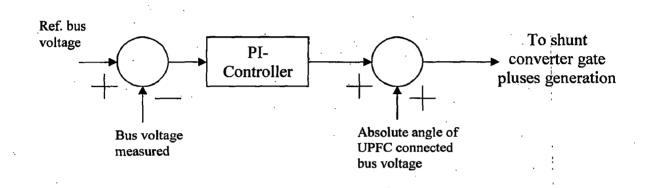

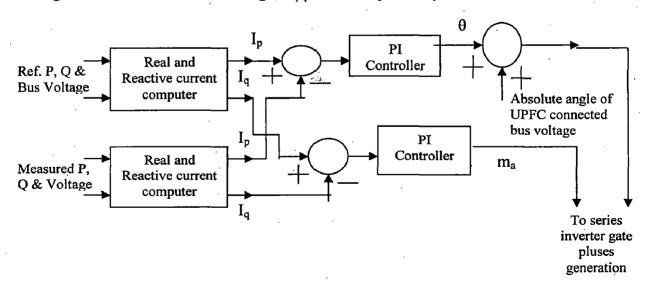

| 3.10   | Block diagram of shunt inverter control                        | 52   |

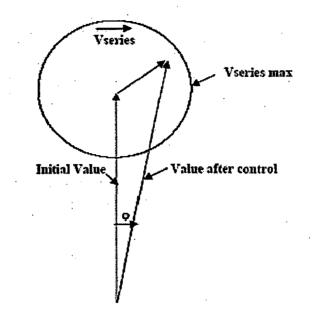

| 3.11   | Principle of operation of the series part of the UPFC          | 53   |

| 3.12   | Block diagram of UPFC series converter control                 | 53   |

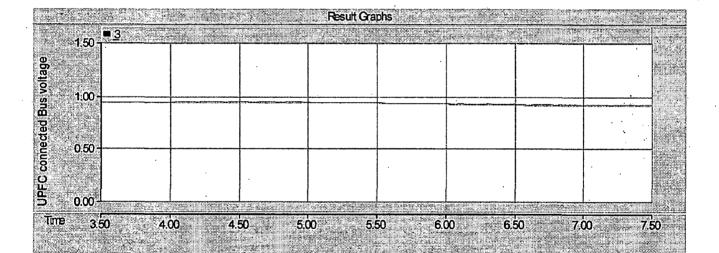

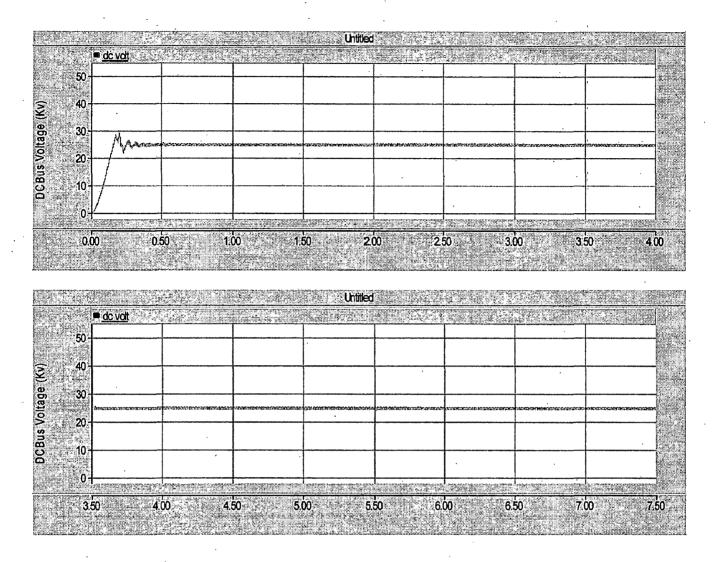

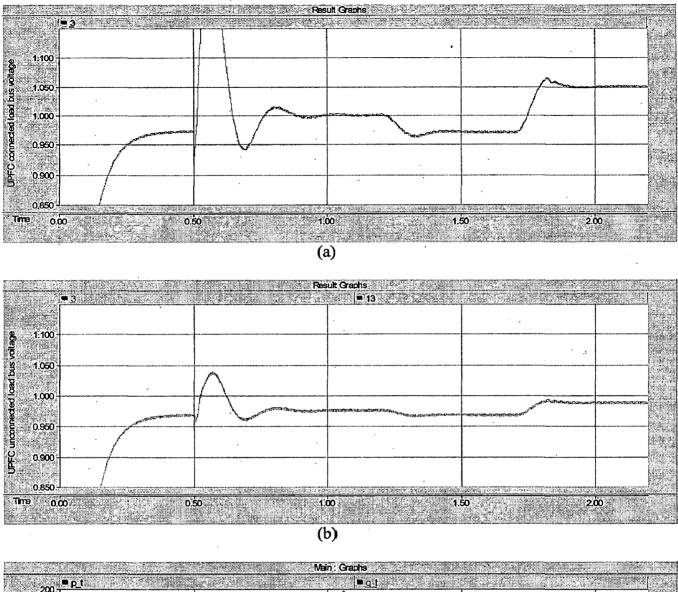

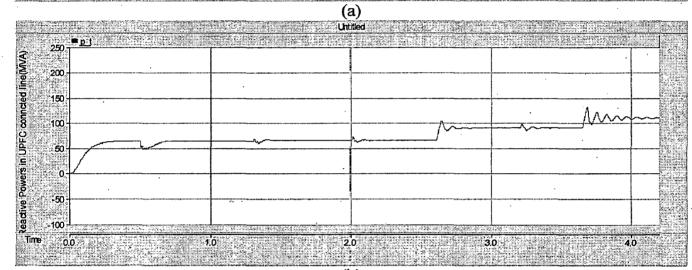

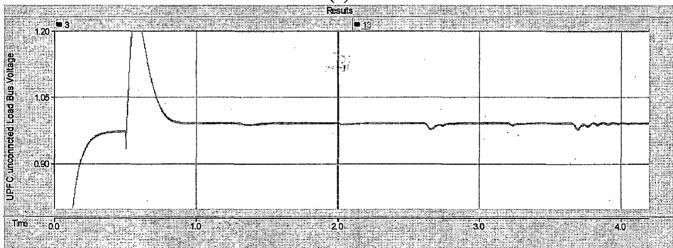

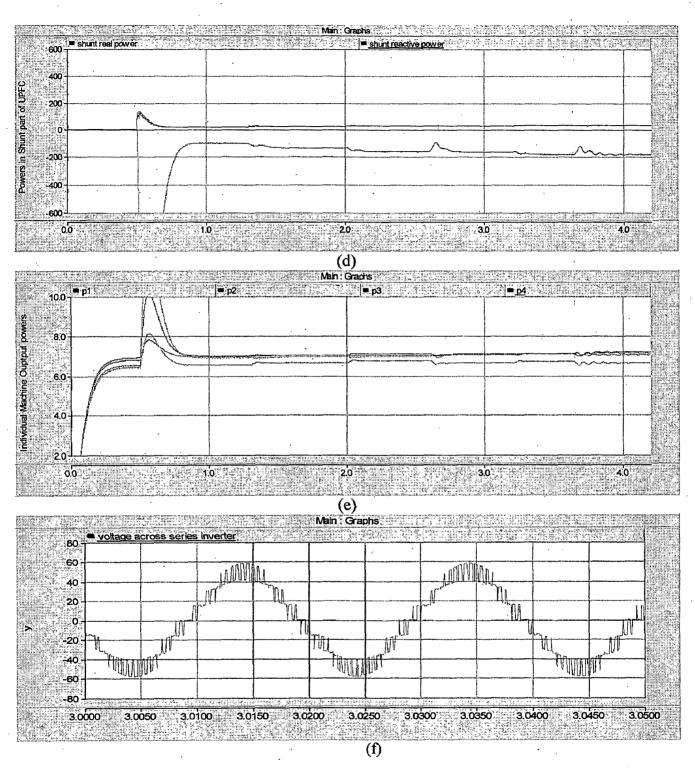

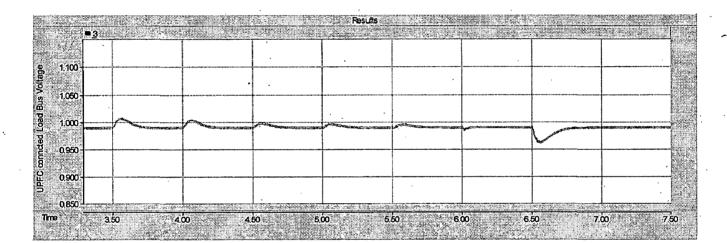

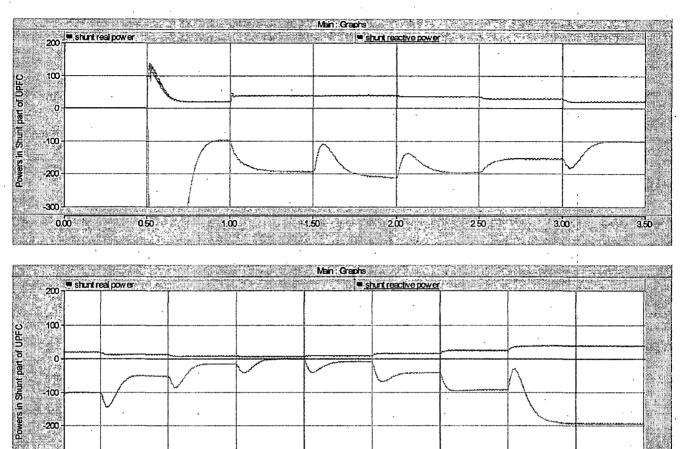

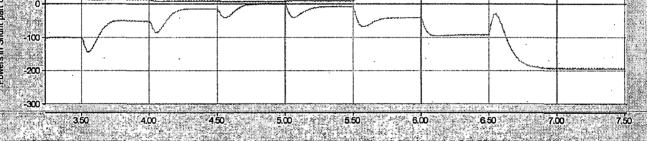

| 3.13   | Simulation results of UPFC as bus voltage control.             | 57   |

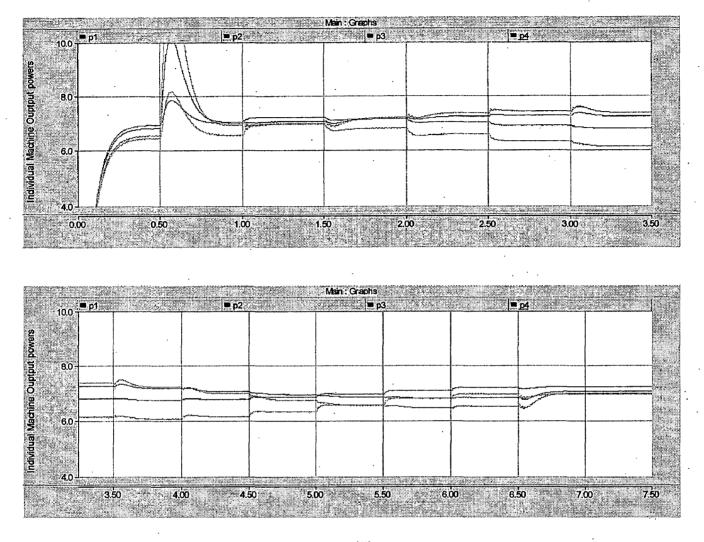

| 3.14   | Simulation results of UPFC in open-loop control.               | 61   |

| 3.15   | Simulation results of UPFC in closed-loop control.             | 64   |

| 4.1    | Single phase m-level structure of cascaded H-bridge inverter   | 67   |

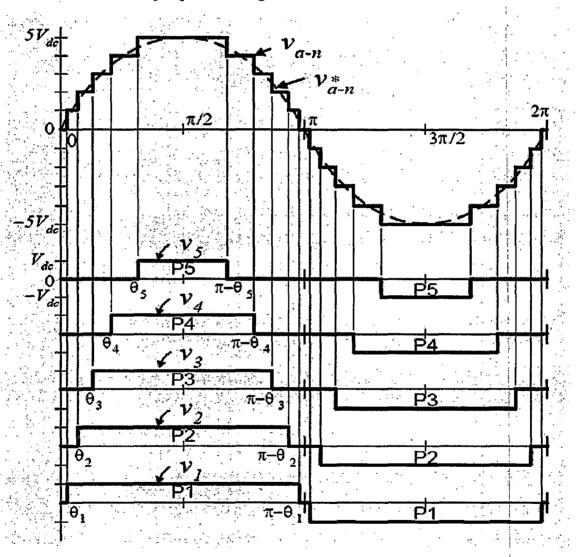

| 4.2    | Typical 11 level line to neutral voltage wave form             | 68   |

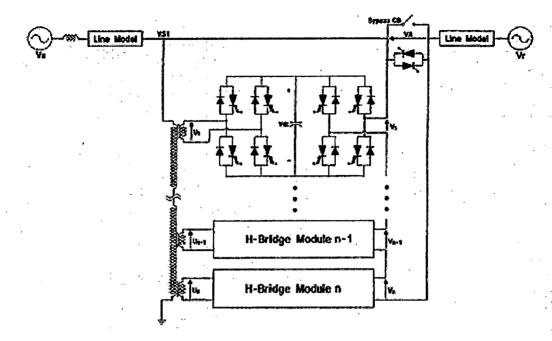

| 4.3    | Configuration of UPFC based in H bridge modules                | 71   |

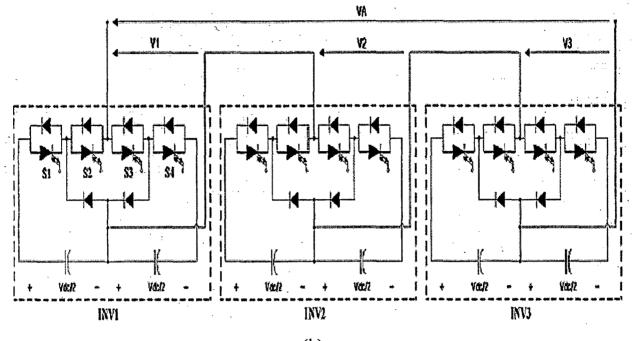

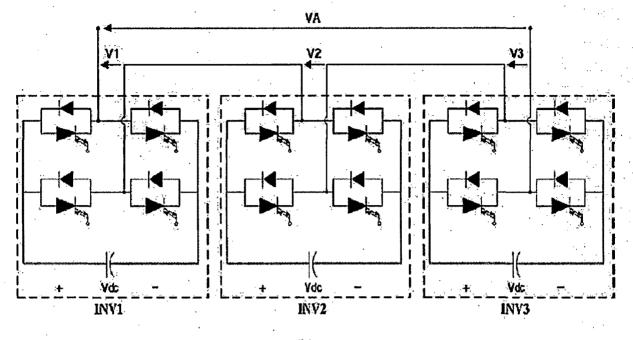

| 4.4    | Converter structure and switching pattern                      | 73   |

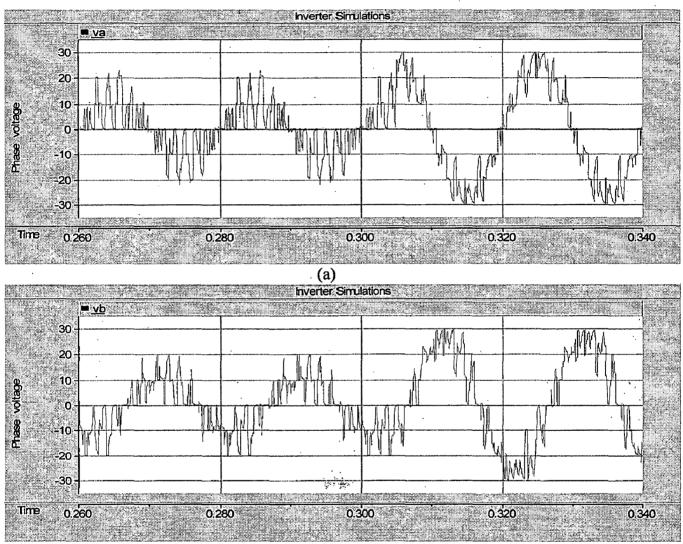

| 4.5    | Principle of gate pulse generation                             | 75   |

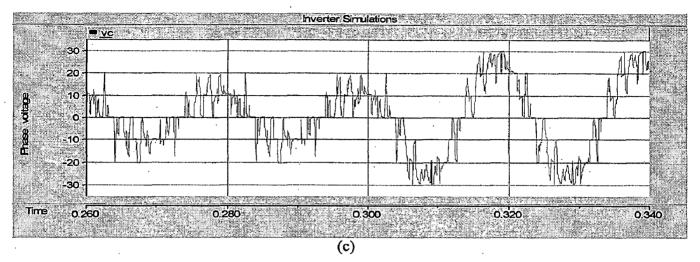

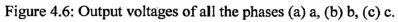

| 4.6        | Output voltages of all the phases-a, b, c.                      | 78    |

|------------|-----------------------------------------------------------------|-------|

| 4.7        | Output voltages of each individual H-bridge modules of phase-a  |       |

| 4.8        | Block diagram of UPFC control                                   | 80    |

| 4.9        | Simulation results of UPFC as bus voltage control               | 83    |

| 4.10       | Simulation results of UPFC in open-loop control                 | 90    |

| 4.11       | Simulation results of UPFC in closed-loop control.              | 94    |

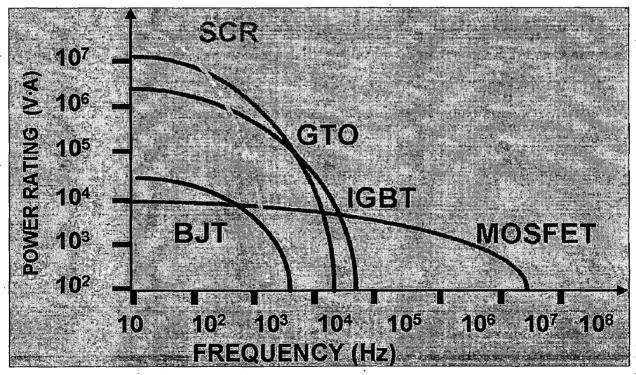

| 5.1        | characteristics of different power devices                      |       |

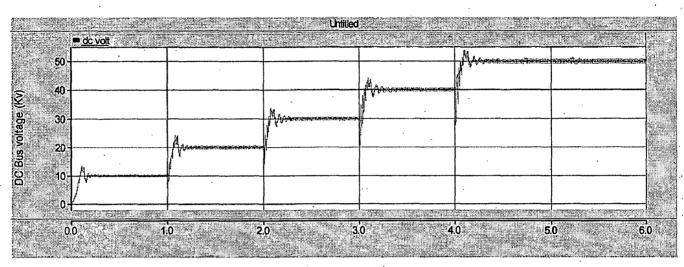

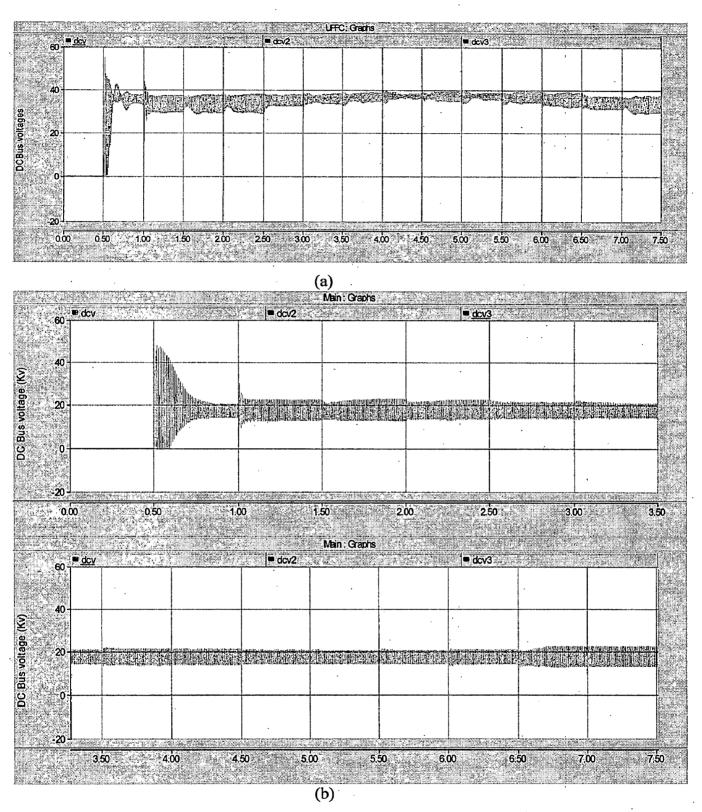

| 5.2        | DC Bus Voltage of UPFC using 2-level VSC                        |       |

| 5.3        | DC Bus voltage profiles                                         |       |

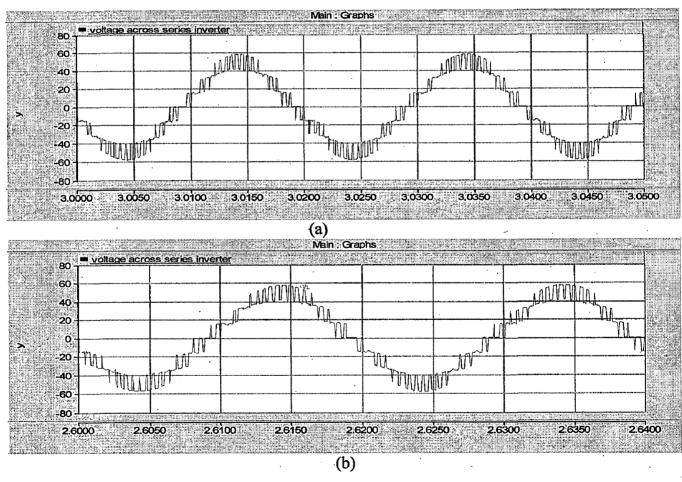

| 5.4        | output voltage of series inverter                               |       |

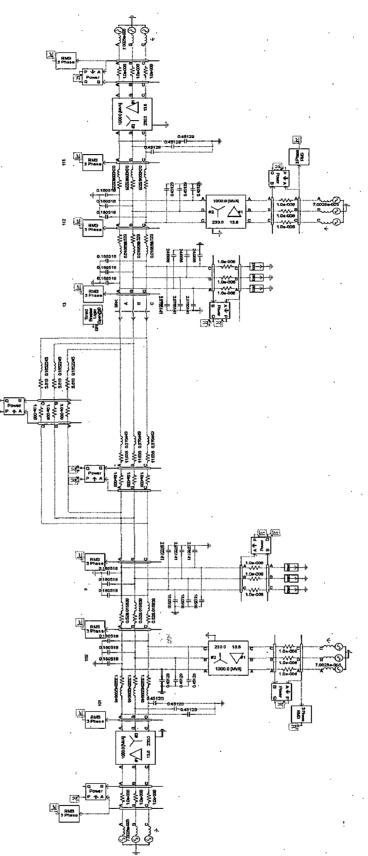

| A-1        | PSCAD view of the simulated test system standalone              | 109   |

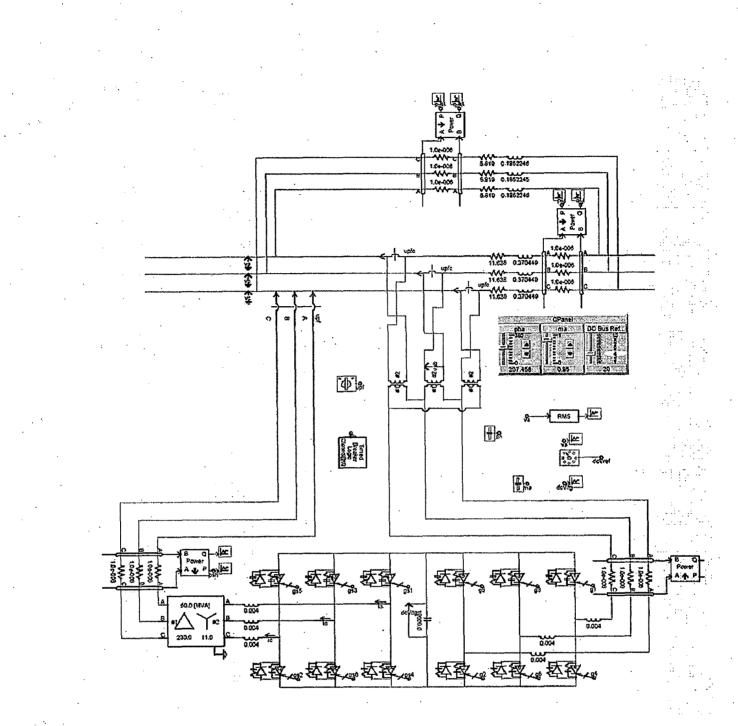

| <b>B-1</b> | Graphical view of the UPFC using 2 level VSC in PSCAD           | 110   |

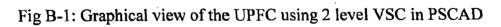

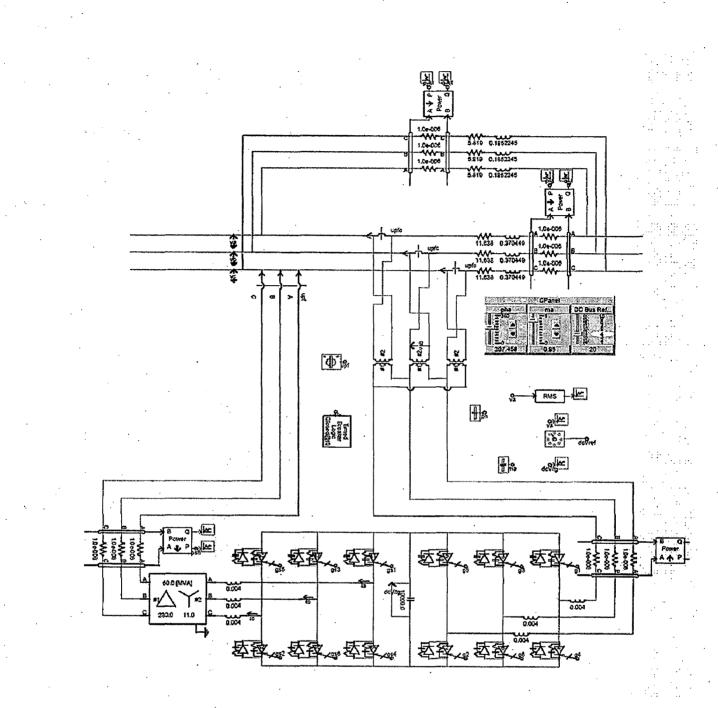

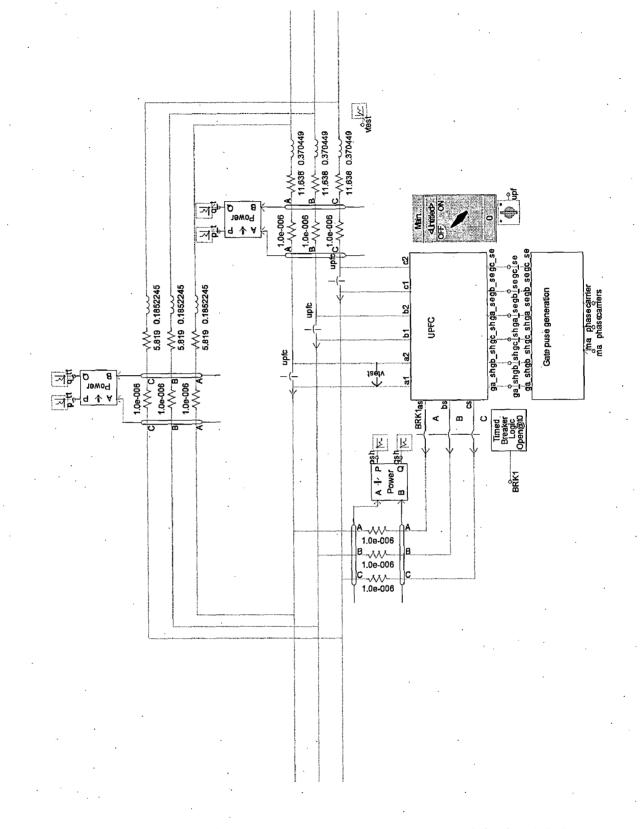

| <b>C-1</b> | Graphical view of the UPFC using DC MLI modules in PSCAD        | 113   |

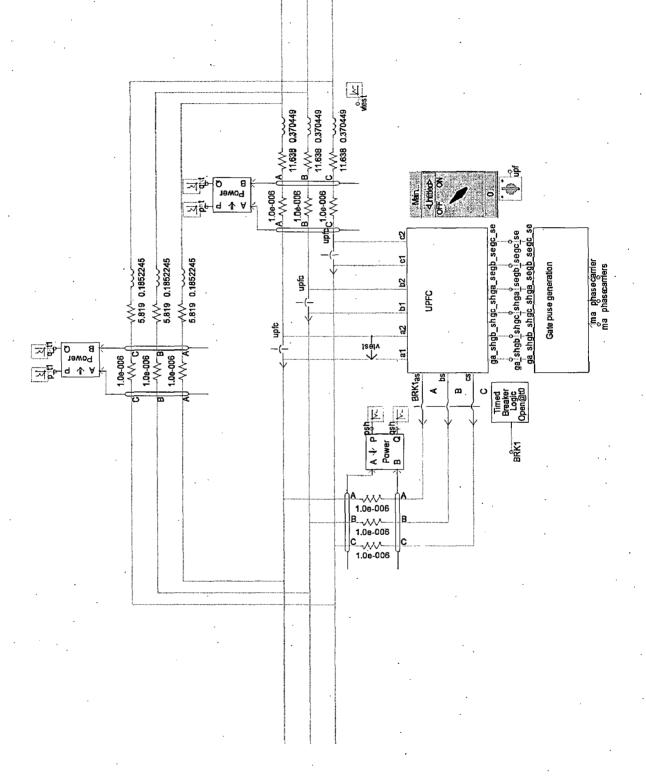

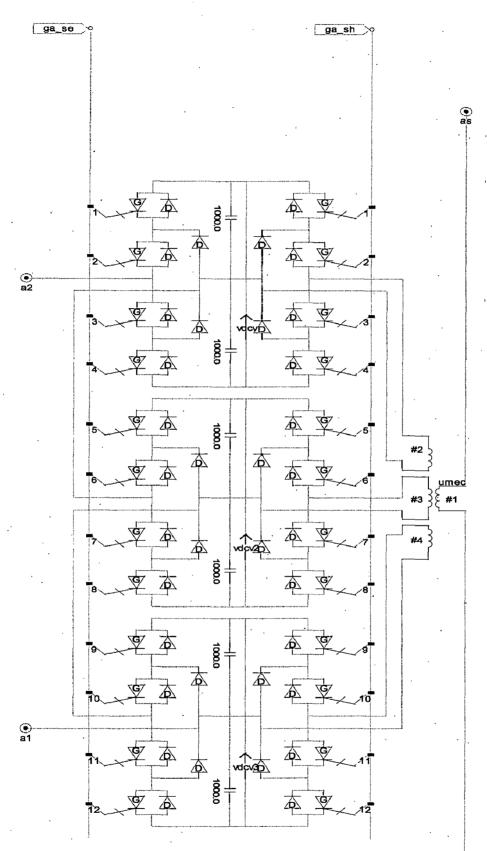

| <b>C-2</b> | Graphical view of the DC MLI inverters PSCAD                    | 114   |

| <b>C-3</b> | Graphical view of the Gate pulse generation scheme for DC MLI   | . 115 |

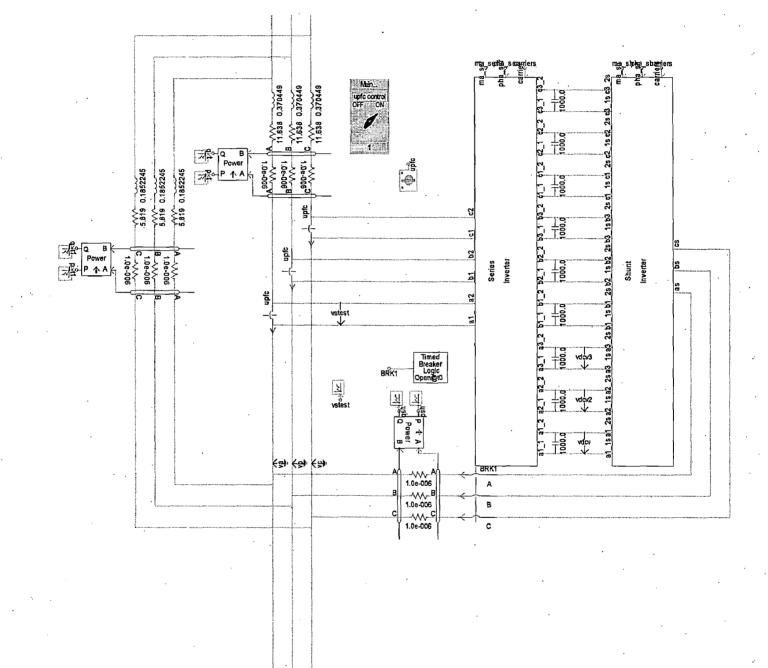

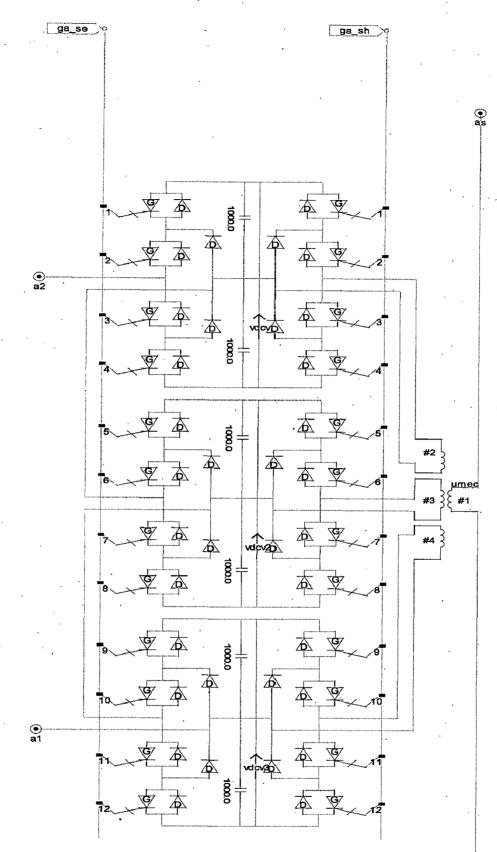

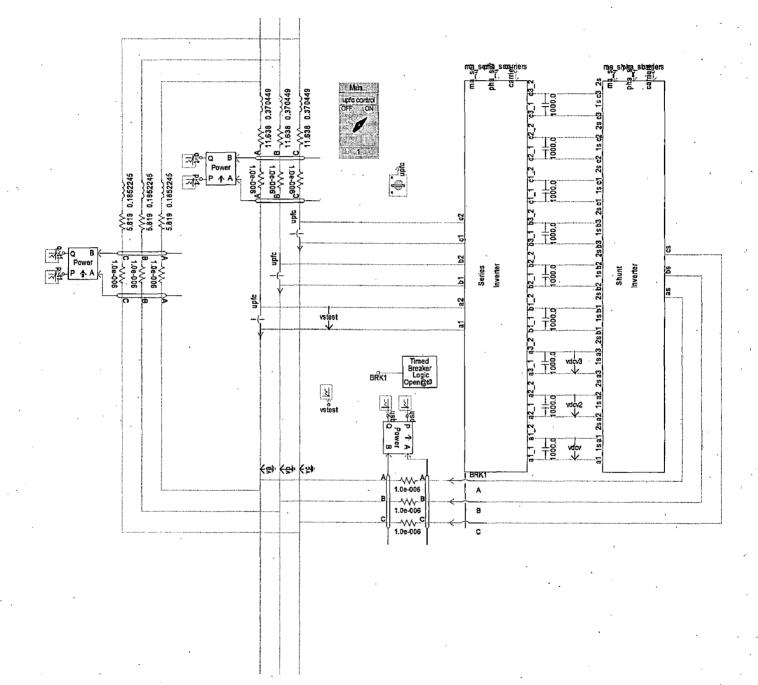

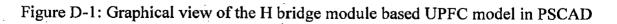

| <b>D-1</b> | Graphical view of the H bridge module based UPFC model in PSCAD | 117   |

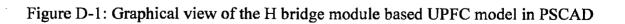

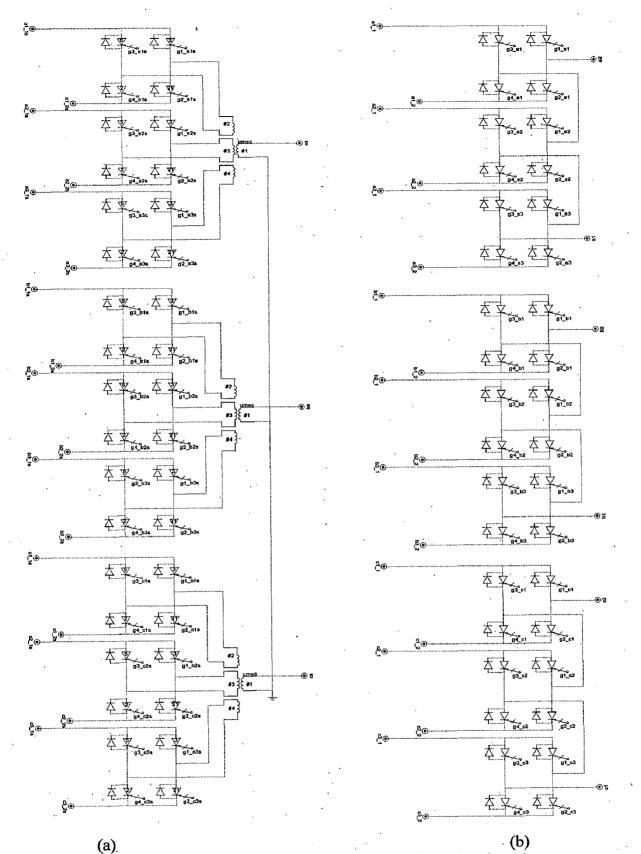

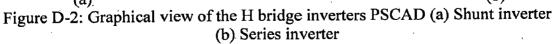

| D-2        | Graphical view of the H bridge inverters PSCAD                  | 118   |

# ABSTRACT

In this thesis, the various configurations of UPFCs have been simulated using the digital simulation tool, PSCAD/EMTDC V4.1. And the comparative analysis is presented, by analyzing the various configurations of UPFCs on the basis of DC Bus voltage magnitude and its variations, physical structure, possible scheme for implementation, switching frequency, harmonic content and rating of UPFC. The simulation studies have been carried out using the four machine, 10 bus, two area standard system. It is concluded that, the compensation provided by the series inverter, and hence the amounts of real and reactive power supplied by the series inverter to the power system are same in both the cases by maintaining the two different DC Bus voltages by two different configurations of the inverters.

CHAPTER: 1

## Introduction

The power system is an interconnection of generating units to load centers through high Voltage electric transmission lines and in general is mechanically controlled. It can be divided into three subsystems: generation, transmission and distribution subsystems. Until recently all three subsystems were under supervision of one body within certain geographical area providing power at regulated rates. In order to provide cheaper electricity the deregulation of power system, which will produce separate generation, transmission and distribution companies, is already being performed. At the same time electric power demand continues to grow and also building of the new generating units and transmission circuits is becoming more difficult because of economic and environmental reasons. Therefore, power utilities are forced to relay on utilization of existing generating units and to load existing transmission lines close to their thermal limits. However, stability has to be maintained at all times. Hence, in order to operate power system effectively, without reduction in the system security and quality of supply, even in the case of contingency conditions such as loss of transmission lines and/or generating units, which occur frequently, and will most probably occur at a higher frequency under deregulation, a new control strategies need to be implemented.

In the late 1980s the Electric Power Research Institute (EPRI) has introduced a new technology program known as Flexible AC Transmission System (FATCS) [1-2]. The main idea behind this program is to increase controllability and optimize the utilization of the existing power system capacities by replacing mechanical controllers by reliable and high speed power electronic devices.

## **1.1 FACTS IN POWER SYSTEMS**

FACTS technology refers to devices that enable flexible electrical power system operation, i.e. controlled active & reactive power flow redirection in transmission paths by controlling different parameters in the transmission system.

It opens up new opportunities for controlling and enhancing the useable capacity of present, as well as new upgraded lines. The possibility that current through a line can be controlled at a reasonable cost enables a large potential of increasing the capacity of existing lines thereby enabling them to carry power closer to their thermal ratings.

Because of their fast response FACTS Controllers can also improve the stability of an electrical power system by helping critically disturbed generators to give away the excess energy gained through the acceleration during fault [2]. This can be done by correctly changing the pattern of power flow. A lot of studies show that the reason for the loss of transient stability in a power system is that some overloads occurred in some lines while some other lines were tripped off after faults. After having adopted FACTS devices, the operating point of the power system can be altered to improve the transient stability to a certain extend.

#### 1.1.1 CONTROLLABLE PARAMETERS FOR FACTS DEVICES [2]

Following are the few basic points regarding the possibilities of power flow control:

- Control of the line impedance X (e.g. with thyristor controlled series capacitor) can provide a powerful means of current control.

- When the angle is not large, which is often the case, control of X or the angle substantially provides the control of active power

- Control of angle (with a phase regulator for example), which in turn controls the driving voltage, provides a powerful means of controlling the current flow and hence active power flow when the angle is not large.

- Injecting a voltage in series with the line, and perpendicular to the current flow, can increase or decrease the magnitude of current flow. Since the current flow

lags the driving voltage by 90 degrees, this means injection of reactive power in series, can provide a powerful means of controlling the line current, and hence the active power when the angle is not large.

- Injecting voltage in series with the line and with any phase angle with respect to the driving voltage can control the magnitude and the phase of the line current. This means that injecting a voltage phasor with variable phase angle can provide powerful means of precisely controlling the active and reactive power flow. This requires injection of both active and reactive power in series

- When the angle is not large, controlling magnitude of one or the other line voltages can be a very cost effective means for the control of reactive power flow through the interconnection

- Combination of the line impedance control with a series controlled and voltage regulation with a shunt controller can also provide a cost effective means to control both the active power flow and reactive power flow between the two systems.

### **1.1.2 TYPES OF FACTS CONTROLLERS [1, 2]**

In general FACTS controllers can be divided into four categories

- a) Series controller

- b) Shunt controller

- c) Combined series-series controllers

- d) Combined series-shunt controllers

#### (a) Series controller [2]:

The series controller could be variable impedance, such as capacitor, reactor, etc or power electronics based variable source of main frequency, sub synchronous and harmonic frequencies to serve the desired need. Fig.1.1 shows the series controller. In principle all the series controllers inject voltage in series with the line. As long as the voltage is in phase quadrature with the line current, the series controller only supply or consumes variable reactive power. Any other phase relationship will involve handling of

real power as well. Series connected controller impacts the driving voltage and hence the current and power flow directly. Therefore, if the purpose of the application is to control the current/ power flow and damp oscillations, the series controller for a given MVA size is several times more powerful than the shunt controller.

Static synchronous series compensator (SSSC), interline power flow controller (IPFC), thyristor controlled switched series capacitor (TCSC) etc are the example of series controllers.

Figure 1.1: Series Controller.

#### (b) Shunt controller [2]:

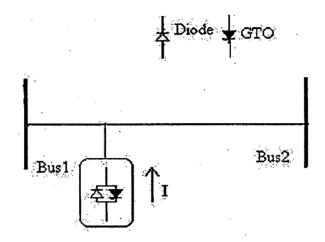

As in the case of series controllers, the shunt controllers may be variable impedance, variable source, or a combination of these. In principle, all shunt controllers inject current into the system at the point of connection. Fig. 1.2 shows the shunt controller.

The shunt controller is like a current source, which draws from or injects current into the line. The shunt controller is therefore a good way to control voltage at and around the point of connection through injection of reactive current (leading or lagging), alone or a combination of active and reactive current for a more effective voltage control and damping of oscillations.

One important advantage of the shunt controller is that it serves the bus node independently of the individual lines connected to the bus. Static synchronous compensator (STATCOM), static synchronous generator (SSG), static VAR compensator

(SVC), thyristor controlled reactor (TCR), thyristor switched capacitor etc are the examples of shunt controllers.

Figure 1.2: Shunt Controller

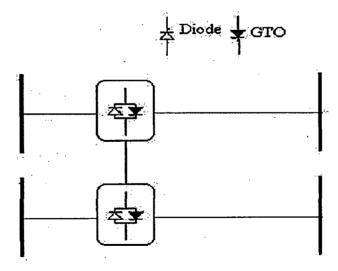

#### (c) Combined series-series controllers [2]:

This could be a combination of separate series controllers, which are controlled in a coordinated manner, in a multi line transmission system or it could be a unified controller, in which series controller provide independent series reactive compensation for each line but also transfer real power among the lines via the power link. Series-series controller is shown in Fig. 1.3.

Figure 1.3: Combined series-series controller

The real power transfer capability of the unified series-series controller, referred as interline power flow controller, makes it possible to balance both the real and reactive power flow in the lines and thereby maximize the utilization of the transmission system.

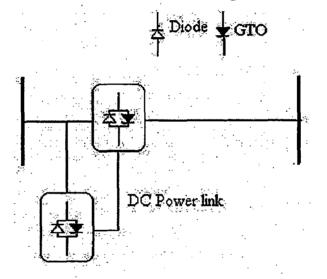

#### (d) Combined series-shunt controllers [2]:

This could be a combination of separate shunt and series controllers, which are controlled in a coordinated manner, or a unified power, flow controller with series and shunt elements. In principle, combined shunt and series controllers inject current into the system with the shunt part of the controller and voltage in series in the line with the series part of the controller. Series-shunt controller is shown in Fig. 1.4.

Figure1.4: Combined series-shunt controller

Unified power flow controllers (UPFC), thyristor controlled phase shifting transformer (TCPST) are the example of shunt series controller.

#### **1.1.3 ADVANTAGES OF FACTS TECHNOLOGY [1, 2]**

FACTS controllers enable the transmission system to obtain one or more of the following benefits:

• Control of power flow as ordered. The use of control of the power flow may be to follow a contract, meet the utilities' own needs, ensure optimum power flow, ride through emergency conditions, or a combination thereof.

- Increase the loading capability of lines to their thermal capabilities, including short term and seasonal. This can be accomplished by overcoming other limitations, and sharing of power among lines according to their capability

- Increase the system security through raising the transient stability limit, limiting short circuit currents and overloads, managing cascading blackouts and damping electromechanical oscillations of power systems and machines.

- Provide secure tie line connections to neighboring utilities and regions thereby decreasing overall generation reserve requirements on both sides.

- Provide greater flexibility in siting new generation

- Upgrade of lines

- Reduce reactive power flows, thus allowing the lines to carry active power

- Reduce loop flows

- Increase utilization of lowest cost generation.

- Balancing the power flow over a wide range of operating conditions, thereby using the power system network most efficiently.

- Balancing the power flow in parallel networks operating at different voltage levels.

A comparison of different features of various FACTS Controllers is given in Table 1.1. From this table, it is observed that among the various FACTS Controllers, Unified Power Flow Controller (UPFC) is the most versatile one.

7.

Table 1.1: Comparison of controllable parameters of different FACTS Controllers

| • • •                                                                                       |                                                                                                                                                                                 |  |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FACTS Controller                                                                            | Control Attributes                                                                                                                                                              |  |

| Static Synchronous Compensator<br>(STATCOM without storage)                                 | Voltage control, VAR compensation, damping oscillations, voltage stability                                                                                                      |  |

| Static Synchronous Compensator<br>(STATCOM with storage, BESS,<br>SMES, large dc capacitor) | Voltage control, VAR compensation, damping<br>oscillations, transient and dynamic stability, voltage<br>stability, AGC                                                          |  |

| Static VAR Compensator (SVC,<br>TCR, TCS, TRS                                               | Voltage control, VAR compensation, damping<br>oscillations, transient and dynamic stability, voltage<br>stability                                                               |  |

| Thyristor-Controlled Braking<br>Resistor (TCBR)                                             | Damping oscillations, transient and dynamic stability                                                                                                                           |  |

| Static Synchronous Series<br>Compensator (SSSC without<br>storage)                          | Current control, damping oscillations, transient and<br>dynamic stability, voltage stability, fault current limiting                                                            |  |

| Static Synchronous Series<br>Compensator (SSSC with storage)                                | Current control, damping oscillations, transient and dynamic stability, voltage stability                                                                                       |  |

| Thrystor-Controlled Series<br>Capacitor (TCSC, TSSC)                                        | Current control, damping oscillations, transient and dynamic stability, voltage stability, fault current limiting                                                               |  |

| Thyristor-Controlled Series Reactor<br>(TCSR, TSSR)                                         | Current control, damping oscillations, transient and dynamic stability, voltage stability, fault current limiting                                                               |  |

| Thyristor-Controlled Phase-Shifting<br>Transformer (TCPST or TCPR)                          | Active power control, damping oscillations, transient and dynamic stability, voltage stability                                                                                  |  |

| Unified Power Flow Controller<br>(UPFC)                                                     | Active and reactive power control, voltage control,<br>VAR compensation, damping oscillations, transient<br>and dynamic stability, voltage stability, fault current<br>limiting |  |

| Thyristor-Controlled Voltage<br>Limiter (TCVL)                                              | Transient and dynamic voltage limit                                                                                                                                             |  |

| Thyristor-Controlled Voltage<br>Regulator (TCVR)                                            | Reactive power control, voltage control, damping<br>oscillations, transient and dynamic stability, voltage<br>stability                                                         |  |

| Interline Power Flow Controller<br>(IPFC)                                                   | Reactive power control, voltage control, damping<br>oscillations, transient and dynamic stability, voltage<br>stability                                                         |  |

|                                                                                             |                                                                                                                                                                                 |  |

|                                                                                             |                                                                                                                                                                                 |  |

**8**.

## **1.2 Unified Power Flow Controller (UPFC)**

The idea of the unified power flow controller (UPFC) was first proposed by Gyugyi in 1992[3]. Since then, as the most sophisticated flexible ac transmission systems (FACTS) device, the UPFC has been researched widely and many papers dealing with UPFC's modeling; analysis, control, and application have been published in the literature.

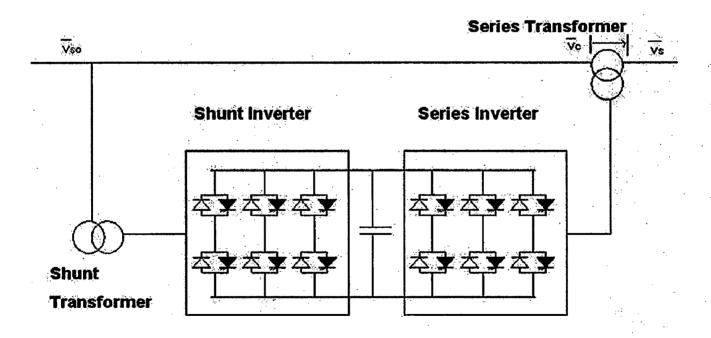

The UPFC combines the functions of several FACTS devices and is capable of realizing voltage regulation, series compensation, and phase angle regulation at the same time, thus realizing the separate control of the active power and reactive power transmitted simultaneously over the line [2-4]. The general configuration of the UPFC is shown in Fig. 1.5. As it can be seen, the UPFC consists of two voltage source inverters. Inverter 1 is in parallel with the transmission line, while Inverter 2 is in series with the transmission line. The two inverters are connected back-to-back through a common dc-link. This arrangement enables real power flow in either direction between the two inverters.

Figure 1.5: Conceptual representation of the UPFC in a power system

### **1.2.1 BASIC OPERATING PRINCIPLE [2, 5]**

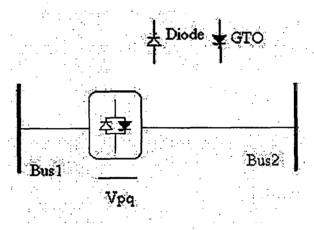

From the conceptual point of viewpoint, the UPFC is a generalized synchronous voltage source (SVS), represented at the fundamental frequency by voltage phasor  $V_{pq}$  with controllable magnitude  $V_{pq}$  ( $0 \le V_{pq} \le V_{pqmax}$ ) and angle  $\rho$  ( $0 \le \rho \le 2\pi$ ), in series with the transmission line. In this functionally unrestricted operation, which clearly includes voltage and angle regulation, the SVS generally exchanges both reactive and real power with the transmission system. But the SVS is able to generate only the reactive power exchanged; the real power must be supplied to it, or absorbed from it, by suitable power supply or sink. In UPFC arrangement the real power exchanged is provided by one of the end buses (e.g. the sending end bus).

In the practical implementation, the UPFC consists of two voltage-sourced converters, as shown in Fig. 1.6. These back-to-back converters, labeled "converter 1" and "converter 2" in the fig, are operated from a common DC link provided by a dc storage capacitor. This arrangement functions as an ideal ac-to-dc power converter in which the real power can freely flow in either direction between the ac terminals of the two converters, and each converter can independently generate or absorb reactive power at its own ac output terminal.

Converter 2 provides the main function of the UPFC by injecting a voltage  $V_{pq}$  with controllable magnitude  $V_{pq}$  and phase angle  $\rho$  in series with the line via an insertion transformer [2, 4]. This injected voltage acts essentially as a synchronous ac voltage source. The transmission line current flows through this voltage source resulting in active and reactive power exchange between it and the ac system. The reactive power is exchanged at the ac terminal (i.e. at the terminal of the series insertion transformer) is generated internally by the converter. The real power exchanged at the ac terminal is converted into dc power, which appears at the dc link as a positive or negative real power demand.

The basic function of converter 1 is to supply or to absorb the real power demanded by converter 2 at the common dc link to support the real power exchange resulting from the series voltage injection. This dc link power demand of converter 2 is

converted back to ac by converter 1 and coupled to the transmission line bus via a shuntconnected transformer. In addition to the real power need of converter 2, converter 1 can also generate or absorb controllable reactive power, if it is desired, and thereby provide independent shunt reactive compensation for the line. There is a closed path for the real power balance by the action of series voltage injection through converter 1 and 2 back to the line, the corresponding reactive power exchanged is supplied or absorbed locally by converter 2 and therefore does not have to be transmitted by the line. Thus, converter 1 can be operated at a unity power factor or to be controlled to have a reactive power exchange with the line independent of the reactive power exchanged by converter 2.

#### **1.2.2** Conventional Transmission Control Capabilities

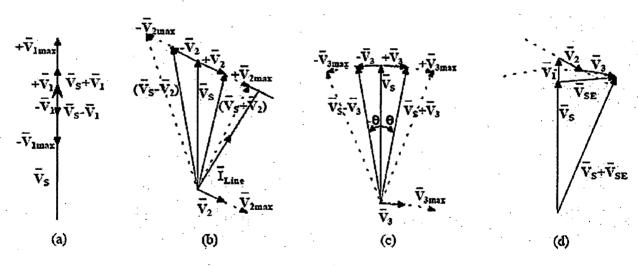

Viewing the operation of the unified power flow controller from the standpoint of traditional power transmission based on reactive shunt compensation, series compensation, and phase angle regulation, the UPFC can fulfill all these functions and thereby meet multiple control objectives by adding the injected voltage  $V_{pq}$ , with appropriate amplitude and phase angle, to the (sending end) terminal voltage  $V_s$ . using phasor representation, the basic UPFC power flow control functions are illustrated in Fig. 1.6.

Figure 1.6: Phasor diagram illustrating the conventional transmission capabilities of the UPFC (a) voltage regulation (b) line impedance compensation (c) phase shifting (d) simultaneous control of voltage, impedance, and angle

çį,

11

÷,

Voltage regulation with continuously variable in-phase/anti-phase voltage injection, is shown in Fig. 1.6(a) for voltage increments  $V_{pq} = \Delta V$  ( $\rho = 0$ ). This is functionally similar to that obtainable with a transformer tap changer having infinitely small steps

Series reactive compensation is shown in Fig. 1.6(b) where  $V_{pq} = V_p$  is injected in quadrature with the line current I. Functionally this is similar to series capacitive and inductive line compensation attained by the SSSC. The injected series compensating voltage can be kept constant, if desired, independent of line current variation, or can be varied in proportion with the line current to imitate the compensation obtained with series capacitor or reactor.

Phase angle regulation is shown in Fig. 1.6(c) where  $V_{pq} = V_{\sigma}$  is injected with an angular relationship with respect to  $V_s$  that achieves the desired  $\sigma$  phase shift without any change in magnitude. Thus the UPFC can function as a perfect phase angle regulator, which can also supply the reactive power involved with the transmission angle by internal VAR generation.

Multifunction power flow control, executed by simultaneous terminal voltage regulation, series capacitive line compensation, and phase shifting, is shown in Fig 1.7(d) where  $V_{pq} = V_q + V_{\sigma} + \Delta V$ . This functional capability is unique to the UPFC. No single conventional equipment has similar multifunctional capability.

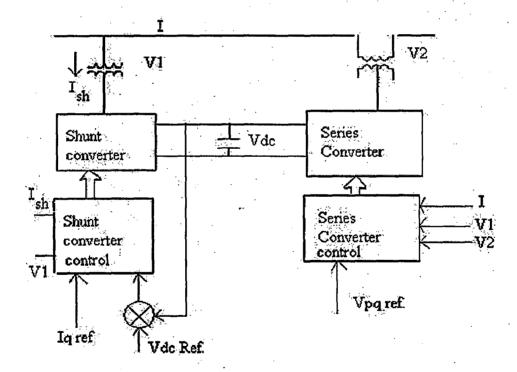

## 1.2.3 Basic Control Structure of UPFC [2, 4, 5]

The superior operating characteristics of the UPFC are due to its unique ability to inject an ac compensating voltage vector with arbitrary magnitude and angle in series with the line upon command, subject only to equipment rating limits. With suitable electronic controls, the UPFC can cause the series injected voltage vector to vary rapidly and continuously in magnitude and angle as desired. Thus, it is not only able to establish an operating point within a wide range of possible P, Q conditions on the line, but also has the inherent capability to transition rapidly from one such achievable operating point to any other.

The UPFC control system can be divided into two parts; internal control and functional operation control. The internal controls operate the two converters so as to produce the commanded series injected voltage and, simultaneously, draw the desired shunt reactive current. The internal controls provide gating signals to the converter valves so that the converter output voltage will properly respond to the internal reference variables,  $i_{pRef}$ ,  $i_{qRef}$  and  $v_{pqRef}$ , in accordance with the basic control structure shown in Fig. 1.7. As can be observed, the series converter responds directly and independently to the demand for series voltage vector injection. Changes in series voltage vector,  $v_{pq}$  can therefore be affected instantaneously. In contrast, the shunt converter operates under a closed loop current control structure whereby the shunt real and reactive power components are independently controlled. The shunt reactive power responds directly to an input demand.

Figure 1.7: Basic UPFC control structure

The external or functional control operation control defines the functional operating mode of the UPFC and is responsible for generating the internal references,

$i_{pRef}$  and  $v_{pqRef}$  for the series and shunt compensation to meet the prevailing demands of the transmission system [2, 6]. The functional operating modes and compensation demands, represented by external reference inputs, can be set manually by the operator or dictated by an automatic system optimization control to meet specific operating contingency requirements [6].

#### **1.2.4 Different configurations of UPFC & literature review**

Essentially, the requirements for implementing the UPFC with different types of converter topologies are [14];

1. To reduce the harmonic distortion in the output of the inverter, i.e. approximating the inverter output to the almost possible sinusoidal.

2. To increase the voltage and hence total power rating of the device.

3. To decrease the voltage stress on each power semi conductor device, by connecting the devices in series.

Recently, multi-level converters of various topologies have emerged as an alternative way of implementing low-distortion and high-power voltage source inverters [7]. In general, these converters synthesize the output voltage from a number of available DC voltage supplies held on storage capacitors. The complex phase shifting transformers of the multi-pulse converter are not needed and, in principle, the series connection of devices can be avoided.

#### **Relevant review of literature**

In [8],The neutral-point-clamped multilevel converter has been shown as an attractive implementation of the unified power flow controller because it facilitates back to back operation, high voltage operation (without direct series connection of devices) and low distortion (without the use of multi-pulse transformers). A UPFC using three converters is proposed. Two phase-shifted converters are required to provide a full range of voltage control of the series connection while ensuring low distortion and a balanced DC link. A single shunt converter is used. A commutation angle solution that balances the voltages of the multiple DC link capacitors is analyzed in terms of the active power

balance at each node. Control of shunt reactive power requires a variable DC link voltage. Control schemes for both shunt and series converters are developed and verified in terms of voltage balancing and power flow control on a micro-scale experimental system, using 5-level converters. This paper describes a back-to-back multi-level converter implementation of a UPFC which achieves independent control of the shunt and series voltage magnitudes, maintains capacitor voltage balance and maintains transmission quality harmonic distortion. The control system required for this UPFC is then examined.

Reference [10] compares four converter topologies for the implementation of flexible ac transmission system (FACTS) controllers: three multilevel topologies (multipoint clamped (MPC), chain, and nested cell) and the well-established multi pulse topology. In keeping with the need to implement very-high-power inverters, switching frequency is restricted to line frequency. The study addresses device count, dc filter ratings, restrictions on voltage control, active power transfer through the dc link, and balancing of dc-link voltages. Emphasis is placed on capacitor sizing because of its impact on the cost and size of the FACTS controller. A method for the dimensioning the dc capacitor filter is presented. It is found that the chain converter is attractive for the implementation of a static compensator or a static synchronous series compensator. The MPC converter is attractive for the implementation of a unified power flow controller or an interline power flow controller, but a special arrangement is required to overcome the limitations on voltage control.

In [14], proposes a novel UPFC based on 3-level half-bridge modules, isolated through single -phase multi winding transformers. The dynamic performance of proposed system was analyzed by simulations with EMTDC, assuming that the UPFC is connected with the 138-kV transmission line of one-machine-infinite-bus power system. The proposed system can be directly connected with the transmission line without series injection transformers. It has flexibility in expanding the operation voltage by increasing the number of 3-level half bridge Modules.

In [15], Operation of UPFC consisting of two VSCs is demonstrated through digital simulations studies on PSCAD/EMTDC software [17]. In this unified power flow

15

. . Di

· a 1 1 2 - \*\*

controller (UPFC) constructed by a back to back connection of a hysteresis current forced (HCF) converter and a pulse width modulated (PWM) inverter. The performance of the proposed switching schemes and associated controllers in providing the desired UPFC internal characteristics such as constant DC bus voltage and bi-directional power transfer capability is illustrated.

In this paper [16], the author has proposed a novel UPFC based on H-bridge modules, isolated through single-phase multi-winding transformers. The dynamic performance of proposed system was analyzed by simulations with EMTDC, assuming that the UPFC is connected with the 138-kV transmission line of one-machine-infinite-bus power system. The proposed system can be directly connected to the transmission line without series injection transformers. It has flexibility in expanding the operation voltage by increasing the number of H-bridge modules. The author has also given the various practical considerations of UPFC and also the realization of a simple power system with UPFC.

In [17], one method of meeting high mega volt ampere specifications by using multiple modules of two-level three-phase converter modules controlled by the phase-shifted triangle carrier technique of the sinusoidal pulse width modulation (SPWM) strategy. Two conceptual designs are presented. The first is the gate-turn-off (GTO)-SPWM-UPFC at the lowest switching rate, fc=fm = 3; to minimize GTO switching loss. The design is based on applying the fundamentals of SPWM theory to overcome unbalances arising from sideband harmonic interferences. The second is the insulated gate bipolar transistor (IGBT)-SPWM-UPFC, at fc=fm = 12 or higher, which SPWM theory assures that direct paralleling of the modules is free of current unbalance. A laboratory UPFC based on six modules of three-phase 5-kVA size IGBT converters operating at the baseline condition of dual unity displacement factor at the sending end and the receiving end has been implemented.

In [19], it is proved here that, as the diode-clamped, multilevel converter has been found to have attractive features for STATCOM application; there is interest in extending it to UPFC application by using multilevel converters as the series and the shunt converters. Unfortunately, as is demonstrated in this paper, the dc voltages at their dc links are inherently unstable. Faced with this impasse, a solution is sought in a system of local feedback controlled Class B choppers to equalize the dc. Laboratory experimental model establishes the feasibility of the proposal. Digital simulations show that current ratings in the choppers need be only 10% of the current ratings in the converters. The chopper cost is estimated as 1% of the cost of the multilevel converters.

## **1.3 OUTLINE OF THE THESIS**

In this thesis three different configurations of UPFCs have been considered. The considered configurations are

(1) UPFC using 2 levels, 6 pulse voltage source converters.

(2) UPFC based on 3-level Half-Bridge DC MLI Modules

(3) H-Bridge inverter module based UPFC.

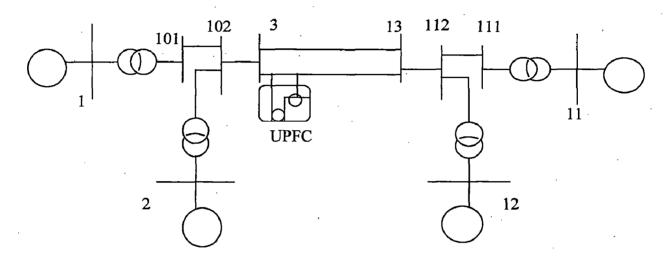

The studies have been carried out through detailed digital simulations on PSCAD/EMTDC V4.1 for investigating the behaviors of UPFCs, the two area 4-M/c, 10 bus system [18] has been chosen.

In Chapter 2, the basic 2-level, 6 pulse voltage source converters are used as shunt and series inverters, which are triggered by two different techniques among the many methods that are available which are listed below. Here, Hysteresis current control (HCC) and PWM switching scheme have been used for the shunt and the series inverter respectively. The simulation results of this UPFC are also discussed at the end of this chapter.

In Chapter 3, the in-depth description of multi level inverters and different types are discussed. The idea and the basic operating principles of diode clamped multi level inverter are also given in this chapter. Later, the UPFC composed of 3 level, diode clamped half bridge inverter modules is being described in detail including the gate pulse generation scheme and structure of this configuration of UPFC. The block diagram of the used control system is also given here. The operation of the proposed system was verified through simulations with PSCAD/EMTDC as said earlier. This system can be directly

17

a la contra a la

connected to the transmission line without series injection transformers. Detailed simulation description is also given including the inverter standalone simulations.

The detailed results of this configuration of UPFC based on 3 level, diode clamped half bridge inverter modules as controlling various parameters like controlling the bus voltage, real power and reactive powers is also given. The automatic power flow controller is also developed and its block diagram is also given and the corresponding results are also included at the end of this chapter.

Chapter 4 describe the operation of H-bridge inverter module based UPFC, isolated through single-phase multi-winding transformers. This system can be directly connected to the transmission line without series injection transformers. Detailed simulation description is also given including the inverter standalone simulations.

The results of this novel UPFC based on H-bridge modules as controlling various parameters like controlling the bus voltage, real power and reactive powers is also given. The automatic power flow controller is also developed and its block diagram is also given and the corresponding results are also included at the end of this chapter.

Chapter 5 broadly compares the different configurations of UPFC, which are simulated & described in above chapters. These configurations of UPFCs are compared on various parameters like, DC bus voltage magnitudes and its oscillations, switching frequency, harmonic content and also on the basis of their physical structure including the required no. of different components to implement practically for designing and put into operation. Finally the conclusions and future scope of thesis work have been presented.

#### **1.3.1 Description of Test System**

In this work, the four synchronous machines of the system are modeled as fixed voltage sources. All the transmission line parameters have been taken as lumped parameters. And the fixed loads at two different buses have been modeled as lumped impedance. The single line diagram of the above described system is as shown in Fig 1.8.

The system data is given in the Appendix. Simulation studies have been carried out by connecting the UPFC (each of the above three configurations) at bus no. 3.0f the

above test system. The single line diagram of the above test system incorporating the UPFC is shown in Fig. 1.8.

The load flow result given in the same standard text book, shown in Appendix I is most accurately achieved in the modeled system using PSCAD/EMTDC V 4.1 and taken as the initial condition for simulating the performance of the UPFC.

Figure 1.8: Single line diagram of the UPFC connected system

The graphical view of the simulated system in PSCAD/EMTDC is given in Appendix A. The steady state results of the above test system achieved with PSCAD/EMTDC are shown in Table 1.2. For comparison, the load flow results are given in [18] are also reproduced in Table 1.2. From this table it can be observed that these two results are close agreement.

Store for

| Table 1.2: comparison of the actual and simulated results of the test system |                           |                       |  |

|------------------------------------------------------------------------------|---------------------------|-----------------------|--|

| Bus No.                                                                      | Voltage mag. Voltage mag. |                       |  |

|                                                                              | Load flow result (pu)     | Simulated result (pu) |  |

| 1                                                                            | 1.03                      | 1.03                  |  |

| 2                                                                            | 1.01                      | 1.01                  |  |

| 11                                                                           | 1.03                      | 1.03                  |  |

| 12                                                                           | 1.01                      | 1.01                  |  |

| 101                                                                          | 1.0108                    | 1.0106                |  |

| 102                                                                          | 0.9875                    | 0.9871                |  |

| 111                                                                          | 1.0095                    | 1.0089                |  |

| 112                                                                          | 0.9850                    | 0.9848                |  |

| 3                                                                            | 0.9761                    | 0.9731                |  |

| 13                                                                           | 0.9716                    | 0.9698                |  |

## 1.4 conclusions

In this chapter, beginning with the introduction to FACTS into power systems and then the various types of FCATS Controllers are described briefly. The comparison of different FACTS controllers is also presented with concluding that, the UPFC is the most versatile Controller among all others. Later, the in-depth description of operating principle and control structure of UPFC are presented. I have finished this chapter by giving introduction to the test system considered for the simulation studies of various configurations of UPFCs.

### CHAPTER: 2

## **UPFC using basic 2-level VSC**

## **2.1 Introduction:**

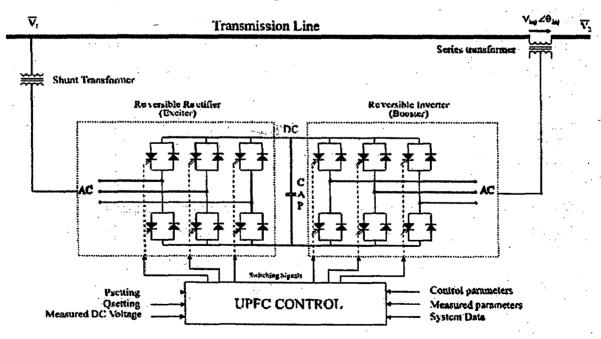

The basic operating principle and the control structure of UPFC are already discussed in previous Chapter 1. A UPFC consists of a shunt inverter, (exciter), a large DC capacitor and a series inverter (booster) as shown schematically in Fig. 2.1 [19].

In this chapter, the basic 2-level, 6 pulse voltage source converters are used as shunt and series inverters, which are triggered by two different techniques among the many methods that are available which are listed below. Hysteresis current control (HCC) and PWM switching scheme have been used for the shunt and the series inverter respectively. Detailed modeling of the UPFC has been carried out using PSCAD/EMTDC to develop a three-phase representation of a UPFC taking into account many practical constraints. The application of the UPFC in power system operation and control are illustrated in the test system described in chapter 1.

21

and a feet of the

## 2.2 Shunt Inverter switching scheme

The function of the exciter is to provide a constant DC bus voltage for the booster whether the power flow within the UPFC is from the exciter toward the booster or in the opposite direction. Hysteresis current forcing (HCF) is used here as the switching scheme for the exciter. The main reasons for selecting this technique are:

- The scheme is very simple to implement and its control technique is very adaptive to non-linear effects such as inductor saturation, switching delays and AC voltage fluctuations [23, 24].

- > Several modules can operate in parallel to provide desired VA rating; and

- The response of the converter to change in power demand is very fast and the converter is robust to the fluctuations of the AC supply.

In HCF switching, the AC side current is forced to track a referenced current by high frequency switching of the switch pairs of the converter bridge. To limit the switching rate a hysteresis band is defined about the reference current and the input current is forced to stay within this band, as shown in the figure. To obtain a constant DC bus voltage, a controller is used to control the switching of the converter. The block diagram of this controller is shown in Fig 2.2. This controller regulates the DC bus voltage by modifying the reference current,  $i_{ref}$  and the hysteresis band, h. In HCF switching scheme, choosing the width of the hysteresis band is important, since a narrow band increases the switching frequency above the rated switching frequency of GTOs, whereas with a wide band a smooth and constant DC bus voltage is not achievable. Moreover, the harmonic distortion of the exciter current is increased with the band. In this HCF scheme for the UPFC, a variable hysteresis band proportional to the AC current is used. This band is selected as 14% of the peak amplitude of the input AC current as described by the following Equation [19].

## $h = 14\% \times Is = 14\% \times \sqrt{2} * P / (\sqrt{3} * 11kV) \approx 0.01 * P$

where P is the three phase real power on the AC side;  $I_s$  the peak amplitude of the input current of the exciter; and h is the hystersis band.

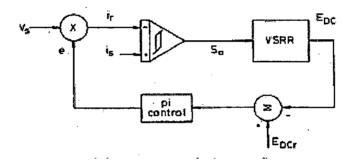

#### 2.2.1 Hysterisis Current Controls [23]

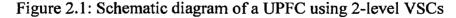

With the hysterisis control, limit bands are set on either side of a signal representing the desired output waveform. The inverter switches are operated as the generated signals within limits. Hysterisis-band PWM is basically an instantaneous feedback current control method of PWM where the actual current continually tracks the command current within a hysterisis band. Fig 2.3 shows the operating principle of hysterisis-band PWM for a half bridge inverter. The control circuit generates the sine reference current wave of desired magnitude and frequency, and it is compared with the actual phase current wave.

Figure 2.2: Simple hysteresis current control scheme

As the current exceeds a prescribed hysterisis band, the upper switch in the halfbridge is turned OFF and the lower switch is turned ON. As a result the output voltage transitions from  $+0.5V_{dc}$  to  $-0.5V_{dc}$ , and the current starts to decay. As the current crosses the lower limit, the lower switch is turned OFF and the upper switch is turned ON [24]. A lock-out time (t<sub>d</sub>) is provided at each transition to prevent a shoot-through fault. The actual current wave is thus forced to track the sine reference wave within the hysterisis band limits.

In a UPFC where  $E_{dc}$  is across a capacitor and is required to equal some reference level under different load conditions, it is necessary to produce a current reference that will cause the correct amount of power to flow in the right direction to maintain the bus voltage [23, 24].

Figure 2.3 Generation of pulses for HCC control

A simple controller that can achieve this again can be explained with the help of Fig 2.2. The signal derived from the supply voltage is multiplied by an error term derived from the DC bus voltage to produce the required current reference, which is then compared with the current to determine which transistors are to be turned on. The process of generation of pulses for HCC scheme is already shown in Figure 2.3 [19].

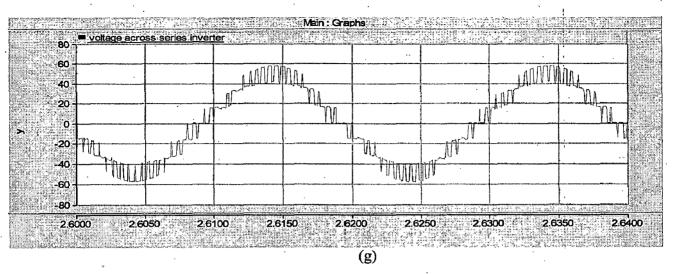

## 2.3 Series Inverter switching scheme

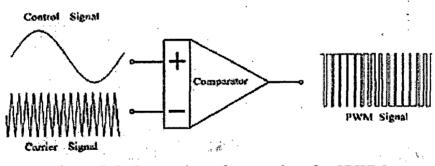

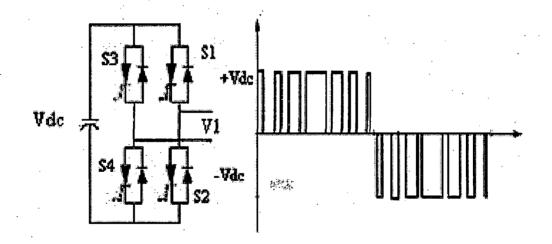

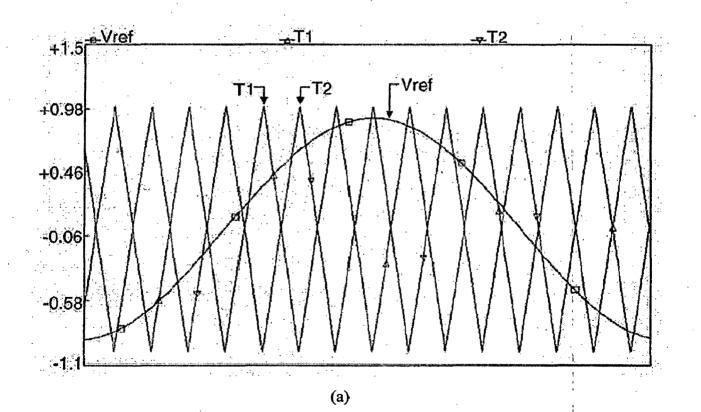

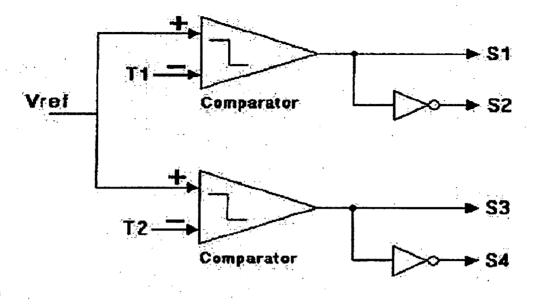

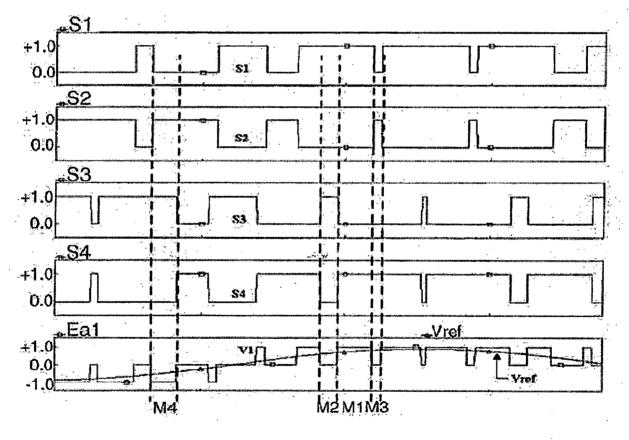

Pulse width modulation (PWM) switching technique is used for the booster [20]. Naturally sampled triangulation method (NST) is implemented on the developed PWM inverter of the booster branch in the UPFC. The typical construction of a naturally sampled triangulation modulator is illustrated in Fig 2.4 [19]. In this technique the PWM switching points are defined by point-on-wave comparisons between a control sinusoidal waveform and a high frequency carrier (triangle) waveform. The comparator output is the PWM signal which determines the switching instants. The magnitude, frequency and phase of the fundamental component of the inverter output voltage can be controlled by changing the frequency, magnitude and phase of the control signal.

### 2.3.1 Sinusoidal Pulse Width Modulation [19, 20]

The sinusoidal PWM technique is very popular for industrial converters. In this, isosceles triangle carrier wave of frequency fc is compared with the fundamental frequency f sinusoidal modulating wave, and the points of intersection determine the switching points of power devices. The notch and pulse widths of Vao wave vary in sinusoidal manner so that average or fundamental component frequency is same as f and its amplitude is proportional to the command modulating voltage. The same carrier wave can be used for all 3 phases.

Fig. 2.4 illustrates the SPWM method. In this method, the switches are turned ON and OFF complimentarily at the instants at which the sinusoidal modulation signal and the triangular carrier signal intersect with each other. This method of encoding the modulating signal through the pulse width is accurate when the frequency of the carrier is sufficiently high. The modulation signal is amplified with a constant gain, without delay. In this regard, three indices are useful to characterize the operation of the SPWM technique.

(a) Modulation Index (M.I) [22] is defined as,

$M.I(Ma) = \frac{Amplitude\_of\_modulating\_wave\_}{Amplitude\_of\_carrier\_wave}$

The properties of the Modulation Index are

- > M.I. determines the fundamental component output voltage

- > If  $0 \le M.I \le 1$ ,  $V_1 = M.I$  ( $V_{in}$ ) where  $V_1, V_{in}$  are the fundamental of the output voltage and input DC voltage respectively

(b) Modulation Ratio (Freq Ratio), M<sub>R</sub> [22]:

$M_{R} = \frac{Frequency\_of\_carrier\_wave}{Frequency\_of\_modulating\_wave}$

- > Modulation ration determines the incident of harmonics in the spectra

- ➤ f=K.M<sub>R</sub> (f<sub>m</sub>), where f<sub>m</sub> is the frequency of modulating signal and k is integer (1, 2, 3....)

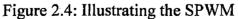

#### (c) Total Harmonics Distortion (THD) [22]:

If  $V_n$  is voltage of  $n^{th}$  harmonic voltage;

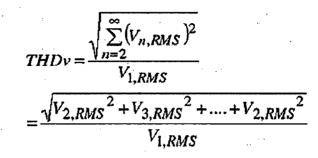

An oscillator is used to generate a triangular carrier waveform at the switching frequency of the carrier signal. A modulated function, control signal, is generated separately and both applied to a comparator. The comparator as shown in Fig 2.5 generates a high output if control signal is greater than carrier signal and a low output when carrier signal is greater than control signal. Hence the output can be interpreted directly as a switching function. Moreover, since the triangle waveform has a voltage linearly dependent on time, the comparator has an output pulse width linearly dependent on the level of control signal

Figure 2.5: Generation of gate pulses for SPWM

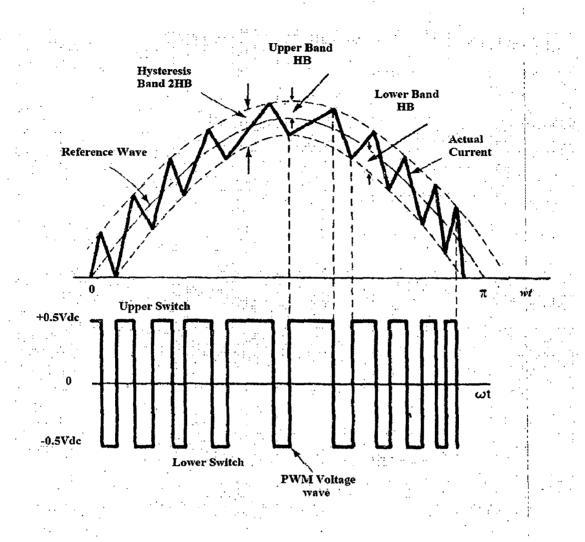

## **2.4 Control Structure**

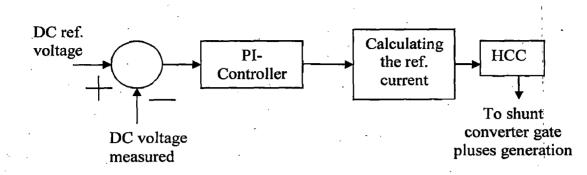

For the purpose of simulating this simple configuration of UPFC, a simple control circuit for controlling the DC bus voltage to a fixed reference value has been chosen. By taking the sys bus voltage waveform and error in the DC bus voltage, passing it to the PI controller, reference current waveform is generated, which is to be tracked by the shunt converter. The block diagram of this controller is as shown in Fig 2.6 below [19].

George -

Figure 2.6: Block diagram of control system.

# 2.5 Simulation results

For simulation of this configuration of UPFC in a grid, the test system as described in chapter 1 has chosen. The PSCAD/EMTDC graphical view is given in Appendix B. The various parameters of the control system and the other apparatus are also given in Appendix B.

#### 2.5.1 Case (I) ·

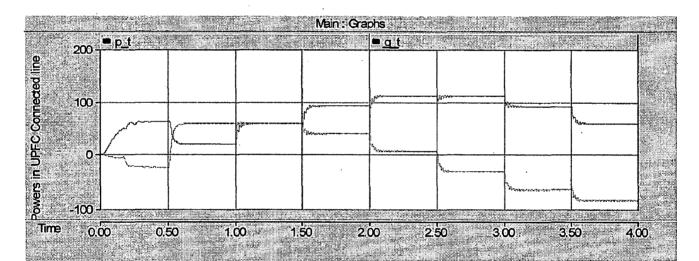

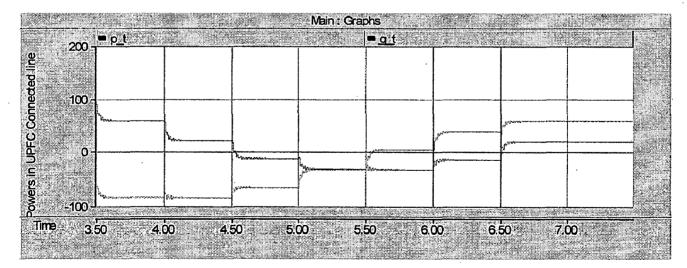

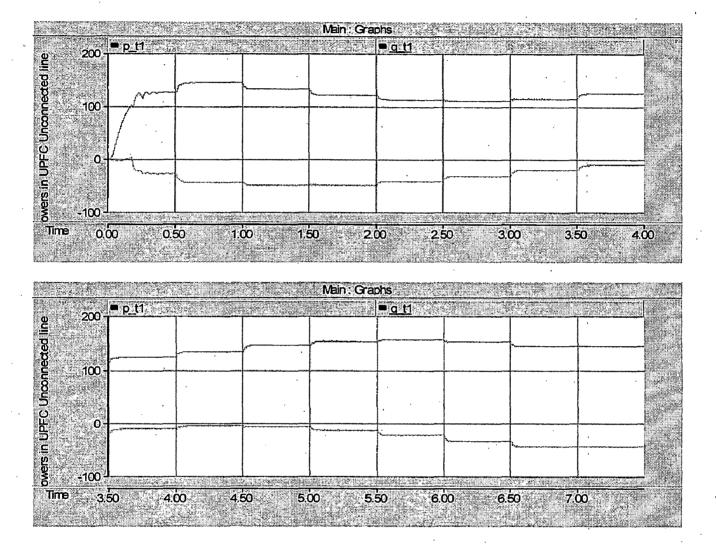

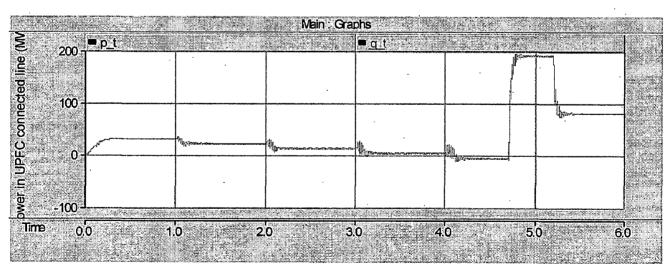

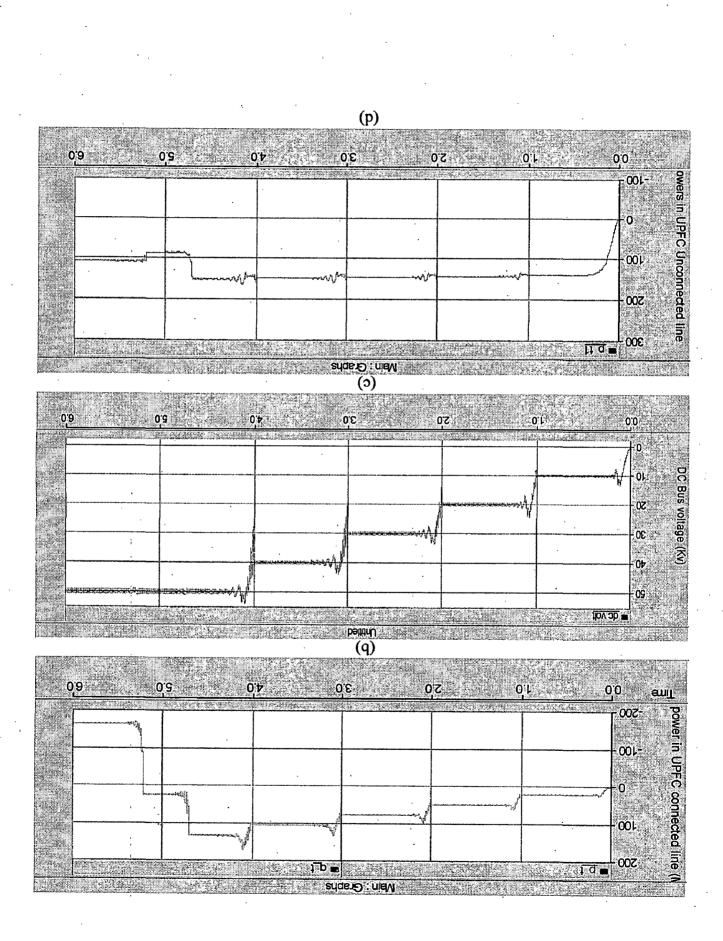

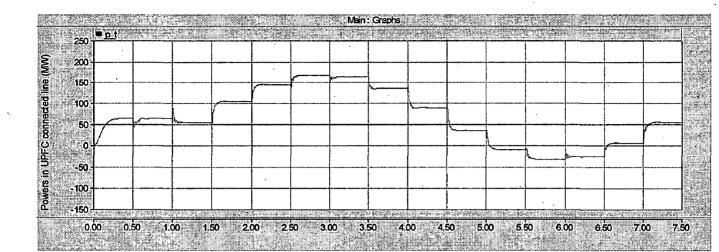

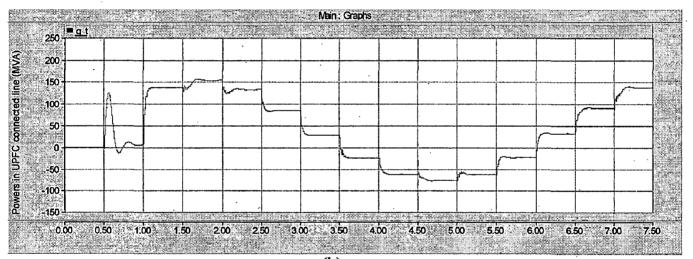

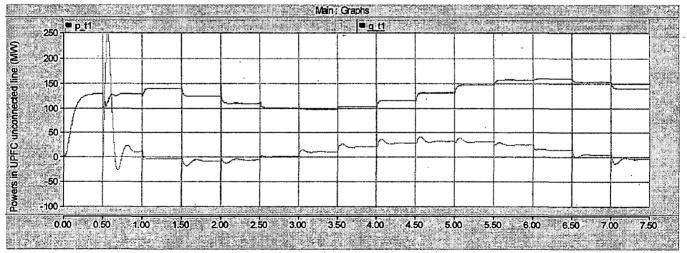

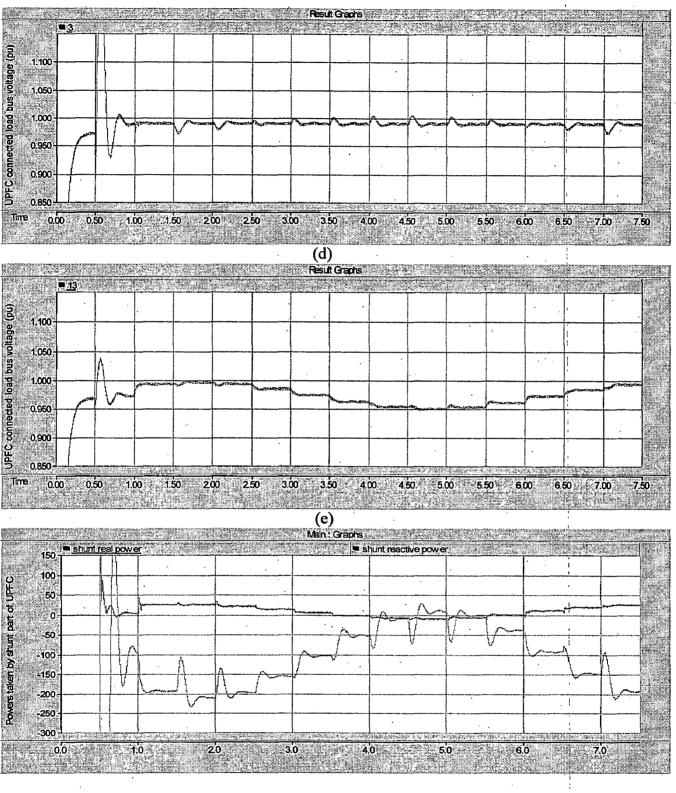

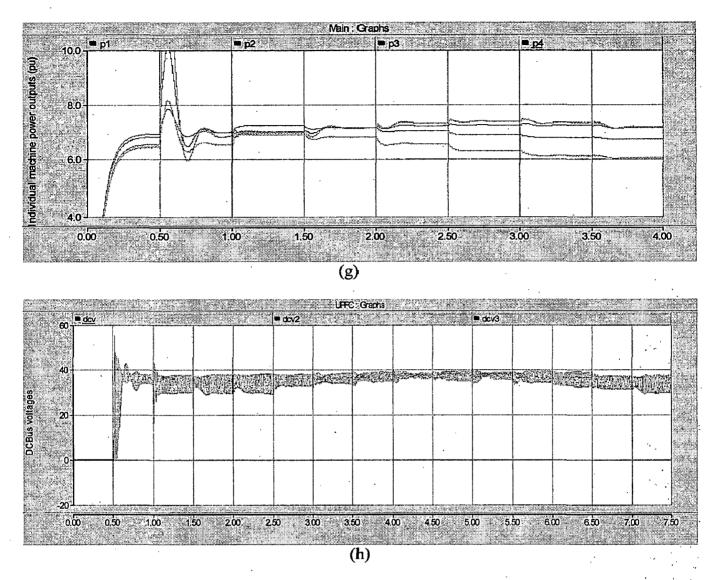

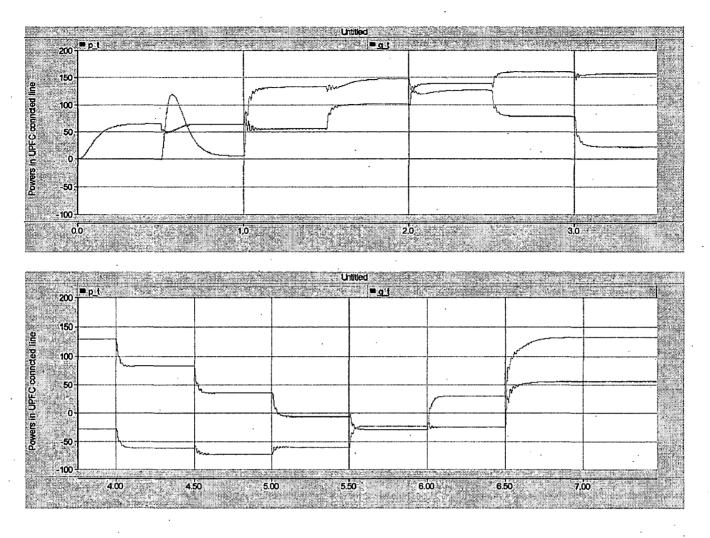

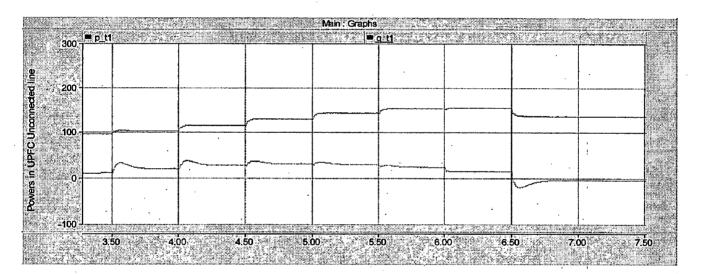

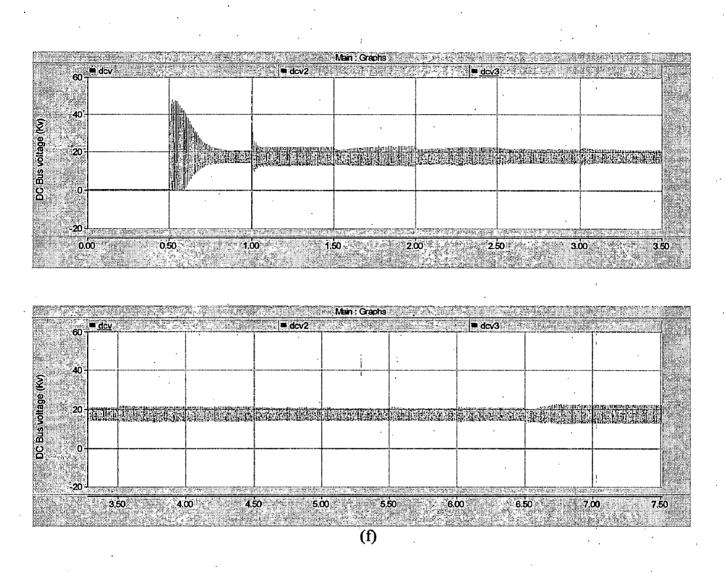

In this case, the parameters of the booster are varied to observe the resultant variations in the real and reactive power flow in the line. Specifically the modulation index of the booster has been kept fixed and phase angle of the injected booster voltage has been changed. The variations of both the real & reactive power flows in the lines, and other parameters are given in Figure 2.7 below. The parameters considered in this work are shown in Table 2.1 below.

| Time Duration  | Ma  | Phase     | DC Bus ref. voltage |

|----------------|-----|-----------|---------------------|

| Sec. (from-to) |     | (degrees) | (Kv)                |

| 0.5-1.0        | 0.9 | 0         | 25                  |

| 1.0-1.5        | 0.9 | 30        | 25                  |

| 1.5-2.0        | 0.9 | 60        | 25                  |

Table 2.1: Simulation parameters used for this UPFC for case (i)

| 2.0-2.5 | 0.9 | 90  | 25 |

|---------|-----|-----|----|

| 2.5-3.0 | 0.9 | 120 | 25 |

| 3.0-3.5 | 0.9 | 150 | 25 |

| 3.5-4.0 | 0.9 | 180 | 25 |

| 4.0-4.5 | 0.9 | 210 | 25 |

| 4.5-5.0 | 0.9 | 240 | 25 |

| 5.0-5.5 | 0.9 | 270 | 25 |

| 5.5-6.0 | 0.9 | 300 | 25 |

| 6.0-6.5 | 0.9 | 330 | 25 |

| 6.5-7.5 | 0.9 | 360 | 25 |

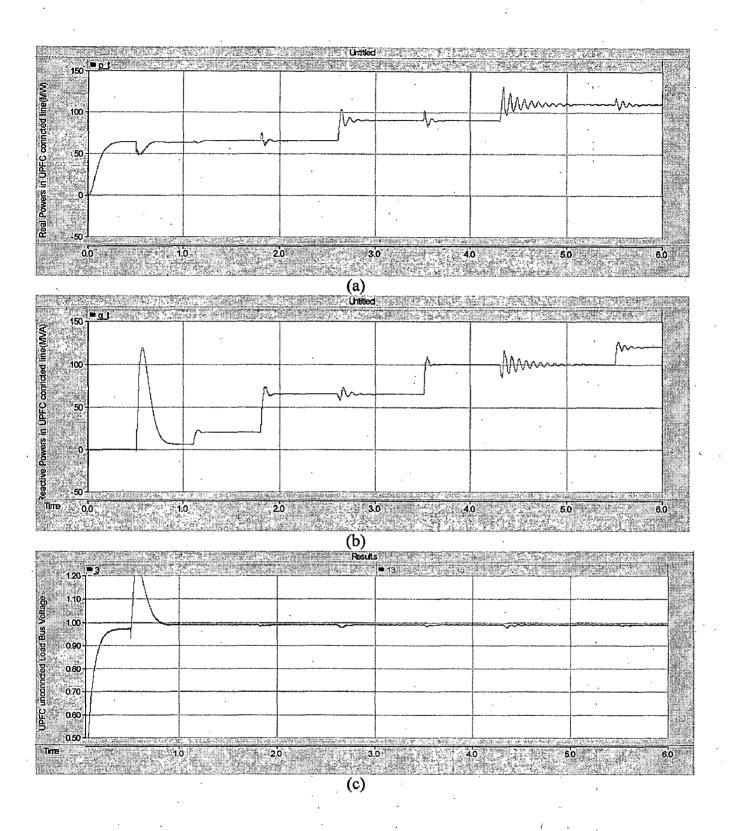

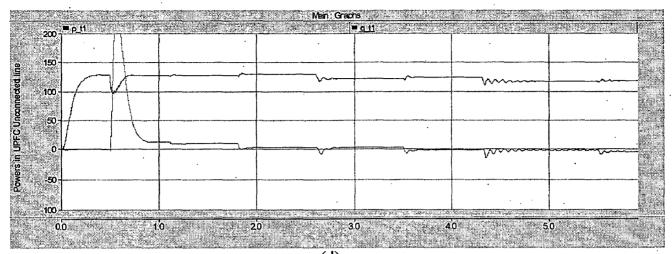

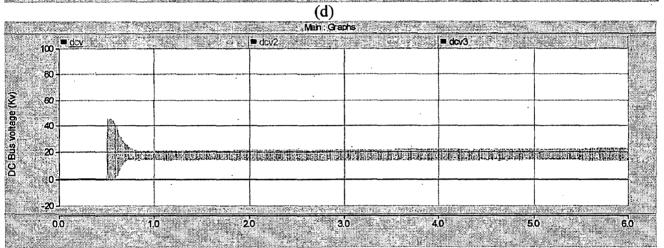

(a)

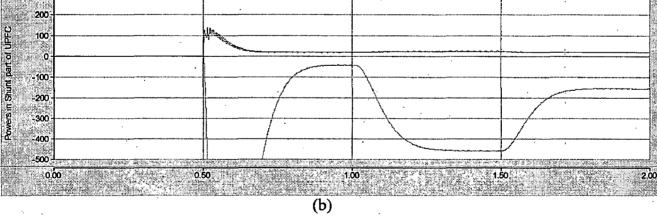

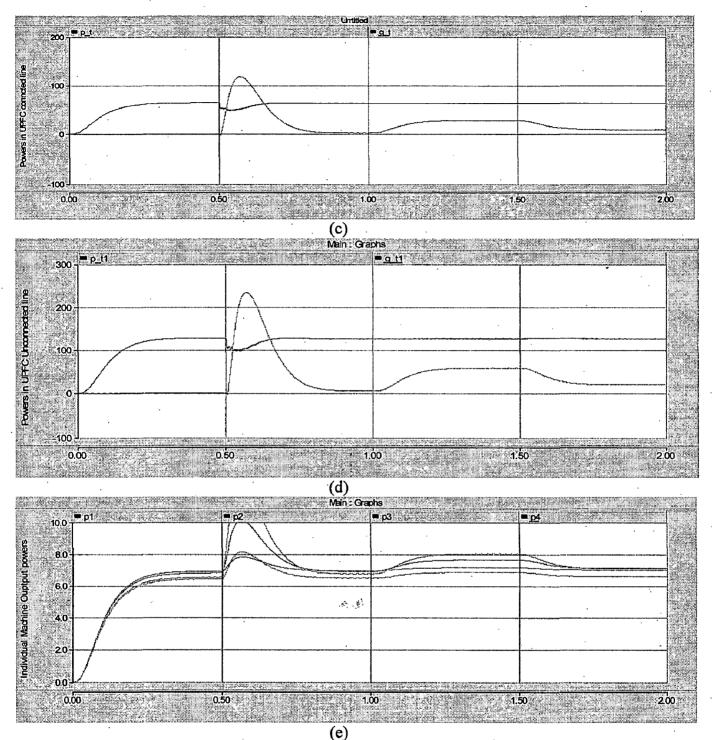

(b)

| 1.50     | 1                                     | <u></u> | ing at the second | <u>erena</u> turra |            |                                                      | internet in the second | -             |

|----------|---------------------------------------|---------|-------------------|--------------------|------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|          |                                       |         |                   |                    |            |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 243           |

|          |                                       |         | 1                 |                    |            |                                                      | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

| 1.00     | · · · · · · · · · · · · · · · · · · · |         |                   |                    |            |                                                      | ļ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

|          |                                       | ·       |                   |                    |            | والأكاف كالثلة بجرب وبالثلاث والمترك ومرادي والمراجع | · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |