# IMPLEMENTATION OF 16 BIT RISC MICROCONTROLLER ON FPGA

# **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree

of

# **MASTER OF TECHNOLOGY**

in

# ELECTRICAL ENGINEERING

(With Specialization in System Engineering & Operations Research)

By

# MOHITE ARUN PANDURANG

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE -247 667 (INDIA) JUNE, 2006

# **CANDIDATE'S DECLARATION**

I hereby declare that the work which is being presented in this dissertation entitled, "IMPLEMENTATION OF 16 BIT RISC MICROCONTROLLER ON FPGA", submitted towards the partial fulfillment of the requirements for the award of the degree of Master of Technology in Electrical Engineering, with specialization in System Engineering and Operations Research, I. I. T. Roorkee, India, is an authentic record of my own work carried out from June 2005 to June 2006 under the supervision of Dr. G. N. Pillai & Prof. M. K. Vasantha, Electrical Engineering Department, Indian Institute of Technology, Roorkee, India.

The matter, embodied in this dissertation report, has not been submitted for the award of any other degree or diploma.

Dated:

Place: Roorkee

Aphrohit

**MOHITE ARUN PANDURANG**

## CERTIFICATE

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

Dr. G. N. Fillai Associate Professor Electrical Department IIT Roorkee Roorkee-247667 (India)

Prof. M. K. Vasantha Professor Electrical Department IIT Roorkee Roorkee-247667 (India)

# ACKNOWLEDGEMENT

I would like to take this opportunity to express my deepest sense of gratitude to my supervisors **Dr. G. N. Pillai** and **Prof. M. K. Vasantha**, Department of Electrical Engineering, I.I.T. Roorkee, for their invaluable support, guidance and suggestions at various stages of this Dissertation. I feel privileged to be associated under them and it was a great pleasure in learning the practical aspects of digital design and verification under their aegis and guidance. I am very much thankful to them for giving me an opportunity to work on a topic which was very much interesting and challenging for me. I remember with great emotion, the constant encouragement and help extended to me by him that went even beyond the realm of academics.

Special mention has to be made of **Dr. (Ms.) Indra Gupta**, in-charge Microprocessor and Computer Laboratory for providing me the computer in the lab and all other facilities including FPGA Kit required for this project as and when needed.

The department of Electrical Engineering of this institute provided me with all kinds of necessary facilities for carrying out my work. My sincere thanks are due to **Prof. S. P. Gupta**, Head of Electrical Engineering department and **Prof. H. O. Gupta**, Ex-head of the department, for making the opportunities available although. My sincere thanks go to all the faculty members of the department for the voluntary help, direct and indirect, extended to me during the course of the work.

I am also thankful to **Dr. S. Dasgupta**, Department of Electronics and telecommunication, IIT Roorkee, for his invaluable discussion and suggestions, regarding various issues of VHDL coding and FPGA implementation.

My sincere regards to staff and my friends at the Department who have directly and indirectly helped me in completing this Report. I am grateful to my hostel mates and my colleagues, for helpful and fruitful discussions and for the good time we spent together.

Last, but not least by any means, I wish to acknowledge my family members for giving me the moral strength and constant encouragement. The work could never reach its present status without their constant support and love.

Dated:

#### **MOHITE ARUN PANDURANG**

M-Tech (System Engineering & Operations Research) Department of Electrical engineering, I. I. T. Roorkee.

Place : Roorkee

ii

# CONTENTS

|               |                 | Title                                                         | Page |

|---------------|-----------------|---------------------------------------------------------------|------|

|               | Candi           | idate's Declaration                                           | i    |

|               | Acknowledgement |                                                               |      |

|               | Acronyms        |                                                               |      |

|               | Abstr           | act                                                           | vii  |

| Ch 1:         | INTR            | ODUCTION                                                      |      |

|               | 1.1             | Introduction                                                  | 1    |

|               | 1.2             | Motivation behind the work                                    | 2    |

|               | 1.3             | Objective of dissertation work                                | 5    |

|               | 1.4             | Introduction to Atmel AVR AT90S1200                           | 5    |

|               | 1.5             | Overview of Microcontroller and Microprocessors               | 5    |

|               | 1.6             | Comparison of Microcontrollers and Microprocessors            | 5    |

|               | 1.7             | Microcontroller Performance Factors                           | 8    |

| •             | 1 <b>.8</b>     | CISC vs. RISC Architecture                                    | 9    |

|               | 1.9             | Microcontroller applications                                  | 11   |

| <b>Ch 2</b> : | MICR            | <b>COCONTROLLER ORGANISATION</b>                              |      |

|               | 2.1             | Tradeoffs in Microcontroller Design                           | 13   |

|               | 2.2             | The Microcontroller Operation                                 | 13   |

|               | 2.3             | Microcontroller organization                                  | 15   |

|               | 2.4             | Description of the microcontroller design Steps               | 17   |

| Ch 3:         | INSTI           | RUCTION SET ARCHITECTURE                                      |      |

|               | 3.1             | Atmel RISC microcontroller Architecture                       | 29   |

|               | 3.2             | Atmel RISC microcontroller Instruction Set & Addressing Modes | 31   |

|               | 3.3             | Machine Cycle Sequence                                        | 32   |

|               | 3.4             | Modeled Architecture                                          | 32   |

| x             | 3.5             | Instruction format                                            | 33   |

|               | 3.6             | Instruction set summary                                       | 35   |

|               | 3.7             | Addressing Modes                                              | 36   |

|               | 3.8             | Brainstorming the Design, the Creative Process                | 36   |

iii

# CONTENTS

|       |                      | Title                                        | Page |  |  |  |  |

|-------|----------------------|----------------------------------------------|------|--|--|--|--|

| Ch 4: | PIPELINE UNIT DESIGN |                                              |      |  |  |  |  |

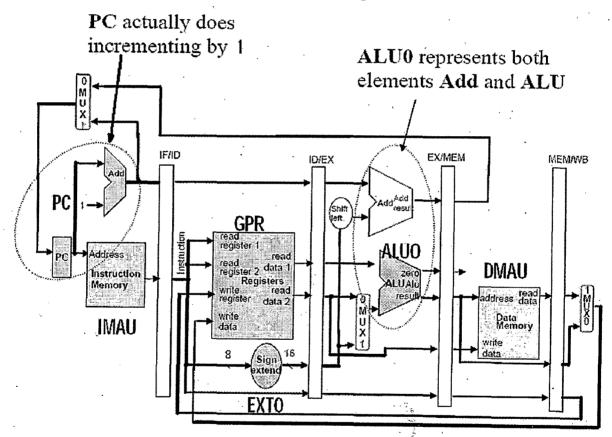

|       | 4.1                  | Instruction fetch unit                       | 41   |  |  |  |  |

| -     |                      | 4.1.1 Program counter                        | 41   |  |  |  |  |

|       |                      | 4.1.2 Instruction memory                     | 42   |  |  |  |  |

|       |                      | 4.1.3 Branch Decide Unit                     | 42   |  |  |  |  |

|       | 4.2                  | Instruction decode unit                      | 42   |  |  |  |  |

|       |                      | 4.2.1 Control unit                           | 42   |  |  |  |  |

|       |                      | 4.2.2 Register file organization             | 42   |  |  |  |  |

|       |                      | 4.2.3 Sign extension unit                    | 43   |  |  |  |  |

|       | 4.3                  | Execution unit                               | 43   |  |  |  |  |

|       | , ·                  | 4.3.1 Branch adder unit                      | 43   |  |  |  |  |

|       |                      | 4.3.2 Arithmetic and logical unit            | 44   |  |  |  |  |

|       |                      | 4.3.3 ALU control unit                       | 45   |  |  |  |  |

|       | 4.4                  | Write back unit                              | 45   |  |  |  |  |

|       |                      | 4.4.1 Data memory organization               | 45   |  |  |  |  |

|       |                      | 4.4.2 Register write unit                    | 45   |  |  |  |  |

|       |                      | 4.4.3 Interrupts and exception handling      | 45   |  |  |  |  |

| :     | 4.5                  | Hazards in pipeline unit                     | 46   |  |  |  |  |

| •     |                      | 4.5.1 Structural hazard                      | 46   |  |  |  |  |

|       |                      | 4.5.2 Data hazard                            | 46   |  |  |  |  |

|       |                      | 4.5.3 Control hazard                         | 47   |  |  |  |  |

| ÷e    | 4.6                  | Hazard detection unit                        | 47   |  |  |  |  |

|       | 4.7                  | Data forward unit                            | 47   |  |  |  |  |

| Ch 5: | CONT                 | TROL UNIT DESIGN                             |      |  |  |  |  |

|       | 5.1                  | Overview of control unit                     | . 49 |  |  |  |  |

|       | 5.2                  | Instruction decode unit                      | 50   |  |  |  |  |

|       | 5.3                  | Control unit                                 |      |  |  |  |  |

|       | 5.4                  | Synchronous Mealy Model Finite State Machine | 51   |  |  |  |  |

|       | 5.5                  | Finite State Machine States                  | 53   |  |  |  |  |

iv

|           |                                                     | Title                               | _    |  |

|-----------|-----------------------------------------------------|-------------------------------------|------|--|

|           |                                                     |                                     | Page |  |

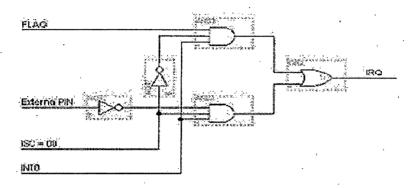

|           | 5.6                                                 | External Interrupt                  | 56   |  |

|           | 5.7                                                 | I/O Decoder                         | 57   |  |

|           | 5.8                                                 | Branch Evaluation Unit              | 57   |  |

|           | 5.9                                                 | Timer                               | 58   |  |

|           | 5.10                                                | Implementation Problems             | 58   |  |

| Ch 6:     | DESIGNING WITH FPGA                                 |                                     |      |  |

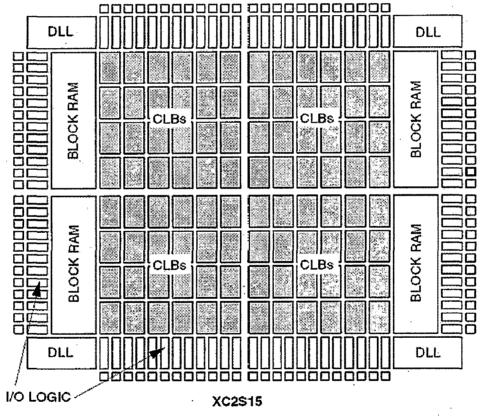

|           | 6.1                                                 | FPGA Architecture                   | 59   |  |

|           | 6.2                                                 | Programming with FPGA               | 60   |  |

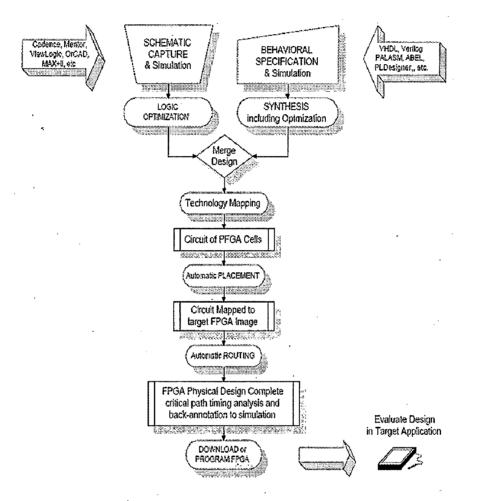

|           | 6.3                                                 | FPGA Design Environment             | 63   |  |

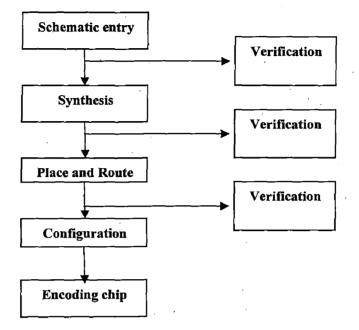

|           | 6.4                                                 | FPGA design flow for implementation | 64   |  |

|           | 6.5                                                 | Verification and testing            | 66   |  |

| Ch 7:     | Results and conclusion                              |                                     |      |  |

|           | 7.1                                                 | Results                             | 67   |  |

|           | 7.2                                                 | Conclusion                          | 67   |  |

|           | 7.3                                                 | future scopes of the work           | 69   |  |

| REFE      | RENC                                                | ES                                  | 70   |  |

| APPE      | NDIX                                                |                                     |      |  |

| <b>A:</b> | Atmel                                               | AVR microcontroller instruction set | 72   |  |

| B:        | Complete instruction set of RISC Microcontroller 74 |                                     |      |  |

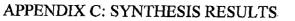

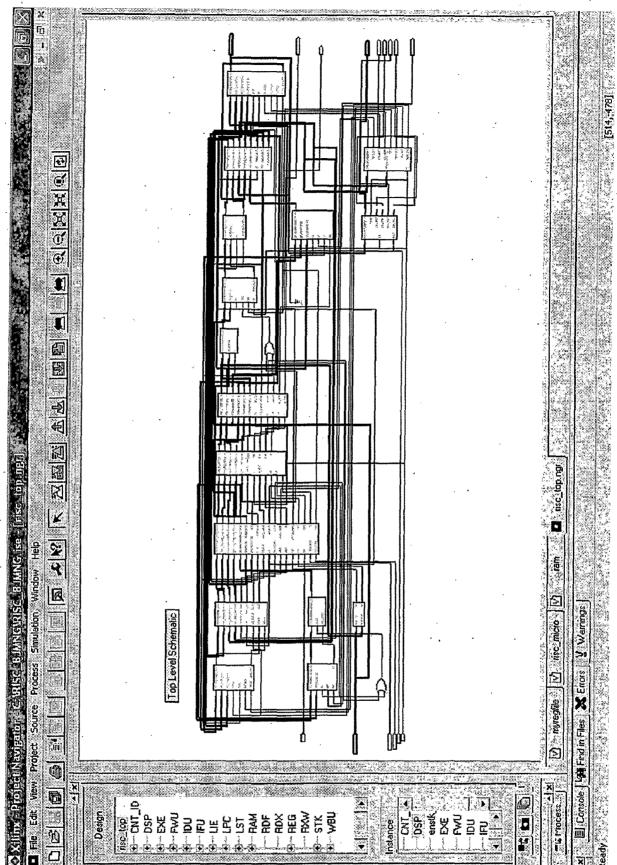

| C:        | Simulation results 75                               |                                     |      |  |

| D:        | Synthesis report 80                                 |                                     | 80   |  |

ν

# **ABBREVIATION AND ACRONYMS**

| FPGA           | Field Programmable Gate Array                       |

|----------------|-----------------------------------------------------|

| VHDL           | VHSIC Hardware Description Language                 |

| VHSIC          | Very High Speed Integrated Circuit                  |

| RISC           | Reduced Instruction Set Computer                    |

| MIPS           | Million Instructions per Second                     |

| SOPC           | System on Programmable Chip                         |

| VERILOG        | An Industry standard HDL (IEEE std. 1364)           |

| XST            | Xilinx's Synthesis Tool                             |

| ASIC           | Application Specific Integrated Circuit             |

| ASIP           | Application Specific Instruction Processor          |

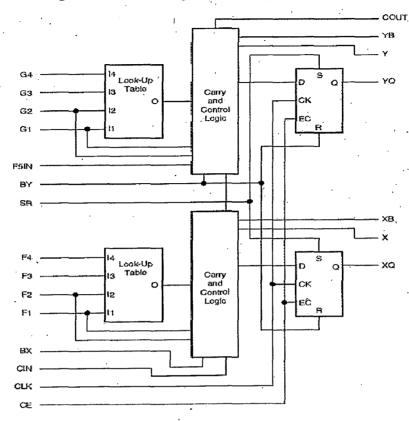

| CLB            | Configurable Logic Block (For Xilinx FPGA)          |

| LUT            | Look Up Table                                       |

| LAB            | Logic Array Block                                   |

| LE             | Logic Element (For Altera FPGA)                     |

| CPLD           | Complex Programmable logic Devices                  |

| PLD            | Programmable Logic Device                           |

| DDR            | Double Data Rate Interface                          |

| FCRAM          | Fast Cycle RAM                                      |

| PLL            | Phase Locked Loops                                  |

| Floor planning | process of choosing best connectivity in a design   |

| IEEE           | Institute of Electrical and Electronics Engineering |

| IOB            | Input/Output Buffer                                 |

| IOE            | Input/Output Element                                |

| VGA            | Video Graphic Adaptor                               |

vi

## ABSTRACT

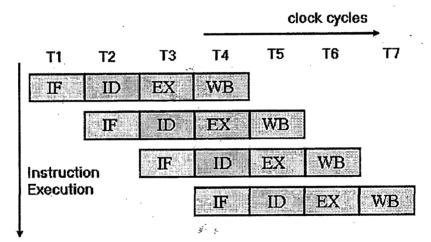

The work presented in this dissertation report describes the implementation of 16-bit RISC Microcontroller in FPGA chip, using VHDL programming at Xilinx ISE 7.1i platform supported by Xilinx ISE and Aldec Active HDL simulation environment. This work explores an application area of FPGA to develop application specific integrated circuit (ASIC) as an independent System on Programmable Chip (SOPC) design. The design is targeted to make a feel of a 16-bit Microcontroller available in FPGA. Microcontroller is organized with 4 stage pipelined RISC architecture and supports a total of 81 instructions. Successful synthesis is done and design is downloaded in Xilinx Spartan II FPGA. Output along with internal states of the embedded processor can be seen on seven segment display of Xilinx Spartan II FPGA kit, available with us in microprocessor and computer lab. Synthesis reports and Place & route reports are also provided to verify the design implementation.

This work focuses on the design methodology based on tools and techniques to capture the design and develop a Hardware Prototype of it. Like any other engineering design, Microcontroller designed is tested consistently and made modifications throughout whenever any problem arose. Pipeline has been modified and remapped for the better performance. Simulation is done using Xilinx ISE and Aldec Active HDL simulation environment to perform functionality test of this code. Synthesis optimization tools were used to convert the chip design in to smaller and faster design. Lastly the synthesized design is verified and various synthesis reports are analyzed to evaluate and verify the performance of the designed chip.

Atmel AVR RISC microcontroller (AT90S1200) is chosen as prototype model for design and all the necessary features of AT90S200 is implemented successfully in Xilinx Spartan 2 FPGA. Microcontroller designed in this dissertation can process 74-86 instructions simulation result of all the instructions are been tested and validated successfully by means of hand calculations. All the important features of a microcontroller are implemented in FPGA, which now behaves as is a microcontroller core.

vii

## **CHAPTER 1: INTRODUCTION**

#### 1.1 Introduction

.

In the ever-changing world of technology, new ideas are born and legacy technologies are left aside to be chronicled in the history books. Although new technologies become available, sometimes it is necessary to maintain older technology when servicing electrical systems for maintenance and redesign of existing systems. The lack of money usually prevents the redesign of systems. Since some systems cannot be replaced using new technology, technicians are challenged to maintain electrical systems with parts that are not procurable by commercial buyers and or government purchasers.

Microcontrollers and microprocessors are the most used devices in electronic equipment. Modern technology demands from any engineer, a basic microcontroller or microprocessor knowledge. The basic difference between them is that microprocessors can be configured for the amount of memory and the input / output system used. The microcontroller has all the computing system (I/O system and memory) built in it. Designer's judgment determines which one should be used [1].

The emphasis of this work will be in the design of complete microcontroller with CPU, RAM, ROM and I/O system in FPGA; microcontroller and microprocessor layout, fabrication process and technology are beyond the scope of this work and will not be considered at all. Design performance parameters like speed, power dissipation, wiring, packing, and transistor sizing are also beyond the scope of this work.

The design methodologies used to develop a Behavioral and Instruction Set model for the Atmel AVR AT90S1200 RISC microcontroller and the results of testing these models will be presented. VHDL is used to create the Behavioral model and the Instruction Set model. It is the intent of this dissertation to develop a model for the Atmel AVR AT90S1200 RISC microcontroller. This will allow for an understanding of how to best replace obsolete parts with new components, especially complex parts. The replacement of obsolete or singled sourced parts by emulation of the existing chip or using remaining die at chip supply houses usually yields a cost effective. Sometimes board or system redesigns are necessary to eliminate a high percentage of system or board level obsolete components. This is often very expensive and time consuming.

The state-of-the-art of digital circuit design now provides for an efficient, CAD oriented methodology for implementing digital designs, by using VHDL. During the 60's-70's system level and microcomputer design entailed building systems out of many individual logic gates manufactured on Integrated Circuits (IC). This design technique was very costly and time consuming. As the technology moved forward from medium-scale integration (MSI) to large-scale integration (LSI), to very large-scale integration (VLSI), the need for new design tools became apparent. With the ability to incorporate many functions on one IC, engineers needed a way to quickly design a function and or circuit and test the design. The standard known as VHDL was first created in 1987, [6].

VHDL allows for hardware description in a text based language. VHDL is similar to Ada, a government standardized, portable, and object oriented software language. VHDL allows a design to model a digital system at many levels of abstraction. A description can be as simple as a 2-input logic circuit or an entire digital system. There are five different levels of modeling: Performance modeling, Behavioral modeling, Instruction Set modeling, RTL modeling, and Gate-Level modeling.

The Behavioral model developed is an abstract model of the Atmel RISC microcontroller that demonstrates a basic understanding of how instructions are fetched and executed. The model was written to give a starting point of understanding to the overall design. Hence the Behavioral model will not have any physical implications pertaining to the original microcontroller.

Once the Behavioral model has been written one can then focus on developing an Instruction Set model. The Instruction Set model developed here allows for exercising a subset of Intel MCS-51 instructions. Since Atmel RISC microcontroller is a feature-reduced version of Atmel RISC microcontroller, it uses MCS-51 instructions.

Increasing performance and gate capacity of recent FPGA devices permits complex logic systems to be implemented on a single programmable device. Such a growing complexity demands design approaches, which can cope with designs containing hundreds of thousands of logic gates, memories, high-speed interfaces, and other high-performance components [26].

#### **1.2 Motivation behind the work**

The motivation for this work comes after the author took the course, "online Computer Application techniques". The author realizes that microcontroller design

could be an opportunity to summarize and apply most of the electronic engineering basic and advanced courses. Basic electronic course, digital logic circuits and advanced digital design are some of the electrical engineering courses used in this work.

Another motivation for this work lies in the author's desire to learn and master the microcontroller concepts, design and operation. For many years literature has been published regarding microcontroller and digital design. Techniques, methods, and procedures have been published, but most of them are usually explained using a symbolic or algorithmic approach. Some examples of this kind of approach can be found in "Computer Organization and Architecture Principles of Structure and Function [8]. Computer Organization and Design The Hardware / Software Interface" [9], The Intel Microprocessors 808X, Pentium and Pentium Pro" [10], "Embedded Systems and Computer Architecture"[3],

To grasp the basic concepts at the starting stage, one may feel more comfortable when they see the theoretical materialization, simulation and execution of hardware circuits, instead of large equations, diagrams, algorithms and symbols that most of the microcontroller information sources offer. The hardware implementation of every concept is what makes this work useful for beginners to learn and understand microcontroller concepts.

One of the main features of this work lies in the fact that it follows a series of steps and makes emphasis on the most important points in each and everyone of those steps. Beginners just have to follow those steps in order to design and simulate their own microcontroller. This work illustrates the design, simulation, testing, and implementation of all microcontroller circuits in each step. Through the whole process you will appreciate the complete microcontroller evolution and transformation from zero to a functional unit.

This method provides mechanisms to change some of the microcontroller parts without affecting others. It makes emphasis on modularization. Through the whole process, modules of each part are designed and can be changed individually without affecting the entire system. This allows experimentation and circuit changes to examine what is happening inside [3].

One possible application of this work is that one can transform microcontroller schematic into VHDL code and download it to an FPGA for prototype simulation. This increases understanding of microcontroller concepts and operation, with hands-on experience; one can examine how the instruction execution is and how the

microcontroller circuits work in every instruction. Also multiple versions of one microcontroller can be developed with slight changes, allowing you to observe the effect of those changes in each design and simulate each prototype on FPGA.

A weak point of this method is that it does not achieve an efficient implementation. Performance is not the main point of this work; just delivering the most important microcontroller concepts. The focus of this work is in the methodology, not in the computational capabilities and features of the microcontroller. Besides its educational approach, another important point is that this method provides a mechanism to design a microcontroller that can be simulated, as said before, on FPGA, but also can be used on real applications. In other words, slight changes can produce a different microcontroller for new applications as needed. Users do not have to buy a new microcontroller but try a different one using this method. Of course this is convenient for experimentation or academic purposes only, not for applications where performance is the critical point.

Modern microcontroller costs are relatively low, and are very useful for many applications but sometimes there are situations that are better handled with specially designed microcontrollers for specific applications. For example, a designer may want to build and control his/her own personal robot, with a specific instruction set. Designers can find in the market some inexpensive microcontrollers that suit design requirements. But those popular microcontrollers perhaps are for general use, but probably lacking features that designers would be looking for. Then, sometimes designers invest huge amounts of time and effort designing and programming assembly routine codes in order to achieve the required microcontroller performance, as to take full control of their robot [4].

Designing a microcontroller for specific needs allows designers to minimize the programming complexity and enhance designers system's performance. Designers also should keep in mind that microcontroller programming is as important as the micro-controller hardware design. Although it is not the intention of this work to discuss the microcontroller programming, this work illustrates the instruction execution of the microcontroller. This helps a lot when we are trying to understand the basic concepts of assembly programming like the addressing modes, clock cycles, and operands.

The quality of the microprogramming is what makes it possible to transform the complex circuits of the microcontroller into something useful. One of the main motivations for this work will be that inexperienced designers will not only gain an

insight of microcontroller design and operation, but also, designers will get a better understanding of the microcontroller assembly programming [2].

#### 1.3 Objectives

The main objective of this dissertation is to design a RISC microcontroller using VHDL and implement it in an FPGA. The microcontroller instruction set and features are based on Atmel AVR AT90S1200 RISC microcontroller. The microcontroller must be able to fit into the targeted FPGA device, which is Xilinx Spartan II xc2s200-5pq208. Features which cannot be implemented on an FPGA (analog comparator, pull-up resistors, etc) and which are not critical to the operation of the CPU (watchdog reset) will be ignored.

#### 1.4 Introduction to Atmel AVR AT90S1200

The AT90S1200 is a low-power CMOS 8-bit microcontroller based on the AVR RISC architecture. By executing powerful instructions in a single clock cycle, the AT90S1200 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed. The AVR core combines a rich instruction set (89 powerful instructions) with the 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.[]

The microcontroller also comes with 1K Bytes of in-system programmable flash as the program memory and 64 bytes of in-system programmable EEPROM. The AT90S1200 is equipped with one 8-bit timer/counter with separate prescaler, one on-chip analog comparator, a watchdog timer with on-chip oscillator and SPI for in system programming. It also features the external and internal interrupt. There are a total of 15 programmable I/O lines. The IC come in 20-pin PDIP and SOIC with 2 speed grades, 0 - 4 MHz for AT90S1200-4 and 0 - 12 MHz for AT90S1200 [25].

#### **1.5 Overview of the Microprocessor and Microcontrollers**

#### **1.5.1 Microprocessors**

A microprocessor, as the term has come to be known, is a general purpose digital computer's central processing unit (CPU). Microprocessor CPU contains arithmetic and

logic unit (ALU), a program counter (PC), a stack pointer (SP), some working, registers, a clock timing circuit, and interrupts circuits.

To make a complete microcomputer, one must add memory; usually read only program memory (ROM) and random-access data memory (RAM), memory decoders, an oscillator, and a number of input/output (I/O) devices, such as parallel and serial data ports. In addition, special-purpose devices, such as interrupt handlers and counters, may be added to relieve the CPU from time consuming counting or timing chores. Equipping the microcomputer with mass storage devices, commonly a floppy and hard disk drives, and I/O peripherals, such as a keyboard and a CRT display, yields a small computer that can be applied to a range of general-purpose software applications [1].

The hardware design of a microprocessor CPU is arranged so that a small or very large system can be configured around the CPU as the application demands. The internal CPU architecture, as well as the resultant machine level code that operates that architecture, is comprehensive but as flexible as possible.

The prime use of a microprocessor is to read data, perform extensive calculations on that data, and store those calculations in a mass storage device or display the results for human use. The programs used by the microprocessor are stored in the mass storage device and loaded into RAM as the user directs. A few microprocessor programs are stored in ROM. The ROM-based programs are primarily small fixed programs that operate peripherals and other fixed devices that are connected to the system. The design of microprocessor is driven by the desire to make it as expandable and flexible as possible, in the expectation of commercial success in the marketplace.

#### **1.5.2 Microcontrollers**

Typically microcontroller is a true computer on a chip. The design incorporates all of the features found in a microprocessor CPU (ALU, PC, SP, and registers). It also has added the other features needed to make a complete computer: ROM, RAM, parallel I/O, serial I/O, timer / counters, interrupt control and a clock circuit.

Like the microprocessor, a microcontroller is a general purpose device, but one that is meant to read data, performs limited calculations on that data, and control its environment based on those calculations. The prime use of a microcontroller is to control the operation of a machine using a fixed program that is stored in ROM and that does not change over the lifetime of the system.

The design approach of the microcontroller mirrors that of the microprocessor:

make a single design that can be used in as many applications as possible in order to sell, hopefully, as many as possible. The microprocessor design accomplishes this goal by having a very flexible and extensive repertoire of multi-byte instructions. These instructions work in a hardware configuration that enables large amounts of memory and I/O to be connected to address and data bus pins on the integrated circuit package. Much of the activity in the microprocessor has to do with moving code and data to and from external memory to the CPU. The architecture features working registers that can be programmed to take part in the memory access process, and the instruction set is aimed at expediting this activity in order to improve throughput. The pins that connect the microprocessor to external memory are unique, each having a single function. Data is handled in byte, or larger, sizes [2].

The microcontroller design uses a much more limited set of single and double byte instructions that are used to move code and data from internal memory to the ALU. Many instructions are coupled with "programmable" pins on the IC package. The microcontroller is concerned with getting data from and to its own pins; architecture and instruction set are optimized to handle data in bit and byte size.

#### **1.6 Comparison of Microcontrollers and Microprocessors**

The microprocessor is an integrated circuit composed by the Control Unit, Arithmetic Logic Unit, Registers and Digital circuit support. The microprocessor uses its data bus pins, address bus pins, and control lines pins to allow connection to other circuits to configure the entire system. The main characteristic of the microprocessor is that it is an open system, which means that its configuration is variable, and can be adapted to many different applications [4].

The microcontroller is a closed system. In which all parts are fixed in the same chip. Just the lines that control the peripherals are the ones that go outside the chip. This characteristic makes microcontrollers suitable for specific applications or for general use. The microcontroller applications range is narrower than the microprocessor's range. The reason is that microcontrollers have all their computing system integrated on the same chip. This reduces the available space inside the microcontroller to include components that the microprocessor has externally like memory and I/O system. This means that a microprocessor can be used for microcontroller applications but microcontrollers cannot always be used for most microprocessor applications. Microcontrollers are preferred when the application is defined and specific. In those situations where important system modifications are needed or applications are not specialized a microprocessor is more convenient.

The contrast between a microcontroller and a microprocessor is best exemplified by the fact that most microprocessors have many operational codes (opcodes) for moving data from external memory to the CPU; microcontrollers may have one or two. Microprocessors may have one or two types of bit handling instructions; microcontrollers will have many.

Microcontrollers are found in small, minimum component designs performing control oriented activities, such as the traffic lights. These designs were often implemented in the past using dozens or even hundreds of ICs. A microcontroller aids in reducing the overall component count. All that is requires is microcontroller, a small number of support components, and a control program in ROM.

To summarize, the microprocessor is concerned with rapid movement of code and data from external addresses to the chip; the microcontroller is concerned with rapid movement of data within the chip. Microcontroller can function as a computer without the addition of any external hardware; microprocessor must have many additional parts to be operational [1].

#### **1.7 Microcontroller Performance Factors**

Microcontroller performance can be defined in terms of speed, size, power, cost, design time and manufacture cost. Each depends on concepts beyond the scope of this work. The main factor that determines the microcontroller performance [5] are its architecture, design features and manufacture process. Thus the microcontroller performance depends on designer's judgment at the design stage. The architecture features determine the remaining microcontroller characteristics. The architecture depends on the microcontroller application. Different applications differ in features and data processing requirements. The Von Neumann architecture and Harvard architecture [3] are the two main architectures used in microcontroller design.

The Harvard architecture is the most popular nowadays. The Von Neumann architecture main characteristic is that it uses one main memory where data and instructions are stored. Only one system bus is used for control, data transfer, processing and addressing. Harvard architecture consists of two different and independent memories in which one contains instructions and the other one contains

data. Both have their own data bus systems for control, data transfer, processing and addressing. Both memories can be accessed simultaneously.

The Architecture and the hardware implementation features transform an idea into a circuit with specific characteristics. Computer simulation allows designers to verify that circuit works as required. When specification constraints and performance requirements are met, it is time for testing and manufacture. Design aspects defined by the architecture determines which manufacture process will be used.

#### **1.8 CISC vs. RISC Architecture**

#### **1.8.1 Complex Instruction Set Computer (CISC)**

In early days, computers had only a small number of instructions and used simple instruction sets, forced mainly by the need to minimize the hardware used to implement them. As digital hardware become cheaper, computer instructions tend to increase both in number and complexity. These computers also employ a variety of data types and a large number of addressing modes. A computer with a large number of instructions, are known as complex instruction set computer, abbreviated CISC. Major characteristics of CISC architecture are:

- A large number of instructions typically from 100 to 250 instructions

- Some instructions that perform specialized tasks and are used infrequently

- A large variety of addressing modes typically from 5 to 20 different modes

- Variable-length instruction formats

- Instructions that manipulate operands in memory

#### **1.8.2 Reduce Instruction Set Computer (RISC)**

In the early 1980s, a number of computer designers were questioning the need for complex instruction sets used in the computer of the time. In studies of popular computer systems, almost 80% of the instructions are rarely being used. So they recommended that computers should have fewer instructions and with simple constructs. This type of computer is classified as reduced instruction set computer.

The first characteristic of RISC is the uniform series of single cycle fetch and execute operations for each instruction implemented on the computer system being developed [9]. A single cycle fetch can be achieved by keeping all the instructions a standard size. The standard instruction size should be equal to the number of data lines

÷2.

in the system bus, connecting the memory (where the program is stored) to the CPU. At any fetch cycle, a complete single instruction will be transferred to the CPU. For instance, if the basic word size is 16 bits, and the data port of the system bus (the data bus) has 16 lines, the standard instruction length should be 16 bits.

Achieving uniform execution of all instructions is much more difficult than achieving a uniform fetch. Some instructions may involve simple logical operations on a CPU register (such as clearing a register) and can be executed in a single CPU clock cycle without any problem. Other instructions may involve memory access (load from or store to memory, fetch data) or multi-cycle operations (multiply, divide, floating point), and may be impossible to be executed in a single cycle.

Some of the necessary conditions to achieve a streamlined operation are:

- 1. Standard, fixed size of the instruction, equal to the computer word length and to the width of the data bus.

- 2. Standard execution time of all instructions, desirably within a single CPU cycle.

Which instructions should be selected to be on the reduced instruction list? The obvious answer is: the ones used most often. It has been established in a number of earlier studies that a relatively small percentage of instructions (10 - 20%) take up about 80% - 90% of execution time in an extended selection of benchmark programs. Among the most often executed instructions were data moves, arithmetic and logic operations. As mentioned earlier, one of the reasons preventing an instruction from being able to execute in a single cycle is the possible need to access memory to fetch operands and/or store results. The conclusion is therefore obvious we should minimize as much as possible number instructions that access memory during execution stage. This consideration brought forward the following RISC principles:

1. Memory access, during execution stage, is done by load/store instructions only.

2. All operations, except load/store, are register-to-register, within the CPU.

Most of the CISC systems are microprogrammed; because of the flexibility that microprogramming offers the designer. Different instructions usually have microroutines of different lengths. This means that each instruction will take a number of different cycles to execute. This contradicts the principle of a uniform, streamlined handling of all instructions. An exception to this rule can be made when each instruction has a one to one correspondence with a single microinstruction. That is, each micro routine consists of a single control word, and still let the designer benefit from the advantages of microprogramming. However, contemporary CAD tools allow

the designer of hardwired control units almost as easy as micro programmed ones. This enables the single cycle rule to be enforced, while reducing transistor count.

In order to facilitate the implementation of most instruction as register-to register operations, a sufficient amount of CPU general purpose registers has to be provided. A sufficiently large register set will permit temporary storage of intermediate results, needed as operands in subsequent operations, in the CPU register file. This, in turn, will reduce the number of memory accesses by reducing the number of load/store operations in the program, speeding up its run time. A minimal number of 32 general purpose CPU registers has been adopted, by most of the industrial RISC system designers.

The characteristics of RISC architecture are summarized as follow:

- Single-cycle instruction execution

- Fixed-length, easily decoded instruction format

- Relatively few instructions

- Relatively few addressing modes

- Memory access limited to load and store instructions

- All operations done within the registers of the CPU

- Hardwired rather than micro programmed control unit

- Relatively large (at least 32) general purpose register file

#### **1.9 Microcontroller Applications**

The microcontroller is one of the most important electronic devices on which modern technology is based on. Microcontroller uses are endless; from toys to TV sets, microwaves, ovens, computers, printers, cars and so on. Digital circuits become larger and larger as more functions need to be executed. In modern digital world, most of the individual digital circuit components are sold in a single chip. Those individual chips need power and space to operate. When the circuit becomes huge, the traditional logic design approach is not the best option and microcontrollers become convenient. Microcontrollers are basically sequential machines because their operation depends on their current status and its inputs. Their power lies in the fact that the hardwire configuration allows its operation to be changed depending on programming. It is not required to use additional logic circuits if the operation is changed [4].

### 2.1 Tradeoffs in Microcontroller Design

An important question that must be answered before attempting to implement a microcontroller is, **Is it necessary to use a special purpose microcontroller?**[3] In addition to having the basic instruction set, special purpose microcontrollers usually have instructions specialized to perform specific tasks. Those microcontrollers include in their design, special hardware that is used for execution and calculation support to execute instructions in their specific applications. The application determines the microcontroller operation, and the operation is executed with specific instructions. Then, the real deal in the design process consists in making tradeoffs between designing more powerful and complex instructions that reduce the programming code, or as another alternative, the operation can be implemented in hardware to save the time-consuming programming of certain tasks and achieve faster execution.

Should an operation be implemented in hardware or software? Is it worth? [3] Answer to those questions depends on many factors like design requirements, available budget, technology used and so on. Hardware instructions implementation result in faster executions but increase design cost. Software implemented operations save hardware and costs but increases the instruction execution time and the programming complexity. There are not defined rules. Designers have to make their choices based on design constraints and available resources to produce the best system performance at lower cost.

#### **2.2 The Microcontroller Operation**

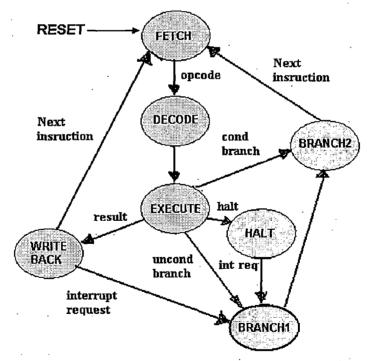

The microcontroller operation consists in four steps:

- 1. Fetch process; the fetch process consists in retrieving one instruction from memory and loads it in the Instruction Register.

- 2. **Decoding**; once the instruction is in the Instruction Register, the control unit receives the operational code from it. The control unit decodes the operational code to identify the instruction to be executed.

- 3. Executing; after the control unit identify the instruction, it start a series of microcontroller hardware signal activations. The control unit ensures that the

12367.

necessary elements are on and off in each clock cycle to accomplish the instruction execution.

4. Storing results: after the execution of the instruction results obtained must be stored at appropriate place.

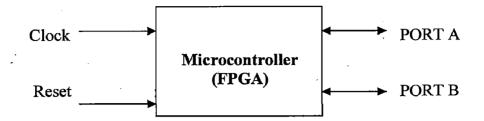

#### Figure 2.1: Microcontroller basic block

Basically the CPU addresses a memory location, obtains (fetches) a program instruction that is stored there, and carries out (executes) the instruction. After completing one instruction, the CPU moves on to the next one. This fetch and execute process is repeated until all of the instructions in a specific program are done. The fetch process clock cycle depend on the Instruction Register size (instruction word) and the number of bits of the data bus. For example if the IR size is 16 bits and the data path is four bits, then four clock cycles will be needed for the fetch process. The memory size will determine how many instructions can be stored in it and indeed the program size that can be stored.

The first step in the hardware design is to prepare the specification of the design. The architecture and the instruction set must be understood thoroughly. The design ideas are then described with VHDL in a text editor. Then, the VHDL code is synthesized with xilinx ISE 7.1i. If synthesized successfully, Xilinx ISE 7.1i will generate a net list files (EDF file). This file is then sent to xilinx ISE 7.1i for compilation and simulation. Results are verified by simulation.

The hardware design process is repeated until the microcontroller is complete without any errors. Hardware implementation is performed by downloading the design into the targeted FPGA device (Xilinx Spartan II xc2s200-5pq208). The hardware implementation tests the design in real physical environment by some control applications. A microcontroller can perform thousands of control applications. For every application, different programs must be written and store into the program ROM of the microcontroller before it can do the job. So, before the microcontroller is downloaded into the FPGA device, the specific program for the application must be written. This program file, together with the EDF file of the complete microcontroller is

then sent to xilinx ISE 7.1i for compilation and device programming. Once programmed into the device, the FPGA is reset to execute the application.

#### 2.3 Microcontroller organization

The microcontroller has 2 input pins (reset & clock) and 2 bi-directional I/O ports. Each I/O port consists of 16 individual I/O pins, total of 32 I/O pins. The clock signal will drive the whole microcontroller directly. Reset is active high; when asserted it resets the microcontroller to the default state even if the clock is not running. Port A and Port B are all 16-bits port. Each bit can be configured to be input or output. All port pins are tri-stated when the microcontroller is reset. Pin B.7 also serves as the external interrupt source and external timer clock source.

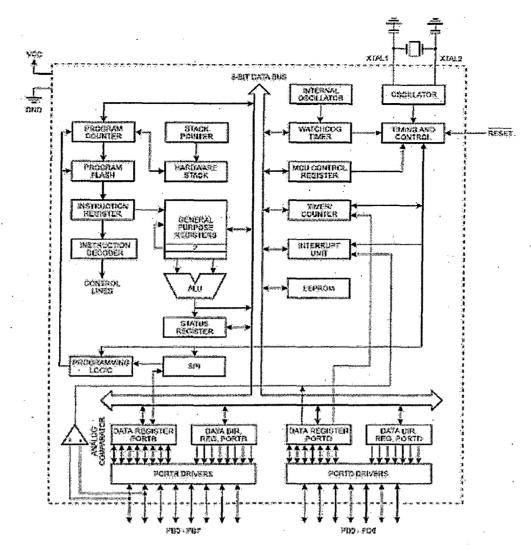

Figure 2.2: Top-level block diagram of the Microcontroller [5].

Figure 2.2 shows the top-level block diagram of the design, the bus structure has been simplified, but every block represents a module to be designed. At first glace, there are 11 modules in the top-level, with the 2 ports sharing the same module. These 11 modules are to be design separately using the top down design approach. Some modules like the instruction register and status register are easy to design, but modules like ALU and the control unit require a lot of understanding. The overall dataflow and bus structure between all the modules must be understood before designing the modules

individually. Buses provide connection between modules. There are many direct buses, such as the connection between program counter and program ROM, between program ROM and IR, between register file and ALU, etc. No control signals are required for direct buses. A common bus is a bus shared by many modules. The data bus is the only common bus in this design. The data bus provides connection between the general purpose register file, ALU, status register, SRAM and all the I/O features. Since there are so many possible data flows, control signals are required to control the correct flow direction. Only one source to the data bus is allowed at a time. If not, logic contentions will happen and the value of the data bus will be invalid. Tri-state bus is used to implement the common data bus. Only the correct source is connected to the data bus while others are in high impedance state. The impedance is so high that it can be seen as unconnected to the bus system. If the ALU is the data source, the data bus will be flooded with the result of the ALU and is available to all the connected modules. Control logic will generate an enable signal for the real destination to receive the data.

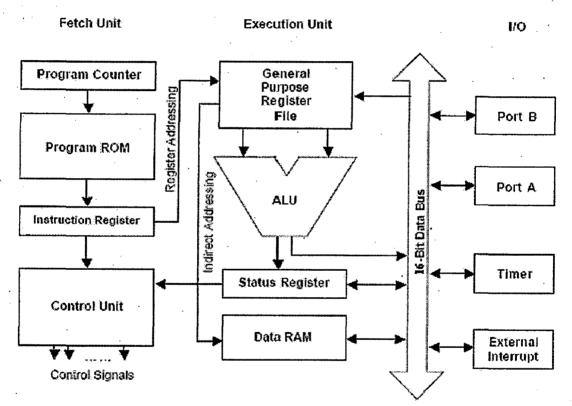

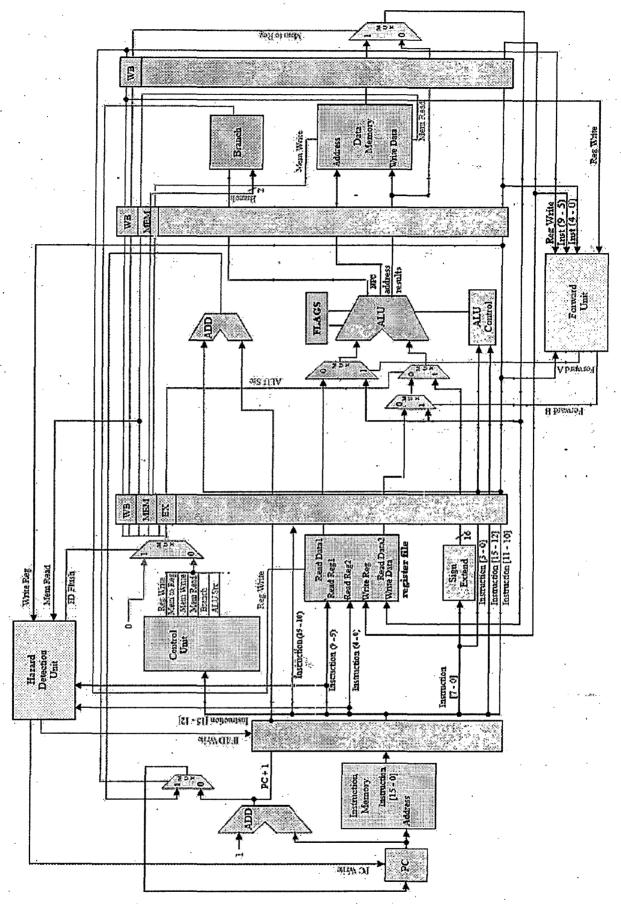

Next is a brief introduction to the whole system. The system can be divided into 5 units, the fetch unit, decode unit, execute unit, write back unit, and I/O unit. Fetch unit is in charge of fetching the next instruction, decode unit decodes instruction and generates necessary control signals, execute unit is in charge of executing the current instruction and the write back unit stores result of various operations performed by microcontroller and interrupt handling is also done. I/O unit provide a connection with the outside world. The fetch unit and execute unit form the CPU of the microcontroller.

The first module of the fetch unit is the program counter (PC). The PC contains the address of the next instruction to be executed. It points to the program ROM to locate the instruction. The instruction from the ROM is then latched into the instruction register (IR). The control unit takes the content of the IR and decodes it. It then asserts the appropriate control signals to execute the instruction. All modules are connected with direct buses.

The execute unit in charge of executing most instructions. Normally, to execute an instruction, 2 operands are output from the register file to the ALU. The ALU then perform the operation and send the result to the data bus. Contents of the data bus (result) are then stored back to the register file. The ALU also evaluate the status register flags and send them directly to the status register (SR). The whole execution process is done in a single cycle. The ALU perform many operations - include passing the contents of a general register to the data bus. SR also has a direct bus connection to

the control unit required for branch evaluation. The register file (destination and source register) is addressed directly by some bits in IR.

A RISC Microcontroller has memory access limited to only LOAD and STORE instructions. Load and store instructions can only transferred data between the RAM and the register file. A load operation sends the RAM data to the general registers through the data bus. A store operation sends the data to ALU, the ALU pass the data to data bus and store into the RAM.

To implement the fetch and execute pipeline in this microcontroller, memory are implemented using the Harvard architecture. Program and data are store in separate memories. As seen in the block diagram, program is stored in the program ROM while data are stored in the data RAM. The advantage of Harvard architecture is the ability to fetch the pre-fetch the next instruction easily. A normal RAM will have initial value zero when powered on. In FPGA, the RAM can have initial values and thus can make it act as a ROM.

All the I/O modules contain many control registers. Data are sent to and receive from it through the common data bus. The Status Register is also mapped into one of the I/O address. IN and OUT instructions are used to transfer data between these control registers and the general registers. The lower half of the control registers (00 h - 1F h, shaded in gray) are directly bit-accessible using the SBI and CBI (Set/Clear Bit in I/O) instructions. In this design, the lower half of control registers is all the I/O ports control registers.

# 2.4 Description of the microcontroller design Steps

#### 2.4.1 Justification for the design

The following are some questions that could guide designers at the implementation decision stage and decide need of microcontroller for the application..

- 1. What is the application? Can the application be implemented with logic circuits? What will be the resulting circuit size? Is it affordable?

- 2. What could be the microcontroller implementation advantage? Microcontroller has hardwired circuits that change its' their operation using programming. Designers should analyze if amount of different applications justify the use of a microcontroller or if the use of individual operational circuits is more convenient.

- 3. What are the advantages or disadvantages of using a microcontroller in terms of efficiency, time, design complexity and cost? Budget and design requirements analyses are necessary to decide if a microcontroller use is convenient or not. Sometimes the use of a micro controller results in a waste of hardware resources and sometimes it is less expensive option. There are situations in which programming is avoided using logic circuit, but this choice could result in larger, expensive and more complex circuits.

- 4. Is a microcontroller result in the best option? How many different operations will be used? How many times one operation is executed? Is it better to use individual circuits for every operation or using a microcontroller is more efficient? Is this difference in time response needed for the application? Is the microcontroller programming complexity worth instead of using individual circuits?

Figure 2.3: Architectural block diagram of microcontroller[9]

### 2.4.2 The Operation Definition

After a careful study of the application, the next step consists in defining the amount of different operations required for the application.

- 1. What are the application operation requirements? Are those operations complex or simple? How many different operations does the application have? Do designers need a new microcontroller to execute one operation or can use an existing one? Does it execute the instruction as required in terms of clock cycle, power & speed?

- 2. Is it more convenient to divide those operations in more simple tasks or not? Depending on the application and design requirements this could or could not be possible. Can the microcontroller with its instruction set, execute those individual and simple tasks, or a new one is needed?

- 3. Can those tasks be executed using more than one instruction, or is one instruction enough?

#### **2.4.3 The Instruction Set Definition**

The instruction set should contain those instructions that the application requires. Tasks executed, amount of hardware used and clock cycles are very important parameters of an instruction.

- How powerful is the instruction? The term powerful means that how many tasks can be executed by single that instruction. This may result in more hardware or more clock cycles per instruction.

- How many instructions are required to perform the operation? This will be determined by the power of the instruction set. The more powerful the instruction set is, fewer instructions are needed per operation.

- What kind of instructions does every microcontroller must have? Every microcontroller must have at least; logic, arithmetic, branch and data transfer instructions.

- How many complex tasks can be executed using the simplest instruction set? The basic instruction set can be combined to execute complex tasks. E.g., multiplication operation can be executed with successive execution of the addition instruction.

- What instructions should be implemented in hardware and which ones in software and why? Instructions frequently executed must be implemented in hardware. This saves programming time and size, allowing faster instruction execution. Software instructions are used depending on the application.

- 18 Ga

#### 2.4.4 The Architecture Definition

The Computer architecture refers to the basic ideas and principles in which a computer system is based on [8]. The Architectural design steps include:

- The Instruction Set.

- The number of used bits to represent data (4, 8, 16, 32 or 64 bits).

- Instruction Format and addressing modes.

- Number of data buses.

- Instruction execution algorithm (best arrangement of hardware to process software).

- Clock cycles per instruction.

- Input / Output mechanisms.

The computer organization must be specially designed to implement a particular architectural specification. The microcontroller task is to execute each and every instruction it receives. This means that each instruction reflects the architecture in use by the microcontroller. After the selection of the desired instructions for the microcontroller, the next step consists in specifying the rest of the architecture.

#### 1. The instruction operation:

The first task must always be to specify each instruction operation. After designers identify the instruction set, they must document: the instruction's name, as well as operands and execution in symbols for each one.

#### 2. The instruction length:

The instruction length refers to the size of the group of bits processed during instruction execution. Using more than the necessary bits may result in excessive hardware use and an increase in circuit size, cost and power consumption.

#### 3. The instruction format:

The instruction format specifies the order of the instruction parameters in the instruction word. Those parameters include the operational code, registers used, and additional necessary data for the instruction execution.

Each instruction word has a group of bits that identifies its specific code. The group of bits used for this code is called the instruction operational code or opcode. This work uses 16 main instructions, so, the minimum number of bits for the opcode decoder is 4, enough to assign each instruction a specific code. There are no standard

rules for the order and meaning of the different groups of bits that compose the instruction word. That depends on designers' judgment and system architecture.

- a. Bits 15-12 stand for opcode. Those bits specifies instruction that will be executed

- b. Bits 11 to 10 represents as function code which gives function of instruction, used depending on the operation.

- c. Bits 9 to 5 labeled as Ra specify the register file address location to store the processed data or the one that has been transferred from memory.

- d. Bits 4 to 0 labeled as Rb, represent register file address location of one operand.

#### 4. The instruction format organization.

The instruction word parameters can be organized as designers want. In this work the operational code will be at the left most side, next are the functional codes, the additional data used for the instruction execution, and finally to the right most side is the registers used during the operation.

#### 5. The Operational Code (Opcode).

The number of instructions decides the necessary bits for the operational code. The operational code identifies each instruction with a unique code for its execution.

#### 6. Addressing modes

The addressing modes decide the amount of registers used for data processing. The addressing modes used during the instruction execution decides if more bits have to be used to address the data or not and this affects the size of the instruction word.

#### 7. Bits used for the Register File.

The number of registers used in the Register File determines how many address bits in the instruction word are required to address one specific location in it.

### 8. Number of data buses.

The number of data buses in use determines the amount of data processed per clock cycle. Using more than one data bus can save clock cycles per instructions, but increases the data path and control unit circuit complexity.

#### 9. Address Bus:

Depending on design requirements the address bus is not necessary if the address bits can be transferred using data bus. A dual role requires additional hardware.

#### 10. I/O Handling:

Will the I/O ports be memory mapped or handled separately? Memory mapped ports do not require special I/O instructions.

192. 199.

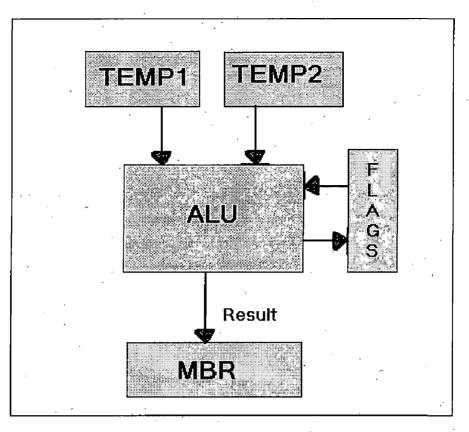

#### 2.4.5 The Arithmetic Logic Unit

In step V, the goal is to design the Arithmetic Logic Unit circuit, which is one of the most fundamental CPU components, where mathematical and logical operations are executed. Techniques used in this work for the ALU design consist in designing all its individual circuits and connecting them in parallel.

1. ALU components: The individual circuits that execute all the arithmetic and logical operations are joined together as one unit to compose the Arithmetic Logic Unit.

2. **Testing:** Designers must ensure that every individual circuit in the ALU correctly does every calculation; flags are added for that purpose.

All mathematical and logical calculations are executed at the same time, but only the desired calculation will be the one released to the ALU output port by means of the tristate buffer activated. Caution should be taken with significance of the input and output bits of every circuit. Mistakes can lead to miscalculations and continue through the rest of the instruction execution.

#### 2.4.6 The Register File

A register is a small high-speed memory circuit that holds binary data. Register File is a group of registers used to store data during the instruction execution. In this step, the Register File is developed. The Register File stores data retrieved from Register, memory or input port resulting from various operations in ALU. All temporary data used by the microcontroller to perform its operations is also stored in the register file. Register File design consists of three stages: register selection stage, input stage and output stage.

#### 1. Implementation alternatives

The number of data buses in the microcontroller determines the Register File design. Sometimes more than one data bus is used to accept and release the data simultaneously in one clock cycle. Designers must decide how many data buses will be used in the microcontroller because Register File will use the same number.

#### 2. The number of registers for the application

The number of registers is an important design parameter because it affects not only The Register File size but also the Instruction Register size because the IR has bits dedicated for the Register File address. Designers must select the number of necessary registers to hold data in each instruction clock cycle.

#### 2.4.6.2 The Register File Selection Stage

The instruction word identifies two parameters: Ra and Rb. Each of this parameter, when referring to registers, is actually addresses that identify a register from the register file. Since Ra and Rb have five bits, the register file has 32 registers. One register is selected by means of a decoder 5x 32. The control unit will activate signals to indicate which register is assigned to Ra or Rb of the instruction word.

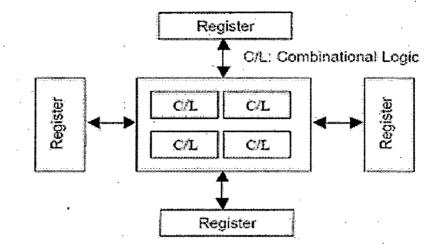

#### 2.4.6.4 Register Transfer

The whole design contains many registers, special purpose registers (IR, PC, MAR, MBR), general purpose registers (R0, R1...R31, I/O control registers) etc. The whole system works by transferring data between these registers (register transfer). Some data are transferred without modification while some are manipulated before transfer to the next register. If the data are to be manipulated, they are manipulated by the combinational logic between these registers. How these data are transferred, how are they being manipulated before transfer, and what does different data inside the register means, will determine whether the design can work as microcontroller. The design will perform a long series of register transfer to form the functioning of a microcontroller. Registers are transferred to another through many levels of the combinational logic.

A read of the status register will bring the contents of the status register to one of the general register directly without manipulation The combinational logic Perform AND operation between two general registers, will pass the two registers through a combinational logic (the logic unit) before writing back to one of the register. Memory (program ROM and data RAM) are treated as a kind of combinational logic. PC is passed through the program ROM to the instruction register. The instruction register will receive instruction in from program ROM pointed by PC.

So, the design process is to design all the registers along with combinational logic and the interconnection between them. This is called the data path of the system. Control signals are then used to determine how the register transfer takes place. Control signals are asserted by the control unit. The data path, along with the control unit forms complete microcontroller. It is important to know what registers exists in the system.

Figure 2.4: Implementation of register transfer

#### 2.4.7 The Instruction Register (IR)

The Instruction Register holds the instruction word that will be executed. The IR is connected to the control unit, the Register File & data path.

#### 1. Implementation alternative:

The IR implementation consists of a register or a group of registers that holds the instruction word.

#### 2. Size:

It will be easier if the size is equal to the word size because then, the instruction word holds all the required information for the instruction execution.

The memory output is connected to the IR to load every single program instruction line. The IR does not have to be the same size of the data bus because it just transfers data and does not contain any other information about the instruction.

#### 2.4.8 Data Path

• The microcontroller data path is the configuration of all the circuits used for data processing. Some key points are very important in this step.

- 1. Layout: Designers must be creative and use strategic thinking to make the best circuit arrangement in order to achieve the instruction execution using the minimum amount of hardware and clock cycles.

- 2. Clock cycles: More data can be processed at the same time depending on the amount of Register File input and output ports. Another important element is the number of additional registers in data path used to hold data between clock cycles. This can make a difference in number of CPI if designers know how to use them.

#### 2.4.8.2 Basic Data Path

In order to make useful all the elements it is necessary to provide a path for communication between them to transfer data from one to another. This data path can perform the basic instructions and will be used as the basis to develop more complex instructions. As more complex instructions are added, this data path undergoes an evolution into a more complex one, adding more hardware in parallel.

To test the feasibility of basic instructions this data path can process data provided by switches. Switches can be used to store values in the Register File. Address lines of Ra and Rb are connected from the IR to Register File to access the data. Register File output port is connected to the ALU input ports to perform logic and mathematical operations. The ALU output port is connected to the Register File input port to store results.

#### 2.4.8.3 Data Path with Immediate Operations

At this point, when adding new hardware to implement new instructions, there are some details that should be taken care of, in particular:

1) Control signals, IR related logic and Connection to buses and other blocks

2) Overall issues such Signal conflict and Delays.

The data path is next modified to include other ALU operations, like, immediate addressing mode operands. The immediate values are put in bits 0 - 7 of the instruction register. The data path modification consists in making a connection between those immediate values in the IR and the ALU. But the connection cannot be done directly because the values in the Register File can cause conflict with those in the data path. To solve this problem a tristate buffer is used to isolate the data in the Register File from those in the data bus. New parts added in the data path are identified with lines.

### 2.4.9 The PC, Jump and data transfer instructions

The instructions developed at this stage use the existing data path hardware and additional necessary circuits added in it for instruction execution.

Those instructions need additional circuit support because some of them make instructions are executed. It is very important to test those circuits before using them for support. Another reason for using additional hardware is that more than one task per clock cycle is executed in those instructions.

- 2. Draw the block diagram to show the added elements: It is convenient to show added elements to the data path to see its transformation into a more complex one.

- 3. Program counter: The program counter is developed at this step. This step presents the PC implementation and interconnection in the microcontroller circuit.

#### 2.4.10. The Control Unit

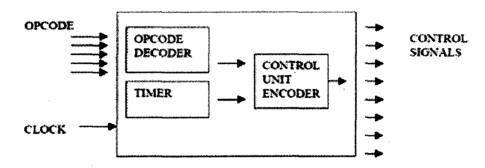

The control unit is the CPU section that decodes program instructions and controls their execution. It takes control of every signal in the microcontroller, activating or deactivating those signals in each clock cycle. The signal activation and deactivation per clock cycle make possible the flow of data through all data path circuits. The circuit arrangement determines the amount of processed data in each clock cycle. Then, as more data is processed per clock cycle fewer of them are needed. The developing method used in this work requires that designers "run" by hand every single instruction and take notes of which circuit signals are activated and deactivated per clock cycle.

#### 1. Operational Code Decoder:

This element receives one specific instruction code and release one signal that indicates the microcontroller to execute it.

#### 2. Control Unit Encoder:

This element receives input signals from opcode decoder and from timer. The Control Unit Encoder activates the corresponding circuit signals that have to be active in the specified instruction in every clock cycle.

#### **3. Implementation Alternatives:**

The preceding explanation of the control unit operation is implemented using logic circuits for the control unit encoder and the opcode decoder. The control unit implementing this approach uses the opcode to identify the instruction location in ROM. Each line code in ROM represents each instruction clock cycle and the code in every line just controls (activates or deactivates) all the data path circuit signals.

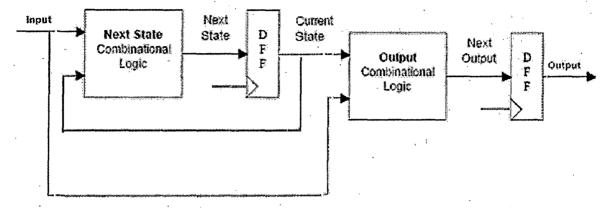

#### 4. Control Signals Characteristics

If the control signals are used to control the data path then the characteristics of the control signals must be understood before one can proceed further. First, a control signal will have at least a length of one clock cycle. It usually asserted at falling clock transition and deactivated a short delay after another falling clock. The data path consists of many registers and combinational logic between them, so there are basically 2 kinds of control signals. The first kind controls the combinational logic and the second kind controls the registers.

When a combinational logic encounters a control signal, it will act towards the signal immediately. The delay to get the valid result is the delay for the input to propagate through the combinational logic. The combinational logic can be functional unit such as adder and shifter, steering logic such as multiplexers and decoders or memory (program ROM and data RAM).

A register control signal requires a falling clock to operate. WR\_REG signal will only latch the data into the destination register of the register file when it encounters the falling clock. the operations is actually happened at the end of the control signal where it meet the falling clock. These kinds of control signals are the enable signals for the registers, or the increment/decrement signal for a counter.

to many embedded control applications. The AT90S1200 AVR is supported with a full suite of program and system development tools including: macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

The Atmel RISC microcontroller is a rather simple machine with quite a bit of flexibility. The 4 I/O ports are perfect for communicating with many external applications. The rich interrupt structure aides well in a control environment. Fig. 3.1 is an architecture block diagram of the Atmel RISC microcontroller. More specifically, register organization is more pronounced and the bus structure is well defined. Atmel RISC microcontroller design is based on Harvard architecture; the data space and the program space are separated. One feature that is noteworthy is the memory-mapped ports. All of the external ports are memory mapped, which simplifies programming control projects. These external data port addresses reside in the memory where registers are given term Special Function Register (SFR). Careful study of architecture gives rise to several SFRs.

Although the special function registers seem to exist as individual registers within the architecture, they are part of the Atmel RISC microcontroller internal RAM structure. The internal RAM of the Atmel RISC microcontroller has four distinct spaces. The upper 128 bytes of RAM contain the SFRs. The lower half of the RAM is further divided into three segments, scratch pad, bit addressing segment, and the register bank area

Though the SFRs as being within the structure of the RAM, it is more likely and is hypothesized that most of the SFRs are physically located outside of the RAM space. Not having these registers in the RAM space would allow for easier placement and access within the datapath. For example, the SFRs for ports P0, P1, P2, and P3 are probably close to the peripheral of the chip, yet they are accessed as though they are physically in the RAM. This could not be verified since Intel keeps these secrets to themselves. Within the lower portion is a scratch pad area for general use.

A bit addressable segment has been included for control applications. The lowest portion of the RAM block contains a bank of registers. The register banks can be accessed by direct or register addressing. The Program Status Word (PSW), which is a SFR located at D0h, contains two bits that shift a pointer to specify with bank to use. Otherwise a programmer may directly request or write data to this space.

Figure 3.1: Architecture block diagram of the Atmel RISC microcontroller

### 3.2 Atmel RISC microcontroller Instruction Set and Addressing Modes

When one writes a program for a microcontroller, close attention is paid to what kind of addressing modes are available to the programmer. The Atmel RISC microcontroller program space is interfaced by four addressing modes: immediate, register, direct, and indirect.[25]