# PERFORMANCE INVESTIGATION OF A HIGH INPUT POWER FACTOR CONVERTER APPLYING SPACE VECTOR MODULATION

## **A DISSERTATION**

# Submitted in partial fulfilment of the requirements for the award of the degree of

MASTER OF TECHNOLOGY

in

#### ELECTRICAL ENGINEERING

(With Specialization in Power Apparatus and Electric Drives)

By

## **D. AMARNATH REDDY**

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA)

**JUNE, 2005**

#### **CANDIDATE'S DECLARATION**

I hereby declare that the work that is being presented in this dissertation report entitled "PERFORMANCE INVESTIGATIONS OF A HIGH INPUT POWER FACTOR CONVERTER APPLYING SPACE VECTOR MODULATION" submitted in partial fulfillment of the requirements for the award of the degree of MASTER OF TECHNOLOGY in ELECTRICAL ENGINEERING with specialization in POWER APPARATUS AND ELECTRIC DRIVE, submitted in the Department of Electrical Engineering, Indian Institute of Technology, Roorkee, is an authentic record of my own work carried out, under the guidance of Dr. Pramod Agrawal, Professor, Department of Electrical Engineering.

The matter embodied in this dissertation report has not been submitted by me for the award of any other degree or diploma.

Date: 27/6/05

Place: Roorkee

EDDY)

This is to certify that the above statement made by the candidate is correct to the

i

best of my knowledge.

(DR. PRAMOD AGRAWAL)

Professor, Department of Electrical Engineering, Indian Institute of Technology, ROORKEE – 247 667, INDIA.

#### ACKNOWLEDGEMENT

I avail this opportunity to express my deep sense of gratitude and sincere thanks to Dr.Pramod Agrawal, Professor, Electrical Engineering Department, Indian Institute of Technology, Roorkee for the invaluable guidance he rendered me during the course of my work. The patience with which he dealt with the various problems encountered during the course of this dissertation is also quite inspiring. His constant encouragement and painstaking efforts have been the sole endeavors to bring this dissertation report in its present form.

I gratefully acknowledge my sincere thanks to all my friends and family members for their inspirational impetus and moral support during the course of this work. I am also grateful to the persons in the electrical engineering department workshop and store for their help and corporation.

Date: 25/6/05

Amonath (D.AMARNATH REDDY)

Place: Roorkee

#### ABSTRACT

Due to the increase of non-linear loads in utility systems, the quality of power has attracted much attention in resent years. The low power factor and large harmonics line currents generated by rectifiers are well known problems that can lead to voltage distortion, and increase losses in the transmission and distribution lines. To overcome these problems active current wave shaping techniques have been developed to provide nearly sinusoidal source current. A SVM-based HCC for the three-phase PWM rectifier is proposed. This technique utilizes advantages of the HCC and SVM technique. This configuration reduces significantly the number of switching and at the same time gives the same state space vectors as those obtained from the SVM technique. The proposed current controller confines state space vectors from a region detector and apply a proper space vector selected according to the HCC for better current shape. A set of state space vectors including the zero vectors is determined from the region detector made up of three comparators. Hard ware implementation circuits and software development have been discussed. Simulation and Experimental results have been discussed.

# . Contents

|         |       |                                                     | Page No. |

|---------|-------|-----------------------------------------------------|----------|

|         |       | Candidate's declaration                             | i        |

|         |       | Acknowledgement                                     | ii       |

|         |       | Abstract                                            | iii      |

|         |       | Contents                                            | iv       |

| Chapter | 1     | Introduction                                        |          |

|         | 1.1   | General                                             | 1        |

|         | 1.2   | Statement of problem                                | 2        |

|         | 1.3   | Organization of this dissertation                   | 3        |

| Chapter | 2     | <b>Background Of Power actor Correction</b>         |          |

|         | 2.1   | Nonlinear loads and their effect on the electricity | 4        |

|         |       | distribution network                                |          |

|         | 2.2   | Standards regulating line current harmonics         | 5        |

|         | 2.3   | Power Factor Correction (PFC) Basics                | 7        |

| Chapter | 3     | <b>High Power Factor Rectifiers</b>                 |          |

|         | 3.1   | Basic operation of High power factor rectifiers     | 13       |

|         | 3.1.1 | Discontinuous mode operation                        | 16       |

|         | 3.2.2 | Continuous mode operation                           | 20       |

|         | 3.2   | Force Commutated Three-Phase Controlled Rectifiers  | 25       |

| Chapter | 4     | Proposed Control Technique                          |          |

|         | 4.1   | Existing Control Technique                          | 35       |

|         | 4.1.1 | Hysteresis Current Control                          | 36       |

|         | 4.1.2 | Space Vector Modulation                             | 38       |

|         | 4.2   | Proposed Control Technique                          | 41       |

| Chapter | 5     | Simulation Results                                  |          |

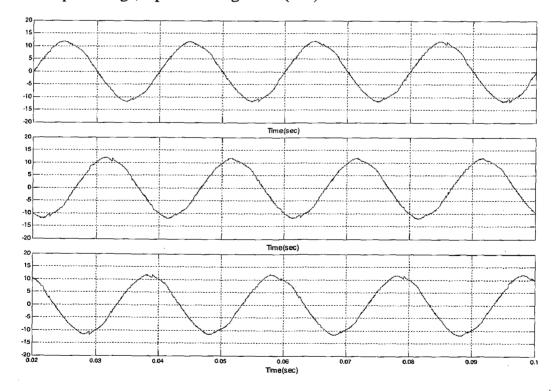

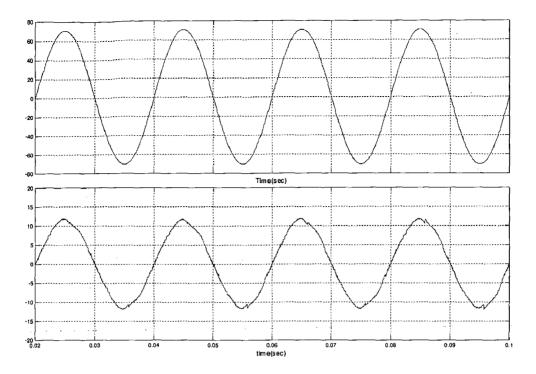

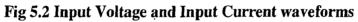

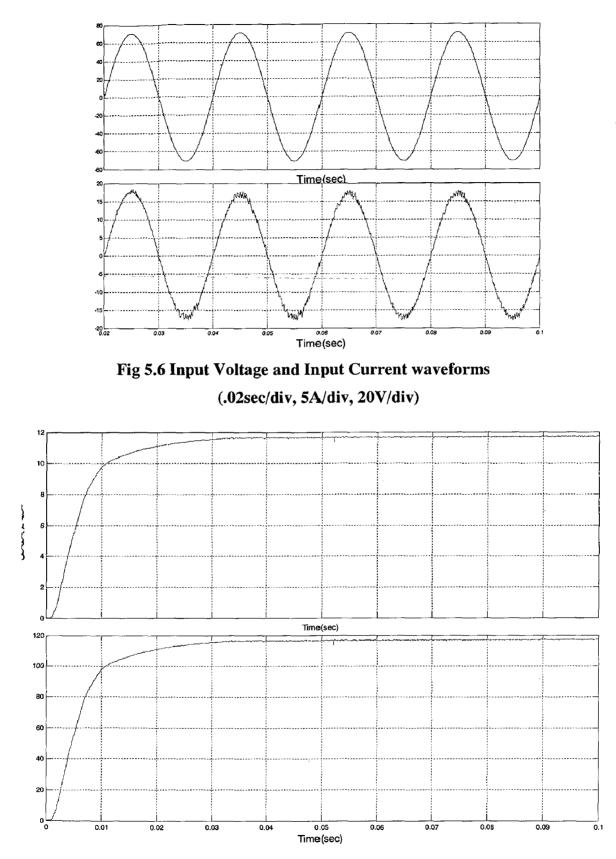

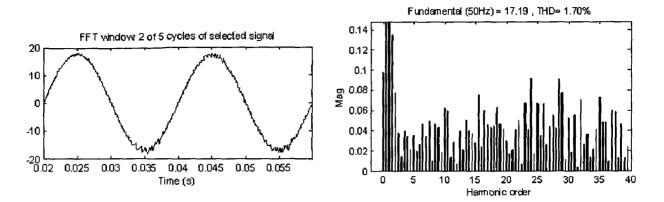

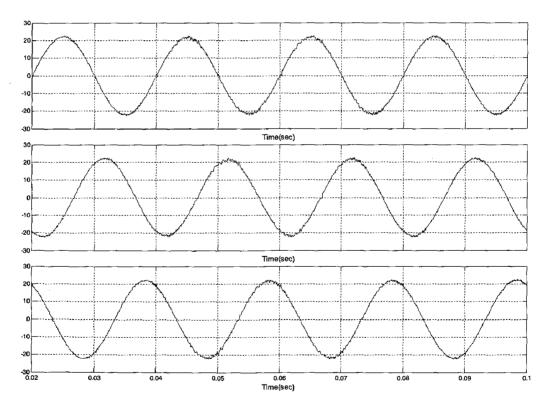

|         | 5.1   | Simulation Results of Experimental Prototype        | 48       |

| Chapter | 6             | System Development                        |    |

|---------|---------------|-------------------------------------------|----|

|         | 6.1           | Hardware development                      | 57 |

|         | <b>6.1</b> .1 | Power circuit                             | 57 |

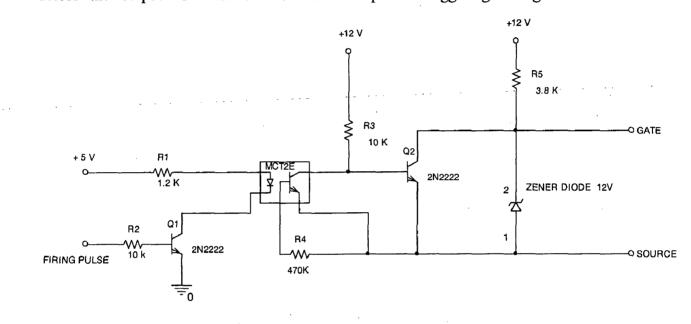

|         | 6.1.2         | Pulse Amplification and Isolation Circuit | 58 |

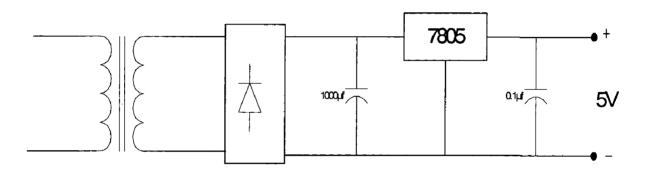

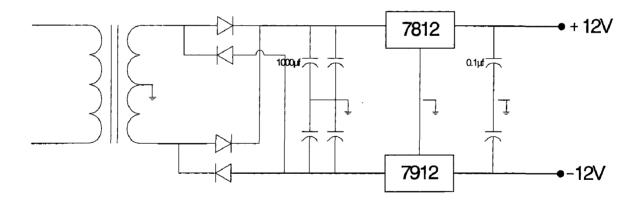

|         | 6.1.3         | Power Supplies                            | 59 |

|         | 6.1.4         | Circuit Protection                        | 61 |

|         | 6.1.5         | Current Sensor Circuit                    | 62 |

|         | 6.1.6         | Control circuit                           | 63 |

|         | 6.1.7         | Generation of Reference Current           | 65 |

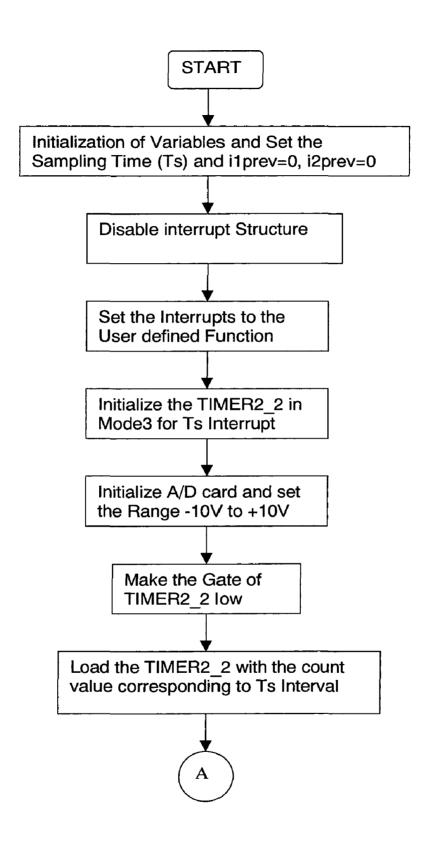

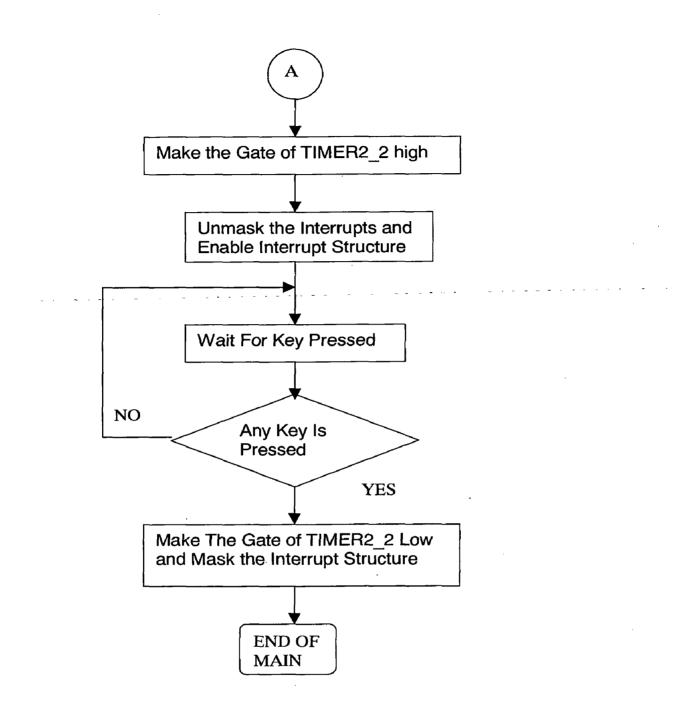

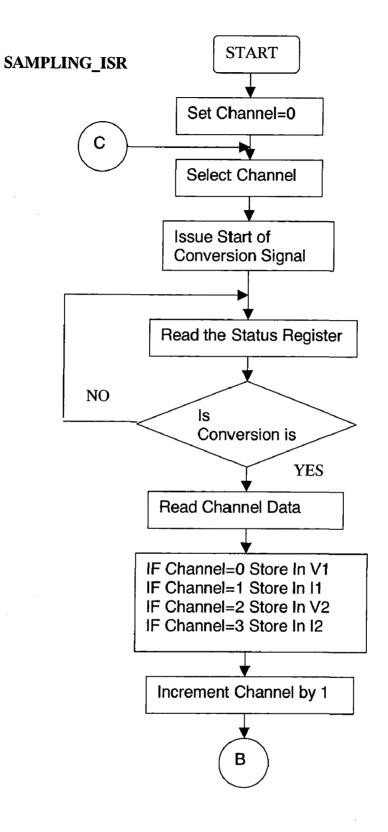

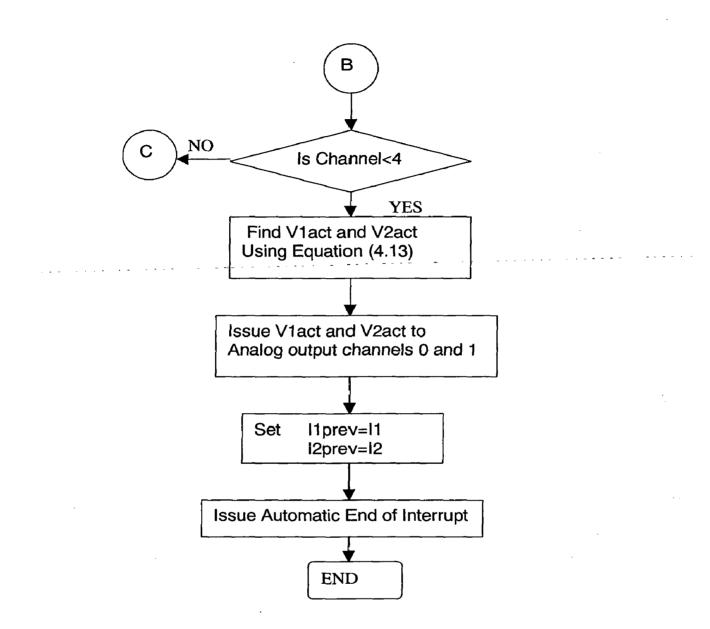

|         | 6.2           | Software development                      | 66 |

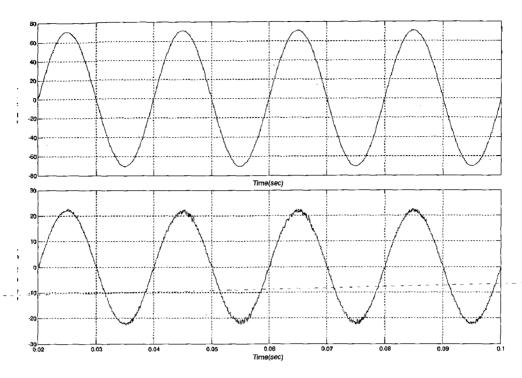

| Chapter | 7             | Experimental Results                      | 72 |

| Chapter | 8             | Conclusion                                | 83 |

|         |               | References                                | 84 |

|         |               | Appendix-A                                | 86 |

|         |               | Appendix-B                                | 88 |

|         |               |                                           |    |

#### **1.1 General**

-

Traditionally, three phase- Controlled or diode rectifiers perform three-phase ACto-DC conversions. Since these rectifiers draw non-sinusoidal currents or reactive power from the source, the power quality of the distribution network is greatly deteriorated, resulting in low efficiency of utilities. Recently, more and more stringent limits on the level of harmonics promote the growth of power factor correction techniques in frontend power converters. Among three-phase ac-to-dc pwm rectifiers, boost-type topologies are frequently used because of continuous input currents and high output voltages. Most popular topology is: a six switch full-bridge boost rectifier. This converter uses six switches to achieve sinusoidal input current control and to share the output power. The inductors and capacitor filter the high-frequency switching harmonics, and have little influence on the low frequency ac components of the waveforms. So its features include continuous input current, excellent power factor, and low switch current rating [1].

The dissertation deals with development of high input p.f converter. The SVM based HCC will be used to control the converter. Current control plays most important role in current controlled pwm converter. In a conventional current control scheme, due to easy implementation, fast dynamic response, maximum current limit, and insensitivity to load parameter variations, the 3 independent hysteresis current controls (HCC) are used. But due to lack of coordination among the individual HCC's of these phases, high switching frequency at lower modulation may happen. In addition the current error is not strictly limited. [3]

On the other hand, the space vector modulation (SVM) scheme has two excellent features in that its maximum out put voltage is larger and the no of switching is less at the same carrier frequency as compared to sinusoidal pwm method. In this a set of space vectors including the zero voltage vectors for changing the current direction can be utilized to reduce the no of switching greatly.

1

The SVM technique confines state space vectors to be applied according to the region where the output voltage vector is located. To minimize the current error between the current command and line current, the SVM technique requires a considerable calculation burden. The space vector approach can provide fast dynamic control, but is quite complicated to implement and requires significant computational resources. High-speed microprocessors or digital signal processors are required. [2]

On the other hand, the HCC can be utilized to make the line current vector track the command vector with almost negligible response time and insensitivity to line voltage and parameter variation. However, the HCC generates other vectors besides the state space vectors required according to the region in the SVM technique and increases the number of switching. If the zero vectors are applied to reduce the magnitude of the line current vector, the line current is decreased with slow slope and the number of switching is decreased. Thus the utilization of non-zero vectors instead of the zero vectors for decreasing the line current increases the number of switching. Therefore, a SVMbased HCC utilizing all features of the HCC and SVM technique needs to be developed.

In the space vector based hysteresis current controller configuration the no of switching reduces, significantly and at the same time gives the same state space vectors as those obtained from the SVM technique. The current controller confine state space vectors from the region detector and applies a proper space vector selected according to the HCC for better current shape. In the dissertation work, SVM based HCC was designed and developed.

#### **1.2 Statement of problem**

- Development of three-phase AC-to-DC converter

- Design and development of SVM based HCC control scheme

- Simulation of the High input power factor converter applying space vector modulation using MATLAB

2

#### **1.3 Organization of this dissertation**

- Chapter 2 defines driving concepts behind requirement of power factor correction.

- Chapter 3 presents the basic operation and different topologies of a high power factor rectifier.

- Chapter 4 discusses about the existing and proposed control techniques to achieve unity power factor input current waveform for a converter.

- Chapter 5 presents the simulation results for the proposed high power factor converter.

- Chapter 6 discusses about the development of hardware setup for the proposed high power factor converter.

12

• Chapter 7 presents the experimental results form the hardware setup.

# CHAPTER-2

### **BACKGROUND OF POWERFACTOR CORRECTION**

#### 2.1 Nonlinear loads and their effect on the electricity distribution

#### Network

The equipment connected to an electricity distribution network usually needs some kind of power conditioning, typically rectification, which produces a non-sinusoidal line current due to the nonlinear input characteristic. The most significant examples of nonlinear loads are reviewed next. Line-frequency diode rectifiers convert AC input voltage into DC output voltage in a un controlled manner. Single-phase diode rectifiers are needed in relatively low power equipment that need some kind of power conditioning, such as electronic equipment (e.g. TVs, office equipment, battery chargers, electronic ballasts) and household appliances. For higher power, three phase diode rectifiers are used, e.g. in variable-speed drives and industrial equipment. In both single- and threephase rectifiers, a large filtering capacitor is connected across the rectifier output to obtain DC output voltage with low ripple. As a consequence, the line current is non sinusoidal. Line-frequency phase-controlled rectifiers are used for controlling the transfer of energy between the AC input and the adjustable DC output. They are applied, for example, in some DC and AC motor drives with regenerative capabilities, or the temperature in resistive heaters. In every case, the line current is non sinusoidal. Gas discharge lamps with line-frequency ballast are nonlinear loads, as well. Hence, their line current is non sinusoidal.

Line current harmonics have a number of undesirable effects on both the distribution network and consumers. These effects include:

- Losses and overheating in transformers shunt capacitors, power cables, AC machines and switchgear, leading to premature aging and failure.

- Reduced power factor, hence less active power available from a wall outlet having a certain apparent power rating.

4

- Electrical resonances in the power system, leading to excessive peak voltages and RMS currents, and causing premature aging and failure of capacitors and insulation.

- Telephone interference, Errors in metering equipment, increased audio noise.

- Cogging or crawling in induction motors, mechanical oscillation in a turbinegenerator combination or in a motor-load system.

# 2.2 Standards regulating line current harmonics

The previously mentioned negative effects of line current distortion have prompted a need for setting limits for the line current harmonics of equipment connected to the electricity distribution network

Standard IEC 1000-3-2 applies to equipment with a rated current up to and including 16Arms per phase, which is to be connected to 50Hz or 60Hz, 220-240Vrms single-phase, or 380-415Vrms three-phase mains. Items of electrical equipment are categorized into four classes (A, B, C and D), for which specific limits are set for the harmonic content of the line current.[7]

| Harmonic order | Maximum permissible |  |  |

|----------------|---------------------|--|--|

|                | Harmonic current    |  |  |

| 'n'            | 'A'                 |  |  |

| Odd            | harmonics           |  |  |

| 3              | 2.30                |  |  |

| 5              | 1.14                |  |  |

| 7              | 0.77                |  |  |

| 9              | 0.40                |  |  |

| 11             | 0.33                |  |  |

| 13             | 0.21                |  |  |

| 15. n. 39      | 0.15 * 15. n        |  |  |

| Even harmonics |                     |  |  |

| 2              | 1.08                |  |  |

| 4              | 0.43                |  |  |

| 6              | 0.30                |  |  |

| 8. n. 40       | 0.23 * 8. n         |  |  |

**Table 2.1**

Class A includes: balanced three-phase equipment; household appliances, excluding equipment identified as Class D, tools, excluding portable tools, dimmers for incandescent lamps; and audio equipment. Equipment not specified in one of the other three classes should be considered as Class A equipment. The limits for Class A are presented in Table 2.1.

Class B equipment includes: portable tools; and nonprofessional arc welding equipment. The limits for this class are those shown in Table 2.1 multiplied by a factor of 1.5.

| Harmonic order | Maximum permissible harmonic current   |

|----------------|----------------------------------------|

|                | Expressed as a percentage of the input |

|                | Current at the fundamental frequency   |

| 'n'            | %                                      |

| 2              | 2                                      |

| 3              | 30.PF *                                |

| 5              | 10                                     |

| 7              | 7                                      |

| 9              | 5                                      |

| 11. n. 39      | 3                                      |

| Pl             | F * is the circuit power factor        |

|                |                                        |

#### Table 2.2

Class C includes lighting equipment. For an active input power greater than 25W, the harmonic currents should not exceed the limits resented in Table 2.2 the harmonic limits for Class D are presented in Table 2.3. They are defined in both power related and absolute terms. These include personal computers, personal computer monitors, and television receivers, equipment having active input power less than or equal to 600W.

| Harmonic order | Maximum permissible  | Maximum permissible |

|----------------|----------------------|---------------------|

|                | Harmonic current per | Harmonic current    |

|                | Watt                 |                     |

| 'n'            | 'mA/W'               | 'A'                 |

| 3              | 3.4                  | 2.30                |

| 5              | 1.9                  | 1.14                |

| 7              | 1.0                  | 0.77                |

| 9              | 0.5                  | 0.44                |

| 11             | 0.35                 | 0.33                |

| 13. n. 39      | 3.85. n              | As in Class A       |

|                | Table 2.2            |                     |

6

The limits for the line current harmonics are given as a percentage of the maximum demand load current  $I_1$  (fundamental frequency component) at the Point of Common Coupling – PCC at the utility. They decrease as the ratio  $I_{sc}/I_1$  decreases, where  $I_{sc}$  is the maximum short-circuit current at the PCC.

#### **2.3 Power Factor Correction (PFC) Basics**

Reduction of line current harmonics is needed in order to comply with the standard. This is commonly referred to as the Power Factor Correction – PFC, which may be misleading. Therefore, some clarification is needed.

The power factor, PF, is defined as the ratio of the active power P to the apparent

power S:

$$PF = \frac{P}{S} PF = \frac{P}{S}$$

For purely sinusoidal voltage and current, the classical definition is obtained:

$$PF = \cos \varphi$$

2.1

Where cos. is the displacement factor of the voltage and current. In a classical sense, PFC means compensation of the displacement factor.

We assume the line voltage to be sinusoidal, since in most cases the total harmonic voltage distortion is quite low, e.g. the total harmonic distortion of the line voltage shown in Fig. 2..1 is  $THD_e=2$ . However, the line current is non sinusoidal when the load is nonlinear. Therefore, the classical definition of the power factor does not apply. For sinusoidal voltage and non-sinusoidal current, P.F can be expressed as:

$$PF = \frac{V_{ms}I_{1rms}\cos\varphi}{V_{ms}I_{rms}} = \frac{I_{1rms}}{I_{rms}}\cos\varphi = K_{p}\cos\varphi \qquad 2..2$$

$$K_{p} = \frac{I_{1rms}}{I_{rms}}, K_{p} \in [0,1] \qquad 2.3$$

The factor  $K_P$  describes the harmonic content of the current with respect to the fundamental. In this case, the power factor depends on both harmonic content and displacement factor. It appears that there is no standard term, which can be used to denote the factor defined by (2.3). Some authors refer to it as the 'purity factor', while others as the 'distortion factor'. We believe that 'purity factor' describes its meaning more

accurately, as the factor is unity f or a pure sinusoidal current, and it decreases as the harmonic content increases. Moreover, defining it as 'distortion factor' is in contradiction with the definition given by the IEEE Standard Dictionary on Electrical and Electronics Terms, which considers it as a synonym for the total harmonic distortion factor, the latter being defined for the line current as:

$$THD_{i} = \frac{\sqrt{\sum_{n=2}^{\infty} I_{nrms}^{2}}}{I_{1rms}} \qquad 2.4$$

It is straightforward to show that the relation between  $K_P$  and  $THD_I$  is:

. . . . . . . .

$$K_p = \frac{1}{\sqrt{1 + THD_i^2}}$$

2.5

Standard IEC 1000-3-2 sets limits on the harmonic content of the current but does not specifically regulate the purity factor  $K_P$  or the total harmonic distortion of the line current *THD*<sub>I</sub>. The values of  $K_P$  and *THD*<sub>I</sub> for which compliance with IEC 1000-3-2 is achieved depend on the power level. For low power level, even a relatively distorted line current may comply with the standard. In addition to this, it can be seen from (2.5) that the distortion factor  $K_P$  of a waveform with a moderate *THD*<sub>I</sub> is close to unity (e.g.  $K_P =$ 0.989 for *THD*<sub>I</sub> =15%)[8].

Considering (2.2) as well, the following statements can be made:

• A high power factor can be achieved even with a substantial harmonic content. The power factor PF is not significantly degraded by harmonics, unless their amplitude is quite large (low  $K_P$ , very large  $THD_I$ ).

• Low harmonic content does not guarantee high power factor ( $K_P$  close to unity, but low cos.).

The supply power factor is critical for an economical design, and efficient and reliable operation of power system. Some of the disadvantages of low power factor are

- Because of large current, the losses in the generators and transmission lines increase causing over heating of the system components.

- It causes poor voltage regulation at the load.

- As the load voltage decreases due to poor voltage regulation the power transfer capacity is adversely affected

- The investment in system facilities per KW of load supplied increases with decrease in supply power factor Improving the power factor brings three benefits:

- Power distribution costs for the electric company are reduced, making the power company much happier. A side benefit is to reduce the tendency of the current peaks to "flatten" the tops of the input voltage sinusoidal waveform.

- More power can be drawn from a line of a given current rating, allowing more powerful equipment to be connected without having to re-wire a building, saving time and money.

- Various governmental and quasi-governmental agencies are passing laws requiring improved power factors on certain types of equipment, especially those which draw a lot of power. These laws make it illegal to sell certain types of equipment without testing and certification of a minimum power factor. To continue to sell medium-to high power supplies in the future, power supply manufacturers will have to deal with power factor correction.[6]

Although the first reason is nice and the second reason saves money, it is the third reason that has given all the impetus to power factor correction development.

Most of the research on PFC for nonlinear loads is actually related to the reduction of the harmonic content of the line current. Methods for limitation and elimination of disturbances and harmonic pollution in the power system have been widely investigated. This problem rapidly intensifies with the increasing amount of electronic equipment (computers, radio set, printers, TV sets etc.). This equipment, a nonlinear load, is a source of current harmonics, which produce increase of reactive power and power losses in transmission lines. The harmonics also cause electromagnetic interference and, sometimes, dangerous resonances. They have negative influence on the control and automatic equipment, protection systems, and other electrical loads, resulting in reduced reliability and availability. Moreover, nonlinear loads and non-sinusoidal currents produce non sinusoidal voltage drops across the network impedances, so that non-

sinusoidal voltages appear at several points of the mains. It brings out overheating of line, transformers and generators due to the iron losses.

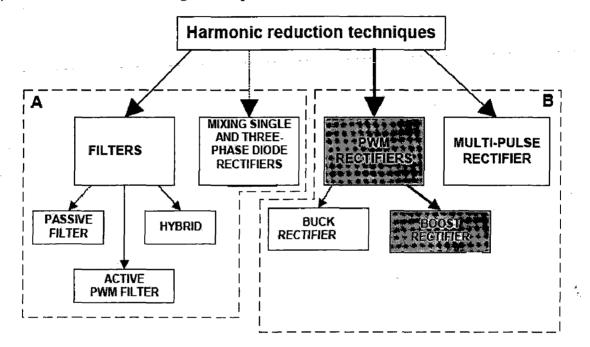

Many of harmonic reduction method exist. These techniques based on passive components, mixing single and three-phase diode rectifiers, and power electronics techniques as: multi pulse rectifiers, active filters and PWM rectifiers (Fig. 2.1). They can be generally divided as:

A) Harmonic reduction of already installed non-linear load.

B) Harmonic reduction through linear power electronics load installation.

Fig. 2.1 Harmonic reduction techniques

The traditional method of current harmonic reduction involves passive filters LC, parallel-connected to the grid. Filters are usually constructed as series-connected legs of capacitors and chokes. The number of legs depends on number of filtered harmonics ( $5^{h}$ ,  $7^{th}$ ,  $11^{th}$ , and 13th). The advantages of passive filters are simplicity and low cost[9]. The disadvantages are:

- Each installation is designed for a particular application (size and placement of the filters elements, risk of resonance problems),

- High fundamental current resulting in extra power losses,

- Filters are heavy and bulky.

In case of diode rectifier, the simpler way to harmonic reduction of current is additional series coils used in the input or output of rectifier (typical 1-5%). The other technique, based on mixing single and three-phase non-linear loads, gives a reduced THD because the 5th and 7th harmonic current of a single-phase diode rectifier often are in counter-phase with the 5th and 7th harmonic current of a three-phase diode rectifier [10].

The other already power electronics techniques is use of multi pulse rectifiers. Although easy to implement, possess several disadvantages such as: bulky and heavy transformer, increased voltage drop, and increased harmonic currents at non-symmetrical load or line voltages.

An alternative to the passive filter is use of the active PWM filter (*AF*), which displays better dynamics and controls the harmonic and fundamental currents. Active filters are mainly divided into two different types: the active shunt filter (current filtering) and the active series filter (voltage filtering).

The three-phase two-level shunt AF consists of six active switches and its topology is identical to the PWM inverter. AF represents a controlled current source  $i_F$  which added to the load current  $I_{Load}$  yields sinusoidal line current  $I_L$  (Fig. 2.2).

AF provides:

- Compensation of fundamental reactive components of load current,

- Load symetrization (from grid point of view),

- Harmonic compensation much better than in passive filters.

In spite of the excellent performance, AF's possess certain disadvantages as complex control, switching losses and EMC problems (switching noise is present in the line current and even in the line voltage). Therefore, for reduction of these effects, inclusion of a small low-pass passive filter between the line and the AF is necessary.

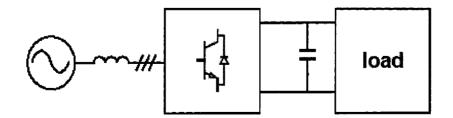

Fig.2.3 PWM rectifier

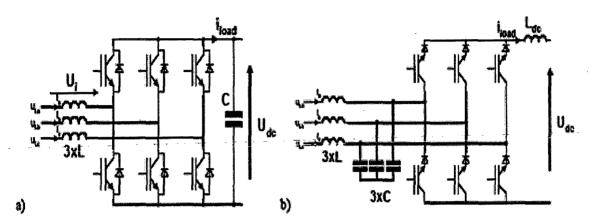

The other interesting reduction technique of current harmonic is a *PWM* (active) rectifier (Fig. 2.3). Two types of *PWM* converters, with a voltage source output (Fig. 2.4a) and a current source output (Fig. 2.4b) can be used. First of them called a *boost* rectifier (increases the voltage) works with fixed DC voltage polarity, and the second, called a *buck* rectifier (reduces the voltage) operates with fixed DC current flow.

Among the main features of PWM rectifiers are:

- Bi-directional power flow,

- Nearly sinusoidal input current,

- Regulation of input power factor to unity,

- Low harmonic distortion of line current (THD below 5%),

- Adjustment and stabilization of DC-link voltage (or current),

- Reduced capacitor (or inductor) size due to the continues current.

Furthermore, it can be properly operated under line voltage distortion and notching, and line voltage frequency variations. Similar to the *PWM* active filter, the PWM rectifier has a complex control structure; the efficiency is lower than the diode rectifier due to extra switching losses. A properly designed low-pass passive filter is needed in front of the *PWM* rectifier due to *EMI* concerns.

The last technique is most promising thanks to advances in power semiconductor devices (enhanced speed and performance, and high ratings) and digital signal processors, which allow fast operation and cost reduction. It offers possibilities for implementation of sophisticated control algorithm.

#### **HIGH POWER FACTOR RECTIFIERS**

#### 3.1 Basic operation of High power factor rectifiers

The high power factor rectifiers can be categorized as single phase and three phases or based on the fact whether the inductor current is continuous or discontinuous.

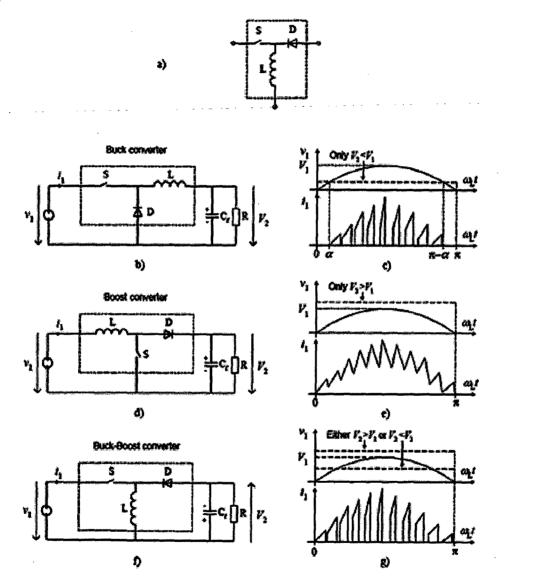

Fig. 3.1 Second-order switching converters and their application for high-frequency active PFC, assuming operation in CICM: a) First-order switching cell, from which second-order switching converter are generated; b) Buck converter, with c) waveforms; d) Boost converter, with e) waveforms; f) Buck-Boost converter, with g) waveforms.

The first-order switching cell is shown in Fig. 3.1 a). The active switch S is controlled by an external control input. In a practical realization, this switch would be implemented, for example, by a MOSFET or an IGBT. The state of the second switch, which is diode D, is indirectly controlled by the state of the active switch and other circuit conditions. The switching cell also contains a storage element, which is the inductor L [7]. In a PFC application, the input voltage is the rectified line voltage

$$V_1(t) = V_1.sin. \ _Lt.$$

3.1

The output voltage  $V_2$  is assumed to be constant. The first characteristic, which is determined by the conversion ratio of the converter, is the relation between the obtainable output voltage  $V_2$  and the amplitude  $V_1$  of the sinusoidal input voltage.

The second characteristic refers to the shape of the filtered (line-frequency) input current. If the converter is able to operate throughout the entire line-cycle, a sinusoidal line current can be obtained. Otherwise the line current is distorted, being zero in a region around the zero-crossings of the line voltage where the converter carnot operate.

The third characteristic is related to the high-frequency content of the input current. We consider that the input current is continuous if it is not interrupted by a switching action. This means that the inductor is placed in series at the input and only the inductor current ripple determines the high-frequency content of the input current. For CICM operation, the inductor current ripple can be relatively low, a situation in which the input current has a reduced high-frequency content. Conversely, the input current is discontinuous if it is periodically interrupted by the switching action of a switch placed in series at the input. In such a case, the high-frequency content of the input current is large, even in CICM operation. The terms continuous/discontinuous input current should not be confused with CICM/DICM, which refer to the inductor current

We now briefly characterize second-order converters in the light of these topology-specific characteristics. The converters are shown in Fig. 3.1 together with waveforms relevant for a PFC application, assuming operation in CICM. We need to clarify here that the given waveforms are only for supporting the explanation of the topology-specific characteristics. In reality, the switching frequency is much higher than the line-frequency and the input current waveform is dependent also on the type of control that is used The Buck converter, shown in Fig. 3.1b), has step-down conversion ratio. Therefore, it is possible to obtain an output voltage V2 lower than the amplitude VI of the input voltage. However, the converter can operate only when the instantaneous input voltage  $V_1$  is higher than the output voltage  $V_2$ , i.e. only during the interval

$$\omega_1 t \varepsilon (\alpha, \pi - \alpha)$$

, where  $\propto = \sin^{-1} \frac{V_2}{V_1}$  3.2

Hence, the line current of a power factor corrector based on a Buck converter has crossover distortions, as illustrated in Fig. 3.1c). Moreover, the input current of the converter is discontinuous. Consequently, even in CICM, the input current has a significant high-frequency component that has to be filtered out.

The Boost converter is shown in Fig. 3.1d). It has a step-up conversion ratio; hence the output voltage  $V_2$  is always higher than the amplitude  $V_1$  of the input voltage. Operation is possible throughout the line-cycle so the input current does not have crossover distortions. As illustrated in Fig. 3.1e), the input current is continuous, because the inductor is placed in series at the input. Hence, an input current with reduced highfrequency content can be obtained when operating in CICM. For these reasons, the Boost converter operating in CICM is widely used for PFC

|            | Conversion characteristics                 | Crossover distortions                                                                                                                 | Input current |

|------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Buck       | Step-down, V <sub>2</sub> <v<sub>1</v<sub> | Yes, because operation is<br>Possible only for<br>$\omega_1 t \varepsilon (\alpha, \pi - \alpha), \alpha = \sin^{-1} \frac{V_2}{V_1}$ | Discontinuous |

| Boost      | Step-up, $V_2 > V_1$                       | NO                                                                                                                                    | Continuous    |

| Buck-Boost | Step-down/up, $V_2 \ge V_1$                | NO                                                                                                                                    | Discontinuous |

#### Table 3.1

The Buck-Boost converter, shown in Fig. 3.1f), can operate either as a step-down or a step up converter. This means that the output voltage $V_2$  can be higher or lower than the amplitude  $V_1$  of the input voltage, which gives freedom in specifying the output voltage. Operation is possible throughout the line-cycle and a sinusoidal line current can be obtained. However, the output voltage is inverted, which translates into higher voltage stress for the switch. Moreover, similar to the Buck converter, the input current is discontinuous with significant high-frequency content, as illustrated in Fig. 3.1g). The topology-specific characteristics are summarized in Table 3.1

One common principle that applies to all three topologies, regardless of operational mode or control method is: In steady state operation, the voltage across the inductor, averaged over each switching cycle, must equal zero. Otherwise, the average inductor current would change, violating the steady state premise. Each of the three basic circuit families has a unique set of relationships between input and output voltages, currents, and duty cycle. For example, the basic buck regulator functions only with output voltage,  $V_o$ , less than  $V_{in}$  and with the same polarity. The basic boost circuit requires  $V_o$  greater than  $V_{in}$  with the same polarity. The fly back topology functions with  $V_o$  either greater or less than  $V_{in}$ , but the polarity must be opposite.

#### **3.1.1 Discontinuous mode operation:**

In the discontinuous inductor current mode, or "discontinuous mode", buck, boost and fly back circuits behave in a similar way. The inductor current is zero (hence discontinuous) during the last part of each switching cycle. During the first part of the cycle, the inductor current increases from zero, storing energy taken from the input. During the second part, all of this stored energy is discharged into the load, pumping energy from input to output.

#### **Three States:**

There are three distinct operational states during each switching cycle:

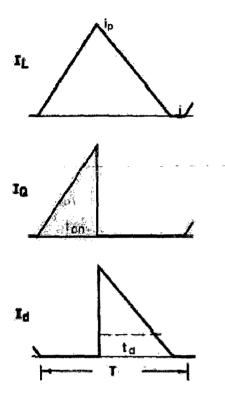

1. During the switch 'S', "on" time, ton, inductor current  $\frac{1}{L}$  rises from zero to the peak value Ip. This peak current equates to energy stored in the inductor,  $\frac{Ll'}{2}$ , at the end of ton. During this time the inductor current is drawn from the input, and this energy stored in the inductor each cycle is power taken from the input source.

2. When the switch turns off, the inductor voltage reverses and its stored energy forces the same peak current to flow through the diode. During the diode conduction time, td, the inductor current drives the output and linearly decreases to zero. At the end of td, all the energy that was stored in the inductor has been delivered to the output. 3. When the current reaches zero, the inductor has no more energy. The current in all switching circuit elements is zero for the remainder of the switching period. During this idle time,  $t_i$ , the circuit waits for the next clock pulse to turn the transistor back on and begin the next cycle.

| Fig 3.2 Inductor, Switch and Diode current wave |

|-------------------------------------------------|

| forms under discontinuous current mode          |

|      | Buck | Boost          | Fly back       |

|------|------|----------------|----------------|

| I in | IQ   | IL             | IQ             |

| Ι    | IL   | I <sub>d</sub> | I <sub>d</sub> |

#### **Discontinuous Mode Boundary**:

When load current is increases, the control circuit causes switch 'S', ton (duty cycle) to increase. Peak inductor current then becomes greater and diode conduction time td must also increase. Consequently, an increase in load current causes a steady state reduction in the idle time, ti. When load current increases to a certain level, ti becomes zero, and the discontinuous mode boundary is reached. If the load current is further increased, the inductor current will no longer discharge to zero every cycle, and continuous mode operation results. The circuit will become unstable because the loop gain compensation required for stable discontinuous mode operation is not adequate to prevent oscillation in the continuous mode. It is imperative for the control circuit to sense and limit the inductor current to prevent crossing this mode boundary [11].

#### **Excellent Closed Loop Response:**

In the discontinuous mode, it is easy to obtain excellent response in correcting disturbances that result from large step changes in line voltage and load current, because the inductor always starts each switching cycle with zero stored energy. This makes it possible for the control circuit to obtain any energy level (and power output) required, from zero to full output, on a cycle-by-cycle basis. The inductor "vanishes" from the small signal closed loop characteristic, leaving only the output capacitor with its 90-degree phase lag. The resulting single-pole characteristic is inherently stable and easy to deal with in closing the loop. The right half plane zero that severely limits closed loop response in continuous mode boost and flyback circuits is not present in the discontinuous mode topologies.

#### **High Peak Current:**

The one main disadvantage of the discontinuous mode is the high peak current through the transistor, diode and output filter capacitor. This requires semiconductors with higher current capability and puts an extreme burden on the output filter capacitor ESR (equivalent series resistance) and RMS current rating requirements. For example, in both boost and fly back circuits, the diode is in the output, and therefore the average diode current, Id, must equal the OC output current, Io. Under full load conditions, if diode time td is 50% of the switching period, the peak current is 4 times the full load Io. In the buck circuit the inductor current with its better form factor drives the output, so the peak current is somewhat less in proportion to the output current. However, the buck topology is seldom used in the discontinuous mode because the continuous mode provides much better performance.

#### Poor Open Loop Line and Load Regulation:

The basic OC equation for the fly back topology operated in discontinuous mode is given below. The boost regulator has a similar but more complex formula. For the fly back circuit

$$V_o = V_{in} D \sqrt{\frac{R_o}{2L_f}} \qquad 3.3$$

It can be seen from this equation that if the duty cycle is fixed (open control loop),  $V_o$  varies directly with  $V_{in}$  and the square root of the output load resistance, Ro. In other words, the open loop line and load regulation is quite poor, and duty cycle D must be changed considerably by the control circuit to maintain the desired out put voltage under the full range of line and load conditions.

#### **Control Method:**

In all three constant frequency control methods (direct duty cycle, voltage feed forward, and current mode), the output voltage is compared with a fixed reference voltage. The resulting error voltage is amplified and used as the closed loop control voltage,  $V_c$ .

#### Direct Duty Cycle Control:

Transistor duty cycle  $D = \frac{t_{on}}{T}$  is varied in proportion to control voltage V<sub>c</sub>. Pooropen loop line and load regulation requires fairly high loop gain for correction. The output filter capacitor is part of the closed loop system and introduces a phase lag, which delays correction of V<sub>in</sub> changes.

#### Voltage Feed forward Control:

A sample of the input voltage is fed directly into the control circuit and causes the duty cycle to vary inversely with  $V_{in}$  as well as directly with  $V_c$

Υÿ

$$D = K \frac{V_c}{V_{in}}$$

If  $V_{in}$  increases, D decreases automatically so that the input volt-seconds ( $V_{in}D$ ) remains constant for a fixed  $V_c$ . Thus,  $V_c$  controls input volt-seconds directly. Open loop line regulation is good, so that less closed loop gain is required to meet DC regulation requirements. Equation 3.3 becomes

$$V_o = K V_c \sqrt{\frac{R_o}{2L_f}} \qquad 3.4$$

Where K is the feed forward ratio =  $\frac{V_{in}D}{V_c}$

#### **Current Mode Control:**

An inner, second control loop compares the peak inductor current,  $I_p$ , to the control voltage, V<sub>c</sub>. In the outer loop, V<sub>c</sub> now controls I<sub>p</sub> directly. The inner loop provides good inherent line regulation, similar to voltage feed forward. Equation 3.3 becomes:

$$V_o = K V_c \sqrt{\frac{R_o L_f}{2}}$$

3.5

Where K is the inner loop current control factor  $K = \frac{\max I_p}{\max V_c}$ .

Either voltage feed forward or current mode control is recommended. They both have essentially the same good effect --improved open loop line regulation, providing instantaneous correction to line changes and requiring less closed loop gain.

#### **3.1.2 Continuous mode operation:**

In the continuous inductor current mode (continuous mode), the inductor current is never zero during any part of the switching cycle. Compared to the discontinuous mode for the same application parameters, the continuous mode requires much greater inductance. The inductor ripple current is small compared to the full load output current.

#### **Current Waveforms**

Continuous mode waveforms are shown in Figure 3.3 Just as with the discontinuous mode, the inductor, transistor and diode current waveforms are exactly the same for the buck, boost or fly back circuits, but the input and output waveforms differ according to which of the three elements are in series with input and output. The boost and fly back circuits have similar behavior. In both cases, the output current is the diode current, Id, which is discontinuous. The peak output current is slightly more than half the value encountered in the discontinuous mode. This reduces the burden on the output capacitor. The buck regulator behaves very differently. Its output current is the inductor current, which is not discontinuous, but has a relatively Figure 3.3 gentle slope and small ripple amplitude. This waveform is easy to filter, substantially reducing the output capacitor ESR and current rating requirements. For this reason, the continuous mode buck regulator is the most popular switching power supply configuration; particularly at higher power

levels where the much higher peak current encountered with all other configurations put an intolerable burden on the output filter capacitor.[11]

| Fig | 3.3   | Inductor,  | Switch   | and    | Diode   | current |

|-----|-------|------------|----------|--------|---------|---------|

| wav | e for | ms under o | continuo | us cui | rrent m | ode     |

|       | Buck             | Boost          | Fly back |

|-------|------------------|----------------|----------|

| I in  | · I <sub>Q</sub> | IL             | IQ       |

| I o · | IL               | I <sub>d</sub> | Id       |

#### **Two States:**

Because the inductor current is never zero, there is no idle time in the continuous mode and only two operational states during each switching cycle.

1. During transistor "on" time, ton, inductor current  $I_L$  increases from an initial value (greater than zero) to a higher value, replacing the inductor energy given up during the "off" time. Current (and power) is drawn from the input.

2. When the transistor is off, the diode conducts for the rest of each cycle. IL declines to the initial value, never reaching zero but giving upenergy to the output.

In continuous mode operation, the up slope and down slope of inductor current are dependent only upon the input and output voltage levels and totally independent of the average inductor current or output load current. Without the flexibility provided by the third (idle) state of the discontinuous mode,  $V_{in}$ , Vo and duty cycle D are related differently for each topology. In the buck regulator, for example, the average voltage at the input side of the inductor is Vinton/T, or  $V_{in}D$ , while the voltage at the inductor output is Vo. In the steady state, the average voltage across the inductor must be zero, so  $V_o = V_{in}D$ . This is the basic DC equation for the buck regulator. There are no terms relating to load current or resistance, which indicates excellent open loop load regulation. When Io changes, steady-state  $I_L$  also changes, but the inductor ripple current and  $V_o$  do not change.

#### **Continuous Mode Boundary:**

Minimum Load Current, when the load current decreases, the duty cycle and inductor ripple current do not change (except momentarily), but the average inductor current declines proportionately.

For the buck regulator  $I_0 = I_L$ ,

For boost and fly back  $I_0 = (1-D) I_L$ .

At a certain critical load current level, the inductor current reaches zero at the minimum of the ripple waveform. This is the boundary for continuous mode operation. If the load current further decreases, the third state idle time appears, and the circuit operates discontinuously, with completely different operating characteristics. DC regulation degrades radically. In a continuous mode regulator, the load current must not be allowed to drop below the critical level where this boundary is crossed. This minimum load requirement is a disadvantage of continuous mode systems.

#### **Poor Closed Loop Response:**

Small signal response of continuous mode regulators is much worse than discontinuous mode circuits because of the two pole second order characteristic of the resonant LC filter. Boost and fly back circuits also have a right half plane zero in their loop gain characteristic. While it is theoretically possible to compensate for the two filter poles, the capacitors used in the compensation network charge to unusual voltage levels during periods of large signal limited operation, when inductor current cannot keep up with changes in load current. This causes output voltage offset errors, which take considerable time for correction. Current mode control overcomes this problem in continuous mode buck regulators by eliminating the inductor pole. Only the single first order filter capacitor pole remains, the same as in the discontinuous mode circuits.

The RHP zero associated with boost and fly back continuous mode circuits is much more difficult to deal with. In buck regulators, output current 10 equals inductor current IL, but in boost and fly back circuits,  $I_0 = I_L[1-D]$ . Consider the process in a fly

22

back regulator. When load current increases, the output capacitor voltage immediately starts to drop. The resulting error voltage temporarily increases the duty cycle, D, causing the inductor current to rise to accommodate the increased load. However, it may take many cycles for the inductor current to complete its rise. During this time, increased D makes [1-D] smaller, so the output current is temporarily decreased, the opposite of what is desired. This additional lag because of the RHP zero inevitably forces the loop gain crossover frequency to be much lower than otherwise desired. There is in addition a large signal problem with continuous mode circuits—the inability to rapidly slew the inductor current as desired with large step changes in load. This is because of the large inductor values used in continuous mode circuits. The problem is most severe when attempting to increase the inductor current when operating near minimum  $V_{in}$ , especially if the circuit has been designed with input volt-second capability,  $V_{in}$  D, only slightly greater than required for steady state operation.

#### Good Open Loop Load Regulation & Poor Line Regulation

| Fly back                    | Boost                        | Buck            |                    |  |

|-----------------------------|------------------------------|-----------------|--------------------|--|

| $V_o = \frac{V_{in}D}{1-D}$ | $V_o = \frac{V_{in}}{1 - D}$ | $V_o = V_{in}D$ | 3 <b>6</b><br>7.55 |  |

| · ·                         |                              | 3.6             |                    |  |

The basic DC equations for the continuous mode are:

Unlike the discontinuous mode, the above equations reveal that the DC output voltage,  $V_o$ , is totally independent of output current or resistance, depending only upon  $V_{in}$  and D. The duty cycle does not change with steady-state changes in load current, but D must be changed to make correction for changes in  $V_{in}$ .

#### **Direct Duty Cycle Control**

Moderately high loop gain is required to correct the inherent poor open loop line regulation. It is difficult to design the closed loop, and many problems cannot be overcome. See earlier comments under "Poor Closed Loop Response." Voltage Feed forward. Voltage feed forward applied in the same way as the discontinuous mode topologies provides good open loop line regulation in the continuous mode buck regulator. Equation 3.6 (buck) becomes:

$$V_o = KV_c \qquad K = \frac{V_{in}D}{V_c} \qquad 3.7$$

Open loop line and load regulation are both good. Closed loop gain is now required only for good dynamic response to changes in load. Boost and fly back topologies in the continuous mode are only partially compensated by this simple feed forward technique. Methods that are more complex will achieve compensation, but they are beyond the scope of this paper.

#### **Current Mode Control**

Applied to continuous mode buck regulators, current mode control provides greatly improved performance. First, the inner current control loop provides inherent good line regulation, even with the outer loop open. Second, the inner loop eliminates the filter inductor pole so that the outer loop no longer has a two-pole second order resonant characteristic, but only the single filter capacitor pole. The gain characteristic becomes very easy to compensate. Third, compensation capacitors at the error amplifier input [which cause output voltage errors after large signal limited operation) are not required because the inductor pole is eliminated. Current mode control has the single disadvantage that it introduces load current dependency, which does need closed loop correction. Buck regulator Equation 4 becomes:

$$V_o = K V_c R_o \qquad K = \frac{\max I_p}{\max V_c} \qquad 3.8$$

Current mode control also facilitates the paralleling of several individual power supply modules. The current control loop insures that each module will always deliver its assigned proportion of the total load current. In the continuous boost and fly back topologies, the performance improvements from current mode control are less dramatic. Only partial voltage feed forward compensation is accomplished. When  $V_{in}$  changes, the inner current control loop maintains IL constant, but 10 will change because the (1-D) factor relating  $I_L$  to  $I_0$  in boost and fly back circuits changes with  $V_{in}$ . Current mode

control does eliminate the inductor pole and thereby simplifies the closed loop design, but it does not eliminate the RHP zero, which is the worst limitation of the continuous mode boost and fly back circuits.

In this operating mode, the inductor current never reaches zero during one switching cycle and there is always energy stored in the inductor. The *volt seconds* applied to the inductor must be balanced throughout the line-cycle by continuously changing the duty-cycle of the converter using an appropriate control method.

# 3.2 FORCE-COMMUTATED THREE-PHASE CONTROLLED RECTIFIERS

Force-commutated rectifiers are built with semiconductor devices with gate turn-off capability. The gate turn-off capability allows full control of the converter, because valves can be switched ON or OFF whenever required. This allows commutation of the valves hundred of times in one period which is not possible with line commutated rectifiers where thyristors are switched ON or OFF only once a cycle.

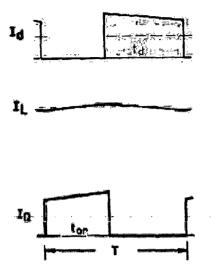

Figure [3.4]: Basic topologies for force-commutated PWM rectifiers A) Current Source Rectifier, B) Voltage Source Rectifier

25

Advantages of Force-commutated rectifiers:

a) The current or the voltage can be modulated (Pulse Width Modulation or PWM), generating less harmonic contamination;

b) Power factor can be controlled; it can be made leading also;

c) They can be built as voltage or current source rectifiers;

d) The reversal of power in thyristor rectifiers is by reversal of voltages at the DC link. Instead, the force-commutated rectifiers can be implemented for both reversal of voltage and reversal of current.

Here are two ways to implement force-commutated three-phase rectifiers

- As a current source rectifier, where the power reversal is by dc voltage reversal

- As voltage source rectifier, where the power reversal is by current reversal at the dc link.

#### **Operation of the voltage source rectifier**

The voltage source rectifier is the most widely used rectifier and because of its duality with the current source rectifier only its operation will be described in detail.

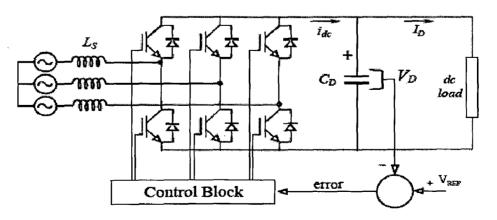

The basic operation principle of the voltage source rectifier consists on keeping the dc link voltage at a desired reference value, using a feedback control loop. To accomplish this task the voltage  $V_D$  is measured and compared with a reference  $V_{REF}$ . The error signal generated from this comparison is used to switch ON and OFF the six valves of the rectifier. In this way the power can come or return to the ac source according to the dc link voltage requirements. The voltage  $V_D$  is measured at the capacitor  $C_D$ .

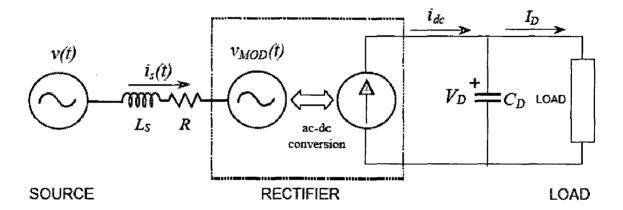

Figure [3.5]: Operation of the Voltage Source Rectifier

When the current  $I_D$  is positive (rectifier operation), the capacitor  $C_D$  is discharged, and the error signal ask the Control Block for more power from the *ac* supply. The Control Block takes the power from the supply by generating the appropriate PWM signals for the six valves. In this way, more current flows from the *ac* to the *dc* side, and the capacitor voltage is recovered. Inversely, when  $I_D$  becomes negative (inverter operation), the capacitor  $C_D$  is overcharged, and the error signal ask the control to discharge the capacitor and return power to the *ac* mains [12].

The PWM Control not only can manage the active power, but reactive power also, allowing this type of rectifier to correct power factor. Besides, the ac current waveforms can be maintained almost sinusoidal, reducing harmonic contamination to the mains supply.

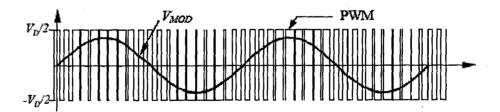

The Pulse-Width-Modulation consists on switching the valves ON and OFF, following a pre-established template. Particularly, this template could be a sinusoidal waveform of voltage or current. For example, the modulation of one phase could be as the one shown in figure [3.6]. This PWM pattern is a periodical waveform whose fundamental is a voltage with the same frequency of the template. The amplitude of this fundamental, called  $V_{MOD}$  in figure [3.6], is also proportional to the amplitude of the template.

Figure [3. 6]: PWM Patten and its fundamental V<sub>MOD</sub>

To make the rectifier works properly; the PWM pattern must generate a fundamental  $V_{MOD}$  with the same frequency of the power source. Changing the amplitude of this fundamental, and its phase-shift with respect to the mains, the rectifier can be controlled to operate in the four quadrants: leading power factor rectifier, lagging power factor rectifier, leading power factor inverter, and lagging power factor inverter. The interaction between  $V_{MOD}$  and V (source voltage) can be seen through a phasor diagram.

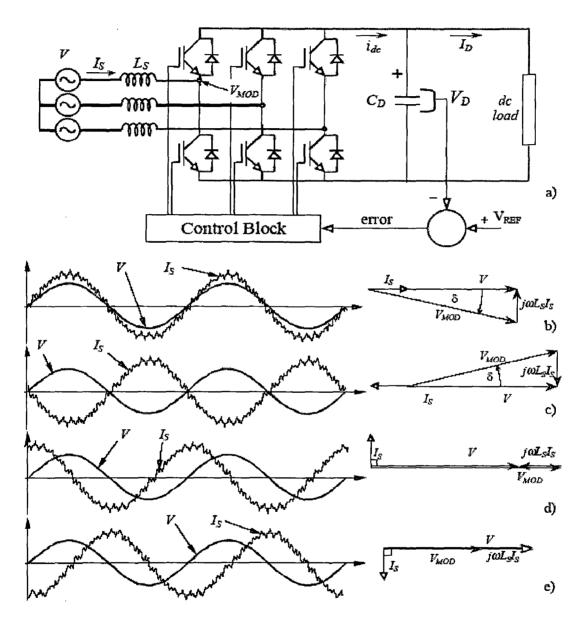

This interaction permits to understand the four-quadrant capability of this rectifier. In the figure [3.8], the following operations are displayed: a) rectifier at unity power factor, b) inverter at unity power factor, c) capacitor (zero power factor), and d) inductor (zero power factor)[13].

Figure [3.8]: Four-quadrant operation of the force commutated rectifier

- a) The PWM force commutated rectifier

- b) Rectifier operation at unity power factor

- c) Inverter operation at unity power factor

- d) Capacitor operation at zero power factor

- e) Inductor operation at zero power factor

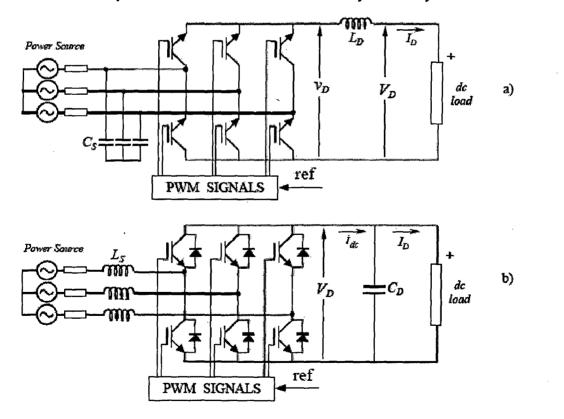

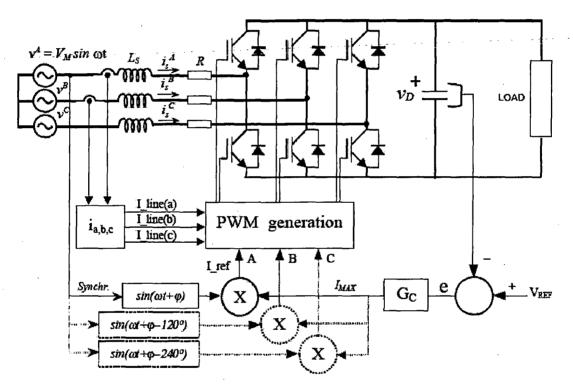

#### **Voltage Source Current Controlled Rectifier:**

This type of control as shown in figure [3. 9] is implemented by measuring the instantaneous phase currents and forcing them to follow a sinusoidal current reference template. The amplitude of the current reference template  $I_{MAX}$  is evaluated using the following equation.

$$I_{MAX} = G_{C.}e = G_{C.}(V_{REF}-v_D)$$

... ... 3.9

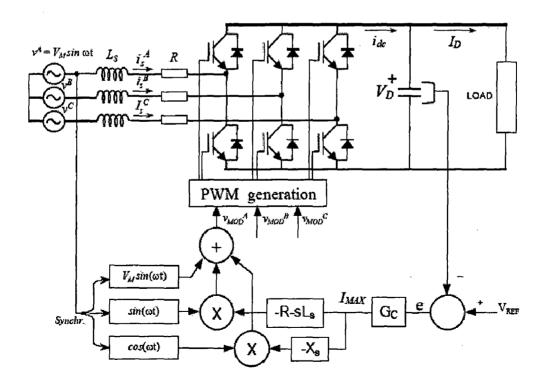

Figure [3. 9]: Voltage Source Current Controlled Rectifier

Where  $G_C$  has been shown in figure [3.9], and represents the controller such as fuzzy, PI, P, and other. The sinusoidal waveform of the template is obtained by multiplying  $I_{MAX}$  with a sine function, with the same frequency of the mains, and with the desired phase-shift angle  $\phi$  as shown in figure [3.9]. Besides, the template must be synchronized with the power supply. After that, the template has been created, and is ready to produce the PWM pattern.

#### Voltage source voltage controlled PWM rectifier

The figure [3.10] shows a one-phase diagram from which the control system for a voltage source voltage controlled rectifier is derived. This diagram represents an equivalent circuit of the fundamentals, i.e., pure sinusoidal at the mains side, and pure dc at the *dc* link side. The control is achieved by creating a sinusoidal voltage template  $V_{MOD}$ , which is modified in amplitude and angle to interact with the mains voltage *V*. In this way the input currents are controlled without measuring them. The template  $V_{MOD}$  is generated using the differential equations that govern the rectifier.

Figure [3. 10]: One-phase Fundamental diagram of the voltage source rectifier

From figure [3.10] the following differential equation can be derived:

Assuming that  $v(t) = V\sqrt{2}\sin(wt)$ , then the solution for  $i_s(t)$ , to get a template  $V_{MOD}$  able to make the rectifier work at constant power factor should be of the form

Equations (3.9) (3.11) and v(t) allows to get a function of time able to modify  $V_{MOD}$  in amplitude and phase, which will make the rectifier work at fixed power factor. Combining these equations with v(t) it yields:

$$v_{MOD}(t) = \left[ V \sqrt{2} + X_s I_{MAX} \sin \phi - \left( R I_{MAX} + L_s \frac{d I_{MAX}}{dt} \right) \cos \phi \right] \sin \omega t - \left[ X_s I_{MAX} \cos \phi + \left( R I_{MAX} + L_s \frac{d I_{MAX}}{dt} \right) \sin \phi \right] \cos \omega t$$

$$3.12$$

The equation (3.12) allows getting a template for  $V_{MOD}$ , which is controlled through variations of the input current amplitude  $I_{MAX}$ . The derivatives of  $I_{MAX}$  into equation (3.12) make sense, because  $I_{MAX}$  changes every time the *dc* load is modified. The term  $X_S$  in eq. (3.12) is  $\omega L_S$ . This equation can also be written for unity power factor operation. In such a case  $\cos \phi = 1$ , and  $\sin \phi = 0$ :

With the Eq no. (3.13), a unity power factor, voltage source, voltage controlled PWM rectifier can be implemented as shown in figure 311]. It can be observed that equations (3.12) and (3.13) have an *in-phase* term with the main supply (sin  $\omega$ t), and an *in-quadrature* term (cos  $\omega$ t). These two terms allow the template V<sub>MOD</sub> to change in magnitude and phase, to have full unity power factor control of the rectifier.

Figure [3.11]: Implementation of the voltage controlled rectifier for unity powerfactor operation

Compared with the control block of figure [3. 3], in the voltage source voltage controlled rectifier of figure [3.10], there is no need to sense the input currents. However, to ensure stability limits as good as the limits of the current controlled rectifier, the blocks '-**R**-sLs' and '-Xs' in figure [3.10], have to emulate and reproduce exactly the real values of R, XS and LS of the power circuit. However, these parameters do not remain constant, and this fact affects the stability of this system, making it less stable than the system showed in figure [3. 5].

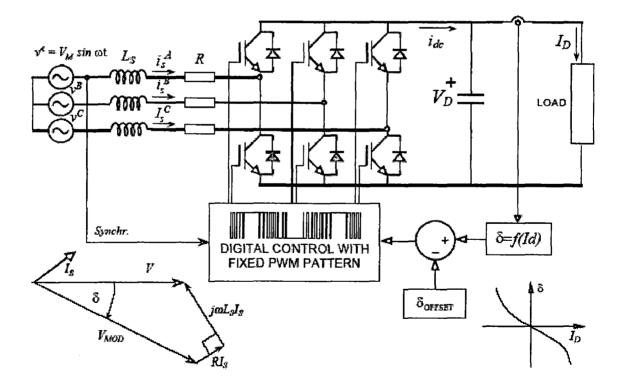

#### Voltage source load controlled PWM rectifier

A simple method of control for small PWM rectifiers (up to 10-20 kW) is based on the direct control of the dc current. The figure [3.11] shows the schematic of this control system. The fundamental voltage  $V_{MOD}$  modulated by the rectifier is produced by a fixed and unique PWM pattern, which can be carefully selected to eliminate most undesirable harmonics. As the PWM does not change, it can be stored in a permanent digital memory (ROM).

Figure 3.12: Voltage Source Load Controlled PWM Rectifier

The control is based on changing the power angle  $\delta$  between the mains voltage Vand fundamental PWM voltage  $V_{MOD}$ . When  $\delta$  changes, the amount of power flow transferred from the *ac* to the *dc* side changes. When the power angle is negative ( $V_{MOD}$ lags V), the power flow goes from the *ac* to the *dc* side. When the power angle is positive, the power flows in the opposite direction. Then, the power angle can be controlled through the current  $I_D$ . The voltage  $V_D$  does not need to be sensed, because this control establishes a stable *dc* voltage operation for each *dc* current and power angle. With these characteristics, it is possible to find a relation between  $I_D$  and  $\delta$ , to get constant *dc* voltage for all load conditions. This relation is given by:

$$ID = f(\delta) = \frac{V\left(\cos\delta - \frac{\omega L_s}{R}\sin\delta - 1\right)}{R\left[1 + \left(\frac{\omega L_s}{R}\right)^2\right]} \qquad \dots \dots 3.14$$

. . . . .

From equation (3.14) a plot and a reciprocal function  $\delta = f(ID)$  is obtained to control the rectifier. The relation between  $I_D$  and  $\delta$  allows leading power factor operation and null regulation. The leading power factor operation is shown in the phasor diagram of figure [3.12]. he control scheme of the voltage source load controlled rectifier is characterized by the following: i) there is neither input current sensors nor dc voltage sensor; ii) it works with a fixed and predefined PWM pattern; iii) it presents a very good stability; iv) its stability does not depend on the size of the *dc* capacitor; v) it can work at leading power factor for all load conditions; and vi) it can be adjusted with eq. (3.14) to work at zero regulation. The drawback appears when *R* in equation (3.14) becomes negligible, because in such a case the control system is unable to find an equilibrium point for the *dc* link voltage. That is the reason why this control method is not applicable to large systems.

The additional advantages of force-commutated rectifiers with respect to linecommutated rectifiers make them better candidates for industrial requirements. They permit new applications such as rectifiers with harmonic elimination capability (active filters), power factor compensators, machine drives with four-quadrant operation, frequency links to connect 50 Hz with 60 Hz systems, and regenerative converters for traction power supplies. The modulation with very fast valves such as IGBTs permits to get almost sinusoidal currents. The dynamics of these rectifiers is so fast that they can reverse power almost instantaneously. In machine drives, current source PWM rectifiers can be used to drive *dc* machines from the three-phase supply. Four-quadrant applications, using voltage source PWM rectifiers, are extended for induction machines, synchronous machines with starting control, and special machines such as brushless-dc motors. Back-to-Back systems are being used in many countries to link power systems with different frequency.

In this chapter I have discussed about basic types of high power factor converters and basic operations continuous and discontinuous current conduction modes in detail. After that I have discussed about types of forced commutated rectifiers and some of the topologies to get unity power factor and better performance.

# CHAPTER-4 PROPOSED CONTROL TECHNIQUE

# 4.1 Existing control techniques

Due to the increase of non-linear loads in utility systems, the quality of power has attracted much attention in resent years. The low power factor and large harmonics line currents generated by uncontrolled rectifiers are well known problems that can lead to voltage distortion, and increase losses in the transmission and distribution lines. To overcome these problems active current wave shaping techniques have been developed to provide nearly sinusoidal source current. [14]

Current control technique plays the most important role in current-controlled pulse-width modulated (PWM) rectifiers. Various techniques for the current controller of the PWM rectifier have been proposed. However, among these techniques, considering Easy implementation, fast dynamic response, Maximum current limit and insensitivity to load parameter variation. The HCC is a rather popular one. Nevertheless, due to lack of coordination among individual hysteresis current controllers of three phases, high switching frequency may happen and the current error is not strictly limited. Some hysteresis current control techniques applying the zero vectors to reduce the number of switching were reported recently.

On the other hand, the space vector modulation (SVM) has been very popular in the past few years; the technique has gained ground as an effective means of generating PWM vector controlled drives. Space vector modulation offers many advantages, compared to the conventional pulse width modulation (PWM) method.

Among these, the key benefits are:

- 15% increase in the maximum line-to-line voltage obtainable, without over modulation, when compared to conventional PWM with Only 87% of the dc link voltage.

- Reduced switching losses converter, and

- Reduced harmonic distortion in the current. [15]

35

The SVM technique confines state space vectors to be applied according to the region where the output voltage vector is located. To minimize the current error between the current command and line current, the SVM technique requires a considerable calculation burden. The space vector approach can provide fast dynamic control, but is quite complicated to implement and requires significant computational resources. High speed microprocessors or digital signal processors are required. [16]

On the other hand, the HCC can be utilized to make the line current vector track the command vector with almost negligible response time and insensitivity to line voltage and parameter variation. However, the HCC generates other vectors besides the state space vectors required according to the region in the SVM technique and increases the number of switching. If the zero vectors are applied to reduce the magnitude of the line current vector, the line current is decreased with slow slope and the number of switching is decreased. Thus the utilization of non-zero vectors instead of the zero vectors for decreasing the line current increases the number of switching. Therefore, a SVM-based HCC utilizing all features of the HCC and SVM technique needs to be developed.

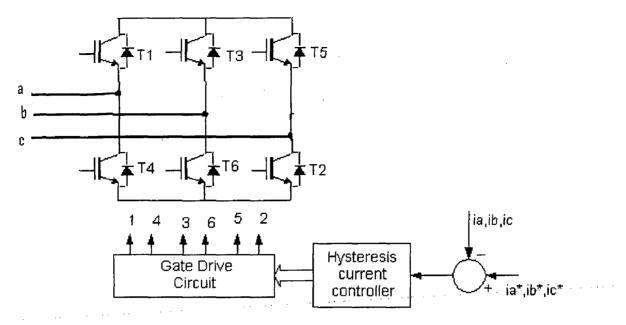

#### 4.1.1 HYSTERESIS CURRENT CONTROL

Hysteresis band current control method is used for the PWM rectifiers. Figure 4.1 Shows the PWM rectifier with the hysteresis current controller. In this system, three line currents are sensed and compared with their respective reference line currents and resulting errors are amplified and send to their respective hysteresis current controllers. The hysteresis current controllers generate switching gate pulses for the switching devices of the converter as shown in figure 4.1 and 4.2. The hysteresis control is lost if error magnitude is smaller than the magnitude of the hysteresis band. The width of the hysteresis band is chosen sufficient small using trail and error method in order to operate the switching devices well below their maximum switching frequency capability, for a maximum line current operation. For narrow hysteresis band, the switching frequency is higher and current wave shape is more sinusoidal, hence using trail and error a compromise is done between switching frequency and quality of current wave shape. With narrow hysteresis band the possibility of loss of hysteresis control is avoided, hence devices having higher switching frequency range should be selected.

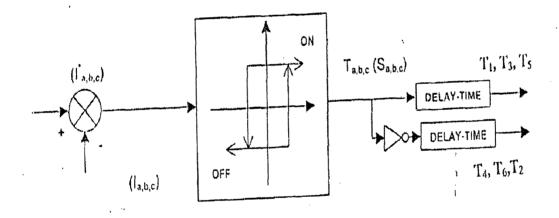

Fig 4.1 Hysterisis current control

#### **Fig.4.2 Hysterisis current controller**

General features of switching table and hysteresis controllers

- The switching frequency depends on the hysteresis wide of active and reactive power comparators.

- Zero vectors decrease switching frequency but it provides short-circuit for the line-to-line voltage.

- Zero vectors  $U_0(000)$  and  $U_7(111)$  should be appropriate chosen

- Switching table with *PLL* sector detection guarantees a very stable and free of disturbances operation, even under distorted and unbalanced line voltages.

# **4.1.2 Space Vector Modulation**

Space vector modulation (SVM) was originally developed as a vector approach to pulse-width modulation (PWM) for three-phase inverters [14]. As SVM has developed, there appears to be some confusion about its characteristics and advantages.

Typical claims made for SVM include the following.

- It achieves the wide linear modulation range associated with PWM thirdharmonic injection automatically, without the need for distorted modulation.

- It has lower base band harmonics than regular PWM or other sine based modulation methods, or otherwise optimizes harmonics.

- Only one switch changes state at a time.

- It is fast and convenient to compute [17]

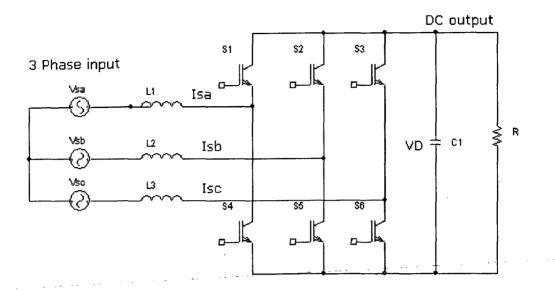

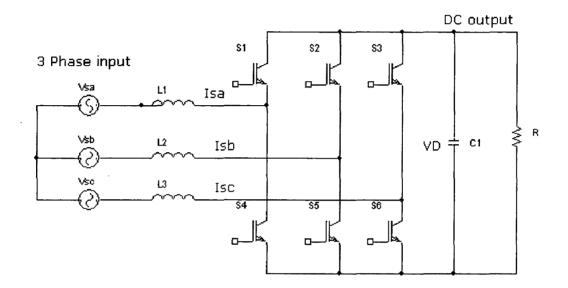

The general power circuit of the PWM rectifier with voltage link is shown in figure 4.2. The switching function for switch  $S_k$  (k=1, 2...6) is defined as

$S_k^* = 1$  when switch  $S_k$  is on  $S_k^* = 0$  when switch  $S_k$  is off

In the PWM rectifier with voltage link, either  $S_1$  or  $S_4$  ( $S_3$  or  $S_6$ ,  $S_5$  or  $S_2$ ) is conducting and only one of them is allowed to conduct in any moment, i.e.

| $S_1^* + S_4^* = 1$ | (4.1) |

|---------------------|-------|

| $S_3^* + S_6^* = 1$ | (4.2) |

| $S_2^* + S_5^* = 1$ | (4.3) |

In the PWM rectifier, the space vector  $\mathbf{V}n$  is represented as

$$V_{n} = 1/3 V_{d} [(S_{1}^{*} - S_{4}^{*}) + (S_{3}^{*} - S_{6}^{*}) e^{j2./3 +} (S_{5}^{*} - S_{2}^{*}) e^{-j2./3}]$$

(4.4)

Where  $V_d$  is the d.c. link voltage. Substituting the switching function, 1 or 0, of each phase into (4.4), the following discrete space vectors are obtained

$$V_n = 2/3 V_d e^{j(n-1)./3}, n=1,2,...,6$$

(4.5)

$V_n = 0, n=0$  (4.6)

#### Fig. 4.3 power circuit of PWM rectifier with link

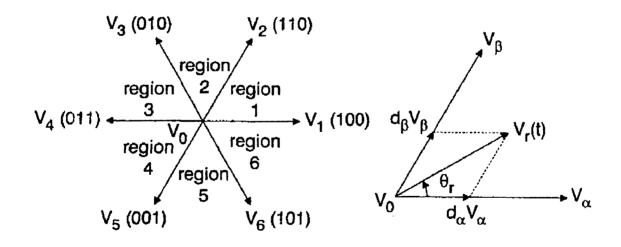

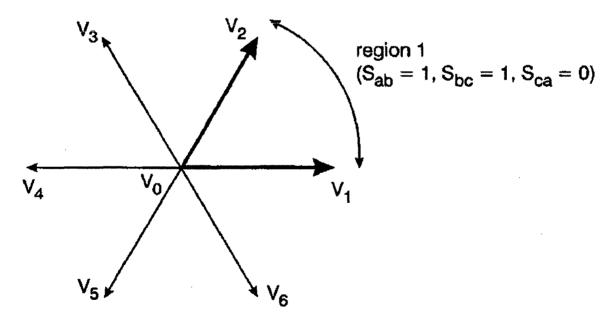

The available space voltage vectors according to eight switch states are shown in figure 4.4(*a*). Among these space voltage vectors, V0 is the zero voltage vectors and it has two switching patterns  $V_0$  (0 0 0) and  $V_0$  (1 1 1). To obtain the required rectifier input space voltage vector  $\mathbf{v}_r(t) = V_{rm} e^{j. st}$ , The conduction times of the switches are modulated according to the amplitude and angle of  $\mathbf{v}_r$ .  $V_{rm}$  and . s are the peak voltage and angular frequency of the space voltage vector  $\mathbf{v}_r$ , respectively. The angle of  $\mathbf{v}_r$  determines a region among six regions in the complex plane. The rectifier input space voltage vector  $\mathbf{v}_r$  in figure 4.4 (*b*) is modulated as:

$$V_r(t) = d_{\alpha}V_{\alpha} + d_{\beta}V_{\beta} \tag{4.7}$$

This is called the space vector modulation. Then the duty cycles  $d_1$  and  $d_2$  of two state space vectors  $V_1$  and  $V_2$  adjacent to the required space vector  $\mathbf{v}_r$  in a given region, and the duty cycle  $d_0$  of the zero vector are given by

$$d_{\alpha} = m \sin\left(\frac{\pi}{3} - \theta_{r}\right)$$

$$d_{\beta} = m \sin\theta_{r}$$

$$d_{o} = 1 - d_{\alpha} - d_{\beta}$$

(4.8)

Where the modulation index m (m 0. m . 1) is defined as

$$M = .3V_{\rm rm} / V_{\rm d}$$

(4.9)

Thus, the SVM technique utilizes three space vectors  $\mathbf{V}_{.}$ ,  $\mathbf{V}_{.}$ , and  $\mathbf{V}_{0}$  to generate the rectifier input voltage vector  $\mathbf{v}_{r}$  in the specified region.

Using Kirchhoff's voltage law from figure 4.1, the following equation is obtained

$$Ldi_{s}/dt = V_{s} - V_{r}$$

(4.10)

Where is  $i_s$  the source line current vector,  $v_s$  is the source voltage vector, L is the inductance of the input filter, and  $v_r$  is the rectifier input space voltage vector. The current error vector  $i_e$  is defined as

$$\mathbf{i}_{e} = \mathbf{i}_{s}^{*} - \mathbf{i}_{s} \tag{4.11}$$

Where  $i_s^*$  is the reference current vector. Substituting (4.11) into (4.10) produces

$$Ldi_{e}/dt = V_{r} - V_{s} + Ldi_{s}/dt \quad (4.12)$$

Thus, the line current error  $i_e$  is influenced by the derivative of the current command, the source voltage and the rectifier input space voltage vector. To obtain the zero current error between the reference current vector  $i_s^*$  and the line current vector  $i_s$ , the desired input voltage vector vr of the rectifier is as follows from (4.12)

$$V_{r}^{*} = V_{s} - Ldi_{s}^{*}/dt$$

(4.13)

Figure 4.4 State space vectors and voltage components of the PWM rectifier with voltage link: (a) state space vectors (b) voltage components.

Since the rectifier input voltage  $\mathbf{v}_r$  is modulated to generate the desired space voltage vector  $\mathbf{v}_r^*$ ,  $\mathbf{v}_r$  is represented by the quantized space vector  $\mathbf{V}_n$ . Then equation (4.12) becomes  $\text{Ldi}_e/\text{dt} = V_n - Vr^*$  (4.14)

Where  $v_r^*$  is the reference space voltage vector required to generate the current reference vector  $i_s^*$  without any current deviation.

## **4.2 PROPOSED CONTROL TECHNIQUE**

#### **SVM-based HCC for the three-phase PWM rectifier**

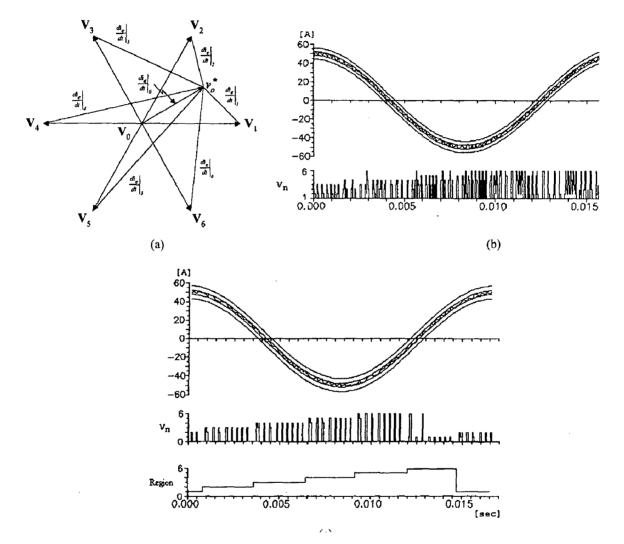

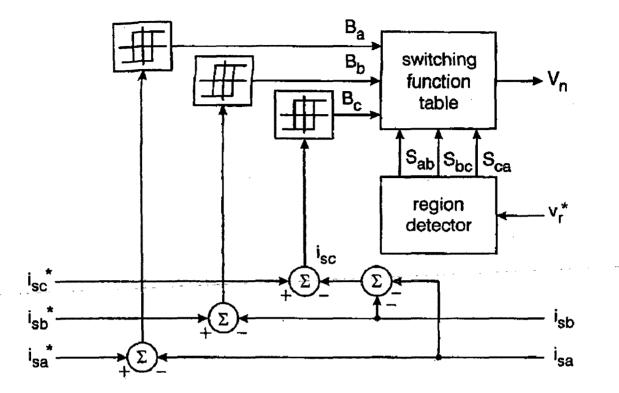

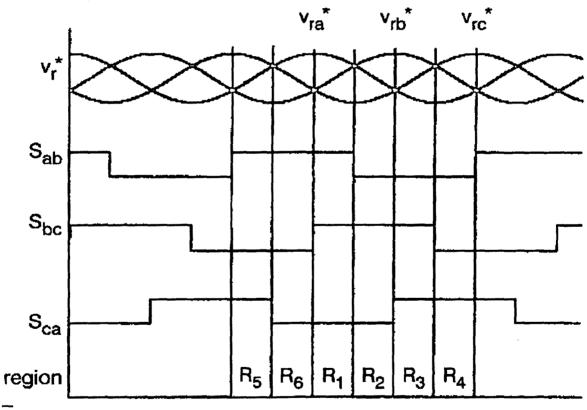

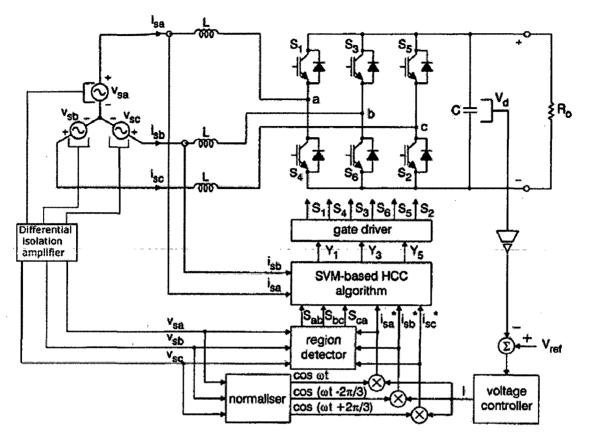

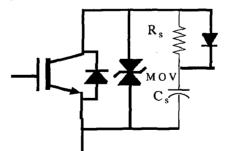

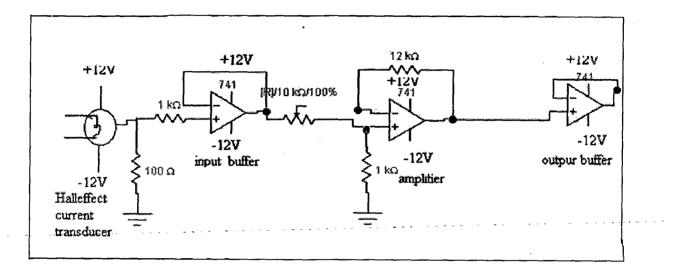

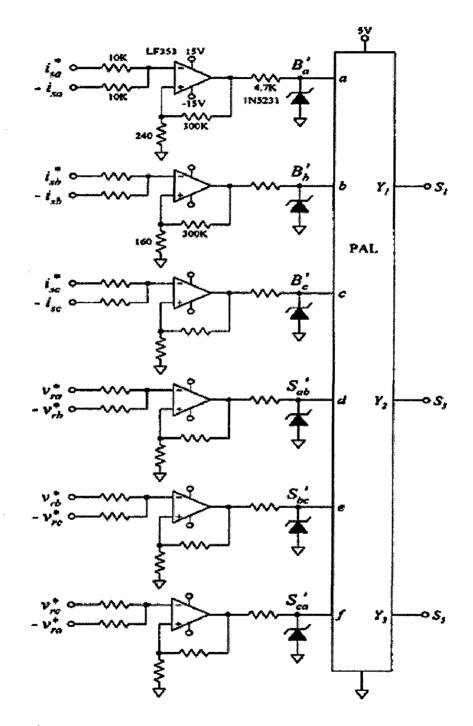

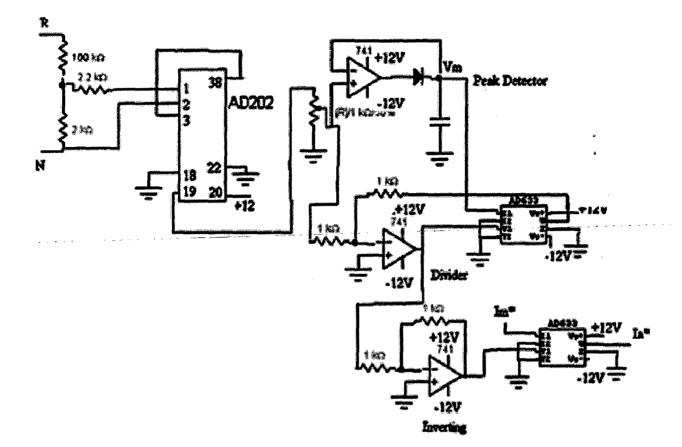

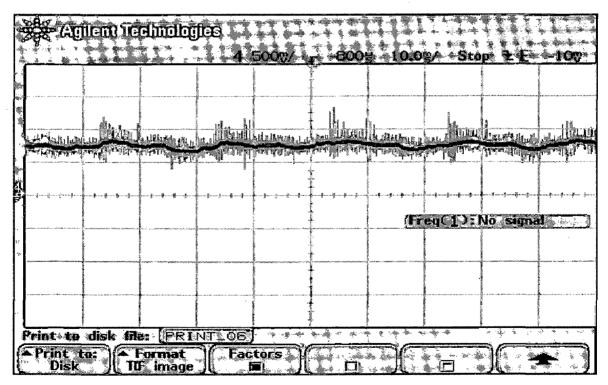

A SVM-based HCC for the three-phase PWM rectifier is proposed. This technique utilizes advantages of the HCC and SVM technique. This configuration reduces significantly the number of switching and at the same time gives the same state space vectors as those obtained from the SVM technique. The proposed current controller confine state space vectors from a region detector and applies a proper space vector selected according to the HCC for better current shape. A set of state space vectors including the zero vectors is determined from the region detector made up of three comparators.