# PERFORMANCE EVALUATION ON MULTI-LEVEL INVERTER FED INDUCTION MOTOR DRIVE

## **A DISSERTATION**

Submitted in partial fulfilment of the requirements for the award of the degree of

MASTER OF TECHNOLOGY

în

ELECTRICAL ENGINEERING

(With Specialization in Power Apparatus and Electric Drives)

By

# **BONDADA SUBBARAO**

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA)

**JUNE, 2005**

I hereby declare that the work that is being presented in this dissertation report entitled "PERFORMANCE EVALUATION ON MULTI-LEVEL INVERTER FED INDUCTION MOTOR DRIVE" submitted in partial fulfillment of the requirements for the award of the degree of Master Of Technology with specialization in Power Apparatus and Electric Drives, to the Department Of Electrical Engineering, Indian Institute Of Technology, Roorkee, is an authentic record of my own work carried out, under the guidance of Dr. Pramod Agrawal, Professor, Department of Electrical Engineering.

The matter embodied in this dissertation report has not been submitted by me for the Award of any other degree or diploma.

Date: 17/06/85 Place: Roorkee

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

(DR. PRAMOD AGRAWAL)

Professor,

Department of Electrical Engineering, Indian Institute of Technology, ROORKEE – 247 667, INDIA.

i

## ACKNOWLEDGEMENT

I wish to express my deep sense of gratitude and sincere thanks to my beloved guide **Dr**. Pramod Agrawal, Prof., Department of Electrical Engineering, IIT Roorkee, for being helpful and a great source of inspiration. His keen interest and constant encouragement gave me the confidence to complete my work. I wish to extend my sincere thanks for his excellent guidance and suggestions for the successful completion of my project work.

I am thankful to Mr. Prashant Sharma, M.Tech, student in PAED group of Electrical Engineering Department for his constant source of encouragement for successful completion of this work. He always boosts my morale

Special thanks to Mr. Rahul Dubey, Ph.D, Research scholar for his valuable guidance and to my friends whose support and encouragement has been a constant source of guidance to me.

I also express sincere thanks to all staff members of Drives lab and Electric workshop for their help in completion of this work.

## (Bondada Subbarao)

## ABSTRACT

All the matter in the universe, the general trend to minimize harmonics in conventional 2-level voltage source inverter (VSI) is towards various PWM techniques. However, this trend invited problems, like the increase of switching frequency increased the switching losses, generating a common mode voltage which becomes significant at high power levels. Multilevel power converters have gained much attention in recent years due to the proven mitigation of various problems sited above. The general structure of the multilevel inverter is such as to synthesize a sinusoidal voltage from several levels of DC voltage. Increasing the number of level produces a fine staircase waveform approaching close to a sinusoidal wave with minimum harmonic distortion.

In this thesis simulation of various inverters (from 2-level to 5-level) is carried and the performance of the inverter is investigated under various operating conditions by changing the load and output frequency. The digital implementation of Space Vector Pulse Width Modulation (SVPWM) technique for both Three phase inverter and Neutral Point Clamped Inverter using '80486 Processor Based PC with Data Acquisition Cards' is described in detail. The work mainly focuses on the improvement in THD of both voltage and current waveforms from normal three-phase inverter to Neutral Point Clamped Inverter. The performance of open loop V/f control of three-phase Induction Motor drive fed from both conventional Three-Phase Inverter and Neutral Point Clamped Inverter is investigated in open loop. Finally the vector control scheme with for three-level inverter using SVPWM is implemented to drive an induction motor for variable speed applications.

iii

|                  |                                                        | Page No |  |  |

|------------------|--------------------------------------------------------|---------|--|--|

| CANDIDATE        | 'S DECLARATION                                         | i       |  |  |

| ACKNOWLE         | DGEMENT                                                | ii      |  |  |

| ABSTRACT         |                                                        | iii     |  |  |

| CHAPTER 1        | : INTRODUCTION                                         |         |  |  |

| 1.1              | General                                                | 1       |  |  |

| 1.2              | VSI Fed Induction Motor Drive                          | 2       |  |  |

| 1.3              | Space Vector Modulation                                | 2       |  |  |

| 1.4              | Multi-level Inverter Fed Induction Motor Drive         | 3       |  |  |

| 1.5              | Microprocessors in Motor Control                       | 5       |  |  |

| 1.6              | Organization of This Thesis                            | 6       |  |  |

| <b>CHAPTER 2</b> | : LITERATURE REVIEW                                    | 9       |  |  |

| CHAPTER 3        | : MULTI-LEVEL INVERTERS                                |         |  |  |

| 3.1              | Introduction                                           | 13      |  |  |

| 3.2              | Basic Principle                                        | 14      |  |  |

| 3.3              | Topologies in Multi-level Inverters                    | 16      |  |  |

| 3.4              | Classification of Multi-level Inverters                |         |  |  |

|                  | 3.4.1 Diode-Clamped Multi-level Inverter(DCMLI)        | 21      |  |  |

|                  | 3.4.2 Capacitor-Clamped Multi-level Inverter(CCMLI)    | 25      |  |  |

|                  | 3.4.3 Cascaded Multicell Inverters                     | 29      |  |  |

| CHAPTER 4        | : SIMULATION OF MULTI-LEVEL INVERTERS                  |         |  |  |

| 4.1              | Two-level Inverter                                     | 31      |  |  |

| 4.2              | Three-level Inverter                                   | 35      |  |  |

| 4.3              | Five-level Inverter                                    |         |  |  |

| CHAPTER 5        | : PULSE WIDTH MODULATION TECHNIQUES                    |         |  |  |

| 5.1              | Introduction                                           | 41      |  |  |

| 5.2              | Sinusoidal Pulse Width Modulation(SPWM)                | 41      |  |  |

| 5.3              | Existing Multi-level carrier Based Methods             | 43      |  |  |

| 5.4              | Space Vector Modulation and Its Digital Implementation |         |  |  |

|                  | 5.4.1 Introduction                                     | 45      |  |  |

|                  | 5.4.2 Space Vector Modulation of 2-level inverter      |         |  |  |

|                  | Using d-q Model                                        | 46      |  |  |

# CONTENTS

.

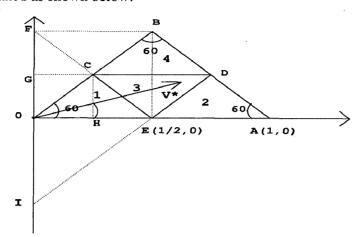

|                  | 5.4.3                                                       | Space Vector Modulation of 3-level Inverter consideri    | ng       |  |  |

|------------------|-------------------------------------------------------------|----------------------------------------------------------|----------|--|--|

|                  |                                                             | DC-link Voltage Balancing Problem                        | 53       |  |  |

| CHAPTER 6        | : INDUC                                                     | TION MOTOR CONTROL                                       |          |  |  |

| 6.1              | Scalar Co                                                   | ontrol or Open-Loop V/Hz Control                         | 62       |  |  |

| 6.2              | Vector C                                                    | ontrol or Field Oriented Control                         | 63       |  |  |

| CHAPTER 7        | : SYSTEN                                                    | A DEVELOPMENT                                            |          |  |  |

| 7.1              | Hardware                                                    | Requirements                                             |          |  |  |

|                  | 7.1.1                                                       | Power Circuit                                            | 69       |  |  |

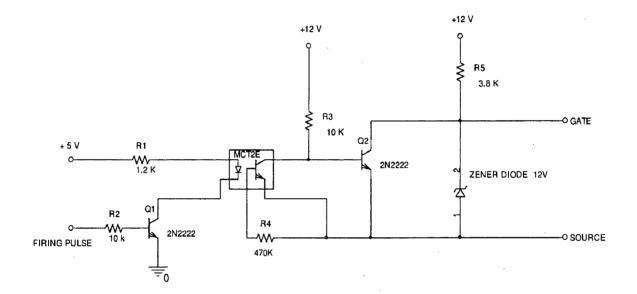

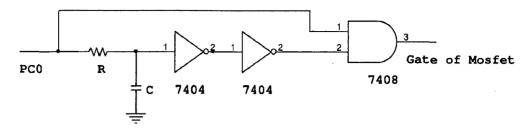

|                  | 7.1.2                                                       | Pulse Amplification and Isolation Circuit                | 70       |  |  |

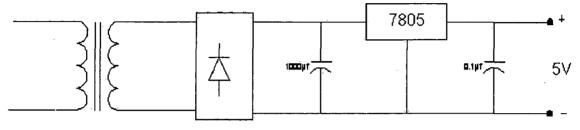

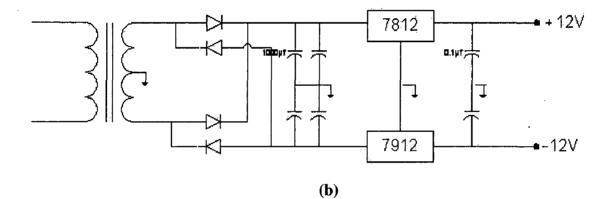

|                  | 7.1.3                                                       | Power Supplies                                           | 71       |  |  |

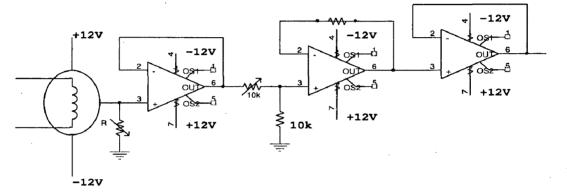

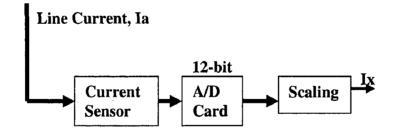

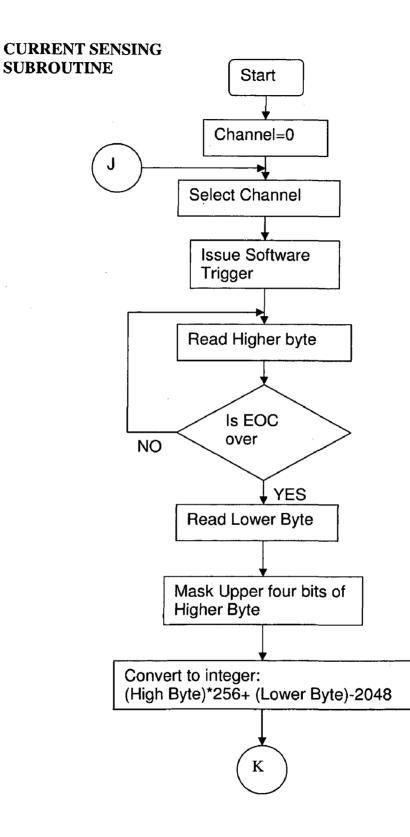

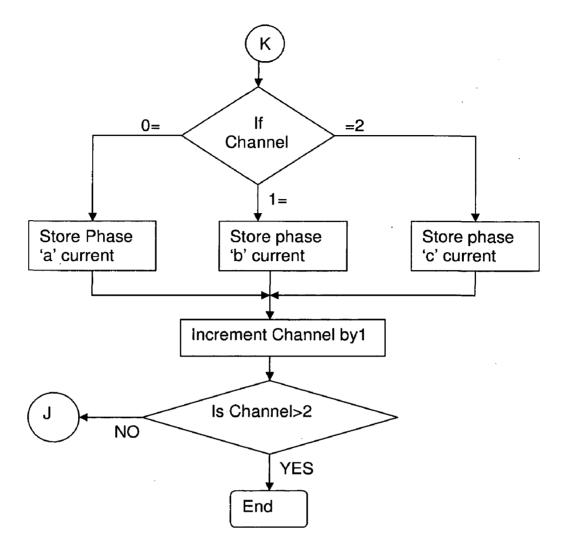

|                  | 7.1.4                                                       | Current Sensing Circuit And Scaling                      | 72       |  |  |

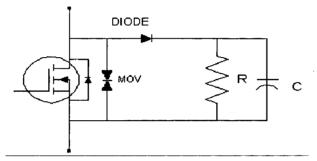

|                  | 7.1.5                                                       | Protection of MOSFETs                                    | 74       |  |  |

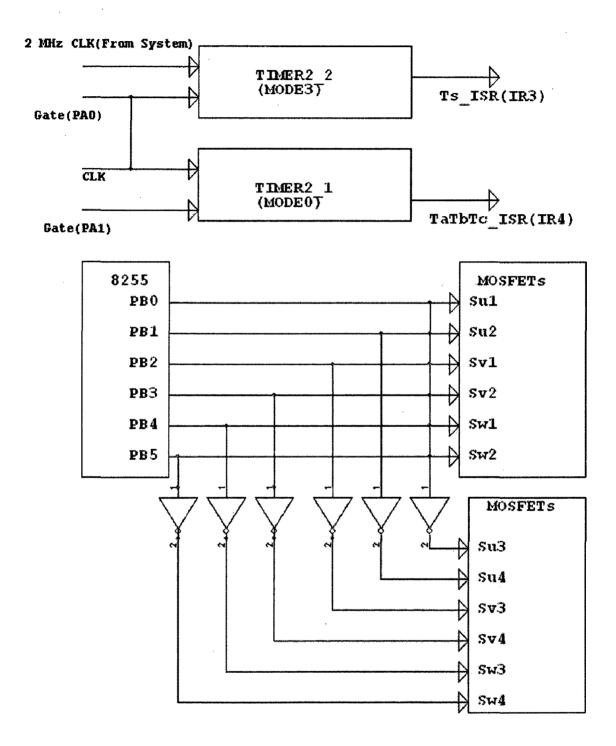

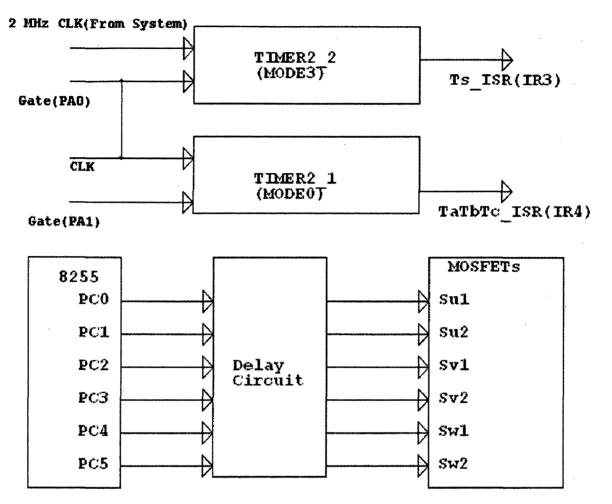

|                  | 7.1.6                                                       | Delay Circuit                                            | 75       |  |  |

| 7.2              | PC Interfacing and Control                                  |                                                          |          |  |  |

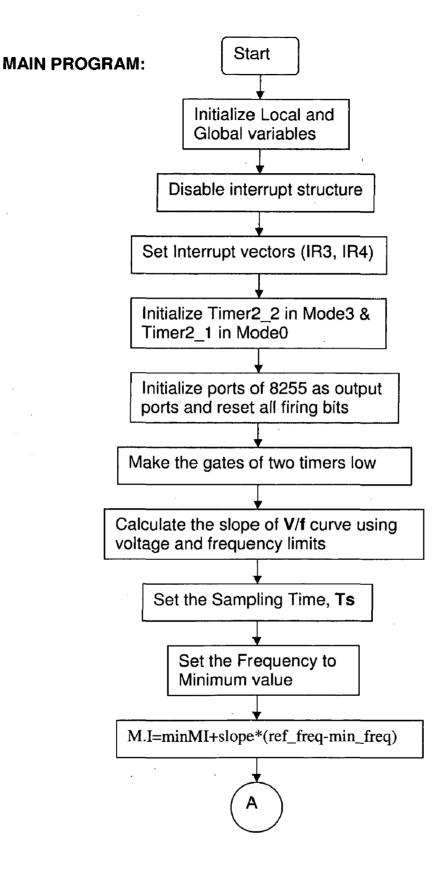

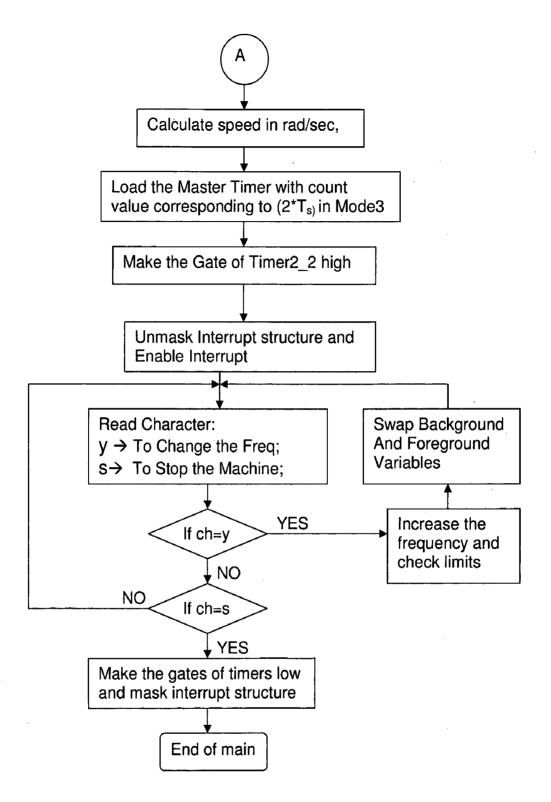

| 7.3              | <b>Control T</b>                                            | echnique and Software Development                        |          |  |  |

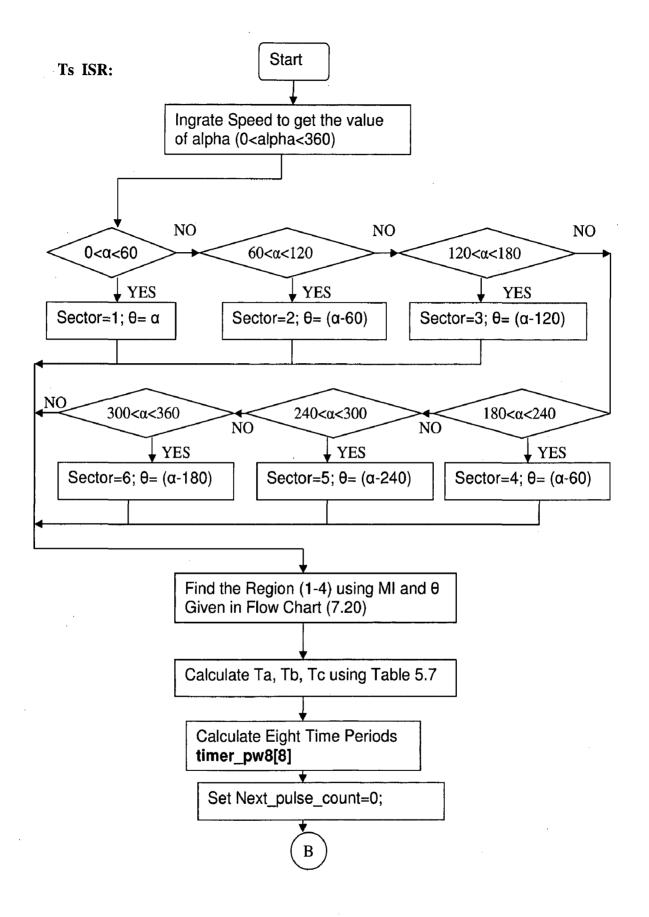

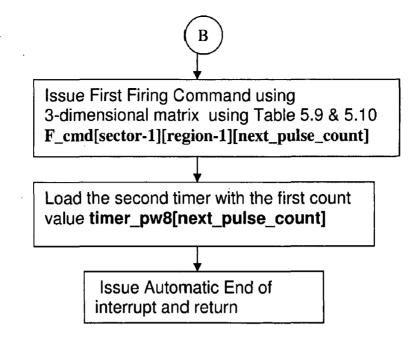

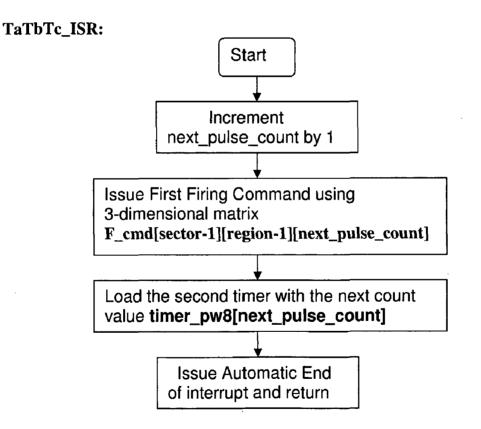

|                  | 7.3.1                                                       | Software Organization                                    | 79       |  |  |

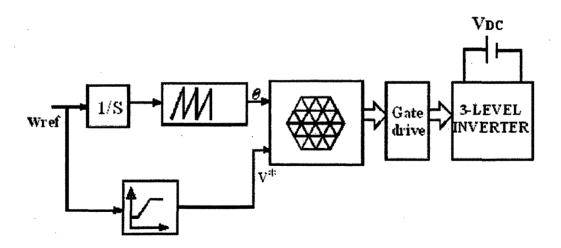

|                  | 7.3.2                                                       | <b>Open Loop V/Hz Control of Neutral Point Clamped</b>   |          |  |  |

|                  |                                                             | Inverter Fed Induction Motor Drive.                      | 80       |  |  |

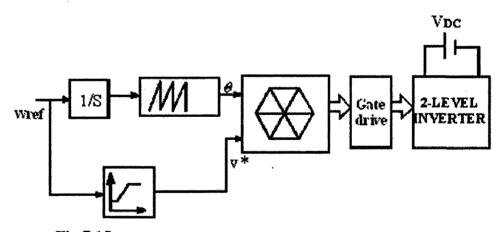

|                  | 7.3.3                                                       | V/Hz Control of Three-Phase Inverter Fed Induction       | •        |  |  |

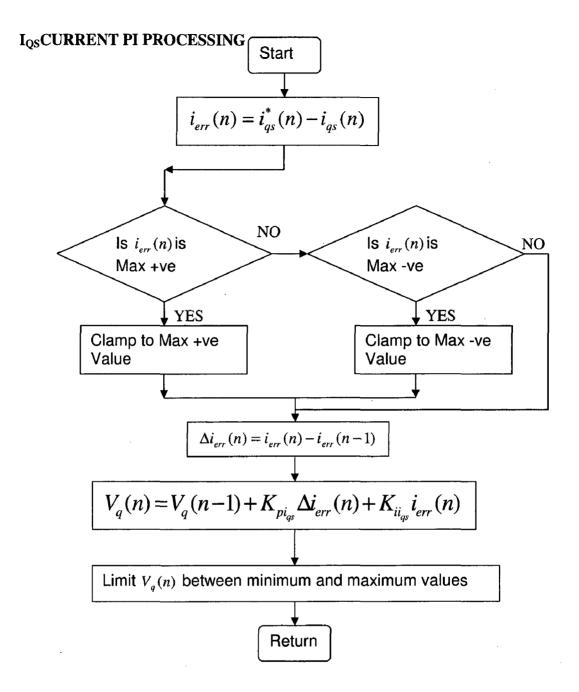

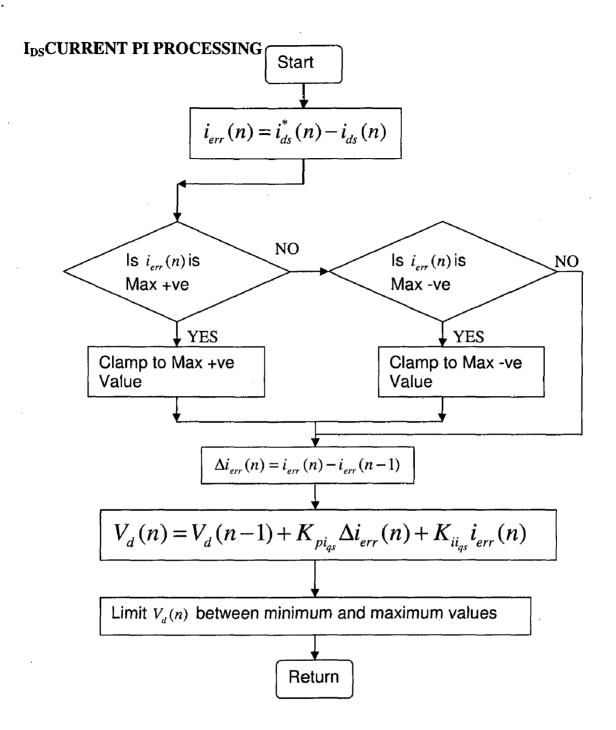

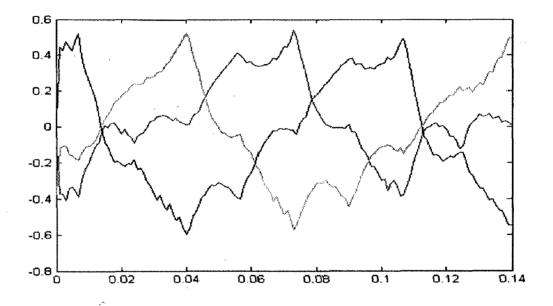

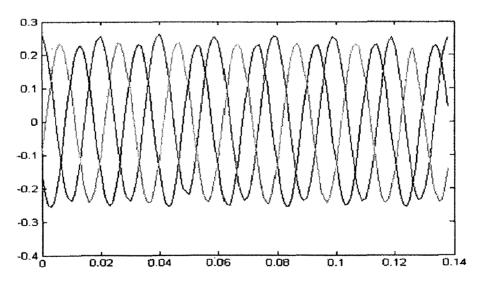

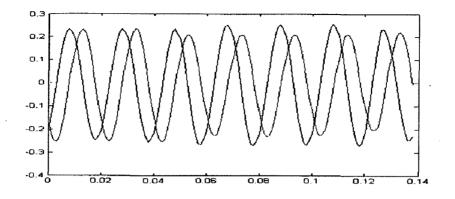

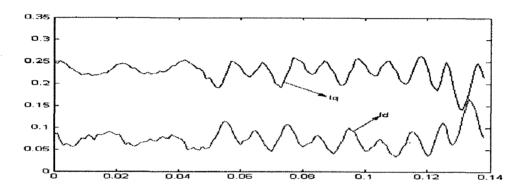

| 7.4              | Impleme                                                     | Motor Drive.<br>ntation of FOC for Induction Motor Drive | 81<br>90 |  |  |

| <b>CHPTARE 8</b> | : EXPERIMENTAL RESULTS                                      |                                                          |          |  |  |

| 8.1              | Performance Investigation of Neutral Point Clamped          |                                                          |          |  |  |

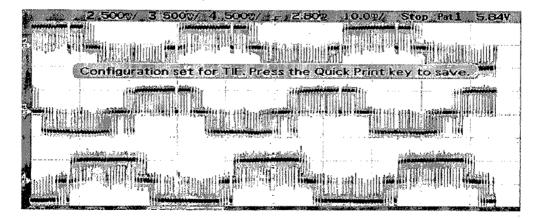

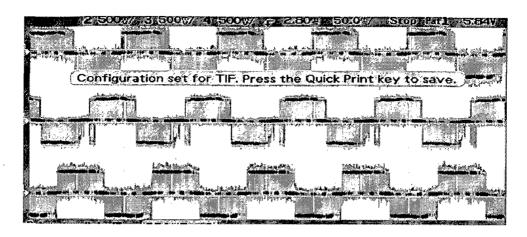

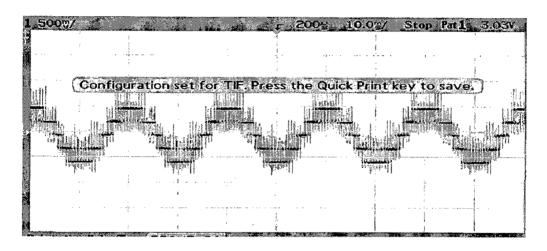

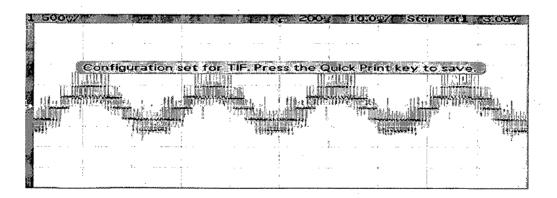

|                  | Three-Le                                                    | vel Inverter                                             | 103      |  |  |

| 8.2              | Performance Investigation of Three-Phase Two-Level Inverter |                                                          |          |  |  |

| 8.3              | -                                                           |                                                          |          |  |  |

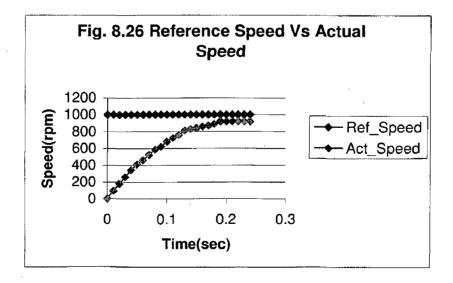

| 8.4              | Perform                                                     | ance Investigation of FOC Of Induction Motor             | 120      |  |  |

| CHAPTER 9        | 9 : CONCLUSION                                              |                                                          |          |  |  |

| REFERENCE        | S                                                           |                                                          | 124      |  |  |

| APPENDIX         | : INFORM                                                    | 1ATION OF DATA ACQUISITION CARDS                         | 127      |  |  |

.

#### **1.1 GENERAL**

Recent years have seen a sea change in factory automation. The manufacturing lines in an industrial plant typically involve one or more variable speed motor drives that serve to various requirements of the plant like, power conveyor belts, robot arms, overhead cranes, steel process lines, paper mills and other processing lines. Prior to 1950s all such applications required the use of DC motor drive as the AC motor were not so flexible with respect to adjustable and smoothly varying speeds. But the inherent disadvantages of the DC drive promoted development on the side and eventually AC drives emerged as cost-effective and rugged compared to their DC counterparts. The reliability was also high. However the control flexibility with these drives is very limited and these proved to be suitable in applications where the speed need be regulated roughly like fan, pump, compressor etc. But high performance applications like machine tools, spindles; high-speed elevators etc need a much more sophisticated regulation of various variables such as speed, position, acceleration etc. Until recently this area was dominated by the DC drives. But with suitable control the induction motor drives are more than a match for DC drives in these high performance applications. The advances in microelectronics have simplified most of the control complexities of these drives and brought about an improved drive performance. The most common drive for the AC motor is the Voltage Source Inverter (VSI) Drive. Before discussing the multilevel-inverter fed drive a brief overview of the existing VSI fed induction motor drives is presented here.

#### **1.2. VSI FED INDUCTION MOTOR DRIVE**

The voltage source inverter (VSI) creates a relatively well-defined switched voltage waveform at the terminals of the motor. This requires stiff DC bus. It is typically sub divided into two types called the six-step inverter and pulse-width modulated inverter. The six-step inverter has six steps in the output line-to-neutral voltage. The harmonics present in the waveform are 6n+1. The Fourier analysis of this waveform reveals a "square-wave" type of geometric progression of the harmonics. That is, the line-to-line and the line-to-neutral waveforms contain1/5<sup>th</sup> of the 5<sup>th</sup> harmonic,1/7<sup>th</sup> of the 7<sup>th</sup> harmonic, 1/11<sup>th</sup> of the 11<sup>th</sup> harmonic and so on. That 20% 5<sup>th</sup> harmonic,14.28% 7<sup>th</sup> harmonic,9.09% 11<sup>th</sup> harmonic and so on which is quite high.

The harmonics in general have two undesirable effects:

- ➢ Harmonic Heating

- Torque Pulsations

The PWM inverter combines both the voltage and frequency control within the inverter itself. Various PWM techniques have been implemented [29]; of these the sinusoidal PWM has been found to be one of the techniques to synthesize the motor currents as near to a sinusoidal as possible. The lower voltage harmonics can be greatly attenuated in this technique. PWM inverter fed motor tends to rotate much more smoothly at low speed. Torque pulsations and harmonic losses are reduced compared to 6-step inverter fed drive. The problems with this drive, as pointed out earlier, is the high dv/dt caused due to high frequency switching between the highest DC levels to zero. This produces common mode voltages across the motor winding that drives currents through the motor bearings resulting in its failure. High dv/dt also causes corona losses in the winding layers. The switching losses in the inverter are also high. Further, the voltage and switching frequency ratings of the devices are required to be high at high-power and high-voltage end applications.

## **1.3. SPACE VECTOR MODULATION (SVM):**

The space-vector PWM (SVPWM) method is an advanced, computationintensive PWM method and is possibly the best among all the PWM techniques for variable-frequency drive applications. Because of its superior performance, it has been finding widespread application in recent years. It is a carrier less method of generating PWM pattern for entire range of operating frequency. The space vector technique has the advantage that harmonics in motor currents are drastically reduced. This technique can be employed on-line with a processor. The synchronization of carrier to modulating signal is not needed, which reduces the burden of control and firing circuit

The PWM methods given in [29] have only considered implementation of a half-bridge of three-phase bridge inverter. If the load neutral is connected to the center

## **1.1 GENERAL**

Recent years have seen a sea change in factory automation. The manufacturing lines in an industrial plant typically involve one or more variable speed motor drives that serve to various requirements of the plant like, power conveyor belts, robot arms, overhead cranes, steel process lines, paper mills and other processing lines. Prior to 1950s all such applications required the use of DC motor drive as the AC motor were not so flexible with respect to adjustable and smoothly varying speeds. But the inherent disadvantages of the DC drive promoted development on the side and eventually AC drives emerged as cost-effective and rugged compared to their DC counterparts. The reliability was also high. However the control flexibility with these drives is very limited and these proved to be suitable in applications where the speed need be regulated roughly like fan, pump, compressor etc. But high performance applications like machine tools, spindles; high-speed elevators etc need a much more sophisticated regulation of various variables such as speed, position, acceleration etc. Until recently this area was dominated by the DC drives. But with suitable control the induction motor drives are more than a match for DC drives in these high performance applications. The advances in microelectronics have simplified most of the control complexities of these drives and brought about an improved drive performance. The most common drive for the AC motor is the Voltage Source Inverter (VSI) Drive. Before discussing the multilevel-inverter fed drive a brief overview of the existing VSI fed induction motor drives is presented here.

## **1.2. VSI FED INDUCTION MOTOR DRIVE**

The voltage source inverter (VSI) creates a relatively well-defined switched voltage waveform at the terminals of the motor. This requires stiff DC bus. It is typically sub divided into two types called the six-step inverter and pulse-width modulated inverter. The six-step inverter has six steps in the output line-to-neutral voltage. The harmonics present in the waveform are 6n+1. The Fourier analysis of this waveform reveals a "square-wave" type of geometric progression of the harmonics. That is, the line-to-line and the line-to-neutral waveforms contain  $1/5^{th}$  of the  $5^{th}$  harmonic,  $1/7^{th}$  of the  $7^{th}$  harmonic,  $1/11^{th}$  of the  $11^{th}$  harmonic and so on. That 20%  $5^{th}$  harmonic, 14.28%  $7^{th}$  harmonic, 9.09%  $11^{th}$  harmonic and so on which is quite high.

The harmonics in general have two undesirable effects:

- ➢ Harmonic Heating

- > Torque Pulsations

The PWM inverter combines both the voltage and frequency control within the inverter itself. Various PWM techniques have been implemented [29]; of these the sinusoidal PWM has been found to be one of the techniques to synthesize the motor currents as near to a sinusoidal as possible. The lower voltage harmonics can be greatly attenuated in this technique. PWM inverter fed motor tends to rotate much more smoothly at low speed. Torque pulsations and harmonic losses are reduced compared to 6-step inverter fed drive. The problems with this drive, as pointed out earlier, is the high dv/dt caused due to high frequency switching between the highest DC levels to zero. This produces common mode voltages across the motor winding that drives currents through the motor bearings resulting in its failure. High dv/dt also causes corona losses in the winding layers. The switching losses in the inverter are also high. Further, the voltage and switching frequency ratings of the devices are required to be high at high-power and high-voltage end applications.

## **1.3. SPACE VECTOR MODULATION (SVM):**

The space-vector PWM (SVPWM) method is an advanced, computationintensive PWM method and is possibly the best among all the PWM techniques for variable-frequency drive applications. Because of its superior performance, it has been finding widespread application in recent years. It is a carrier less method of generating PWM pattern for entire range of operating frequency. The space vector technique has the advantage that harmonics in motor currents are drastically reduced. This technique can be employed on-line with a processor. The synchronization of carrier to modulating signal is not needed, which reduces the burden of control and firing circuit

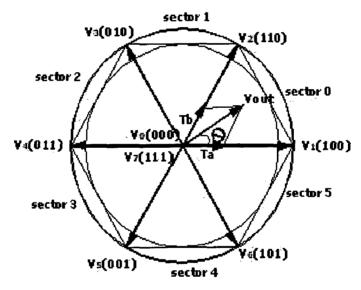

The PWM methods given in [29] have only considered implementation of a half-bridge of three-phase bridge inverter. If the load neutral is connected to the center tape of dc supply all the three bridges operate independently, giving satisfactory PWM performance. With a machine load, the load neutral is normally isolated, which causes the interaction among the phases. This intersection was not considered before in the PWM discussions. The SVM technique considers this interaction of the phases and optimizes the harmonic content of the three-phase isolated neutral load.

## **1.4. MULTI-LEVEL INVERTER FED INDUCTION MOTOR DRIVE**

The multi level starts with the three-level which is also known as neutral point clamped three-level inverter proposed by Akari Nabae [1]. Recently, with the dramatic improvements in high voltage technologies, high voltage insulated gate bipolar transistor (HVIGBT) and gate commutated thyristor (GCT) are expanding the area of their application. For the high performance ac drive systems at increased power level, high quality inverter output with low harmonic loss and torque pulsation is necessary. In case of the conventional two-level inverter configuration, the harmonic contents reduction of an inverter output current is achieved mainly by raising the switching frequency.

However in the field of high voltage, high power applications and the switching frequency of the power device has to be restricted below 1 KHz, even with the HVIGBT and GCT, due to the increased switching loss. So the harmonic reduction by raised switching frequency of a two-level inverter becomes more difficult in high power applications. In addition, as the dc link voltage of a two-level inverter is limited by voltage ratings of switching devices, the problematic series connection of switching devices is required to raise the dc link voltage. By series connection, the maximum allowable switching frequency has to be more lowered, thus the harmonic reduction becomes more difficult. From the aspect of harmonic reduction and high dc-link voltage level; three-level approach seems to be the most promising alternative. The harmonic contents of a three-level inverter are less than that of a two-level inverter at the same switching frequency and the blocking voltage of the switching device is half of the de-link voltage. So the three-level inverter topology is generally used in realizing the high performance, high voltage ac drive systems [1]. However, the inherent neutral-point potential variation of a three-level inverter has to be effectively suppressed to fully utilize

the above-mentioned advantages of a three-level inverter. So many PWM strategies have been proposed to solve the neutral-point potential unbalance problem [5], [8], [9].

In this thesis, a simple SVPWM method for three-level inverter is proposed. By using the new PWM strategy, dwelling time calculation and switching sequence selection are easily done like conventional two-level inverter. And the neutralpoint voltage control algorithm can be easily implemented. In this paper, the proposed three-level SVPWM method is explained in detail.

Multilevel inverters are based on the fact that a sine-wave can be approximated to a stepped waveform having large number of steps. The steps being supplied from different DC levels supported by series connected batteries or capacitors. Multilevel inverters have gained importance recently in power applications because of the problems reported by the industry with regard to two-level PWM based adjustablespeed drives (ASD's). The problems reported were mainly of motor damage, particularly motor bearings failure and motor winding insulation break-down because of circulating currents, dielectric stresses, voltage surges and corona discharge. The problems have attributed to high-rate-of change of voltage (dv/dt), of these inverters, which produces common voltage across motor windings. It has been shown that in general, increasing the switching frequency in voltage-source inverters (VSIs), better voltage/current waveforms are obtained. Advances in the semi-conductor device technology (<1ms required for turn on and turn off) have permitted to advance in his direction. This has allowed faster PWM carrier frequencies to be used, increasing the motor running efficiency. But the associated dv/dt and hence di-electric stresses between winding turns also increased greatly. At the inverter end the high frequency switching increased the switching losses.

Multilevel inverters overcome most of the problems cited above for earlier VSI and PWM techniques. The individual switches in multi-level configuration have a much lower dv/dt per switching, eliminating the problems of voltage stresses and corona discharge. Also multi-level inverters operate at high efficiencies because they can at a much lower frequency than PWM controlled inverter.

The unique structure of multi-level inverters allows them to reach higher voltages and therefore lower voltage-rating devices can be used. As the number of levels increases, the synthesized output waveform has more steps, producing a very fine stair

case wave and approaching very closely to the desired sine wave. It can be easily understood that as more and more steps are included in the waveform, the harmonic distortion of the output wave decreases, approaching zero as the number of levels approaches infinity.

Some of the problems associated with multilevel inverters.

- > Difficult and very complex to achieve series redundancy

- Capacitor voltage balancing

- > More complex PWM control strategy for higher levels

- Circuit complexity for higher levels

- ➤ Large device control

In spite of these problems, multi-level inverters offer a great potential for improving the drive performance in the industry. For a moderate number of levels the number of devices can be limited and combined with modular design, the overall designing of the inverter can be further simplified.

#### **1.5. MICROPROCESSORS IN MOTOR CONTROL**

Market analysis shows that most of all industrial motor applications use AC induction motors. The reasons for this include high robustness, reliability, low price and high efficiency (up to 80%). However, the use of induction motors also has its disadvantages, these lie mostly in its difficult controllability, due to its complex mathematical model, its non linear behavior during saturation effect and the electrical parameter oscillation which depends on the physical influence of the temperature. Traditionally motor control was designed with analog components; they are easy to design and can be implemented with relatively inexpensive components. However, there are several drawbacks with analog systems. Aging and temperature can bring about component variation causing the system to need regular adjustment, as the parts count increase the reliability of the system decreases. Analog components raise tolerance issues and upgrades are difficult as the design is hardwired. Digital systems offer improvements over analog designs. Drift is eliminated since most functions are performed digitally, upgrades can easily be made in software and part count is also reduced since digital systems can handle several functions on chips.

Hyo L. Liu, Nam S. Choi and Gyu H. Cho in their publication[5] titled " DSP based Space Vector PWM For Three-Level Inverter With DC-link voltage balancing", presented a new PWM method for three-level inverter considering DC-link capacitor balancing problem using Motorola DSP 56000. In this paper each voltage vector on space vector plane is classified in relation to charging discharging action of DC capacitors.

Masato Koyama, Toshiyuki Fuzzi, Ryohei Uchida, Takao Kawabata in their publication [6] titled, "Space Voltage Vector-Based New PWM Method For Large Capacity Three-Level GTO Inverter" presented new PWM method for three-level inverter based on the space voltage vectors. This PWM method can minimize the harmonic components of the output voltage under the minimum pulse width limitation of GTO's and also suppress the fluctuation of the neutral-point voltage.

Yo-Han Lee, Bum-Seok Suh, Dong-Seok Hyun in their publication [7] titled "A Novel PWM scheme for a Three-Level Voltage Inverter with GTO Thyristors" presents a new PWM method for the three-level GTO inverters based on the space voltage vectors and with this method the harmonic components of the output voltage by avoiding minimum pulse with limitation problem of GTO thyristors and keeping the voltage balancing of the dc-link capacitors.

Annette von Jouanne, Shaoan Dai, Haoran Zhang in their publication [8] titled "A multilevel Inverter Approach Providing DC-link Balancing, Ride – Through Enhancement, and Common-Mode Voltage Elimination ", presents a simple control method for balancing the dc-link voltage of three-level neutral-point-clamped inverters, while providing enhanced ride-through and common-mode voltage(CMV) elimination.

Sun-Kyoung Lim, Jun-Ha Kim and Kwanghee Nam in their publication [9] titled, "A DC-Link Voltage Balancing Algorithm for 3-level Converter Using the Zero Sequence Current " have given a method of balancing DC link voltage by using the zero-sequence current flowing in the link made between the neutral point the source transformer on the AC side and the mid-point of DC-link for the 3-level case. This problem has been tackled by various other techniques by numerous authors [6],[10],[13].

case wave and approaching very closely to the desired sine wave. It can be easily understood that as more and more steps are included in the waveform, the harmonic distortion of the output wave decreases, approaching zero as the number of levels approaches infinity.

Some of the problems associated with multilevel inverters.

- > Difficult and very complex to achieve series redundancy

- Capacitor voltage balancing

- More complex PWM control strategy for higher levels

- Circuit complexity for higher levels

- > Large device control

In spite of these problems, multi-level inverters offer a great potential for improving the drive performance in the industry. For a moderate number of levels the number of devices can be limited and combined with modular design, the overall designing of the inverter can be further simplified.

#### **1.5. MICROPROCESSORS IN MOTOR CONTROL**

Market analysis shows that most of all industrial motor applications use AC induction motors. The reasons for this include high robustness, reliability, low price and high efficiency (up to 80%). However, the use of induction motors also has its disadvantages, these lie mostly in its difficult controllability, due to its complex mathematical model, its non linear behavior during saturation effect and the electrical parameter oscillation which depends on the physical influence of the temperature. Traditionally motor control was designed with analog components; they are easy to design and can be implemented with relatively inexpensive components. However, there are several drawbacks with analog systems. Aging and temperature can bring about component variation causing the system to need regular adjustment, as the parts count increase the reliability of the system decreases. Analog components raise tolerance issues and upgrades are difficult as the design is hardwired. Digital systems offer improvements over analog designs. Drift is eliminated since most functions are performed digitally, upgrades can easily be made in software and part count is also reduced since digital systems can handle several functions on chips. Micro Processors go on further to provide high speed, high resolution and sensor less algorithms in order to reduce system costs. Providing a more precise control to achieve better consumption or radiation performances often means performing more calculations speeds-up calculations. Generally fixed point Micro Processors are preferred for motor control for two reasons.

### **Benefits of the Micro Processor Controllers**

The performances of an AC induction motor are strongly dependent on its control. Micro Processors controllers enable enhanced real time algorithms as well as sensorless control. The combination of both allows to reduce the number of components and to optimize the design of silicon, to achieve a system cost reduction.

- Favours system cost reduction by an efficient control in all speed range implying right dimensioning of power device circuits

- Performs high level algorithms due to reduced torque ripple, resulting in lower vibration and longer life time.

- Enables a reduction of harmonics using enhanced algorithms, to meet easier requirements and to reduce filters cost.

- Removes speed or position sensors by the implementation of sensor less algorithms.

- Decreases the number of look-up tables which reduces the amount of memory required.

- Real-time generation of smooth near-optimal reference profiles and move trajectories, resulting in better-performing.

- Controls power switching inverters and generates high-resolution PWM outputs.

- Provides single chip control system.

Microcontroller has the disadvantage of signal quantization and sampling delay. It is sluggish as compared to dedicated hardware. One of the main difficulties with conventional tracking controllers for electric drives is their inability to capture the unknown load characteristics very a widely ranging operating point. This makes the tuning of the respective controller parameters difficult.

## **1.6. ORGANIZATION OF THIS THESIS**

**CHAPTER 2:** This chapter a review of the various publications in this field has been discussed briefly.

**CHAPTER 3:** This chapter focuses on the basic principle of obtaining a multilevel waveform, different topologies and classification of multi-level inverters, which includes some of the recently developed circuit topologies. The salient features of each topology have been presented and relative comparison has also been made.

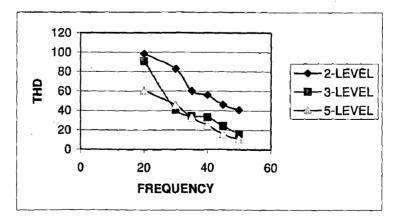

**CHAPTER 4:** This chapter includes the simulation of various inverters (2-level, 3-level, 5-level) using 'MATLAB 6.5' software. The performance of these inverters was investigated under various conditions of the load (Both R-L and Induction Motor) by changing output frequency using Sinusoidal Pulse Width Modulation Technique. The main aim of this chapter is to investigate the effect on harmonic spectra and THD as number of levels increased from conventional 2-level to 5-level inverters

**CHAPTER 5:** This chapter discusses the various PWM techniques for multilevel inverters and briefly explains the theory and digital implementation of Space Vector PWM for both conventional Three-phase Inverter and Neutral-Point Clamped Inverter.

**CHAPTER 6:** This chapter explains the theory and implementation of open loop V/Hz control and Field Oriented Control for Induction Motor Drive.

CHAPTER 7: This chapter consists of three sections.

- Hardware development

- ➢ Software development

- > PC interfacing and control

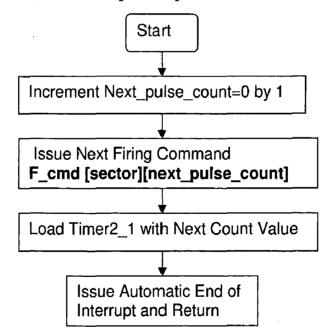

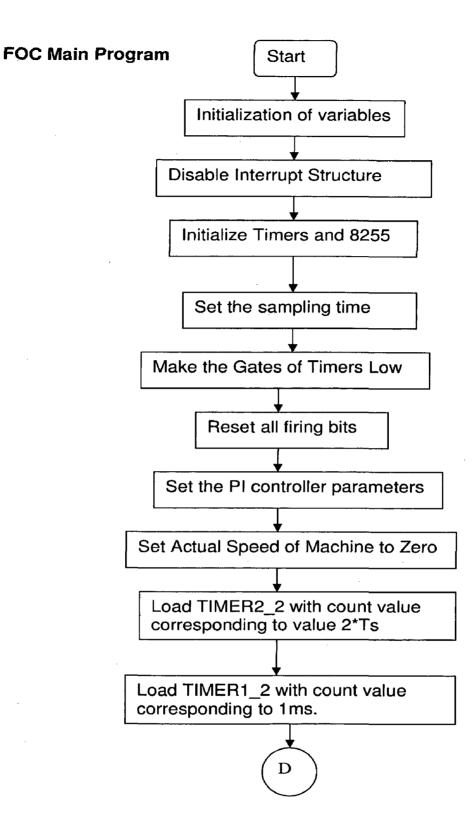

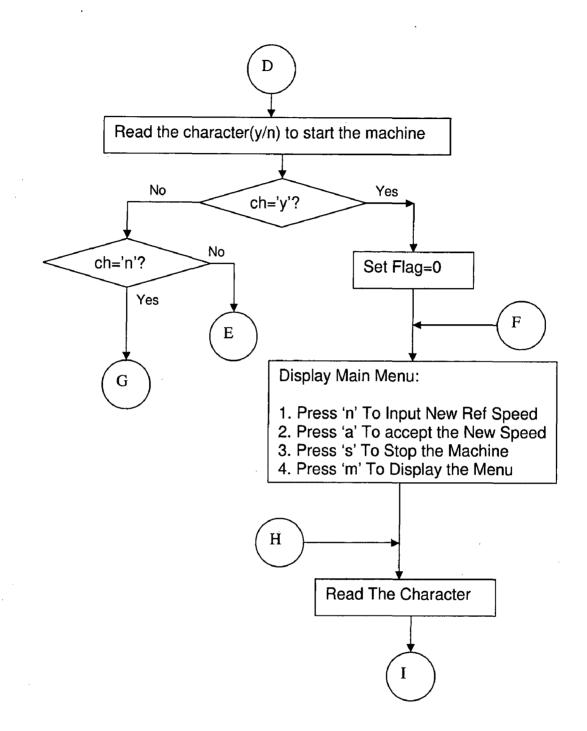

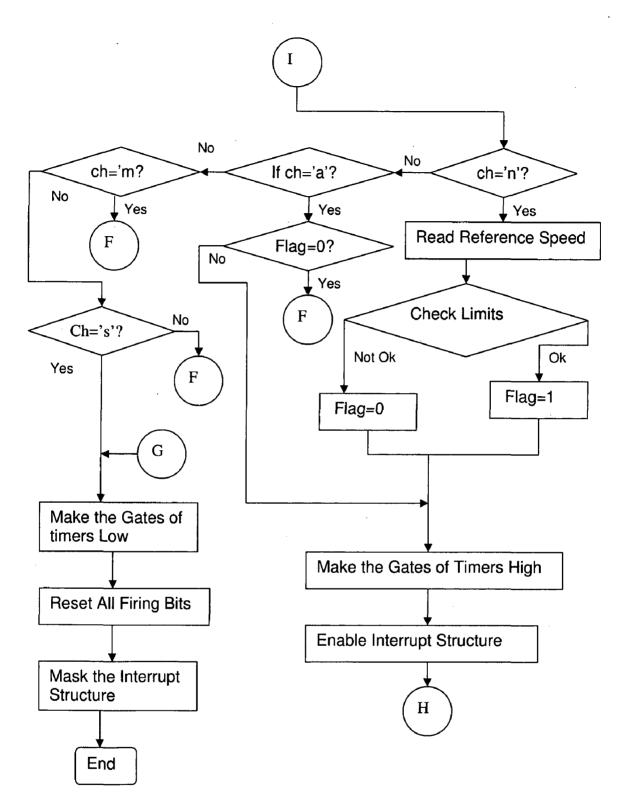

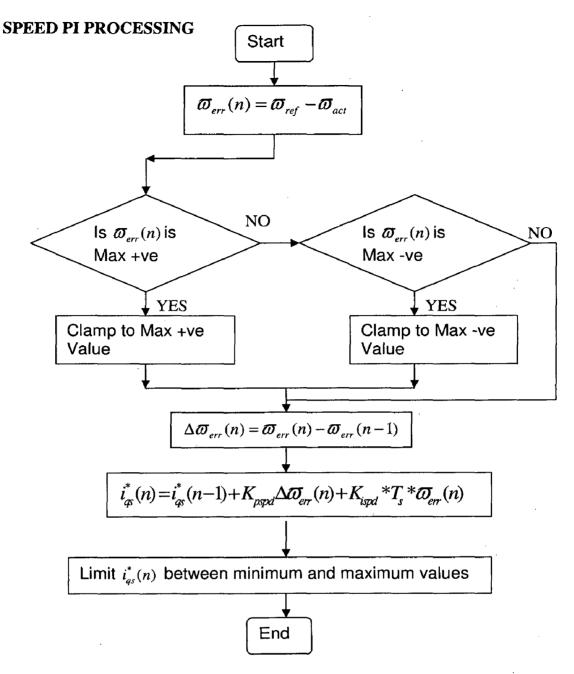

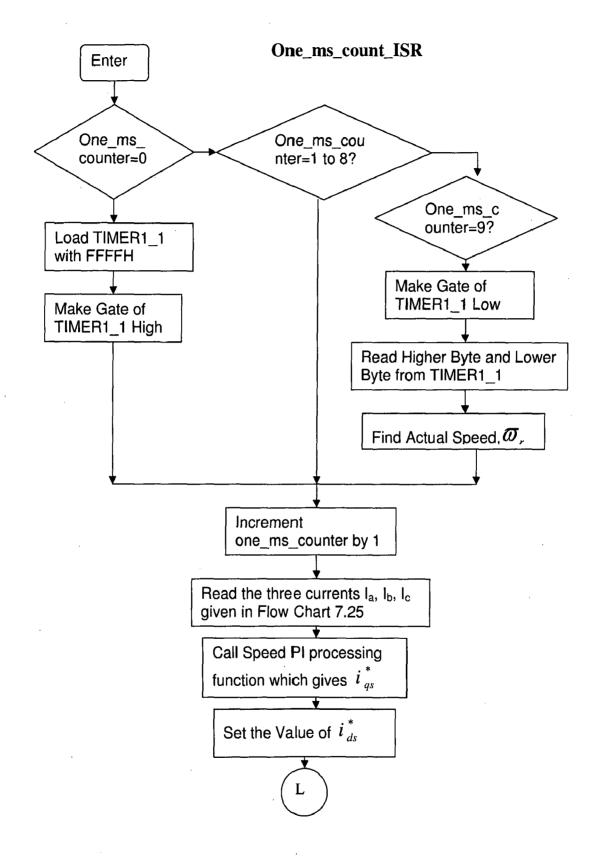

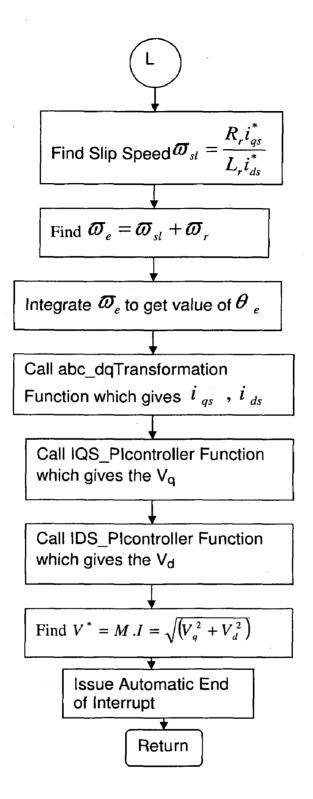

In Hardware development, hardware requirement for the realization of the Thee-level Neutral Point Clamped inverter and Three-phase inverter has been given, and design of various circuits like power supplies, current measurement, delay circuit, snubber circuit for MOSFET are explained in detail. In software development section Open Loop V/f control of induction motor using both conventional Three-phase inverter and Neutral-Point Clamped Inverter has been explained with the flowcharts. PC interfacing with the hardware is discussed briefly. The complete software for the Field Oriented Control of Induction Motor consisting of current measurement, current PI processing, speed measurement, speed PI processing has been discussed briefly with the

·7

help of flowcharts. Only the pictorial representation of software has been given. The complete software has been written using 'C- Language'

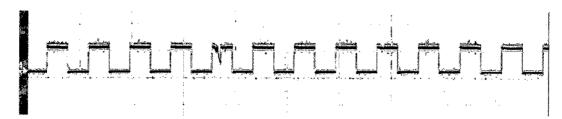

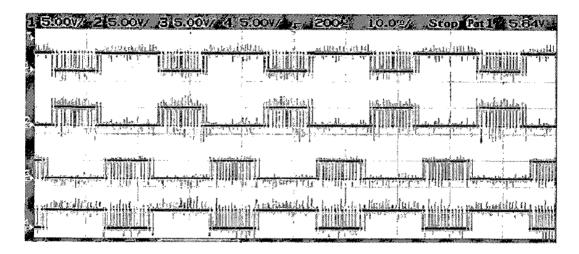

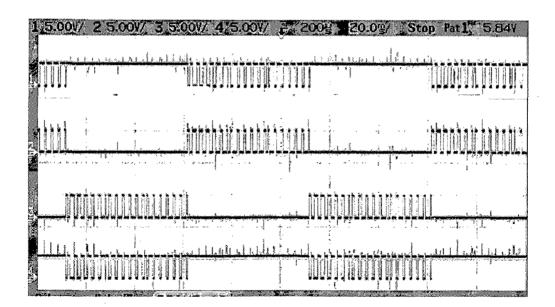

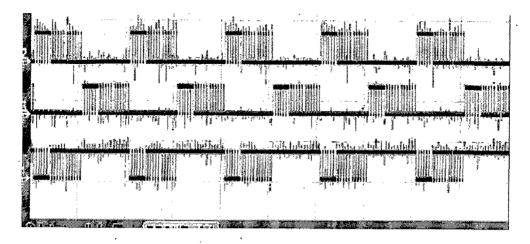

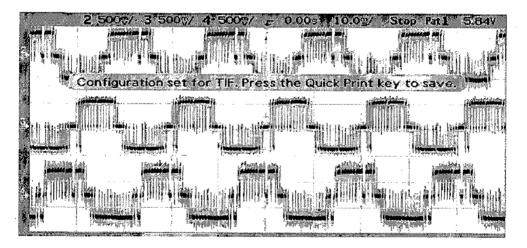

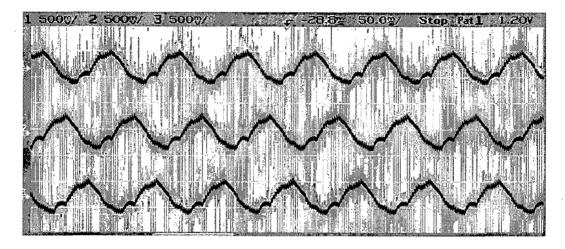

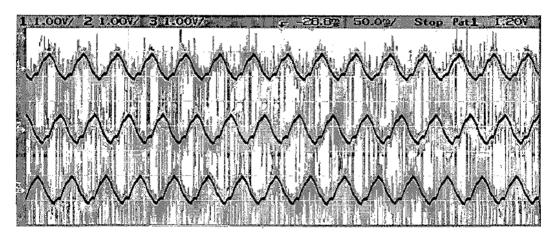

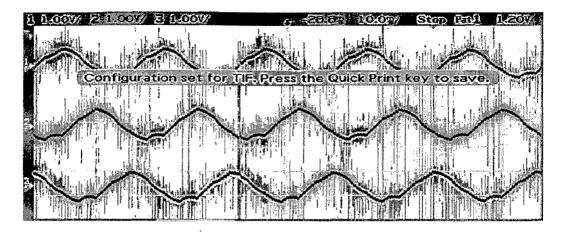

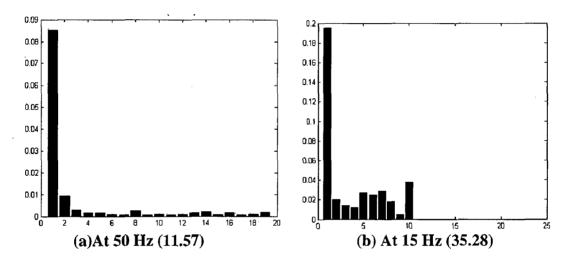

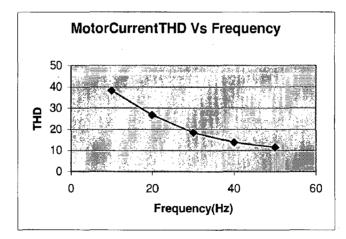

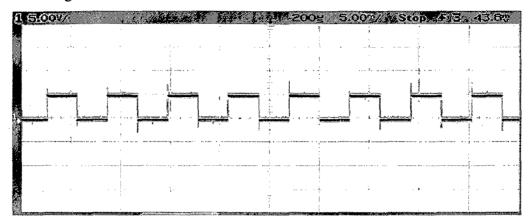

**CHAPTER 8:** This chapter presents the experimental results such as firing pulses to MOSFETs, line voltages and their THDs, phase voltages, line currents and their THDs under various conditions of load at different frequencies using both the inverters. And relative comparison of line currents THDs between 2-level and 3-level inverters has been presented with the help of charts.

CHAPTER 9: This chapter presents the conclusion of this thesis and scope for future work in this area.

## LITERATURE REVIEW

Harmonic distortion was one of the most important factors in the evolution of the multilevel inverters. Akira Nabae et. al. [1] in their publication titled, "A New Neutral-Point-Clamped PWM Inverter", has made a clear distinction between the conventional and the multilevel inverters vis-a-vis the harmonic spectra. The multilevel technique was introduced here in combination with the already existing PWM technique.

Jih-Sheng Lai and Fang Zheng Peng in their publication [2] titled, "Multilevel Converters - A New Breed of Power Converters", bring out clearly the working of each of the three basic types of multilevel inverters. The potential applications like reactive power compensation, back-to-back intertie and adjustable speed drives has been presented.

Jose Rodriguez, Jih-Shing Lai and Fang Zheng Peng in their publication [3] titled "Multilevel Inverters: A survey of Topologies, Controls, and Applications", presents the most important topologies like diode-clamped inverter (neutral-point clamped), capacitor-clamped (flying capacitor), and cascaded multicell with separate dc sources. Emerging topologies like asymmetric hybrid cells and soft-switched multilevel inverters are also discussed. This paper also presents the most relevant control and modulation methods developed for this family of converters: multilevel sinusoidal pulse width modulation, multilevel selective harmonic elimination, and space-vector modulation.

Texas Instruments application note no. SPRA284a [4] titled "AC Induction Motor Control Using Constant V/Hz Principle and Space Vector PWM Technique with TMS320C240" presents digital implementation of space vector modulation using d-q model and principles of constant V/Hz control for AC Induction motor. Two different implementations are presented. Implementation issues such as command voltage generation, switching pattern determination, speed measurement and scaling are discussed.

Hyo L. Liu, Nam S. Choi and Gyu H. Cho in their publication[5] titled " DSP based Space Vector PWM For Three-Level Inverter With DC-link voltage balancing", presented a new PWM method for three-level inverter considering DC-link capacitor balancing problem using Motorola DSP 56000. In this paper each voltage vector on space vector plane is classified in relation to charging discharging action of DC capacitors.

Masato Koyama, Toshiyuki Fuzzi, Ryohei Uchida, Takao Kawabata in their publication [6] titled, "Space Voltage Vector-Based New PWM Method For Large Capacity Three-Level GTO Inverter" presented new PWM method for three-level inverter based on the space voltage vectors. This PWM method can minimize the harmonic components of the output voltage under the minimum pulse width limitation of GTO's and also suppress the fluctuation of the neutral-point voltage.

Yo-Han Lee, Bum-Seok Suh, Dong-Seok Hyun in their publication [7] titled "A Novel PWM scheme for a Three-Level Voltage Inverter with GTO Thyristors" presents a new PWM method for the three-level GTO inverters based on the space voltage vectors and with this method the harmonic components of the output voltage by avoiding minimum pulse with limitation problem of GTO thyristors and keeping the voltage balancing of the dc-link capacitors.

Annette von Jouanne, Shaoan Dai, Haoran Zhang in their publication [8] titled "A multilevel Inverter Approach Providing DC-link Balancing, Ride – Through Enhancement, and Common-Mode Voltage Elimination ", presents a simple control method for balancing the dc-link voltage of three-level neutral-point-clamped inverters, while providing enhanced ride-through and common-mode voltage(CMV) elimination.

Sun-Kyoung Lim, Jun-Ha Kim and Kwanghee Nam in their publication [9] titled, "A DC-Link Voltage Balancing Algorithm for 3-level Converter Using the Zero Sequence Current " have given a method of balancing DC link voltage by using the zero-sequence current flowing in the link made between the neutral point the source transformer on the AC side and the mid-point of DC-link for the 3-level case. This problem has been tackled by various other techniques by numerous authors [6],[10],[13].

Fang Zheng Peng in his publication [10] titled, "A Generalized Multilevel Inverter Topology with Self Voltage Balancing", has presented a generalized topology from which any type and any level multilevel inverter can be deduced. The topology proposed has a self-voltage balancing property. But for higher levels, the device count becomes quite high.

Leon M. Tolbert, Fang Z. Peng , Thomas G. Habetler in their publication[11] titled "Multilevel Inverters for Electric Vehicle Applications" presented applications of multilevel inverters for all-electric vehicle(EV) and hybrid-electric(HEV) motor drives. This paper explores the benefits and discussed the control schemes of the cascade inverter for use as an EV motor drive or a parallel HEV drive and the diode clamped inverter as a series HEV motor drive.

Leon M. Tolben, Fang Zheng Peng and Thomas G. Habetler in their publication [12] titled, "Multilevel Converters for Large Electric Drives", have proved the suitability of multilevel converters for high power and/or high voltage electric motor drives. The cascaded inverter has been shown to be a natural fit for large automotive all-electric drives because it uses several levels of DC voltage sources, which would be available from batteries or fuel cells. Also a back-to-back diode clamped converter has been found to be ideal where a source of AC voltage is available, such as in a hybrid electric vehicle.

Texas Instruments application note no. SPRU485A [13] titled "Digital Motor Control, Software Library "describes briefly the digital implementations of PI controllers, Park's transformation, Clark's transformation, Integrator, speed measurement, current measurement through 'C' language.

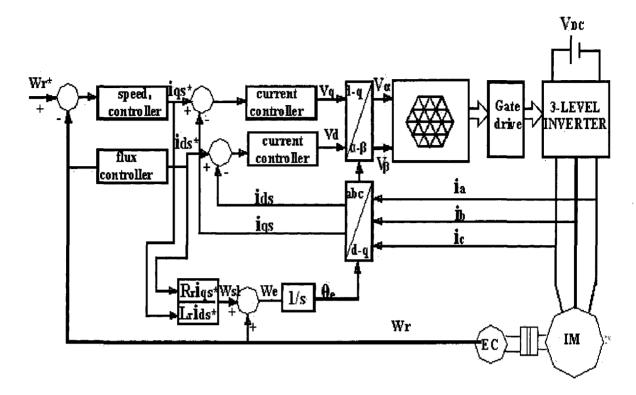

Texas Instruments Literature Number BPRA076 titled [14] "Implementation of a Speed Field Orientated Control of Three Phase AC Induction Motor using TMS320F240", It consists of two sections The first section deals with the presentation of the field orientated controlled AC induction drive; it explains the AC induction motor, the control hardware, the power electronics hardware as well as the complete FOC structure. The second section deals with the implementation of TMS320F240 drive speed control. Here, the details of how and why the software is

organized, the Per Unit model, the numerical consideration, the current and speed sensing and scaling, the regulators, the system transformations, the current model, the field weakening and the space vector modulation are fully explained step by step.

## CHAPTER-3

## MULTILEVEL INVERTERS

This chapter focuses on the basic principle of obtaining a multilevel waveform, classification of multi-level inverters and their operation, which includes some of recently developed circuit topologies. The salient features of each topology have been presented and a relative comparison has also been made.

#### **3.1. INTRODUCTION**

Multilevel inverter technology has emerged recently as a very important alternative in the area of high-power medium-voltage energy control. The term multilevel starts with the 3-level inverter introduced by "Akari Nabae "in 1981[1]. By increasing the number of levels in inverter the output voltages have more steps generating staircase waveform which has reduced harmonic distortion. Multilevel inverters include an array of power semiconductors and capacitor voltage sources, the output of which generate voltages with stepped waveforms. The commutation of the switches permits the addition of capacitor voltages, which reach high voltage at output, while power semiconductors must withstand only reduced voltages.

Multi level inverters are based on the fact that sine wave can be approximated to a stepped wave form having large number of steps. The steps being supplied from different DC levels supported by series connected batteries or capacitors. The individual devices in multilevel configuration have a much lower dv/dt per switching at a much lower frequency than PWM- controlled inverter. The unique structure of multi level inverters allows them to reach high voltages and therefore lower voltage rating devices can be used.

As the number of levels increases the synthesized output waveform has more steps producing a very fine stair case wave and approaching very closely to the desired sine wave. It can be easily understood that as the more and more steps are included in the waveform the harmonic distortion of the output wave decreases approaching zero as the number of levels approaching infinity. Hence multi level inverters offer a better choice at a high power end because the high volt-ampere ratings are possible with these inverters without the problems of high dv/dt and the other associated ones.

## **3.2. BASIC PRINCIPLE**

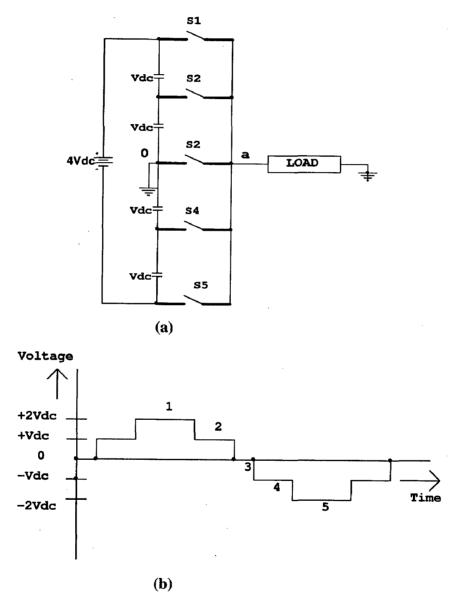

To understand the concept of multilevel inverters consider the circuit shown in Fig 3.1. Here capacitors are connected in series and across the main DC source  $4 V_{dc}$ .

Fig.3.1 Basic principle of Multi-level inverter (a) Circuit (b) output voltage Here capacitors are connected in series and across the main DC source  $V_{dc}$ . The switches  $S_1$ - $S_5$  are closed one at a time for a fixed duration of time. The load voltage which is

measured with respect to the reference point 0, in shown in the form of waveform in Fig.3.2. Table3.1 lists the switching states and output voltage obtained for each state of switches. Switch state '1' means ON and '0' means OFF. It can be seen that a stepped wave is output to the load. The stepped can be approximated to a sine wave by adding more number of capacitors (levels) in series. Also it can be noted that 5-level waveform requires four capacitors and so on. In general an inverter consists of m-1 capacitors on the DC bus and produces m-levels of the phase voltage.

| V <sub>ao</sub>   | Switching States |                |                |            |                |  |  |

|-------------------|------------------|----------------|----------------|------------|----------------|--|--|

|                   | S <sub>1</sub>   | S <sub>2</sub> | S <sub>3</sub> | <b>S</b> 4 | S <sub>5</sub> |  |  |

| 0                 | 0                | 0              | 1              | 0          | 0              |  |  |

| V <sub>dc</sub>   | 0                | 1              | 0              | 0          | 0              |  |  |

| 2V <sub>dc</sub>  | 1                | 0              | 0              | 0          | 0              |  |  |

| V <sub>dc</sub>   | 0                | 1              | 0              | 0          | 0              |  |  |

| 0                 | 0                | 0              | 1              | 0          | 1              |  |  |

| -V <sub>dc</sub>  | 0                | 0              | 0              | 1          | 1              |  |  |

| -2V <sub>dc</sub> | 0                | 0              | 0              | 0          | 1              |  |  |

| -V <sub>dc</sub>  | 0                | 0              | 0              | 1          | 0              |  |  |

## **Table 3.1 Switching States of Multi-level Inverter**

## **Features of Multilevel Inverters**

- This can generate output voltages with extremely low distortion and lower dv/dt.

- They draw input current with very low distortion

- They generate smaller common mode voltages thus reducing the stress in the motor bearings. In addition using sophisticated modulation methods, common mode voltages can be eliminated.

- They can operate with a lower switching frequency.

- Excellent dynamic response

- Smooth torque/speed control over full speed range

- Increase frequencies up to 200Hz

- Improved AC supply power factor

- Lesser Torque pulsations

- Lower audible noise levels

## **Problems associated with Multilevel Inverters**

Some of the problems associated with multilevel inverters.

- Difficult and very complex to achieve series redundancy

- Capacitor voltage balancing

- More complex PWM control strategy for higher levels

- Circuit complexity for higher levels

- Large device control

## 3.3. THE TOPOLOGIES IN MULTILEVEL INVERTERS

The topologies available have been given as:

- Series connected 2-level inverter(SC2L)

- ➤ 3-level neutral point clamped MLI(3LNPC)

- ➤ Multilevel Inverter.

## **Series Connected 2-Level Inverter**

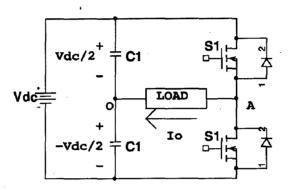

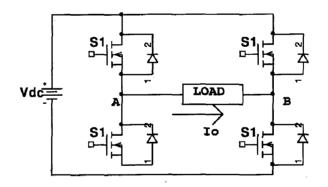

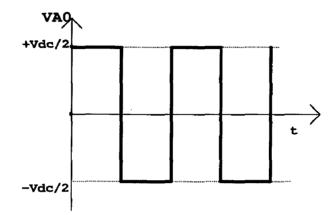

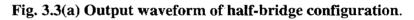

Switch-mode dc-to-ac inverters used in ac power supplies and ac motor drives where the objective is to produce a sinusoidal ac output whose magnitude and frequency can both be controlled. Practically, we use an inverter in both single-phase and three-phase ac systems. A half-bridge is the simplest topology, which is used to produce a two-level square-wave output waveform. A center-tapped voltage source supply is needed in such a topology. It may be possible to use a simple supply with two wellmatched capacitors in series to provide the center tap. The full-bridge topology is used to synthesize a three-level square-wave output waveform. The half-bridge and full-bridge configurations of the single-phase voltage source inverter are shown in Fig. 3.3 and Fig. 3.4 respectively. In a single-phase half-bridge inverter, only two switches are needed. To avoid shoot-through fault, both switches are never turned on at the same time.  $S_1$  is turned on and  $S_2$  is turned off to give a load voltage,  $V_{AO}$  in Fig. 3.2(a), of  $V_{dc}/2$ . To complete one cycle,  $S_1$  is turned off and  $S_2$  is turned on to give a load voltage,  $V_{AO}$  of  $-V_{dc}/2$ . In full bridge configuration, turning on  $S_1$  and  $S_4$  and turning off  $S_2$  and  $S_3$  give a voltage of  $V_{dc}$  between point A and B ( $V_{AB}$ ) in Fig. 3.2(b), while turning off  $S_1$  and  $S_4$  and turning on  $S_2$  and  $S_3$  give a voltage of  $-V_{dc}/2$ .

Fig. 3.2(a) Half Bridge Configuration

Fig. 3.2(b) Full Bridge Configuration

Note that  $S_1$  and  $S_3$  should not be closed at the same time, nor should  $S_2$  and  $S_4$ . Otherwise, a short circuit would exist across the dc source. The output waveform of half-bridge and full-bridge of single-phase voltage source inverter are shown in Fig. 3.3(a) and 3.3(b) respectively.

devices  $S_{1U}$  and  $S_{4U}$  function as main devices (like two level inverter ), and  $S_{2U}$  and  $S_{3U}$  function as auxiliary devices which help to clamp the output potential to the neutral point with the help of clamping diodes  $D_1$  and  $D_2$ .

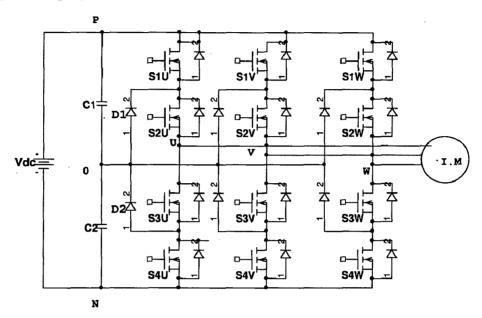

Fig 3.4 Neutral Point Clamped Three-level Inverter

The harmonic contents of a three-level inverter are less than that of a twolevel inverter at the same switching frequency and the blocking voltage of the switching device is half of the de-link voltage.

However, the concept of three level inverter introduced a new zero voltage level (also called neutral point), other than the positive and negative voltage levels in comparison to two level inverter. This type of DC links inherently associated with neutral point variations and results in a voltage unbalance problems between the lower and upper capacitor dc-link capacitors, causing undesirable uneven voltage stress at the upper and lower array of switching elements[9][23][26]. The inherent neutral point potential variation of a three-level inverter has to be effectively suppressed to fully utilize the advantages of three-level inverter. More complex PWM control is needed than 2-level. And requires mid point voltage balance control and neutral point voltage control. So many PWM techniques have been proposed in literature [22], [23], [25] and [26] to solve the above mentioned problems. In a single-phase half-bridge inverter, only two switches are needed. To avoid shoot-through fault, both switches are never turned on at the same time.  $S_1$  is turned on and  $S_2$  is turned off to give a load voltage,  $V_{AO}$  in Fig. 3.2(a), of  $V_{dc}/2$ . To complete one cycle,  $S_1$  is turned off and  $S_2$  is turned on to give a load voltage,  $V_{AO}$  of  $-V_{dc}/2$ . In full bridge configuration, turning on  $S_1$  and  $S_4$  and turning off  $S_2$  and  $S_3$  give a voltage of  $V_{dc}$  between point A and B ( $V_{AB}$ ) in Fig. 3.2(b), while turning off  $S_1$  and  $S_4$  and turning on  $S_2$  and  $S_3$  give a voltage of  $-V_{dc}/2$ .

Fig. 3.2(a) Half Bridge Configuration

Fig. 3.2(b) Full Bridge Configuration

Note that  $S_1$  and  $S_3$  should not be closed at the same time, nor should  $S_2$  and  $S_4$ . Otherwise, a short circuit would exist across the dc source. The output waveform of half-bridge and full-bridge of single-phase voltage source inverter are shown in Fig. 3.3(a) and 3.3(b) respectively.

| Conducting Switches      | Load Voltage V <sub>AB</sub> |

|--------------------------|------------------------------|

| S1,S4                    | +V <sub>dc</sub>             |

| S2,S3                    | -V <sub>dc</sub>             |

| $S_1, S_2$ or $S_3, S_4$ | 0                            |

Table 3.2 Load Voltage With Corresponding Switching States

Fig. 3.3 (b) Output waveform of Full-bridge configuration.

## **Advantages**

- 1. Simple and proven technology

- 2. Same converter design over supply voltage range

- 3. Standard fully developed PWM Control

#### Disadvantages

- 1. Static and dynamic voltage sharing of series devices

- 2. High dv/dt due to synchronous commutation of series devices

- 3. High switching frequency harmonic content in inverter output voltage.

## **Three-Level Neutral Point Clamped MLI**

In case of the conventional two-level inverter configuration, the harmonic contents reduction of an inverter output current is achieved mainly by raising the switching frequency. However in the field of high voltage, high power applications the switching frequency of the power device has to be restricted below 1 KHz, even with the HVIGBT and GCT, due to the increased switching loss. So the harmonic reduction by raised switching frequency of a two-level inverter becomes more difficult in high power applications. In addition, as the dc link voltage of a two-level inverter is limited by voltage ratings of switching devices, the problematic series connection of switching devices is required to raise the dc link voltage. By series connection, the maximum allowable switching frequency has to be more lowered, thus the harmonic reduction becomes more difficult.

From the aspect of harmonic reduction and high de-link voltage level; three-level approach seems to be the most promising alternative. The harmonic contents of a three-level inverter are less than that of a two-level inverter at the same switching frequency and the blocking voltage of the switching device is half of the de-link voltage. So the three-level inverter topology is generally used in realizing the high performance, high voltage ac drive systems.

For power/high voltage applications, the NPC inverter has advantages such that the blocking voltage of each switch is clamped to the half of DC –link voltage and the output voltage and current waveforms contain low harmonics compared to the conventional two -level inverter operating with the same switching frequency.

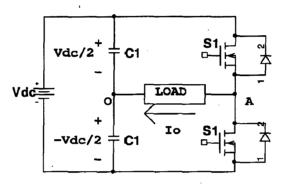

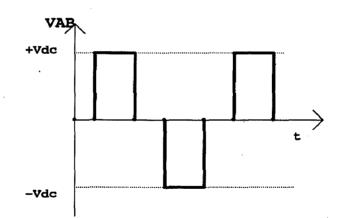

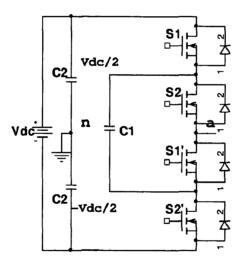

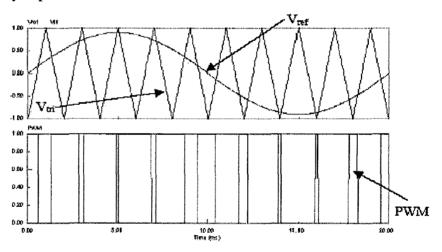

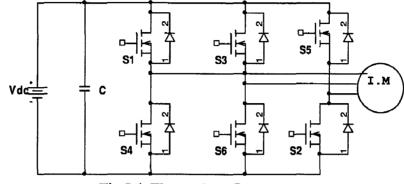

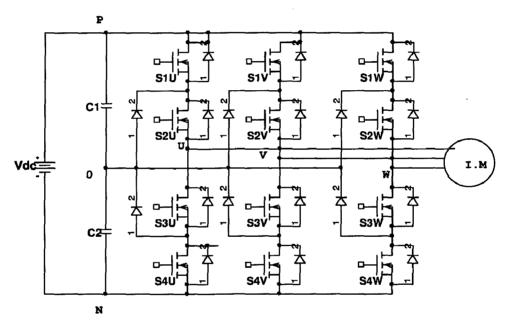

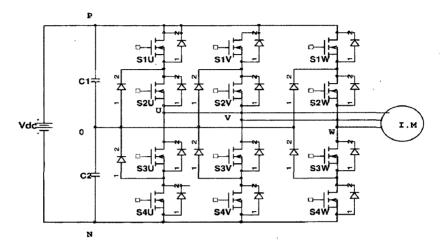

Fig 3.4 shows the circuit of a Neutral Point Clamped Three Level, three phase inverter using MOSFET devices. The dc link capacitor C has been split to create the neutral point 0. A pair of devices with bypass diodes is connected in series with an additional diode connected between the neutral point and the center of the pair. The

devices  $S_{1U}$  and  $S_{4U}$  function as main devices (like two level inverter ), and  $S_{2U}$  and  $S_{3U}$  function as auxiliary devices which help to clamp the output potential to the neutral point with the help of clamping diodes  $D_1$  and  $D_2$ .

Fig 3.4 Neutral Point Clamped Three-level Inverter

The harmonic contents of a three-level inverter are less than that of a twolevel inverter at the same switching frequency and the blocking voltage of the switching device is half of the de-link voltage.

However, the concept of three level inverter introduced a new zero voltage level (also called neutral point), other than the positive and negative voltage levels in comparison to two level inverter. This type of DC links inherently associated with neutral point variations and results in a voltage unbalance problems between the lower and upper capacitor dc-link capacitors, causing undesirable uneven voltage stress at the upper and lower array of switching elements[9][23][26]. The inherent neutral point potential variation of a three-level inverter has to be effectively suppressed to fully utilize the advantages of three-level inverter. More complex PWM control is needed than 2-level. And requires mid point voltage balance control and neutral point voltage control. So many PWM techniques have been proposed in literature [22], [23], [25] and [26] to solve the above mentioned problems.

## **Multilevel Inverters**

Since these are of three types, viz., Diode clamped multilevel inverter (DCMLI), Capacitor clamped (CCMLI) (or flying capacitor) multilevel inverter and Cascaded multi cell inverters, an overall comparison is made here [2],[3] and [12].

## The advantages are

- ▶ Reduced harmonic content.

- $\triangleright$  Reduced dv/dt.

- Snubberless operation (for CCMLI).

- $\triangleright$  Modular design.

- ▶ Low switching frequency devices.

- $\triangleright$  Low switching losses.

- > High voltage/power output with reduced rating of individual devices.

## The disadvantages are

- Large device count(DCMLI)

- ➢ Complex PWM control.

- Requirement of split DC link.

- Voltage balancing of DC link capacitors.

- Series redundancy difficult to achieve.

- Separate DC link sources(for ISHB)

- Uneven current stresses on power devices.

#### **3.4 CLASSIFICATION OF MULTI LEVEL INVERTRS**

## 3.4.1. DIODE-CLAMPED MULTI-LEVEL INVERTER (DCMLI)

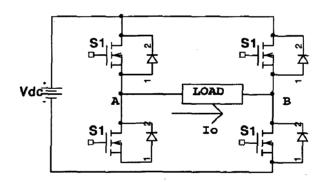

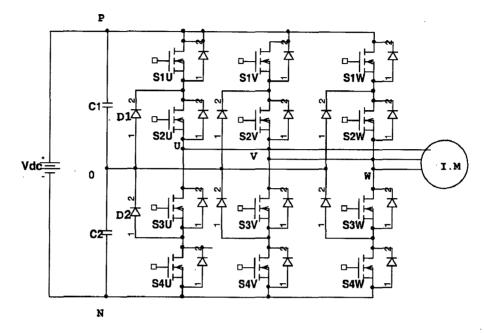

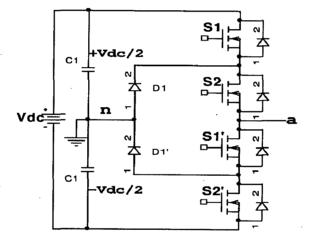

A three-level diode-clamped inverter is shown in Fig 3.5(a). In this circuit, the dc-bus voltage is split into three levels by two series-connected bulk capacitors,  $C_1$  and  $C_2$ . The middle point of the two capacitors *n* can be defined as the neutral point. The output voltage  $V_{an}$  has three states:  $V_{dc/2}$ , 0, and  $-V_{dc/2}$ . For voltage level  $V_{dc}/2$ , switches S<sub>1</sub> and S<sub>2</sub> need to be turned on; for  $-V_{dc/2}$ , switches S<sub>1</sub>' and S<sub>2</sub>' need to be turned on; and for the 0 level, S<sub>2</sub> and S<sub>1</sub>' need to be turned on.

The key components that distinguish this circuit from a conventional twolevel inverter are  $D_1$  and  $D_{\lambda}^{l}$ . These two diodes clamp the switch voltage to half the level of the dc-bus voltage. When both  $S_1$  and  $S_2$  turn on, the voltage across a and n is  $V_{dc}$ , i.e.,  $V_{an} = V_{dc}$ . In this case,  $d_1$  balances out the voltage sharing between  $S_1$ ' and  $S_2$ ' with  $S_1$ ' blocking the voltage across  $C_1$  and  $S_2$ ' blocking the voltage across  $C_2$ . Notice that output voltage  $v_{an}$  is ac, and  $v_{a0}$  is dc. The difference between  $v_{an}$  and  $v_{a0}$  is the voltage across  $C_2$ , which is  $V_{dc/2}$

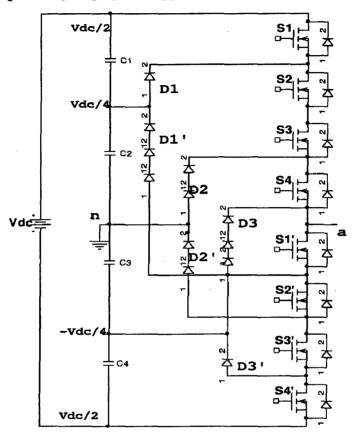

Fig. 3.5(b) shows a five-level diode-clamped converter in which the dc bus consists of four capacitors, C1,  $C_2$ ,  $C_3$ , and C4. For de-bus voltage V<sub>dc</sub>, the voltage across each capacitor is V<sub>dc</sub>/4, and each device voltage stress will be limited to one capacitor voltage level V<sub>dc/4</sub> through clamping diodes.

Fig 3.5(a) 3-level Diode-clamped Inverter

Although each active switching device is only required to block a voltage level of  $V_{dc}/(m - 1)$  where m is number of levels, the clamping diodes must have different voltage ratings for reverse voltage blocking. Using  $d_1$  of Fig. 3.5(b) as an example, when lower devices  $S_2$ ' to  $S_4$ ' are turned on,  $D_1$  and needs to block three capacitor voltages, or 3  $V_{dc/4}$ . Similarly,  $D_2$  and  $D_2$ ' need to block  $2V_{dc/4}$ , and  $D_3$  and  $D_3$ ' needs to block 3  $V_{dc/4}$ . Assuming that each blocking diode voltage rating is the same as the active device voltage rating, the number of diodes required for each phase will be  $(m - 1) \times (m - 2)$ . This number represents a quadratic increase in *m*. When *m* is sufficiently high, the number of diodes required will make the system impractical to implement. If the inverter runs under

PWM, the diode reverse recovery of these clamping diodes becomes the major design challenge in high-voltage high-power applications.

Fig3.5 (b) 5-level Diode Clamped Inverter

|                    | ]          |                |                       |    |   |   | · ·     |         |  |

|--------------------|------------|----------------|-----------------------|----|---|---|---------|---------|--|

| Output             | <b>S</b> 1 | S <sub>2</sub> | <b>S</b> <sub>3</sub> | S4 |   |   | $S_3^I$ | $S_4^I$ |  |

| V <sub>dc</sub>    | 1          | 1              | 1                     | 1  | 0 | 0 | 0       | 0       |  |

| V <sub>dc/4</sub>  | 0          | 1              | 1                     | 1  | 1 | 0 | 0       | 0       |  |

| 0                  | 0          | 0              | 1                     | 1  | 1 | 1 | 0       | 0       |  |

| -V <sub>dc/4</sub> | 0          | 0              | 0                     | 1  | 1 | 1 | 1       | 0       |  |

| -V <sub>dc/2</sub> | 0          | 0              | 0                     | 0  | 1 | 1 | 1       | 1       |  |

There are 5 switch combinations to synthesize five level voltages across a and n.

Table. 3.3. Switching Combinations Vs Output Voltage

#### **Unequal device rating and Capacitor Voltage Unbalance**

The switch S1 conducts only during  $V_{a0} = V_{dc/2}$ , while switch S<sub>4</sub> conducts over the entire cycle except  $V_{a0}=0$ . Such an unequal conduction duty requires different current for switching devices, the outer switches may be oversized and the inner switches may be undersized. A power needs to transfer real power from ac to dc (rectifier) or dc to ac (inverter). When operating at unity power factor, the charging time for rectifier operation or discharging time for inverter operation for each capacitor is different. The voltage unbalance problem is solved by several approaches, such as replacing capacitors by a controlled constant dc voltages source such as pulse width modulation (PWM) voltage regulators or batteries. The use of controlled dc voltage results in system complexity and cost penalties. The converter switching frequency should be kept, minimum to avoid switching losses and electromagnetic interference problems. When operating at zero power factor, the capacitor voltages can be balanced equal charge and discharge in one half cycle.

The voltage unbalance problem in multilevel inverter can be solved by several approaches proposed in the literature [8,9]. A simple solution would be to replace capacitors by constant DC voltage sources, voltage regulators or batteries. But this makes the system complex and costly.

In ref. [8] a simple method of balancing the capacitor voltages has been given. The method is based on buck-boost converter, where half cycle charging of inductors is used for compensating the loss of charge in the capacitors. The method although simple, requires extra components including inductors. Also it exposes the system to over –voltages that can damage the system devices.

In ref. [9], a method using the zero sequence current to control the capacitor voltages for a three-level inverter has been presented. The system is slightly complex and the complexity increases for higher levels.

In ref. [10], the generalized topology has been presented. The topology has a true modular structure with a basic cell and does not require extra components like clamping diodes and voltage balancing capacitors. The generalized topology presents a structure from which any type and any level inverter can be deduced with self voltagevoltage balancing. For higher levels the device count for this topology is excessive. The diode-clamp Multi Level Inverter can be therefore summarized with the following advantages and disadvantages.

#### Advantages

- Large number of levels reduces the harmonic content and avoids the needs for filters.

- Since all devices are switched at fundamental frequency, the efficiency is high because of low switching losses.

- Reactive power flow can be controlled

#### **Disadvantages**

➢ For large number of levels, the number of clamping diodes required is very high,(m-1)x(m-2) for each phase for m-level inverter.

÷.,

> Real power flow control is difficult for the individual converter.

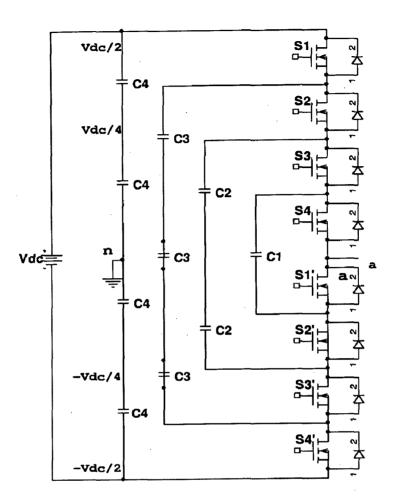

#### 3.4.2 CAPACITOR-CLAMPED MULTI-LEVEL INVERTER(CCMLI)

For high-voltage applications, some problems have been encountered while dealing with the practical control and implementation of main topologies. These include,

- Voltages unbalance between split dc capacitors.

- Indirect clamping of inner switching devices.

- Series connected clamping diodes.

To overcome these problems, a multilevel structure with flying capacitors was proposed. This approach obviously overcomes the limitation of diode-clamped multilevel inverters. The flying capacitor multilevel inverter has not been widely applied in industry. Nevertheless it seems that it has important advantages over the diode clamp multilevel converter. This is because it uses a clamping capacitor across a two-switch pair. In spite of this, there is a fundamental problem dealing with voltage balancing between flying capacitors and each leg under practical operation. This leads to voltage unbalance and thus, unsafe operation. For its balancing, FCMLI requires the symmetric switching of control signals with a phase shift. Up to now, there has been very little work done to solve a fundamental problem in the FCMLI applications. Since most of the research was focused on uni-directional dc-dc converter applications, this problem was not considered to be a major concern.

Through simulation and experimentation, it was discovered that this topology is not available for bi-directional applications without adding a passive voltage balancing circuit or voltage control loops. For voltage balancing between flying capacitors, various approaches can be considered using voltage stabilizers and switching modulations.

- First, controlling each capacitor voltage within a few cycles makes it possible to maintain a voltage balance.

- ➤ The capacitor voltage can be controlled by a modulation scheme, which introduces small changes in the switching instants. In this case, the suggested approach changes slight distortions to the voltage but allow selective charging of each capacitor without requiring an increase in the number of switching events.

Fig 3.6(a) Three -level Capacitor Clamped MLI

Fig. 3.6(b) illustrates the fundamental building block of a phase-leg capacitor-clamped inverter. Clamping capacitor  $C_1$  is charged when  $S_1$  and  $S_1$ ' are turned on, and is discharged when  $S_2$  and  $S_2$ ' are turned on. The voltage synthesis in a five-level capacitor-clamped converter has more flexibility than a diode-clamped converter. Using Fig. 3.2(b) as the example, the voltage of the five-level phase-leg *a* output with respect to the neutral point *n*,  $V_{an}$  can be synthesized by the following switch combinations.

÷

#### Fig 3.6(b) Five -level Capacitor Clamped MLI

- 1) For voltage level  $V_{an} = V_{dc/2}$ , turn on all upper switches  $S_1 S_4$ .

- 2) For voltage level  $V_{an} = V_{dc/4}$ , there are three combinations

- a)  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_i'$  ( $V_{an} = V_{dc/2}$  of upper  $C_4$ 's- $V_{dc/4}$  of  $C_1$ );

b)

$$S_2$$

,  $S_3$ ,  $S_4$ ,  $S_4'$  ( $V_{on} = 3V_{dc}/4$  of  $C_3$ 's -Vdc/2 of lower  $C_4$ 's); and

c)

$$S_1$$

,  $S_3$ ,  $S_4$ ,  $S_3'$  ( $V_{an} = Vdc/2$  of upper C<sub>4</sub>'s- $3V_{dc}/4$  of C<sub>3</sub>'s + $V_{dc}/2$  of C<sub>4</sub>'s)

- 3) For voltage level  $V_{an} = 0$ , there are six combinations:

- a)  $S_1$ ,  $S_2$ ,  $S_1'$ ,  $S_2'$  ( $V_{an} = V_{dc}/2$  of upper C<sub>4</sub>'s-V<sub>dc/2</sub> of C<sub>2</sub>'s);

- b)  $S_3, S_4, S_3', S_4' (V_{an} = V_{dc}/2 \text{ of } C_2 V_{dc/2} \text{ of lower } C_4);$

- c)  $S_1, S_3, S_1', S_3' (V_{an} = V_{dc}/2 \text{ of upper } C_4' \text{s} 3V_{dc}/4 \text{ of } C_3' \text{s} + V_{dc}/2 \text{ of } C_2' \text{s} V_{dc}/4 \text{ of } C_1);$

- d)  $S_1, S_4, S_2', S_3' (V_{on} = V_{dc}/2 \text{ of upper } C_4's 3V_{dc}/4 \text{ of } CVs + V_{dc}/4 \text{ of } C_1);$

- e)  $S_2$ ,  $S_4$ ,  $S_2'$ ,  $S_4'$  ( $V_{an} = 3Vdc/4$  of  $C_3$ 's  $V_{dc}/2$  of  $C_2$ 's + $V_{dc}/4$  of  $C_1$   $V_{dc}/2$  of lower  $C_4$ 's); and

- f)  $S_2$ ,  $S_3$ ,  $S_1'$ ,  $S_4'$  ( $V_{an} = 3V_{dc}/4$  of  $C_3$ 's  $-V_{dc}/4$  of  $C_1$   $-V_{dc}/2$  of lower  $C_4$ 's).

- 4) For voltage level  $V_{an} = -V_{dc}/4$ , there are three combinations:

- a)  $S_1, S_1', S_2', S_3' (V_{an} = V_{dc}/2 \text{ of upper } C_4's 3 V_{dc}/4 \text{ of } C_3's);$

- b)  $S_4, S_2', S_3', S_4' (V_{an} = V_{dc} / 4 \text{ of } C_1 V_{dc} / 2 \text{ of lower } C_4's)$ ; and

- c)  $S_3$ ,  $S_1'$ ,  $S_3'$ ,  $S_4'$  ( $V_{an} = V_{dc}/2$  of  $C_2$ 's  $V_{dc}/4$  of  $C_1$   $V_{dc}/2$  of lower  $C_4$ 's).

- 5) For voltage level  $V_{an} = -V_{do}/2$ , turn on all lower switches,  $S_1'-S_4'$ .

In the preceding description, the capacitors with positive signs are in discharging mode, while those with negative sign are in charging mode. By proper selection of capacitor combinations, it is possible to balance the capacitor charge. Similar to diode clamping, the capacitor clamping requires a large number of bulk capacitors to clamp the voltage. Provided that the voltage rating of each capacitor used is the same as that of the main power switch, an m-level converter will require a total of  $(m - 1) \times (m - 2)/2$  clamping capacitors per phase leg in addition to (m - 1) main de-bus capacitors.

#### Advantages

- Large no of storage capacitors provides extra ride through capabilities during power outage.

- Provides switch combination redundancy for balancing different voltage levels.

- When the no. of levels is high enough, harmonic content will be low enough to avoid the need for filters

- Both real and reactor power flow can be controlled.

#### Disadvantages

- An excessive no of storage capacitors is required when the no. of levels is high.

- The inverter control will be complicated and switching frequency losses will be high for real power transmission.

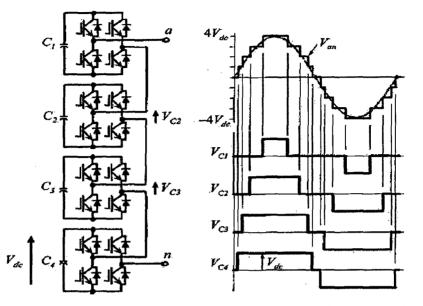

#### 3.4.3. CASCADED MULTICELL INVERTERS:

Fig3.7: Cascaded Inverter circuit Topology and its associated waveform

A different converter topology is introduced here, which is based on the series connection of single-phase inverters with separate dc sources [3]. Fig. 3.7 shows the power circuit for one phase leg of a nine-level inverter with four cells in each phase. The resulting phase voltage is synthesized by the addition of the voltages generated by the different cells. Each single-phase full-bridge inverter generates three voltages at the output:  $+V_{dc}$ , 0, and  $-V_{dc}$ . This is made possible by connecting the capacitors sequentially to the ac side via the four power switches. The resulting output ac voltage swings from  $-4V_{dc}$  to  $+4V_{dc}$  with nine levels and the staircase waveform is nearly sinusoidal, even without filtering.

#### **Advantages**

- Requires the least no. of components among all the multilevel inverters to achieve the same number of voltage levels

- Modularized circuit lay out and packaging is possible since each level has the same structure and there are no extra clamping diodes or voltage balancing capacitors.

- Soft switching is possible to avoid bulky and lossy resistor capacitor diode snubbers.

# Disadvantages

Needs separate dc sources for real power conversions and thus its applications are somewhat limited.

| <b>Inverter Configuration</b> | Diode-clamped | Flying-capacitors | Cascaded-inverters |

|-------------------------------|---------------|-------------------|--------------------|

| Main switching devices        | 2(m-1)        | 2(m-1)            | 2(m-1)             |

| Main diodes                   | 2(m-1)        | 2(m-1)            | 2(m-1)             |

| Clamping diodes               | (m-1)(m-1)    | 0                 | 0                  |

| DC bus capacitors             | (m-1)         | (m-1)             | (m-1)/2            |

| Balancing capacitors          | 0             | (m-1)(m-2)/2      | 0                  |

# Table.3.4 Comparison of power component requirements per phase leg among three multilevel inverters

.

#### **CHAPTER-4**

# SIMULATION OF MULTI-LEVEL INVERTERS

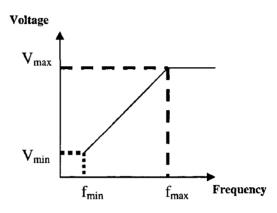

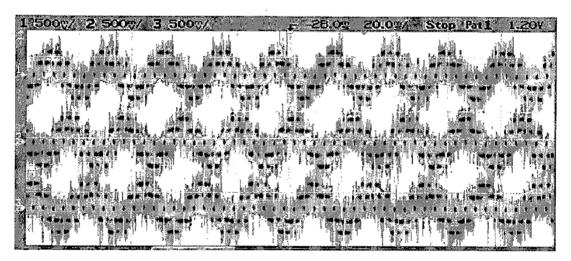

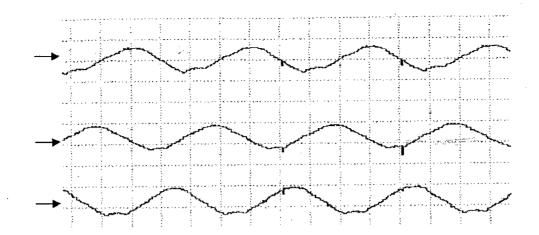

In this chapter simulation of various inverters using sinusoidal pulse width modulation was carried out with the help of "MATLAB 6.5". The main objective of this chapter is to observe the improvement in the line voltage THD and Line Current THD for both R-L Load, Motor Load as the inverter level increases from 2-level to 5-level. V/f analysis of the drive has been done using 2-level, 3-level and 5-level inverters. Here it has been assumed that modulation index is proportional to output voltage of inverter.

$MI=K*V_1(V_1$ - Fundamental Component)

where k is constant. So for variable speed drive at different frequencies following quantities have been observed.

- ➤ Line Voltage waveform

- Line current waveform for both R-L load and Motor Load

- Variation of Line Voltage THD and frequency

#### Load Specifications:

(a) R-L load:  $R=10\Omega$ , L=30mH

(b) Motor Load: 1 HP, RPM: 1440, Current: 2 Amps.

#### **4.1. TWO-LEVEL INVERTER**

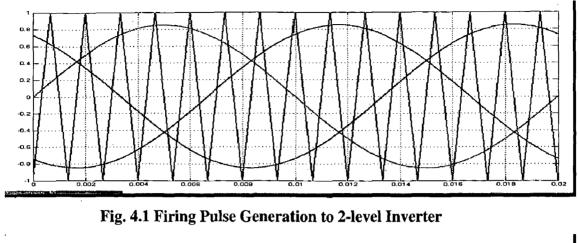

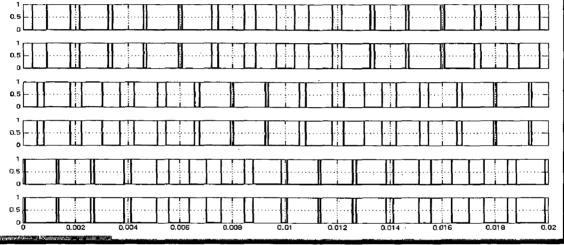

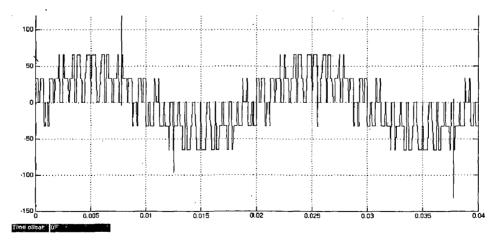

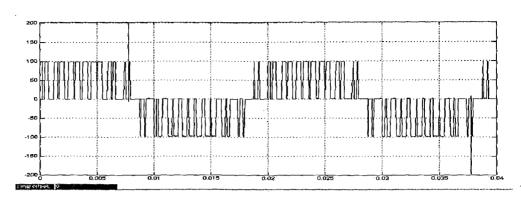

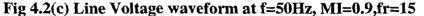

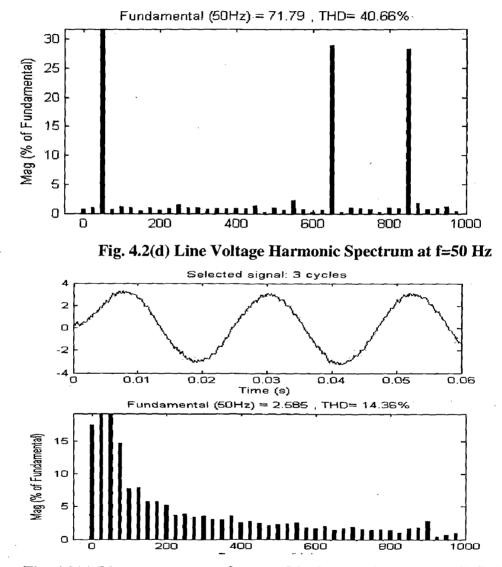

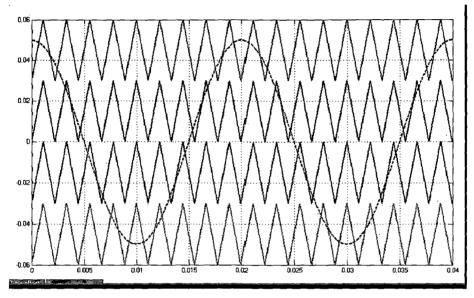

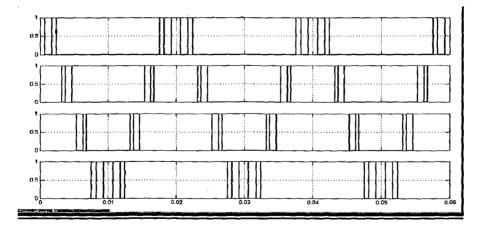

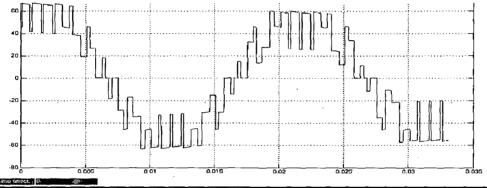

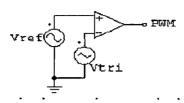

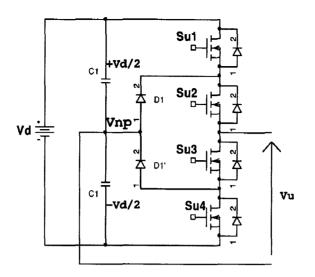

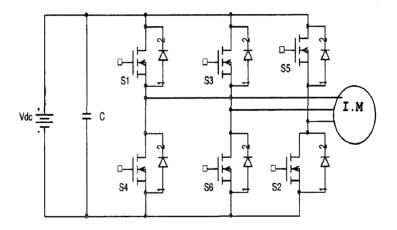

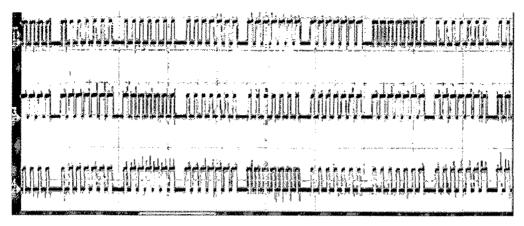

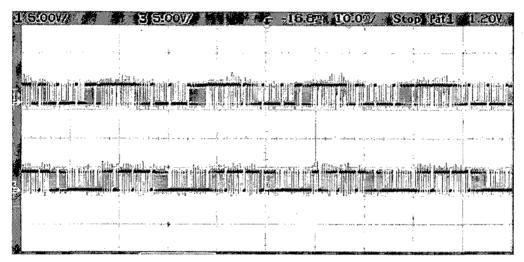

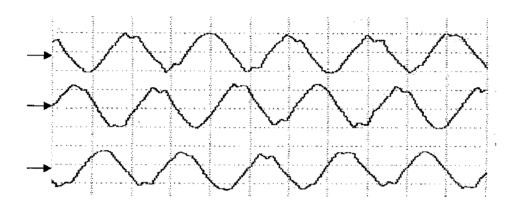

In 2-level inverter one triangular wave is compared with one sine wave as shown in Fig 4.1. Fig 4.2(a) to Fig 4.2(f) shows the firing pulses to the six MOSFETs, phase voltage line voltage waveform and its harmonic spectrum, line current waveforms and its harmonic spectrum for both R-L load and Induction Motor load respectively.

Fig. 4.2(a) Firing Pulses to Six MOSFETs S1, S4, S3, S6, S5, S2 from Top to Bottom

Fig. 4.2(e) Line current waveform and its harmonic spectrum(R-L Load)

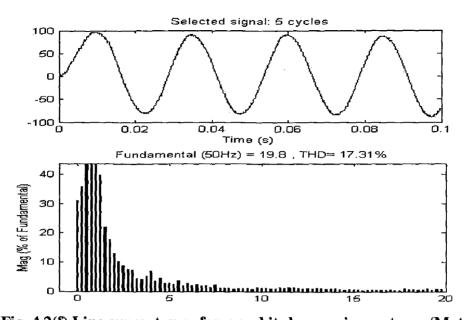

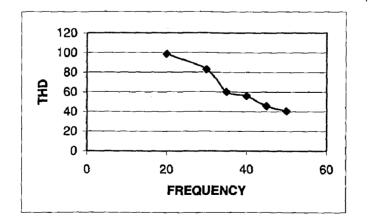

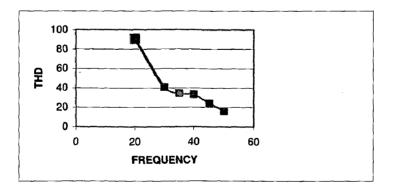

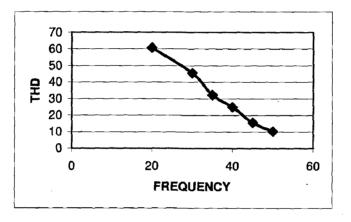

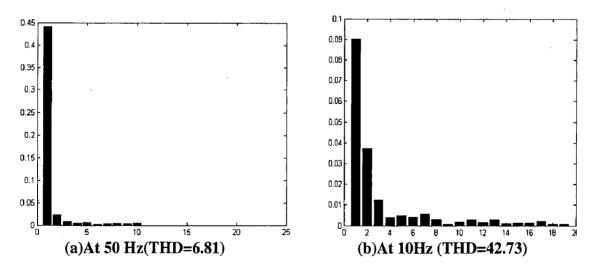

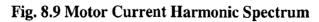

Fig. 4.2(f) Line current waveform and its harmonic spectrum (Motor Load) Table 4.1 shows V/f analysis of Three-level Inverter along with the THD variation. Fig. 4.3 shows variation of 2-level Line voltage THD with the frequency.

| Freq<br>(Hz) | (MI) | Line Current<br>THD% | Line Voltage<br>THD % |

|--------------|------|----------------------|-----------------------|

| 50           | 0.9  | 14.36                | 40.66                 |

| 45           | 0.81 | 19.32                | 45.83                 |

| 40           | 0.72 | 30.00                | 55.98                 |

| 35           | 0.63 | 35.73                | 60.23                 |

| 30           | 0.54 | 45.47                | 82.76                 |

| 20           | 0.36 | 50.04                | 98.53                 |

Table 4.1 Analysis of Two-level Inverter as V/f drive

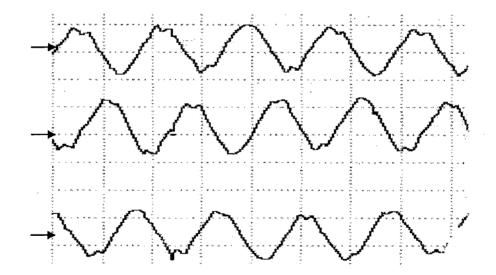

#### **4.2. THREE-LEVEL INVERTER:**

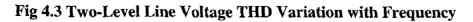

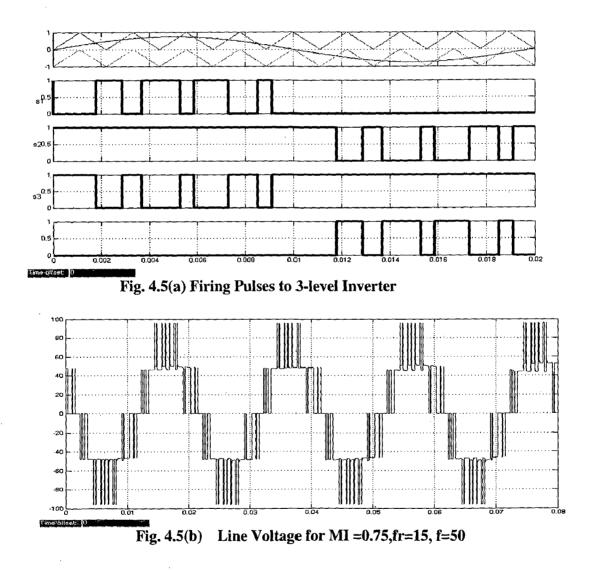

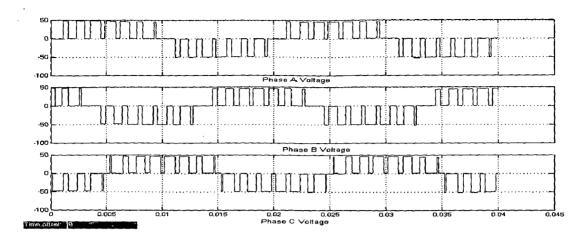

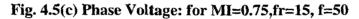

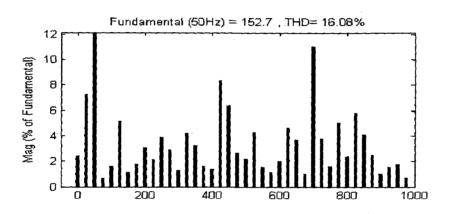

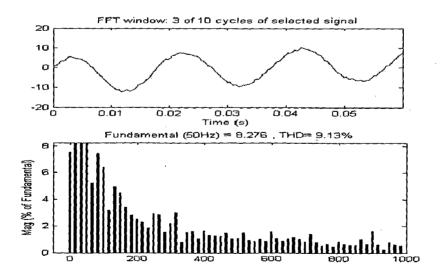

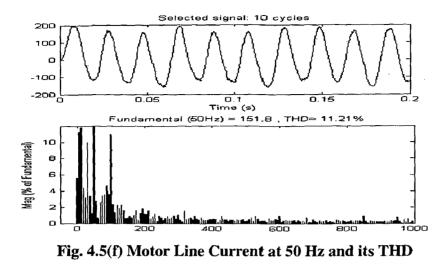

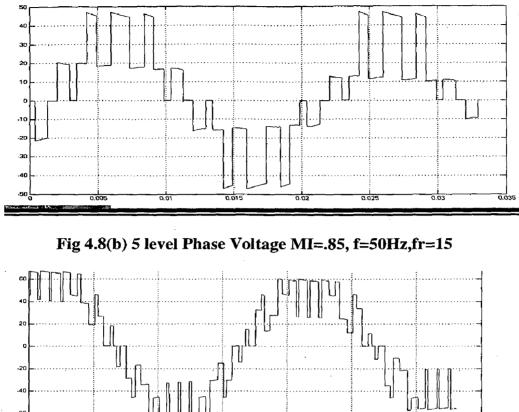

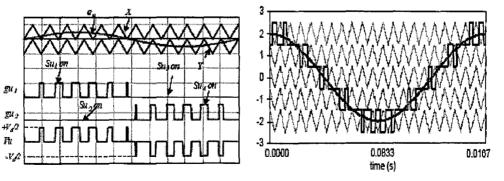

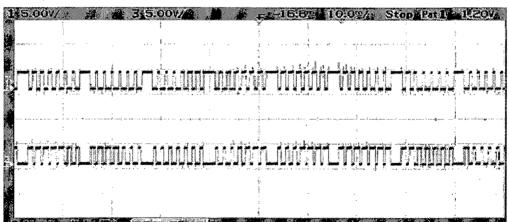

In 3-level inverter two triangular waves are compared with one sine wave as shown Fig 4.4. Firing pulses are generated according to logic given in previous chapter. Fig 4.5(a) to Fig 4.5(f) shows the firing pulses four MOSFETs in one phase, phase voltage line voltage waveform and its harmonic spectrum, line current waveforms and its harmonic spectrum for both R-L load and Induction Motor load respectively

35

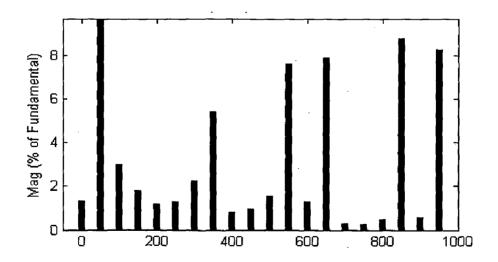

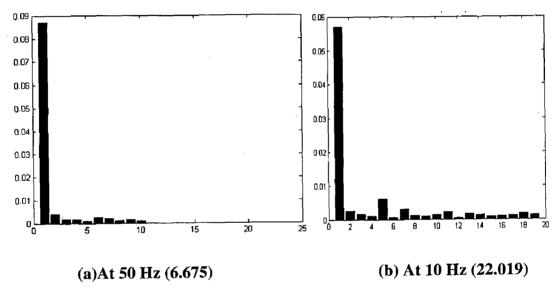

Fig 4.5(d) Harmonic Spectrum 3-Level Inverter f=50, MI=0.9, THD=16.08

Fig. 4.5(e) Line Current and its harmonic spectrum

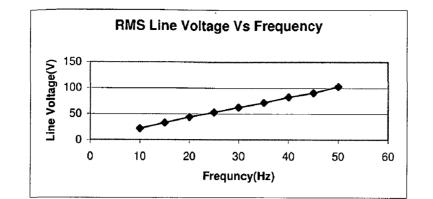

Table 4.2 shows V/f analysis of Three-level Inverter along with the THD variation. Fig. 4.6 shows variation of 3-level Line voltage THD with the frequency.

| Freq<br>(Hz) | (MI) | Line Current<br>THD% | Line Voltage<br>THD % |

|--------------|------|----------------------|-----------------------|

| 50           | 0.9  | 9.13                 | 16.08                 |

| 45           | 0.81 | 15.32                | 24.06                 |

| 40           | 0.72 | 23.00                | 33.06                 |

| 35           | 0.63 | 28.73                | 34.34                 |

| 30           | 0.54 | 32.47                | 40.54                 |

| 20           | 0.36 | 45.04                | 90.74                 |

Table 4.2 Analysis of Three-level Inverter as V/f drive